Patents

Literature

115results about How to "Prevent capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

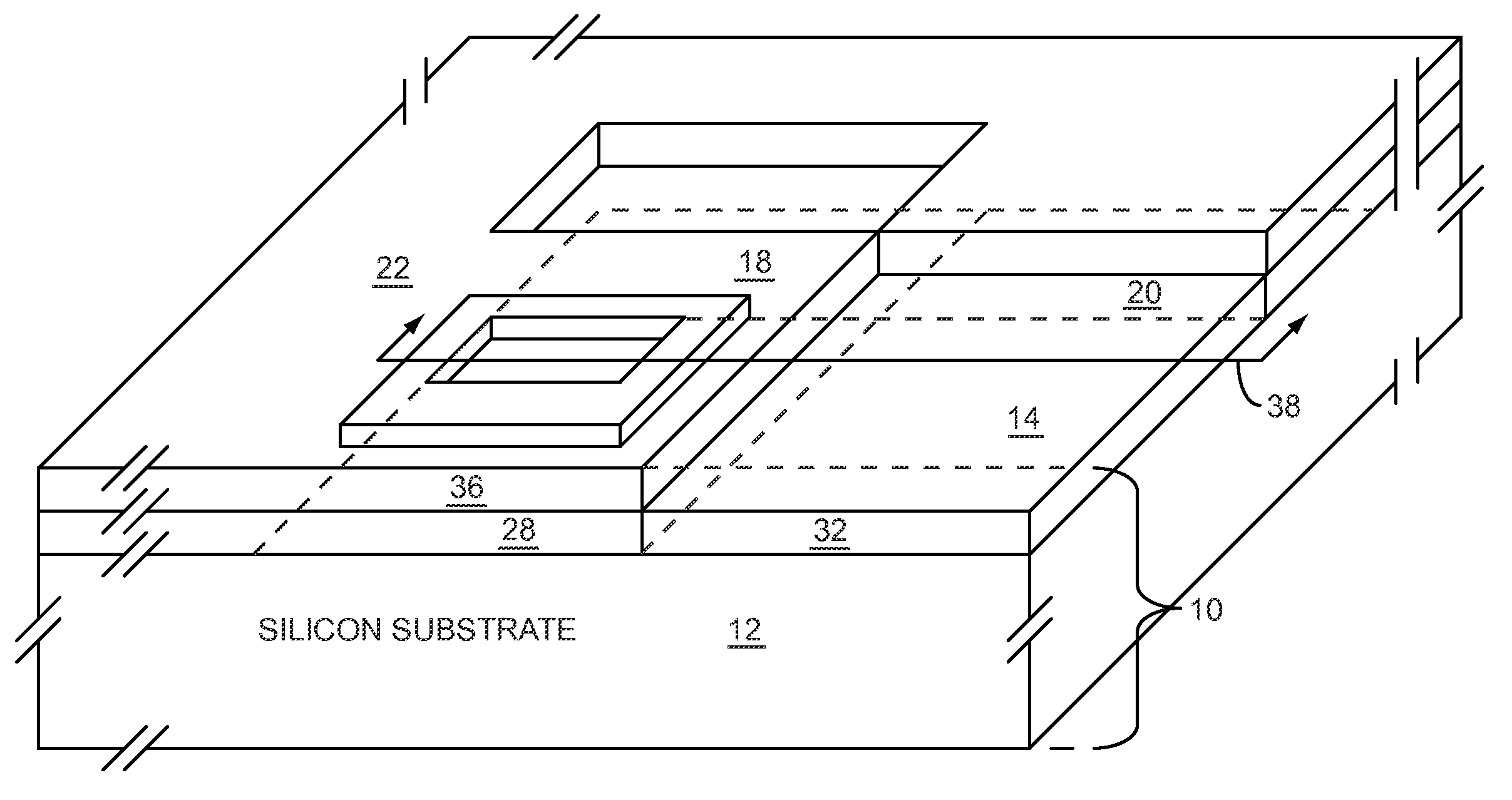

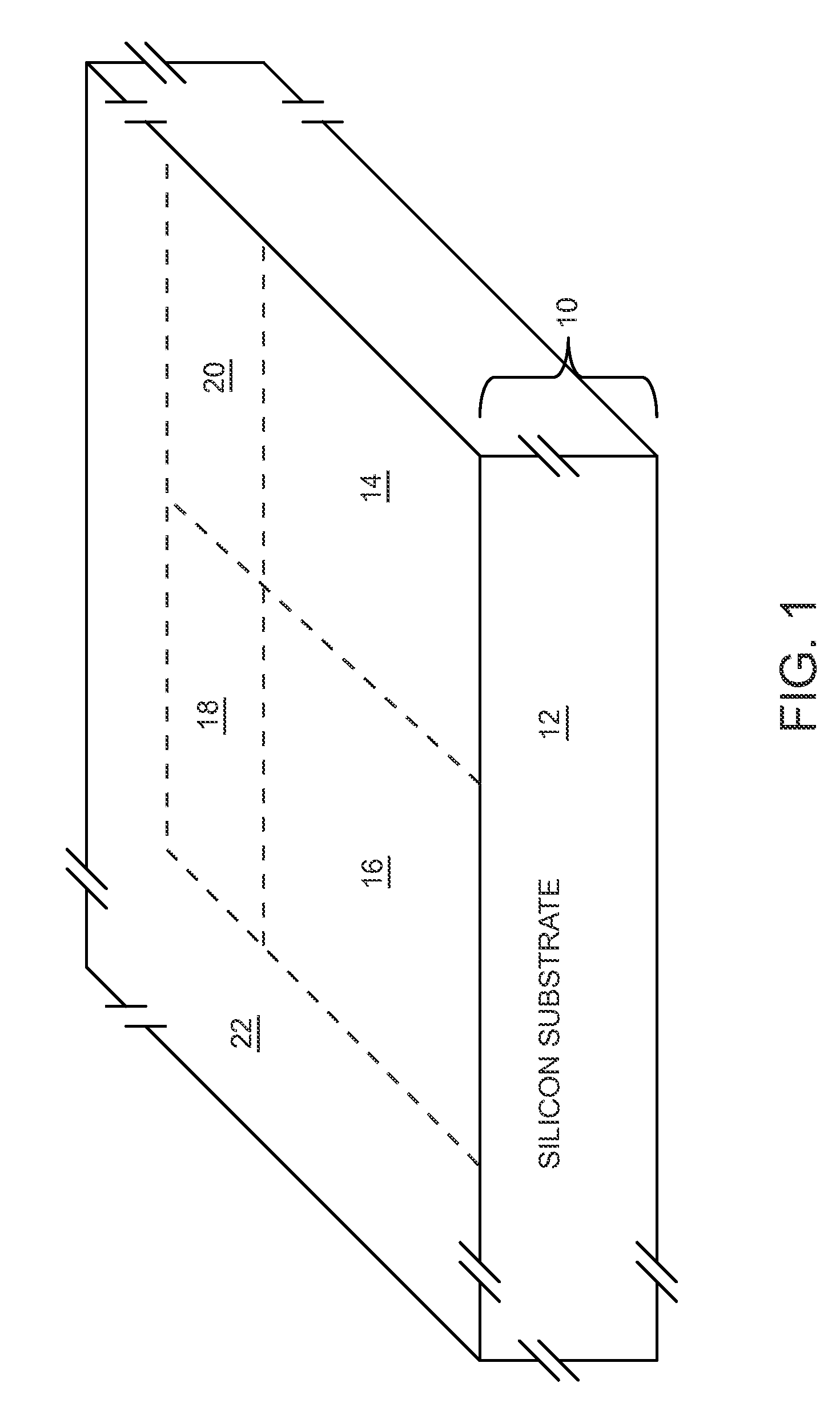

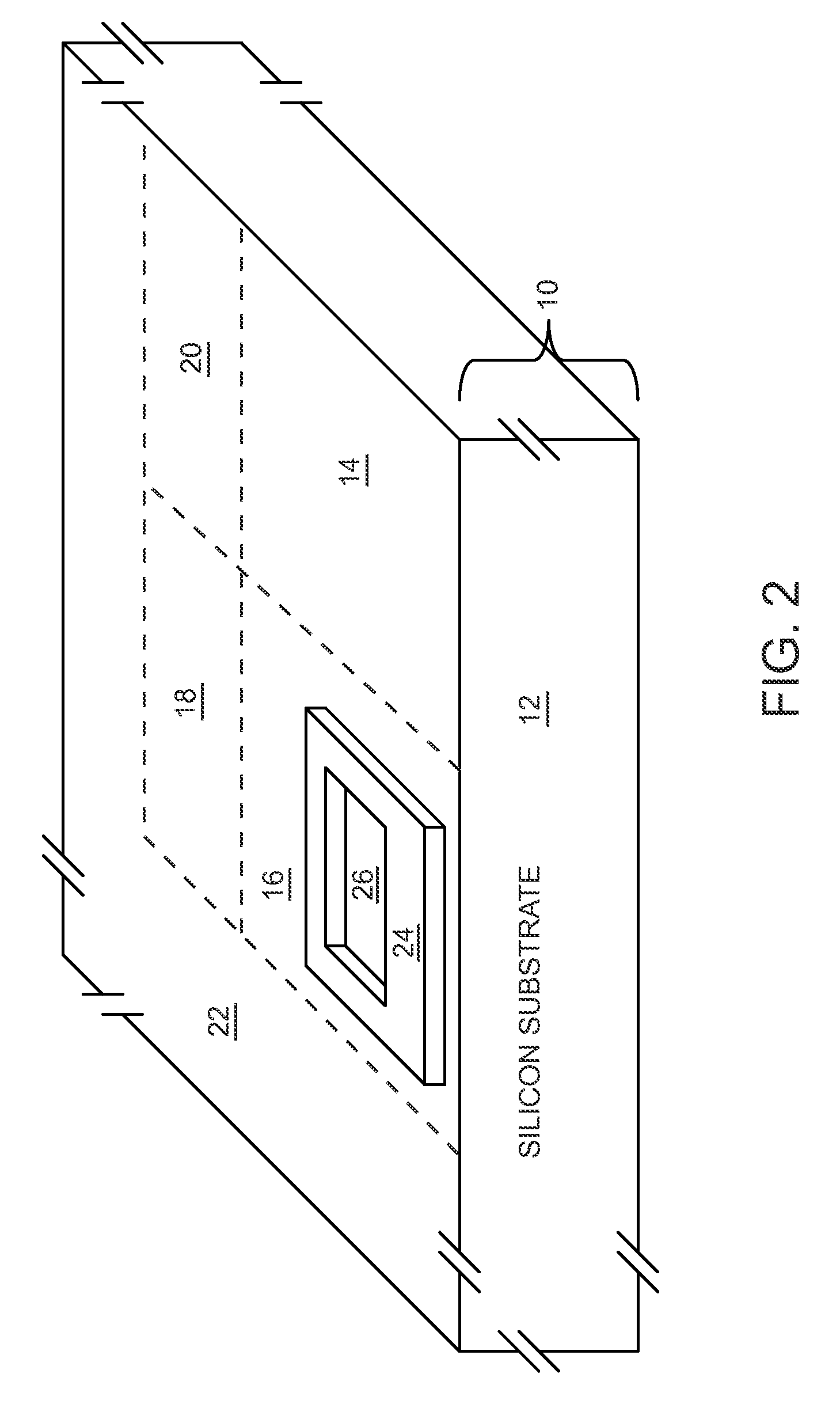

Linearity improvements of semiconductor substrate based radio frequency devices

ActiveUS7868419B1Effectively layerPrevent capacitance changeSemiconductor/solid-state device detailsSolid-state devicesCapacitanceHigh density

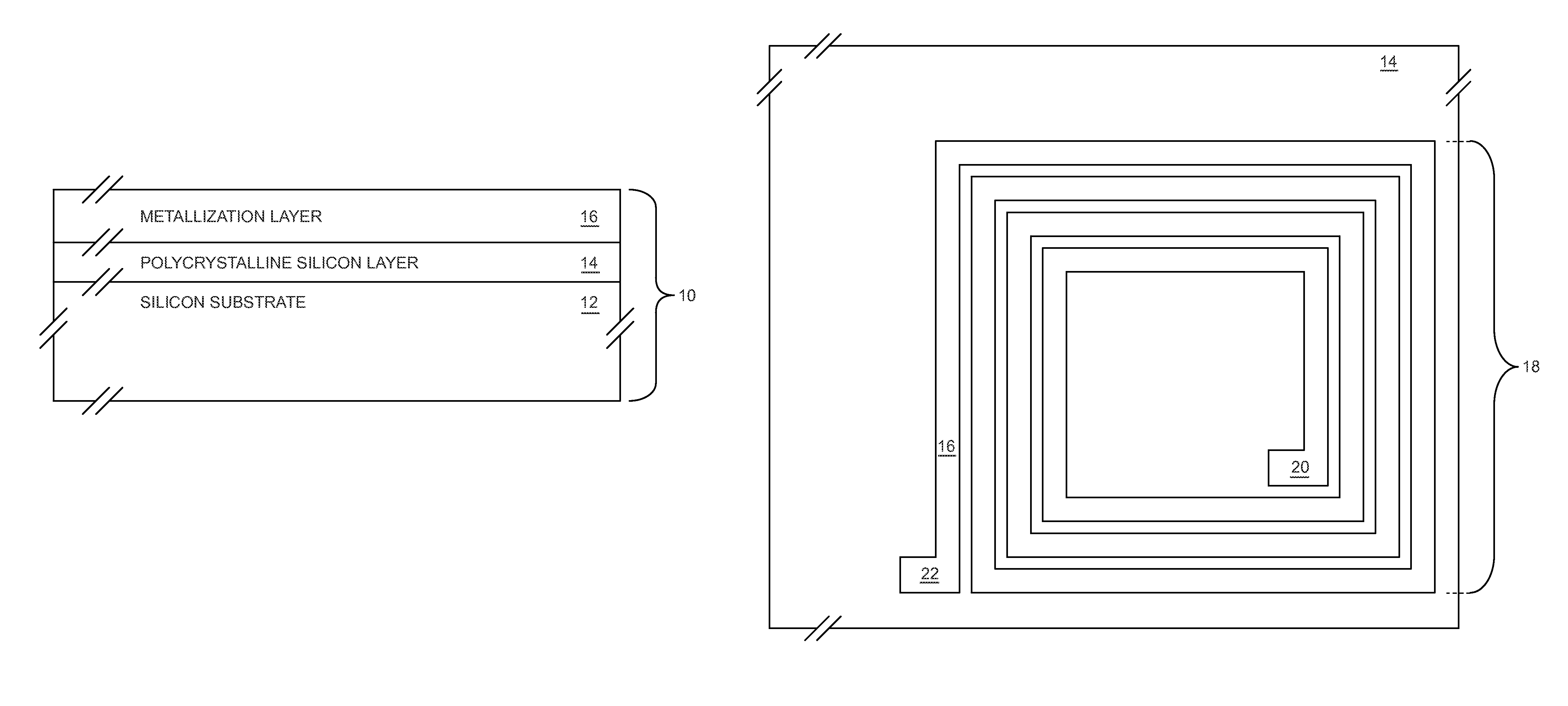

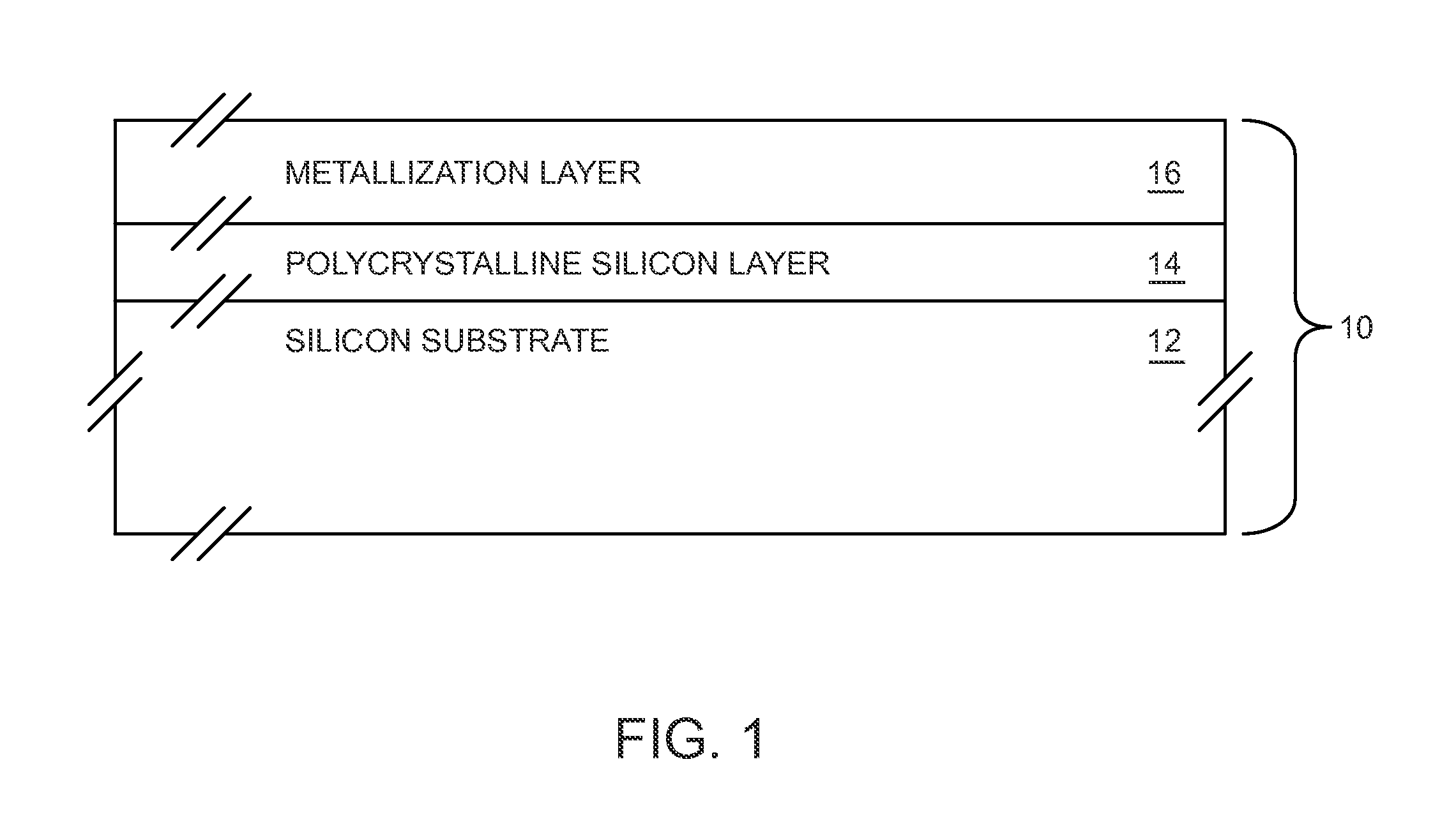

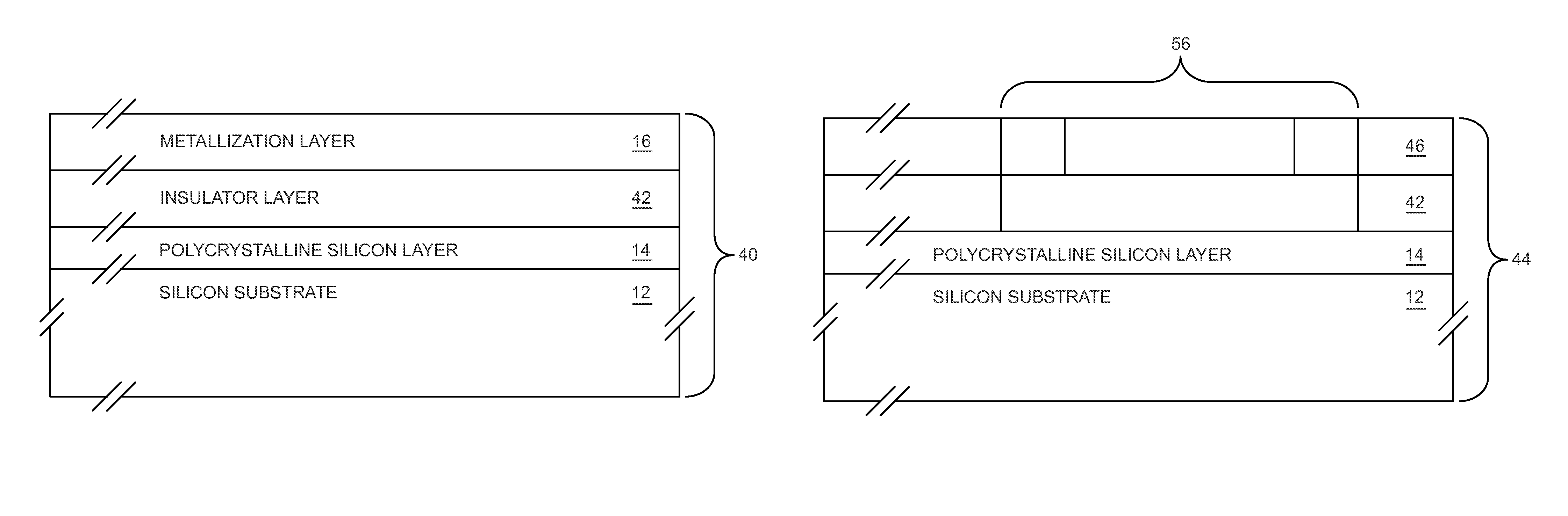

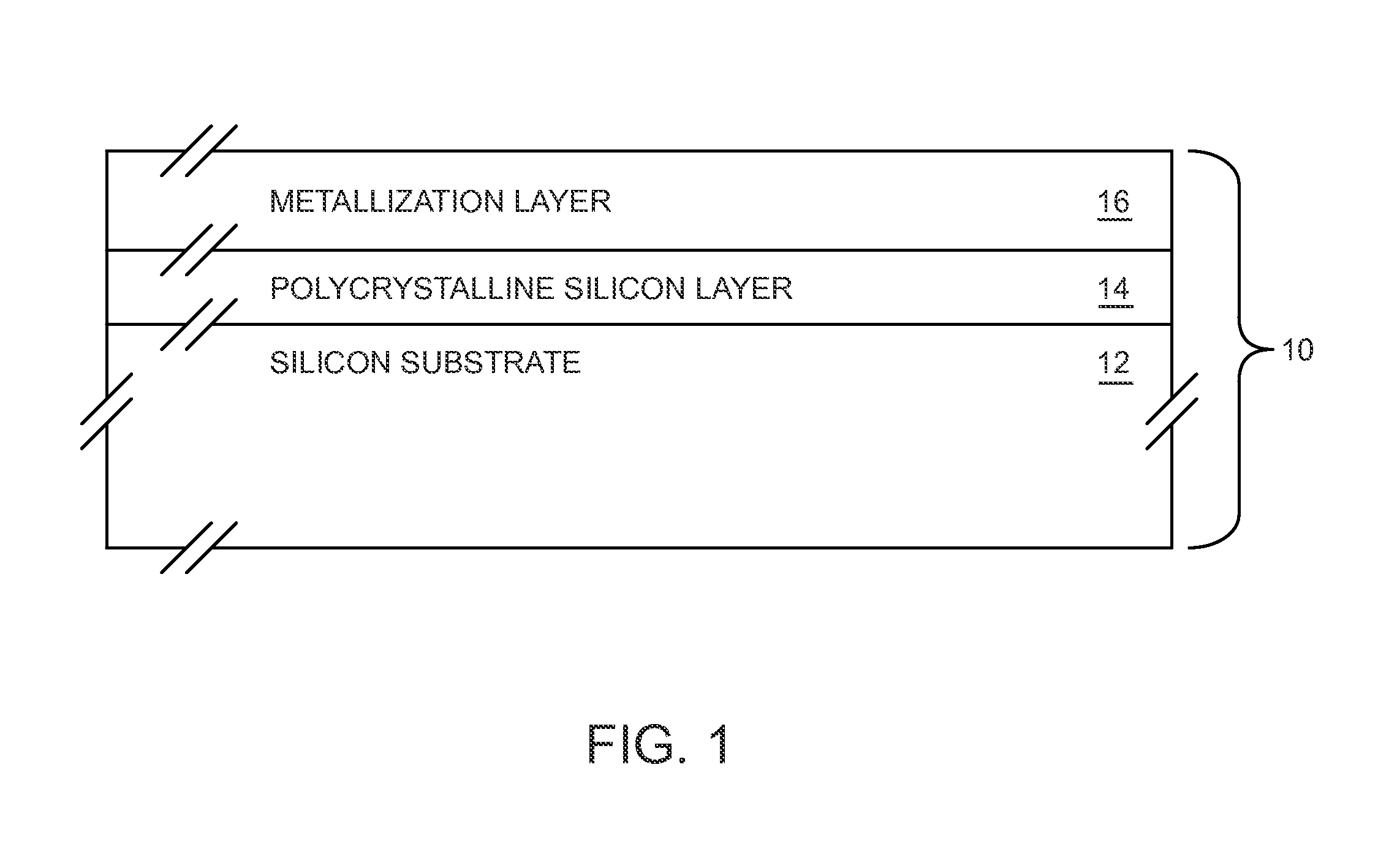

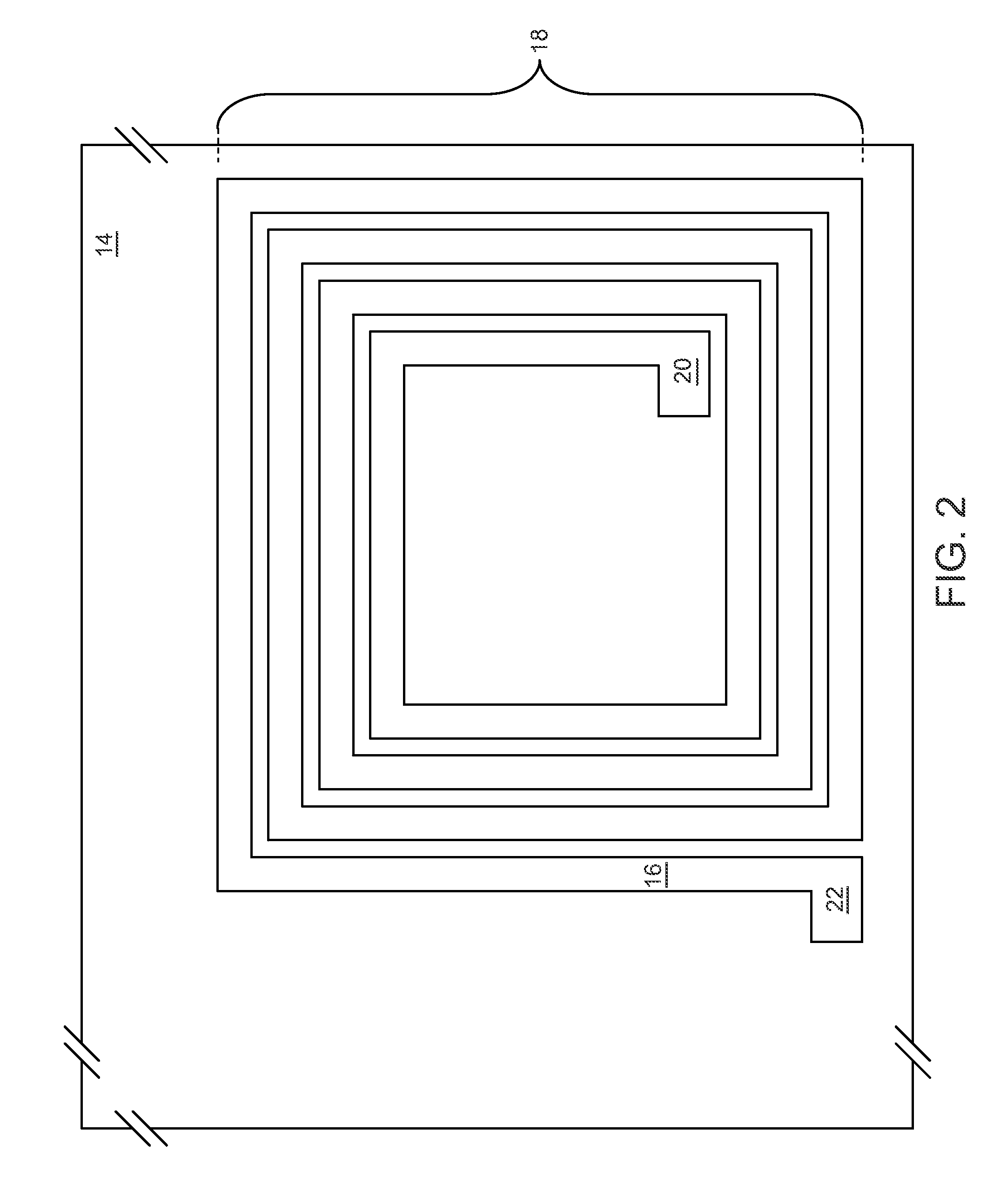

The present invention relates to using a trap-rich layer, such as a polycrystalline Silicon layer, over a semiconductor substrate to substantially immobilize a surface conduction layer at the surface of the semiconductor substrate at radio frequency (RF) frequencies. The trap-rich layer may have a high density of traps that trap carriers from the surface conduction layer. The average release time from the traps may be longer than the period of any present RF signals, thereby effectively immobilizing the surface conduction layer, which may substantially prevent capacitance and inductance changes due to the RF signals. Therefore, harmonic distortion of the RF signals may be significantly reduced or eliminated. The semiconductor substrate may be a Silicon substrate, a Gallium Arsenide substrate, or another substrate.

Owner:QORVO US INC

Linearity improvements of semiconductor substrate based radio frequency devices

ActiveUS8076750B1Effectively immobilizing the surface conduction layerPrevent capacitanceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceRelease time

The present invention relates to using a trap-rich layer, such as a polycrystalline Silicon layer, over a semiconductor substrate to substantially immobilize a surface conduction layer at the surface of the semiconductor substrate at radio frequency (RF) frequencies. The trap-rich layer may have a high density of traps that trap carriers from the surface conduction layer. The average release time from the traps may be longer than the period of any present RF signals, thereby effectively immobilizing the surface conduction layer, which may substantially prevent capacitance and inductance changes due to the RF signals. Therefore, harmonic distortion of the RF signals may be significantly reduced or eliminated. The semiconductor substrate may be a Silicon substrate, a Gallium Arsenide substrate, or another substrate.

Owner:QORVO US INC

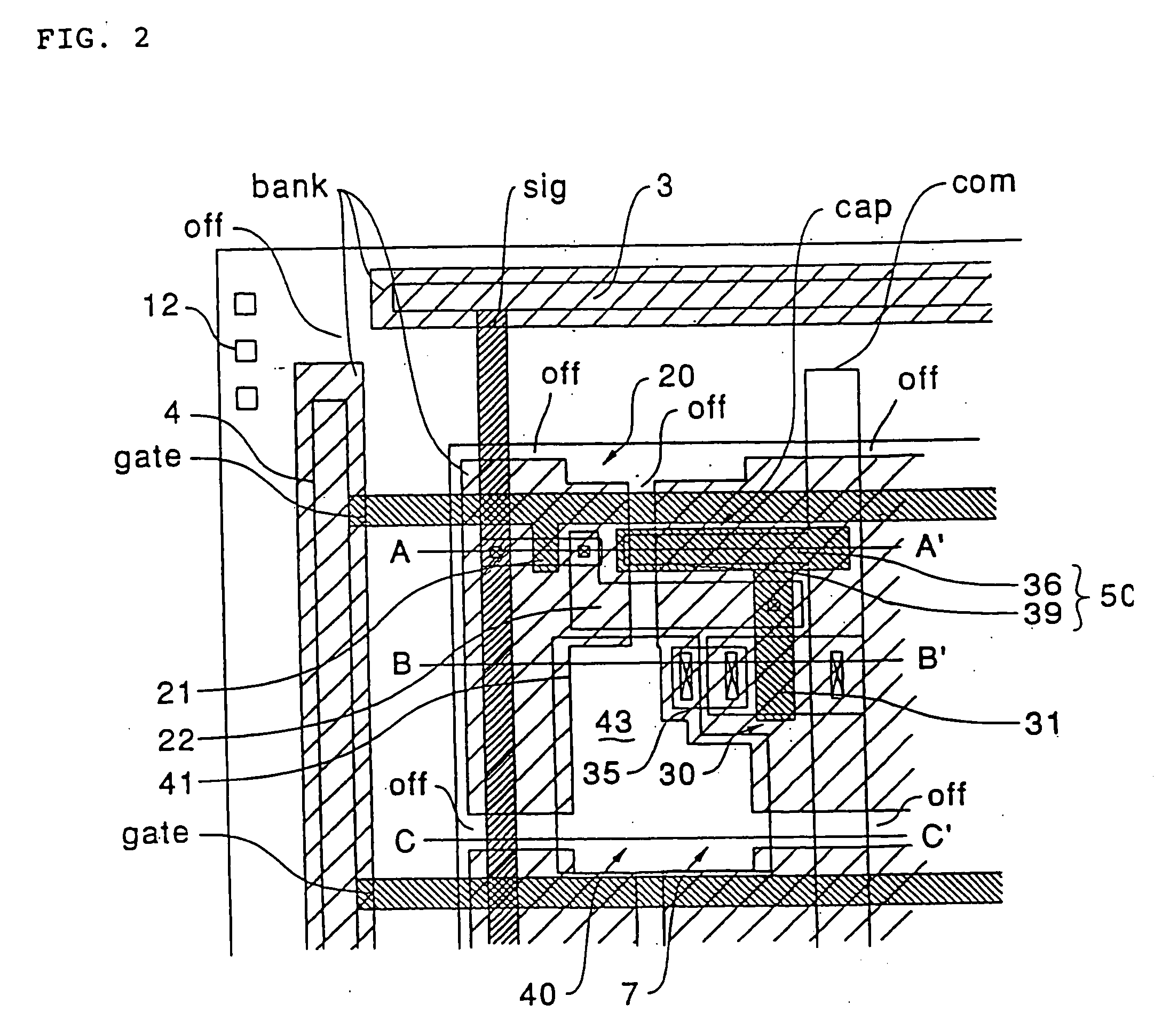

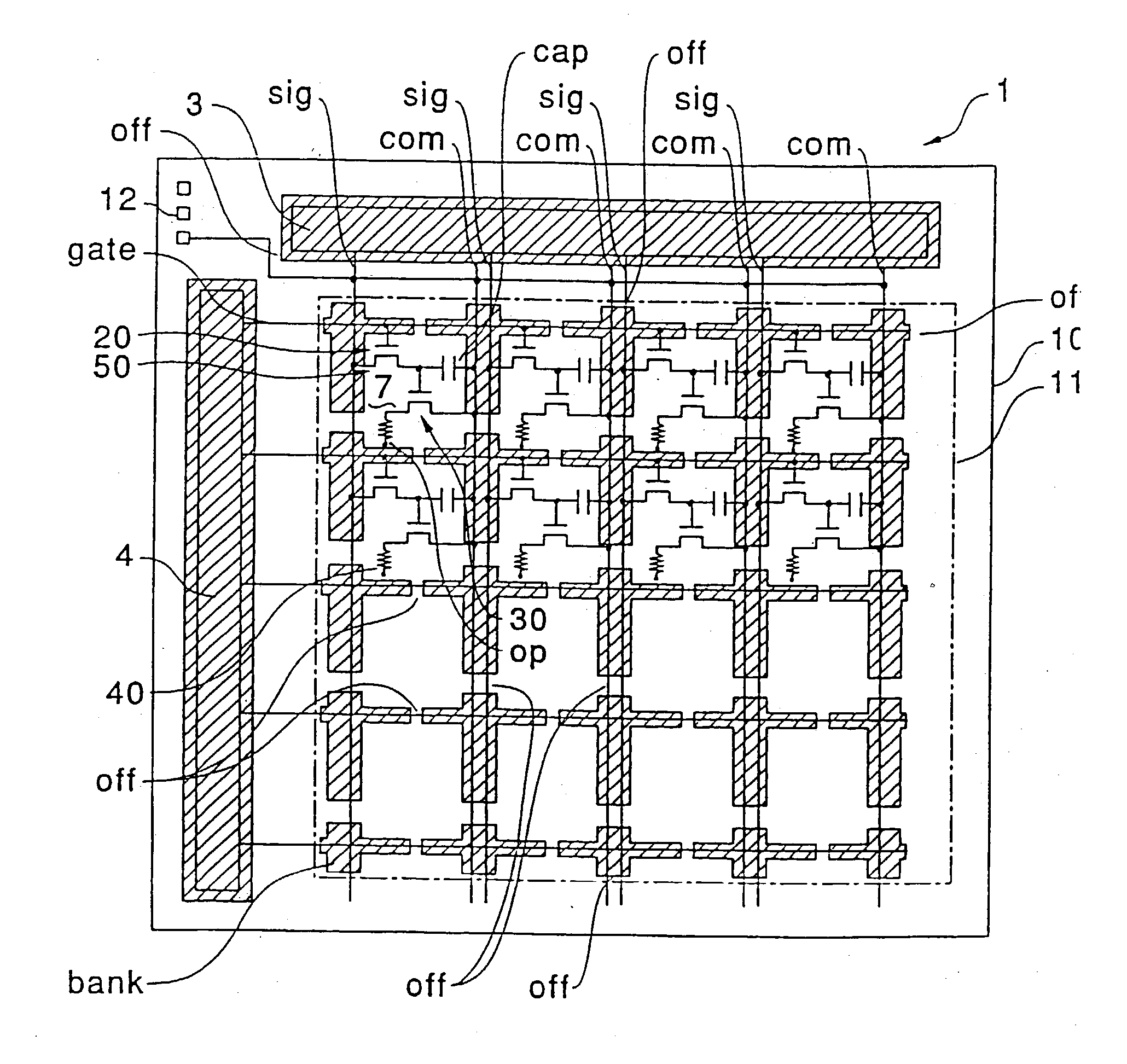

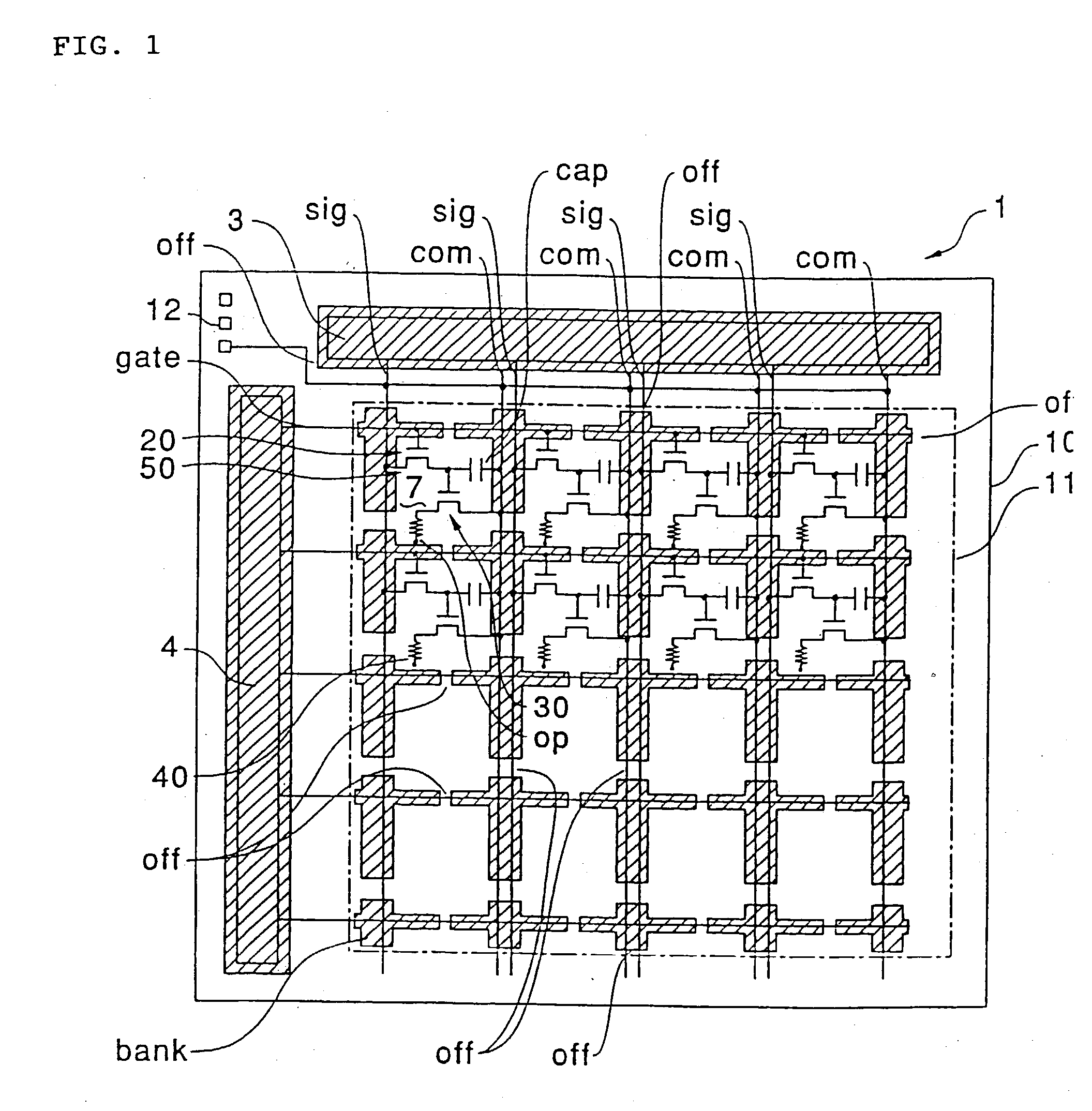

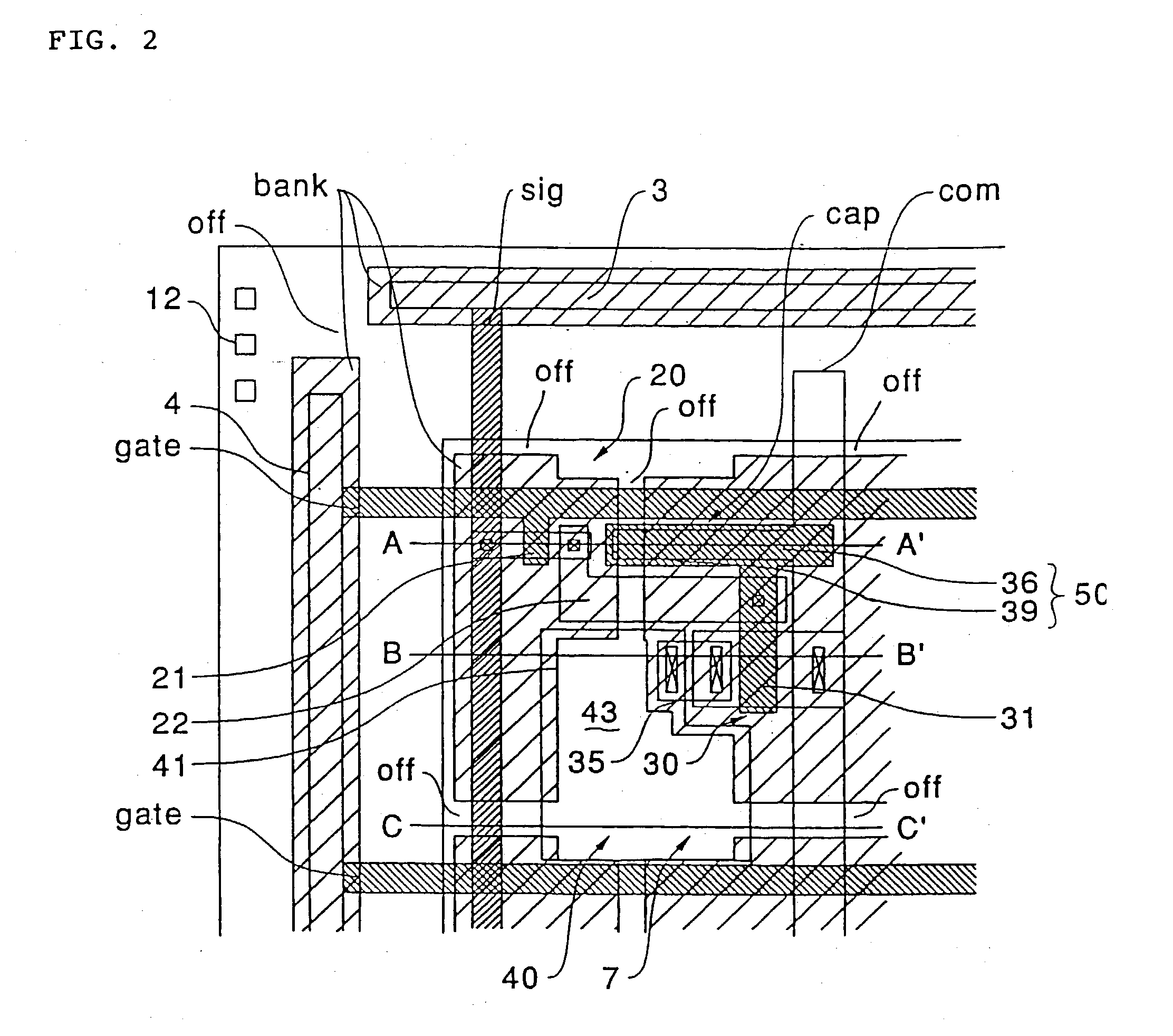

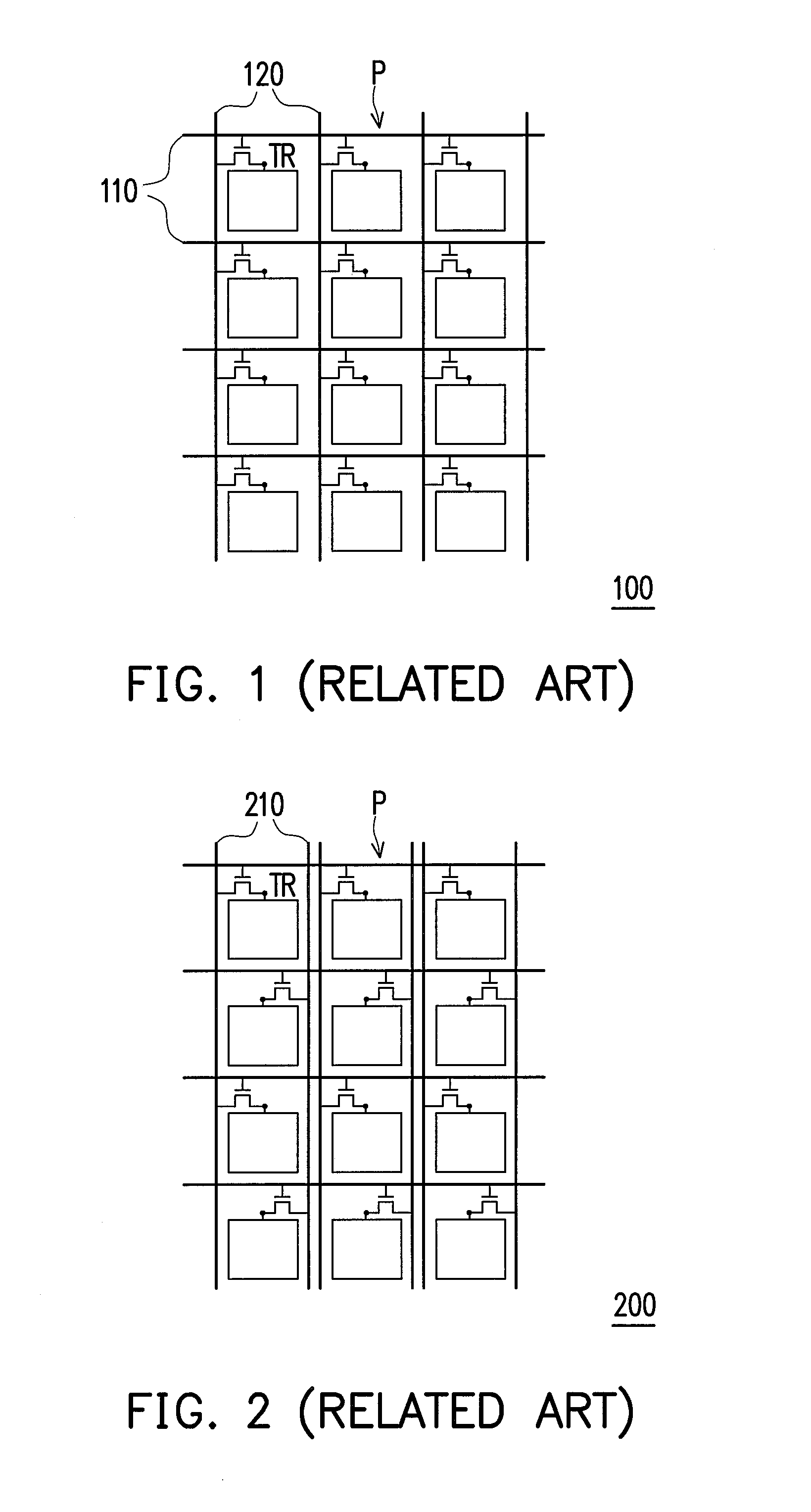

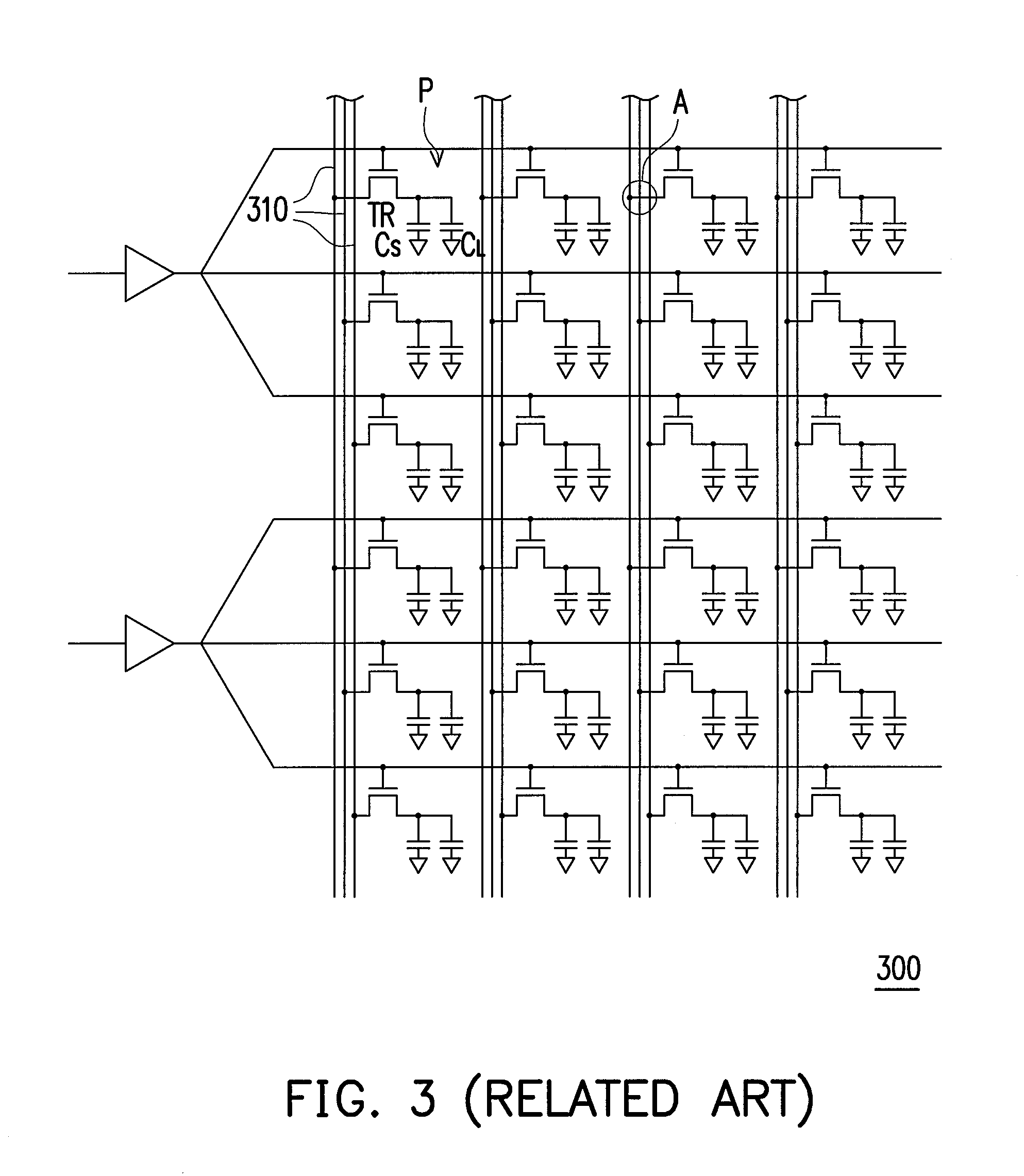

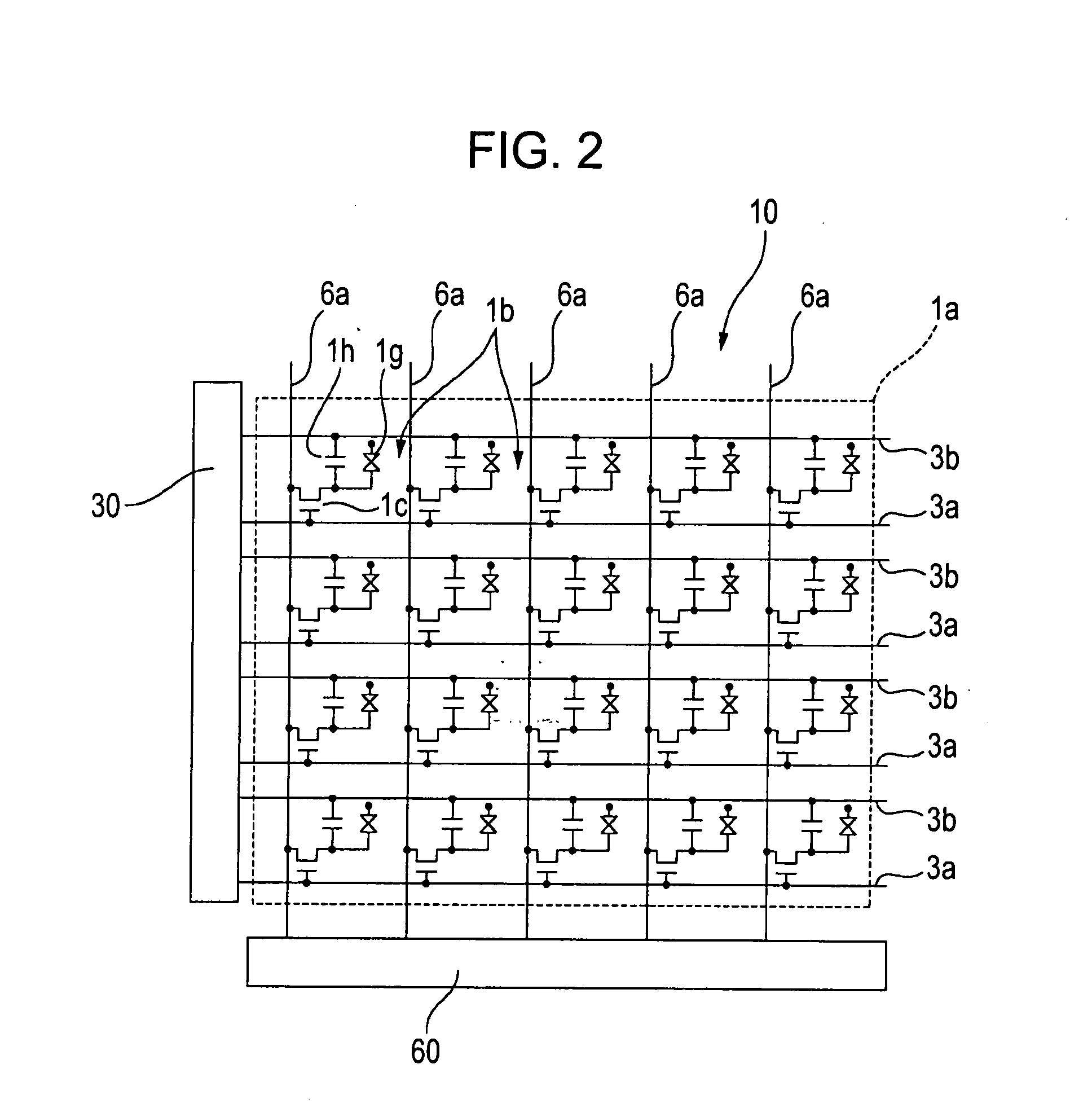

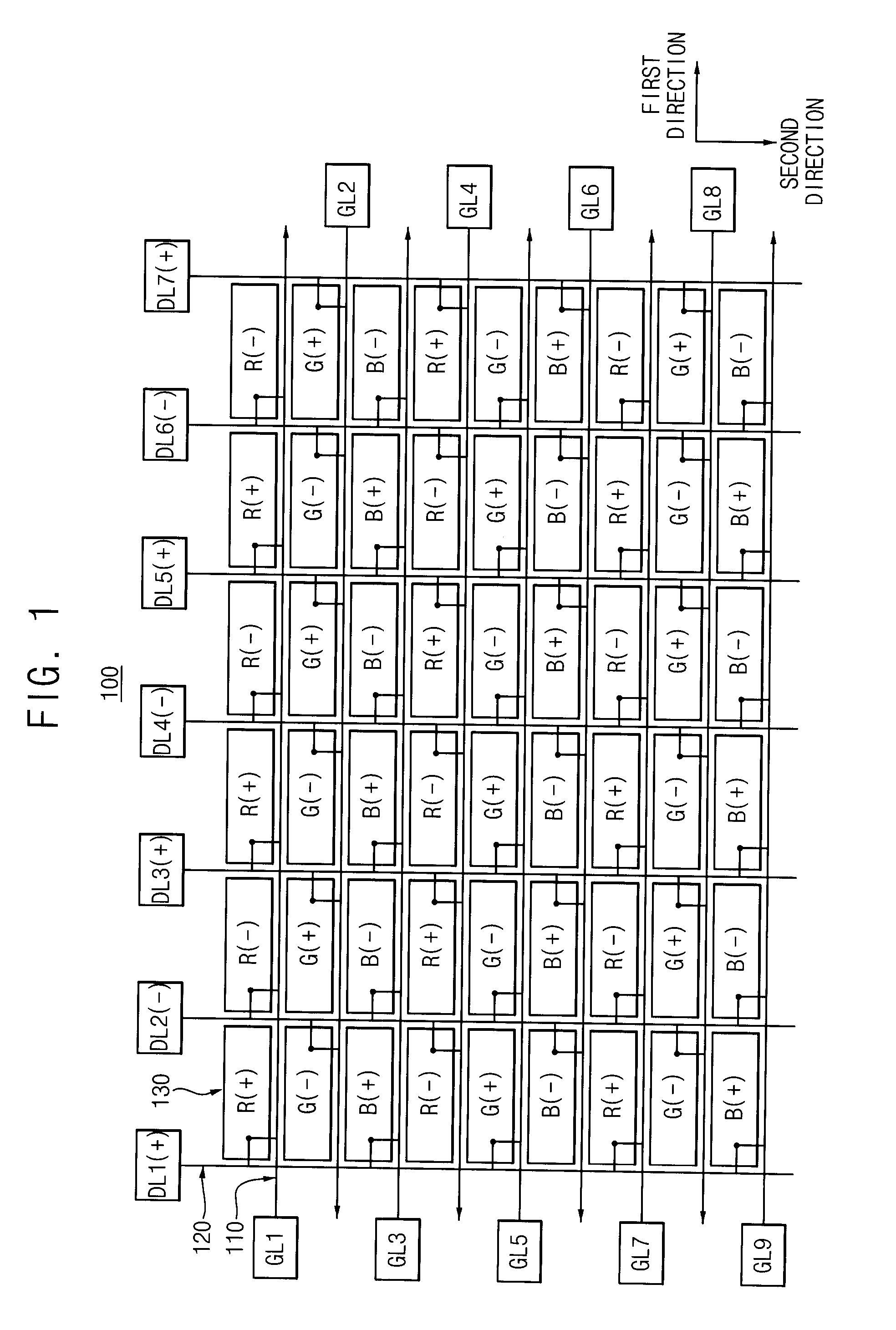

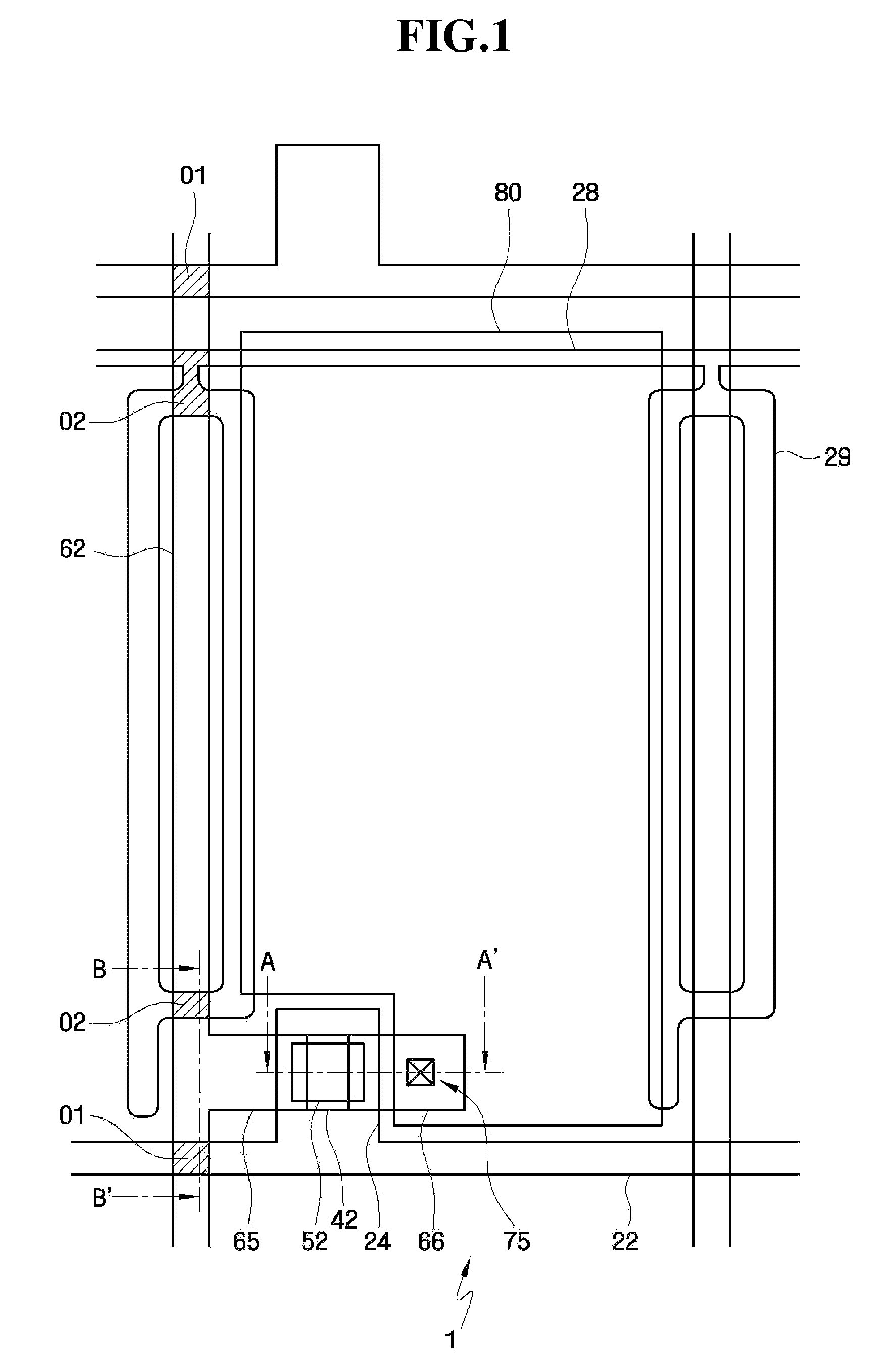

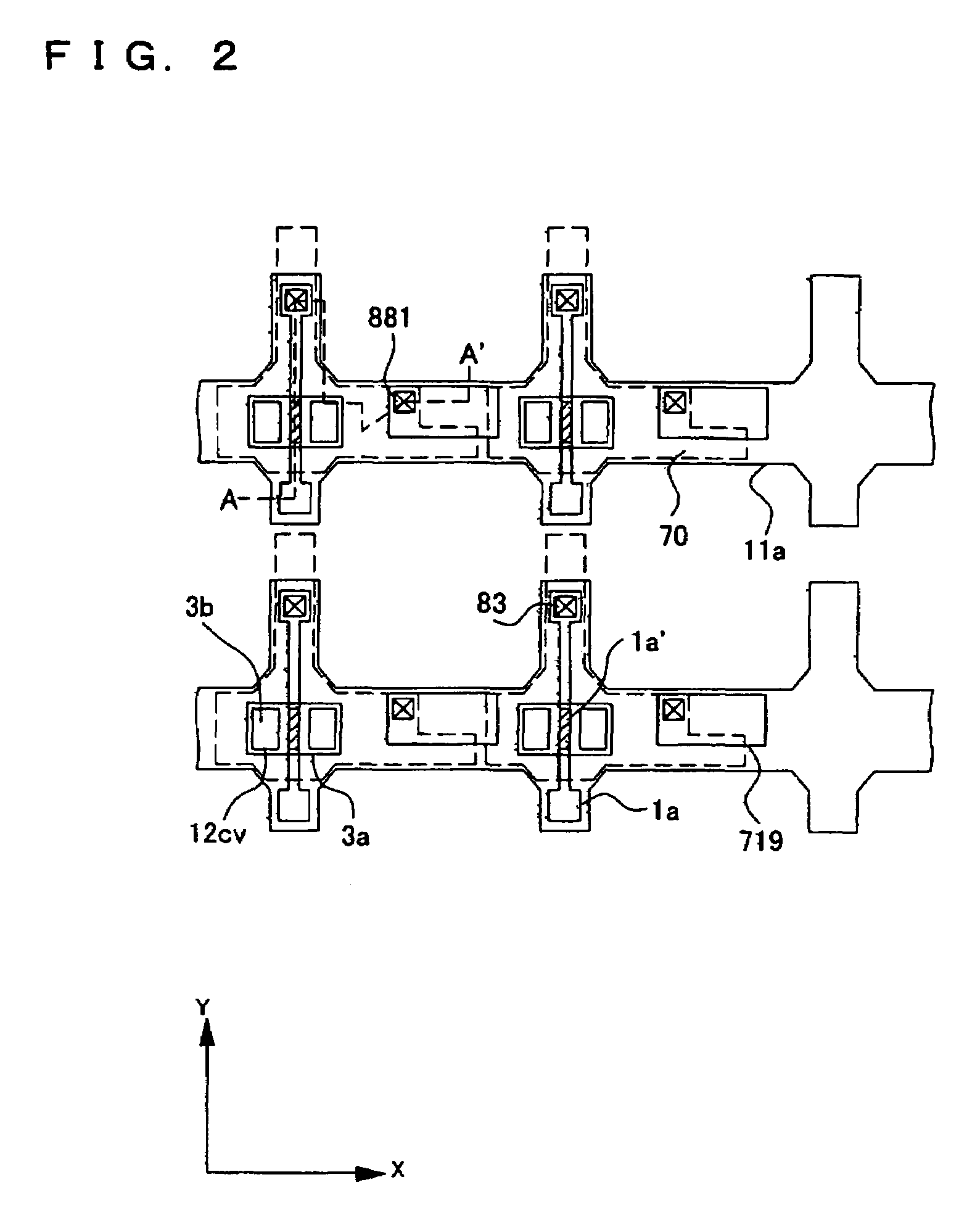

Active matrix display device

InactiveUS20080036699A1Reduce dataReduce capacitanceStatic indicating devicesElectroluminescent light sourcesResistActive matrix

Owner:INTELLECTUAL KEYSTONE TECH LLC

Active matrix display device

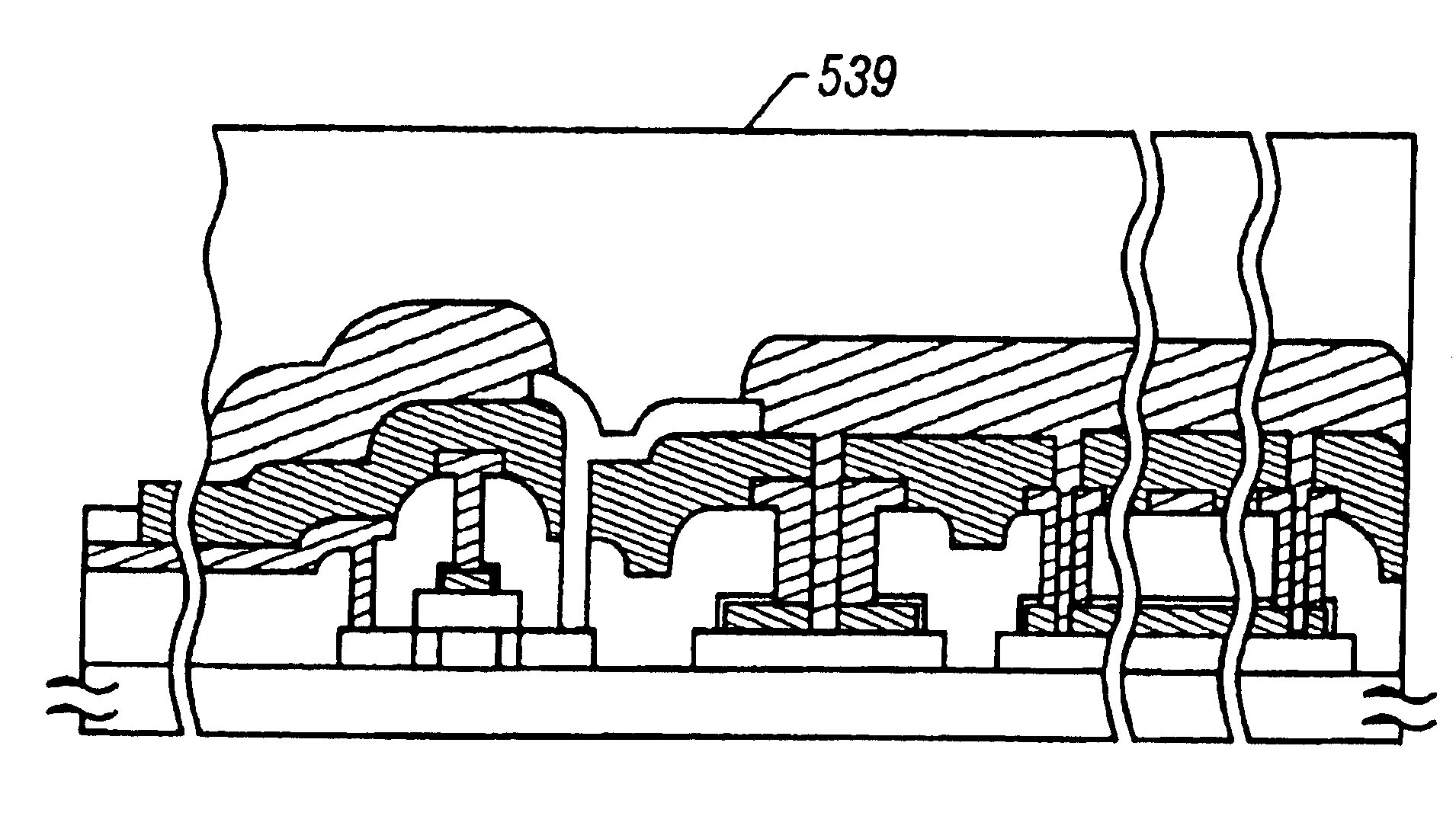

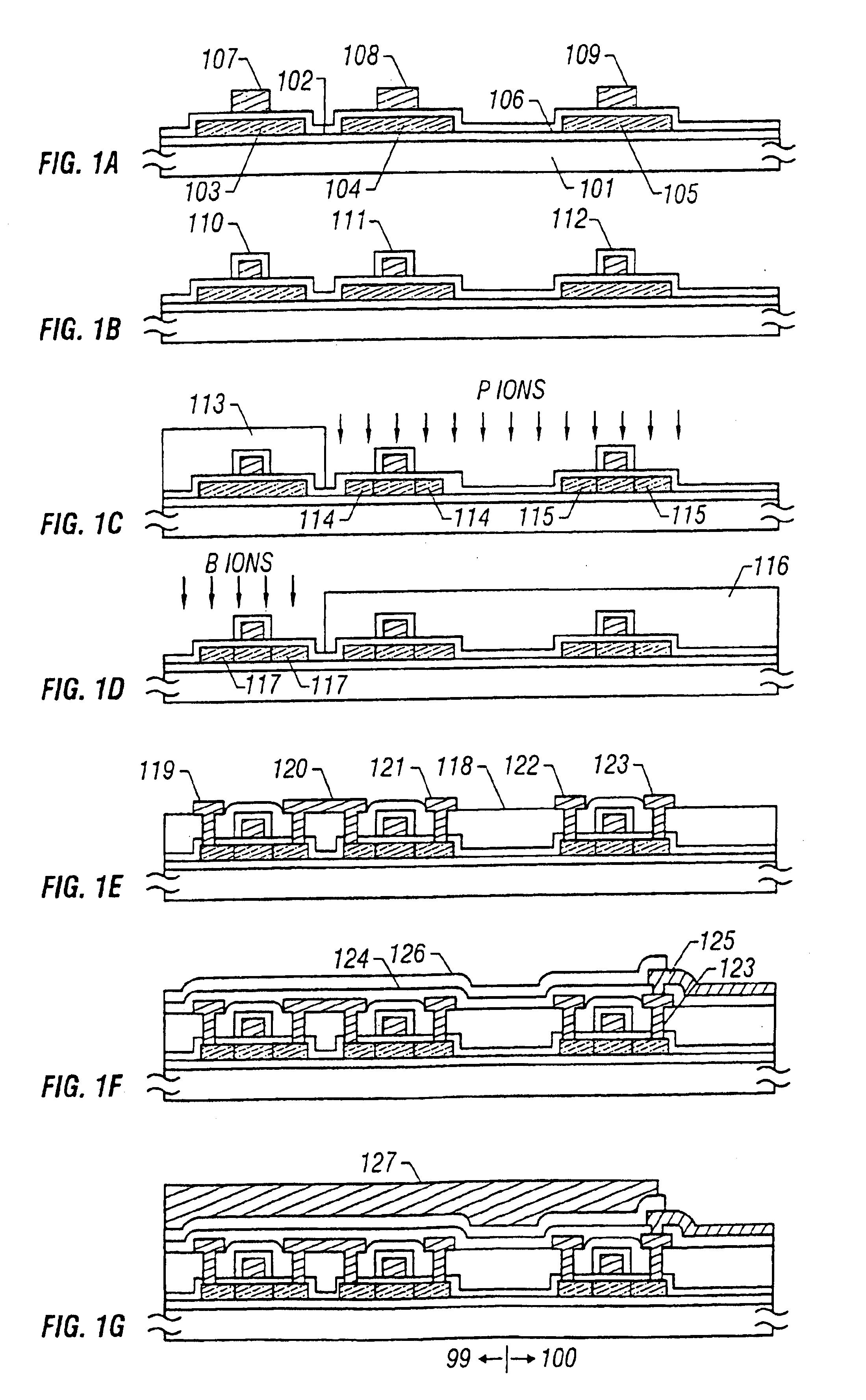

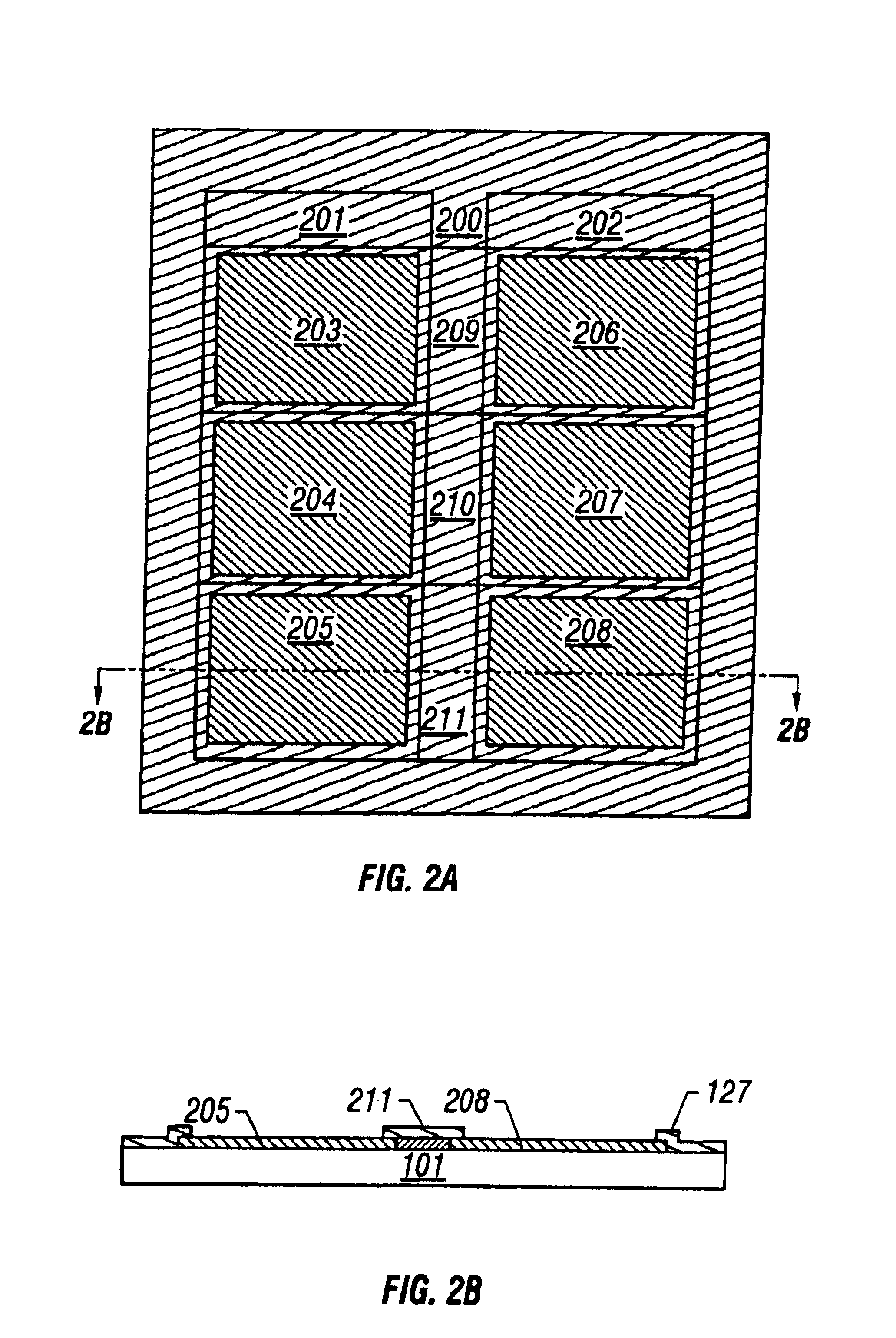

InactiveUS20030206144A1Reduce power consumptionPrevent capacitanceStatic indicating devicesElectroluminescent light sourcesResistCapacitance

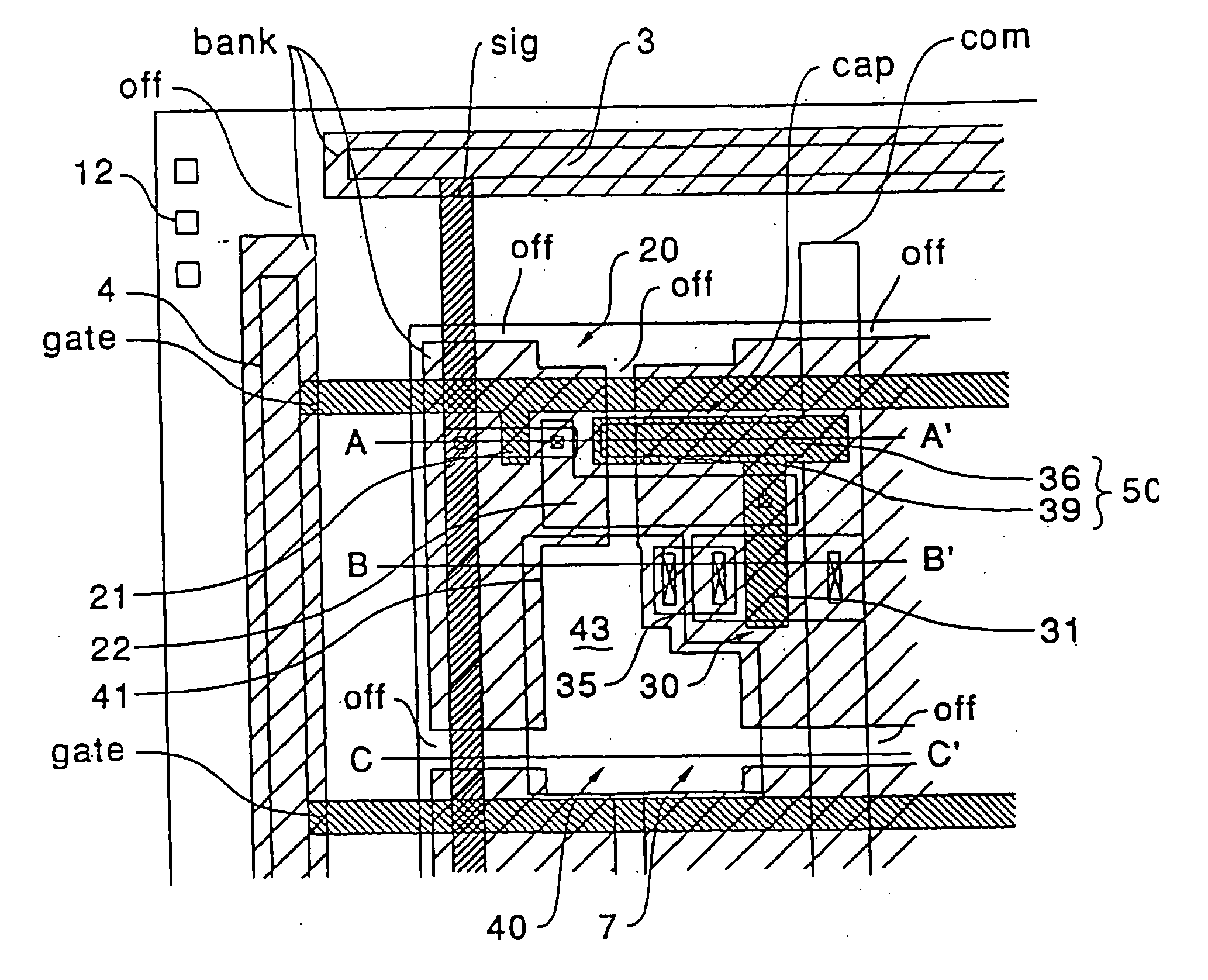

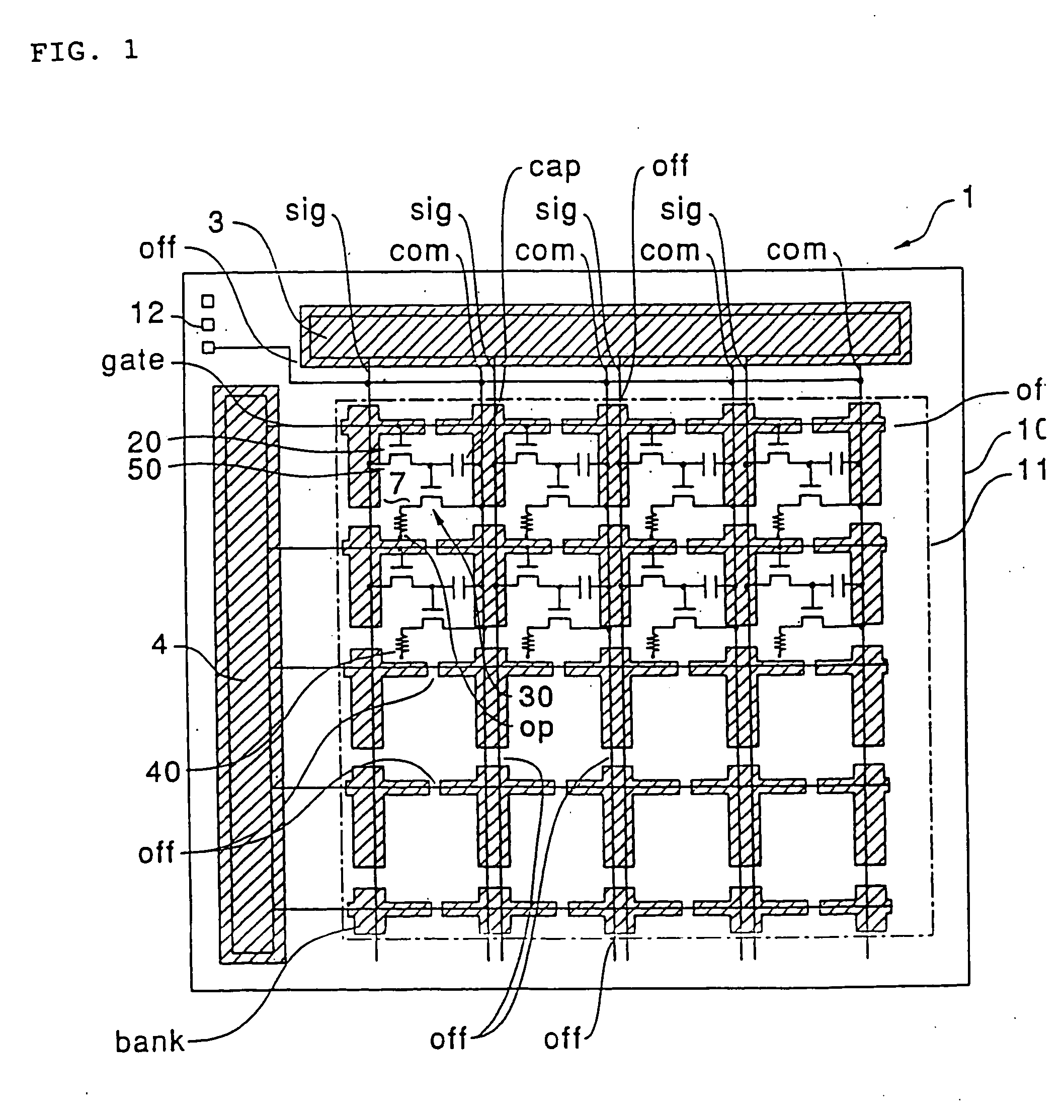

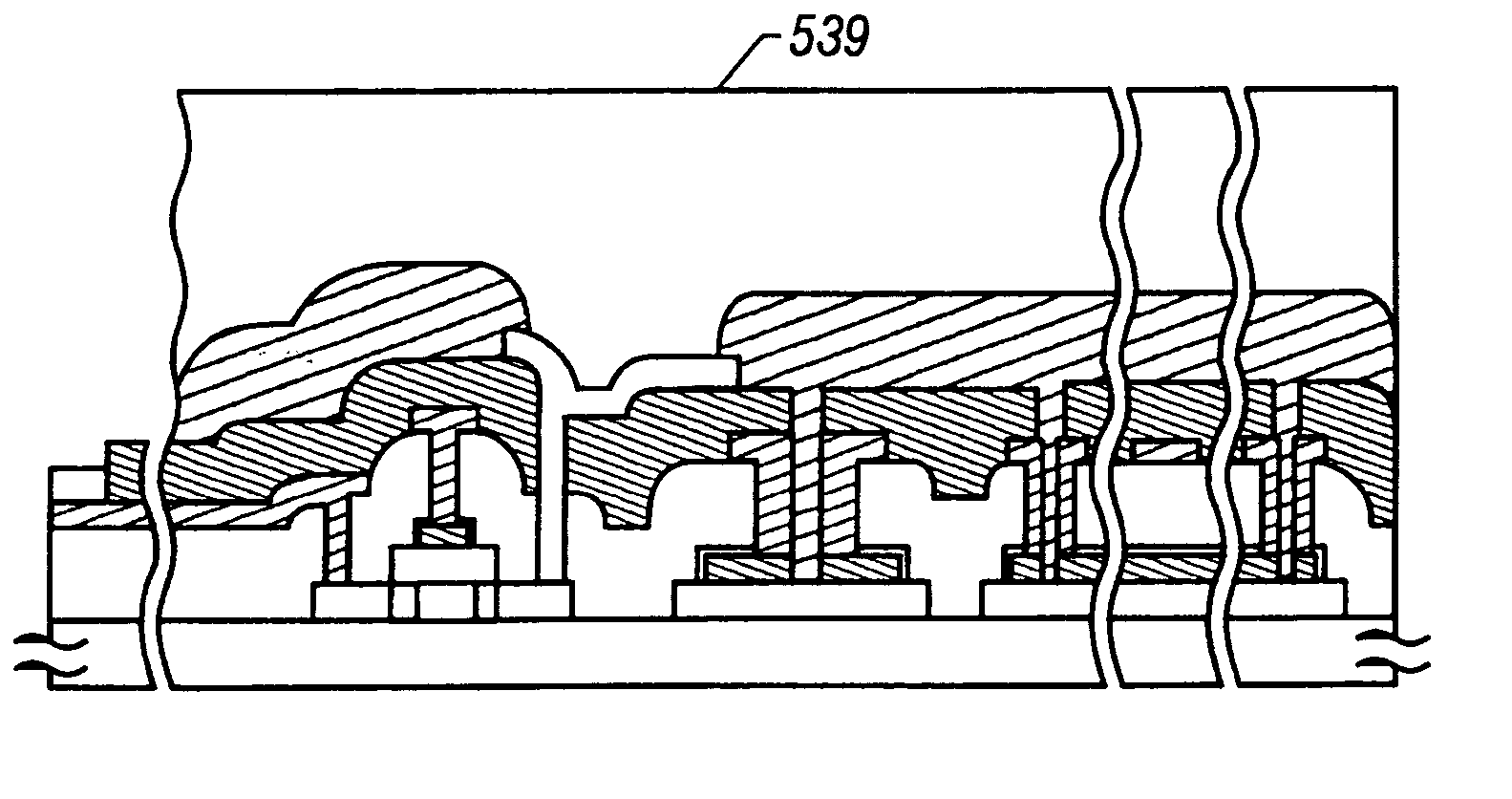

An active matrix display device is provided in which parasistic capacitance or the like is suppressed by forming a thick insulating film around an organic semiconductor film, and disconnection or the like does not occur in an opposing electrode formed on the upper layer of the thick insulating film. In the active matrix display device, first, a bank layer composed of a resist film is formed along data lines and scanning lines. By depositing an opposing electrode of a thin film luminescent element on the upper layer side of the bank layer, capacitance that parasitizes the data lines can be suppressed. Additionally, a discontinuities portion is formed in the bank layer. Since the discontinuities portion is a planar section which does not have any a step due to the existence of the bank layer, disconnection of opposing electrode does not occur at this section. When an organic semiconductor film is formed by an ink jet process, a liquid material discharged from an ink jet head is blocked by the bank layer.

Owner:SEIKO EPSON CORP

Capacitor structure

InactiveUS20070102745A1Increase capacitanceMatching worsenedTransistorSemiconductor/solid-state device detailsCapacitorElectrical and Electronics engineering

A capacitor structure is described, including a first capacitor and a second capacitor. The first capacitor includes a first electrode, a second electrode and a first insulating layer, wherein the second electrode is disposed under the first electrode and the first insulating layer between the first electrode and the second electrode. The second capacitor is disposed under the first capacitor and coupled thereto in parallel. The second capacitor includes multiple patterned metal layers and via plugs that constitute a third electrode and a fourth electrode, and a second insulating layer. The patterned metal layers are stacked in the second insulating layer and connected by the via plugs, wherein each patterned metal layer includes a portion of the third electrode and a portion of the fourth electrode that are separated by the second insulating layer.

Owner:UNITED MICROELECTRONICS CORP

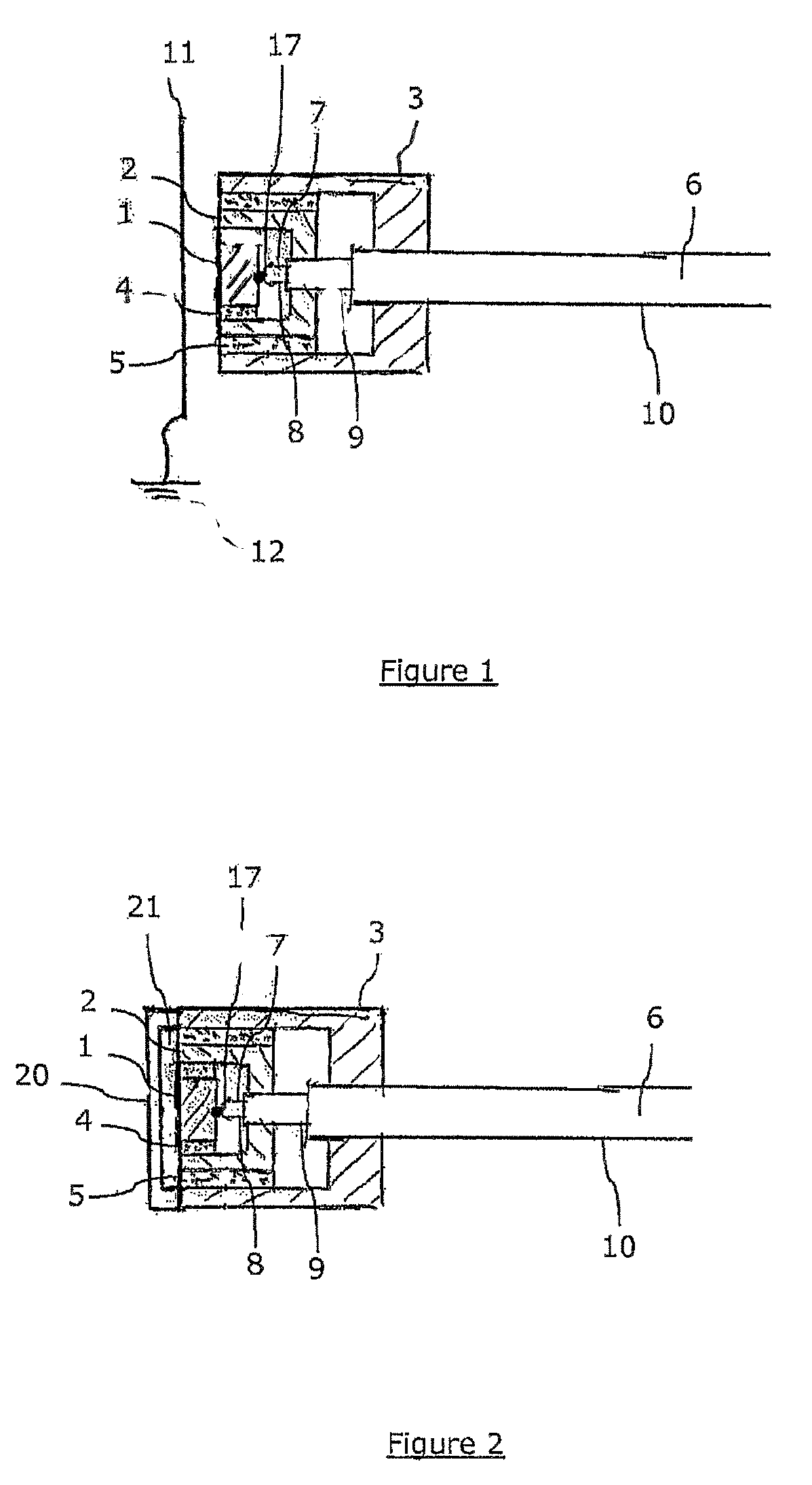

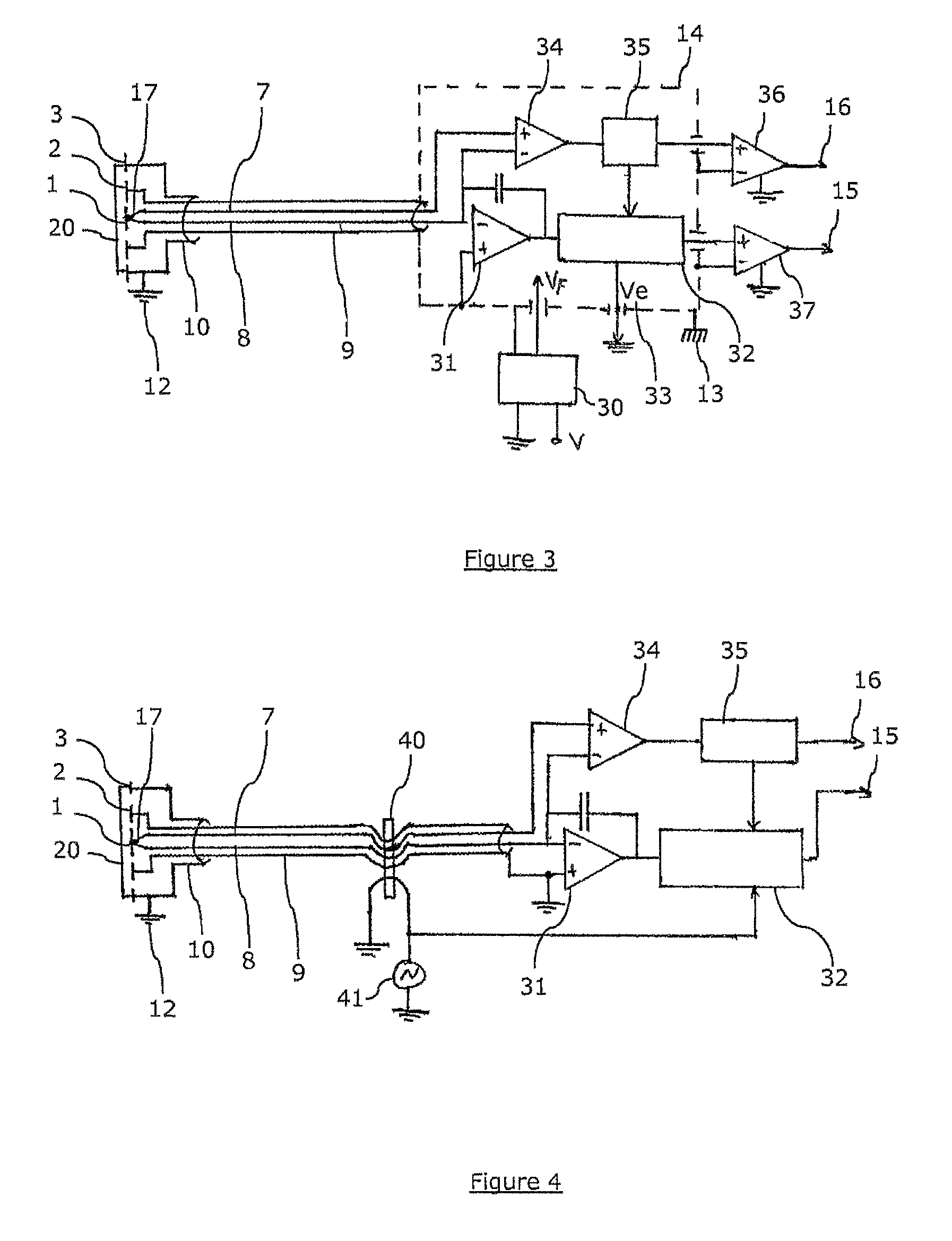

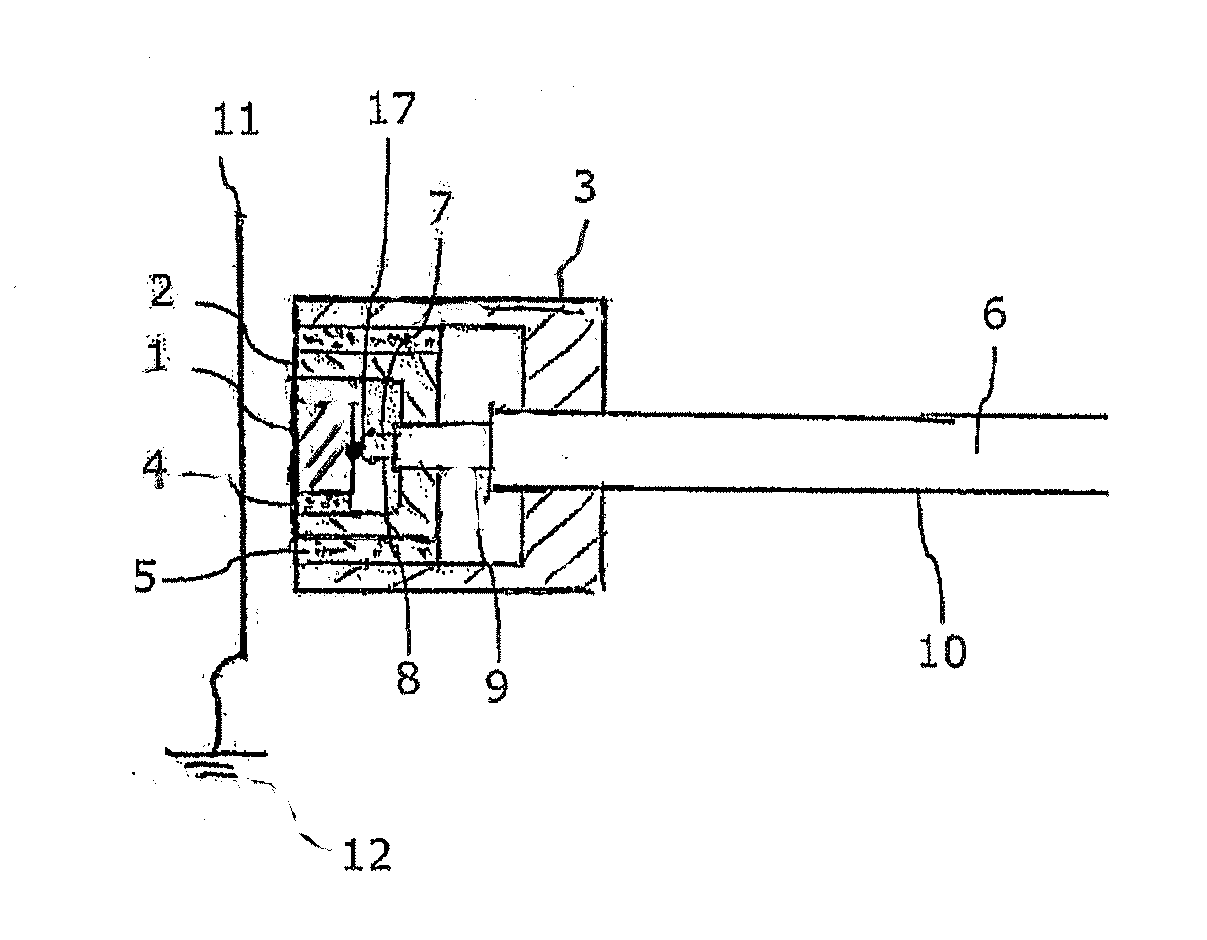

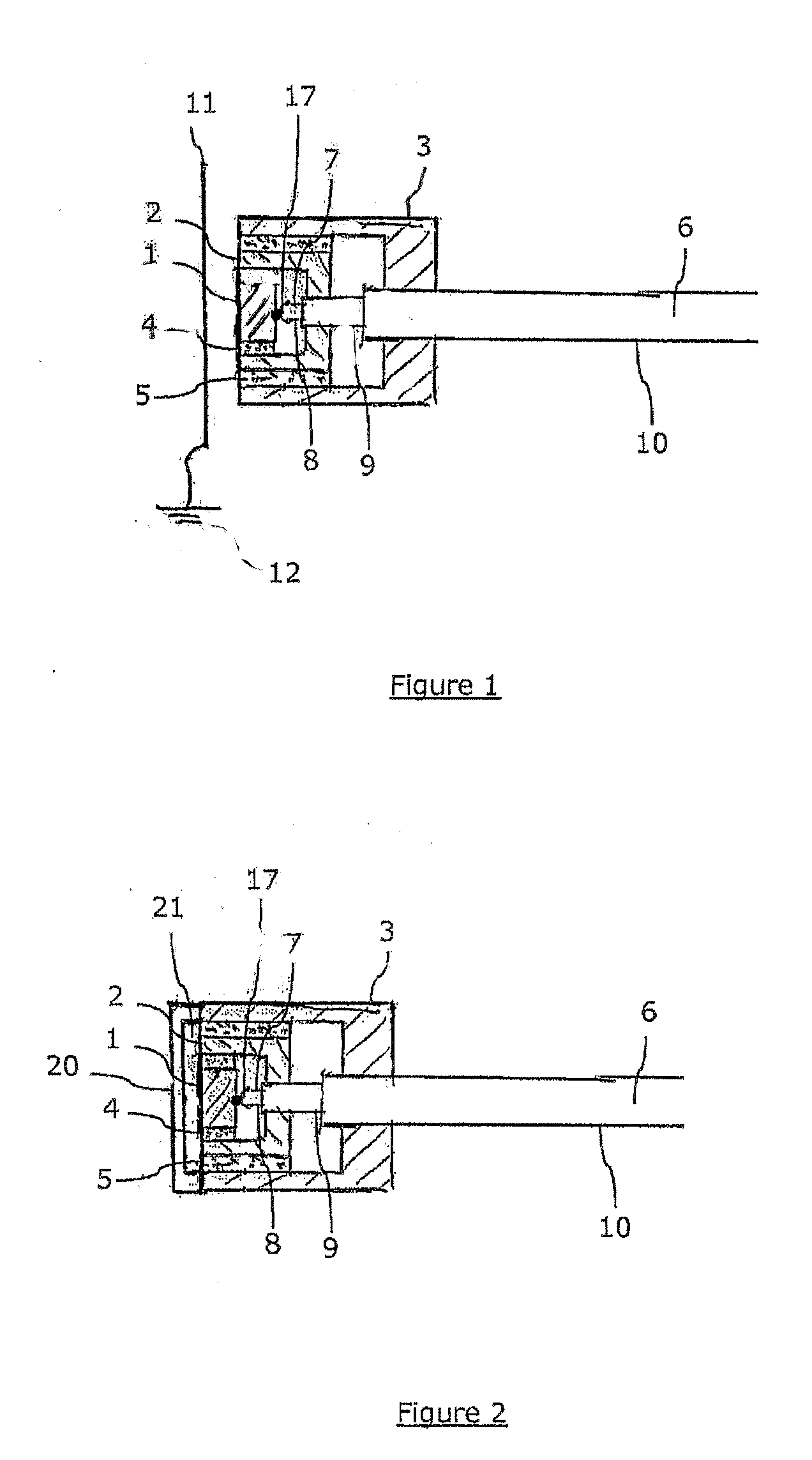

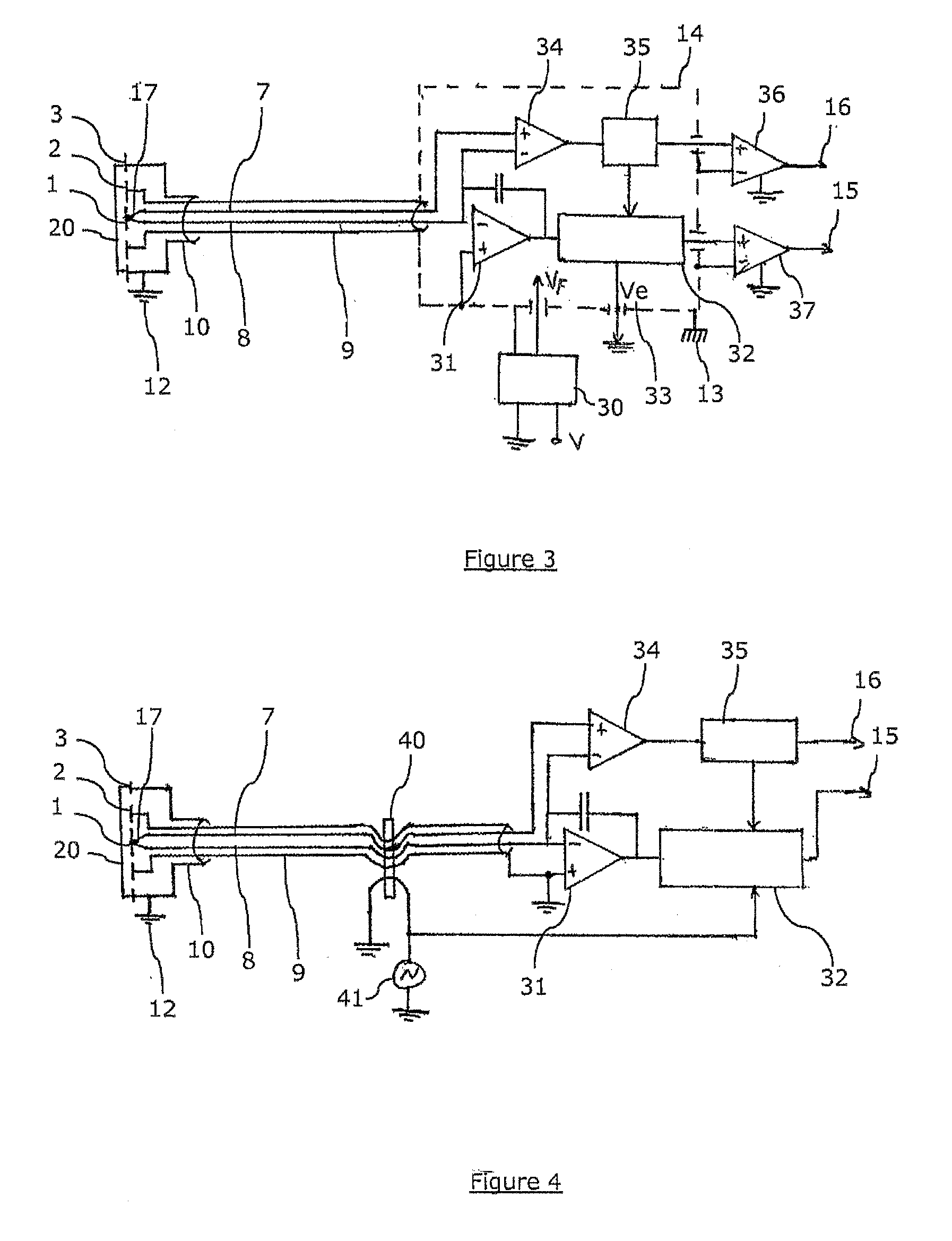

Capactive pressure sensor incorporating a temperature measurement and compatible with hot environments

ActiveUS8770033B2Improve accuracyPrevent capacitanceConverting sensor output electrically/magneticallyFluid pressure measurement using capacitance variationCapacitive pressure sensorMeasurement device

A capacitive measurement device including first measurement device designed to carry out a first measurement function in relation to a nearby object, the first measurement device including a body and, a capacity electrode, both of a substantially conductive material, and a guard electrode placed between the body and the capacitive electrode and insulated from the body on the one hand and from the capacitive electrode on the other hand by dielectric elements; an excitation apparatus which maintains the capacitive electrode and the guard electrode to a desired AC electrical potential; a first electronic apparatus, connected to the capacitive and guard electrodes, for measuring the capacitance between the capacitive electrode and the object; and a second measurement device designed to carry out a second measurement function, which are located in the vicinity of either the capacitive or guard electrode, and maintained by the excitation apparatus to a desired AC electrical potential.

Owner:FOGALE NANOTECH SA

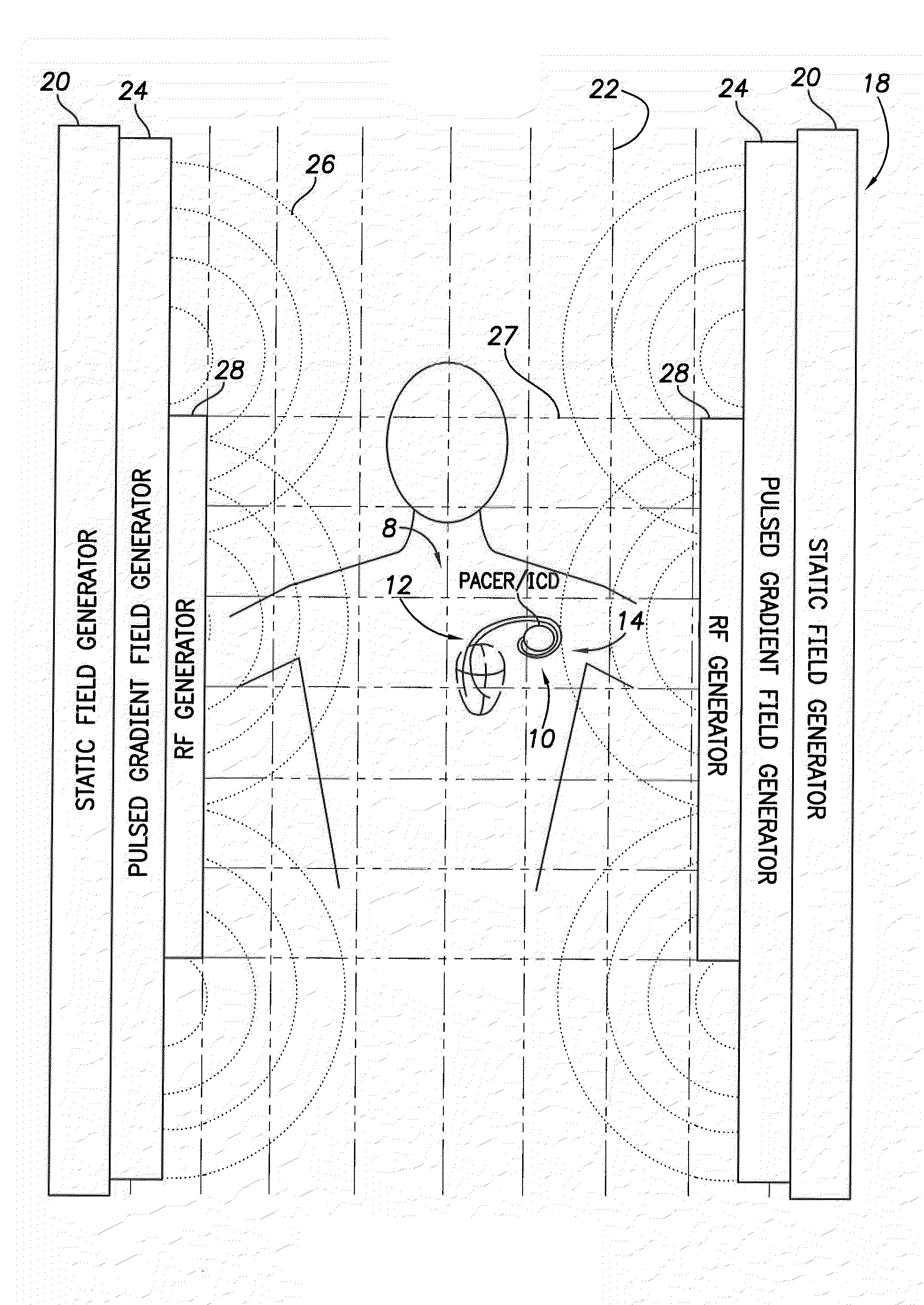

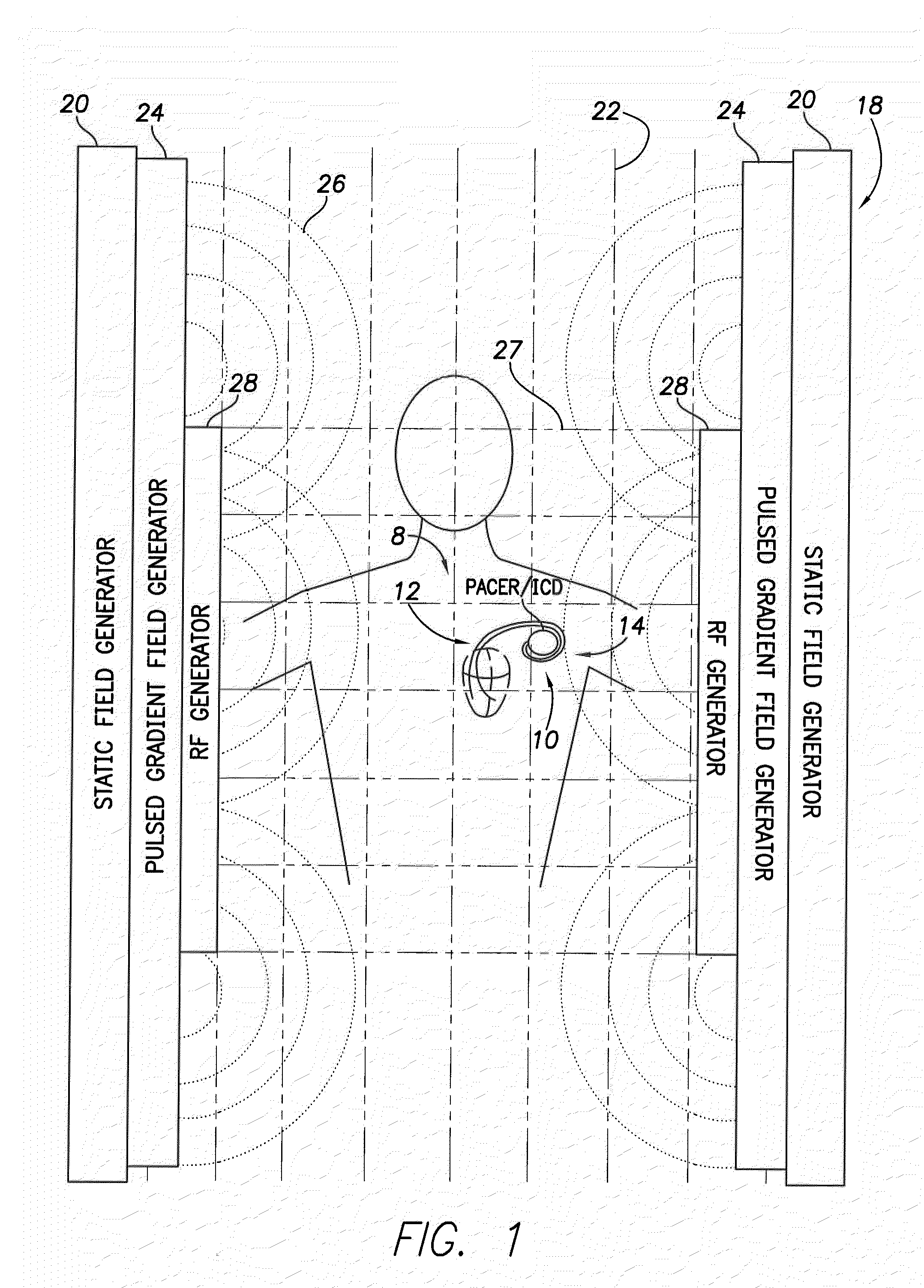

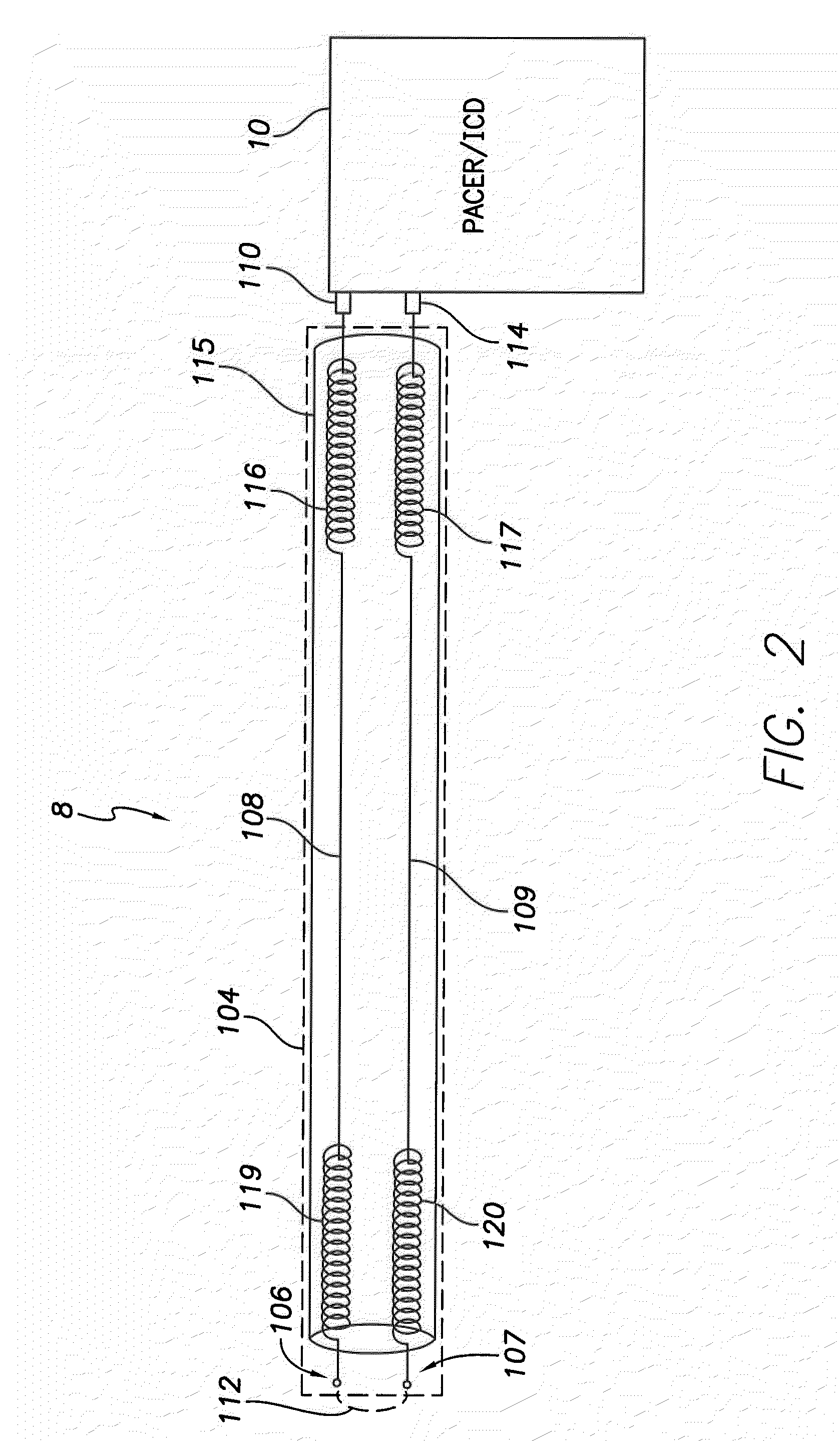

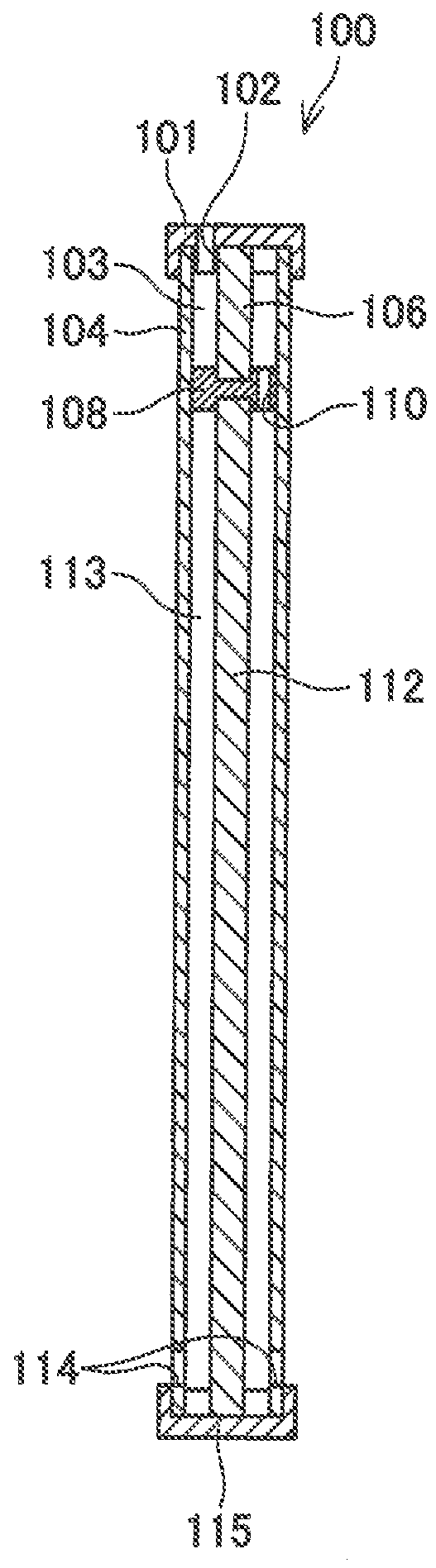

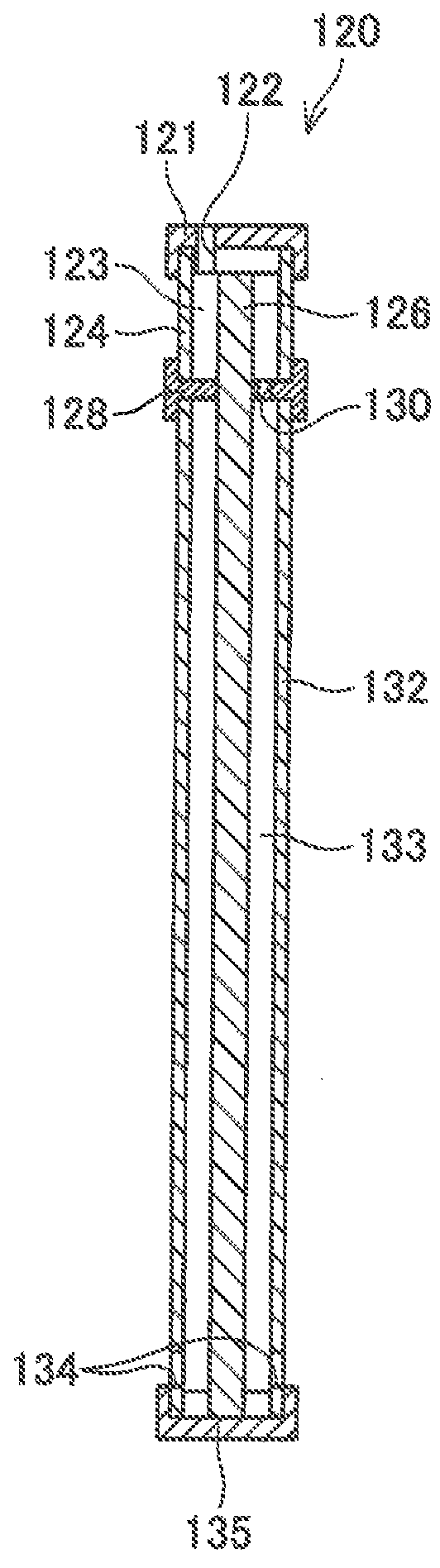

Implantable medical device lead incorporating a conductive sheath surrounding insulated coils to reduce lead heating during MRI

InactiveUS20110034983A1Reduce couplingReduce heatInternal electrodesExternal electrodesDevice implantConductive polymer

A conducting sheath is provided along at least a portion of an implantable medical device lead, and preferably along substantially its entire length, for mitigating heating problems arising during magnetic resonance imaging (MRI) procedures, particularly problems arising due to a problem described herein as the “coiling effect.” During device implant, the clinician may elect to wrap or coil excess proximal portions of leads around or under the medical device being implanted. Thereafter, during MRI procedures, shunt capacitance may develop between the housing of the implantable device and insulated coils within the proximal portions of the lead that are near the device, resulting in greater lead heating during the MRI. The conducting sheath helps suppress induced currents and also reduces or eliminates shunt capacitance. The conducting sheath may be, for example, formed using a metal mesh or a conducting polymer tube incorporating non-ferrous metal powders. The sheath may be formed in ¼ wavelength segments.

Owner:PACESETTER INC

Capactive pressure sensor incorporating a temperature measurement and compatible with hot environments

ActiveUS20120132006A1Improve accuracyPrevent capacitanceConverting sensor output electrically/magneticallyFluid pressure measurement using capacitance variationCapacitive pressure sensorMeasurement device

A capacitive measurement device including first measurement device designed to carry out a first measurement function in relation to a nearby object, the first measurement device including a body and, a capacity electrode, both of a substantially conductive material, and a guard electrode placed between the body and the capacitive electrode and insulated from the body on the one hand and from the capacitive electrode on the other hand by dielectric elements; an excitation apparatus which maintains the capacitive electrode and the guard electrode to a desired AC electrical potential; a first electronic apparatus, connected to the capacitive and guard electrodes, for measuring the capacitance between the capacitive electrode and the object; and a second measurement device designed to carry out a second measurement function, which are located in the vicinity of either the capacitive or guard electrode, and maintained by the excitation apparatus to a desired AC electrical potential.

Owner:FOGALE NANOTECH SA

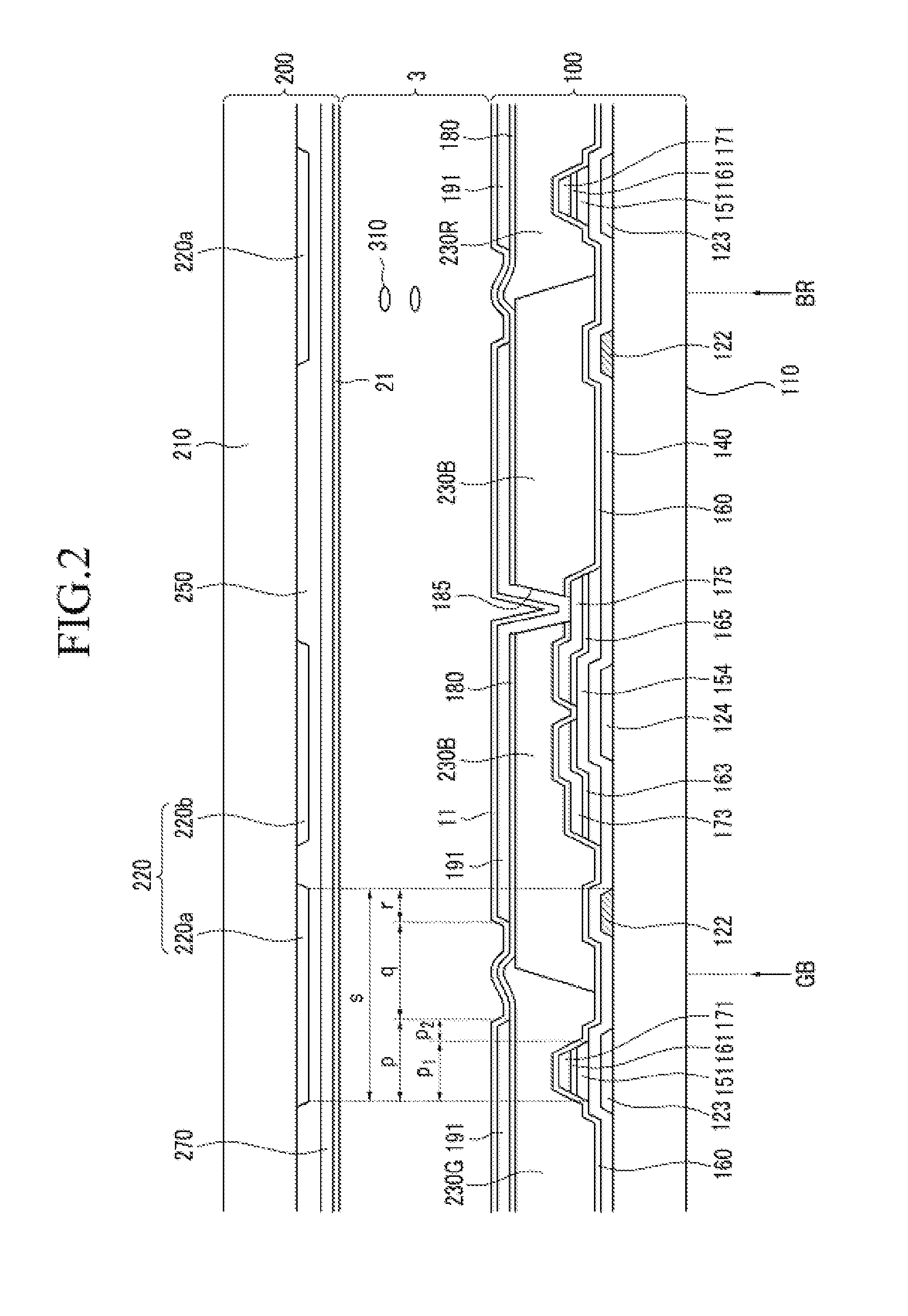

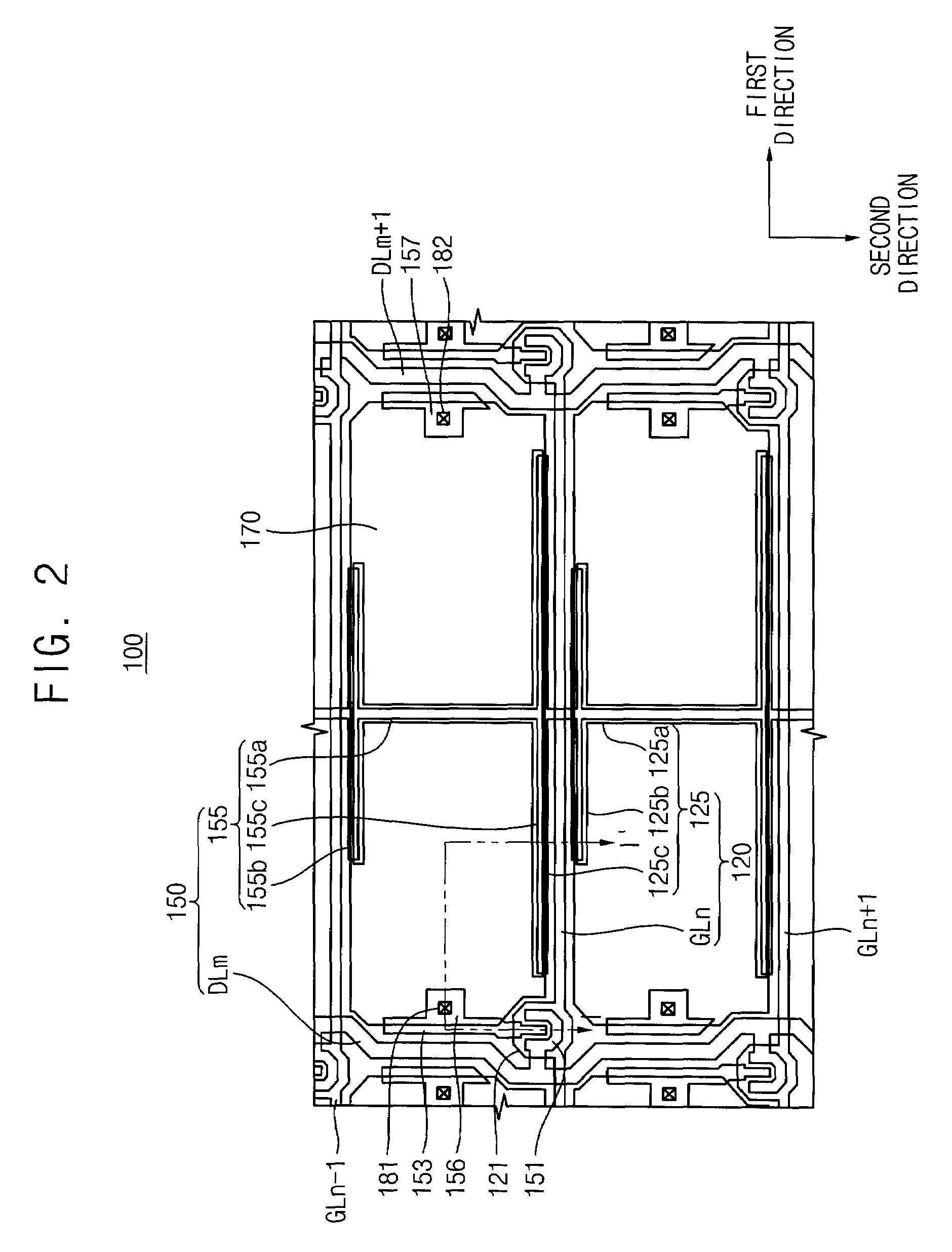

Display device

InactiveUS20090225017A1Good step coverageUniformity of cell gapStatic indicating devicesNon-linear opticsDisplay deviceComputer science

A display device includes; a first substrate, a first pixel electrode disposed on the first substrate, a second pixel electrode disposed on the first substrate and neighboring the first pixel electrode, a first color filter disposed under the first pixel electrode, a second color filter disposed under the second pixel electrode and overlapping the first color filter in an area between the first pixel electrode and the second pixel electrode, and a data line including a first portion and a second portion respectively disposed on left and right sides of the area wherein the first and second color filters overlap.

Owner:SAMSUNG DISPLAY CO LTD

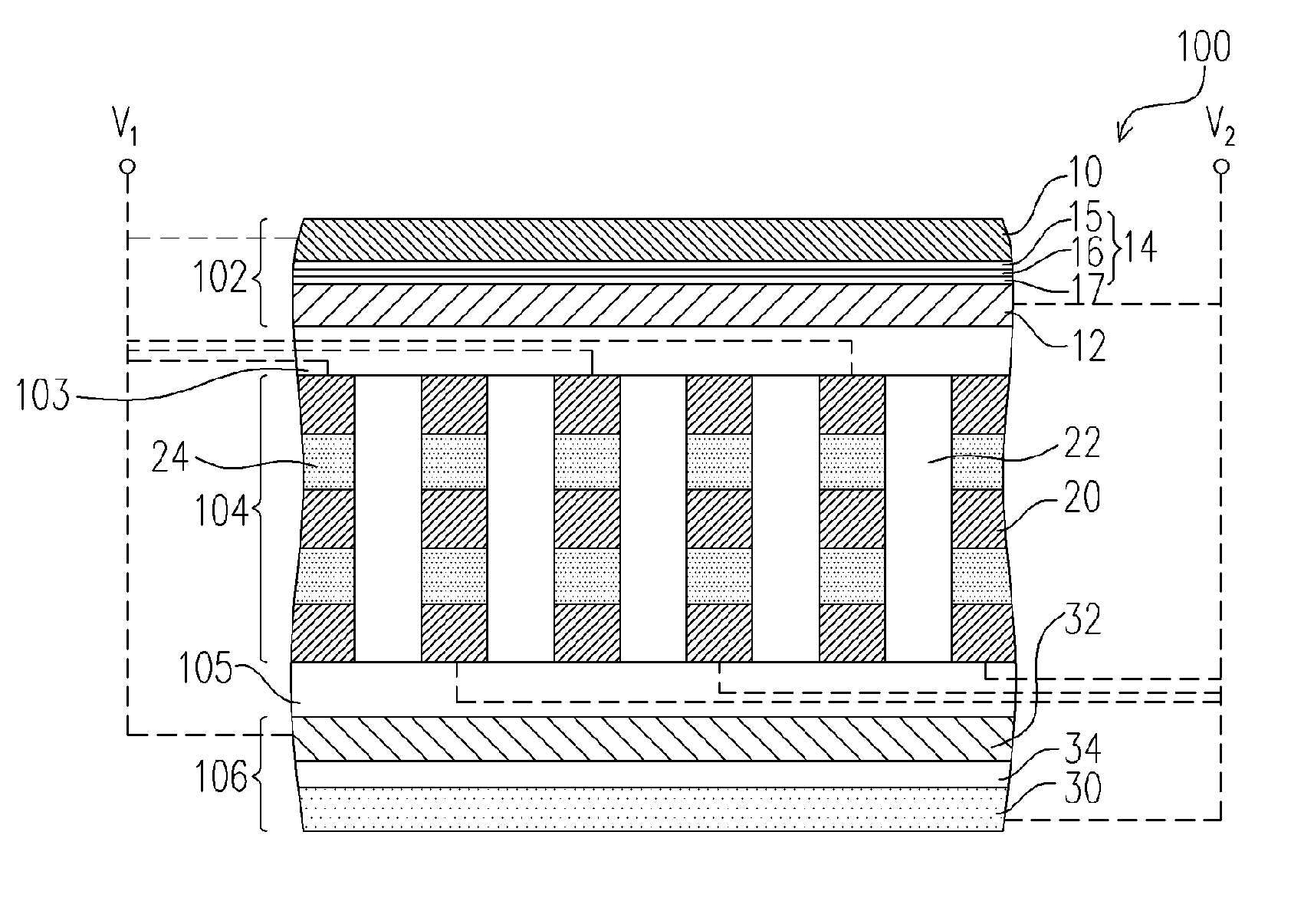

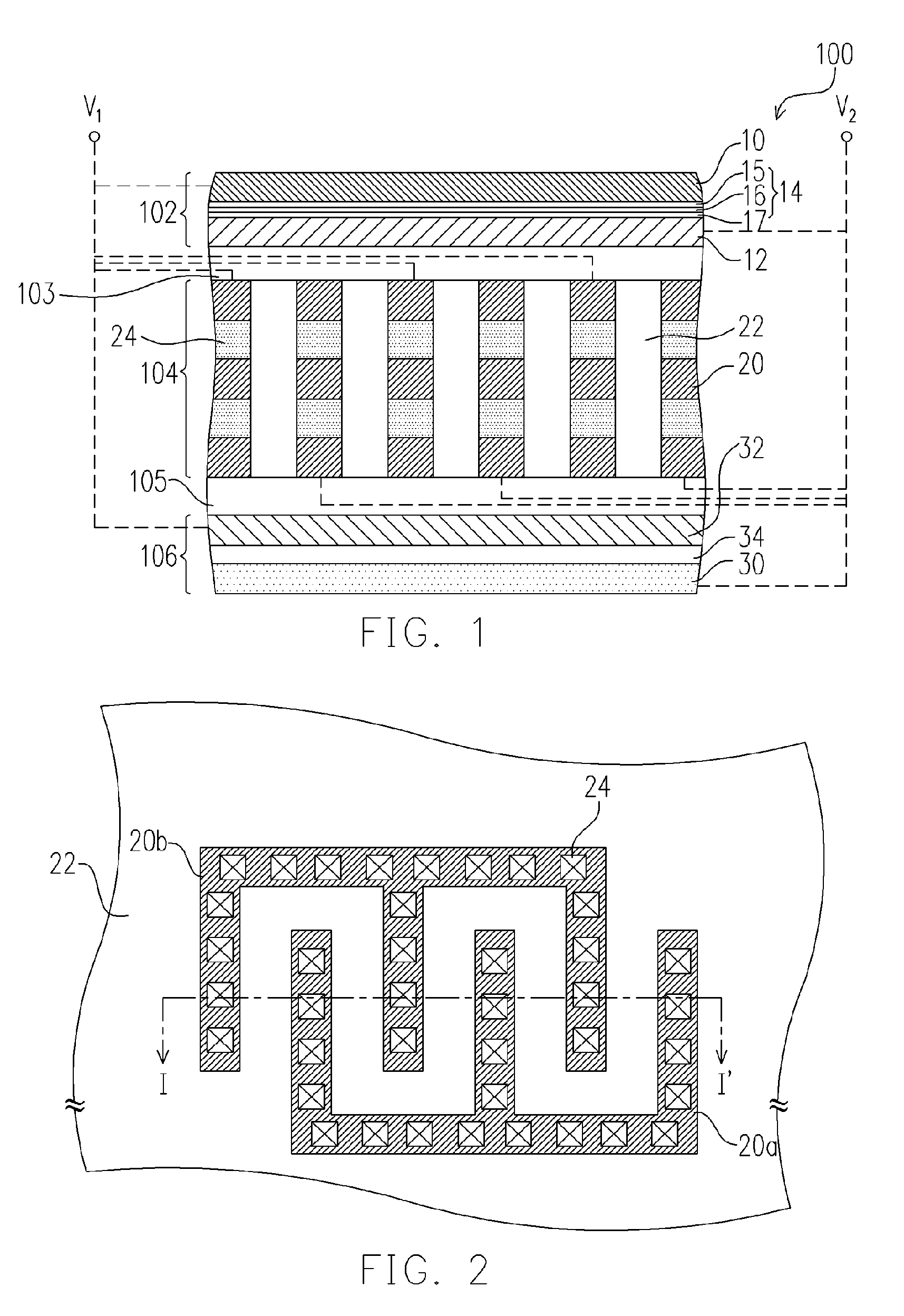

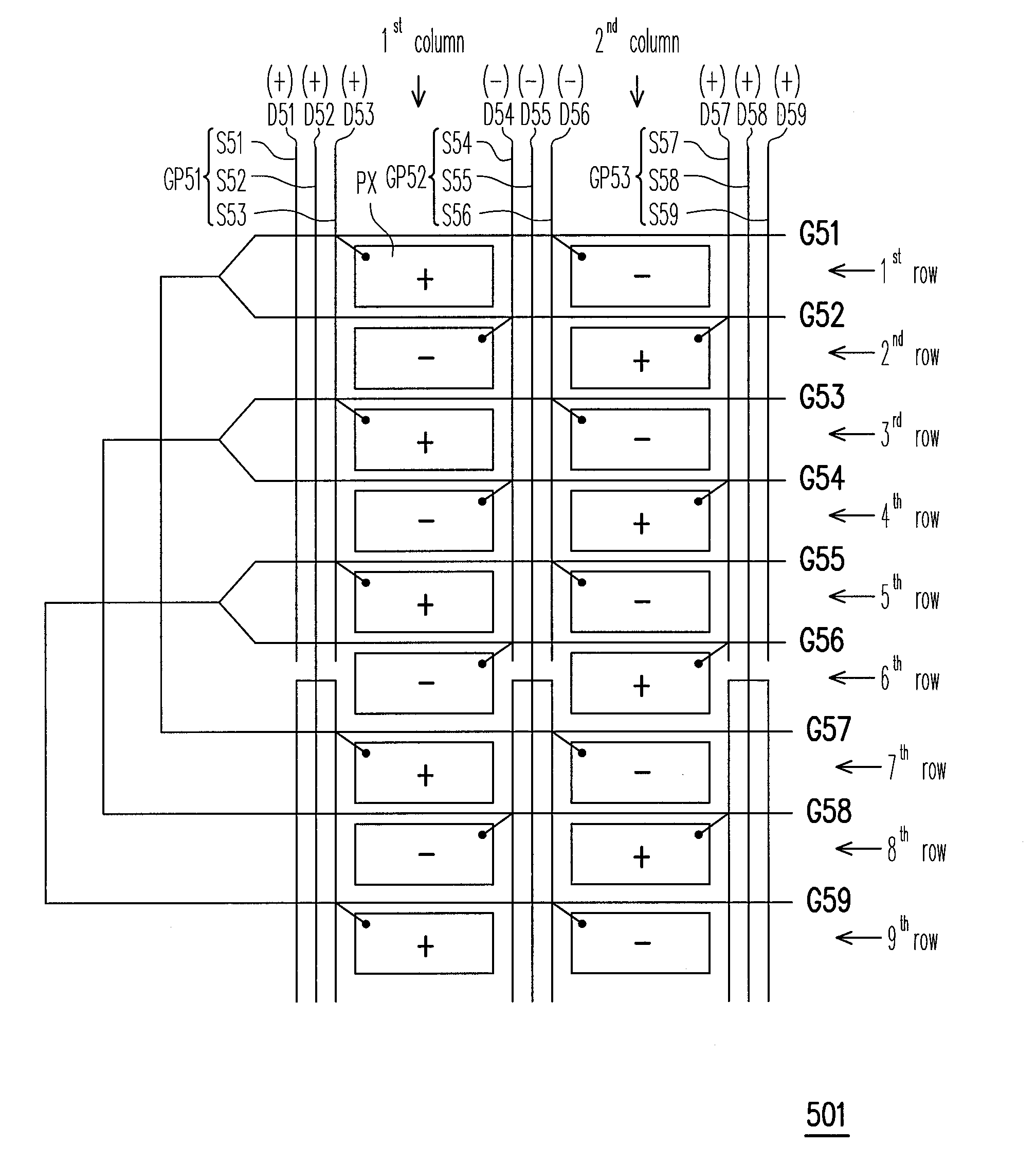

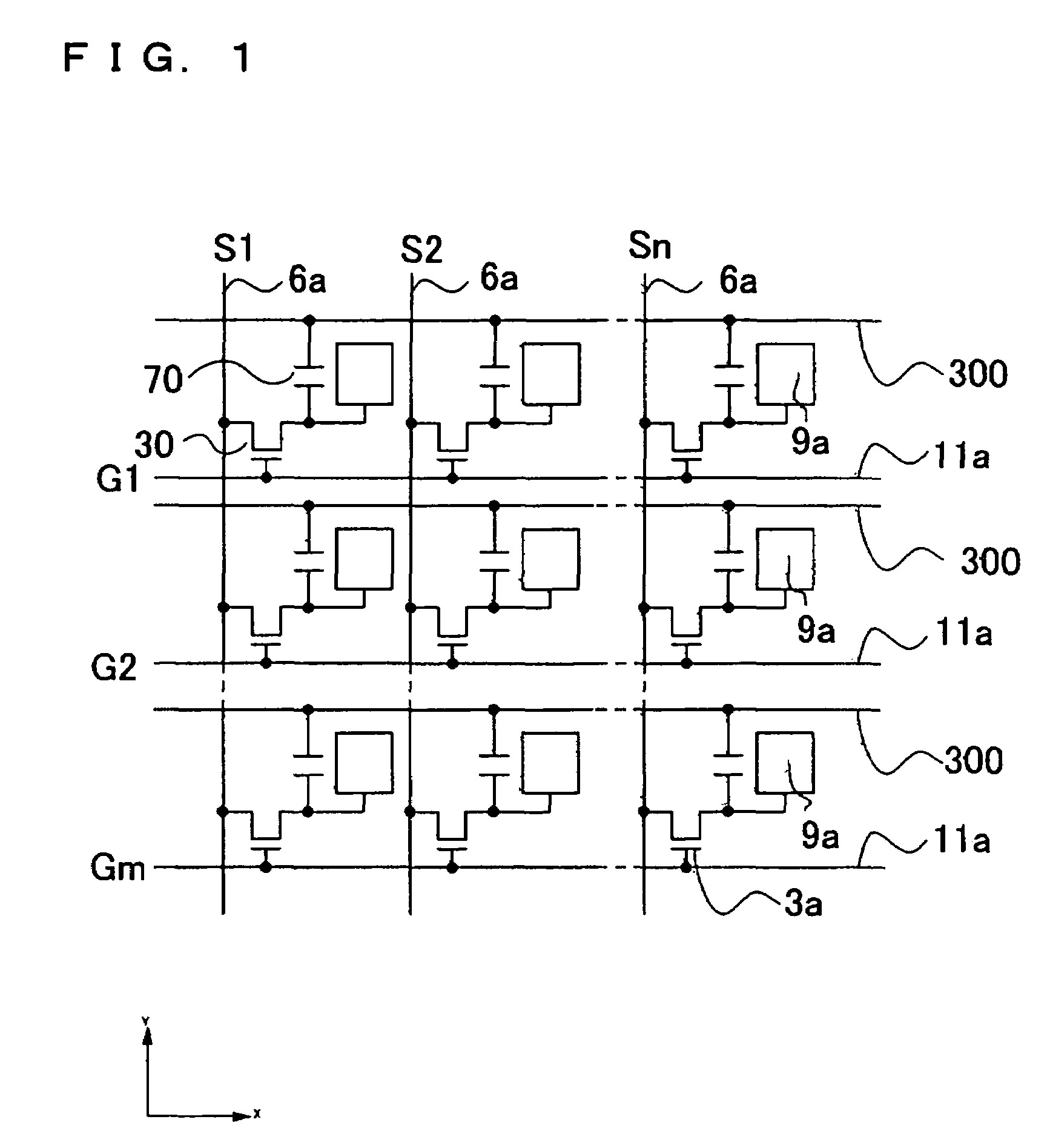

Display and display panel thereof

ActiveUS20110241526A1Prevent capacitanceInhibit productionControl electrodesStatic indicating devicesScan lineComputer science

A display panel including a plurality of scan lines, a plurality of data lines, and a plurality of pixels is provided. The data lines are disposed substantially perpendicular to the scan lines Each of the pixels is electrically connected with the corresponding data line and the corresponding scan line and the pixels are arranged as an array. The data lines are grouped into a plurality of groups and each of the groups is disposed between two adjacent pixel columns and has N data lines, where N is a positive integer greater than or equal to 3. A portion of the data lines of at least a first group among the groups cross over a portion of the scan lines. The rest data lines of the first group cross over all the scan lines.

Owner:AU OPTRONICS CORP

Linearity improvements of semiconductor substrate using passivation

ActiveUS7915706B1Effectively layerPrevent capacitance changeTransistorSolid-state devicesCapacitanceRelease time

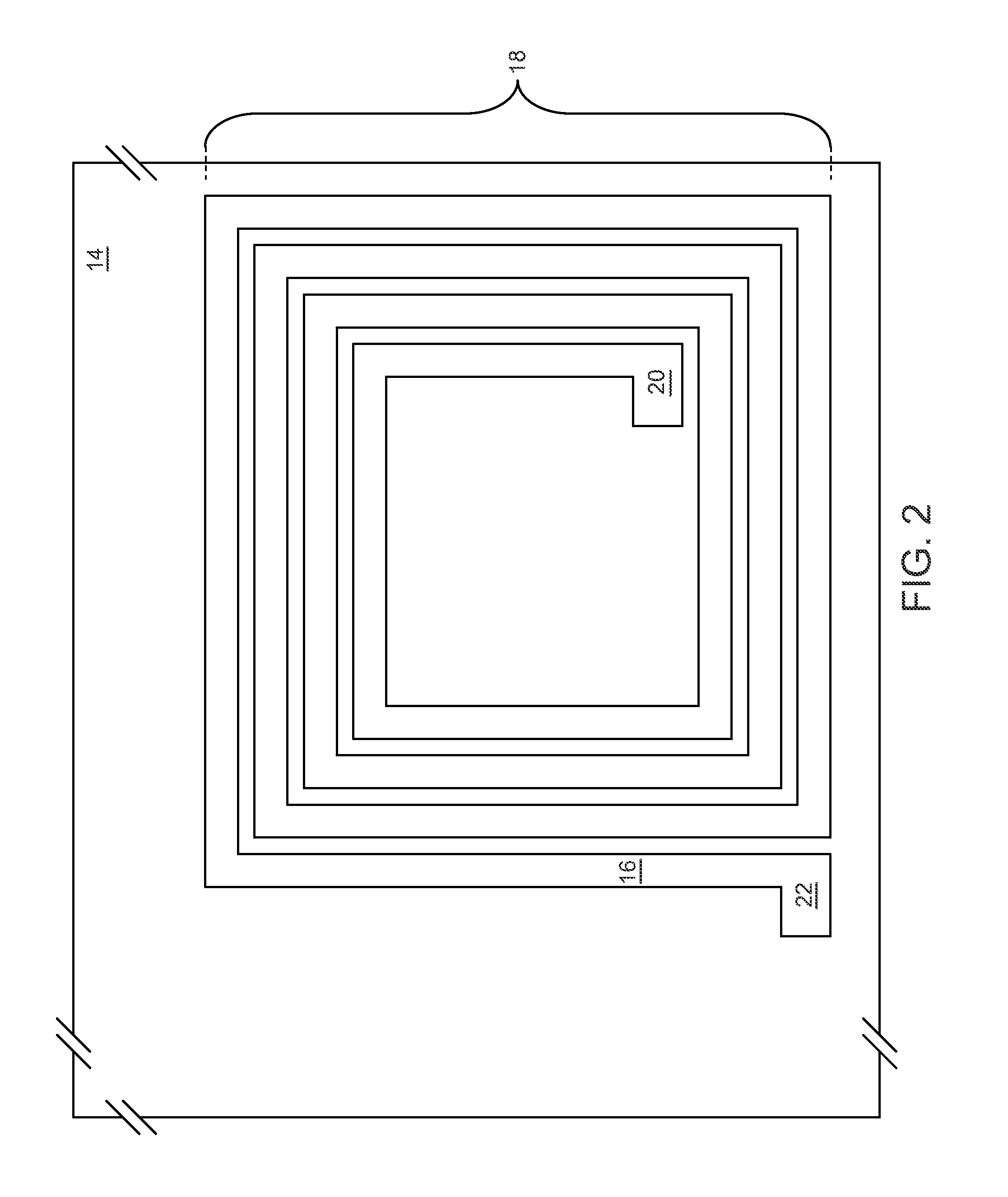

The present invention relates to using a potentially trap-rich layer, such as a polycrystalline Silicon layer, over a passivation region of a semiconductor substrate or a Silicon-on-insulator (SOI) device layer to substantially immobilize a surface conduction layer at the surface of the semiconductor substrate or SOI device layer at radio frequency (RF) frequencies. The potentially trap-rich layer may have a high density of traps that trap carriers from the surface conduction layer. The average release time from the traps may be longer than the period of any present RF signals, thereby effectively immobilizing the surface conduction layer, which may substantially prevent capacitance and inductance changes due to the RF signals. Therefore, harmonic distortion of the RF signals may be significantly reduced or eliminated. The semiconductor substrate may be a Silicon substrate, a Gallium Arsenide substrate, or another substrate.

Owner:QORVO US INC

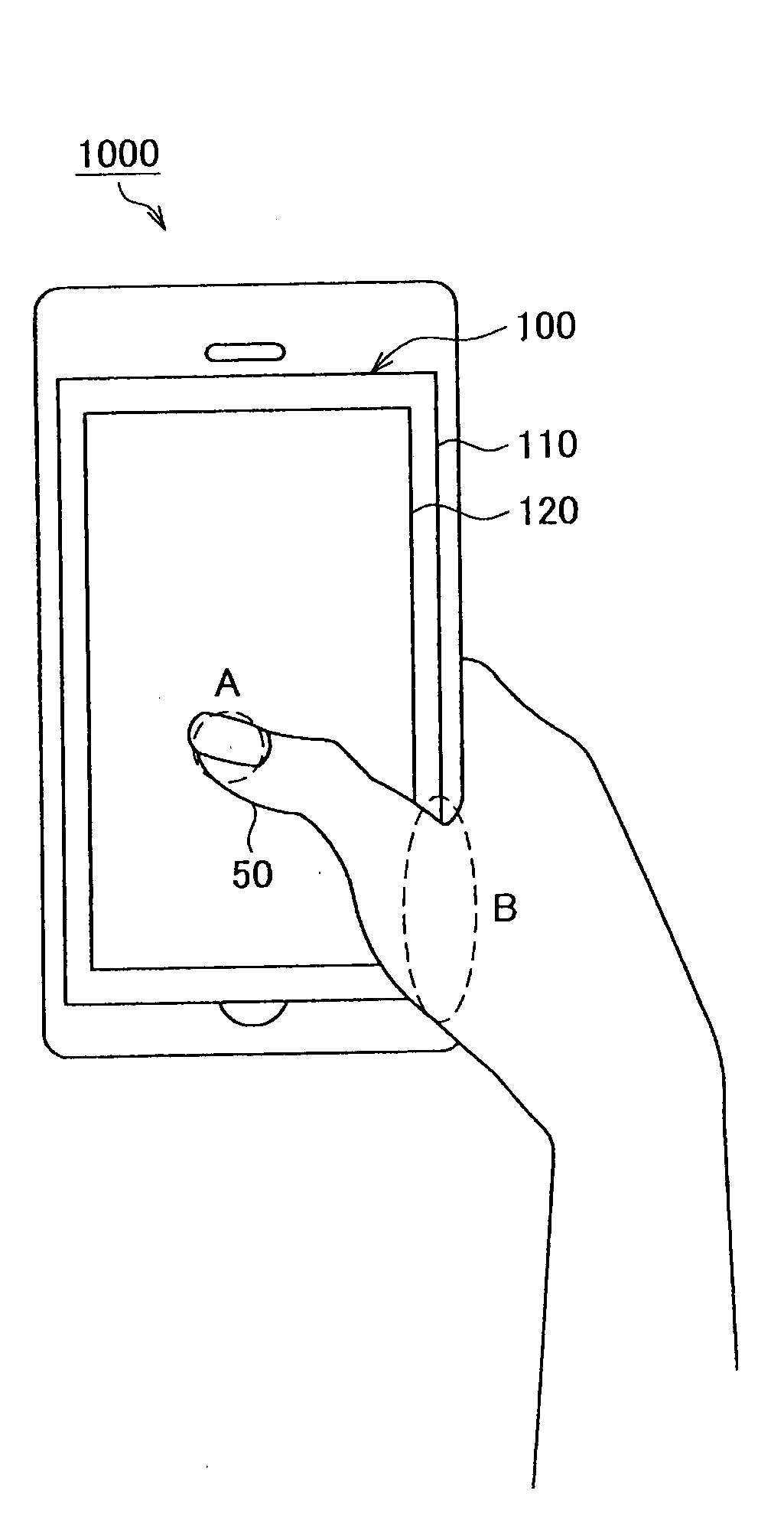

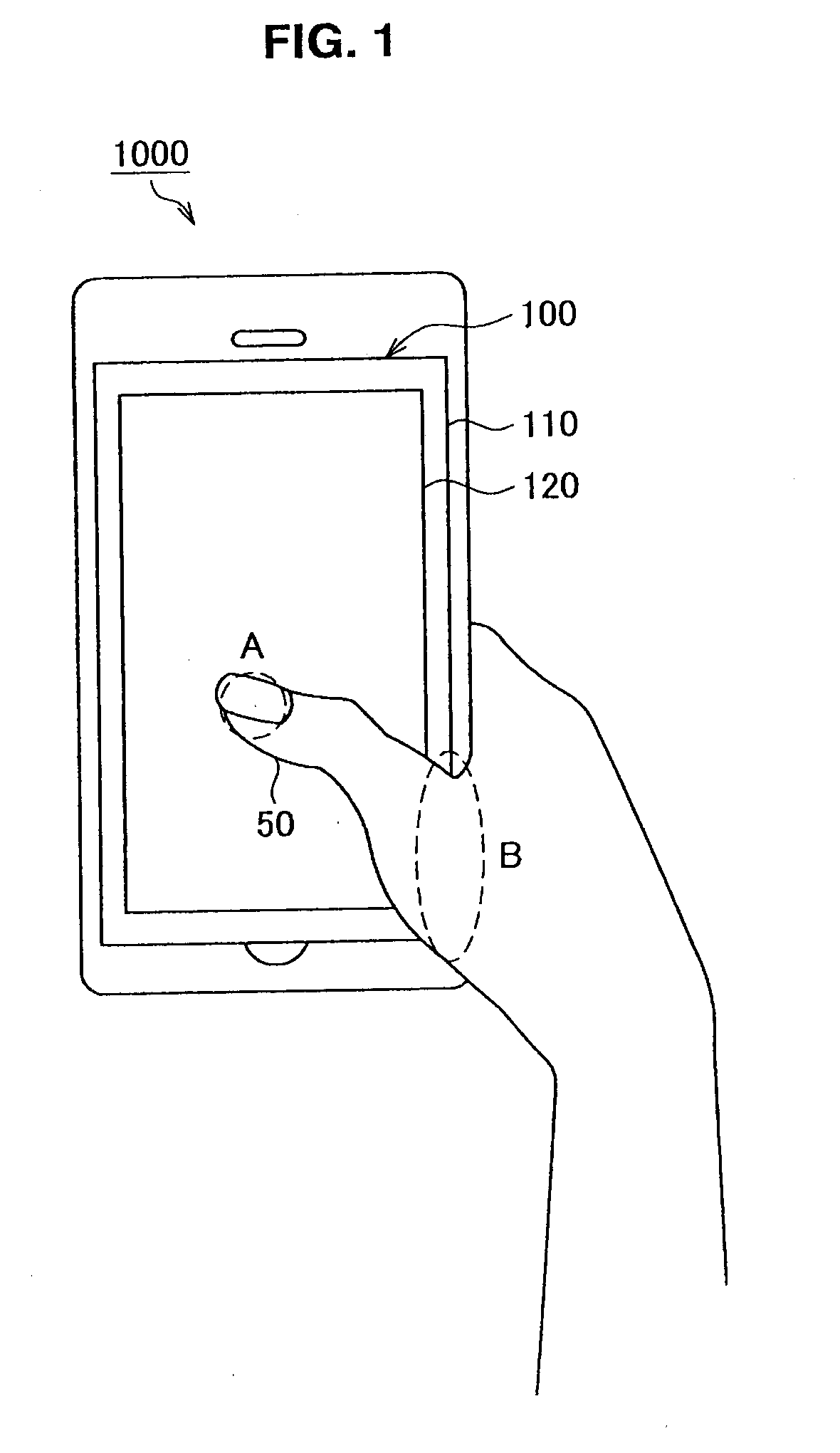

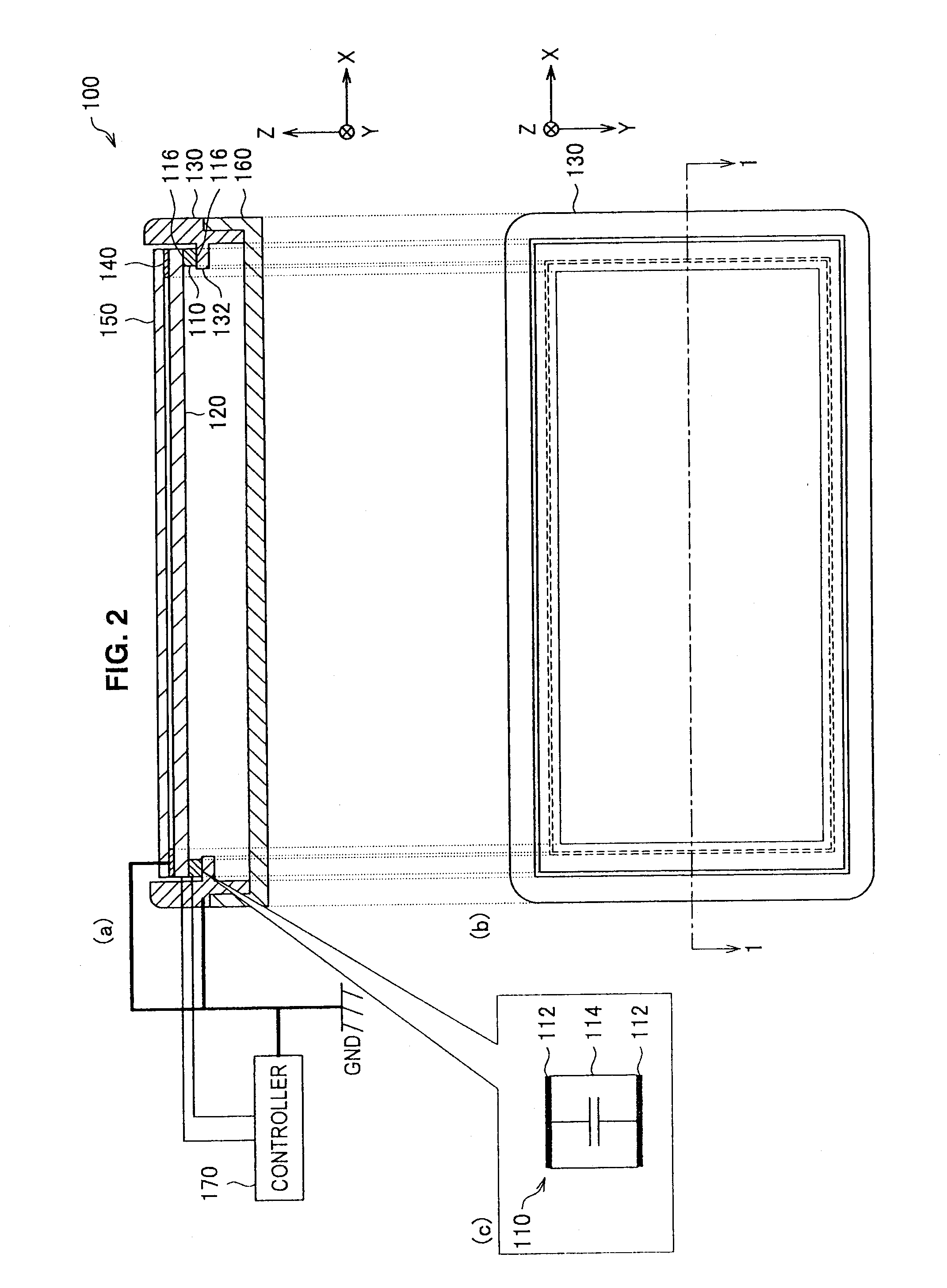

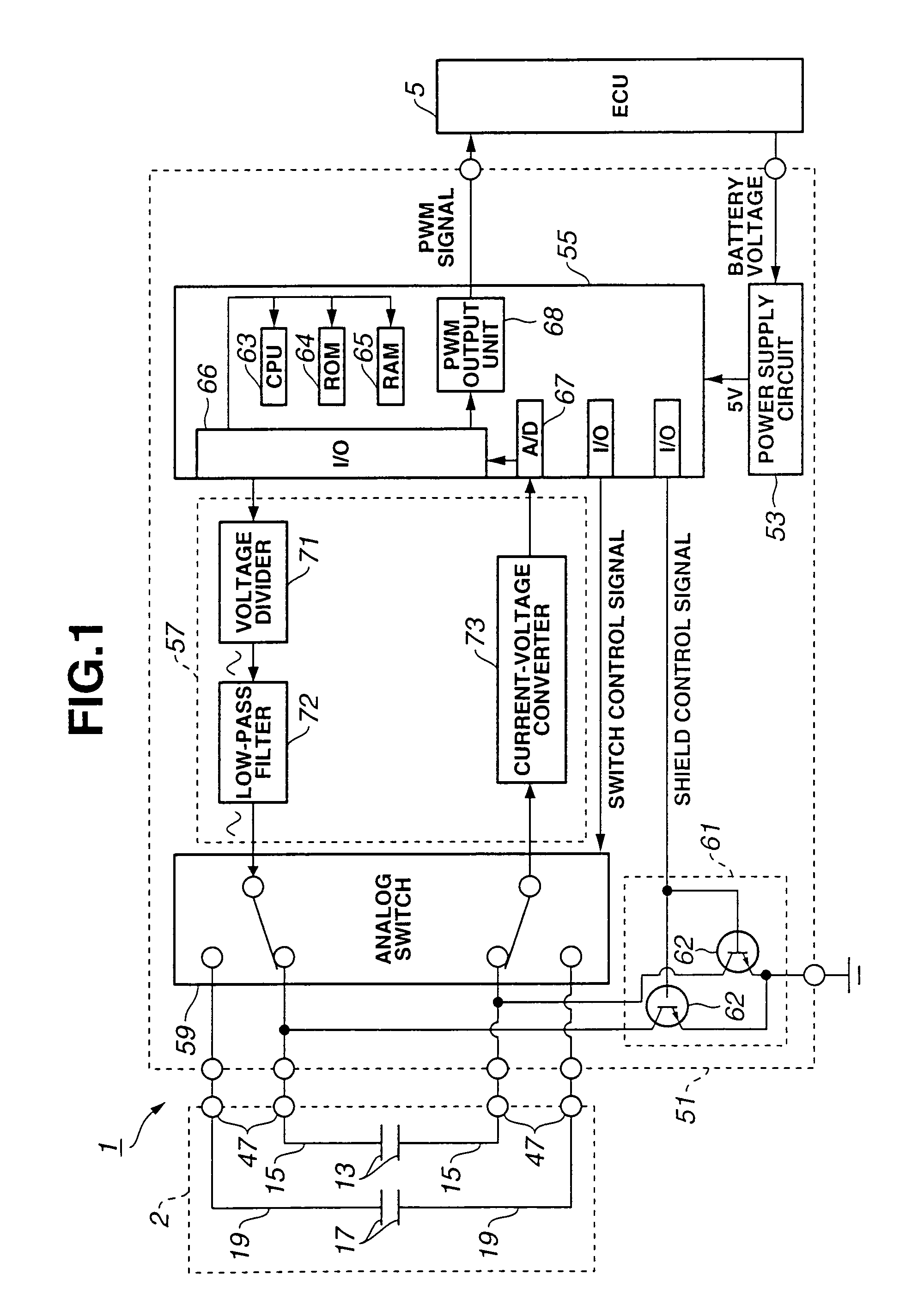

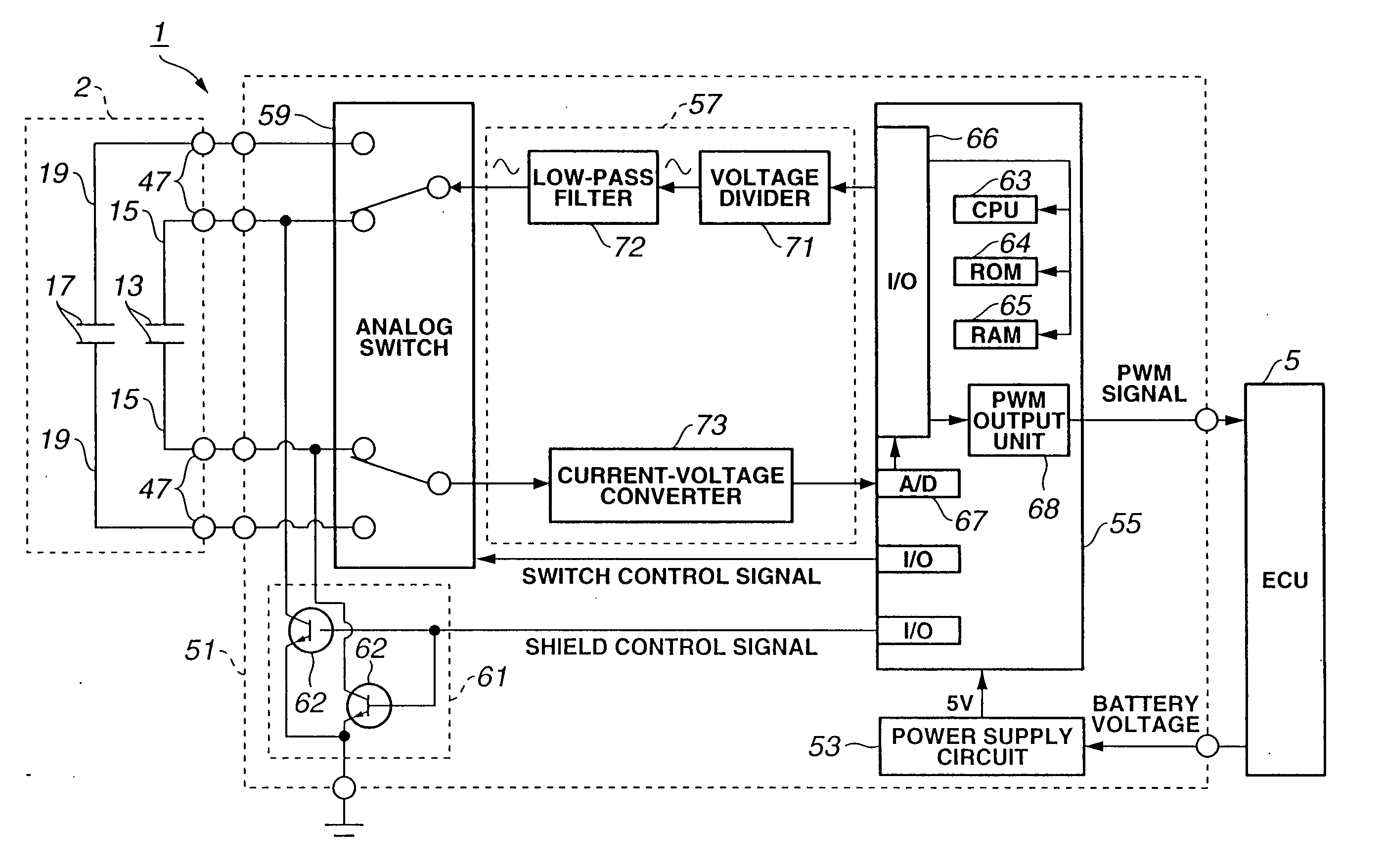

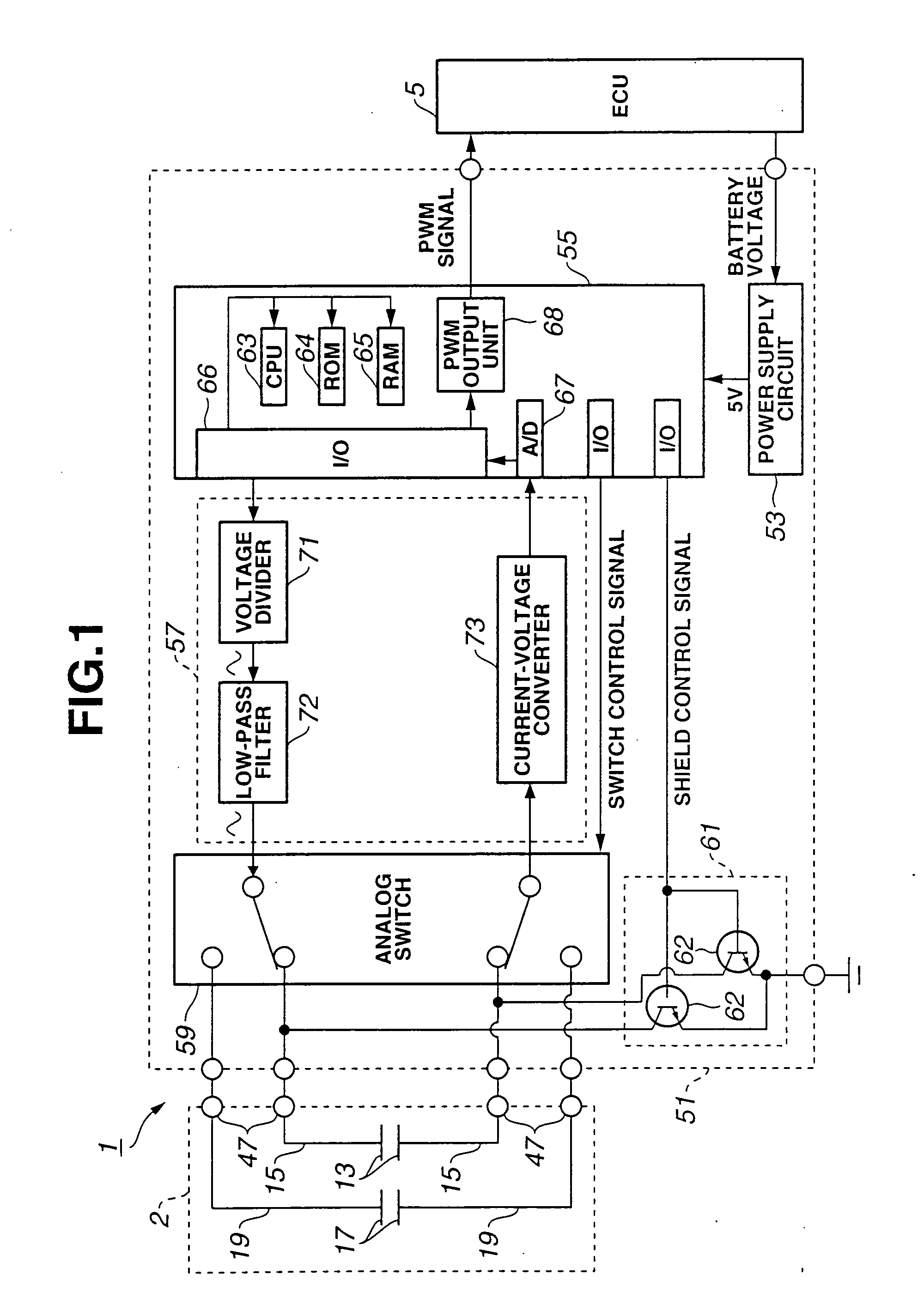

Sensor Device and Information Processing Device

ActiveUS20110057904A1Prevents change in capacitancePrevent change in capacitanceCapacitor with electrode distance variationPulse techniqueCapacitanceInformation processing

A sensor device is provided which includes a pressure-sensitive sensor which changes shape in response to pressing of an operation tool and which detects change in capacitance due to the change in shape, and a barrier which covers at least a part of the pressure-sensitive sensor and which prevents change in capacitance of the pressure-sensitive sensor due to capacitive coupling that occurs with approach between the pressure-sensitive sensor and the operation tool.

Owner:SONY CORP

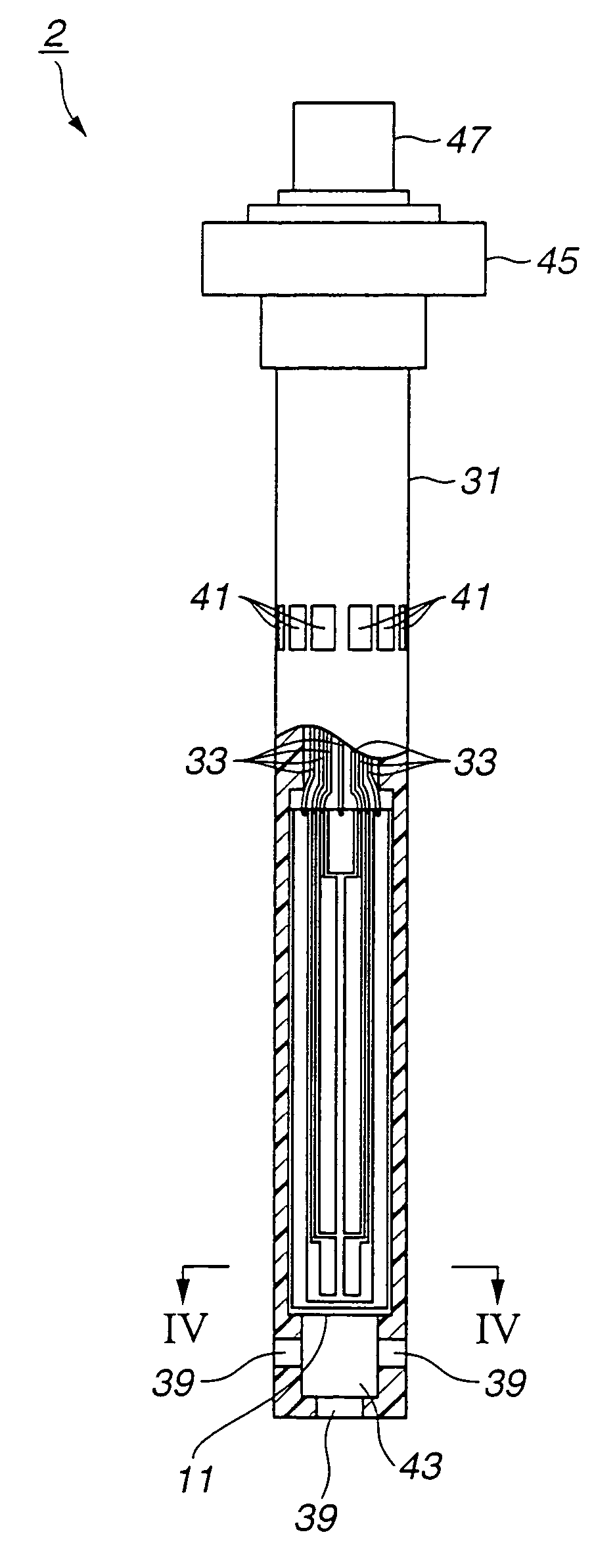

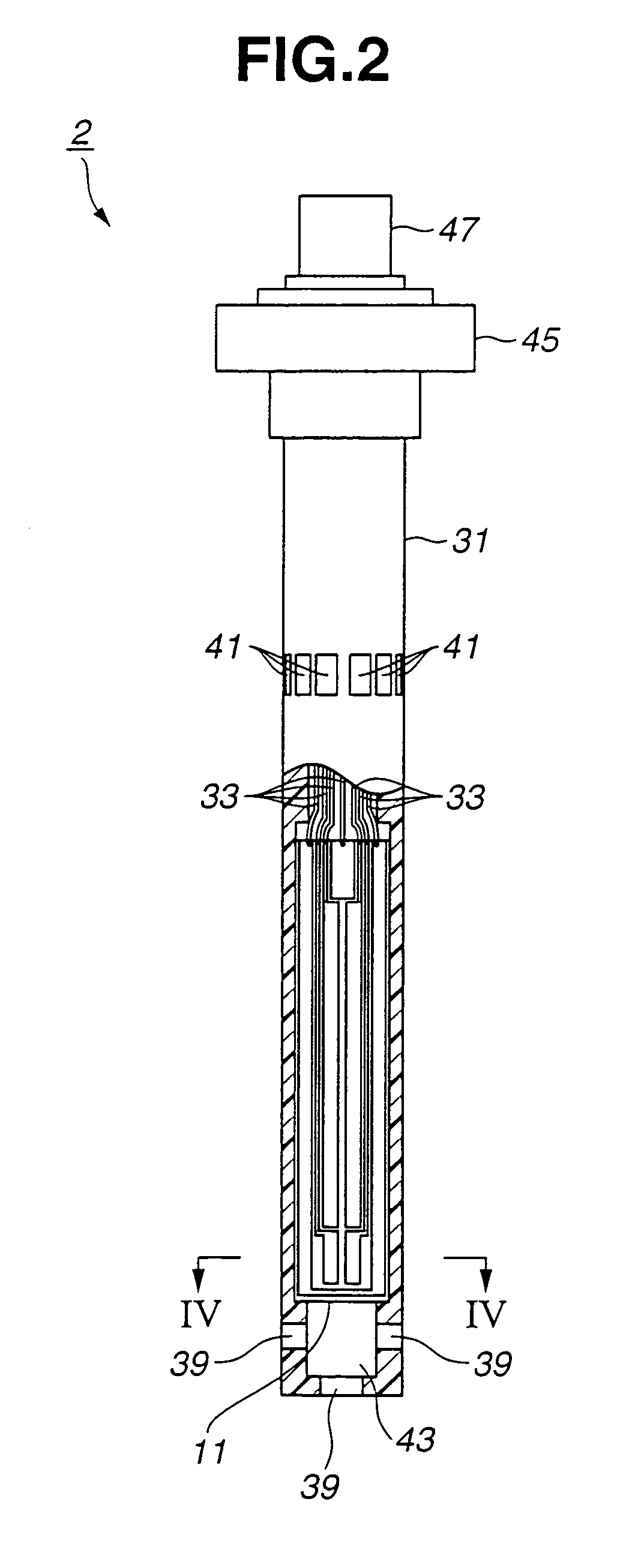

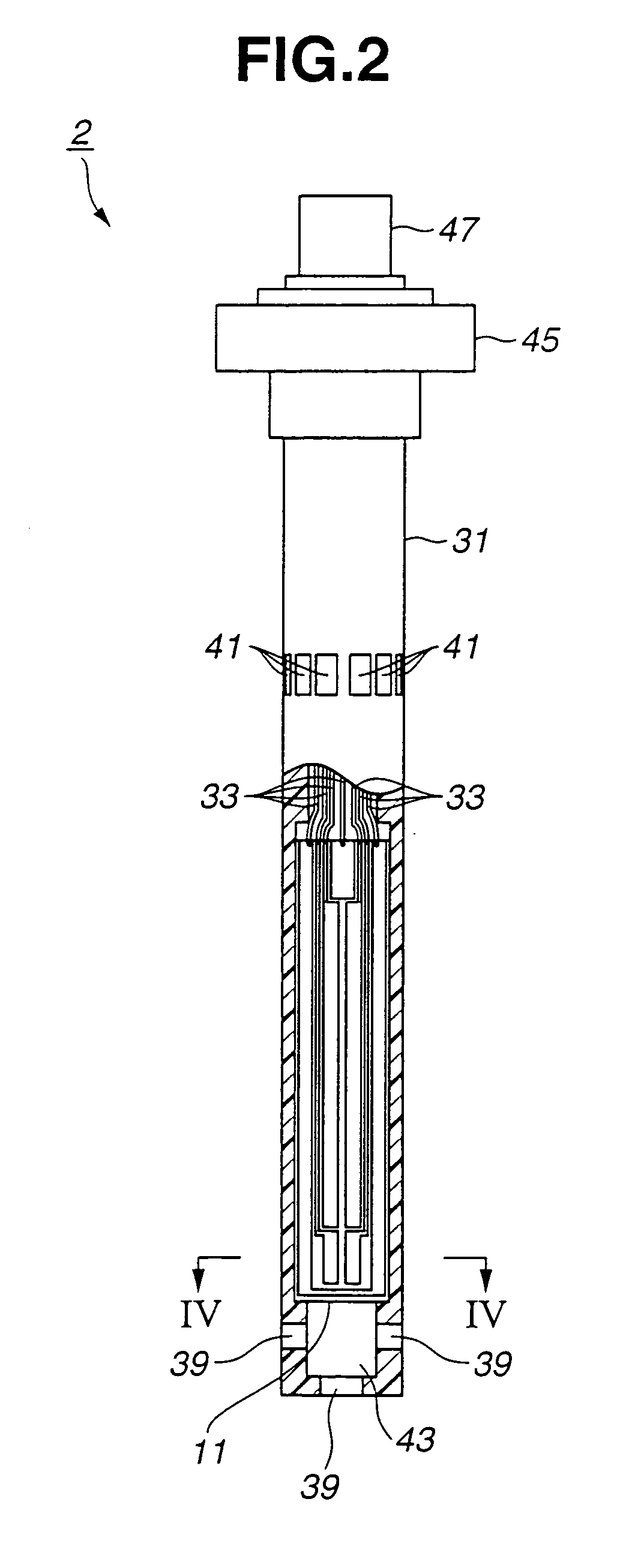

Liquid level detection apparatus

InactiveUS7114391B2Inhibit deteriorationIncrease in electrode arrangement areaMachines/enginesLubrication indication devicesCapacitanceEngineering

Owner:NGK SPARK PLUG CO LTD

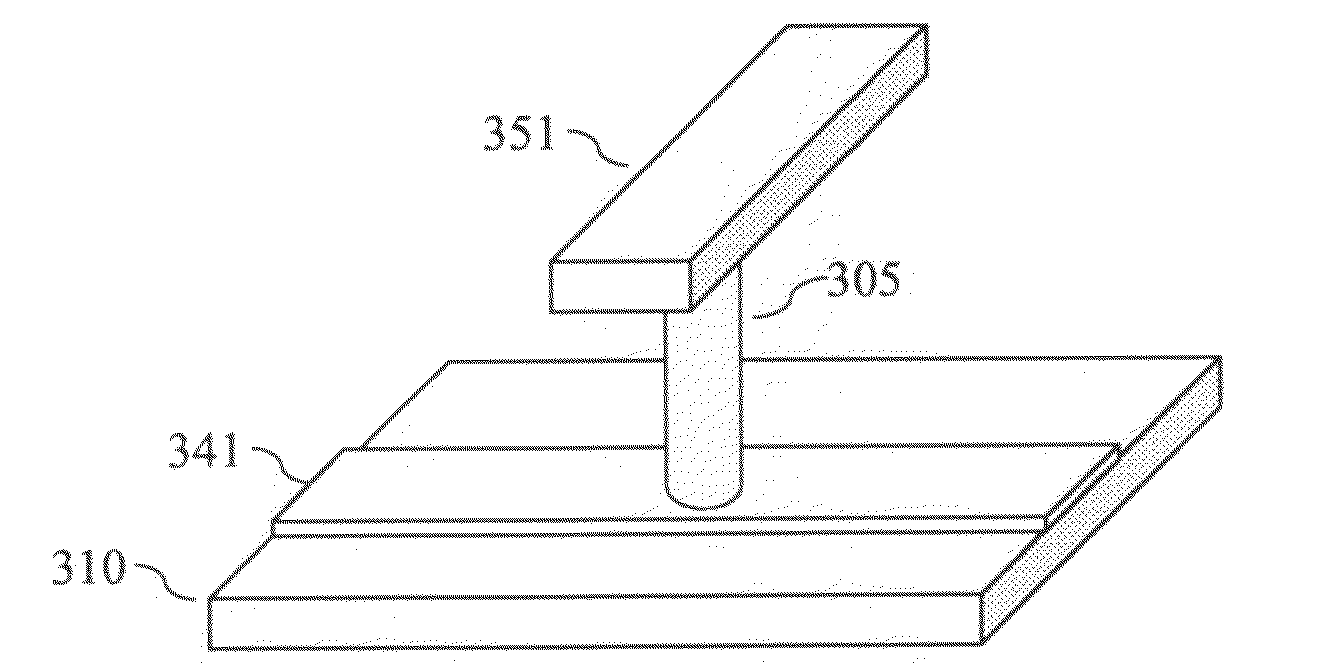

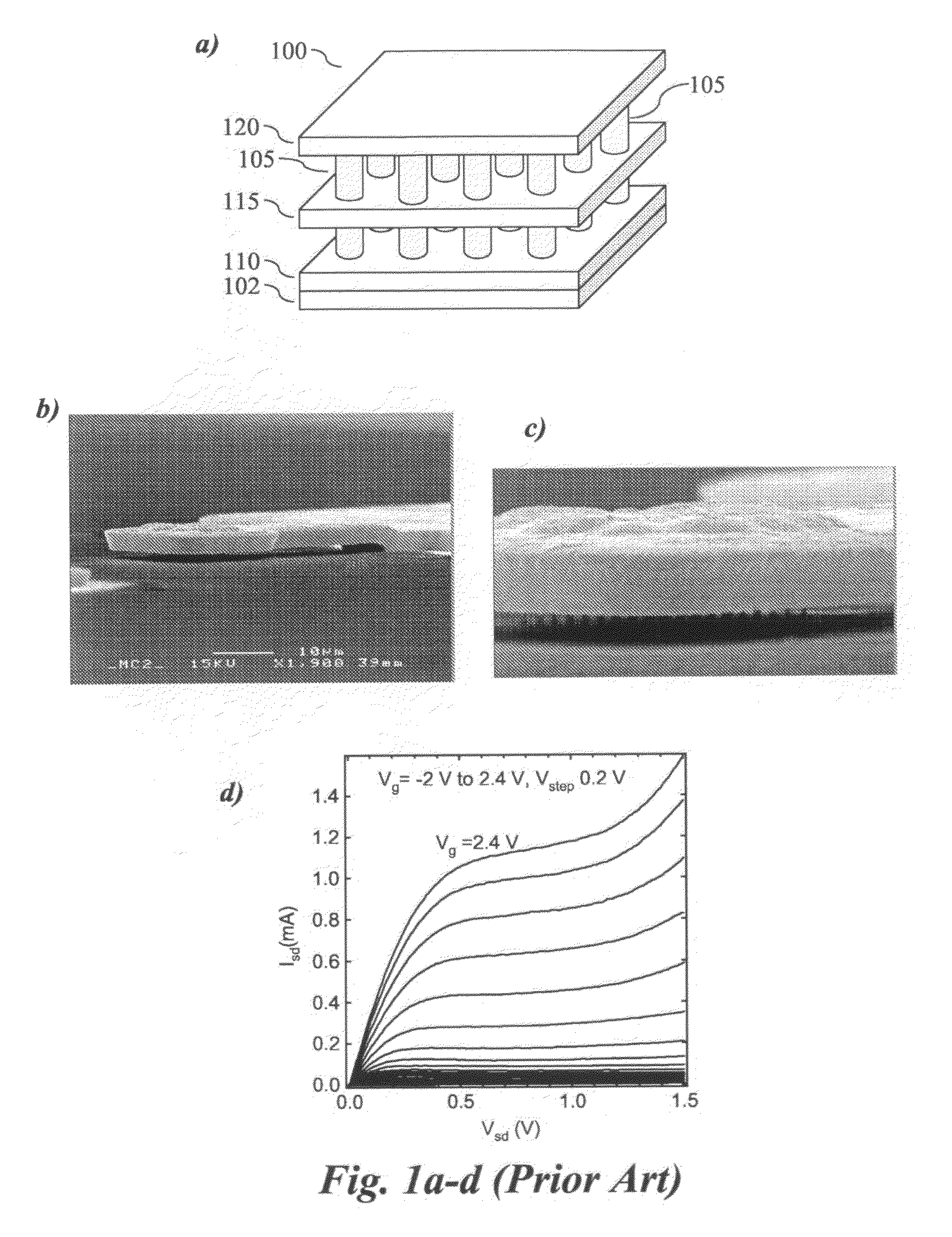

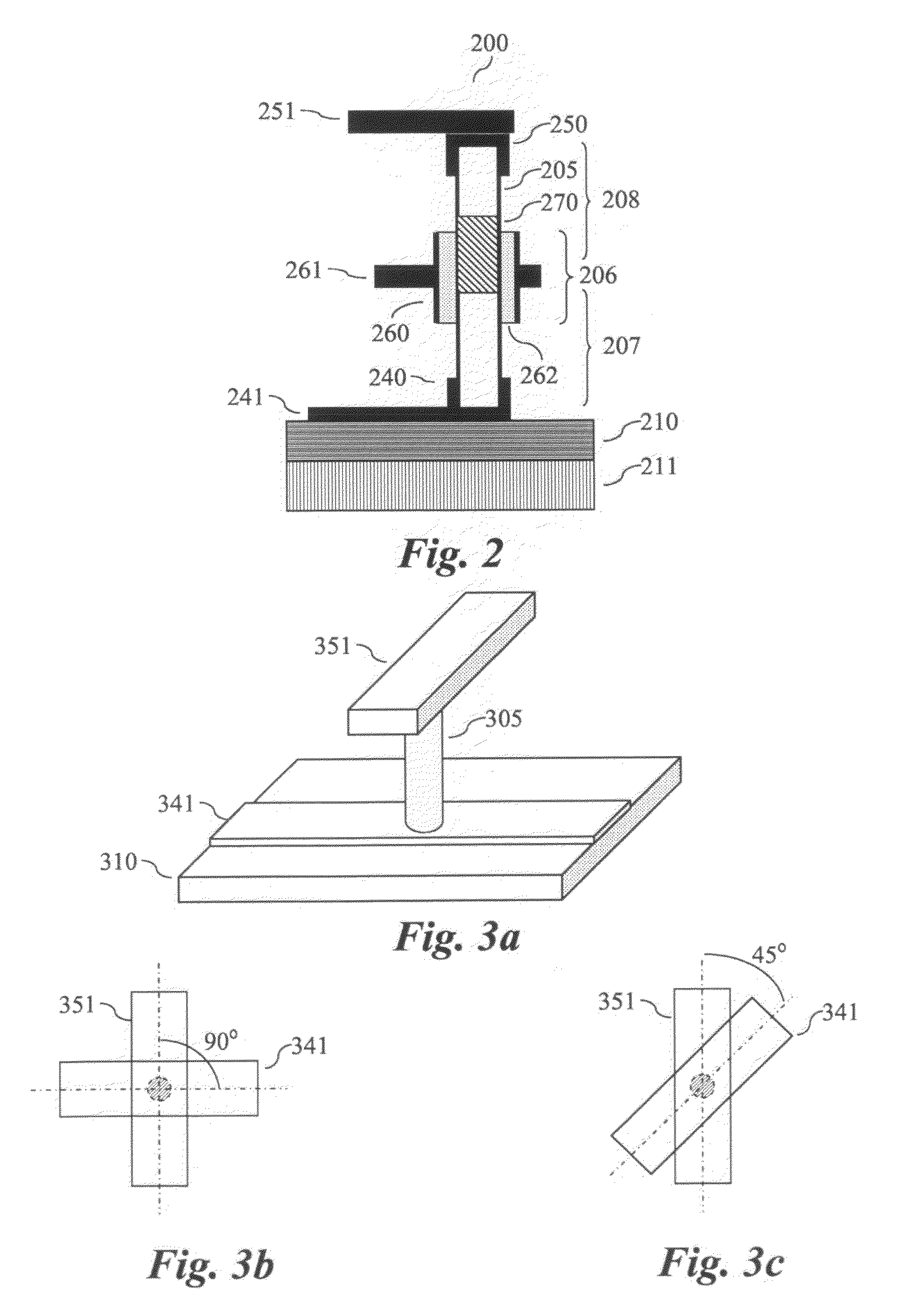

Semiconductor Nanowire Vertical Device Architecture

ActiveUS20090294757A1Minimise overlayPrevent leakageIndividual molecule manipulationSemiconductor/solid-state device detailsCapacitanceNanowire

The present invention relates to nanoscaled electronic devices with a vertical nanowire as a functional part. Contacts are arranged on the nanowire at different parts of the nanowire, for example drain and source contacts. In connection to the nanowire contacts are external electrodes, that connect at different levels, as seen from the substrate, of the device. The external electrodes are elongated, and typically and preferably stripe-like. According to the invention a first external electrode, or contacts, associated with contact(s) at a first part of the nanowire, and a second external electrode, associated with contact(s) at a second part of the nanowire are arranged in a cross-bar configuration. The cross-bar configuration minimizes the overlay of the external electrodes, hence, parasitic capacitances and current leakage can be reduced, and the performance of the device improved.

Owner:QUNANO

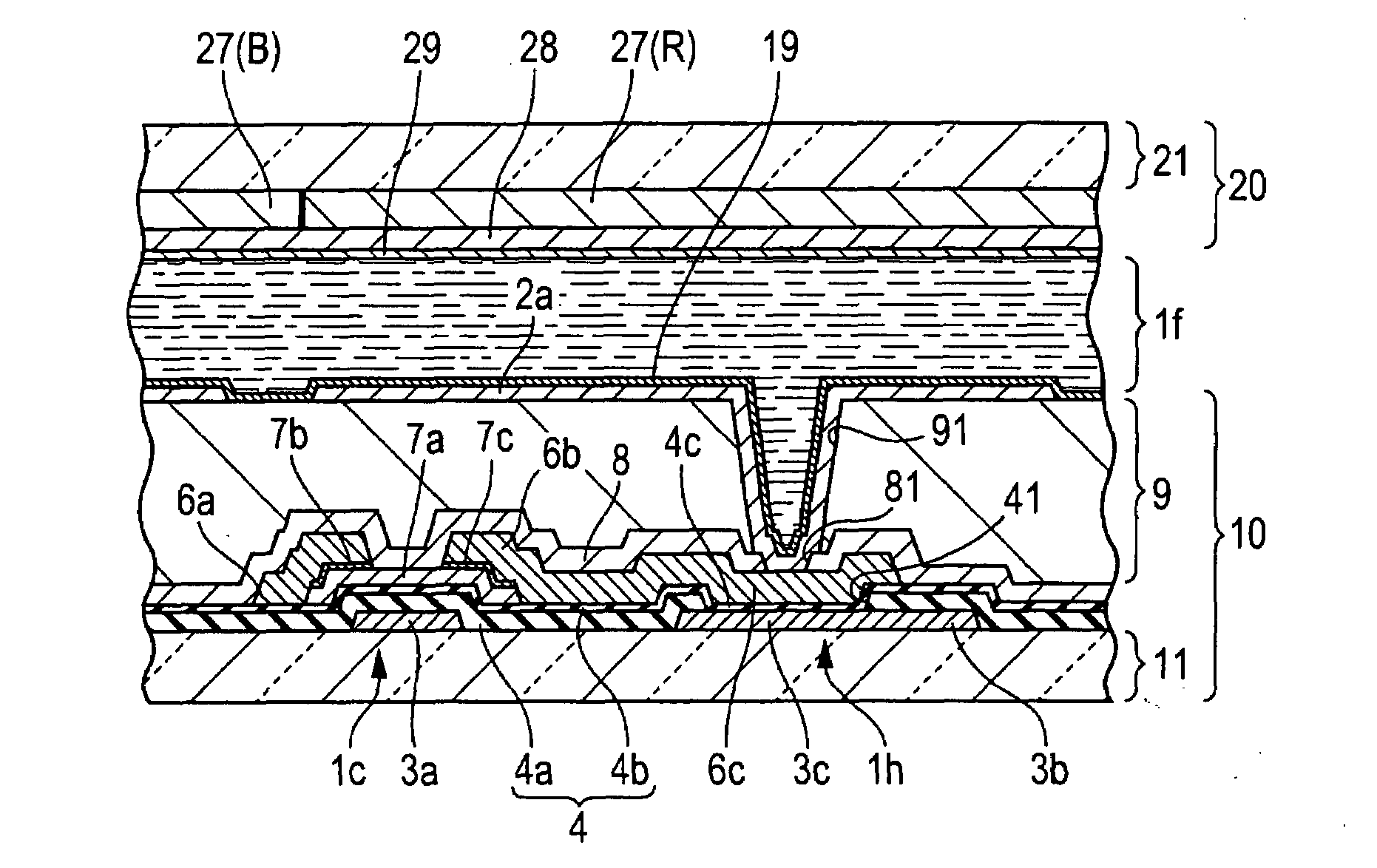

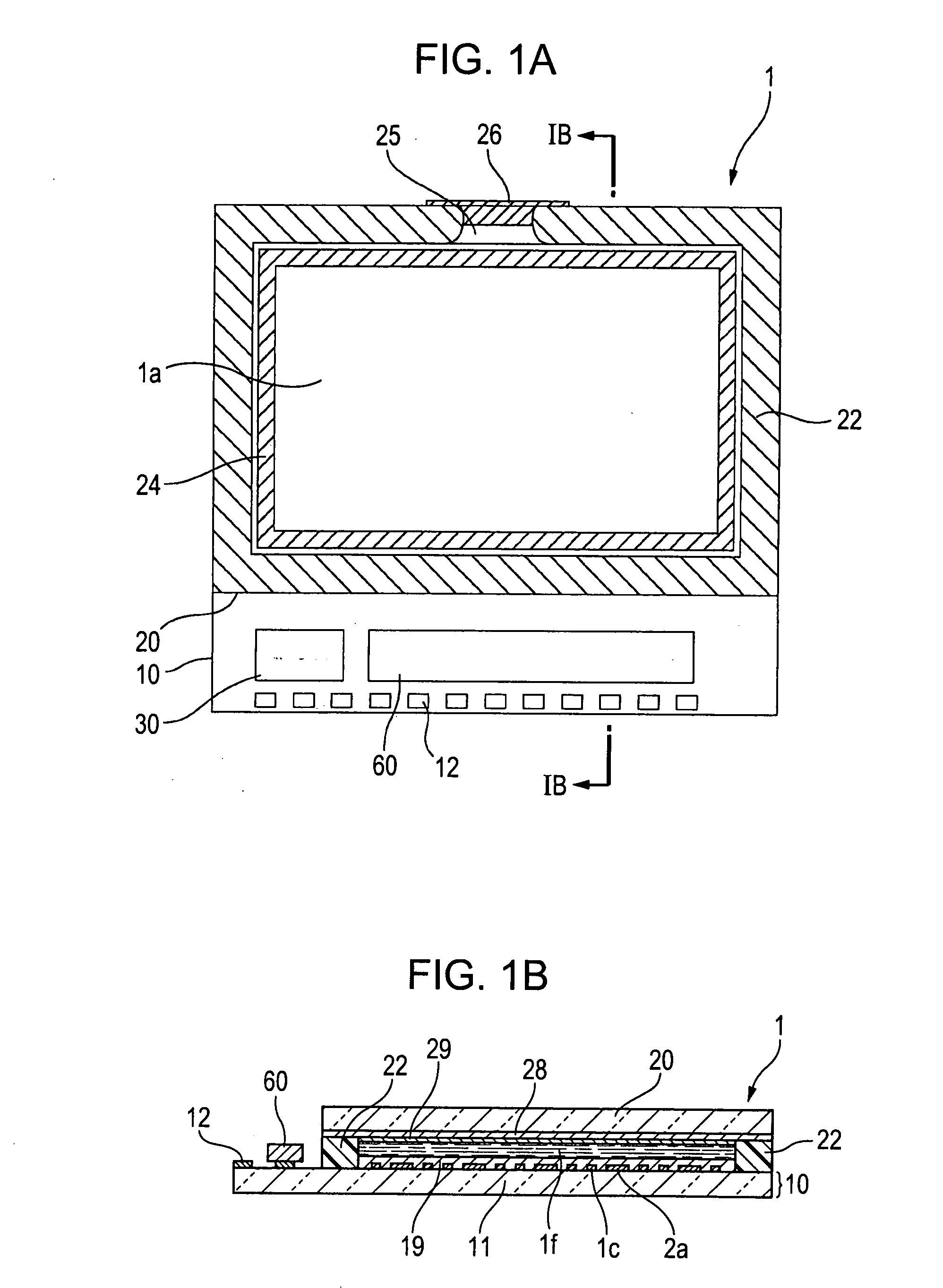

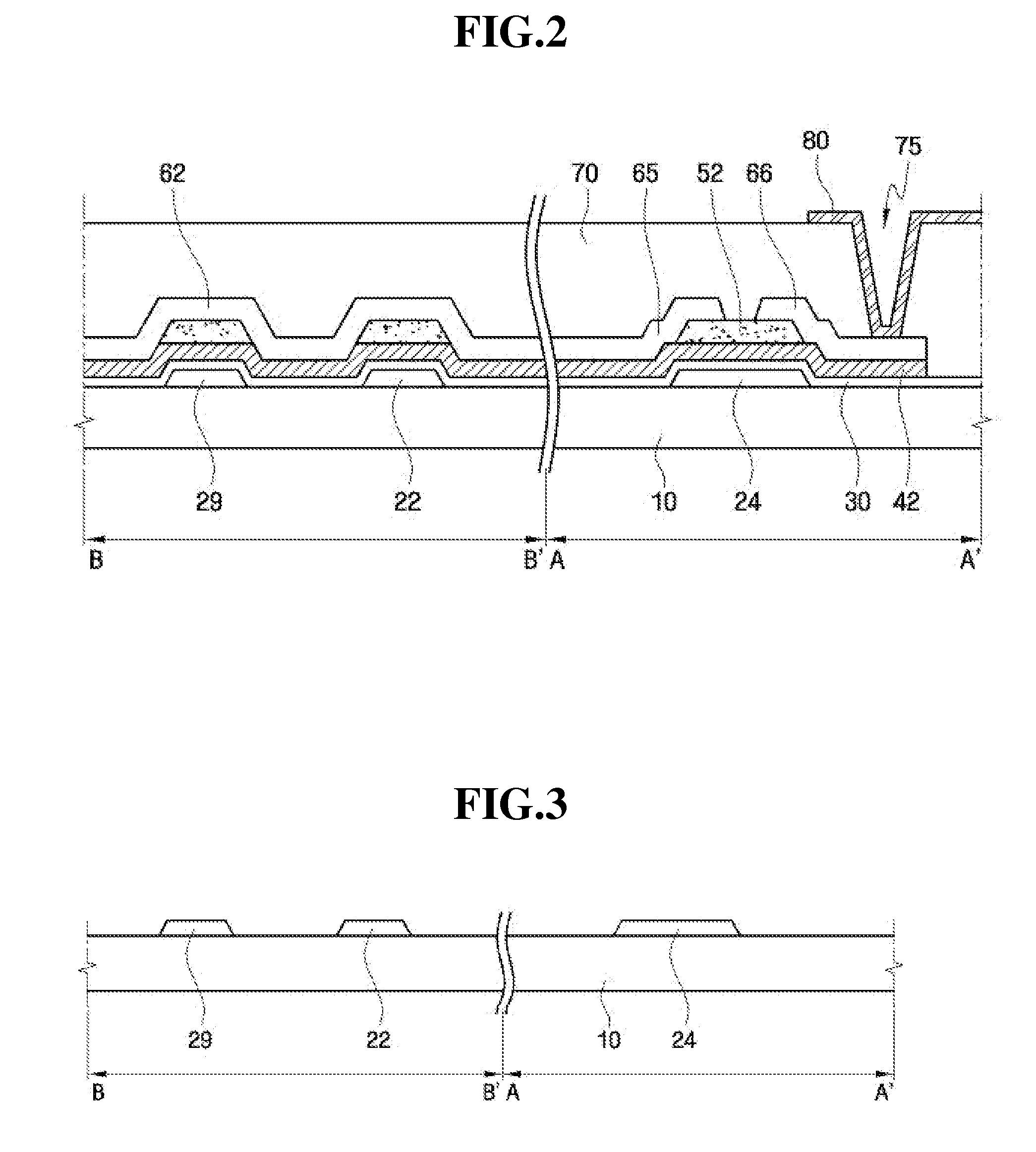

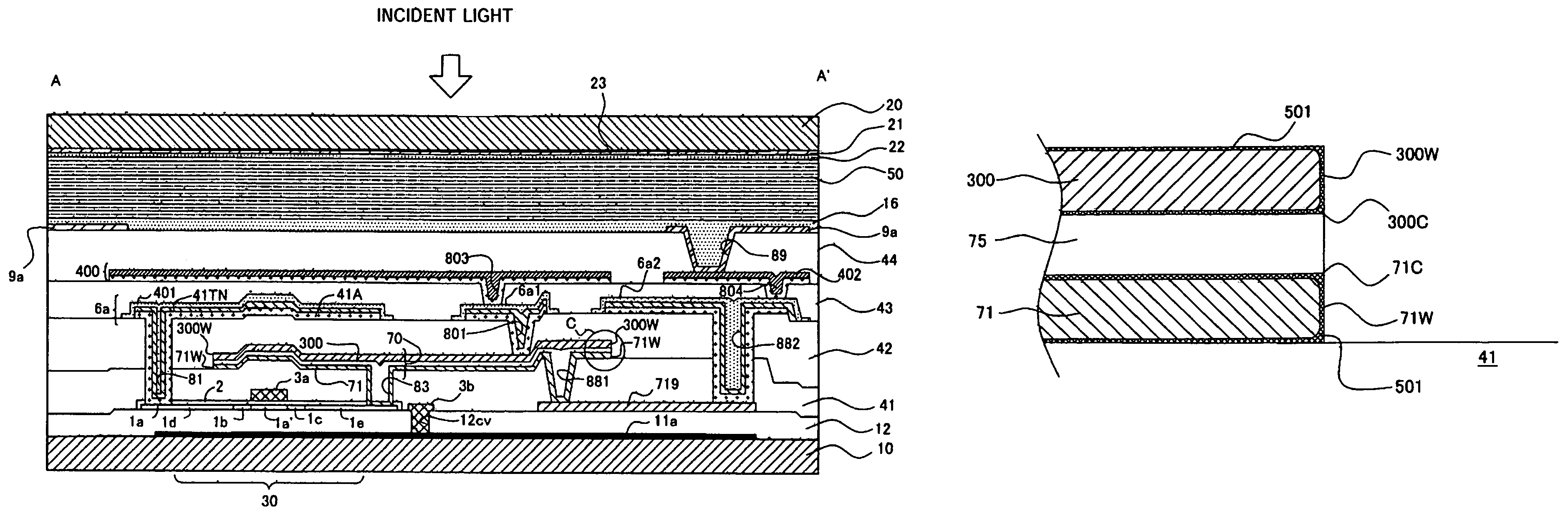

Electro-optical device and electronic apparatus

ActiveUS20070262352A1Reduce thicknessReduced dielectric strengthSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

An electro-optical device includes an element substrate having a plurality of pixel regions; thin-film transistors, arranged in the pixel regions, including gate electrodes, portions of a gate insulating layer, and semiconductor layers; pixel electrodes electrically connected to drain regions of the thin-film transistors; and storage capacitors including lower electrodes and upper electrodes that are opposed to the lower electrodes with insulating layers disposed therebetween, the insulating layers being made of the same material as that for forming the gate insulating layer. The upper electrodes overlap with some of end portions of the lower electrodes. The gate insulating layer has thin portions located in inner portions of regions overlapping with the lower and upper electrodes and thick portions which are located in regions overlapping with the upper electrodes and the end portions of the lower electrodes and which have a thickness greater than that of the thin portions.

Owner:JAPAN DISPLAY WEST

Liquid level detection apparatus

InactiveUS20050156962A1Inhibit deteriorationIncrease in electrode arrangement areaPrintingLevel indicators by physical variable measurementCapacitanceEngineering

There is provided a liquid level detection apparatus for detecting the level of a liquid, including a pair of first electrodes, a pair of second electrodes arranged at a different height to that of the first electrodes, a pair of electrode leads having respective ends connected with the first electrodes and sandwiching therebetween the second electrodes, a grounding unit that changes, between a current-carrying state and an open state, a second electrode current bypass from the second electrodes to a ground line, a first electrode capacitance measurement unit that measures a first electrode capacitance between the first electrodes, with the second electrode current bypass set in the current-carrying state to establish a connection from the second electrodes to the ground line, and a level determination unit that determines the liquid level based on the first electrode capacitance between the first electrodes and a second electrode capacitance between the second electrodes.

Owner:NGK SPARK PLUG CO LTD

Display device having resin black matrix over counter substrate

InactiveUS6900855B1Improve fitting accuracyReduce widthNon-linear opticsSemiconductor devicesDisplay deviceEngineering

A display device is disclosed. The display device has a first substrate having a thin film transistor connected to a pixel electrode. Further, the display device has a second substrate opposed to the first substrate and having a resin black matrix.

Owner:SEMICON ENERGY LAB CO LTD

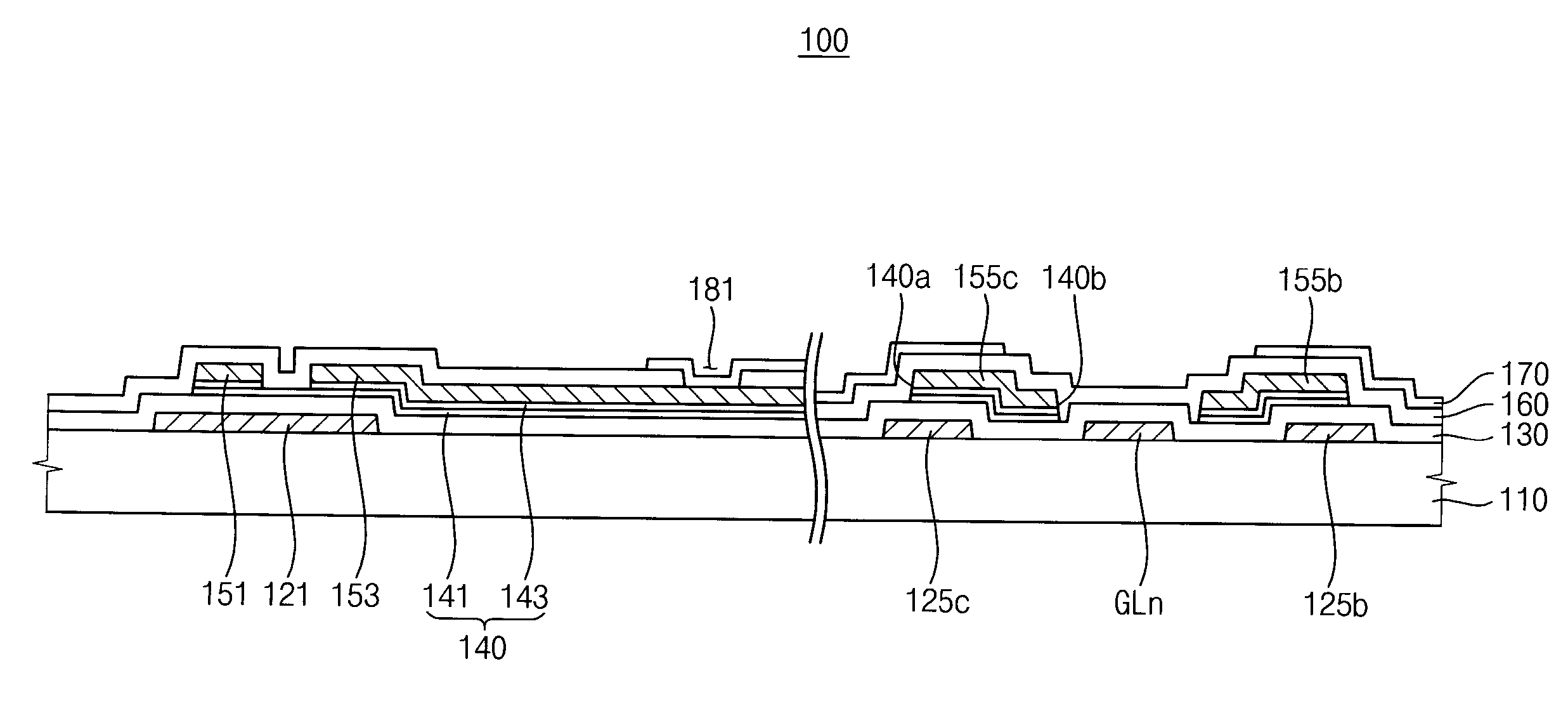

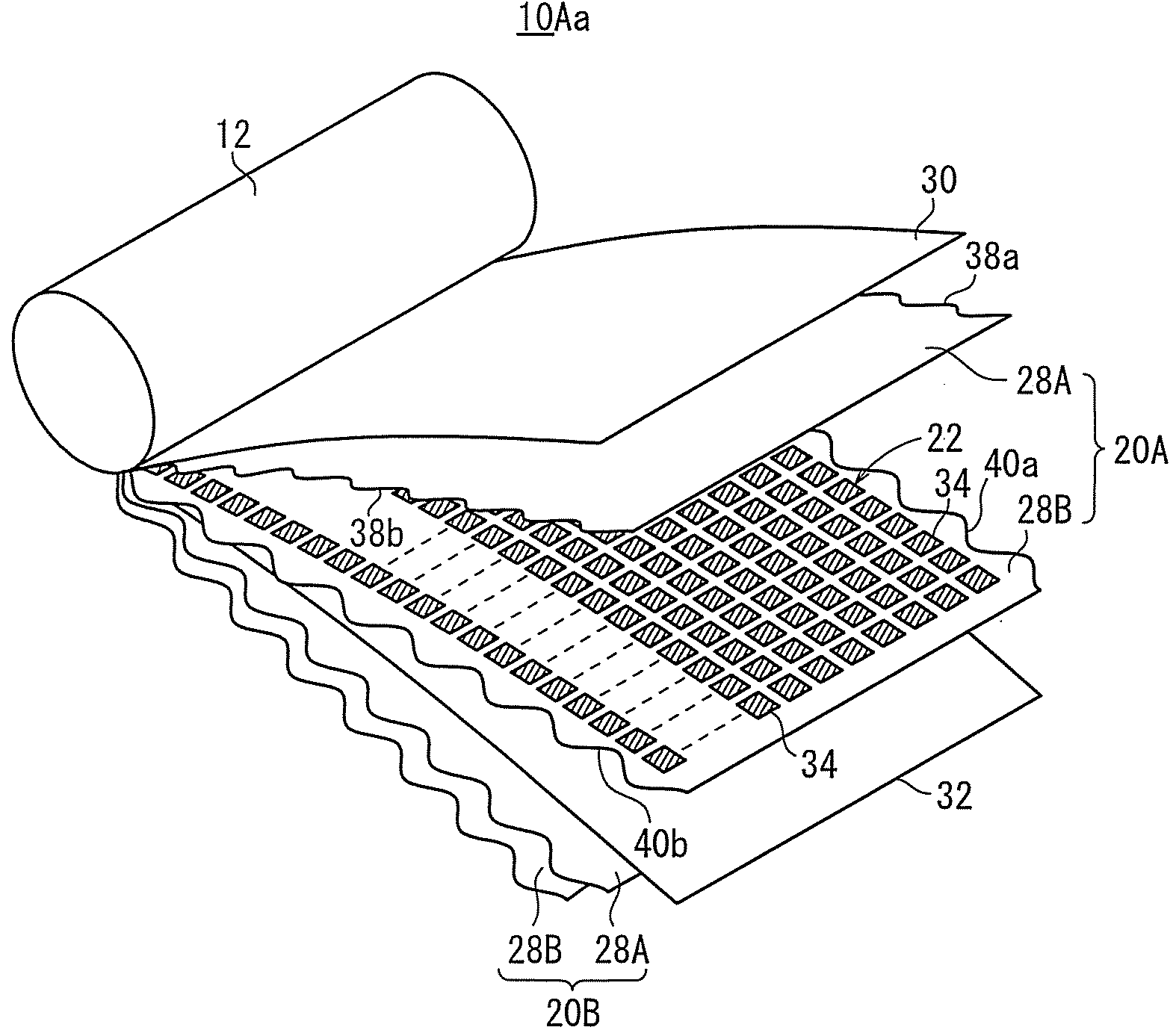

Array substrate and method for manufacturing the same

ActiveUS20090166633A1Storage capacitance can be preventedImprove display image qualitySolid-state devicesSemiconductor/solid-state device manufacturingLight energyCapacitor

In an array substrate capable of improving the quality of displayed images and a method for manufacturing the array substrate, the array substrate includes a base substrate, a first conductive pattern including a gate line and a first light-blocking pattern, a semiconductor layer overlapping the light-blocking pattern, a second conductive pattern including a data line and a storage line overlapping the first light-blocking pattern, and a pixel electrode overlapping the storage line to form a storage capacitor. The first conductive pattern may further include a second light-blocking pattern overlapping the semiconductor layer which is formed under the data line. The first and second light-blocking patterns block light proceeding toward the semiconductor layer formed under the storage line and under the data line, respectively, so that the semiconductor layer may be prevented from being excited by light energy.

Owner:SAMSUNG DISPLAY CO LTD

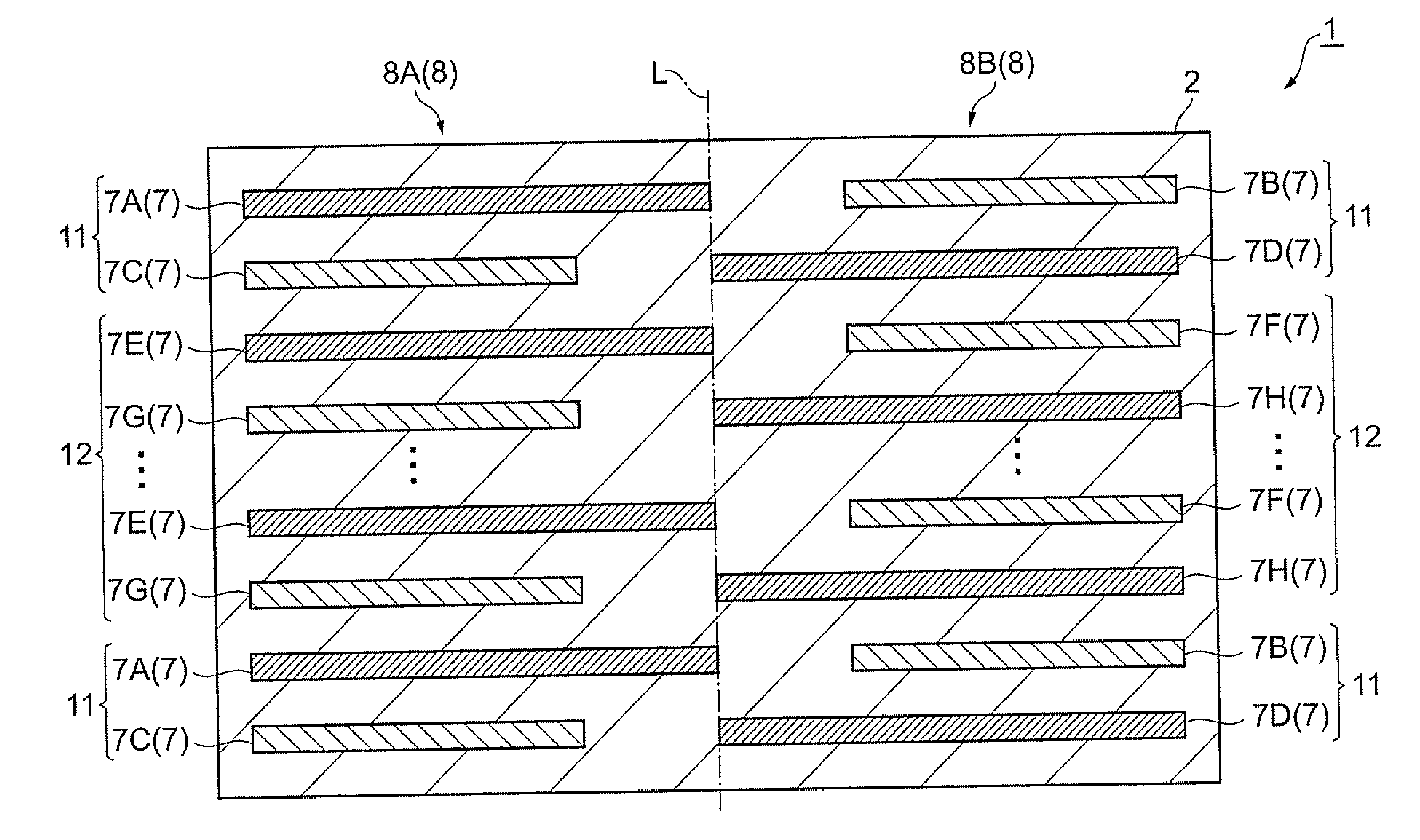

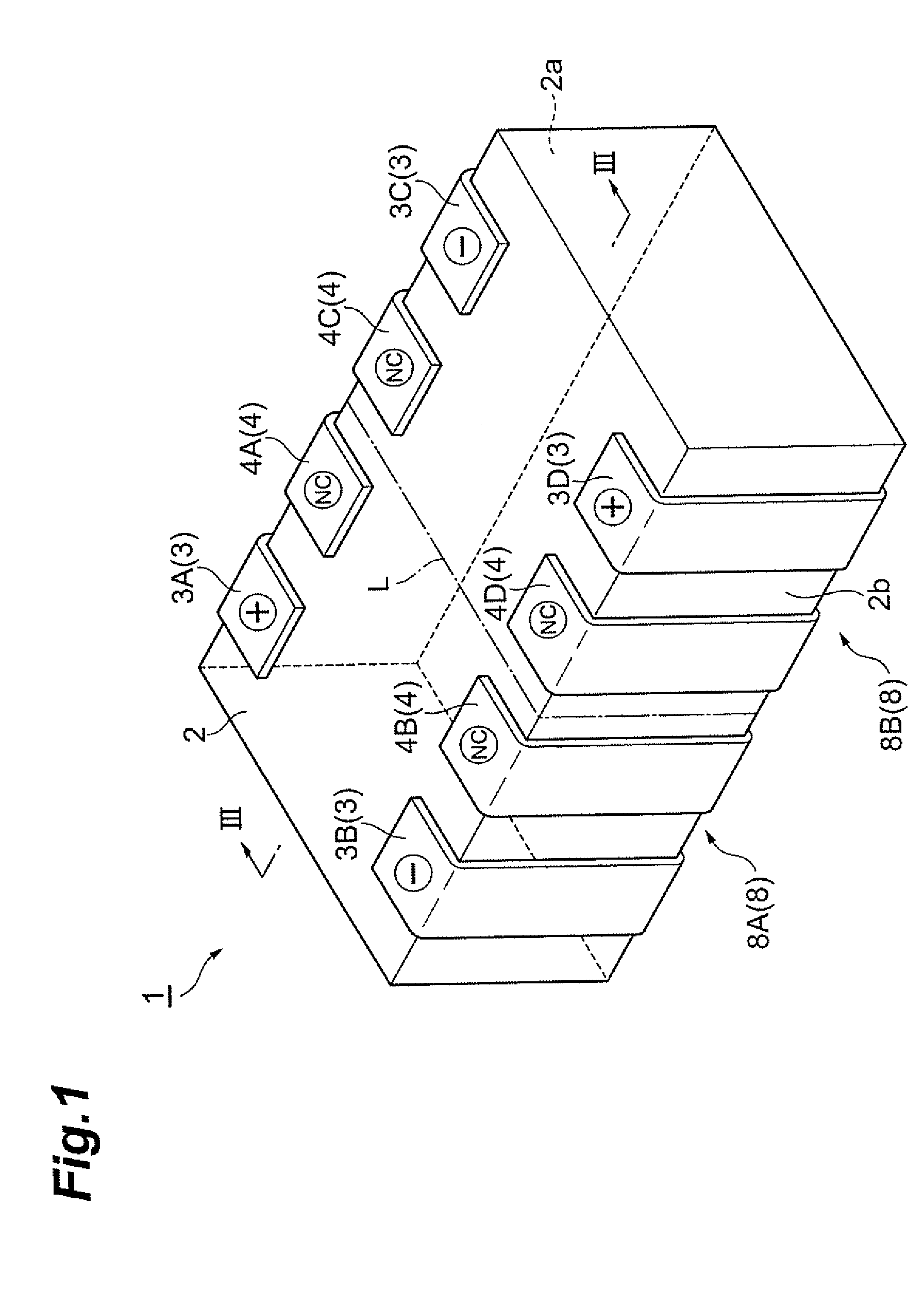

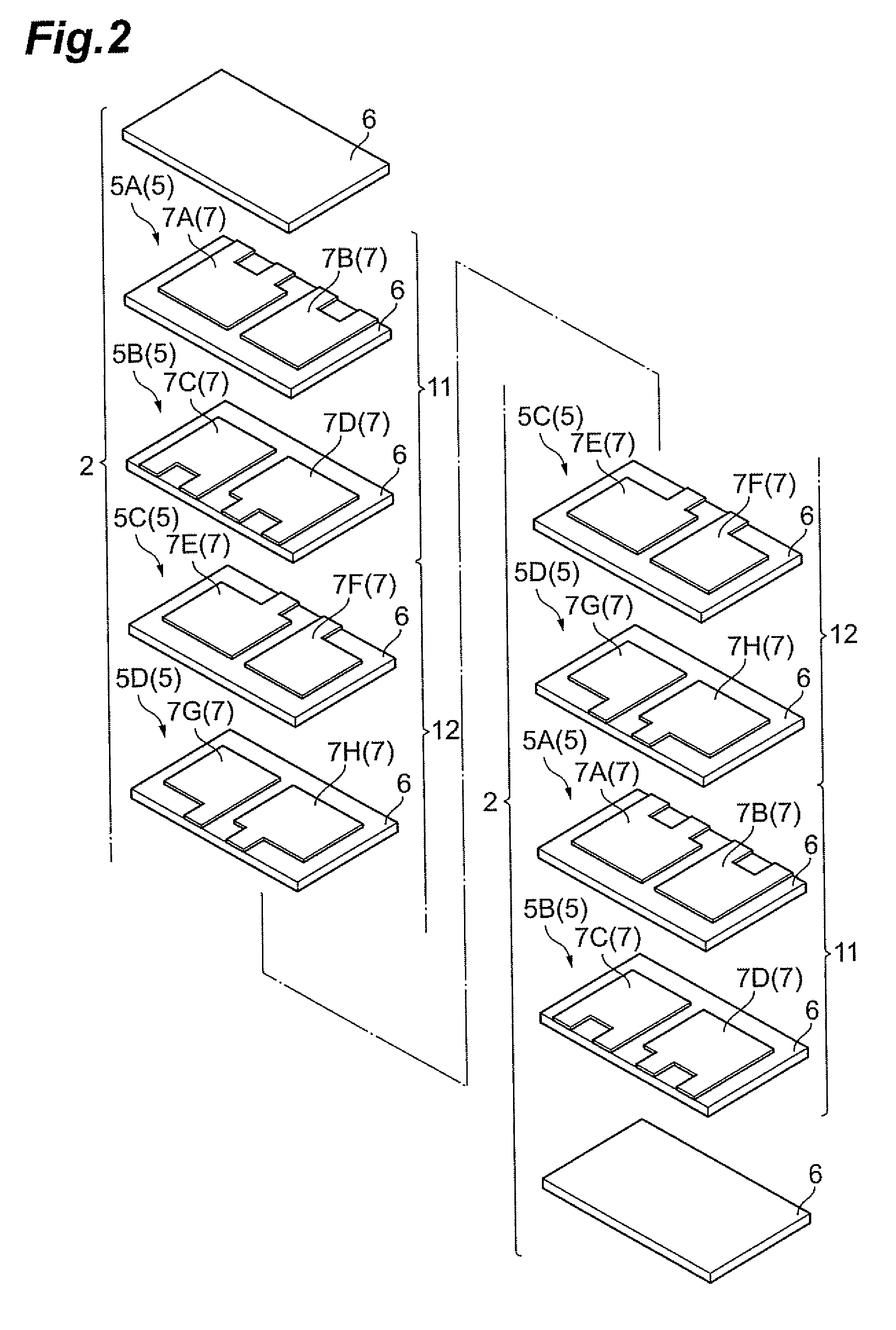

Multilayer capacitor array having terminal conductor, to which internal electrodes are connected in parallel, connected in series to external electrodes

ActiveUS8107214B2High ESRStress relief concentrationFixed capacitor electrodesFixed capacitor dielectricStress concentrationCapacitance

A multilayer capacitor array achieves a high ESR because terminal conductors to which internal electrodes in capacitance sections are connected in parallel are connected in series through internal electrodes in ESR control sections to external electrodes. Since in the multilayer capacitor array the internal electrodes extend as far as a boundary between capacitor element portions, electrostriction occurs in an entire laminate including a region near the boundary between the capacitor element portions, with application of a voltage from the outside. Therefore, concentration of stress due to electrostriction is avoided, so as to suppress occurrence of cracking or the like.

Owner:TDK CORPARATION

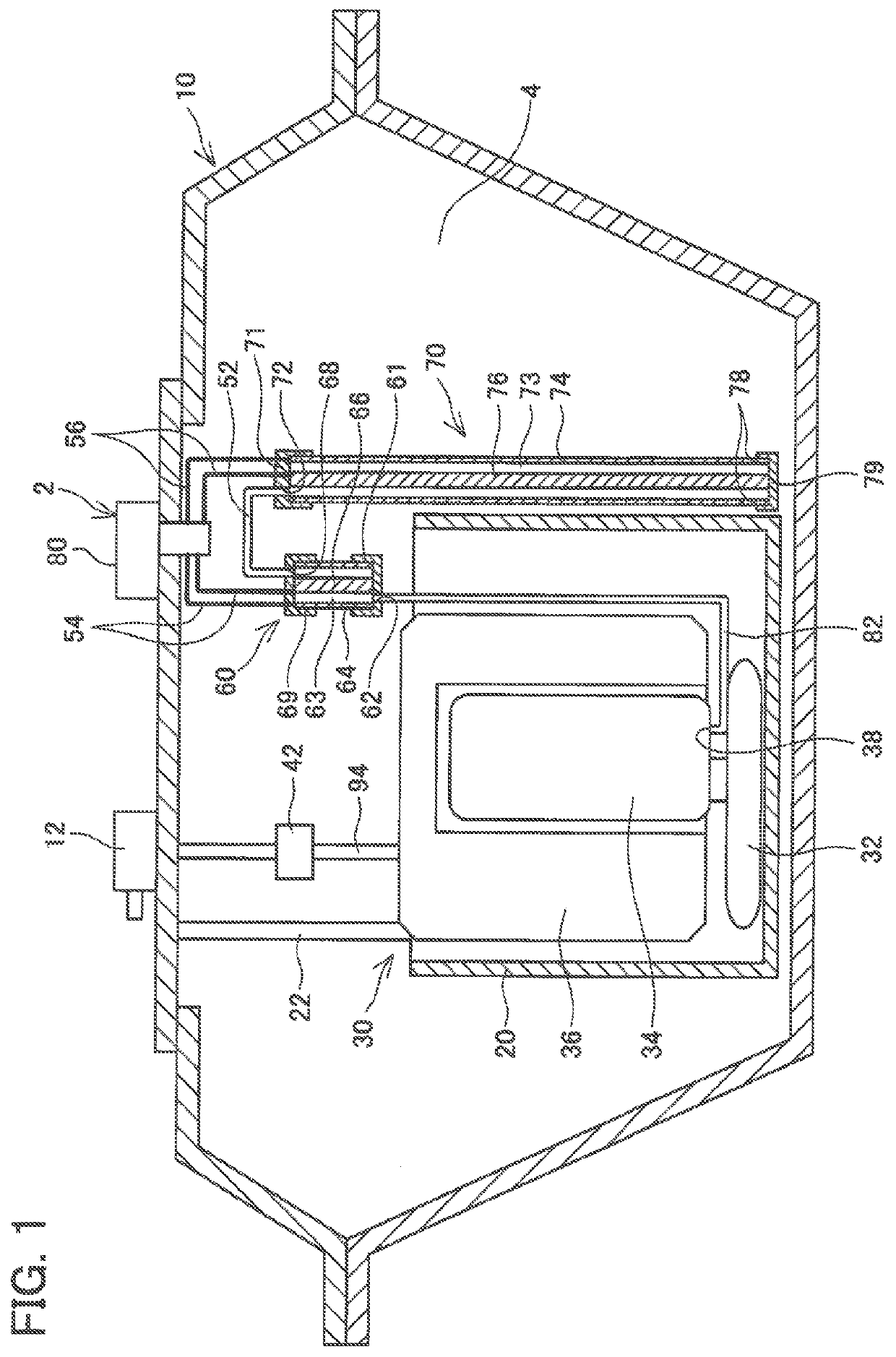

Liquid level measuring device

InactiveUS9383245B2Prevent capacitanceUnderstructuresLevel indicators by physical variable measurementEngineeringLevel measurement

A liquid level measuring device for measuring a liquid level of liquid stored in a container may comprise a discharging unit, a first storing space, and an electrode unit. The discharging unit may be configured to discharge the liquid compressed by a pump. The pump may be configured to suck the liquid stored in the container and feed the liquid toward a liquid usage device by pressure. The first storing space may be located in the container and configured to accept the liquid discharged from the discharging unit. The electrode unit may be disposed in the first storing space and comprising a first pair of electrodes configured to measure the liquid level of the liquid within the first storing space. The electrode unit may compose at least a part of a wall surface defining the first storing space.

Owner:AISAN IND CO LTD

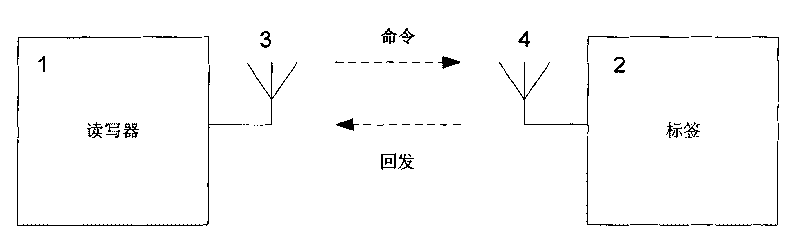

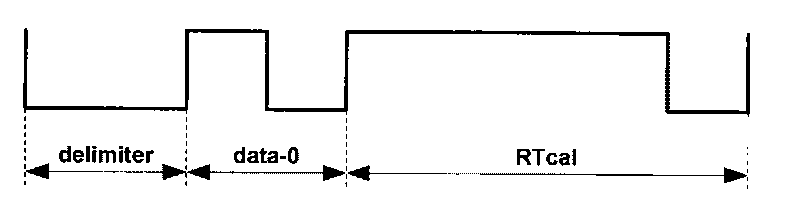

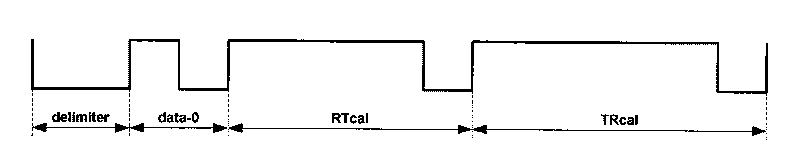

Radio frequency identification tag and method for calibrating clock signals

ActiveCN101727601AControl power consumptionIncrease reading and writing distancePulse automatic controlSensing record carriersElectricityReader writer

The invention provides a radio frequency identification (RFID) tag circuit and method for calibrating clock signals. An RFID tag circuit counts the specific duration signal emitted by a reader-writer, adjusts the clock calibration bit segment according to the counting results and writes the clock calibration bit segment into a nonvolatile memory of the tag. During next electrifying, the tag needs not to calibrate the clock again and only needs to read the clock calibration bit segment from the nonvolatile memory and adopts the clock calibration bit segment to control the circuit of an oscillator of the tag to obtain accurate clock signals. The invention ensures the clock signals generated by the tag circuit to meet the requirement of RFID protocol, correctly decodes the data sent by the reader-writer to the tag, correctly posts data back to the reader-writer, simultaneously controls the power consumption of the tag and enlarges the read-write distance of the tag.

Owner:SHANGHAI FUDAN MICROELECTRONICS GROUP

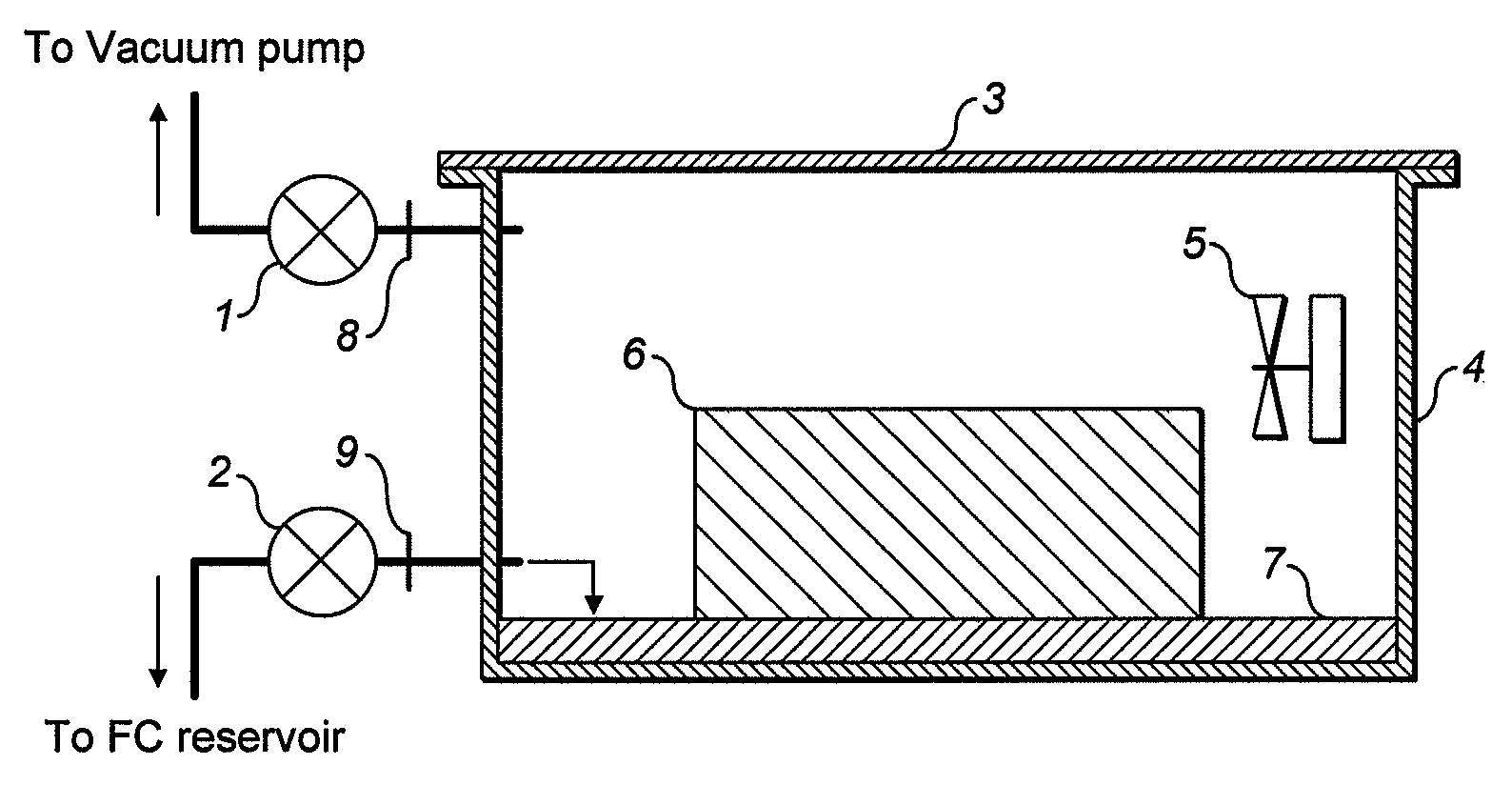

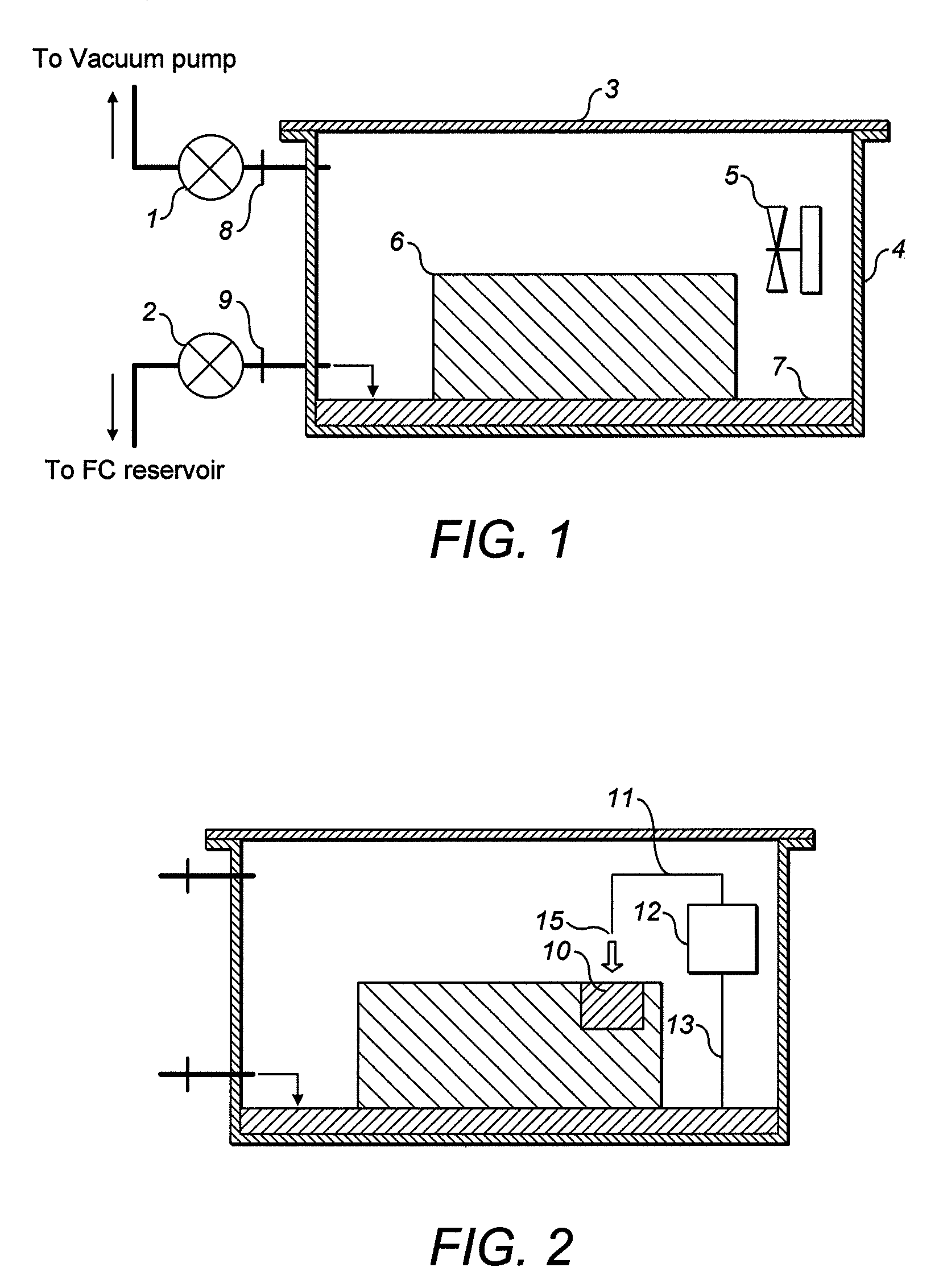

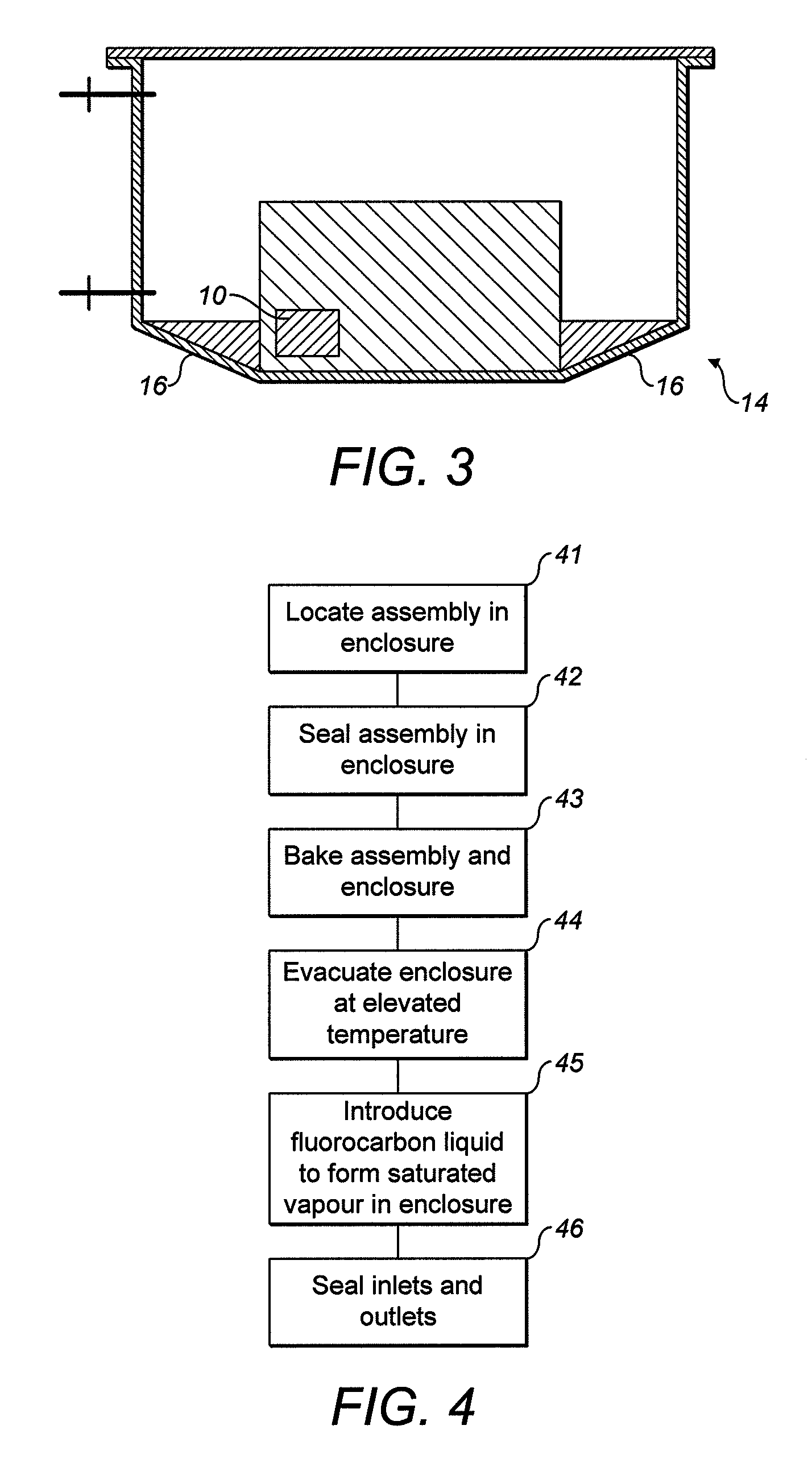

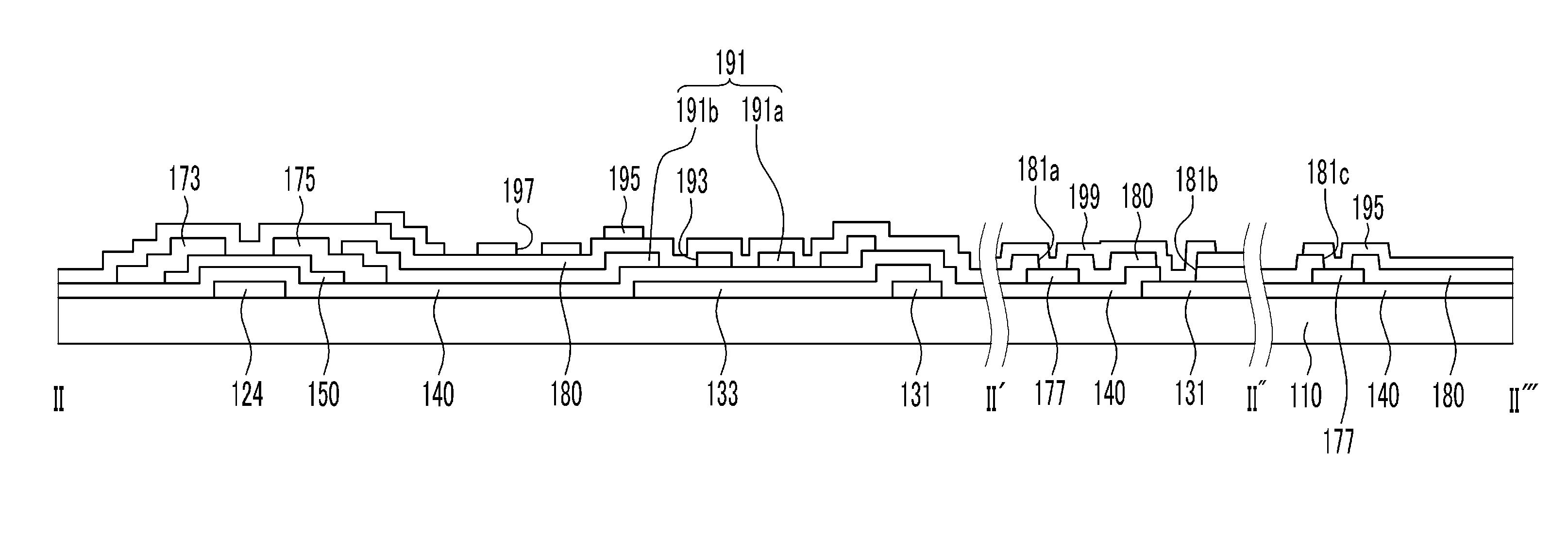

Sealed and cooled enclosure with voltage isolation

InactiveUS7923630B2Electrical isolation is improvedLow dielectric constantLiquid organic insulatorsSubstation/switching arrangement cooling/ventilationElectricityCapacitance

An enclosure (4) for electrical apparatus (6) has a sealable outlet (8) for partially evacuating the enclosure and a sealable inlet (9)for partially filling the enclosure with a liquid (7) having a vapor pressure at operating temperatures of the apparatus suitable to enhance electrical isolation of the electrical apparatus and suitable to provide convective cooling of the electrical apparatus. The vapor preferably provides a voltage hold-off sufficiently high for operating voltages of the electrical apparatus and has a relative permittivity sufficiently low to prevent stray capacitance in the electrical apparatus above a predetermined limit.

Owner:E2V TECH (UK) LTD

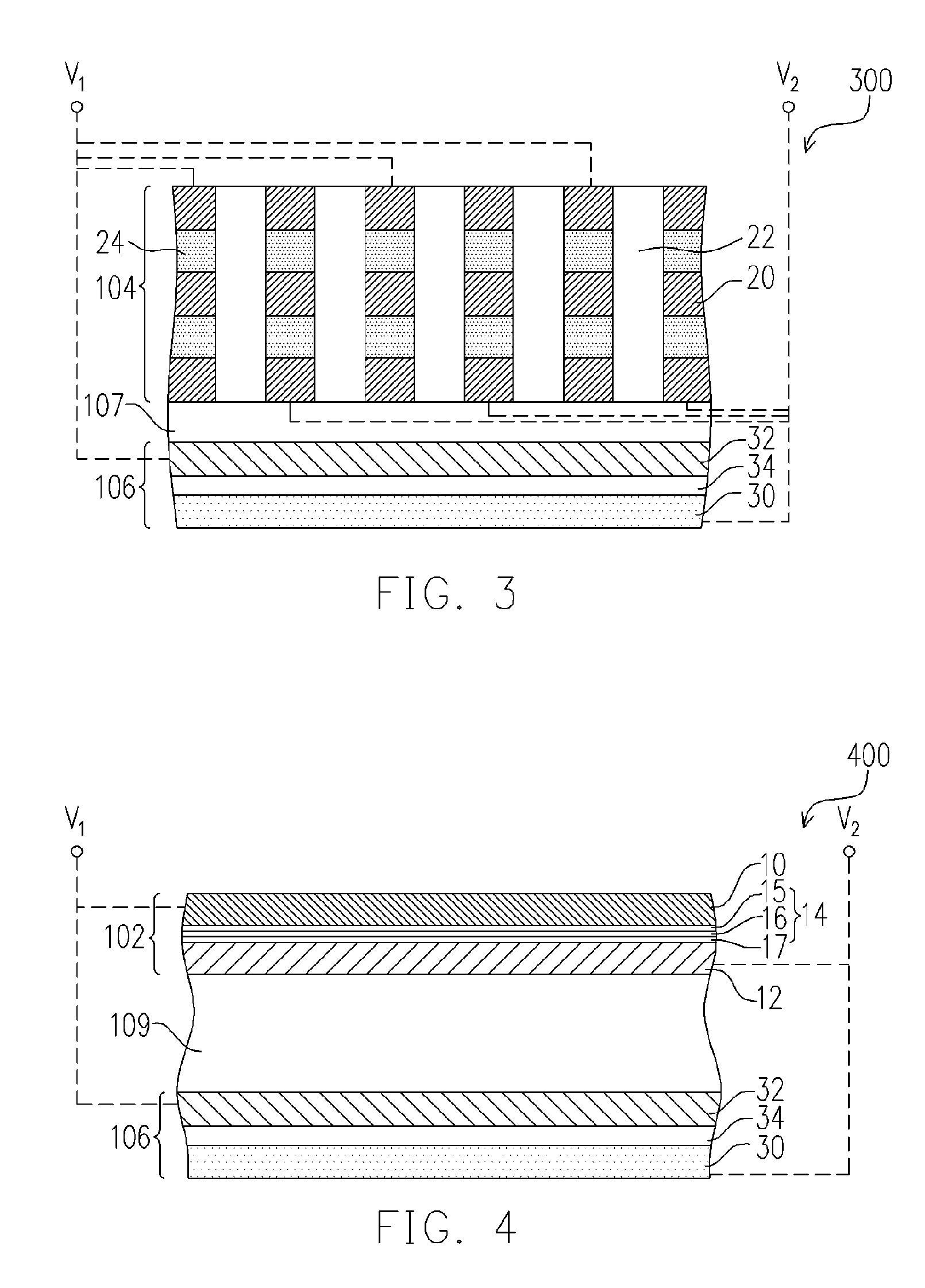

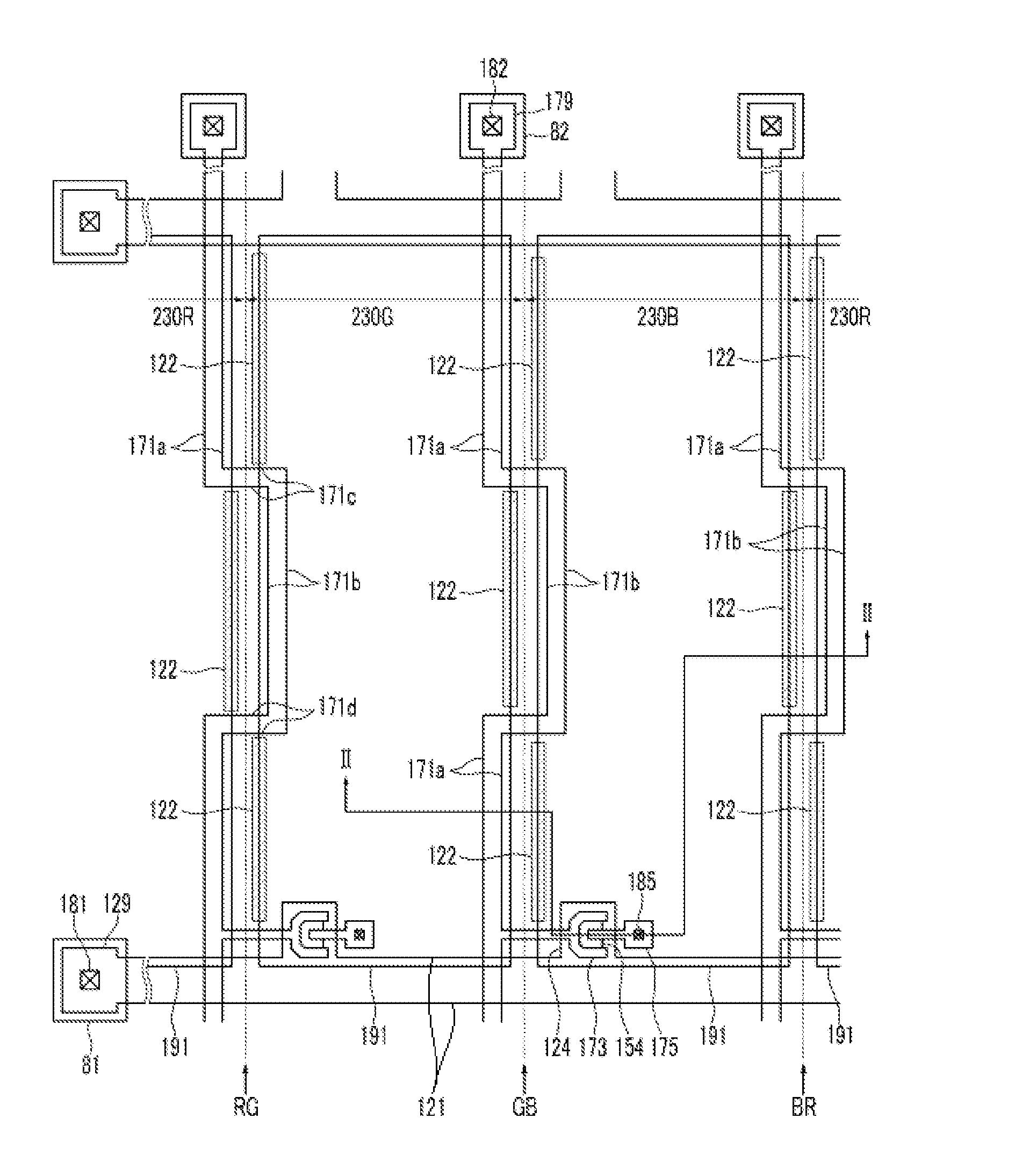

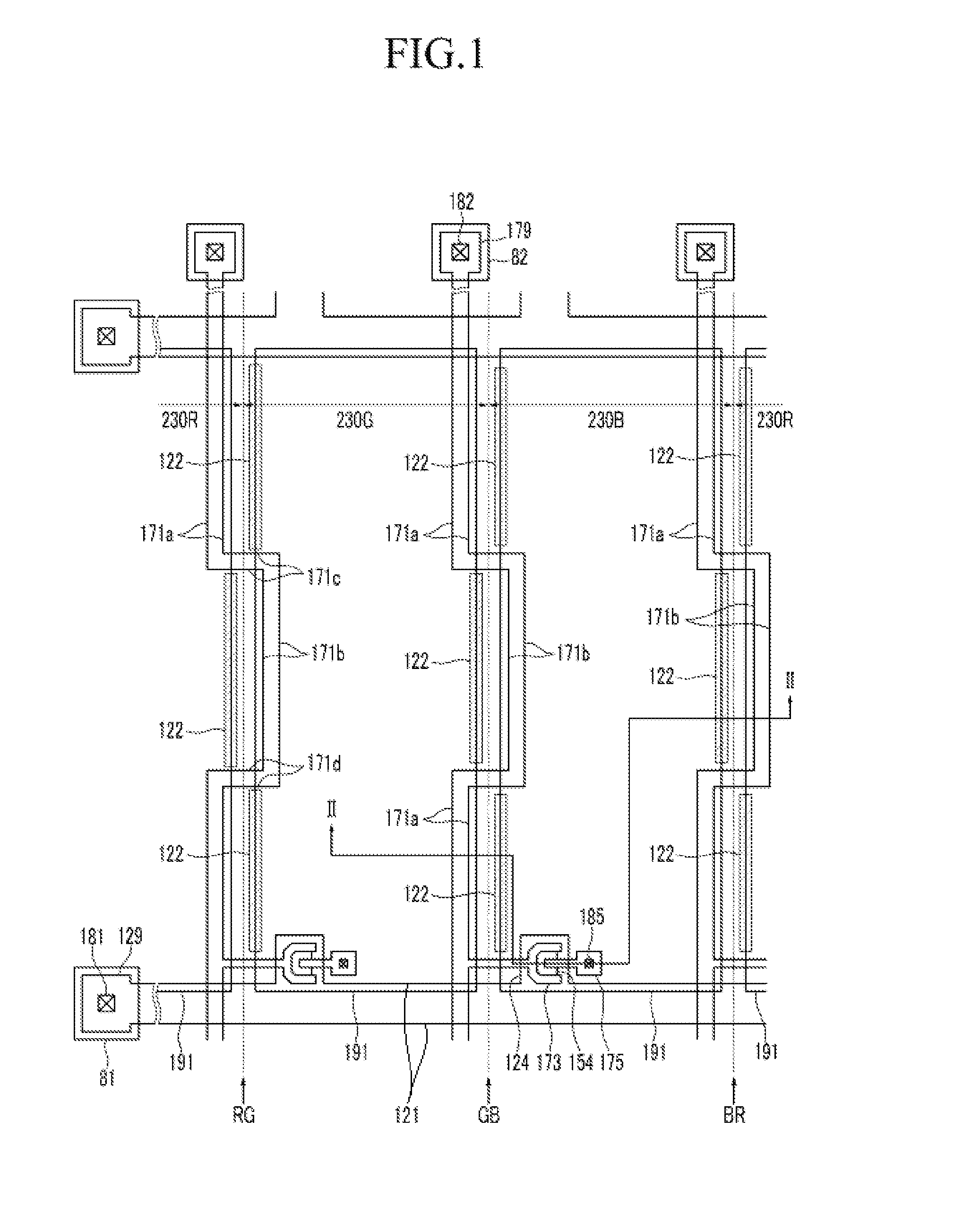

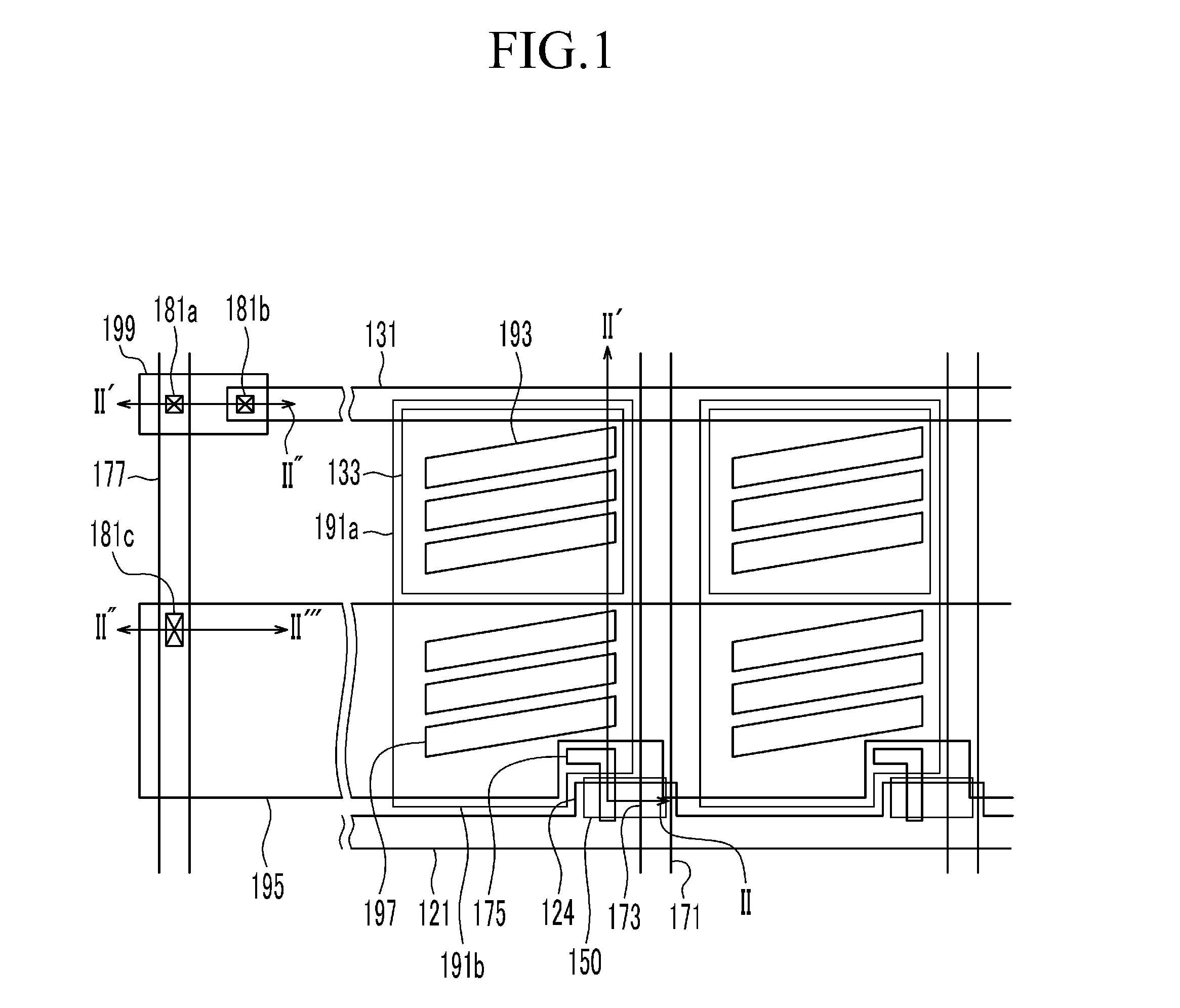

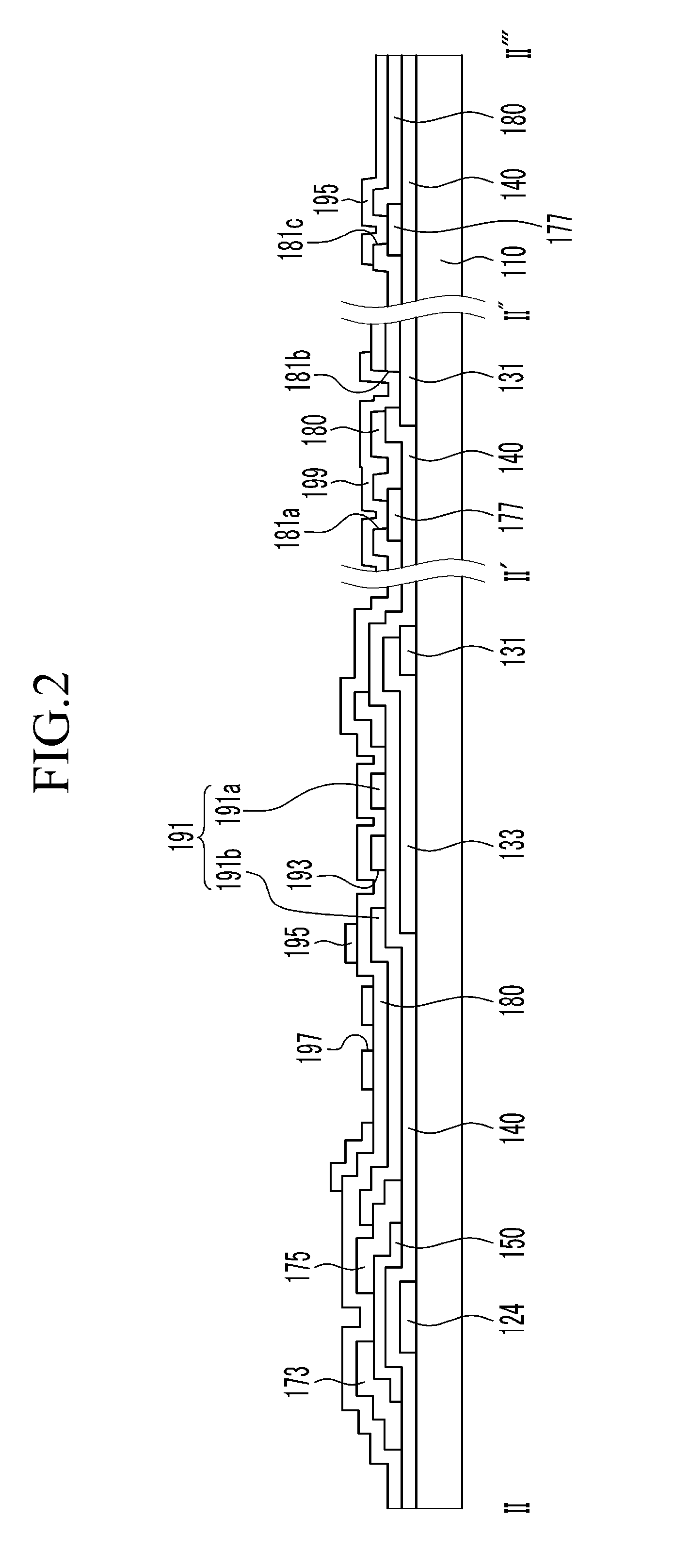

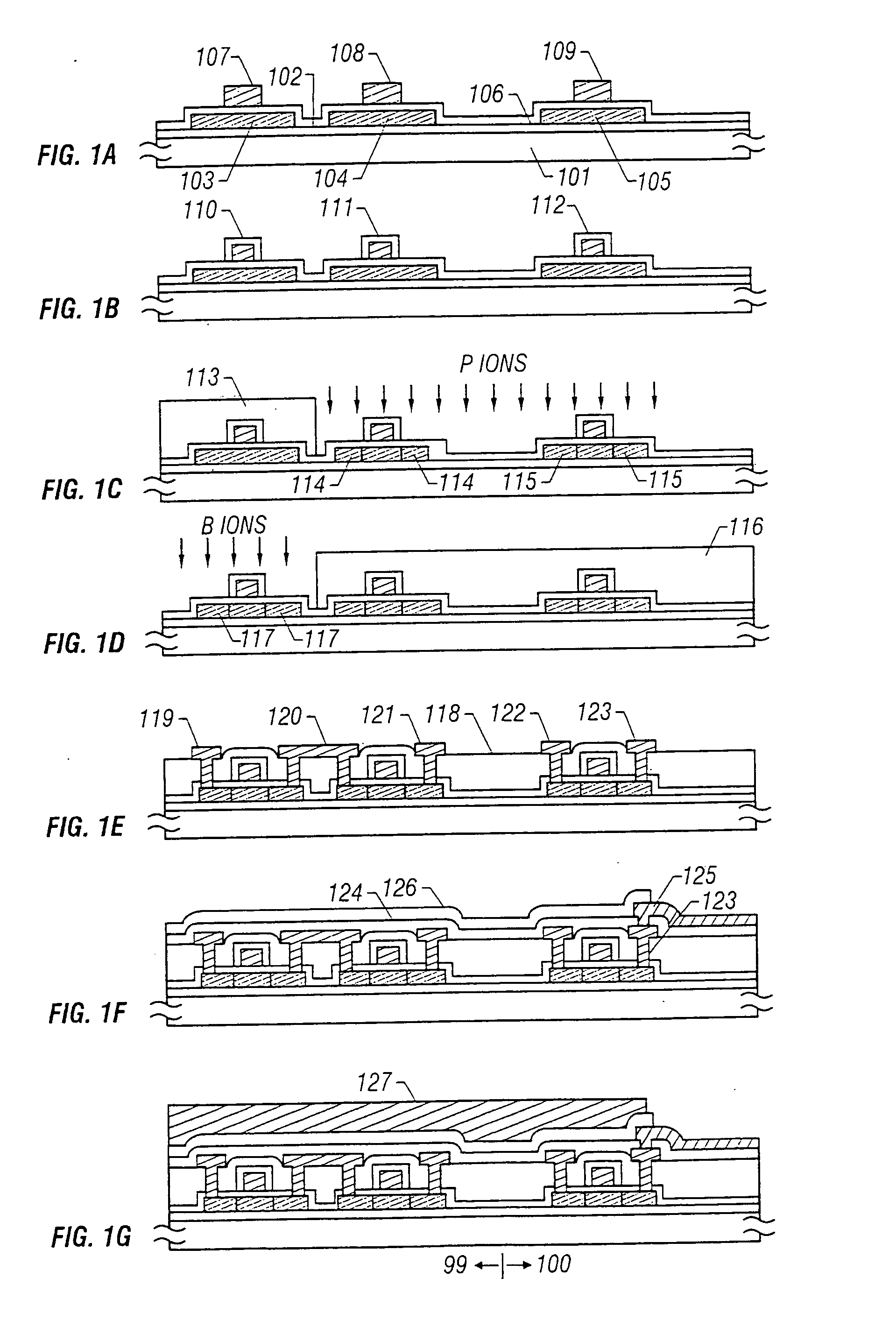

Thin film transistor array panel and the method for manufacturing thereof

ActiveUS20120104392A1Prevent difference of capacitancePrevent capacitanceSolid-state devicesNon-linear opticsEngineeringTransistor

Provided is a thin film transistor array panel that includes: a substrate; a gate line and a data line formed on the substrate and at least partially defining a pixel area; a thin film transistor connected to the gate line and the data line; a pixel electrode connected to the thin film transistor and formed in the pixel area; a first common electrode formed under the pixel electrode; a second common electrode formed on the pixel electrode. The pixel area includes an upper pixel area and a lower pixel area, the first common electrode is formed in the upper pixel area, and the second common electrode is formed in the lower pixel area. The pixel electrode includes an upper pixel electrode formed in the upper pixel area and a lower pixel electrode formed in the lower pixel area.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

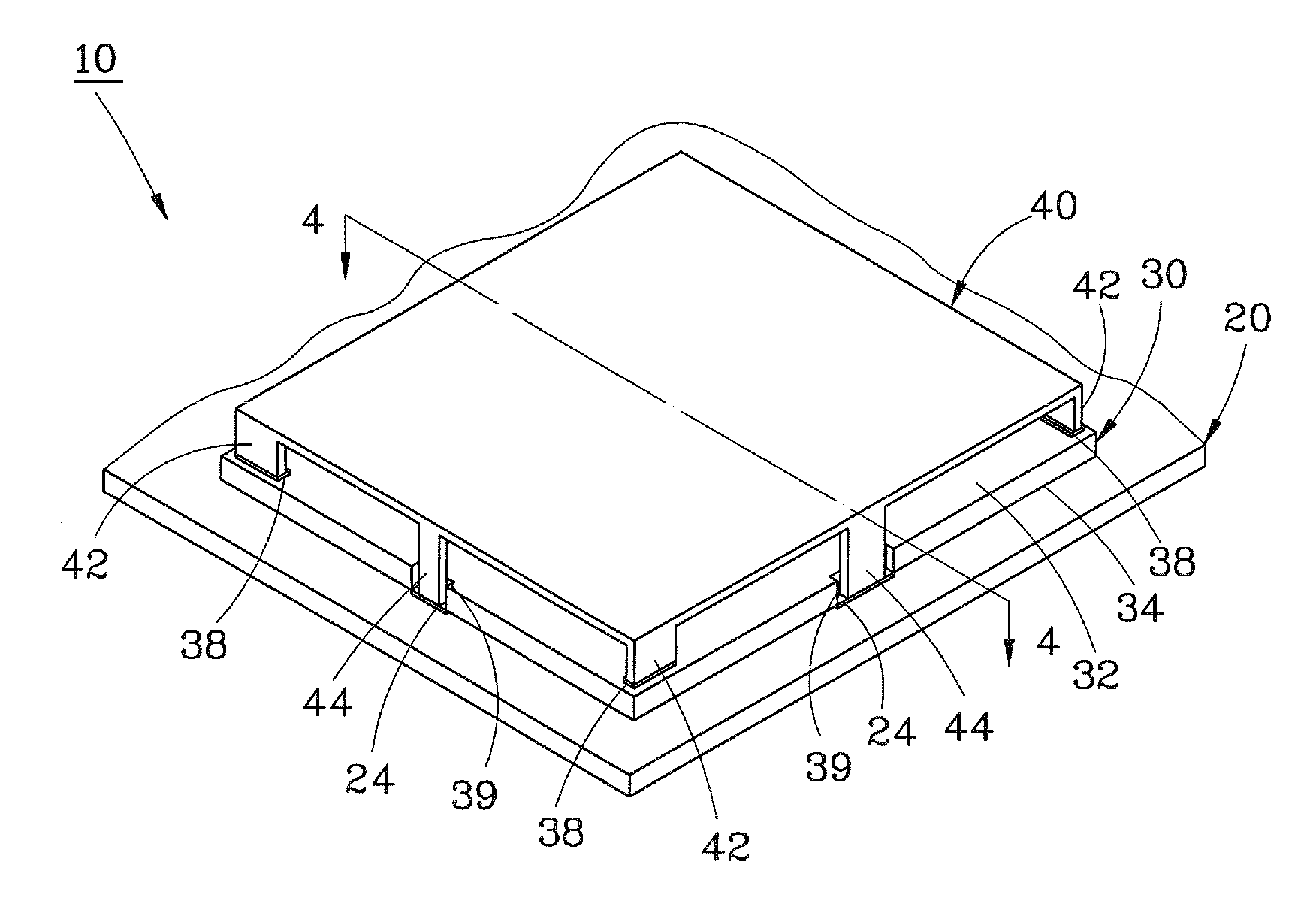

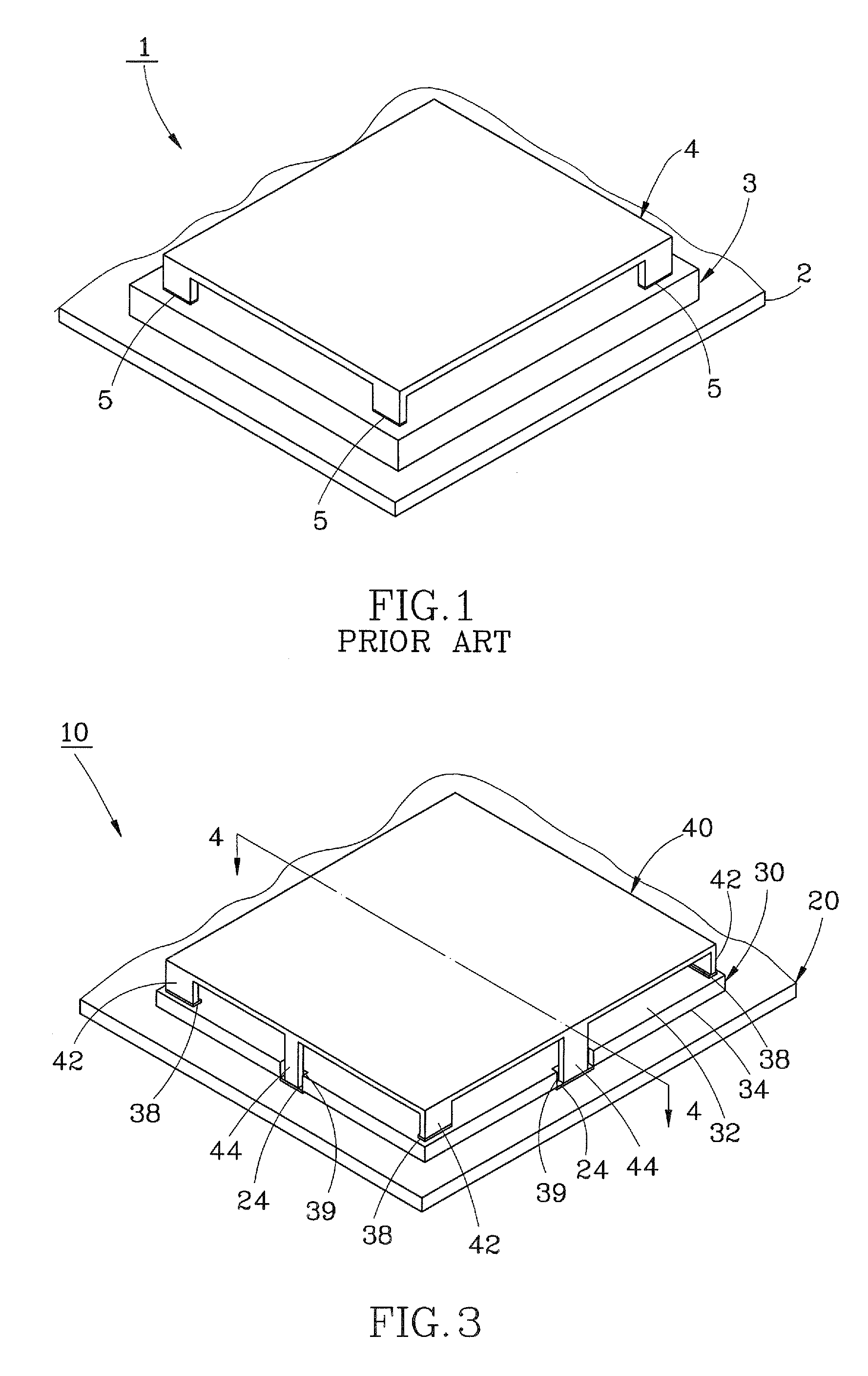

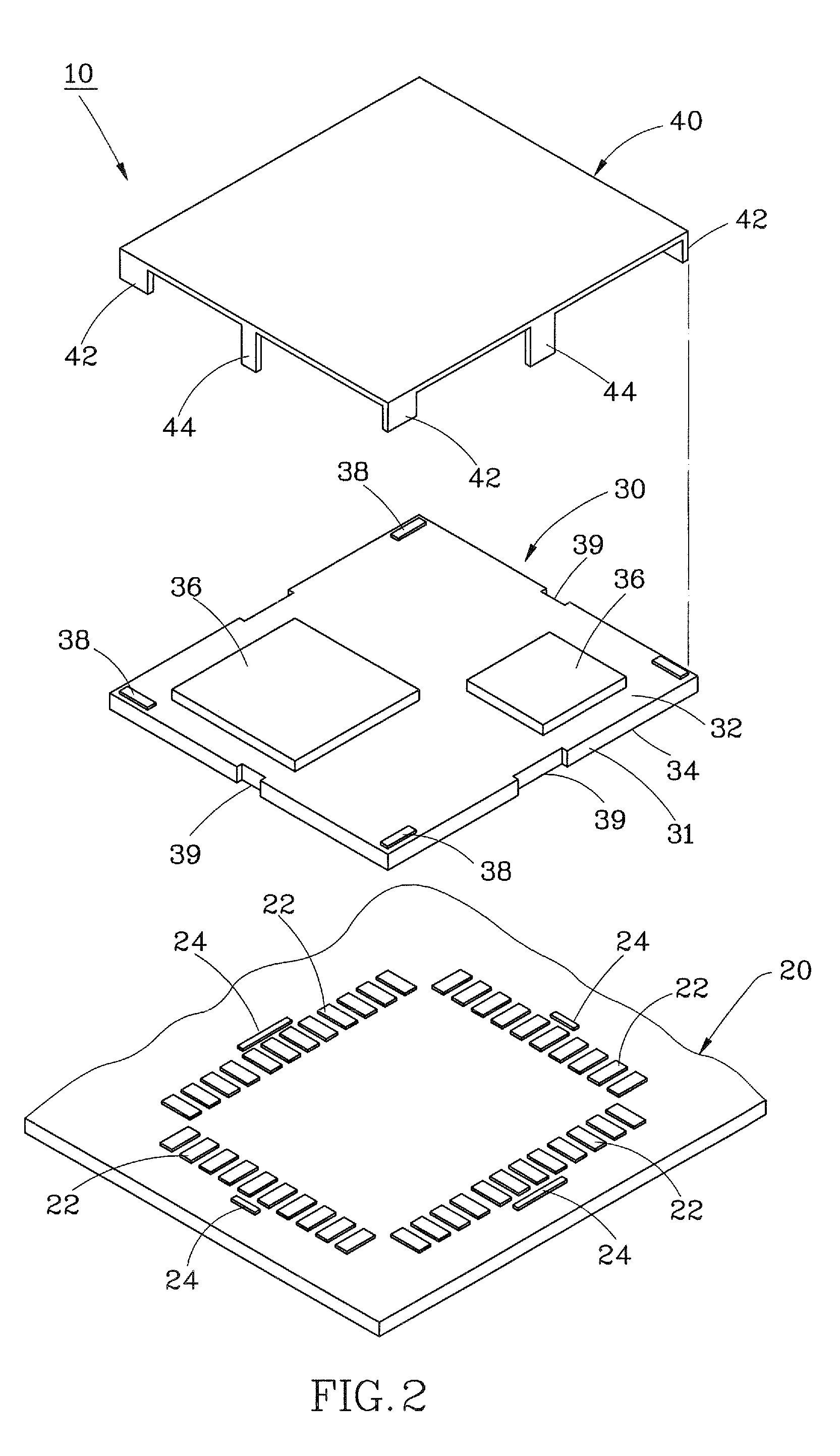

Wireless communication nodule assembly

InactiveUS20080291654A1Good groundingMinimizing electromagnetic interferenceLocalised screeningPrinted circuit aspectsEngineeringWireless

A wireless communication module assembly includes a main board having a top surface on which a plurality of grounding pads are provided, a circuit board unit, and a metal cap. The circuit board unit has a bottom surface electrically mounted on the top surface of the main board, a top surface with a plurality of grounding pads, and a plurality of notches corresponding to the grounding pads of the main board. The metal cap covers the circuit board unit and has first mounting legs respectively and electrically connected with the grounding pads of the circuit board unit, and second mounting legs respectively passing through the notches of the circuit board unit and electrically connected with the grounding pads of the main board.

Owner:UNIVERSAL SCI IND CO LTD

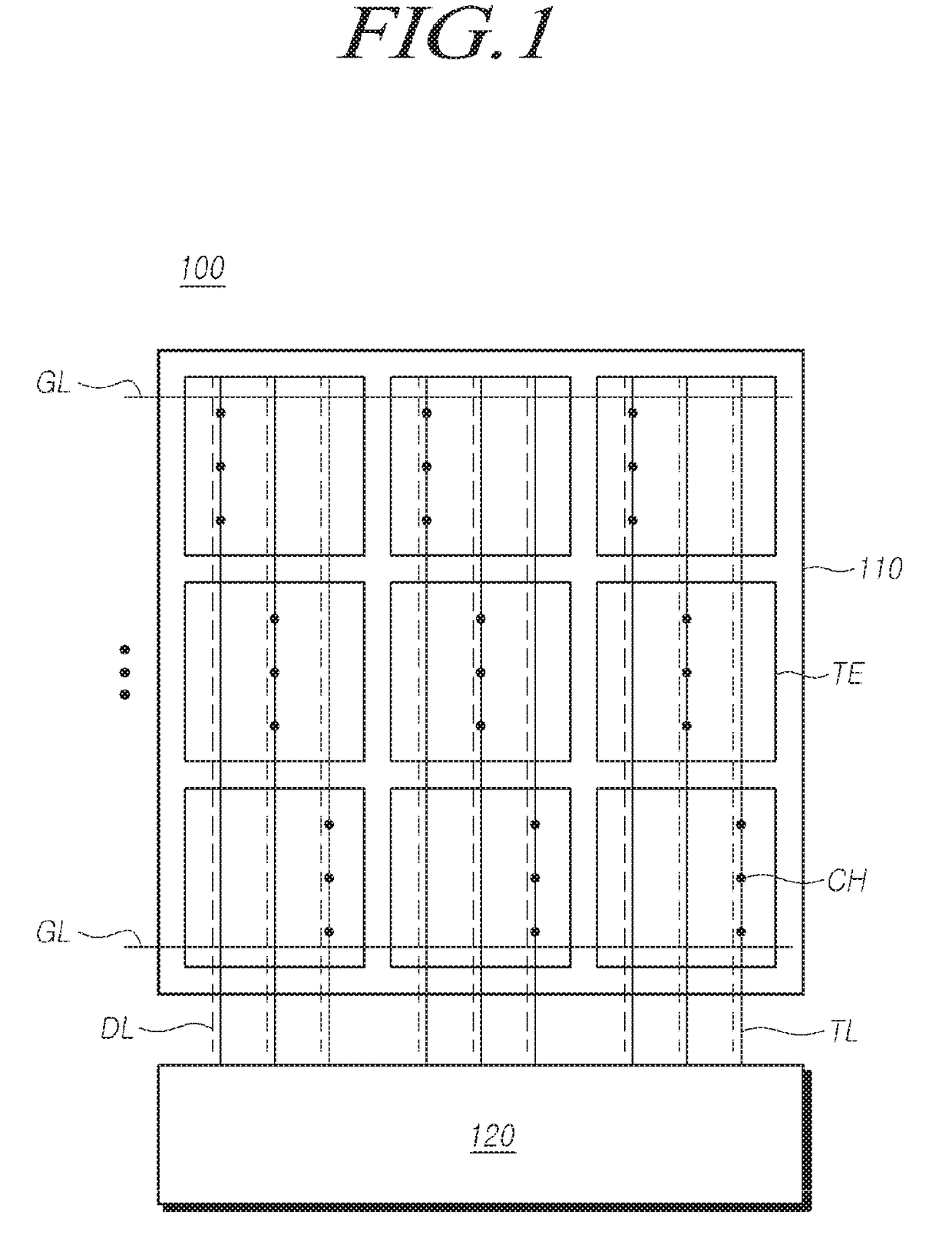

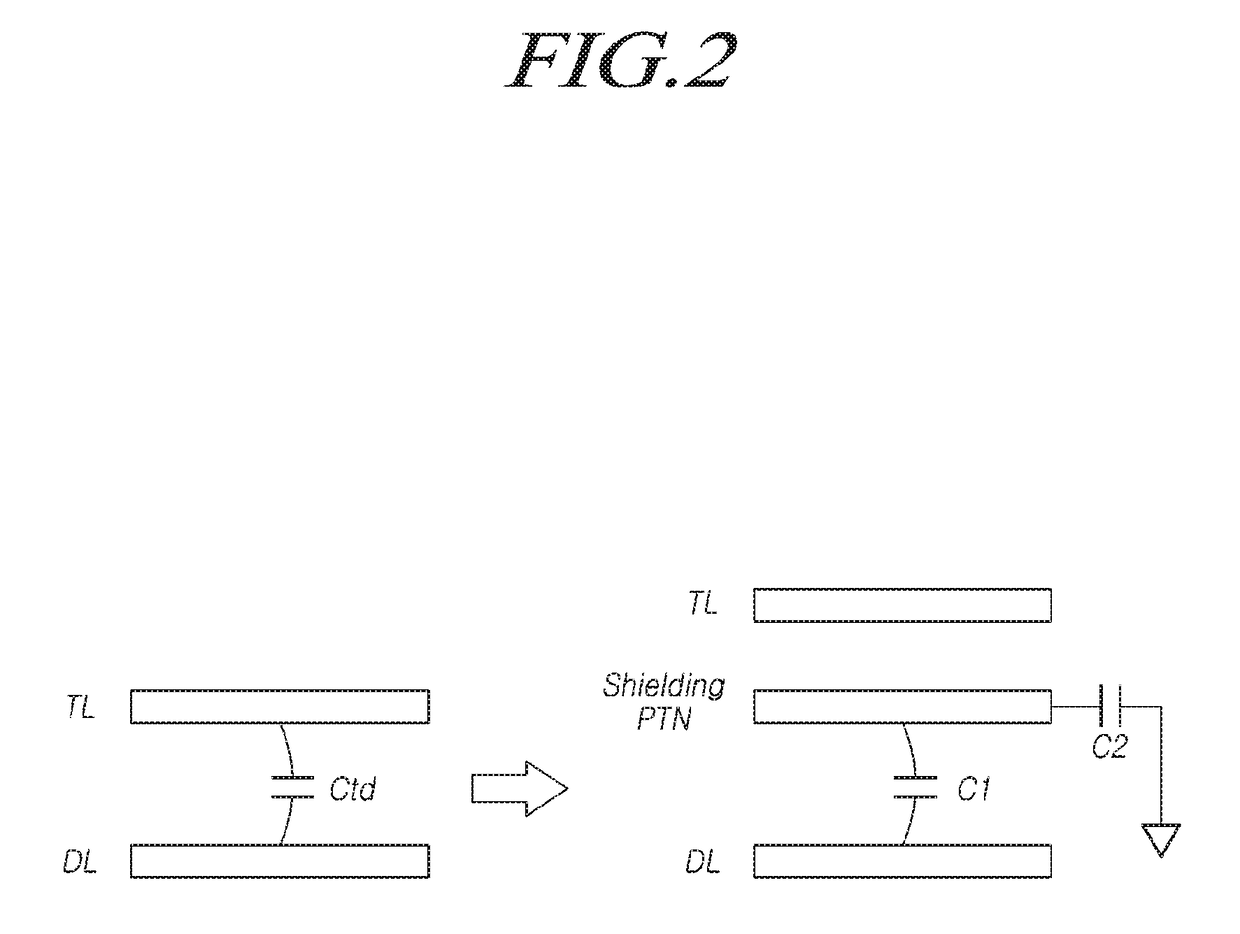

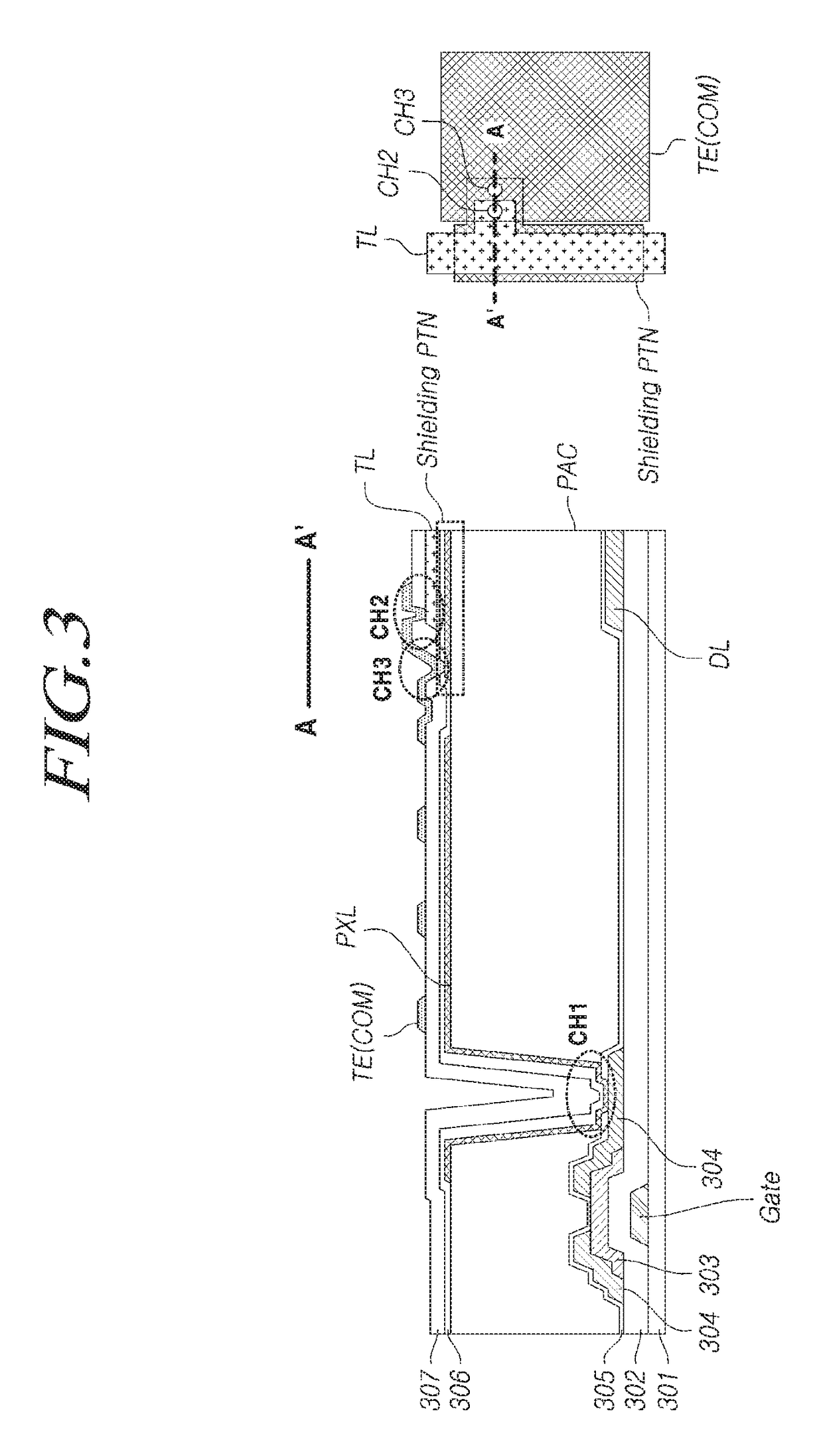

Touch display panel and touch display device

ActiveUS20190079623A1Avoid formingLarge capacitanceStatic indicating devicesNon-linear opticsCapacitanceTouch Senses

Embodiments disclosed herein relate to a touch display panel and a touch display device. By arranging a shielding structure, which is connected to a touch electrode in a region where a touch line and a data line overlap each other or is applied with a shielding signal corresponding to a touch driving signal from an outside circuit, between the touch line and the data line, it is possible to prevent direct capacitance from being formed between the touch line and the data line, and to prevent the capacitance formed due to the data line from causing noise on a touch sensing signal. In addition, by arranging a touch load reduction layer between the shielding structure and the touch line, it is also possible to reduce the capacitance between the touch line and the data line arranged in the horizontal direction, thereby improving touch sensing performance.

Owner:LG DISPLAY CO LTD

Film capacitor

ActiveUS20090185326A1Improve pressure resistancePrevent capacitanceFixed capacitor electrodesFixed capacitor dielectricFloating electrodeFilm capacitor

A film capacitor comprises a wound body, a first terminal part electrically connected to one end of the wound body, and a second terminal part electrically connected to the other end of the wound body. The wound body is structured by winding into a laminate a first film laminate formed of a laminate of dielectric films and having therein a floating electrode and a second film laminate formed of a laminate of first and second metal films sandwiching the first film laminate and dielectric films and having therein a floating electrode. Each of the floating electrodes is composed of integrated small electrodes independent of each other.

Owner:SOSHIN ELECTRIC

Display device having resin layer

InactiveUS20050206797A1Reduce widthImprove fitting accuracyNon-linear opticsSemiconductor devicesDisplay deviceOptoelectronics

A display device is disclosed. The display device has a first substrate having a thin film transistor connected to a pixel electrode. Further, the display device has a second substrate opposed to the first substrate and having a resin black matrix.

Owner:SEMICON ENERGY LAB CO LTD

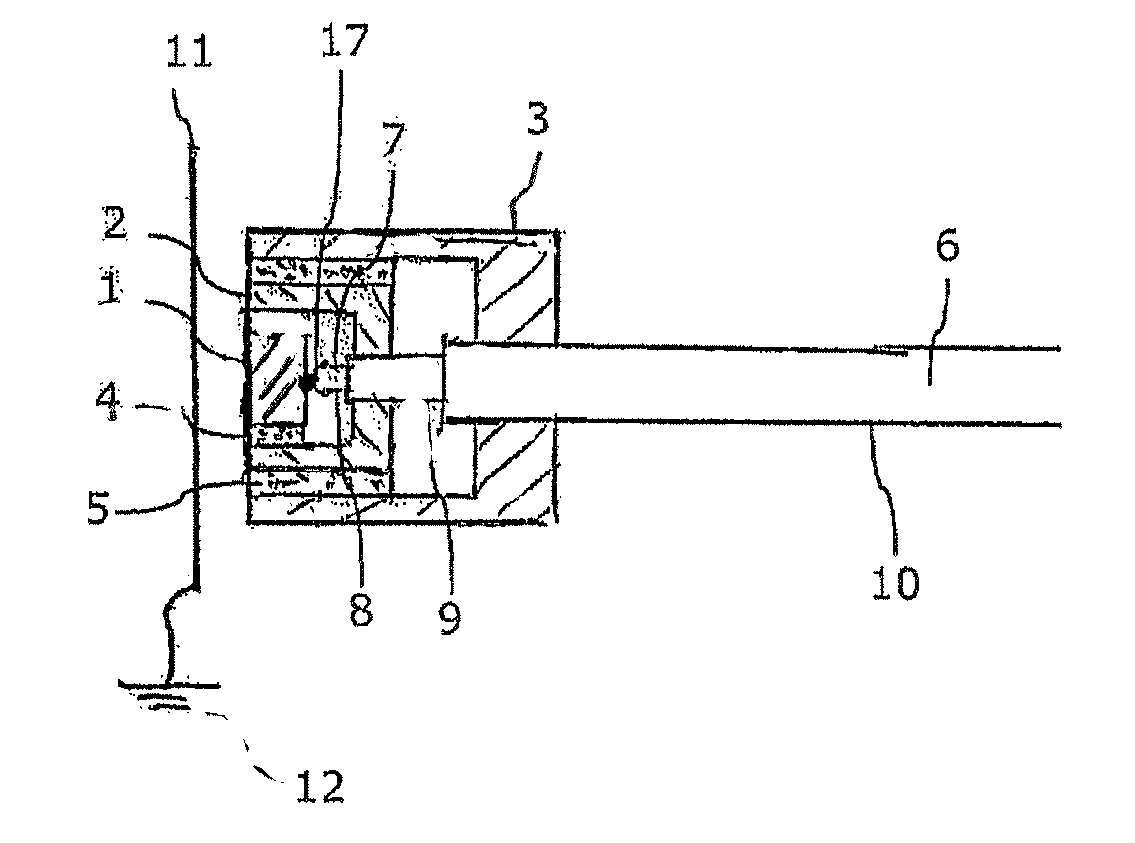

Device for measuring a fluid meniscus

ActiveUS20110204902A1Accurately measuring geometryAccurate measurementCapacitance measurementsElectric/magnetic contours/curvatures measurementsCapacitanceMultiplexer

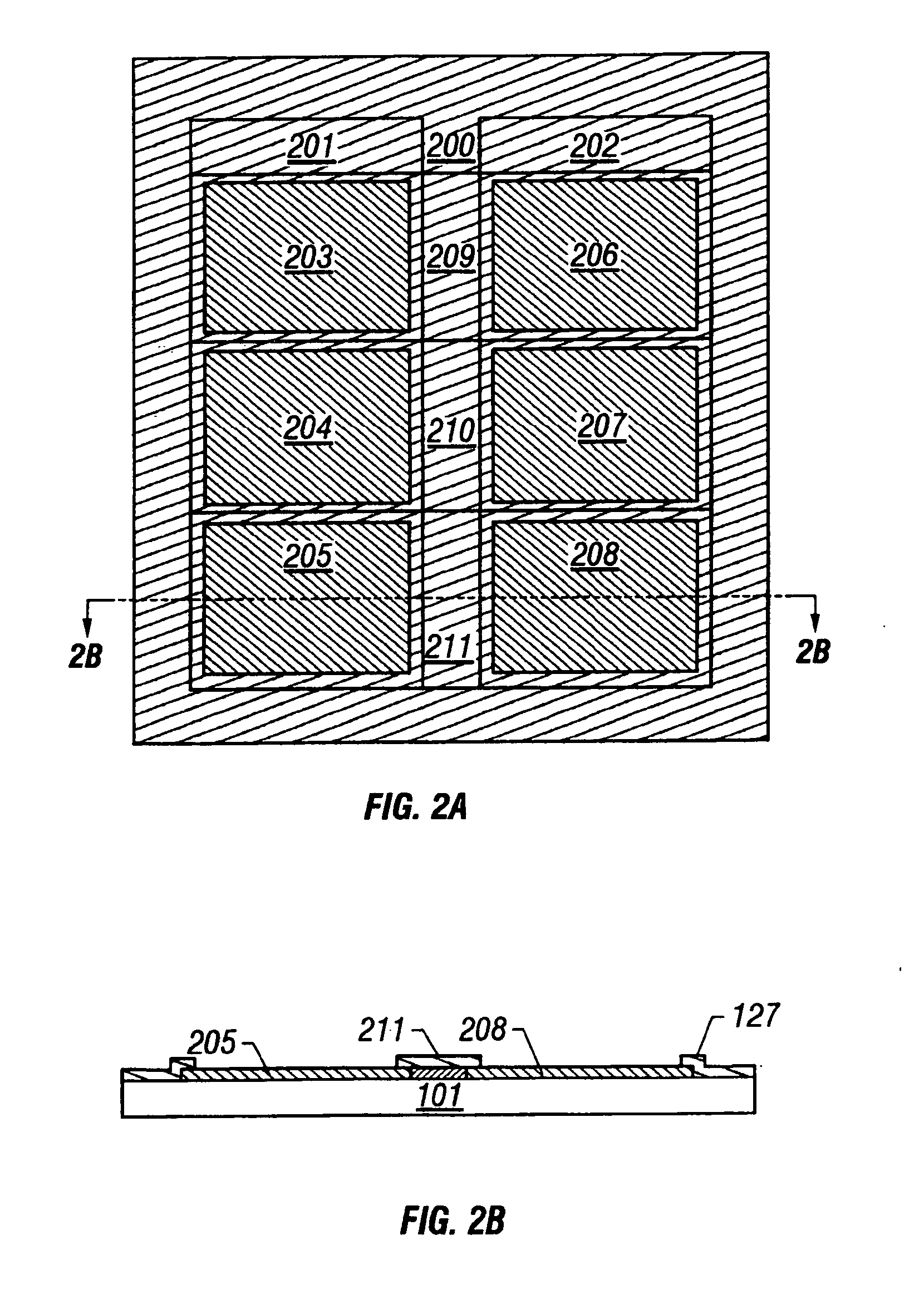

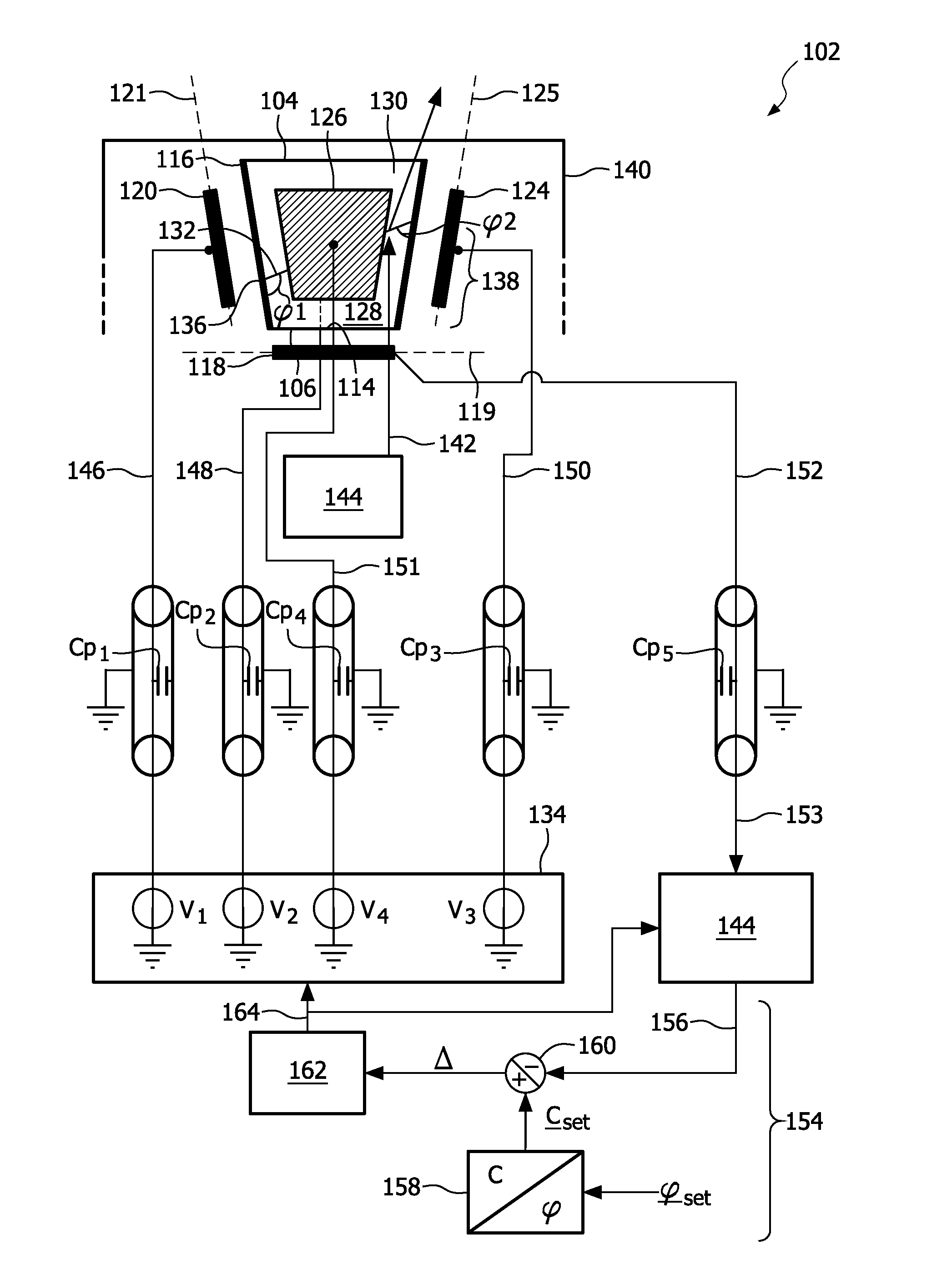

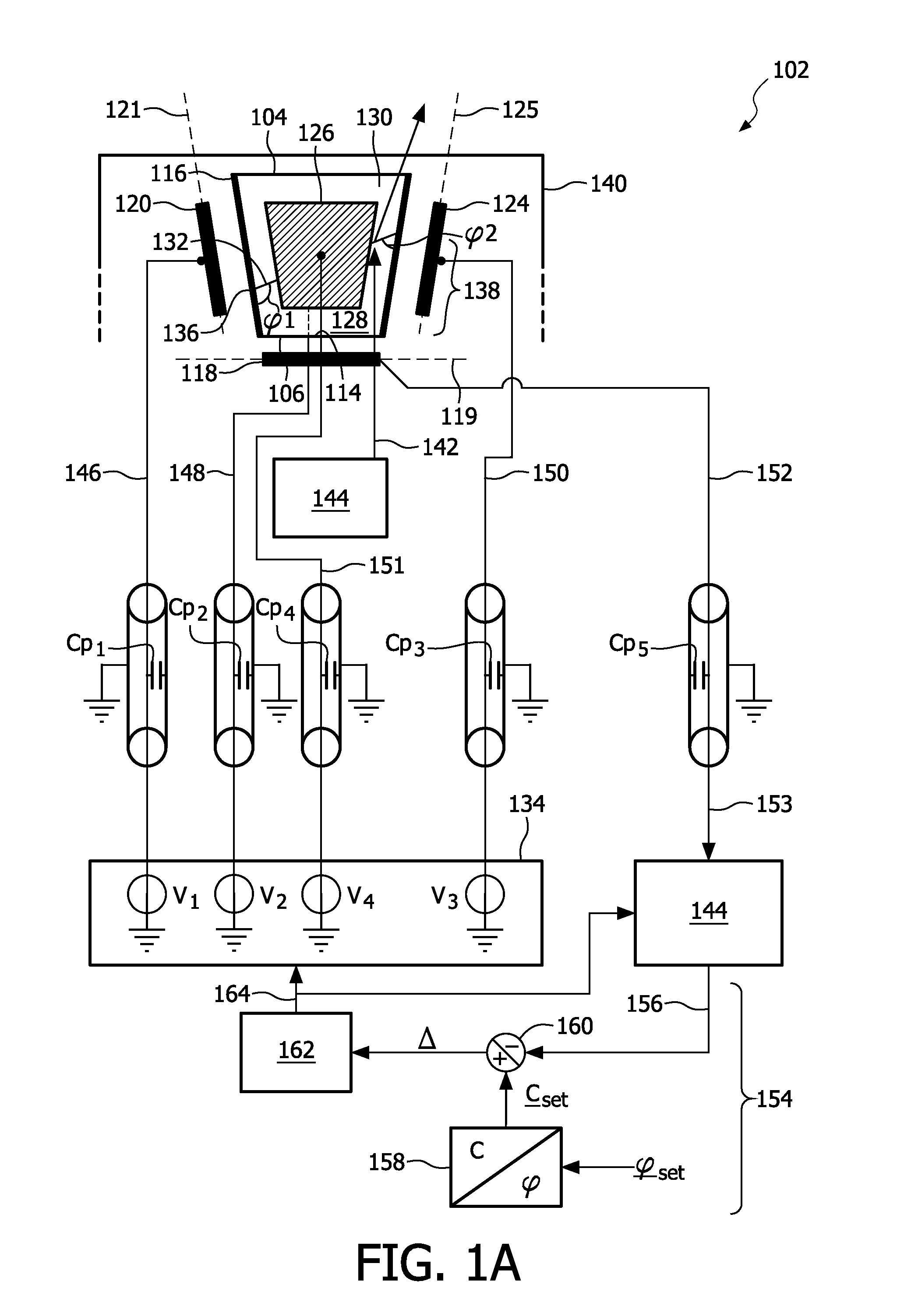

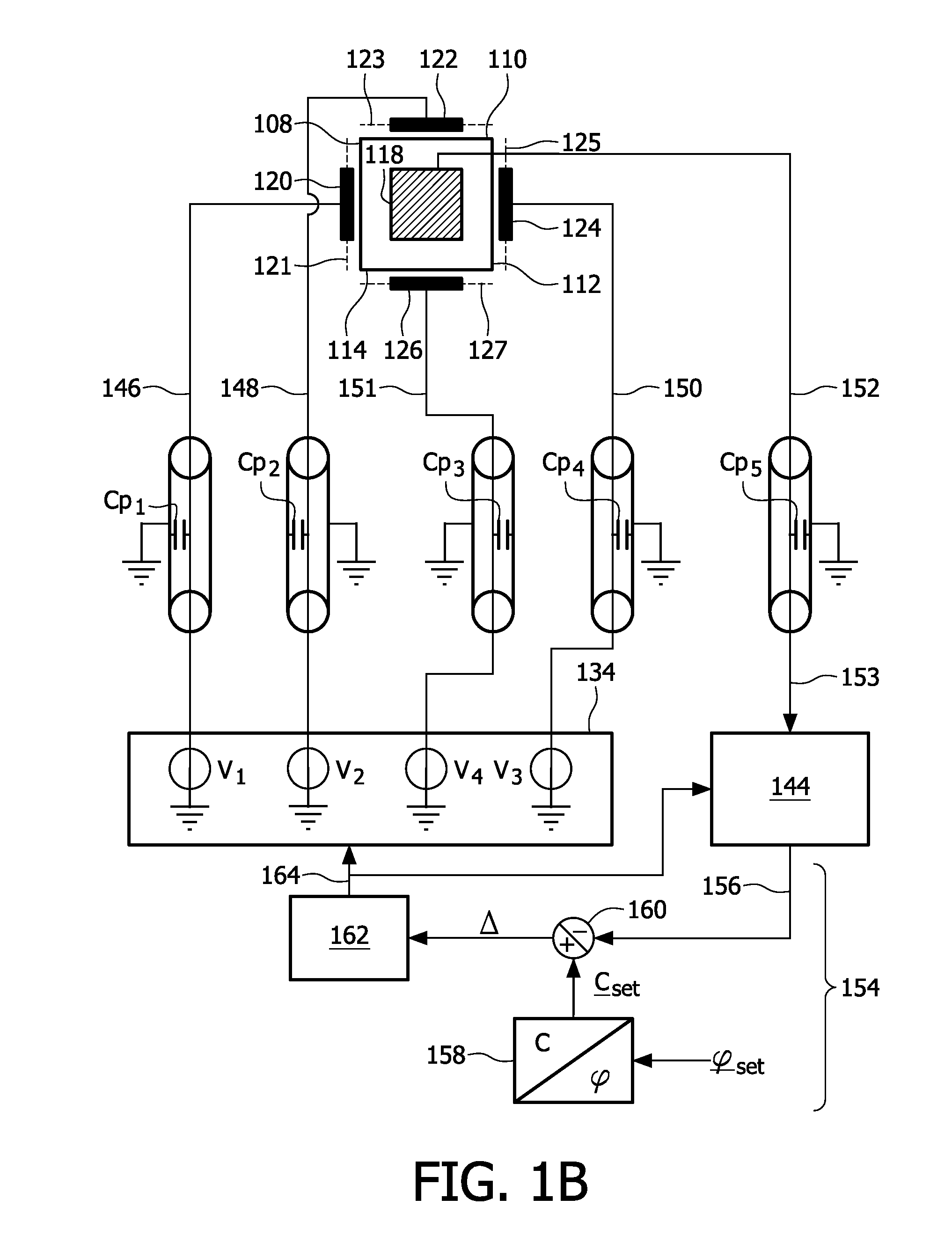

The invention relates to a device (102) arranged for measuring a geometry of a fluid meniscus (132). The device comprises a fluid chamber (104) storing a first electrically conductive fluid (128) and a second electrically insulating fluid (324). The fluids are mutually immiscible and define a fluid meniscus (132) in between them. Furthermore a main electrowetting electrode (118) and auxiliary electrowetting electrodes (120, 122, 124, 126) are provided for controlling the geometry of the fluid meniscus. Hereto a voltage source (134) for providing a voltage between the main electrowetting electrode and the auxiliary electrowetting electrodes is comprised, as well as a measurement circuit (144) for separately measuring capacitances between the main electrowetting electrode and at least two of the auxiliary electrowetting electrodes. For this purpose the measurement circuit comprises a multiplexer for demodulating a signal indicative for said capacitances. The invention further relates to a method for measuring a fluid meniscus.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Thin film transistor array substrate and manufacturing method thereof

ActiveUS8450736B2Prevent capacitancePreventing deterioration of the oxide semiconductor layerTransistorSolid-state devicesEngineeringSemiconductor

A thin film transistor (TFT) array substrate and a manufacturing method thereof are provided. The TFT array substrate may include a gate line disposed on a substrate and including a gate line and a gate electrode, an oxide semiconductor layer pattern disposed on the gate electrode, a data line disposed on the oxide semiconductor layer pattern and including a source electrode and a drain electrode of a thin film transistor (TFT) together with the gate electrode, and a data line extending in a direction intersecting the gate line, and etch stop patterns disposed at an area where the TFT is formed between the source / drain electrodes and the oxide semiconductor layer pattern and at an area where the gate line and the data line overlap each other between the gate line and the data line.

Owner:SAMSUNG DISPLAY CO LTD

Electro-optical device, method of manufacturing the same, and electronic apparatus

ActiveUS7388225B2Reduce and prevent portionReduction and minuteness in sizeSolid-state devicesSemiconductor/solid-state device manufacturingElectricityEngineering

Exemplary embodiments of the present invention include an electro-optical device including storage capacitors having excellent breakdown-voltage performance to function properly. Exemplary embodiments further include an electro-optical device including data lines, scanning lines, thin film transistors, and pixel electrodes formed on a substrate. The electro-optical device also includes storage capacitors composed of first electrodes electrically connected to the thin film transistors and the pixel electrodes, second electrodes that are arranged to face the first electrodes, and dielectric films arranged between the first electrodes and the second electrodes, and oxidation films obtained by oxidizing part or all of the surfaces of at least one of the first electrodes and the second electrodes.

Owner:SEIKO EPSON CORP