Reduced integrated circuit chip leakage and method of reducing leakage

A technology of integrated circuits and chips, applied in the field of reducing the power consumption of static random access memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

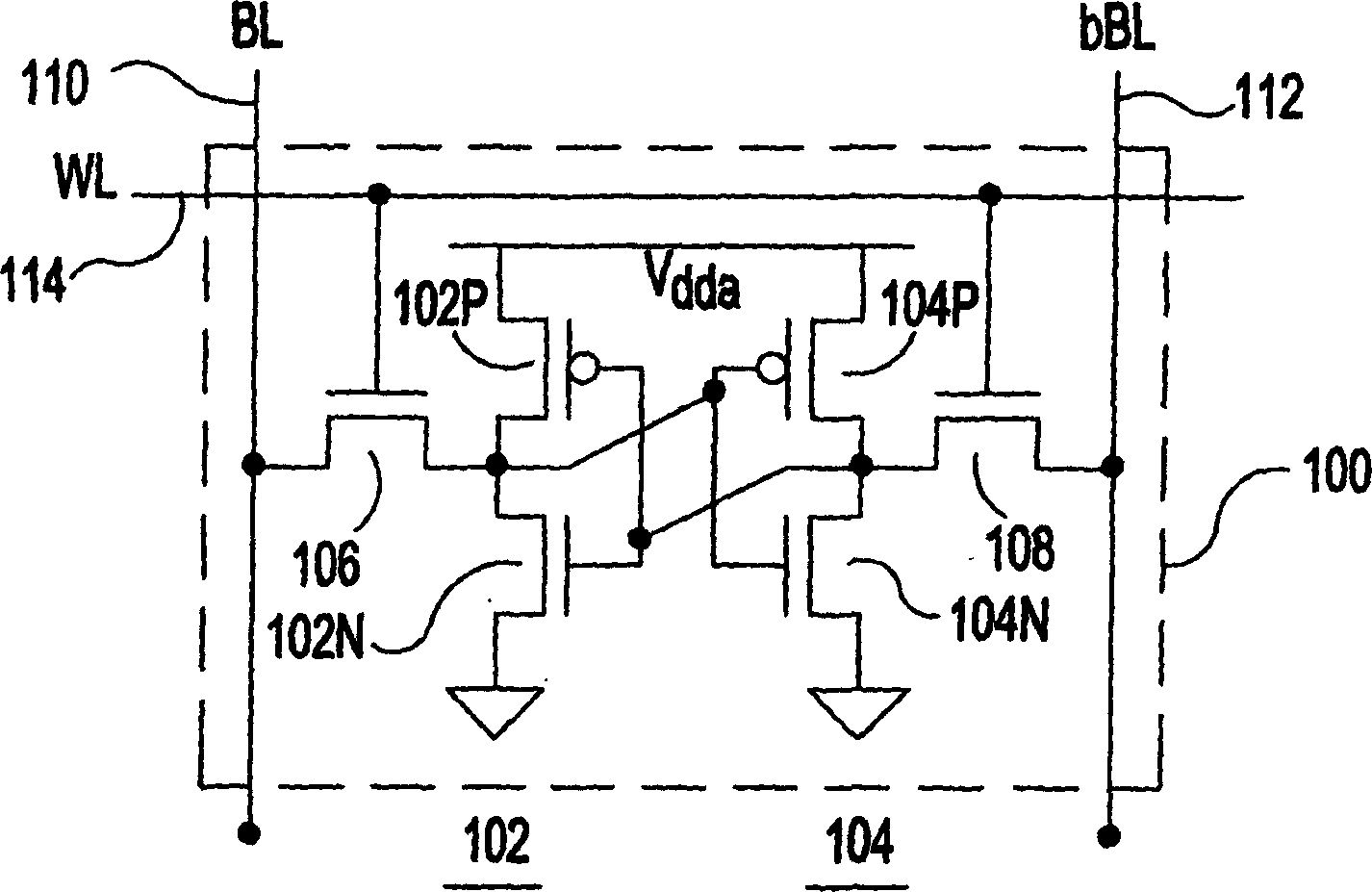

[0020] Referring now to the accompanying drawings, and more specifically, figure 1 A preferred embodiment of a six-transistor (6T) memory latch, e.g., static random access memory (SRAM) cell 100 in the well-known complementary insulated gate field-effect transistor (FET) technology known as CMOS is shown. Examples of embodiments. The technology has a stated design or design rule gate oxide thickness. Preferably, cell 100 is of what is known as partially depleted (PD) silicon-on-insulator (SOI) technology. By selectively providing increased threshold voltages (V T ) to reduce cell leakage, for example, by selectively thickening the gate oxide above the specified design gate oxide thickness, or forming the gate oxide with a high-k dielectric for these FETs. Thus, by using a suitable high-k gate dielectric or by increasing the thickness of the gate oxide or both, the threshold of the selected device is increased and thus the leakage of the device is reduced. Examples of high-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More