Patents

Literature

85results about How to "Sufficient form" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

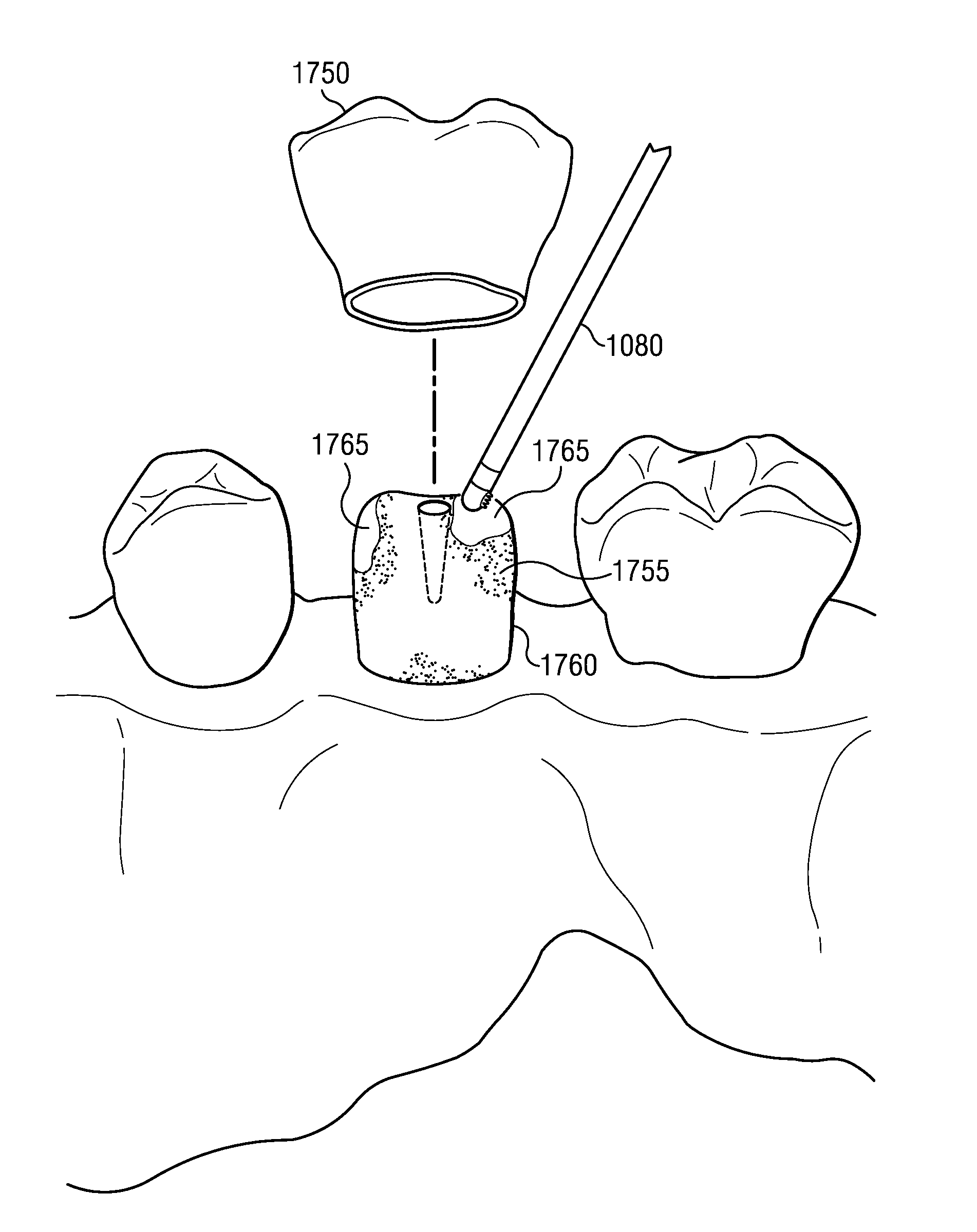

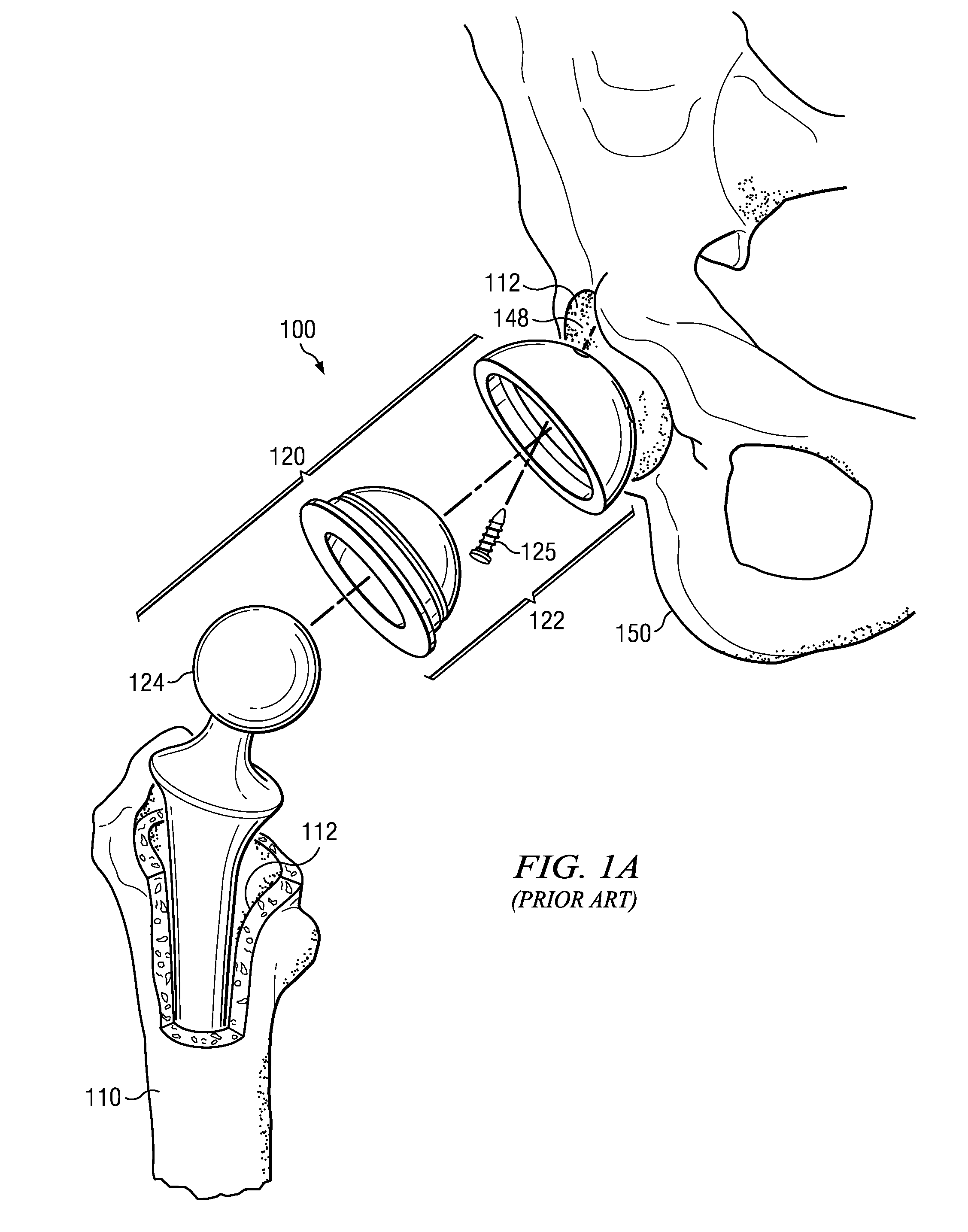

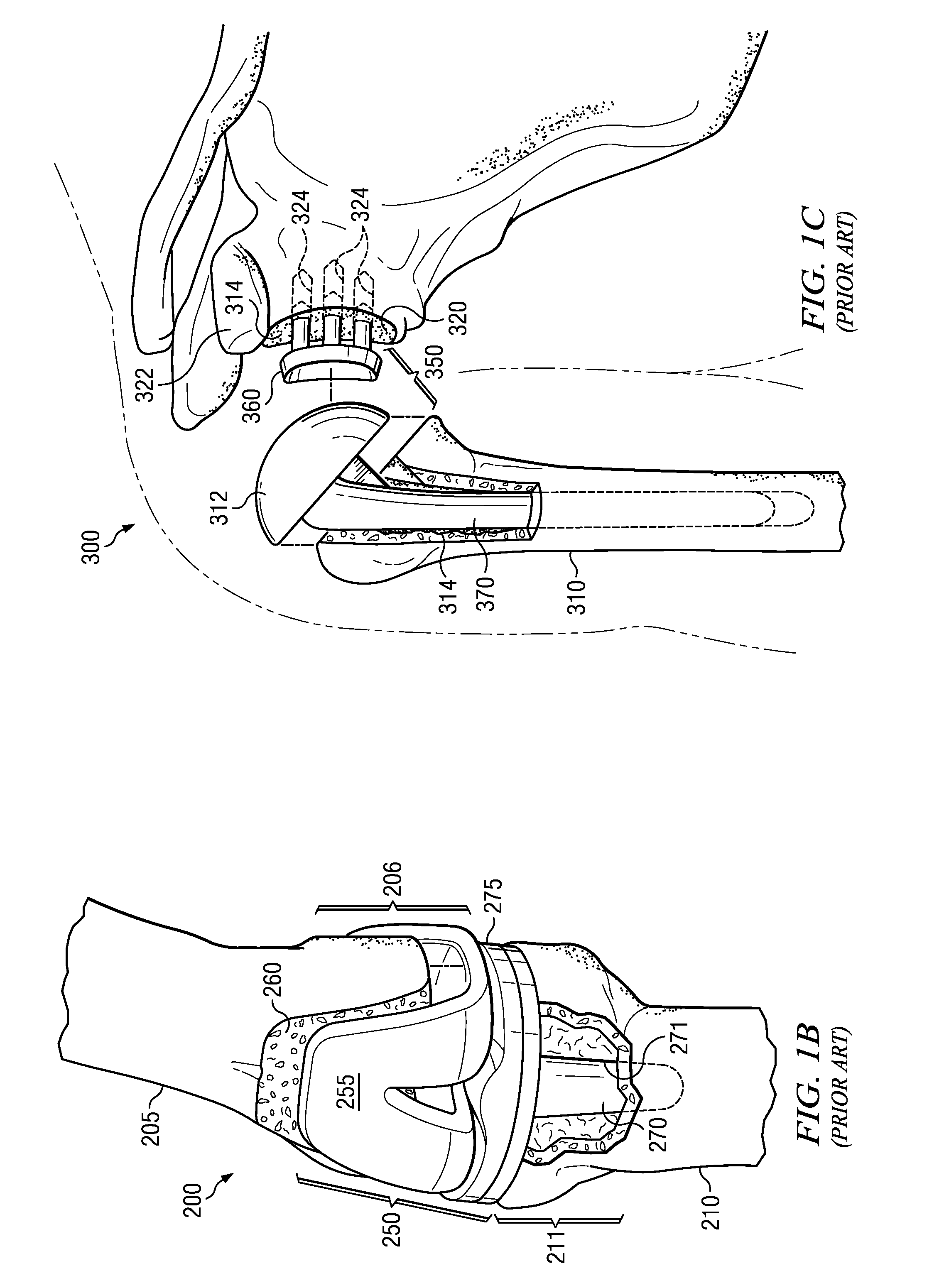

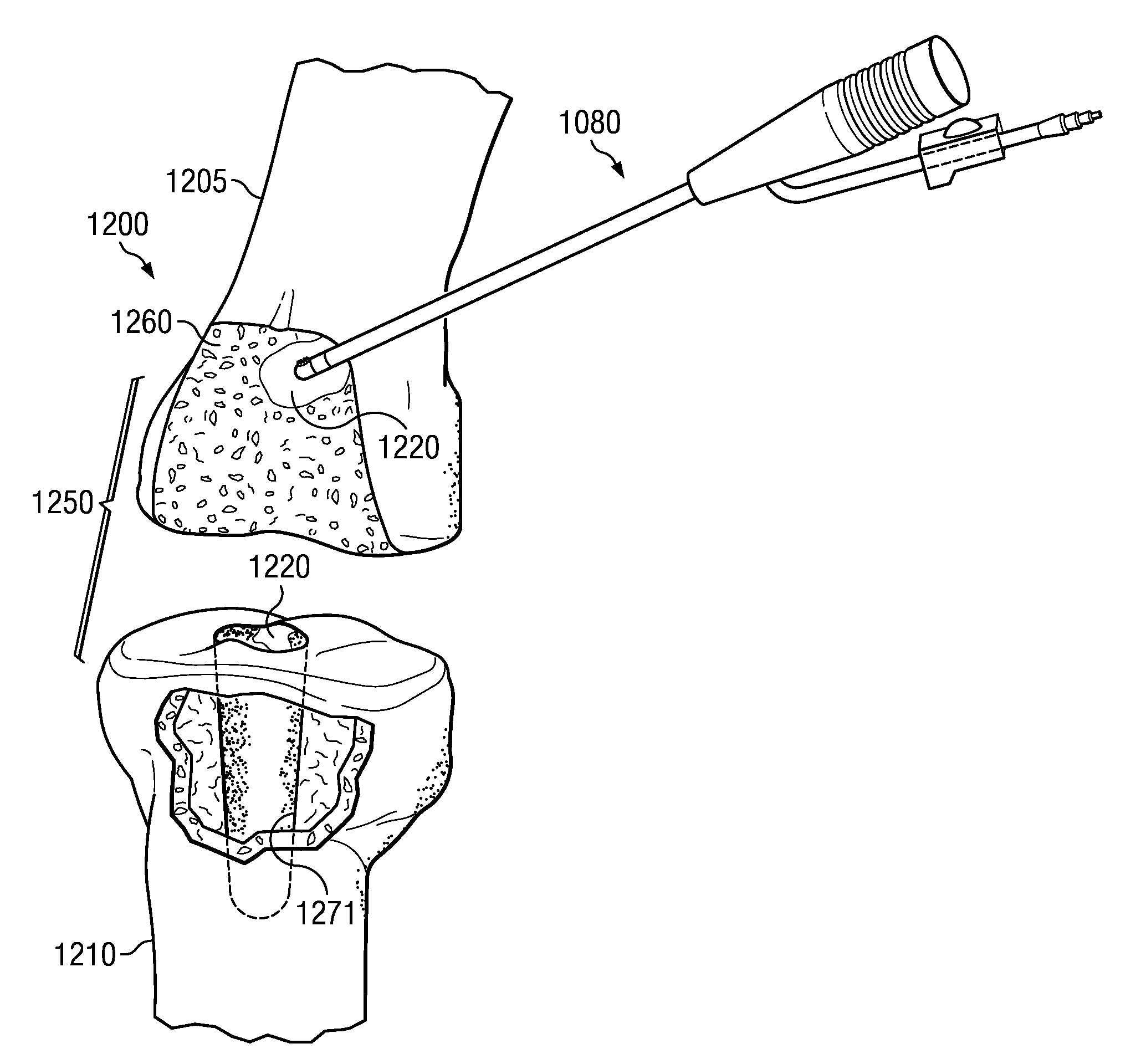

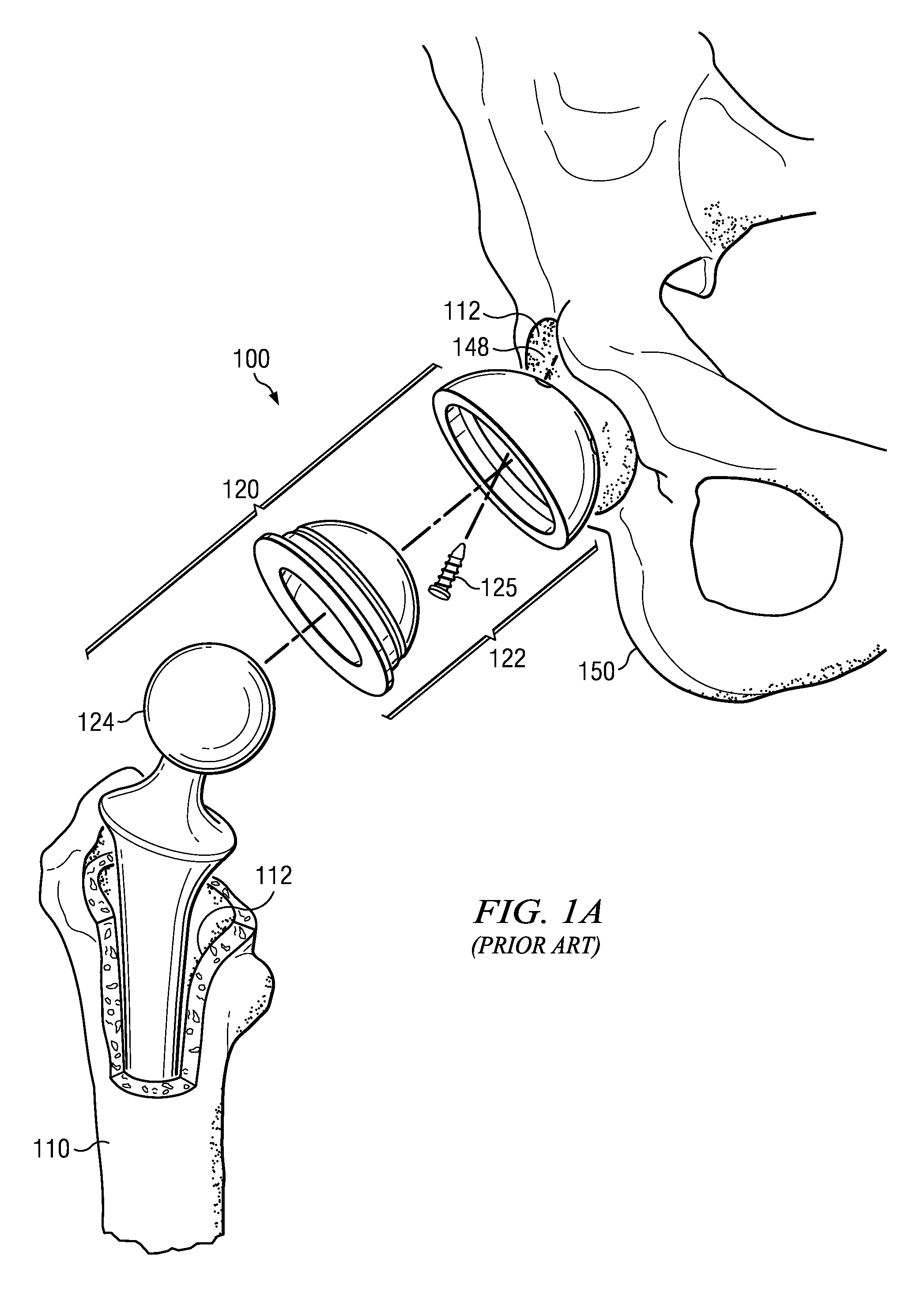

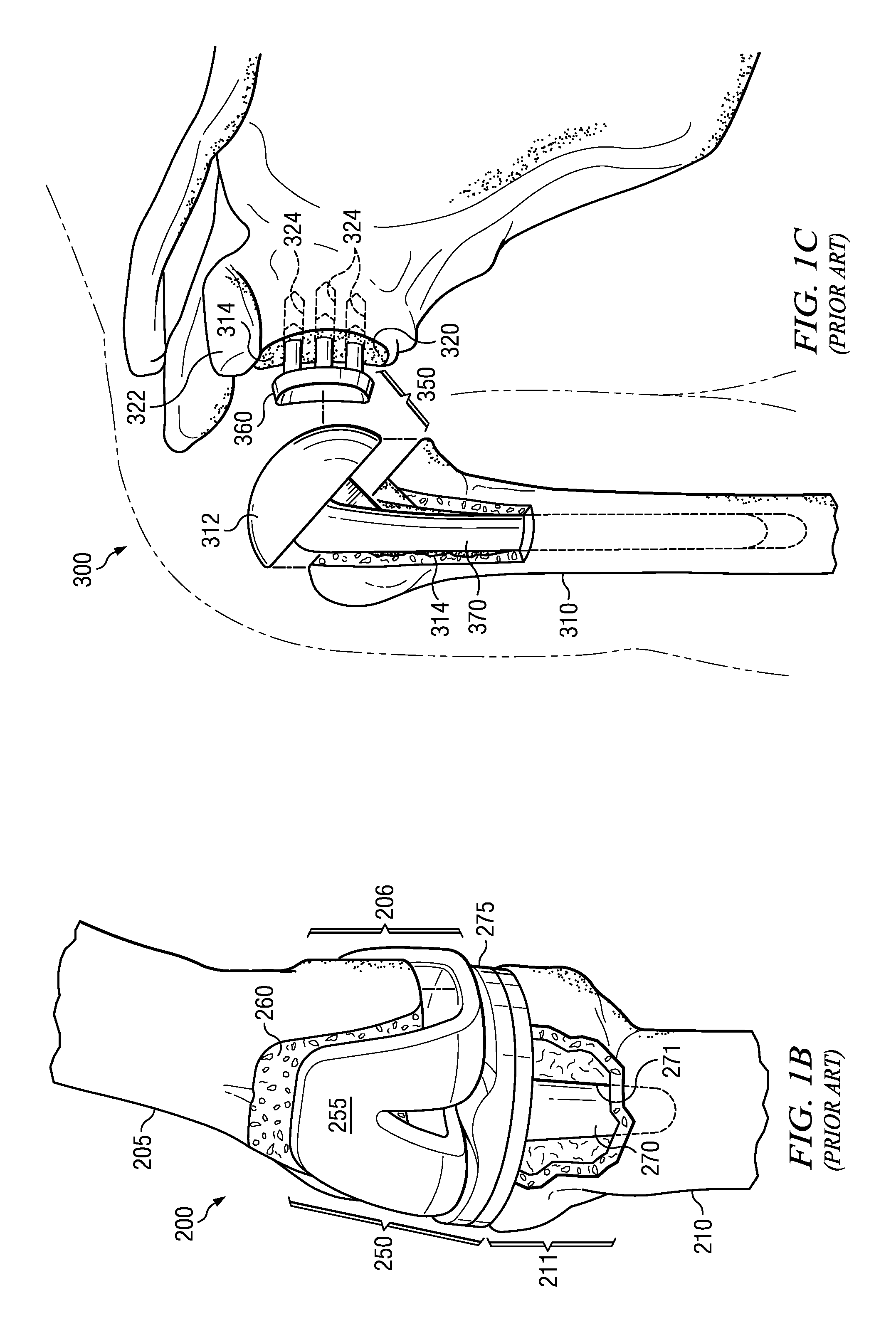

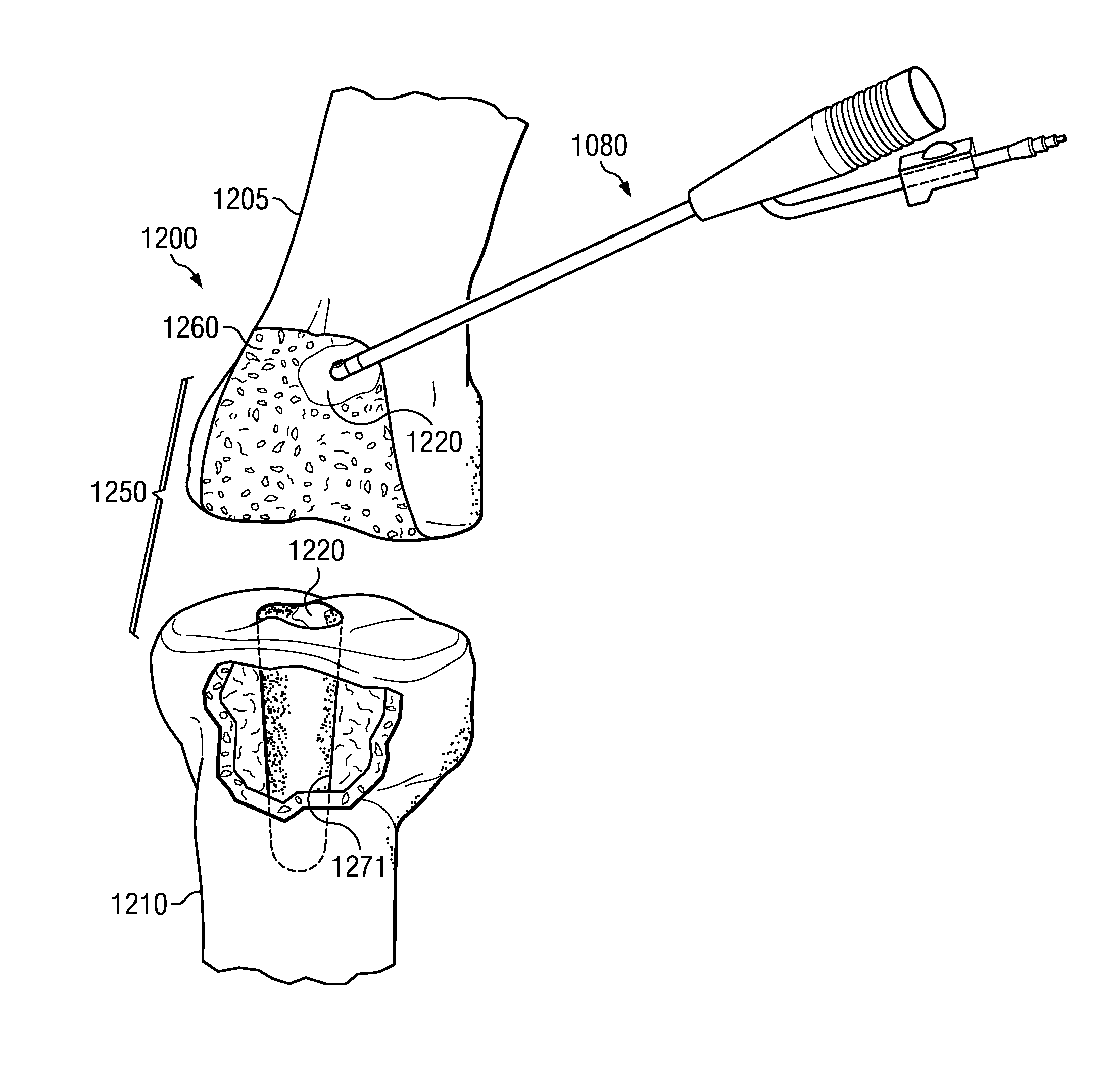

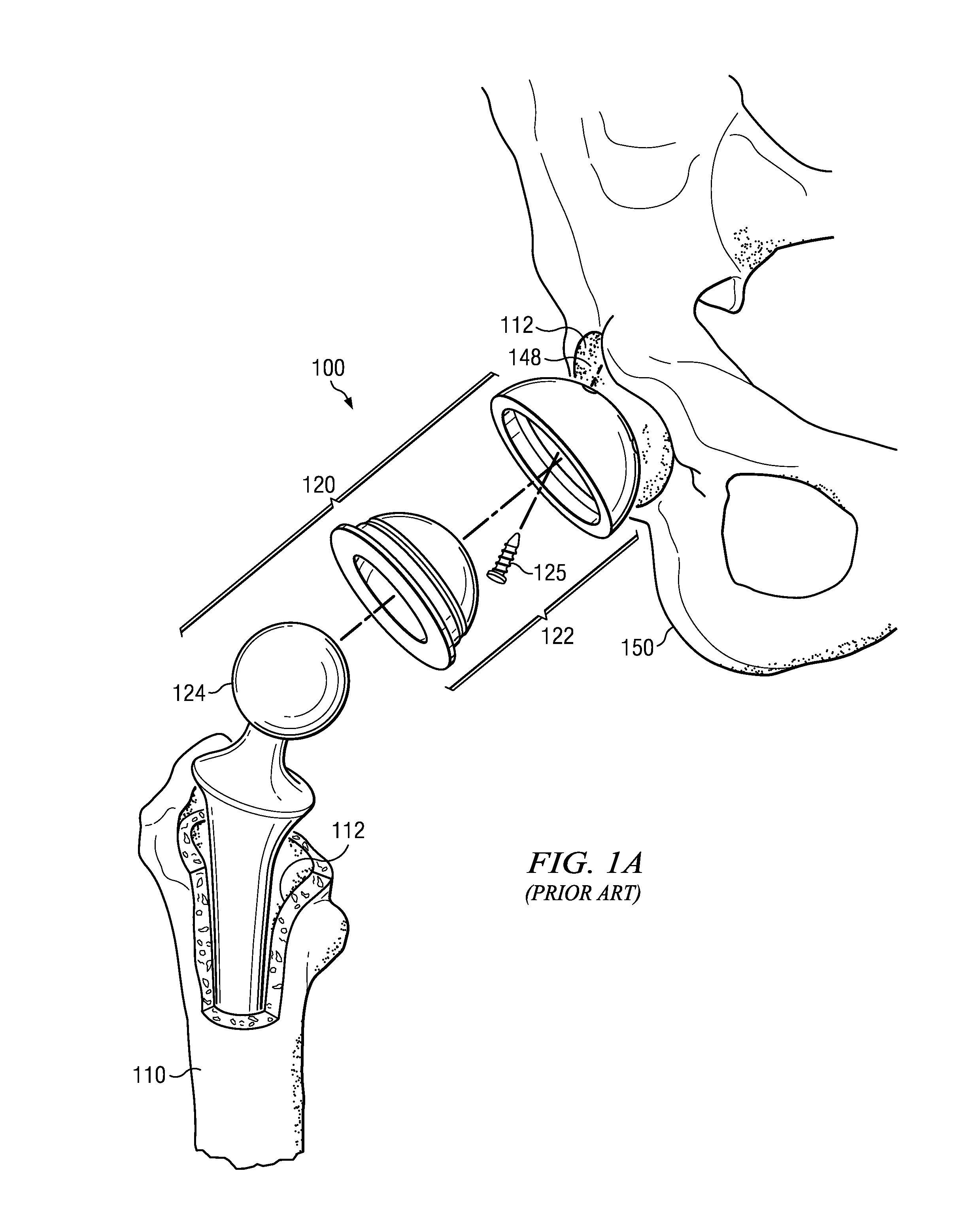

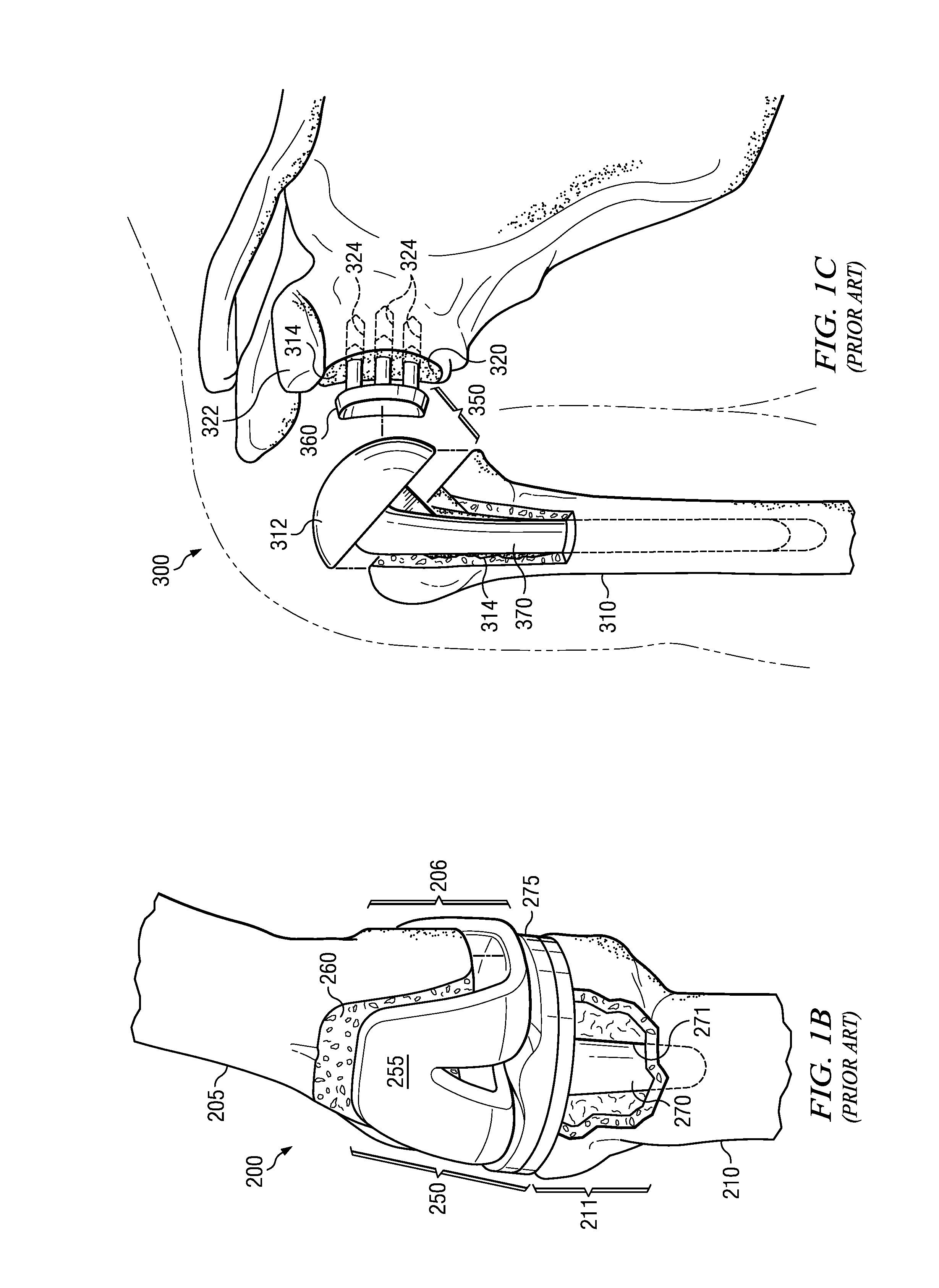

Electrosurgical system and method for treating hard body tissue

InactiveUS20120196251A1Improve sterilizationReduce inflammationGum massageTeeth fillingActive electrodeBlood plasma

A method of preparing a target hard body tissue, such as osseous or dental tissue, to receive an implant component including; positioning an active electrode in proximity to a target tissue and proximate an electrically conductive fluid, followed by applying a high frequency voltage between the active electrode and a return electrode, the high frequency voltage sufficient to form a plasma. This plasma modifies at least a portion of the target tissue. An implant component may then be placed adjacent at least a portion of the modified target tissue.

Owner:ARTHROCARE

Electrosurgical system and method for treating hard body tissue

ActiveUS20120197344A1Improve sterilizationReduce inflammationElectrotherapySurgical instruments for aspiration of substancesActive electrodeBlood plasma

A method of preparing a target hard body tissue, such as osseous or dental tissue, to receive an implant component including; positioning an active electrode in proximity to a target tissue and proximate an electrically conductive fluid, followed by applying a high frequency voltage between the active electrode and a return electrode, the high frequency voltage sufficient to form a plasma. This plasma modifies at least a portion of the target tissue. An implant component may then be placed adjacent at least a portion of the modified target tissue.

Owner:ARTHROCARE

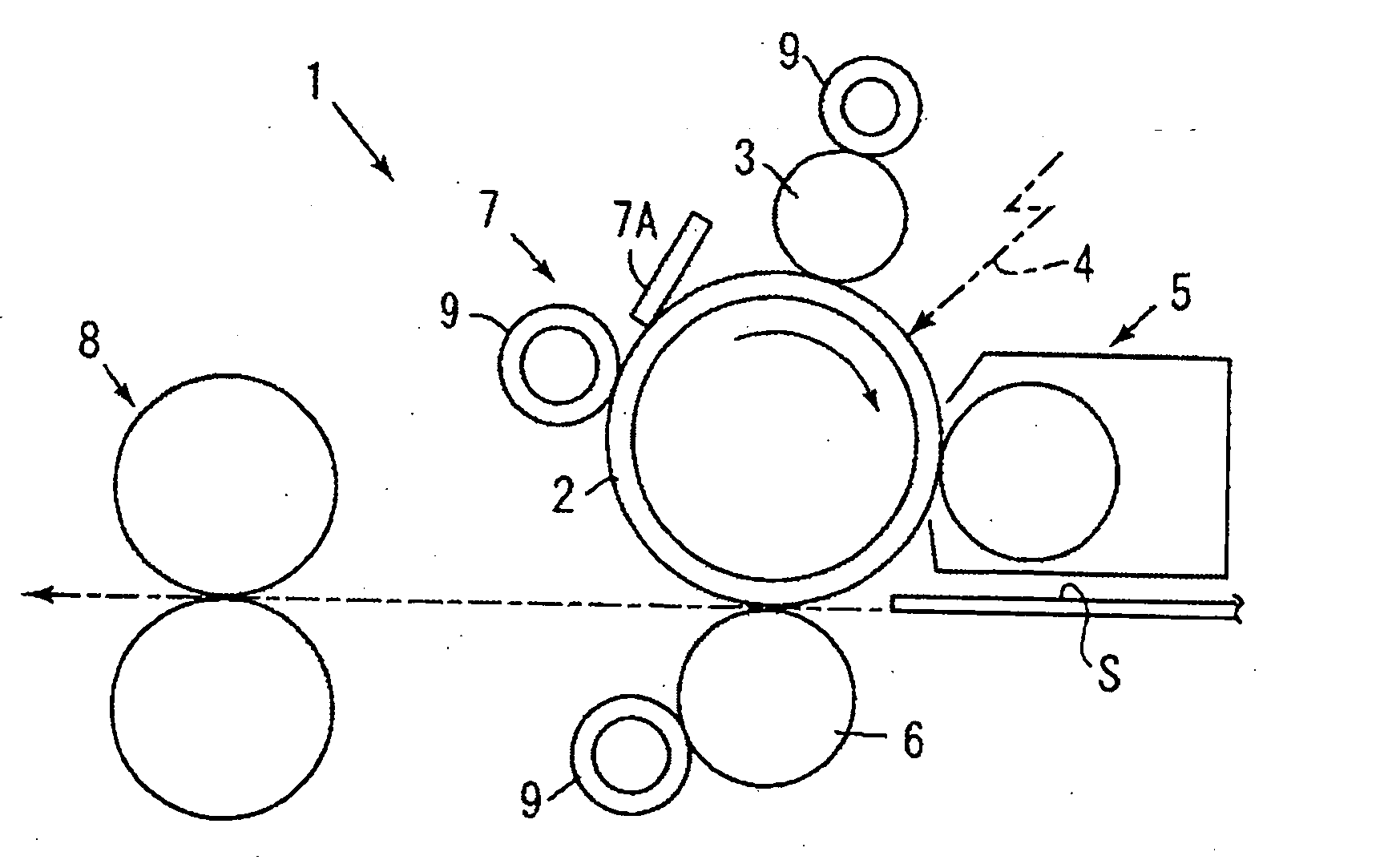

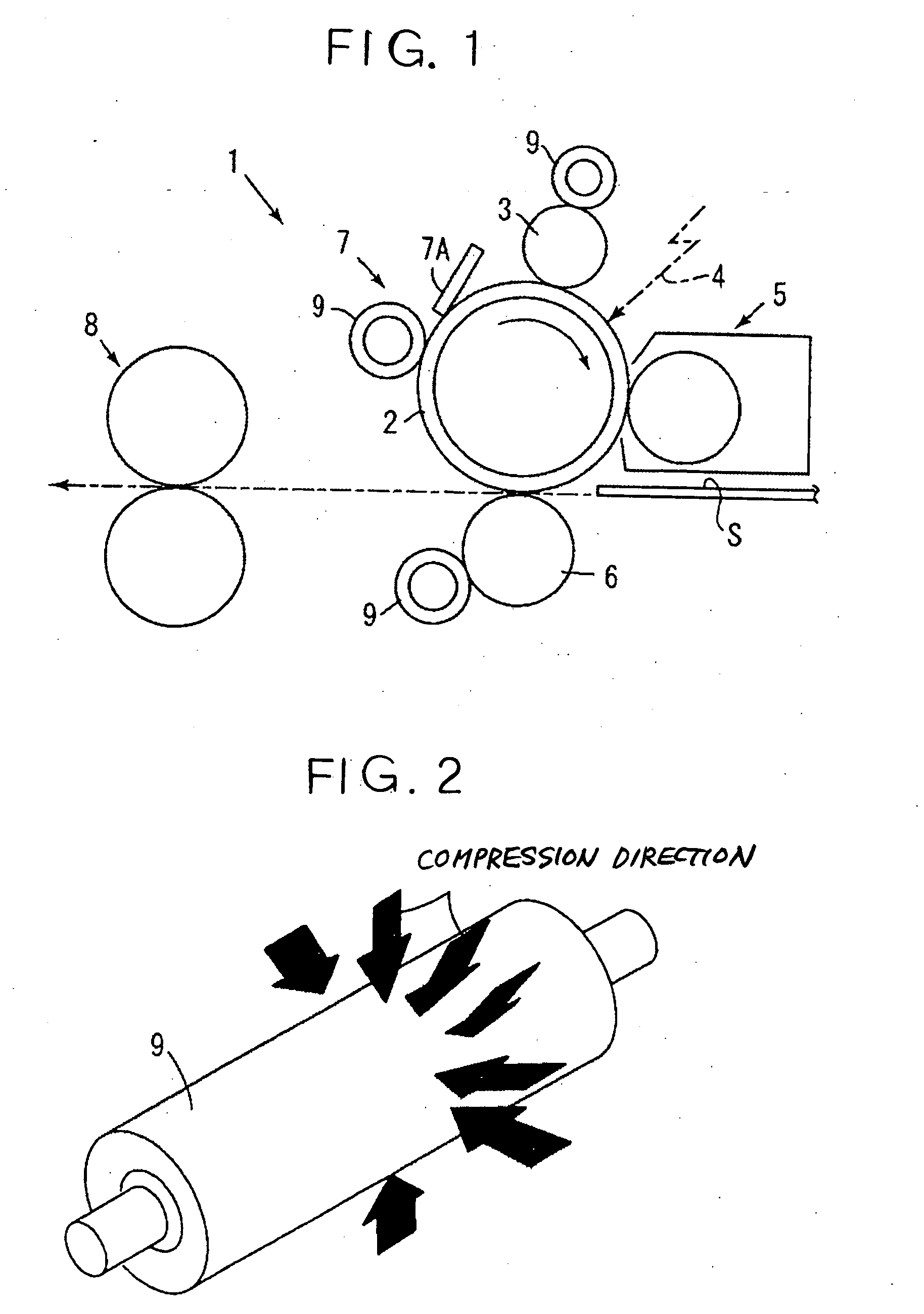

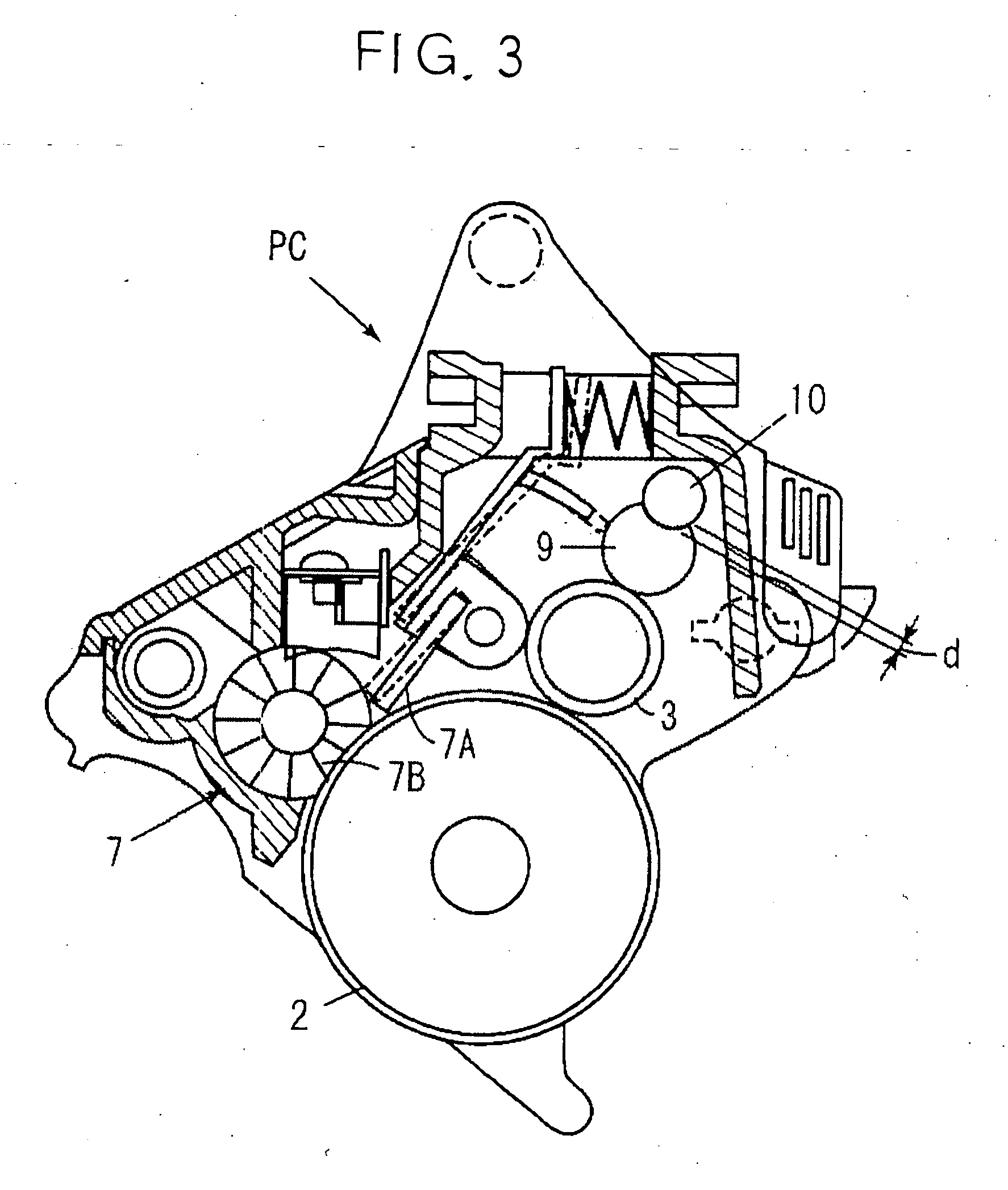

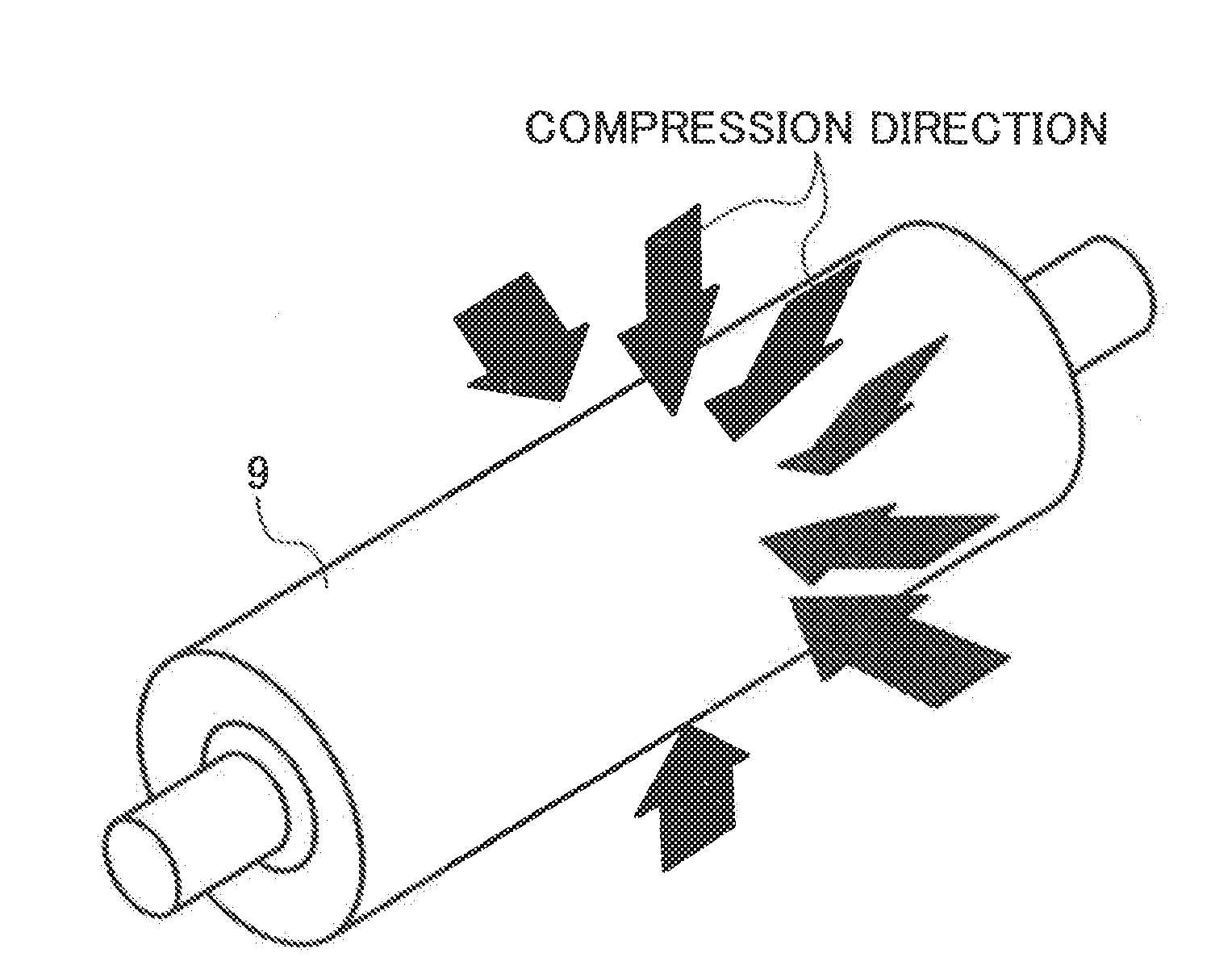

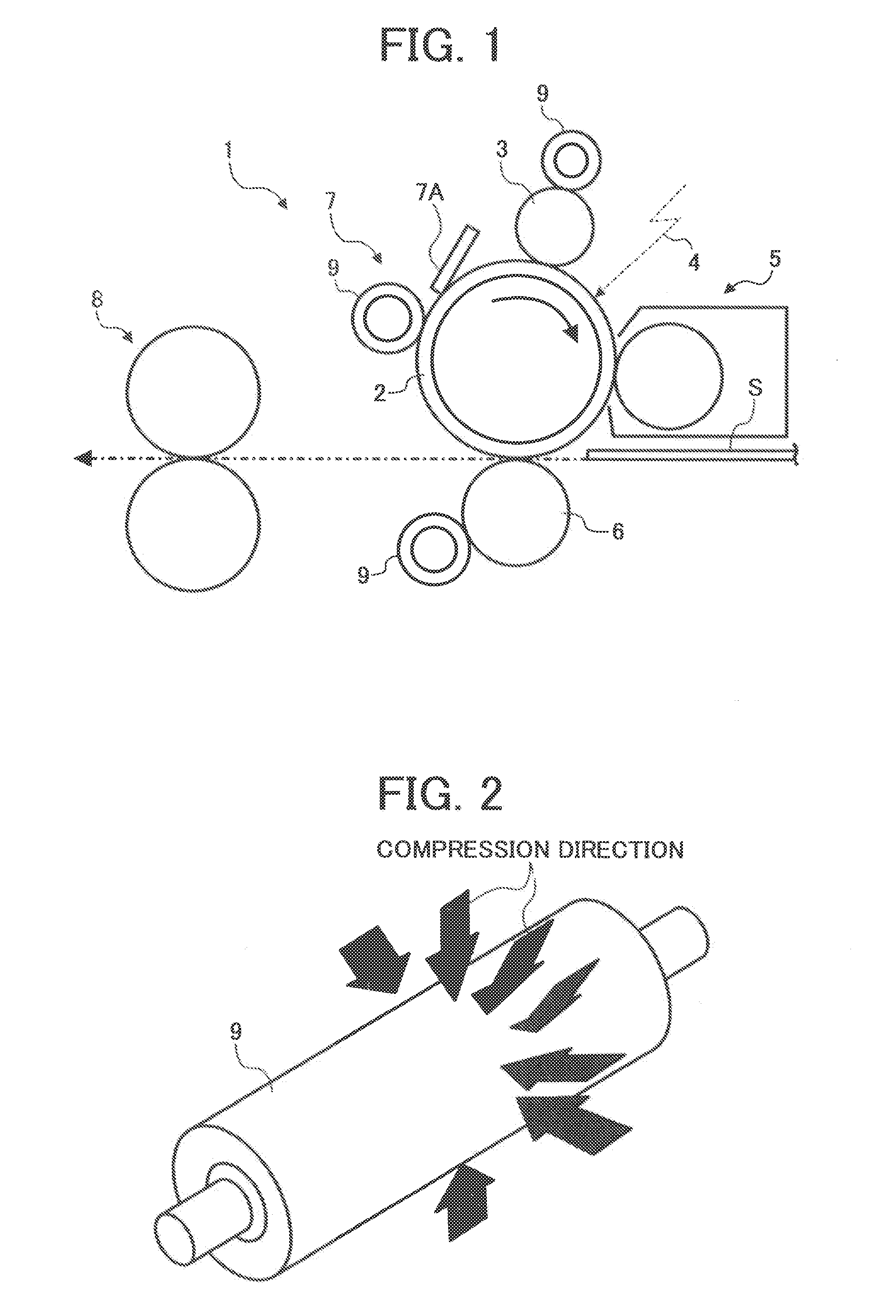

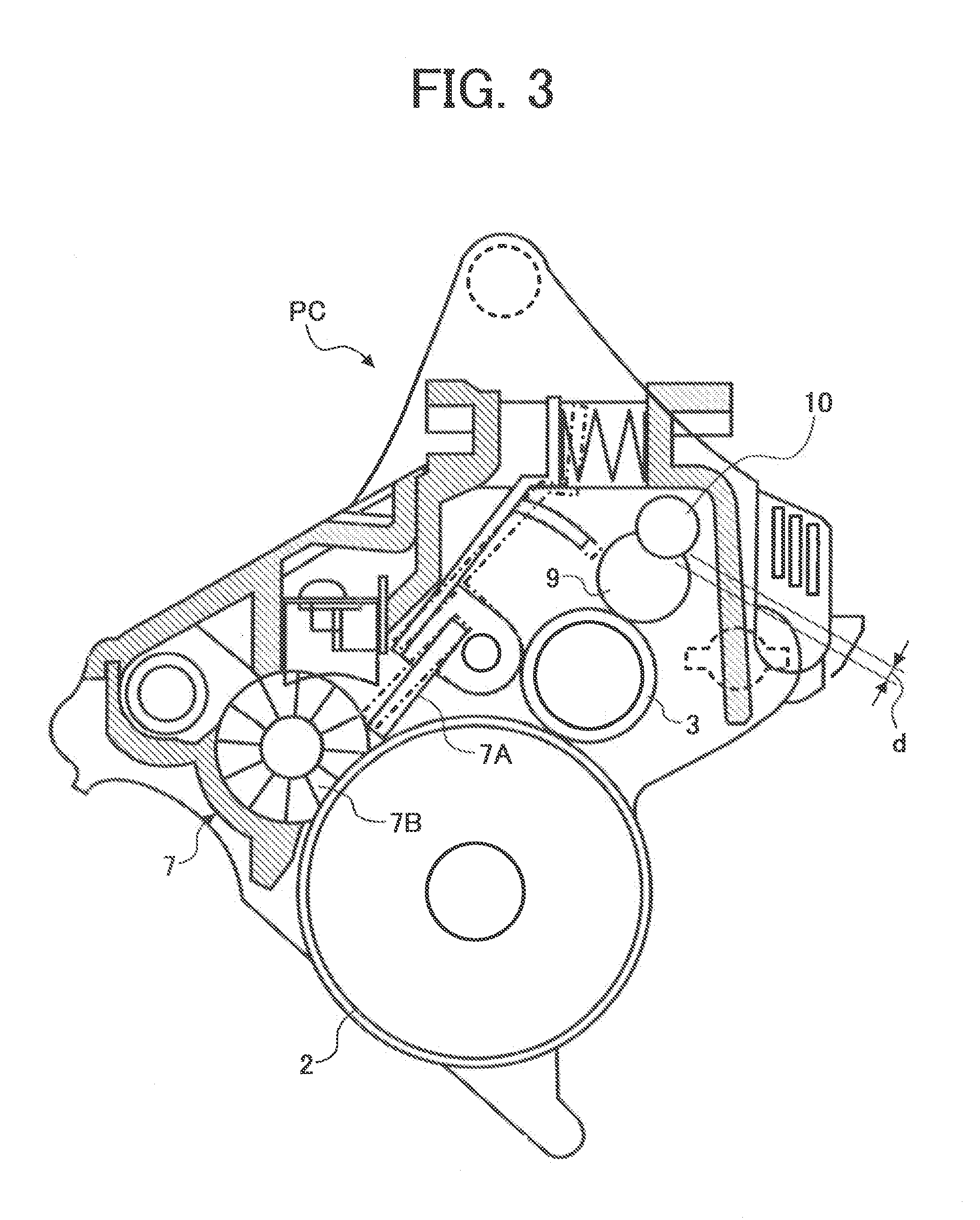

Charged device, cleaning device, process cartridge, toner, and image-forming device that uses these

ActiveUS20050191081A1Increase costReduce image qualityElectrographic process apparatusCorona dischargeForeign matterImaging quality

There is provided a cleaning device for an image-forming device configured so as to be capable of preventing the image quality from deteriorating by being able to prevent the deterioration of the charging state caused by deposits of foreign matter without increasing costs. There is also provided a cleaning member that can make contact with the cleaning target-members. The cleaning member has a portion composed of melamine resin foam for making contact with at least the cleaning target members, and the melamine resin foam has an Asker F hardness of 5 to 25 points and a hardness variation of 5 points or less, and is used on the cleaning target members in a state obtained by heat compression from the original shape. The pressing member is furthermore disposed in contact with the cleaning member.

Owner:RICOH KK

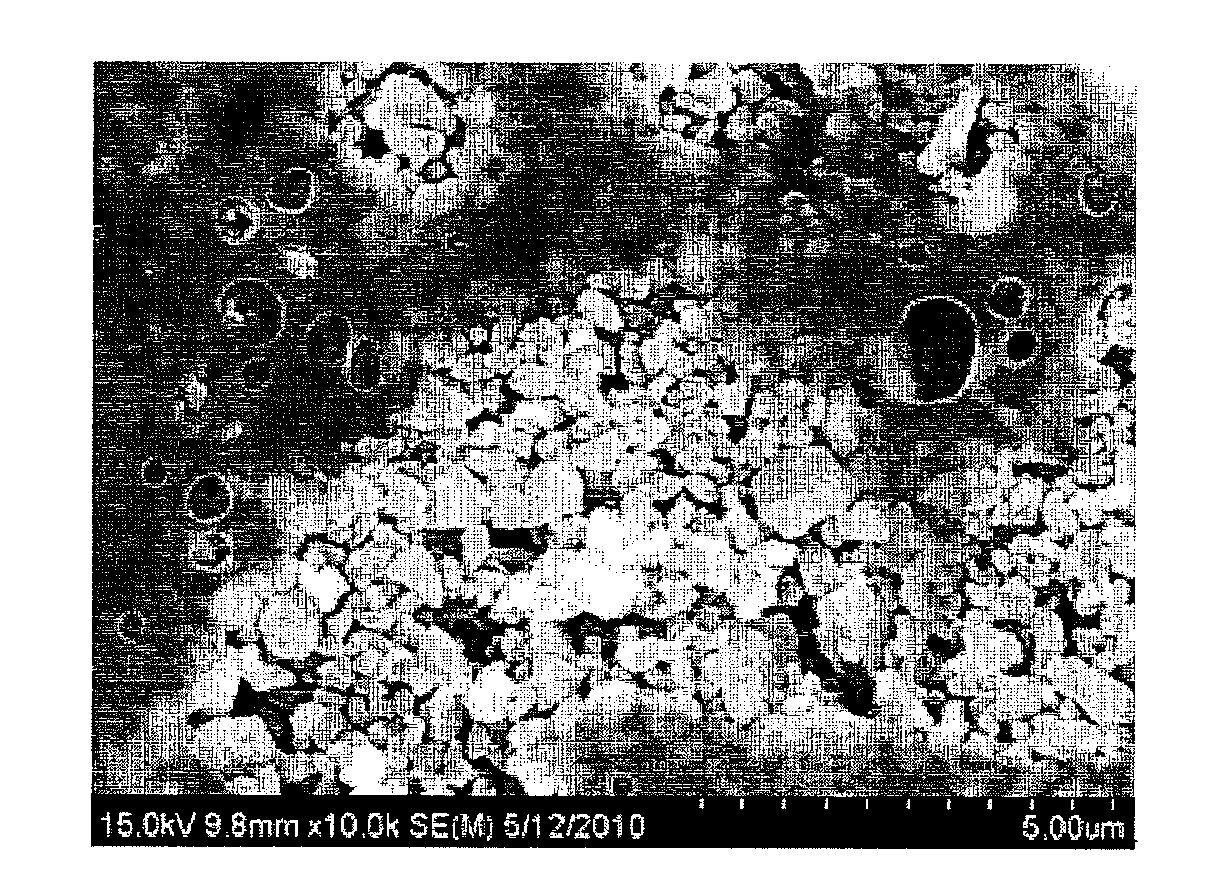

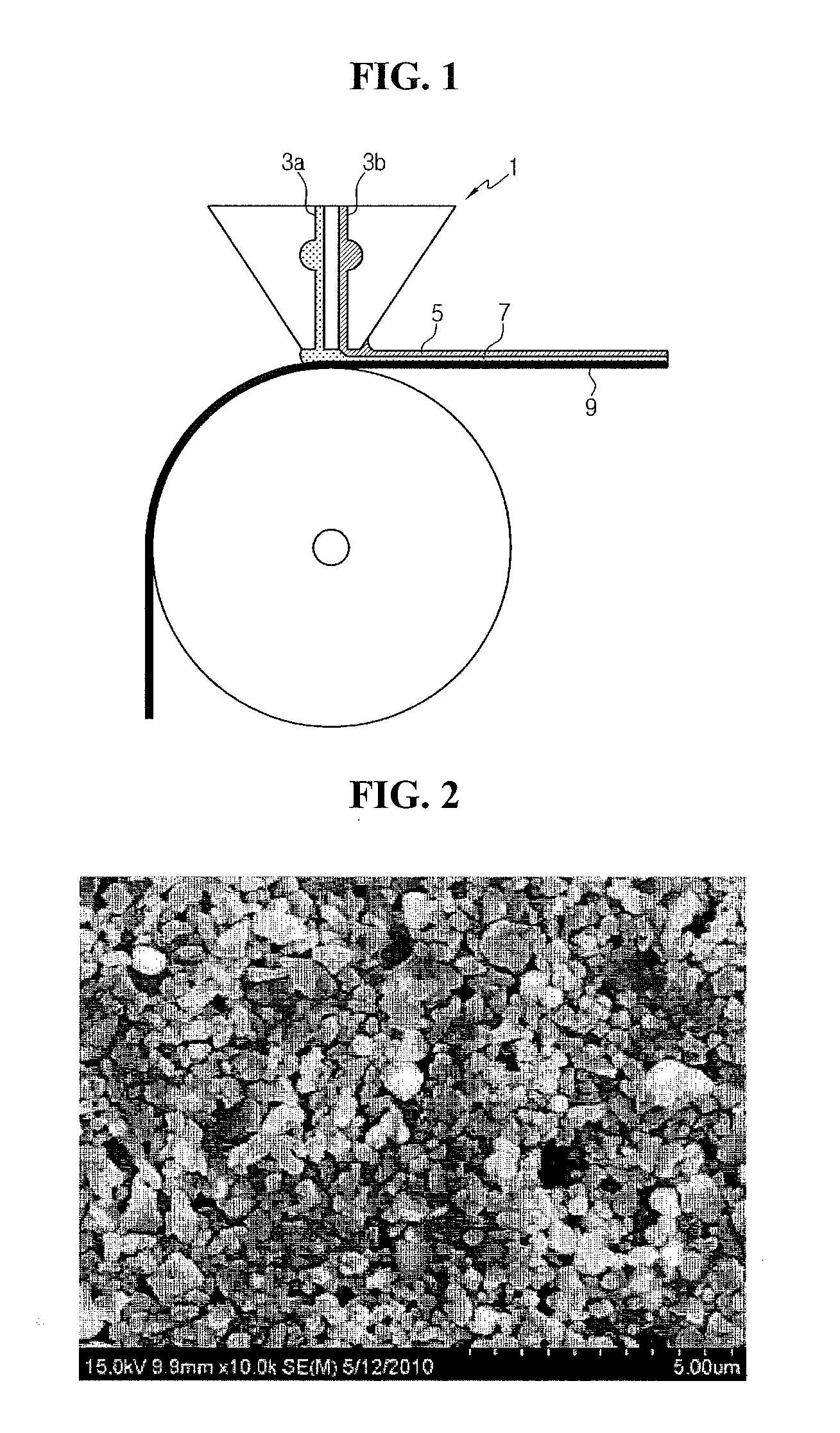

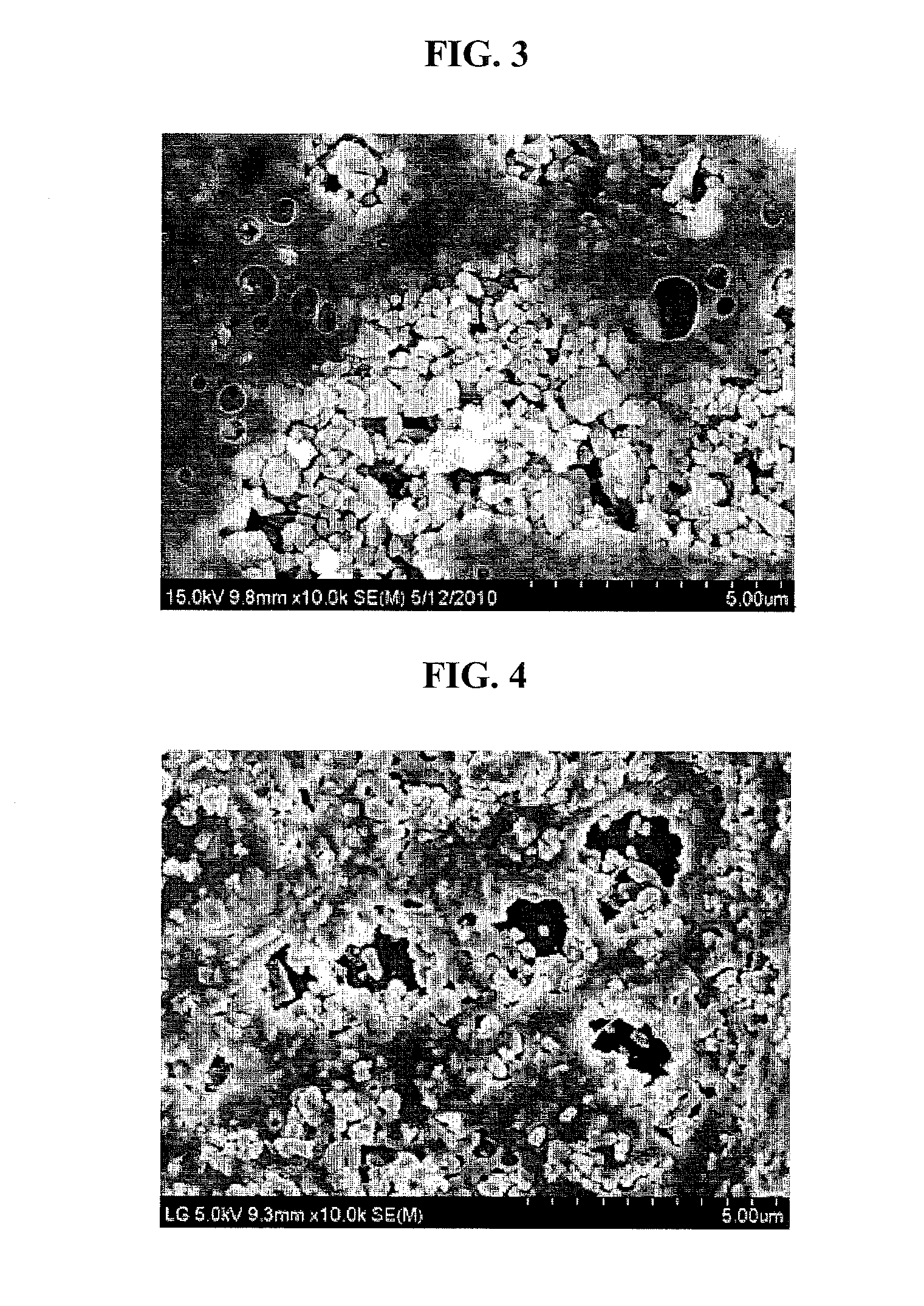

Method for manufacturing separator, separator manufactured therefrom and method for manufacturing electrochemical device having the same

ActiveUS20110259505A1Improve adhesionEasy laminationLamination ancillary operationsCell seperators/membranes/diaphragms/spacersInorganic particleInorganic particles

Disclosed is a method for manufacturing a separator for an electrochemical device. The method contributes to formation of a separator with good bondability to electrodes and prevents inorganic particles from detaching during an assembling process of an electrochemical device.

Owner:TORAY BATTERY SEPARATOR FILM +1

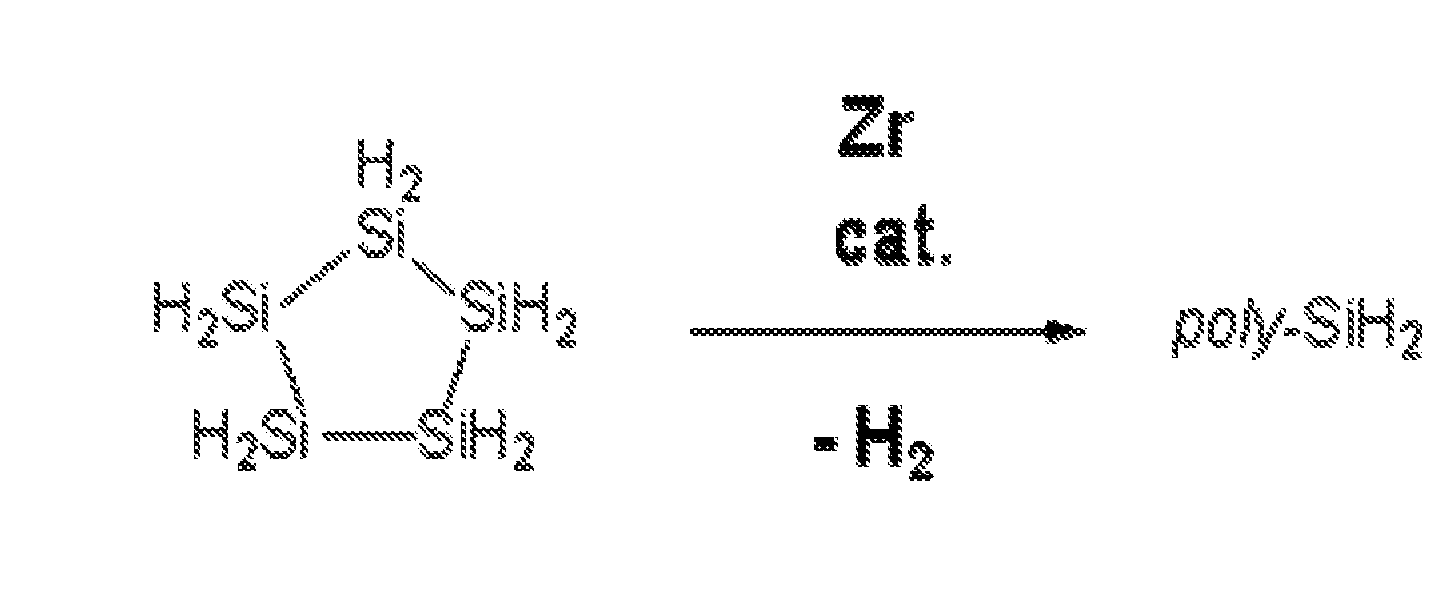

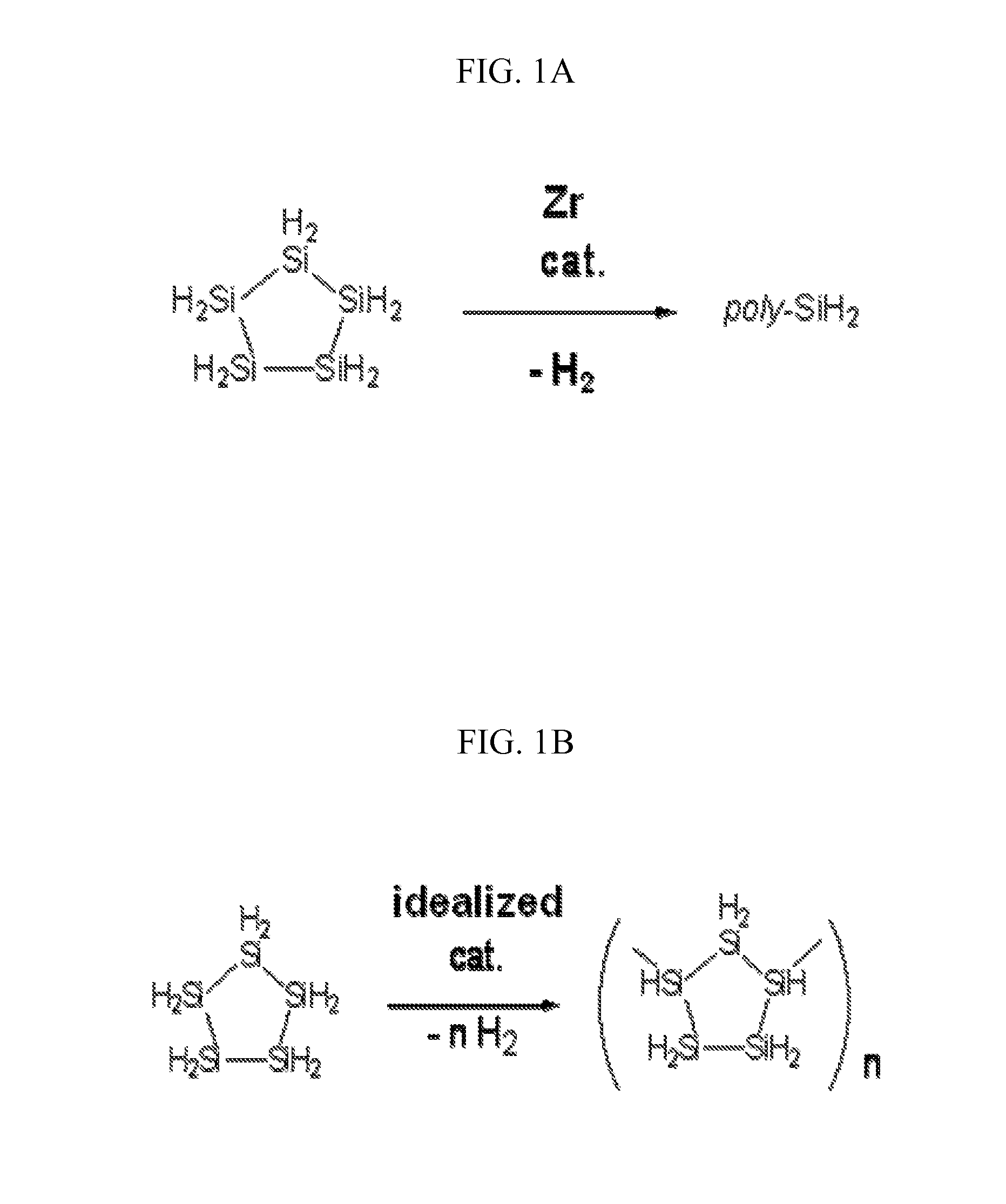

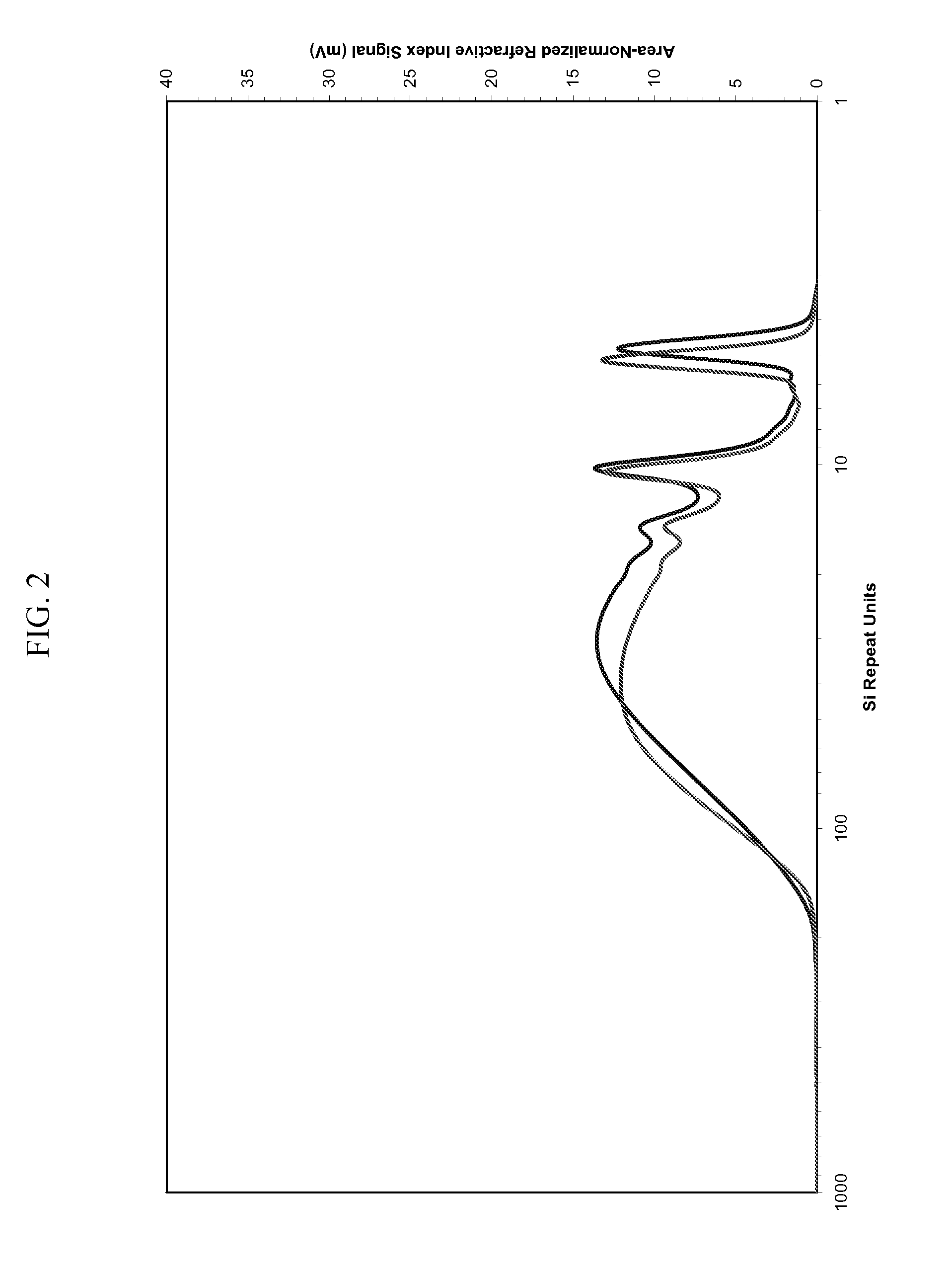

Silicon Polymers, Methods of Polymerizing Silicon Compounds, and Methods of Forming Thin Films from Such Silicon Polymers

ActiveUS20080085373A1Reduce hydrogen contentSufficient formSilicon organic compoundsSolid-state devicesSilanesCompound (substance)

Compositions and methods for controlled polymerization and / or oligomerization of hydrosilanes compounds including those of the general formulae SinH2n and SinH2n+2 as well as alkyl- and arylsilanes, to produce soluble silicon polymers as a precursor to silicon films having low carbon content.

Owner:ENSURGE MICROPOWER ASA

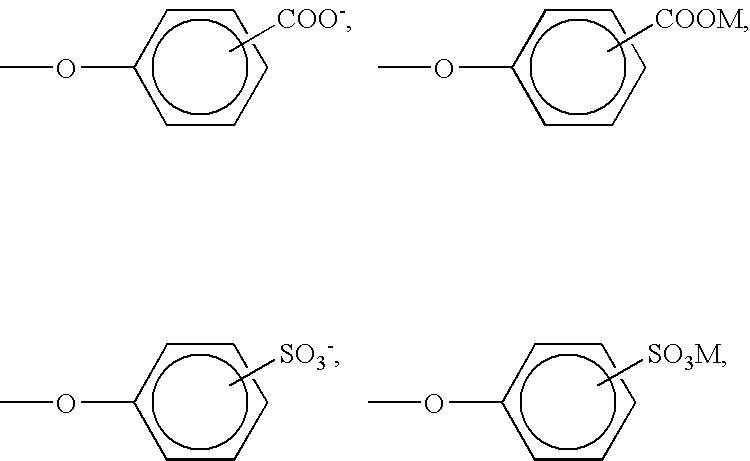

Acid stable membranes for nanofiltration

InactiveUS20030121857A1Good rejectionImprove permeabilityGeneral water supply conservationUltrafiltrationNanofiltrationOrganic compound

Semi-permeable membranes are described that allow for the efficient processing of many liquid based feed solutions, particularly those that contain acids. The membranes of this invention are able to process such feeds with high permeate rates while maintaining excellent retention of dissolved metals, cations, and organic compounds, even in the presence of hot concentrated acids. The semi-permeable membranes of this invention are able to conduct such separations for a useful period of time due to their chemical stability towards acids and their ability to permeate acids.

Owner:GE OSMONICS INC

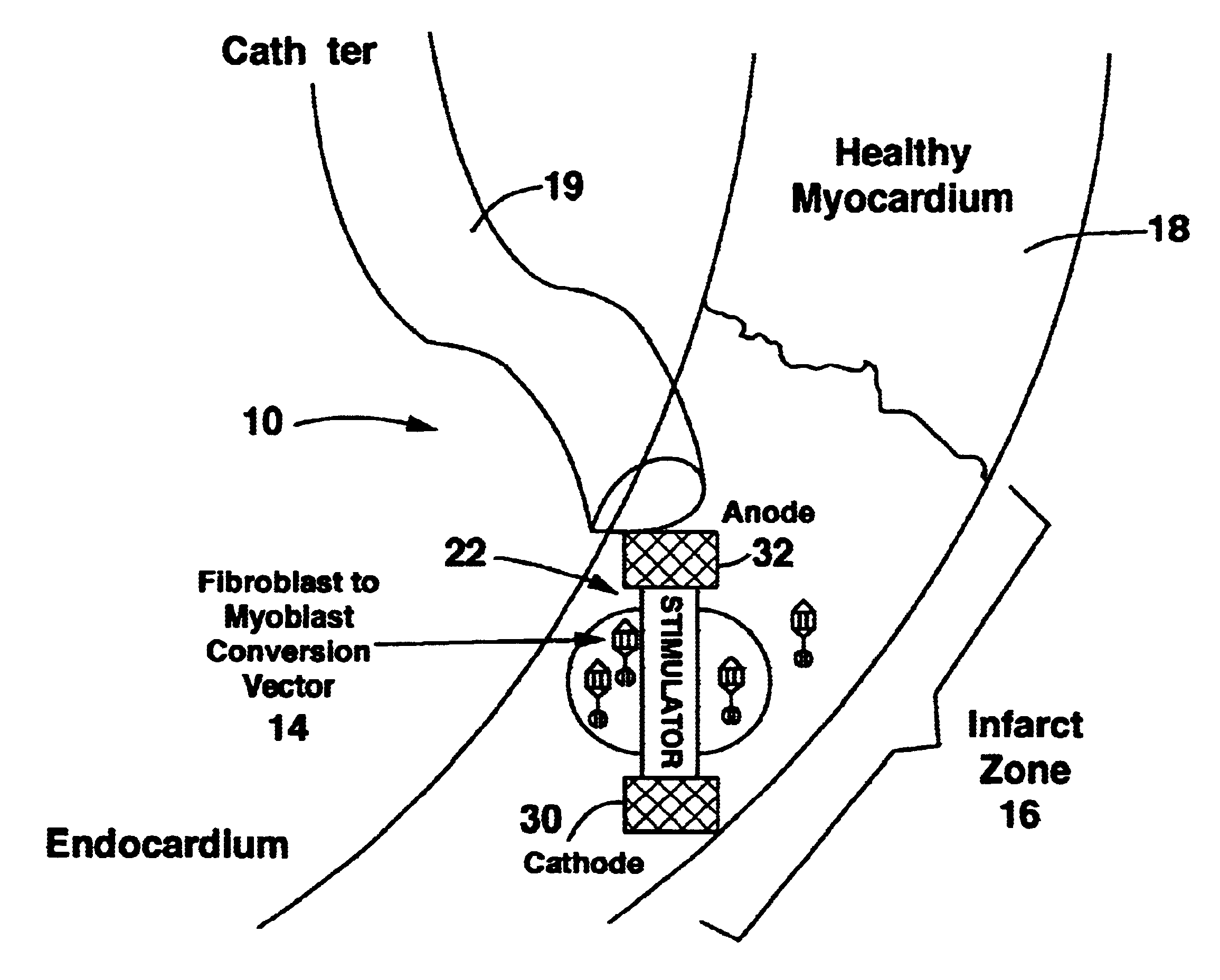

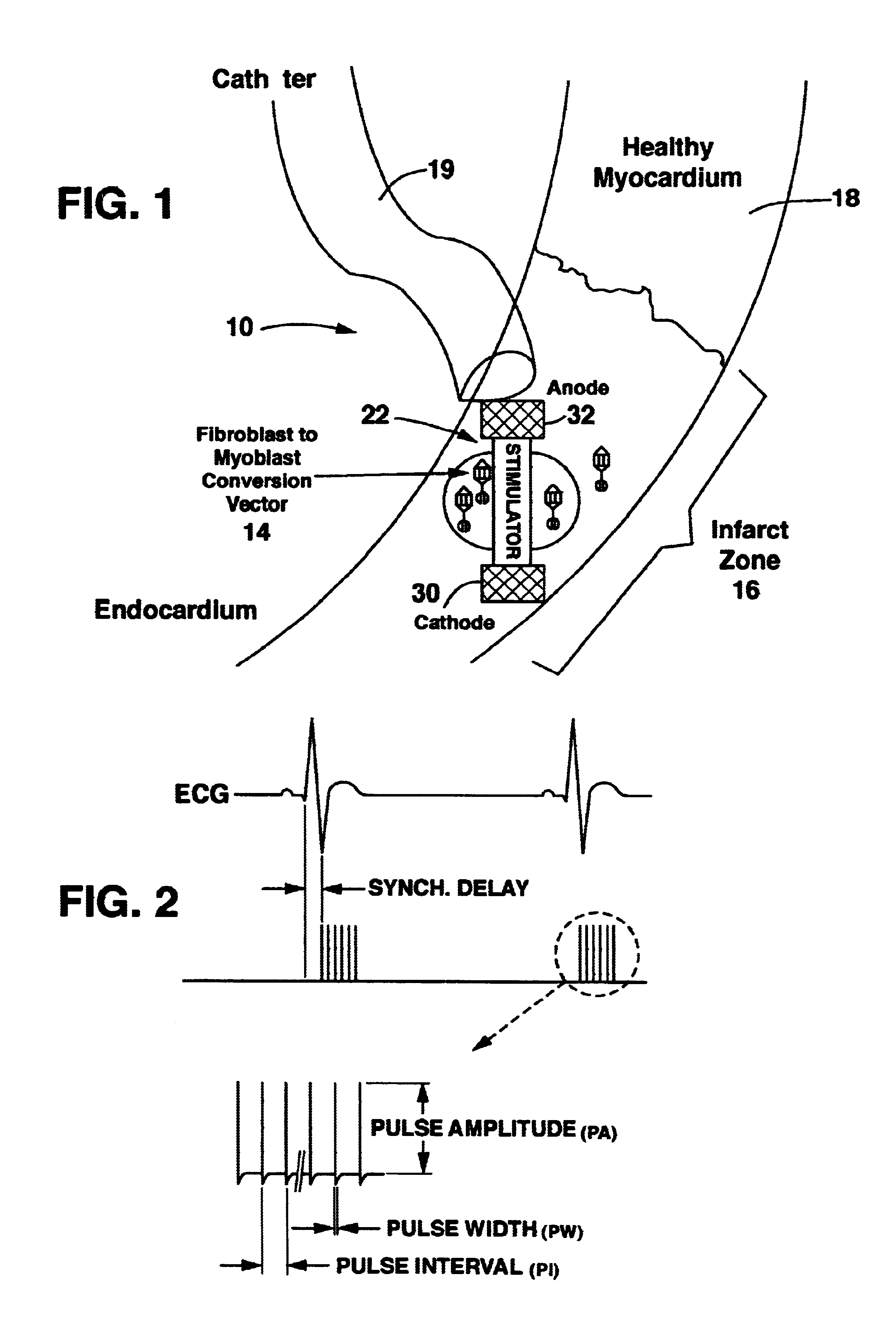

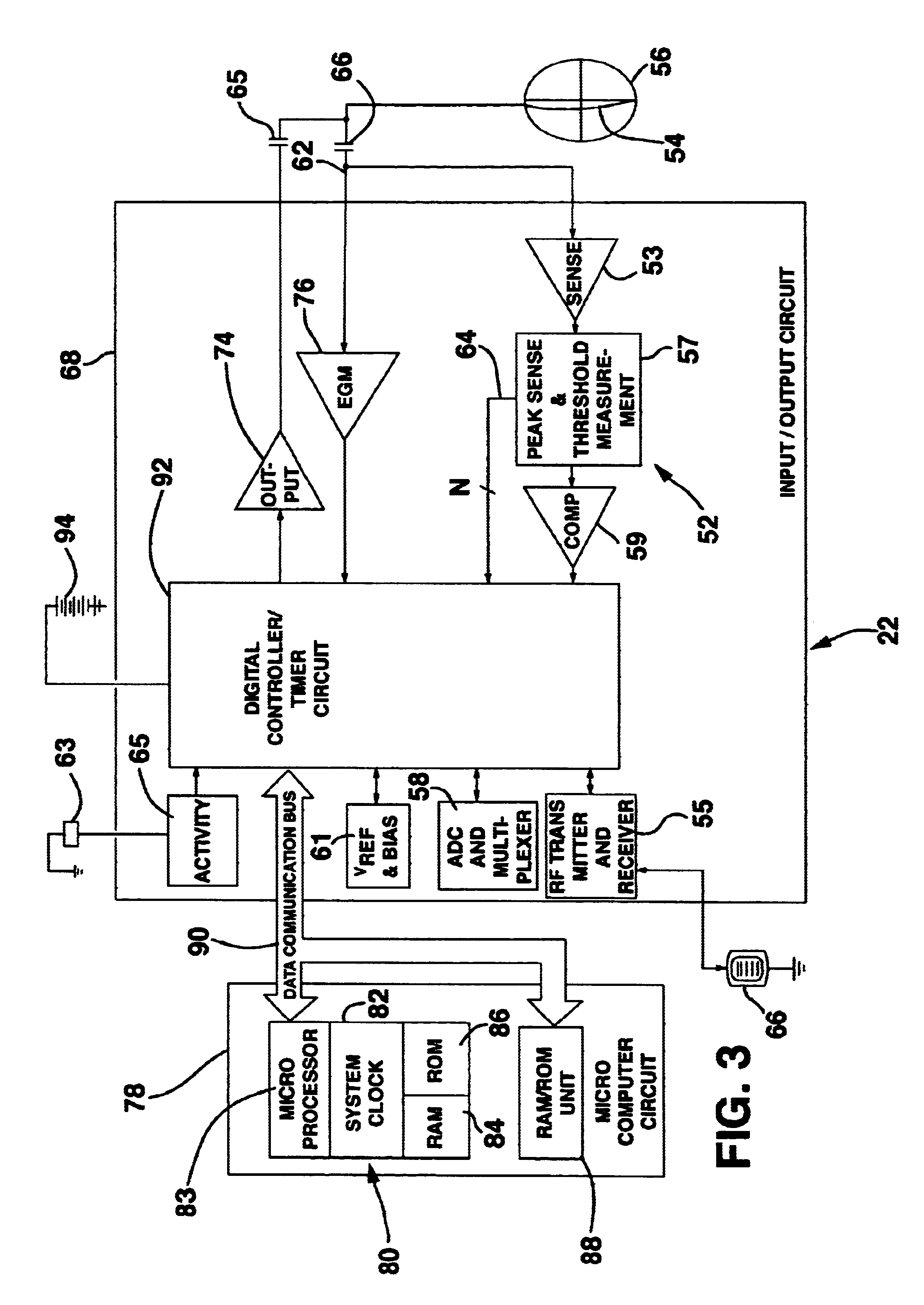

Method and system for myocardial infarction repair

InactiveUS6671558B1Restore elasticityRestoration of contractilityElectrotherapyArtificial respirationGenetic MaterialsCardiac muscle

An implantable system is provided that includes: a cell repopulation source comprising genetic material, undifferentiated and / or differentiated contractile cells, or a combination thereof capable of forming new contractile tissue in and / or near an infarct zone of a patient's myocardium; and an electrical stimulation device for electrically stimulating the new contractile tissue in and / or near the infarct zone of the patient's myocardium or otherwise damaged or diseased myocardial tissue.

Owner:MEDTRONIC INC

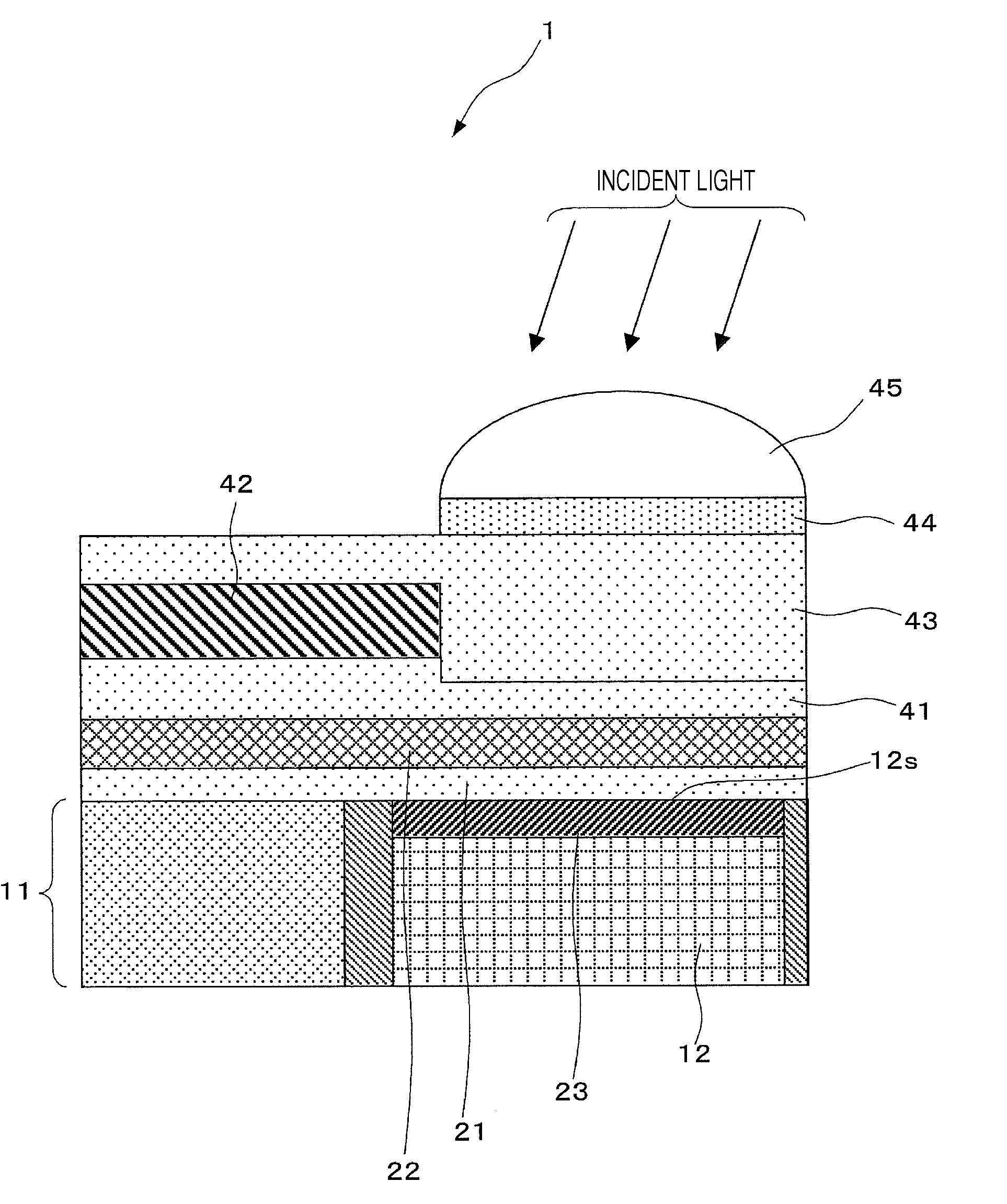

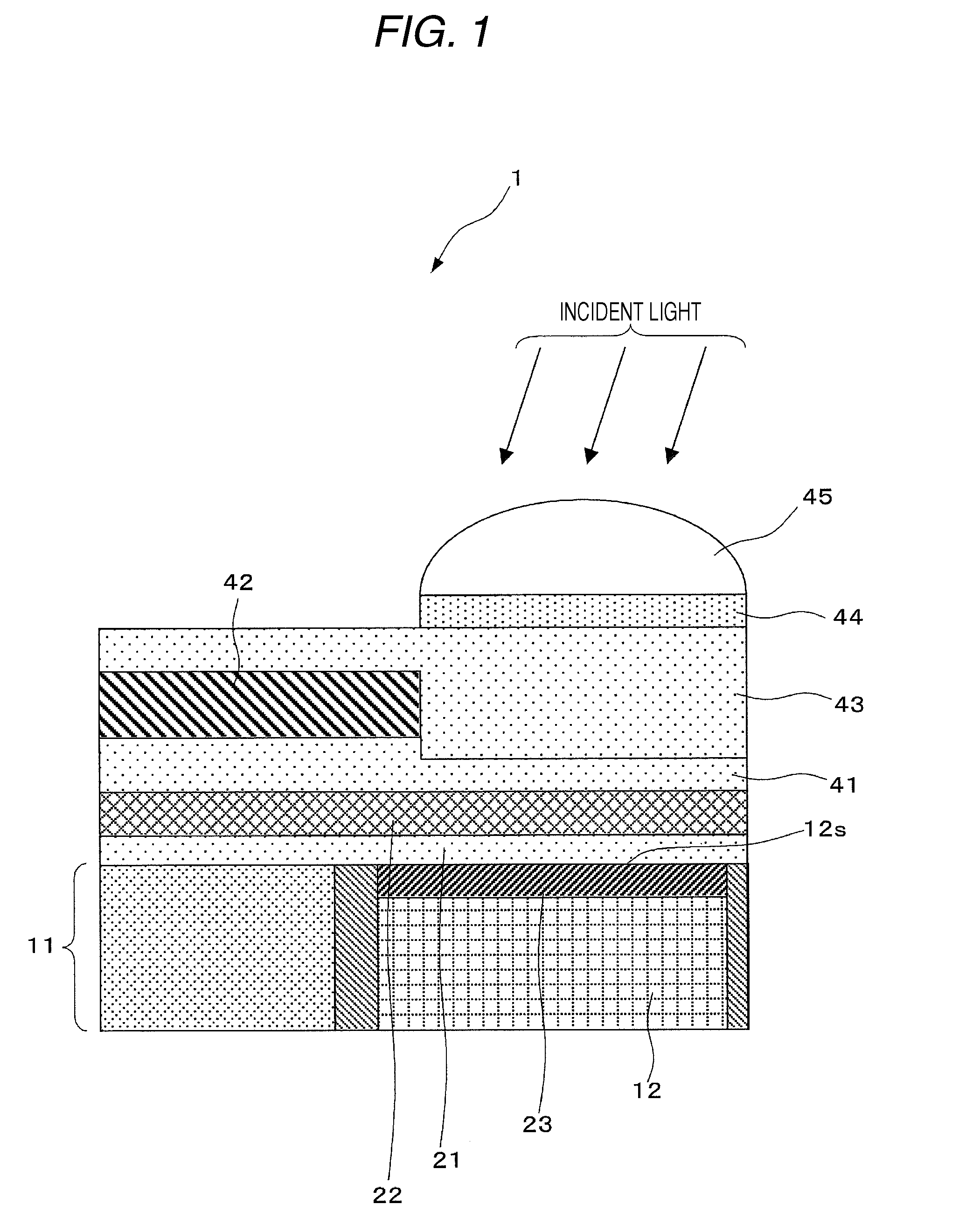

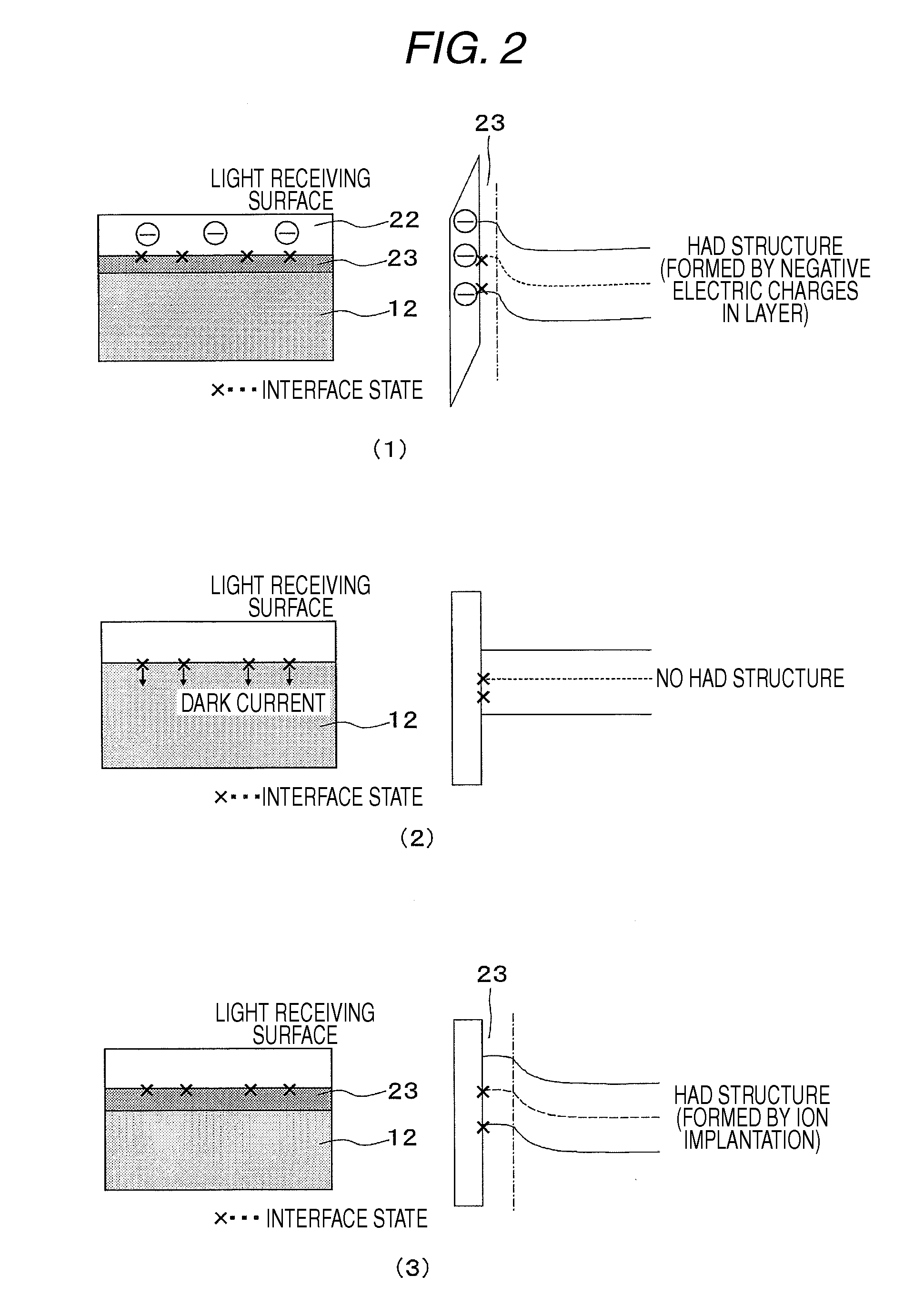

Solid state imaging device, method of manufacturing the same, and imaging apparatus

ActiveUS20090096049A1High quality imagingReduce noise imagingTelevision system detailsSolid-state devicesLight sensingPhotoelectric conversion

A solid state imaging device having a light sensing section that performs photoelectric conversion of incident light includes: an insulating layer formed on a light receiving surface of the light sensing section; a layer having negative electric charges formed on the insulating layer; and a hole accumulation layer formed on the light receiving surface of the light sensing section.

Owner:SONY CORP

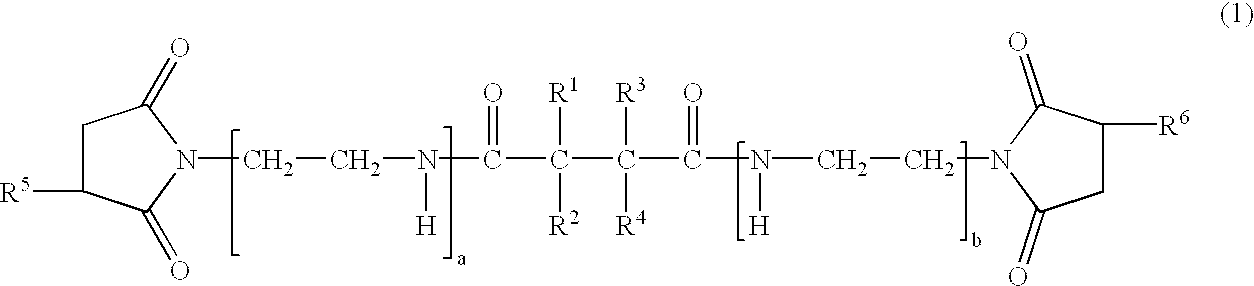

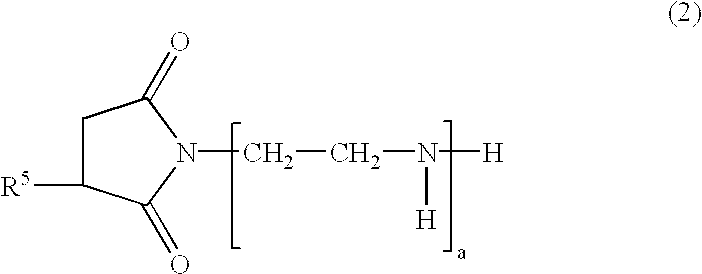

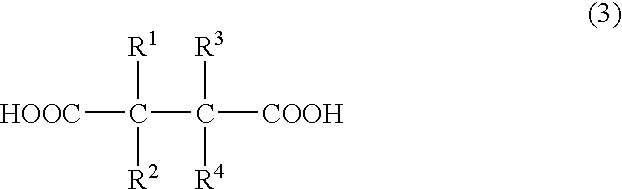

Lubricant compositions

InactiveUS20020119896A1Improve abilitiesSuppress increase of viscosityOrganic chemistryOrganic compound preparationViscosity indexZinc dithiophosphate

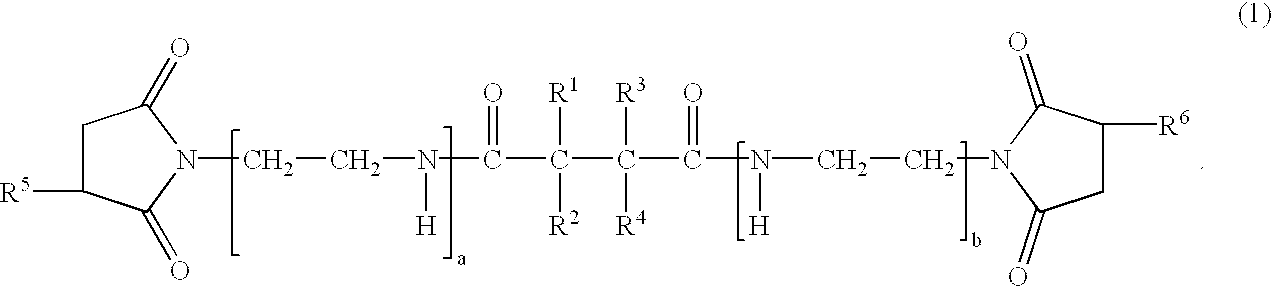

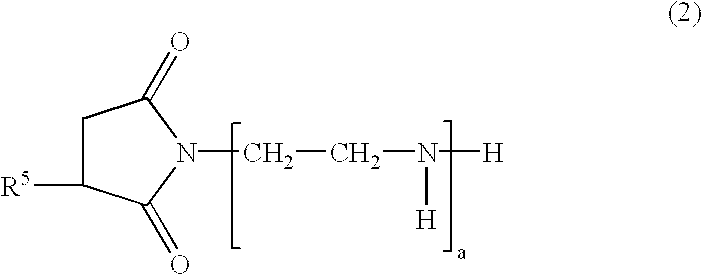

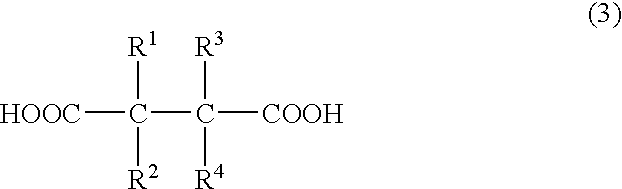

Lubricant compositions comprise a lubricant base oil, and (A) a mono substituted amide type bissuccinimide in an amount from 0.5 to 20 percent by mass, (B) zinc dithiophosphate in an amount from 0.05 to 0.3 percent by mass of phosphorus, and (C) a metal-based detergent in an amount form 0.5 to 4.0 percent by mass of sulfated ash, based on the total mass of the composition. Lubricant compositions preferably further comprises (D) a dispersant type viscosity index improver in an amount from 0.1 to 20 percent by mass, based on the total mass of the composition.

Owner:NIPPON MITSUBISHI OIL CORP

Electrosurgical system and method for treating hard body tissue

ActiveUS9131597B2Improve bindingSufficient formElectrotherapySurgical instruments for heatingActive electrodeBlood plasma

A method of preparing a target hard body tissue, such as osseous or dental tissue, to receive an implant component including; positioning an active electrode in proximity to a target tissue and proximate an electrically conductive fluid, followed by applying a high frequency voltage between the active electrode and a return electrode, the high frequency voltage sufficient to form a plasma. This plasma modifies at least a portion of the target tissue. An implant component may then be placed adjacent at least a portion of the modified target tissue.

Owner:ARTHROCARE

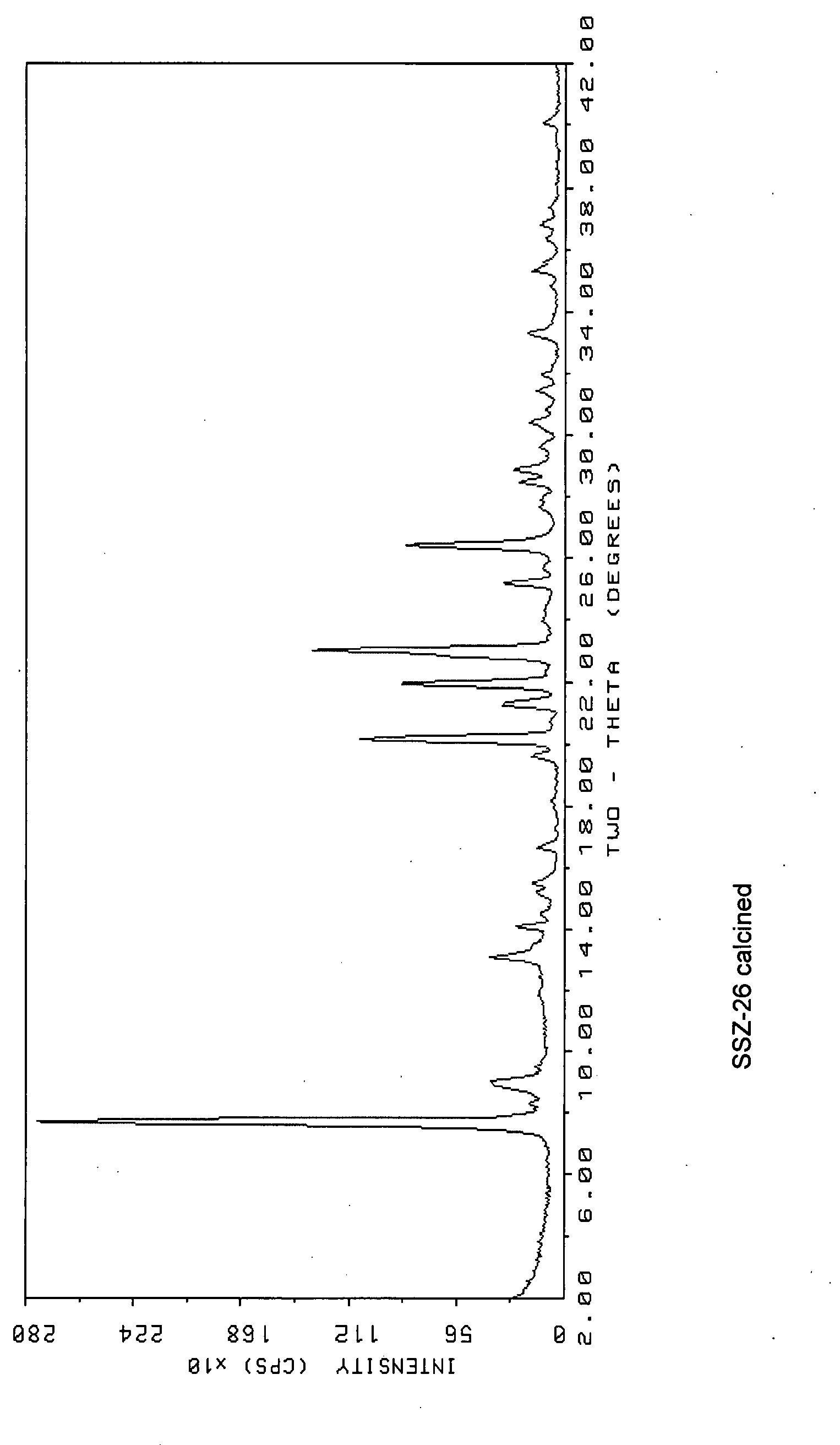

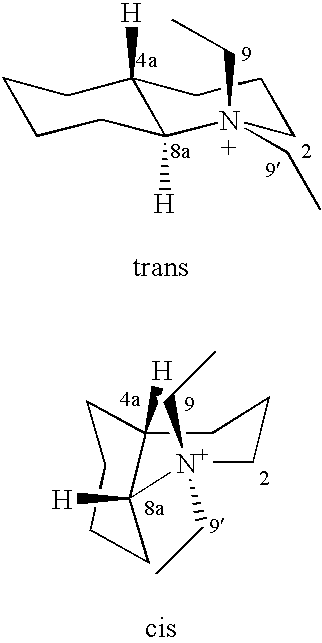

Process for preparing aluminum-containing molecular sieve ssz-26

InactiveUS20080089835A1Sufficient formAluminium compoundsAluminium silicatesMolecular sieveOrganic chemistry

A process for directly preparing aluminum-containing molecular sieve SSZ-26 using a structure directing agent comprising a cis-N,N-diethyldecahydroquinolinium cation or mixture of a cis-N,N-diethyldecahydroquinolinium cation and a trans-N,N-diethyldecahydroquinolinium cation.

Owner:CHEVROU USA INC

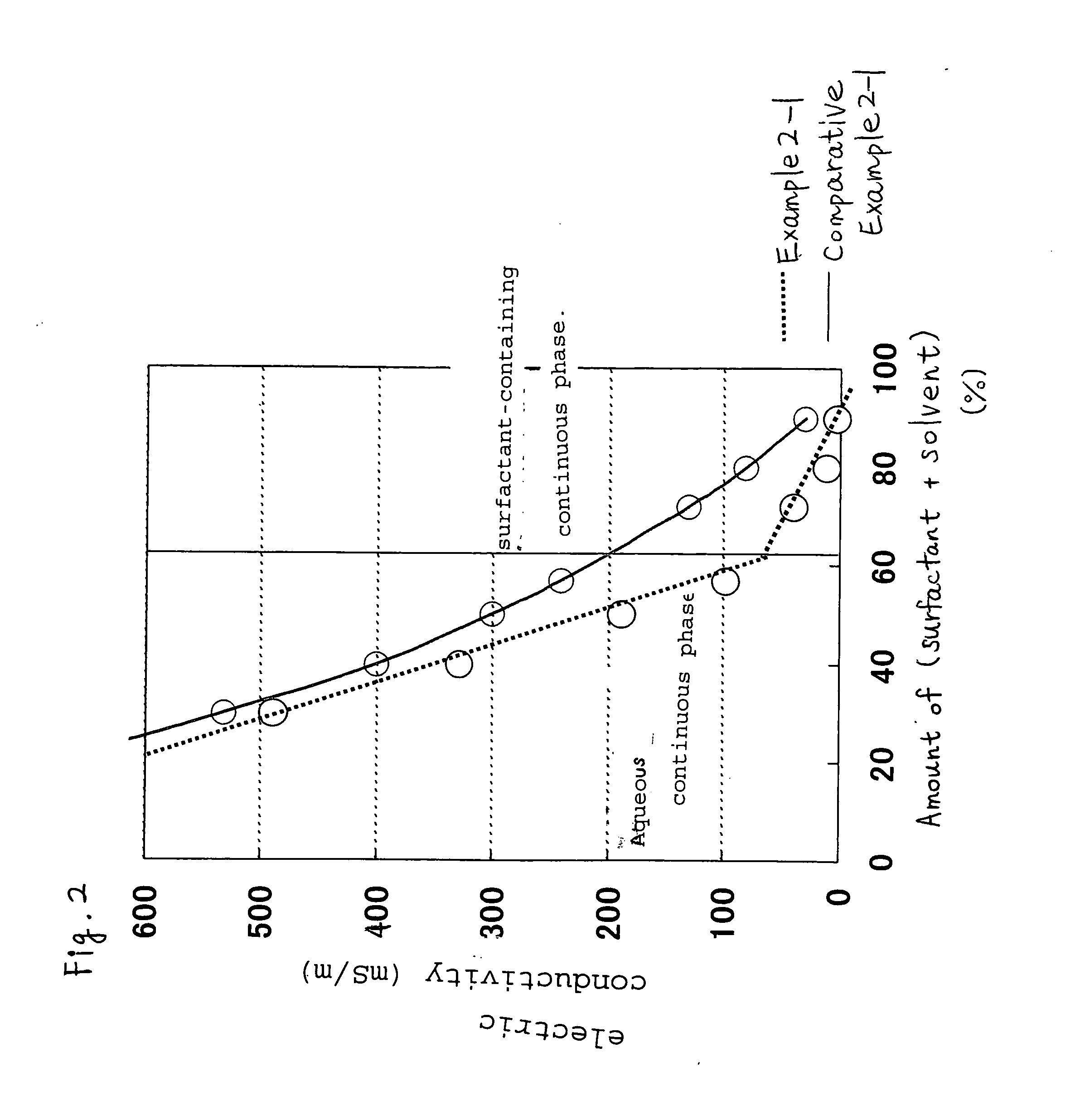

Liquid Detergent Composition

InactiveUS20090249557A1Sufficient formImprove stabilityNon-ionic surface-active compoundsOrganic detergent compounding agentsBoric acidBleach activator

The present invention relates to a liquid detergent composition containing (a) hydrogen peroxide or a compound forming hydrogen peroxide in water, 0.1 to 10 mass % of (b) a bleaching activator, 45 to 80 mass % of (c) a nonionic surfactant, (d) water, (e) at least one or more compounds selected from boric acid, borax and borate, and (f) a polyol compound, said liquid detergent composition having a pH value of 4 to 7 at 20° C.

Owner:KAO CORP

Lubricant compositions

InactiveUS6569819B2Reduce fluid resistanceImprove the lubrication effectOrganic chemistryOrganic compound preparationSulfateViscosity index

Lubricant compositions comprise a lubricant base oil, and (A) a mono substituted amide type bissuccinimide in an amount from 0.5 to 20 percent by mass, (B) zinc dithiophosphate in an amount from 0.05 to 0.3 percent by mass of phosphorus, and (C) a metal-based detergent in an amount form 0.5 to 4.0 percent by mass of sulfated ash, based on the total mass of the composition. Lubricant compositions preferably further comprises (D) a dispersant type viscosity index improver in an amount from 0.1 to 20 percent by mass, based on the total mass of the composition.

Owner:NIPPON MITSUBISHI OIL CORP

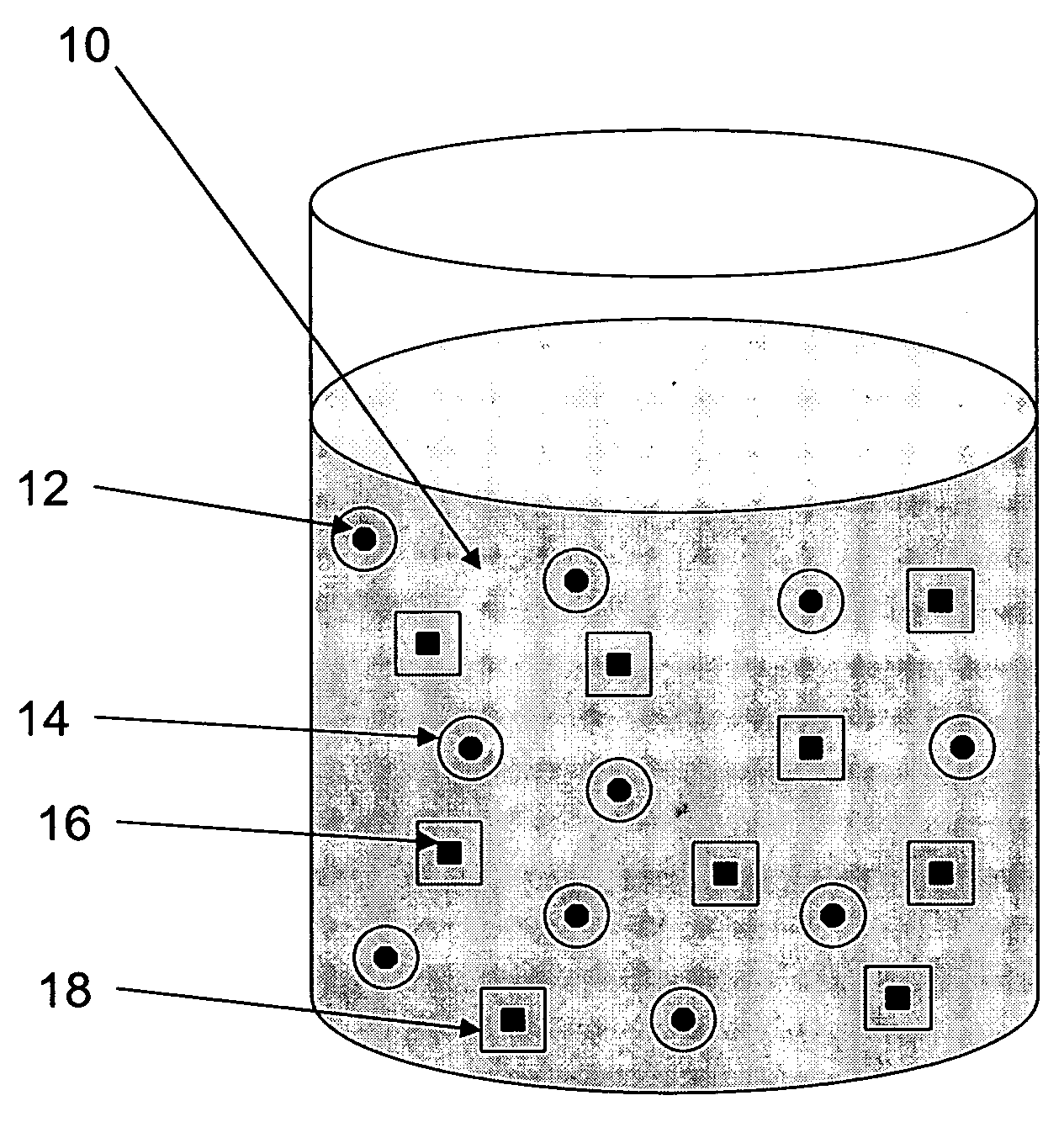

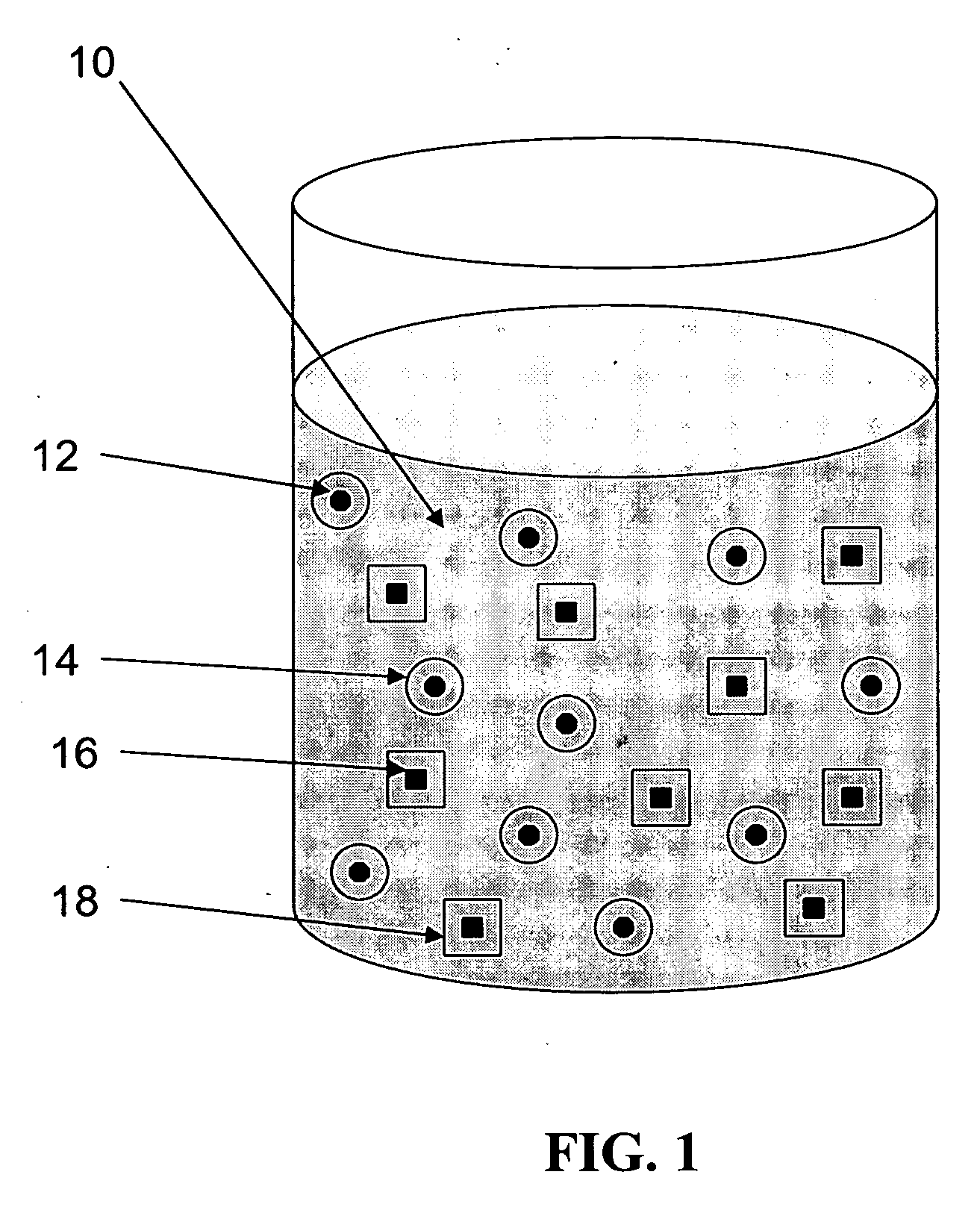

Compositions and methods comprising magnetic particles for health use

The present invention provides a topical composition comprising a topical composition base and a plurality of magnetic particles. The topical composition can further comprise one or more active agents. The magnetic particles and / or active agent(s) can optionally be encapsulated and / or coated. Methods for making and using the topical composition are also provided.

Owner:SPECTOR DONALD

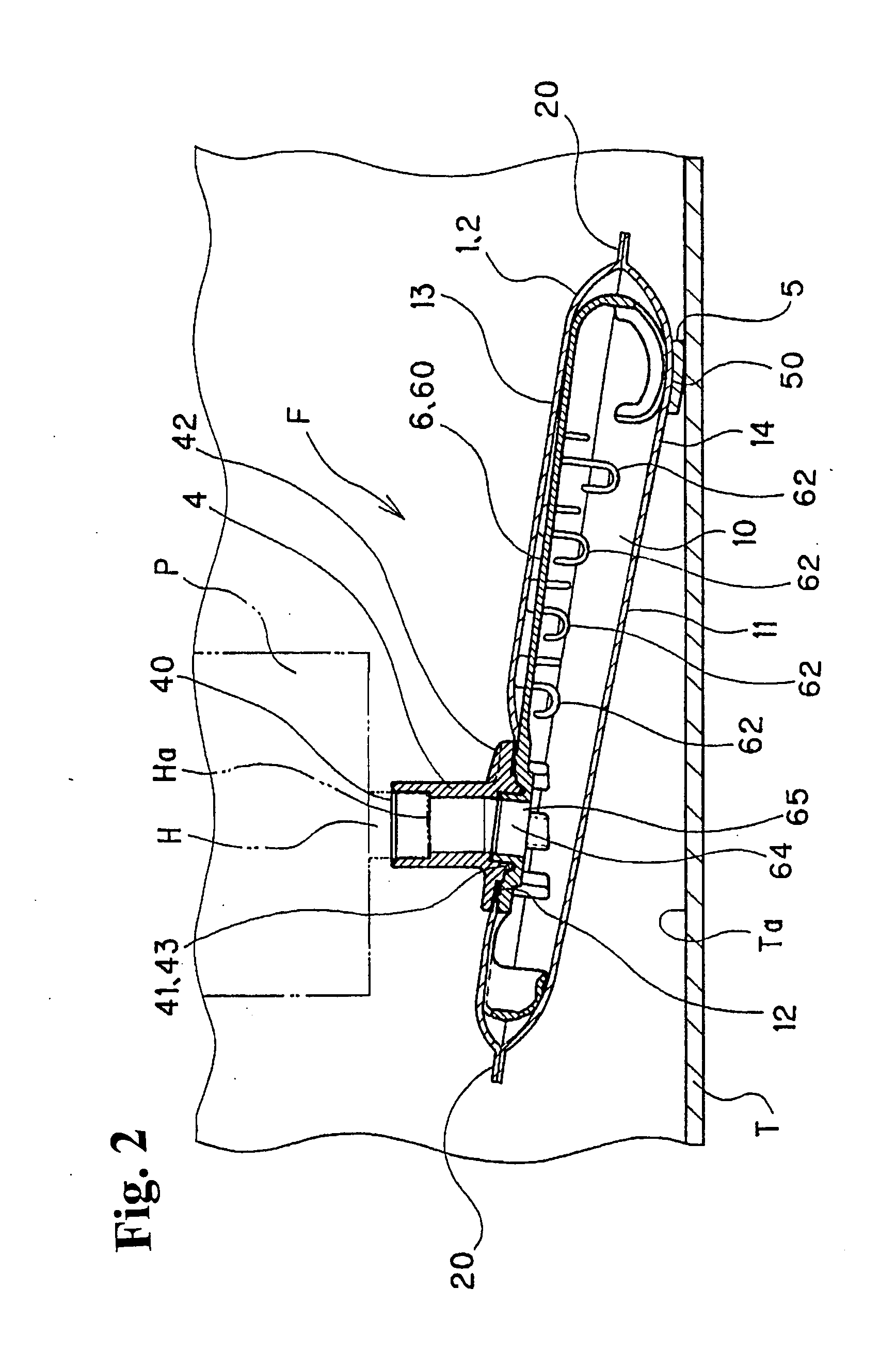

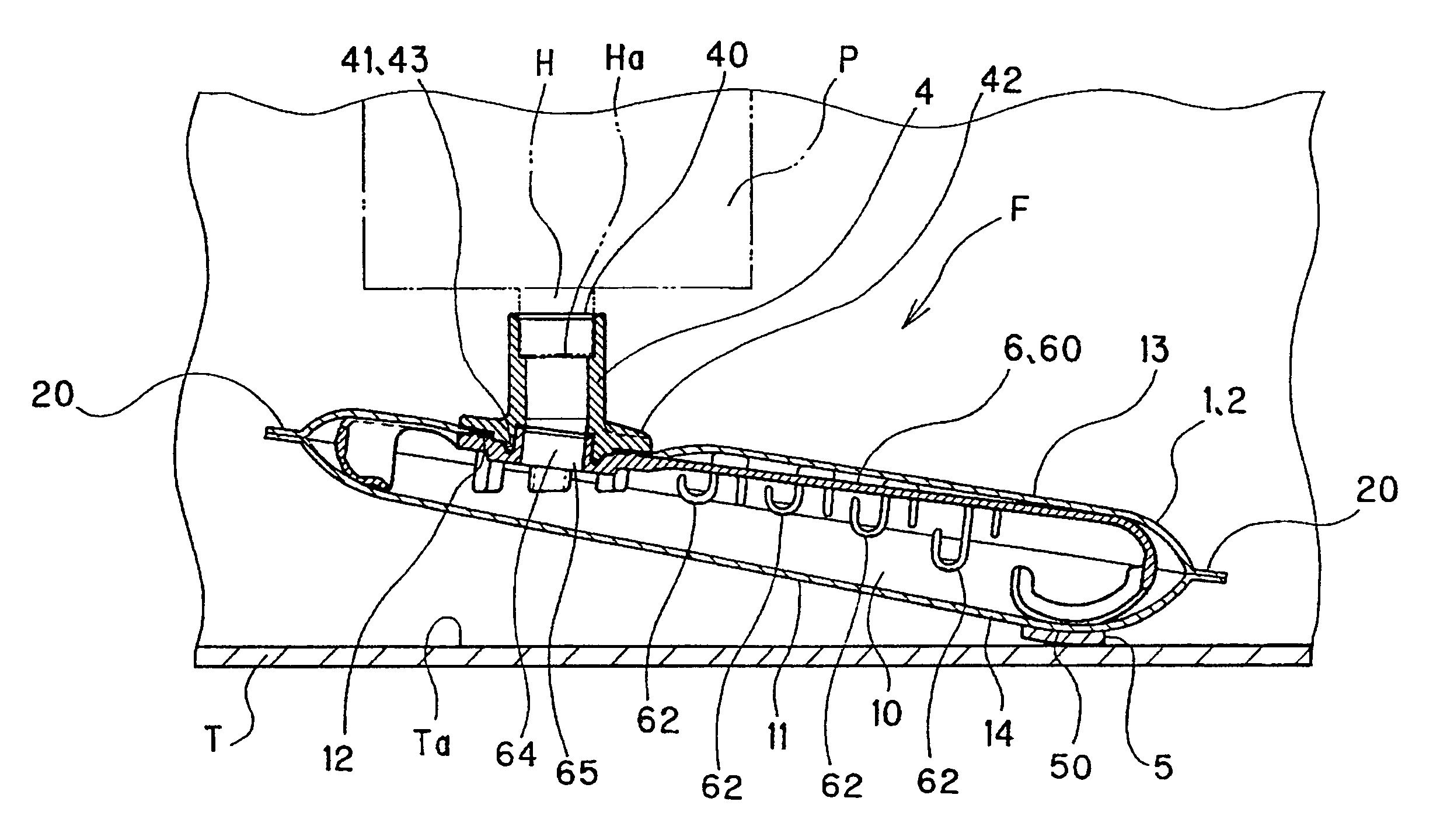

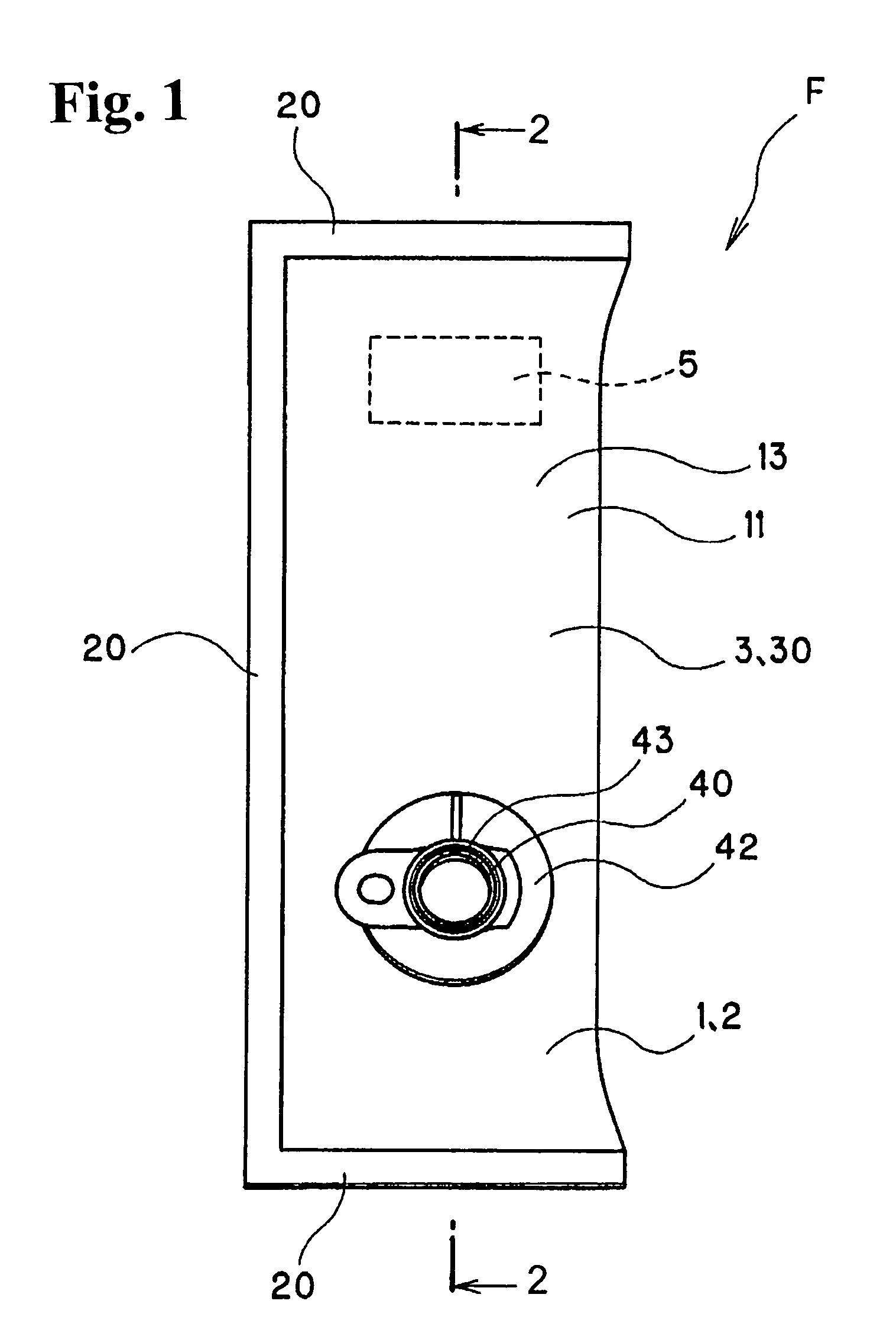

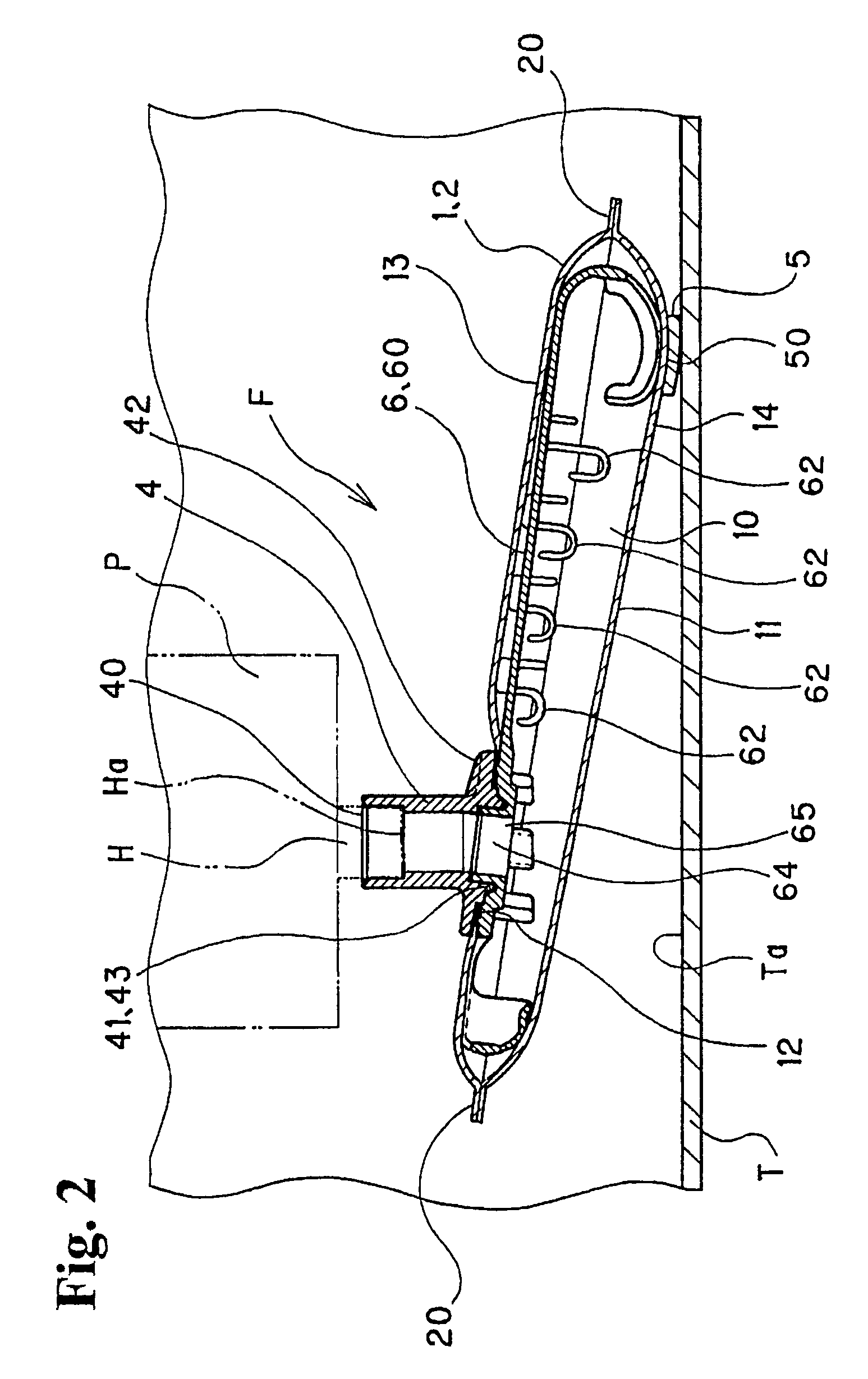

Fuel-filtering device

InactiveUS20050150826A1Easy to separateEfficient separationWater/sewage treatmentMachines/enginesFuel tankEngineering

A fuel-filtering device is disposed inside a fuel tank for filtering a fuel. The fuel-filtering device includes a filter body having a bag shape and a communication hole, and is formed of a plurality of laminated filter layers. The laminated filter layers includes an outside filter layer formed of a woven mesh, an inside filter layer formed of a non-woven fabric, and at least one intermediate filter layer disposed between the outside filter layer and the inside filter layer and formed of a non-woven fabric. The filter body is formed of at least one of a polyethylene fiber and a polypropylene fiber and has mesh sizes decreasing from the outside filter layer toward the inside filter layer.

Owner:NIFCO INC

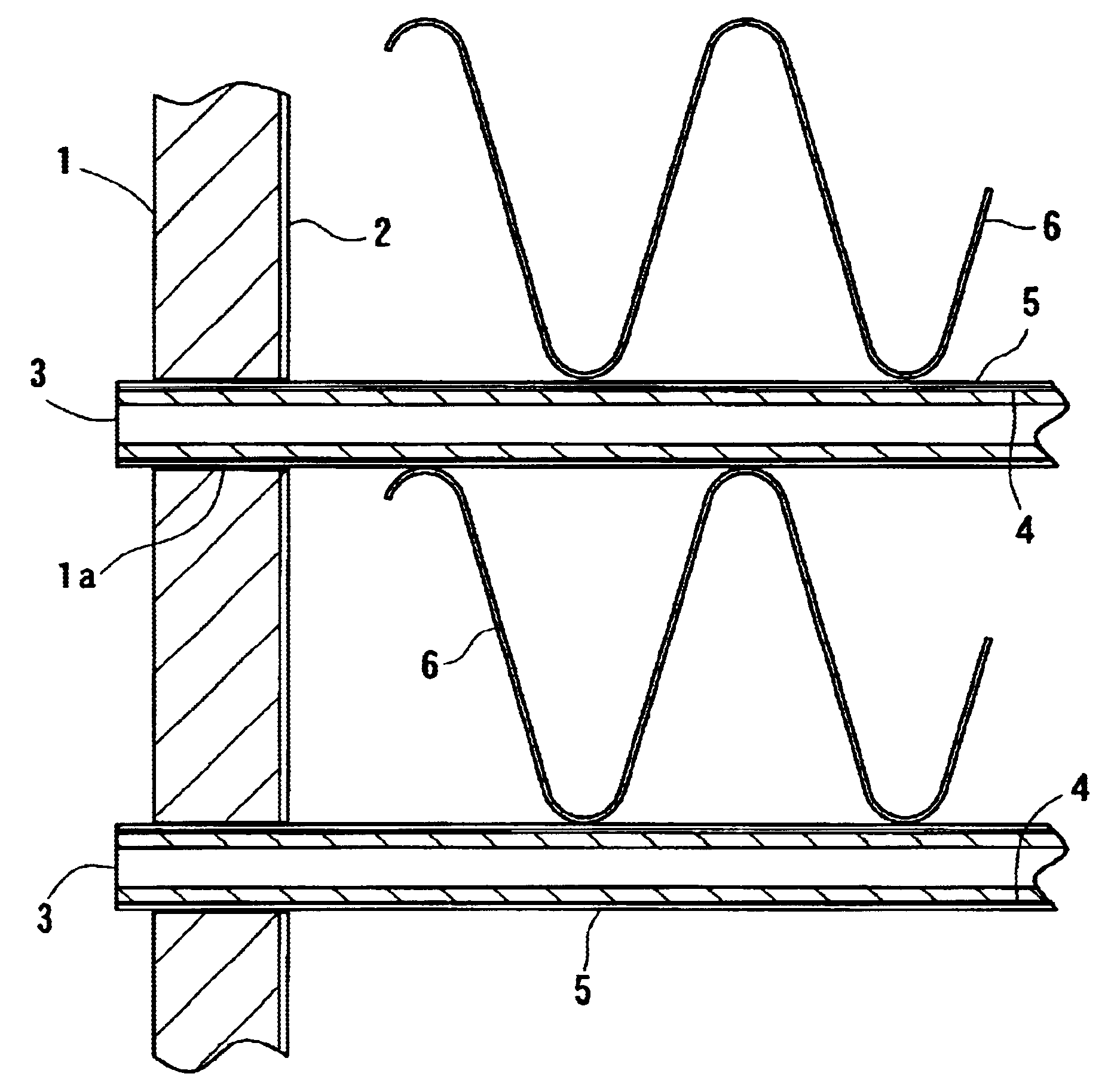

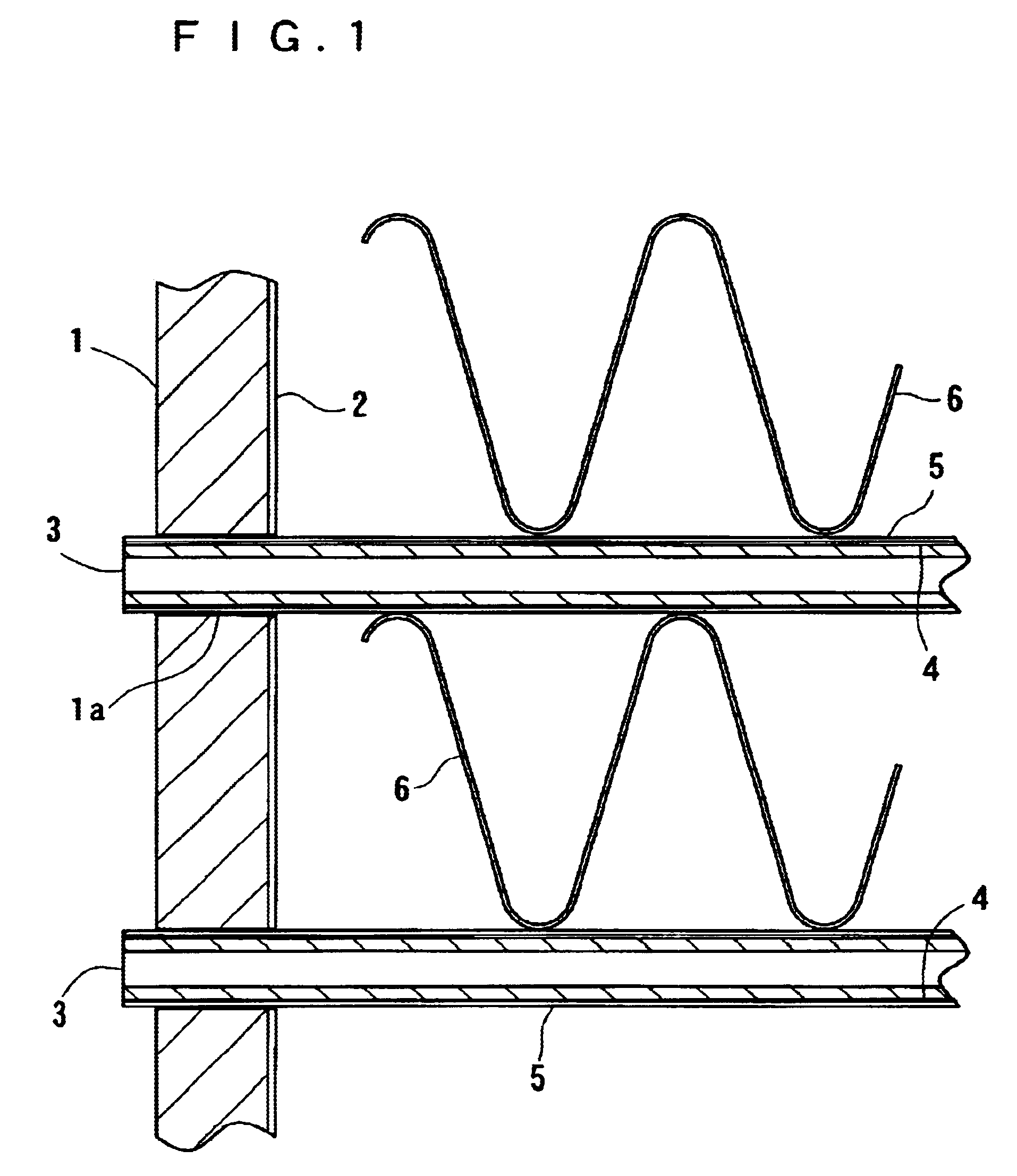

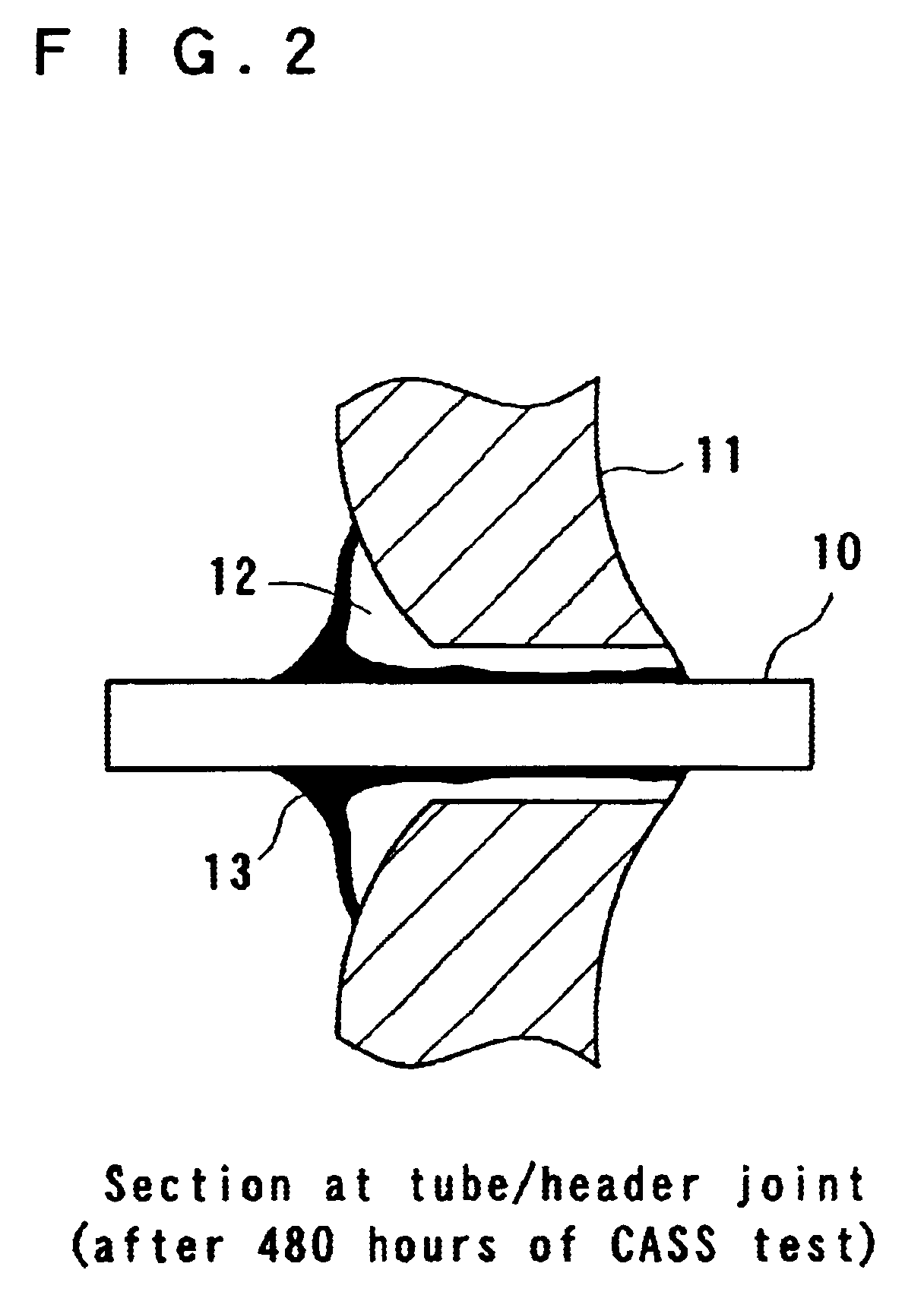

Method for production of heat exchanger

InactiveUS6708869B2Improve corrosion resistanceFacilitated DiffusionMolten spray coatingHeat exchanger casingsPlate heat exchangerAlloy

A heat exchanger, characterized in that Al or Al alloy tubes, each having a thermally Zn-sprayed layer formed on the surface of it, and having a brazing filler metal layer formed on said thermally Zn-sprayed layer using a powdery brazing filler Al alloy composed of 5 to 60 weight % of Si and the balance of Al and unavoidable impurities, are combined with and brazed to an Al or Al alloy header having a brazing filler metal layer formed using a powdery brazing filler Al alloy composed of 5 to 60 weight % of Si and the balance of Al and unavoidable impurities. The tubes and the header are strongly bonded to each other, and Zn is uniformly diffused and distributed. So, the heat exchanger shows good corrosion resistance.

Owner:MITSUBISHI ALUMINUM CO LTD

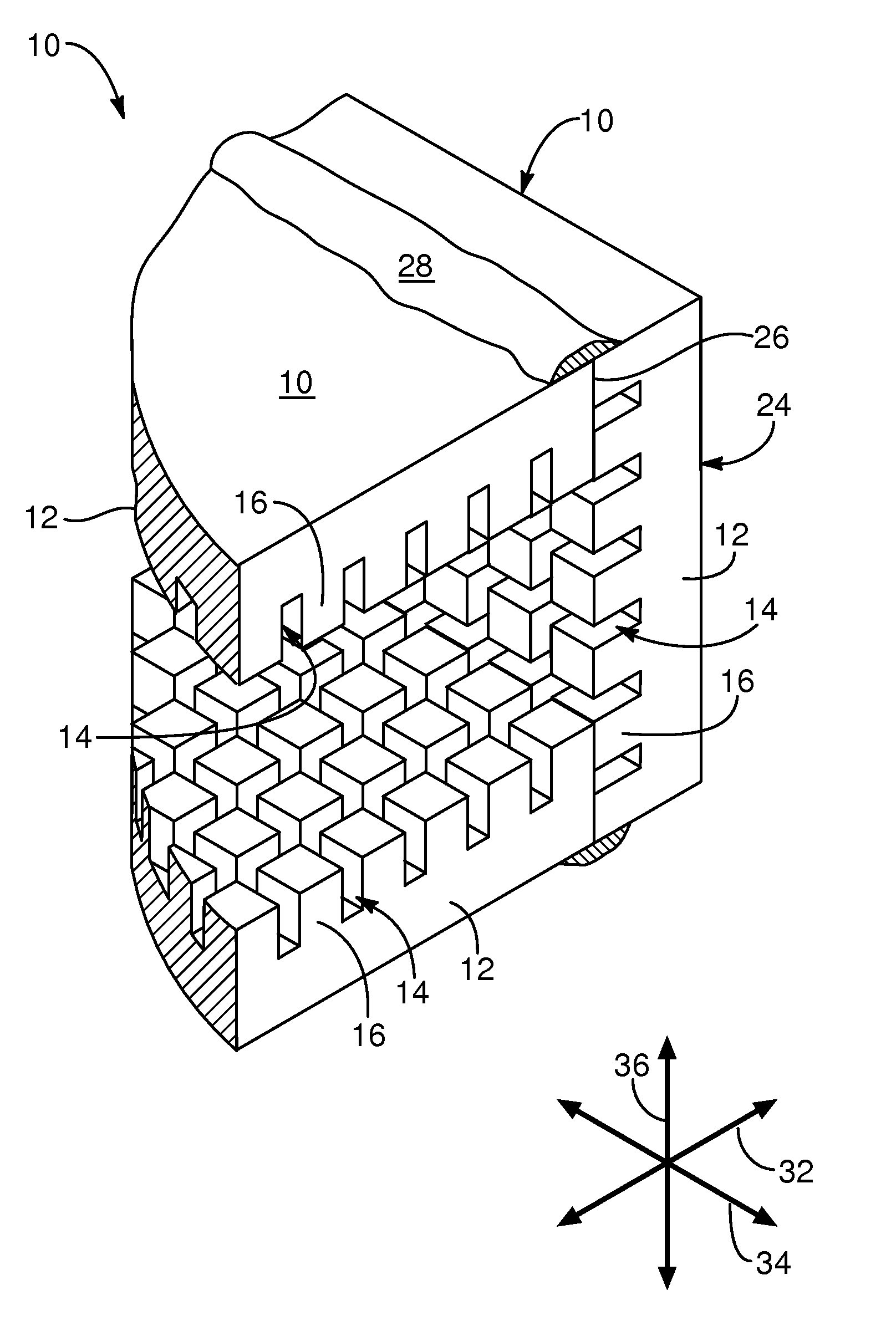

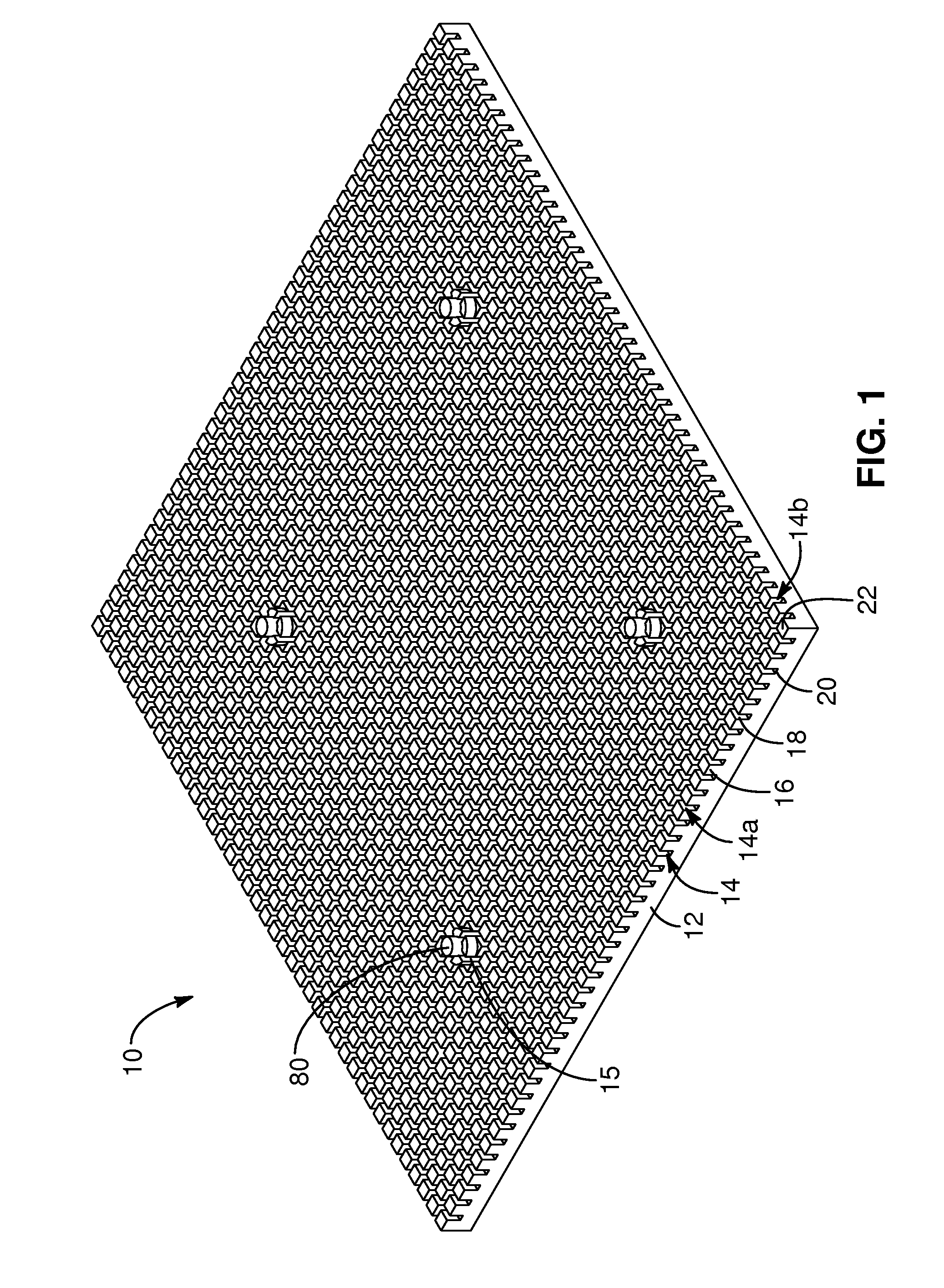

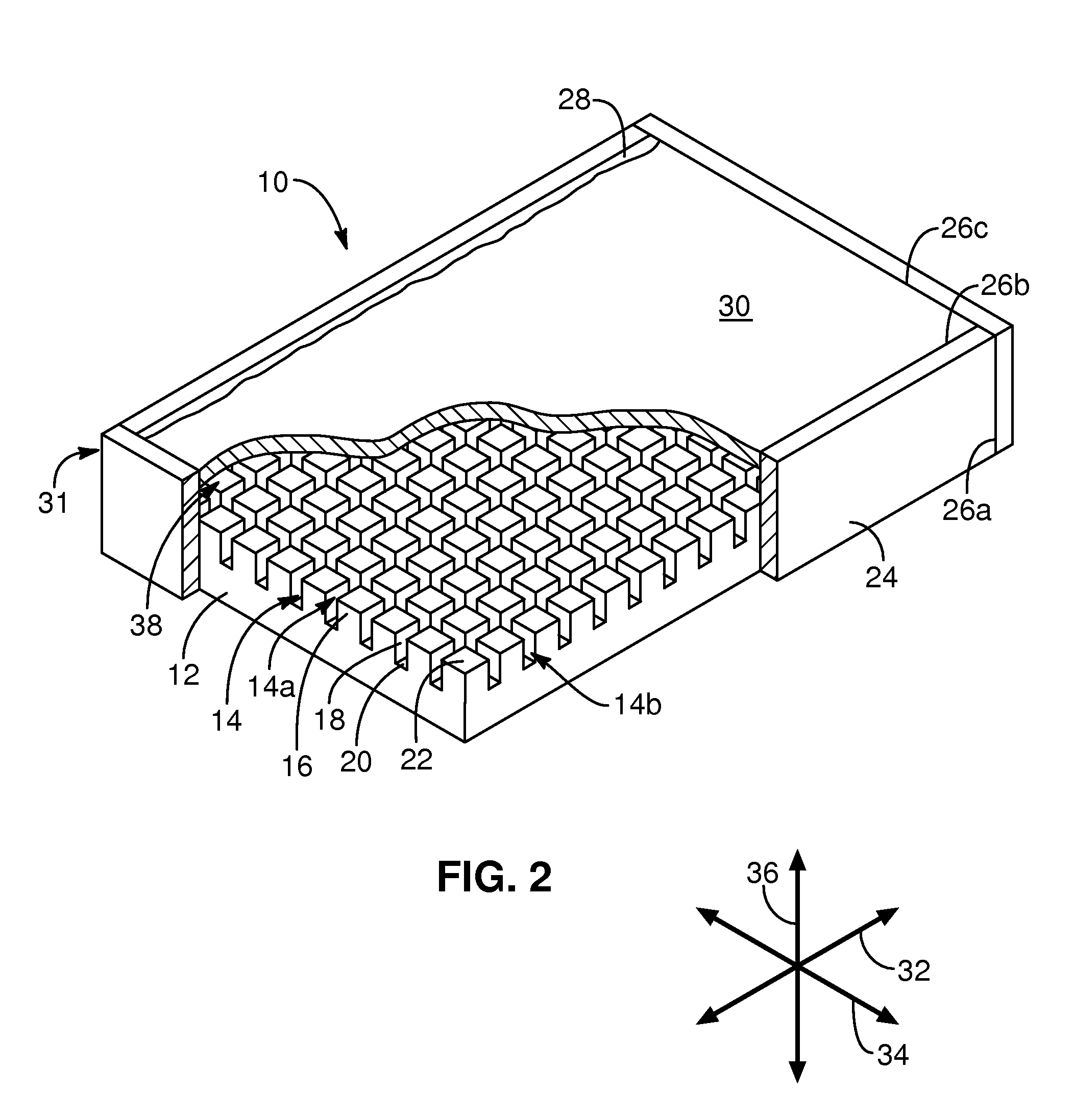

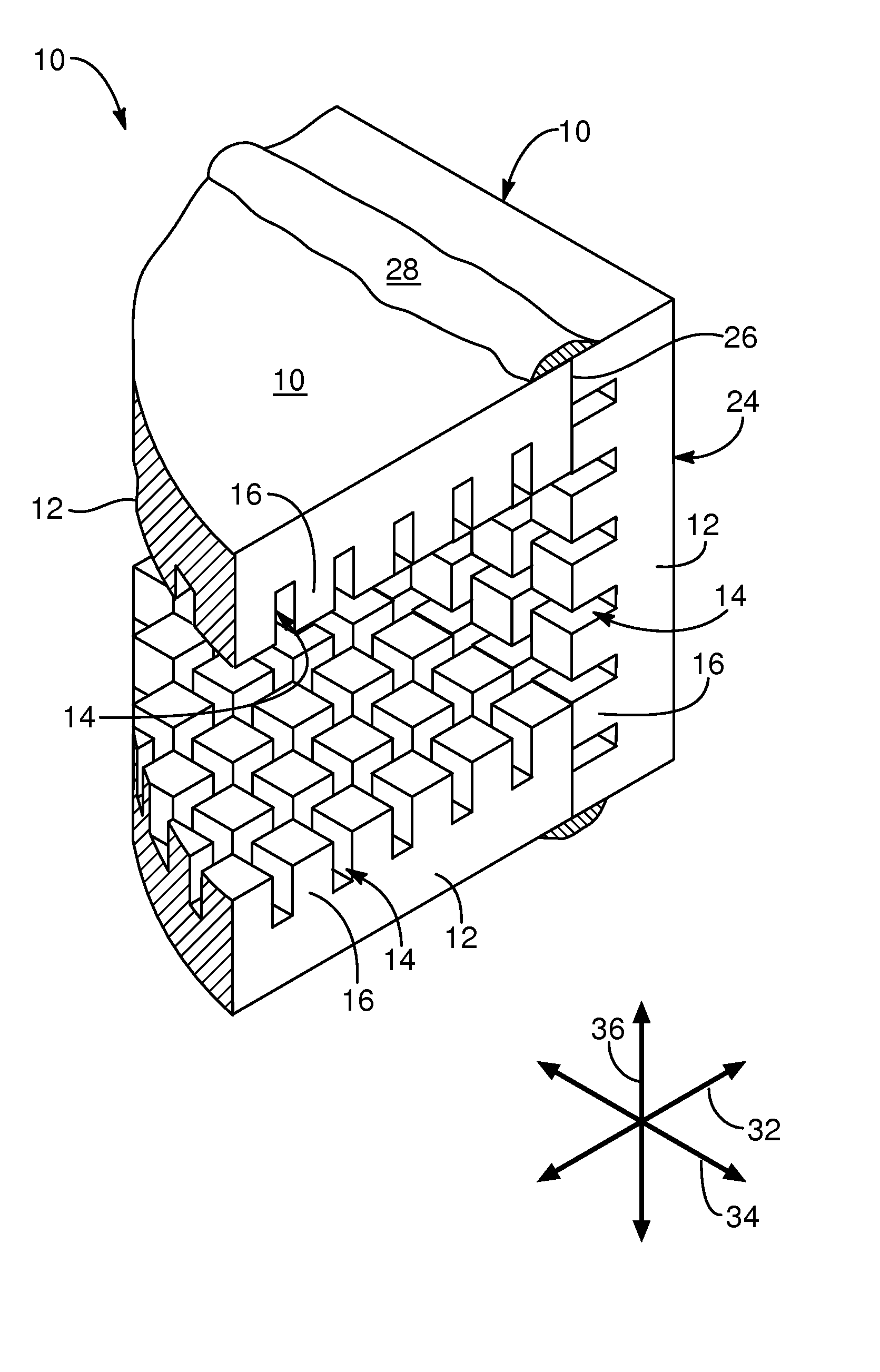

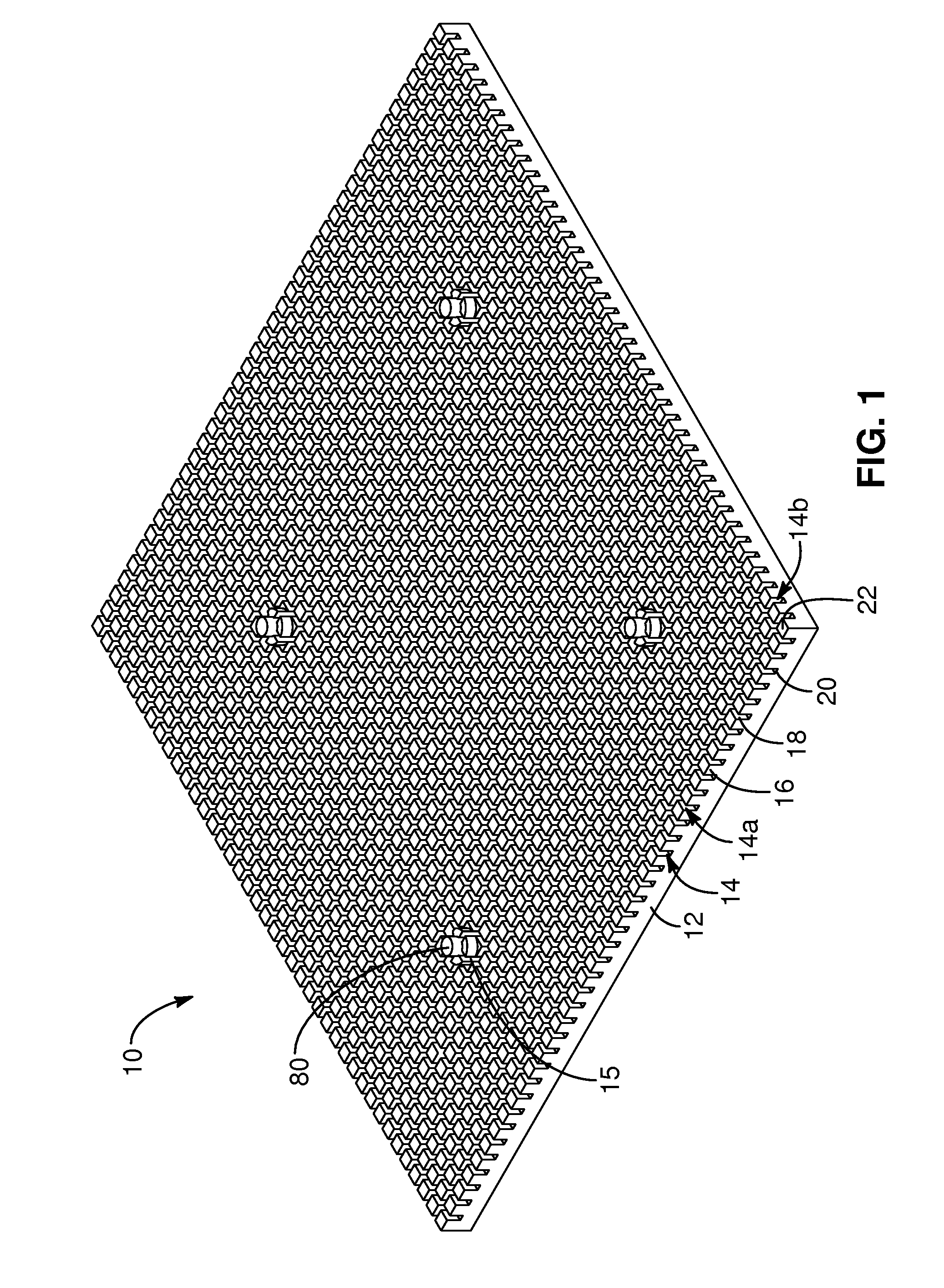

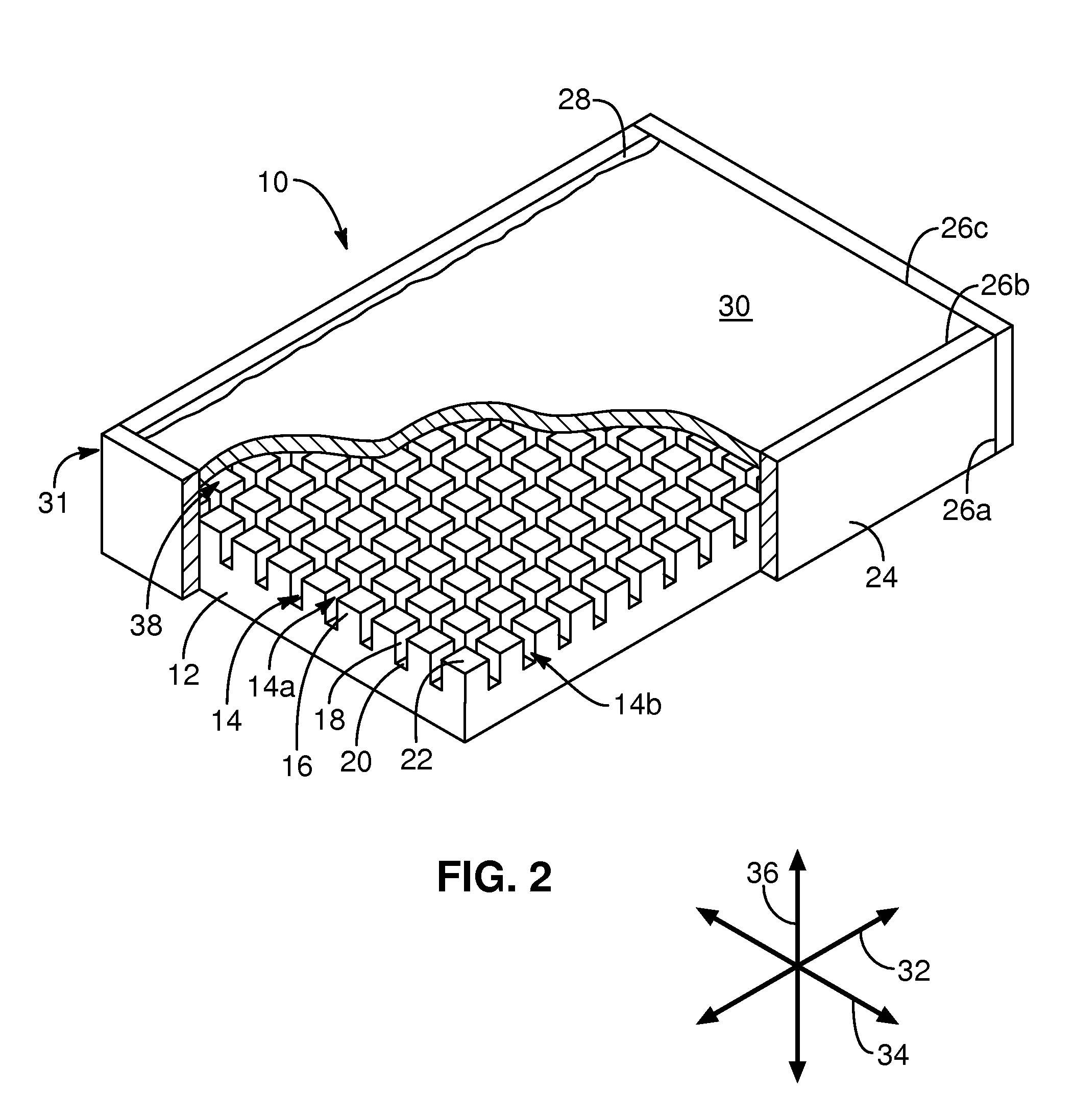

Minimal-Temperature-Differential, Omni-Directional-Reflux, Heat Exchanger

ActiveUS20100132923A1Easy to moveSufficient formIndirect heat exchangersHeat transfer modificationWorking fluidGas phase

A substrate formed of a suitable conductive-heat-transfer material is formed with small channels of a size selected to provide surface tension forces dominating a motion of a liquid-phase working fluid. A space above the channels of the substrate provides comparatively unobstructed space for the transport motion of a vapor phase of the working fluid effecting a heat-pipe effect in a multi-dimensional device. Channels may typically be formed in an orthogonal grid providing capillary return of liquids from a comparatively cooler condensation region to a comparatively warmer evaporation region, without any wicks other that the adhesion of the liquid phase working fluid to the vertices of the channels. Interference between the boundary layers of the liquid phase and the vapor phase of the working fluid are minimized by the depth of the channels, and the pedestals formed by the channel walls. Extremely small temperature differentials are thereby achieved between an outer surface of the substrate and an inner surface of the substrate when the liquid phase floods the substrate.

Owner:UTAH STATE UNIVERSITY

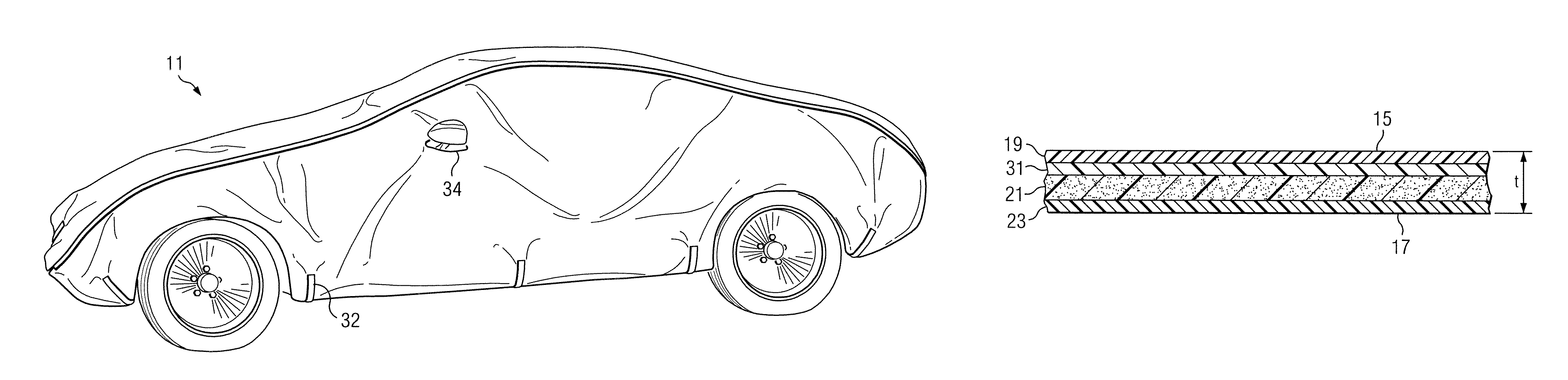

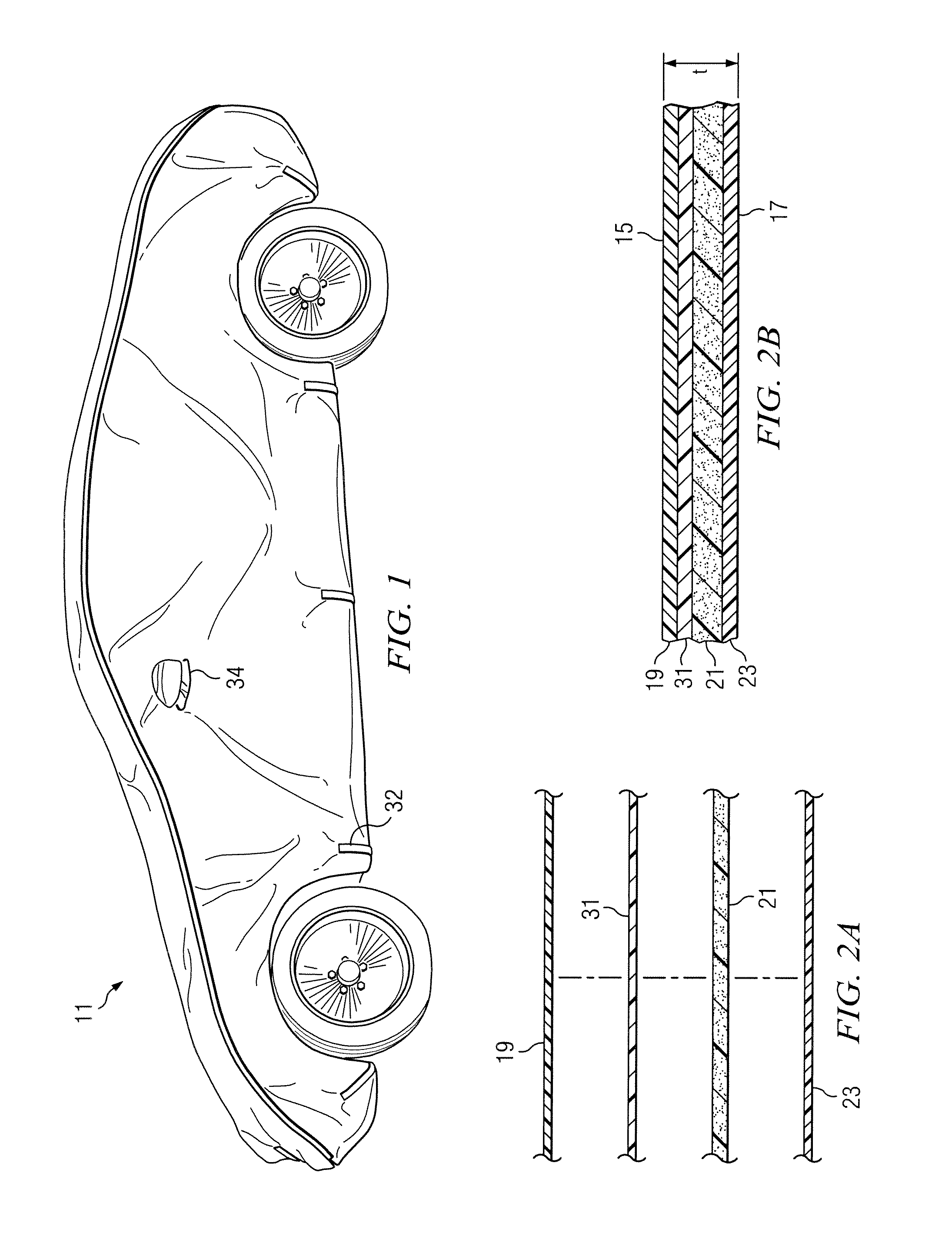

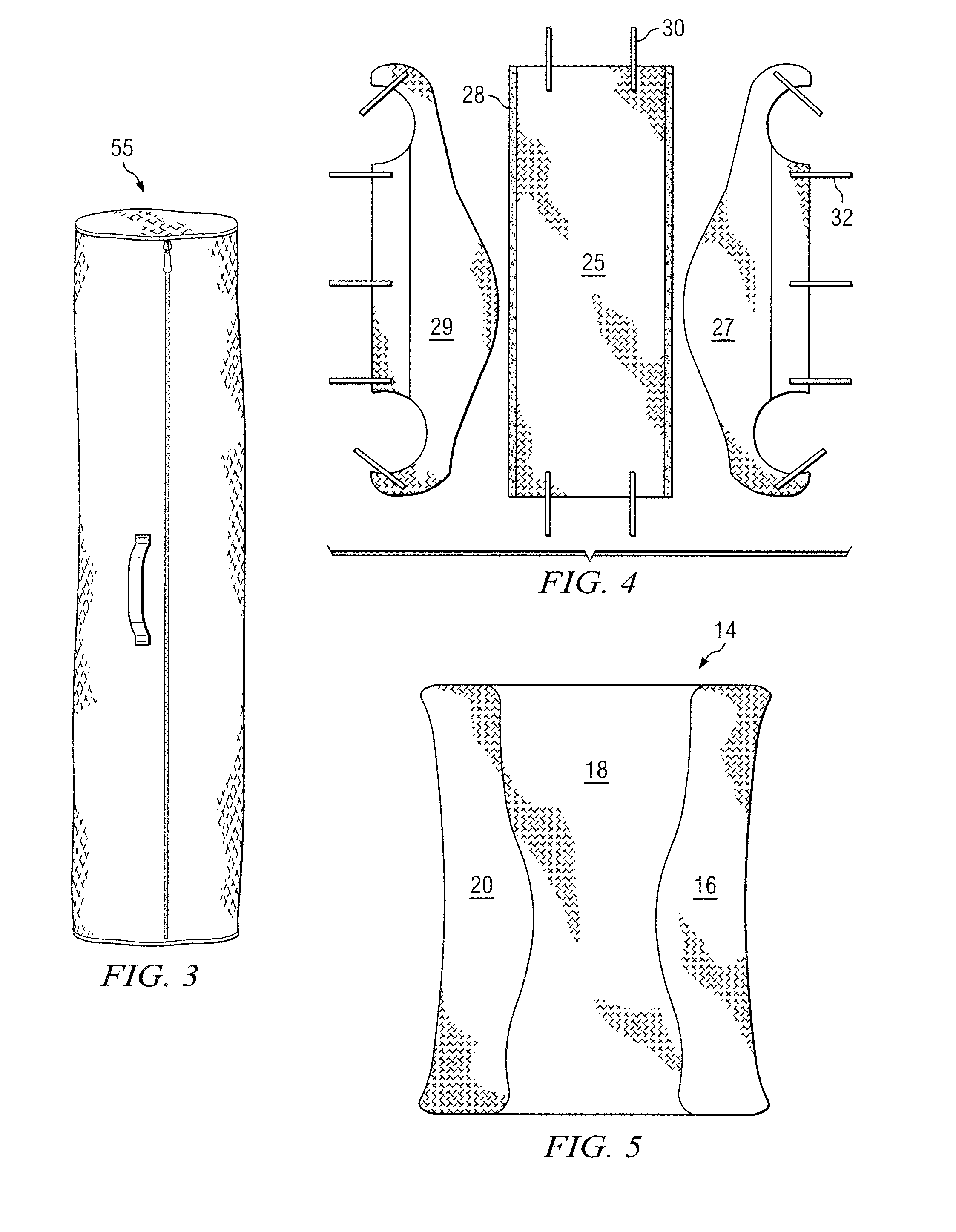

Protective vehicle cover

A protective vehicle cover is shown for protecting an outer surface of a vehicle from hail and other falling objects. The cover includes a flexible blanket having a front side, a back side and a thickness therebetween. The blanket is made up of an outer fabric cover and a protective central region, the protective central region being made up of a layer of foam cushioning material covered with a layer of flexible plastic-type material which together provide a cushioning effect to protect the outer surface of the vehicle from hail and other falling objects; Fastening elements are provided for attaching the flexible blanket to the outer surface of the vehicle.

Owner:DEVEREAUX CAREY

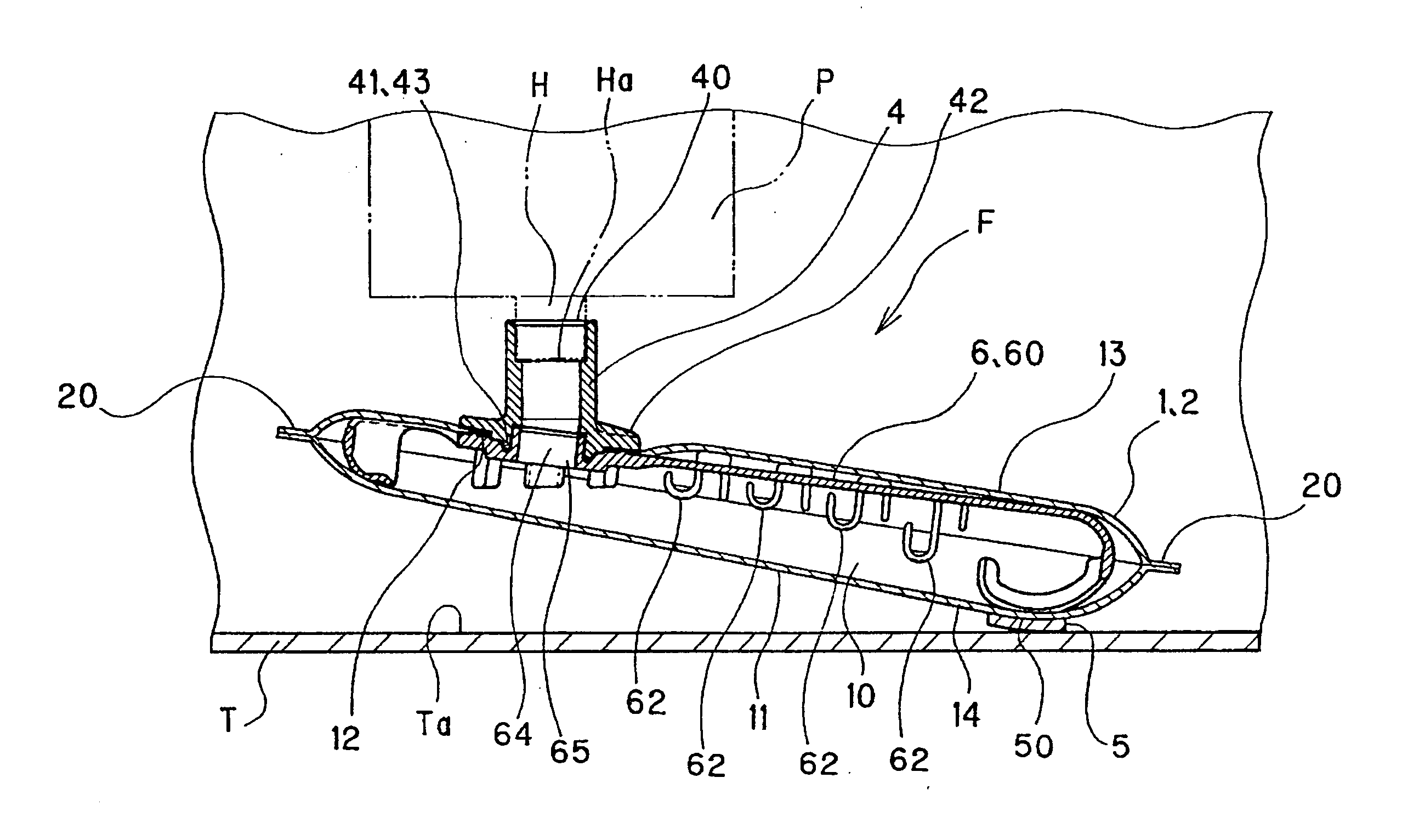

Fuel-filtering device

InactiveUS7478729B2Easy to separateEfficient separationWater/sewage treatmentMachines/enginesFuel tankFuel filter

A fuel-filtering device is disposed inside a fuel tank for filtering a fuel. The fuel-filtering device includes a filter body having a bag shape and a communication hole, and is formed of a plurality of laminated filter layers. The laminated filter layers includes an outside filter layer formed of a woven mesh, an inside filter layer formed of a non-woven fabric, and at least one intermediate filter layer disposed between the outside filter layer and the inside filter layer and formed of a non-woven fabric. The filter body is formed of at least one of a polyethylene fiber and a polypropylene fiber and has mesh sizes decreasing from the outside filter layer toward the inside filter layer.

Owner:NIFCO INC

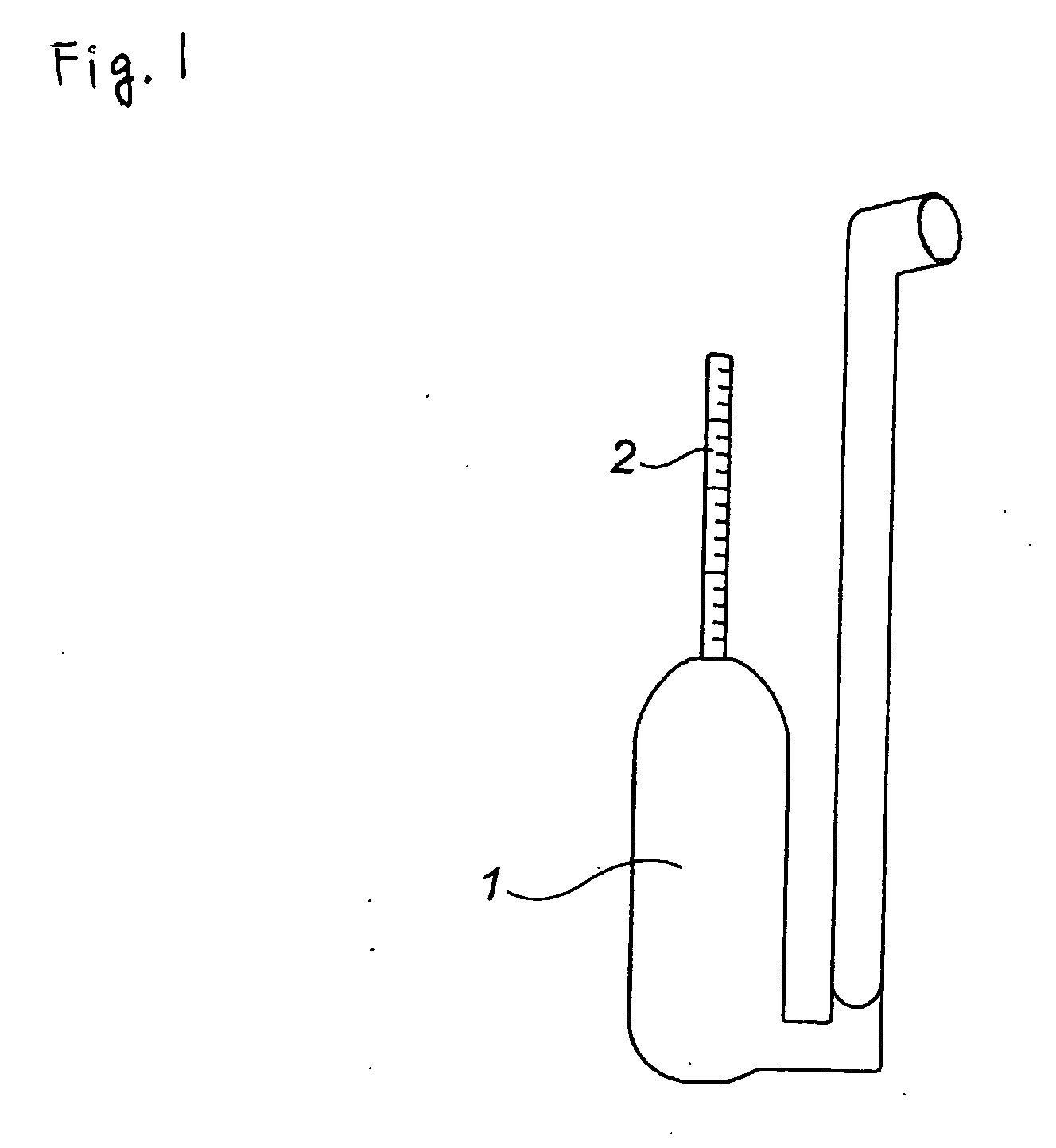

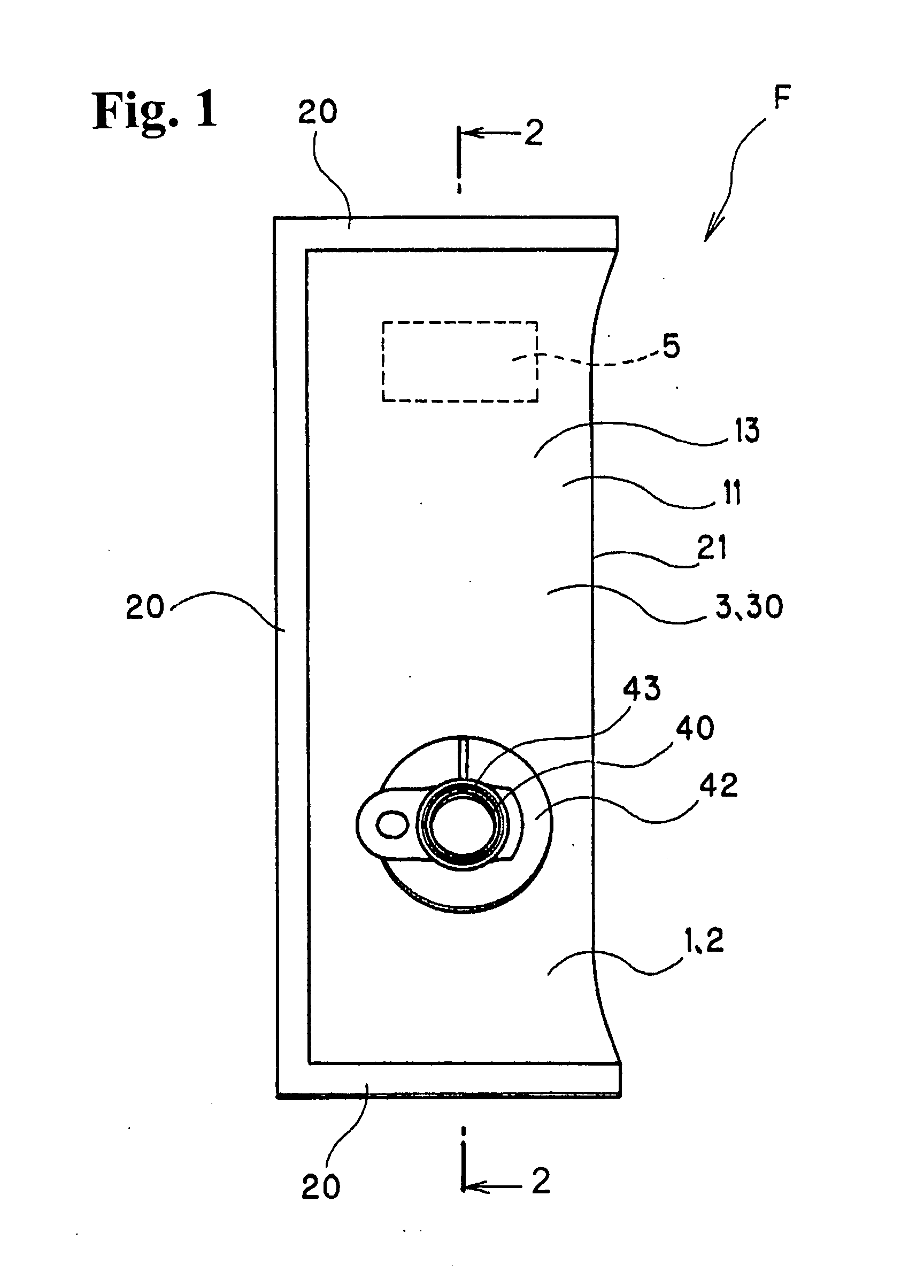

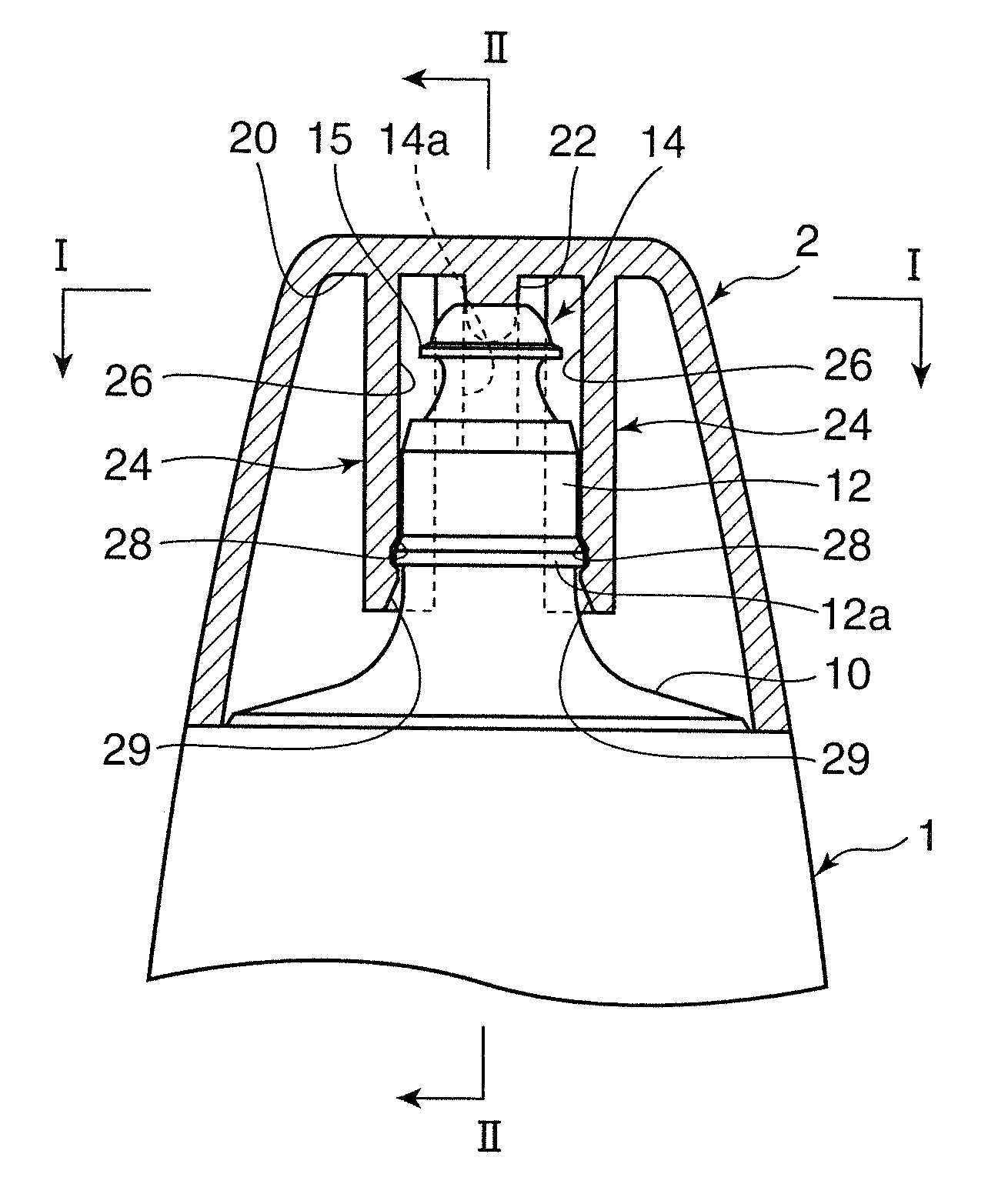

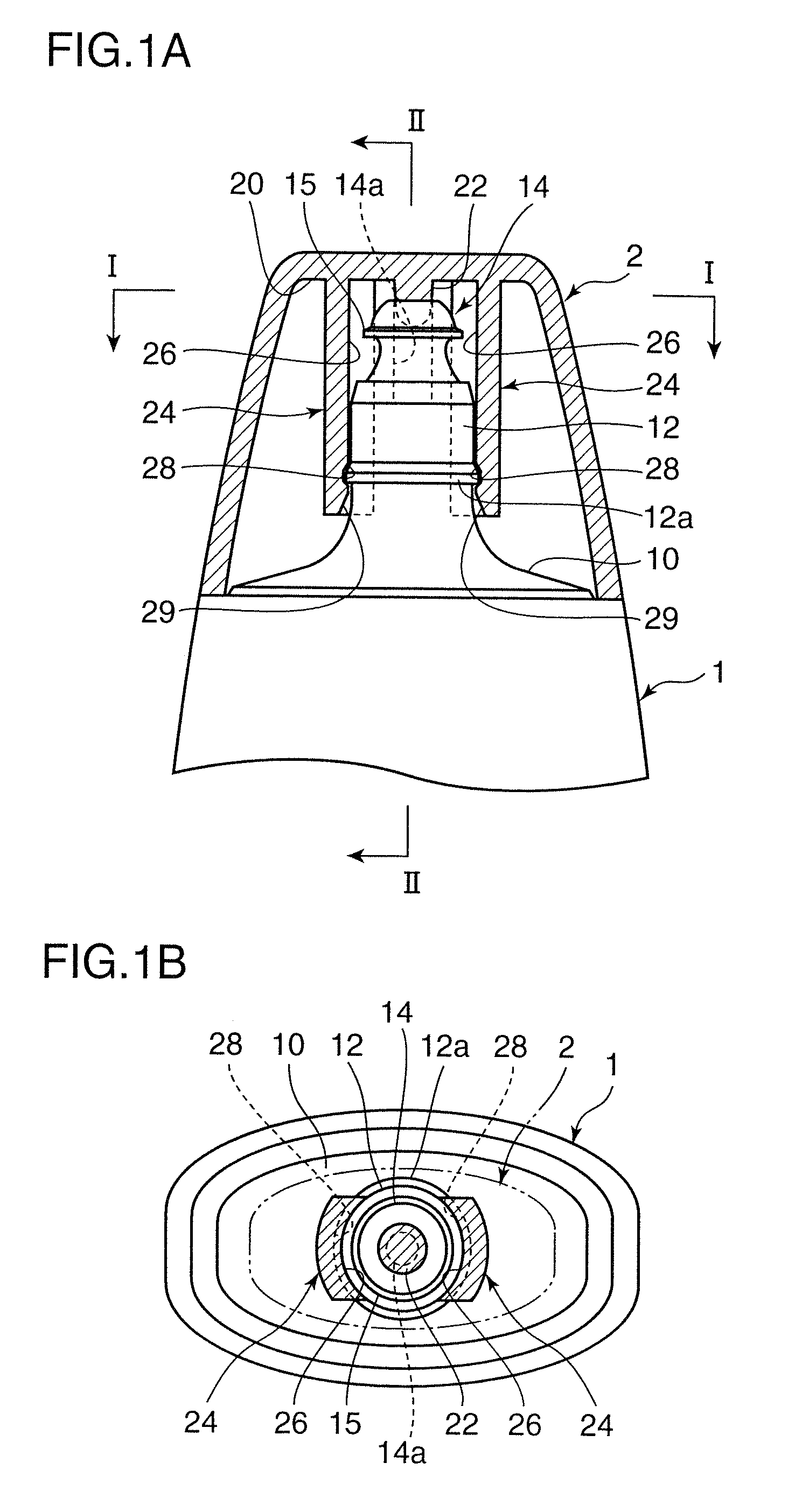

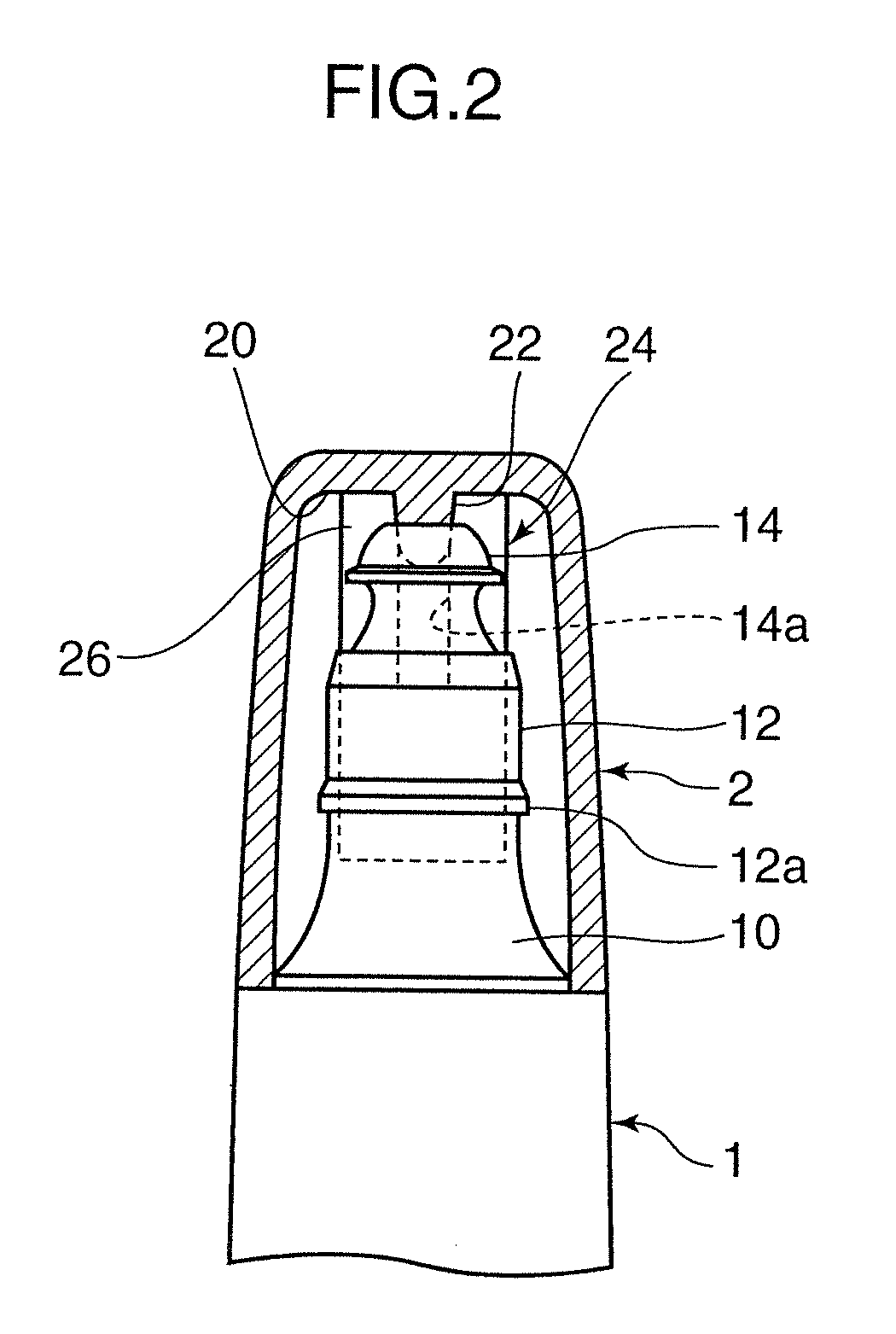

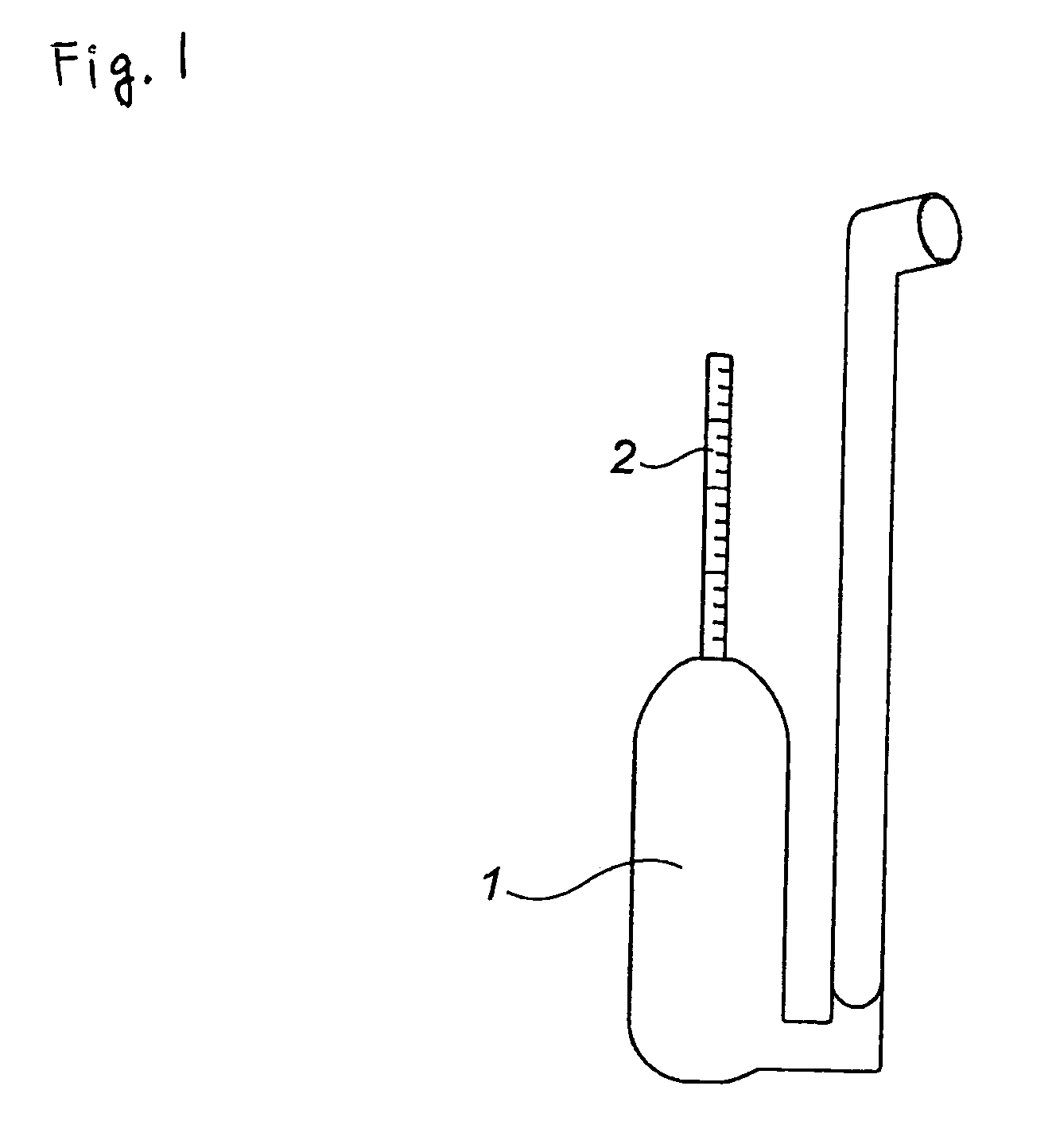

Liquid container

InactiveUS20110024426A1Improve instillation performancePrevent deformationClosure capsDischarging meansMaximum diameterBiomedical engineering

A liquid container has a body (1) and a cap (2). A circular tubular neck (12) of the body (1) has an outer diameter greater than a maximum diameter of a nozzle (14), and a locking protrusion (124) for the cap (2) is provided on an outer peripheral surface of the circular tubular neck. The cap (2) has two lockable arms (24). The lockable arms (24) are locked onto the locking protrusion (12a) while attaching the cap (2) to the body (1). Opposing surfaces (26) of the lockable arms (24) define guide surfaces that contact the outer peripheral surface of the circular tubular neck (12) during the cap attaching operation to guide the cap (2) along the circular tubular neck (12) so as to allow a plug protrusion (22) of the cap (2) and a nozzle hole (14a) to oppose each other.

Owner:ROHTO PHARM CO LTD

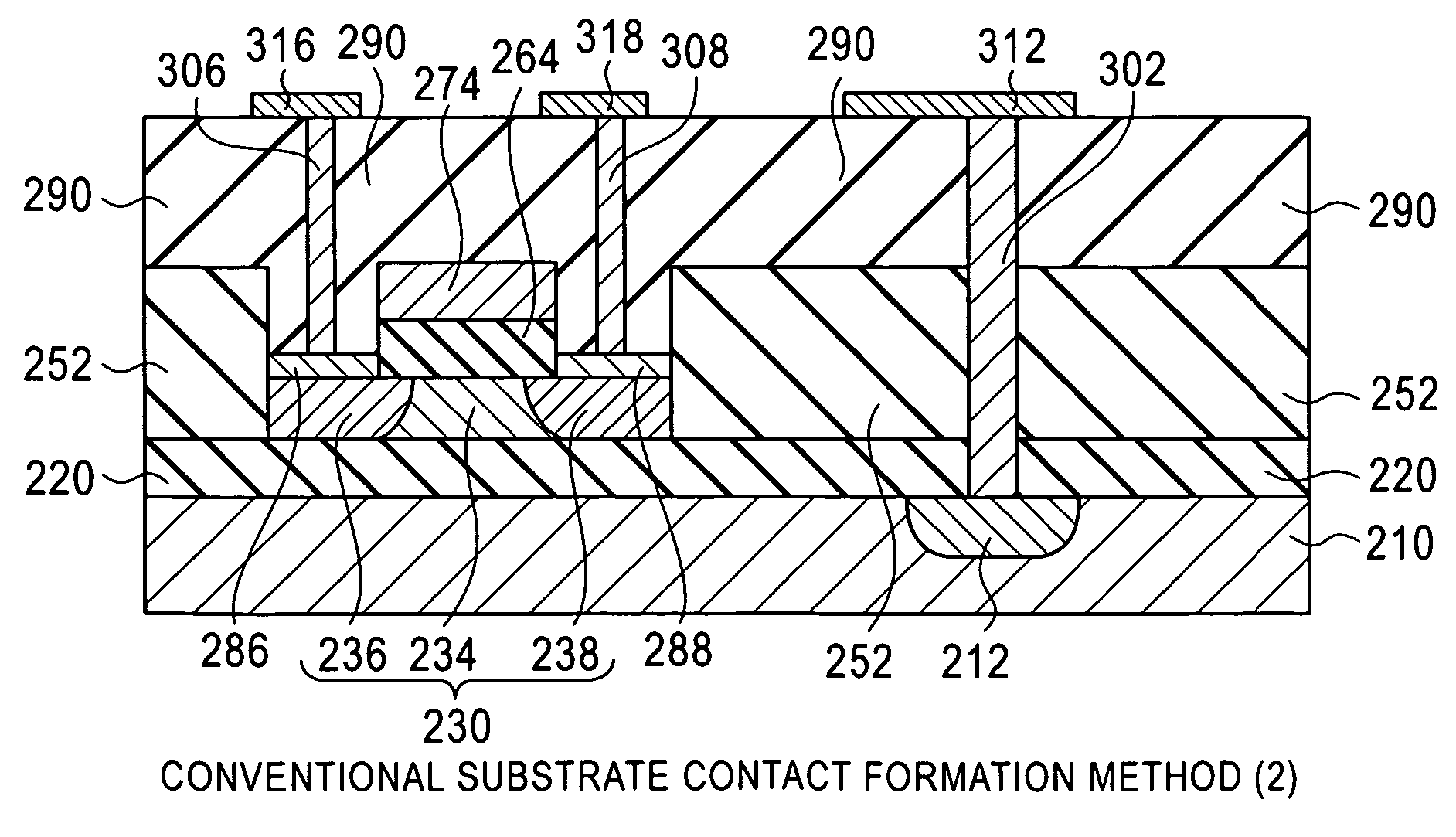

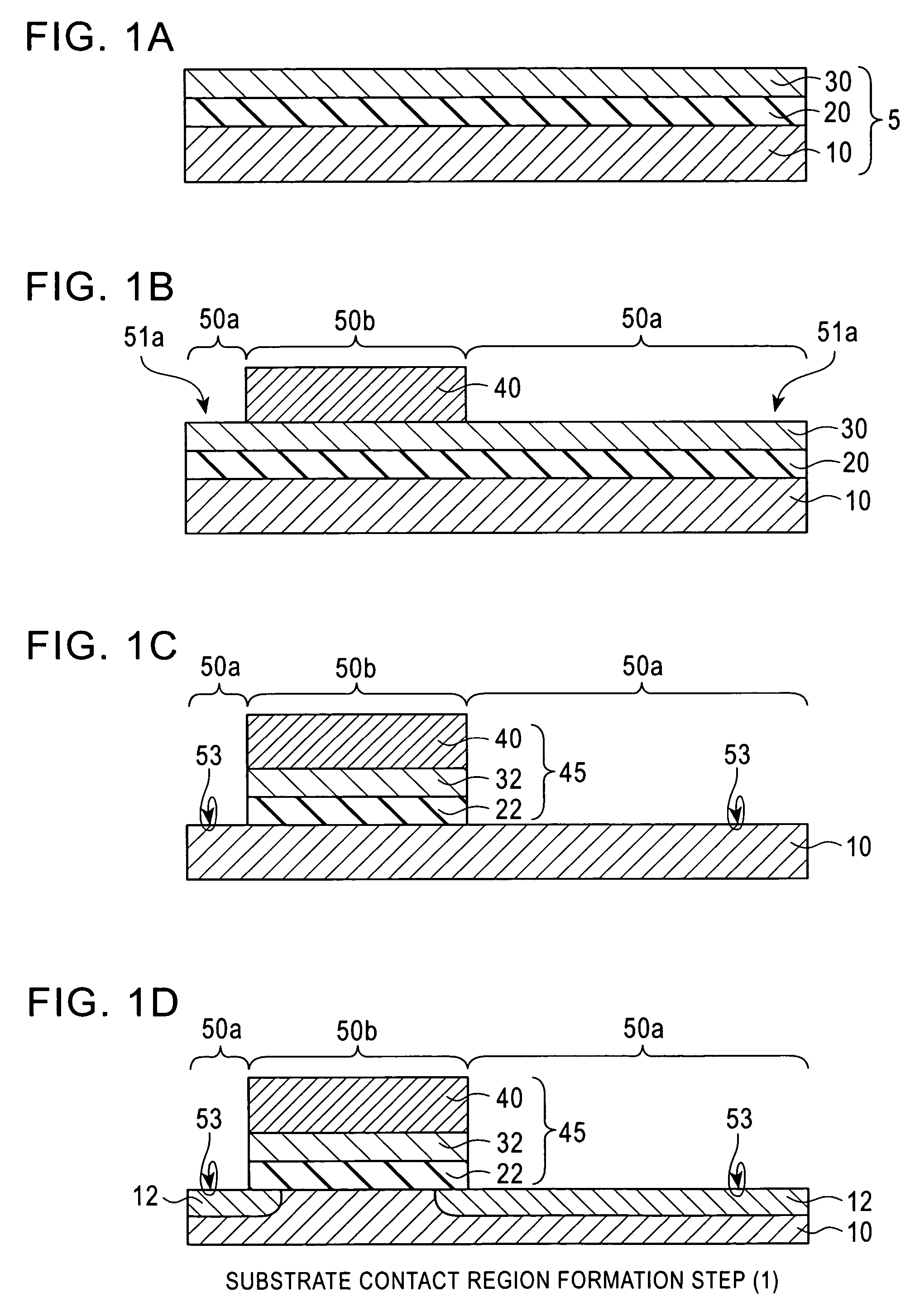

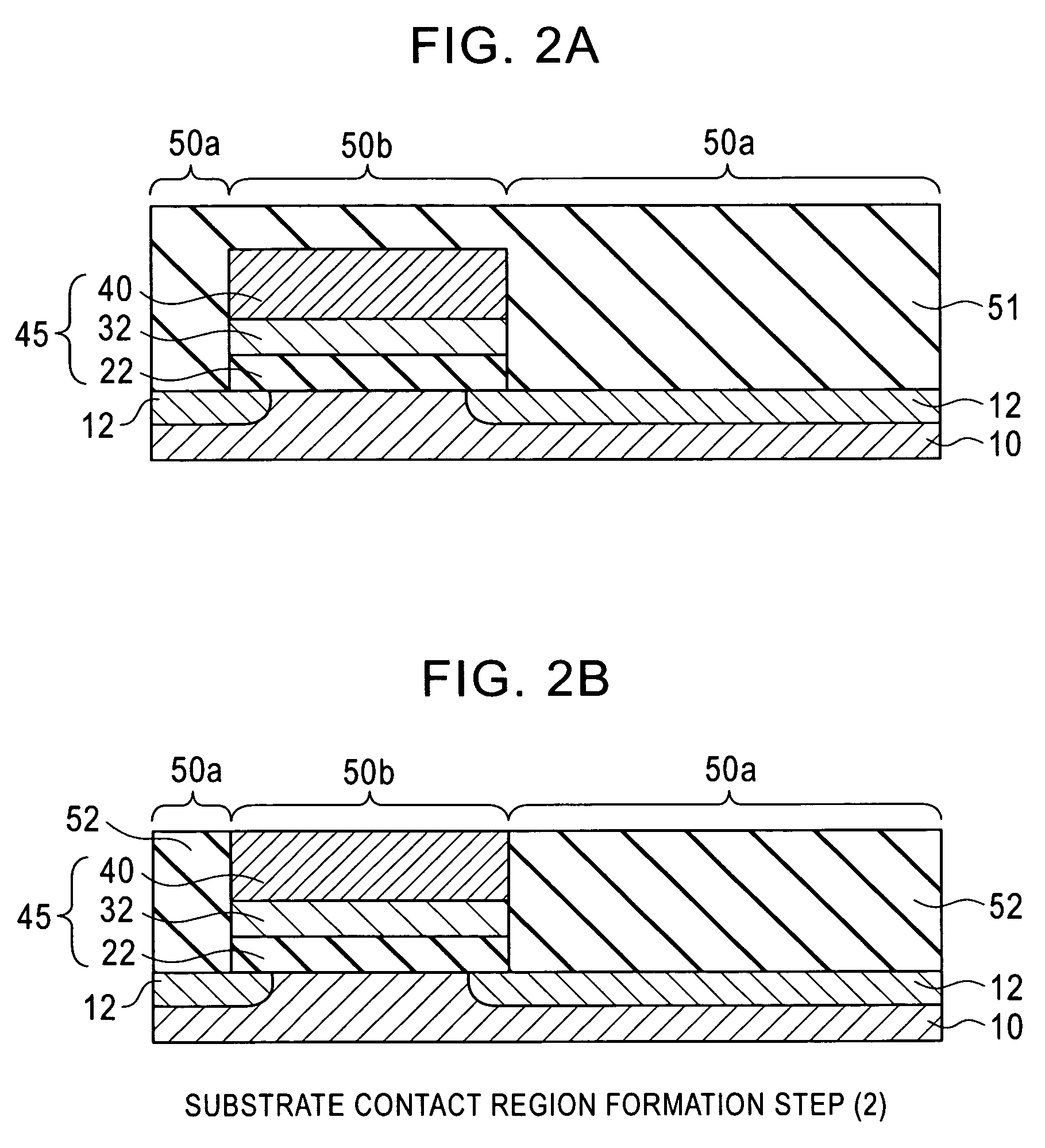

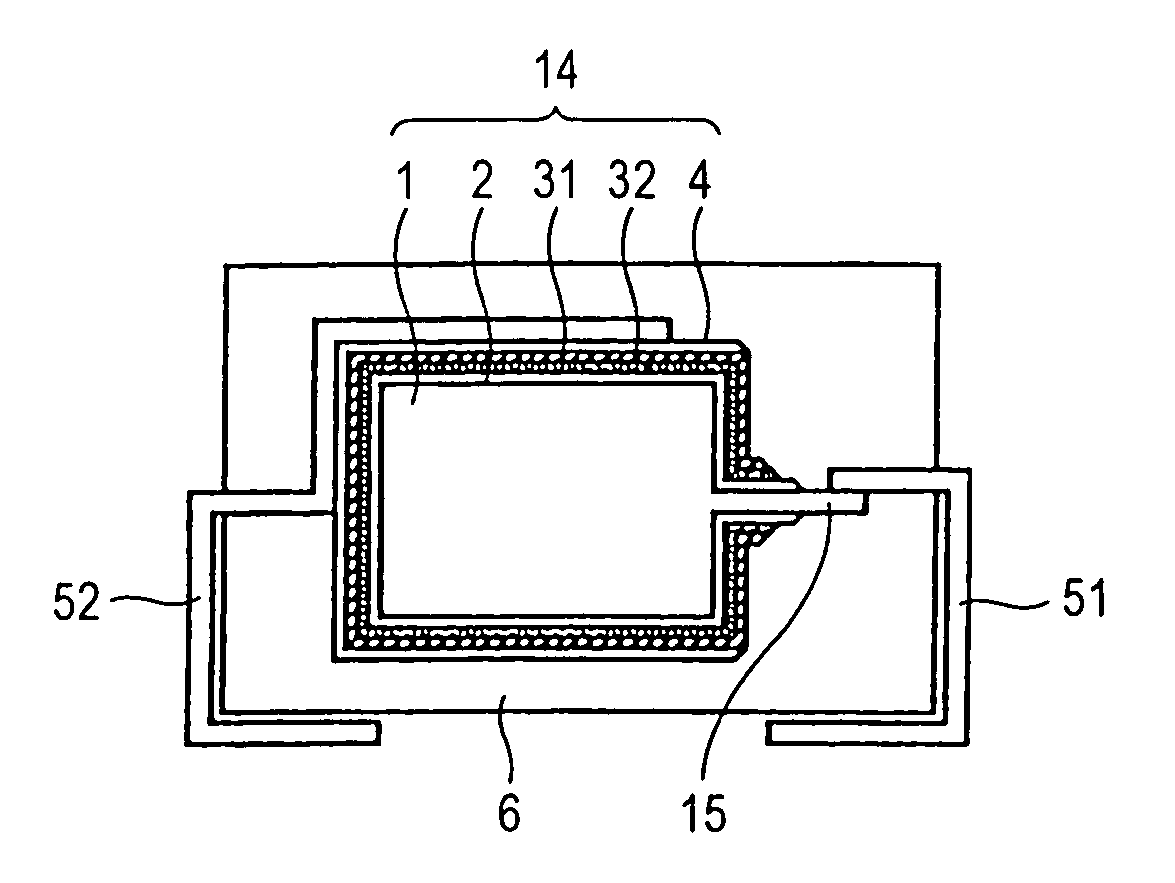

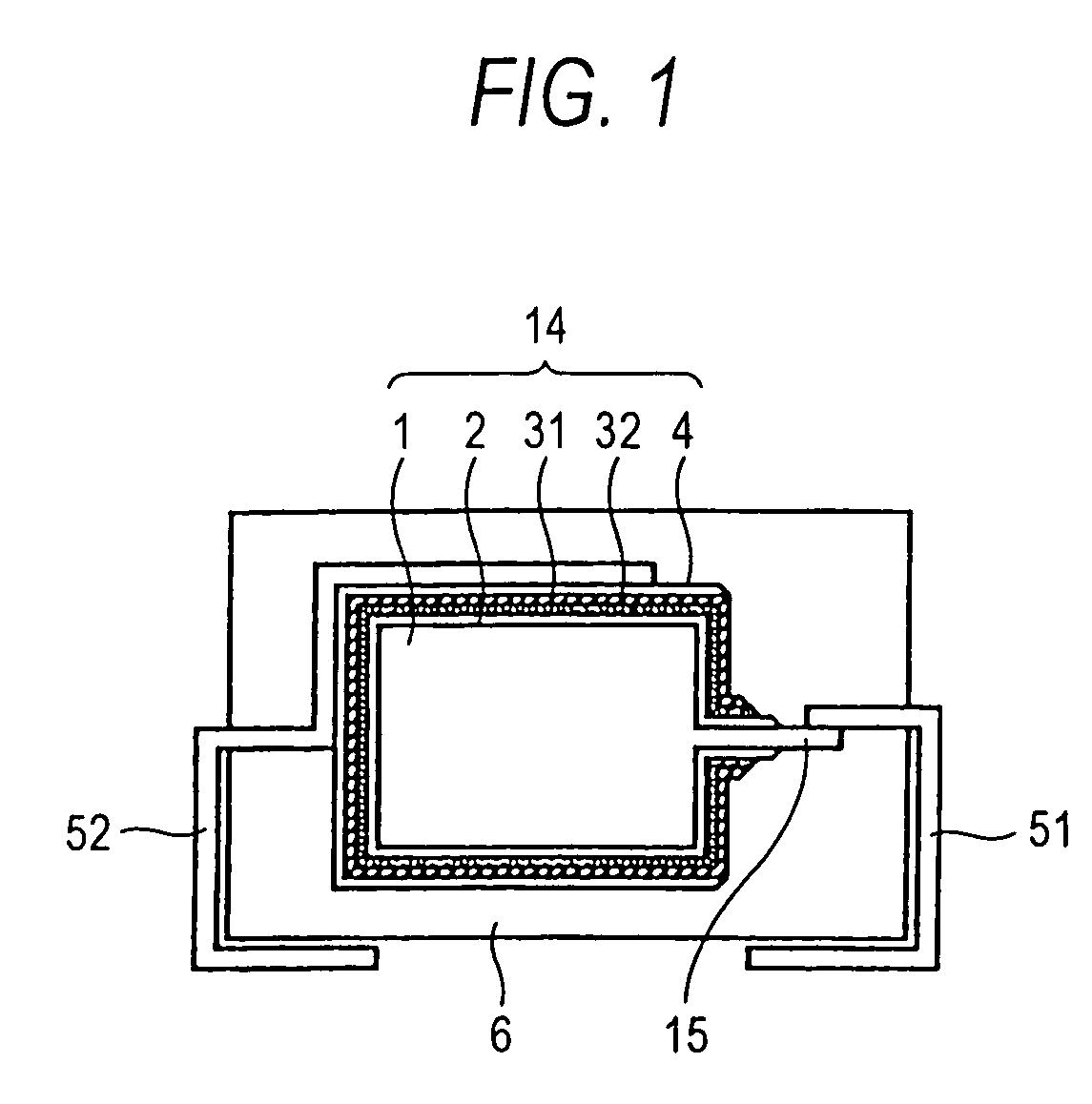

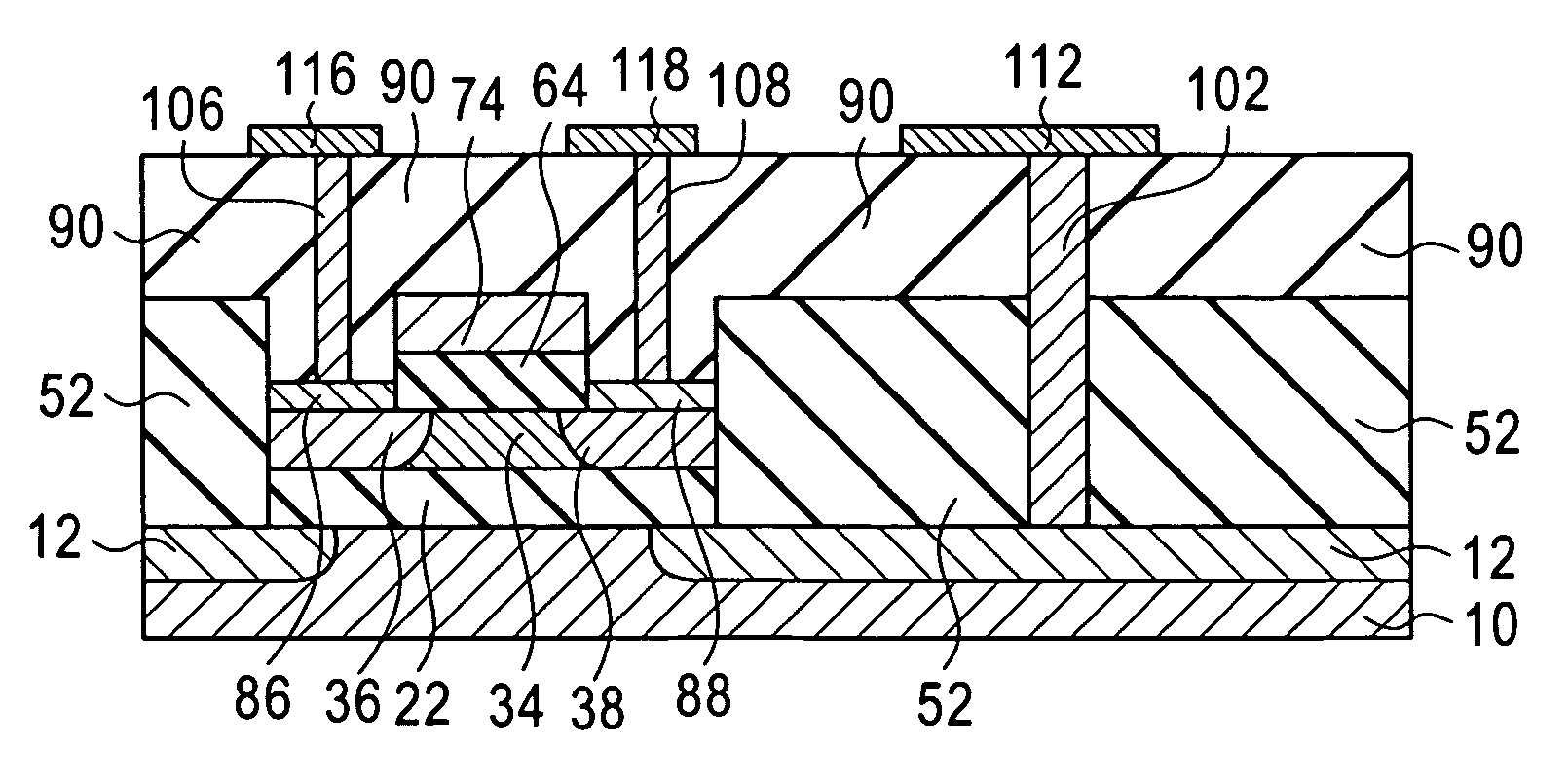

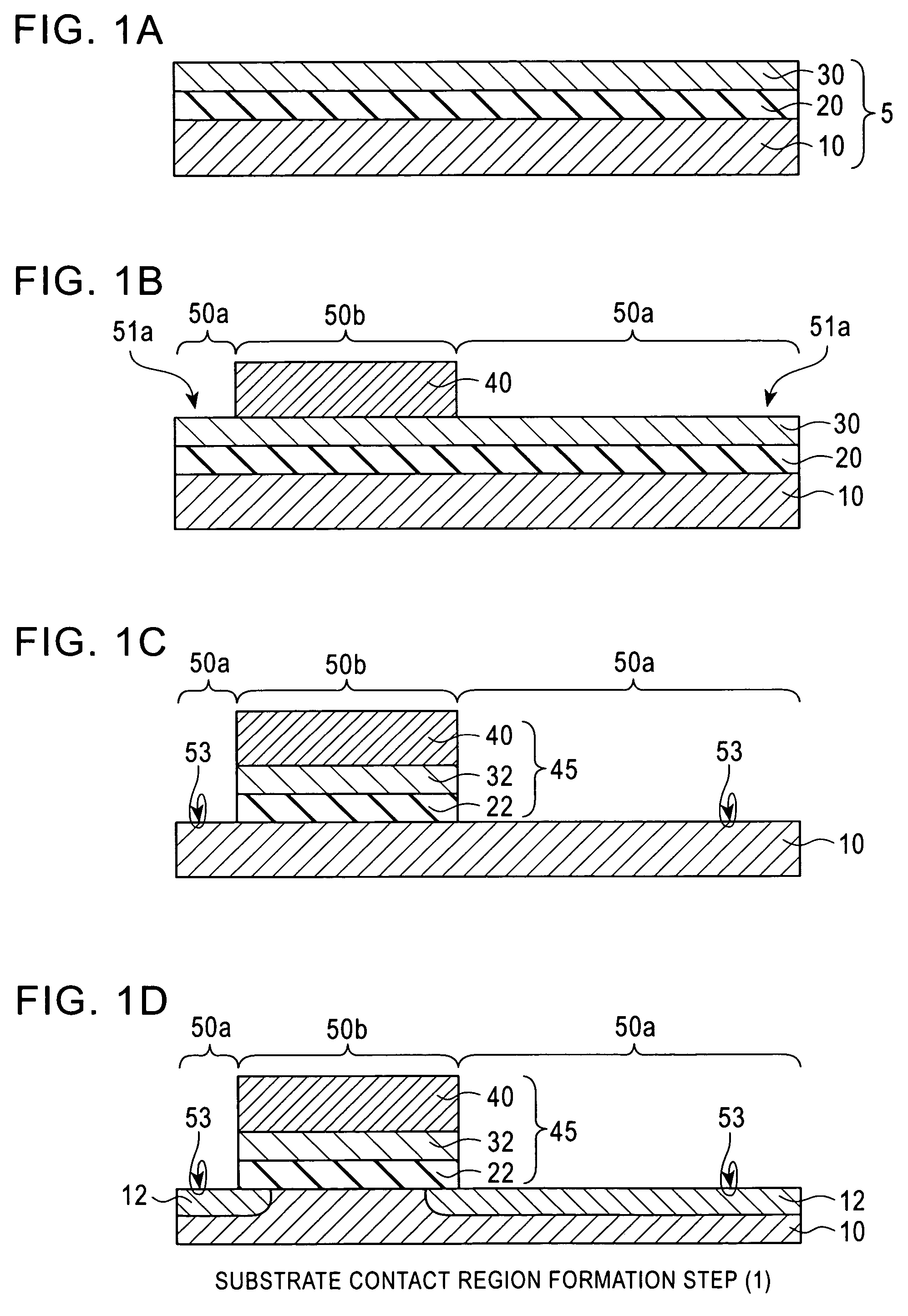

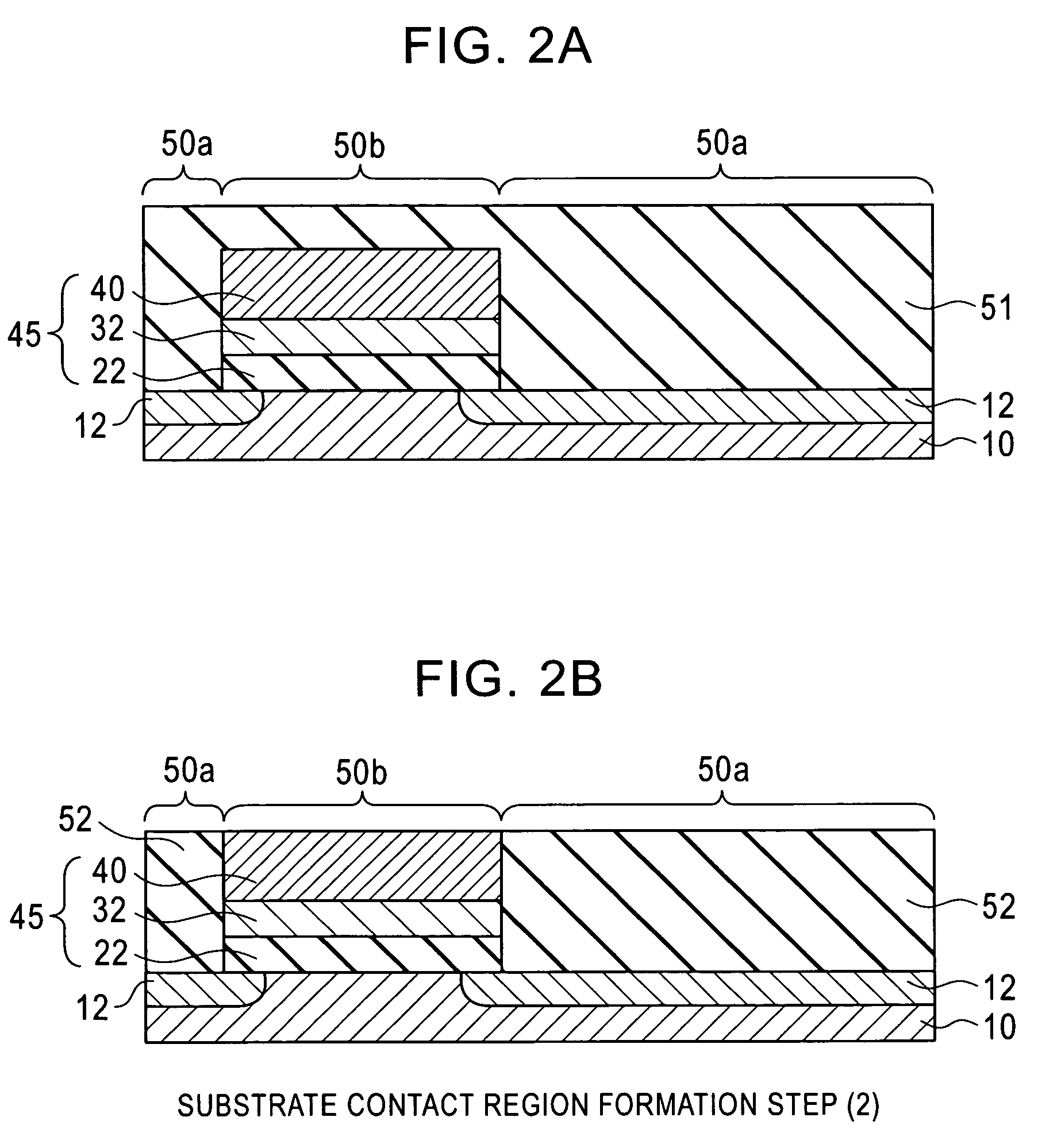

Semiconductor device fabrication method

The present invention adequately activates a substrate contact region of a support substrate without substantially changing the conventional SOI-CMOS device formation process. An exposed face of the support substrate is formed in an element isolation region of a layered substrate, which includes a support substrate having a first semiconductor layer, an insulating layer provided on the support substrate, and a second semiconductor layer provided on the insulating layer, by etching away the insulating layer and the second semiconductor layer. A substrate contact region is then formed in the support substrate by performing ion implantation from the side of the exposed face of the support substrate. Thereafter, an element isolation insulation layer is formed on the exposed face of the support substrate and a gate oxide film and a gate electrode are formed on the remaining second semiconductor layer. In addition, drain and source regions are formed by performing the ion implantation to the remaining second semiconductor layer with the gate electrode serving as a mask. Annealing to activate the substrate contact region, the drain region and the source region is then performed. Thereafter, a metal layer with a high melting point is formed on the drain and source regions and the metal layer is silicided through heat treatment.

Owner:LAPIS SEMICON CO LTD

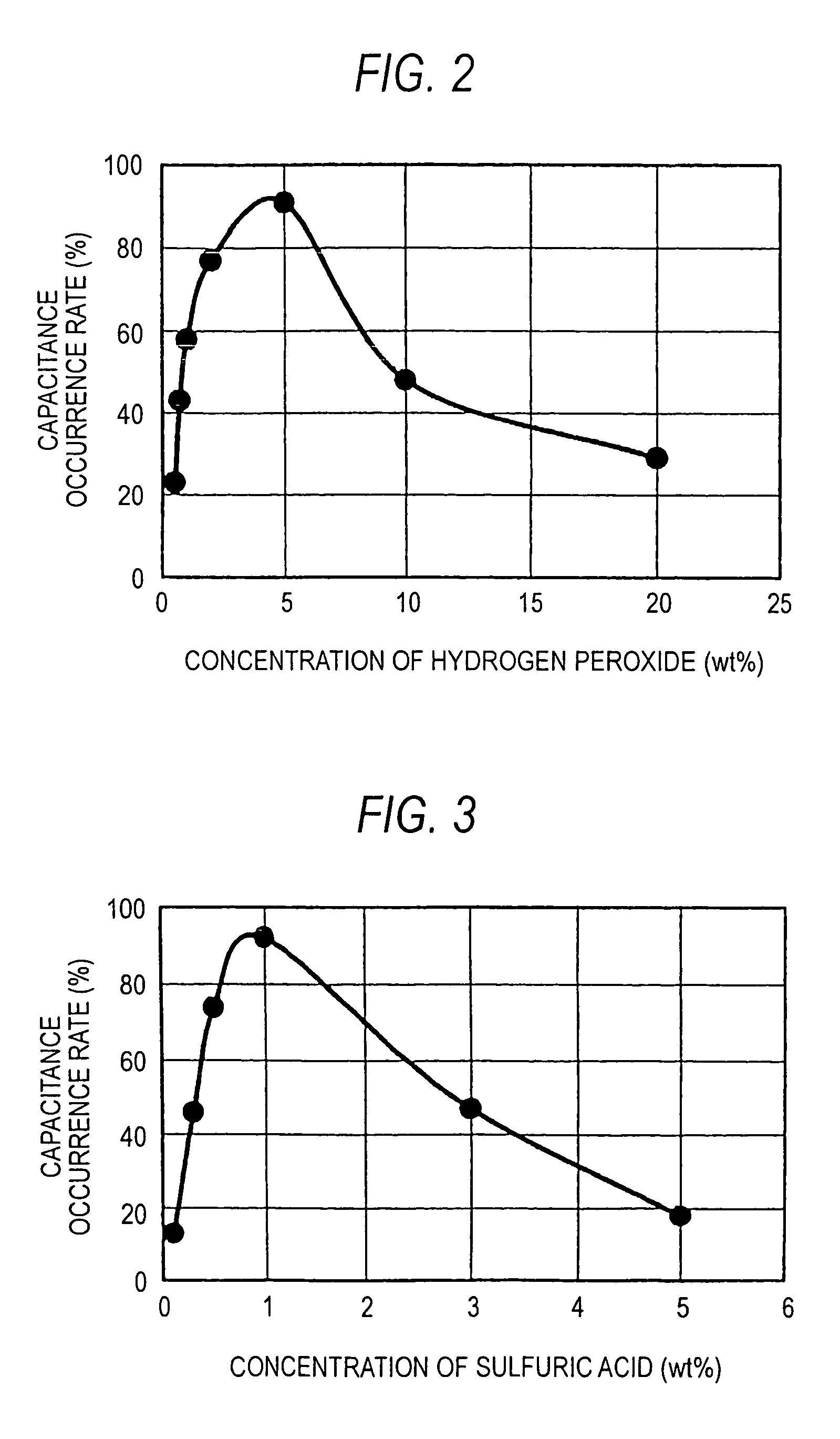

Method of producing solid electrolytic capacitor

InactiveUS7125764B2Increase capacitanceReduce leakage currentEmergency protective circuit arrangementsCapacitor electrolytes/absorbentsDielectricSupporting electrolyte

Owner:SAN DENSHI INDS

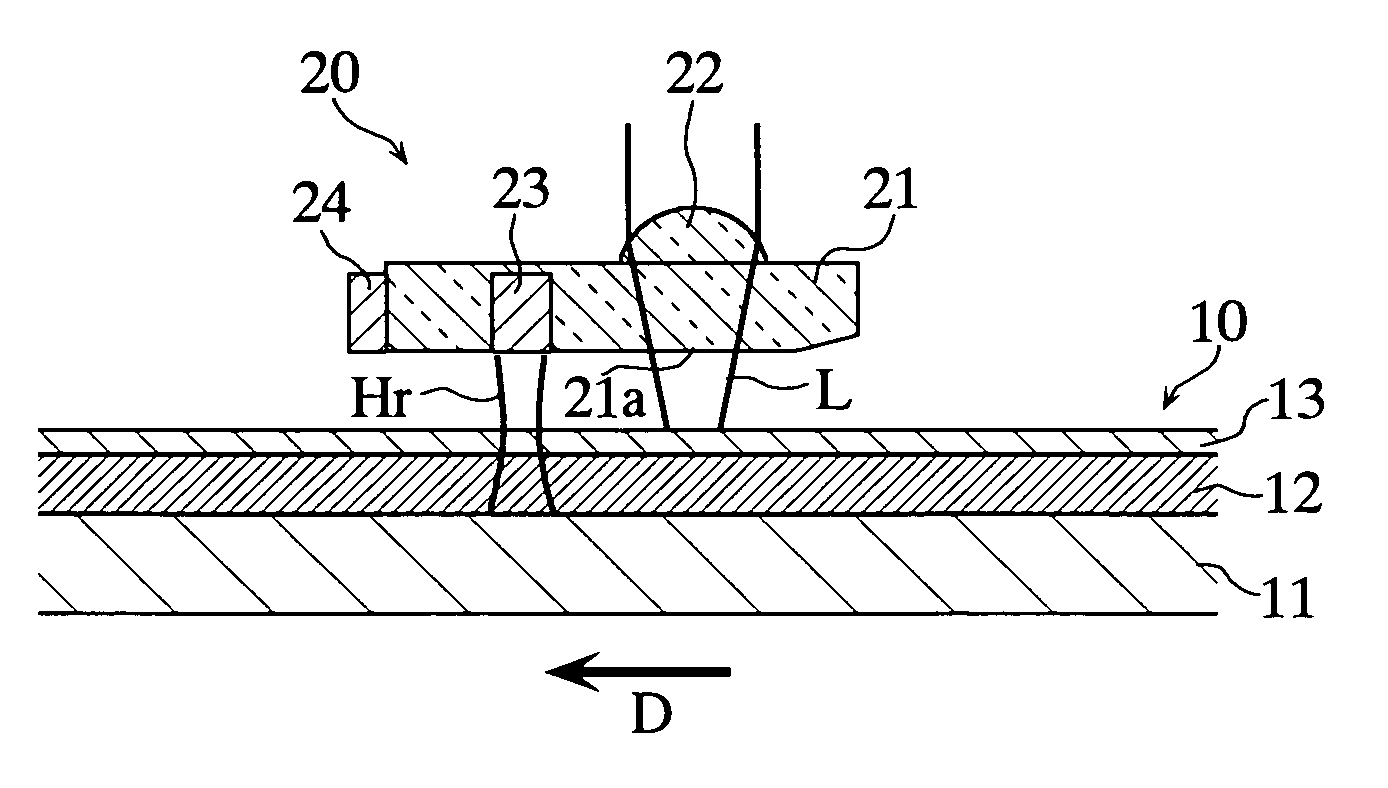

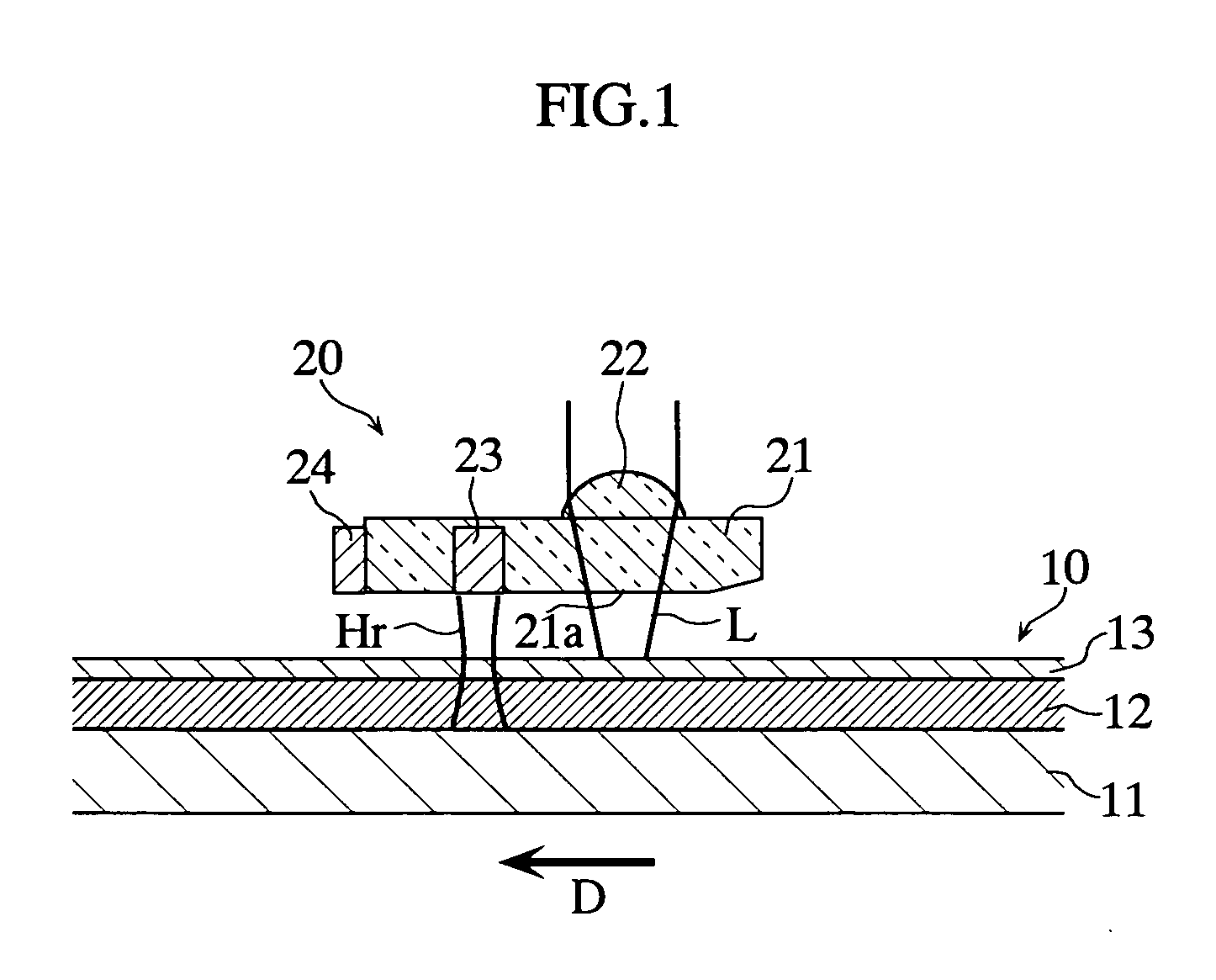

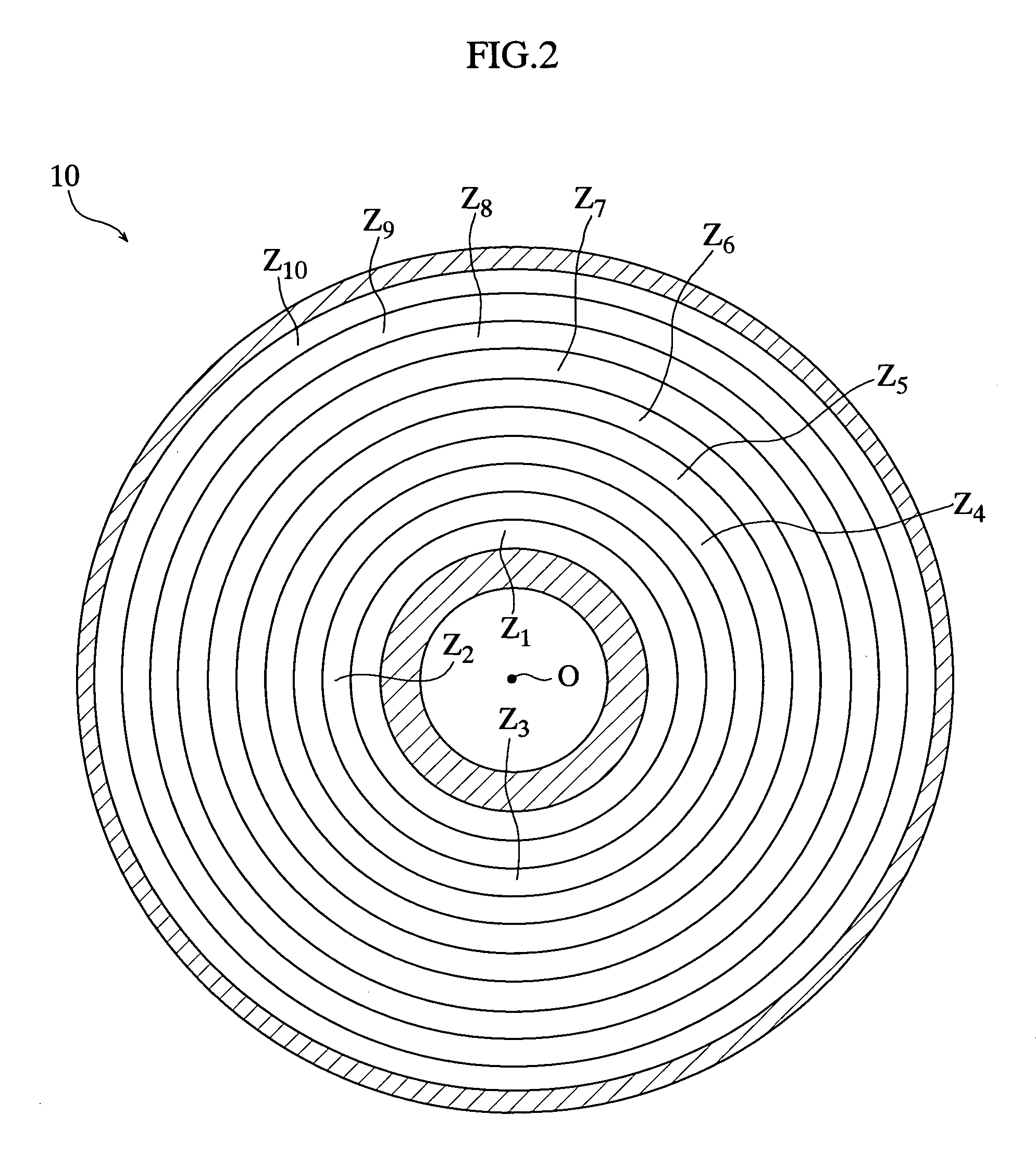

Heat-assisted magnetic recording method and test record reproduction method

ActiveUS20060117333A1Avoid demagnetization effectsFull adjustmentRecord information storageRecording/reproducing/erasing methodsHeat-assisted magnetic recordingLaser beams

A heat-assisted magnetic recording method is provided for implementing information recording on a recording magnetic film of a magnetic recording medium rotated around a rotation center. The method includes the steps of: illuminating a recording region in the magnetic film with a laser beam for locally heating the recording region; and applying a recording magnetic field to the heated recording region. The power of the laser beam illuminating the recording region is selected in accordance with the distance between the rotation center and the recording region.

Owner:KK TOSHIBA

Semiconductor device fabrication method

InactiveUS7205190B2Sufficient formHigh melting pointTransistorSemiconductor/solid-state device detailsSoi cmosInsulation layer

The present invention adequately activates a substrate contact region of a support substrate without substantially changing the conventional SOI-CMOS device formation process. An exposed face of the support substrate is formed in an element isolation region of a layered substrate, which includes a support substrate having a first semiconductor layer, an insulating layer provided on the support substrate, and a second semiconductor layer provided on the insulating layer, by etching away the insulating layer and the second semiconductor layer. A substrate contact region is then formed in the support substrate by performing ion implantation from the side of the exposed face of the support substrate. Thereafter, an element isolation insulation layer is formed on the exposed face of the support substrate and a gate oxide film and a gate electrode are formed on the remaining second semiconductor layer. In addition, drain and source regions are formed by performing the ion implantation to the remaining second semiconductor layer with the gate electrode serving as a mask. Annealing to activate the substrate contact region, the drain region and the source region is then performed. Thereafter, a metal layer with a high melting point is formed on the drain and source regions and the metal layer is silicided through heat treatment.

Owner:LAPIS SEMICON CO LTD

Liquid detergent composition

InactiveUS7863234B2Sufficient formImprove stabilityInorganic/elemental detergent compounding agentsOrganic detergent compounding agentsBoric acidBleach activator

The present invention relates to a liquid detergent composition containing (a) hydrogen peroxide or a compound forming hydrogen peroxide in water, 0.1 to 10 mass % of (b) a bleaching activator, 45 to 80 mass % of (c) a nonionic surfactant, (d) water, (e) at least one or more compounds selected from boric acid, borax and borate, and (f) a polyol compound, said liquid detergent composition having a pH value of 4 to 7 at 20° C.

Owner:KAO CORP

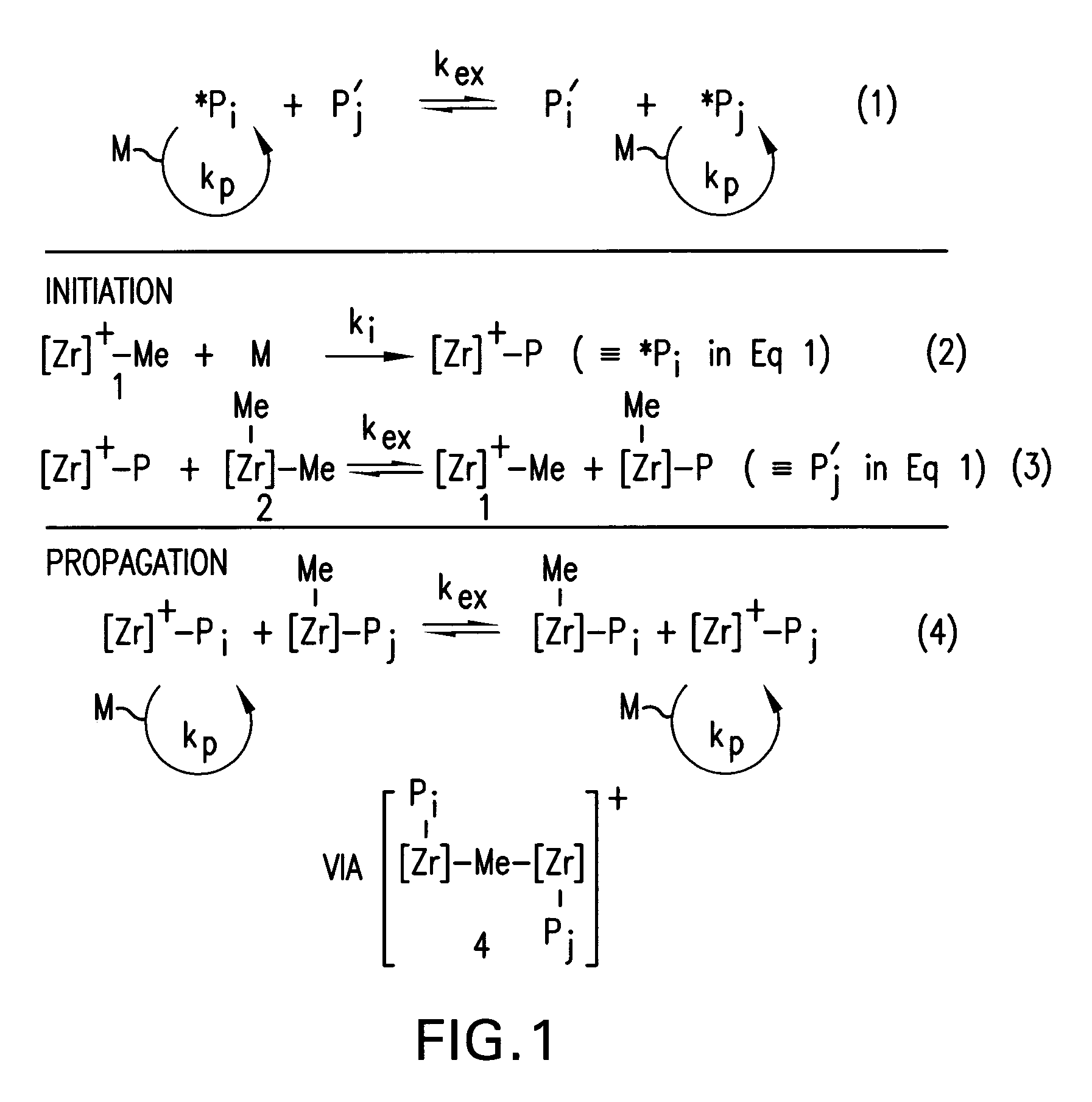

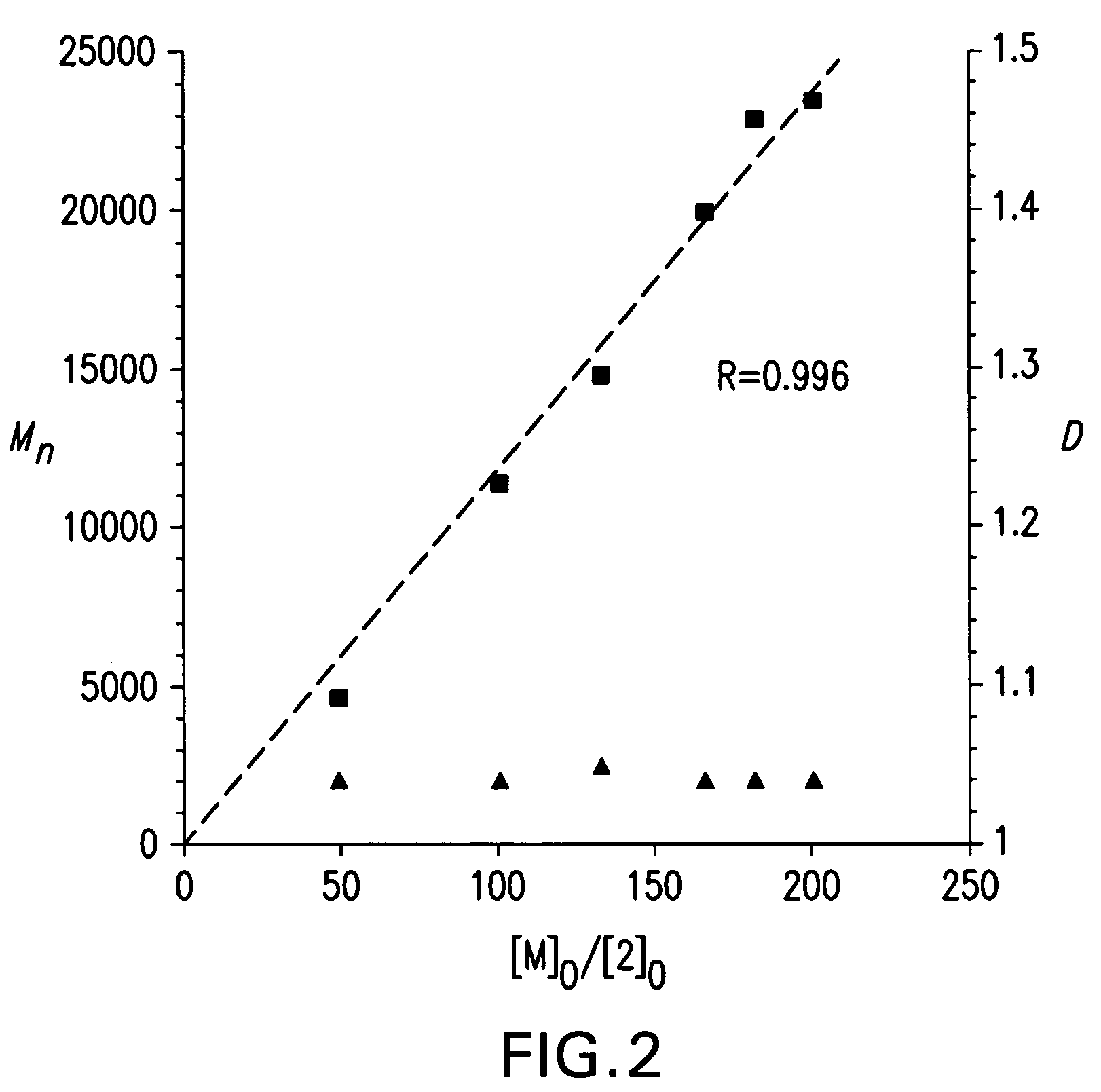

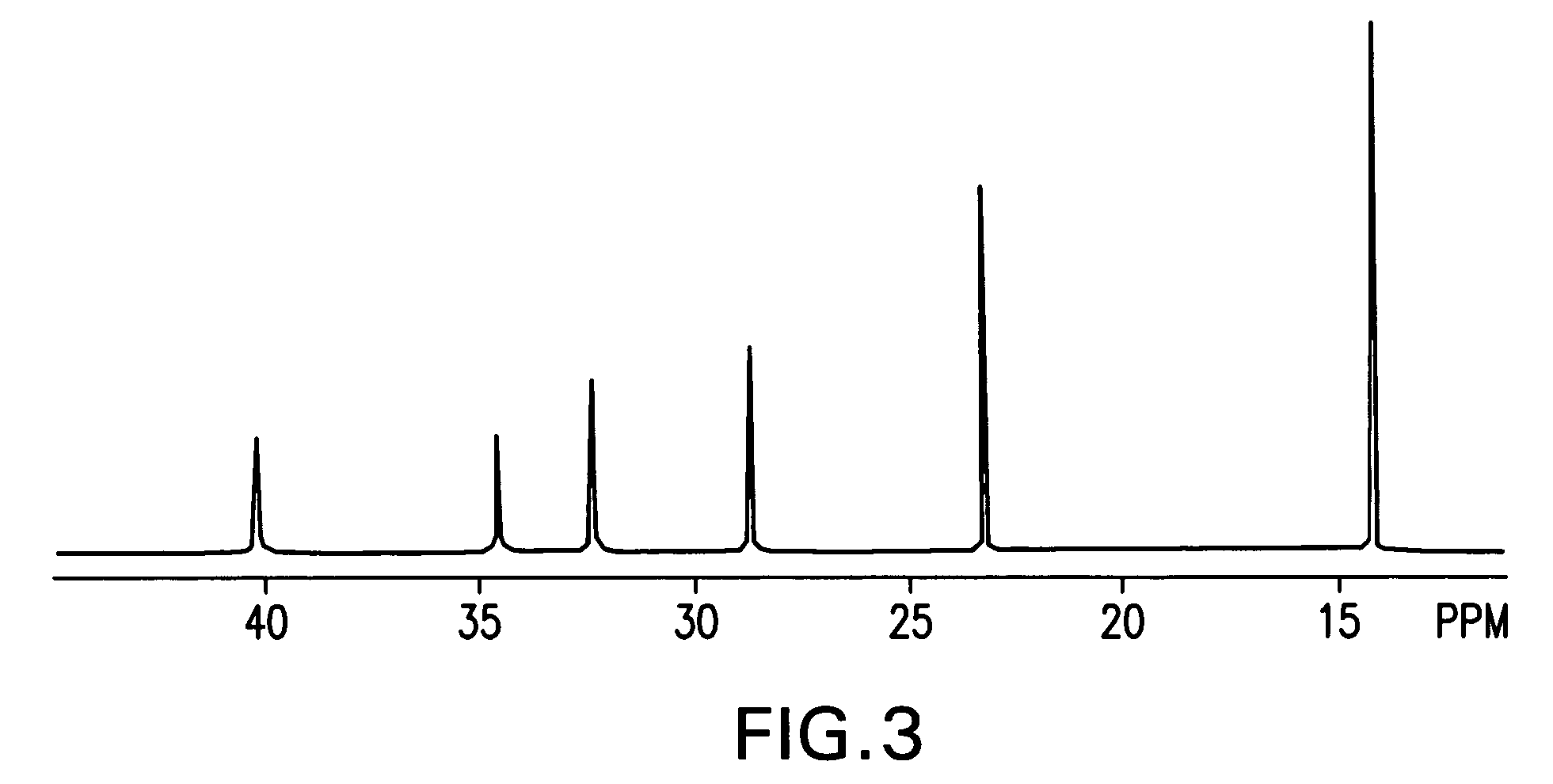

Process for preparation of polyolefins via degenerative transfer polymerization

Disclosed is a method of producing a polyolefin composition comprising contacting a metallocene pre-catalyst with a substoichiometric amount of a co-catalyst; adding a first olefin monomer; and polymerizing the first monomer for a time sufficient to form the polyolefin. The method allows for the use of a minimum amount of activating co-catalyst, and allows for the production of stereoregular and non-stereoregular polyolefins. The use of configurationally stable metallocene pre-catalysts allows for the production of monomodal isotactic polyolefins having narrow polydispersity. The use of configurationally unstable metallocene pre-catalysts allows for the production of monomodal atactic polyolefins having narrow polydispersity. The method of the present invention optionally further comprises contacting the polyolefin with a second amount of said co-catalyst; adding a second olefin monomer; polymerizing said second olefin monomer to form a block-polyolefin composition. Also disclosed are monomodal diblock copolymer compositions made according to the present invention.

Owner:UNIV OF MARYLAND

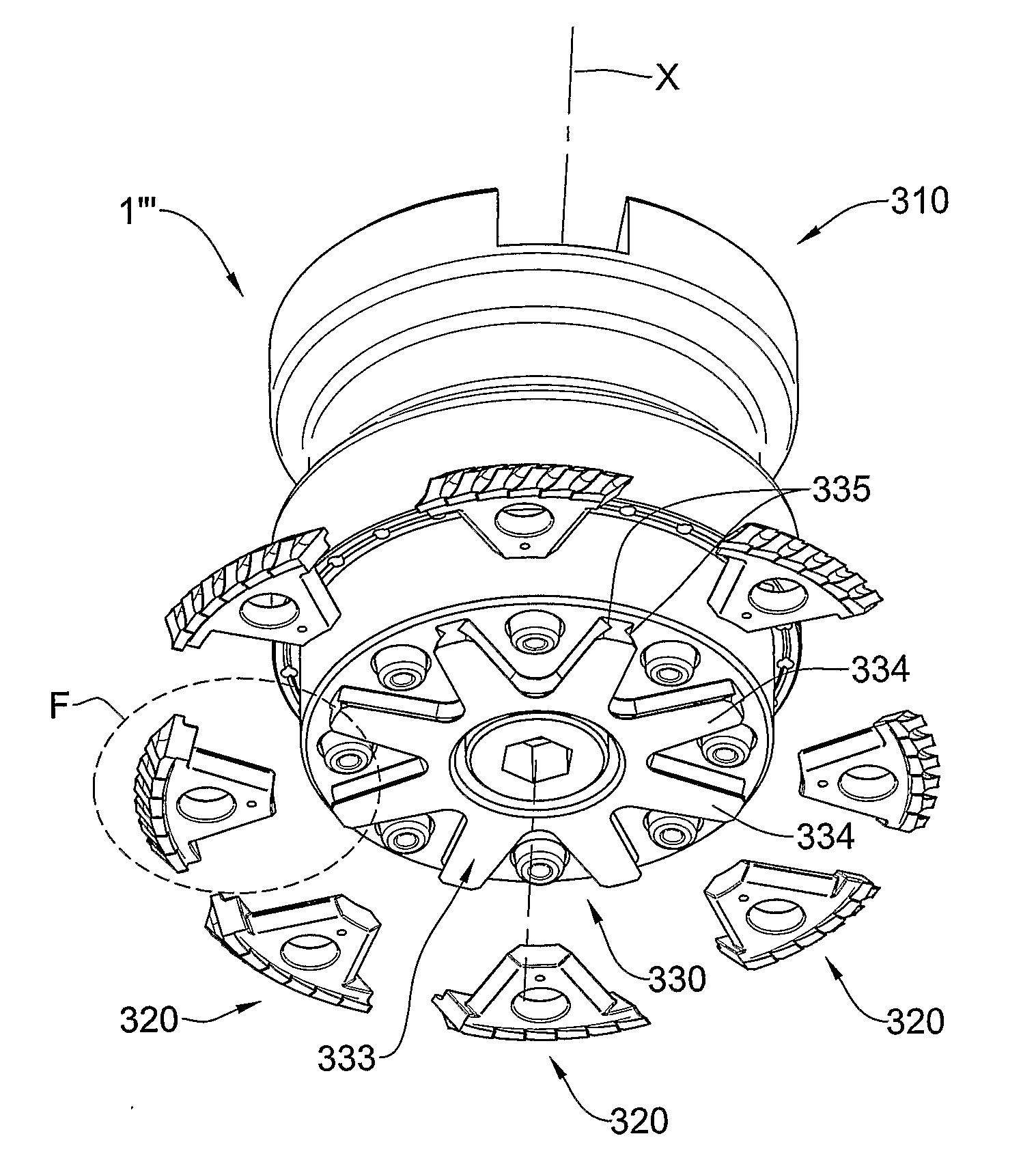

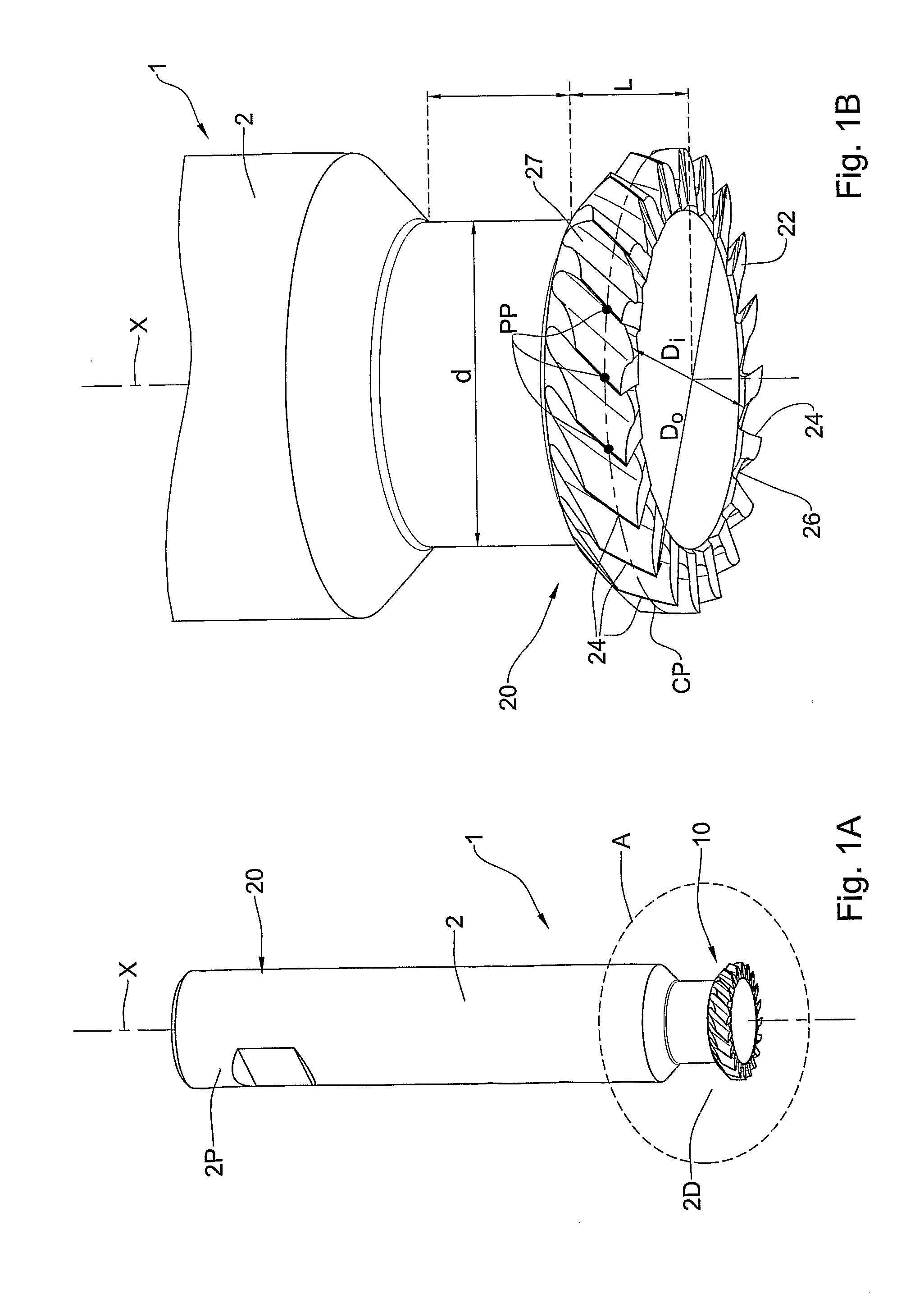

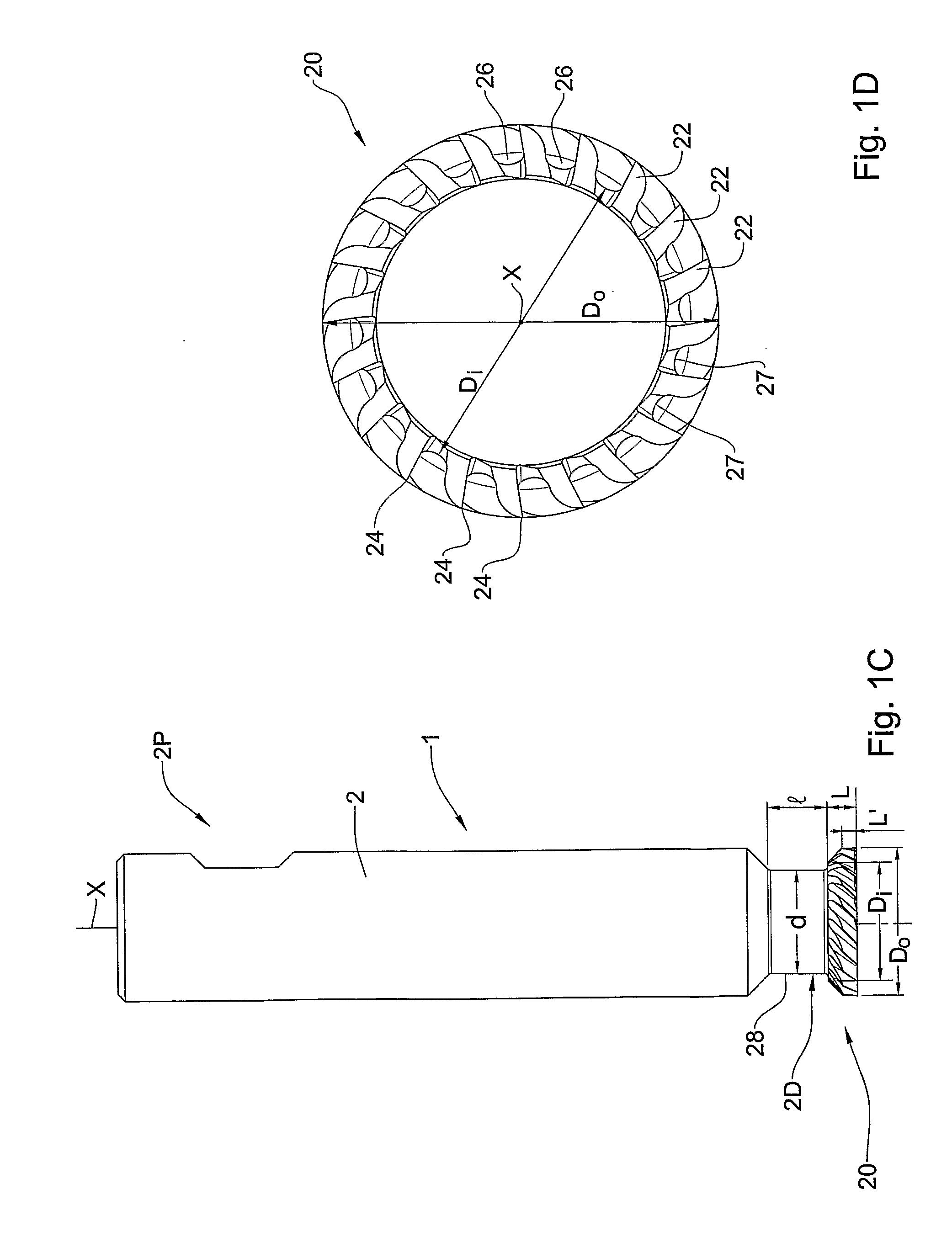

Multi-edge cutting head and an insert used therein

InactiveUS20110311327A1Prevent from rotateSufficient formMilling cuttersShaping cuttersKnife bladesEngineering

A cutting portion of an integral cutting tool or of a cutting insert adapted for mounting onto a cutting tool holder to form a cutting tool, which comprises a plurality n of cutting edges. The cutting portion extends along a cutting path about a central axis. The cutting path (CP) passes through a point of each of the cutting edges which is at a maximal radial space R from the central axis, such that (formula I), where D=2R and θ is the angular extension of the cutting path about the central axis (X). At any given point along the cutting portion, (formula II), where L is one of the following: i. the extension of the cutting portion in a direction perpendicular to the cutting path; and ii. the extension of the cutting edges in a direction perpendicular to the cutting path.

Owner:SIMATATE

Minimal-temperature-differential, omni-directional-reflux, heat exchanger

InactiveUS8042606B2Sufficient formFacilitates capillary actionIndirect heat exchangersHeat transfer modificationWorking fluidGas phase

A substrate formed of a suitable conductive-heat-transfer material is formed with small channels of a size selected to provide surface tension forces dominating a motion of a liquid-phase working fluid. A space above the channels of the substrate provides comparatively unobstructed space for the transport motion of a vapor phase of the working fluid effecting a heat-pipe effect in a multi-dimensional device. Channels may typically be formed in an orthogonal grid providing capillary return of liquids from a comparatively cooler condensation region to a comparatively warmer evaporation region, without any wicks other that the adhesion of the liquid phase working fluid to the vertices of the channels. Interference between the boundary layers of the liquid phase and the vapor phase of the working fluid are minimized by the depth of the channels, and the pedestals formed by the channel walls. Extremely small temperature differentials are thereby achieved between an outer surface of the substrate and an inner surface of the substrate when the liquid phase floods the substrate.

Owner:UTAH STATE UNIVERSITY

Charged device, cleaning device, process cartridge, toner, and image-forming device that uses these

ActiveUS7477862B2Increasing costQuality improvementElectrographic process apparatusCorona dischargeForeign matterImaging quality

Owner:RICOH KK

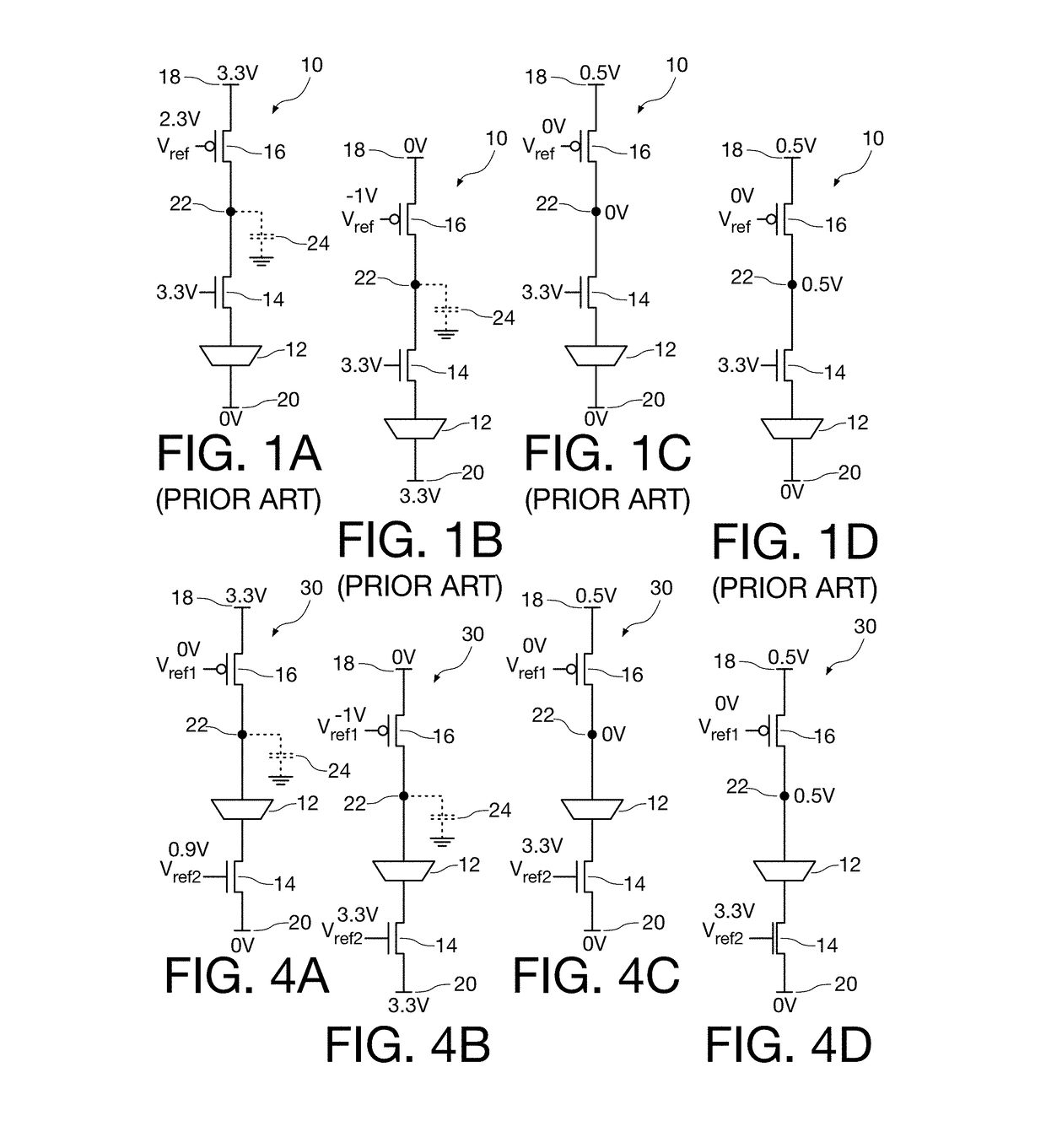

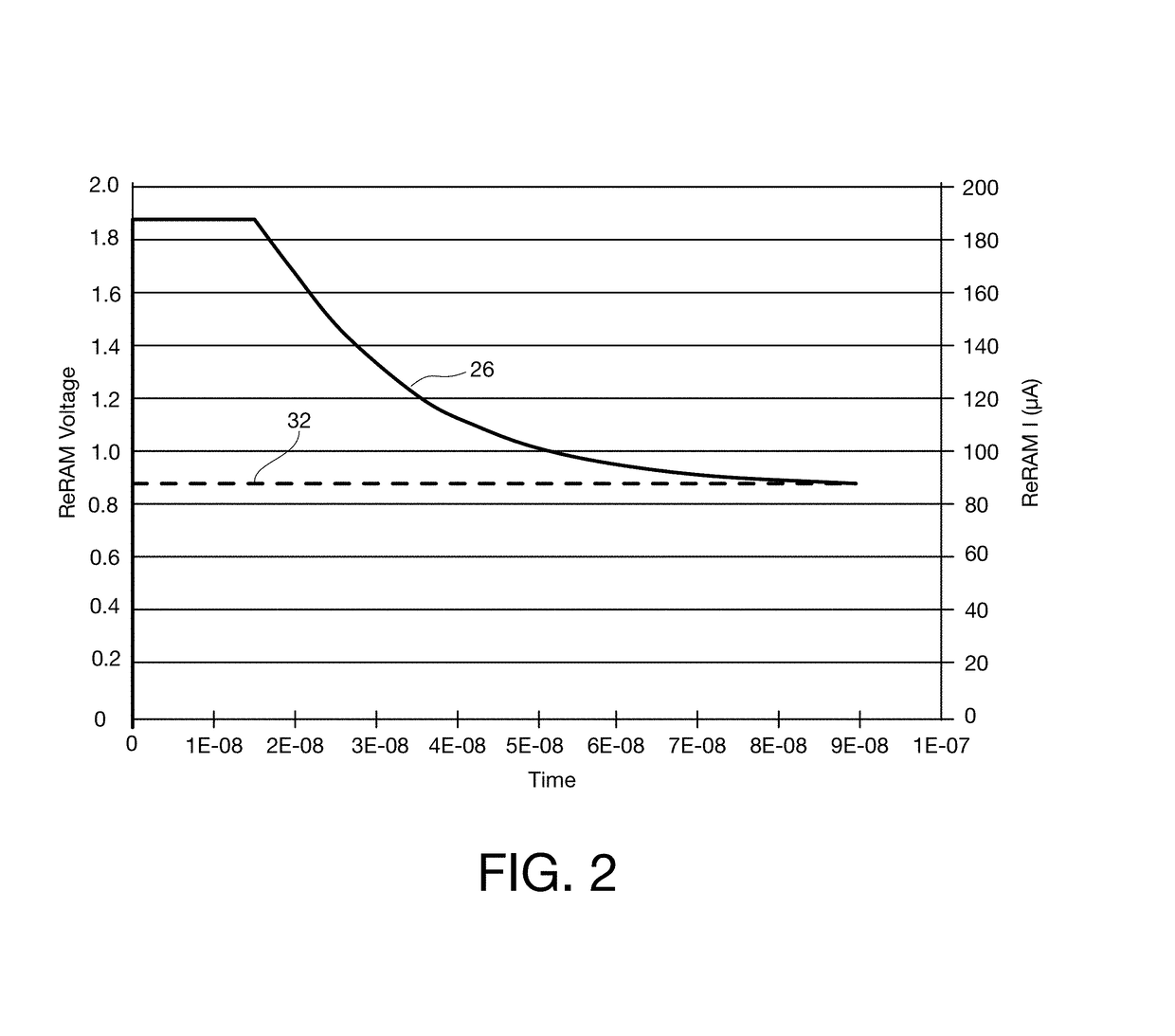

Circuitry and methods for programming resistive random access memory devices

ActiveUS20190051352A1Increase currentIncrease in sizeSolid-state devicesDigital storageVoltage pulseEngineering

A method for programming a ReRAM cell including a ReRAM device connected in series with an access transistor includes biasing the ReRAM cell with a programming potential that configures the access transistor in a common-source configuration and applying at least one programming voltage pulse to a gate of the access transistor, the programming voltage pulse having a magnitude selected to limit programming current to a preselected value.

Owner:MICROSEMI SOC