Patents

Literature

374 results about "Weighted average method" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Weighted Average Method Overview. The weighted average method is used to assign the average cost of production to a product. Weighted average costing is commonly used in situations where: Inventory items are so intermingled that it is impossible to assign a specific cost to an individual unit.

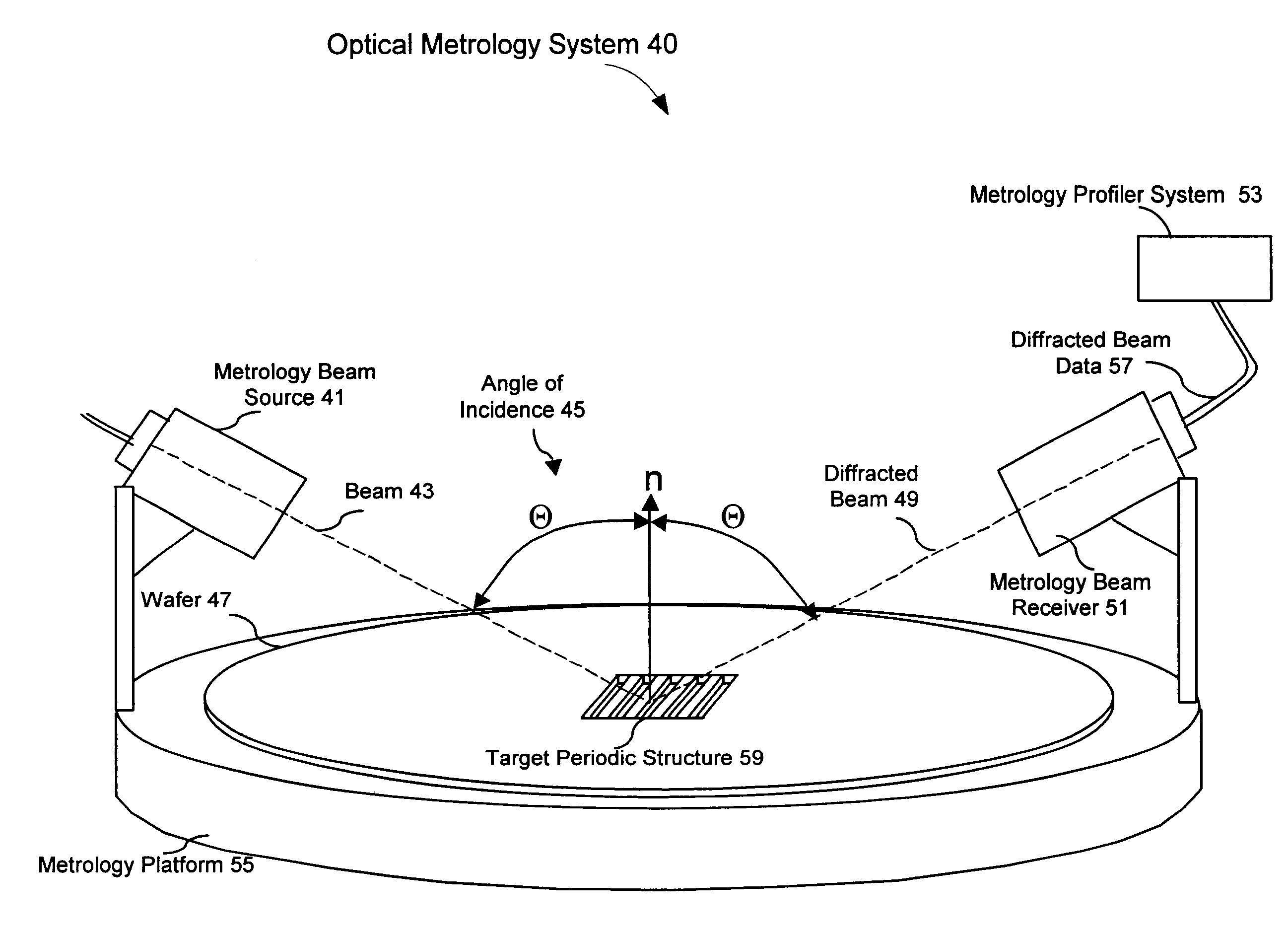

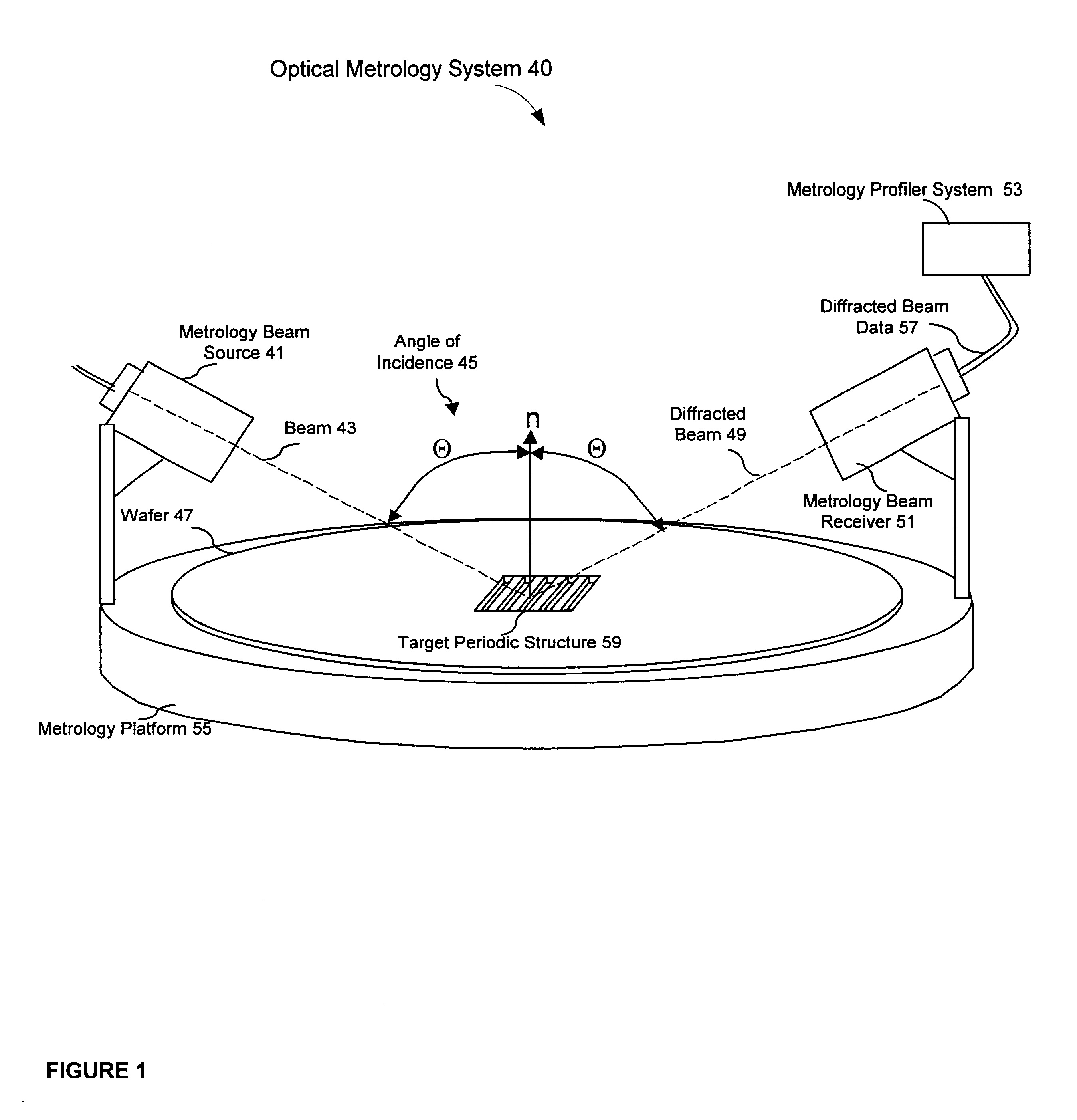

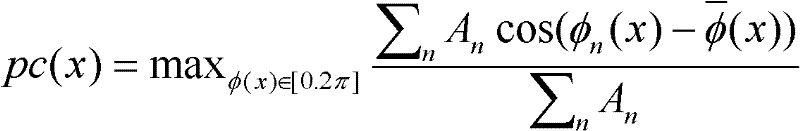

Profile refinement for integrated circuit metrology

InactiveUS6609086B1Minimize cost functionAmplifier modifications to reduce noise influenceScattering properties measurementsMetrologyData space

The present invention includes a method and system for determining the profile of a structure in an integrated circuit from a measured signal, the signal measured off the structure with a metrology device, selecting a best match of the measured signal in a profile data space, the profile data space having data points with a specified extent of non-linearity, and performing a refinement procedure to determine refined profile parameters. One embodiment includes a refinement procedure comprising finding a polyhedron in a function domain of cost functions of the profile library signals and profile parameters and minimizing the total cost function using the weighted average method. Other embodiments include profile parameter refinement procedures using sensitivity analysis, a clustering approach, regression-based methods, localized fine-resolution refinement library method, iterative library refinement method, and other cost optimization or refinement algorithms, procedures, and methods. Refinement of profile parameters may be invoked automatically or invoked based on predetermined criteria such as exceeding an error metric between the measured signal versus the best match profile library.

Owner:TOKYO ELECTRON US HOLDINGS INC

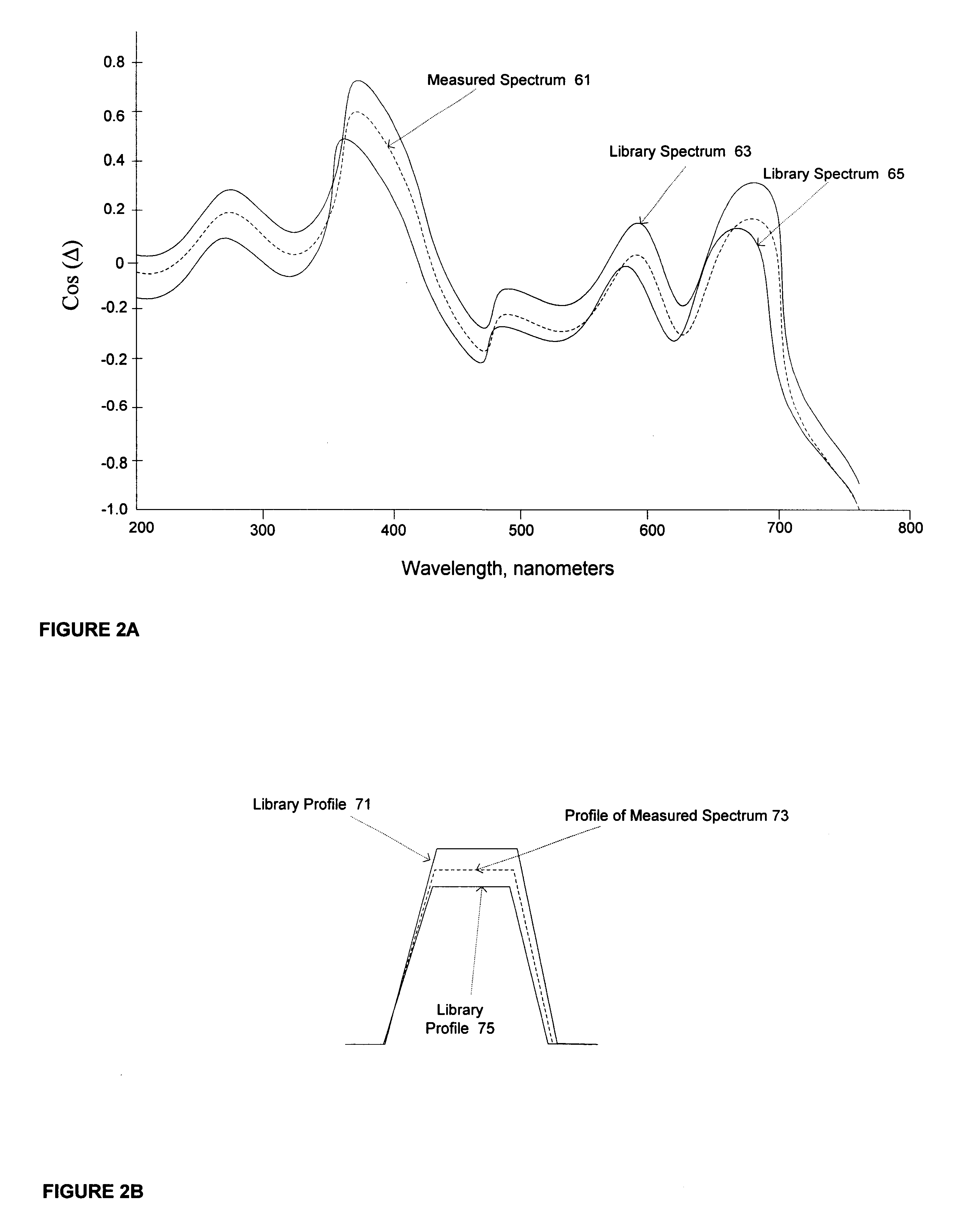

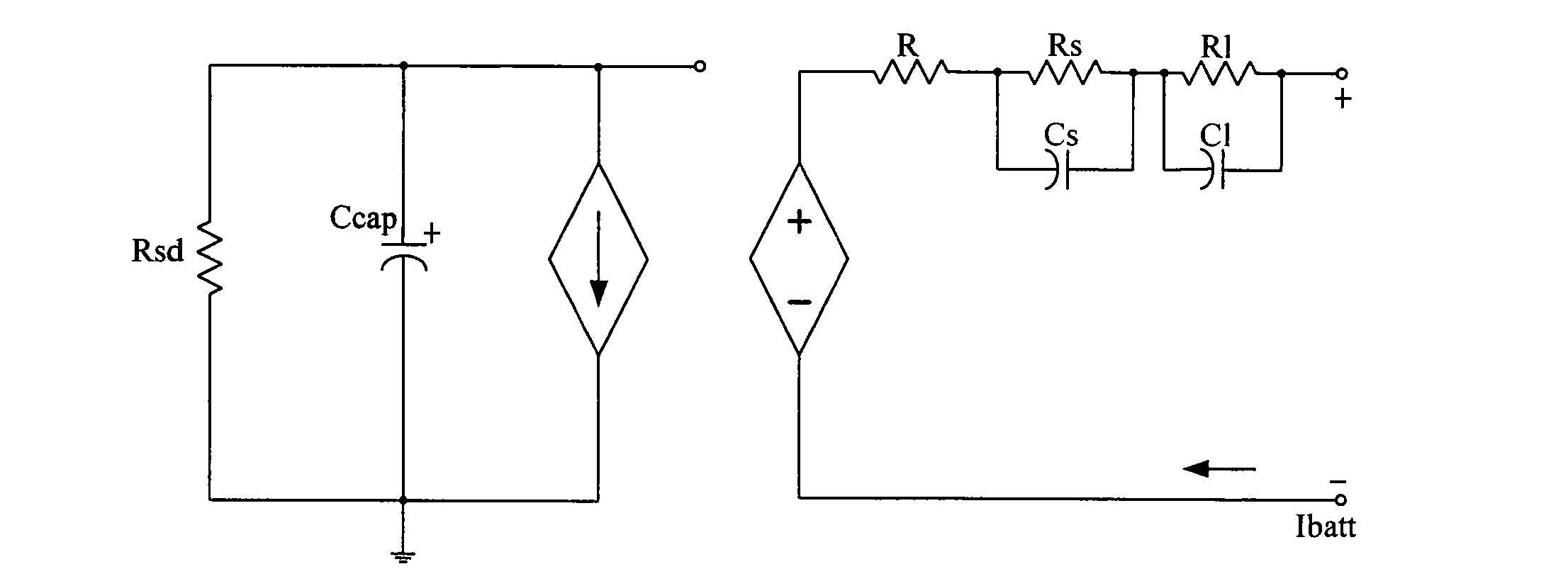

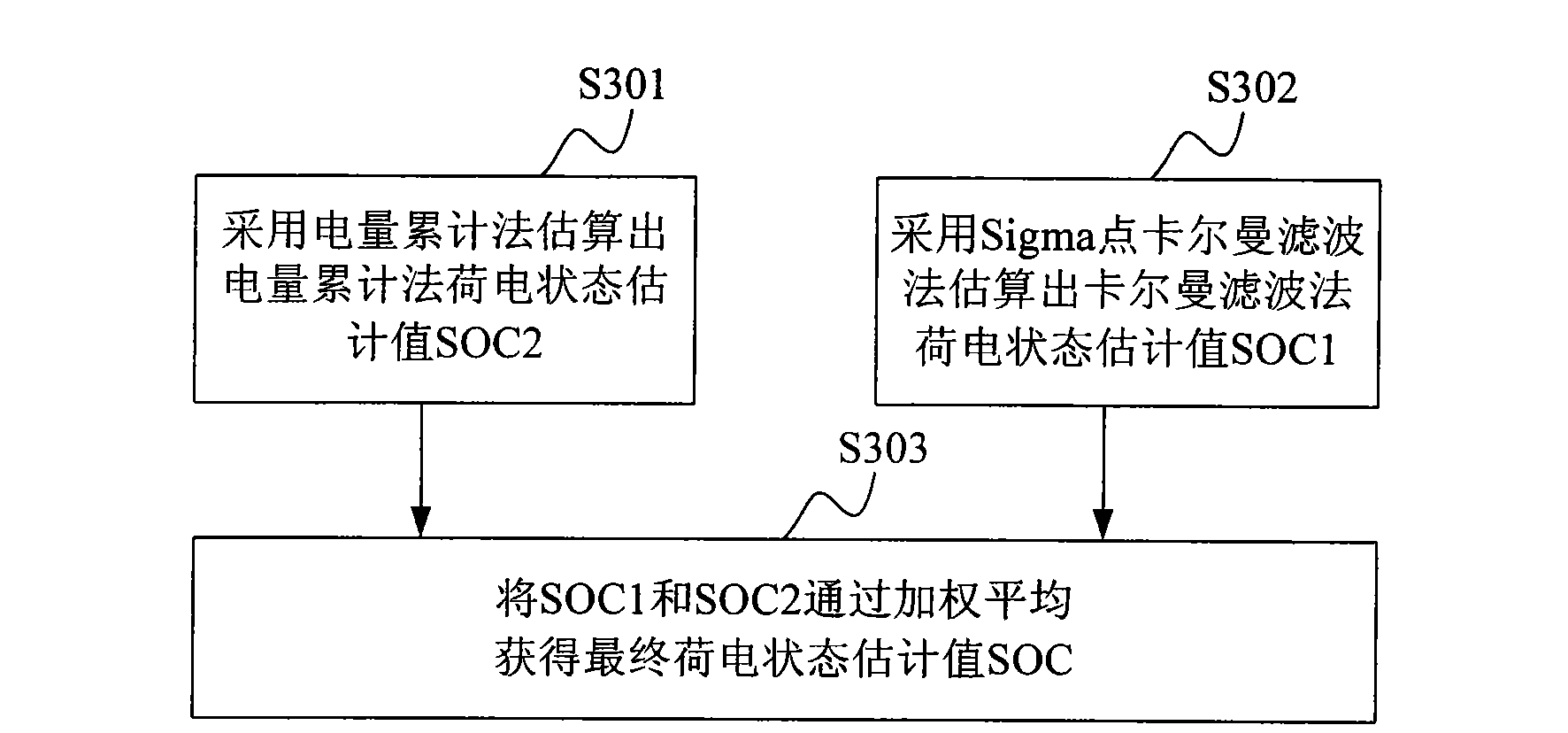

Estimation method and system of state of charge (SOC) of power battery

ActiveCN102062841AAvoid oscillationAvoid Cumulative ErrorsElectrical testingState of chargeWeighted average method

The invention discloses an estimation method of state of charge (SOC) of a power battery. The method comprises the following steps: estimating the SOC estimated value SOC2 of the power battery by an electricity accumulative method; taking a Sigma-point Kalman filter (SPKF) as a basic estimation tool, taking a dual-RC circuit battery model as a time and measurement update engine of the SPKF, and estimating the SOC estimated value SOC1 of the power battery by a Kalman filter method; and obtaining the final SOC estimated value SOC based on the SOC estimated value SOC2 by the electricity accumulative method and the SOC estimated value SOC1 by the Kalman filter method by utilizing a weighted average method. Correspondingly, the invention further discloses an estimation system of the SOC of thepower battery. The invention has the advantages of high SOC estimation accuracy, stable operation and the like, and is convenient in real-time estimation, thus being applicable to pure electric vehicles and hybrid electric vehicles in need of the power battery.

Owner:BEIQI FOTON MOTOR CO LTD

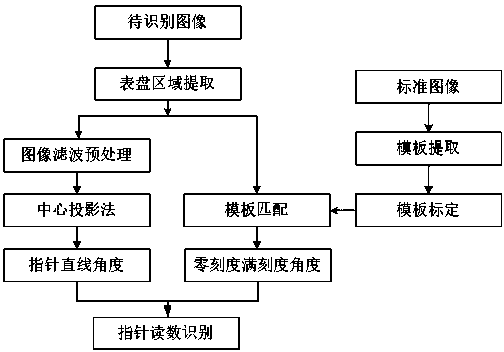

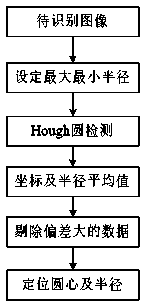

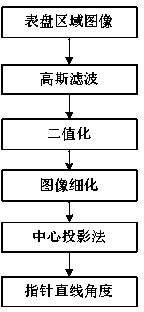

Image processing method for automatic pointer-type instrument reading recognition

ActiveCN104392206ASmall amount of calculationHigh positioning accuracyCharacter and pattern recognitionTemplate matchingImaging processing

The invention discloses an image processing method for automatic pointer-type instrument reading recognition. The method comprises the following steps: (1) Hough circle detection is carried out on the image, a weighted average method is used for positioning the circle center and the radius of a dial, and a dial region square image is extracted; (2) the image is pre-treated, and a binary thinning image of the instrument pointer is extracted; (3) a central projection method is used for determining a pointer angle; (4) a zero graduation line and full graduation line position templates are extracted, and a range starting point and ending point positions are calibrated; (5) by using template matching, zero graduation line and full graduation line angles are obtained; and (6) according to the pointer angle, the zero graduation line angle and the full graduation line angle, the pointer reading is obtained through calculation. Thus, the problem that the instrument dial position on the acquired image is not fixed as the relative position between a camera and the pointer-type instrument is not fixed can be solved, subjective errors as the reading of the instrument is read manually can be eliminated, the efficiency and the precision can be improved, safety of people is ensured, the application range is wide, and robustness is strong.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

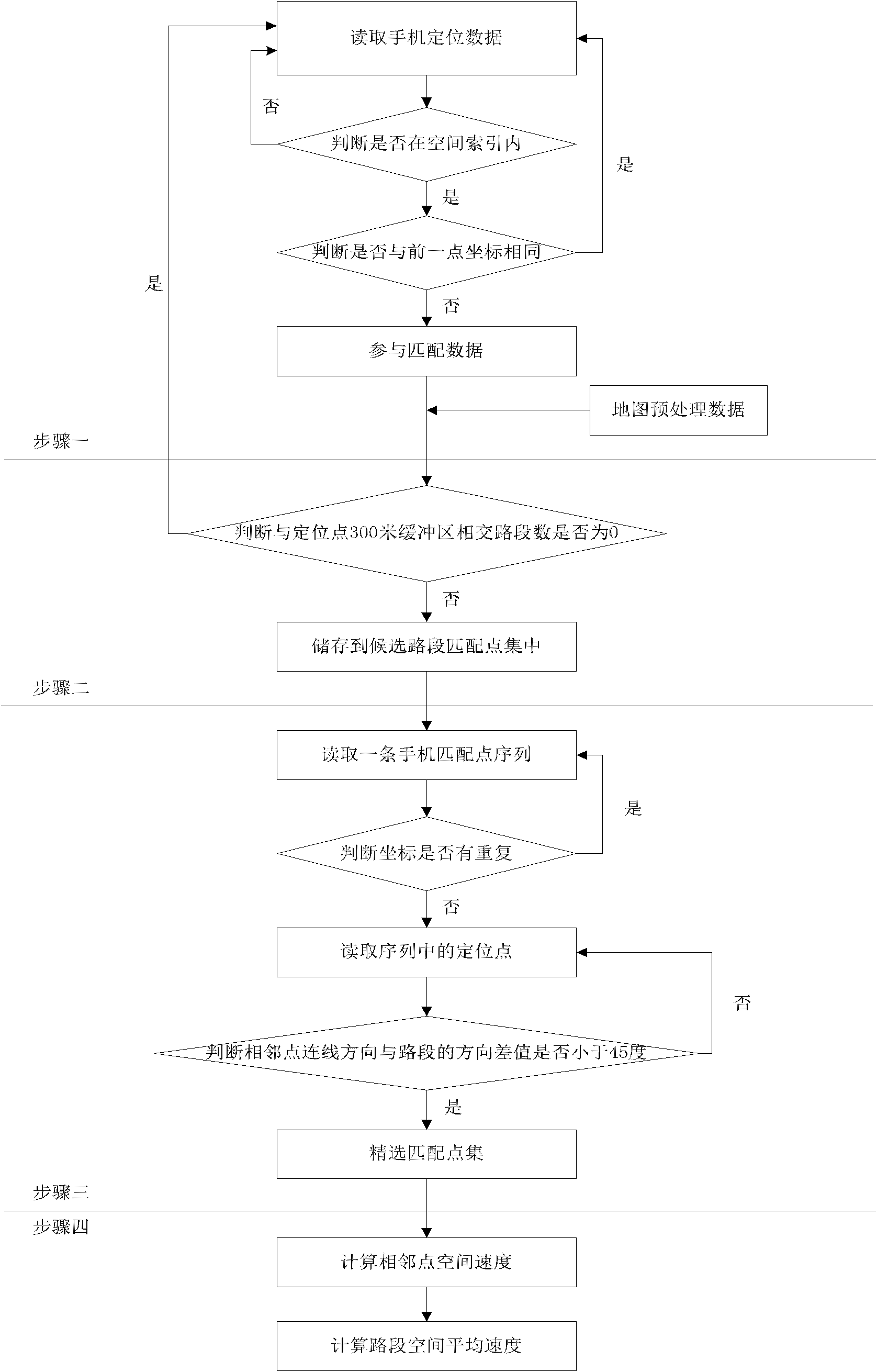

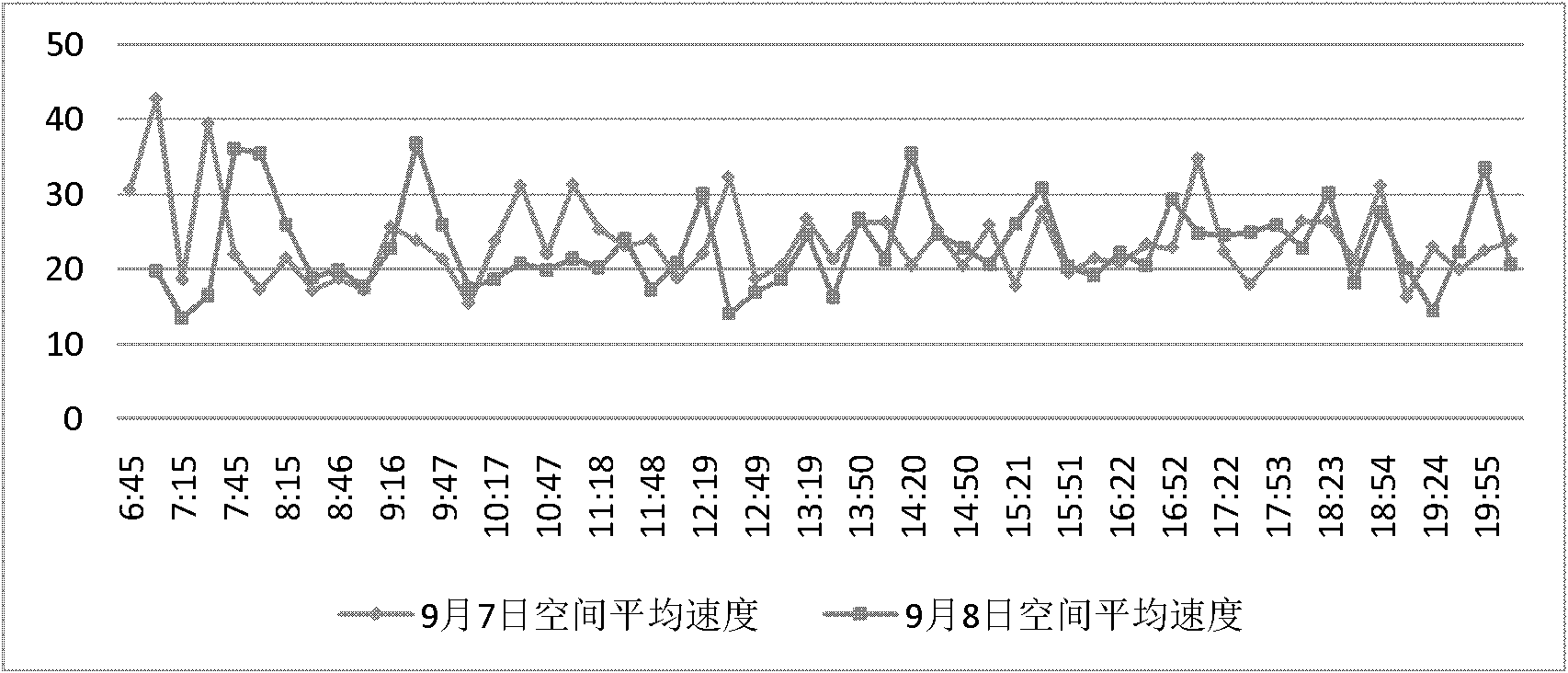

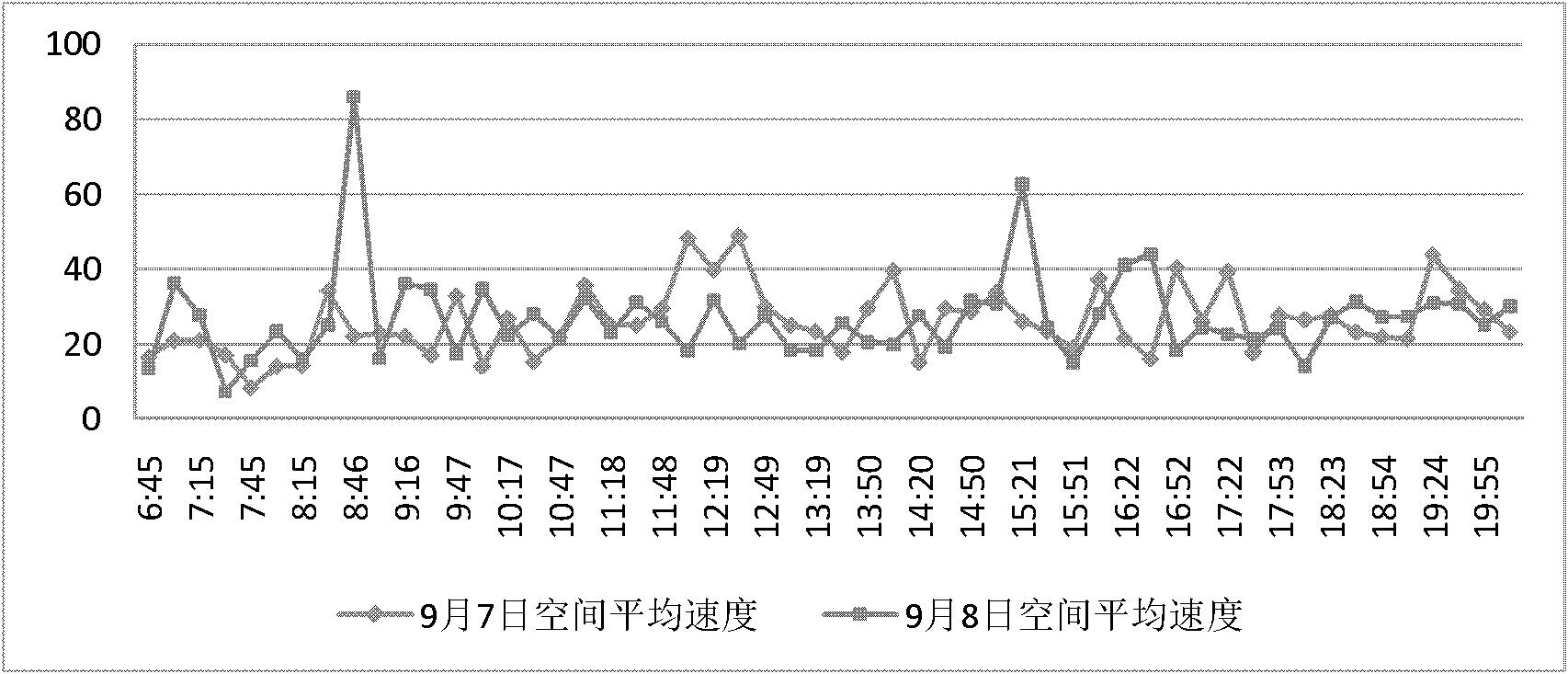

Method for extracting real-time urban road traffic flow data based on mobile phone positioning data

InactiveCN102332210ADetection of traffic movementLocation information based serviceTransit systemWeighted average method

The invention discloses a method for extracting real-time urban road traffic flow data based on mobile phone positioning data. The method comprises the following steps of: 1, preprocessing the mobile phone positioning data and map data; 2, determining a candidate matching road section of the mobile phone positioning data and a rough matching point set of each road section; 3, extracting vehicle-mounted mobile phone data, namely determining a fine matching point set of each road section; and 4, calculating space mean speed of the road section by a space speed weighted average method. The method is a dynamic and real-time traffic flow data acquisition method with a large coverage area and low acquisition cost; a traffic information acquisition mode and a source of an intelligent transportation system are enriched; and the method has positive significance to constructing the urban intelligent transportation system and improving the road operation management level.

Owner:SOUTHEAST UNIV +1

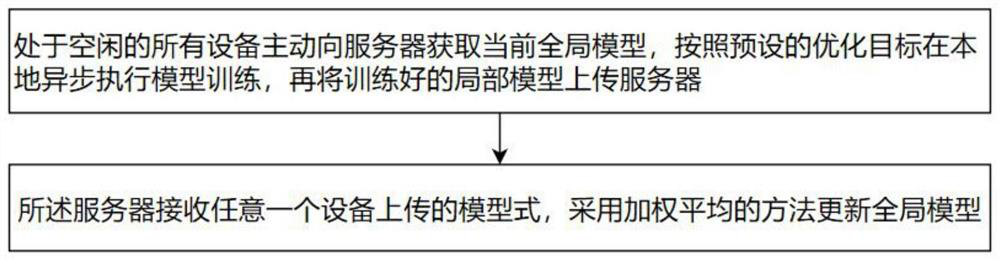

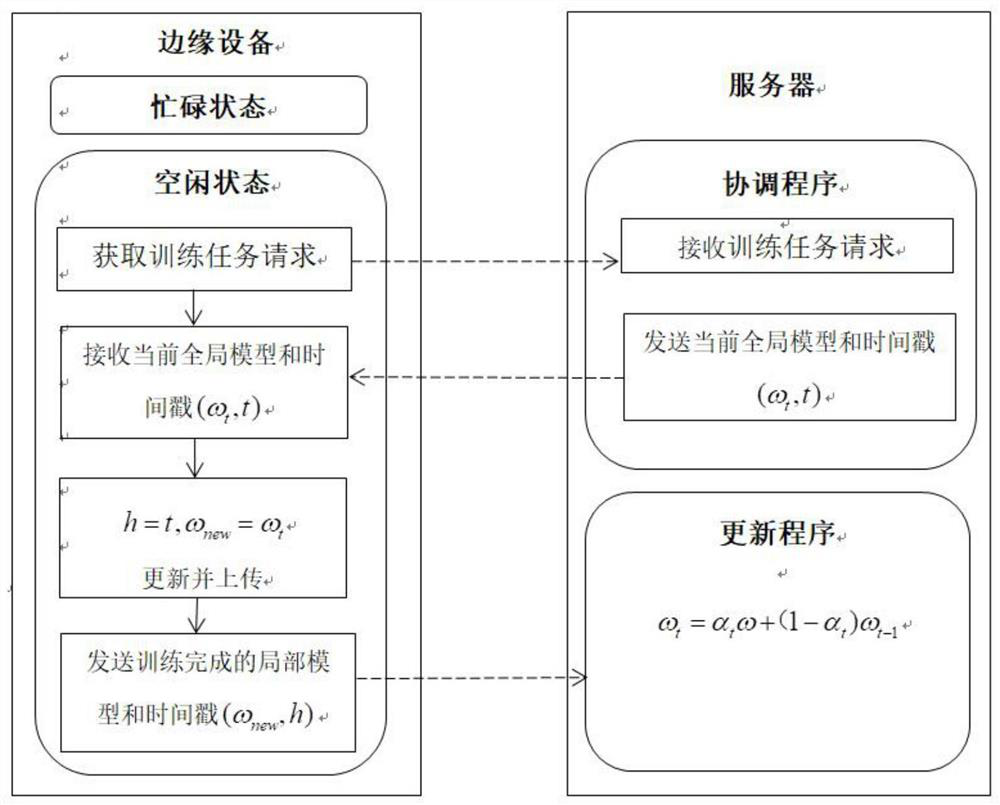

Edge computing-oriented federated learning method

InactiveCN111708640AEfficient training processMake the most of free timeResource allocationMachine learningEdge computingWeighted average method

The invention provides an edge computing-oriented federated learning method, which comprises the following steps that: all idle devices actively acquire a current global model from a server, asynchronously execute model training locally according to a preset optimization target, and upload the trained local model to the server; and the server receives the model formula uploaded by any one device and updates the global model by adopting a weighted average method. According to the method, asynchronous training and federation learning can be combined, in asynchronous federation optimization, allidle devices are used for asynchronous model training, a server updates a global model through weighted average, idle time of all edge devices is fully utilized, and model training is more efficient.

Owner:苏州联电能源发展有限公司

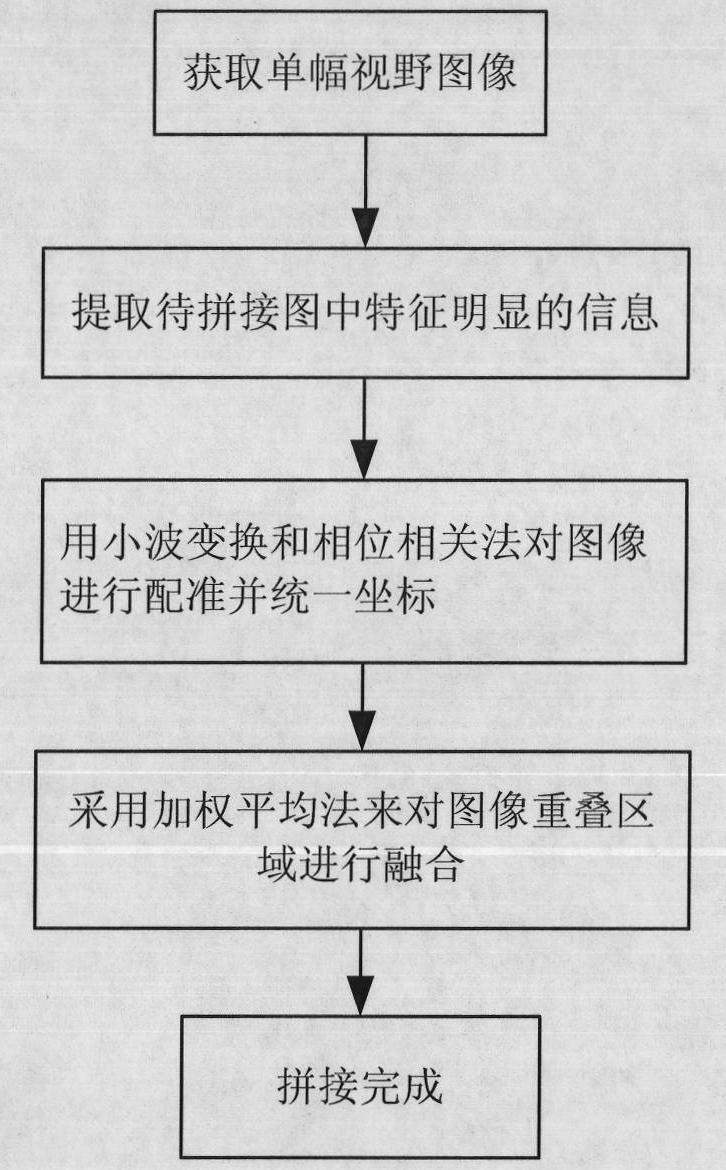

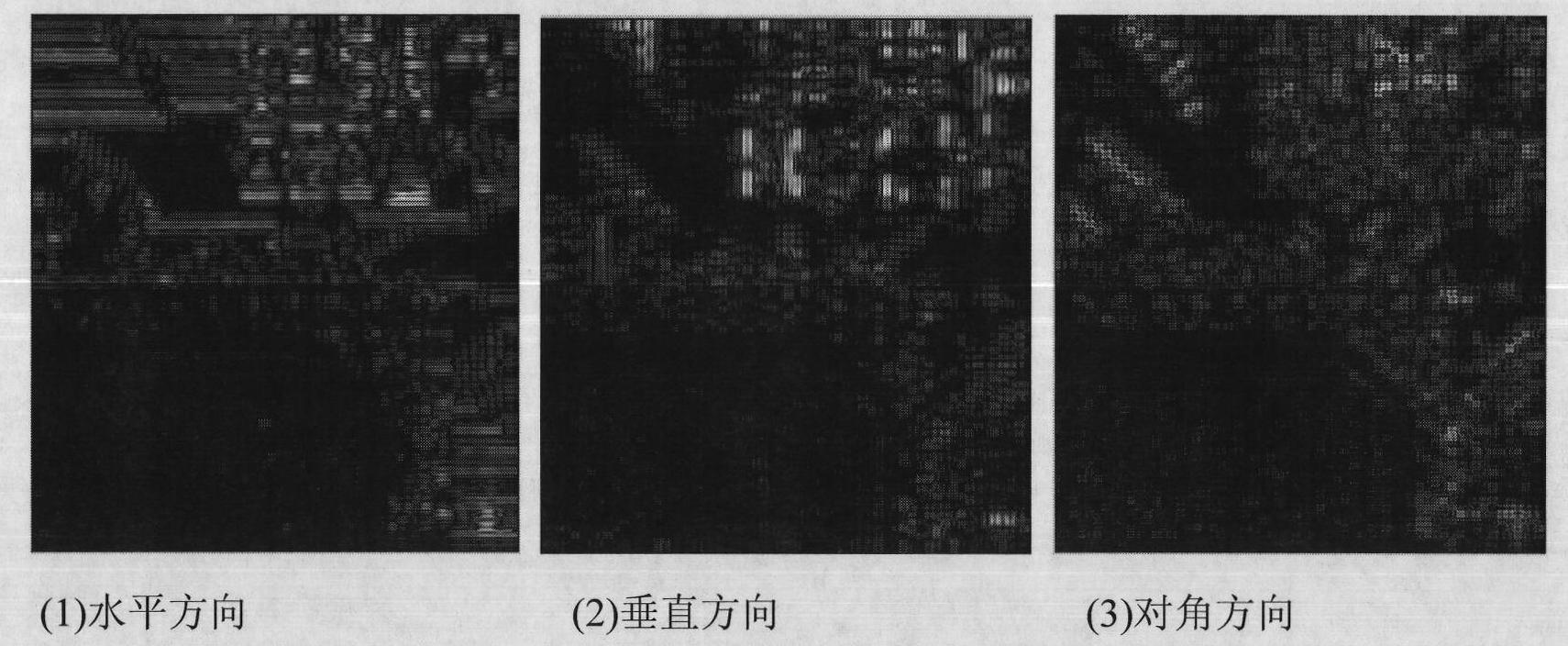

Fast image splicing method

InactiveCN101840570AAchieve integrationQuick stitchingImage enhancementImage analysisPhase correlationComputation complexity

The invention discloses a fast image splicing method, which is characterized by comprising the following steps of: (1) acquiring a single-breadth field image; (2) extracting characteristic information in an image to be spliced; (3) performing two-dimensional wavelet transform on the image to be spliced to obtain high-frequency coefficients reflecting the profile of change in a horizontal direction and a vertical direction of the image, and realizing overlapped position alignment in combination with a phase correlation method; and (4) adopting a weighted mean method to fuse overlapped areas of the image to finish the splicing. In the method, low-energy coefficients reflecting the gradual change of illumination are removed by performing the two-dimensional wavelet transform on the image and then the high-frequency coefficients reflecting the profile of the change in the horizontal direction and the vertical direction of the image are obtained, which can effectively reduce calculation complexity; and simultaneously, the fast and accurate overlapped position alignment is realized in combination with the phase correlation method and the fusion of the image is realized by adopting the weighted mean method so as to realize the fast and accurate splicing of PCB images of various specifications and various colors.

Owner:GUANGDONG UNIV OF TECH

Sight tracking method based on stepwise regression analysis mapping model

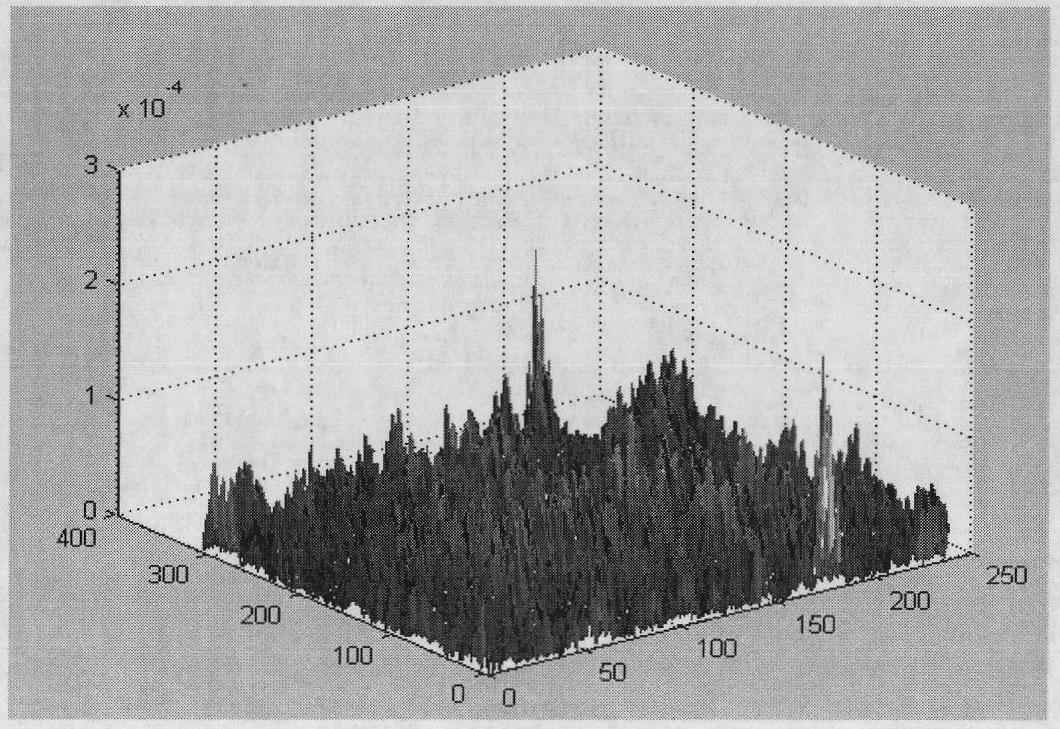

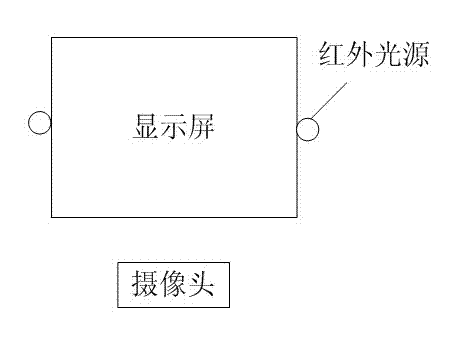

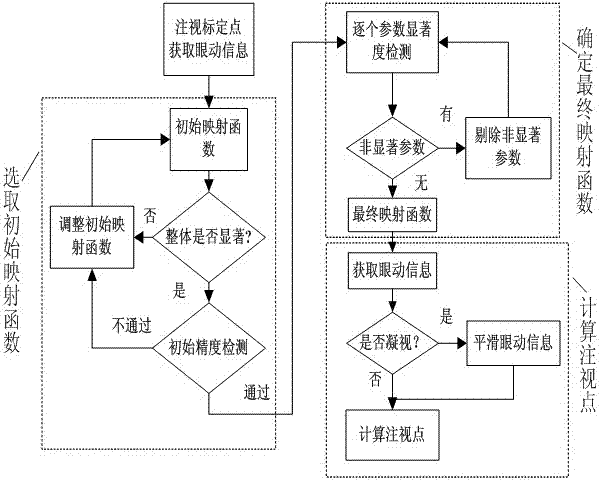

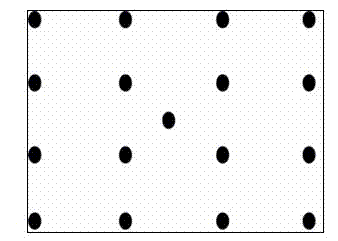

InactiveCN102520796AImprove computing efficiencyImprove fitting accuracyInput/output for user-computer interactionGraph readingWeighted average methodComputer science

The invention discloses a sight tracking method based on a stepwise regression analysis mapping model. The method comprises the steps of firstly, extracting eye movement characteristic information when human eyes watch a fixed point; then selecting an initial mapping model function; after the initial mapping model is selected, checking significances of all items of a mapping model function, rejecting the non-significant items, and in the process of continuously rejecting the items and reconstructing the mapping model function, finding the mapping model function with the highest fitting precision at last; and finally, utilizing the mapping model function for calculating the watching point, and when the human eyes are in a gazing state, adopting a Gaussian weighted average method to smooth the eye movement characteristic information, thus solving the problem of eye shaking. According to the method, the robustness is good, and the precision is high.

Owner:SOUTH CHINA UNIV OF TECH

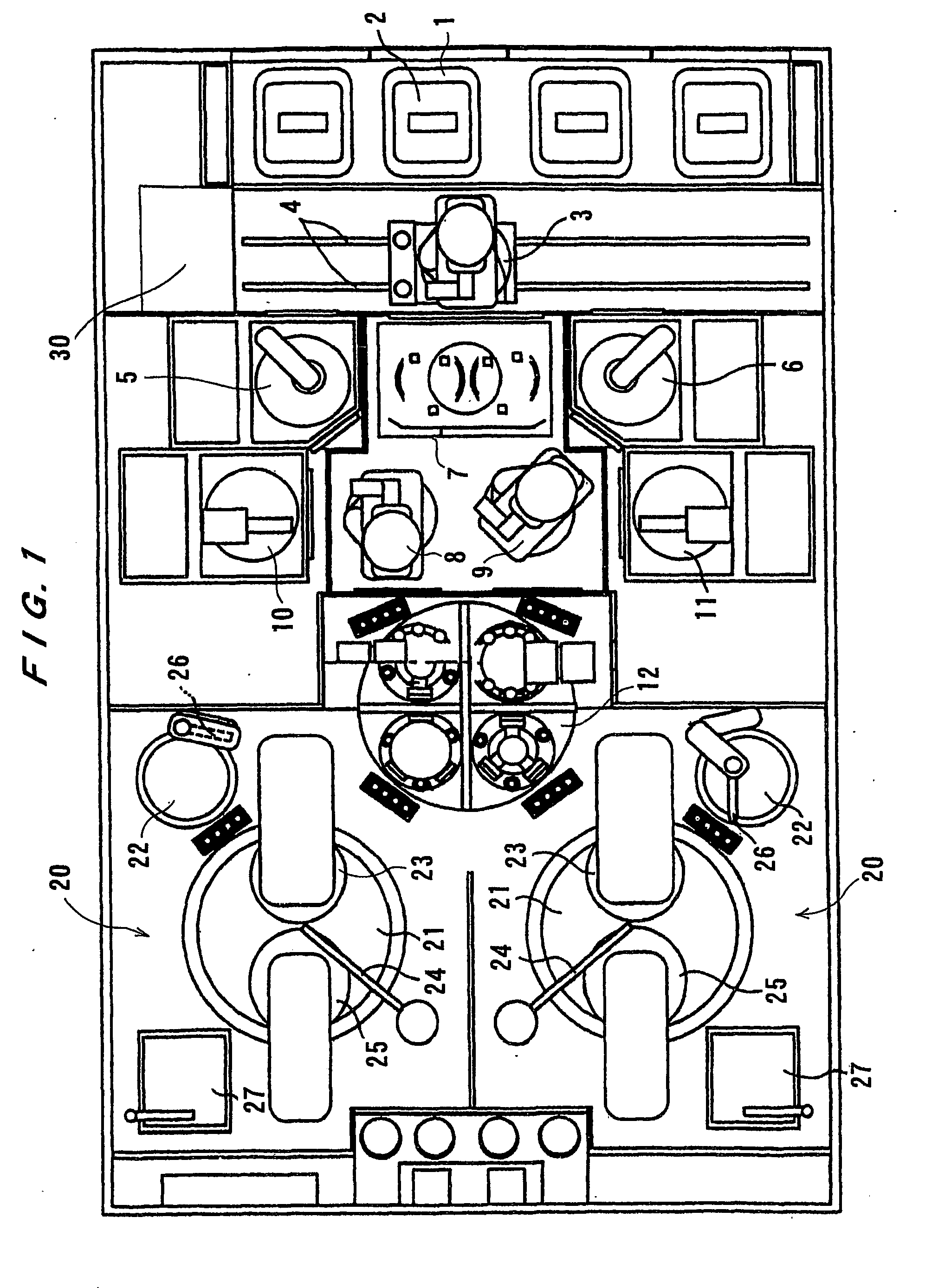

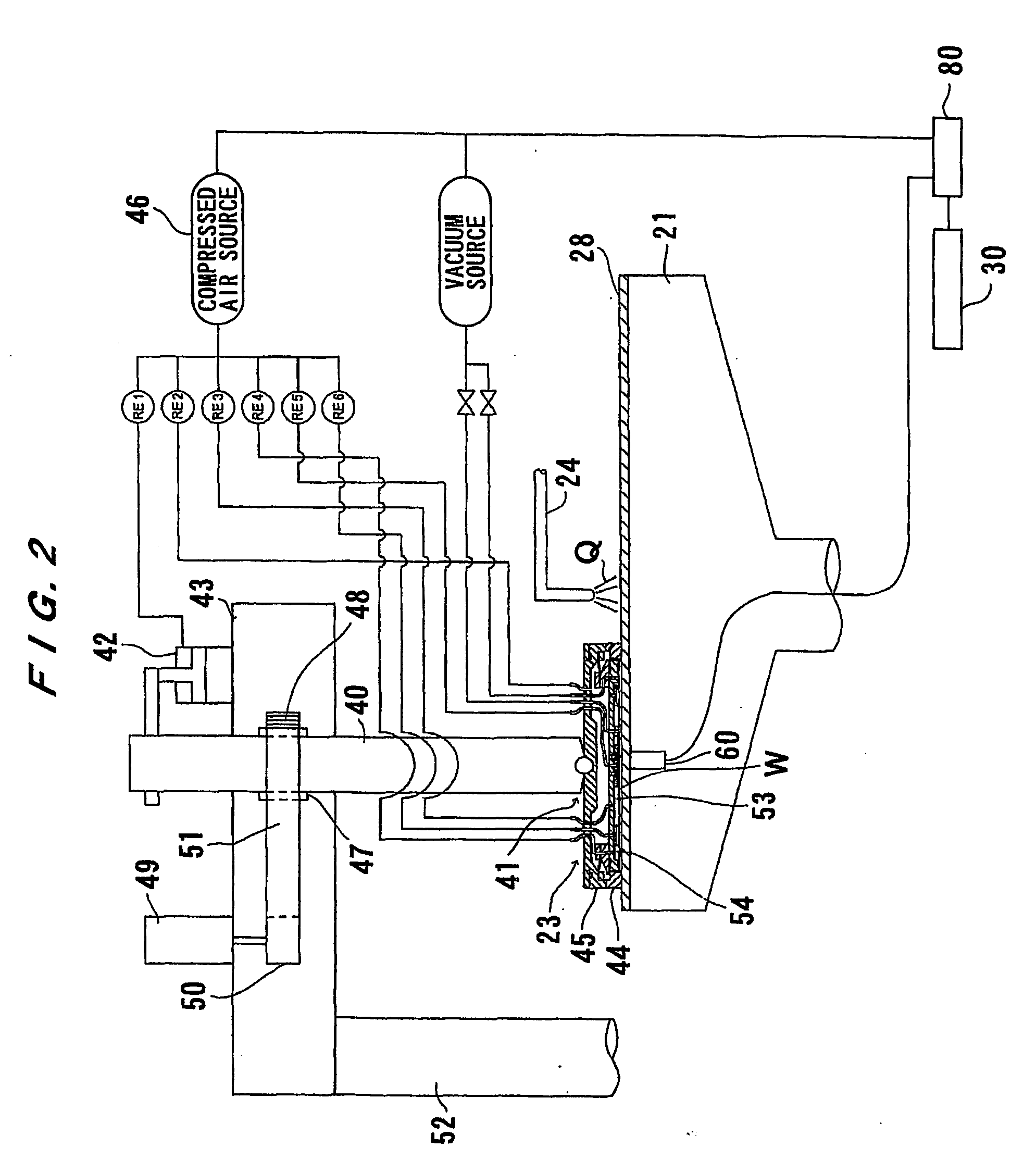

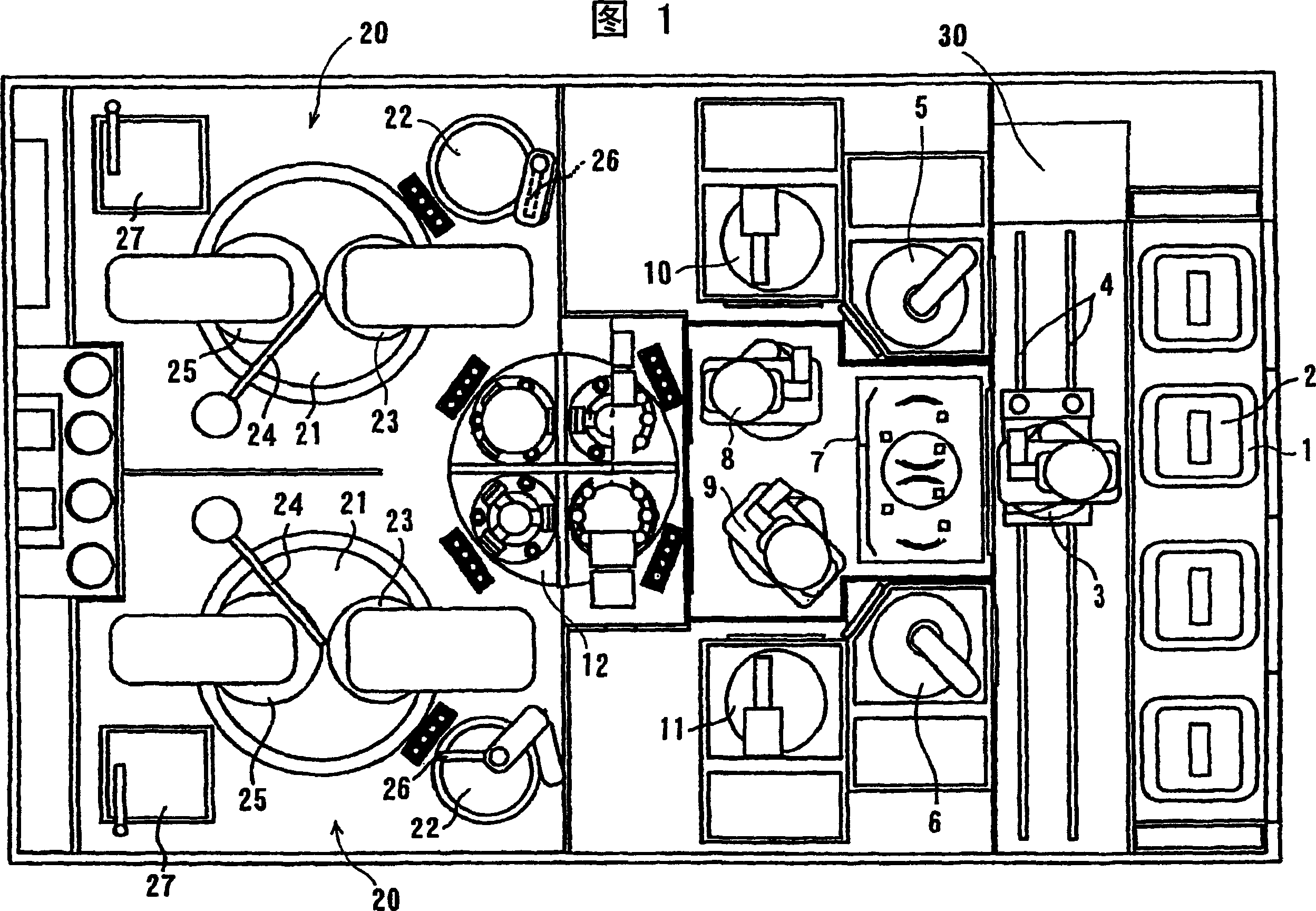

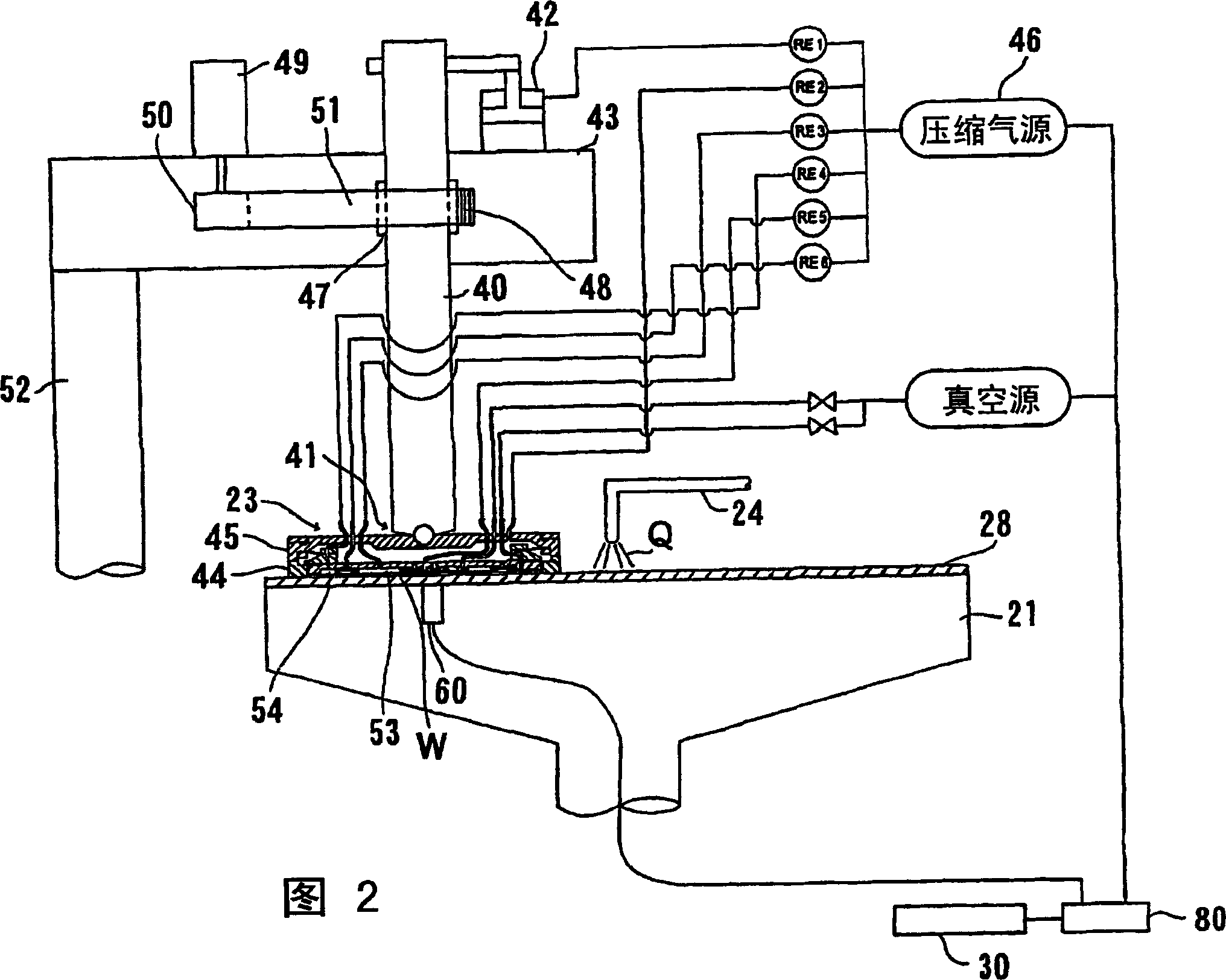

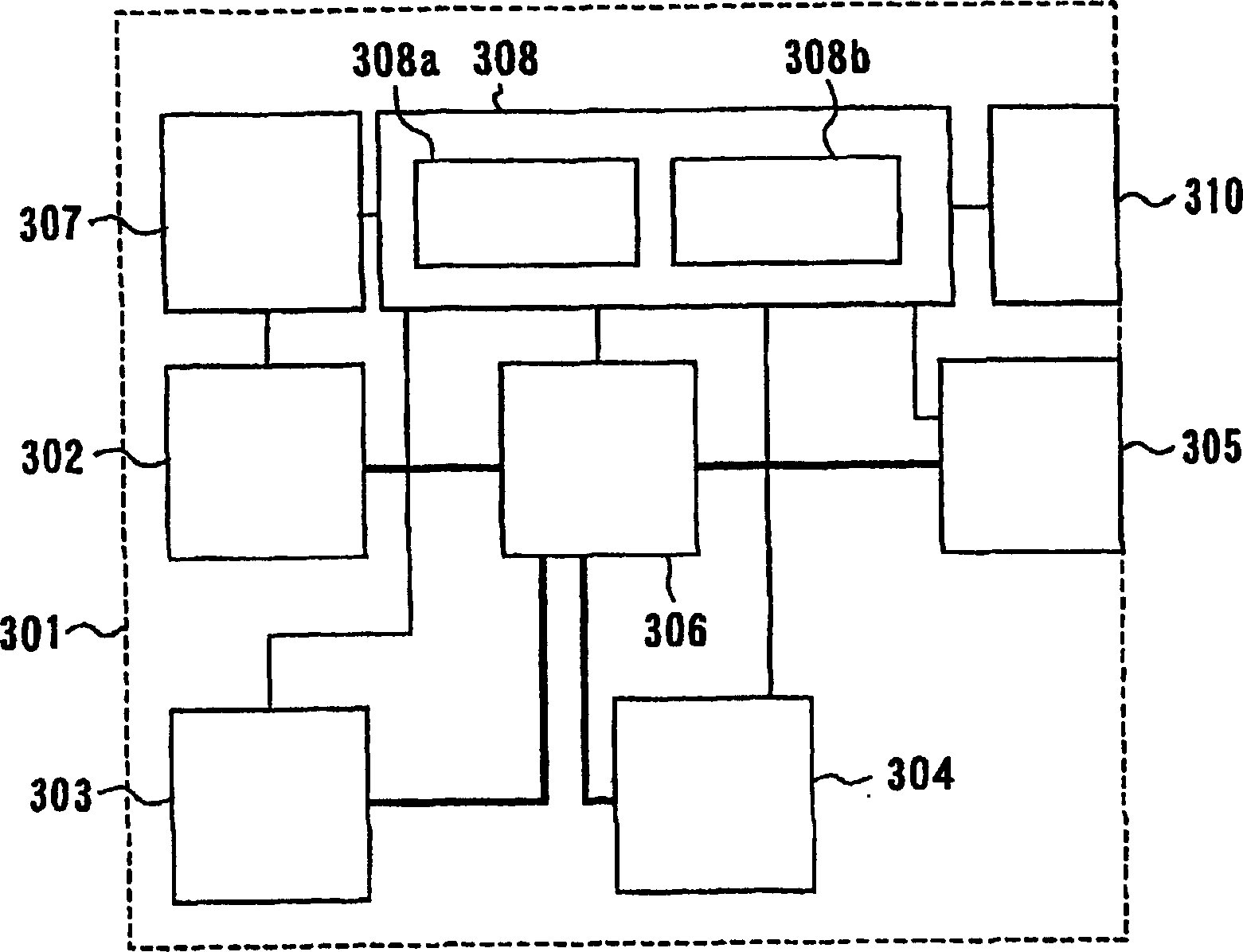

Polishing apparatus and polishing method

ActiveUS20060166503A1Prevent manufacturing yieldIncrease manufacturing costDecorative surface effectsSemiconductor/solid-state device manufacturingWeighted average methodEngineering

A polishing apparatus has a polishing section (302) configured to polish a substrate and a measurement section (307) configured to measure a thickness of a film formed on the substrate. The polishing apparatus also has an interface (310) configured to input a desired thickness of a film formed on a substrate to be polished and a storage device (308a) configured to store polishing rate data on at least one past substrate therein. The polishing apparatus includes an arithmetic unit (308b) operable to calculate a polishing rate and an optimal polishing time based on the polishing rate data and the desired thickness by using a weighted average method which weights the polishing rate data on a lately polished substrate.

Owner:EBARA CORP

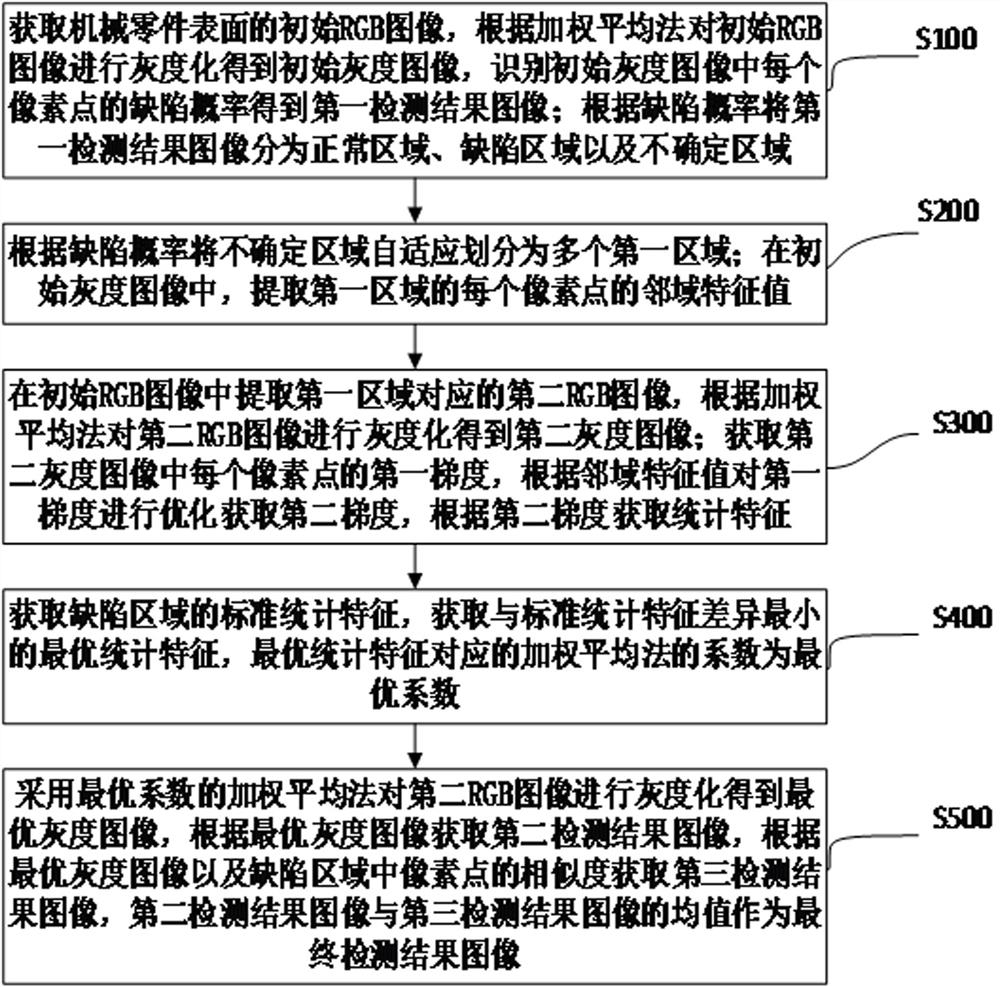

Mechanical part stress corrosion detection method and system based on image processing

ActiveCN113689428AImprove accuracyImprove detection accuracyImage enhancementImage analysisPattern recognitionImaging processing

The invention relates to the technical field of artificial intelligence, in particular to a mechanical part stress corrosion detection method and system based on image processing. The method comprises the following steps: obtaining an initial grayscale image of a mechanical part according to a weighted average method, identifying the defect probability of each pixel point to obtain a first detection result image, extracting an uncertain region in the first detection result image, and adaptively dividing the uncertain region into a plurality of first regions; extracting a neighborhood feature value of the pixel points of the first region, and obtaining a second gray level image according to a weighted average method; obtaining a second gradient according to the neighborhood feature value, obtaining an optimal statistical feature having the smallest difference with the standard statistical feature according to the second gradient, and further obtaining an optimal coefficient; and obtaining an optimal grayscale image by adopting the optimal coefficient, and obtaining a final detection result image according to the optimal grayscale image. Through the feature enhancement of the image, the detection accuracy of the stress corrosion area is improved, and the detection efficiency is also improved while the detection accuracy is improved.

Owner:江苏南通元辰钢结构制造有限公司

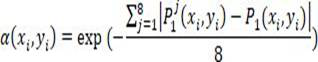

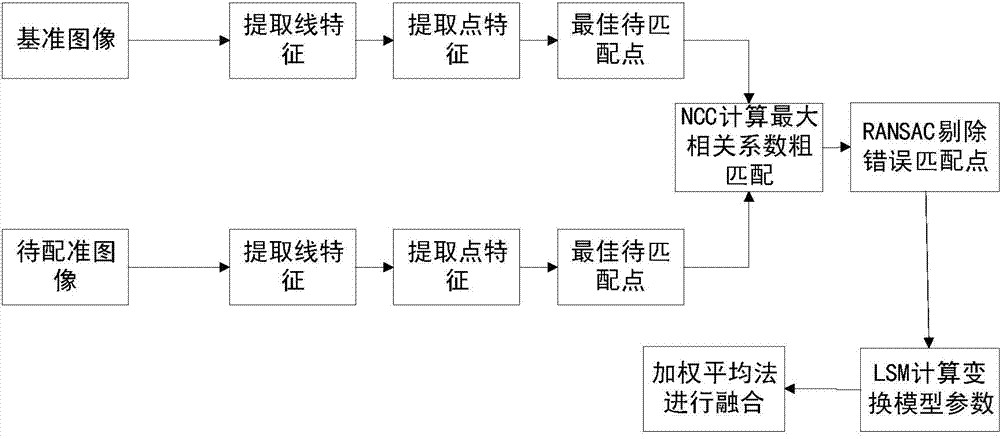

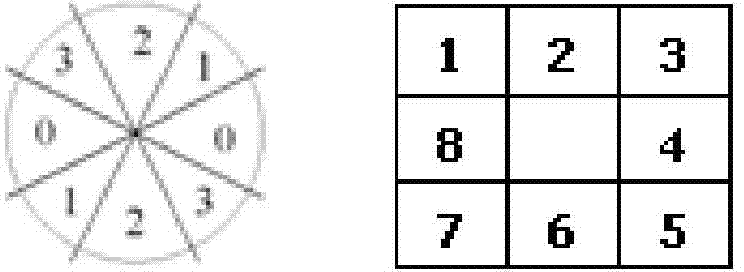

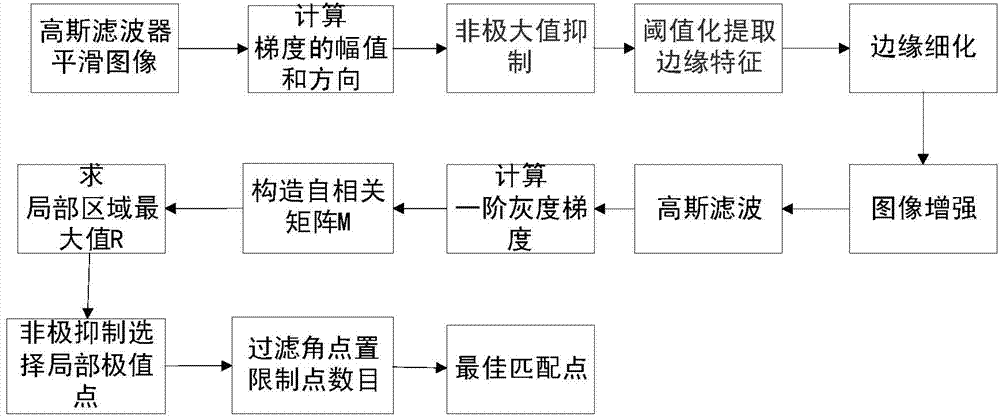

Rapid image splicing method based on point and line features

ActiveCN103679636AImprove stitching qualityAvoid lossImage enhancementGeometric image transformationWeighted average methodModel parameters

The invention provides a rapid image splicing method based on feature matching. The method includes the steps: respectively extracting line features and point features of images by the aid of a Canny edge detection algorithm and a Harris corner point detection algorithm and combining the line features and the point features to obtain the best feature points; roughly matching the feature points by the aid of similarity metric NCC (normalized cross correlation), removing mismatched points by the aid of an RANSAC (random sample consensus) algorithm to improve image matching accuracy, and calculating transformation model parameters by an LSM (least square method); finally, fusing the spliced images by a weighted average method and eliminating splicing gaps. The points to the matched are determined according to the point and line image features, image details can be enhanced, image matching errors caused by underexposure, overexposure, camera shake and the like are avoided, and image splicing quality is improved to a certain degree.

Owner:JIANGSU R & D CENTER FOR INTERNET OF THINGS

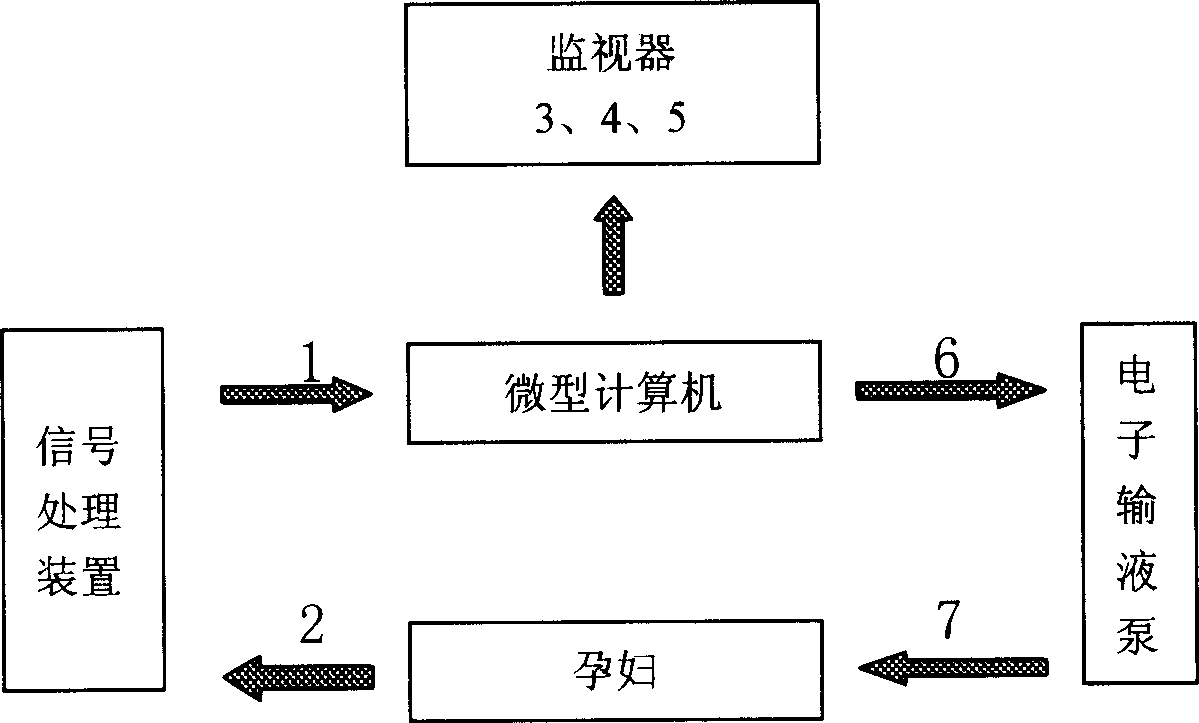

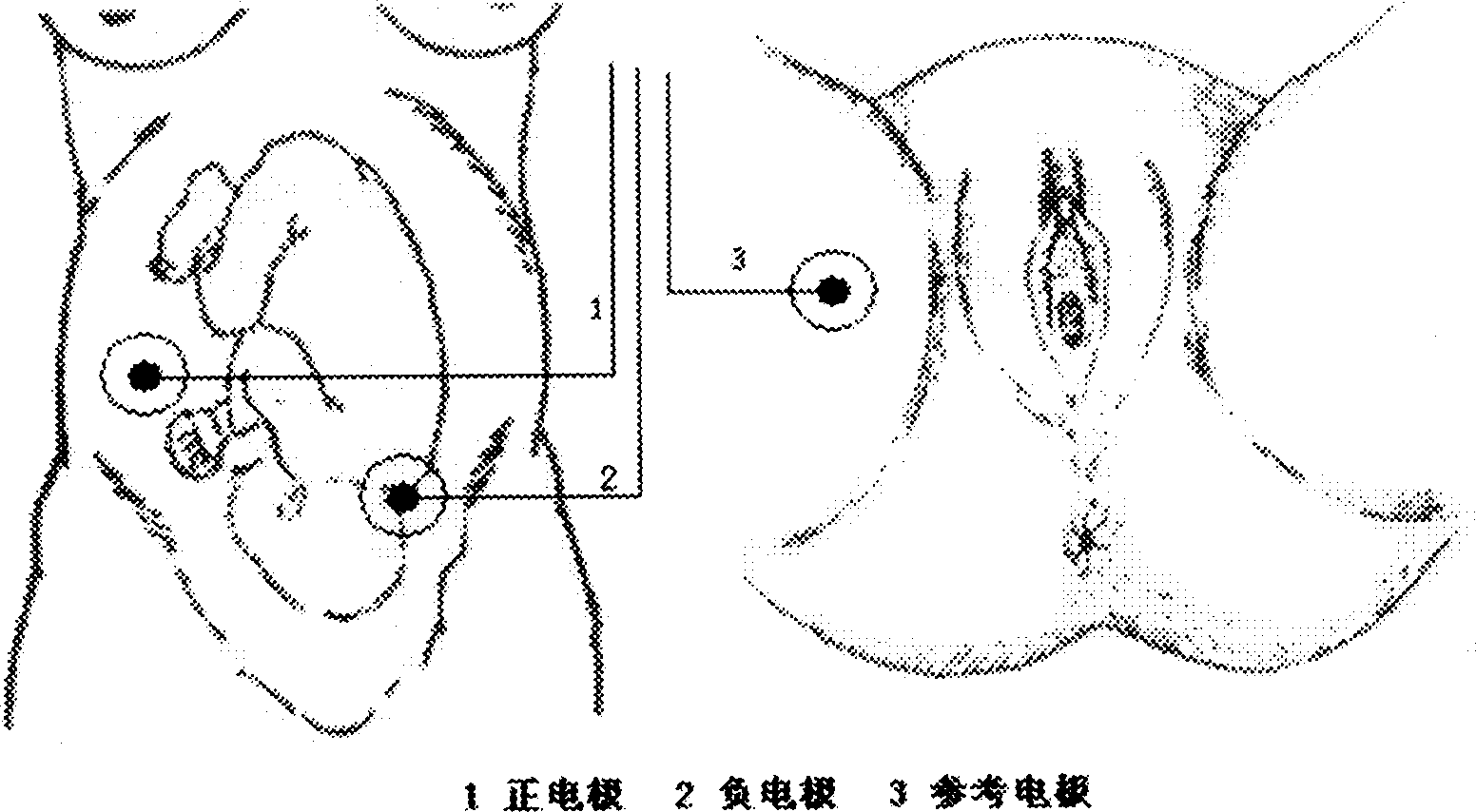

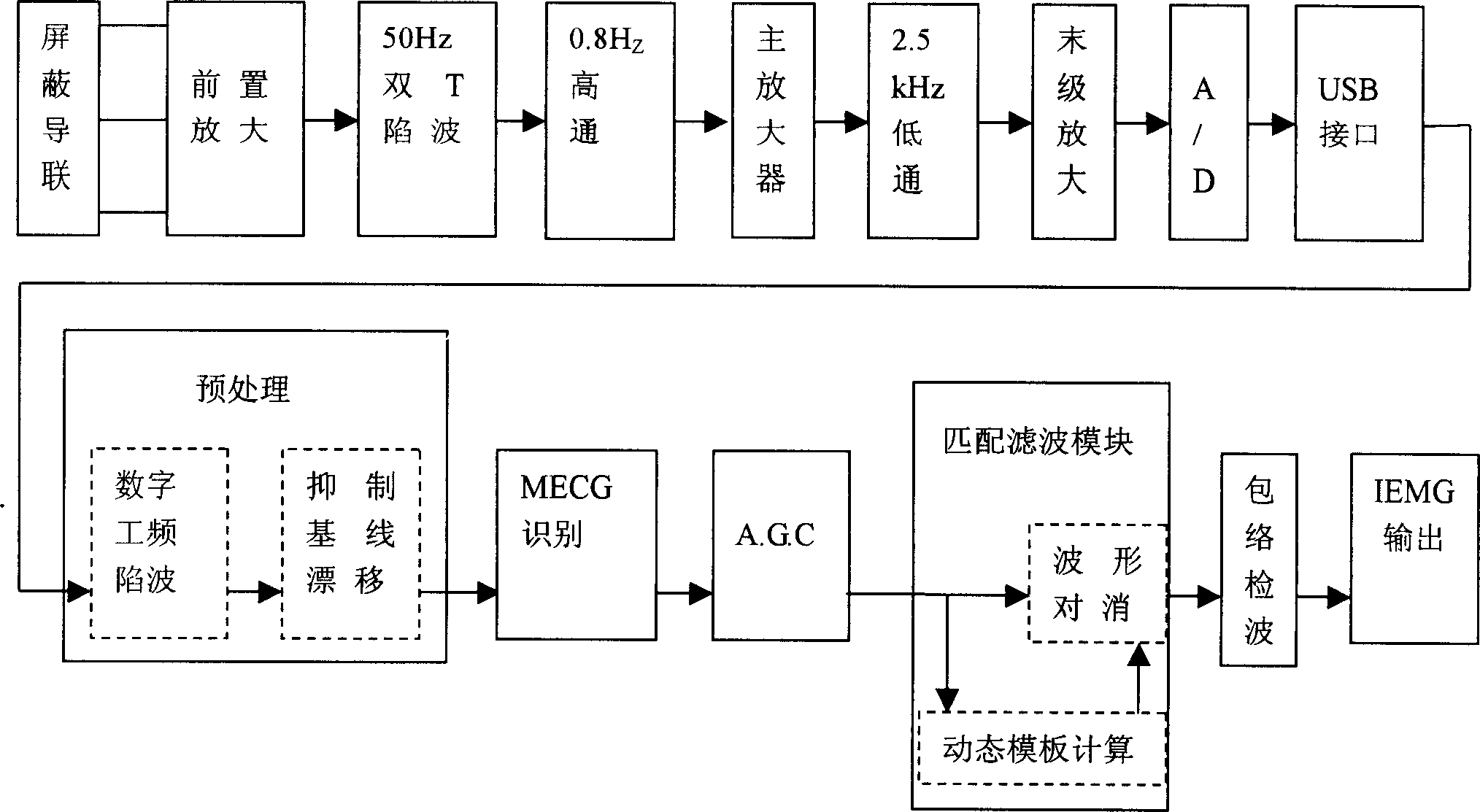

Method and device for monitoring contraction activities of mother womb and controlling childbirth process

InactiveCN1444905AConvenient and effective extractionEfficient extractionAnimal reproductionDiagnostic recording/measuringDigital signal processingWeighted average method

A method and equipment for monitoring the uterine contraction of mother and controlling the delivery process features that an abdominal electrode including method is used to sample all abdominal signals including the noisese, such as mother ECG, fetal ECG and electromagnetic interference, and AGC module is designed for suppressing said noises, and a digital signal processor is used as the core unit to eliminate mother ECG. Its advantages are high reliability, no damage, and less distortion.

Owner:GUANGZHOU SUNRAY MEDICAL APP +1

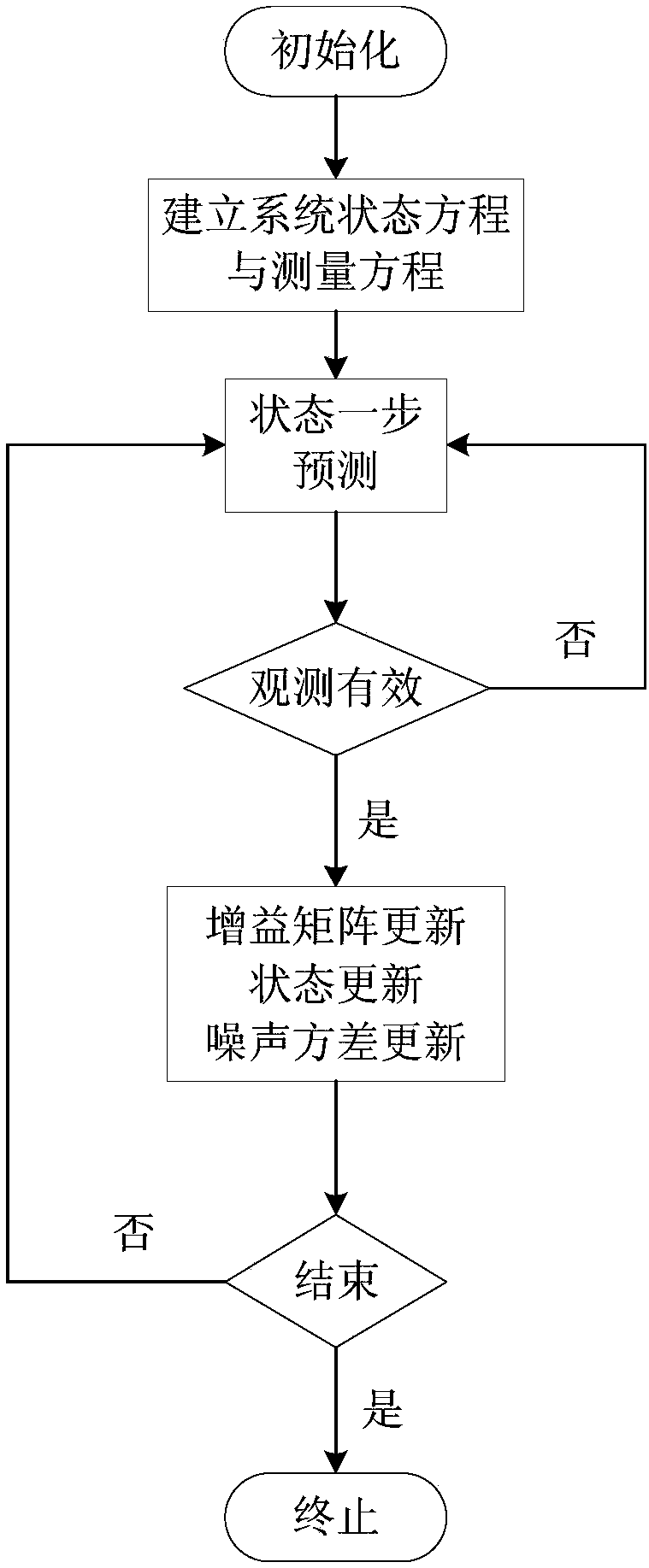

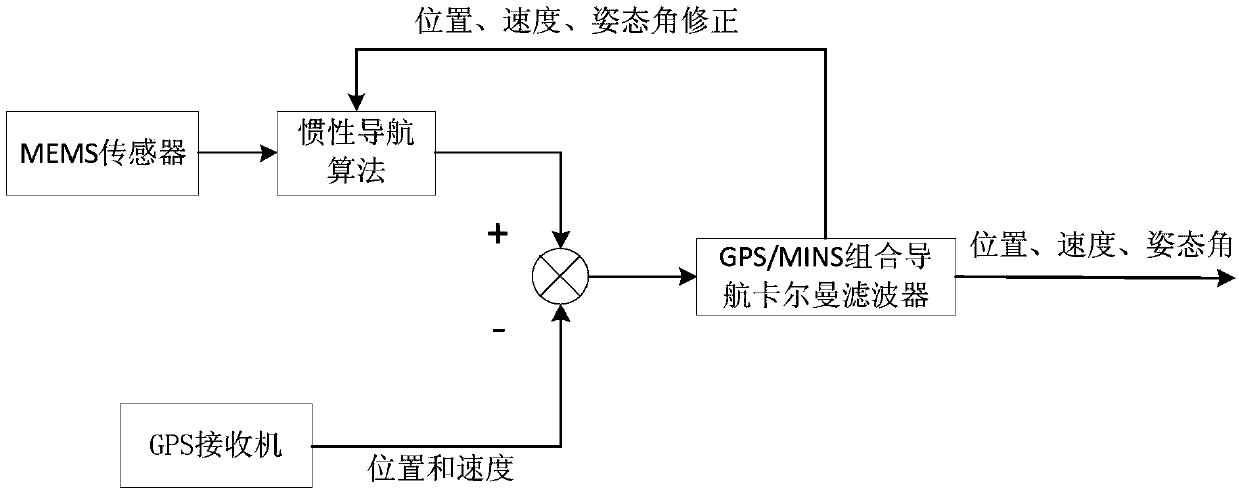

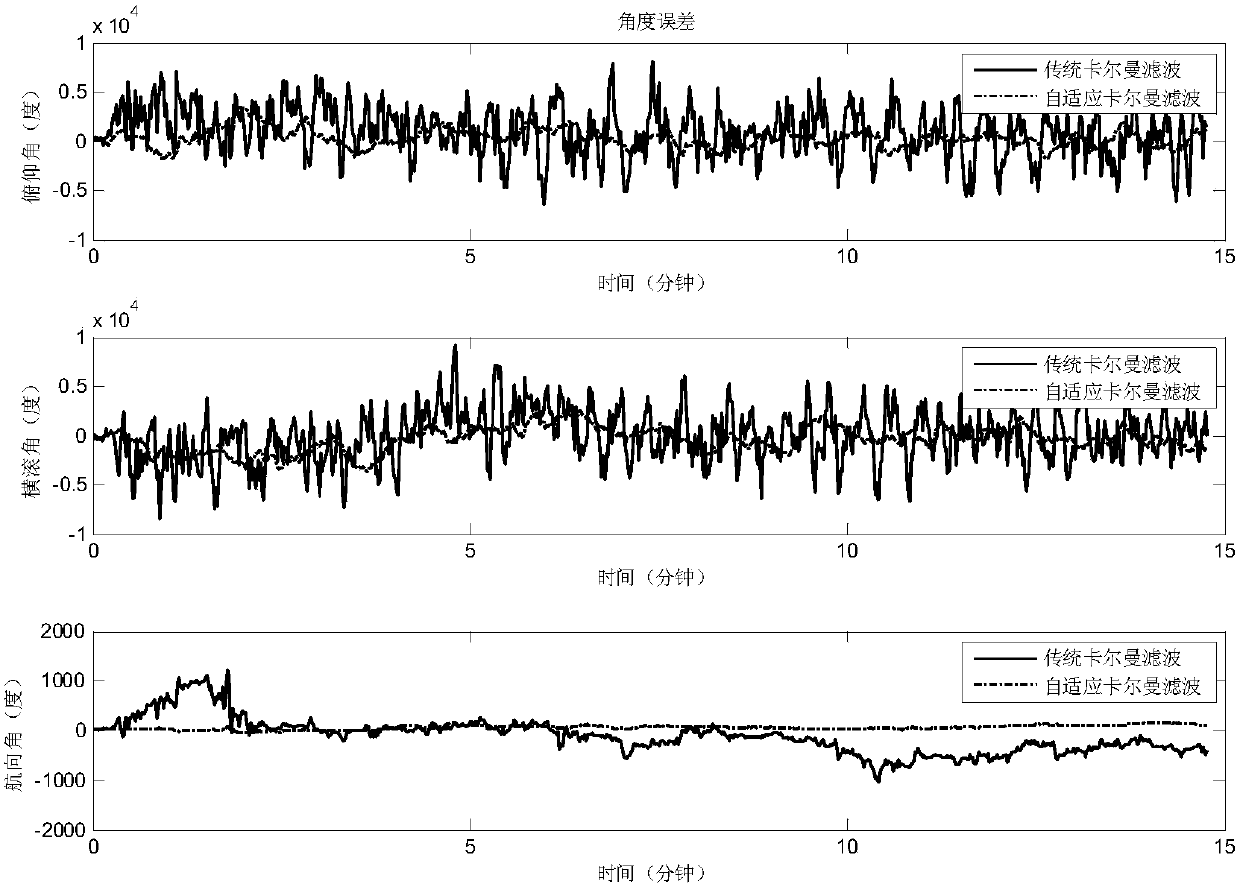

Adaptive Kalman filtering method of vehicle-mounted microinertia/satellite integrated navigation system

ActiveCN107621264AEffective calculationHigh positioning accuracyInstruments for road network navigationNavigational calculation instrumentsIn vehicleWeighted average method

The invention discloses an adaptive Kalman filtering method of a vehicle-mounted microinertia / satellite integrated navigation system. By the adaptive Kalman filtering method, when a state estimating error parameter and a measured noise parameter of the integrated navigation system are unknown or time-varying, a measured noise variance matrix and a state noise variance matrix are updated in real time according to measured output and state information while state estimation is performed. An exponential fading memory weighted average method is used for fading influence of the old measured noise and the system noise; moreover, in view of the problem that the noise variance matrix may lose positive definiteness, a sequential filtering method is introduced for the size of each element on a diagonal in the matrix is limited. The adaptive Kalman filtering method is small in calculation amount and high in robustness; and compared with conventional Kalman filtering, the adaptive Kalman filteringmethod has the advantages as follows: by the adaptive Kalman filtering method, the position information, the speed information and the attitude information of a vehicle with higher accuracy can be obtained.

Owner:SOUTH CHINA UNIV OF TECH

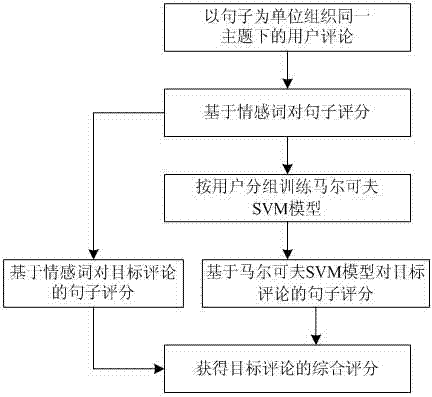

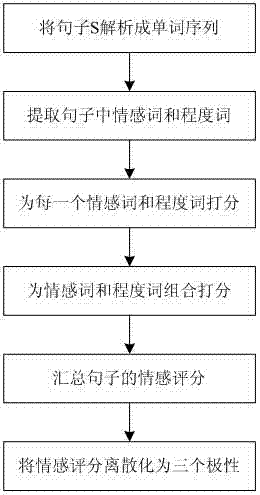

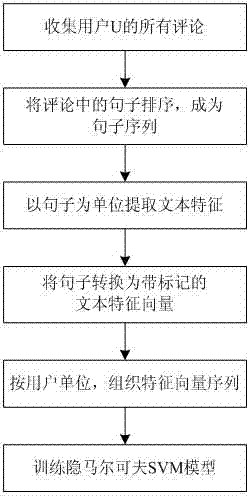

Recommendation level scoring method for theme-based network user comments

ActiveCN104331451AImprove accuracyQuick auto-gradingNatural language data processingSpecial data processing applicationsSupport vector machineWeighted average method

The invention discloses a recommendation level scoring method for theme-based network user comments. The method comprises the following steps: (1) acquiring the user comments under the same theme in network and organizing the comments by taking sentences as units; (2) performing emotional scoring on the sentences based on emotional words in the sentences; (3) taking the sentences and the corresponding emotional scoring as inputs and training a hidden Markov SVM (Support Vector Machine) model according to user units; (4) scoring each sentence by using the model aiming at a target comment to be scored; (5) scoring each sentence by using the step (2) aiming at the target comment to be scored; (6) combining the scoring in the two aspects by using a weighted average method to acquire the recommendation level scoring of the target comment. According to the method, an unsupervised mode is adopted, artificial evaluation is not required by applying a public emotional word library, and the calculation cost is simple; the method is suitable for the situation of quick updating of the network comments; the theme characteristics can be mined, the emotional tendency of other user comments and the influence of the theme on the target user comment are fully considered, and the accuracy and the timeliness of scoring are improved.

Owner:NANJING UNIV

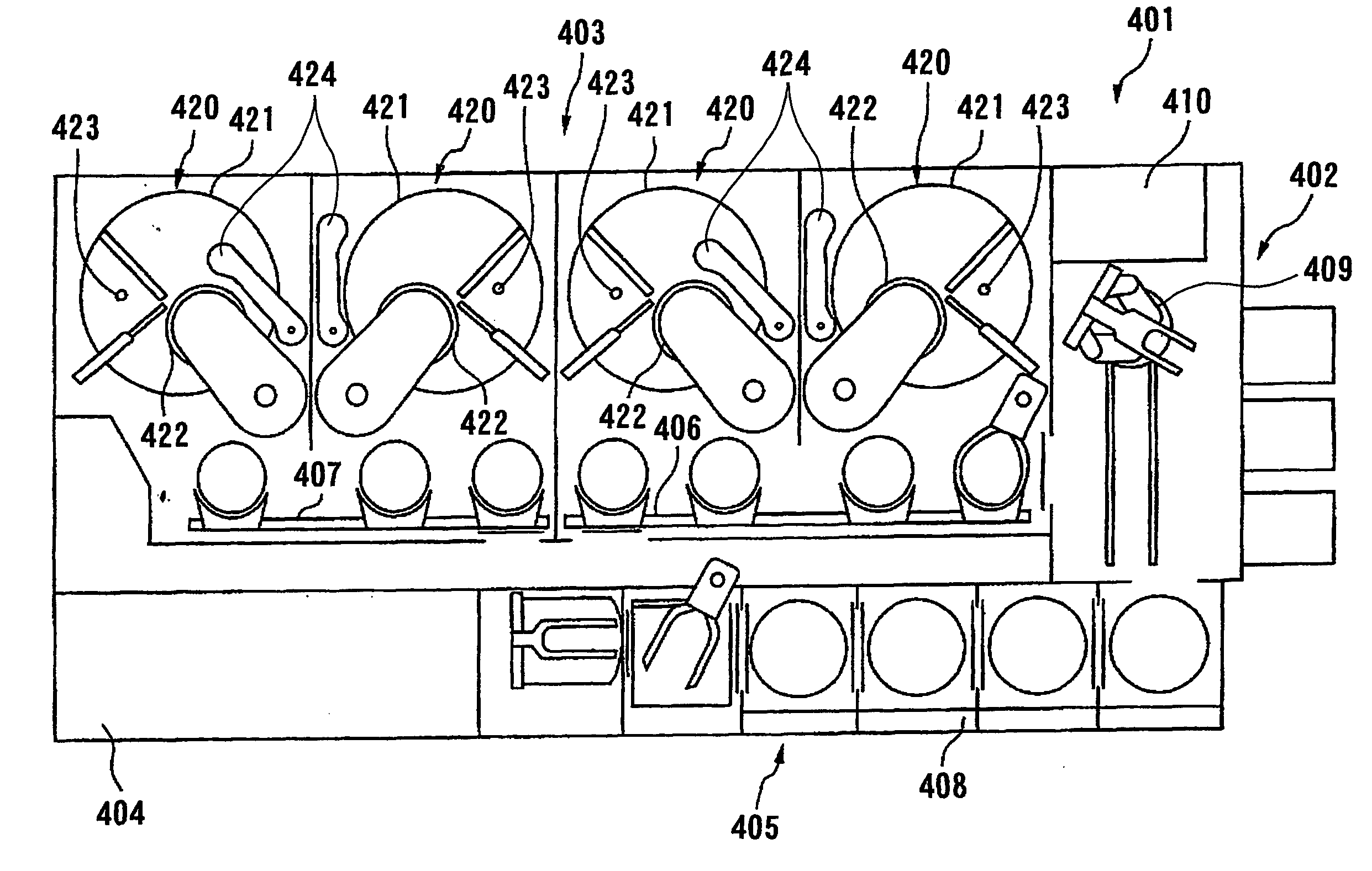

Polishing apparatus and polishing method

ActiveCN1813340AOptimize polishing timeAvoid yield lossSemiconductor/solid-state device manufacturingLapping machinesWeighted average methodEngineering

A polishing apparatus is disclosed, comprising a polishing section configured to polish a substrate, wherein the substrate has a plurality of laminating films including an upper layer and a lower layer; a measurement section configured to measure a thickness of a film formed on the substrate; an interface configured to input a desired thickness of a film formed on a substrate to be polished; an arithmetic unit operable to calculate a polishing rate and an optimal polishing time based on the polishing rate data and the desired thickness by using a weighted average method which weights the polishing rate data on a lately polished substrate. The invention also discloses a polishing method.

Owner:EBARA CORP

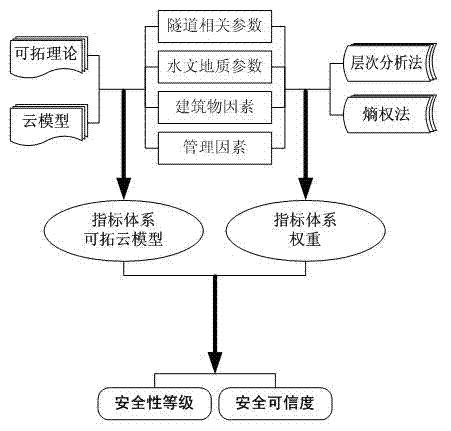

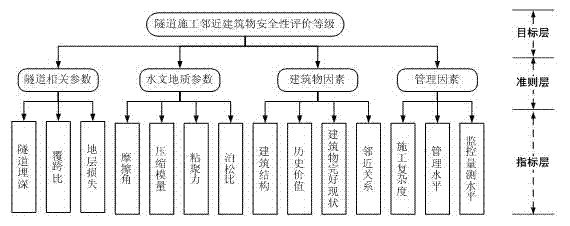

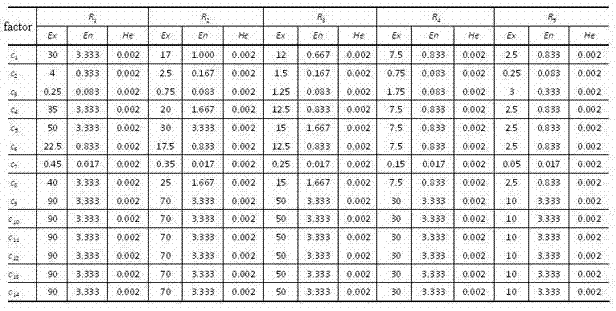

Adjacent building safety quantitative evaluation method in tunnel construction

ActiveCN103093400AEliminate the normalization processAvoid information lossData processing applicationsWeighted average methodEngineering

The invention belongs to the field of engineering risk evaluation, and particularly relates to an adjacent building safety quantitative evaluation method in tunnel construction. The adjacent building safety quantitative evaluation method in the tunnel construction mainly comprises the following steps of step 1, building an evaluation index system, step 2, building a standard extensible cloud model of evaluation indexes, step 3, computing and obtaining a weight matrix of the evaluation indexes through a subjective and objective weighting method, step 4, computing a relevancy matrix of a to-be-evaluated object through cloud relevancy computing, and obtaining a safety evaluation grade of the to-be-evaluated object through a weighted average method and combination of an evaluation index weighted value and the relevancy matrix, and step 5, measuring the reliability of safety evaluation grade. The adjacent building safety quantitative evaluation method in the tunnel construction combines advantages of a cloud model and an extensible theory, and provides effective decision support advices for protection and control of an adjacent building of different safety grades.

Owner:HUAZHONG UNIV OF SCI & TECH

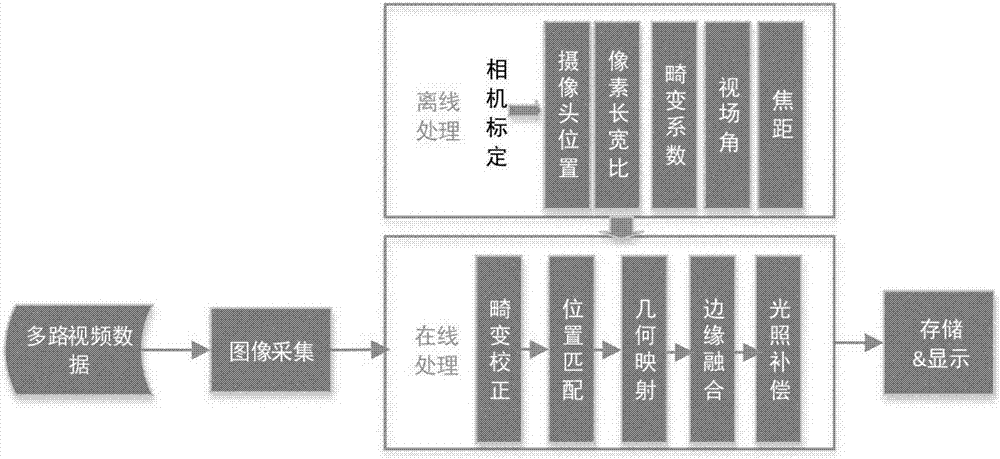

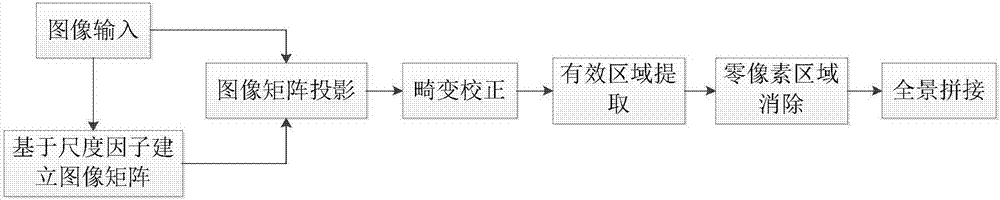

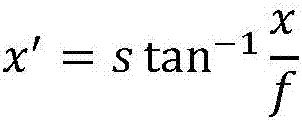

Spherical panoramic stitching method based on improved radial distortion correction

InactiveCN107424118ALossless and Accurate StitchingImage enhancementImage analysisWide areaImage resolution

The invention belongs to the technical field of computer vision, and provides a spherical panoramic stitching method in order to overcome the defects of prior art, such as the failure to meet requirements for wide-area and long-time monitoring which is often caused by low resolution and small area of monitoring. According to the invention, the technical solution discloses a spherical panoramic stitching method which can eliminate image loss caused by command distortion correction by improving radial distortion correction, then completes paranomic stitching through the spherical stitching algorithm, and eventually eliminates interference in repeated areas and light differences of different cameras based on the weighted average method and the optical equalization fusion algorithm, and achieves high resolution and wide area photographing. According to the invention, the method herein is applied to the processing of computer vision.

Owner:TIANJIN UNIV

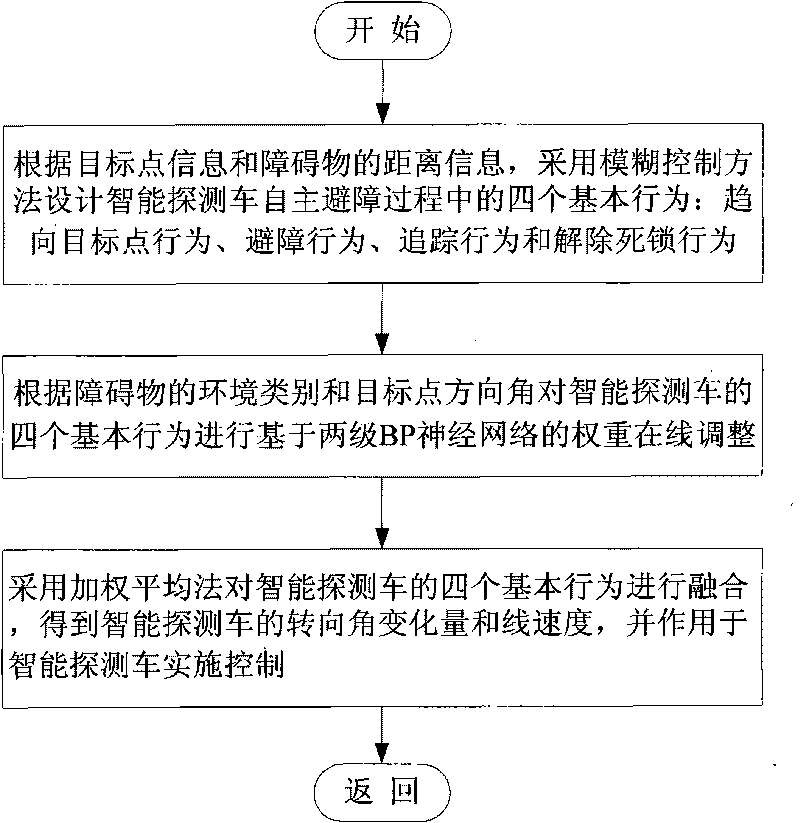

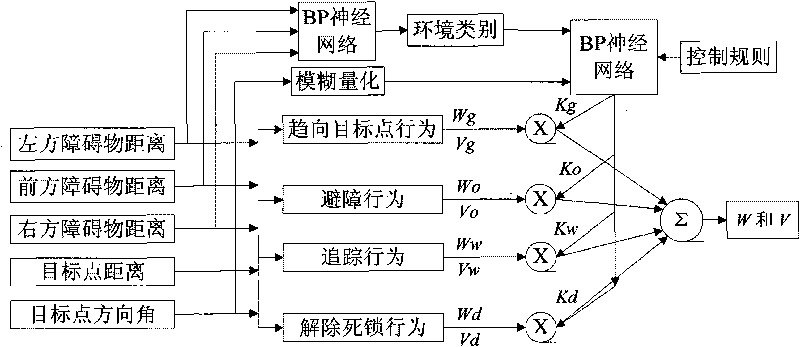

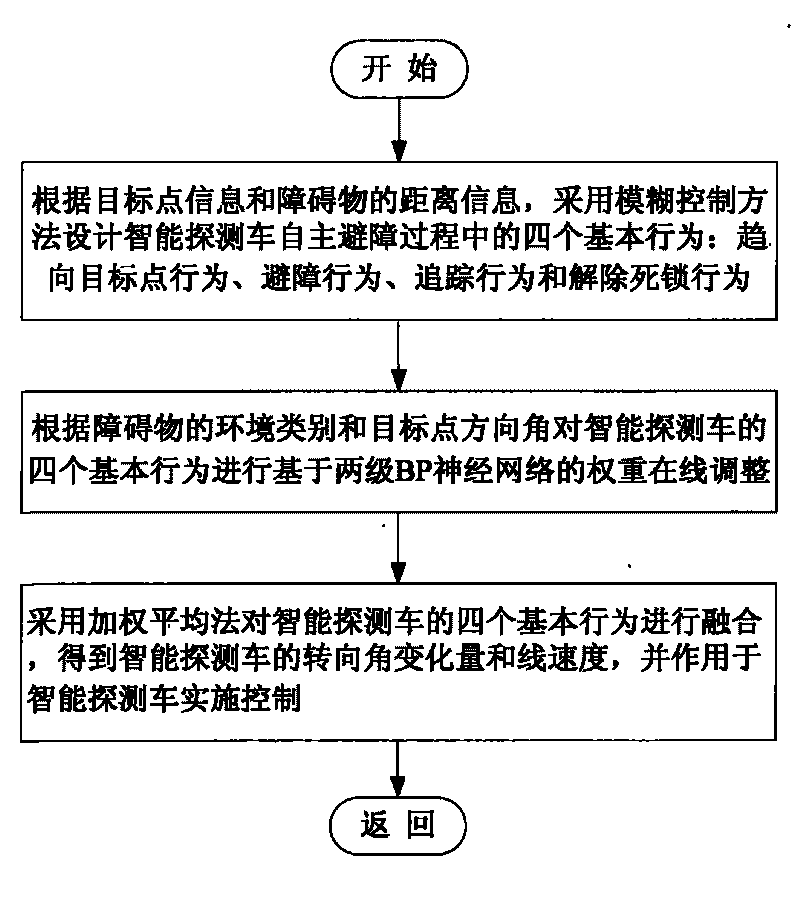

Automatic obstacle avoiding method of intelligent detection vehicle based on behavior fusion in unknown environment

InactiveCN101758827ARealize autonomous obstacle avoidanceSelf-learning abilityAcoustic wave reradiationSteering angleWeighted average method

The invention discloses an automatic obstacle avoiding method of an intelligent detection vehicle based on behavior fusion in unknown environment, which comprises the following steps: the first step, adopting a fuzzy control method for designing four basic behaviors in the automatic obstacle avoiding process of the intelligent detection vehicle according to information of target points and distance information of obstacles; the second step, carrying out online regulation based on the weighing of two grades of BP neuronic network on the four basic behaviors of the intelligent detection vehicleaccording to the environment types of the obstacles and the direction angles of the target points; and the third step, adopting a weighing average method for fusing the four basic behaviors of the intelligent detection vehicle to obtain the steering angle change amount and the linear speed of the intelligent detection vehicle, and exerting the steering angle change amount and the linear speed of the intelligent detection vehicle on the intelligent detection vehicle for implementing the control. The invention combines the fuzzy control method, the neuronic network method and the intelligent control method based on the behavior fusion, and realizes the automatic obstacle avoidance of the intelligent detection vehicle in the unknown environment. Compared with the existing algorithm, the method of the invention has the advantages of good obstacle avoiding effect, strong robustness, high real-time performance and strong learning capability.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

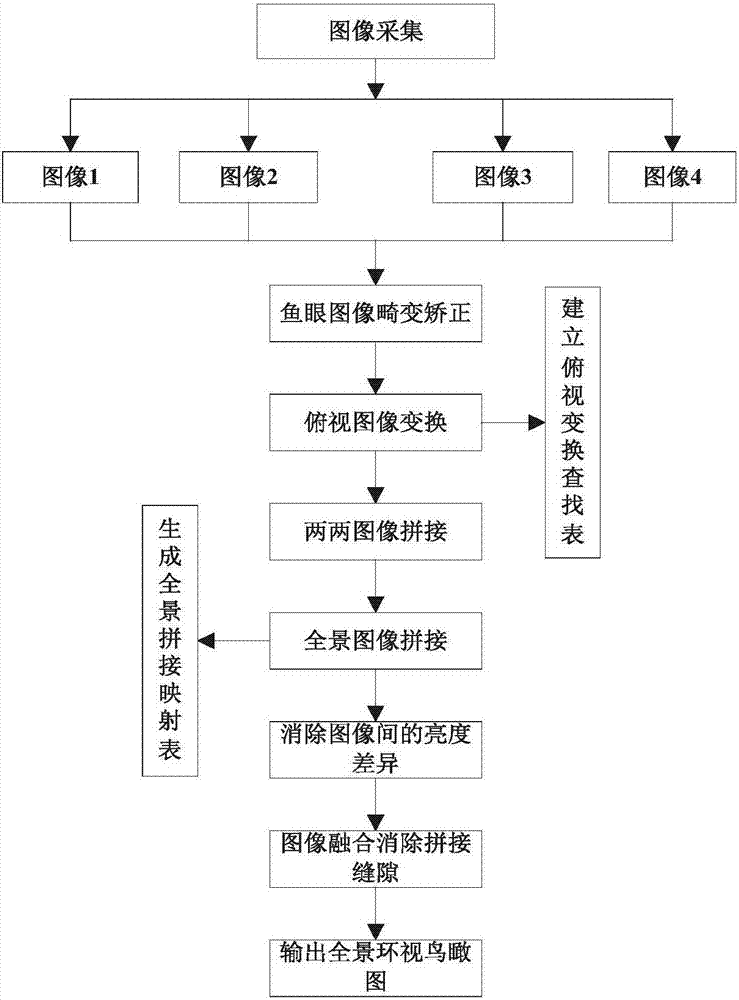

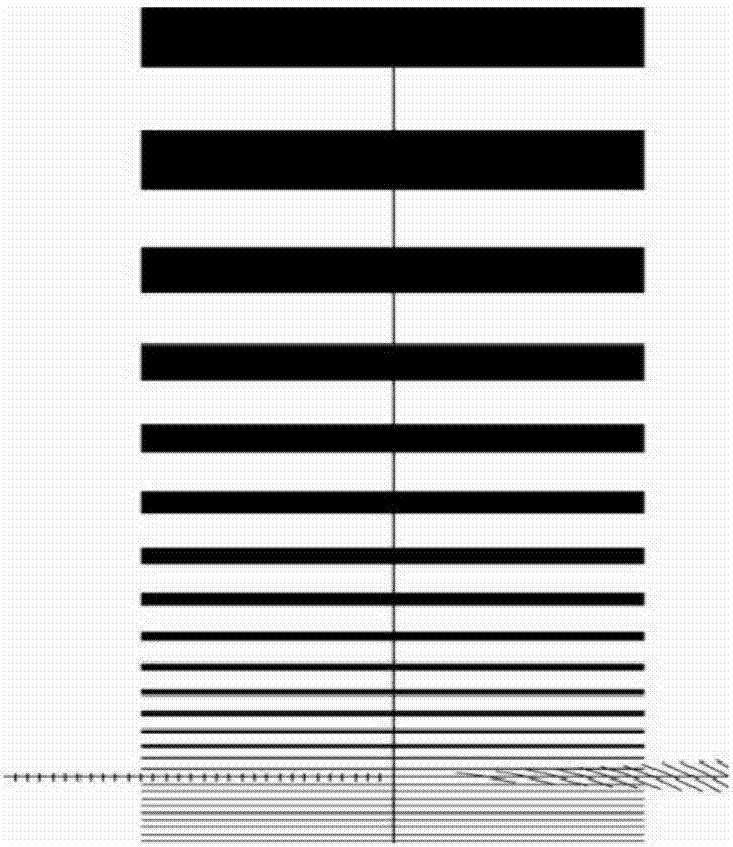

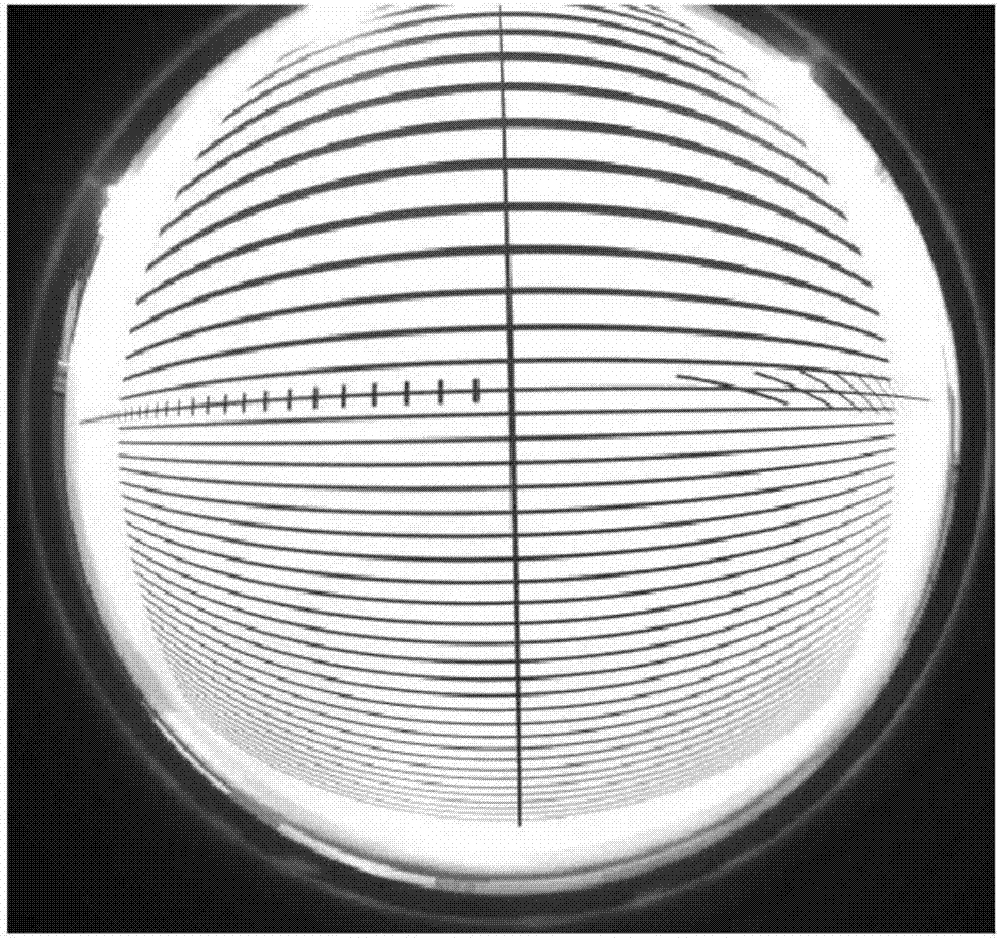

Image stitching method in panoramic surround-view system

InactiveCN107424120ASolve the problem of fuzzy edge informationFast top-down transitionImage enhancementImage analysisWeighted average methodVisual perception

The invention relates to an image stitching method in a panoramic surround-view system, and relates to the field of computer vision. The method includes the steps of 1) correcting the fisheye image distortion by combining a spaced line training model and a SVM algorithm; 2) establishing an image overlook transformation look-up table to achieve a quick overlook transformation and obtaining a bird's-eye view; 3) generating a panoramic image stitching mapping table, and quickly obtaining a panoramic surround-view bird's-eye view by looking up the panoramic image stitching mapping table; and 4) solving the brightness difference between every two stitched images by using an improved brightness tuning processing algorithm, and then further eliminating stitching seams by using an image fusion method of a weighted average method. The method of the invention effectively reduces the system overhead, quickly achieves the seamless image stitching, and obtains the panoramic surround-view bird's-eye view.

Owner:HUNAN VISION SPLEND PHOTOELECTRIC TECH

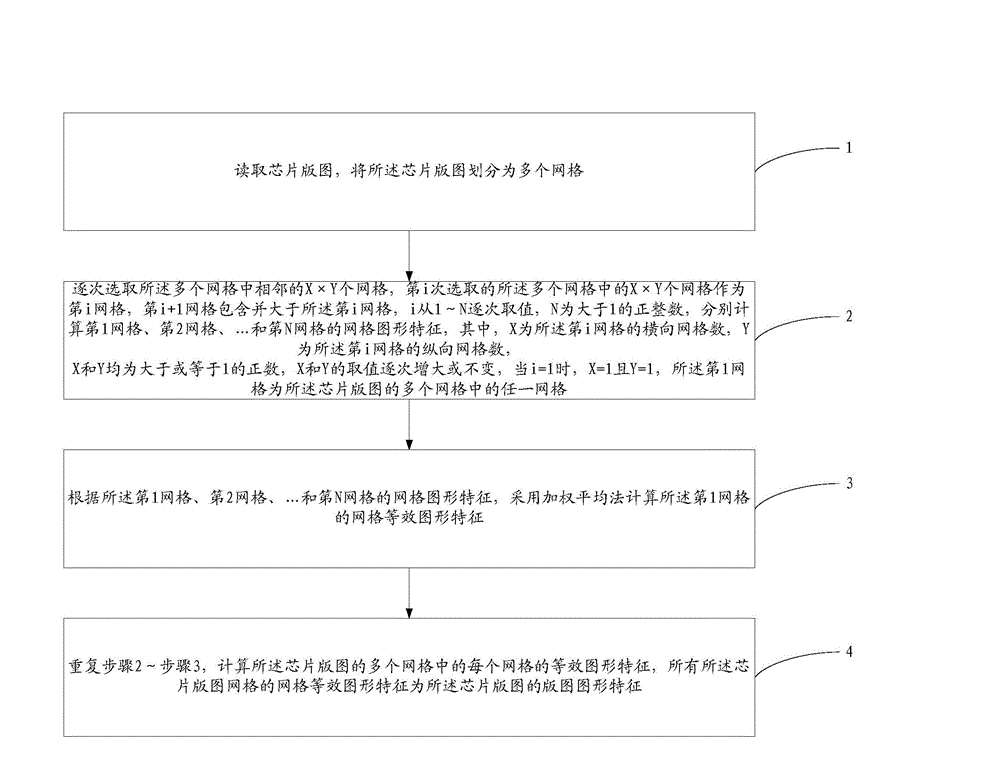

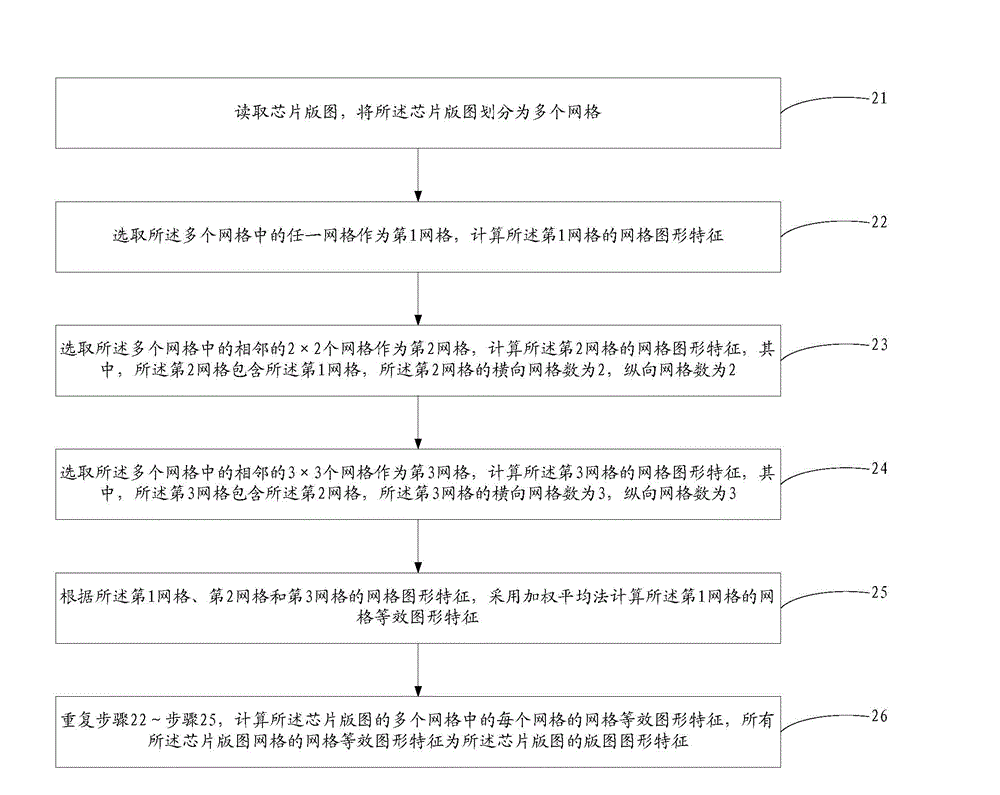

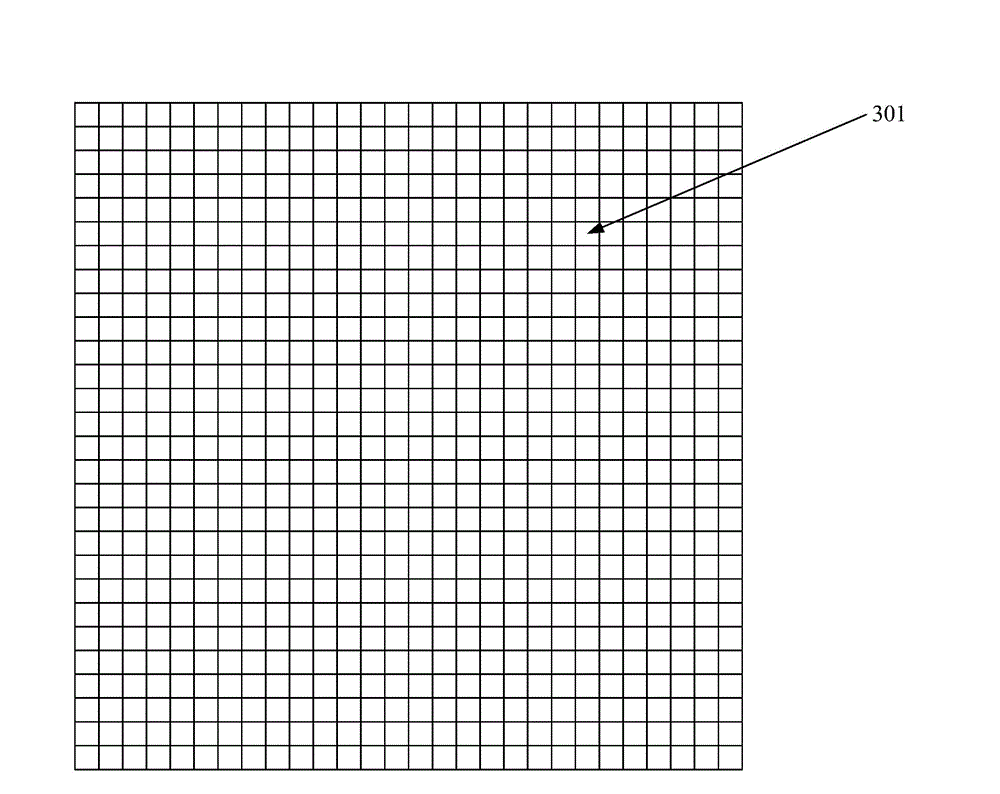

Method for extracting graphic features of layout of chip and CMP simulation method

ActiveCN103559364AImprove accuracyAccurate predictionSpecial data processing applicationsGraphicsWeighted average method

The invention provides a method for extracting graphic features of the layout of a chip and a CMP (chemical mechanical polishing) simulation method. In the process of extracting the graphic features of the layout, an incremental partition method is adopted, firstly, the layout of the chip is partitioned into a plurality of grids, then any one grid is selected, the graphic feature of the selected grid is calculated, based on the grid, the size of the grid is gradually increased, the graphic feature of the grid after each increase in size is calculated, a method of weighted mean is adopted to calculate to obtain an equivalent grid graphic feature of the selected grid, then the same method is adopted to calculate to obtain the equivalent grid graphic feature of each of the rest grids of the layout of the chip, and all equivalent grid graphic features are used as the graphic features of the layout. According to the method, the incremental partition method is adopted as a correlative mechanism about proximity effects of all partitioned grids of the layout of the chip, the graphic proximity effects of different grids in the CMP process are taken into full consideration, the accurate prediction about the surface topography of the layout of the chip is realized, and the accuracy in simulation in the CMP process is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

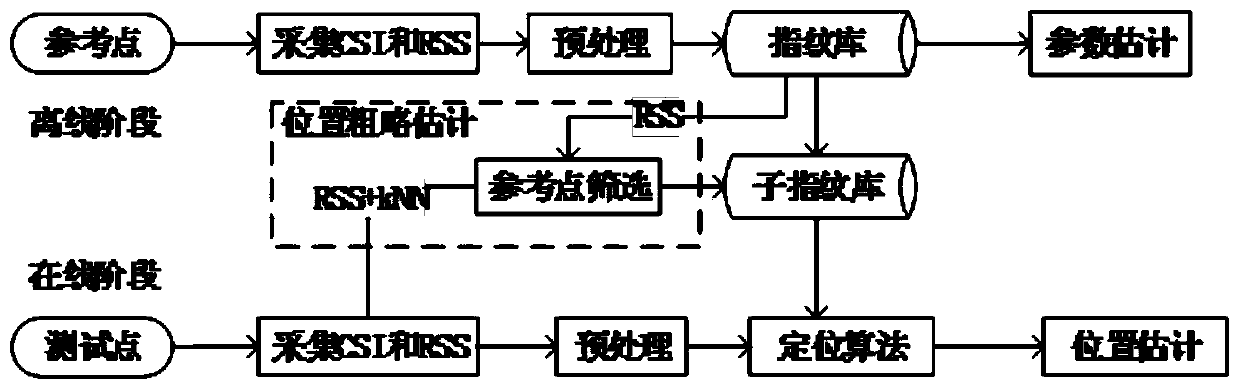

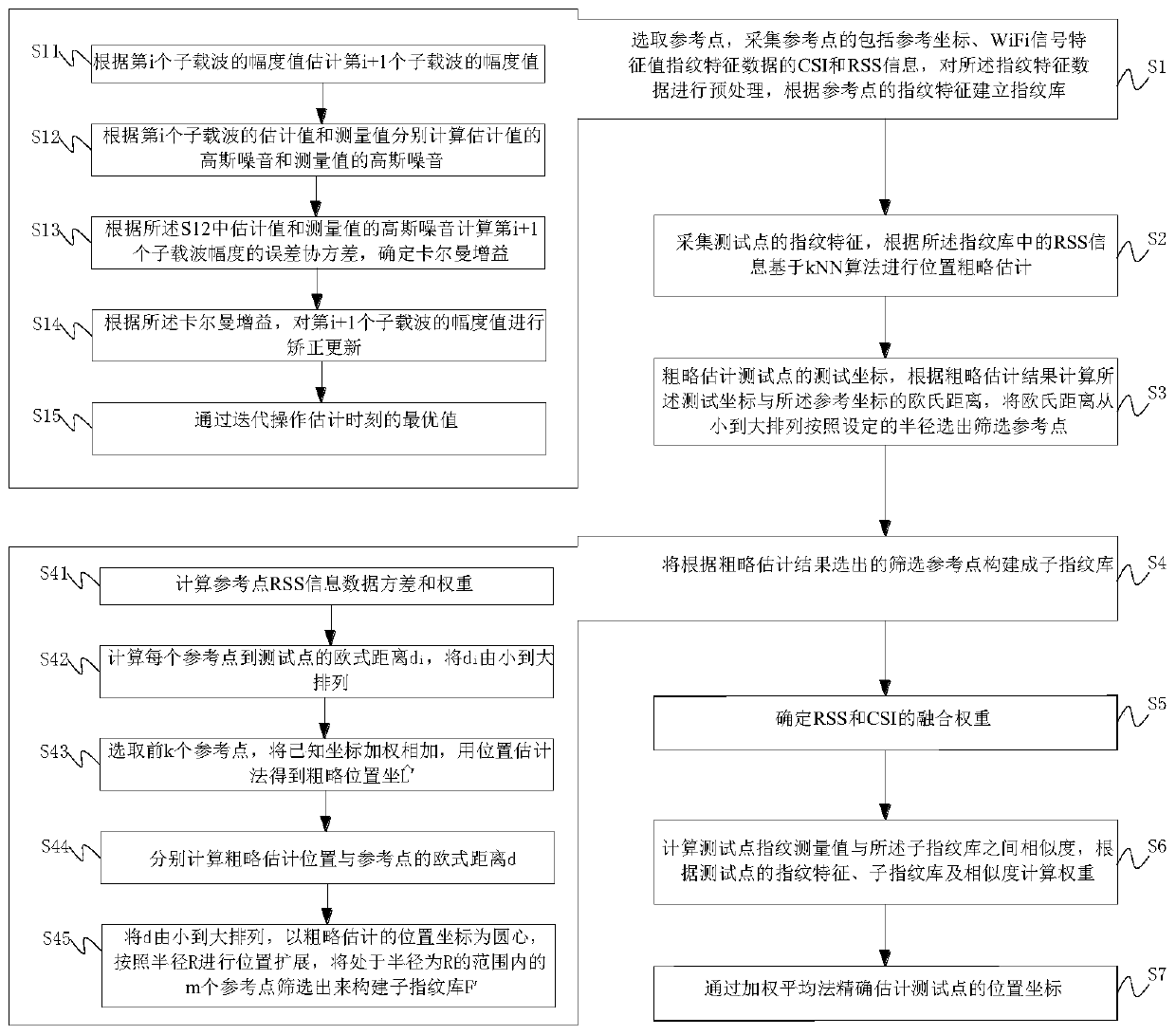

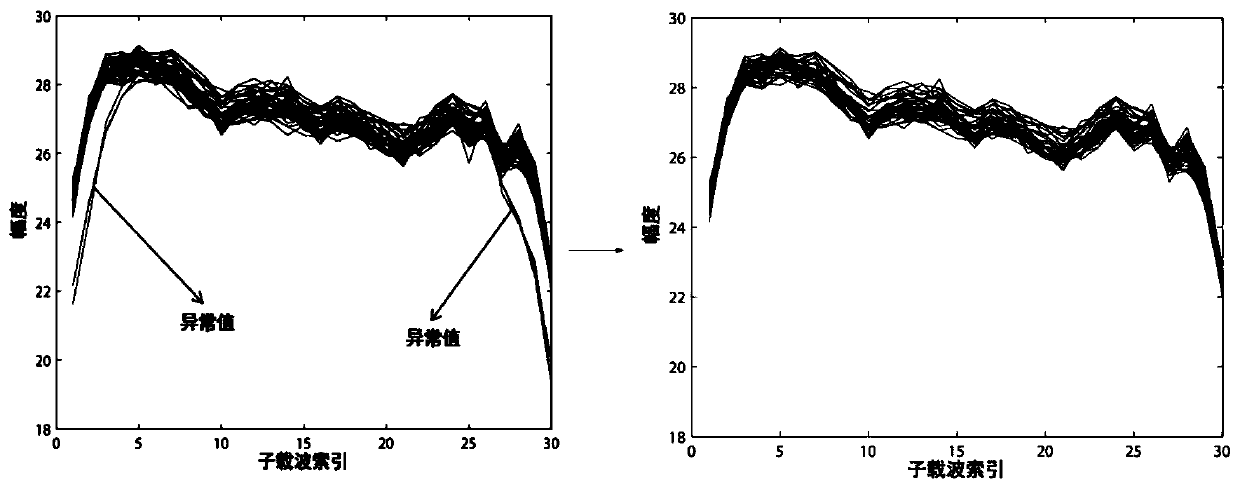

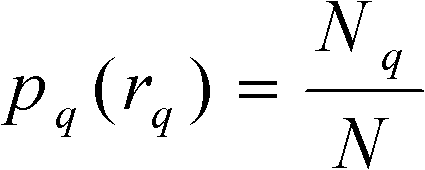

RSS and CSI integrated indoor positioning method based on WiFi signal

InactiveCN109951807AAccurate estimateReduce positioning errorsParticular environment based servicesLocation information based serviceWeighted average methodData mining

The invention discloses an RSS and CSI integrated indoor positioning method based on a WiFi signal, and the method comprises the steps: collecting CSI and RSS information of reference points which comprises reference coordinates and WiFi signal characteristic value fingerprint characteristic data, carrying out the preprocessing of the fingerprint characteristic data, and building a fingerprint database; collecting fingerprint characteristics of a test point, and roughly estimating the position based on a kNN algorithm according to the RSS information in the fingerprint database; roughly estimating the test coordinates of the test point, calculating the Euclidean distance between the test coordinates and the reference coordinates according to a rough estimation result, arranging the Euclidean distance from small to large, and selecting and screening the reference points according to a set radius; constructing a sub-fingerprint database from the screened reference points selected according to the rough estimation result; calculating the similarity between the fingerprint measurement value of the test point and the sub-fingerprint database, and calculating the weight according to thefingerprint characteristics of the test point, the sub-fingerprint database and the similarity; and accurately estimating the position coordinates of the test point through a weighted average method.Positioning errors are reduced, and positioning precision is improved.

Owner:NORTHWEST NORMAL UNIVERSITY

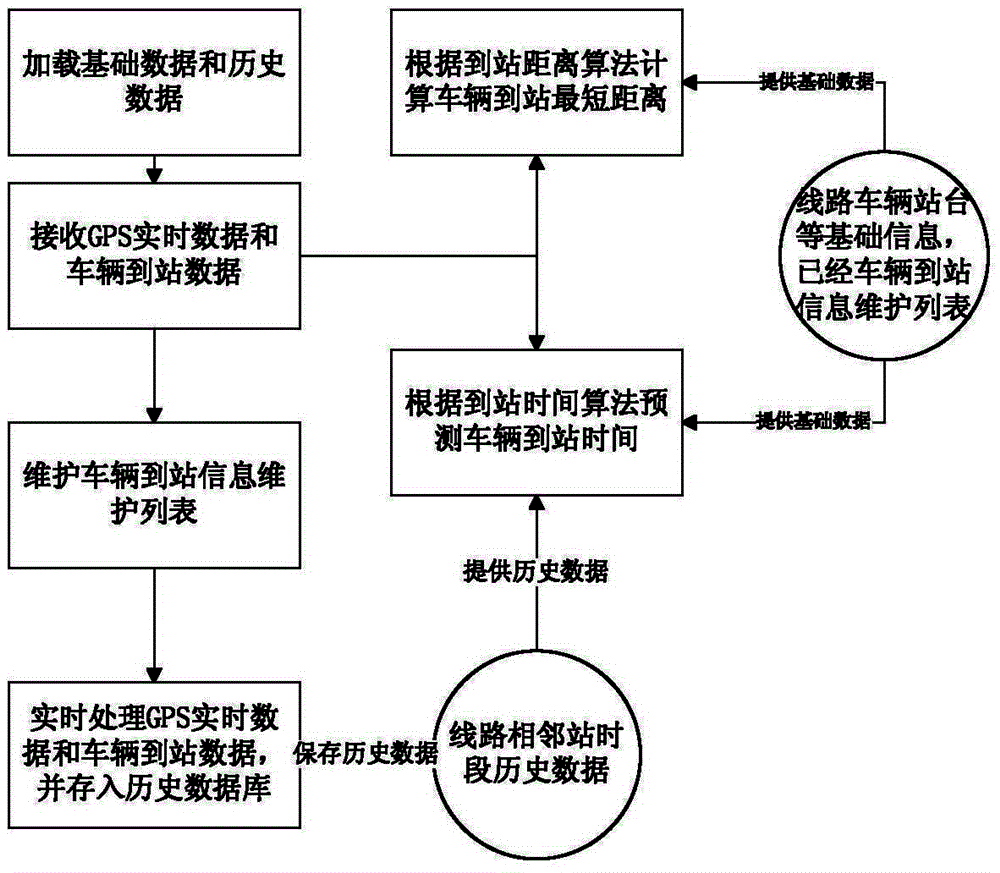

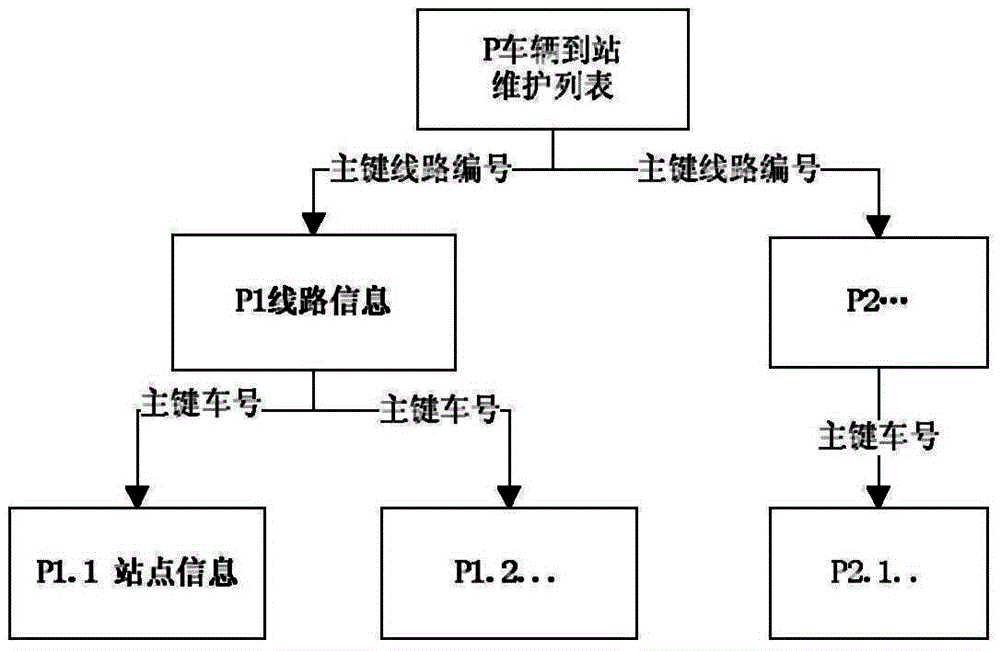

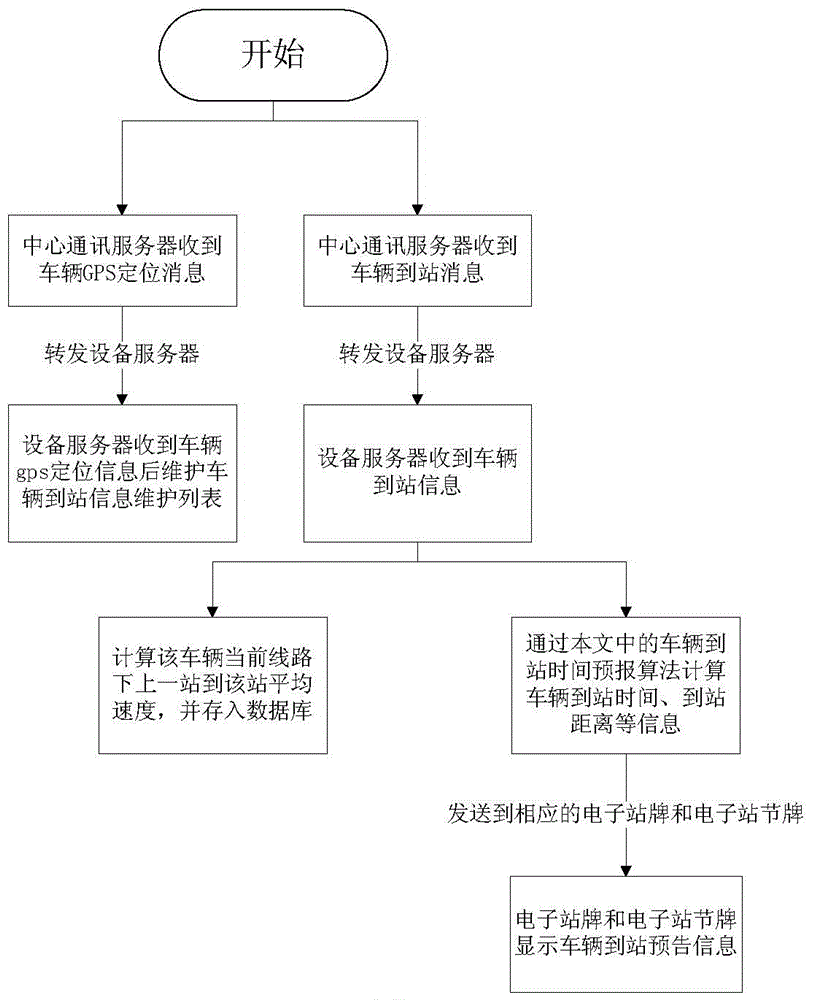

Public transport vehicle arrival time prediction method based on history data

ActiveCN104064024AOvercome the problem of not being able to locate long distancesAccurate acquisition in real timeRoad vehicles traffic controlInformation dataPublic transport

A public transport vehicle arrival time prediction method based on history data comprises the following steps: a)receiving GPS real-time data uploaded by a GPS device on a public transport vehicle and vehicle arrival information data in real time; b) processing the GPS real-time data after the GPS real-time data of the vehicle is obtained successfully; and c) after the vehicle arrival information is obtained successfully, searching station devices to send information from on-line station devices according to the line serial number and the running direction in the vehicle arrival information and obtaining the closet vehicle distance of a target station; and through obtaining the history data and today's data of the running speed of a vehicle between adjacent stations on the line at set time running period, by utilizing a weighted average method to estimate the average running speed of the vehicle between the adjacent stations on the current line and at the current time period, and on the basis of the bypassed inter-station distances and inter-station average running speed of the vehicle running to the station, each inter-station running time of the vehicle can be estimated, and the vehicle arrival time can be predicted jointly. With the method, the prediction distance is long, the real-time performance is good and the accuracy is good.

Owner:ENJOYOR COMPANY LIMITED

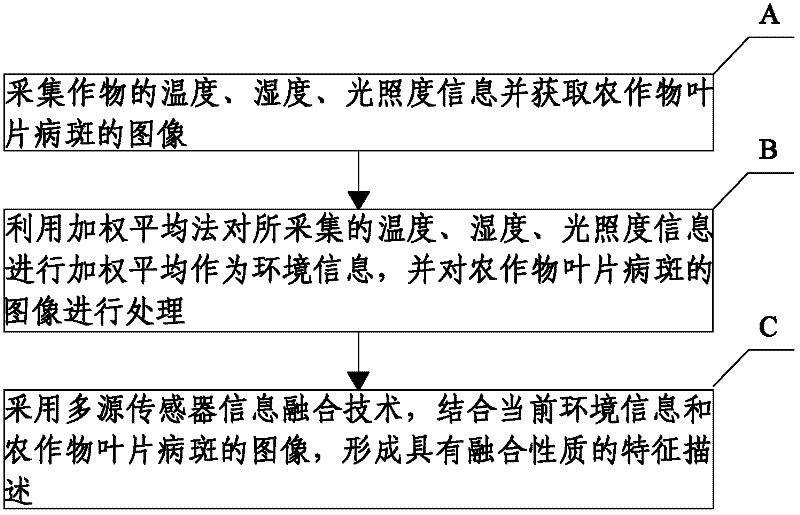

Crop information fusion method and disease monitoring system

InactiveCN102523953ARealize automated monitoringAvoid troubles caused by communication blind spotsTransmissionHorticulture methodsDisease monitoringIlluminance

The invention discloses a crop information fusion method and a disease monitoring system, and relates to the technical field of agricultural information monitoring. The method comprises the following steps of: A, acquiring temperature, humidity and illumination information of a crop and acquiring an image of spots of leaves of the crop; B, performing weighted average on the acquired temperature, humidity and illumination information as environment information by using a weighted average method and processing the image of the spots of the leaves of the crop; and C, forming characteristic description with fusion property in combination with current environment information and the image of the spots of the leaves of the crop by using a multi-sensor information fusion technology. According to the crop information fusion method and the disease monitoring system, automatic monitoring of crop diseases can be realized, the information query speed is high, and the system has low application barrier.

Owner:BEIJING RES CENT FOR INFORMATION TECH & AGRI

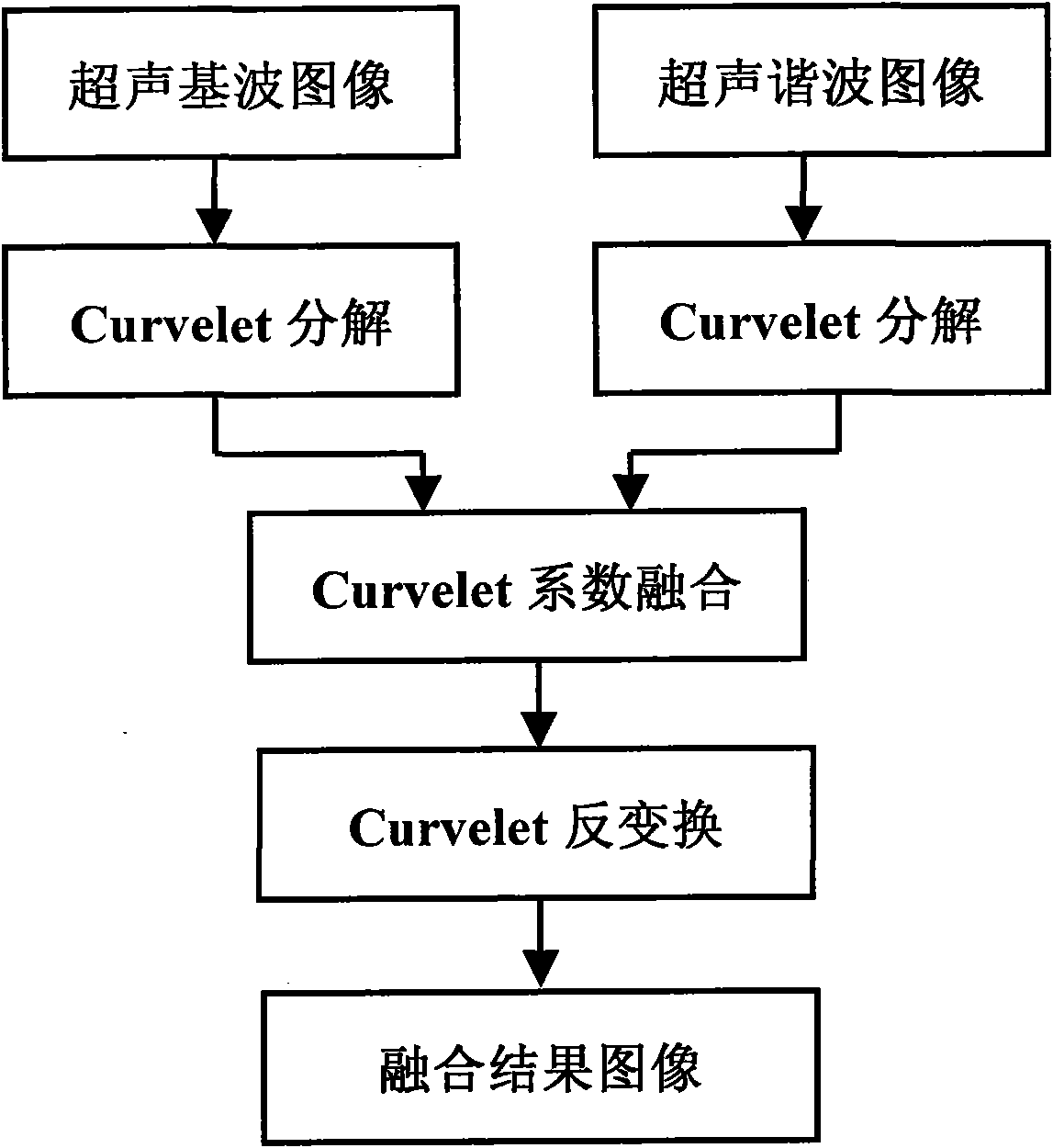

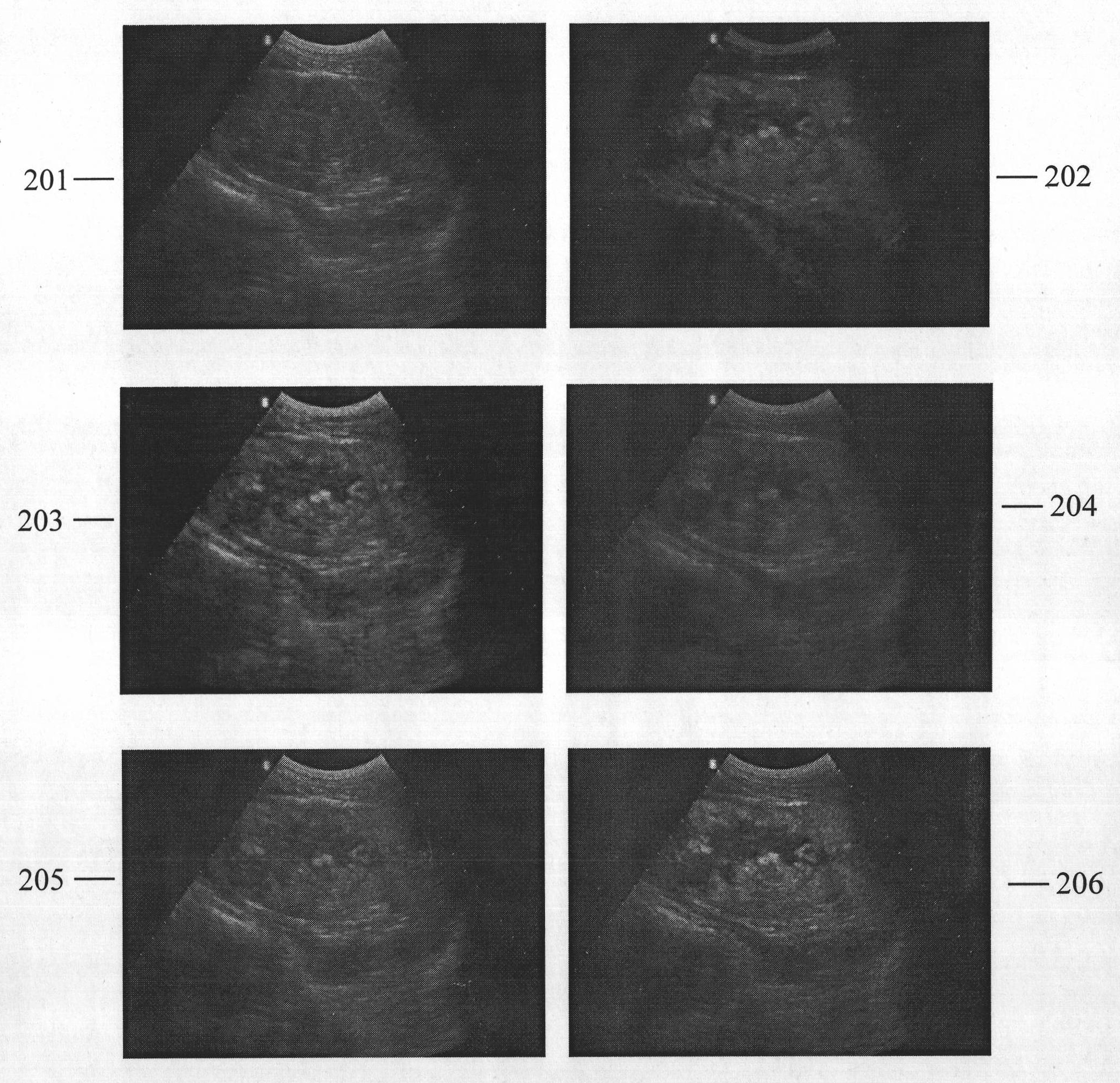

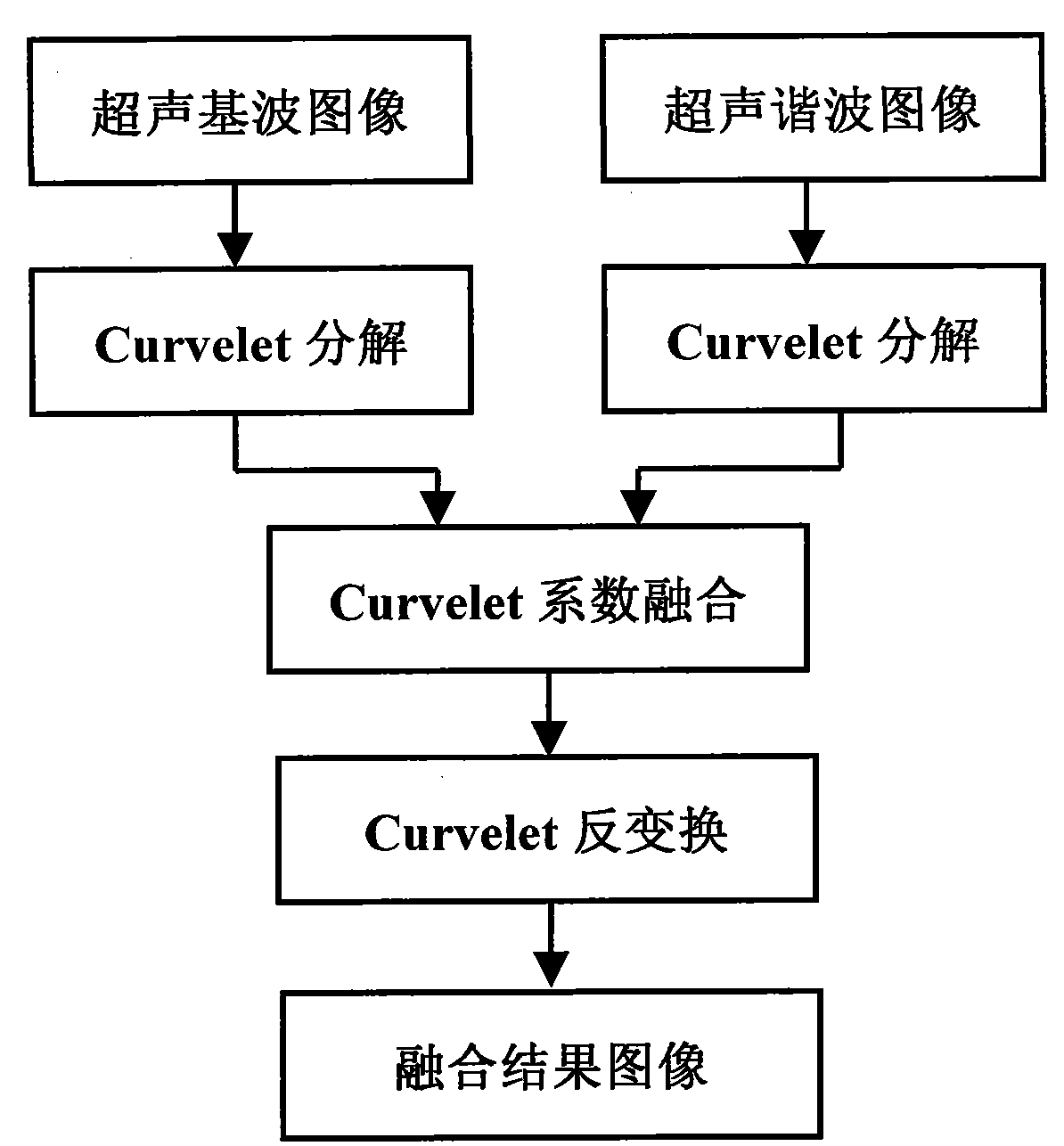

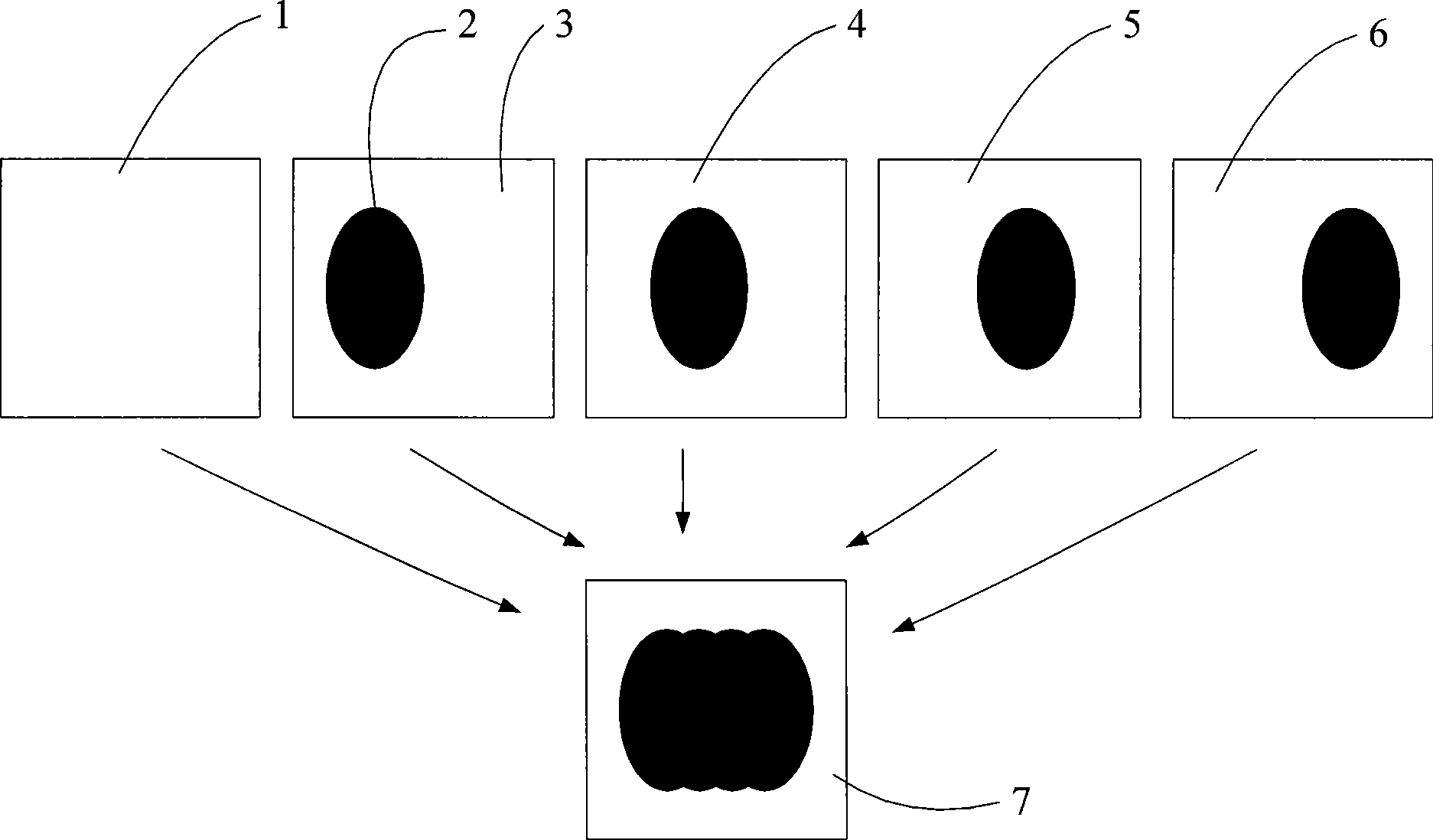

Medical ultrasonic fundamental wave and harmonic wave image fusion method

The invention provides a medical ultrasonic fundamental wave and harmonic wave image fusion method, which comprises the following steps: firstly, performing Curvelet decomposition of an ultrasonic fundamental wave and harmonic wave image to obtain a Curvelet coefficient; secondly, performing fusion treatment of the Curvelet coefficient, and obtaining a fusion Curvelet coefficient by using a weighted average method for a low-frequency part and an absolute value maximum selection method for a high-frequency part; and thirdly, reconstructing a fusion result image by Curvelet inverse transformation according to the Curvelet coefficient obtained by the fusion treatment. In the invention, according to the characteristics of the ultrasonic fundamental wave and harmonic wave image, the fusion of the ultrasonic fundamental wave and harmonic wave image is performed by using a Curvelet method to obtain an image with clear organizational boundaries and interior, the problems of blurred edges, difficult organization positioning and the like of common imaging harmonic wave imaging are solved, and the method can be widely used in the processing of medical ultrasonic images.

Owner:HARBIN INST OF TECH AT WEIHAI

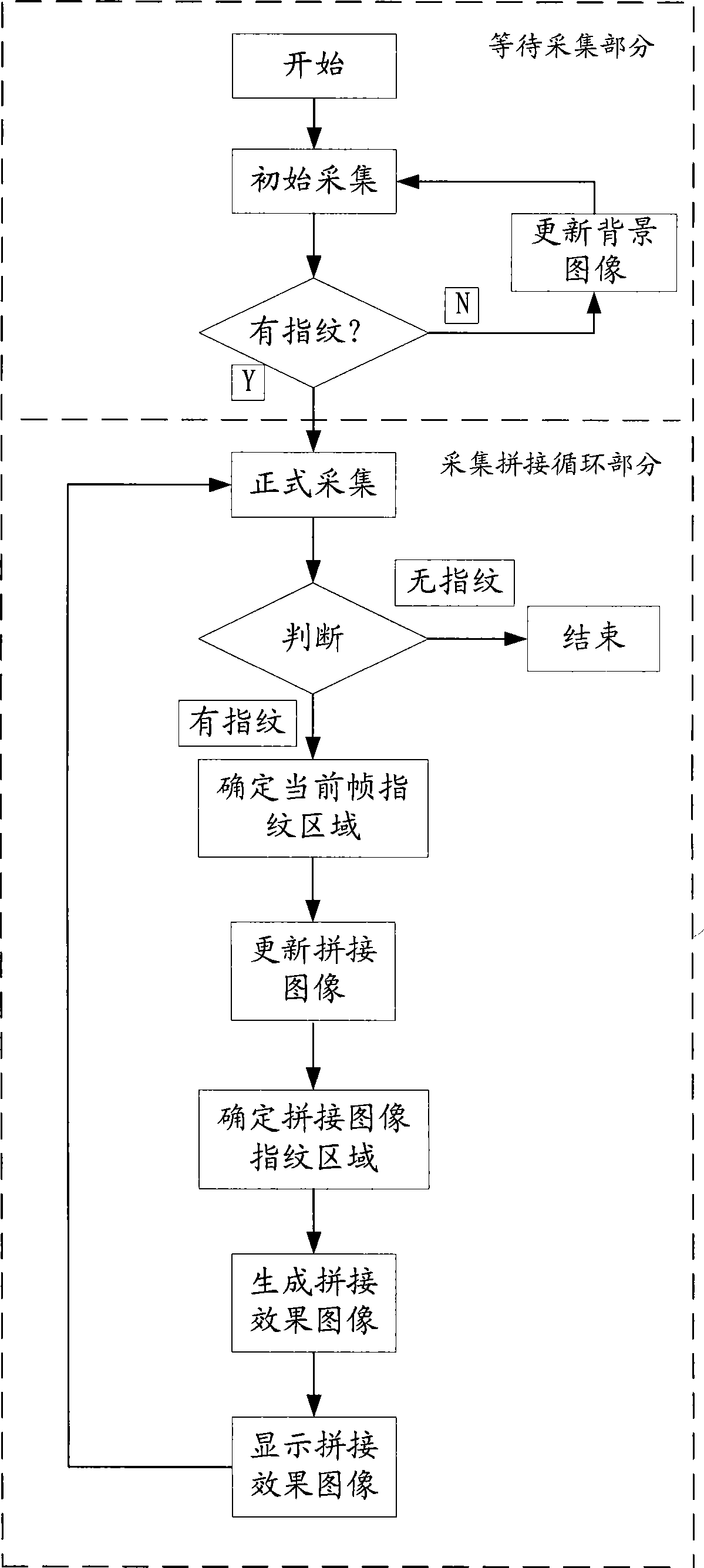

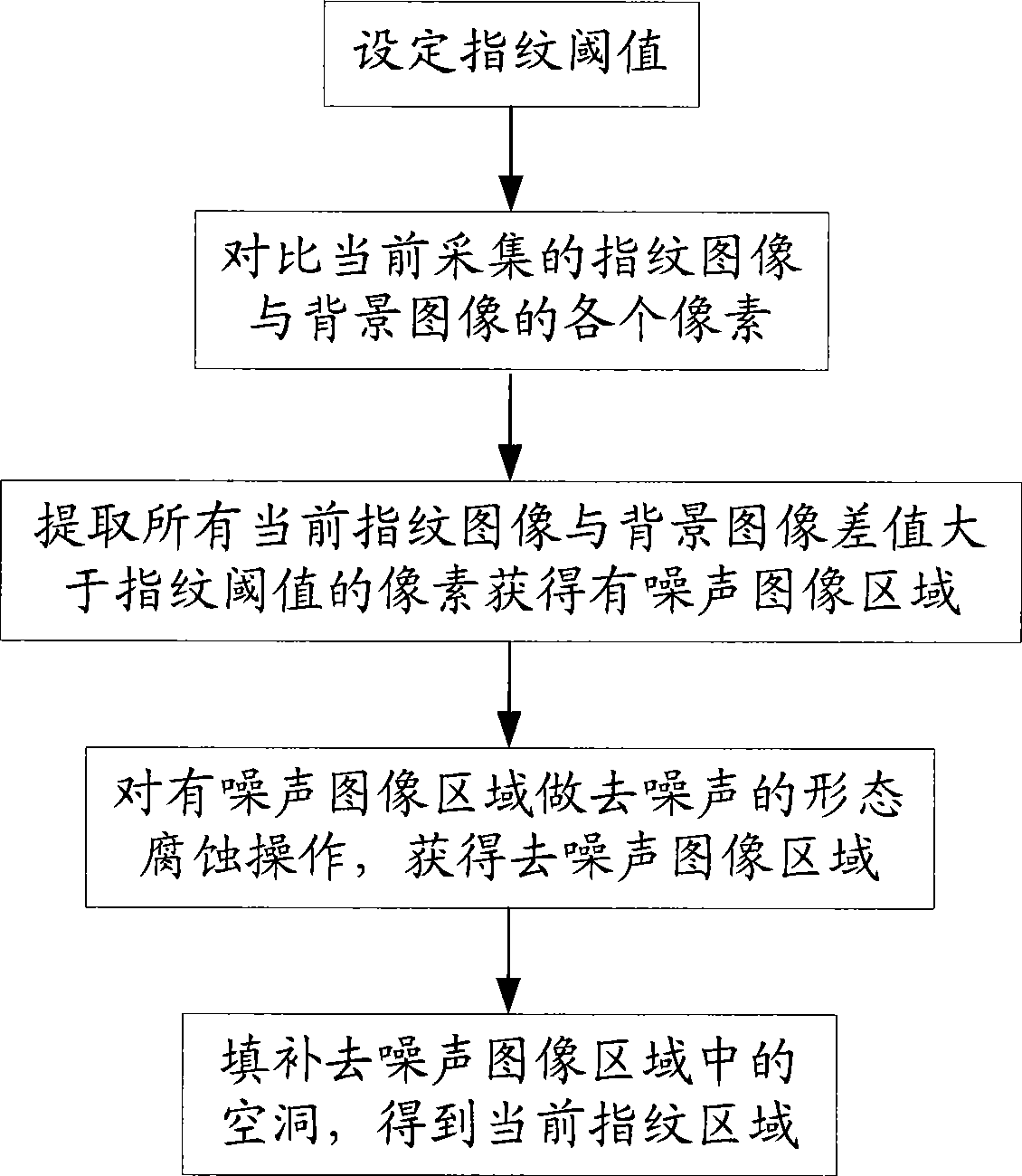

Finger print collecting and joining method supporting arbitrary directional rolling

ActiveCN101383002ANatural effectSmooth effectCharacter and pattern recognitionGraphicsPattern recognition

The invention relates to a method for collecting and splicing a fingerprint, which can support the rolling in any direction and is a method for identifying and processing a fingerprint picture. The method applies a fingerprint collecting system which is composed of a fingerprint collector, a computer and a fingerprint collecting and splicing program, and comprises the steps of starting the initialization of the fingerprint collecting and splicing program, initial collecting, formal collecting, determining a fingerprint area of a current frame, updating a spliced picture, determining a fingerprint area of the spliced picture, generating a picture with splicing effects and displaying the picture with splicing effects. The method adopts a picture splicing method with a background picture as a reference and eliminates the restriction of the rolling direction during a fingerprint collecting process by rolling so that a complete fingerprint splicing picture can be formed with a finger to roll on a fingerprint collecting surface in any direction. In addition, the method also applies the weighted average method to process edges of the fingerprint splicing picture to ensure that the spliced fingerprint picture can be more natural and smooth.

Owner:北京海鑫科金高科技股份有限公司

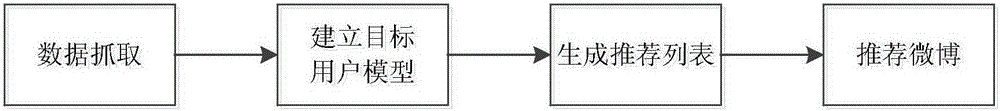

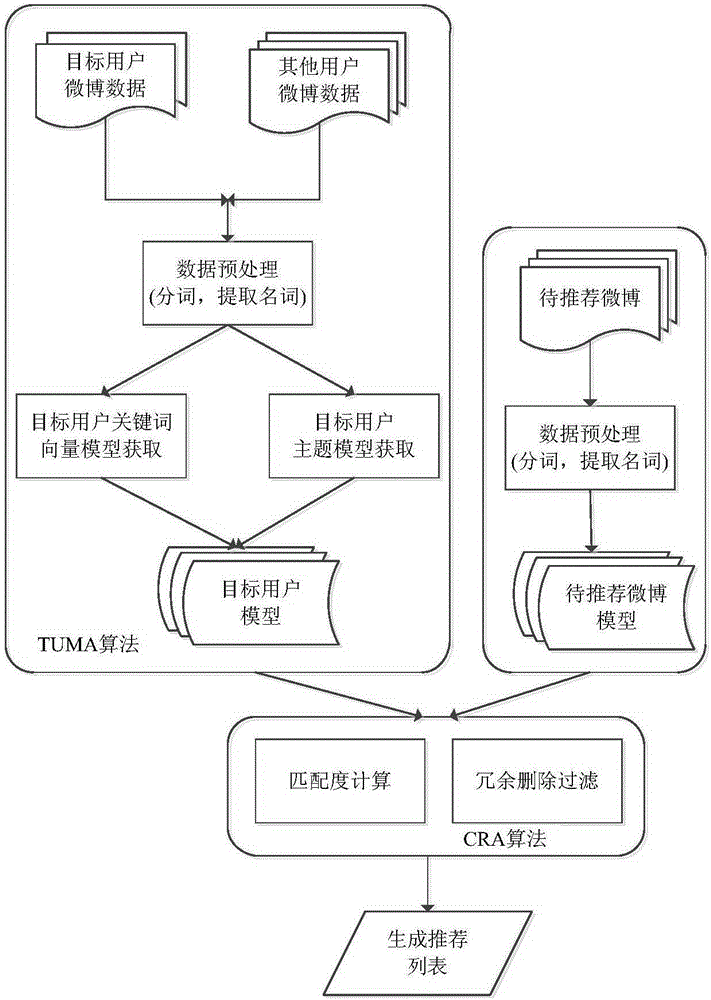

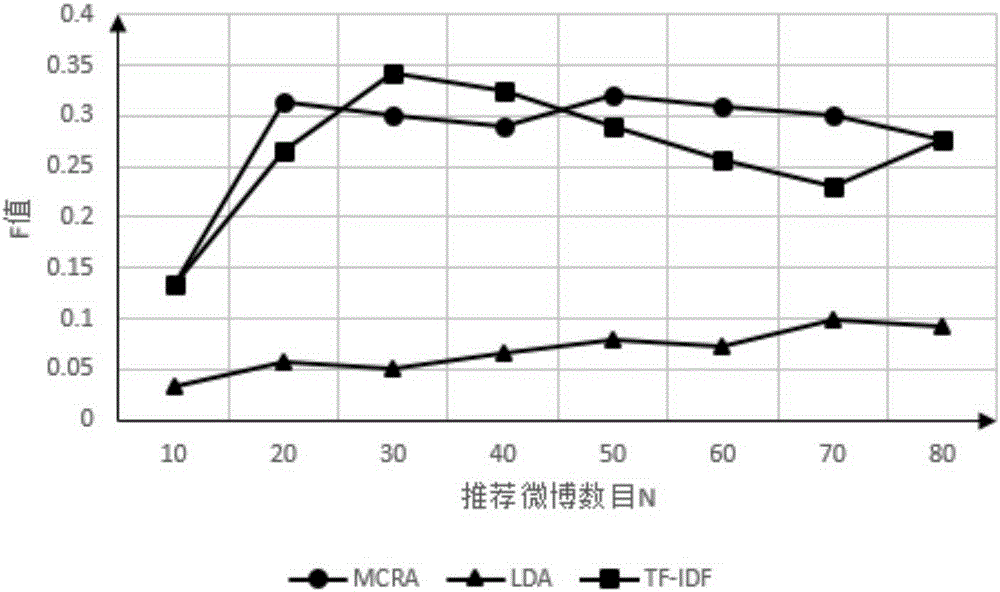

User model based microblogging text recommendation method and recommendation apparatus thereof

ActiveCN105183833AAccurate modeling effectsControl specific gravityData processing applicationsSpecial data processing applicationsMicrobloggingWeighted average method

The present invention discloses a user model based microblogging text recommendation method and a recommendation apparatus thereof. The method comprises: obtaining microblogging data, forming a microblogging document, and performing preprocessing on the mircroblogging document; establishing a target user theme model according to an LDA theme model, and calculating a matching degree between a candidate microblog and the target user theme model; establishing a target user keyword vector model based on a TF-IDF algorithm, and calculating a matching degree between the candidate microblog and the target user keyword vector model; and calculating a matching degree between the candidate microblog and a target user model with reference to the two matching degrees by using a weighted average method, using the matching degree as a score of the candidate microblog, and sorting on the score. The apparatus comprises an obtaining and preprocessing module, a first calculating module, a second calculation module, and a sorting module. According to the present invention, microblogging information in which a target user can be interested can be found and recommended to the target user, and connection among users is enhanced, so as to improve vitality of microblog.

Owner:TIANJIN UNIV

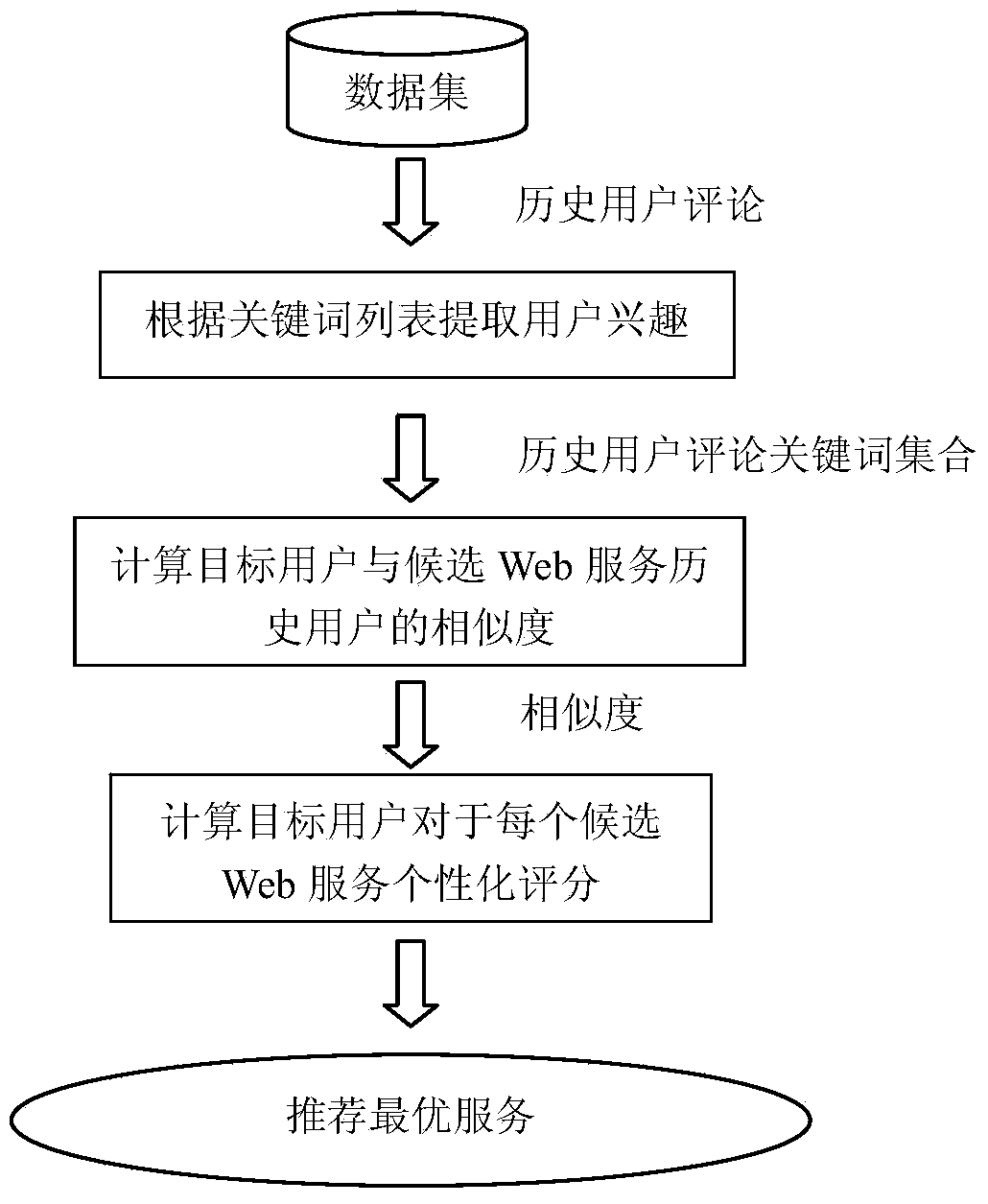

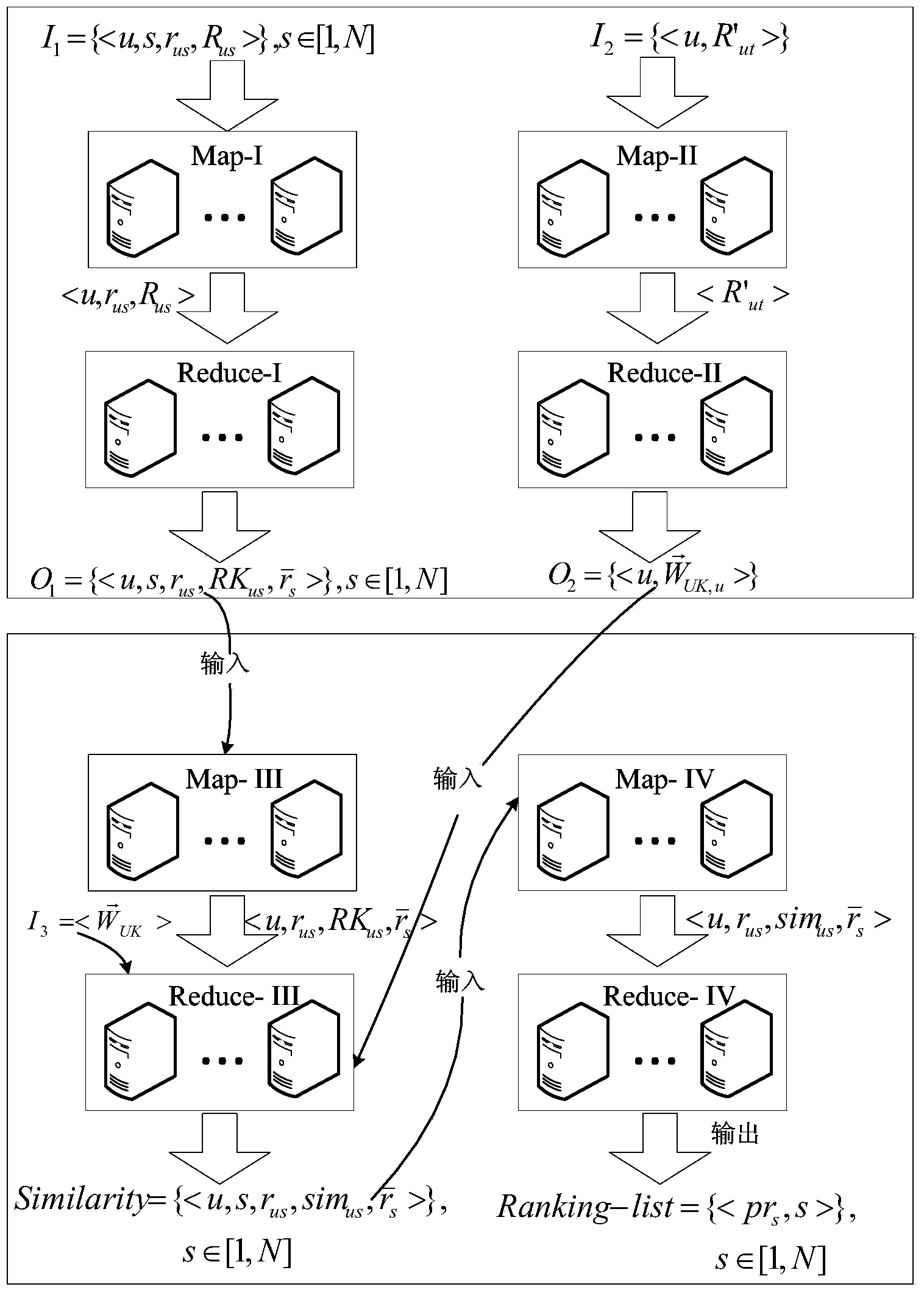

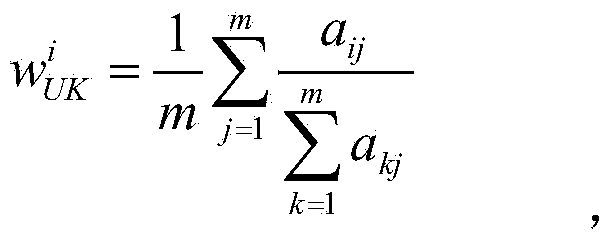

Interest aware service recommendation method based on MapReduce model

ActiveCN103455613AReliable extractionImprove acceleration performanceSpecial data processing applicationsPersonalizationMap reduce

The invention discloses an interest aware service recommendation method based on a MapReduce model. The method comprises the following steps of 1, acquiring a data set through the comment of a history user; 2, extracting the interests of an object user and the history user according to the corresponding keyword list and field word bank provided by the method, wherein the object user refers to the current user required to be recommended; 3, for each candidate Web service, calculating the similarity between the object user and the history user of the candidate Web service for searching users similar to the object user; 4, after calculating the similarity between the object user and the history user, predicting an individual score of the candidate Web service for the object user and providing an individual service ranking list according to a weighted average method, and recommending for the user according to the individual ranking list; 5, realizing the steps 2 to 4 through a Map-Reduce programming framework through four stages for parallel arrangement.

Owner:NANJING UNIV

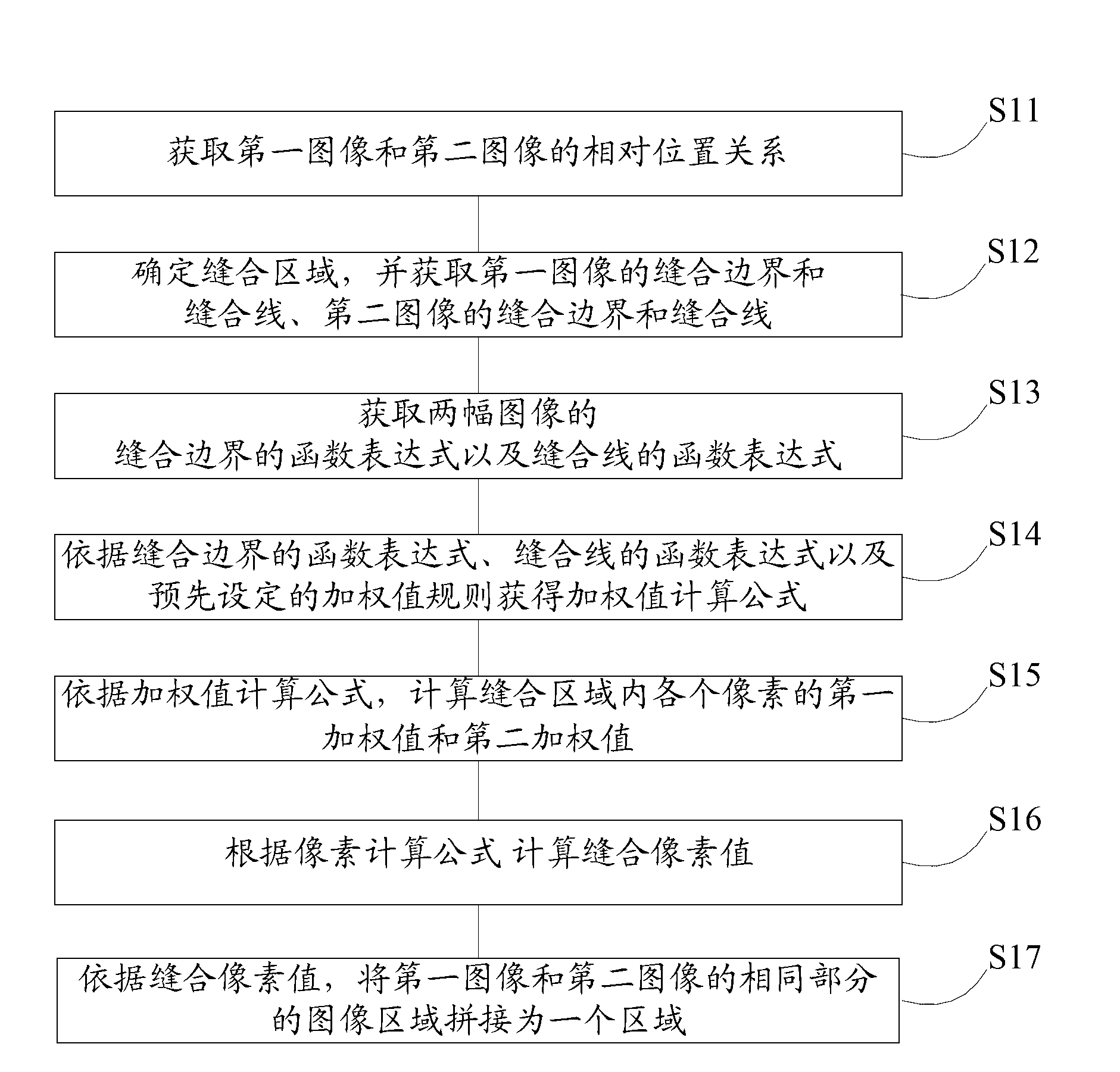

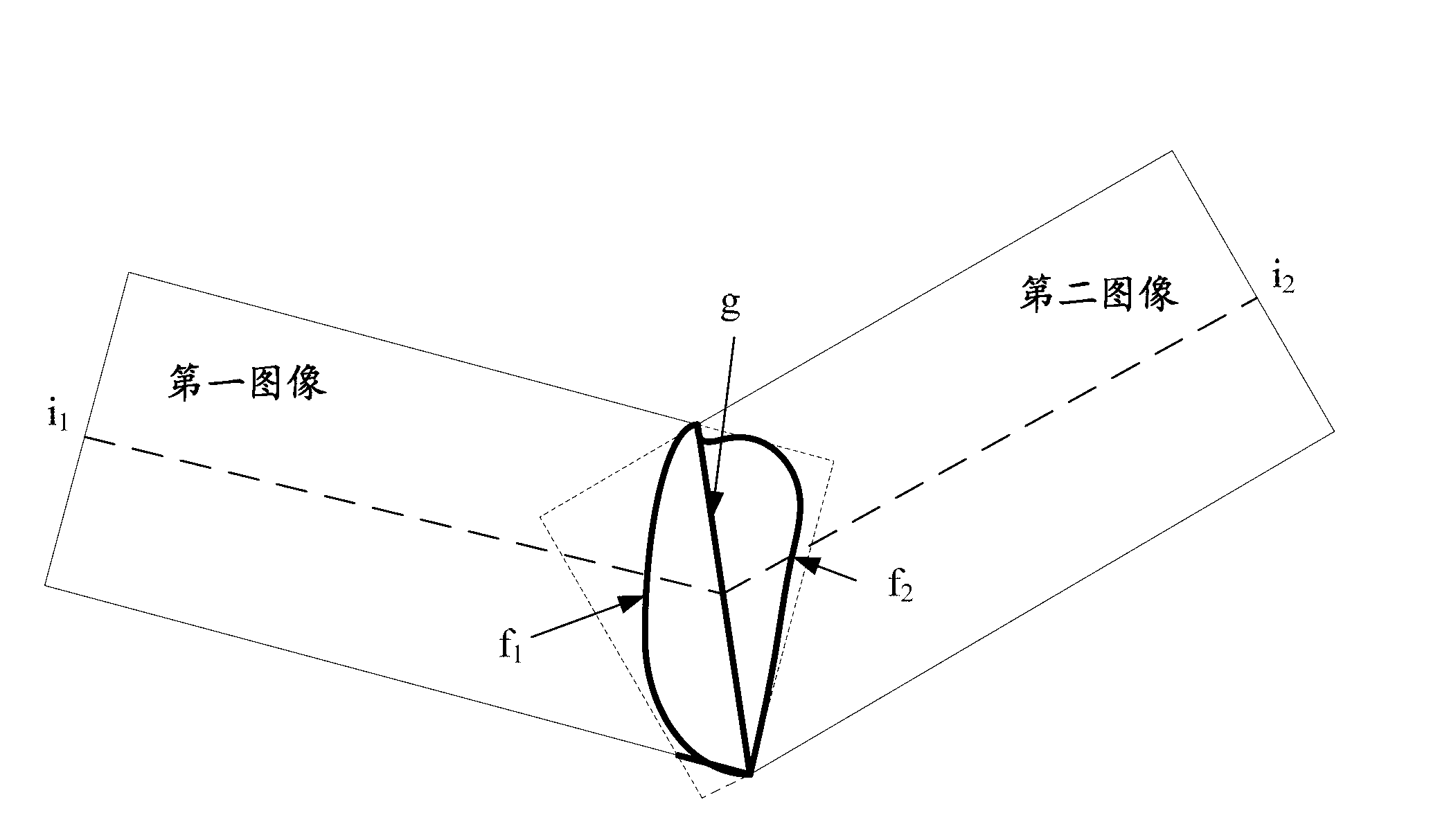

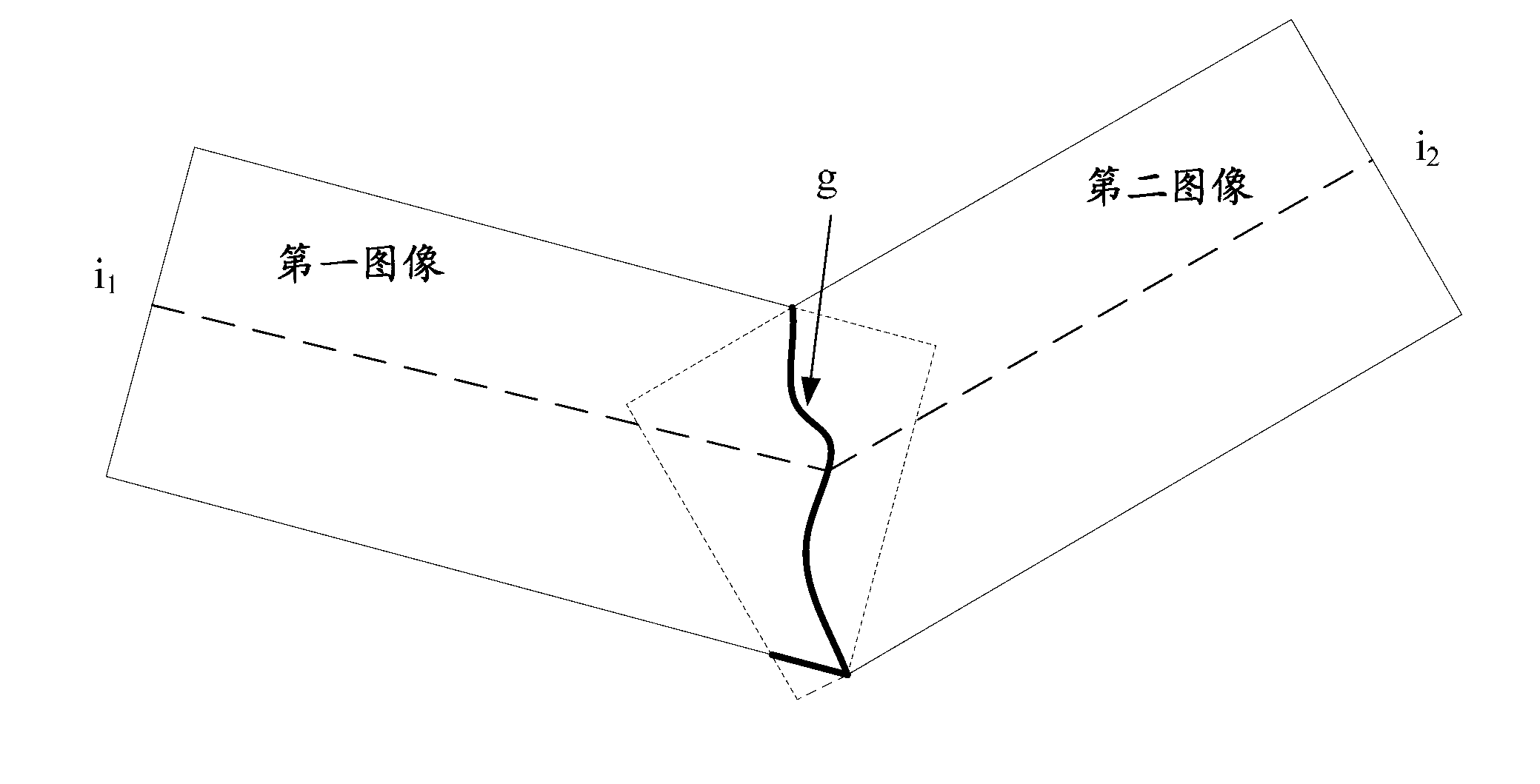

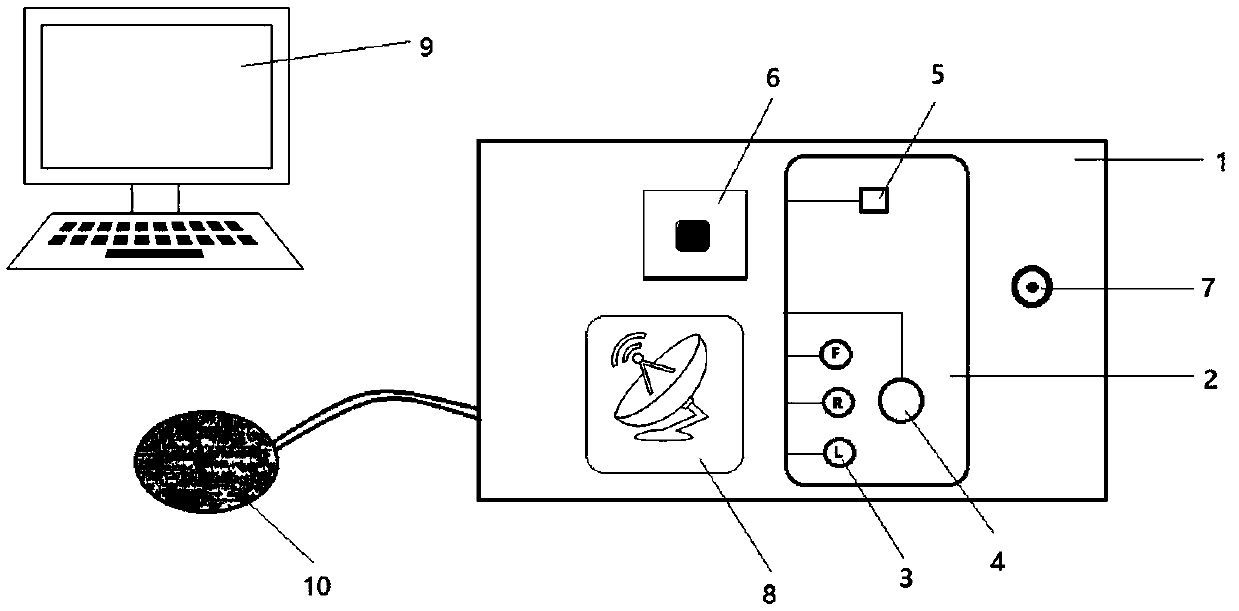

Method and system for stitching spatial domain images based on weighted average method

ActiveCN103020938AImprove versatilityImage transitions are naturalImage enhancementGeometric image transformationWeighted average methodImage area

The invention relates to a method and a system for stitching spatial domain images based on a weighted average method. The method for stitching the spatial domain images includes the steps: acquiring a weighted value calculation formula according to a preset weighted value rule and calculating a first weighted value and a second weighted value of each pixel in a stitching area according to the weighted value calculation formula; multiplying pixel values of optional pixels in different images in the stitching area with weighted values corresponding to the pixel values in the different images to obtain weighted pixel values, and adding the weighted pixel values to obtain stitching pixel values serving as pixel values corresponding to the pixels in the stitching area; and splicing image areas of the same portion of a first image and a second image into an area according to the stitching pixel values. Therefore, the weighted value calculation formula is universally used for optional stitching borders and optional stitching lines of overlap areas, and universality of the method is improved.

Owner:BEIJING JINGWEI HIRAIN TECH CO INC

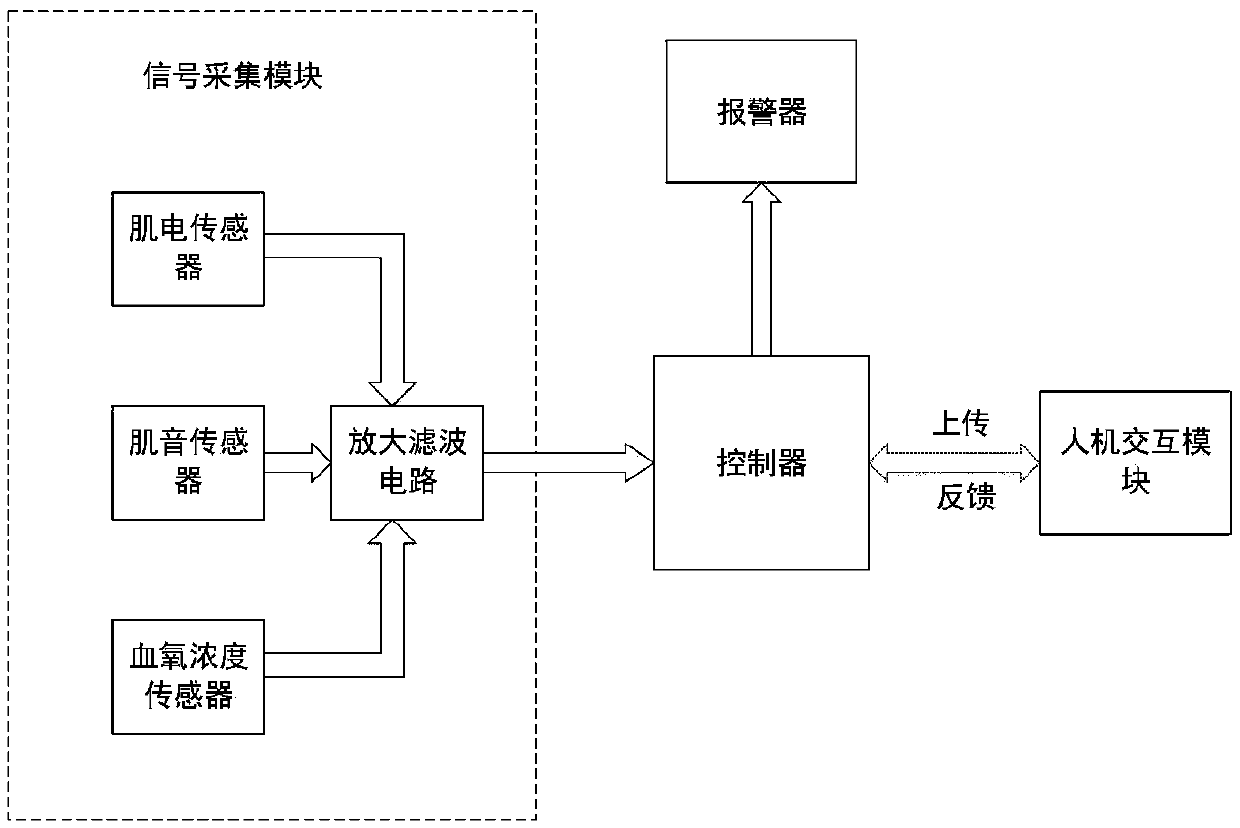

Wearable human upper limb muscle fatigue detection and training system based on multi-sensor data fusion

PendingCN109222969AResolve distortionSolve the noiseDiagnostic recording/measuringSensorsUpper limb muscleMuscle strength

The invention discloses a wearable human upper limb muscle fatigue detection and training system based on multi-sensor data fusion. The system comprises a signal acquisition module, a data processingmodule, an alarm module and a human-computer interaction module. A surface electromyography sensor, a muscular sound sensor and a blood oxygen saturation sensor constitute a multi-sensor acquisition array which are worn on that measured upper limb part, and data fusion is carry out based on a weighted average method to synthetically calculate the muscle fatigue parameters of the upper limb, thereby greatly improving the detection accuracy of the muscle fatigue of the upper limb. If the parameter reaches the preset value, the system can give the fatigue alarm reminder. The system also has the function of muscle strength training, By collecting surface electromyography signals and muscle tone signals to judge human upper limb movements and muscle strength, and real-time monitoring muscle fatigue status, using wireless transmission mode to upload data to the human-computer interaction module, matching with the virtual game, make the upper limb muscle strength training process more interesting, and effectively improve its training effect.

Owner:ZHENGZHOU UNIV

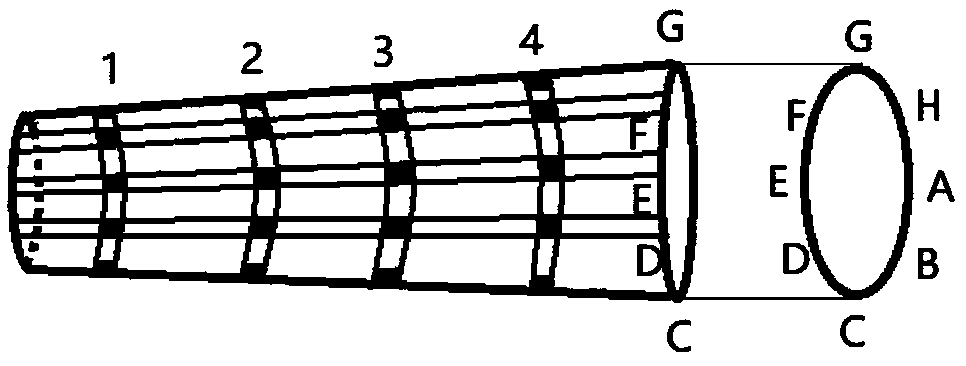

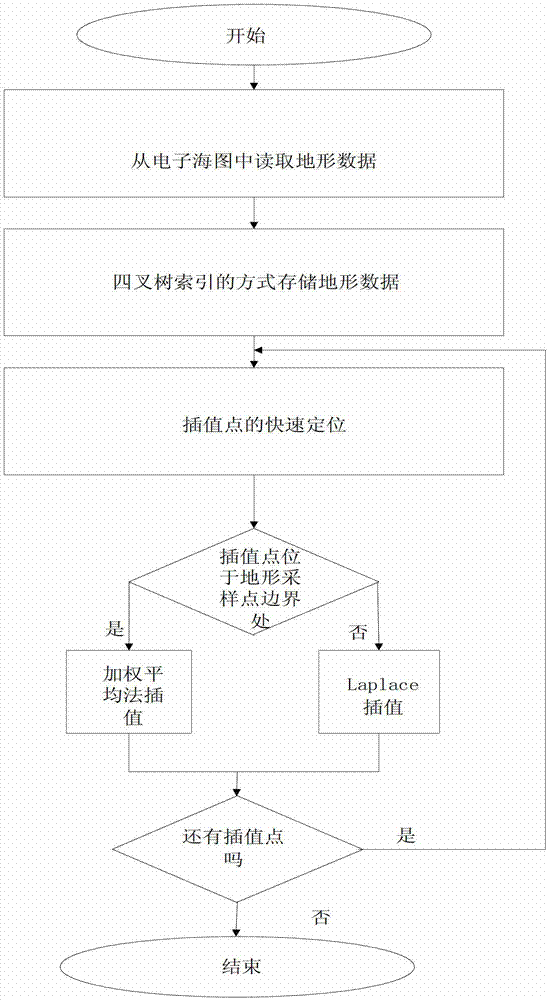

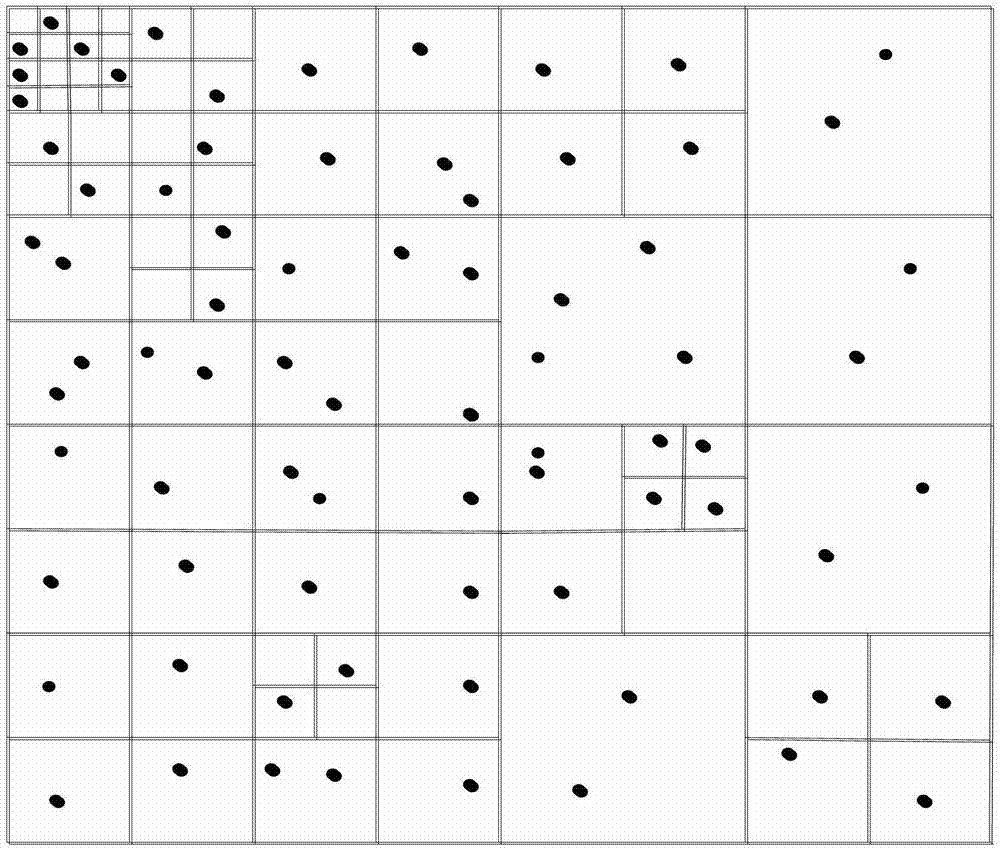

Submarine topography data establishment method based on topographical sampling point positions

ActiveCN102819568AReduce Terrain Interpolation ErrorsMaps/plans/chartsSpecial data processing applicationsOcean bottomWeighted average method

The invention discloses a submarine topography data establishment method based on topographical sampling point positions, belonging to the space field of a Geographical Information System (GIS). The method comprises the following steps of: firstly, extracting submarine topography sampling point data from an electronic chart, and performing a quad-tree space index on submarine topography sampling data, searching positions of interpolation points in the quad-tree space index; obtaining a proper interpolation method in accordance with the positions of the interpolation points; and finally comparing a time of interpolations having been carried out and a total time of interpolations required, and continuing to perform an interpolation process if the times subjected to the interpolation is less than the total times required to be interpolated, otherwise, ending the interpolation process. According to a characteristic that the interpolation points at the boundary of the submarine topography sampling data cannot acquire annularly-connected natural neighbouring points, a mixed interpolation way of the natural neighbor interpolation method and a method of weighted mean is adopted in the method of the invention, thus sufficiently taking the advantages of an interpolation method into account and effectively reducing topography interpolation errors.

Owner:哈尔滨哈船导航技术有限公司

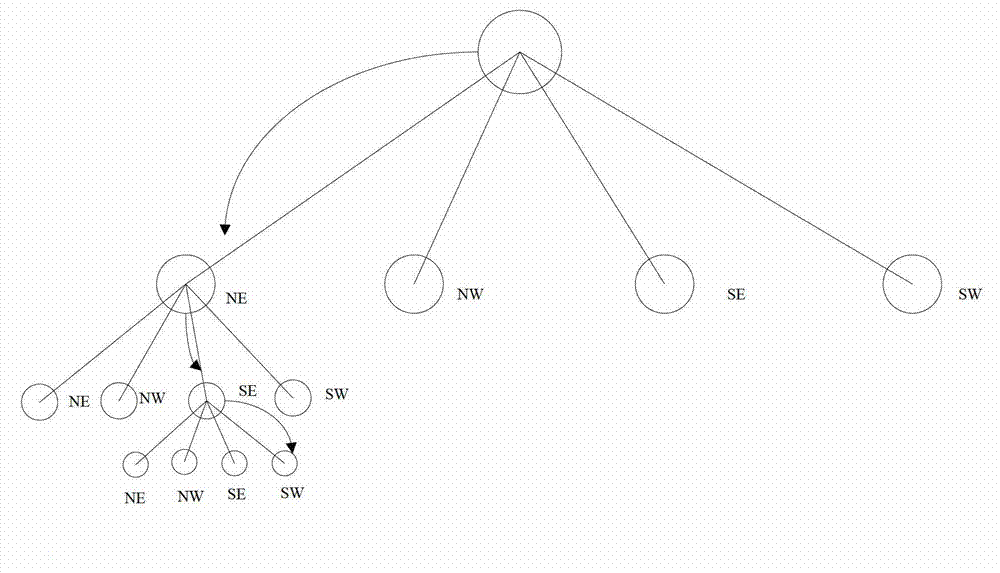

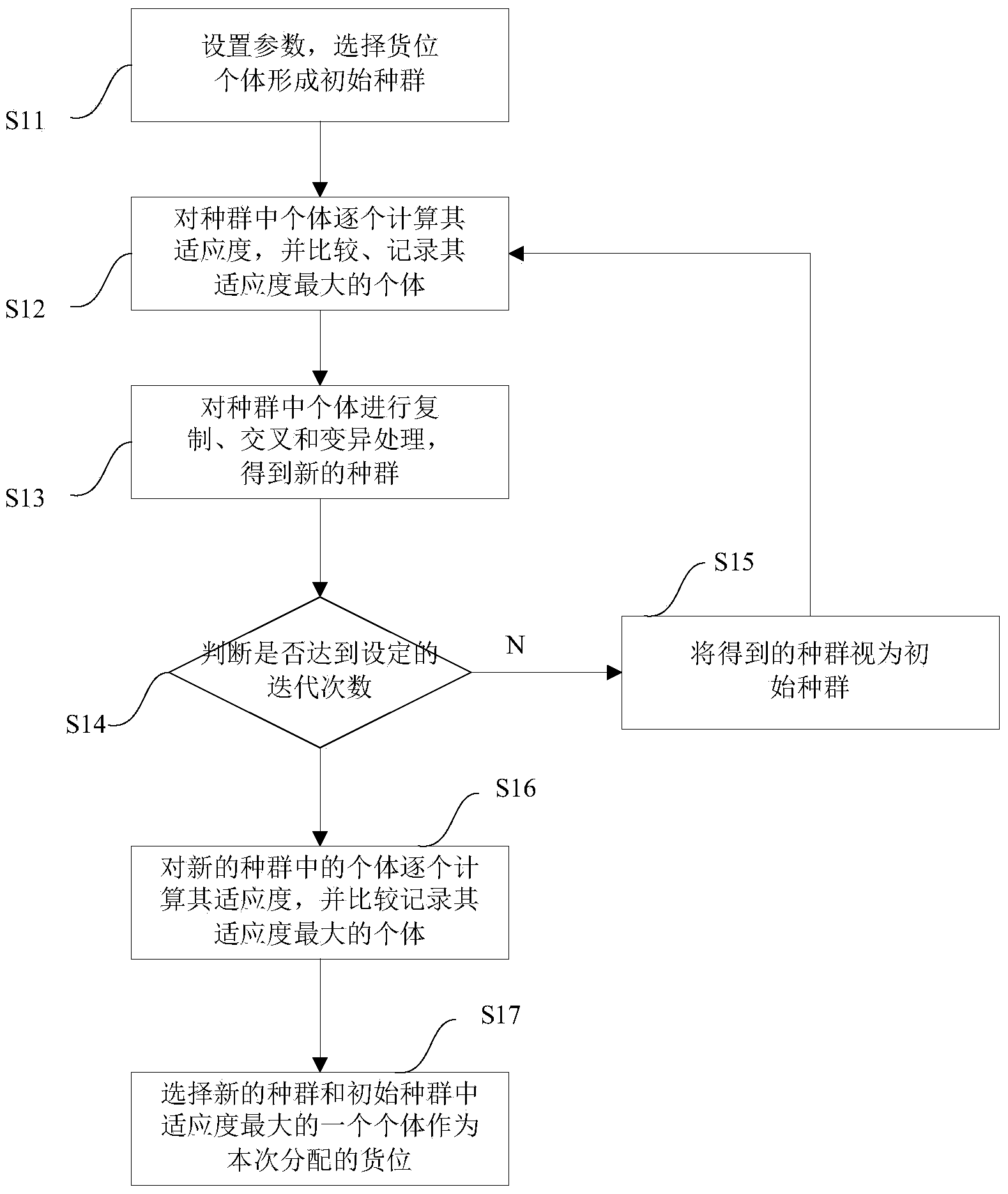

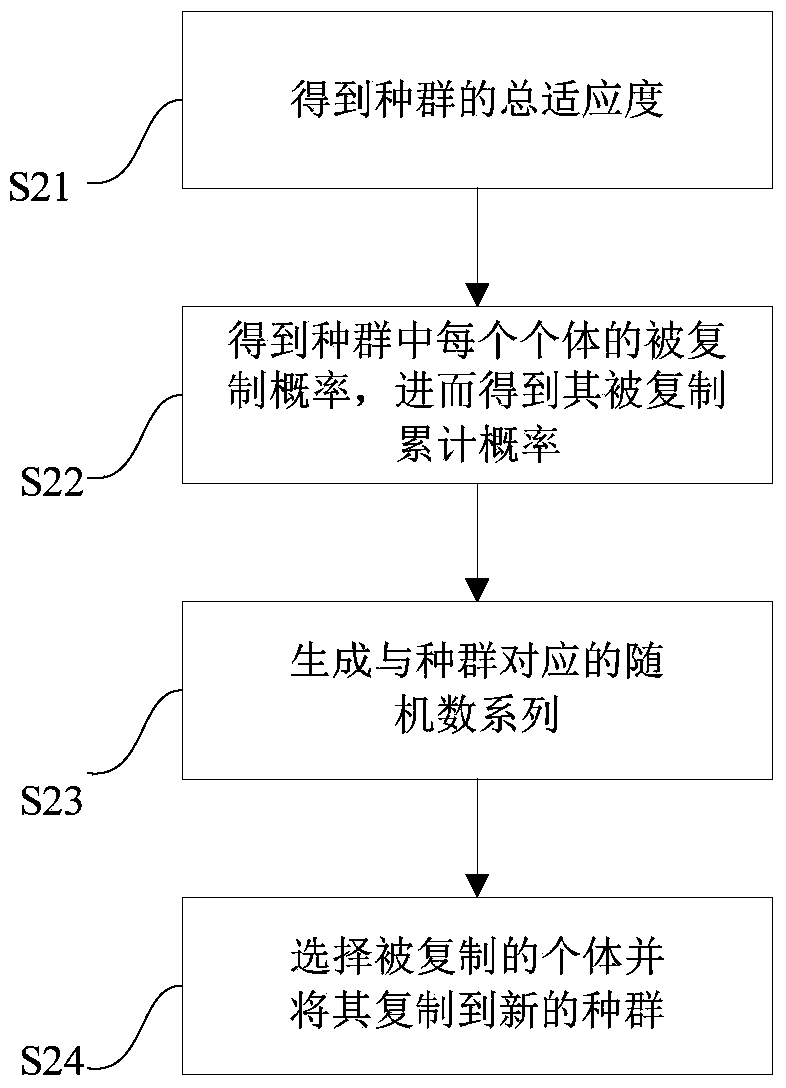

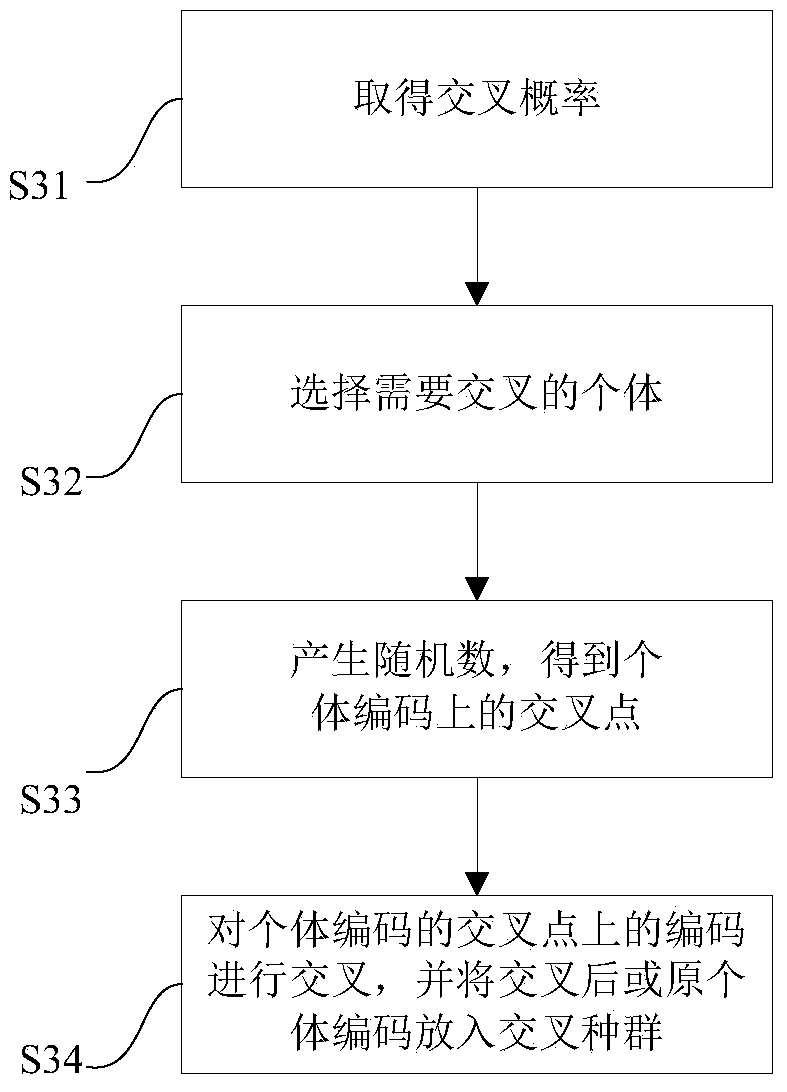

Method for allocating cargo positions for cargoes in three-dimensional warehouse

The invention relates to a method for allocating cargo positions for cargoes in a three-dimensional warehouse. The method comprises the following steps that an original group is obtained; the weighted average method is used for calculating the individual fitness of each cargo position represented with position coordinates; comparing is carried out, and the individual with the highest fitness is recorded; the genetic algorithm is adopted to carry out individual copy, cross, variation and individual variation on the individuals in the original group, and a new group is obtained; whether the set number of iterations is achieved or not is judged, if yes, the weighted average algorithm is used for calculating the individual fitness for the new group; comparing is carried out, and the individual with the highest fitness is recorded; the highest fitness of the new group and the highest fitness of the original group are compared, the individual with the highest fitness is selected, and the cargo position represented by the individual is obtained; or otherwise, the obtained new group serves as the original group, and processing is carried out again. The method for allocating the cargo positions for the cargoes in the three-dimensional warehouse has the advantages that the time for searching for the warehouse is shortened, and cost is low.

Owner:INVENGO INFORMATION TECH