Method for extracting graphic features of layout of chip and CMP simulation method

A graphic feature and layout technology, applied in special data processing applications, instruments, calculations, etc., can solve problems such as inaccurate simulation results, achieve accurate prediction, and improve accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

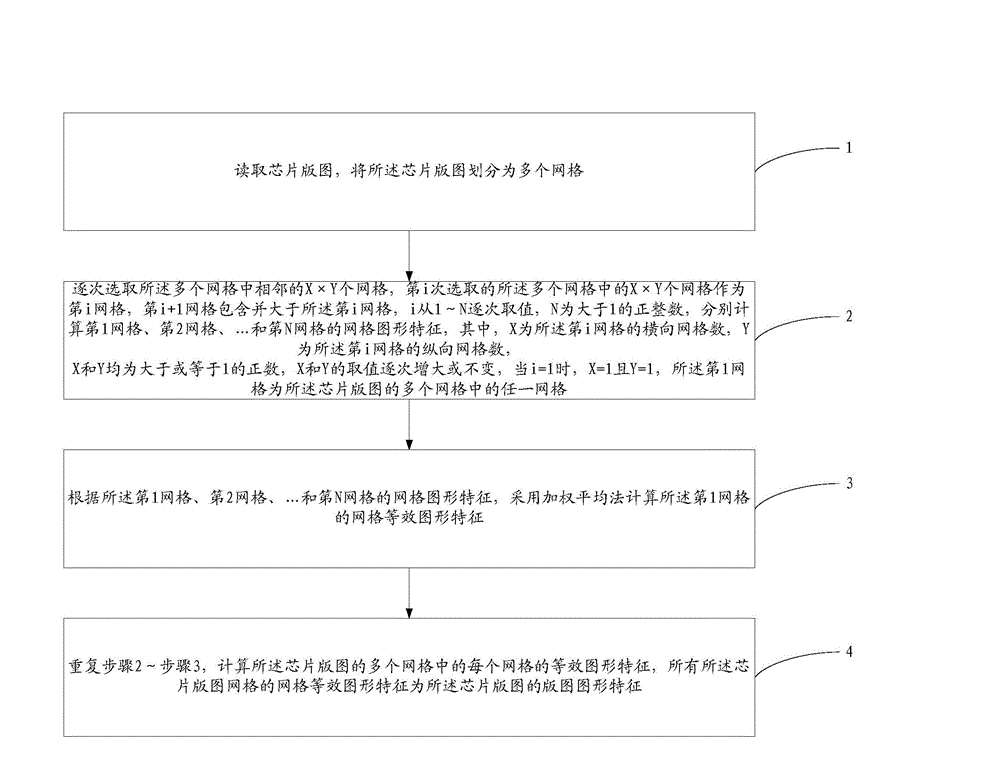

[0054] This embodiment provides a method for extracting layout graphic features of chip layout, such as figure 1 As shown, the method includes the following steps:

[0055] Step 1: read the chip layout, and divide the chip layout into multiple grids;

[0056] Considering that the current chip layout is usually a hierarchical structure, a preprocessing step of flattening the chip layout is required before layout division.

[0057] In order to reduce the amount of calculation, the plurality of divided grids are preferably squares with the same size. However, in actual application, the layout can also be divided into grids of other shapes as required, and the sizes of the divided grids can be different.

[0058] Due to the different ups and downs in different areas of the chip layout, the size of the divided grid needs to be selected. Generally, the principle of selecting the grid size is: not less than the planarization length of the layout; the so-called planarization length ...

Embodiment 2

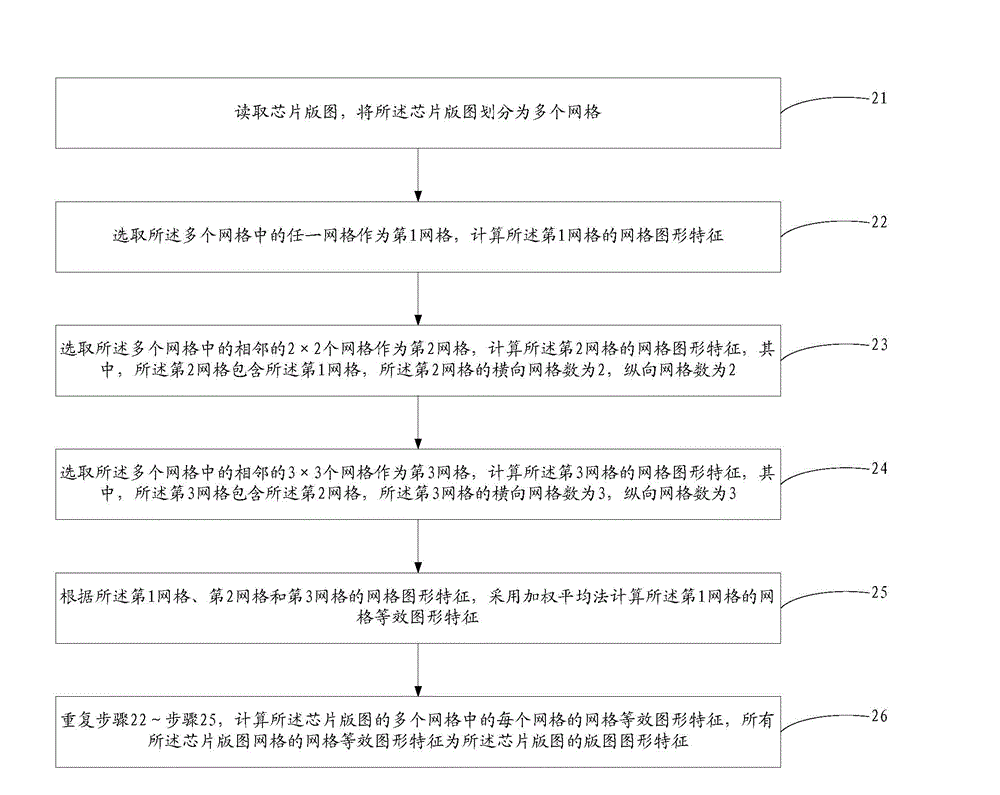

[0090] Based on Embodiment 1, this embodiment specifically introduces the method provided in Embodiment 1 by taking N=3 as an example. N=3 means that multiple grids of the chip layout are selected three times. Such as figure 2 As shown, the method includes the following steps:

[0091] Step 21: read the chip layout, and divide the chip layout into multiple grids;

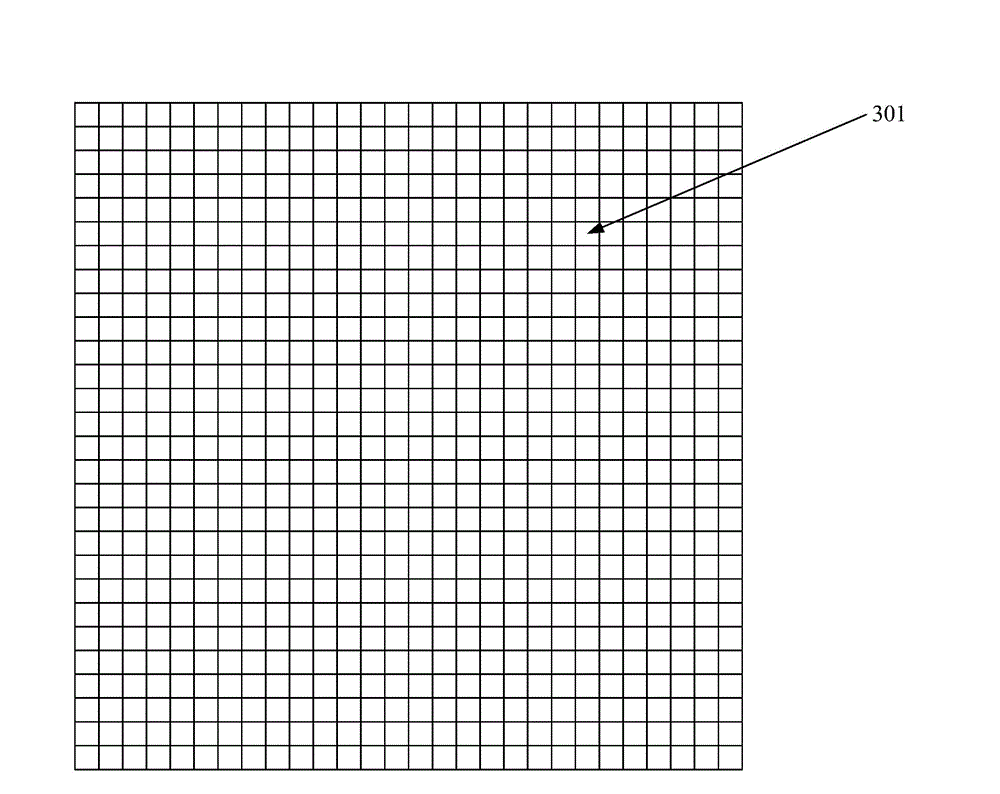

[0092] Such as image 3 As shown, the chip layout is divided into a plurality of square grids 301 with the same shape and size, the size of the grid 301 is less than or equal to the planarization length of the chip layout, and the size of the grid 301 is D 1 .

[0093] Step 22: selecting any one of the plurality of grids as the first grid, and calculating the grid graphic features of the first grid;

[0094] Such as Figure 4 As shown, select any grid as the first grid 401, and the size of the first grid 401 is D 2 , the first grid 401 contains a plurality of graphic areas, and these graphic areas are defined...

Embodiment 3

[0111] Based on embodiment one and embodiment two, this embodiment provides a kind of CMP emulation method, and this method comprises the following steps:

[0112] Using the method described in Embodiment 1 and Embodiment 2 to extract the layout graphic features of the chip layout;

[0113] A CMP model is selected, and the layout graphic features of the chip layout are used as parameters of the CMP model to perform CMP process simulation.

[0114] The CMP simulation method provided in this embodiment can consider the proximity effect of different graphics in the layout to a greater extent, and consider various characteristic parameters of the layout graphics in a more comprehensive manner. The simulation accuracy is high, and the calculation amount is small, which is convenient for implementation; Assisting the foundry to realize the process prediction can save the cost of process tape-out and testing, and enable the foundry to produce chips that meet the design ideas of the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More