Patents

Literature

508results about How to "Improve welfare" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

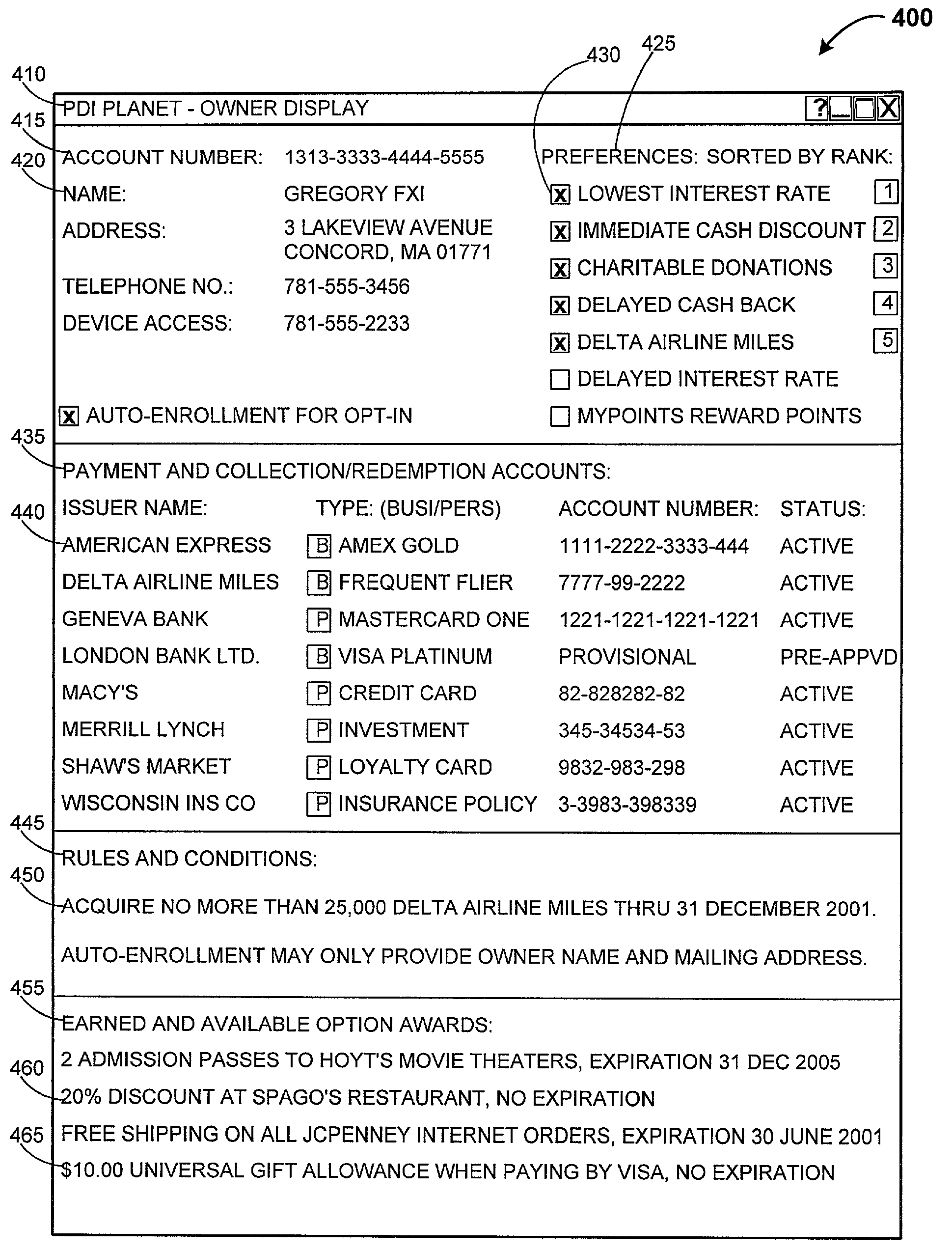

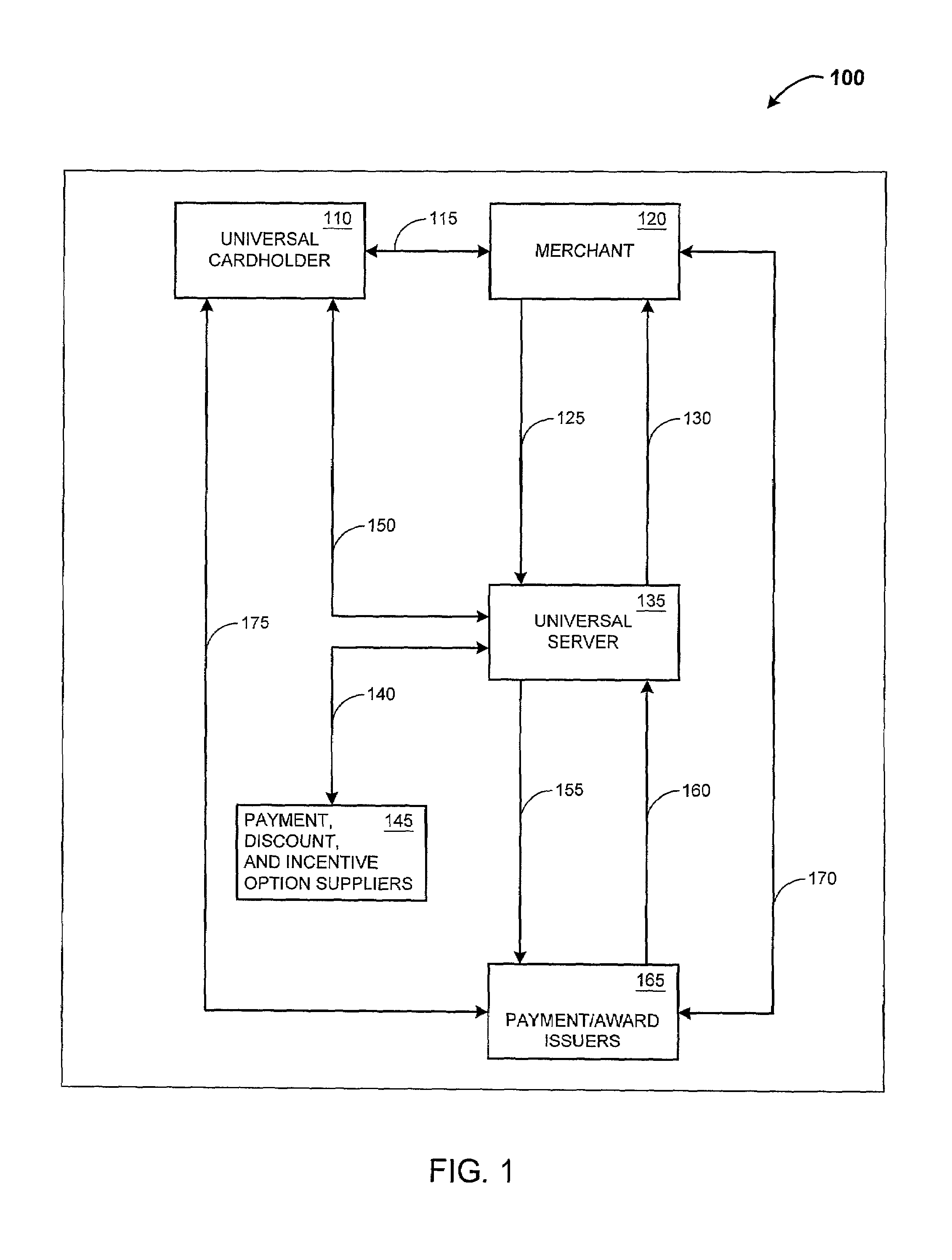

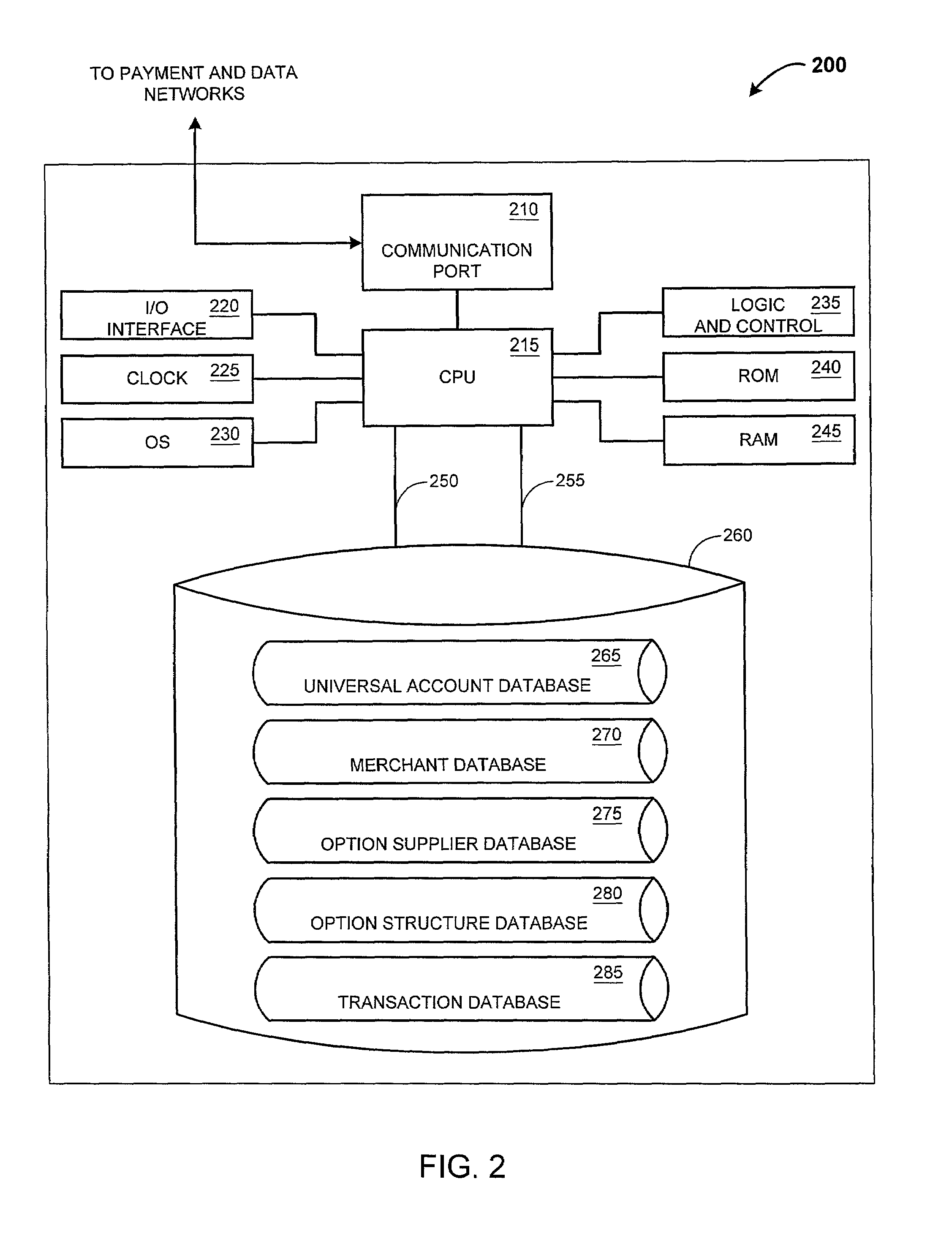

System and method for an automated benefit recognition, acquisition, value exchange, and transaction settlement system using multivariable linear and nonlinear modeling

InactiveUS7318049B2Convenient transactionReduce identity theft and economic lossesDiscounts/incentivesFinanceRandom mutationPayment

A system and process that provides an on-line, interactive, and fully integrated benefit-driven value exchange and settlement program that monitors, evaluates, and manages economic and personal benefits and executes functions to produce and acquire the maximum or preferred benefit items for users by guiding and automating appropriate payment and settlement actions. The present invention finds useful patterns in data; produces conclusions based on rules and experience; responds to environmental changes with or without human intervention; and, may evolve through selecting the best results from random mutations all of which are intended to maximise user value.

Owner:IANNACCI GREGORY FX

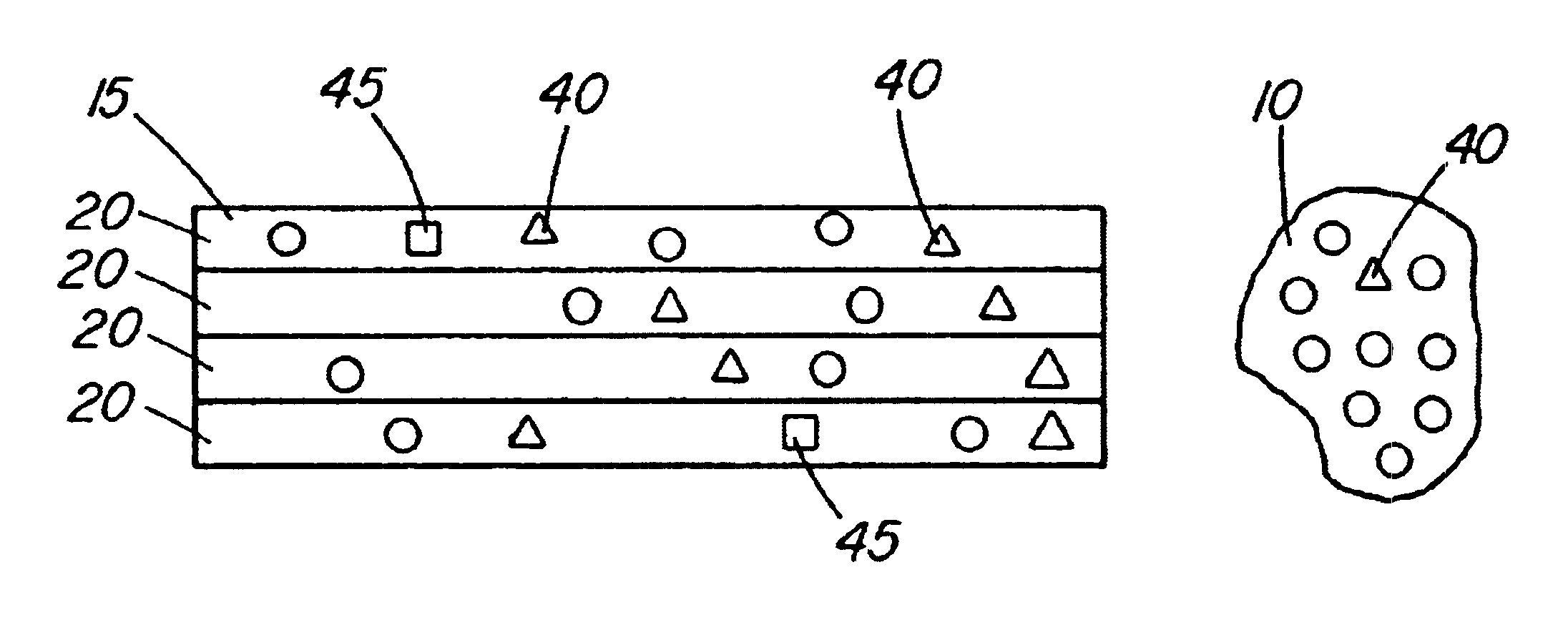

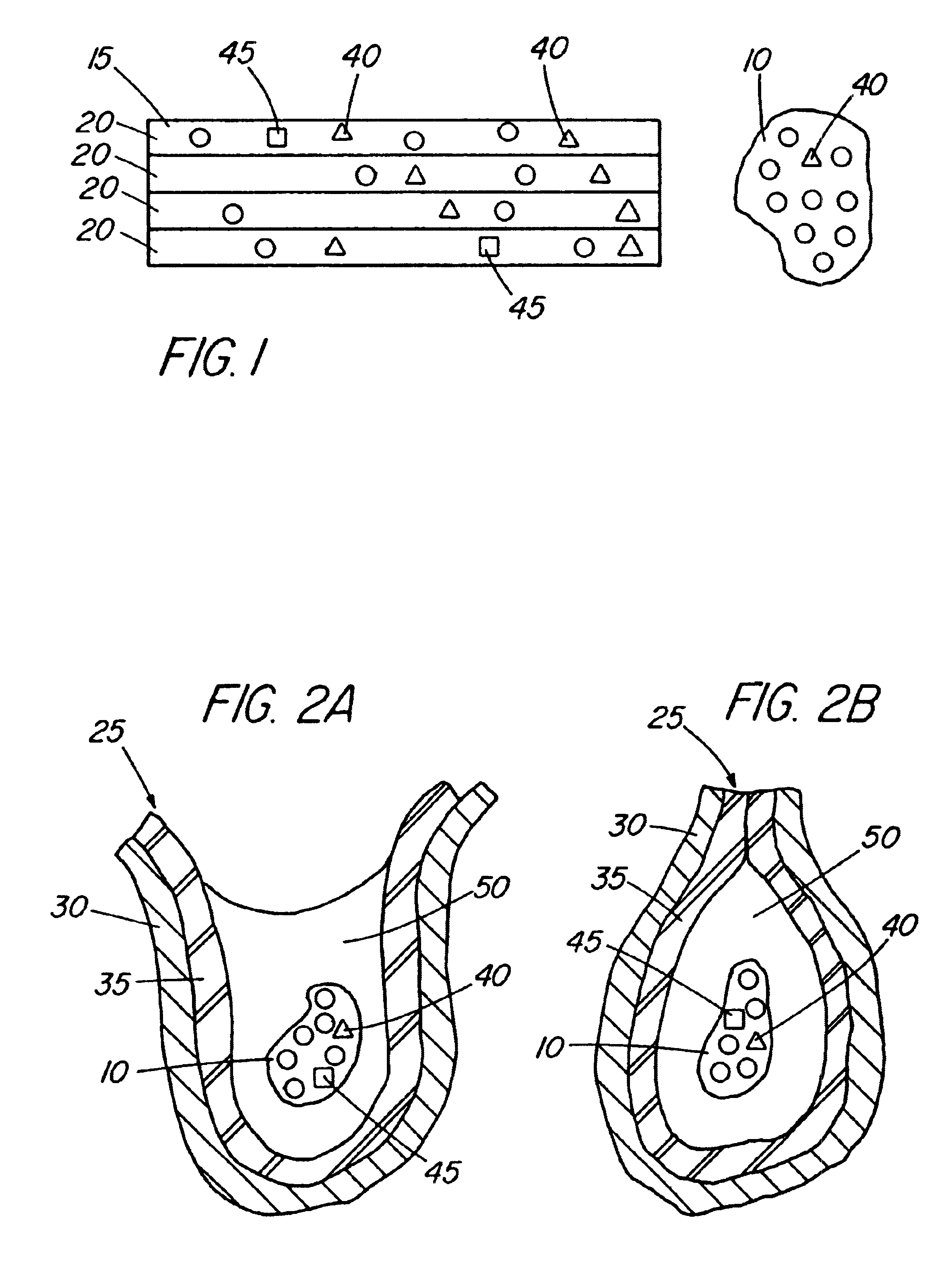

Multi-formed collagenous biomaterial medical device

InactiveUS6666892B2Great benefitFavorable immune responseStentsSurgical adhesivesBiomedical engineeringMedical device

Owner:COOK BIOTECH

Topically Bioavailable Acne and Rosacea Treatment Compositions

InactiveUS20040156873A1Reduce stimulationSynergistic superior anti-acneBiocideCosmetic preparationsAdditive ingredientIrritation

The present invention relates to acne and rosacea compositions by a six-prong synergistic combination treatment strategy that includes (1) control of excess sebum production, (2) control of undesirable bacteria or mites, (3) control of inflammation, (4) enhanced desquamation of follicular infundibulum cells, (5) reduction of irritation from anti-acne or rosacea compositions themselves, and (6) enhancement of the topical bioavailability of anti-acne and rosacea compositions. This is achieved by a synergistic combination of commonly utilized topical anti-acne and rosacea ingredients with a topical bioavailability enhancement composition, which results in enhanced anti-acne and rosacea action from such ingredients. Moreover, additional inclusion of an anti-inflammatory composition, and also a vascular micro-circulation enhancement composition, further results in synergistic superior anti-acne and rosacea benefits from such compositions. The present invention discloses additional surprising synergistic combinations for the control of acne and rosacea that are suitable for a variety of delivery systems and packaging forms.

Owner:GUPTA SHYAM K

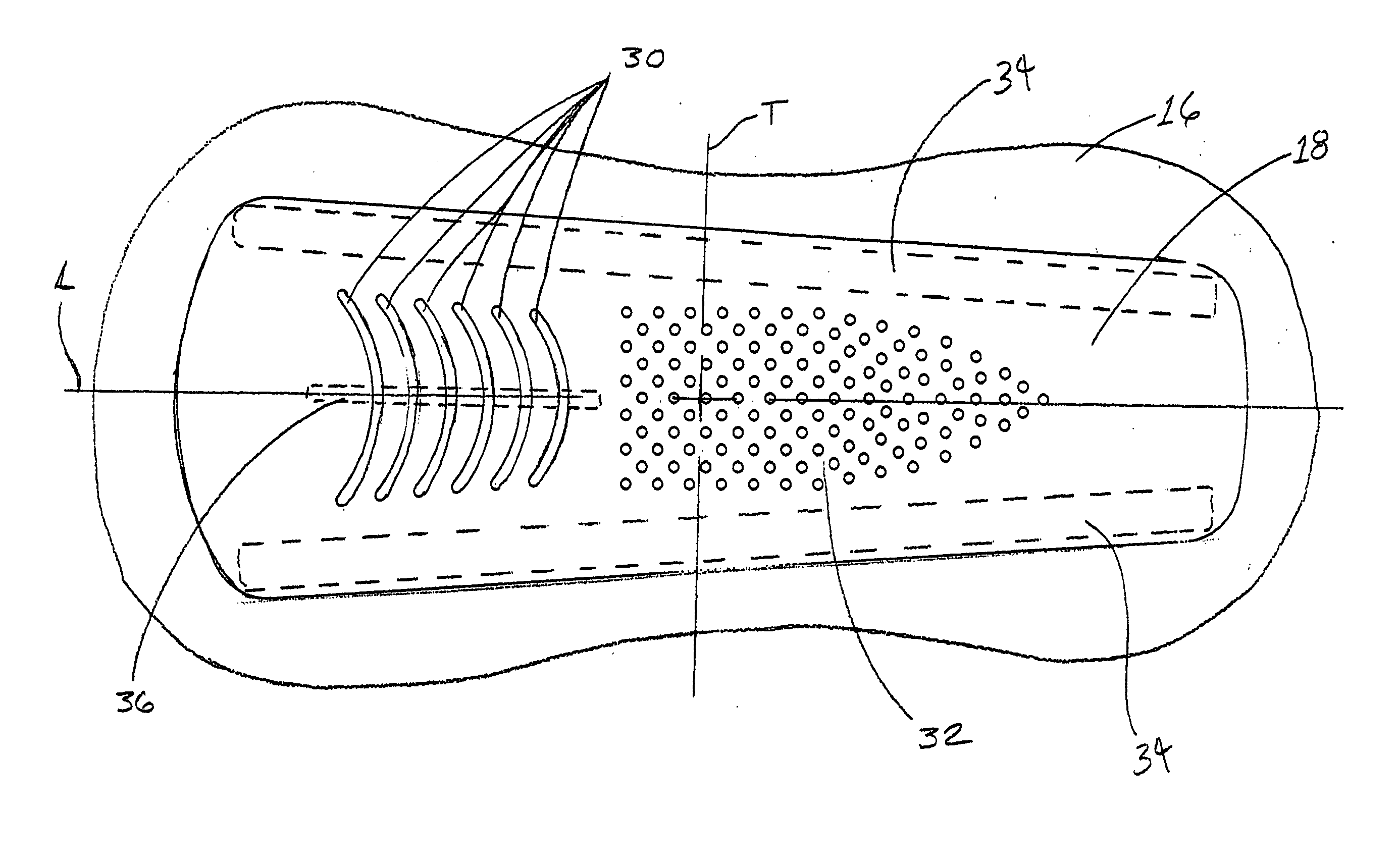

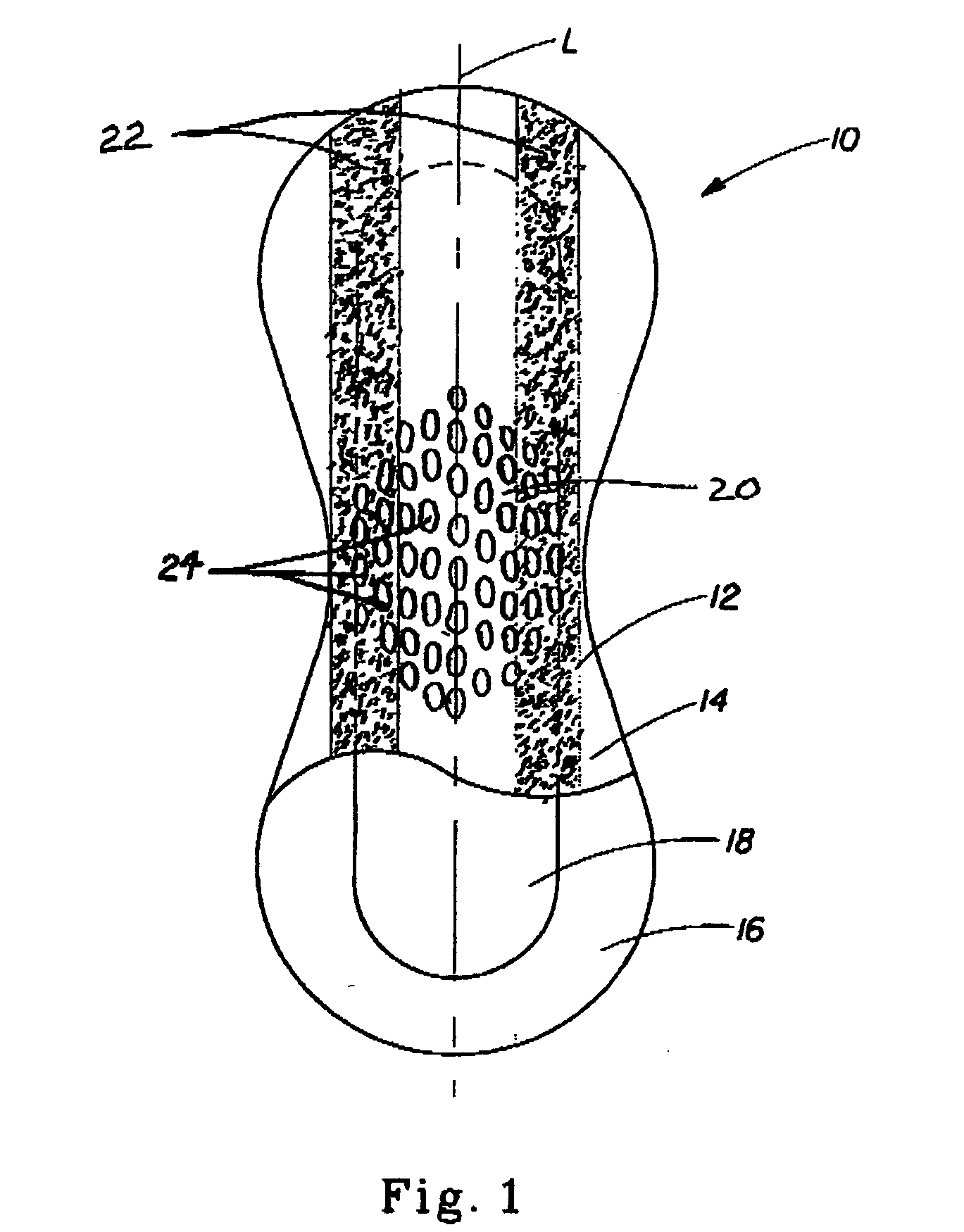

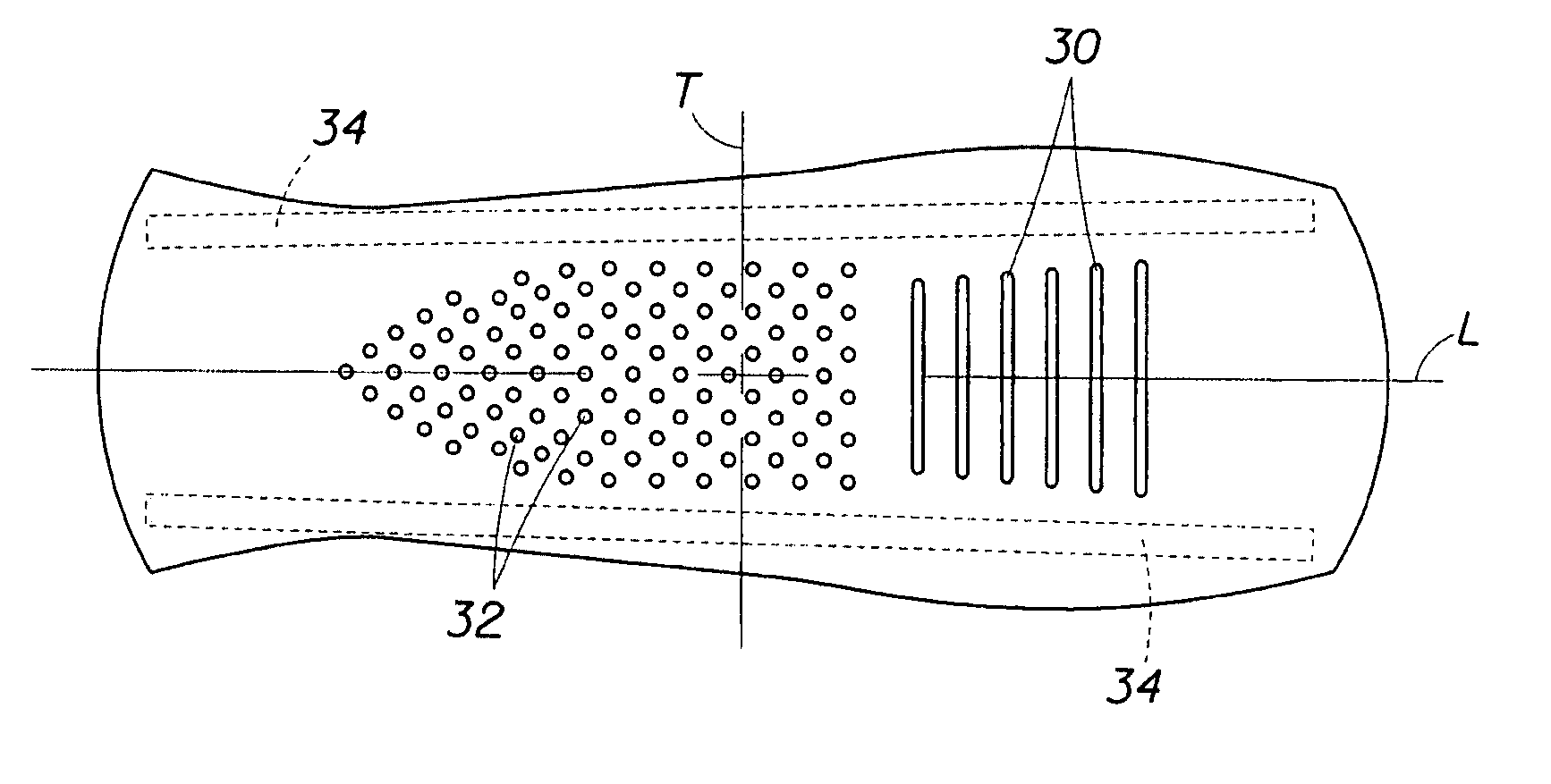

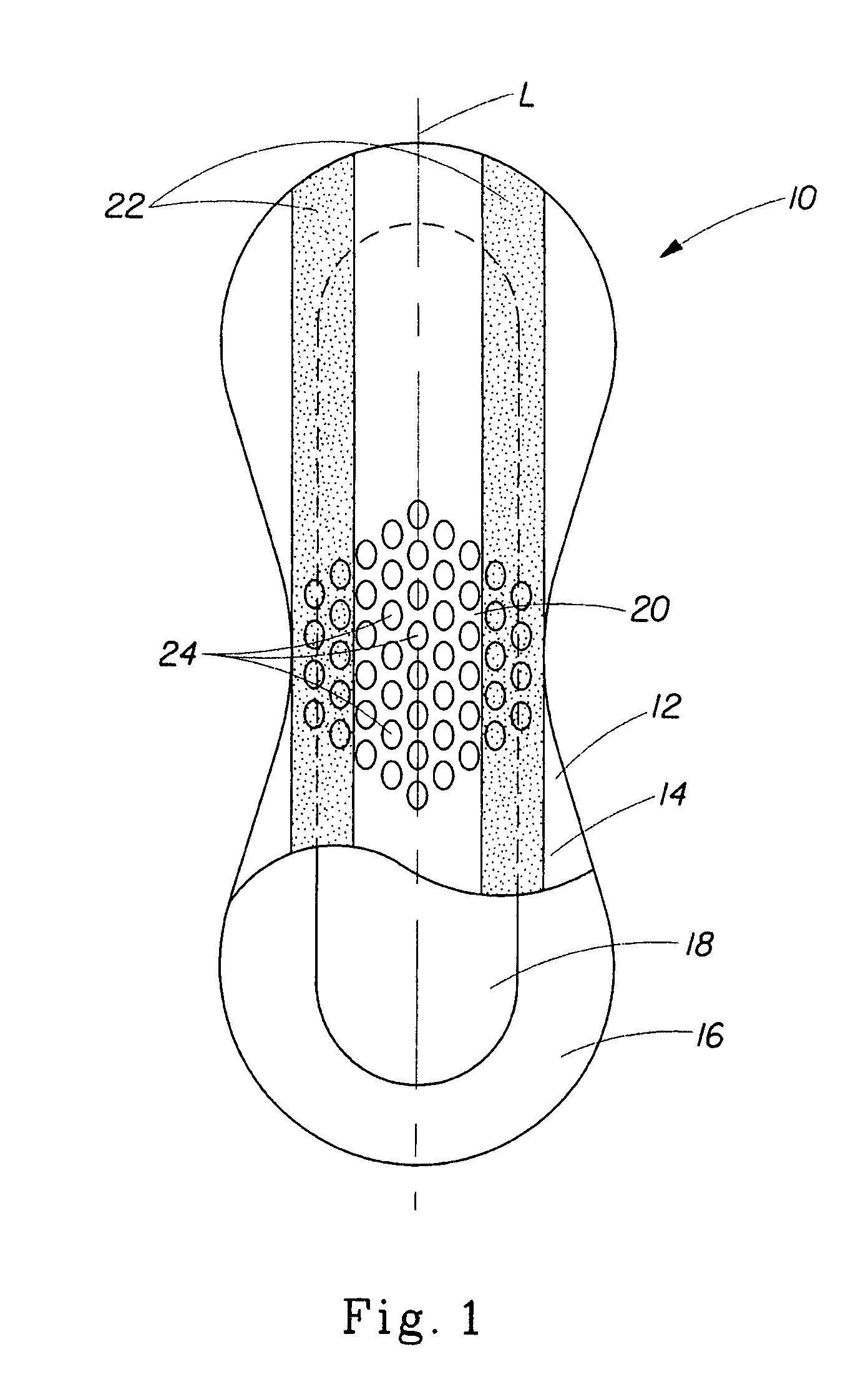

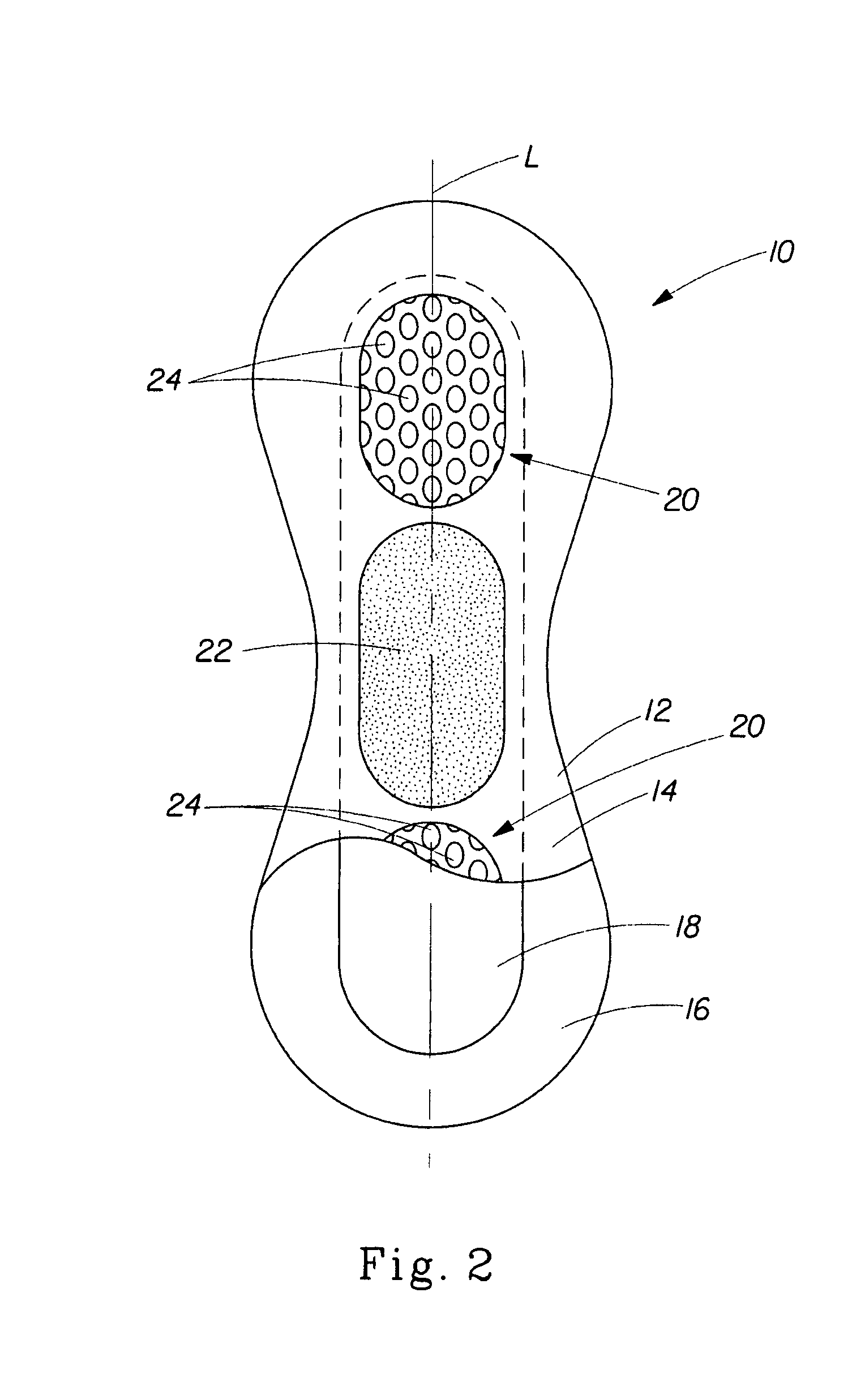

Sanitary napkins capable of taking complex three-dimensional shape in use

ActiveUS20060184150A1Superior benefitGreat viscosityBaby linensTamponsThree dimensional shapeBiomedical engineering

Owner:THE PROCTER & GAMBNE CO

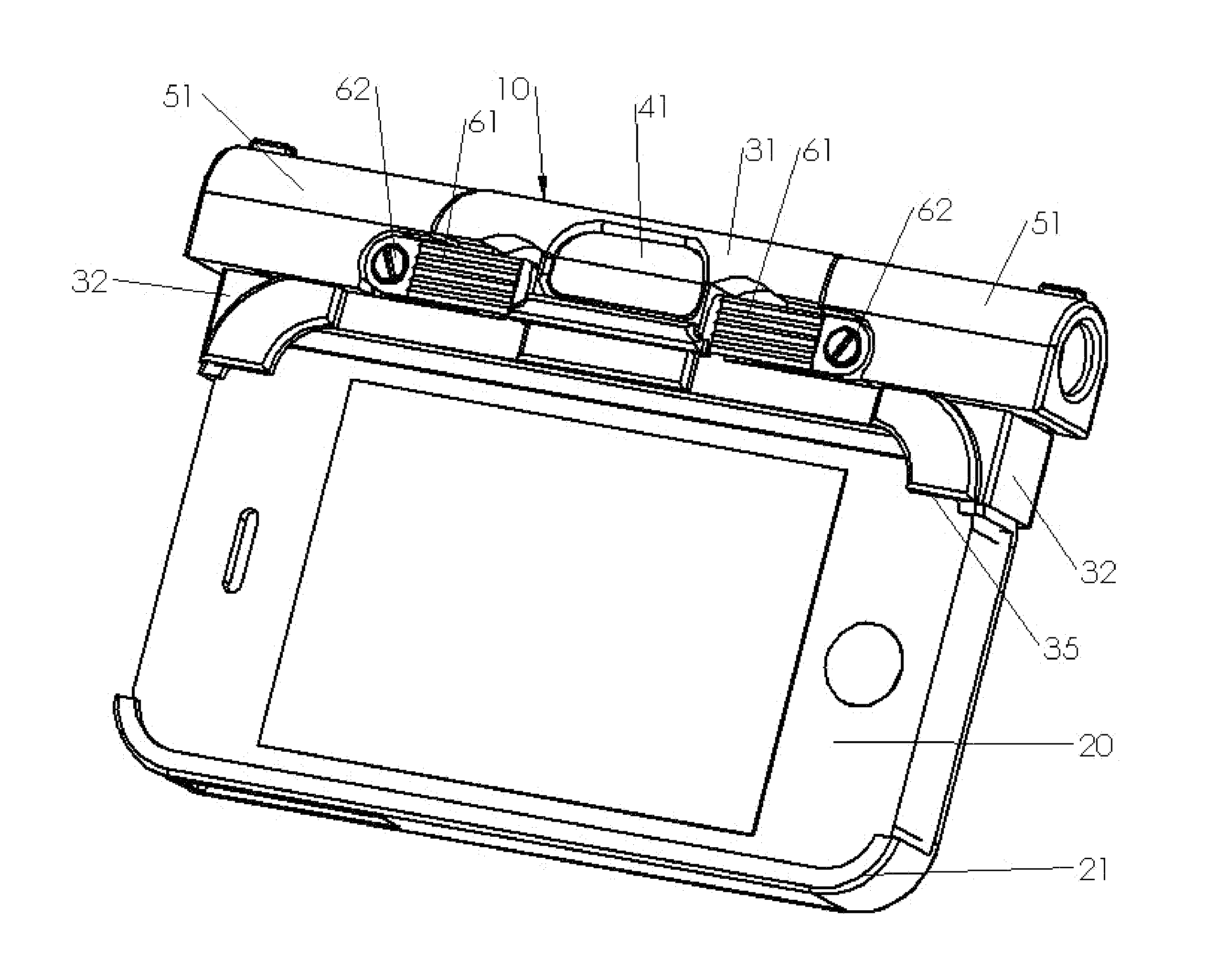

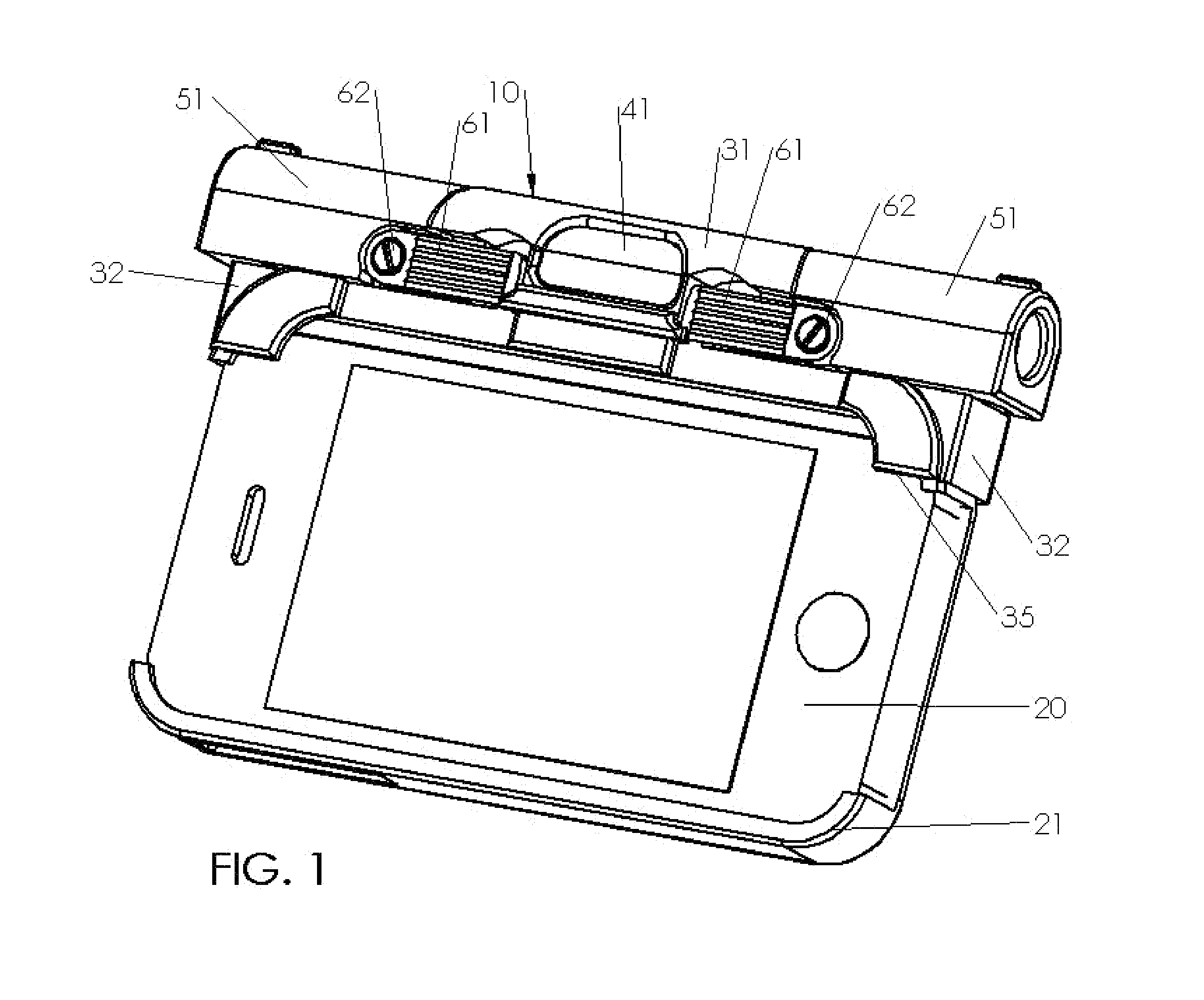

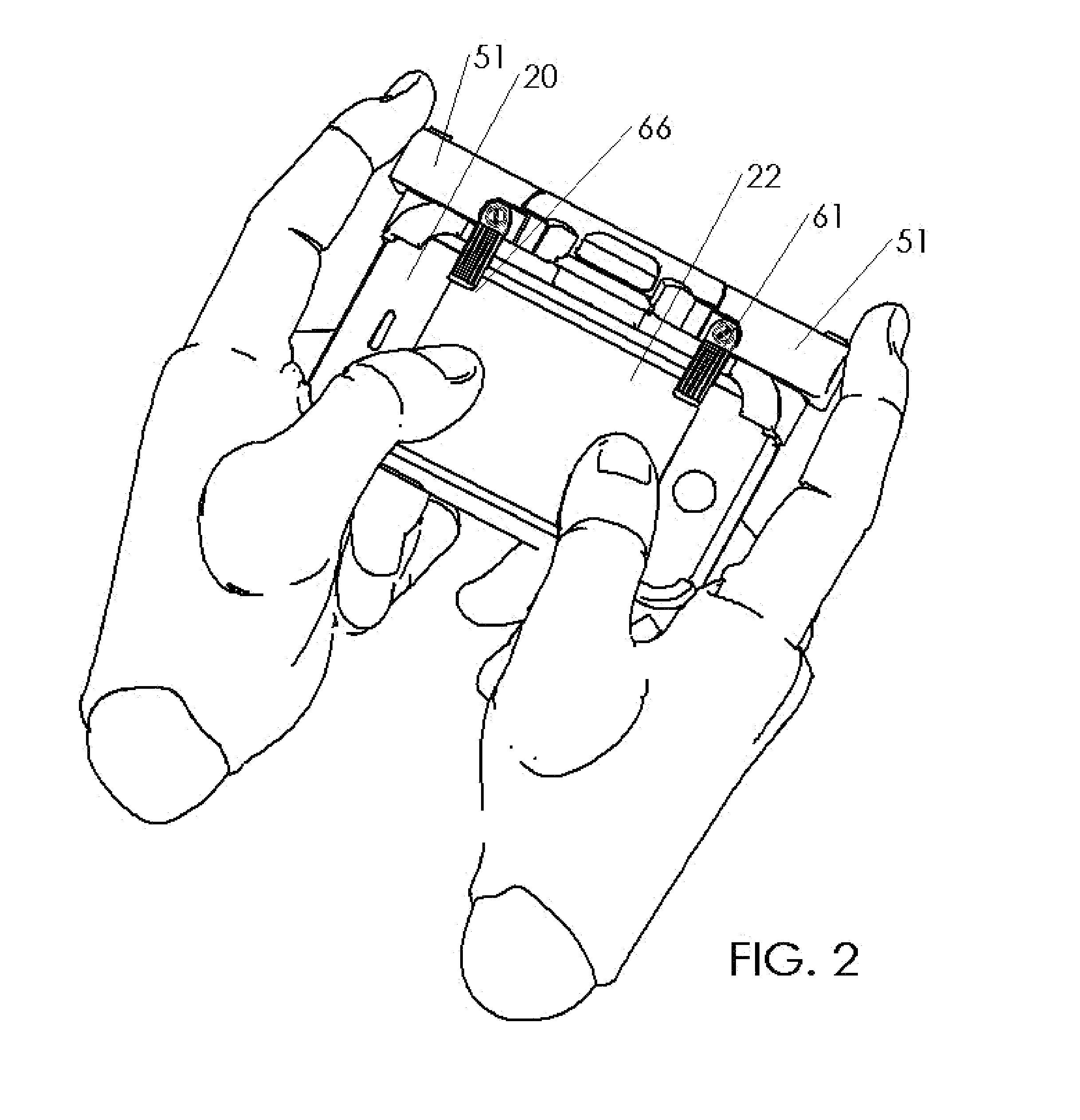

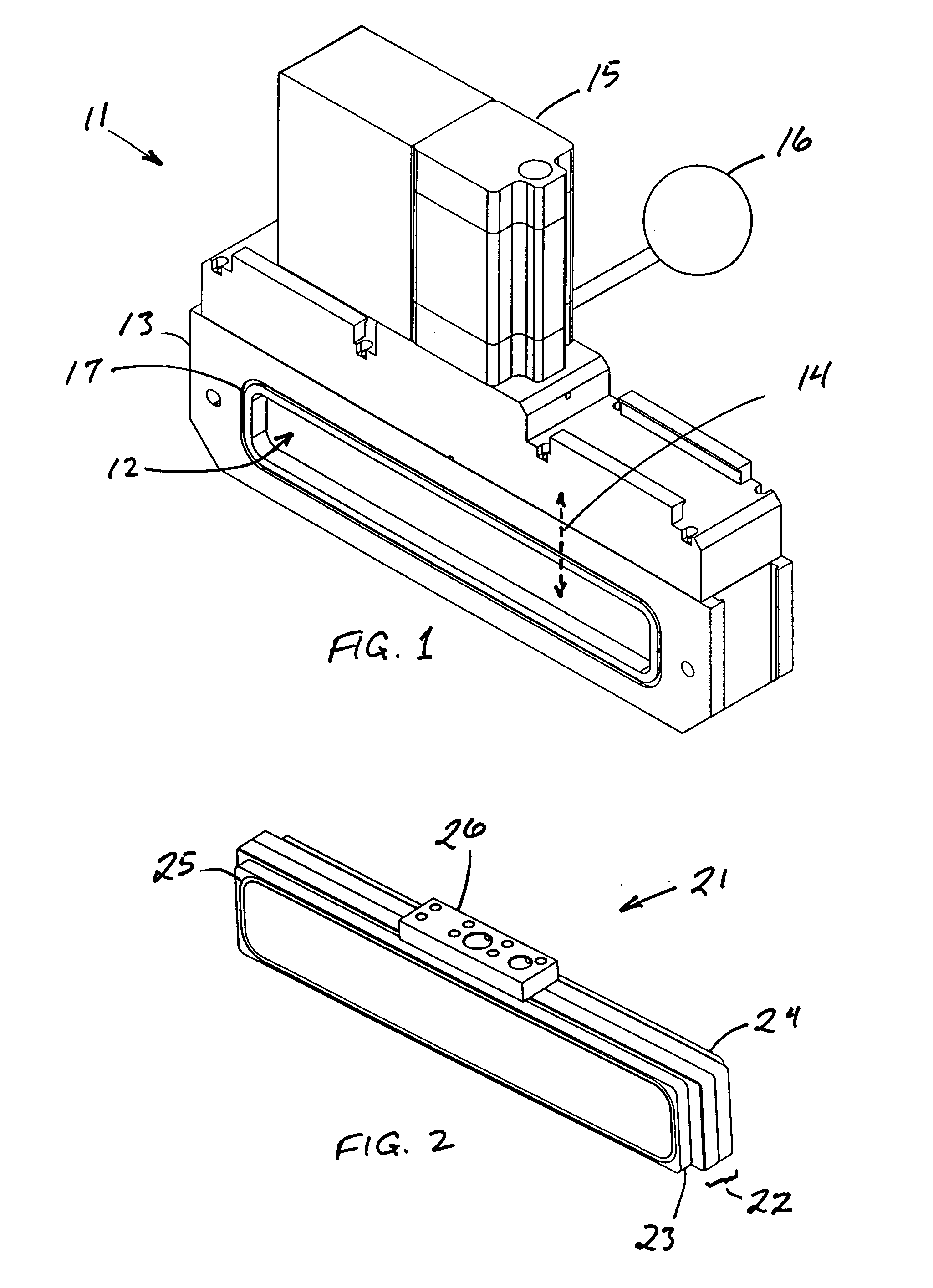

Multi-touch input device

InactiveUS20130120258A1Impair game playInhibit migrationInput/output for user-computer interactionDigital data processing detailsCapacitanceTablet computer

An interface is provided for a device having a touch screen such as a smart phone or tablet computer that extends the touch screen input to areas outside the touch screen area. The interface has a housing which attaches to the device. One or more input controls are mounted on the housing. The controls can be joysticks, buttons, touch pads, levers, triggers, keyboards, etc. Conductive pads are connected to the housing and and capacitively interact with the touch screen. The interface contains circuitry that transmits an electrical or capacitive signal from the user's manipulation of the controls to the conductive pads in order to activate selected areas of the touch screen. The housing may be made in multiple pieces to connect to different sides of the touch screen device.

Owner:MAUS DARYL D

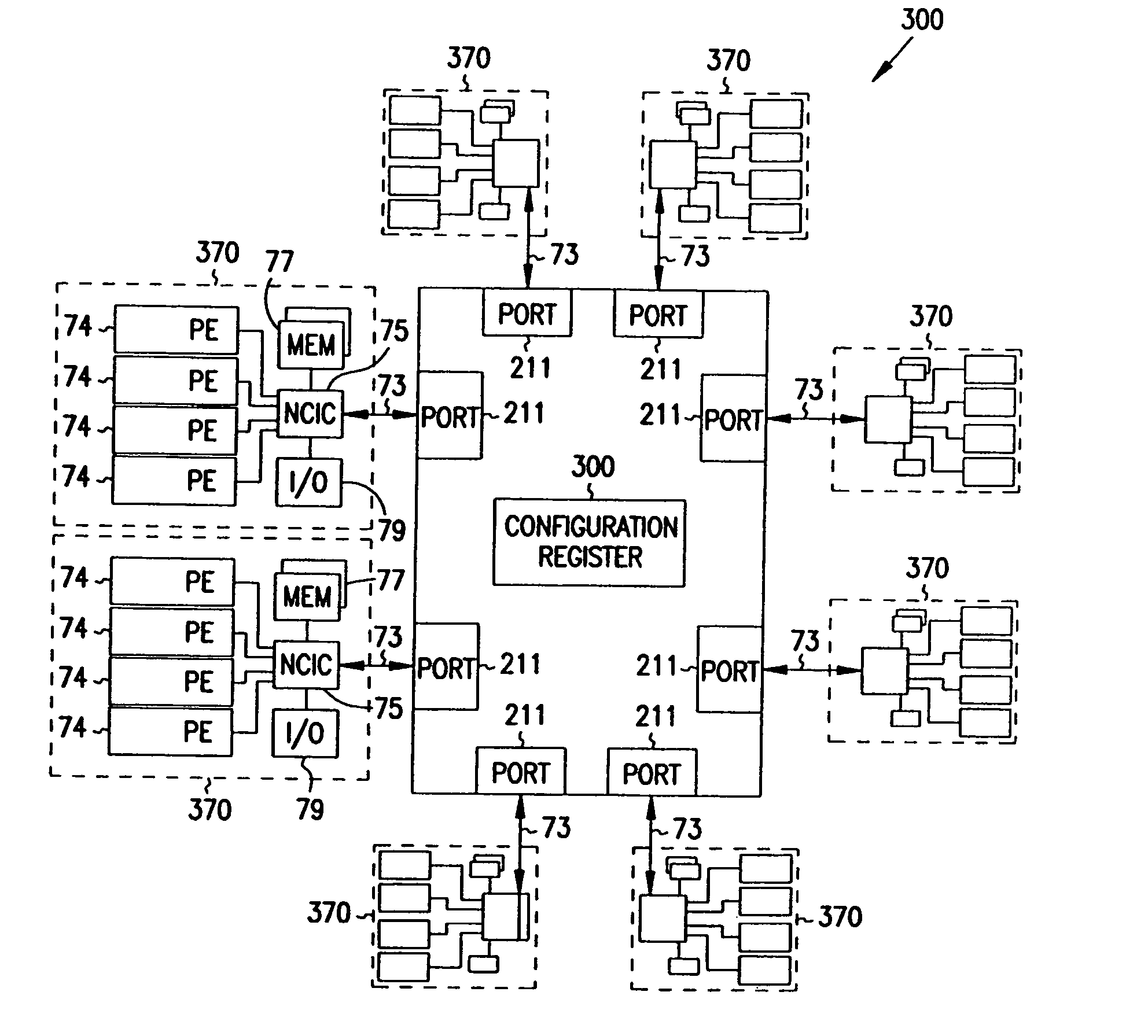

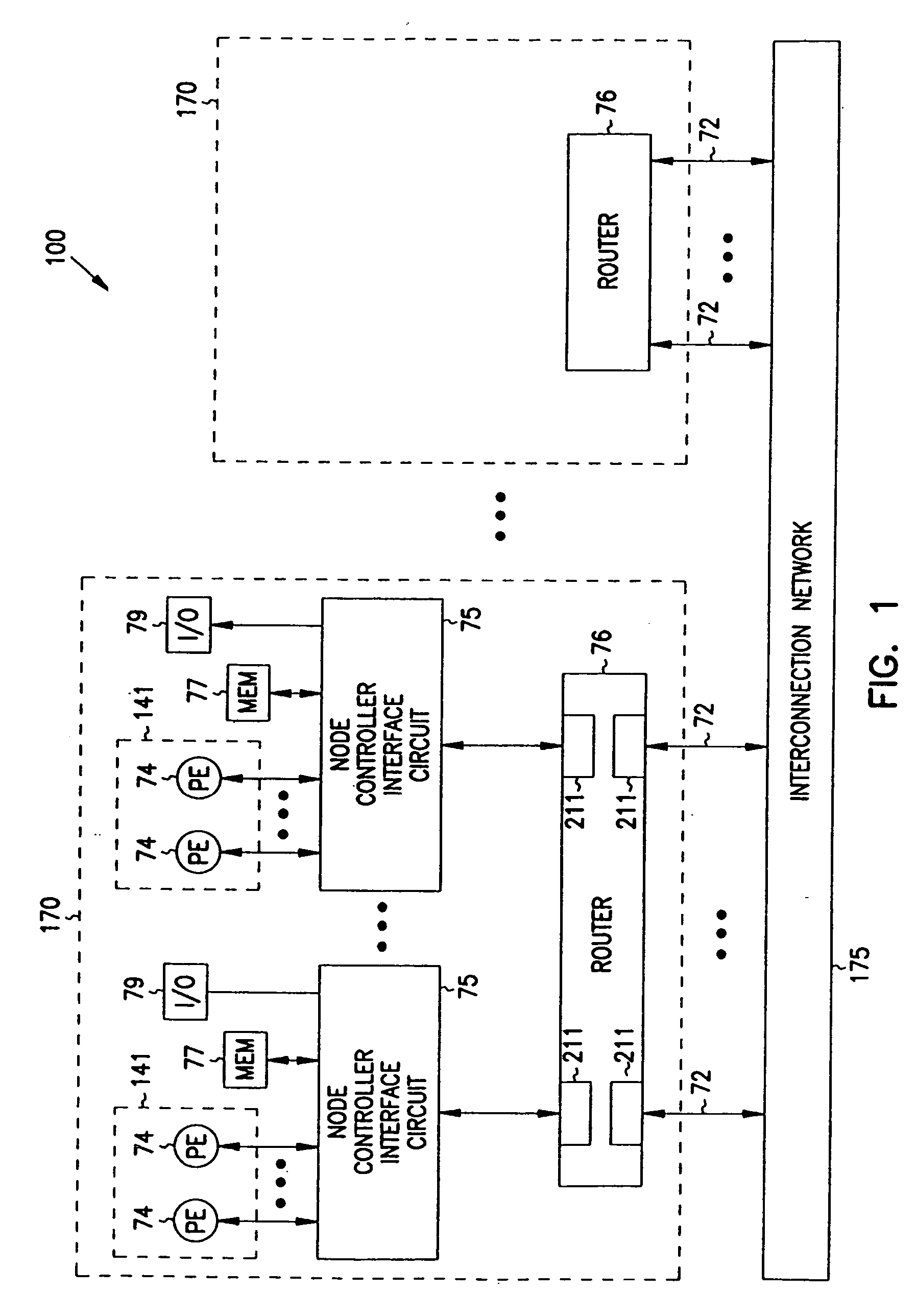

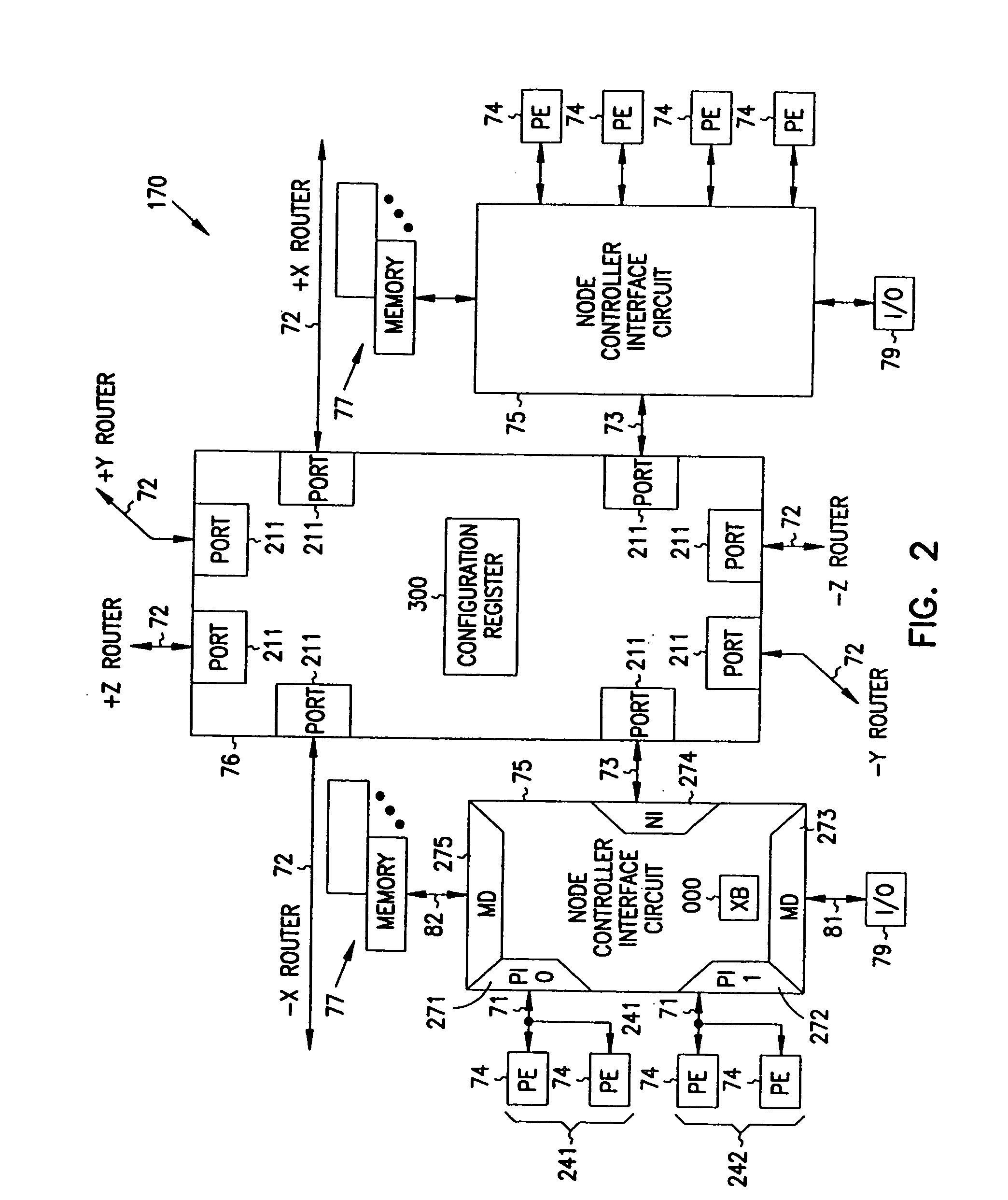

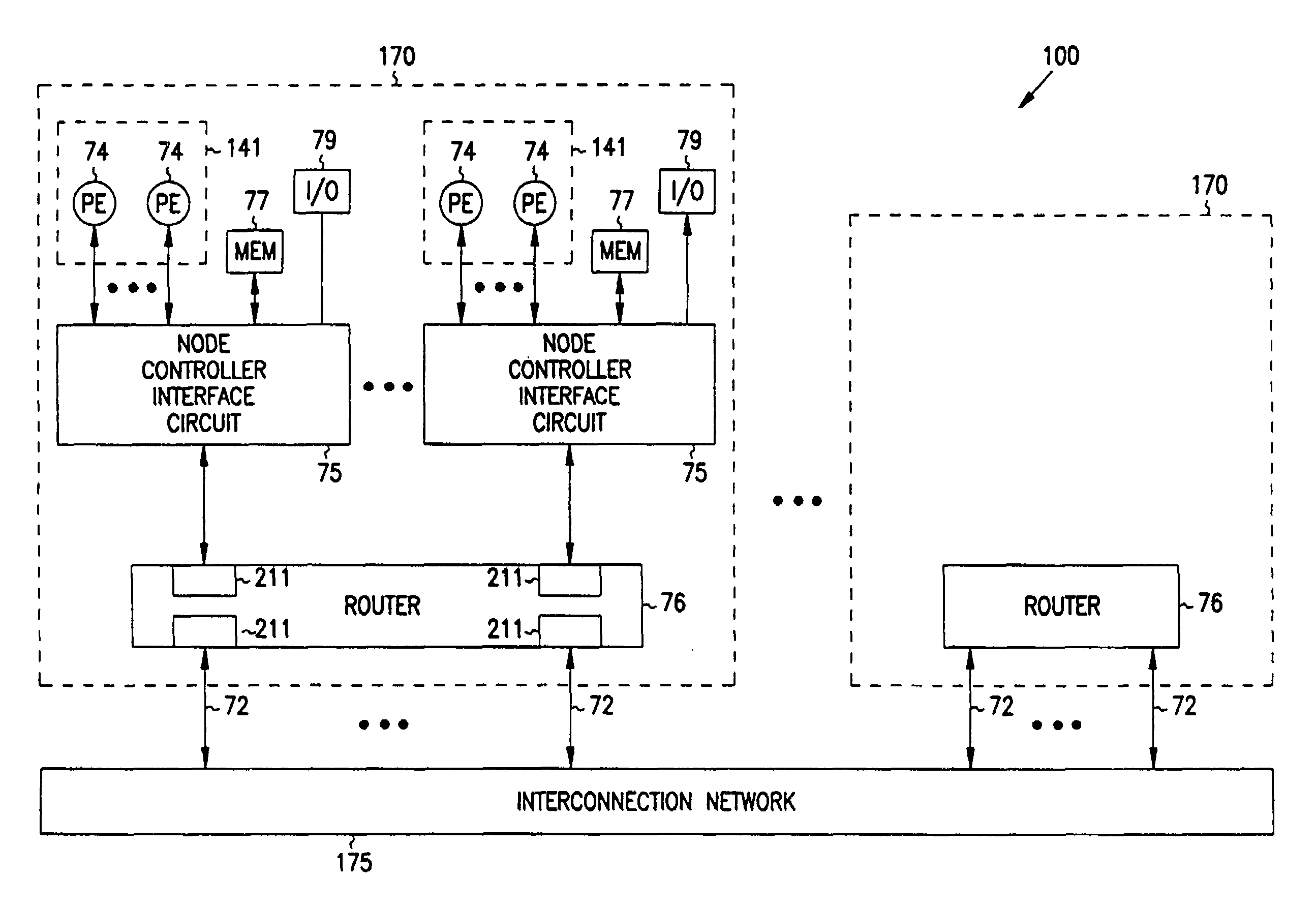

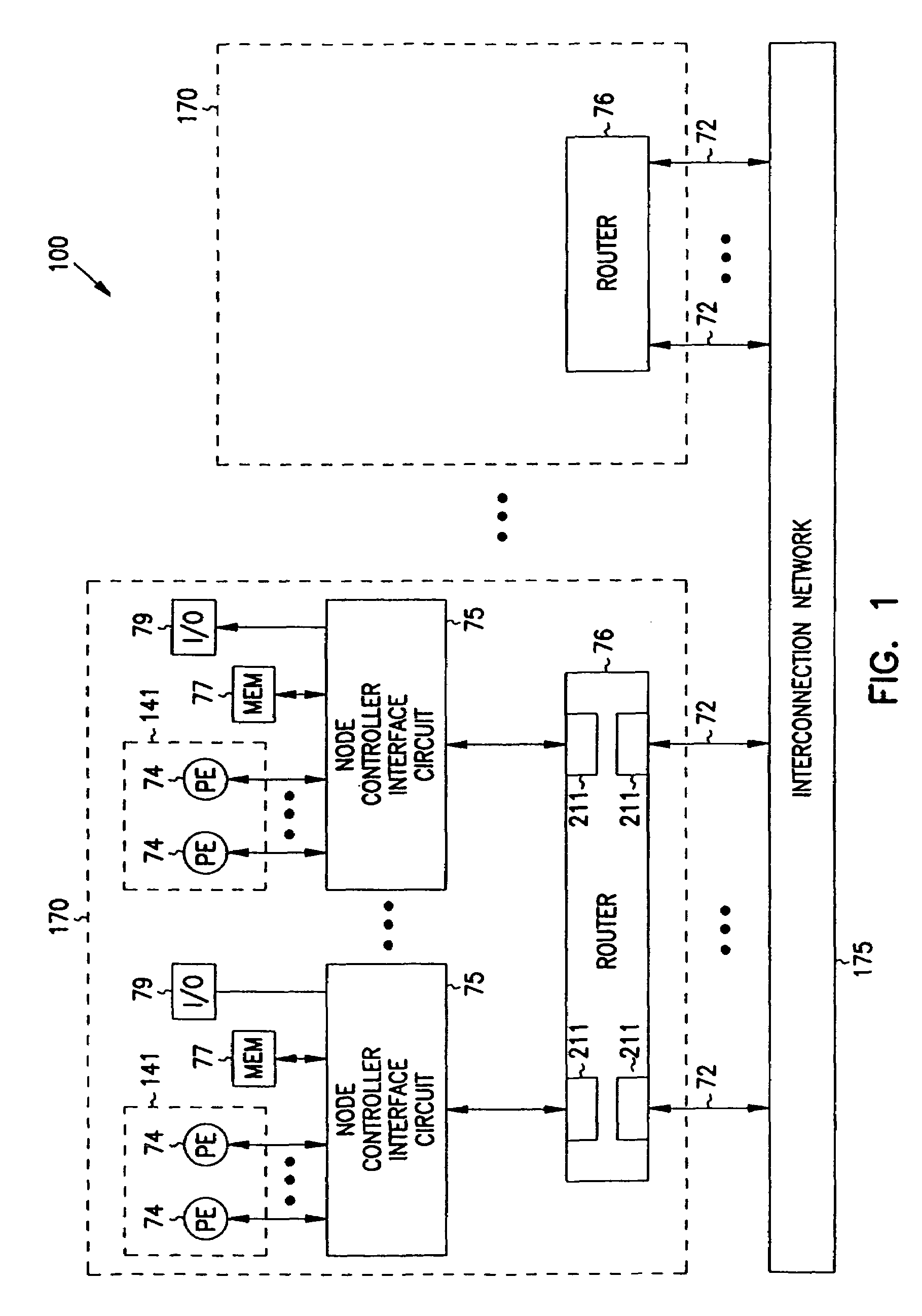

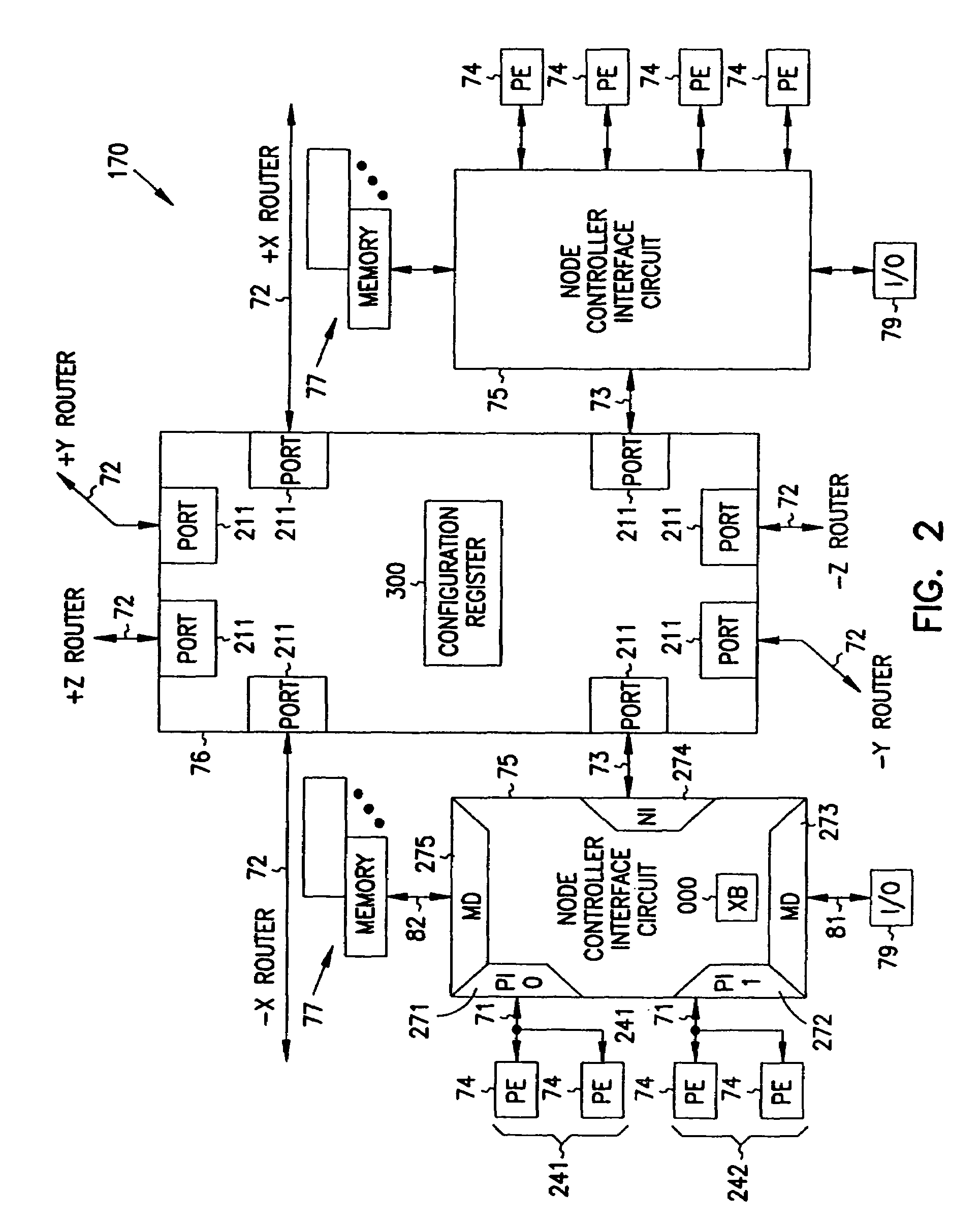

Multiprocessor node controller circuit and method

InactiveUS20050053057A1Ease of parallel processingImprove welfareMultiplex system selection arrangementsMemory adressing/allocation/relocationMemory addressCrossbar switch

Improved method and apparatus for parallel processing. One embodiment provides a multiprocessor computer system that includes a first and second node controller, a number of processors being connected to each node controller, a memory connected to each controller, a first input / output system connected to the first node controller, and a communications network connected between the node controllers. The first node controller includes: a crossbar unit to which are connected a memory port, an input / output port, a network port, and a plurality of independent processor ports. A first and a second processor port connected between the crossbar unit and a first subset and a second subset, respectively, of the processors. In some embodiments of the system, the first node controller is fabricated onto a single integrated-circuit chip. Optionally, the memory is packaged on plugable memory / directory cards wherein each card includes a plurality of memory chips including a first subset dedicated to holding memory data and a second subset dedicated to holding directory data. Further, the memory port includes a memory data port including a memory data bus and a memory address bus coupled to the first subset of memory chips, and a directory data port including a directory data bus and a directory address bus coupled to the second subset of memory chips. In some such embodiments, the ratio of (memory data space) to (directory data space) on each card is set to a value that is based on a size of the multiprocessor computer system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

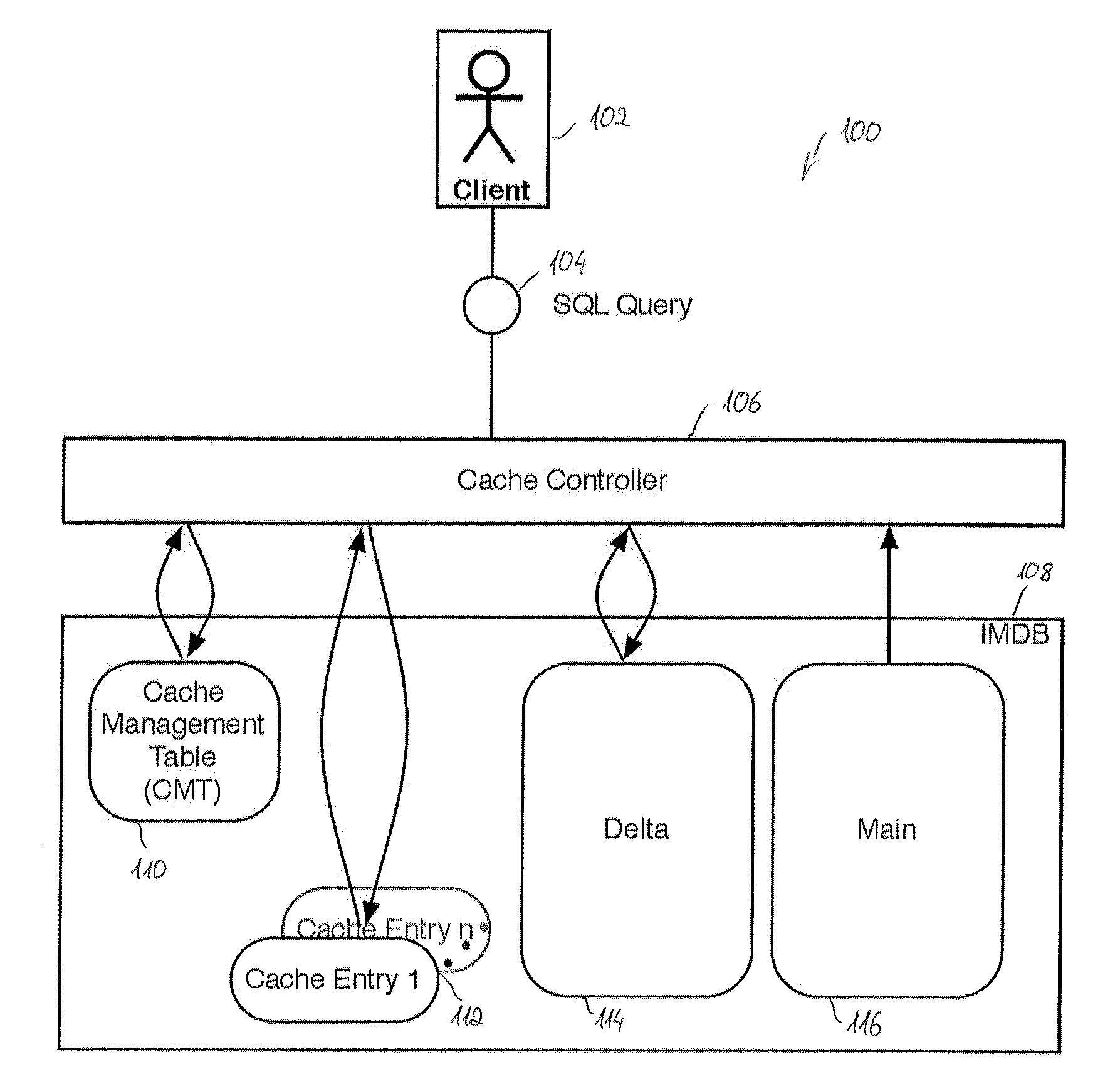

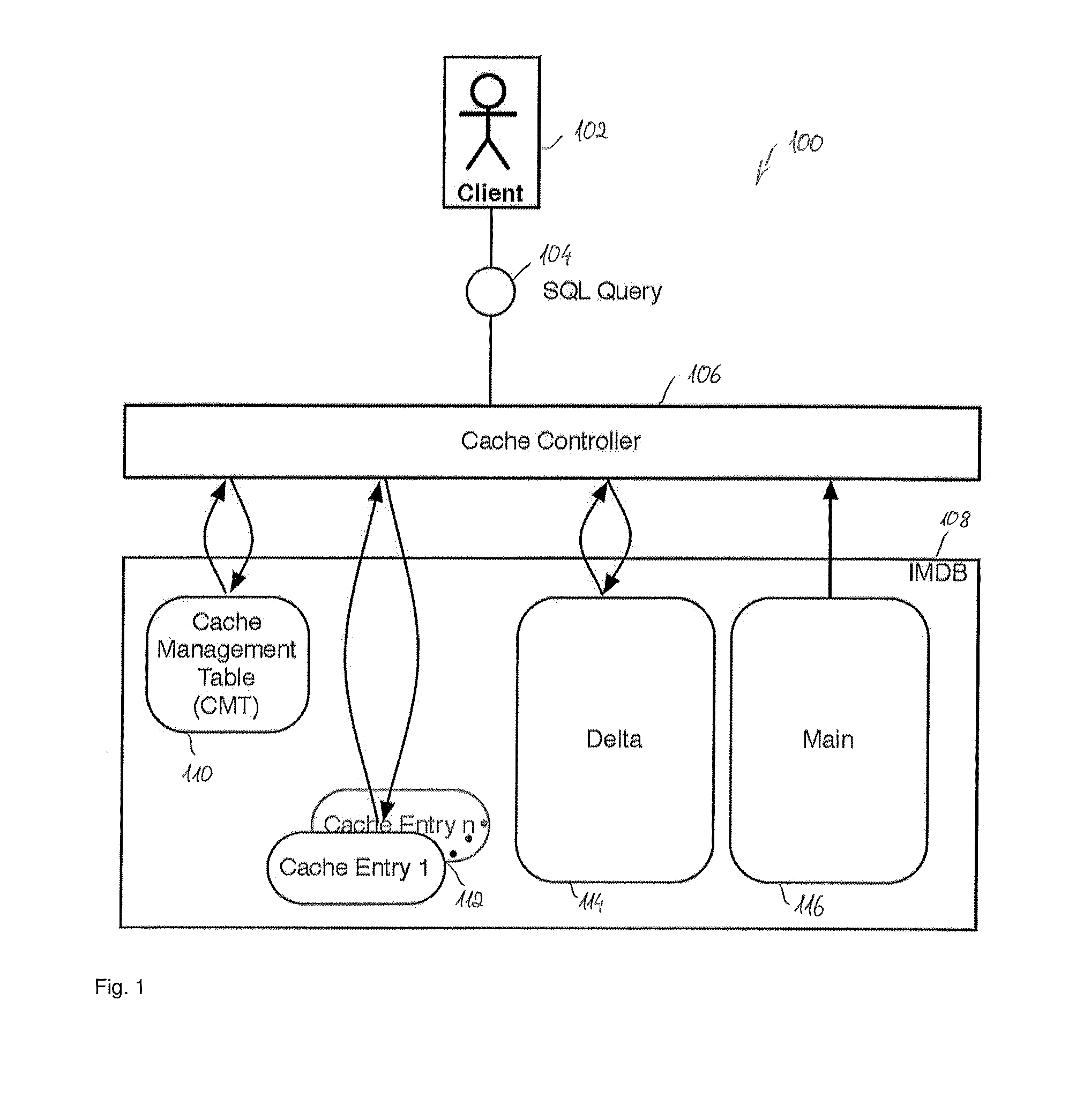

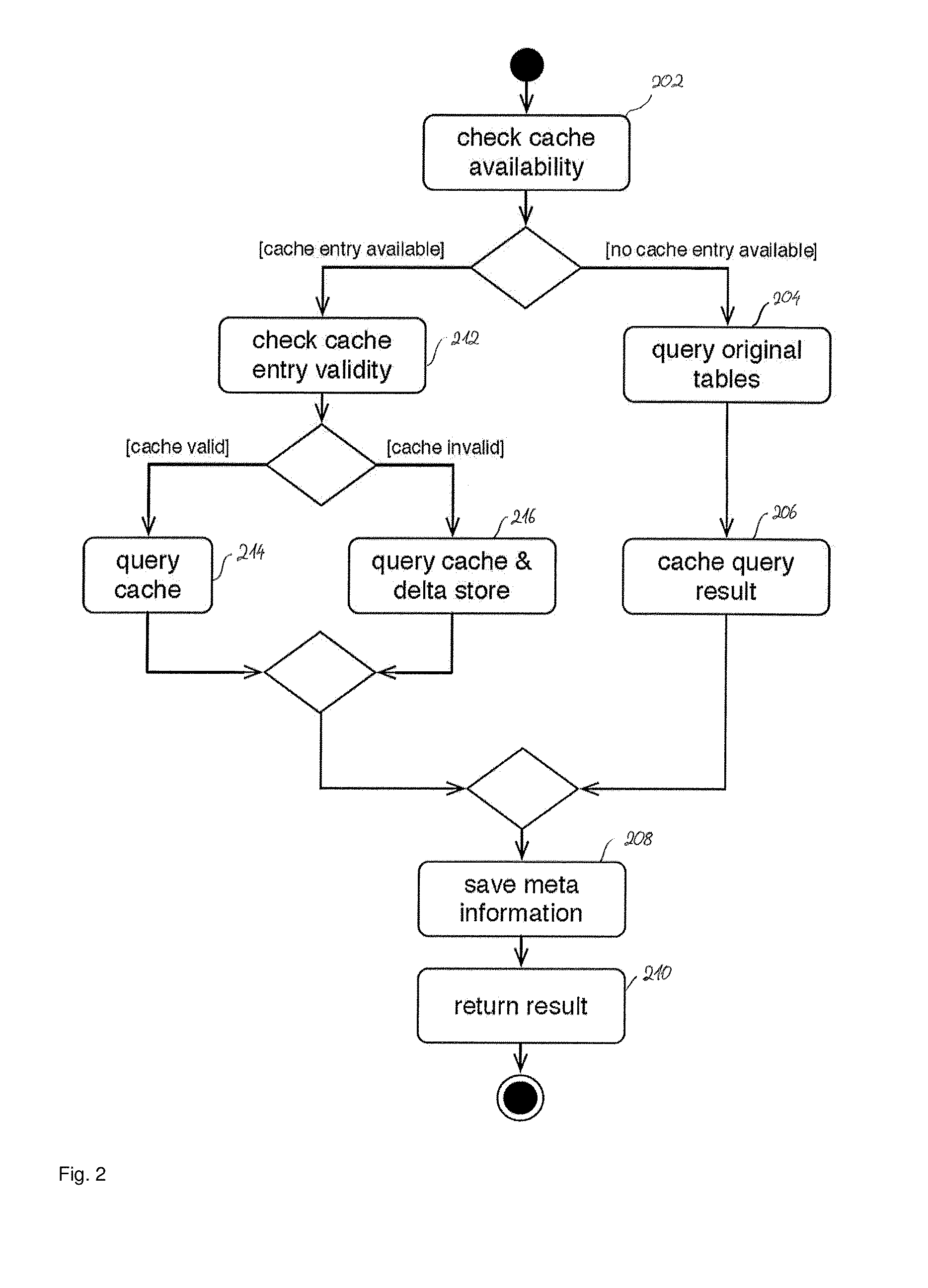

Aggregate query-caching in databases architectures with a differential buffer and a main store

ActiveUS20140310232A1Shorten the timeImprove welfareDigital data information retrievalDigital data processing detailsOn line analytical processingOnline transaction processing

The invention relates to a computer system for both online transaction processing and online analytical processing, comprising: a processor coupled to a database, the database comprising the database comprising: a main store (116) for storing records, a differential buffer (114) for receiving and buffering added or deleted or modified records, the differential buffer being coupled to the main store, a schema comprising records stored in the main store and records stored in the differential buffer, and a cache store (112) for caching a result of a query against the schema; and a cache controller (106) executable by the processor and communicatively coupled to the database, the cache controller being configured for: storing the result of the query in the cache store; receiving an analytical request; and determining, in response to the received request, an up-to-date result of the query by (216): accessing the cache store to obtain the cached result; determining the records of the schema that have been added or deleted or modified since the step of storing the cached result in the cache store on the basis of the records stored in the differential buffer; and incrementally deriving the up-to-date result from the cached result and from the records determined in the previous step.

Owner:HASSO PLATTNER INSTITUT FUR SOFTWARESYSTTECHN

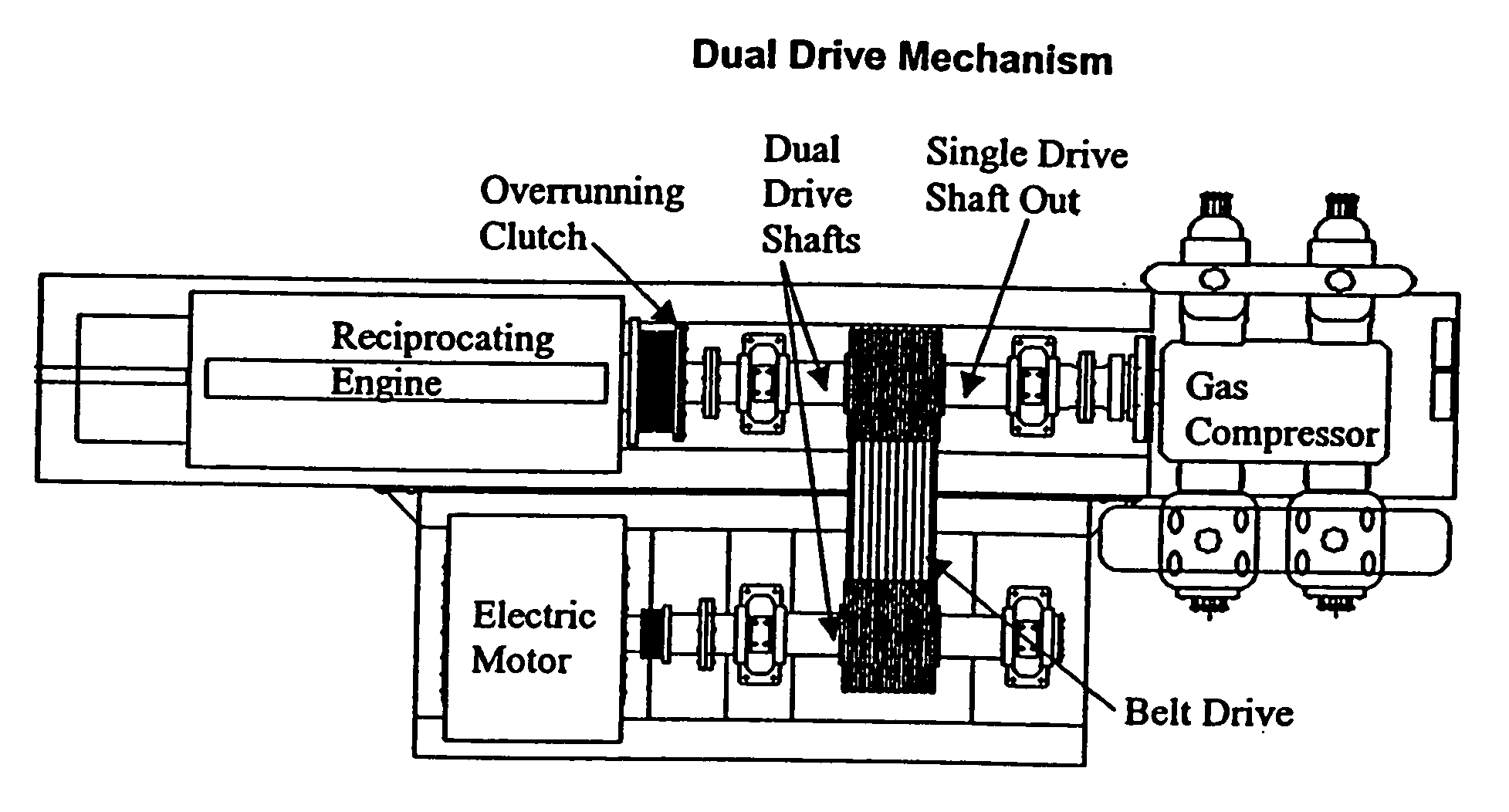

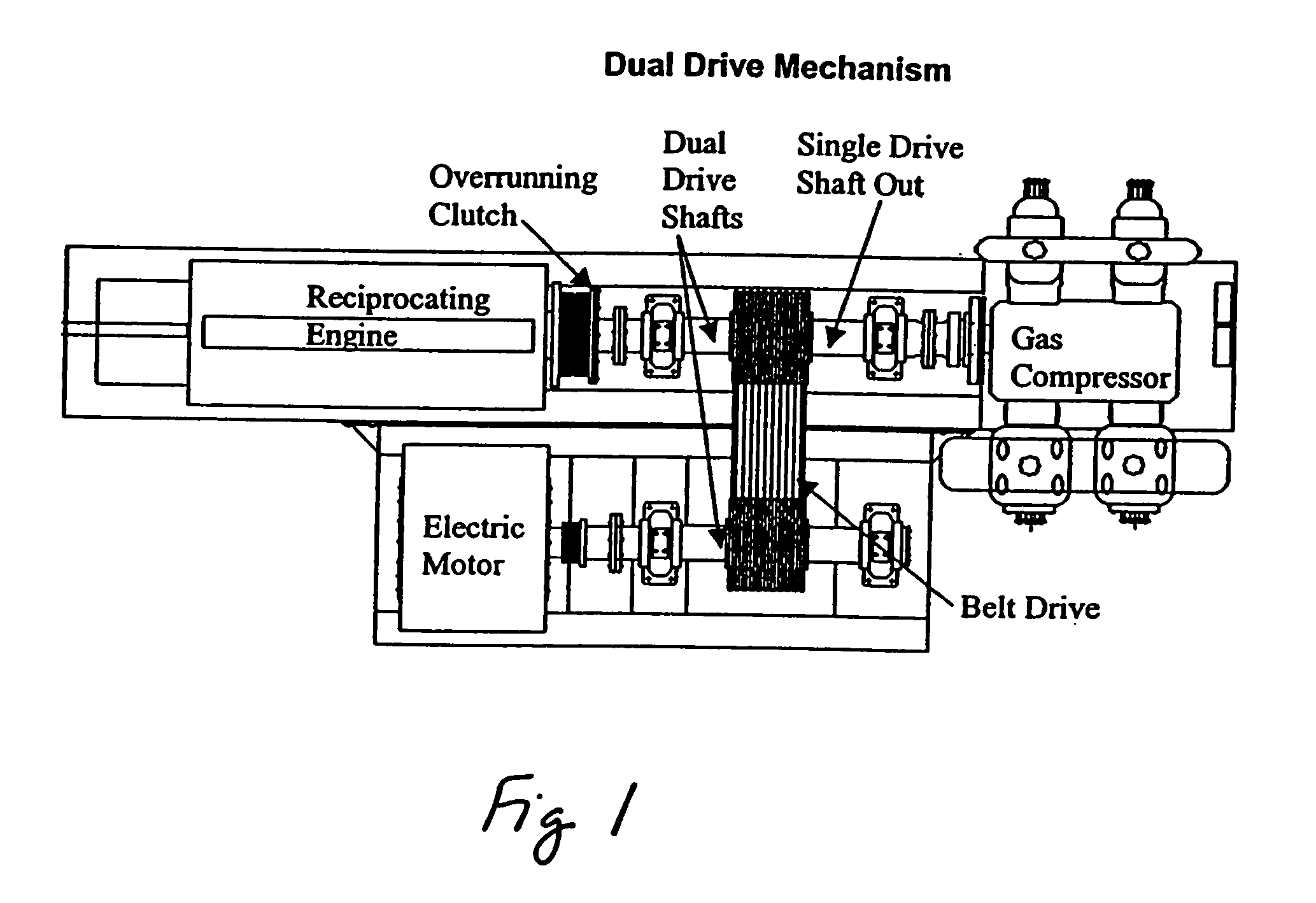

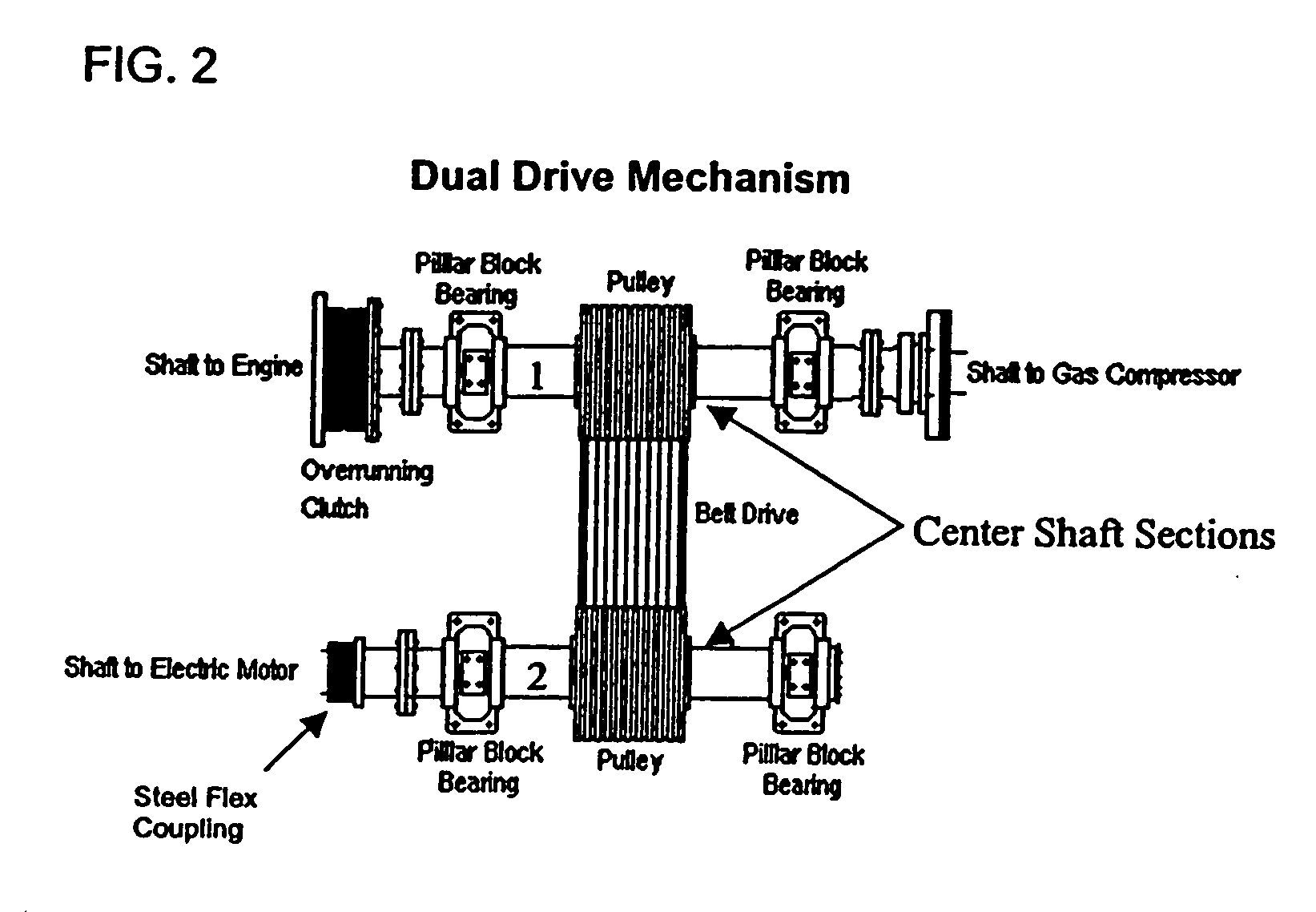

Gas compressor dual drive mechanism

InactiveUS20050196298A1Increase redundancyIncrease productivityPiston pumpsPositive-displacement liquid enginesGas compressorElectric power

A dual drive mechanism for a gas compressor includes a pulley and belt drive system to provide power to a gas compressor using either an electric motor or a reciprocating engine. The source of the power can be chosen by the operator of the system depending on a number of variables, including the cost of electric power.

Owner:MANNING JOHN B

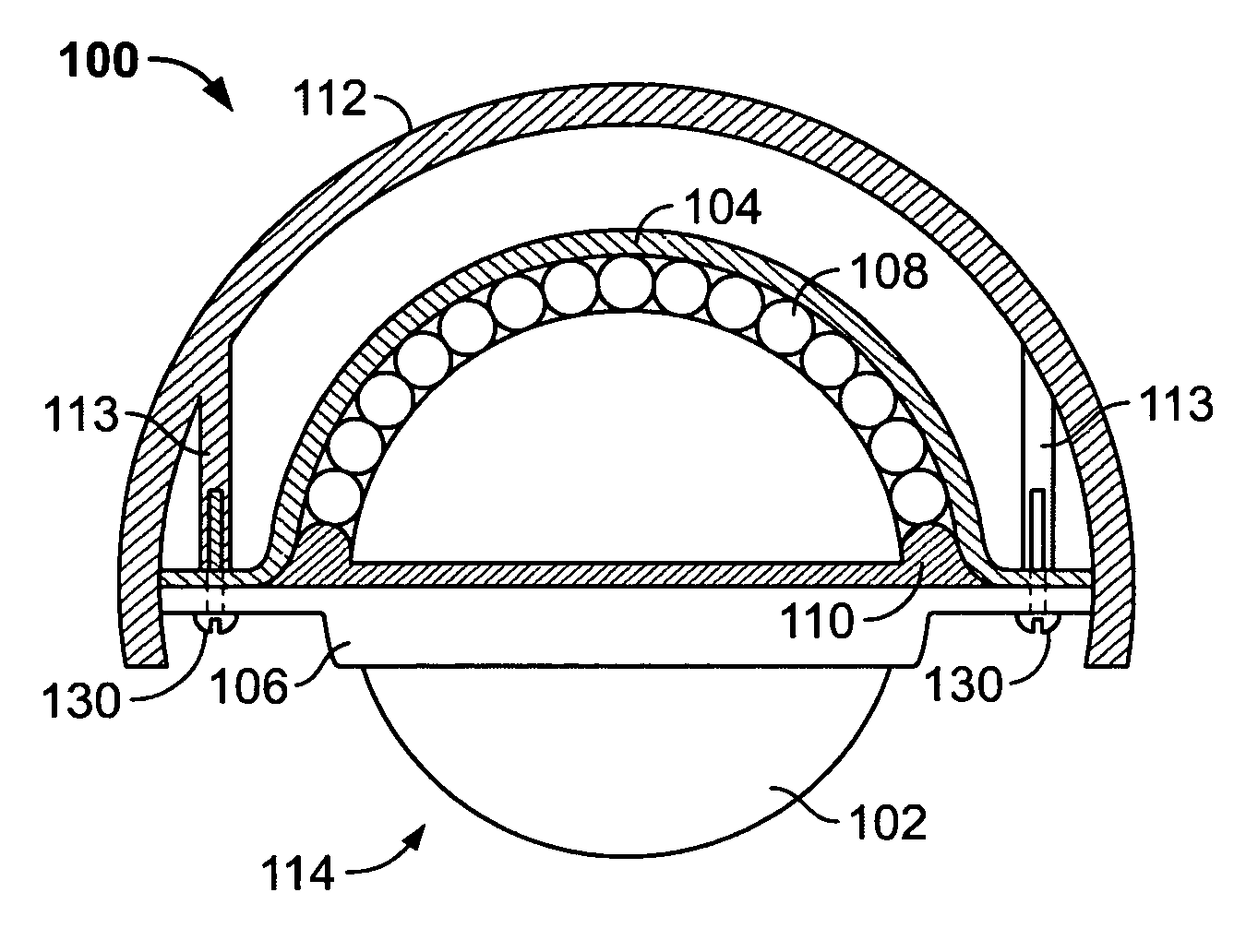

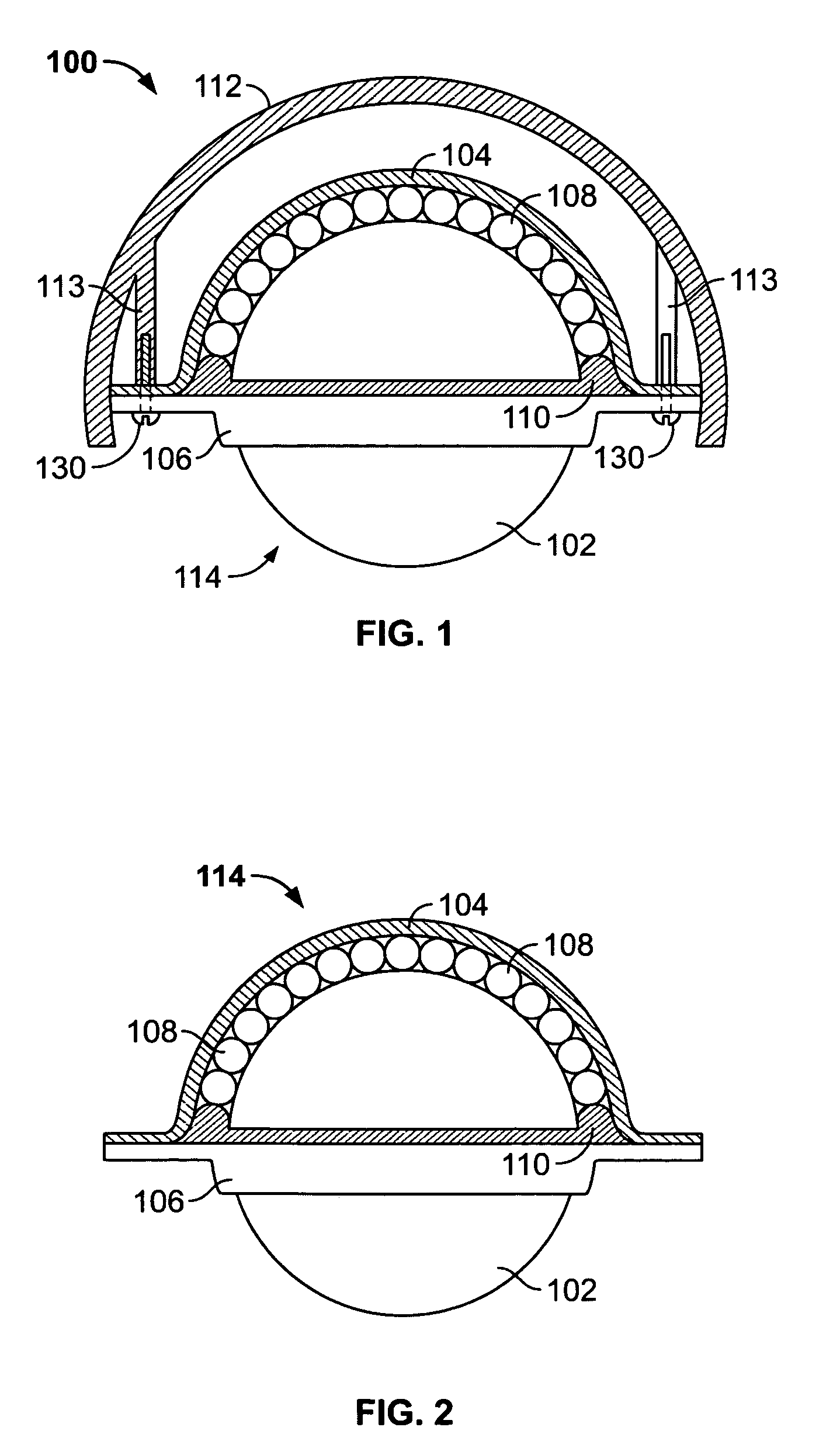

Apparatus and method for exercise using an omnidirectional roller

ActiveUS7621858B2Suitable weightIncrease valueMuscle exercising devicesMovement coordination devicesFree rotationBall bearing

The invention provides an exercise apparatus with a hemispherical support frame and a rigid ball mounted to the support frame with a low-friction bearing system in between the ball and the support frame so that the ball is freely rotatable in any direction. In one embodiment, the bearing system comprises a plurality of ball bearings and a retainer. The present invention also provides for an exercise system with two omnidirectional rolling apparatuses and a band that tethers the pair of apparatuses. The present invention also provides for methods of using the apparatus and system to perform isotonic exercises.

Owner:GOOD NATURED PROD

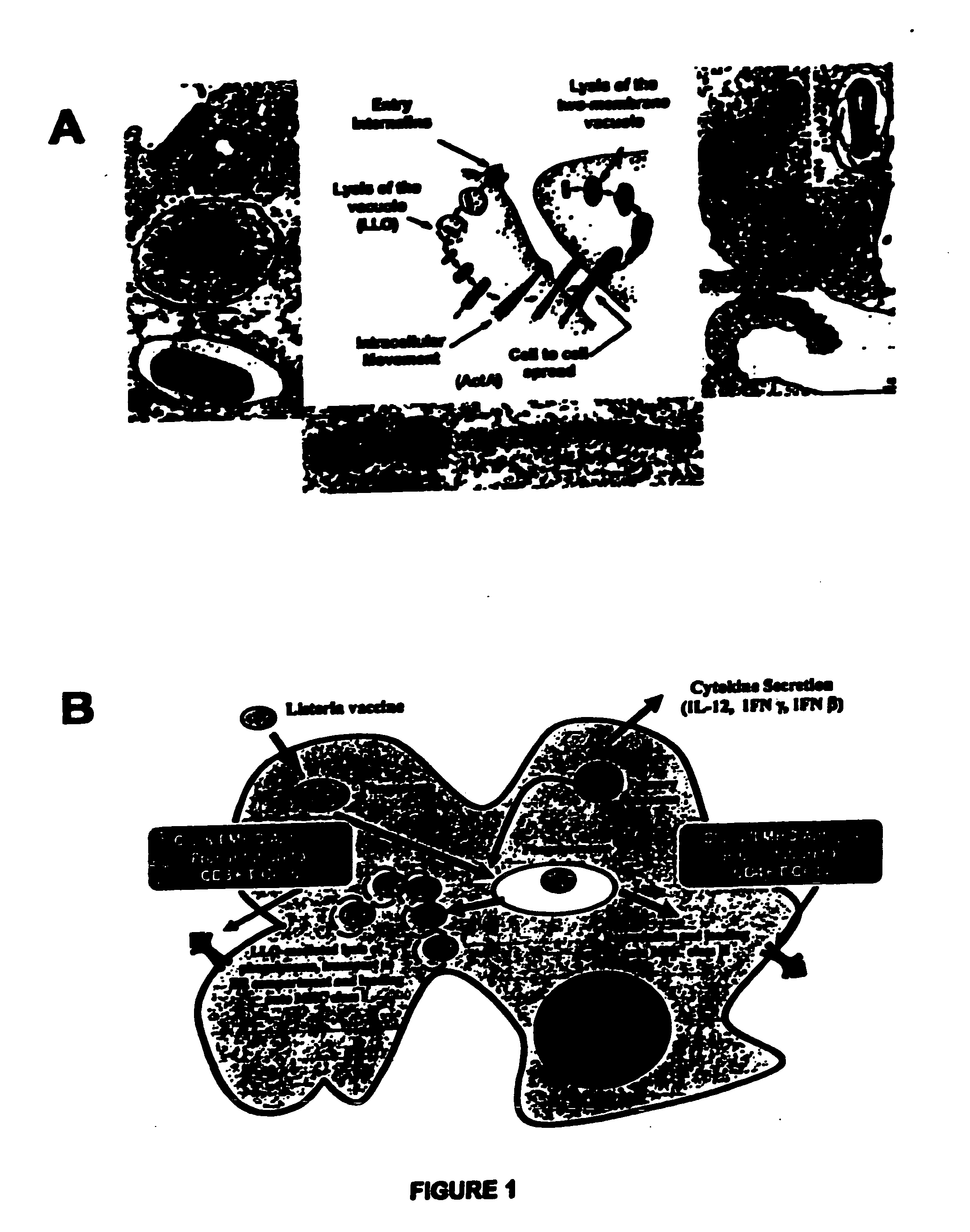

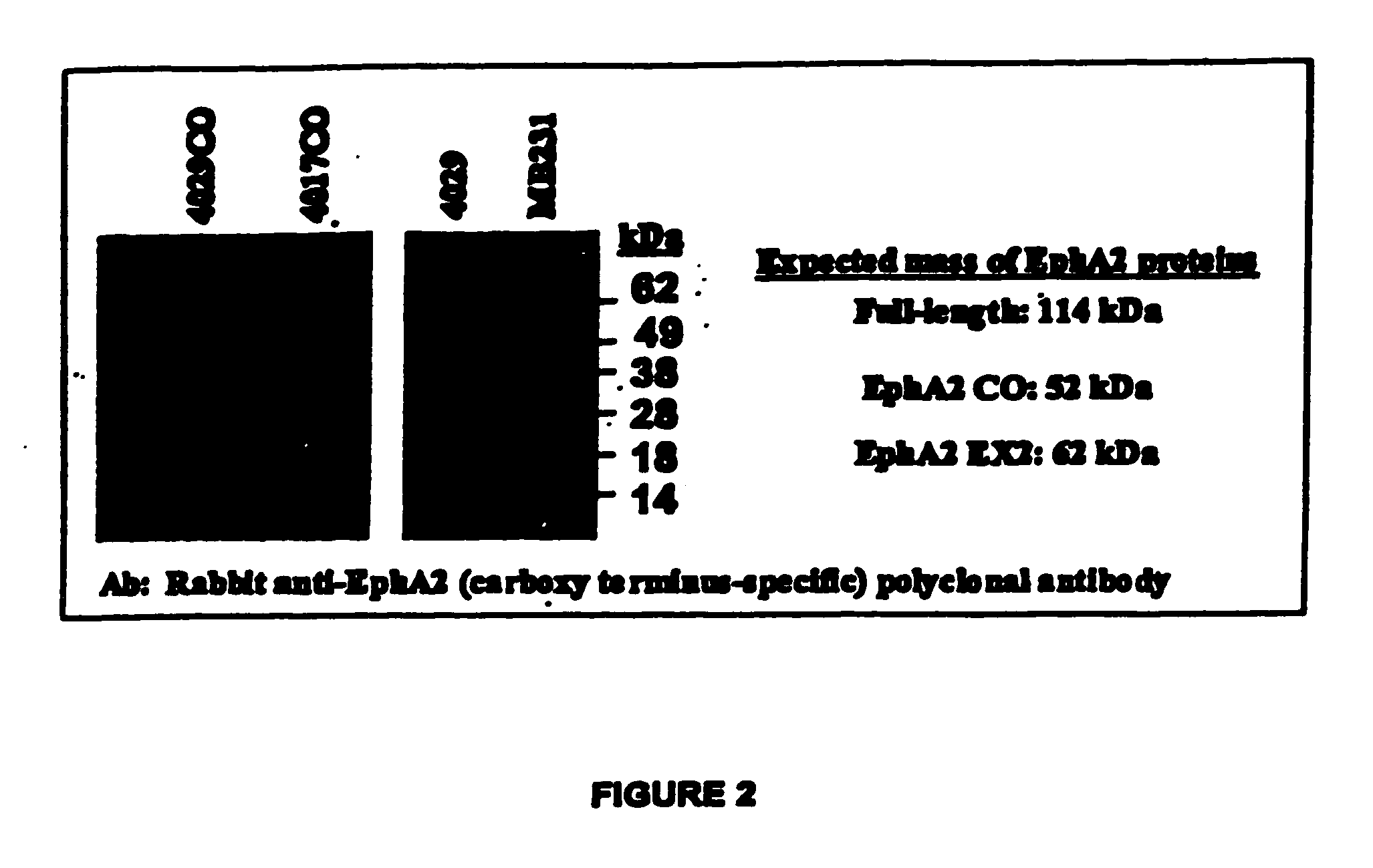

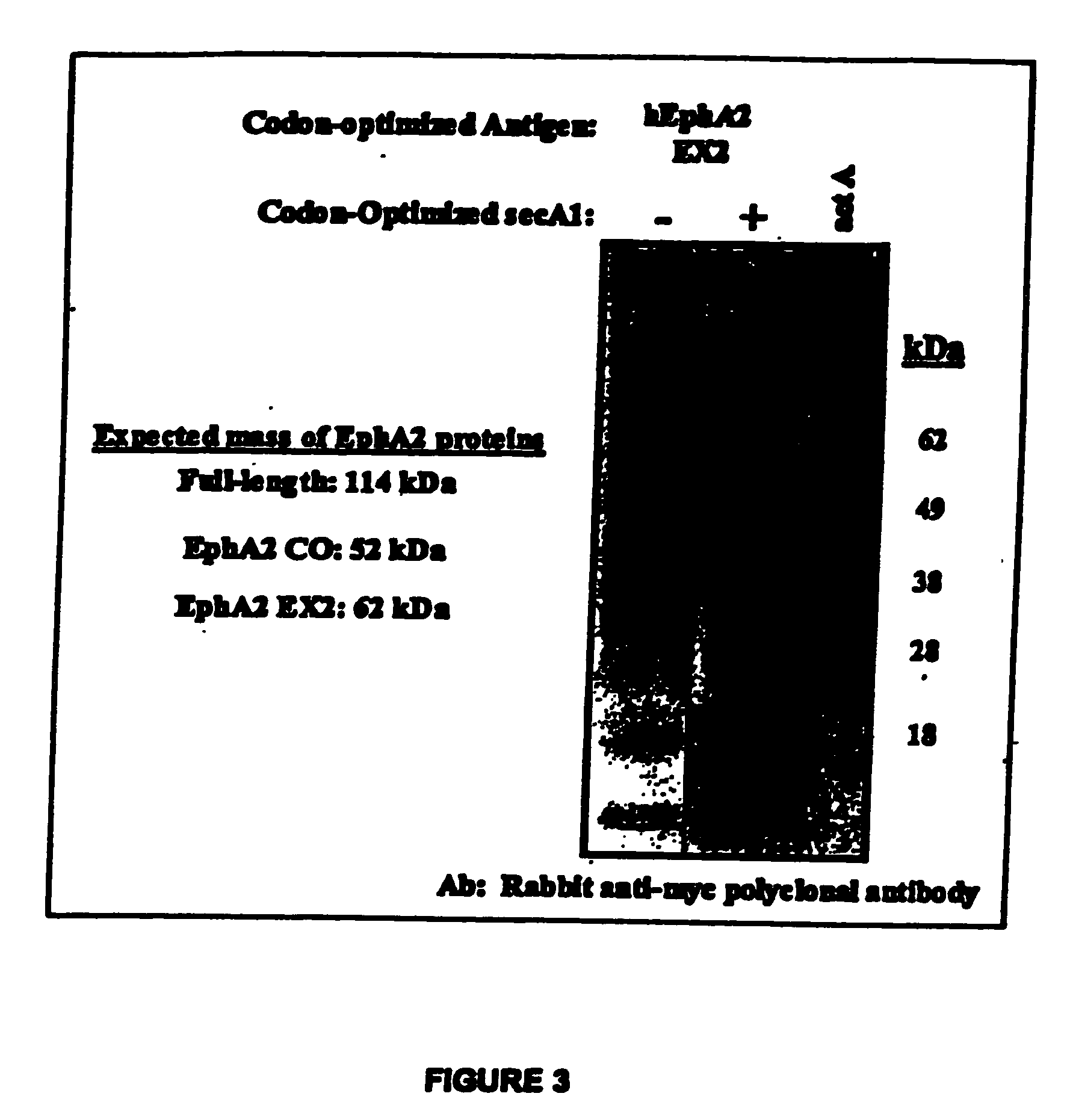

Listeria-based EphA2 vaccines

InactiveUS20050281783A1Beneficial therapeuticBeneficial prophylactic benefitBiocideSenses disorderCancer preventionCancer therapy

The present invention relates to methods and compositions designed for the treatment, management, or prevention of cancer, particularly metastatic cancer and cancers of T cell origin, and hyperproliferative diseases involving EphA2-expressing cells. The methods of the invention entail the use of a Listeria-based EphA2 vaccine. The invention also provides pharmaceutical compositions comprising one or more Listeria-based vaccines of the invention either alone or in combination with one or more other agents useful for cancer therapy. In certain aspects of the invention, the methods entail eliciting both CD4+ and CD8+ T-cell responses against EphA2 and / or EphA2-expressing cells.

Owner:CERUS CORP

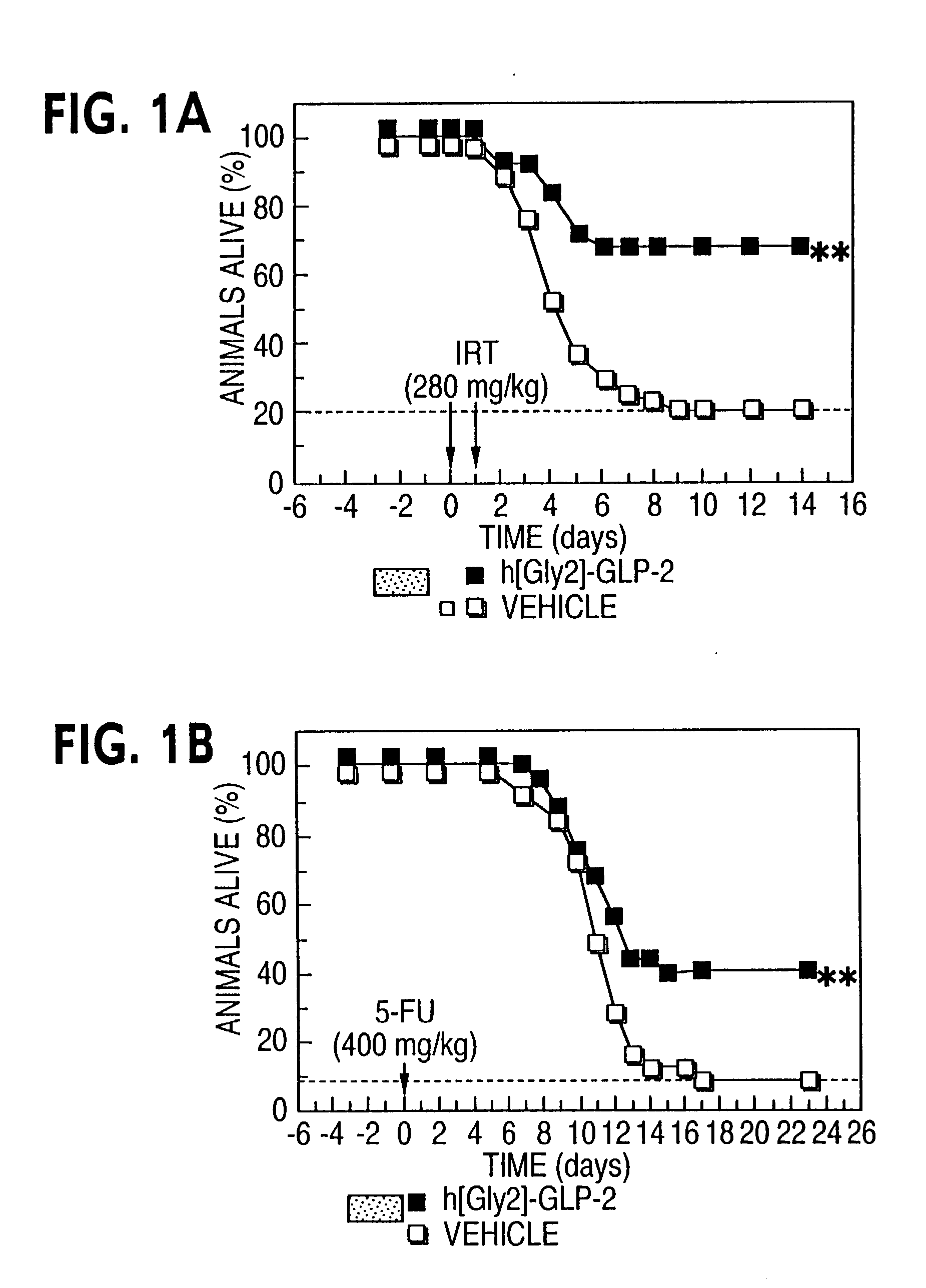

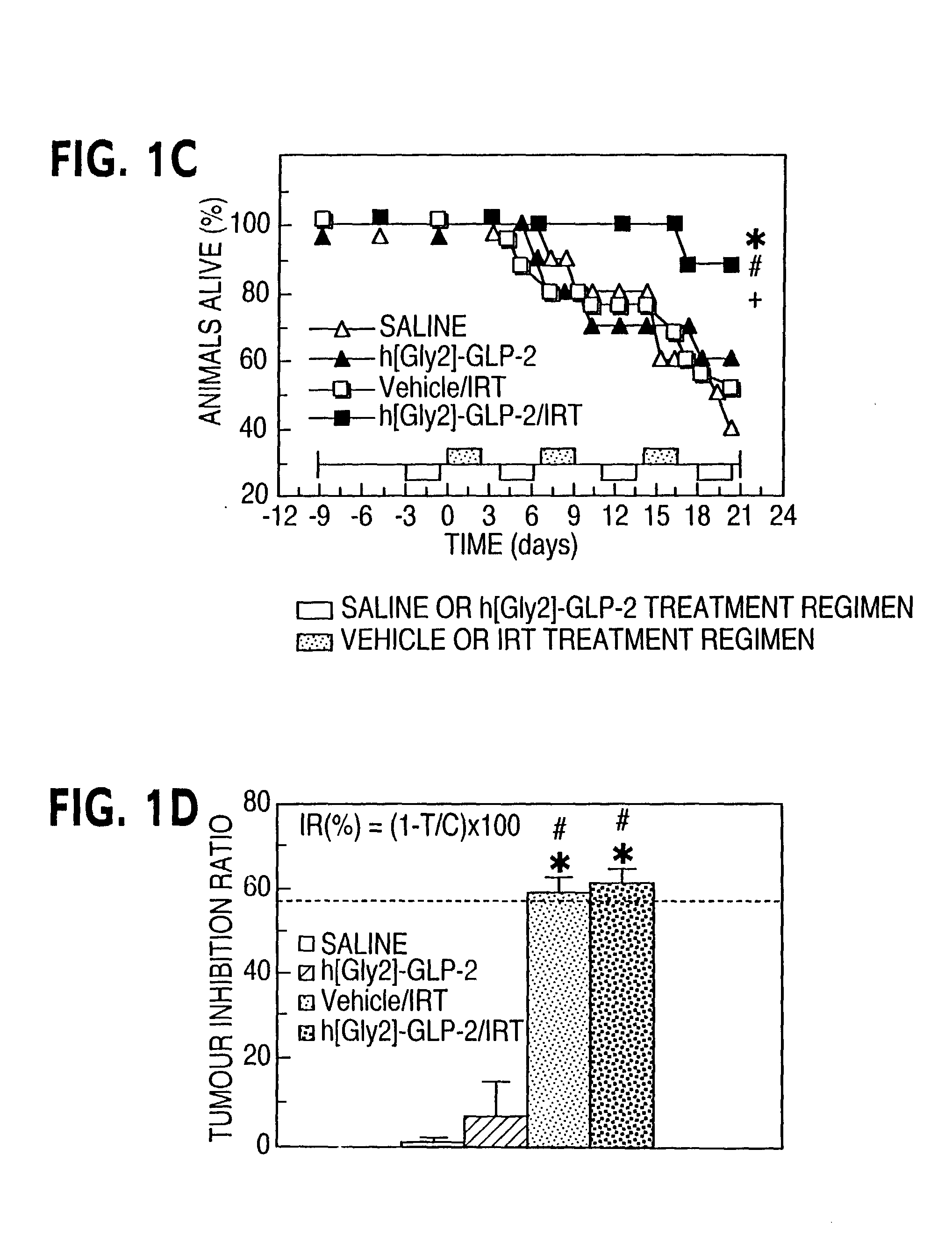

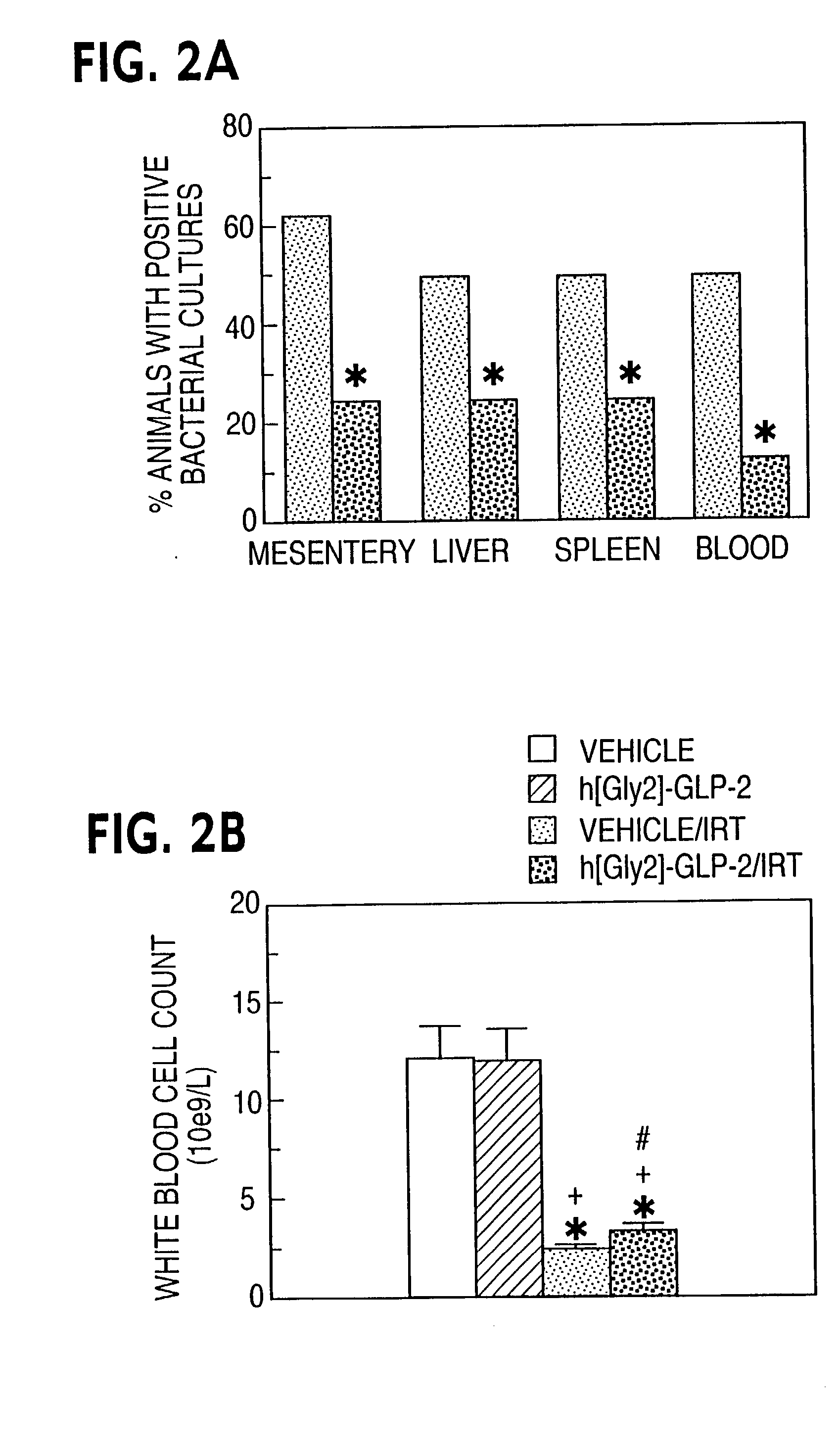

Chemotherapy treatment

InactiveUS20030040478A1Improve welfareImprove survivalBiocideOrganic active ingredientsRegimenApoptosis

This invention provides a treatment regimen that is effective in inhibiting chemotherapy-induced apoptosis and promoting cell survival. The invention also relates to a treatment regimen that confers resistance to caspase activation, thereby inhibiting caspase-mediated, proteolytic cleavage of functional cellular enzymes. Specifically, subjects undergoing chemotherapy are first exposed to a pretreatment regimen. Under this regimen, a GLP-2 receptor activator, such as h[GLY2]-GLP2, is administered each day for a predetermined beneficial period, e.g., three consecutive days. Approximately about 1 week following pretreatment, the subjects are exposed to an appropriate chemotherapy treatment regimen. Pretreatment with a GLP-2 receptor activator followed by administration of chemotherapeutic agents improves cell survival, reduces bacteremia, attenuates epithelial injury, and inhibits cellular apoptosis. Moreover, it does not impair the effectiveness of chemotherapy nor result in weight loss. The anti-apoptotic effects of GLP-2 may be useful in the reduction of cytoxicity and bacterial infection induced by chemotherapeutic agents.

Owner:1149336 ONTARIO

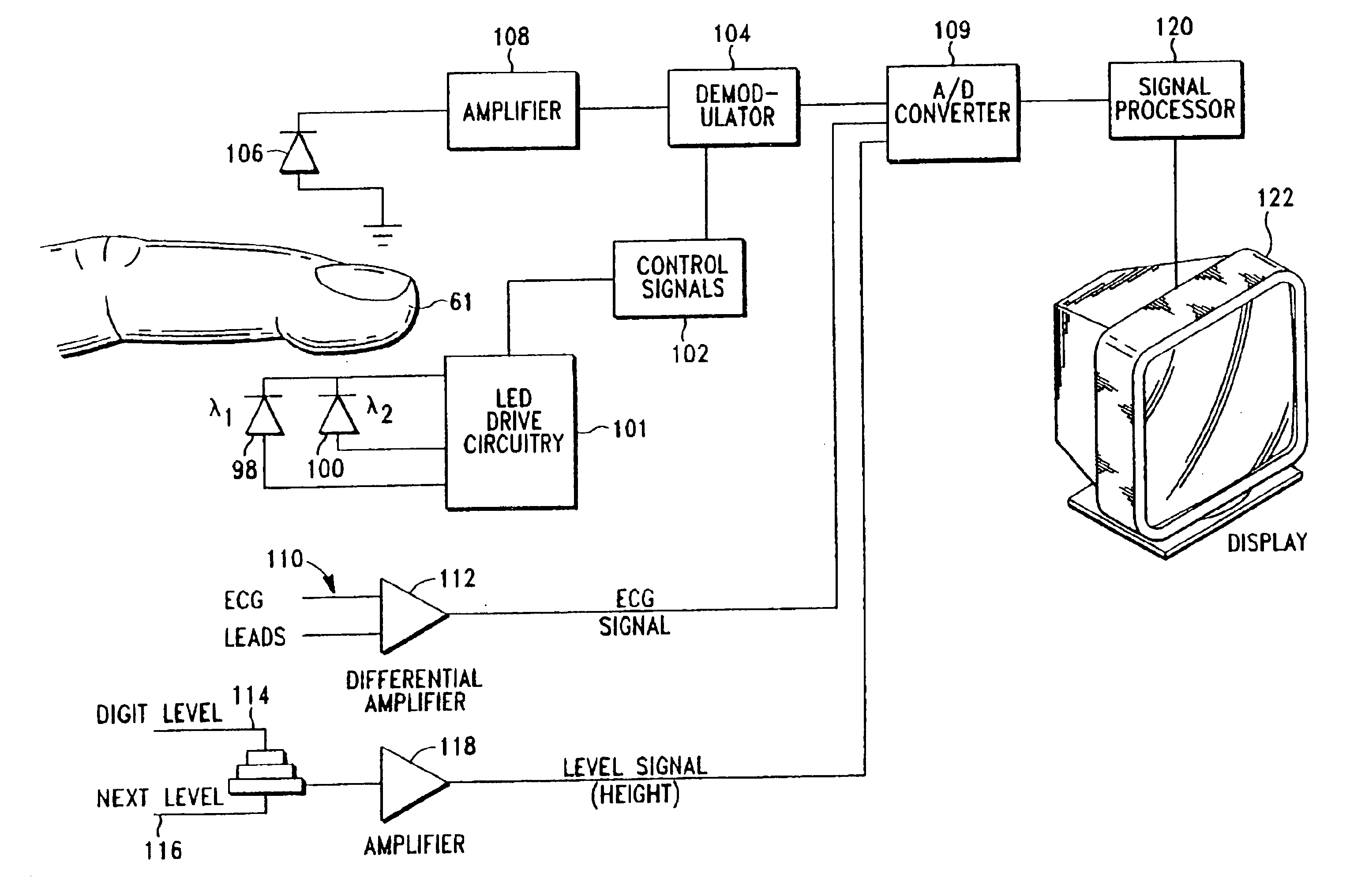

Device and method for noninvasive continuous determination of physiologic characteristics

InactiveUS6921367B2Eliminate needEasy to take care ofElectrocardiographyEvaluation of blood vesselsHydrostatic pressureArrival time

The invention comprises devices for noninvasively monitoring physiological characteristics of a patient's blood. Generally, probes having radiation emitters and detectors are used to determine absorbance of blood within the patient's tissue to determine various blood parameters. The device also has either a position sensor for determining the position of the probe with respect to the patient's heart or a movement generator for altering the position of the probe with respect to the patient's heart. The invention also comprises methods for noninvasively monitoring the physiological characteristics. In one embodiemnt, induced positional changes create differential hydrostatic pressures to facilitate measurement of blood parameters by absorbance. In a second embodiment, delays in pulse arrival times in coupled organs or members on opposite sides of the body are measured to determine cardiac output. The two methods are such that they can advantageously be used together.

Owner:WOOLSTHORPE TECH

Packaged product having a reactive label and a method of its use

InactiveUS20110140844A1Improve overall senseImprove welfareStampsContainer decorationsReflectivityPersonalization

A reactive label is capable of reacting with a shopper that peruses the label while considering the purchase of the labeled product. The label includes sensors and a display unit and is powered by incorporated batteries or photovoltaic cells. The sensors can include a timer that provides the shopper with additional information from a ROM by displaying it sequentially on an LCD screen or the like. The sensors can also include a sensor such as an optical sensor that measures such factors as hair reflectance and can inform the shopper as to the suitability of the product (if, for example, it is a shampoo) for their personal use. The reactive label gives the shopper a previously unattainable sense of product personalization and will thereby enhance a sense of loyalty to and confidence in the product.

Owner:THE PROCTER & GAMBLE COMPANY

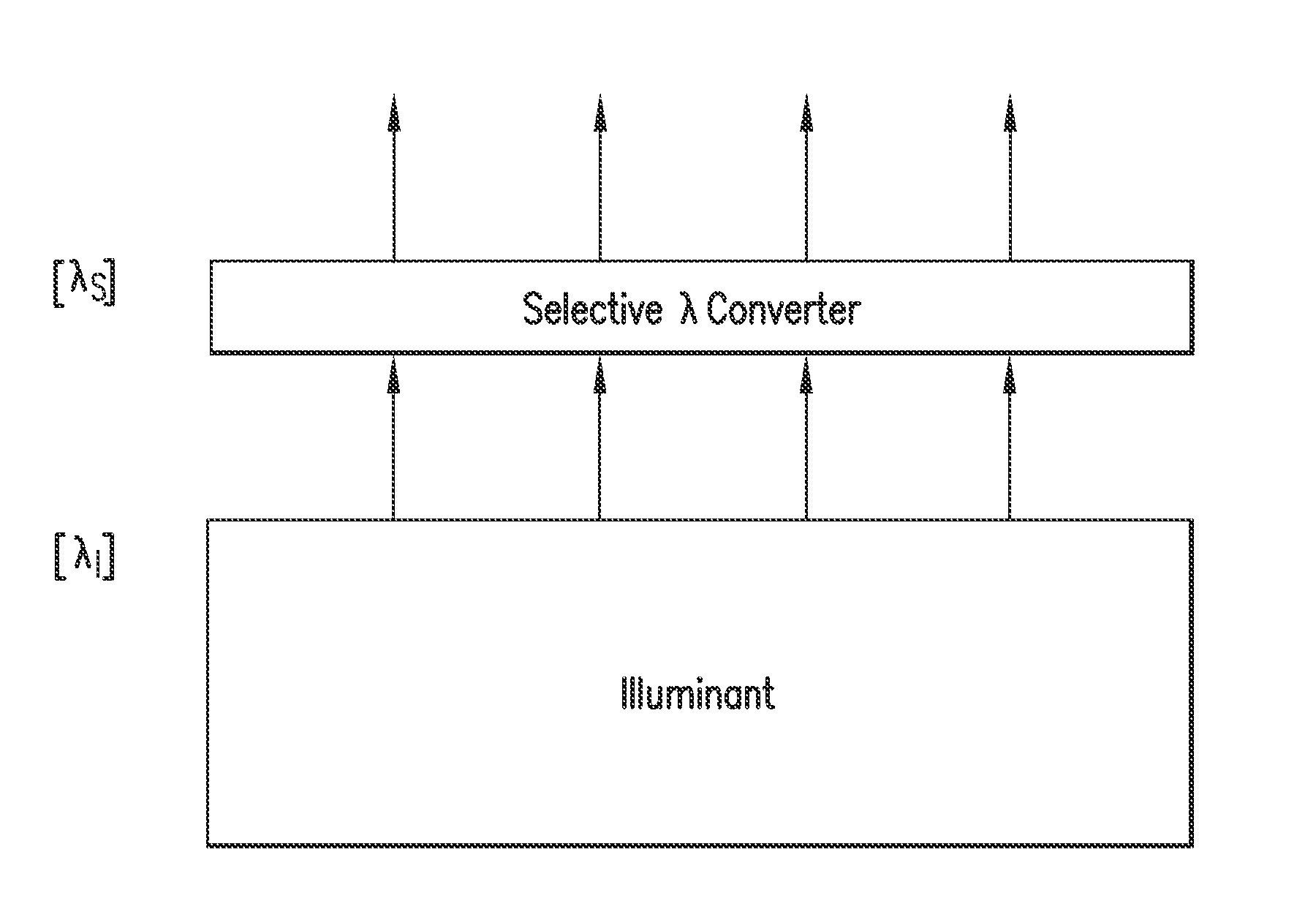

Light Sources Adapted to Spectral Sensitivity of Diurnal Avians and Humans

ActiveUS20110228515A1Improve welfareImprove lifetime developmentElectrical apparatusAnimal housingLight-emitting diodeVisual perception

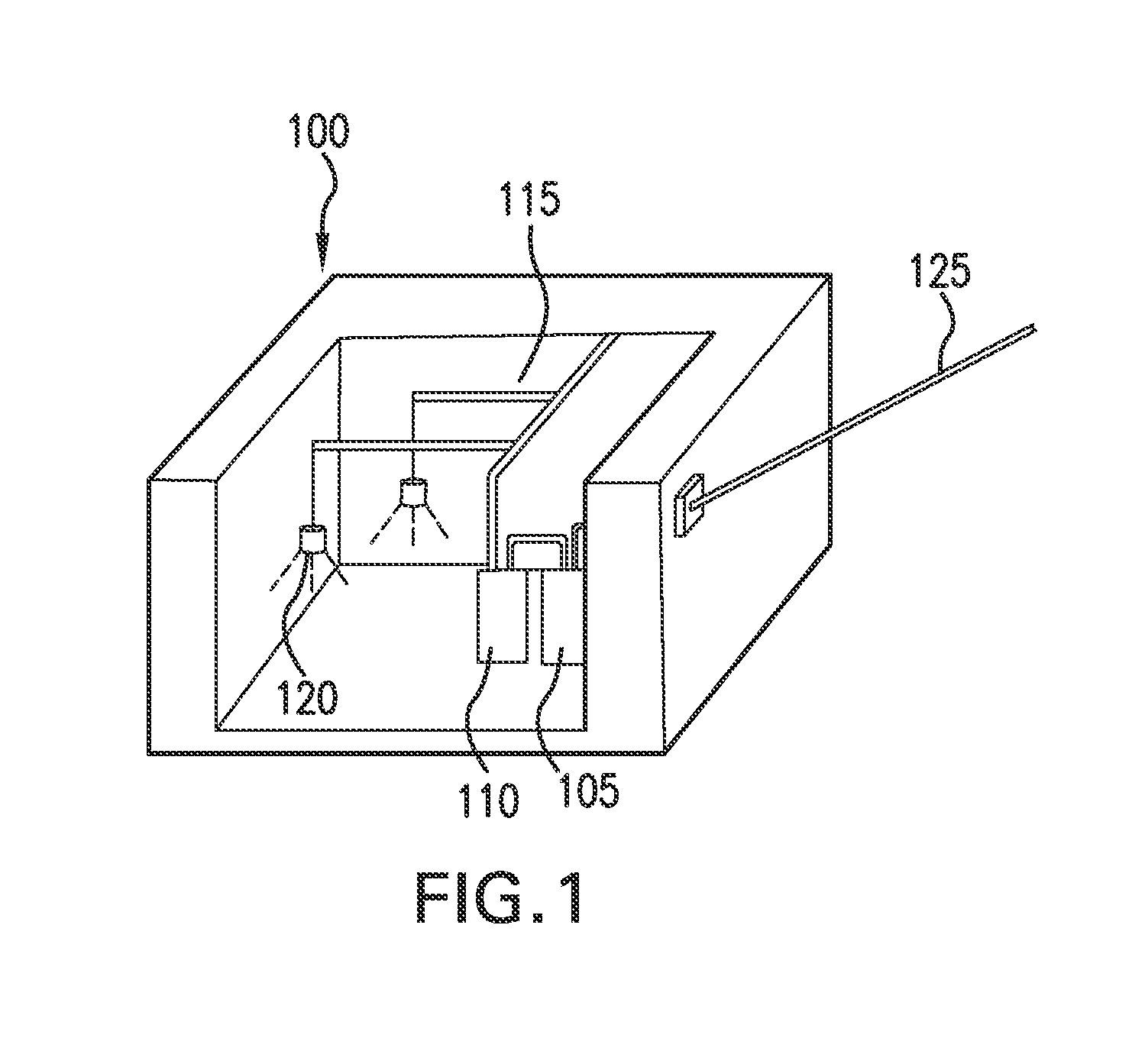

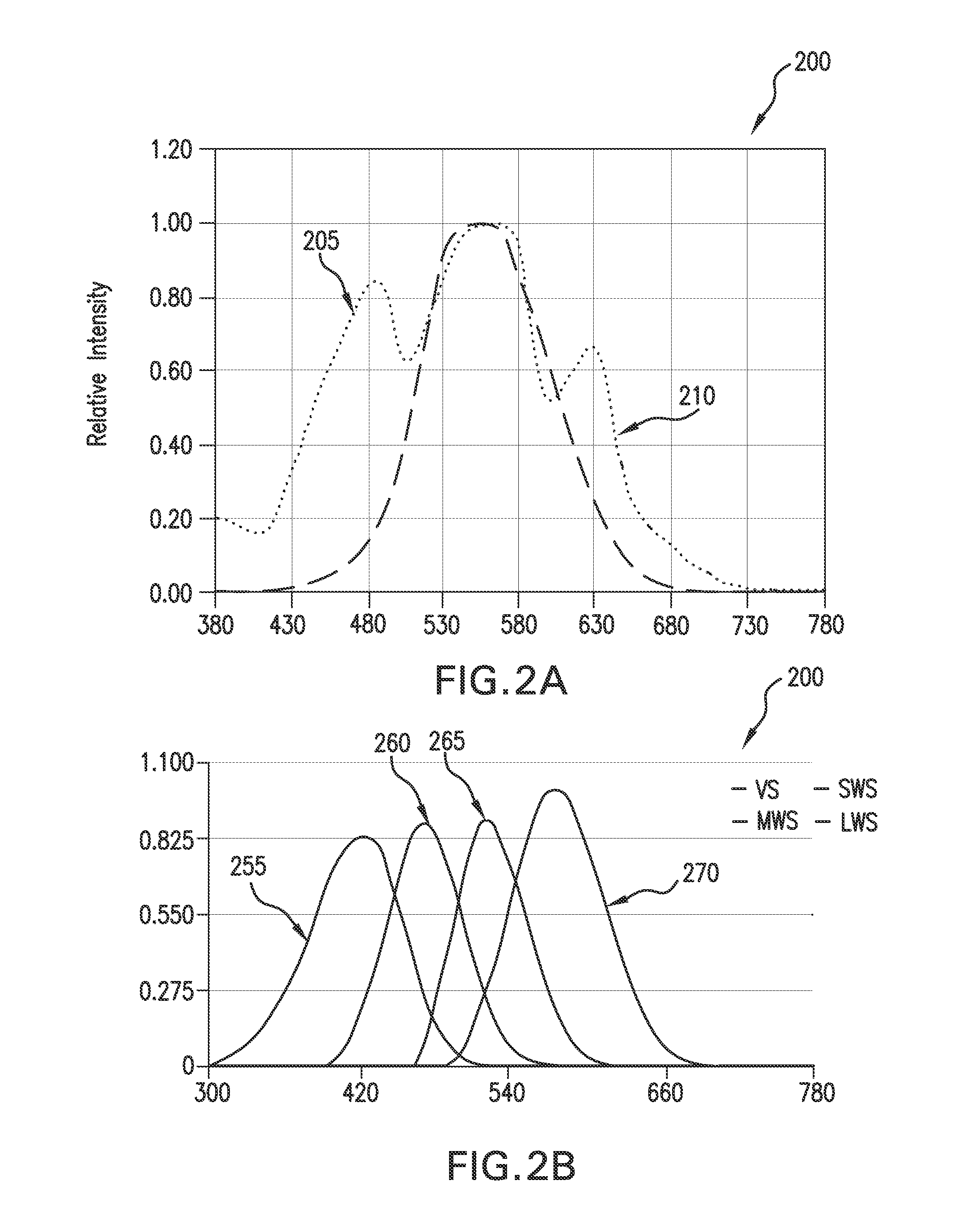

Various apparatus and associated methods involve a light source that provides light at wavelengths that substantially correlate to local maxima in the spectral sensitivity of a diurnal avian. In an illustrative example, the light source may output light primarily in wavelength bands that are not substantially absorbed by colored oil droplets and / or visual pigment in at least one type of cone in the eye of a diurnal avian. In some embodiments, the light source may include a light-emitting diode (LED) light source. Exemplary light sources may output spectral components to illuminate diurnal avians with local maxima of intensity at wavelengths that substantially correspond to local maxima in a spectral sensitivity visual response characteristic of the diurnal avians.

Owner:SIGNIFY NORTH AMERICA CORP

Sanitary napkins capable of taking complex three-dimensional shape in use

ActiveUS8211078B2Easy to handleImprove welfareSanitary towelsBaby linensThree dimensional shapeBiomedical engineering

Owner:PROCTER & GAMBLE CO

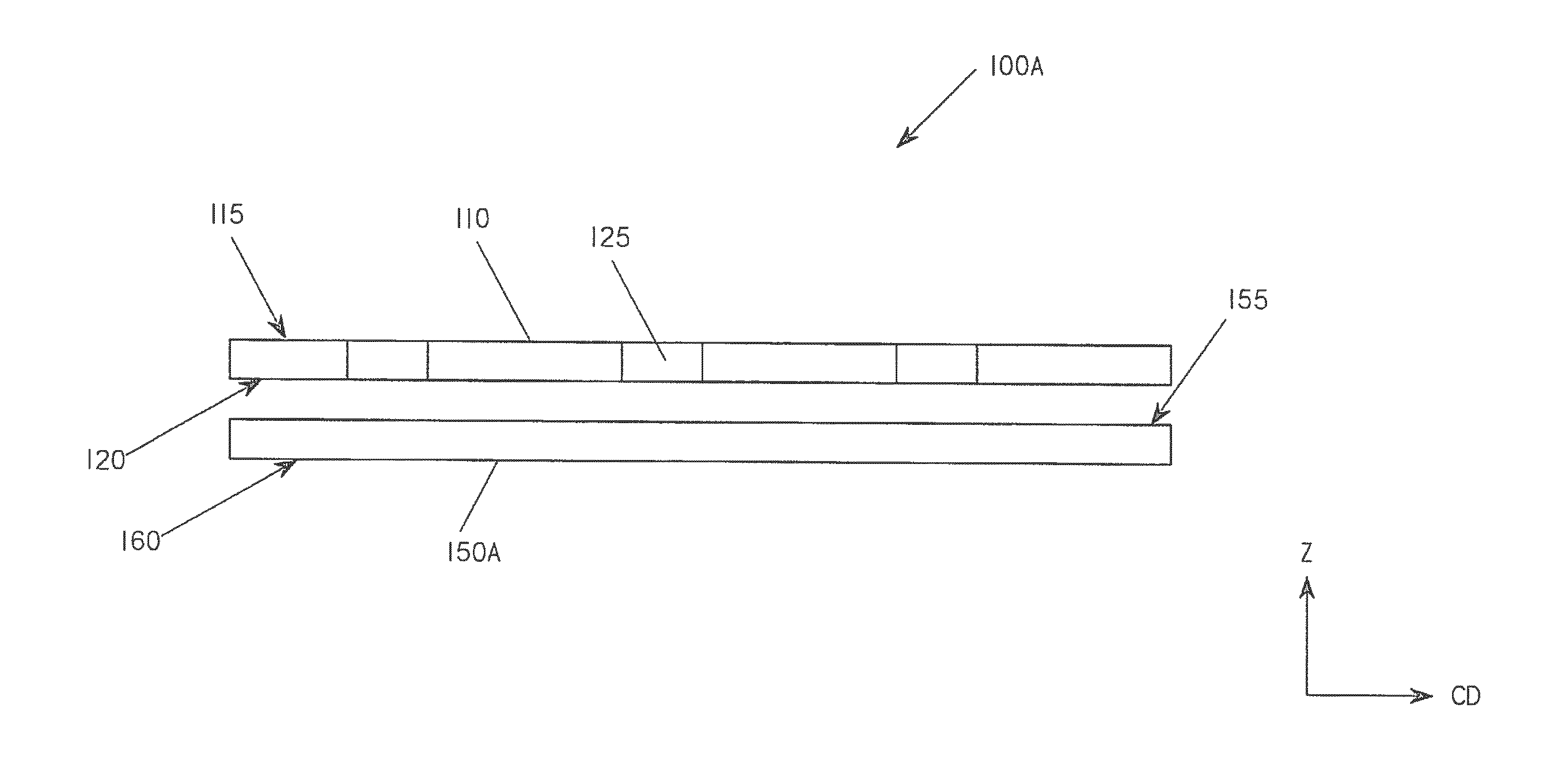

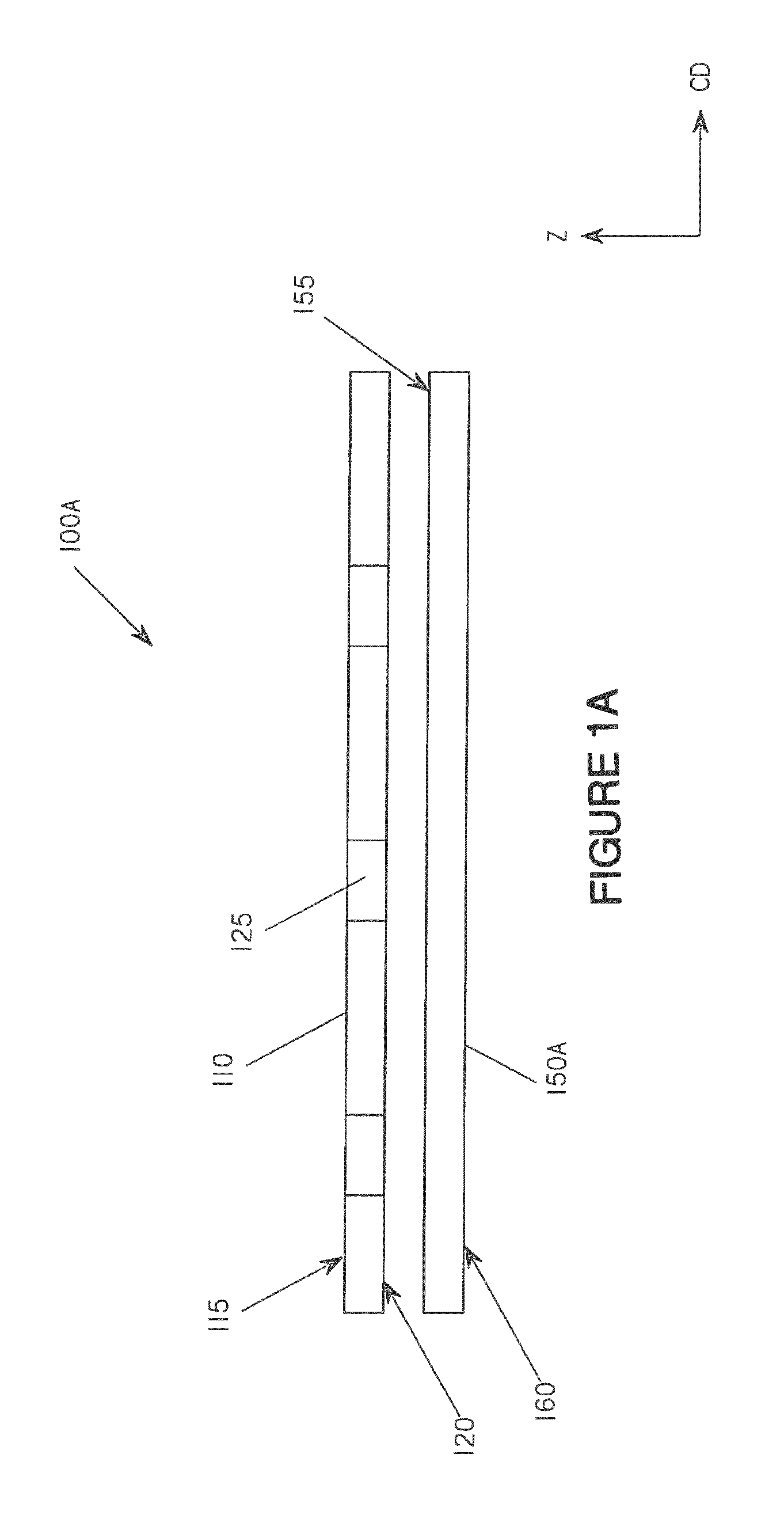

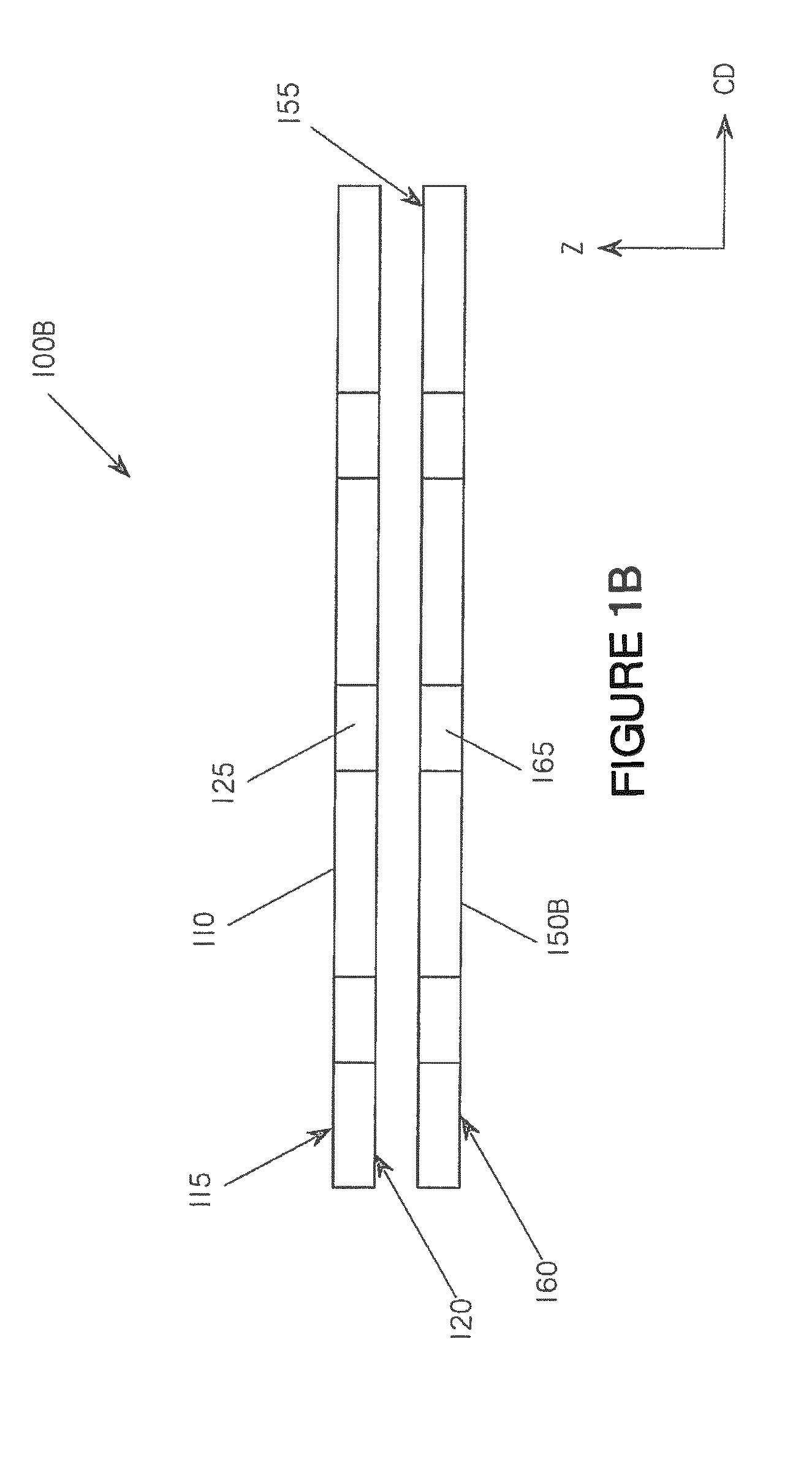

Nonwoven Web

InactiveUS20160067118A1Soft touchGood blurring/masking benefitPersonal careSynthetic resin layered productsFiberEngineering

Owner:THE PROCTER & GAMBLE COMPANY

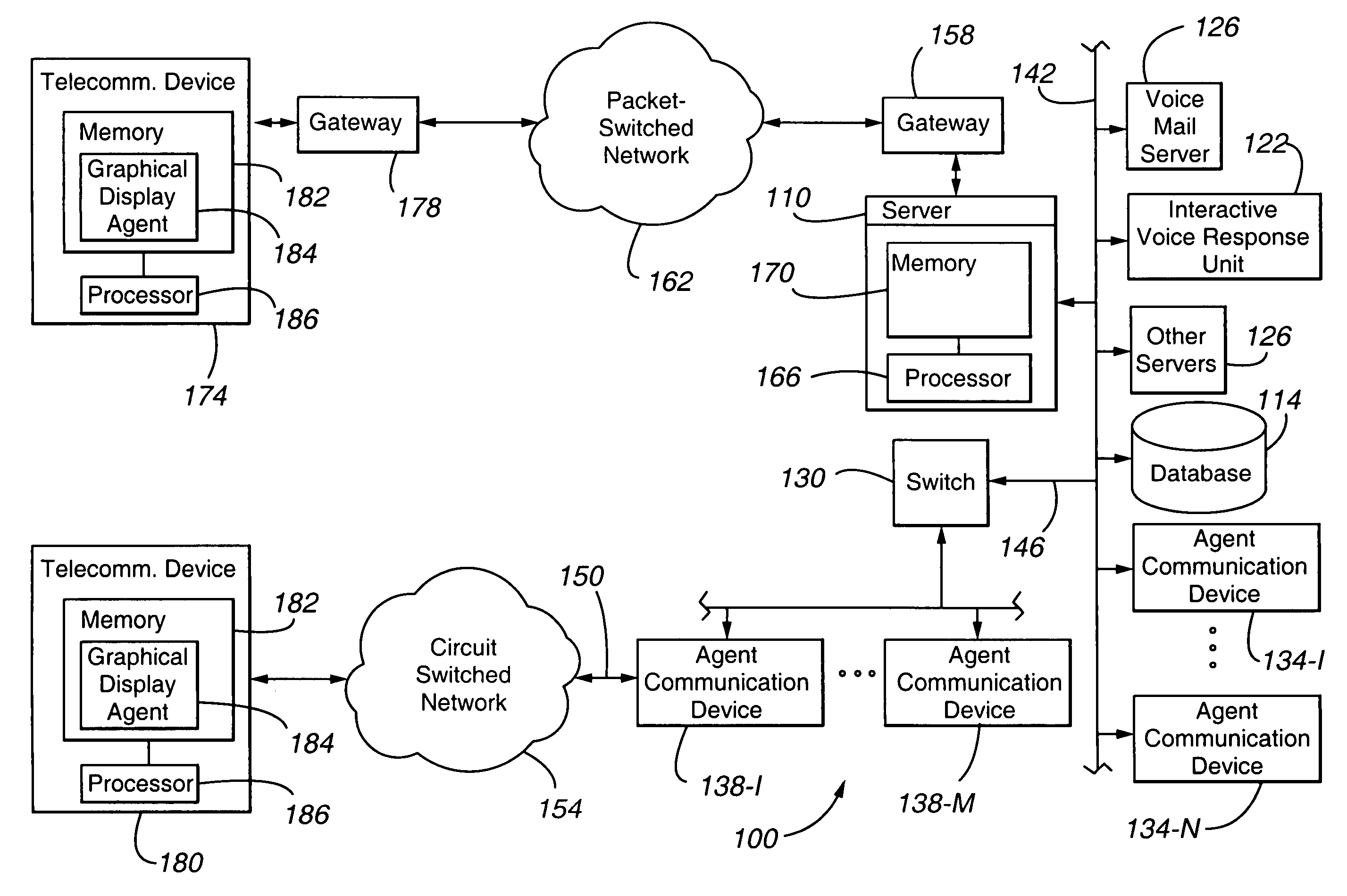

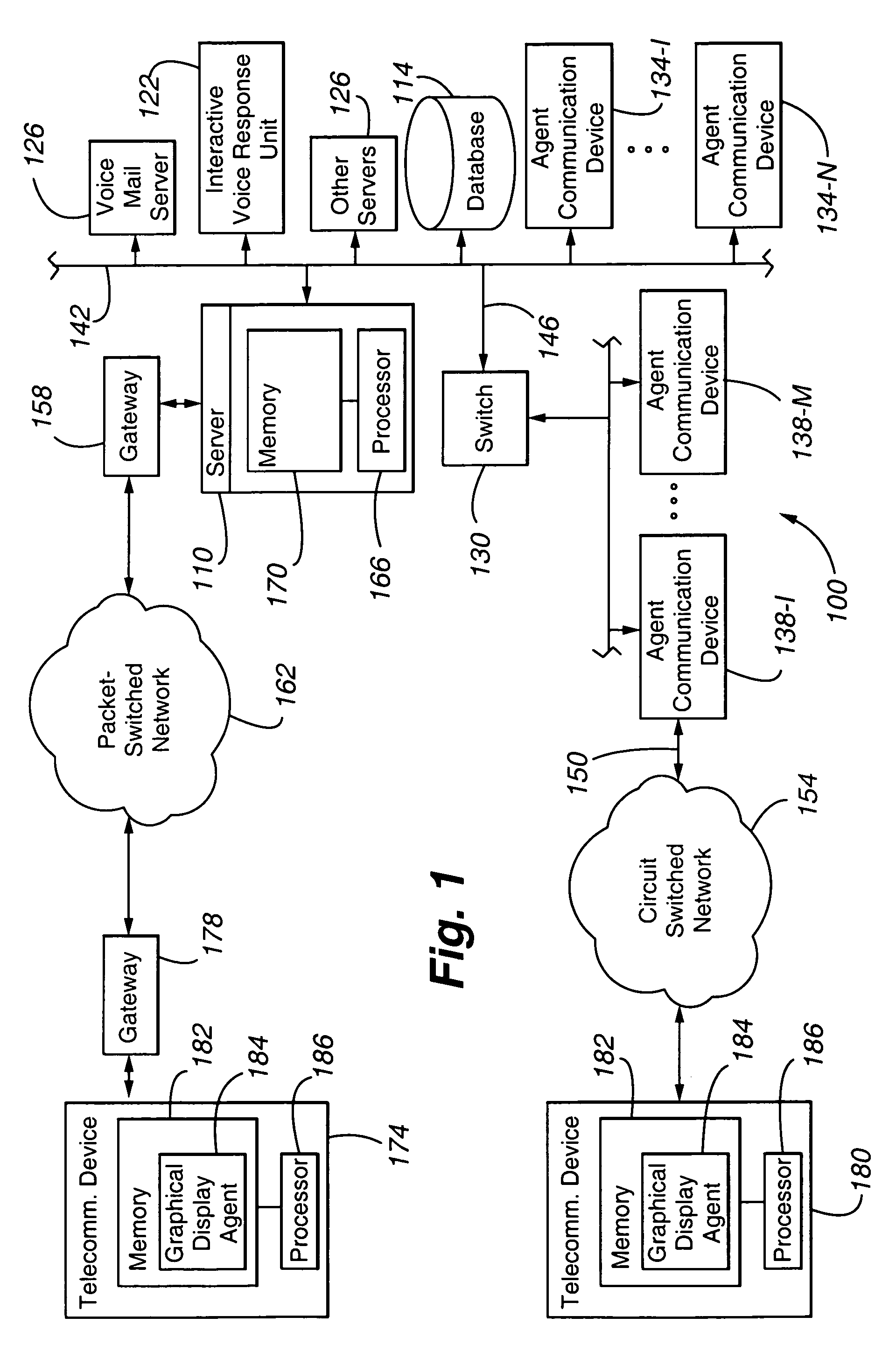

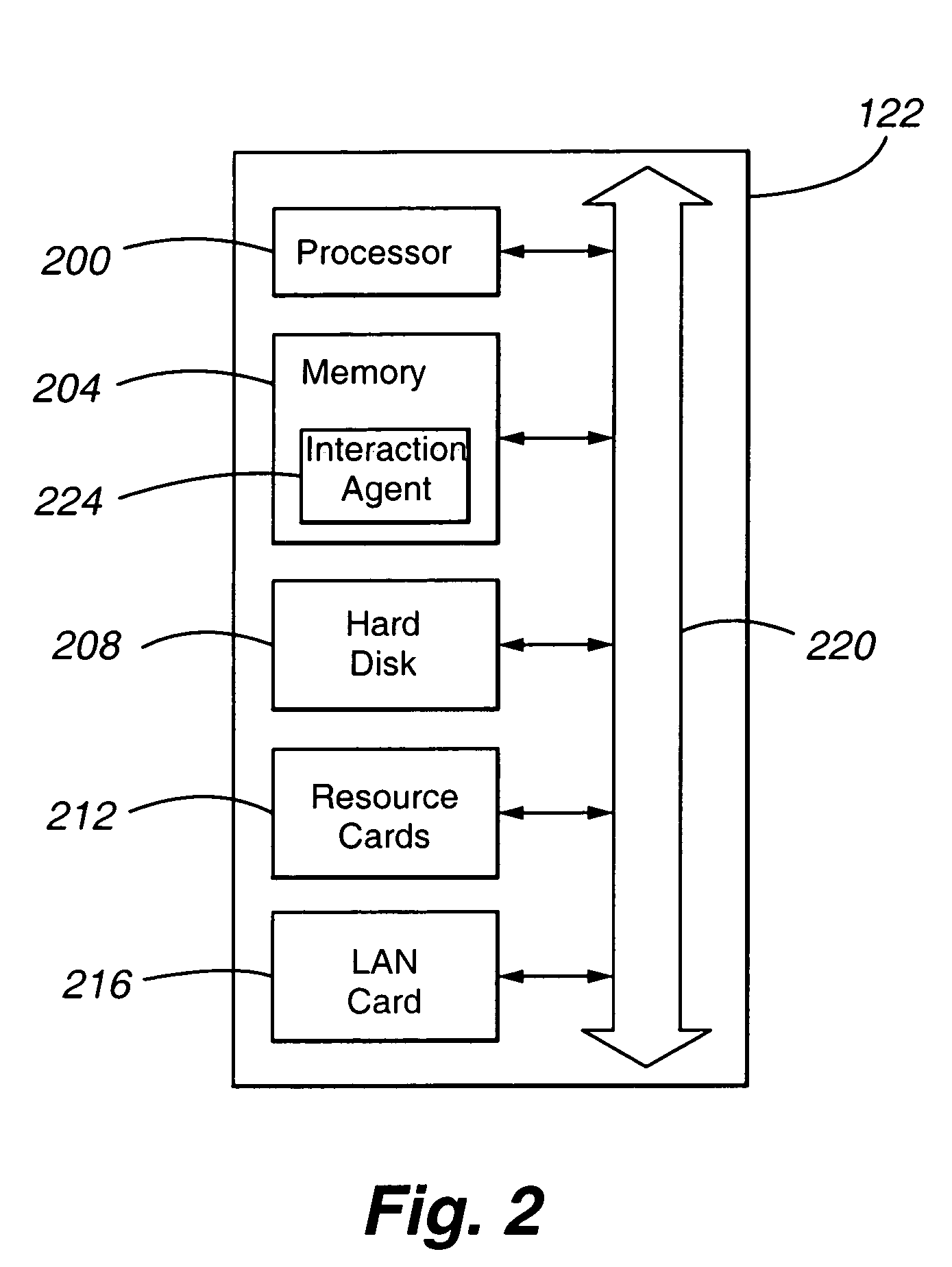

Interactive voice response unit response display

ActiveUS7136478B1Reduce frustrationImprove the level ofSpecial service for subscribersManual exchangesLive voiceVoice communication

The present invention is directed to a telecommunication device 174 or 180 including (a) an input operable to receive from an endpoint, as part of a live voice communication, a text message and an audio message, the audio message being a voiced version of the text message; (b) a character display; (c) at least one activator; and (d) a graphical display agent 184 operable to (i) display the text message on an associated character display 300 and (ii) audibly play the audio message.

Owner:AVAYA INC

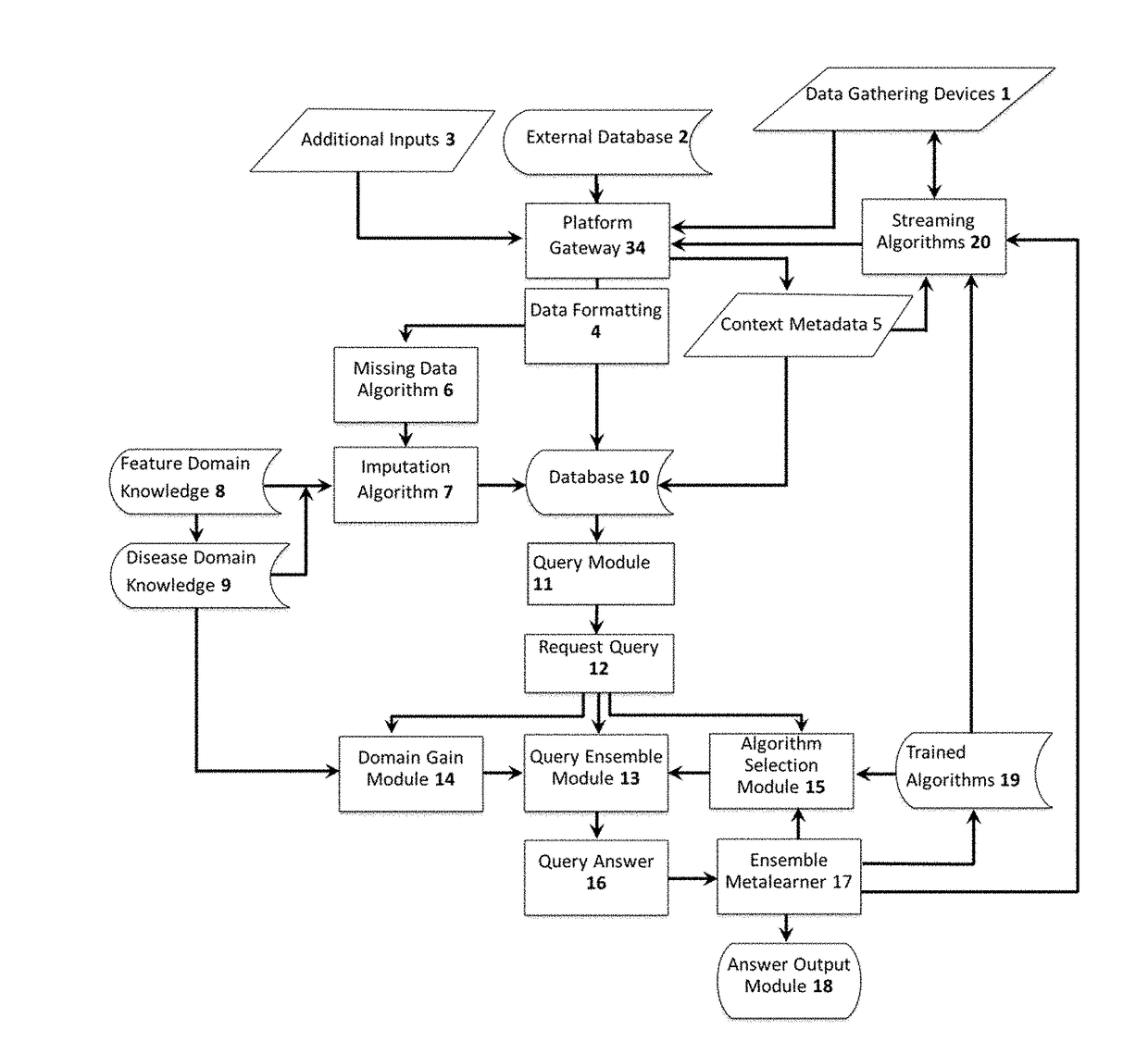

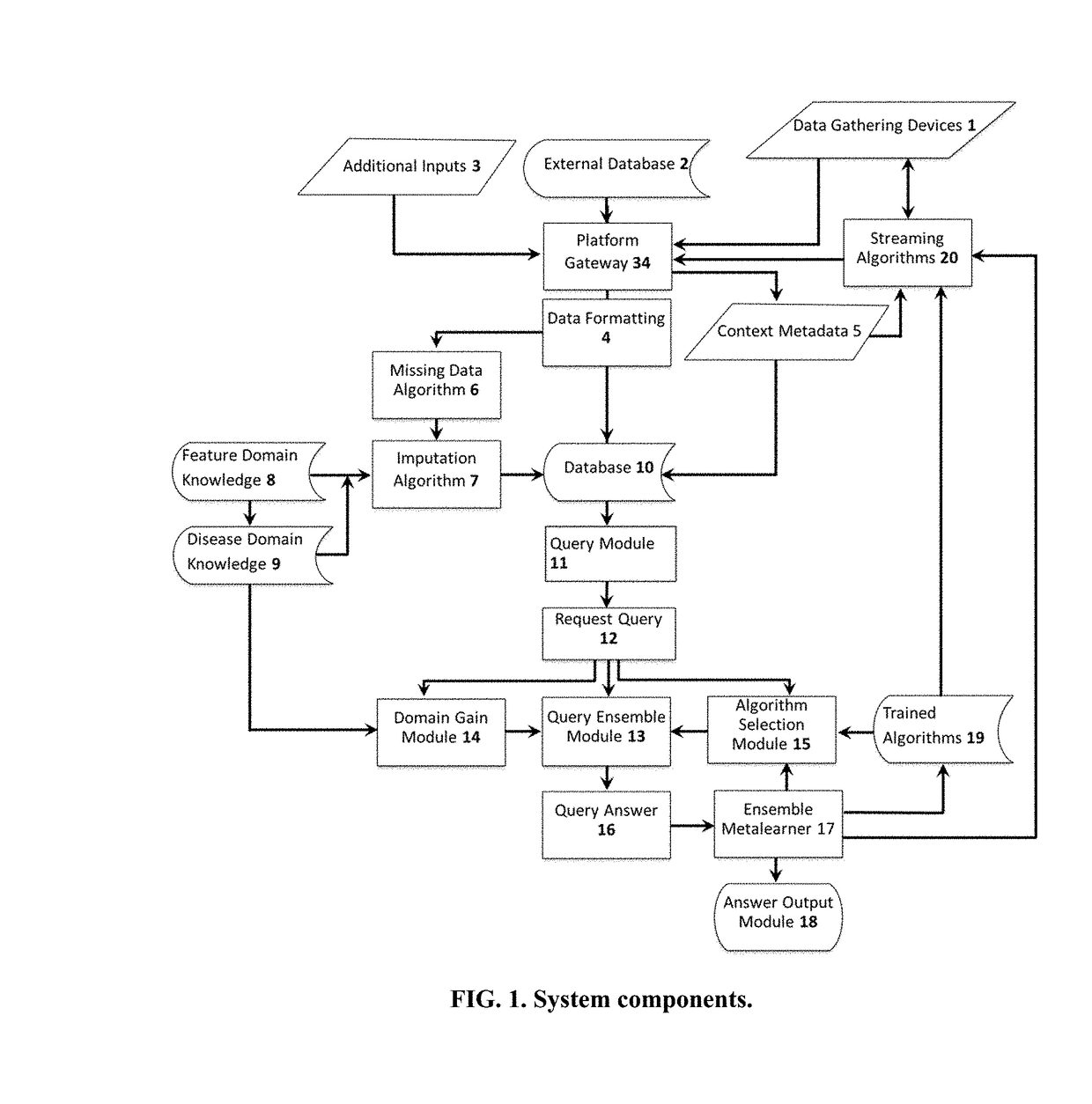

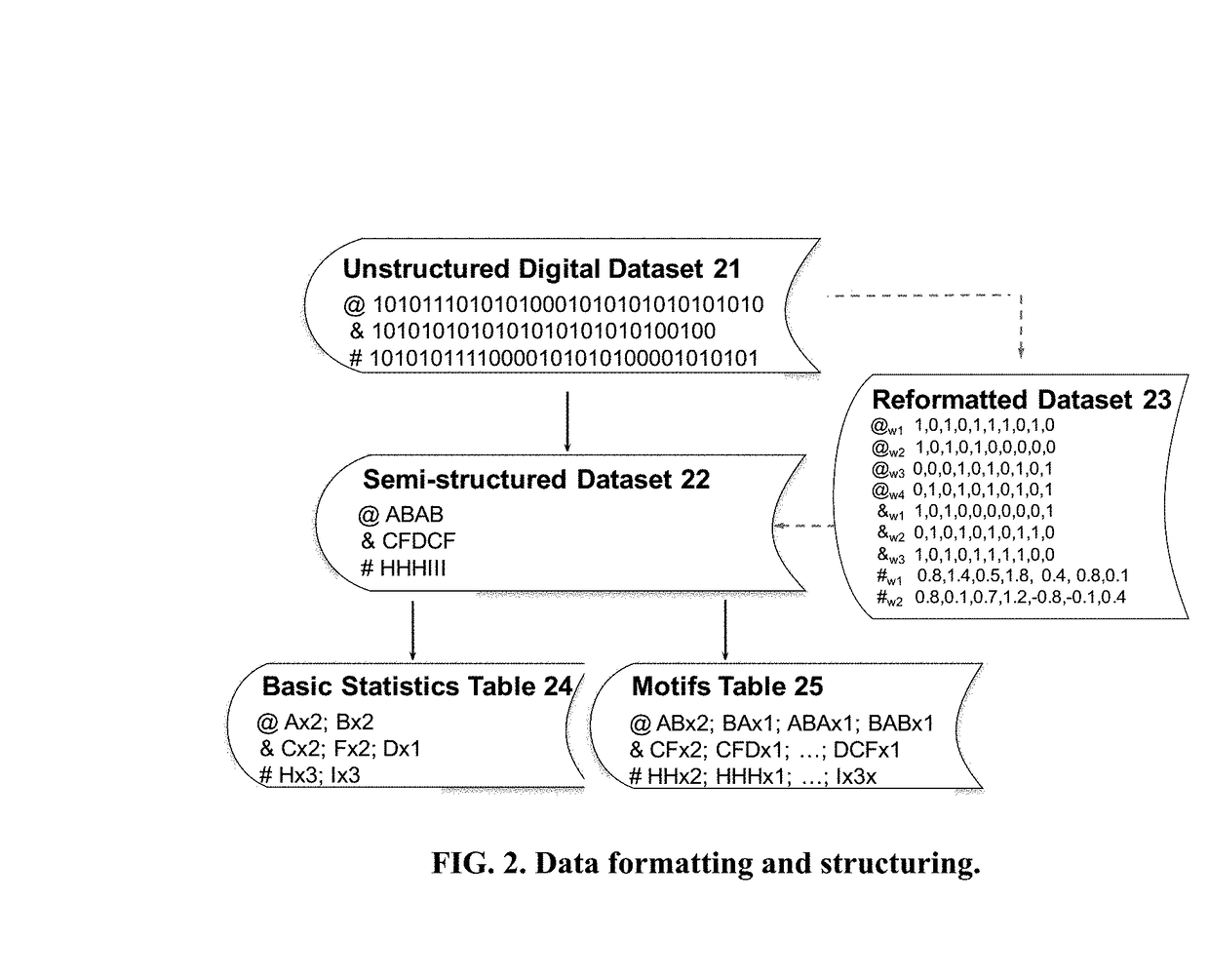

Multi-format, multi-domain and multi-algorithm metalearner system and method for monitoring human health, and deriving health status and trajectory

InactiveUS20170249434A1Effective therapyAccurate trackingDigital data information retrievalTelemedicinePersonalizationDisease monitoring

Real-time and individualized disease monitoring is central to rapidly evolving medical sciences and technologies, but for the vast majority of patients, disease progression and treatment are monitored only in an irregular and discontinuous fashion. Consequently, disease progression and relapse are often allowed to proceed too far before they are detected, compromising the possibility of any effective treatment. For one patient, this can mean becoming refractory to the few early drug treatments that are available; for another, missing early detection may be deadly. This invention provides a method for the detection of early signals of disease and recovery thereof comprising a universal yet personalized health-monitoring solution using cell phones or other wearable smart device data that generate extensive real-time data. The invention further provides a system and method to provide answers to a variety of questions related to the patient health status and health trajectory. Its flexibility and generality is designed for a preferred application to rare disorders and rare questions for which other analytical system are lacking.

Owner:EARLY SIGNAL LLC

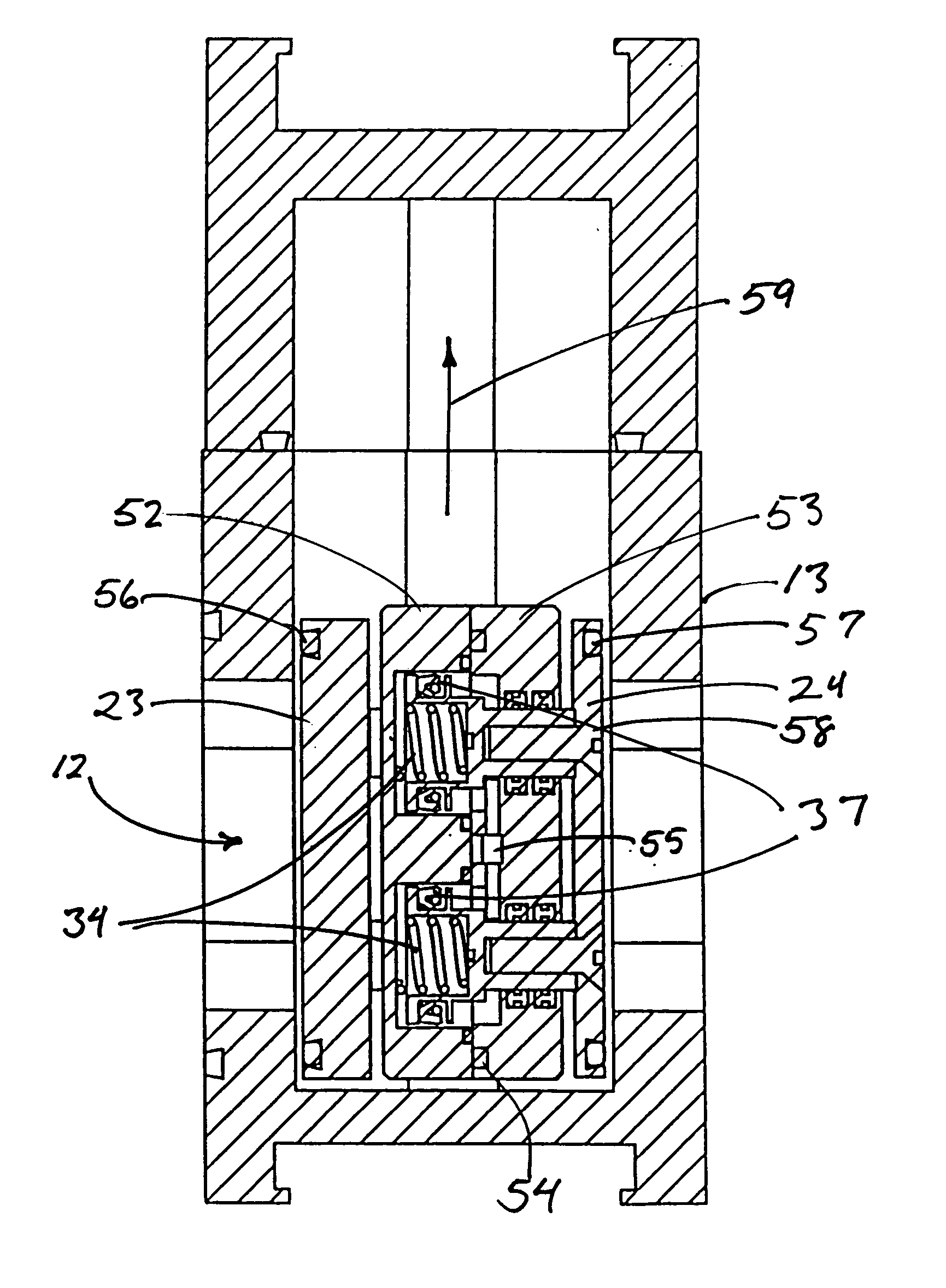

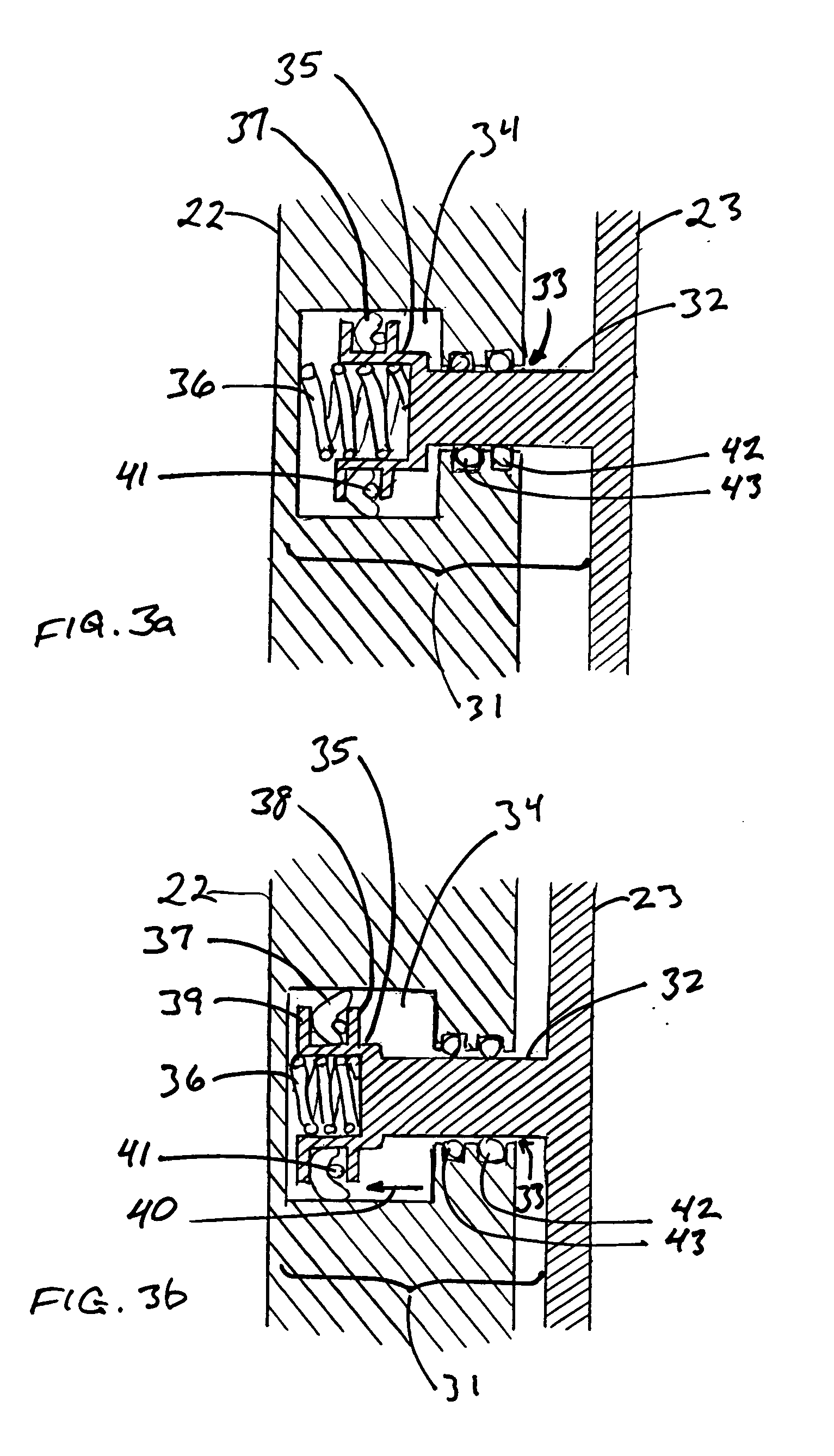

High-vacuum valve with retractable valve plate to eliminate abrasion

InactiveUS20040079915A1High yieldIncreased operating lifeSlide valveValve member-seat contactsEngineeringVALVE PORT

A valve achieves a high-vacuum seal and opens and closes with no sliding or otherwise abrading contact between the sealing plate and the valve seat, while maintaining pressure of the plate against the valve seat in the event of a failure in the valve actuation mechanism. These results are attained by use of a composite valve plate that includes a sealing plate joined to a support block through a retractable resilient connector. During retraction, the sealing plate is drawing close to the block by a pneumatic actuator internal to the composite valve plate, the actuator arranged to oppose and overcome a mechanical resilient element also contained within the valve plate that urges the sealing plate outward from the support block to effect the seal when the actuator is not engaged.

Owner:MDC VACUUM PRODS

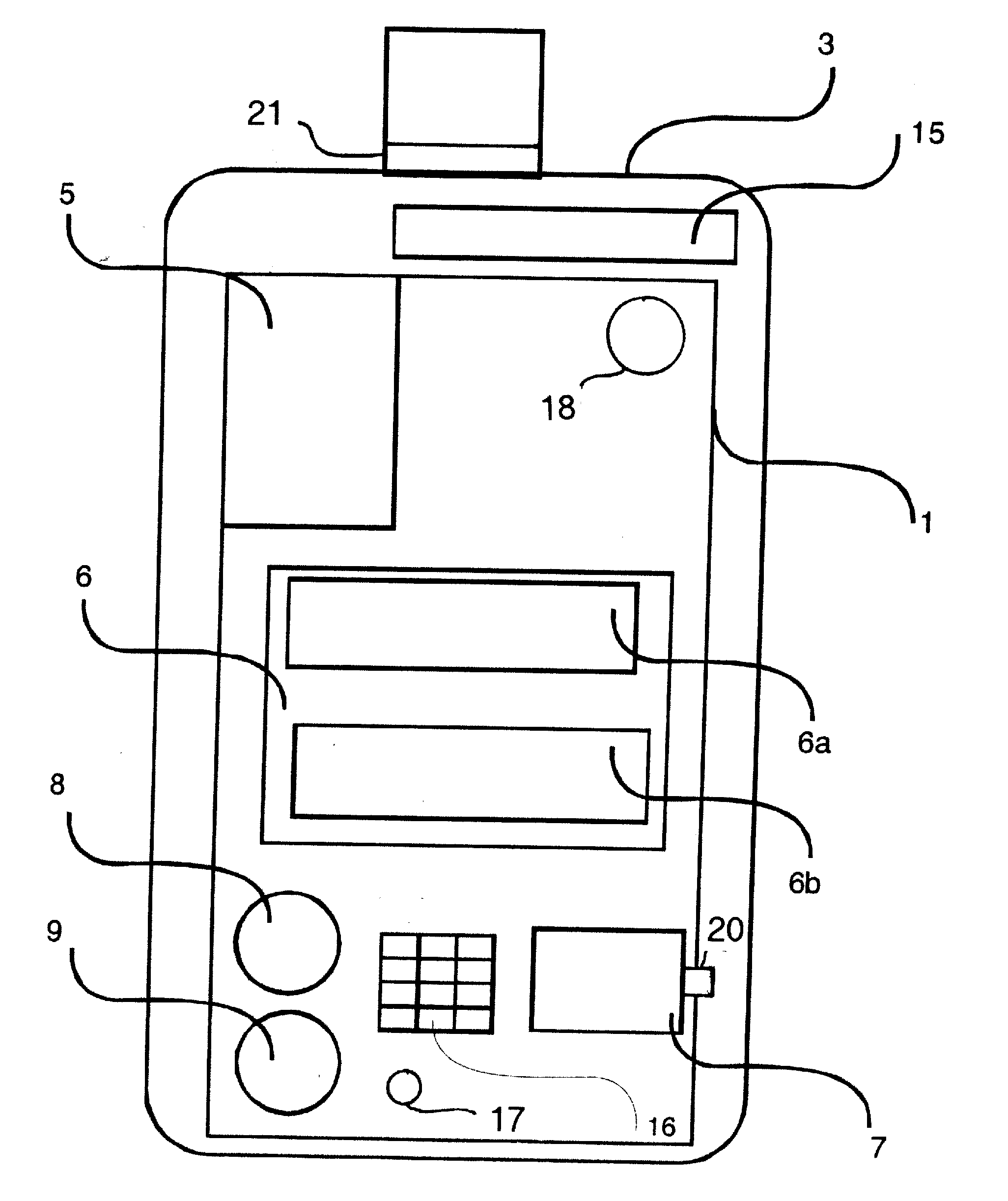

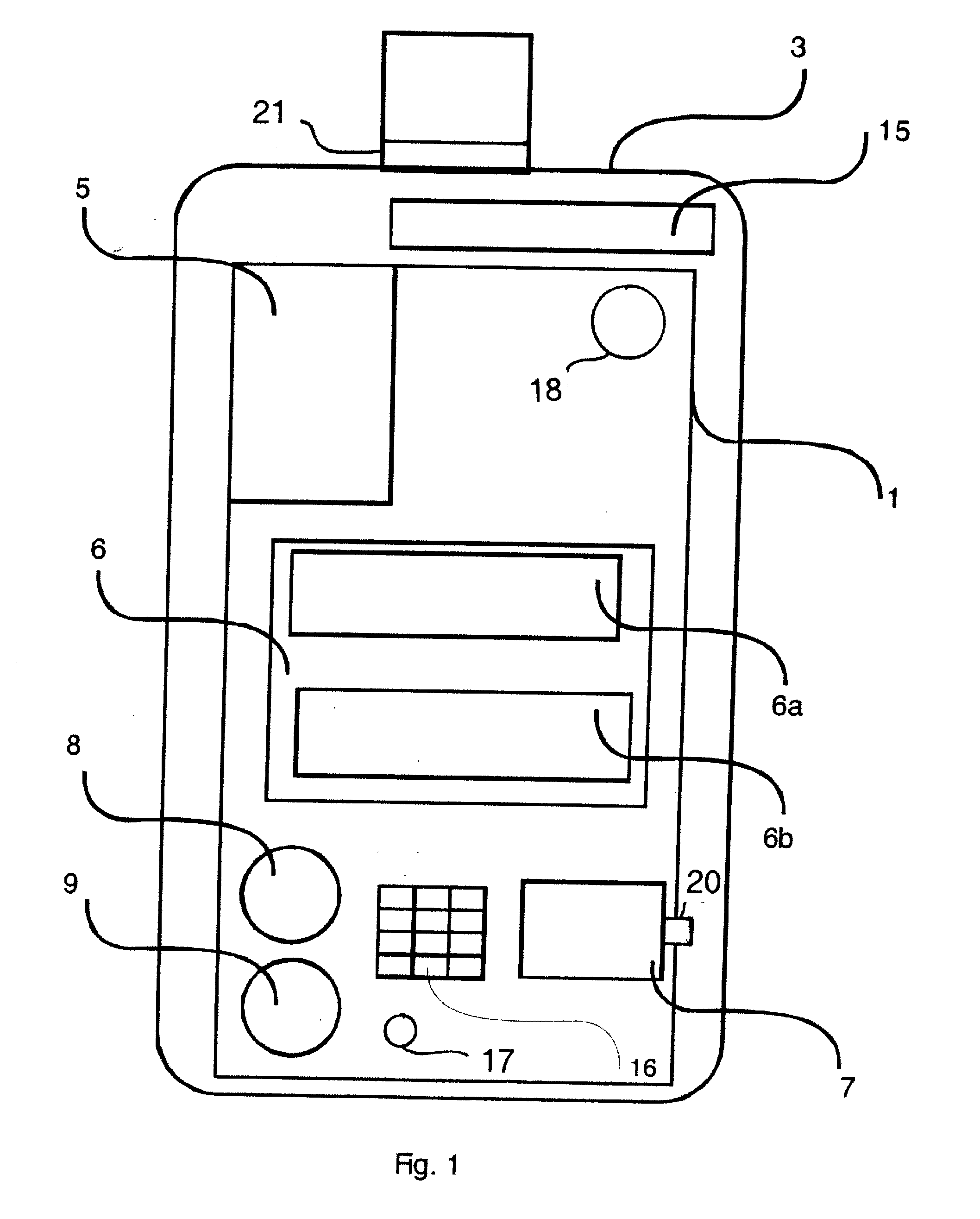

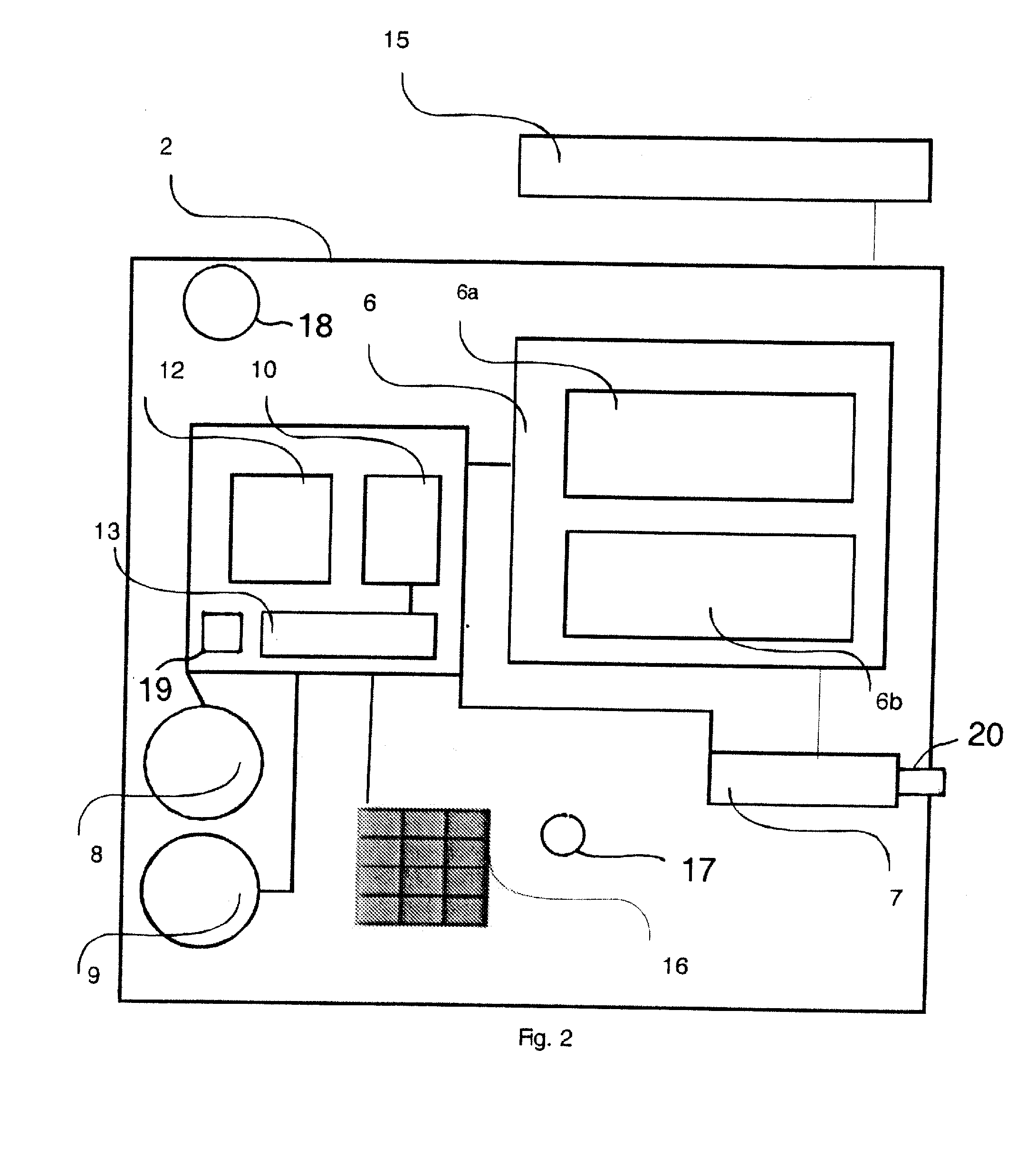

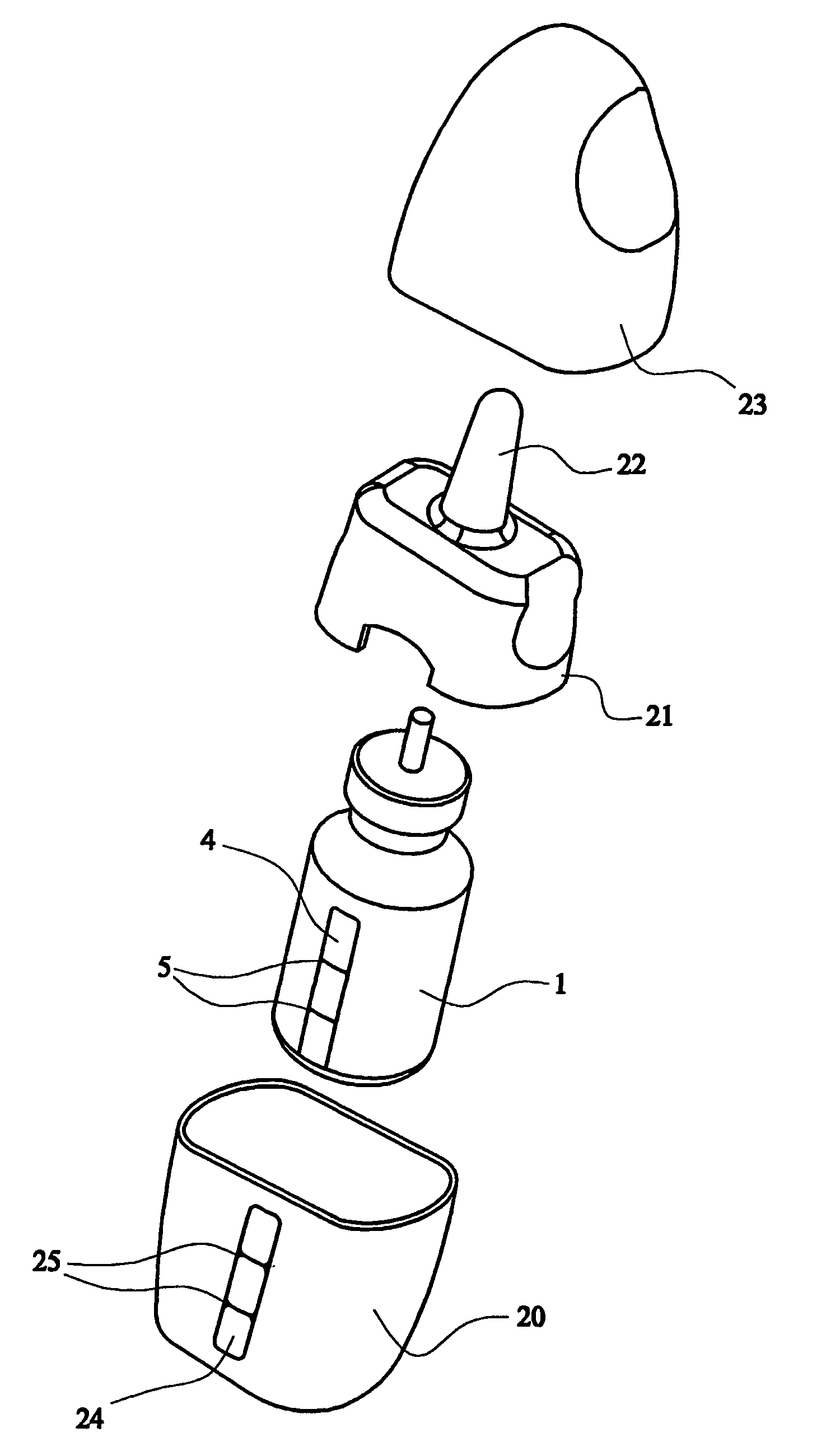

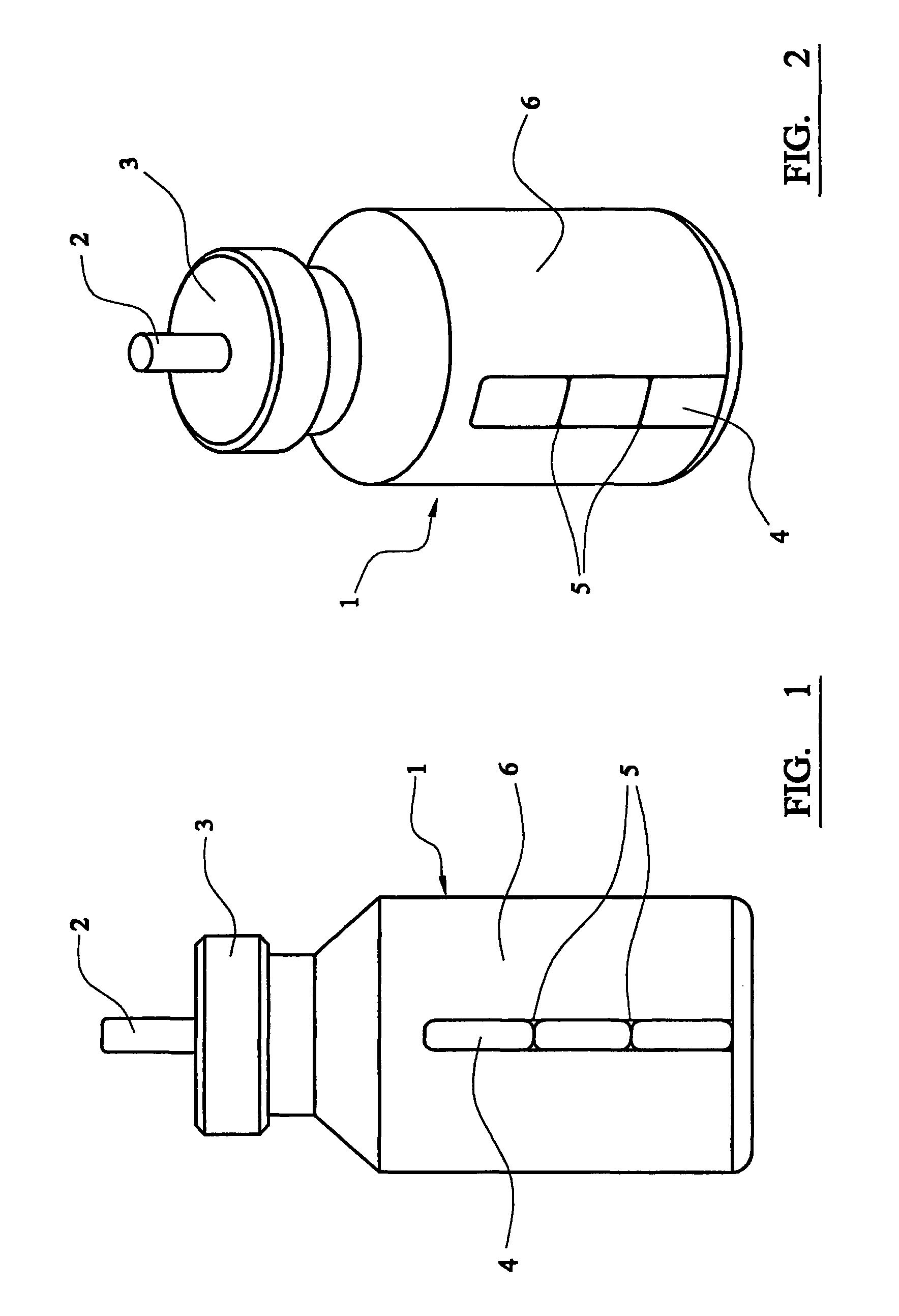

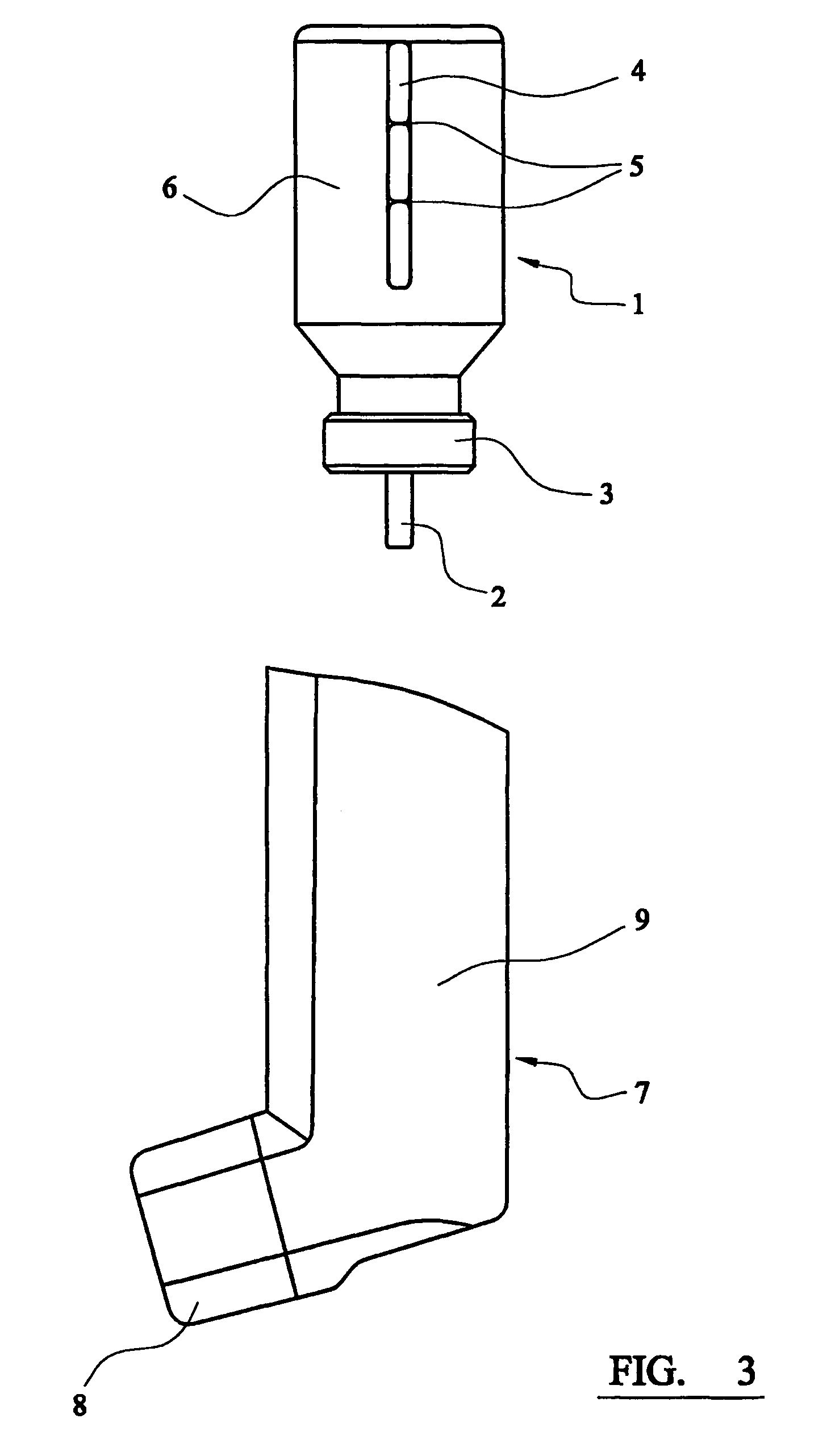

Spray device

InactiveUS7845346B2Welfare of a subjectRapid and reliableRespiratory disorderLiquid spraying apparatusBiomedical engineeringPolymer

The present invention relates to a spray device (e.g., an inhaler) comprising an aerosol formulation administered to the respiratory or nasal tract in which the level of formulation remaining in the device can be readily inspected. The device comprises a glass vial (1) coated with a coating of polymeric material having at least one clear or translucent portion (4).

Owner:NORTON HEALTHCARE

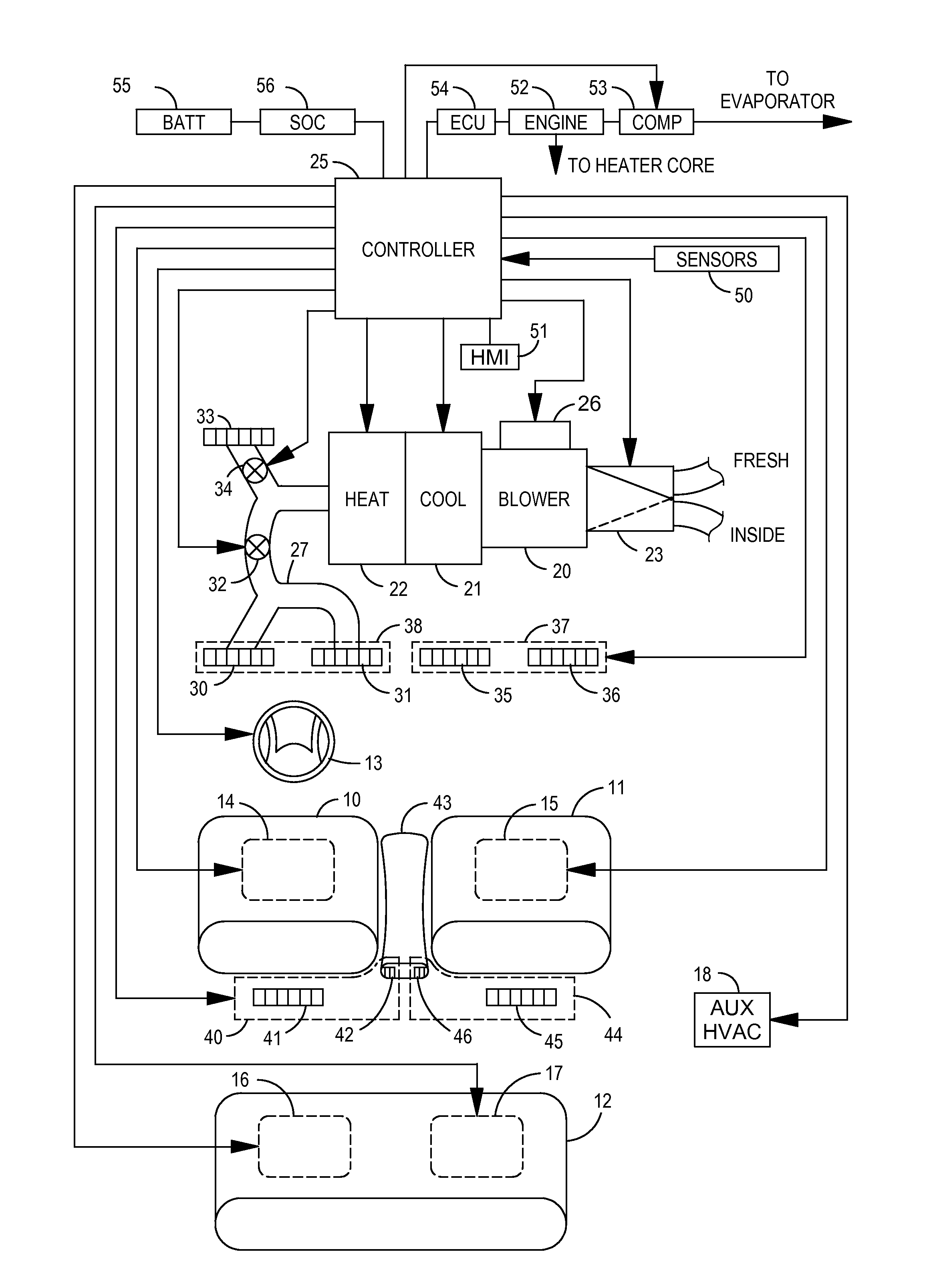

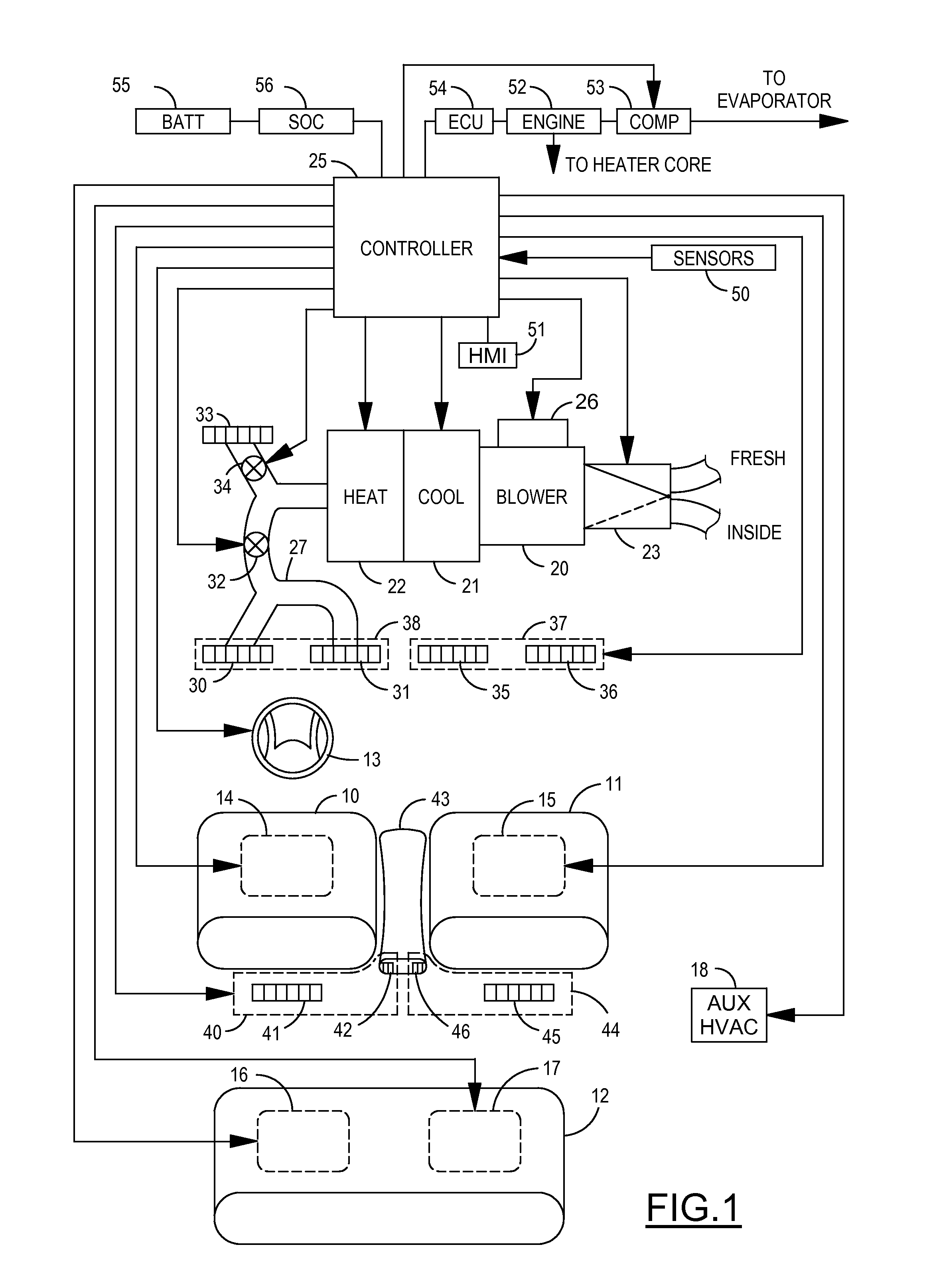

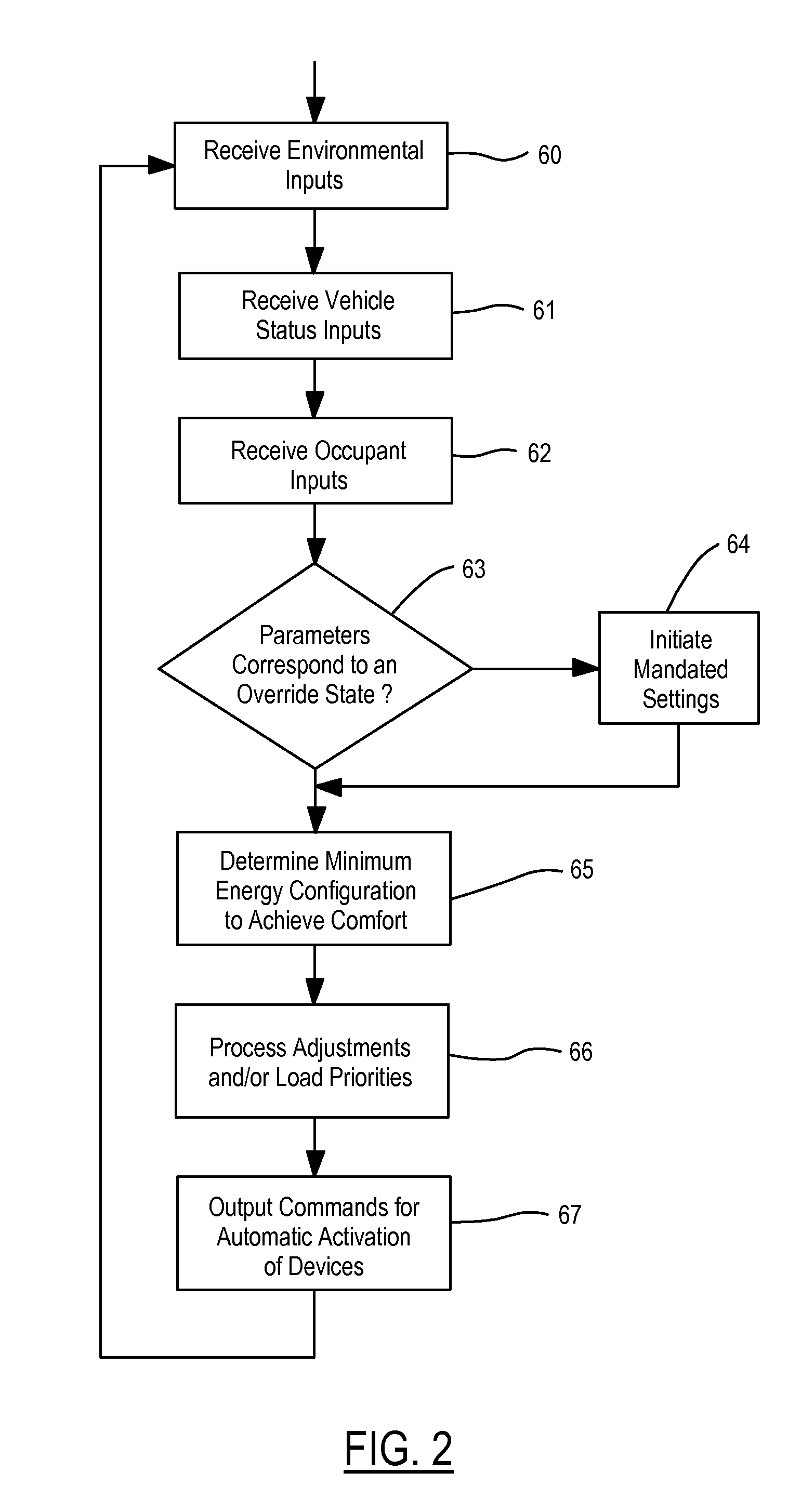

Vehicle comfort system with efficient coordination of complementary thermal units

ActiveUS20120312520A1Great comfort benefitReduce energy useAir-treating devicesSeat heating/ventillating devicesState parameterEngineering

An HVAC comfort system operates in a cabin of a vehicle. A plurality of vehicle status parameters are measured including a cabin temperature and a seat occupancy configuration. The method detects whether the vehicle status parameters correspond to a predetermined override state. When the vehicle status parameters correspond to the predetermined override state, then a respective mandated setting is automatically activated. Unless prevented by the mandated setting, one of a plurality of HVAC modes is automatically selected in response to the cabin temperature and other inputs, wherein the HVAC modes include an extremity heating mode and a panel circulation mode. The extremity heating mode is comprised of automatic activation of a touchpoint heated surface and other outputs in response to the seat occupancy configuration. The panel circulation mode is comprised of automatic activation of one or more zones for convective cooling in response to the seat occupancy configuration and may include activating other cooling devices.

Owner:FORD GLOBAL TECH LLC

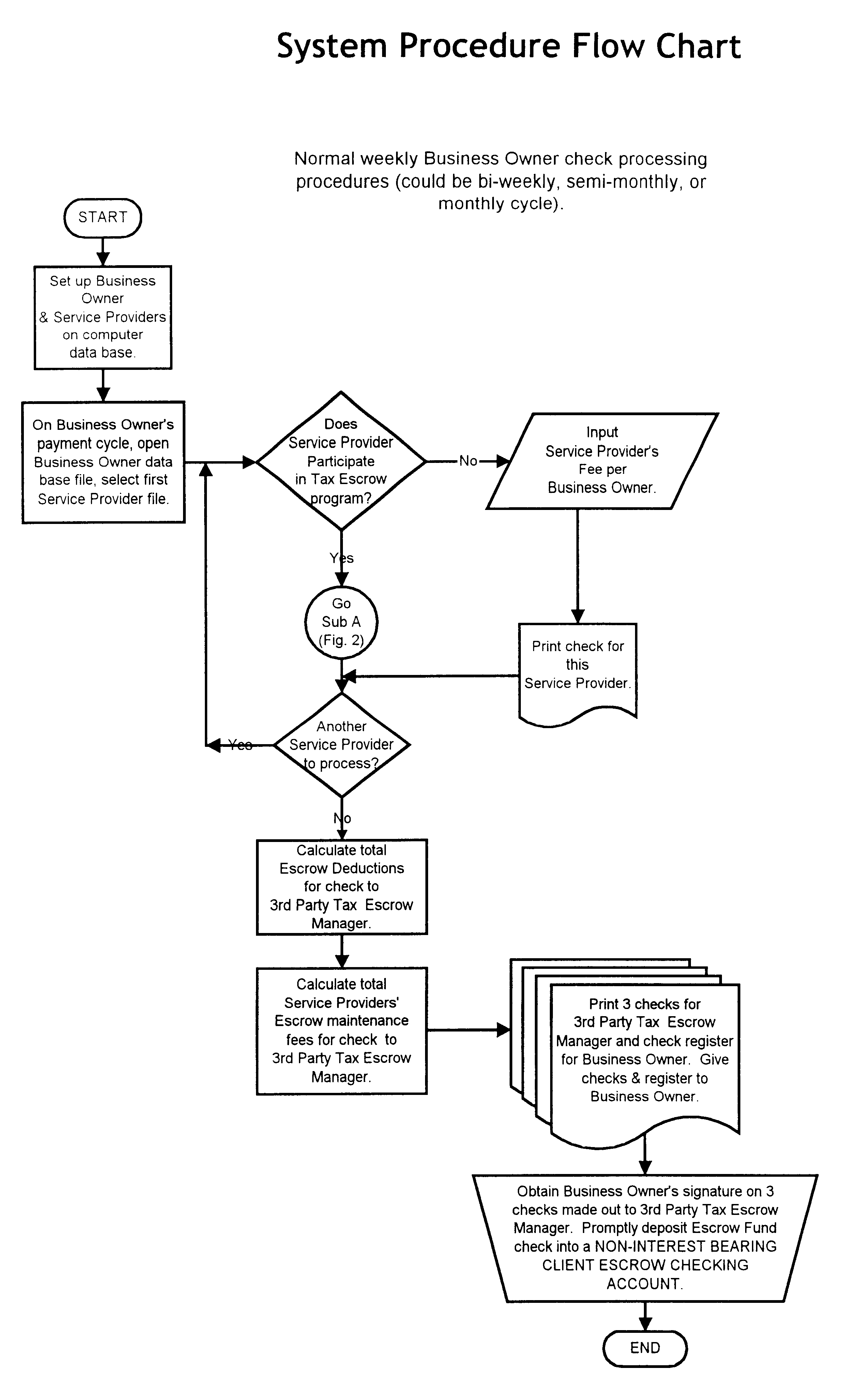

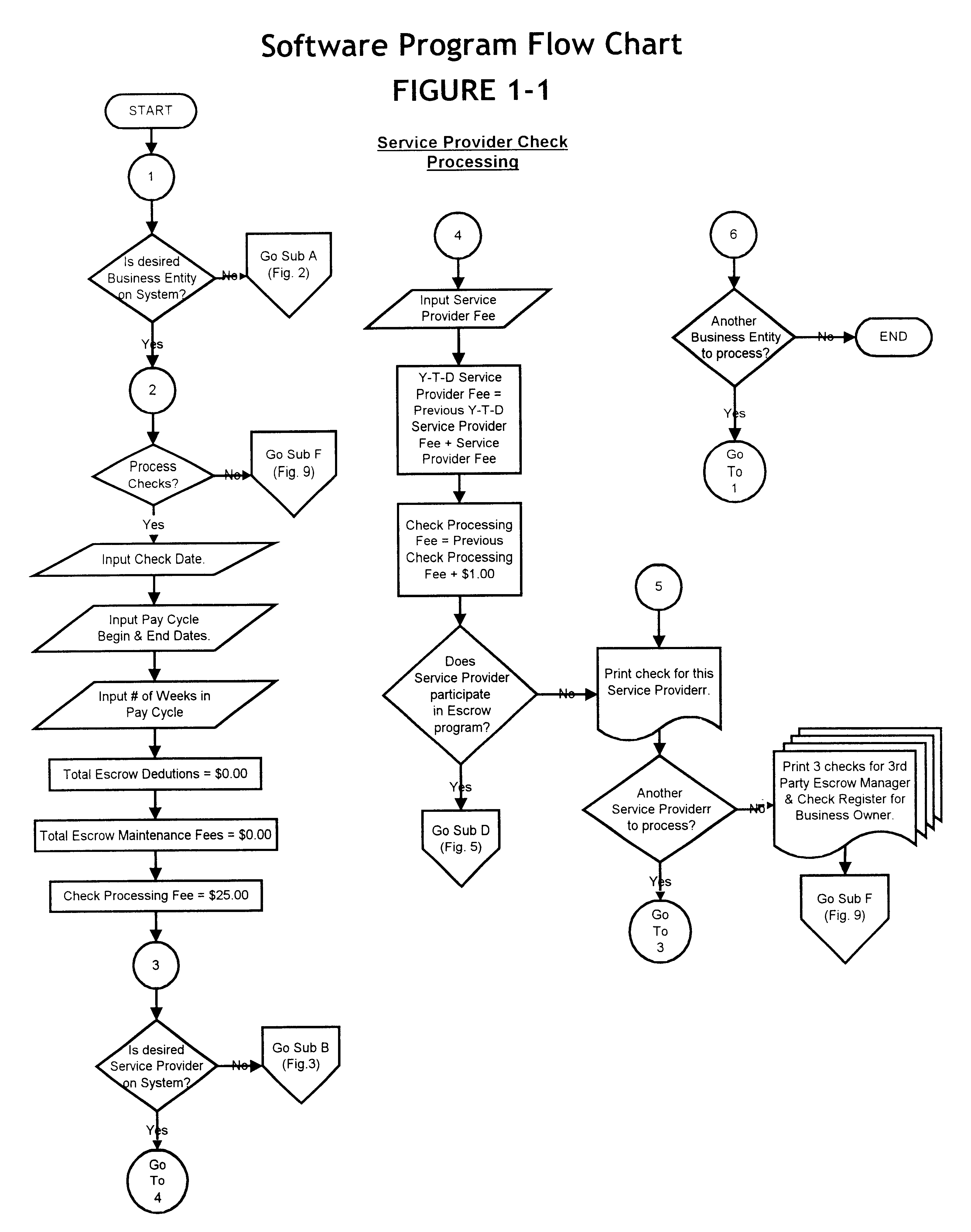

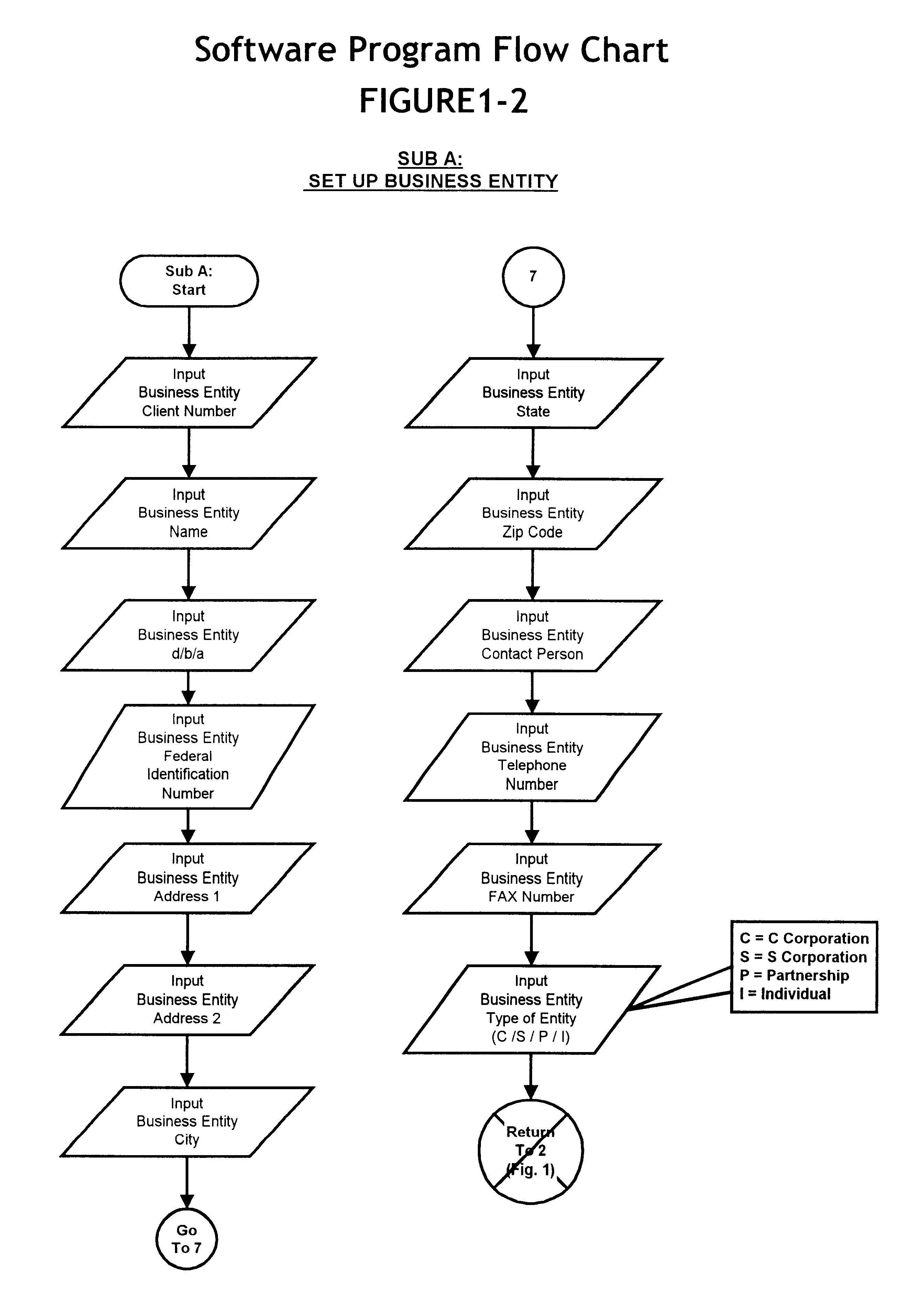

Tax escrow system for independent contractors

InactiveUS6898573B1Reducing noncompliance and nonpayment of taxesReduce paperworkComplete banking machinesFinanceThird partyInternet privacy

The system ensures the timely payment of taxes due a taxing authority while protecting the solvency of an independent service provider. The contracting entity retains a third-party escrow manager who oversees payments made by the contracting entity to an independent service provider. The third-party escrow manager estimates tax liability owed by the independent service provider to a tax authority based upon data provided to the third-party escrow manager by the independent service provider. The third-party escrow manager deposits a portion of monies owed to the independent service provider by the contracting entity for services provided in an escrow account. The escrow account is used by the independent contractor to pay monies owed to the taxing authority in a timely manner when due.

Owner:E PAYCON

Multiprocessor node controller circuit and method

InactiveUS7406086B2Ease of parallel processingImprove welfareMultiplex system selection arrangementsMemory adressing/allocation/relocationMemory addressMemory chip

Improved method and apparatus for parallel processing. One embodiment provides a multiprocessor computer system that includes a first and second node controller, a number of processors being connected to each node controller, a memory connected to each controller, a first input / output system connected to the first node controller, and a communications network connected between the node controllers. The first node controller includes: a crossbar unit to which are connected a memory port, an input / output port, a network port, and a plurality of independent processor ports. A first and a second processor port connected between the crossbar unit and a first subset and a second subset, respectively, of the processors. In some embodiments of the system, the first node controller is fabricated onto a single integrated-circuit chip. Optionally, the memory is packaged on plugable memory / directory cards wherein each card includes a plurality of memory chips including a first subset dedicated to holding memory data and a second subset dedicated to holding directory data. Further, the memory port includes a memory data port including a memory data bus and a memory address bus coupled to the first subset of memory chips, and a directory data port including a directory data bus and a directory address bus coupled to the second subset of memory chips. In some such embodiments, the ratio of (memory data space) to (directory data space) on each card is set to a value that is based on a size of the multiprocessor computer system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

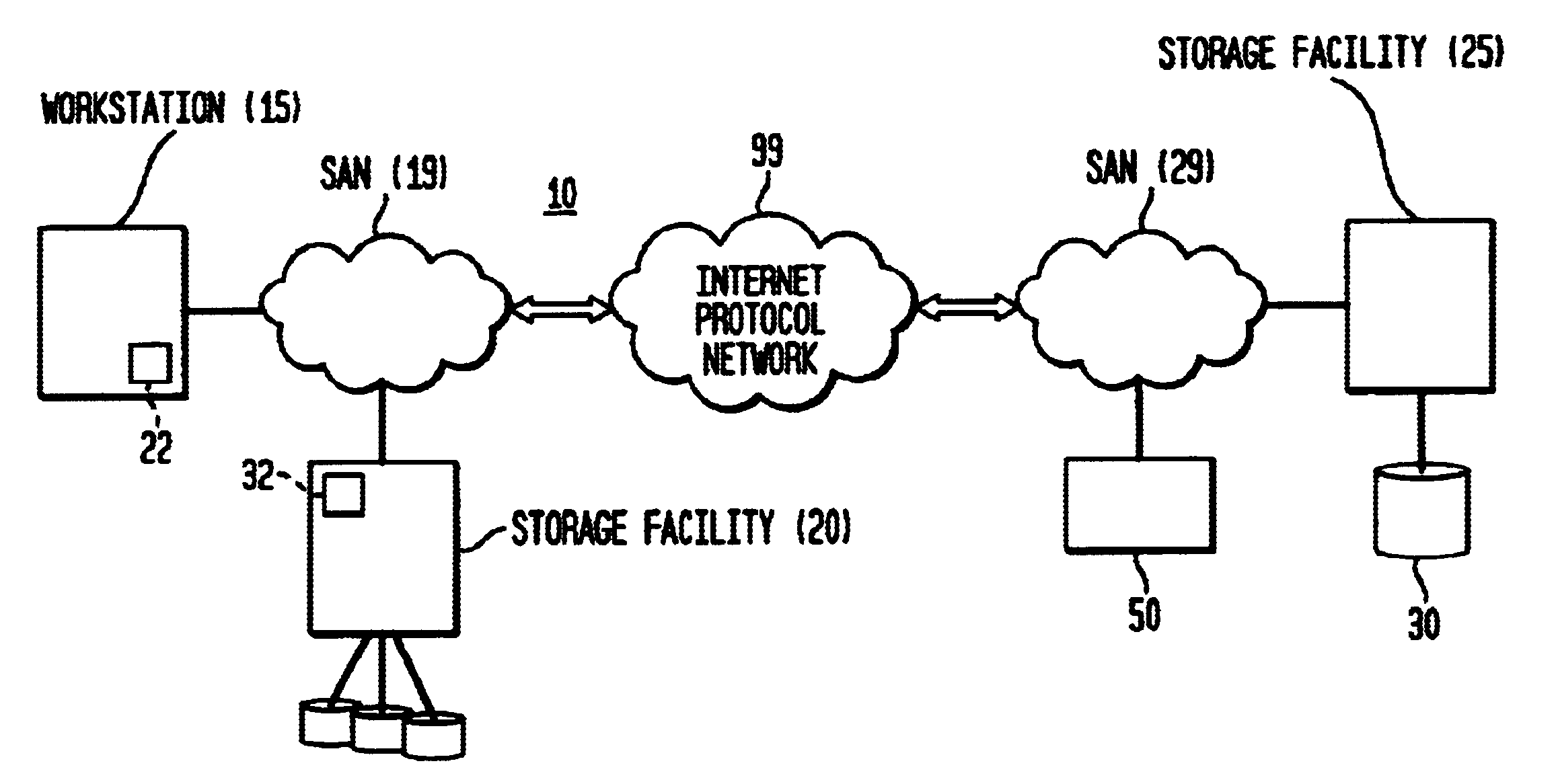

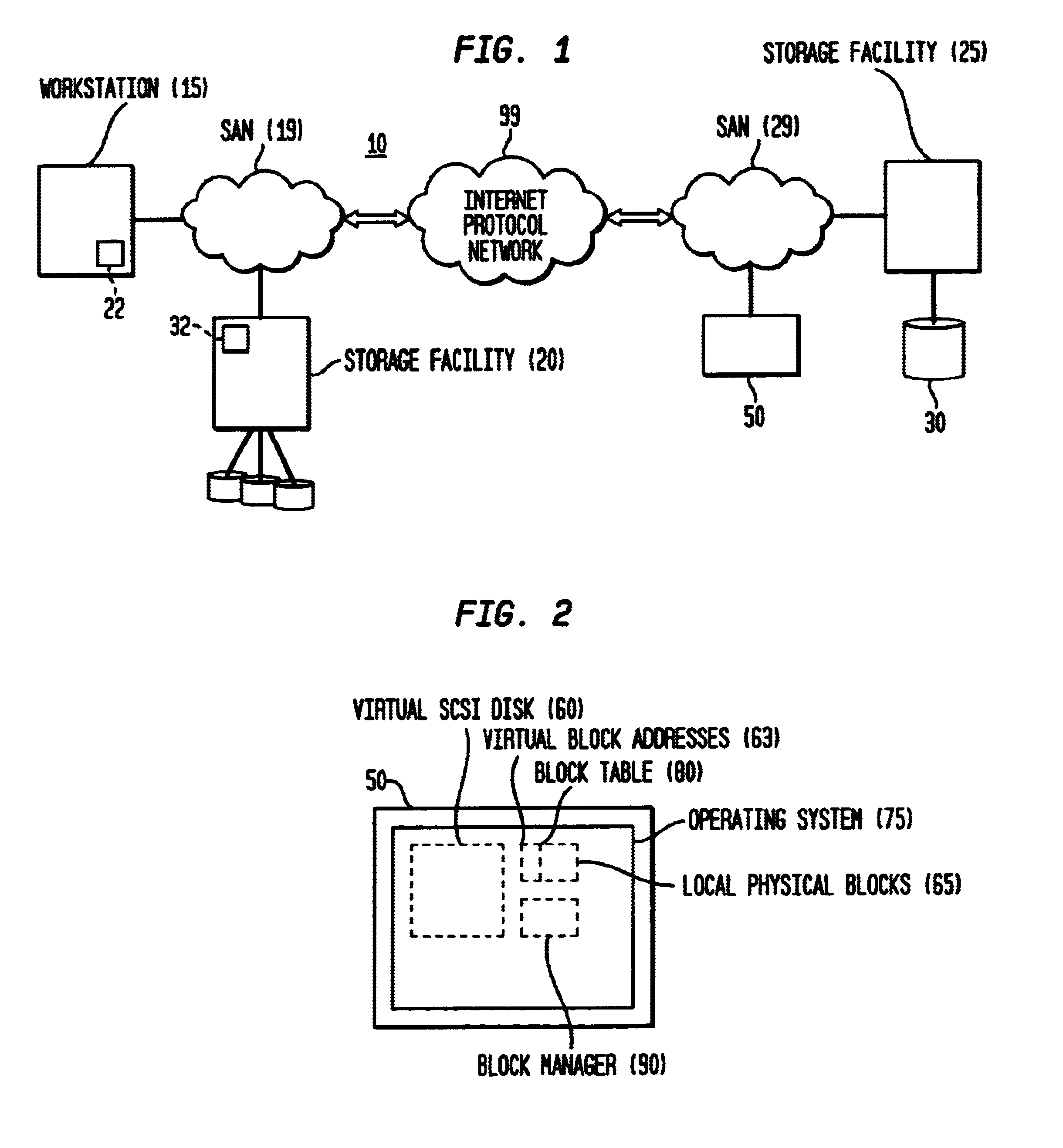

Virtual disk image system with local cache disk for iSCSI communications

InactiveUS6925533B2Improve speed performanceImprove welfareInput/output to record carriersMemory adressing/allocation/relocationTransmission protocolSCSI

A system and method for caching data received over a network connection comprising: a target device for receiving requests for routing data packetized for transport according to an Internet SCSI (iSCSI) transport protocol, the target device including an iSCSI drive for processing received SCSI commands; an initiator device for generating SCSI commands for reading data and writing data from / to storage devices associated with the iSCSI drive; a local disk at the initiator device for storing a copy of data read from or written to the storage devices associated with the iSCSI drive; and, a mapping device for mapping addresses associated with data stored at storage devices associated with the iSCSI drive with local data storage units in the local disk device, wherein seamless local caching of data at the initiator from data at remote data storage devices associated with the iSCSI drive is provided.

Owner:IBM CORP

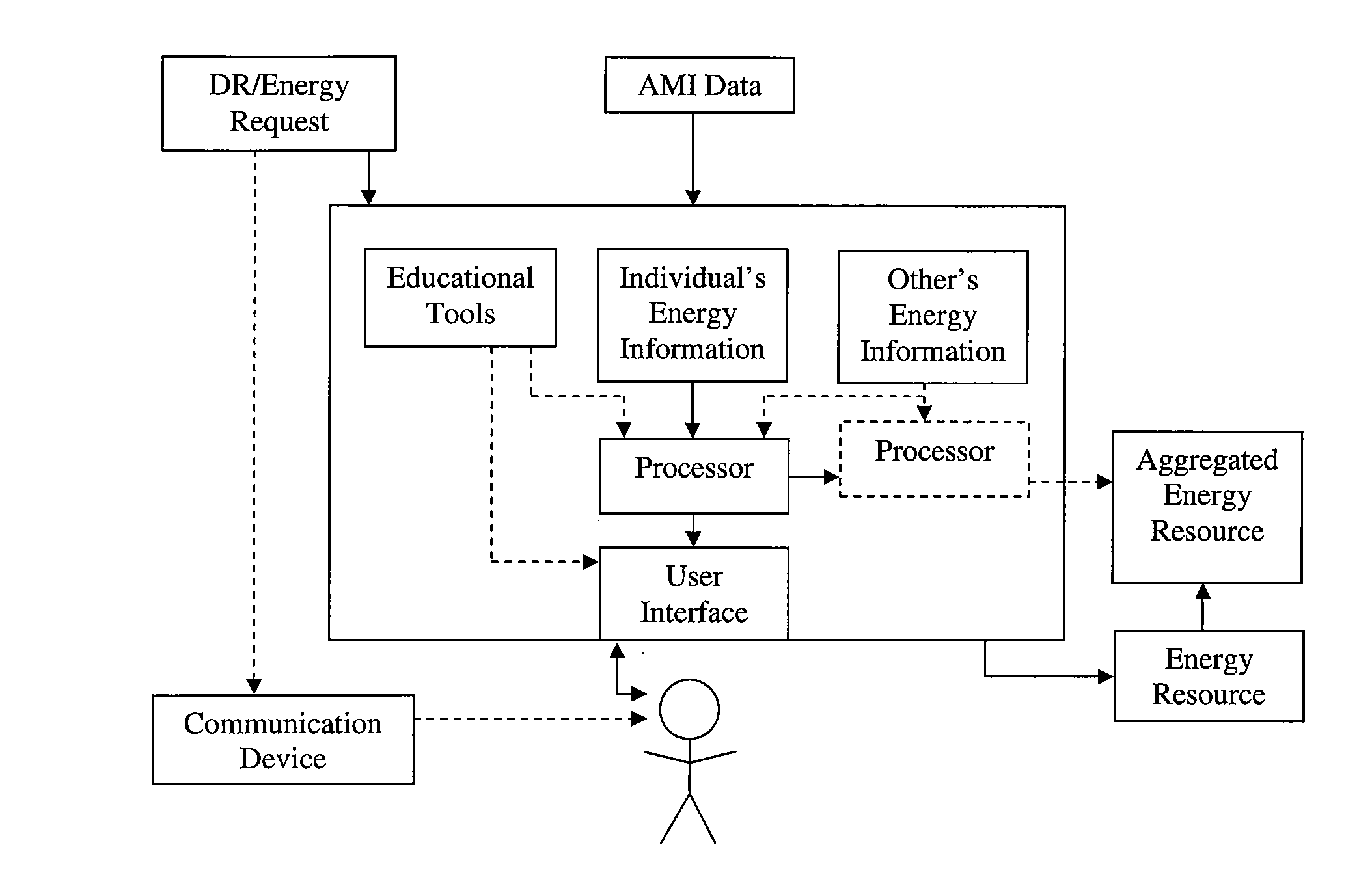

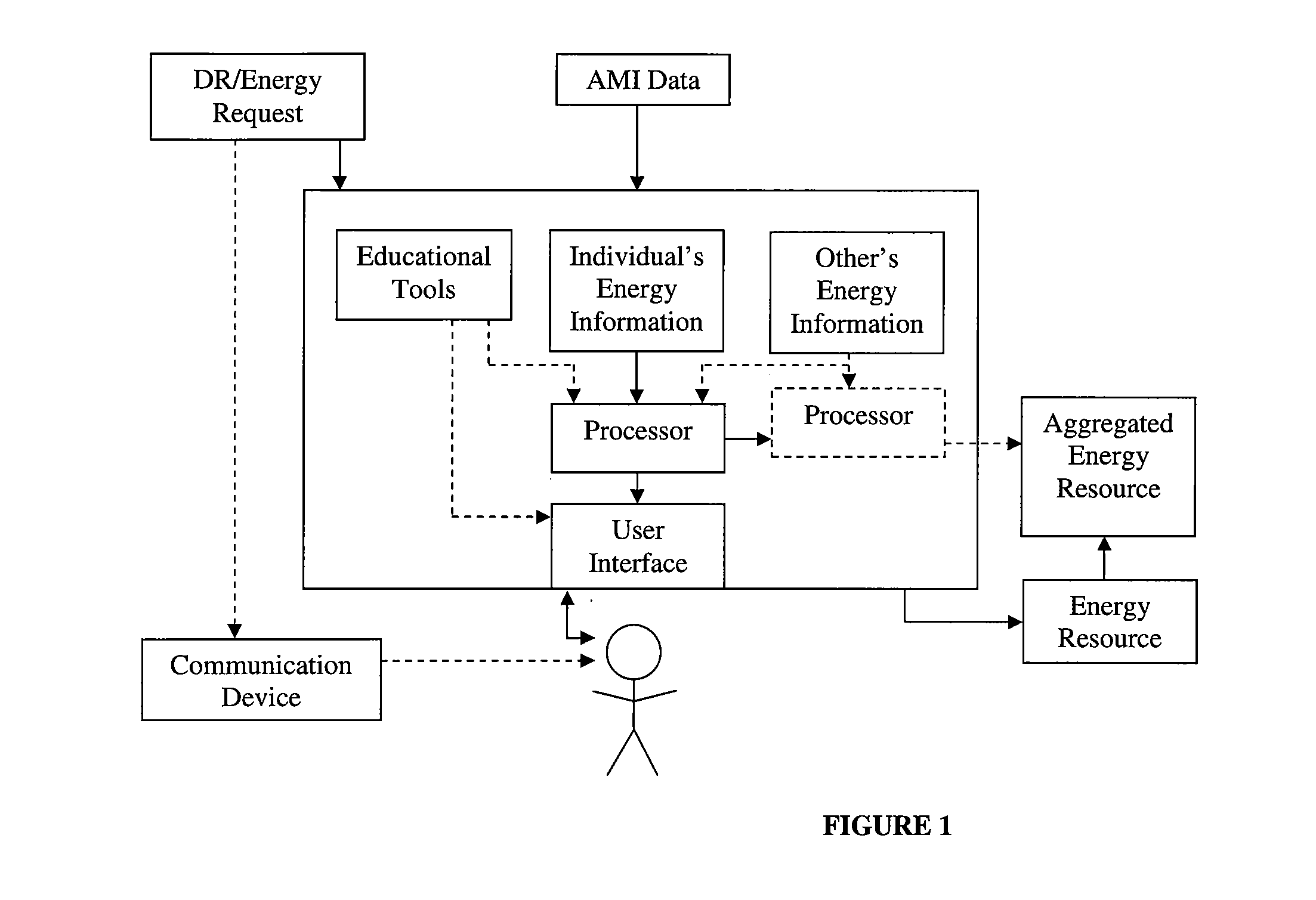

Coordinated energy resource generation

InactiveUS20100211443A1Great demand response benefitValuable energy resourceMechanical power/torque controlDiscounts/incentivesEngineeringEnergy expenditure

Demand response to reduce energy consumption by individual consumers is provided by aggregating individual consumers, and providing feedback to such consumers regarding their energy consumption relative to other energy consumers in a group. The resulting feedback may result in reduced energy consumption by the individual consumer.

Owner:CLEANTECH BUSINESS SOLUTIONS

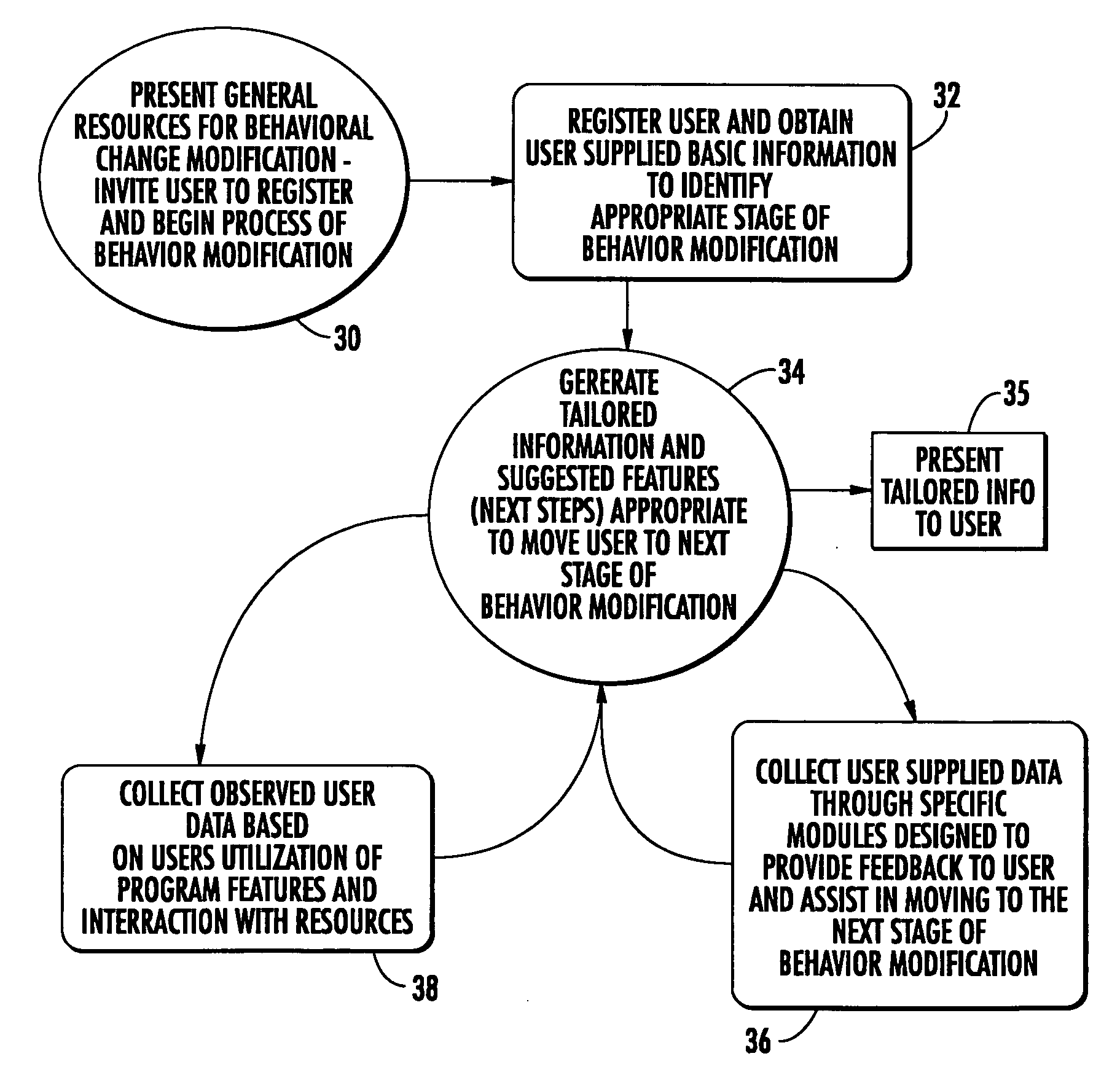

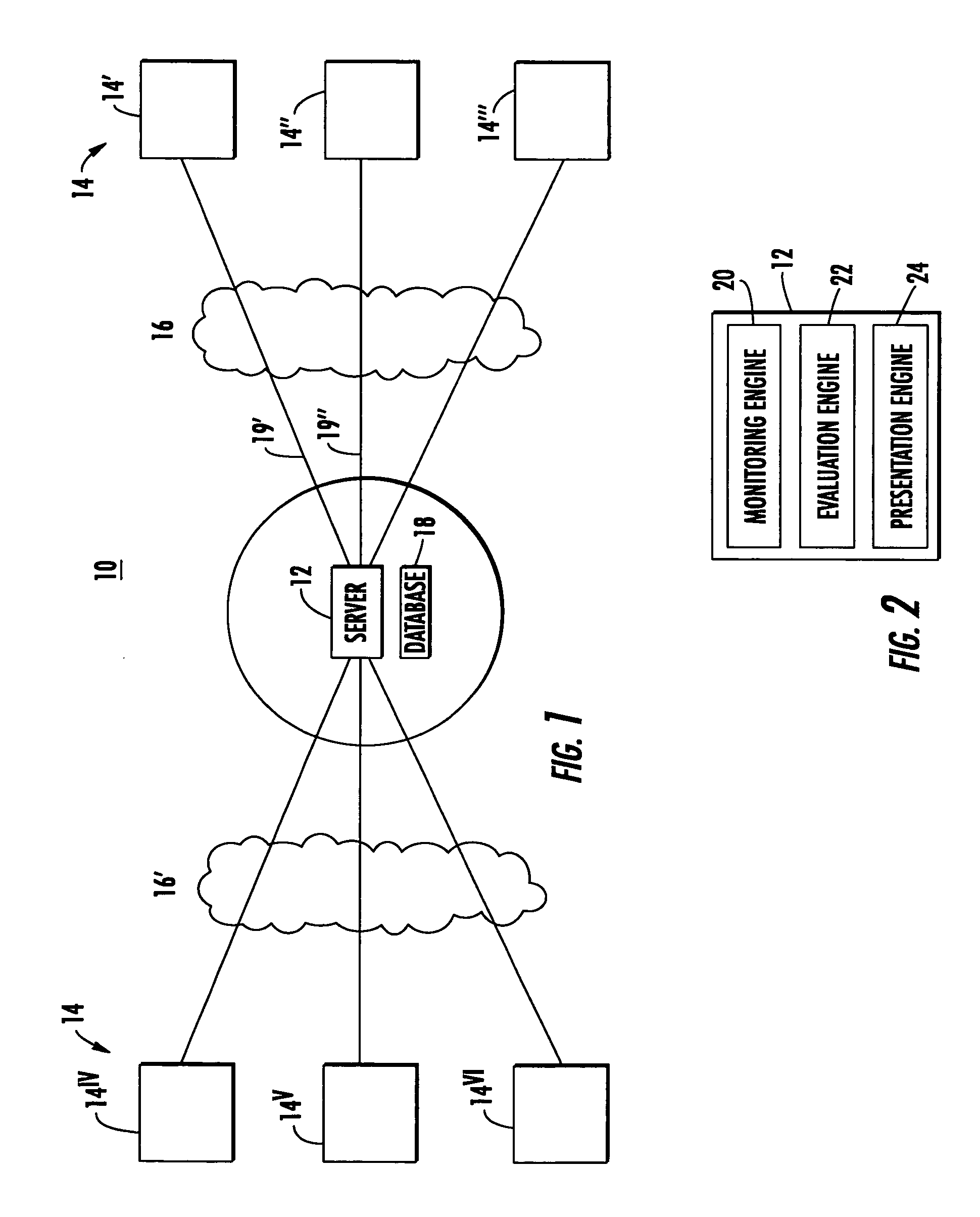

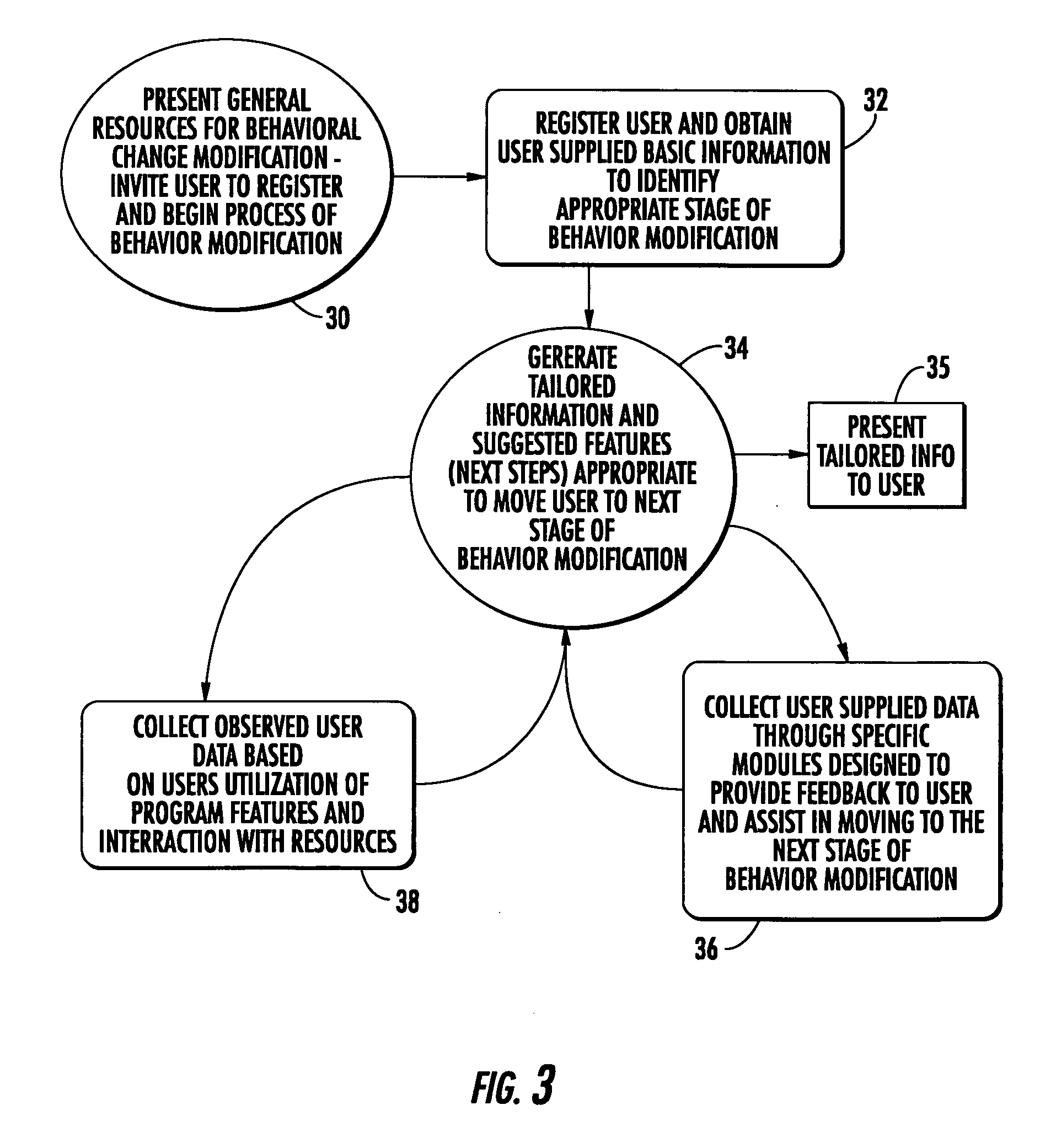

Method and system for delivering behavior modification information over a network

InactiveUS20070168501A1Great benefitEfficient combinationDrug and medicationsDigital computer detailsInformation deliveryBehavior modification

This invention features a method of delivering information over one or more information delivery networks, the method including: monitoring the actions of a user on the one or more networks to obtain observed user data relating to a desired behavior modification; obtaining user supplied data relating to the desired behavior modification; evaluating the observed user data and the use supplied data to generate tailored information for progressing a user towards the desired behavior modification; presenting the tailored information to the user over at least one of the networks; and repeating steps a), b), c) and d) until the desired behavior modification is achieved. The user is continually provided with re-tailored information resulting from an iterative process of obtaining and evaluating data that progresses the user towards a desired behavior modification. The desired behavior modification can be, for example, the cessation of smoking.

Owner:COBB NATHAN KNIGHT +5

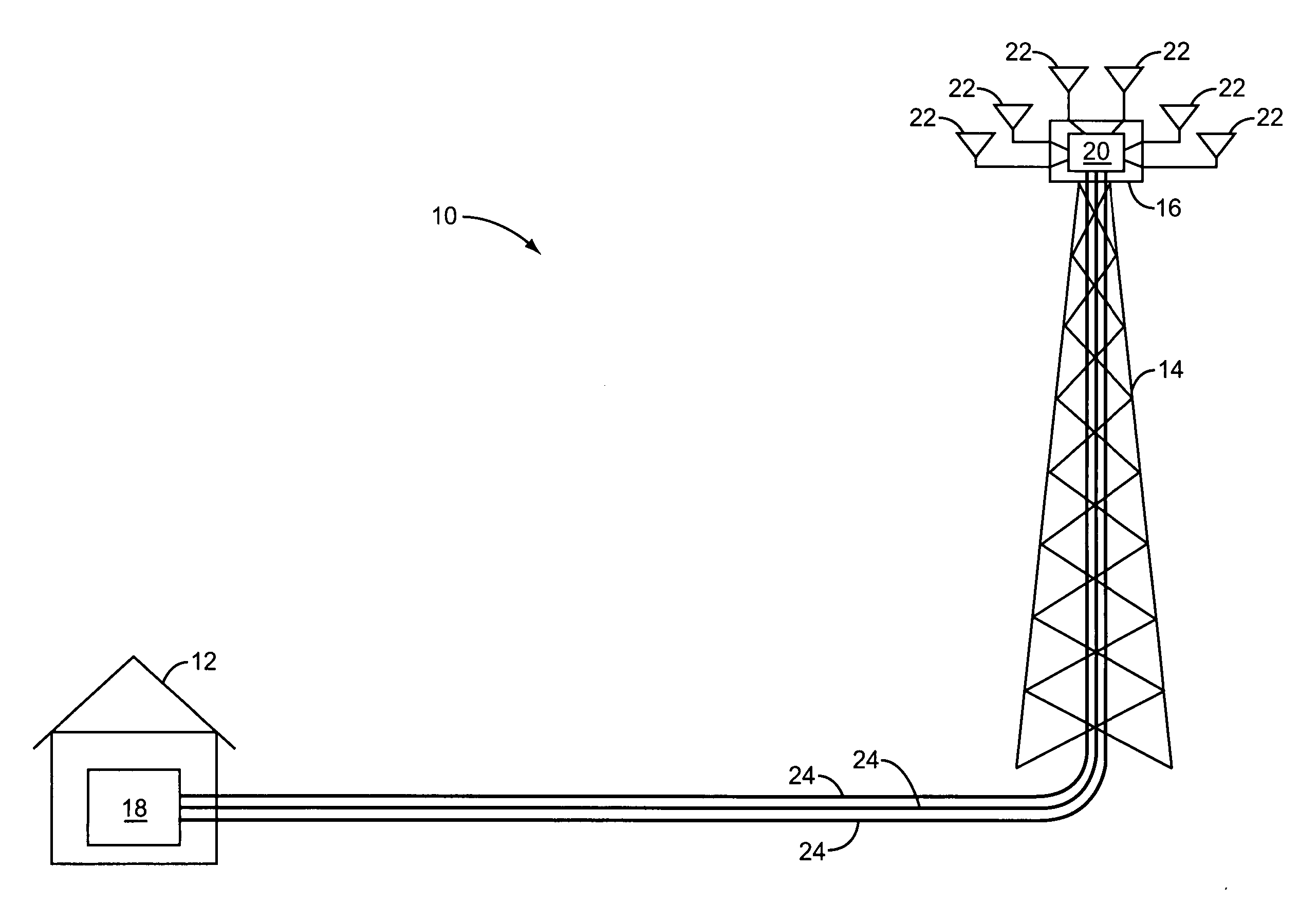

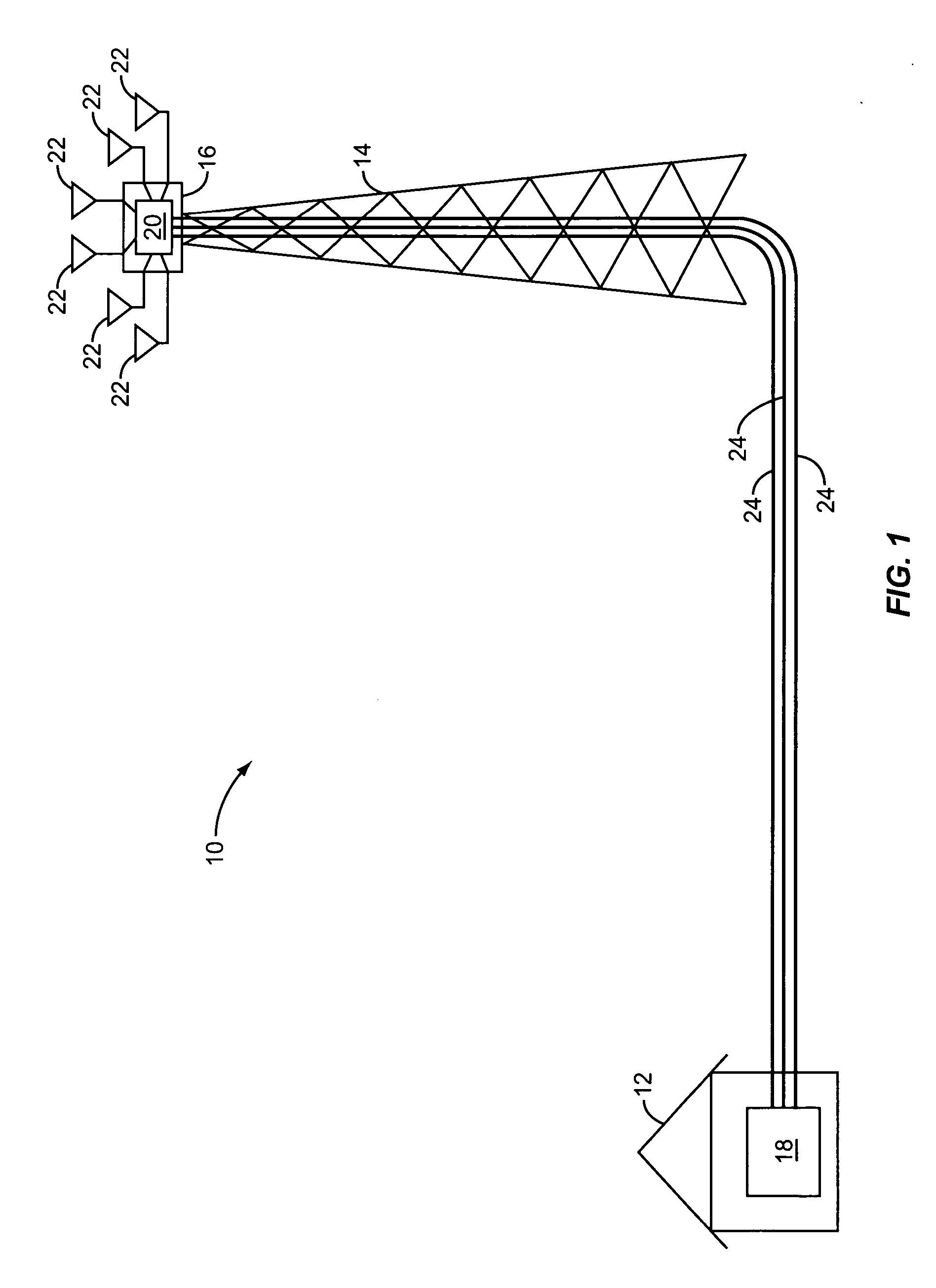

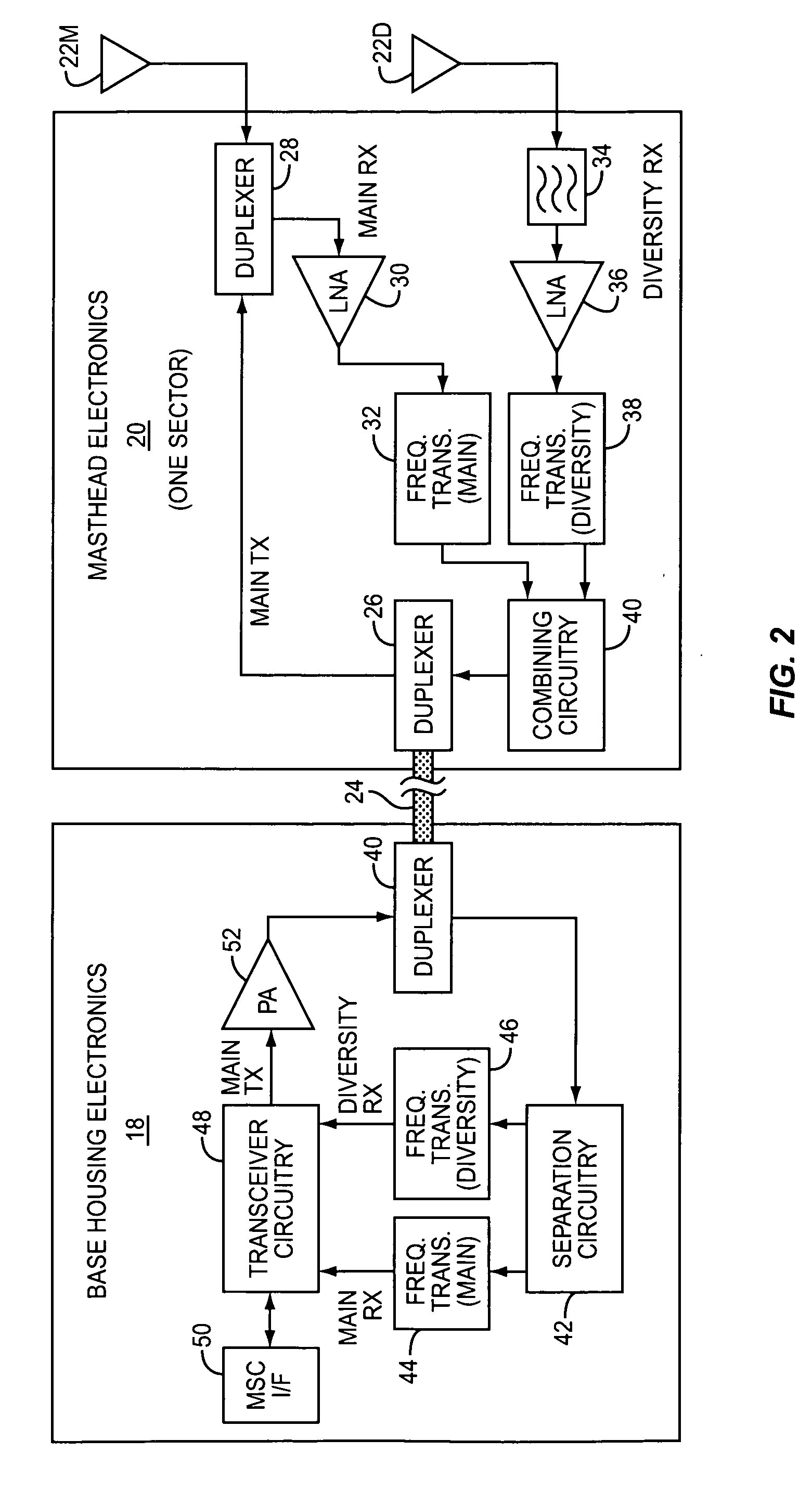

Feeder cable reduction

InactiveUS20050215288A1Improve welfareSpatial transmit diversityFrequency-division multiplex detailsTransceiverEngineering

The present invention allows transmission of multiple signals between masthead electronics and base housing electronics in a base station environment. At least some of the received signals from the multiple antennas are translated to being centered about different center frequencies, such that the translated signals may be combined into a composite signal including each of the received signals. The composite signal is then sent over a single feeder cable to base housing electronics, wherein the received signals are separated and processed by transceiver circuitry. Prior to being provided to the transceiver circuitry, those signals that were translated from being centered about one frequency to another may be retranslated to being centered about the original center frequency.

Owner:APPLE INC

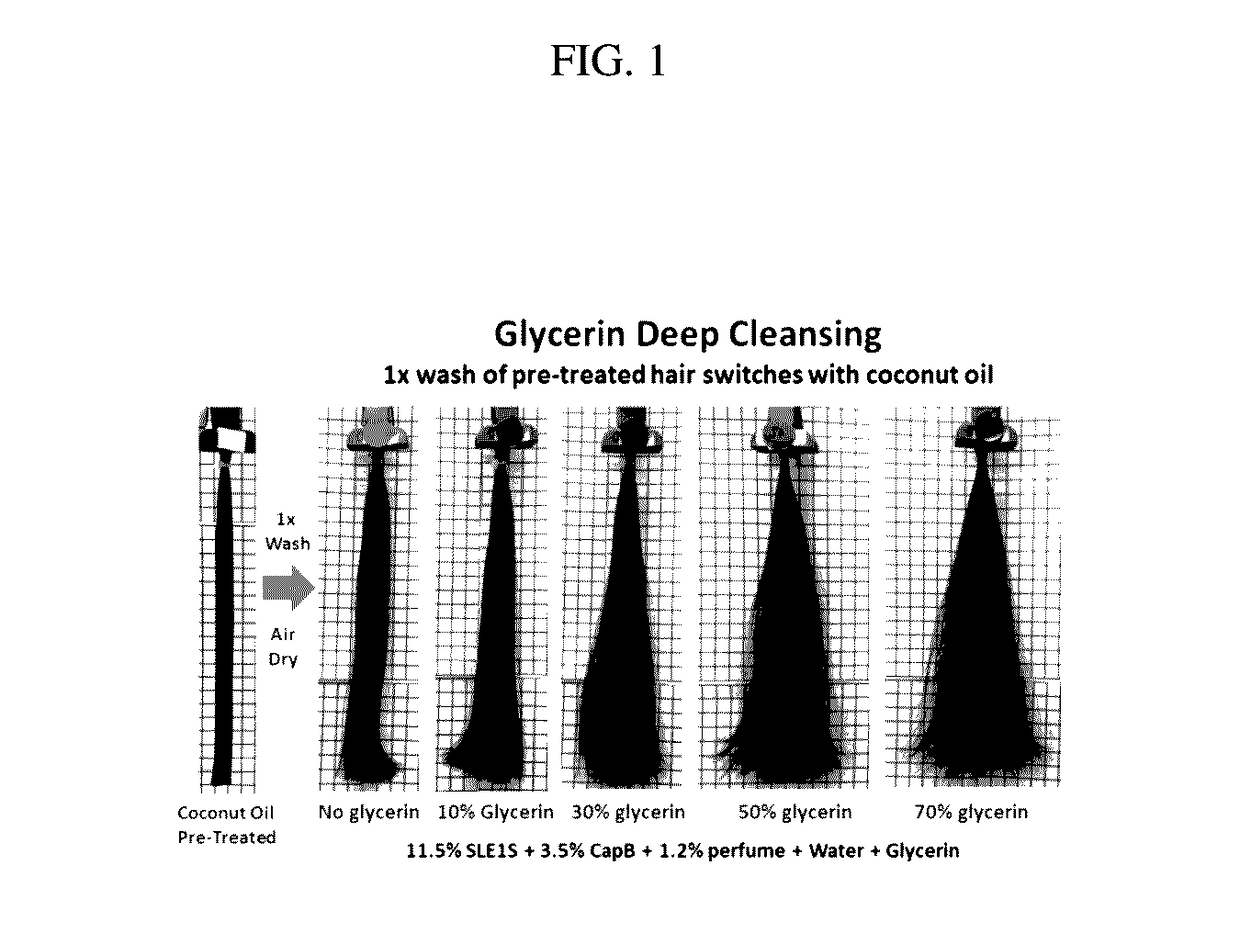

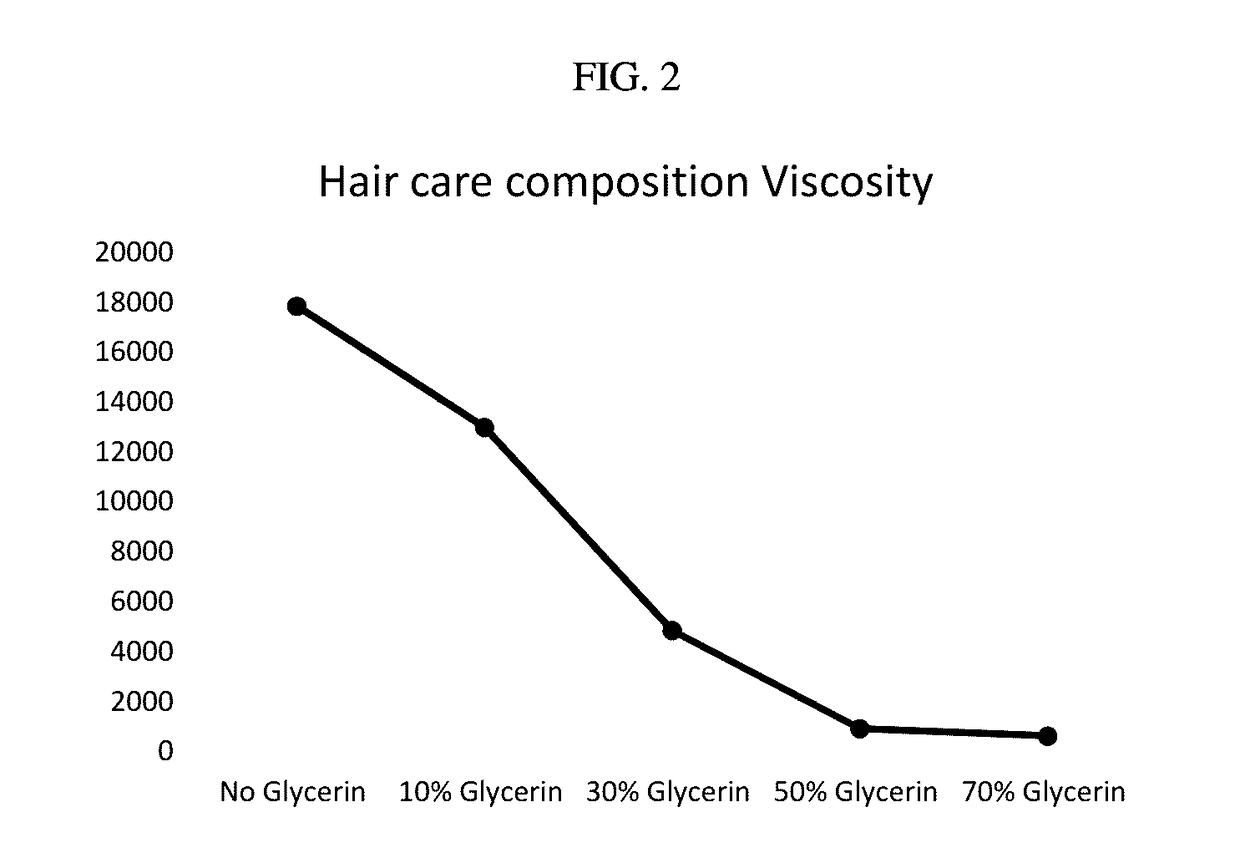

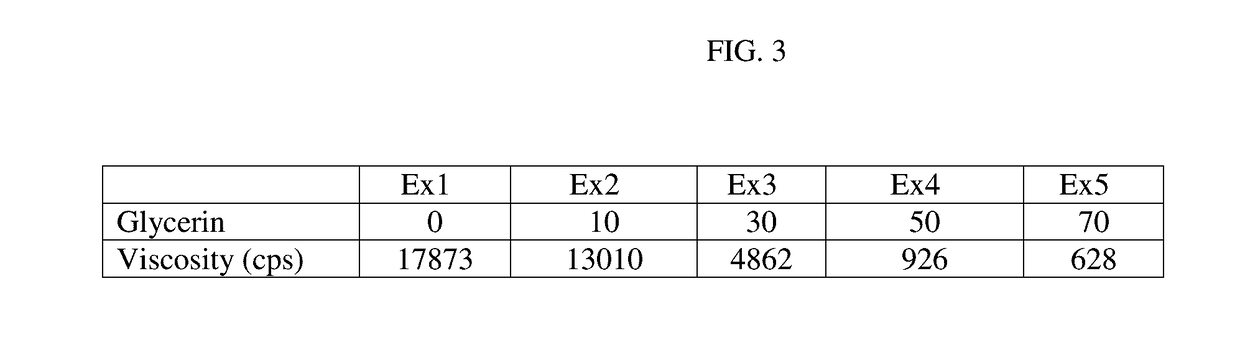

Deep cleansing hair care composition

InactiveUS20170165164A1Deep cleansingIncrease experienceCosmetic preparationsHair cosmeticsPolyolSURFACTANT BLEND

A shampoo composition is disclosed that has from about 5 to about 40 weight % of one or more detersive surfactants and an aqueous carrier comprising water and one or more polyols, wherein the weight ratio of one or more polyols to water is higher than or equal to about 0.4, and the water content is higher than or equal to about 9% by weight of the composition. The composition delivers thorough hair cleansing, good lather, good conditioning wet feel, clean rinse feel during use, leaving hair with very low residue on the hair surface. The use of the shampoo composition also provides high hair volume, smooth dry hair feel, and bouncy hair that is easy to style.

Owner:THE PROCTER & GAMBLE COMPANY

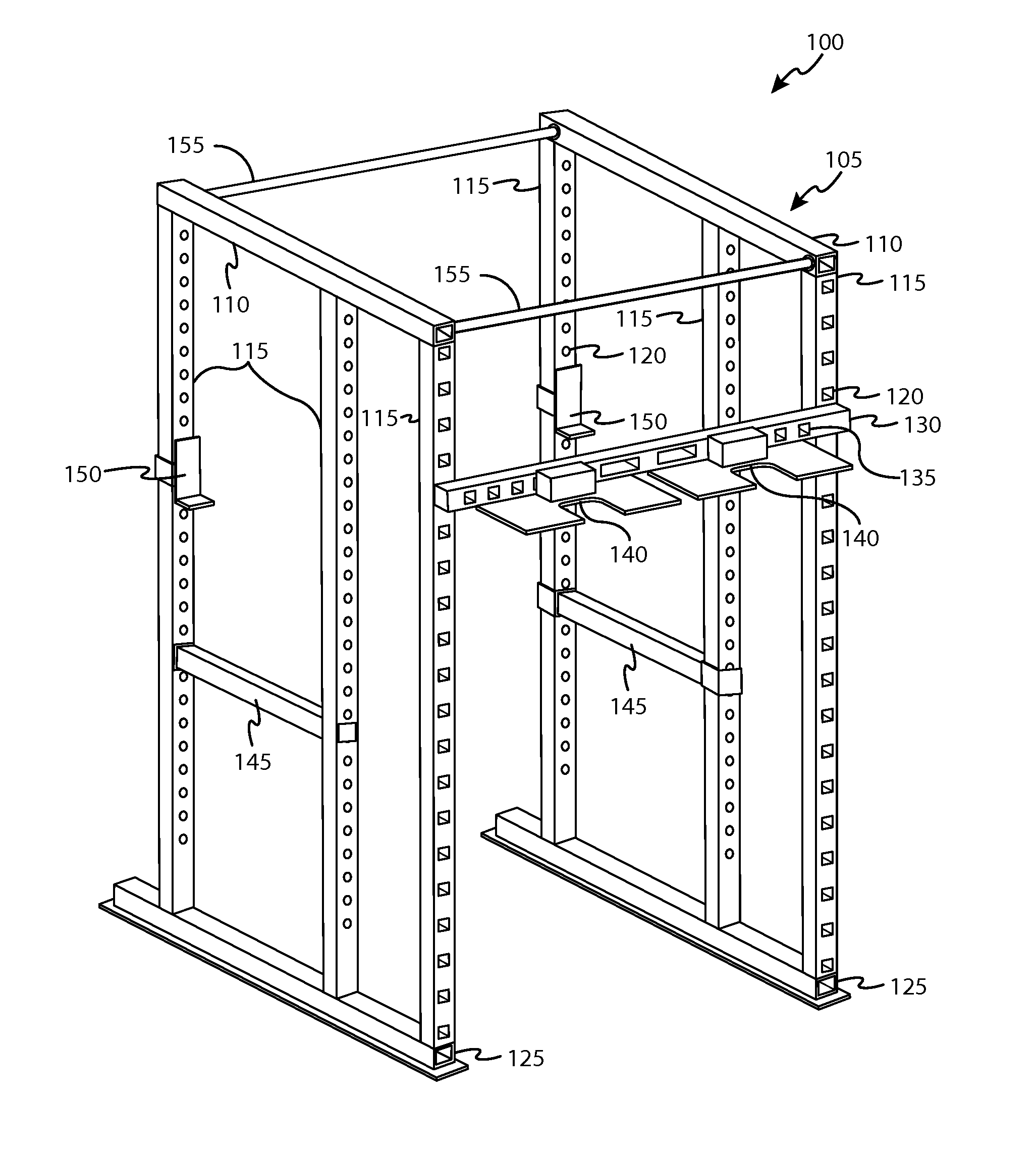

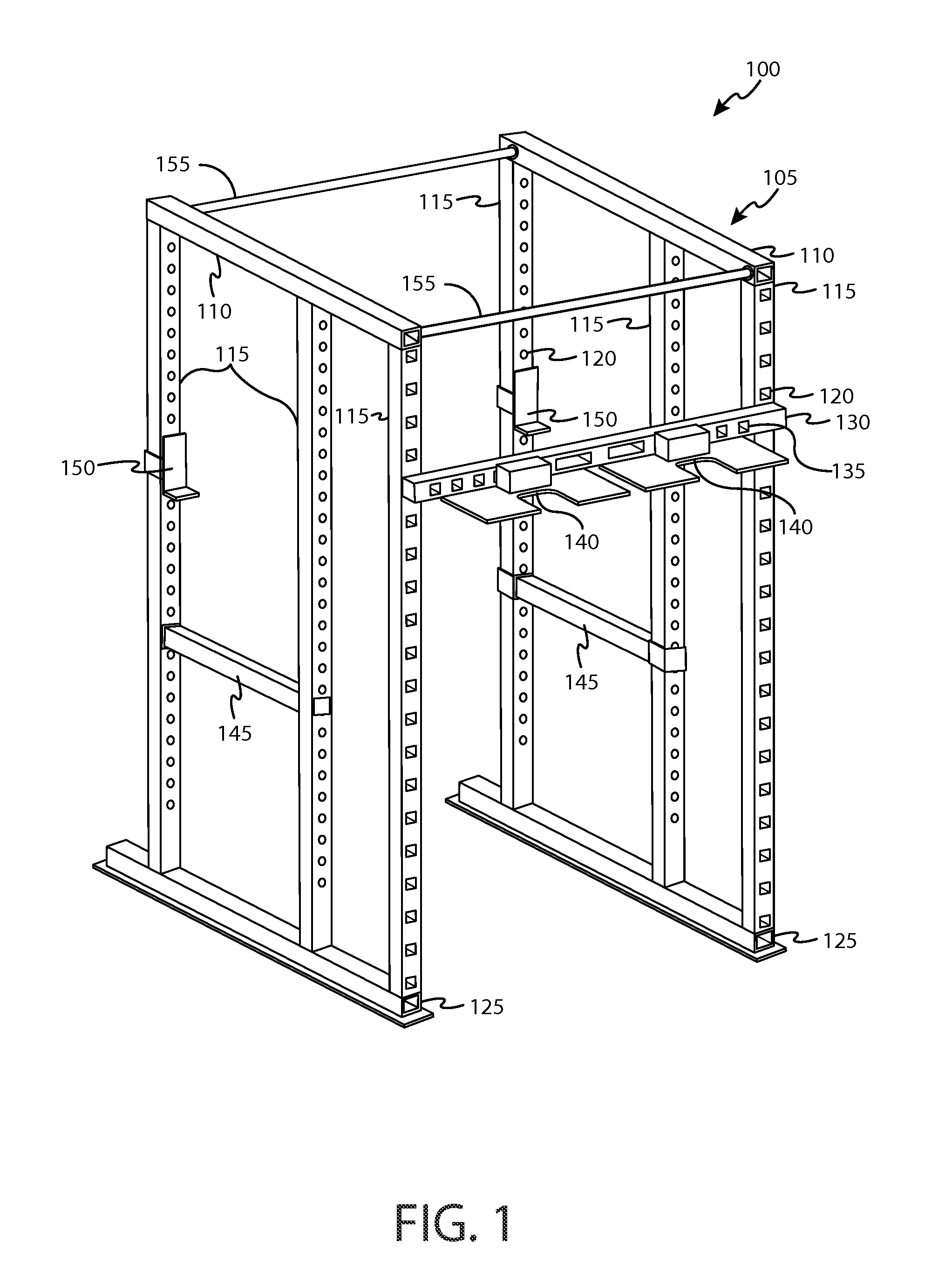

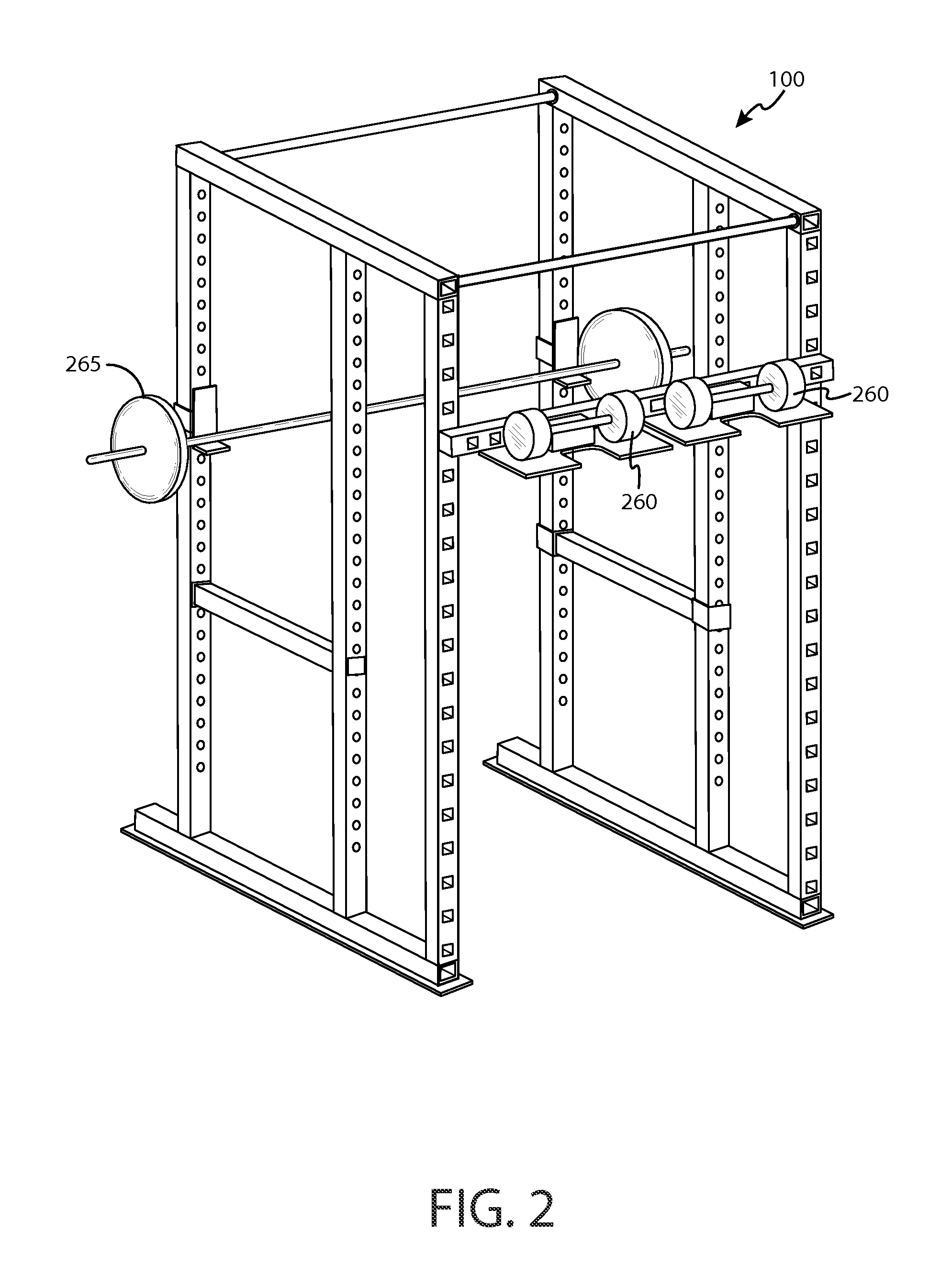

Dumbbell power rack apparatus

ActiveUS9492701B1Reduce usageSimple designDumb-bellsHorizontal barsDumbbellElectrical and Electronics engineering

The present invention provides, in at least one embodiment, a power rack apparatus for lifting dumbbells. The apparatus can have a conventional cage design or a novel cage design with dual pull up bars. The apparatus also has novel dumbbell trays configured to attach to a novel horizontal support. The horizontal support is configured to attach to the cage in a plurality of vertical positions and the horizontal support contains a plurality of slots for horizontal width adjustment of the dumbbell trays. The slots on the horizontal support are configured to receive a plurality of inclined dumbbell trays. The apparatus can be a combo power rack configured to hold barbells and dumbbells or a simplified power rack apparatus configured to just hold dumbbells.

Owner:BOGNATZ DON

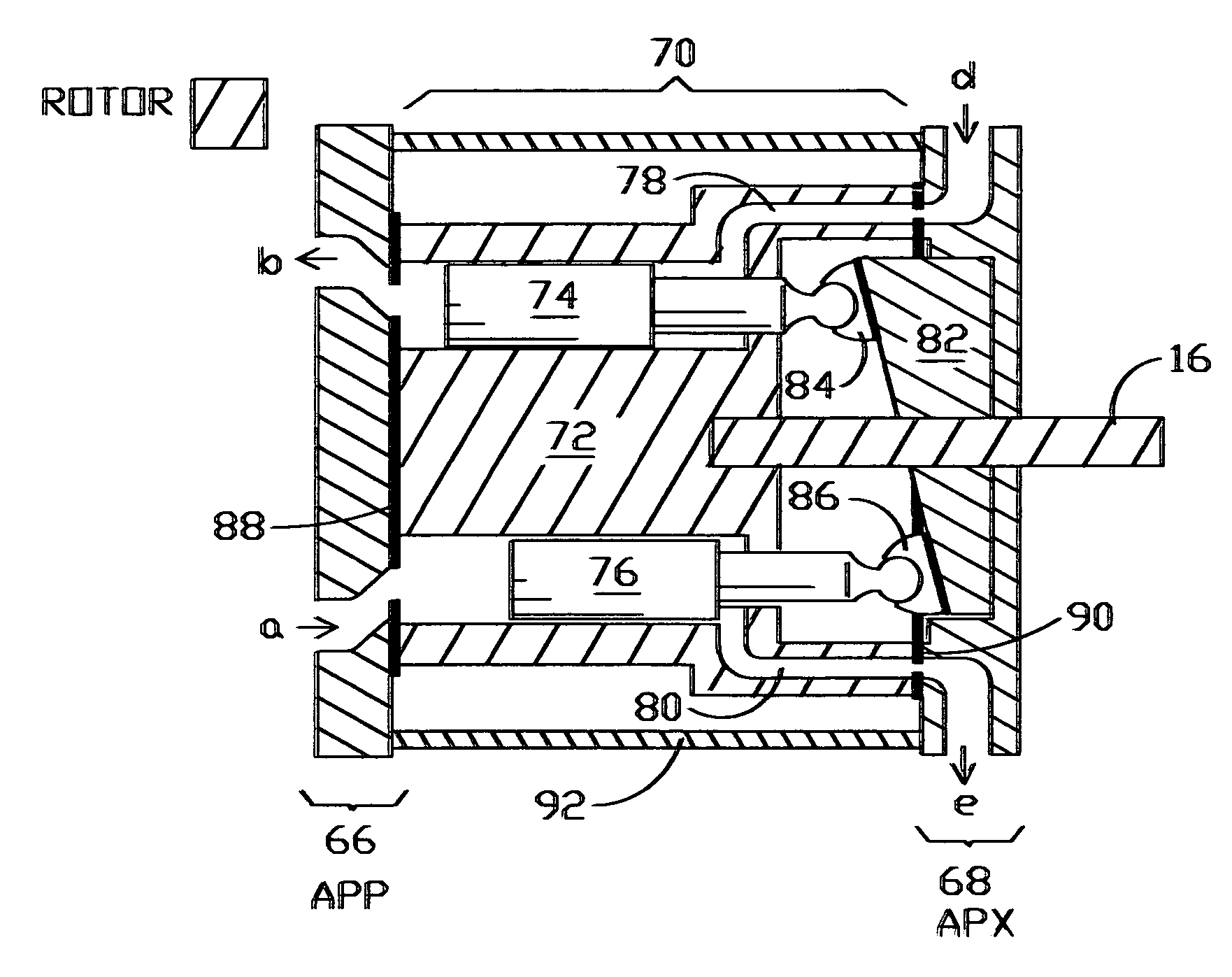

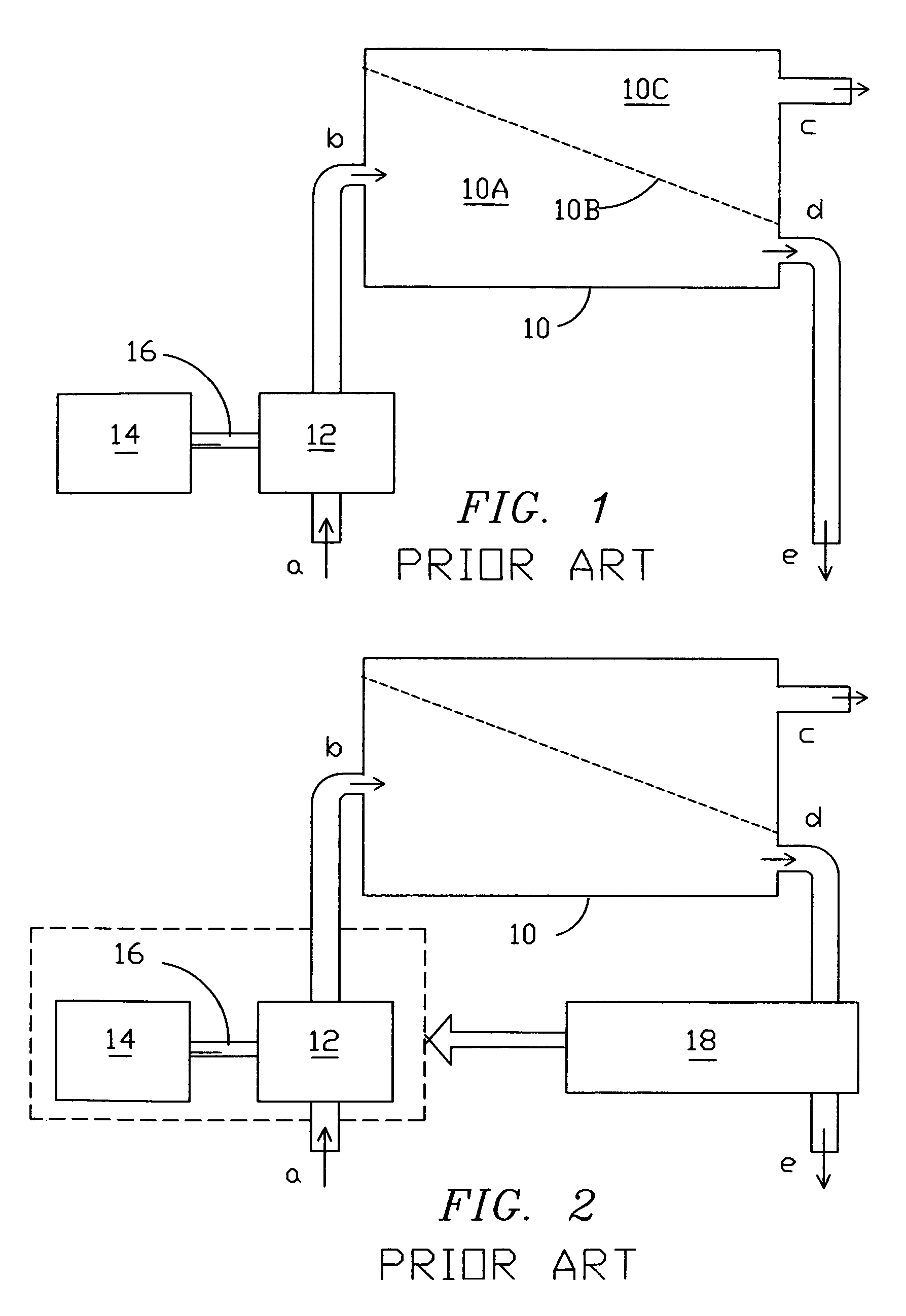

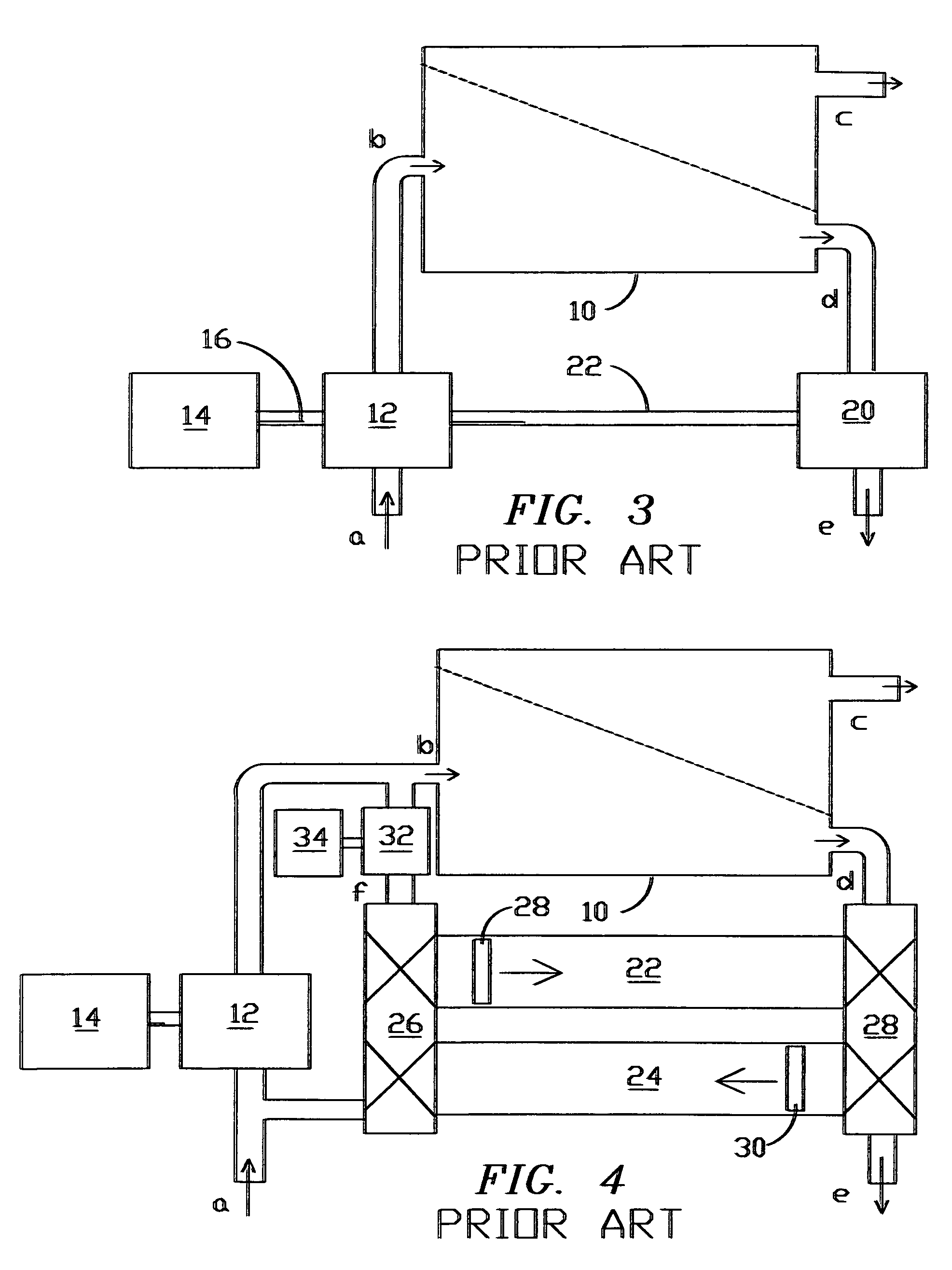

Combined axial piston liquid pump and energy recovery pressure exchanger

InactiveUS7799221B1Improve welfareMinimize the numberMembranesGeneral water supply conservationReciprocating motionEnergy recovery

A pumping machine, that can serve a system as the sole main pump for pressurizing a primary liquid flow, incorporates, in a single machine, a rotor-drum type AP (axial piston) pump and a PX (pressure exchanger) that recovers energy from a secondary liquid flow such as the brine discharge from an RO seawater desalination system, with benefits including fewer moving parts and small machine size along with lower capital and operating costs. A single rotor-drum containing the cylinders and pistons is located between two end blocks, one or both configured with manifold passageways, ports and sliding valves. A swash-plate at one end reciprocates the pistons axially when the rotor-drum is rotated. Two working chambers, primary and secondary, are formed at opposite ends of a single piston in each cylinder, thus enabling the single rotor-drum to function as a primary liquid-pressurizing axial pump (AP) with sliding valves at the primary end enabling primary liquid pumping, and as a secondary outflow-driven pressure exchanger (PX) recovering energy from pressure drop in the secondary liquid flow and thus contributing work to primary pumping, saving energy and reducing operating costs.

Owner:OCEAN PACIFIC TECH