Silicon-based heterojunction solar cell and preparation method thereof

A solar cell and heterojunction technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve problems such as small variable range of work function, achieve the effects of increasing short-circuit current density, improving conversion efficiency, and low process temperature

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

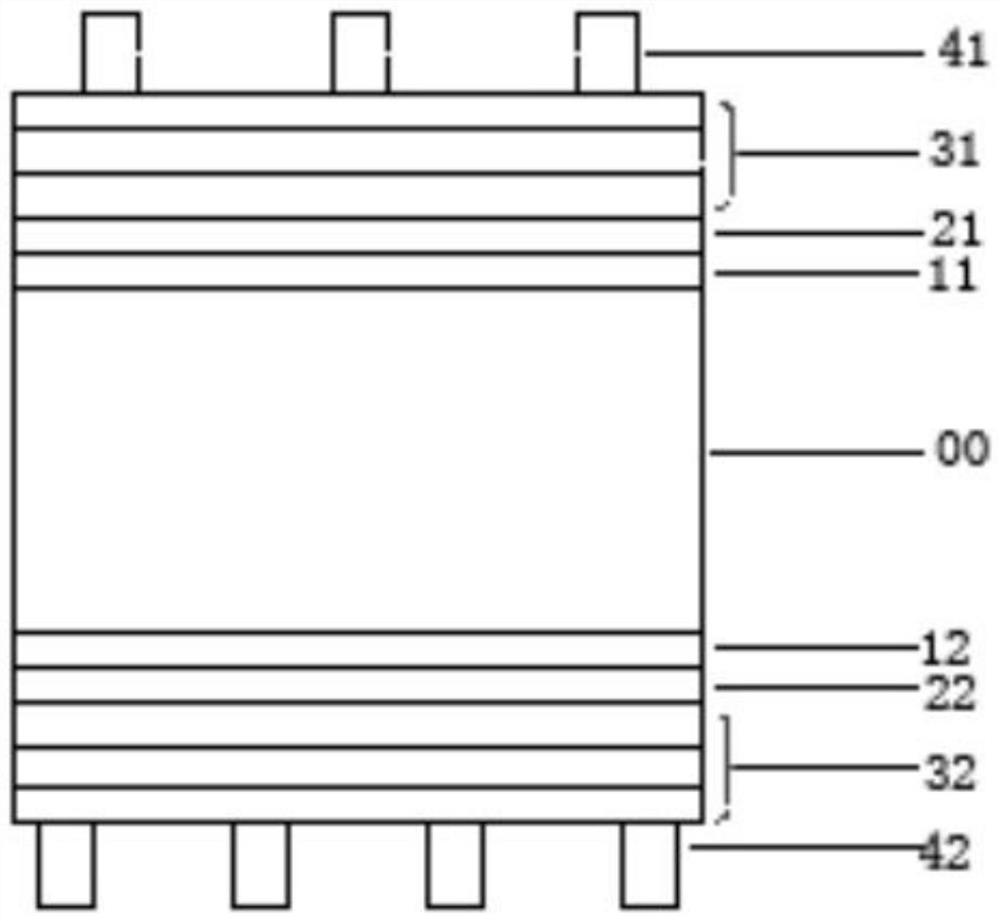

[0049] A method for preparing a silicon-based heterojunction solar cell, specifically comprising the following steps:

[0050] (1) Texturing and cleaning the crystalline silicon wafer to obtain the crystalline silicon substrate 00;

[0051] (2) Utilizing plasma chemical vapor deposition, depositing the first intrinsic amorphous silicon layer 11 and the first doped layer 21 sequentially on the upper surface of the crystalline silicon substrate 00, and depositing the first intrinsic amorphous silicon layer 21 sequentially on the lower surface of the crystalline silicon substrate 00. Two intrinsic amorphous silicon layers 12 and a second doped layer 22;

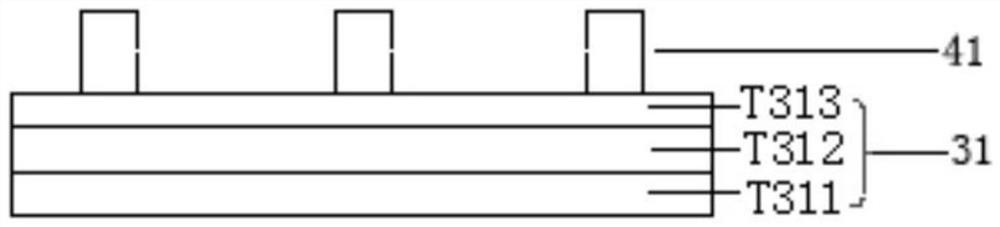

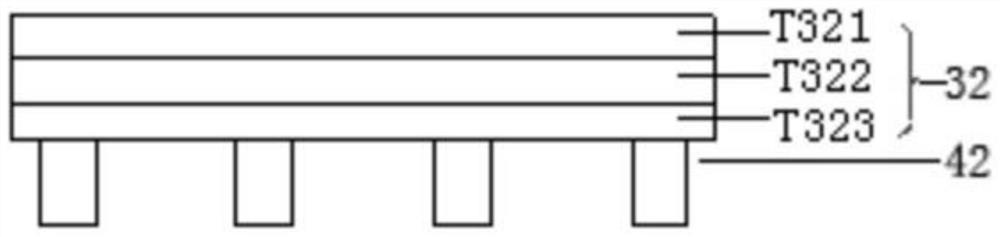

[0052] (4) Utilize the magnetron sputtering mode, deposit the first TCO film 311, the second TCO film 312 and the 3rd TCO film 313 successively on the upper surface of the first doped layer 21, meanwhile, process and first doped layer 21 (n-type amorphous silicon) contact with the first TCO film 311, use plasma chemical vapor d...

Embodiment 2

[0056] A method for preparing a silicon-based heterojunction solar cell, specifically comprising the following steps:

[0057] (1) Texturing and cleaning the crystalline silicon wafer to obtain the crystalline silicon substrate 00;

[0058] (2) Utilizing plasma chemical vapor deposition, depositing the first intrinsic amorphous silicon layer 11 and the first doped layer 21 sequentially on the upper surface of the crystalline silicon substrate 00, and depositing the first intrinsic amorphous silicon layer 21 sequentially on the lower surface of the crystalline silicon substrate 00. Two intrinsic amorphous silicon layers 12 and a second doped layer 22;

[0059] (4) Utilize the electron beam evaporation mode, deposit the first TCO thin film 311, the second TCO thin film 312 and the third TCO thin film 313 successively on the upper surface of the first doped layer 21, meanwhile, process and first doped layer 21 (n-type amorphous silicon) contact with the first TCO thin film 311, ...

Embodiment 3

[0063] A method for preparing a silicon-based heterojunction solar cell, specifically comprising the following steps:

[0064] (1) Texturing and cleaning the crystalline silicon wafer to obtain the crystalline silicon substrate 00;

[0065] (2) Utilizing plasma chemical vapor deposition, depositing the first intrinsic amorphous silicon layer 11 and the first doped layer 21 sequentially on the upper surface of the crystalline silicon substrate 00, and depositing the first intrinsic amorphous silicon layer 21 sequentially on the lower surface of the crystalline silicon substrate 00. Two intrinsic amorphous silicon layers 12 and a second doped layer 22;

[0066] (4) Utilize the reactive plasma deposition method, deposit the first TCO thin film 311, the second TCO thin film 312 and the third TCO thin film 313 successively on the upper surface of the first doped layer 21, meanwhile, process and first doped layer 21 (n-type amorphous silicon) contact with the first TCO film 311, use ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More