Patents

Literature

43results about How to "Lower Schottky Barrier Height" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

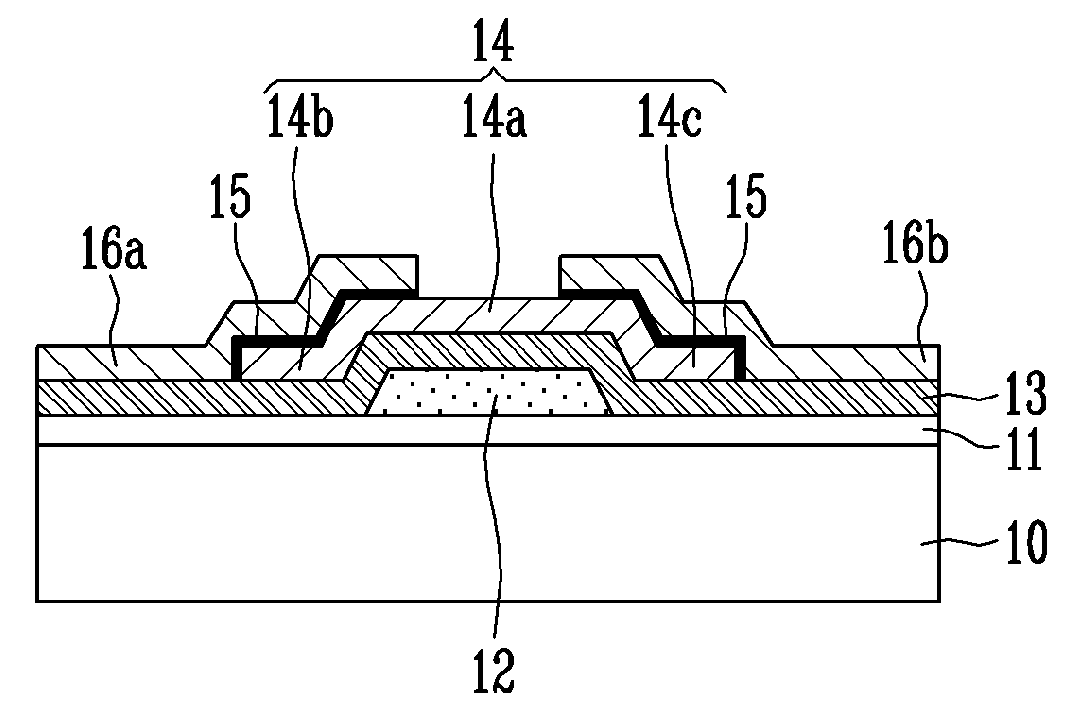

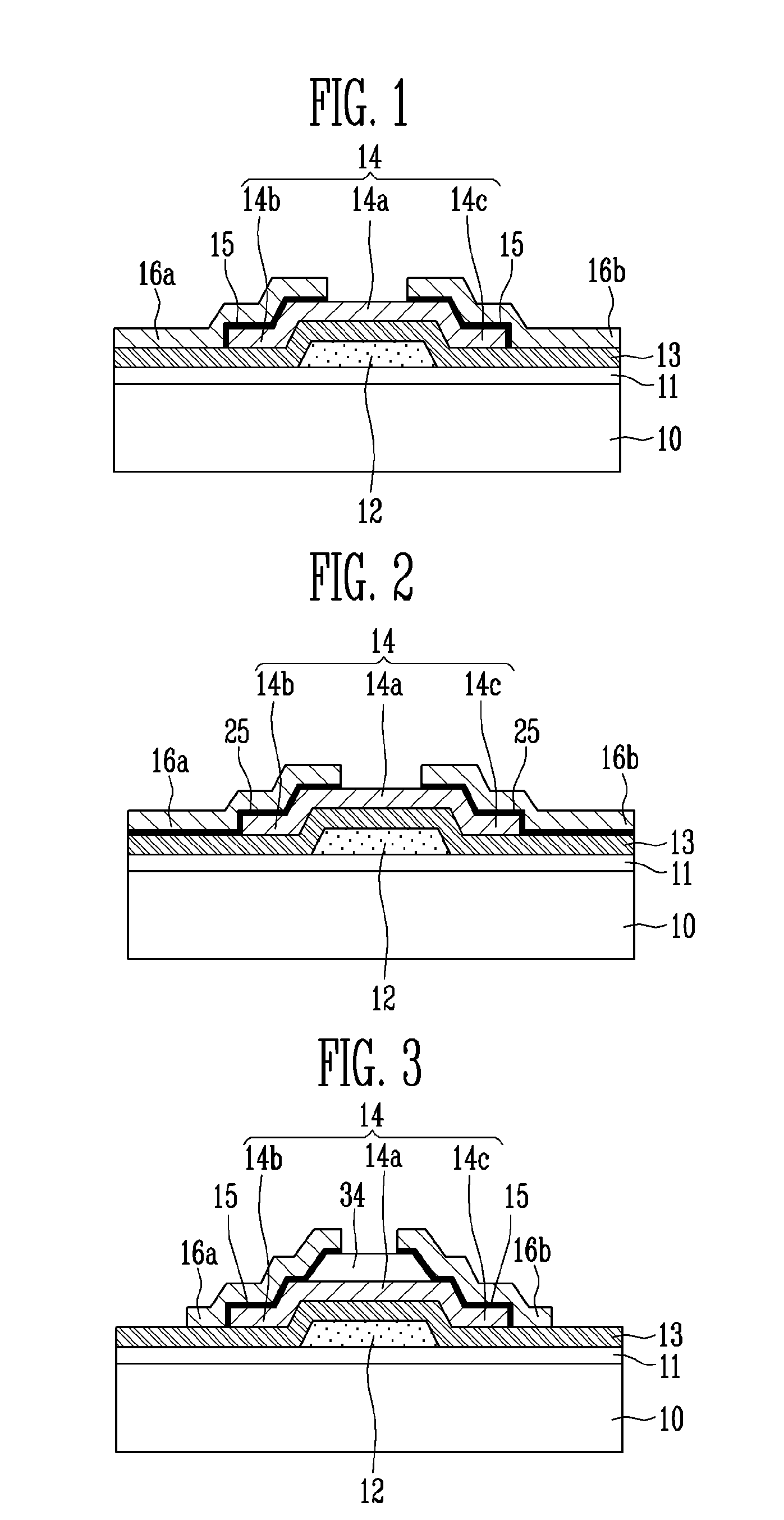

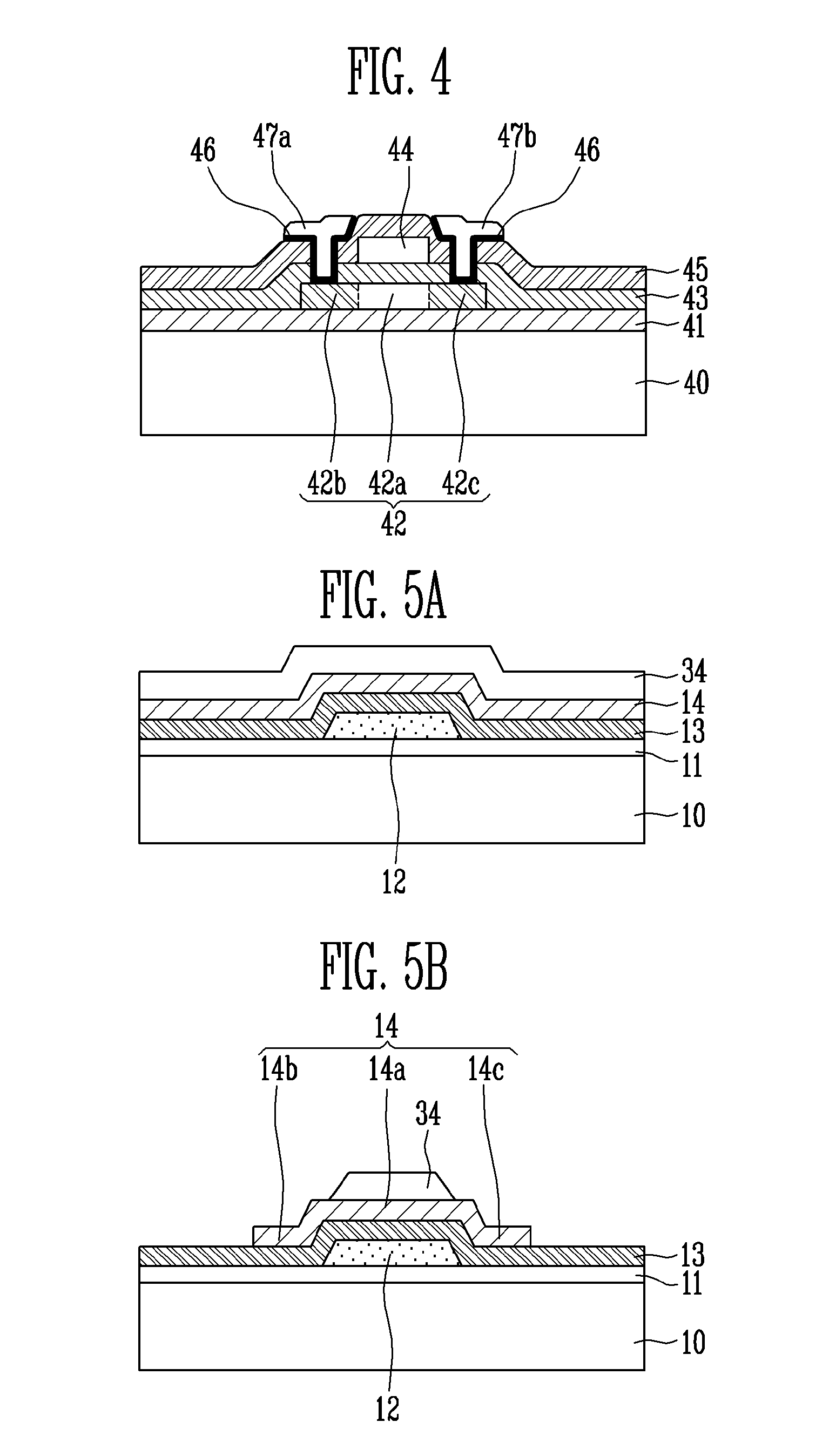

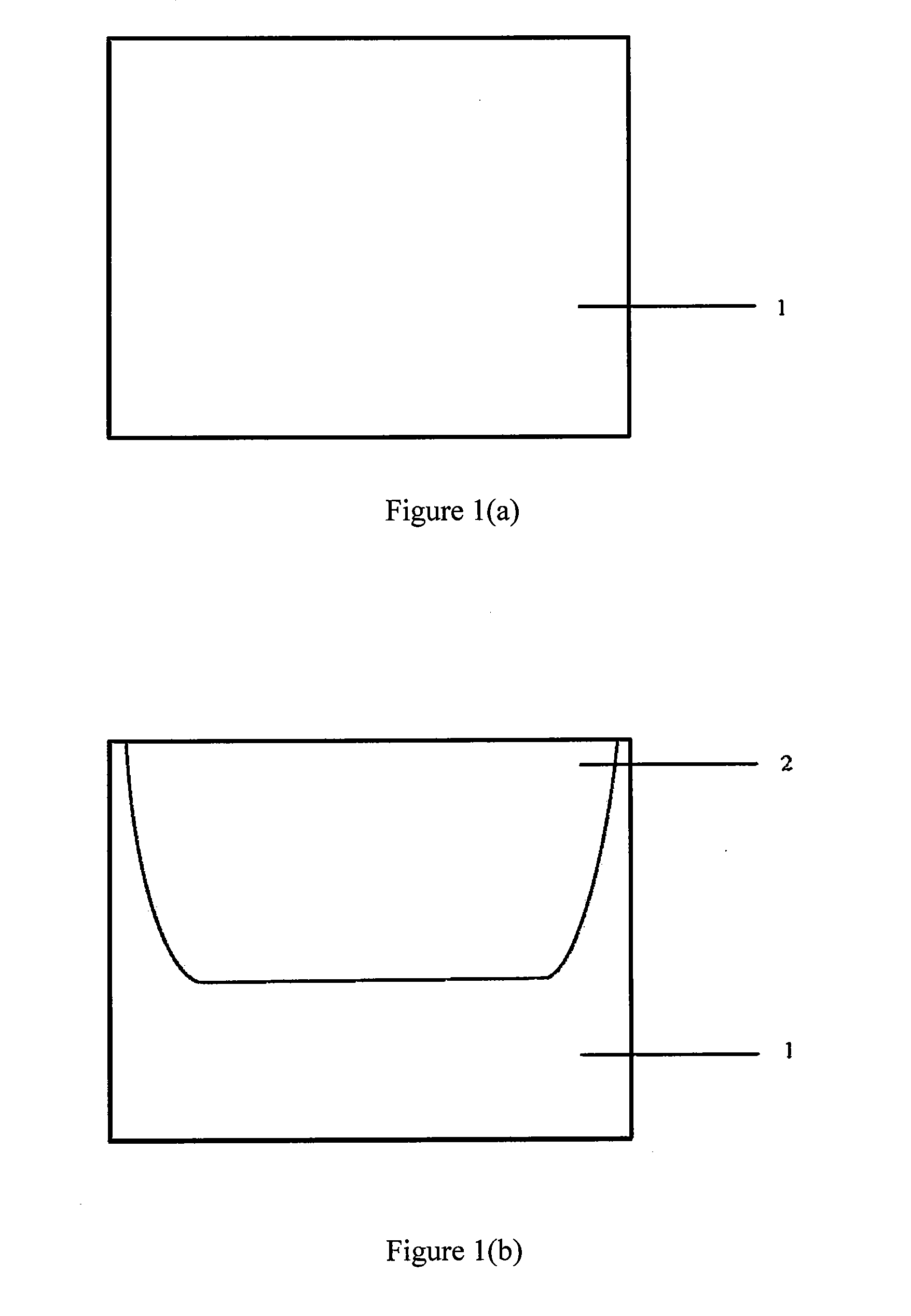

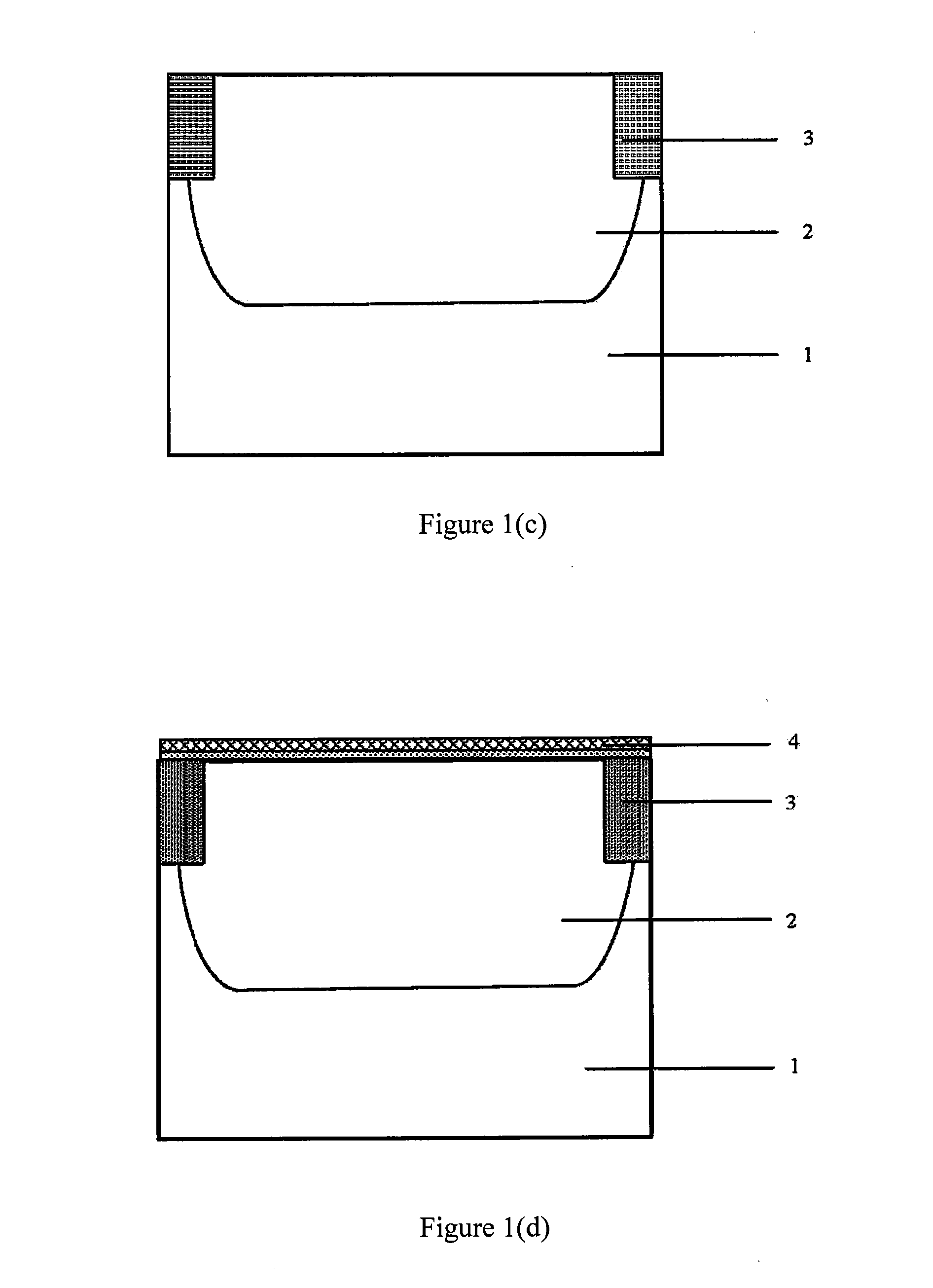

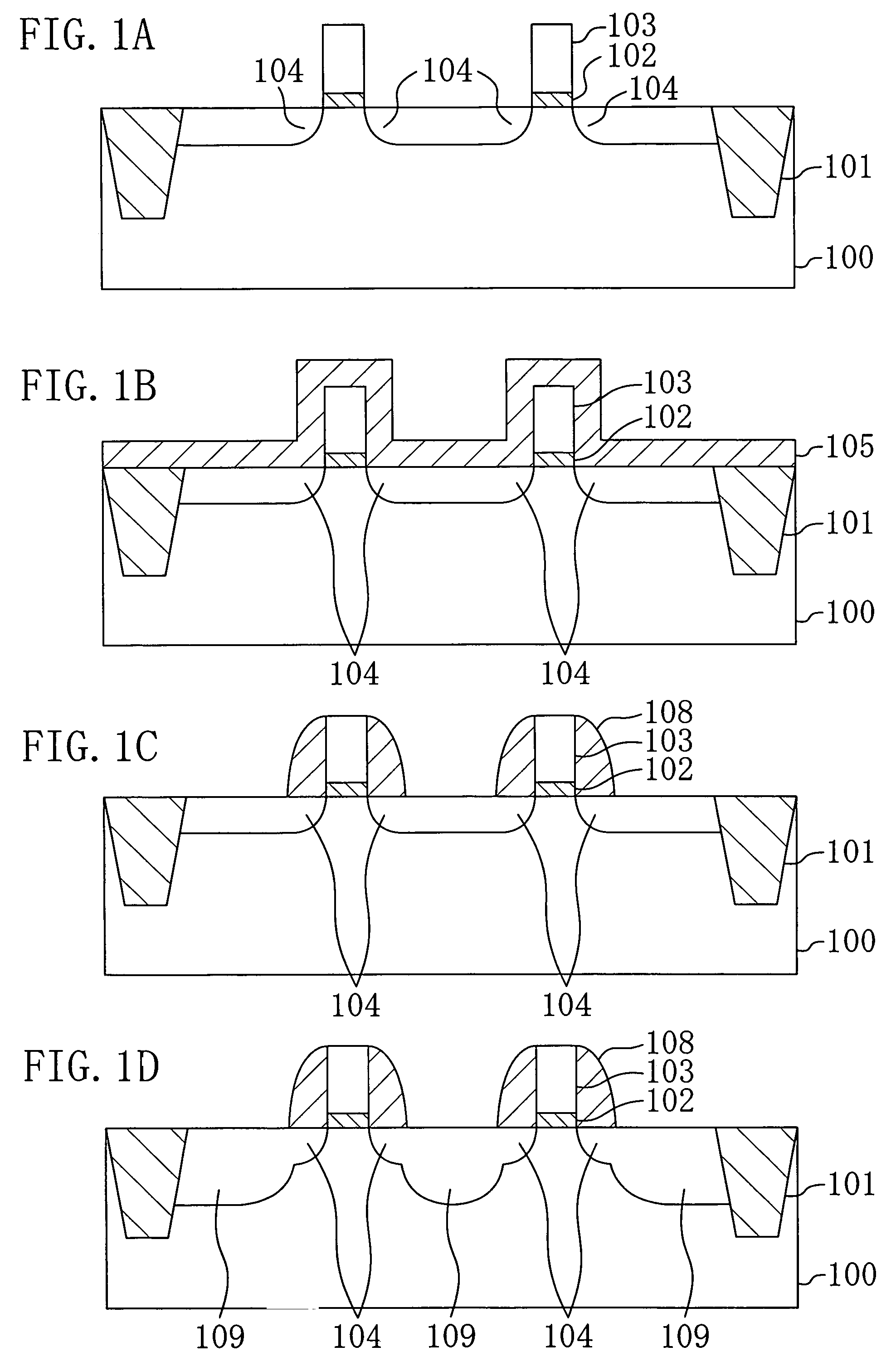

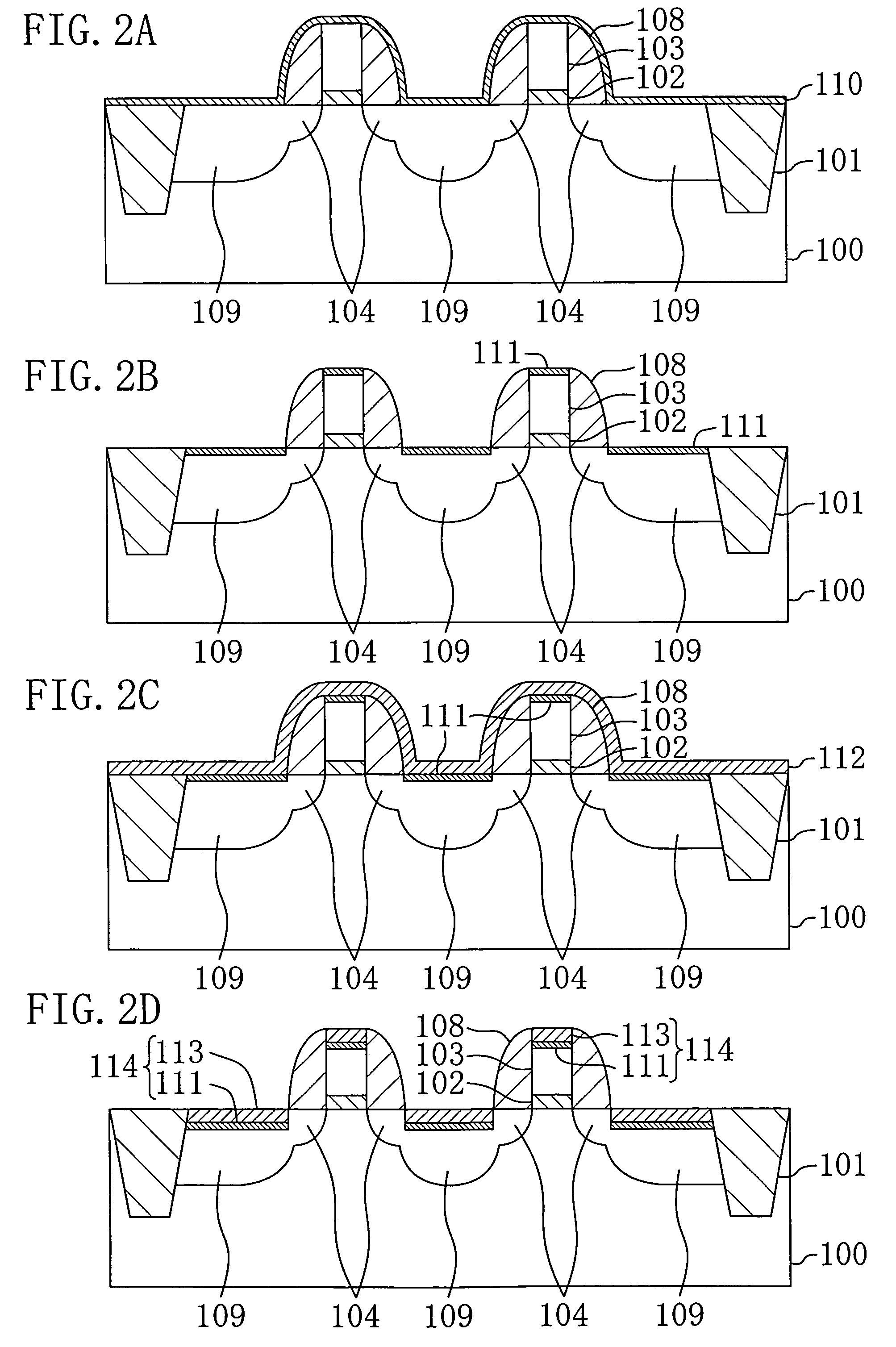

Thin film transistor, method of manufacturing the same, and flat panel display device haviing the same

InactiveUS20090315026A1Good ohmic contactLower Schottky Barrier HeightTransistorNon-linear opticsOhmic contactEngineering

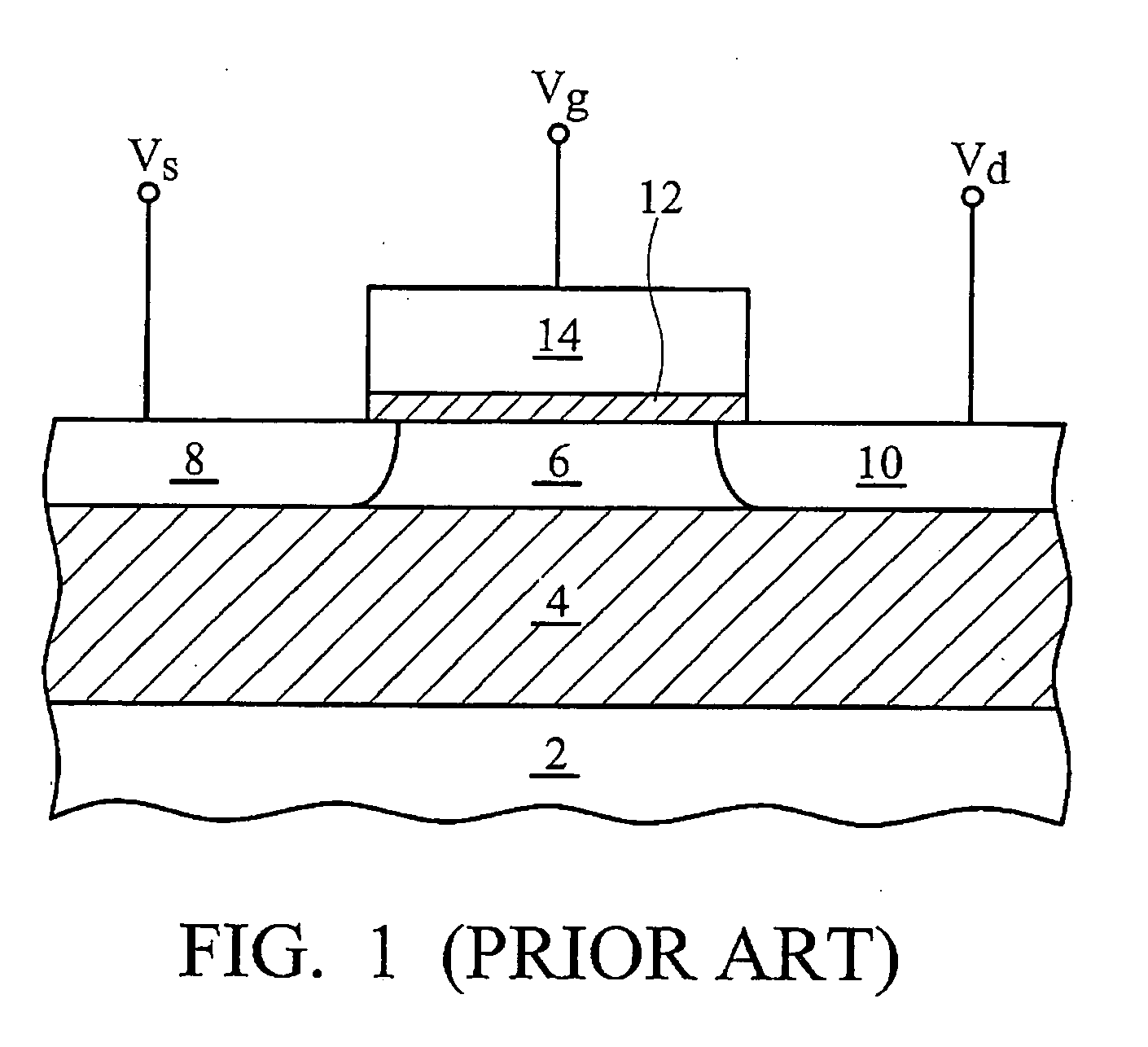

A thin film transistor, a method of manufacturing the same, and a flat panel display device having the same use an oxide semiconductor as an active layer, wherein the thin film transistor includes: an oxide semiconductor layer formed on a substrate and having a channel region, a source region, and a drain region; a gate electrode insulated from the oxide semiconductor layer by a gate insulating layer; an ohmic contact layer formed on the source region and the drain region of the oxide semiconductor layer; and a source electrode and a drain electrode coupled to the source region and the drain region through the ohmic contact layer, the ohmic contact layer being formed of a metal having a lower work function lower than work functions of the source electrode and the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

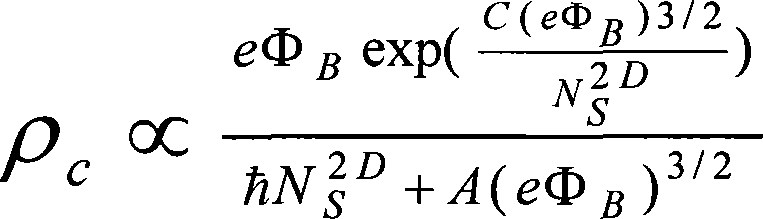

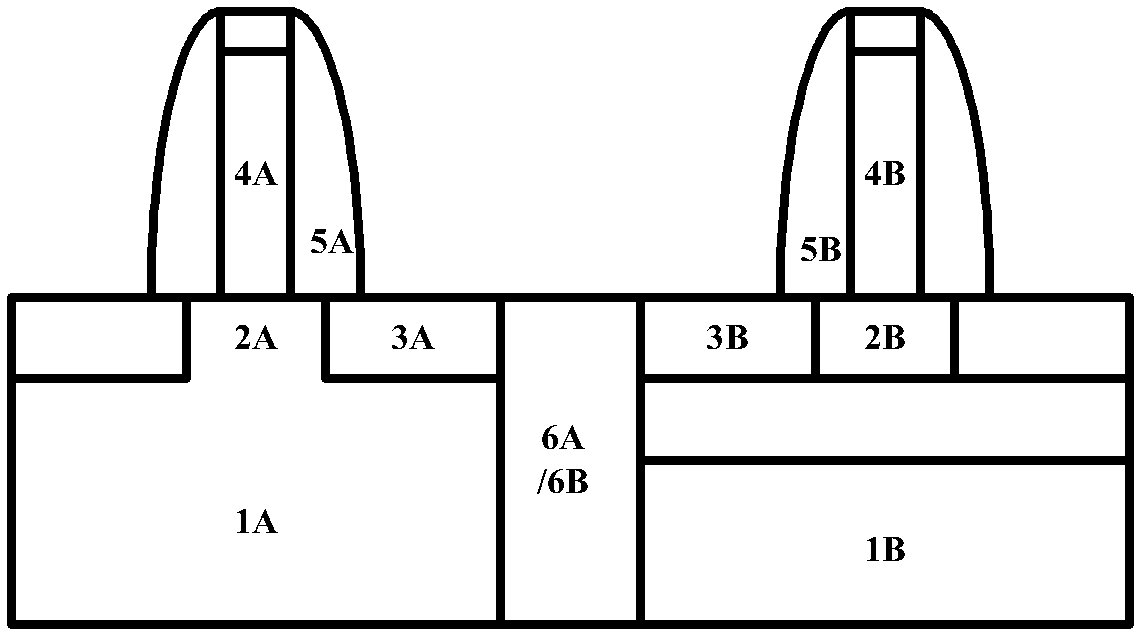

Capacitor-less 1T-DRAM cell with Schottky source and drain

InactiveUS20060125121A1Improve equipment reliabilityLower bandgapTransistorSolid-state devicesCapacitanceGate dielectric

A tunneling injection based Schottky source / drain memory cell comprising: a first semiconductor layer with a first conductivity type overlying an insulating layer, wherein the first semiconductor acts as a body region; a gate dielectric overlying the semiconductor layer; a gate electrode overlying the gate dielectric; a pair of spacers on sides of the gate electrodes; and a first Schottky barrier junction formed on a source region and a second Schottky barrier junction formed on a drain region on opposing sides of the body region. The source and the regions have an overlapping portion with the gate electrode and length of overlapping portion is preferably greater than about 5 Å. Interfacial layers are formed between the first and the second Schottky barrier regions.

Owner:TAIWAN SEMICON MFG CO LTD

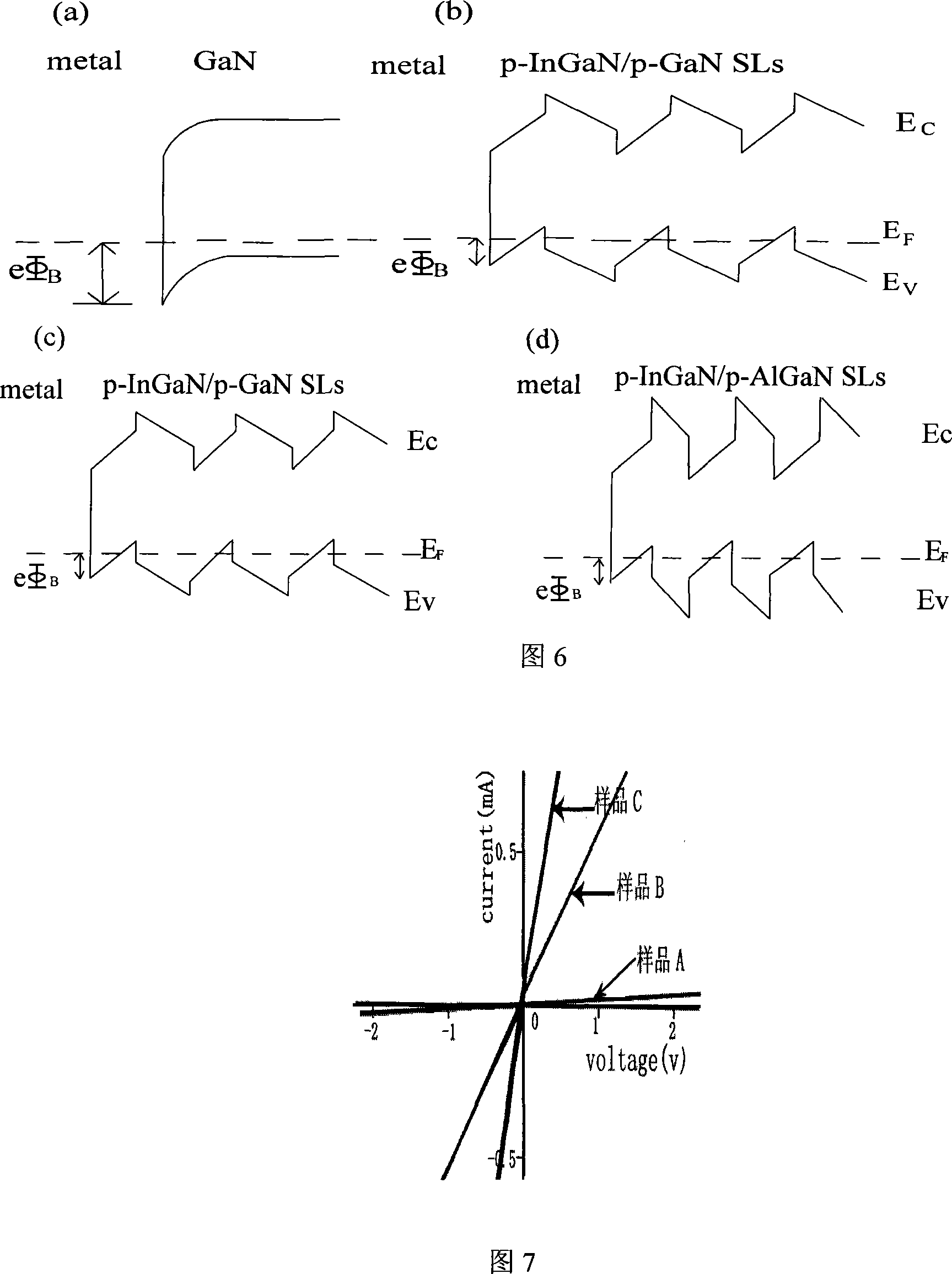

Method of producing p-GaN low-resistance Ohm contact

InactiveCN101183642AImprove surface qualityIncrease hole concentrationFinal product manufactureSemiconductor/solid-state device manufacturingOhmic contactGallium nitride

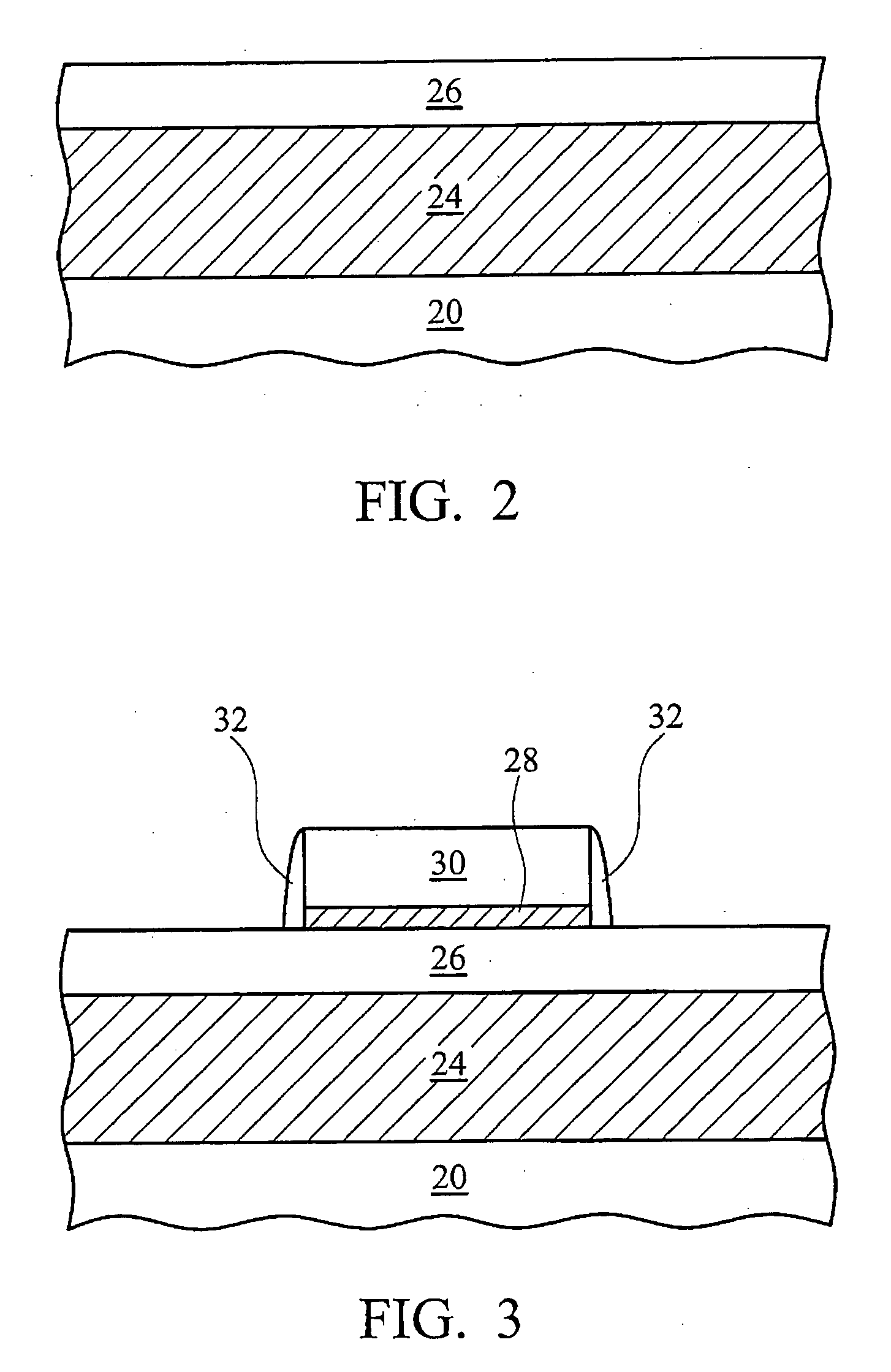

The invention discloses a preparation method of the p-GaN ohmic contact with a low resistance, relating to a p-GaN, and provides a preparation method of a low resistance p-GaN ohmic contact. The invention comprises the following steps: a (0001) oriented sapphire substrate is arranged in a reaction chamber and heated in an atmosphere of H2, and then is cooled, and a nitriding treatment is performed on the substrate; cooling the material and a GaN buffer layer grows on the material, then the material is heated to recrystallize the GaN buffer layer; a layer of GaN grows on the epitaxy of the material; the material is cooled to grows a GaN layer doping Mg; the material is cooled to grow five cycles of p-InGaN / p-AlGaN superlattice layer; a p-InGaN top layer grows on the five cycles of p-InGaN / p-AlGaN superlattice layer. The result shows that adopting the p-InGaN / p-AlGaN superlattice layer as a top layer can provide a lower specific contact resistance.

Owner:EPITOP PHOTOELECTRIC TECH

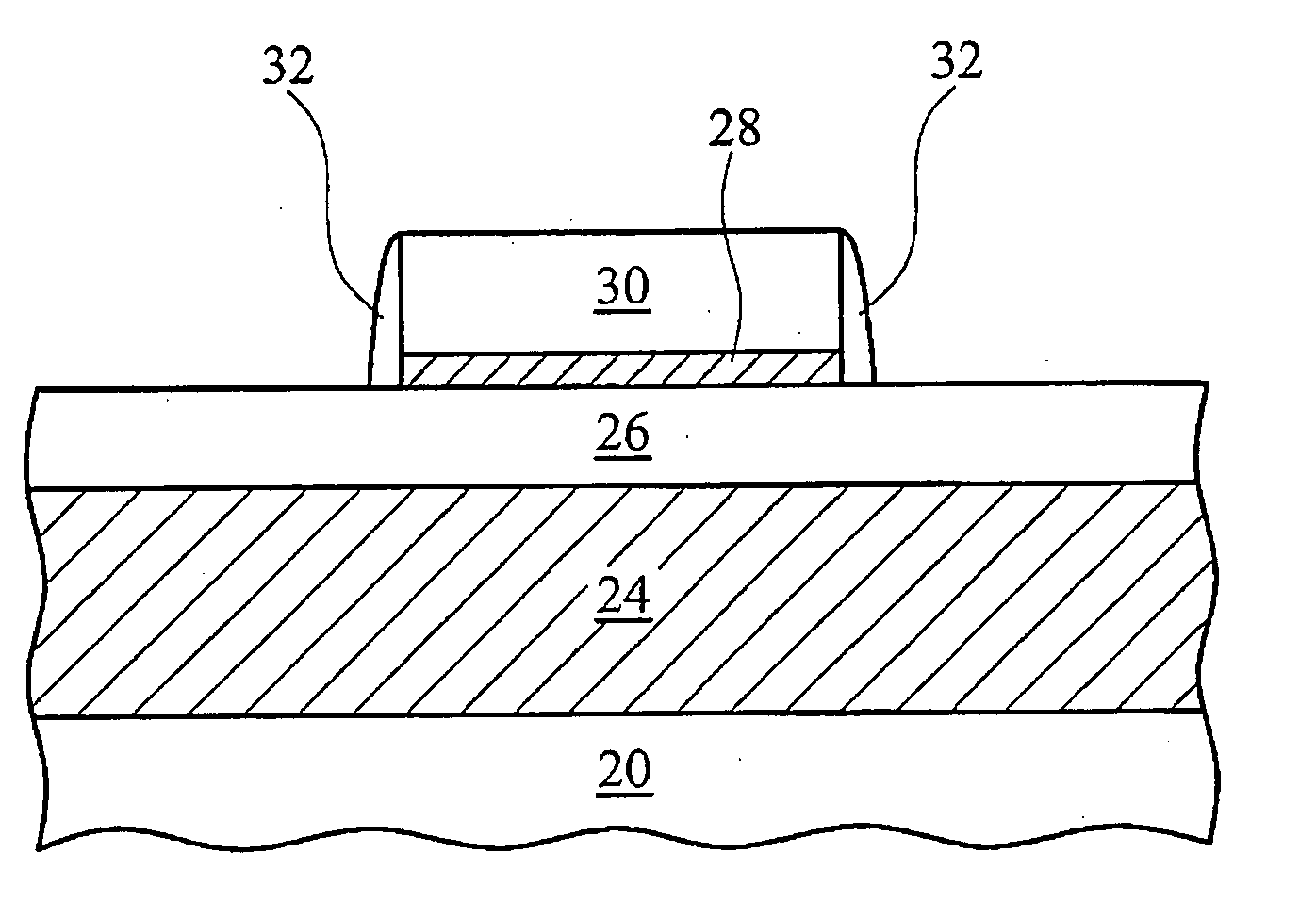

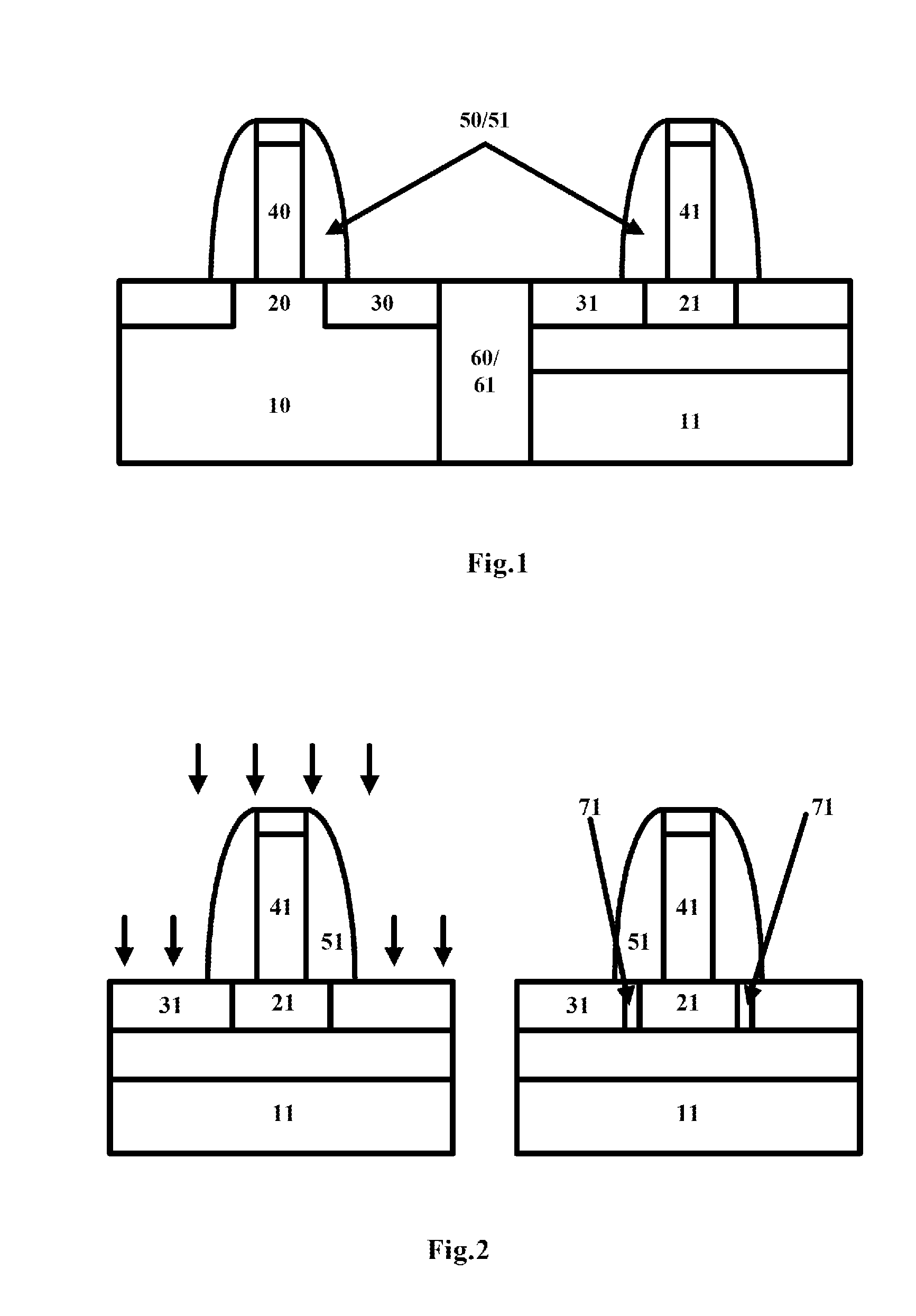

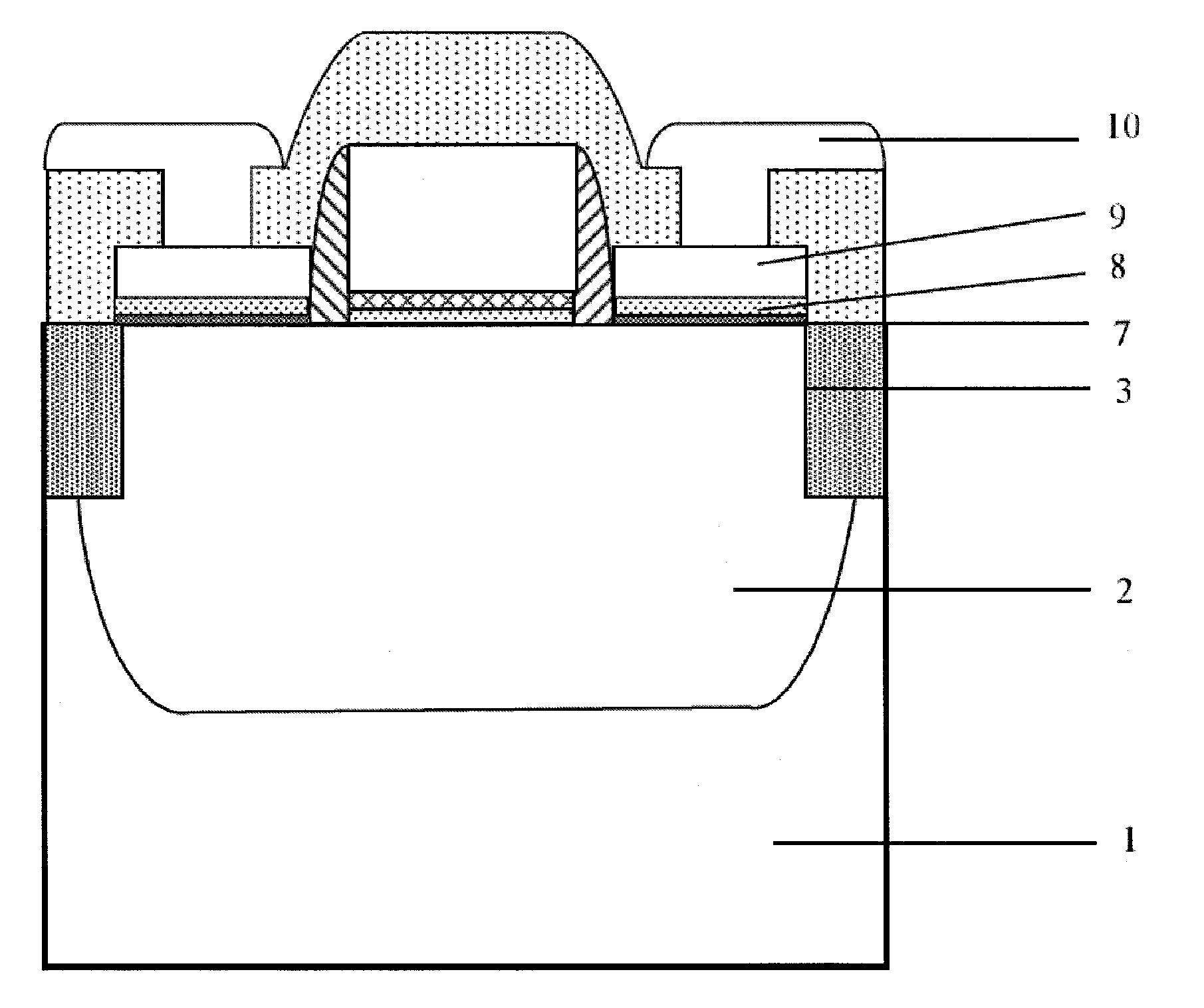

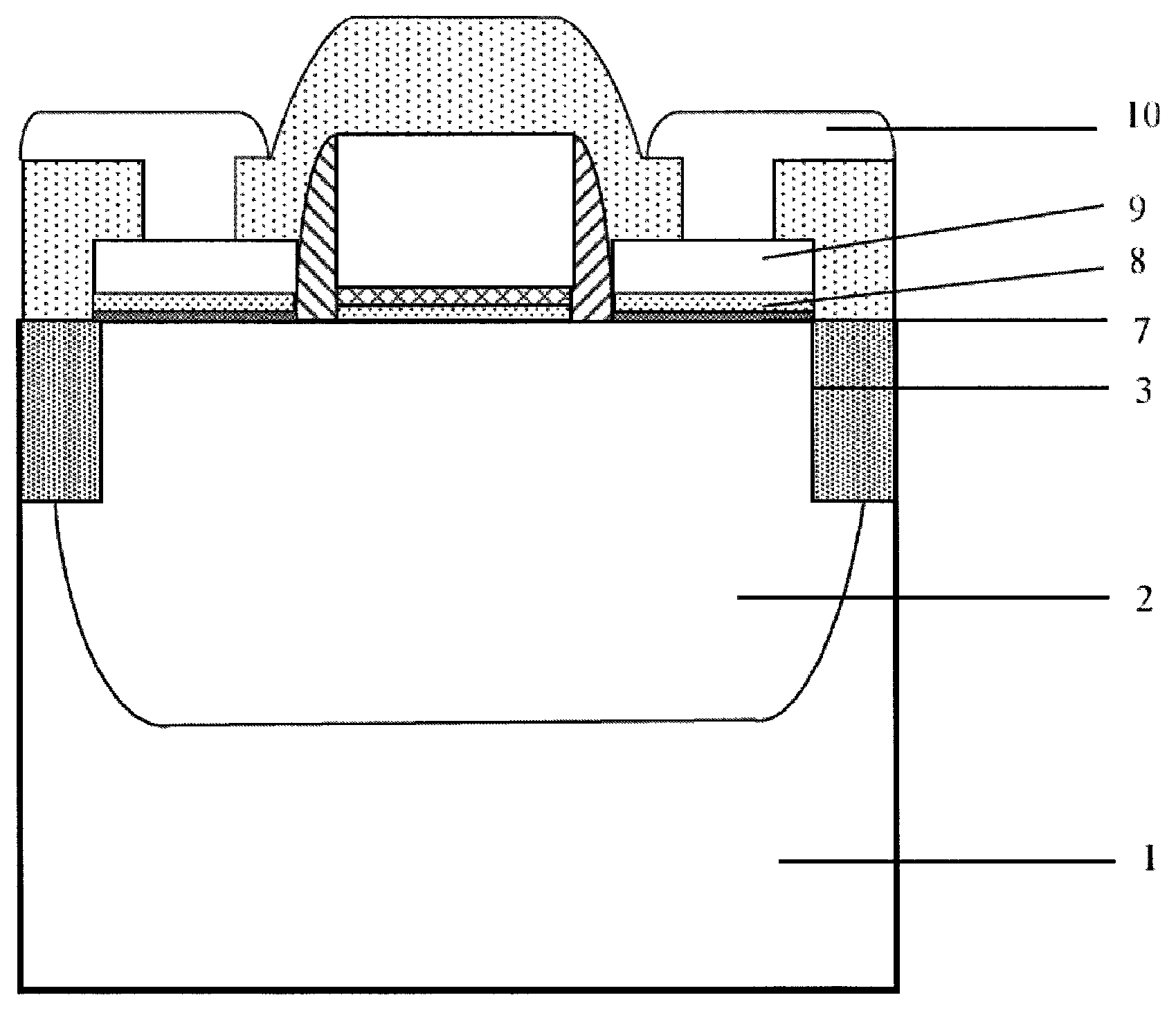

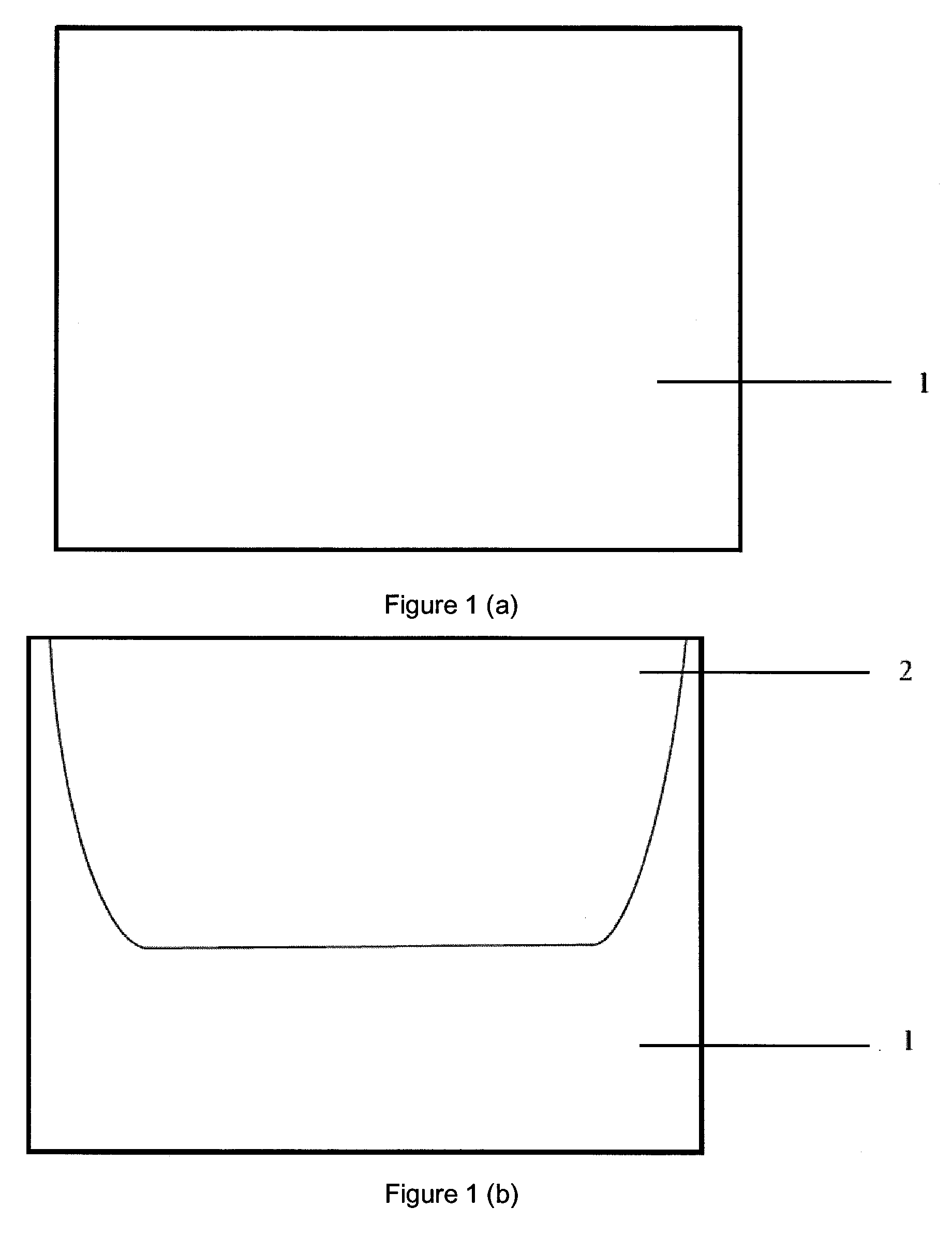

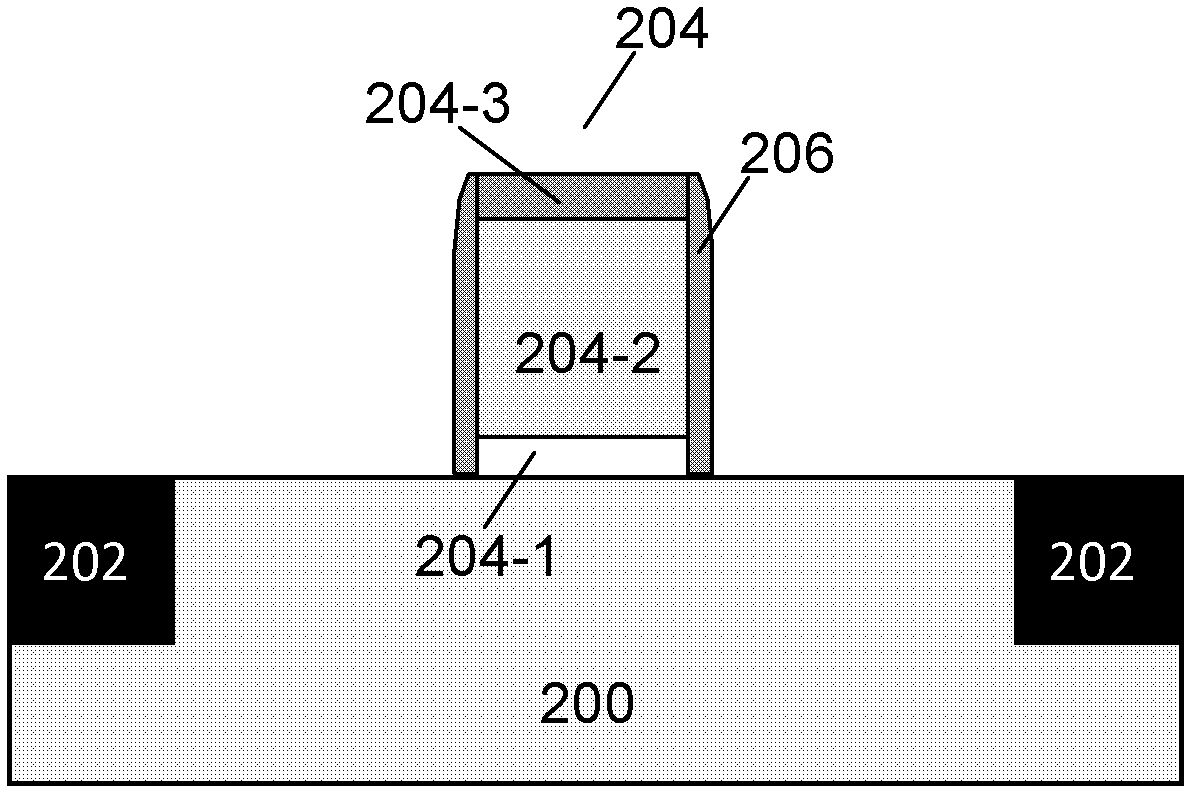

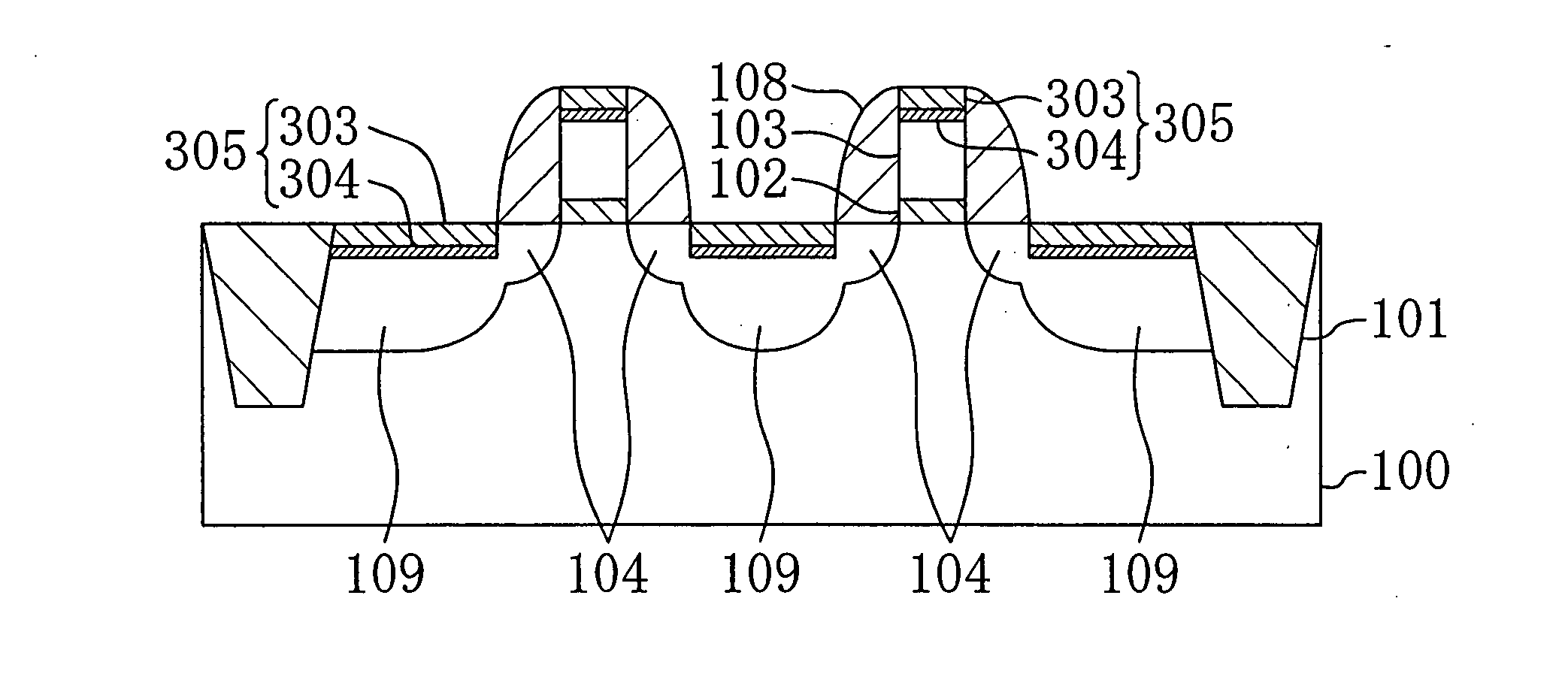

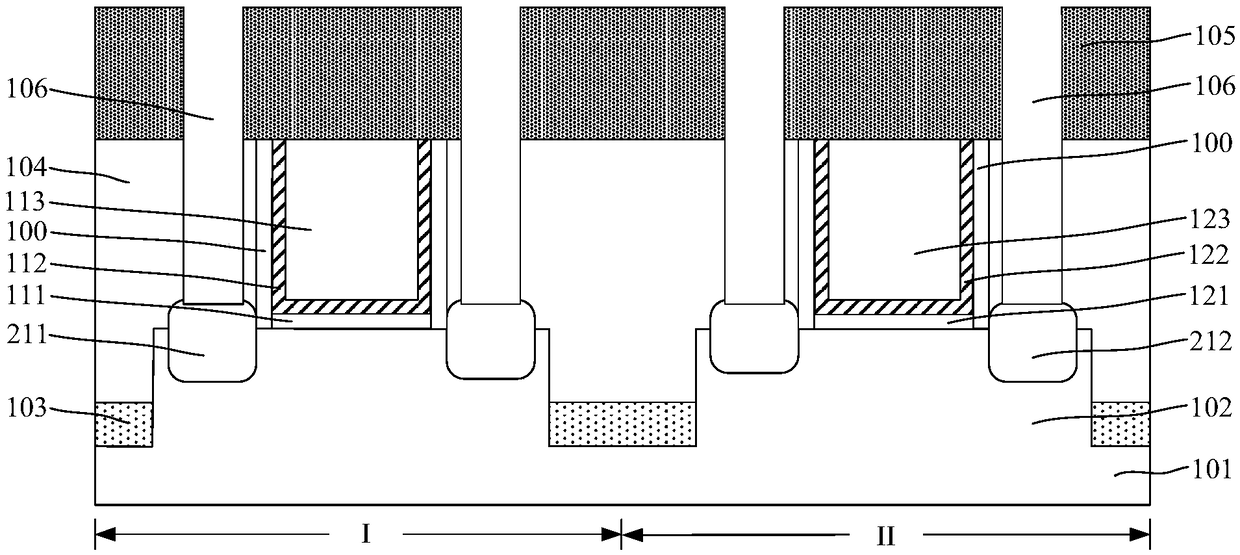

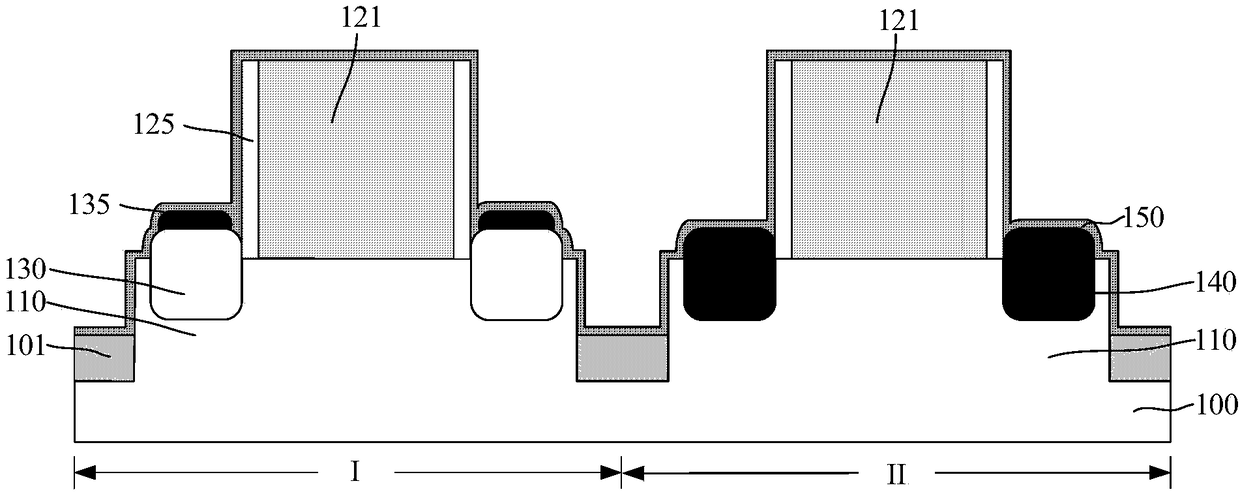

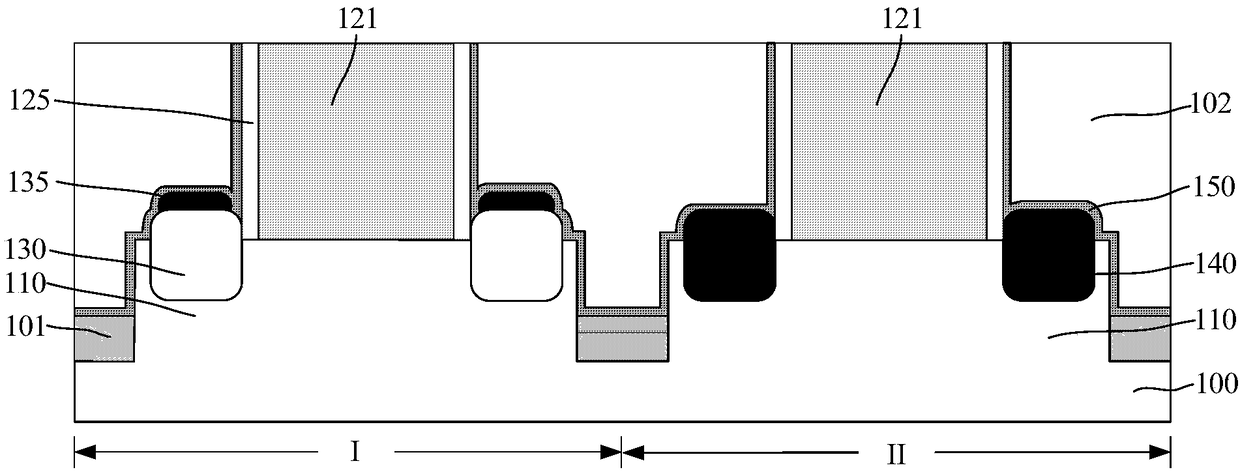

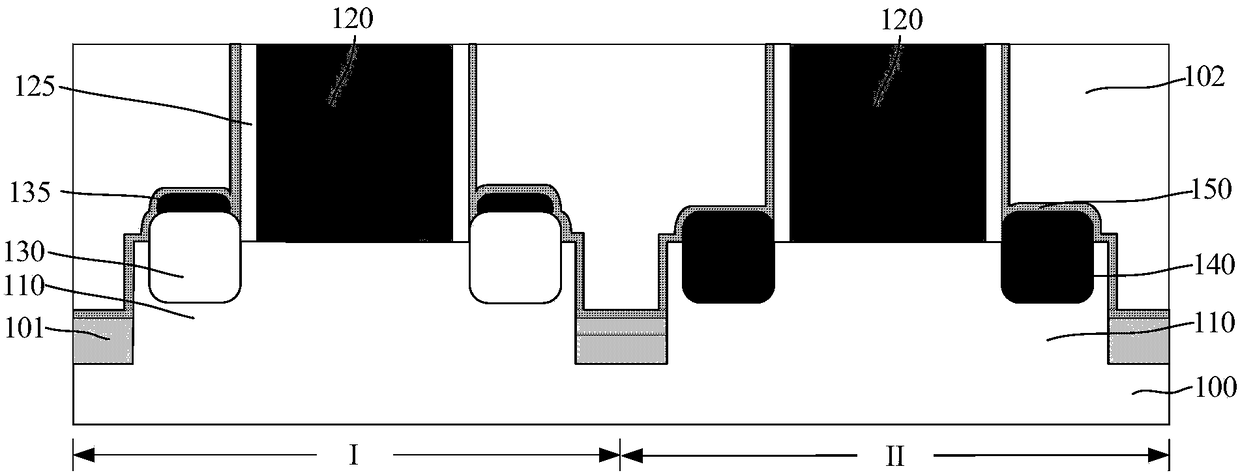

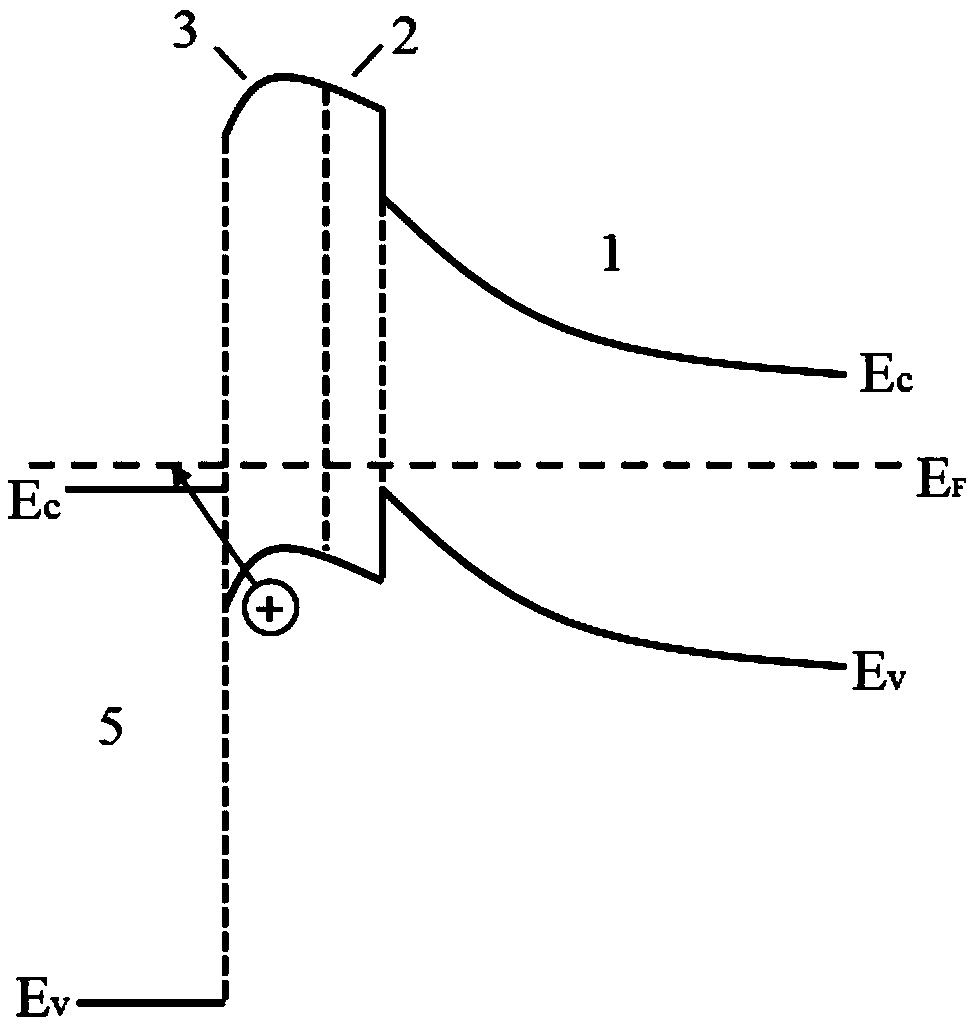

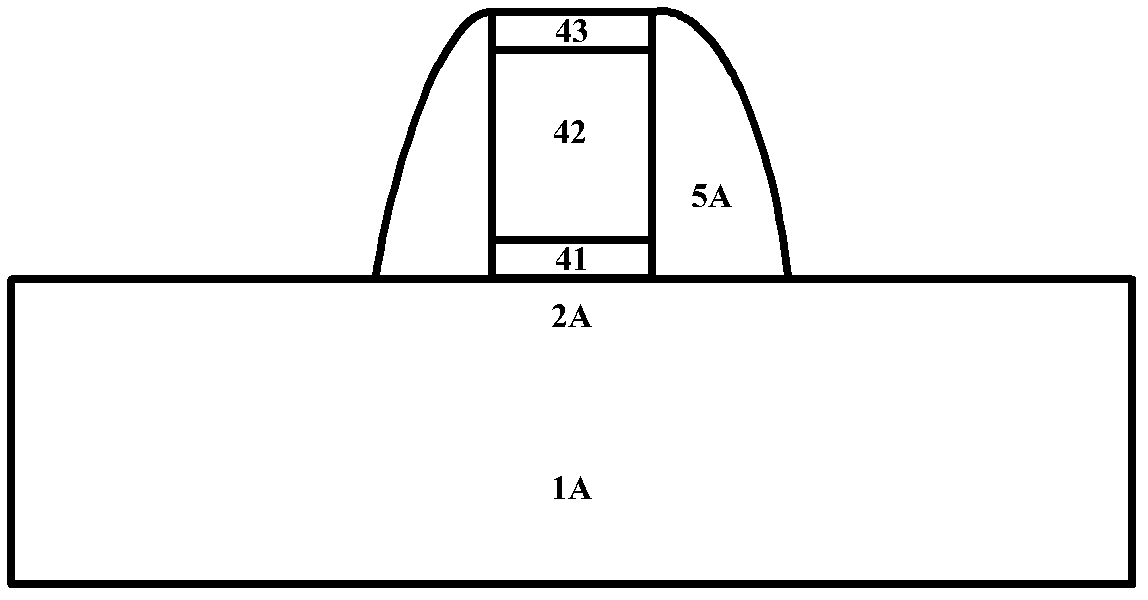

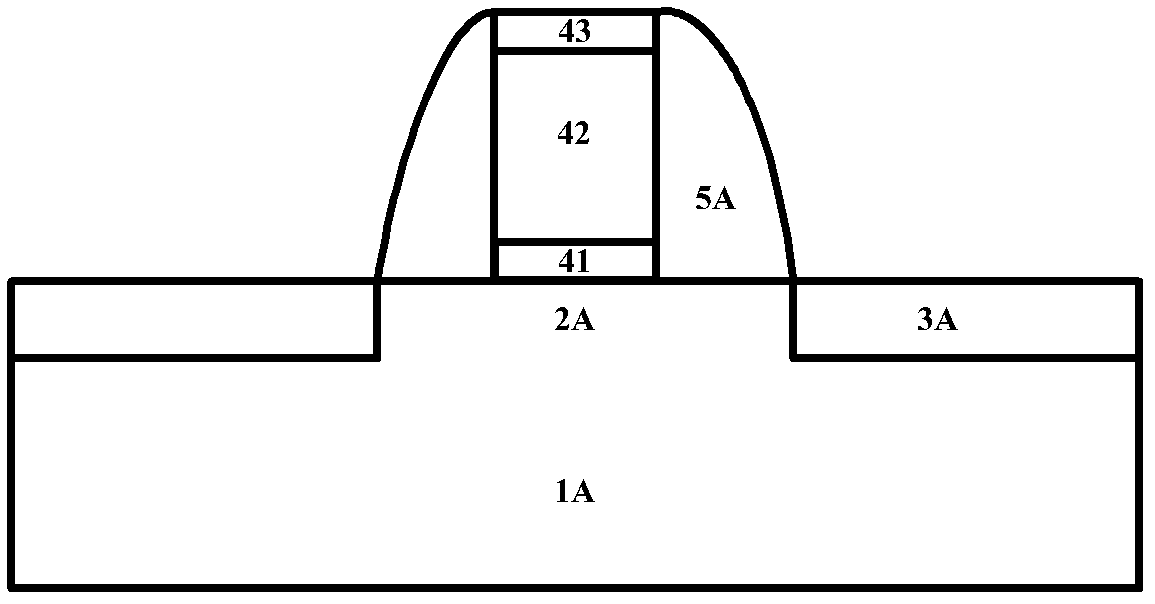

Semiconductor device and method of manufacturing the same

InactiveUS20120139047A1Improve thermal stabilityDrive capability can be improvedSolid-state devicesSemiconductor/solid-state device manufacturingDopantPower semiconductor device

Disclosed is a semiconductor device, comprising a substrate, a channel region in the substrate, source / drain regions on both sides of the channel region, a gate structure on the channel region, and gate sidewall spacers formed on the sidewalls of the gate structure, characterized in that each of the source / drain regions comprises an epitaxially grown metal silicide region, and dopant segregation regions are formed at the interfaces between the epitaxially grown metal silicide source / drain regions and the channel region. By employing the semiconductor device and the method for manufacturing the same according to embodiments of the present invention, the Schottkey Barrier Height of the MOSFETs with epitaxially grown ultrathin metal silicide source / drain may be lowered, thereby improving the driving capability.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

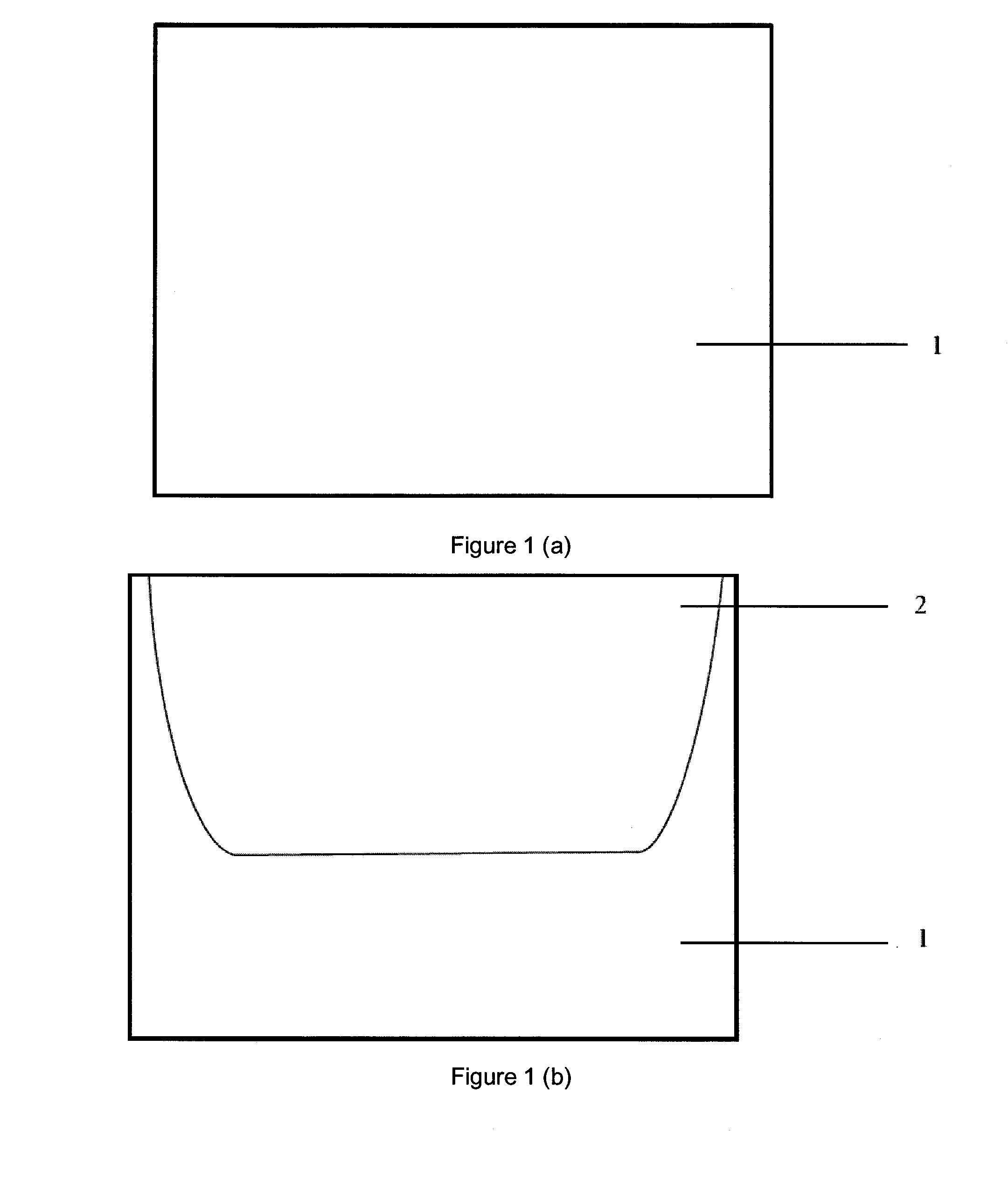

Ge-based nmos device and method for fabricating the same

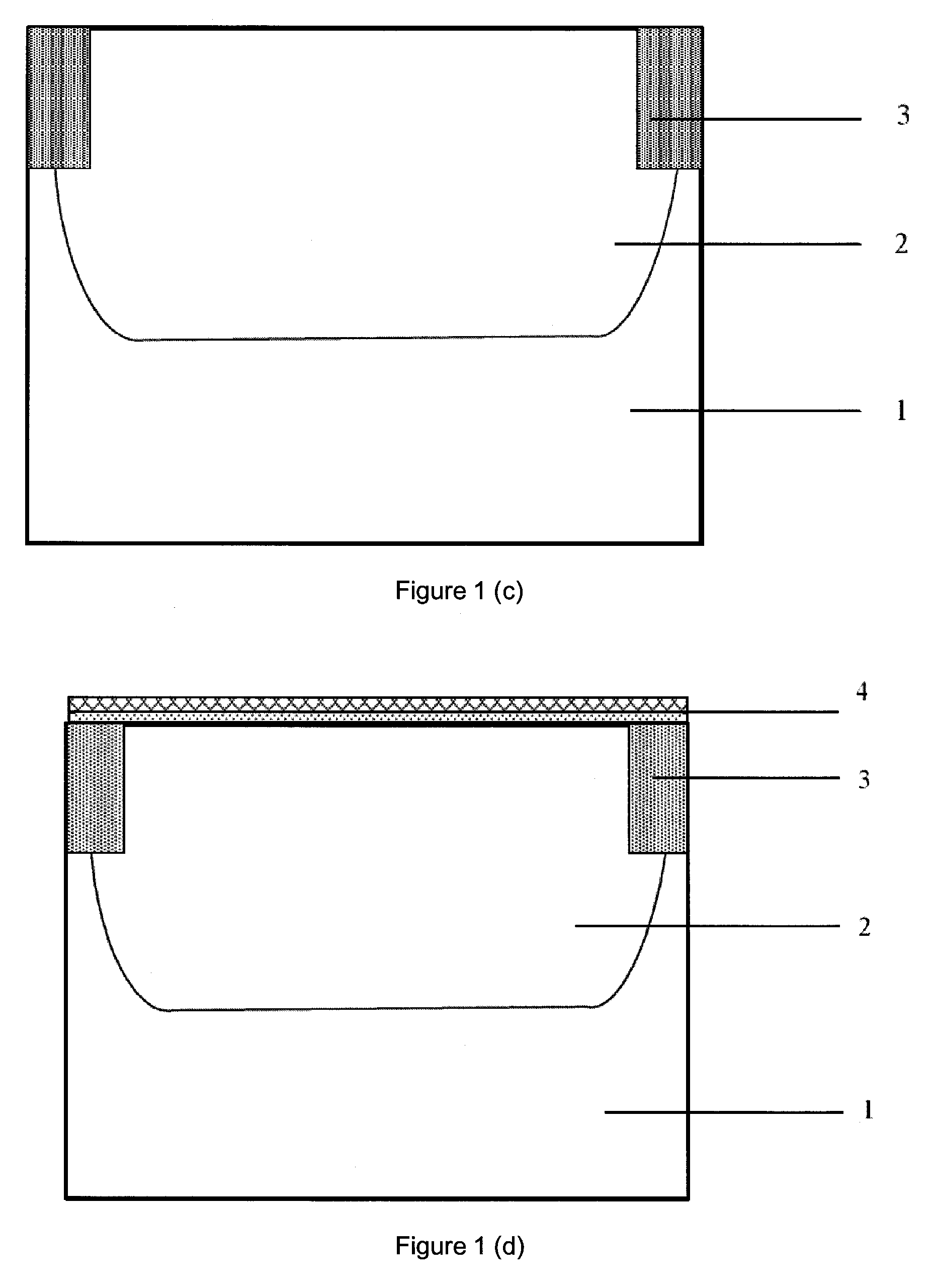

ActiveUS20140117465A1Alleviate Fermi level pinning effectReduce electron barrierSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierDielectric layer

The embodiments of the present invention provide a Ge-based NMOS device structure and a method for fabricating the same. By using the method, double dielectric layers of germanium oxide (GeO2) and metal oxide are deposited between the source / drain region and the substrate. The present invention not only reduces the electron Schottky barrier height of metal / Ge contact, but also improves the current switching ratio of the Ge-based Schottky and therefore, it will improve the performance of the Ge-based Schottky NMOS transistor. In addition, the fabrication process is very easy and completely compatible with the silicon CMOS process. As compared with conventional fabrication method, the Ge-based NMOS device structure and the fabrication method in the present invention can easily and effectively improve the performance of the Ge-based Schottky NMOS transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

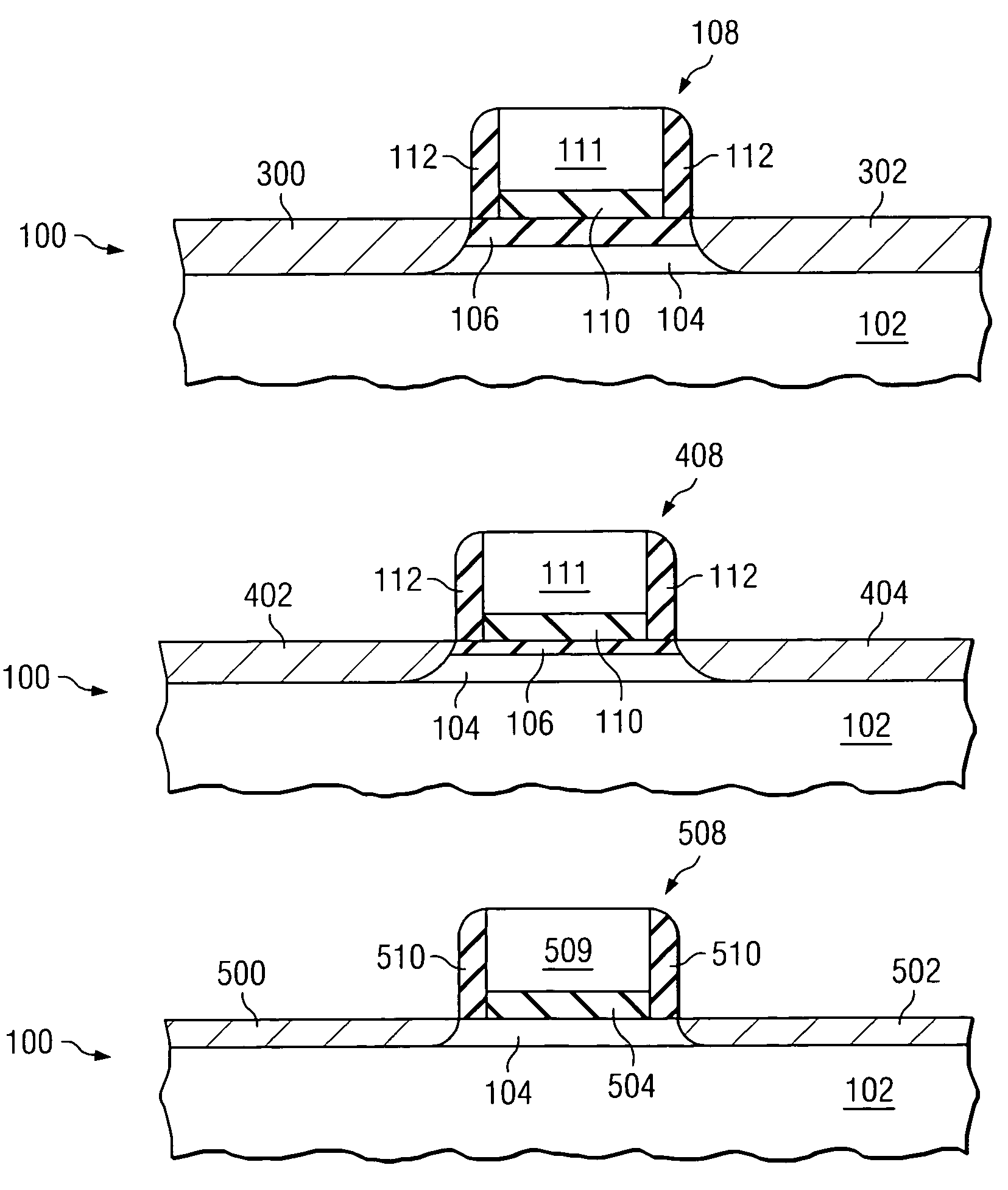

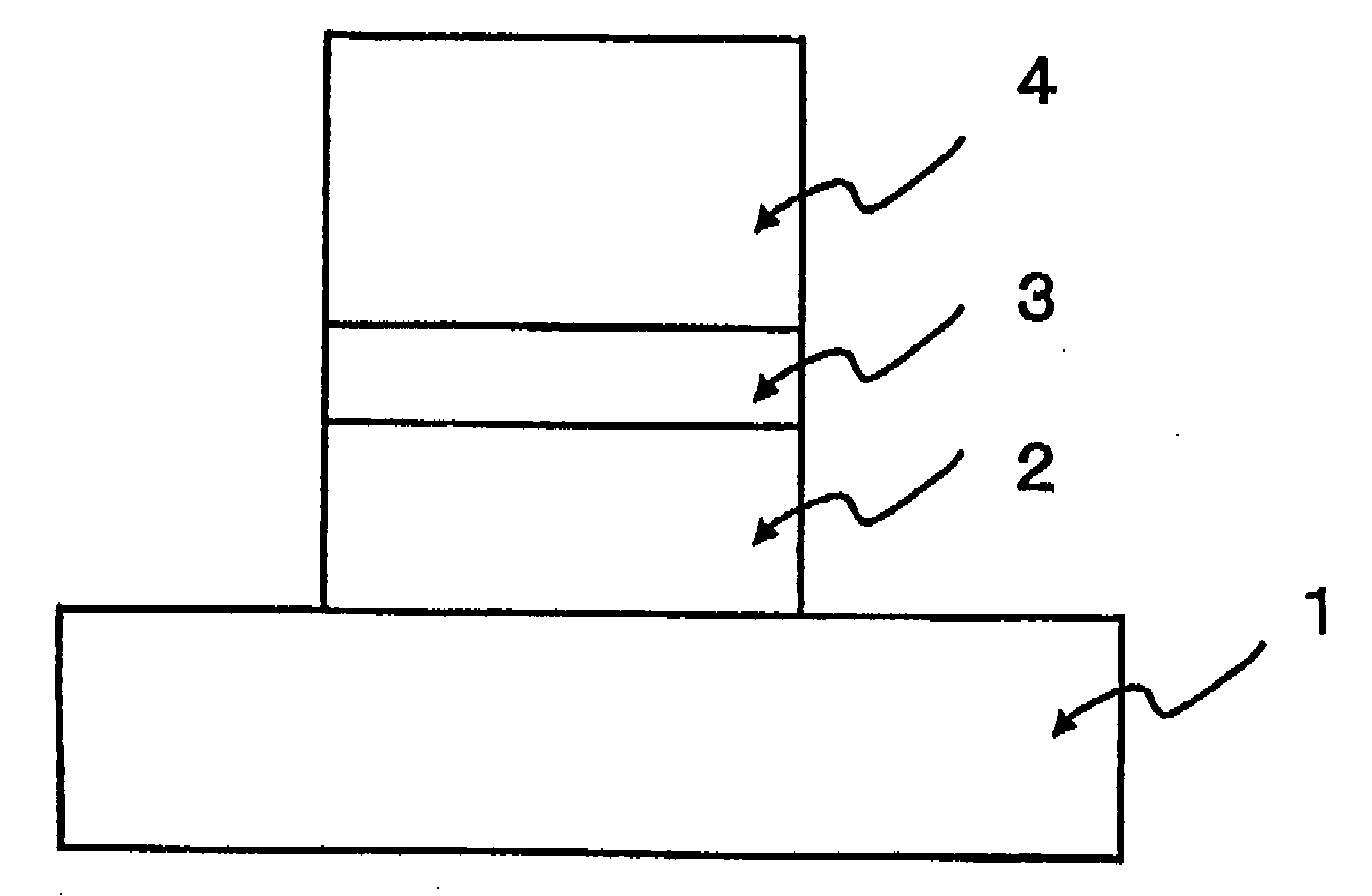

System and method for integrating low schottky barrier metal source/drain

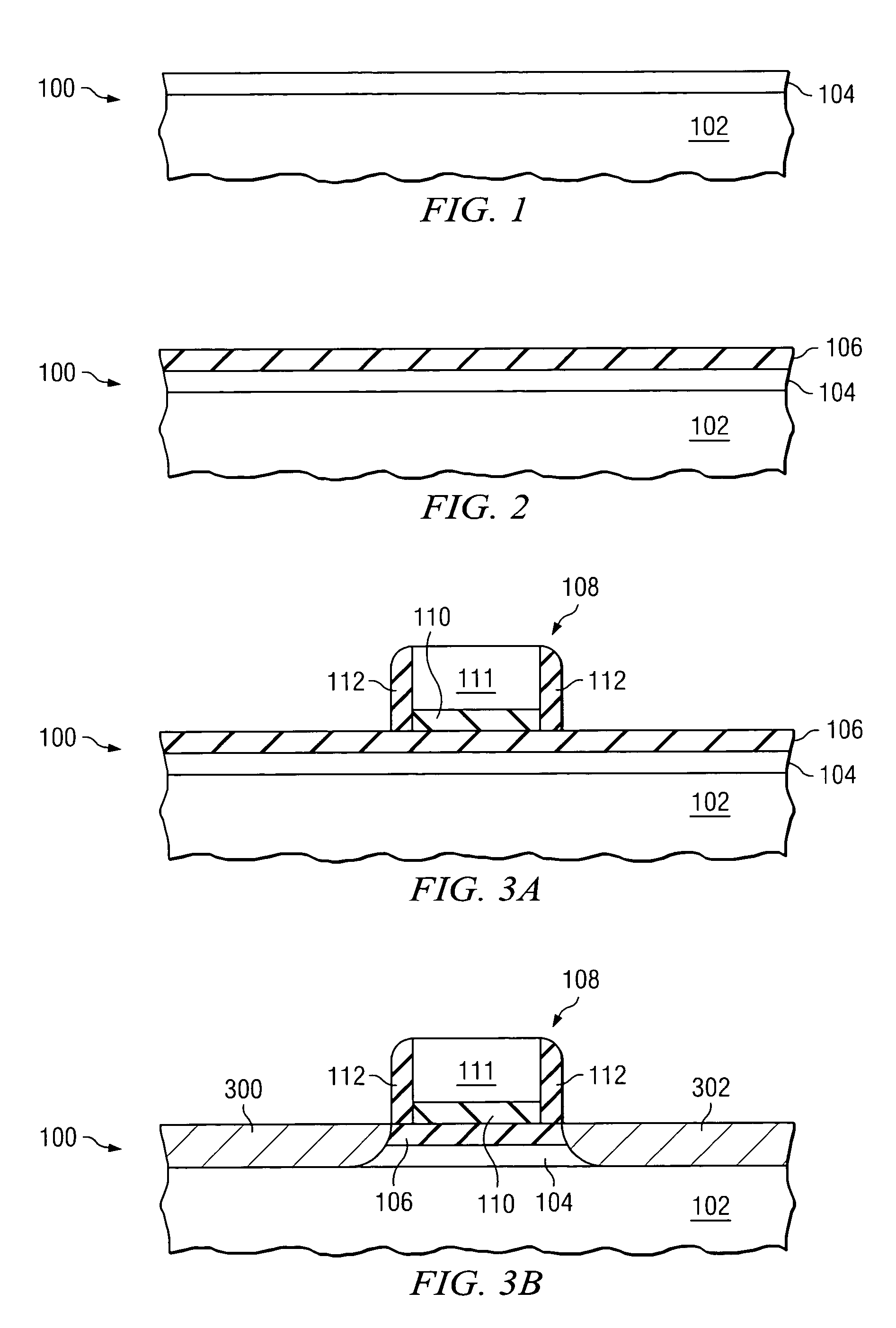

ActiveUS7238567B2Lower Schottky Barrier HeightLower barrier heightTransistorSolid-state devicesSchottky barrierOptoelectronics

According to one embodiment of the invention, a method for integrating low Schottky barrier metal source / drain includes providing a substrate, forming an epitaxial SiGe layer outwardly from the substrate, forming an epitaxial Si layer outwardly from the SiGe layer, and forming a metal source and a metal drain.

Owner:TEXAS INSTR INC

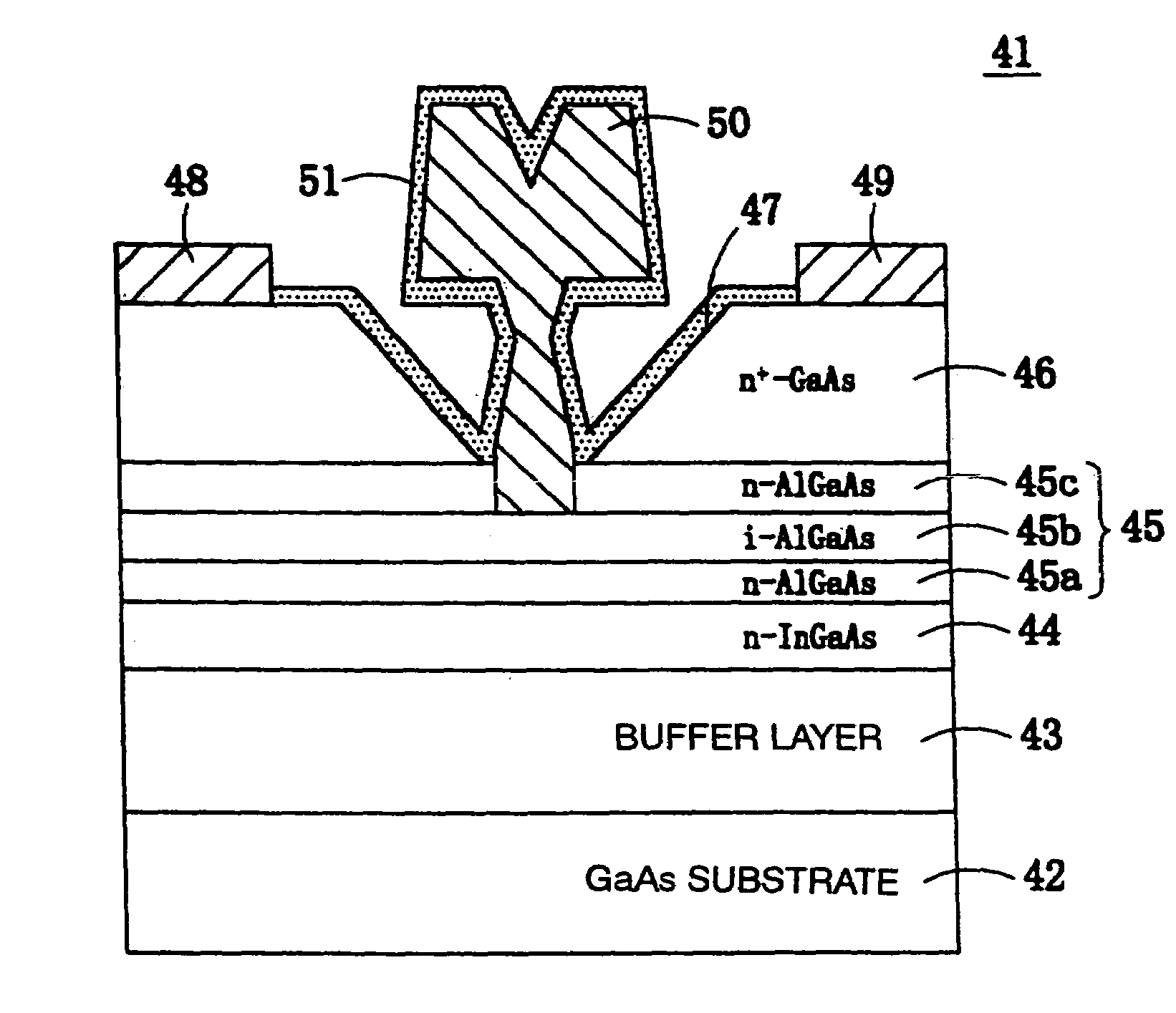

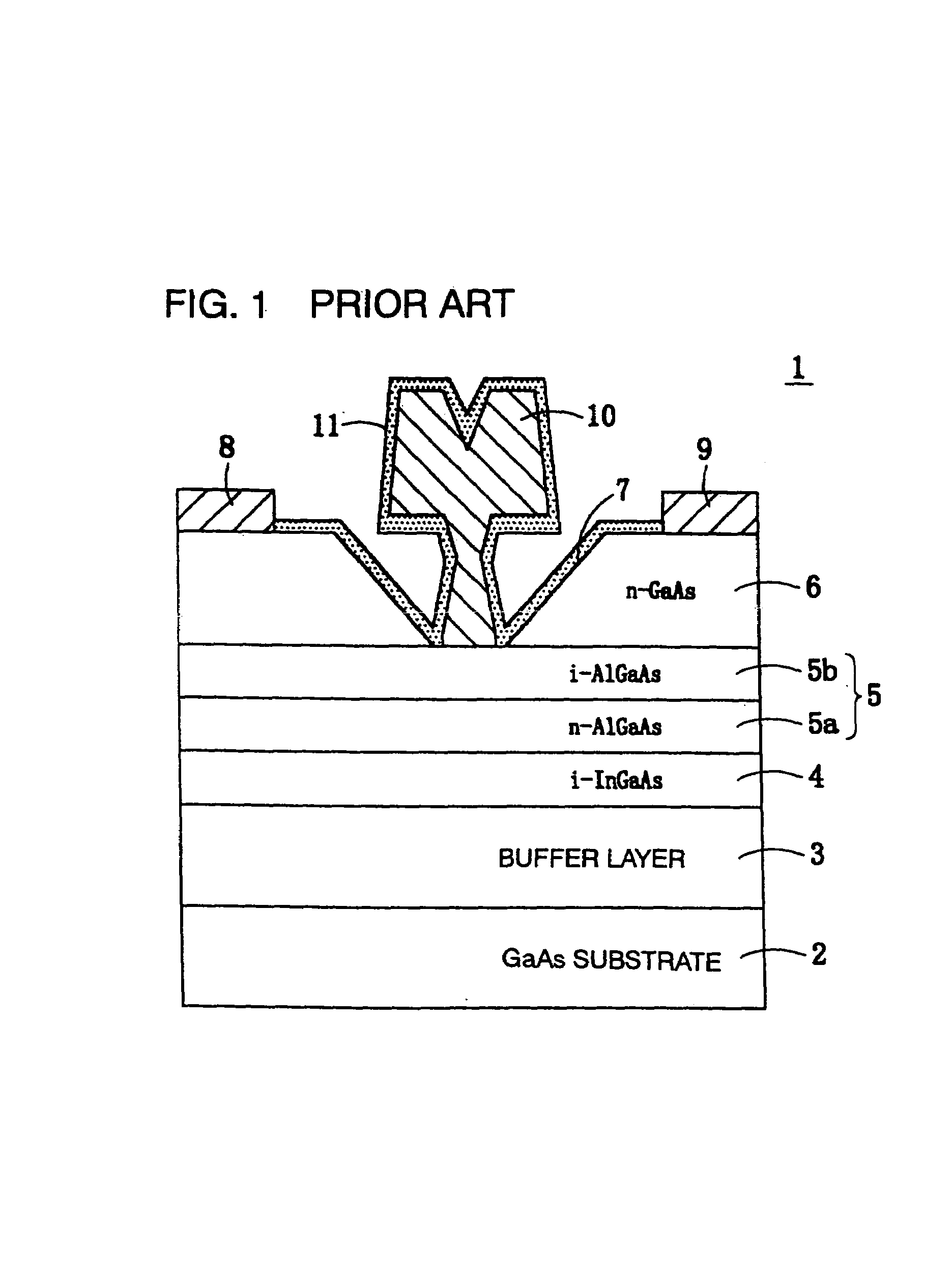

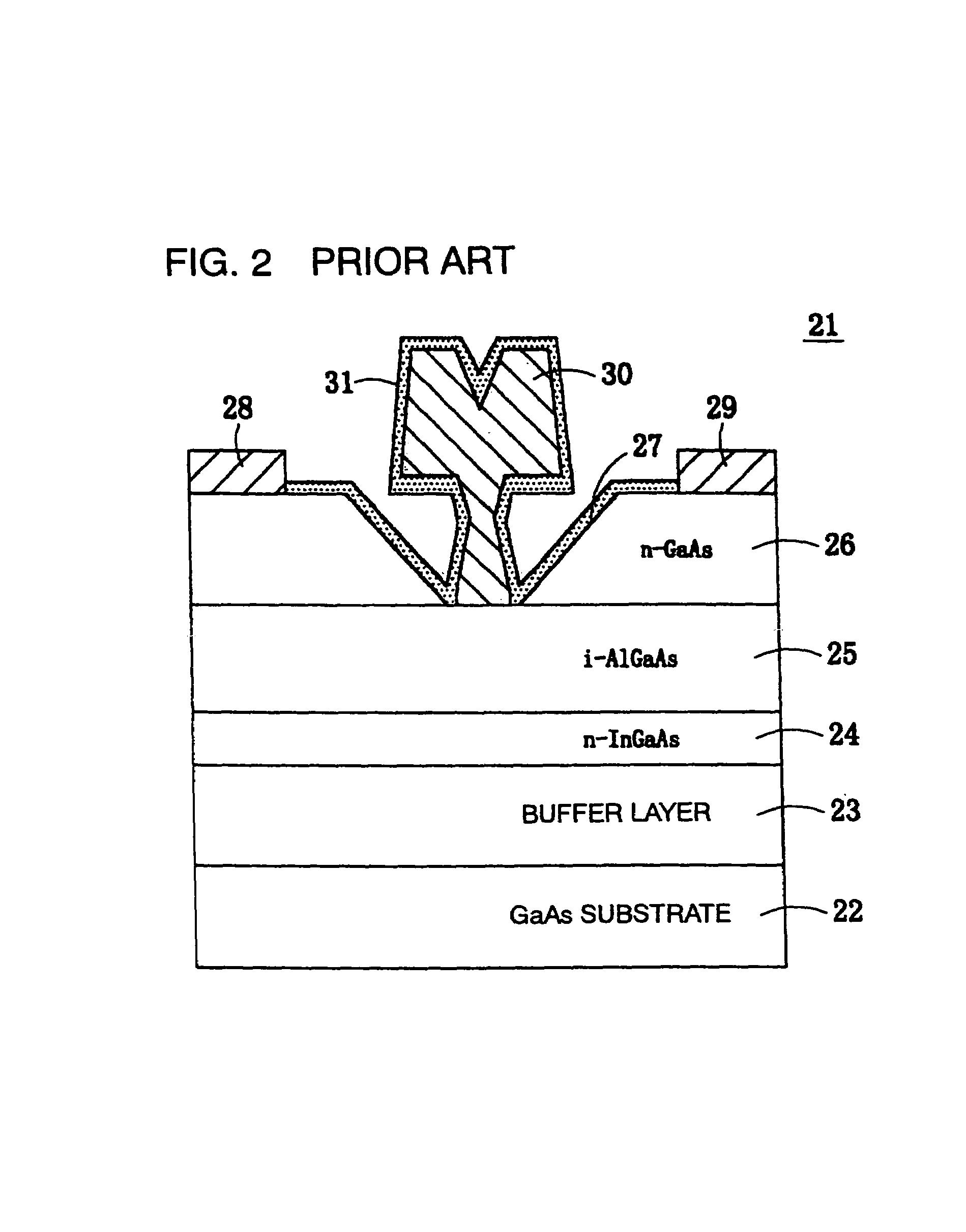

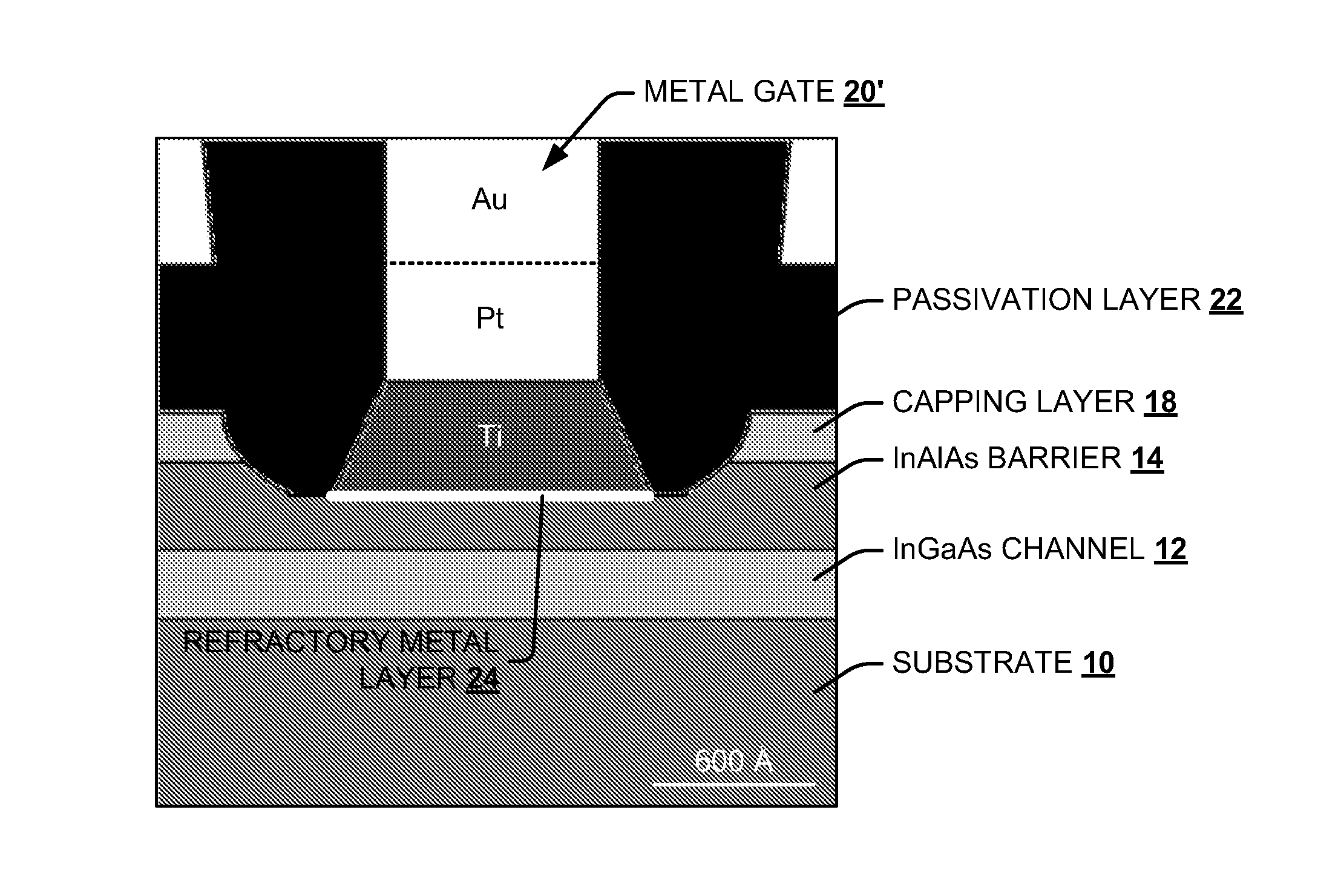

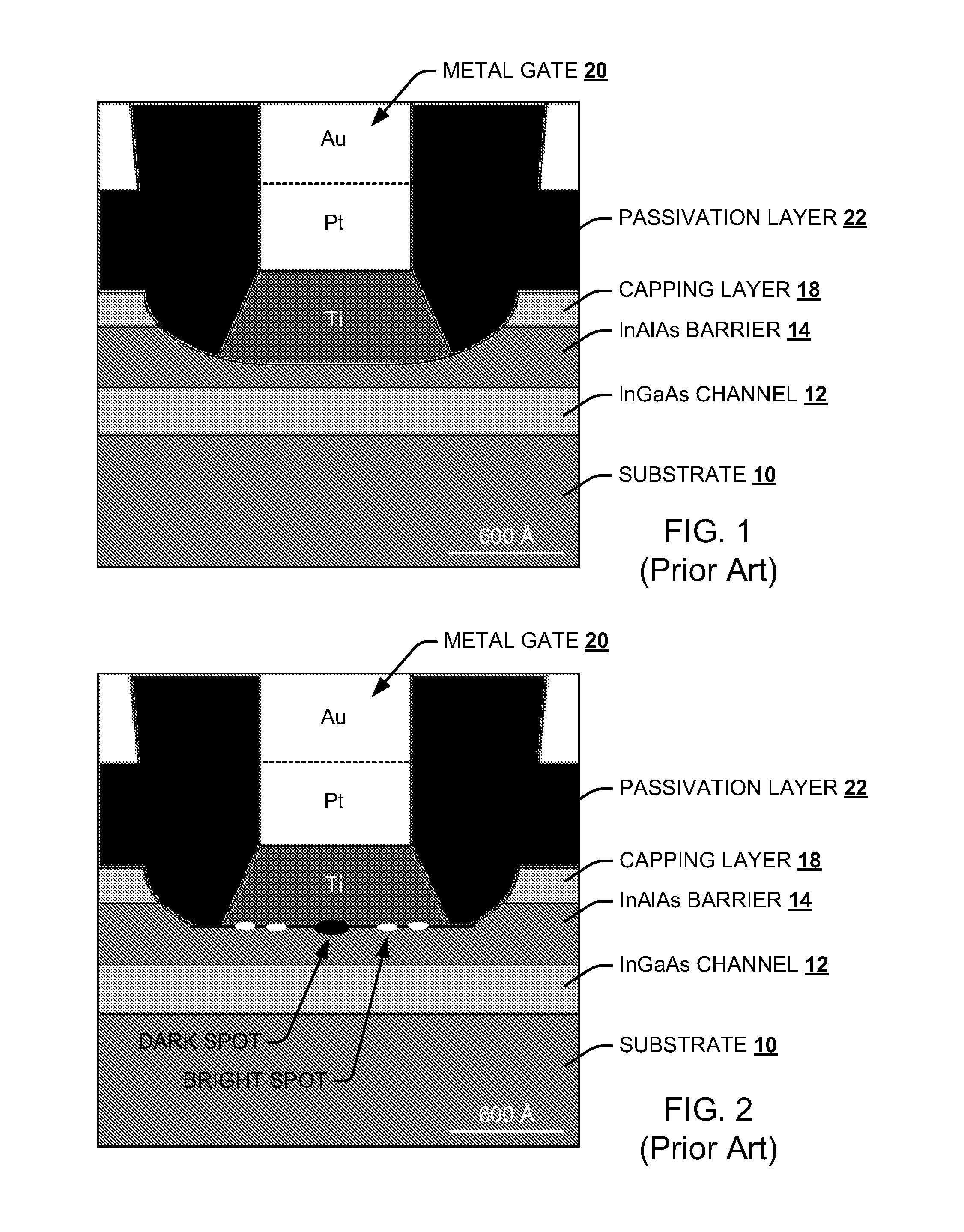

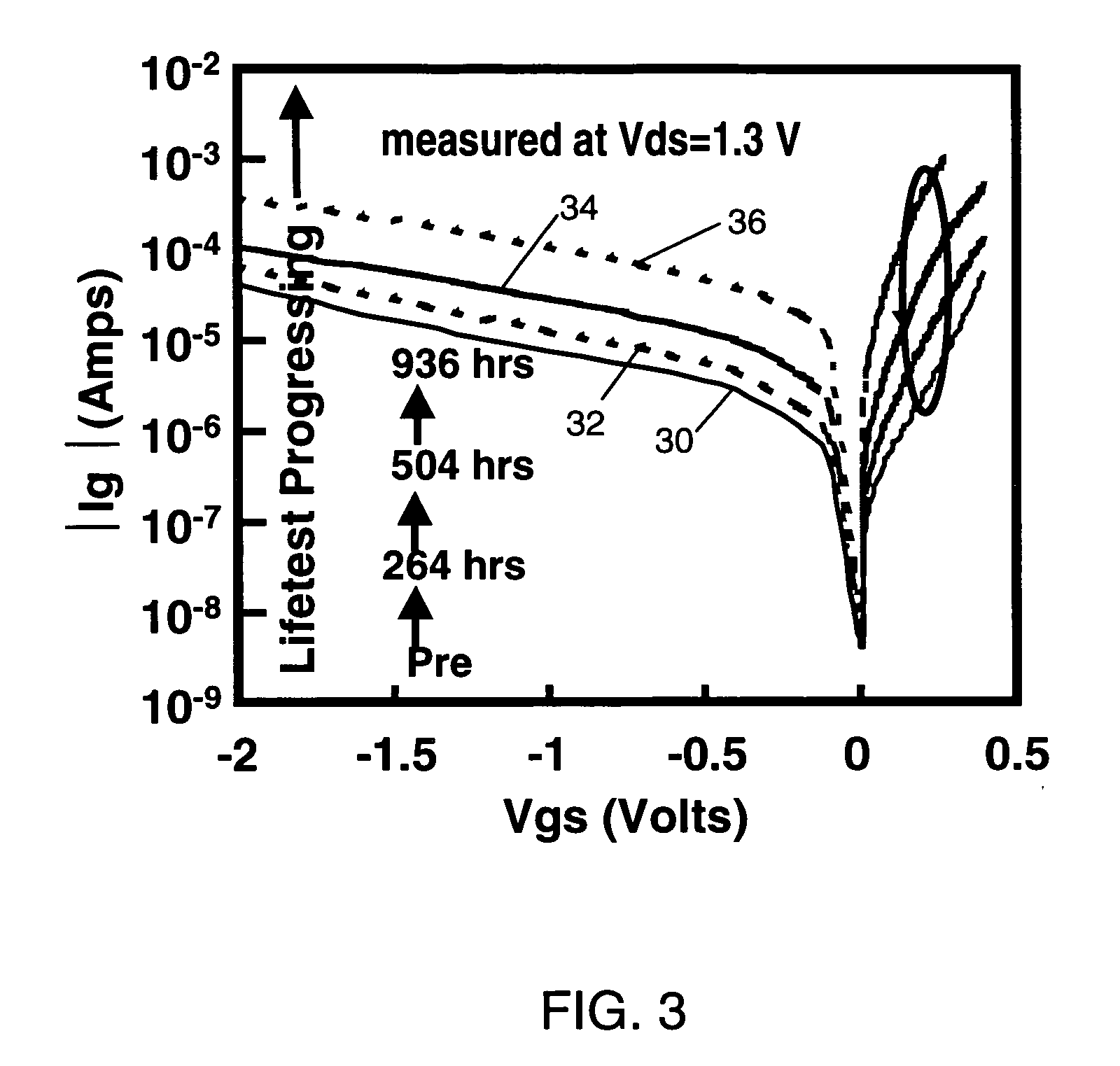

High electron mobility transistor (HEMT) structure with refractory gate metal

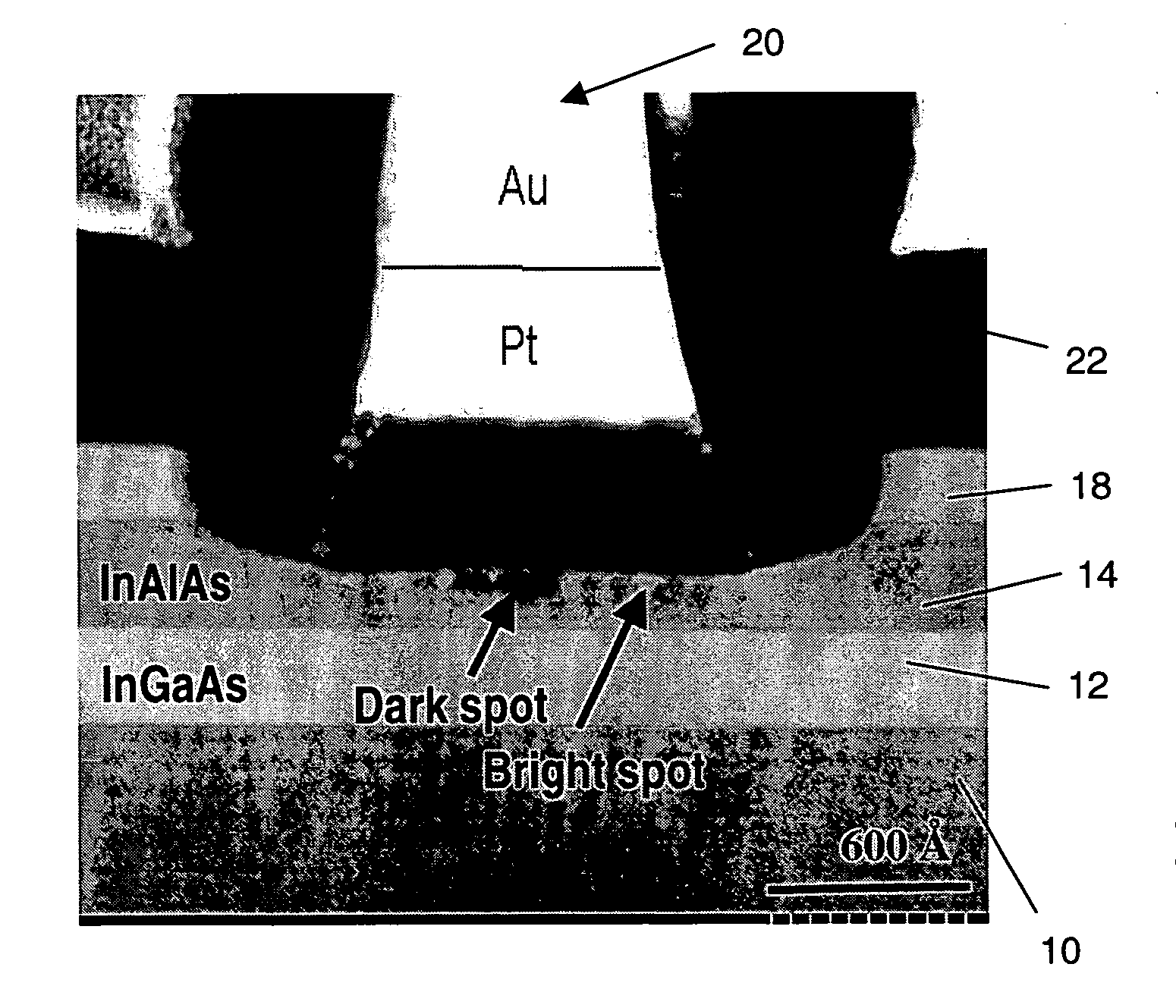

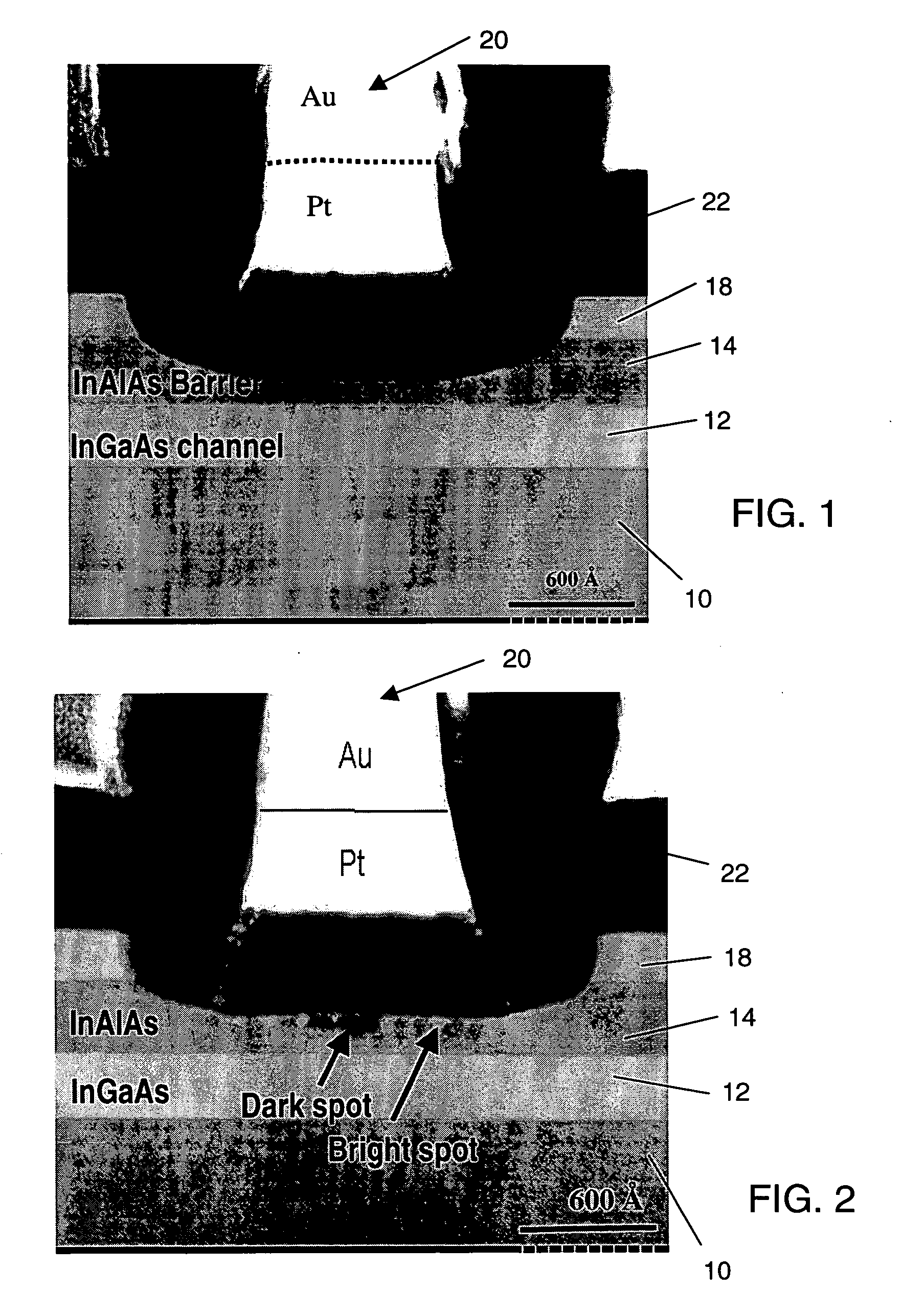

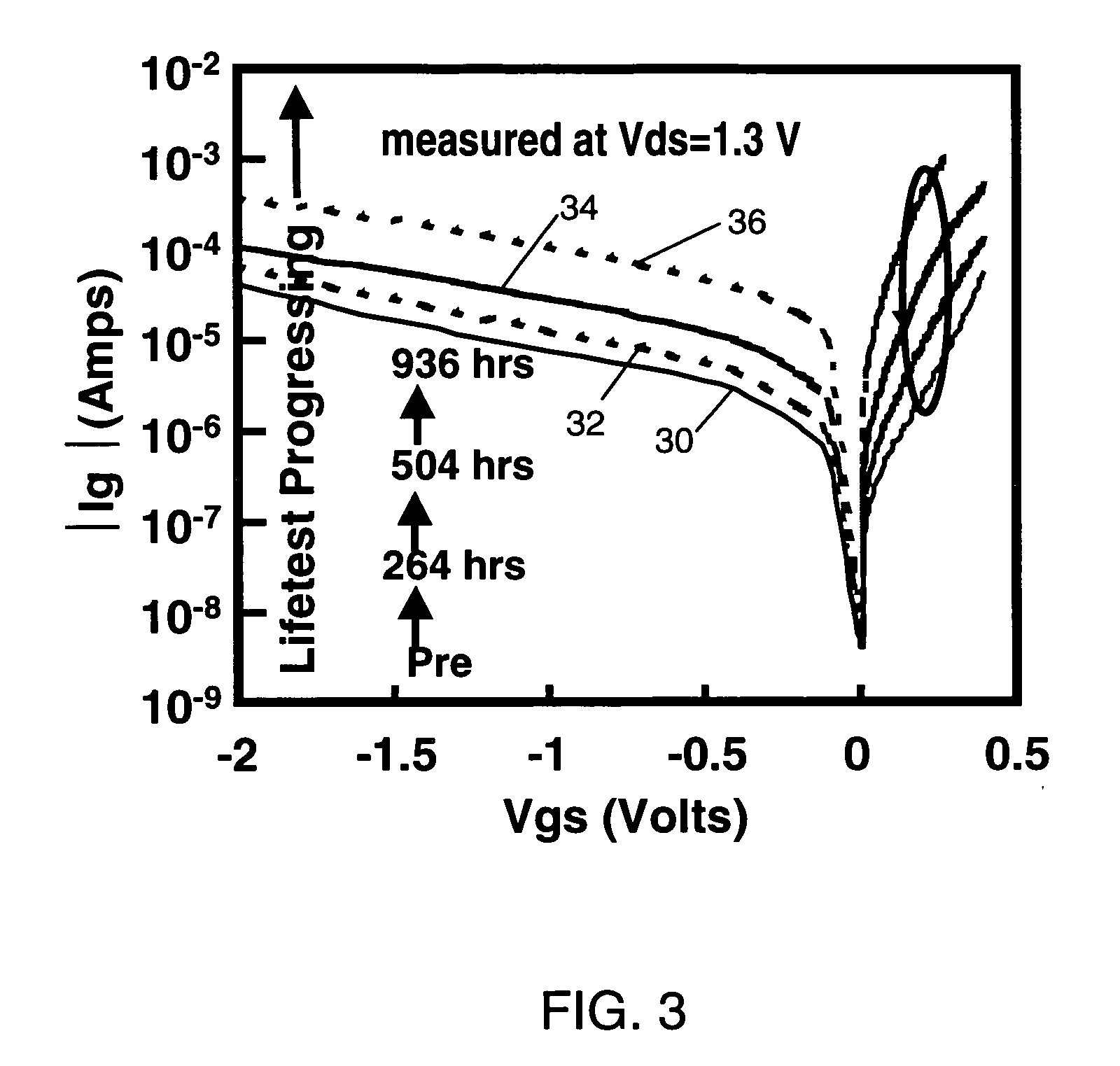

ActiveUS20060244009A1Improve long-term reliabilityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPlatinumLong term degradation

An InP high electron mobility transistor (HEMT) structure in which a gate metal stack includes an additional thin layer of a refractory metal, such as molybdenum (Mo) or platinum (Pt) at a junction between the gate metal stack and a Schottky barrier layer in the HEMT structure. The refractory metal layer reduces or eliminates long-term degradation of the Schottky junction between the gate metal and the barrier layer, thereby dramatically improving long-term reliability of InP HEMTs, but without sacrifice in HEMT performance, whether used as a discrete device or in an integrated circuit.

Owner:NORTHROP GRUMMAN SYST CORP

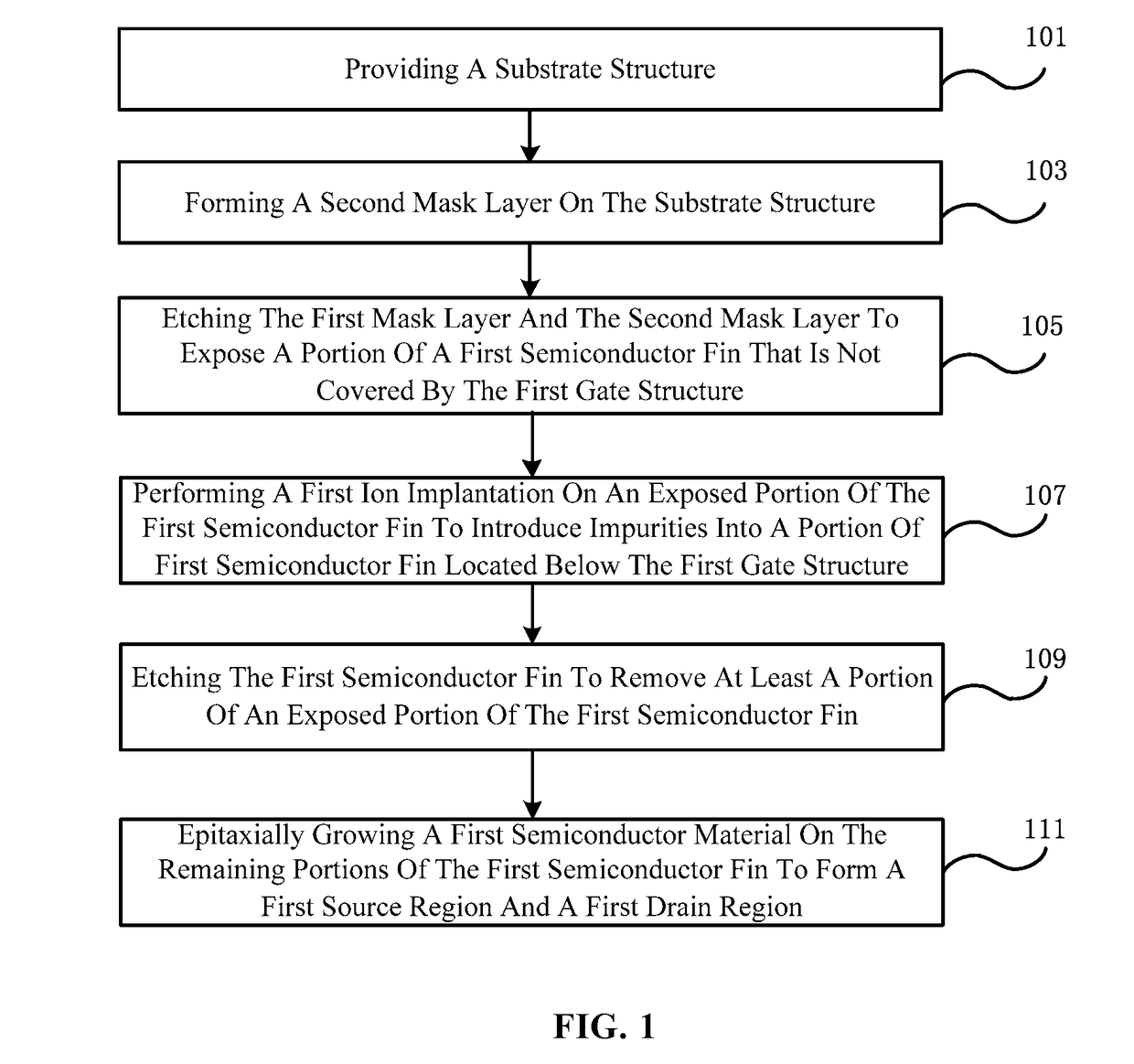

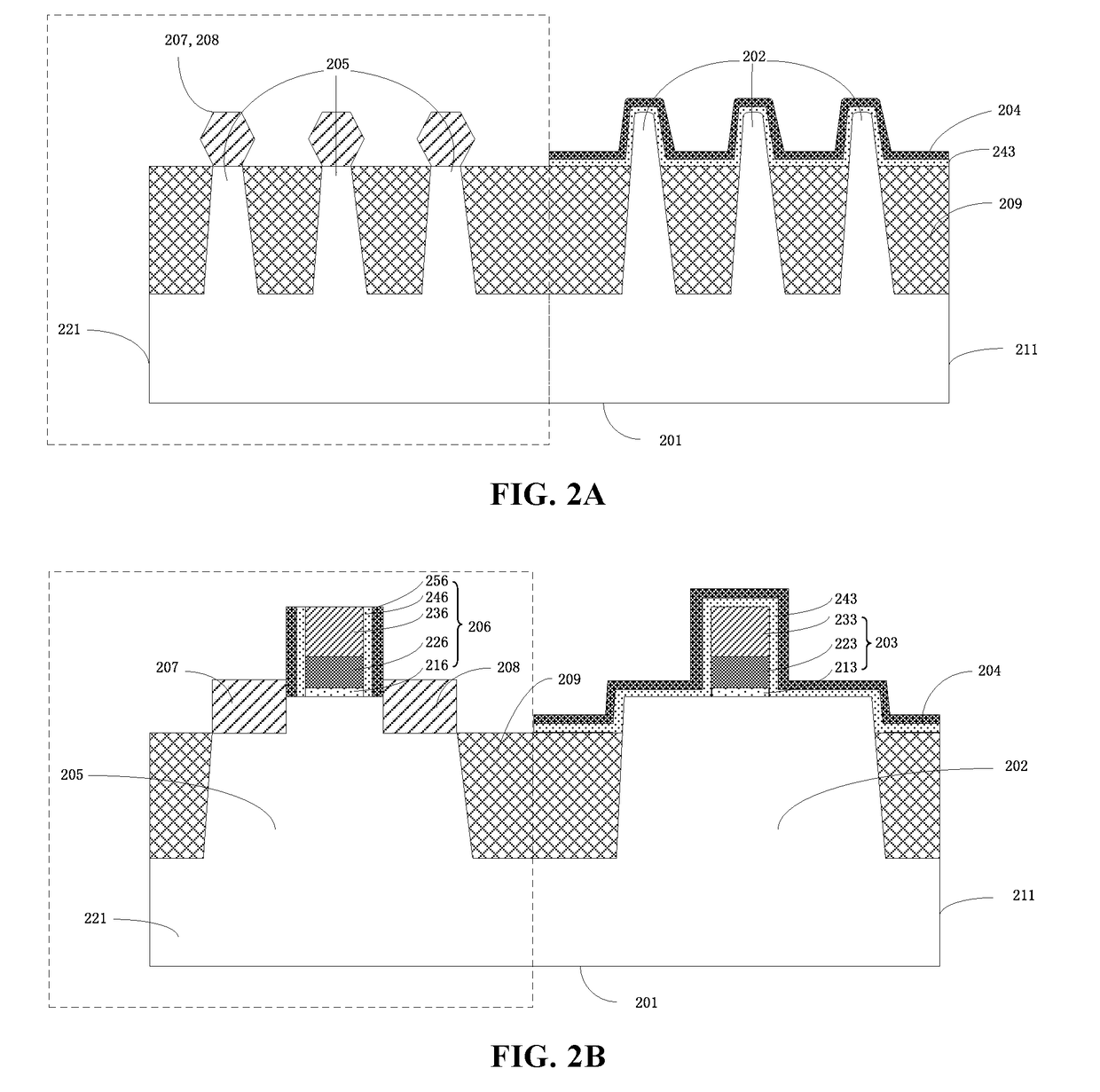

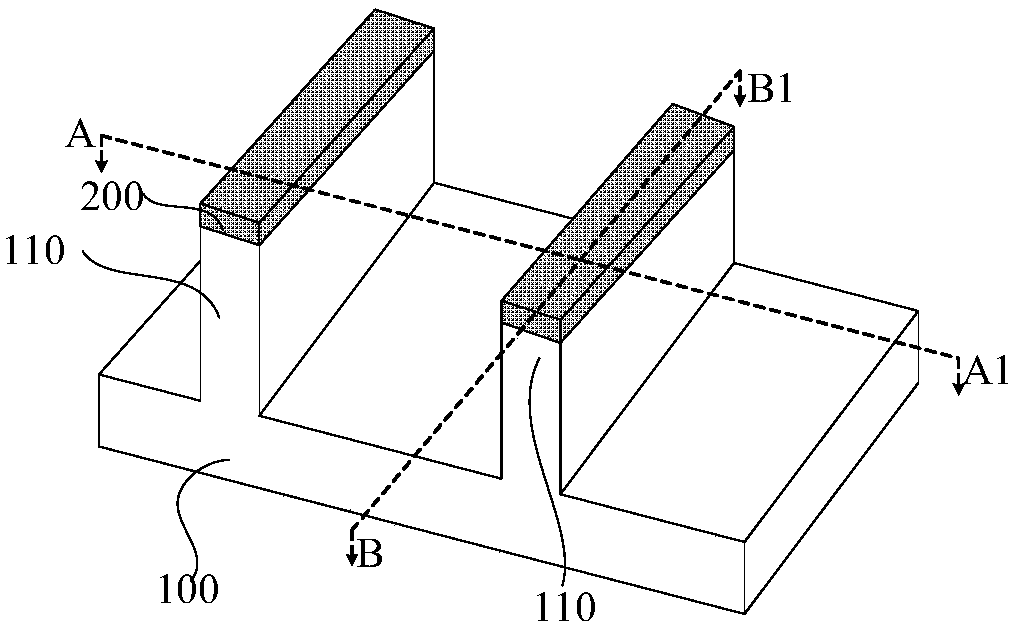

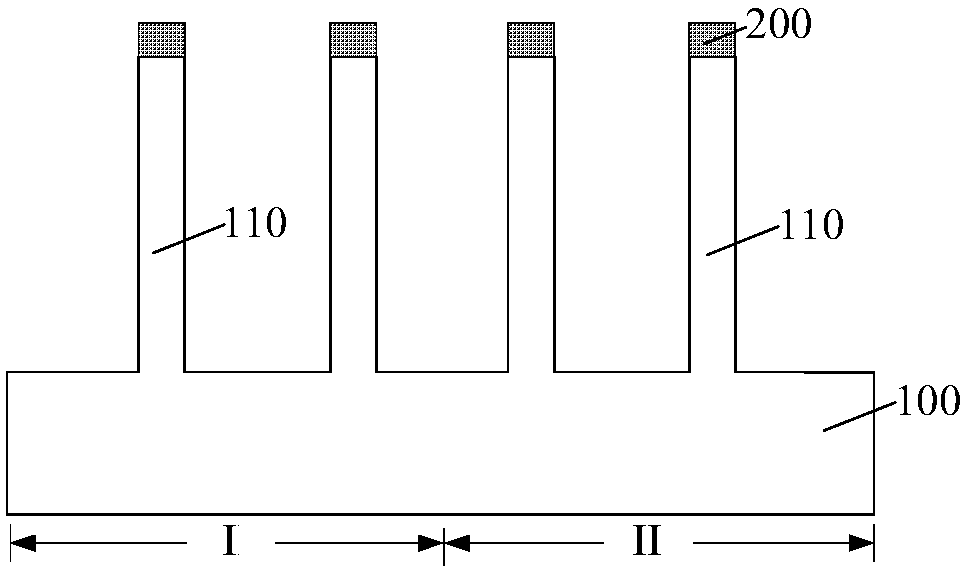

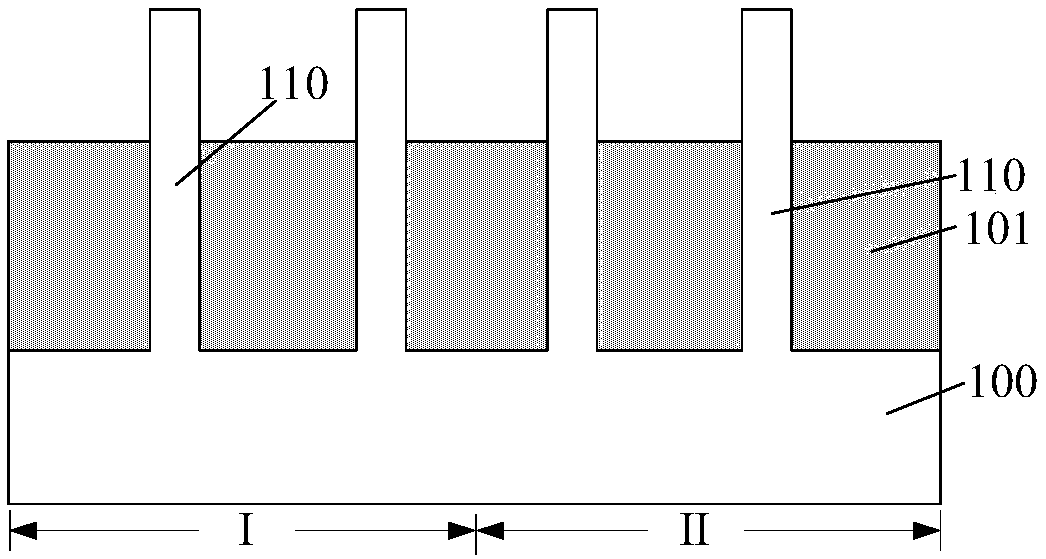

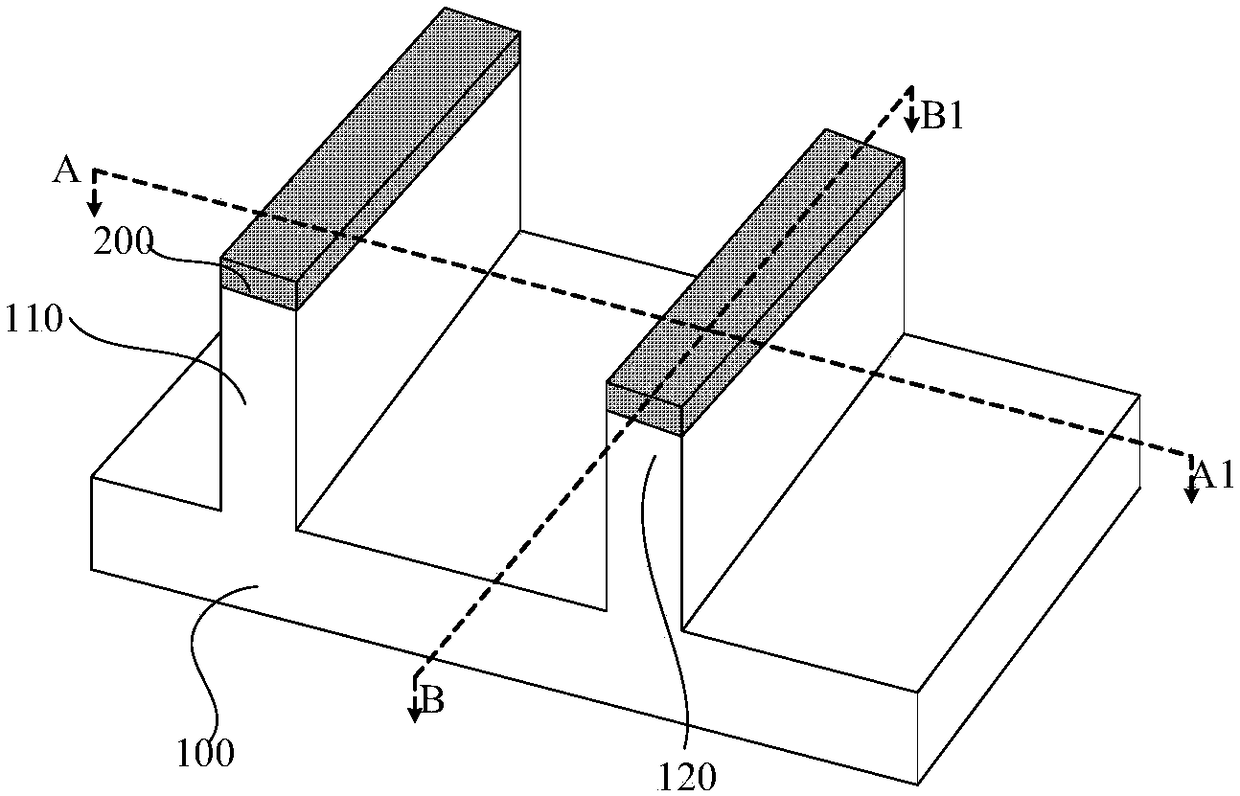

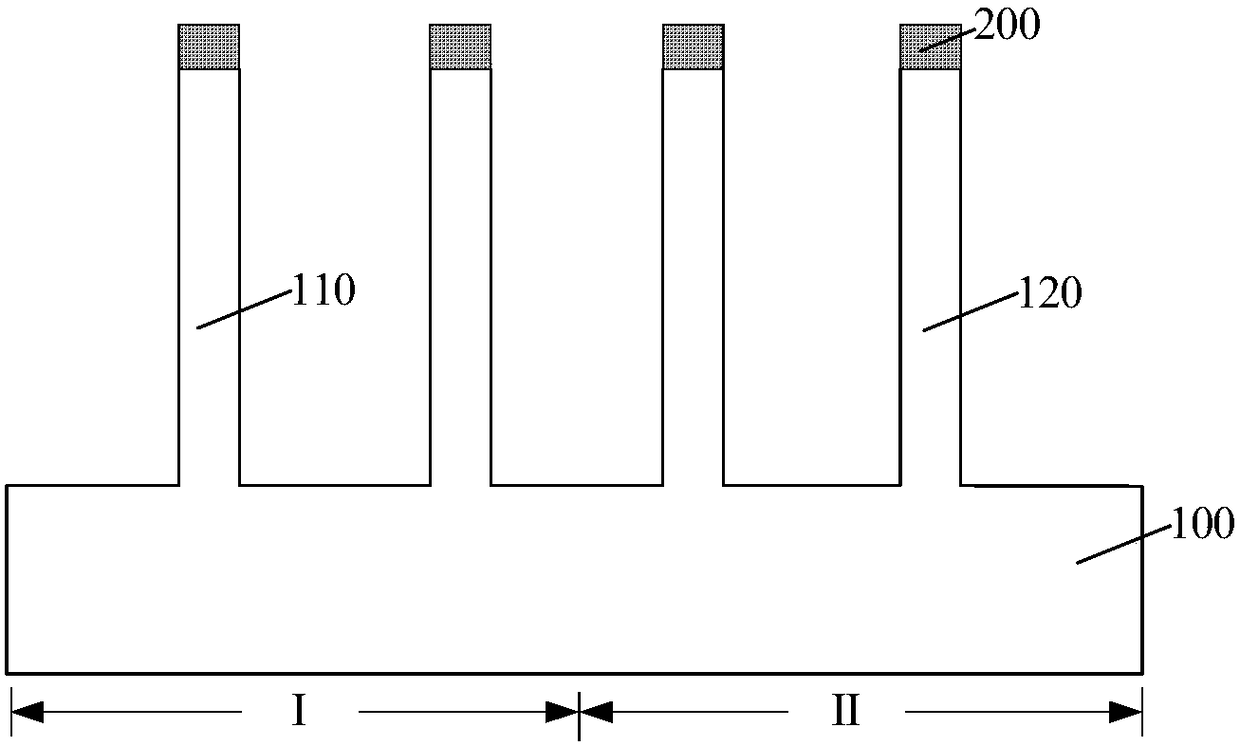

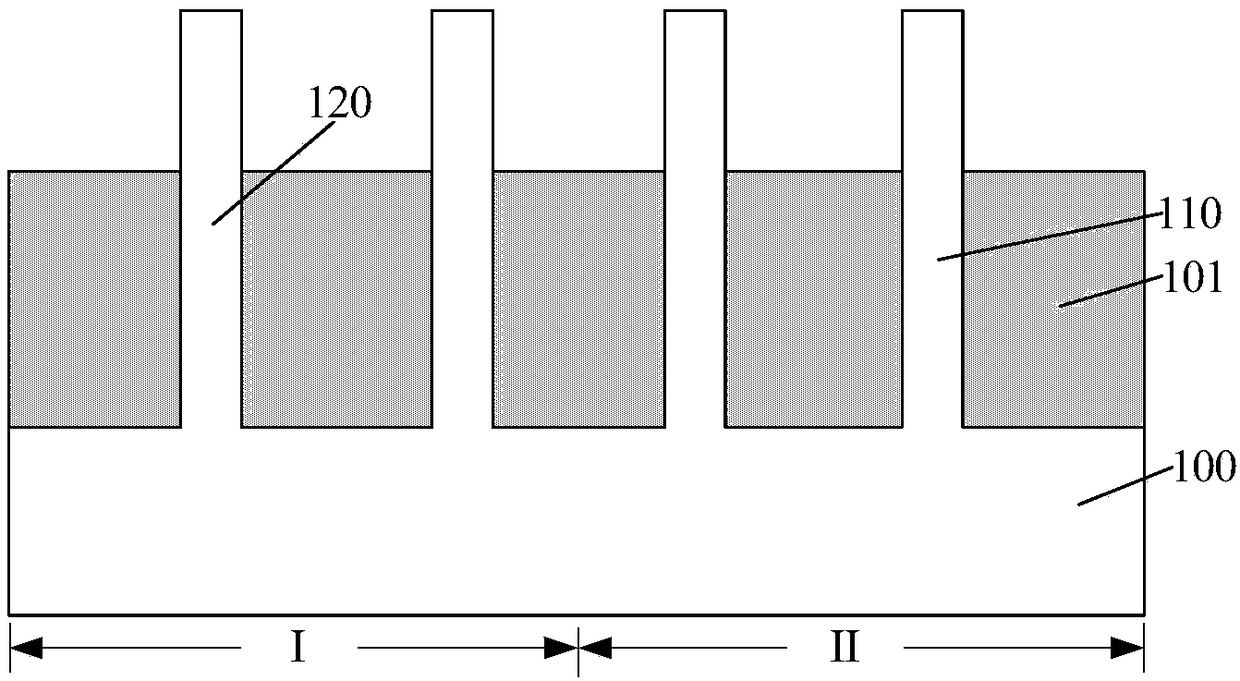

Method for reducing n-type finfet source and drain resistance

ActiveUS20170352595A1Increase in sizeBring more stressTransistorSolid-state devicesSemiconductor materialsEngineering

A method of manufacturing a semiconductor device includes providing a substrate structure, the substrate structure having a semiconductor substrate including a first semiconductor fin, a first gate structure, and a first mask layer on a first semiconductor region. The method includes forming a second mask layer on the substrate structure, etching first mask layer and second mask layer to expose a portion of a first semiconductor fin not covered by the first gate structure, performing a first ion implantation on an exposed portion of the first semiconductor fin to introduce impurities into a portion of the first semiconductor fin located below the first gate structure, etching the first semiconductor fin to remove a portion of an exposed portion of the first semiconductor fin, and epitaxially growing a first semiconductor material on the remaining portions of the first semiconductor fin to form a first source region and a first drain region.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

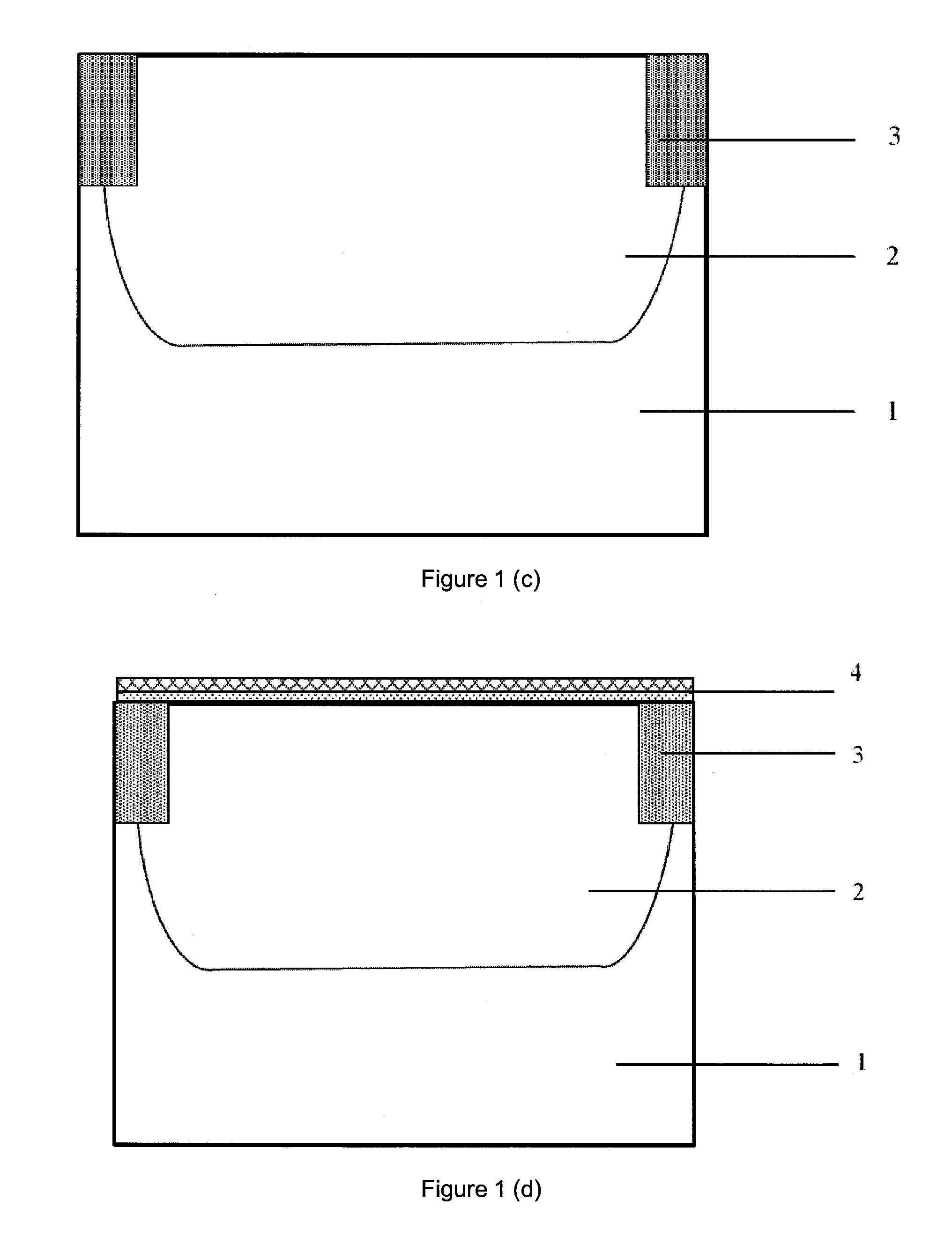

Germanium-based nmos device and method for fabricating the same

InactiveUS20130069126A1On-off ratio can be increasedLittle resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon oxideHafnium

An embodiment of the invention provides a germanium-based NMOS device and a method for fabricating the same, which relates to fabrication process technology of an ultra-large-scale-integrated (ULSI) circuit. The germanium-based NMOS device has two dielectric layer interposed between a metal source / drain and a substrate. The bottom dielectric layer includes a dielectric material having a high pinning coefficient S such as hafnium oxide, silicon nitride, hafnium silicon oxide or the like, and the top dielectric layer includes a dielectric material having a low conduction band offset ΔEC such as titanium oxide, gallium oxide, strontium titanium oxide or the like. According to the method, Fermi level pinning effect can be alleviated, electron barrier height can be lowered, and thus performance of the germanium-based Schottky NMOS device can be improved. Compared with a conventional single dielectric layer such as aluminum oxide (Al2O3), Schottky barrier height can be lowered while low source / drain resistances can be maintained, and thus performance of the device can be significantly improved.

Owner:PEKING UNIV

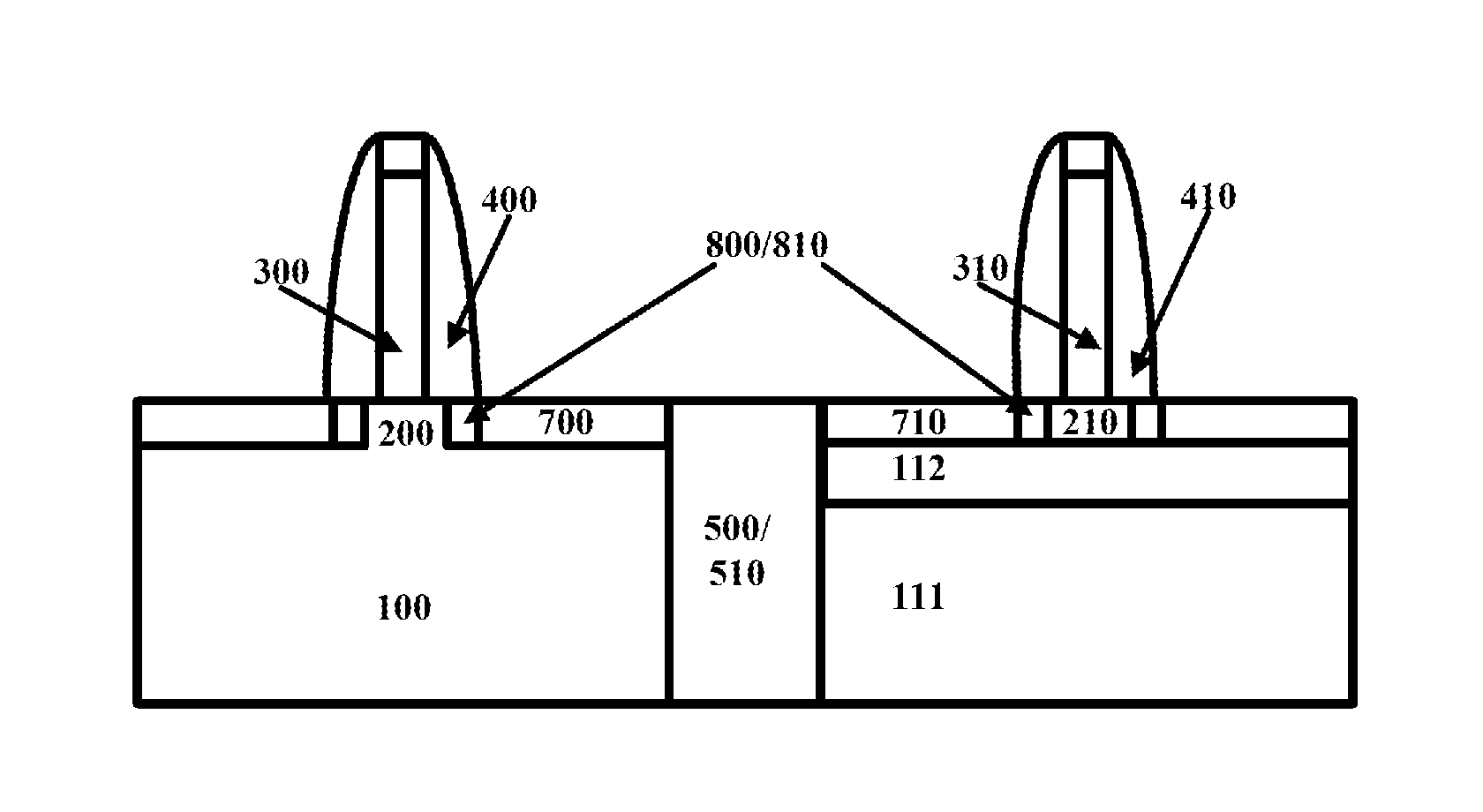

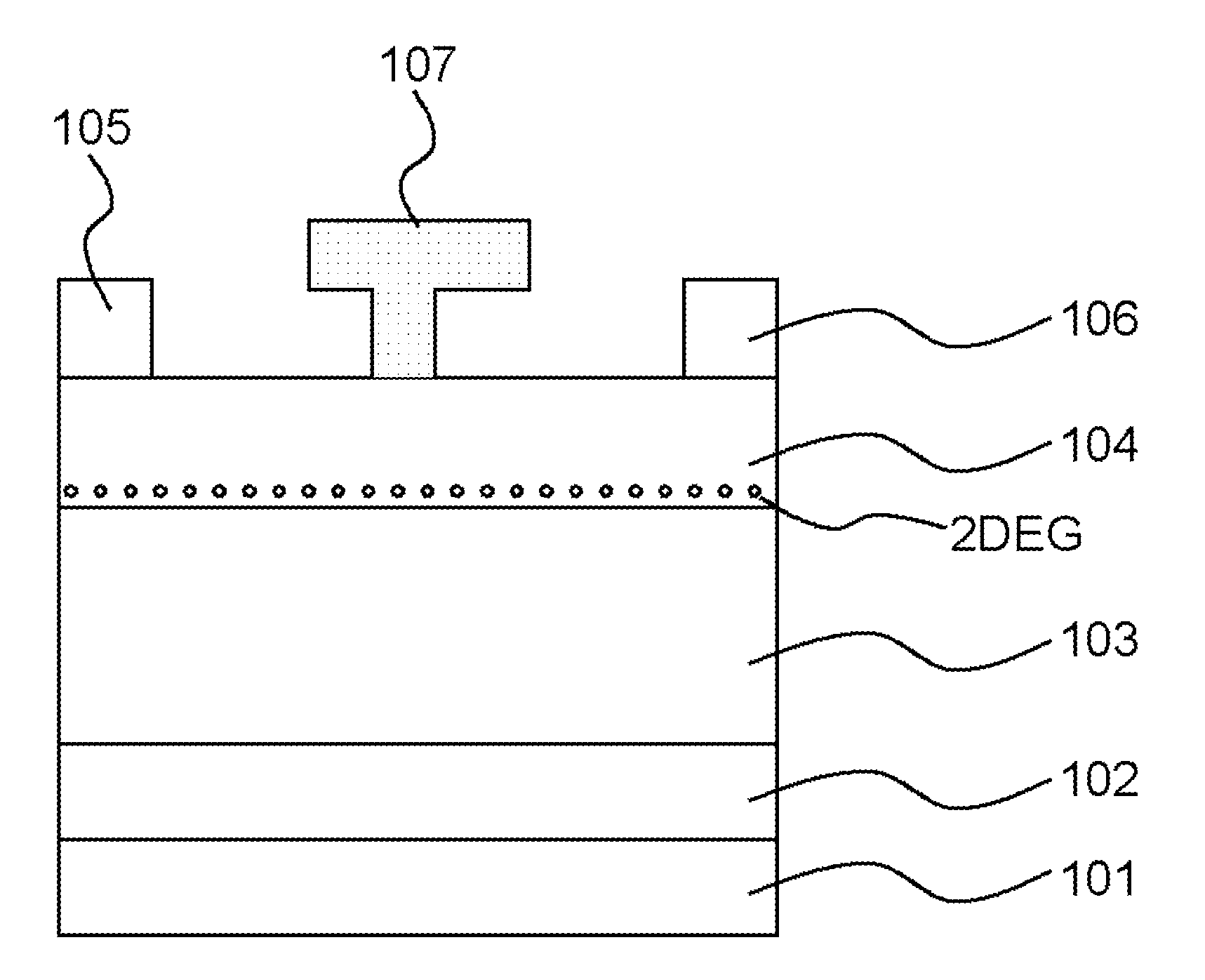

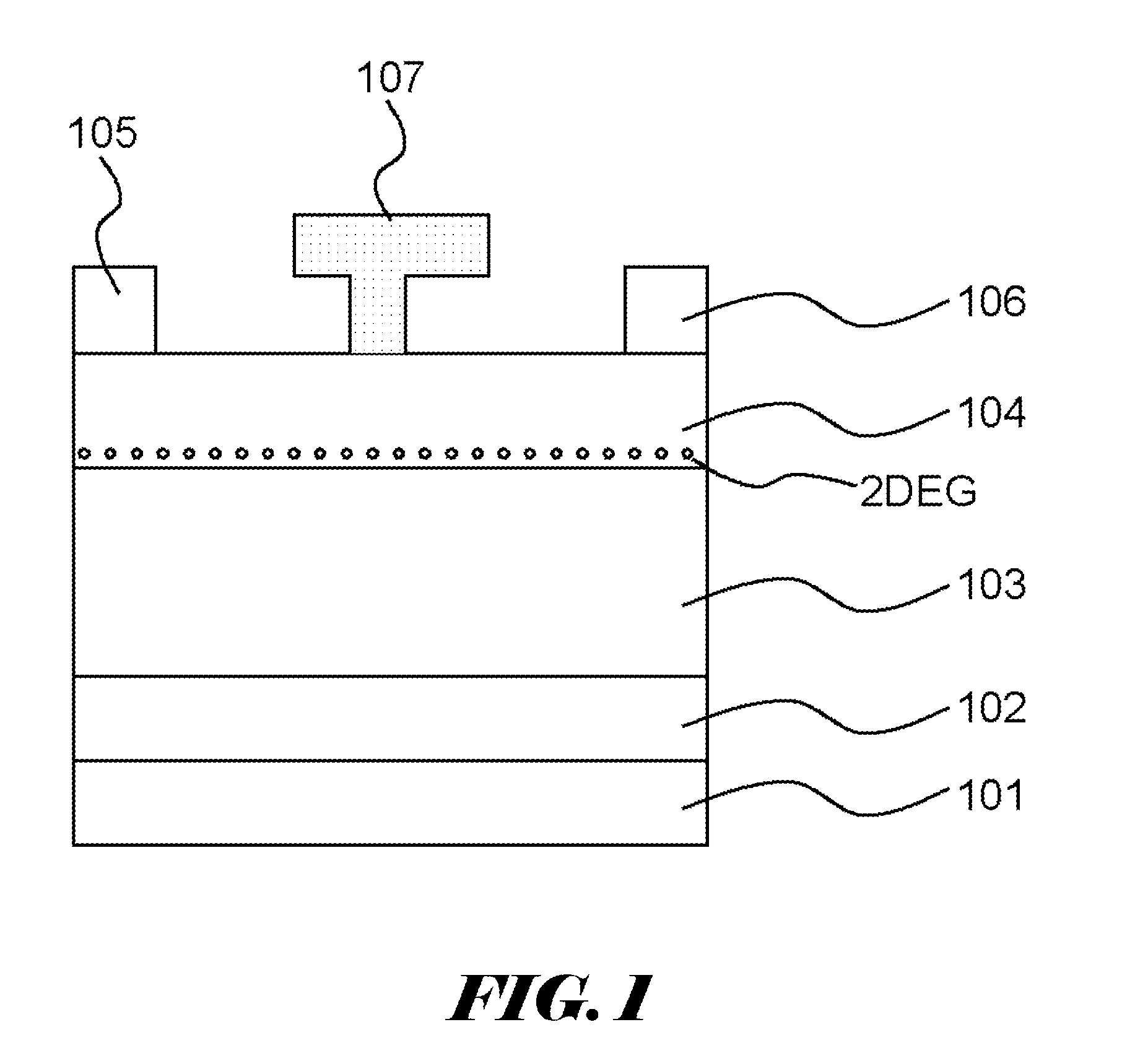

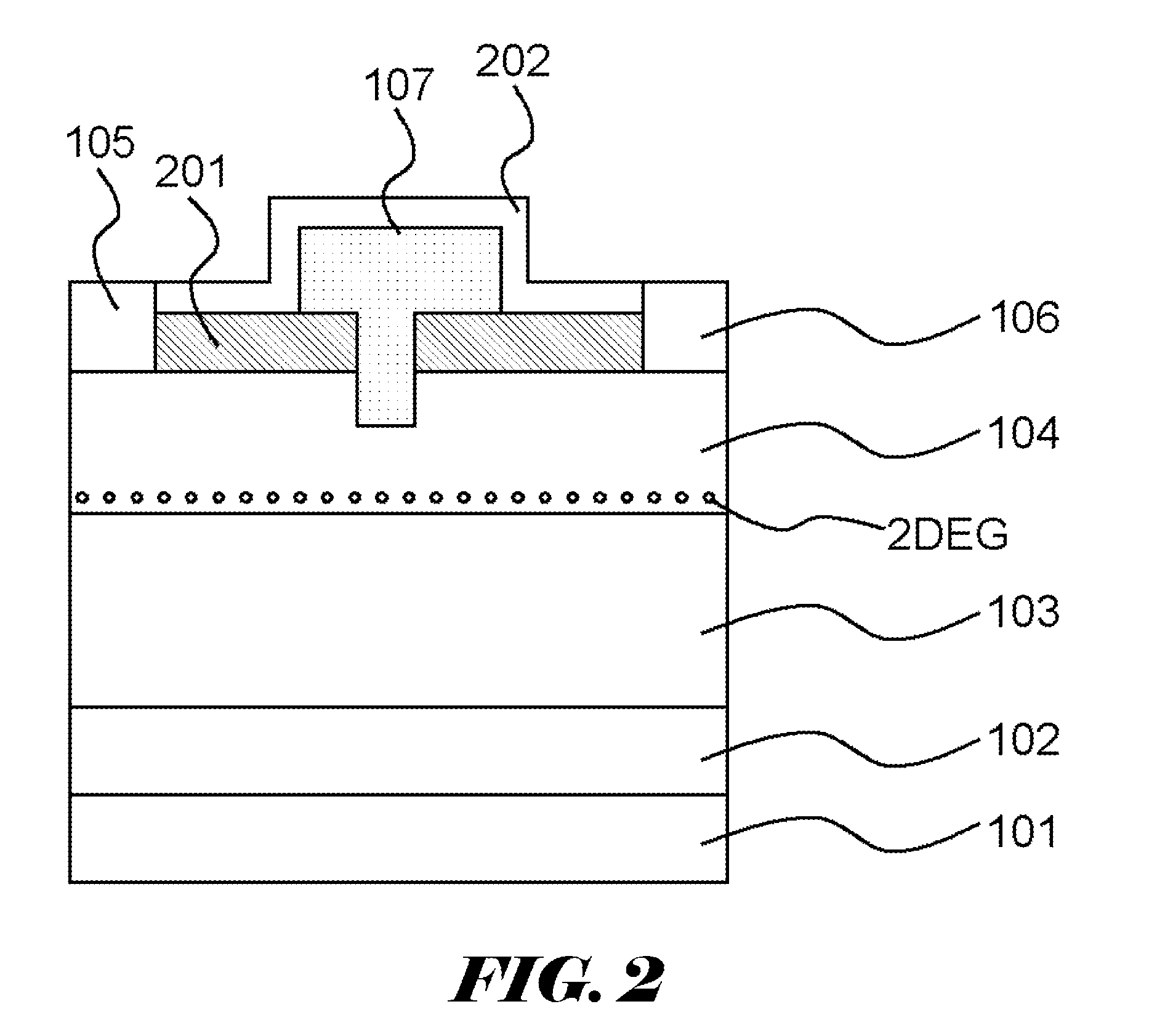

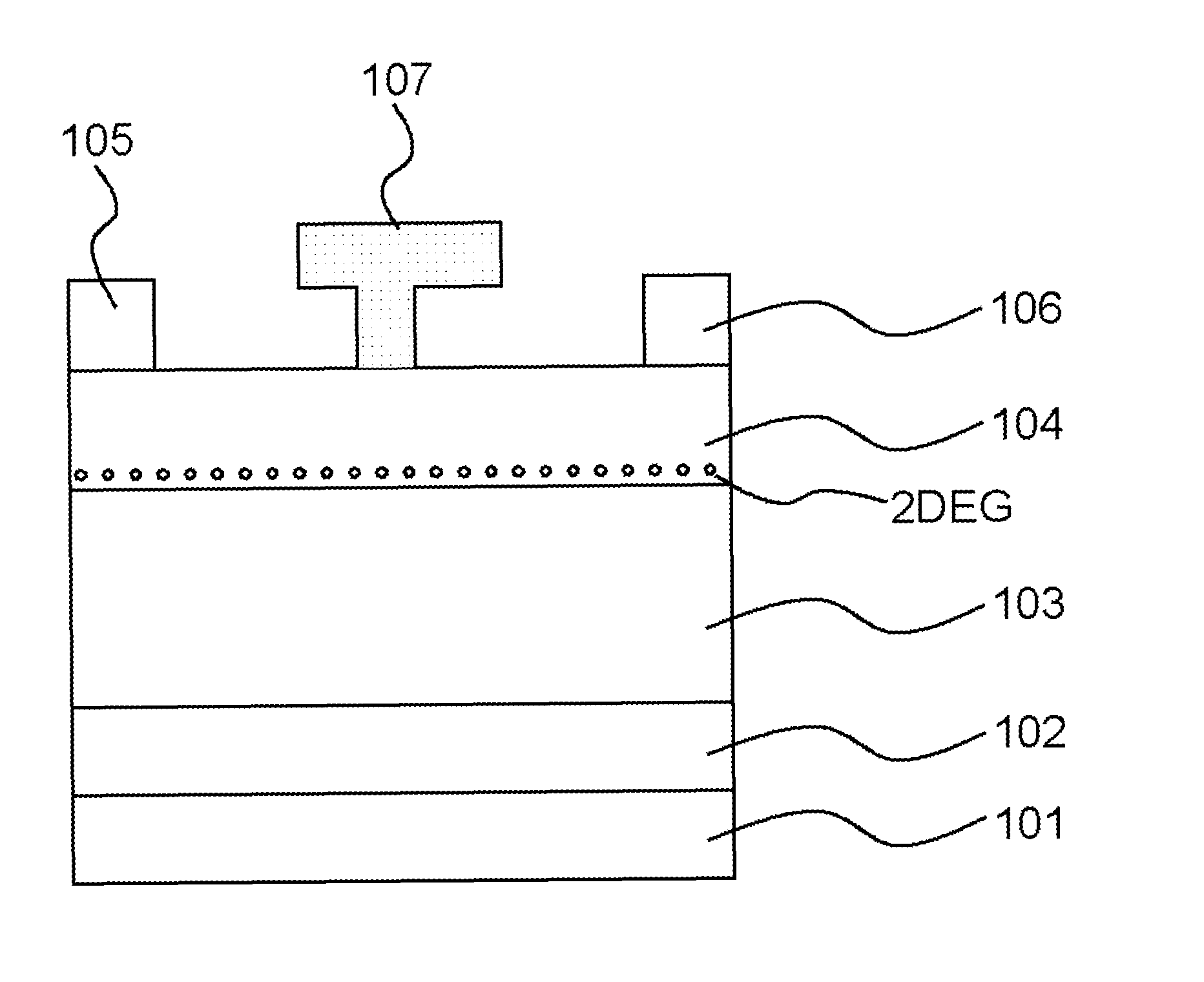

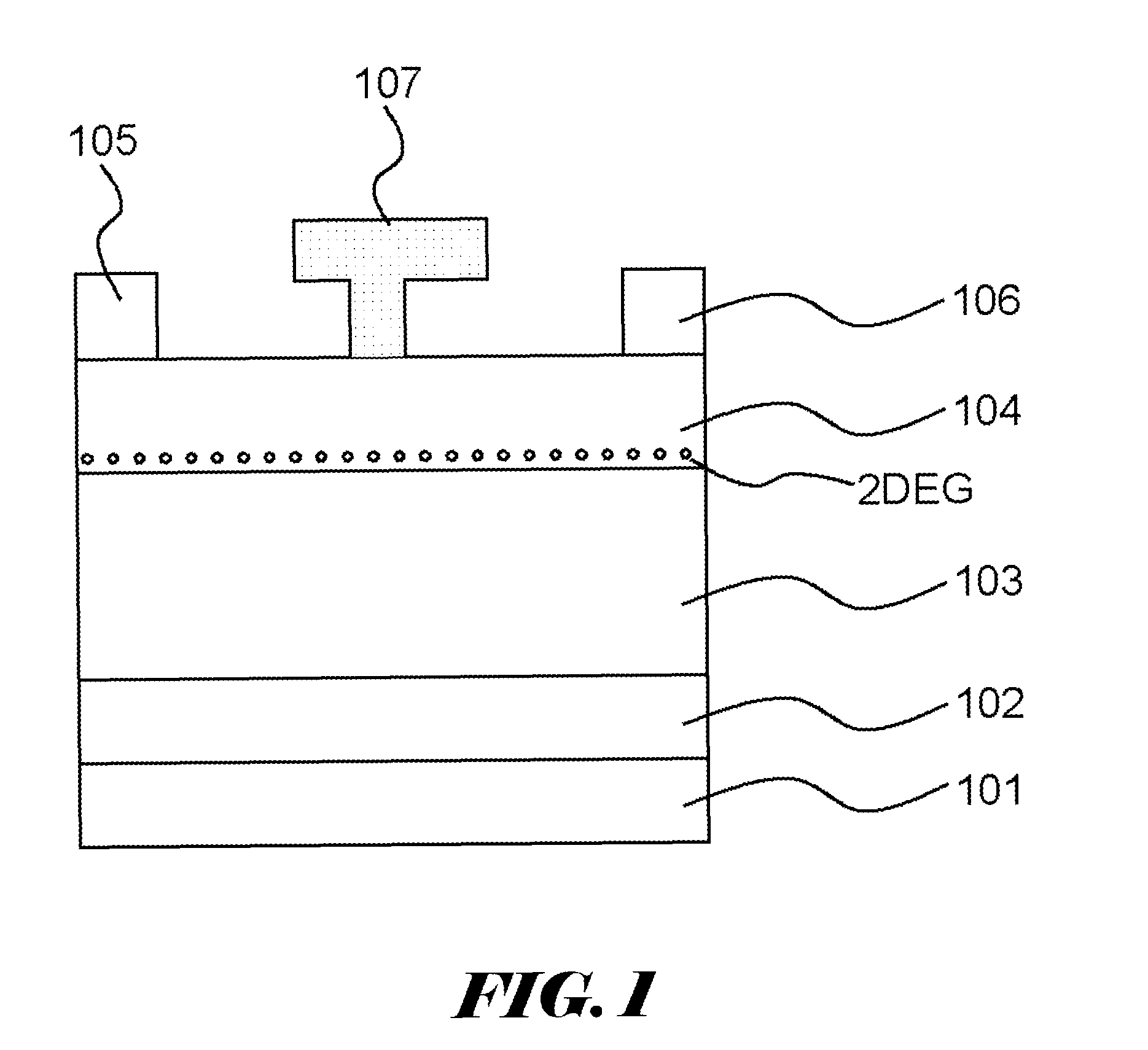

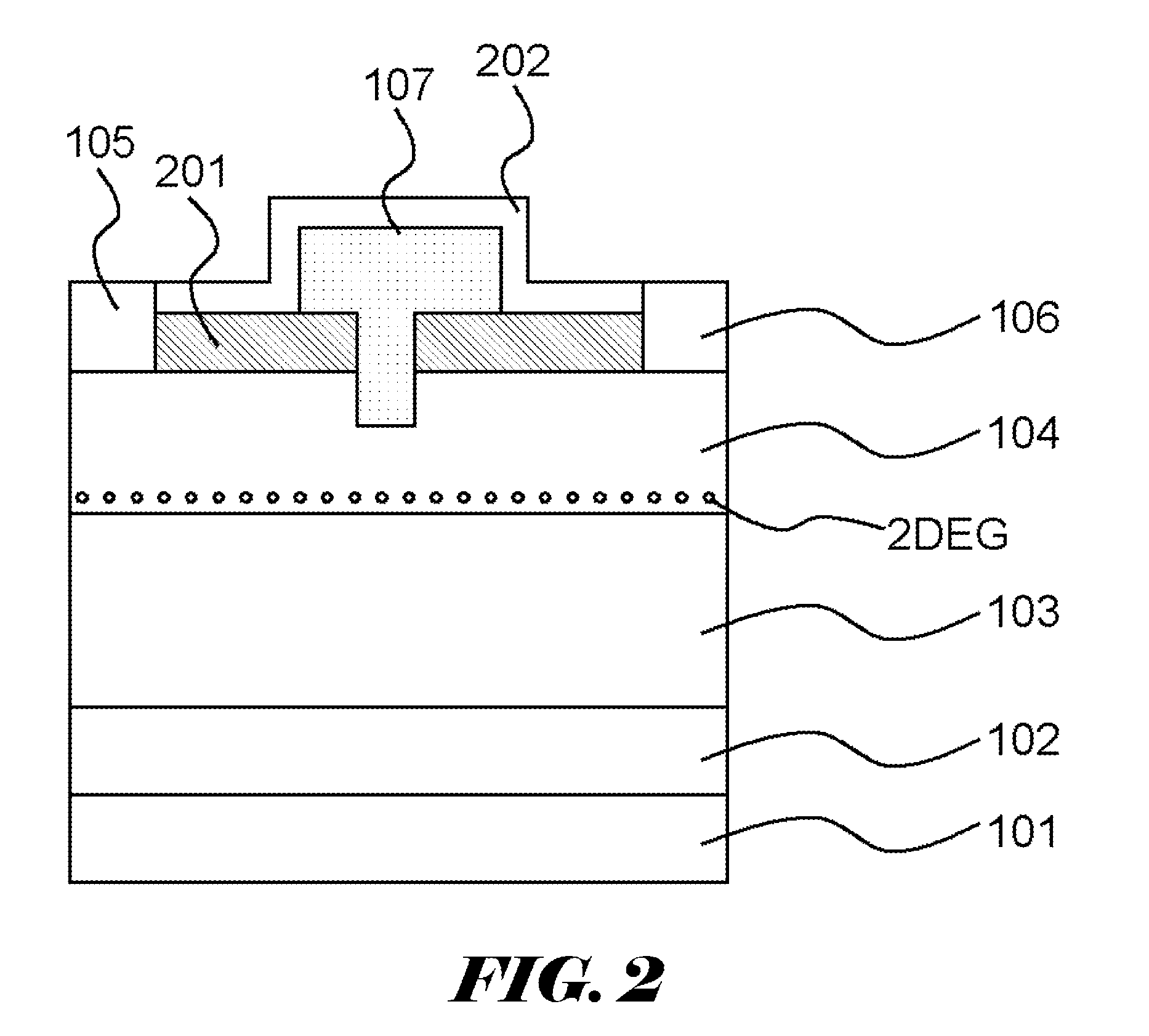

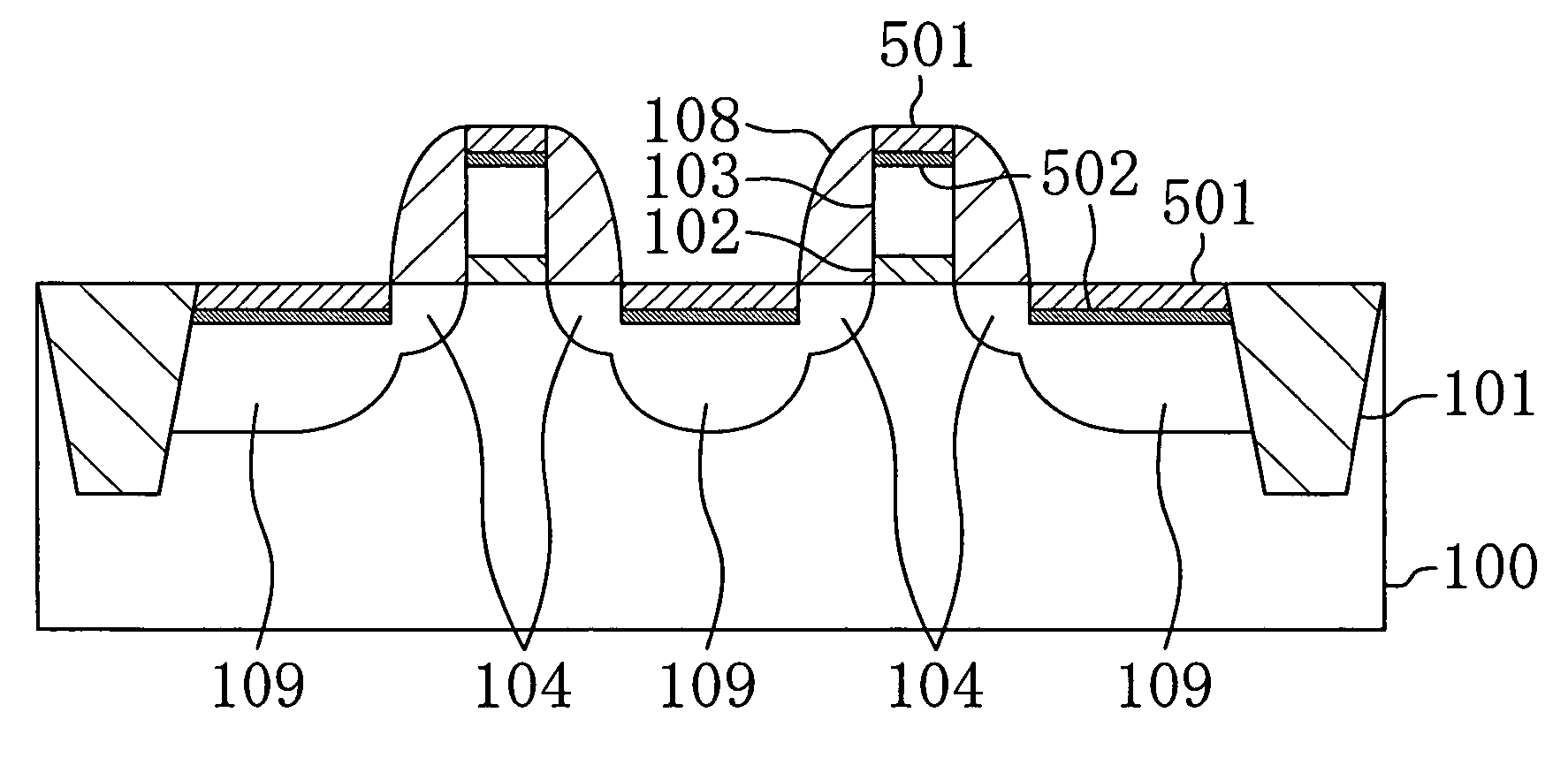

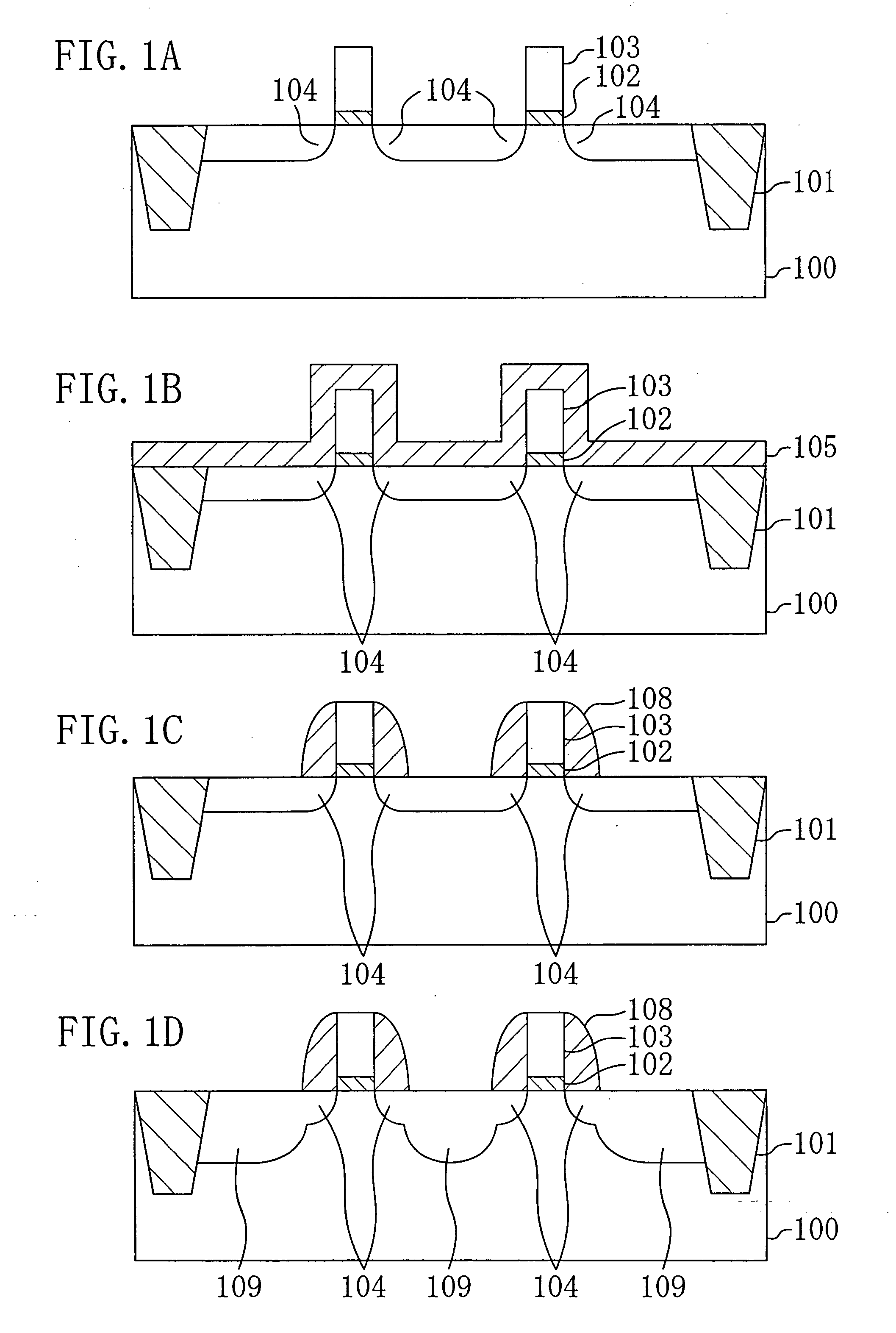

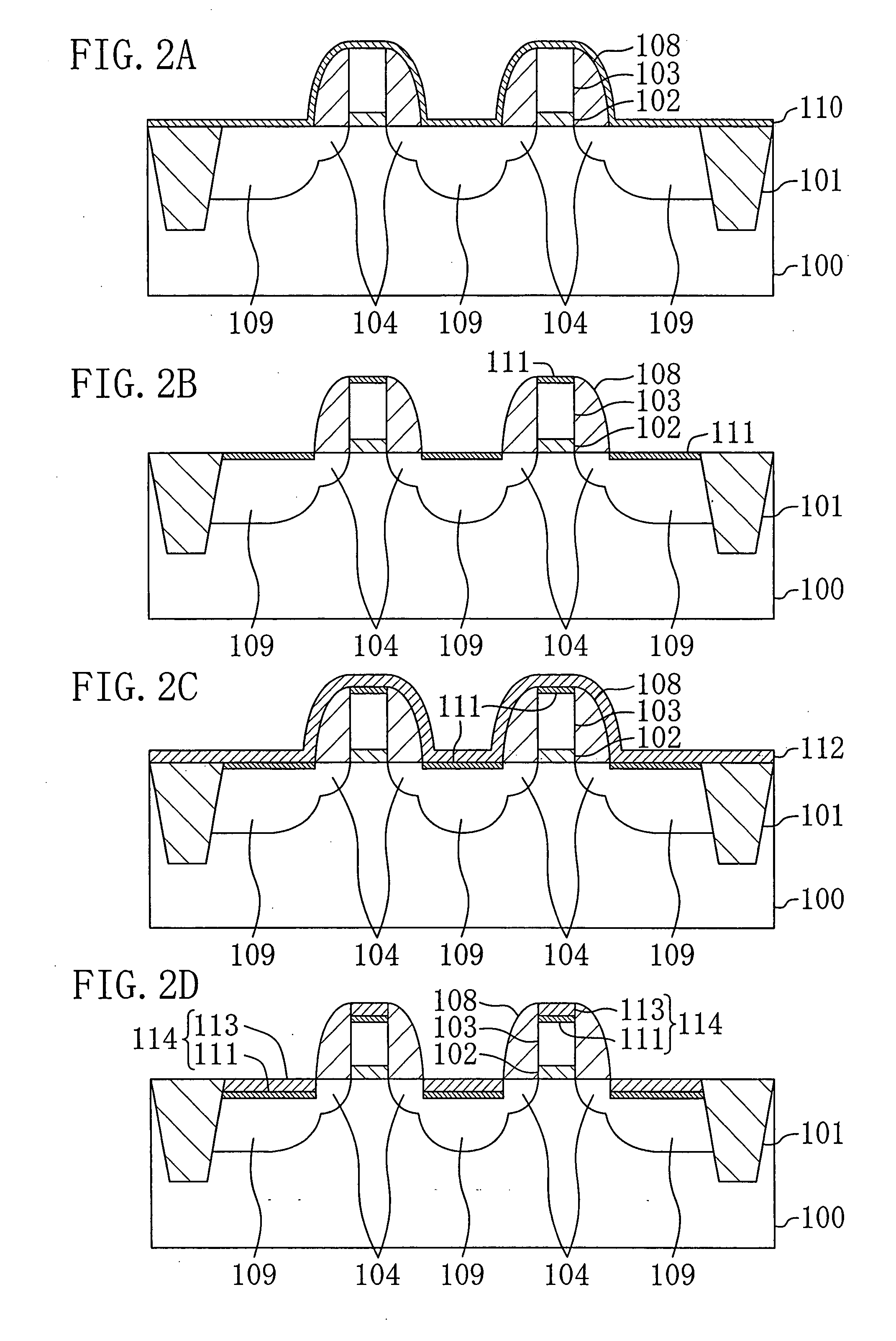

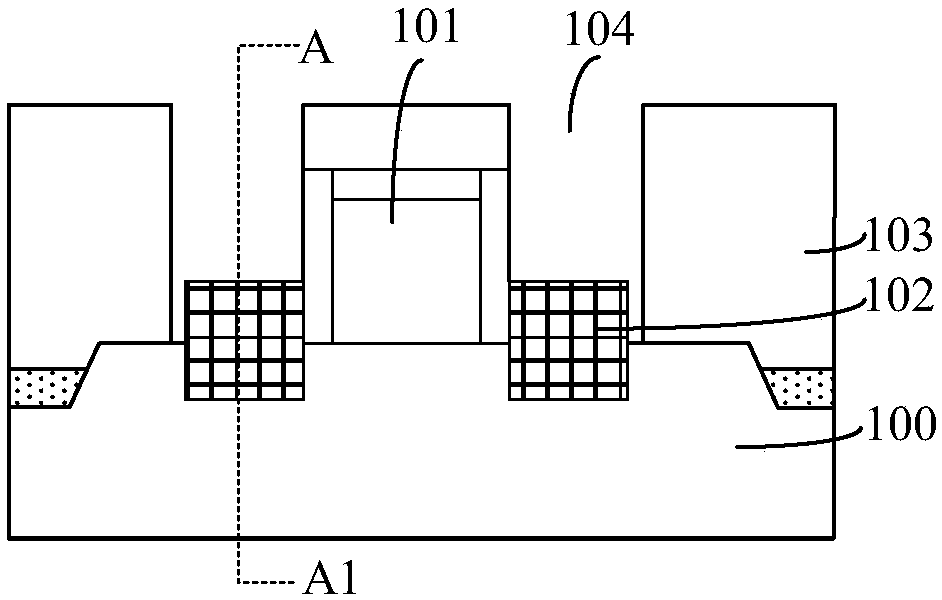

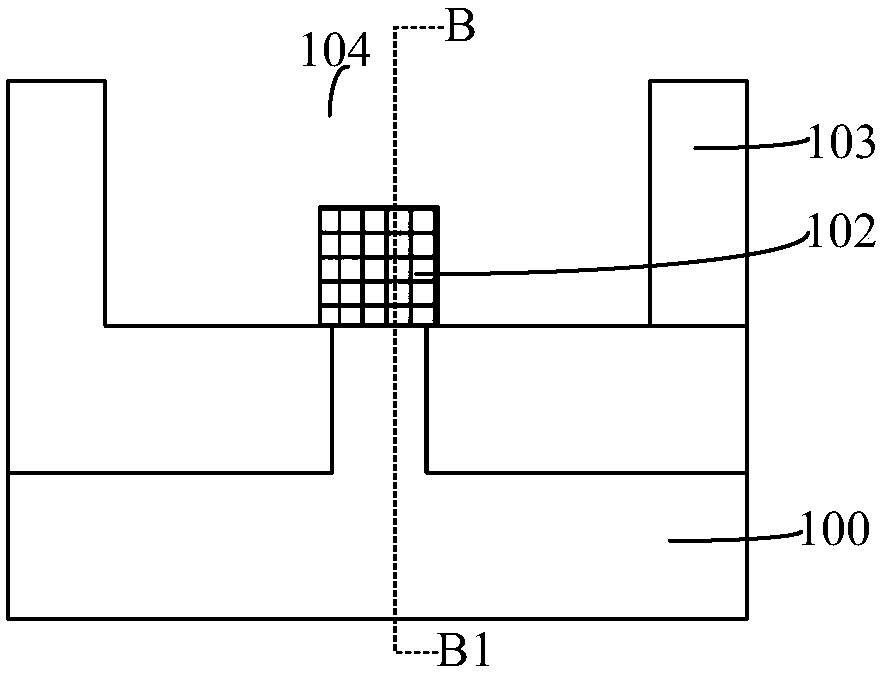

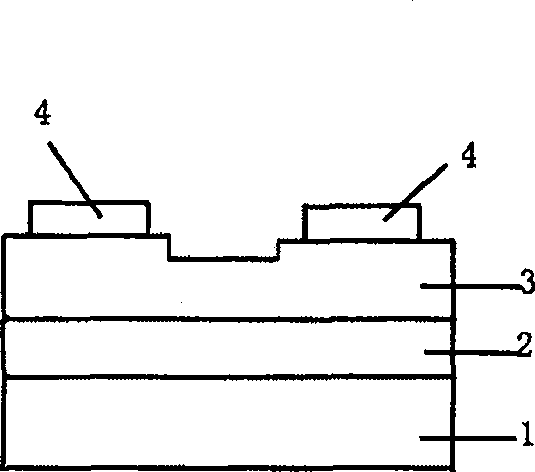

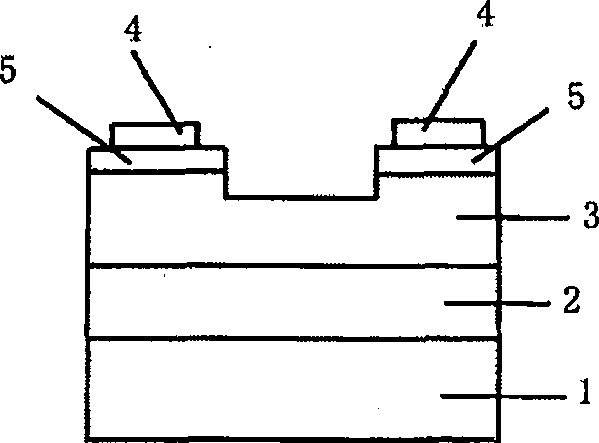

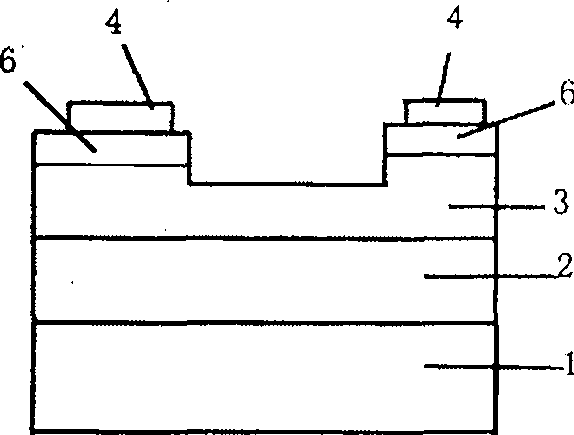

Iii-nitride semiconductor field effect transistor

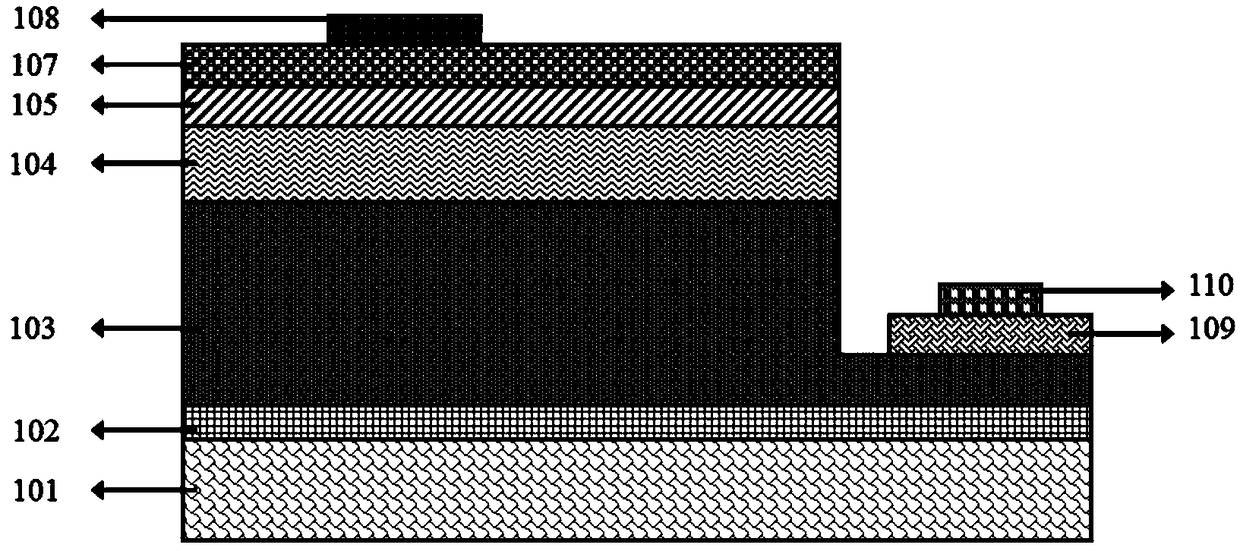

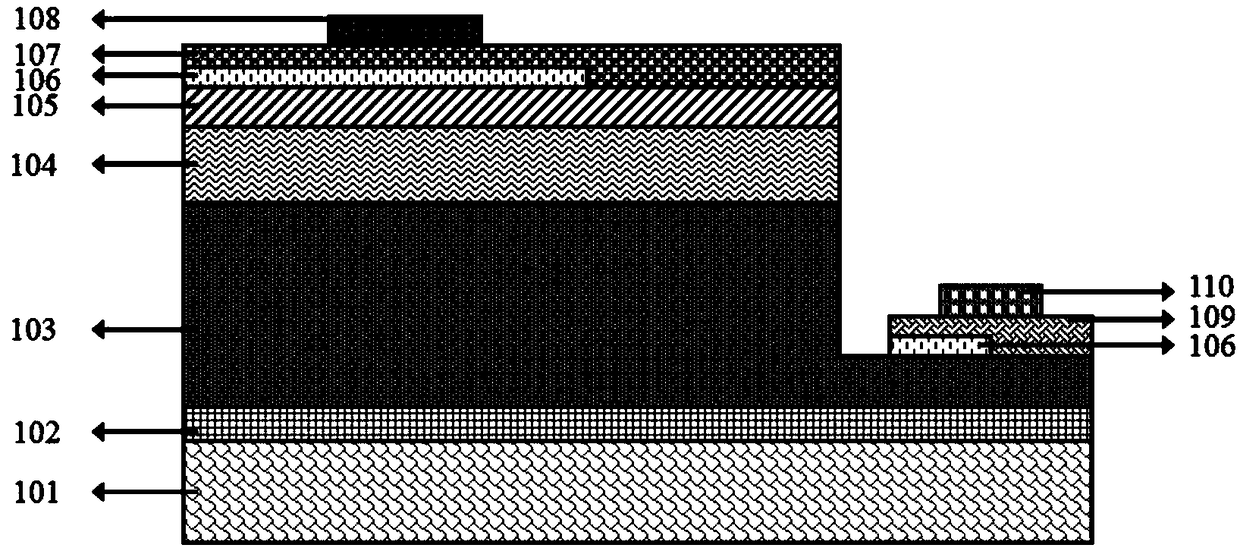

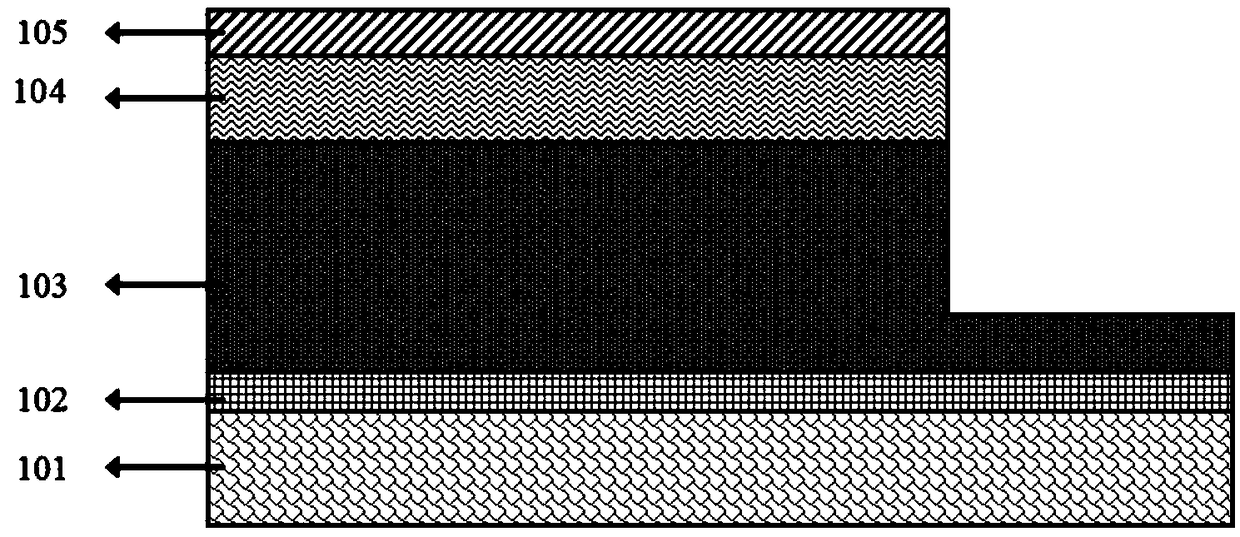

ActiveUS20100038680A1Reduce contact resistanceLower Schottky Barrier HeightSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsOhm

Provided is a semiconductor device that can reduce the contact resistance, has a small current collapse, and can improve the pinch-off characteristic upon a high-frequency operation. A field effect transistor using a wurtzite (having (0001) as the main plane) type III-nitride semiconductor includes: a substrate (101); an undercoat layer (103) of a first III-nitride semiconductor; and a carrier travel layer (104) of a second III-nitride semiconductor. The undercoat layer (103) (101) and the carrier travel layer (104) is formed on the substrate in this order. The field effect transistor includes source / drain electrodes (105, 106) in ohmic contact, and a gate electrode (107) in Schottky contact directly or via another layer on the carrier travel layer (104). The undercoat layer (103) has an average lattice constant greater than that of the carrier travel layer (104) and a band gap greater than that of the carrier travel layer (104).

Owner:MITSUBISHI ELECTRIC CORP

III-nitride semiconductor field effect transistor

ActiveUS7985984B2Reduce contact resistanceLower Schottky Barrier HeightSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialOhmic contact

Provided is a semiconductor device that can reduce the contact resistance, has a small current collapse, and can improve the pinch-off characteristic upon a high-frequency operation. A field effect transistor using a wurtzite (having (0001) as the main plane) type III-nitride semiconductor includes: a substrate (101); an undercoat layer (103) of a first III-nitride semiconductor; and a carrier travel layer (104) of a second III-nitride semiconductor. The undercoat layer (103) (101) and the carrier travel layer (104) is formed on the substrate in this order. The field effect transistor includes source / drain electrodes (105, 106) in ohmic contact, and a gate electrode (107) in Schottky contact directly or via another layer on the carrier travel layer (104). The undercoat layer (103) has an average lattice constant greater than that of the carrier travel layer (104) and a band gap greater than that of the carrier travel layer (104).

Owner:MITSUBISHI ELECTRIC CORP

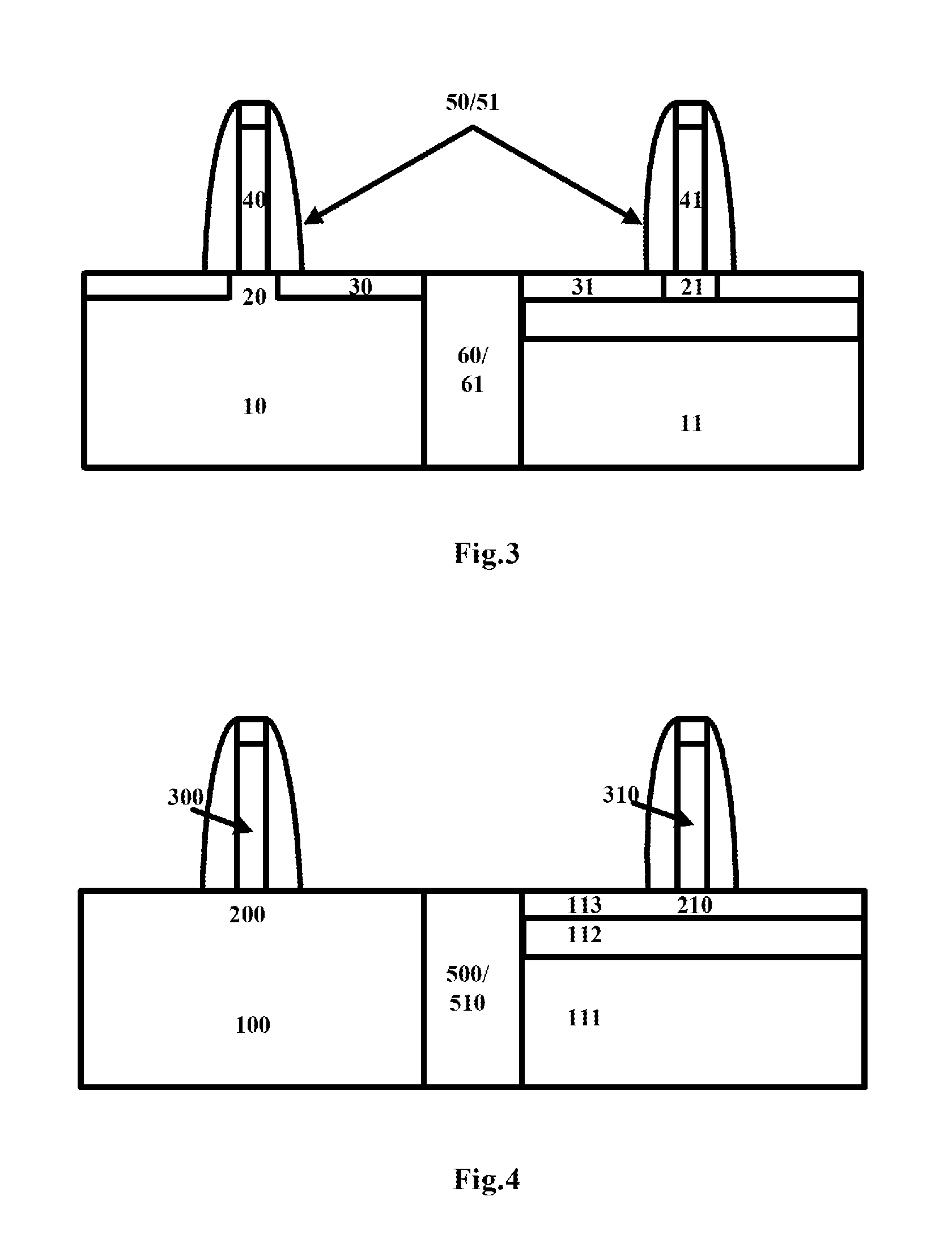

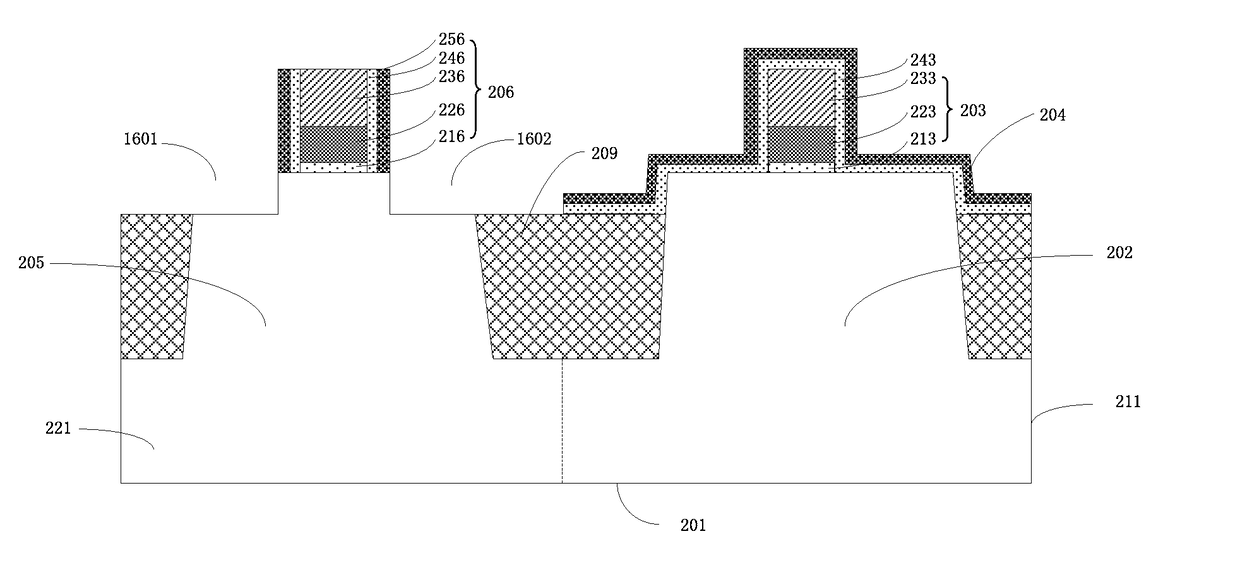

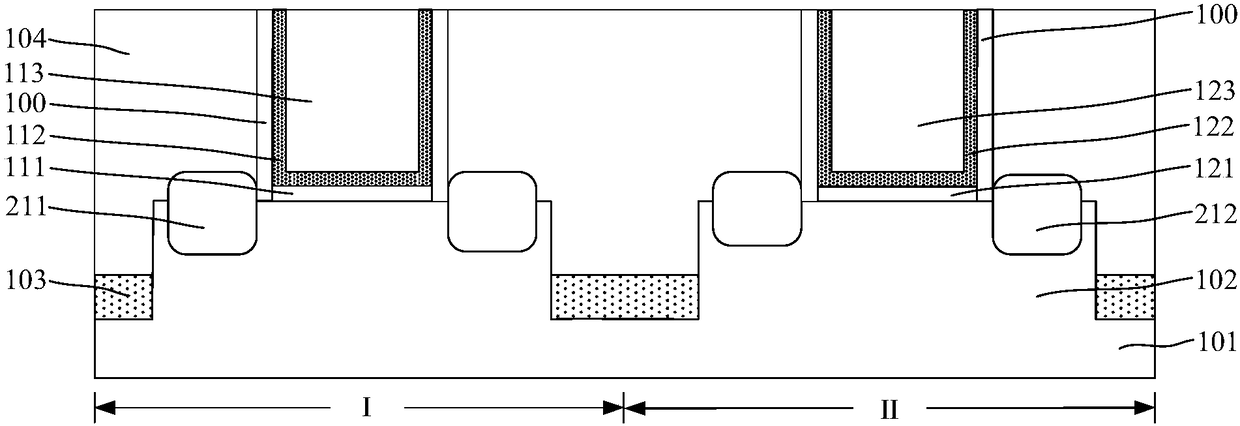

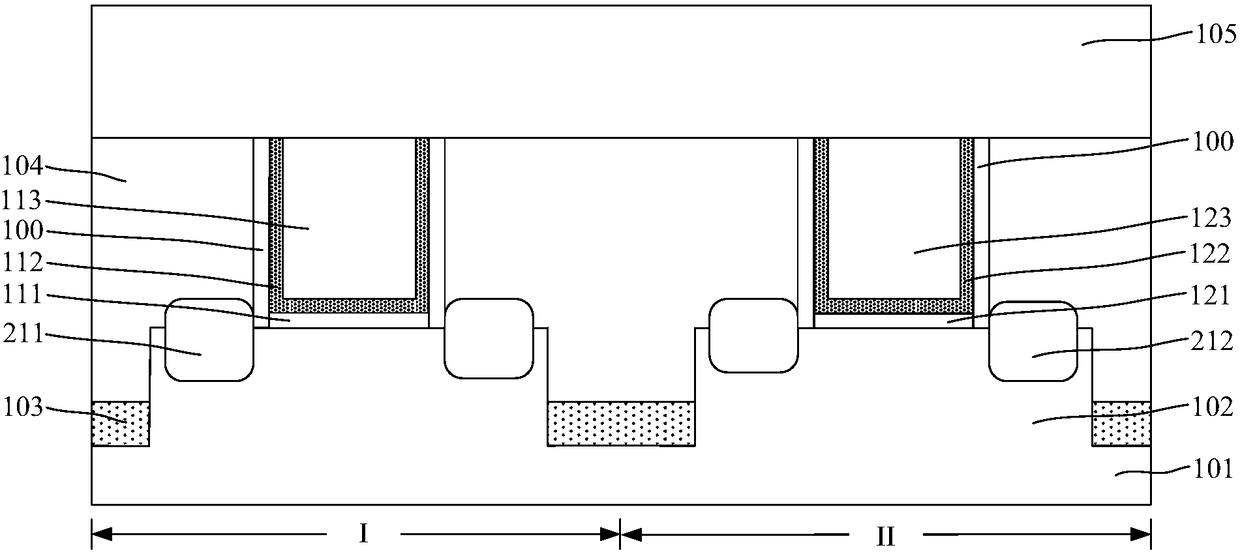

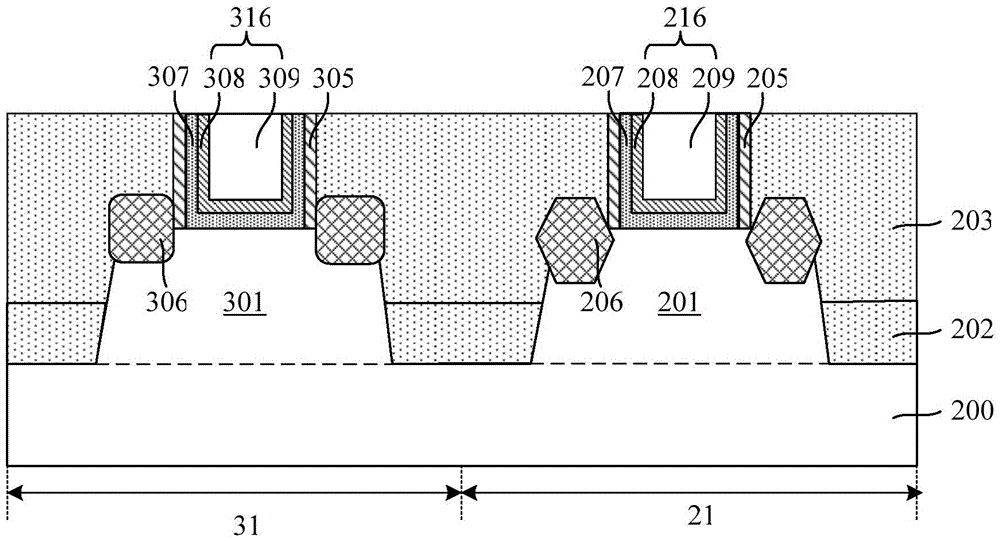

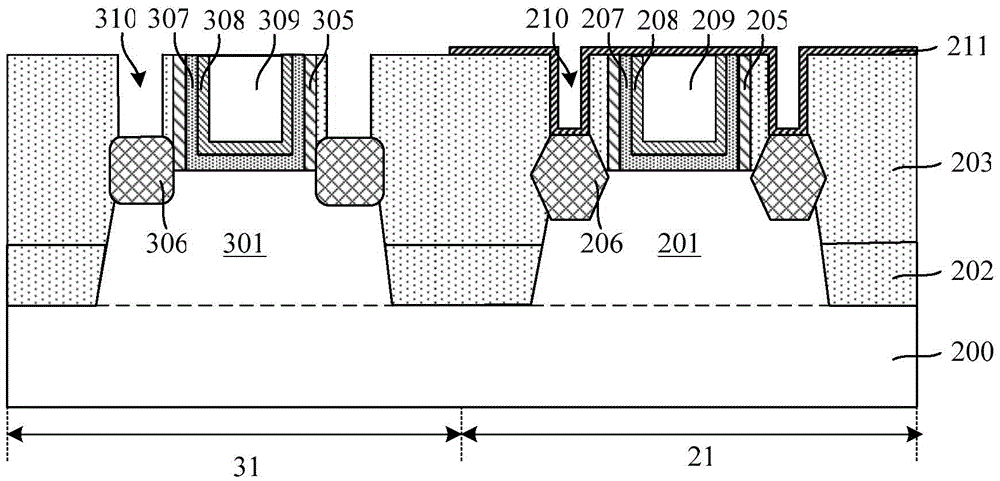

Semiconductor structure and formation method thereof

ActiveCN108695257AReduce adverse effectsIncrease drive currentTransistorSolid-state devicesSemiconductor structureMetal silicide

The invention relates to a semiconductor structure and a formation method thereof. The formation method includes the following steps that: a substrate is provided, gate structures are arranged on thesubstrate, source-drain doping regions located at two sides of each gate structure are formed in the substrate, an interlayer dielectric layer is formed on the substrate which is not covered by the gate structure, and the interlayer dielectric layer covers the tops of the gate structures; first contact openings exposing the source / drain doping regions are formed in the interlayer dielectric layerat two sides of each gate structure; second contact openings which pass through the interlayer dielectric layer above the gate structures are formed; after the second contact openings are formed, pre-amorphization implantation is performed on the source / drain doping regions; after the pre-amorphization implantation process, metal silicide layers are formed at the bottoms of the first contact openings; and after the metal silicide layers are formed, first contact hole plugs are formed in the first contact openings, and second contact hole plugs are formed in the second contact openings. With the formation method of the present invention adopted, amorphous layers formed at the bottoms of the first contact openings can be prevented from being oxidized during the formation of the second contact openings, and therefore, the problem that the metal silicide layers are difficult to form can be avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor device and method for fabricating the same

ActiveUS7202147B2Reduce interface resistanceStructuredTransistorSemiconductor/solid-state device manufacturingSalicideMetal silicide

Owner:PANNOVA SEMIC

Field-effect semiconductor device

InactiveUS7208777B1Reduce series resistanceReduced series resistanceTransistorSemiconductor/solid-state device manufacturingSemiconductor structureField effect

The field-effect semiconductor device includes a channel layer; a contact layer; a semiconductor structure having an electron-affinity different from those of the channel layer and the contact layer and formed between the channel layer and the contact layer; an ohmic electrode formed on the contact layer; and a Schottky electrode formed on the semiconductor structure. The junction face between the channel layer and the semiconductor structure and the junction face between the contact layer and the semiconductor structure are iso-type heterojunctions.

Owner:MURATA MFG CO LTD

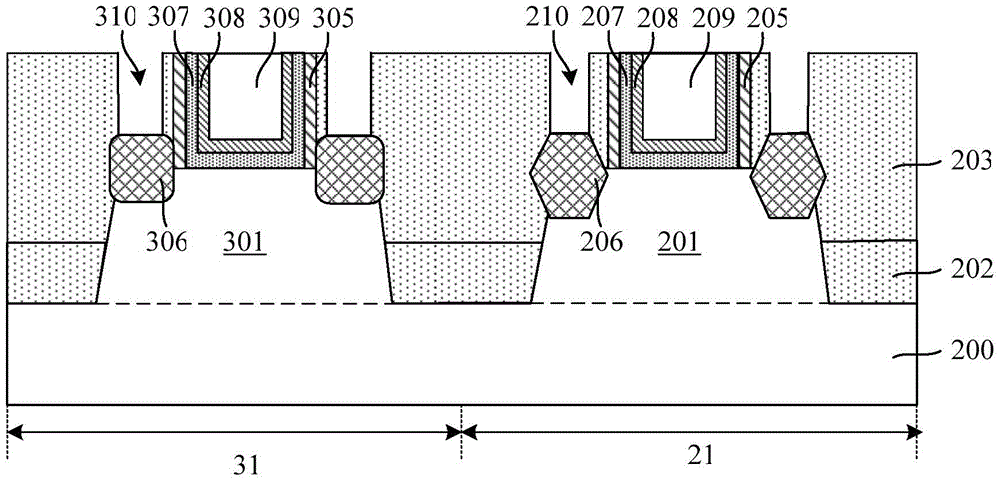

Semiconductor structure and formation method thereof

ActiveCN108257916AReduce manufacturing costReduce the impactTransistorSolid-state devicesDopantSemiconductor structure

Disclosed are a semiconductor structure and a formation method thereof. The formation method comprises the steps of forming a base, wherein the base comprises a substrate, a gate structure positionedon the substrate, source and drain doped regions positioned in the base on the two sides of the gate structure, and an interlayer dielectric layer positioned on the base and for covering the top of the gate structure, and the substrate comprises a first region for forming a P type device and a second region for forming an N type device; forming a first contact opening for exposing the source and drain doped regions in the interlayer dielectric layer on the two sides of the gate structure; performing a P type dopant segregated schottky doping process on the source and drain doped regions exposed from the first contact opening in the first region and the second region; forming a metal silicide layer at the bottom of the first contact opening; and forming a first contact hole inserting plug in the first contact opening. By adjusting the doping concentration of the source and drain doped regions in the second region, use of a photomask can be avoided when the P type dopant segregated schottky doping process is performed, so that lowering of the process cost is realized, and the N type device suffers from relatively low influence.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

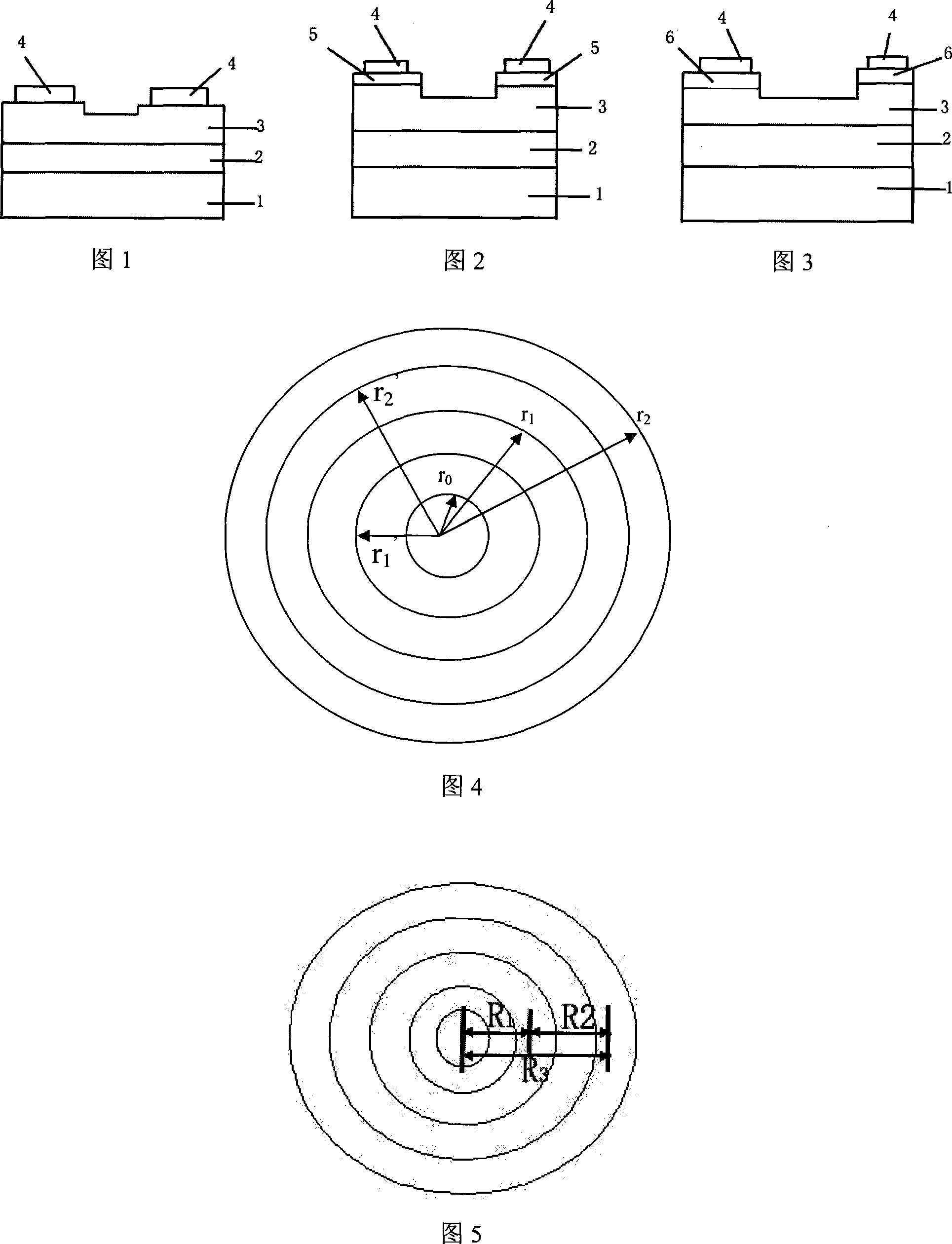

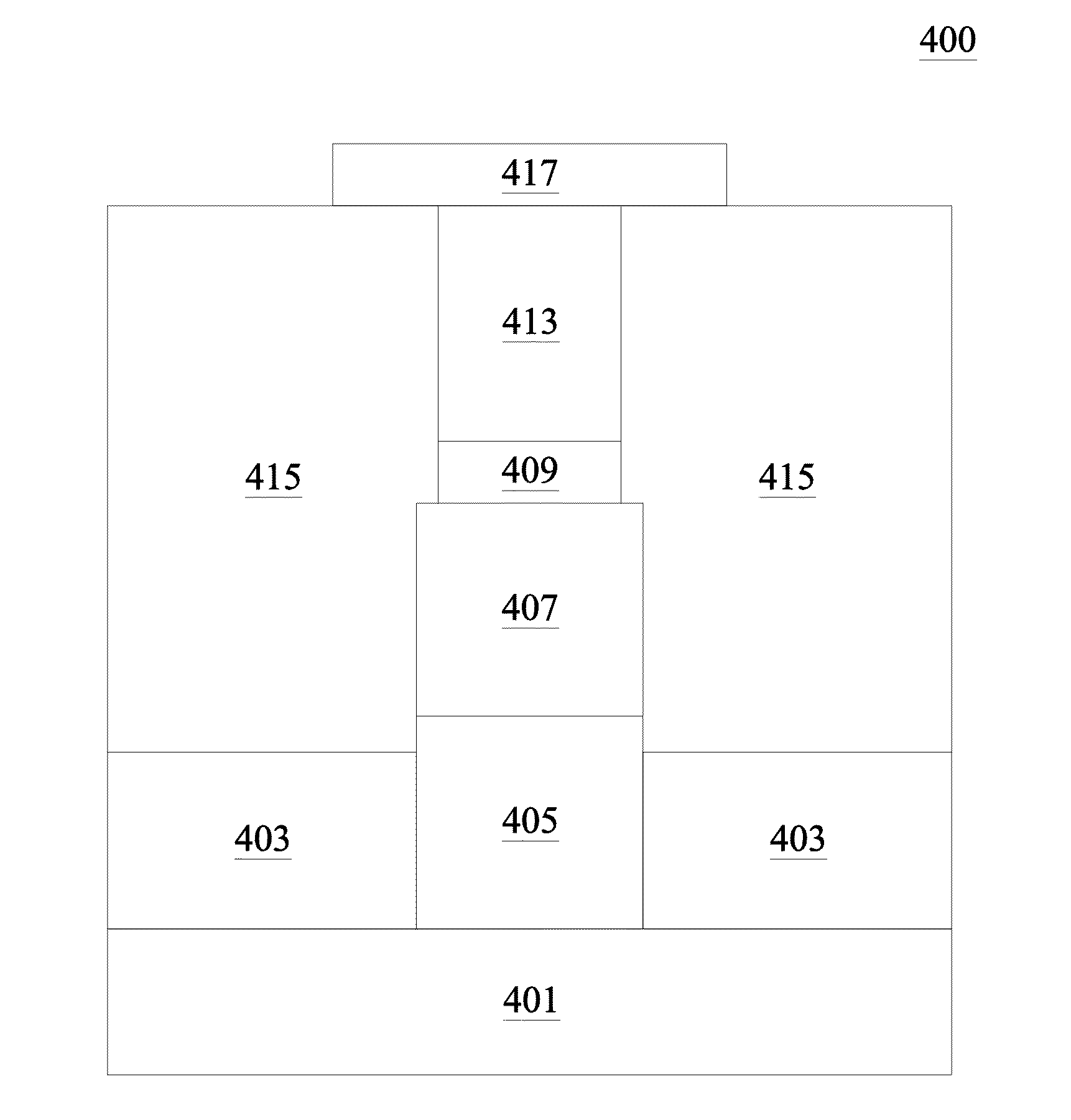

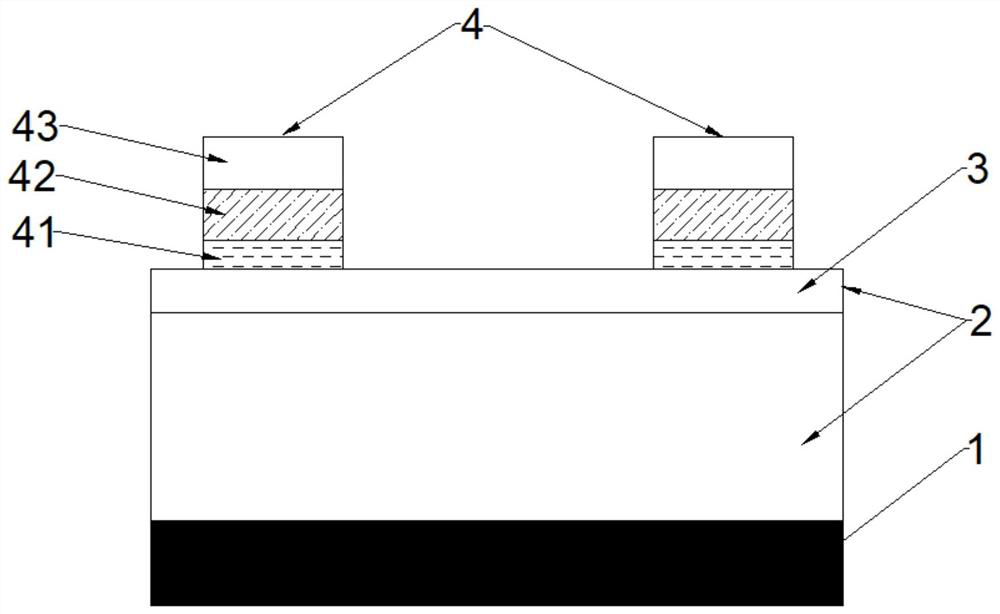

Chip epitaxial structure of low-resistance LED and preparation method thereof

PendingCN108538982AReduce contact resistanceLower Schottky Barrier HeightSemiconductor devicesInsulation layerSemiconductor materials

The present invention provides a chip epitaxial structure of a low-resistance LED and a preparation method thereof. The structure comprises a substrate, a buffer layer, an N-type semiconductor material layer, a multi-quantum well layer, a P-type semiconductor material layer, a current expanding layer and a P-type Ohmic electrode in order in an epitaxial growth direction. The current expanding layer and the N-type semiconductor material layer are respectively embedded with insulation layers. The epitaxial structure further comprises an N-pole Ohmic contact layer and an N-type Ohmic electrode; the N-pole Ohmic contact layer is located on part of the N-type semiconductor material layer; and the N-type Ohmic electrode is located on the N-pole Ohmic contact layer. The preparation method is simple, high in operability and low in cost, can increase the injection efficiency of carriers to a certain extent on the basis of further reduction of the Ohmic contact resistance, and greatly improves the implementation performances.

Owner:HEBEI UNIV OF TECH

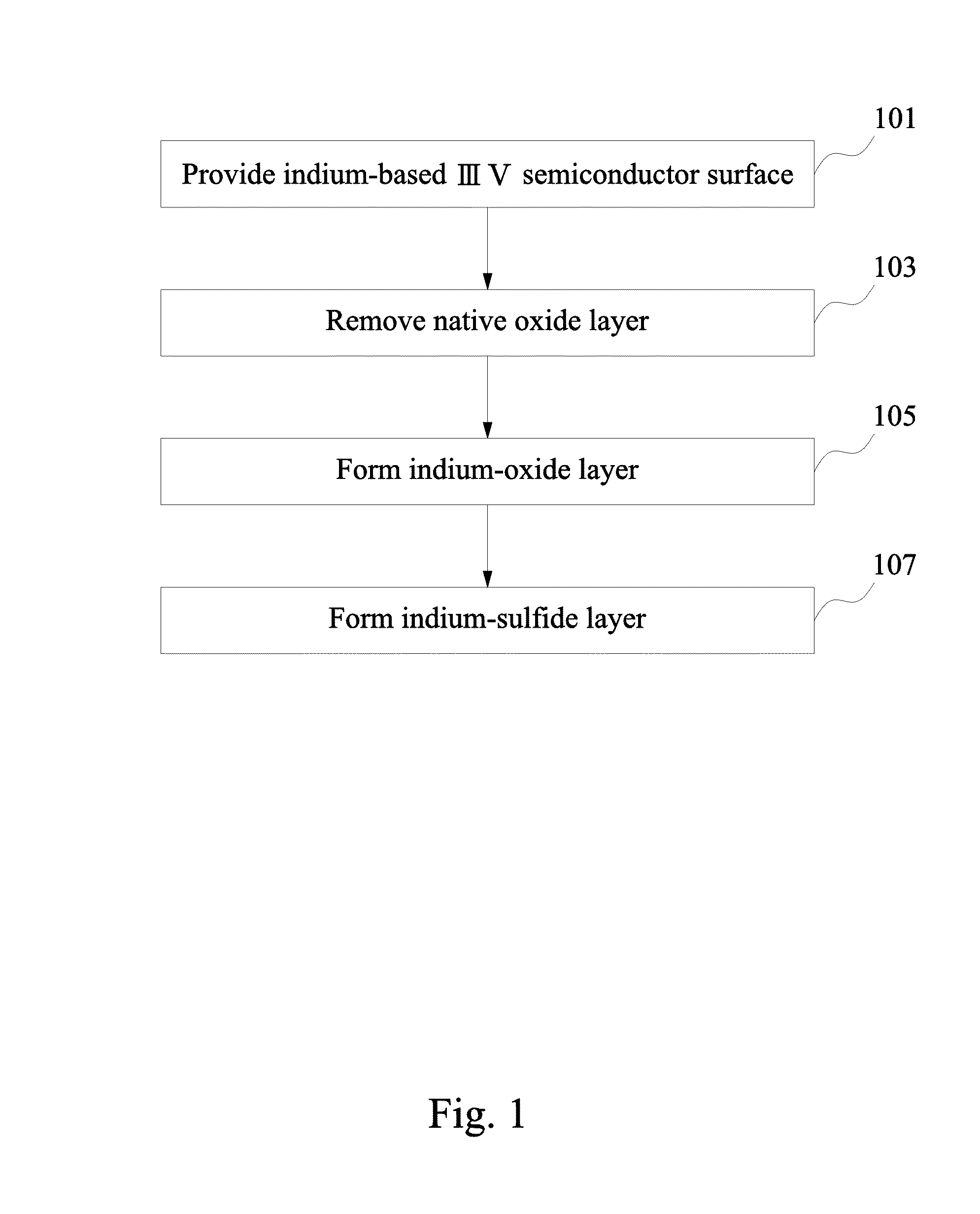

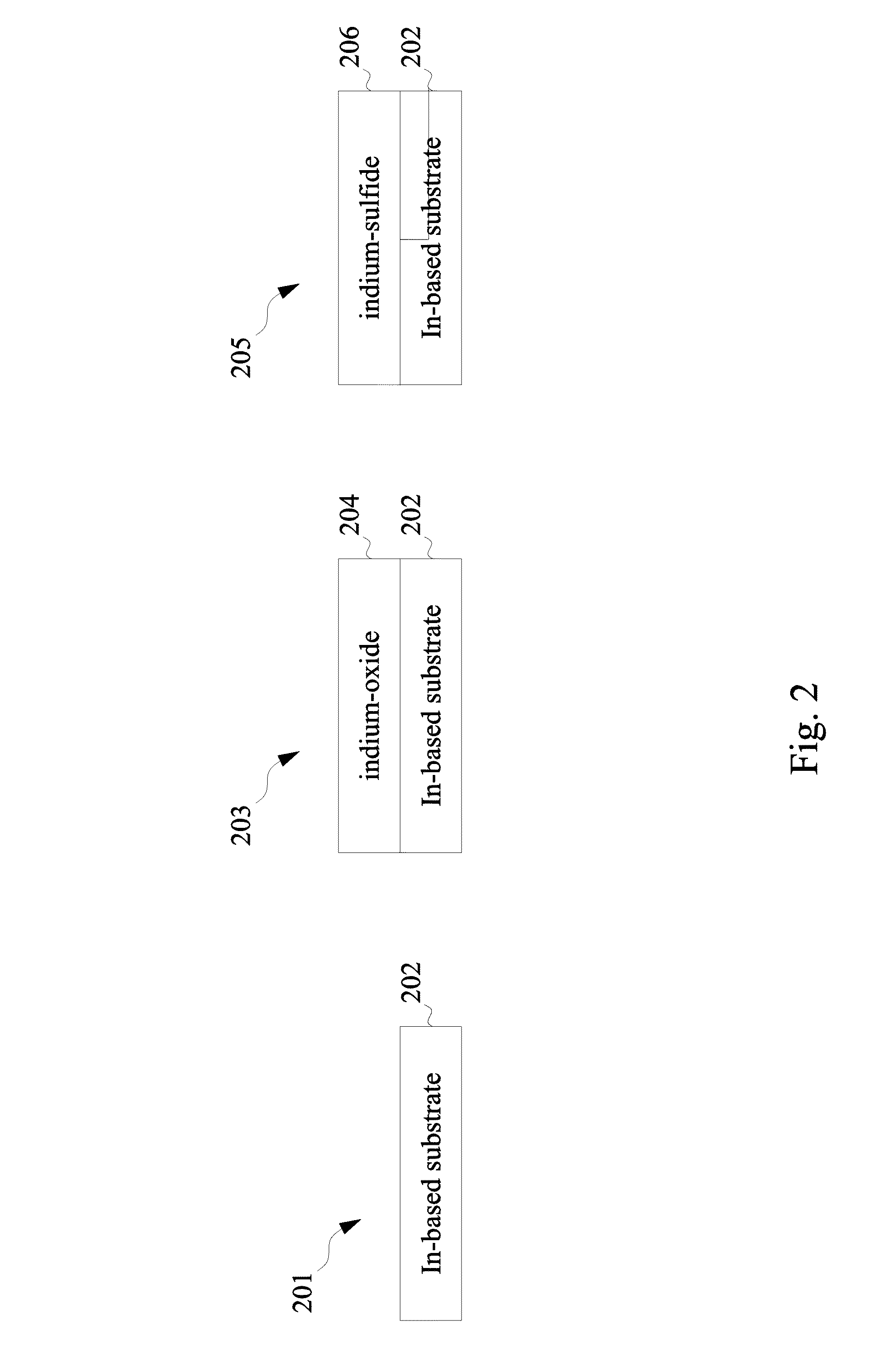

Surface passivation on indium-based materials

ActiveUS20160268122A1Inhibition formationLow densitySemiconductor/solid-state device detailsSolid-state devicesIndiumSemiconductor structure

The present disclosure provides a semiconductor structure in accordance with some embodiments. The semiconductor structure includes a semiconductor feature, a passivation layer that includes indium sulfide formed over a surface of the semiconductor feature. More particularly, the surface of the semiconductor feature comprises indium-based III-V compound semiconductor material.

Owner:TAIWAN SEMICON MFG CO LTD

Ge-based NMOS device and method for fabricating the same

ActiveUS8865543B2Improve performanceGuaranteed flatnessSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierPower flow

The embodiments of the present invention provide a Ge-based NMOS device structure and a method for fabricating the same. By using the method, double dielectric layers of germanium oxide (GeO2) and metal oxide are deposited between the source / drain region and the substrate. The present invention not only reduces the electron Schottky barrier height of metal / Ge contact, but also improves the current switching ratio of the Ge-based Schottky and therefore, it will improve the performance of the Ge-based Schottky NMOS transistor. In addition, the fabrication process is very easy and completely compatible with the silicon CMOS process. As compared with conventional fabrication method, the Ge-based NMOS device structure and the fabrication method in the present invention can easily and effectively improve the performance of the Ge-based Schottky NMOS transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

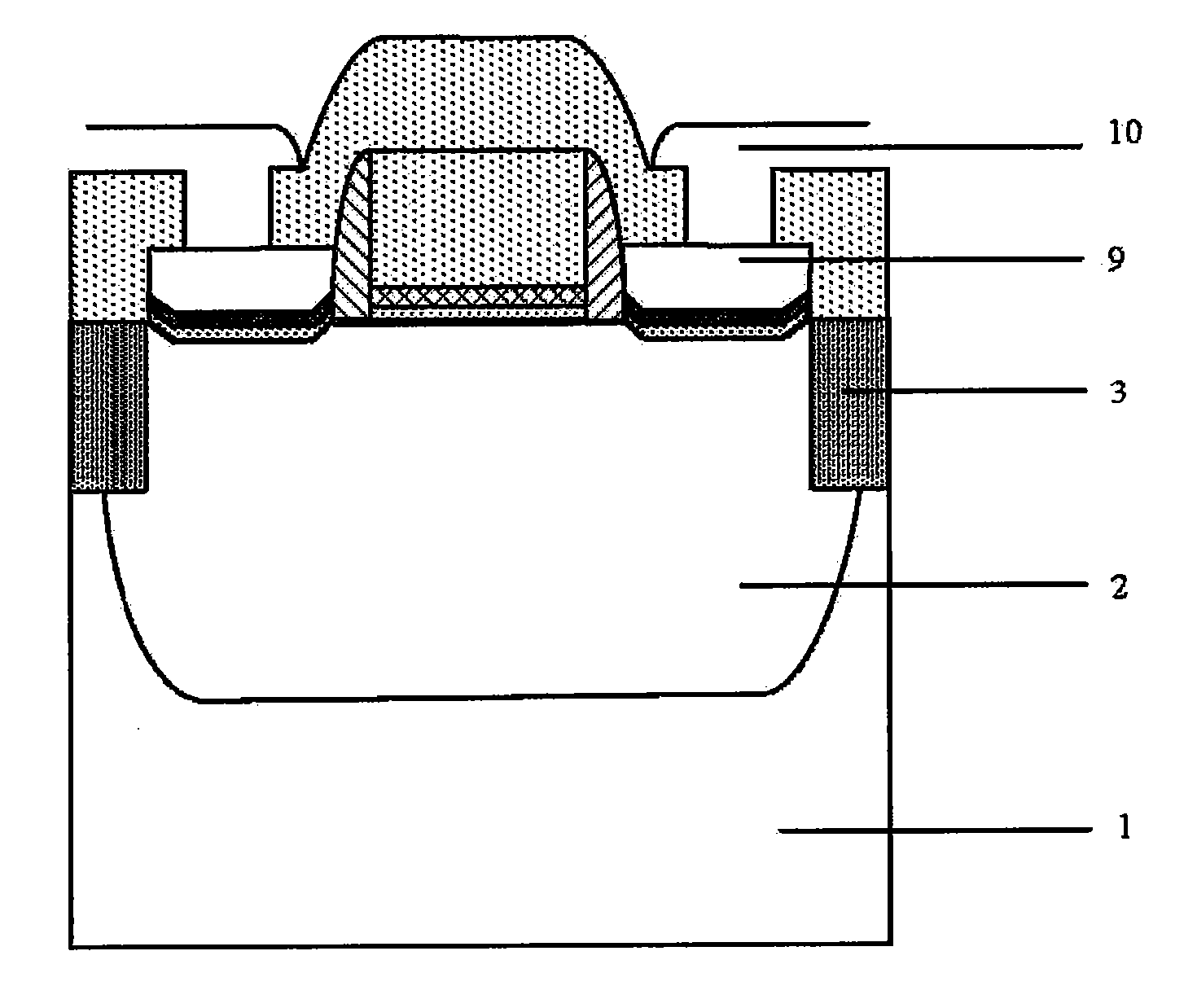

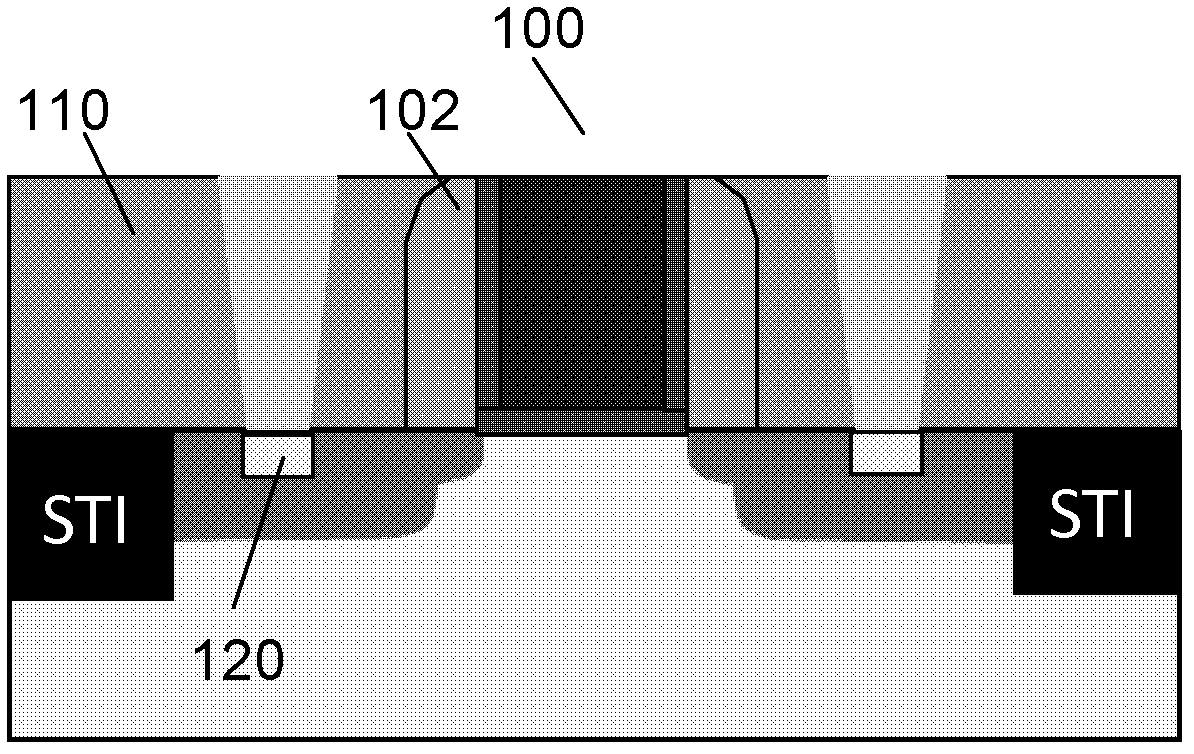

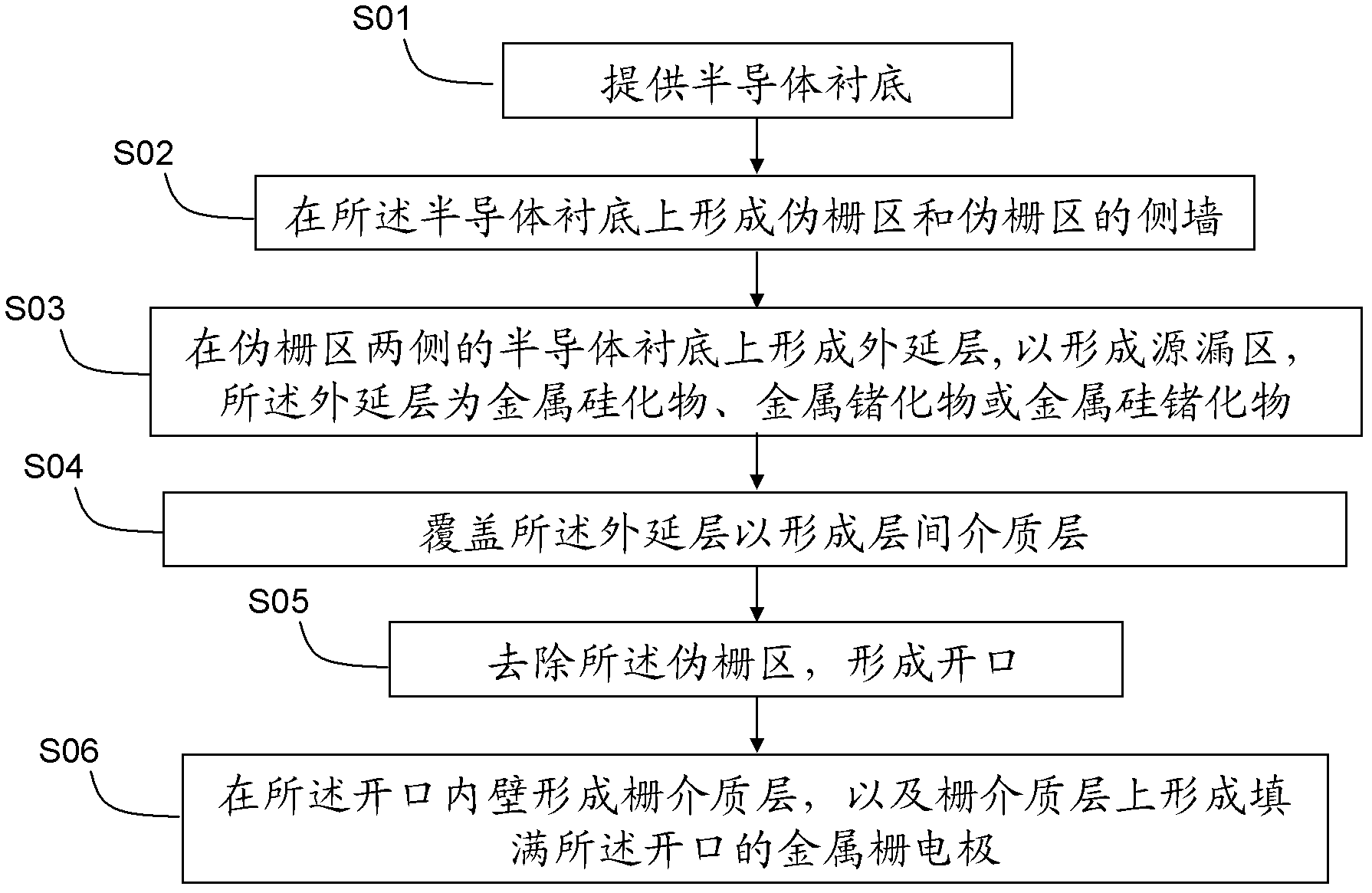

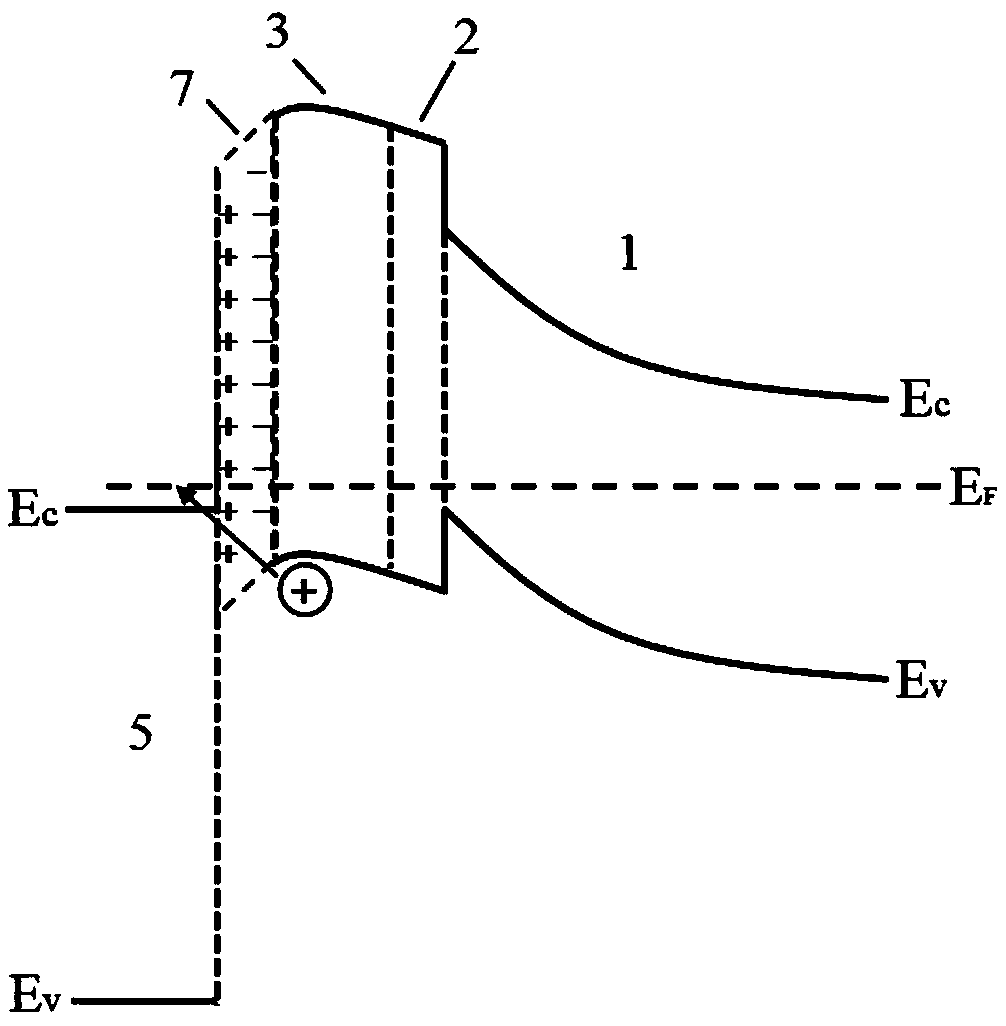

Semiconductor device and manufacturing method thereof

InactiveCN102931085AReduce parasitic resistanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierMetal silicide

The invention discloses a semiconductor device and a manufacturing method thereof. The method comprises the following steps of: providing a semiconductor substrate; forming a pseudo-gate region and side walls of the pseudo-gate region on the semiconductor substrate; forming epitaxial layers on the semiconductor substrate on the two sides of the pseudo-gate region to form source and drain regions, wherein the epitaxial layers are made of metal silicide, metal germanide or metal silicon germanide; forming interlayer dielectric layers to cover the epitaxial metal silicide layers of the source and drain regions; removing the pseudo-gate region to form an opening; and forming a gate dielectric layer on the inner walls of the opening, and forming a metal gate electrode on the gate dielectric layer to fill the opening. Before a substitute gate is formed, the epitaxial layers are formed on the semiconductor substrate on the two sides of the gate region and cover the whole source and drain regions of a Schottky barrier field effect transistor device, and the height of a Schottky barrier between the epitaxial source and drain regions and a channel is effectively reduced, so that the source and drain parasitic resistance of the device is obviously reduced, and the performance of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor device and method for fabricating the same

InactiveUS20070158760A1Reduce interface resistanceStructuredTransistorSemiconductor/solid-state device manufacturingDevice materialMetal silicide

Owner:PANASONIC CORP

High electron mobility transistor (HEMT) structure with refractory gate metal

ActiveUS7411226B2Degree of reductionImprove long-term reliabilityTransistorSemiconductor/solid-state device manufacturingPlatinumSchottky barrier

An InP high electron mobility transistor (HEMT) structure in which a gate metal stack includes an additional thin layer of a refractory metal, such as molybdenum (Mo) or platinum (Pt) at a junction between the gate metal stack and a Schottky barrier layer in the HEMT structure. The refractory metal layer reduces or eliminates long-term degradation of the Schottky junction between the gate metal and the barrier layer, thereby dramatically improving long-term reliability of InP HEMTs, but without sacrifice in HEMT performance, whether used as a discrete device or in an integrated circuit.

Owner:NORTHROP GRUMMAN SYST CORP

Semiconductor device and formation method thereof

InactiveCN108231762AIncrease speedLower Schottky Barrier HeightTransistorSolid-state devicesElectrical performanceContact layer

The invention relates to a semiconductor device and a formation method thereof. The formation method comprises that pre-non-crystallization processing is carried out on a source-drain doped region exposed out of the bottom of a first through hole; after pre-non-crystallization processing, a protection layer is formed on the source-drain doped region exposed out of the bottom of the first through hole; a pattern layer filling the first through hole is formed on the protection layer, and the pattern layer positioned in the top of a dielectric layer includes an opening; the dielectric layer is etched along the opening till the top of a gate structure is exposed, and a second through hole out of which the top of the gate structure is exposed is formed in the dielectric layer; the pattern layeris removed in the oxygen-containing atmosphere; the protection layer is removed; a metal contact layer is formed on the source-drain doped region exposed out of the bottom of the first through hole;and a conductive plug filling the first through hole is formed on the metal contact layer, and a gate plug filling the second through hole is formed at the same time. The contact resistance between the source-drain doped region and the metal contact layer is reduced, and the electrical performance of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and forming method thereof

ActiveCN109817525AHigh second atomic percent concentrationNot easy to spreadSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureCondensed matter physics

The invention discloses a semiconductor structure and a forming method thereof, and the method comprises the steps: providing a substrate which comprises a first region; forming a first gate structureand a first source-drain doped region located in the substrate at two sides of the first gate structure on the substrate with the first region, wherein the first source-drain doped region has first doped ions, and the first doped ions in the first source-drain doped region have a first atomic percentage concentration; and after the first gate structure and the first source-drain doped region areformed, forming a first improvement layer at the top of the first source-drain doped region, the first doped ions in the first improvement layer have a second atomic percentage concentration, and thesecond atomic percentage concentration is greater than the first atomic percentage concentration. According to the semiconductor device formed by the method, the contact resistance between the first source-drain doped region and the subsequently formed plug can be reduced, and meanwhile, the short-channel effect can be inhibited.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and forming method thereof

ActiveCN109216278ALower Schottky Barrier HeightLower barrier heightTransistorSolid-state devicesSchottky barrierSemiconductor structure

A method for for a semiconductor structure includes for a substrate including a PMOS region, forming a gate structure on that substrate, forming a P-type doped epitaxial lay in the substrate on both sides of the gate structure of the PMOS region, forming a silicon layer on the surface of the P-type doped epitaxial layer, and forming an interlayer dielectric layer covering the top of the gate structure on the substrate; Contact openings exposing the silicon layer are formed in the interlayer dielectric layers on both sides of the gate structure of the PMOS region. The silicon layer is doped bymetal segregation Schottky method; Forming a metal layer at the bottom of the contact opening; The metal layer and the silicon layer are reacted to form a metal silicide layer by annealing treatment;A contact hole plug is formed in the contact opening. The solid solubility of metal segregated Schottky doped ions in the metal silicide layer is lower than that in the silicon layer, Therefore, dopedions precipitate from the metal silicide layer and segregate at the interface between the metal silicide layer and the P-type doped epitaxial layer, thus lowering the Schottky barrier height of PMOS,thereby reducing the contact resistance of the PMOS region.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

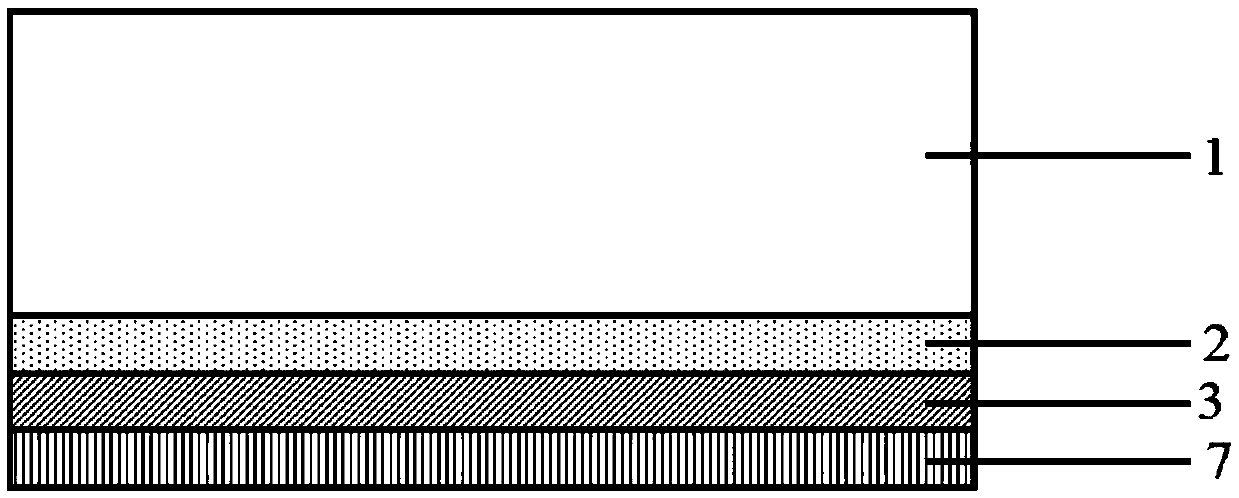

Silicon heterojunction solar cell and emitter thereof, and preparation method of emitter

PendingCN111370521AImprove conversion efficiencyLower electron affinityFinal product manufacturePhotovoltaic energy generationFill factorMolecular physics

The invention discloses a silicon heterojunction solar cell emitter, which comprises: an n-type silicon substrate having an emitter surface; a first intrinsic passivation layer formed on the emitter surface; a p-type silicon doped layer formed on the first intrinsic passivation layer; and an adsorption atom layer formed on the p-type silicon doped layer, wherein the adsorption atom layer comprisesadsorption atoms which are deposited on the surface of the p-type silicon doped layer and form a positive dipole moment potential field with the silicon atoms on the surface of the p-type silicon doped layer. The invention also discloses a preparation method of the silicon heterojunction solar cell emitter and a silicon heterojunction solar cell. The height of the Schottky barrier of the p-type silicon doped layer and the TCO interface of the emitter to the hole of the n-type silicon substrate is low, and the fill factor and the conversion efficiency of the silicon heterojunction solar cell are high.

Owner:德运创鑫(北京)科技有限公司

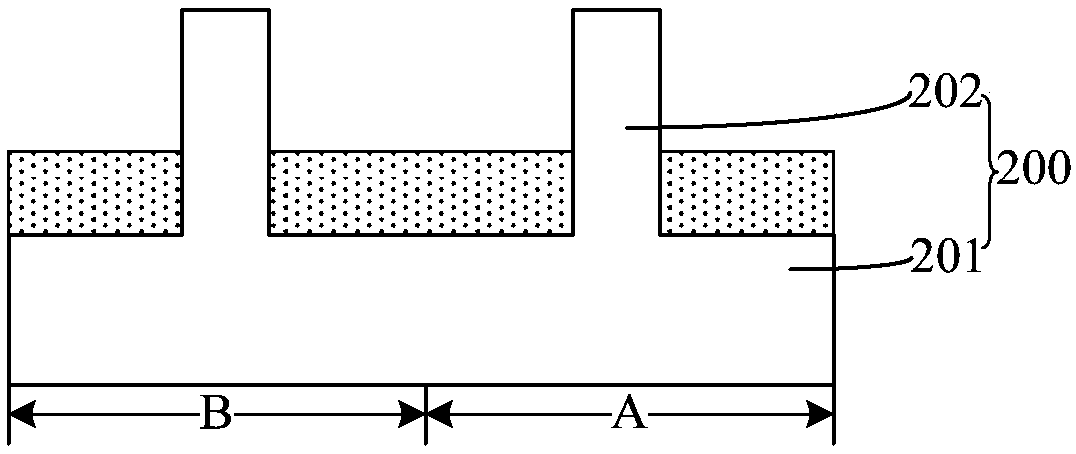

Method of forming fin-type field effect transistor

ActiveCN106783742AImprove thickness uniformityUniform distribution of aluminum ion concentrationSemiconductor/solid-state device manufacturingSeleniumEngineering

A method of forming a fin-type field effect transistor comprises: forming a first etch hole that exposes a first source region and a first drain region surface in a dielectric layer, and a second etch hole exposing a second source region and a second drain region; forming a second oxide layer containing aluminum on the side wall and the bottom surface of the second etch hole; forming a first oxide layer containing sulfur or selenium on the side wall and the bottom surface of the first etch hole; performing annealing such that sulfur ions or selenium ions in the first oxide layer containing sulfur or selenium diffuse into the first source region and the first drain region at the bottom of the first etch hole, aluminum ions in the second oxide layer containing aluminum diffuse into the second source region and the second drain region at the bottom of the second etch hole; and removing the first oxide layer and the second oxide layer, forming a first metal silicide on the surfaces of the first source region and the first drain region, and forming a second metal silicide layer on the surfaces of the second source region and the second drain region. The method of the present invention reduces the Schottky barrier height of the fin-type field effect transistor source-drain region.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Electrode of p-type gallium nitride-based device as well as preparation method and application thereof

PendingCN113488530ASolving the Schottky Barrier Height ElevationReduced ohmic contact resistanceSemiconductor devicesPhysicsCMOS

The invention provides an electrode of a p-type gallium nitride-based device as well as a preparation method and application thereof. The electrode comprises a nickel oxide layer, a platinum layer and a gold layer which are sequentially stacked, wherein the nickel oxide layer is of a P-type structure, the platinum layer is located between the P-type nickel oxide layer and the gold layer, and the nickel oxide layer is an ohmic contact layer of the p-type gallium nitride-based device. The electrode of the p-type gallium nitride-based device is used for a source electrode and a drain electrode of the p-type gallium nitride-based device, more carriers flow between metal and a semiconductor by introducing a Schottky barrier height of the P-type NiO layer, the transition metal and the semiconductor interface, and meanwhile, by means of ultrahigh vacuum heat treatment, the problem that the height of the Schottky barrier is increased due to a Ga2O3 pollution layer is solved, the ohmic contact resistance of the source electrode and the drain electrode of the device is reduced, the performance of a p-type gallium nitride-based transistor is improved, the p-type gallium nitride-based device can play a greater role in a CMOS circuit, and the defect is changed into the advantage.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA +1

Schottky Electrode of Nitride Semiconductor Device and Process for Production Thereof

InactiveUS20080006853A1Suppressing chargeLower Schottky Barrier HeightSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceMetallic materials

The present invention provides a Schottky electrode for a nitride semiconductor device having a high barrier height, a low leak current performance and a low resistance and being thermally stable, and a process for production thereof. The Schottky electrode for a nitride semiconductor has a layered structure that comprises a copper (Cu) layer being in contact with the nitride semiconductor and a first electrode material layer formed on the copper (Cu) layer as an upper layer. As the first electrode material, a metal material which has a thermal expansion coefficient smaller than the thermal expansion coefficient of copper (Cu) and starts to undergo a solid phase reaction with copper (Cu) at a temperature of 400° C. or higher is employed.

Owner:NEC CORP

Semiconductor device manufacturing method

ActiveCN103137486AImprove driving abilityImprove solid solubilityTransistorSolid-state devicesHigh concentrationSalicide

The invention discloses a semiconductor device manufacturing method which comprises the steps of forming a grid stack structure on a substrate containing silicon; depositing nickel metal layers on the substrate and the grid stack structure; primarily annealing to enable silicon in the substrate to react with the nickel metal layer to form nickel-rick phase metal silicide; injecting ions to enable doping ions to be injected into the nickel-rich phase metal silicide; secondarily annealing to enable the nickel-rick phase metal silicide to be converted into nickel metal silicide source leakage and simultaneously forming separation and condensation zone at the interface between the nickel metal silicide source leakage and the substrate. According to the semiconductor device manufacturing method, doping ions are injected into the nickel-rick phase metal silicide to be annealed, solid solubility of the doping ions is improved to form the high-concentration doping ion separation and condensation zone, schottky barrier height between the nickel metal silicide and a silicon channel is effectively reduced, and driving capacity of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method of producing p-GaN low-resistance Ohm contact

InactiveCN100514558CImprove surface qualityIncrease hole concentrationFinal product manufactureSemiconductor/solid-state device manufacturingOhmic contactGallium nitride

Owner:EPITOP PHOTOELECTRIC TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com