Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, applied in the field of semiconductor structure and its formation, can solve problems such as different contact resistance effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

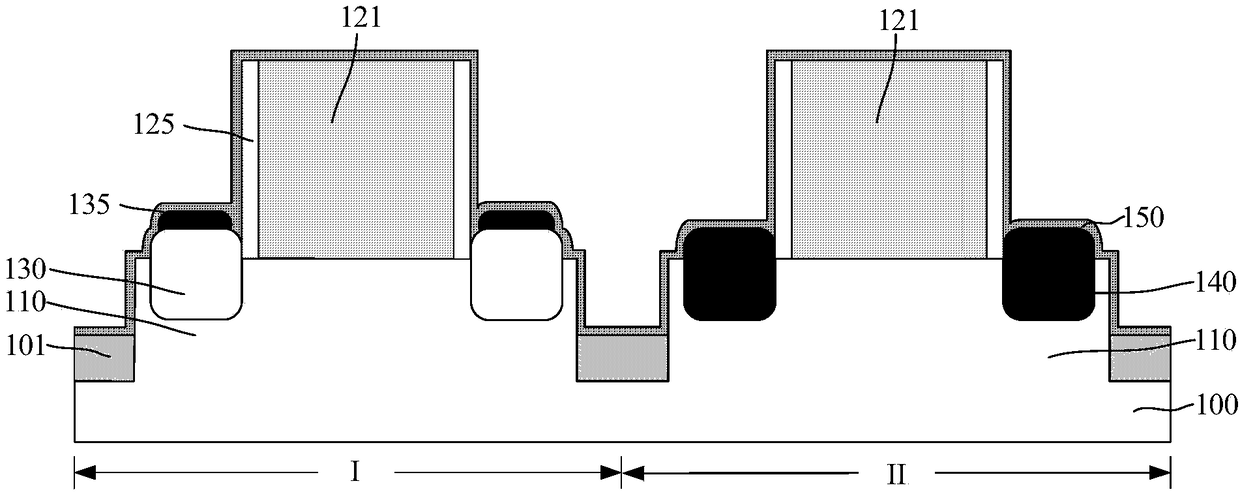

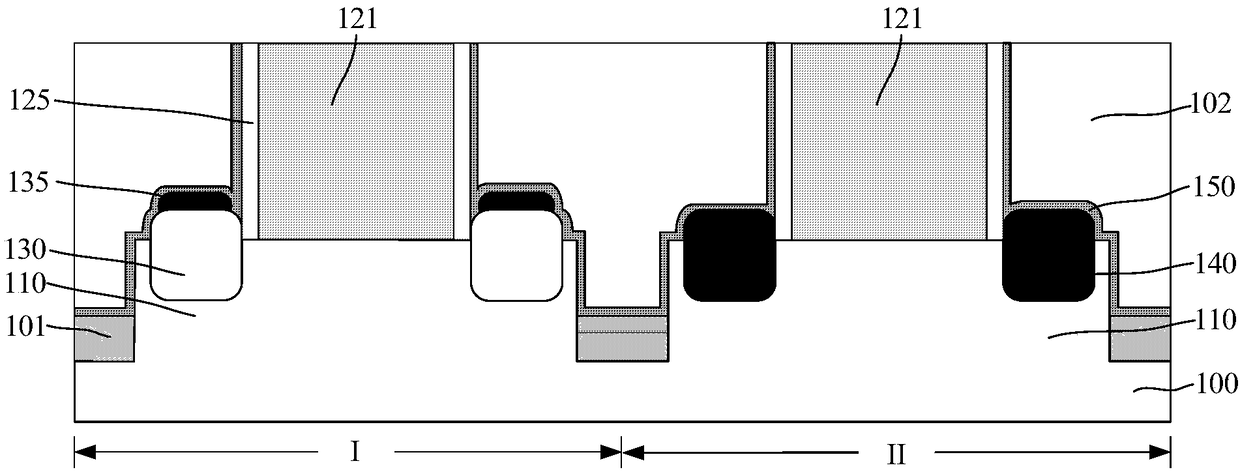

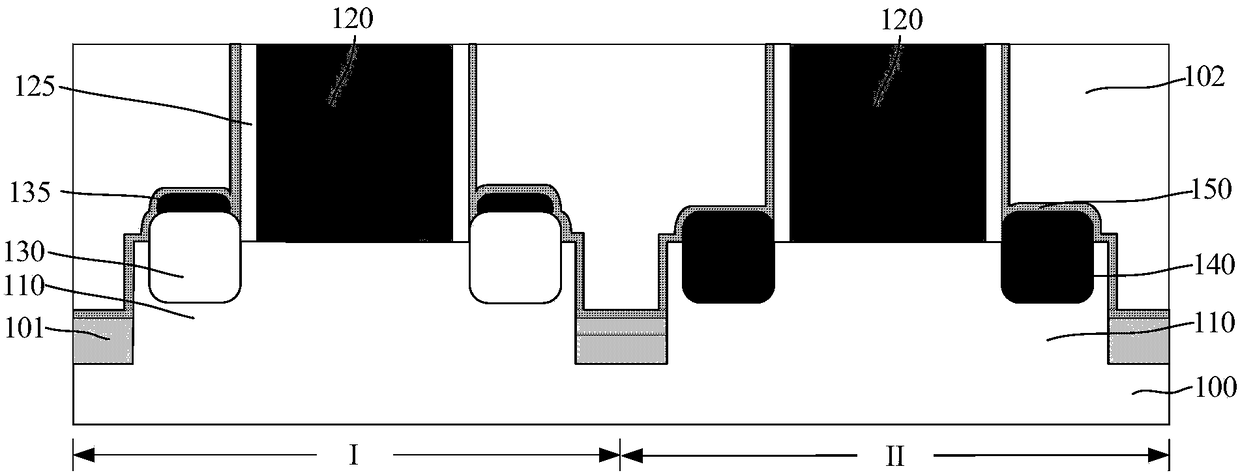

[0033] It is known from the background technology that the contact resistance of the PMOS region needs to be reduced.

[0034] During the formation of the semiconductor structure, the metal silicide layer is usually formed by the reaction between the metal layer and the doped epitaxial layer. Currently, the main material used for the metal layer is Ti. For the NMOS region, the use of a Ti metal layer can effectively reduce the Schottky barrier height of NMOS; but for the PMOS region, when the material is Ti metal layer, the Schottky barrier of PMOS The height is still large, resulting in the insignificant effect of reducing the contact resistance.

[0035] In order to solve the technical problem, the present invention performs metal segregation Schottky doping treatment on the silicon layer exposed by the contact opening after forming the contact opening exposing the silicon layer; due to the metal segregation Schottky doping The solid solubility of the treated dopant ions in the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com