Method of forming fin-type field effect transistor

A fin-type field effect and transistor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of transistor performance to be improved, and achieve the effect of uniform aluminum ion concentration distribution and high thickness uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] As mentioned in the background technology, the performance of the existing fin field effect transistor still needs to be improved. For example, the resistance of the metal silicide formed in the source region and the drain region of the fin field effect transistor formed in the prior art is still relatively large. The Schottky Barrier Height (Schottky Barrier Height, SBH) is still large, affecting the performance of the FinFET.

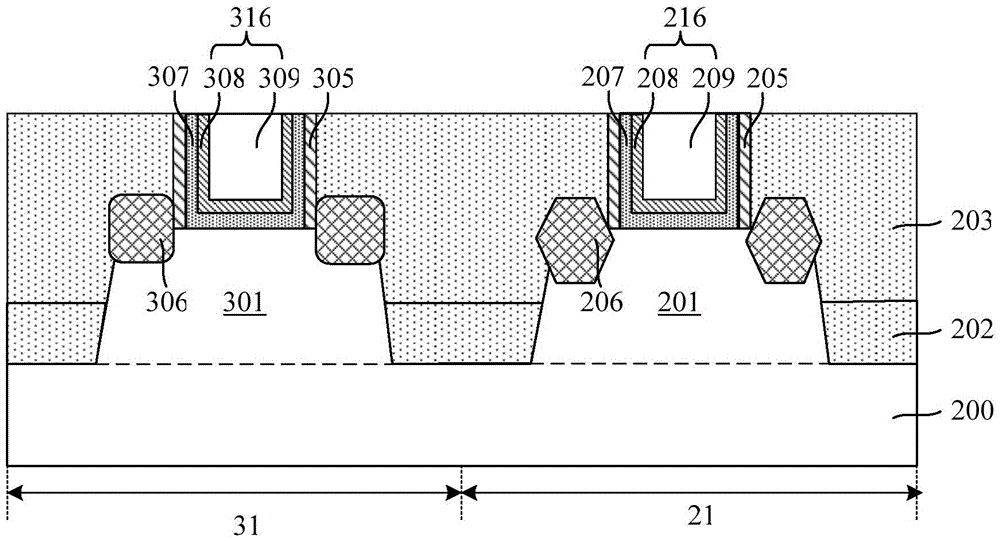

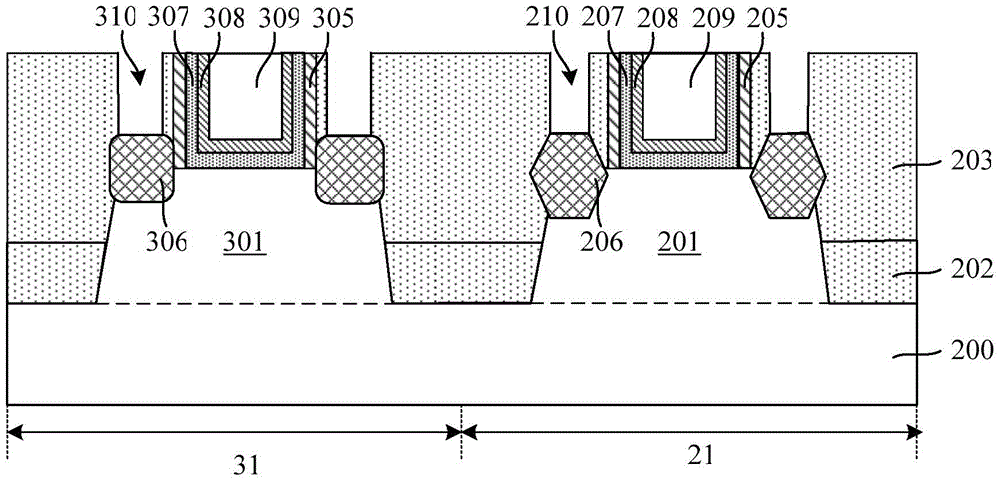

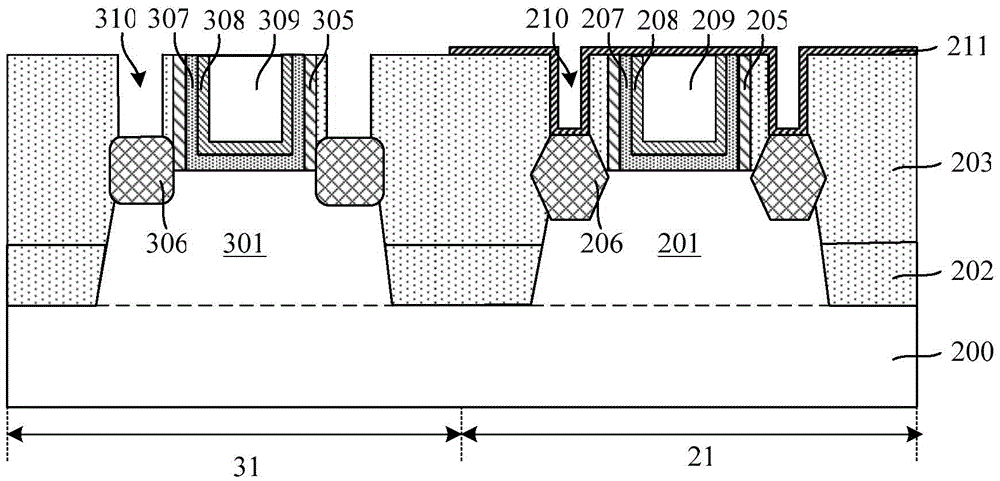

[0030] To this end, an embodiment of the present invention provides a method for forming a Fin Field Effect Transistor. A semiconductor substrate is provided, the semiconductor substrate includes an NMOS region and a PMOS region, and a first fin is formed on the semiconductor substrate of the NMOS region. portion, across the first gate covering the sidewall and top surface of the first fin, and the first source region and the first drain region in the first fin located on both sides of the first gate, the semiconductor substrate of the PMOS regi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More