Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, applied in the field of semiconductor structure and its formation, can solve problems such as poor performance of fin field effect transistors, and achieve the effects of improving performance, suppressing short-channel effect, and reducing contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background, FinFETs have poor performance.

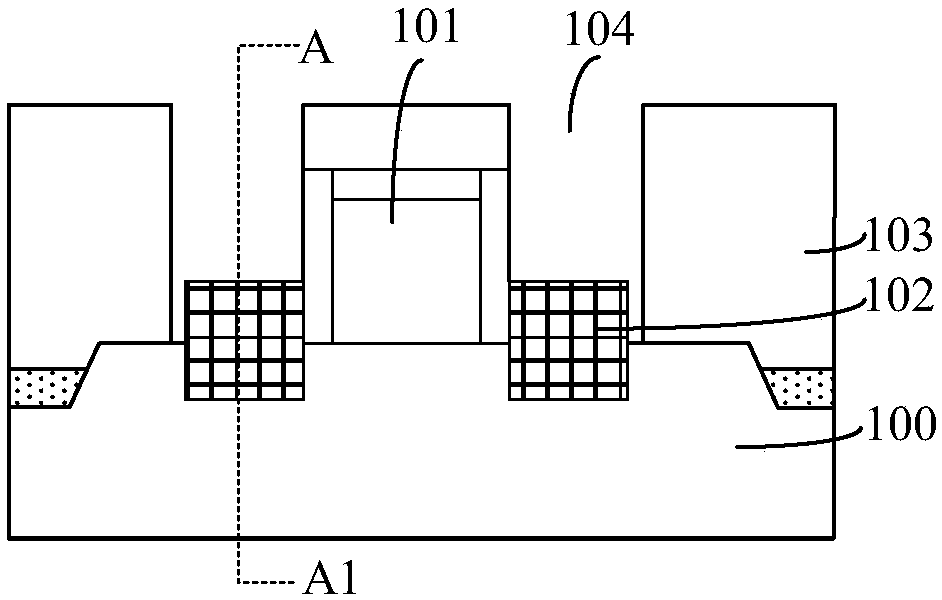

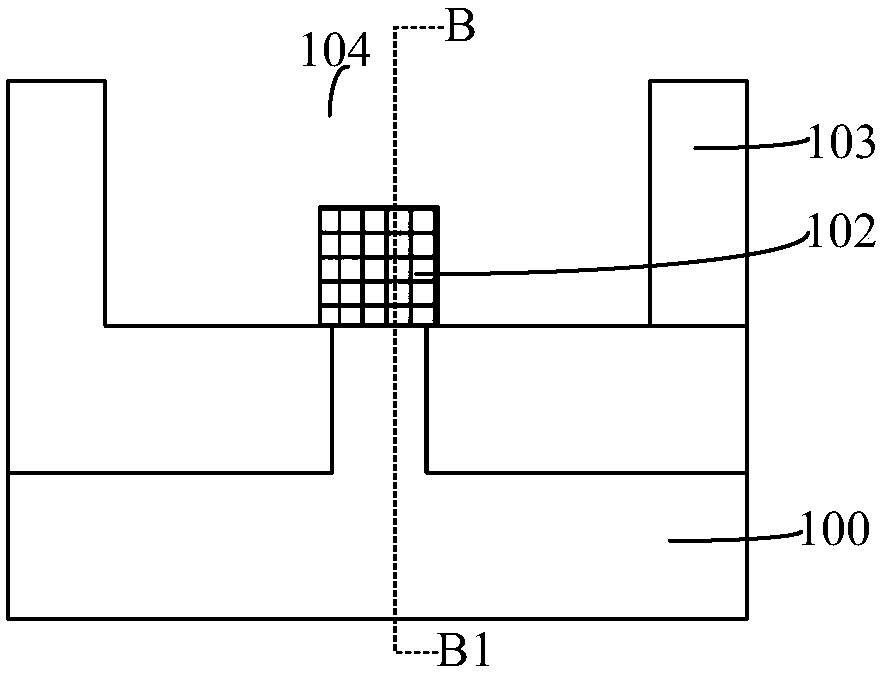

[0034] figure 1 and figure 2 It is a schematic diagram of the structure of a fin field effect transistor.

[0035] Please refer to figure 1 and figure 2 , figure 2 yes figure 1 A schematic sectional view along line A-A1, figure 1 yes figure 2 A schematic cross-sectional view along the line B-B1, a substrate 100 with a gate structure 101 on it; source and drain doped regions 102 located in the substrate 100 on both sides of the gate structure 101; located on the substrate 100 and the gate structure 101 The above dielectric layer 103 has a contact hole 104 exposing the source-drain doped region 102 in the dielectric layer 103 .

[0036] In the above structure, with the continuous improvement of the integration degree of semiconductor devices, the size of the source-drain doped region 102 is continuously reduced, so that the subsequent contact area between the plug in the contact hole 104 and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More