Patents

Literature

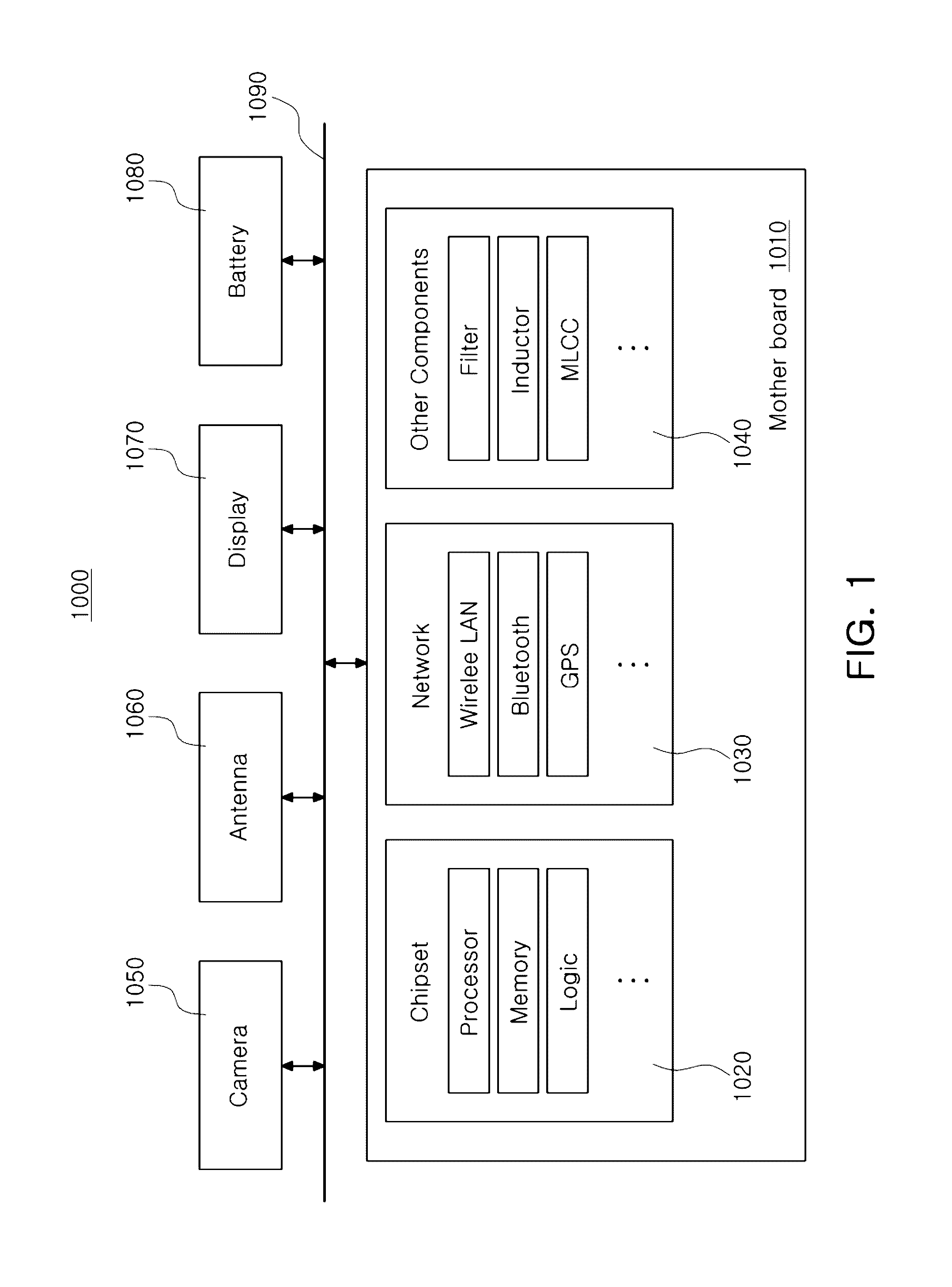

2248results about "Printed circuits stress/warp reduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

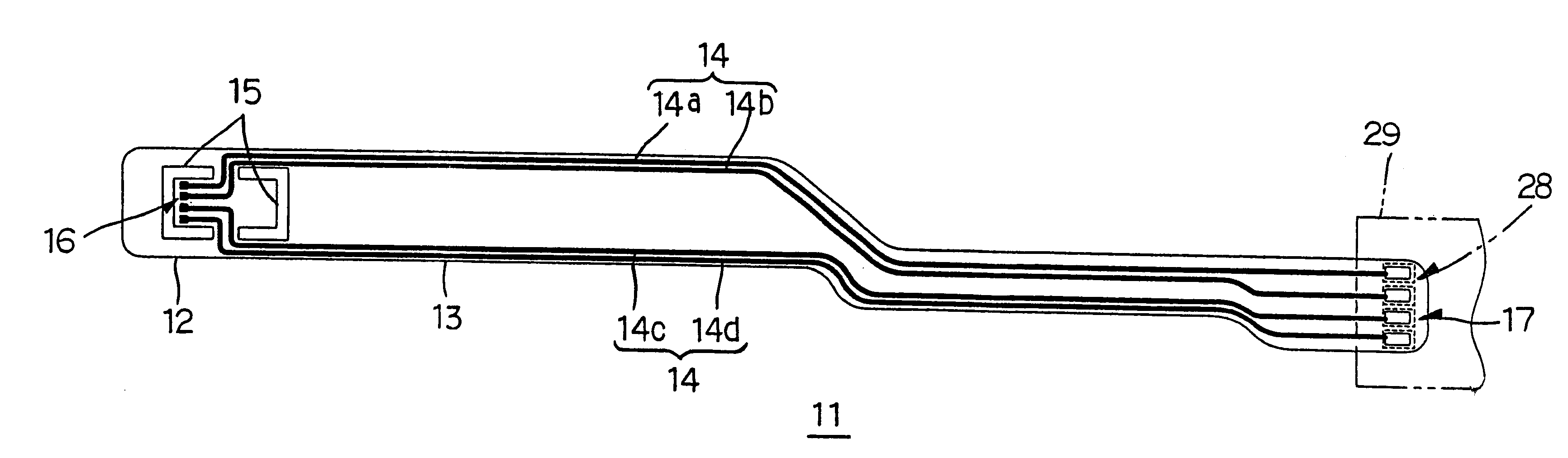

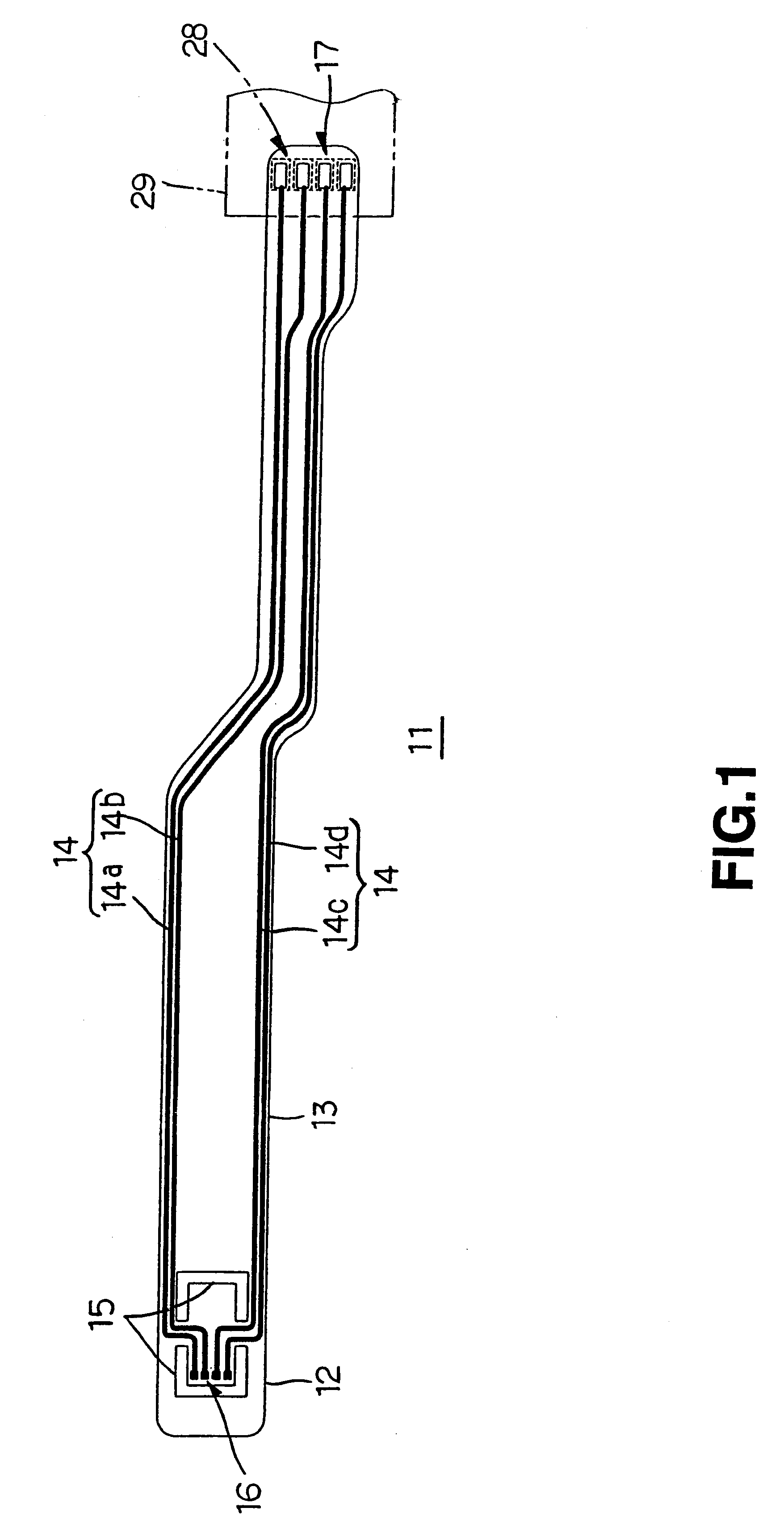

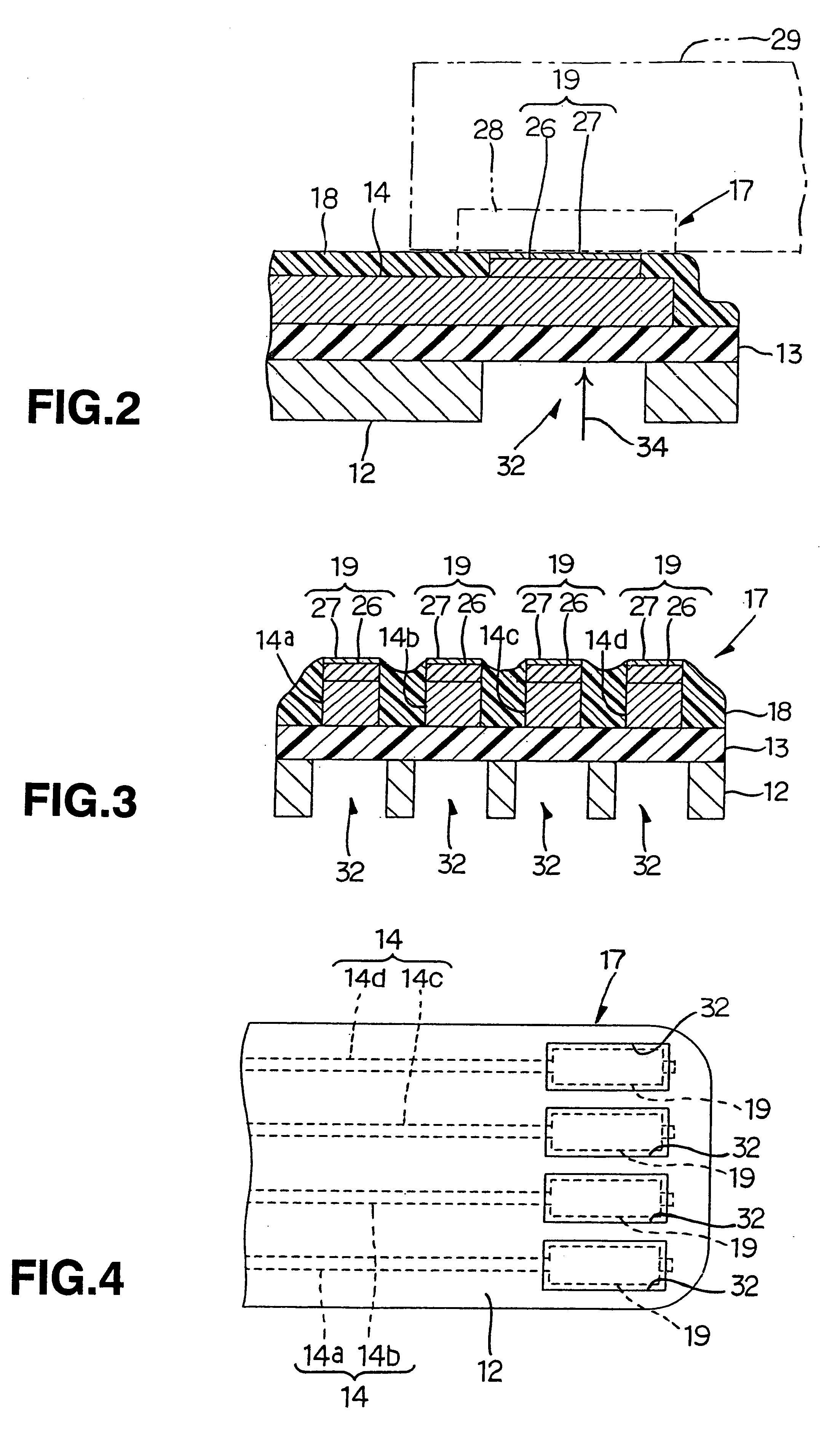

Suspension board with circuit

InactiveUS6399899B1High strengthSimple structureRelieving strain on wire connectionRecord information storageExternal connectionEngineering

To provide a suspension board with circuit that enables its terminals to be bonded to the other terminals with sufficient strength with simple structure, to ensure sufficient bonding reliability, the suspension board with circuit 11 includes a suspension board 12, a base layer 13 formed on the suspension board 12, and a conductive layer 14 formed on the base layer 13 and a cover layer 18 with which the conductive layer 14 is covered, wherein external connection terminals 17 to be bonded to terminals 28 of a read / write board 29 are formed without the suspension board 12 and / or the base layer 13 being formed.

Owner:NITTO DENKO CORP

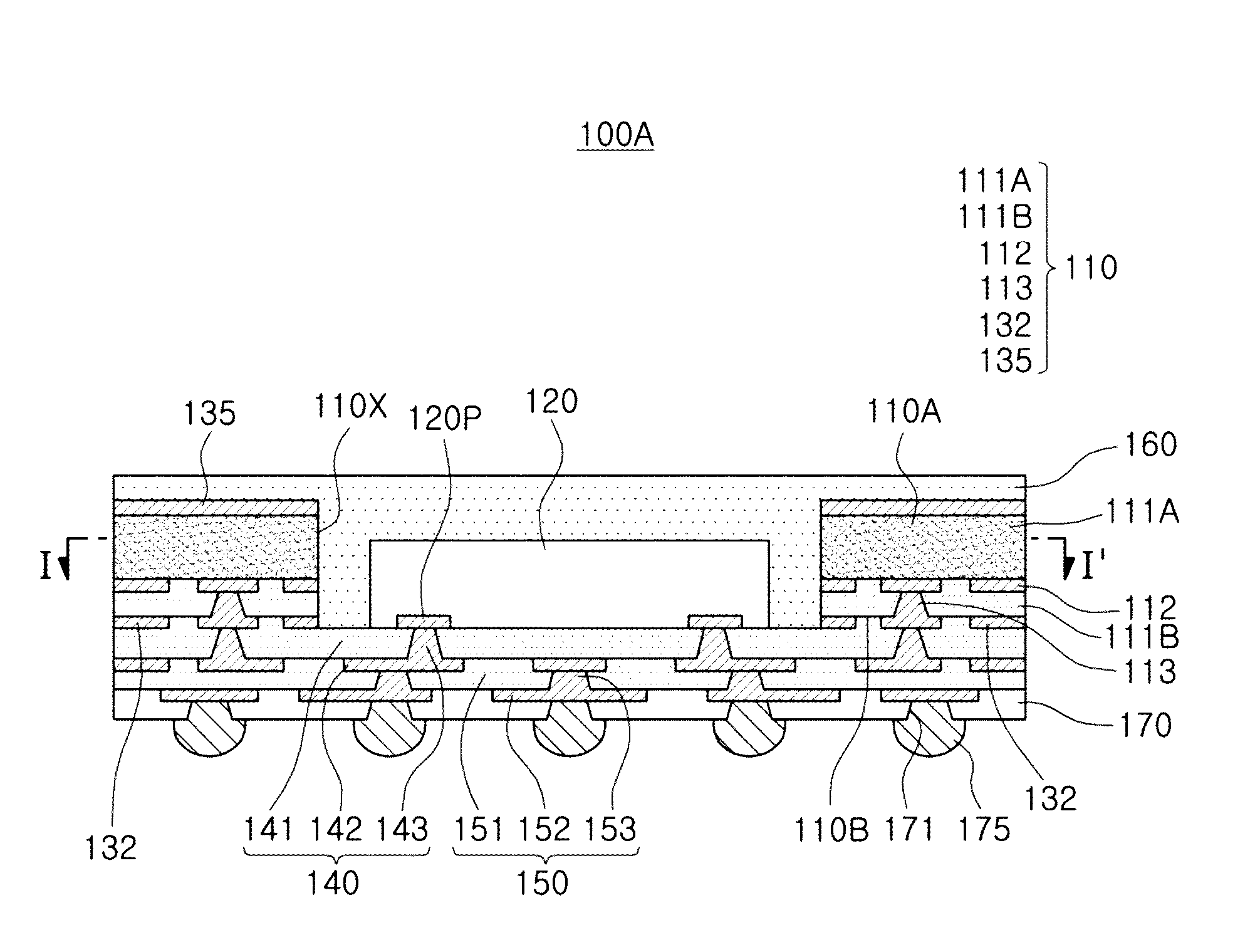

Electronic component package and method of manufacturing the same

ActiveUS20160338202A1Reduce yieldPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringElectronic component

An electronic component package and a method of manufacturing the same are provided. The electronic component package includes a frame having a through-hole, an electronic component disposed in the through-hole of the frame, and a redistribution part disposed at one side of the frame and the electronic component. One or more first wiring layers of the frame are electrically connected to the electronic component through the redistribution part.

Owner:SAMSUNG ELECTRONICS CO LTD

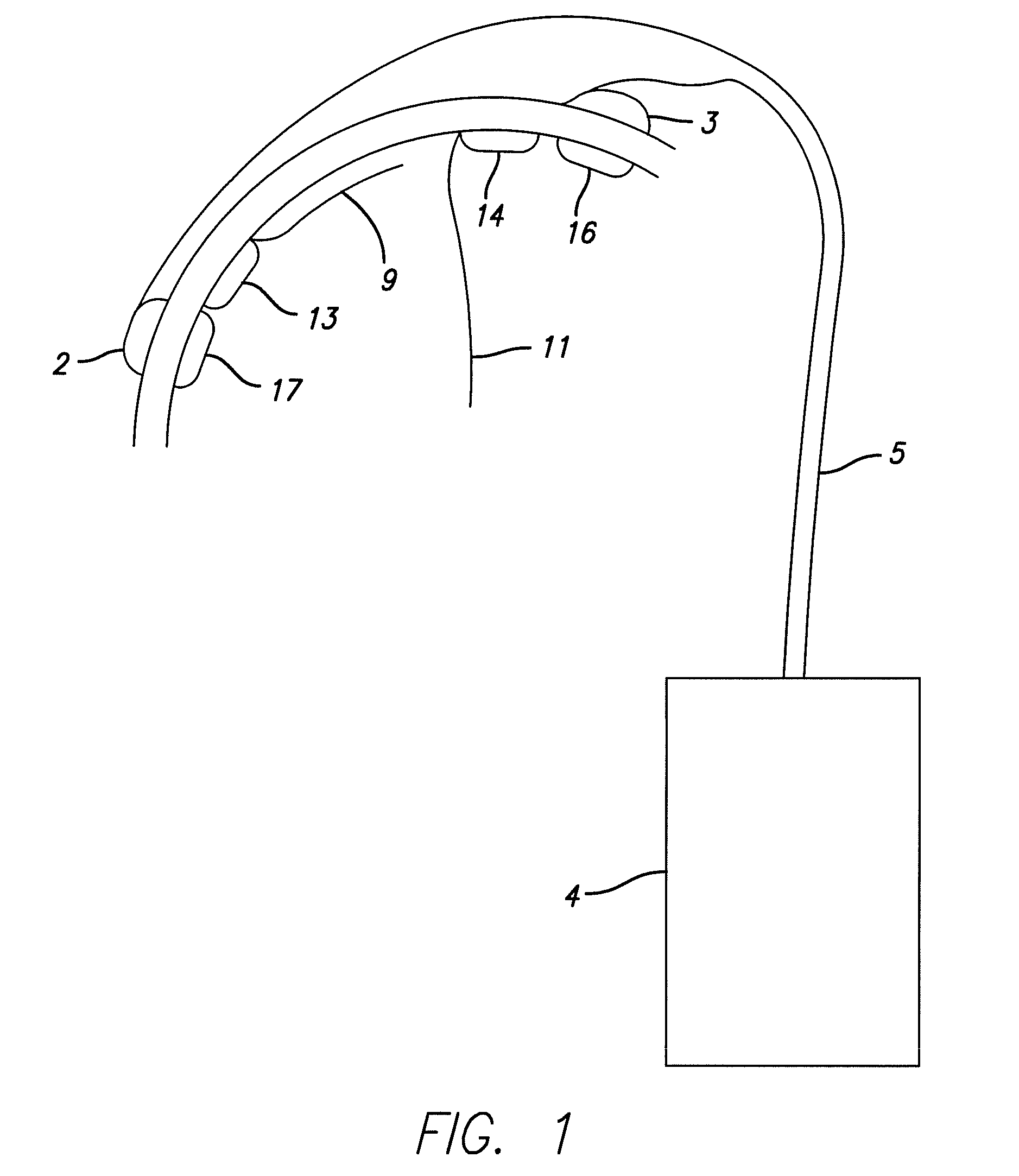

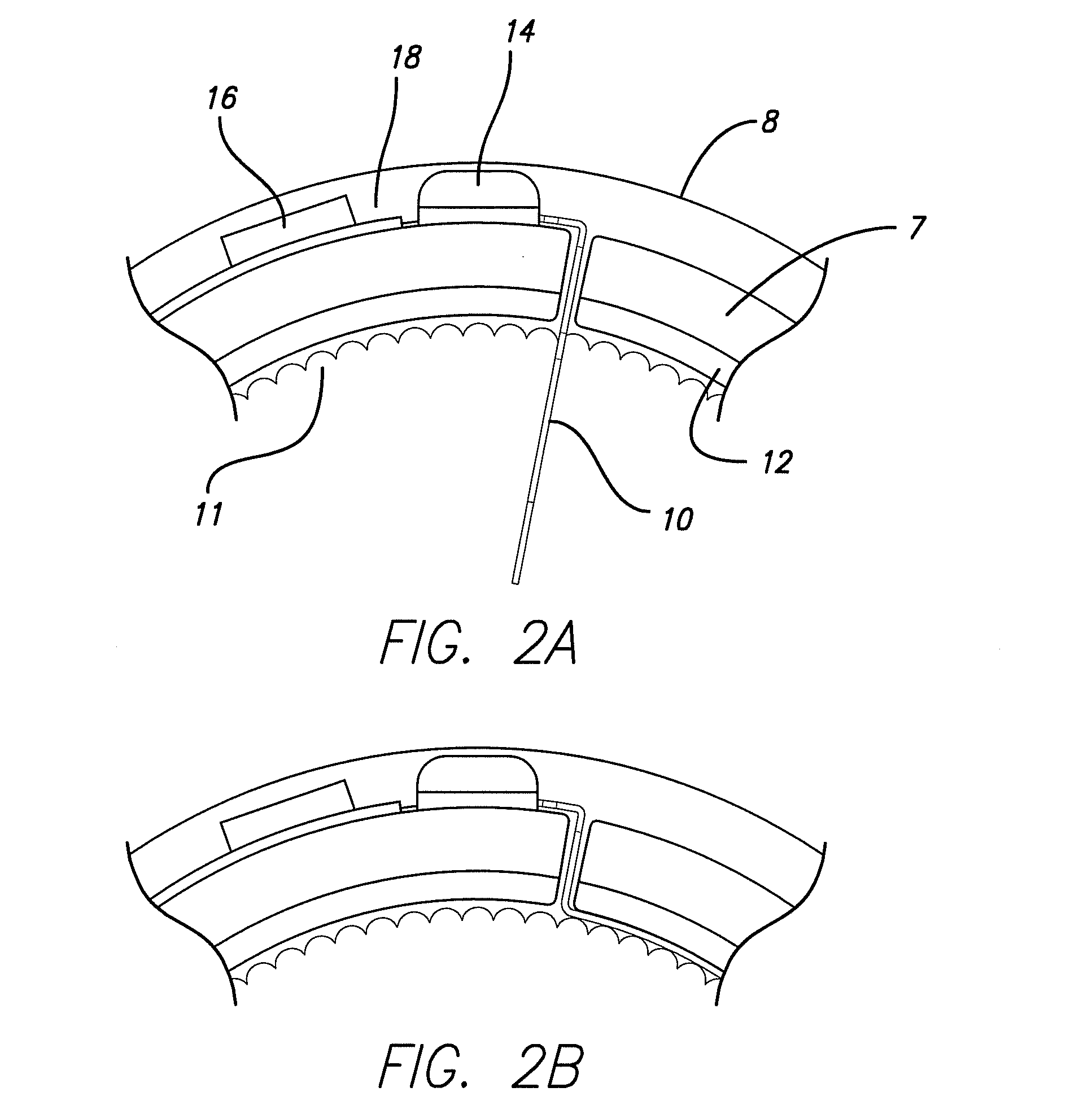

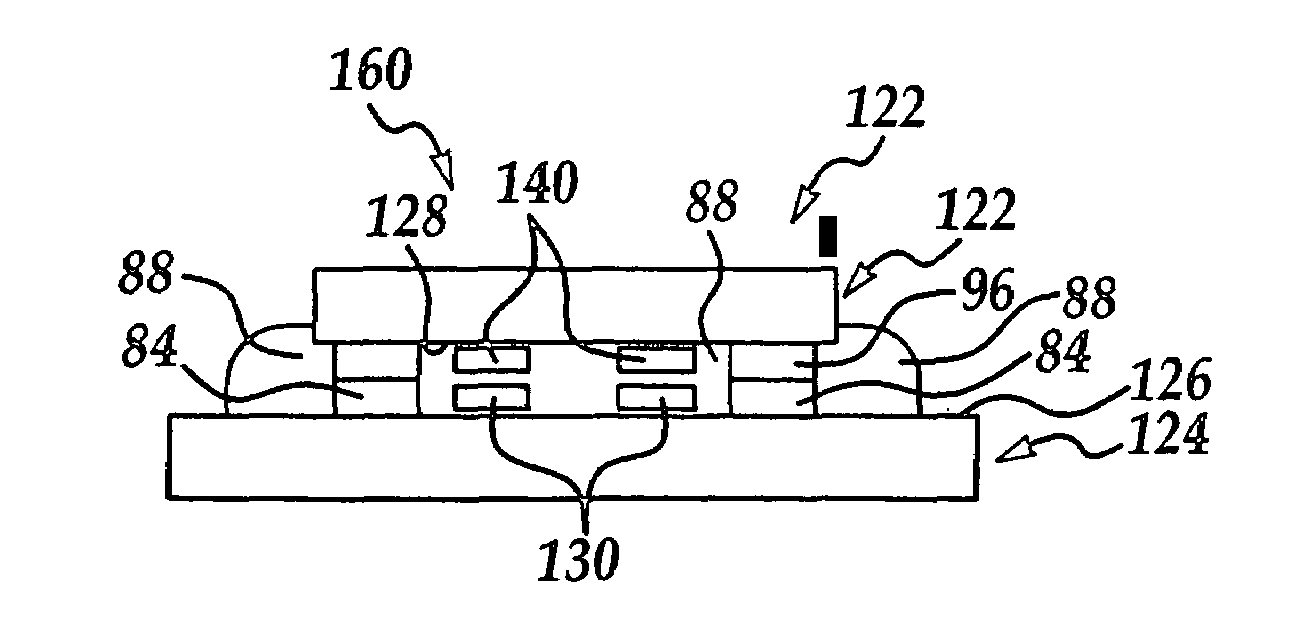

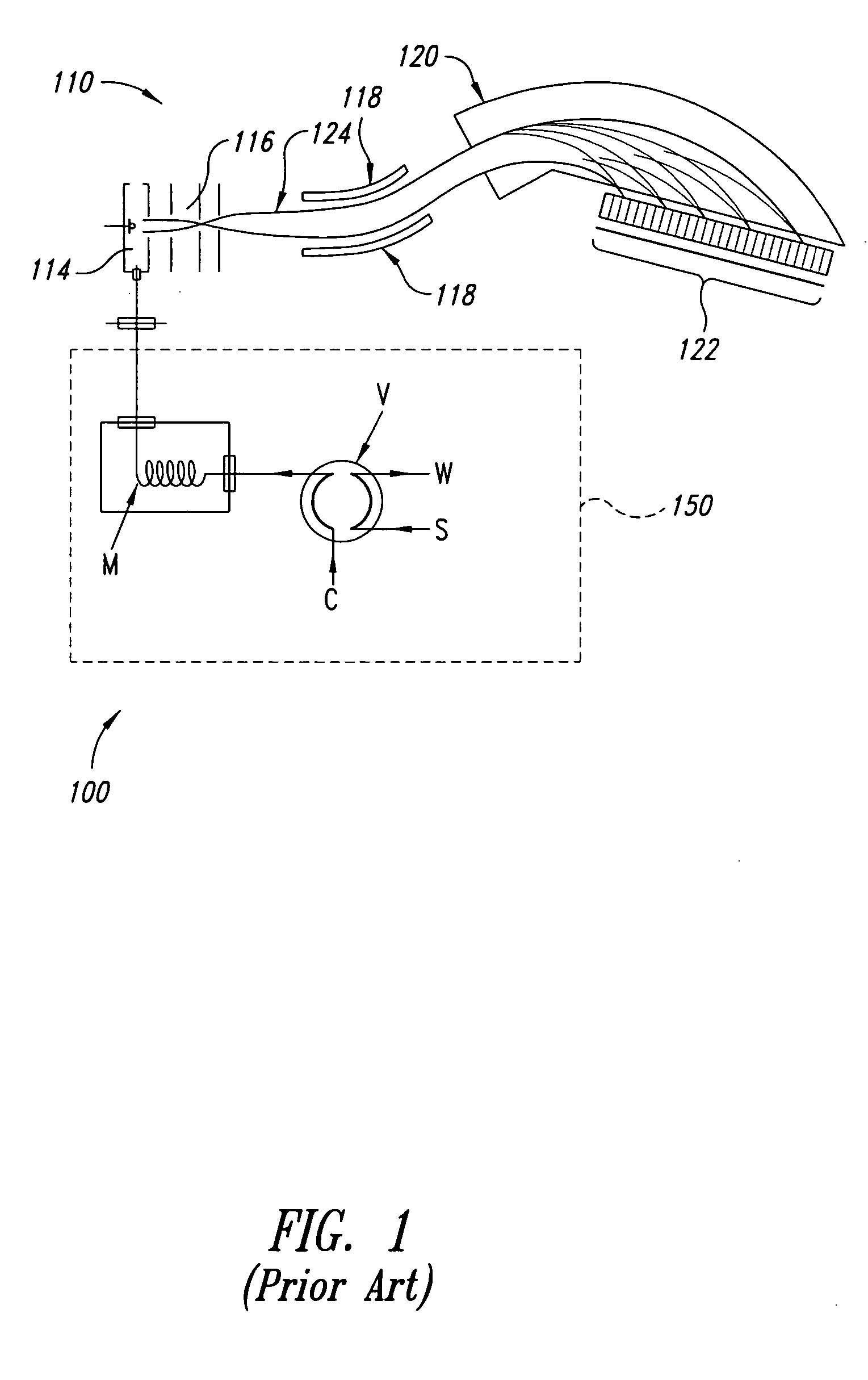

Cortical Implant System for Brain Stimulation and Recording

ActiveUS20150157862A1Shorter electrode arraysLess distortionSemiconductor/solid-state device detailsLaminating printed circuit boardsDiseaseEngineering

The present invention consists of an implantable device with at least one package that houses electronics that sends and receives data or signals, and optionally power, from an external system through at least one coil attached to at least one package and processes the data, including recordings of neural activity, and delivers electrical pulses to neural tissue through at least one array of multiple electrodes that are attached to the at least one package. The device is adapted to electrocorticographic (ECoG) and local field potential (LFP) signals. A brain stimulator, preferably a deep brain stimulator, stimulates the brain in response to neural recordings in a closed feedback loop. The device is advantageous in providing neuromodulation therapies for neurological disorders such as chronic pain, post traumatic stress disorder (PTSD), major depression, or similar disorders. The invention and components thereof are intended to be installed in the head, or on or in the cranium or on the dura, or on or in the brain.

Owner:CORTIGENT INC

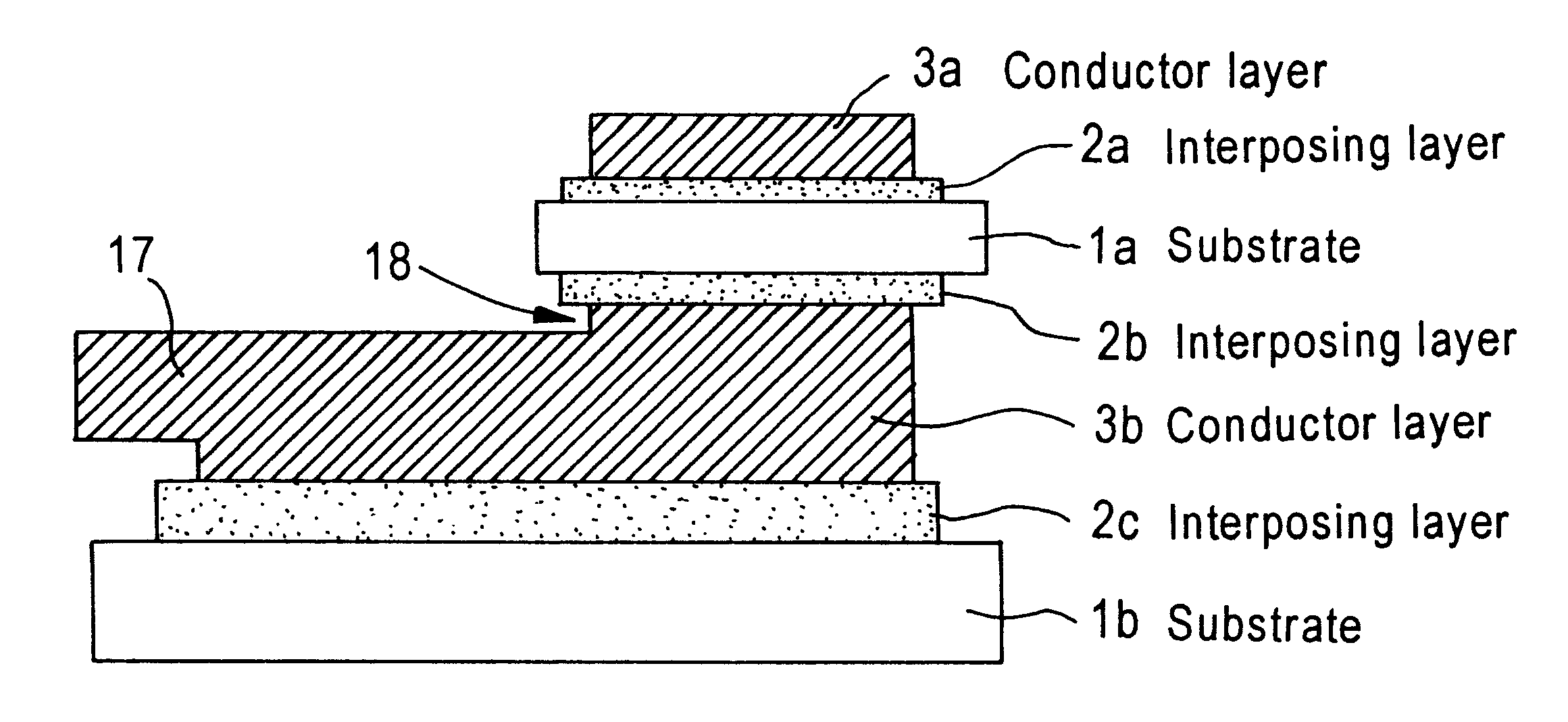

Copper circuit junction substrate and method of producing the same

InactiveUS6261703B1Avoid discharge phenomenonHigh concentration of thermal stressInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsElectrical conductorCopper oxide

A highly reliable copper circuit-joined board that, in mounting a semiconductor element, a lead frame or the like on a ceramic substrate, enables the semiconductor element, the lead frame or the like to be strongly joined to the substrate without breaking or deformation of the substrate found in conventional joining methods, such as brazing and joining using a copper / copper oxide eutectic crystal. Any one of an interposing layer comprising a brazing material layer comprising silver and / or copper as a main component and an active metal or an interposing layer having a two-layer structure comprising a first interposing layer comprising the brazing material layer or a high-melting metallizing layer and a second interposing layer, having a melting point of 1000.degree. C. or below, comprising Ni, Fe, Cu as a main component in that order from the substrate side, is formed on a ceramic substrate, and a conductor layer, comprising copper as a main component, which, in both the lengthwise and widthwise directions, is at least 0.05 mm shorter than the interposing layer, is formed on the interposing layer to prepare a copper circuit-joined board. The copper circuit-joined board may comprise the base board having thereon an outer layer comprising Ni as a main component. A semiconductor element is mounted on the copper circuit-joined board to prepare a semiconductor device.

Owner:SUMITOMO ELECTRIC IND LTD

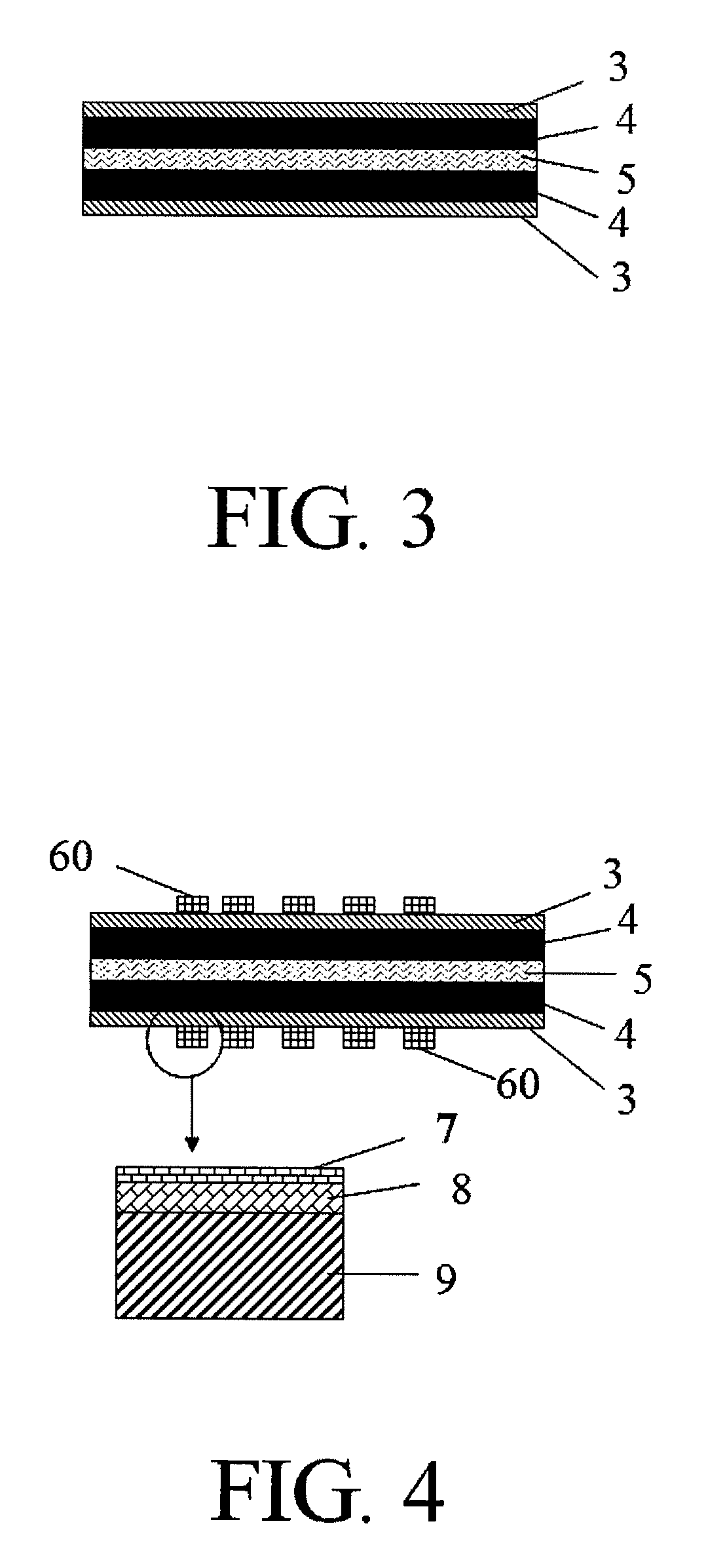

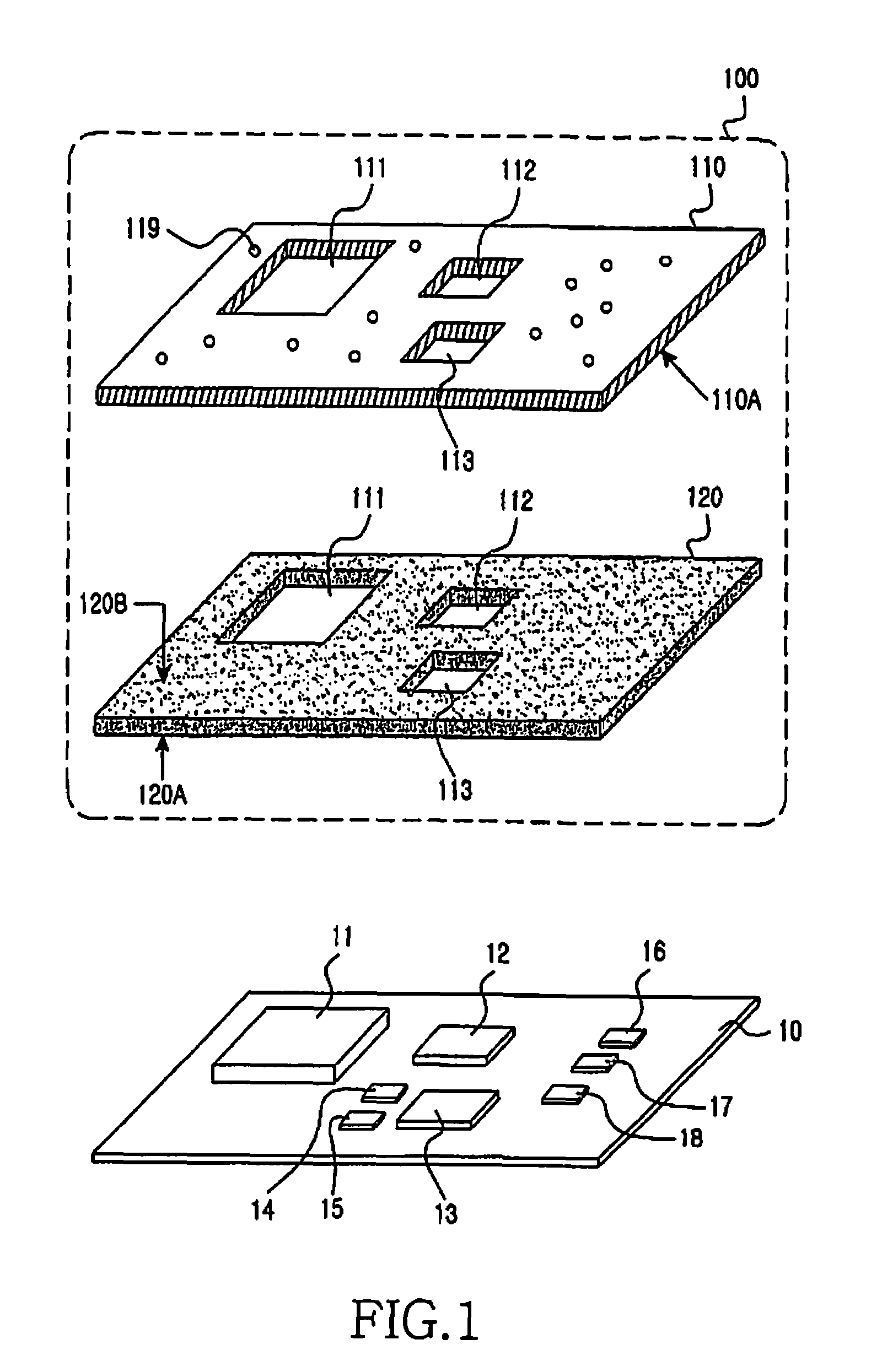

Functional-device-embedded circuit board, method for manufacturing the same, and electronic equipment

InactiveUS20100103634A1Improve reliabilityLow costPrinted electric component incorporationSemiconductor/solid-state device detailsElectrical conductorInterconnection

A circuit board includes a functional device, a circuit board embedding therein the functional device, and first and second conductive-wiring layers formed on the front and rear surfaces of the circuit board to sandwich therebetween the functional device and each include at least one conductor layer. The surface of each of the outermost patterned interconnections of the first conductive-wiring layer is exposed, and the surface of a first dielectric layer isolating the outermost patterned interconnections from one another protrudes from the surface of the each of the patterned interconnections. The patterned interconnections of the second conductive-wiring layer are connected to respective electrode terminals of the functional device, and the surface of a second dielectric layer isolating the electrode terminals from one another is substrate within the same plane as the surface of the electrode terminals disposed adjacent to the second dielectric layer.

Owner:NEC CORP

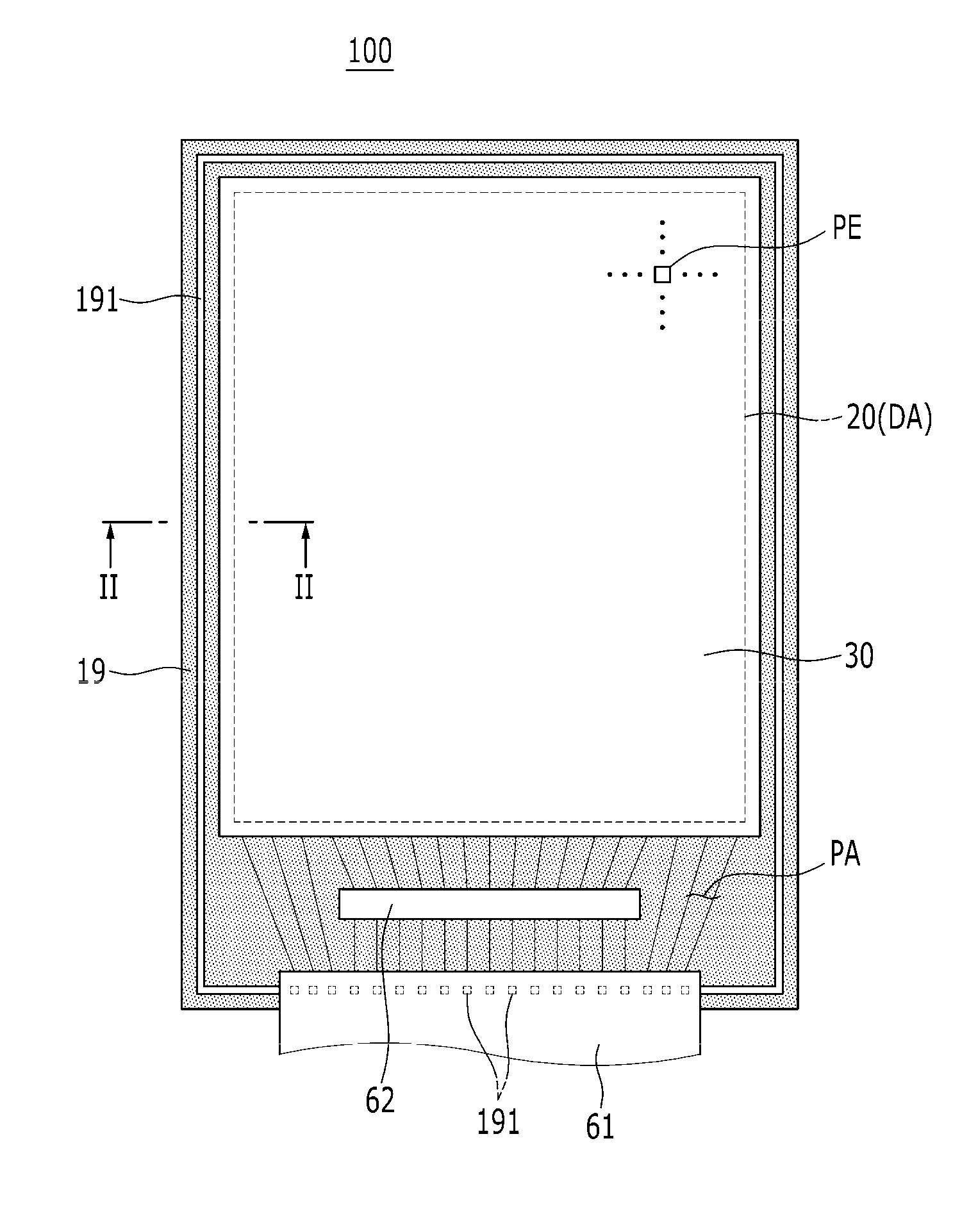

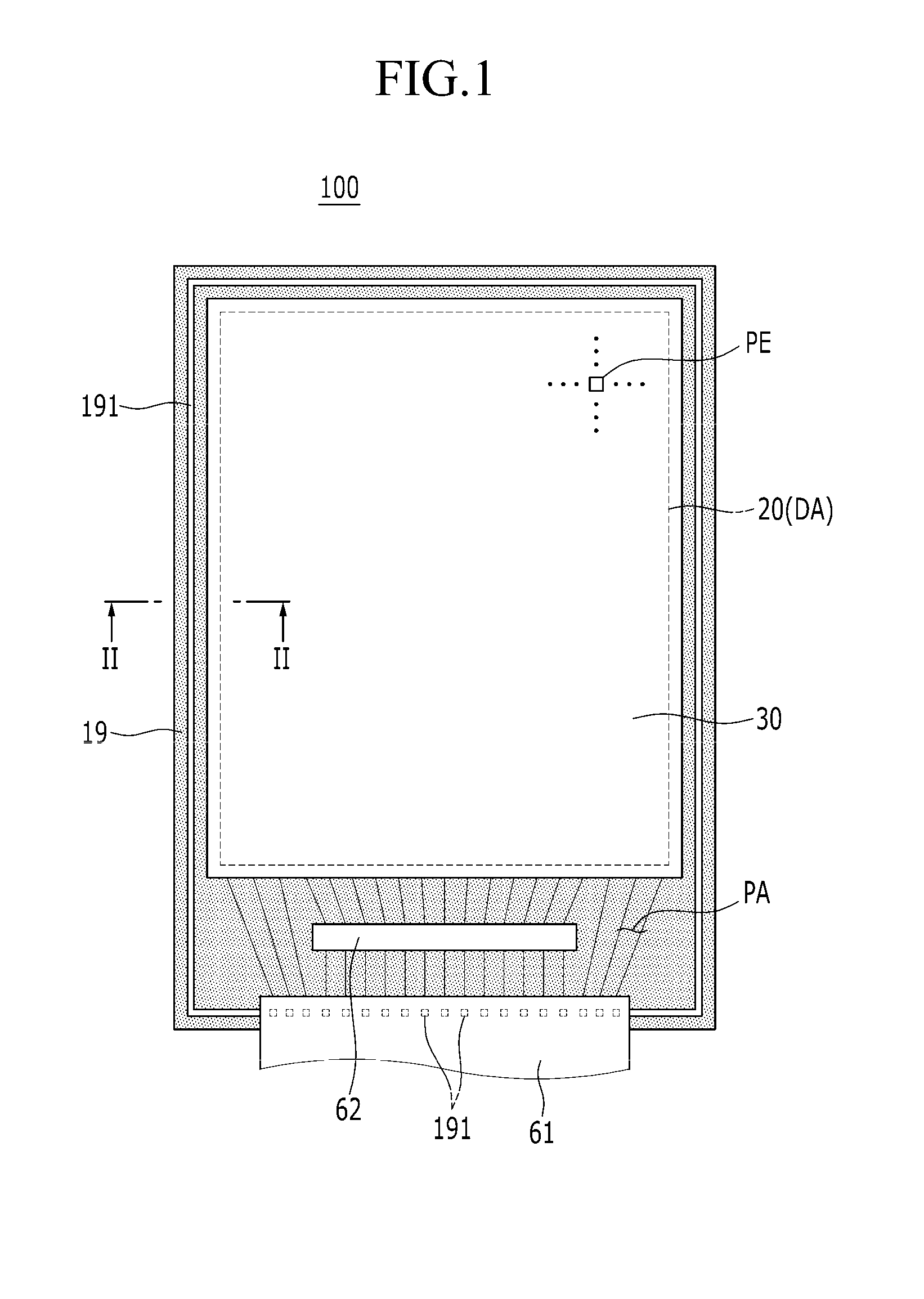

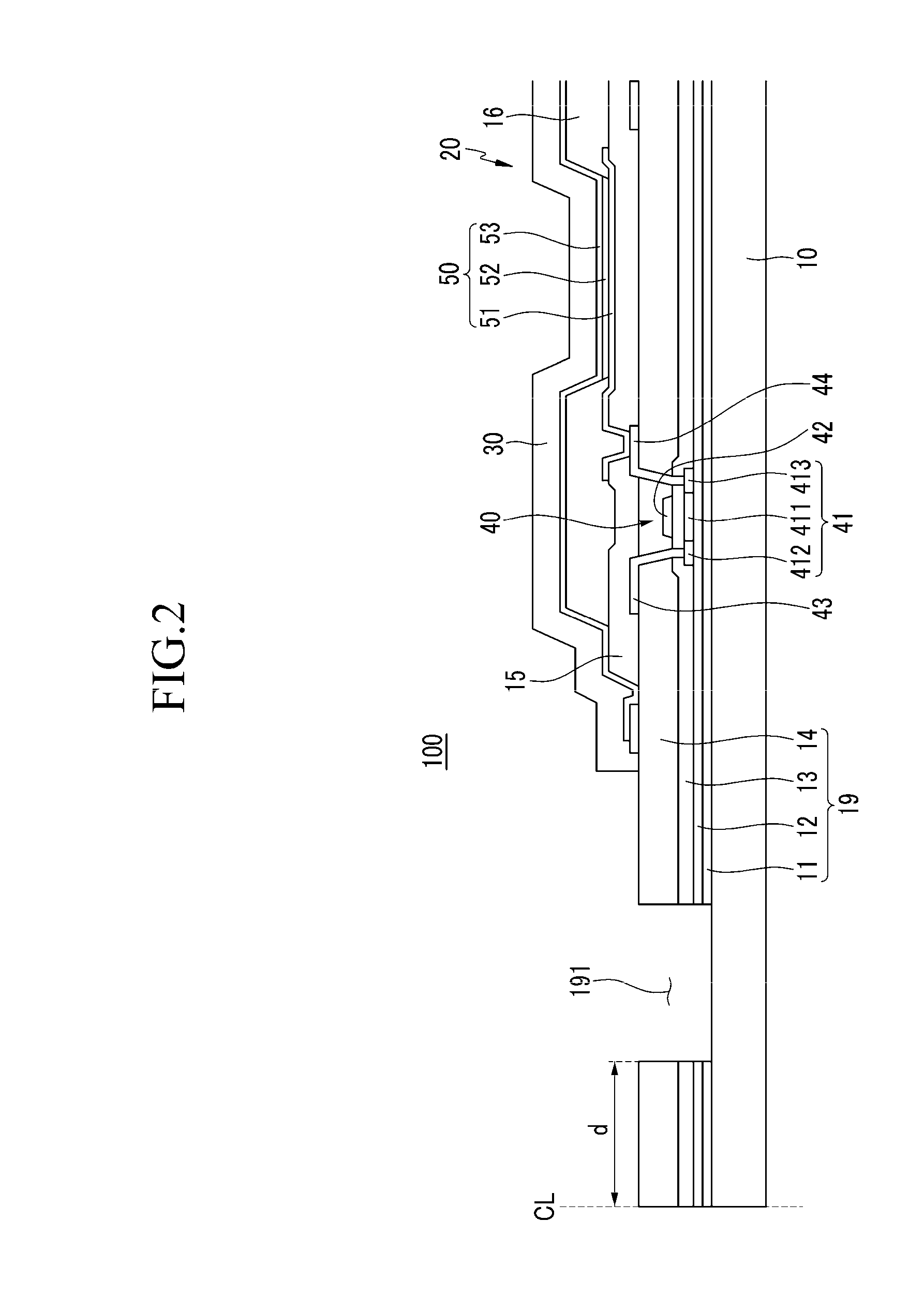

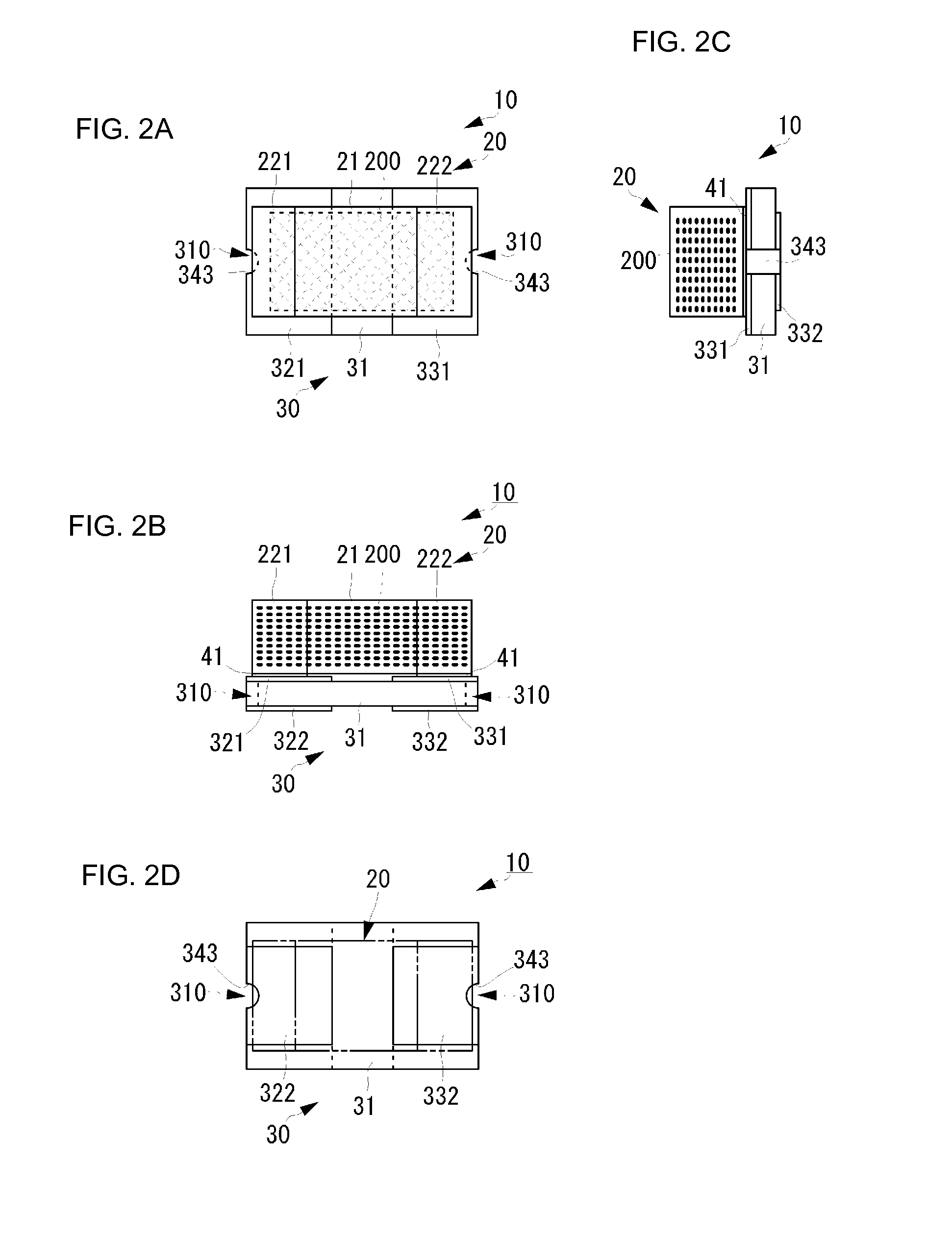

Flexible display device

ActiveUS20150036299A1Improve production yieldSuppressing panel shrinkageFinal product manufactureFlexible printed circuitsFlexible displayComputer science

A flexible display device that can suppress spread of cracks of an inorganic layer is provided. A flexible display device includes a flexible substrate including a display area and a periphery surrounding the display area, an inorganic layer formed on the flexible substrate, a display unit formed on the display area, and a thin film encapsulation layer covering the display unit. The inorganic layer includes an opening disposed on a periphery between edges of the flexible substrate and the thin film encapsulation layer.

Owner:SAMSUNG DISPLAY CO LTD

Wiring substrate, semiconductor device, and method of manufacturing the same

InactiveUS20080012140A1Easy to installImprove productivitySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorInterconnection

A wiring substrate includes a base insulating film, a first interconnection formed on a top surface side of the base insulating film, a via conductor provided in a via hole formed in the base insulating film, and a second interconnection provided on a bottom surface side of the base insulating film, the second interconnection being connected to the first interconnection via the via conductor. The wiring substrate includes divided-substrate-unit regions, in each of which the first interconnection, the via conductor, and the second interconnection are formed. The wiring substrate includes a warpage-controlling pattern on the base insulating film, and has a warped shape such that when the wiring substrate is left at rest on a horizontal plate, at least a central part of each side of a plane surface of the substrate contacts the horizontal plate, with both ends of the side raised, where each of the sides extends along a second direction perpendicular to a first direction in the plane surface of the substrate.

Owner:RENESAS ELECTRONICS CORP +1

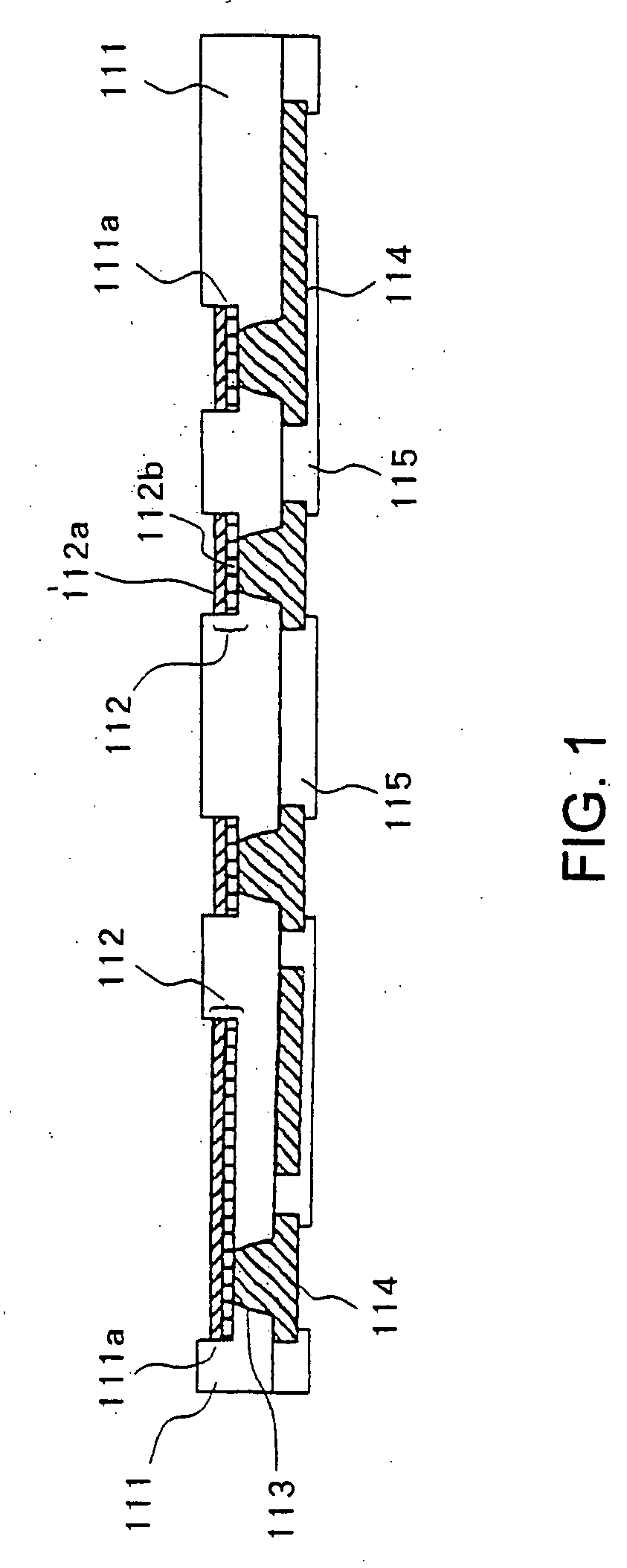

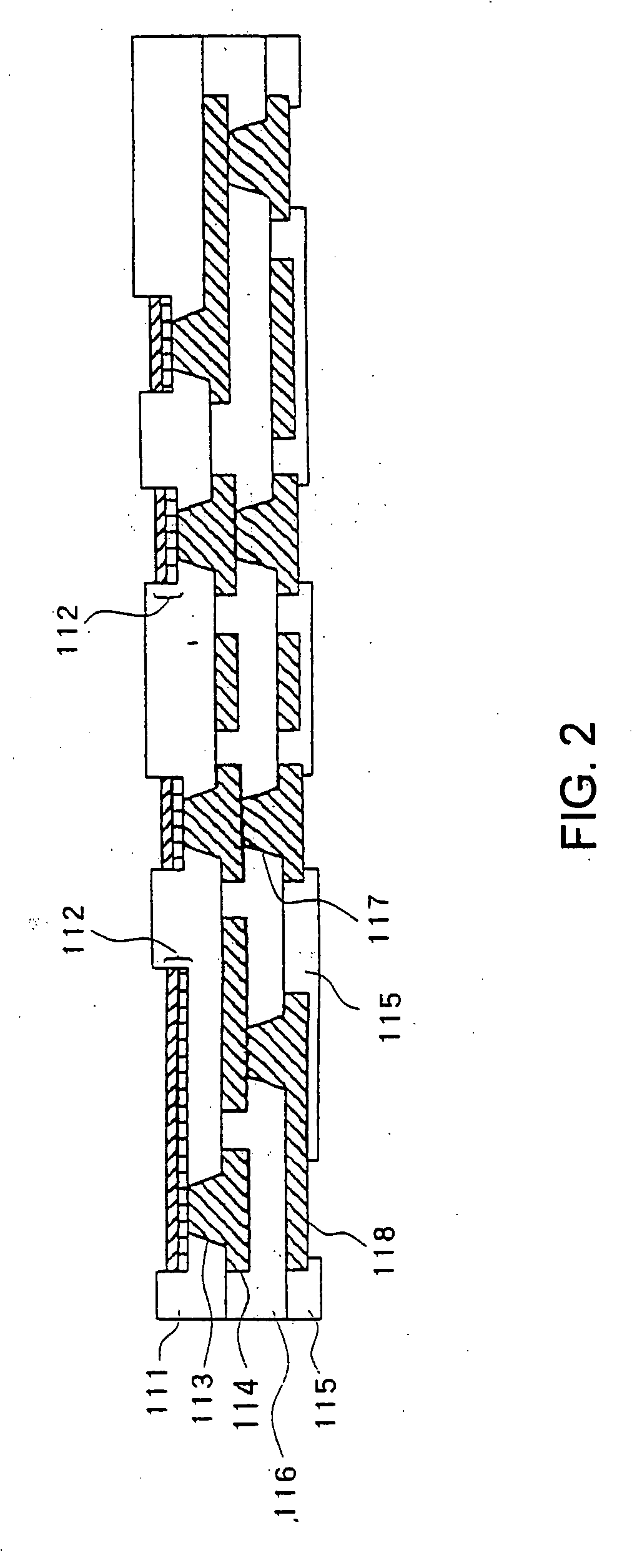

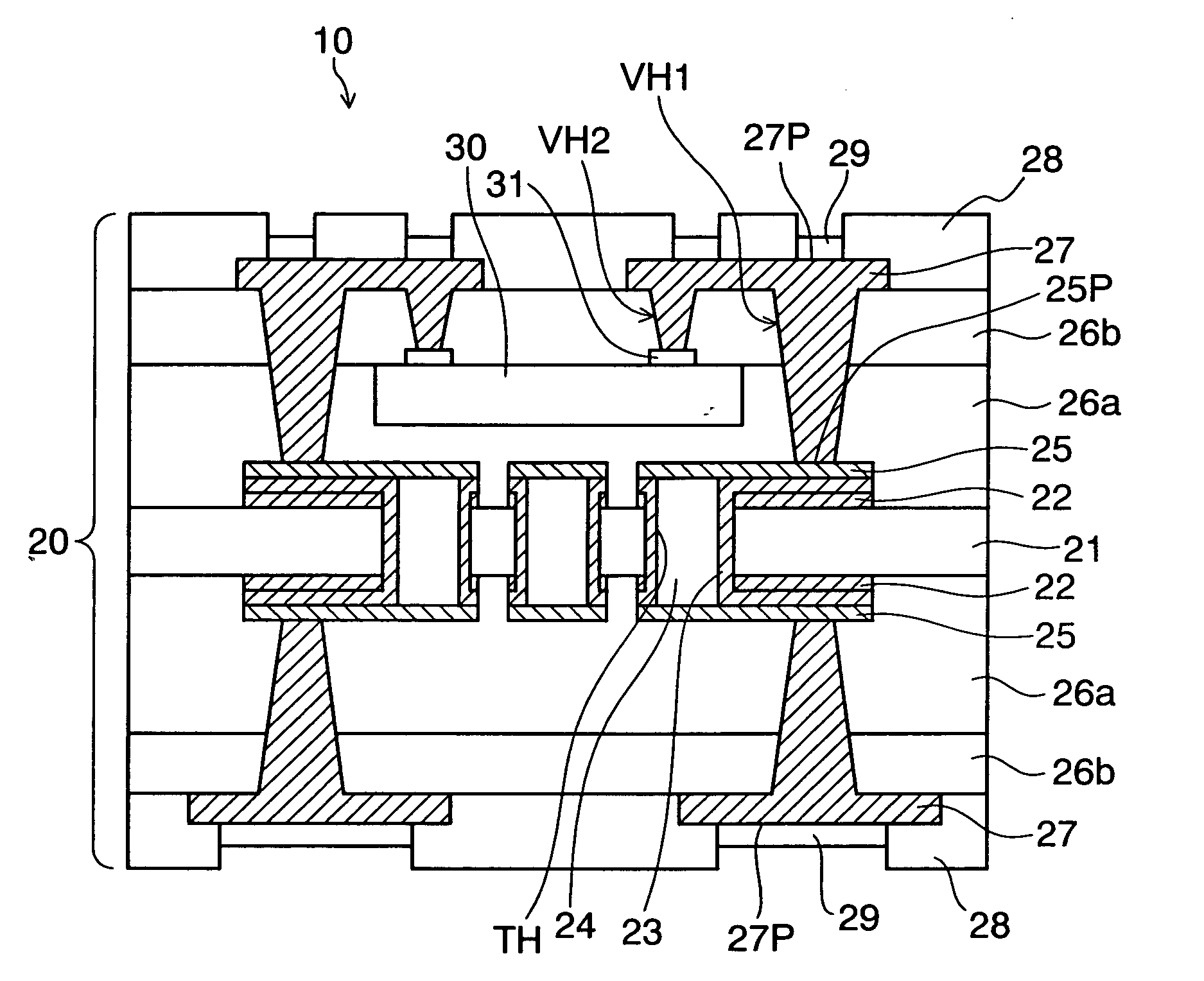

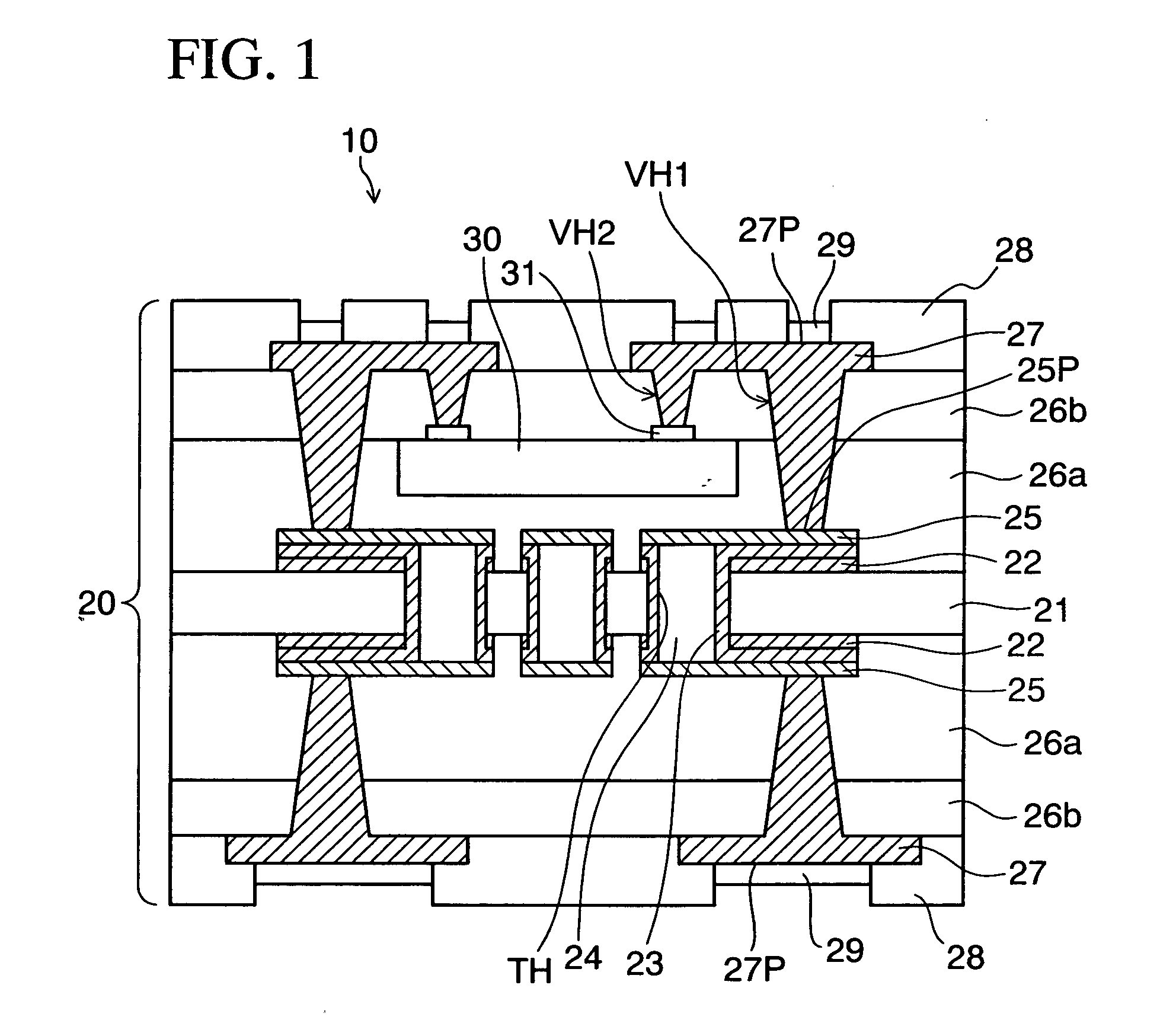

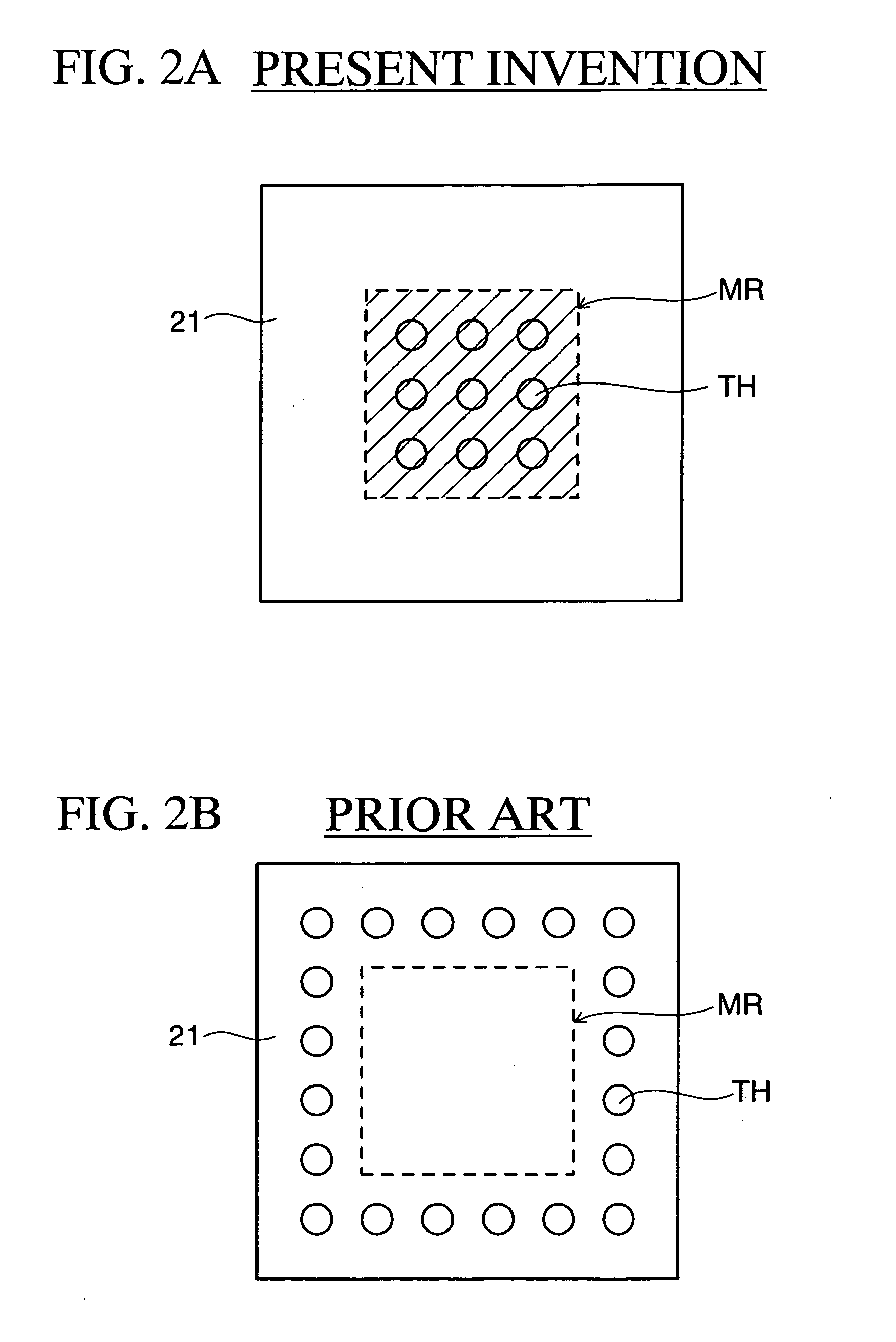

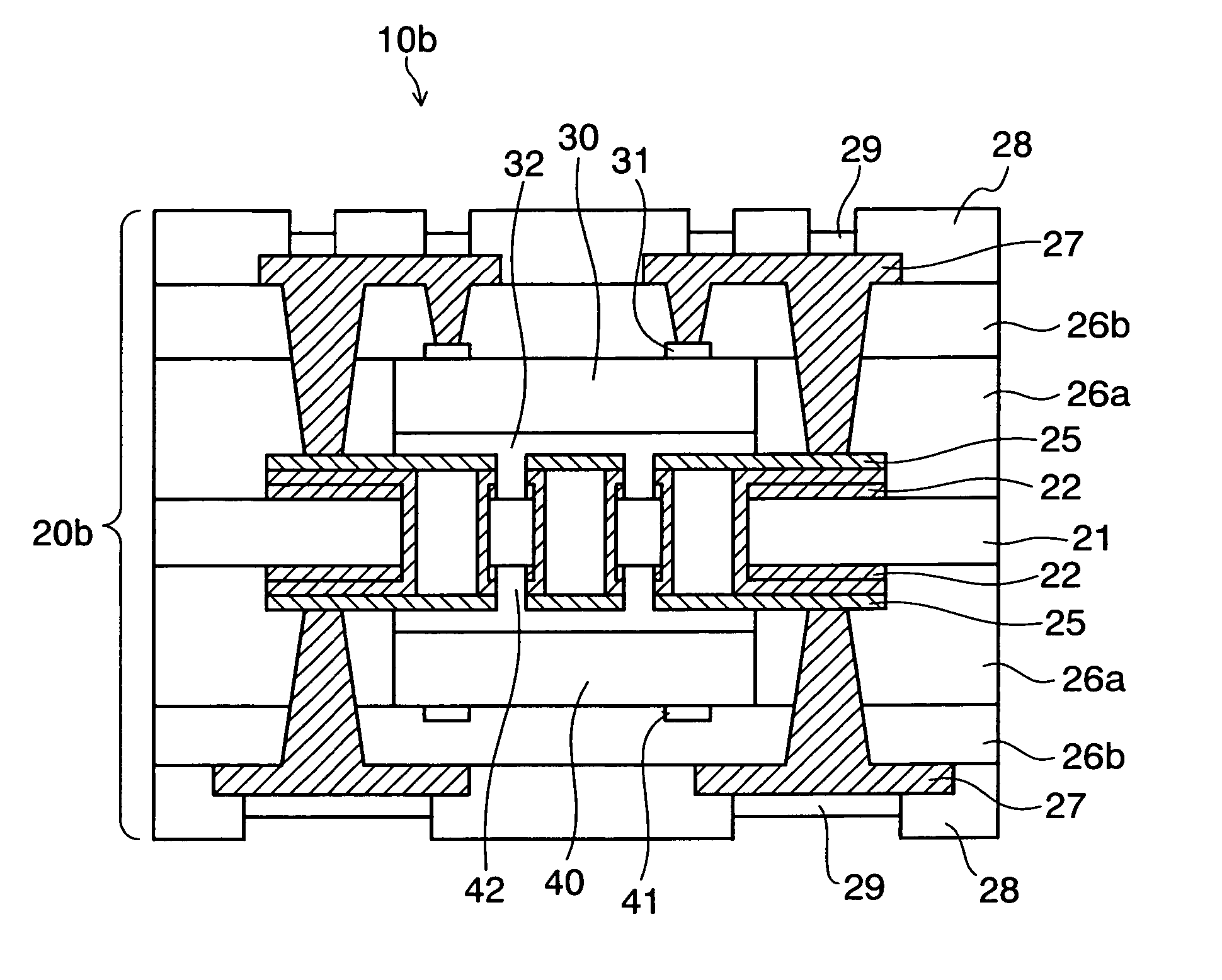

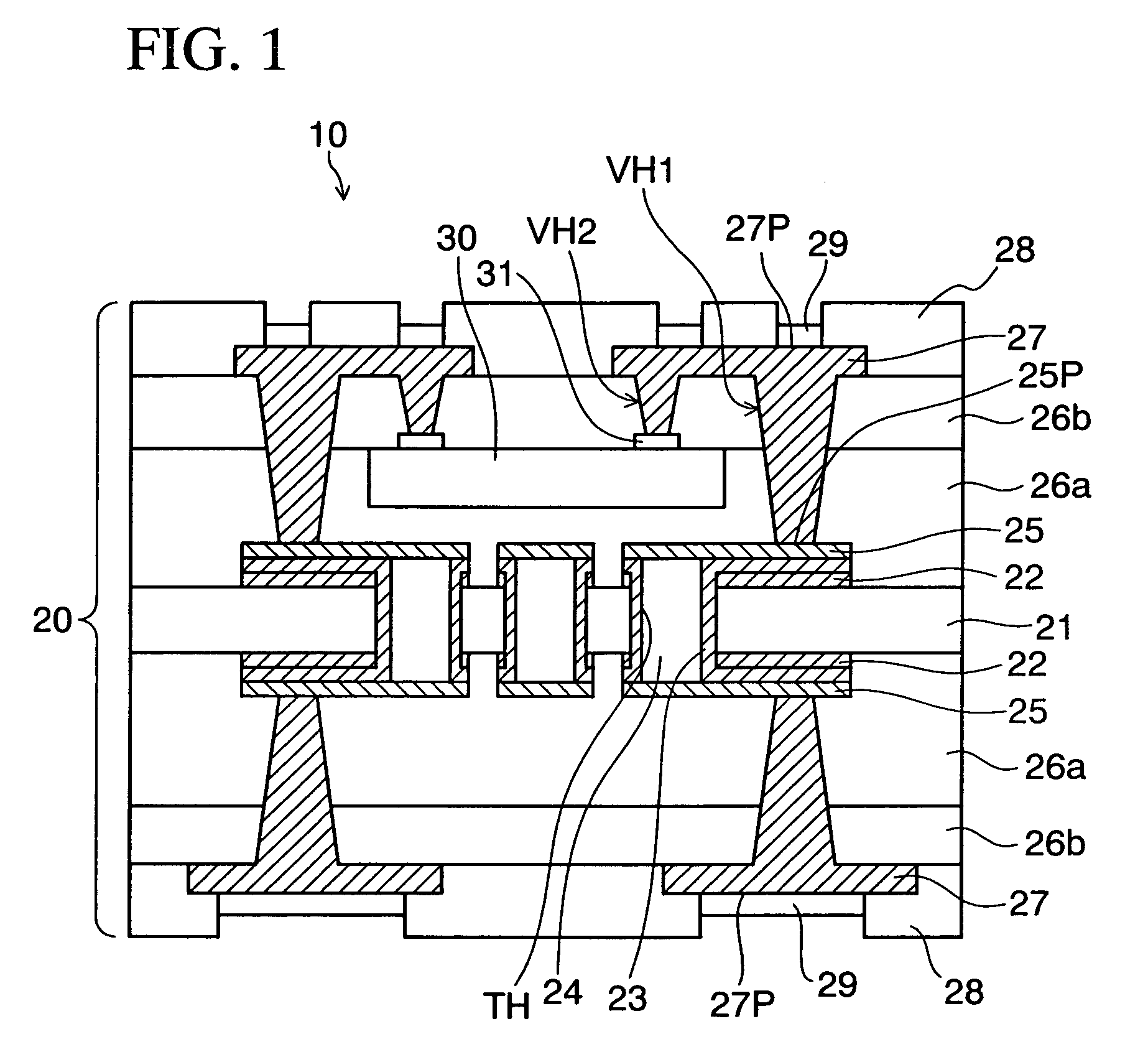

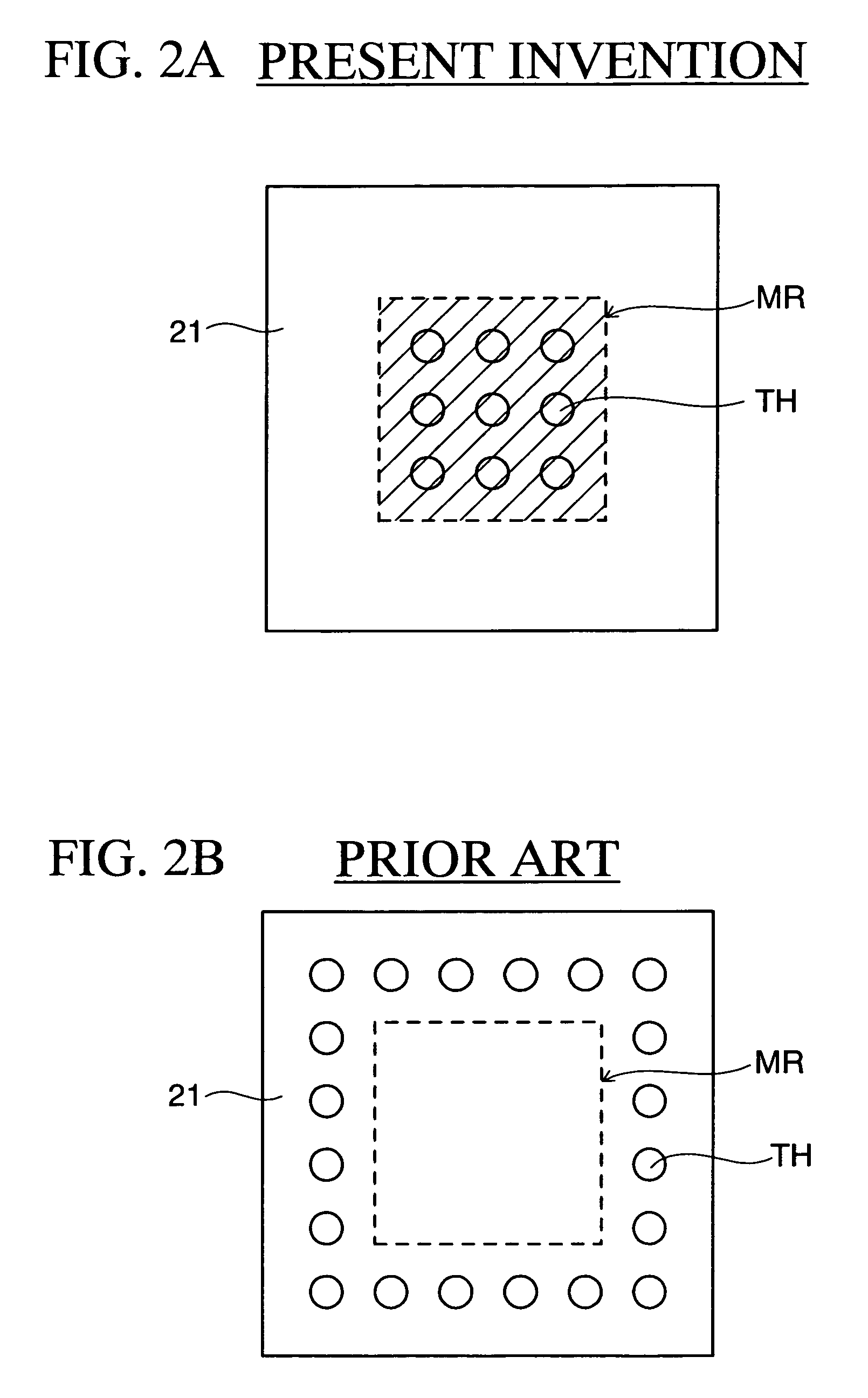

Semiconductor device

ActiveUS20050230835A1Avoid crackingImprove reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorDevice material

In a semiconductor device, a plurality of wiring layers each patterned in a required shape are laminated over both surfaces of an insulating base material with insulating layers interposed therebetween, and electrically connected to one another through via holes piercing the insulating layers in the direction of thickness. A chip is mounted in an embedded manner in one insulating layer over at least one surface of the insulating base material. Electrodes of the chip are connected to one wiring layer. Through holes are formed in portions of the insulating base material, the portions corresponding to a mount area for the chip. Via holes are formed on outwardly extending portions (pad portions) of the wiring layer connected to a conductor layer formed at least on the inner walls of the through holes.

Owner:SHINKO ELECTRIC IND CO LTD

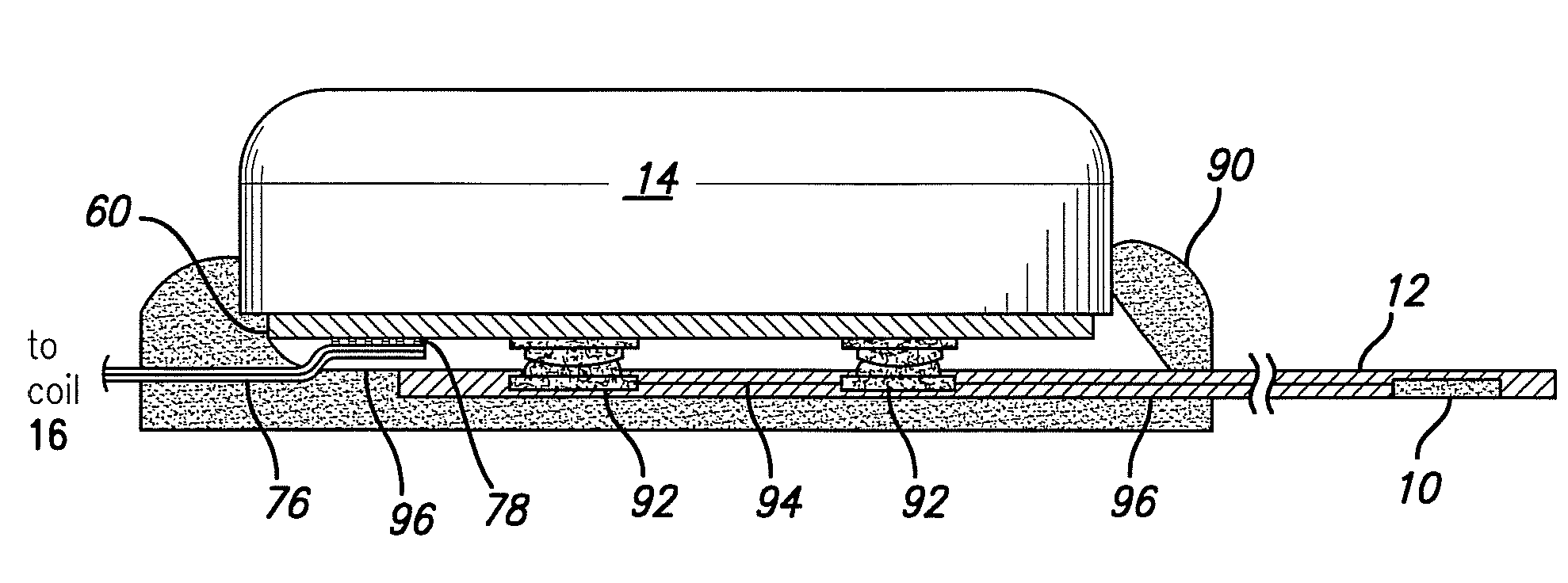

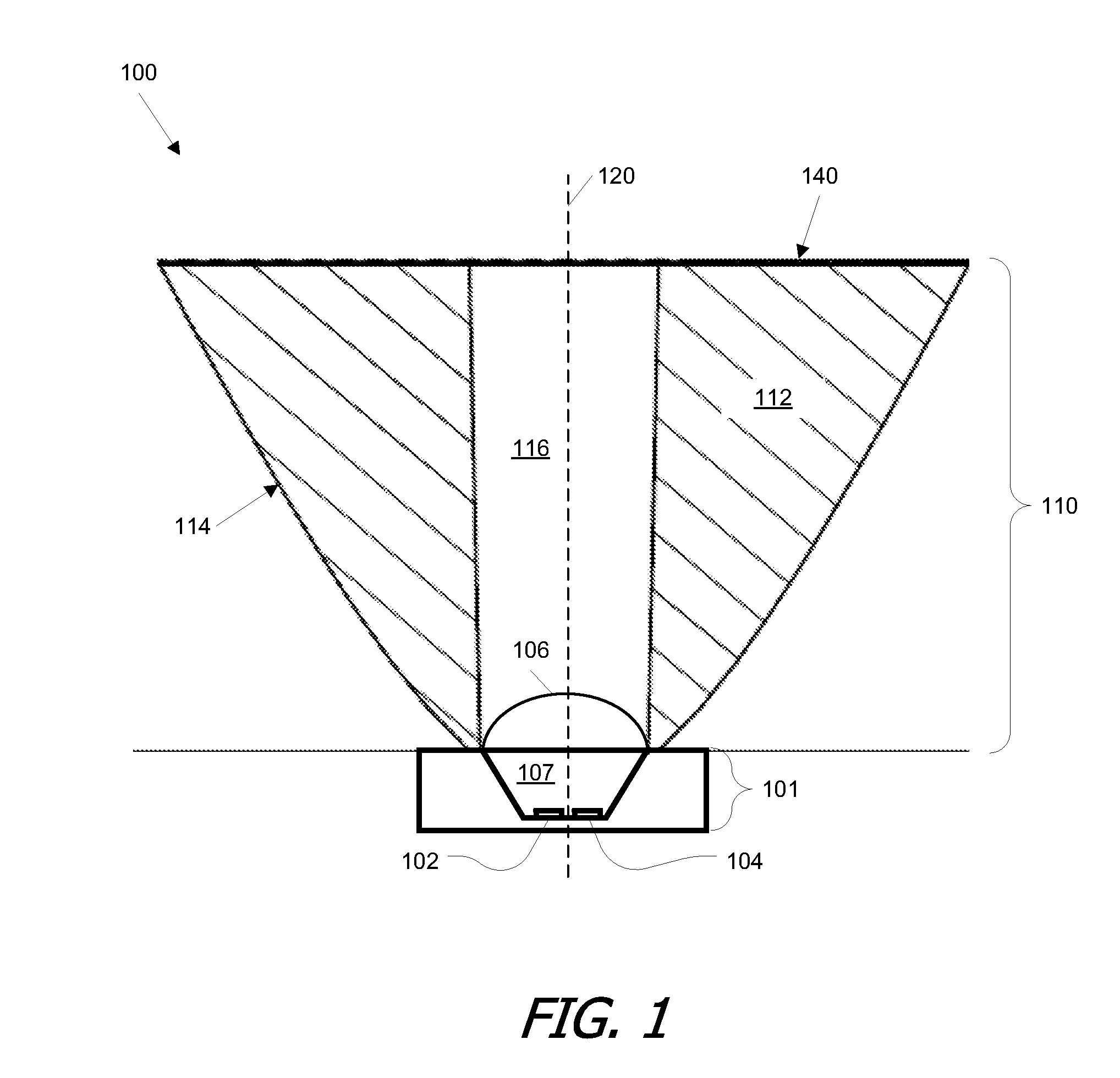

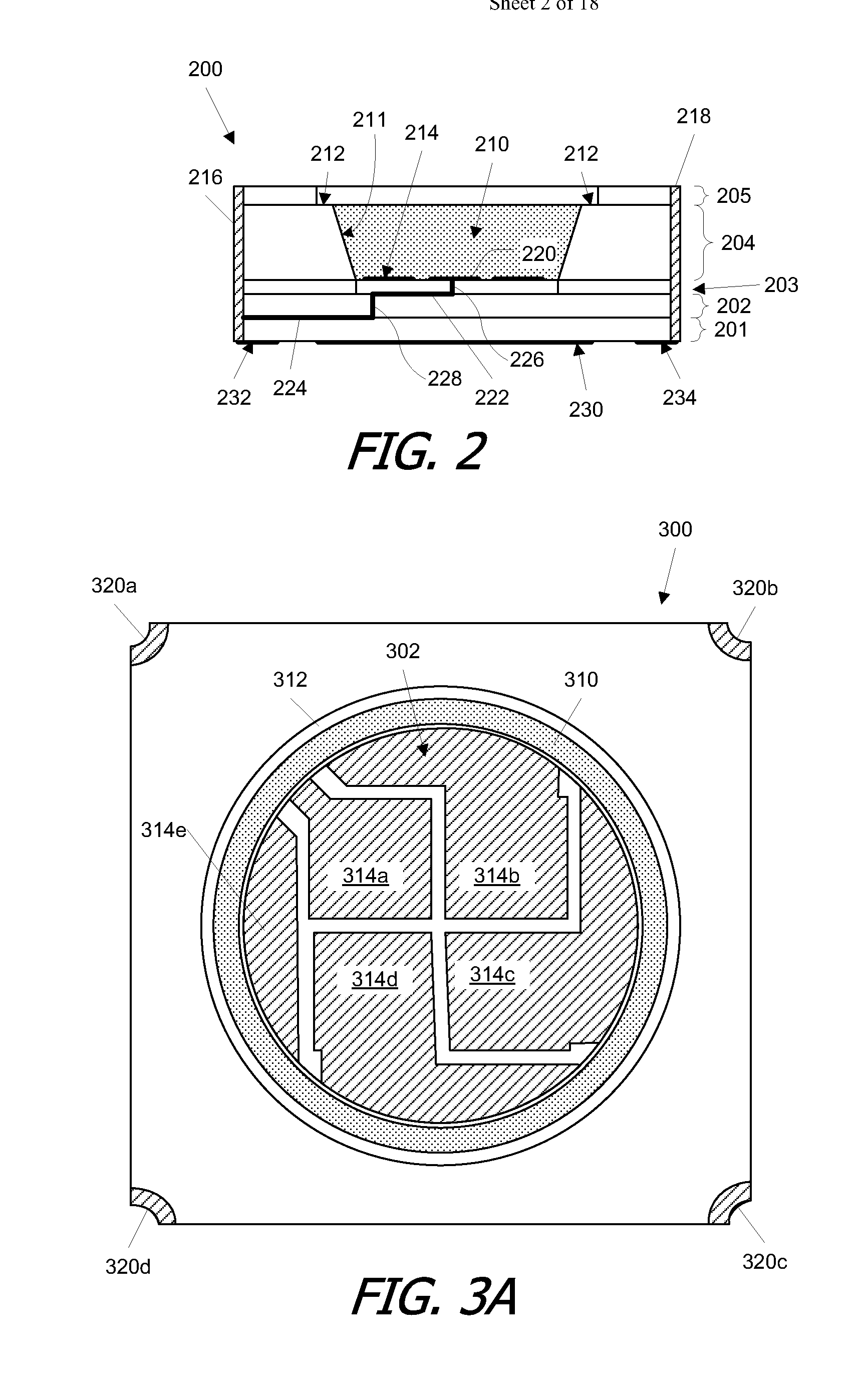

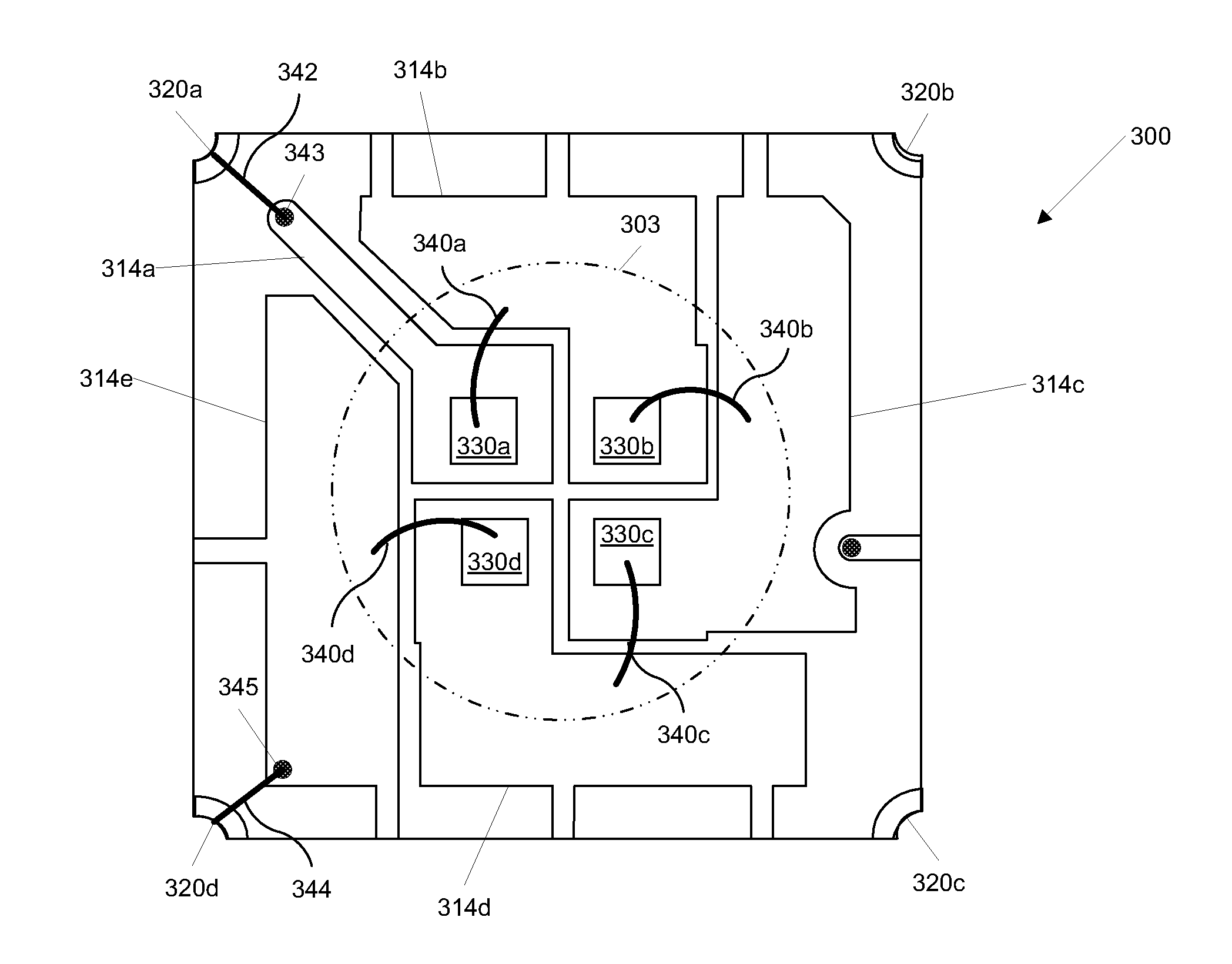

Package for multiple light emitting diodes

ActiveUS20100259930A1Improve controlImprove thermal efficiencyLighting support devicesPoint-like light sourceElectricityLight-emitting diode

Substrates and packages for LED-based light devices can significantly improve thermal performance and provide separate electrical and thermal paths through the substrate. One substrate includes multiple electrically insulating base layers. On a top one of these layers are disposed top-side electrical contacts, including light device pads to accommodate a plurality of light devices. External electrical contacts are disposed on an exterior surface of the substrate. Electrical paths connect the top-side electrical contacts to the external electrical contacts. At least portions of some of the electrical paths are disposed between the electrically insulating base layers. The electrical paths can be arranged such that different subsets of the light device pads are addressable independently of each other. A heat dissipation plate can be formed on the bottom surface of a bottom one of the base layers.

Owner:LEDENGIN

Wiring substrate with reinforcing member

InactiveUS20080308305A1Warpage suppressionEasy to shape3D rigid printed circuitsSemiconductor/solid-state device detailsElectrical conductorEngineering

A wiring substrate with a reinforcing member includes: a resin wiring substrate having a substrate principal surface, a substrate rear surface, and substrate side surfaces, forming a rectangular shape having four sides in plan view, and including a resin insulating layer and a conductor layer; and a reinforcing member formed in a rectangular frame shape which surrounds the four sides of the resin wiring substrate, and provided with an inner wall having a depression surface-joined to at least one of the substrate side surfaces, an outer peripheral portion of the substrate principal surface, and an outer peripheral portion of the substrate rear surface.

Owner:NGK SPARK PLUG CO LTD

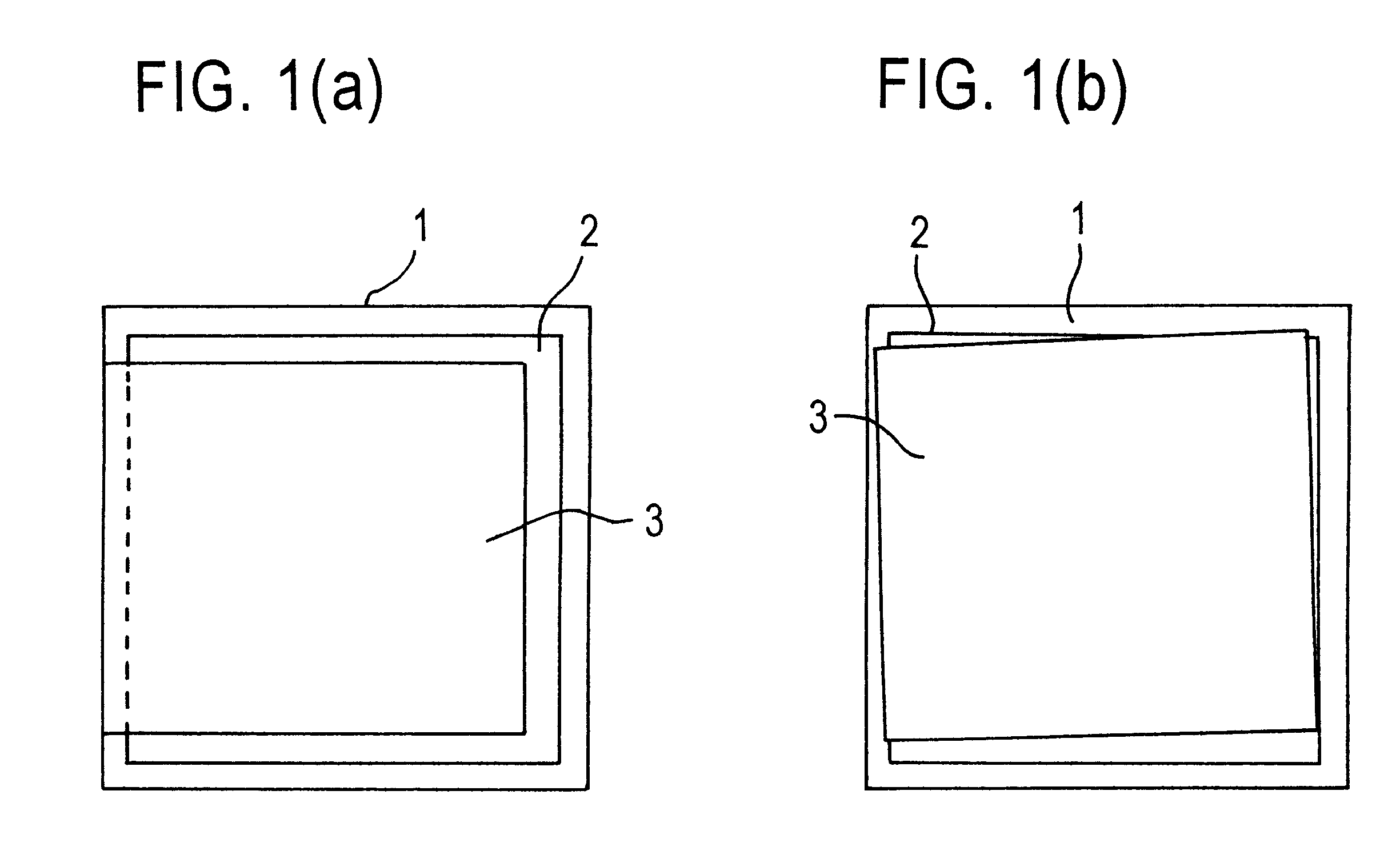

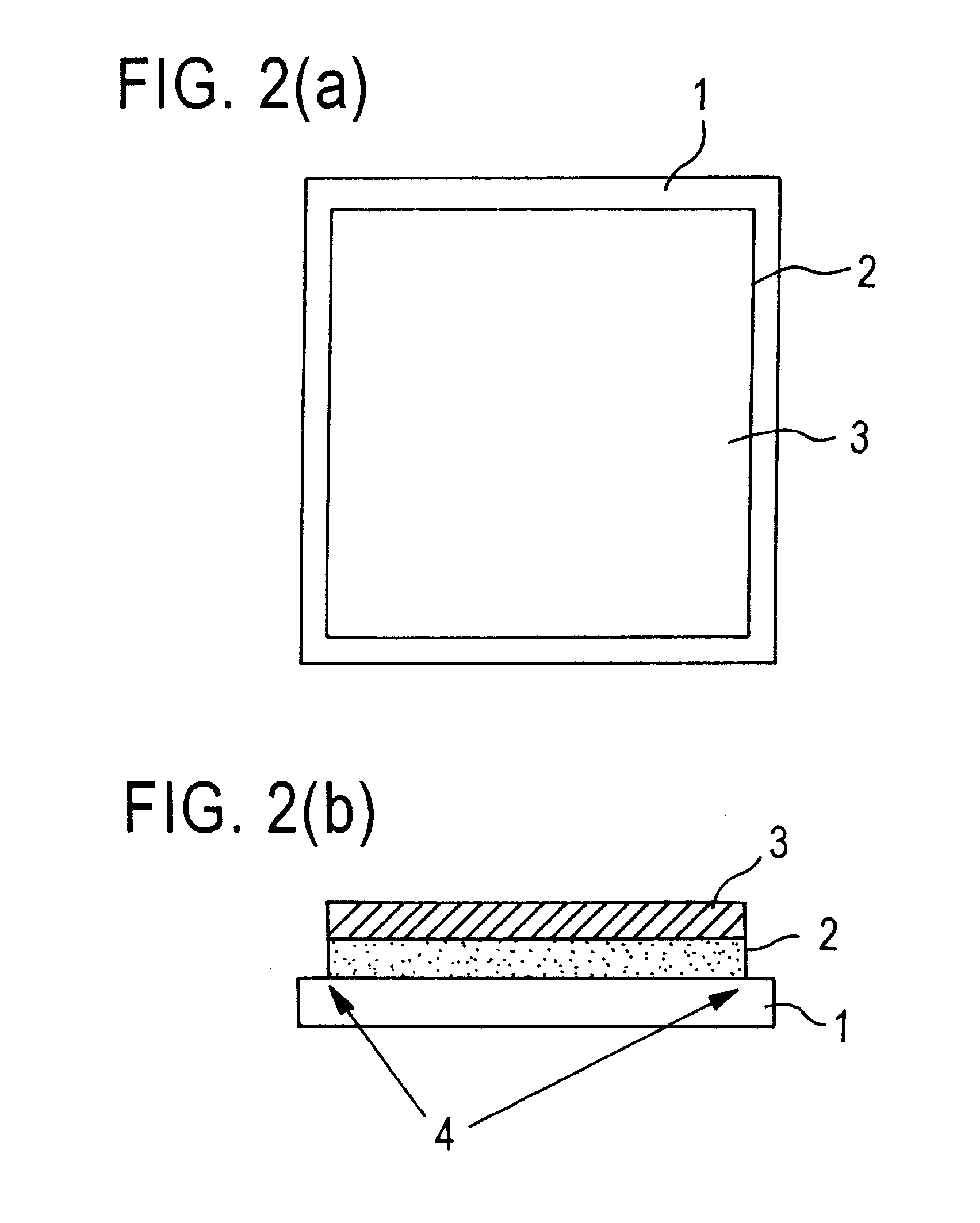

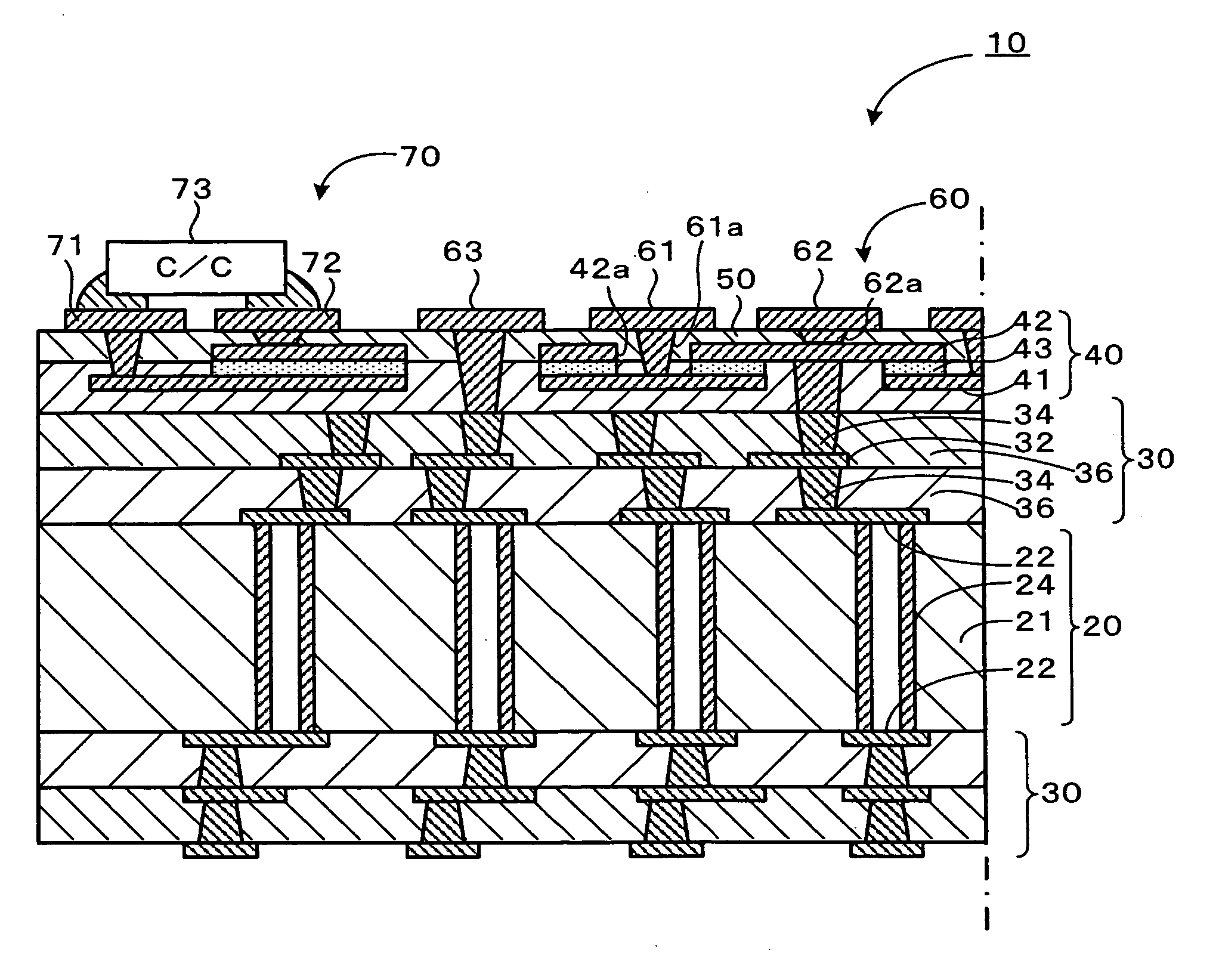

Interposer, and multilayer printed wiring board

InactiveUS20060202322A1Avoid it happening againPrinted circuit assemblingSemiconductor/solid-state device detailsInterposerEngineering

An interposer capable of preventing breaking of a wiring pattern with an IC chip loaded on a package substrate. Stress due to a difference in thermal expansion coefficient between a multilayer printed wiring board having a large thermal expansion and the IC chip having a small thermal expansion can be absorbed by locating the interposer between the package substrate and the IC chip. Particularly by using an insulation substrate whose Young's modulus is 55 to 440 Gpa as the insulation substrate constituting the interposer, stress is absorbed within the interposer.

Owner:IBIDEN CO LTD

Method of manufacture of ceramic composite wiring structures for semiconductor devices

InactiveUS7047637B2Increase volume fractionEasy to removeSemiconductor/solid-state device detailsSolid-state devicesDielectricCeramic composite

Method of manufacture of a composite wiring structure for use with at least one semiconductor device, the structure having a first conductive member upon which the semiconductor device can be mounted for electrical connection thereto. A dielectric member, made of ceramic or organo-ceramic composite material, is bonded to the first conductive member and contains embedded therein a conductive network and a thermal distribution network. A second conductive member may be incorporated with the composite wiring structure, with a capacitor electrically connected between the conductive network and the second conductive member. Bonding between the dielectric member and the conductive members may be in the form of a direct covalent bond formed at a temperature insufficient to adversely effect the structural integrity of the conductive network and the thermal distribution network.

Owner:L PIERRE DEROCHEMONT C2 TECH

Printed circuit board and electronic package using same

InactiveUS6985362B2Reduce stress concentrationImprove abilitiesPrinted circuit assemblingPrinted electric component incorporationSemiconductor chipPrinted circuit board

A printed circuit board on which a semiconductor chip is flip chip mounted, comprising a circuit pattern to which a conductive bump, provided in a corner portion of a semiconductor chip, is connected, an insulating layer for holding the circuit pattern, and a protection pad which is positioned on the insulating layer relative to the circuit pattern, to which the conductive bump is connected.

Owner:IBM CORP

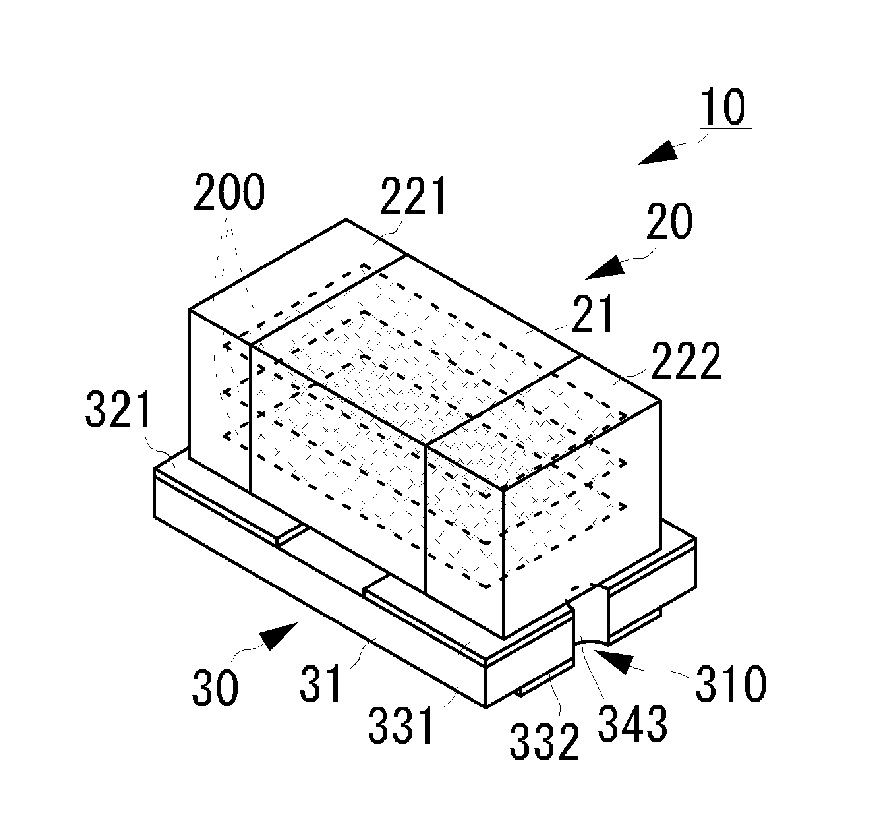

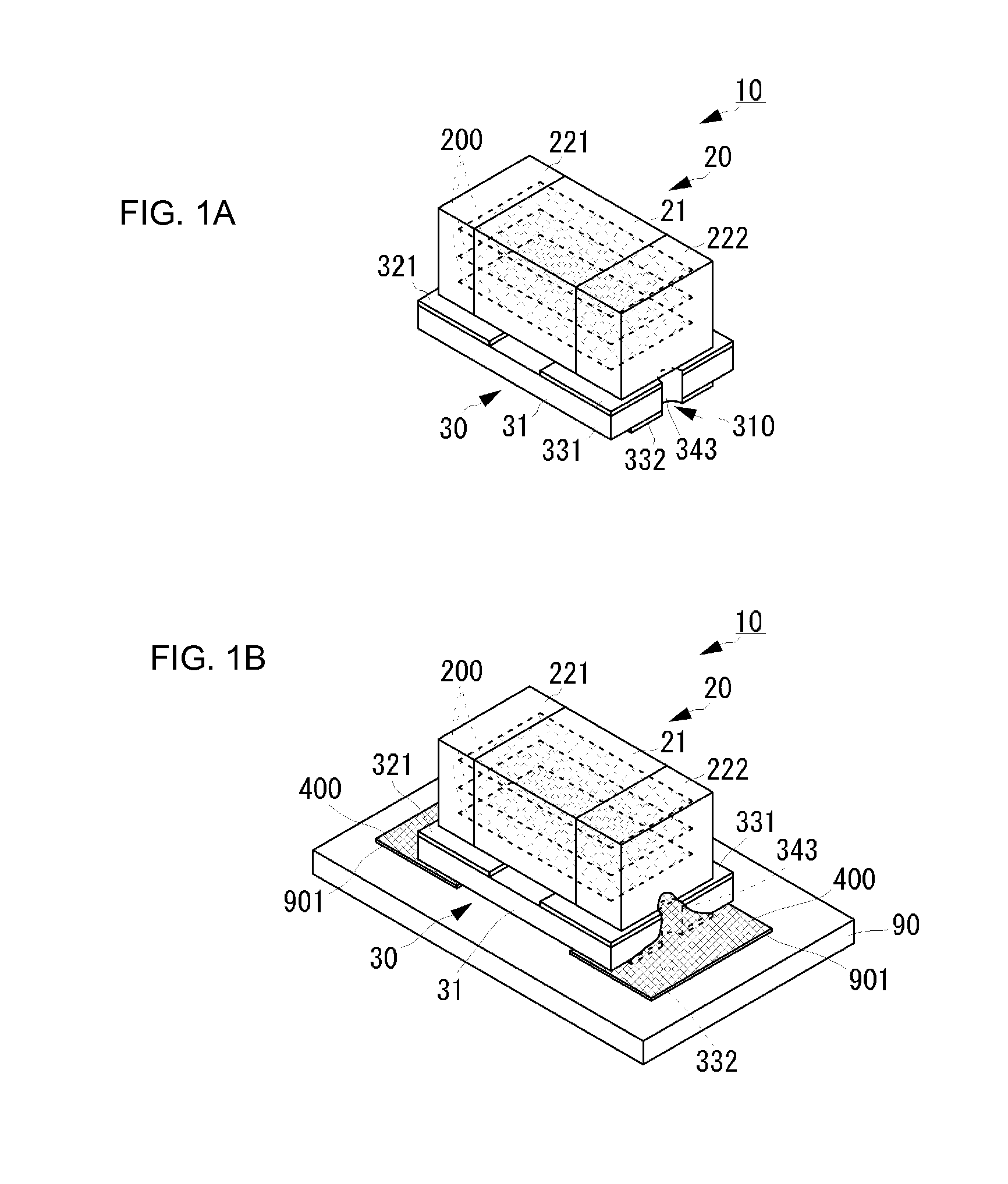

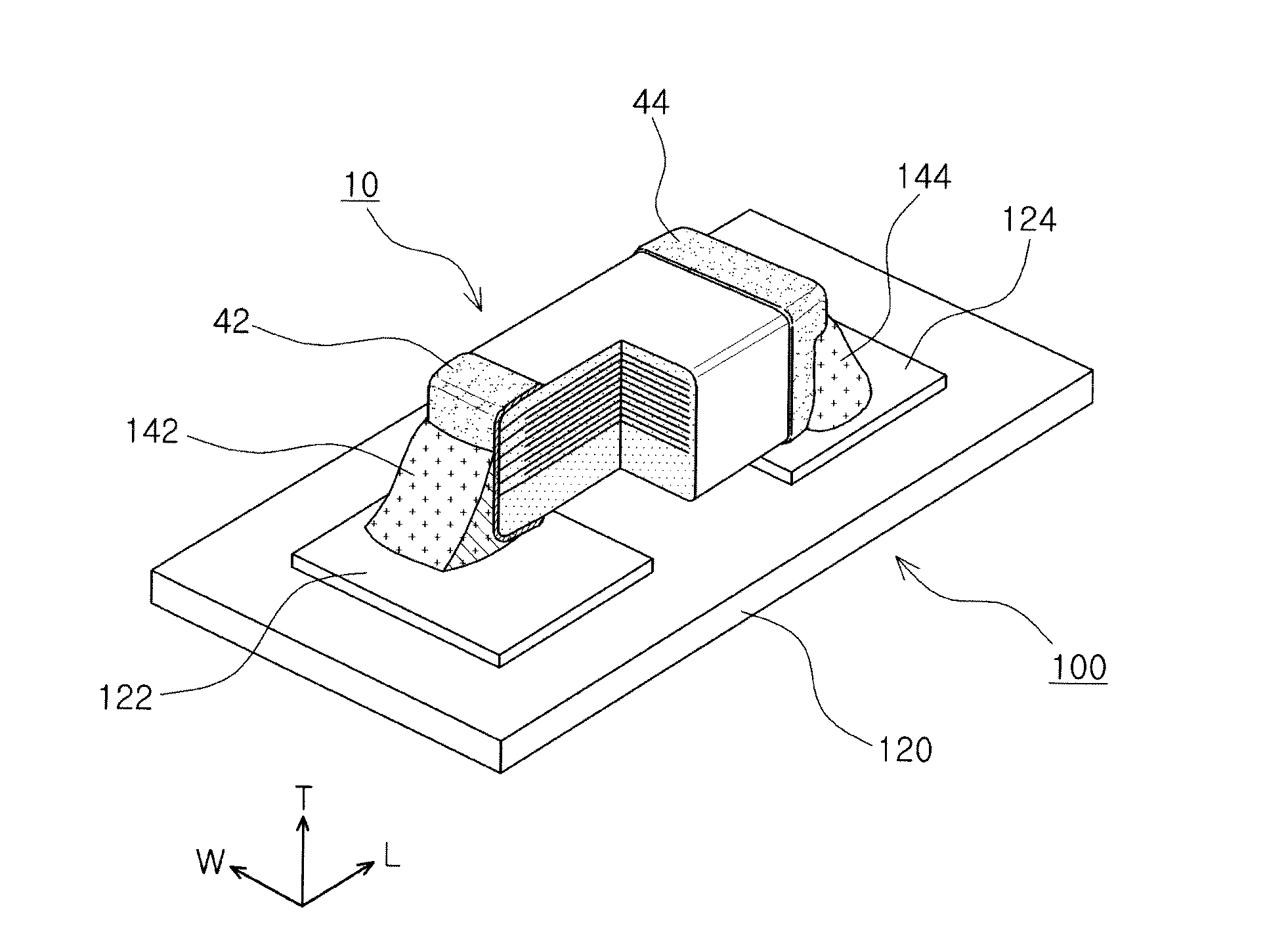

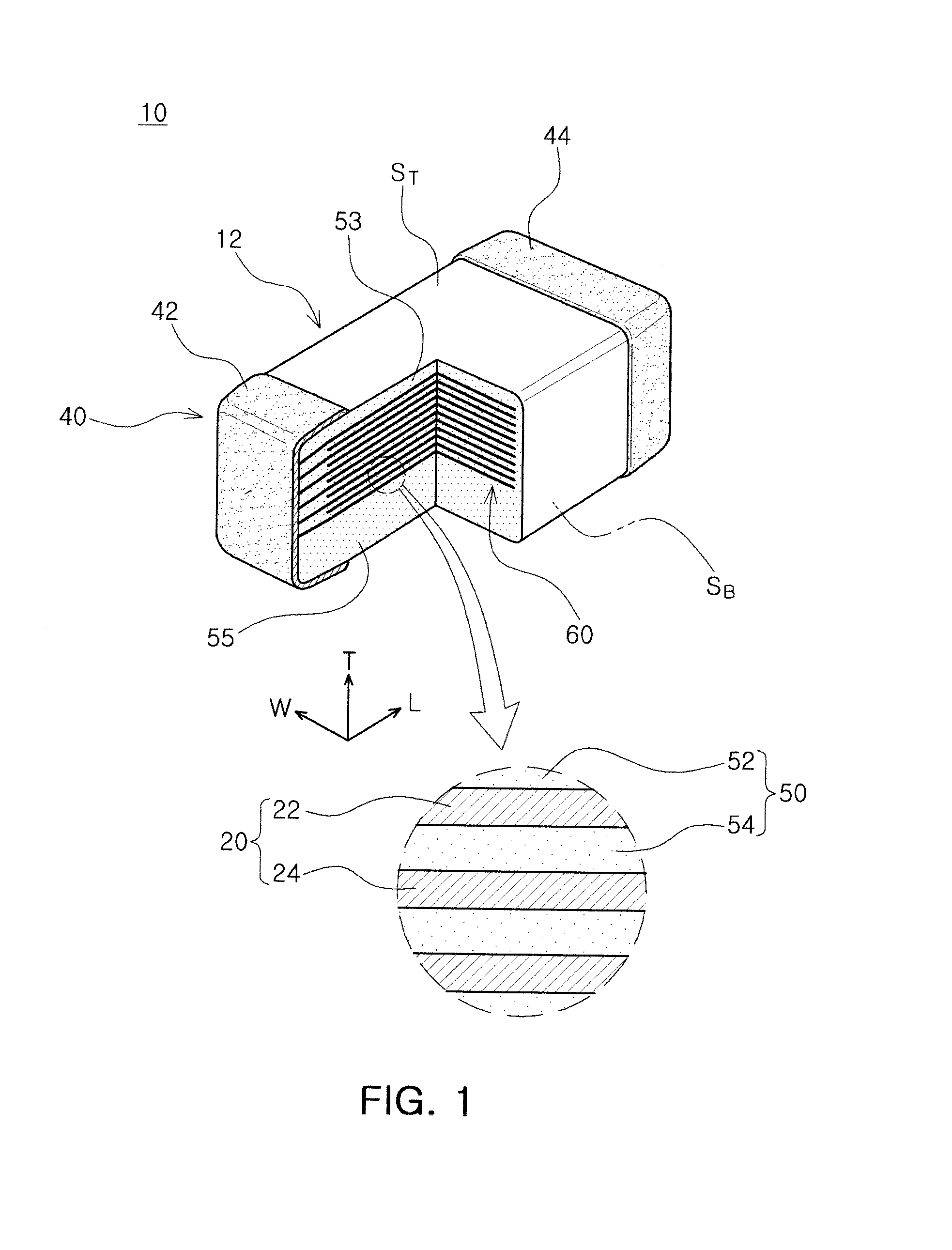

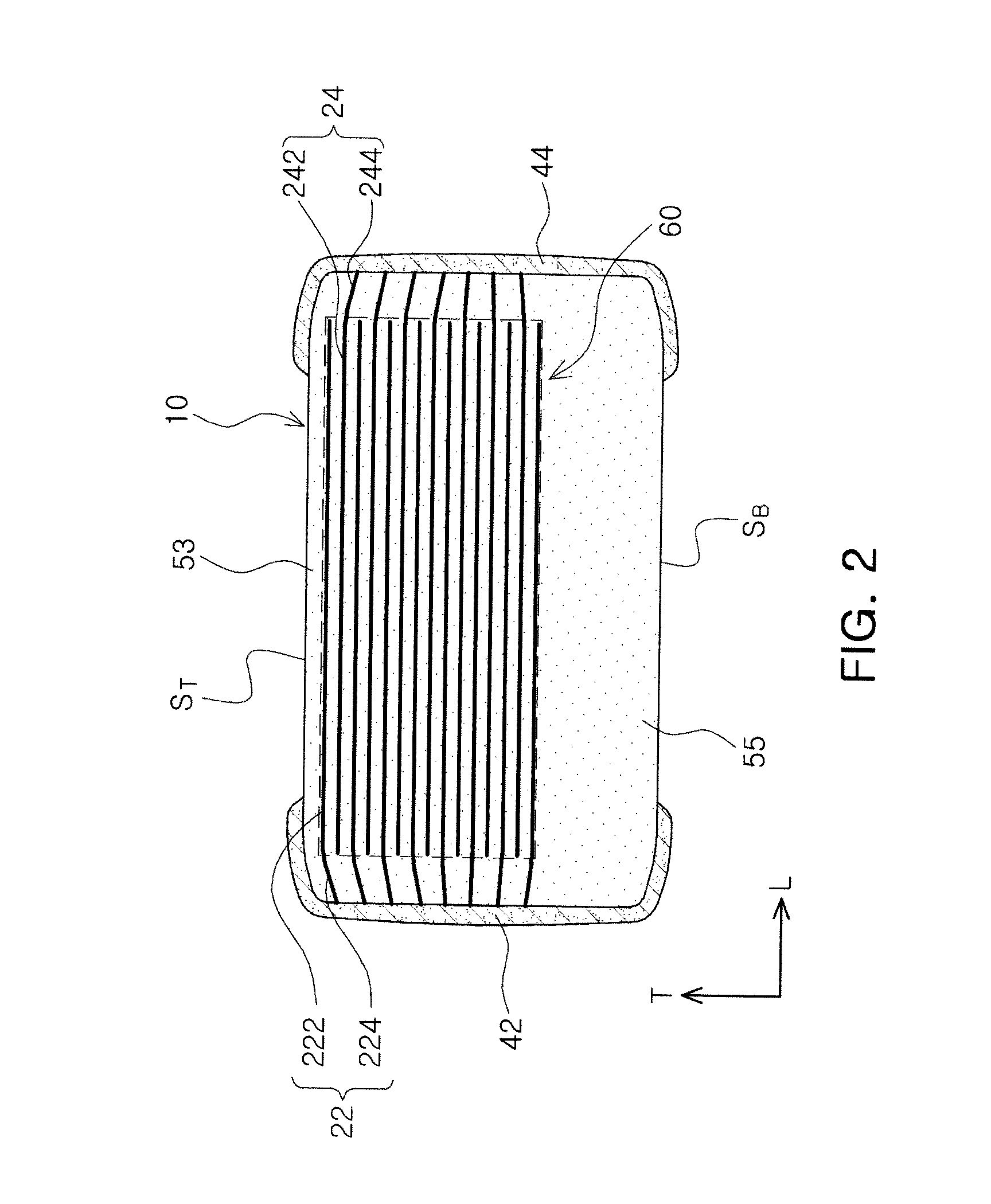

Electronic component

ActiveUS20140016242A1Reduce adhesionSimple structureFixed capacitor electrodesFinal product manufactureCeramic capacitorInterposer

A multilayer ceramic capacitor includes flat-shaped inner electrodes that are laminated. An interposer includes an insulating substrate that is larger than contours of the multilayer ceramic capacitor. A first mounting electrode that mounts the multilayer ceramic capacitor is located on a first principal surface of the insulating substrate, and a first external connection electrode for connection to an external circuit board located on a second principal surface. The multilayer ceramic capacitor is mounted onto the interposer in such a way that the principal surfaces of the inner electrodes are parallel or substantially parallel to the principal surface of the interposer, that is, the first and second principal surfaces of the insulating substrate.

Owner:MURATA MFG CO LTD

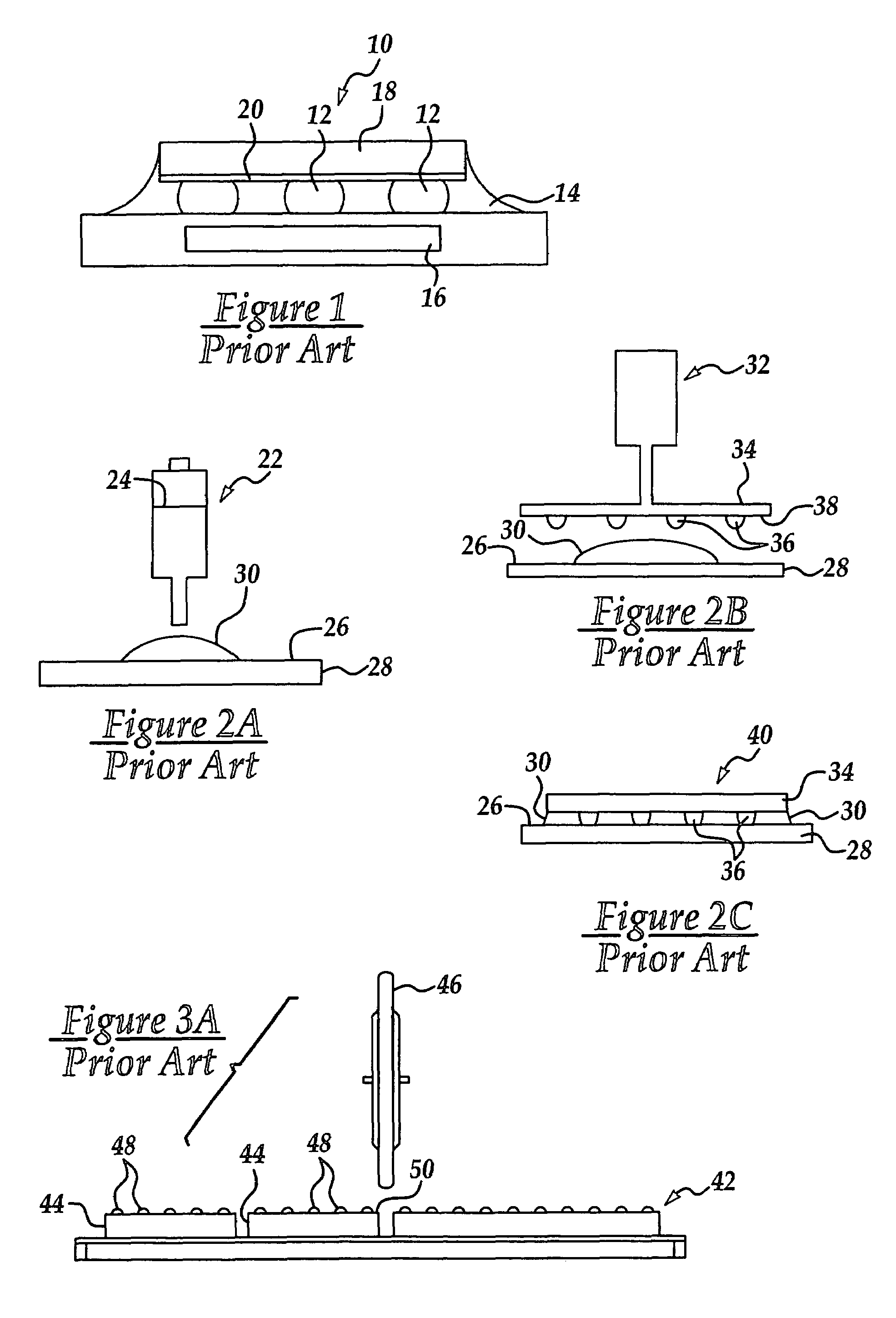

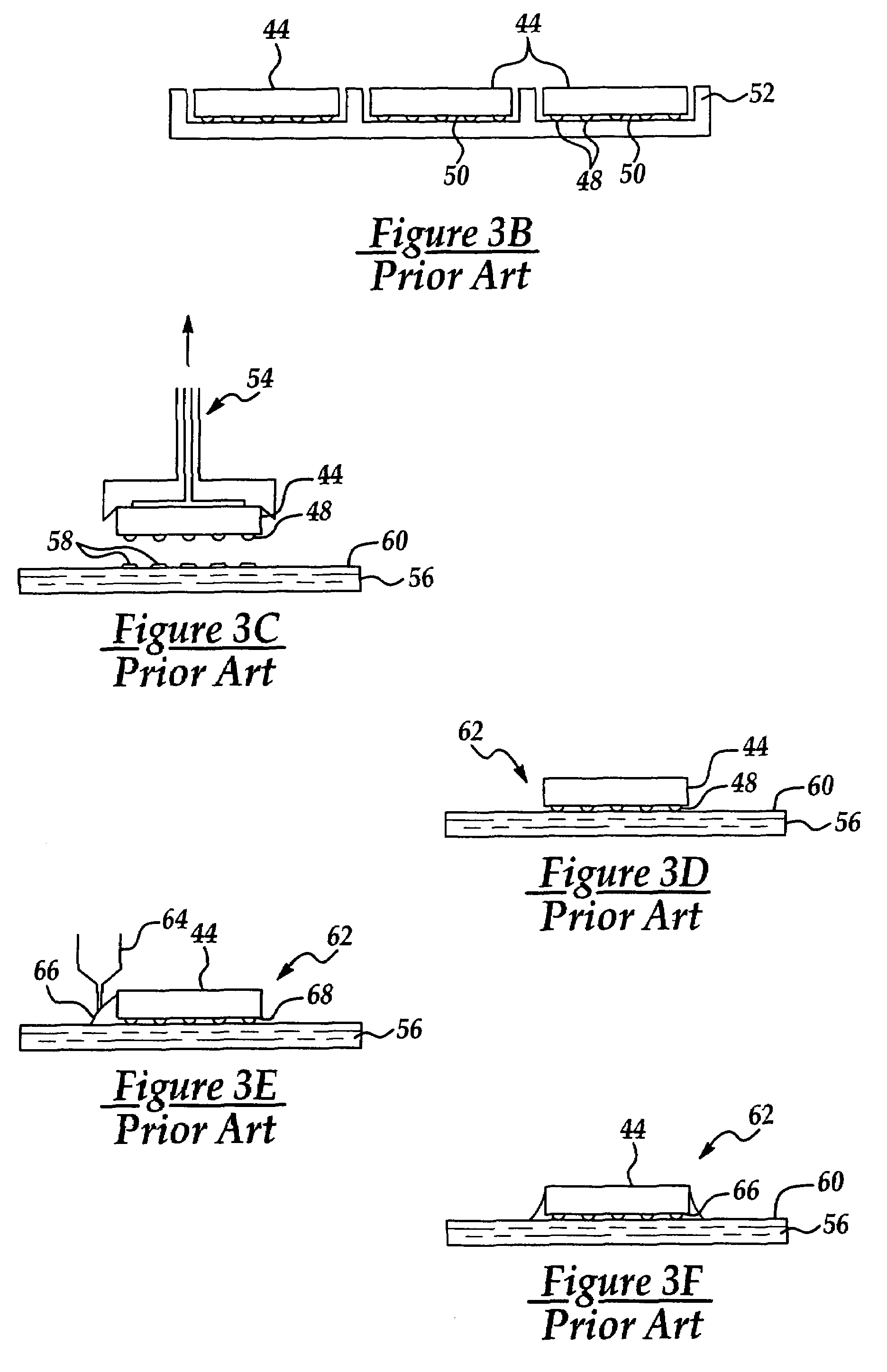

Method for bonding IC chips to substrates incorporating dummy bumps and non-conductive adhesive and structures formed

InactiveUS6919642B2Printed circuit assemblingSemiconductor/solid-state device detailsAdhesiveEngineering

An IC chip / substrate assembly bonded together by a non-conductive adhesive and a method for forming the assembly. The assembly consists of an IC chip that has bumps formed on an active surface, a substrate that has bond pads formed on a top surface, wherein at least one of the IC chip and the substrate has dummy bumps formed in-between the bumps or the bond pads, and a non-conductive adhesive disposed in between and bonding the IC chip and the substrate together in a face-to-face relationship with the bumps in electrical communication with the bond pads.

Owner:IND TECH RES INST

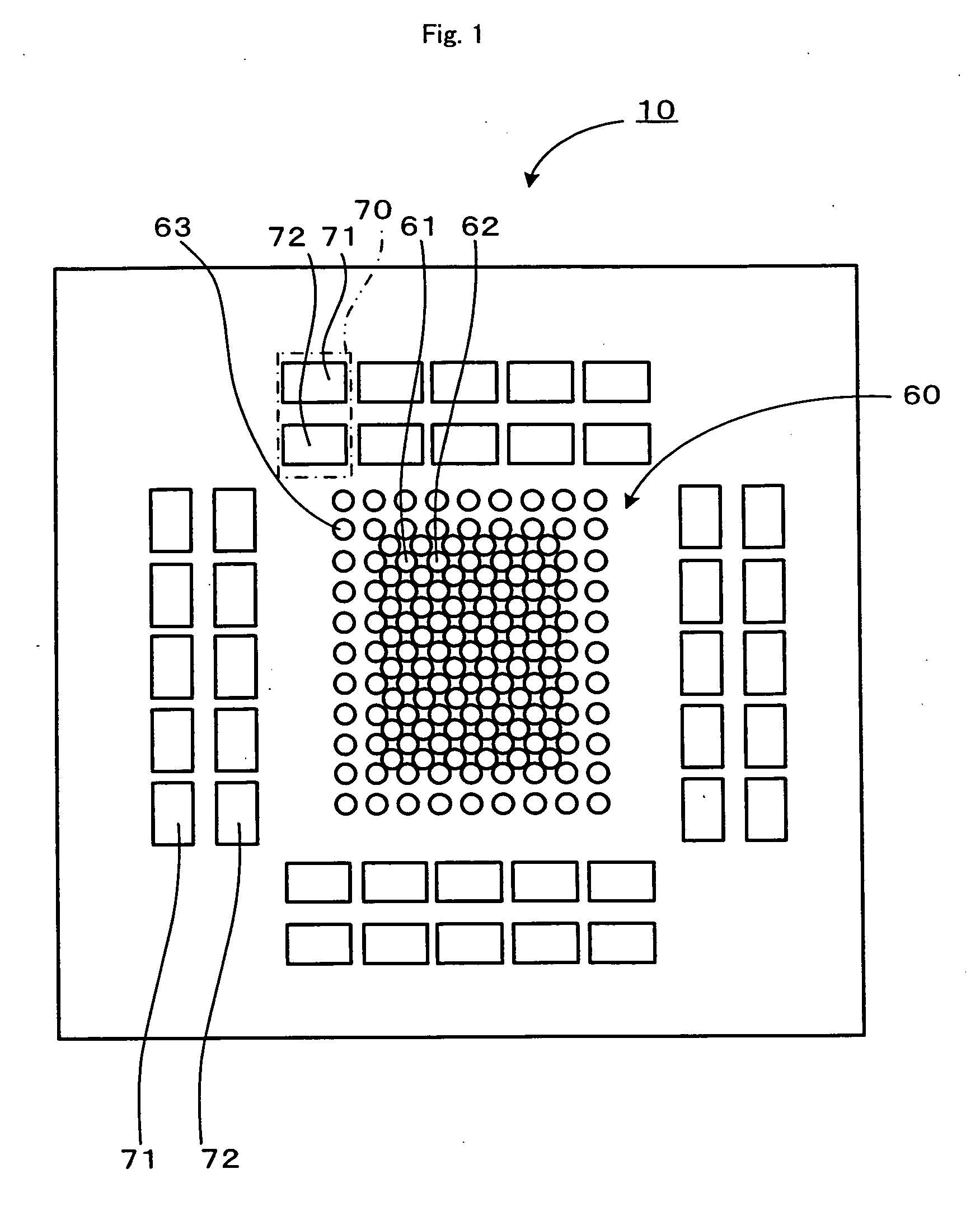

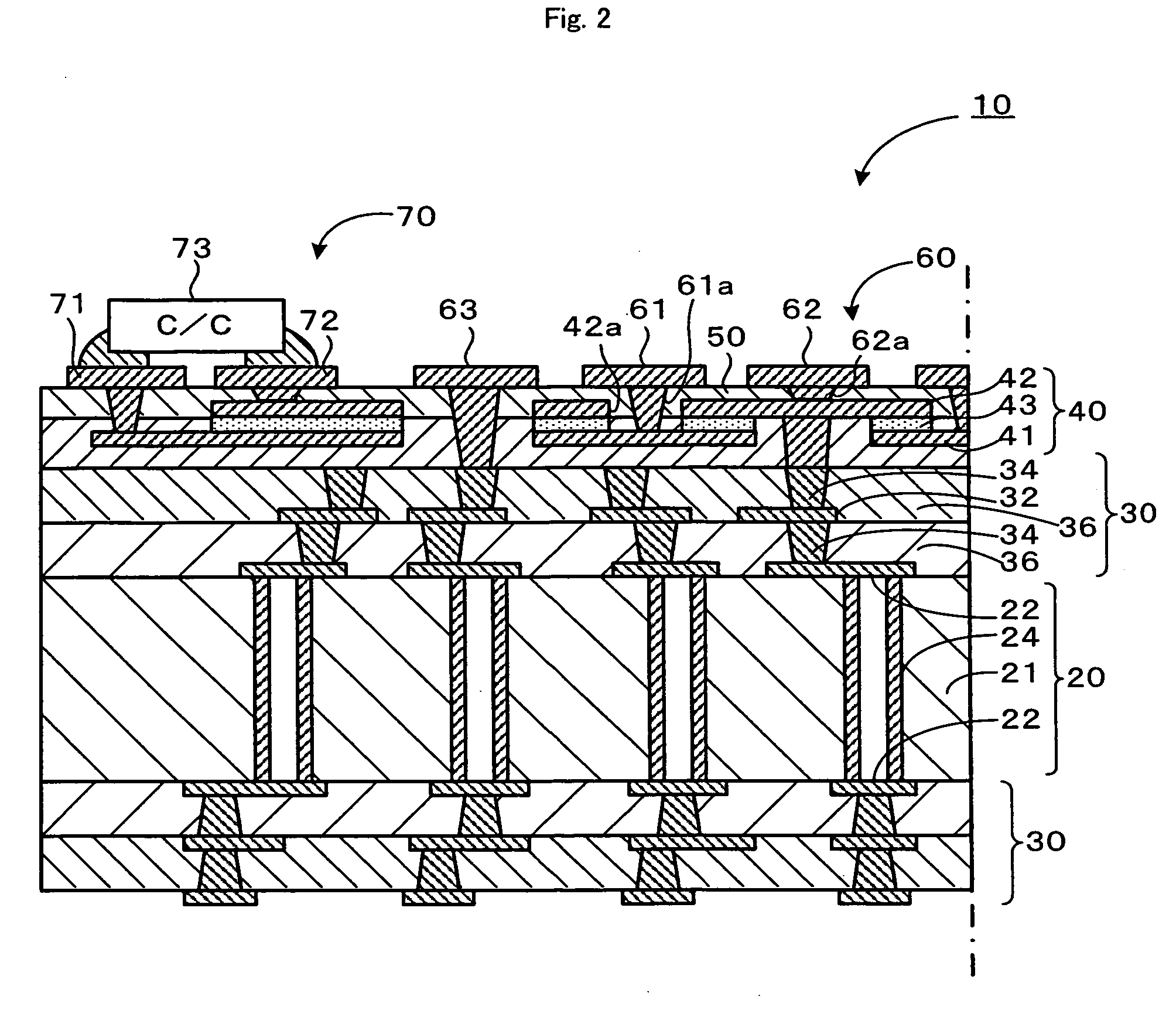

Multilayer printed wiring board

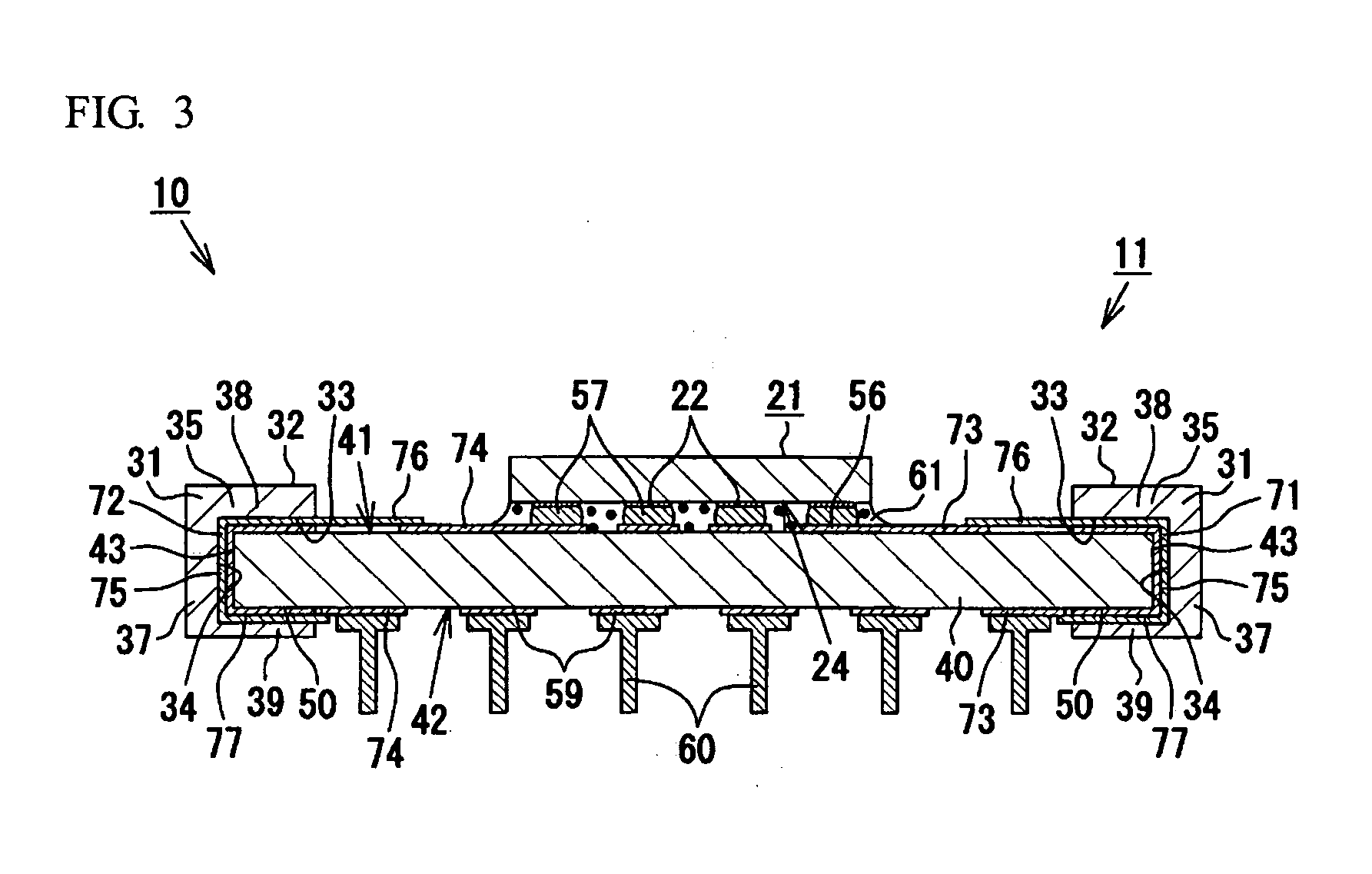

ActiveUS20060137905A1High capacitanceAdequate decoupling effectCross-talk/noise/interference reductionPrinted circuits stress/warp reductionCapacitanceEngineering

A multilayer printed wiring board 10 includes: a mounting portion 60 on the top surface of which is mounted a semiconductor element that is electrically connected to a wiring pattern 32, etc.; and a capacitor portion 40 having a high dielectric constant layer 43, formed of ceramic and first and second layer electrodes 41 and 42 that sandwich the high dielectric constant layer 43. One of either of the first and second layer electrodes 41 and 42 is connected to a power supply line of the semiconductor element and the other of either of the first and second layer electrodes 41 and 42 is connected to a ground line. In this multilayer printed wiring board 10, high dielectric constant layer 43 included in the layered capacitor portion 40, which is connected between the power supply line and the ground line, is formed of ceramic. With this structure, the static capacitance of the layered capacitor portion 40 can be high, and an adequate decoupling effect is exhibited even under circumstances in which instantaneous potential drops occur readily.

Owner:IBIDEN CO LTD

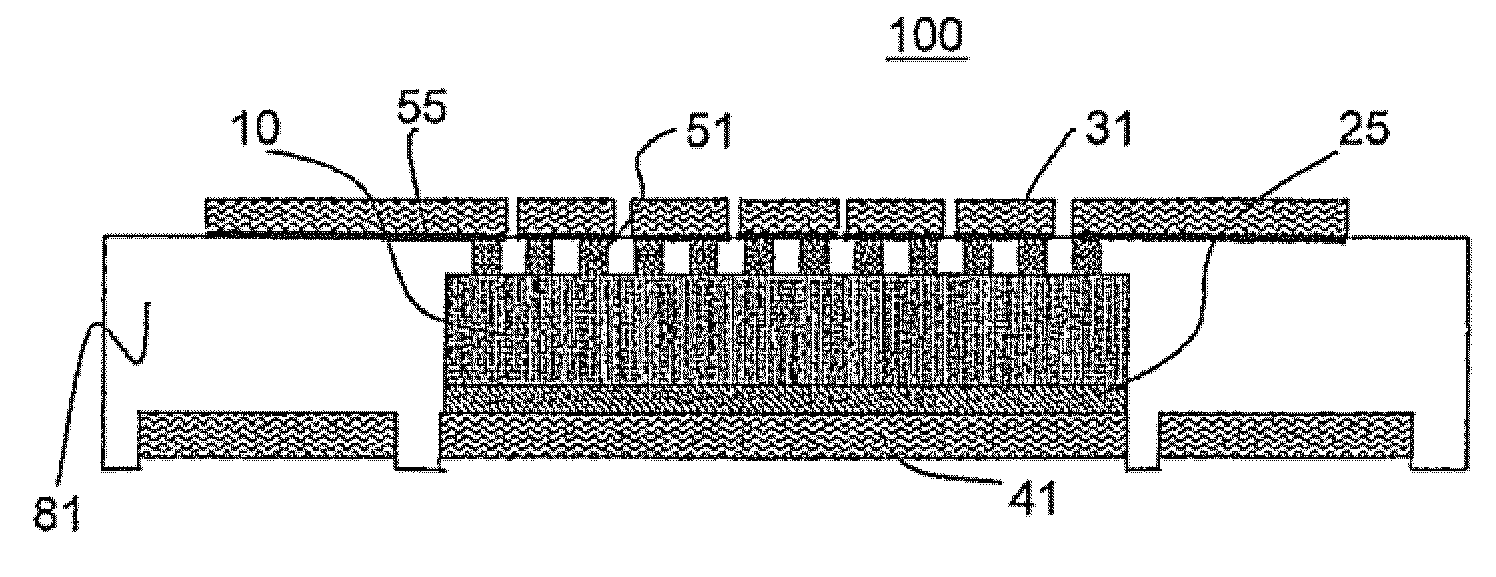

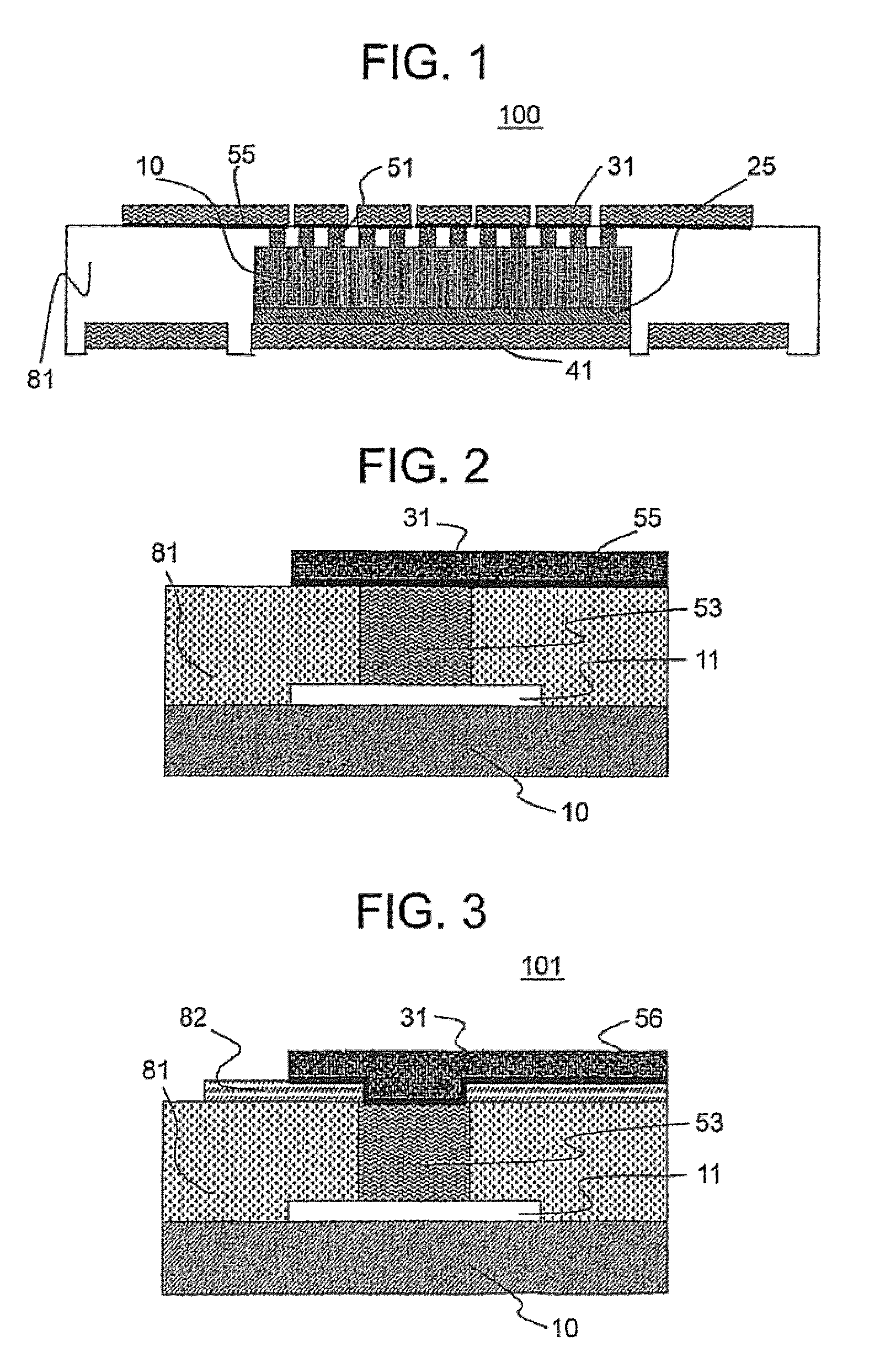

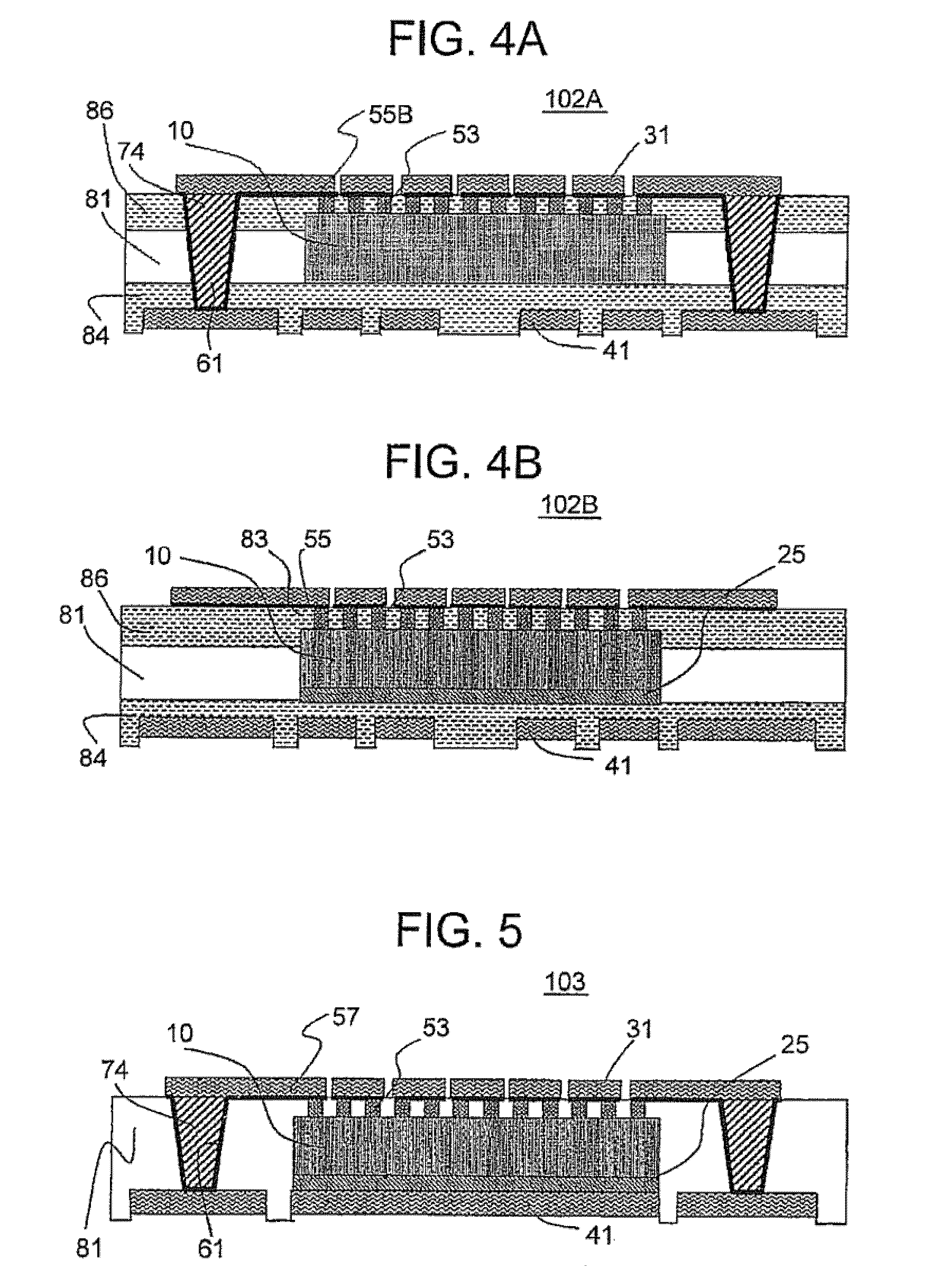

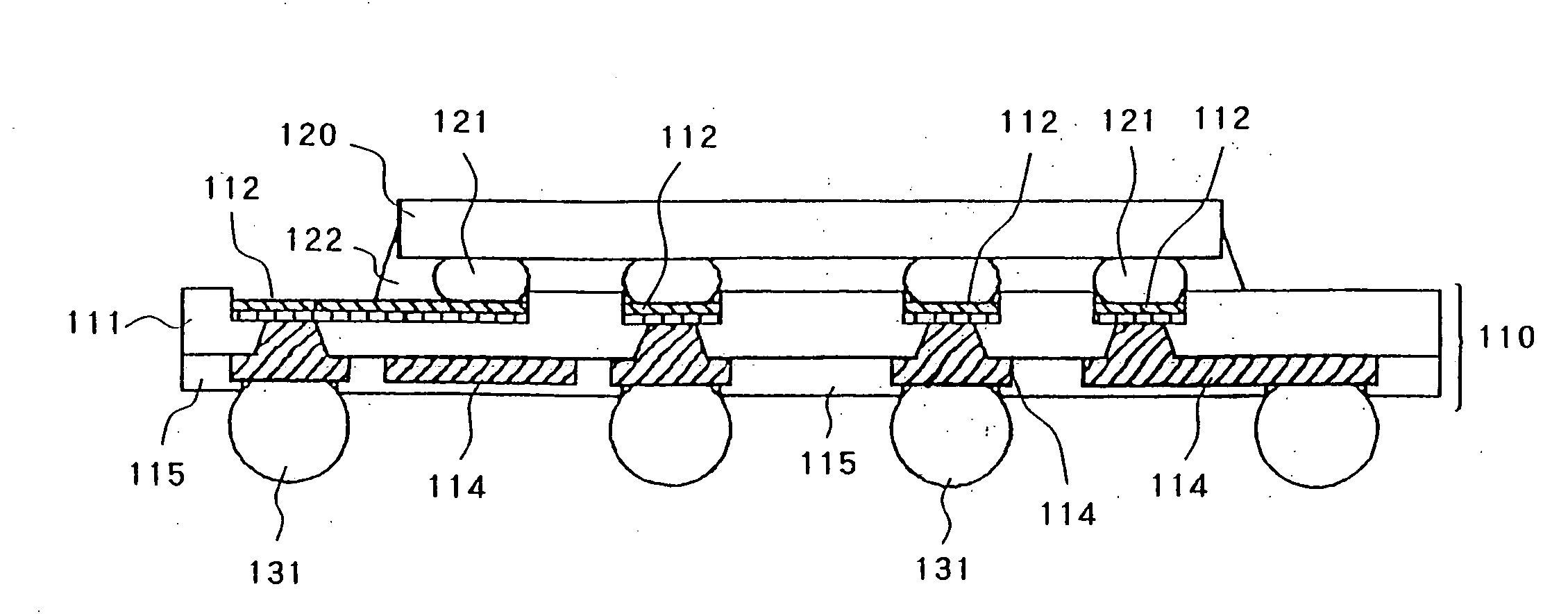

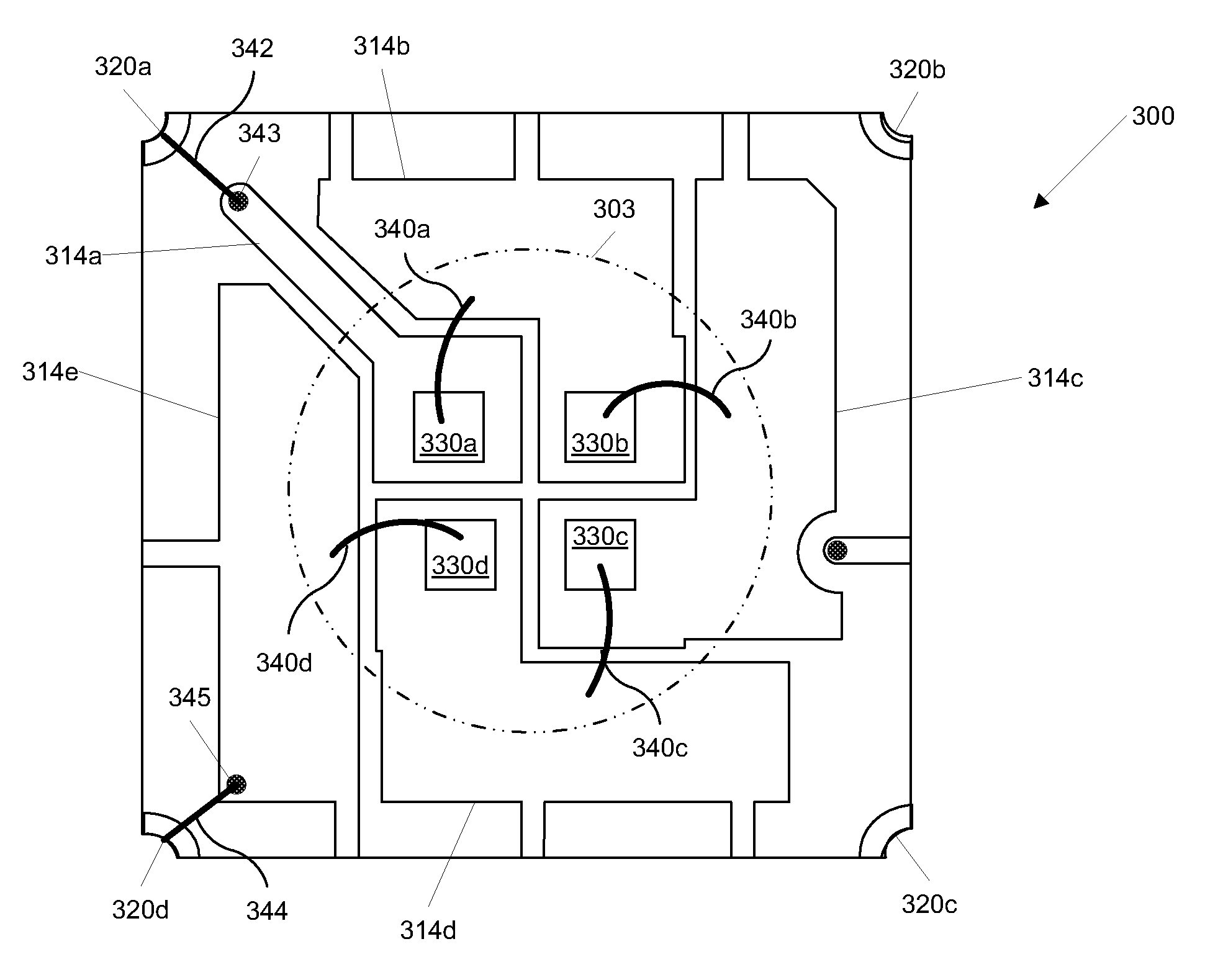

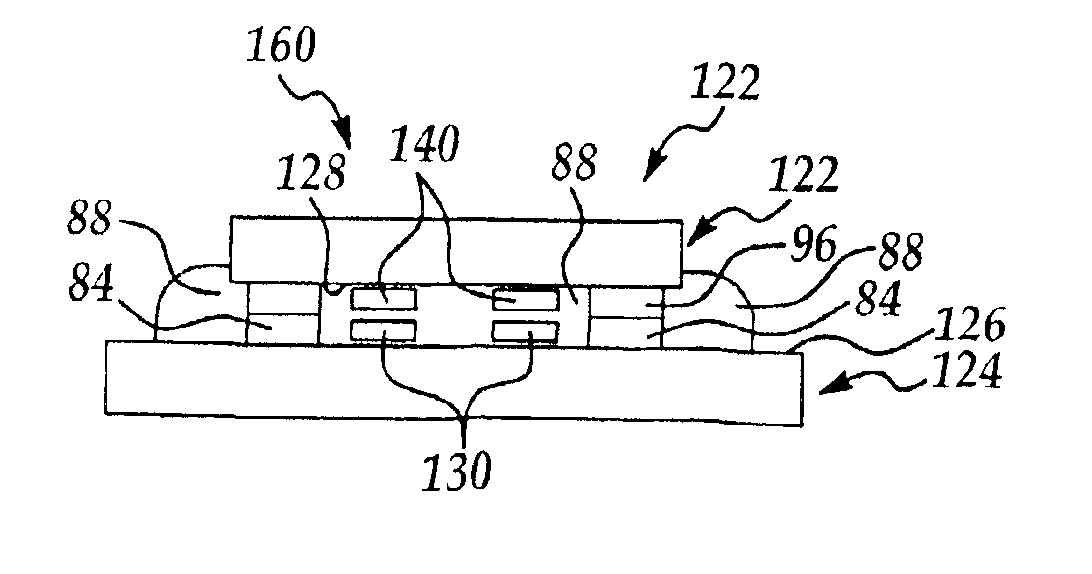

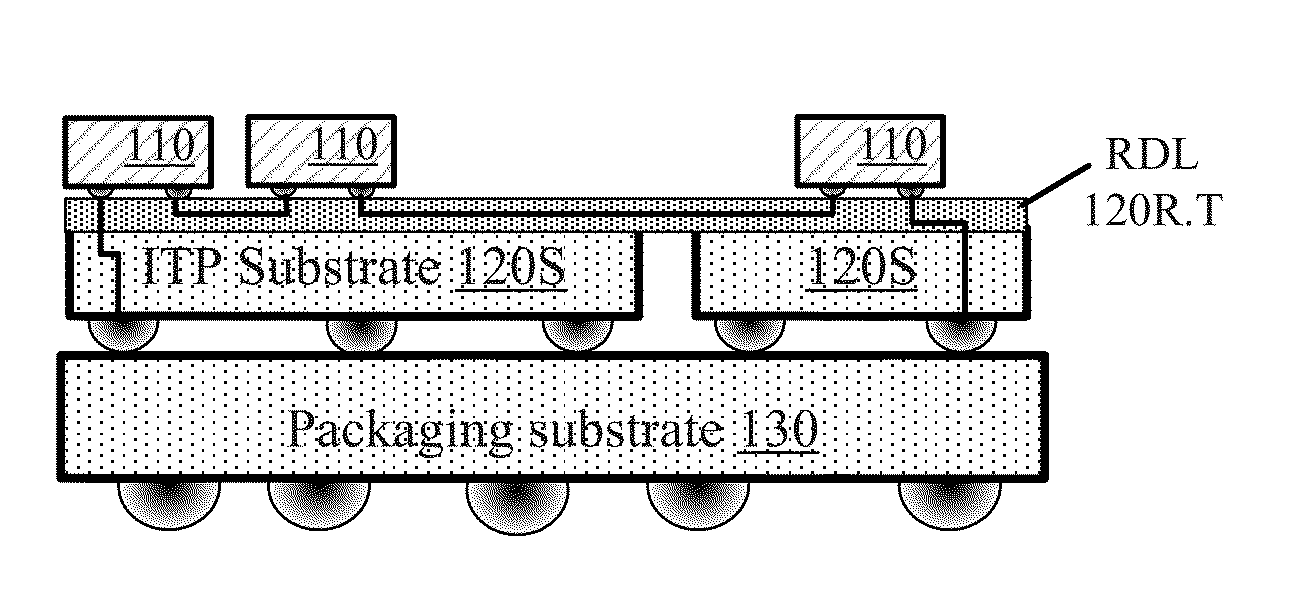

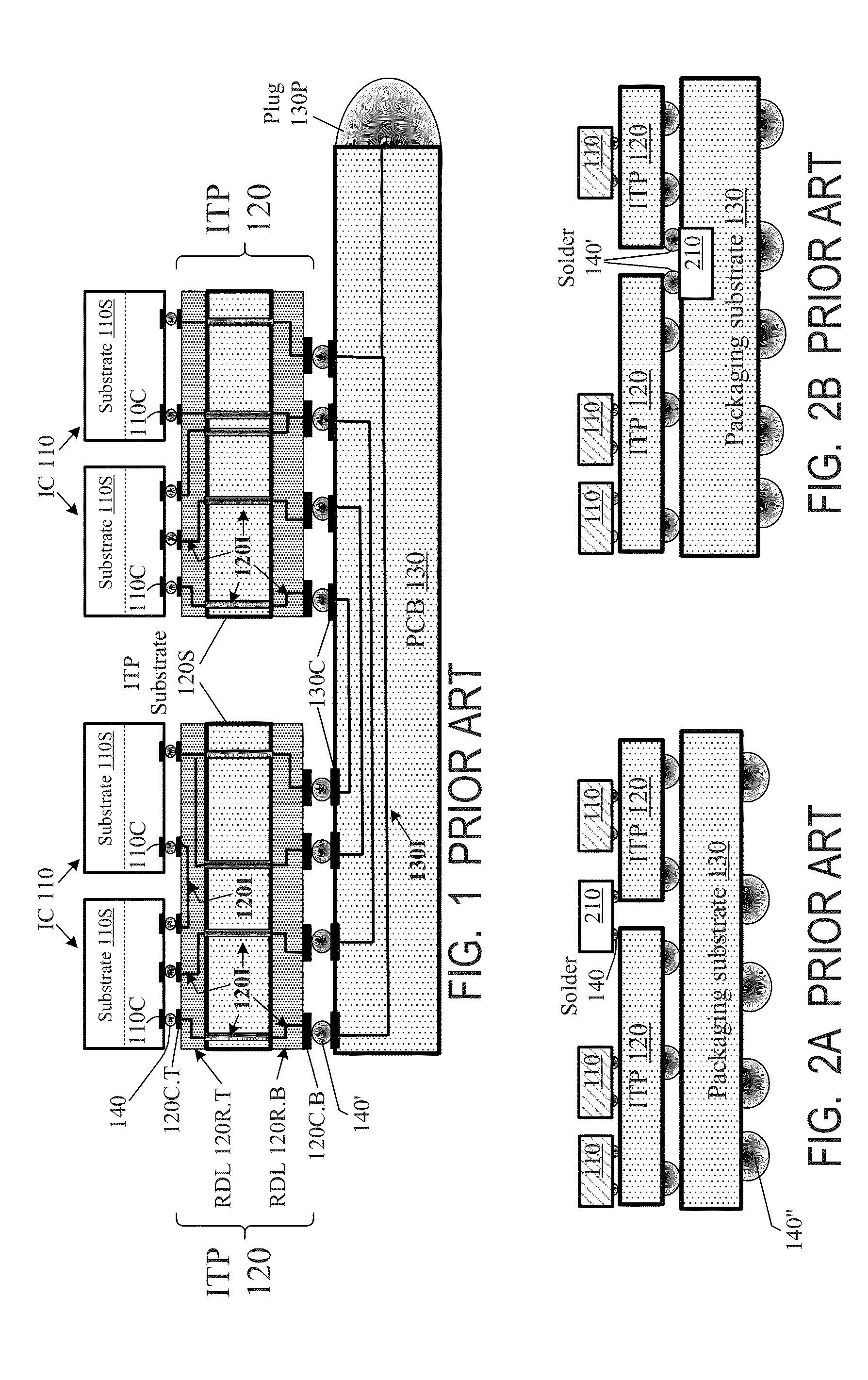

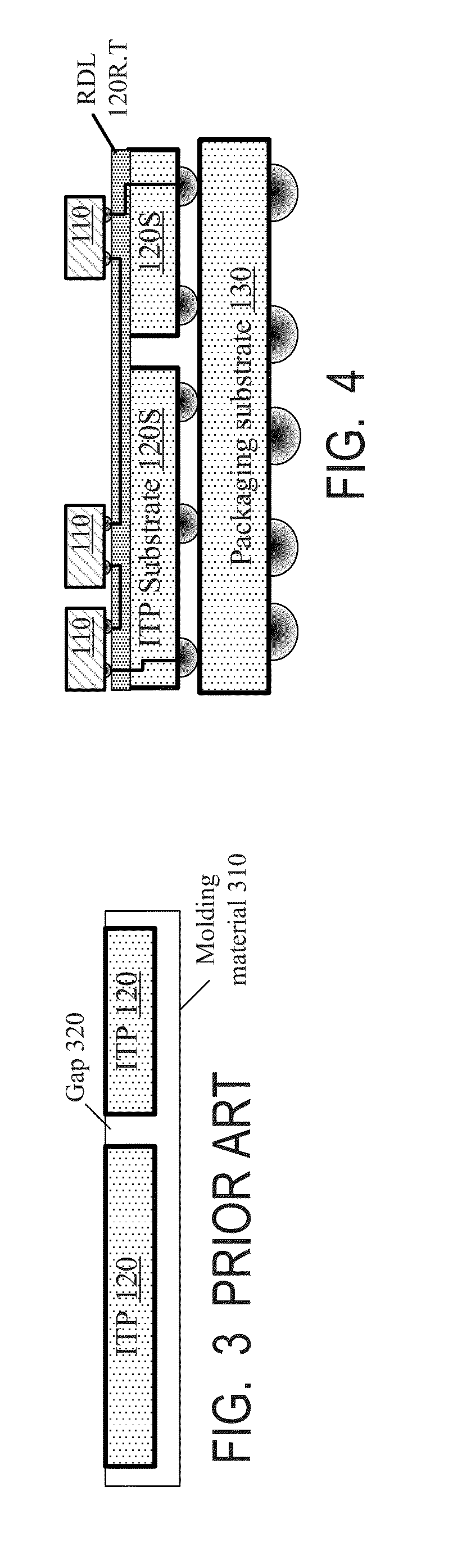

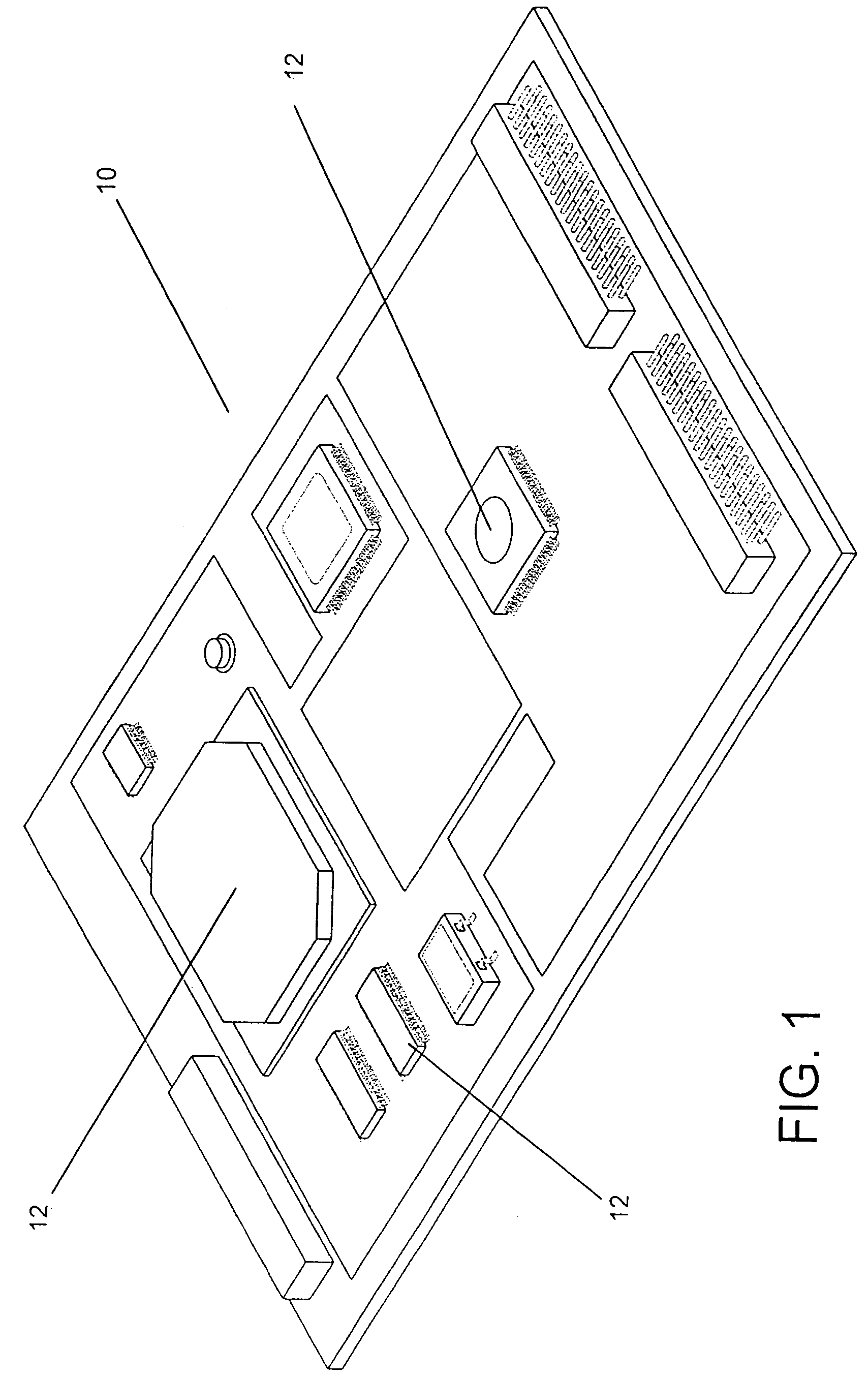

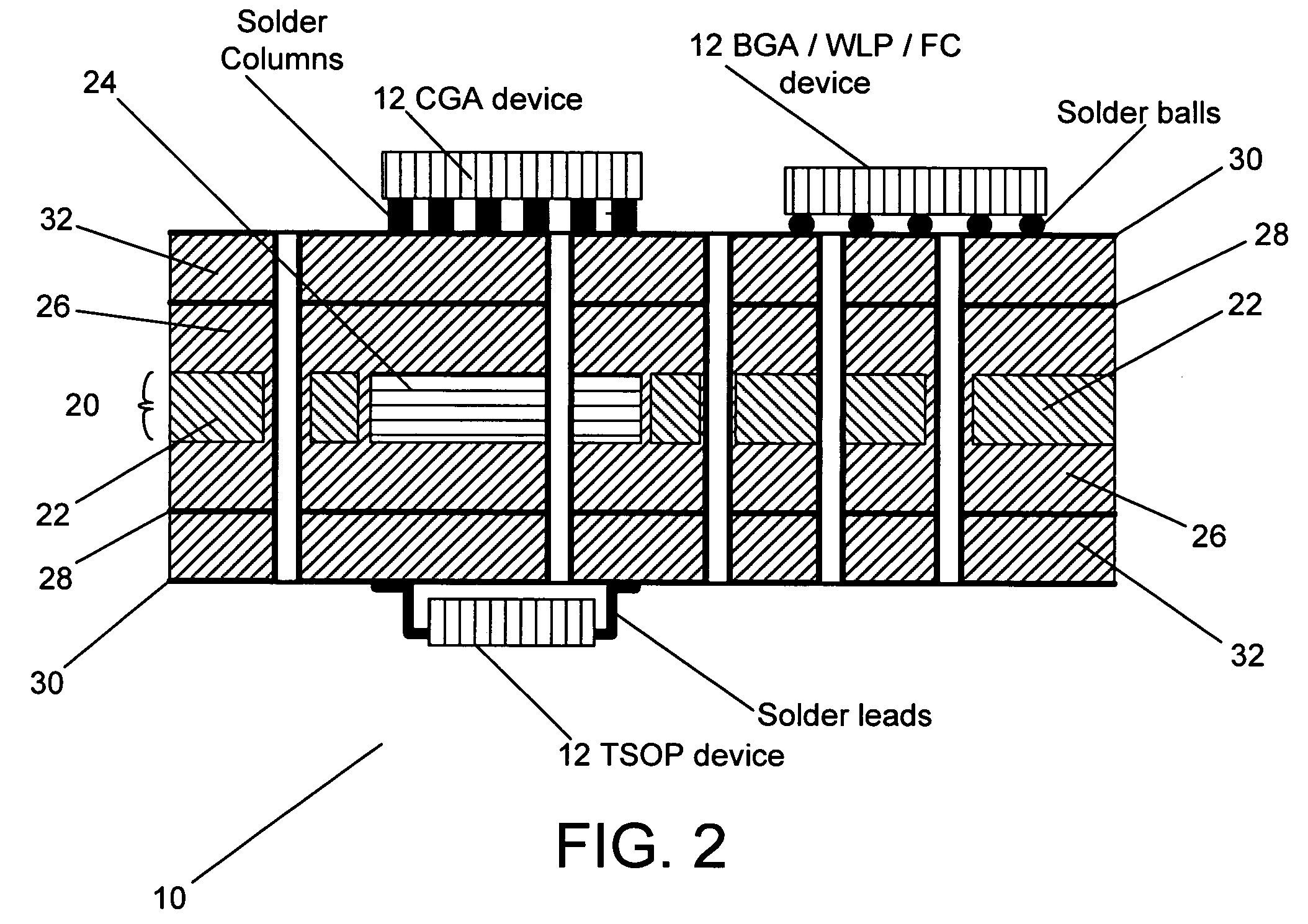

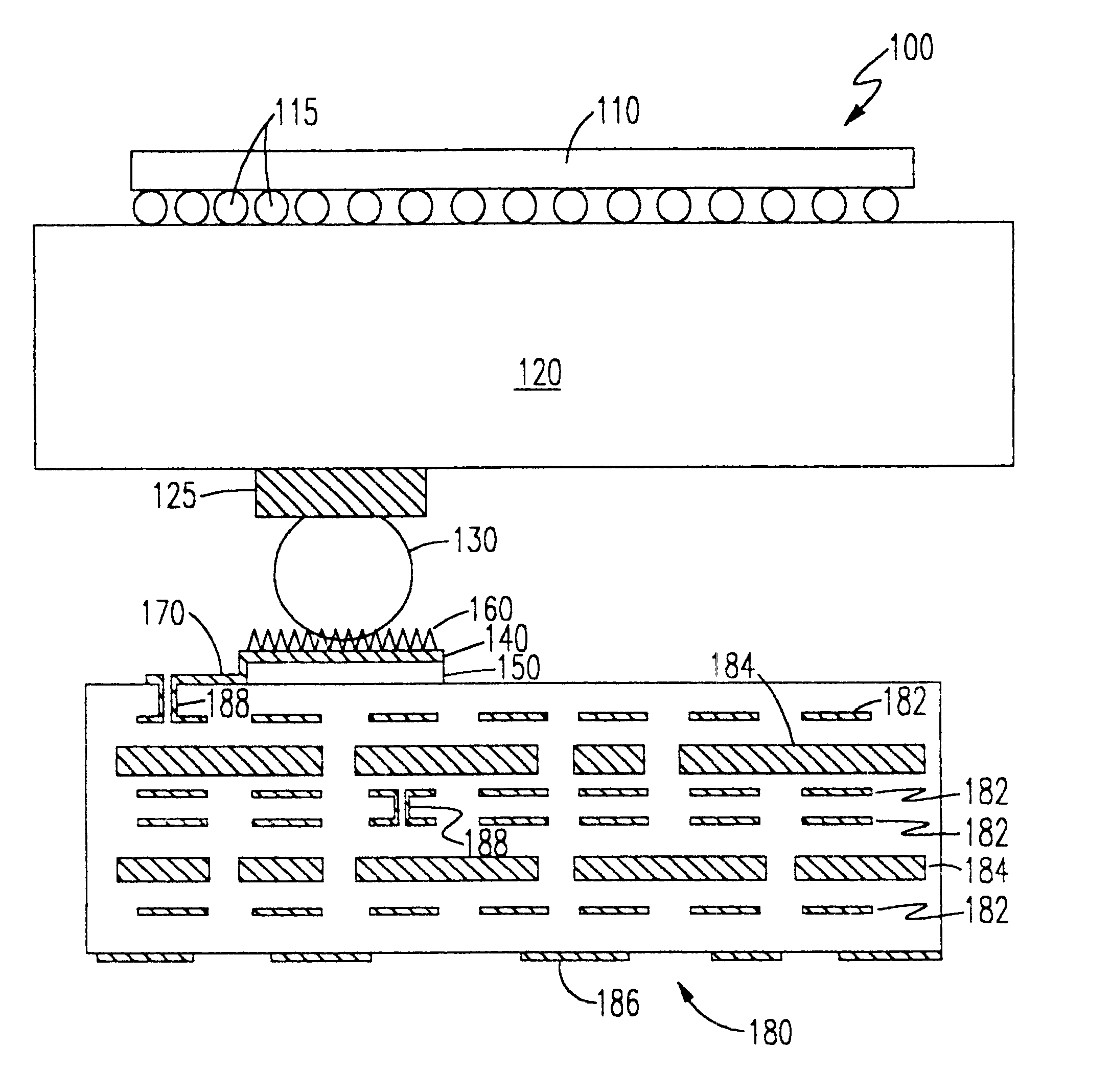

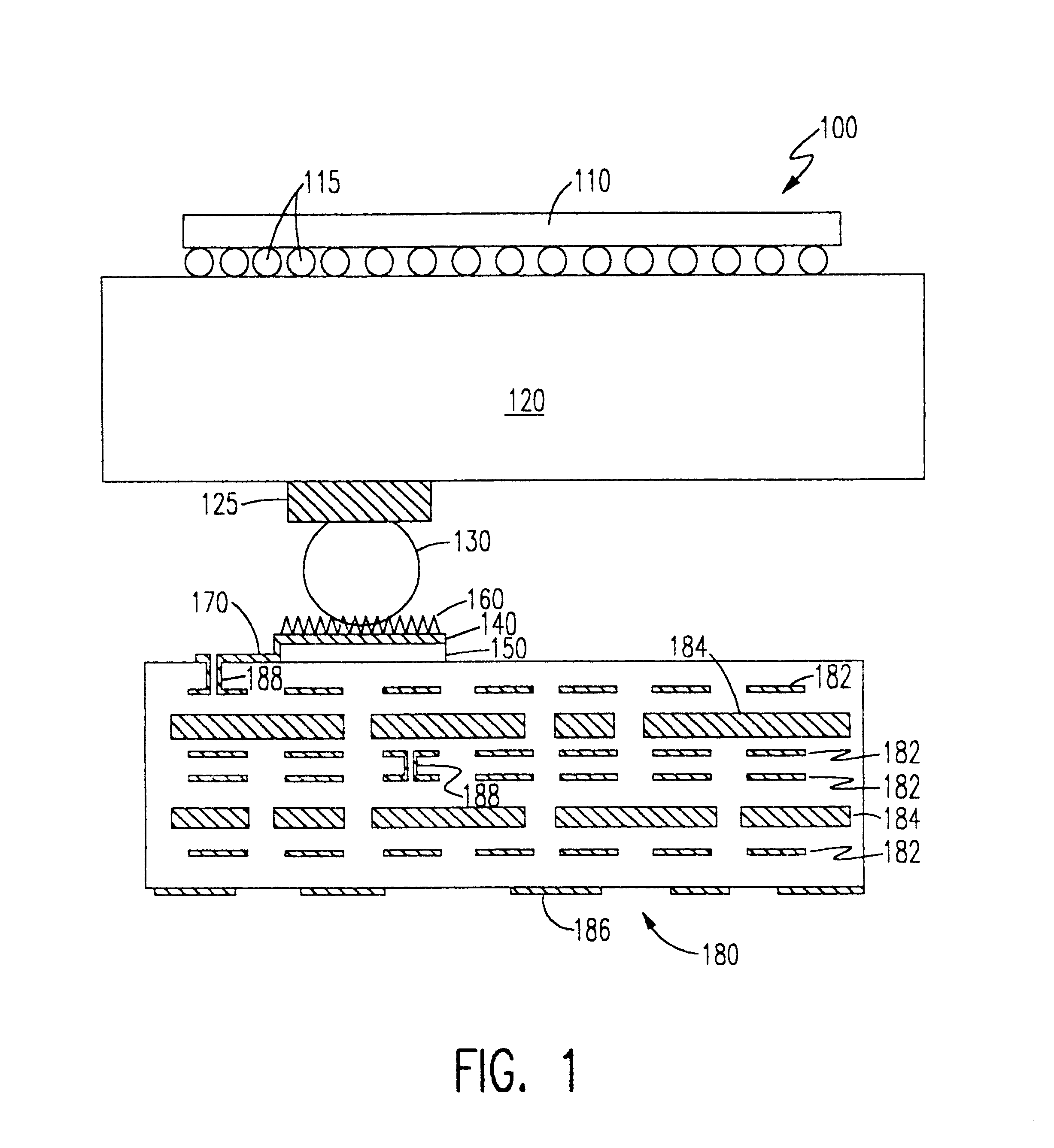

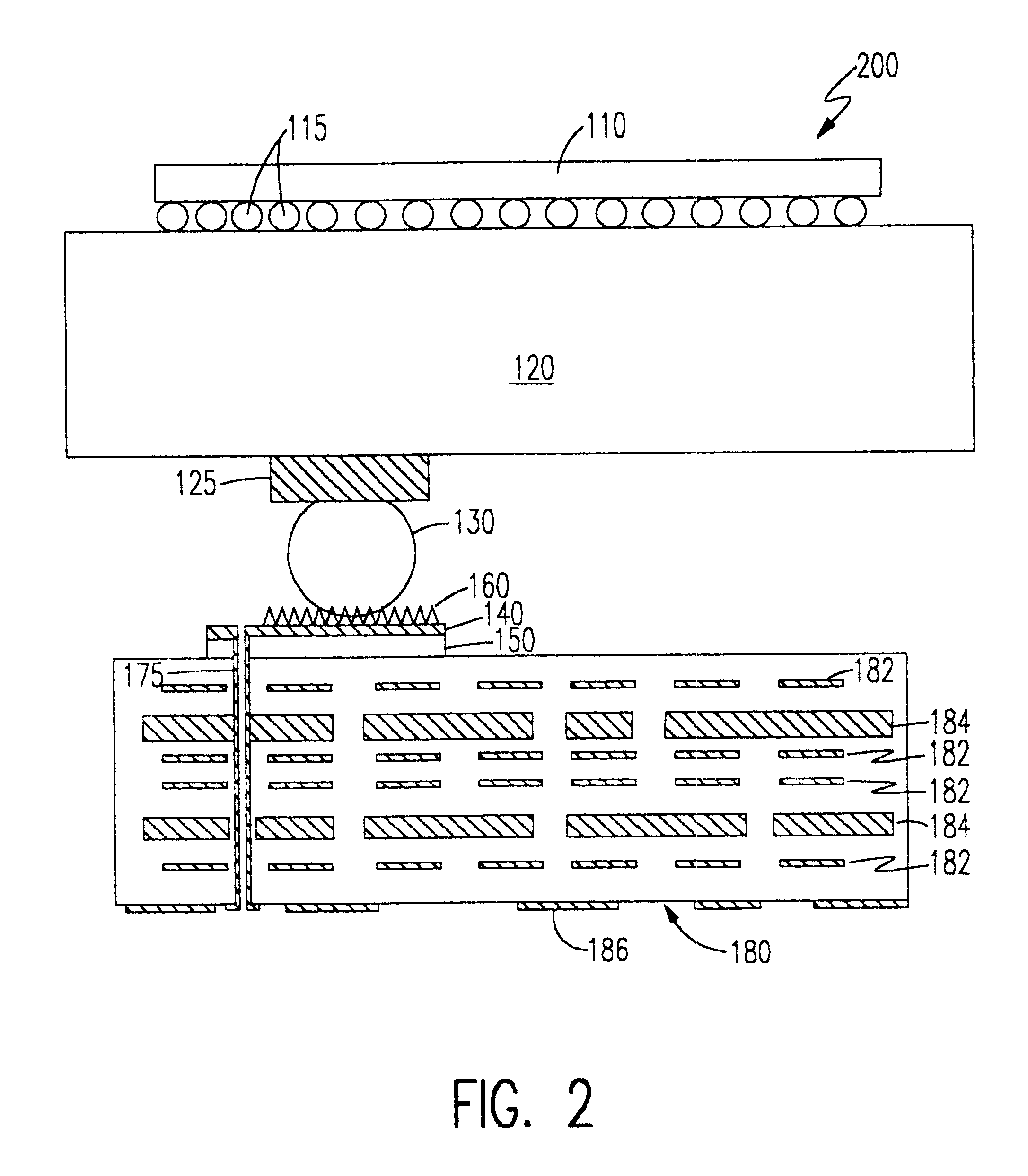

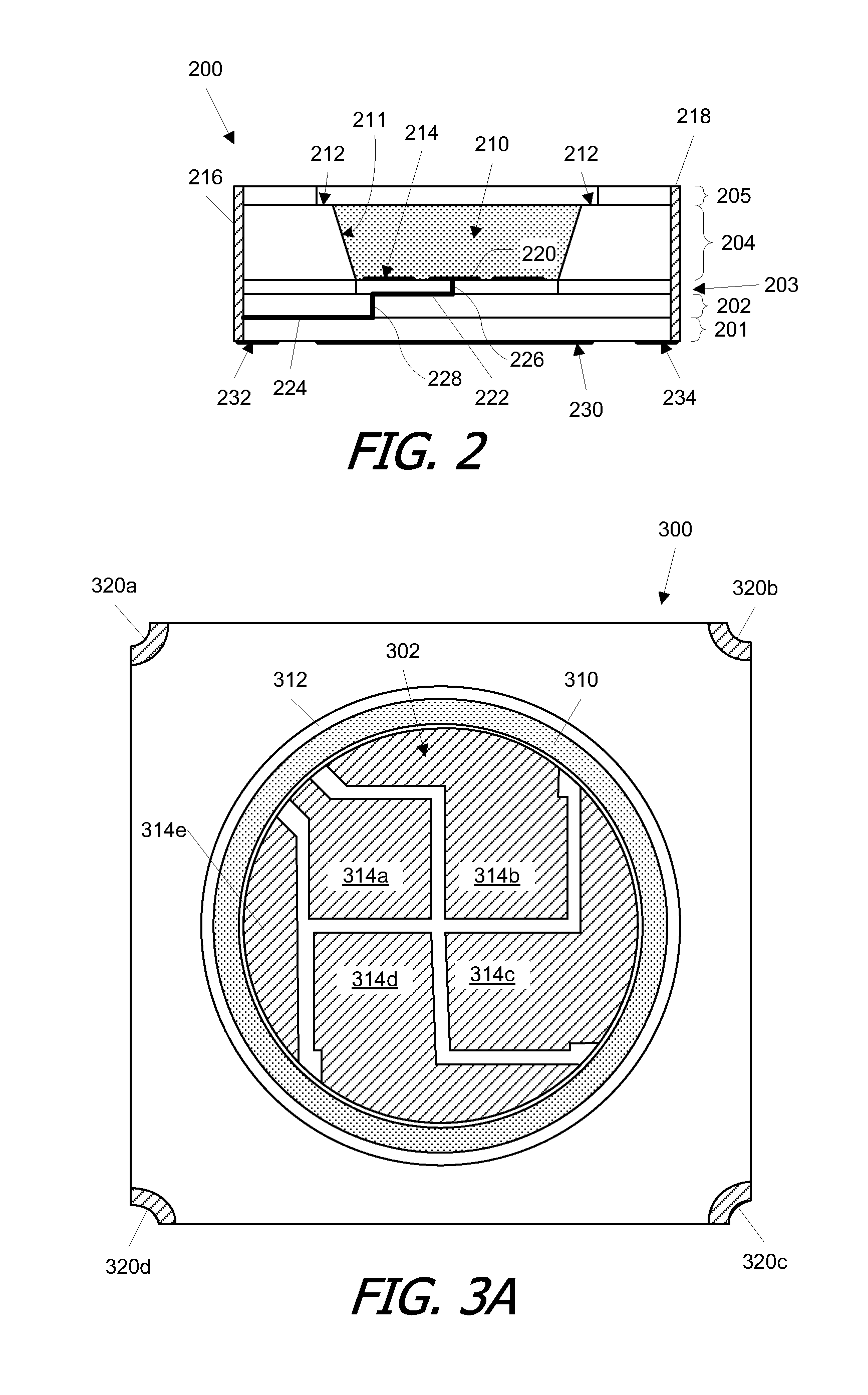

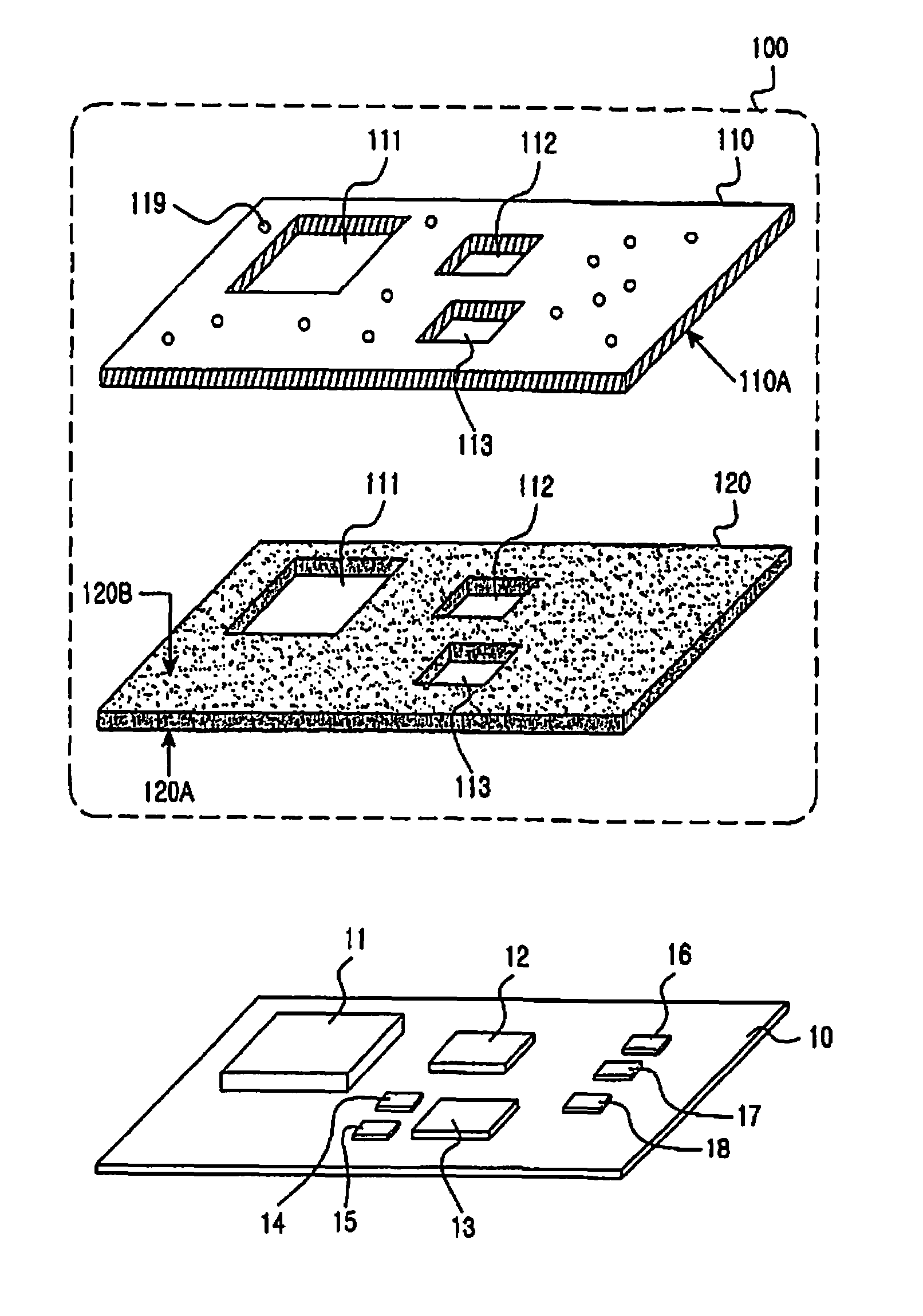

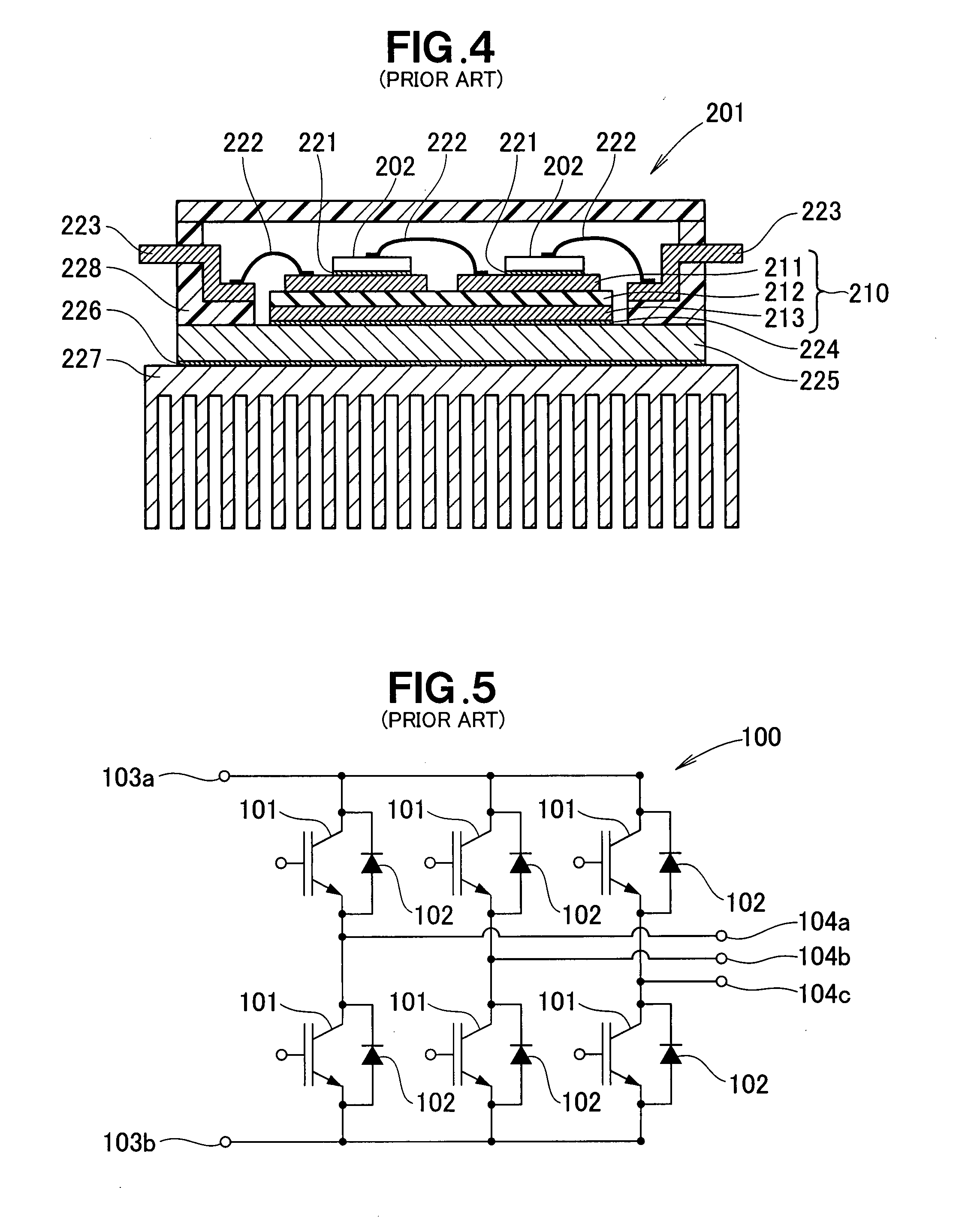

Circuit assemblies with multiple interposer substrates, and methods of fabrication

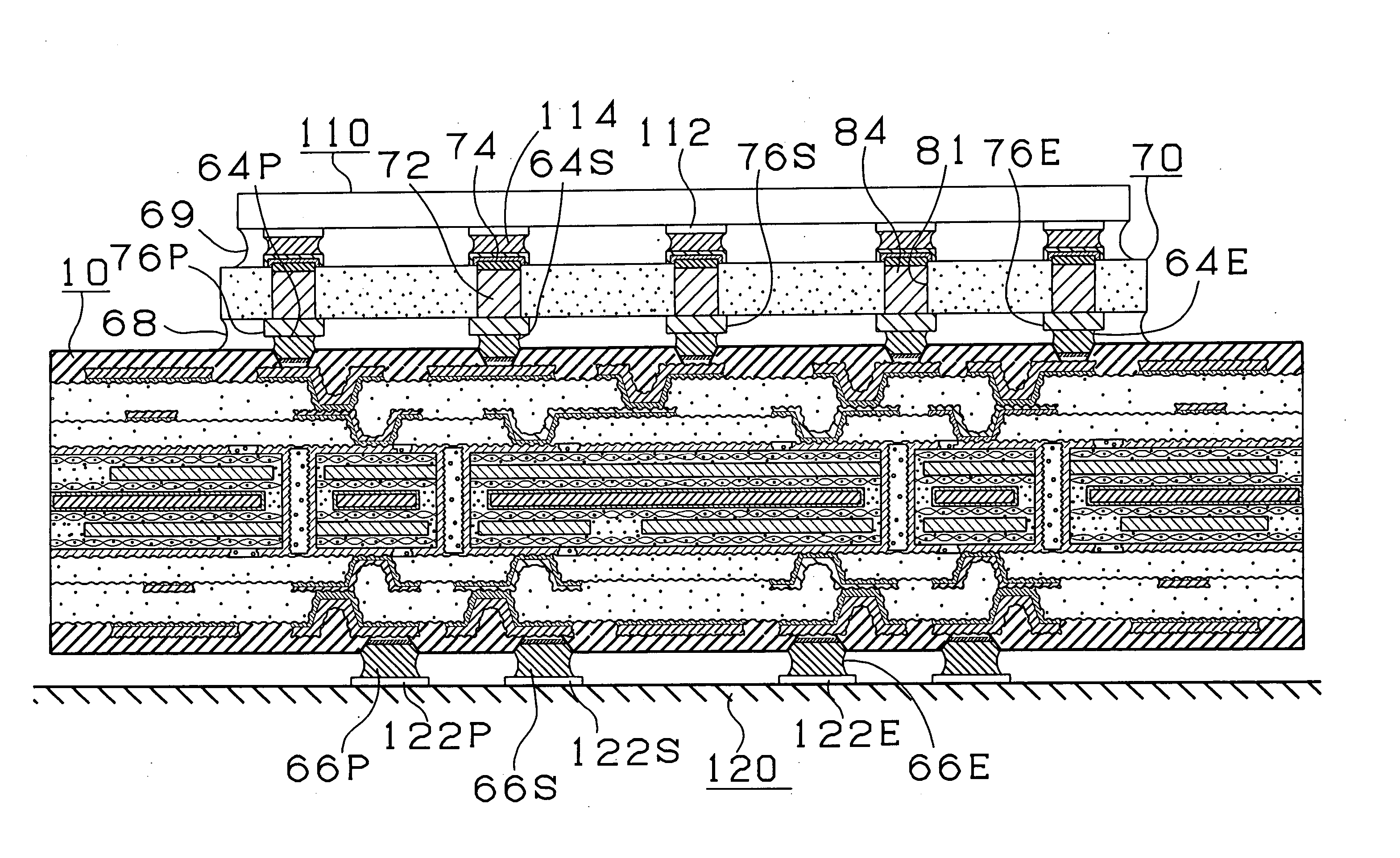

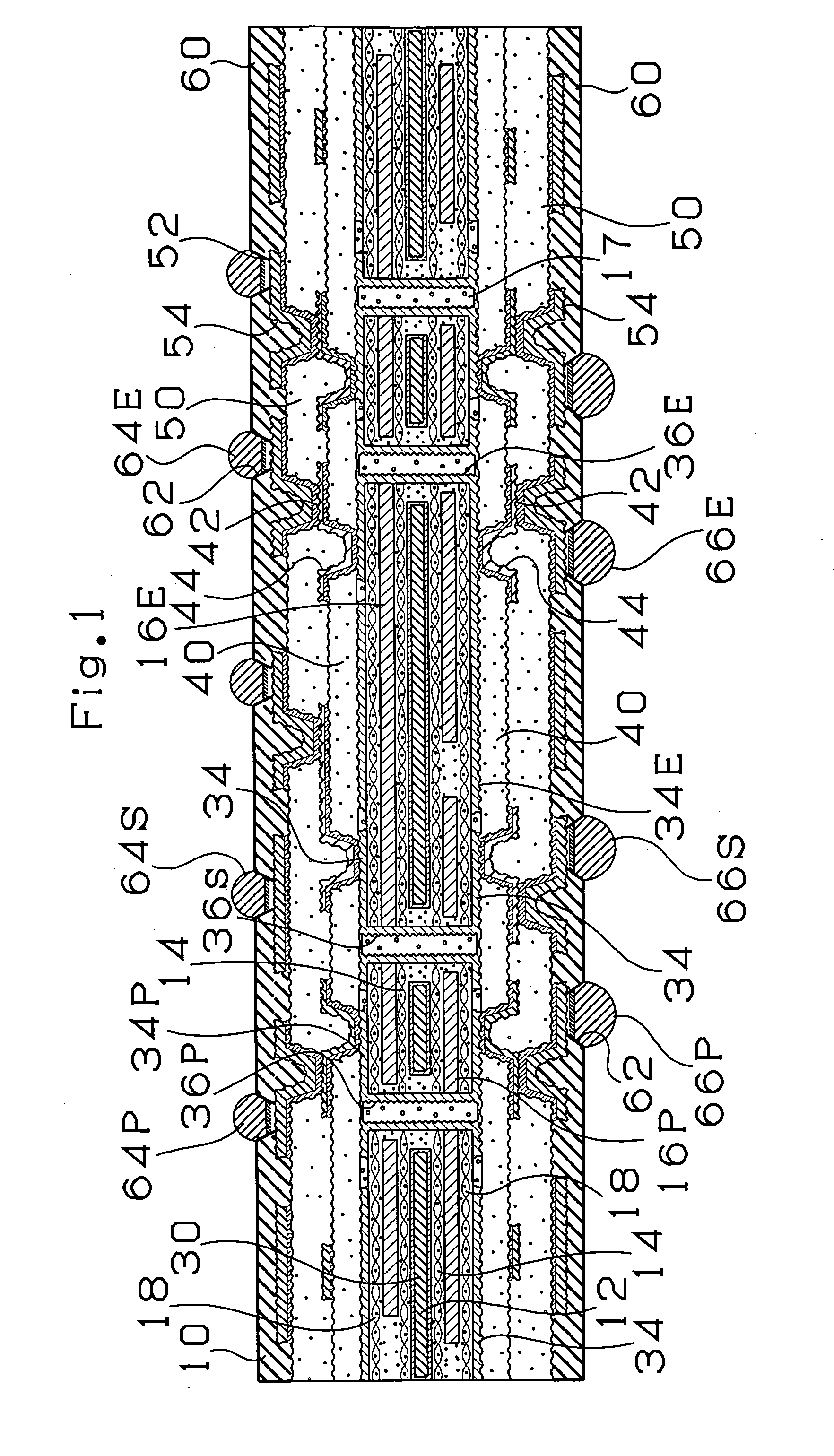

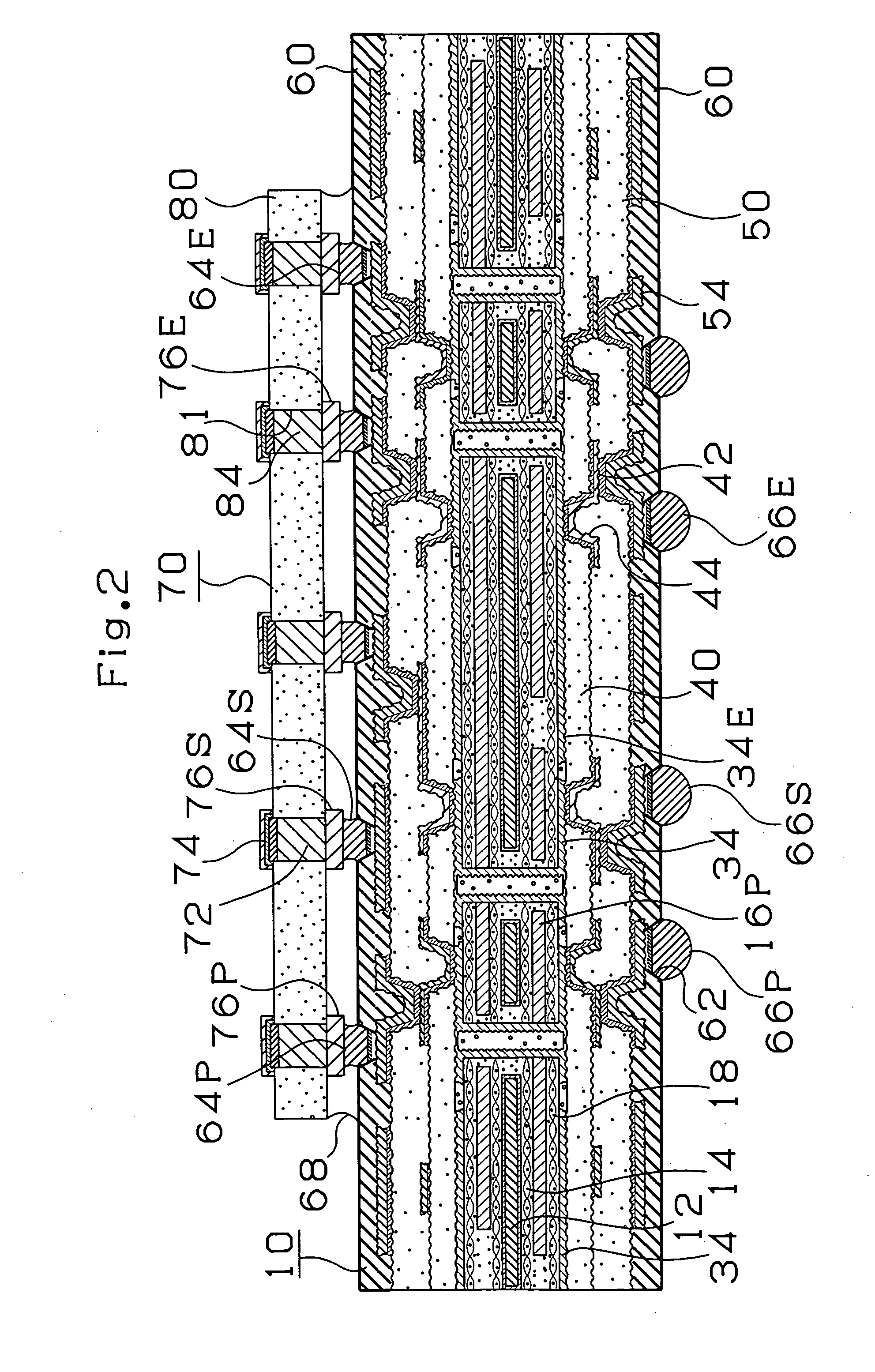

ActiveUS20150327367A1High strengthImproves heat dissipation propertySemiconductor/solid-state device detailsSolid-state devicesRedistribution layerInterposer

A combined interposer (120) includes multiple constituent interposers (120.i), each with its own substrate (120.iS) and with a circuit layer (e.g. redistribution layer) on top and / or bottom of the substrate. The top circuit layers can be part of a common circuit layer (120R.T) which can interconnect different interposers. Likewise, the bottom circuit layers can be part of a common circuit layer (120R.B). The constituent interposer substrates (120.iS) are initially part of a common wafer, and the common top circuit layer is fabricated before separation of the constituent interposer substrates from the wafer. Use of separated substrates reduces stress compared to use of a single large substrate. Other features are also provided.

Owner:INVENSAS CORP

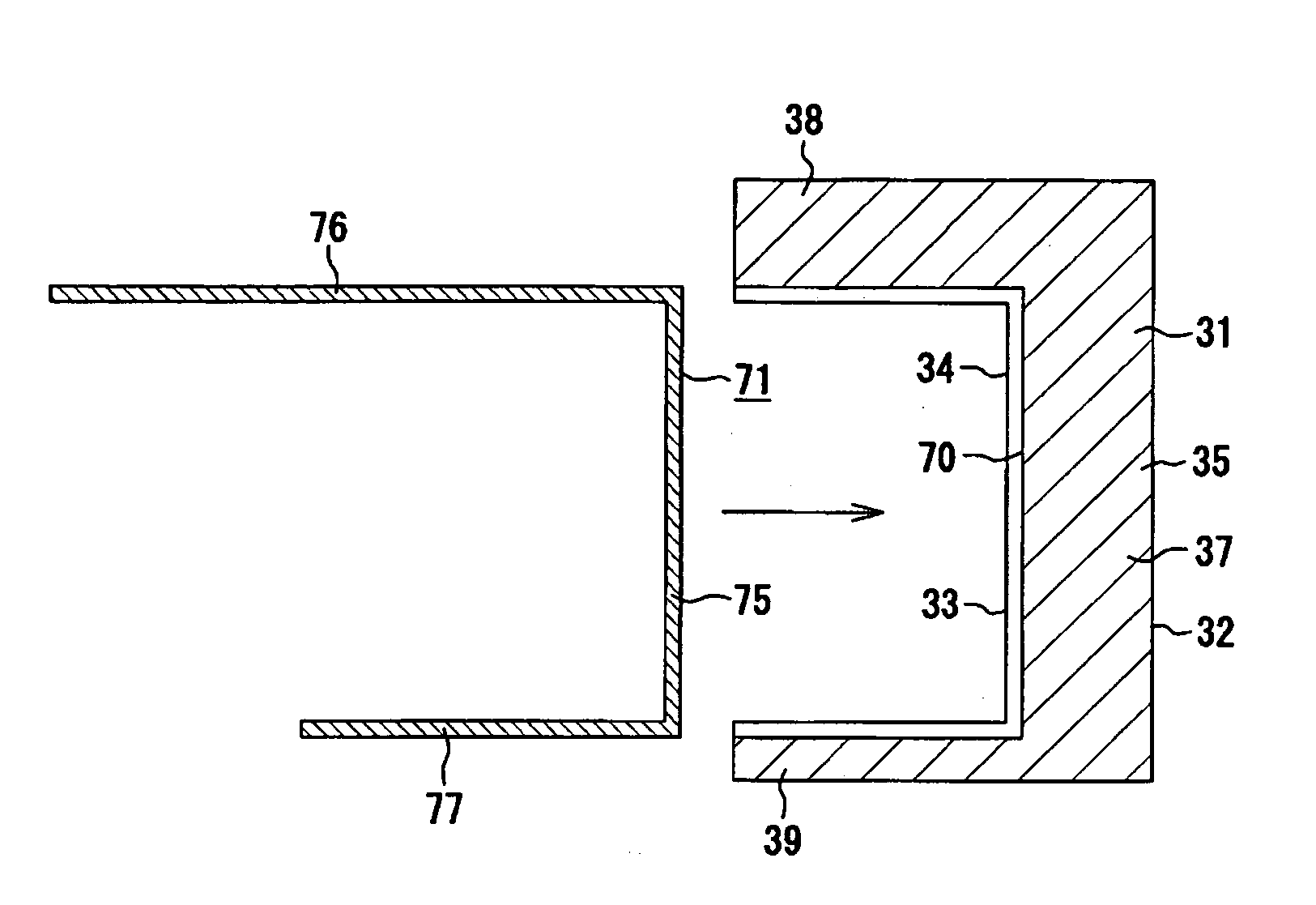

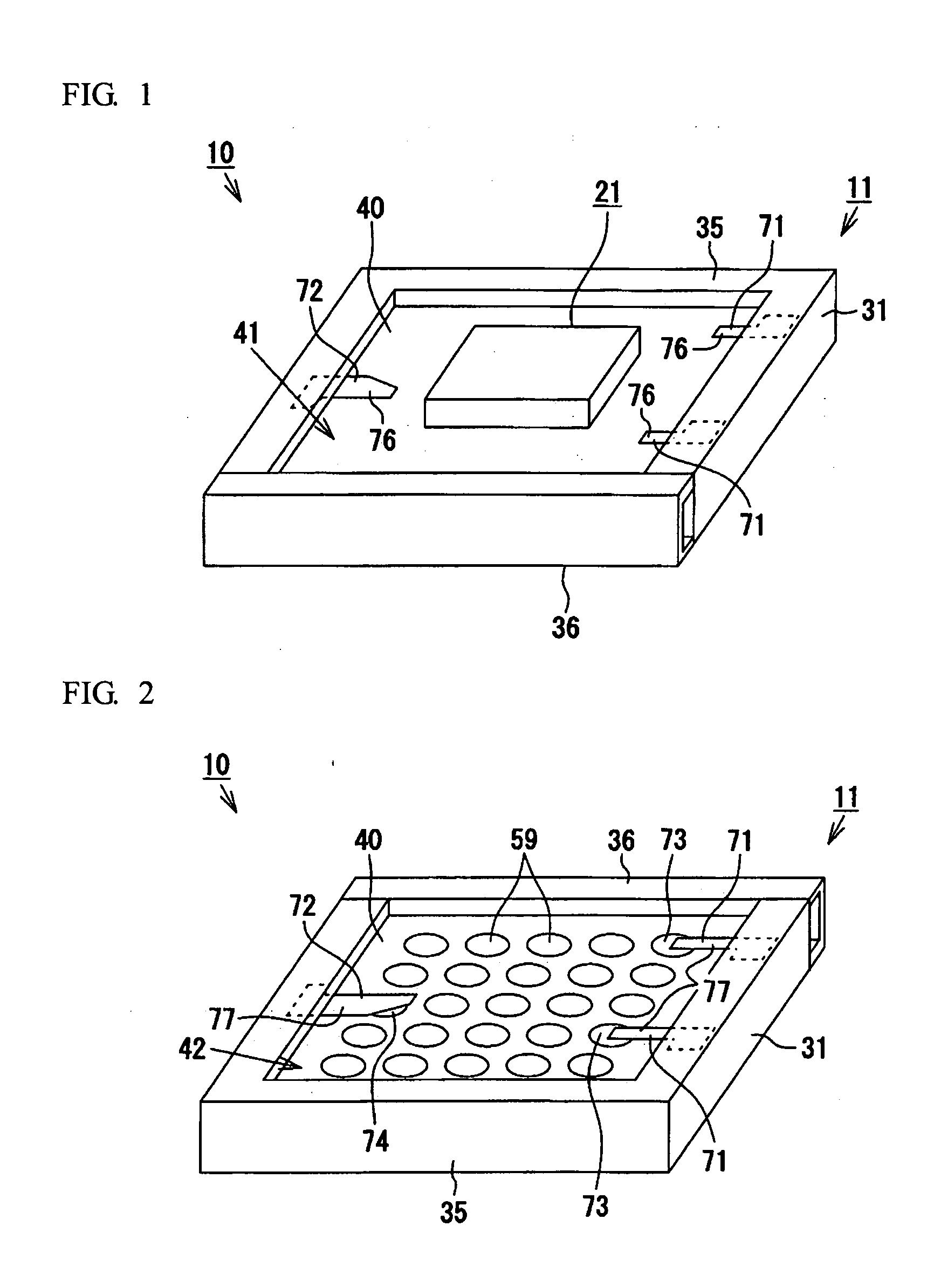

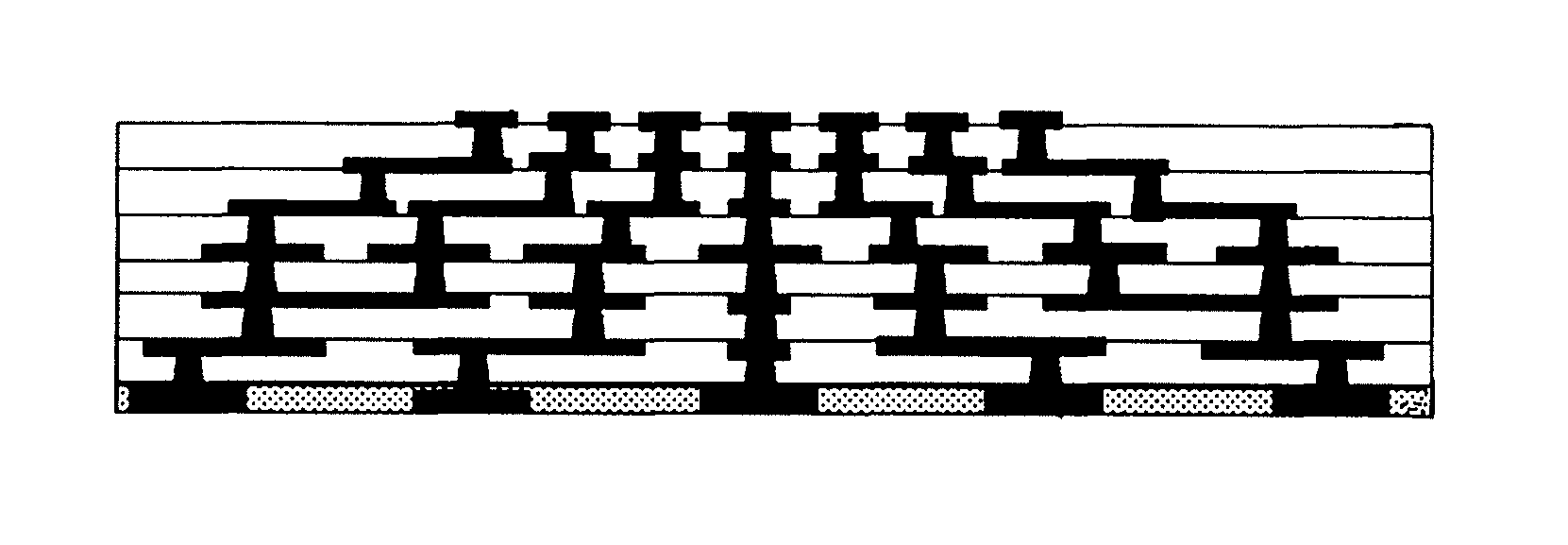

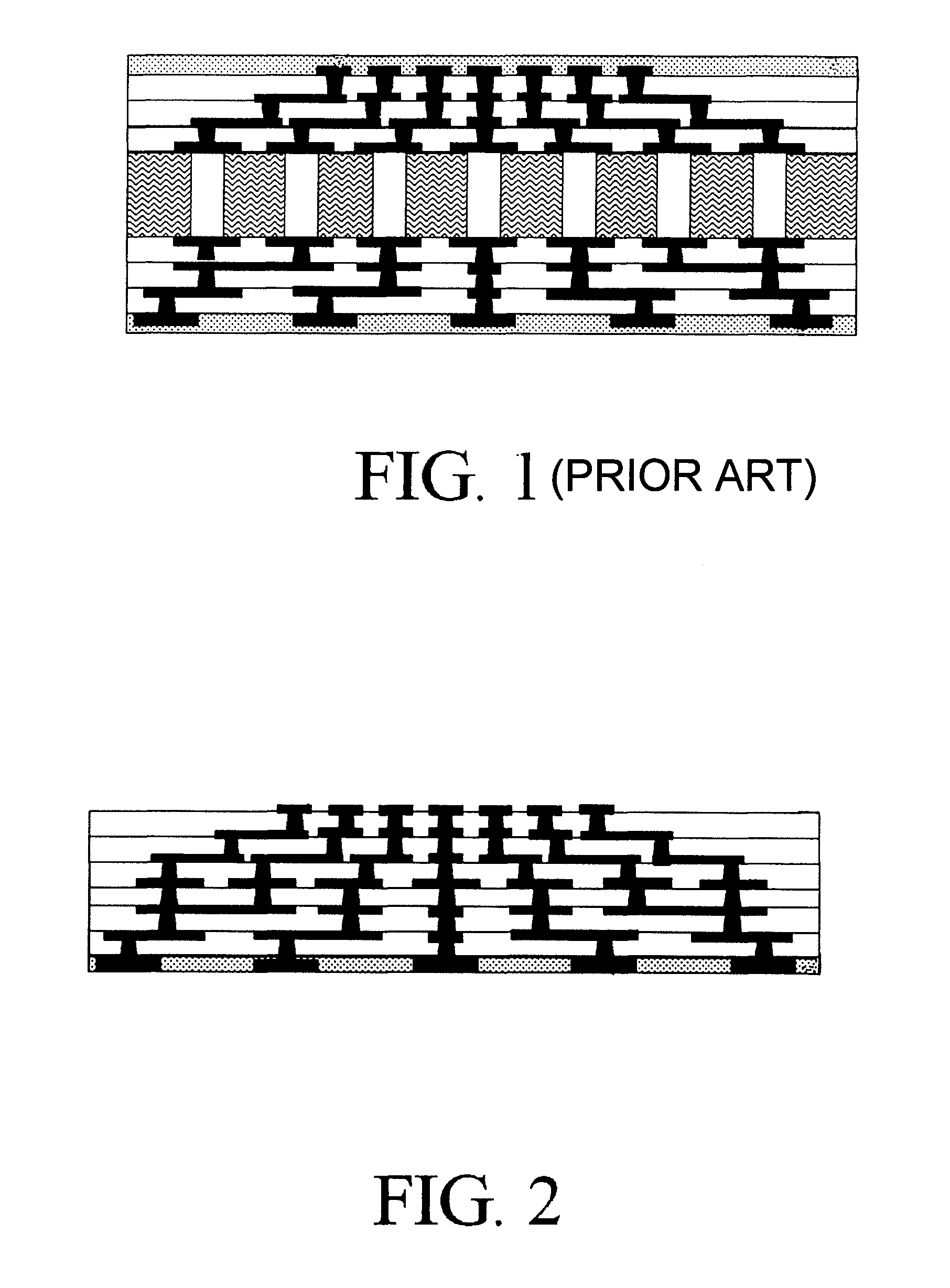

Multilayered circuit board and semiconductor device

InactiveUS8227703B2Avoid deformationImprove connection reliabilityPrinted electric component incorporationSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multilayered circuit board of the present invention has a single-side laminated structure and does not include a core substrate having via-holes formed therethrough and vias for providing electrical connection through the via-holes. The multilayered circuit board includes a plurality of pairs of layers, each pair including a conductor circuit layer and an insulator layer, wherein a glass transition temperature of each insulator layer is 170° C. or higher, a coefficient of thermal expansion at the glass transition temperature or lower of each insulator layer is 35 ppm or less, and a modulus of elasticity of each insulator layer is 5 GPa or more.

Owner:SUMITOMO BAKELITE CO LTD

Laminated chip electronic component, board for mounting the same, and packing unit thereof

ActiveUS20130319741A1Reduce noiseFixed capacitor electrodesFinal product manufactureCapacitanceEngineering

A laminated chip electronic component includes: a ceramic body including internal electrodes and dielectric layers; external electrodes formed to cover both end portions of the ceramic body in a length direction; an active layer in which the internal electrodes are disposed in an opposing manner, while having the dielectric layers interposed therebetween, to form capacitance; and upper and lower cover layers formed on upper and lower portions of the active layer in a thickness direction, the lower cover layer having a thickness greater than that of the upper cover layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

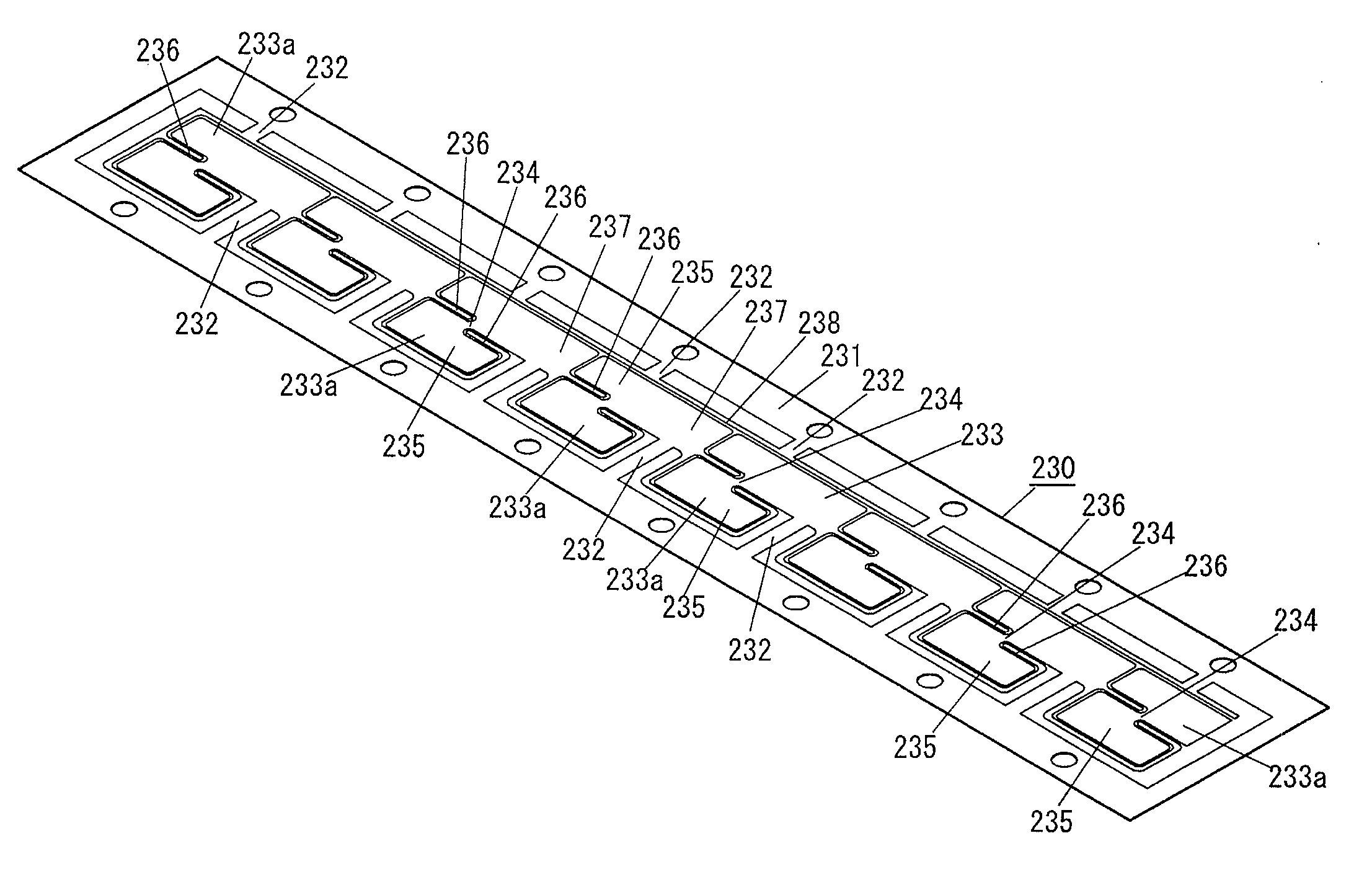

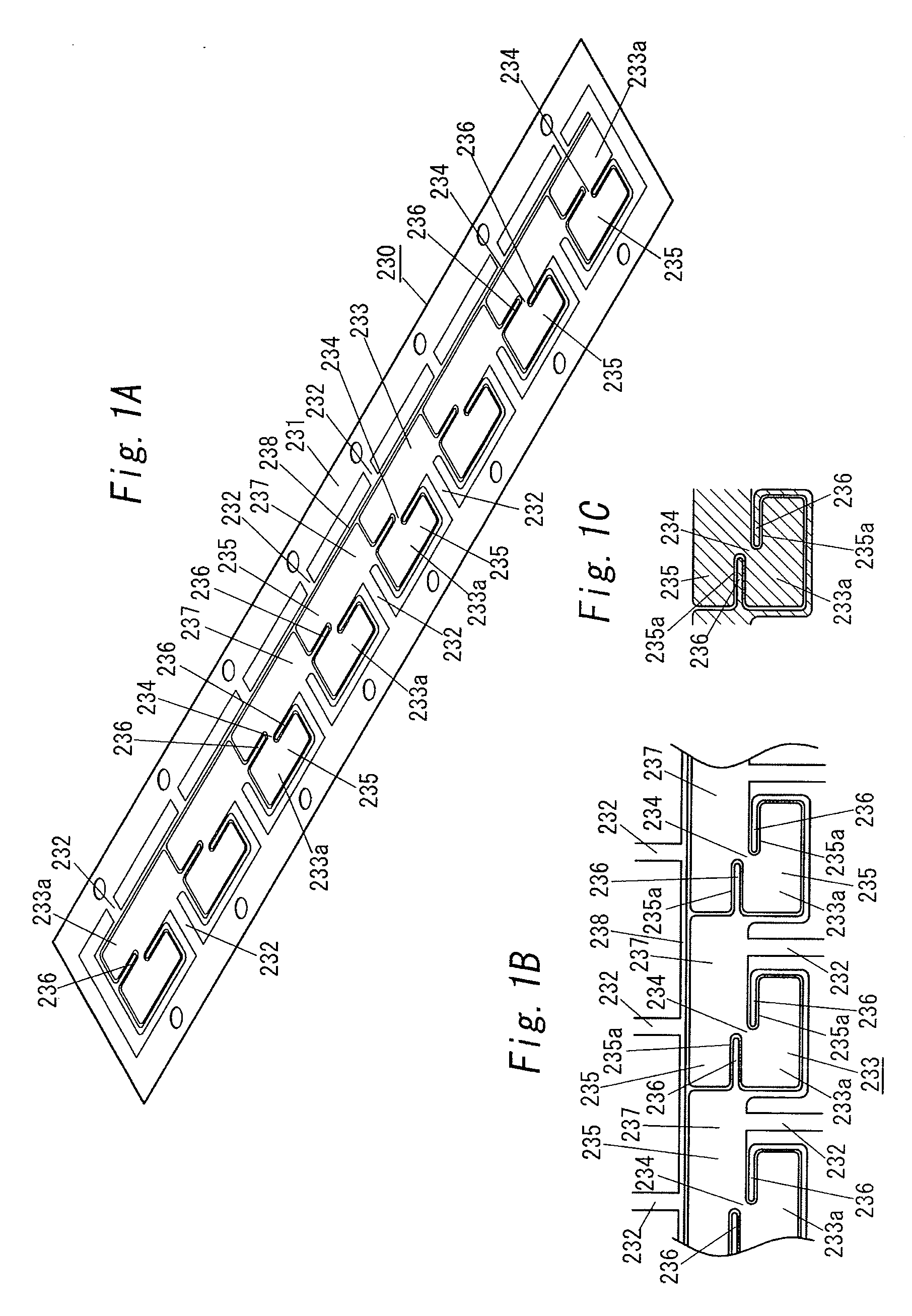

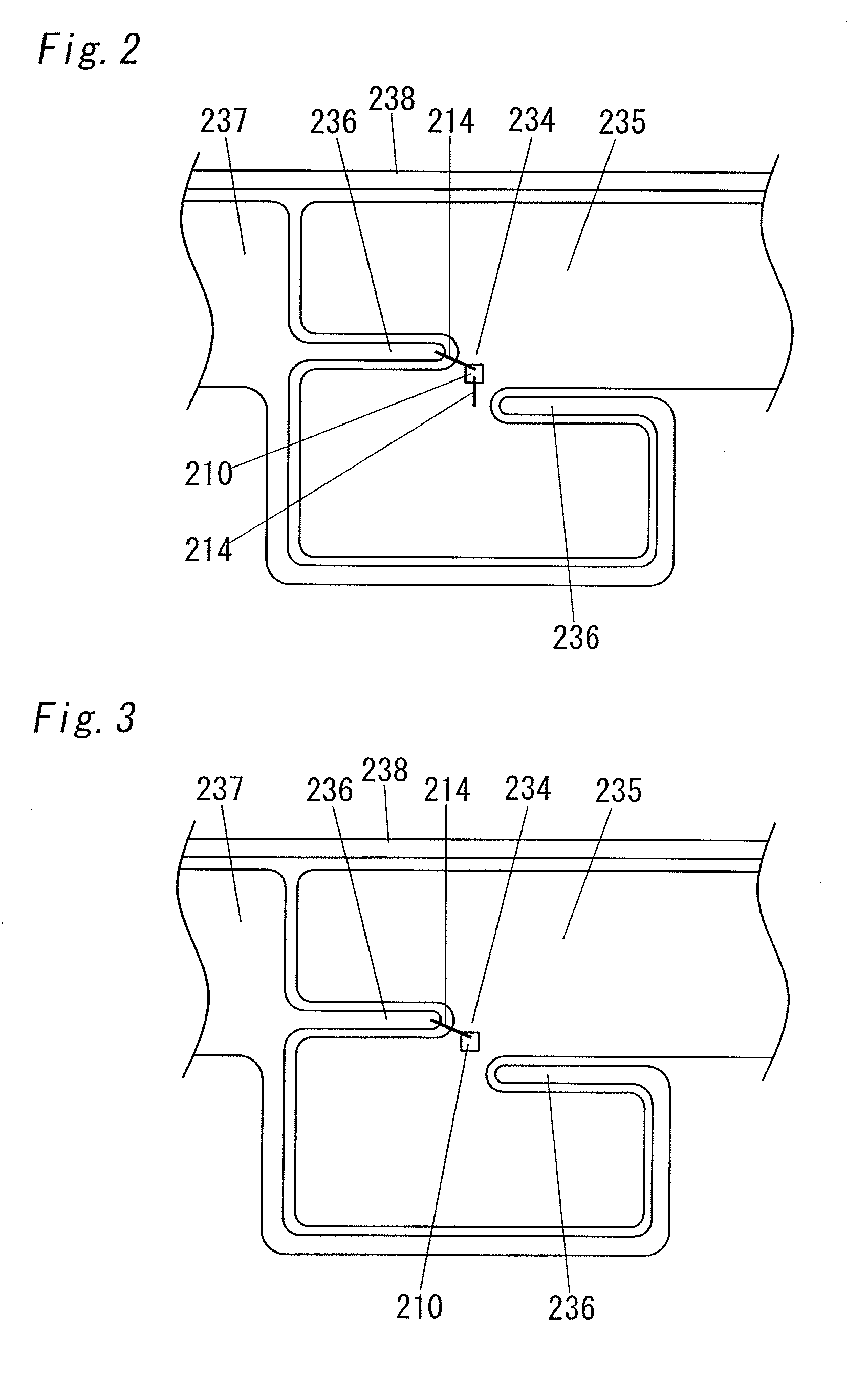

Lead frame, wiring board, light emitting unit, and illuminating apparatus

InactiveUS20130070452A1Improve light outputImprove cooling effectPlanar light sourcesPoint-like light sourceElectricityEngineering

Provided is lead frame in which a wiring pattern supported by a support piece inside of a one-pitch outer frame section comprises a plurality of base units, each of which comprises a die pad on which a solid-state light emitting element is mounted, a heat sink extending from die pad so as to surround die pad electrically connected to one electrode of the element, and a lead electrically connected to the other electrode of the element. Lead of one base unit among adjacent base units and heat sink of the other base unit are coupled and electrically connected in series. Increase in temperature of the element is inhibited, light output is increased, and cost of a light emitting unit in which a plurality of solid-state light emitting elements connected in series are used is reduced. Also provided are wiring board, light emitting unit, and illuminating apparatus.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Printed wiring boards possessing regions with different coefficients of thermal expansion

InactiveUS7301105B2Printed circuit aspectsSecuring/insulating coupling contact membersThermal expansionEngineering

Printed wiring boards are disclosed that include regions having different coefficients of thermal expansion. In one aspect of the invention, the regions can be matched to the coefficients of thermal expansion of devices mounted on the printed wiring board. In one embodiment, the invention includes a layer including a base material and at least one insert material that are combined using a resin. In addition, the base material and insert material are located within the same plane.

Owner:STABLCOR TECH

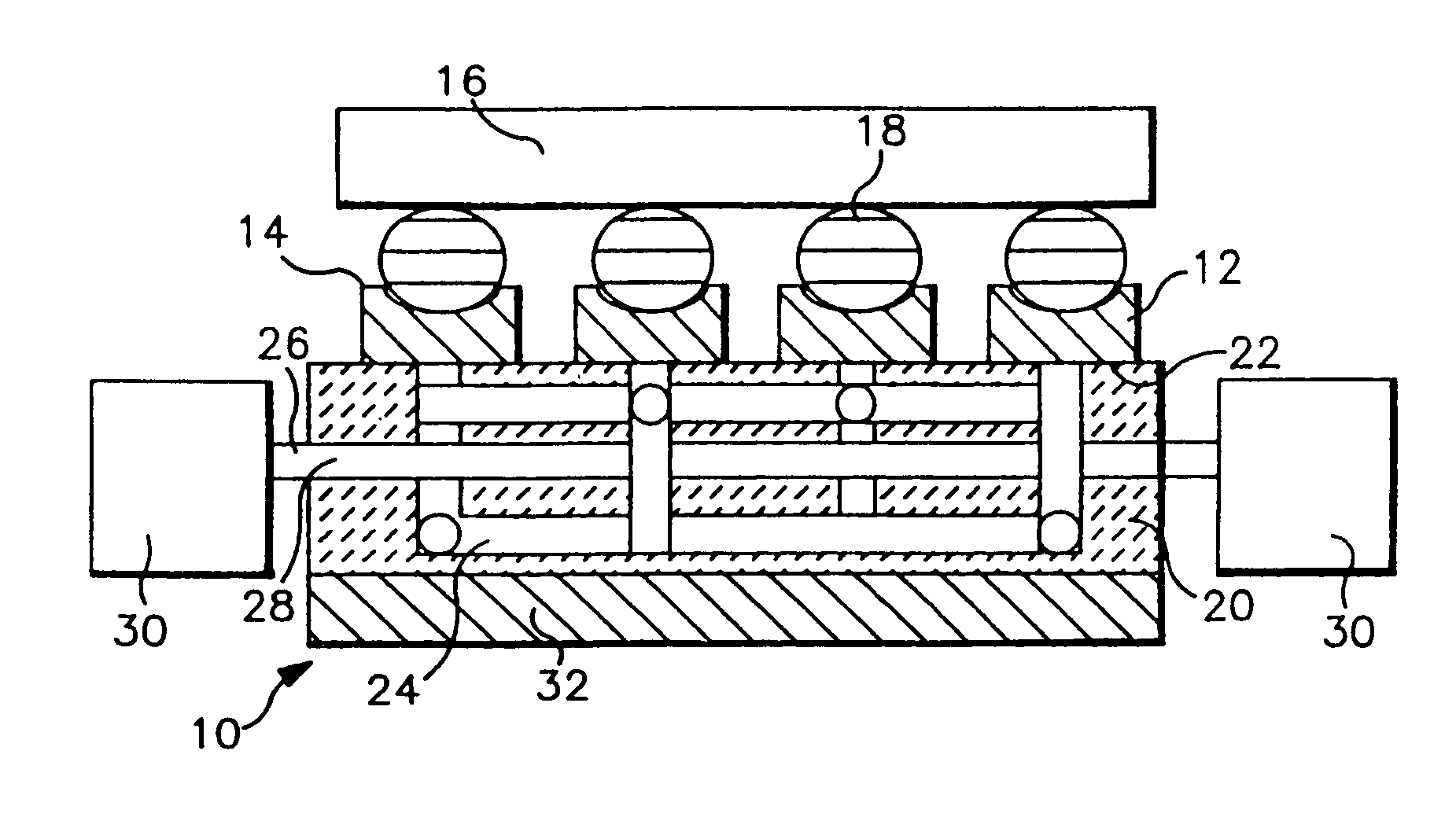

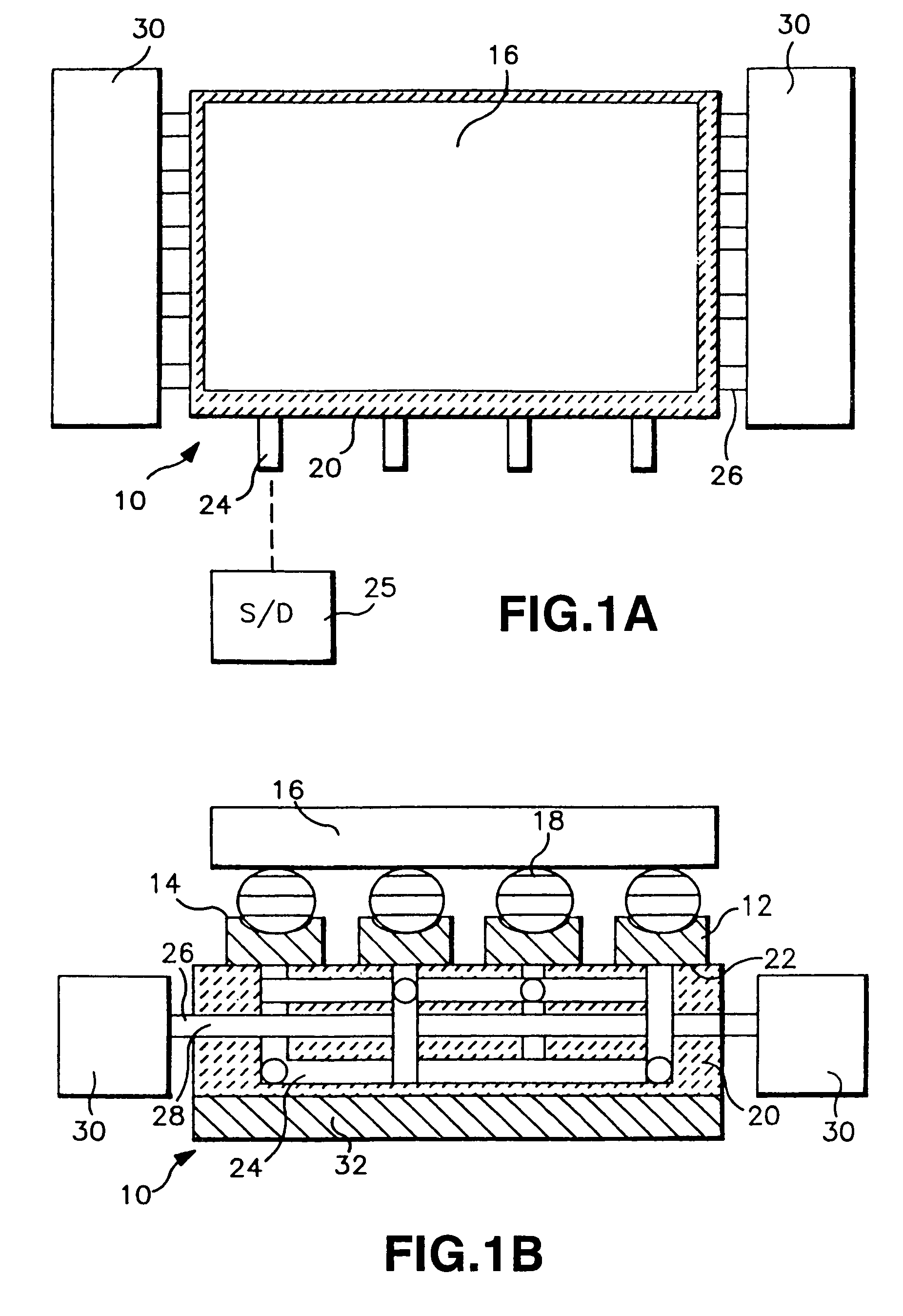

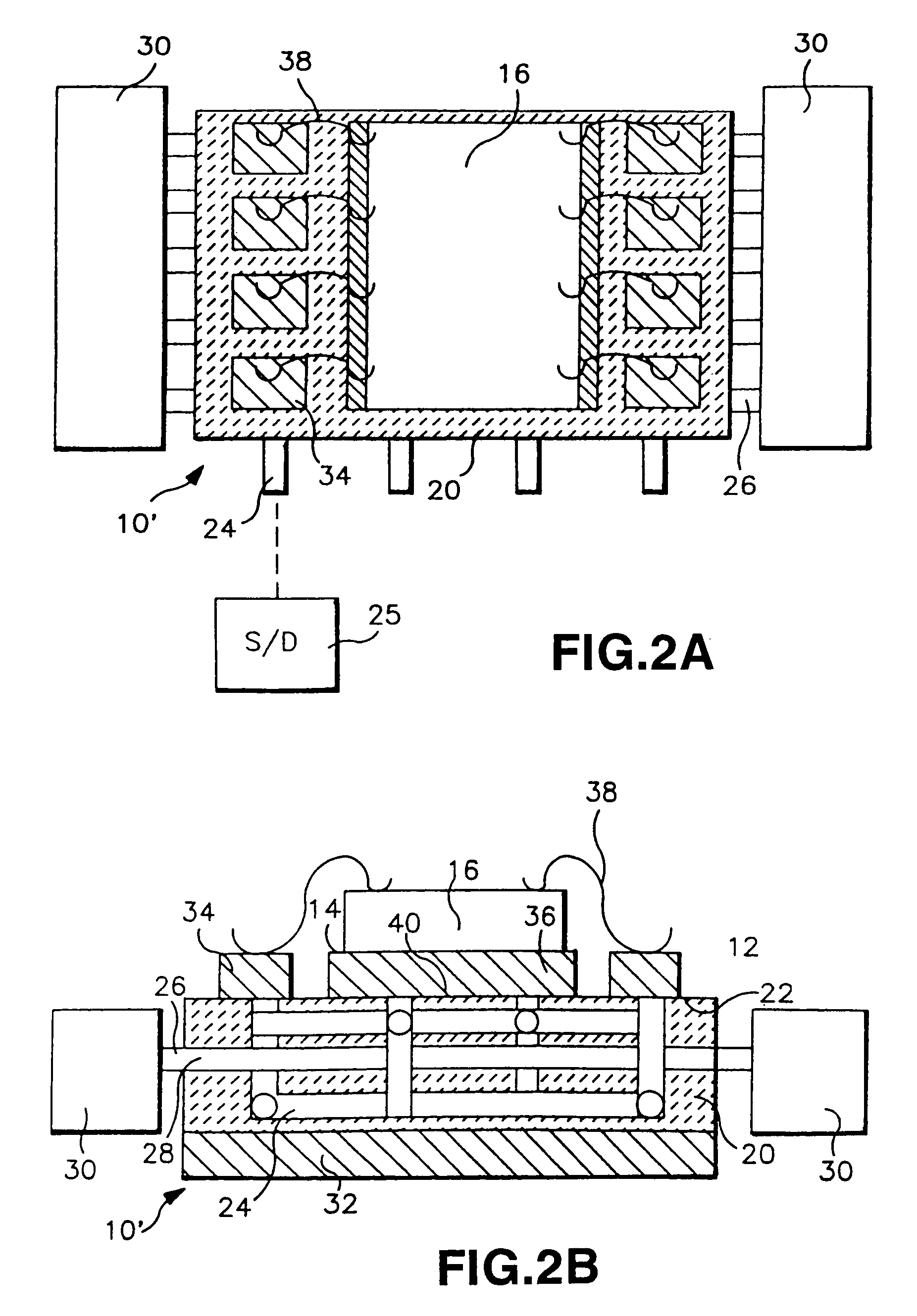

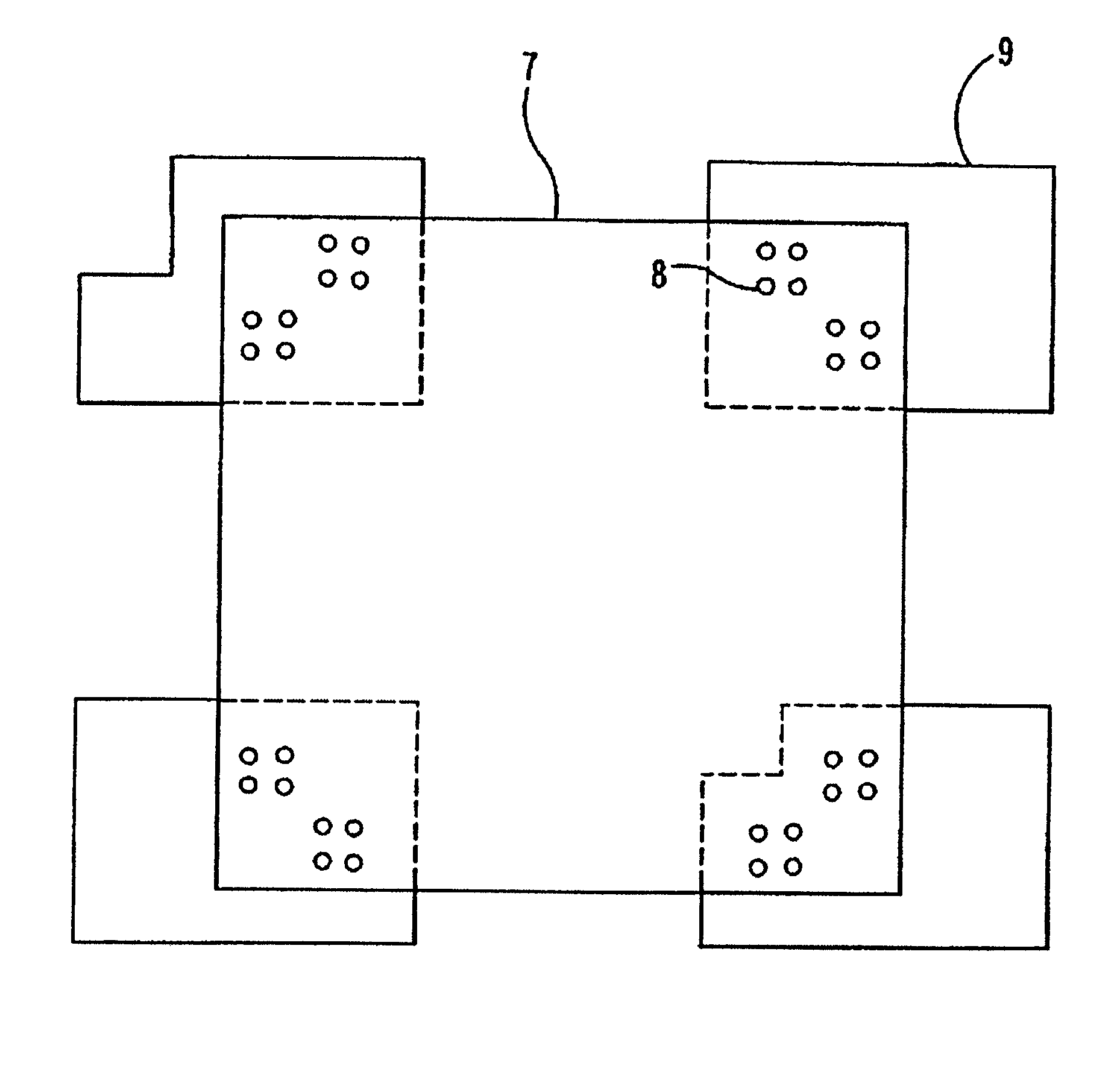

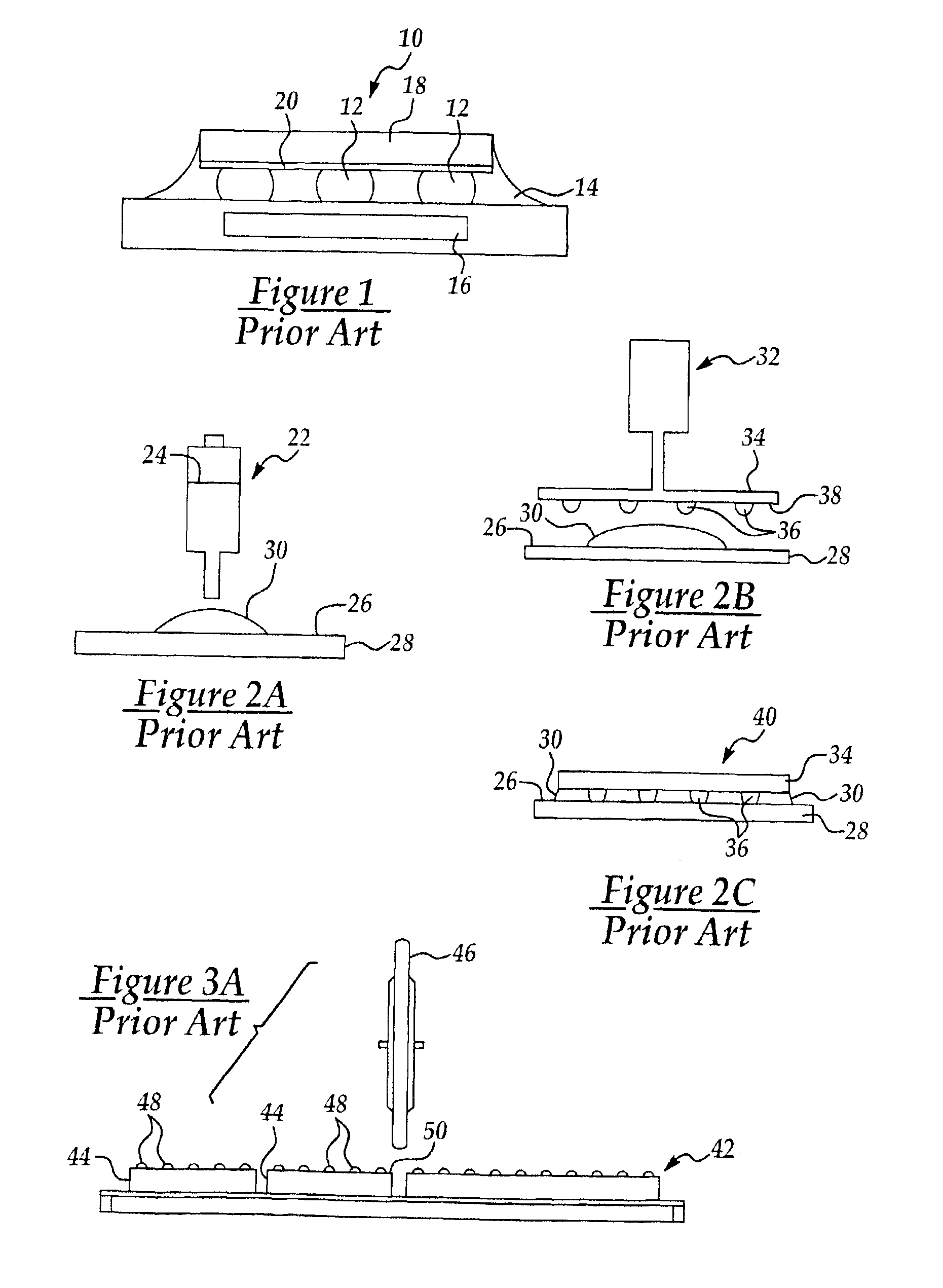

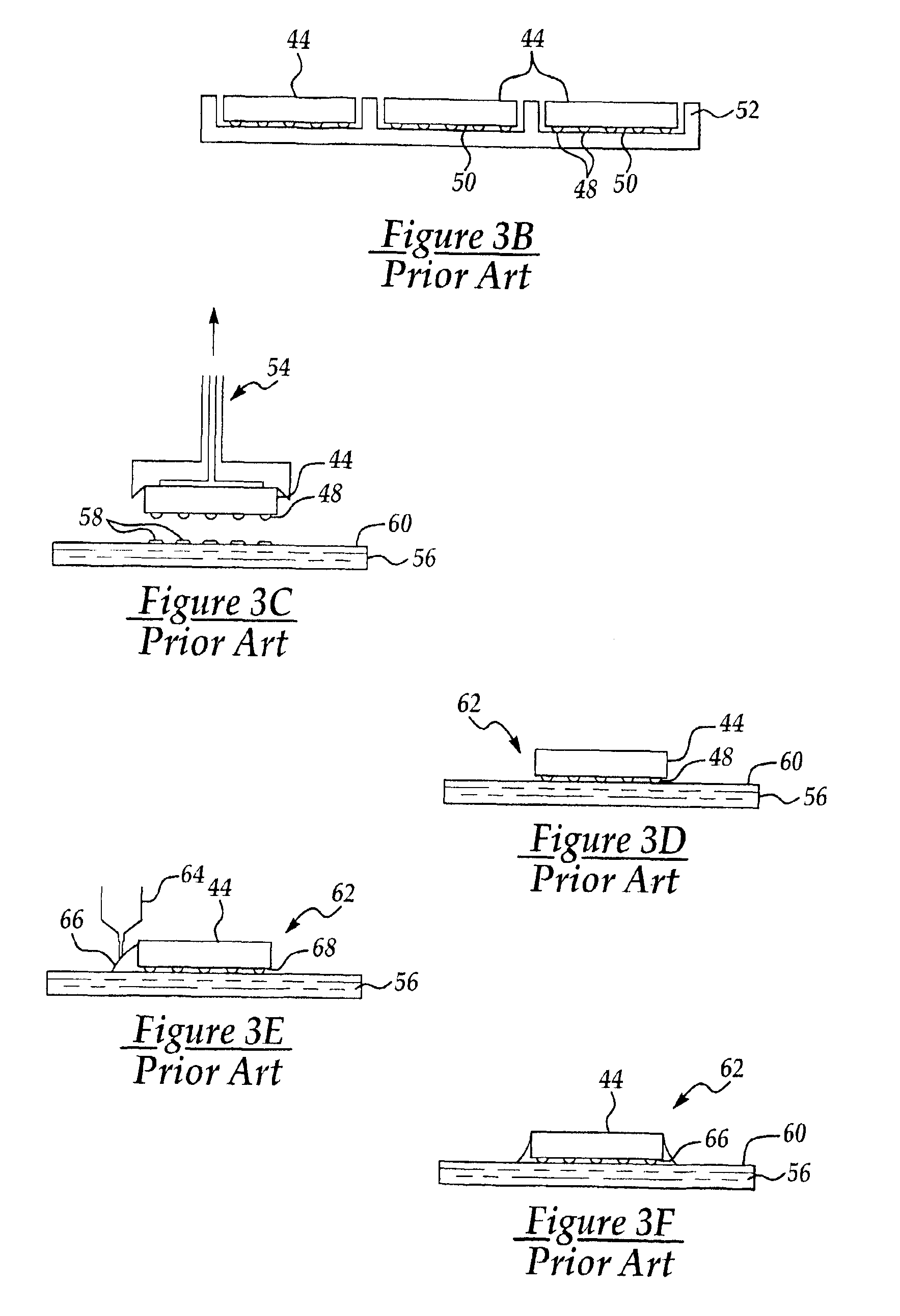

Circuit package having low modulus, conformal mounting pads

InactiveUS6399896B1Increase in number and sizeClosely matchedSemiconductor/solid-state device detailsSolid-state devicesElastomerThermal expansion

Reliability of circuit packaging while accommodating larger chips and increased temperature excursions is achieved by use of compliant pads only at the locations of connections between packaging levels, preferably between a laminated chip carrier and a printed circuit board. The invention allows the coefficient of thermal expansion of the chip carrier to be economically well-matched to the CTE of the chip and accommodation of significant differences in CTEs of package materials to be accommodated at a single packaging level. The compliant pads are preferably of low aspect ratio which are not significantly deflected by accelerations and can be formed on a surface or recessed into it. Connections can be made through surface connections and / or plated through holes. Connection enhancements such as solder wettable surfaces or dendritic textures are provided in a conductive metal or alloy layer over a compliant rubber or elastomer layer which may be conductive or non-conductive.

Owner:IBM CORP

Method for bonding IC chips to substrates incorporating dummy bumps and non-conductive adhesive

InactiveUS7300865B2Printed circuit assemblingPrinted circuits stress/warp reductionAdhesiveActive surface

An IC chip / substrate assembly bonded together by a non-conductive adhesive and a method for forming the assembly. The assembly consists of an IC chip that has bumps formed on an active surface, a substrate that has bond pads formed on a top surface, wherein at least one of the IC chip and the substrate has dummy bumps formed in-between the bumps or the bond pads, and a non-conductive adhesive disposed in between and bonding the IC chip and the substrate together in a face-to-face relationship with the bumps in electrical communication with the bond pads.

Owner:IND TECH RES INST

Semiconductor device

ActiveUS7122901B2Avoid crackingImprove reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorEngineering

In a semiconductor device, a plurality of wiring layers each patterned in a required shape are laminated over both surfaces of an insulating base material with insulating layers interposed therebetween, and electrically connected to one another through via holes piercing the insulating layers in the direction of thickness. A chip is mounted in an embedded manner in one insulating layer over at least one surface of the insulating base material. Electrodes of the chip are connected to one wiring layer. Through holes are formed in portions of the insulating base material, the portions corresponding to a mount area for the chip. Via holes are formed on outwardly extending portions (pad portions) of the wiring layer connected to a conductor layer formed at least on the inner walls of the through holes.

Owner:SHINKO ELECTRIC IND CO LTD

Package for multiple light emitting diodes

ActiveUS8384097B2Improve controlImprove thermal efficiencyPoint-like light sourceLighting support devicesEngineeringLight-emitting diode

Substrates and packages for LED-based light devices can significantly improve thermal performance and provide separate electrical and thermal paths through the substrate. One substrate includes multiple electrically insulating base layers. On a top one of these layers are disposed top-side electrical contacts, including light device pads to accommodate a plurality of light devices. External electrical contacts are disposed on an exterior surface of the substrate. Electrical paths connect the top-side electrical contacts to the external electrical contacts. At least portions of some of the electrical paths are disposed between the electrically insulating base layers. The electrical paths can be arranged such that different subsets of the light device pads are addressable independently of each other. A heat dissipation plate can be formed on the bottom surface of a bottom one of the base layers.

Owner:LEDENGIN

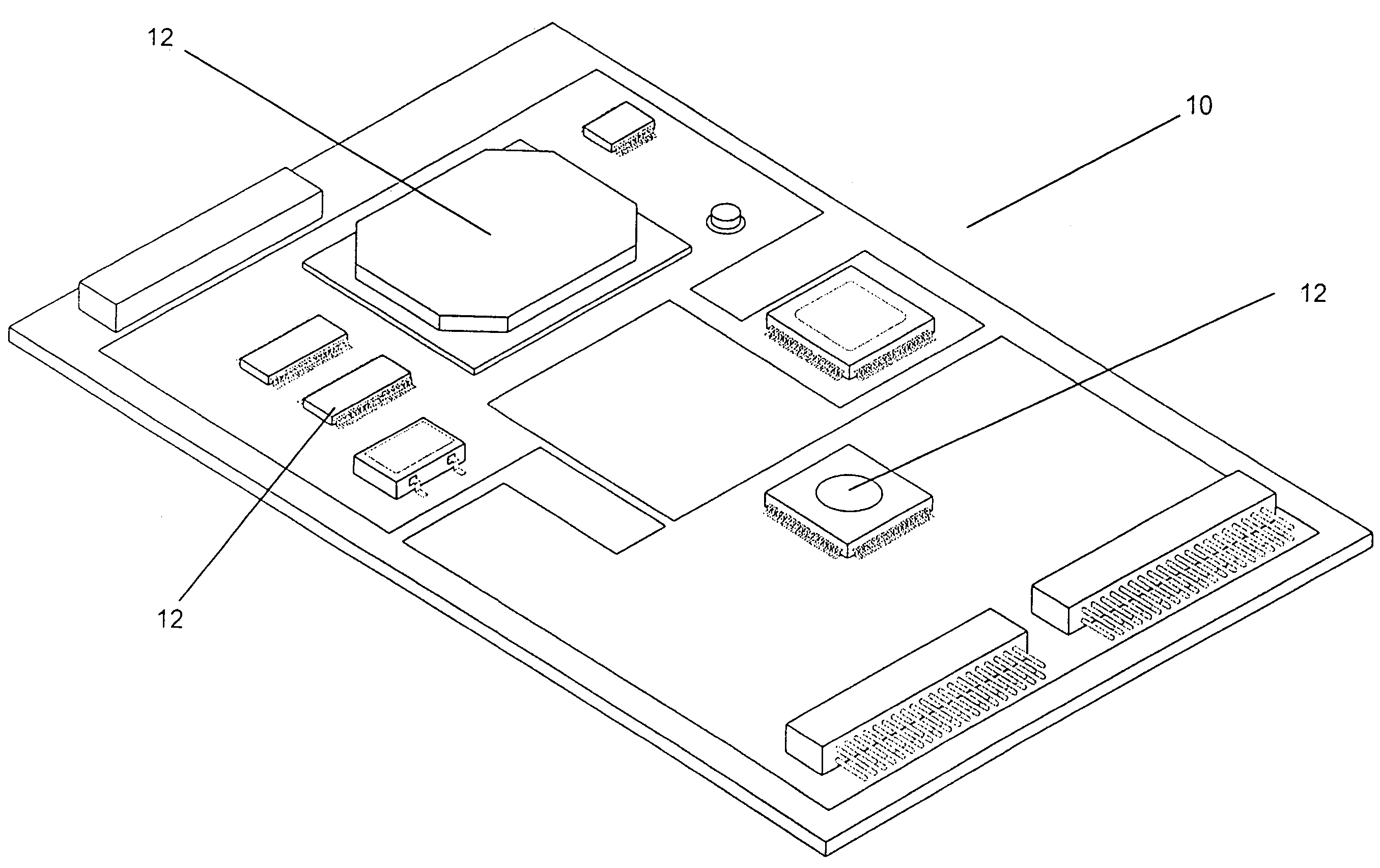

Printed circuit board reinforcement structure and integrated circuit package using the same

InactiveUS8059384B2Reduce thicknessMaintain rigidityMake-and-break ignitionPrinted electric component incorporationSoft layerSurface mounting

A printed circuit board reinforcement structure for a printed circuit board receiving a plurality of surface mounting devices, and an integrated circuit package using the same. The structure includes a hard layer having one or more openings formed at areas corresponding to one or more surface mounting devices with a thickness exceeding a predetermined thickness; and a soft layer bonded to a side of the hard layer so that the soft layer can accommodate the protrusion of the surface mounting devices. The structure prevents defects of a printed circuit board, such as deformation, fracture or the like, while substantially reducing the size of a package by applying a reinforcement structure to a thin printed circuit board, thereby reinforcing the rigidity (mechanical strength) of the thin printed circuit board.

Owner:SAMSUNG ELECTRONICS CO LTD

Power semiconductor module

InactiveUS20070262387A1Improve reliabilityIncrease temperatureInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsEngineeringThermal expansion

A power semiconductor module having an integral circuit board with a metal substrate electrode, an insulation substrate and a heat sink joined is disclosed. A SiC semiconductor power device is joined to a top of the metal substrate electrode of the circuit board. A difference in average coefficients of thermal expansion between constituent materials of the circuit board in a temperature range from room to joining time temperatures is 2.0 ppm / ° C. or less, and a difference in expansion, produced by a difference between a lowest operating temperature and a joining temperature, of the circuit-board constituent materials is 2,000 ppm or less.

Owner:HONDA MOTOR CO LTD

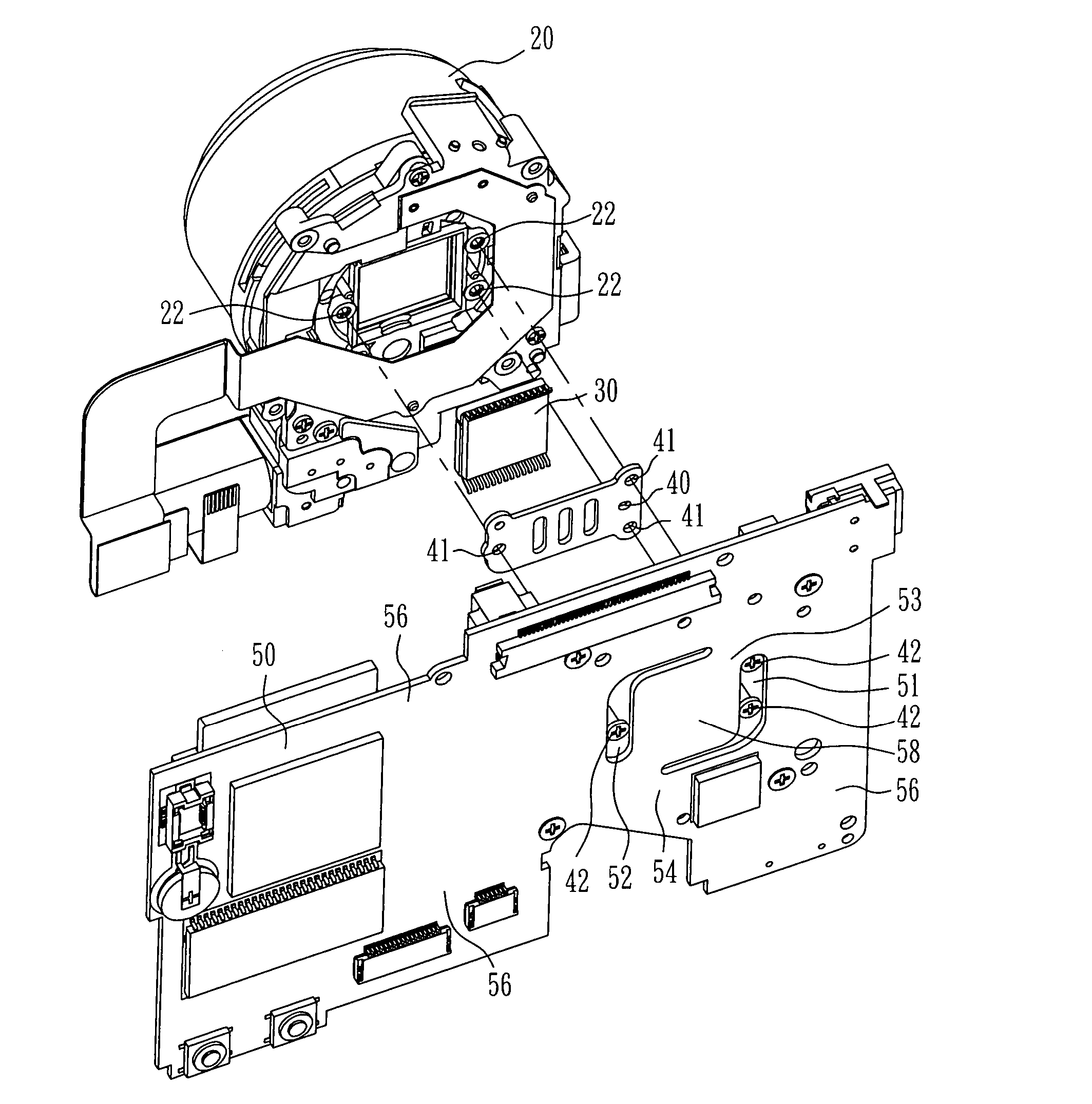

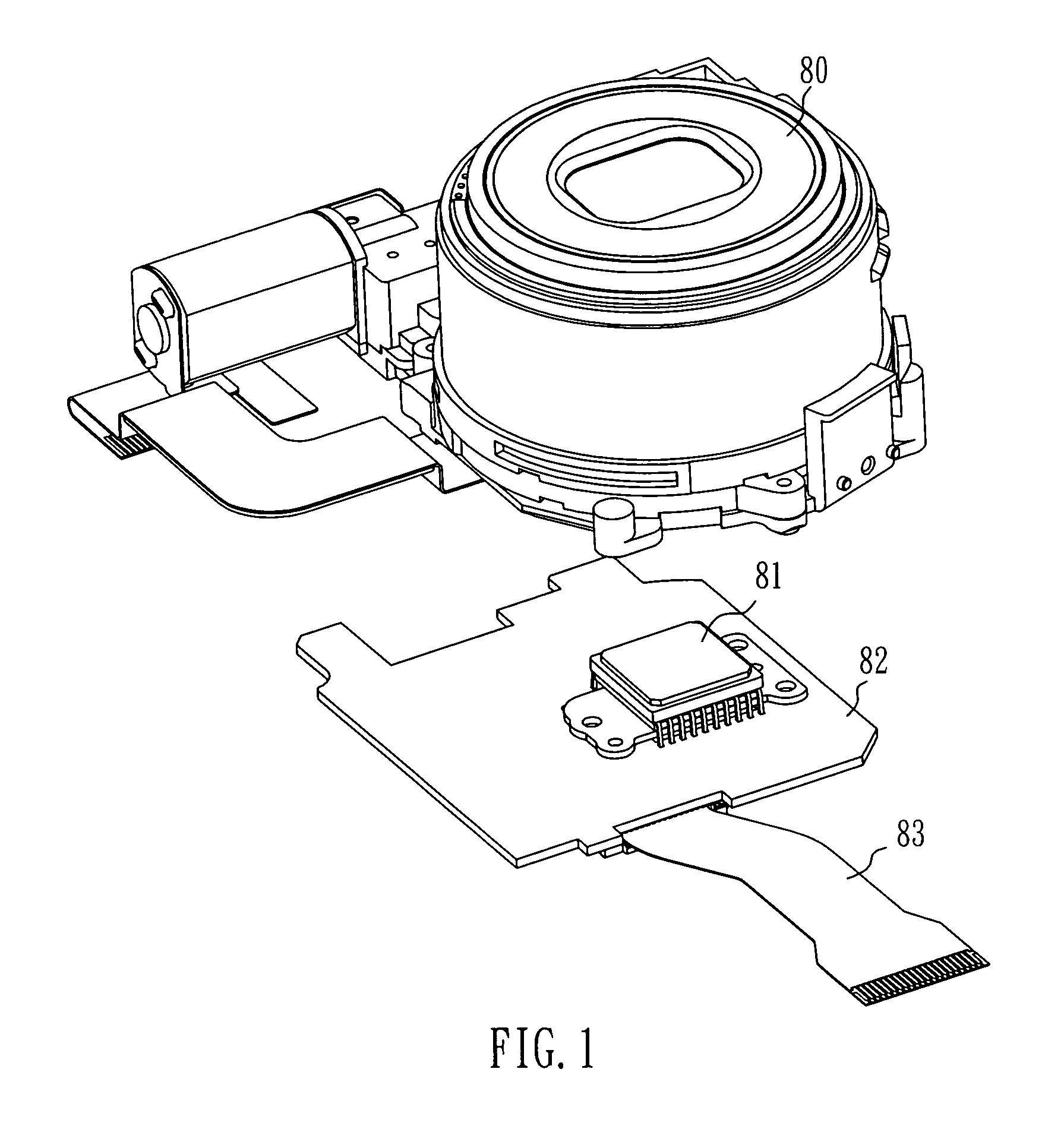

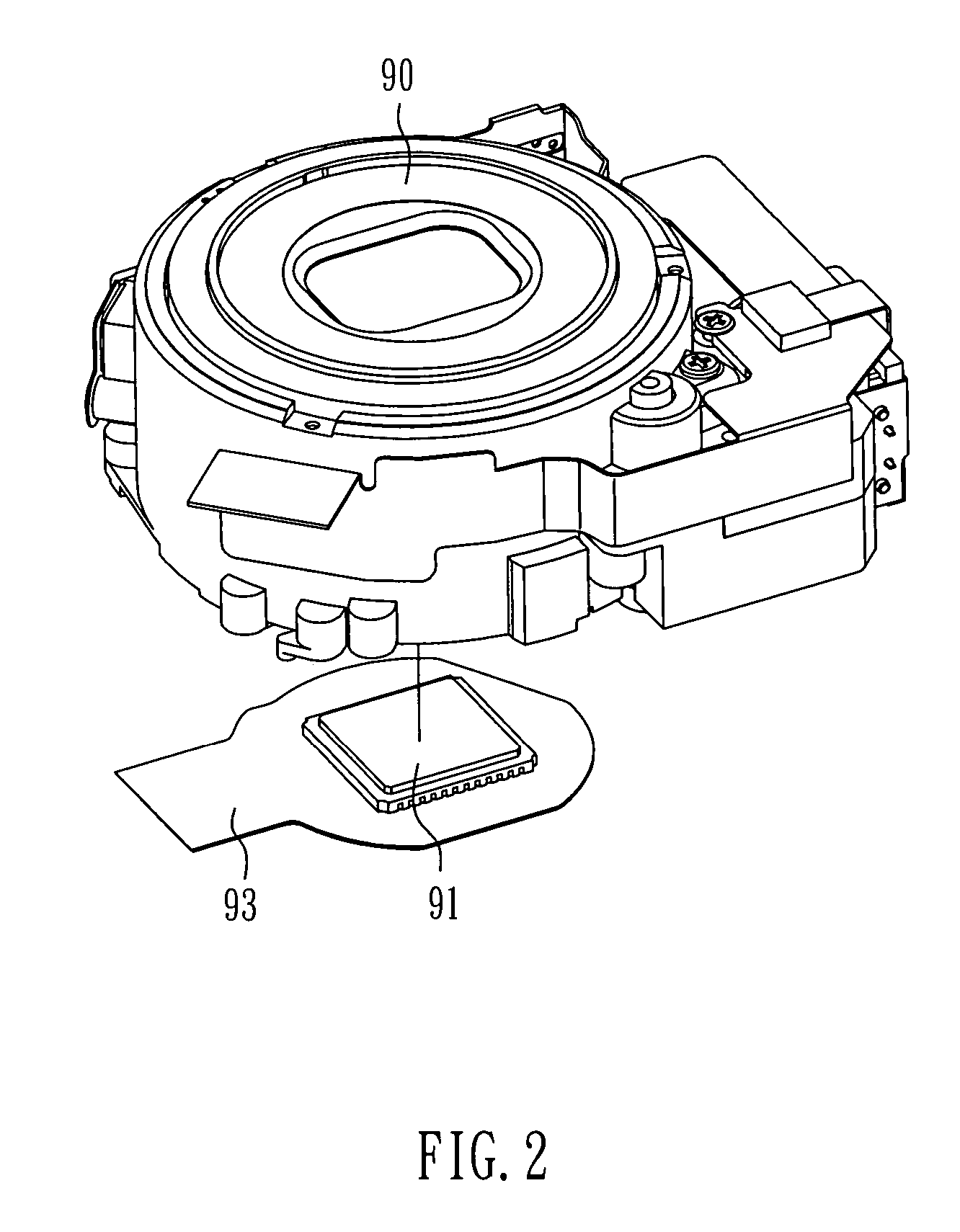

Digital camera

InactiveUS20070127915A1Low production costReduce the number of productsTelevision system detailsPrinted circuit aspectsEngineeringFlexible character

A digital camera has a printed circuit board which comprises a main area and a flexible area. An optical sensor chip (e.g. a CCD) is fixed onto the flexible area. The flexible area has flexible character relative to the main area. Therefore, even if the printed circuit board is stressed, such stress will be almost or completely eliminated in the flexible area, so that the optical sensor chip and an optical lens can be coupled together in a precise manner.

Owner:HON HAI PRECISION IND CO LTD

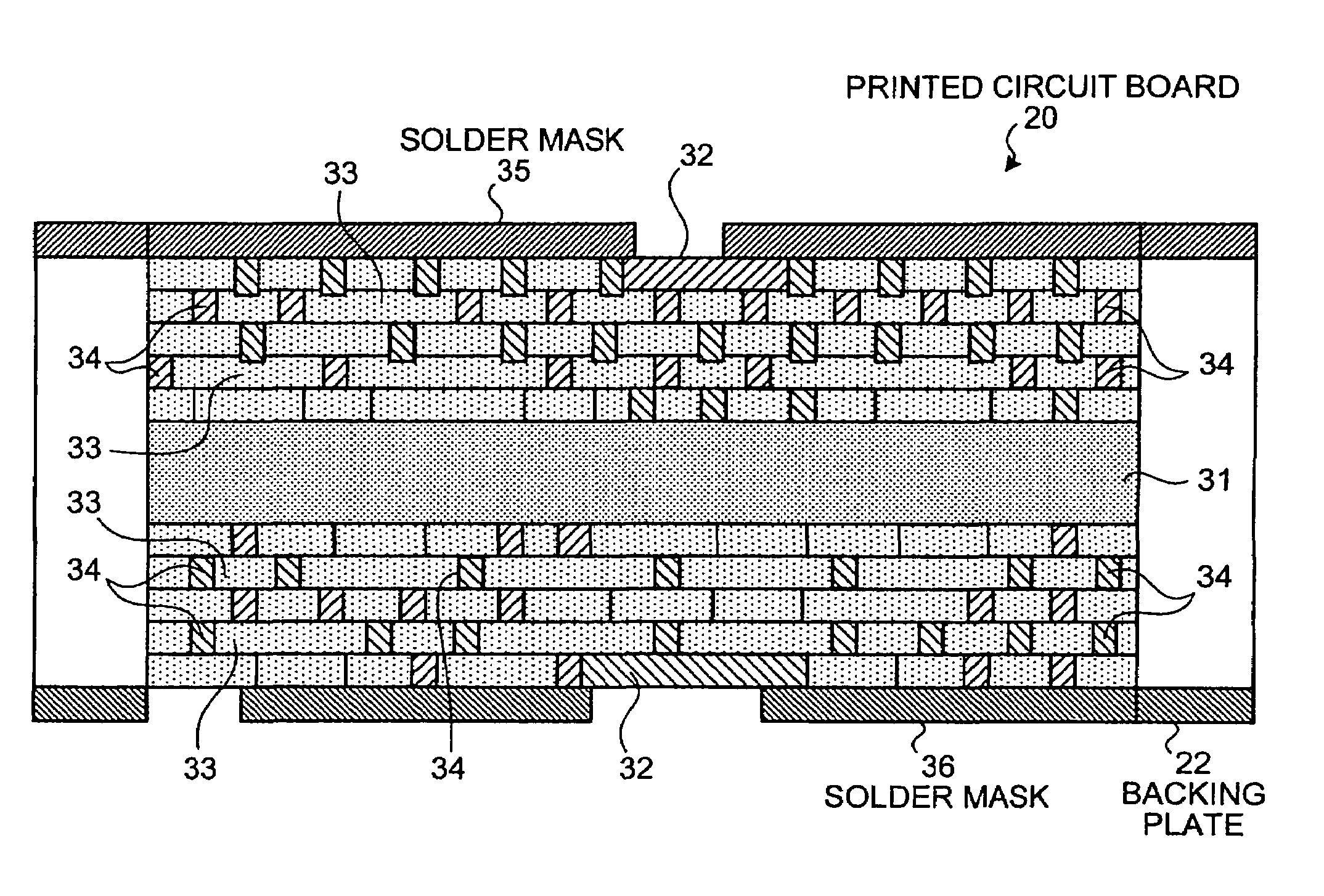

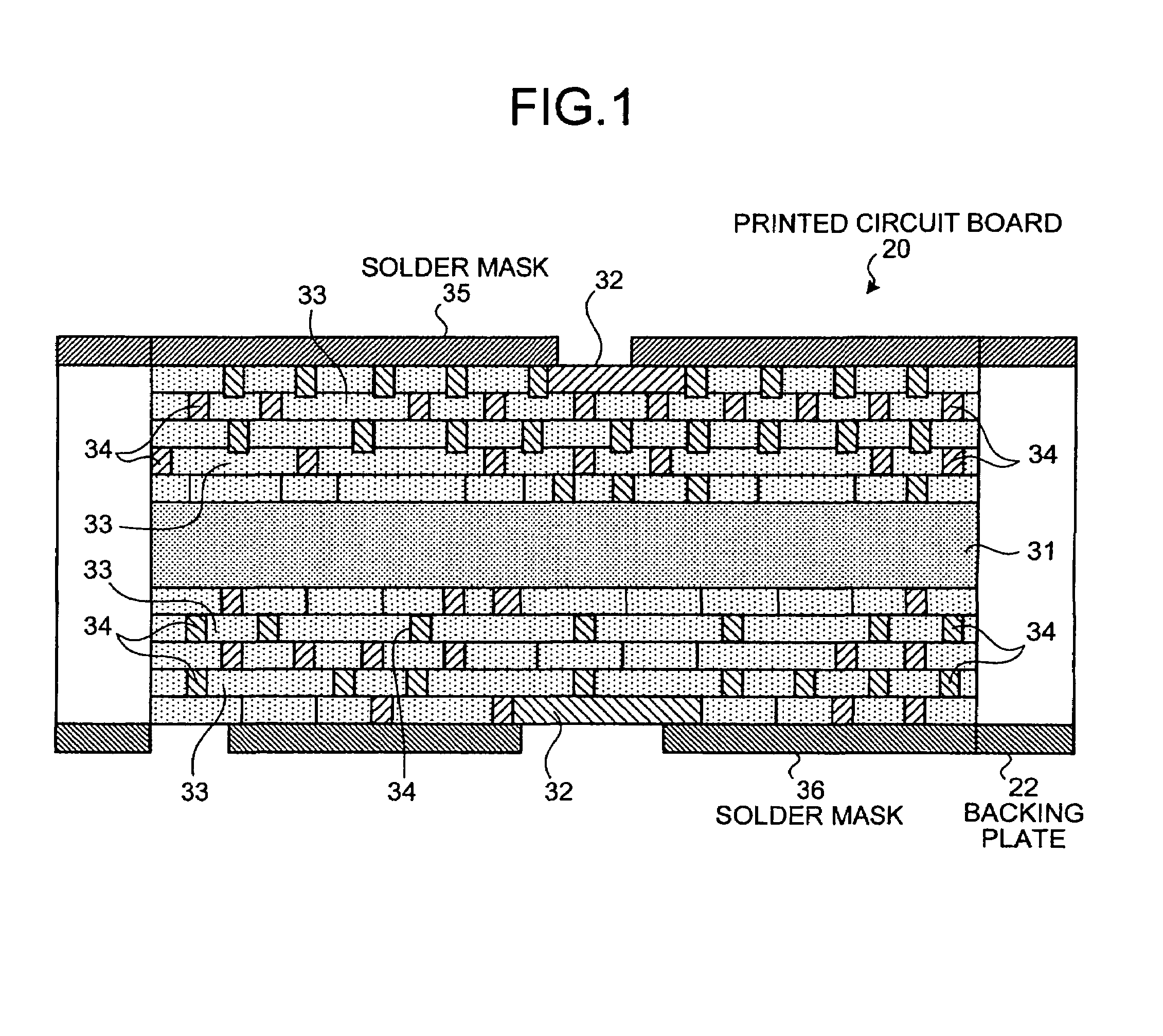

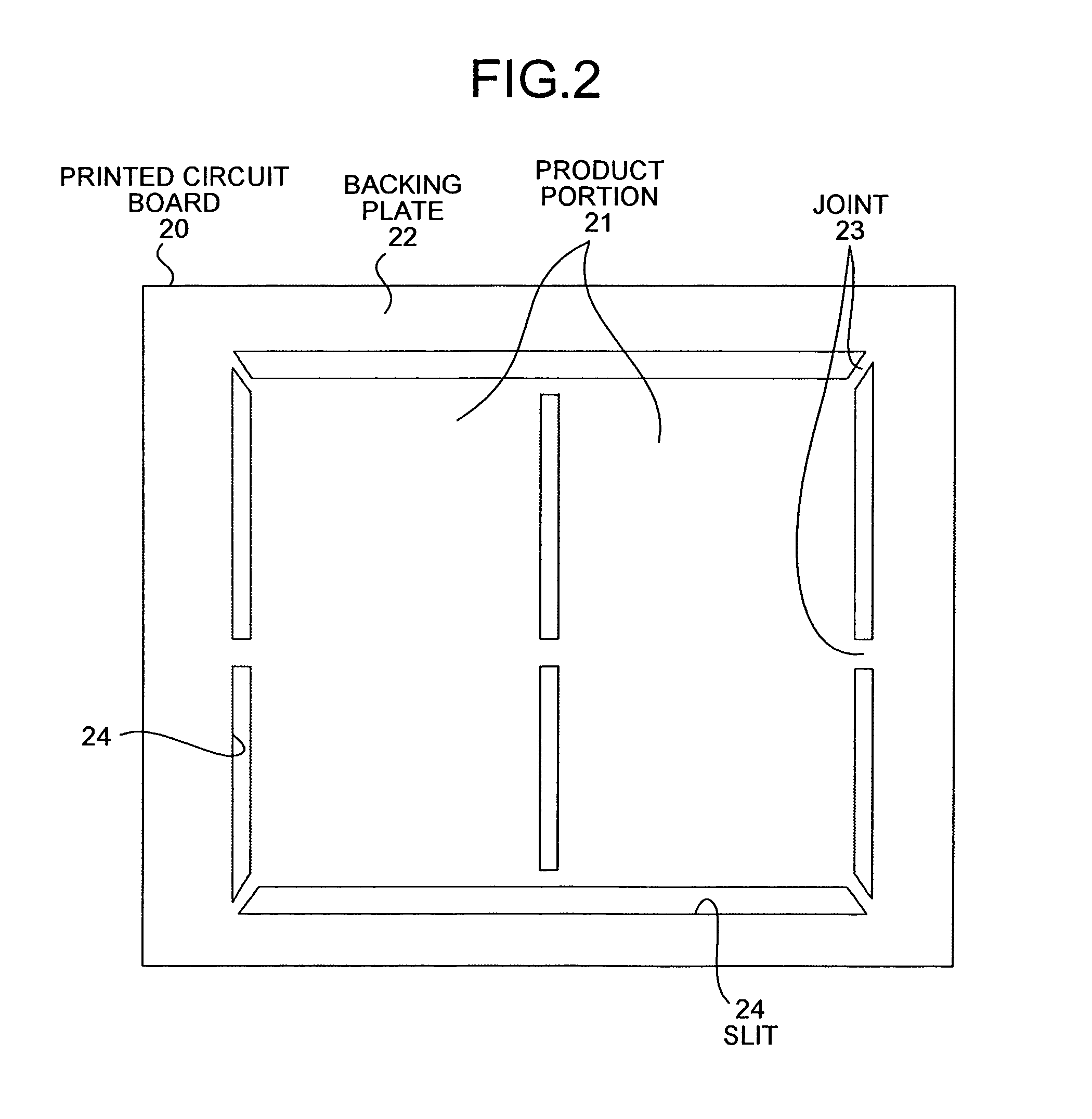

Multilayer printed circuit board and manufacturing method thereof

ActiveUS7498522B2Printed electric component incorporationPrinted circuit aspectsSolder maskMechanical engineering

A printed circuit board includes a product portion and a backing plate. Upper and lower surfaces of the backing plate are coated with solder masks with different material characteristics.

Owner:FUJITSU LTD

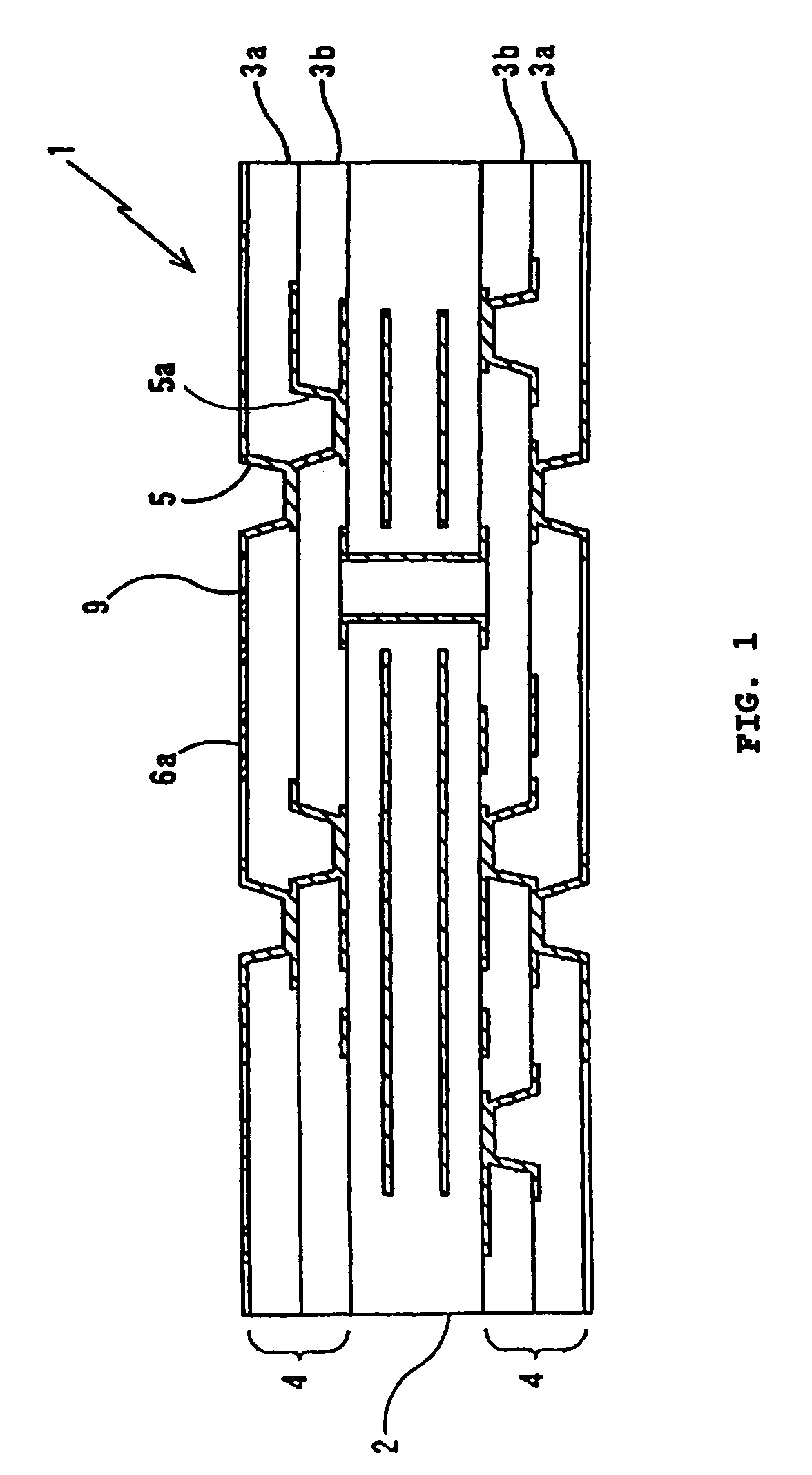

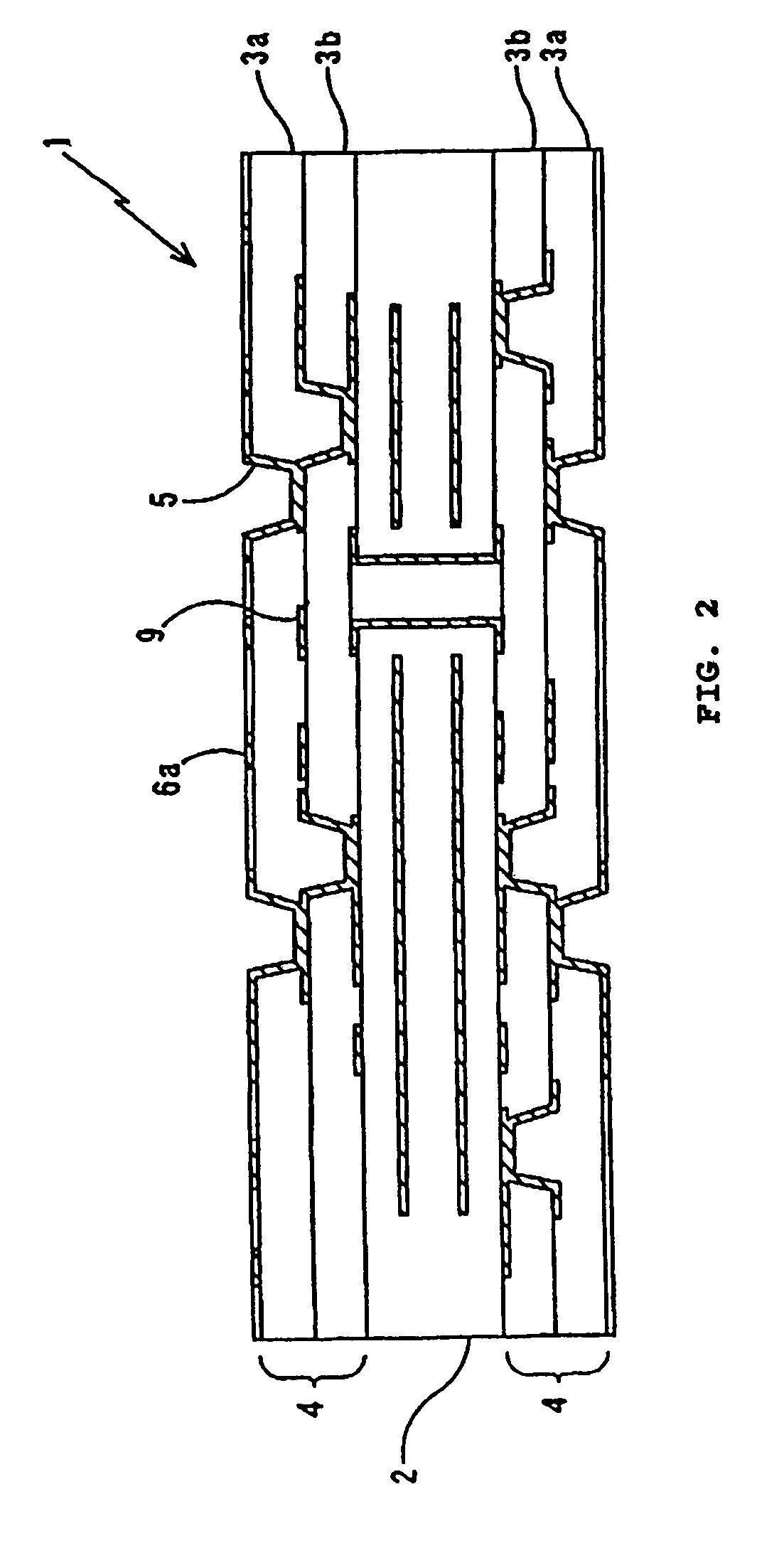

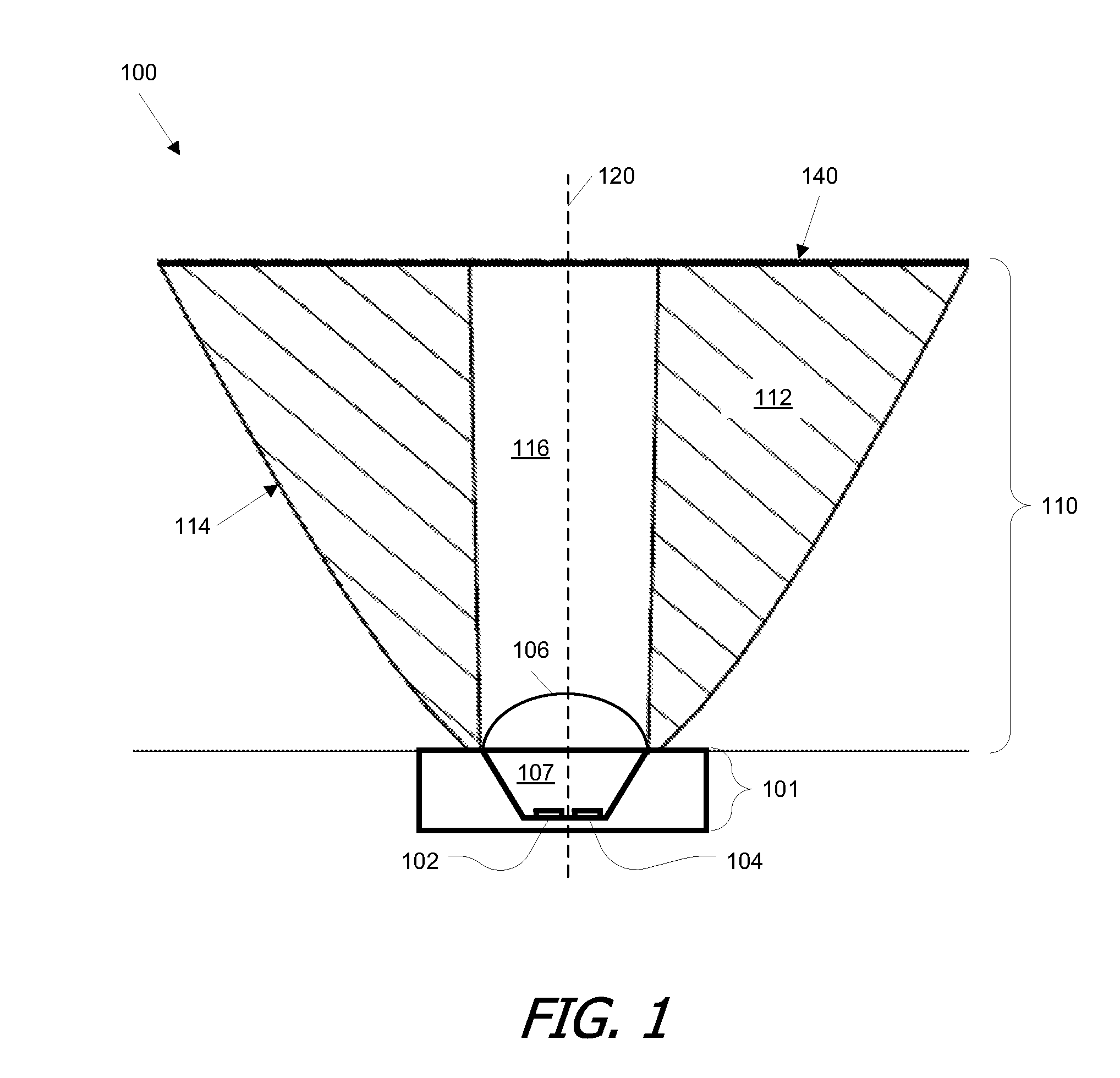

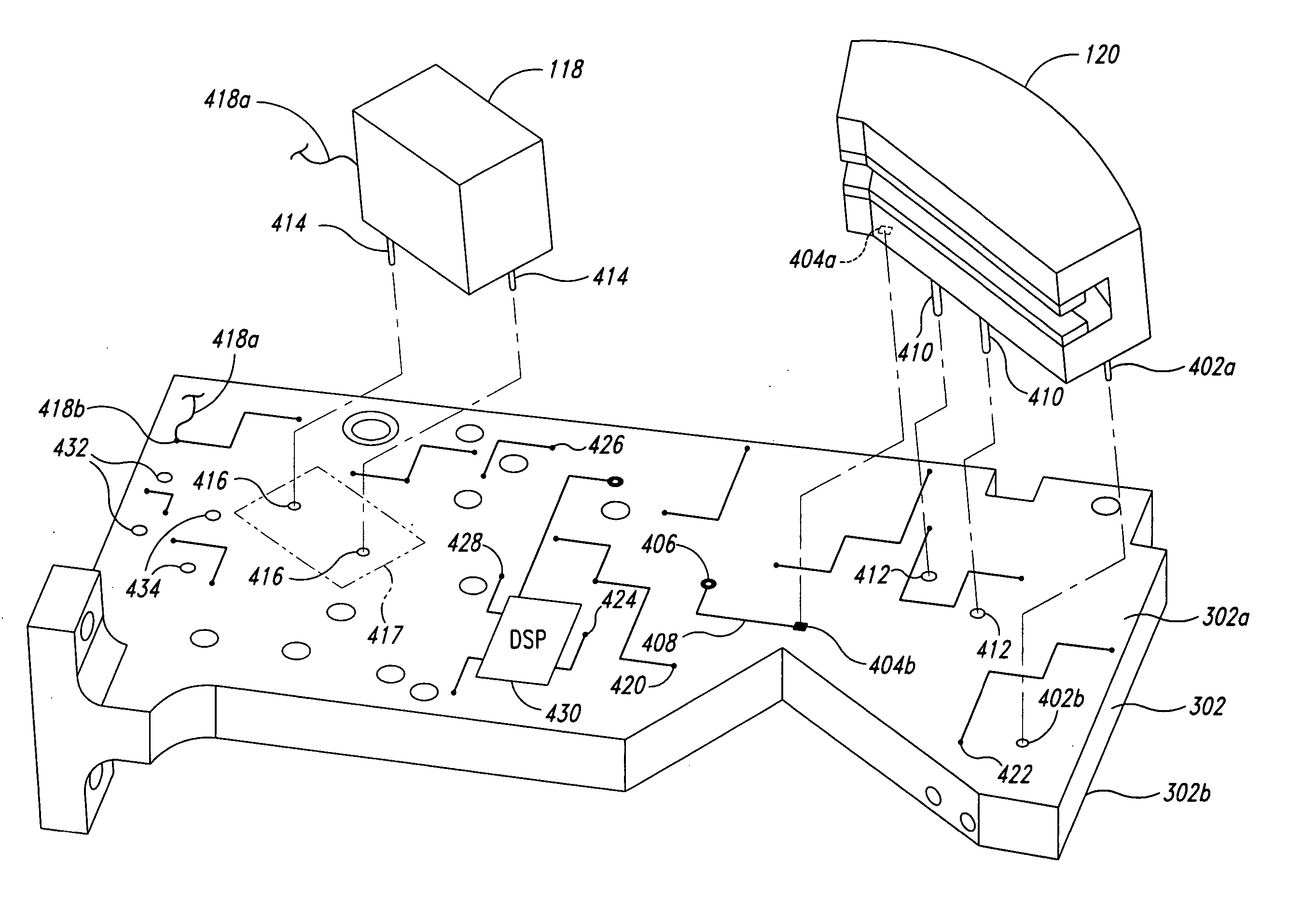

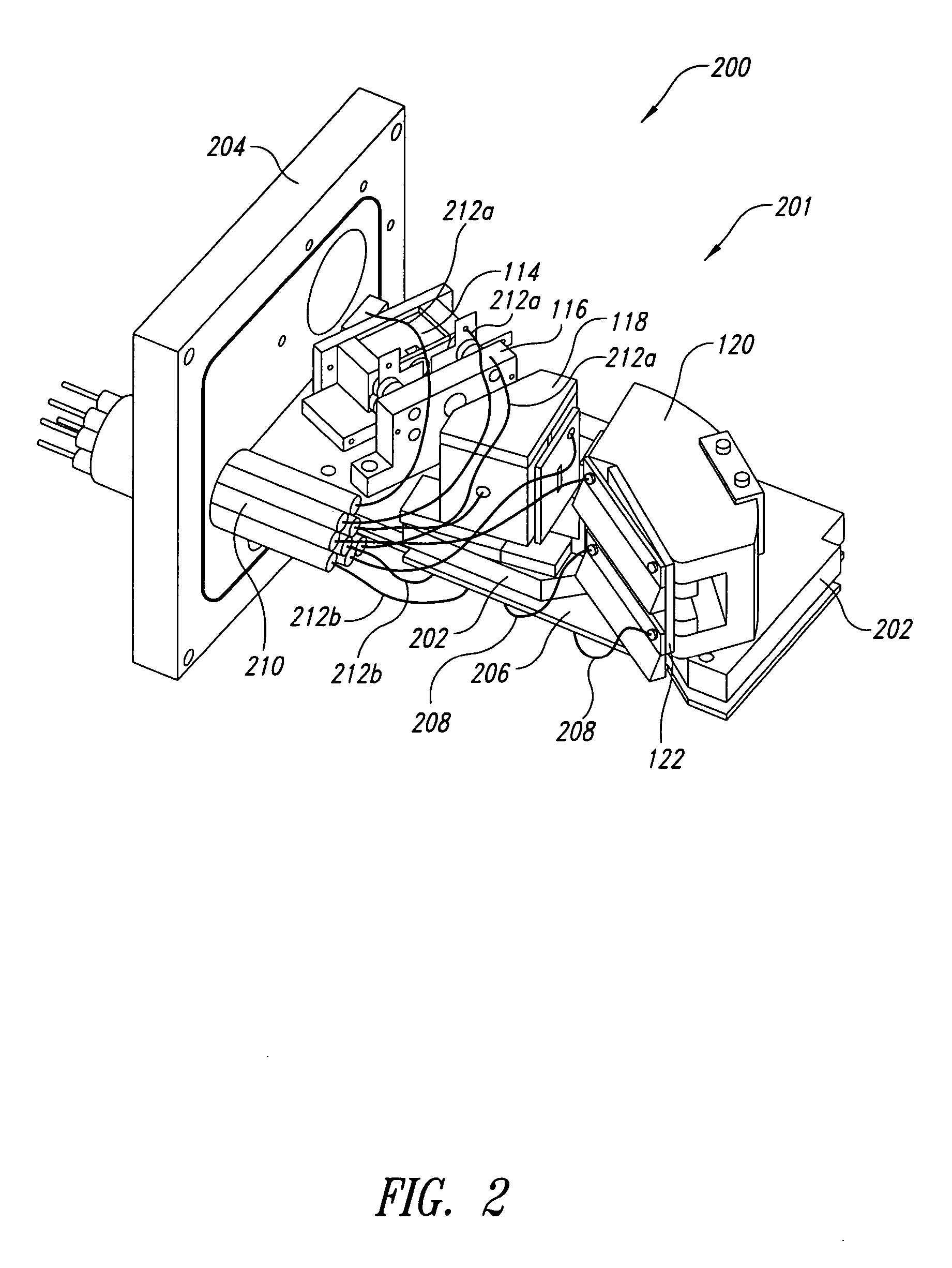

Optical bench for a mass spectrometer system

ActiveUS20060076483A1Improve drawing legibility3D rigid printed circuitsPrinted circuit aspectsAnalyteMass analyzer

Mass spectrometer systems for measuring mass / charge ratios of analytes are described. A mass spectrometer system includes a vacuum flange, a PCB base plate coupled to the vacuum flange, and an ion optic assembly coupled to the PCB base plate. The PCB base plate may include signal-processing electronics. The system may include an electrical cable coupled to the PCB base plate for supplying power, control, and I / O to the ion optic assembly and the signal processing electronics. Alternatively, a mass spectrometer system includes a PCB base plate and an ion optic assembly. The PCB base plate has a sealant portion and an electrical portion. The ion optic assembly is coupled to the electrical portion. The system may include a vacuum housing for enclosing the ion optic assembly. The vacuum housing is coupled to the sealant portion of the PCB base plate for sustaining a vacuum while the system is in operation.

Owner:O I CORP

Popular searches

Fluid-dynamic spacing of heads Computer periphery connectors Electrical connection printed elements Circuit susbtrate materials Support for heads Soldered/welded conductive connections Conductive pattern reinforcement Non-metallic protective coating application Semiconductor/solid-state device manufacturing Printed circuit non-printed electric components association