Patents

Literature

340results about "Radiation-sensitive masks exposure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

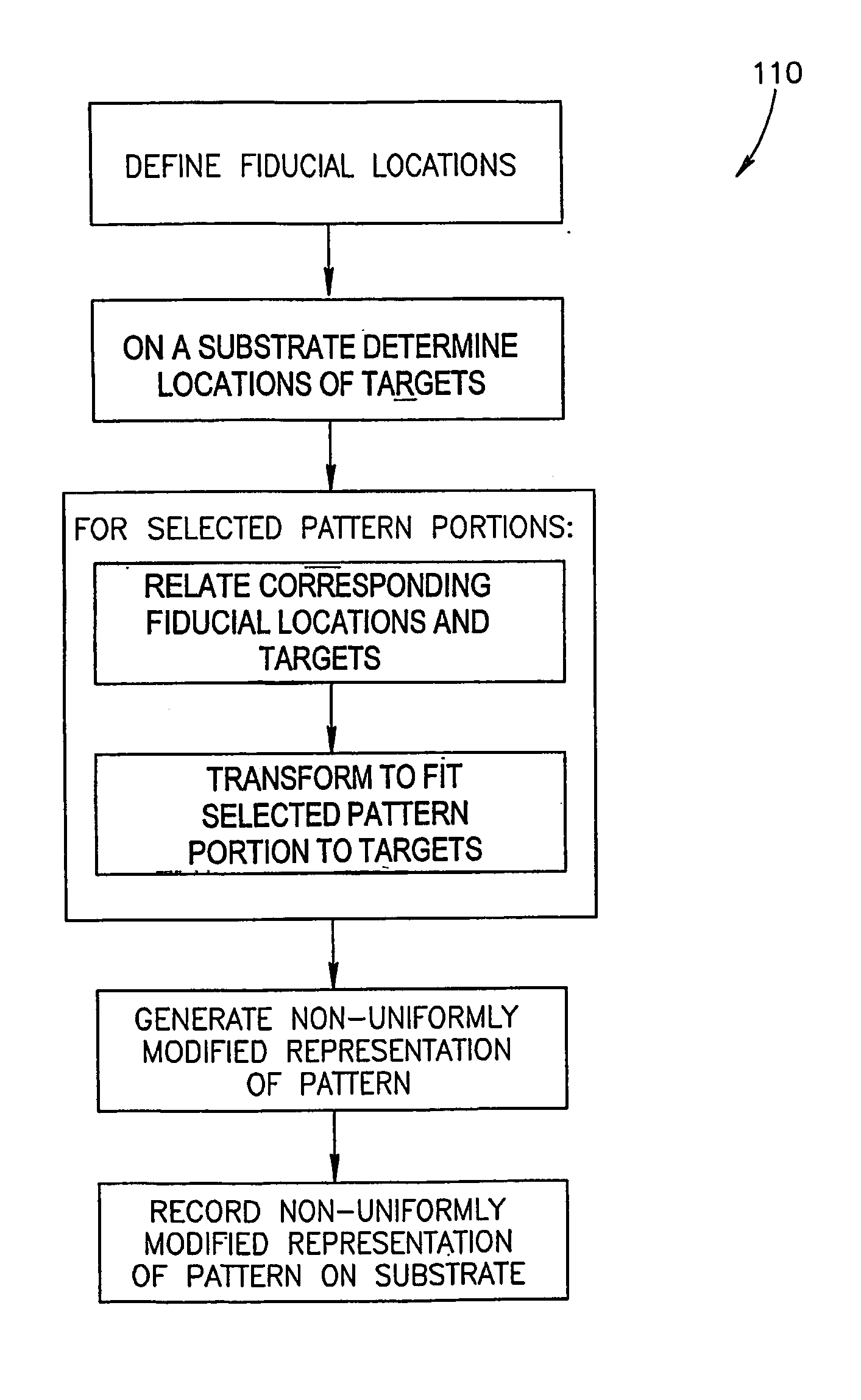

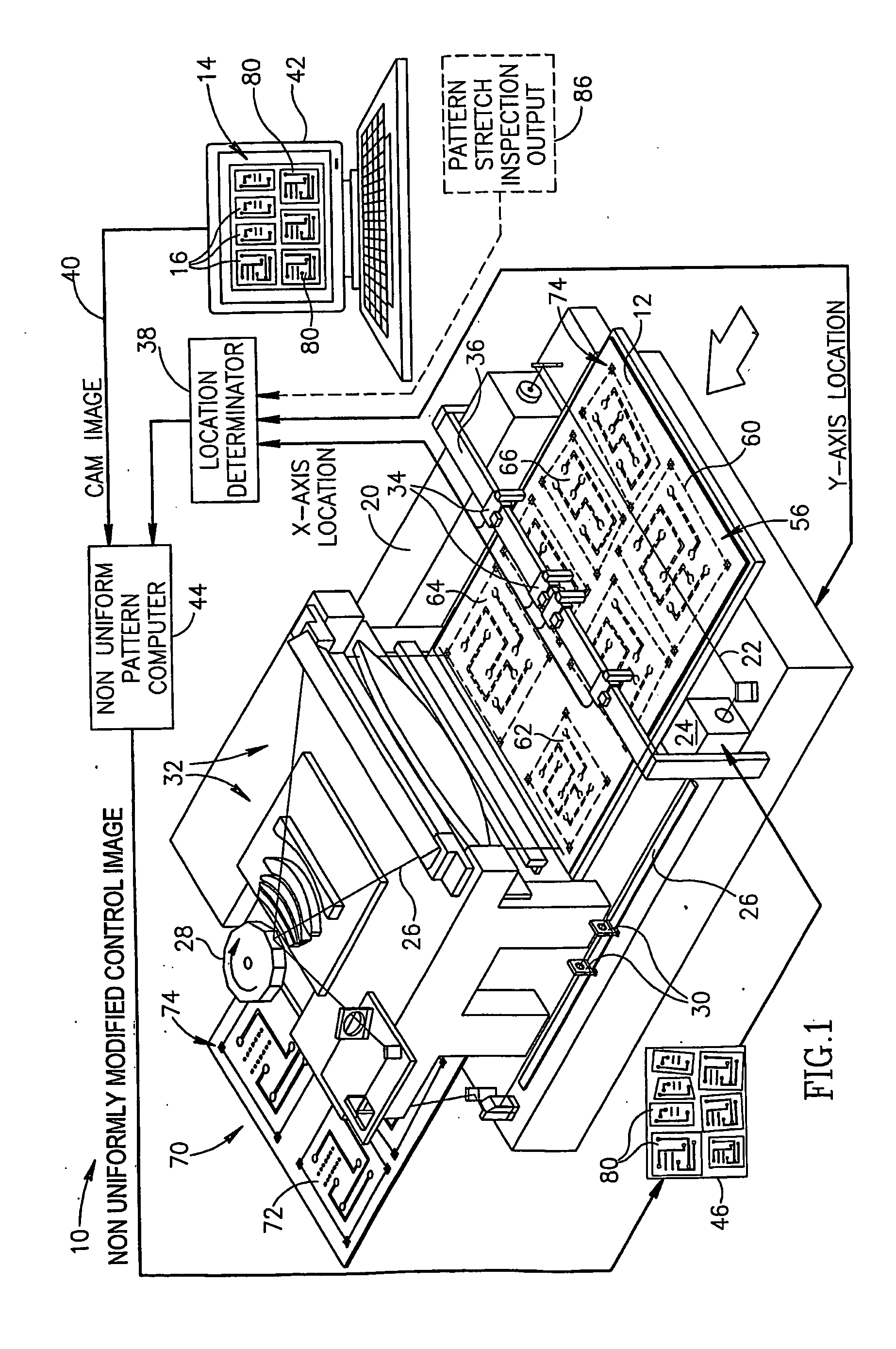

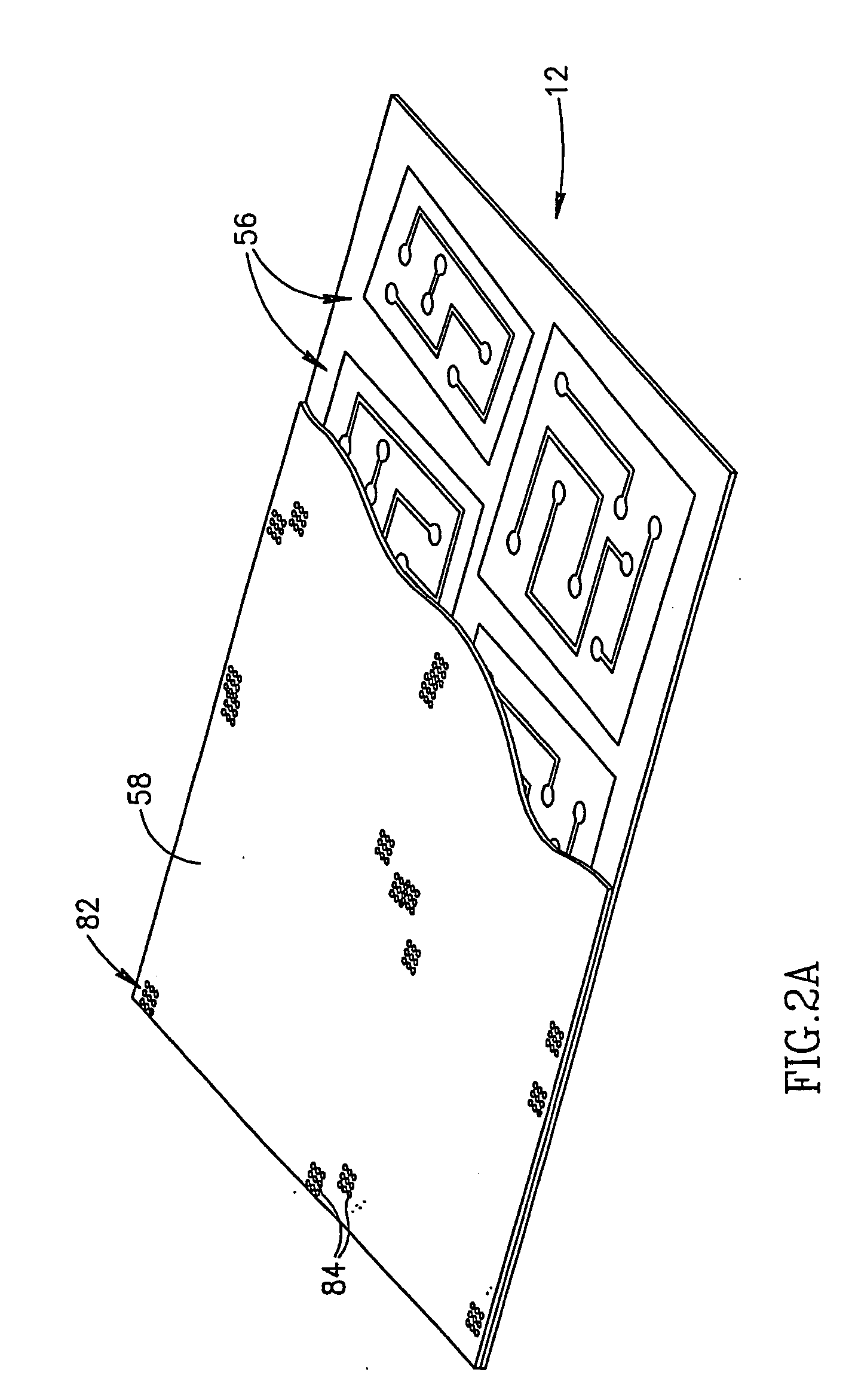

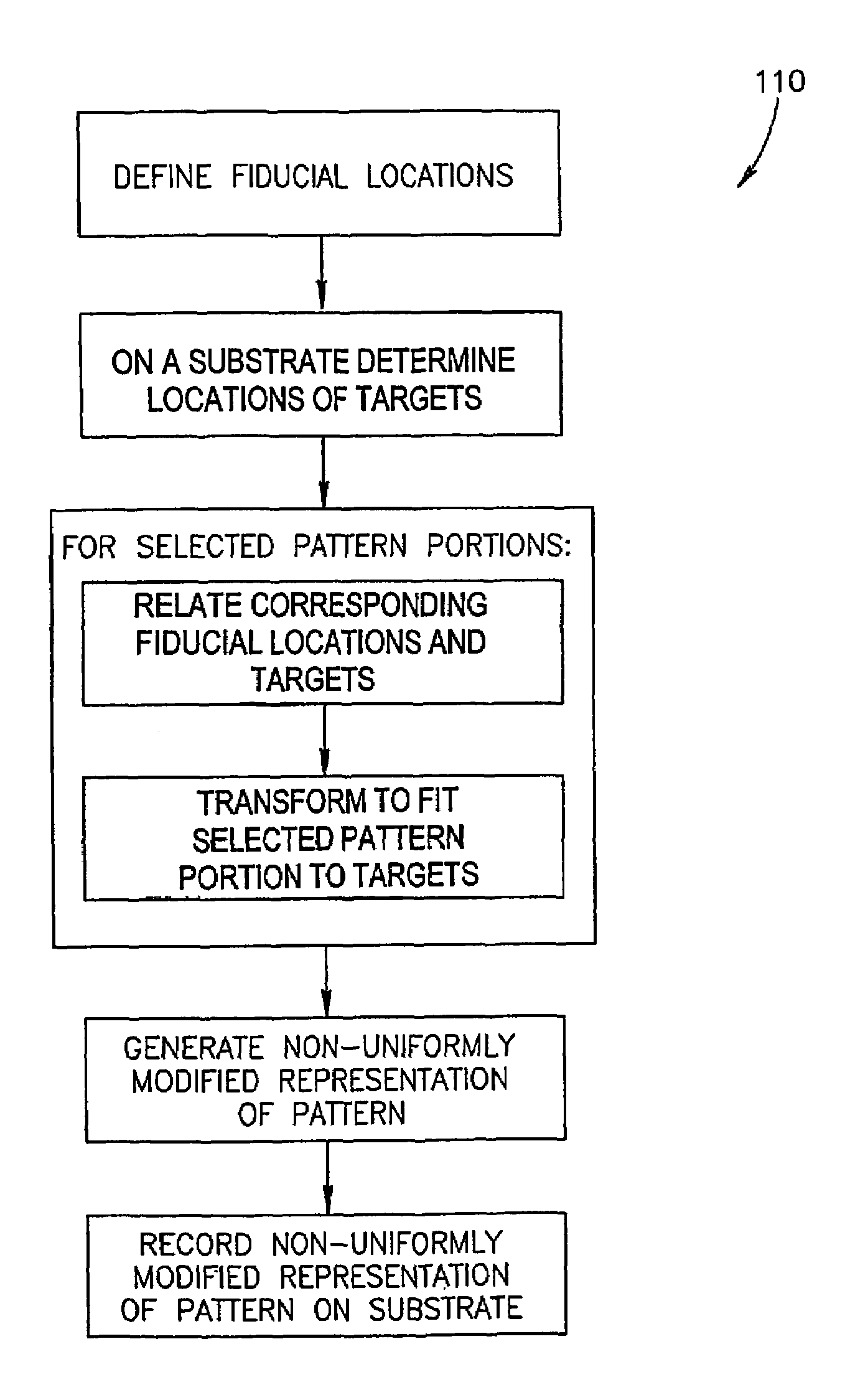

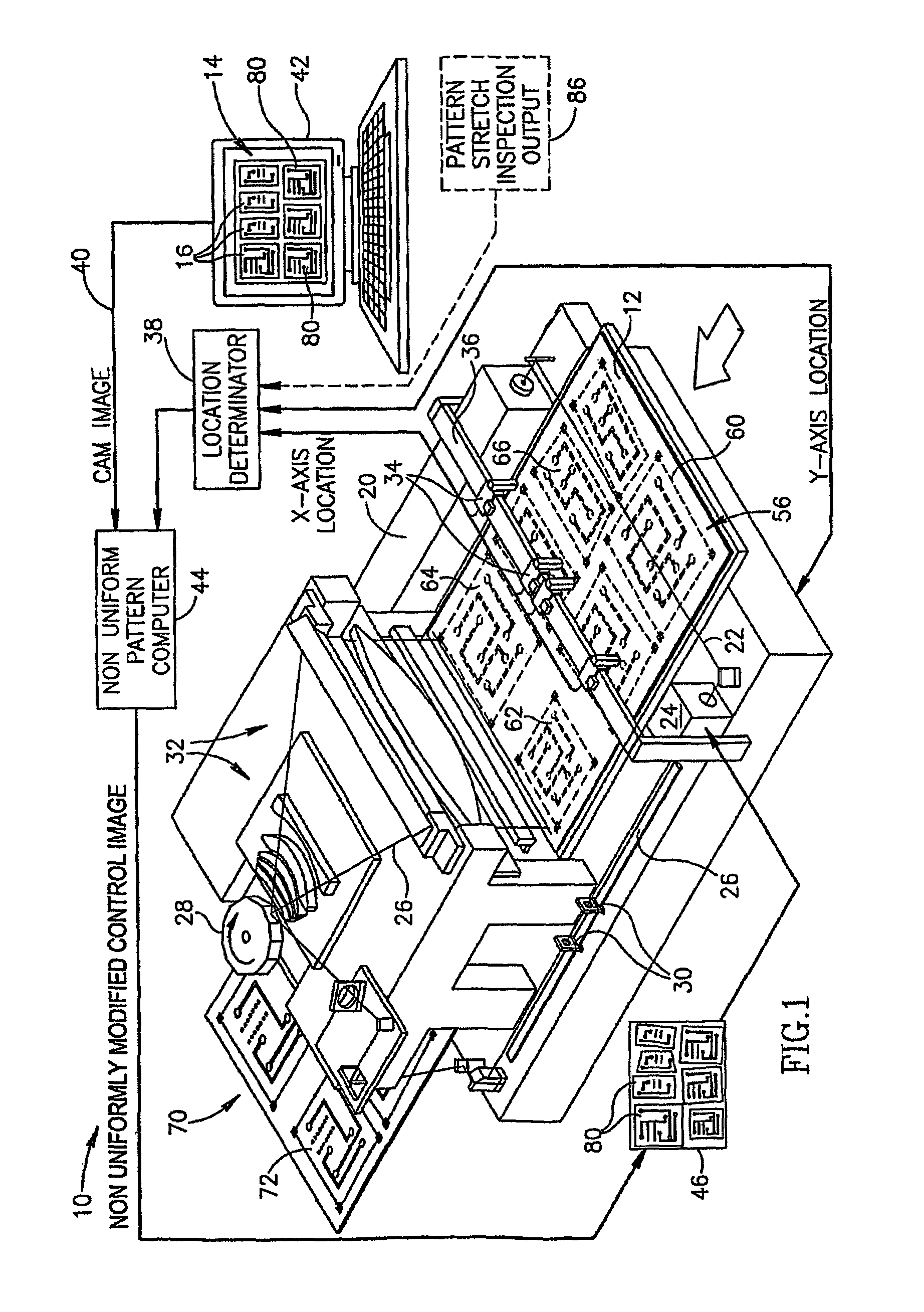

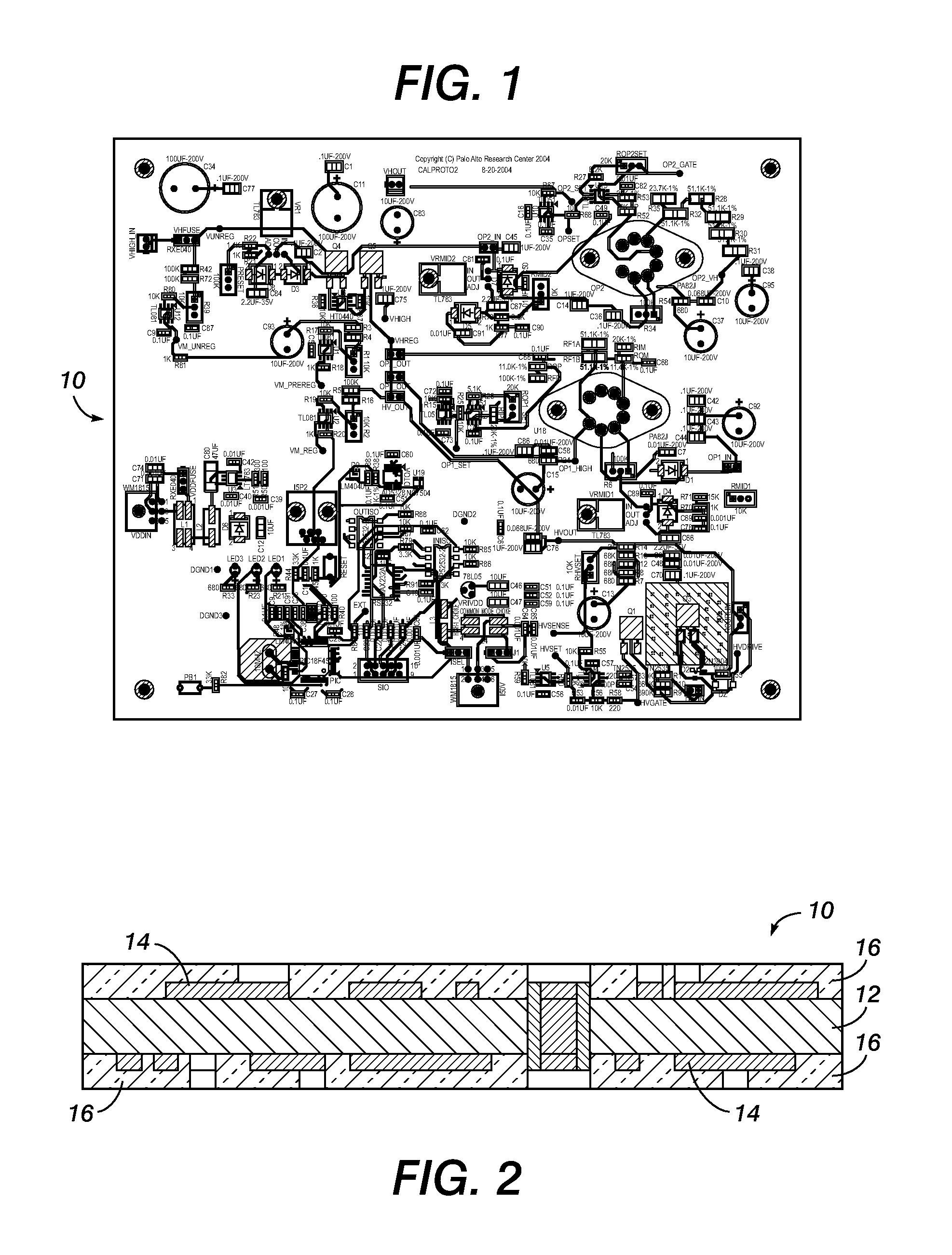

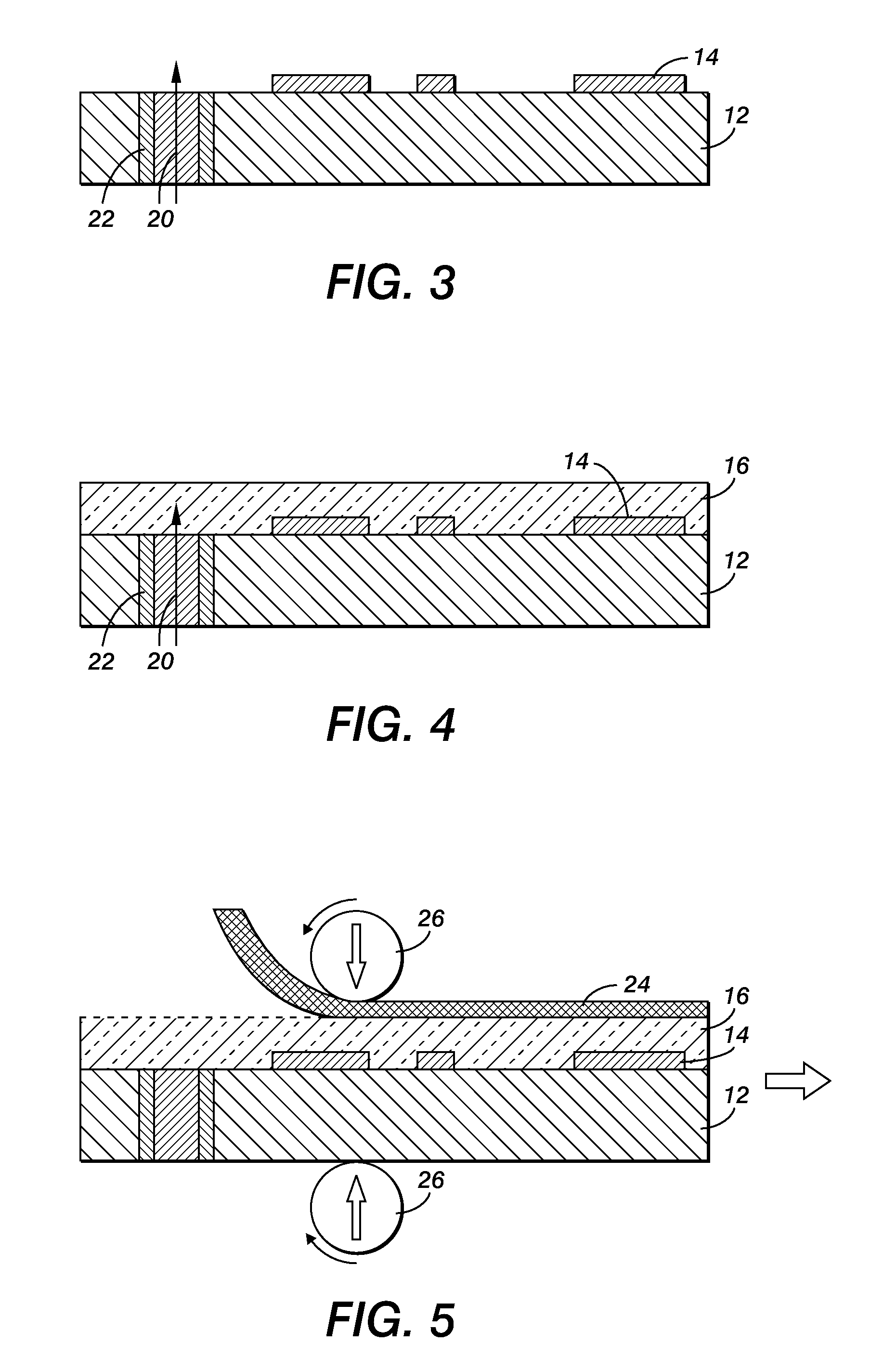

System and method for manufacturing printed circuit boards employing non-uniformly modified images

ActiveUS20050213806A1Non uniformCharacter and pattern recognitionCircuit board tools positioningEngineeringDigital control

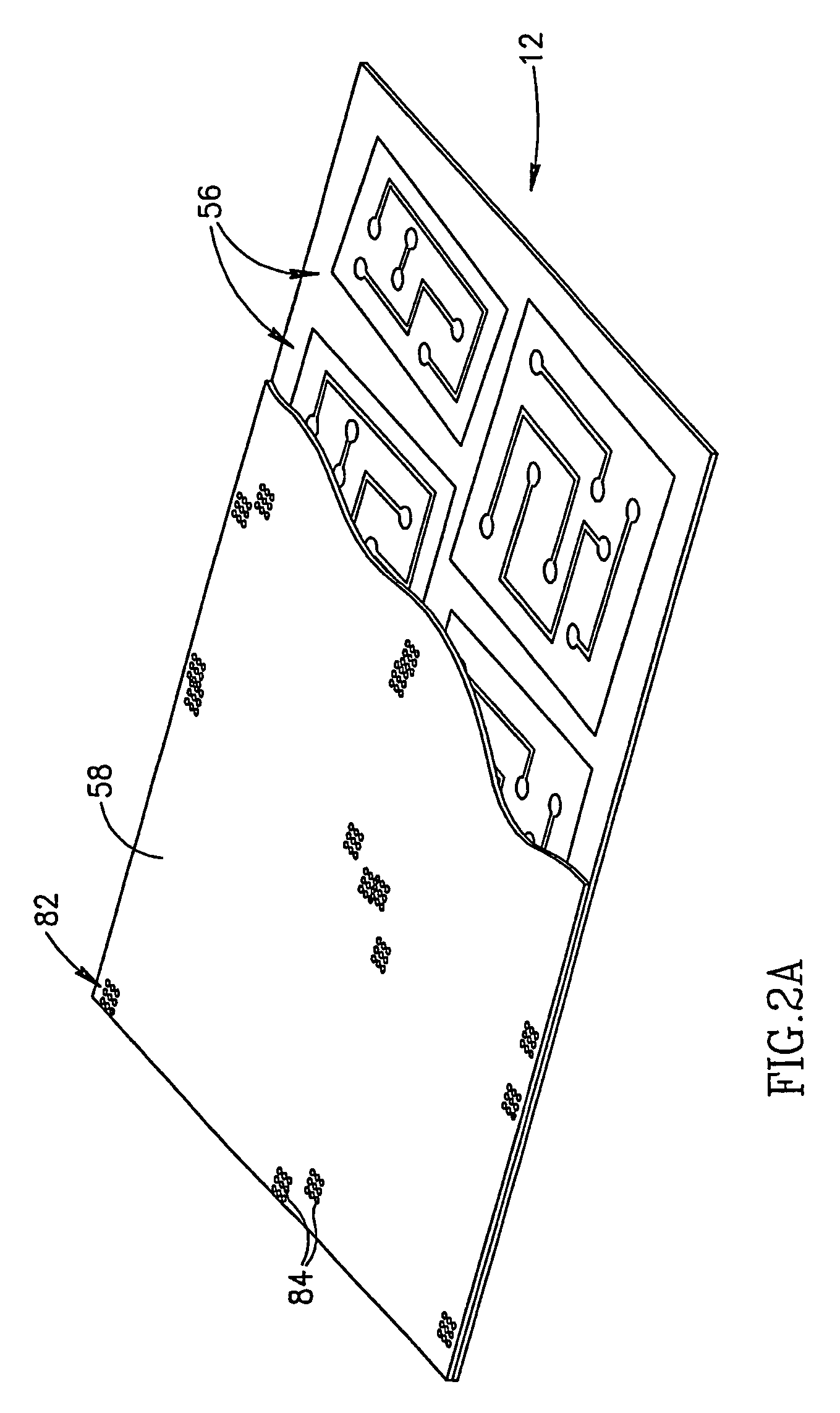

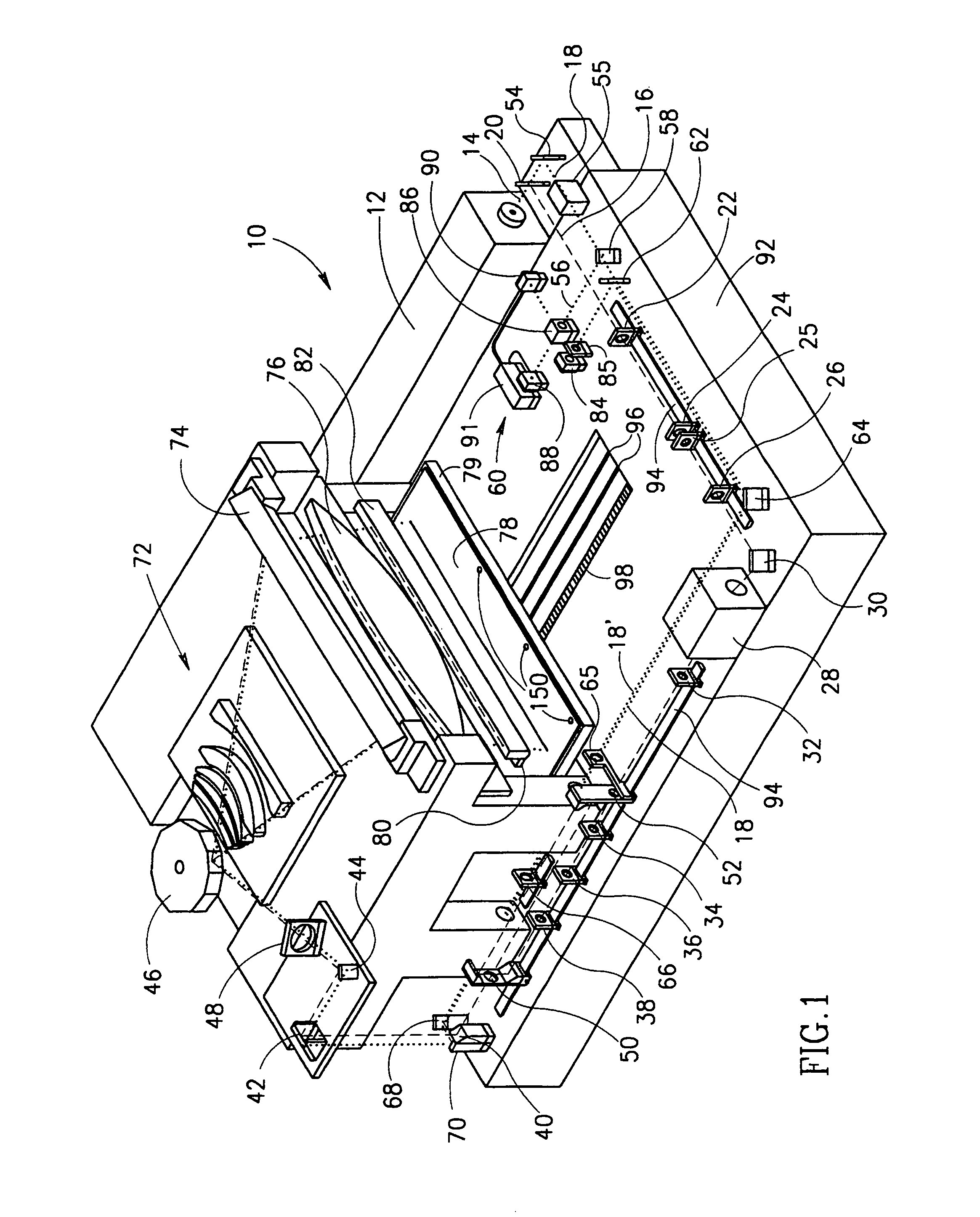

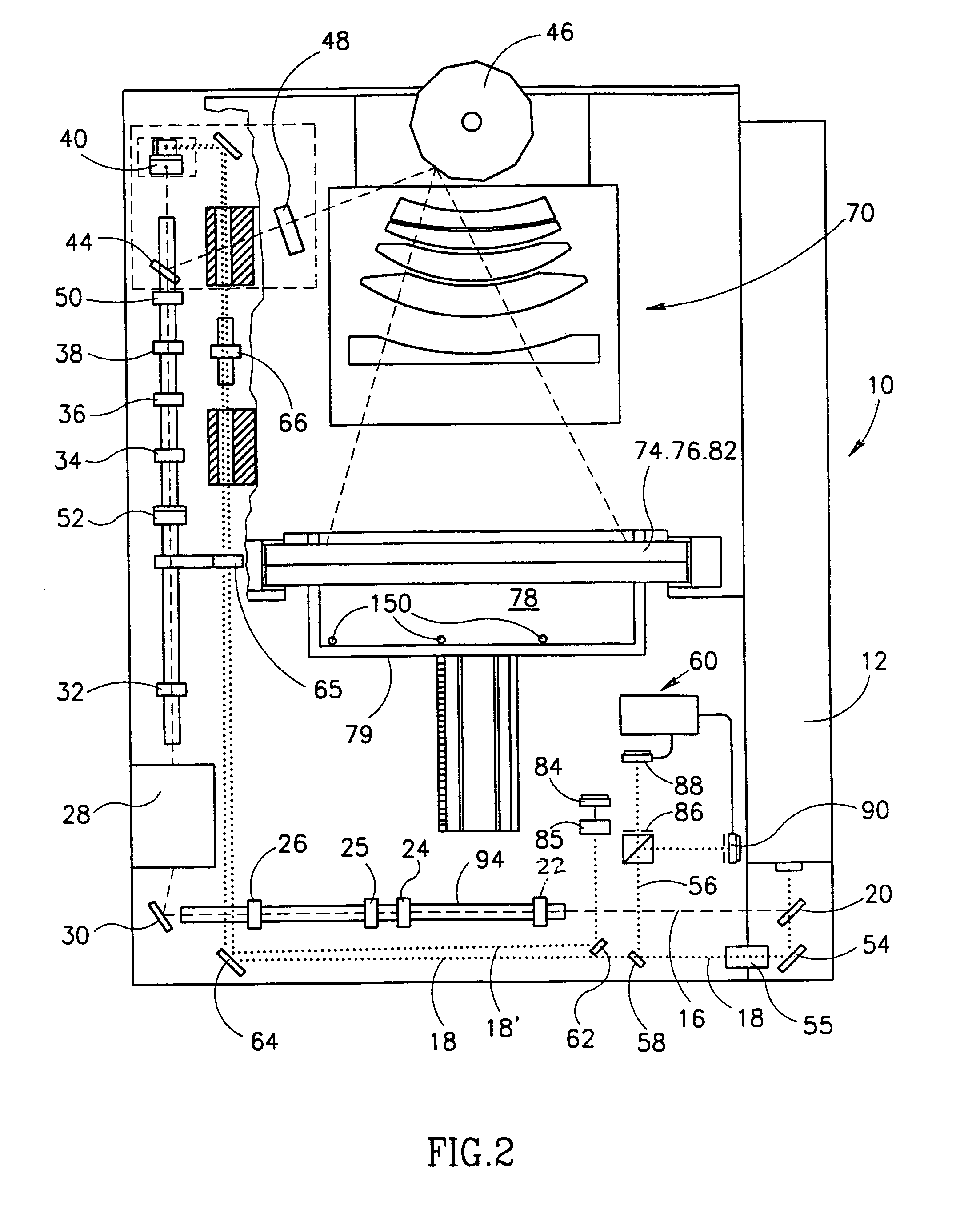

A system and method for fabricating an electrical circuit in which a digital control image (46) is generated by non-uniformly modifying (44) a representation of an electrical circuit (40), such that an electrical circuit pattern (72) recorded on a substrate (12) using the digital control image (46) precisely fits an already formed electrical circuit portion (62).

Owner:ORBOTECH LTD

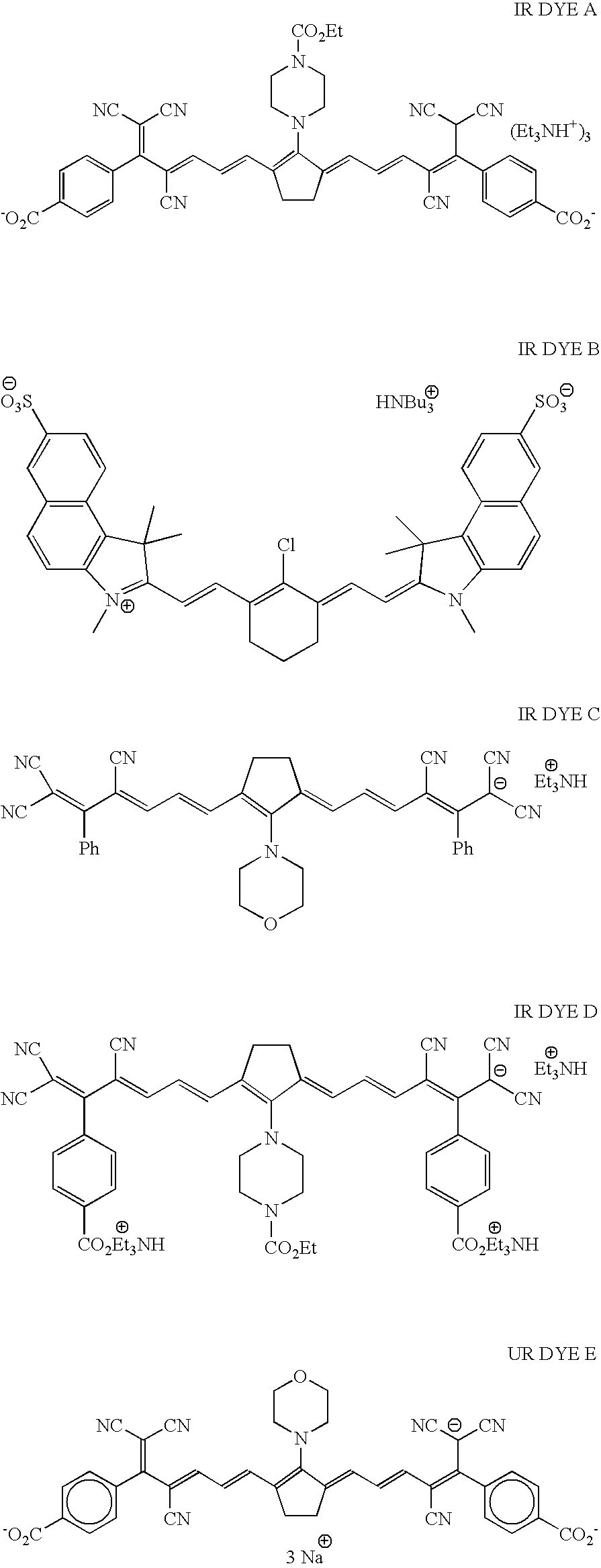

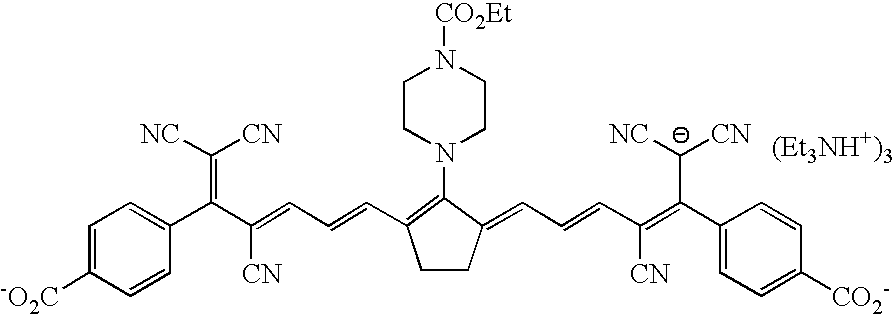

Nanopastes as patterning compositions for electronic parts

InactiveUS6921626B2Good dispersionLow viscosityRadiation applicationsSemiconductor/solid-state device manufacturingInorganic nanoparticlesElectrically conductive

The present invention provides methods of making an electronic part in which a nanopaste composed of inorganic nanoparticles and a carrier is applied onto a surface of a substrate. The composition is then processed to form an electrically conductive pattern area that adheres to the surface of the substrate. Optionally, the conductivity of the pattern area may be improved by heating.

Owner:KODAK POLYCHROME GRAPHICS

System and method for manufacturing printed circuit boards employing non-uniformly modified images

ActiveUS7508515B2Circuit board tools positioningCharacter and pattern recognitionEngineeringDigital control

A system and method for fabricating an electrical circuit in which a digital control image (46) is generated by non-uniformly modifying (44) a representation of an electrical circuit (40), such that an electrical circuit pattern (72) recorded on a substrate (12) using the digital control image (46) precisely fits an already formed electrical circuit portion (62).

Owner:ORBOTECH LTD

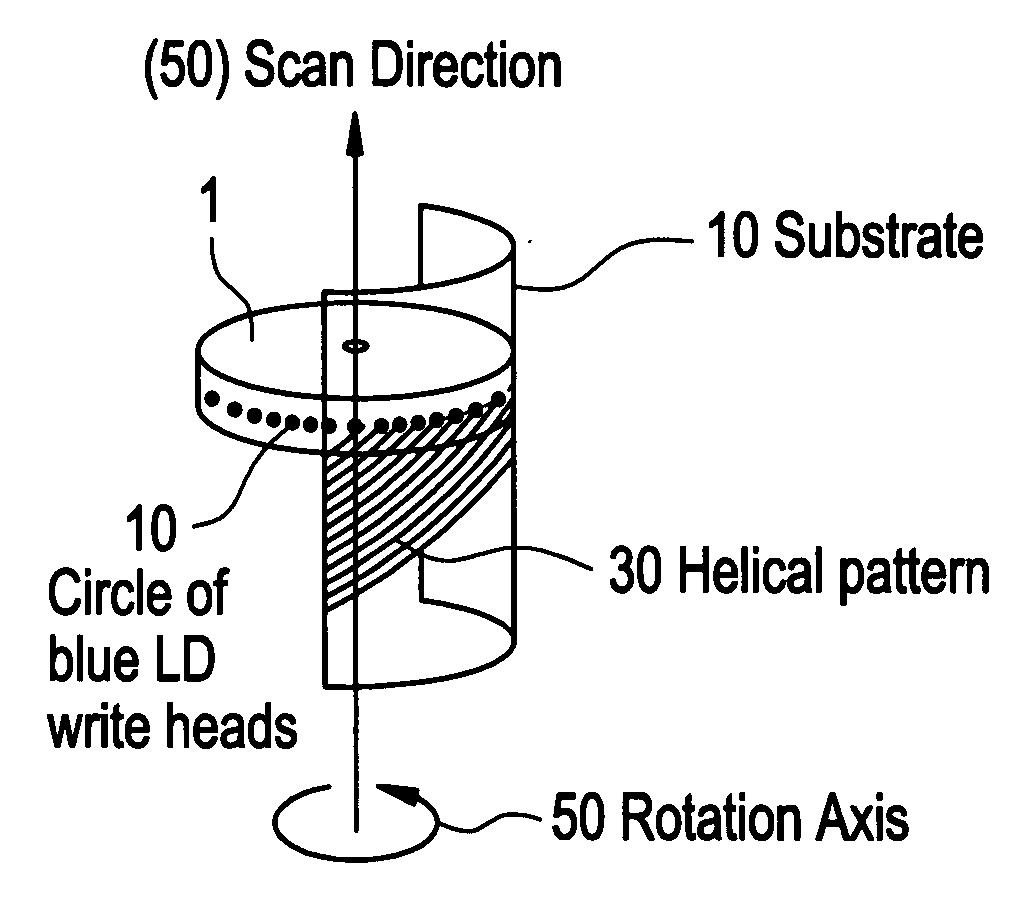

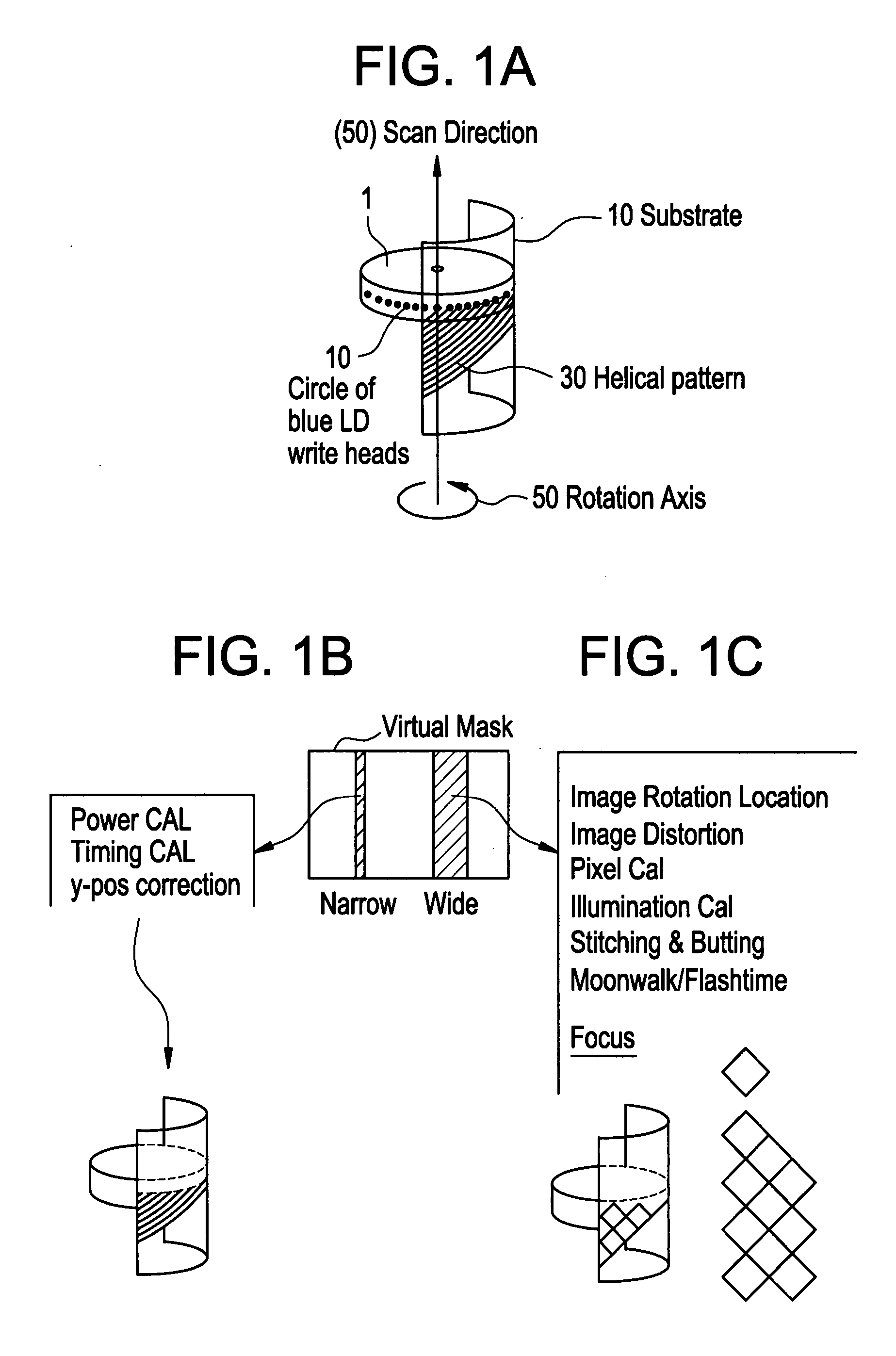

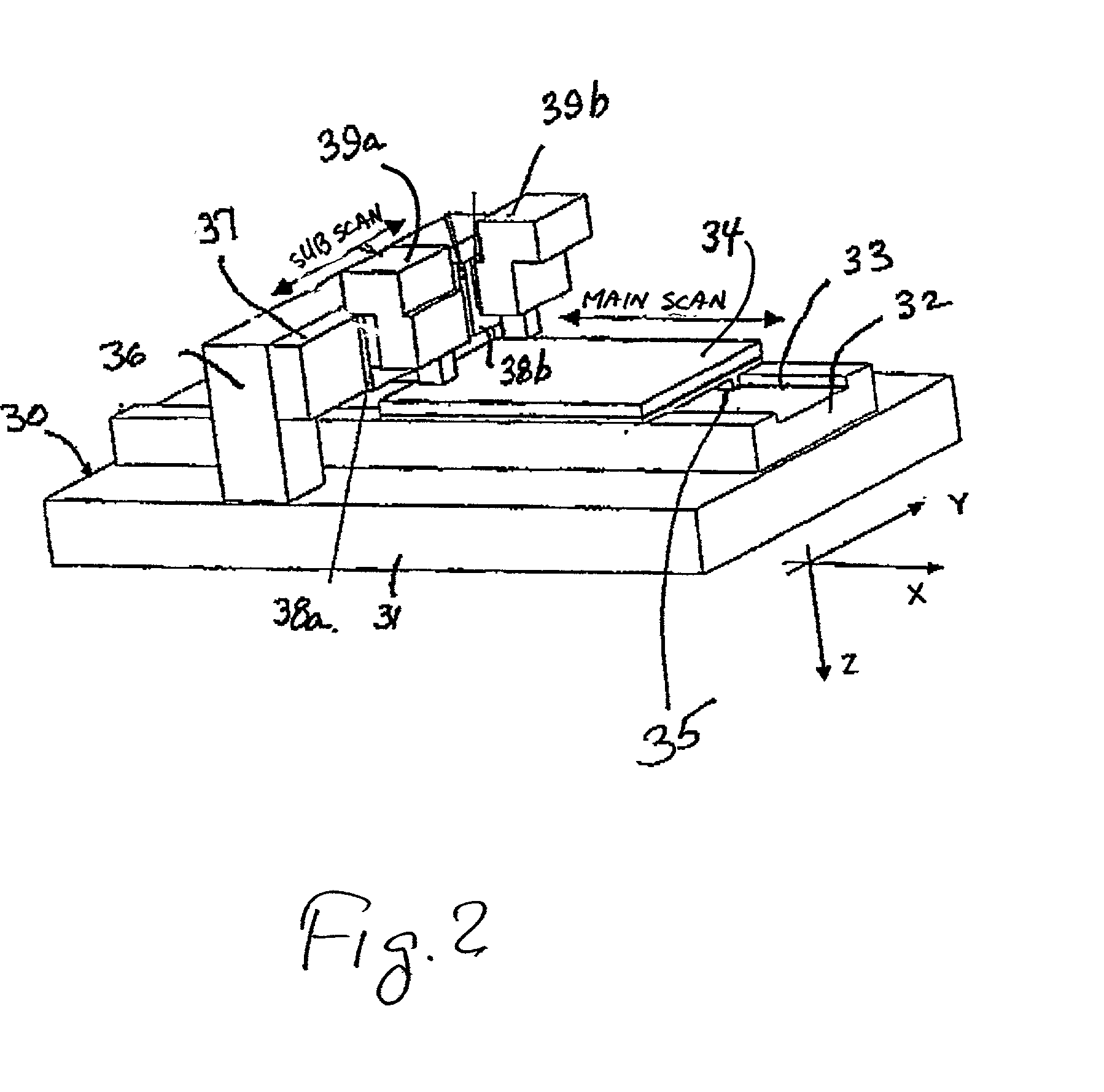

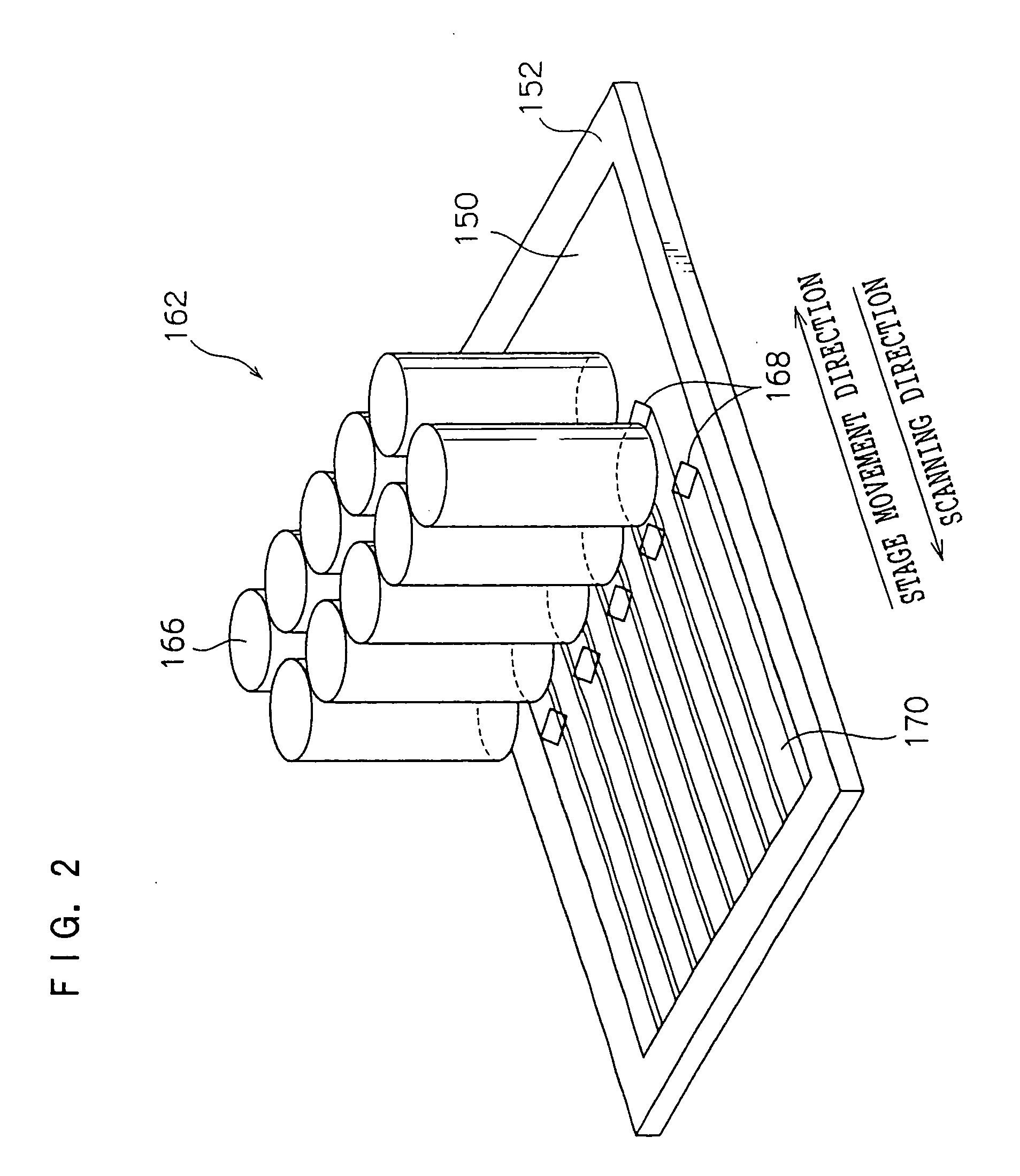

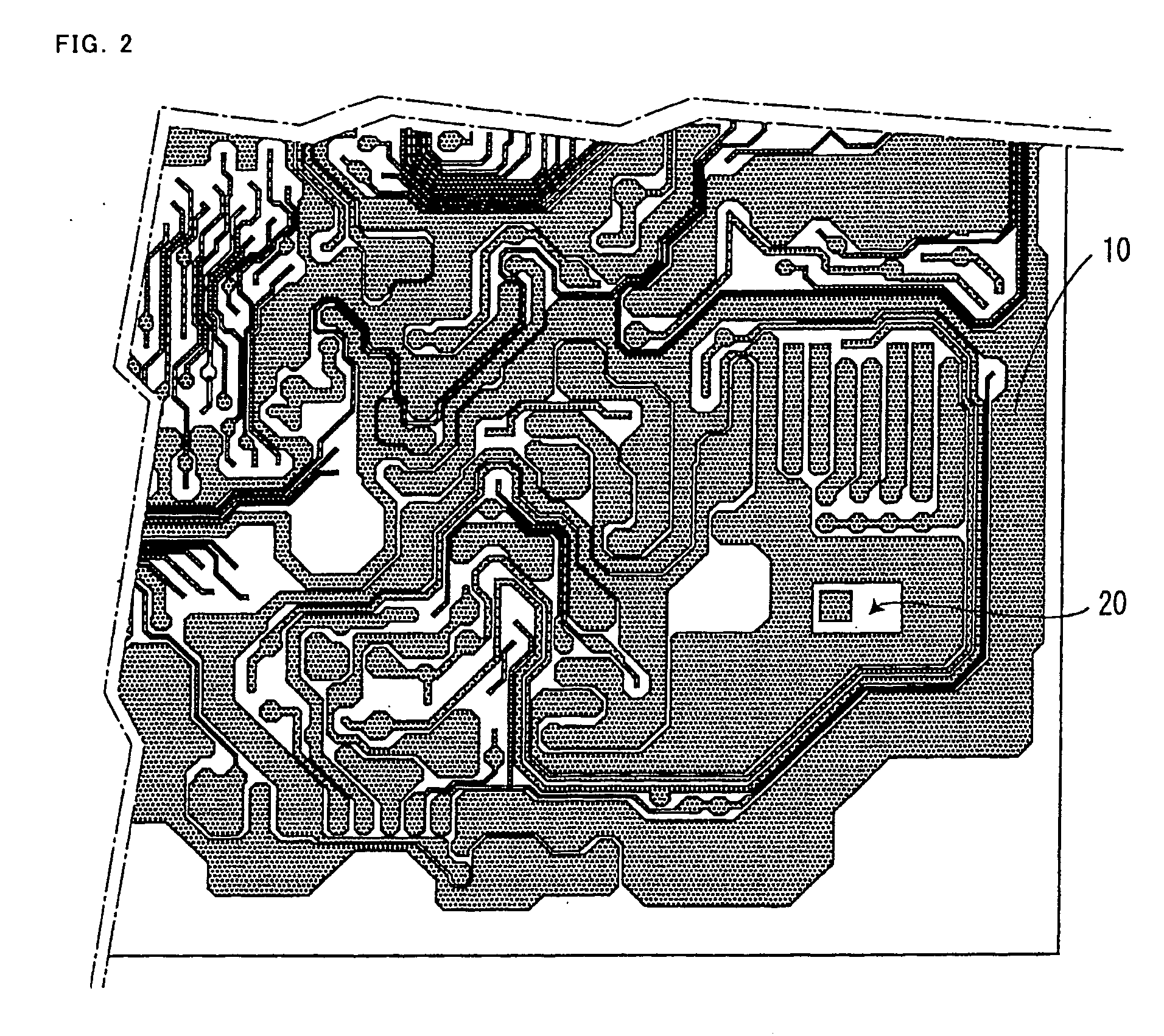

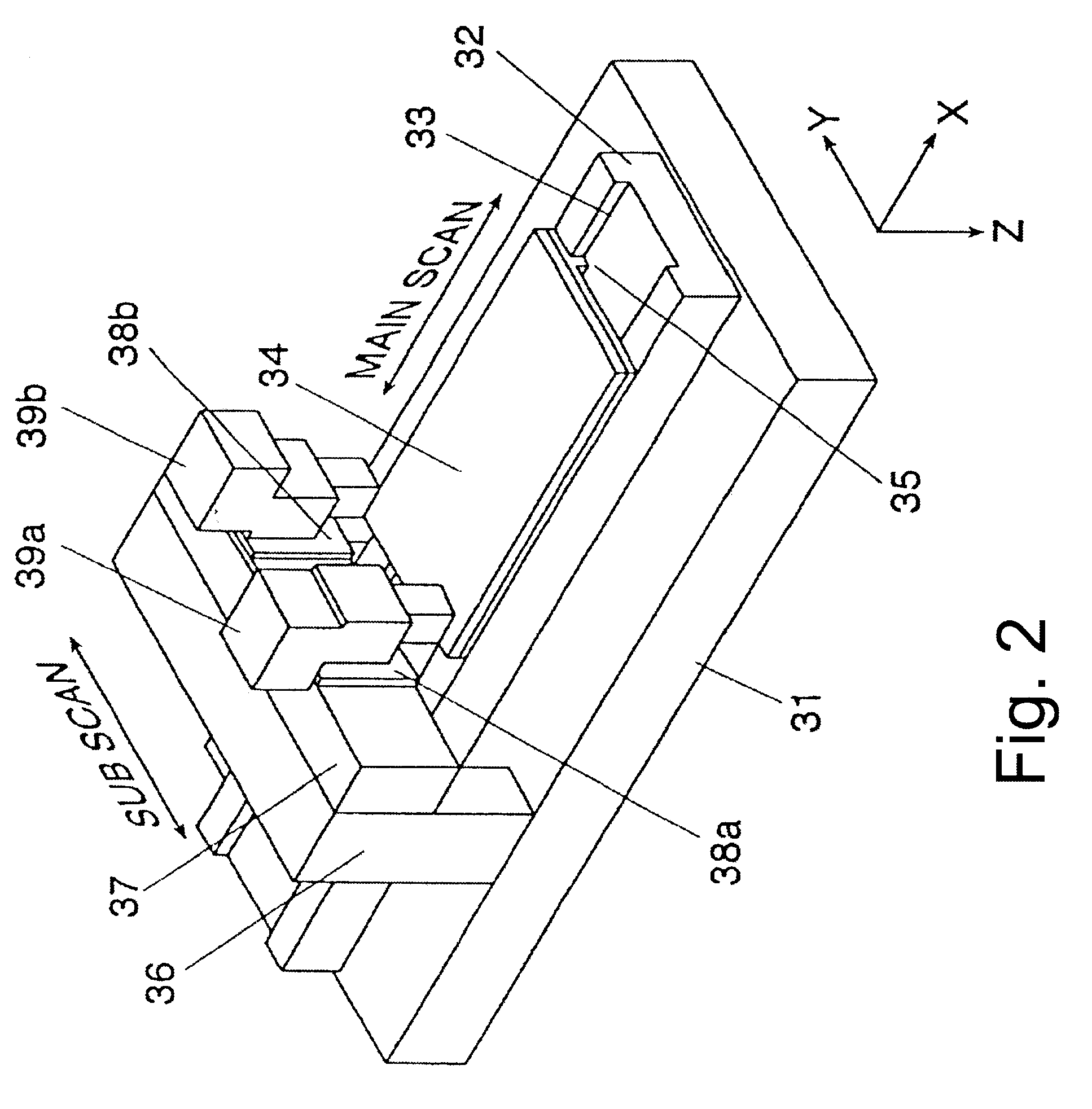

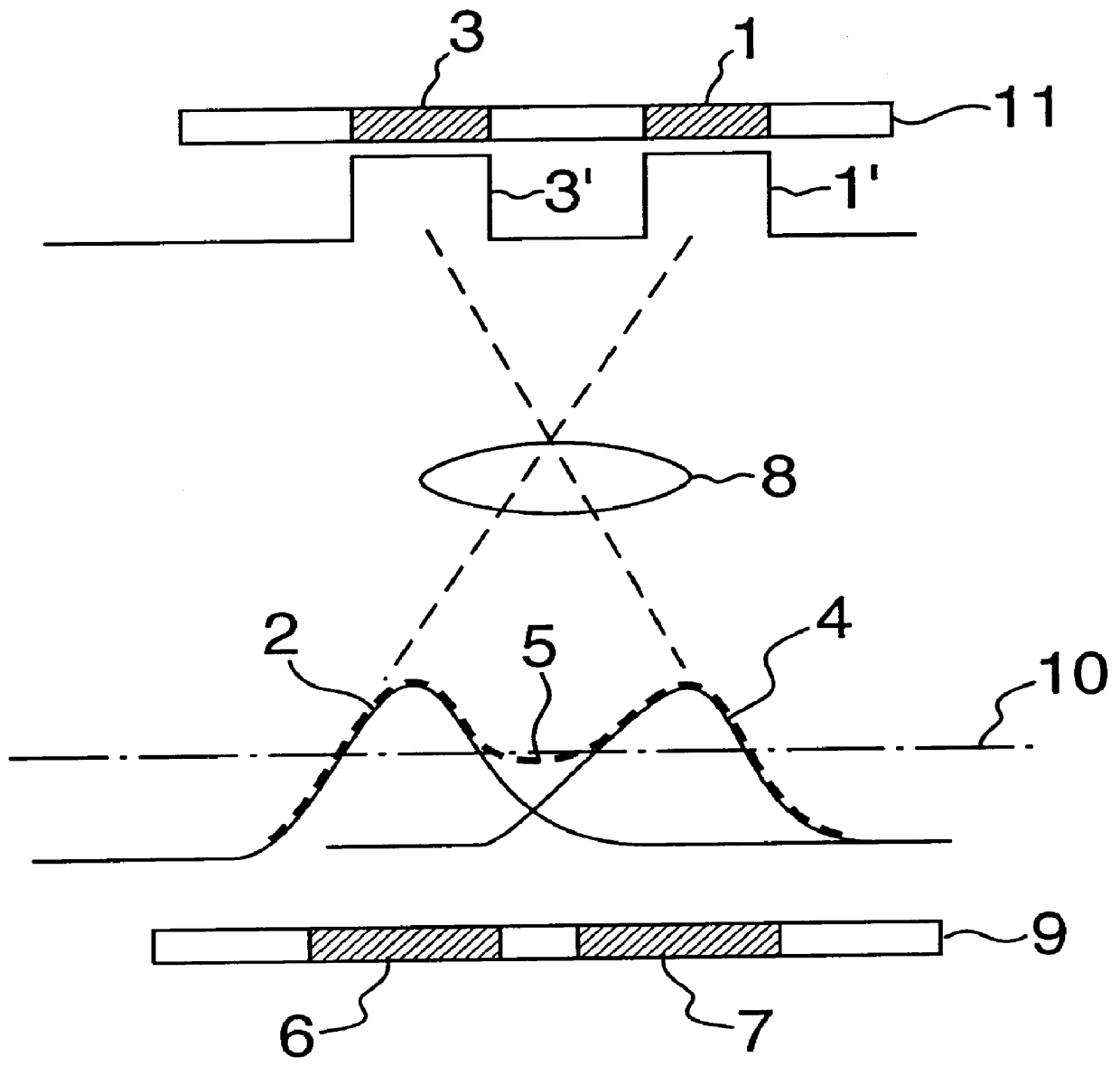

Scanner system

InactiveUS7046266B1Reduce laser powerLose sensitivityElectrographic process apparatusPhotomechanical exposure apparatusSerial scanningLight beam

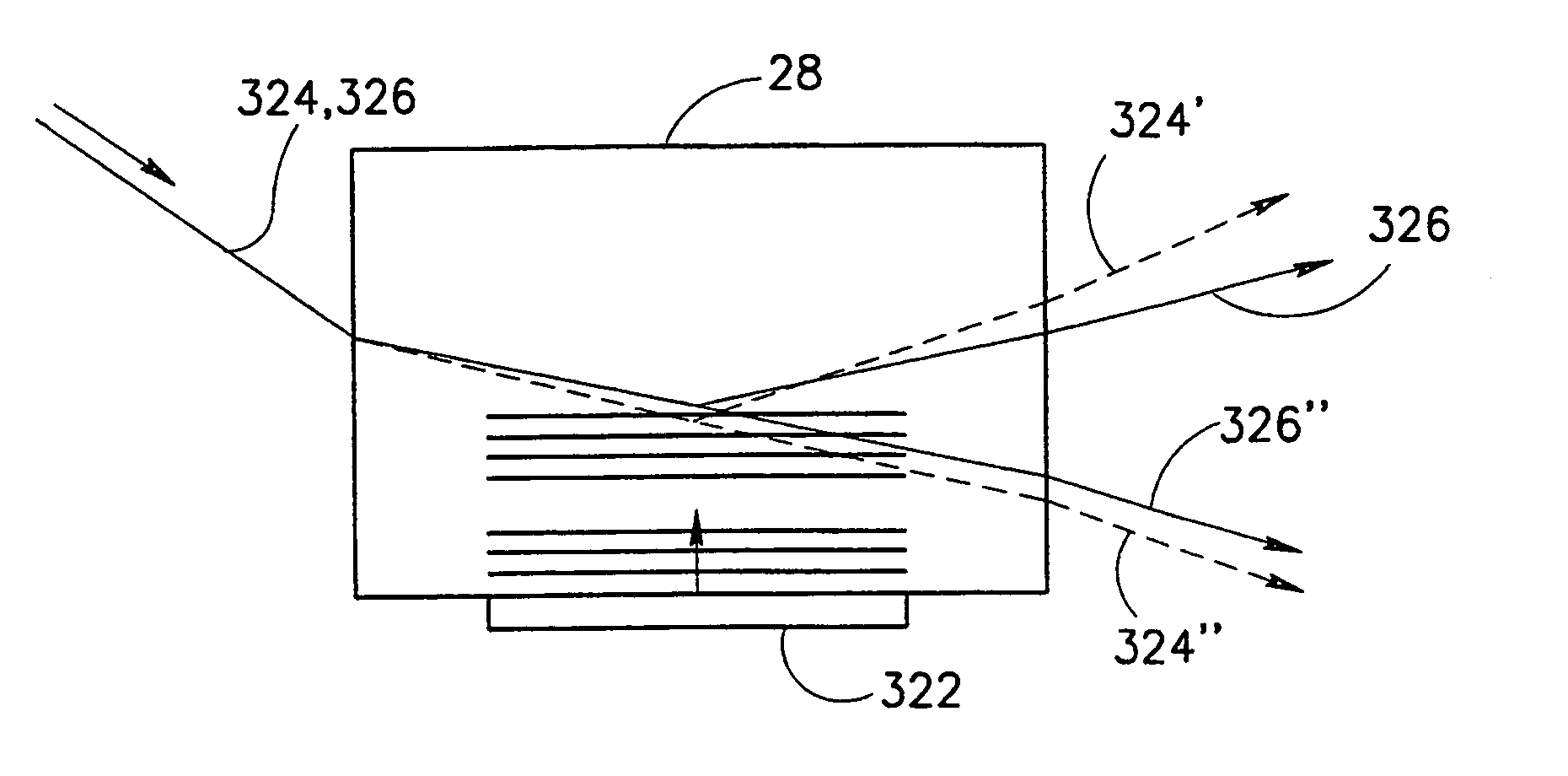

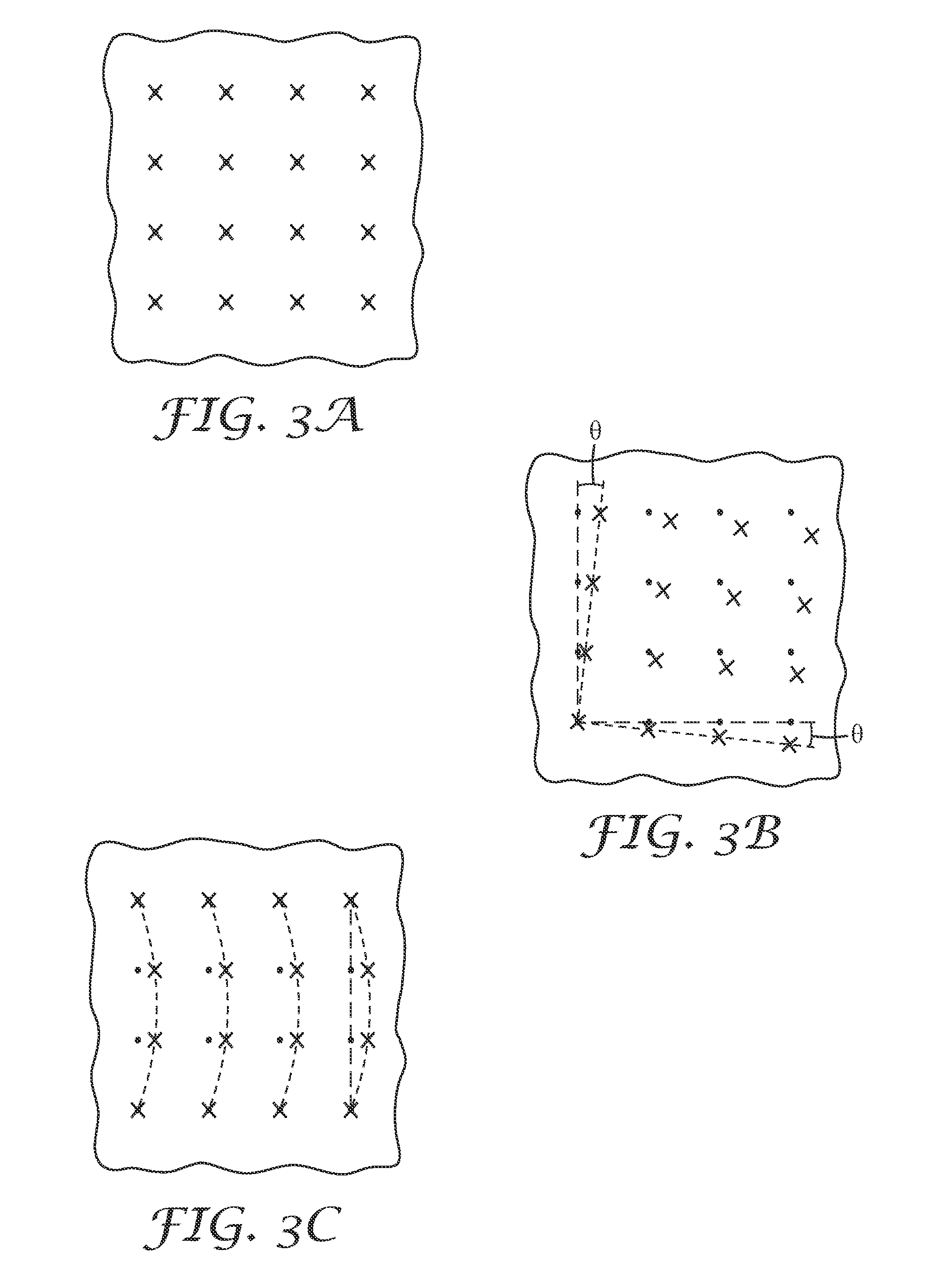

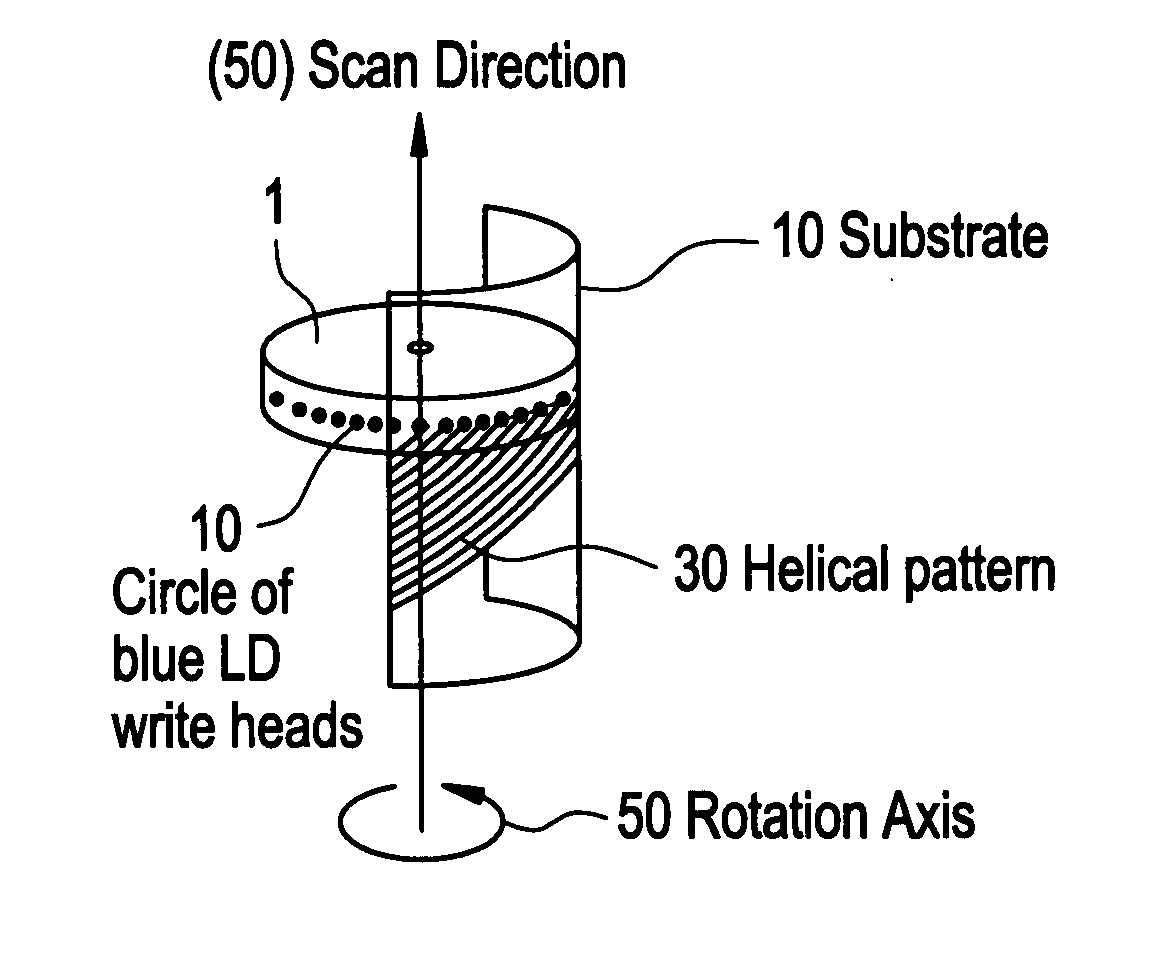

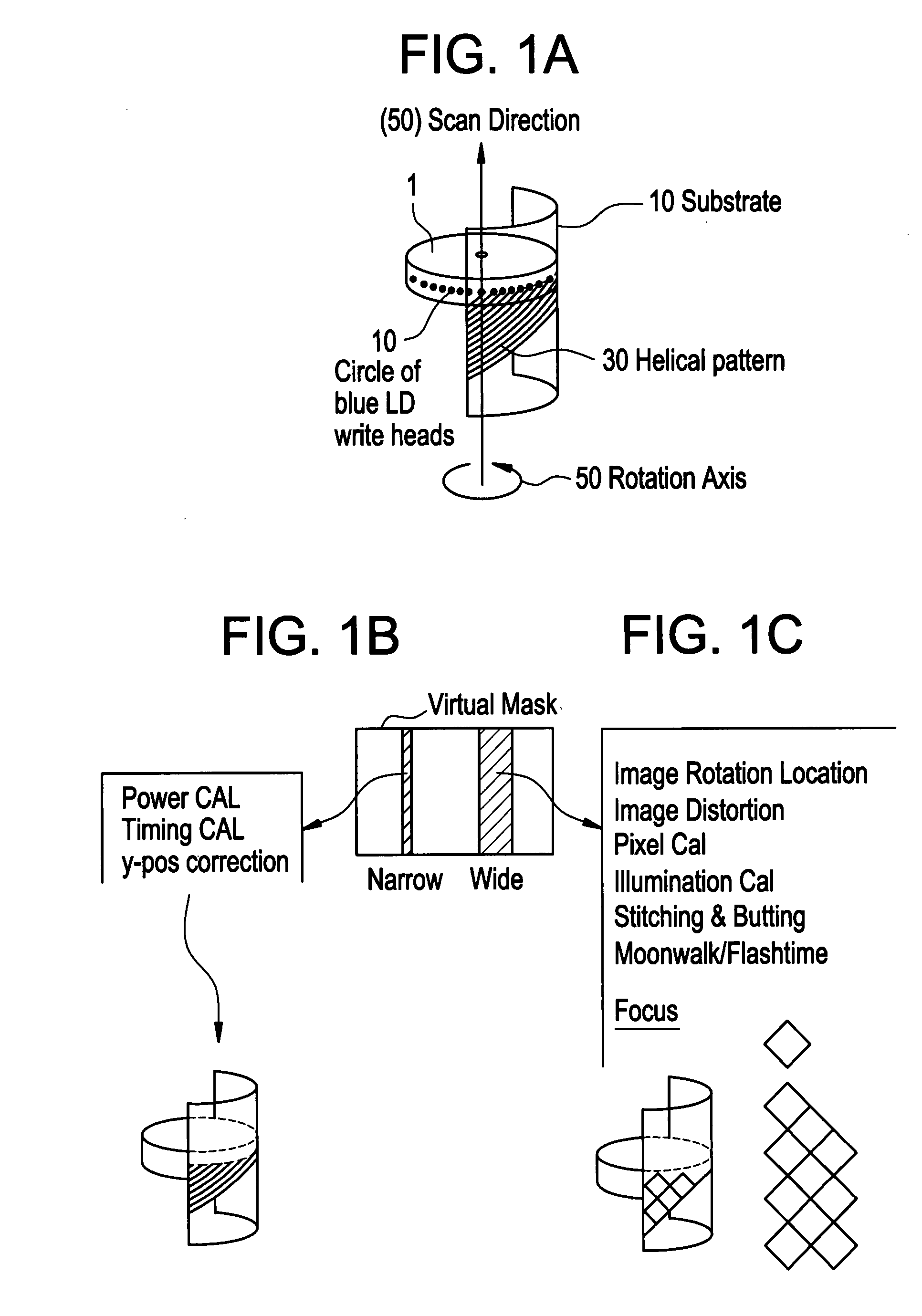

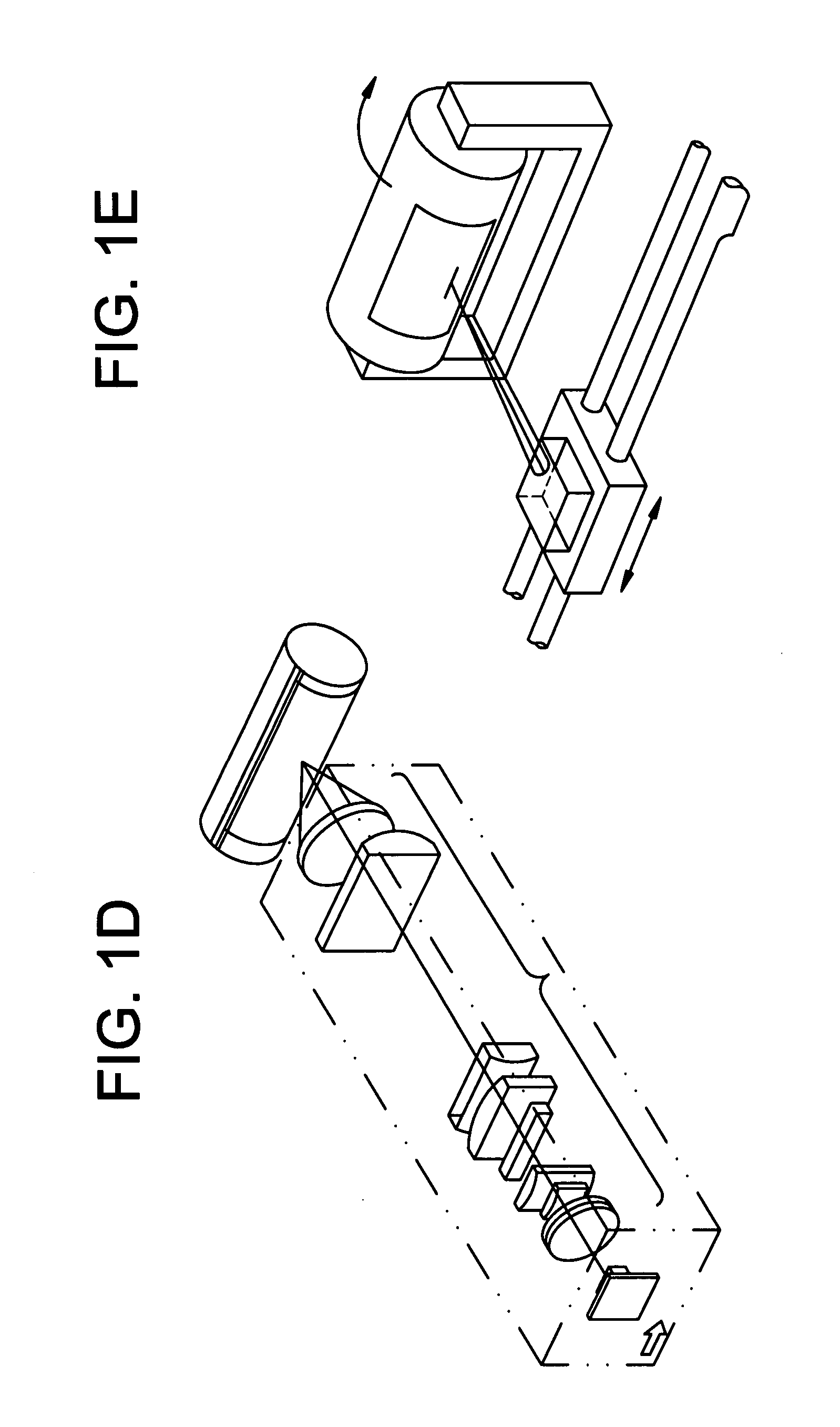

A method of scanning for writing a pattern on a surface, including providing a scanning beam comprised of a plurality of independently addressable sub-beams, scanning the surface with the scanning beam a plurality of times, the sub-beams scanning the surface side-by-side in the cross-scan direction, each sub-beam being modulated to reflect information to be written, and overlapping the beams in successive scans in the cross scan direction such that all written areas of the surface are written on during at least two scans.

Owner:LASER IMAGING SYST

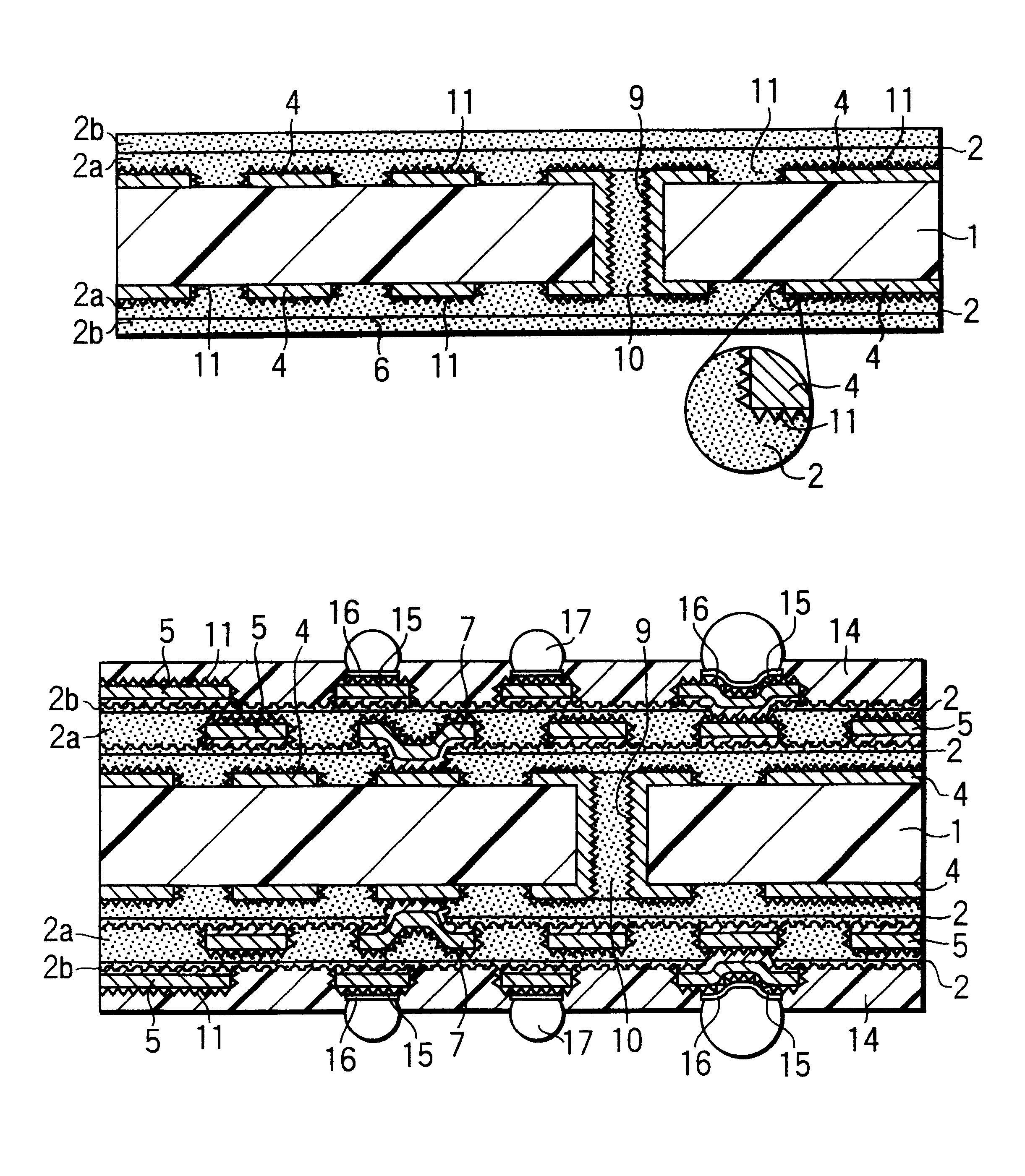

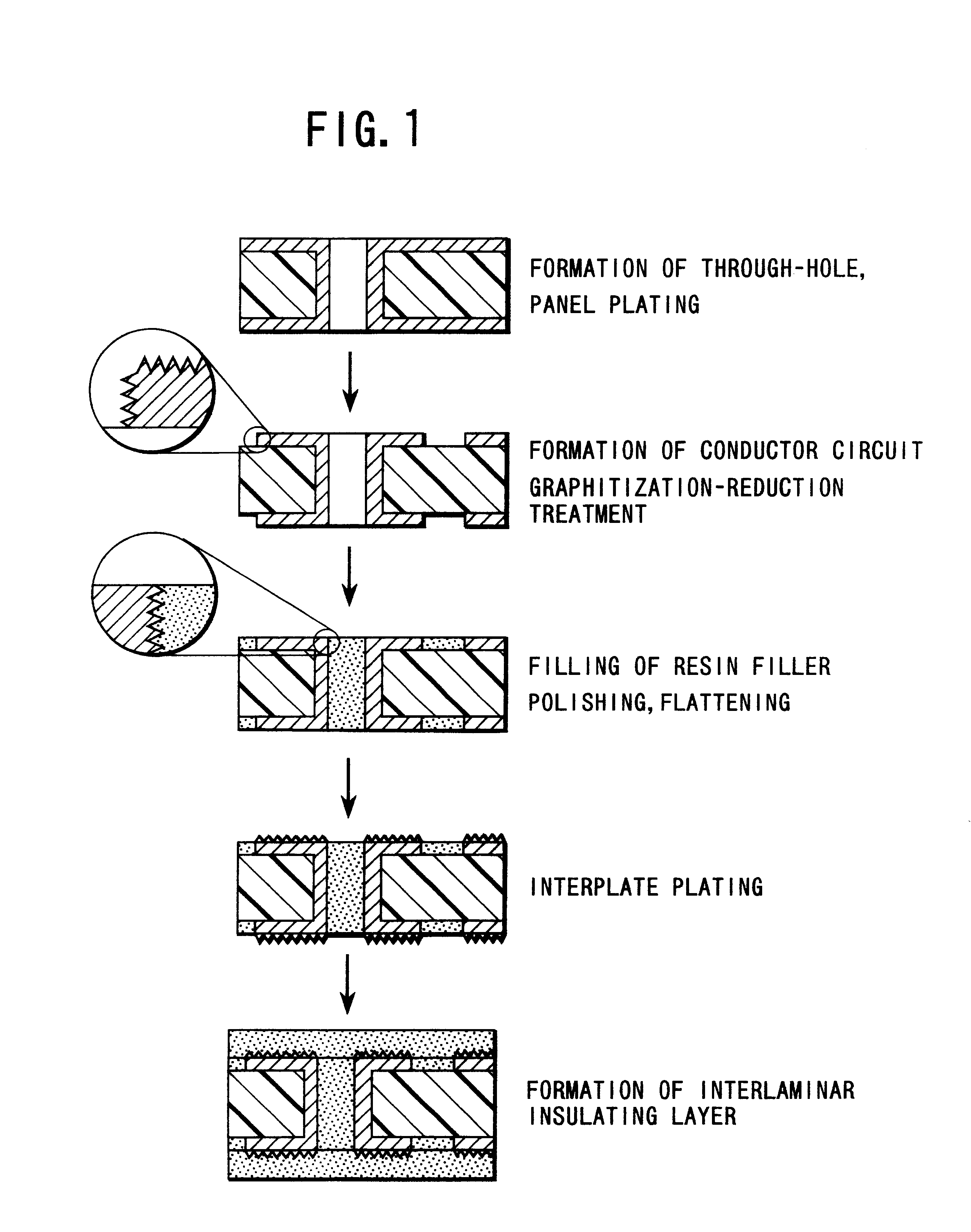

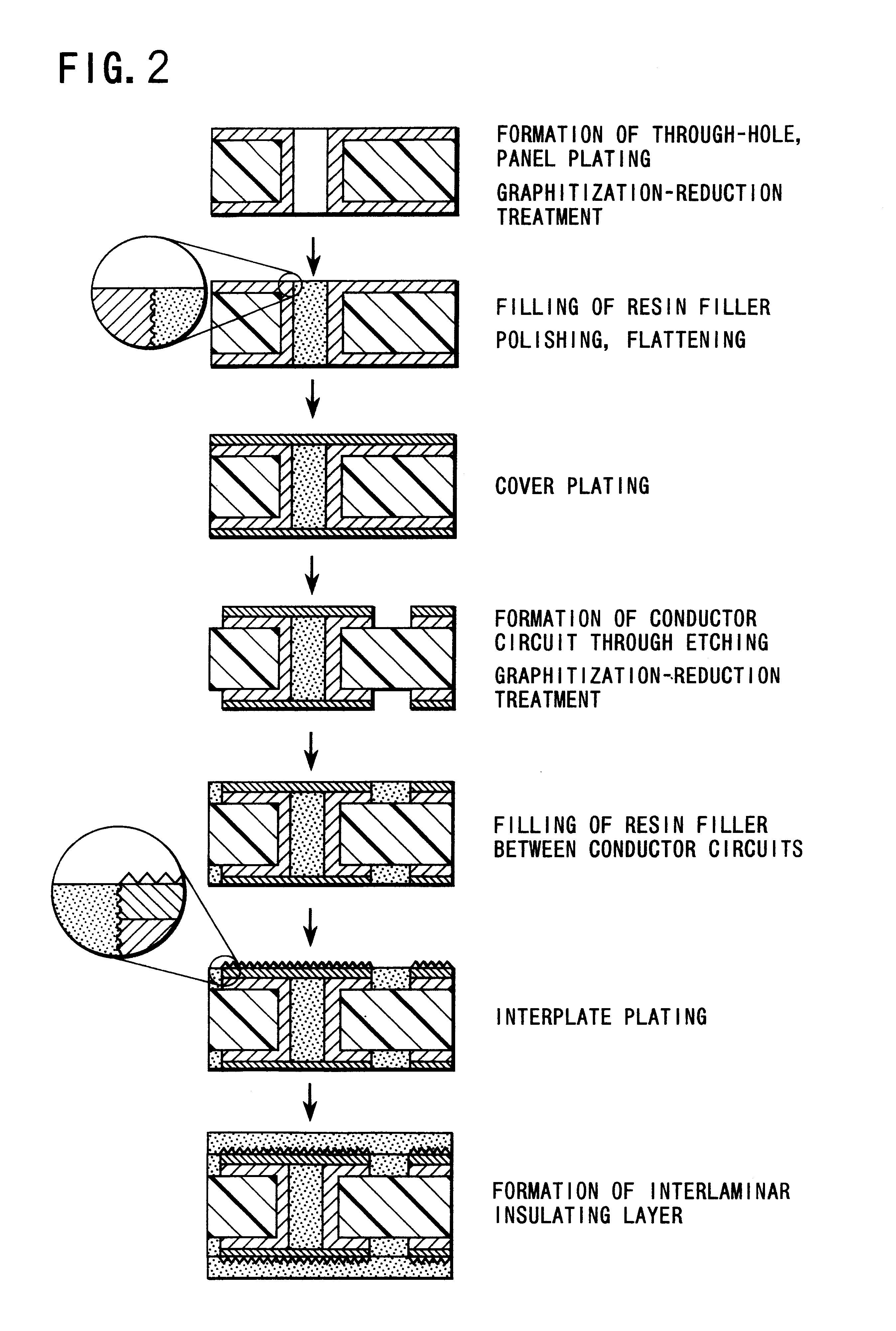

Multilayer printed wiring board having a roughened inner conductor layer and production method thereof

InactiveUS6512186B1Low peel strengthPoor mountingInsulating substrate metal adhesion improvementTransparent dielectricsCrack resistanceElectrical conductor

A multilayer printed wiring board has such a structure that conductor circuit patterns are formed on a core substrate through interlaminar resin insulating layers and through-holes are formed in the core substrate and a filler is filled in the through-hole. The interlaminar resin insulating layer formed on the substrate is flat and the same kind of roughened layer is formed on the conductor circuit pattern on the substrate over a full surface including a side surface thereof. A cover plated layer is formed just above the through-hole, and the roughened layers are formed on the conductor layer and the conductor circuit pattern located at the same level as the conductor layer over a full surface including side surfaces thereof, and the interlaminar resin insulating layer is formed so as to cover the surfaces of these roughened layers and filled in recess portions between the conductors and flattened on its surface. Thus, it is excellent in the crack resistance under heat cycle condition or the like and does not cause the damage of the cover plated layer.

Owner:IBIDEN CO LTD

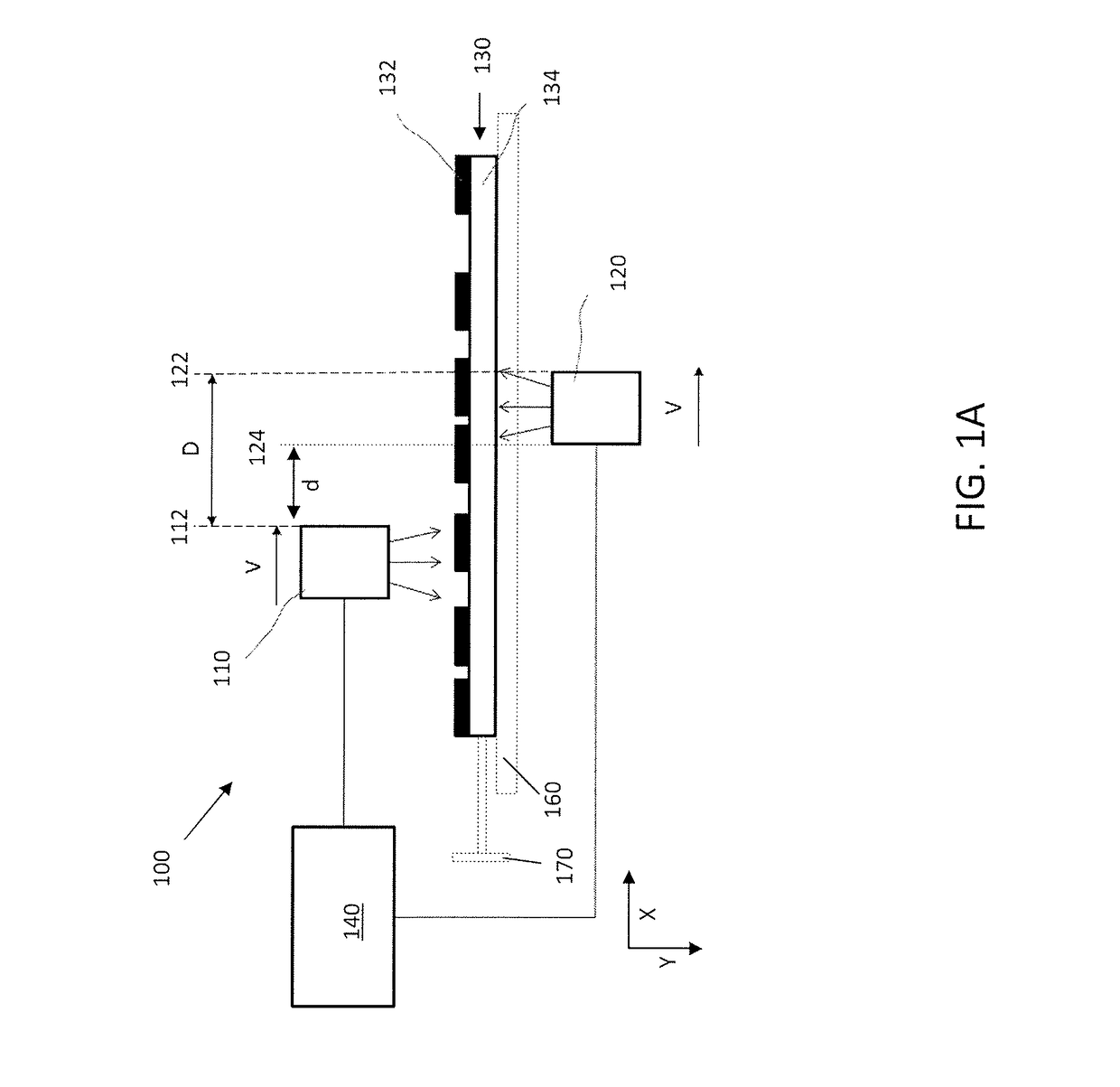

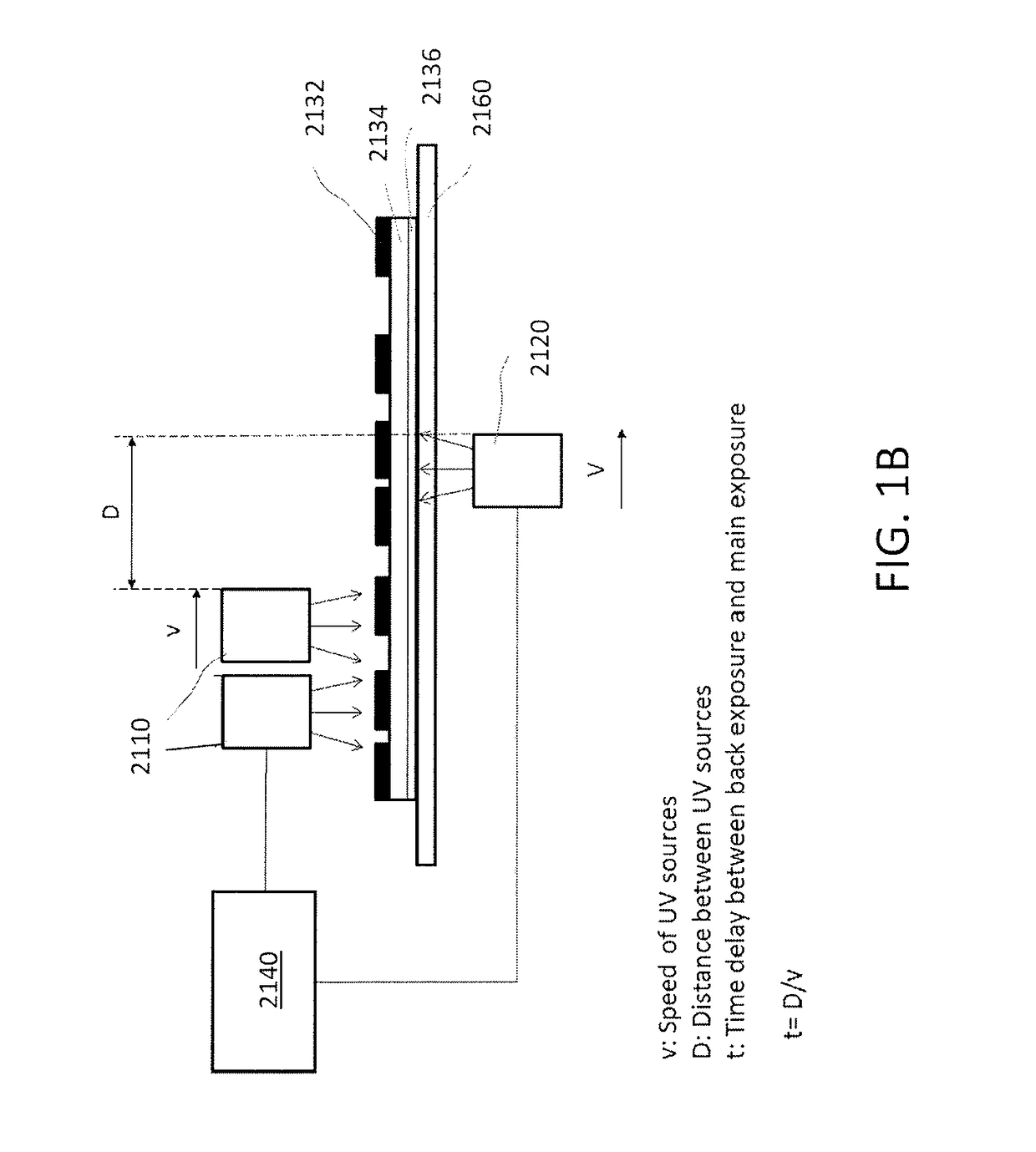

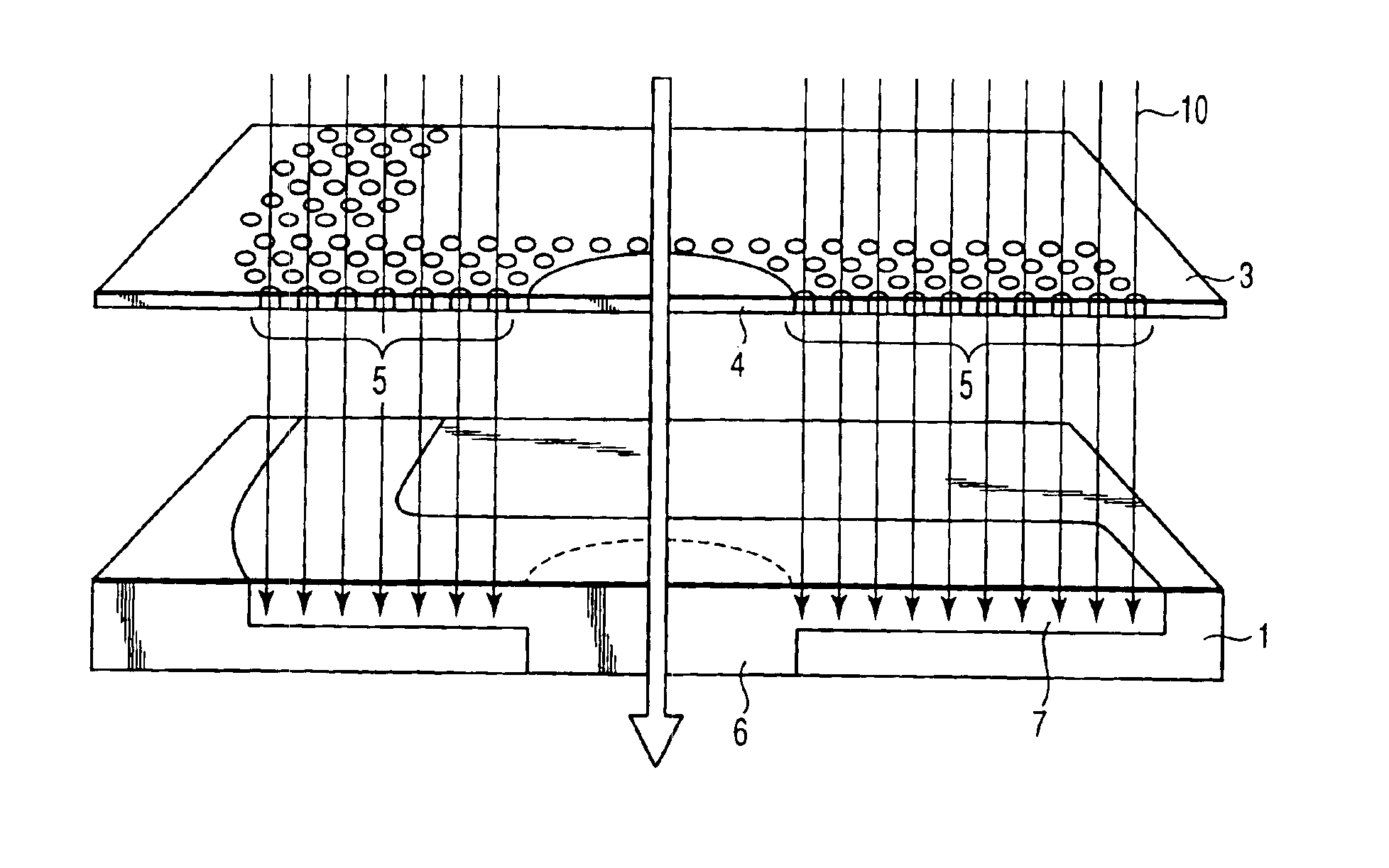

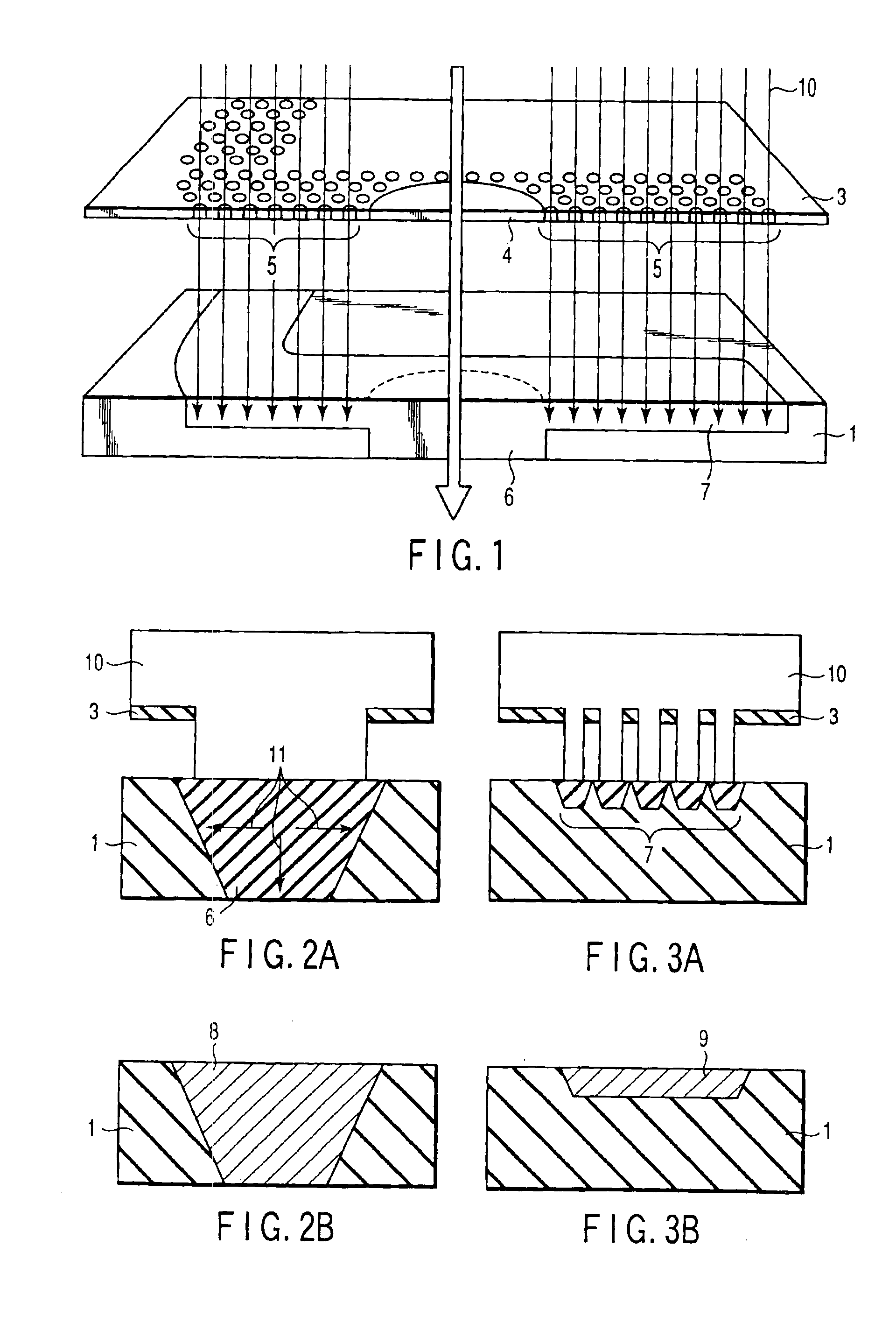

Process and apparatus for controlled exposure of flexographic printing plates and adjusting the floor thereof

ActiveUS20180210345A1Photomechanical exposure apparatusMicrolithography exposure apparatusSingle elementTime delays

A method and apparatus to expose photosensitive printing plates with a predetermined radiation density from the main side (top) and a predetermined radiation density from the back side (bottom). The method comprises executing the main exposure with a time delay after the back exposure. The time delay between back exposure and main exposure is optimized to create smaller stable single dot elements on the photosensitive printing plate after processing and smaller single element dot sizes printed on the print substrate. The plate floor may be adjusted by performing a back-side-only exposure prior to executing the combined back and main exposure with the time delay.

Owner:ESKO GRAPHICS IMAGING

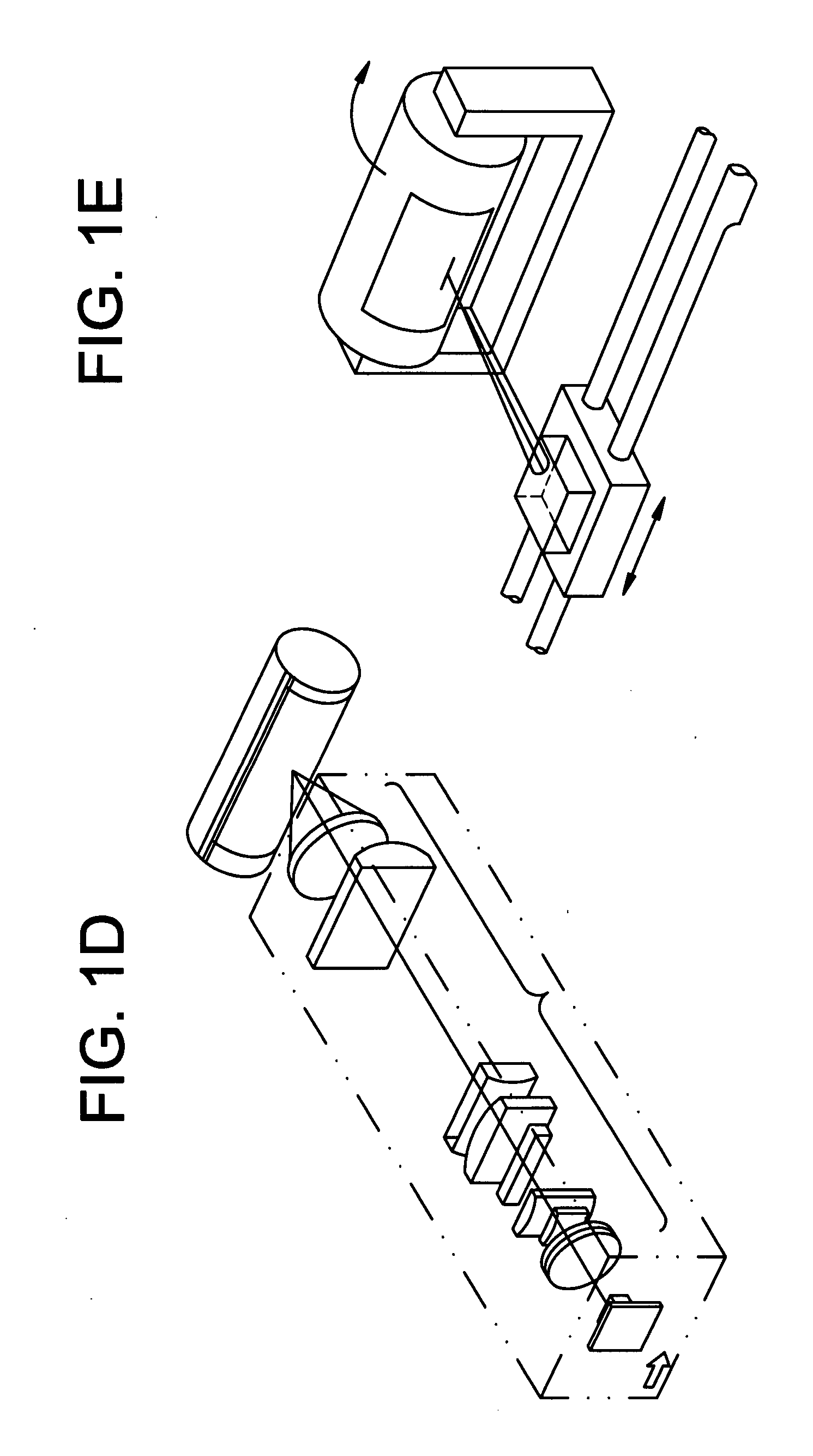

Writing apparatuses and methods

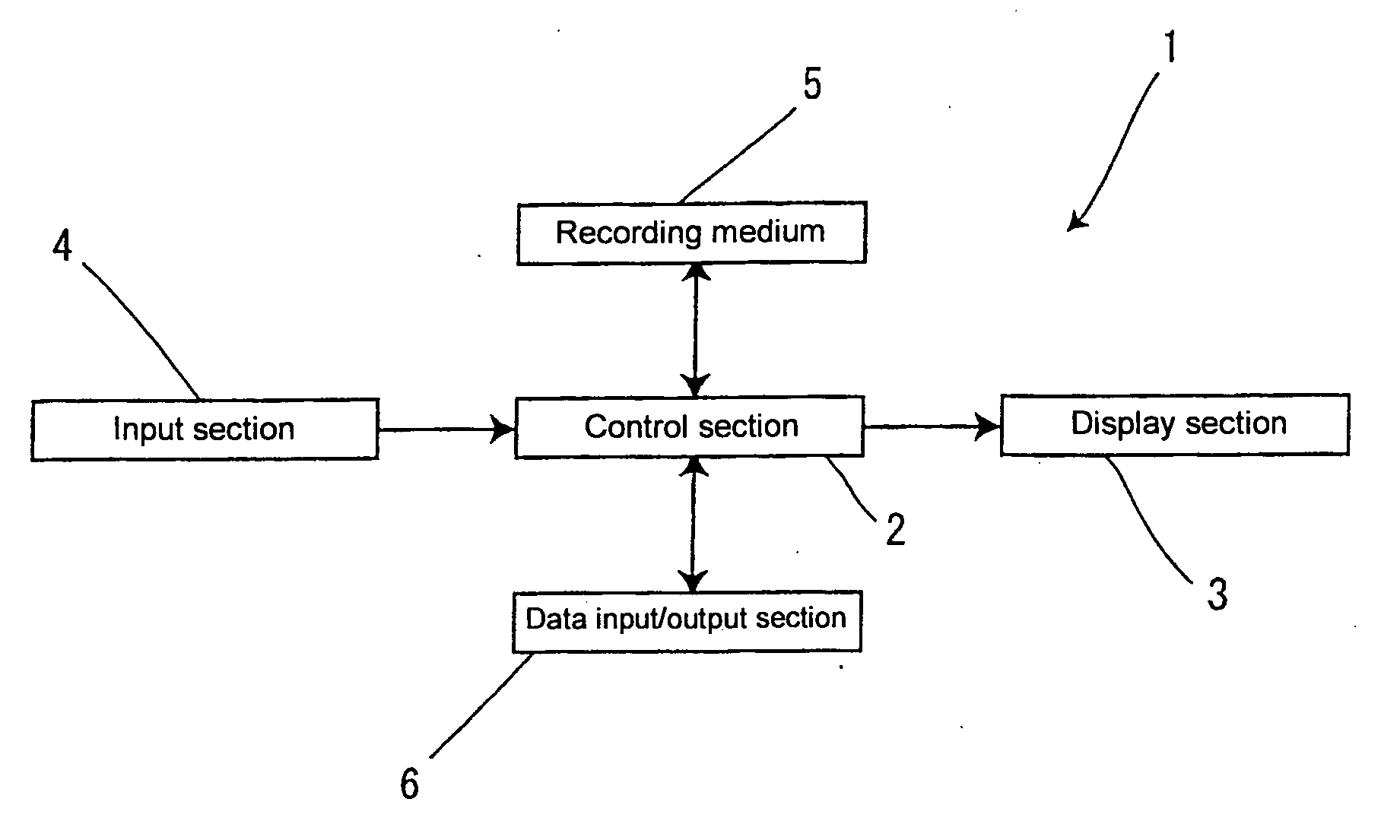

InactiveUS20070182808A1Simple methodIncrease heightRecording apparatusPhotomechanical exposure apparatusDisplay deviceEngineering

Owner:MICRONIC LASER SYST AB

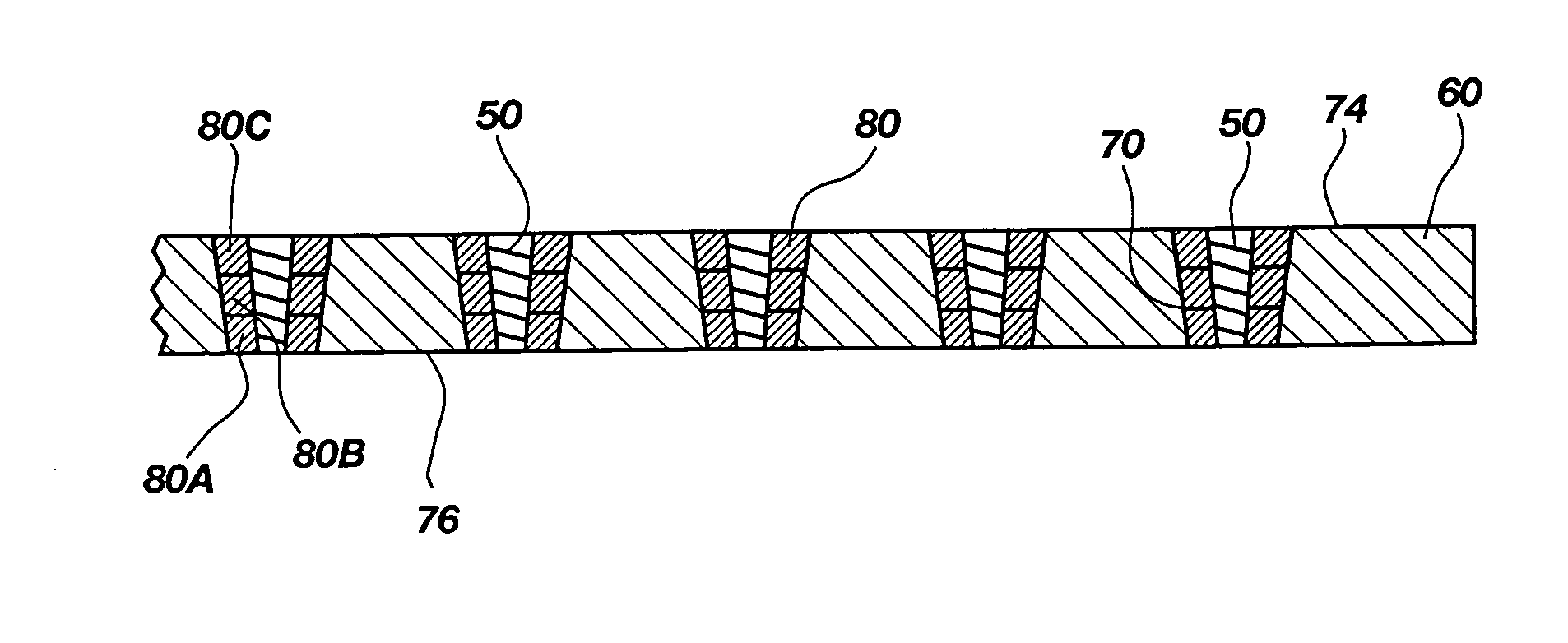

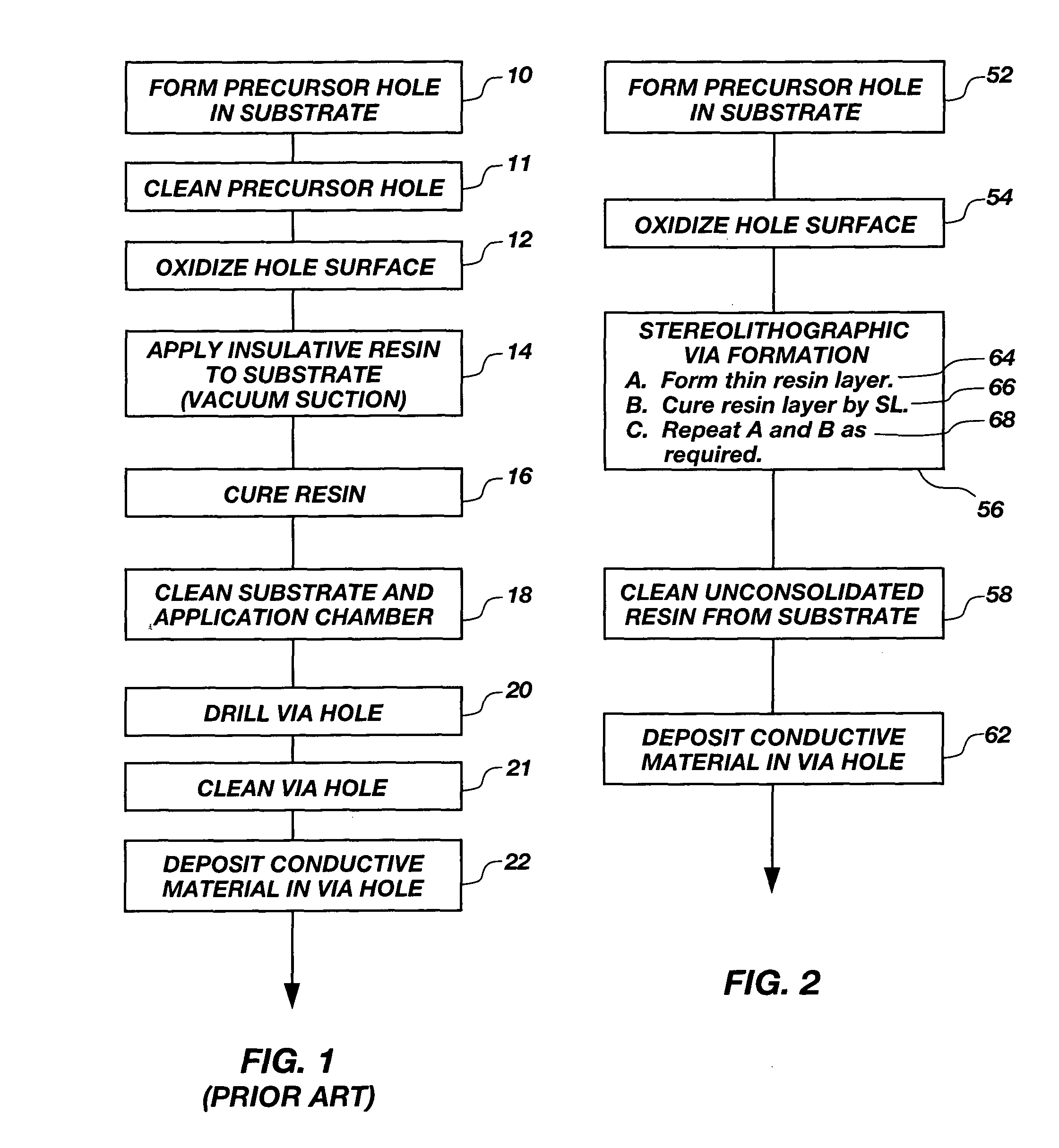

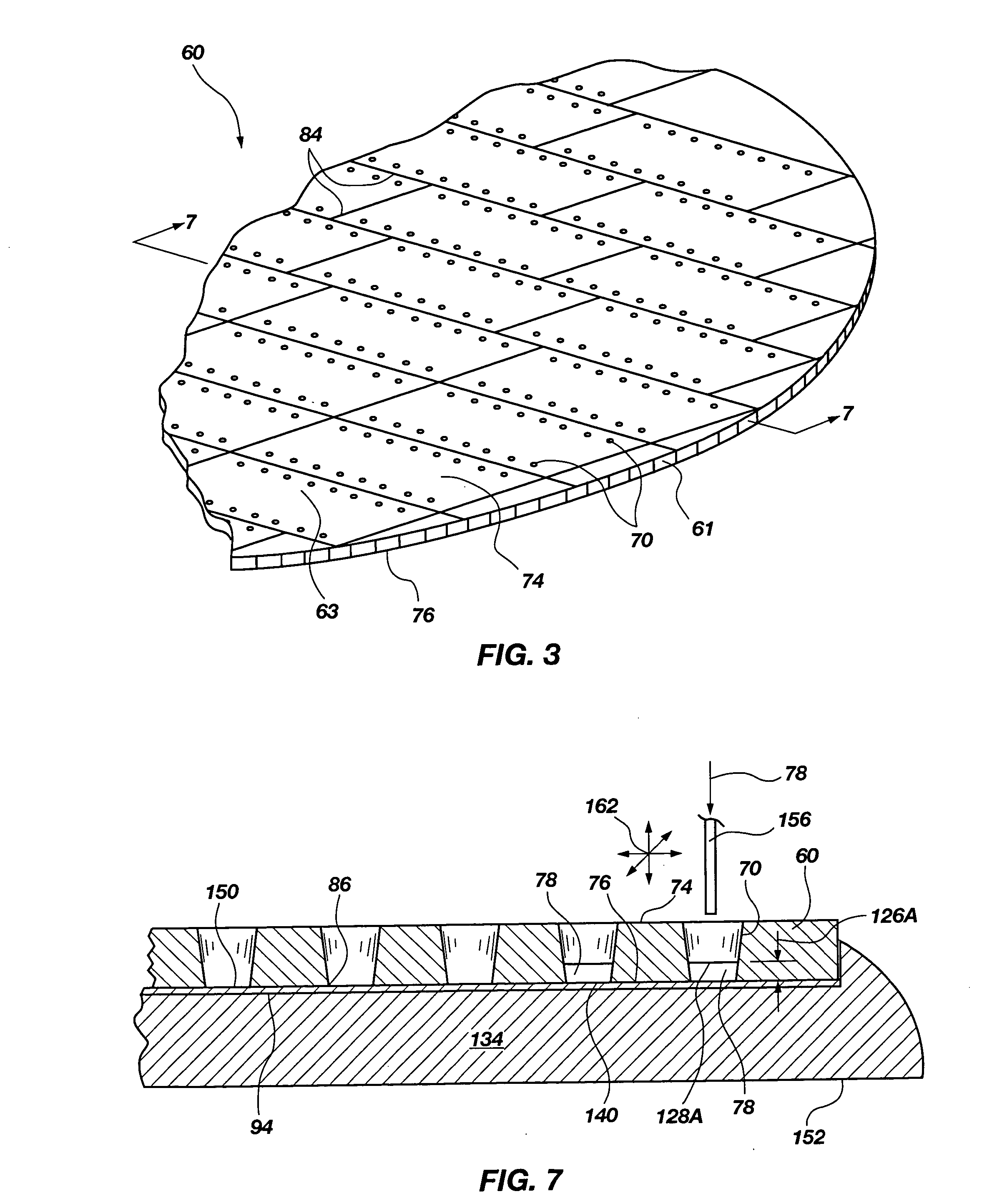

Stereolithographic method for forming insulative coatings for via holes in semiconductor devices, insulative coatings so formed, systems for forming the insulative coatings, and semiconductor devices including via holes with the insulative coatings

InactiveUS20050056913A1Reduce wasteSemiconductor/solid-state device detailsSolid-state devicesSemiconductorMaterials science

A method for forming insulating precursors to via holes formed through conductive and semiconductive substrates includes use of stereolithographic processes. An unconsolidated material is introduced into a precursor hole, then regions of the unconsolidated material that are located adjacent to the surface of each precursor hole are selectively consolidated to form an insulative coating thereon. This process may be conducted once to form a single-layered insulative coating or multiple times to form multilayered insulative coatings. Subsequently, unconsolidated material may be removed to expose a via hole that extends through the insulative coating. Structures that include via holes and conductive vias that have been insulated in this manner are also disclosed, as are systems for forming the insulative coatings.

Owner:MICRON TECH INC

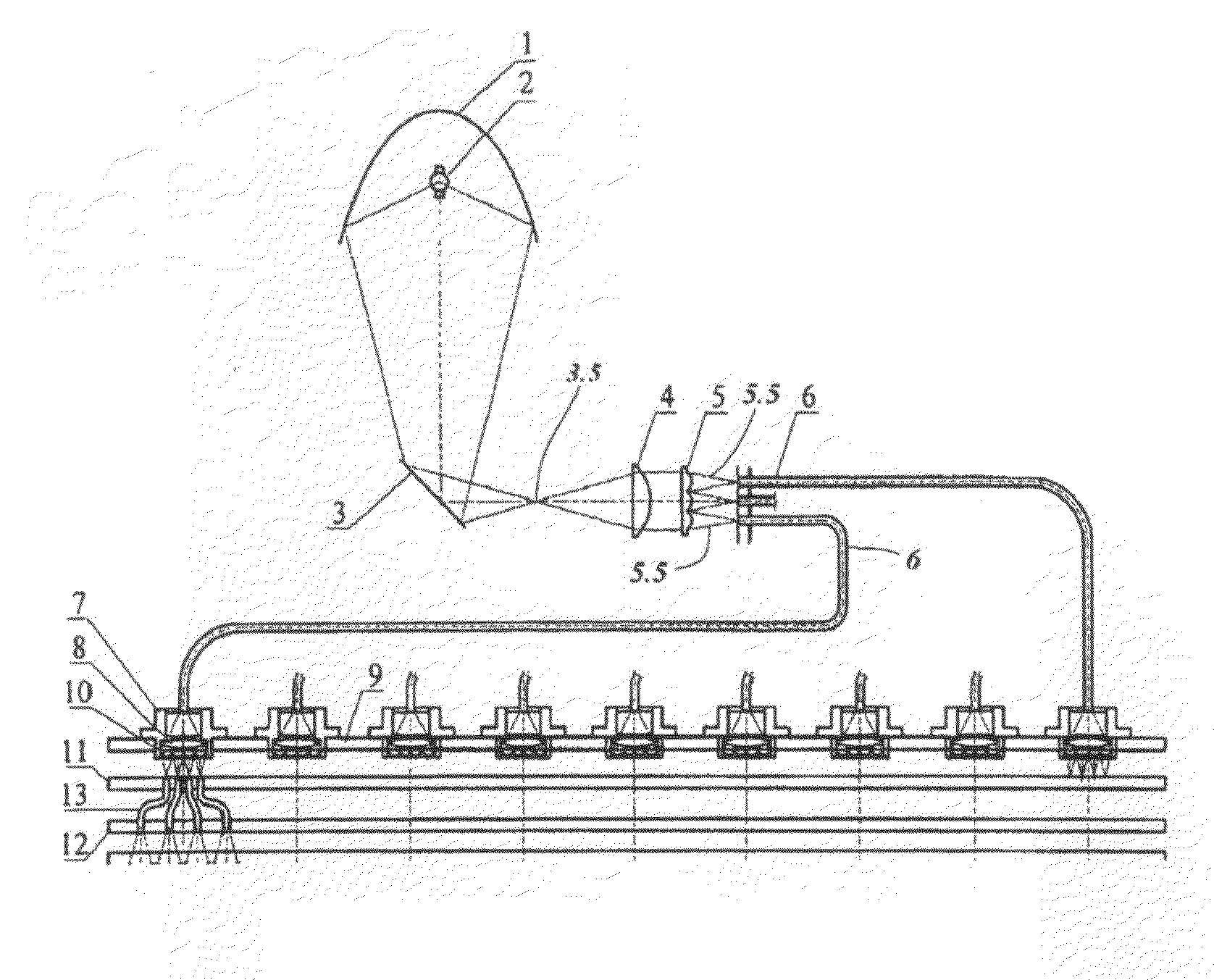

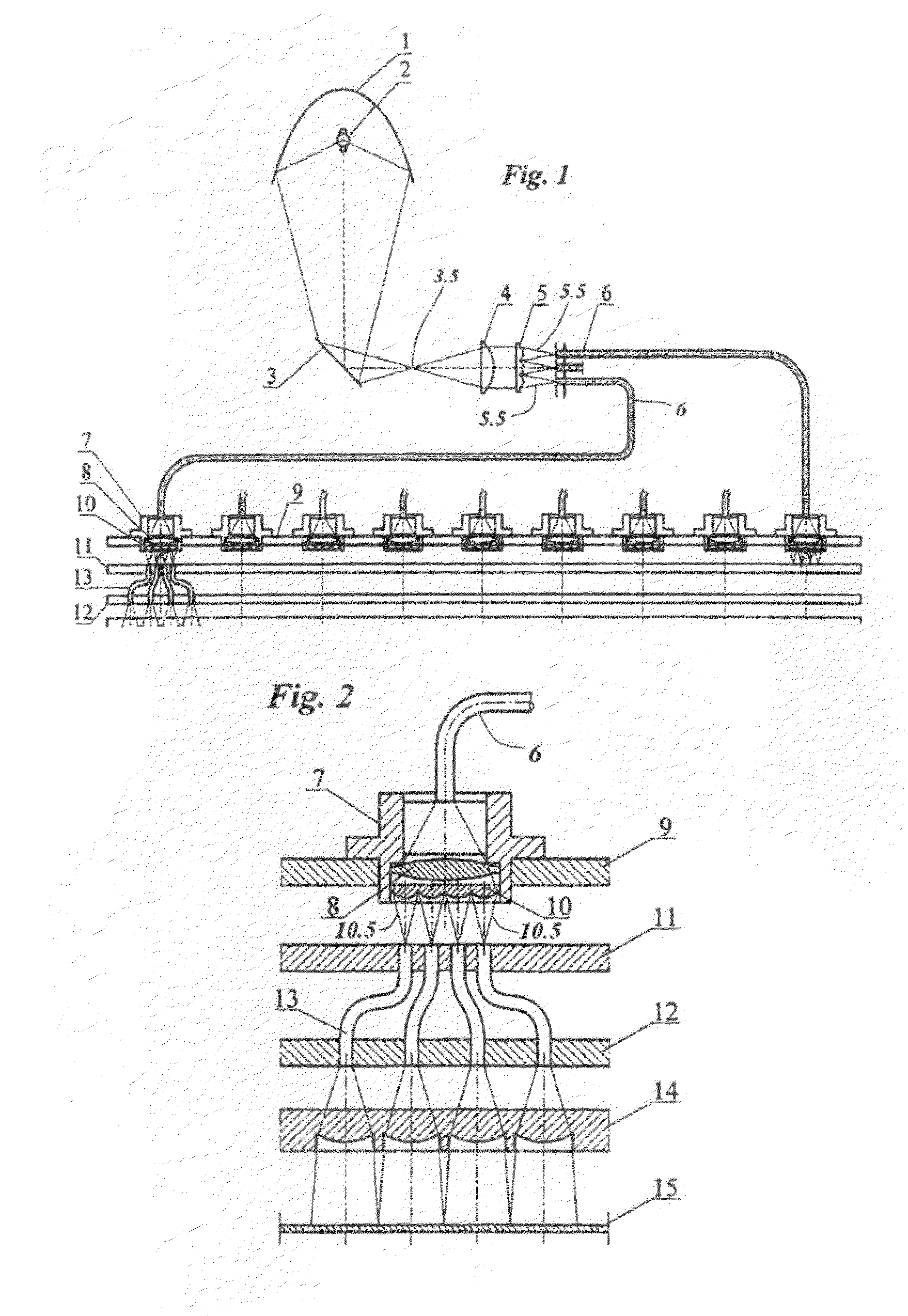

Process and apparatus for the production of collimated UV rays for photolithographic transfer

InactiveUS20090244510A1Shorten the optical lengthSpeed up the processPhotomechanical apparatusPhotographic printingPhysicsRadiation

The present invention provides an improved process and an apparatus for producing collimated UV radiation for exposing printed circuit boards. The process consists in shortening the optical length of the downstream optics by dividing the UV radiation over many radiation sources, and in distributing the UV radiation uniformly on the substrate by using a scanning slide.

Owner:RADOVE

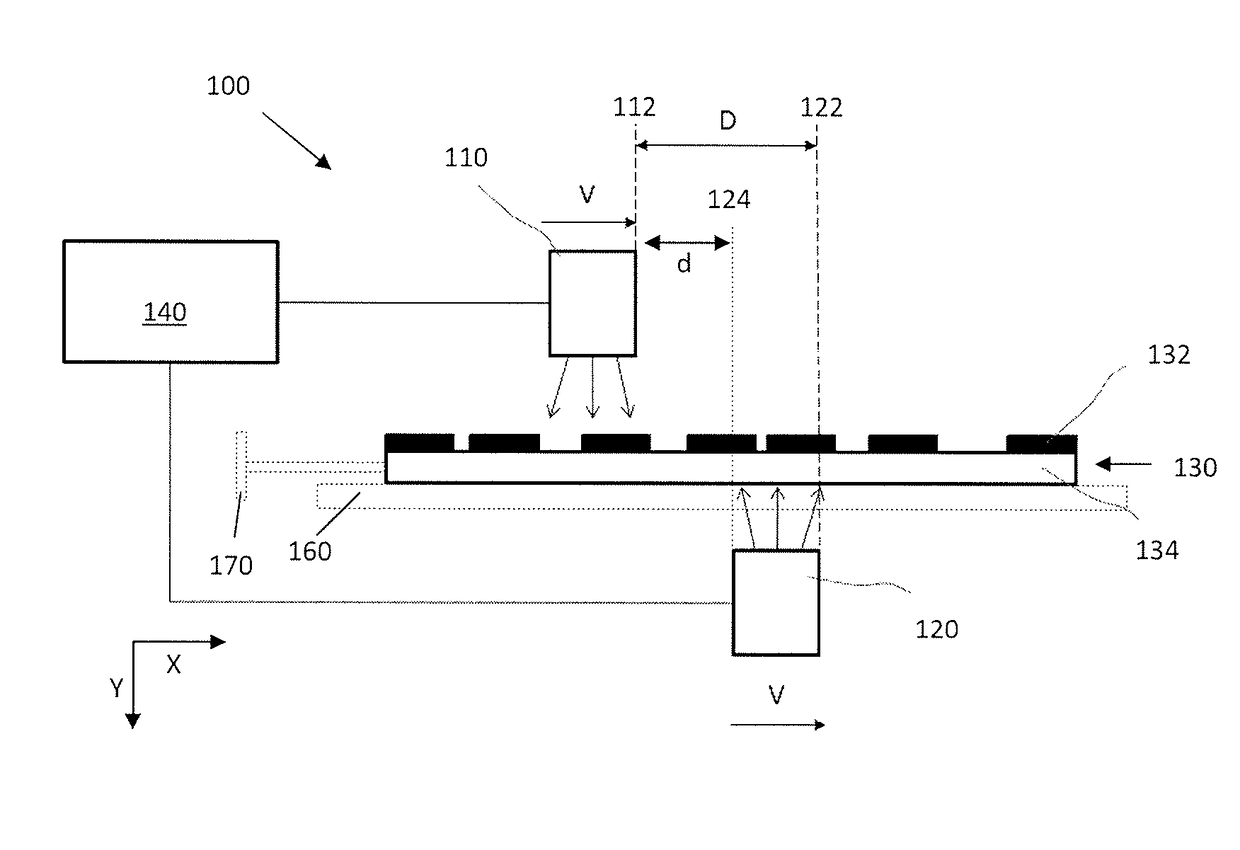

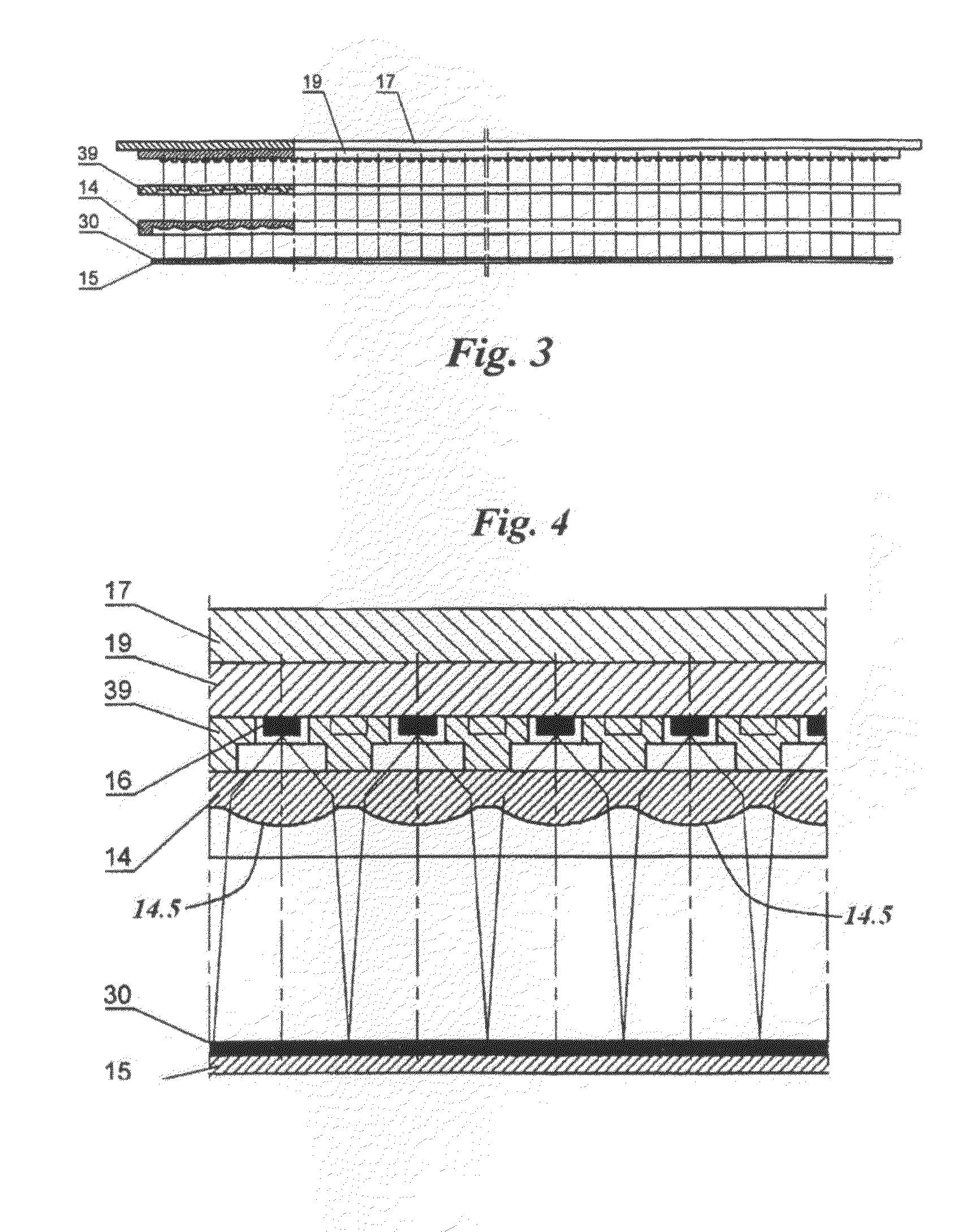

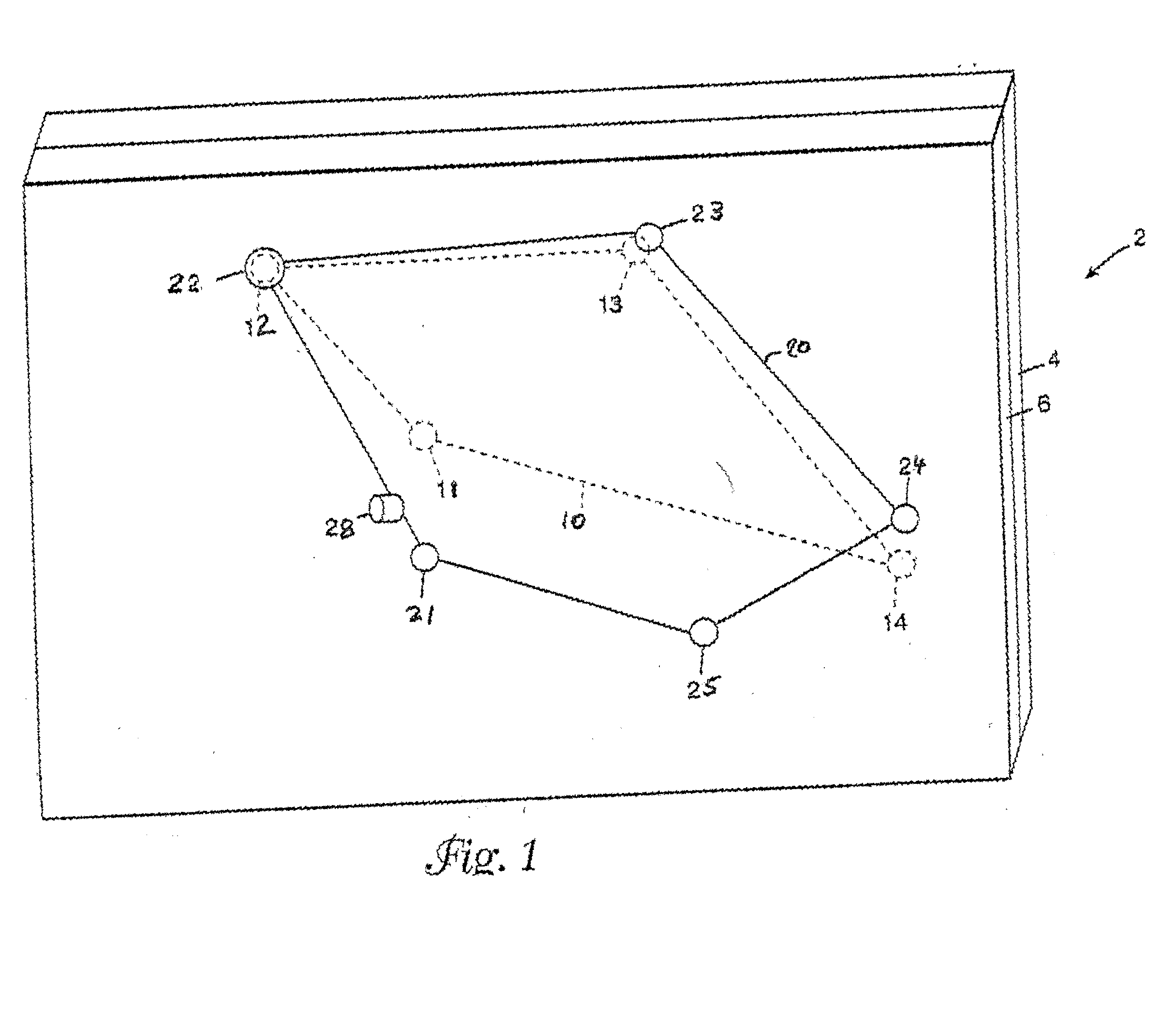

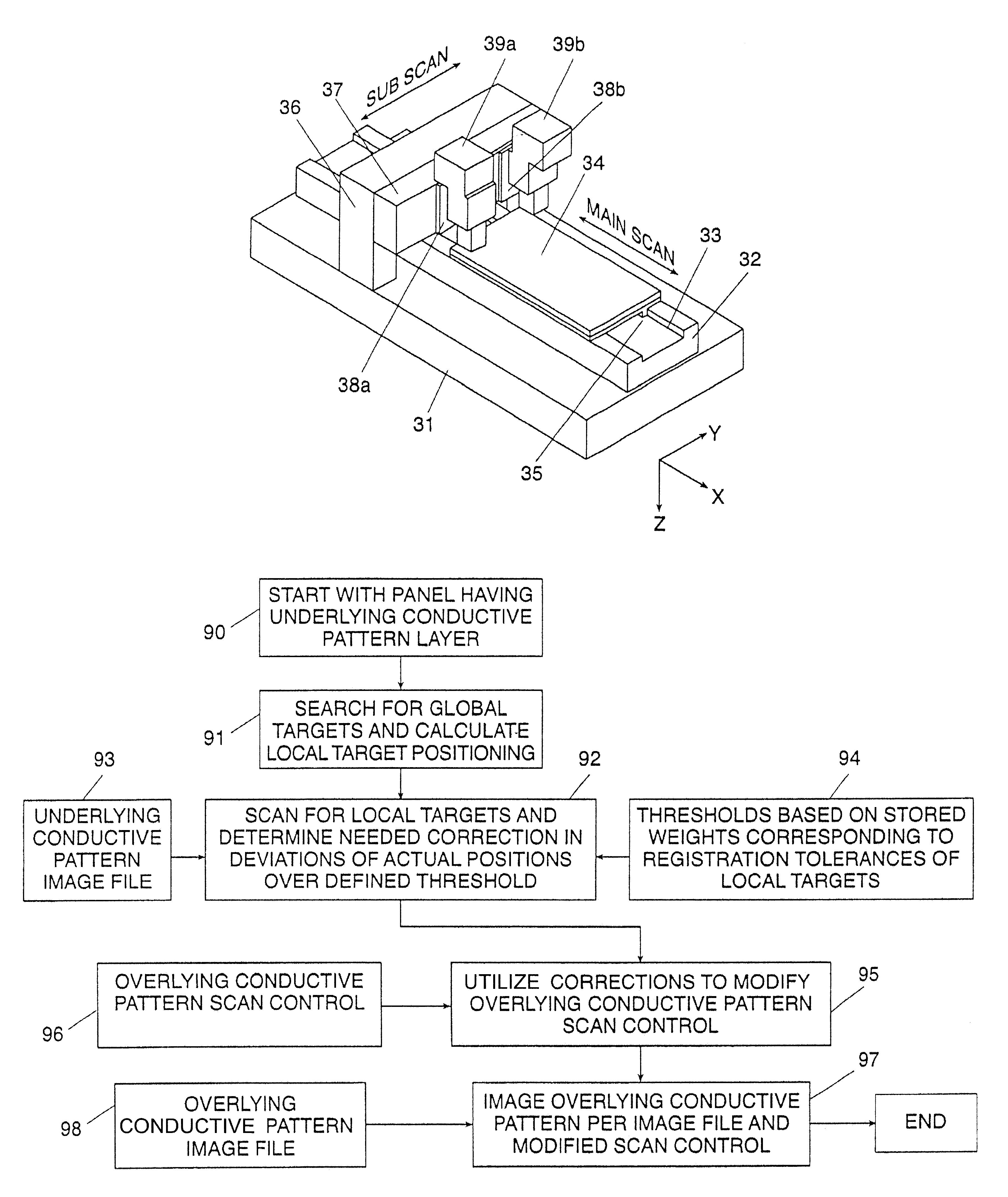

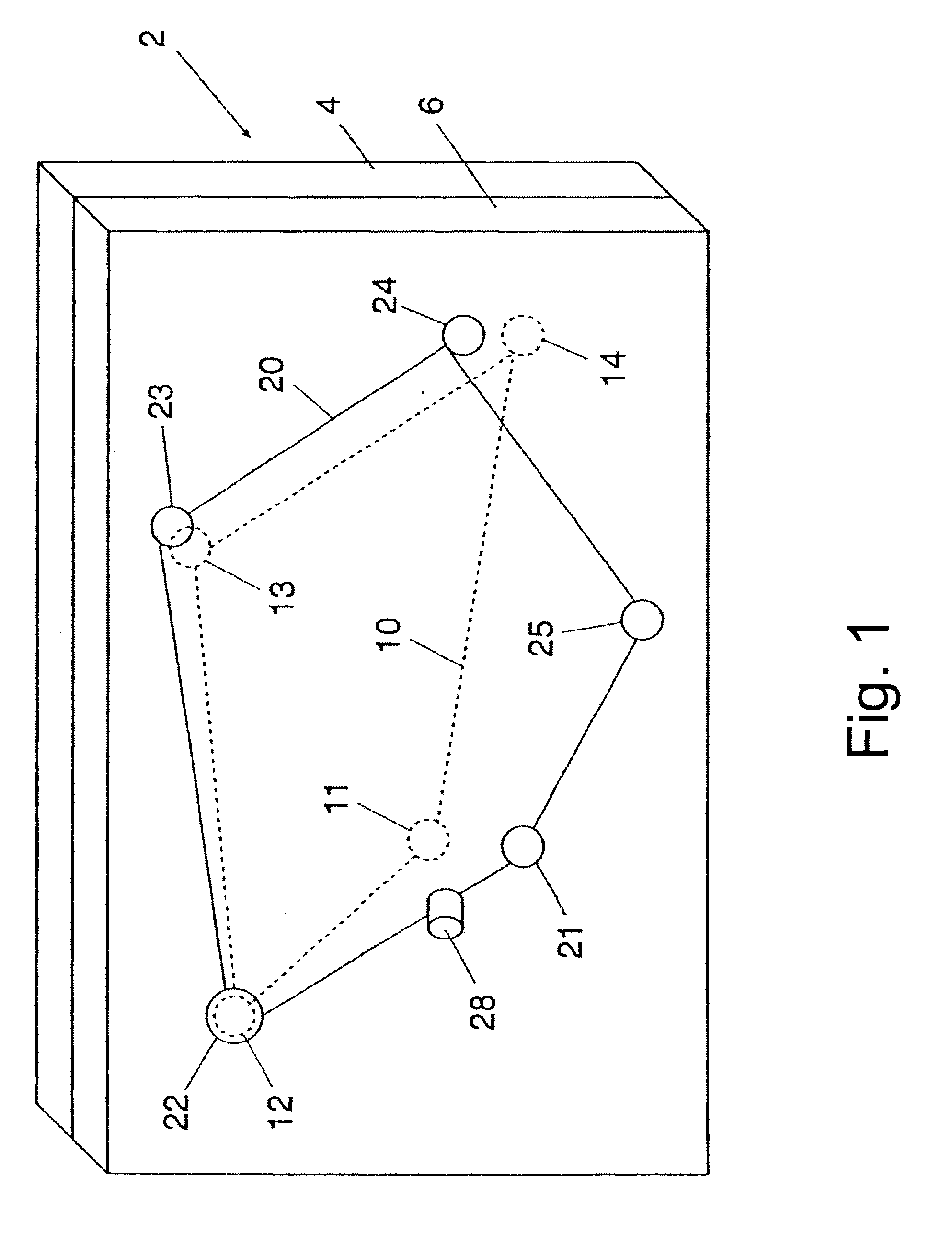

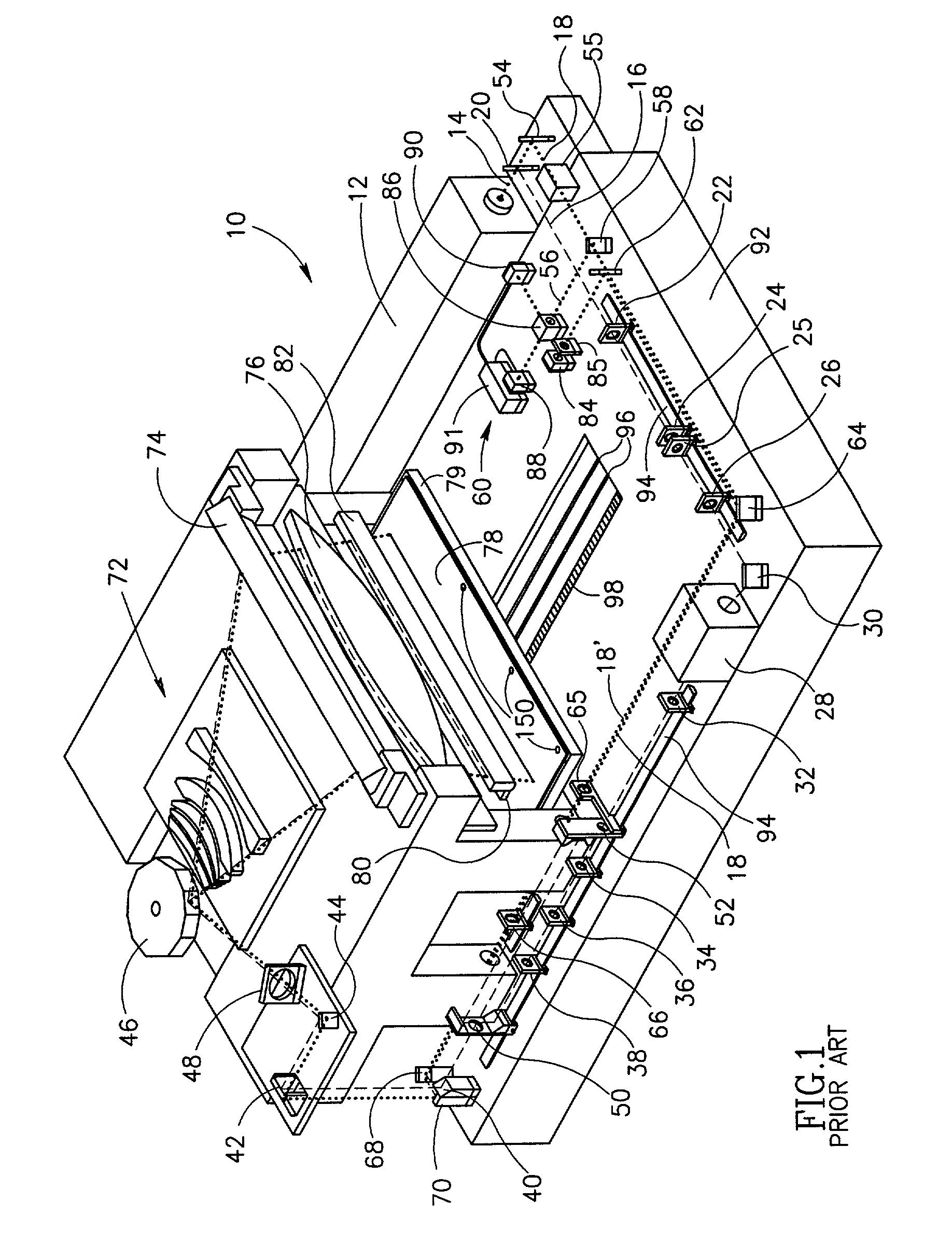

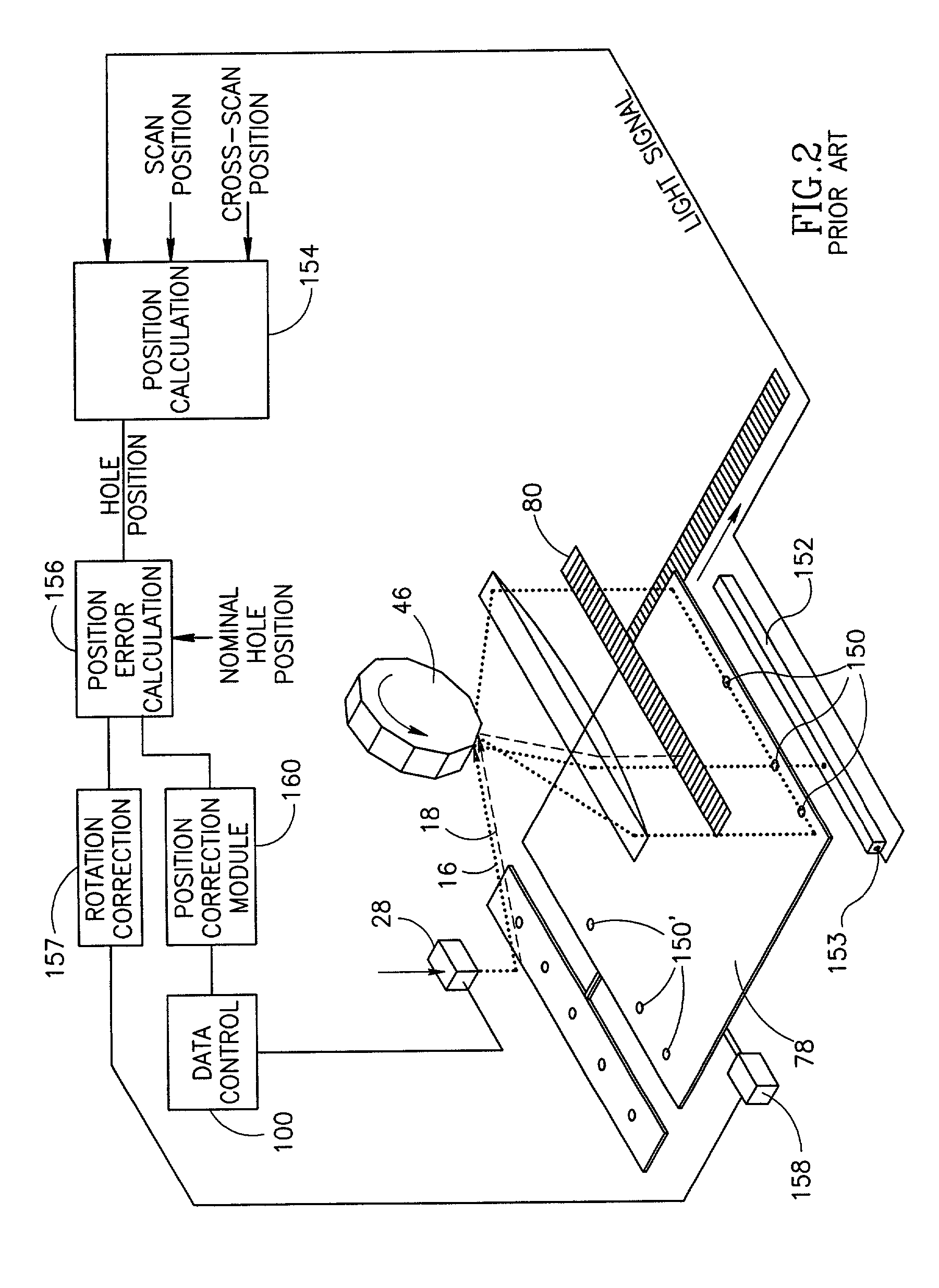

Method and apparatus for registration control in production by imaging

InactiveUS20020118350A1Reduce misregistrationSemiconductor/solid-state device manufacturingCircuit board tools positioningControl dataEngineering

A method and apparatus for imaging an overlying conductive pattern over an underlying conductive pattern on a substrate, by determining deviations between the actual locations and the nominal locations of predetermined reference targets in the underlying conductive pattern on the substrate; and utilizing the determined deviations for modifying the scanning control data used for imaging the image data of the overlying conductive pattern in order to reduce misregistration thereof with respect to the underlying conductive pattern. Preferably, the reference targets are predetermined connection sites in the underlying conductive pattern to be precisely located with respect to connection sites in the overlying conductive pattern. The reference features may be assigned different weights according to their registration importance, and the deviations may be determined according to a threshold which varies with the weight assigned to the respective reference feature.

Owner:KODAK IL

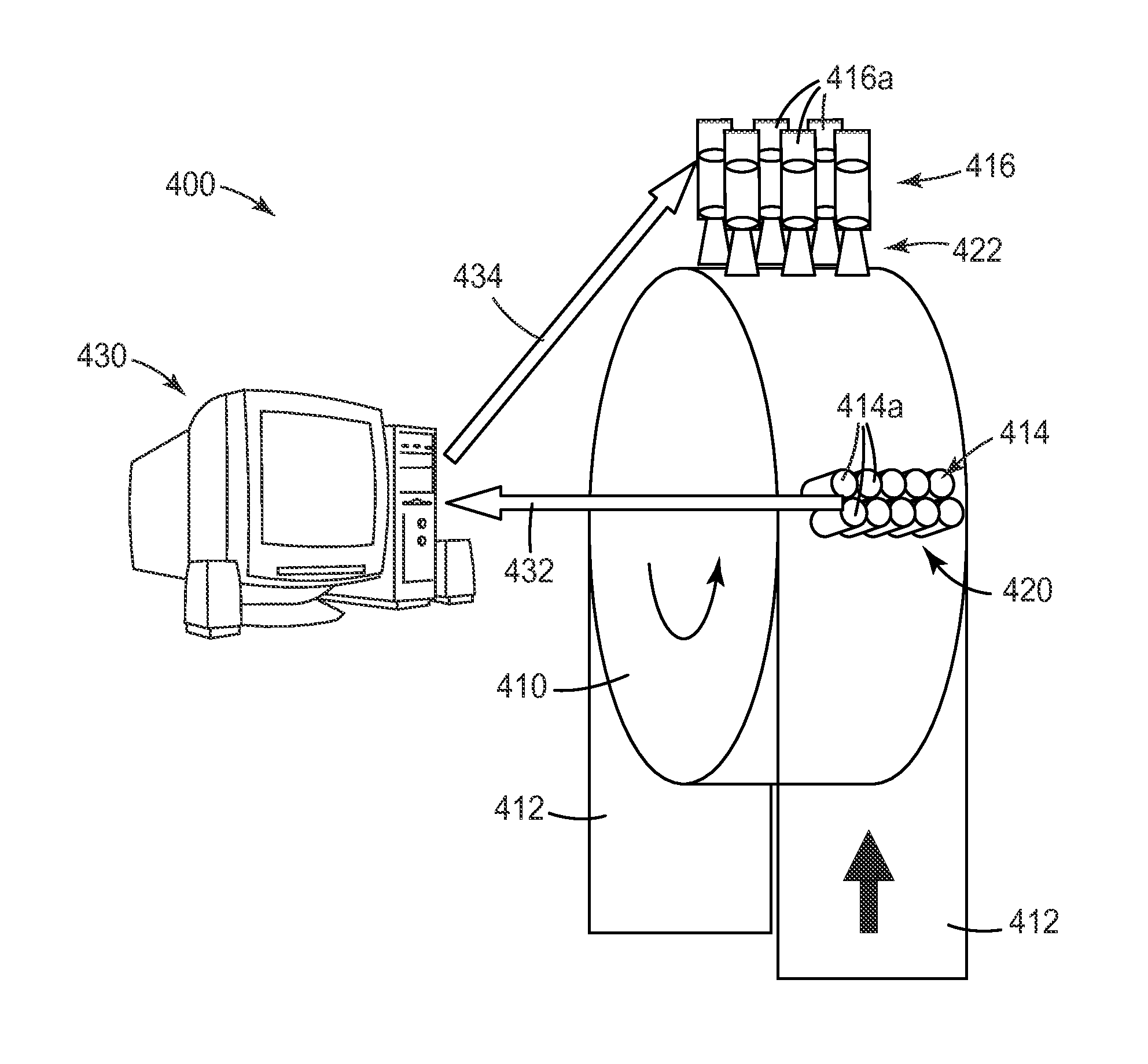

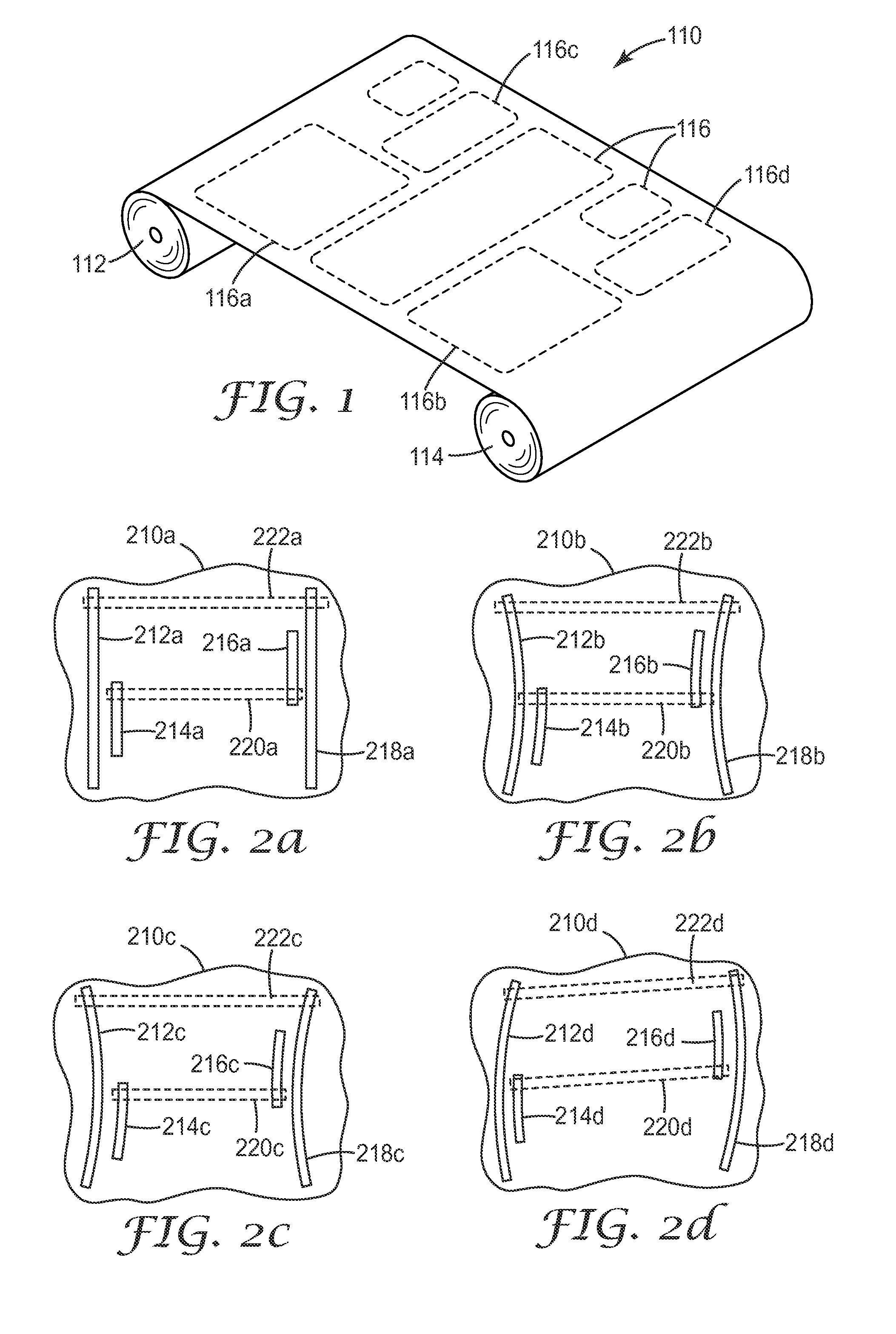

Roll-to-roll digital photolithography

InactiveUS20110253425A1Alignment error is smallFunctionality and performance improvementsPrinted circuit aspectsSemiconductor/solid-state device manufacturingFlexible circuitsEngineering

Methods of making flexible circuit films include providing a polymer film or other flexible substrate having a plurality of alignment marks and a photosensitive material thereon. The substrate passes around a suitable roller, belt, or other inelastic conveyor such that the substrate and the conveyor move together at least from a first location to a second location. Positions of a first set of the alignment marks on a first portion of the substrate are measured when such portion is at the first location, and the measured positions can be used to calculate a distortion of the substrate. The photosensitive material is then patternwise exposed when the first portion of the substrate has moved to the second location. The patternwise exposing is based on the measured positions of the first set of alignment marks, and may include exposing the web with a distortion-adjusted pattern. Related systems and articles are also disclosed.

Owner:3M INNOVATIVE PROPERTIES CO

Writing apparatuses and methods

ActiveUS20070188591A1Increase heightRecording apparatusPhotomechanical exposure apparatusDisplay deviceEngineering

Owner:MICRONIC LASER SYST AB

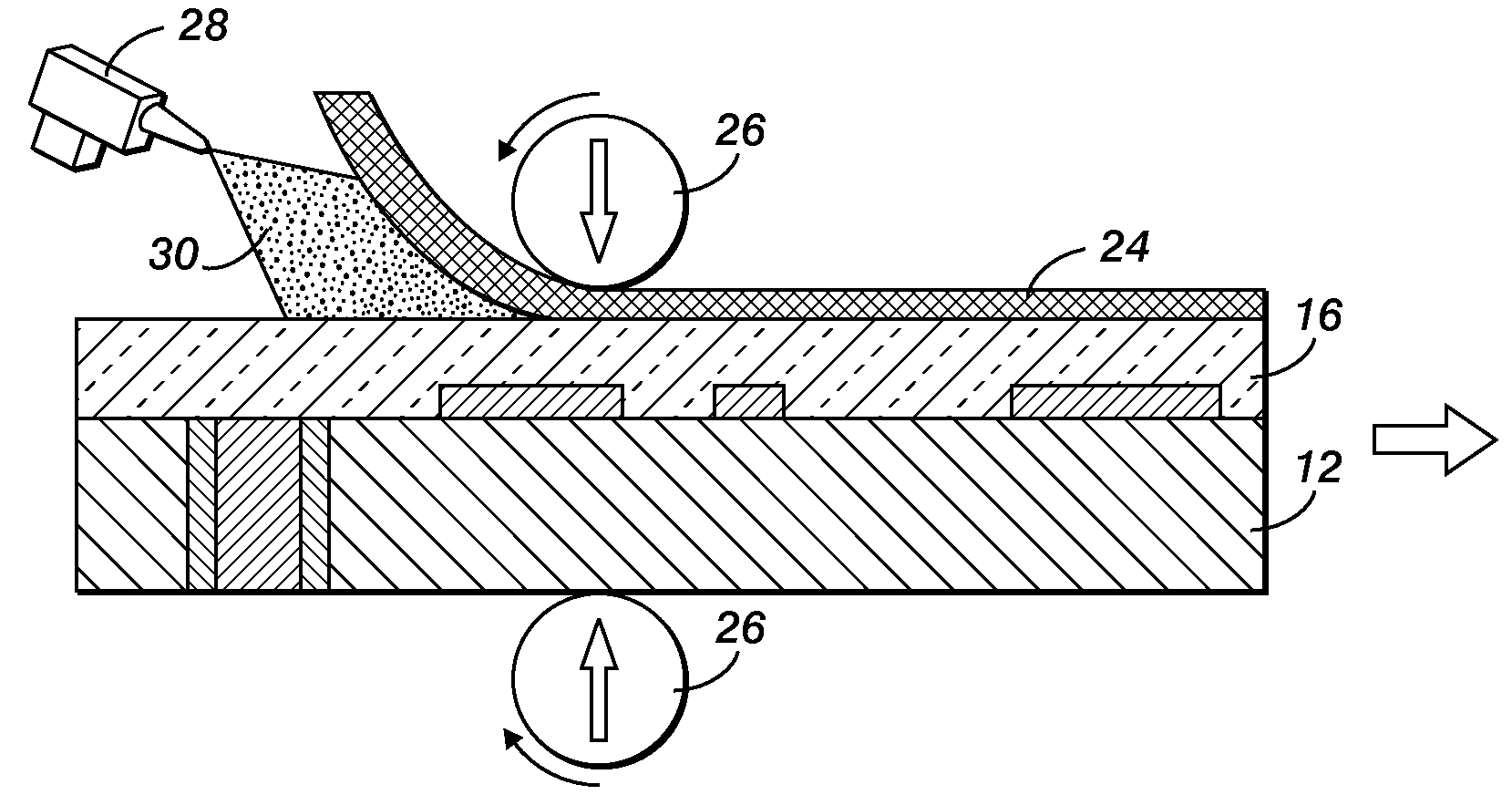

Lamination for Printed Photomask

InactiveUS20090123873A1Increase costExtended production timePhotosensitive materialsPrinted circuit aspectsResistAdhesive

A method for masking regions of photoresist in the manufacture of a soldermask for printed circuit boards is disclosed. Following application of photoresist over patterned traces on a substrate, a sheet-like thin film is applied over the photosensitive material. The thin film may adhere to the photosensitive material by way of the adhesive state of the photosensitive material or by way of an adhesive applied to the photosensitive material or the thin film or carried by the thin film. Digital mask printing may proceed on the surface of the thin film. The photosensitive material may then be exposed through the printed photomask, the thin film (with photomask) removed, and the photosensitive material developed.

Owner:PALO ALTO RES CERNTER

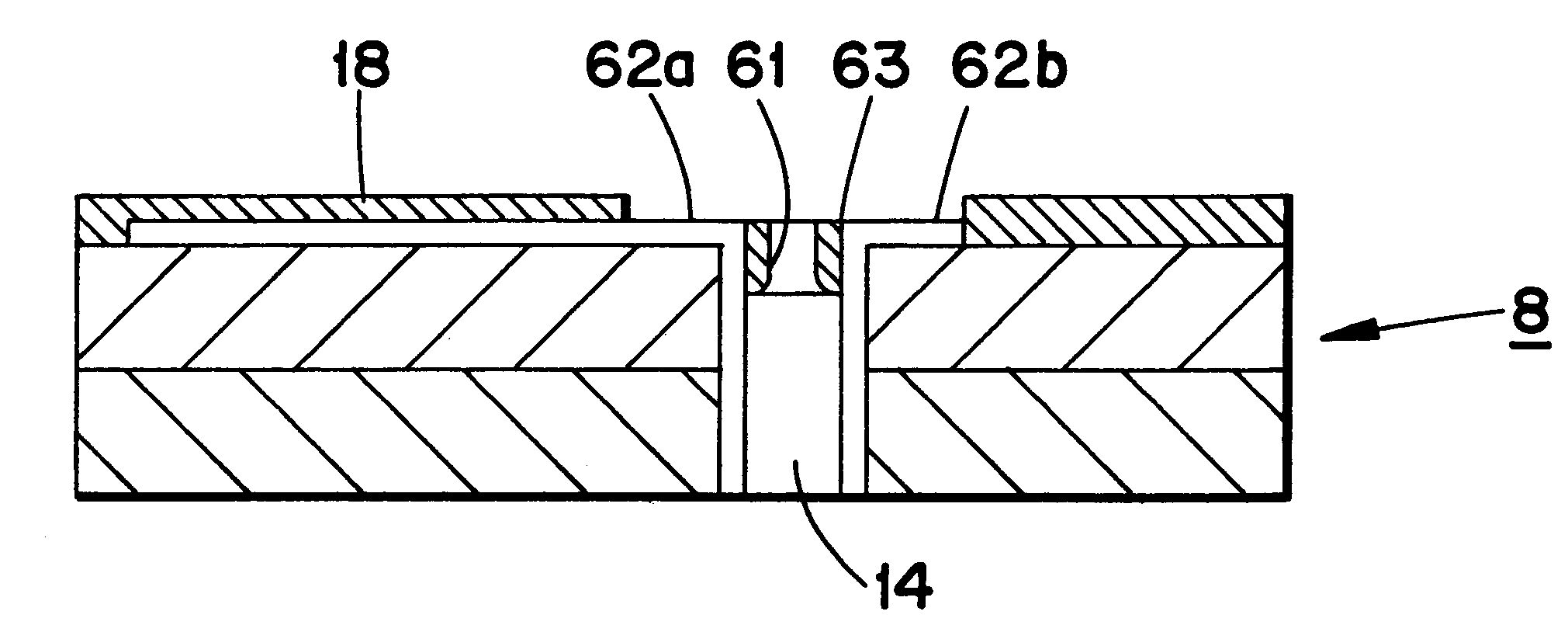

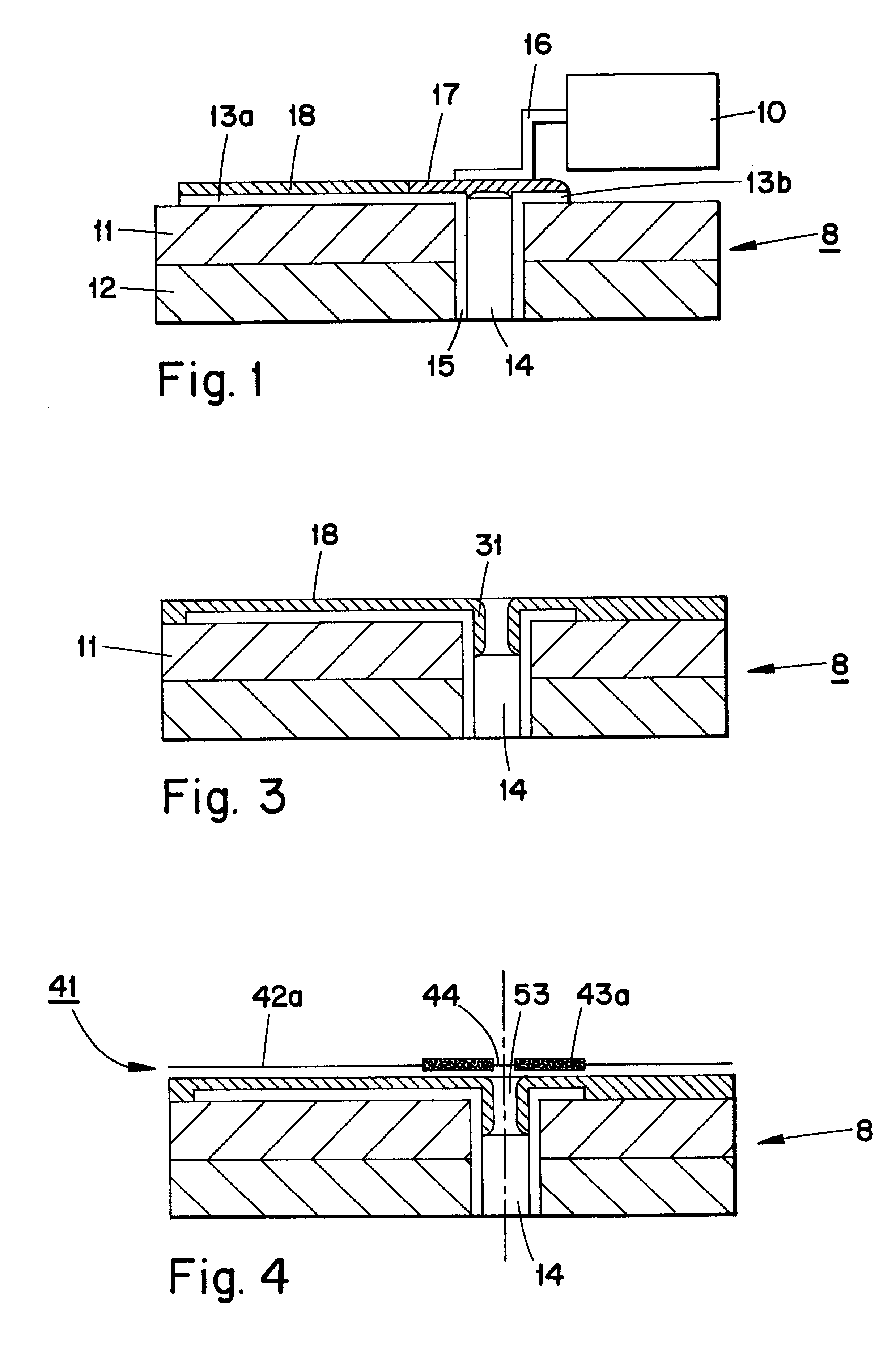

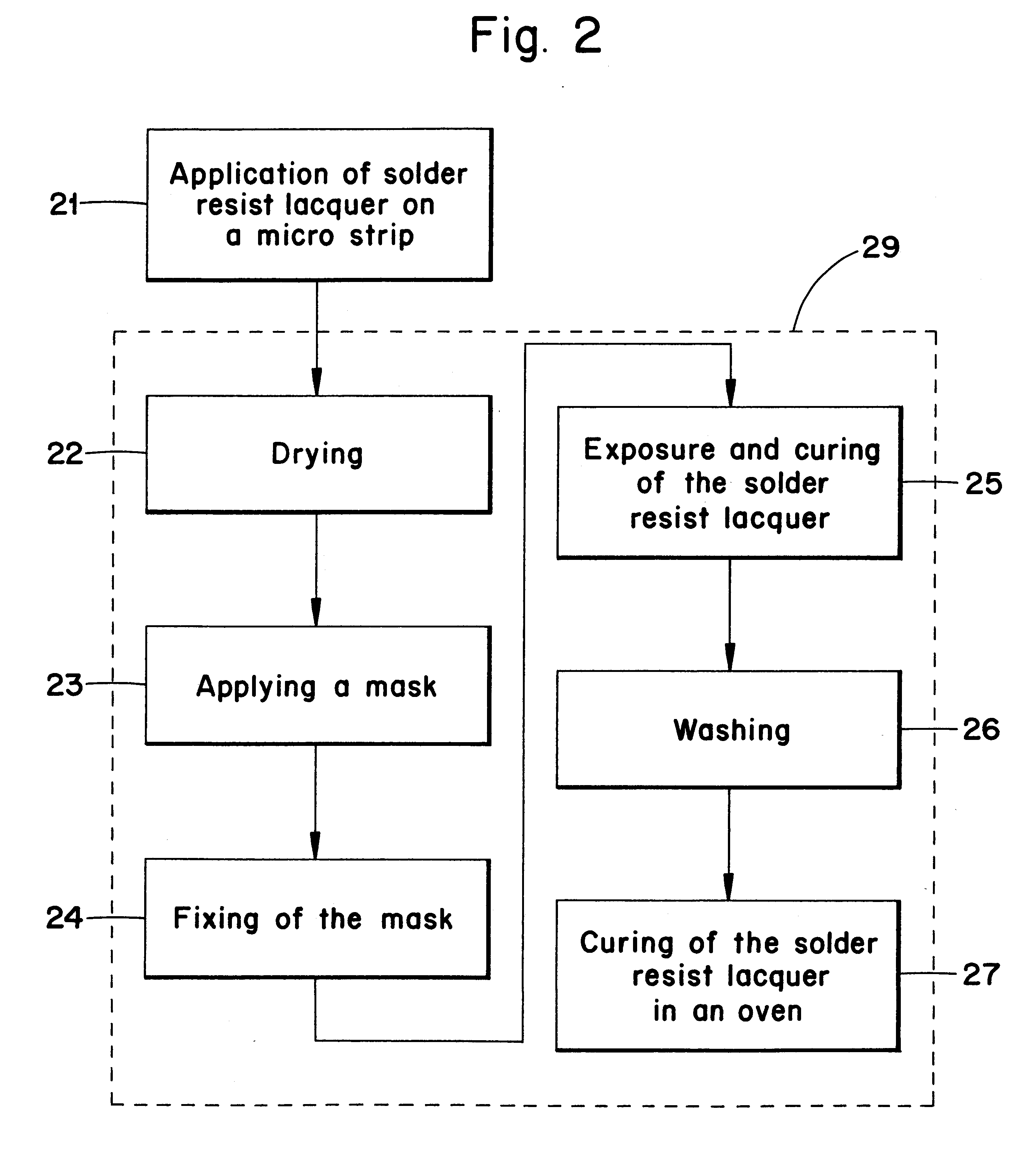

Method and device on printed boards

The present invention relates to a solder stop in through-plated through-holes on micro strip boards (8). A solder resist lacquer (18) with a certain viscosity is applied on a micro strip board (8) wherein the solder resist lacquer (18) flows out over the micro strip (8) and down into a top portion of the through-plated through-hole and dried. A ring-shaped portion of the solder resist lacquer (18) is retained in the top part of the through-plated through-hole.

Owner:TELEFON AB LM ERICSSON (PUBL)

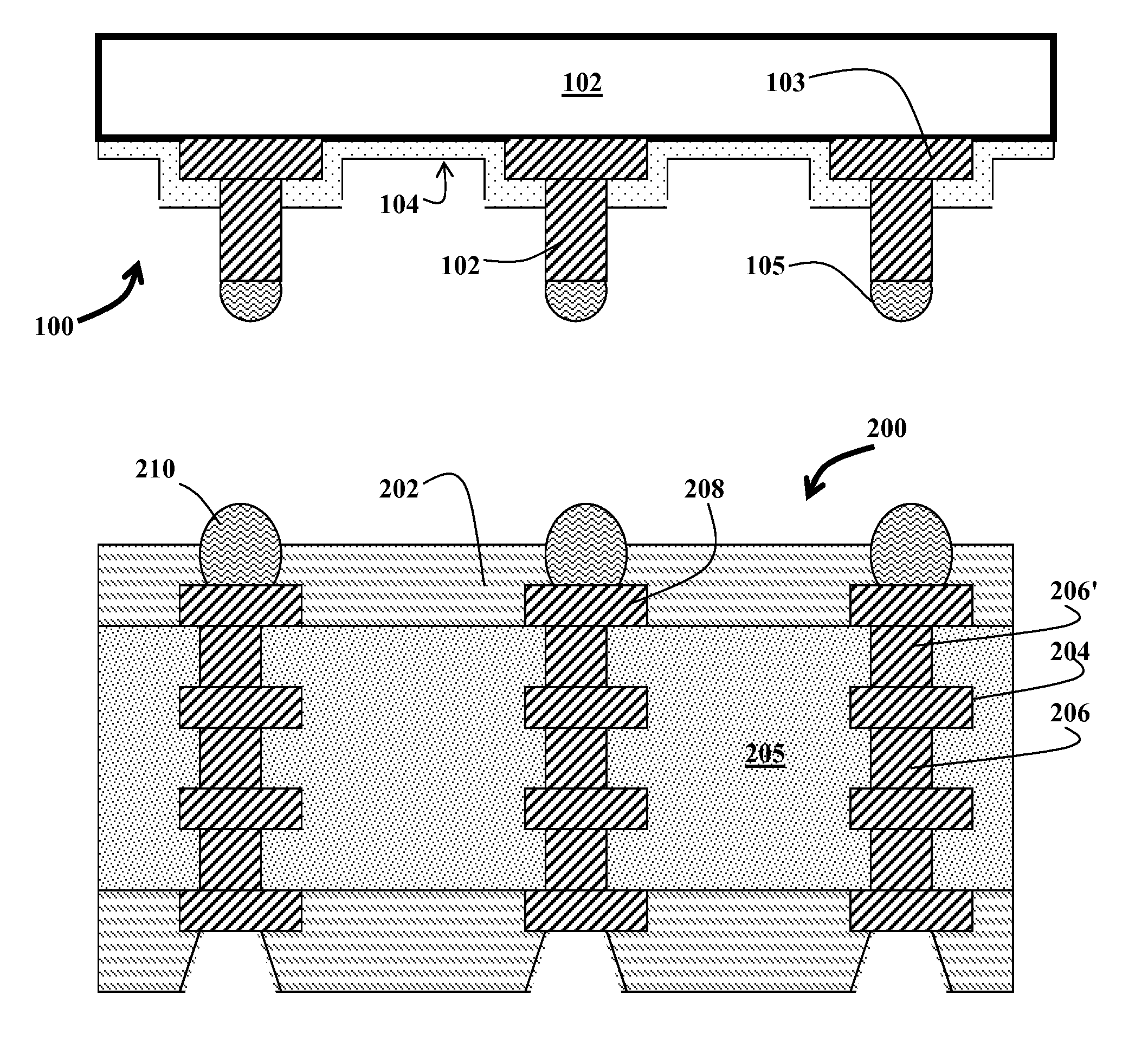

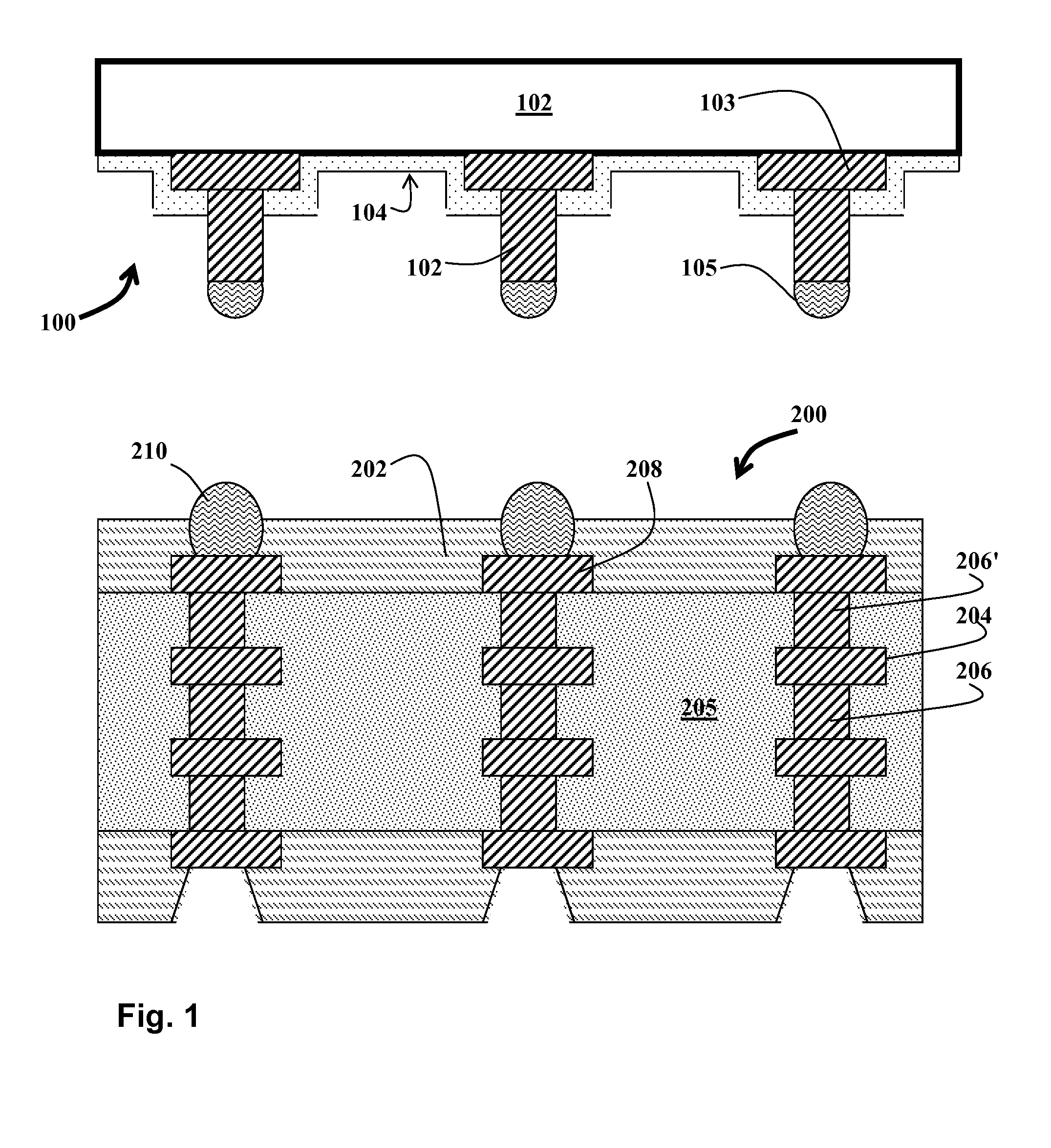

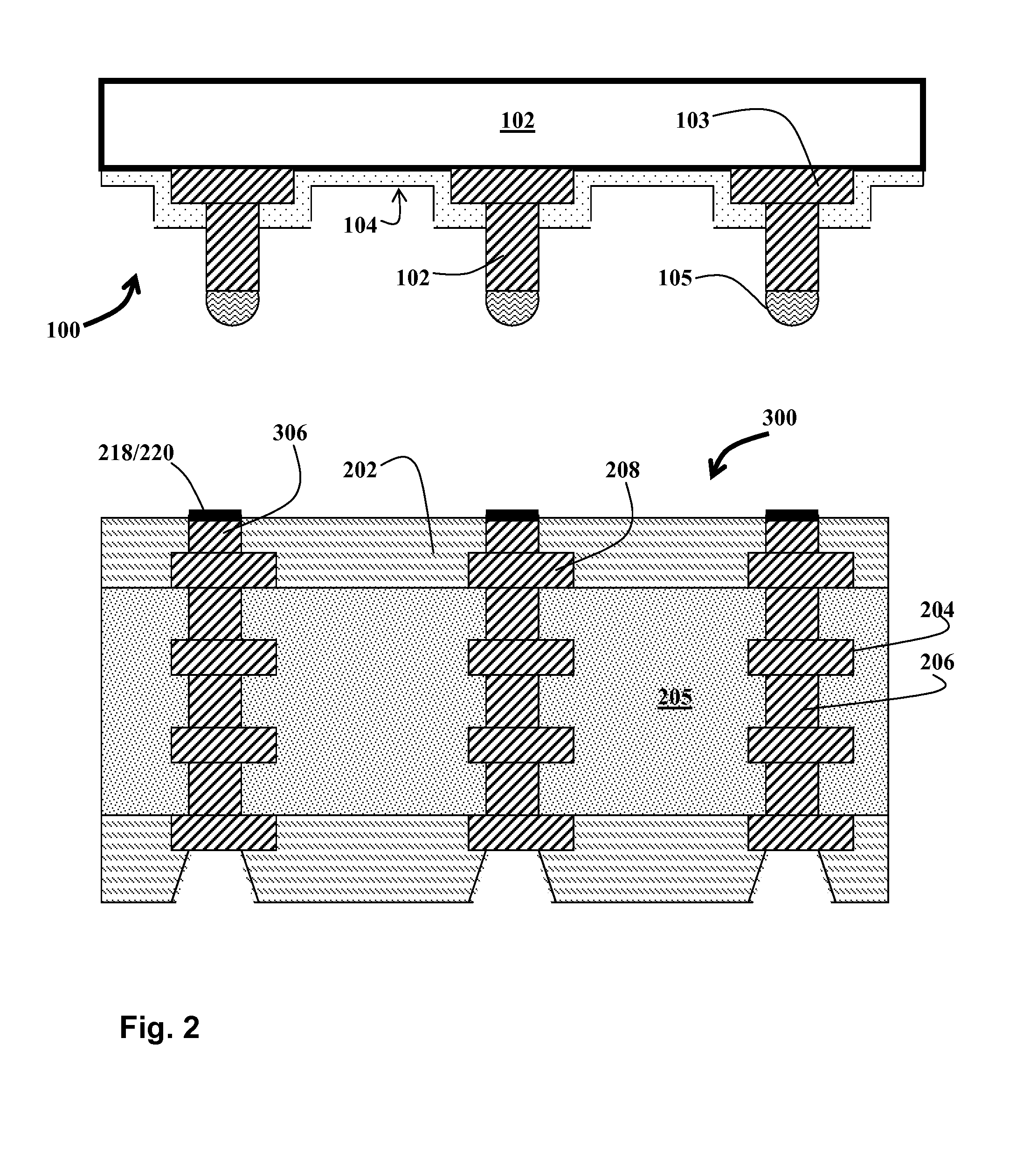

Novel Terminations and Couplings Between Chips and Substrates

ActiveUS20140363927A1High yieldLess limited pitchSemiconductor/solid-state device detailsPrinted circuit aspectsDielectricSolder mask

A method of attaching a chip to the substrate with an outer layer comprising via pillars embedded in a dielectric such as solder mask, with ends of the via pillars flush with said dielectric, the method comprising the steps of: (o) optionally removing organic varnish, (p) positioning a chip having legs terminated with solder bumps in contact with exposed ends of the via pillars, and (q) applying heat to melt the solder bumps and to wet the ends of the vias with solder.

Owner:ZHUHAI ADVANCED CHIP CARRIERS & ELECTRONICS SUBSTRATE SOLUTIONS TECH

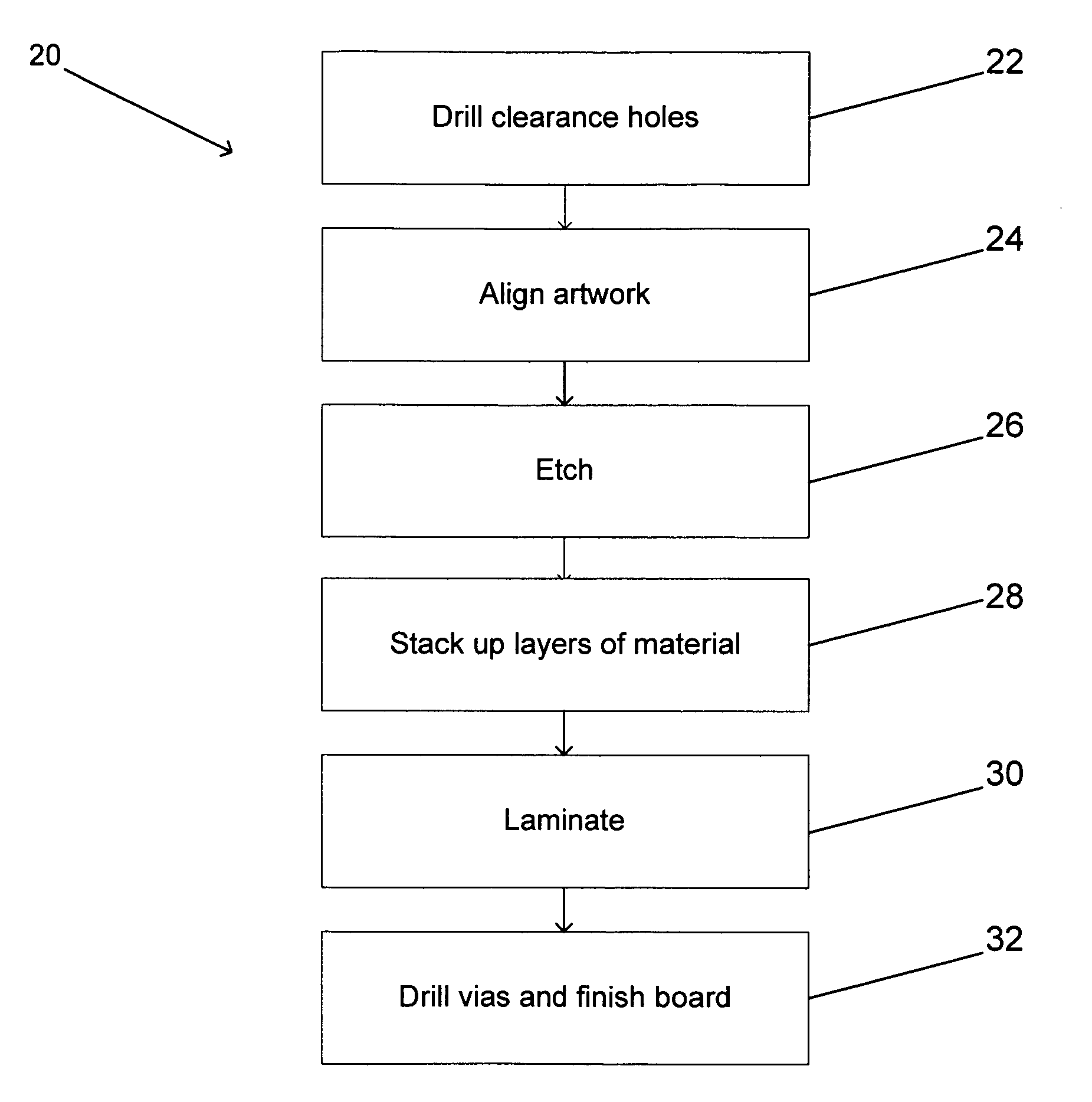

Manufacturing process: how to construct constraining core material into printed wiring board

InactiveUS20060231198A1Precise alignmentImprove manufacturing yieldLamination ancillary operationsPrinted circuit aspectsManufacturing technologyEngineering

Processes for manufacturing printed wiring boards including electrically conductive constraining cores are disclosed. Several of the processes enable precise alignment of tooling holes used by tools to perform processes with respect to various panels and subassemblies used to form finished printed wiring boards. Modifications to Gerber files that can increase manufacturing yield and provide the ability to detect faulty printed wiring boards in a panelized array of printed wiring boards are also discussed. One embodiment of the invention includes aligning the weave of a woven panel of electrically conductive material relative to a tool surface using at least a pair of references and forming tooling holes in the panel of electrically conductive material.

Owner:STABLCOR TECH

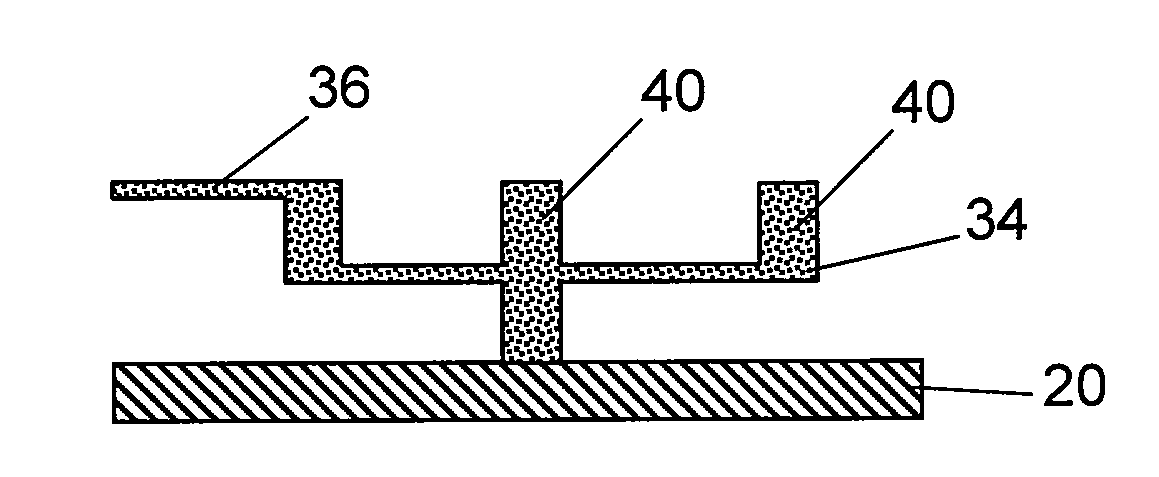

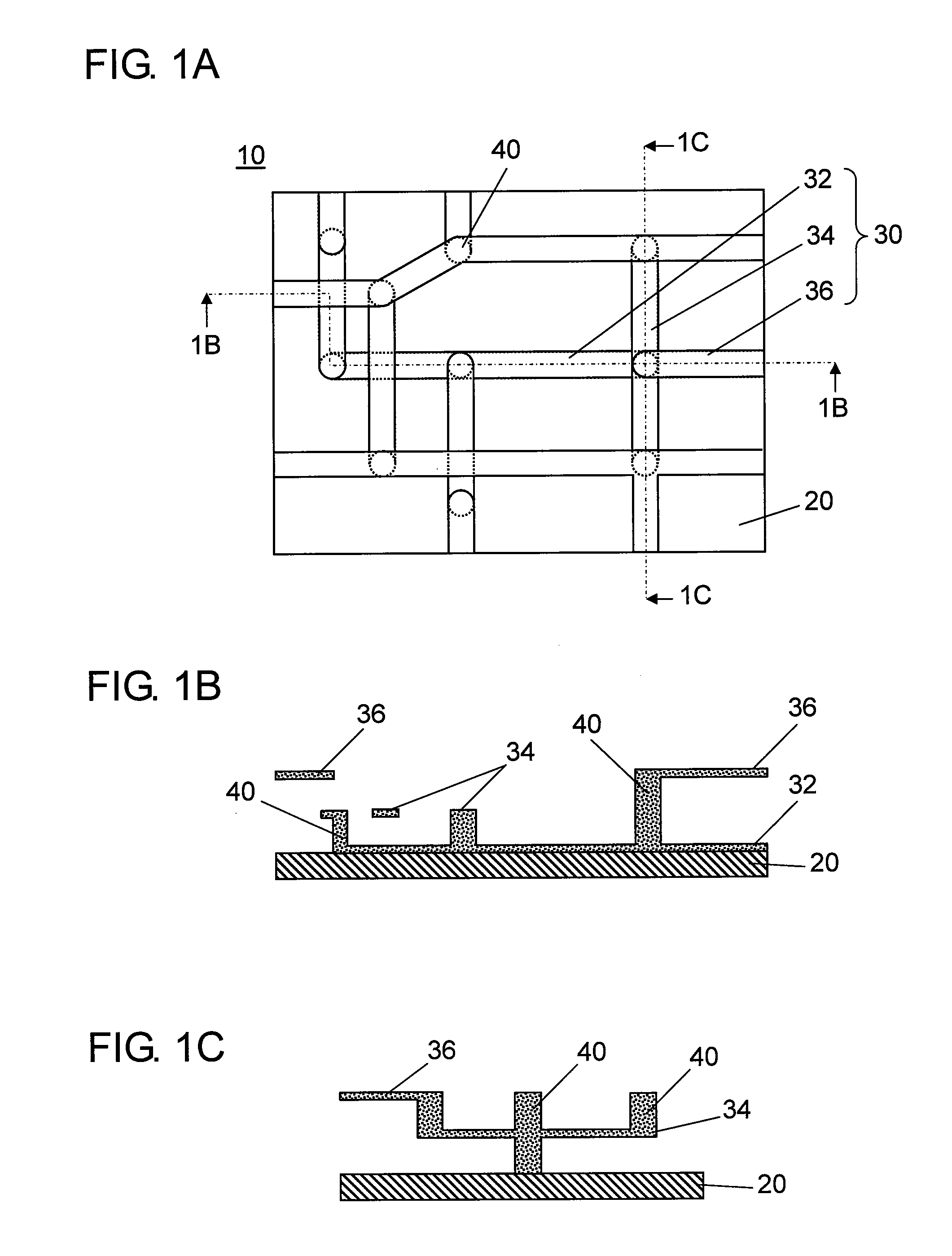

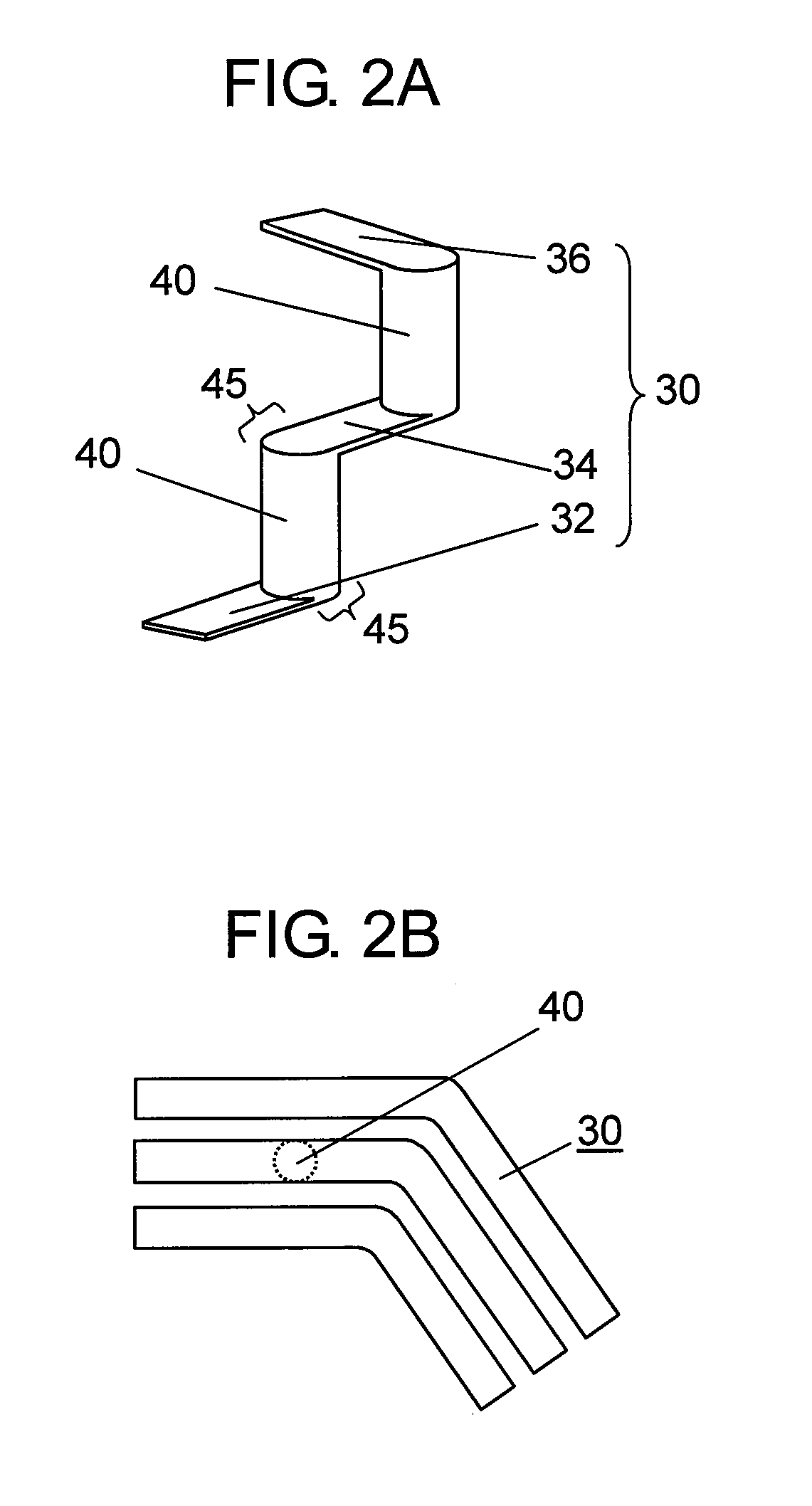

Three-dimensional circuit board and its manufacturing method

InactiveUS20090266582A1High densityImprove reliabilityPrinted circuit aspectsSolid-state devicesEngineeringElectrical and Electronics engineering

A three-dimensional circuit board is formed by comprising a board, a first wiring-electrode group provided on a plurality of steps above the board, and a second wiring-electrode connected to the first wiring-electrode group at least in an altitude direction, in which at least a connecting portion between the first wiring-electrode group and the second wiring-electrode is integrated in a continuously identical shape.

Owner:PANASONIC CORP

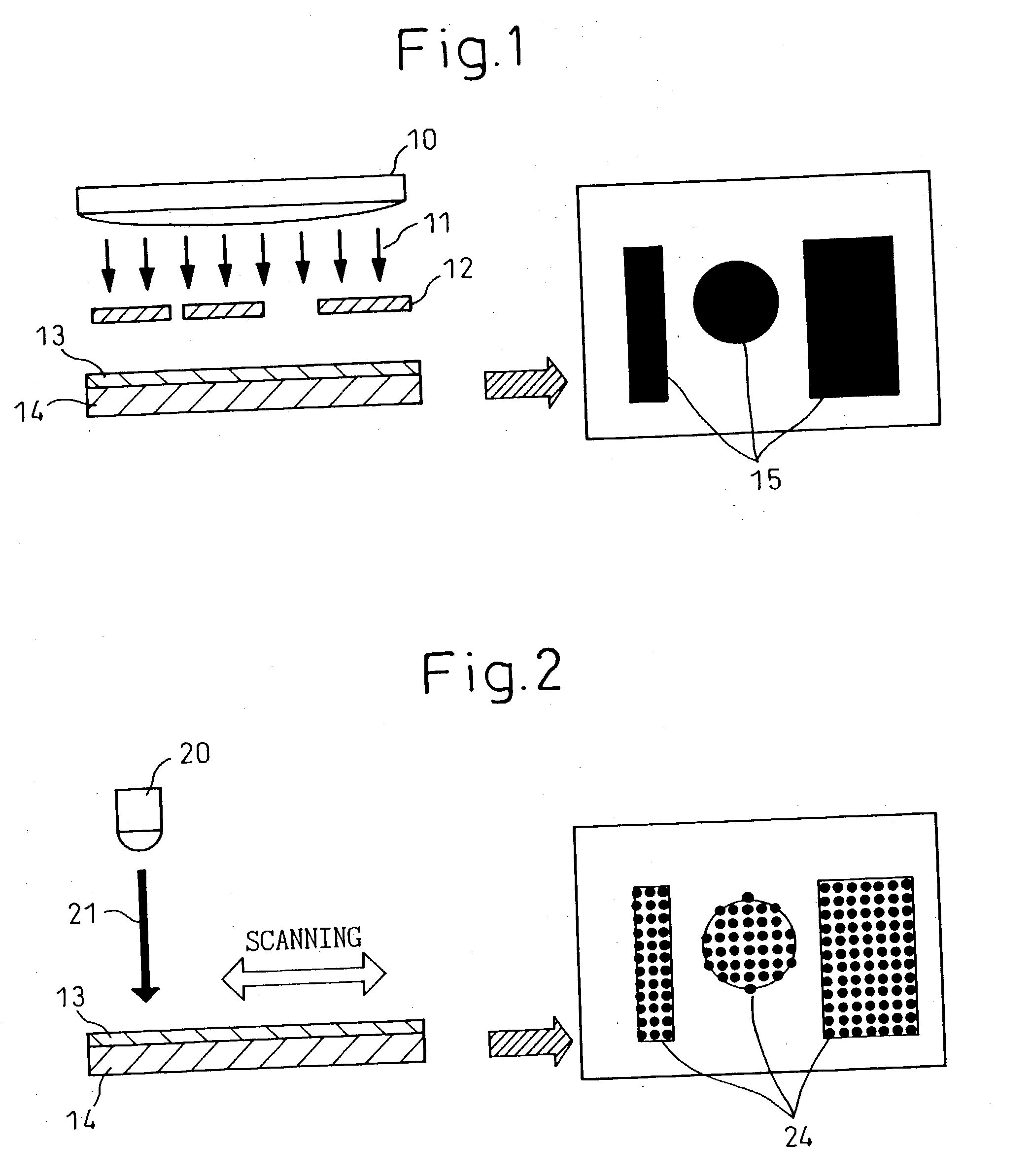

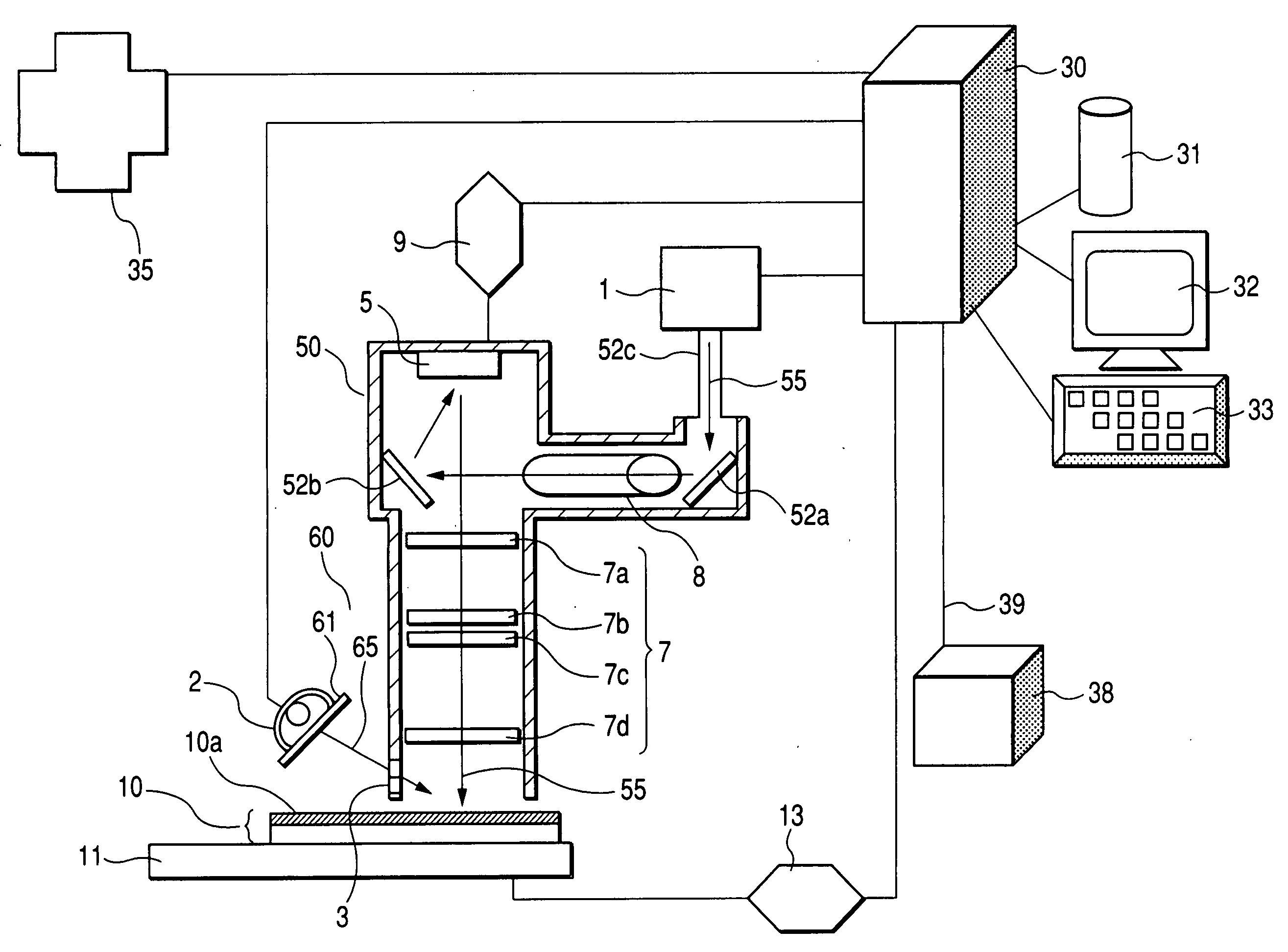

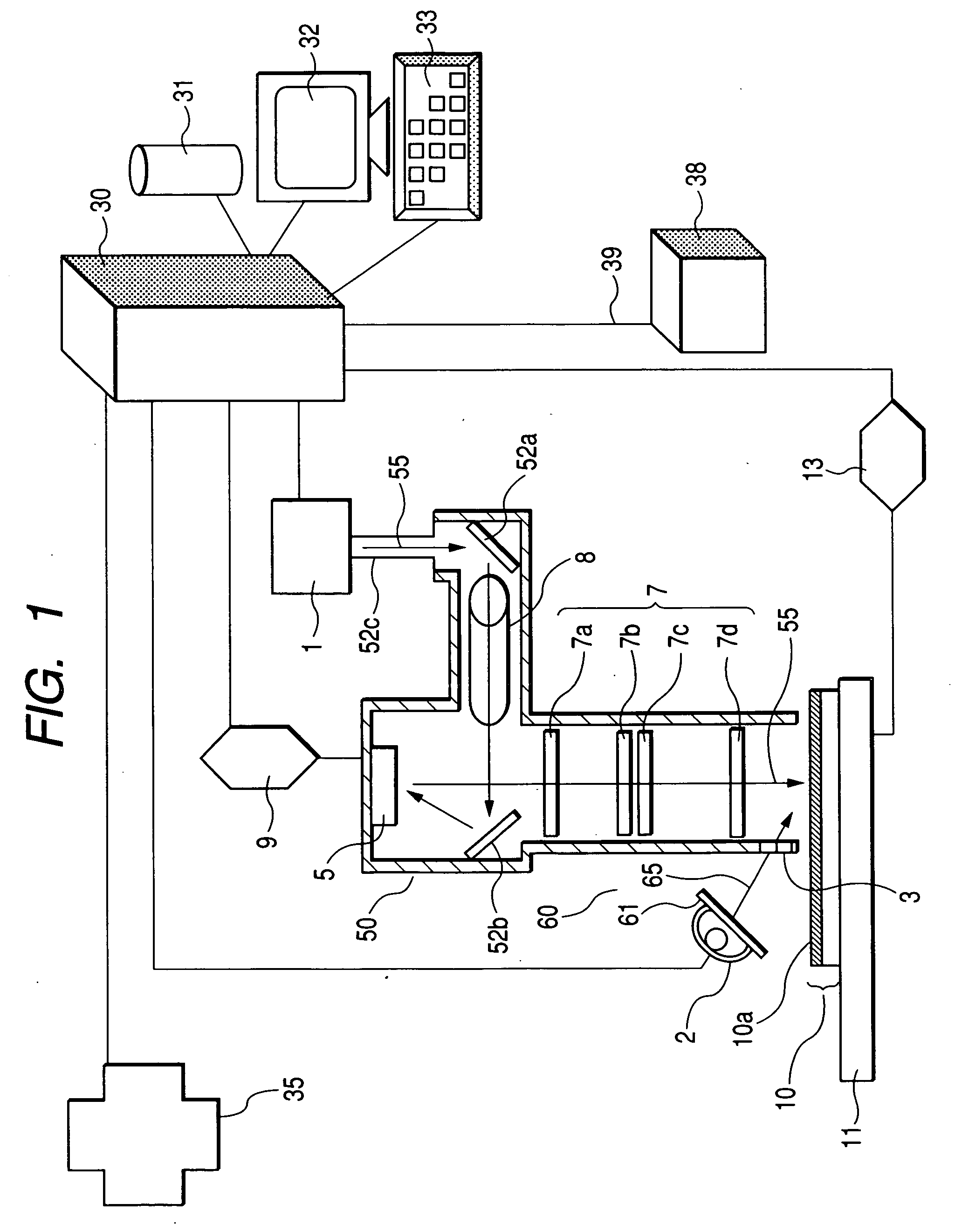

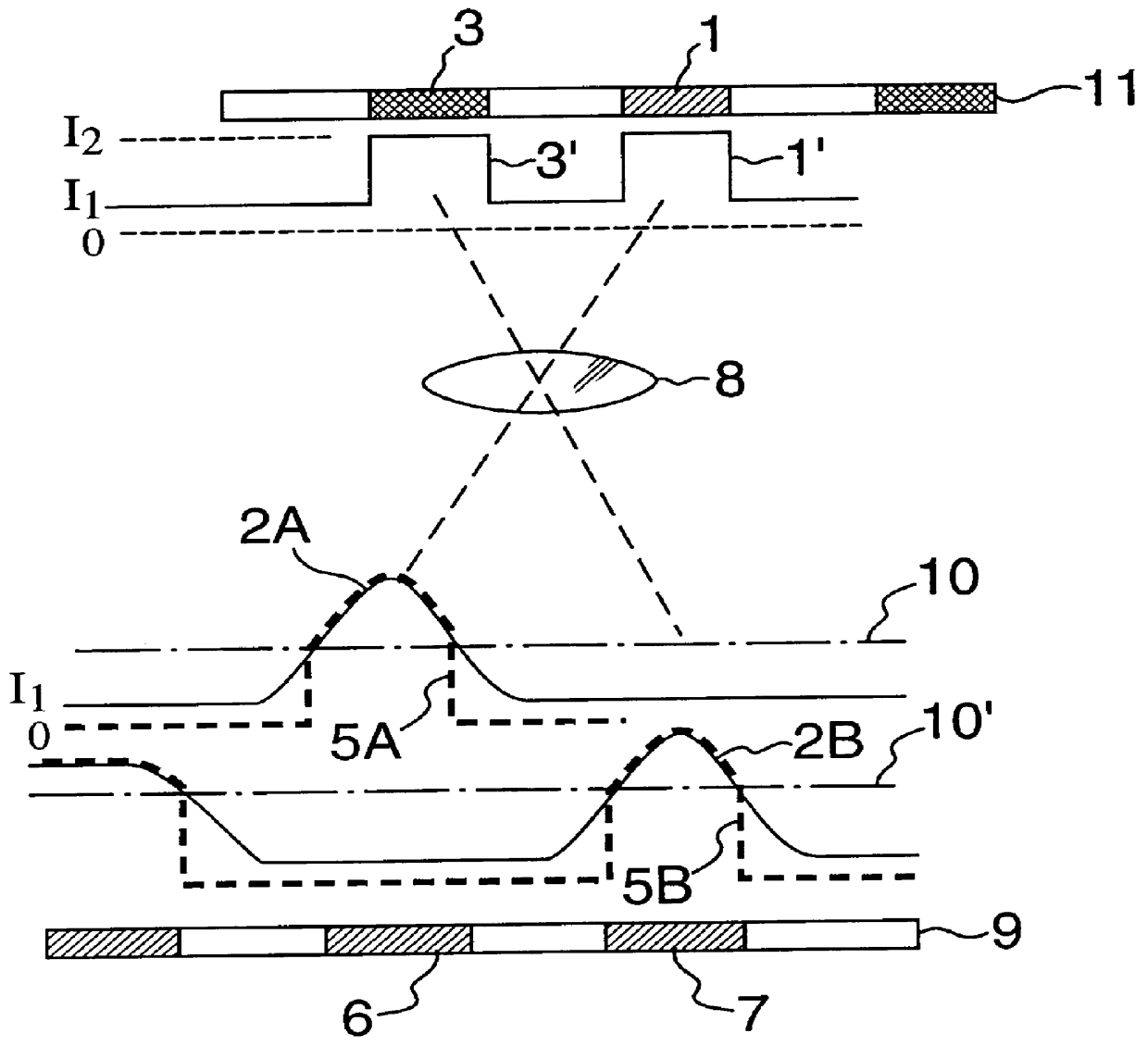

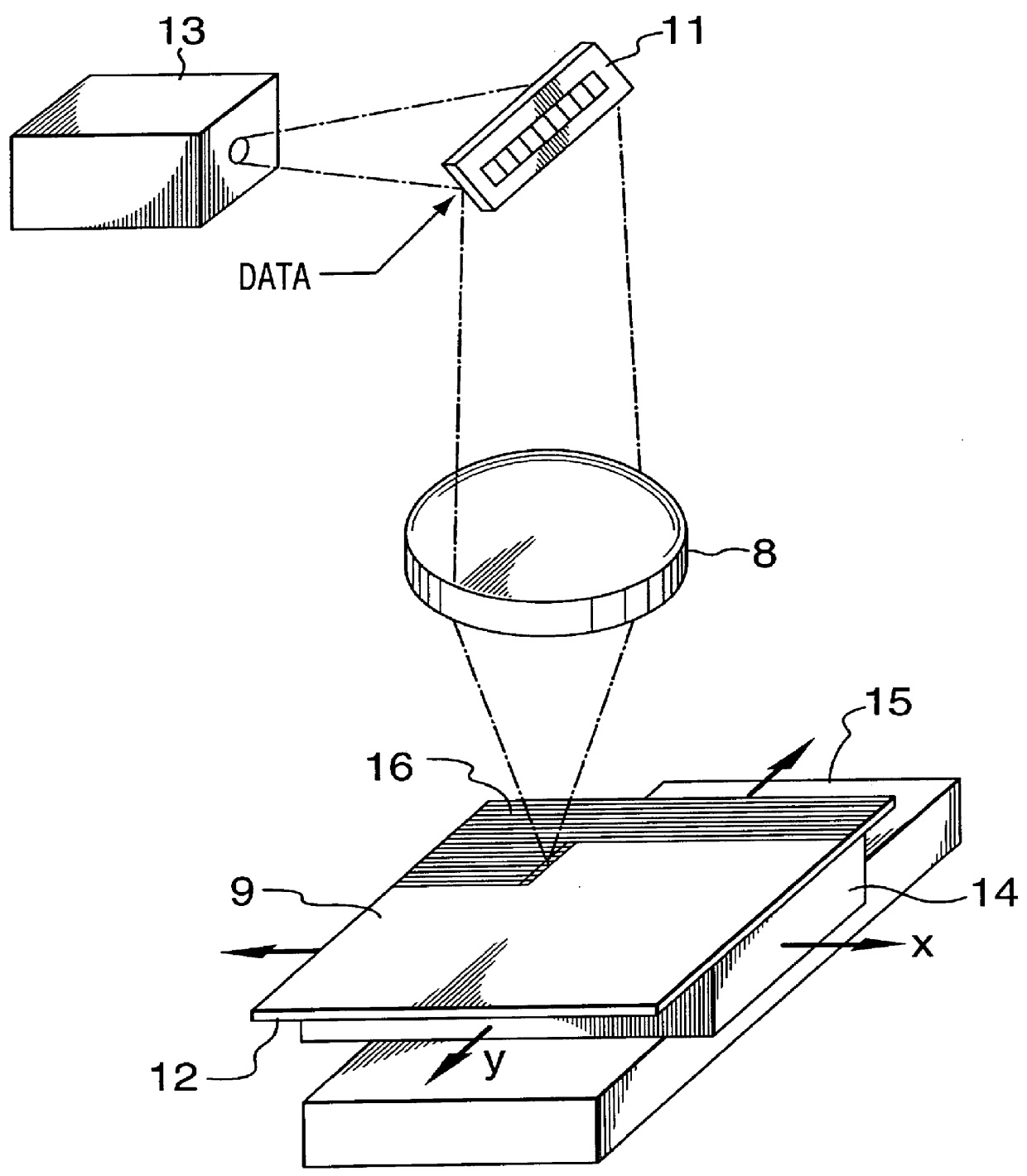

Exposure method and device for forming patterns on printed wiring board

InactiveUS20030124463A1Improve throughputSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusEngineeringSemiconductor

An optical exposure method and a device are used for forming patterns on a printed board wiring or semiconductor board. A single exposing region of a surface to be exposed is irradiated with a plurality of optical beams having different irradiating areas and different scanning speeds, such as, a peripheral area is irradiated with an optical beam having a smaller irradiating area and an inner area is irradiated with an optical beam having a larger irradiating area.

Owner:SHINKO ELECTRIC IND CO LTD

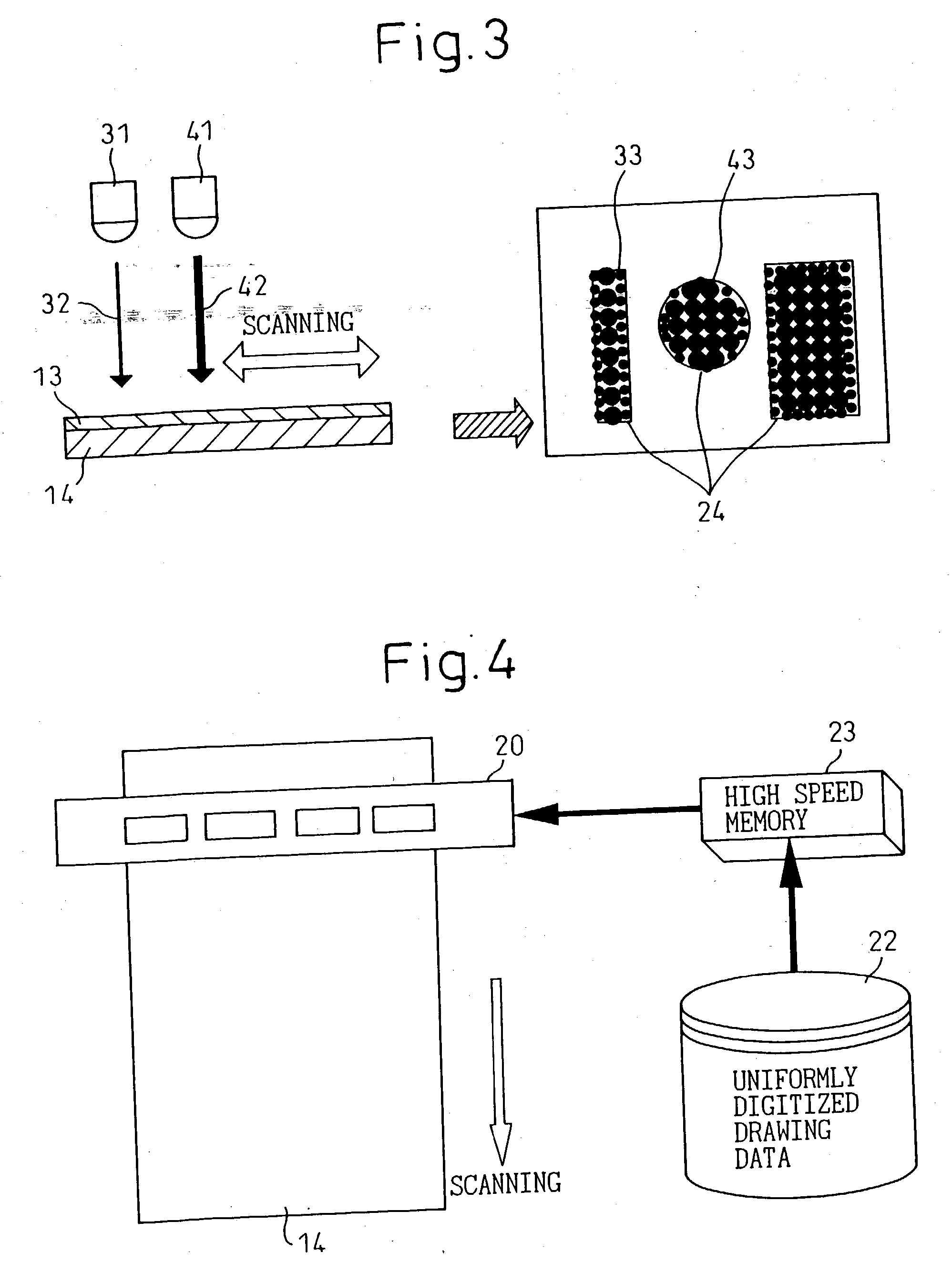

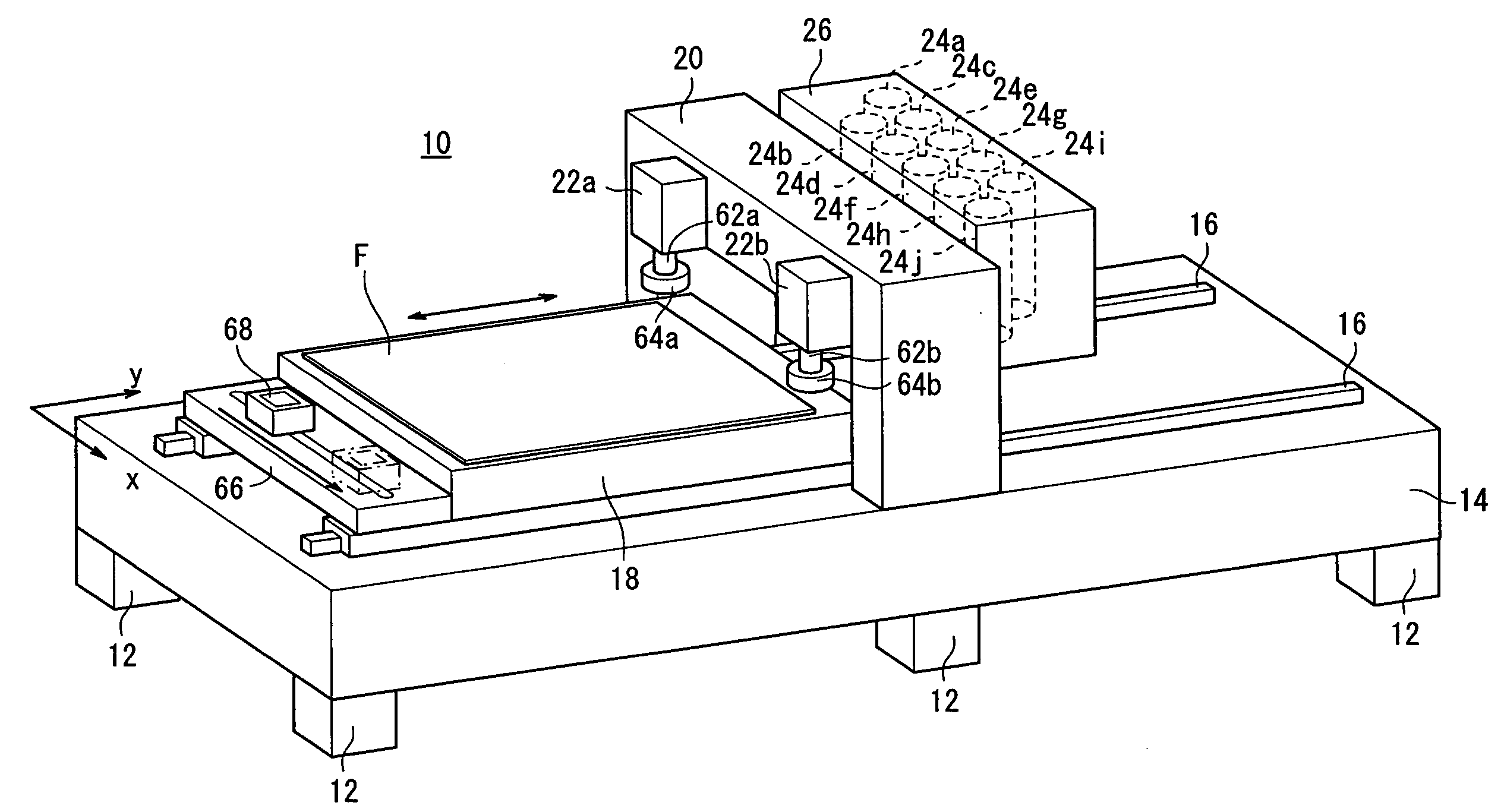

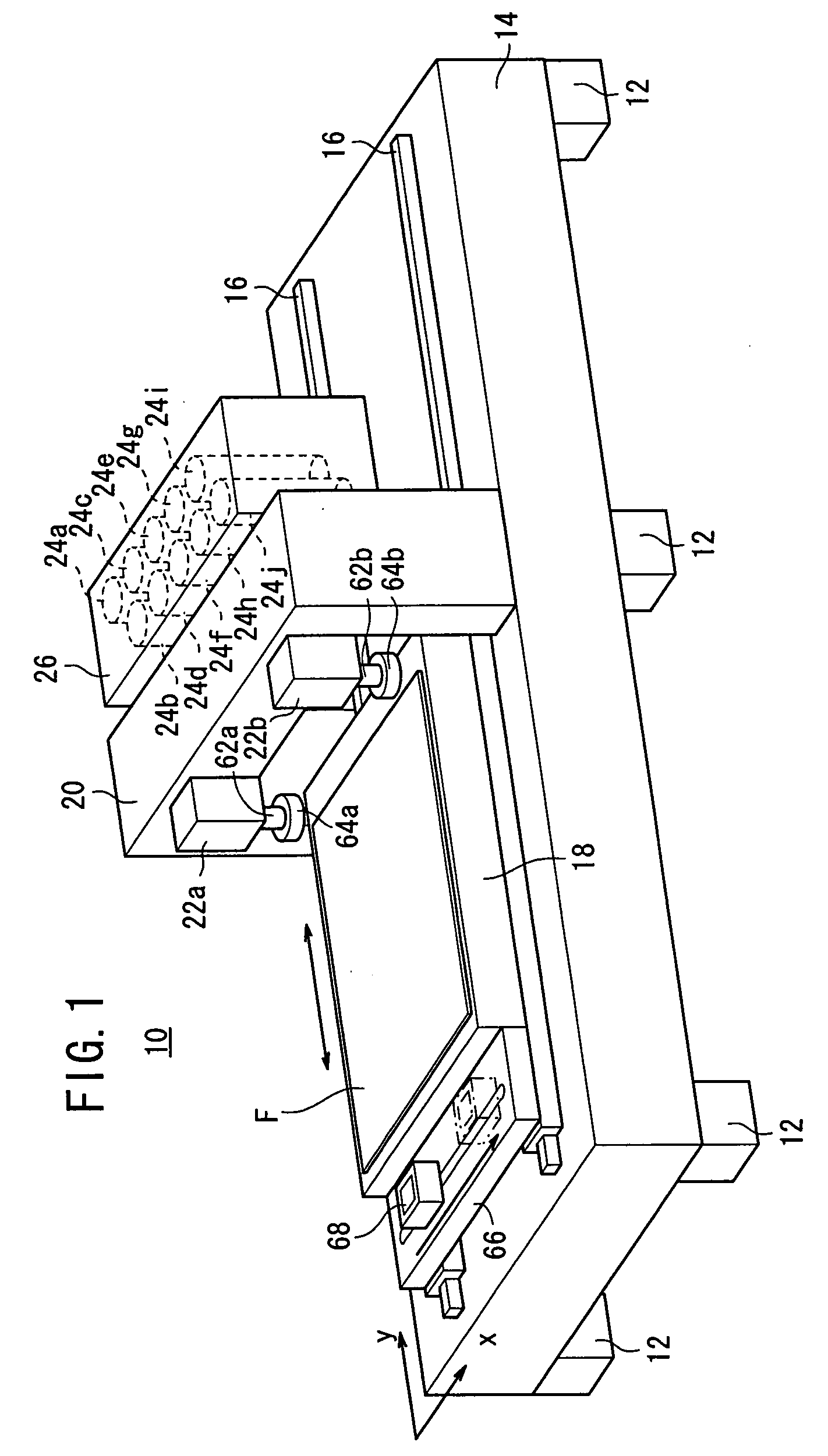

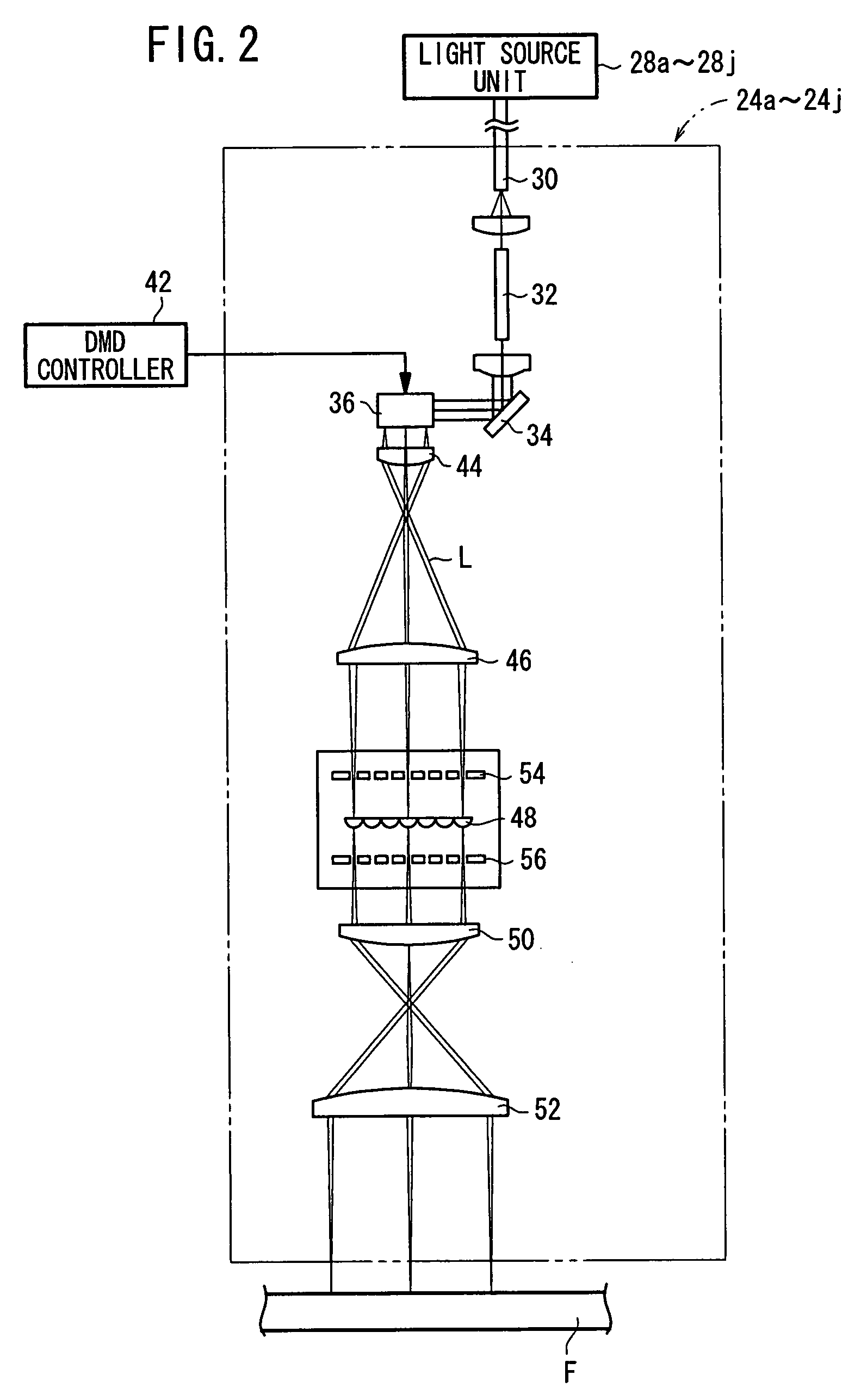

Light Quantity Adjustment Method, Image Recording Method, and Device

InactiveUS20080316458A1Accurate imagingPrinted circuit aspectsPhotomechanical apparatusData setLine width

According to test data supplied from a test data memory (80), a test pattern is formed on a substrate (F) and its line width is measured. Light source units (28a to 28j) are adjusted by a light source control unit (89) and the line width change amount between exposure heads (24a to 24j) is corrected so as to set the obtained light quantity. In a mask data setting unit (86), mask data is set so as to control a particular micro mirror of DMD constituting the exposure heads (24a to 24j) to OFF state. By using the mask data, the output data is corrected and a desired image is exposed / recorded on a substrate (F).

Owner:FUJIFILM CORP

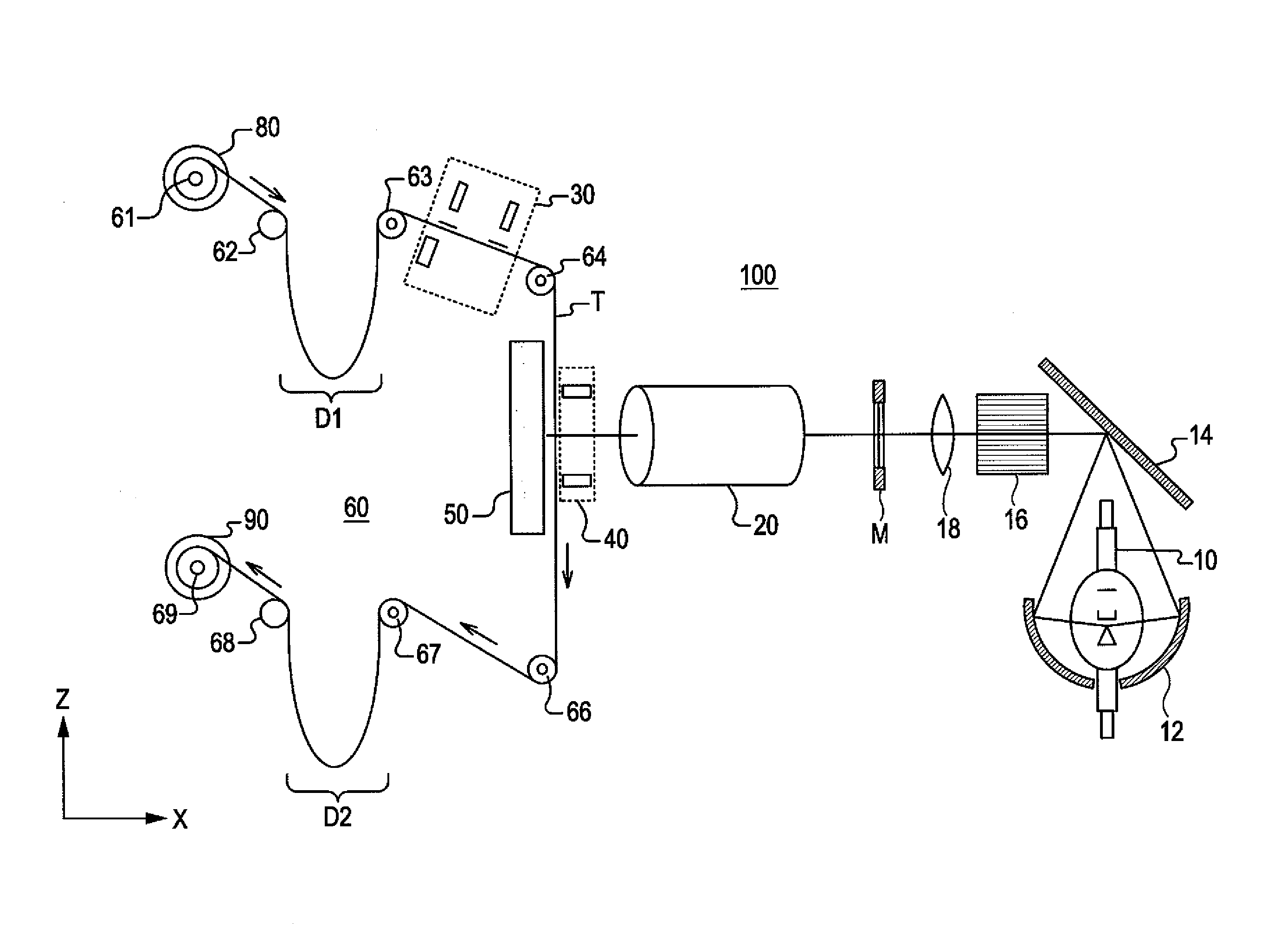

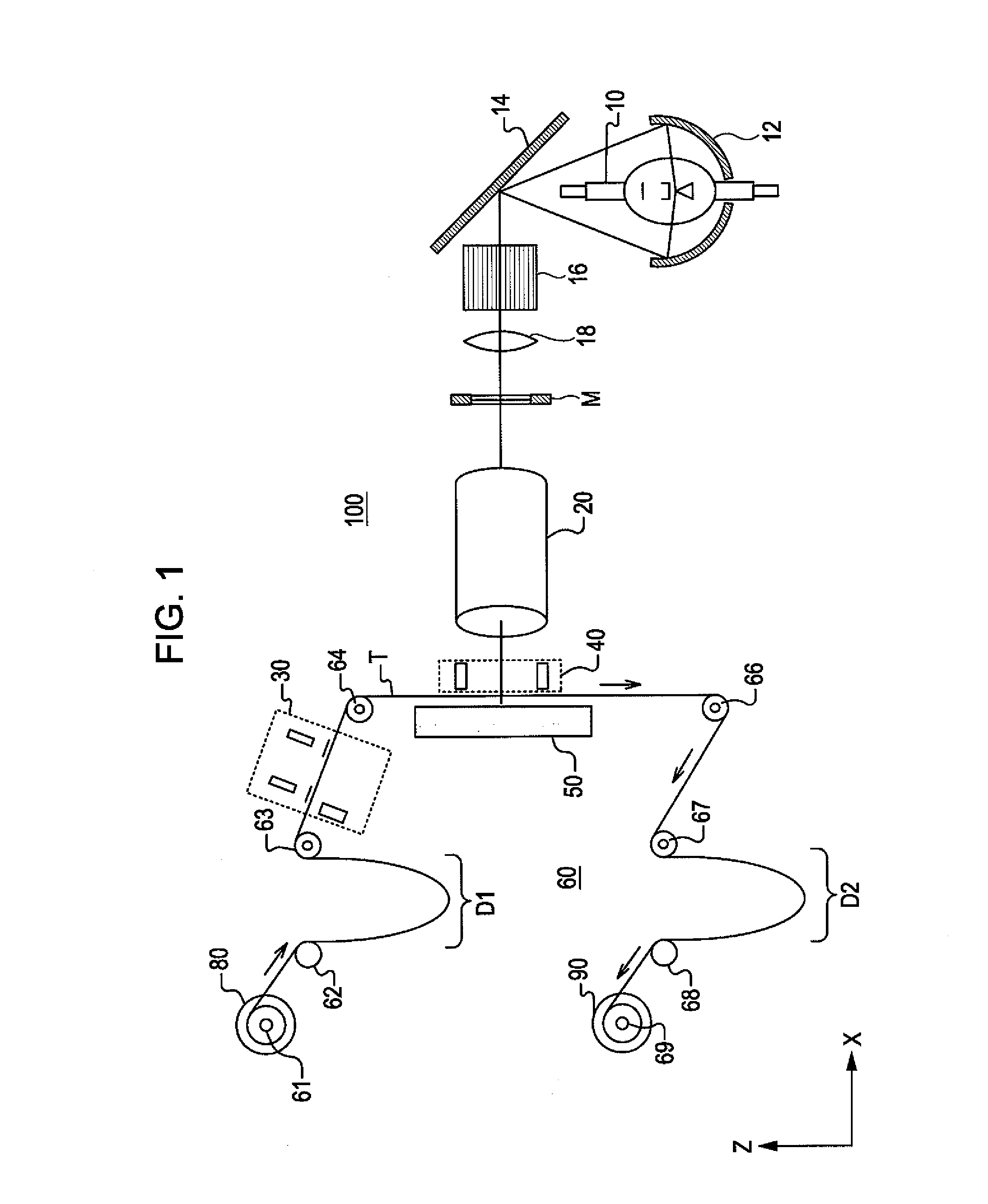

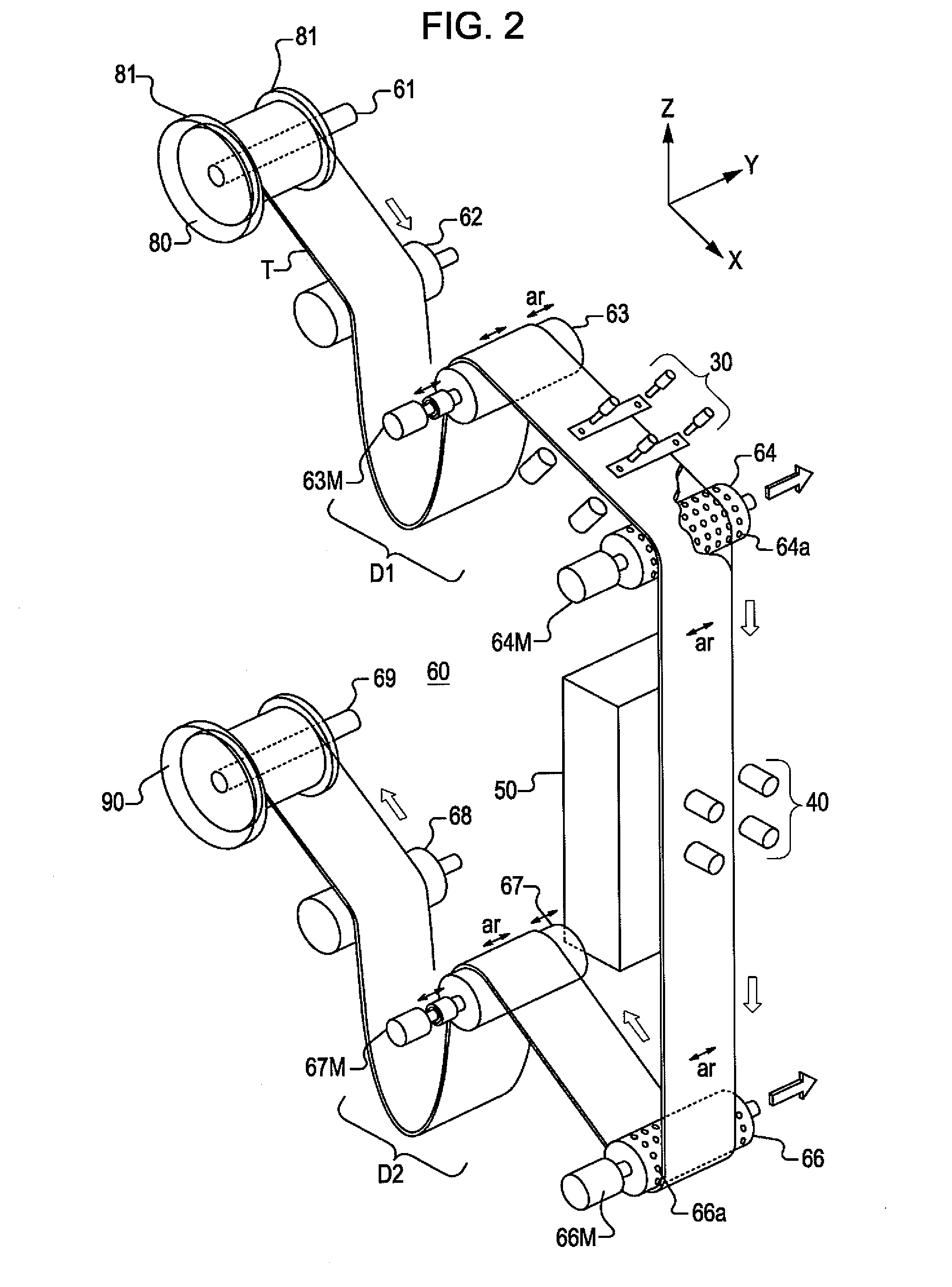

Exposure device with mechanism for forming alignment marks and exposure process conducted by the same

ActiveUS20090059195A1Accurate transferReduce riskPrinted circuit aspectsSolid-state devicesEngineeringRoll film

The present invention relates to an exposure device for transferring circuit patterns of a mask to a roll-film-shaped object. The exposure device includes a supply reel rotation section that is constituted by a supply reel around which the object is wound and that feeds the object by rotating the supply reel, at least one guide roller for guiding the object fed from the supply reel rotation section, an exposure stage on which the circuit patterns are transferred to the object guided by the guide roller, and an alignment mark forming section which forms, on the object, alignment marks that are used to align the mask with the object and which is positioned between the guide roller and the exposure stage.

Owner:ORC MFG

Image-recording apparatus and image-recording process

InactiveUS20050161426A1Eliminate the problemPolycrystalline material growthPrinted circuit aspectsGratingImage recording

An image-recording apparatus and image-recording process capable of suppressing mispositioning of recording of an image from an ideal position while correcting for mispositioning of the recording of the image in a case in which a recording medium is deformed to an arbitrary shape. When a wiring pattern is to be recorded on a PWB (printed wiring board) using raster data, deformation information representing a state of deformation of the PWB is acquired beforehand. On the basis of this deformation information, the raster data is converted such that the wiring pattern that is recorded will, after the deformation, have the same shape as the wiring pattern represented by the unconverted raster data. On the basis of the converted raster data, the wiring pattern is recorded at the PWB before the deformation.

Owner:FUJIFILM HLDG CORP +1

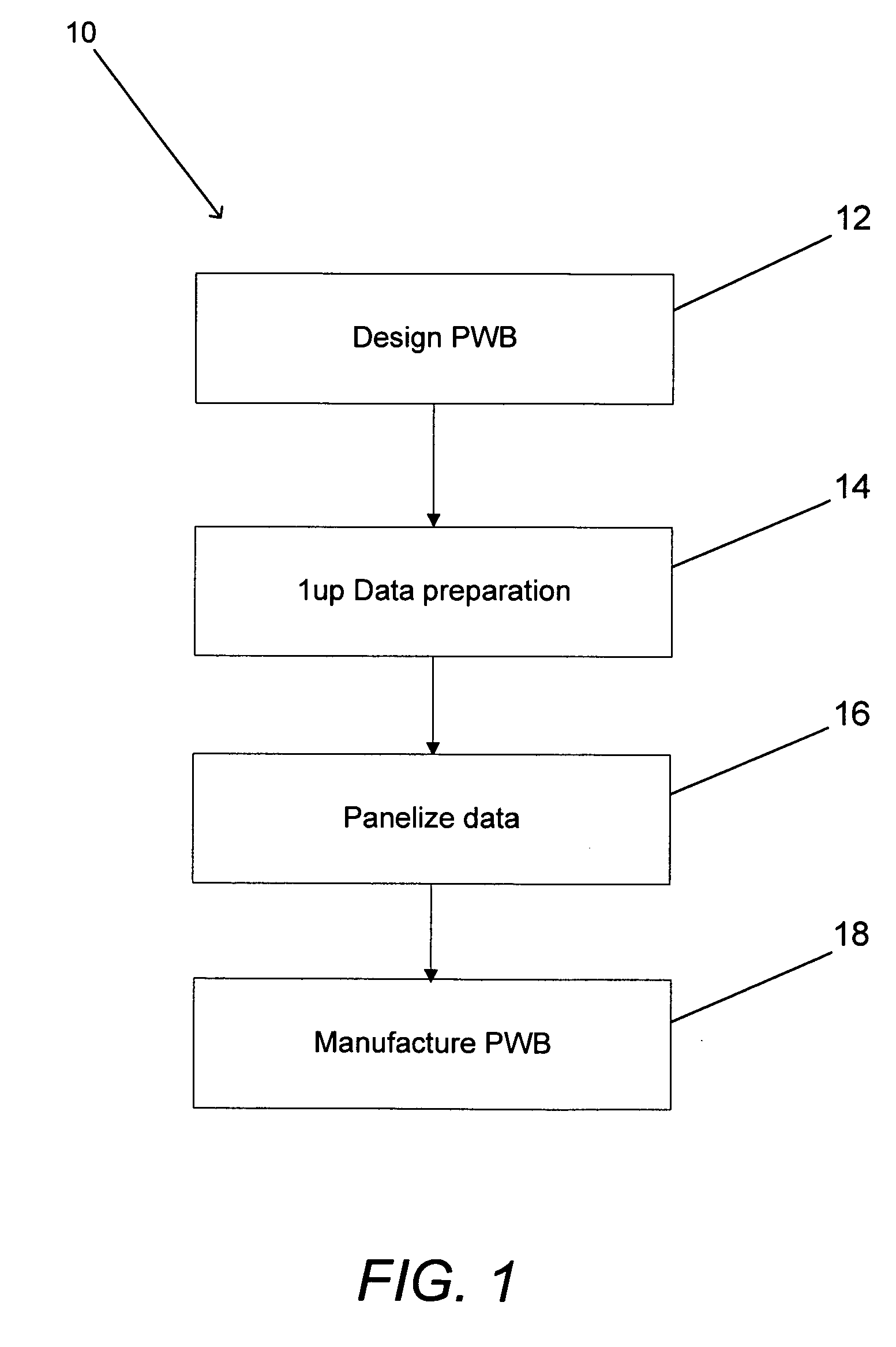

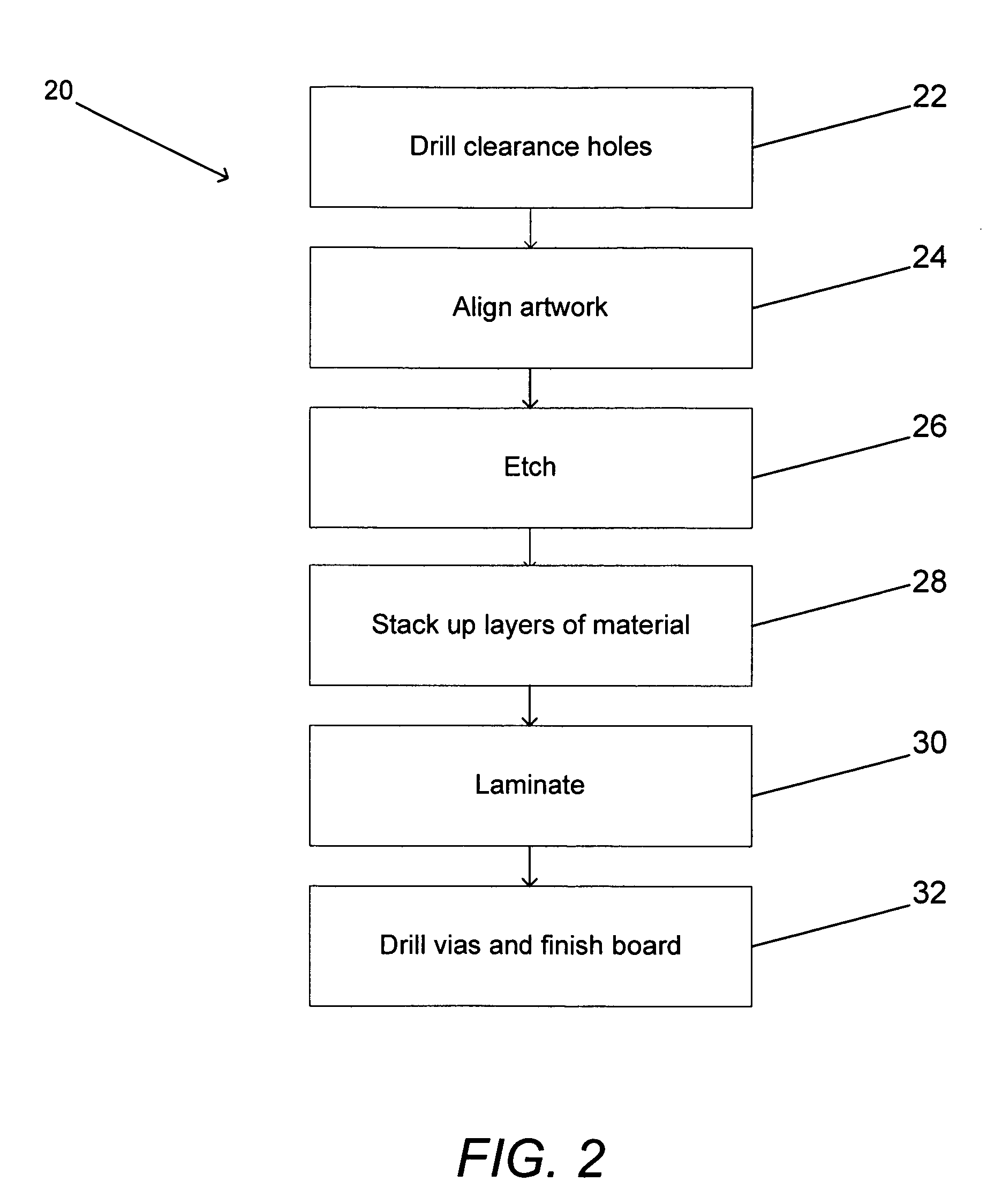

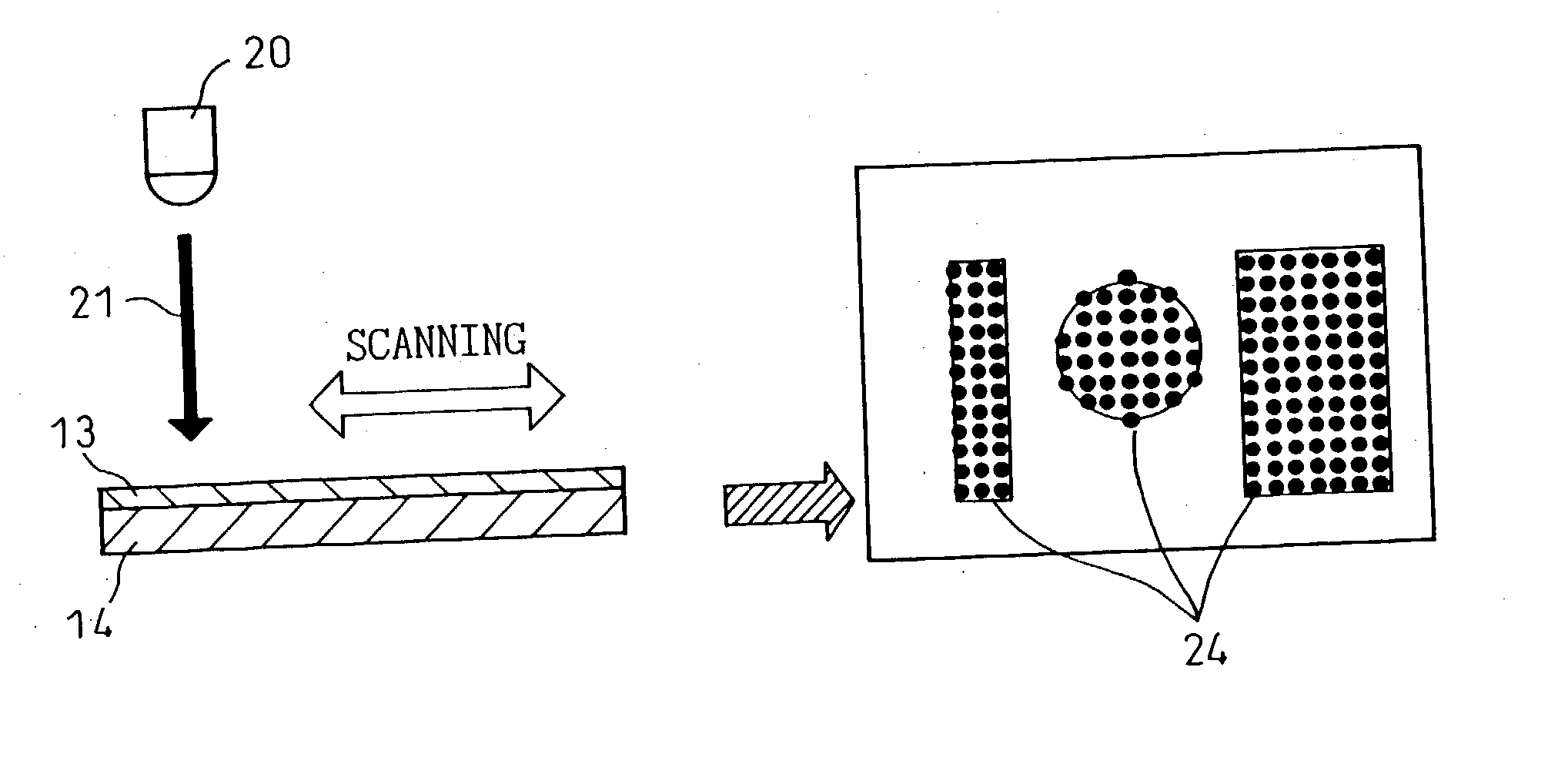

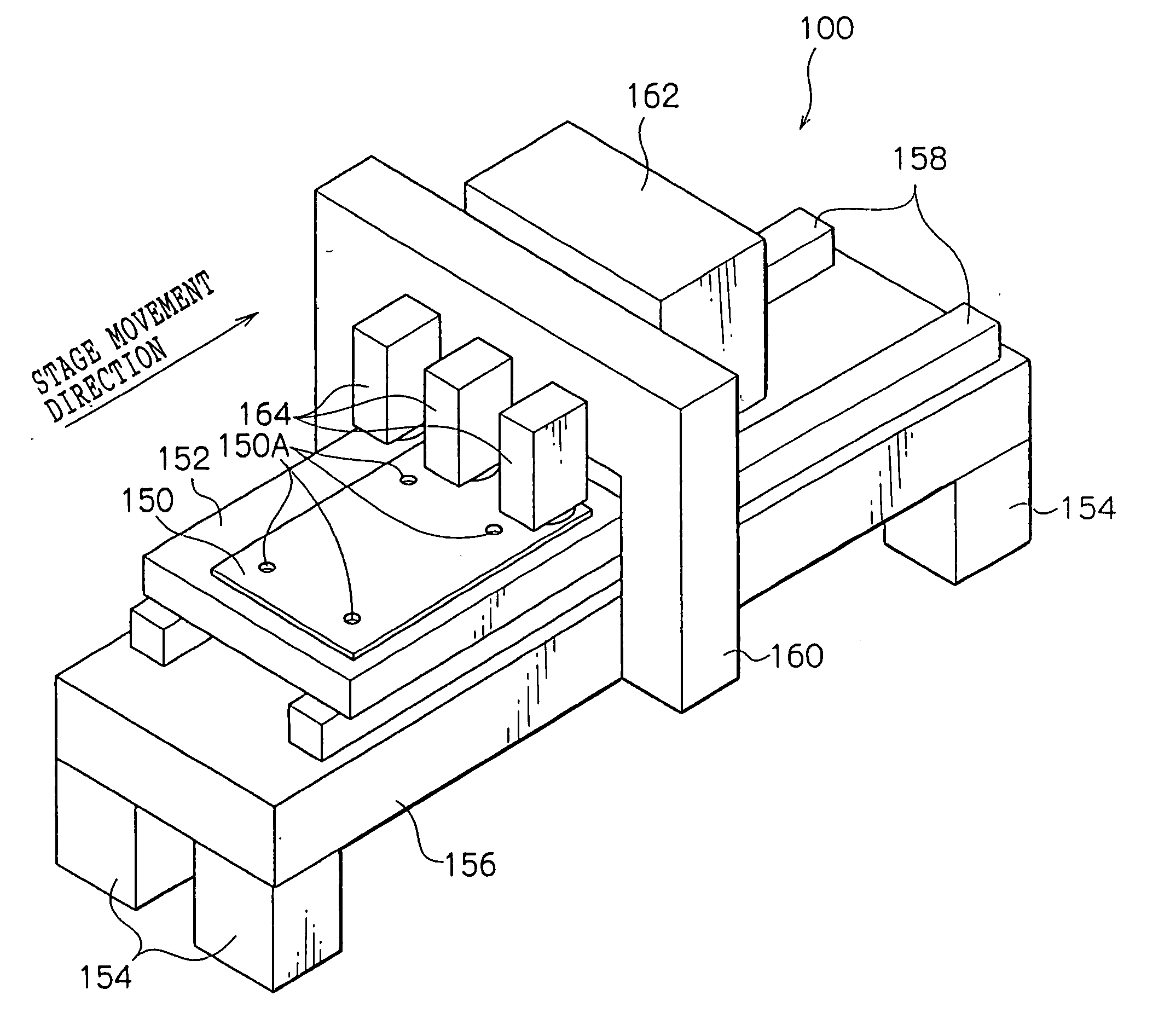

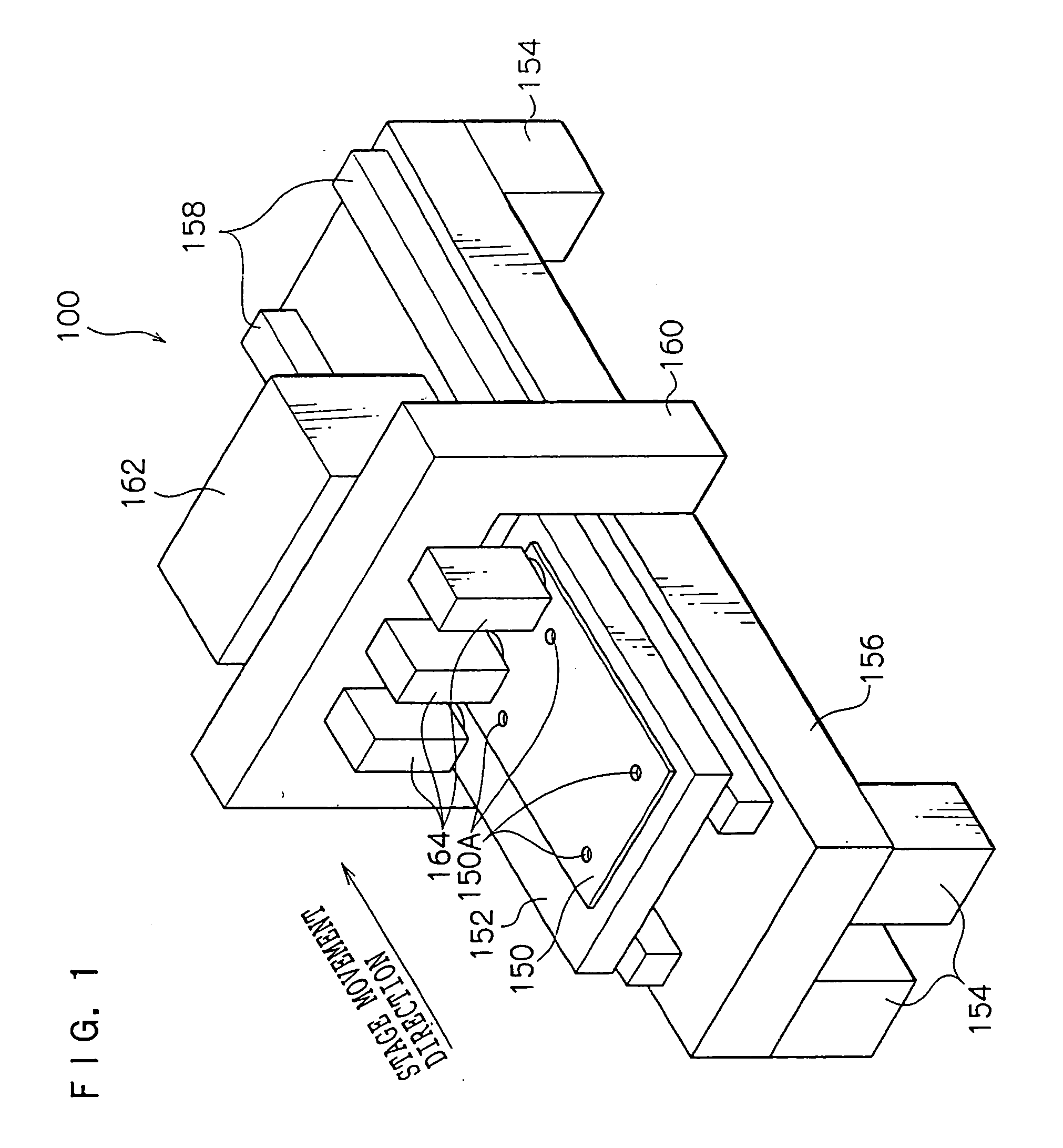

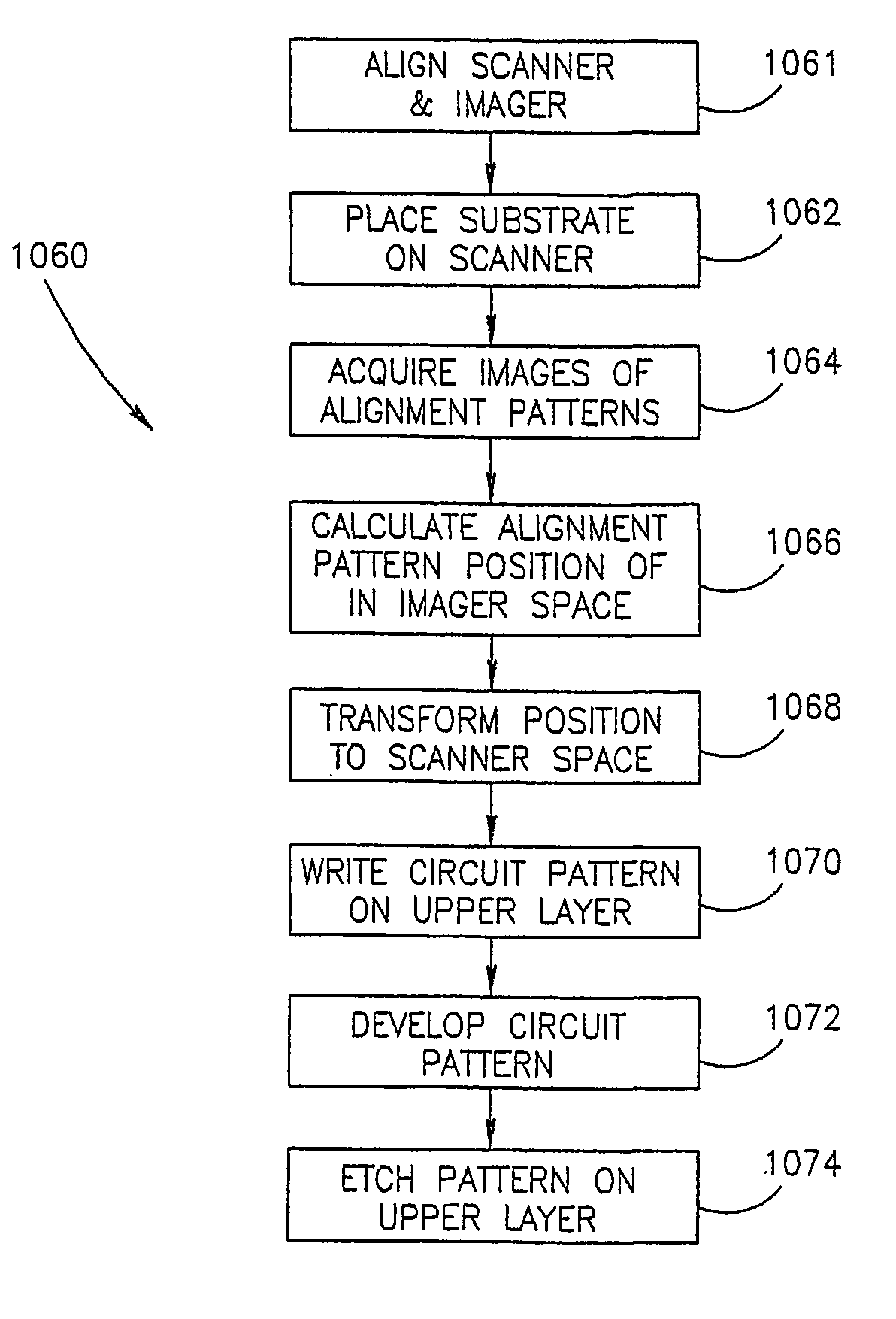

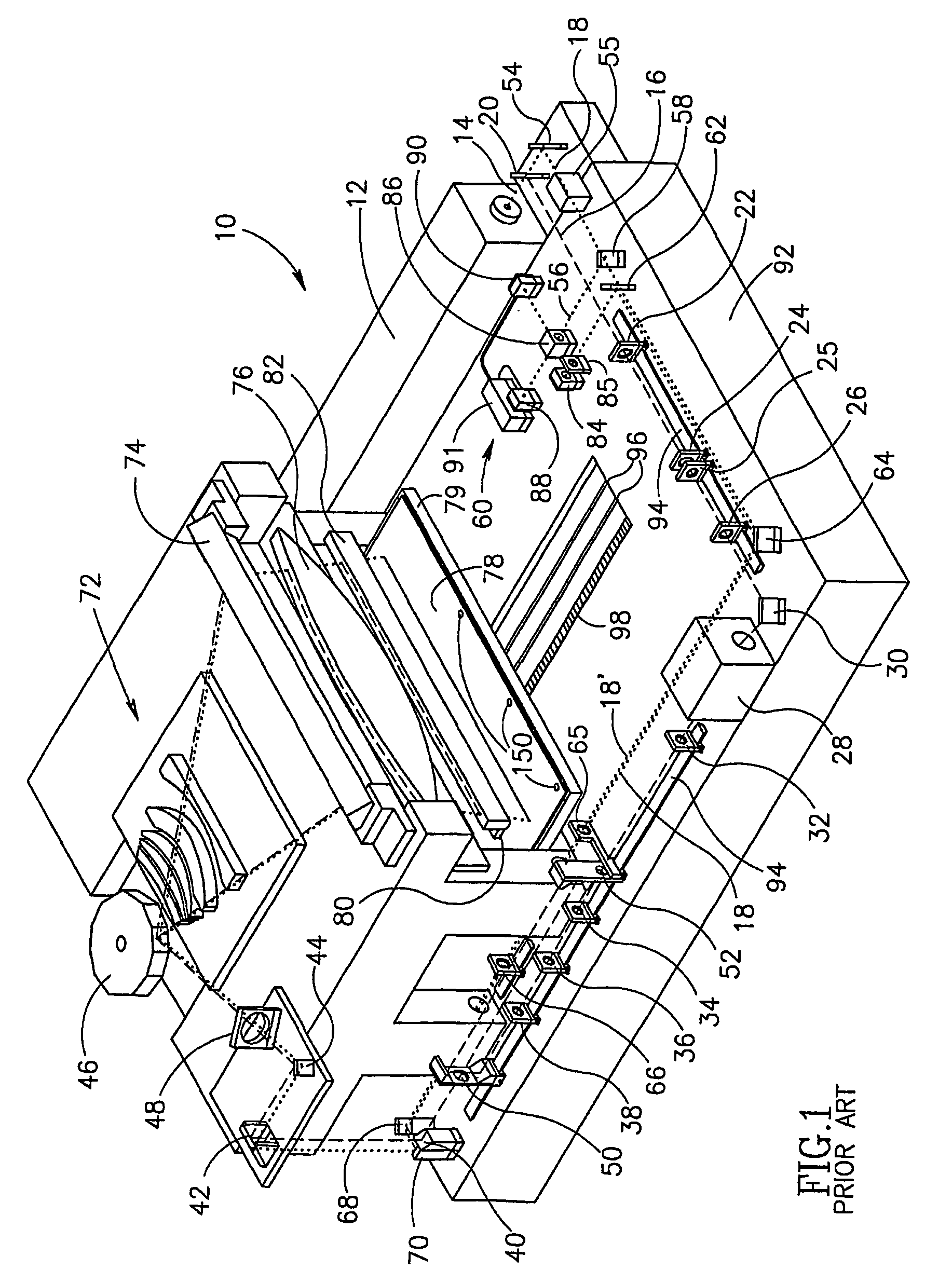

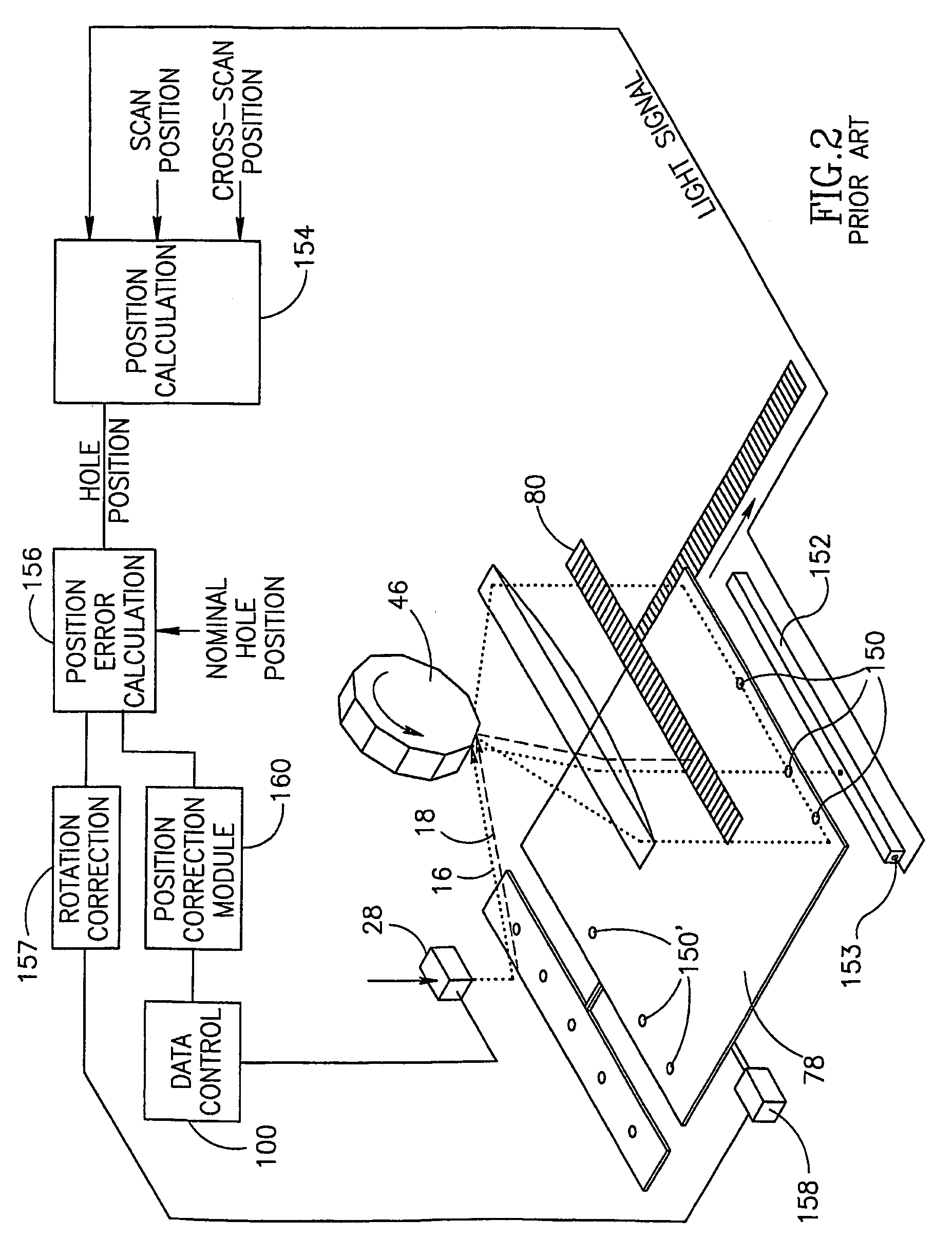

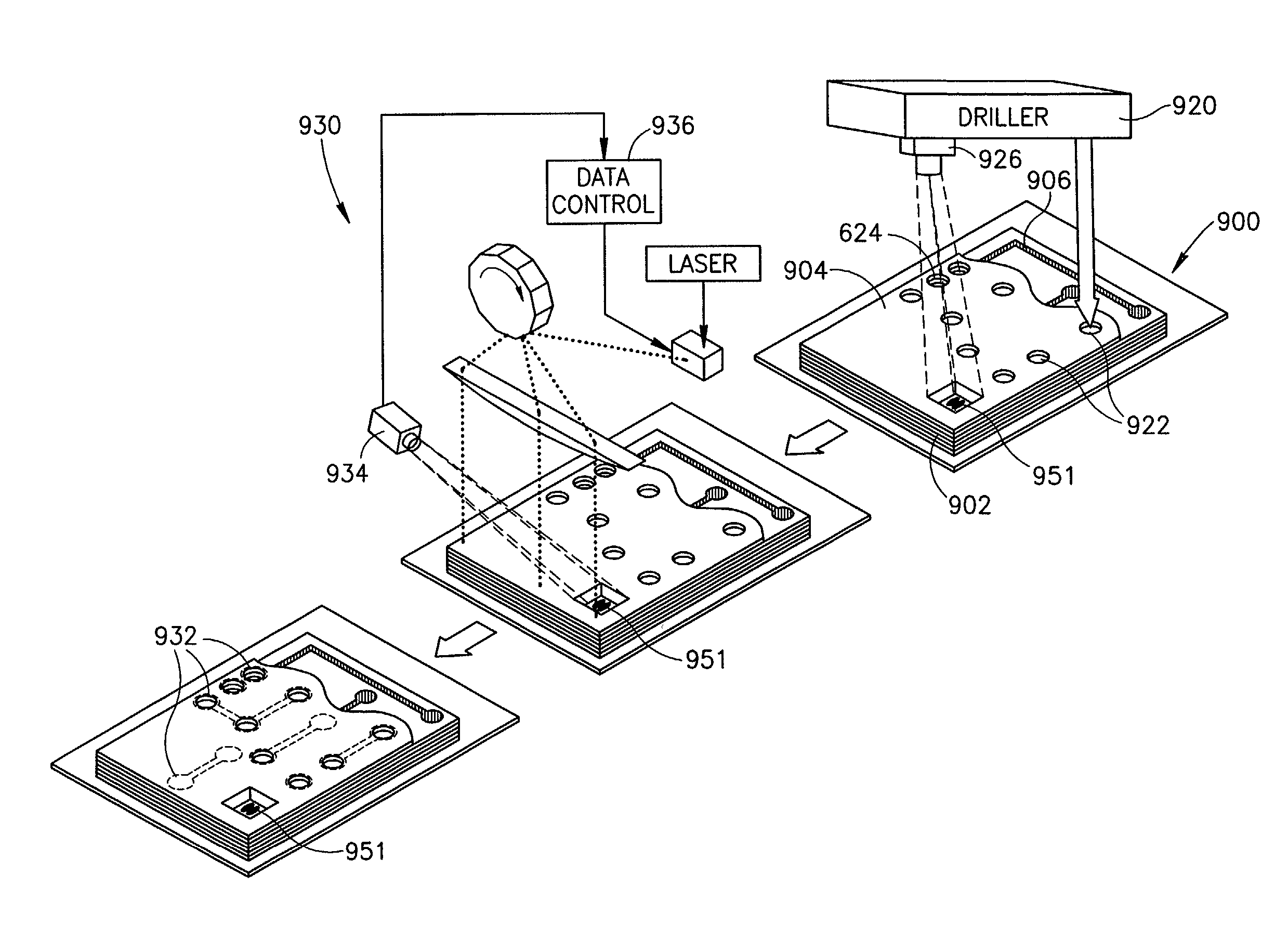

Multi-layer printed circuit board fabrication system and method

InactiveUS7062354B2Printed circuit aspectsSemiconductor/solid-state device manufacturingPrinted circuit boardComputer science

A method for aligning an image to be recorded by a direct image scanner on an upper layer of a printed circuit board with an image recorded on a lower layer thereof, the method comprising visually imaging a portion of the image on the lower layer and recording a pattern on the upper layer, referenced to coordinates of the visual image of the portion.

Owner:ORBOTECH LTD

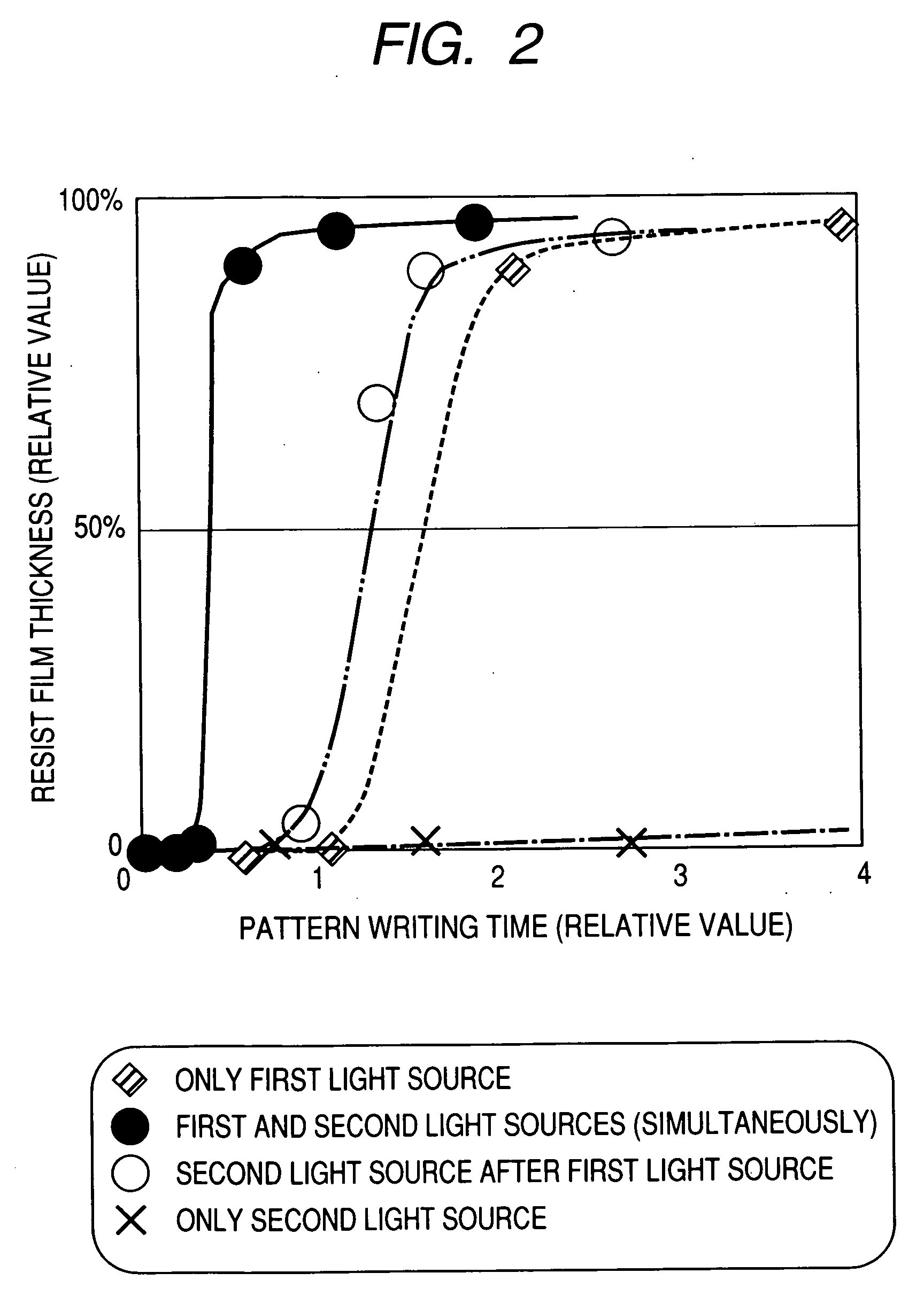

Exposure apparatus and exposing method and method of manufacturing a printed wiring board

ActiveUS20060215143A1Low costImprove stabilityPhotomechanical apparatusPhotographic printingLight irradiationUltraviolet

The mask-less exposure apparatus includes: a stage which moves with the substrate having a photosensitive resin layer with sensitivity to ultraviolet radiation formed thereon; a first light source for emitting light containing a wavelength component in the wavelength range of 300 to 410 nm; a first light irradiation optical system for modulating a radiant flux emitted from the first light source based on data of a desired exposure pattern to image a pattern on the photosensitive resin layer; a second light source for emitting light containing a wavelength component in the wavelength range of 450 to 2500 nm; and a second light irradiation optical system for guiding a radiant flux emitted from the second light source to a second light irradiation area that is set so as to include at least a first light irradiation area.

Owner:ADTEC ENG

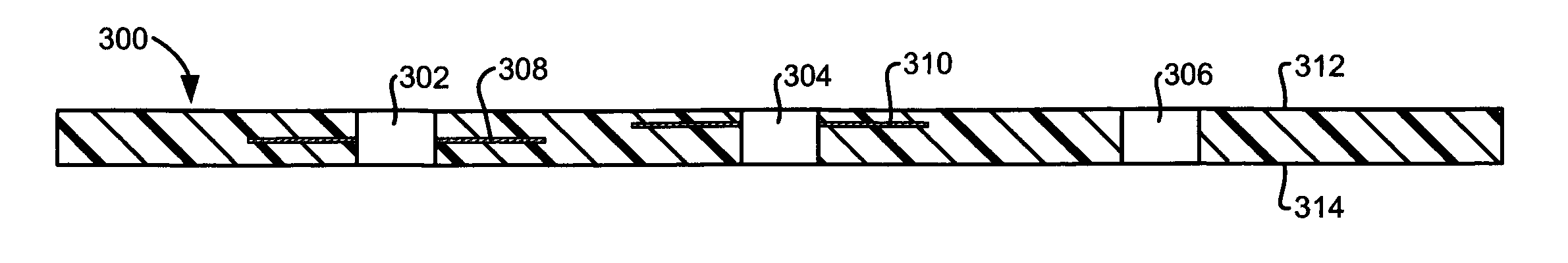

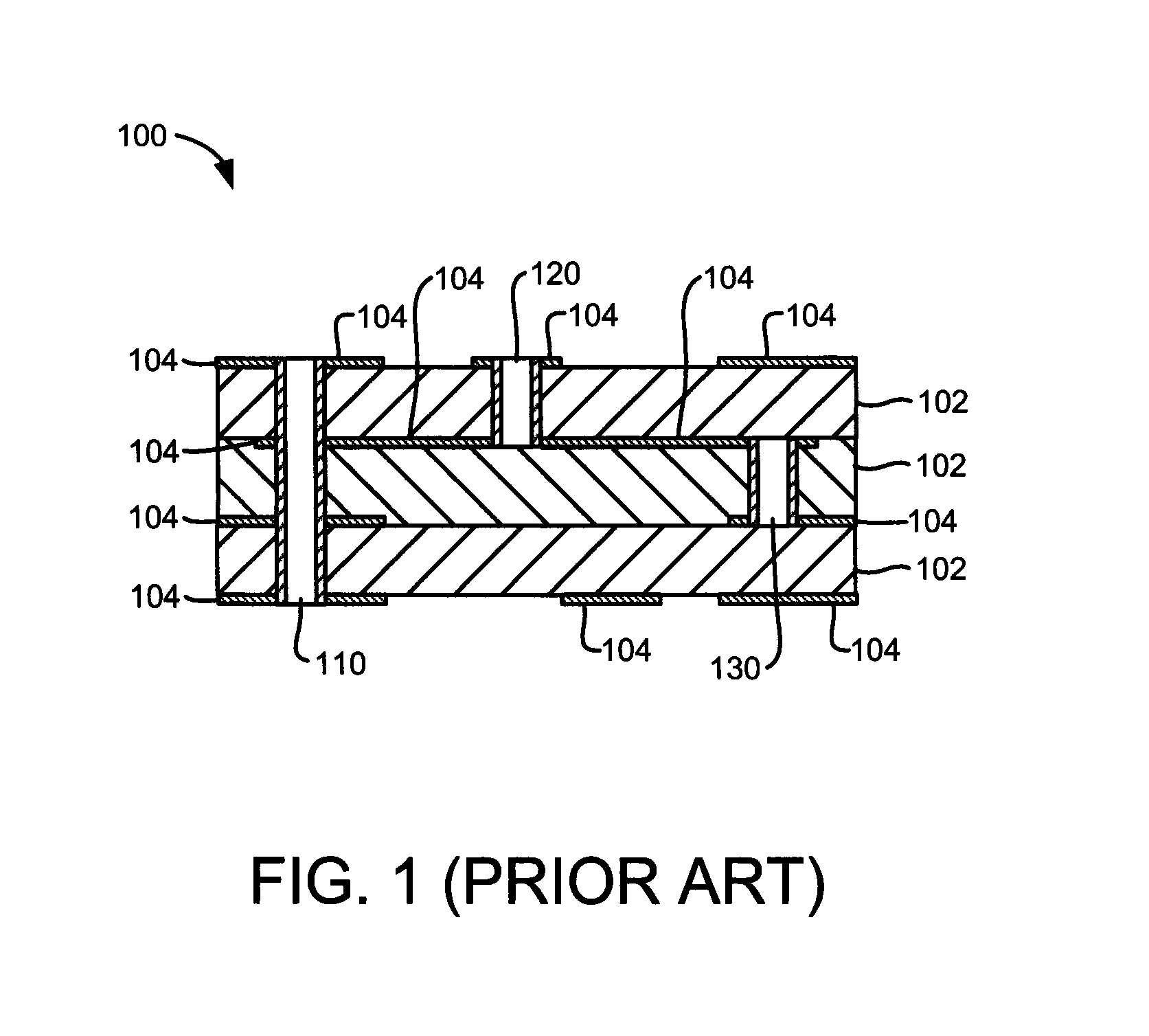

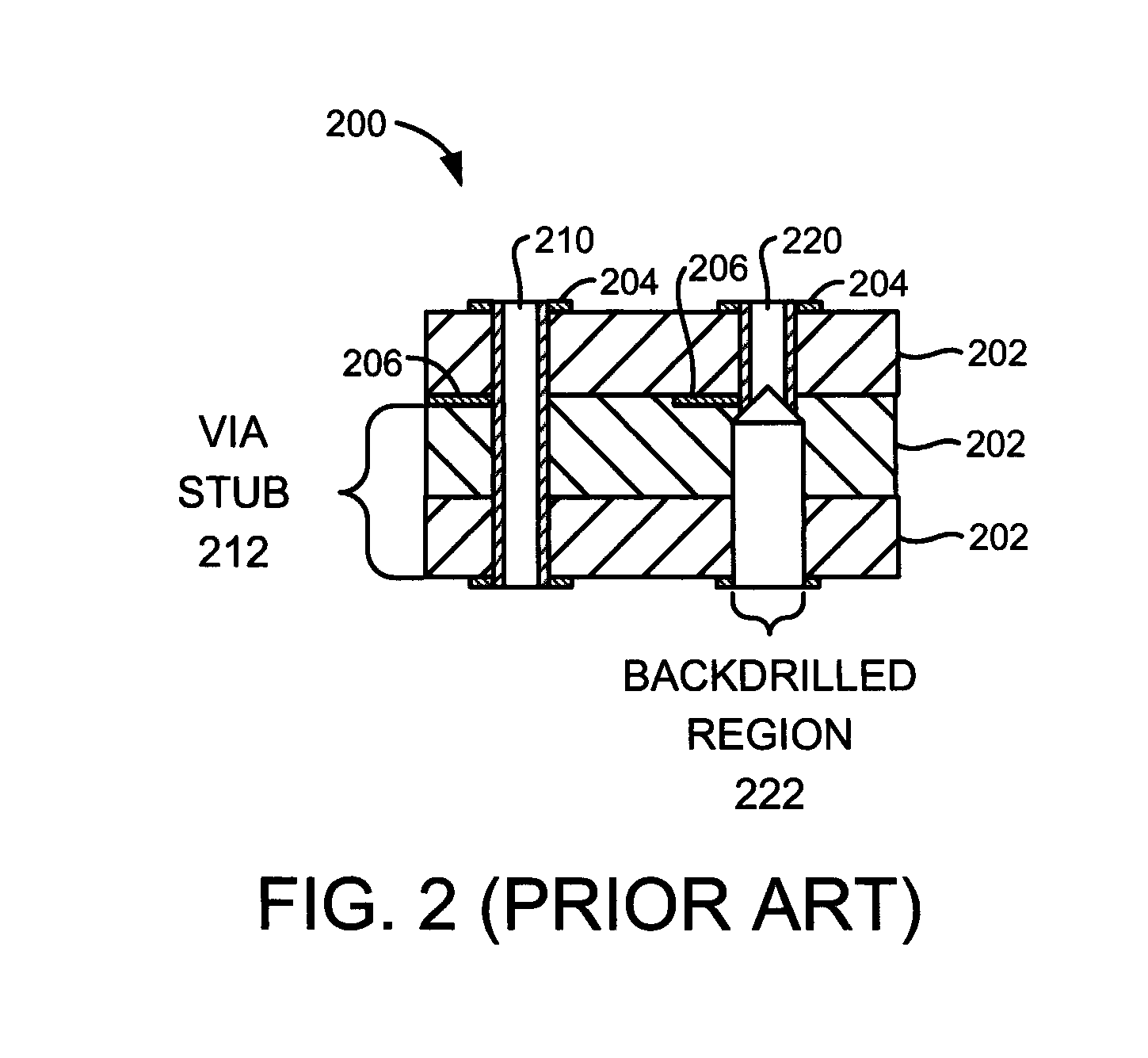

Via Stub Elimination

InactiveUS20100044095A1Eliminates costlyTime-consuming to eliminatePrinted circuit assemblingAdditive manufacturing apparatusTime-ConsumingPhotomask

An enhanced mechanism is disclosed for via stub elimination in printed wiring boards (PWBs) and other substrates. In one embodiment, the substrate includes a plurality of insulator layers and internal conductive traces. First and second through-holes extend completely through the substrate and respectively pass through first and second ones of the internal conductive traces, which are at different depths within the substrate. Photolithographic techniques are used to generate plated-through-hole (PTH) plugs of controlled, variable depth in the through-holes before first and second conductive vias are respectively plated onto the first and second through-holes. The depth of these PTH plugs is controlled (e.g., using a photomask and / or variable laser power) to prevent the first and second conductive vias from extending substantially beyond the first and second internal conductive traces, respectively, and thereby prevent via stubs from being formed in the first place. This advantageously eliminates the costly and time consuming process of via stub backdrilling.

Owner:GLOBALFOUNDRIES INC

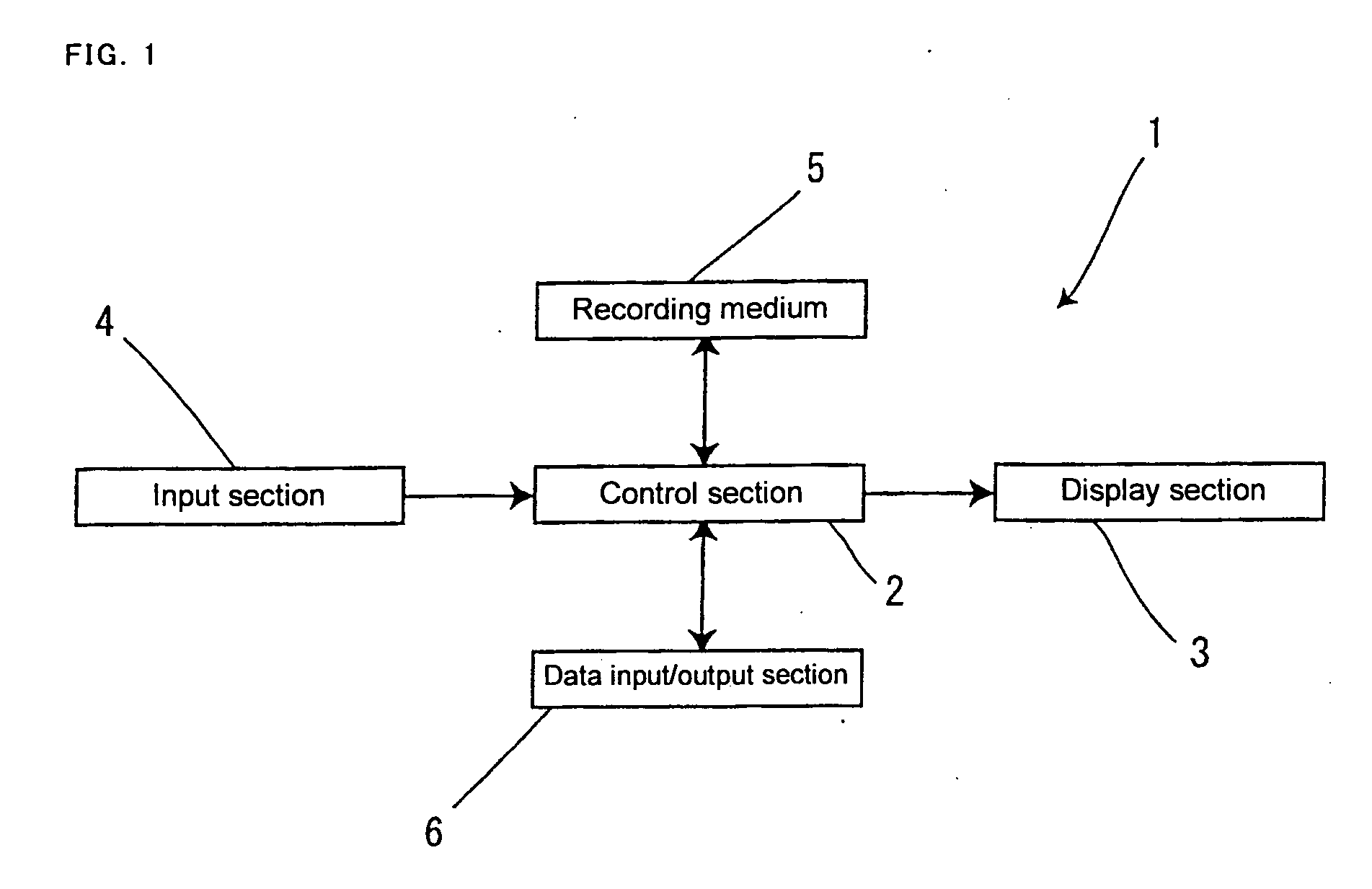

CAD system for a printed circuit board

InactiveUS20060200332A1Valid checkReasonable judgmentPrinted circuit aspectsAnalogue computers for electric apparatusEngineeringPrinted circuit board

A pattern design of a film for manufacturing a printed circuit board is made by using a CAD system, and a plurality of types of Gerber data are produced in which a series of various data has been encoded. For example, a pattern film is formed by combining pattern Gerber data with pattern cut Gerber data. Data for check marks whose sizes are different from each other is added as well as pattern data to each Gerber data such that their central coordinates are to be the same. In this manner, a judgment mark having the check marks combined therewith is formed on the pattern film having the items of Gerber data combined therewith.

Owner:ORION ELECTRIC CO LTD

Method and apparatus for registration control in production by imaging

InactiveUS6493064B2Reduce misregistrationPrinted circuit aspectsCircuit board tools positioningControl dataEngineering

A method and apparatus for imaging an overlying conductive pattern over an underlying conductive pattern on a substrate, by determining deviations between the actual locations and the nominal locations of predetermined reference targets in the underlying conductive pattern on the substrate; and utilizing the determined deviations for modifying the scanning control data used for imaging the image data of the overlying conductive pattern in order to reduce misregistration thereof with respect to the underlying conductive pattern. Preferably, the reference targets are predetermined connection sites in the underlying conductive pattern to be precisely located with respect to connection sites in the overlying conductive pattern. The reference features may be assigned different weights according to their registration importance, and the deviations may be determined according to a threshold which varies with the weight assigned to the respective reference feature.

Owner:KODAK IL

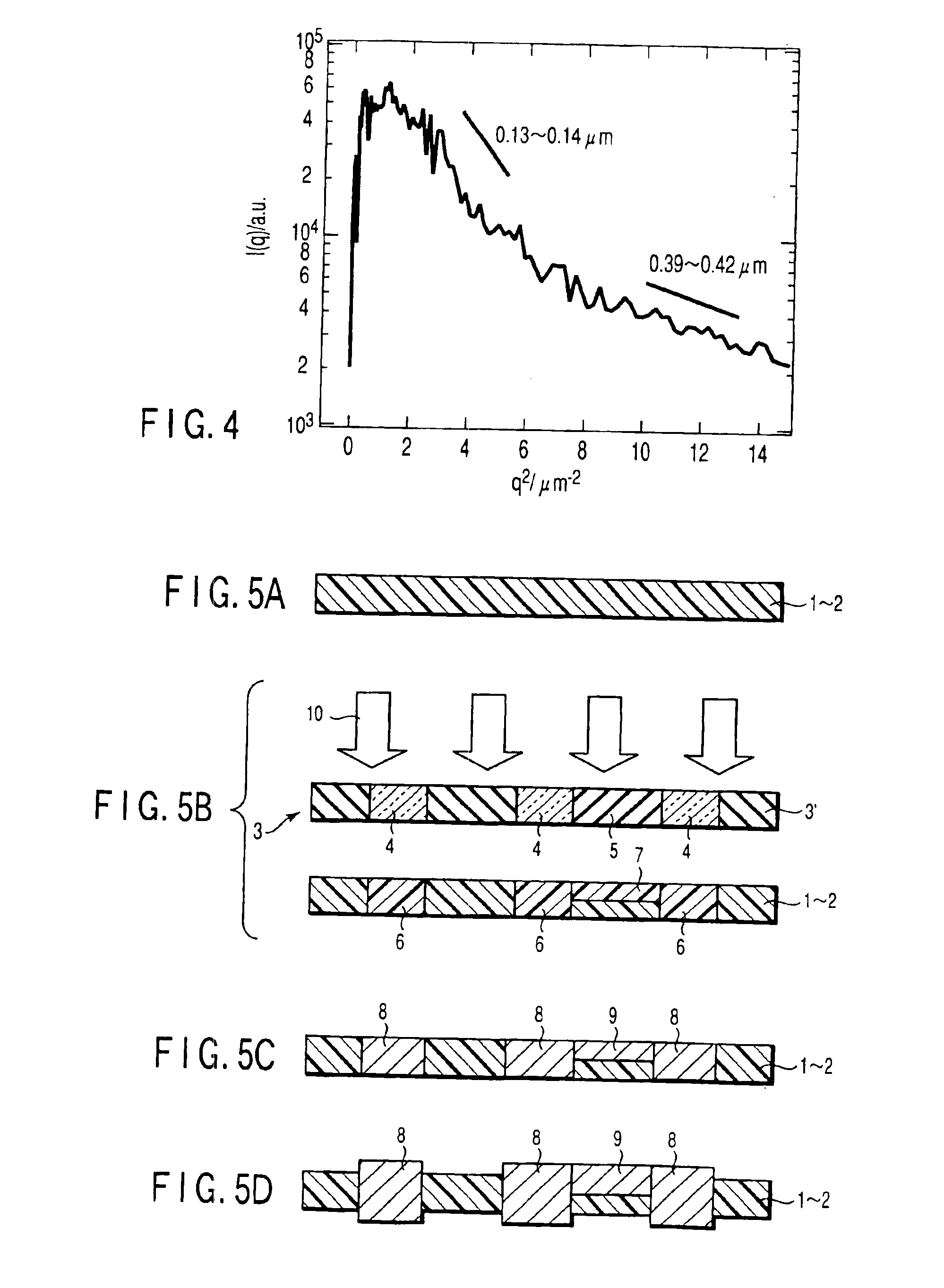

Mask used for exposing a porous substrate

InactiveUS6906423B1Increase freedomPorous dielectricsLayered productsPorous substrateConductive materials

A mask used for exposing a porous substrate to form a first region and a second region, the first region being filled with a conductive material piercing through the entire thickness of the porous substrate to constitute an interfacial conductive portion, the second region being filled with a conductive material not piercing the entire thickness of the porous substrate to constitute a non-interfacial conductive portion. The mask includes a first light-transmitting region for exposing the first region, and a second light-transmitting region for exposing the second region, said second light-transmitting region including an aggregation of fine patterns of which an average aperture ratio is not more than 50% of an average aperture ratio of the first light-transmitting region and a size of said fine patterns of the second light-transmitting region being in the range of 0.1 μm to 10 μm.

Owner:KK TOSHIBA

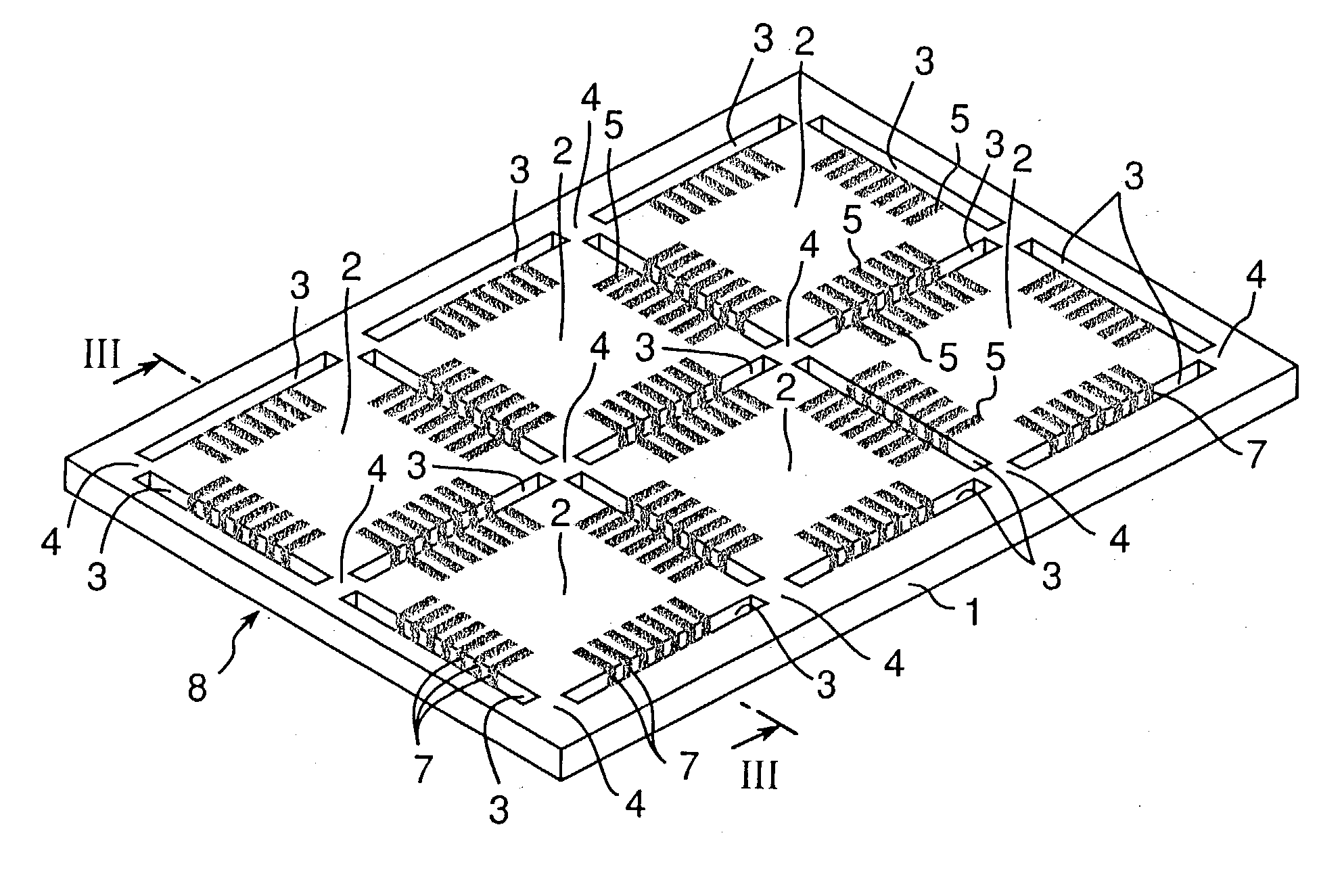

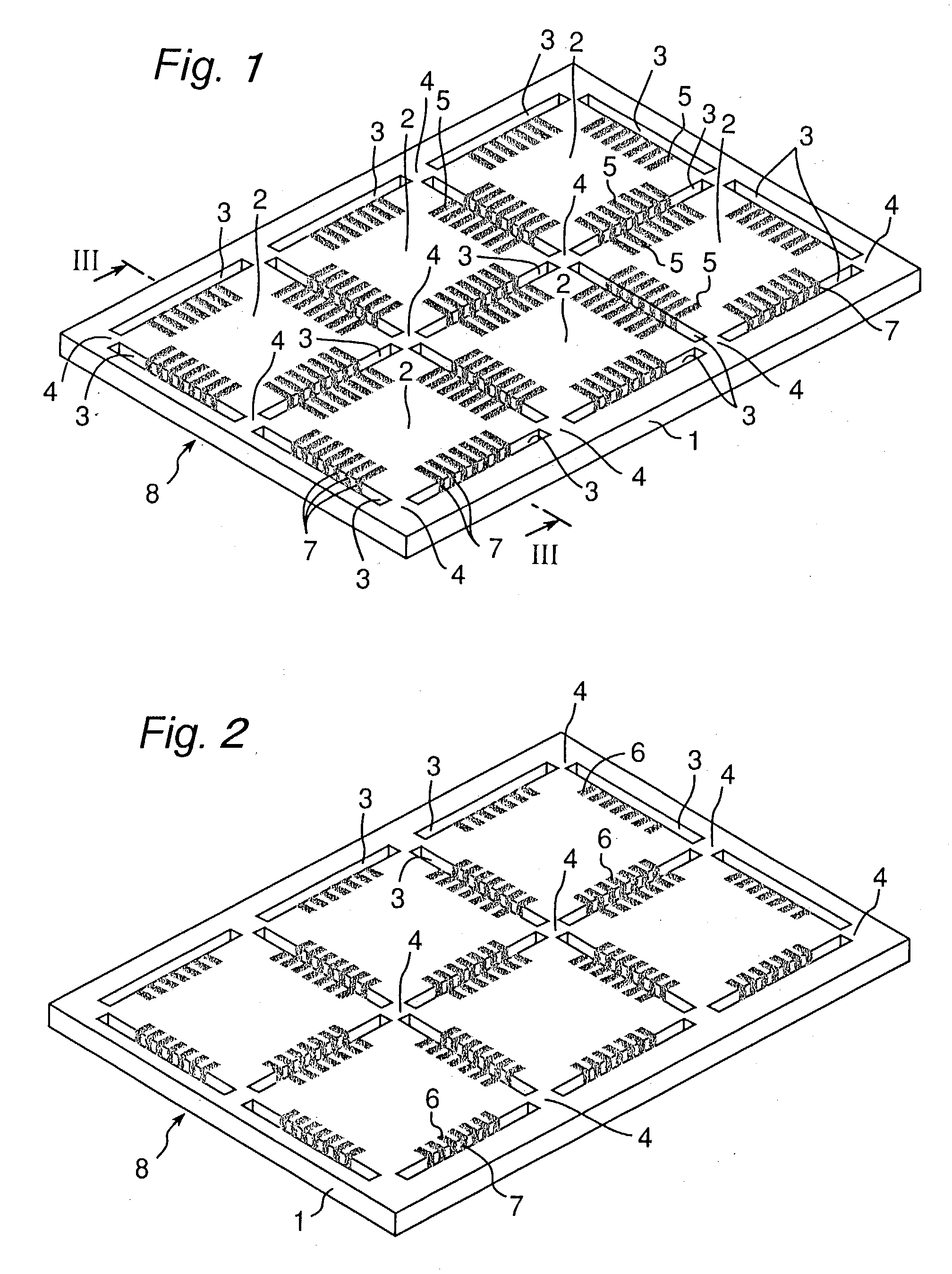

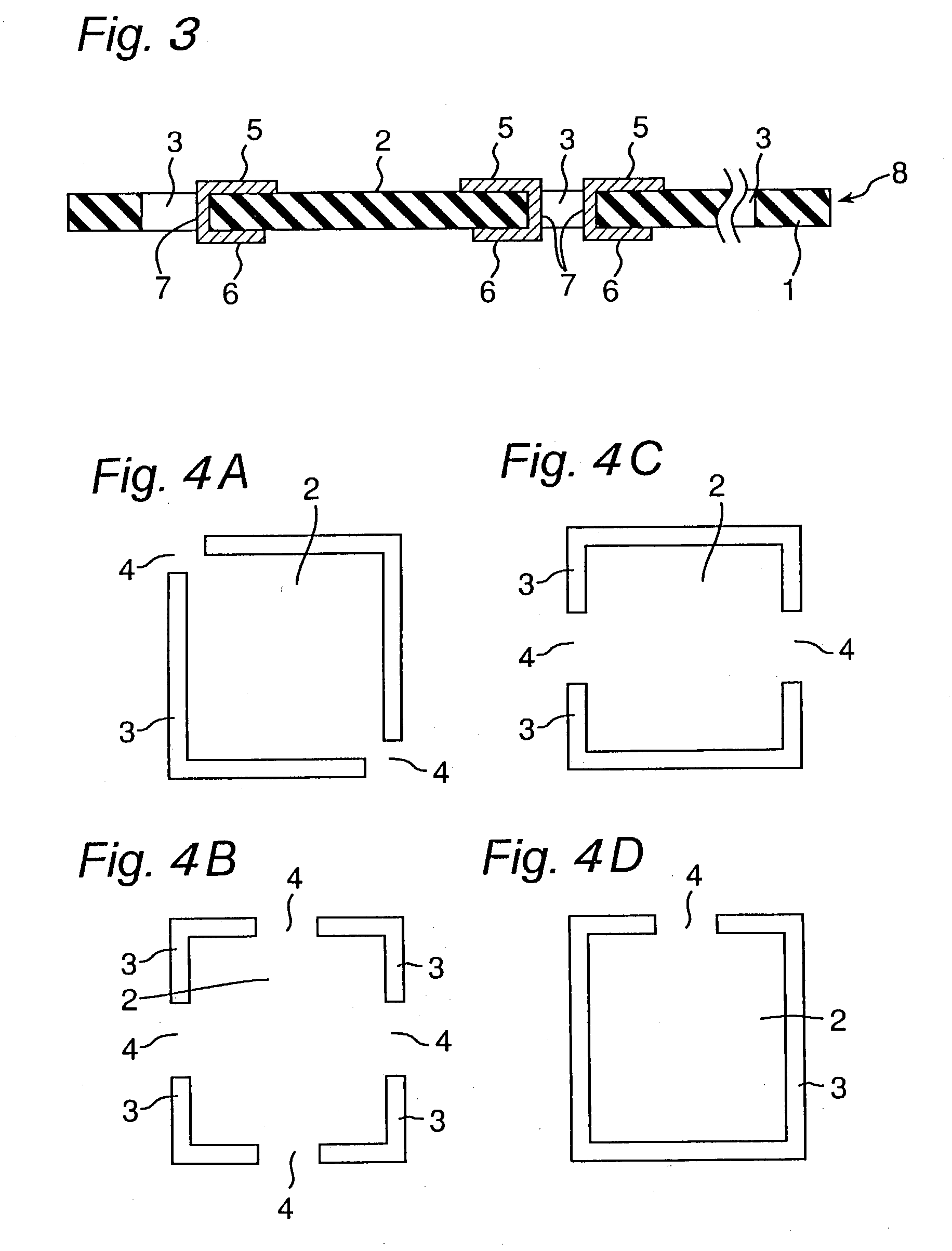

Semiconductor module substrate sheet, semiconductor module substrate sheet fabricating method and semiconductor module

InactiveUS20030157437A1Firm supportEfficiently formedSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

Through holes are formed at four peripheral edges of a plurality of semiconductor chip placement regions of an insulating substrate, except for coupling portions partially arranged thereat. A substrate sheet for semiconductor module is used in which connecting portions between inner lead portions and outer lead portions arranged on both surfaces of the substrate are formed in pattern on the side wall surface of the through hole. The semiconductor chip is mounted on each region, electrode terminals thereof and the inner lead portions are electrically connected to each other, the chip is sealed, and then the coupling portions are cut.

Owner:NISSHA PRINTING COMPANY

Multi-layer printed circuit board fabrication system and method

InactiveUS7283660B2Semiconductor/solid-state device testing/measurementGeometric image transformationComputer sciencePrinted circuit board

A method for aligning an image to be recorded by a direct image scanner on an upper layer of a printed circuit board with an image recorded on a lower layer thereof, the method comprising:visually imaging a portion of the image on the lower layer; andrecording a pattern on the upper layer, referenced to coordinates of the visual image of the portion.

Owner:ORBOTECH LTD

Method of exposing thermoresist

Low contrast optics, including low contrast linear light valves, can be used to create high resolution patterns by using thermoresist instead of photoresist and by using multiple exposures of the same area, preferably exposing different features of the pattern in each exposure. When using thermoresist, the stray light from imaging the individual features does not add up, as the stray heat it creates will dissipate between exposures. The method is particularly useful for imaging thermoresists using UV light for manufacturing of integrated circuits.

Owner:CREO PRODS