Patents

Literature

385 results about "Quantum circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

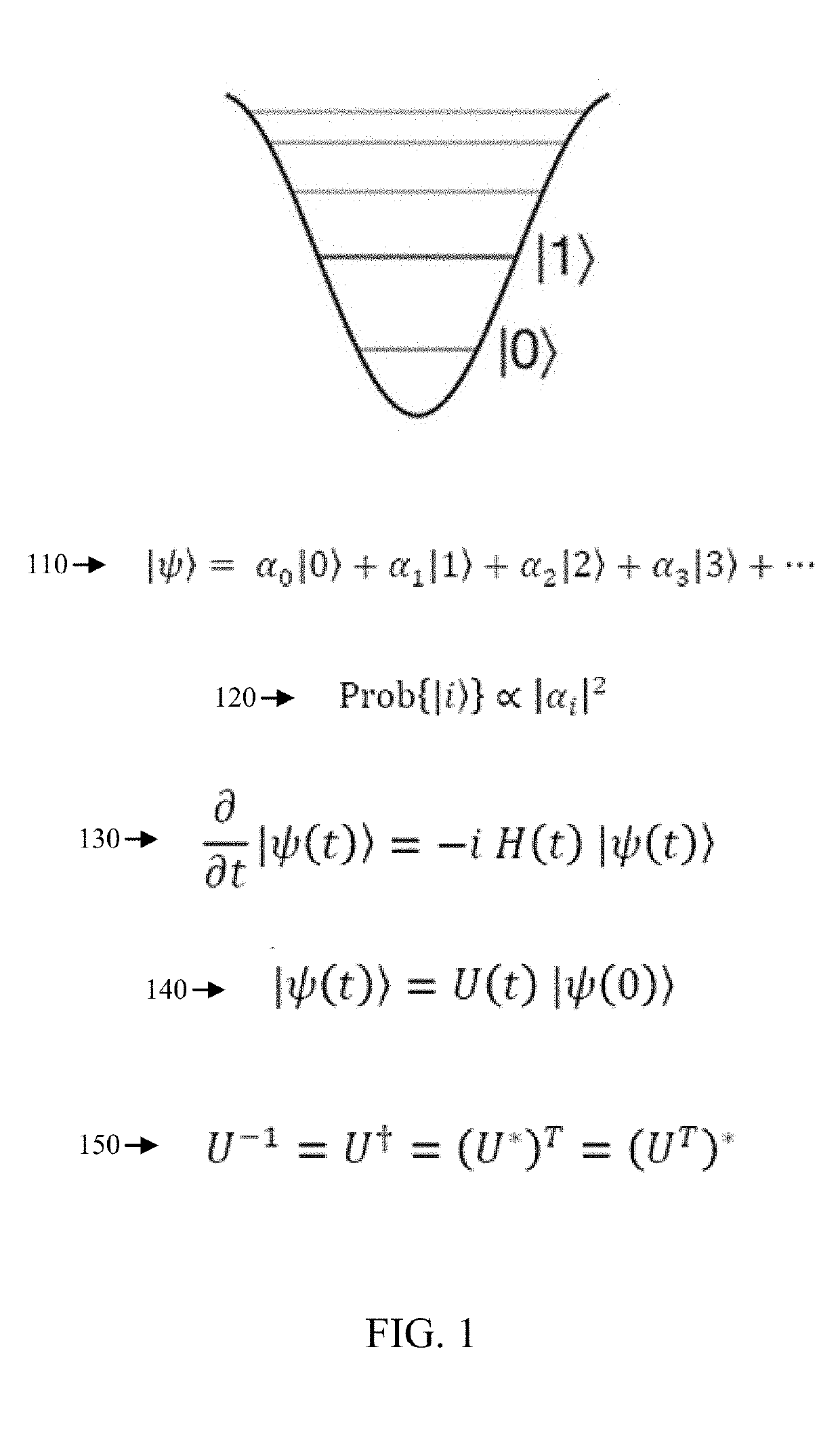

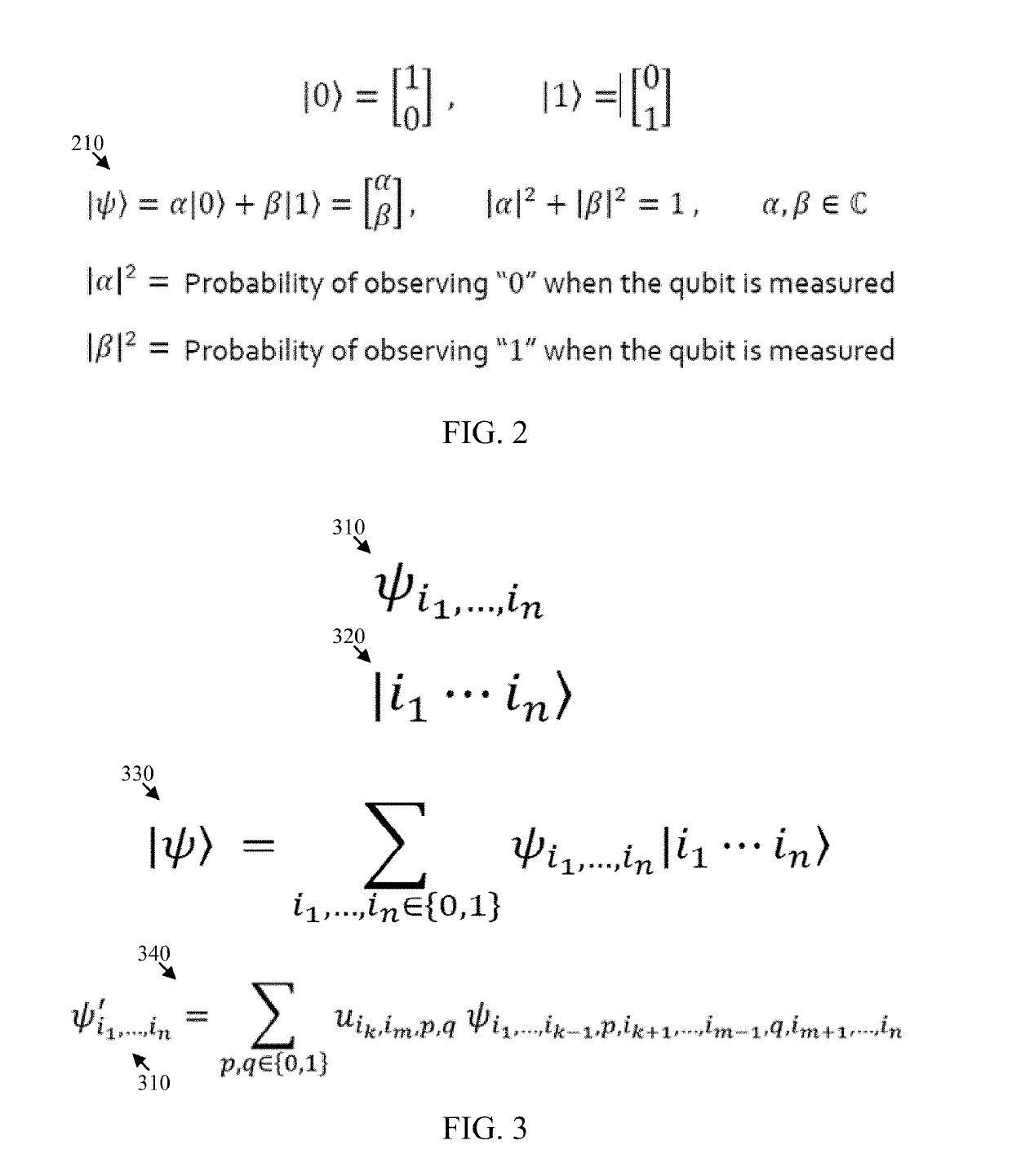

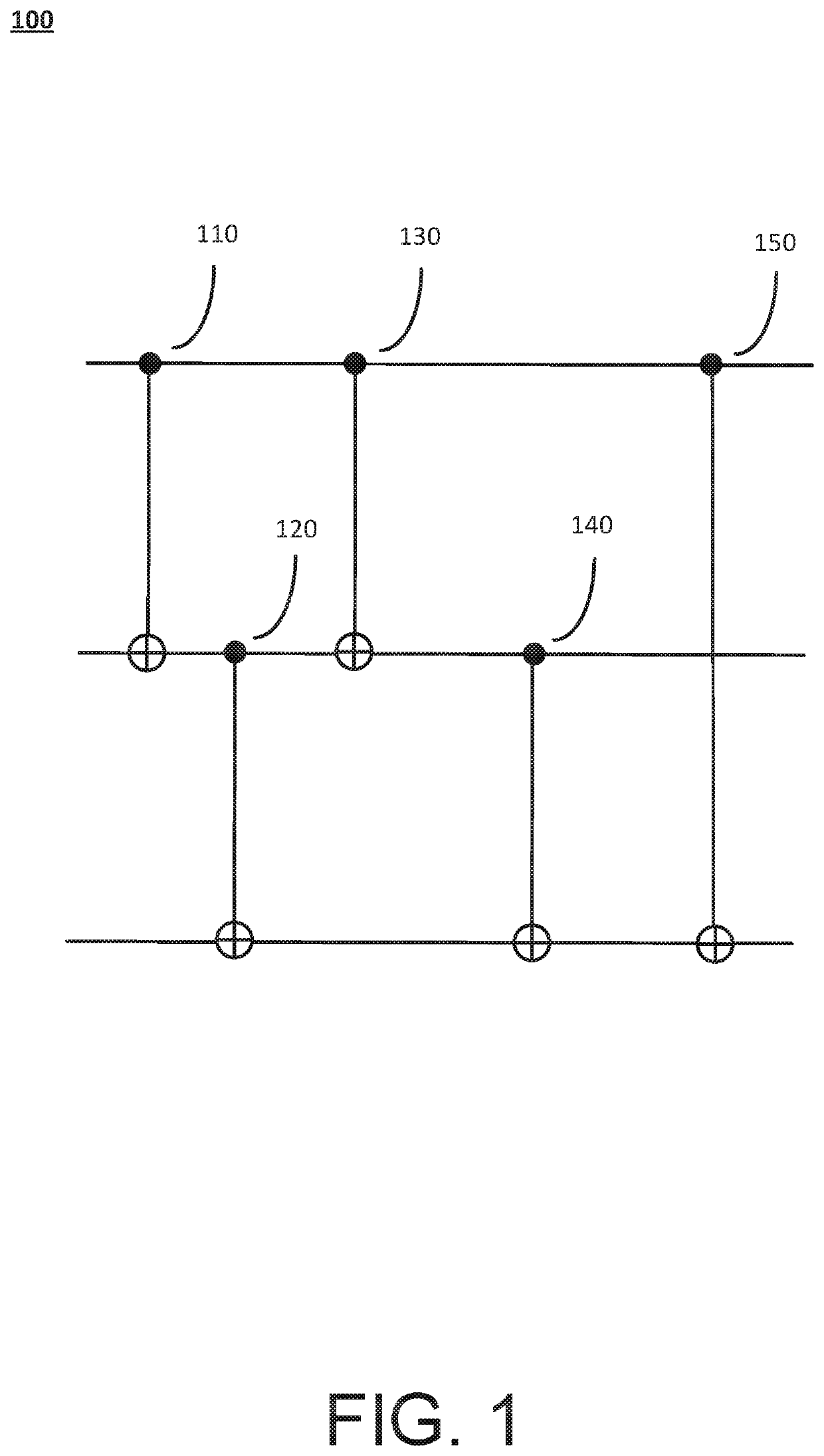

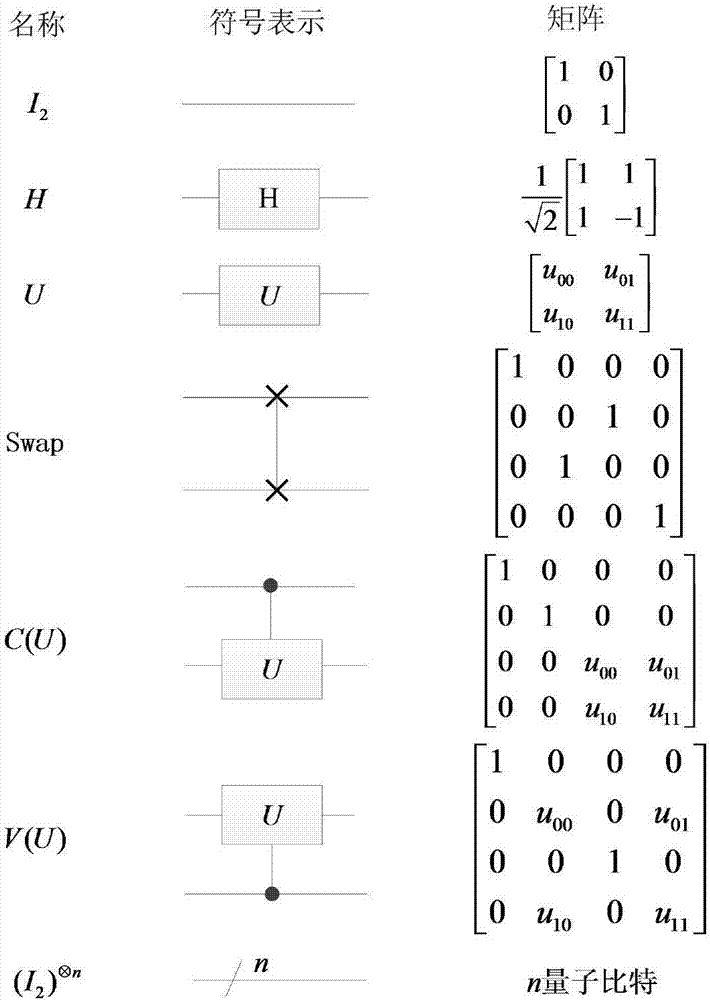

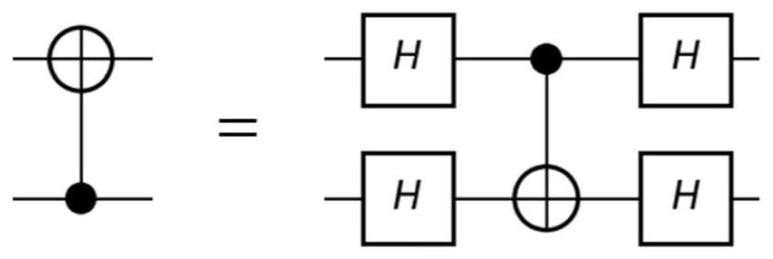

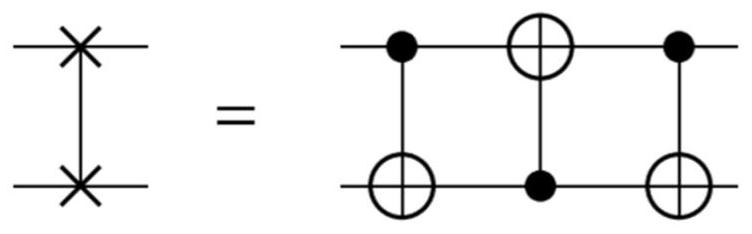

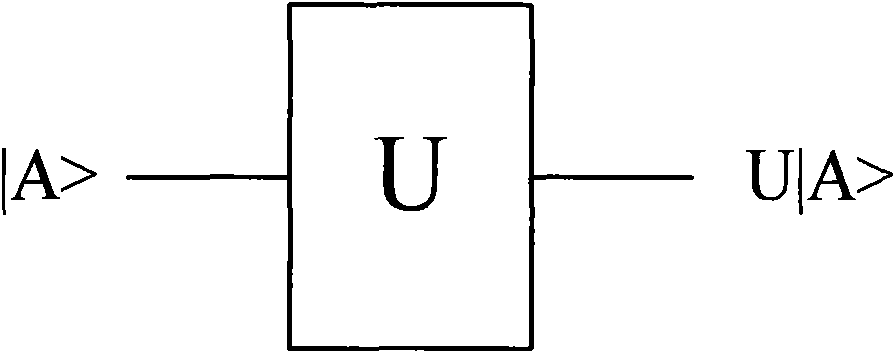

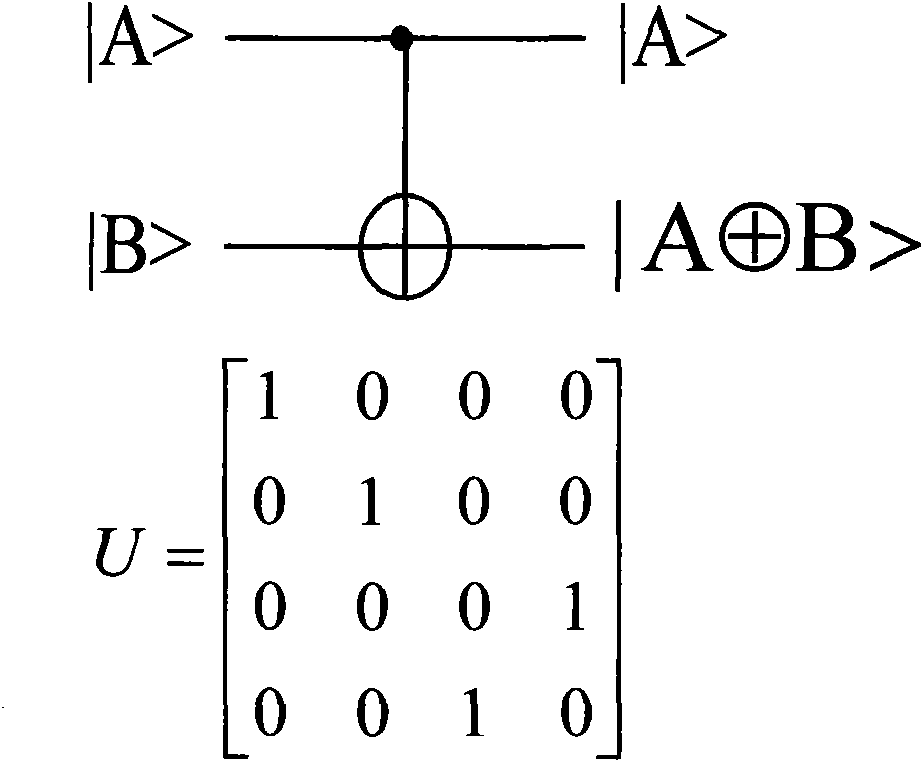

In quantum information theory, a quantum circuit is a model for quantum computation in which a computation is a sequence of quantum gates, which are reversible transformations on a quantum mechanical analog of an n-bit register. This analogous structure is referred to as an n-qubit register.

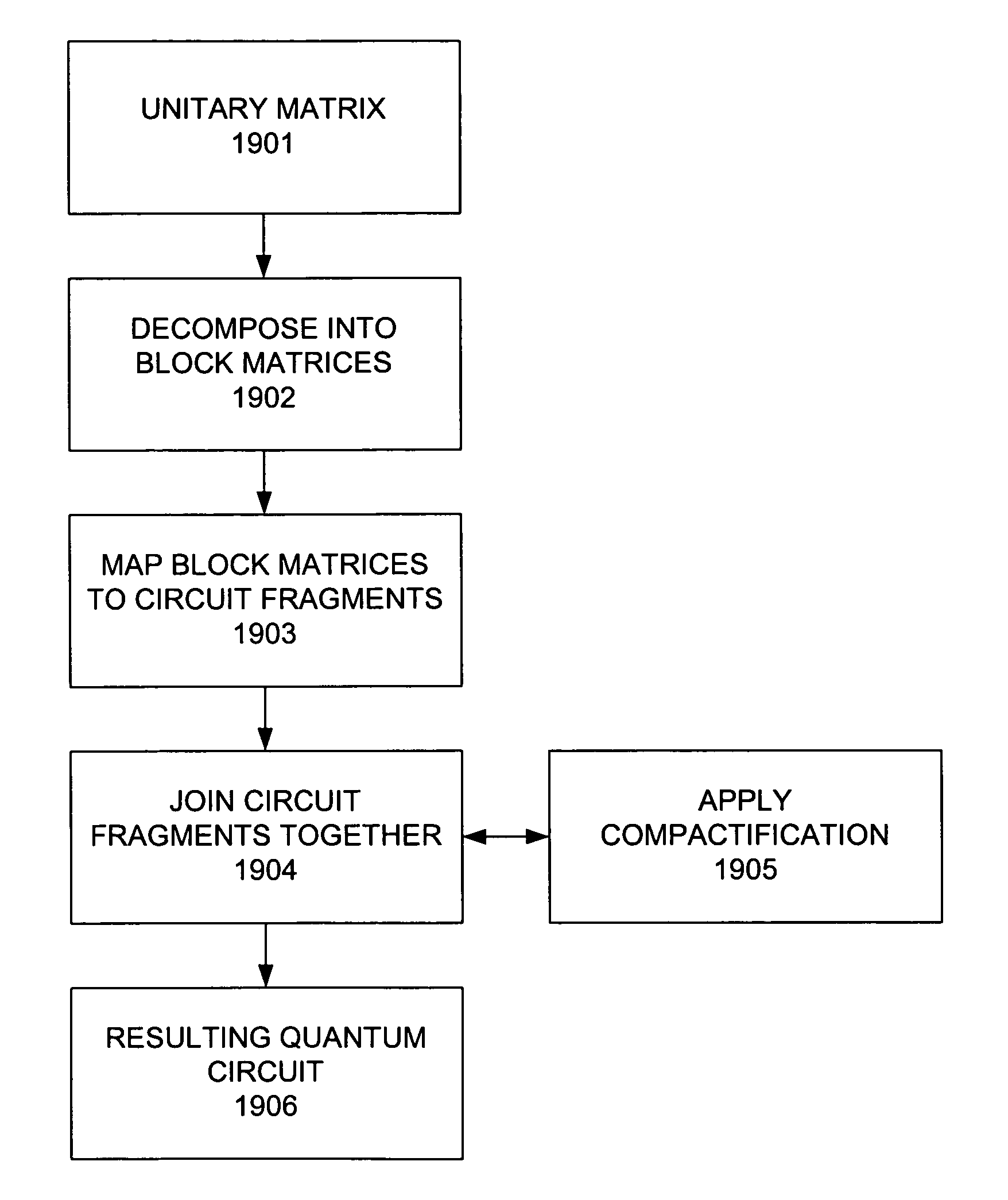

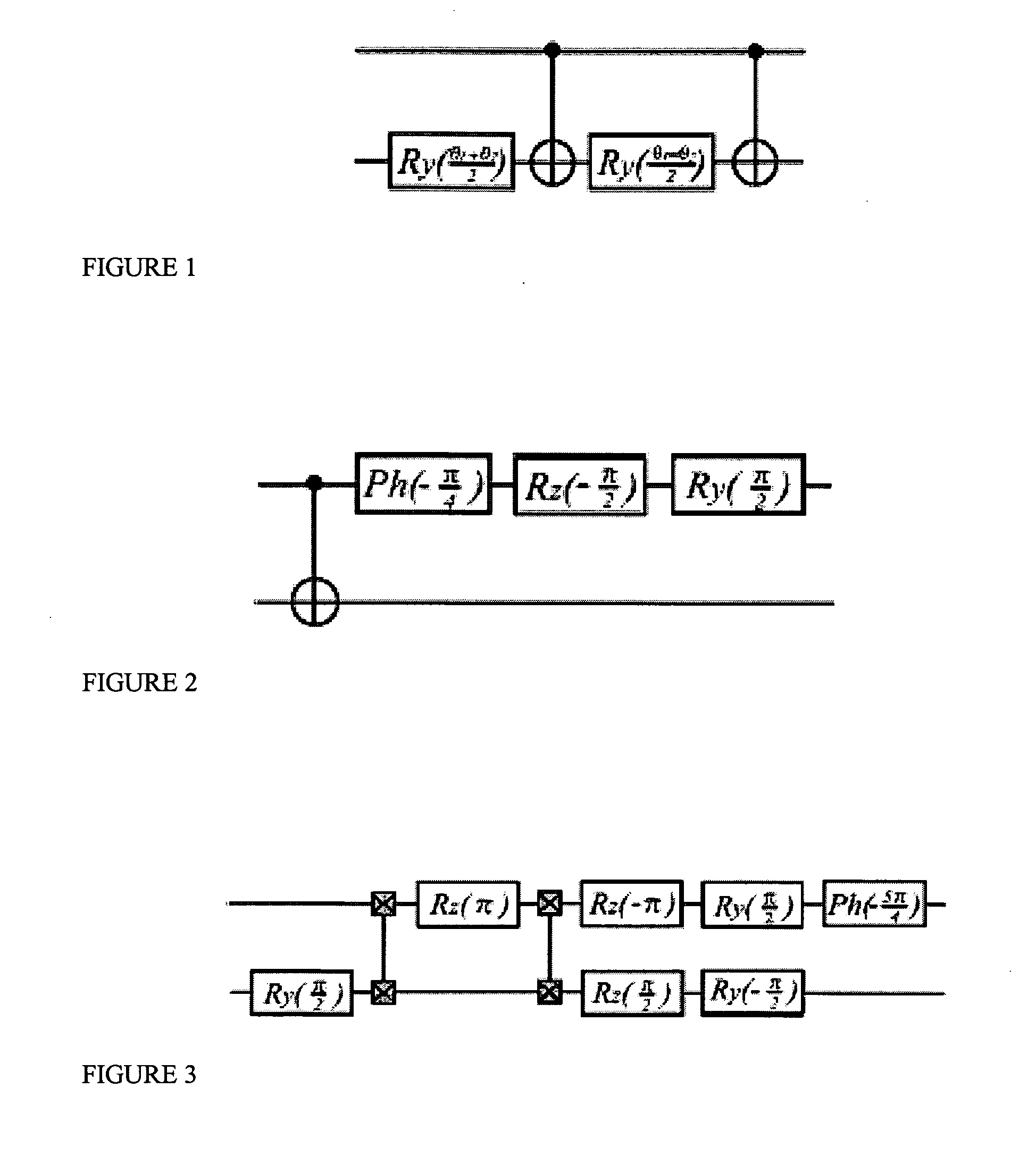

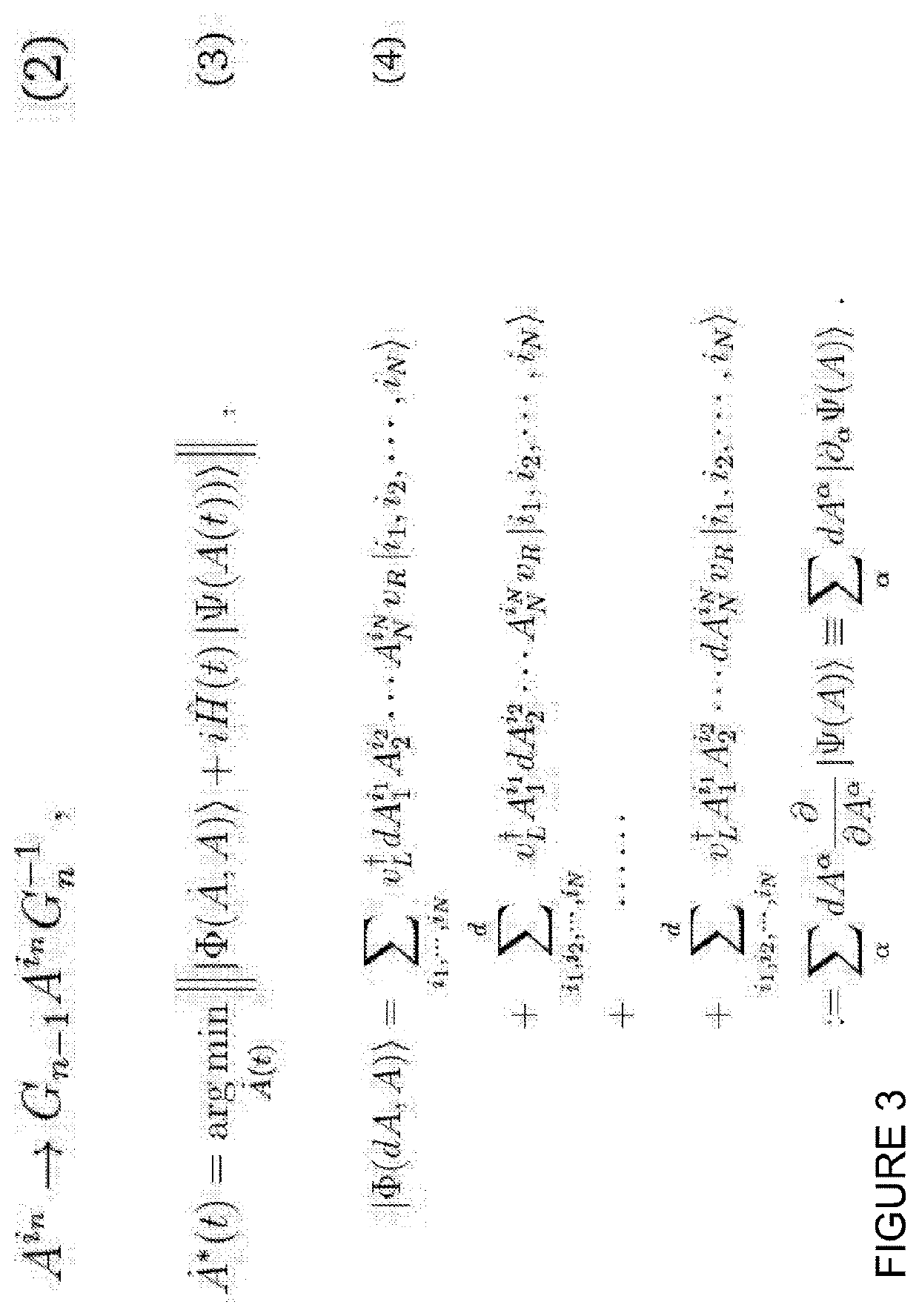

Method and apparatus for automated design of quantum circuits

The present invention provides an algebraic approach to quantum circuit design based on using a GSVD (Generalized Singular Value Decomposition) to map a unitary matrix, representing a desired quantum computation, into a product of block diagonal unitary matrices, each of which can then be mapped into equivalent circuit fragments. The invention describes a number of rules allowing such circuits to be compactified.

Owner:CALIFORNIA INST OF TECH

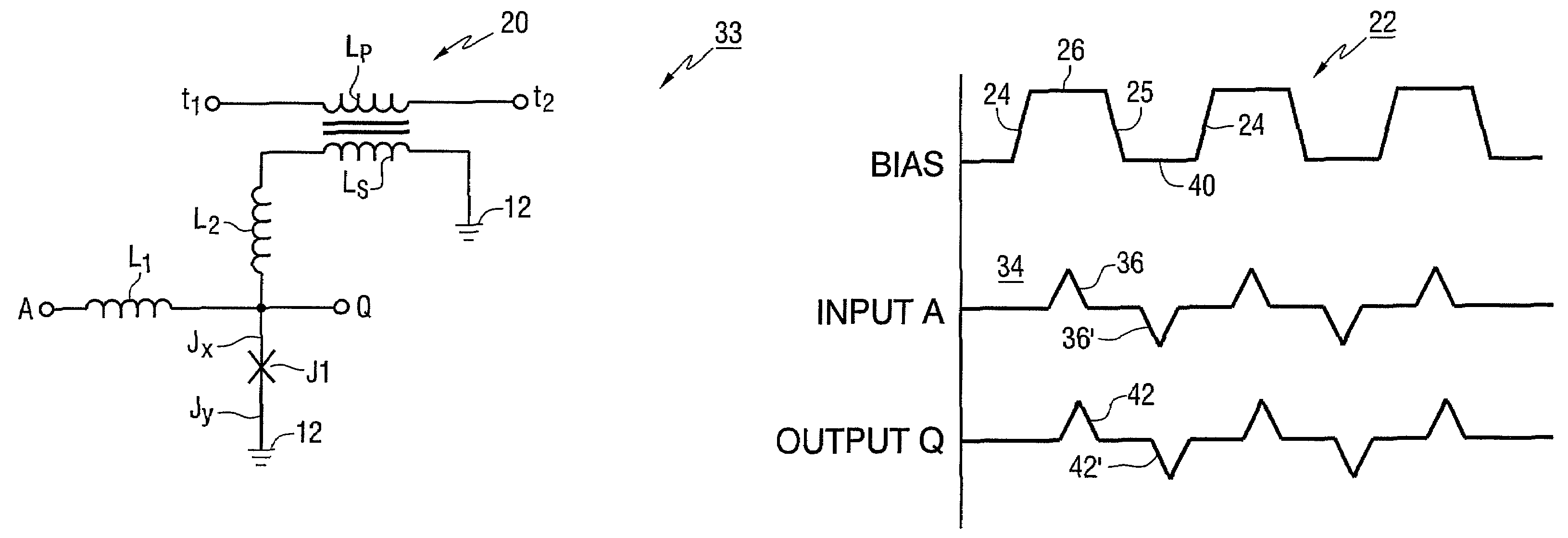

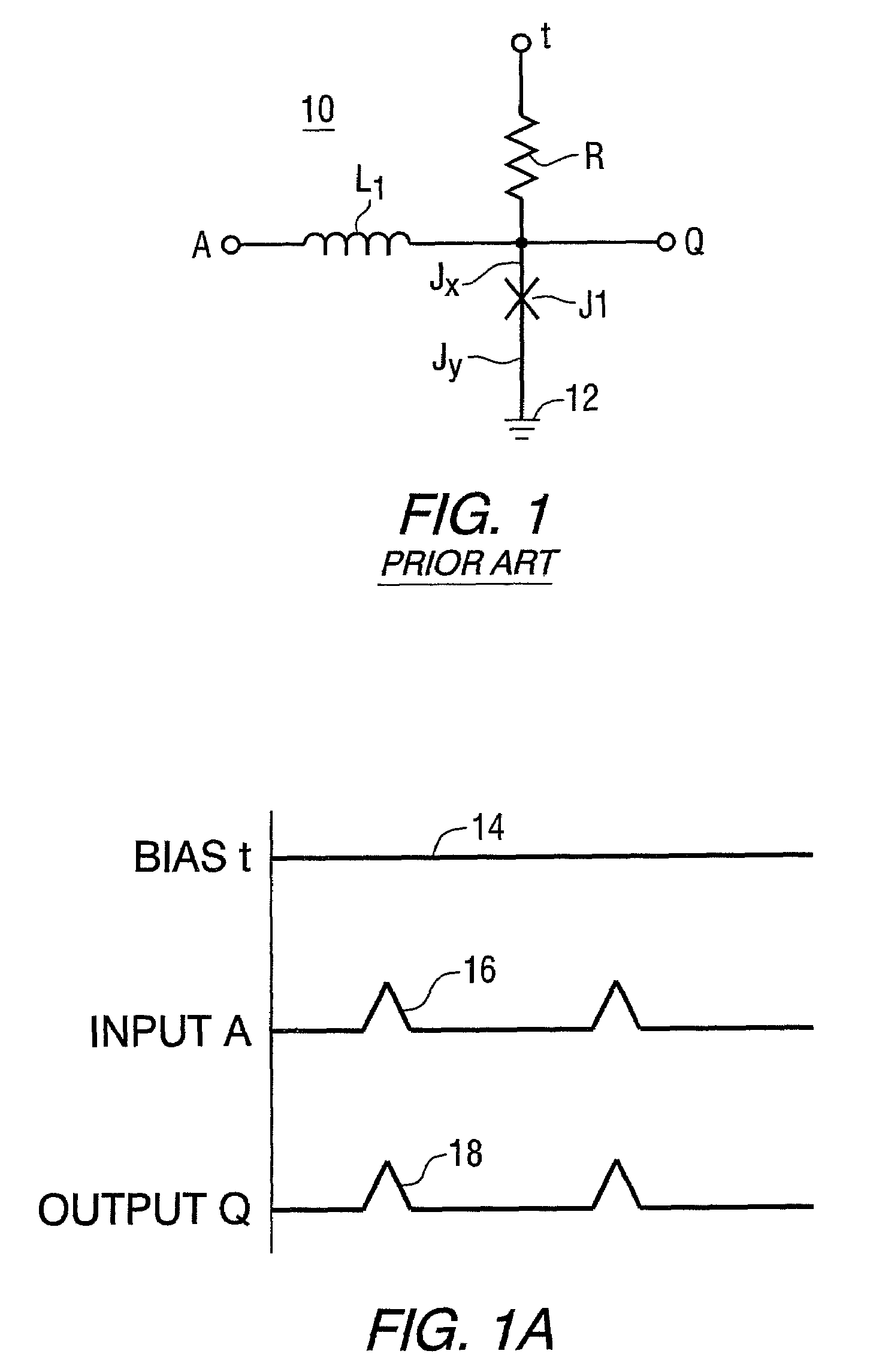

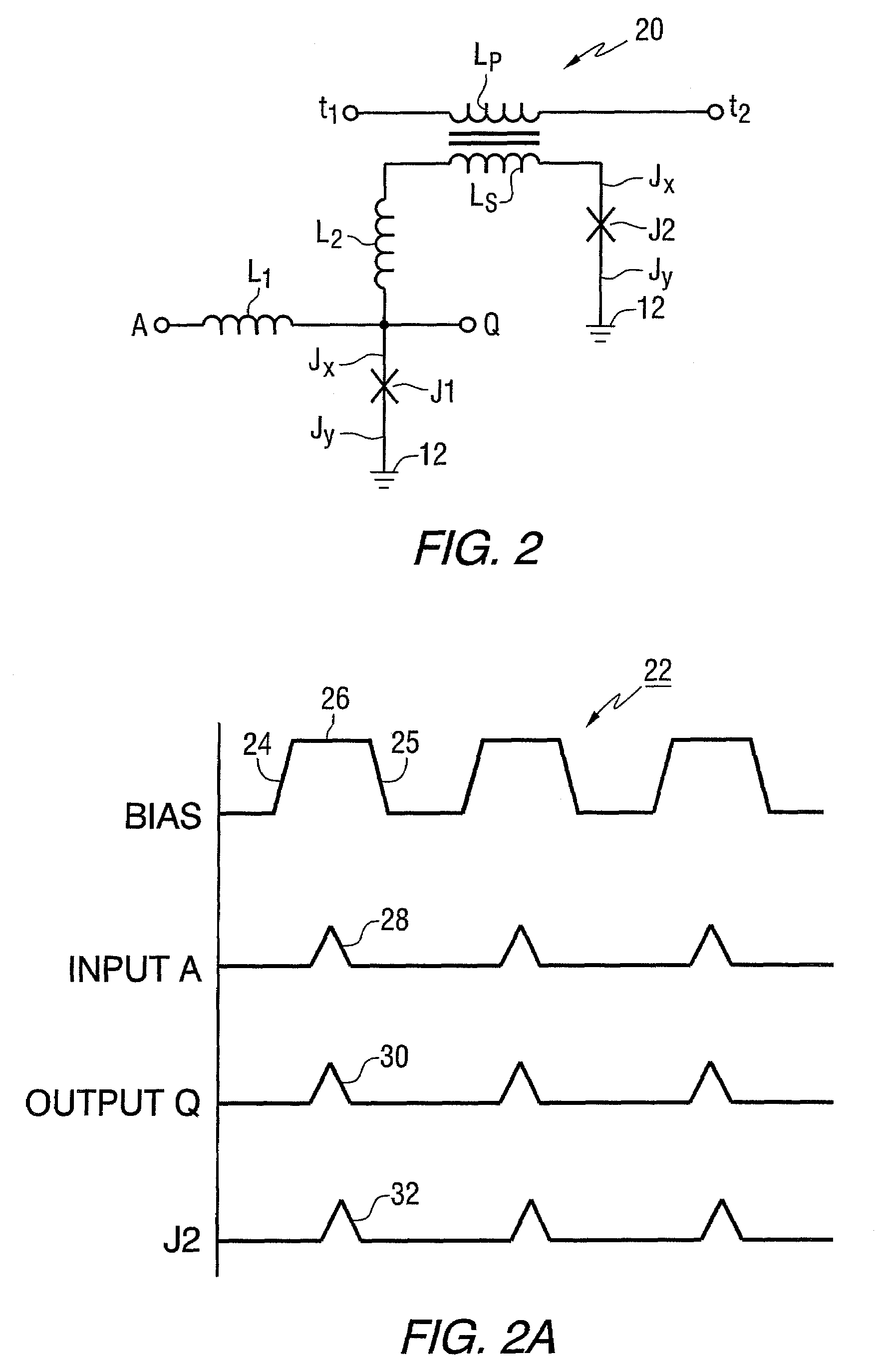

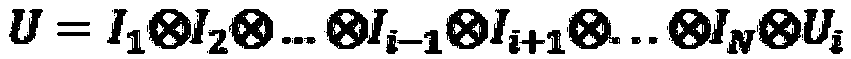

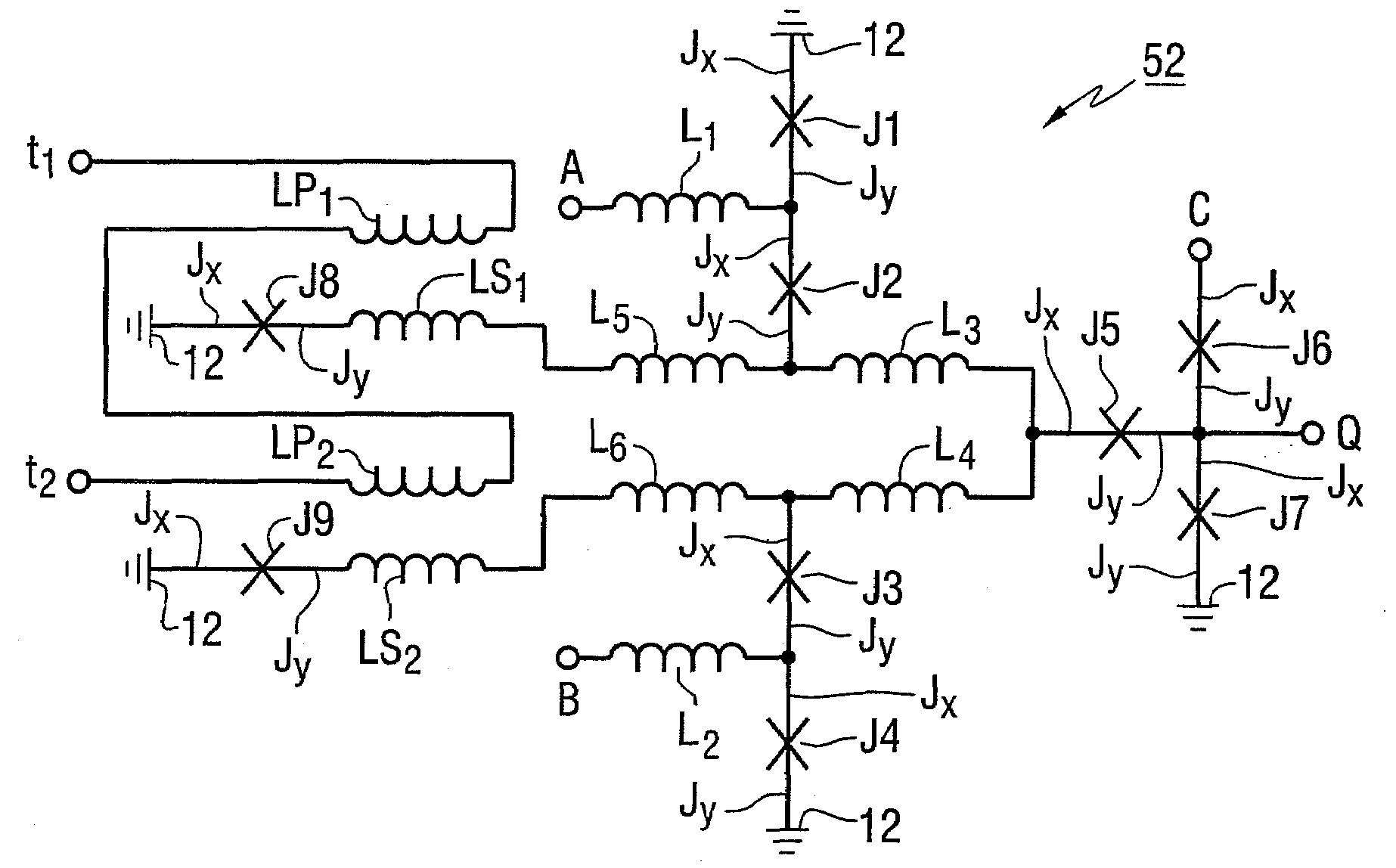

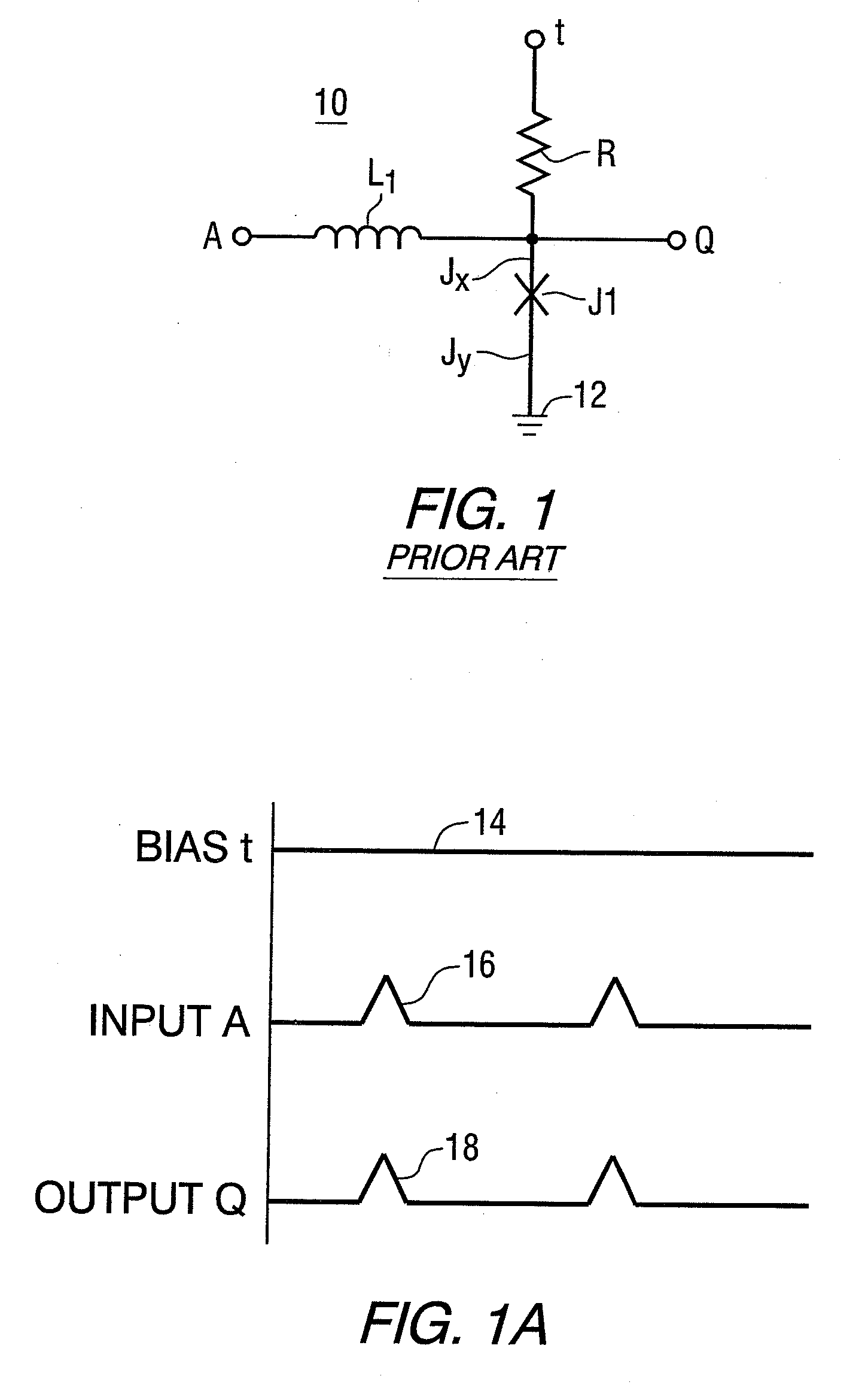

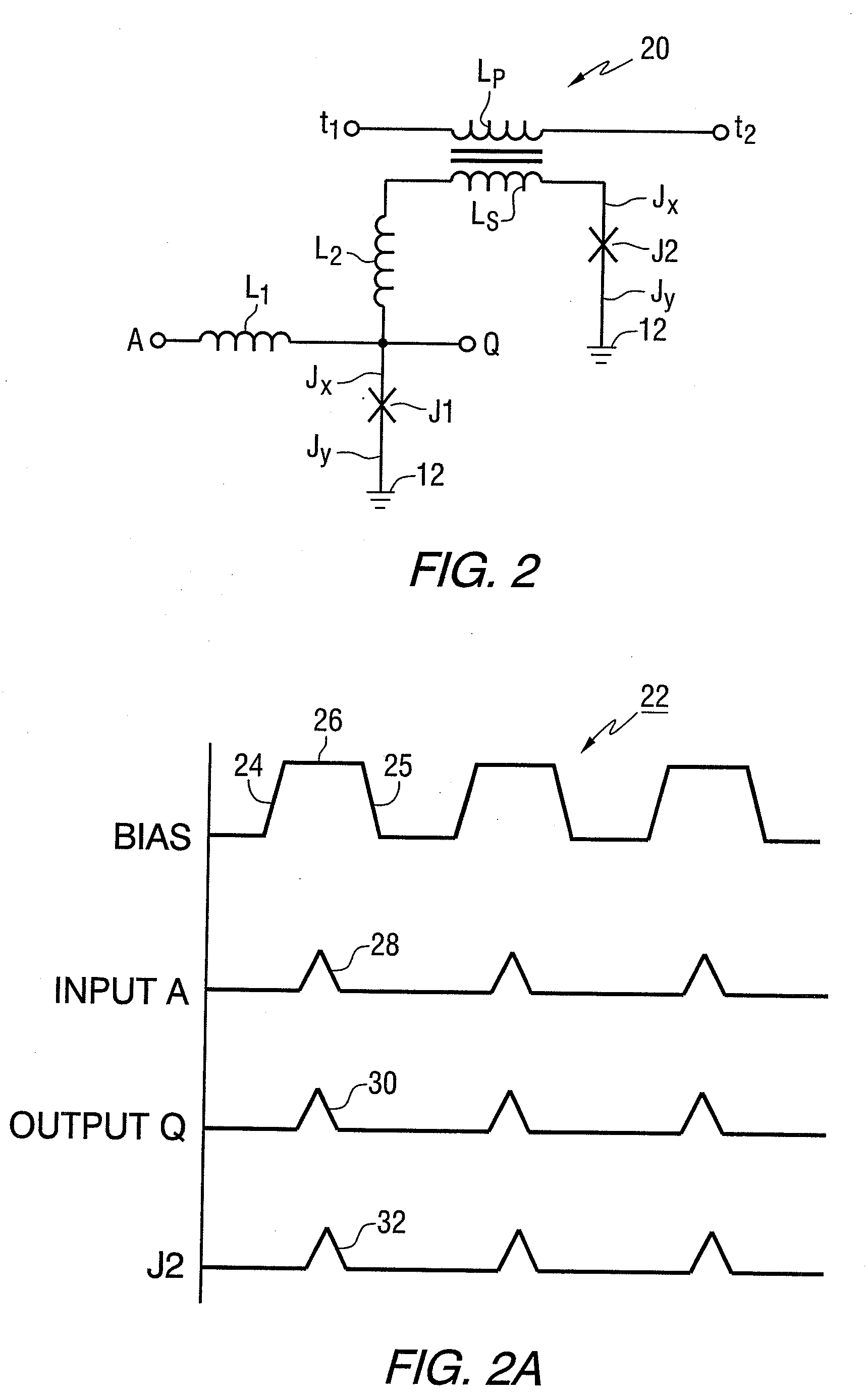

Single flux quantum circuits

ActiveUS7724020B2Reduce and eliminate unnecessary power dissipationQuantum computersPower consumption reductionQuantum circuitTransformer

Superconducting single flux quantum circuits are disclosed herein, each having at least one Josephson junction which will flip when the current through it exceeds a critical current. Bias current for the Josephson junction is provided by a biasing transformer instead of a resistor. The lack of any bias resistors ensures that unwanted power dissipation is eliminated.

Owner:NORTHROP GRUMMAN SYST CORP

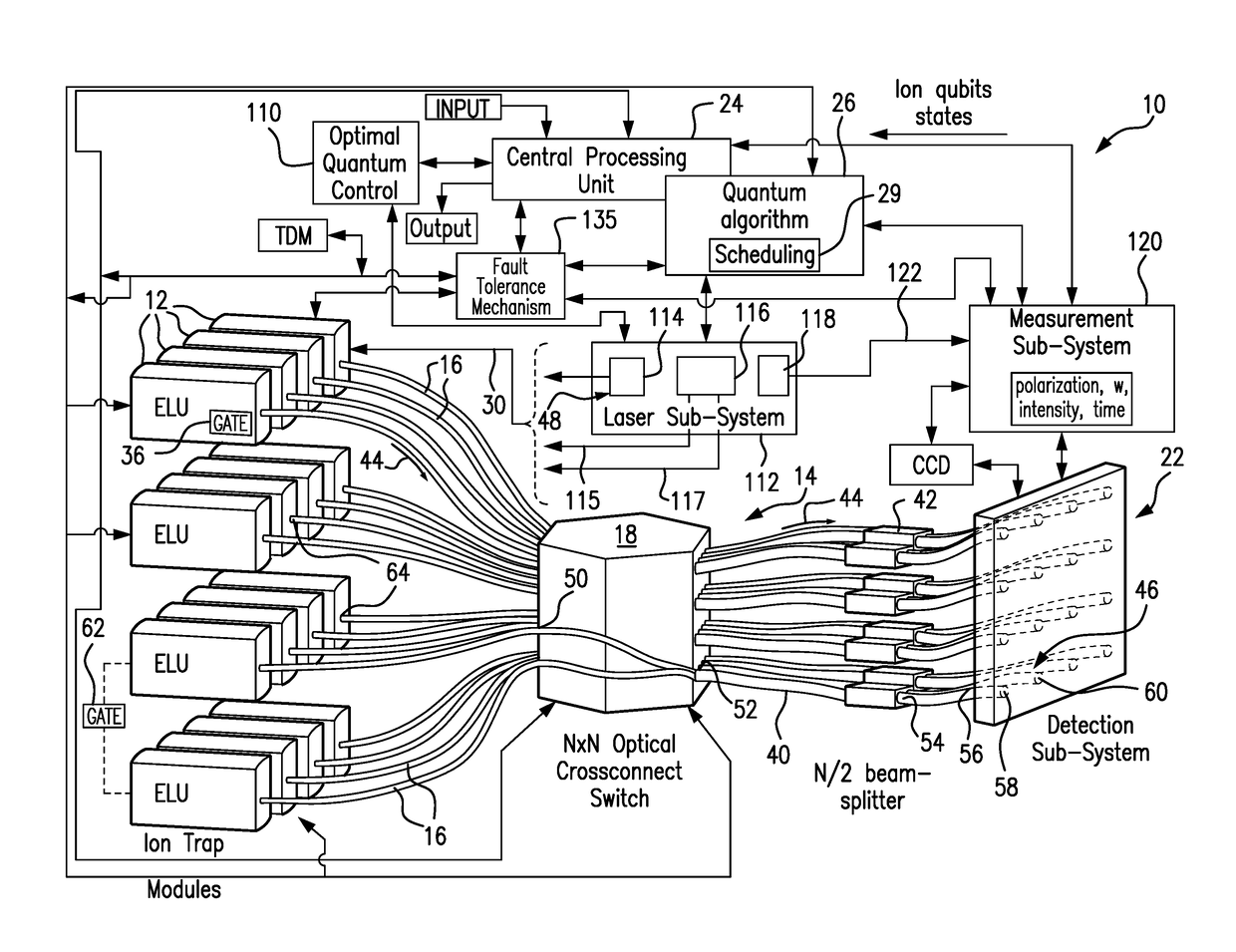

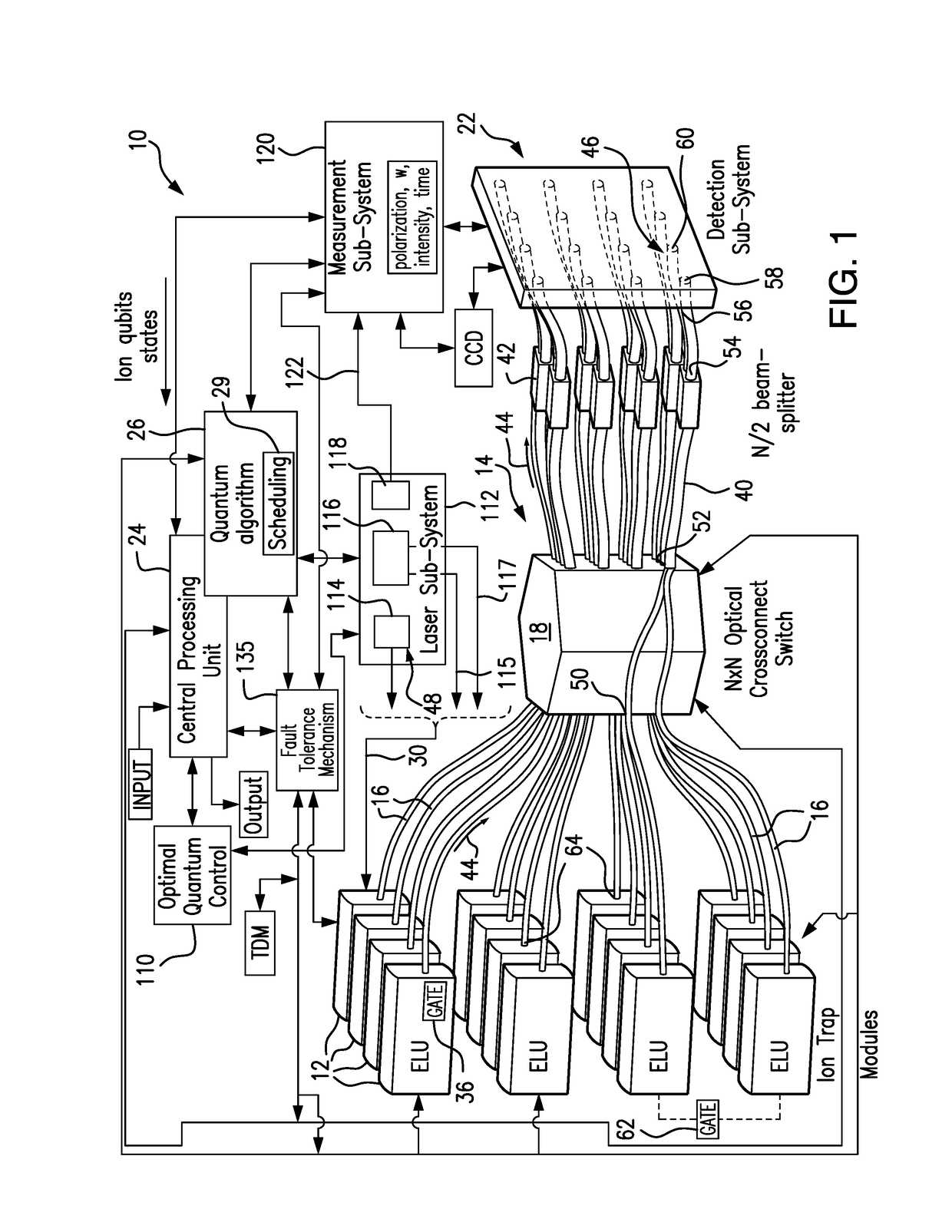

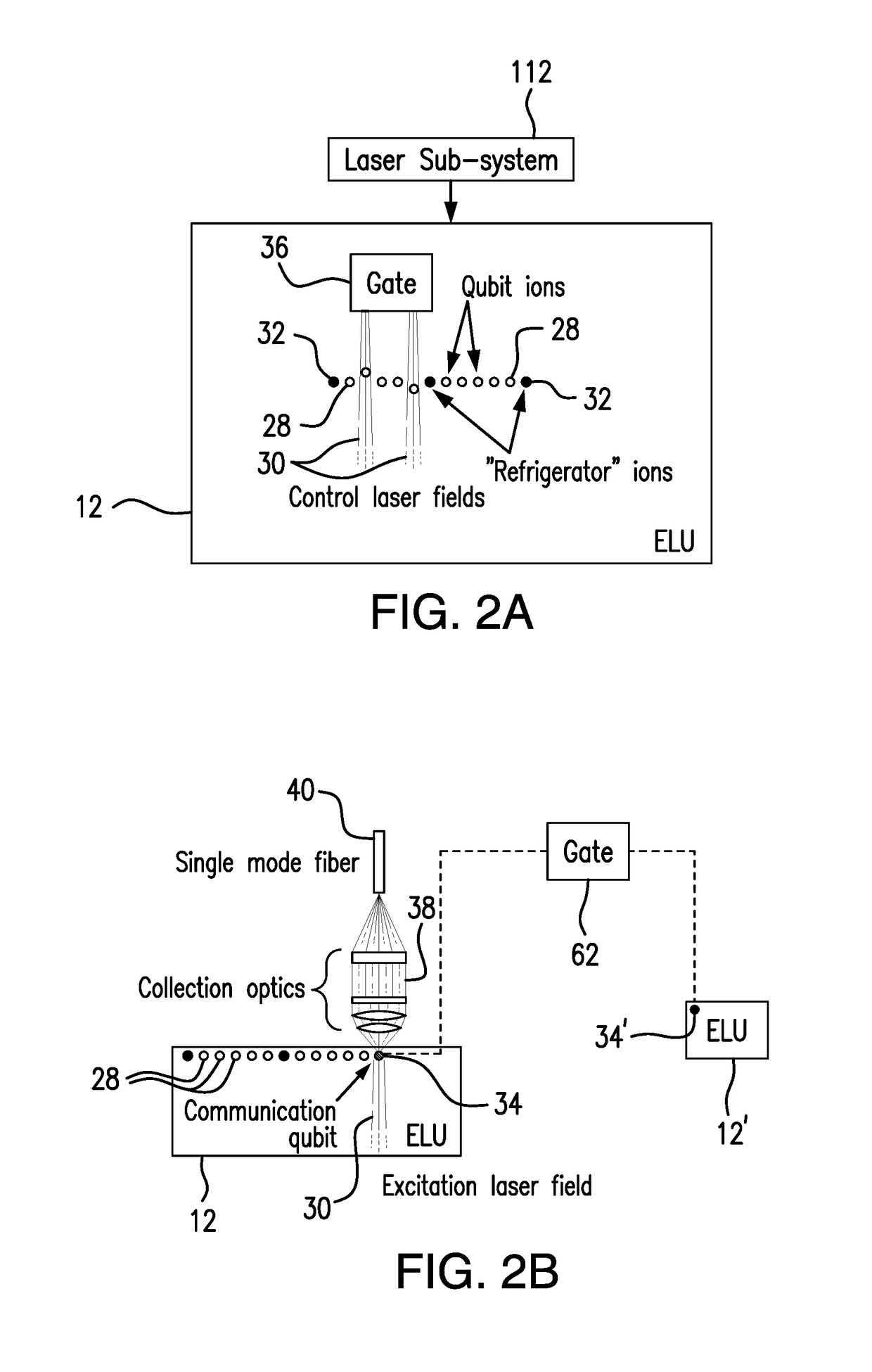

Fault-tolerant scalable modular quantum computer architecture with an enhanced control of multi-mode couplings between trapped ion qubits

ActiveUS20180114138A1Effective and reliableQuantum computersGeneral purpose stored program computerPhotonicsLarge distance

A modular quantum computer architecture is developed with a hierarchy of interactions that can scale to very large numbers of qubits. Local entangling quantum gates between qubit memories within a single modular register are accomplished using natural interactions between the qubits, and entanglement between separate modular registers is completed via a probabilistic photonic interface between qubits in different registers, even over large distances. This architecture is suitable for the implementation of complex quantum circuits utilizing the flexible connectivity provided by a reconfigurable photonic interconnect network. The subject architecture is made fault-tolerant which is a prerequisite for scalability. An optimal quantum control of multimode couplings between qubits is accomplished via individual addressing the qubits with segmented optical pulses to suppress crosstalk in each register, thus enabling high-fidelity gates that can be scaled to larger qubit registers for quantum computation and simulation.

Owner:DUKE UNIV +2

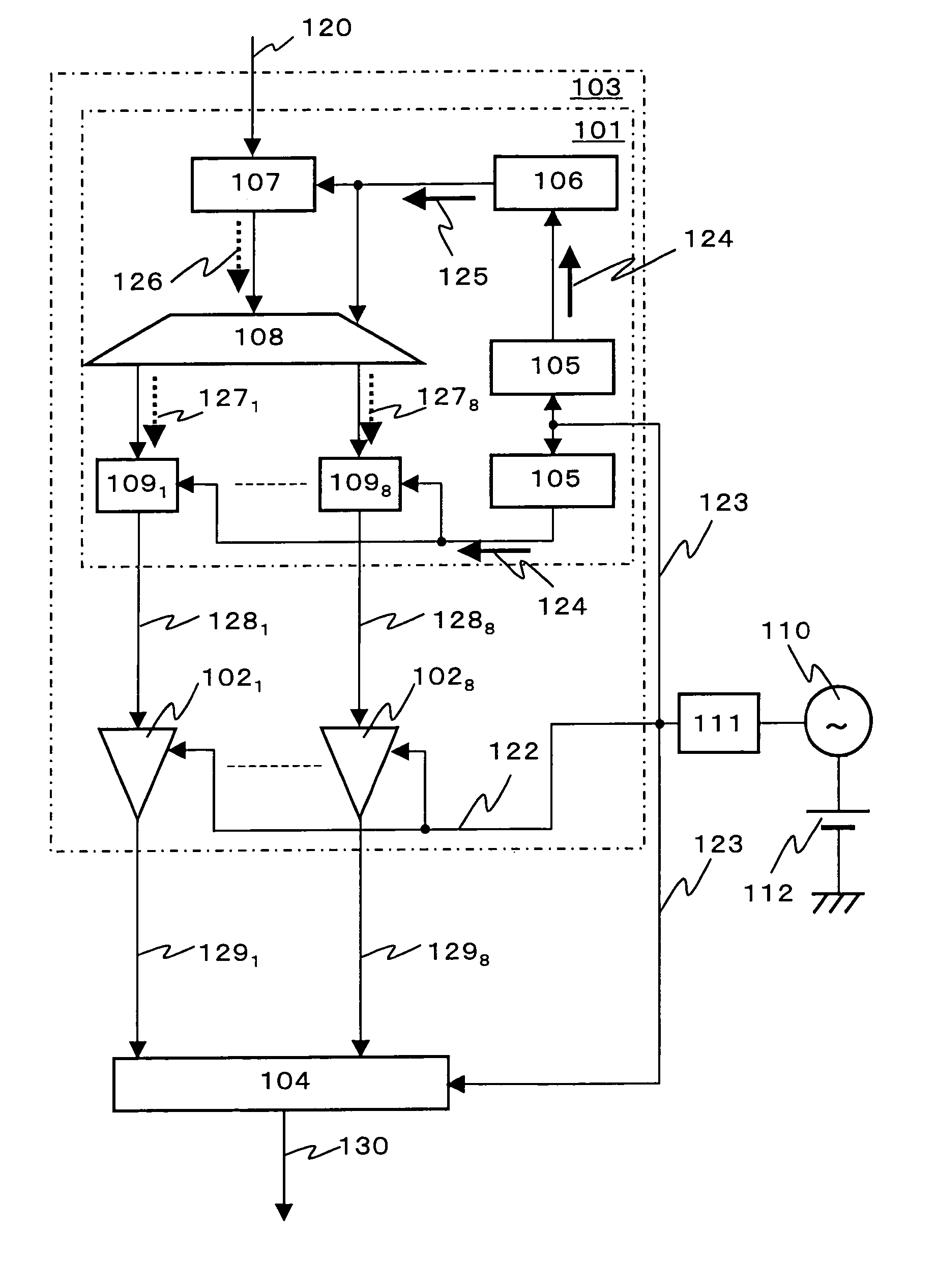

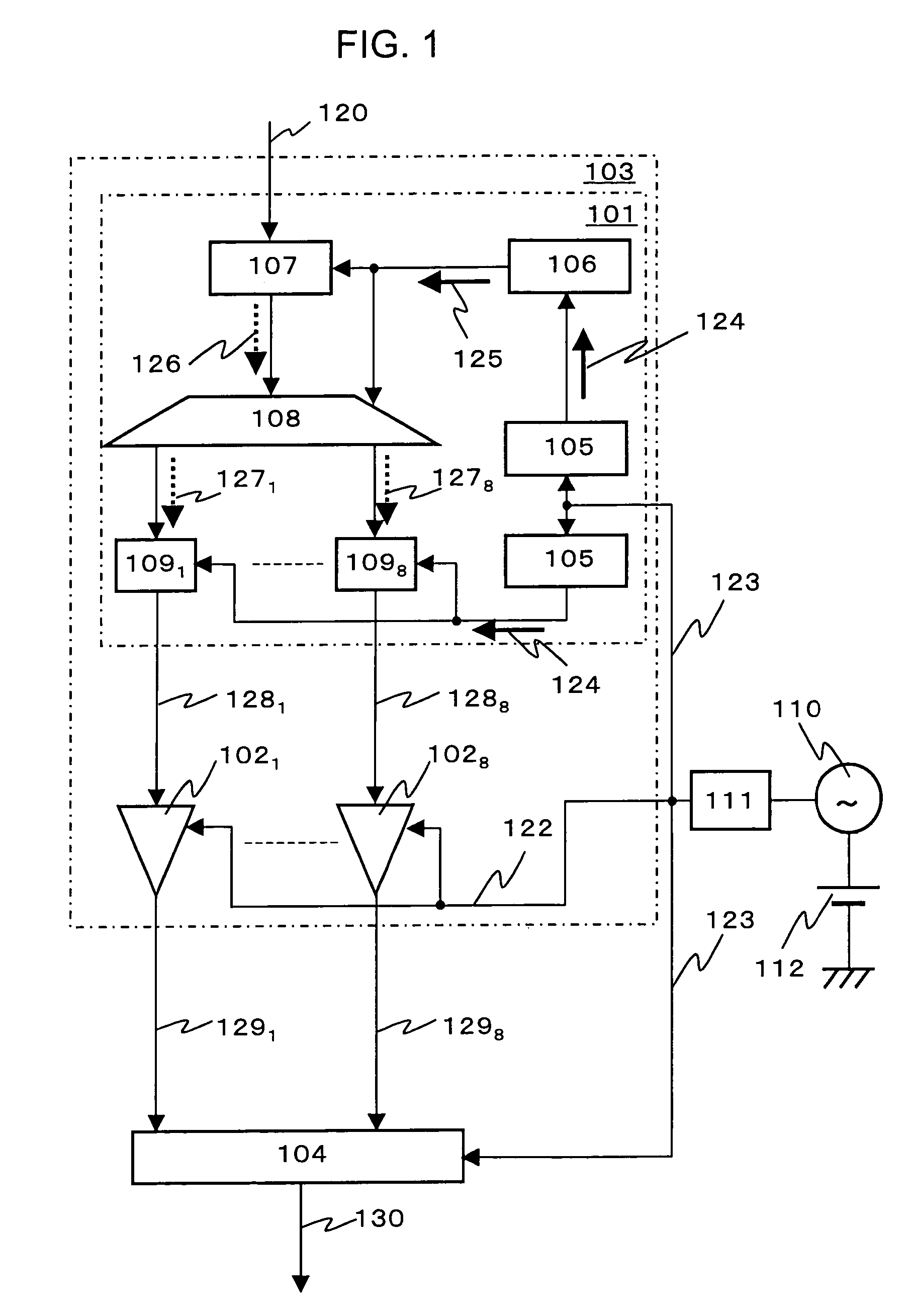

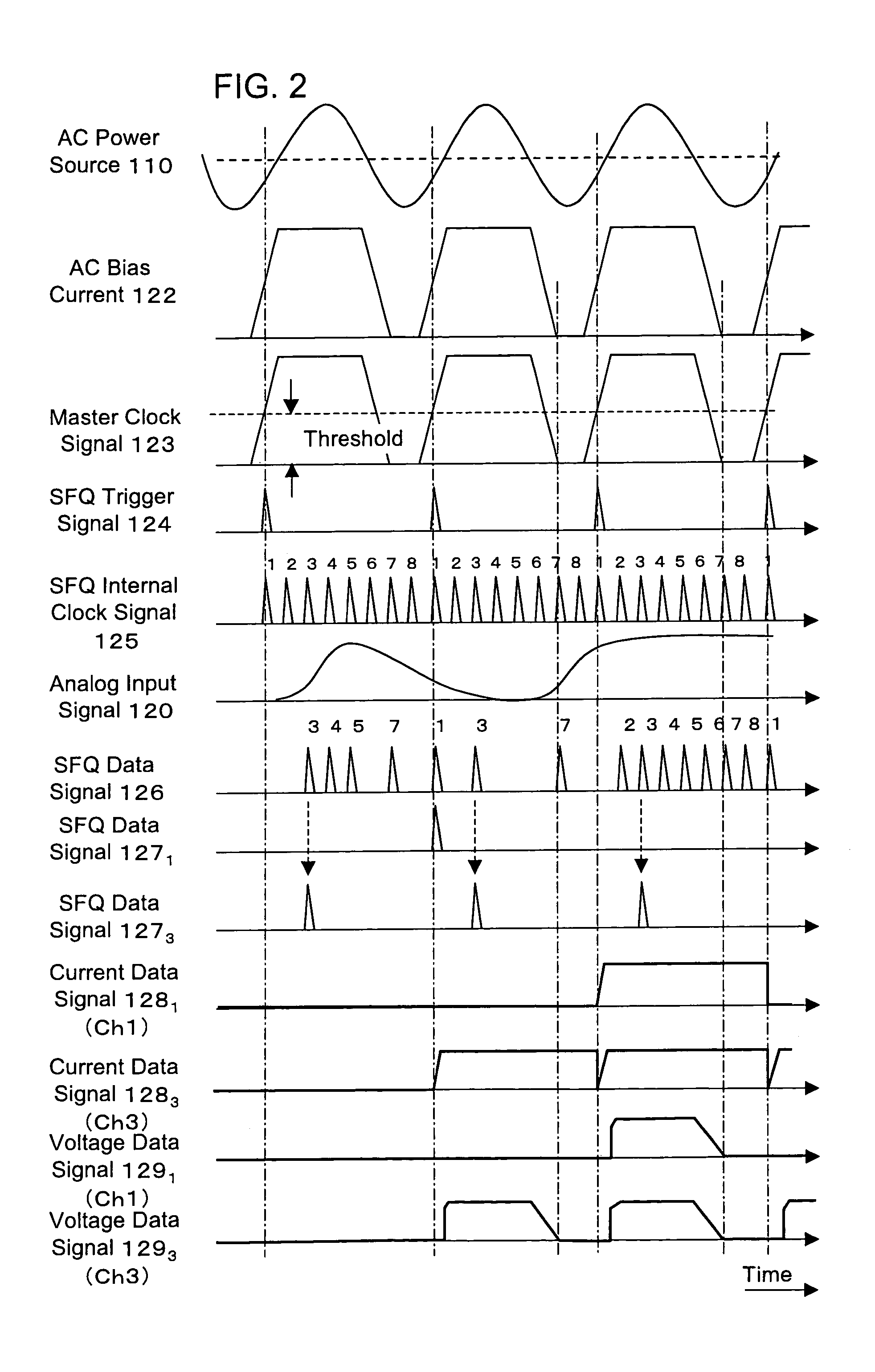

Superconductor semiconductor integrated circuit

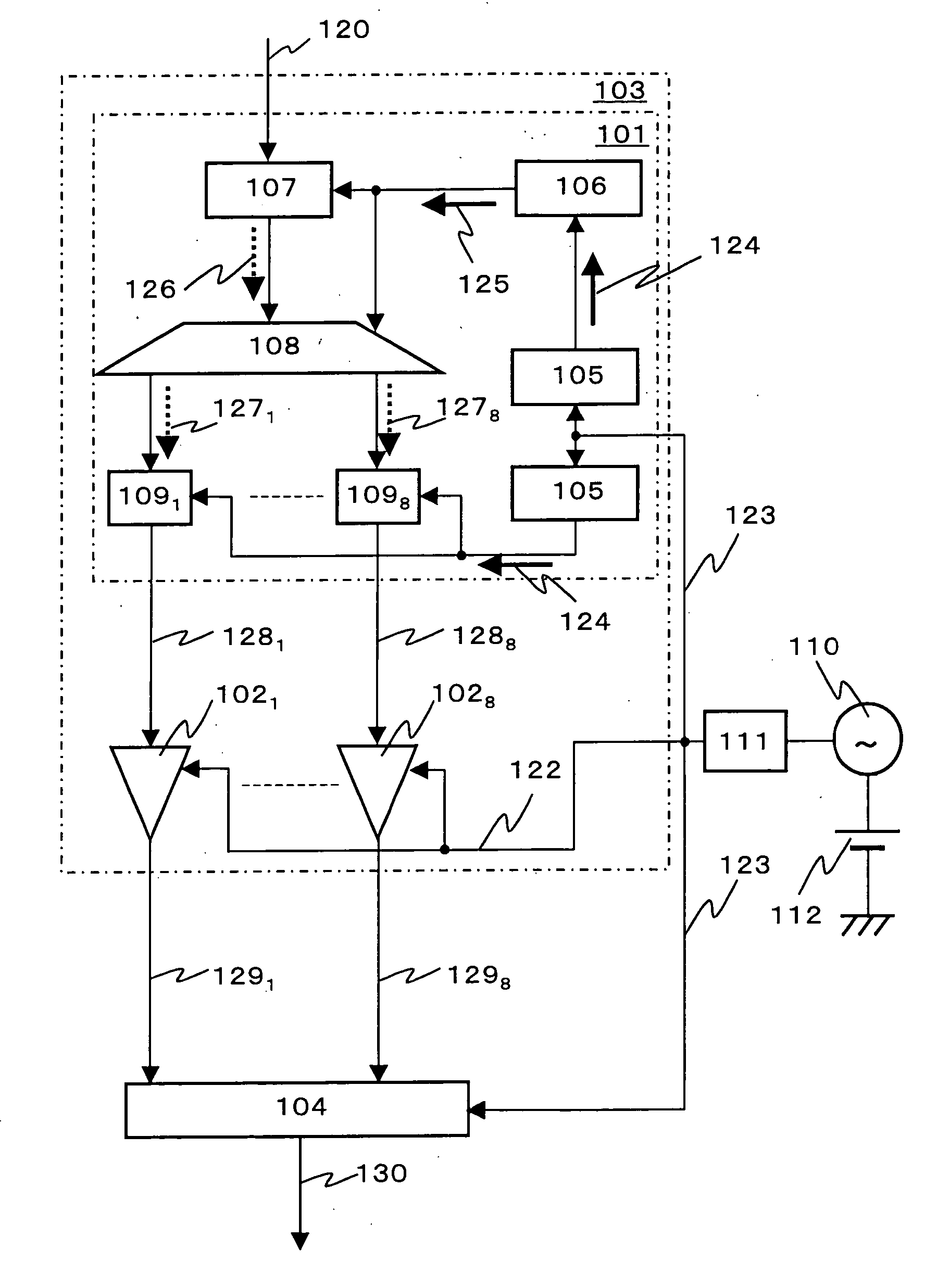

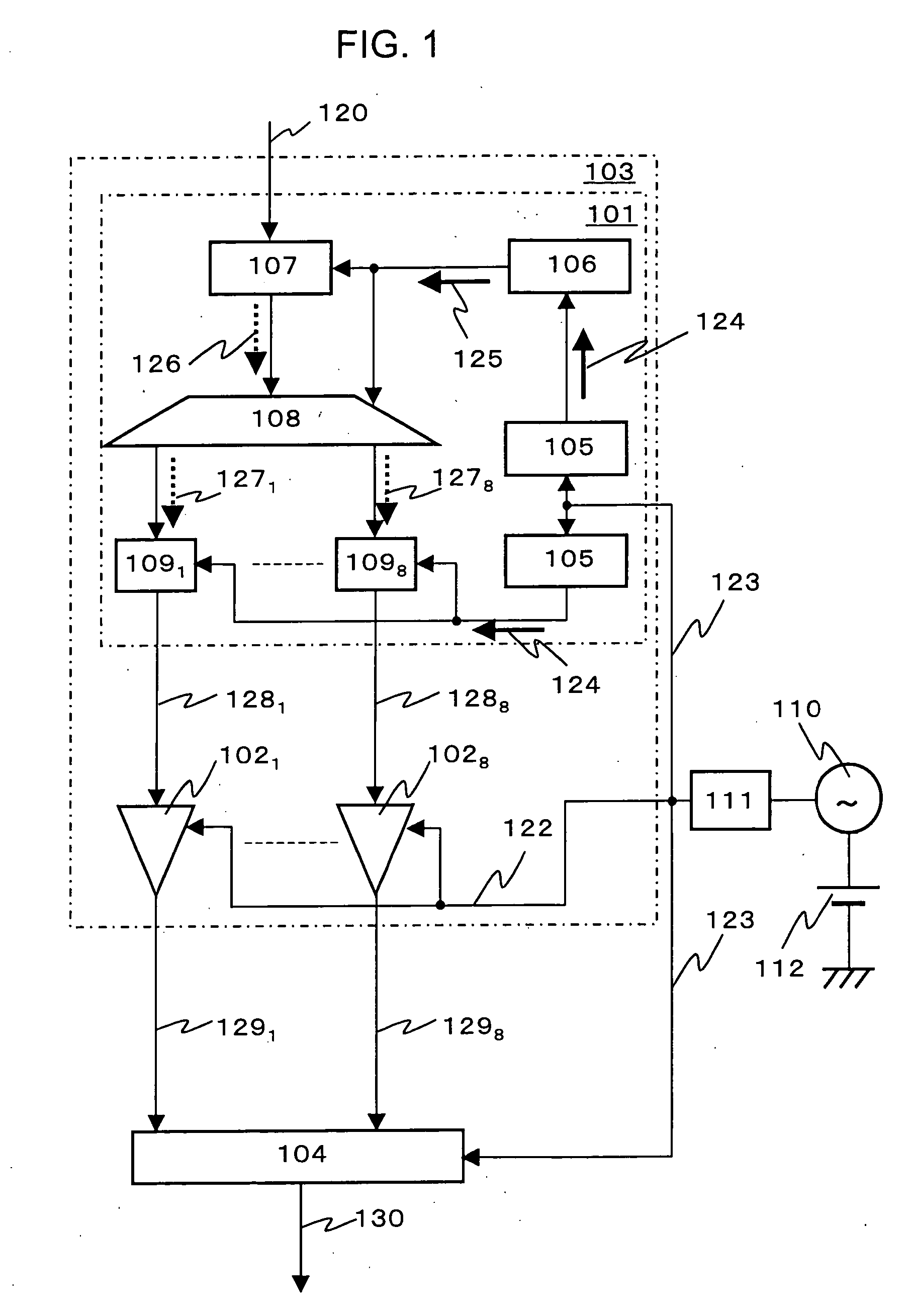

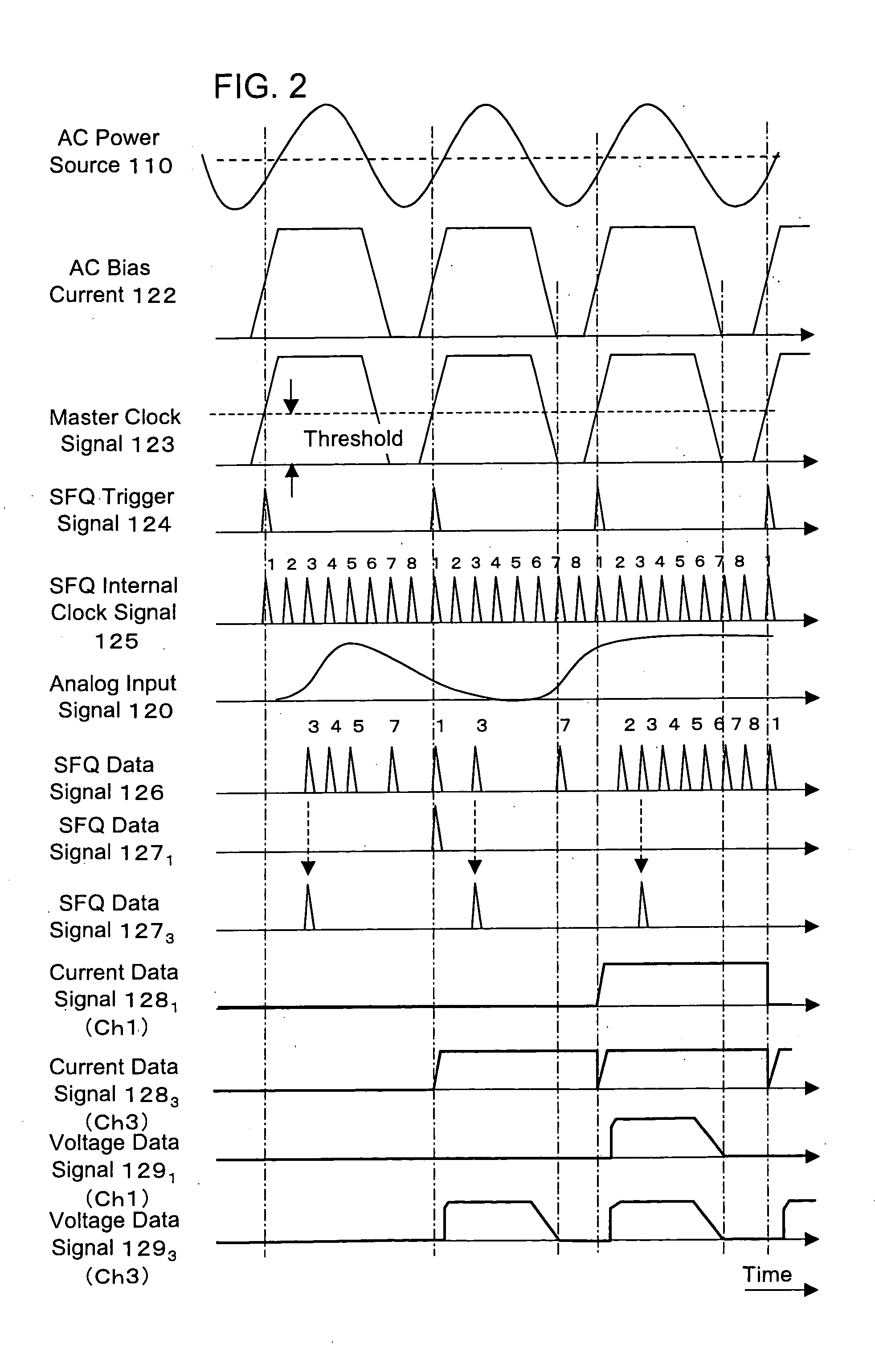

InactiveUS7129869B2Timing design is facilitatedReduce frequencyElectric signal transmission systemsDigital storageQuantum circuitFrequency multiplier

In an A / D converter having a single flux quantum circuit having a flux quantum as an information carrier, a superconducting amplifier circuit driven by an AC current, and a semiconductor circuit, the operations of the circuits are synchronized with each other and a data signal from the single flux quantum circuit is transmitted to the semiconductor circuit.An AC current as the power source of a superconducting amplifier circuit is inputted as a master clock signal to the single flux quantum circuit and the semiconductor circuit to synchronize the operations of the circuits with the master clock signal. The single flux quantum circuit has a clock signal frequency multiplier circuit, a demultiplexing circuit and a memory circuit.

Owner:HITACHI LTD +1

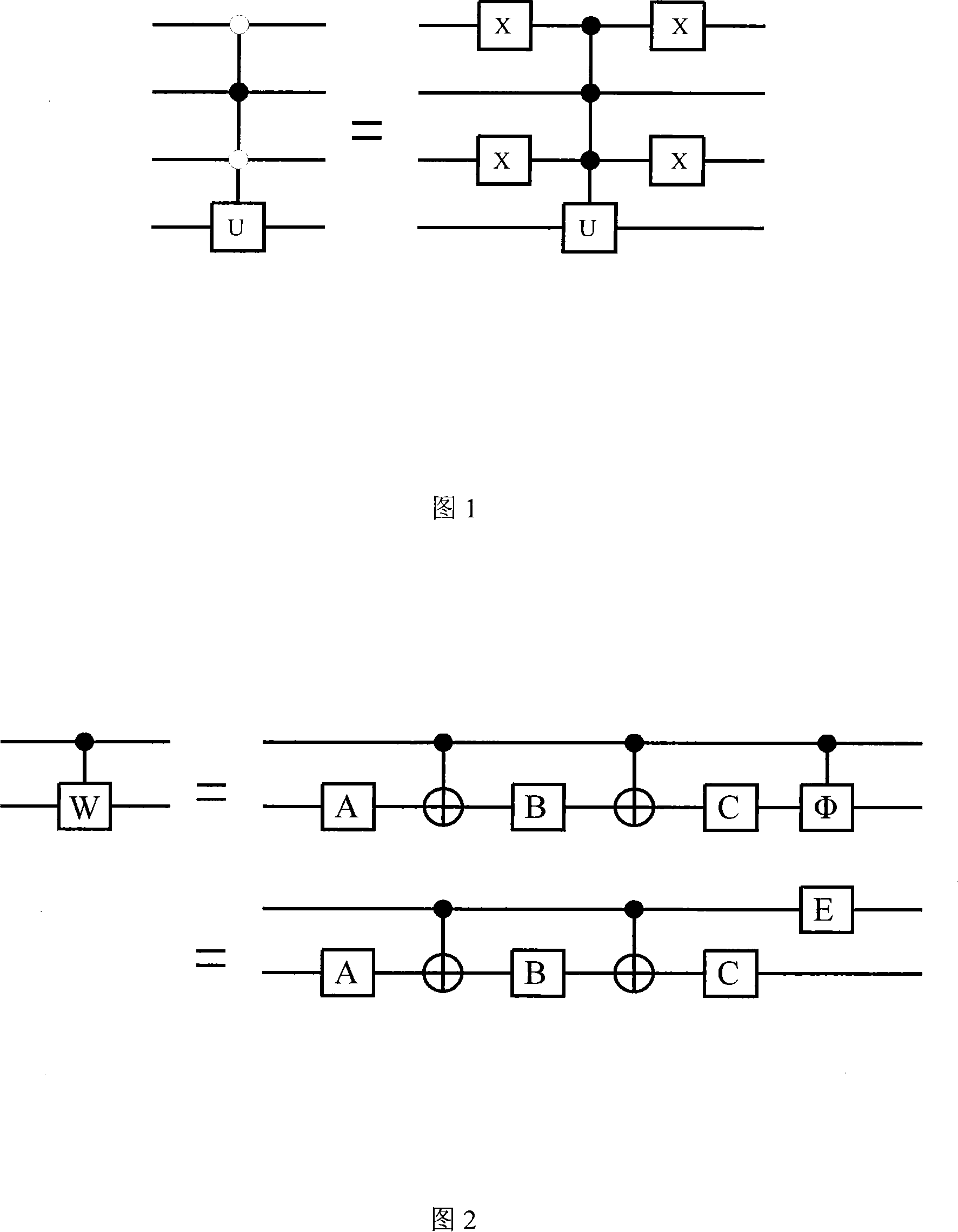

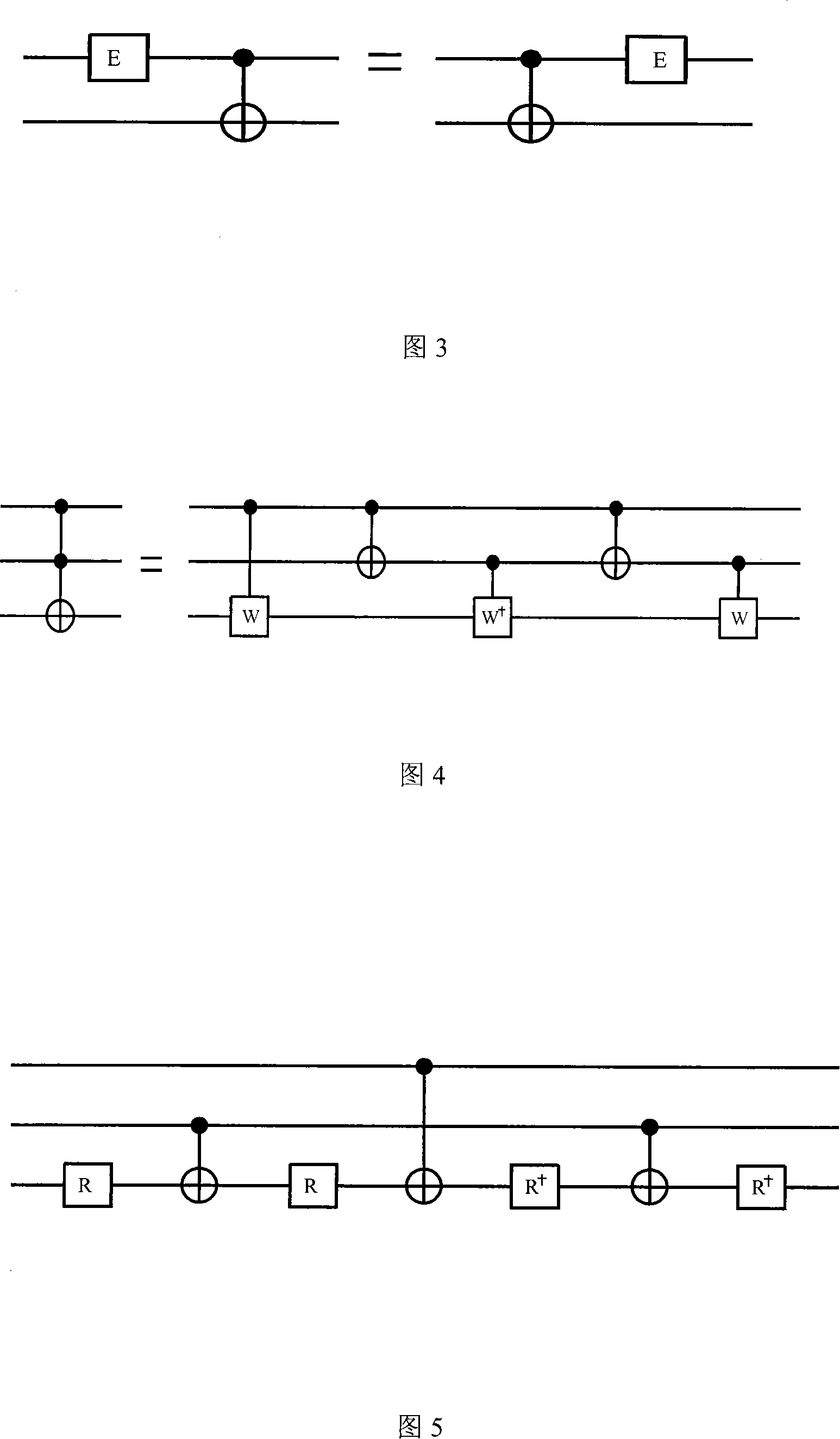

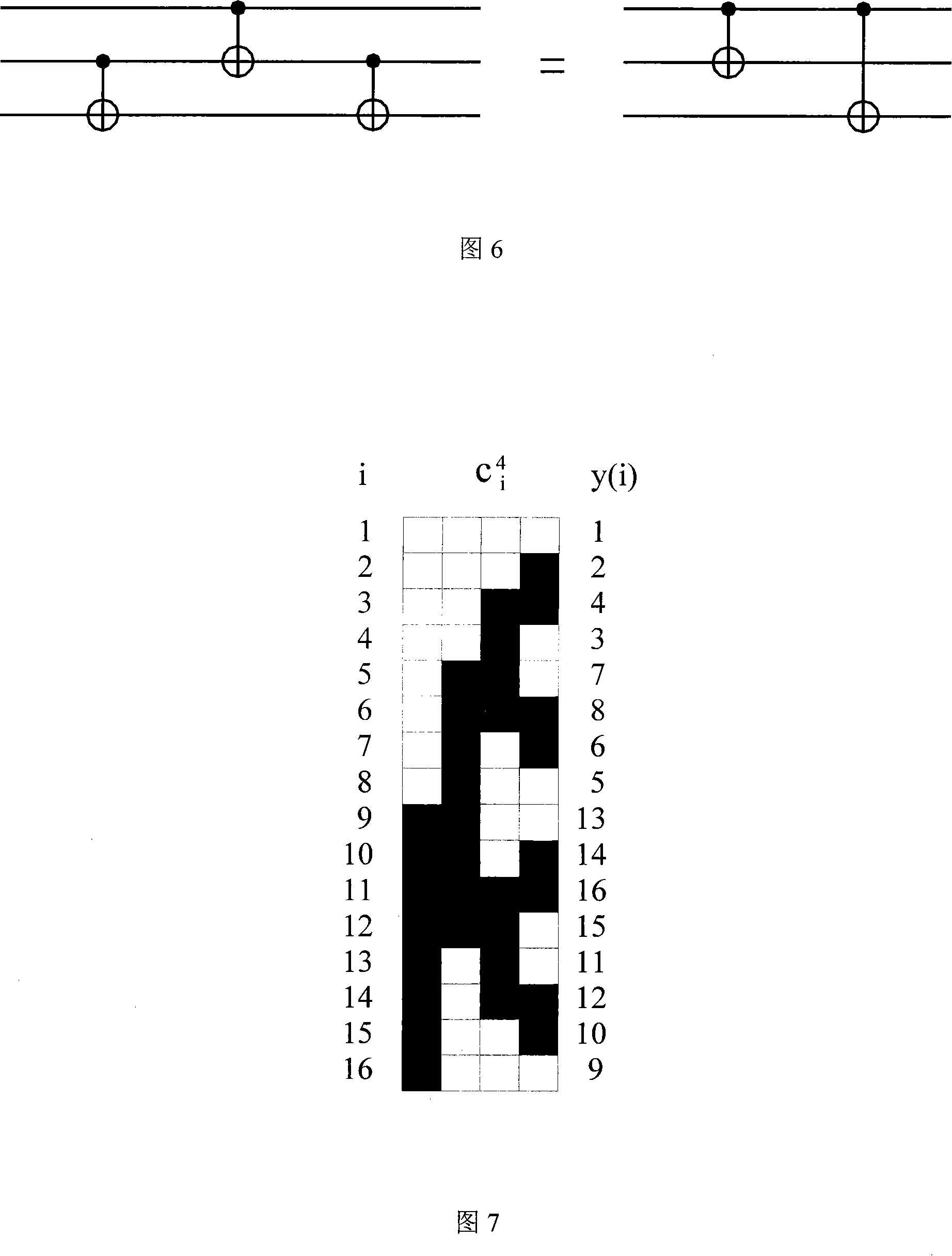

Decompose method for arbitrarily quantum bit gate

ActiveCN101118608AReduce complexityReduce the numberComputing modelsCircuit complexityQuantum circuit

The present invention discloses a decomposition method for a random quantum bit gate, and belongs to the field of the quantum state manipulating technology. The method includes: the bit gate U of a random quantum n is decomposed into a plurality of uninterrupted Cn (U) and the decomposition of a random quantum bit gate is achieved by adopting an index decomposition mode and a polynomial decomposition mode with circuit complexities of O (2n) and O (n2) respectively through the fundamental segment and the correcting segment of the structure and utilizing the mode of nested recursion. The present invention achieves that a random quantum bit gate is decomposed into a qubit index form and a polynomial form of complexities, gives the quantum circuit and the relevant analytical expression containing only two quantum bit CNOTs and a single quantum bit accurately, thereby achieving an arbitrary operation to a quantum state in the transmission process of the quantum state, figures out the number of a basic logic gate that the two decomposed forms need, uses a phaseshift approximate gate to replace the Toffolin gate and reduces the complexity of the circuit greatly.

Owner:TSINGHUA UNIV

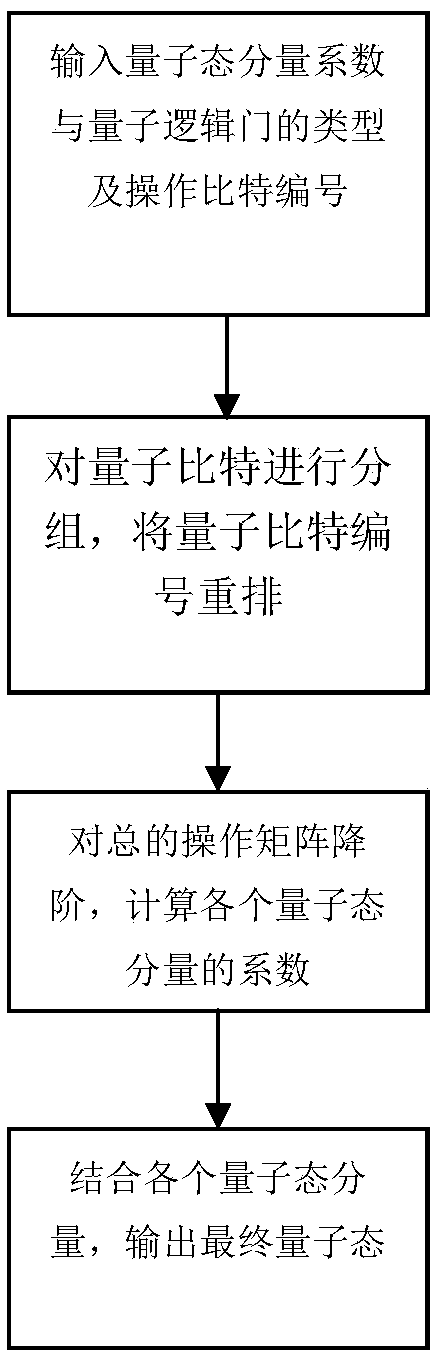

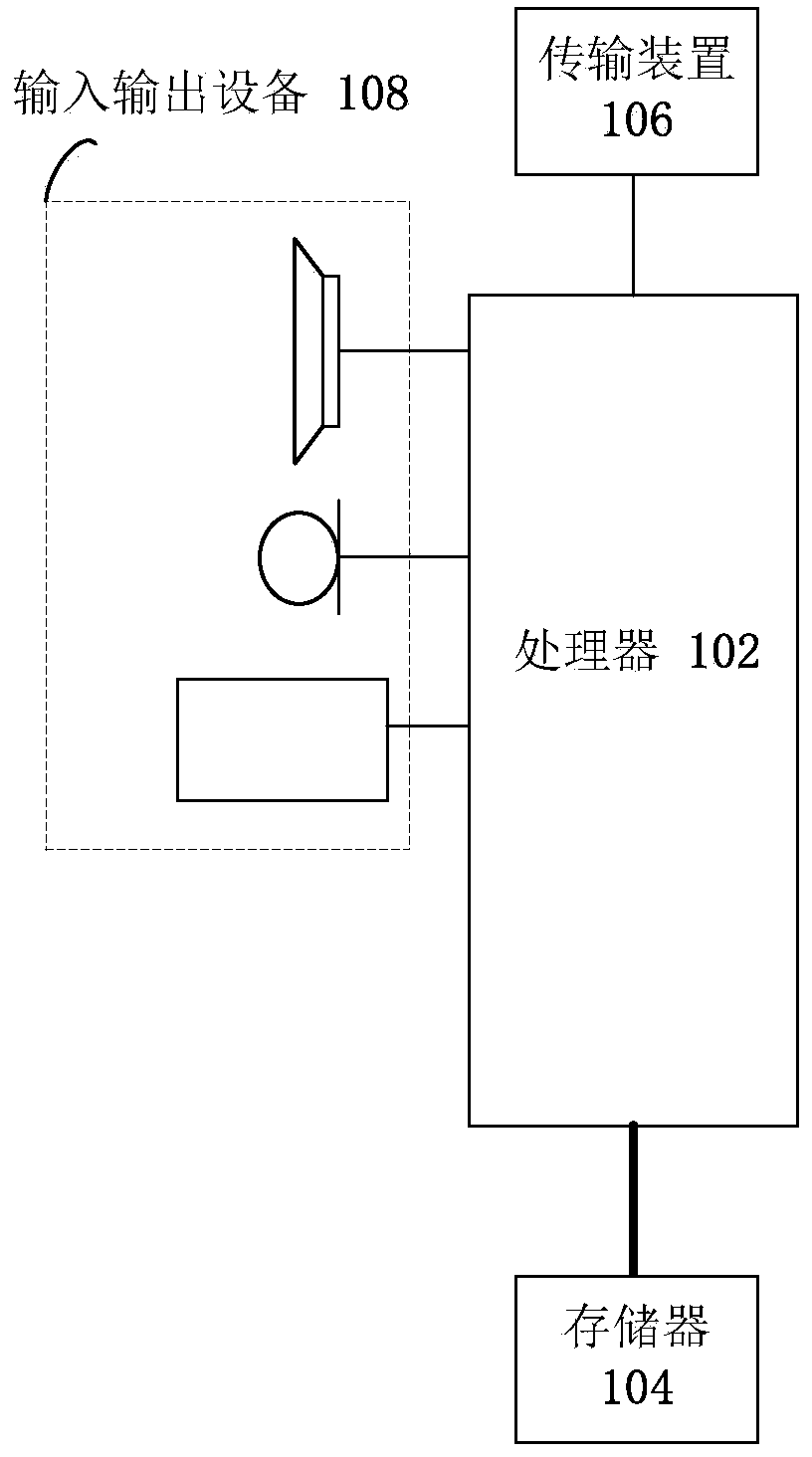

Low-complexity quantum circuit simulation system

ActiveCN108154240AScalableAvoid the disadvantage of too manyQuantum computersSupercomputerQuantum logic

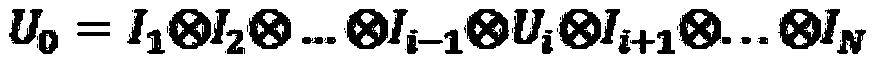

The invention discloses a low-complexity quantum circuit simulation system, and belongs to the field of quantum computing. The low-complexity quantum circuit simulation system overcomes the technicalproblems in the prior art that the quantum circuit simulation storage space is too large and the calculation time is too long. The system comprises an input module, a storage module and an output module, the storage process of the storage module for data is as follows: (1) a mathematical model is established to represent the operation of a quantum state and quantum logic gate; (2) quantum bits aregrouped and the serial numbers of the quantum bits are rearranged; (3) degree reduction is conducted on a total operation matrix U0, and an output state is calculated. According to the system, a matrix element of a quantum state vector is directly operated by using an connotative inherent law of a quantum logic gate, at the same time, the method has expandability, in the future, a supercomputer can be used to simulate a quantum computer with more bits.

Owner:ORIGIN QUANTUM COMPUTING TECH (HEFEI) CO LTD

Single flux quantum circuits

ActiveUS20090153180A1Reduce and eliminate unnecessary power dissipationQuantum computersPower consumption reductionQuantum circuitTransformer

Superconducting single flux quantum circuits are disclosed herein, each having at least one Josephson junction which will flip when the current through it exceeds a critical current. Bias current for the Josephson junction is provided by a biasing transformer instead of a resistor. The lack of any bias resistors ensures that unwanted power dissipation is eliminated.

Owner:NORTHROP GRUMMAN SYST CORP

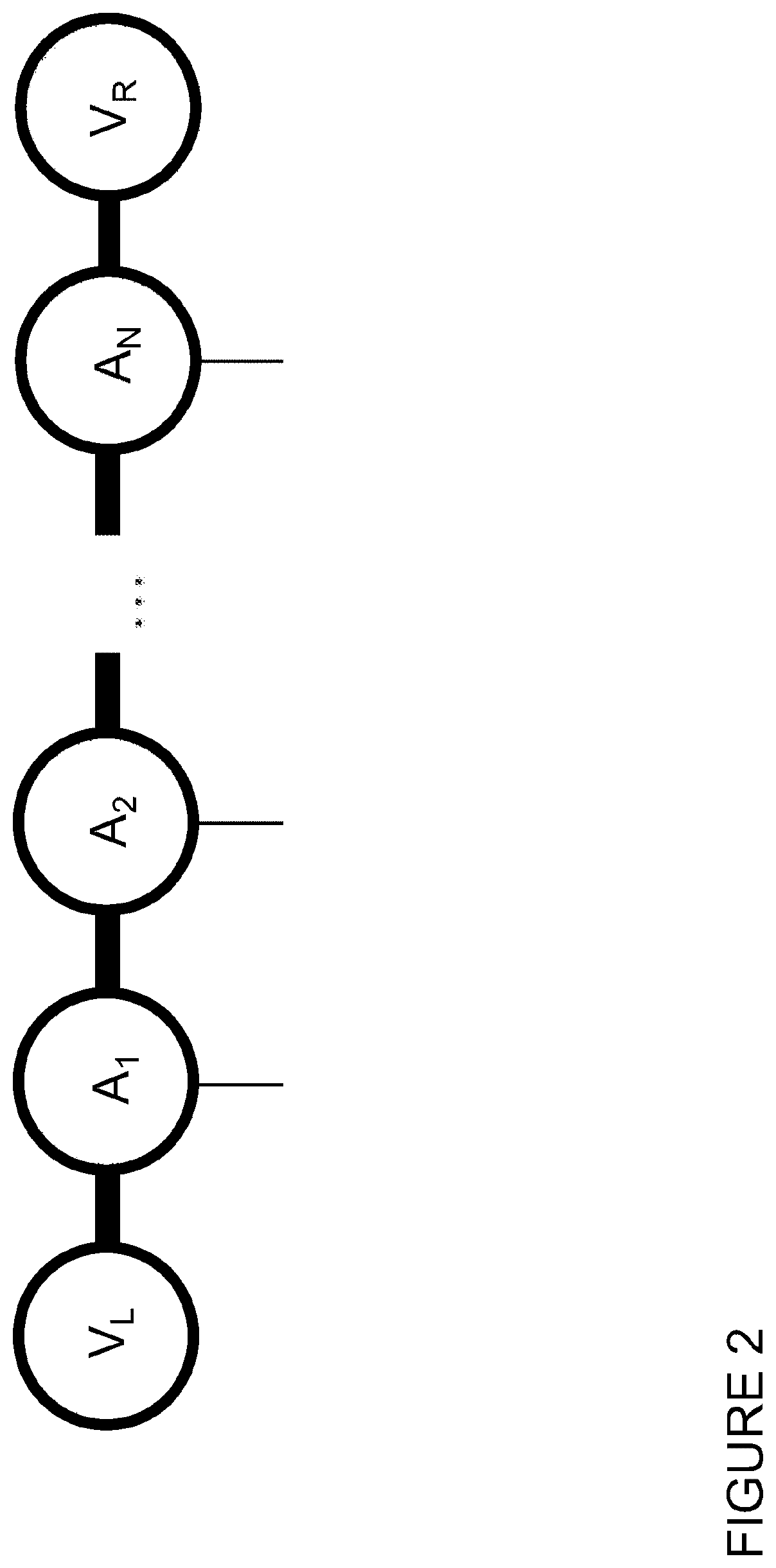

Simulating quantum circuits

A computer implemented method includes receiving a digital description of a quantum circuit, partitioning the digital description of the quantum circuit into a plurality of quantum sub-circuits wherein each quantum sub-circuit of the plurality of quantum sub-circuits comprises one or more quantum gates, determining sub-circuit dependencies for the plurality of quantum sub-circuits, simulating the plurality of quantum sub-circuits according to the sub-circuit dependencies to produce simulation results for each quantum sub-circuit of the plurality of quantum sub-circuits, wherein a first and a second quantum sub-circuit of the plurality of quantum sub-circuits each contain one or more gates that are applied to a common qubit, and wherein the first and the second quantum sub-circuit are simulated independently using an entangled tensor index. A corresponding computer system and computer program product are also disclosed herein.

Owner:IBM CORP

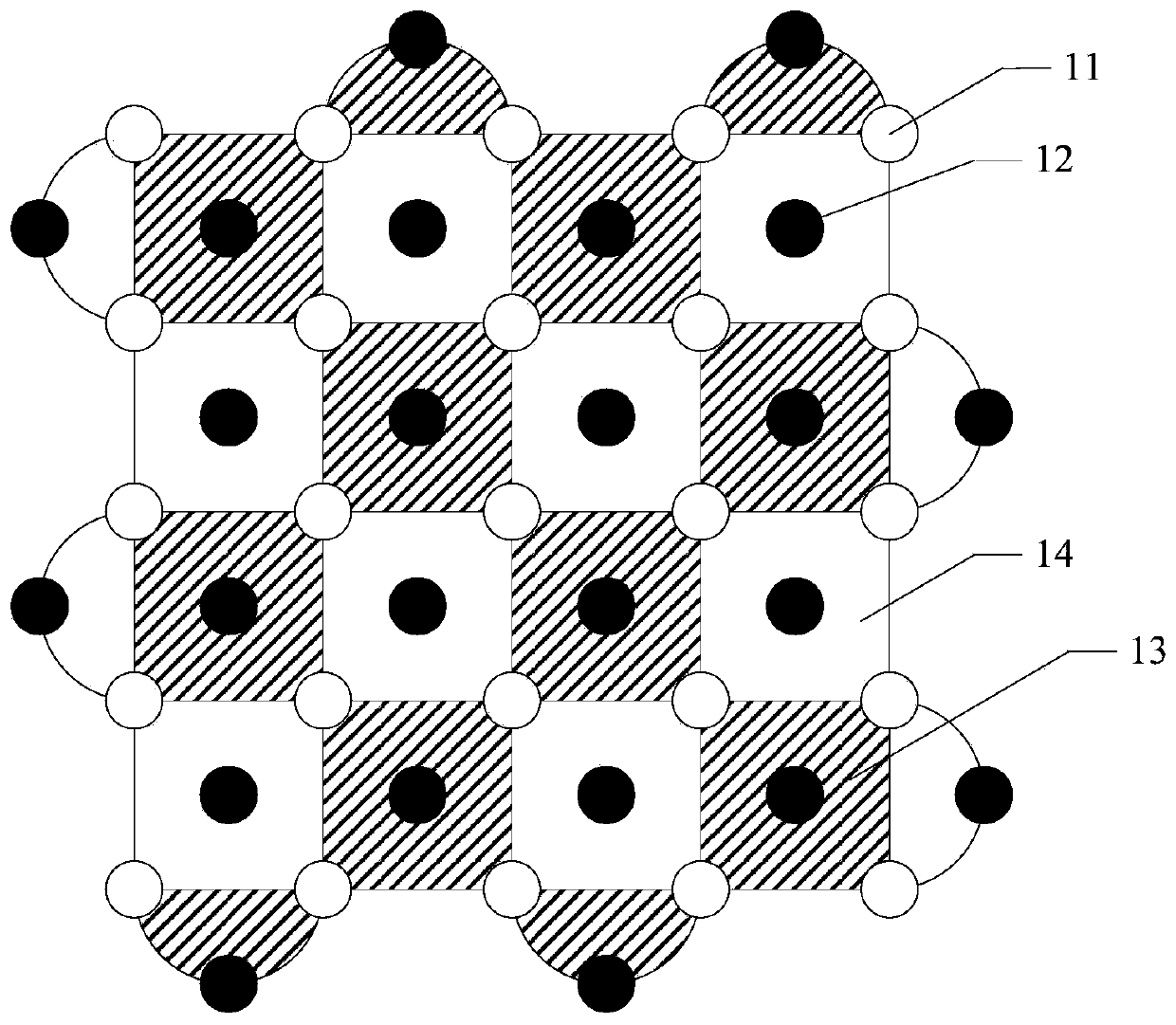

Quantum error correction decoding method and device based on neural network, and chip

ActiveCN111510157AReduce the number of channelsReduce in quantityQuantum computersError detection/correctionDecoding methodsQuantum circuit

The invention discloses a quantum error correction decoding method and a quantum error correction decoding device based on a neural network, and a chip, which relate to the technical field of artificial intelligence and quanta. The quantum error correction decoding method comprises the following steps of: acquiring error symptom information of a quantum circuit; performing block feature extractionon the error symptom information through using a neural network decoder to obtain feature information; and subjecting the feature information to fusion decoding processing through using the neural network decoder to obtain error result information, wherein the error result information is used for determining error data quantum bits and corresponding error types in the quantum circuit. According to the quantum error correction decoding method and the quantum error correction decoding device, a block feature extraction mode is adopted, the number of channels of the feature information obtainedby each feature extraction is reduced, and the input data of the next feature extraction is reduced, thereby being conductive to reducing the number of feature extraction layers in the neural networkdecoder, further reducing the depth of the neural network decoder, shortening the decoding time of the neural network decoder correspondingly, and satisfying the requirement of real-time error correction.

Owner:TENCENT TECH (SHENZHEN) CO LTD

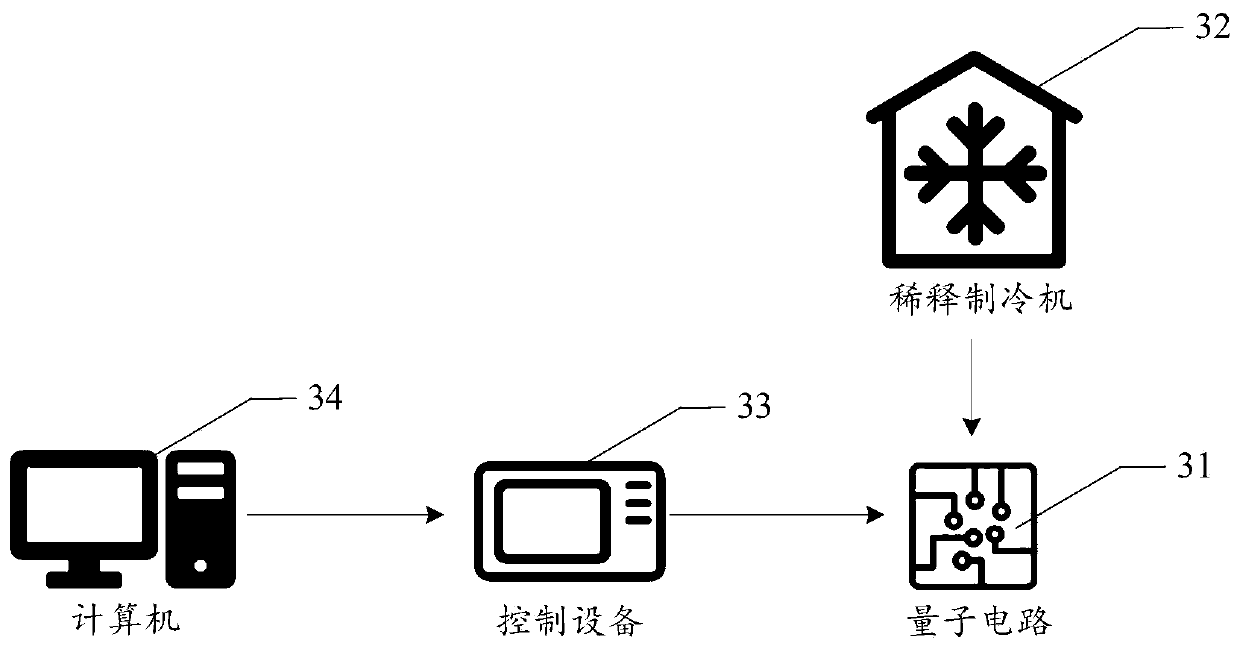

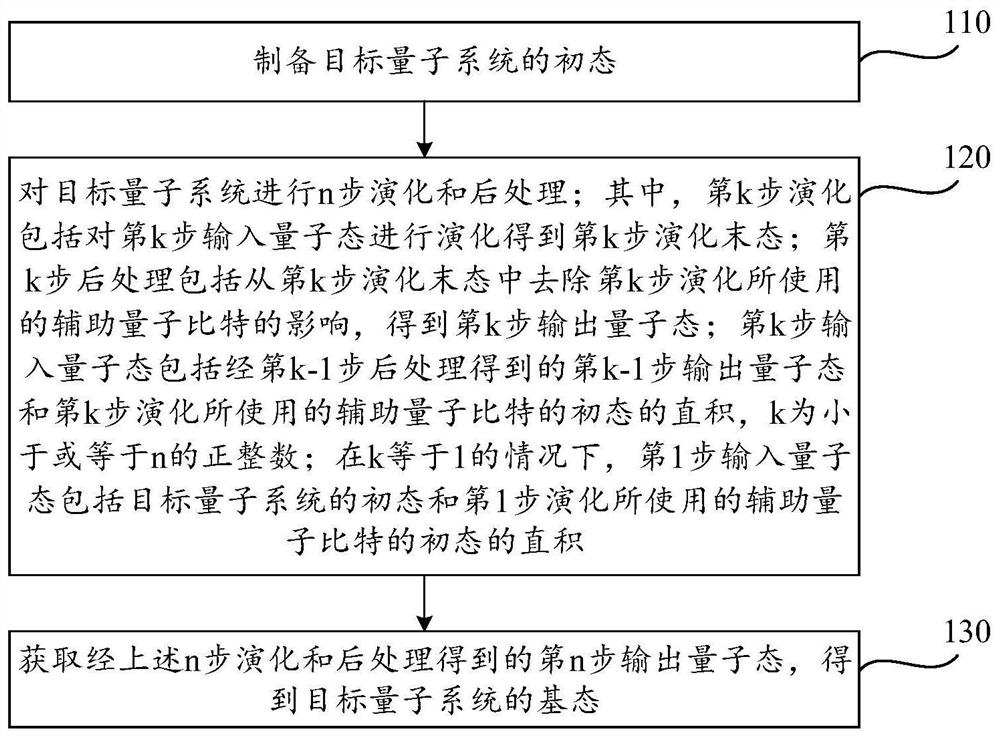

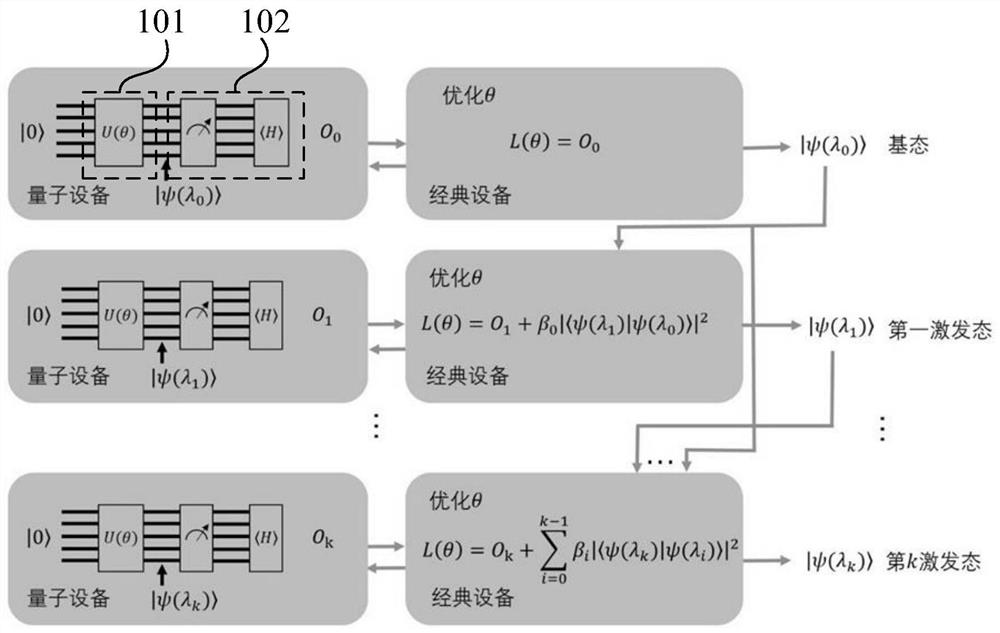

Ground state acquisition method and device of quantum system, equipment and storage medium

The invention discloses a ground state acquisition method and device of a quantum system, equipment and a storage medium, and relates to the technical field of quantum. The method comprises the following steps: preparing an initial state of a target quantum system; performing n steps of evolution and post-processing on the target quantum system, wherein the kth step of evolution comprises evolving the kth step of input quantum state to obtain a kth step of evolution final state, and the kth step of post-processing comprises removing the influence of auxiliary quantum bits used by the kth step of evolution from the kth step of evolution final state to obtain a kth step of output quantum state; and obtaining an nth-step of output quantum state obtained through the n-step of evolution and post-processing, and obtaining a ground state of the target quantum system. According to the quantum simulation algorithm based on the non-Hermite process, the ground state of a quantum system is simulated, the effect of virtual-real evolution is achieved through real-time unitary evolution related to the Hamiltonian of the system, ground state simulation is clearly and clearly achieved theoretically, the process can be directly achieved through a quantum circuit, and the operability of the scheme is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

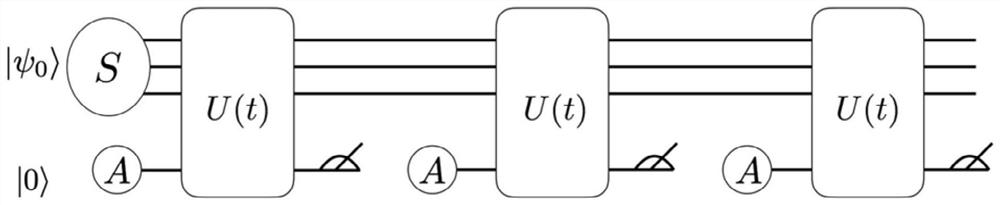

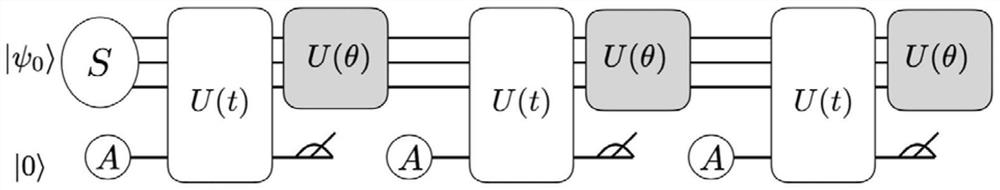

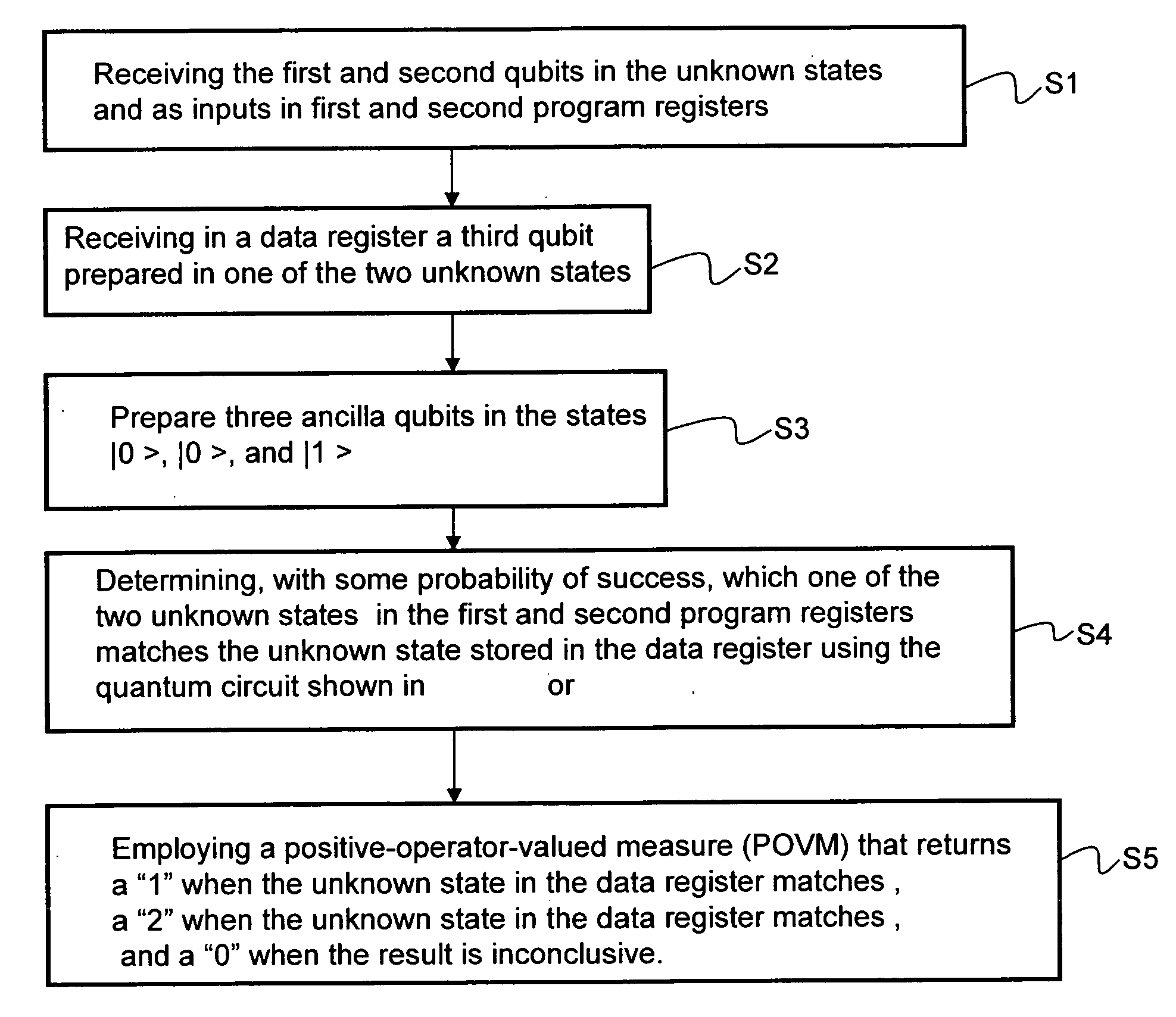

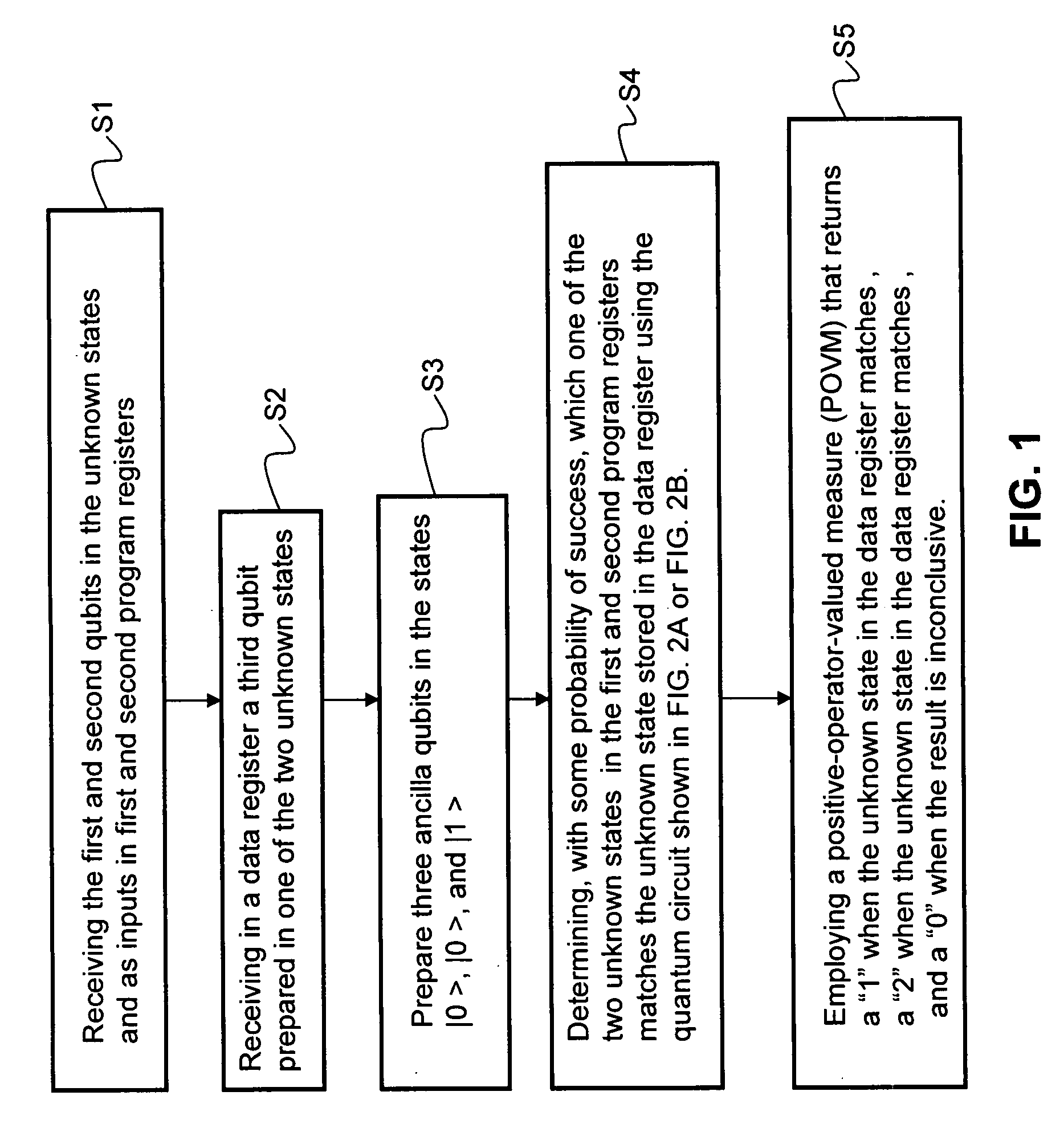

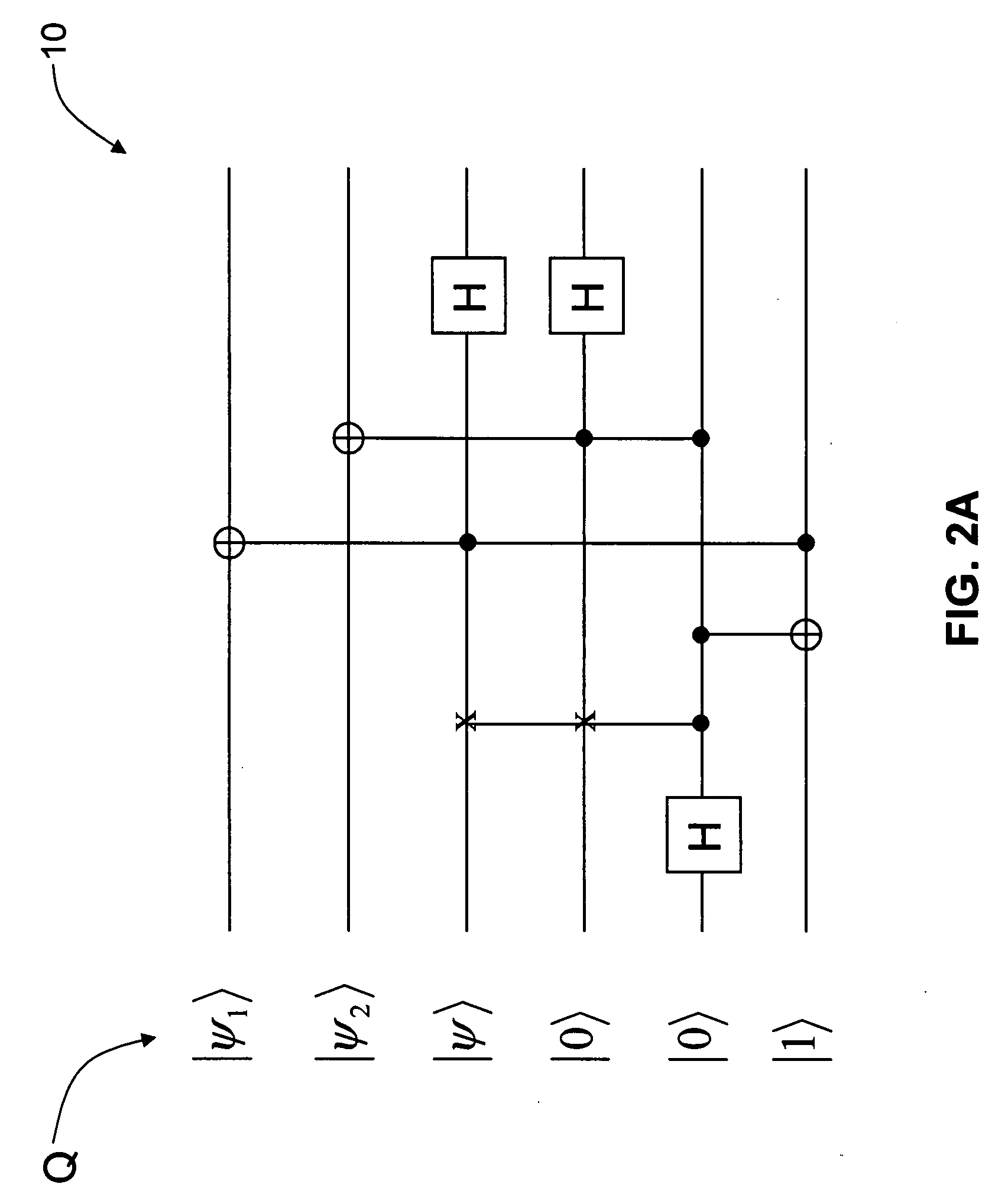

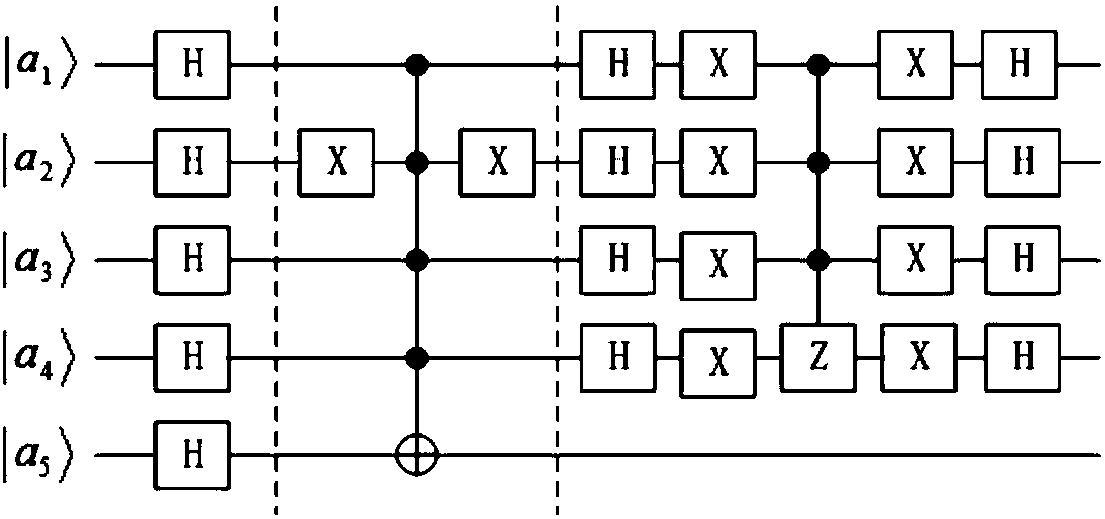

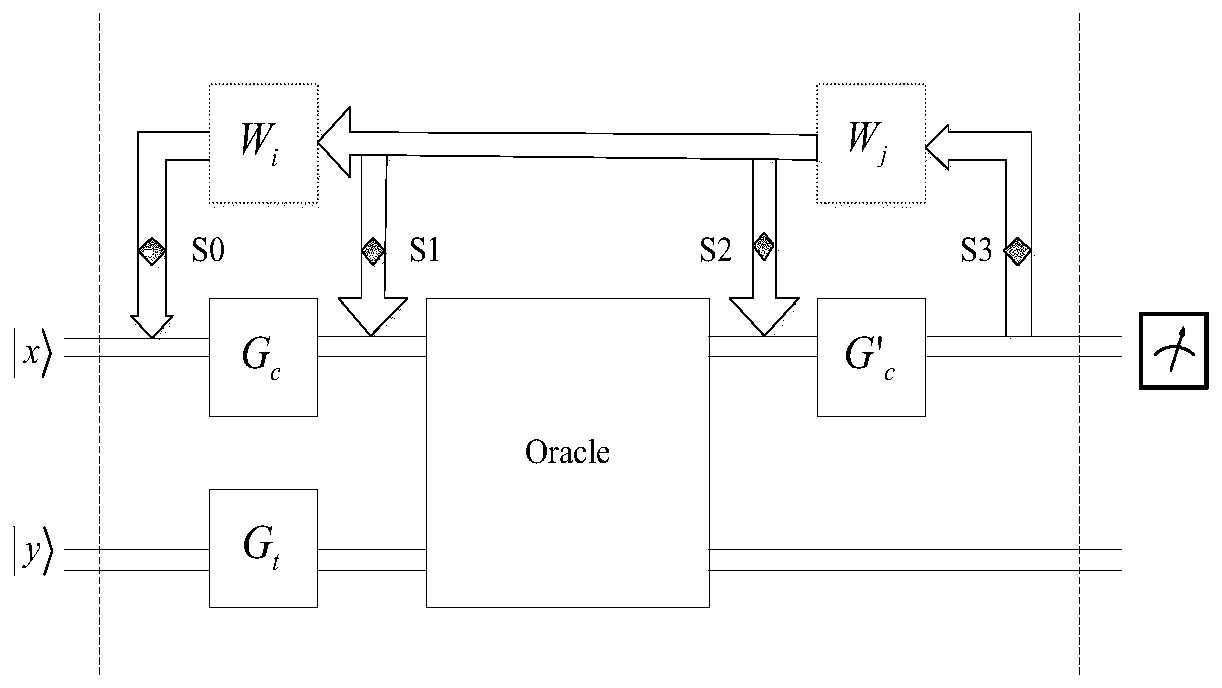

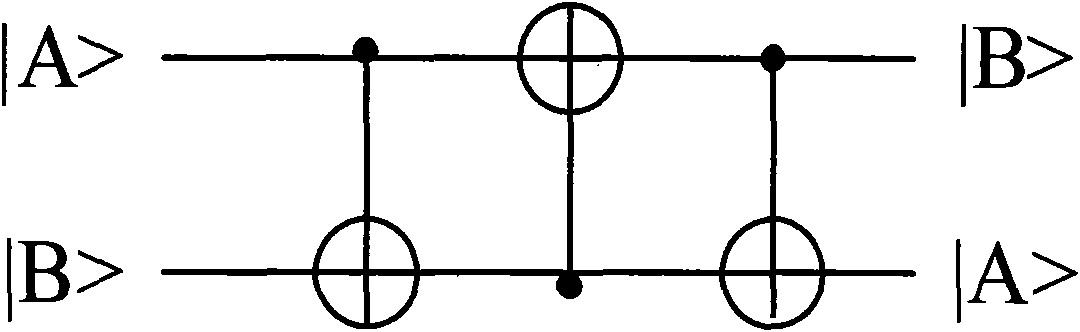

Quantum circuit for quantum state discrimination

The invention is a quantum circuit that unambiguously discriminates between two unknown quantum states of qubits. The circuit receives the qubits in the unknown states as inputs, or programs, in first and second program registers. A data register also receive a third qubit prepared in one of the two states stored in the program registers. The circuit, with some probability of success, determines which unknown state of the qubit in the data register matches the state stored in the first or second program registers. The optimal circuit, i.e., one that maximizes the probability of success, is universal because it does not depend on the actual unknown states to be discriminated. The quantum circuit has industrial applicability to quantum information, and in particular to quantum computing.

Owner:MAGIQ TECH INC

Superconductor semiconductor integrated circuit

InactiveUS20050047245A1Transmission easilyTiming design is facilitatedElectric signal transmission systemsDigital storageQuantum circuitFrequency multiplier

In an A / D converter having a single flux quantum circuit having a flux quantum as an information carrier, a superconducting amplifier circuit driven by an AC current, and a semiconductor circuit, the operations of the circuits are synchronized with each other and a data signal from the single flux quantum circuit is transmitted to the semiconductor circuit. An AC current as the power source of a superconducting amplifier circuit is inputted as a master clock signal to the single flux quantum circuit and the semiconductor circuit to synchronize the operations of the circuits with the master clock signal. The single flux quantum circuit has a clock signal frequency multiplier circuit, a demultiplexing circuit and a memory circuit.

Owner:HITACHI LTD +1

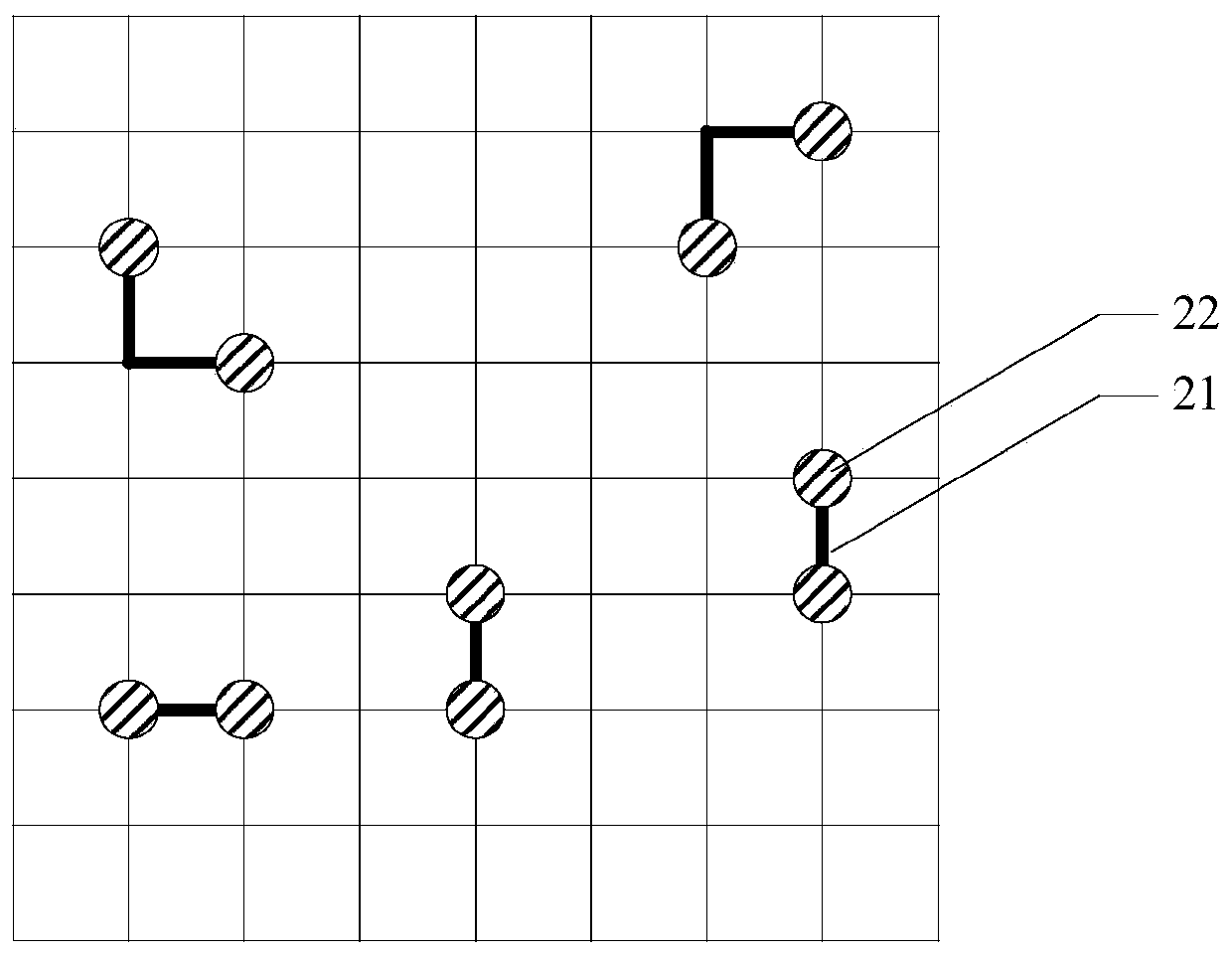

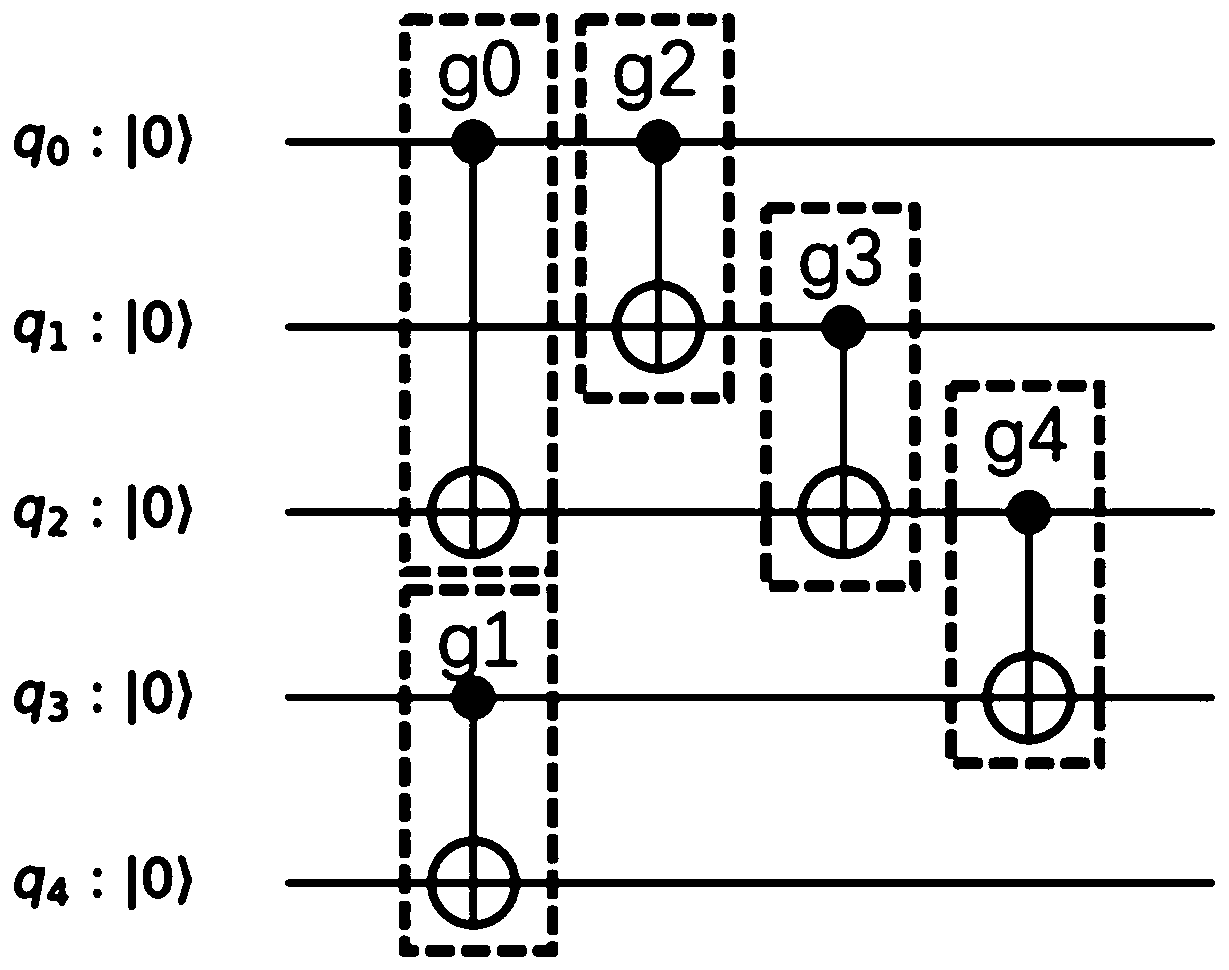

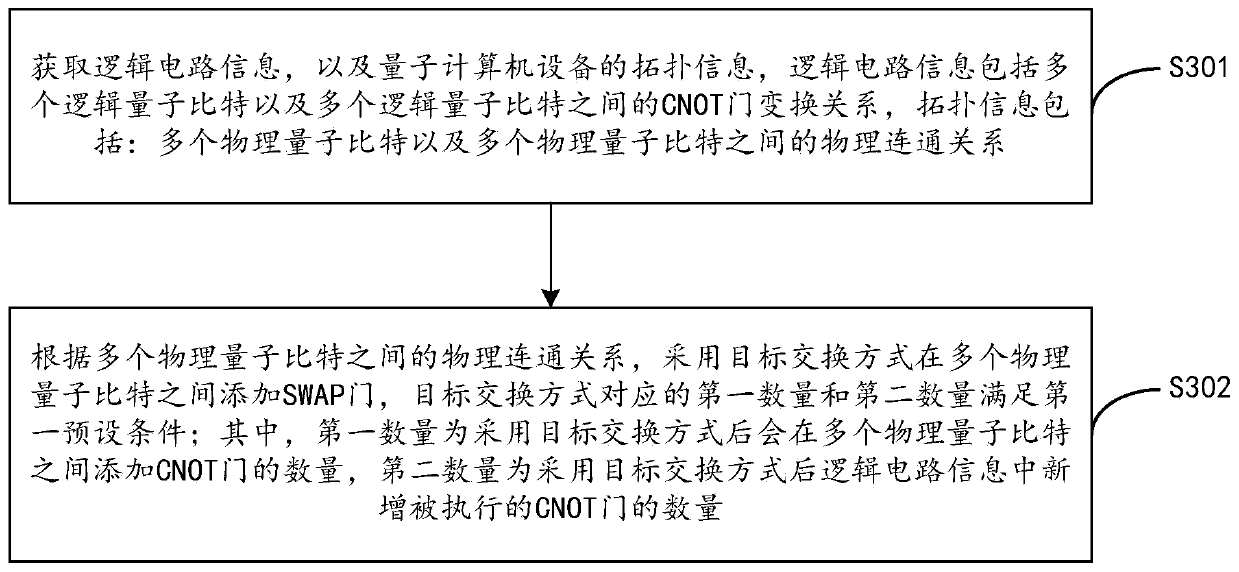

Quantum circuit processing method, device and apparatus

The invention discloses a quantum circuit processing method, device and apparatus, and relates to the technical field of quantum computing. According to the technical scheme, the method comprises thesteps that according to a physical connection relationship among the plurality of physical quantum bits; adding an SWAP gate among the plurality of physical quantum bits by adopting a target exchangemode, when the SWAP gate is added, considering the number of CNOT gates added among a plurality of physical quantum bits after a target switching mode is adopted and the number of newly added executedCNOT gates in logic circuit information after the target switching mode is adopted. Therefore, it can be avoided that a large number of CNOT gates are additionally introduced into the converted circuit, so that quantum fidelity in quantum calculation is prevented from being reduced, and the precision of a quantum calculation result is improved.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

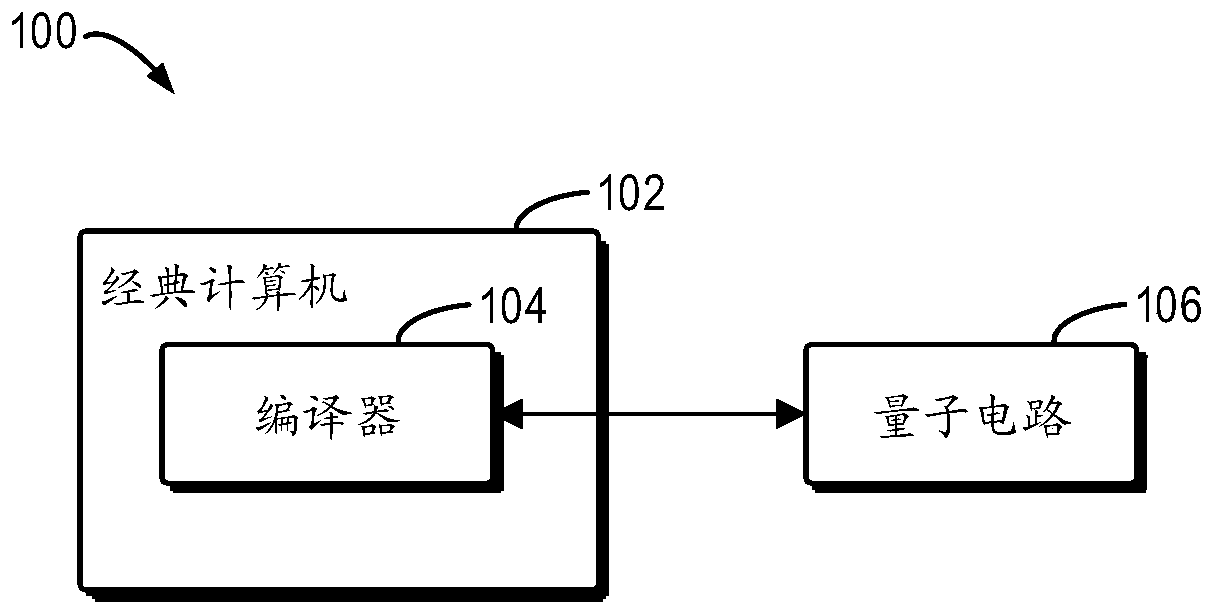

Method and device for compiling quantum circuit, equipment, and computer readable storage medium

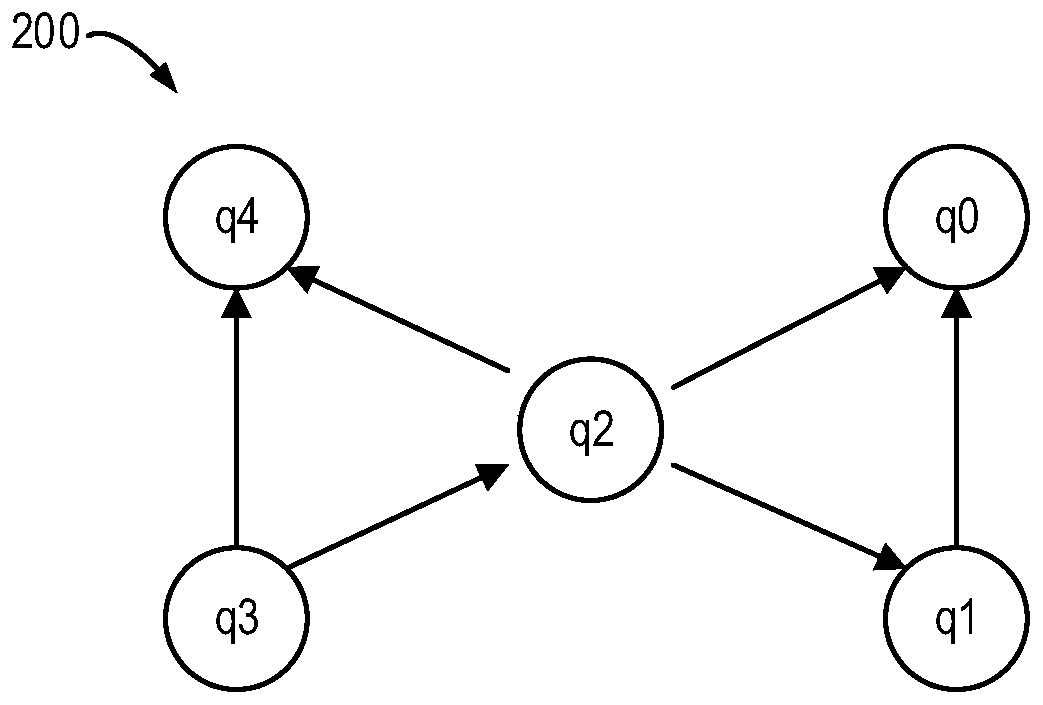

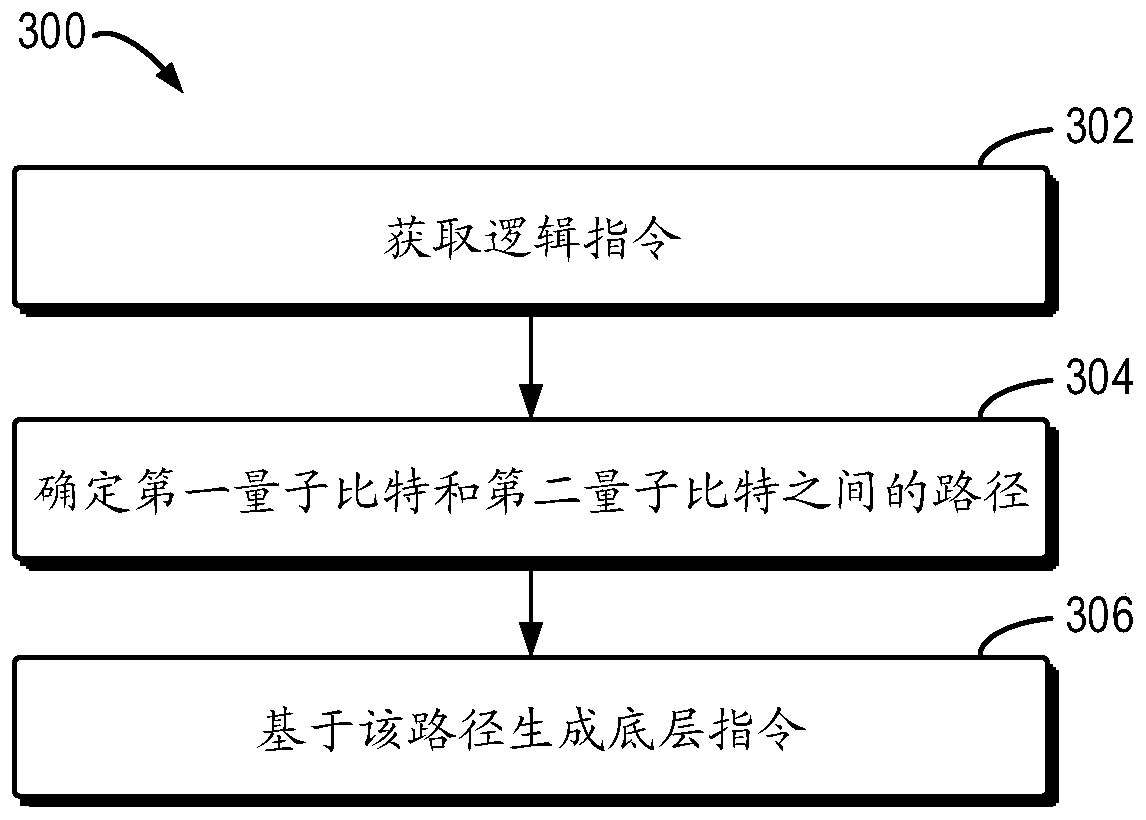

Embodiments of the present disclosure relate to a method and device for compiling quantum circuit, equipment, and a computer readable storage medium. The method comprises: obtaining a logic instruction to be compiled for a quantum circuit, the quantum circuit comprising a plurality of qubits, the logic instruction being associated with a first qubit and a second qubit of the plurality of qubits, at least a portion of the plurality of qubits being operable using a dual-bit quantum gate; determining a path between the first qubit and the second qubit in the quantum circuit; and generating an underlying instruction for the quantum circuit corresponding to the logic instruction by adding a single-bit quantum gate based on the path.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

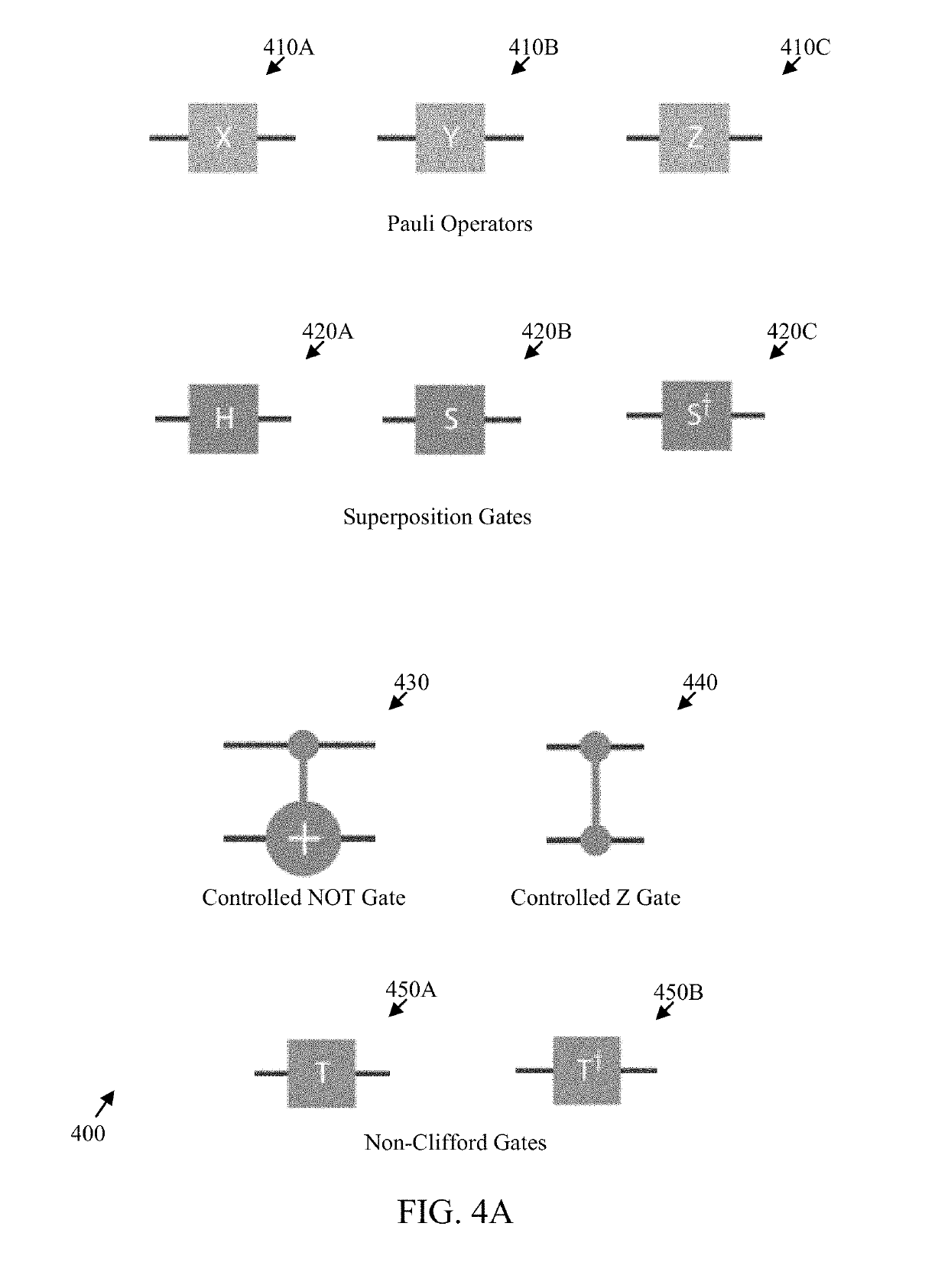

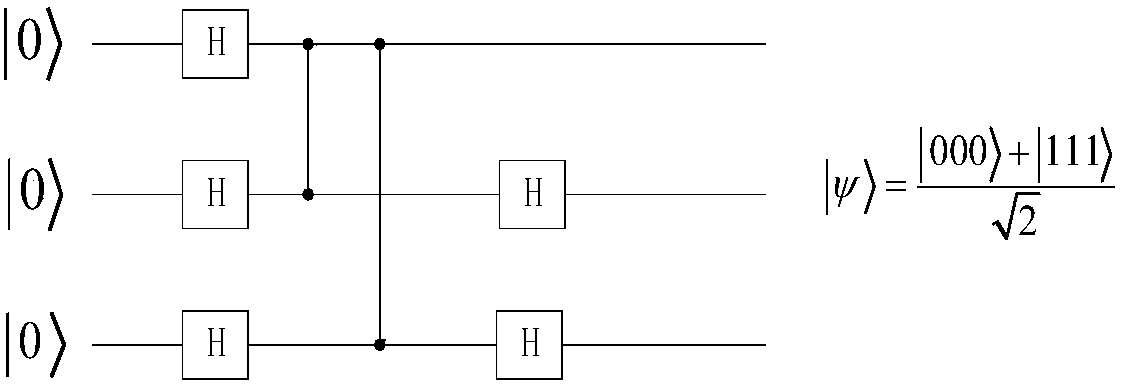

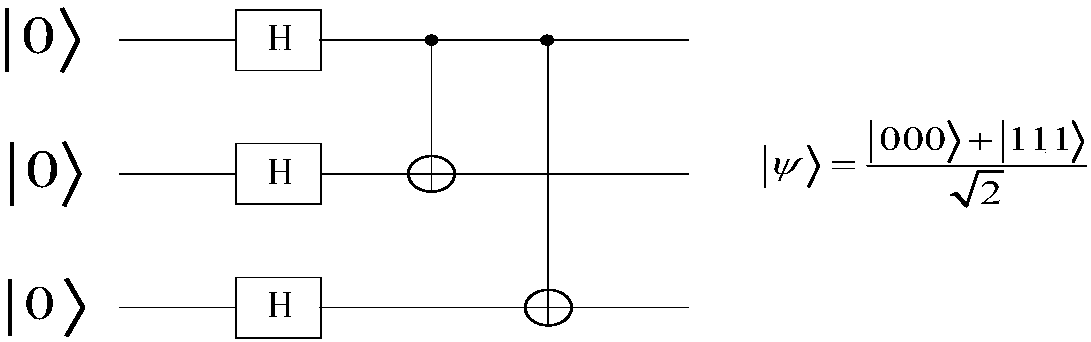

Novel universal quantum gate and quantum circuit optimization method

PendingCN108334952AReduce typesReduce the numberQuantum computersDesign optimisation/simulationQuantum circuitGrover's algorithm

The invention discloses a novel universal quantum gate and a quantum circuit optimization method. The method comprises the following contents: analyzing the effect of a basic quantum gate and the variation process of the probability amplitude, the relation of equivalence between the existing universal quantum gate combination and the quantum gate, and the data dependence in the quantum gate simulation process in a GPU environment, proposing a novel universal quantum gate {C-Z, H, T}, meanwhile, simulating a basic quantum gate operation by using the GPU environment, inputting corresponding quantum gates as needed in the simulation process, and optimizing a GHZ state quantum circuit and a quantum Grover algorithm circuit by using the novel universal quantum gate combination and quantum gatedecomposition and merging strategy. The availability and efficiency of the optimized circuit are verified in the simulation environment.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

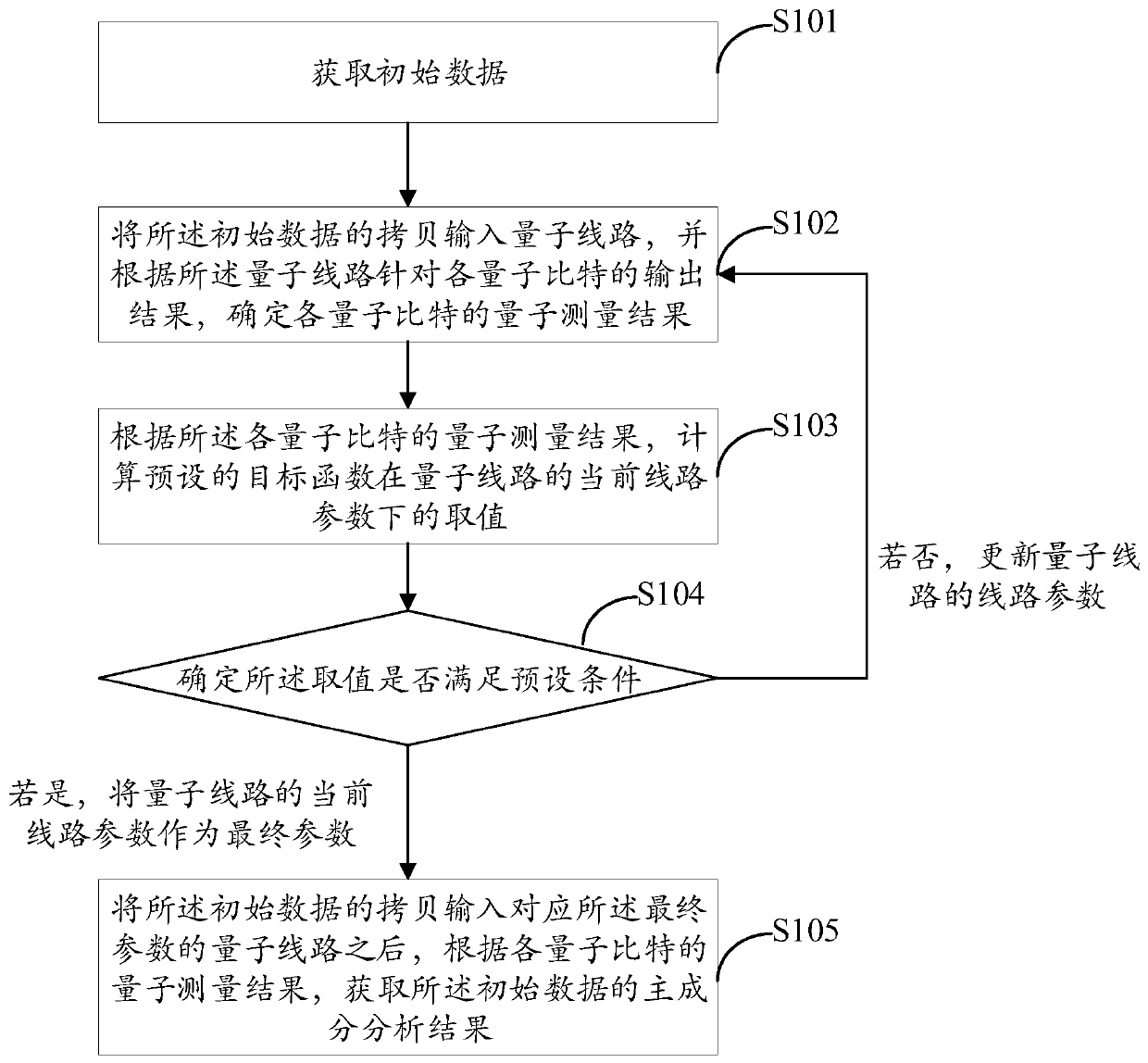

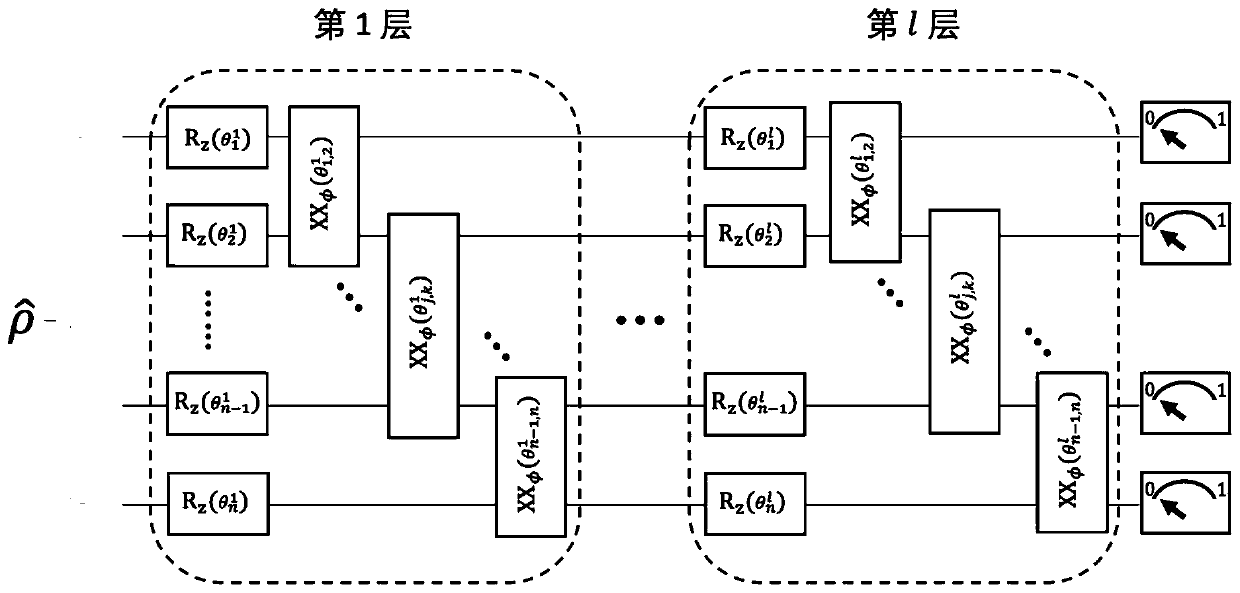

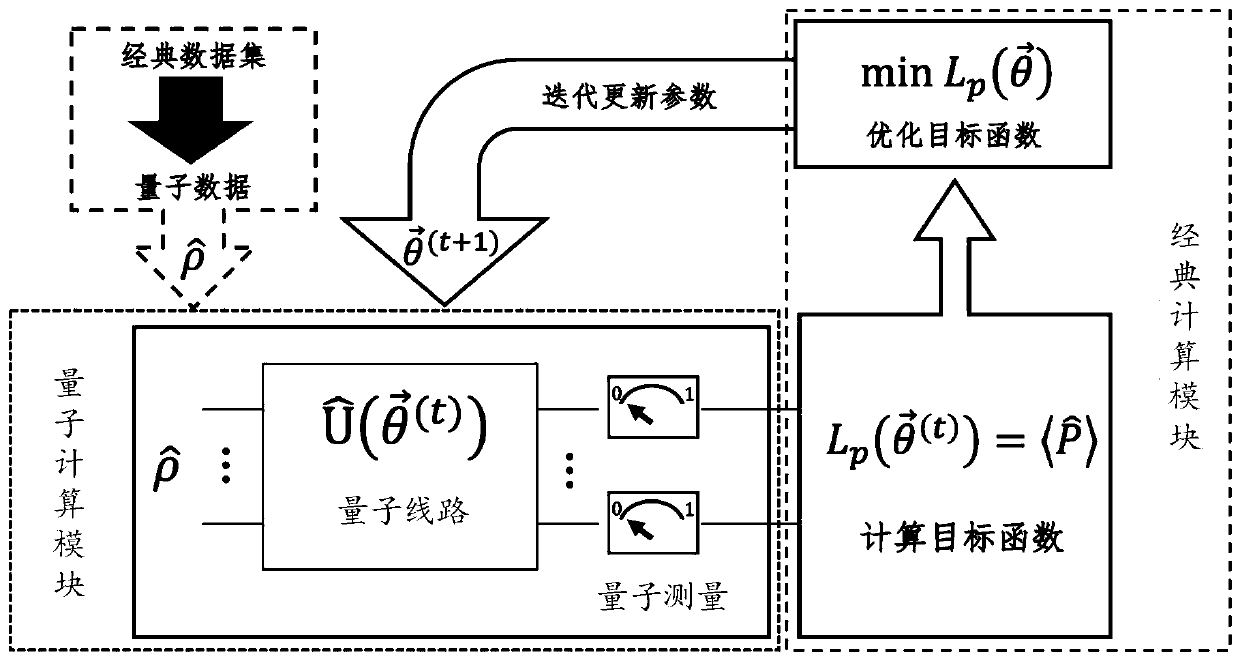

Quantum principal component analysis method and device, electronic equipment and computer readable storage medium

The invention discloses a quantum principal component analysis method and device, electronic equipment and a computer readable storage medium, and relates to the technical field of quantum computing.The implementation scheme adopted during quantum principal component analysis comprises the steps: acquiring initial data; copying and inputting the initial data into a quantum circuit, and determining a quantum measurement result of each quantum bit; according to the quantum measurement result of each quantum bit, calculating the value of a preset target function under the current circuit parameter of the quantum circuit; determining whether the value meets a preset condition or not, if the value does not meet the preset condition, updating the circuit parameter of the quantum circuit, turning to execute inputting of the copy of the initial data into the quantum circuit to determine a quantum measurement result, iteratively executing the process until the value meets the preset condition,and taking the current circuit parameter of the quantum circuit as a final parameter; and inputting the copy of the initial data into the quantum circuit corresponding to the final parameter, and obtaining a principal component analysis result of the initial data according to the quantum measurement result of each quantum bit.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

Quantum circuit optimization

Technologies are described herein to implement an optimizer that receives portions of a quantum circuit; identifies, from within the received portions of the quantum circuit, a pattern of quantum gates to perform a quantum function; searches a library for a replacement pattern of quantum gates, which is also to perform the quantum function, for the identified pattern of quantum gates; determines that a quantum cost of the replacement pattern of quantum gates is lower than a quantum cost of the identified pattern of quantum gates; and replaces the identified pattern of quantum gates with the replacement pattern of quantum gates.

Owner:IONQ INC

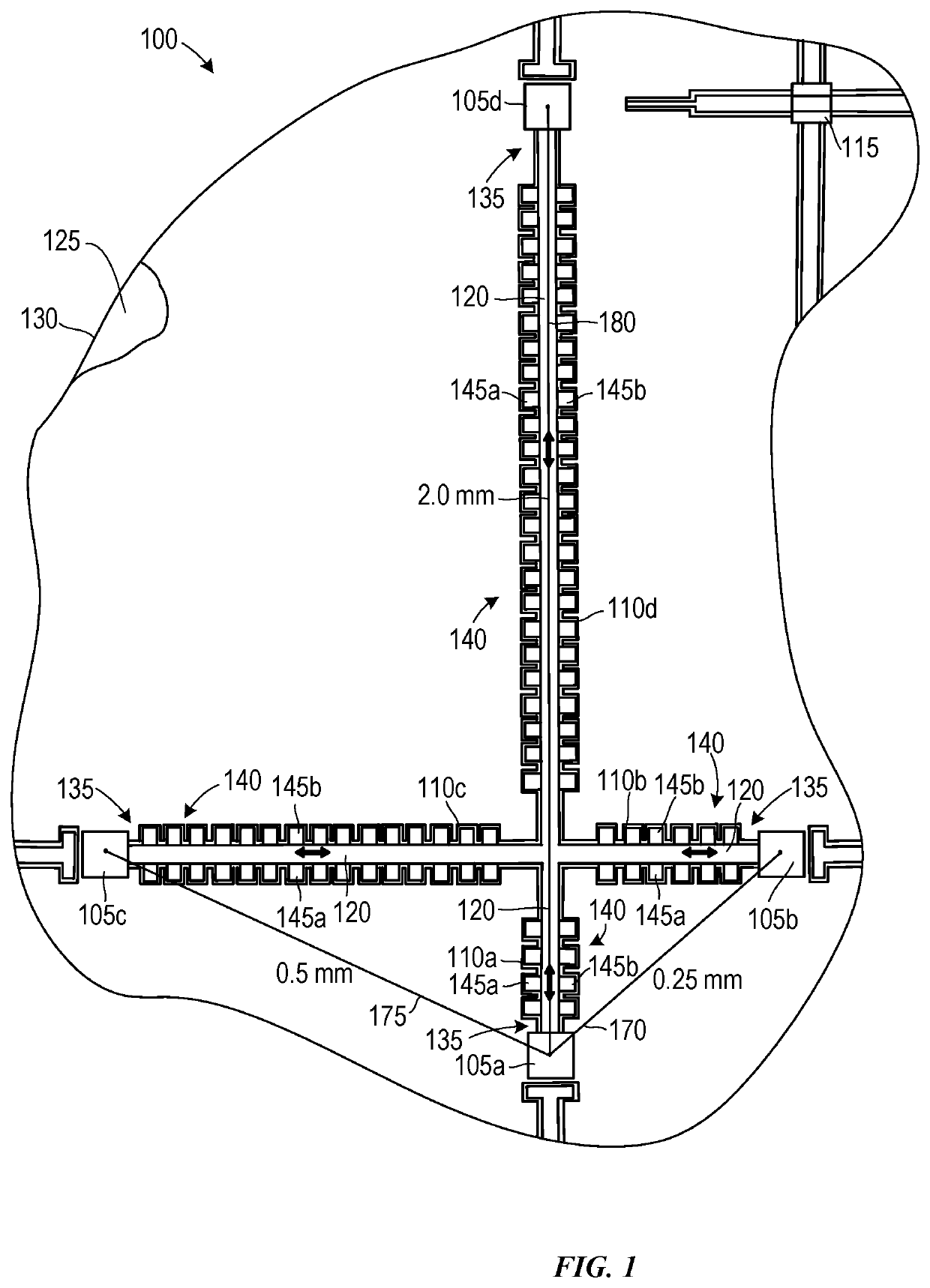

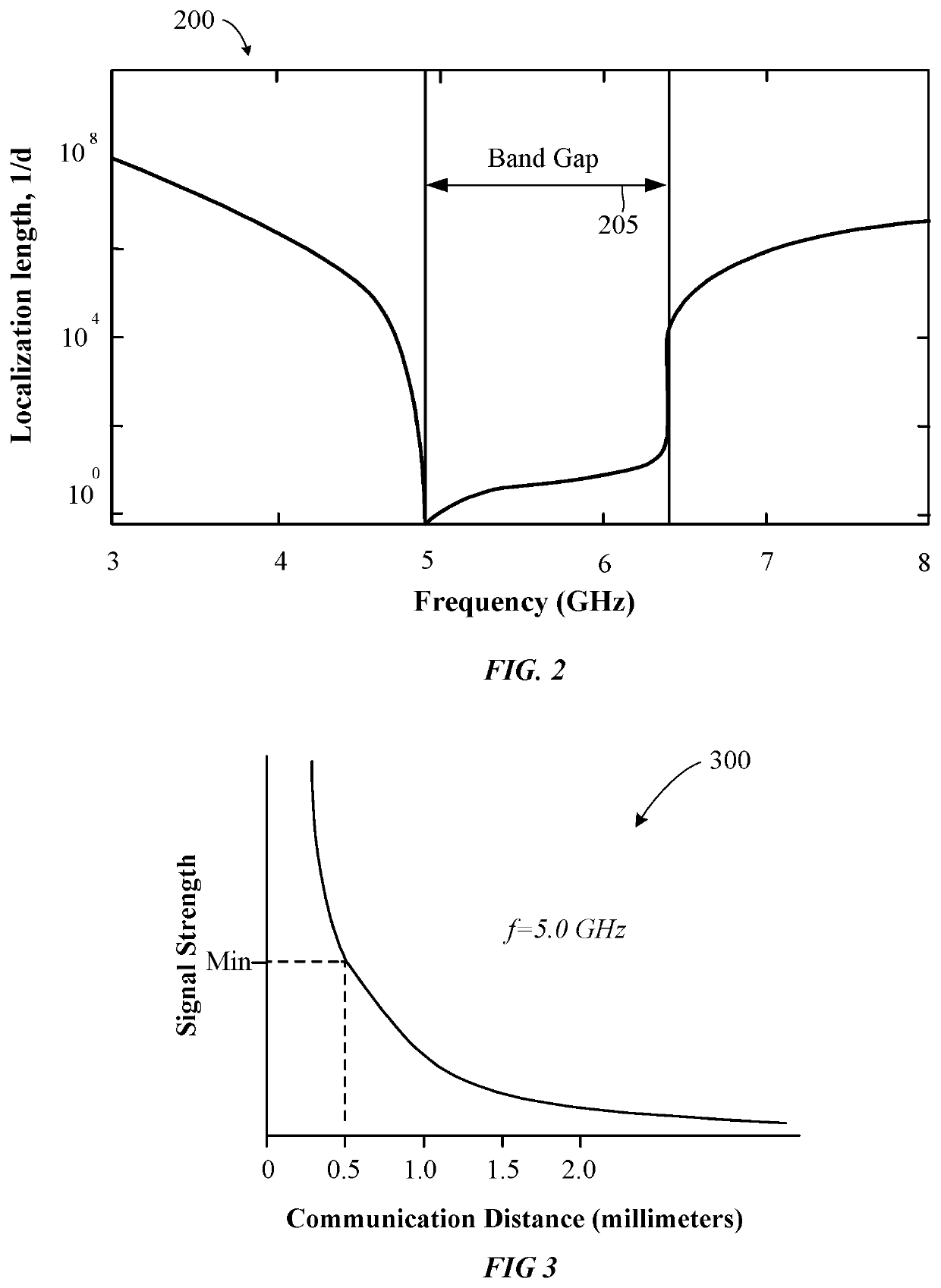

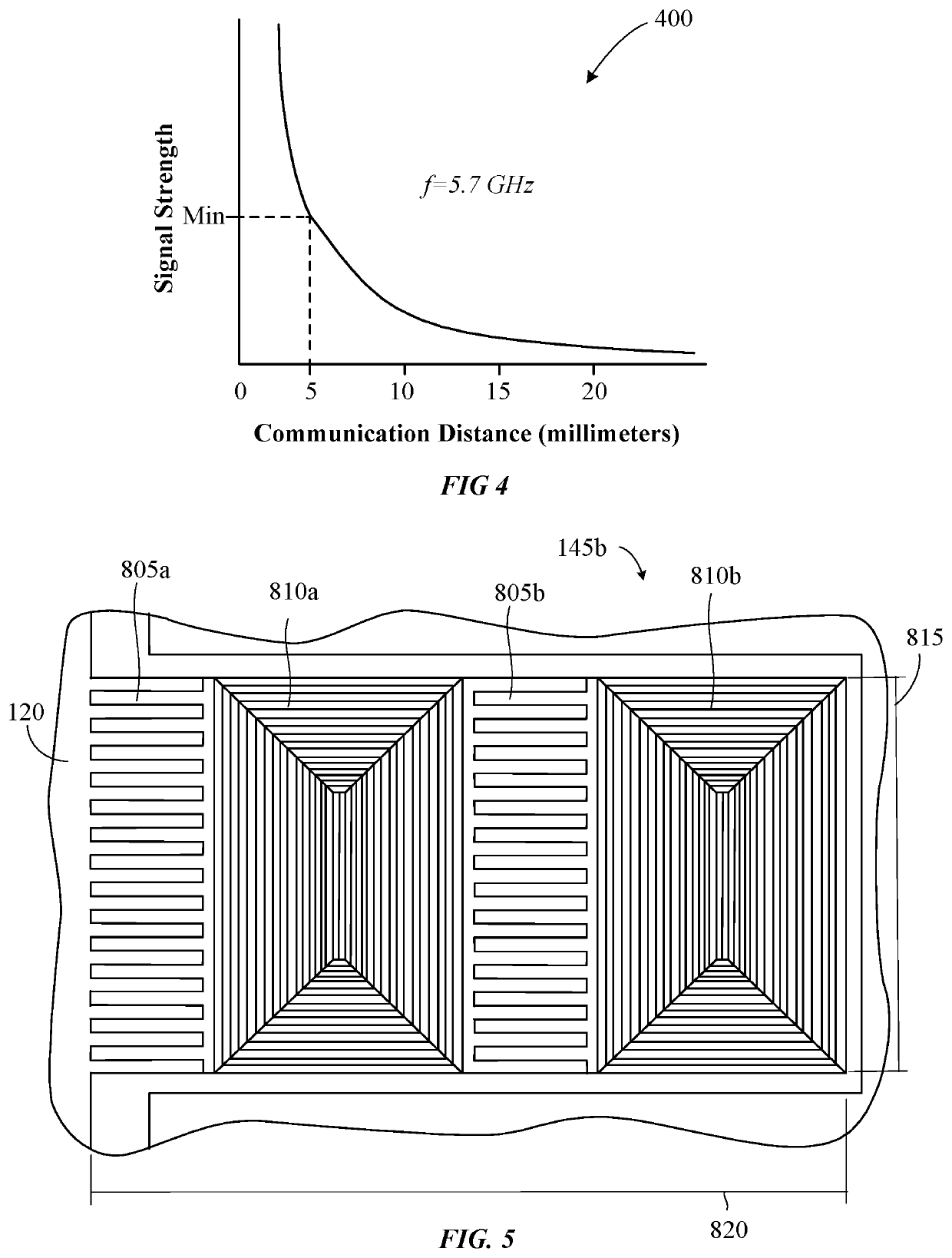

Metamaterial waveguides and shielded bridges for quantum circuits

Metamaterial waveguides and shielded bridges are employed to improve the scalability and routing of quantum computing circuits. A metamaterial waveguide includes a signal conductor that has a periodic array of lumped element resonators distributed along and electrically coupled to a signal conductor. The periodic array of lumped element resonator pairs defines a bandgap within an operating bandwidth of the waveguide. Qubits can communicate within the operating bandwidth of the waveguide and communications via the waveguide can be controlled by changing a center frequency of the qubits. A shielded bridge is used to cross over high frequency communications and control CPW's in a quantum computing circuit. The shielded bridge includes a signal bridge that is elevated and extends over a separate CPW, and a ground bridge positioned between the signal bridge and the separate CPW.

Owner:CALIFORNIA INST OF TECH

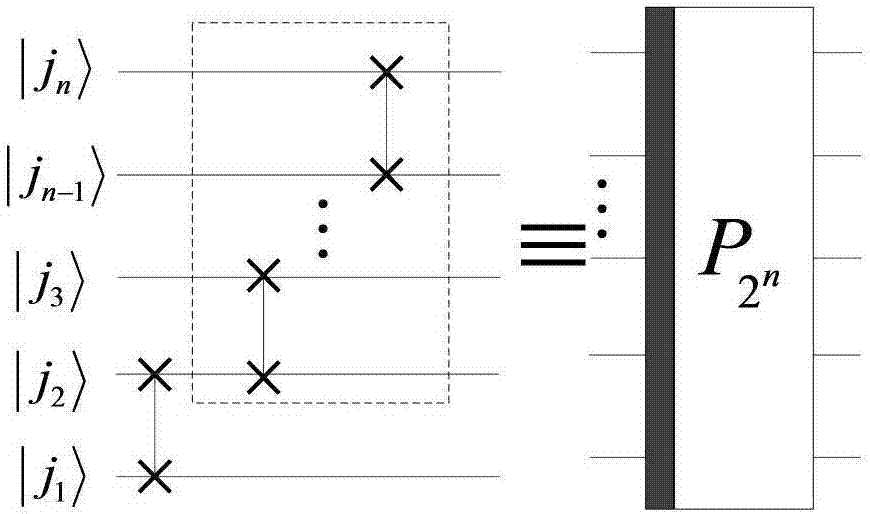

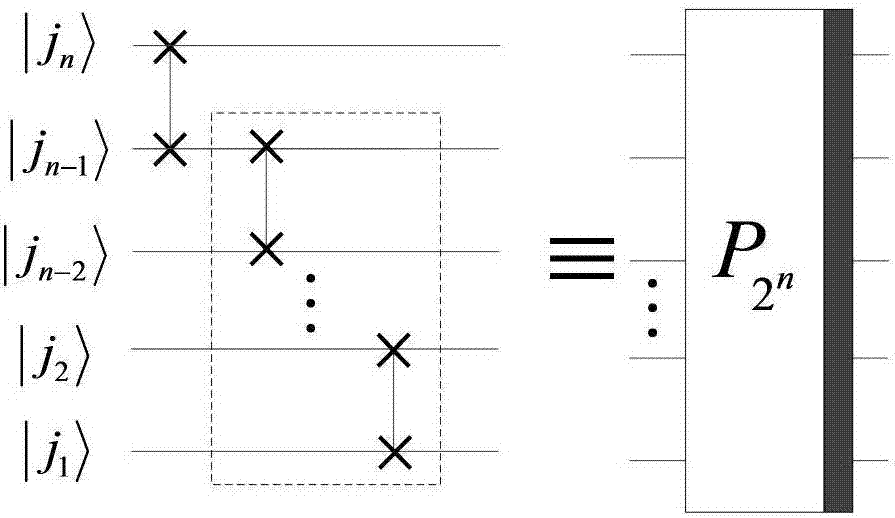

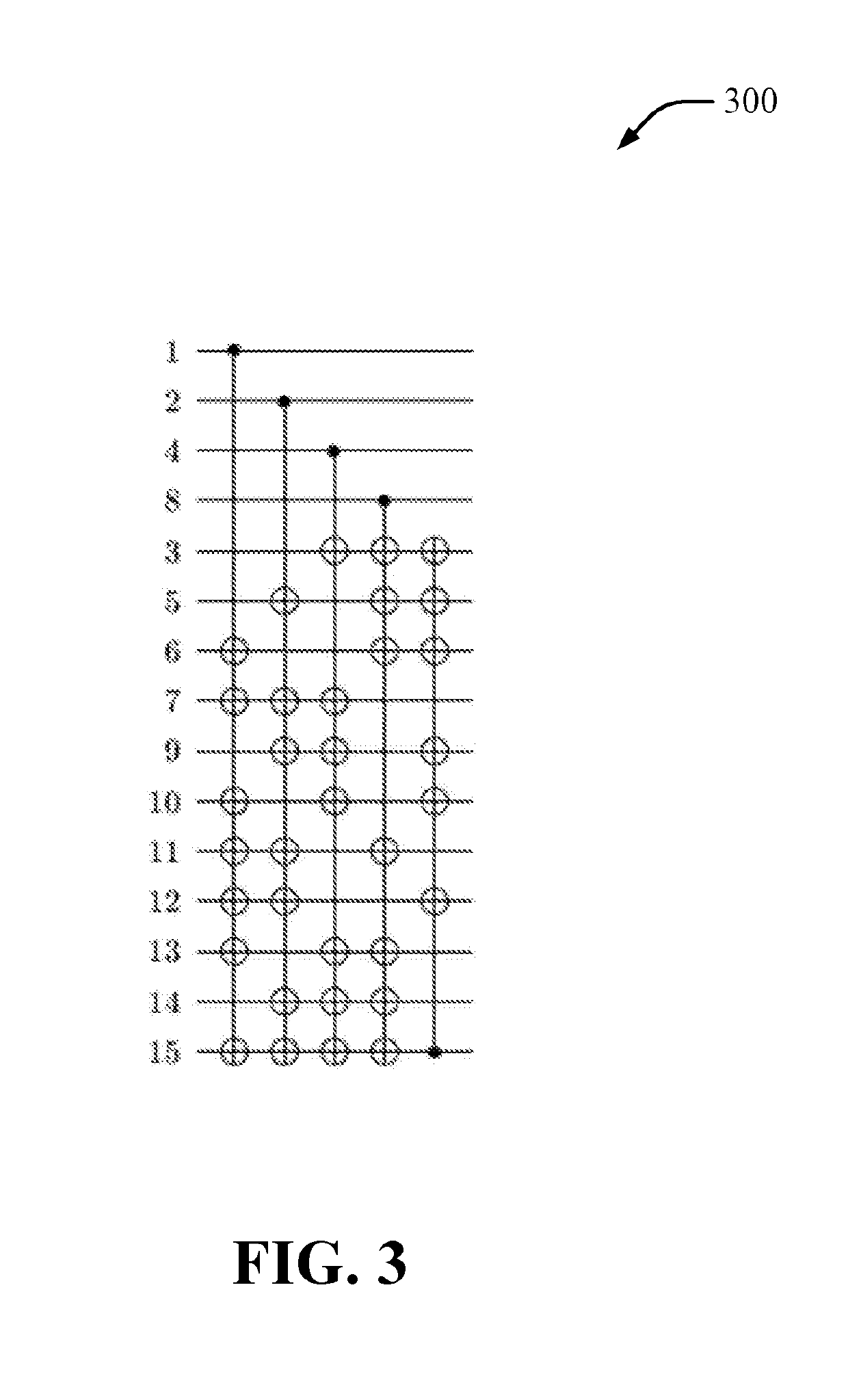

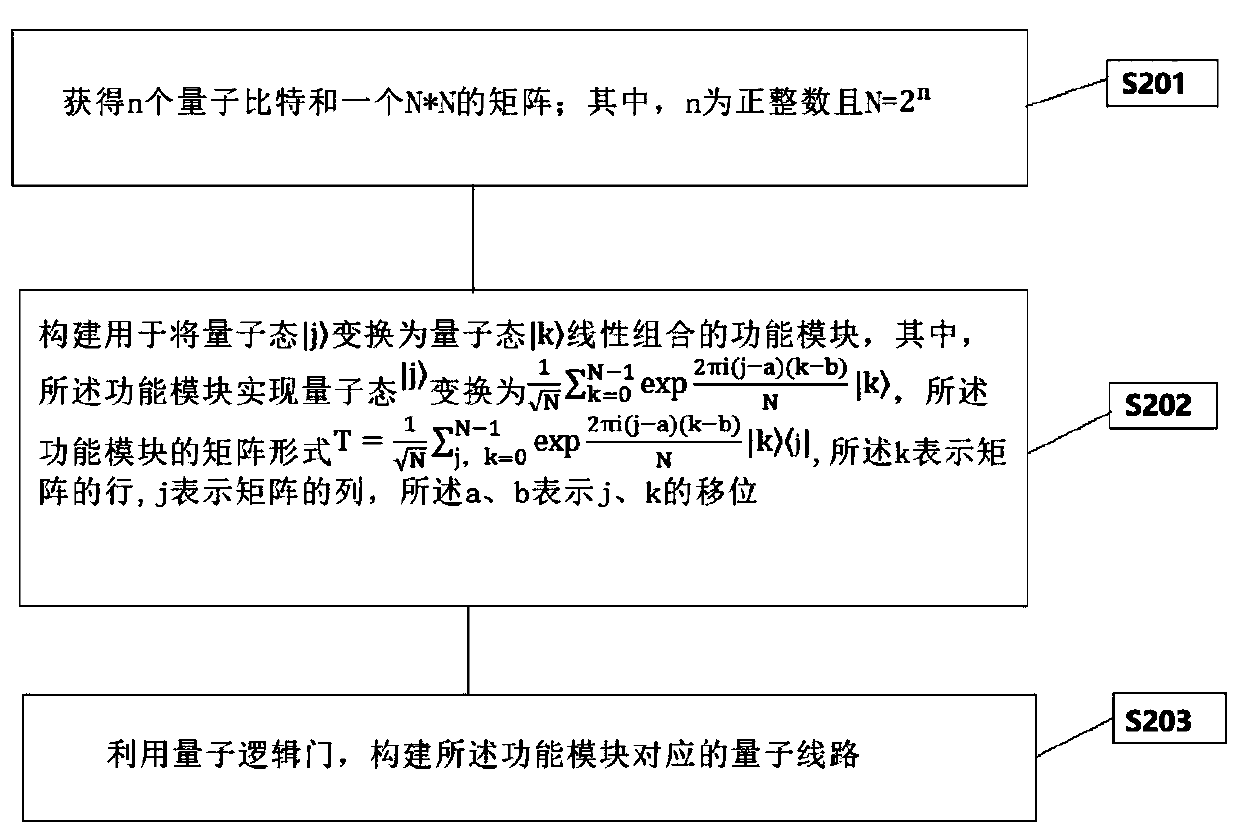

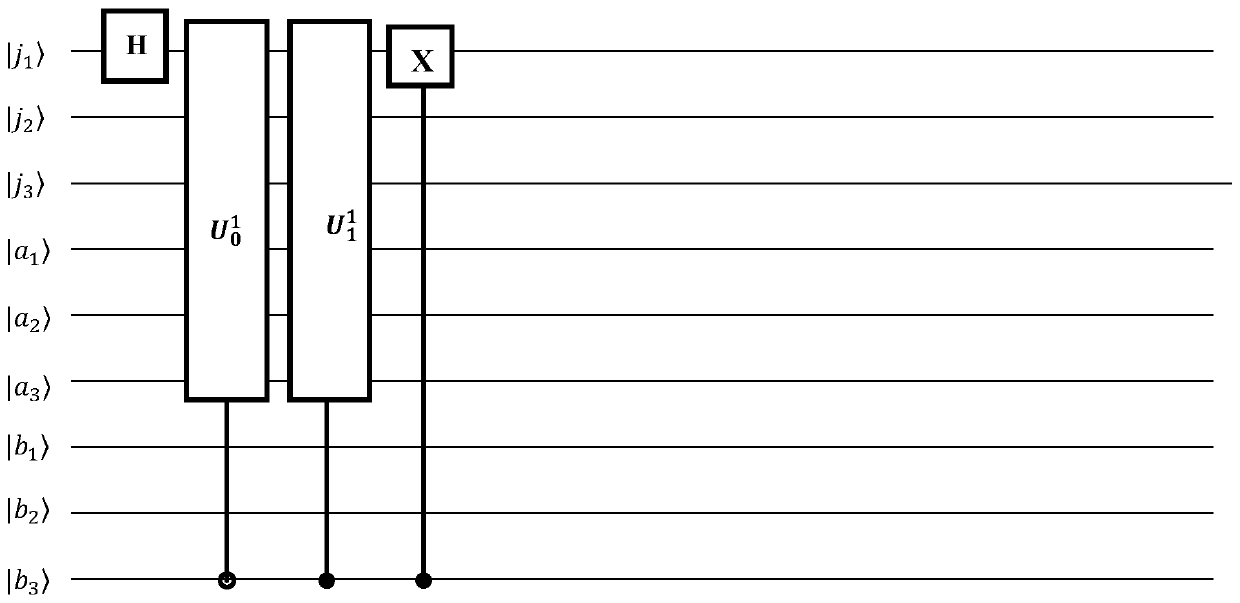

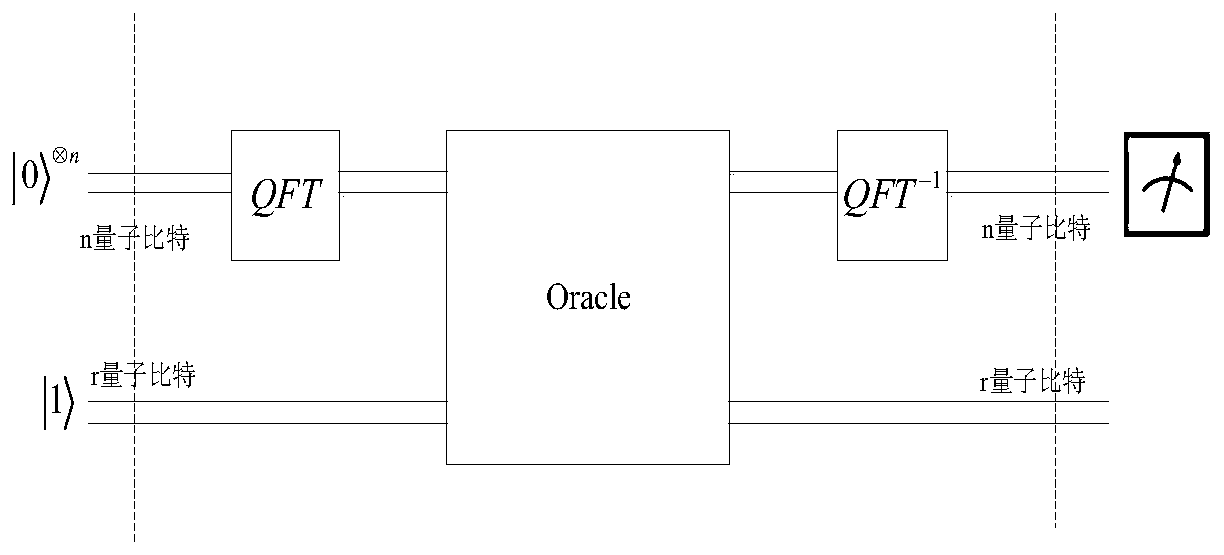

Method for realizing quantum circuit design through quantum Fourier transform

The invention provides a method for realizing quantum circuit design through quantum Fourier transform and belongs to the field of circuit design. A conventional quantum Fourier transform implementation technology is perfected and improved with the method due to the fact that a Bit Reverse circuit is absent in conventional quantum Fourier transform implementation circuits. Four quantum Fourier transform implementation circuits are constructed by an extended tensor product and basic quantum bit gates including quantum bit controlled gates and single quantum bit gates; on the basis of analysis for complexity of the quantum Fourier transform implementation circuits, complexity of the four quantum Fourier transform implementation circuits is theta(n<2>) in terms of a data set comprising 2<n> elements, which cannot be achieved by any other classic fast Fourier transform. The method is suitable for many application fields of actual information processing, for instance, efficient Fourier transform is required for algorithms of image compression, denoising, encryption, decryption and the like, and the method has great significance in perfection of the quantum computing theory and popularization of application.

Owner:GUANGXI NORMAL UNIV

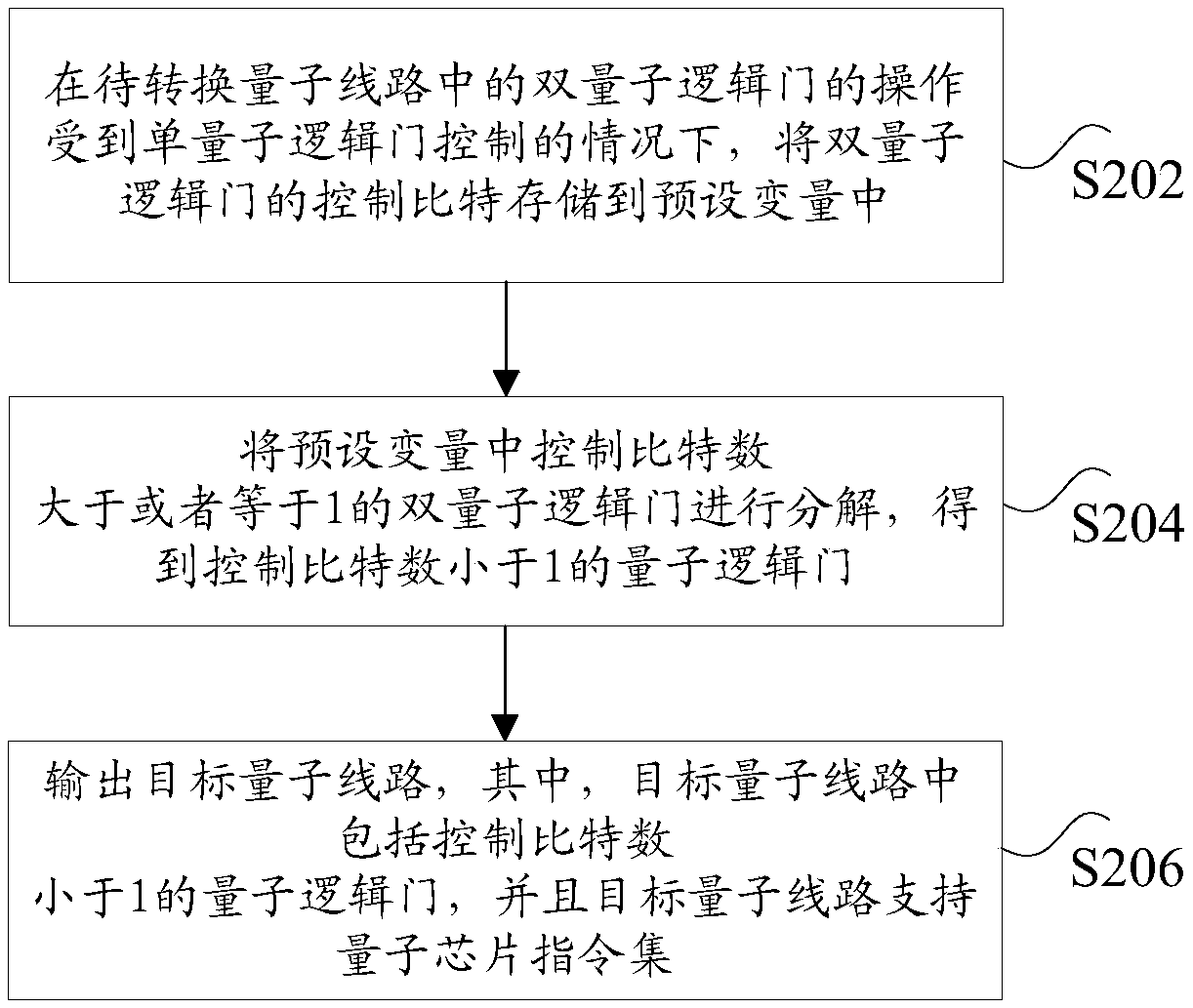

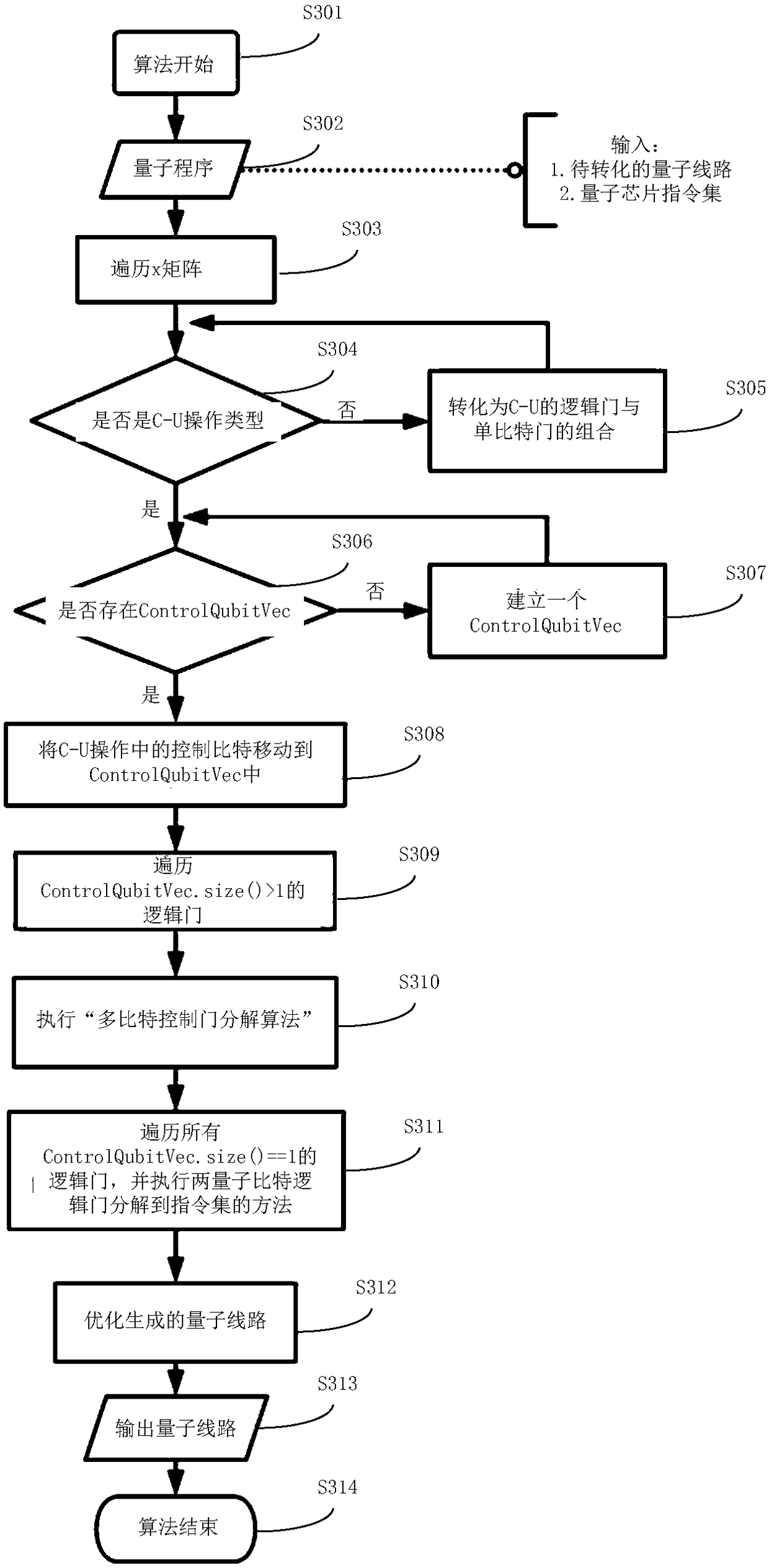

Processing method and device of a quantum circuit, storage medium and electronic device

InactiveCN109165741ATroubleshoot technical issues with conversionQuantum computersQuantum circuitLogic gate

The invention discloses a processing method and device of a quantum circuit, a storage medium and an electronic device. The method comprises the following steps: when the operation of the double quantum logic gates in the quantum circuit to be converted is controlled by a single quantum logic gate, the control bits of the double quantum logic gates are stored in a preset variable; a double quantumlogic gate whose control bit number is greater than or equal to 1 in a preset variable is decomposed to obtain a quantum logic gate whose control bit number is less than 1; a target quantum circuit is output, wherein the target quantum circuit includes a quantum logic gate having a control number of bits less than 1, and the target quantum circuit supports a quantum chip instruction set. The invention solves the technical problem that the two-bit logic gate of the quantum circuit cannot be converted in the related art.

Owner:ORIGIN QUANTUM COMPUTING TECH (HEFEI) CO LTD

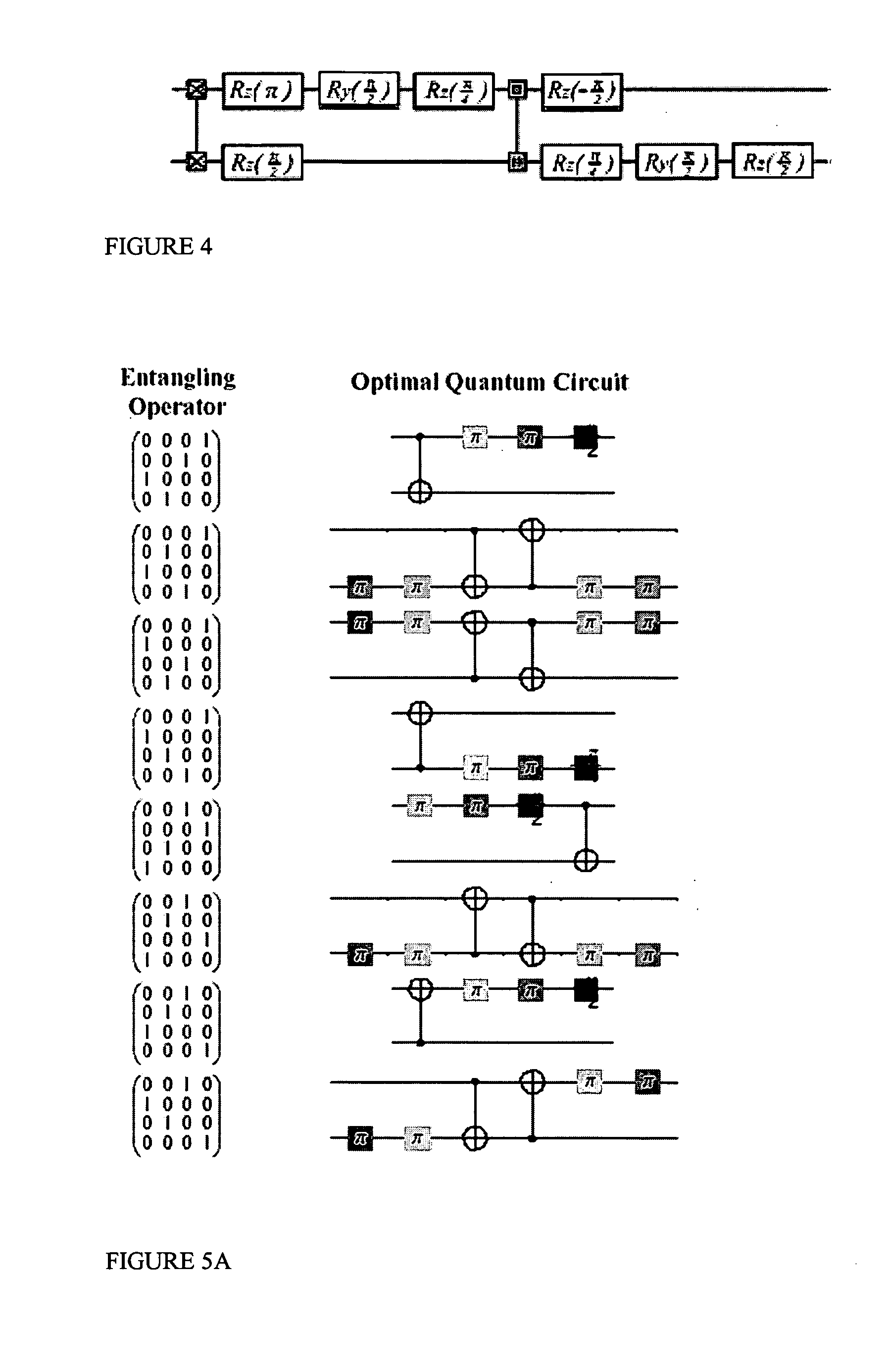

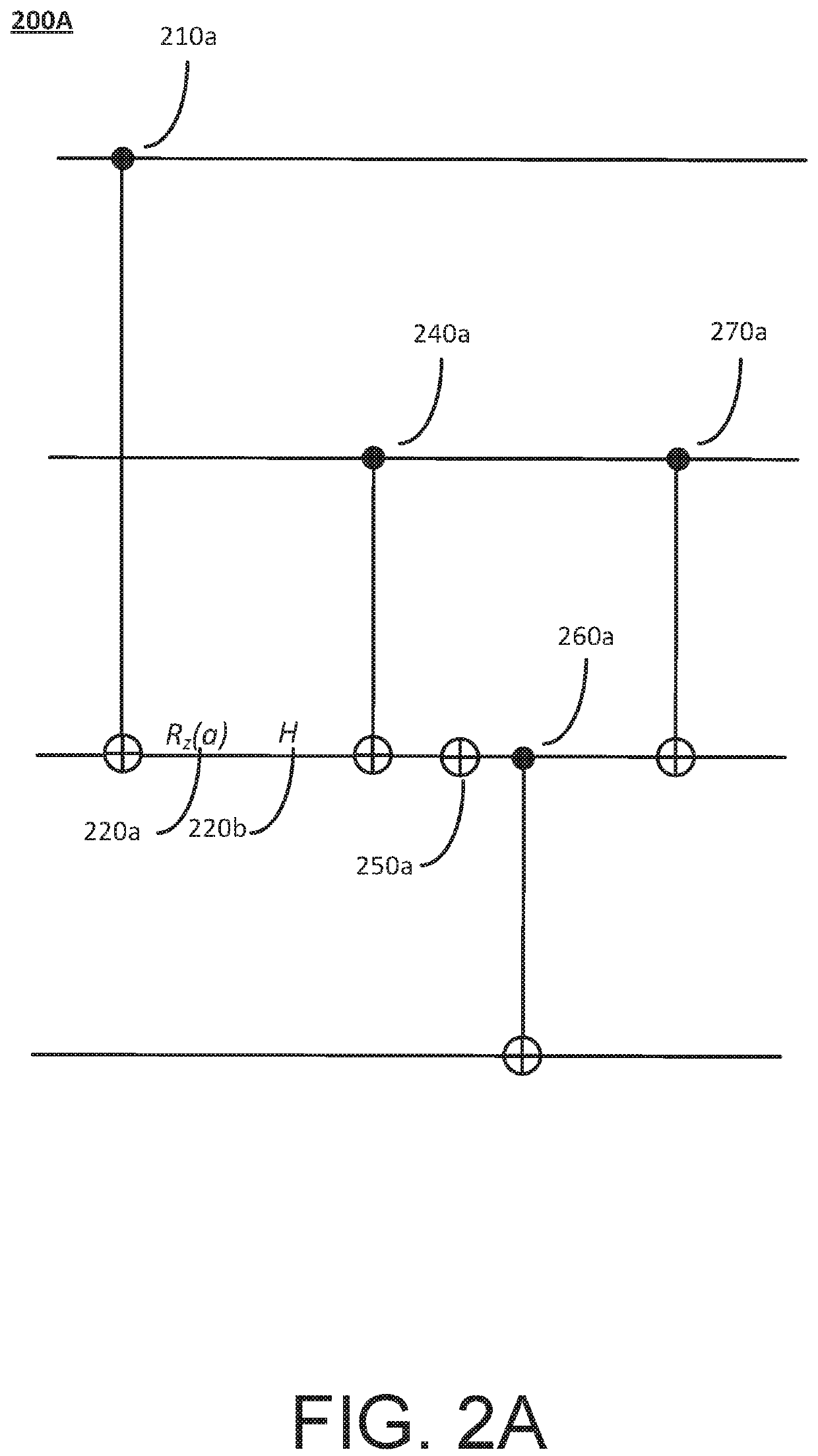

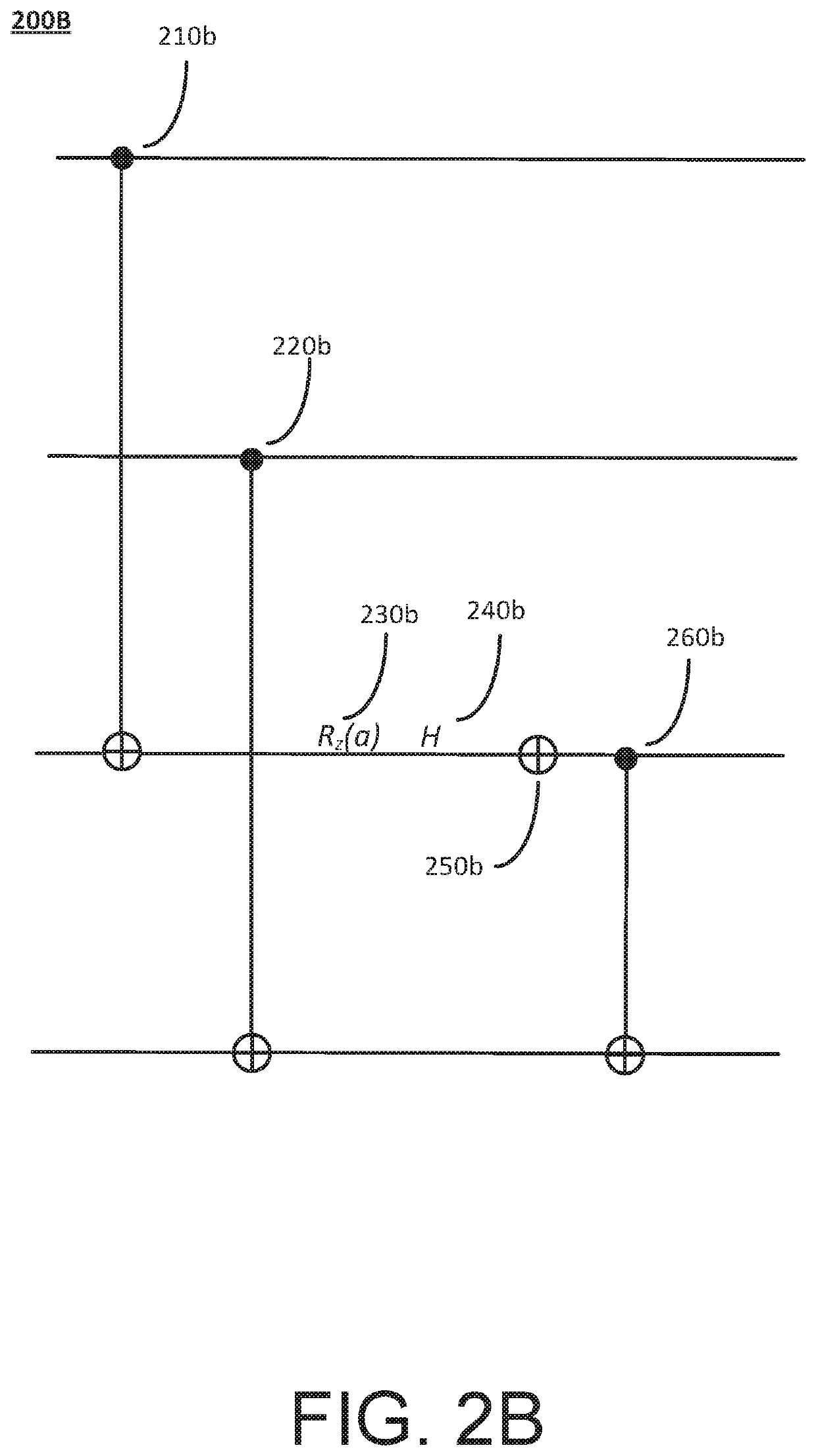

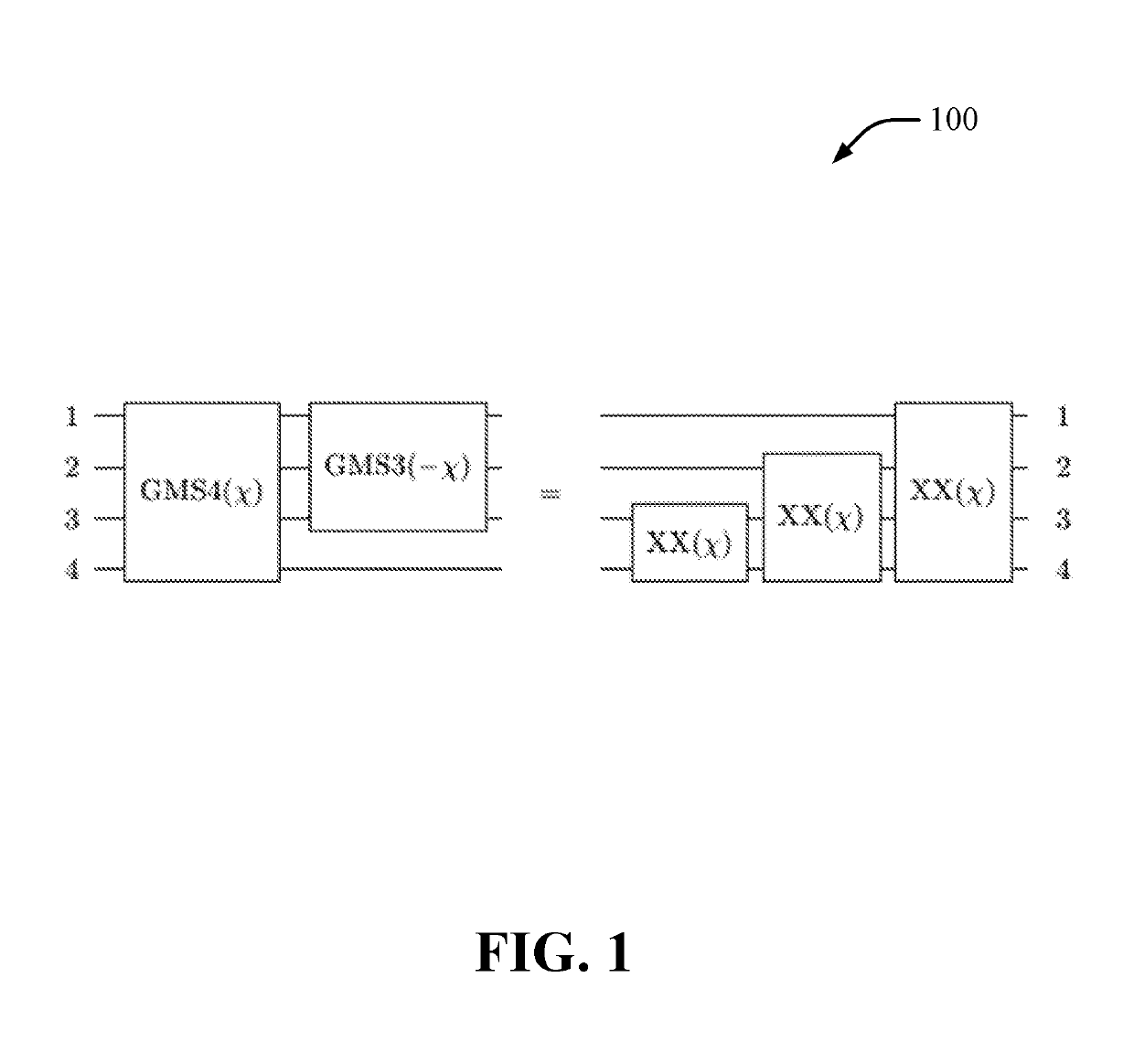

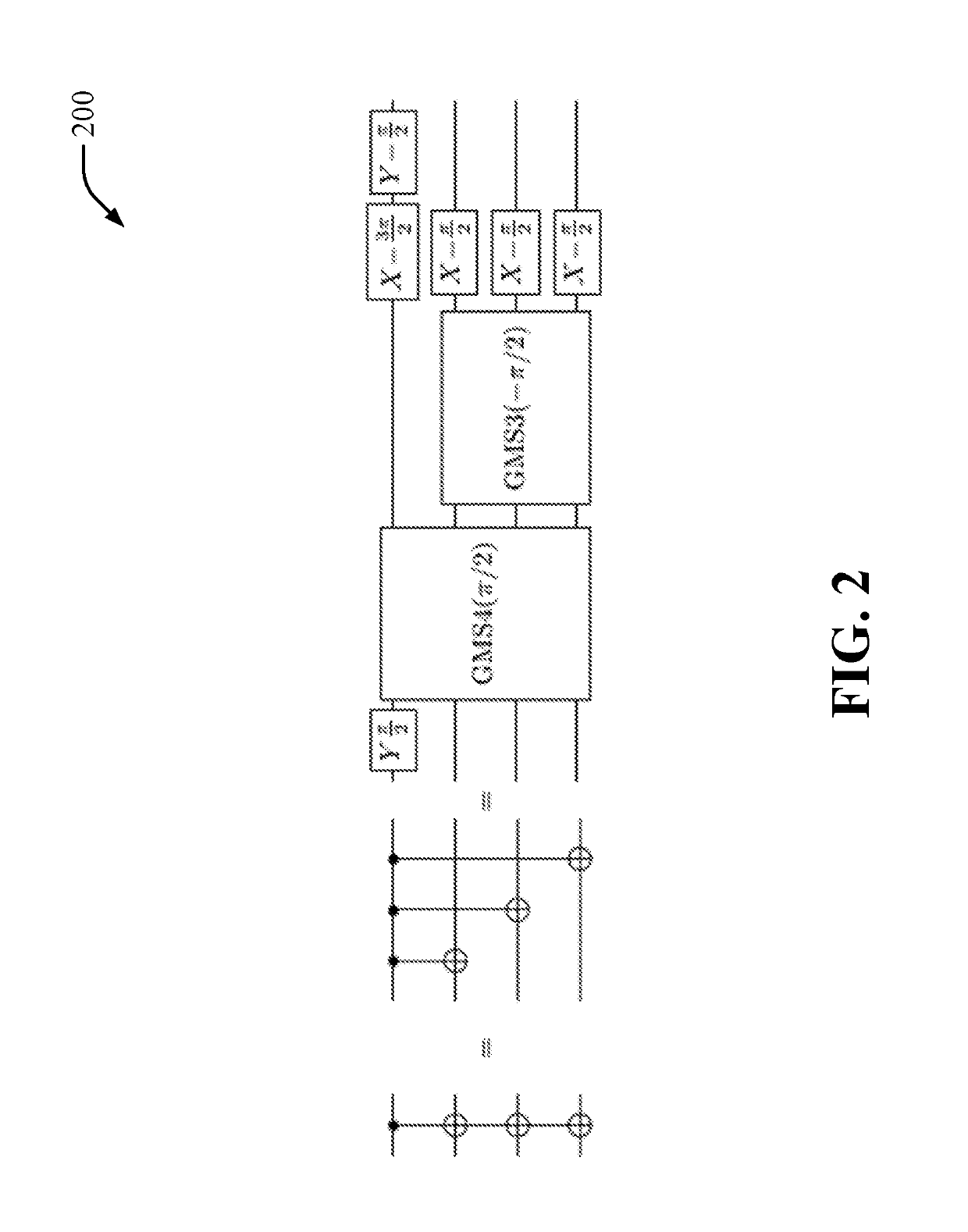

Use of global interactions in efficient quantum circuit constructions

ActiveUS20190205783A1Improve accessibilityEasy to useQuantum computersSingle instruction multiple data multiprocessorsQuantum Fourier transformQuantum circuit

The disclosure describes various aspects of techniques for using global interactions in efficient quantum circuit constructions. More specifically, this disclosure describes ways to use a global entangling operator to efficiently implement circuitry common to a selection of important quantum algorithms. The circuits may be constructed with global Ising entangling gates (e.g., global Mølmer-Sørenson gates or GMS gates) and arbitrary addressable single-qubit gates. Examples of the types of circuits that can be implemented include stabilizer circuits, Toffoli-4 gates, Toffoli-n gates, quantum Fourier transformation (QTF) circuits, and quantum Fourier adder (QFA) circuits. In certain instances, the use of global operations can substantially improve the entangling gate count.

Owner:UNIV OF MARYLAND +1

Quantum circuit construction method and device

PendingCN111582491ASolve simulation problemsQuantum computersEnergy efficient computingQuantum circuitEngineering

Owner:ORIGIN QUANTUM COMPUTING TECH (HEFEI) CO LTD

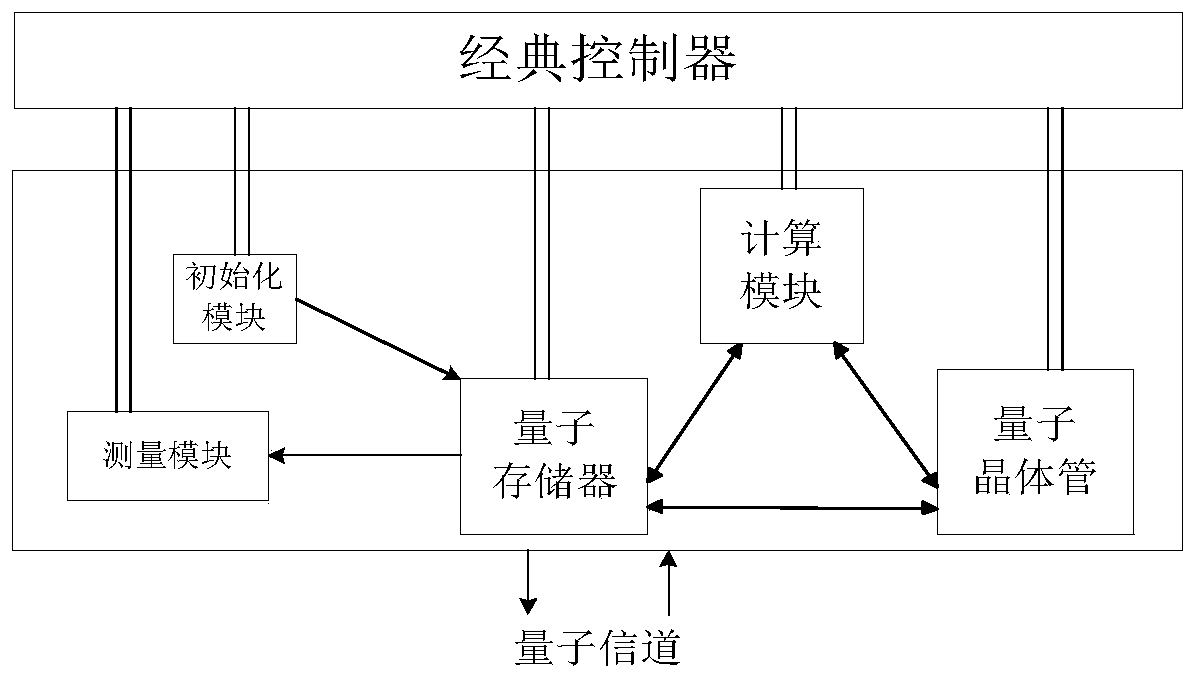

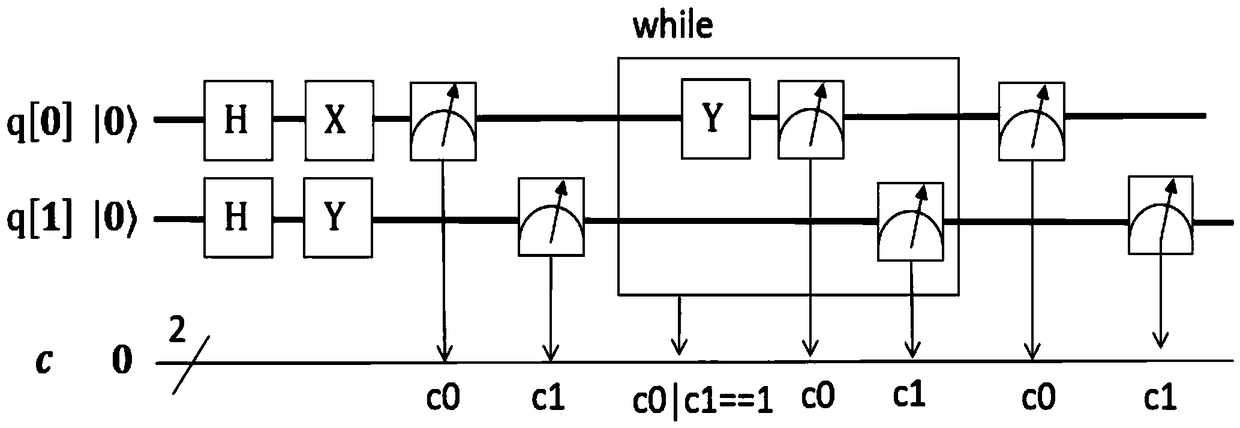

Quantum computer quantum processing unit, quantum circuit and quantum circuit quantum algorithm

ActiveCN110490327AAchieve performanceGuaranteed cycle lookupQuantum computersEnergy efficient computingQuantum circuitDecomposition

The invention relates to a quantum computer quantum processing unit, a quantum circuit and a quantum circuit quantum algorithm, and belongs to the technical field of computers. The quantum processingunit (QPU) is composed of five modules and is controlled by a classic device. The quantum circuit defines two n quantum bit inputs |x) and |y) based on an SHOR algorithm. A control register and a target register are arranged. Gates Gc, G'c and Gt are defined for each algorithm. The quantum circuit quantum algorithm is a design scheme of a quantum processing architecture based on a Shor algorithm.The influence of feedback control on the proposed architecture is considered. The period searching during large number decomposition can be effectively ensured by utilizing feedback adjustment, so that the optimal performance of the quantum algorithm is effectively realized.

Owner:HUBEI UNIV OF TECH

Data processing method and device based on quantum circuit, electronic equipment and medium

PendingCN113496285ASave resourcesQuick extractionQuantum computersCharacter and pattern recognitionHemt circuitsEngineering

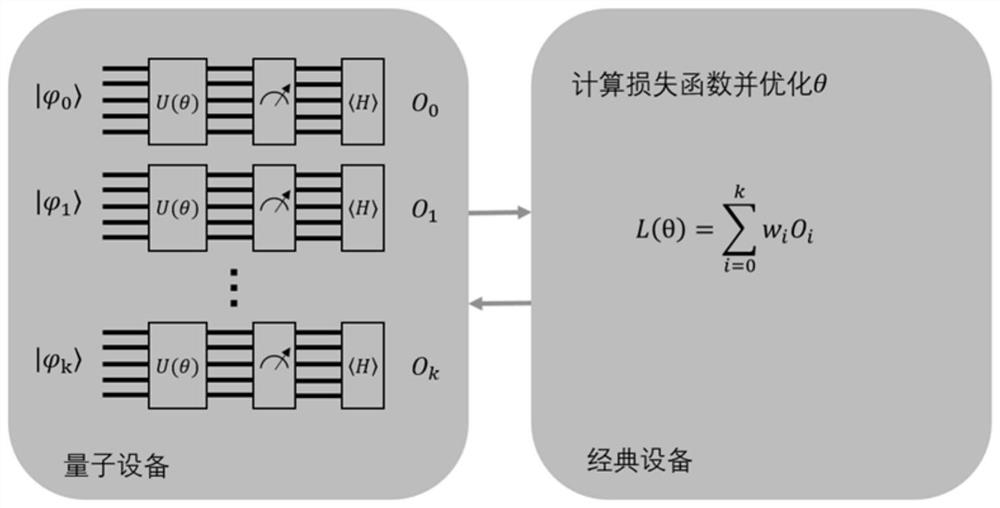

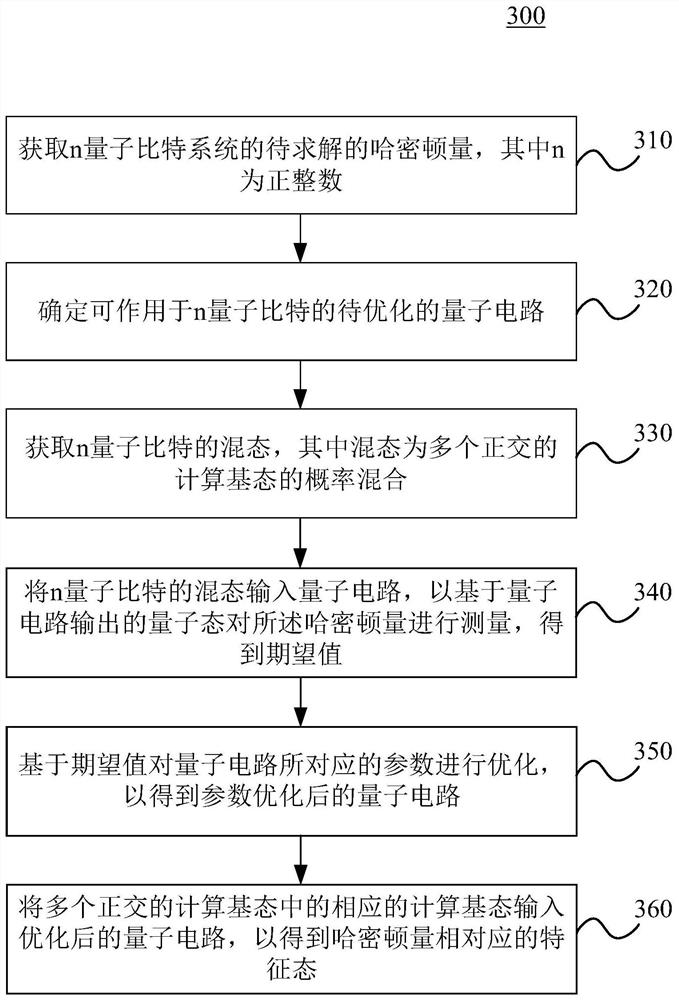

The invention provides a data processing method and device based on a quantum circuit, electronic equipment, a computer readable storage medium and a computer program product, and relates to the field of quantum computing, in particular to the technical field of data processing. According to the implementation scheme, the method includes obtaining a to-be-solved Hamiltonian of an n quantum bit system, wherein n is a positive integer; determining a to-be-optimized quantum circuit capable of acting on the n quantum bits; obtaining a mixed state of n quantum bits, wherein the mixed state is a probability mixture of a plurality of orthogonal calculation ground states; inputting the mixed state of the n quantum bits into a quantum circuit, and measuring the Hamiltonian based on the quantum state output by the quantum circuit to obtain an expected value; optimizing the parameters corresponding to the quantum circuit based on the expected value to obtain the quantum circuit after parameter optimization; and inputting a corresponding calculation ground state in a plurality of orthogonal calculation ground states into the optimized quantum circuit to obtain a characteristic state corresponding to the Hamiltonian.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

Data structure representing quantum program

InactiveCN109063844AEasy to useImprove development efficiencyComputing modelsRelevant informationQuantum circuit

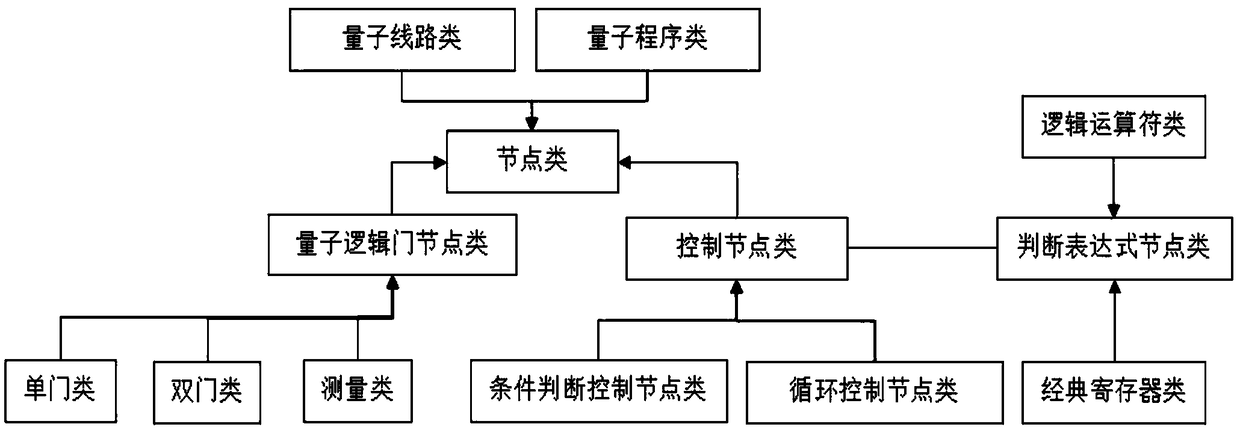

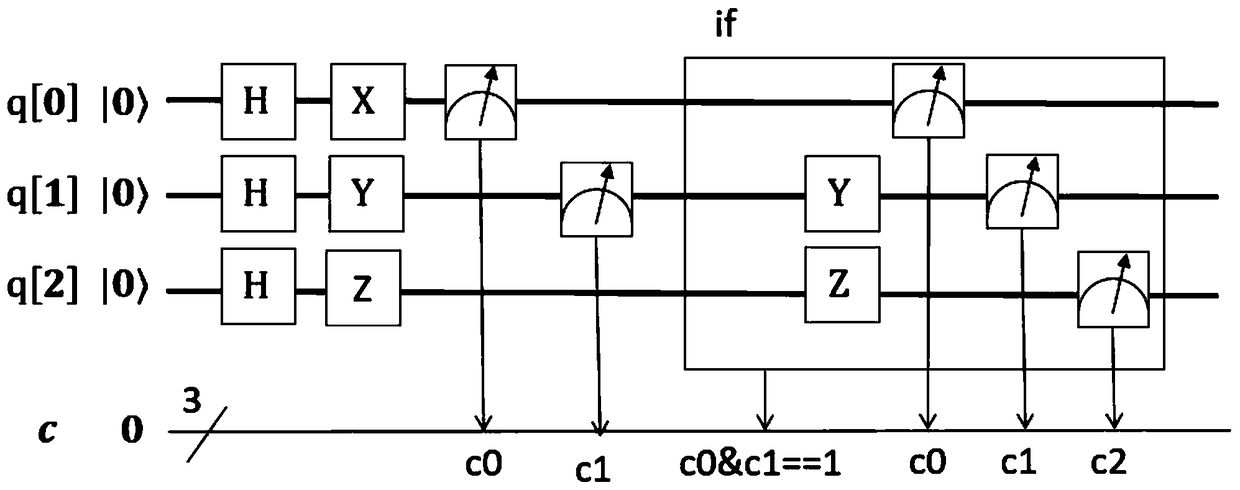

The invention discloses a data structure representing a quantum program, the data structure includes: quantum circuit class, quantum program class, Node Class, Quantum Logic Gate Node Class, Control node class, Determine Expression Node Class, the quantum circuit class is used for storing a set of quantum logic gates using a container, the quantum program class is used for storing a set of node classes using a container, The node class is a quantum circuit class, a quantum program class, a quantum logic gate node class, and a parent class of the control node class. The quantum logic gate nodeclass is used for storing the qubits of the operation of the quantum logic gate, the unitary matrix corresponding to the quantum logic gate, and the judgment expression node class is used for storingthe related information of the judgment expression. The invention has the advantages that the execution sequence of the recordable quantum instructions, the reusable quantum circuit, the condition judgment expression input by the developer can be recorded by the control node type, and finally the executable quantum circuit of the quantum program can be judged according to the final result.

Owner:ORIGIN QUANTUM COMPUTING TECH (HEFEI) CO LTD

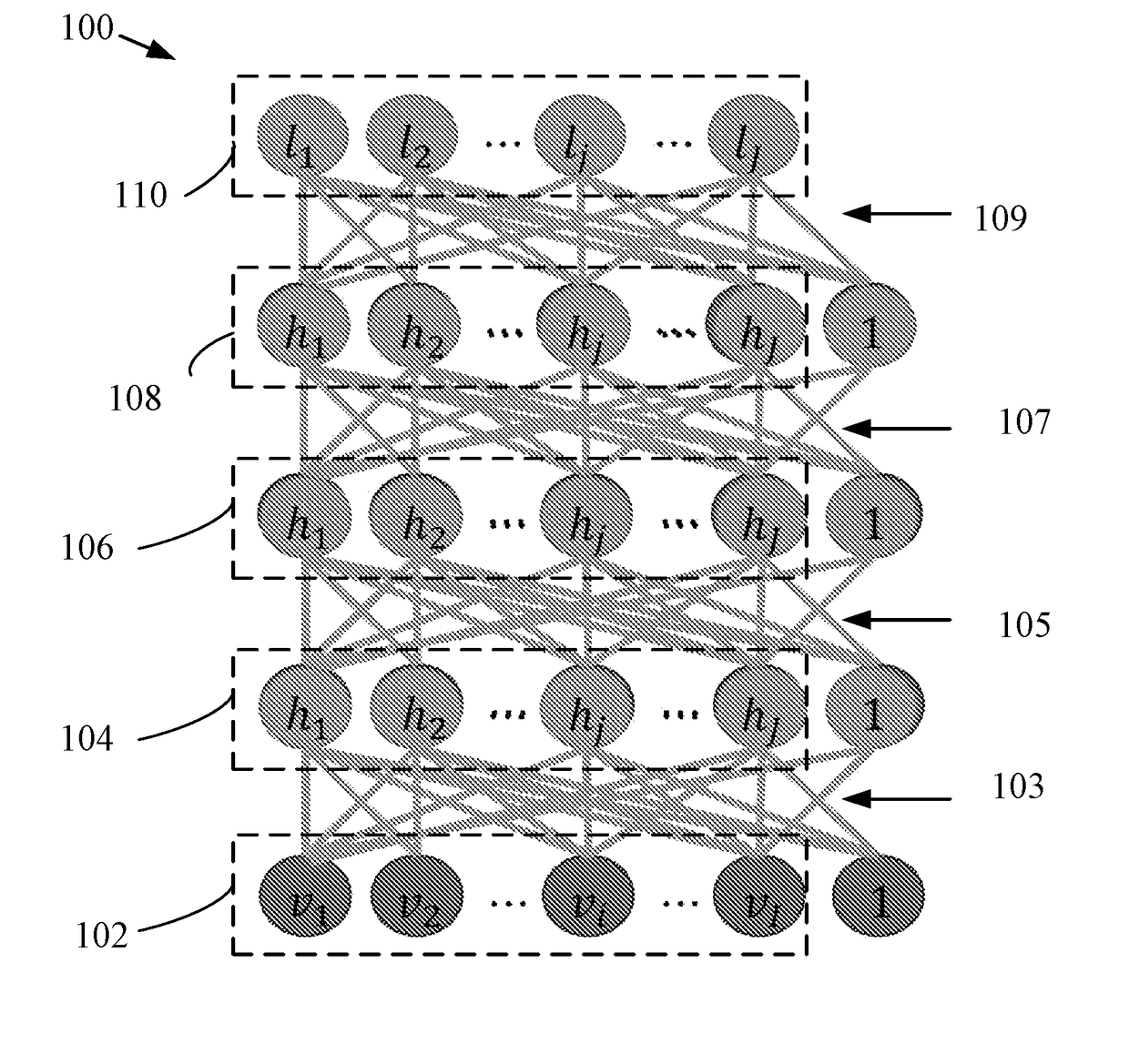

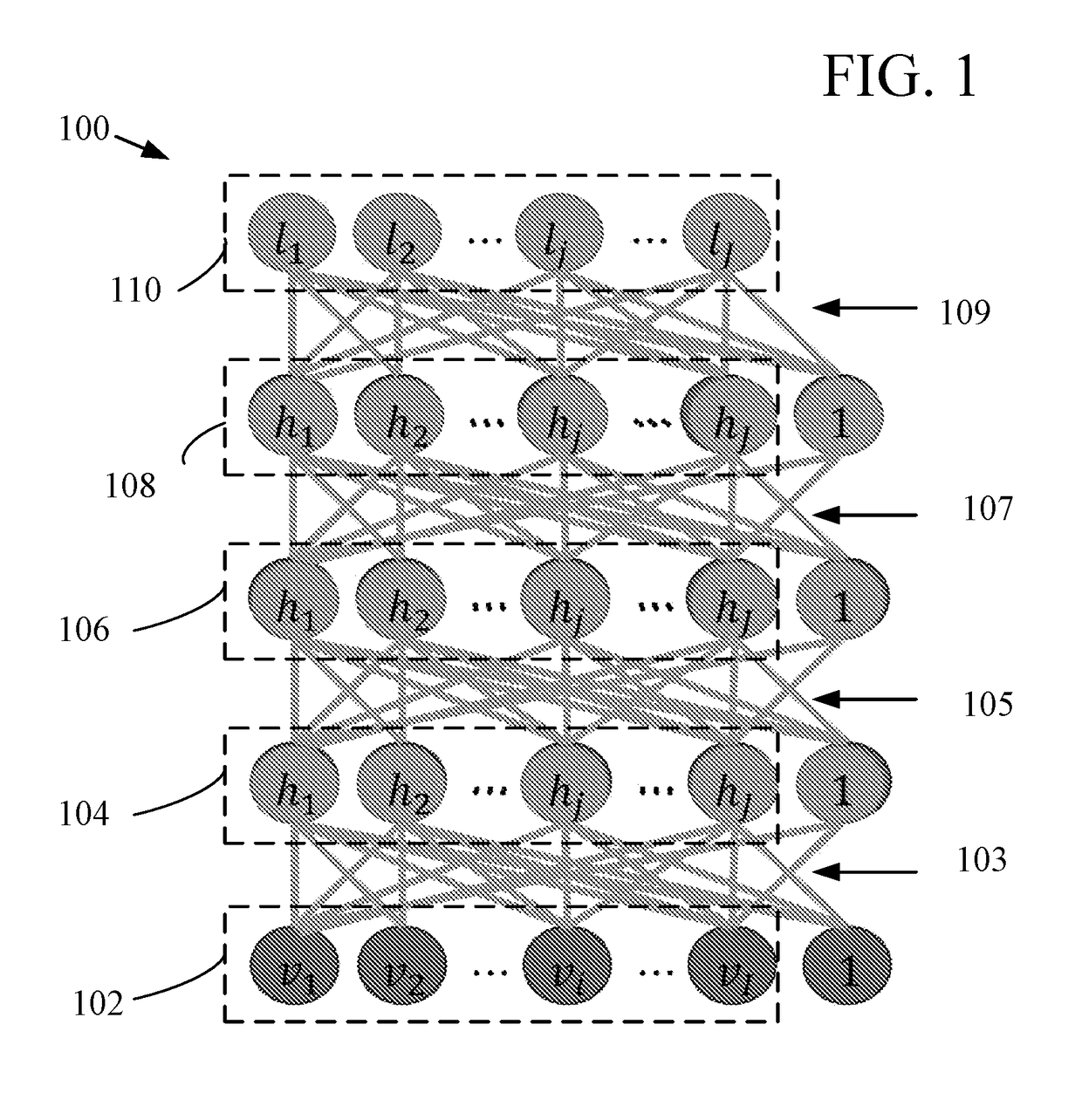

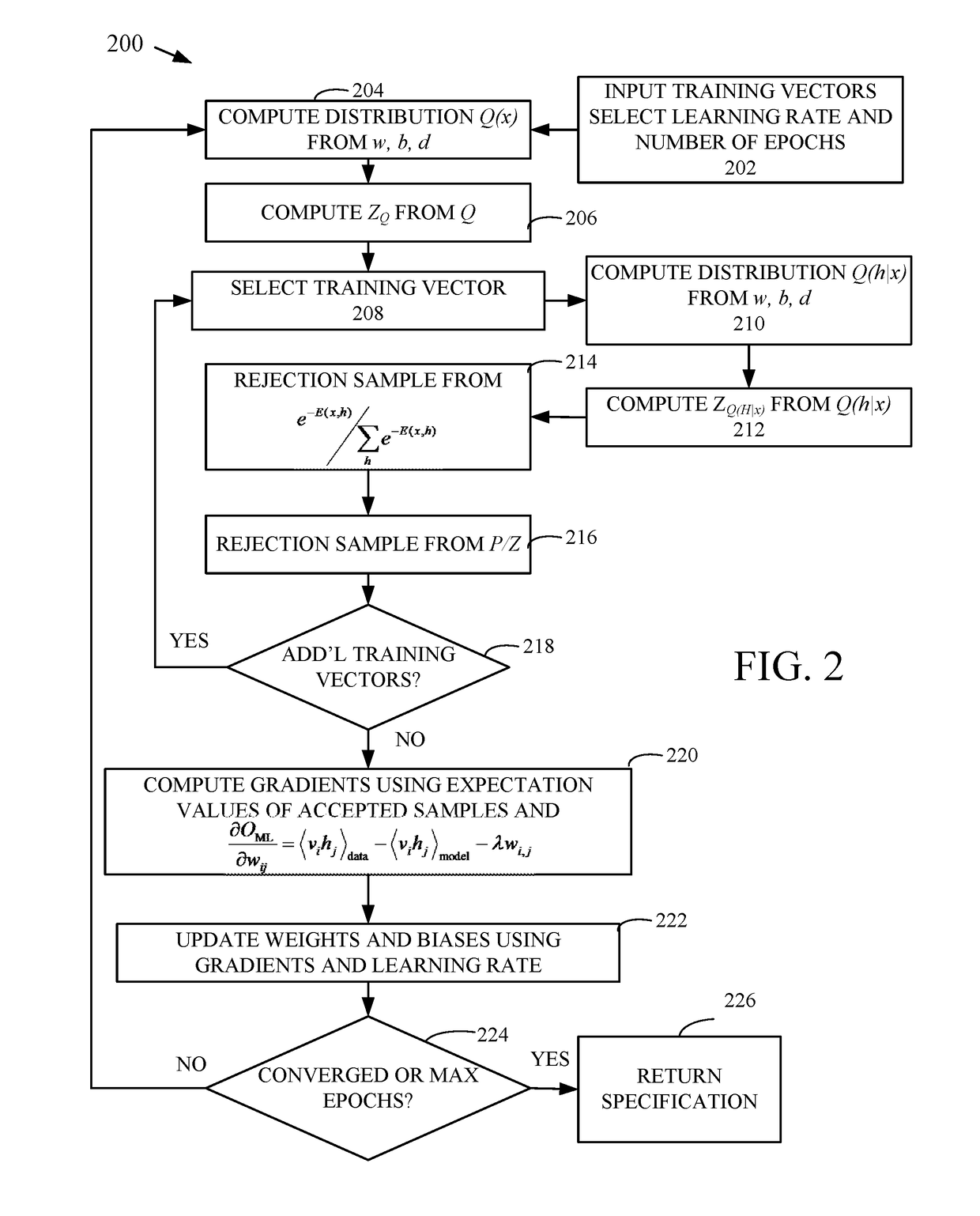

Fast low-memory methods for bayesian inference, gibbs sampling and deep learning

InactiveUS20180137422A1Easy to sampleQuantum computersCharacter and pattern recognitionQuantum circuitGibbs sampling

Methods of training Boltzmann machines include rejection sampling to approximate a Gibbs distribution associated with layers of the Boltzmann machine. Accepted sample values obtained using a set of training vectors and a set of model values associate with a model distribution are processed to obtain gradients of an objective function so that the Boltzmann machine specification can be updated. In other examples, a Gibbs distribution is estimated or a quantum circuit is specified so at to produce eigenphases of a unitary.

Owner:MICROSOFT TECH LICENSING LLC

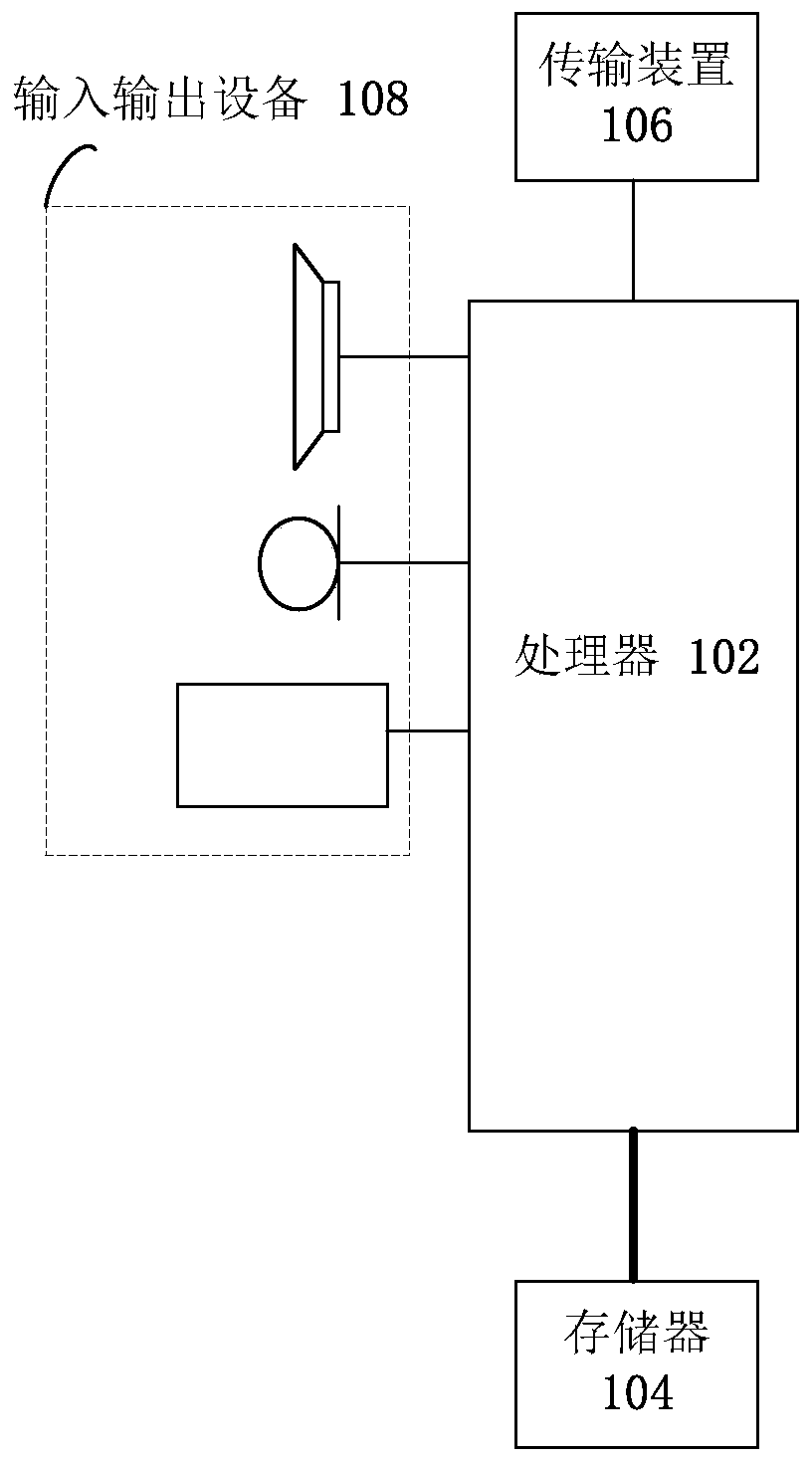

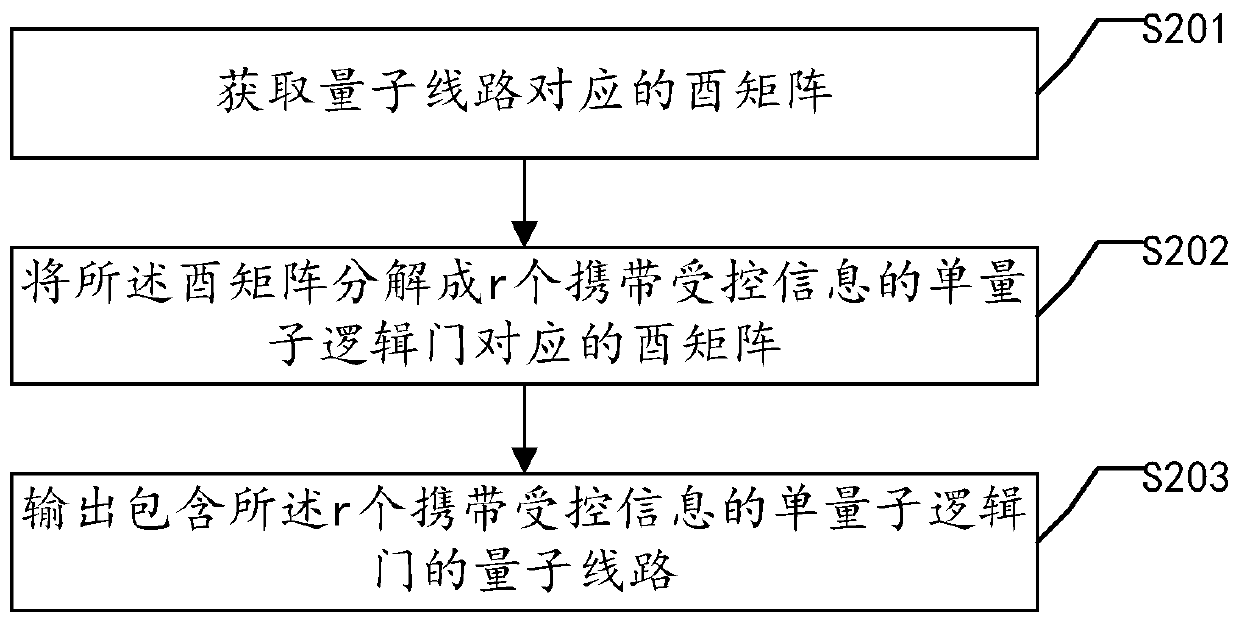

Quantum circuit decomposition method and device, storage medium and electronic device

PendingCN111563599AImprove Simulation EfficiencyReduce occupancyQuantum computersEnergy efficient computingQuantum circuitEngineering

The invention discloses a quantum circuit decomposition method and device, a storage medium and an electronic device. The method comprises the steps of obtaining a unitary matrix U corresponding to aquantum circuit, wherein the order N of the unitary matrix is equal to 2n, and n is the total number of quantum bits contained in the quantum circuit; decomposing the unitary matrix U into r unitary matrixes corresponding to single quantum logic gates carrying controlled information, wherein Ur... Ui... U1U = IN, Ui is a unitary matrix corresponding to the ith single quantum logic gate carrying the controlled information, i is greater than or equal to 1 and less than or equal to r, and IN is an N-order unit matrix; and outputting a quantum circuit containing the r single quantum logic gates carrying the controlled information. By utilizing the embodiment of the invention, the calculation amount of the quantum circuit can be reduced, the simulation efficiency of the quantum circuit is improved, and the occupation of hardware resources is reduced.

Owner:ORIGIN QUANTUM COMPUTING TECH (HEFEI) CO LTD

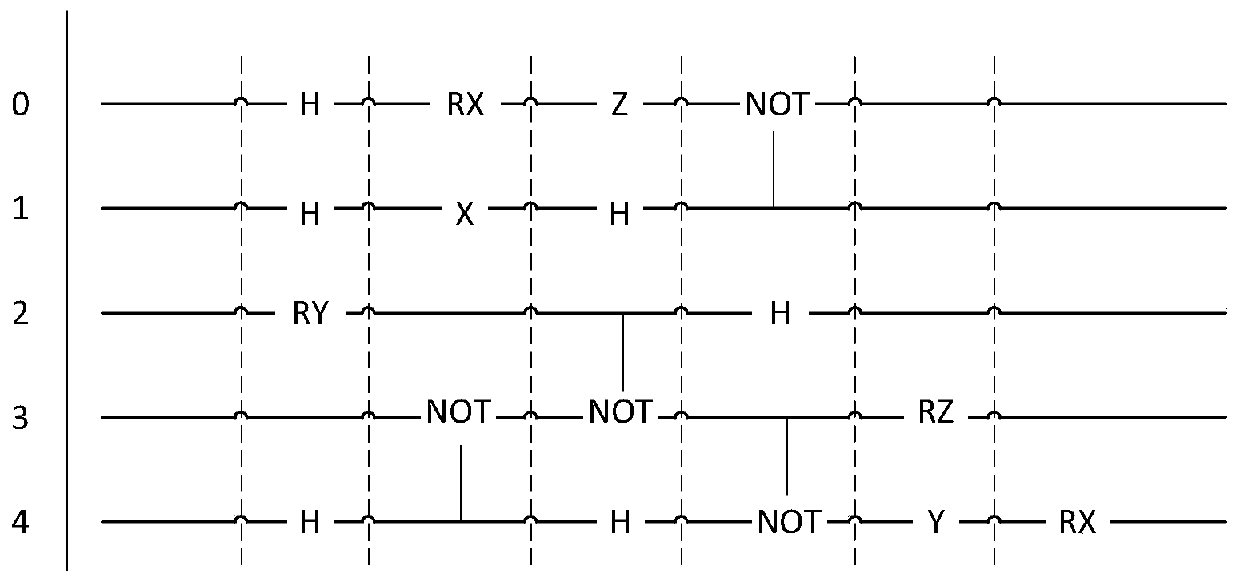

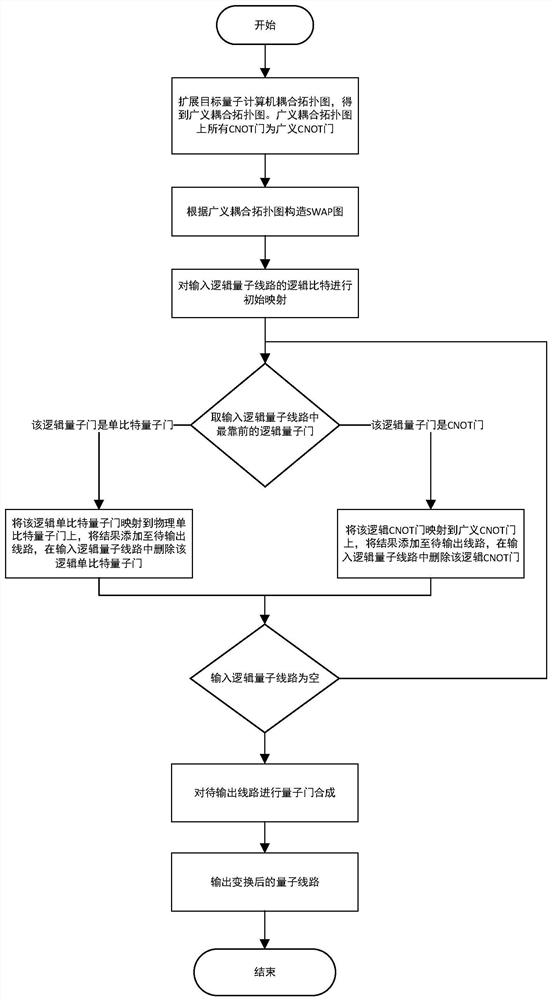

A circuit transformation method for quantum compilation

The invention discloses a circuit transformation method for quantum compilation. The circuit transformation method comprises the steps of expanding a target quantum computer coupling topological graphto obtain a generalized coupling topological graph; constructing an SWAP graph according to the generalized coupling topological graph; carrying out initial mapping on logic bits in an input logic quantum circuit; taking a logic quantum gate at the top in the input logic quantum circuit; mapping a logic CNOT gate to a generalized CNOT gate, and mapping a logic single-bit quantum gate to a physical single-bit quantum gate; performing quantum gate synthesis on the to-be-output circuit to obtain a converted quantum circuit. The method can be executed on a target quantum computer, and the fidelity of the converted quantum circuit is improved.

Owner:SOUTHEAST UNIV

Design and realization method of array multiplier based on reversible 'ZS' series gate

InactiveCN101923457AFast addition operationRegularComputation using non-contact making devicesLogic gateQuantum system

The invention relates to a design and realization method of an array multiplier based on the reversible 'ZS' series of gates. The method establishes a one-to-one relationship between the reversible definitions in a quantum computer and the inputs or outputs in a truth table and designs a series of reversible logic gates-'ZS1', 'ZS2' and 'ZS3' gates, which have the one-to-one relationship with theinputs or outputs in the truth table, and a quantum circuit diagram of the series of gates only containing double-quantum bit controlled gate and single bit gate. The method is based on Toffoli gate and designs three adding circuits which receive different symbol inputs and obtain the corresponding symbol outputs; the method is based on the 'ZS' series of gates and designs a multiplication circuit structure with the best reversible optimization, namely a quantum array multiplier. The reversible array multiplier can adopt a method similar to the manual calculation to complete the multiply operation with symbolic number in a higher computing speed; and the regularity of the internal structure is high and the internal structure is easy to extend. The design and realization method of the invention is applicable to the circuit design and application of the quantum system and realizes a certain promotion to the design and realization of the quantum large scale integrated circuits.

Owner:EAST CHINA JIAOTONG UNIVERSITY