Patents

Literature

196 results about "Quantum error correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

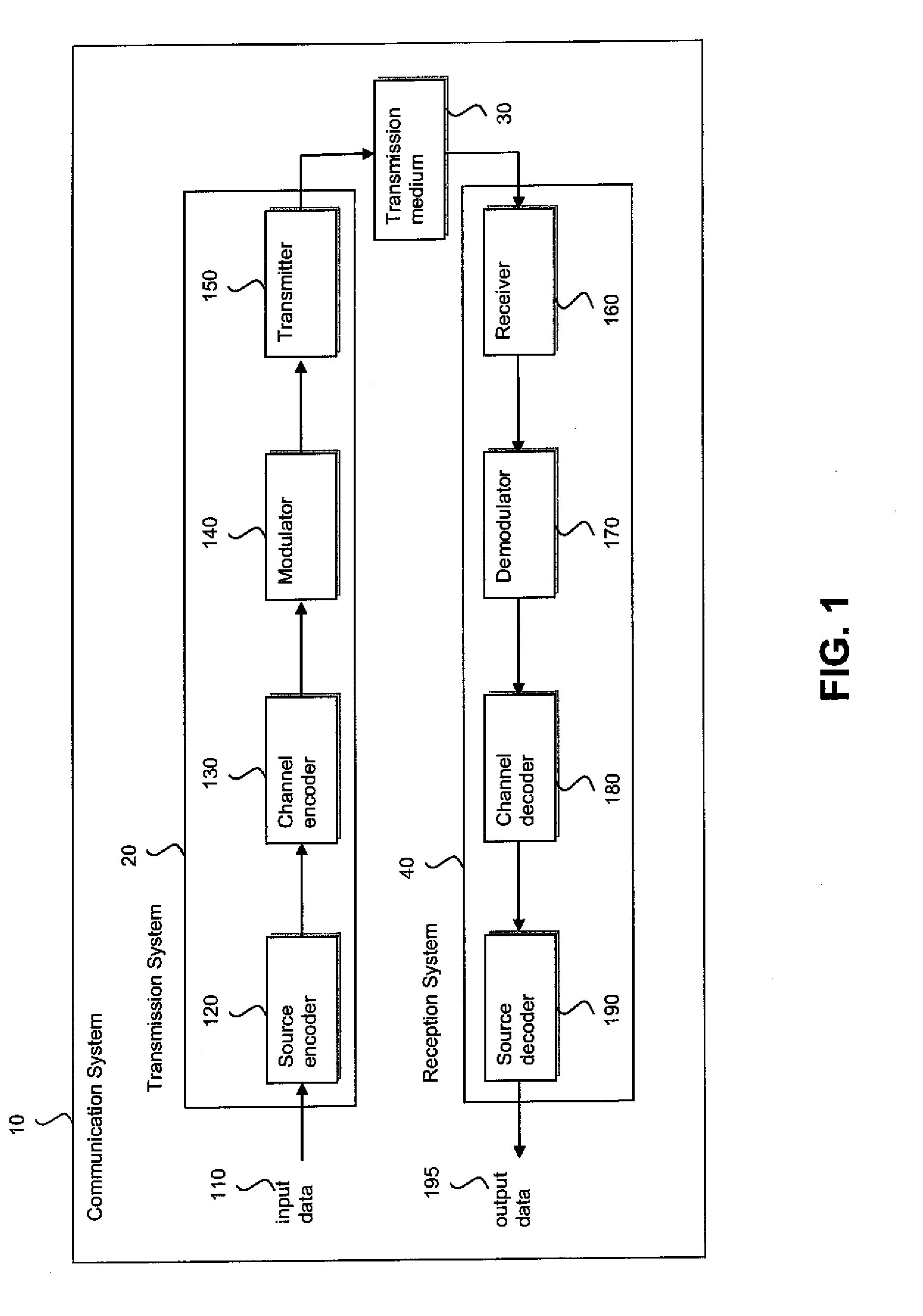

Quantum error correction (QEC) is used in quantum computing to protect quantum information from errors due to decoherence and other quantum noise. Quantum error correction is essential if one is to achieve fault-tolerant quantum computation that can deal not only with noise on stored quantum information, but also with faulty quantum gates, faulty quantum preparation, and faulty measurements.

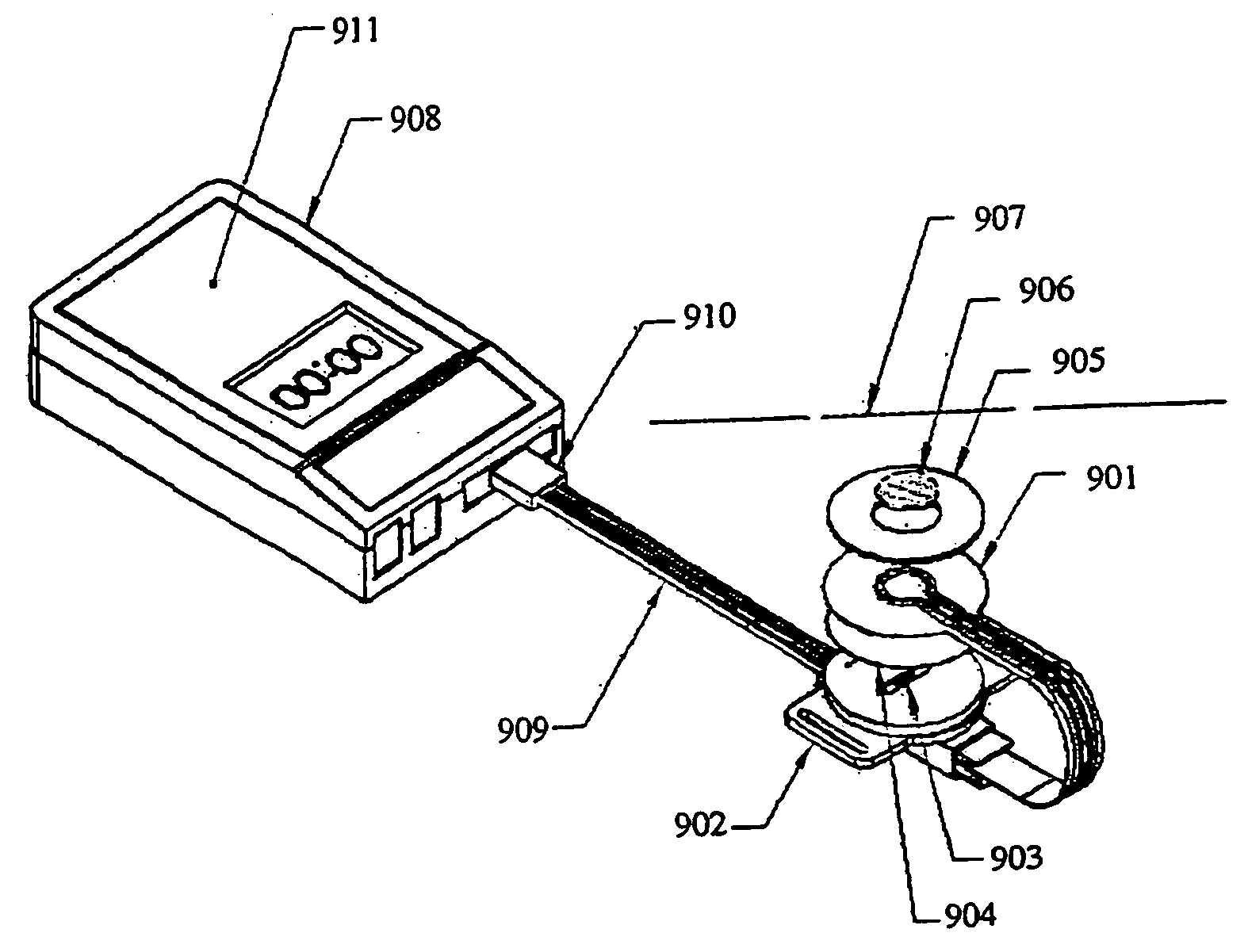

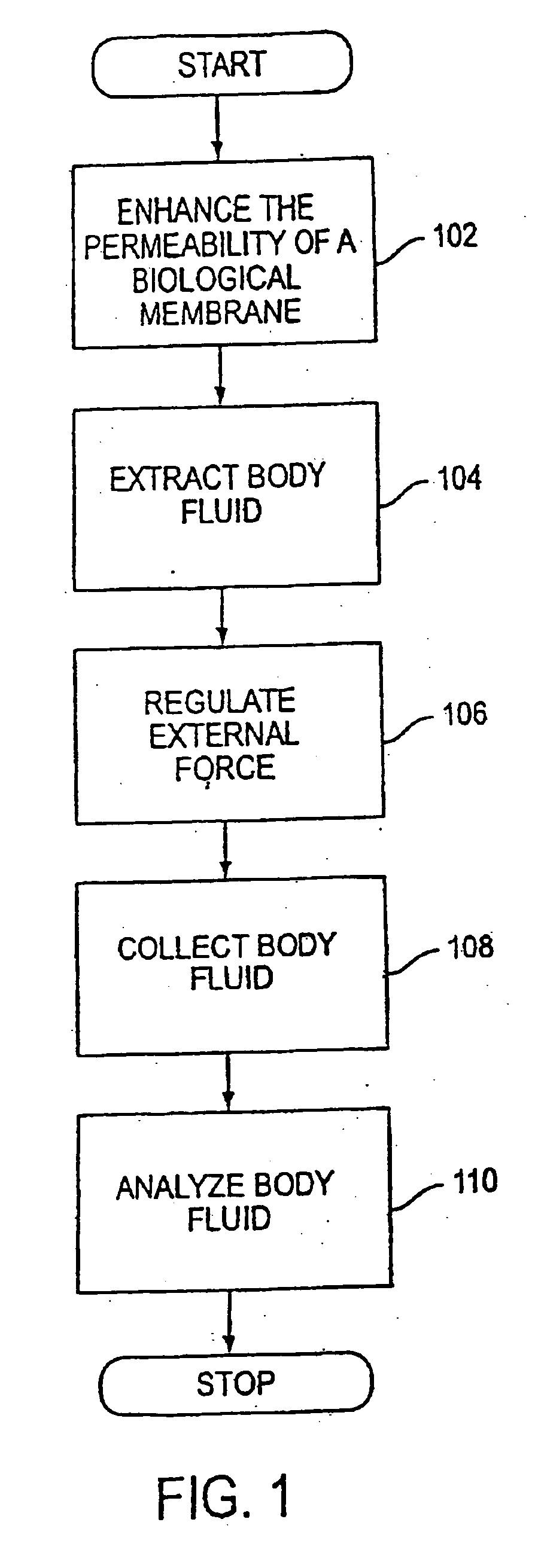

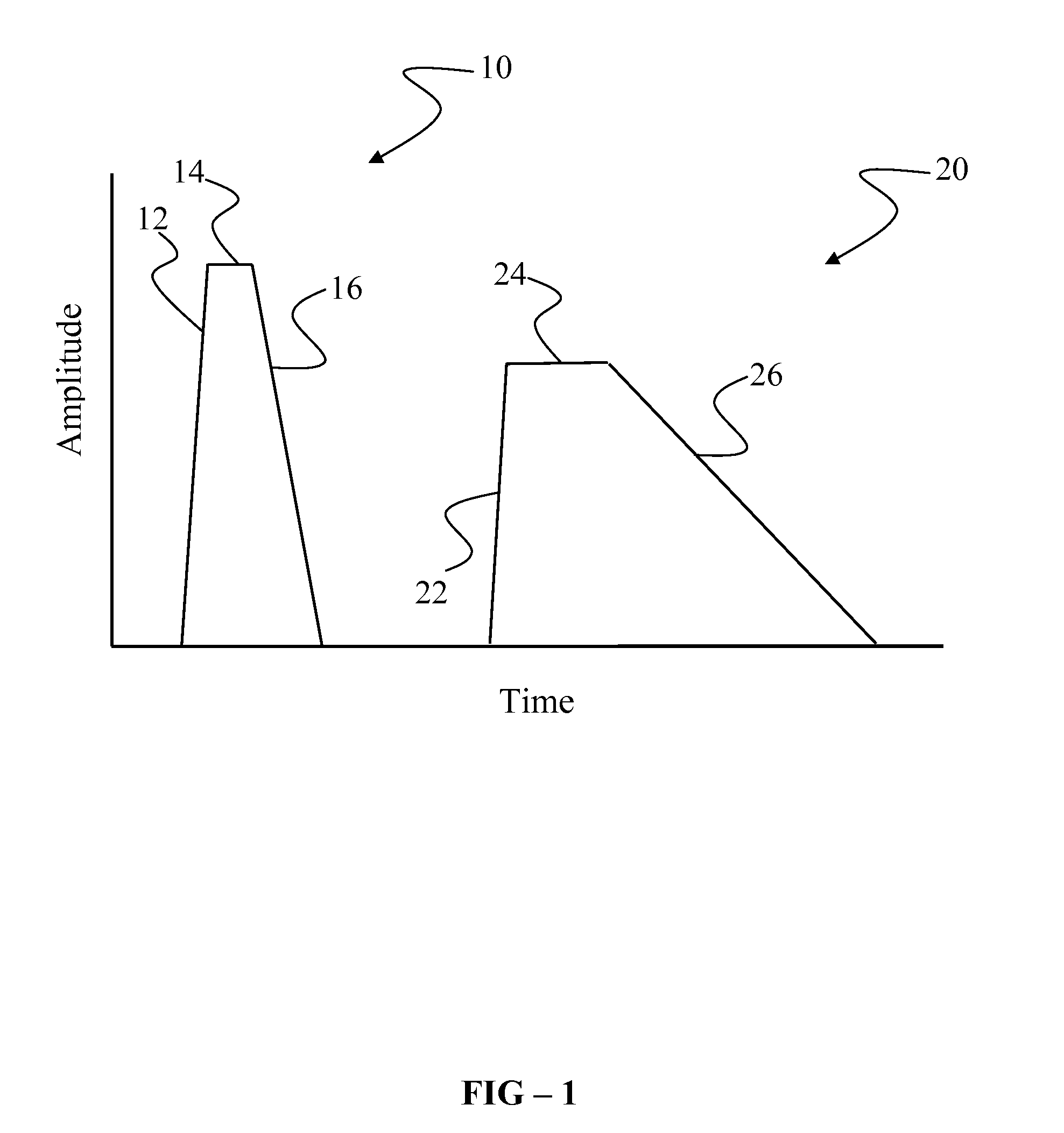

System and method for analyte sampling and analysis with error correction

InactiveUS20060094944A1SurgeryMaterial analysis by electric/magnetic meansPolyethylene glycolCorrection method

The invention relates to a transdermal analyte monitoring system comprising a medium adapted to interface with a biological membrane and to receive an analyte from the biological membrane and an electrode assembly comprising a plurality of electrodes, wherein the medium is adapted to react continuously with the analyte, an electrical signal is detected by the electrode assembly, and the electrical signal correlates to an analyte value. The analyte value may be the flux of the analyte through the biological membrane or the concentration of the analyte in a body fluid of a subject. The medium may comprise a vinyl acetate based hydrogel, an agarose based hydrogel, or a polyethylene glycol diacrylate (PEG-DA) based hydrogel, for example. The surface region of the electrode may comprise pure platinum. The system may include an interference filter located between the biological membrane and the electrode assembly for reducing interference in the system. The system may comprise a processor programmed to implement an error correction method that corrects for sensor drift.

Owner:SONTRA MEDICAL CORP

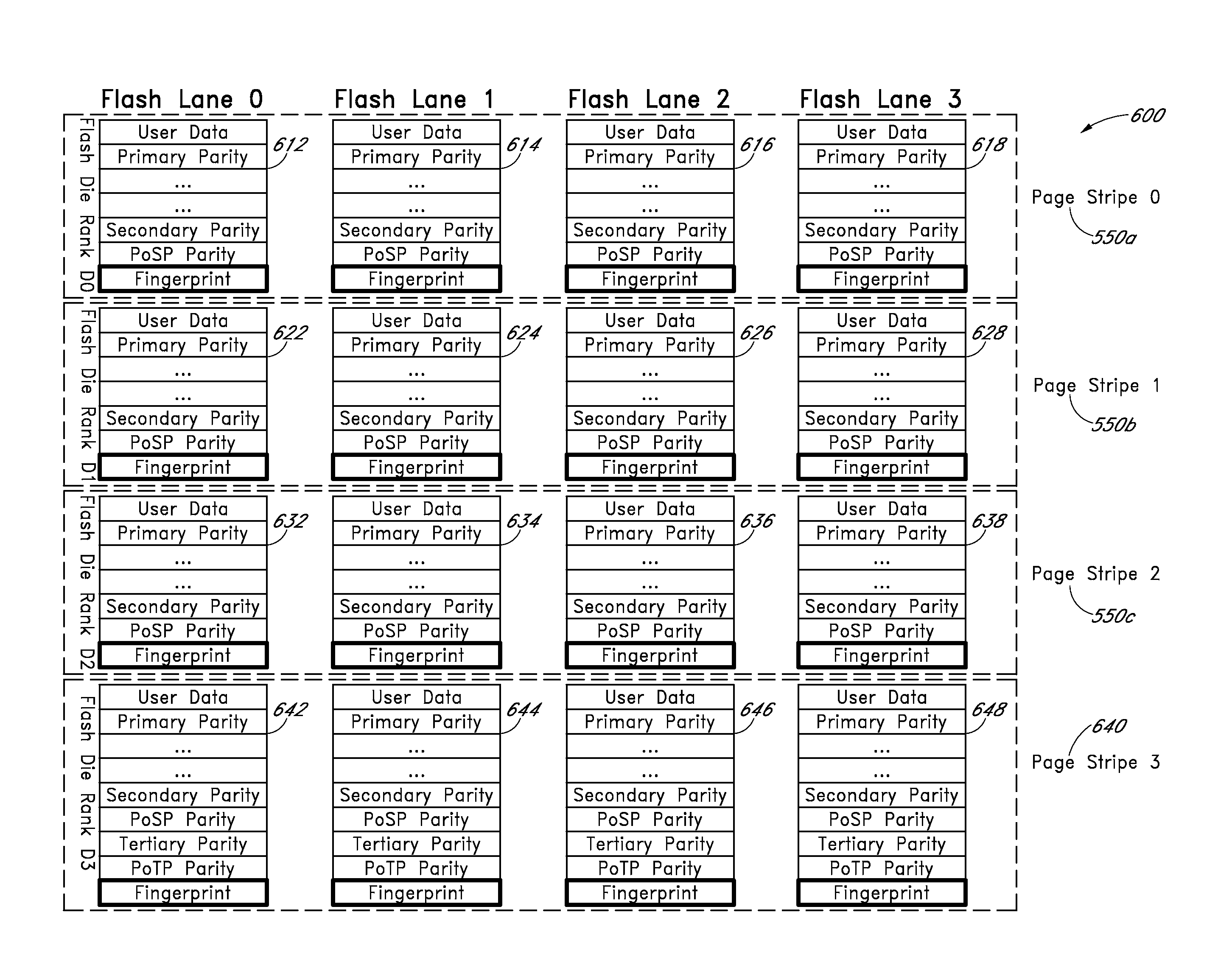

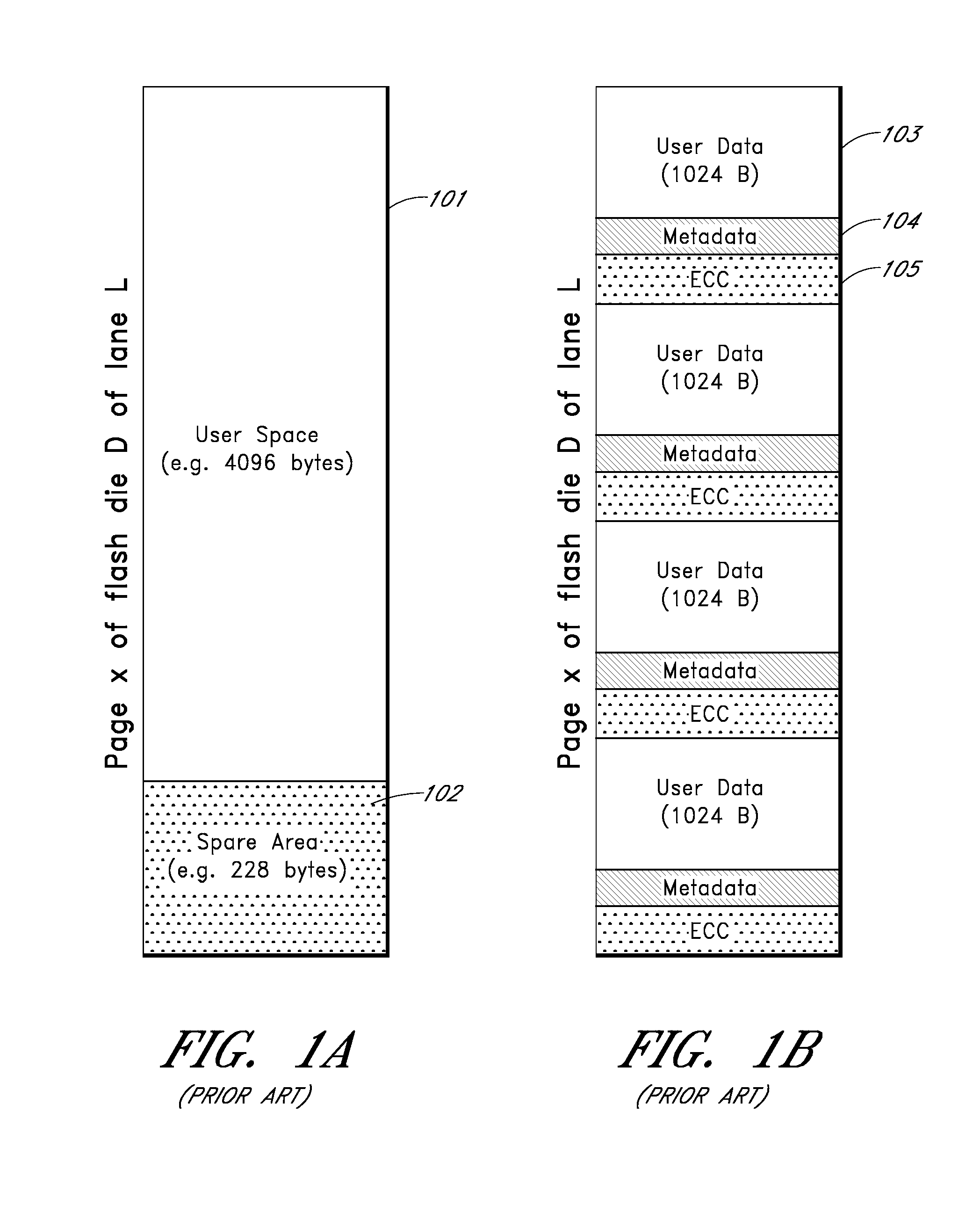

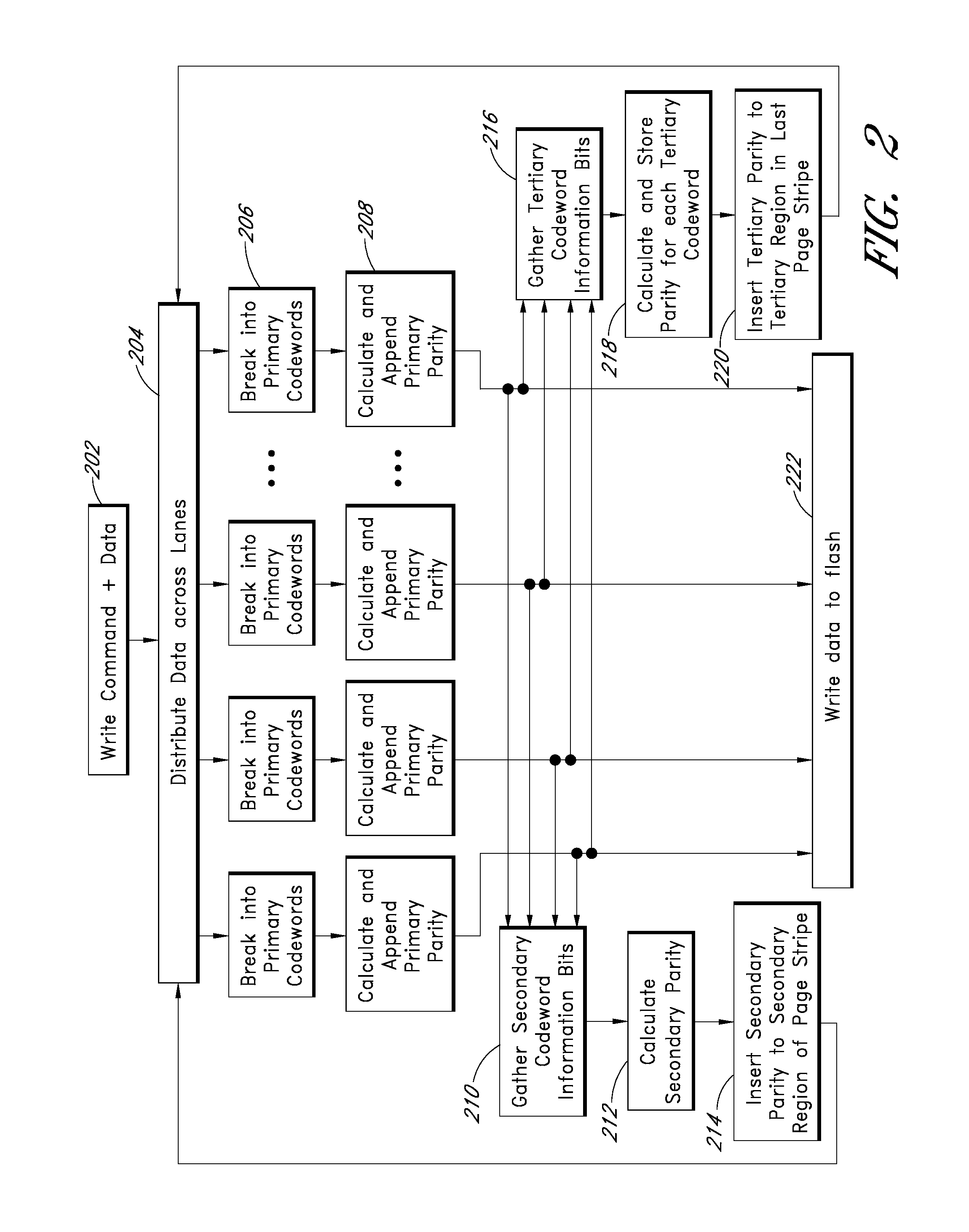

Systems and methods for adaptively selecting from among a plurality of error correction coding schemes in a flash drive for robustness and low latency

ActiveUS9183085B1Low uncorrectable bit error rateSolution to short lifeRedundant data error correctionWrite amplificationLatency (engineering)

Owner:POLARIS POWERLED TECH LLC

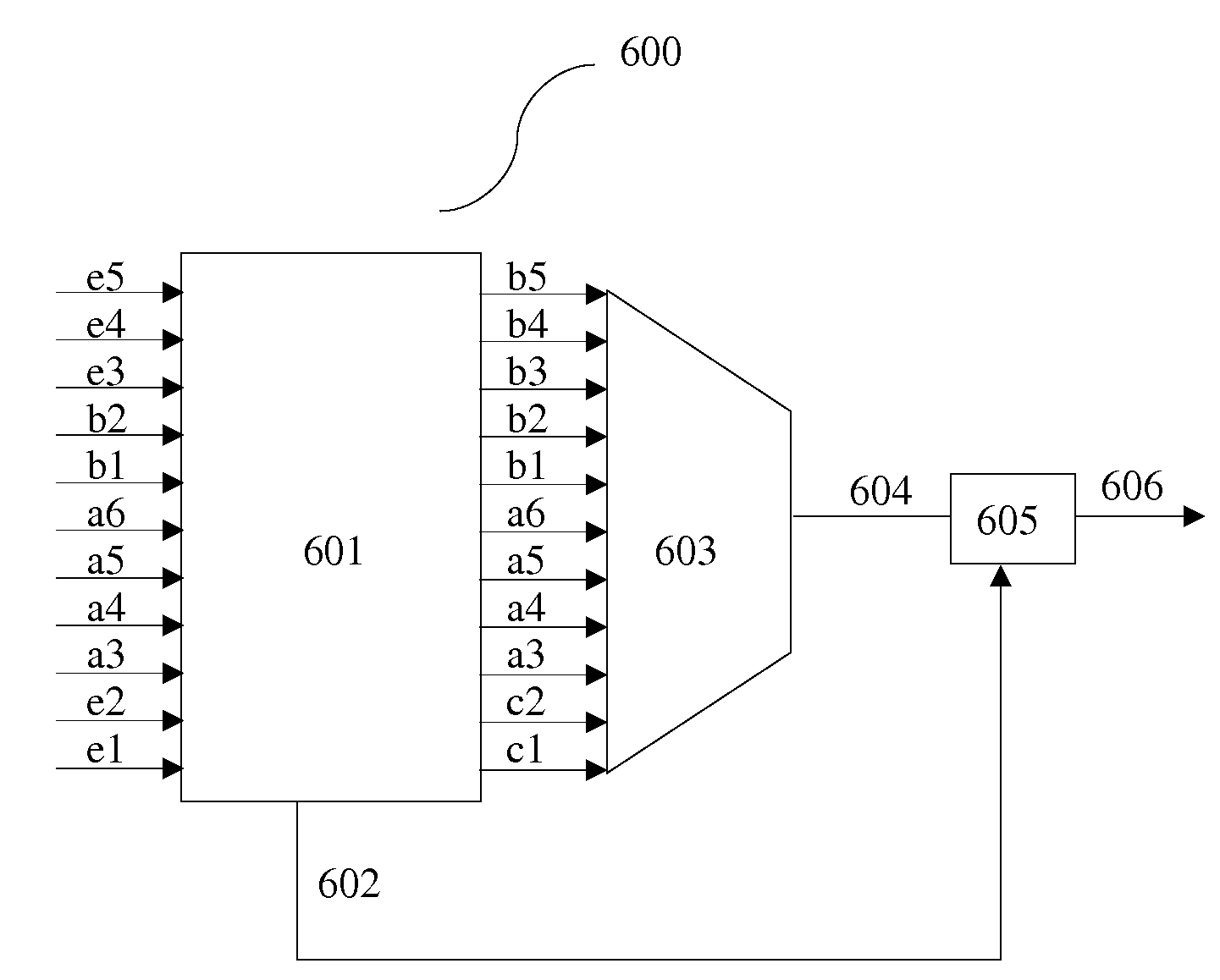

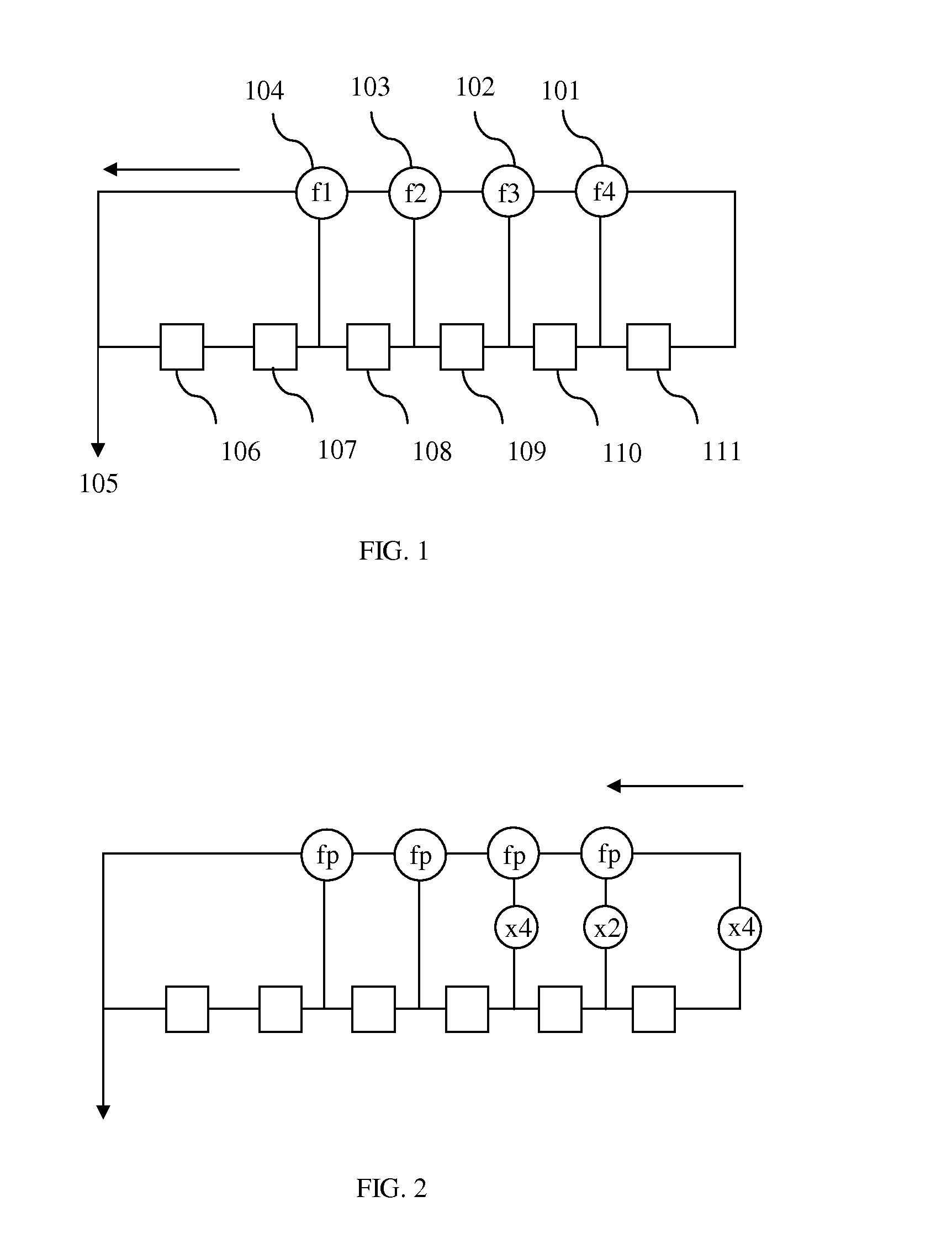

Error correction by symbol reconstruction in binary and multi-valued cyclic codes

InactiveUS20080016431A1Rapidly detect and correct errorCode conversionCyclic codesAlgorithmSymbol of a differential operator

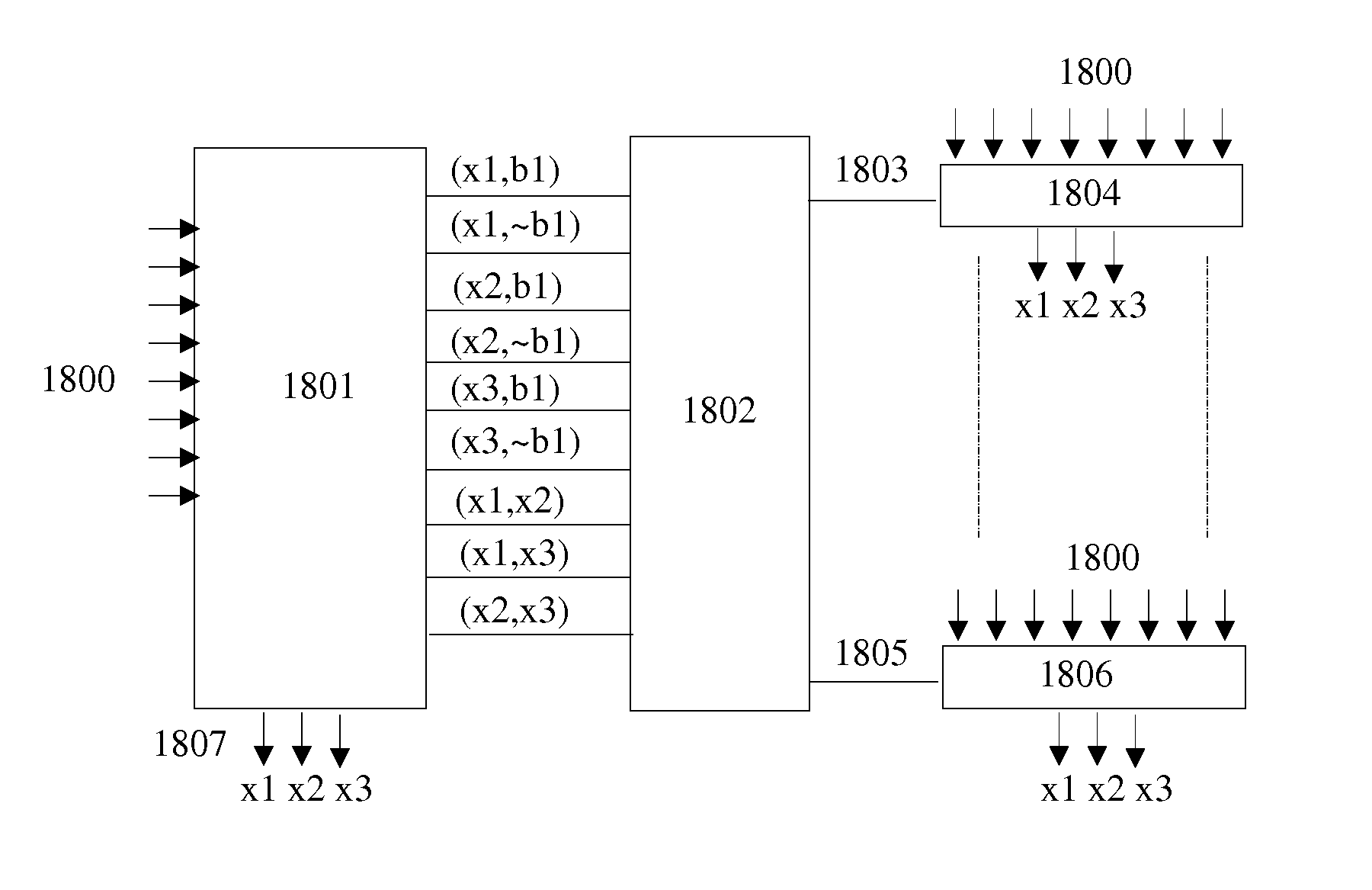

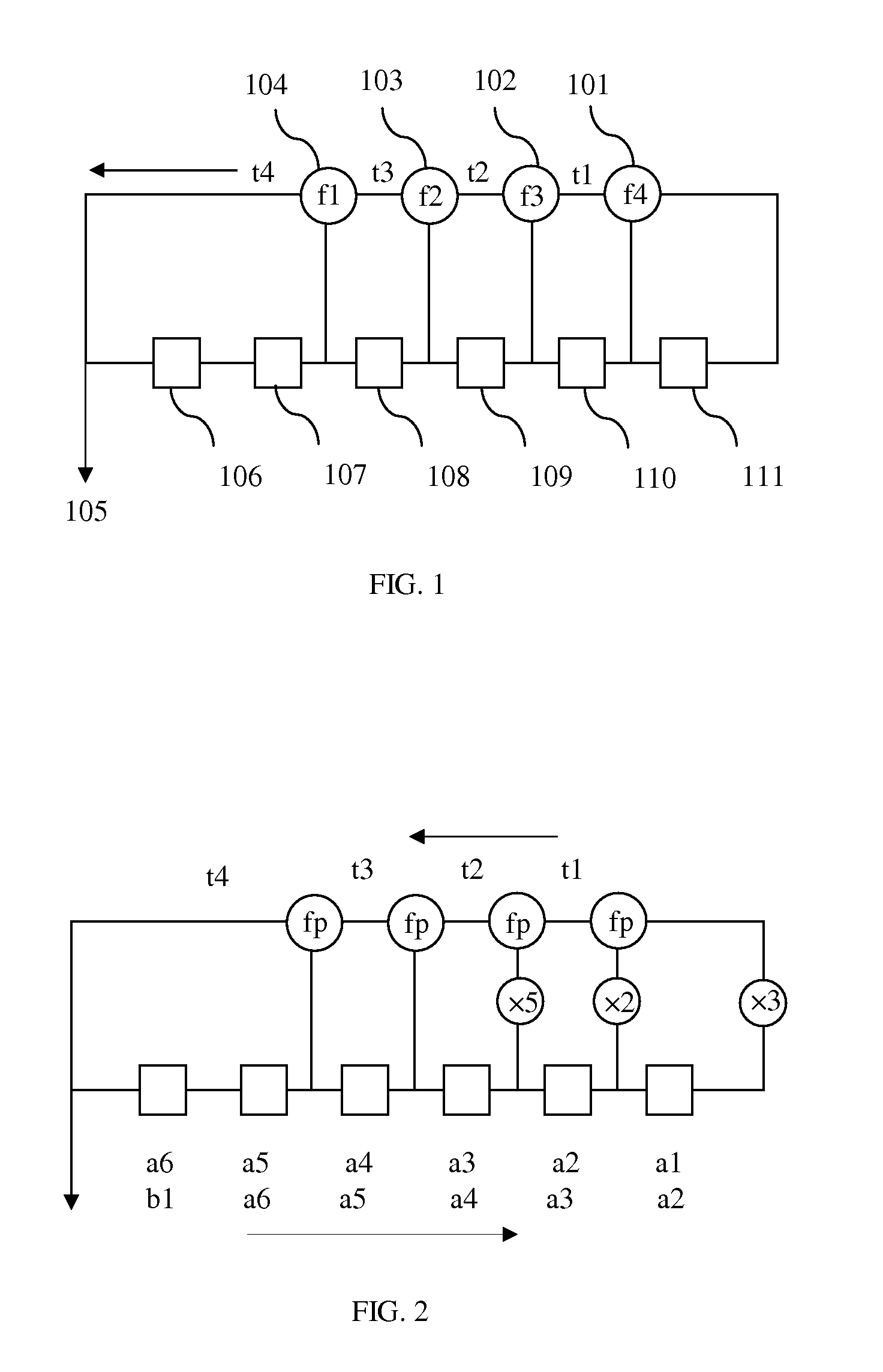

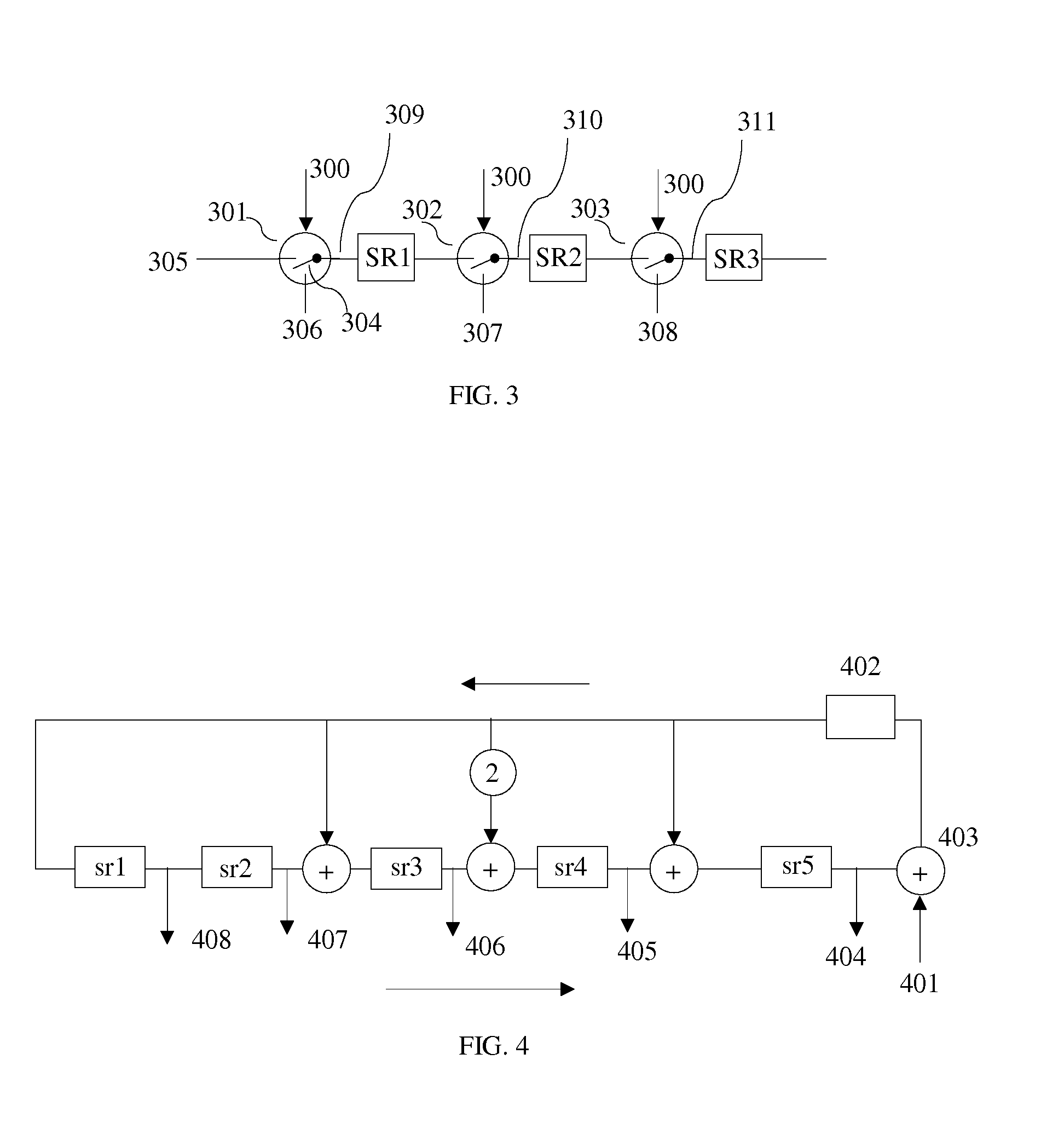

Methods, apparatus and systems for error correction of n-valued symbols in codewords of p n-valued symbols with n>2 and for n=2 and k information symbols have been disclosed. Coders and decoders using a Linear Feedback Shift Registers (LFSR) are applied to generate codewords and detect the presence of errors. An LFSR can be in Fibonacci or Galois configuration. Errors can be corrected by execution of an n-valued expression in a deterministic non-iterative way. Deterministic error correction methods based on known symbols in error are provided. Corrected codewords can be identified by comparison with received codewords in error. N-valued LFSR based pseudo-noise generators and methods to determine if an LFSR is appropriate for generating error correcting codes are also disclosed. Methods and apparatus applying error free assumed windows and error assumed windows are disclosed. Systems using the error correcting methods, including communication systems and data storage systems are also provided.

Owner:TERNARYLOGIC

Error corrected quantum computer

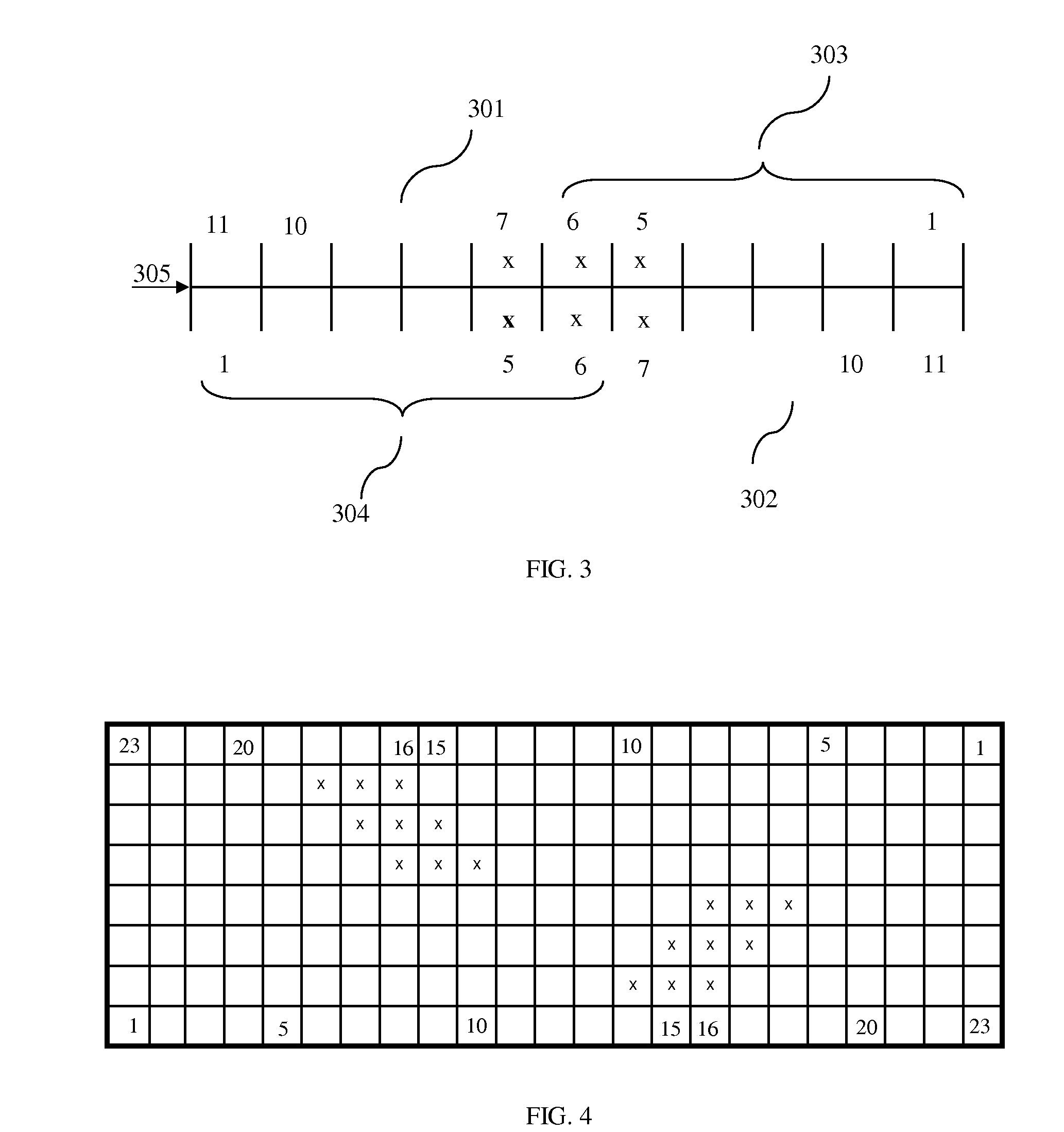

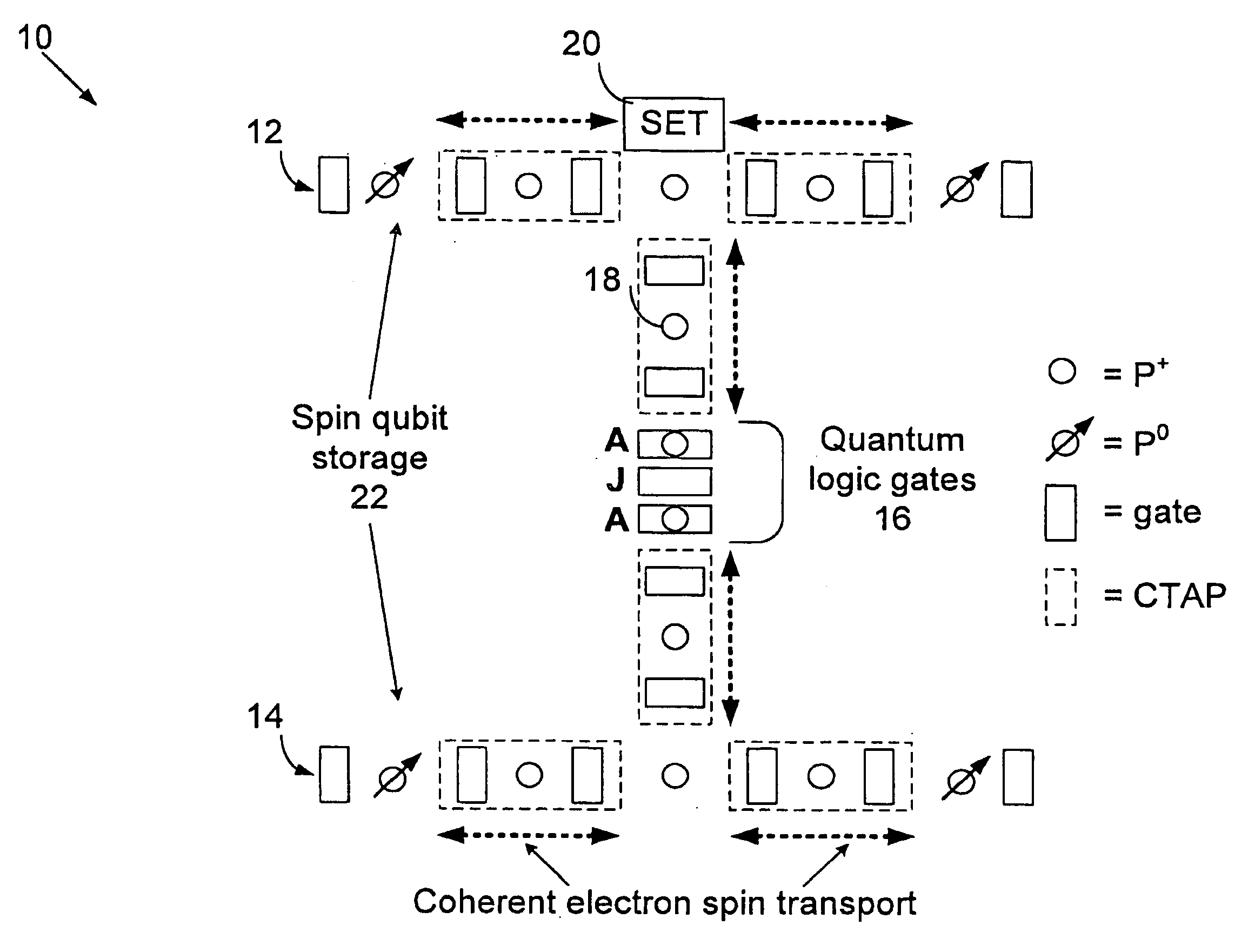

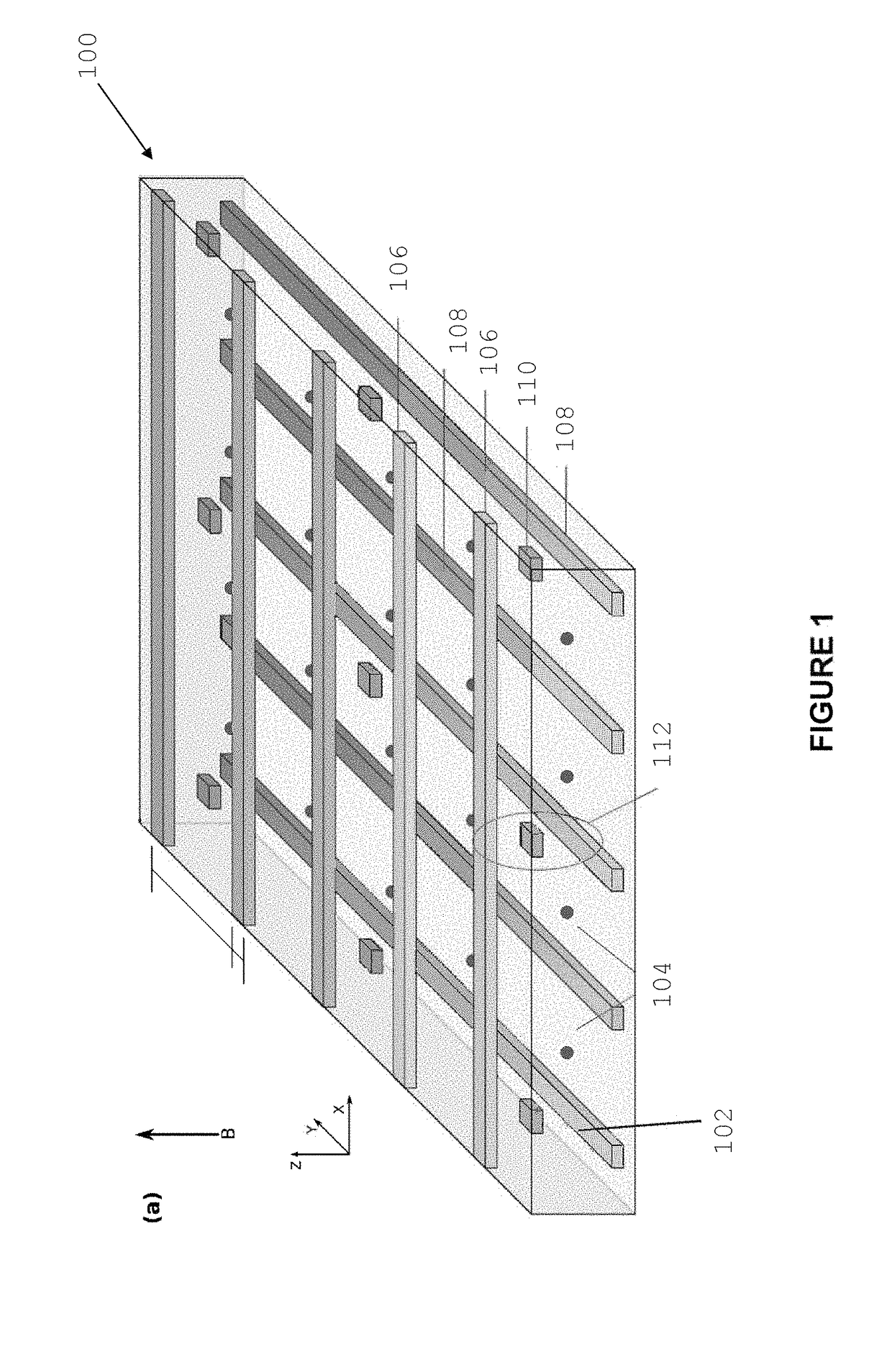

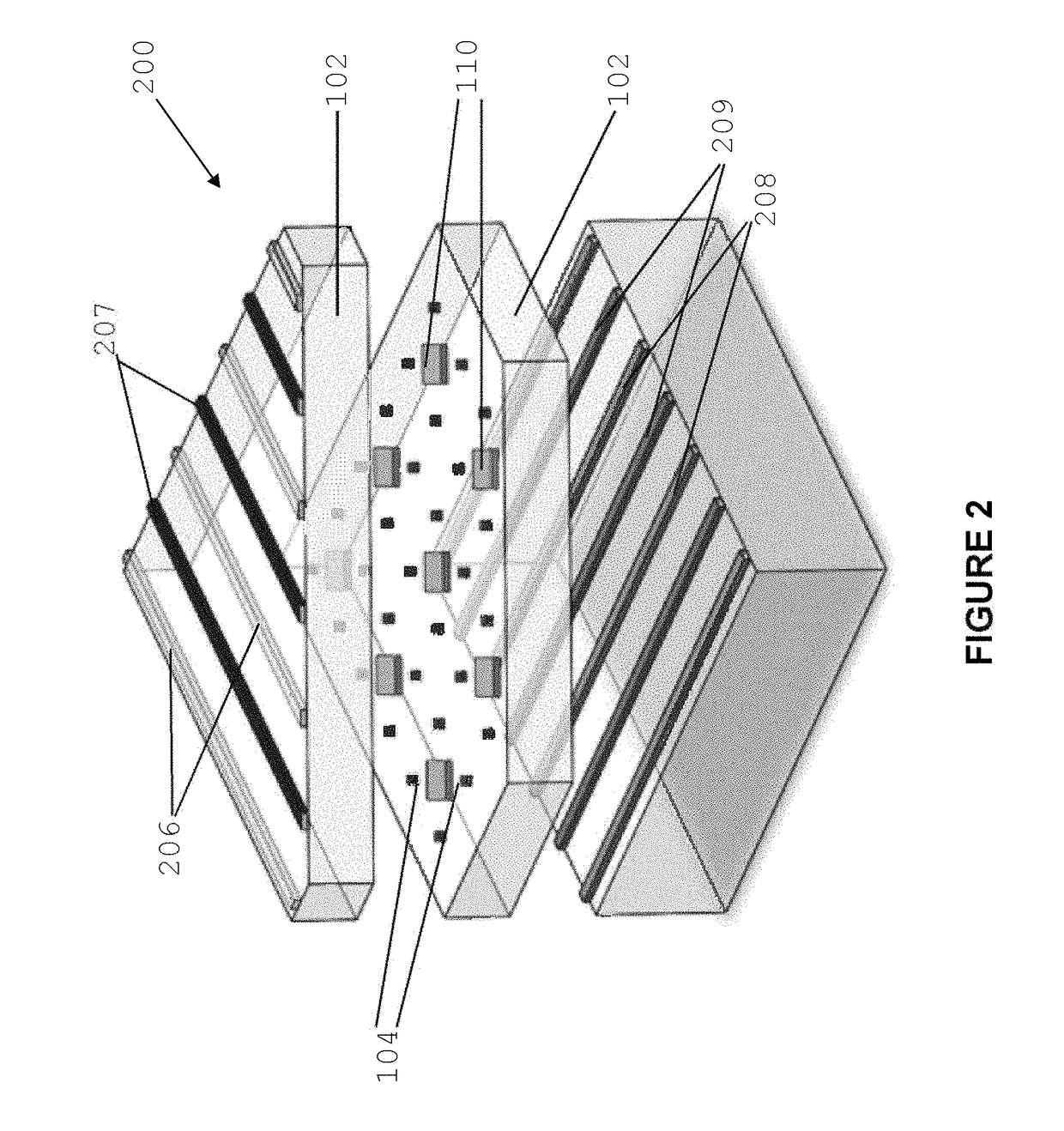

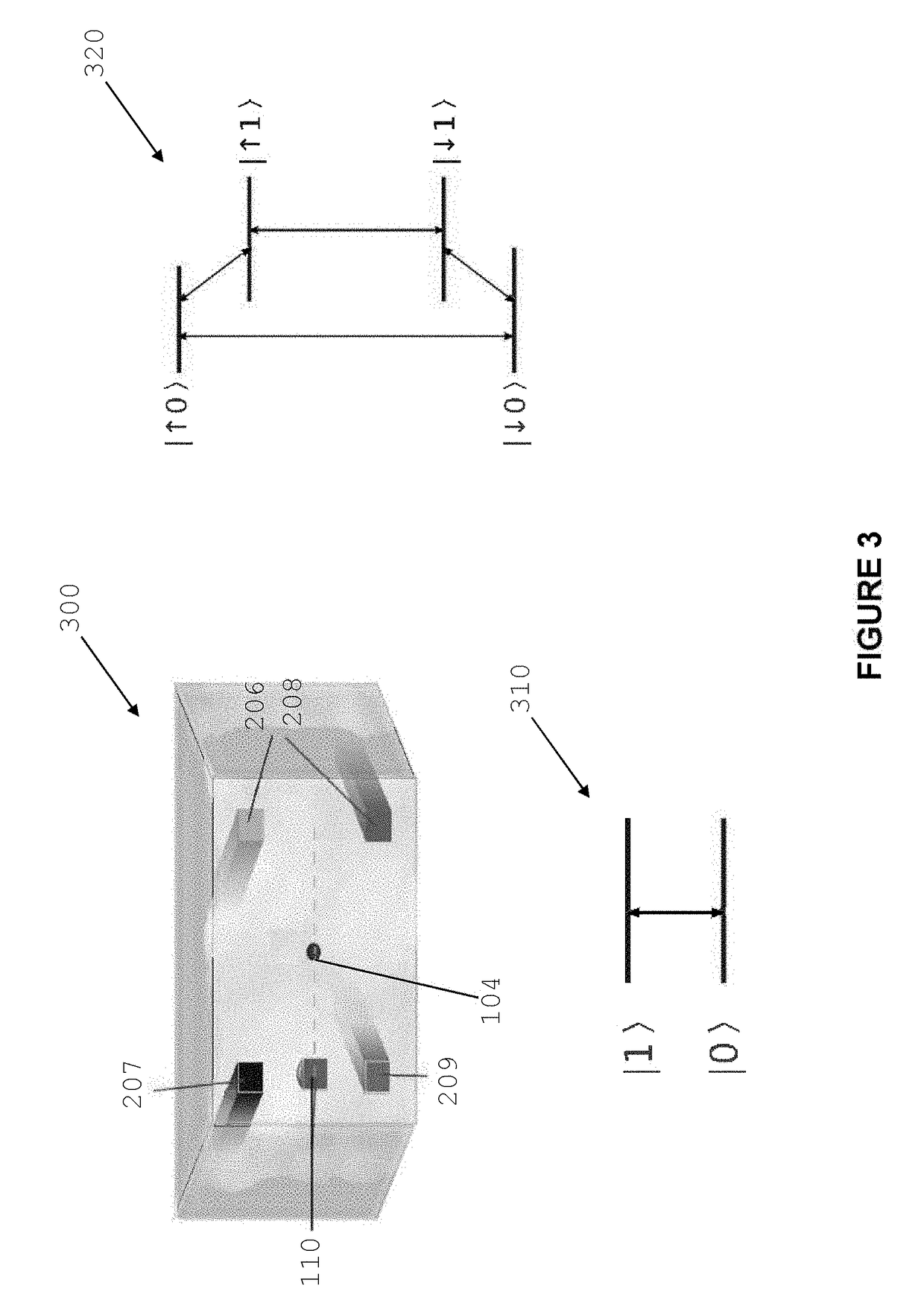

This invention concerns quantum error correction, that is the correction of errors in the transport and processing of qubits, by use of logical qubits made up of a plurality of physical qubits. The process takes place on a spatial array of physical qubit sites arranged with a quasi-2-dimensional topology having a first line of physical qubit sites and second line of physical qubit sites, where the first and second lines are arranged in parallel, with the sites of the first line in registration with corresponding sites in the second line. Between the first and second lines of physical qubit sites are a plurality of logic function gates, each comprised of a first physical qubit gate site associated with a first physical qubit site in the first line, and a second physical qubit gate site associated with the physical qubit site in the second line that corresponds to the first physical qubit site. The temporal process comprises the following steps: Creating a logical qubit in a section of the array by initialising an equal plurality of physical data and ancilla qubits at respective sites of the first and second lines within the section. Clocking each physical qubit site in the section at the same time. Permitting the physical data and ancilla qubits to move to an adjacent site in a clock cycle, provided that no site may contain more than one physical qubit at any time. Controlling the sites to achieve movement of ancilla qubits in the array to bring pairs of the ancilla qubits to respective first and second physical gate sites of logic function gates over the course of a number of clock cycles. Permitting logic operations to be performed at logic function gates which have both of their gate sites occupied by a physical ancilla qubit. Controlling the gate sites of the logic function gate to achieve the logic operation. Controlling the sites to achieve movement of the qubits in the array to bring pairs of all the data and ancilla qubits to respective logic function gates over the course of a number of clock cycles. Controlling the gate sites of the logic function gate to achieve the logic operation between each pair of data and ancilla qubits. Controlling the sites to achieve movement of the qubits in the array to bring all the data and ancilla qubits to respective sites where they can be read out. And, Using the values of the ancilla qubits read out to correct errors arising in the data qubits they have been gated with.

Owner:NEWSOUTH INNOVATIONS PTY LTD

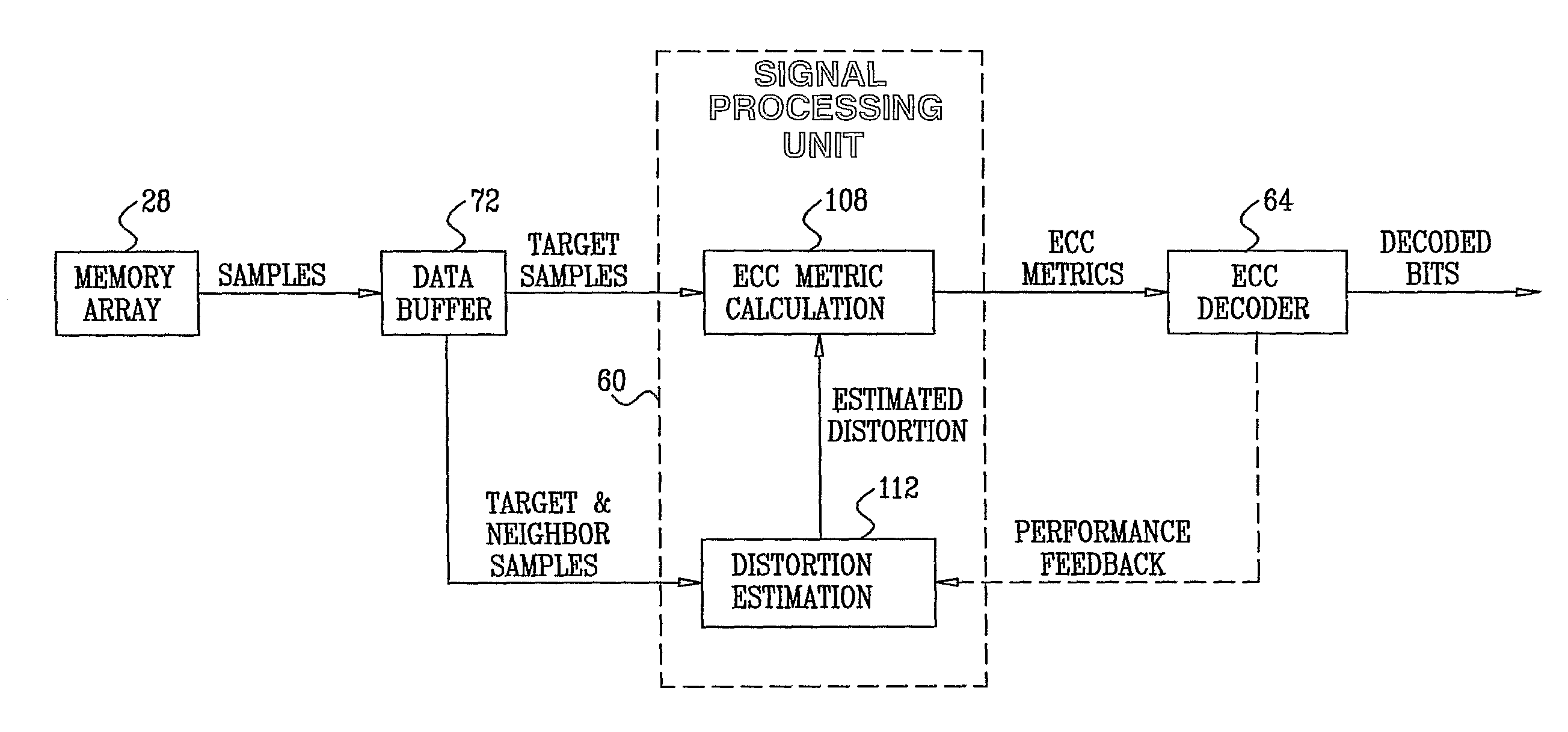

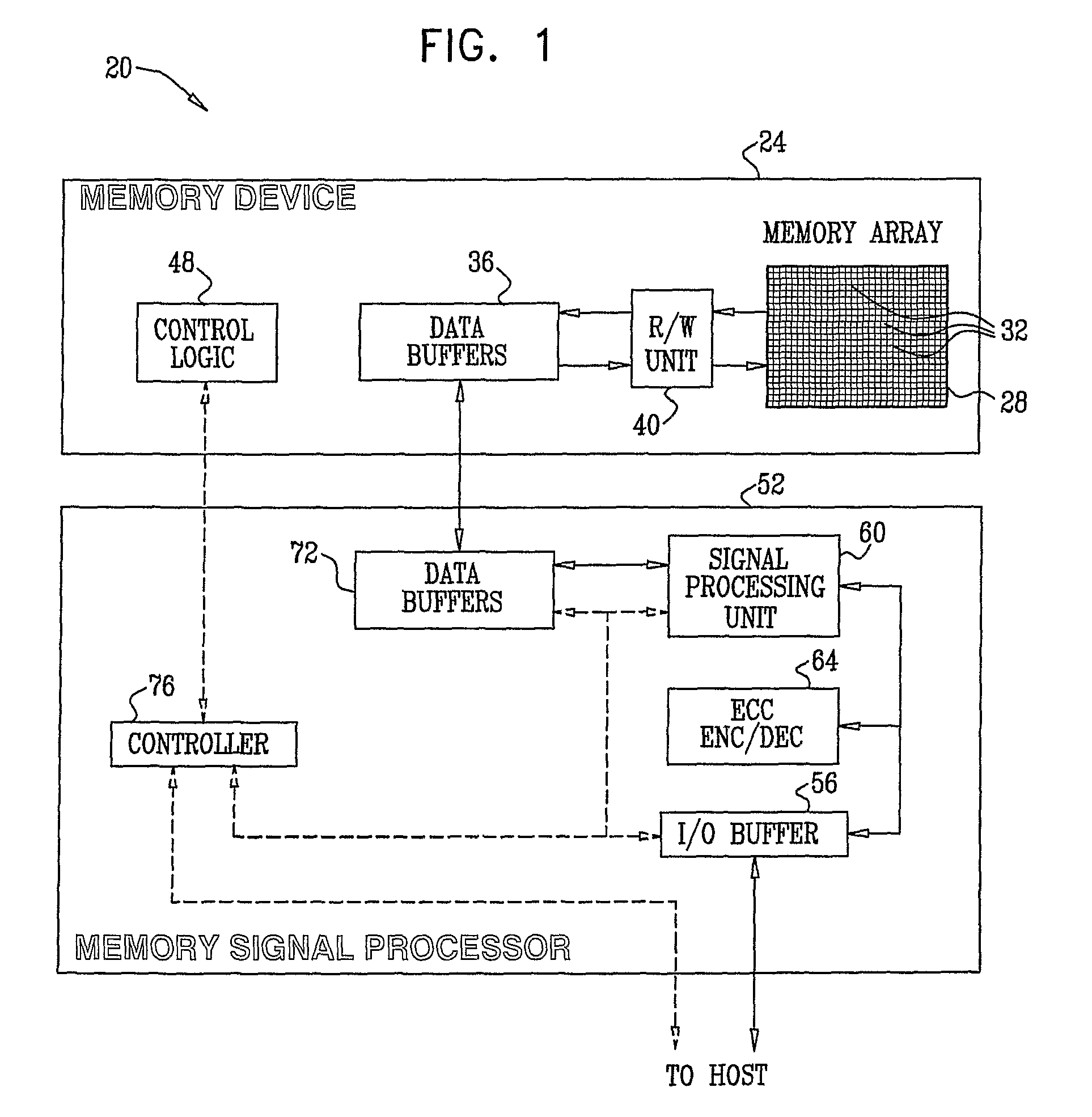

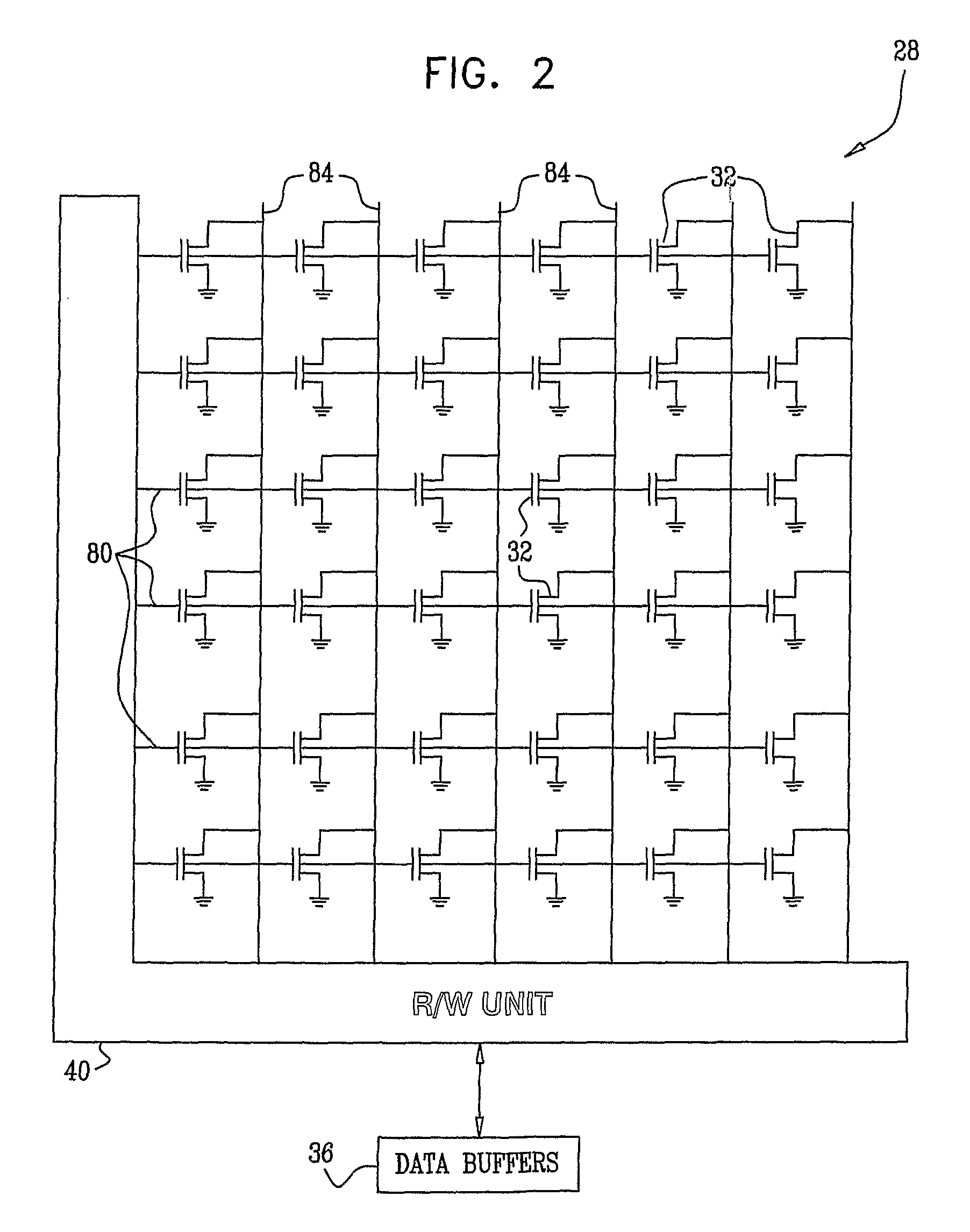

Combined distortion estimation and error correction coding for memory devices

ActiveUS8156403B2Improve performanceData representation error detection/correctionError detection/correctionCalculation errorForward error correction

Owner:APPLE INC

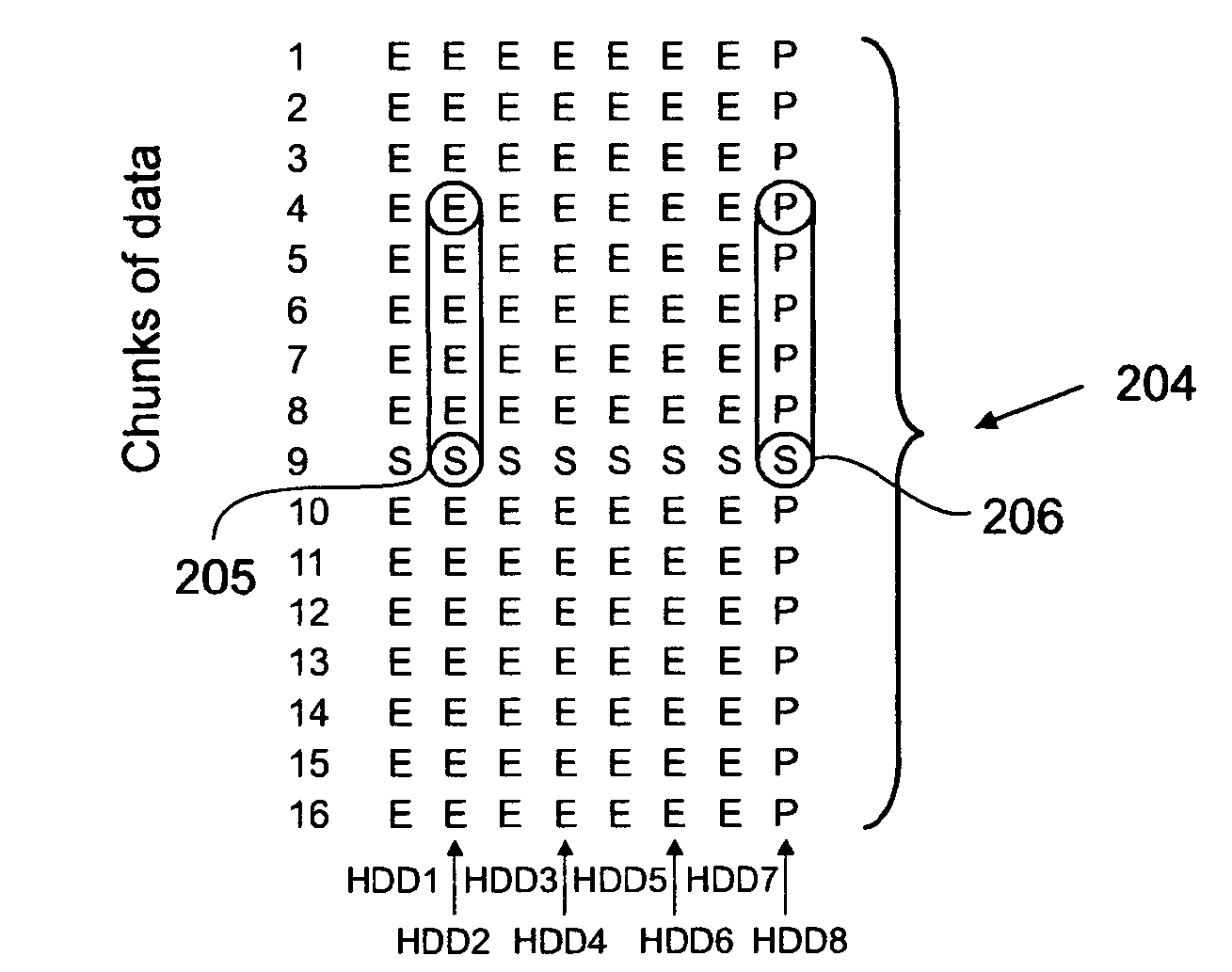

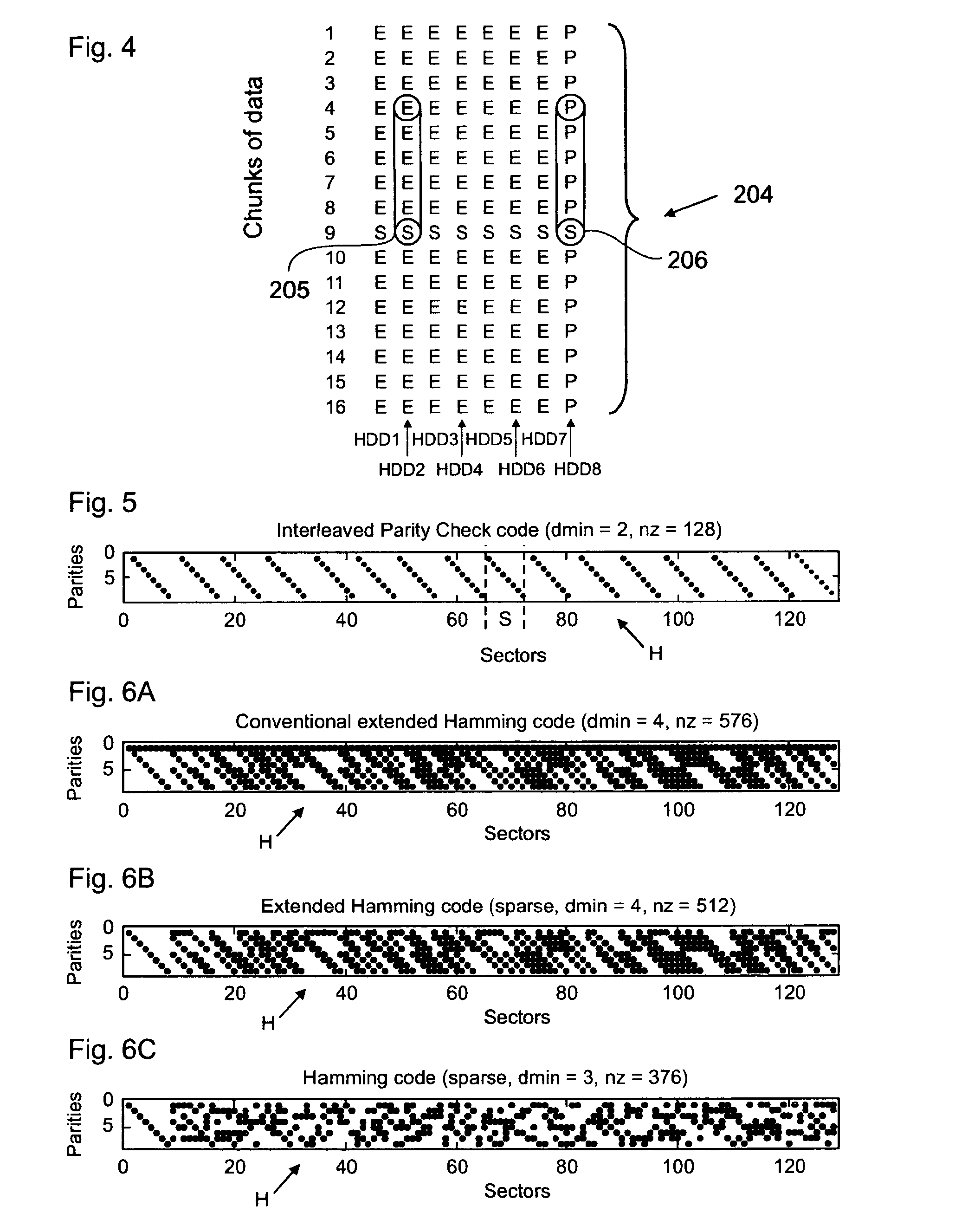

Method for creating an error correction coding scheme

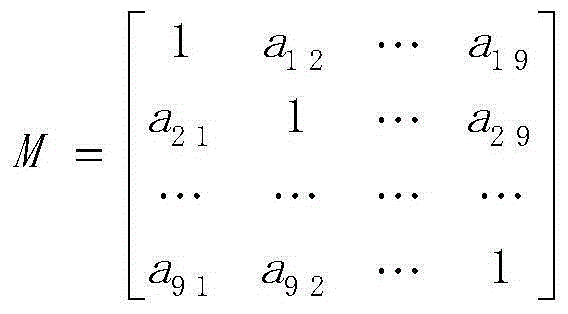

InactiveUS20080244353A1Reduce data lossEasy constructionBurst error correctionCode conversionMain diagonalData set

The present invention relates to a method for reducing data loss comprising a first computing step for computing an intermediate result for each redundancy information entity of a redundancy set by processing respectively associated data information entities of a given data set on at least two main diagonals of a parity check matrix representing an error correction coding scheme. The method further comprises a second computing step for computing the information content of the respective redundancy information entity dependent on the respective intermediate result.

Owner:GLOBALFOUNDRIES INC

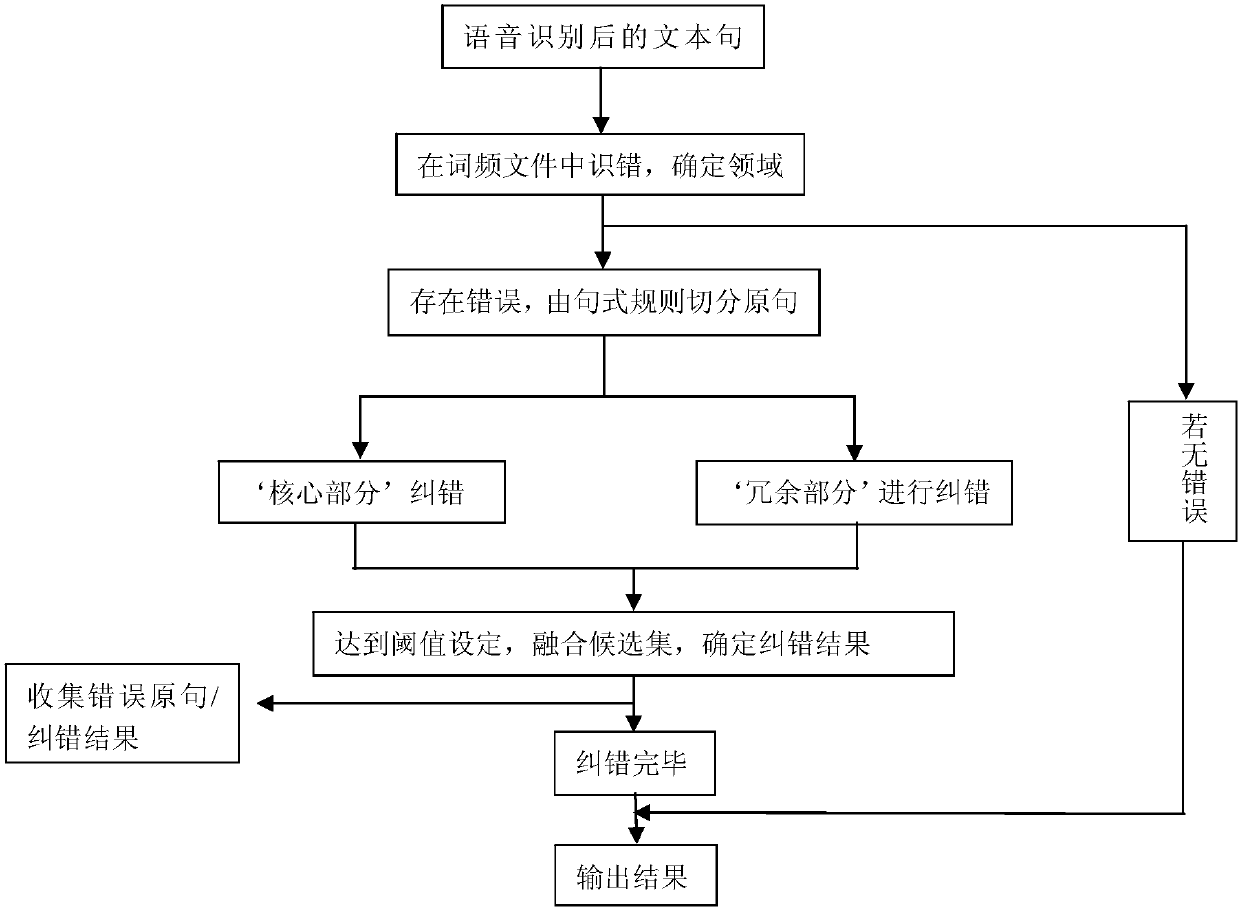

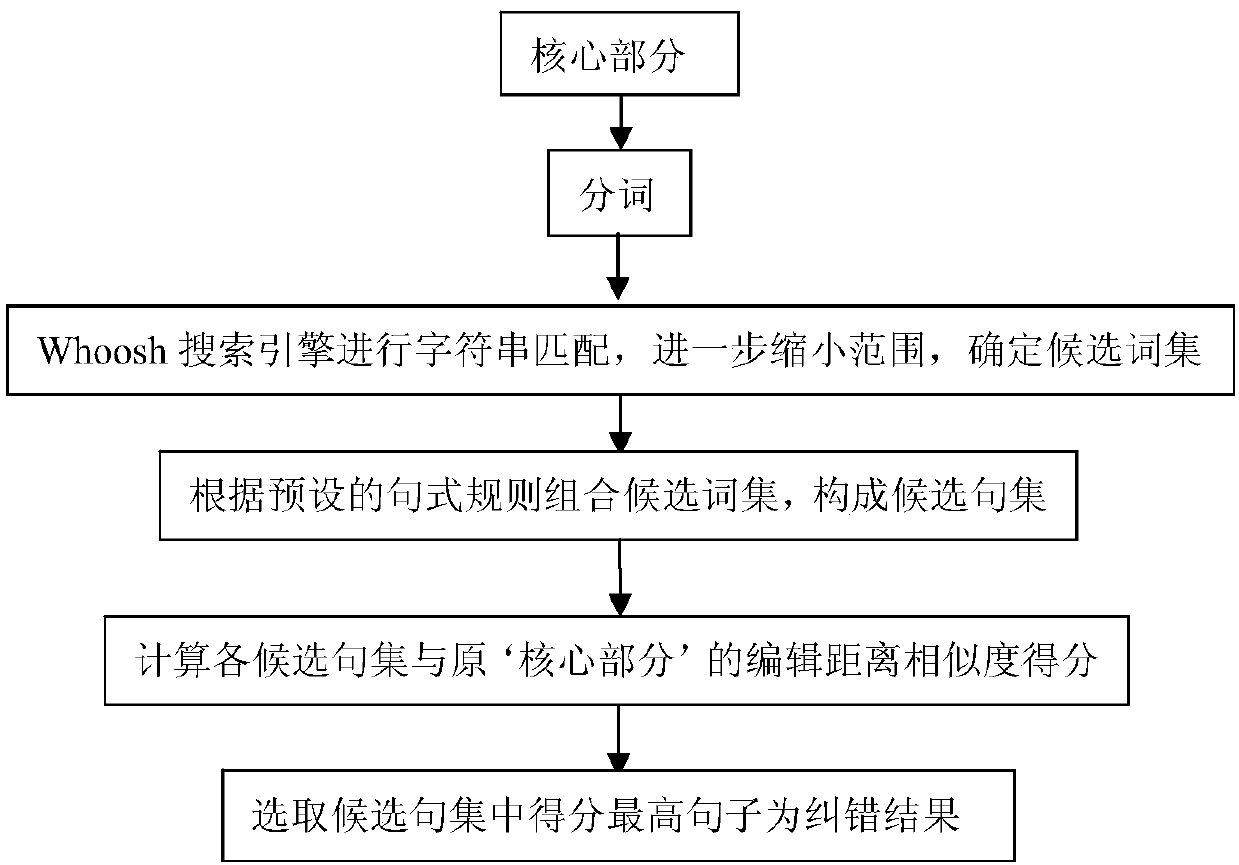

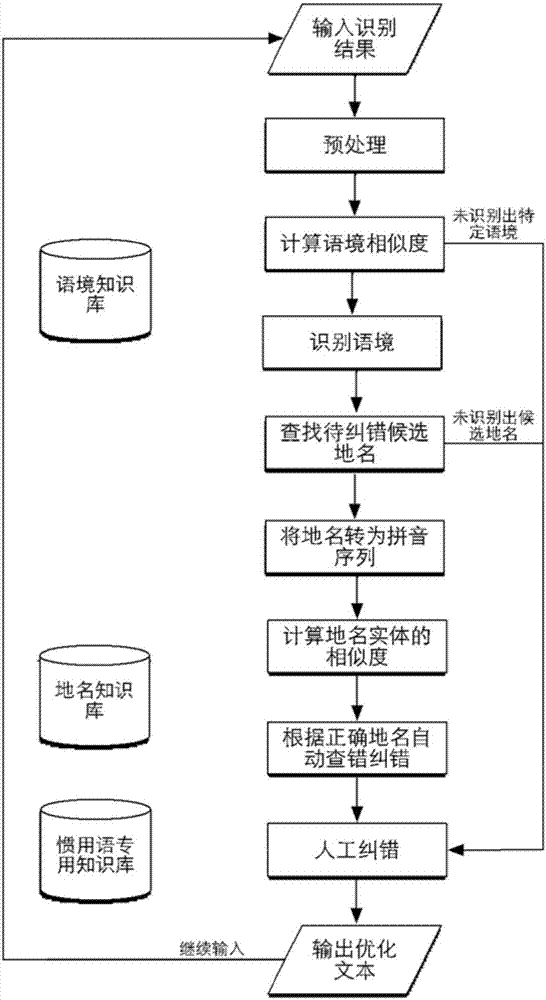

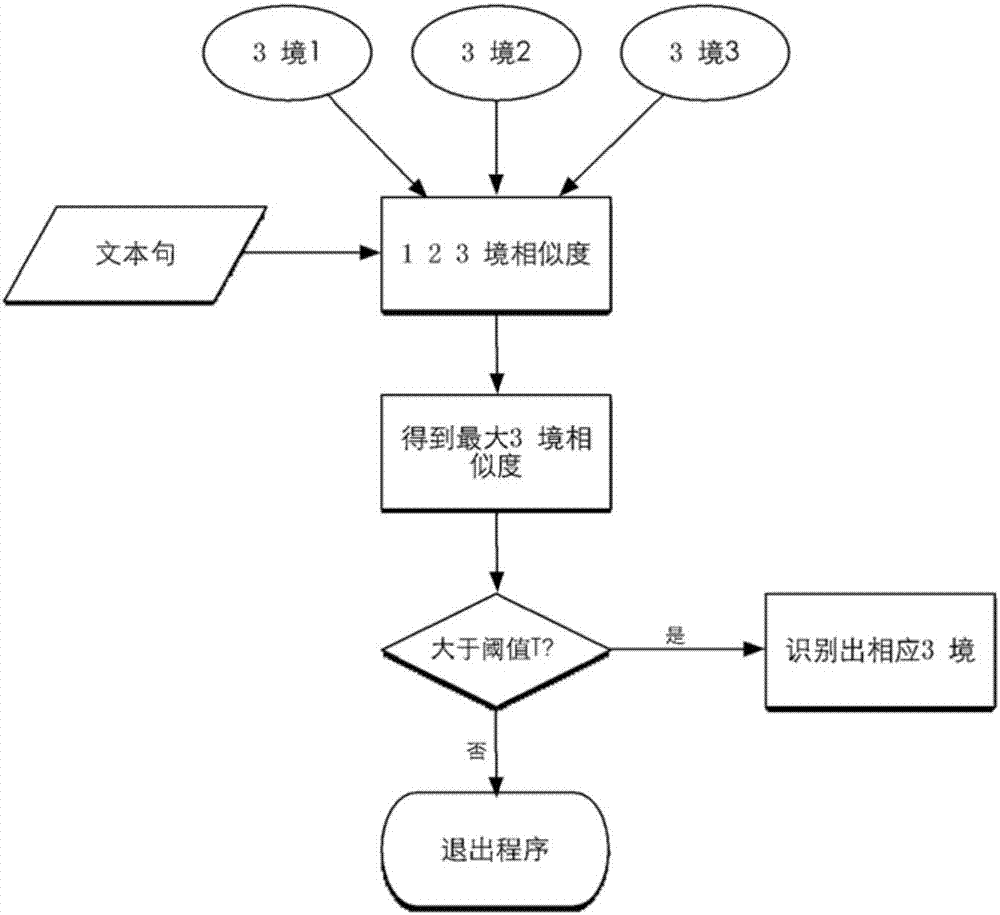

Method for text error correction after voice recognition based on domain identification

ActiveCN107741928ALess error-correcting processImprove the effect of practiceNatural language data processingSpeech recognitionSpeech identificationEdit distance

The invention belongs to the field of voice recognition text processing and discloses a method for text error correction after voice recognition based on domain identification and aims at solving theproblem that a processing method in the prior art needs lots of labor for intervention, is low in error correction efficiency and cannot conduct error correction on proper names. The method comprisesthe following steps that (a) error knowing and analysis are conducted on texts obtained after voice recognition, and the field which text sentences belong to are primarily determined; (b) sentences toundergo error correction are segmented according to predefined syntax rules and are divided into redundancy portions and core portions; (c) a search engine is utilized to perform character string fuzzy matching and determine candidate specific word bank sets of the core portions of the sentences; (d) similarity scores are calculated according editing distances, and error correction is conducted on the redundancy portions and the core portions; (e) the redundancy portions and core portions undergoing the error correction are fused, and then error correction results are output.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

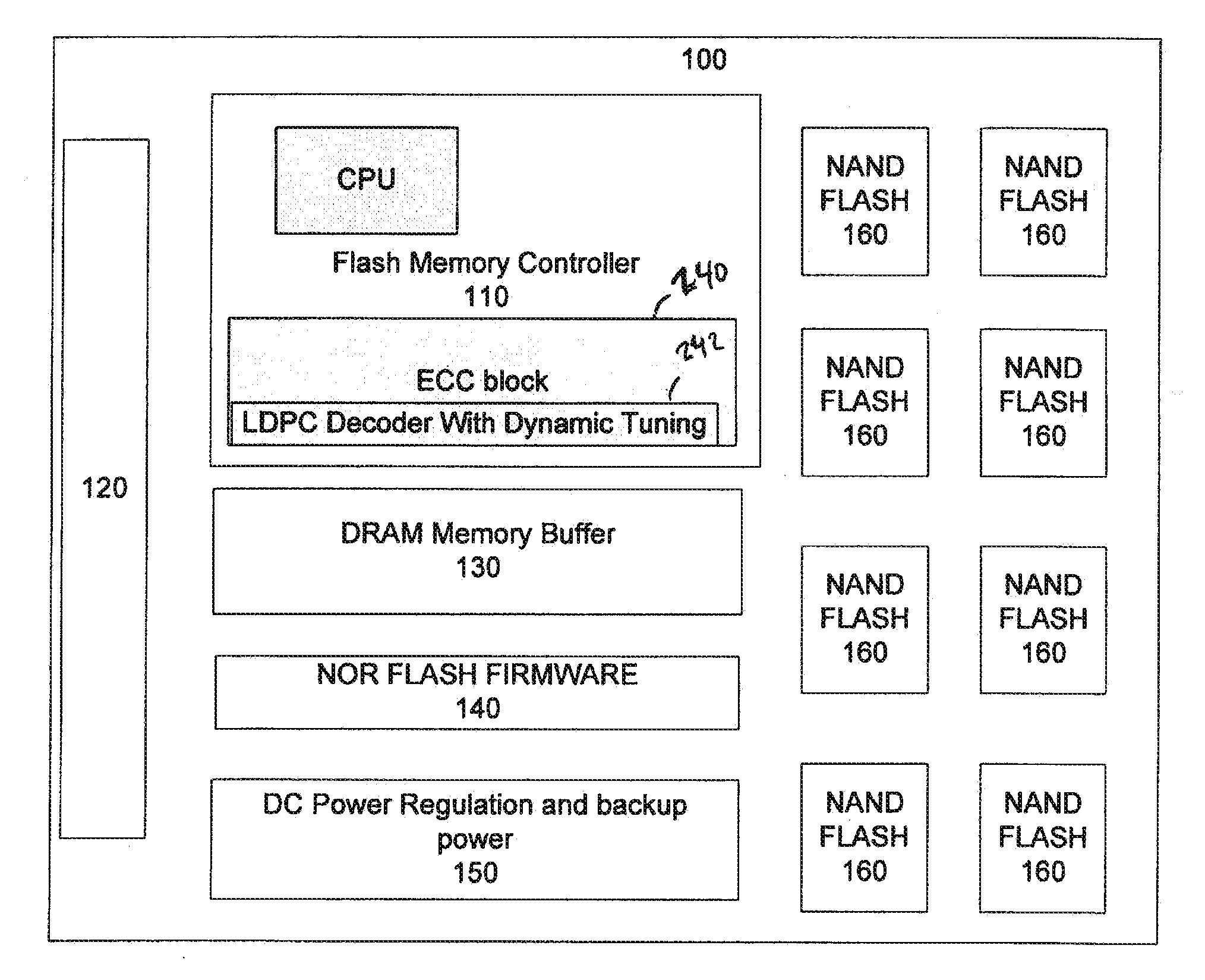

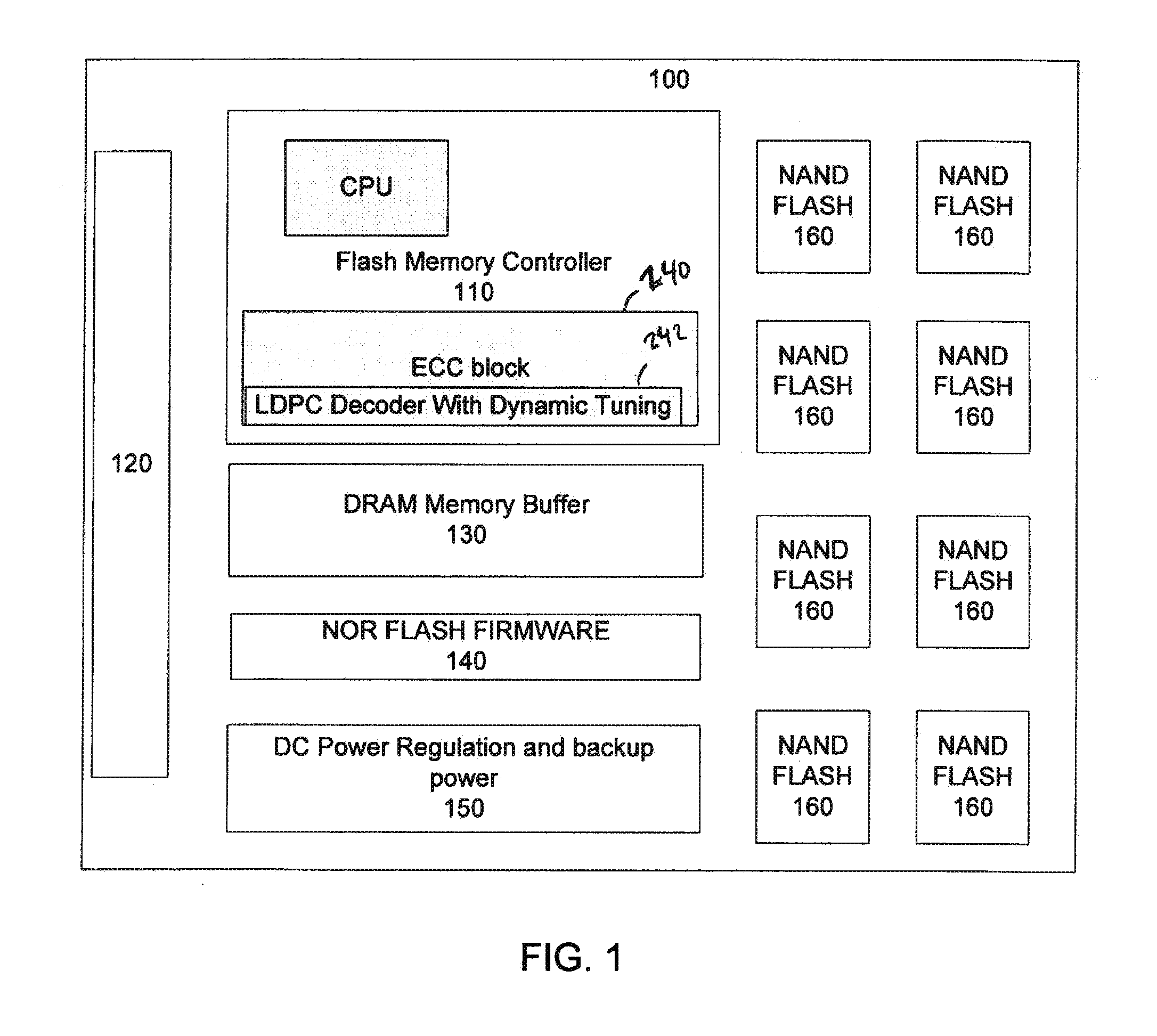

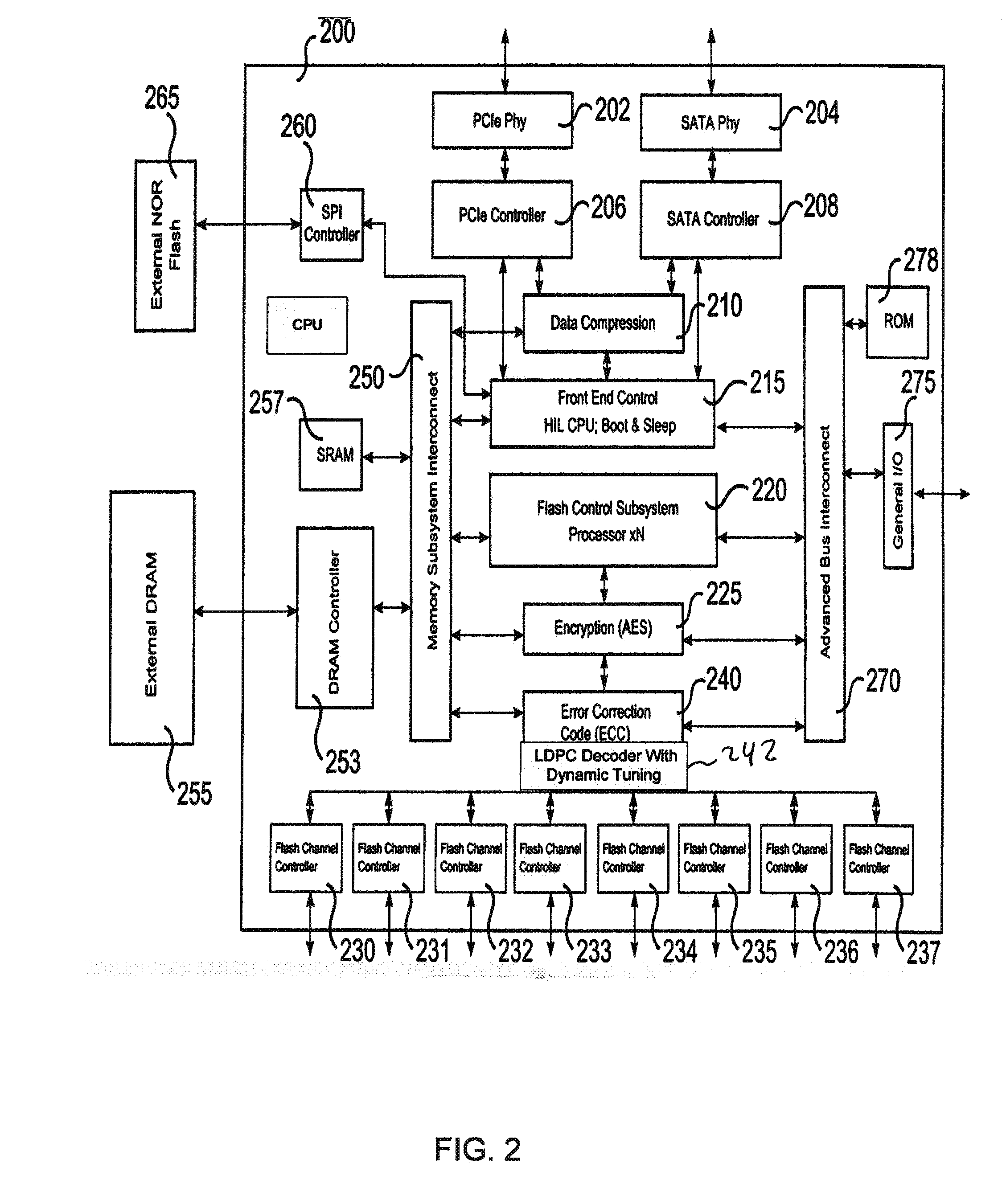

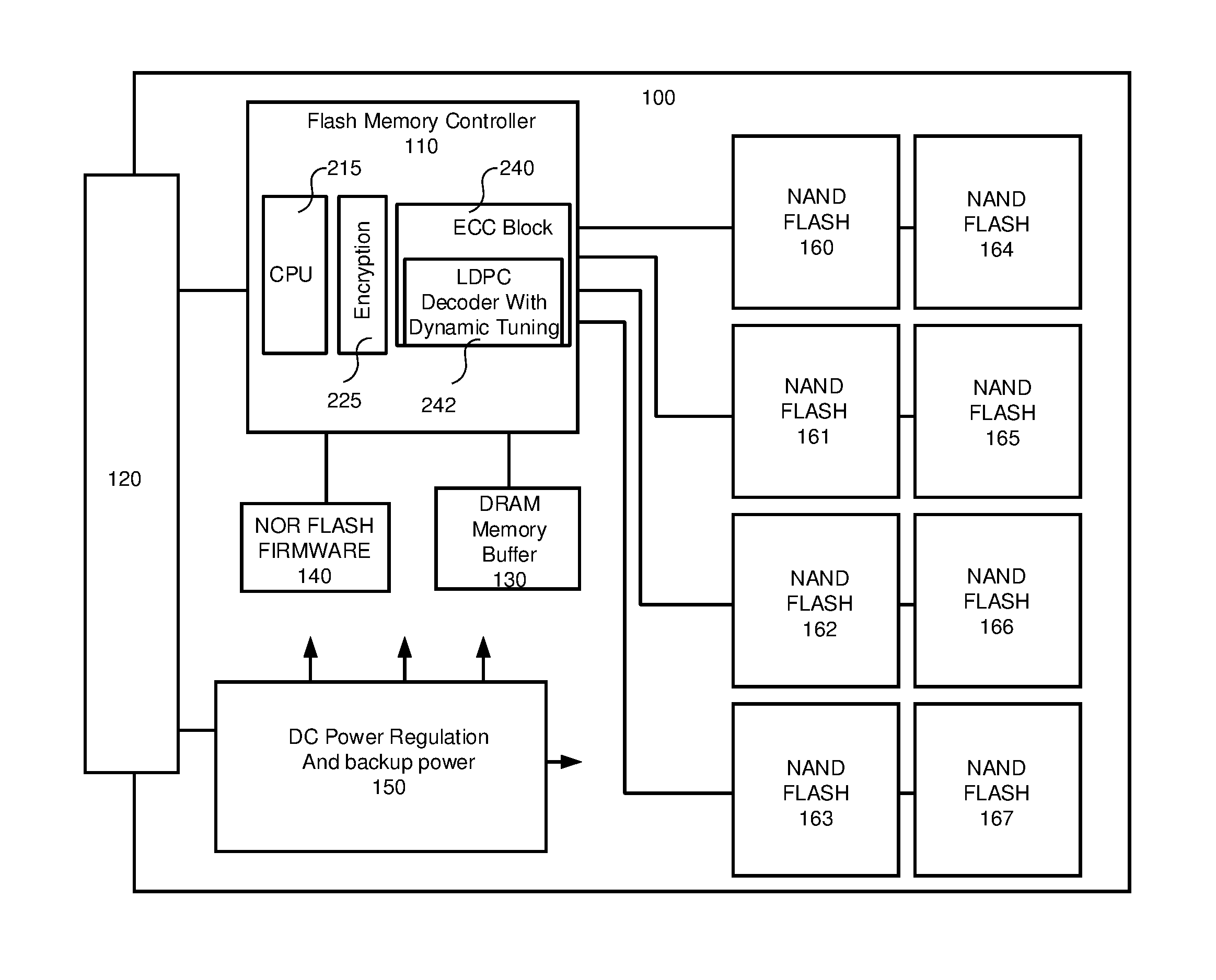

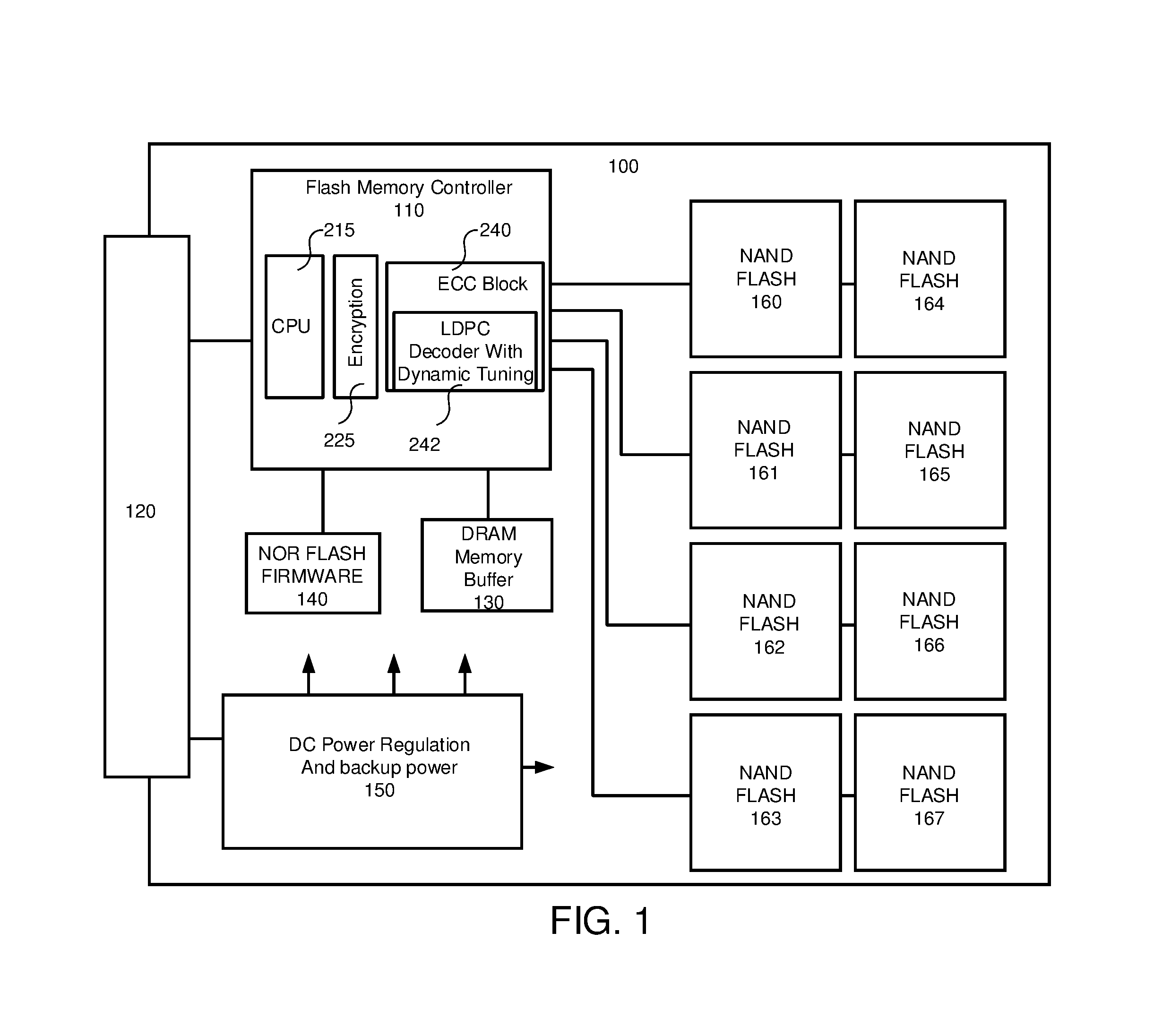

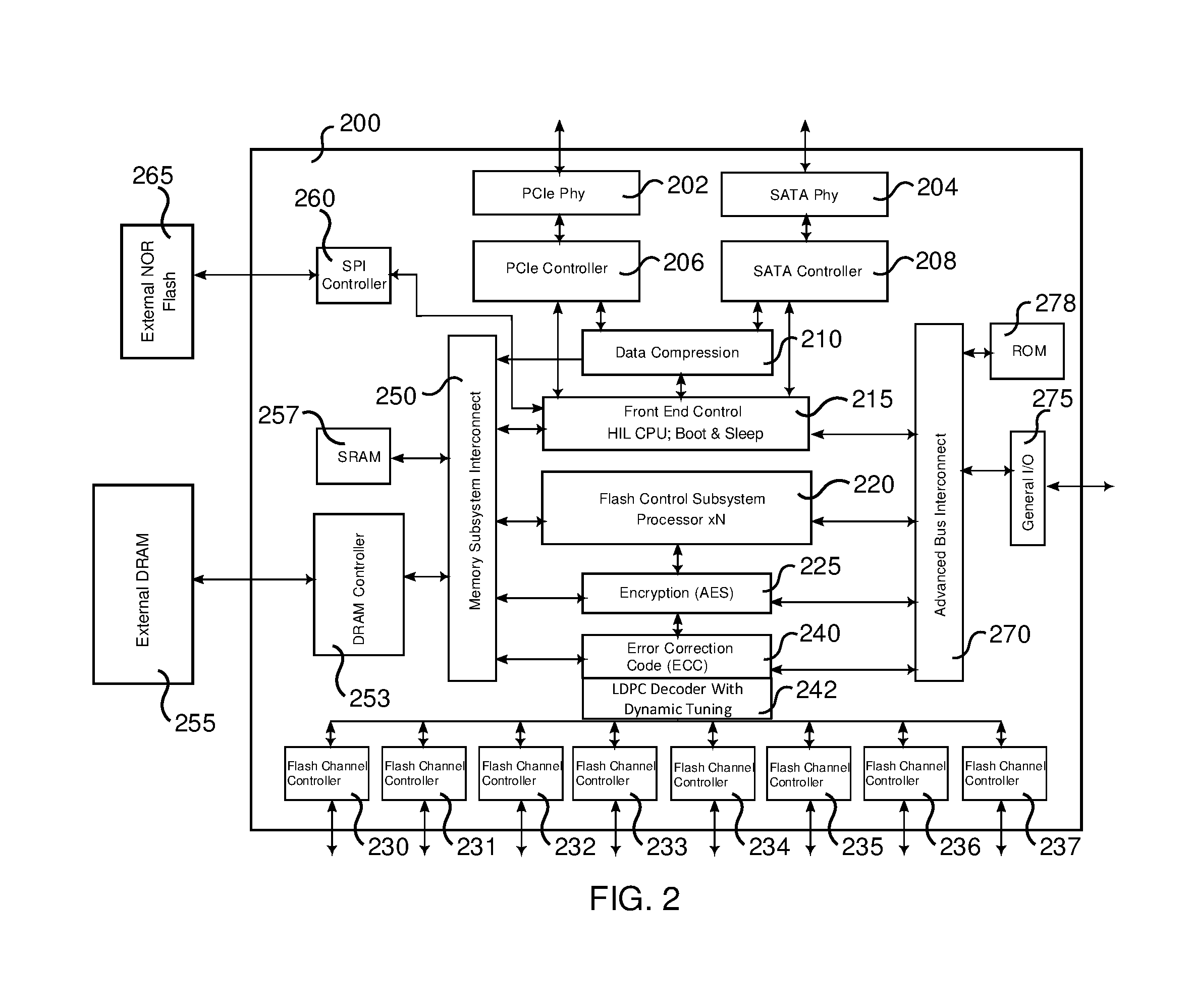

Non-volatile memory controller with error correction (ECC) tuning via error statistics collection

ActiveUS20160006462A1Easy to operateImprove performanceOther decoding techniquesError correction/detection using multiple parity bitsForward error correctionSolid-state drive

A non-volatile memory controller for a solid state drive includes a soft-decision LDPC decoder. The soft-decision LDPC decoder includes a probability generation module. A processor reads collected statistics collated from decoded frames and tunes the performance of the soft-decision LDPC decoder performance. Additional parameters may also be taken into account, such as the scramble seed and the type of non-volatile memory. An asymmetry in errors may also be detected and provided to a hard-decision LDPC decoder to adjust its performance.

Owner:KIOXIA CORP

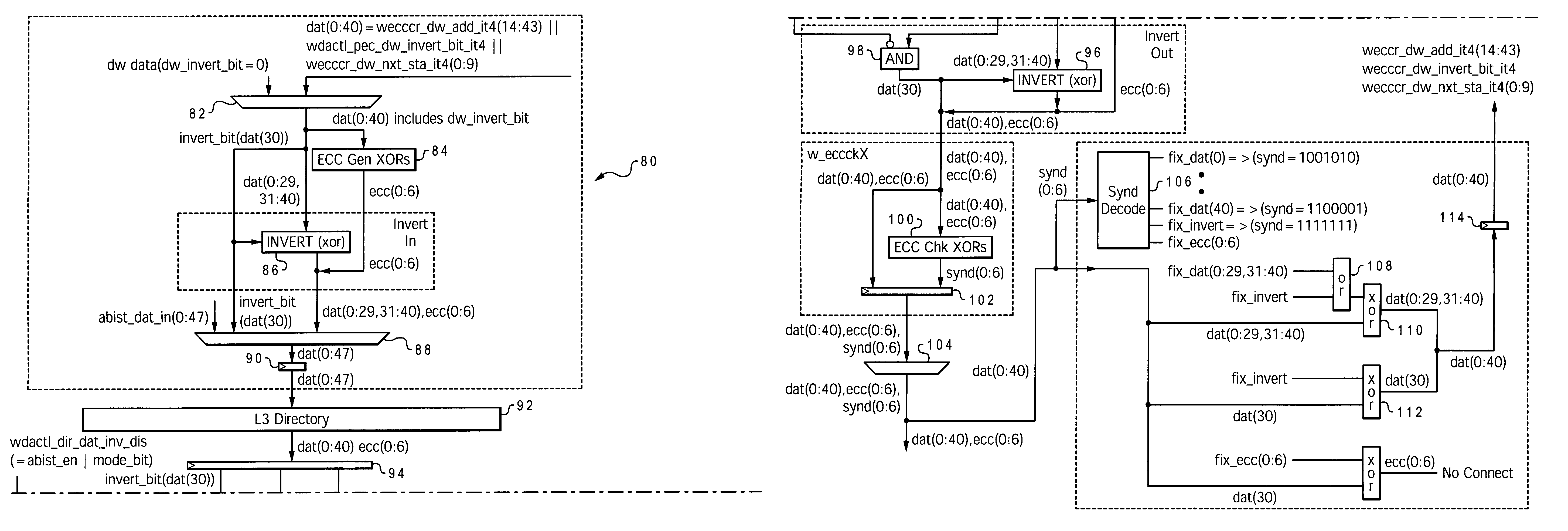

Cache directory array recovery mechanism to support special ECC stuck bit matrix

InactiveUS7272773B2Simple structureEasy to useMemory adressing/allocation/relocationCode conversionData applicationCorrection code

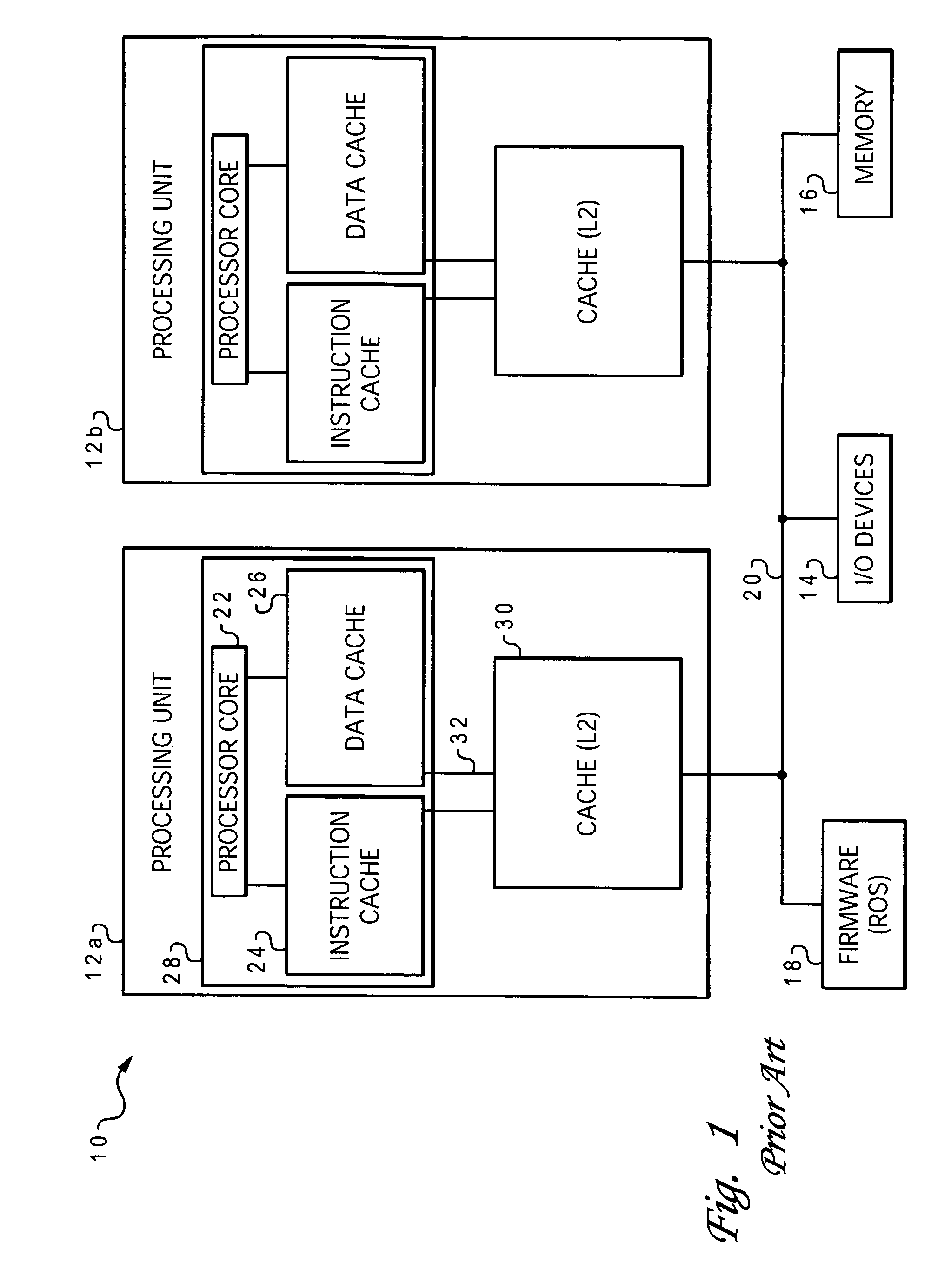

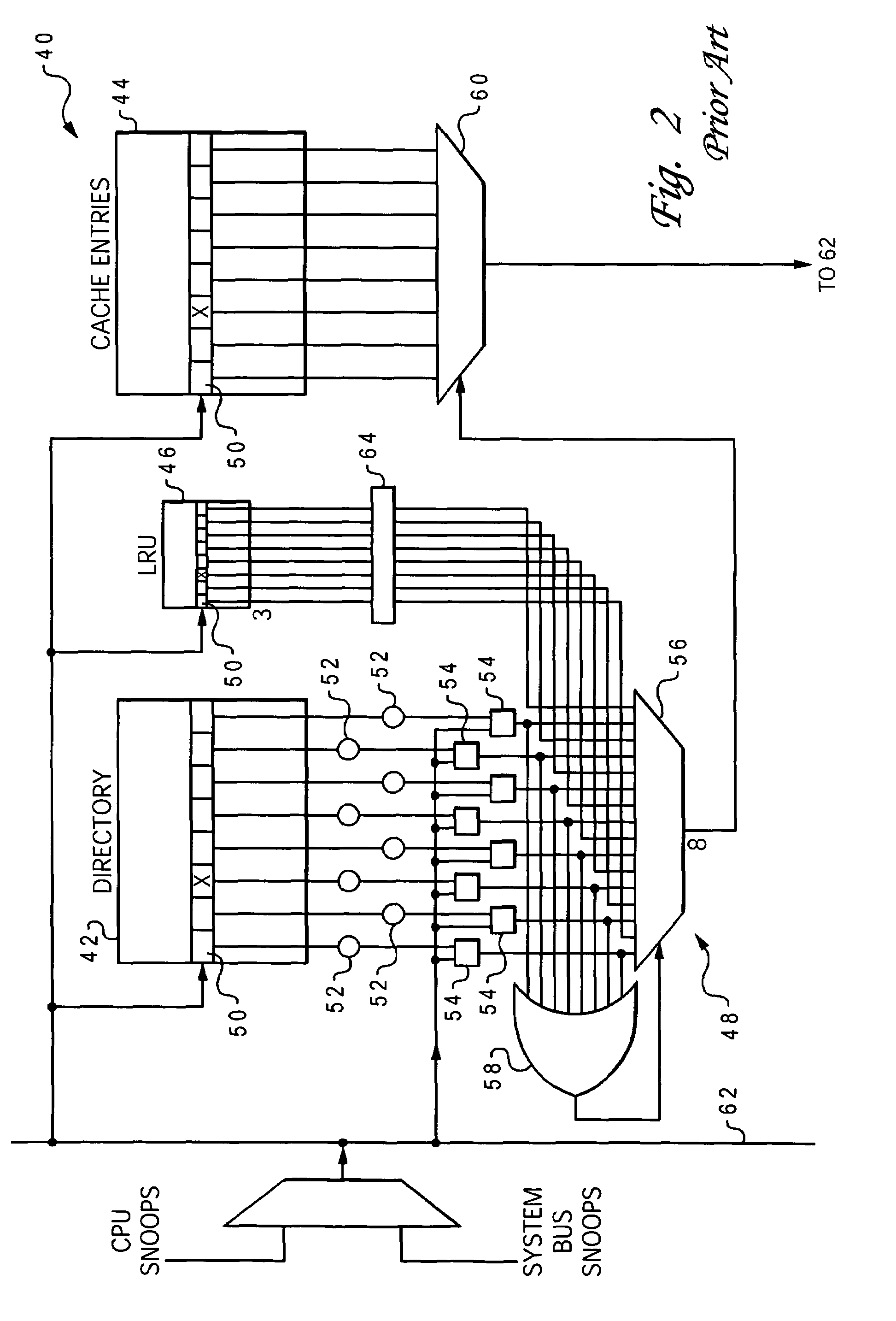

A method of correcting an error in an ECC protected mechanism of a computer system, such as a cache or system bus, by applying data with a number of bits N to an error correction code (ECC) matrix to yield an error detection syndrome, wherein the ECC matrix has a plurality of rows and columns with a given column corresponding to a respective one of the data bits, and selected bits are set in the ECC matrix along each column and each row such that encoding for the ECC matrix allows N-bit error correction and (N−1)-bit error detection. When an error is detected and after it is corrected, the corrected data is inverted and then rewritten to the cache array. The corresponding inversion bit for this entry is accordingly set to indicate that the data as currently stored is inverted.

Owner:INT BUSINESS MASCH CORP

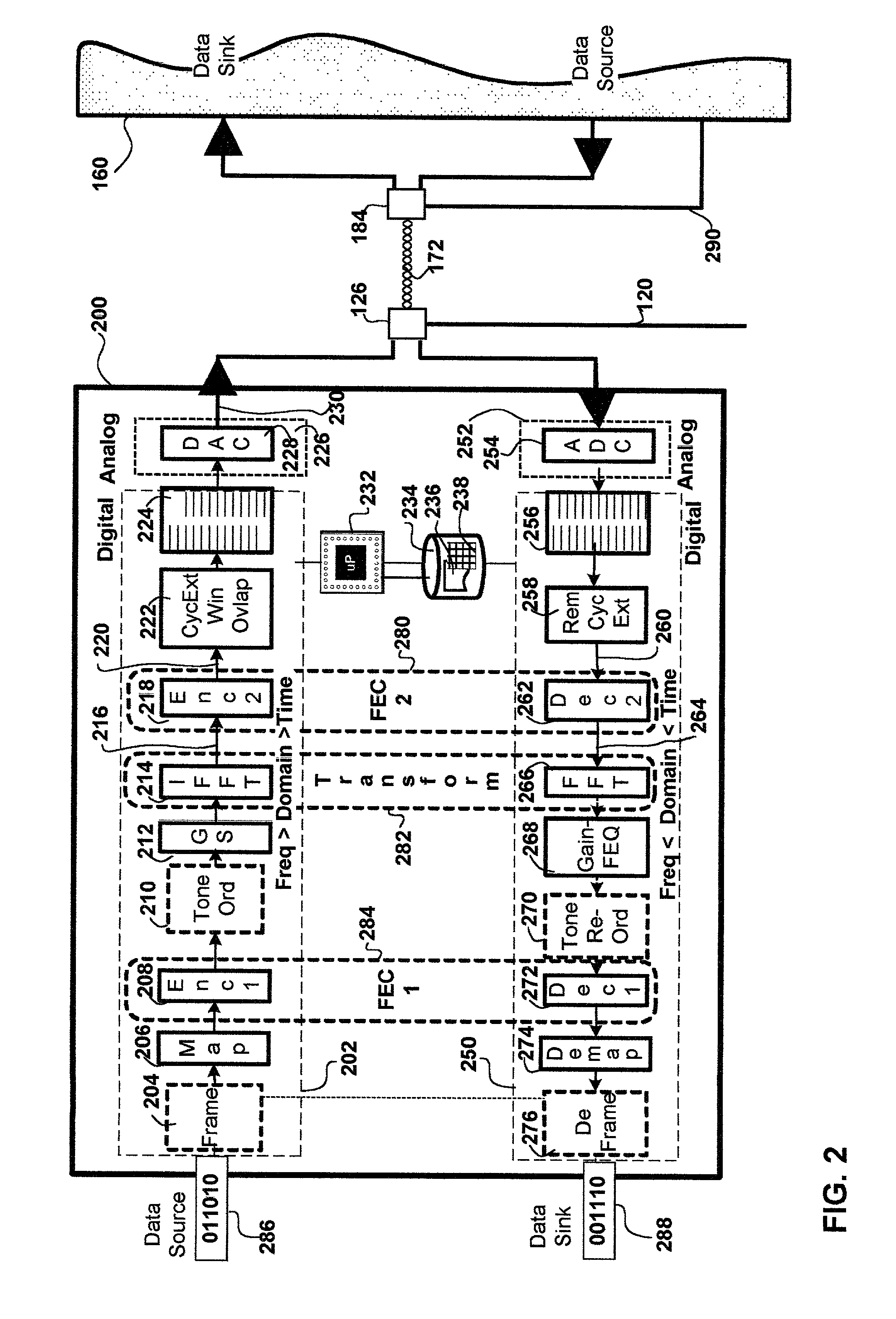

Method and apparatus for time-frequency domain forward error correction for digital communication systems

InactiveUS6976202B1Reduce overheadData representation error detection/correctionTransmission path divisionTime domainModem device

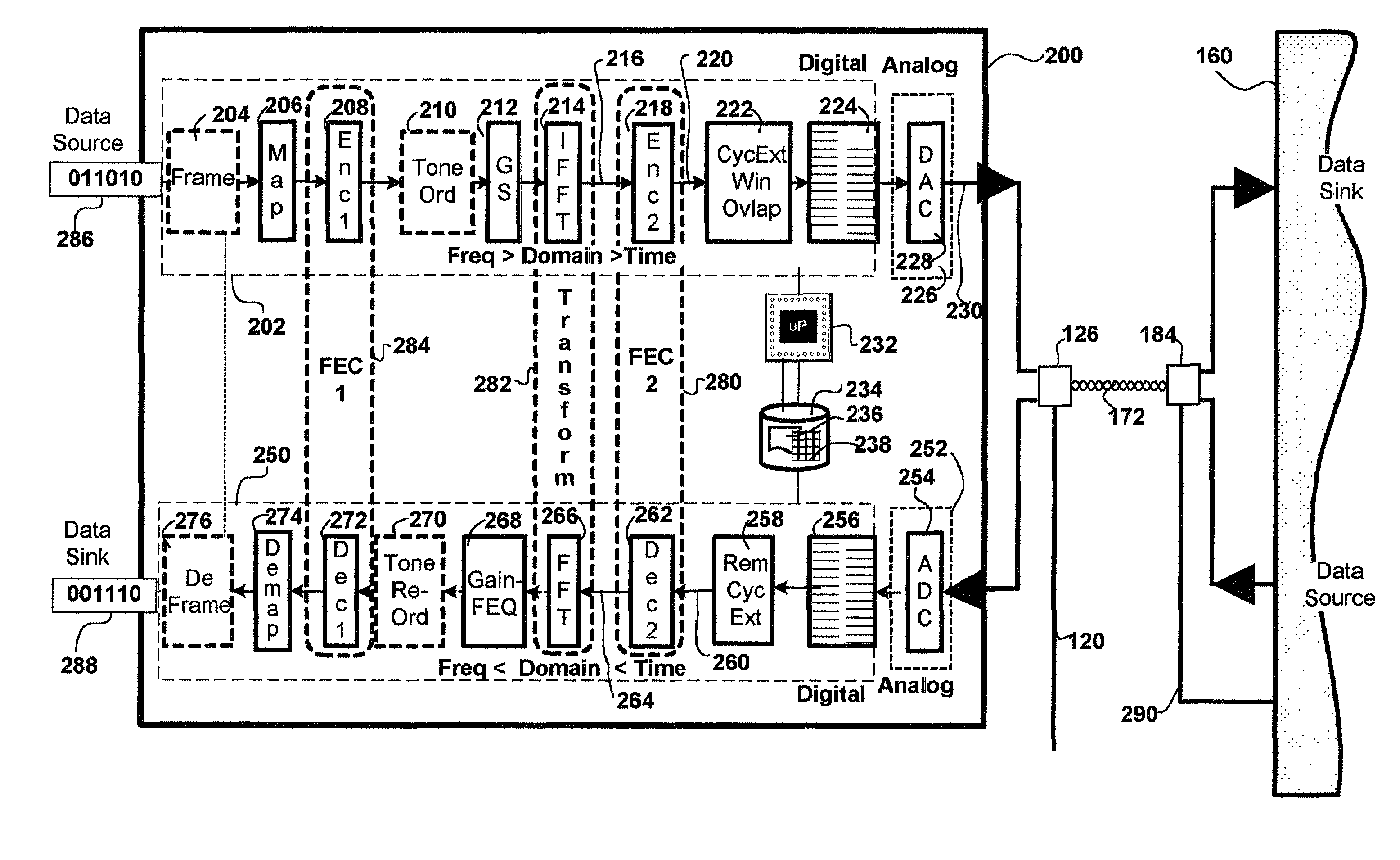

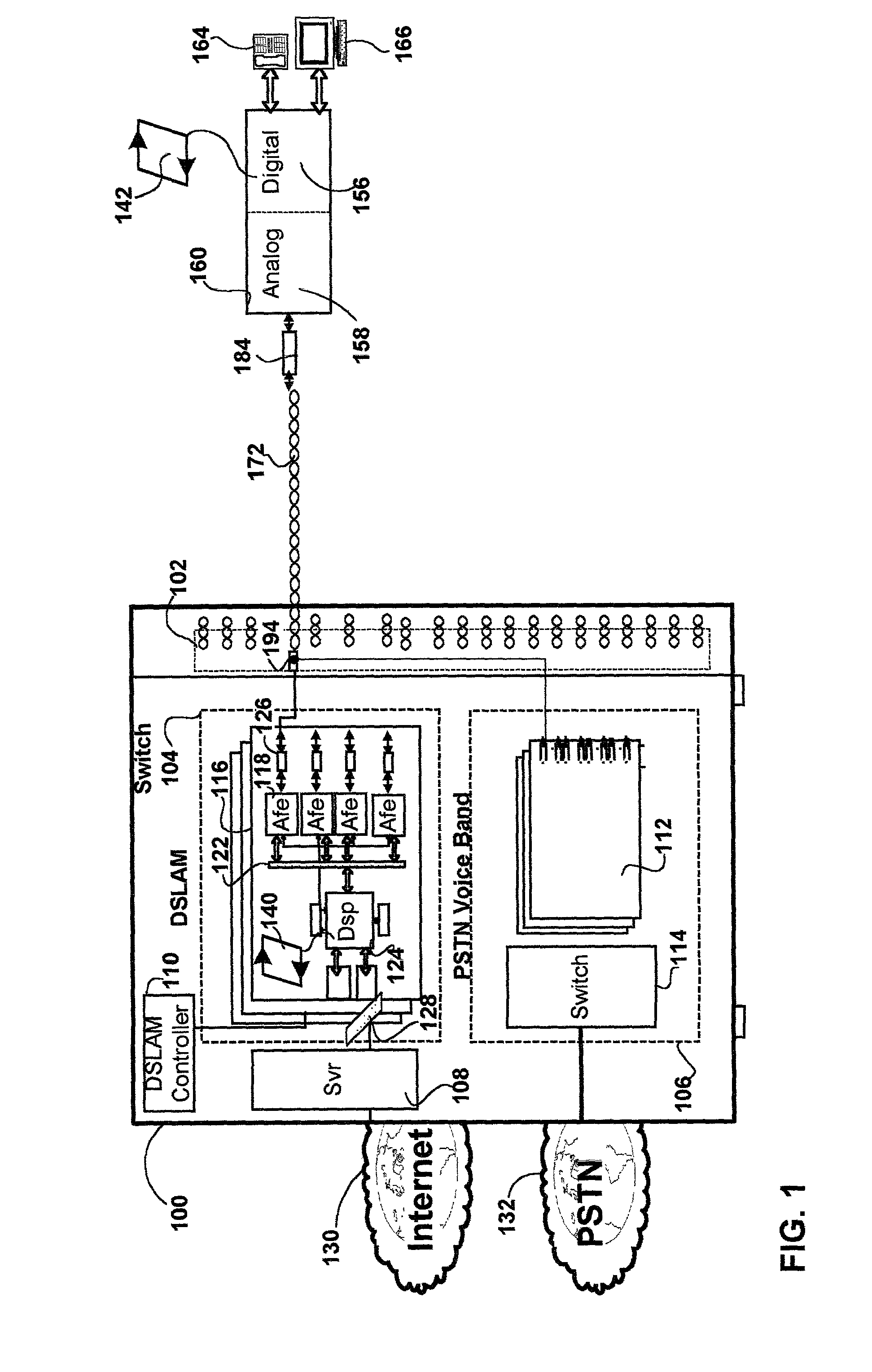

A method and apparatus for time and frequency domain forward error correction (FEC) in a modem which communicates data using multiple discrete sub-channels is provided. The invention may be implemented in hardware, software or firmware. In an embodiment of the invention a modem with a plurality of components forming a transmit path and a receive path is disclosed. The modem communicates data across a wired or wireless communication medium using a multiplicity of discrete sub-channels. The modem includes a transform component and a time domain FEC component. The transform component transforms the multiplicity of discrete sub-channels of a communication between a time domain and a frequency domain on the receive path and vice-versa on the transmit path. The time domain FEC component couples to the transform component. The time domain FEC component has a complementary encoder and decoder portion on the transmit and receive paths respectively. The encoder and decoder portions encode and decode respectively the multiplicity of discrete sub-channels in the time domain.

Owner:IKANOS COMMUNICATIONS

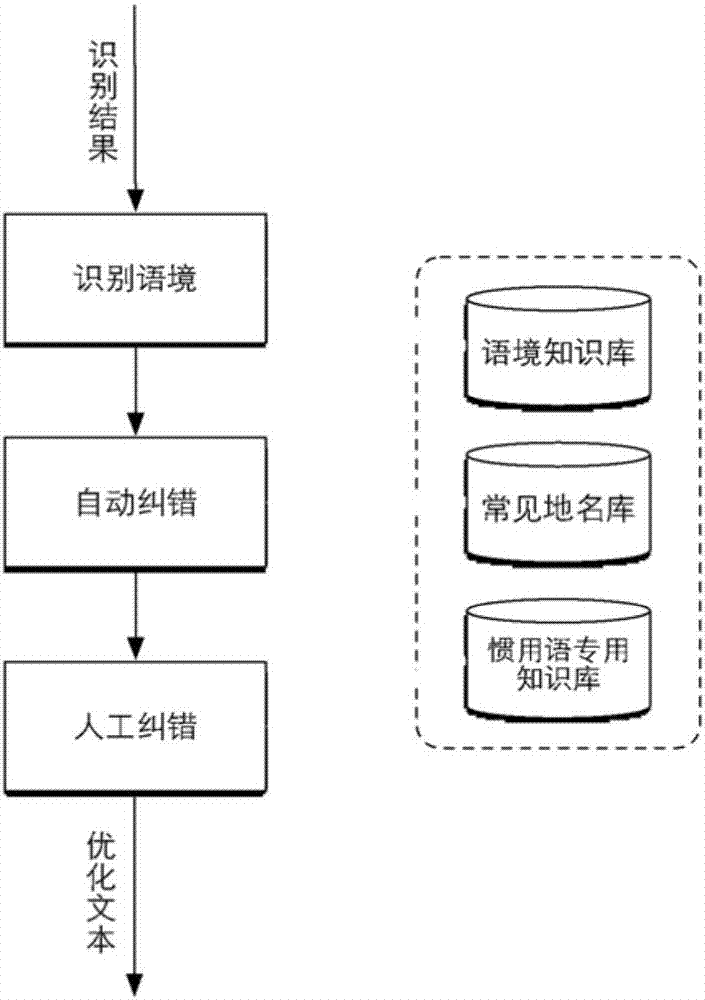

Method for correcting error-prone words in voice interaction

InactiveCN107305768AEnhance typo-correcting abilityIncrease weightSpeech recognitionNamed-entity recognitionContext recognition

The invention provides a method for correcting error-prone words in voice interaction. The method comprises the steps of context recognition, automatic error correction based on semantic restriction, and artificial error correction based on semantic feedback. Through voice interaction with users and perception and recognition of the context of a topic, automatic error correction of an entity with a specific meaning can be achieved by using the named entity recognition technology within the limited semantic range, additional semantics can be obtained through artificial feedback so as to conduct error correction, and higher input efficiency and more convenient wrong word correction than existing voice recognition software are realized.

Owner:SHANGHAI JIAO TONG UNIV

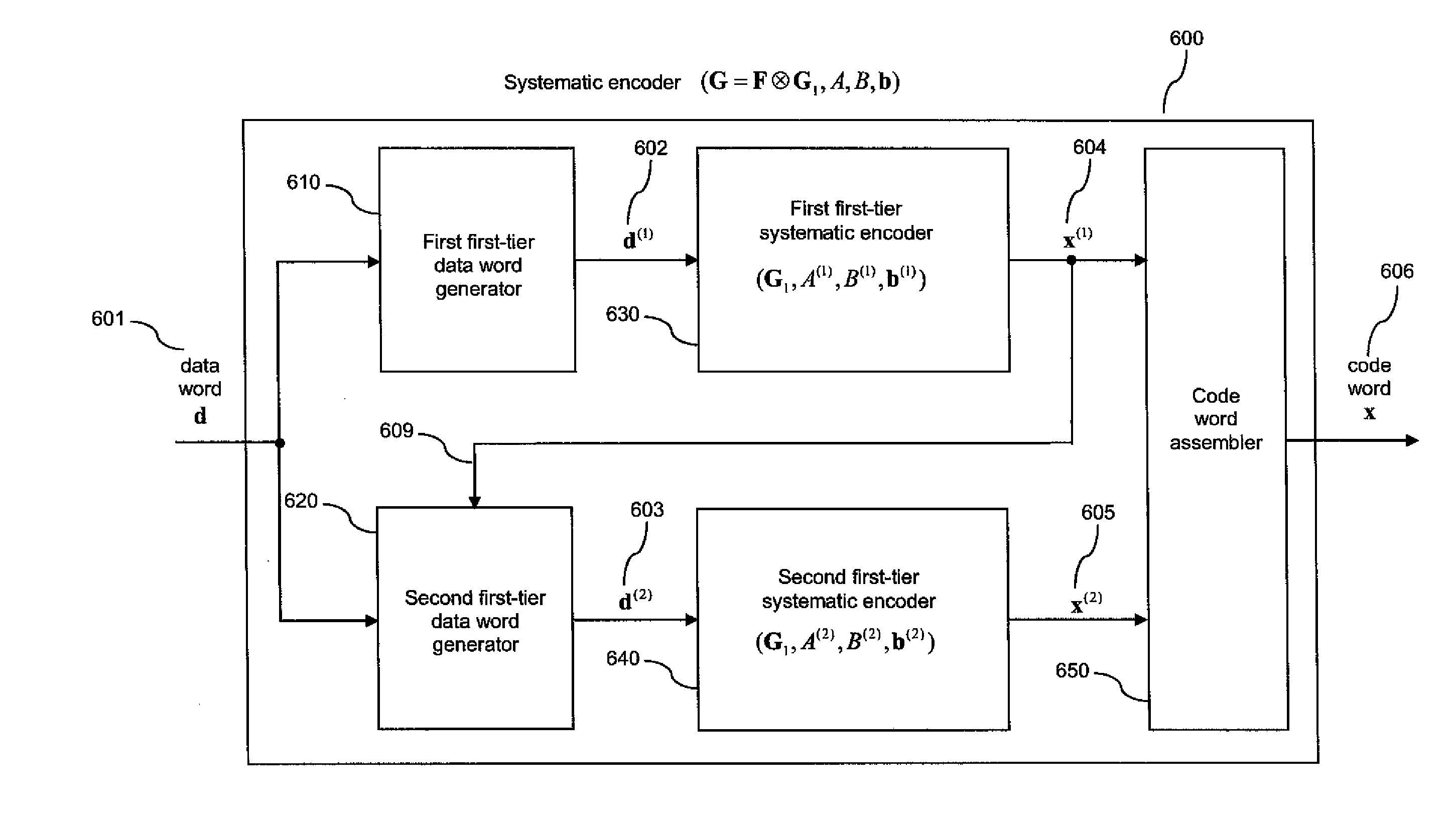

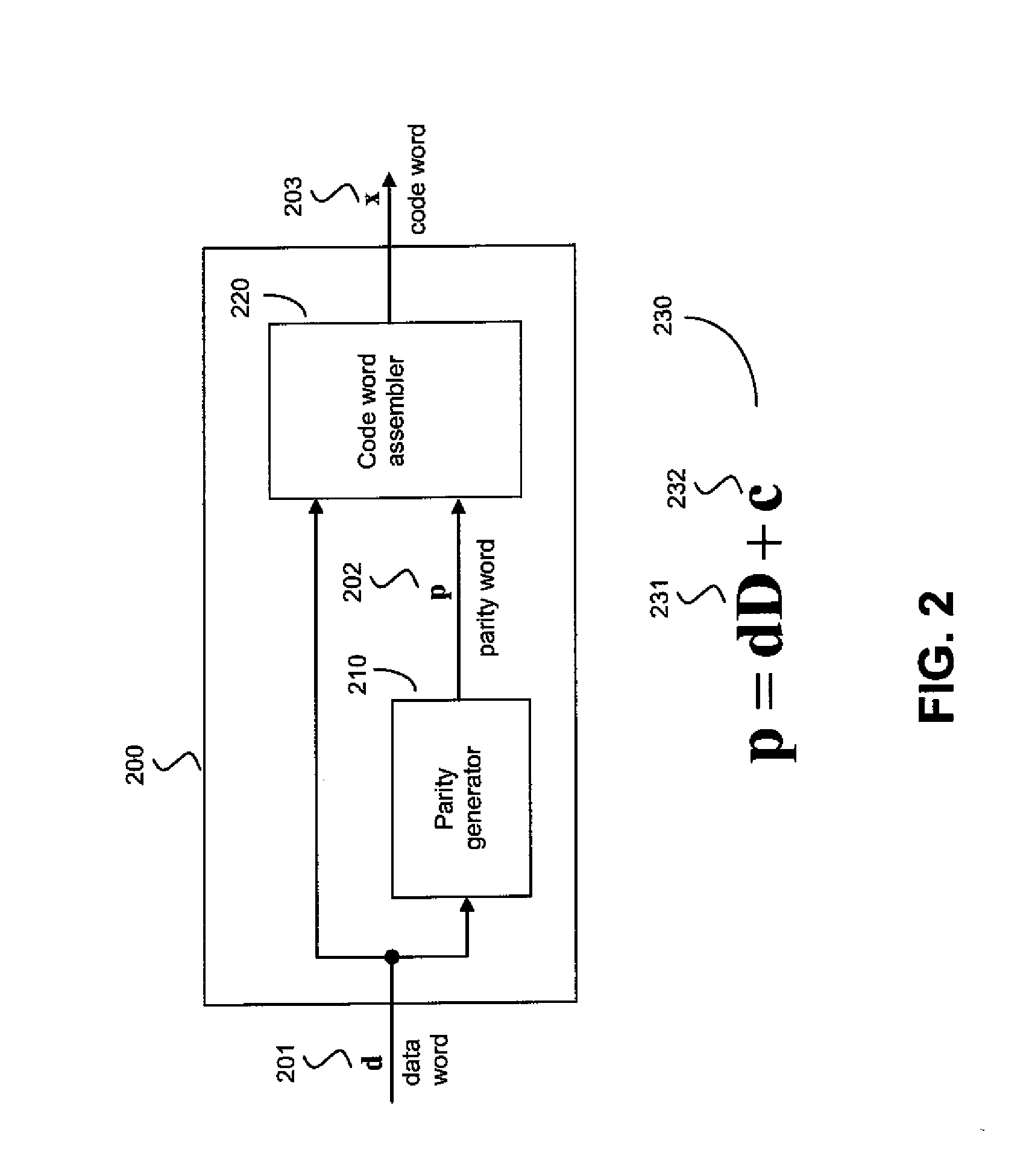

Method and system for error correction in transmitting data using low complexity systematic encoder

ActiveUS20130283116A1Improve performanceImprove Noise PerformanceCode conversionChannel coding adaptationTransmission channelForward error correction

Owner:POLARAN HABERLESME TEKNOLOJILERI ANONIM SIRKETI

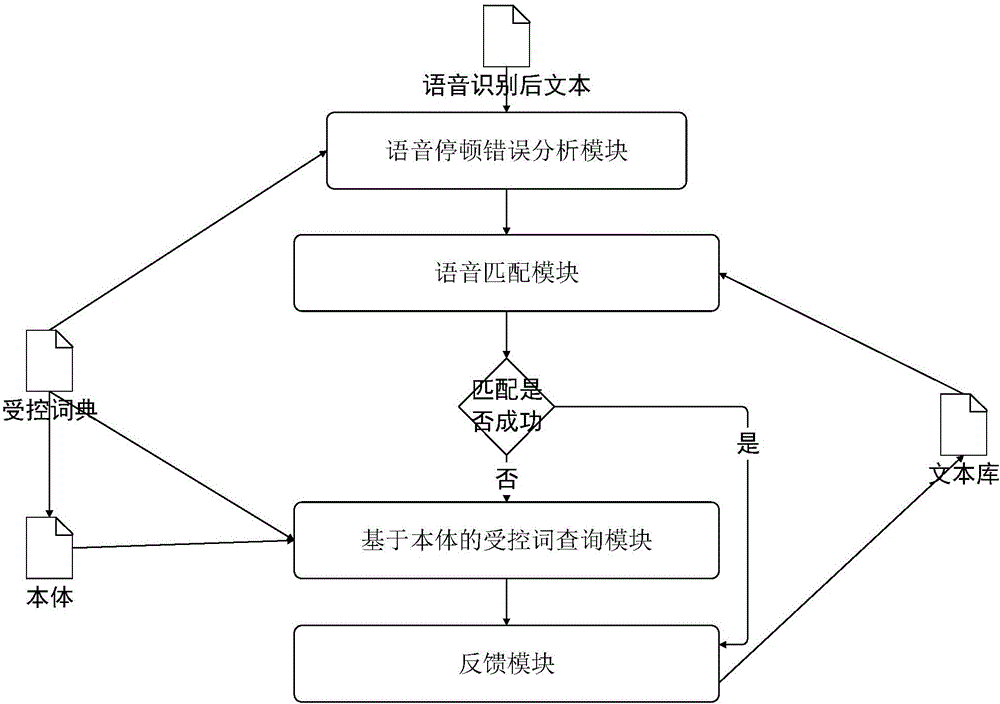

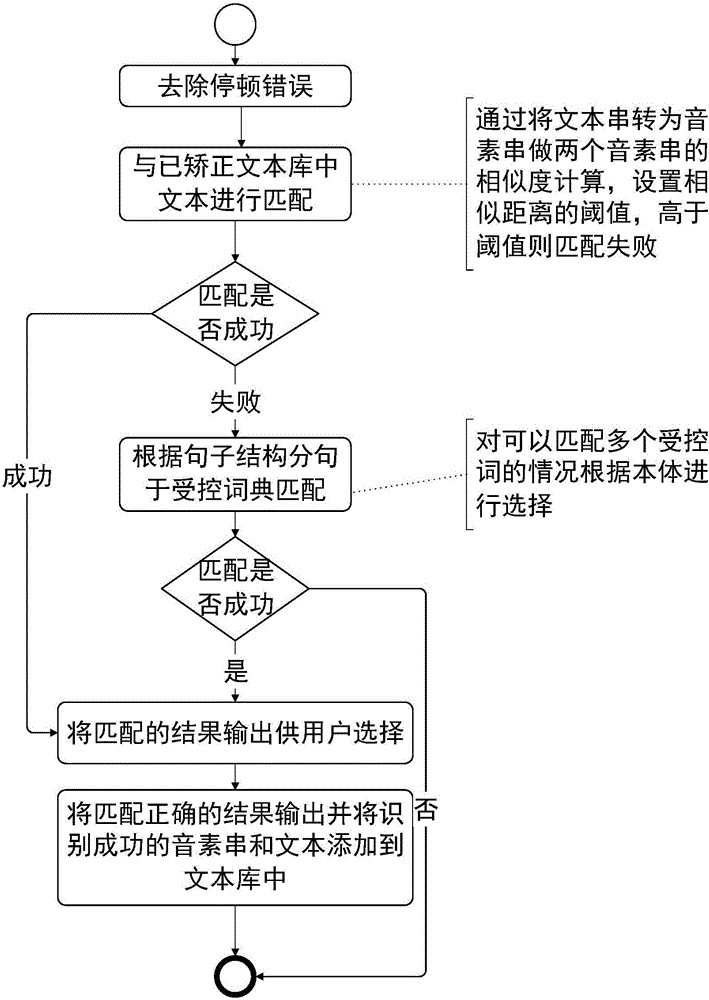

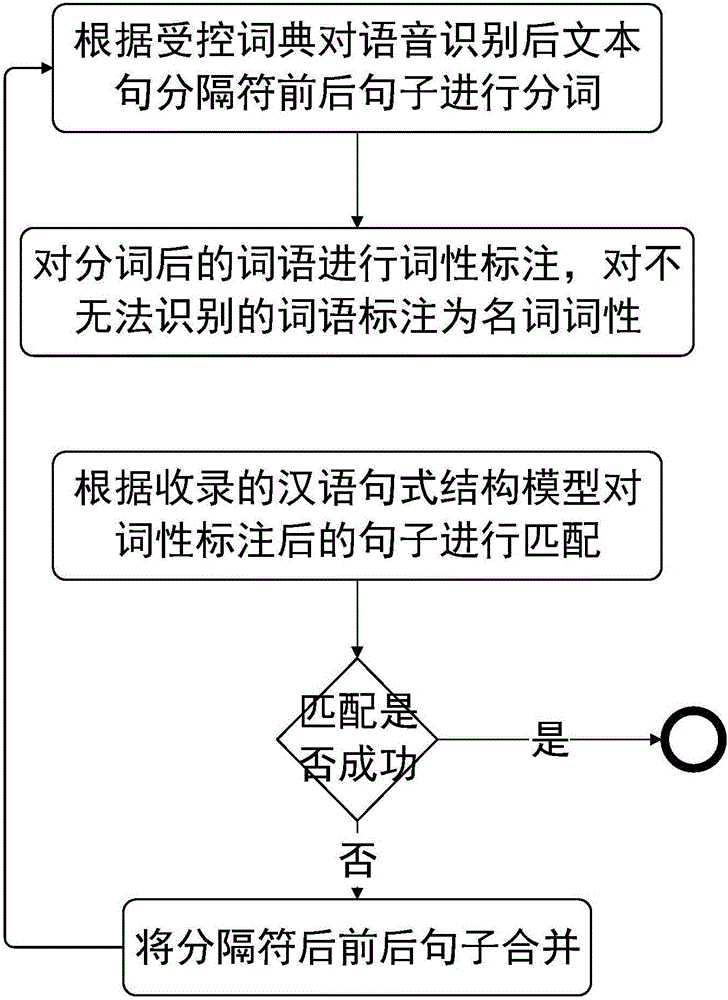

Field-based method and system for feeding back text error correction after speech recognition

The invention discloses a field-based method for feeding back text error correction after speech recognition, and belongs to the speech recognition field. Text sentences after speech recognition are analyzed based on errors of speed pauses of Chinese sentence structures. The method is characterized by detecting whether structures before and after a sentence separator meet the sentence pattern rules of Chinese language, finding pause errors, calculating and dividing sentences based on phoneme string similarity and converting into pinyin, converting pinyin into phoneme strings according to a phoneme table, finding sentences corresponding to the phoneme strings similar to the strings in a corpus, establishing a body based on a body controlled word query module through the controlled word table of the field, correcting the errors related to the field in the text after speech recognition through the body, outputting the matching result by a feedback module, and adding the correct identification result selected by a user and the original phoneme strings in the corpus. According to the method and system, the originally correct result of speech recognition may not be affected, and the speech recognition accuracy can be better determined through a body and feedback mechanism.

Owner:CHONGQING UNIV

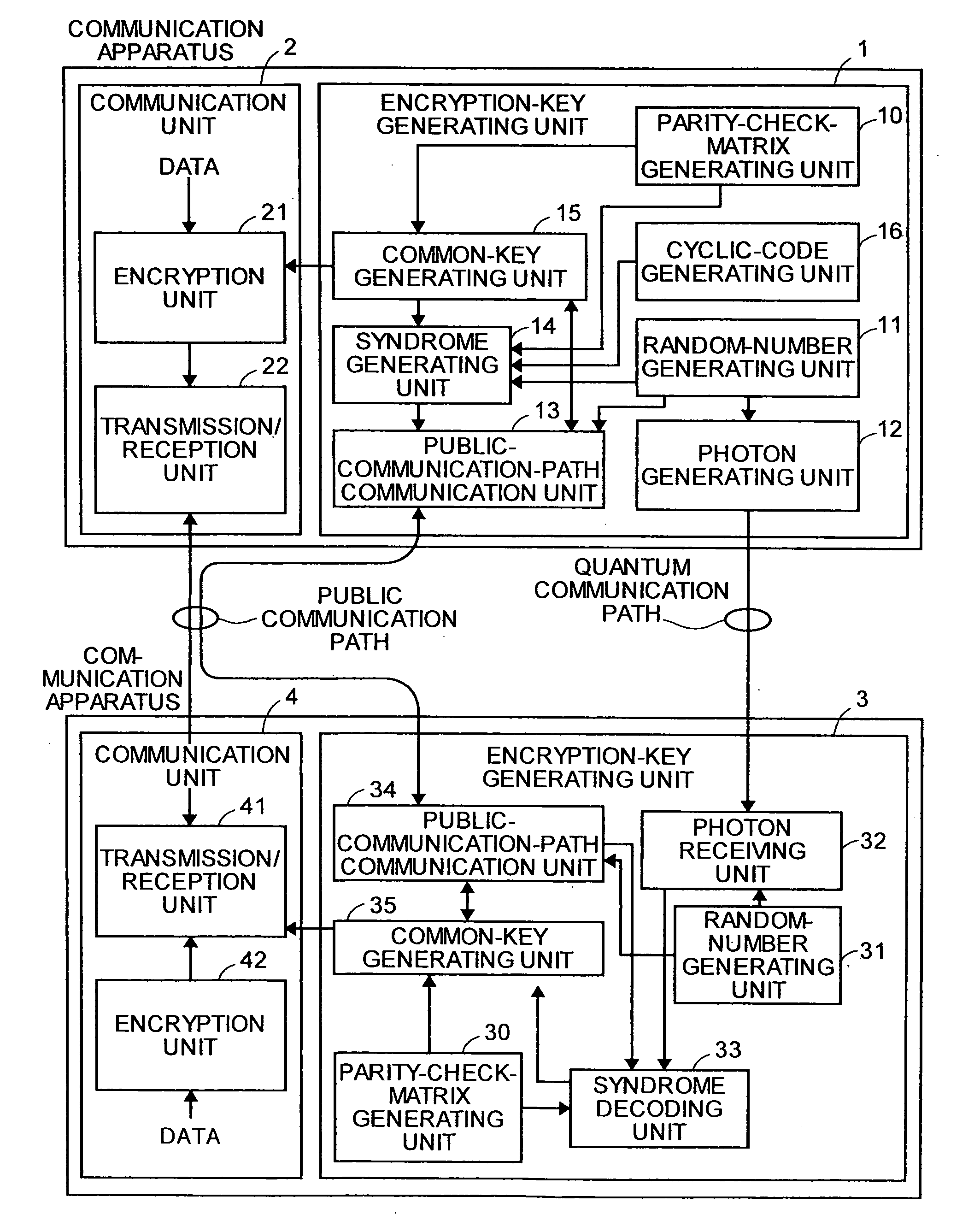

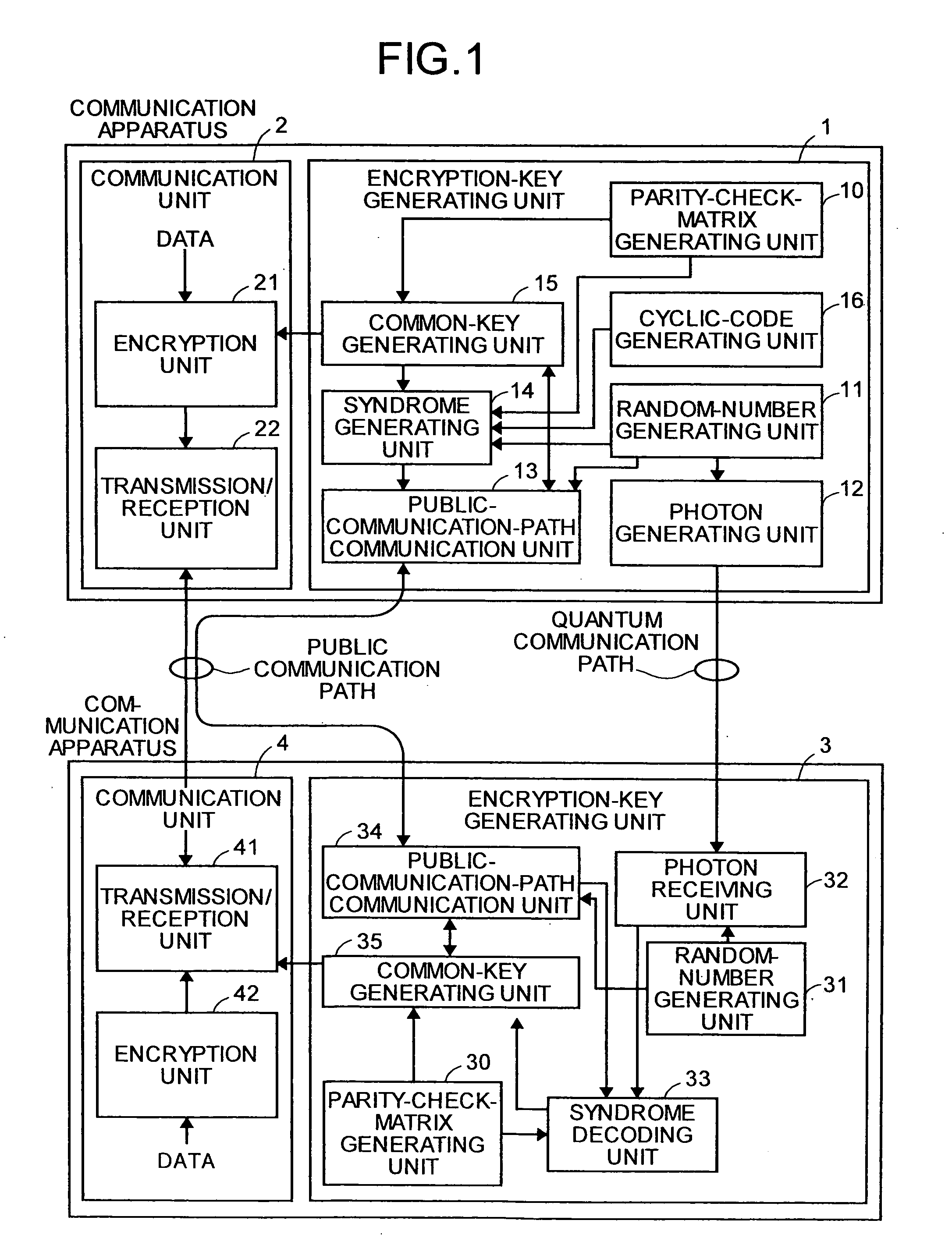

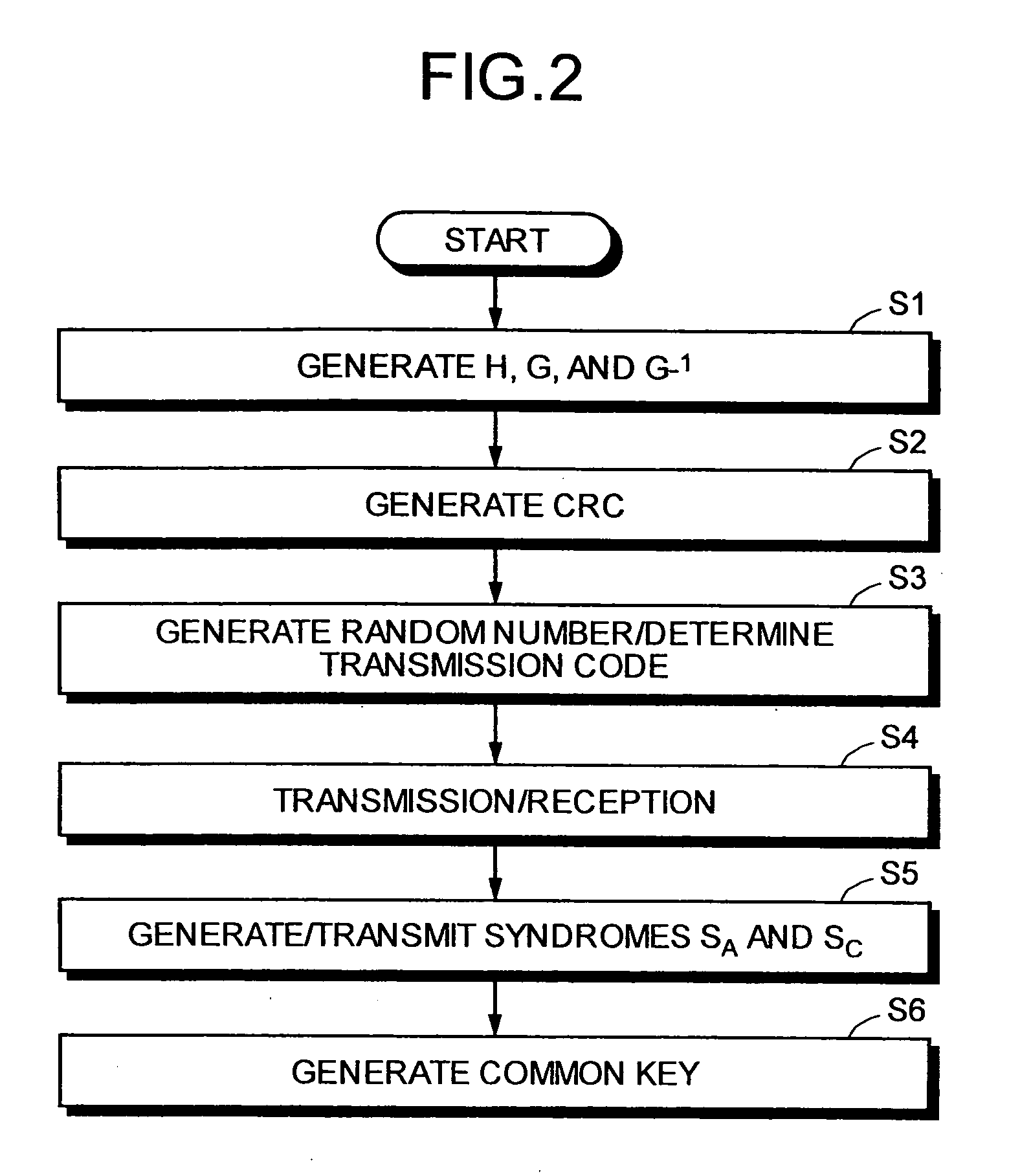

Quantum Key Distribution Method and Communication Apparatus

InactiveUS20080144833A1Stable characteristicsKey distribution for secure communicationSynchronising transmission/receiving encryption devicesComputer hardwareParity-check matrix

In a quantum key distributing method of the present invention, a communication apparatus on a reception side performs error correction using parity check matrixes for an LDPC code that have an extremely high error correction ability. In the quantum key distributing method of the present invention, a cyclic code syndrome generated by a communication apparatus on a transmission side and an estimated cyclic code syndrome generated based on an estimated word after error correction are compared to perform error detection for the estimated word.

Owner:MITSUBISHI ELECTRIC CORP

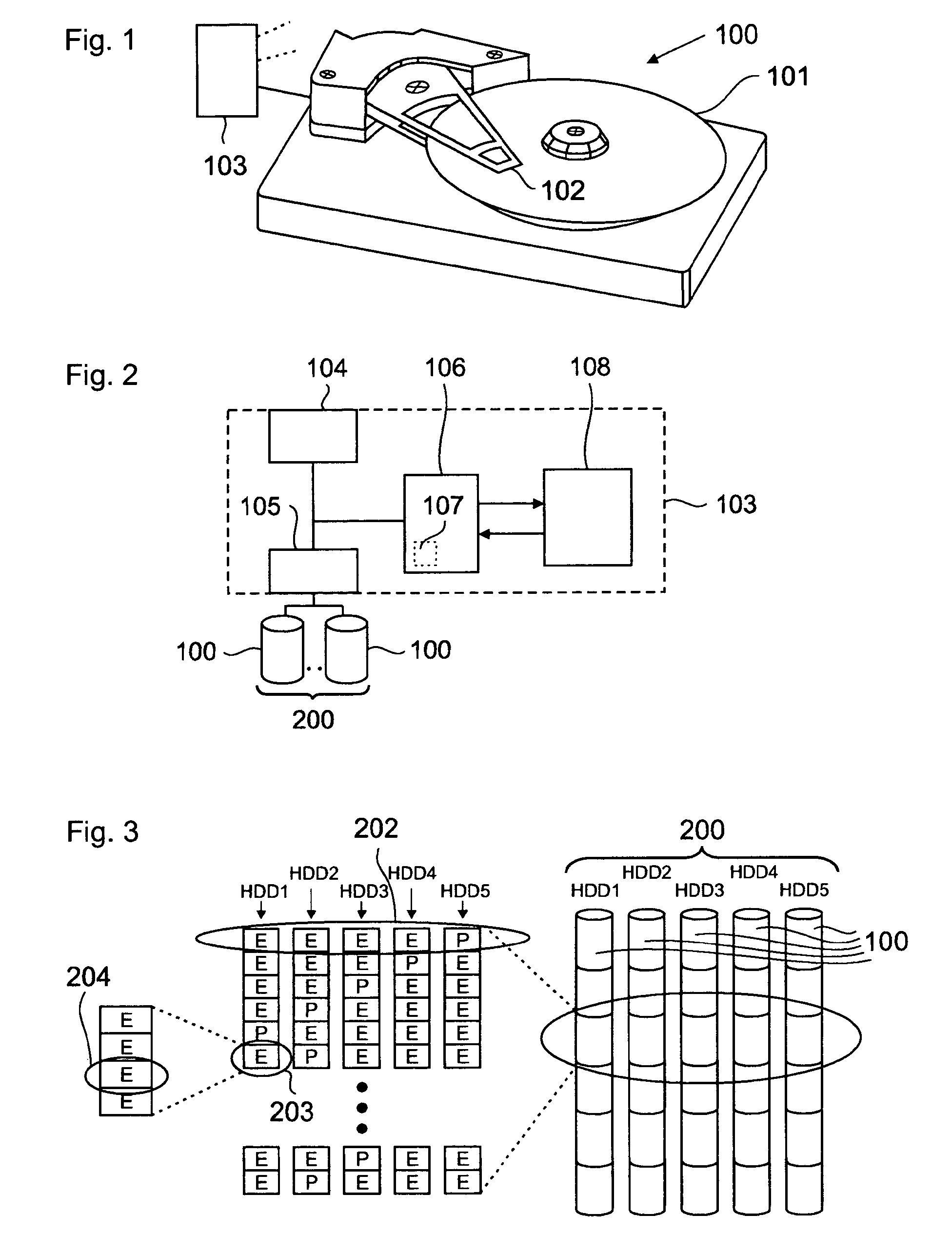

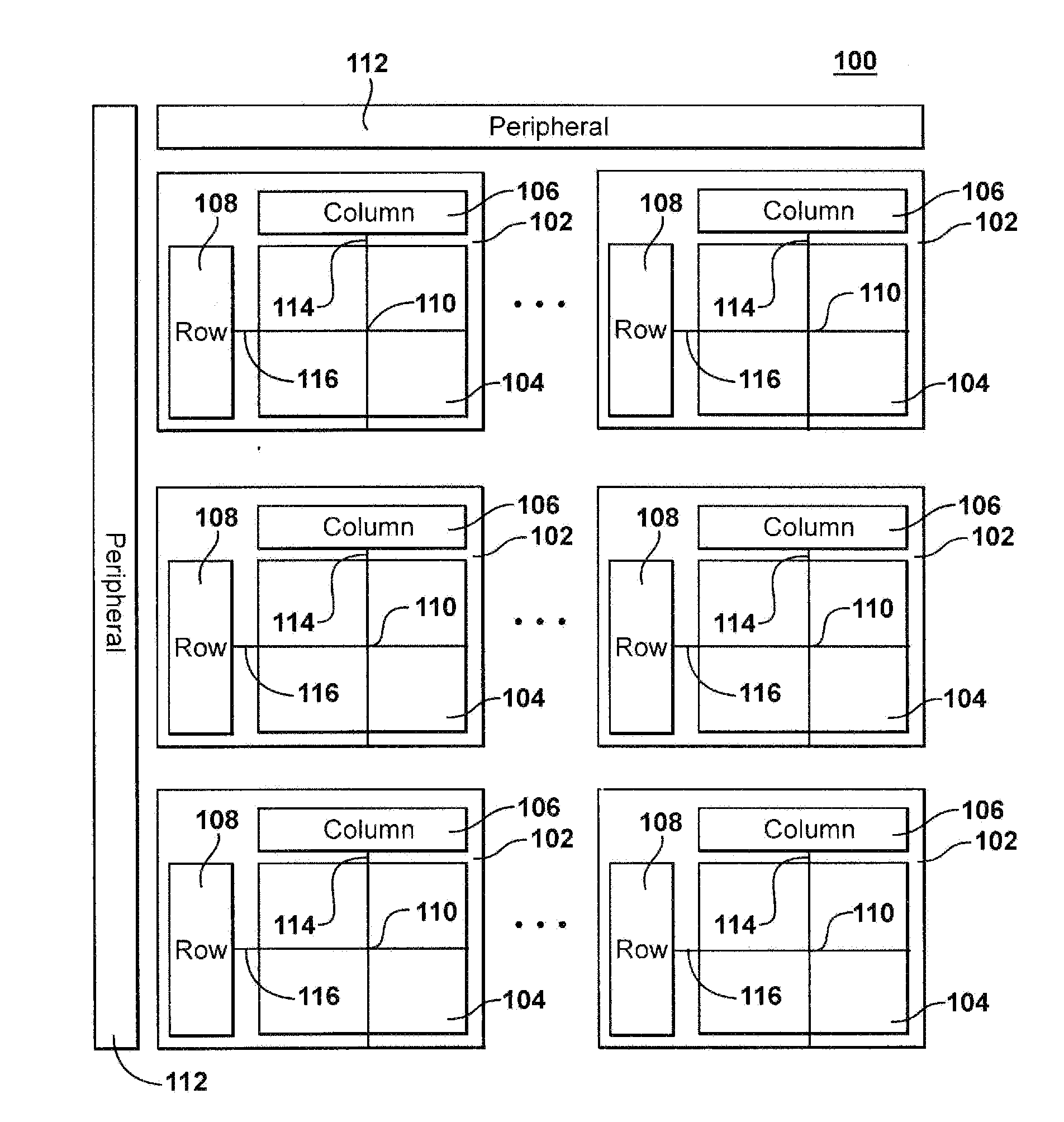

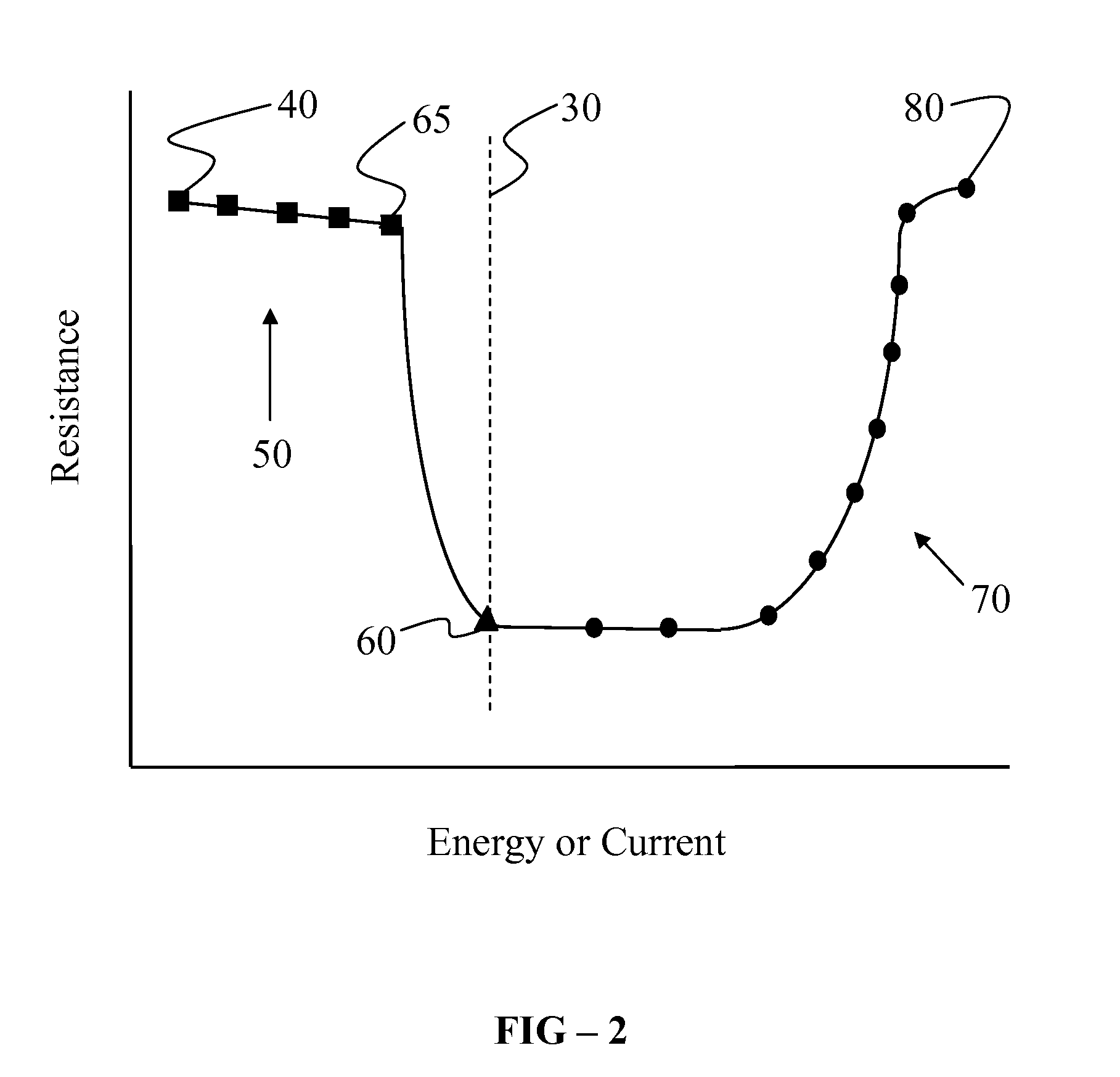

Sector Array Addressing for ECC Management

ActiveUS20120069622A1Minimizes effect of configurationReduce in quantityDigital storagePhase-change memoryArray data structure

An addressing scheme for non-volatile memory arrays having short circuit defects that manages the demand for error correction. The scheme generally avoids simultaneous active driving of the row line and column line of the selected cell during write. Instead, only a single row or column line is actively driven at any one time and all other array lines are left floating. In addition, the number of memory cells accessed from a given row or column during a fetch may be limited. The benefits of the scheme include preventing short circuits from drawing excess currents through the array and limiting the frequency of read or write failures caused by short circuits to a manageable number. In one embodiment, the scheme maintains the demand for error correction to within the error correction capability of a flash controller. Exemplary embodiments include phase-change memory arrays.

Owner:OVONYX MEMORY TECH LLC

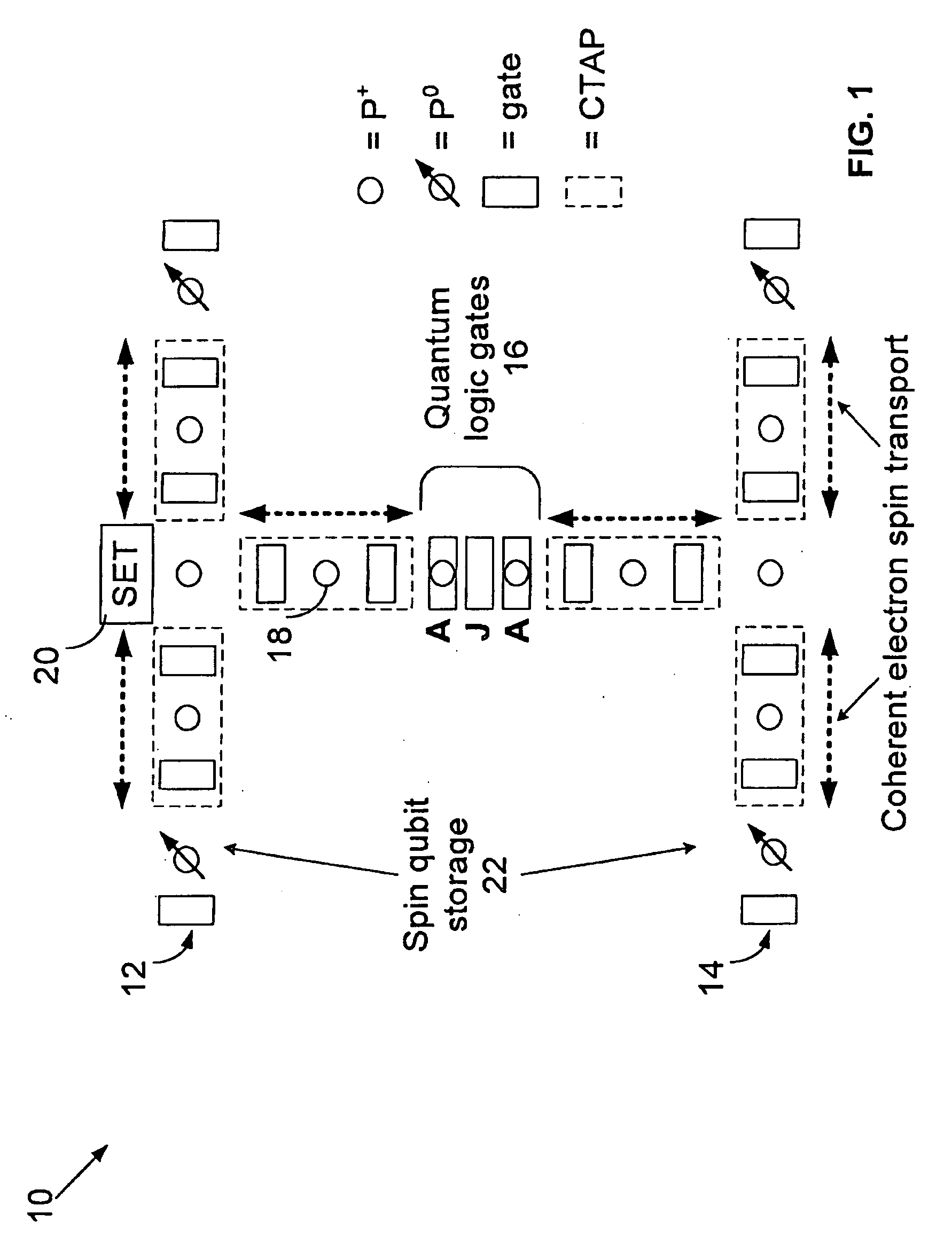

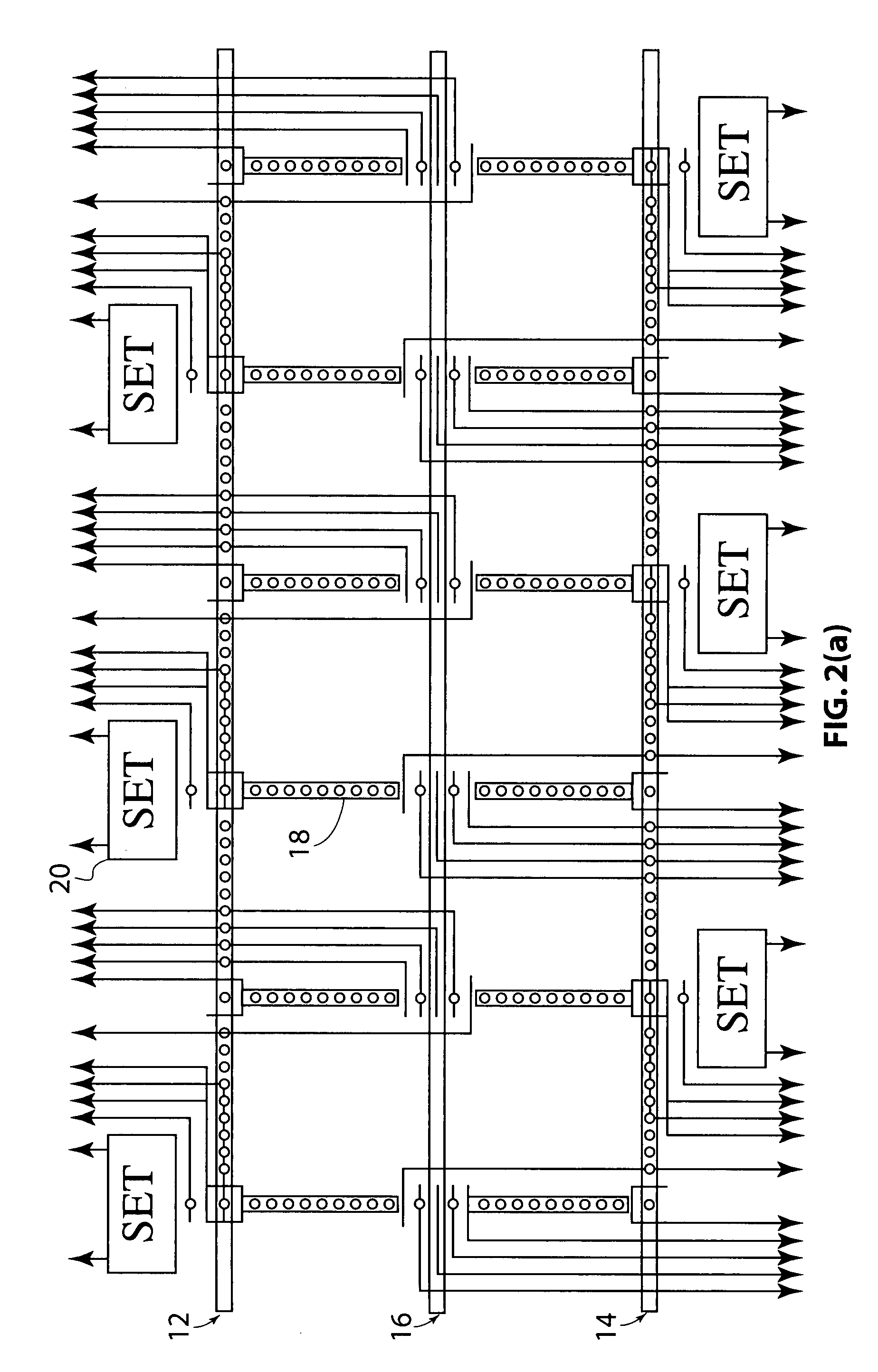

Apparatus and method for quantum processing

ActiveUS10229365B2Reduce variationPrevent unwanted tunnelingQuantum computersSolid-state devicesSemiconductor materialsSpins

The present disclosure provides a quantum processor realized in a semiconductor material and method to operate the quantum processor to implement error corrected quantum computation. The quantum processor comprises a plurality of qubit elements disposed in a two-dimensional matrix arrangement. The qubits are implemented using the nuclear or electron spin of phosphorus donor atoms. Further, the processor comprises a control structure with a plurality of control members, each arranged to control a plurality of qubits disposed along a line or a column of the matrix. The control structure is controllable to perform topological quantum error corrected computation.

Owner:NEWSOUTH INNOVATIONS PTY LTD +1

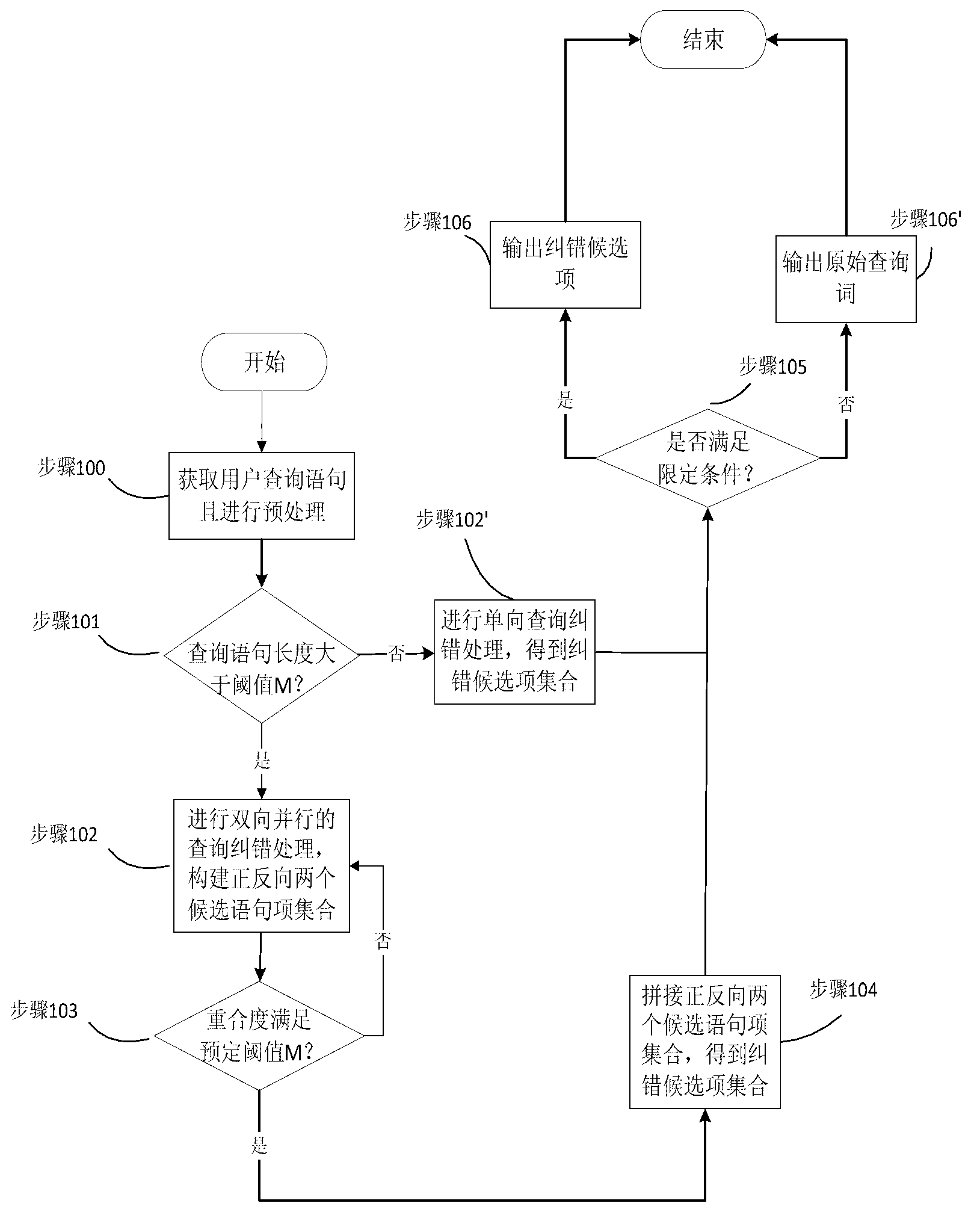

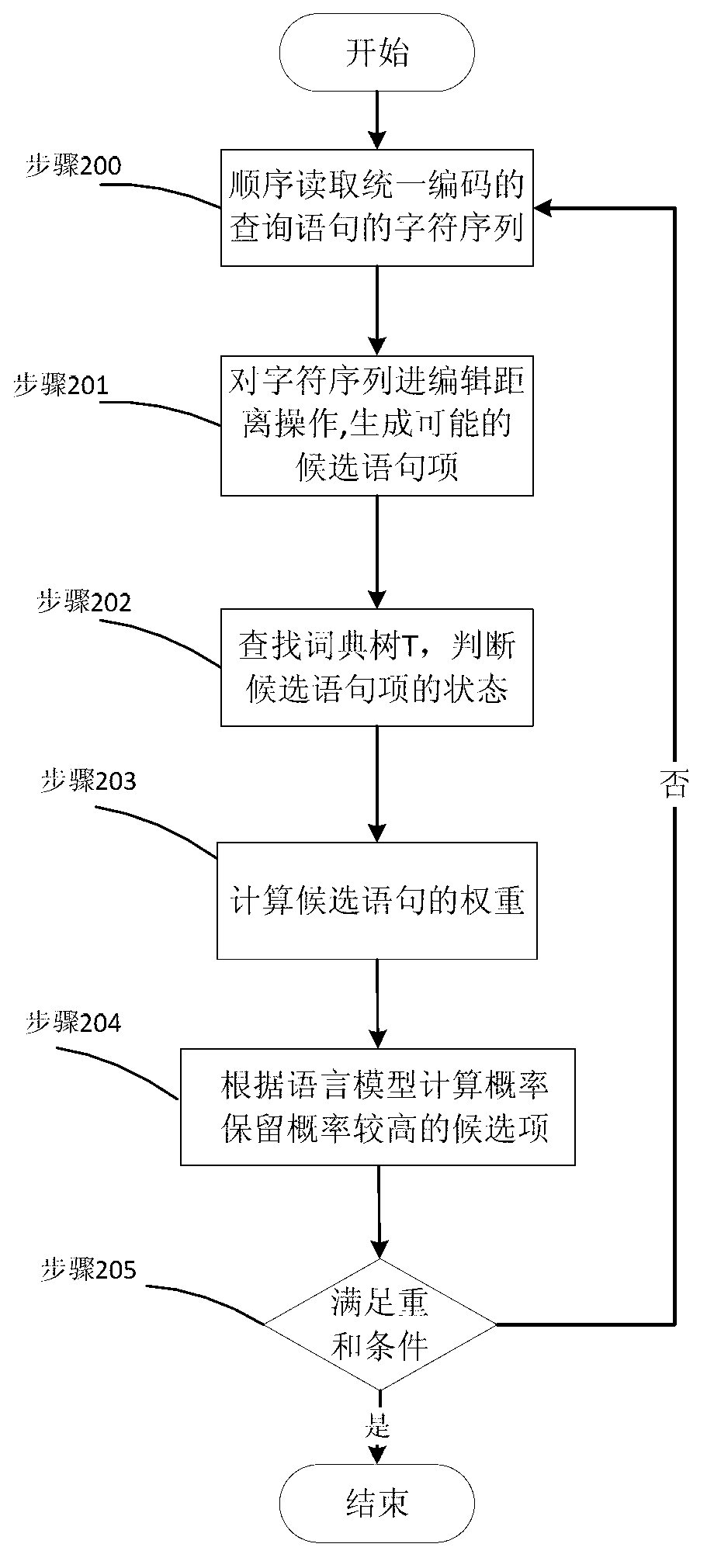

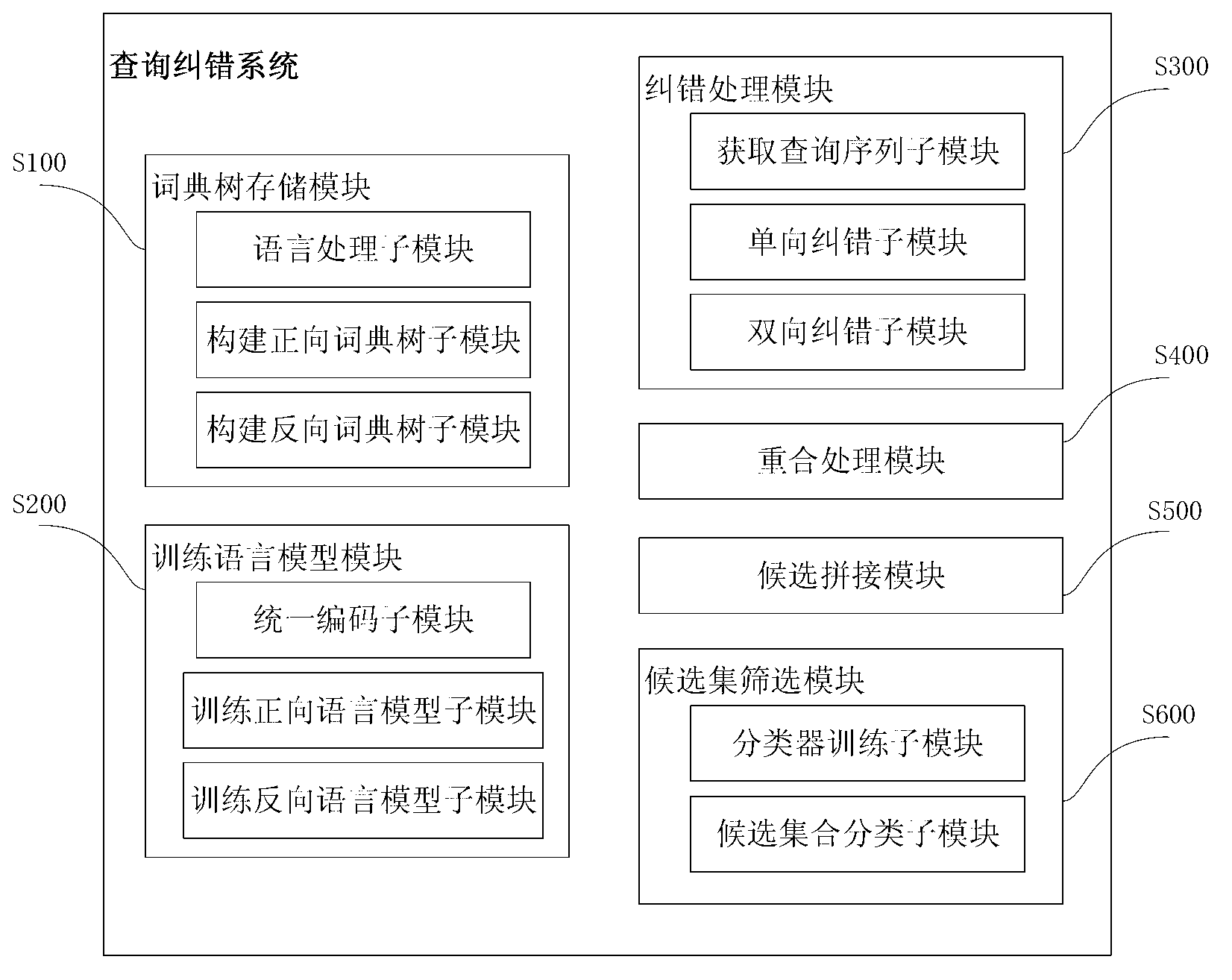

Method and system for query error correction

ActiveCN103198149AMeet the needs of fast error correctionReduce processing timeSpecial data processing applicationsQuantum error correctionSpeech recognition

The invention provides a method and a system for query error correction. The method includes: converting an query sentence into a character sequence, and judging whether the length of the character sequence is larger than a preset threshold value delta or not; simultaneously performing forward and reverse error correction to the character sequence with the length larger than delta until the number of characters under overlap processing reaches a threshold value M, and obtaining forward and reverse candidate sentence item set; and splicing candidate sentences where rear M characters in the forward candidate sentence item set are identical with front M characters in the reverse candidate sentence item set, spliced candidate sentence items form an error correction candidate item set. The method supports query sentences with Chinese and English characters mixed and allows for parallel forward and reverse query error correction to long queries, and by the parallel processing mode, accuracy is guaranteed while processing time of query error correction is saved.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

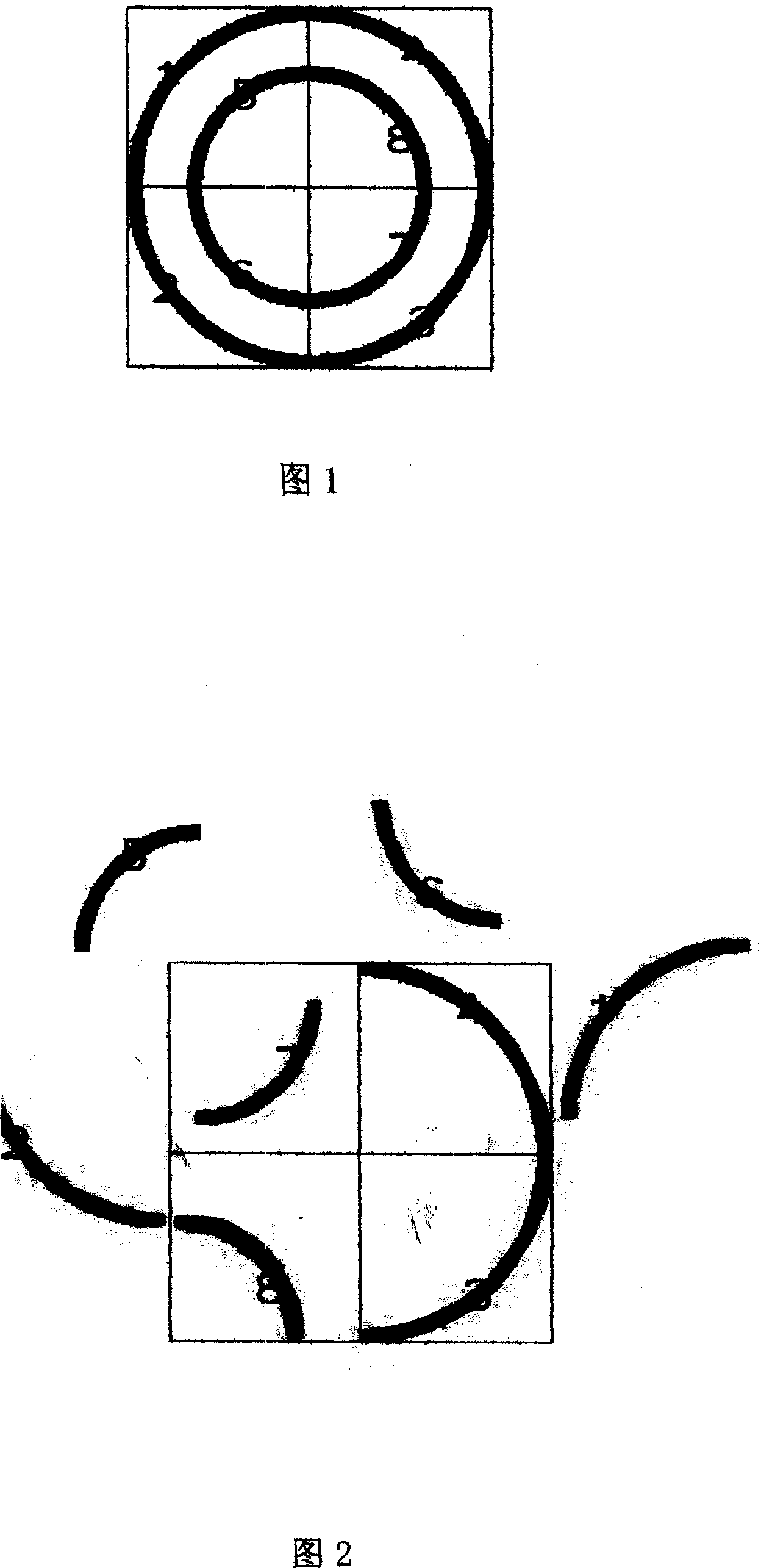

Printing registration test method

A printing register detection method includes the following steps: (1) printing required various color registered graphs on printed matter; (2) grasp shooting the printing registered graphs through cameras installed on the printer in the printing process, and transmitting the information to computer; (3) digital anglicizing the grasp shooted registered graphs by computer, calculating various color chromatic error, and transmitting the error data to the servo-actuator of printer to correcting the error; after several timely capture images properly, calculating error and error correction, then the printing register achieves best status. The method has convenient operation, can fast and accurately detect chromatic error, the detection effect is audio-visual and clean; it can complete vertical and horizontal two directions error detection once and has a very good extension value.

Owner:LUOYANG SUNRAY TECH

Non-volatile memory controller with error correction (ECC) tuning via error statistics collection

ActiveUS9407294B2Easy to operateImprove performanceOther decoding techniquesError correction/detection using multiple parity bitsForward error correctionSolid-state drive

A non-volatile memory controller for a solid state drive includes a soft-decision LDPC decoder. The soft-decision LDPC decoder includes a probability generation module. A processor reads collected statistics collated from decoded frames and tunes the performance of the soft-decision LDPC decoder performance. Additional parameters may also be taken into account, such as the scramble seed and the type of non-volatile memory. An asymmetry in errors may also be detected and provided to a hard-decision LDPC decoder to adjust its performance.

Owner:KIOXIA CORP

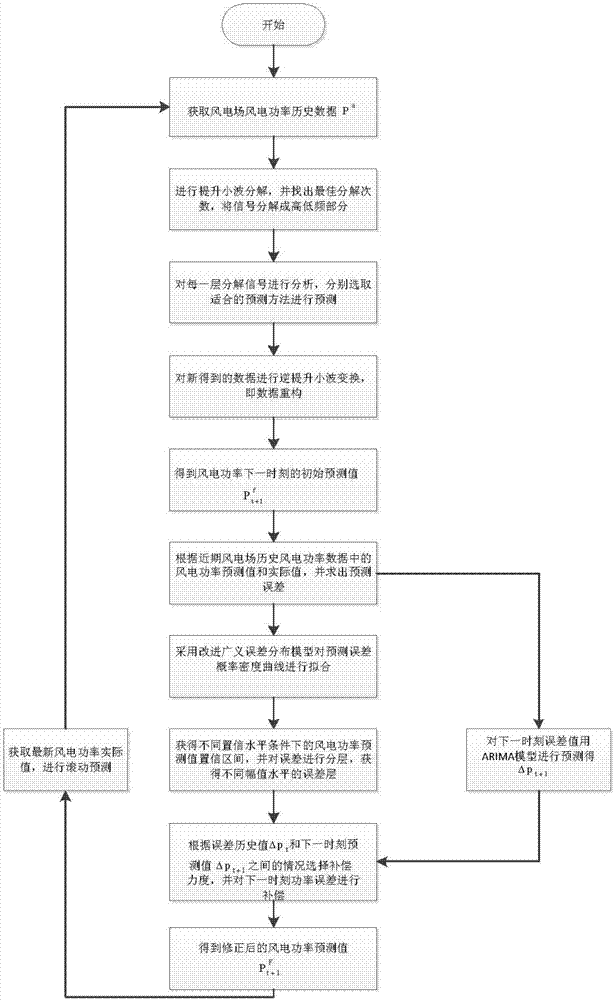

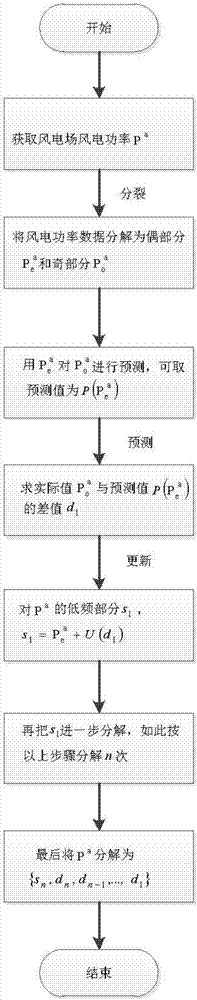

Wind power forecast method based on error correction and promotion wavelet combination forecast model

InactiveCN107230977ACancel noiseEliminate deficienciesForecastingAc network circuit arrangementsWavelet decompositionForward error correction

The invention discloses a wind power forecast method based on an error correction and promotion wavelet combination forecast model. According to the method, wind power history data is processed through utilization of a promotion wavelet decomposition technology, main characteristics of a power data sequence can be improved, frequency components with relatively obvious characteristics can be obtained, and the denoising effect can be achieved, thereby applying to various forecast algorithms. A suitable forecast model is selected according to the characteristics of high and low frequency components, the deficiency of a single forecast method can be removed, and the forecast precision can be greatly improved. According to the method, processing errors are corrected through utilization of an error layered analysis method. Compared with the method of obtaining a next moment error forecast value by directly using the forecast model, the method has the advantage that under the condition that relatively high fluctuation occurs in the errors, the next moment error condition and compensation strength can be analyzed precisely, the errors resulting from an error forecast process can be reduced, and the errors of the integrated forecast method can be reduced.

Owner:ZHEJIANG GONGSHANG UNIVERSITY

Error Correction in Multi-Valued (p,k) Codes

InactiveUS20080016432A1Rapidly detect and correct errorCode conversionCyclic codesCommunications systemError location

Methods, apparatus and systems for error correction of n-valued symbols in (p,k) codewords including Reed Solomon codes of p n-valued symbols with n>2 and k information symbols have been disclosed. Coders and decoders using a Linear Feedback Shift Registers (LFSR) are applied. An LFSR can be in Fibonacci or Galois configuration. Errors can be corrected by execution of an n-valued expression in a deterministic way. Error correcting methods using Galois arithmetic are disclosed. Methods using Cramer's rule are also disclosed. Deterministic error correction methods based on known symbols in error are provided, making first determining error magnitudes not necessary. An error location methods using up and down state tracking is provided. Methods and apparatus executing the methods with binary circuits are also disclosed. Systems using the error correcting methods, including communication systems and data storage systems are also provided.

Owner:TERNARYLOGIC

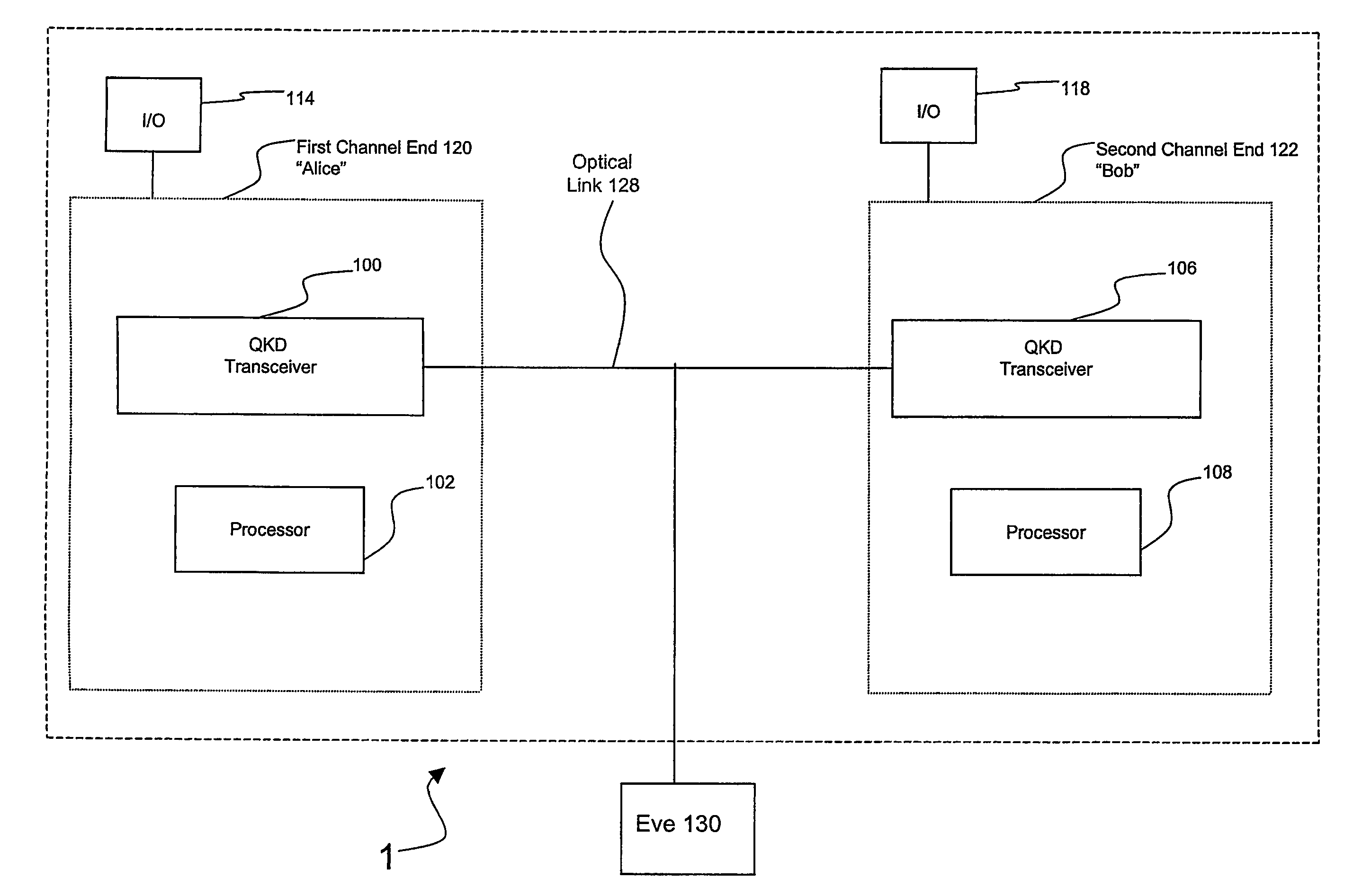

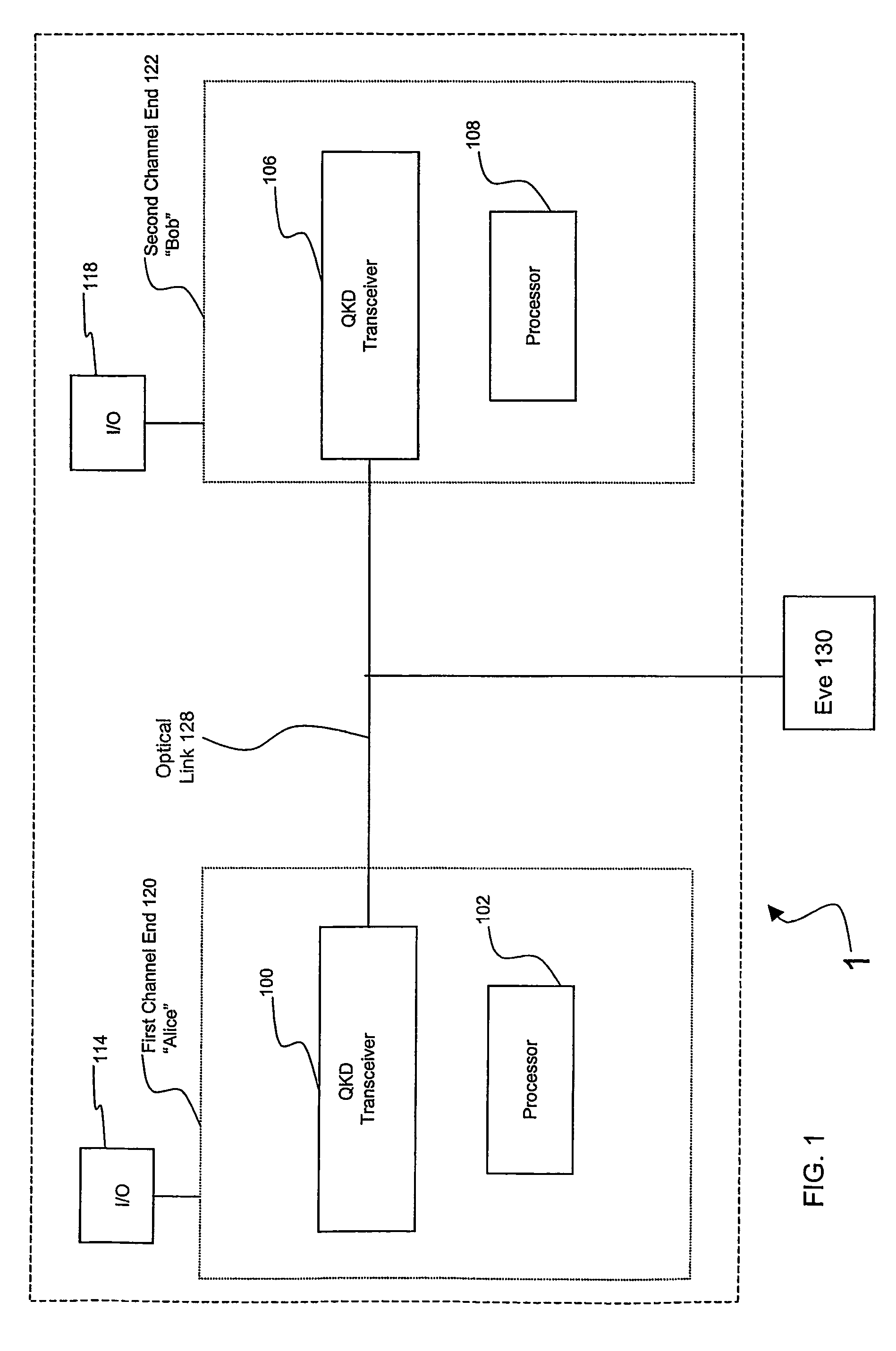

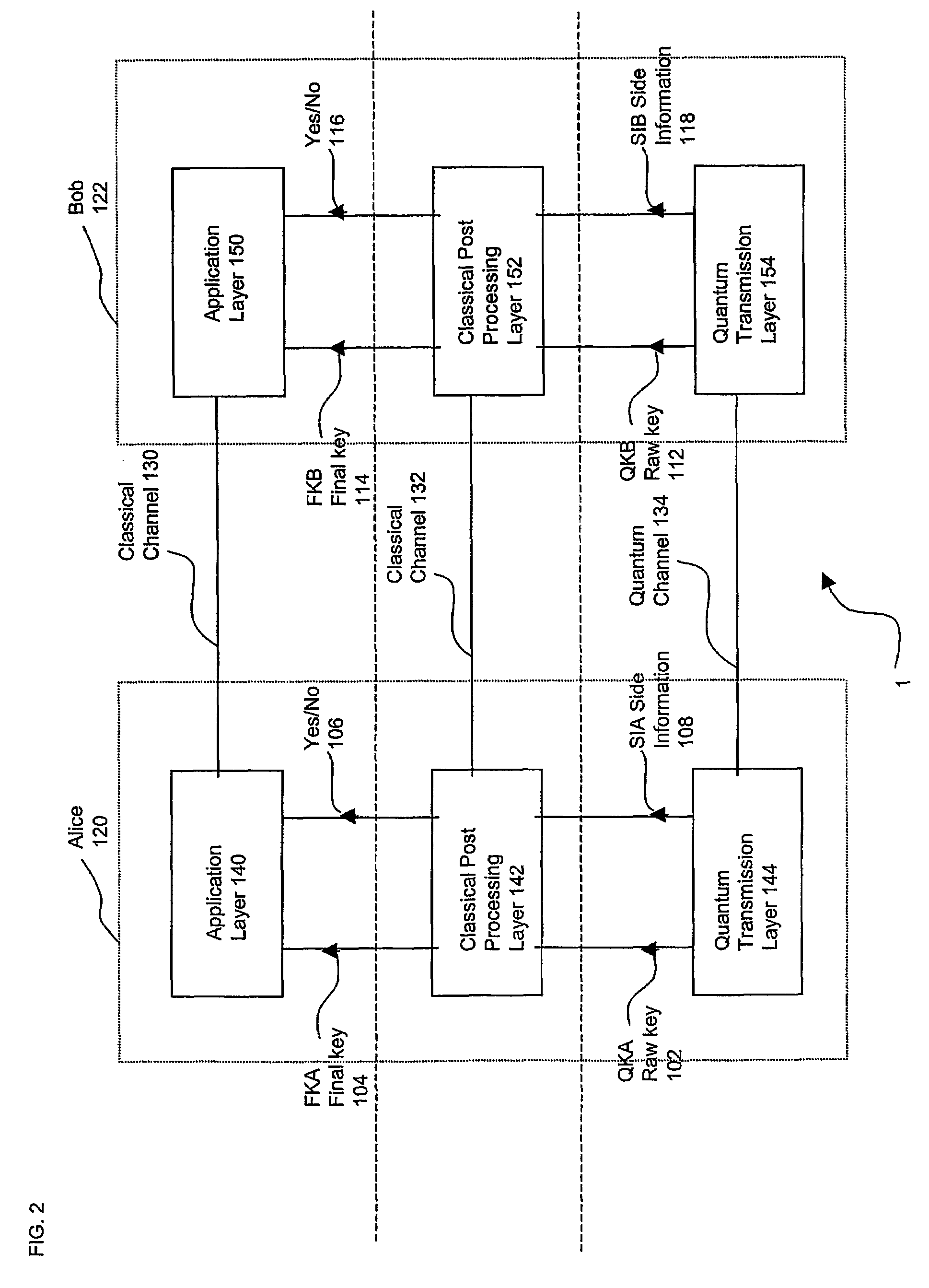

Decoupling error correction from privacy amplification in quantum key distribution

InactiveUS7570767B2Key distribution for secure communicationError preventionComputer hardwareComputerized system

An apparatus (1) and method for decoupling error correction from privacy amplification in a quantum key distribution (QKD 100) system includes two or more computer systems (102, 108) linked by quantum and classical channels (120, 122) where each computer system determines a generalized error syndrome associated with quantum communication between the systems, encrypts the generalized error syndrome using a sequence of values, and communicates the encrypted generalized error syndrome via a classical channel (128) to the other system, which uses the encrypted generalized error syndromes to compute error correction for the quantum transmission.

Owner:MAGIQ TECH INC

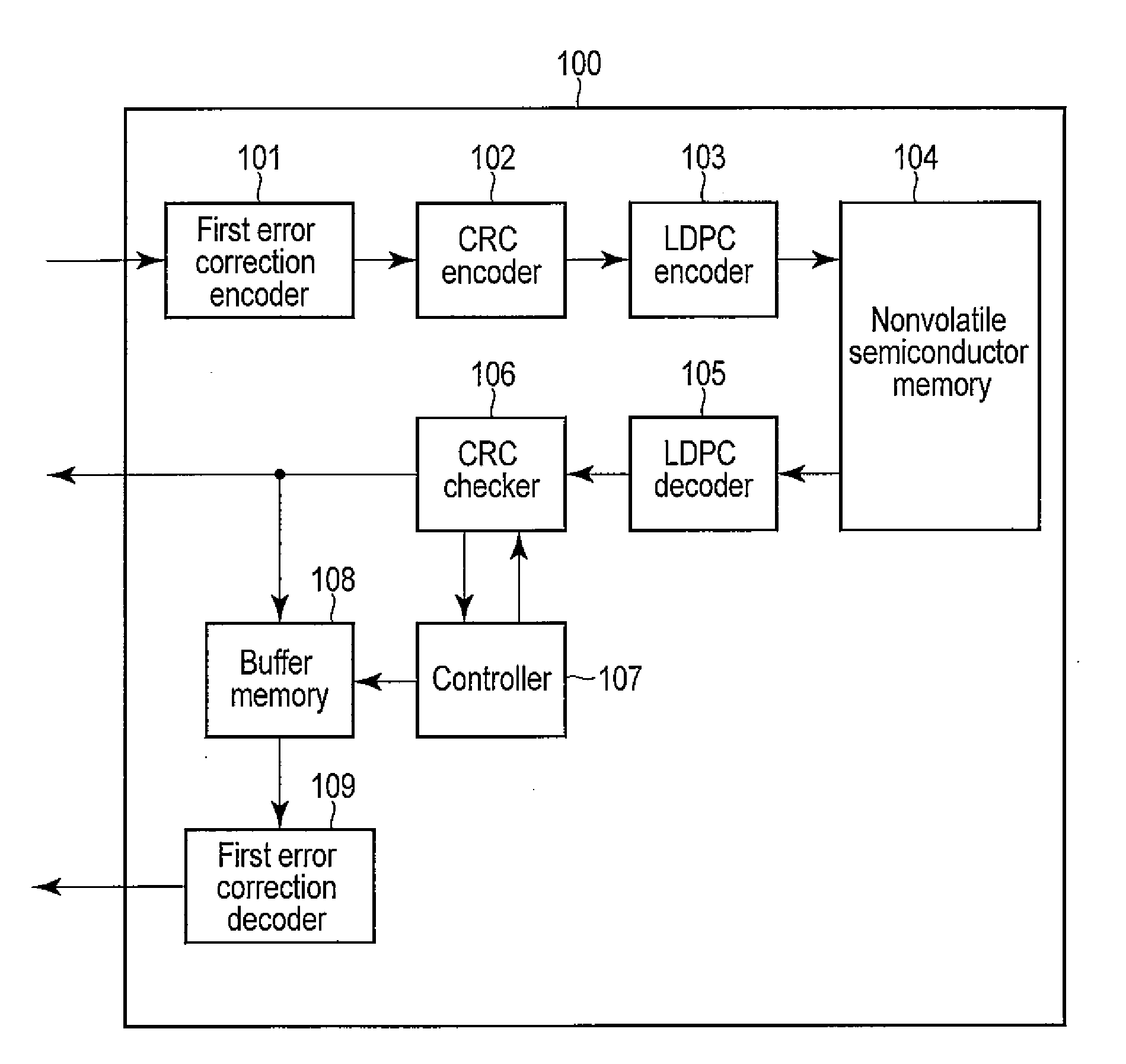

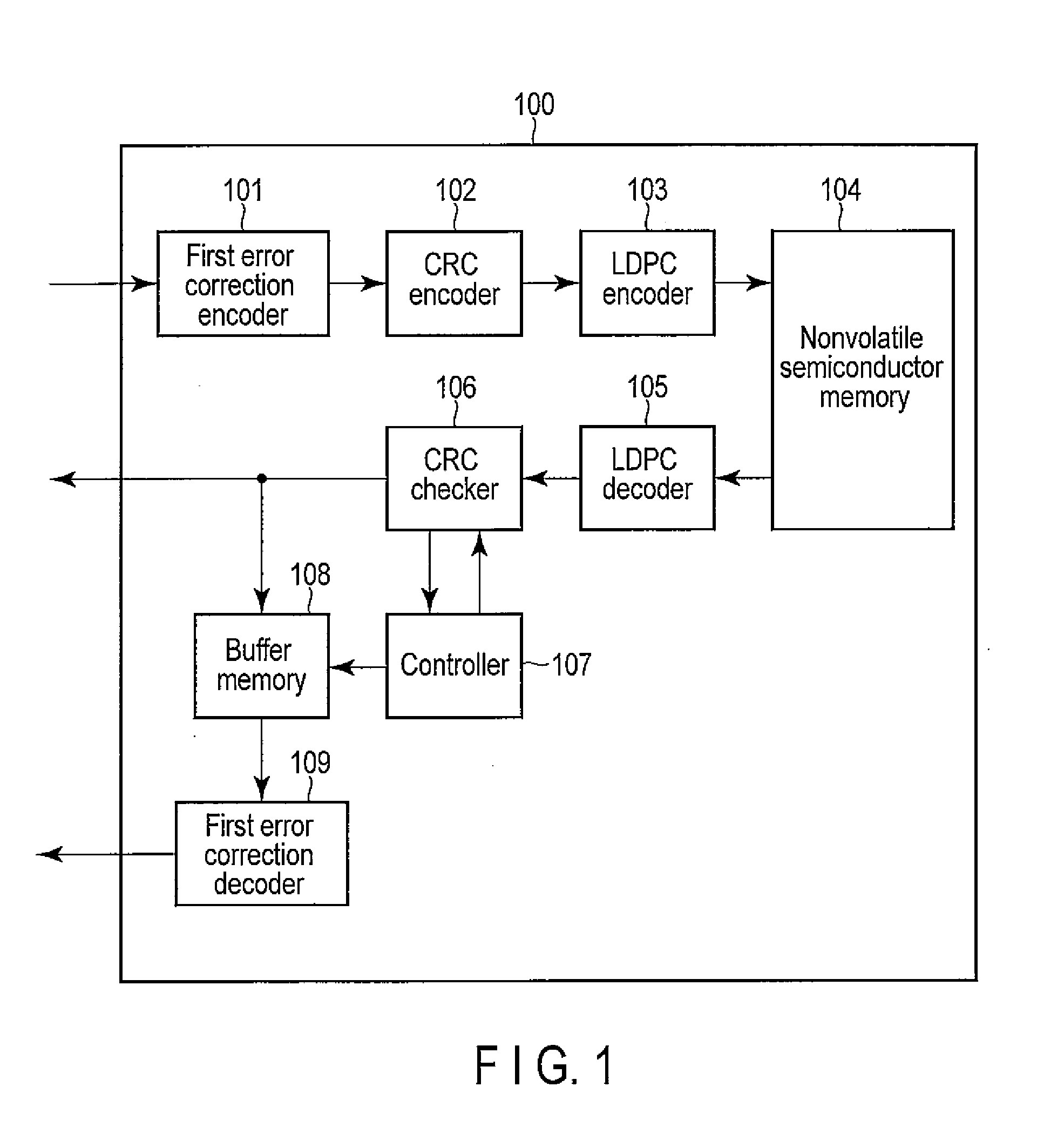

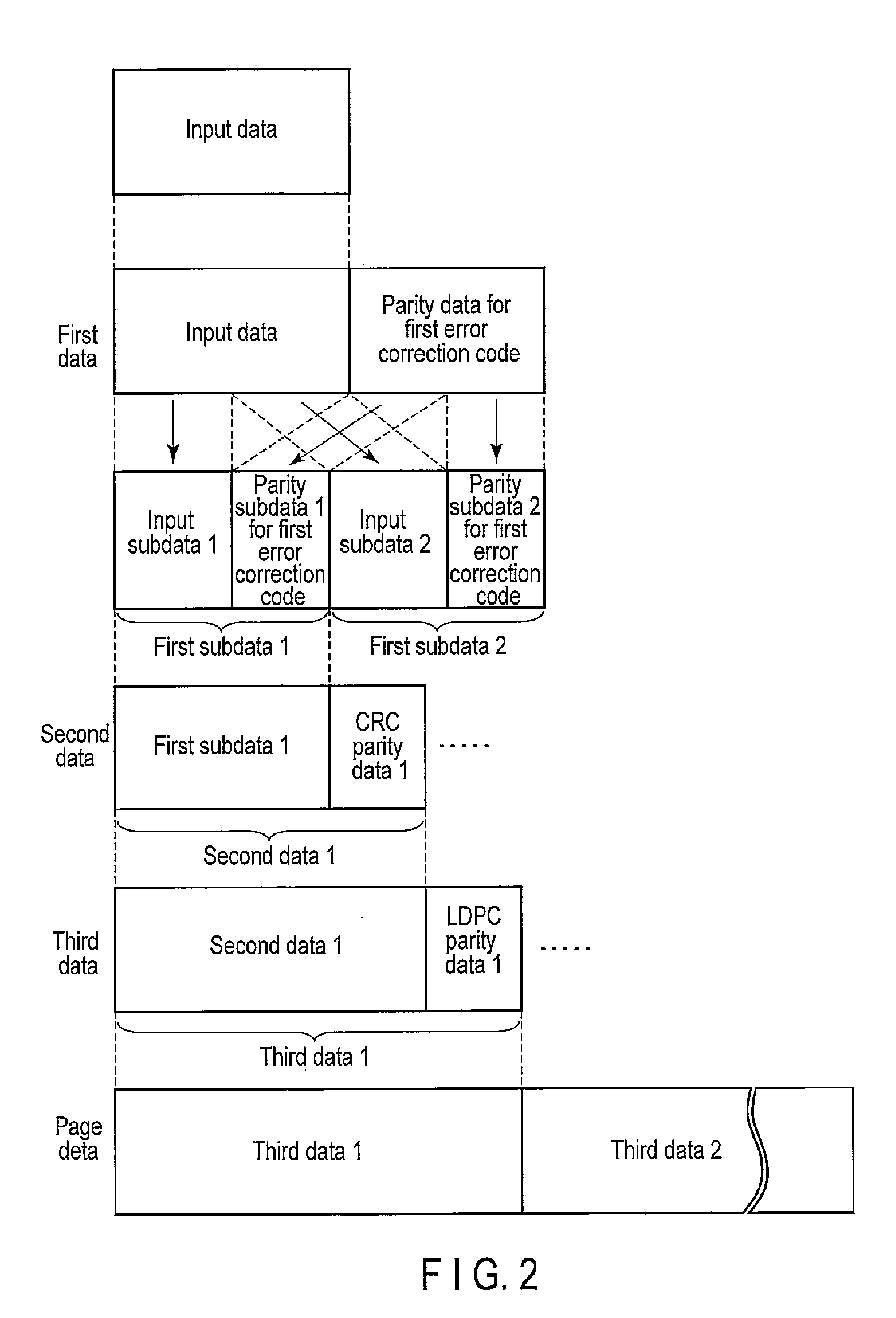

Error correction encoding apparatus, error correction decoding apparatus, nonvolatile semiconductor memory system, and parity check matrix generation method

ActiveUS20130055050A1Code conversionChecking code calculationsLinear codingTheoretical computer science

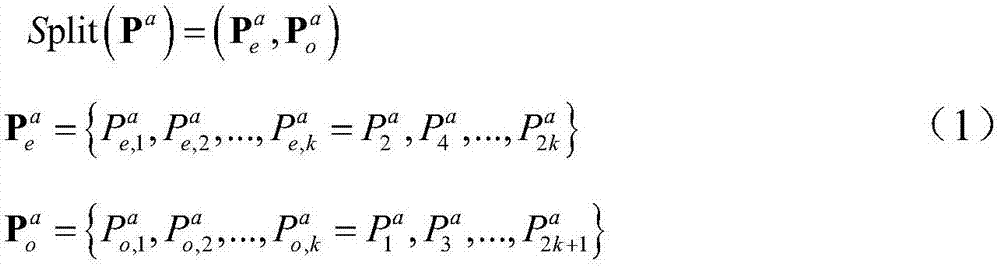

According to one embodiment, an error correction encoding apparatus includes a linear encoder and a low-density parity check (LDPC) encoder. The linear encoder supports a linear coding scheme enabling a parity check to be carried out by a division using a generating polynomial and applies the generating polynomial to input data to obtain linear coded data. The LDPC encoder applies a generator matrix corresponding to a parity check matrix for an LDPC code to the linear coded data to obtain output data. The parity check matrix satisfies Expression (1) shown in the specification.

Owner:KIOXIA CORP

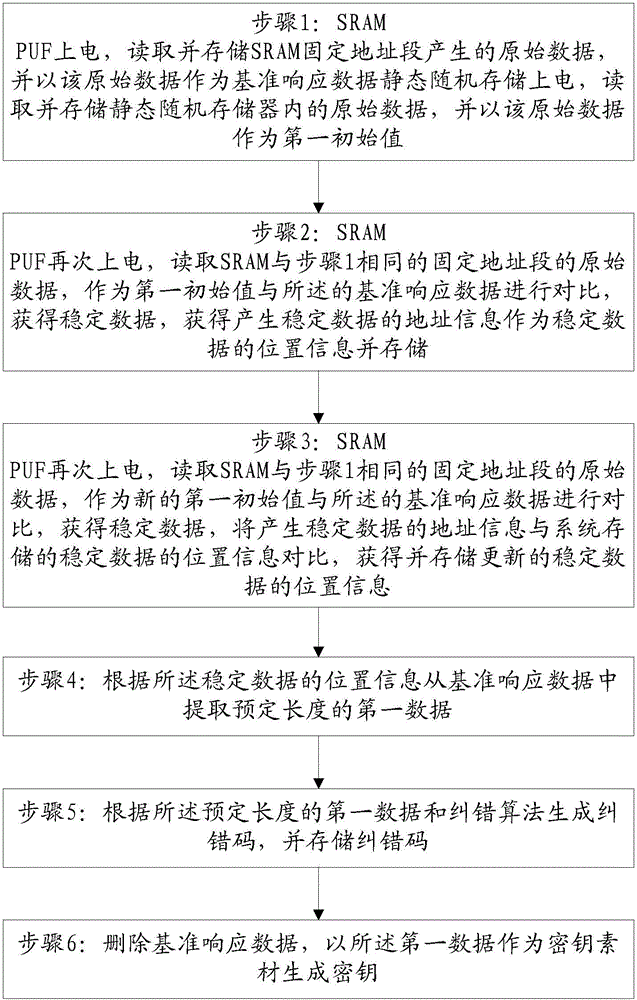

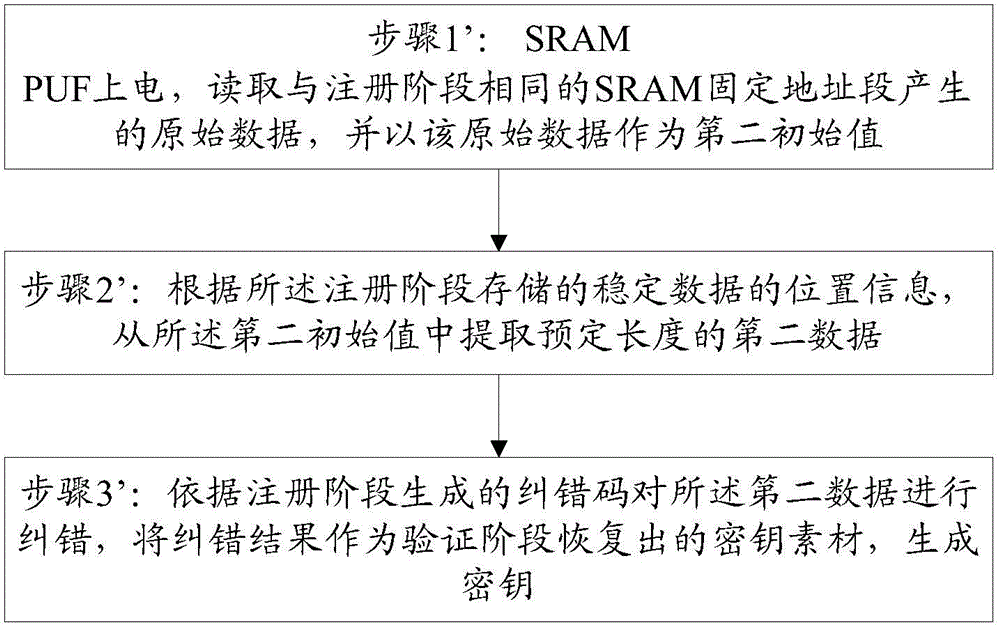

Secret key extraction method and system based on SRAM PUF

InactiveCN105530097AReduce error rateImprove system efficiencyUser identity/authority verificationComputer hardwareCorrection algorithm

The invention discloses a secret key extraction method and a secret key extraction system based on an SRAM PUF. The secret key extraction method comprises a registration phase and an authentication phase. The registration phase comprises the steps of: reading original data generated by an SRAM fixed address field, and regarding the original data as an initial value; carrying out powering-on for many times, comparing the plurality of obtained initial values, and eliminating addresses corresponding to error-prone data bits in the initial values to obtain a stable address; and using an initial values generated by the stable address as a secret key material for generating a secret key, and generating an error correction code of the secret key material by adopting an error correction algorithm. Thus, the error rate of an SRAM address field for generating the secret key material is reduced, the system can select the simple error correction algorithm for carrying out error correction on the short original data when extracting the secret key material the next time, and the system efficiency is improved. The authentication phase comprises the steps of: extracting the original data with low error rate from the stable address obtained in the registration phase, carrying out error correction by adopting the same error correction algorithm, and finally recovering the secret key material.

Owner:DATA ASSURANCE & COMM SECURITY CENT CHINESE ACADEMY OF SCI

Etl diagnostics

ActiveUS20170068595A1Well formedNon-redundant fault processingRedundant data error correctionCloud baseForward error correction

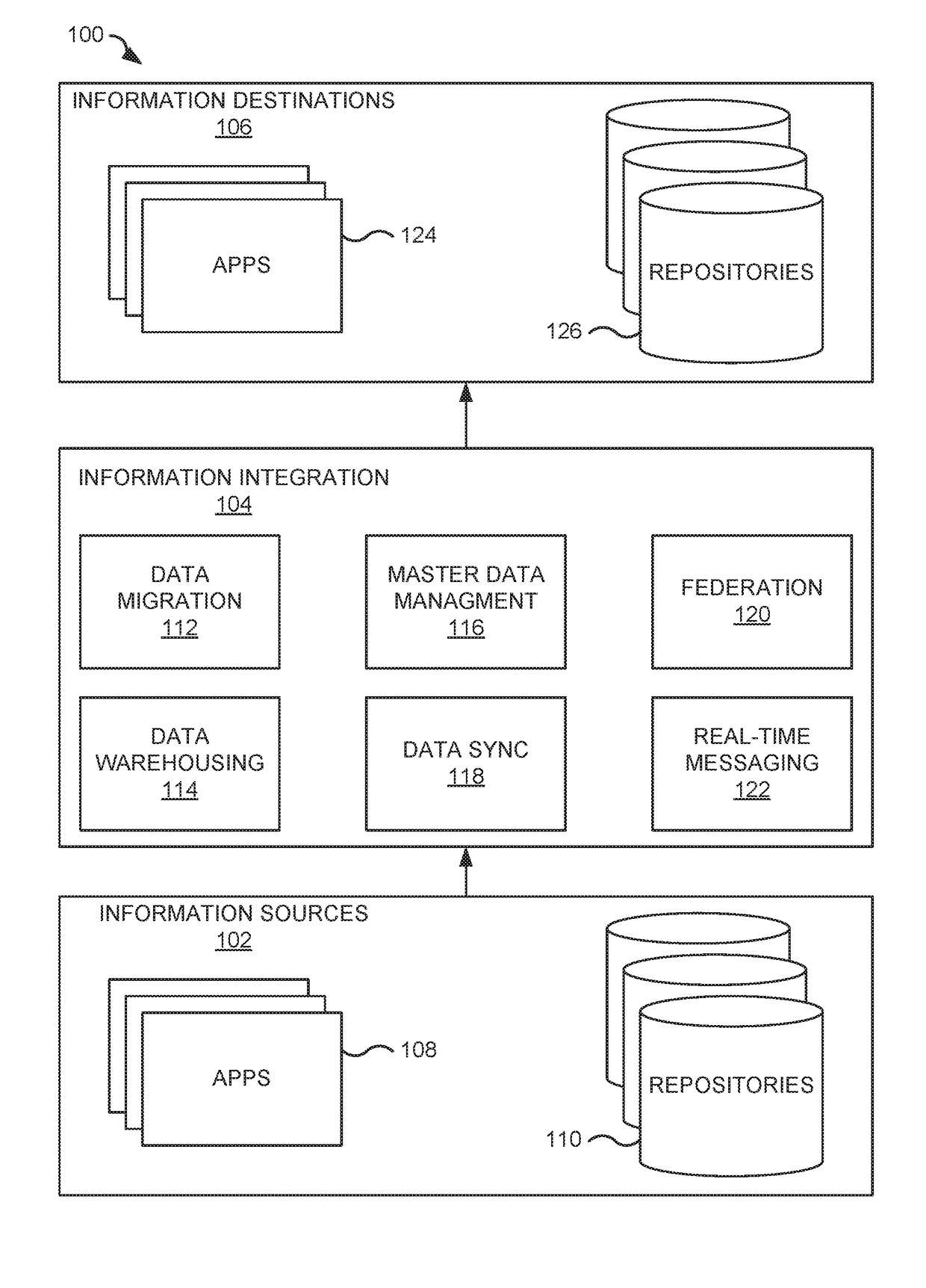

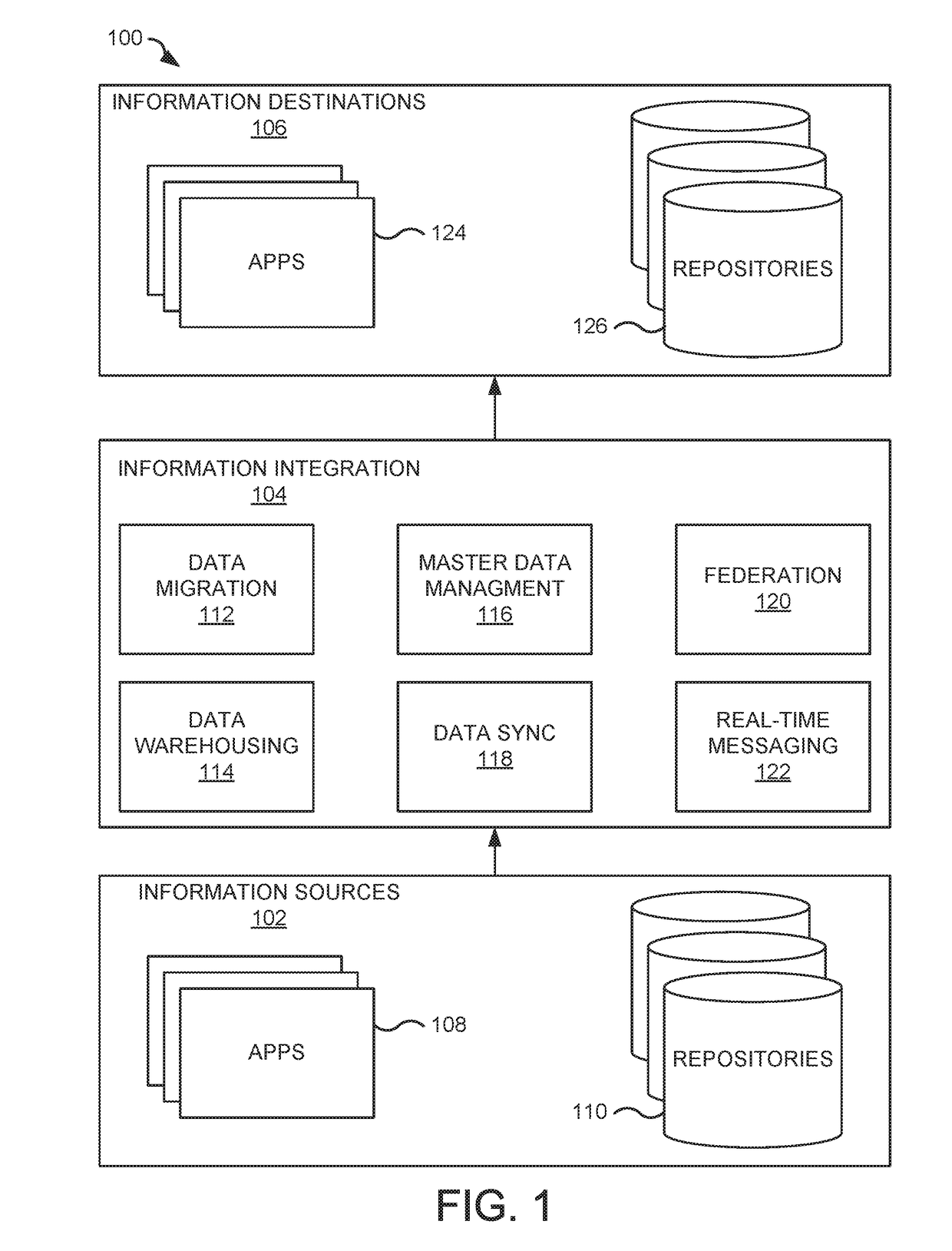

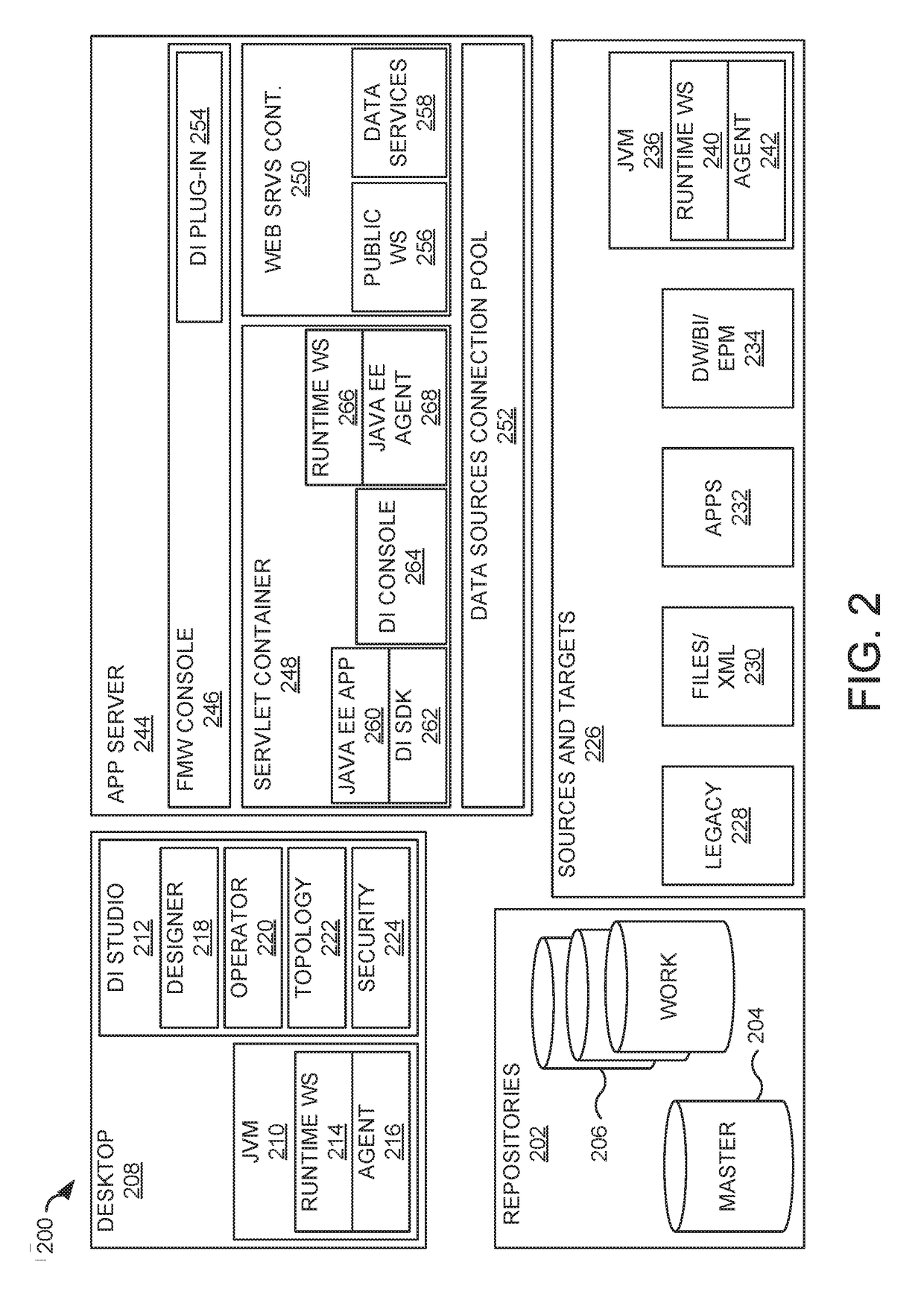

A cloud-based ETL system provides error detection, error correction and reporting of data integration flows hosted by cloud services. Categories of errors are identified using one or more checks at different points of a data integration flow and one or more actions selected based at least in part on the error category. A determination can be made whether the error category is fault tolerant and one or more actions can be selected based at least in part on the error fault tolerance to correct the error, restart a flow, or generate a notification assisting a user to correct the error.

Owner:ORACLE INT CORP

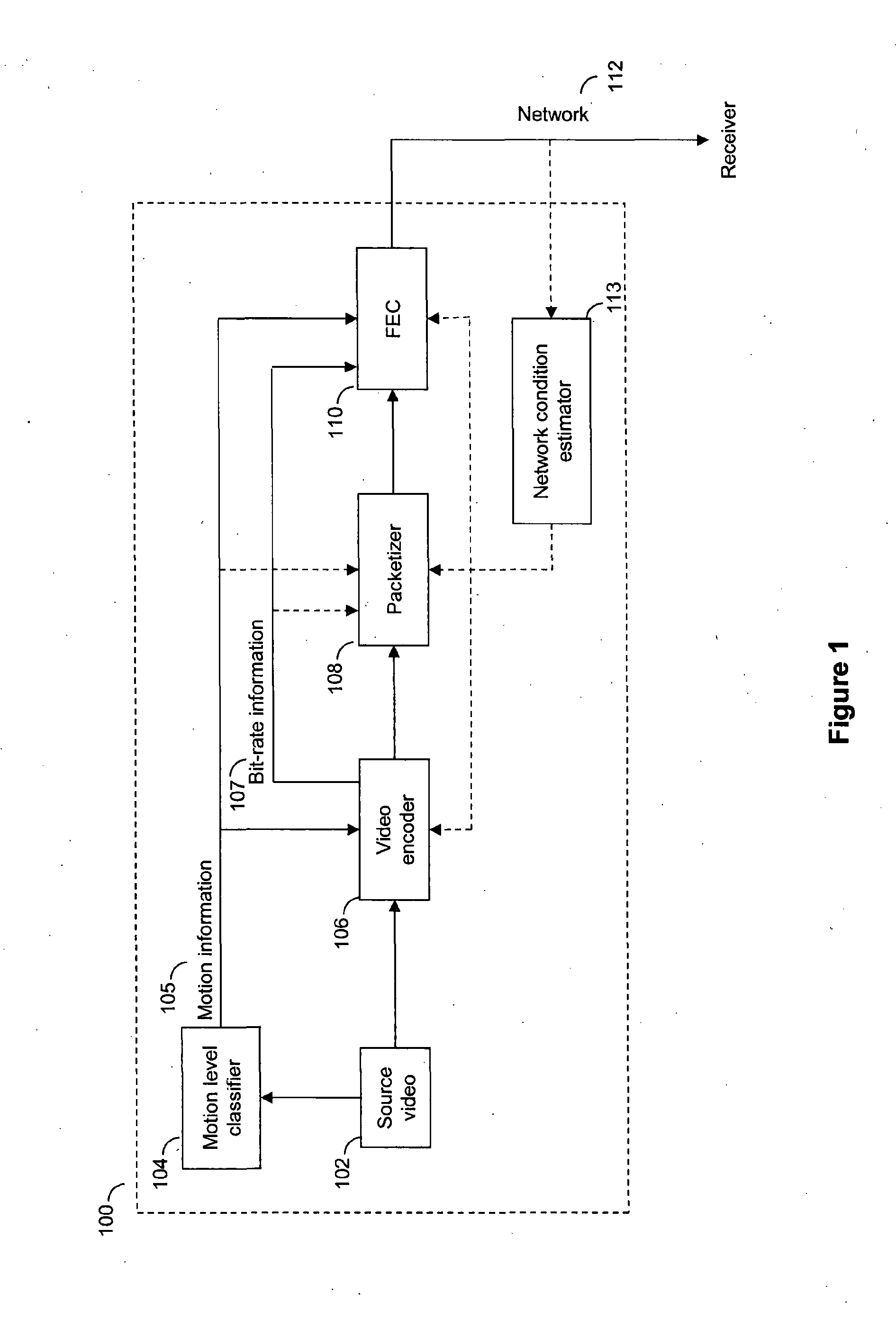

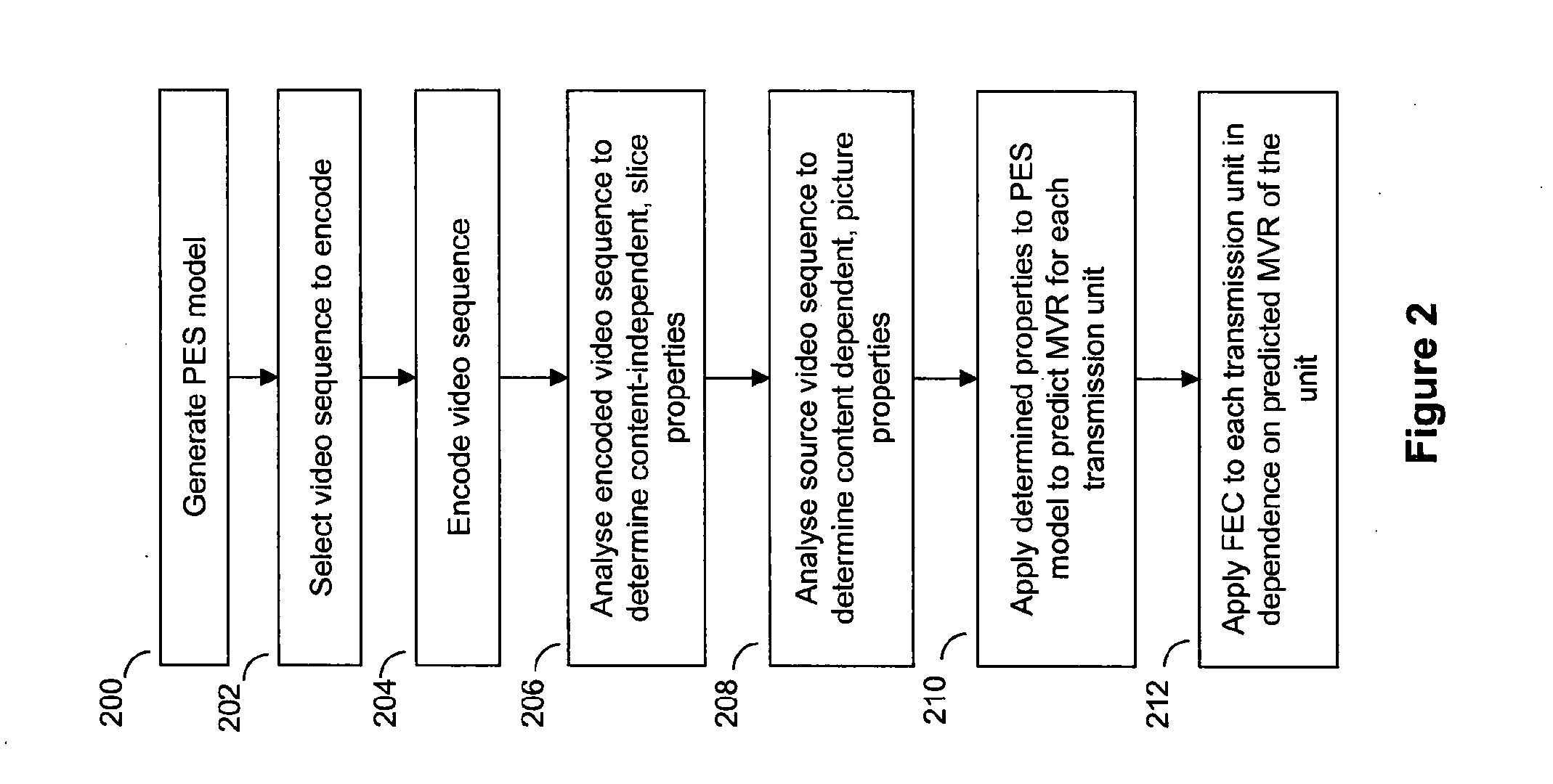

Perceptually driven error correction for video transmission

InactiveUS20150296224A1Measure resulting error visibility is avoidedLess computationally intensiveColor television with pulse code modulationColor television with bandwidth reductionPacket lossVideo transmission

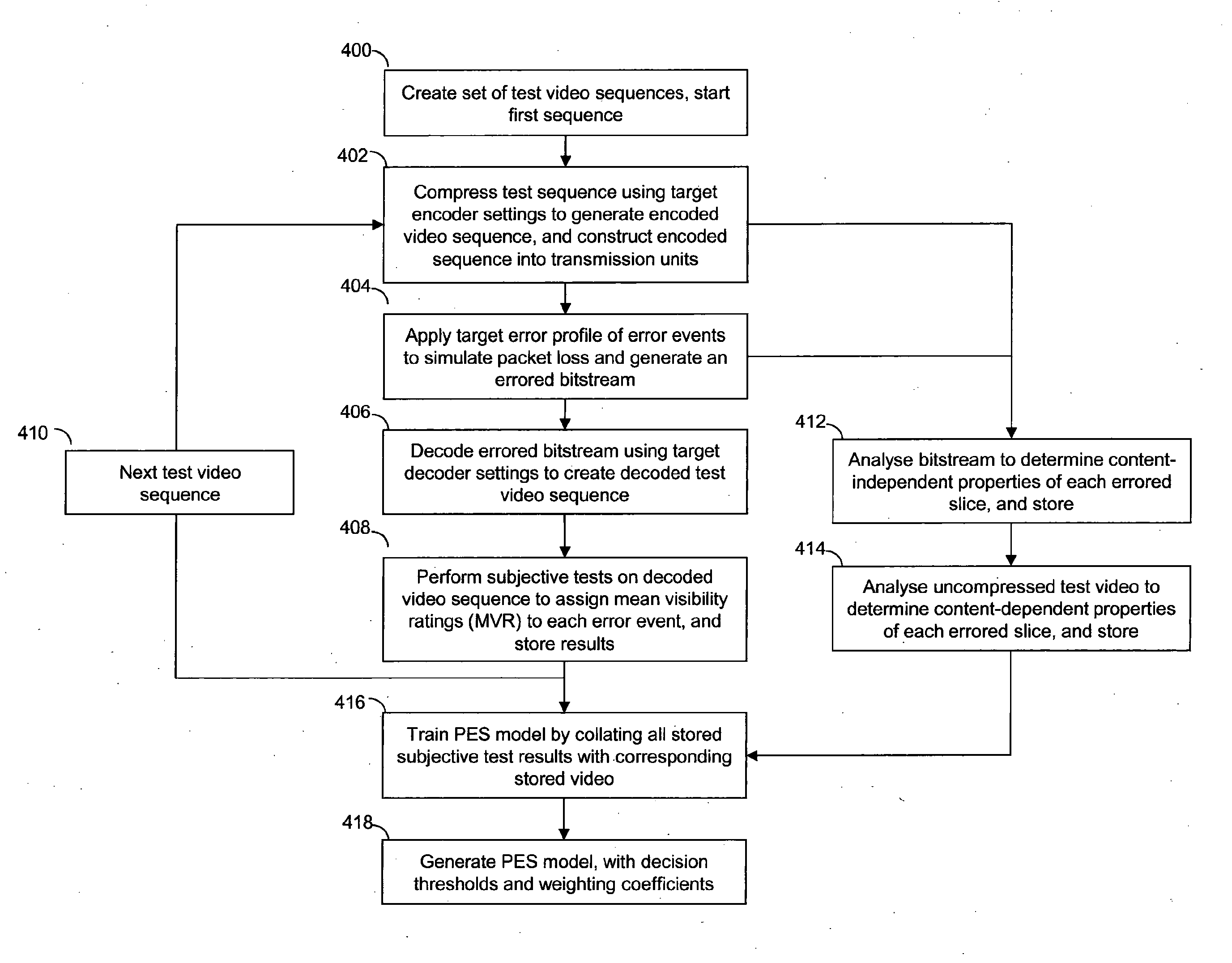

The invention presents a method of applying forward error correction selectively to an encoded video sequence before it is transmitted. Forward error correction is targeted at portions of the video that will be most noticeably affected by any potential packet loss during transmission. The targeting is done using a perceptual error sensitivity model, which effectively maps an error visibility rating onto content-dependent and content-independent properties associated with a given portion video. The encoder and decoder settings will be used for the actual video sequence where forward error correction is to be applied are used in the training of the model, as they have a significant effect on the perception of any errors. Then, to adaptively apply forward error correction, a selected video sequence is encoded, and the encoded bitstream is analysed to determine content-independent properties. A decoded version of the video sequence is also analysed to determine content-dependent properties being determined. The content-independent and content-dependent properties are used in conjunction with the perceptual error sensitivity model to predict which slices of the video sequence will be most significantly affected perceptually by packet loss, and thus target FEC to those areas accordingly.

Owner:BRITISH TELECOMM PLC

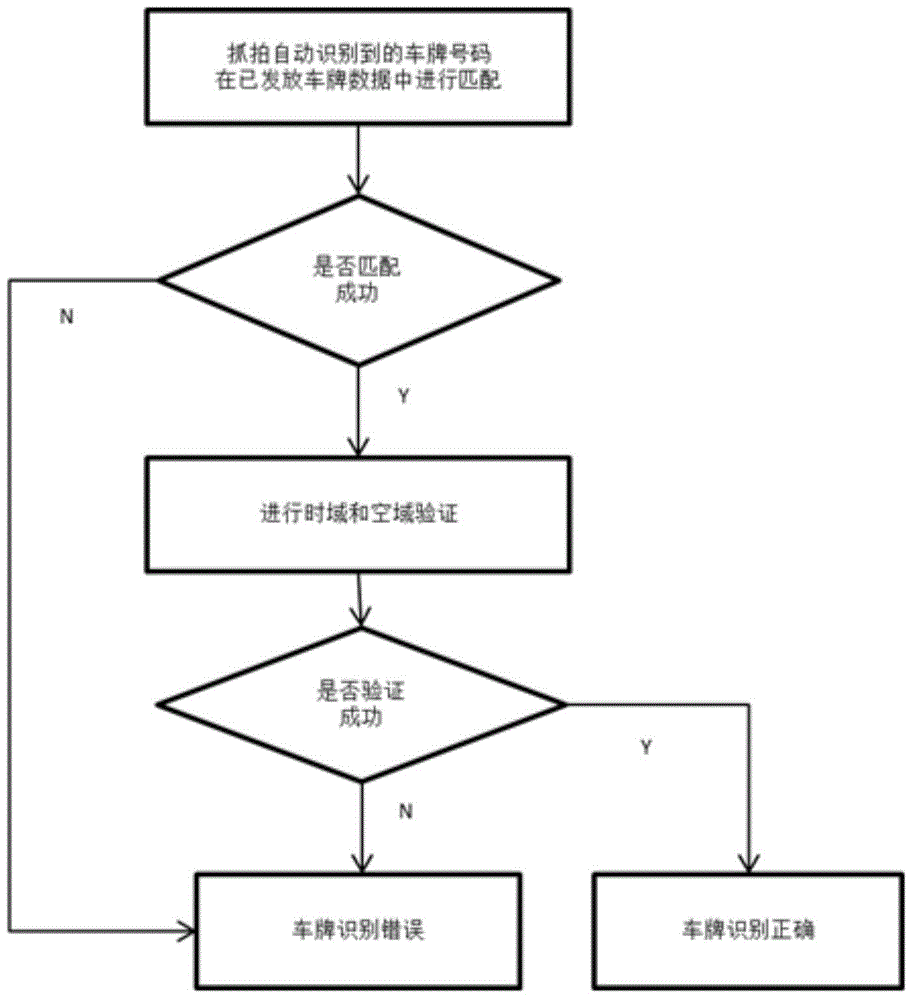

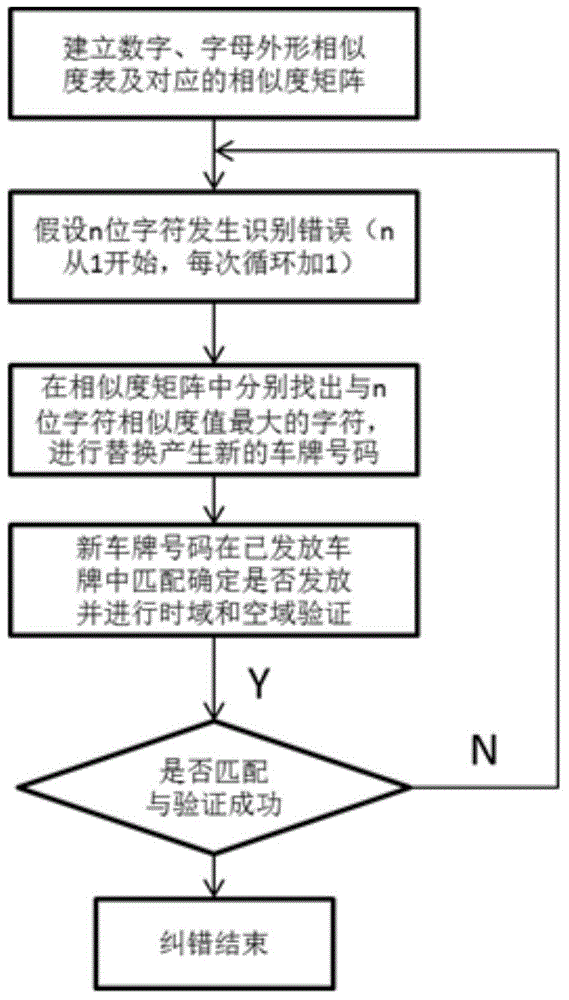

Method of correcting license plate number automatically recognized in traffic snapshot

ActiveCN105118300AFast error correctionImprove accuracyRoad vehicles traffic controlCharacter and pattern recognitionIn vehicleForward error correction

The invention discloses a method of correcting a license plate number automatically recognized in traffic snapshot. The method comprises steps: 1, error detection is carried out: license plate numbers in vehicle passing records are matched with the existing already-issued license plate numbers; and if a certain license plate number succeeds in matching in the above step, whether the license plate number is correctly recognized is verified next; and 2, error correction is carried out: through carrying out the above error detection on the license plate numbers, a large number of wrongly-recognized license plate numbers are obtained, and the error correction process is to correct the wrongly-recognized license plate numbers to be actually true license plate numbers of vehicles.

Owner:广东启功实业集团有限公司

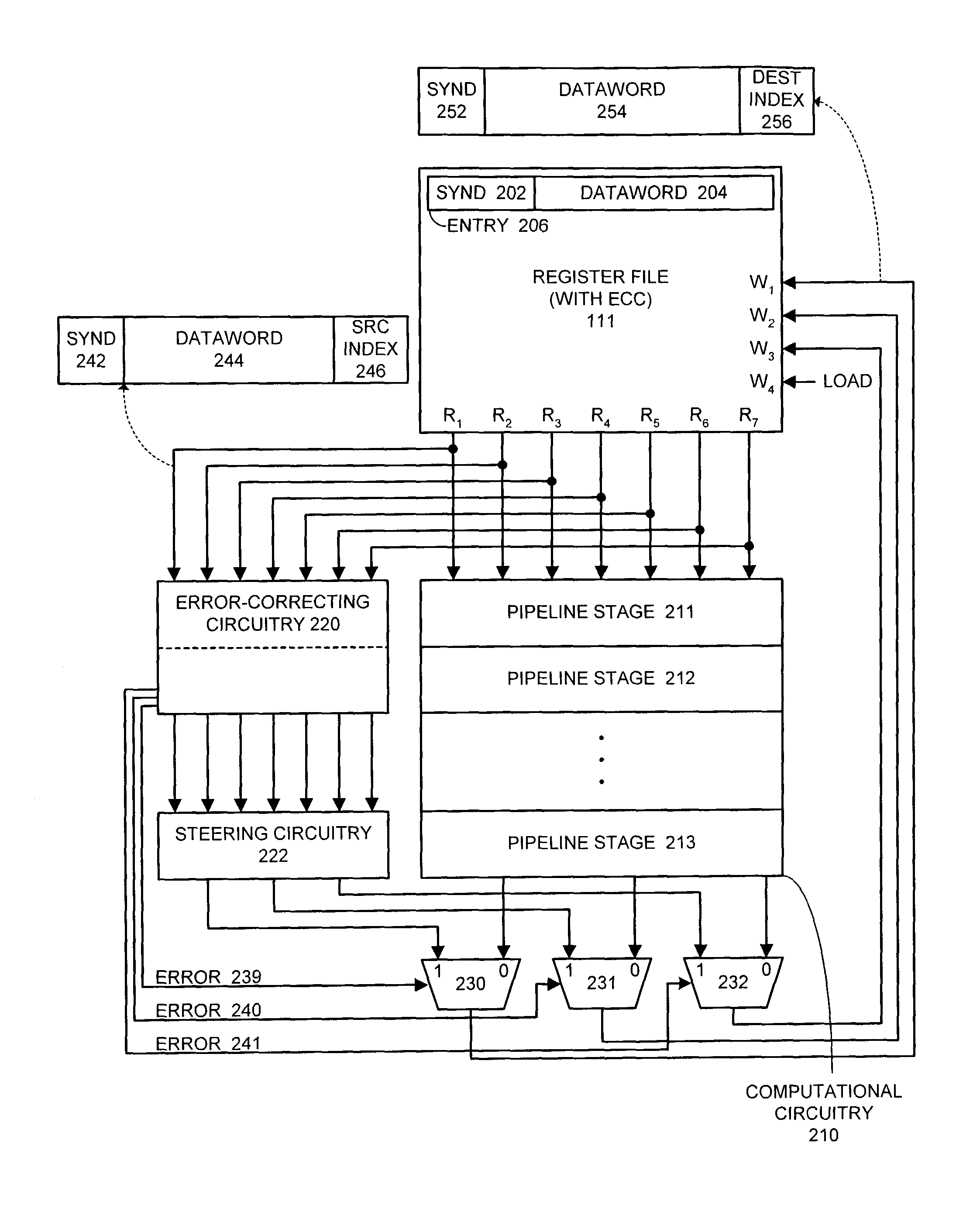

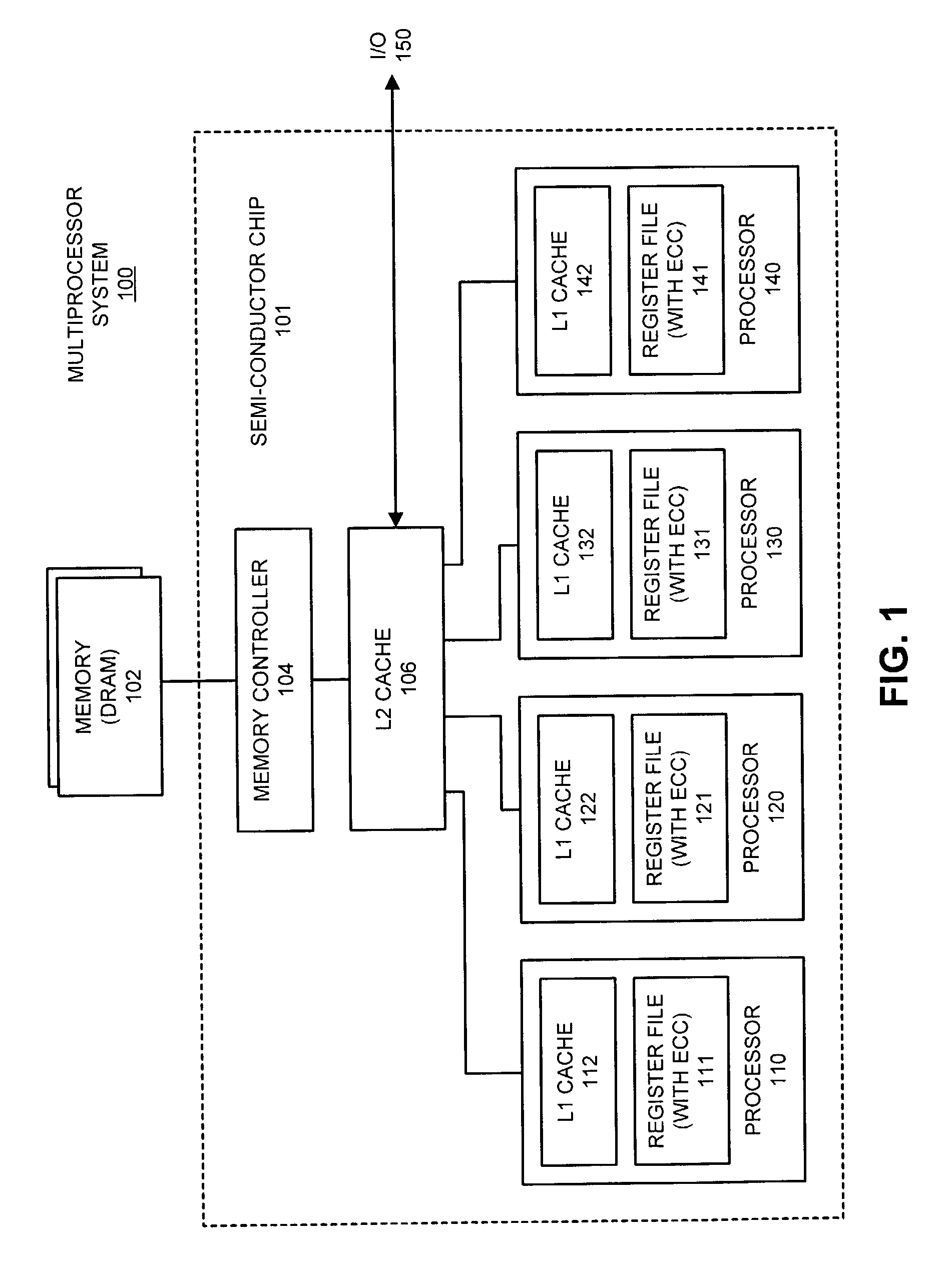

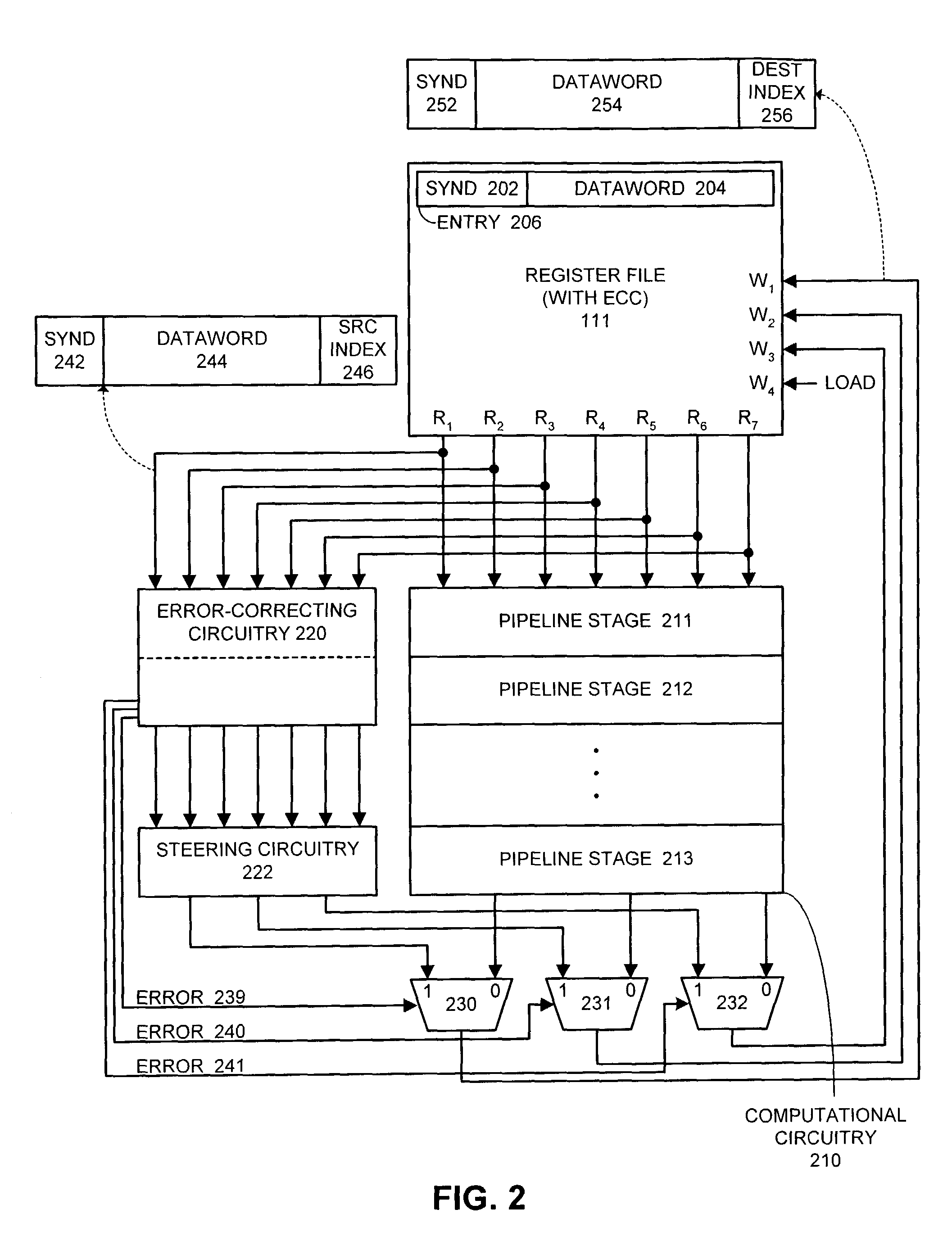

Method and apparatus for providing error correction within a register file of a CPU

InactiveUS7058877B2Easy to correctAvoid performanceData representation error detection/correctionCode conversionProcessor registerInstruction pipeline

A system that facilitates error correction within a register file in a central processing unit (CPU). During execution of an instruction by the CPU, the system retrieves a dataword and an associated syndrome from a source register in the register file. Next, the system uses information in the dataword and the associated syndrome to detect, and if necessary correct, an error in the dataword or associated syndrome. This error detection and correction takes place in parallel with using the dataword to perform a computational operation specified by the instruction. If an error is detected, the system prevents the instruction from performing a writeback to a destination register in the register file. The system also writes a corrected dataword to the source register in the register file. Next, the system flushes the instruction pipeline, and restarts execution of the instruction so that the corrected dataword is retrieved for the computational operation.

Owner:ORACLE INT CORP

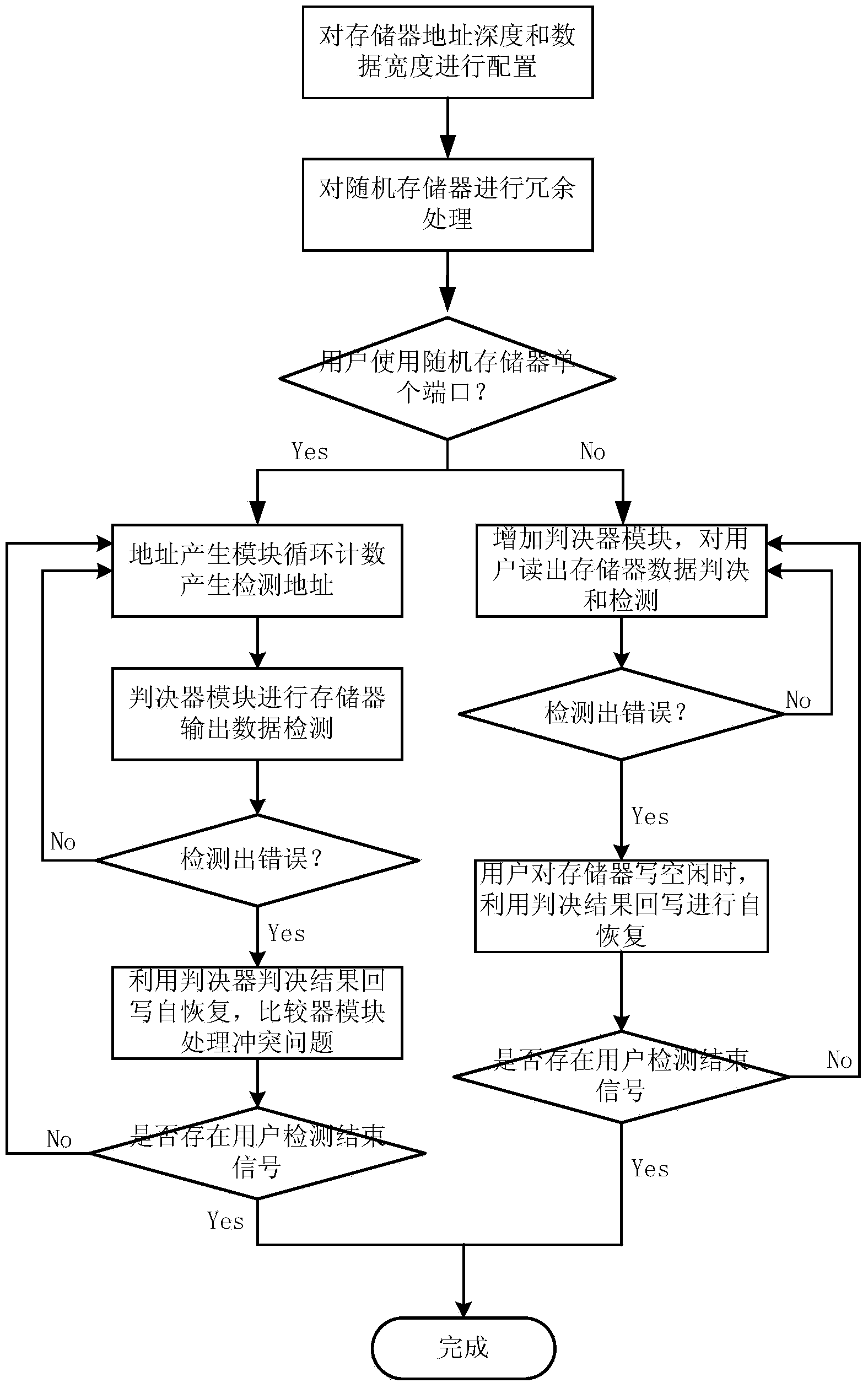

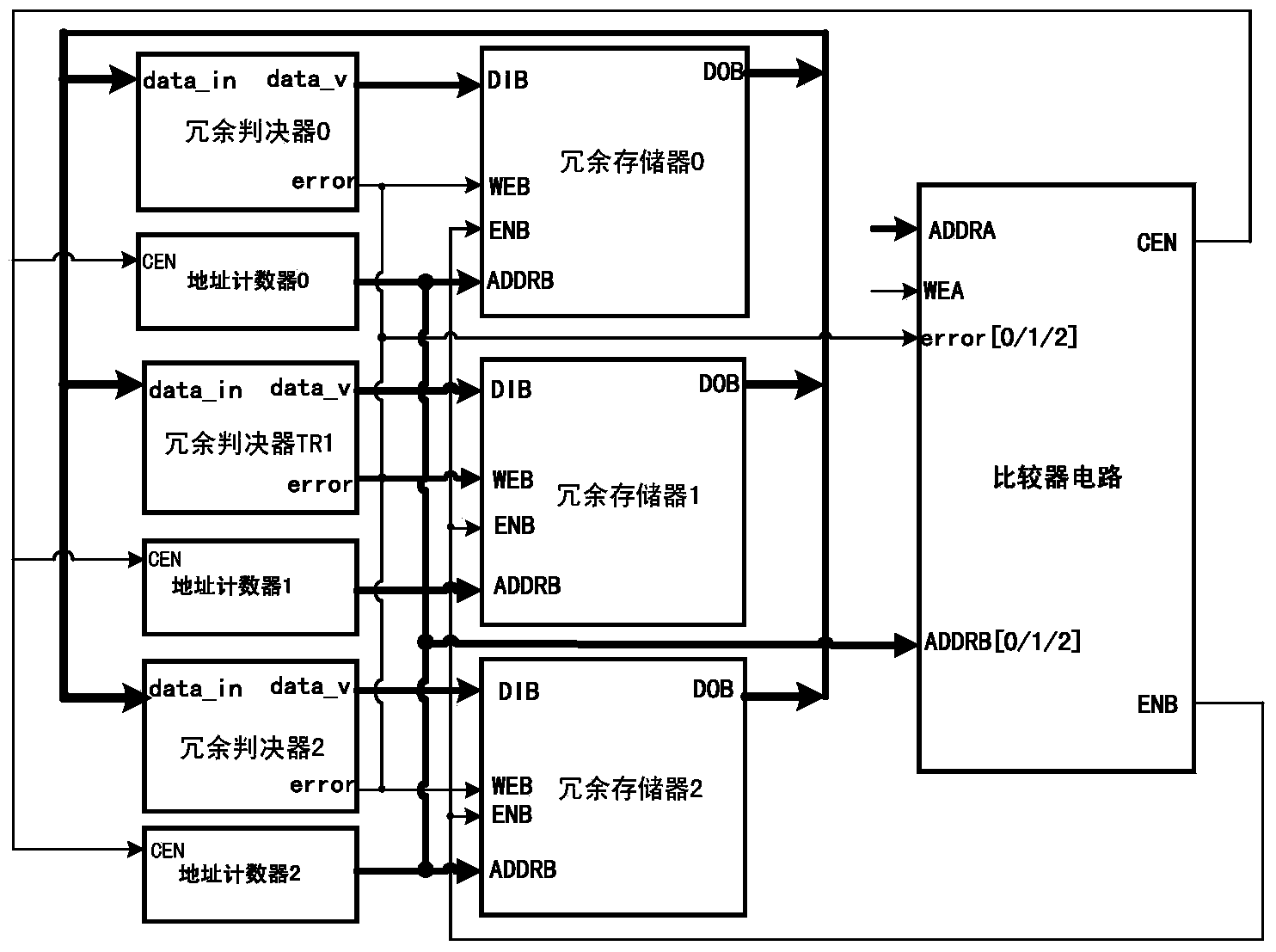

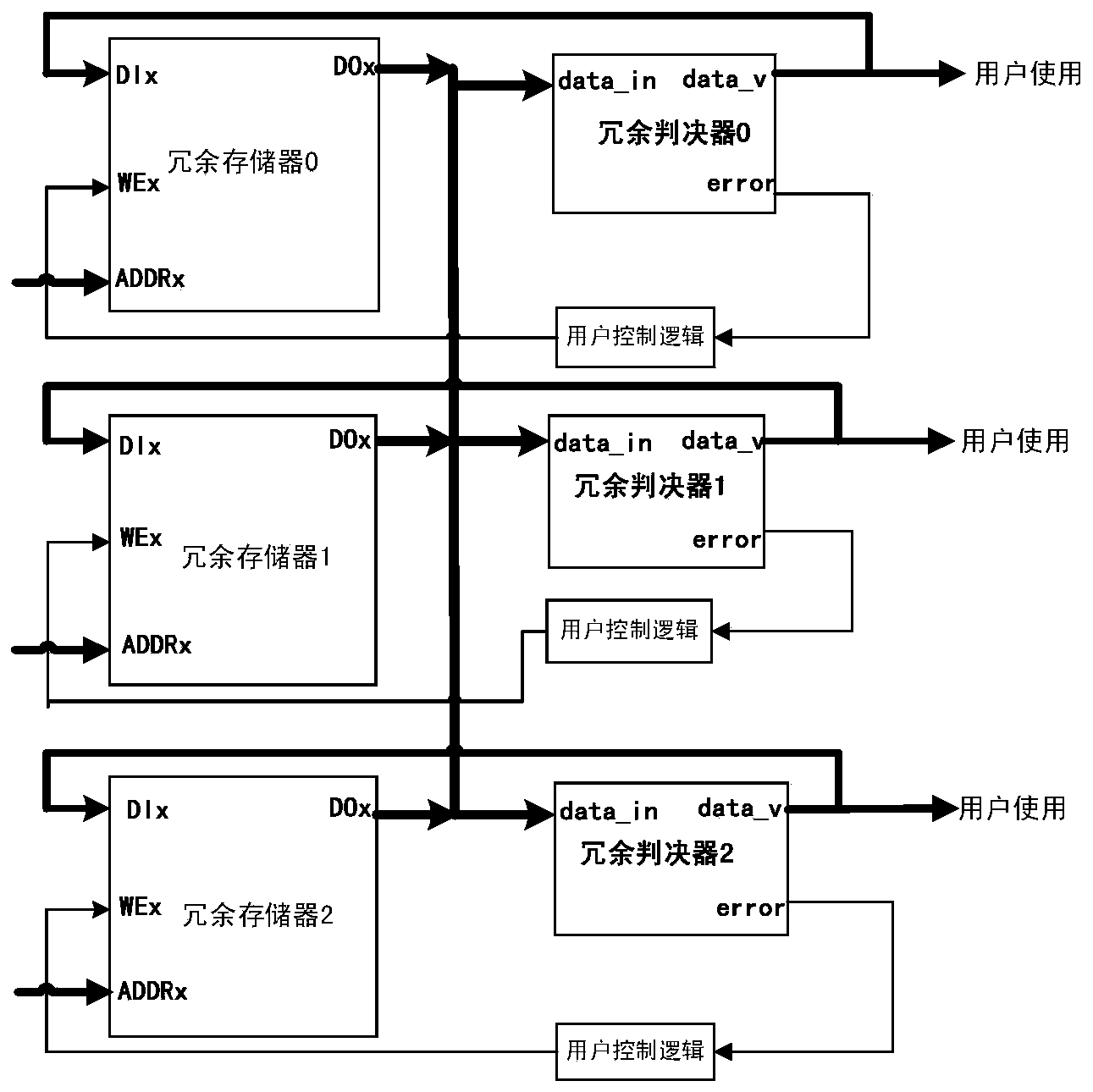

Periodic self-checking recovery method of random access memory

ActiveCN103680639AEffective Single Event Effect ProtectionUnlimited by error correction capabilitiesStatic storageRecovery methodStatic random-access memory

The invention discloses a periodic self-checking recovery method of a random access memory, which can perform error tolerance and correction design on the random access memory. The method comprises the steps of firstly performing redundancy processing on the random access memory, performing three-evaluation and two-judgment and consistency comparison on redundancy output results through a design judgment module, taking judgment results as error correction input data, and taking consistency comparison results as error correction enabling data. Simultaneously an address generating module periodically generates memory read addresses, so as to realize error detection control. The invention can provide an error detection and correction method for the random access memory which easily generates error caused by external causes (such as space radiation environment and the like), and improves the problem of error accumulate invalidation of the traditional redundancy error tolerance technology, the error correction capability is not limited by error correction and detection algorithm, and the memory is effectively protected.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

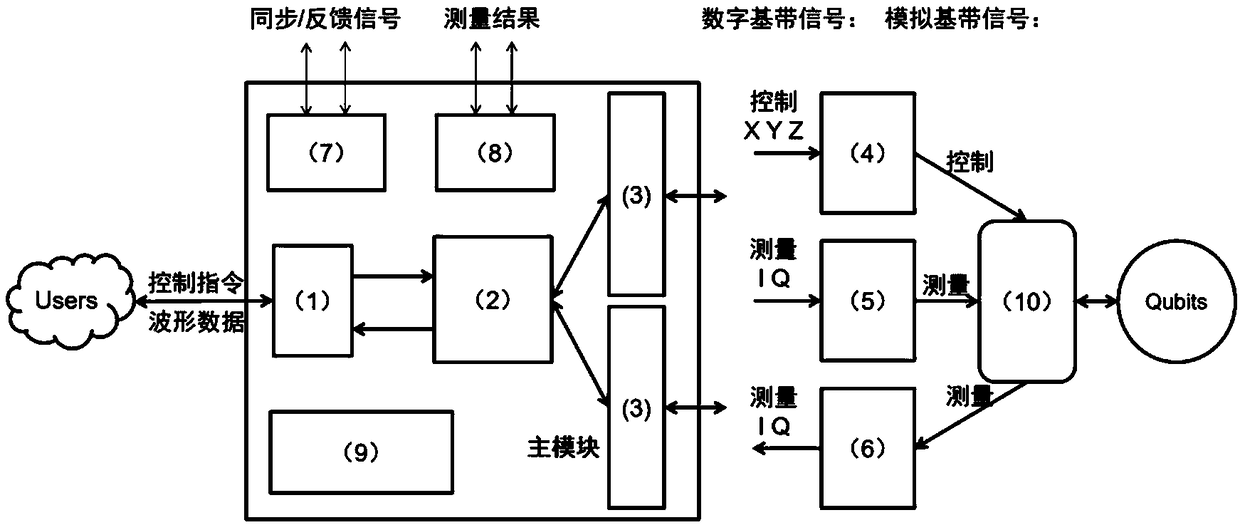

Scalable low-latency feedback control device for quantum bits

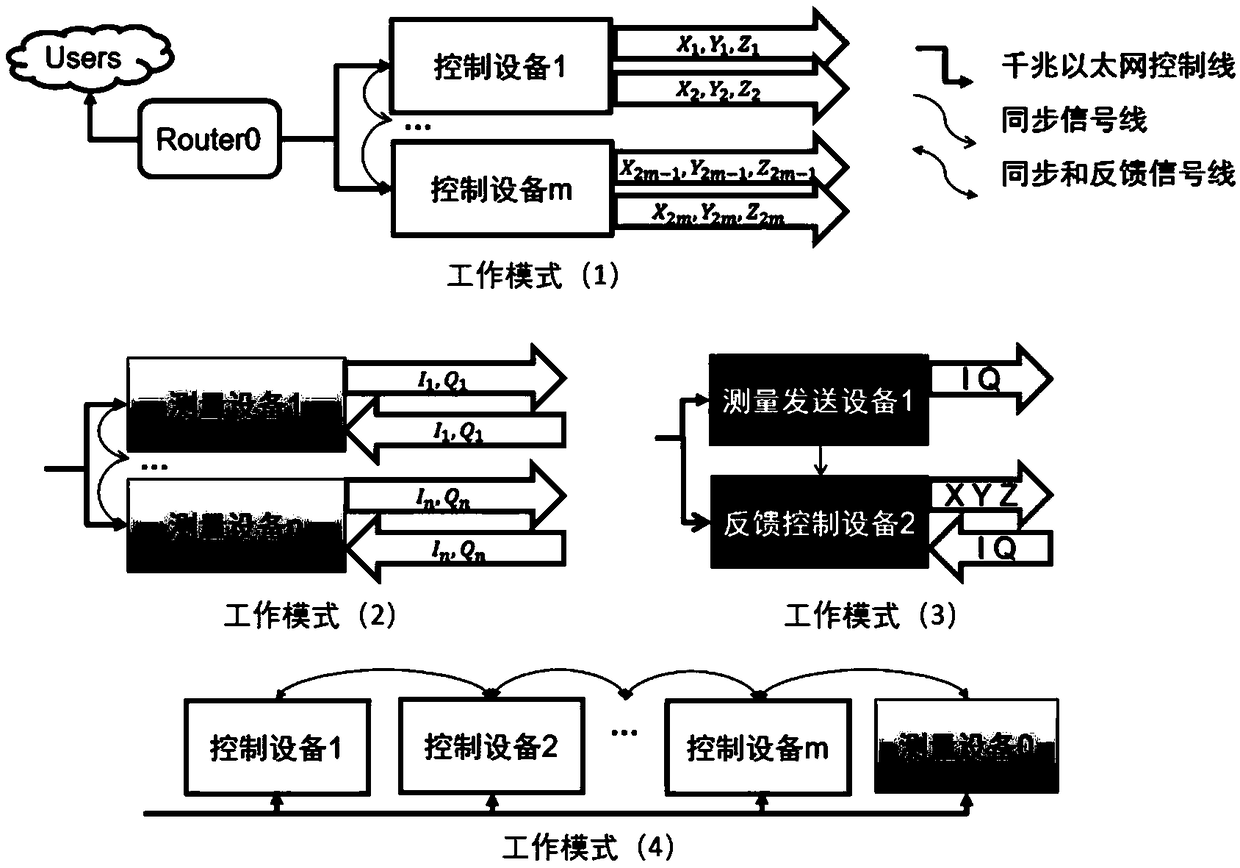

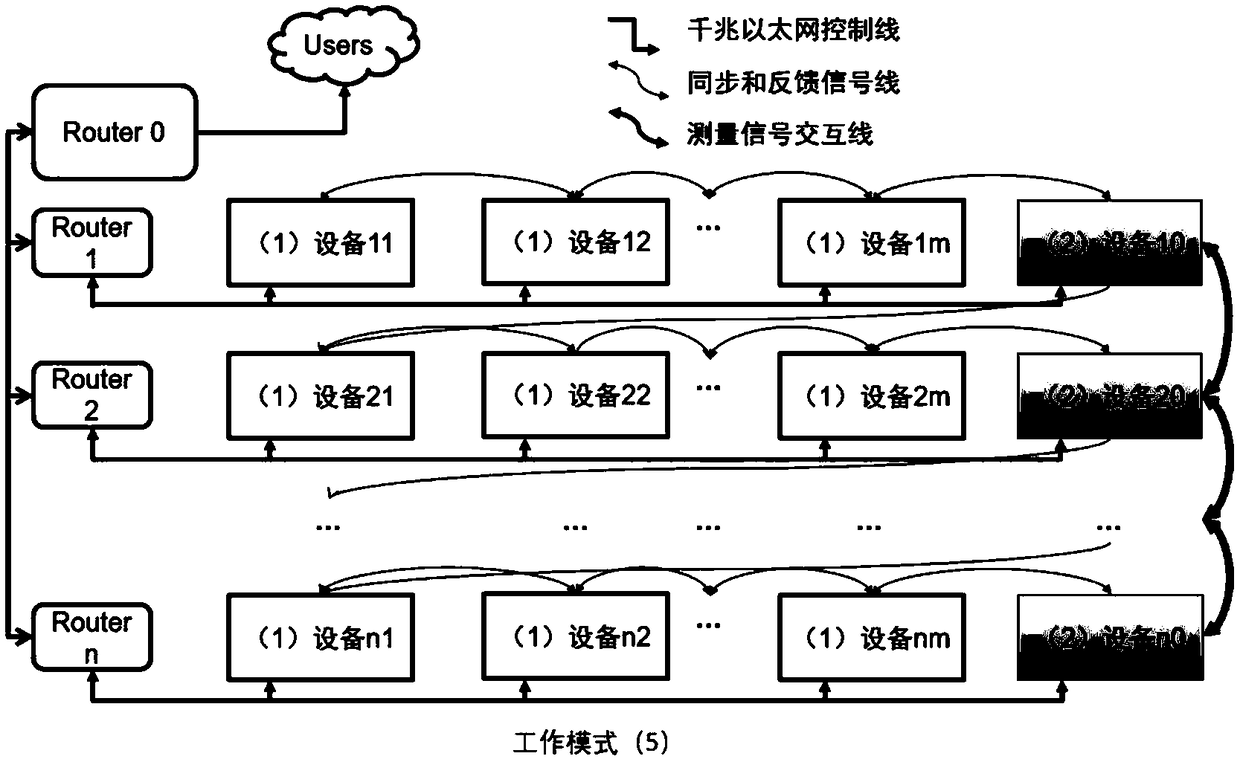

ActiveCN109217939AEnabling Quantum MeasurementsImplement Feedback ControlPhotonic quantum communicationDigital signal processingFeedback control

The invention discloses a scalable low-latency feedback control device for quantum bits. The device realizes the feedback control of the quantum states of multiple quantum bits by means of digital signal processing technology and a quantum mechanical principle based on a high-speed microwave baseband signal transceiving hardware circuit board. The quantum feedback control device designed in the present invention is different from the feedback control applied in the classic field, and can generate synchronous microwave pulses for operating superconducting quantum bits, can accurately define thenumber of times, the time and the strength of quantum measurement, demodulates measurement signals in real time, deploys a quantum feedback algorithm on an FPGA, and has extremely low feedback delayand excellent scalability so as to accurately control a system integrating multiple quantum bits and to satisfy a requirement for running a measurement-based quantum error correction algorithm on a quantum chip.

Owner:ZHEJIANG UNIV