Resetting method and resetting control device of register inside chip based on scanning chain

A reset method and scan chain technology, which are applied in the field of scan chain-based chip internal register reset method and reset control device, can solve the problems of chip physical implementation, chip design and implementation, and hardware resource consumption, and achieve simple structure and high performance. Low-impact, physically simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

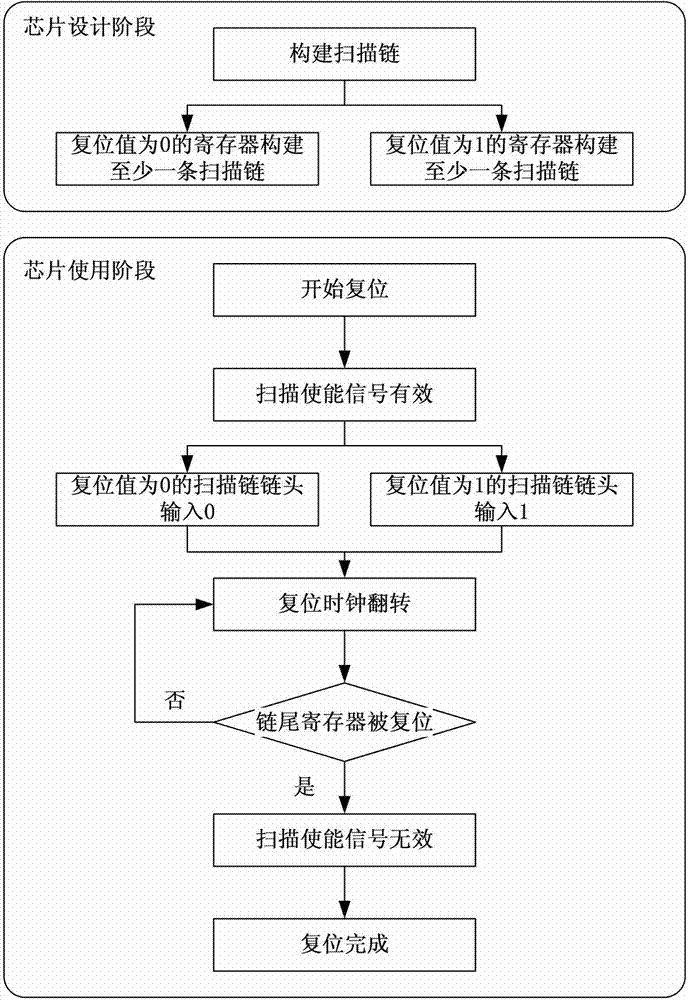

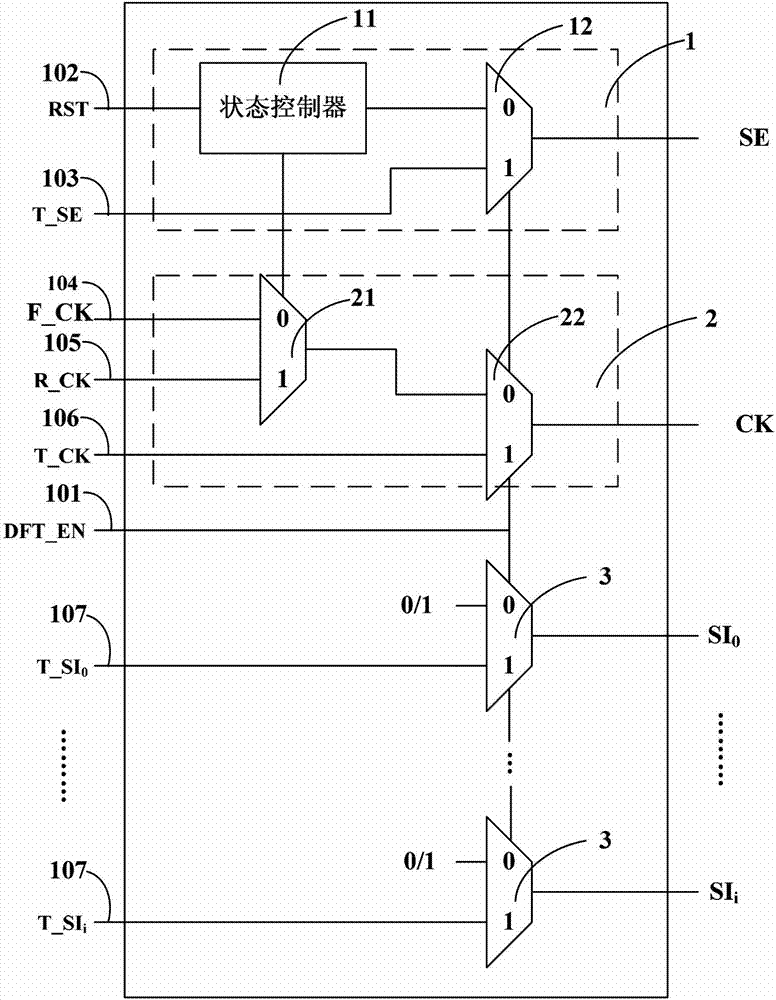

[0020] Such as figure 1 As shown, the implementation steps of the chip internal register reset method based on the scan chain in the embodiment of the present invention are as follows:

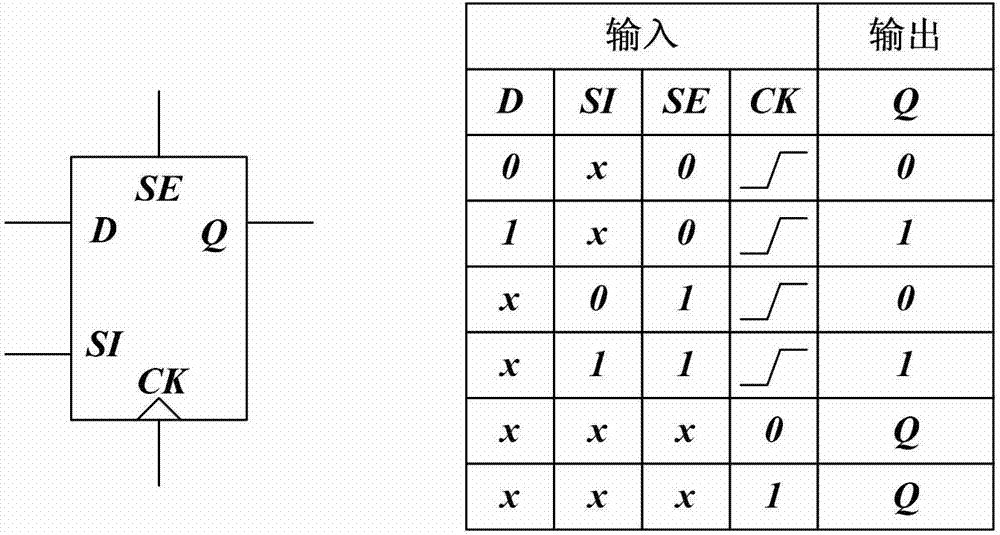

[0021] 1) In the chip design stage, build at least one scan chain for the registers that need to be reset to 0, and at least one scan chain for the registers that need to be reset to 1, and the scan output of the previous register in the same scan chain The scan input of a register is connected;

[0022] 2) In the chip use stage, enable the scan enable signal of each register in the chip, input the reset value 0 at the head of the scan chain composed of the registers that need to be reset to 0, and input the reset value 0 in the scan chain composed of the registers that need to be reset to 1 The scan chain head inputs a reset value of 1 and provides a reset clock to control each scan chain to enter the reset scanning state. Under the control of the input reset clock, the reset value is sequen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More