Patents

Literature

1000 results about "Page buffers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor memory device and method of operating the same

ActiveUS8526239B2Minimizing deteriorationImprove reliabilityRead-only memoriesDigital storageComputer architectureControl circuit

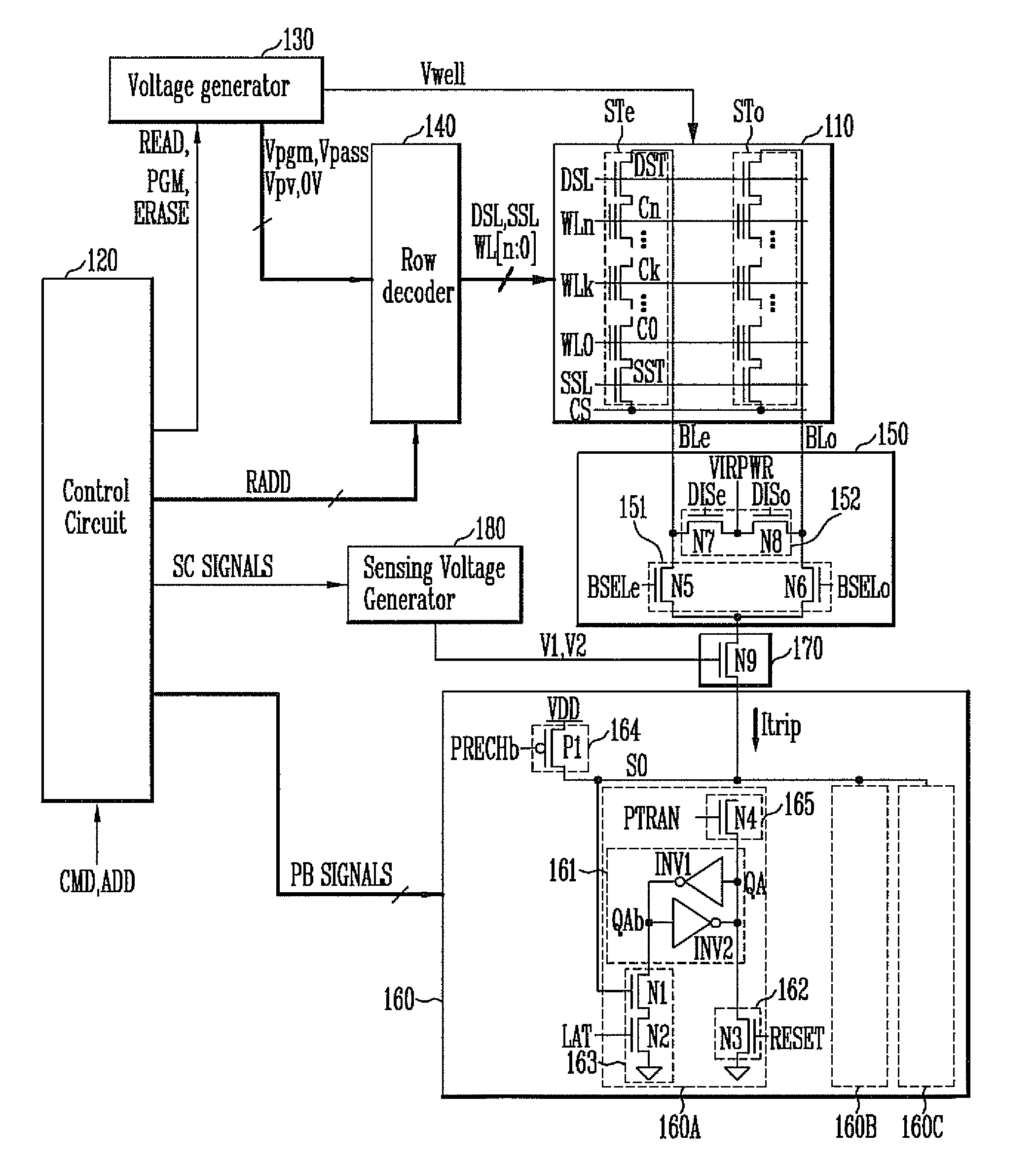

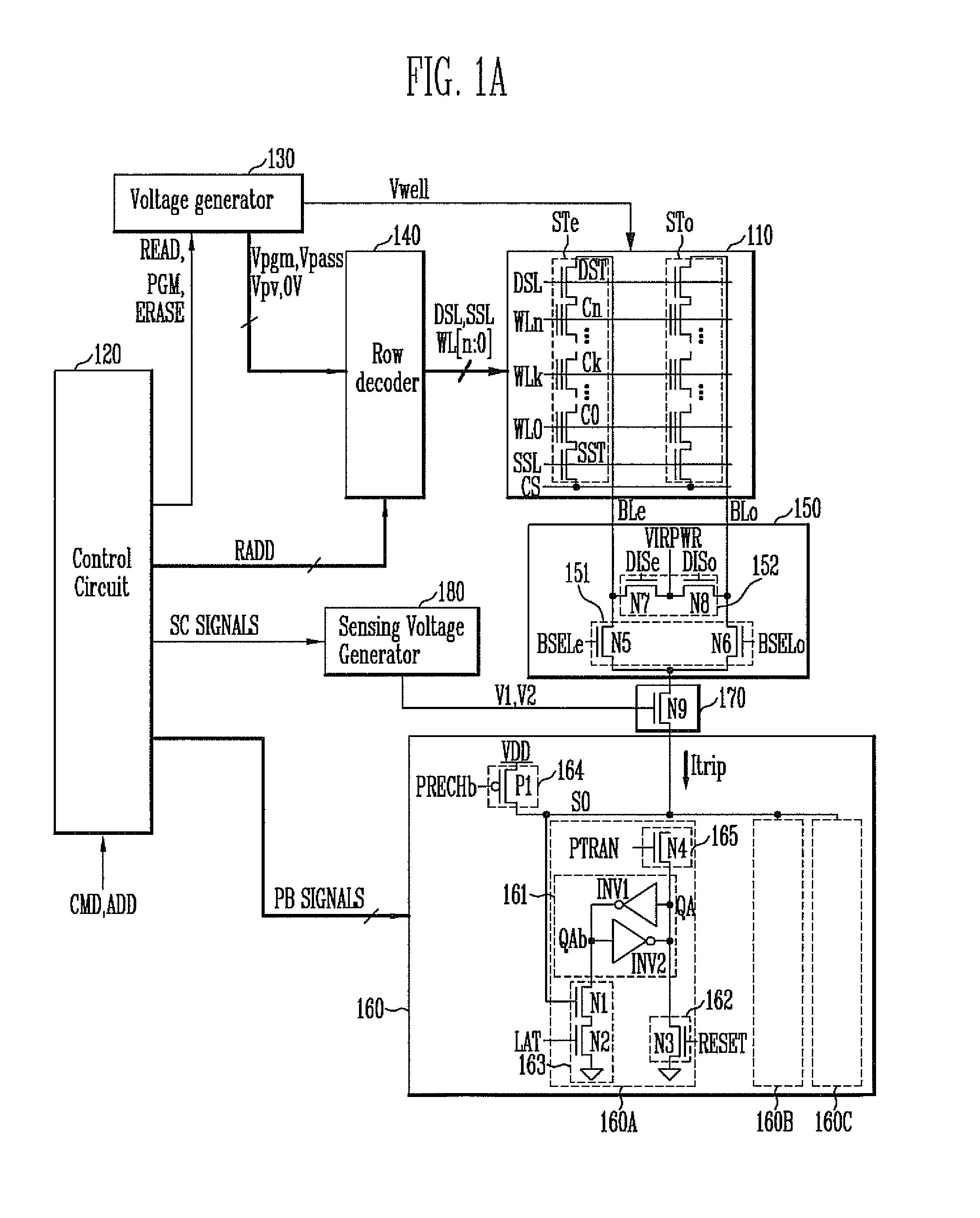

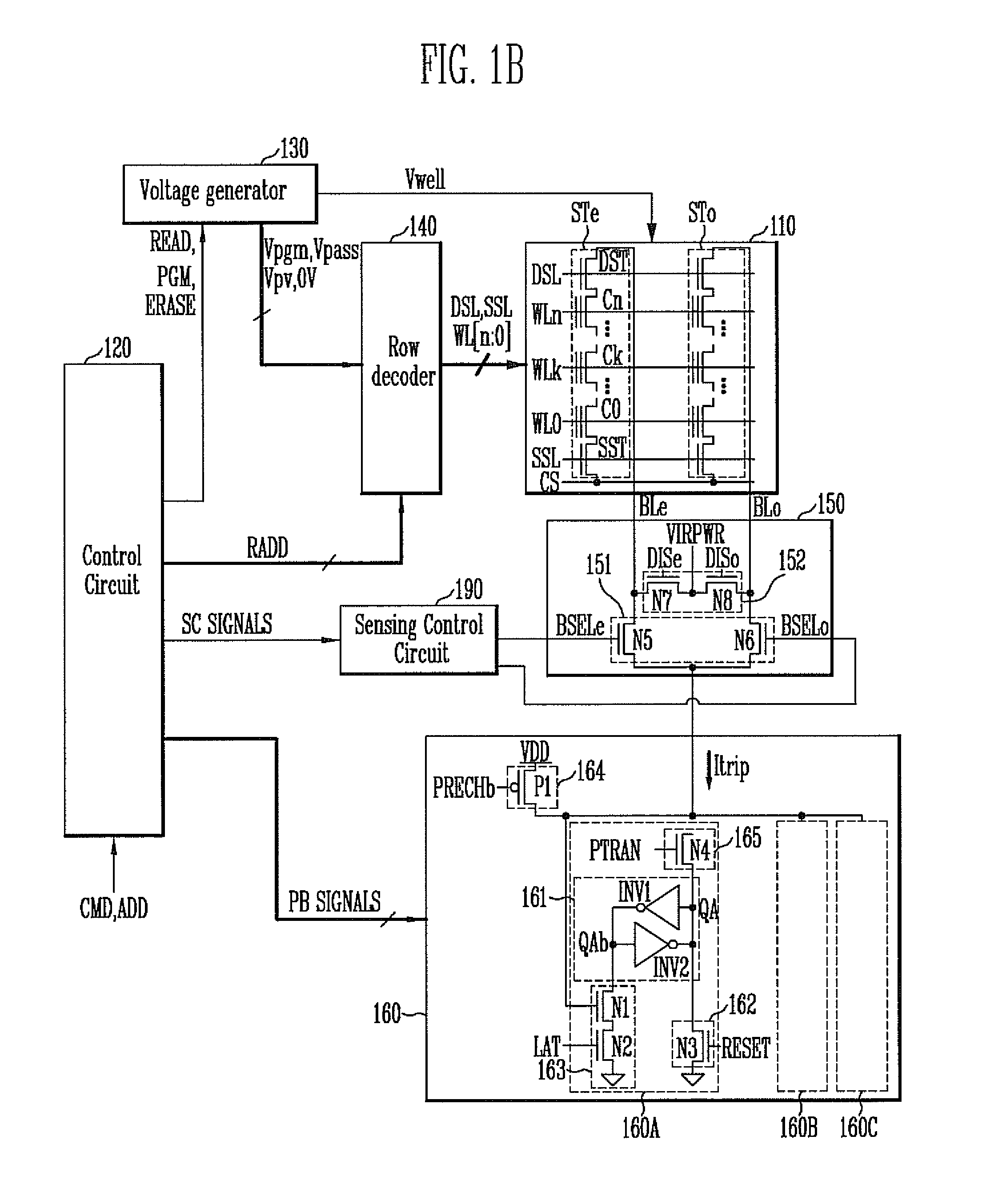

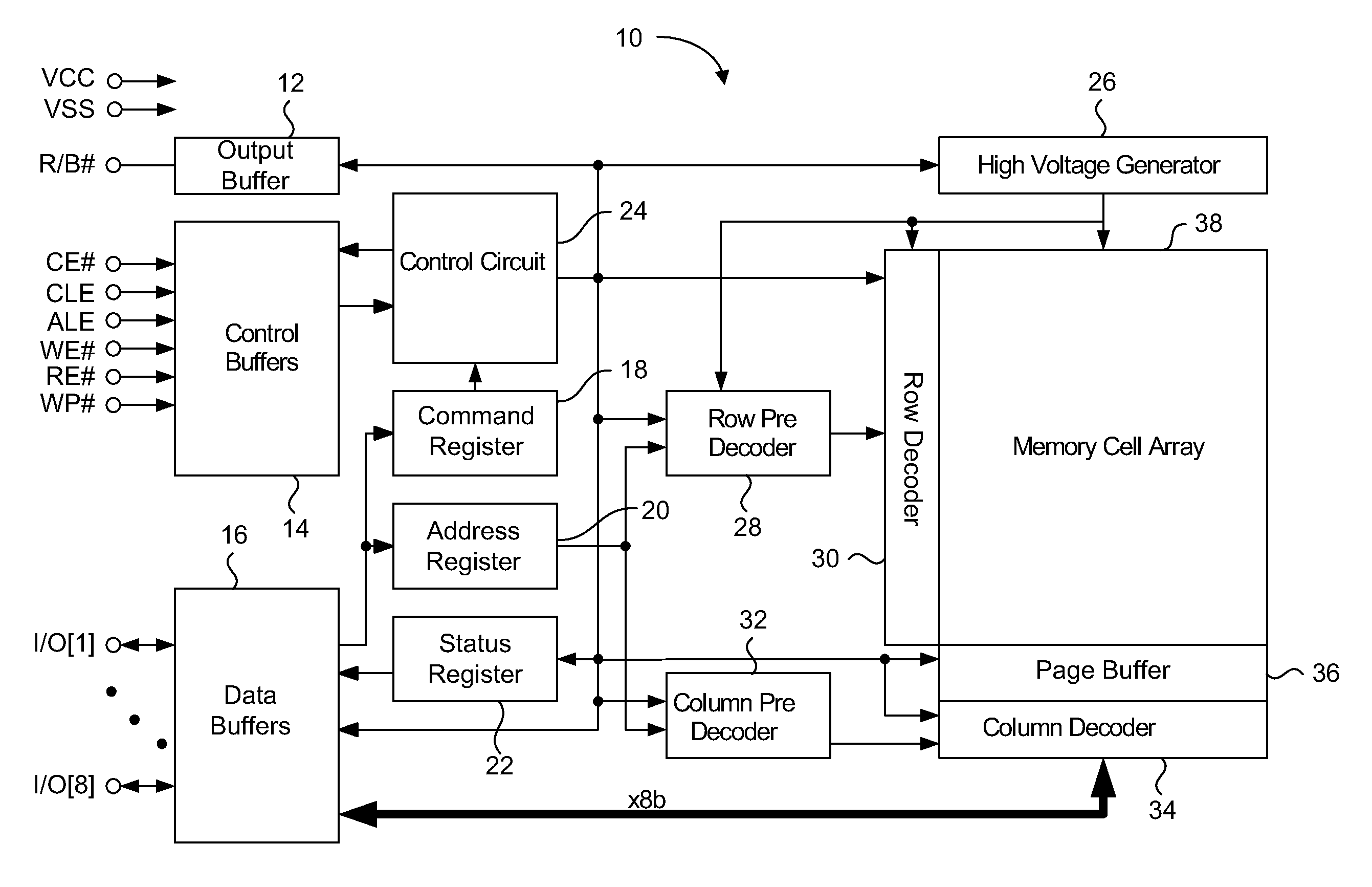

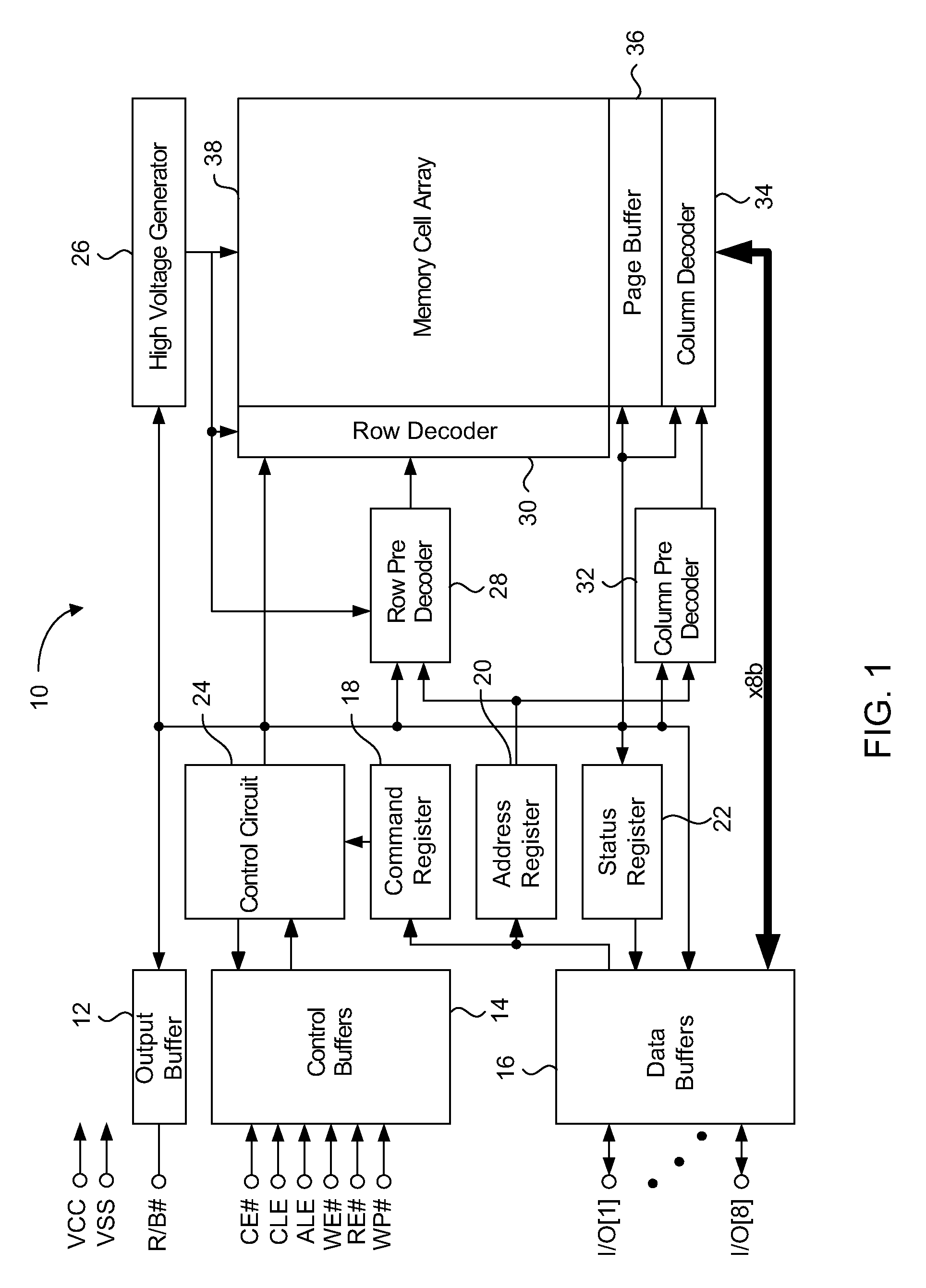

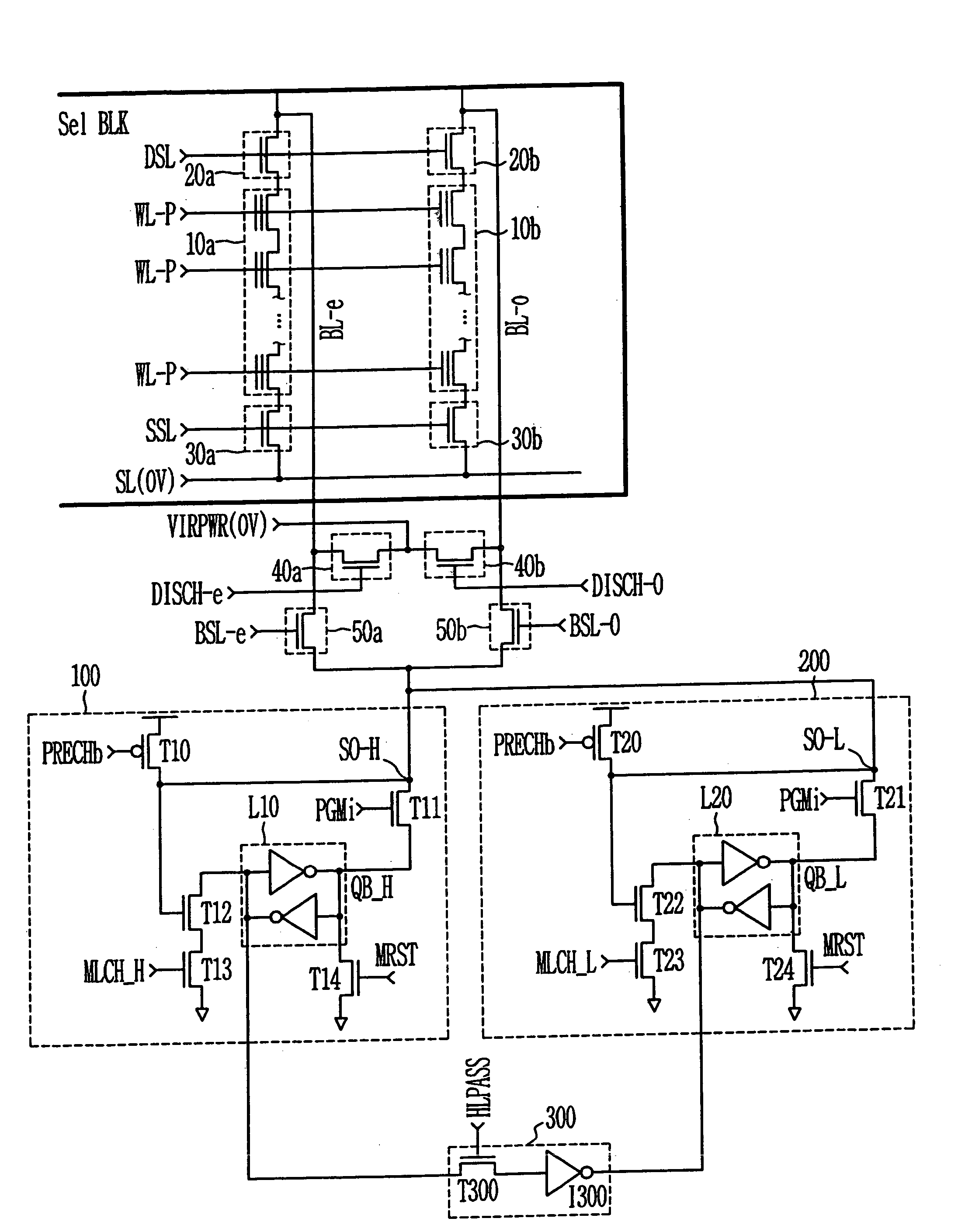

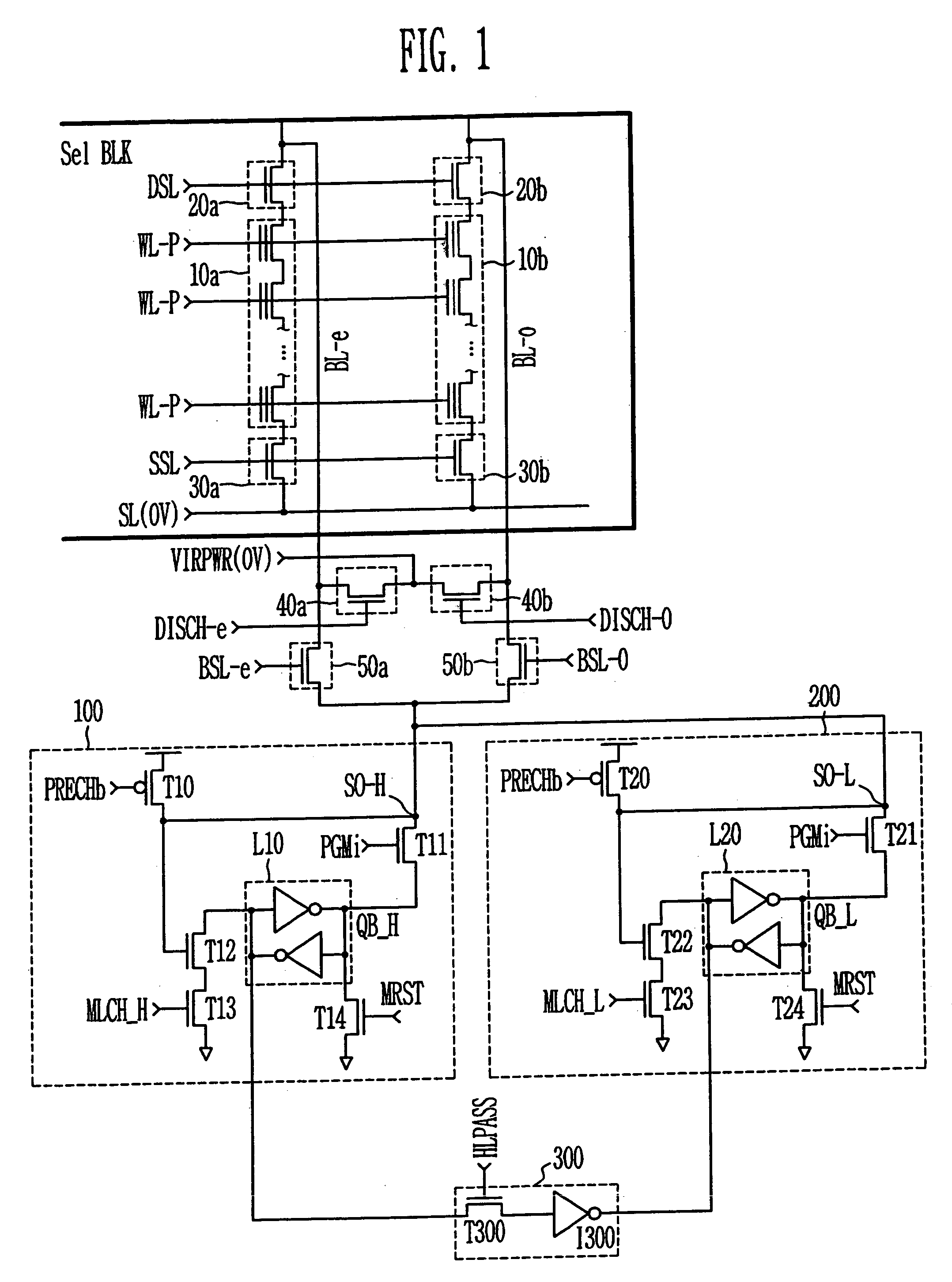

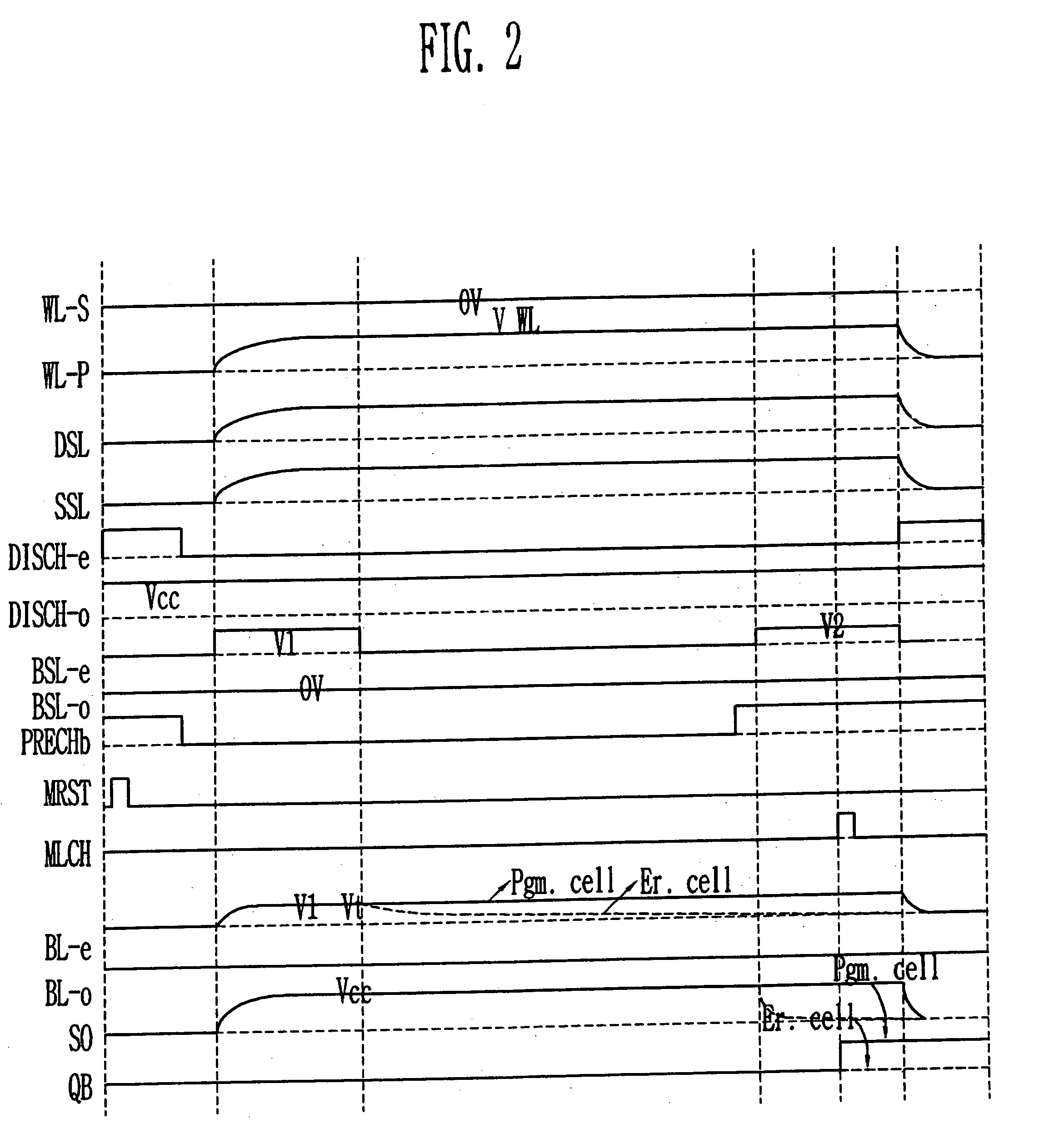

A semiconductor memory device includes a memory string coupled to a bit line, a page buffer configured to sense a sensing current of the bit line in an erase verification operation or a program verification operation, and a sensing control circuit configured to differently set a level of the sensing current in the erase verification operation and the program verification operation in order to sense the threshold voltage level of a selected memory cell of the memory string.

Owner:SK HYNIX INC

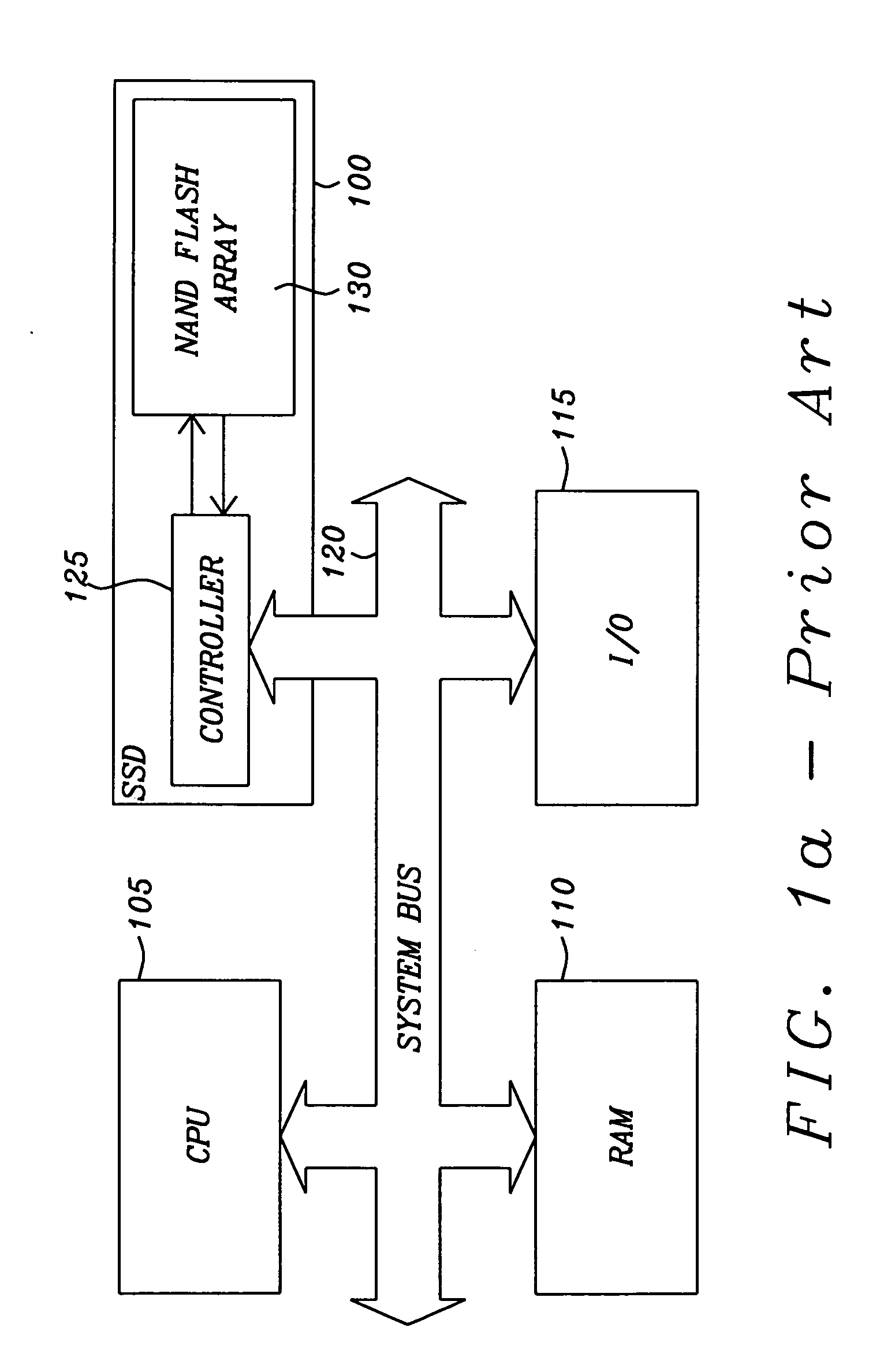

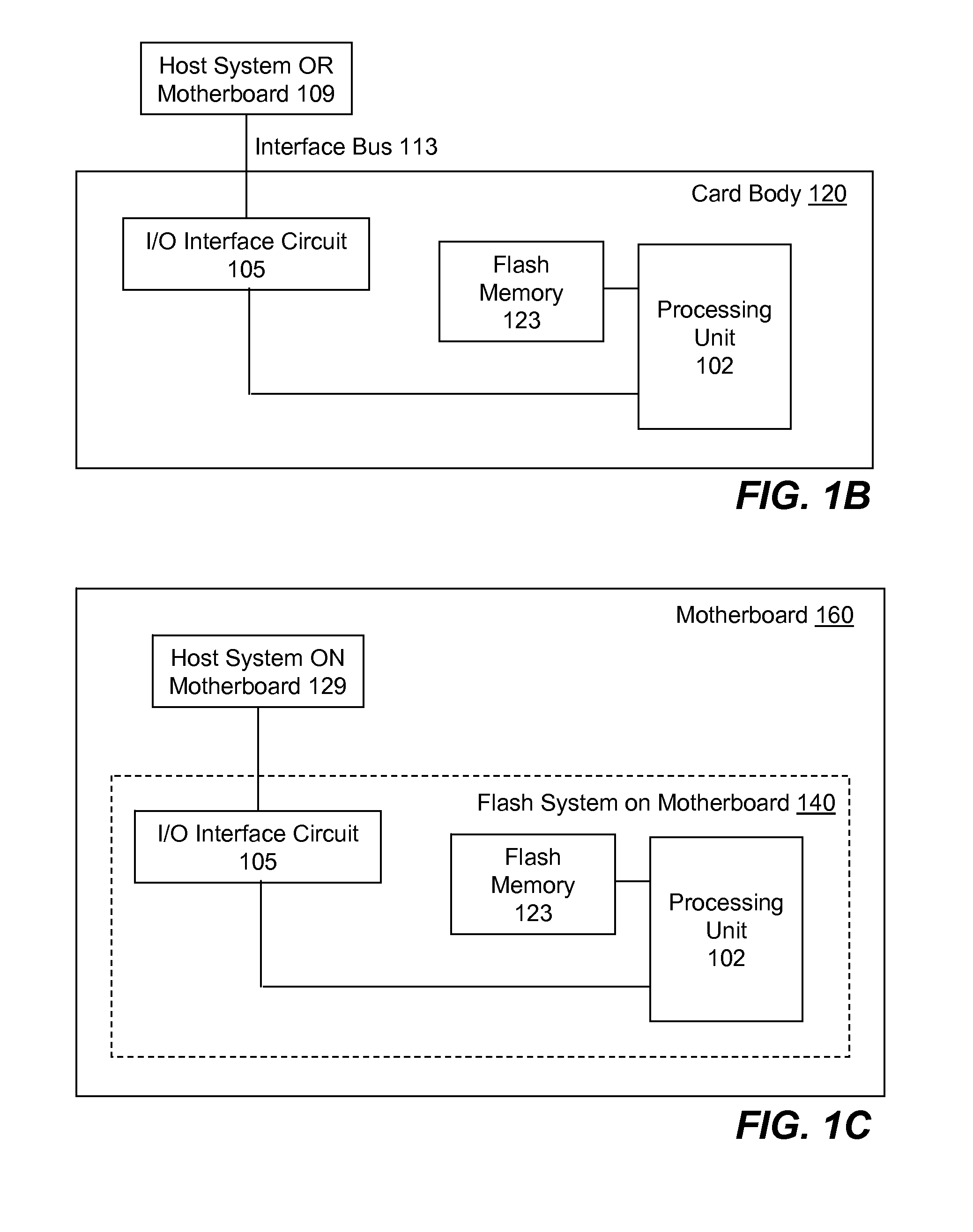

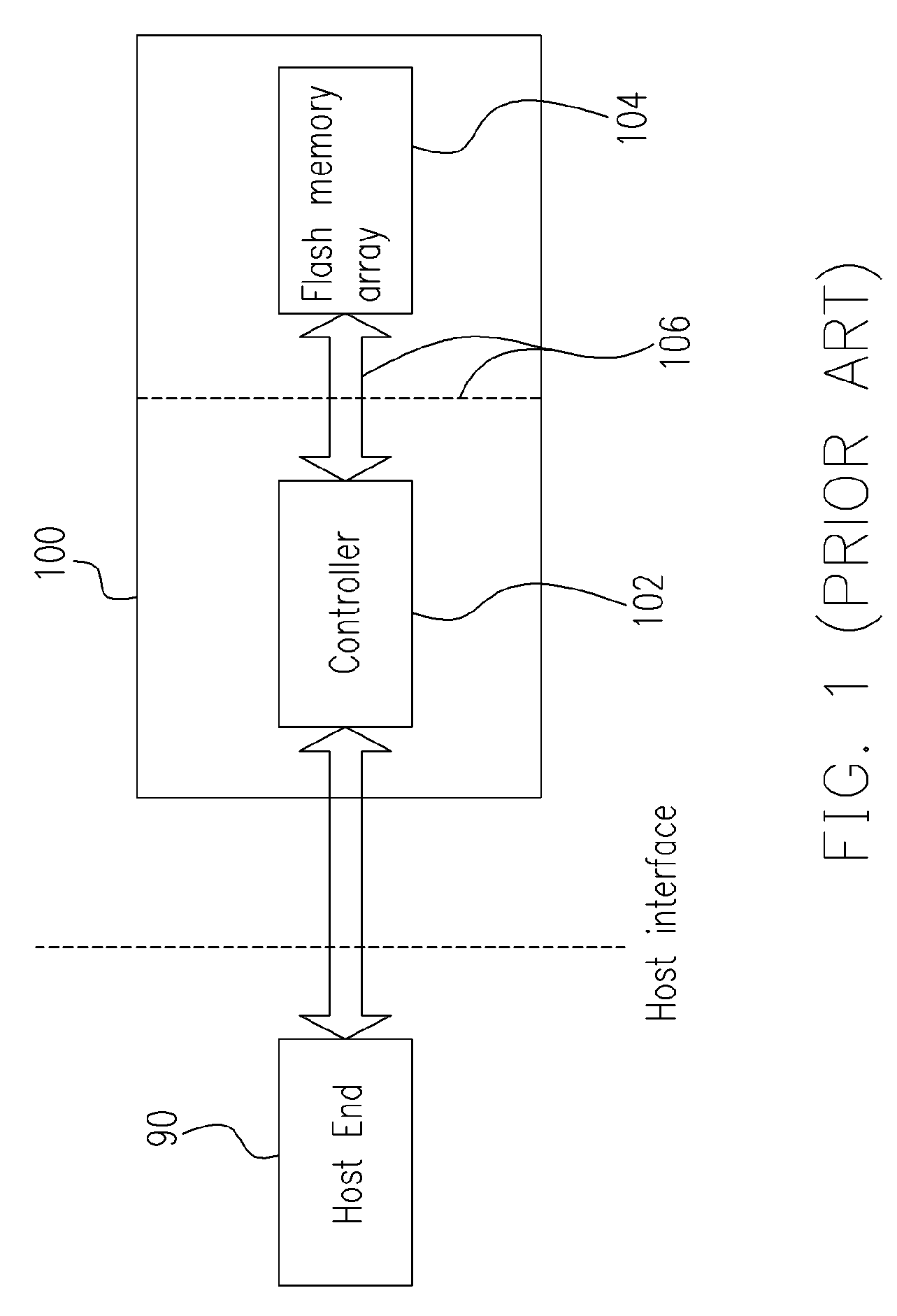

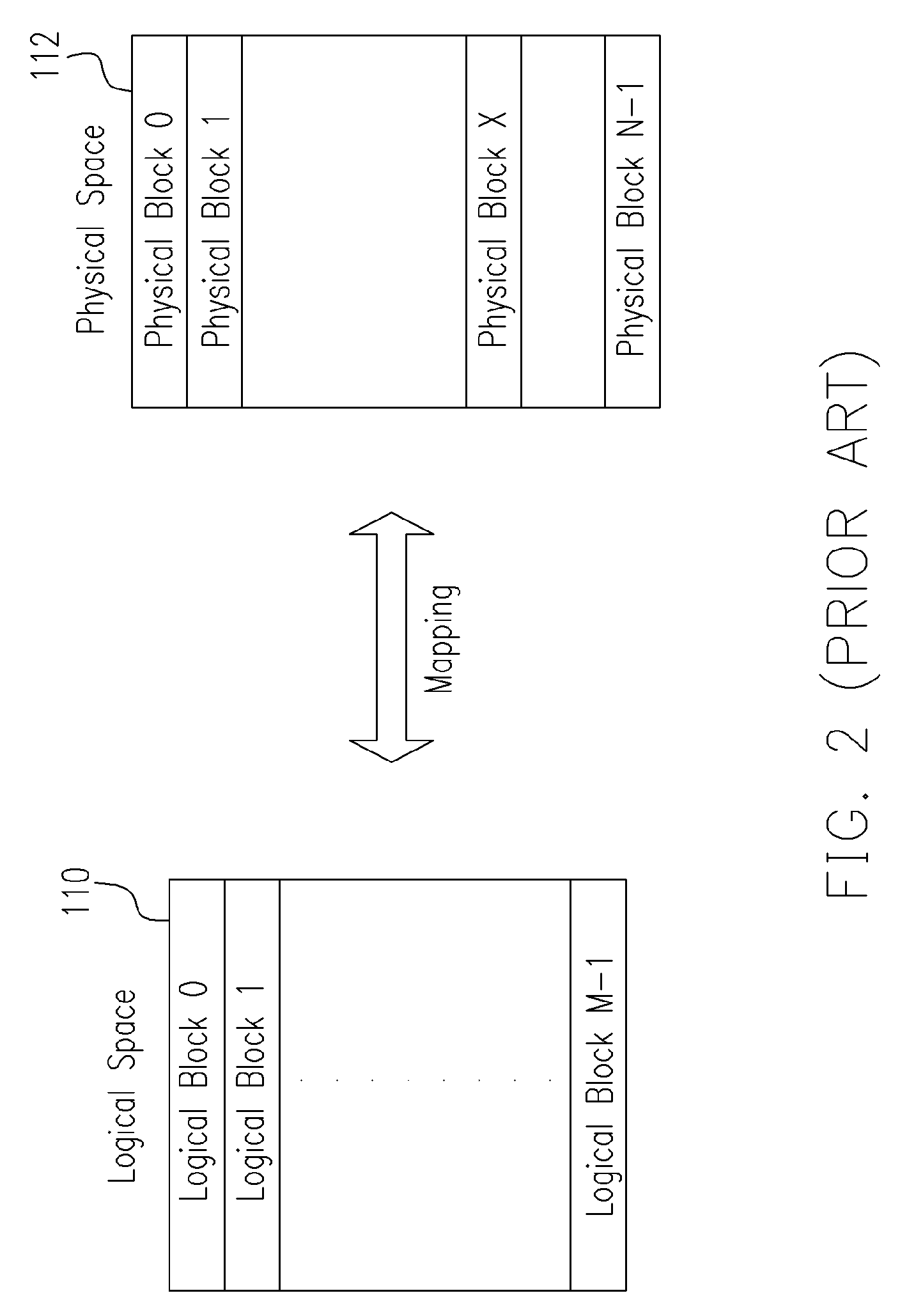

Page based management of flash storage

InactiveUS20110055458A1Memory architecture accessing/allocationMemory adressing/allocation/relocationControl signalPaging

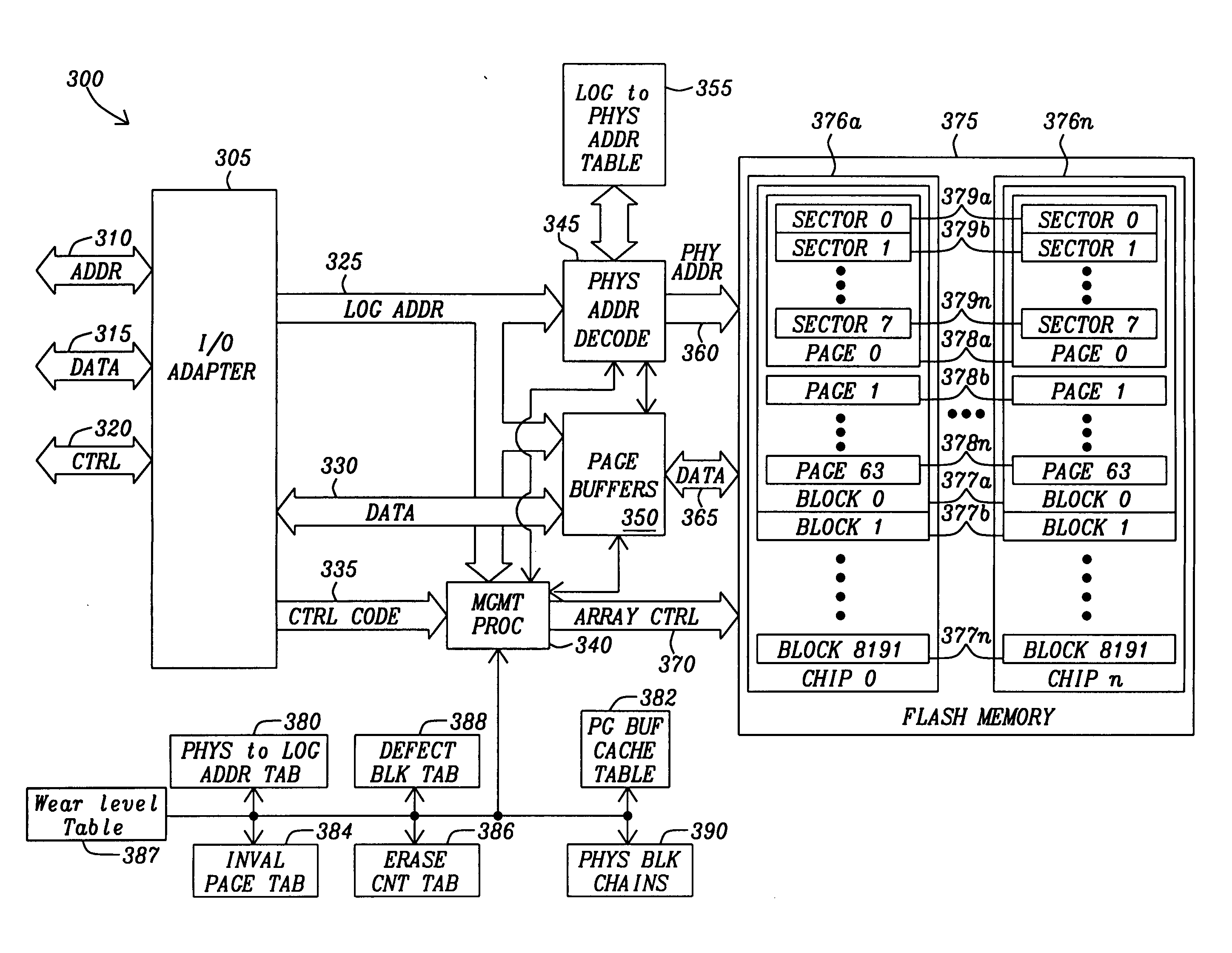

Methods and circuits for page based management of an array of Flash RAM nonvolatile memory devices provide paged base reading and writing and block erasure of a flash storage system. The memory management system includes a management processor, a page buffer, and a logical-to-physical translation table. The management processor is in communication with an array of nonvolatile memory devices within the flash storage system to provide control signals for the programming of selected pages, erasing selected blocks, and reading selected pages of the array of nonvolatile memory devices.

Owner:PIONEER CHIP TECH

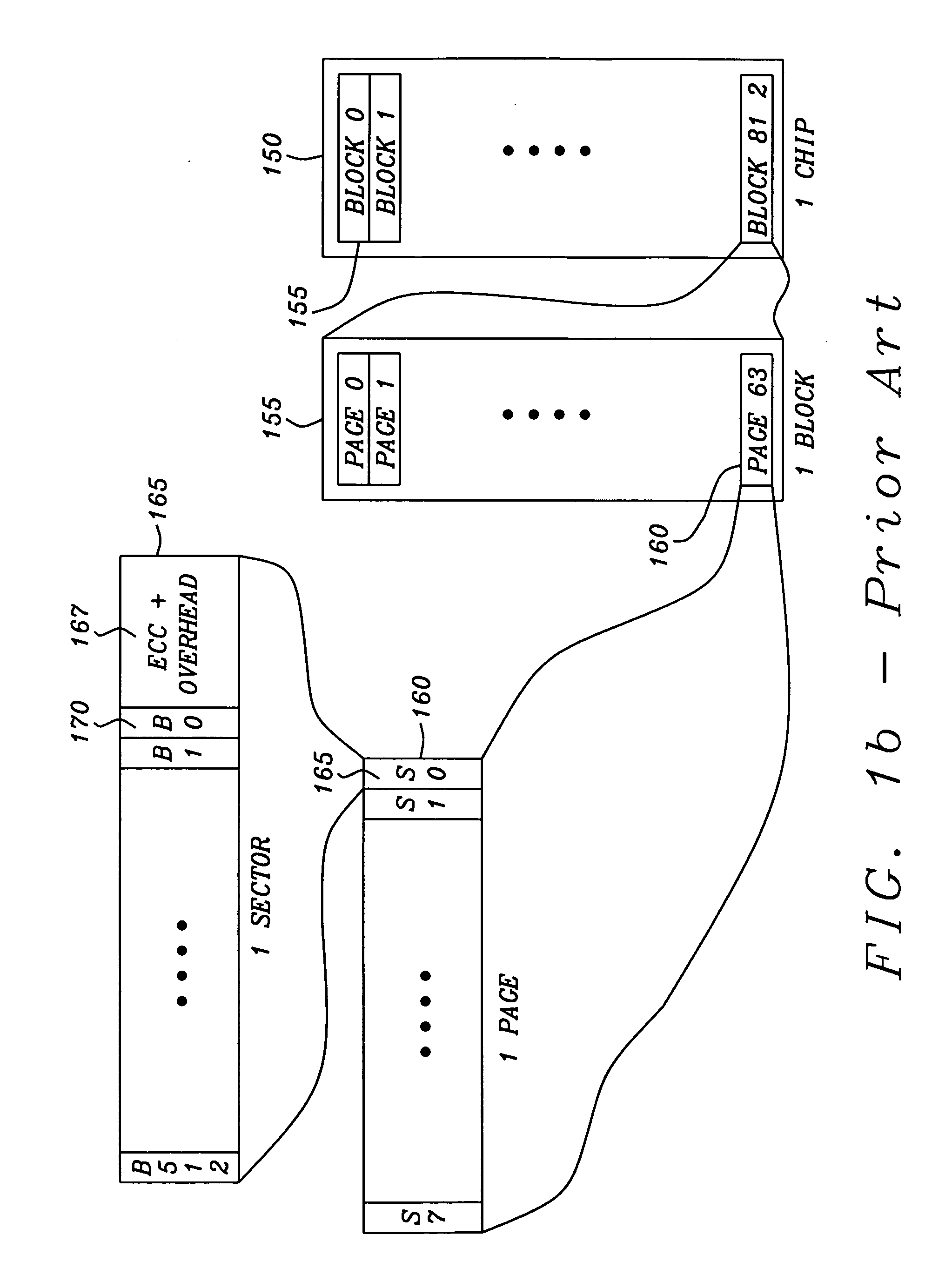

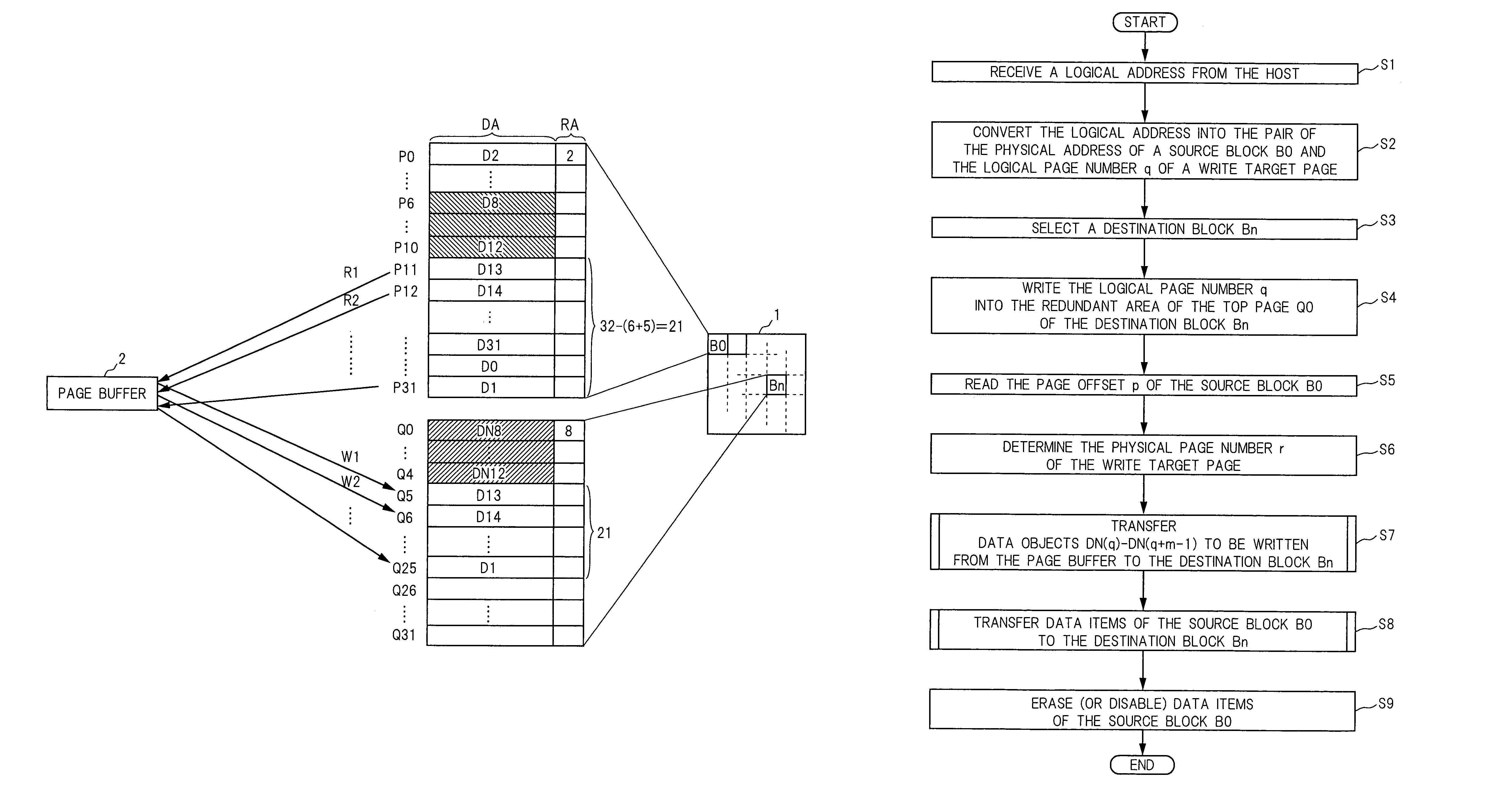

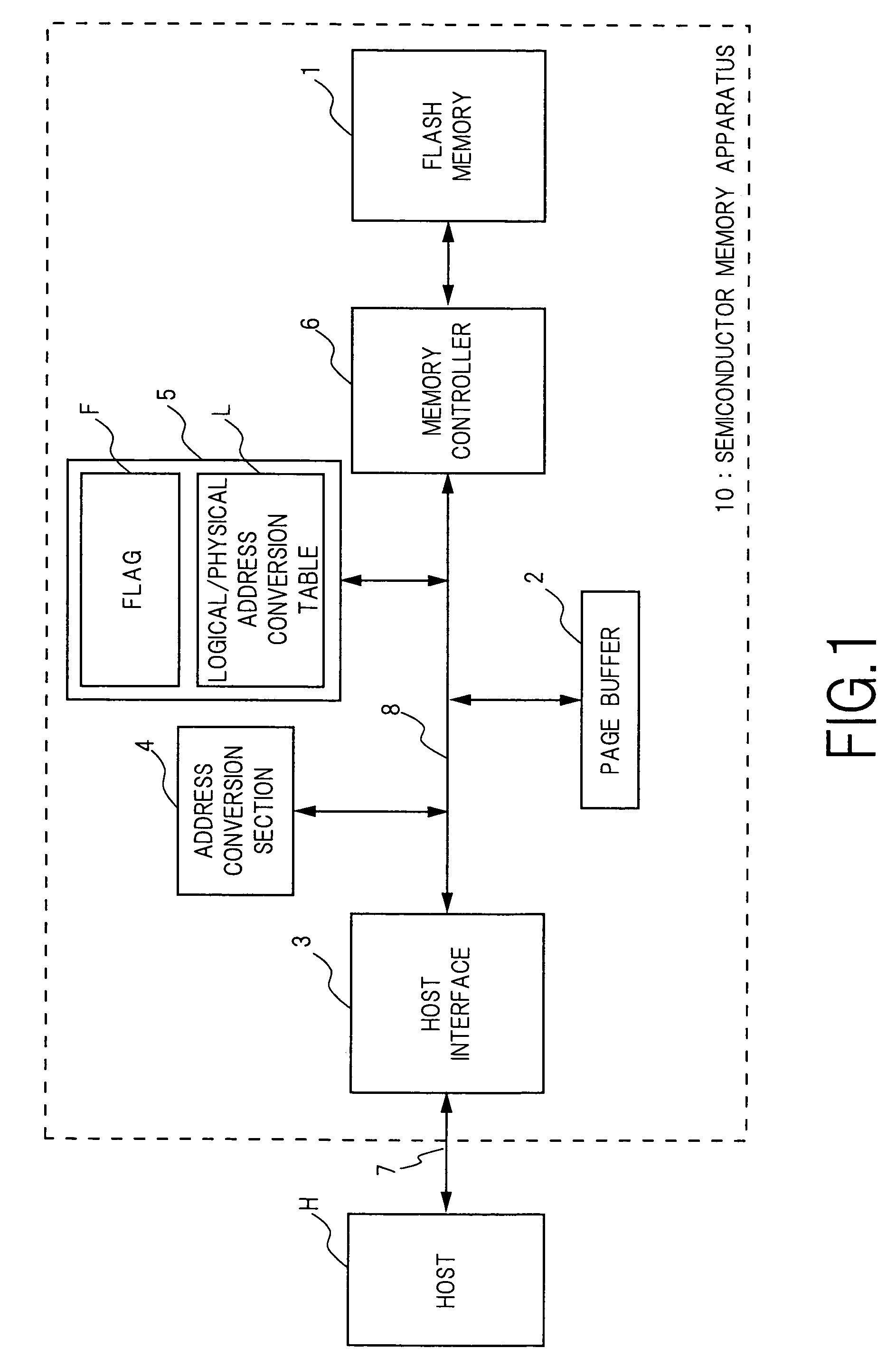

Semiconductor memory device and method for writing data into flash memory

ActiveUS7107389B2Small sizeReduce waiting timeMemory architecture accessing/allocationMemory adressing/allocation/relocationHome pageDatabase

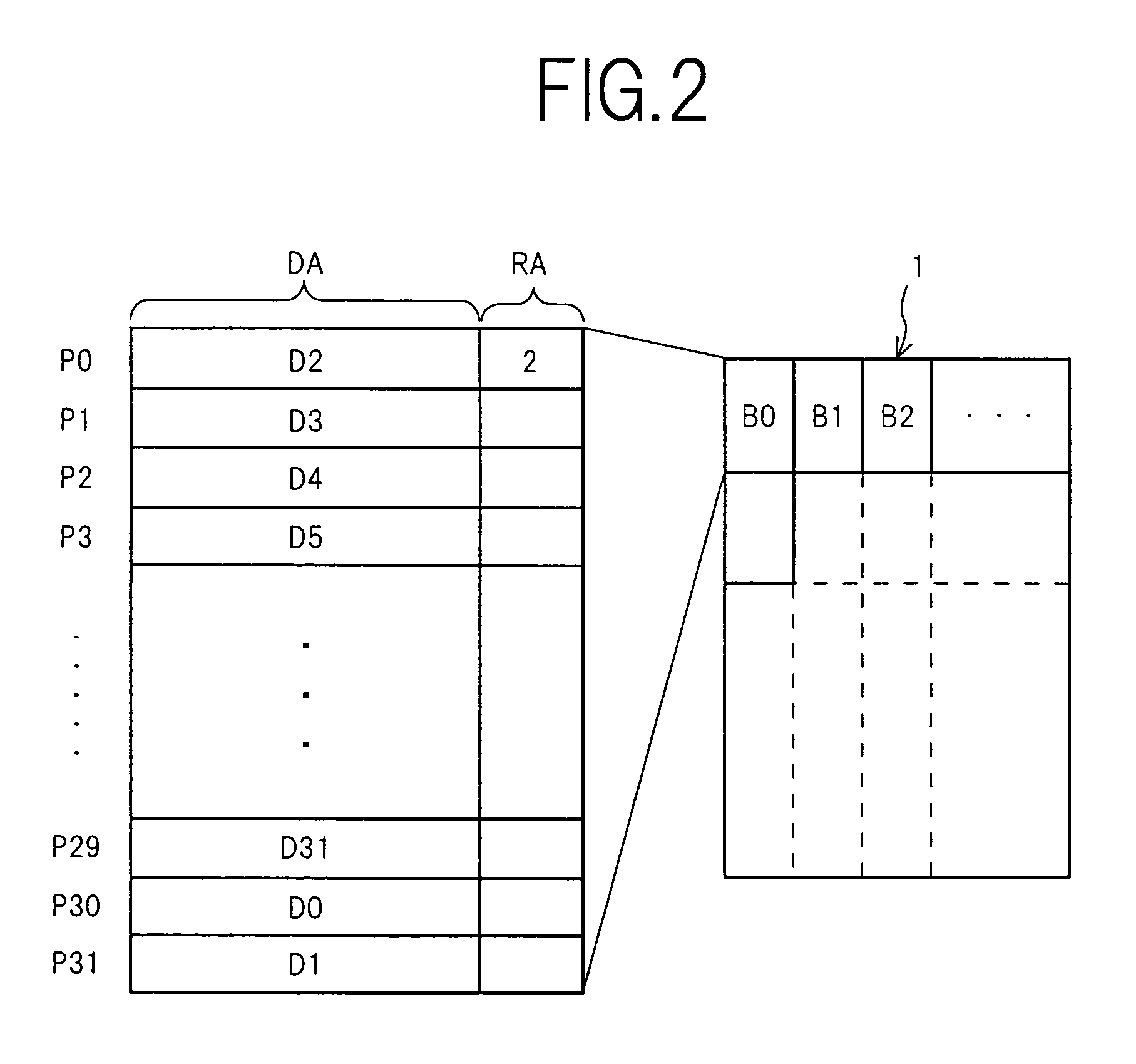

A source block (B0) and the logical page number (“8”) of a write target page are identified from the logical address of the write target page. Data objects (DN8, DN9, . . . , DN12) to be written, which a host stores in a page buffer (2), are written into the data areas (DA) of the pages (Q0, Q1, . . . , Q4) of a destination block (Bn), starting from the top page (Q0) in sequence. The logical page number (“8”) of the write target page is written into the redundant area (RA) of the top page (Q0). The physical page number (“6=8−2”) of the write target page is identified, based on the logical page number (“8”) of the write target page and the page offset (“2”) of the source block (B0). When notified by the host of the end of the sending of the data objects (DN8, . . . , DN12), the data items (D13, . . . , D31, D0, D1, . . . , D7) in the source block (B0) are transferred to the pages (Q5, Q6, . . . , Q31) in the destination block (Bn) via the page buffer (2) sequentially and cyclically, starting from the page (P11) situated cyclically behind the write target page (P6) by the number (“5”) of pages of the data objects (DN8, . . . , DN12).

Owner:PANASONIC CORP

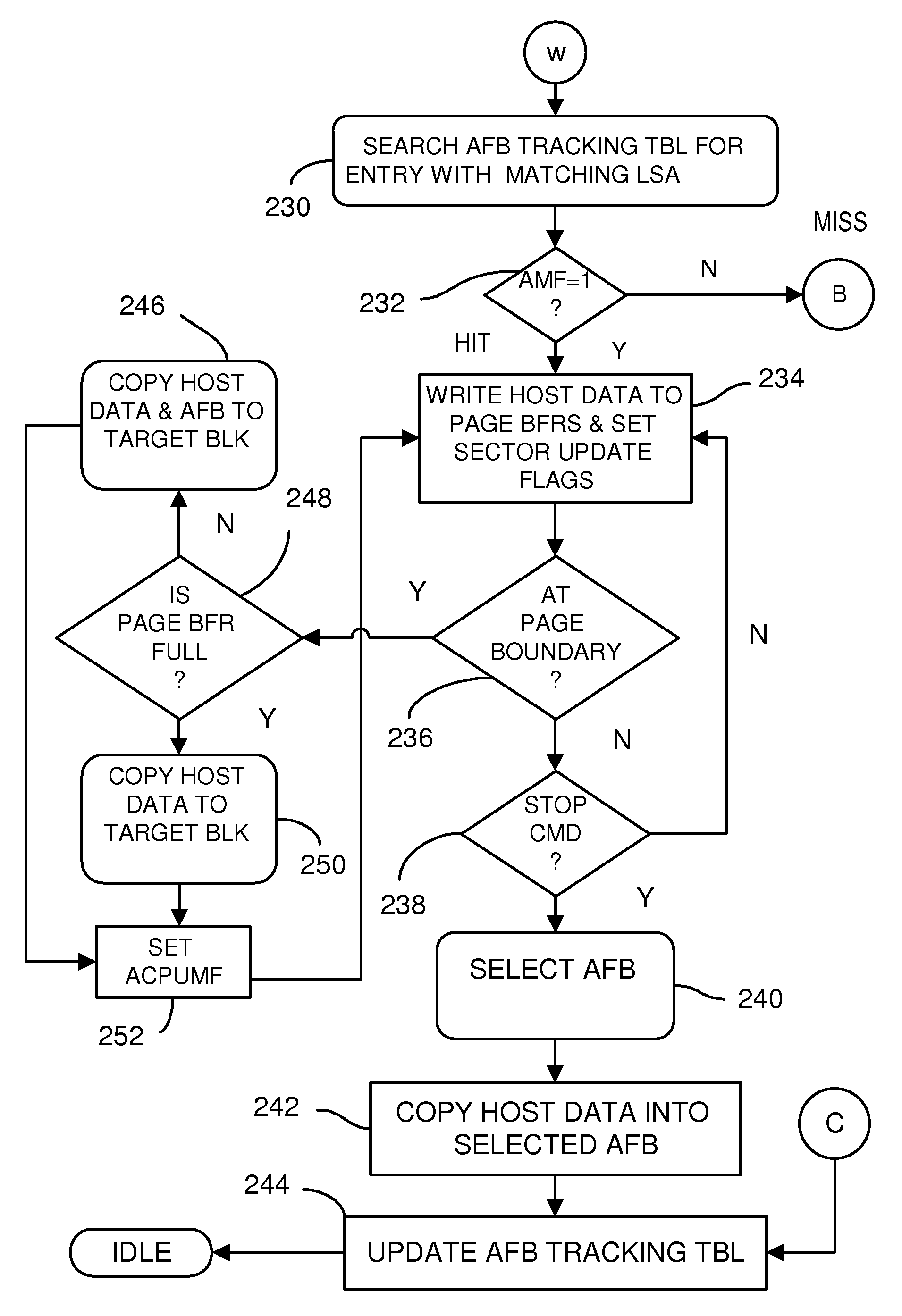

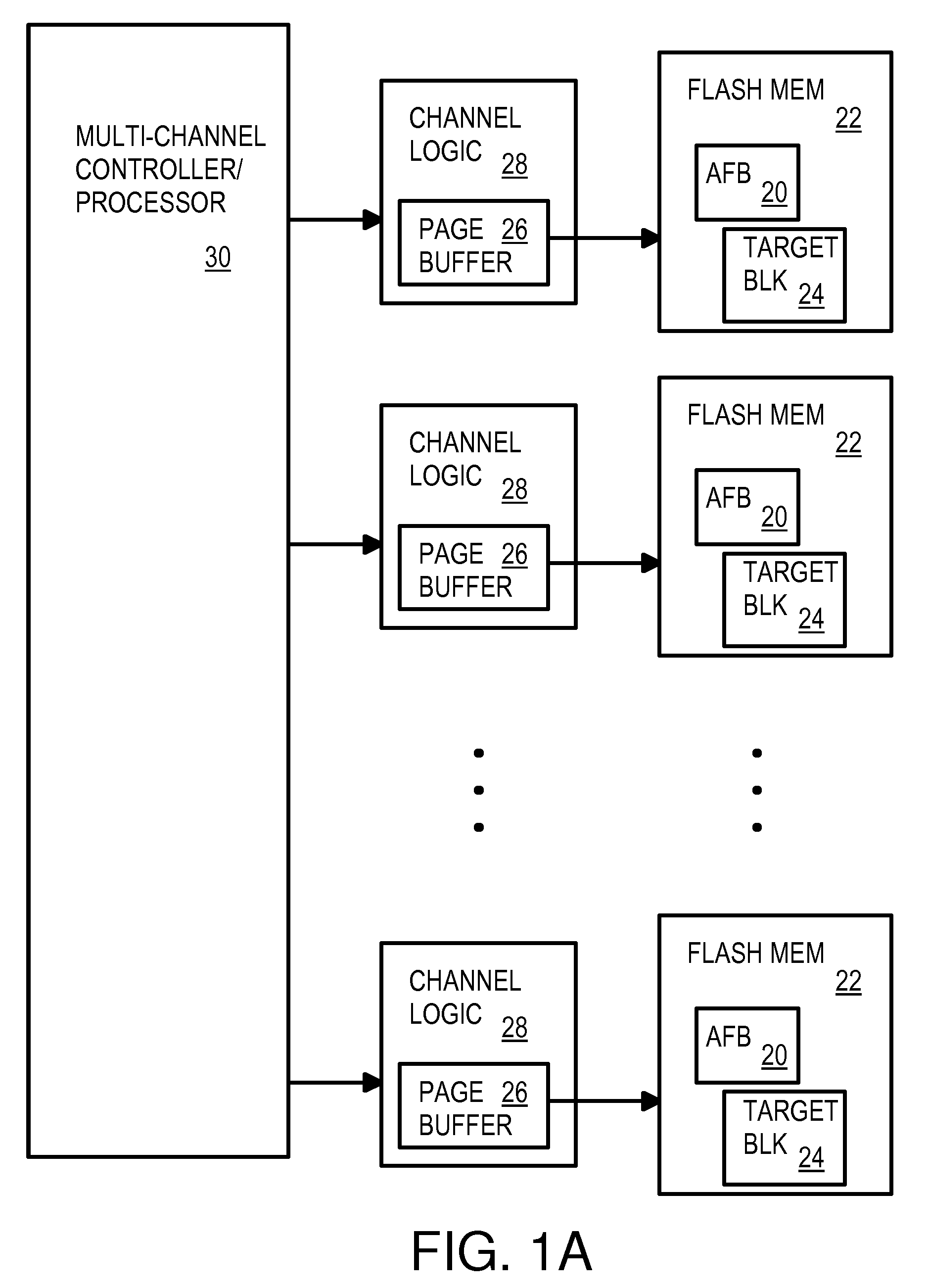

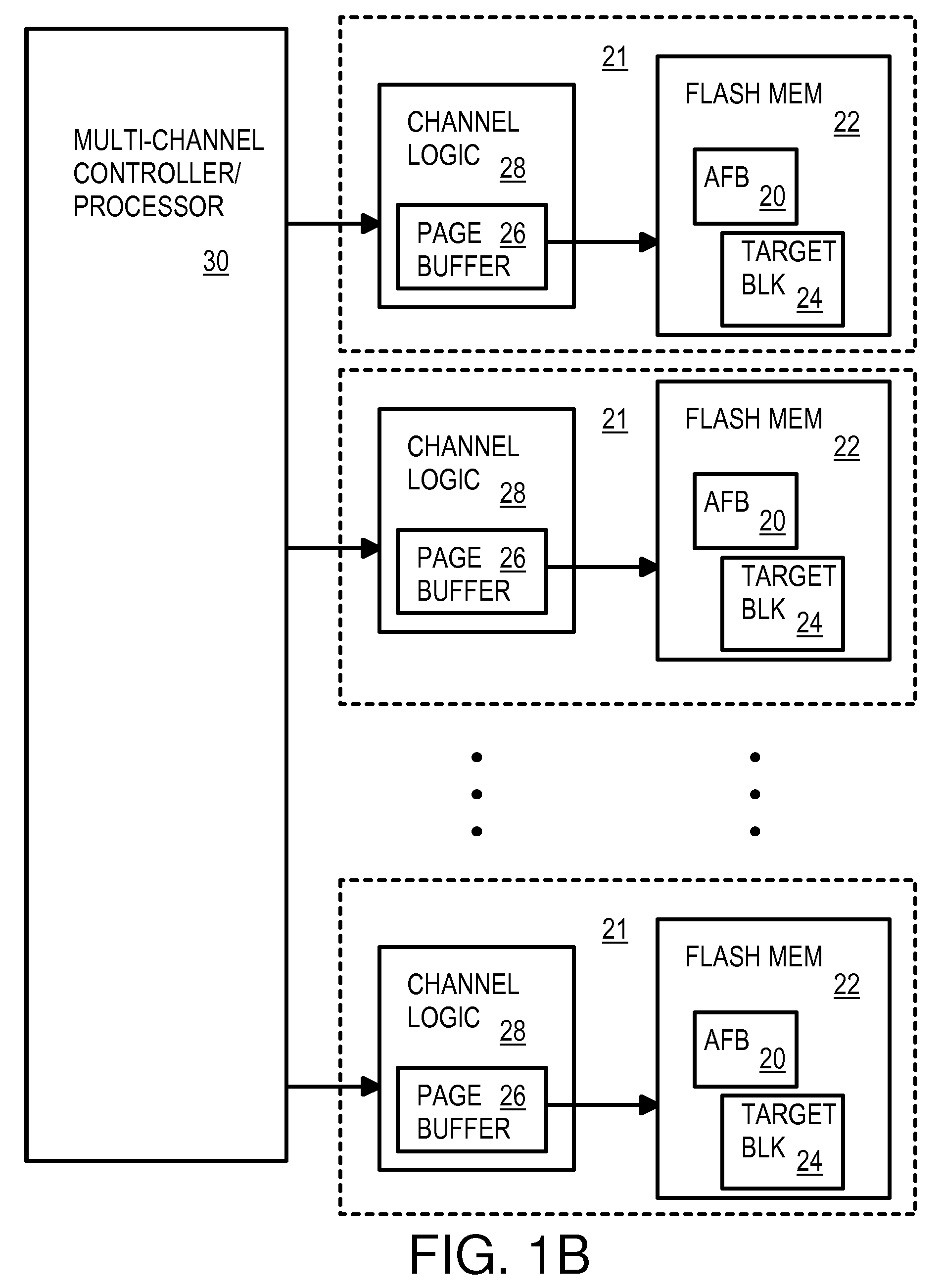

Multi-Operation Write Aggregator Using a Page Buffer and a Scratch Flash Block in Each of Multiple Channels of a Large Array of Flash Memory to Reduce Block Wear

InactiveUS20080250195A1Memory architecture accessing/allocationMemory adressing/allocation/relocationSmall fragmentPage buffers

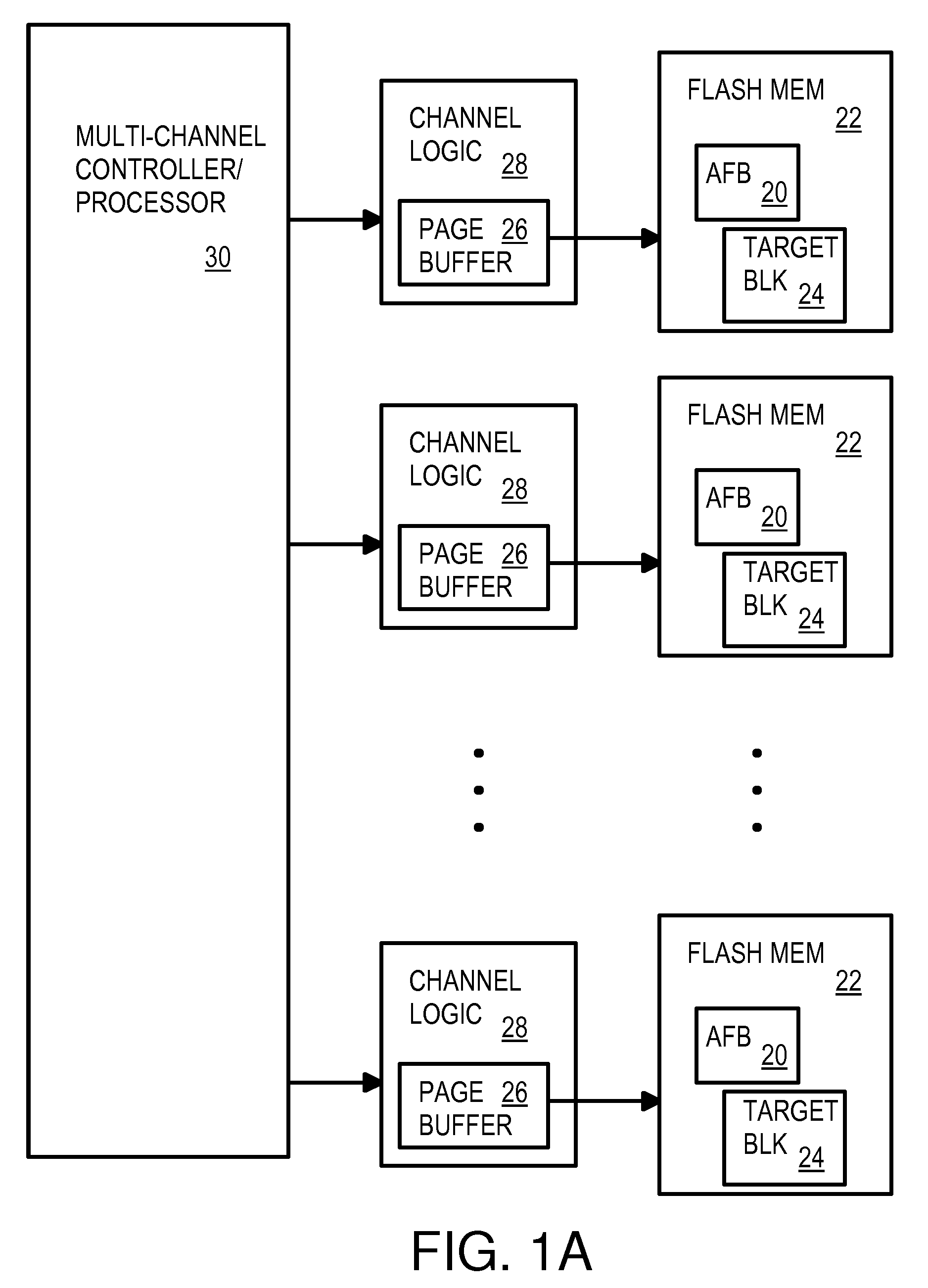

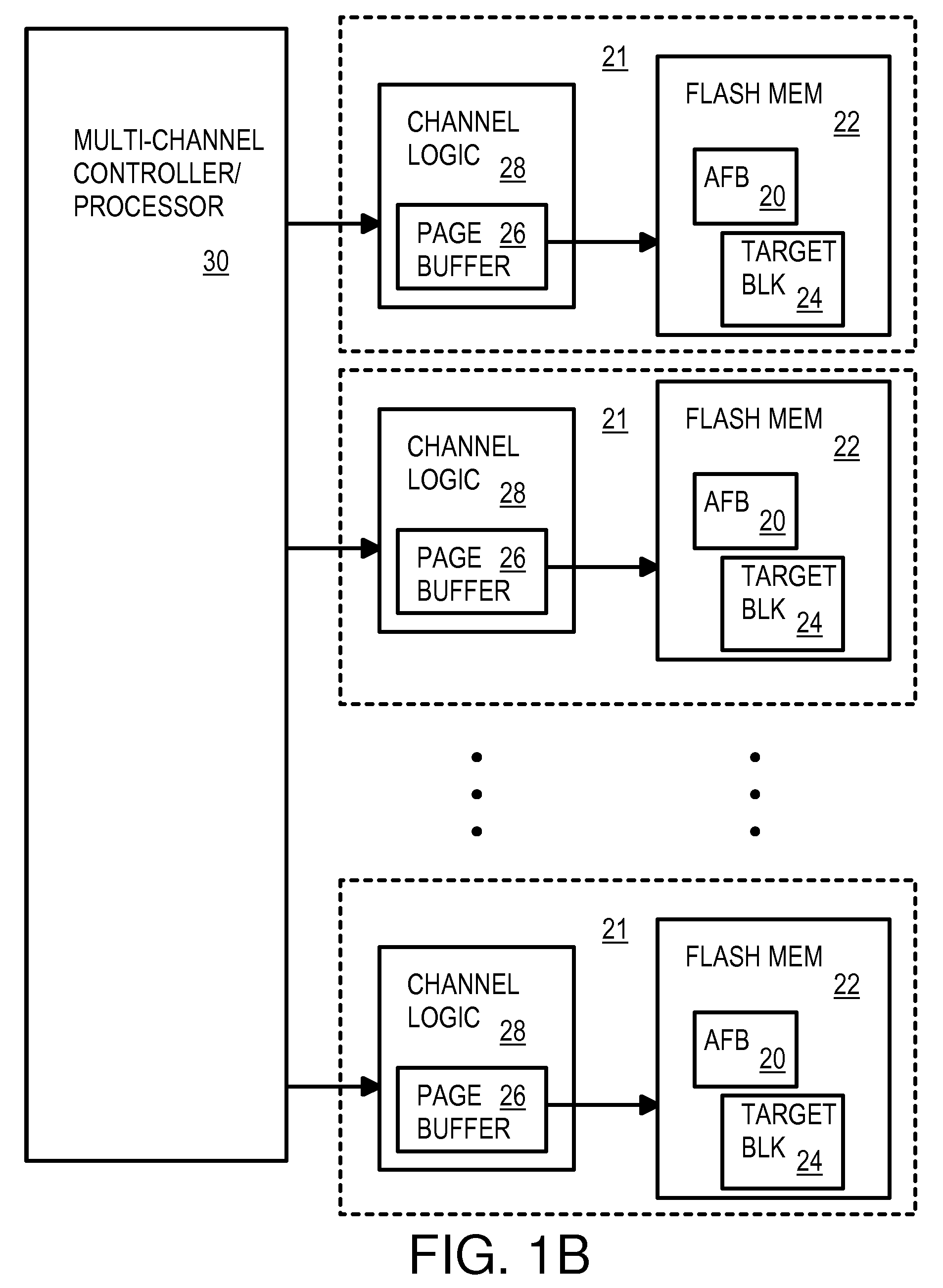

A flash system has multiple channels of flash memory chips that can be accessed in parallel. Host data is assigned to one of the channels by a multi-channel controller processor and accumulated in a multi-channel page buffer. When a page boundary in the page buffer is reached, the page buffer is written to a target physical block if full, or combined with old data fragments in an Aggregating Flash Block (AFB) when the logical-sector addresses (LSA's) match. Thus small fragments are aggregated using the AFB, reducing erases and wear of flash blocks. The page buffer is copied to the AFB when a STOP command occurs. Each channel has one or more AFB's, which are tracked by an AFB tracking table.

Owner:SUPER TALENT TECH CORP

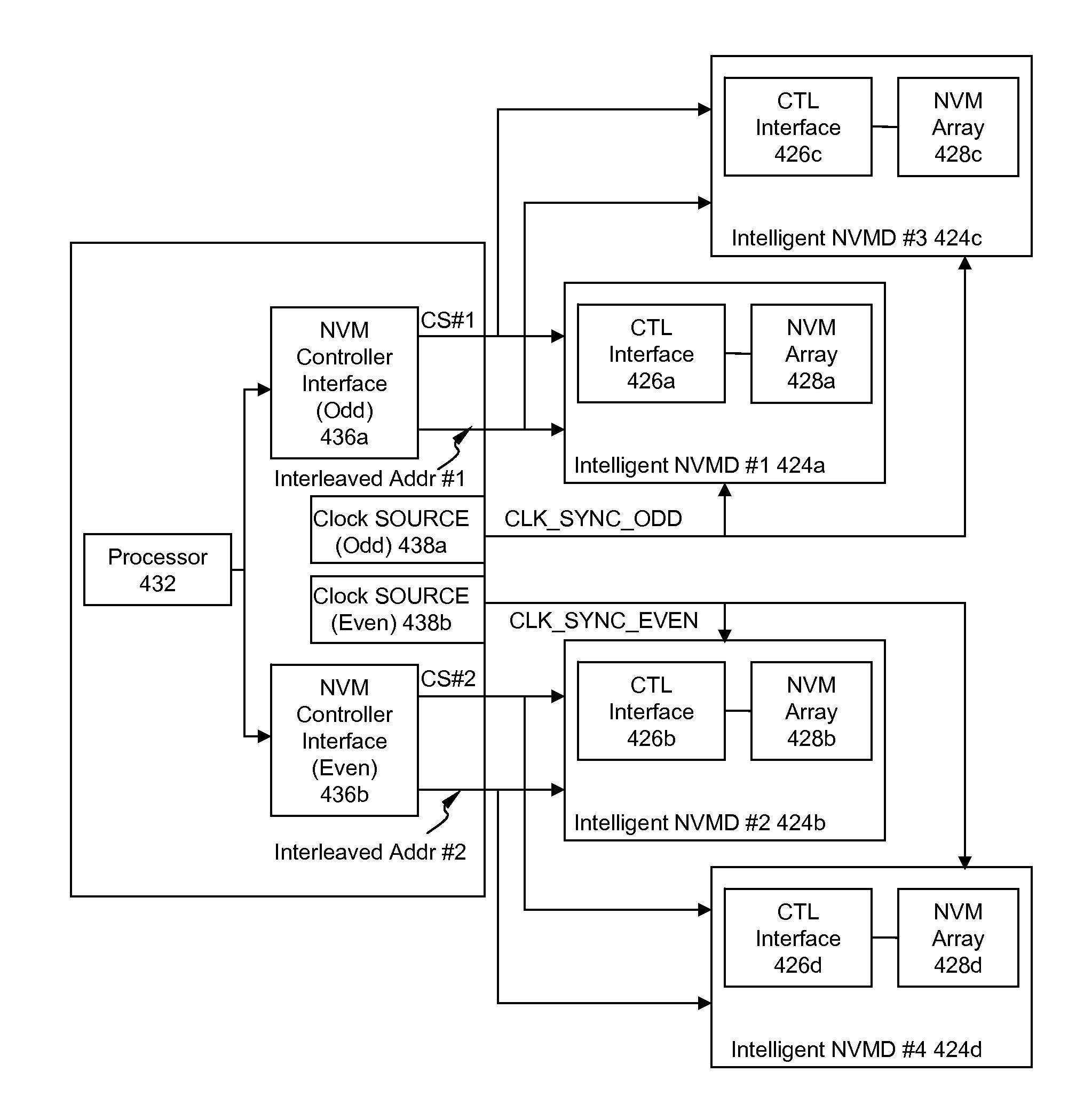

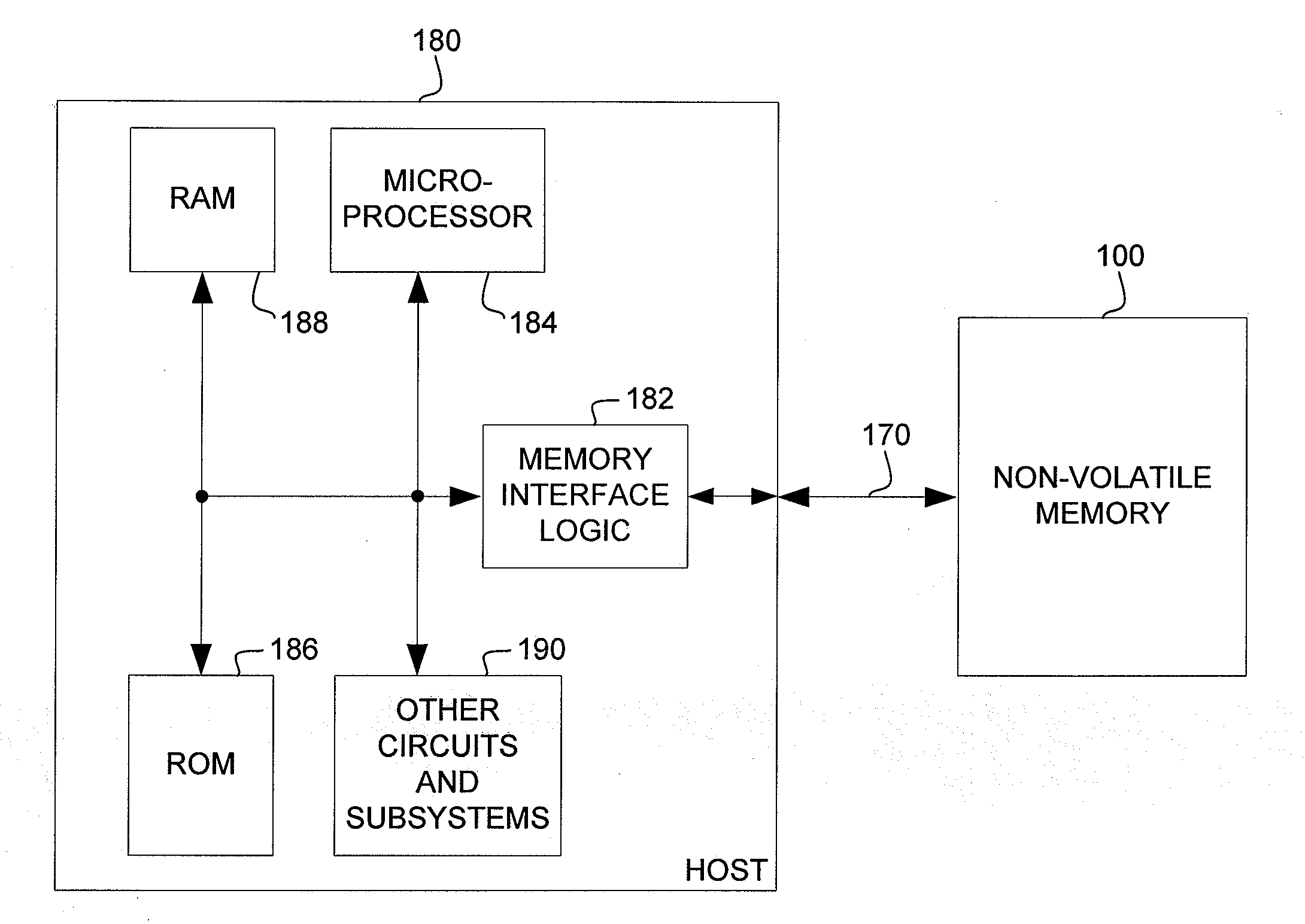

High Performance and Endurance Non-volatile Memory Based Storage Systems

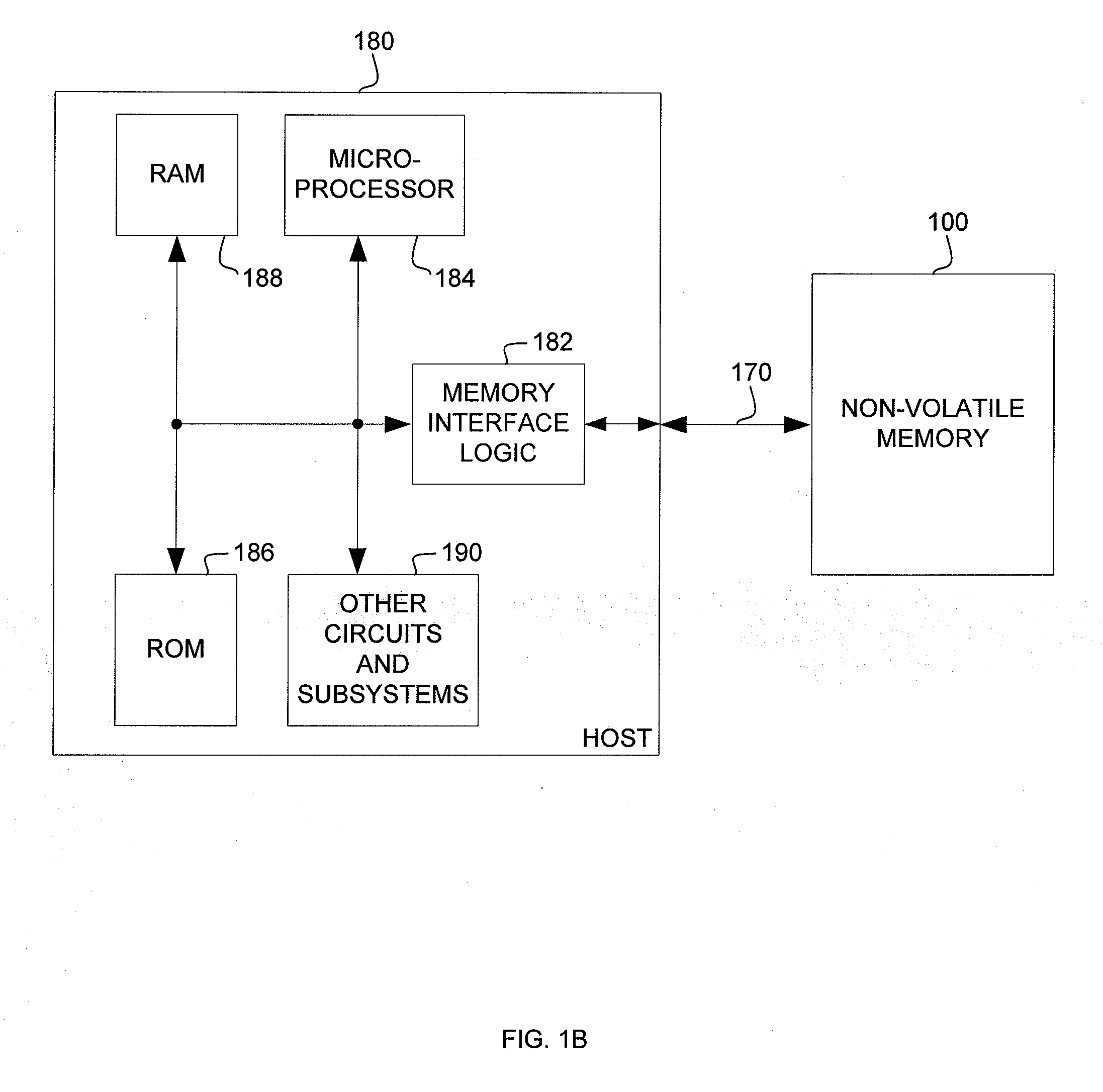

InactiveUS20080320209A1Reduce dataEndurance of the NVM based storage system is increasedMemory architecture accessing/allocationMemory adressing/allocation/relocationPhase locked loop circuitPhysical address

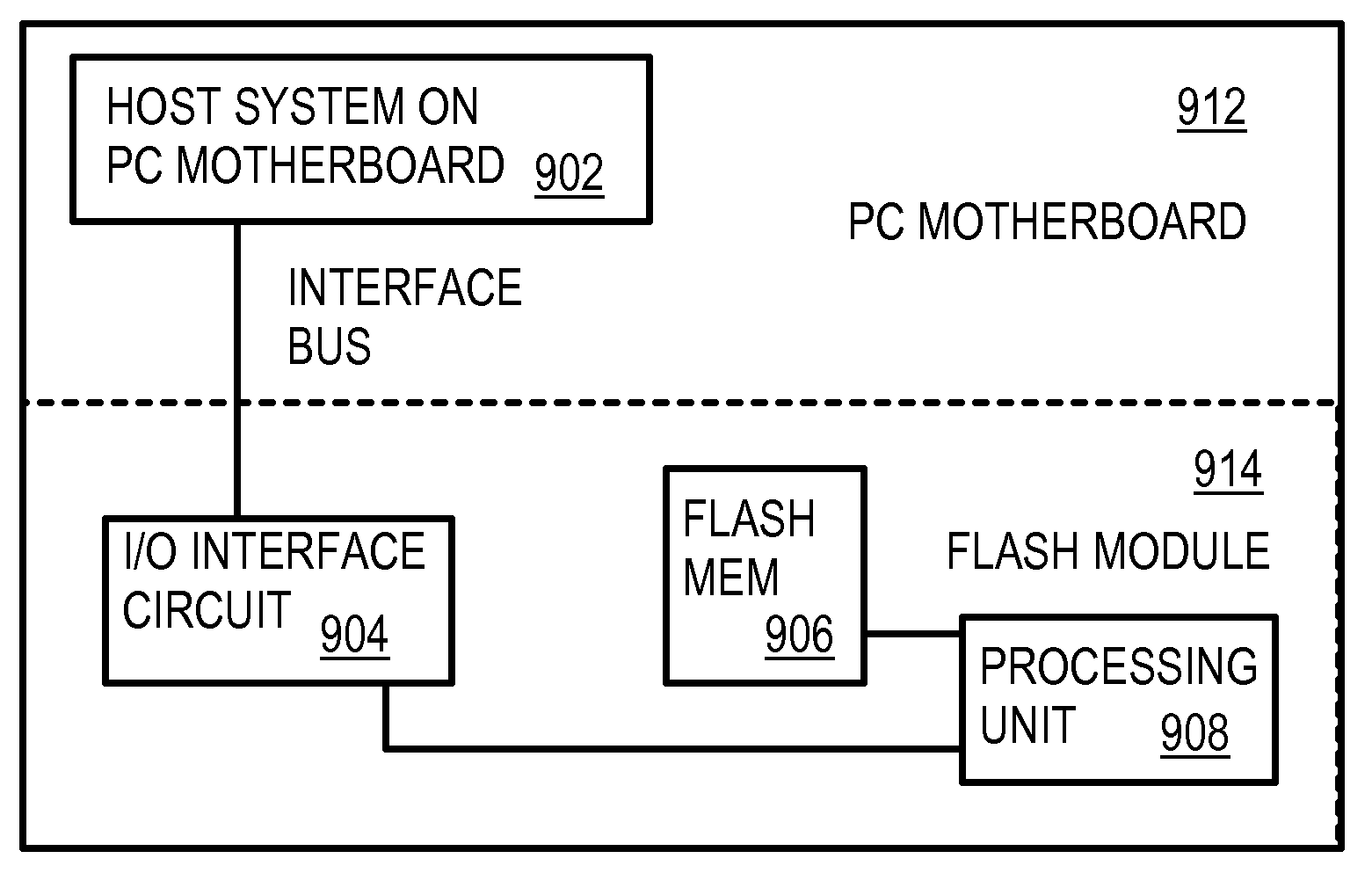

High performance and endurance non-volatile memory (NVM) based storage systems are disclosed. According to one aspect of the present invention, a NVM based storage system comprises at least one intelligent NVM device. Each intelligent NVM device includes a control interface logic and NVM. Logical-to-physical address conversion is performed within the control interface logic, thereby eliminating the need of address conversion in a storage system level controller. In another aspect, a volatile memory buffer together with corresponding volatile memory controller and phase-locked loop circuit is included in a NVM based storage system. The volatile memory buffer is partitioned to two parts: a command queue; and one or more page buffers. The command queue is configured to hold received data transfer commands by the storage protocol interface bridge, while the page buffers are configured to hold data to be transmitted between the host computer and the at least one NVM device.

Owner:SUPER TALENT ELECTRONICS

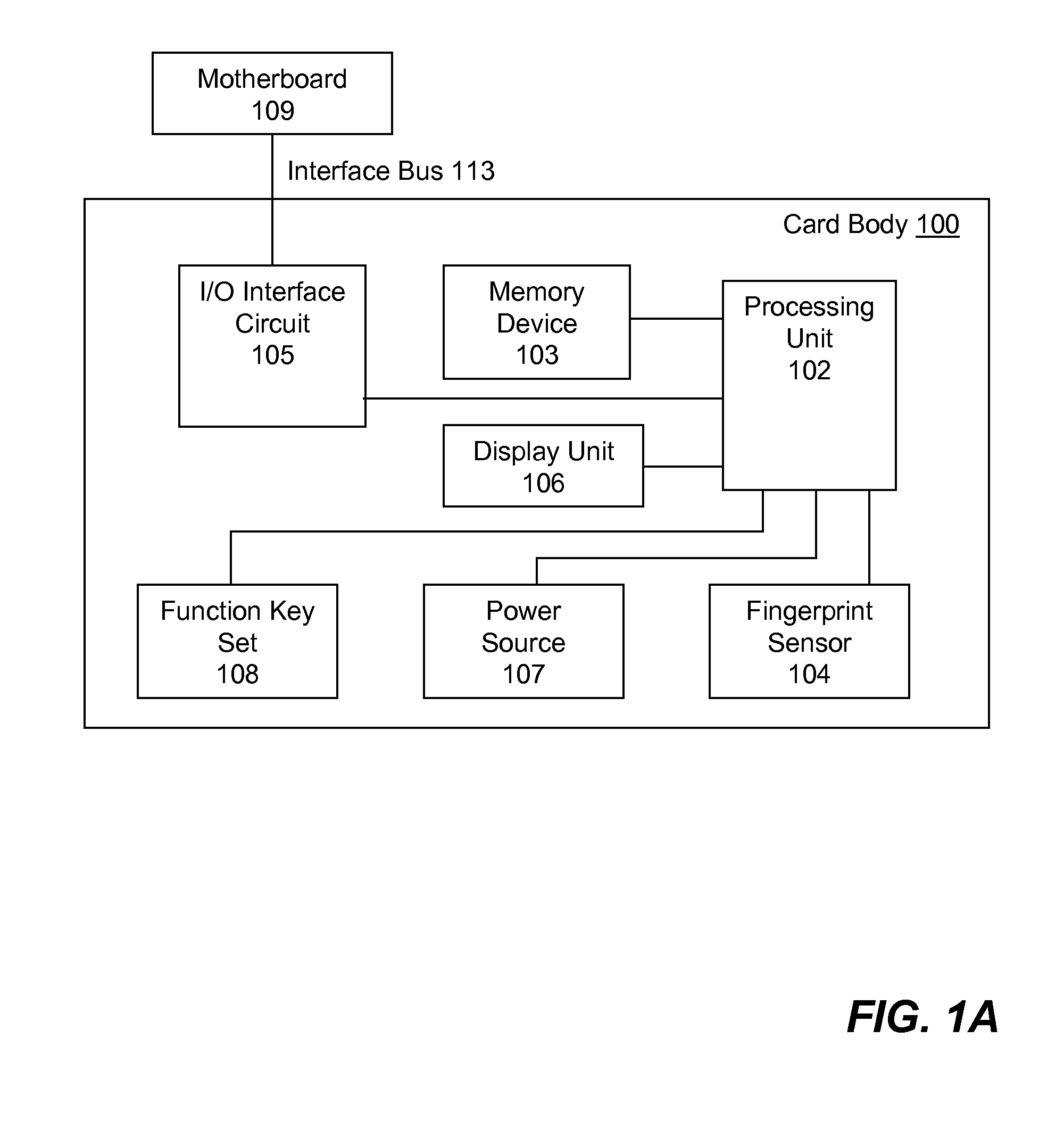

Writing control method and writing control system of semiconductor storage device, and portable electronic apparatus

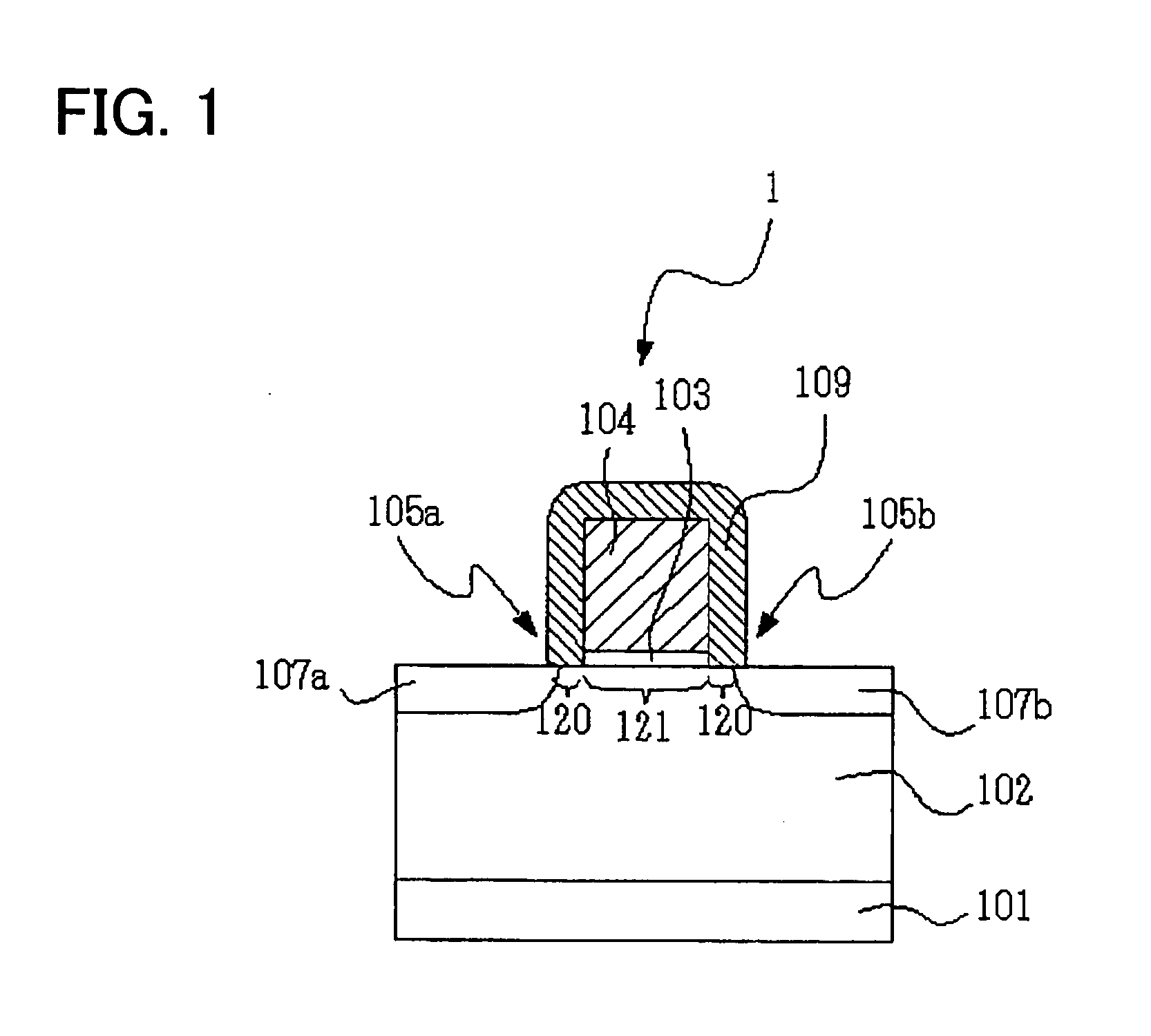

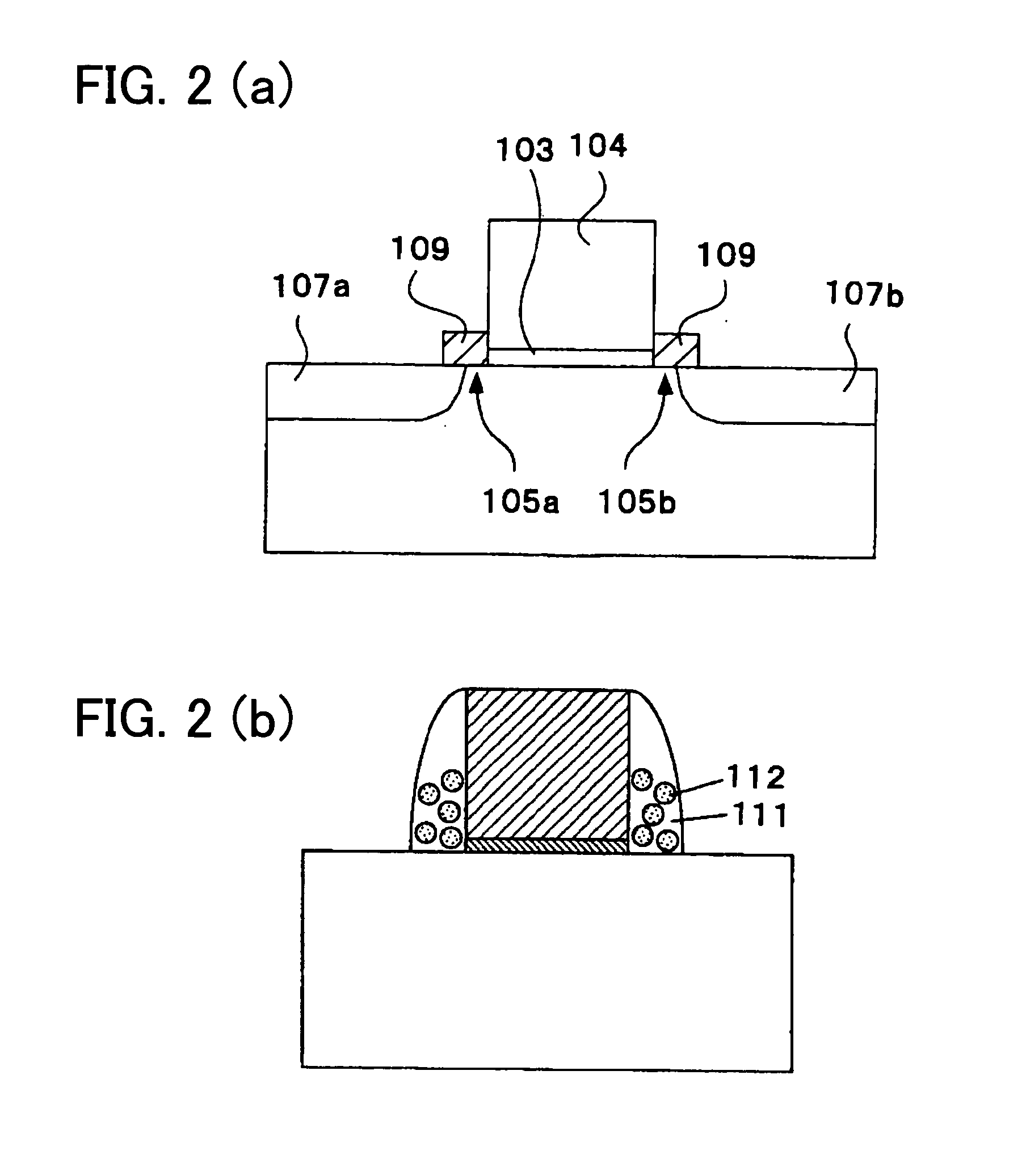

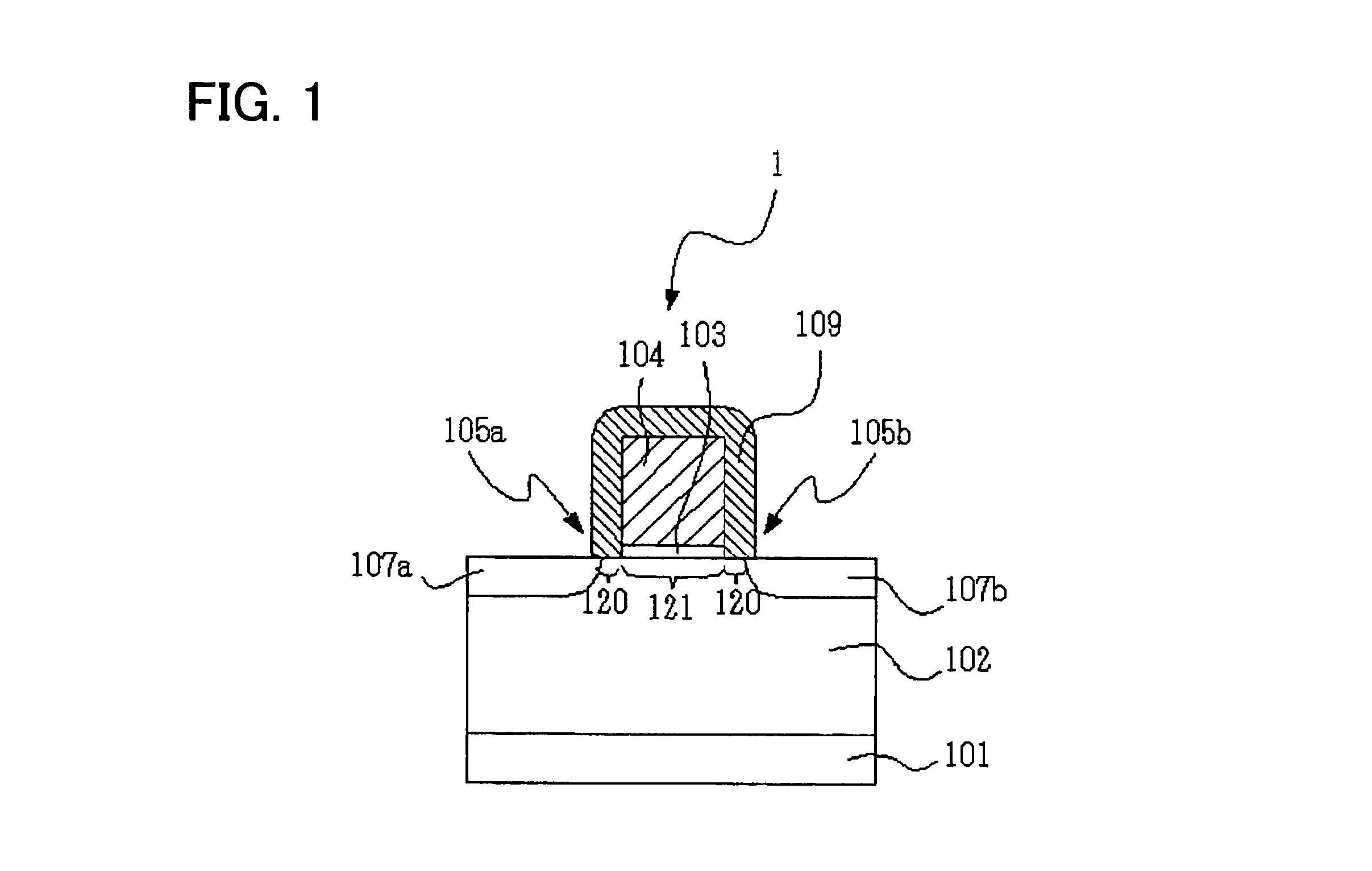

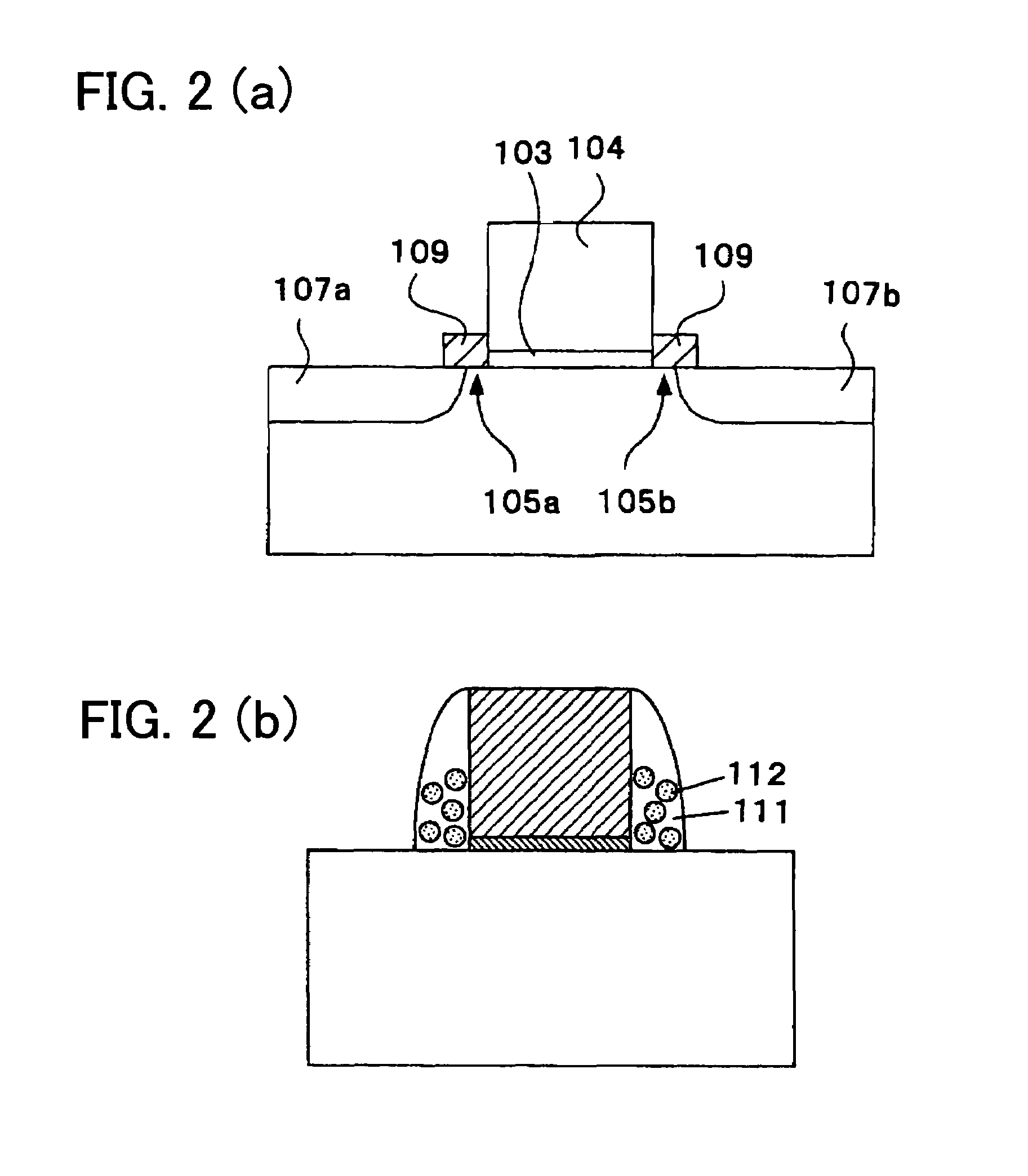

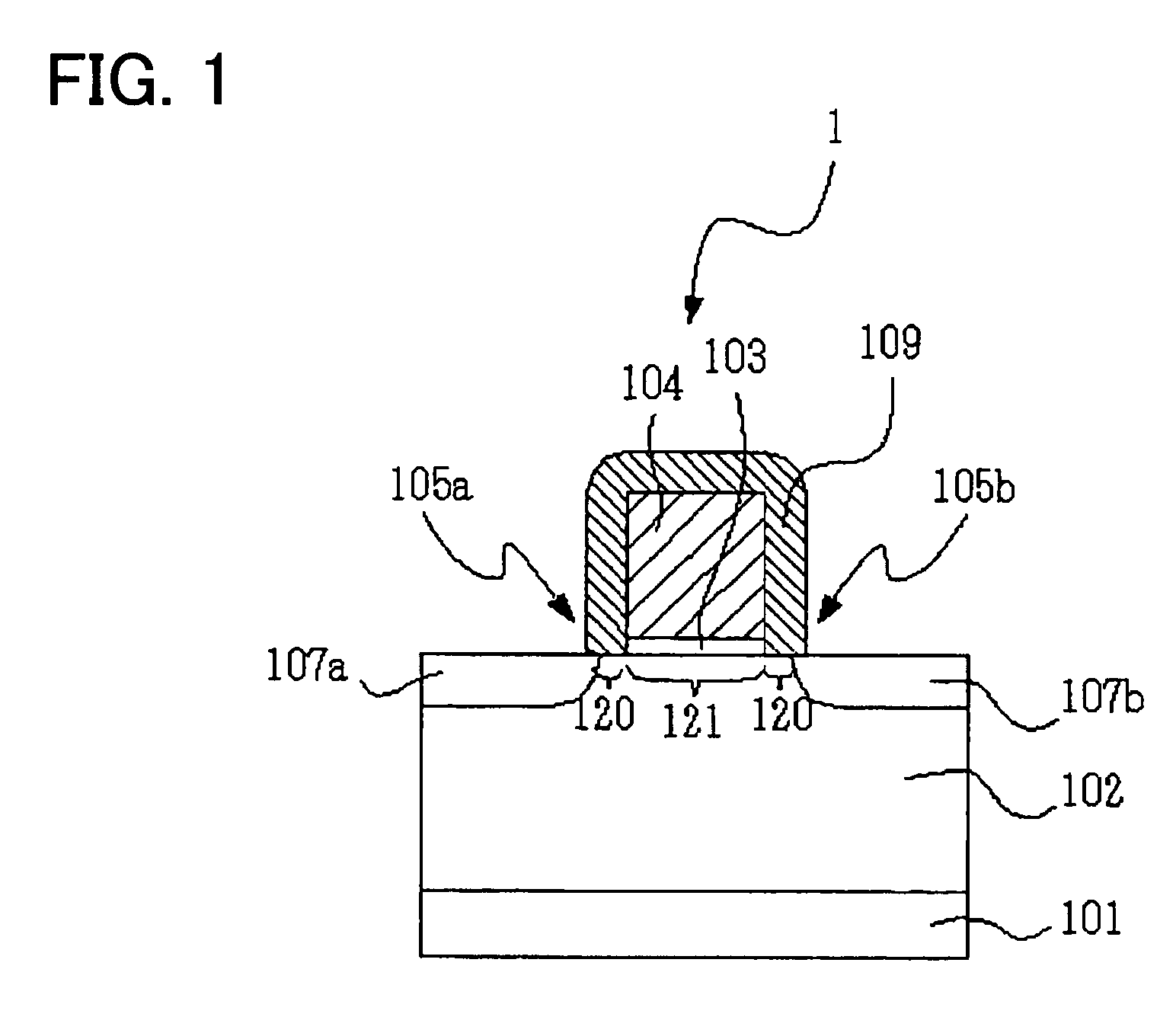

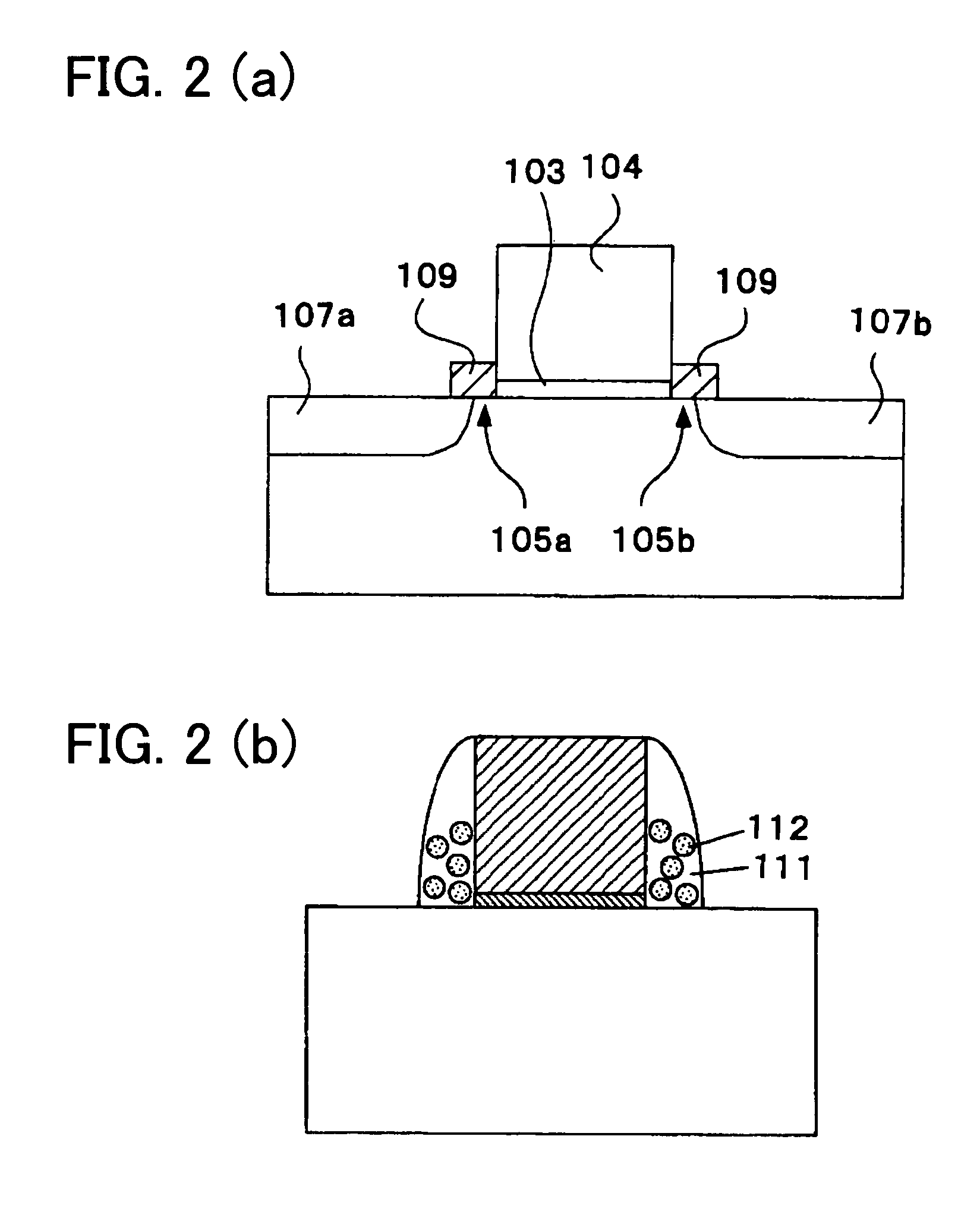

InactiveUS20050002263A1Easily-realized finerSpeedup of writingTransistorSolid-state devicesSemiconductor storage devicesEngineering

A writing control system providing high-speed writing to a nonvolatile semiconductor storage device, includes (a) a plurality of memory elements each having: a gate electrode provided on a semiconductor layer with an intervening gate insulating film; a channel region provided beneath the gate electrode; a diffusion region provided on both sides of the channel region, having an opposite polarity to the channel region; and a memory functioning member, provided on both sides of the gate electrode, having a function of holding electric charges, (b) a memory array including a page buffer circuit, and (c) CPU controlling writing to the memory array. The CPU loads a first plane of the page buffer circuit with a first byte of data and writes with the first byte of data stored in the first plane. Further, the CPU writes a second byte of data into the second plane and writes the second byte of data having been stored in the second plane while writing the first byte of data having been stored in the first plane into the memory array.

Owner:SHARP KK

Writing control method and writing control system of semiconductor storage device, and portable electronic apparatus

InactiveUS7050337B2The implementation process is simpleSpeedup of writingTransistorSolid-state devicesSemiconductor storage devicesHemt circuits

A writing control system providing high-speed writing to a nonvolatile semiconductor storage device, includes (a) a plurality of memory elements each having: a gate electrode provided on a semiconductor layer with an intervening gate insulating film; a channel region provided beneath the gate electrode; a diffusion region provided on both sides of the channel region, having an opposite polarity to the channel region; and a memory functioning member, provided on both sides of the gate electrode, having a function of holding electric charges, (b) a memory array including a page buffer circuit, and (c) CPU controlling writing to the memory array. The CPU loads a first plane of the page buffer circuit with a first byte of data and writes with the first byte of data stored in the first plane. Further, the CPU writes a second byte of data into the second plane and writes the second byte of data having been stored in the second plane while writing the first byte of data having been stored in the first plane into the memory array.

Owner:SHARP KK

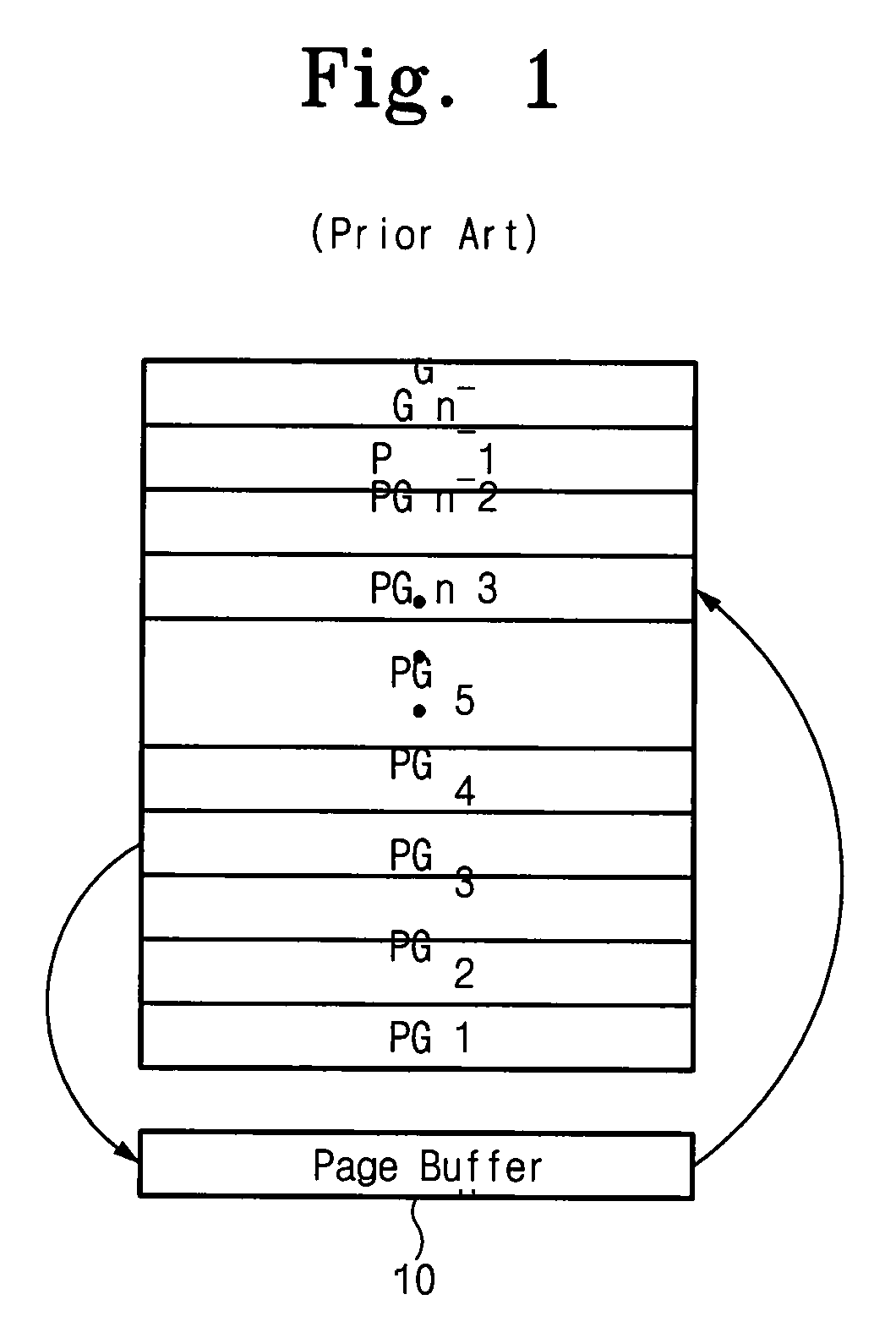

Nonvolatile memory with error correction for page copy operation and method thereof

InactiveUS20080163030A1Transcription errorMaintain integrityMemory loss protectionMemory adressing/allocation/relocationError checkingData storing

The disclosure is a NAND flash memory with the function of error checking and correction during a page copy operation. The NAND flash memory is able to prohibit transcription of erroneous bits to a duplicate page from a source page. Embodiments of the inventive flash memory include a correction circuit for correcting bit errors of source data stored in a page buffer, a circuit configured to provide the source data to the correction circuit and to provide correction data to the page buffer, and a copy circuit configured to copy the source data to the page buffer, and to store the correction data in the other page from the page buffer.

Owner:SAMSUNG ELECTRONICS CO LTD

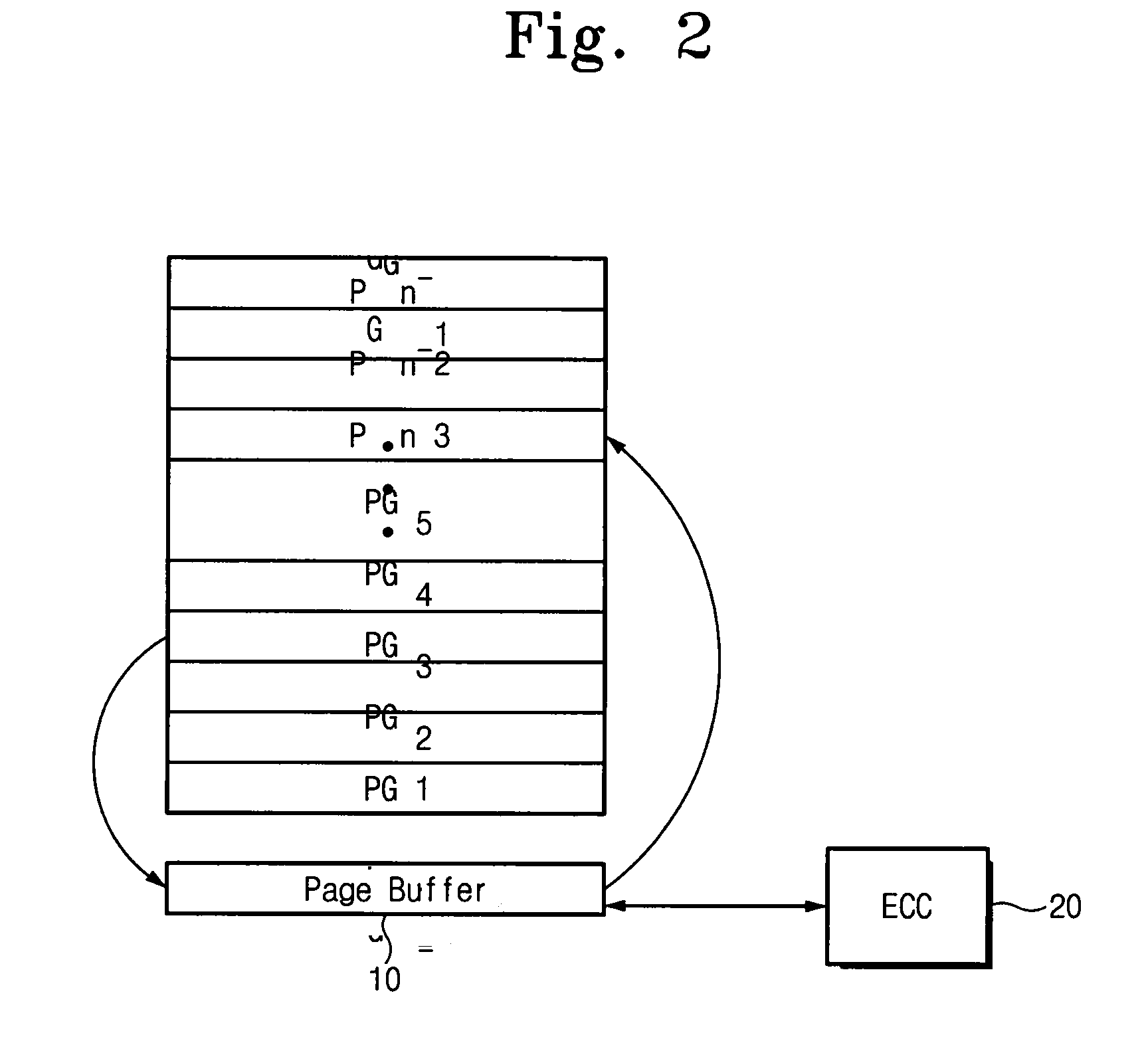

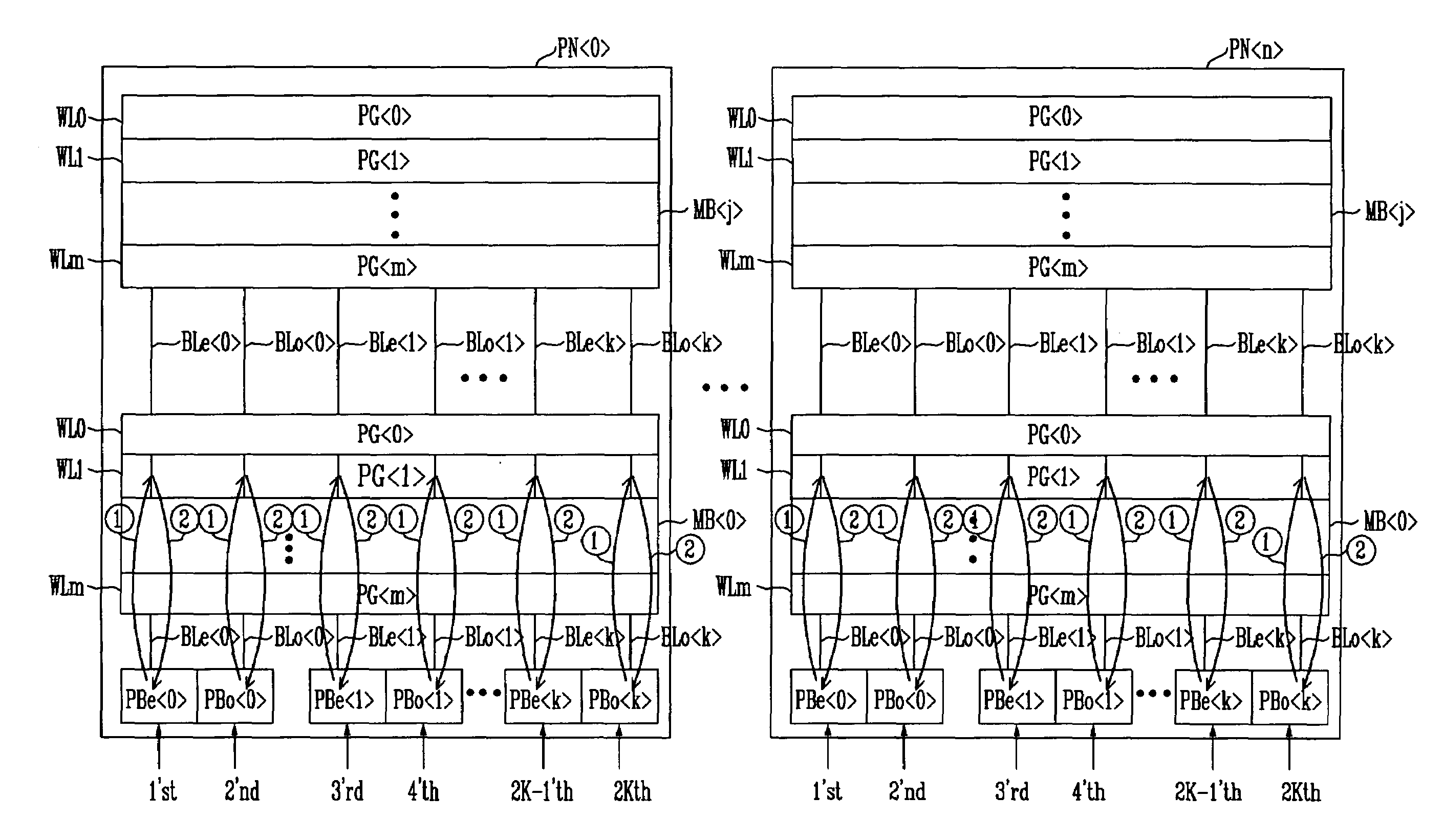

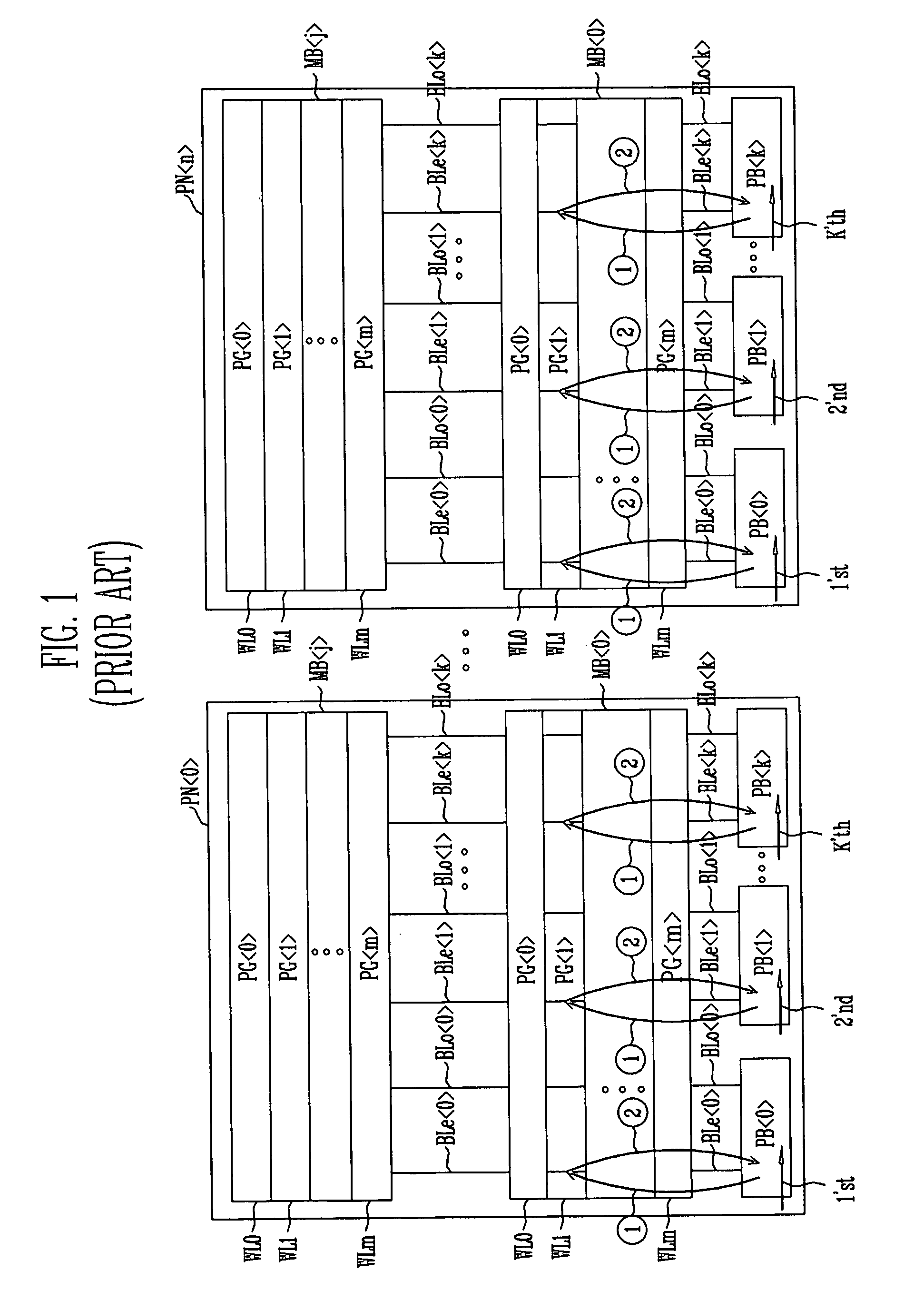

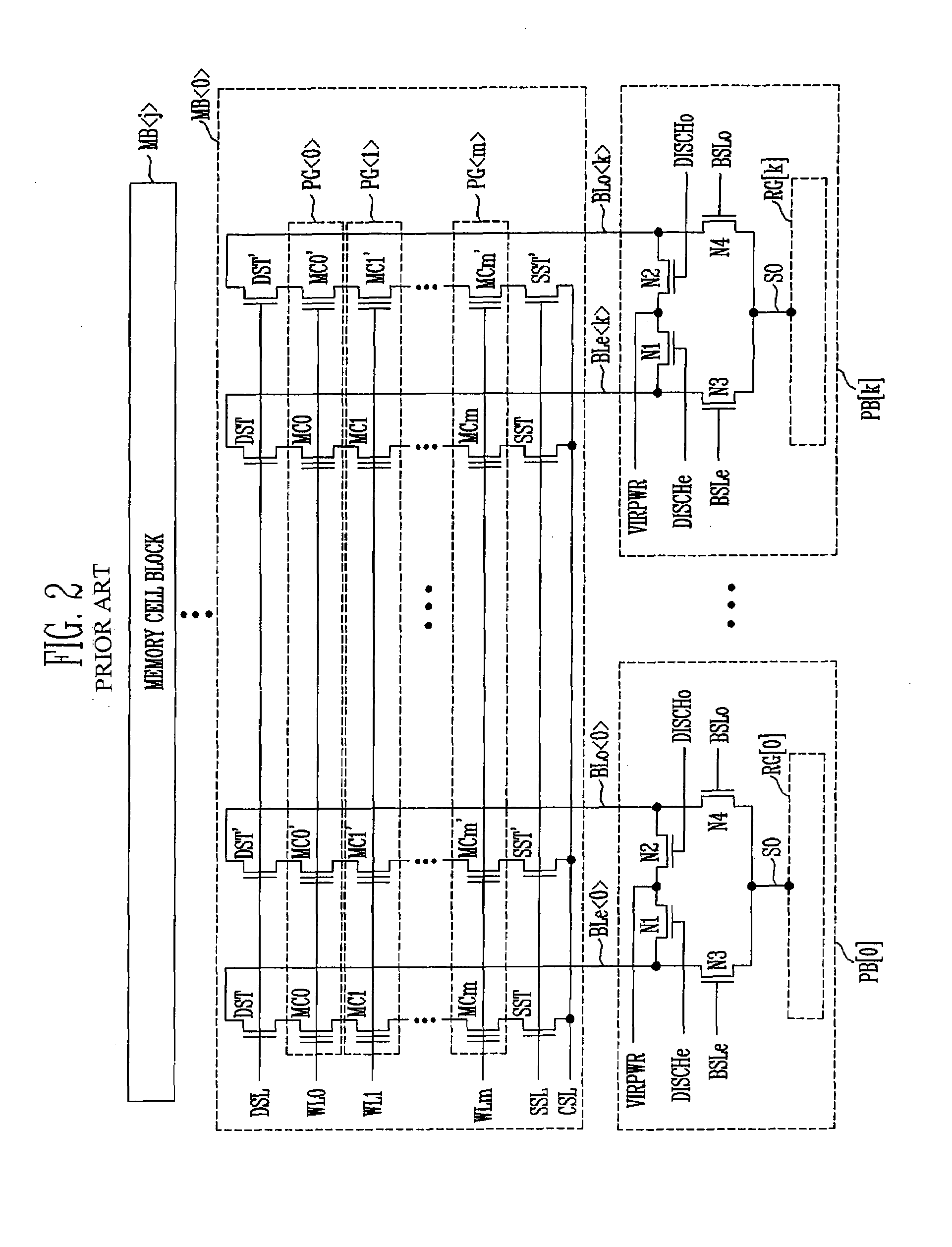

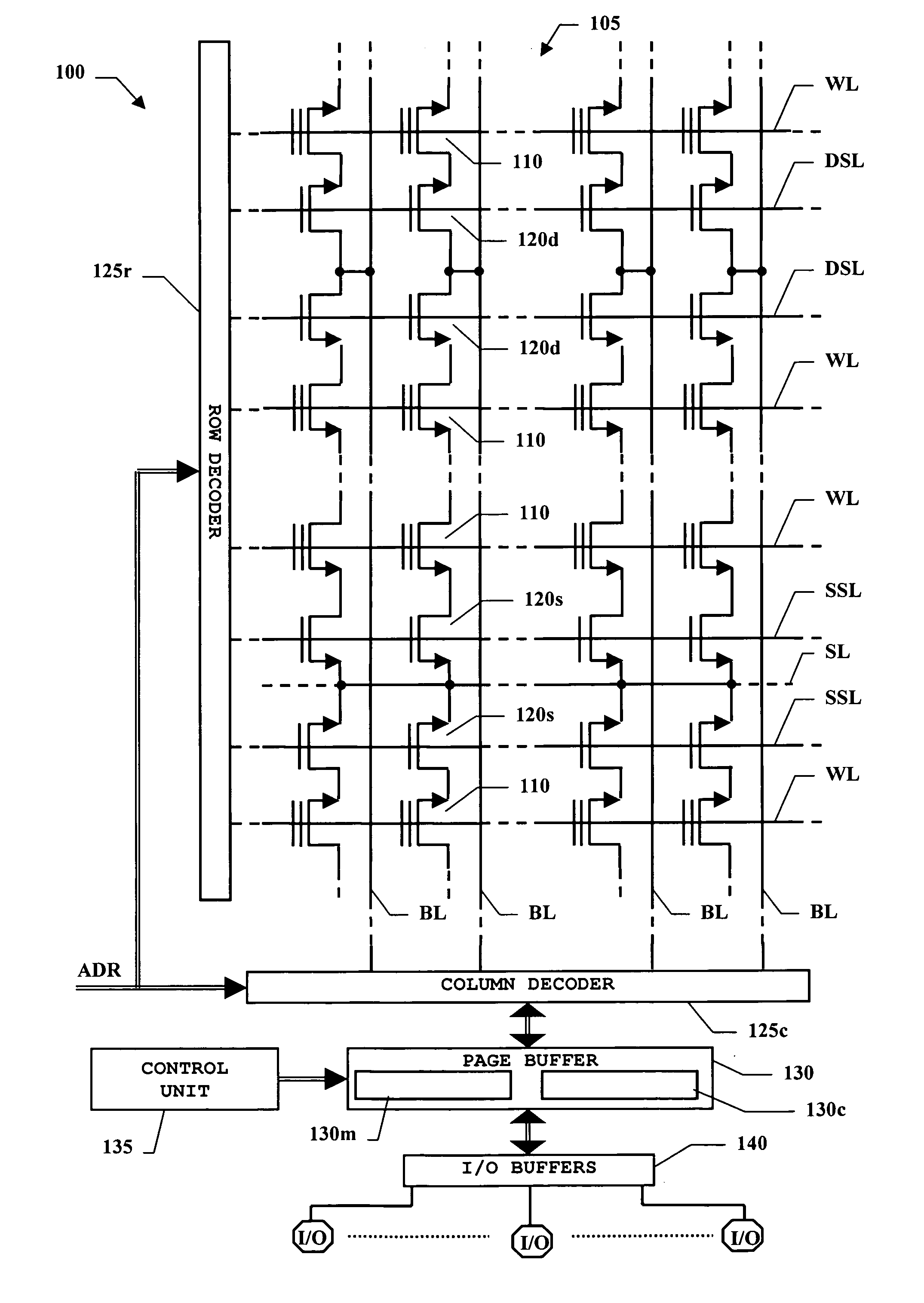

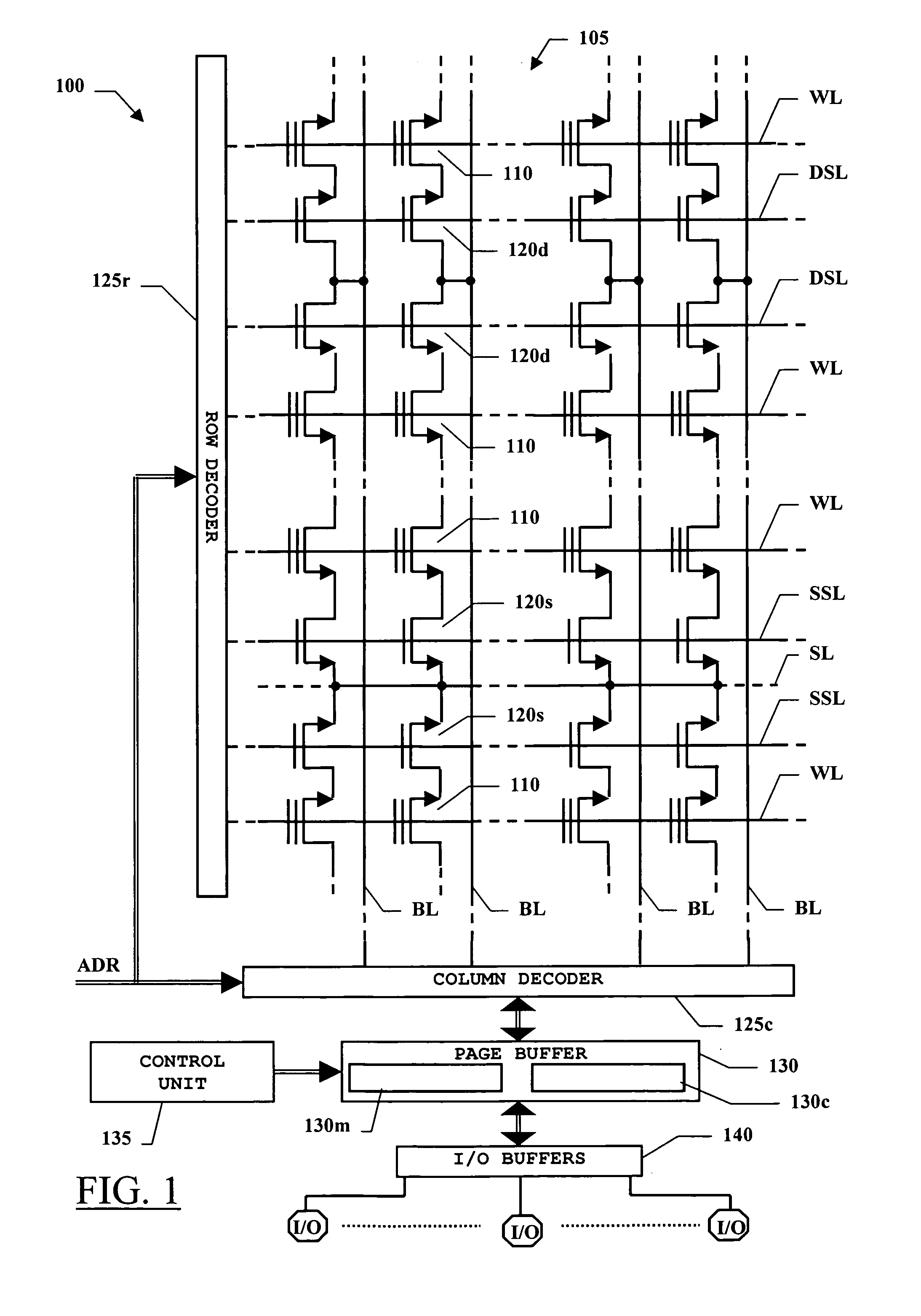

Non-volatile memory device, and multi-page program, read and copyback program method thereof

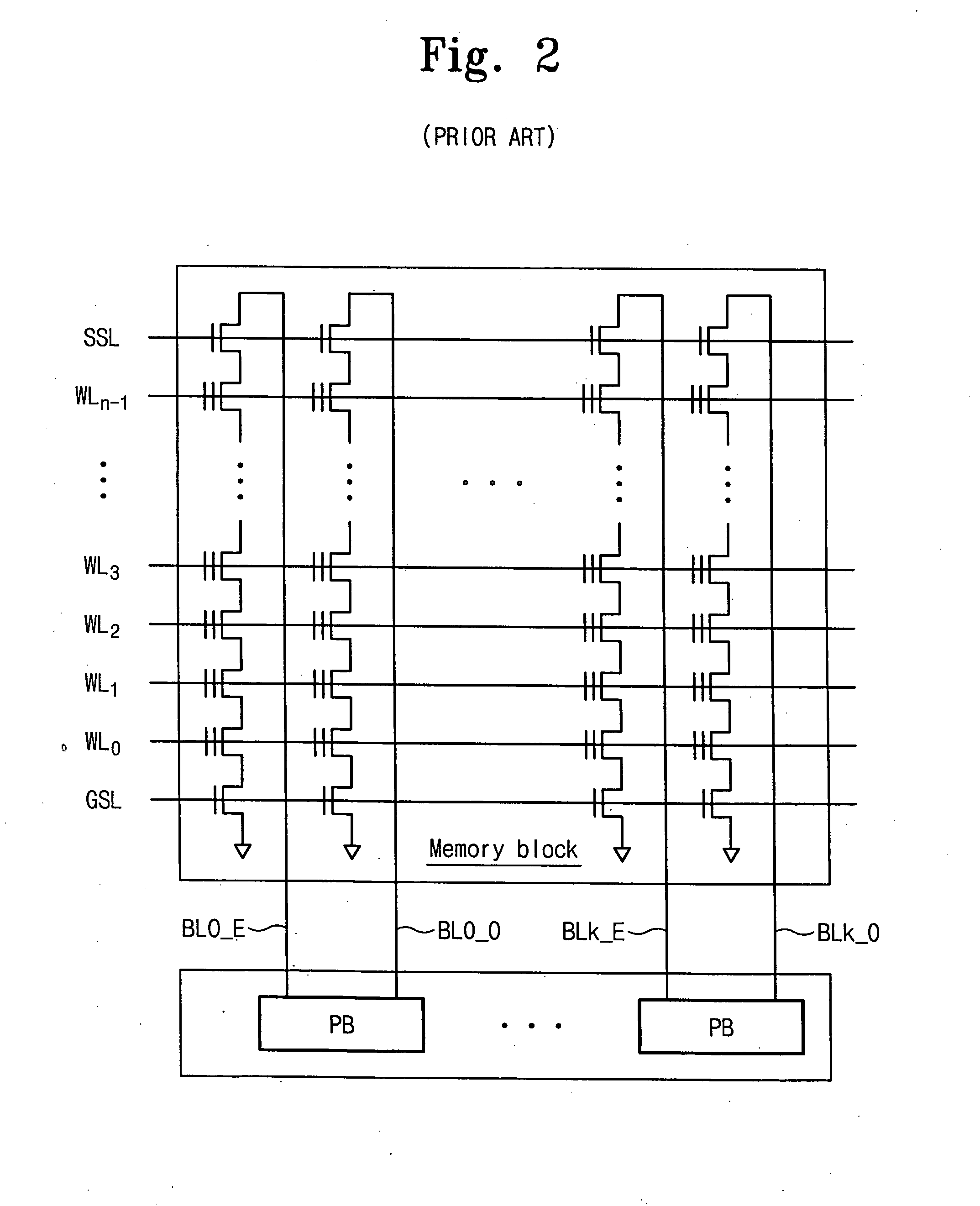

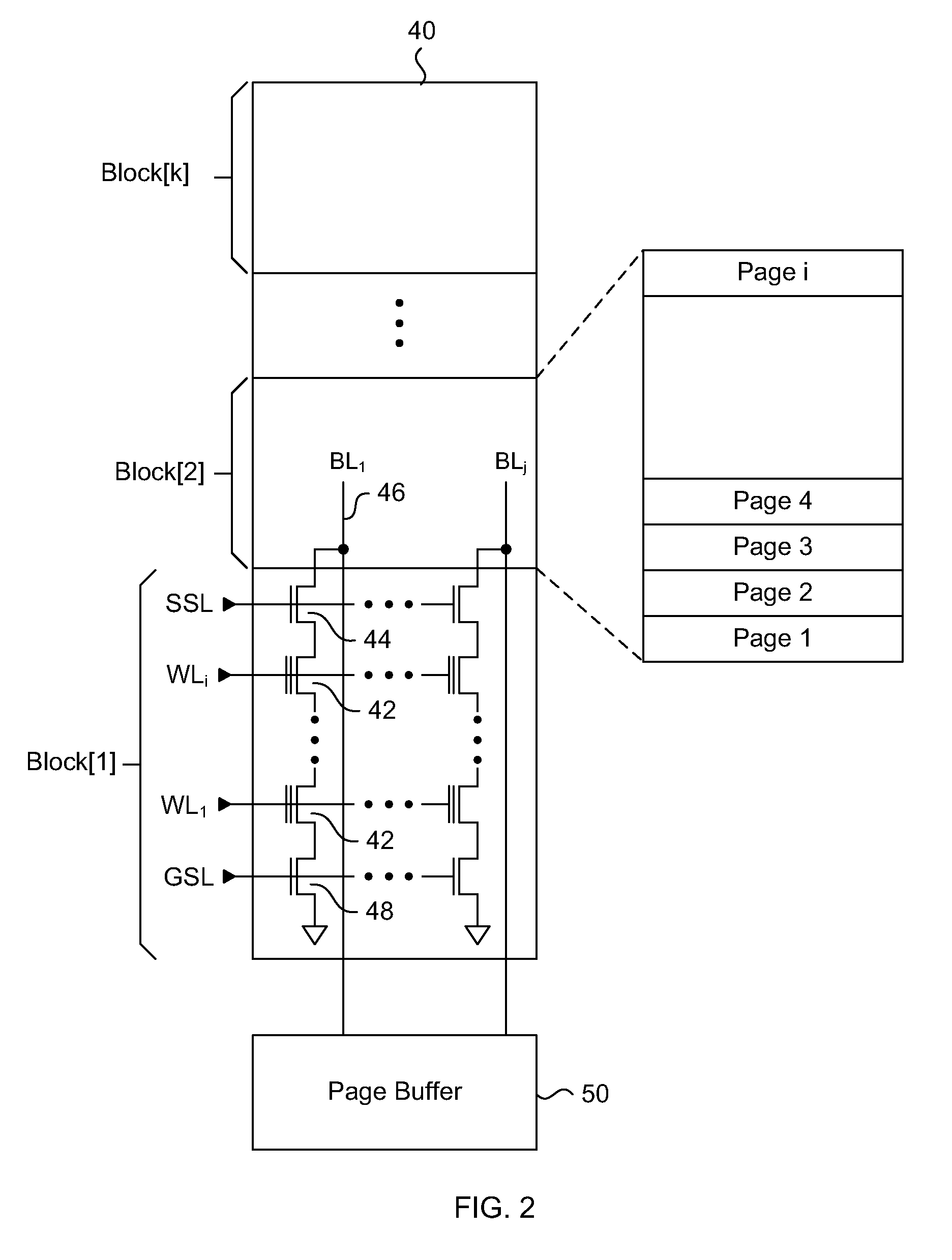

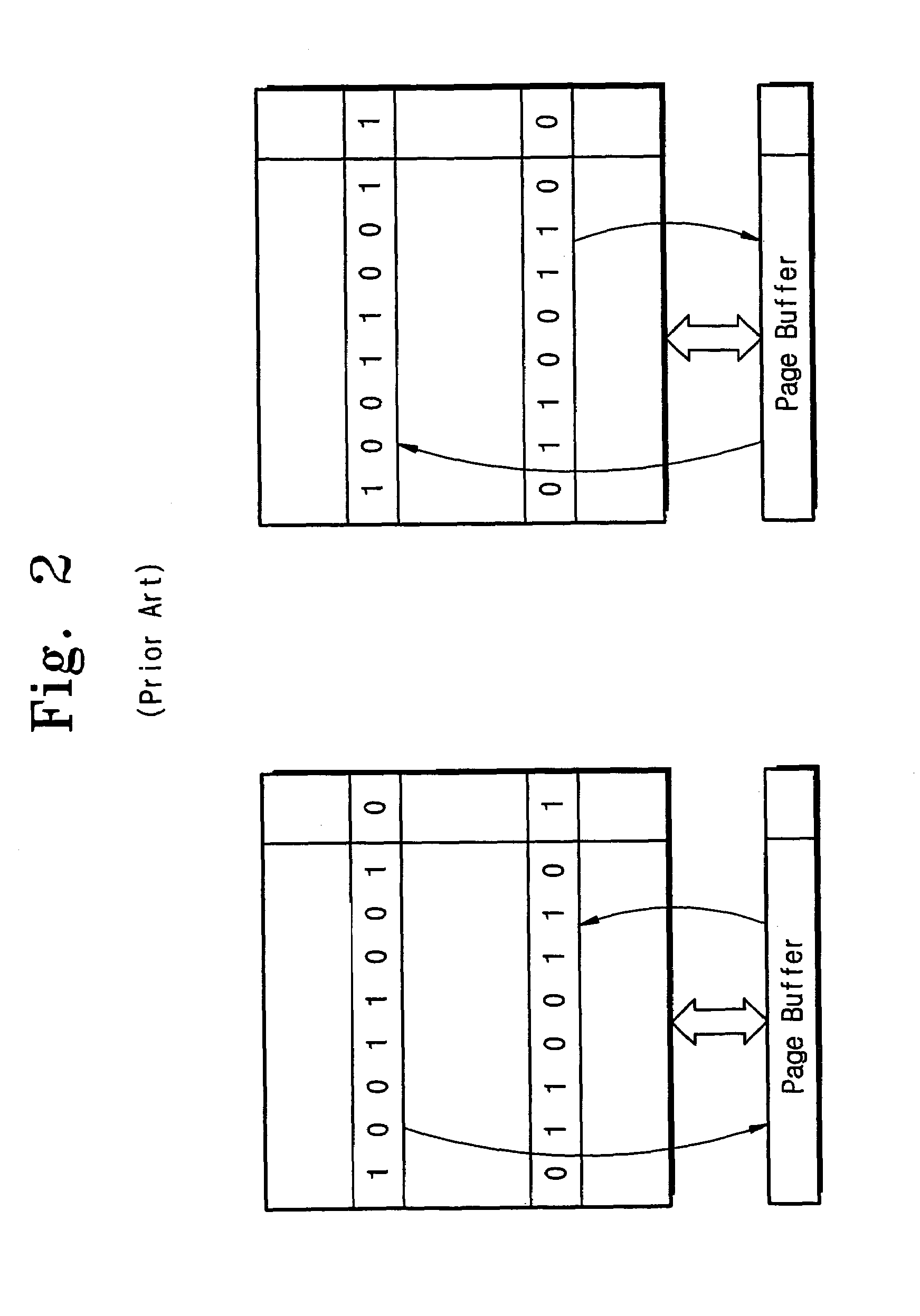

A NAND-type flash memory device has a multi-plane structure. Page buffers are divided into even page buffers and odd page buffers and are driven at the same time. Cells connected to even bit lines within one page and cell connected to odd bit lines within one page are programmed, read and copyback programmed at the same time.

Owner:SK HYNIX INC

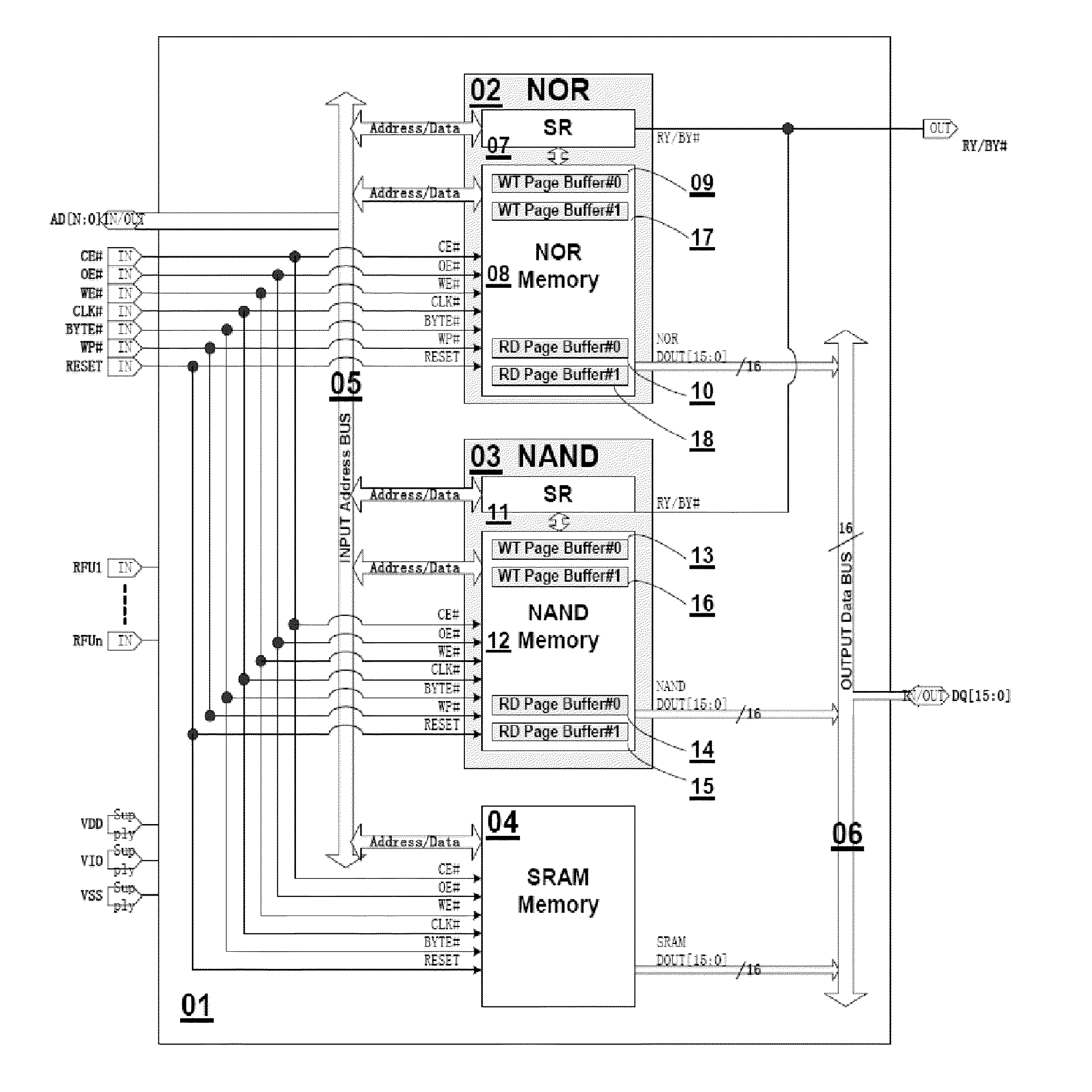

Memory system having NAND-based nor and NAND flashes and SRAM integrated in one chip for hybrid data, code and cache storage

InactiveUS20100329011A1Faster and improved read and write operation of memoryEasy to operateMemory adressing/allocation/relocationRead-only memoriesAddress busMemory map

A memory system includes a NAND flash memory, a NOR flash memory and a SRAM manufactured on a single chip. Both NAND and NOR memories are manufactured by the same NAND manufacturing process and NAND cells. The three memories share the same address bus, data bus, and pins of the single chip. The address bus is bi-directional for receiving codes, data and addresses and transmitting output. The data bus is also bi-directional for receiving and transmitting data. One external chip enable pin and one external output enable pin are shared by the three memories to reduce the number of pins required for the single chip. Both NAND and NOR memories have dual read page buffers and dual write page buffers for Read-While-Load and Write-While-Program operations to accelerate the read and write operations respectively. A memory-mapped method is used to select different memories, status registers and dual read or write page buffers.

Owner:APLUS FLASH TECH

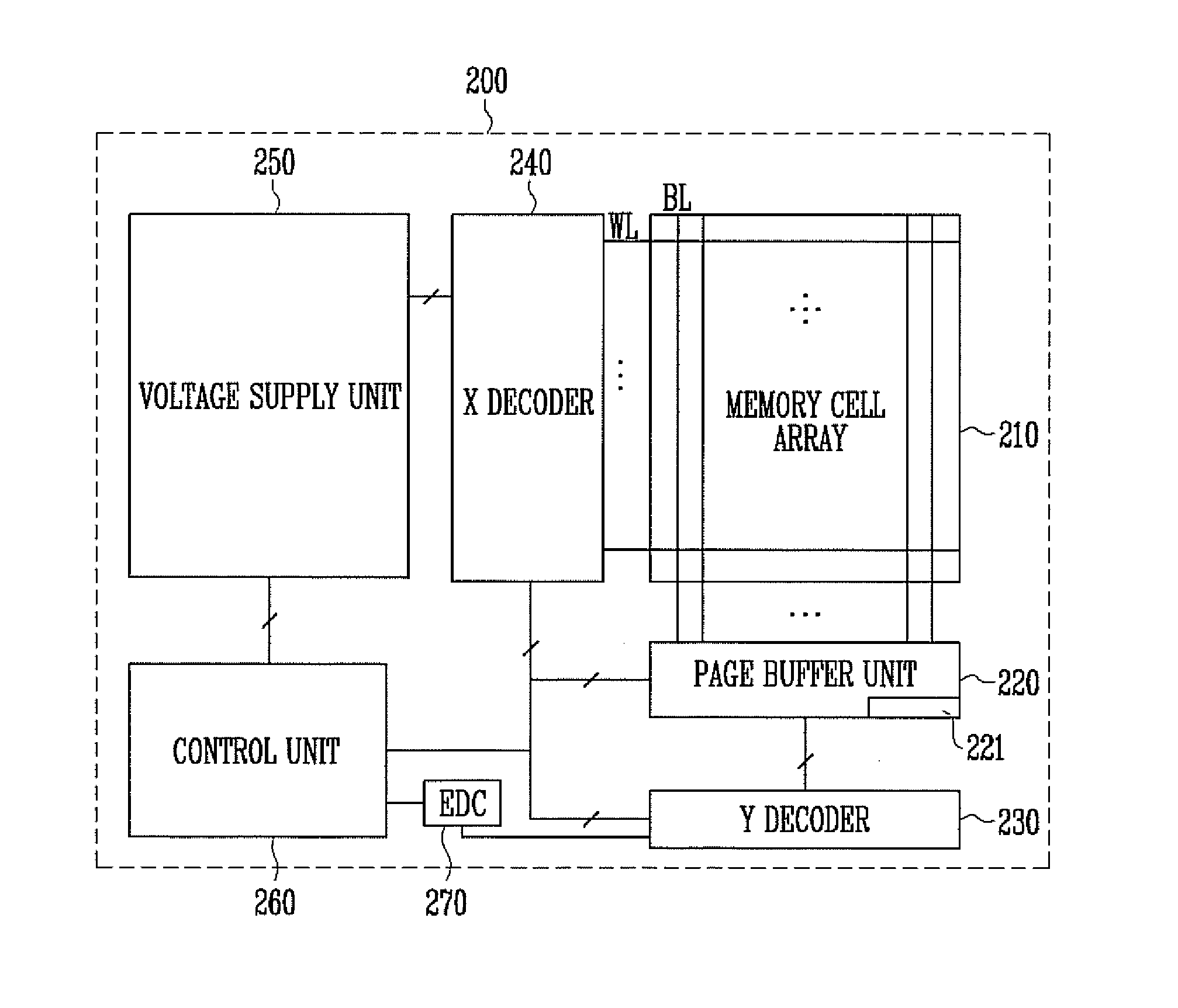

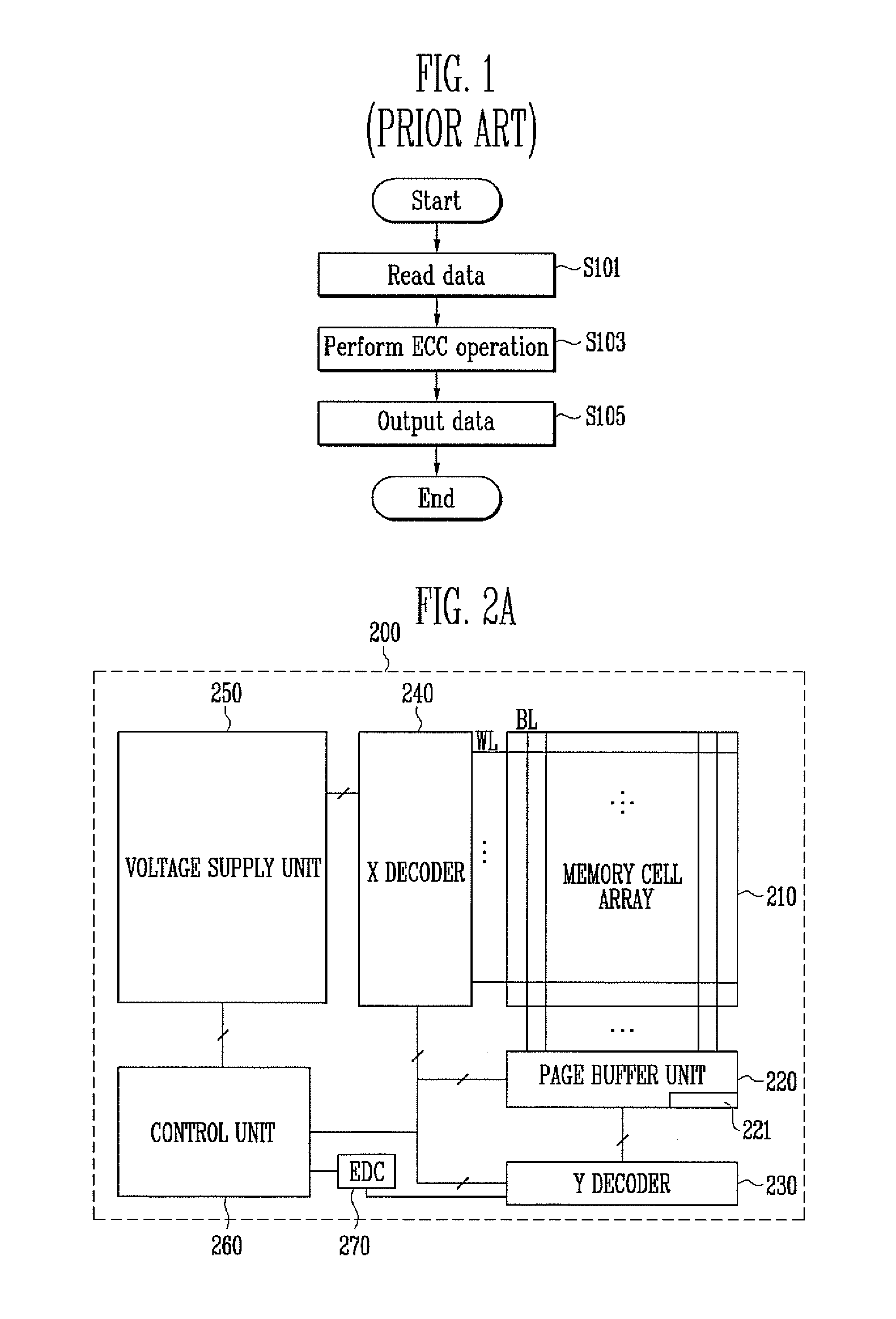

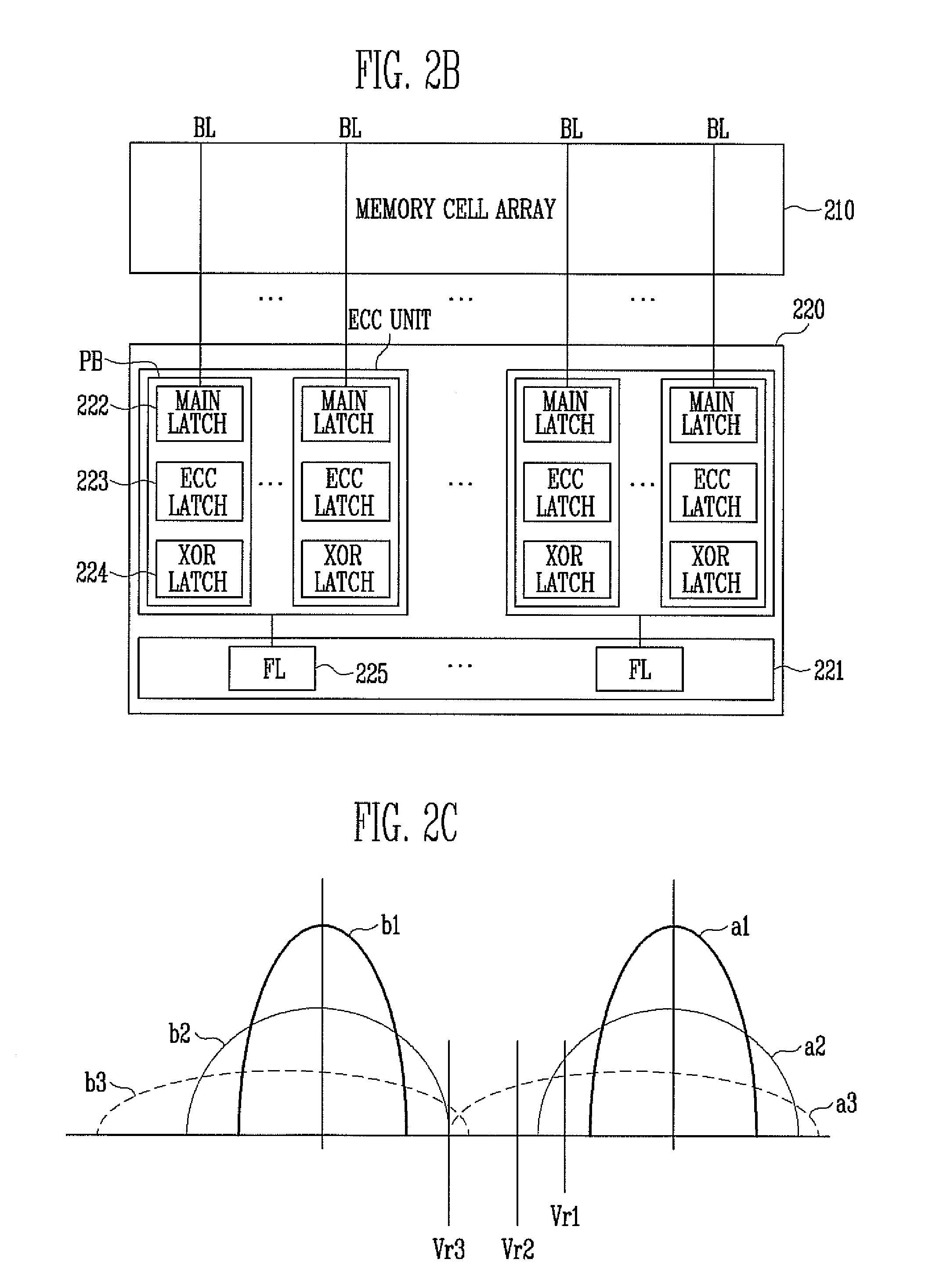

Nonvolatile memory device and method of operating the same

ActiveUS20100199138A1Correction errorError preventionTransmission systemsLogical operationsError detection coding

A nonvolatile memory device includes a memory cell array configured to comprise memory cells coupled by bit lines and word lines, a page buffer unit configured to comprise page buffers and flag latches, wherein the page buffers, coupled to one or more of the bit lines, each are configured to comprise a plurality of latches for storing logic operation results for error correction and configured to store data read using a read voltage, and the flag latches each are configured to classify the page buffers into some page buffer groups each having a predetermined number and to store flag information indicating whether an error has occurred in each group, and an error detection code (EDC) checker configured to determine whether an error has occurred in each of the page buffer groups.

Owner:SK HYNIX INC

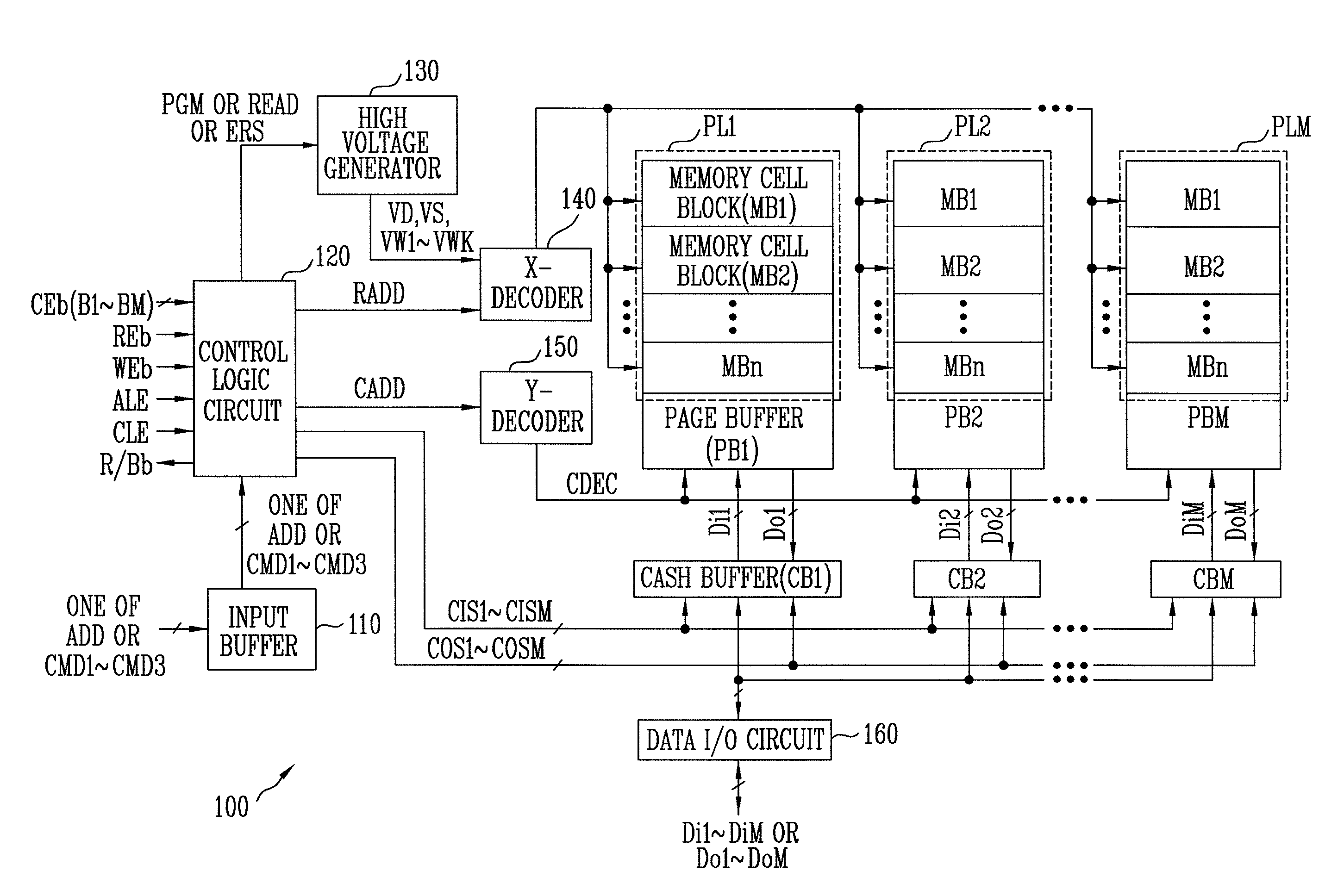

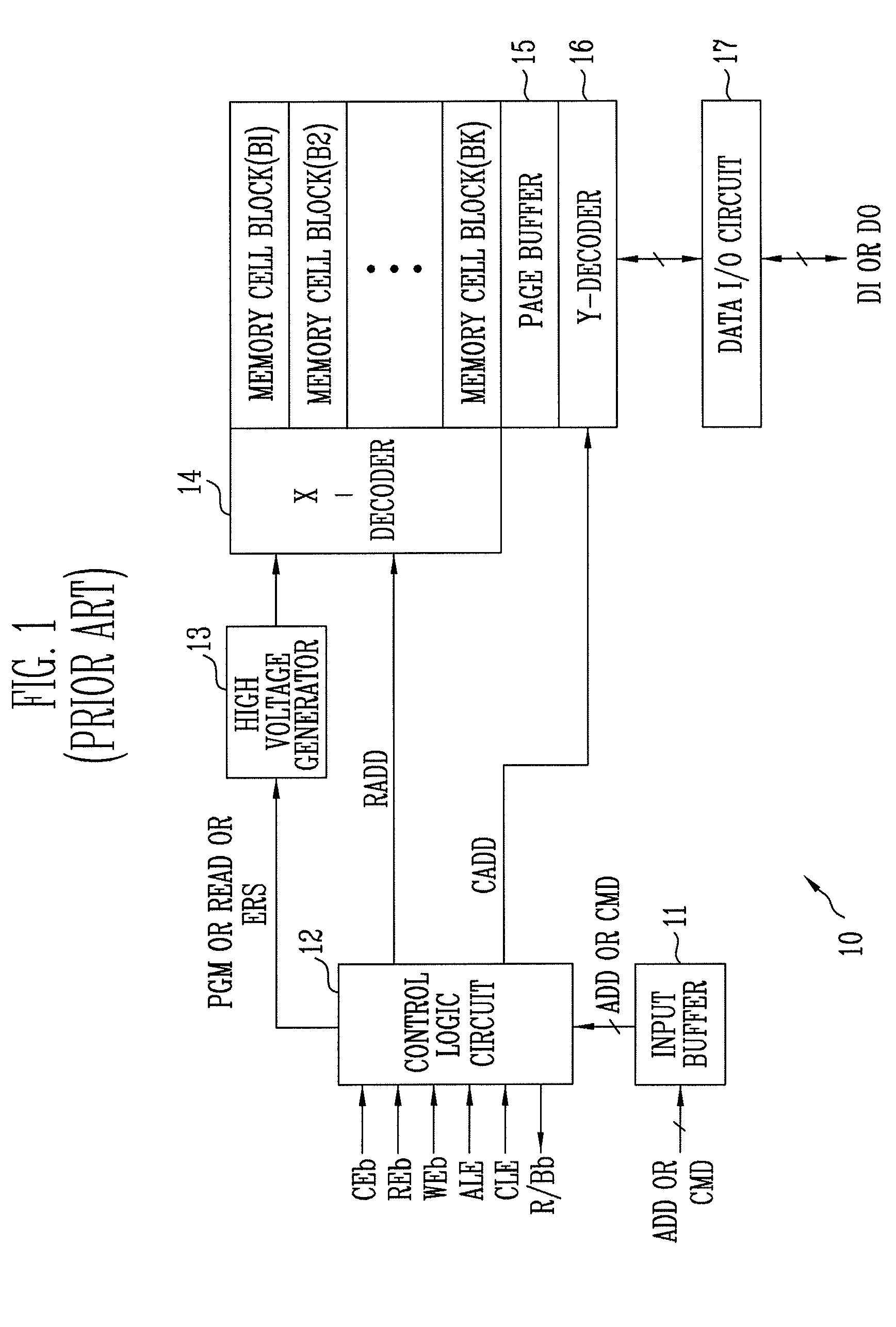

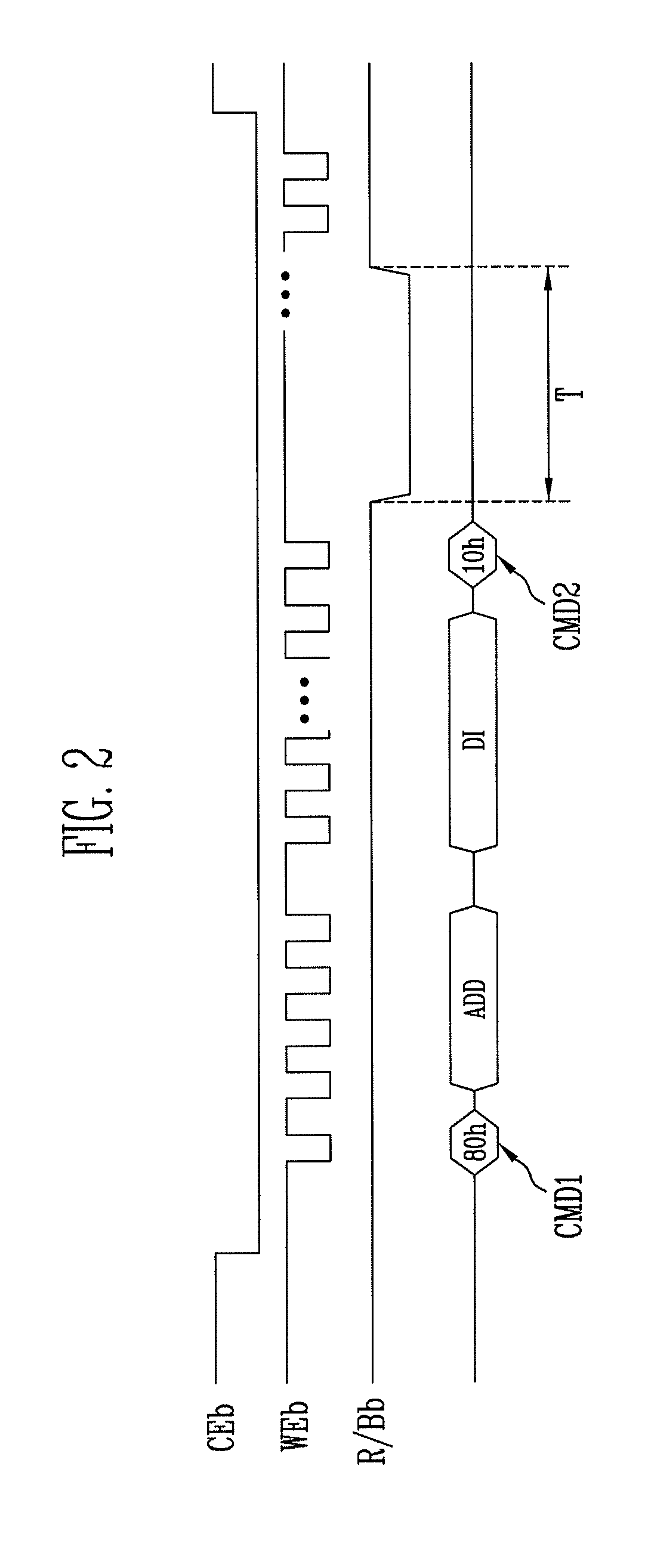

Multi-plane type flash memory and methods of controlling program and read operations thereof

ActiveUS8347042B2Data augmentationIncrease speedRead-only memoriesDigital storageControl signalInput control

A multi-plane type flash memory device comprises a plurality of planes each including a plurality of memory cell blocks, page buffers each latching an input data bit to be output to its corresponding plane or latching an output data bit to be received from the corresponding plane, cache buffers each storing an input or output data bits in response to one of cache input control signals and each transferring the stored data bit to the page buffer or an external device in response to one of cache output control signals, and a control logic circuit generating the cache input and output control signals in response to command and chip enable signals containing plural bits. The program and read operations for the plural planes are conducted simultaneously in response to the chip enable signal containing the plural bits, which increases an operation speed and data throughput processed therein.

Owner:SK HYNIX INC

Multi-operation write aggregator using a page buffer and a scratch flash block in each of multiple channels of a large array of flash memory to reduce block wear

InactiveUS8108590B2Memory architecture accessing/allocationMemory adressing/allocation/relocationSmall fragmentPage buffers

A flash system has multiple channels of flash memory chips that can be accessed in parallel. Host data is assigned to one of the channels by a multi-channel controller processor and accumulated in a multi-channel page buffer. When a page boundary in the page buffer is reached, the page buffer is written to a target physical block if full, or combined with old data fragments in an Aggregating Flash Block (AFB) when the logical-sector addresses (LSA's) match. Thus small fragments are aggregated using the AFB, reducing erases and wear of flash blocks. The page buffer is copied to the AFB when a STOP command occurs. Each channel has one or more AFB's, which are tracked by an AFB tracking table.

Owner:SUPER TALENT TECH CORP

Method And System For Virtual Fast Access Non-Volatile RAM

ActiveUS20100023672A1Fast read accessFast write accessMemory architecture accessing/allocationMemory adressing/allocation/relocationData spaceDatabase

A method of writing data to a non-volatile memory with minimum units of erase of a block, a page being a unit of programming of a block, may read a page of stored data addressable in a first increment of address from the memory into a page buffer, the page of stored data comprising an allocated data space addressable in a second increment of address, pointed to by an address pointer, and comprising obsolete data. The first increment of address is greater than the second increment of address. A portion of stored data in the page buffer may be updated with the data to form an updated page of data. Storage space for the updated page of data may be allocated. The updated page of data may be written to the allocated storage space. The address pointer may be updated with a location of the allocated storage space.

Owner:SANDISK TECH LLC

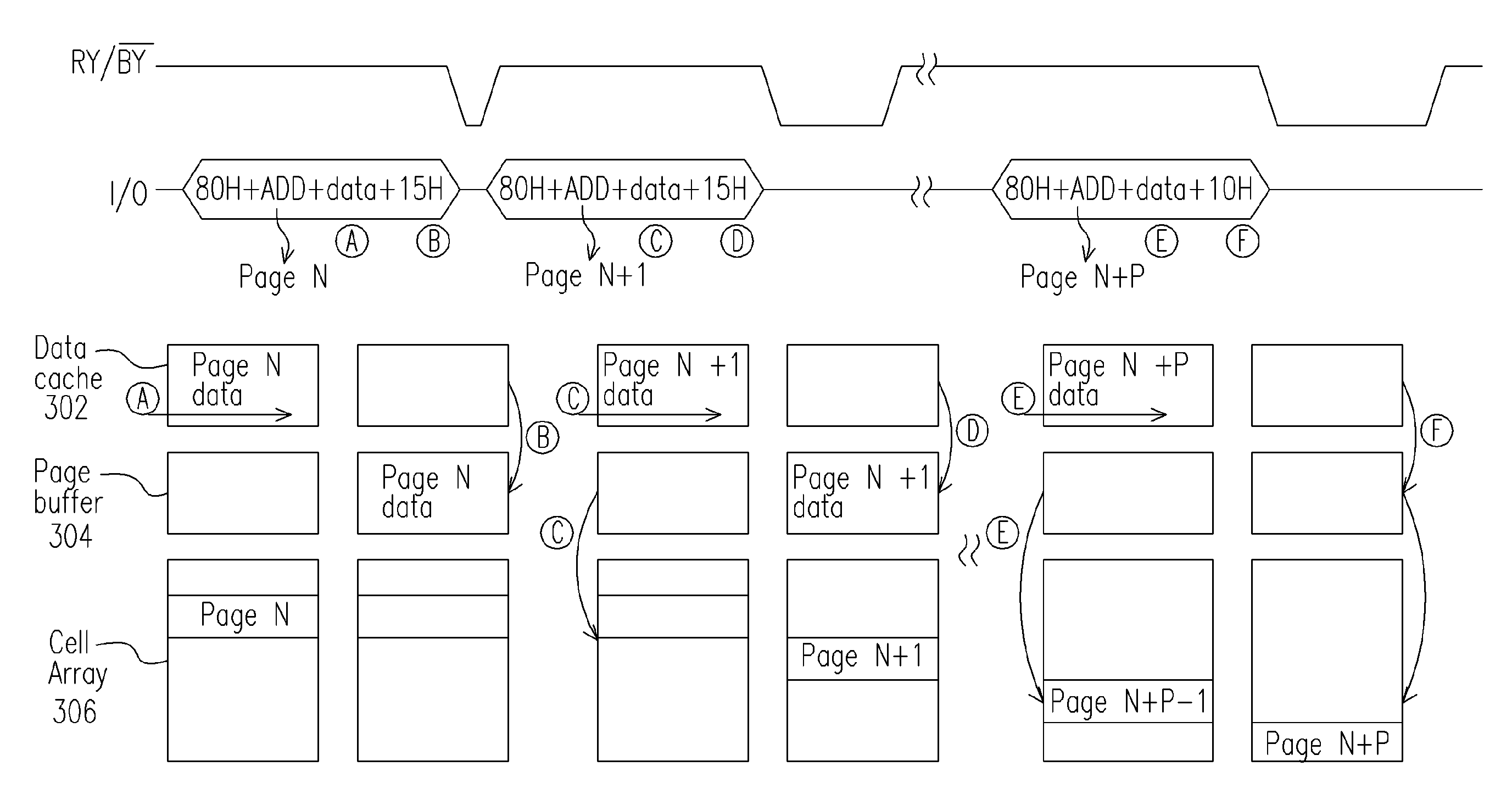

Pipeline accessing method to a large block memory

ActiveUS7076598B2Reduce frequencyReduce busy timeMemory architecture accessing/allocationMemory adressing/allocation/relocationAccess methodPage buffers

A pipeline accessing method to a large block memory is described. The large block flash memory has a plurality of pages and each page has a plurality of sectors. The memory device has a controller to control an access operation between a host and a cell array of the large block flash memory with a page buffer. The controller includes at least two buffers, when the host intends to program the memory device. In the method, data sectors are transferred between the host and the large block flash memory by alternatively using the buffers. After transferring N data sectors with respect to one page, a start program command is issued by the controller for programming the data.

Owner:SOLID STATE SYST

Flash memories and processing systems including the same

InactiveUS20060224789A1Improve reading speedIncrease write speedRead-only memoriesDigital storageExternal storageData shipping

A memory may include first and second buffer memories and a memory core. The memory core may include memory blocks each having a plurality of pages and a page buffer for reading data from a selected memory block. A control logic may control the first and second buffer memories and the memory core. The control logic may have a register for storing address and command information of the memory core. The control logic may control the memory core so that data read periods for pages of the selected memory block are carried out according to the stored address and command information. The control logic may control the first and second buffer memories and the memory core so that data in the page buffer may be transferred to the first and / or second buffer memories during the data read periods. The control logic may deactivate an interrupt signal when data in the page buffer is transferred to the first and / or second buffer memory and may activate the interrupt signal when data in the first and / or second buffer memory is transferred to an external storage.

Owner:SAMSUNG ELECTRONICS CO LTD

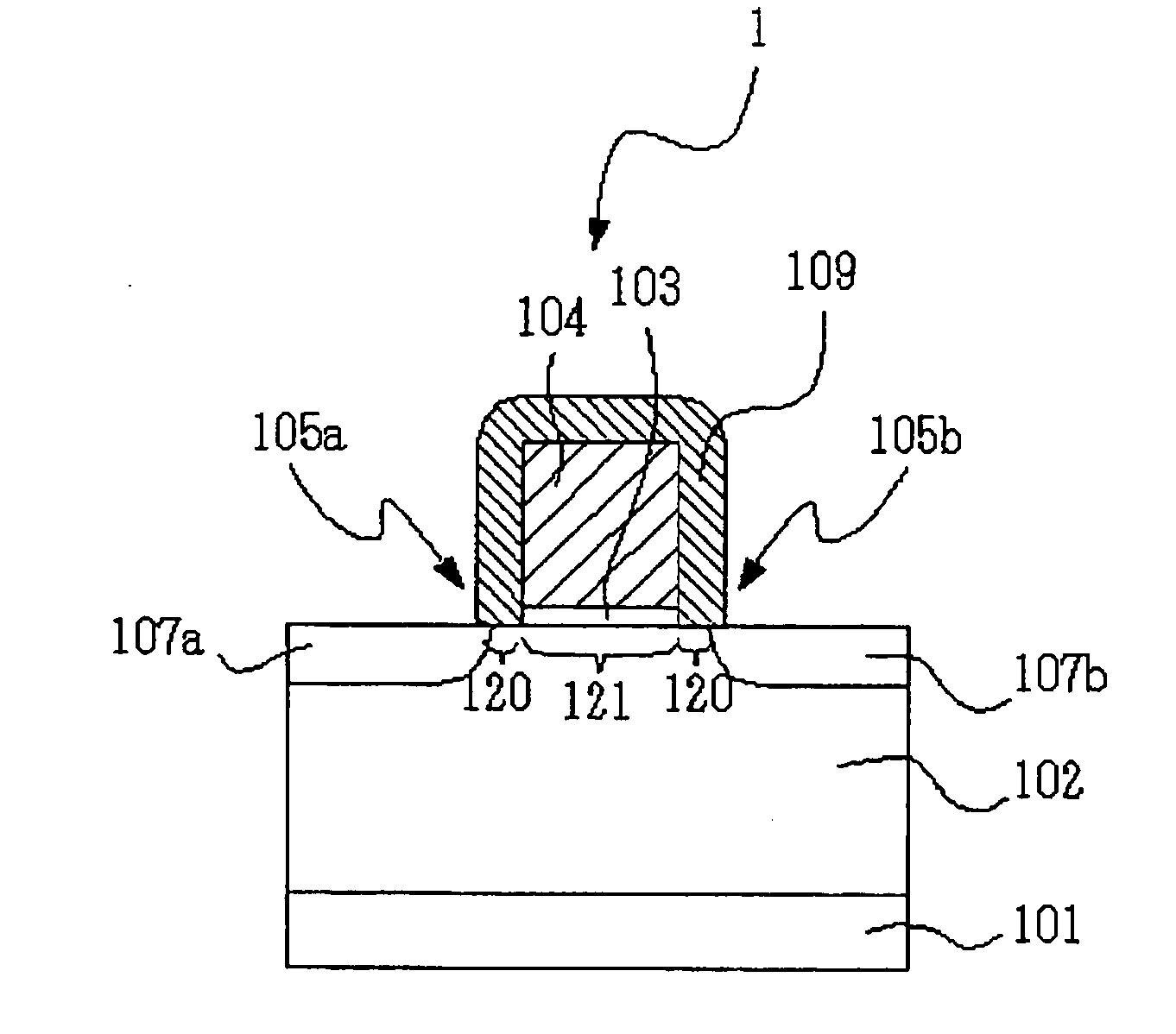

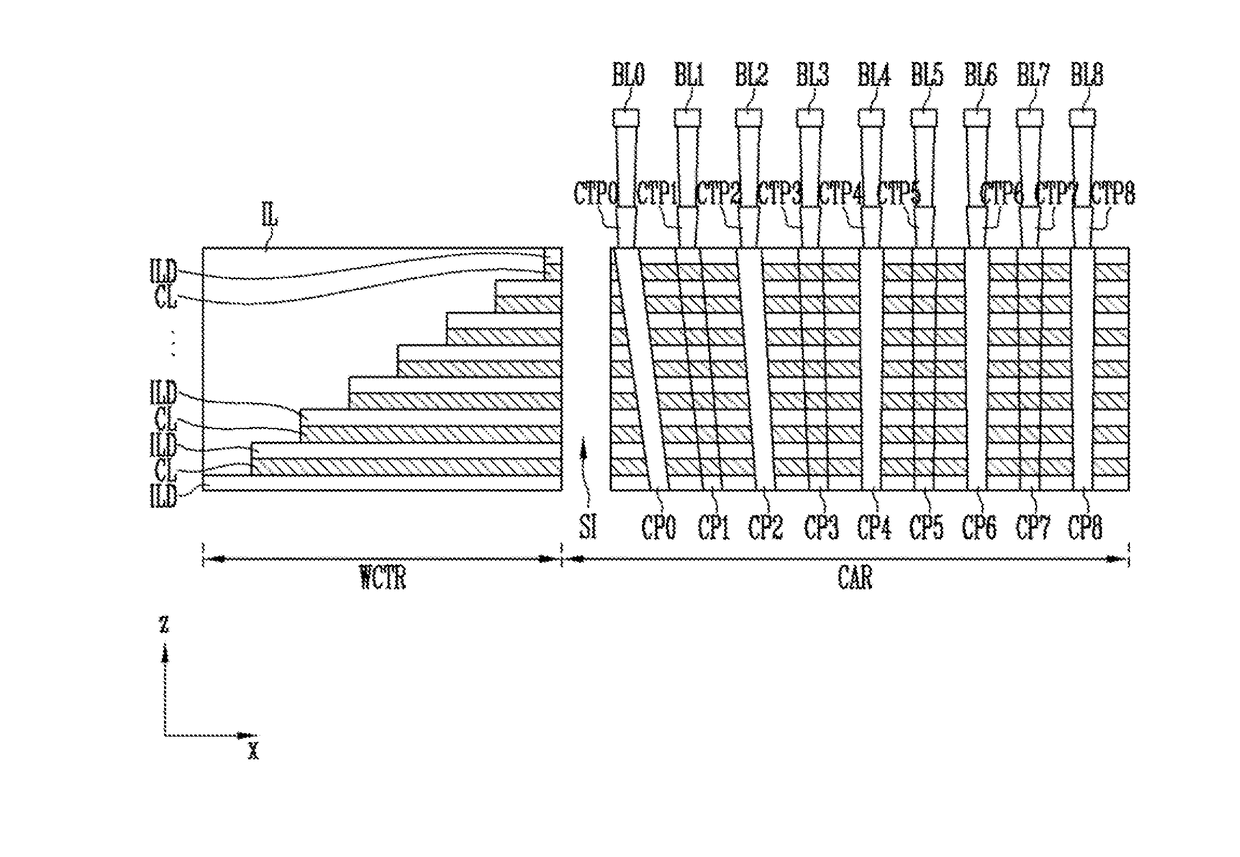

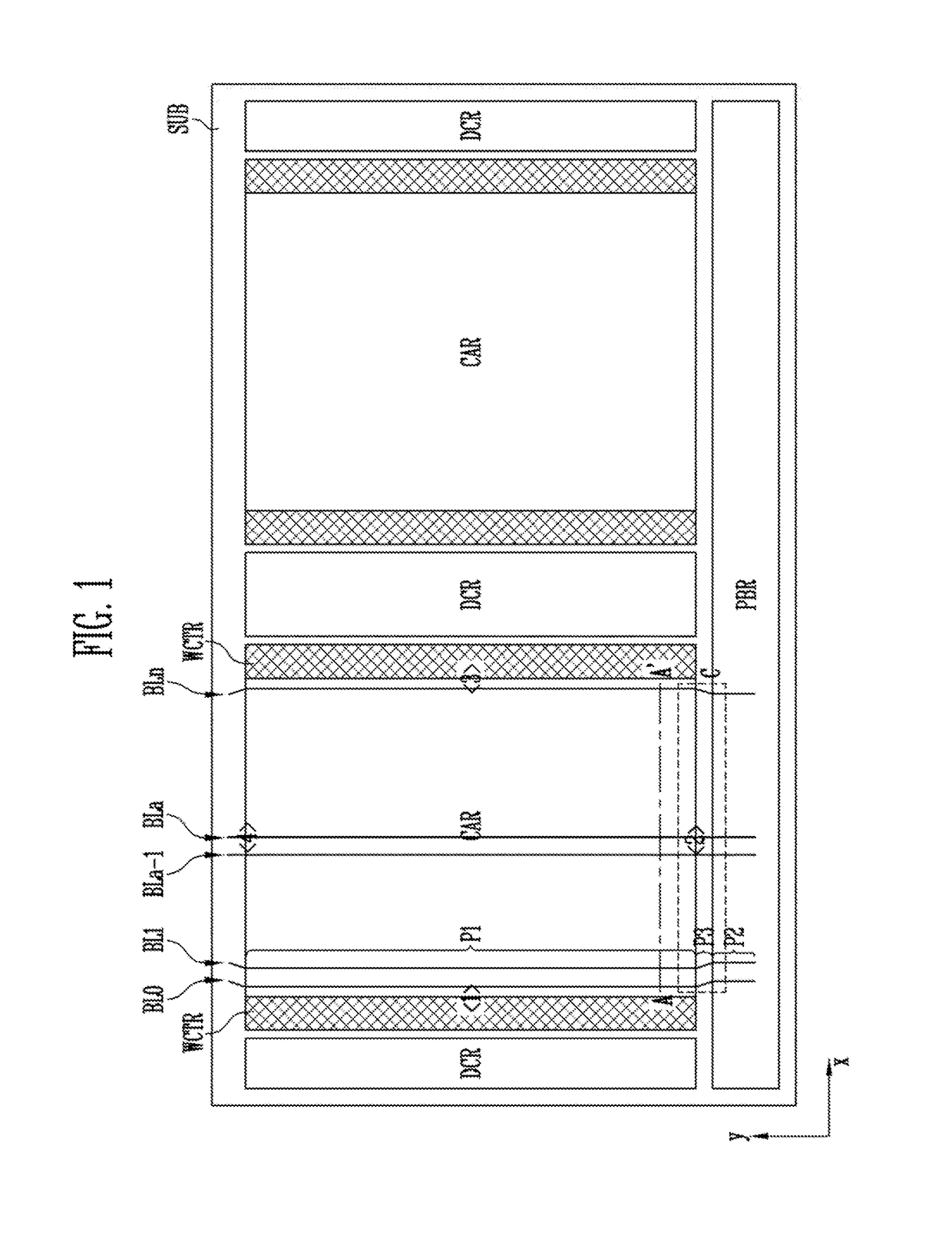

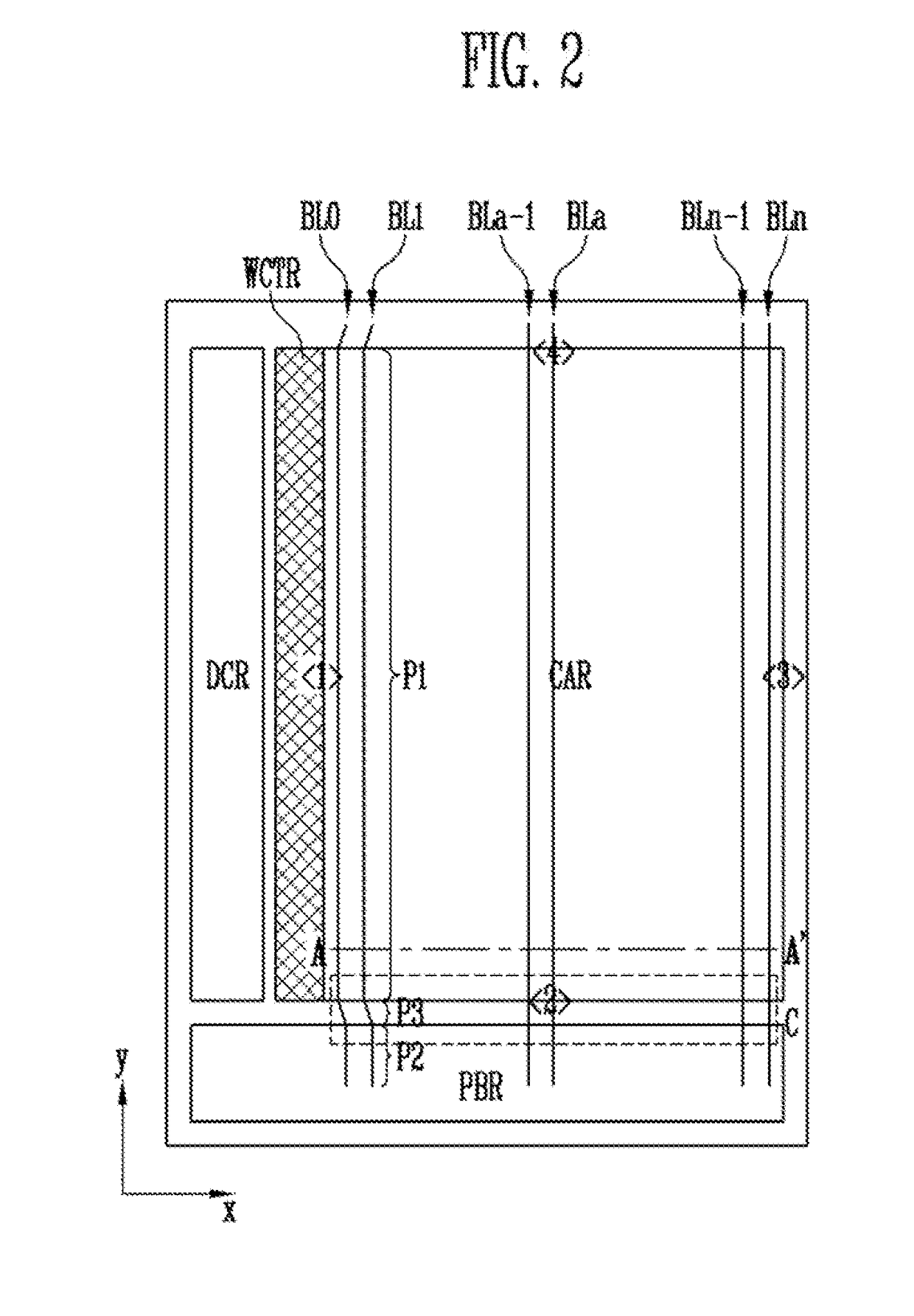

Semiconductor memory device

ActiveUS20180130818A1Operational reliability is increasedSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor memory device includes a cell array region formed on a substrate, a word line contact region, and a page buffer region coupled to the cell array region through bit lines, wherein at least one of the bit lines has a curved structure toward the word line contact region. According to an embodiment, a misalignment between a cell plug and a contact plug caused by a natural cell plug bending phenomenon may be reduced to improve operational reliability of a semiconductor memory device.

Owner:SK HYNIX INC

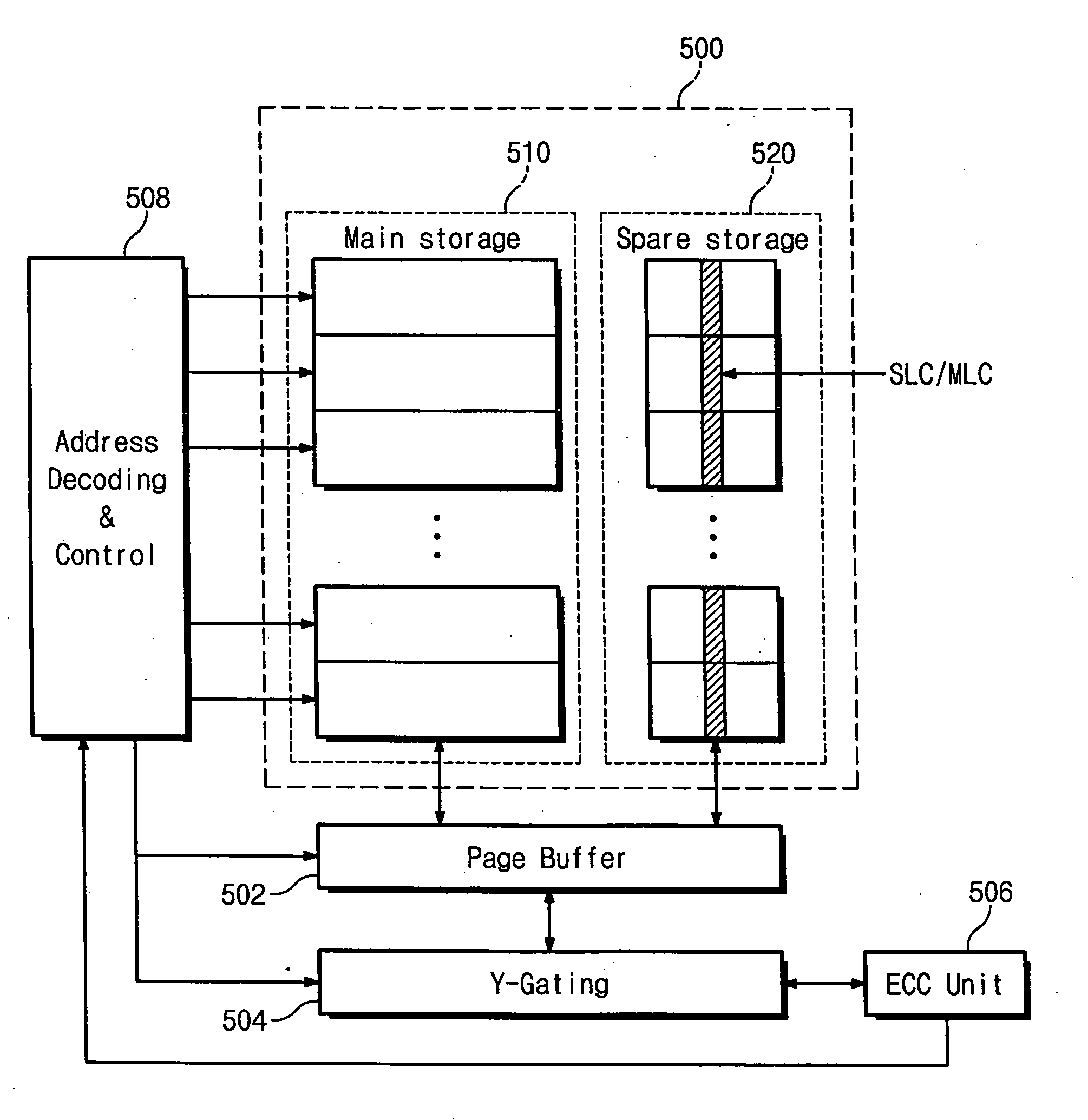

Multi-bit memory device and memory system

ActiveUS20070234183A1Reduce in quantityCorrection capabilityRead-only memoriesDigital storageData storingControl circuit

A nonvolatile memory device, memory system and read method are disclosed. The memory device comprises a memory cell array comprising a plurality of memory blocks each having a plurality of memory cells adapted to store N bits, where N is an integer greater than 1, a page buffer configured to perform a read operation adapted to read data from the memory cell array and output read data, an error correction circuit configured to detect and correct an error in read data stored in a memory block K and generate corresponding error information, and a control circuit configured to reduce the number of bits stored in the plurality of memory cells for memory block K from N to J, where J is an integer less than N but greater than zero, in response to the error information.

Owner:SAMSUNG ELECTRONICS CO LTD

Non-volatile memory device having configurable page size

A flash memory device having at least one bank, where the each bank has an independently configurable page size. Each bank includes at least two memory planes having corresponding page buffers, where any number and combination of the memory planes are selectively accessed at the same time in response to configuration data and address data. The configuration data can be loaded into the memory device upon power up for a static page configuration of the bank, or the configuration data can be received with each command to allow for dynamic page configuration of the bank. By selectively adjusting a page size the memory bank, the block size is correspondingly adjusted.

Owner:MOSAID TECH

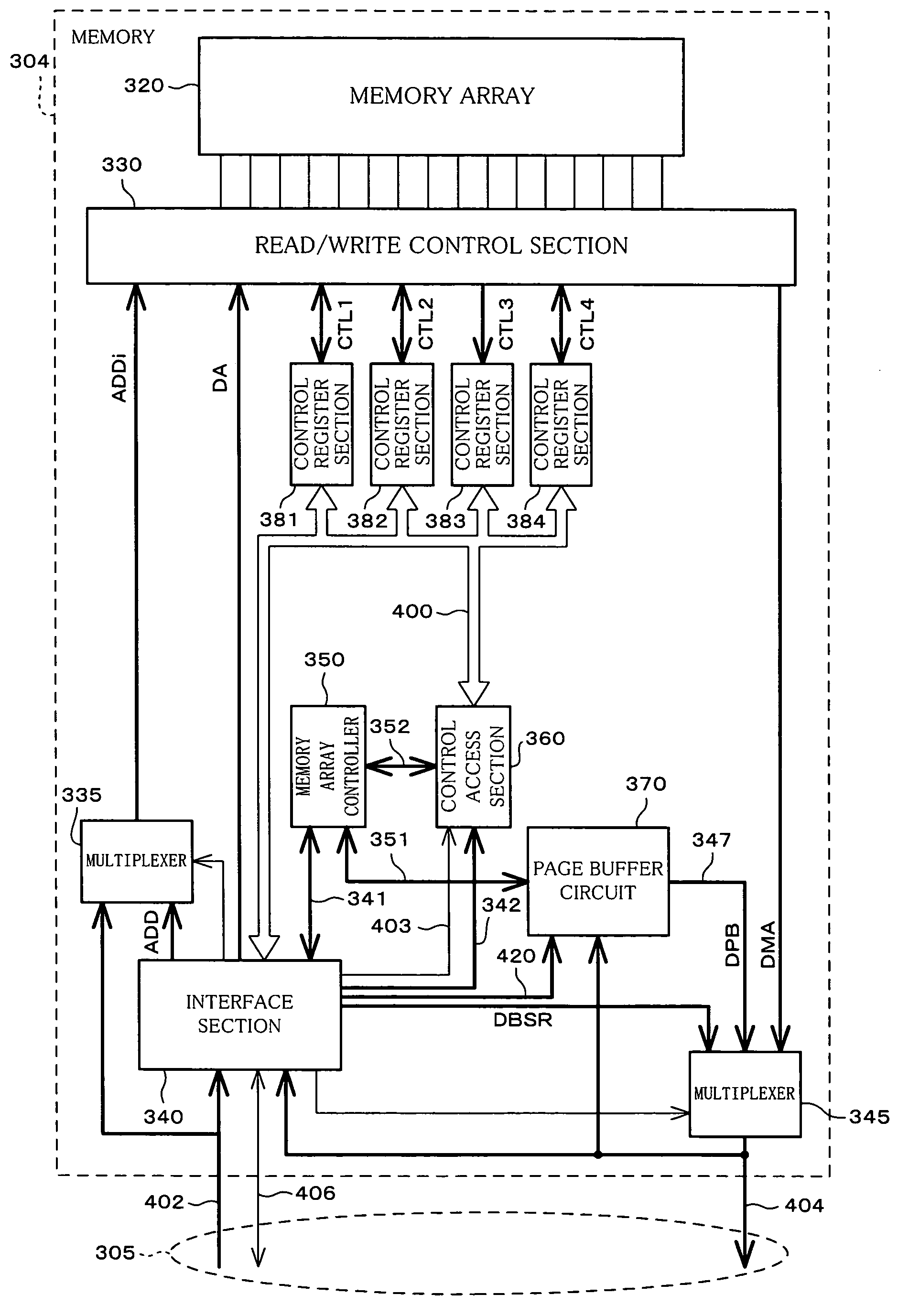

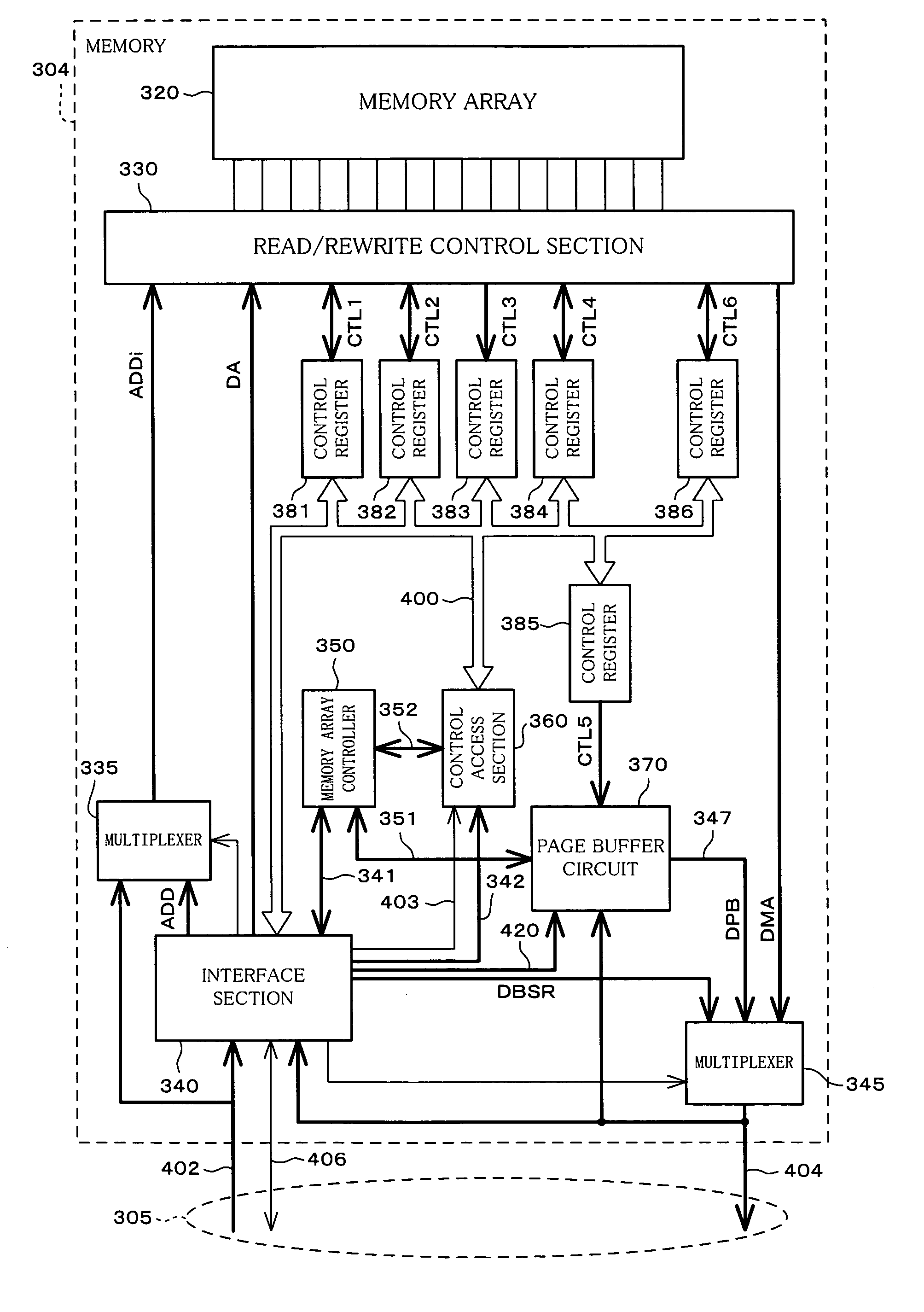

Semiconductor memory device, page buffer resource assigning method and circuit therefor, computer system and mobile electronic device

InactiveUS7405974B2Readily scaled down in sizeReadily access page planeTransistorSolid-state devicesMode controlMobile electronics

A semiconductor memory device includes a page buffer circuit and an arrangement of memory elements each including: a gate electrode provided on a semiconductor layer with an intervening gate insulating film; a channel region provided beneath the gate electrode; a diffusion area provided on both sides of the channel region, having an opposite polarity to the channel region; and a memory functioning member provided on both sides of the gate electrodes, having a function of storing electric charge. The page buffer circuit provides a common resource shared between a memory array controller and a user. The page buffer circuit has two planes containing random access memory arrays. The page buffer circuit also includes a mode control section to facilitate access to the planes over a main bus in user mode and access to the planes by the memory array controller in memory control mode.

Owner:SHARP KK

Page buffer for a programmable memory device

A page buffer is provided for an electrically programmable memory that includes multiple memory cells forming multiple memory pages. The page buffer includes a register for at least temporarily storing data read from or to be written to the memory cells of a selected memory page. The register includes multiple latches and multiple buffer elements. Each of the latches is coupled to at least one signal line for transferring the data bit that is stored in the latch. Each of the buffer elements decouples an output of a corresponding one of the latches from the signal line, with the buffer element driving the signal line according to the data bit stored in the corresponding latch. Also provided is a method of transferring data from a register to signal lines in an electrically programmable memory.

Owner:STMICROELECTRONICS SRL +1

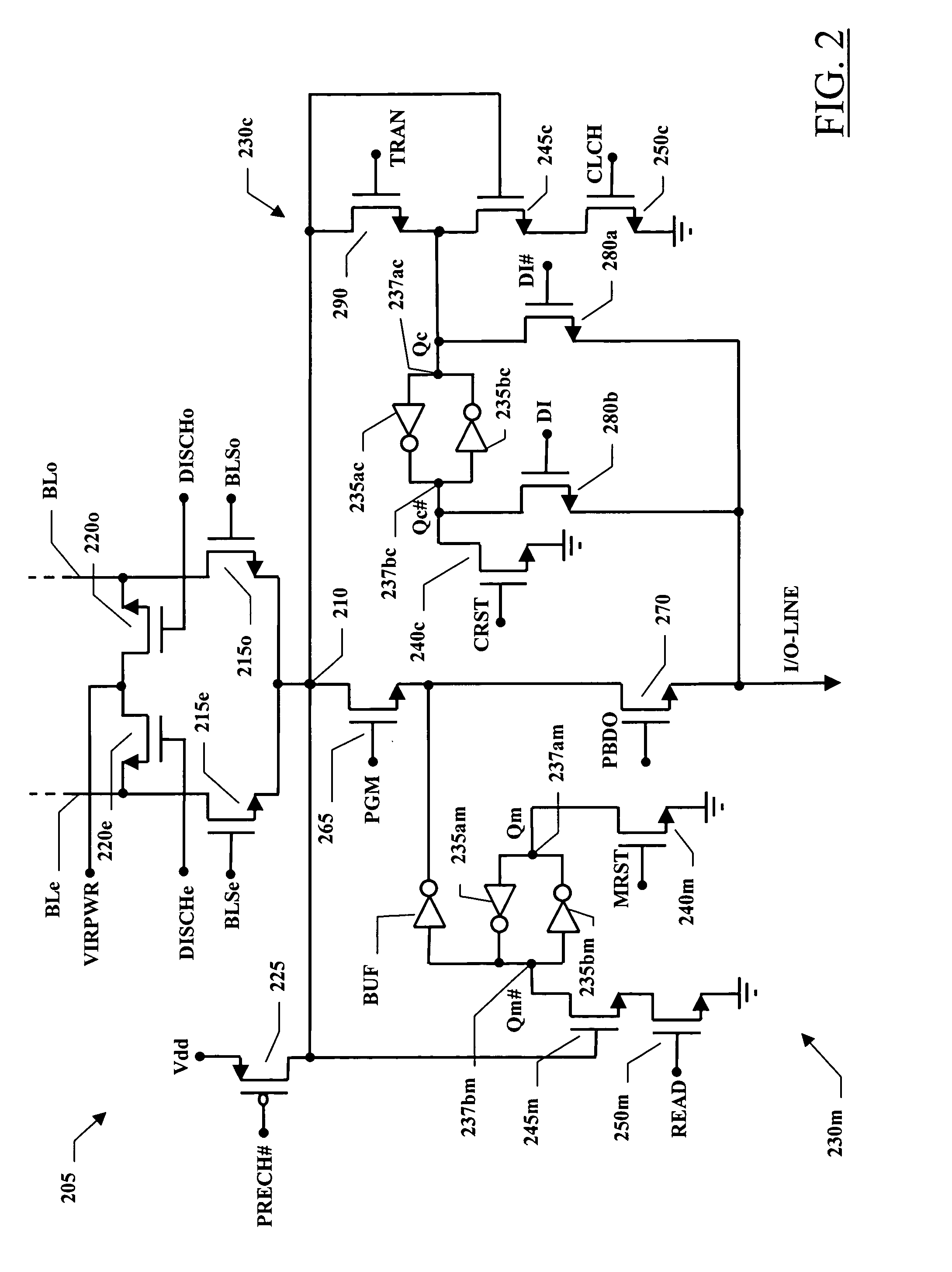

Memory devices with page buffer having dual registers and method of using the same

A nonvolatile memory device and programming method and apparatus therefore are described that include operatively coupled first and second sense amplifiers having first and second data registers or latches, a storage circuit for storing a data of the second amplifier, a pass / fail check circuit for checking the content of the second data register whether a cell of the memory device has been sufficiently programmed and a restore circuit for resetting the second data register for reprogramming the device until sufficiently programmed.

Owner:SAMSUNG ELECTRONICS CO LTD

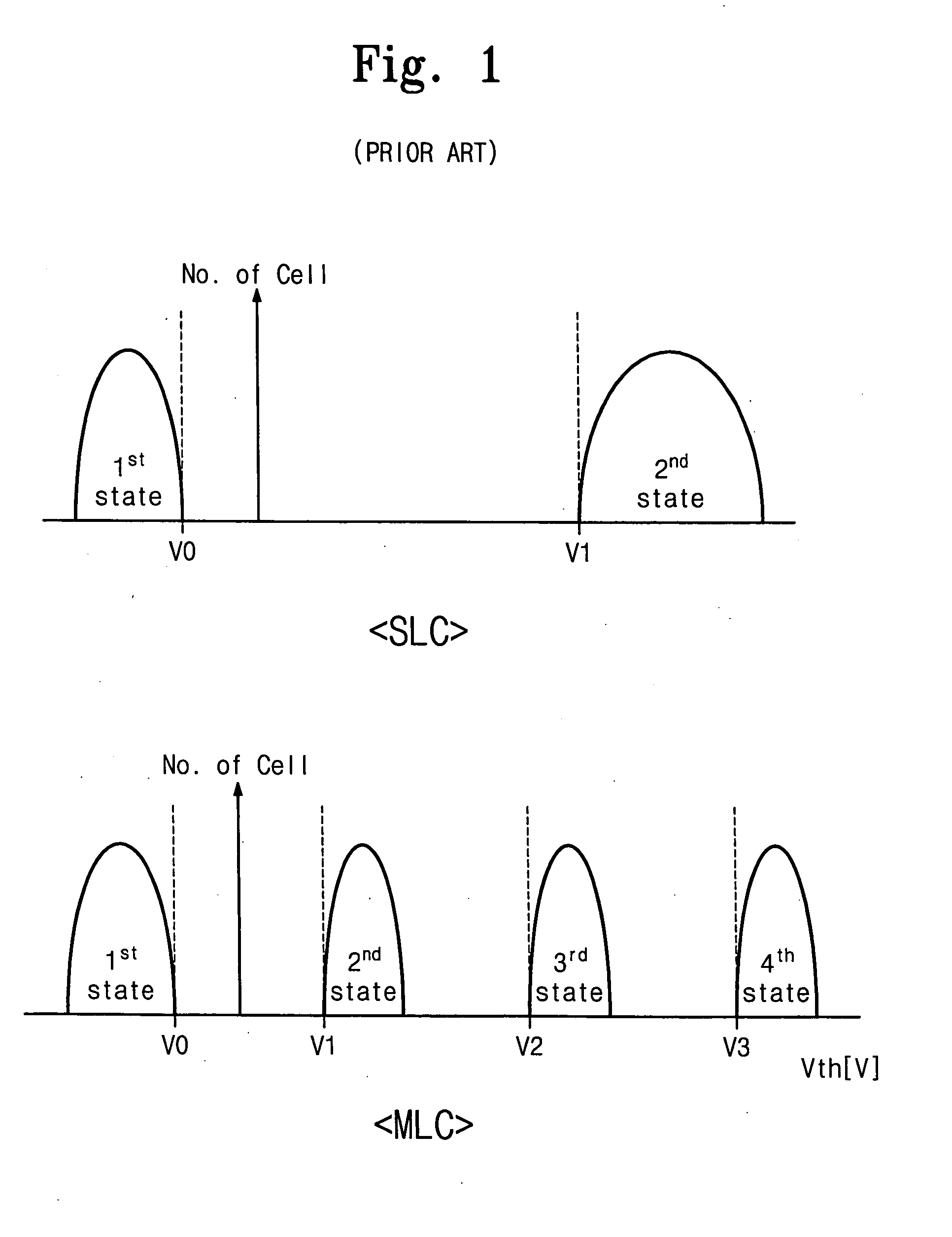

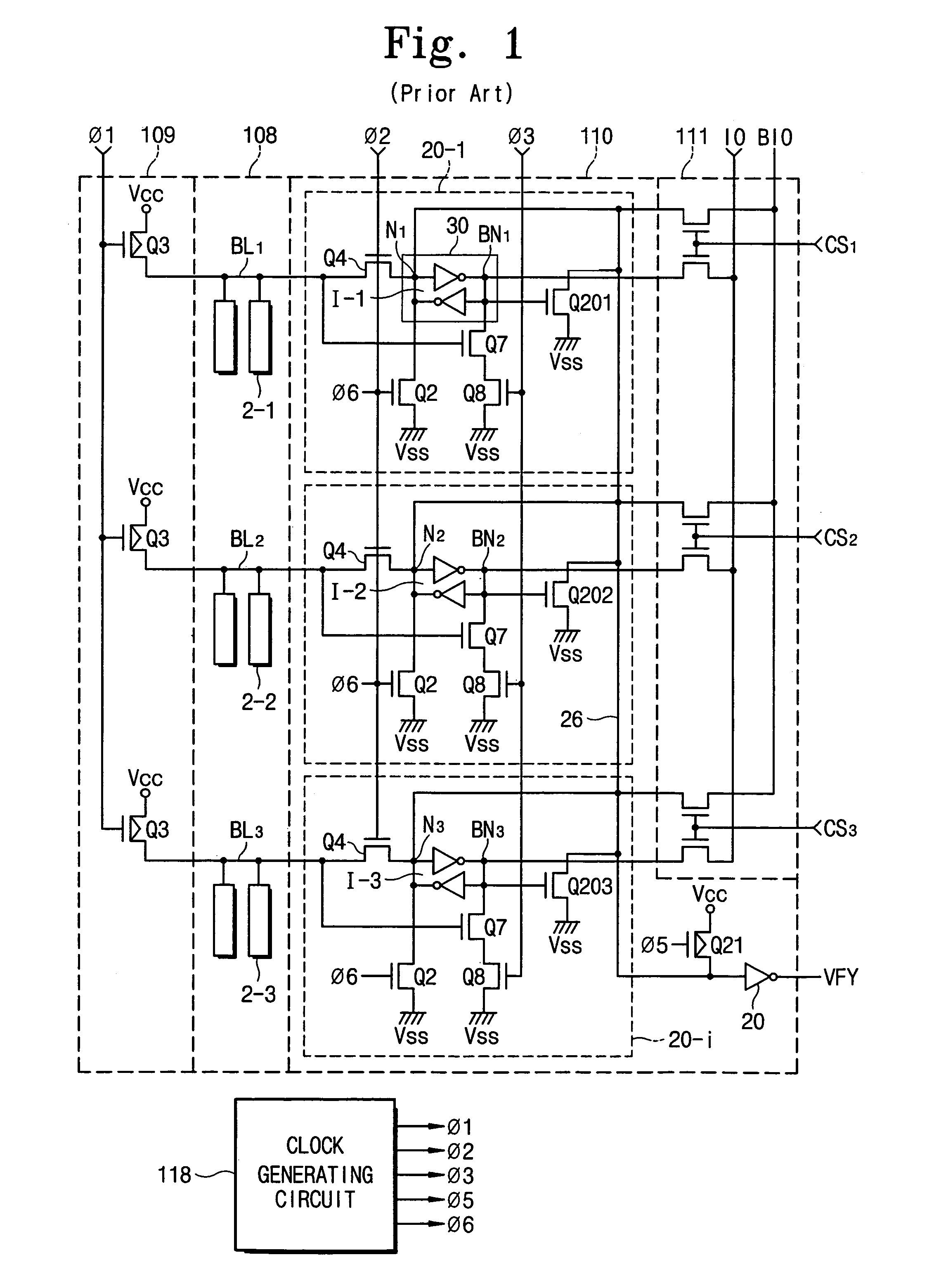

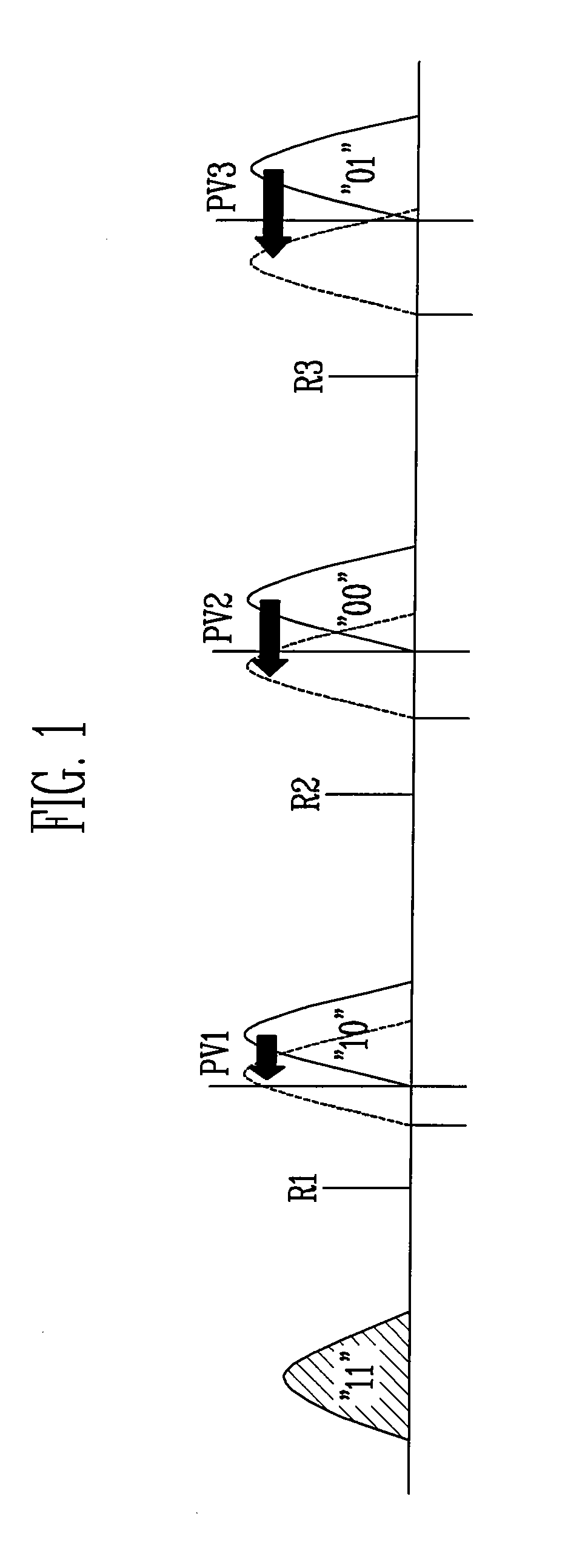

Method of reading multi-level nand flash memory cell and circuit for the same

The disclosed is a method of reading a multi-level NAND flash memory cell and a circuit for the same. The read circuit for the NAND flash memory device includes a NAND flash memory cell having multi-level information, a first page buffer for storing an upper-bit, a second page buffer for storing a lower bit, and pass transistor for changing information of the second page buffer according to a variation of the first page buffer. In accordance with the present invention, “00” or “01” information is read out by applying a first voltage to a word line of the cell. “00”, “01”, or “11” information is read out by applying a second voltage to the word line. A latch pass control signal is applied to a pass transistor. Thus, it is possible to read out “00”, “01”, “11”, or “10” information.

Owner:STMICROELECTRONICS SRL +1

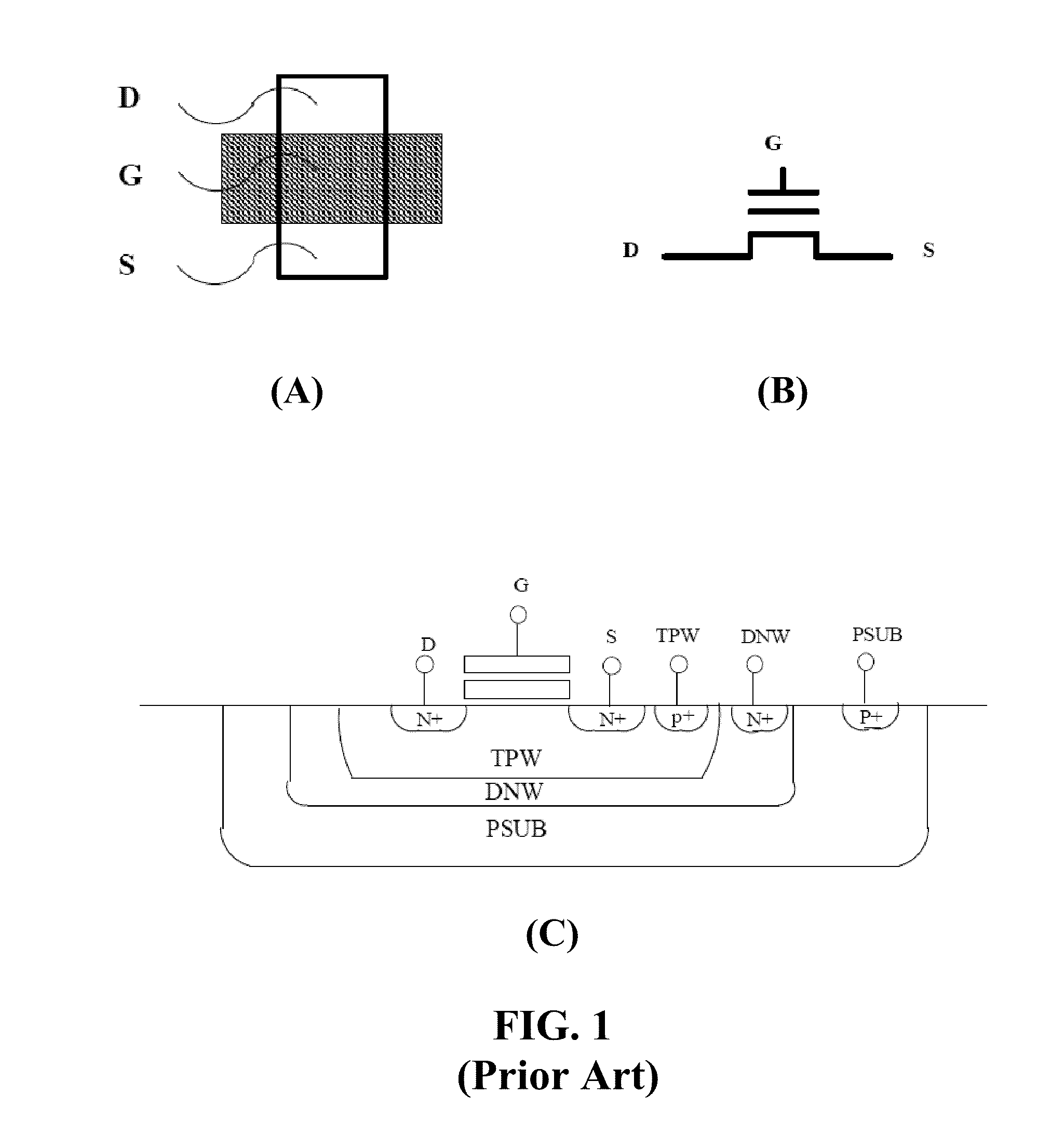

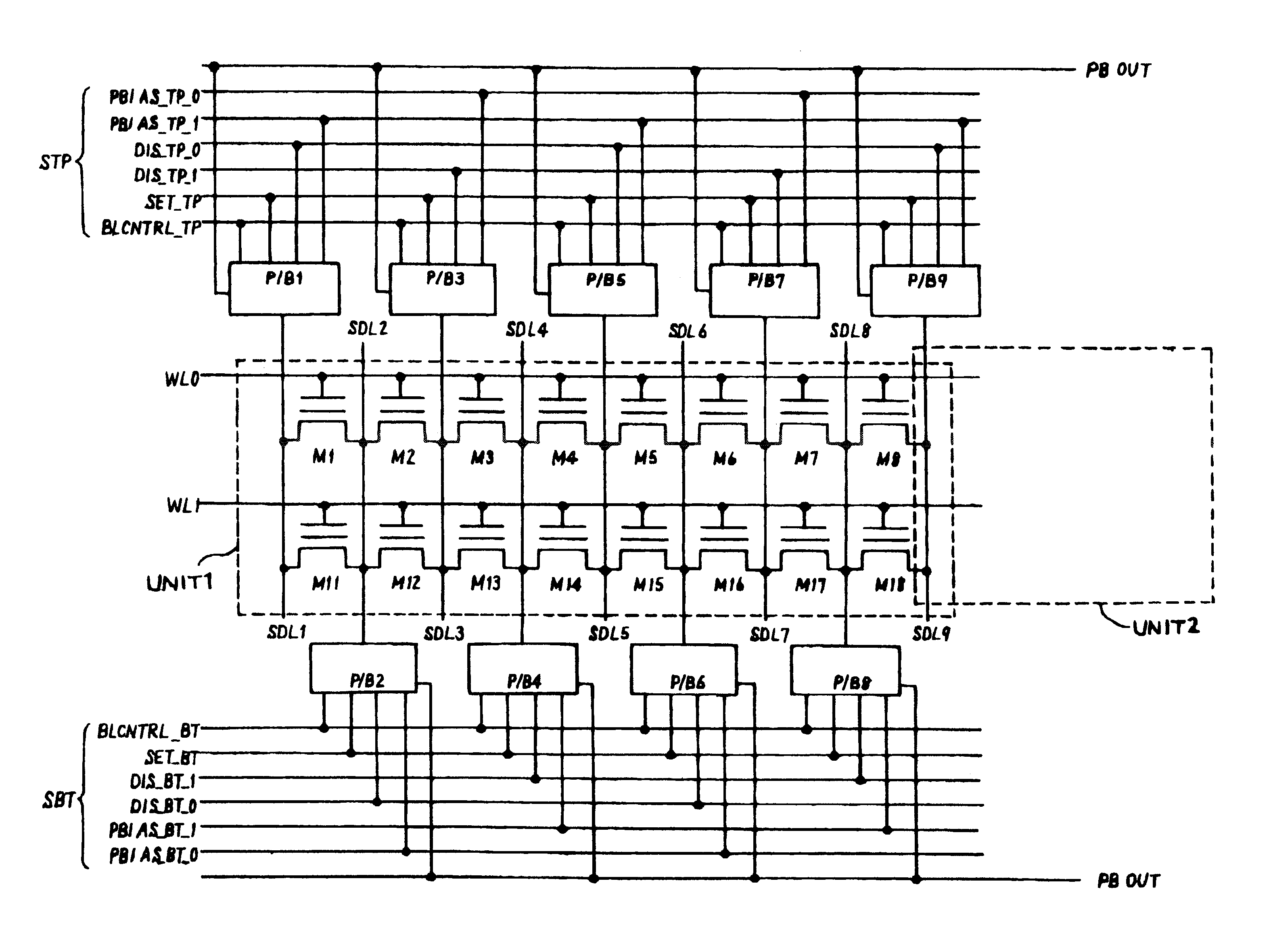

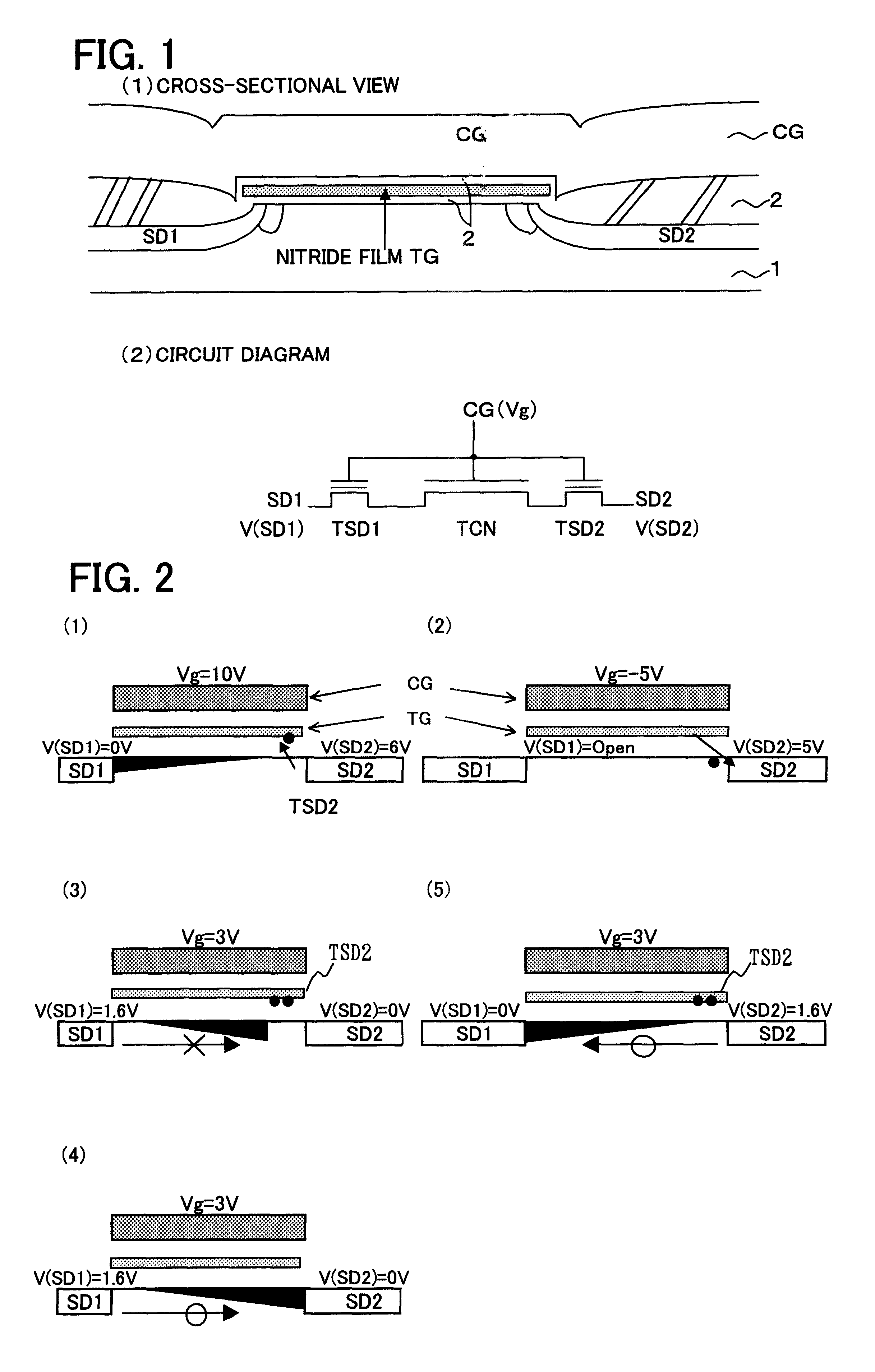

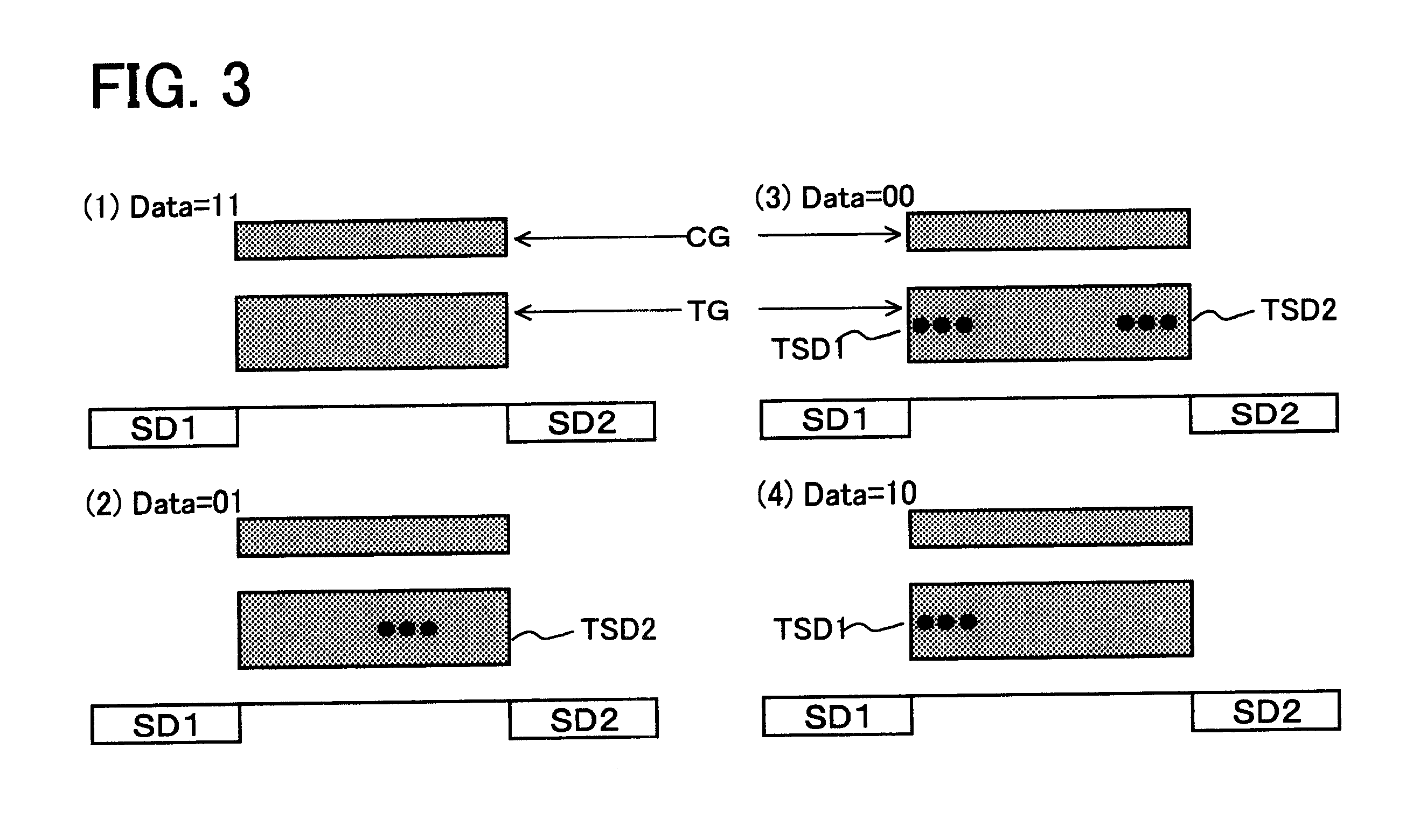

Nonvolatile memory circuit for recording multiple bit information

The present invention provides a multi-bits non-volatile memory circuit having a cell transistor with non-conductive trap gate which has a cell array capable of reading a plural data simultaneously. The present invention is a non-volatile memory circuit in which a plurality of cell transistors M having a non-conductive trapping gate TG are arranged, comprising: a plurality of source-drain lines SDL, which are connected commonly with the source-drain regions SD1, SD2 of cell transistors adjacent in row direction, wherein these adjacent source-drain lines are set to a floating state F, a read-out voltage application state BL, a reference voltage state OV, a read-out voltage state BL, and a floating state F, and the source-drain lines SDL in the read-out voltage state is caused to function as bit lines, such that a plurality of data are read out simultaneously. The above states are generated by the page buffer P / B connected to the source-drain line. The data read and hold are performed by the page buffer.

Owner:SPANSION INC +1

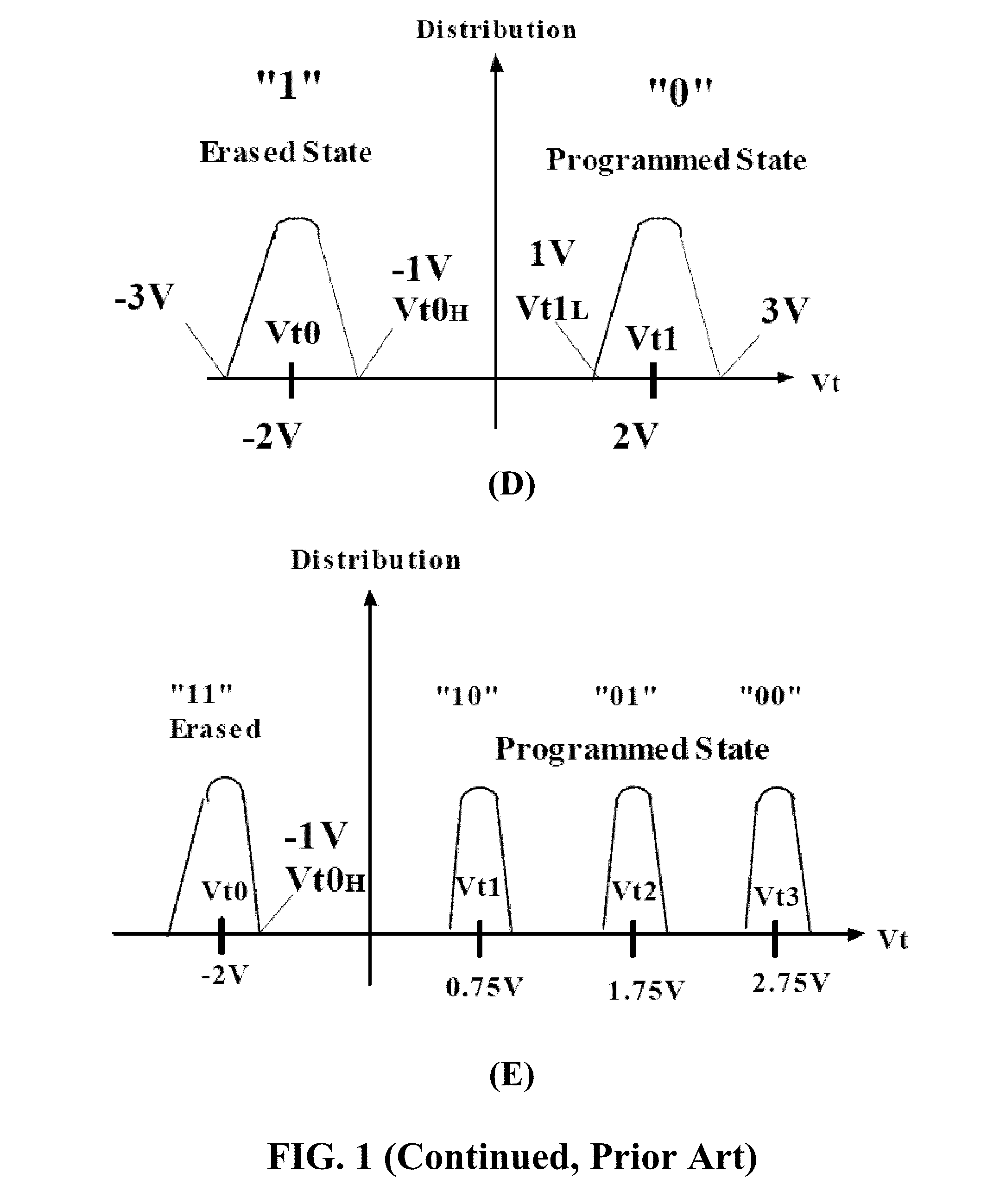

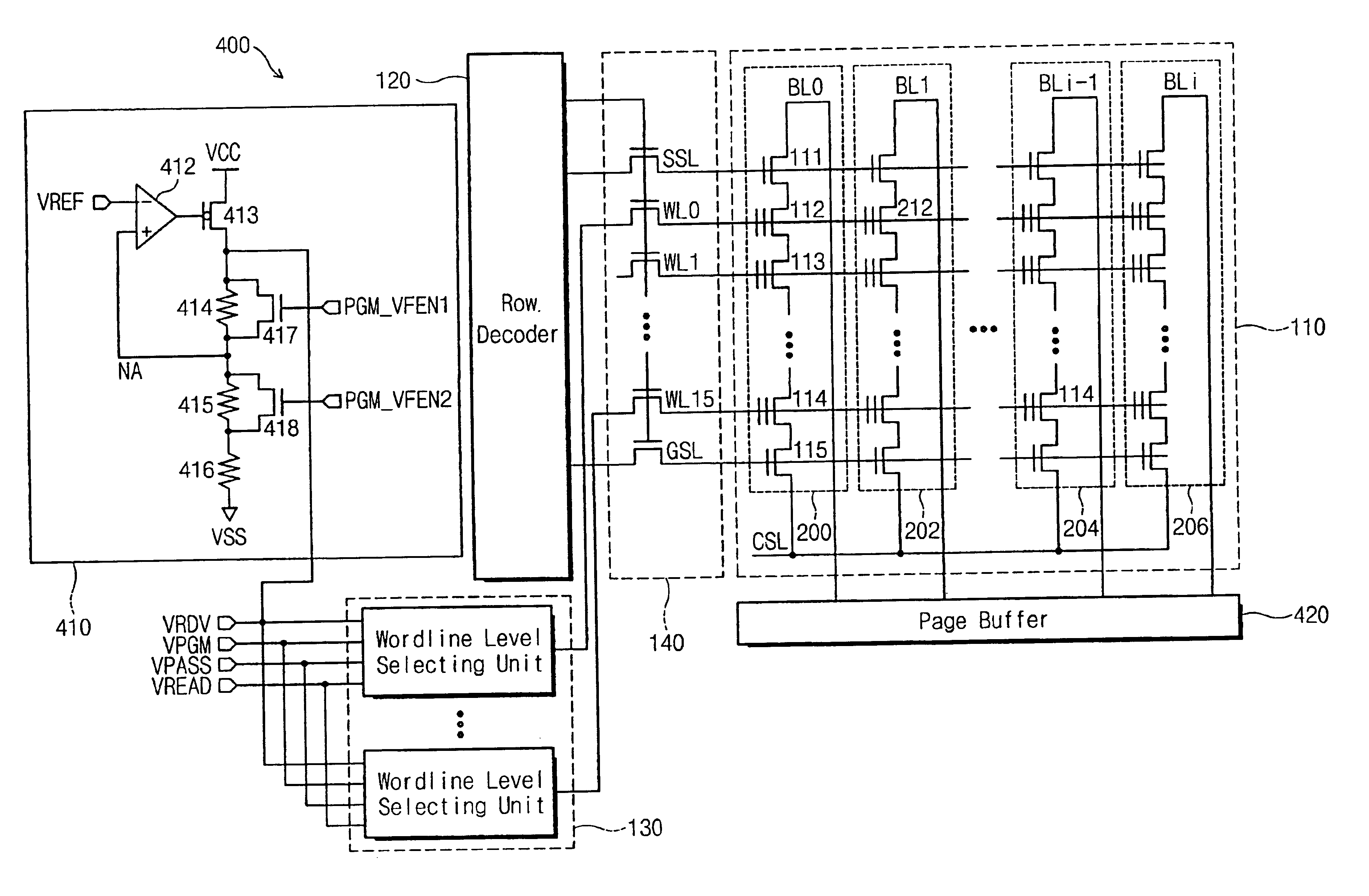

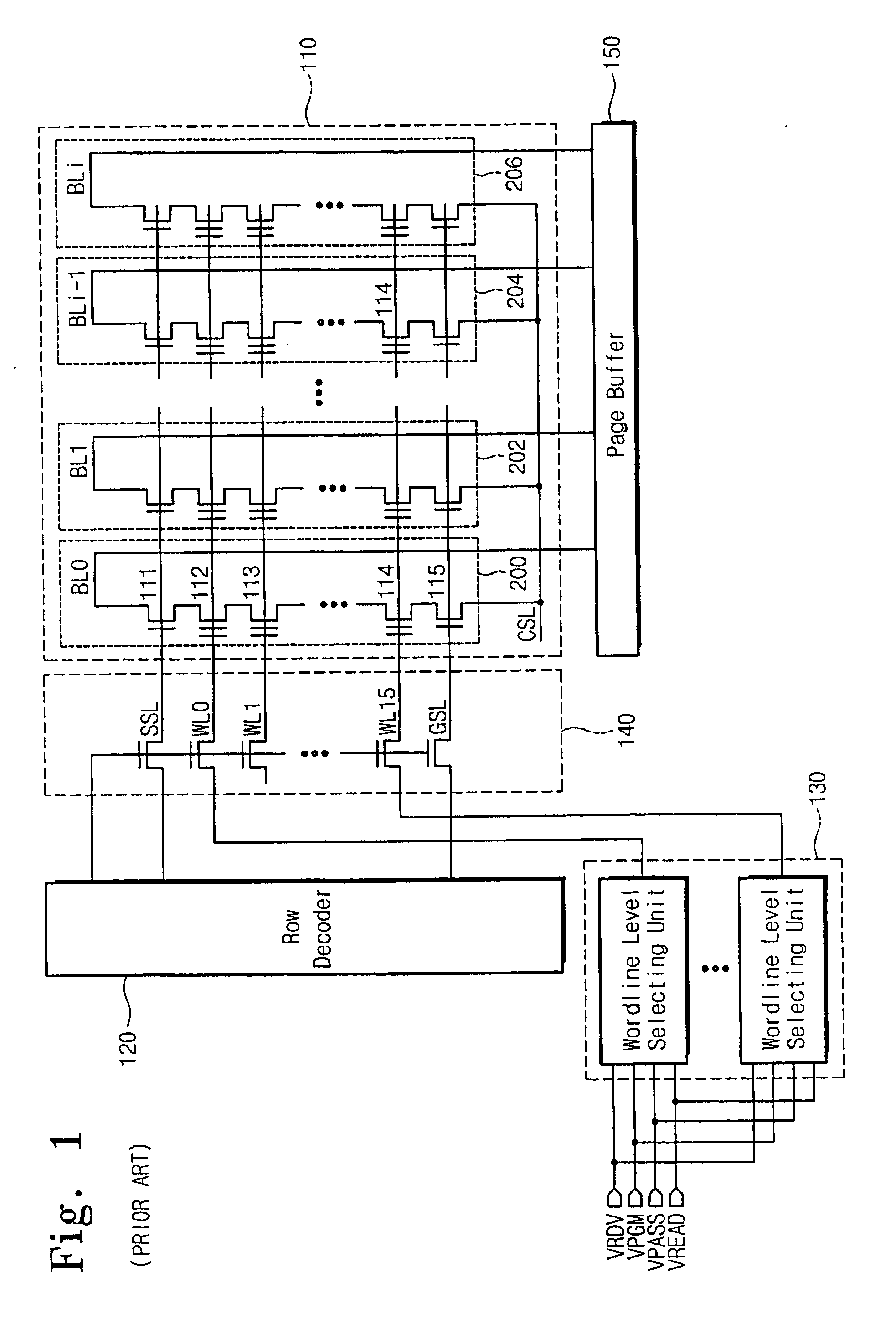

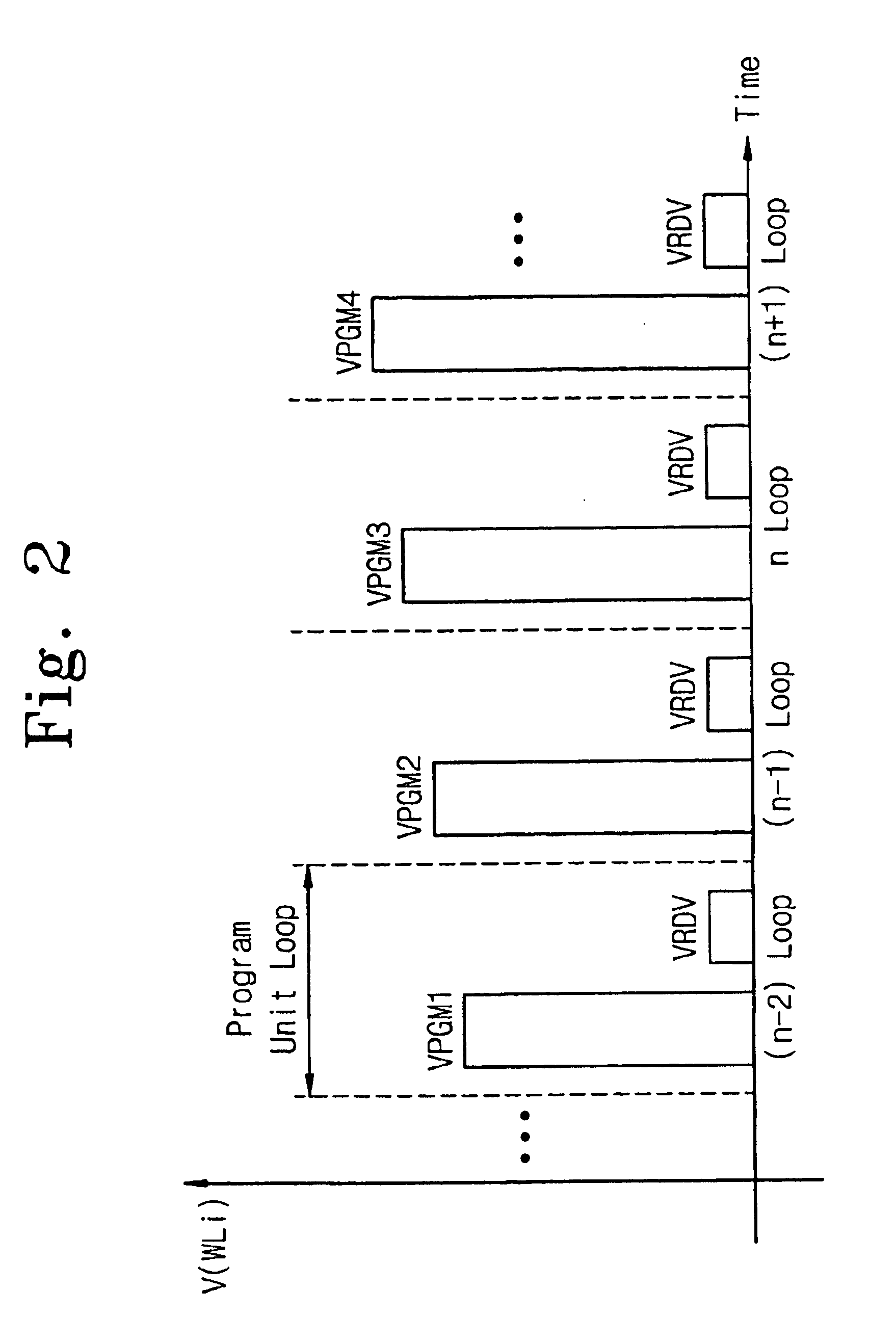

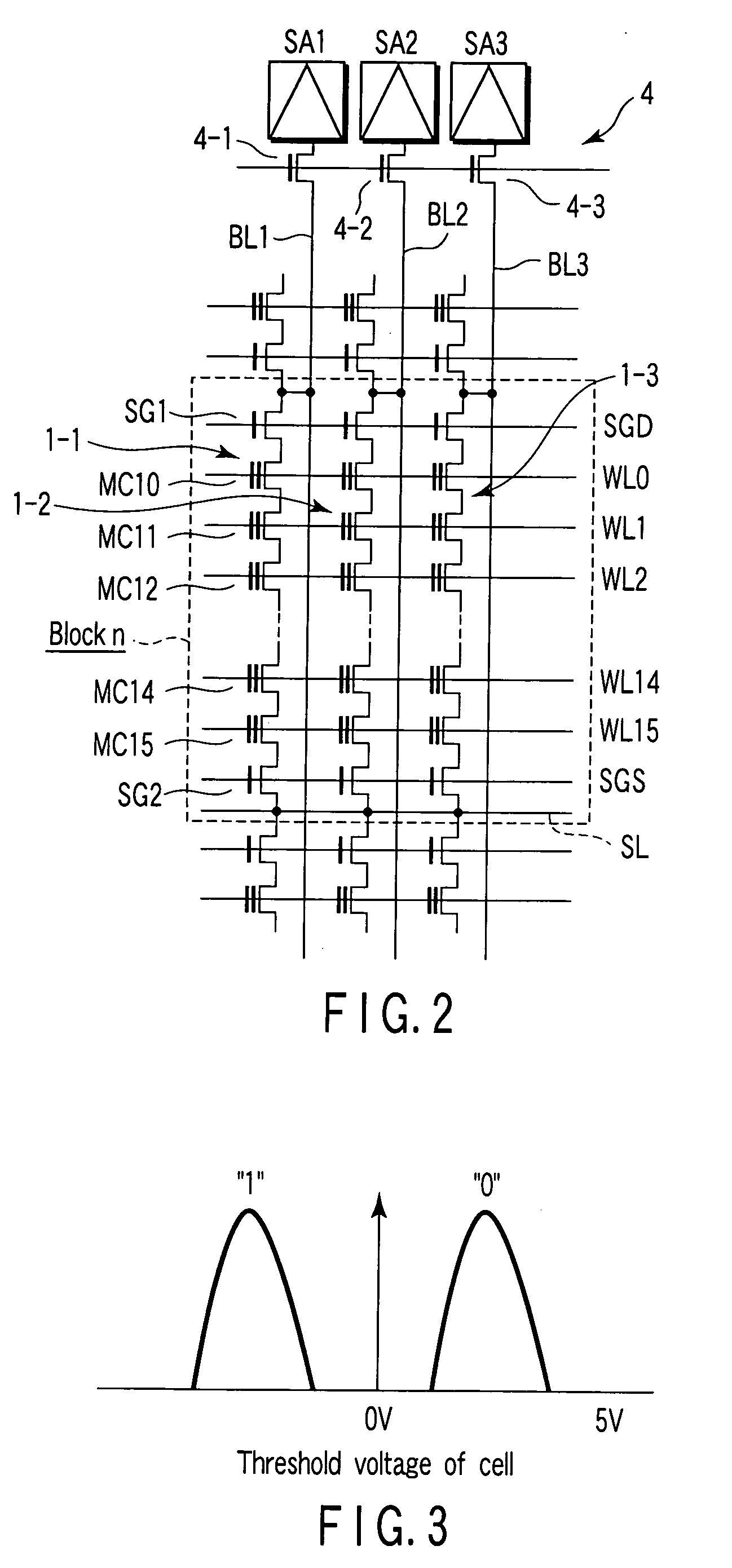

Flash memory device having uniform threshold voltage distribution and method for verifying same

ActiveUS6853585B2Voltage balanceEvenly distributedRead-only memoriesDigital storageValidation methodsPage buffers

A flash memory device including a memory cell array block including a plurality of flash memory cells. A program verify voltage generating unit variably generates a program verify voltage that verifies flash memory cells programming. A wordline level selecting unit transfers the program verify voltage to the flash memory cells. And a page buffer, including a latch, stores flash memory cell data and resets the latch whenever the program verify voltage is lowered.

Owner:SAMSUNG ELECTRONICS CO LTD

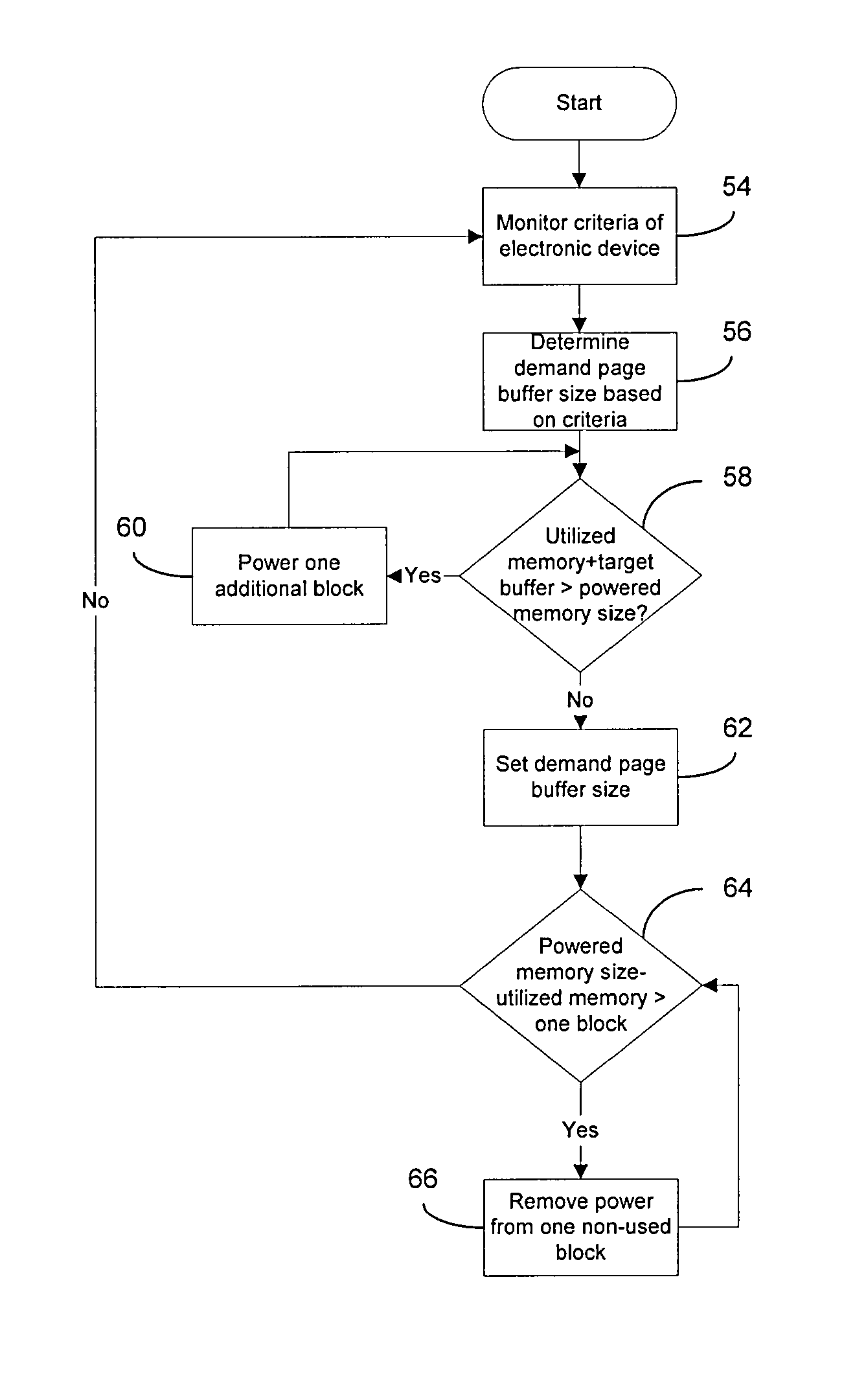

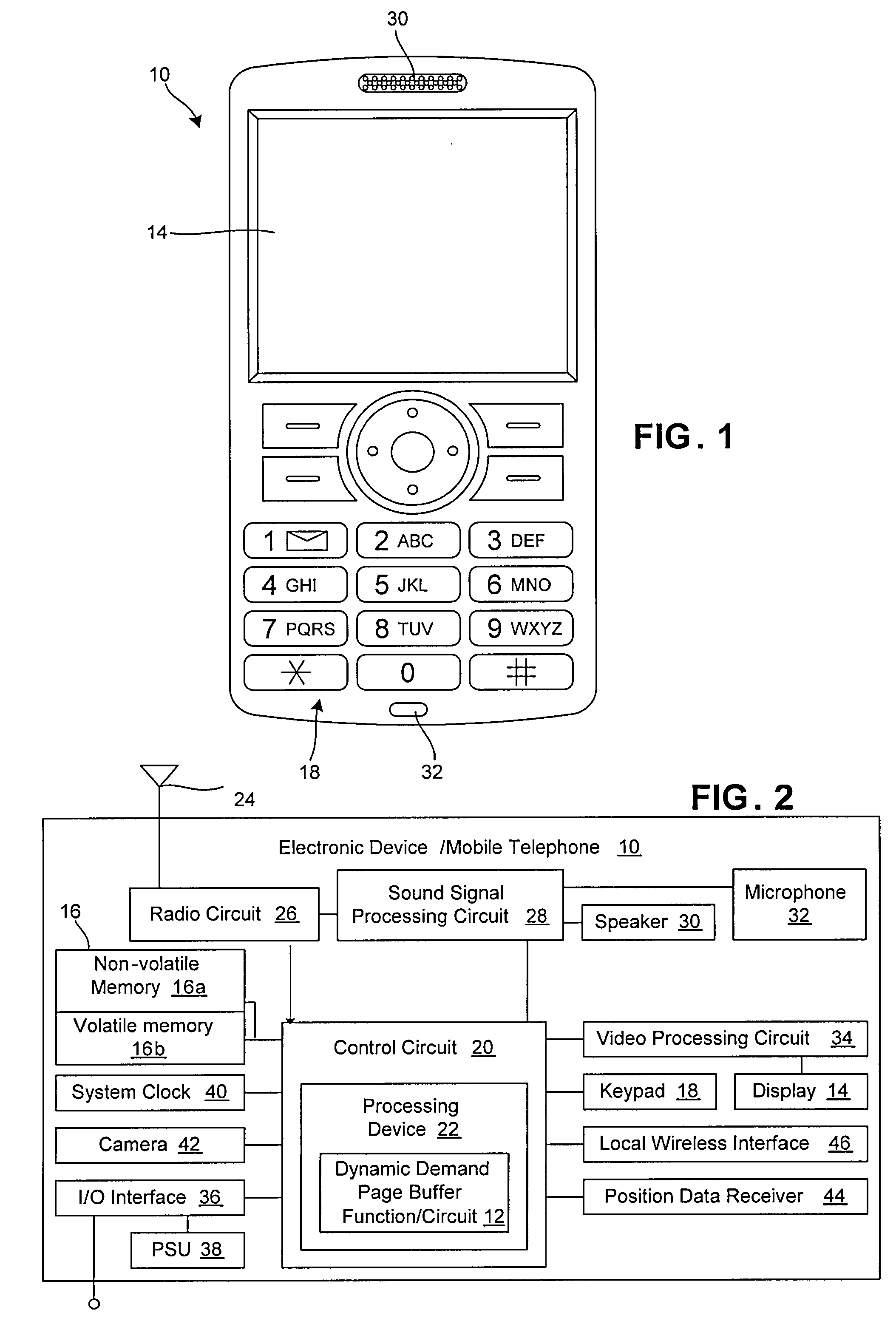

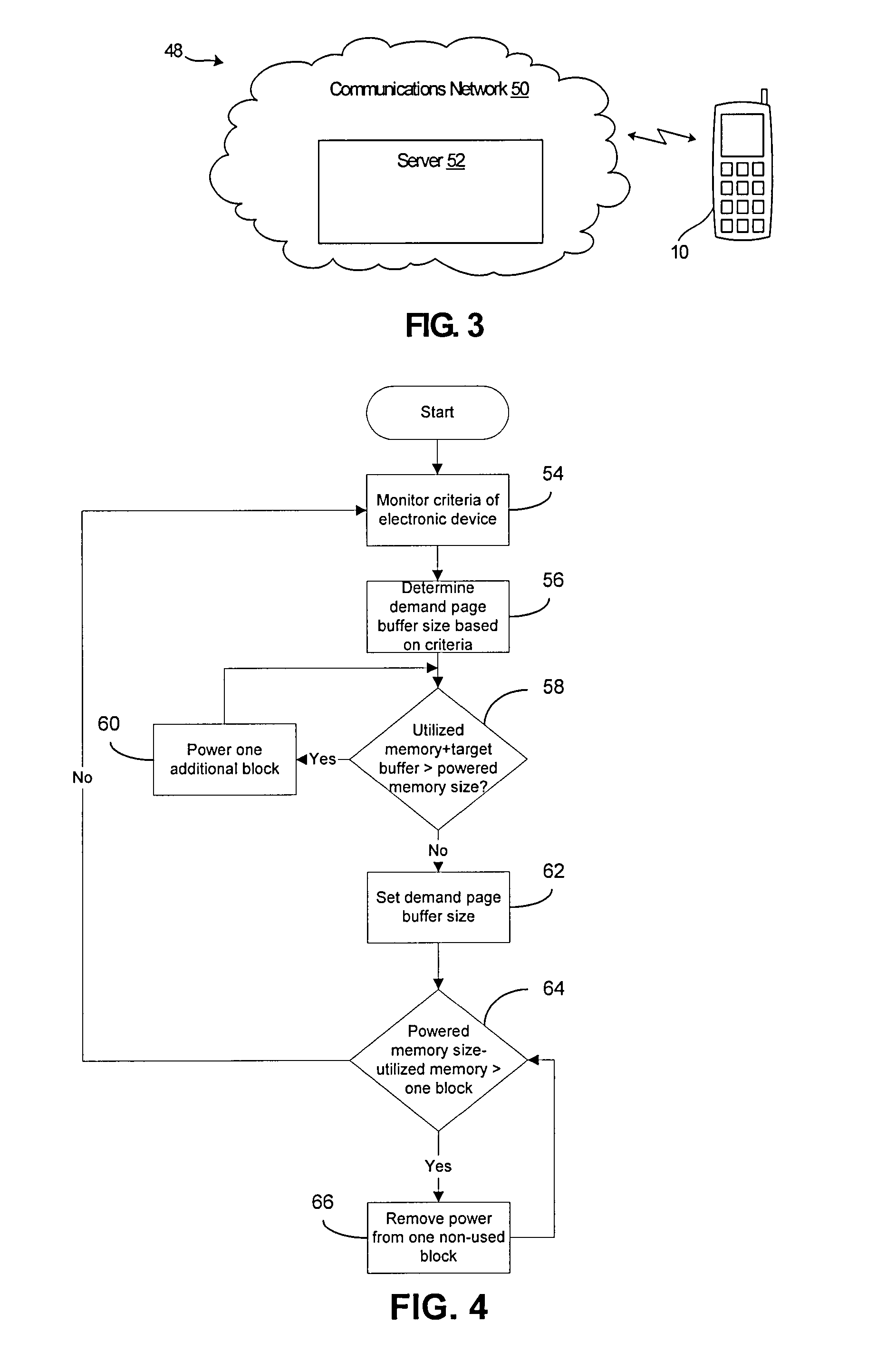

Dynamic page on demand buffer size for power savings

InactiveUS20080229050A1Short timeAverage power consumptionEnergy efficient ICTDigital data processing detailsOn demandPage buffers

A portable electronic device includes a processing device, a memory operatively coupled to said processing device, said memory comprising a plurality of blocks, wherein at least one block of the plurality of blocks may be powered independent of other blocks of the plurality of blocks, and a logic circuit operative to dynamically adjust a demand page buffer size within the memory and utilized by the processor, thereby permitting a corresponding adjustment of a number of powered memory blocks within the memory.

Owner:SONY ERICSSON MOBILE COMM AB

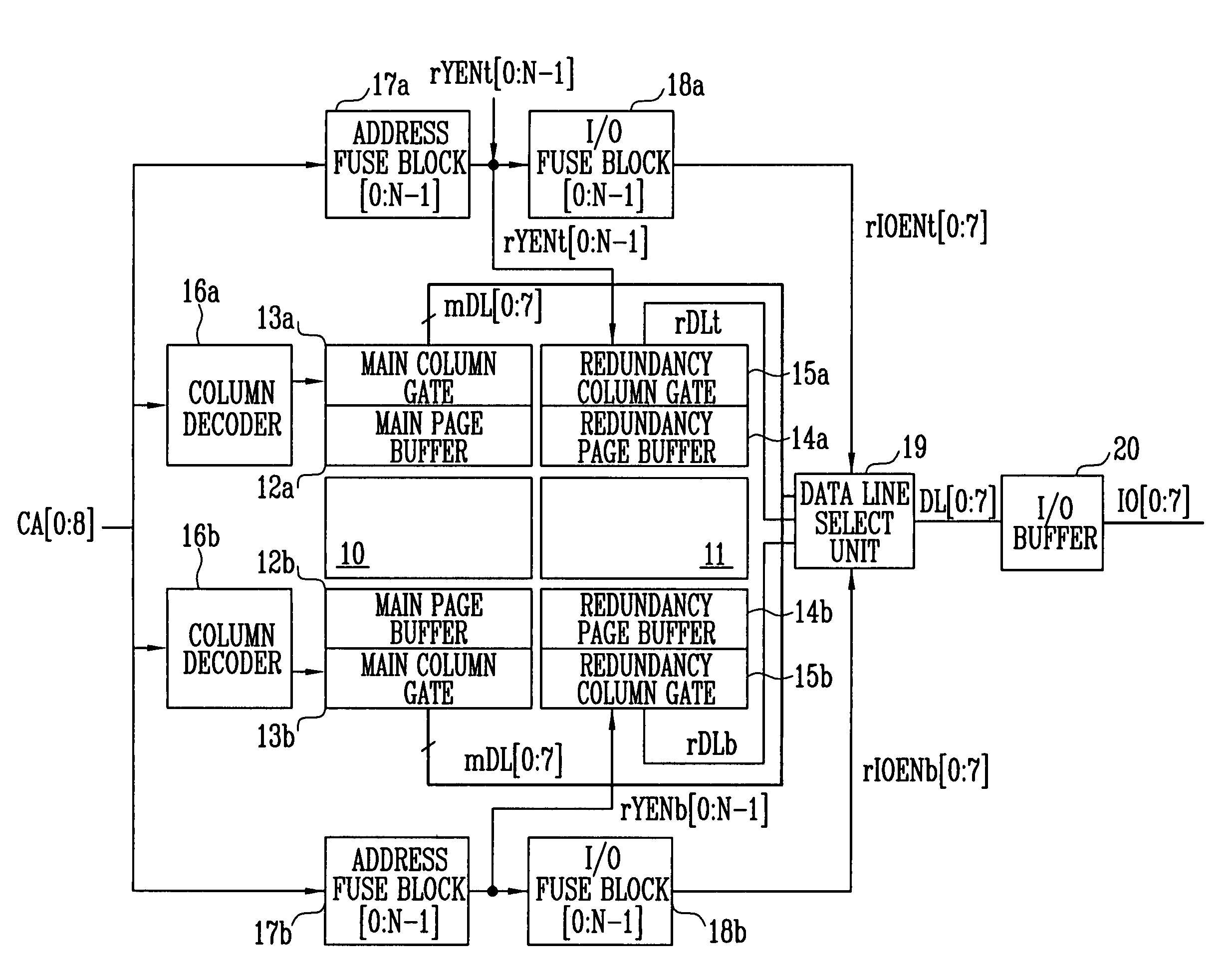

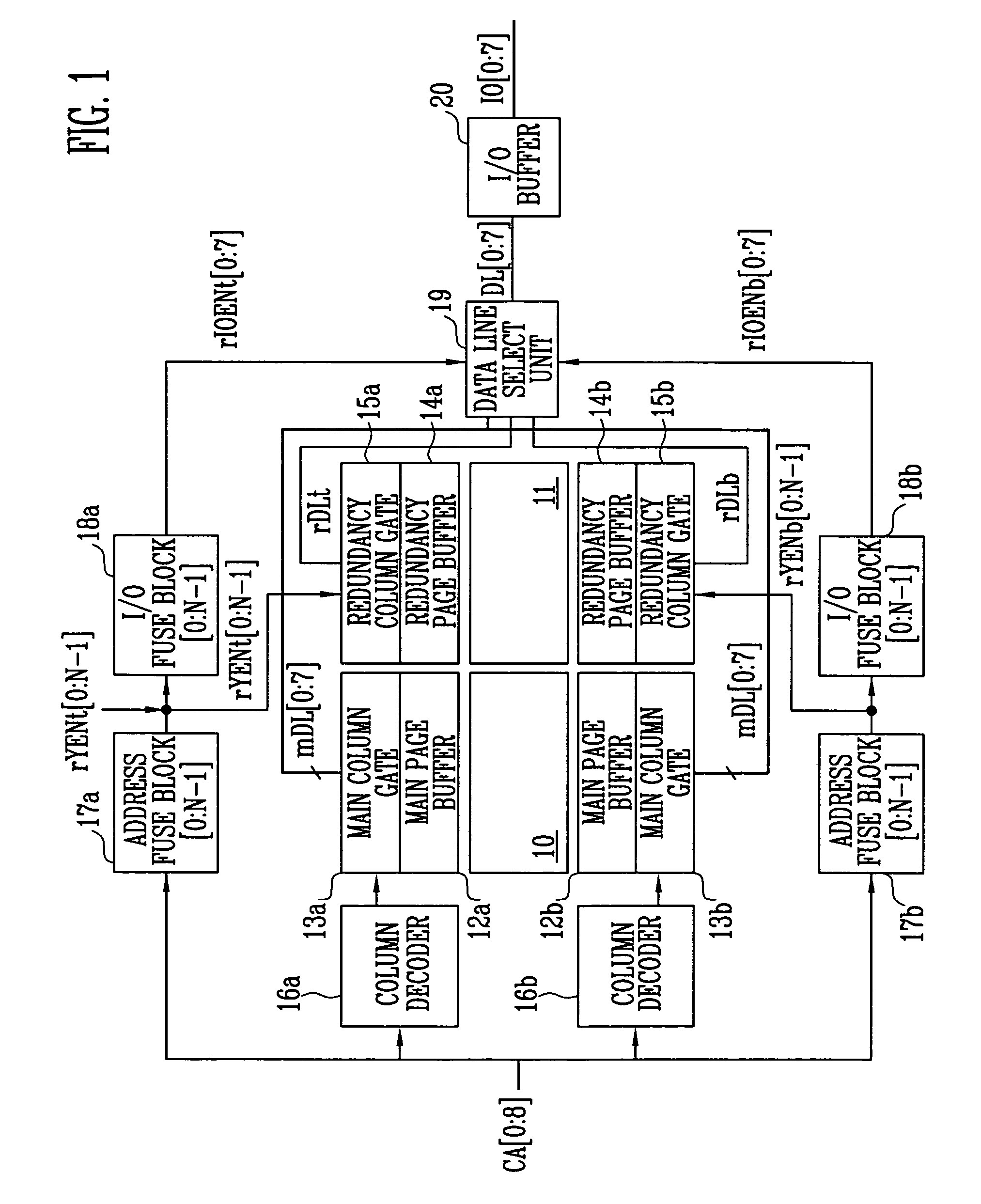

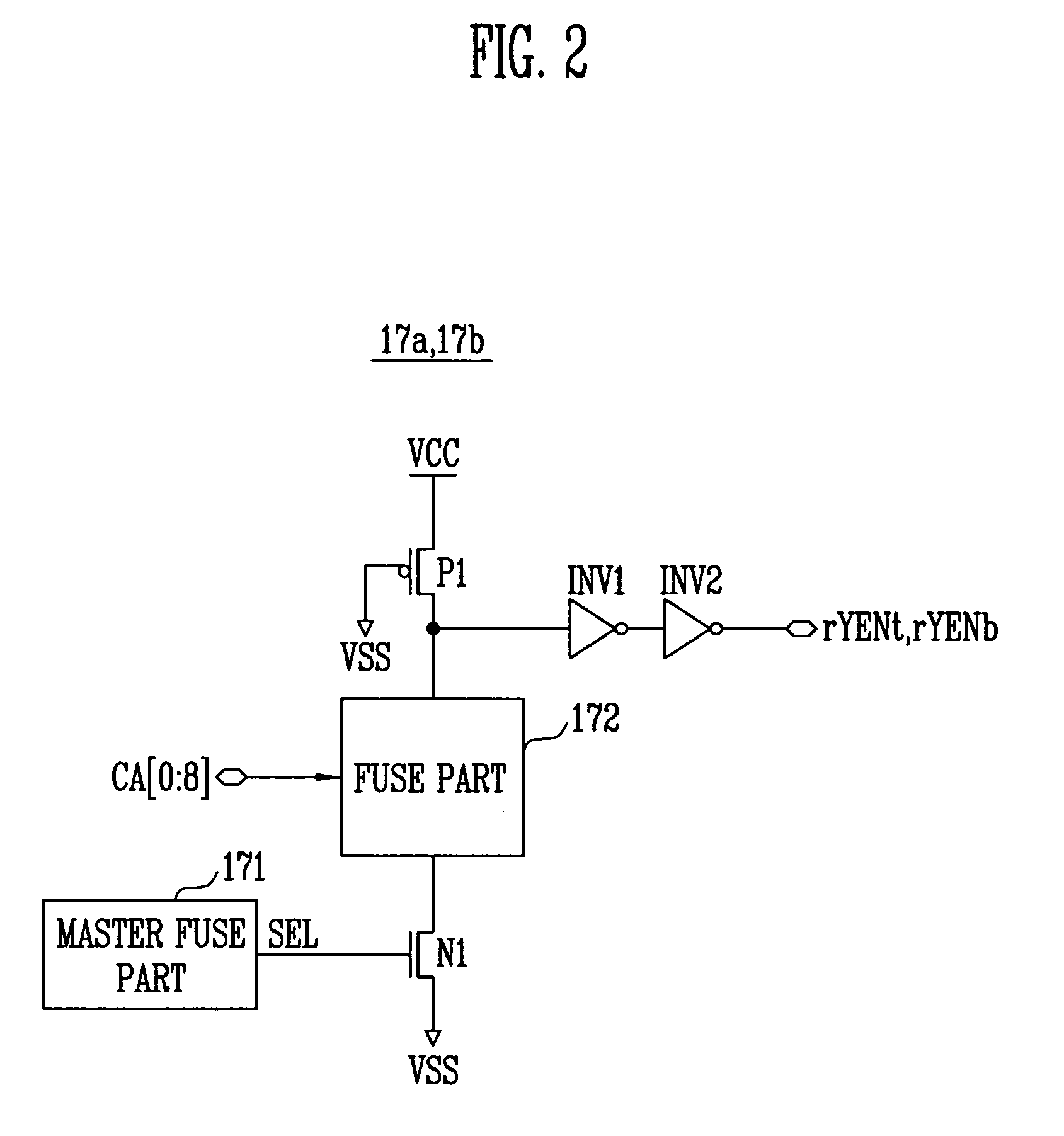

Multi-input/output repair method of NAND flash memory device and NAND flash memory device thereof

A multi-I / O repair method of a NAND flash memory device and a NAND flash memory device thereof are disclosed. A NAND flash memory device is disclosed in which page buffers are positioned at the top and bottom of a main array and a redundancy array and have different data lines. The top / bottom page buffers of the redundancy array are all selected according to an external address and data is transmitted over redundancy data lines, and this data is finally selected through a data line select unit. Accordingly, if main columns having different addresses are to be repaired, they can be replaced with redundancy columns one to one and multi-I / O repair of two main columns having the same address is thus possible.

Owner:STMICROELECTRONICS SRL +1

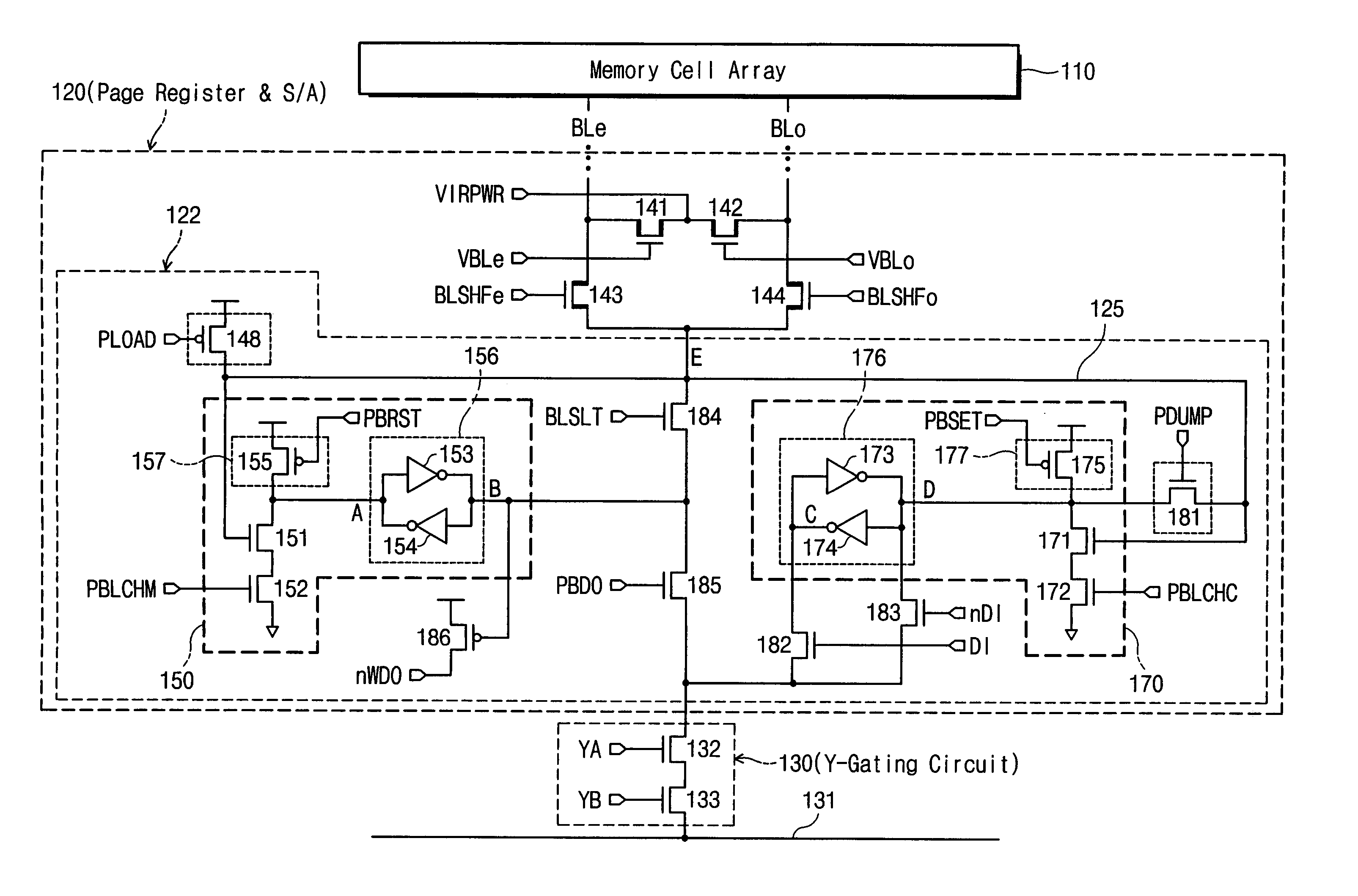

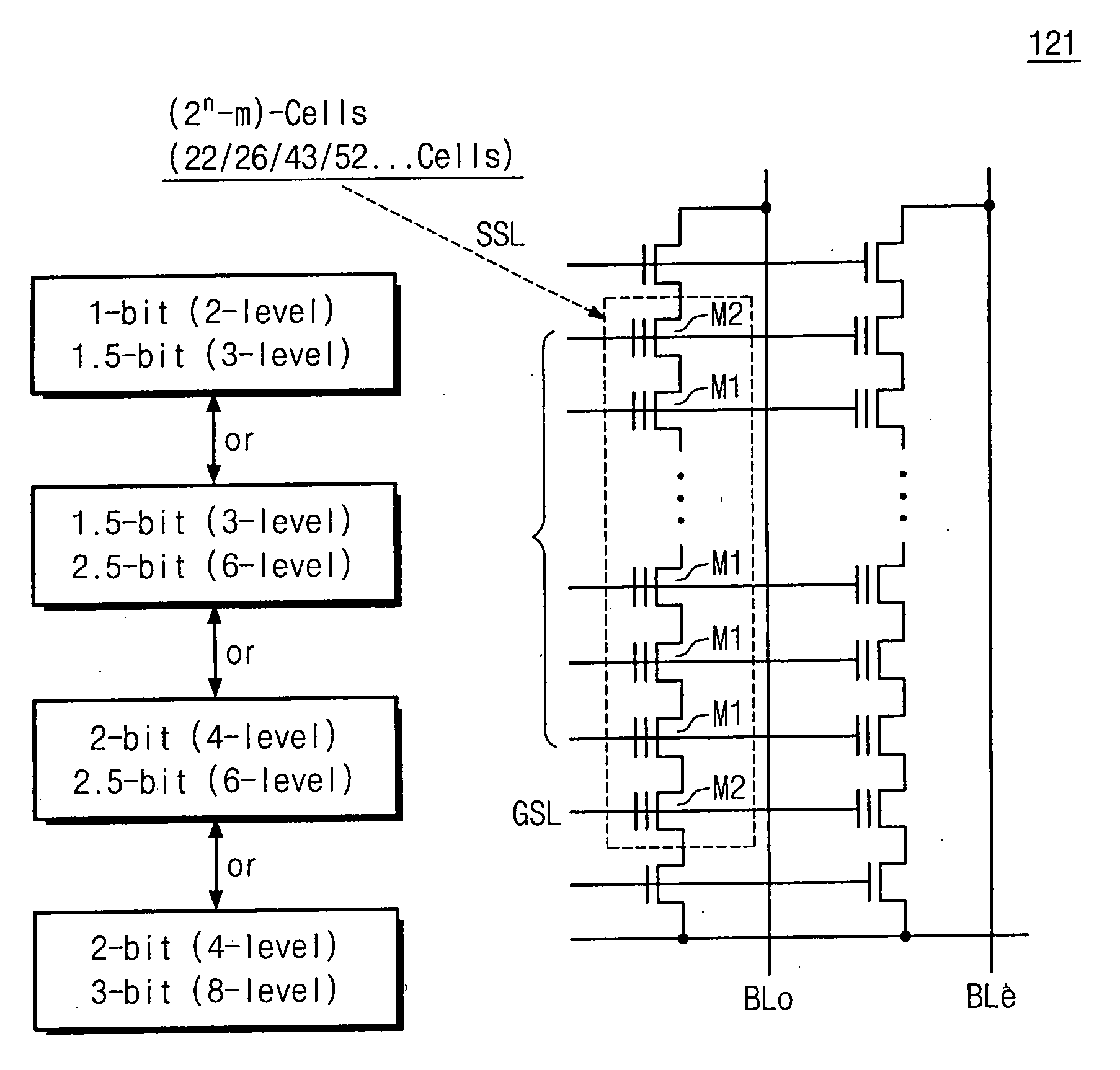

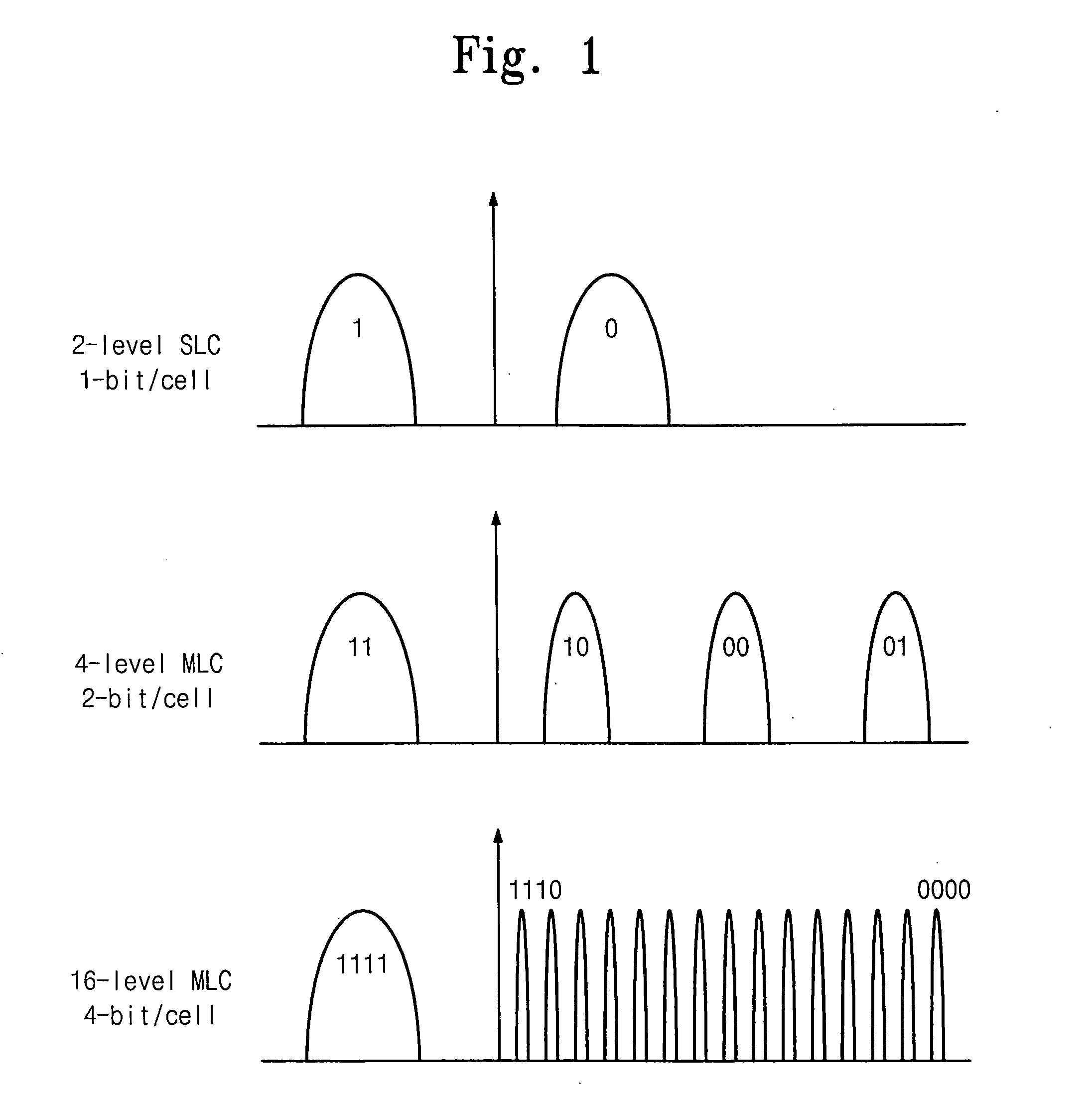

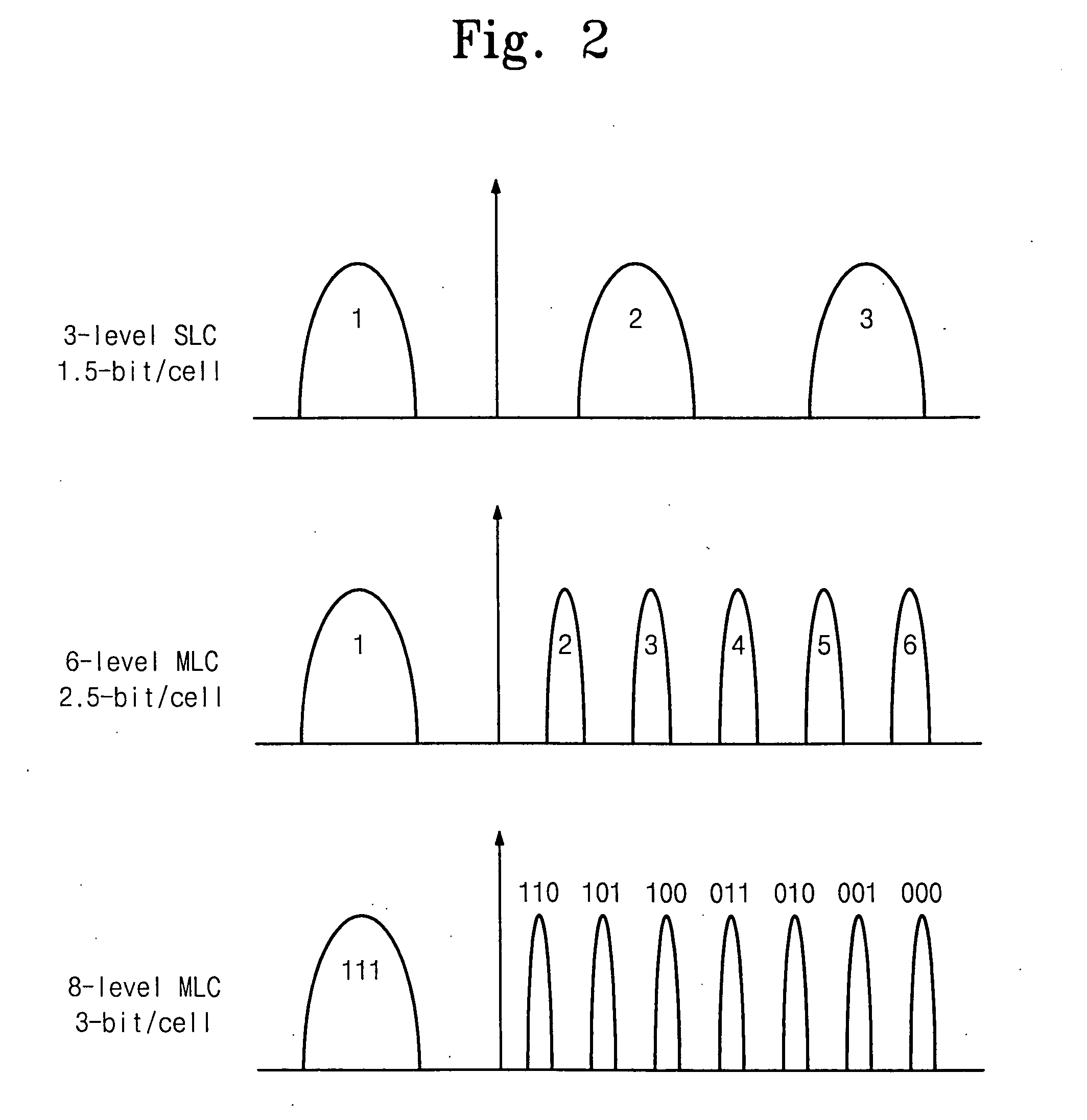

Multi-bit flash memory device including memory cells storing different numbers of bits

A flash memory device comprises an array of memory cells capable of storing different numbers of bits per cell. A page buffer circuit for the flash memory device comprises a plurality of page buffers, each operating during programming, erasing, and reading operations of the memory cells. A control logic unit controls functions of the page buffers in accordance with the number of bits stored in corresponding memory cells.

Owner:SAMSUNG ELECTRONICS CO LTD

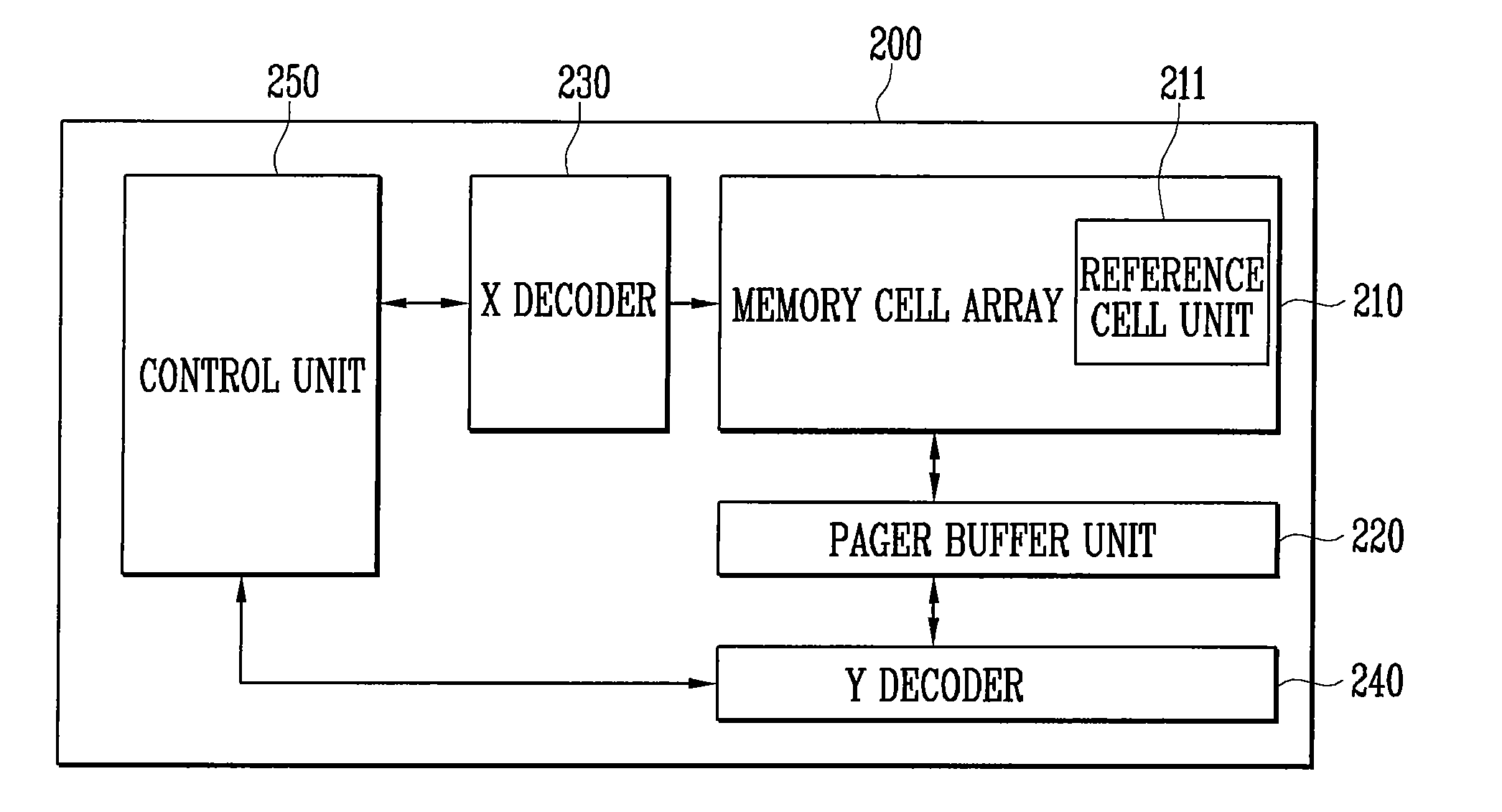

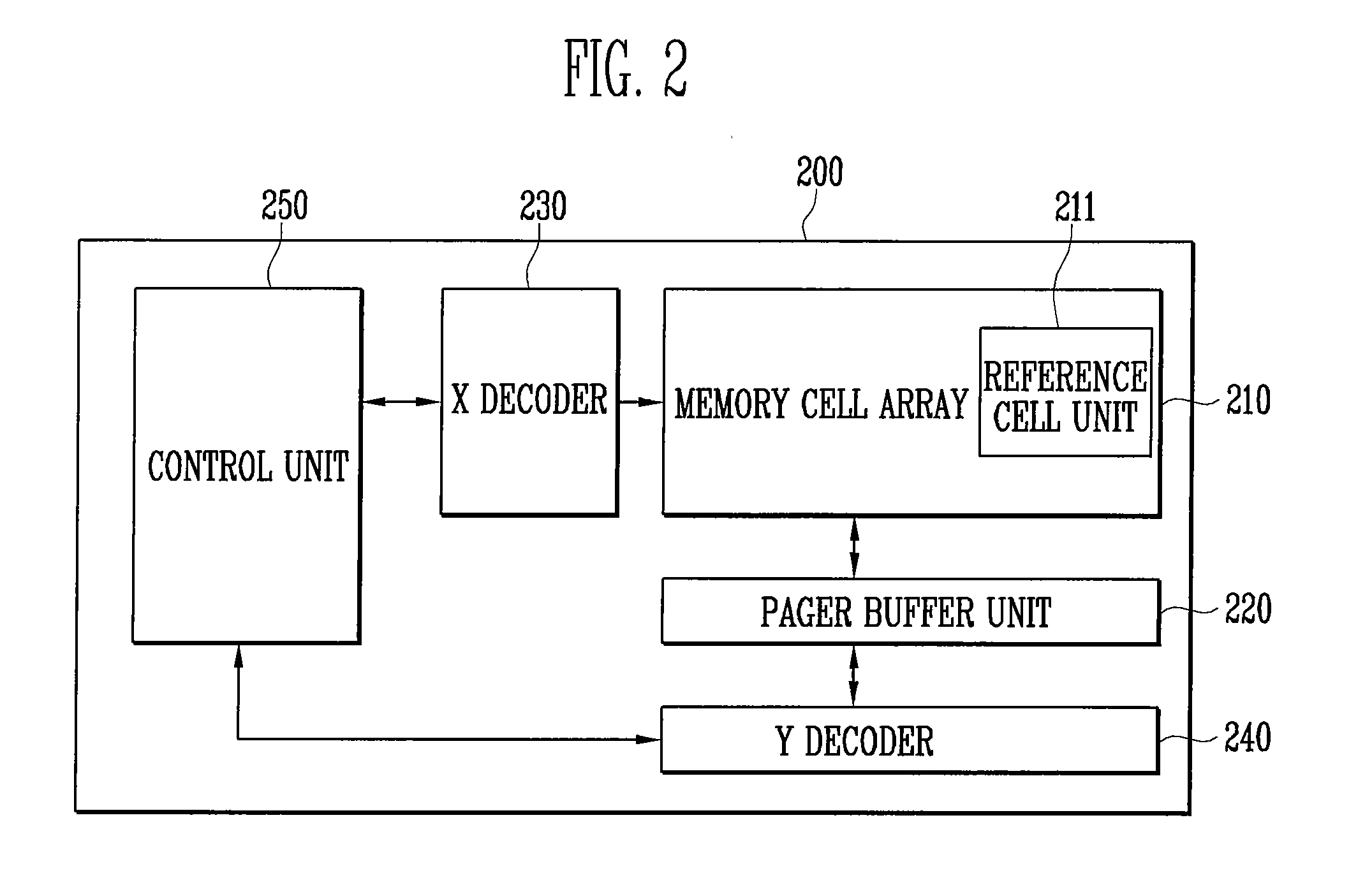

Non-volatile memory device and self-compensation method thereof

InactiveUS20080175055A1Compensation Threshold VoltageAvoid failureRead-only memoriesDigital storageVoltagePage buffers

A non-volatile memory device includes a memory cell array at least one block having a plurality of memory cells, and at least one reference cell with respect to each block, an X decoder and a Y decoder for selecting a memory cell for an operation according to an input address, a page buffer for programming data into a memory cell selected by the X decoder and the Y decoder or reading programmed data, and a controller for controlling the memory cell array, the X decoder, the Y decoder and the page buffers to calculate a change in a threshold voltage of the memory cells and compensate for a changed threshold voltage of a memory cell based on a change in a threshold voltage of the reference cell.

Owner:SK HYNIX INC

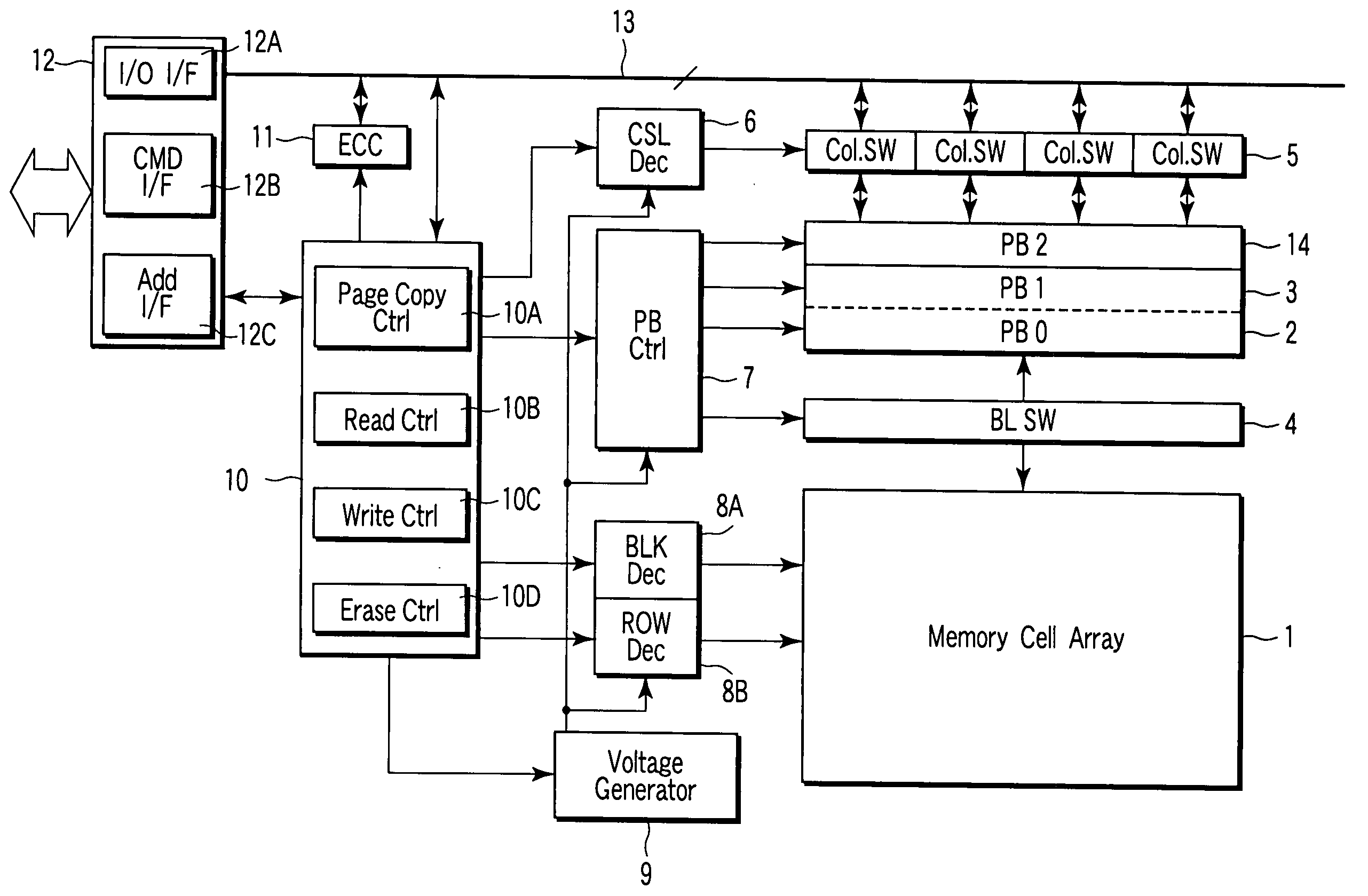

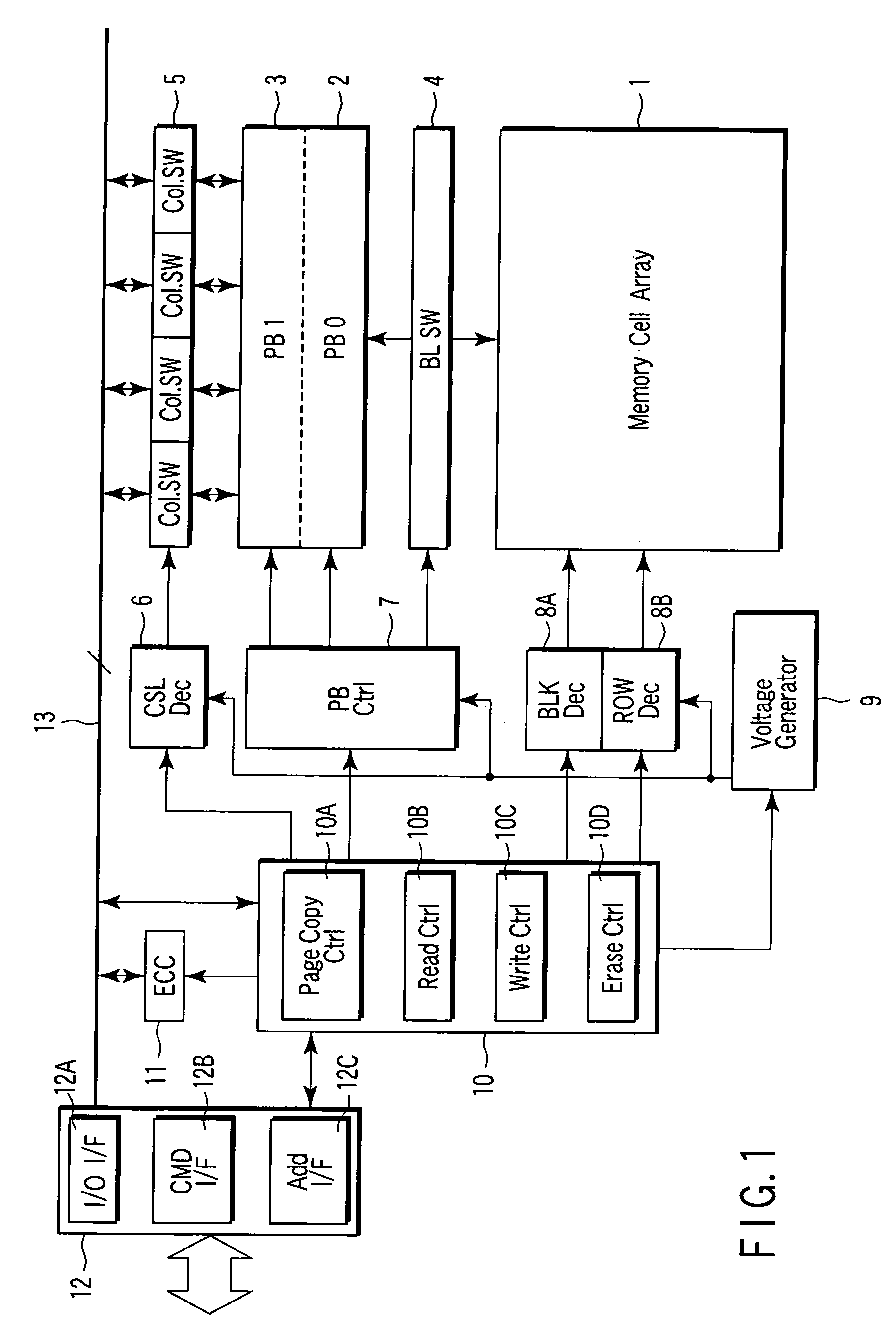

Memory system which copies successive pages, and data copy method therefor

A memory system includes a memory cell array, a bit line switch, first and second page buffers, a column switch, an error correction circuit, and control circuits. The second page buffer can swap data with the first page buffer. The control circuits controls the bit line switch and the first and second page buffers, sequentially reads, page by page, one or more pages from the mth (m is a positive integer) page to the nth (n is an integer greater than m) page of the first block in the memory cell array, controls the error correction circuit to perform error correction calculation by the error correction circuit, controls the first and second data buffers and the bit line switch, and controls to perform write in the second block in the erase state in the memory cell array.

Owner:SOLID STATE SYST +1