Method for making polysilicon layer

A polysilicon layer and manufacturing method technology, which can be applied in the directions of polycrystalline material growth, chemical instruments and methods, crystal growth, etc., and can solve problems such as grain size limitation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

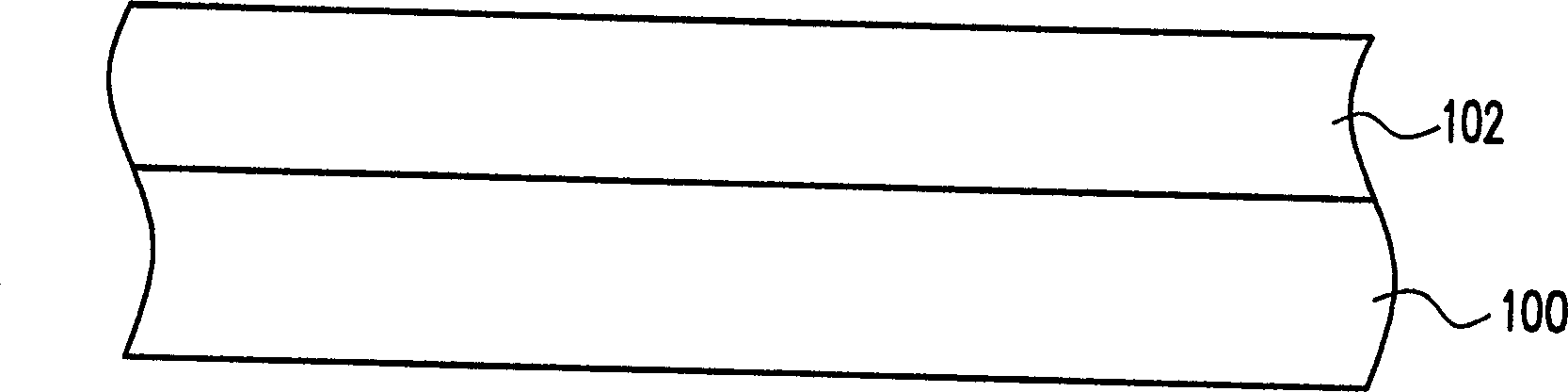

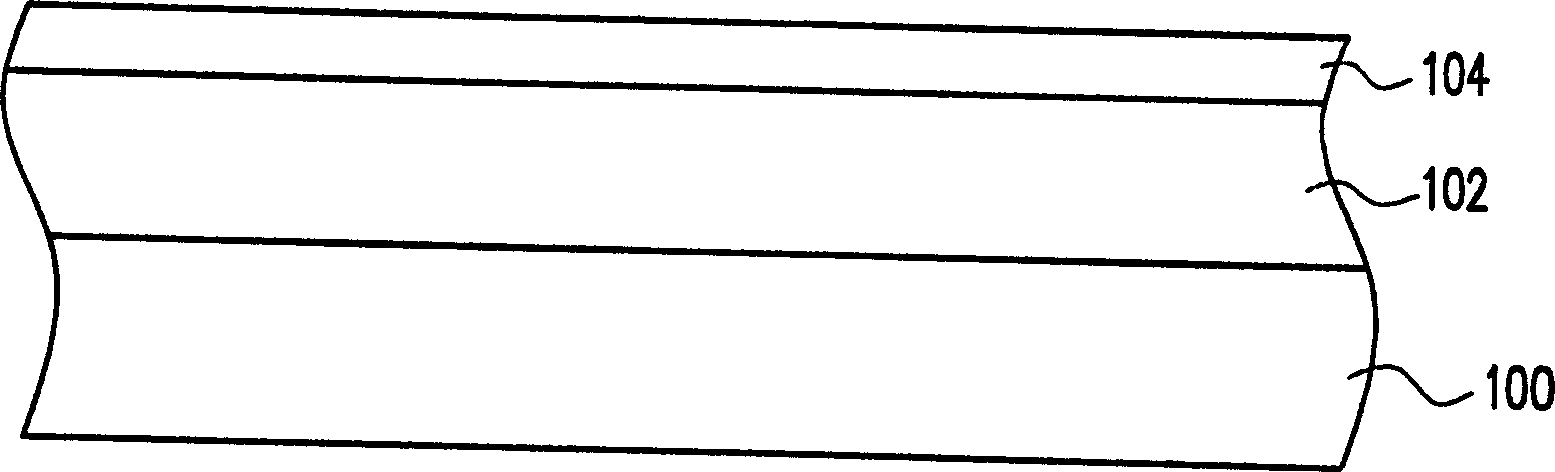

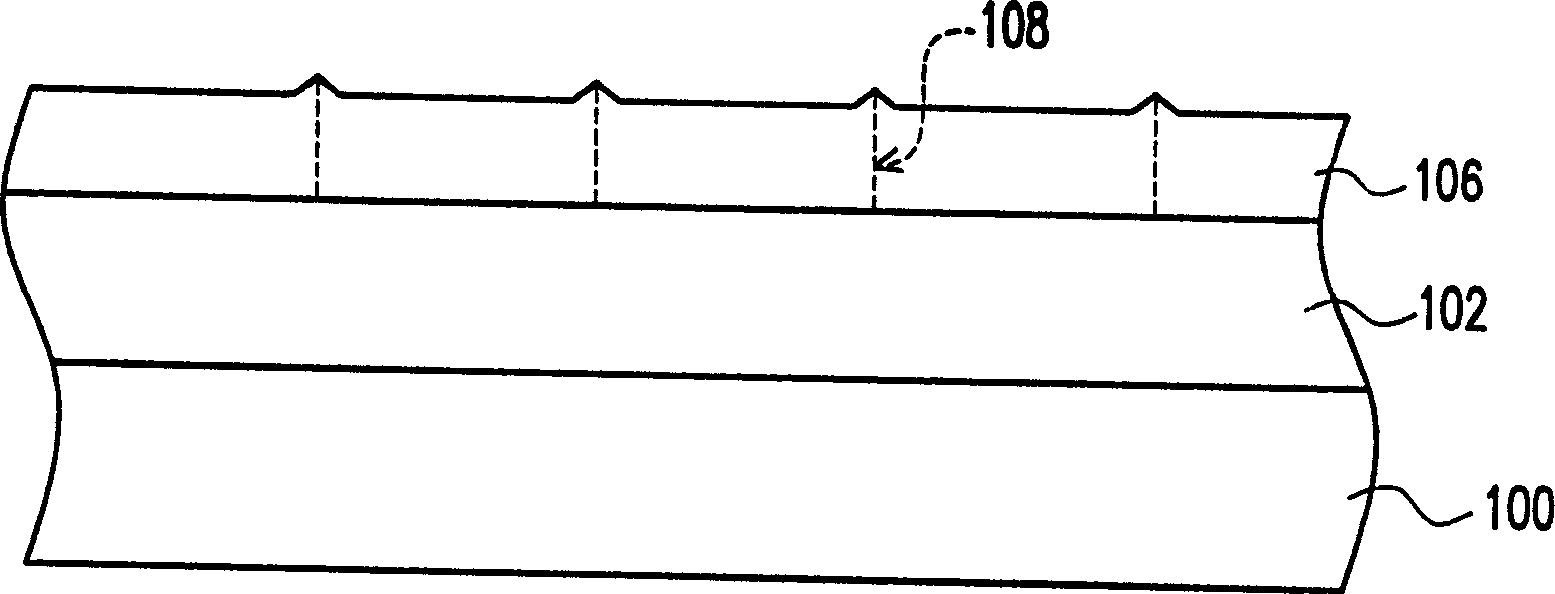

[0033] Figure 4 It is a schematic diagram of forming a polysilicon layer through a trench on a buffer layer according to a preferred embodiment of the present invention. Please refer to Figure 4 , providing a substrate 400, the substrate 400 is usually a glass substrate. Next, a buffer layer 402 is formed on the substrate 400 . The buffer layer 402 is, for example, a laminated structure including a silicon nitride layer and a silicon oxide layer (details will be described later). In order to improve the crystal size, uniformity and process margin in the formed polysilicon layer, in this embodiment, a plurality of parallel first trenches 404 are formed in the buffer layer 402, and these first trenches 404 are formed in the subsequent excimer In the laser thermal annealing process, it will play the role of providing crystallization nuclei. During excimer laser thermal annealing, the amorphous silicon layer (not shown) on the region outside the first trench 404 will be compl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More