Memory with memory cells that include a MIM type capacitor with a lower electrode made for reduced resistance at an interface with a metal film

a memory cell and capacitor technology, applied in the field of semiconductor devices, can solve the problems of increasing the leak current of the capacitor, and increasing the thickness of the film on the side wall and the bottom portion, so as to reduce the process margin for layer alignment, small leak current, and the effect of not increasing the number of fabrication processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0086] (1) Structure

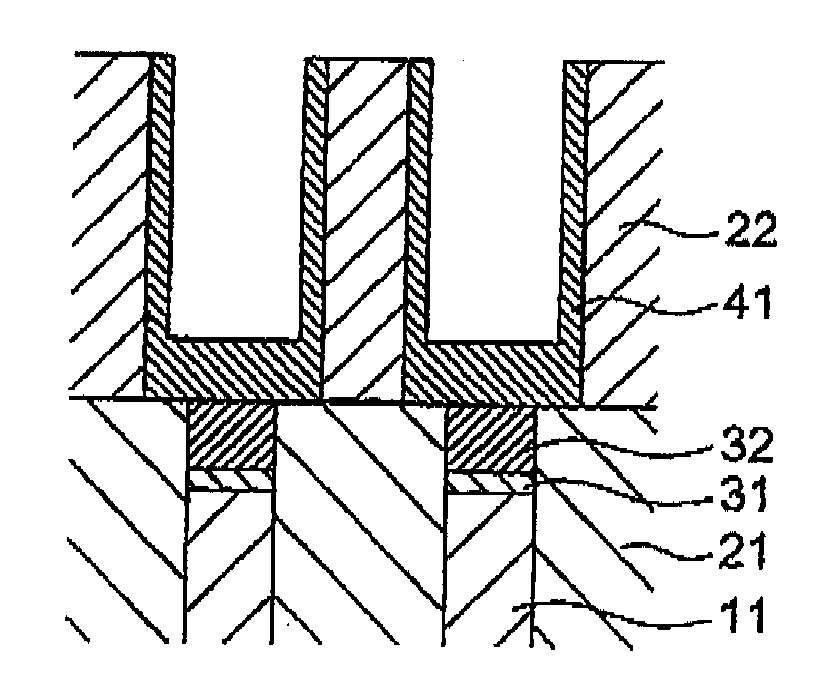

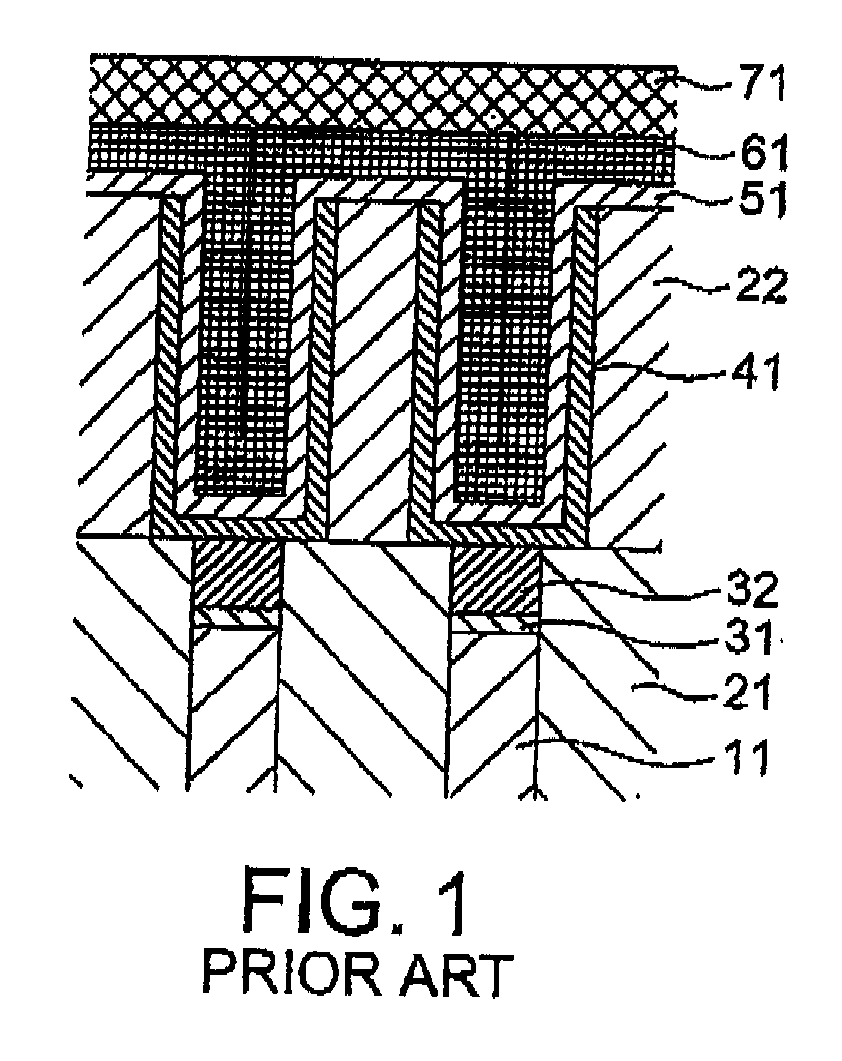

[0087]FIG. 5 is a longitudinal cross-sectional view showing illustrating a capacitor according to the first embodiment of the present invention.

[0088] The capacitor according to the embodiment is formed on an interlayer insulating film 21 which covers an underlying device. The capacitor is constructed by laminating a ruthenium film 41 as a lower electrode, a ruthenium film 61 as an upper electrode and a tantalum oxide film 51 as a capacitive insulating film in a hole provided in an interlayer insulating film 22 formed on the interlayer insulating film 21.

[0089] The lower electrode 41 is connected at its bottom to a barrier metal film 32 which is connected at its bottom surface to a polysilicon plug 11 via a contact metal film 31. The polysilicon plug 11 is further connected to a diffusion layer region (equivalent to “6” in FIG. 2) via an underlying polysilicon plug (equivalent to “12” in FIG. 2).

[0090] In the embodiment, as the bottom portion of the lower ele...

second embodiment

[0126] (1) Structure

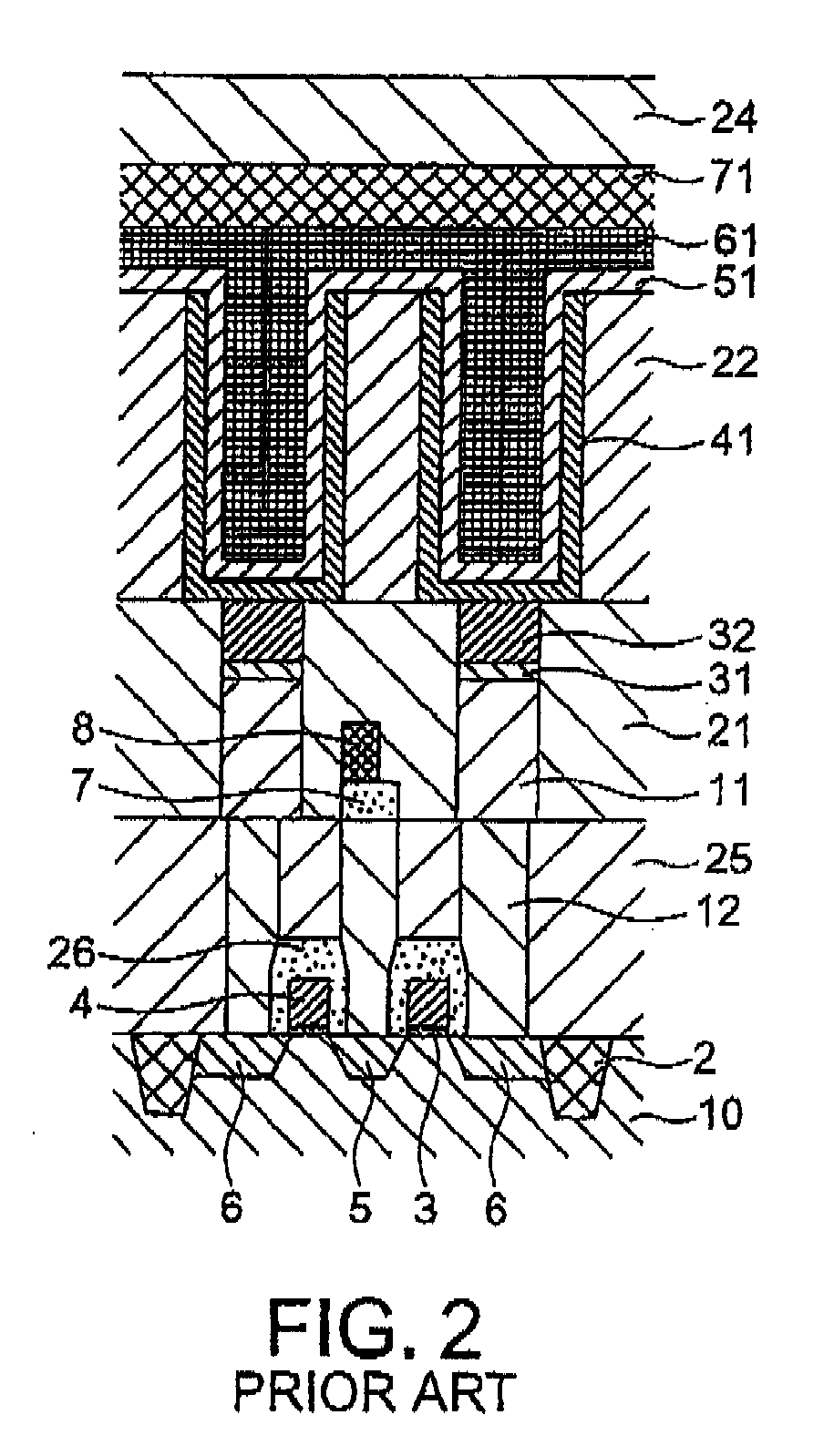

[0127]FIG. 25 is a longitudinal cross-sectional view showing illustrating a capacitor according to the second embodiment of the present invention. The second embodiment is an application example in which a metal plug 35 is used in place of the polysilicon plug and barrier metal film in the first embodiment (FIG. 5).

[0128] The lower electrode 41 of the capacitor according to the second embodiment is connected at its bottom to the metal plug 35 which comprises a tungsten film 37 and a titanium nitride film 36. The metal plug 35 is connected to a diffusion layer region (equivalent to “6” in FIG. 2) via an underlying polysilicon plug (equivalent to “12” in FIG. 2).

[0129] As the bottom portion of the lower electrode 41 is thick, the diffusion of oxygen is sufficiently restrained, so that even when a tungsten film which is inferior in oxidation resistance to a titanium nitride film is connected directly to the lower electrode 41, there does not arise a problem that ...

third embodiment

[0135] (1) Structure

[0136]FIG. 29 is a longitudinal cross-sectional view showing illustrating a capacitor according to the third embodiment of the present invention. The third embodiment is an application example in which a titanium nitride film is used for the lower electrode and the upper electrode of the in the second embodiment (FIG. 25) in place of the ruthenium film.

[0137] The capacitor according to the embodiment is formed on the interlayer insulating film 21 which covers an underlying device. The capacitor is constructed by laminating a titanium nitride film 46 as the lower electrode, a titanium nitride film 66 as the upper electrode and the tantalum oxide film 51 as the capacitive insulating film in a hole provided in the interlayer insulating film 22 formed on the interlayer insulating film 21.

[0138] The lower electrode 46 of the capacitor is connected at its bottom to the metal plug 35 which comprises the tungsten film 37 and the titanium nitride film 36. The metal plu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More