Semiconductor device, a method of manufacturing the semiconductor device and a method of deleting information from the semiconductor device

a semiconductor device and information deletion technology, applied in the direction of semiconductor devices, radiocontrolled devices, electrical devices, etc., can solve the problems of difficult photolithography process patterned polysilicon films, inability to meet one of the important requirements, and number of processes, so as to achieve easy and proper formation and increase process margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

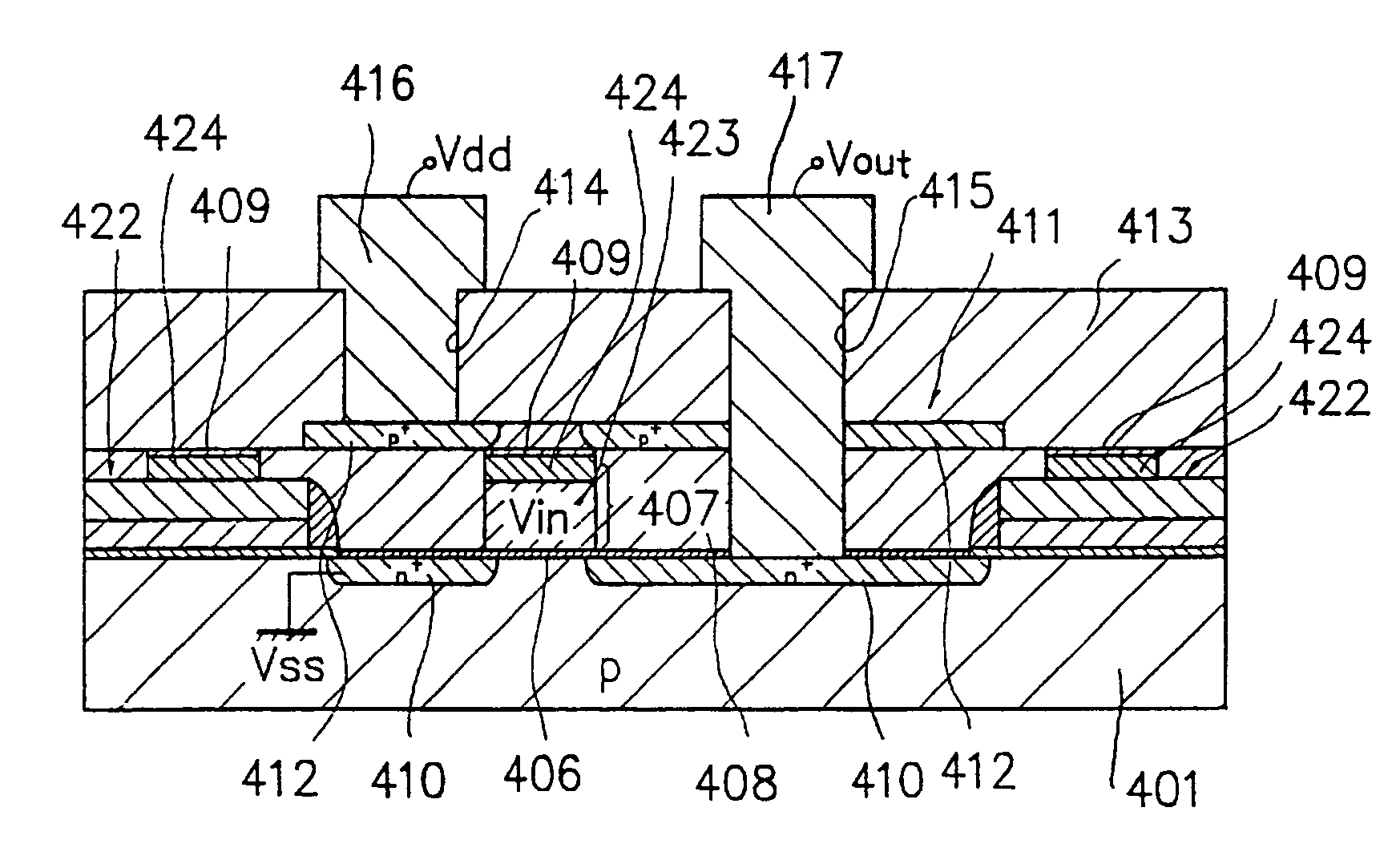

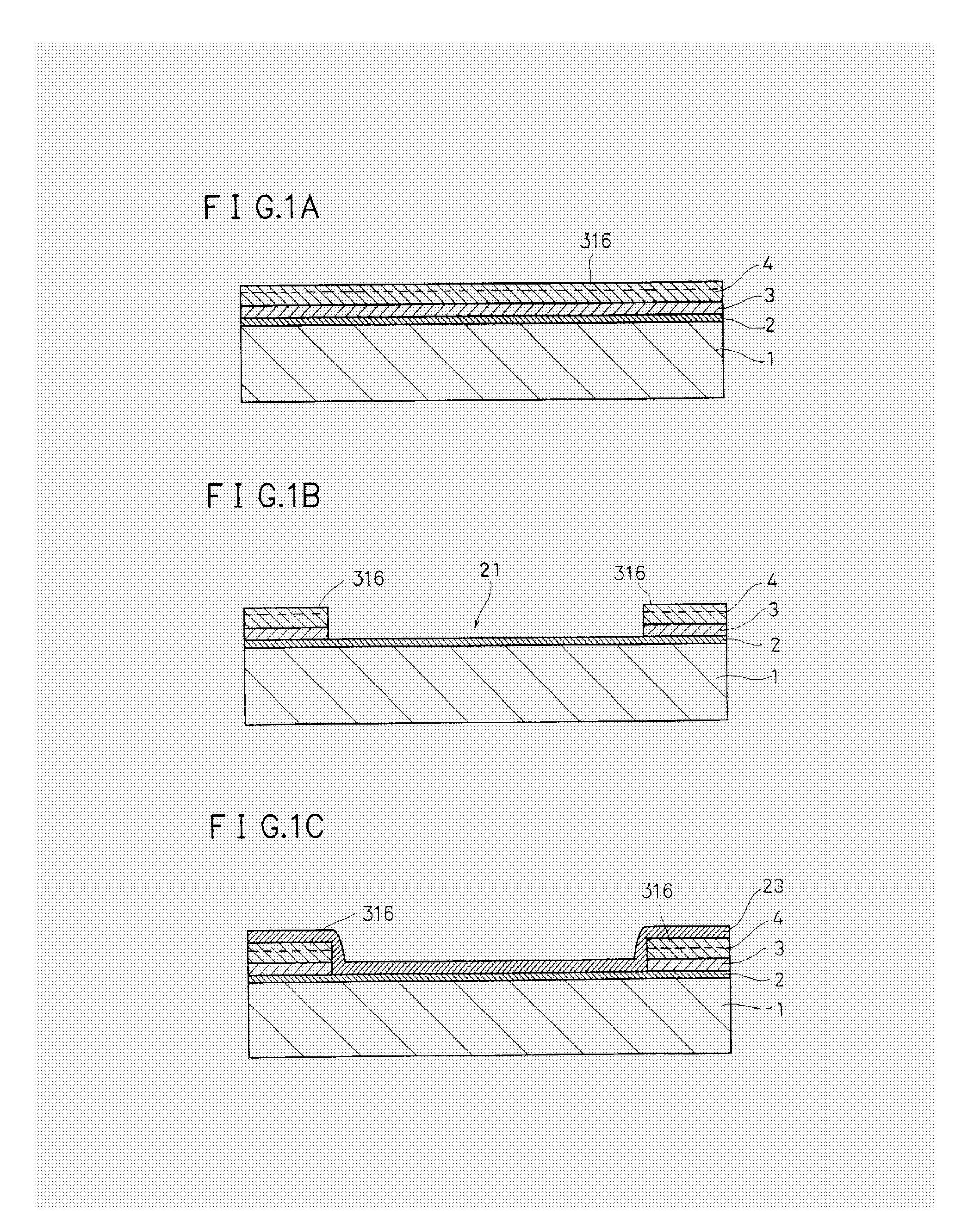

[0113] The first embodiment will be described first. In the first embodiment, an example in which the present invention is applied to a MOS transistor will be described. In the first embodiment, the structure of the MOS transistor and a manufacturing method therefore will be described together. FIGS. 1A to 1J are schematic sectional views showing steps in manufacturing the MOS transistor.

[0114] An element isolation structure is formed in an element isolation region on a p-type silicon semiconductor substrate by a so-called field shield element isolation method, thereby demarcating an element formation region.

[0115] More specifically, as shown in FIG. 1A, a silicon oxide film 2, a polysilicon film 3, and a silicon oxide film 4 are formed on a p-type silicon semiconductor substrate 1 to thicknesses of, e.g., about 50 nm, 200 nm, and 200 nm, respectively. A silicon nitride film 316 having a thickness of about 200 nm may be formed on the entire surface of the silicon oxide film 4 by C...

second embodiment

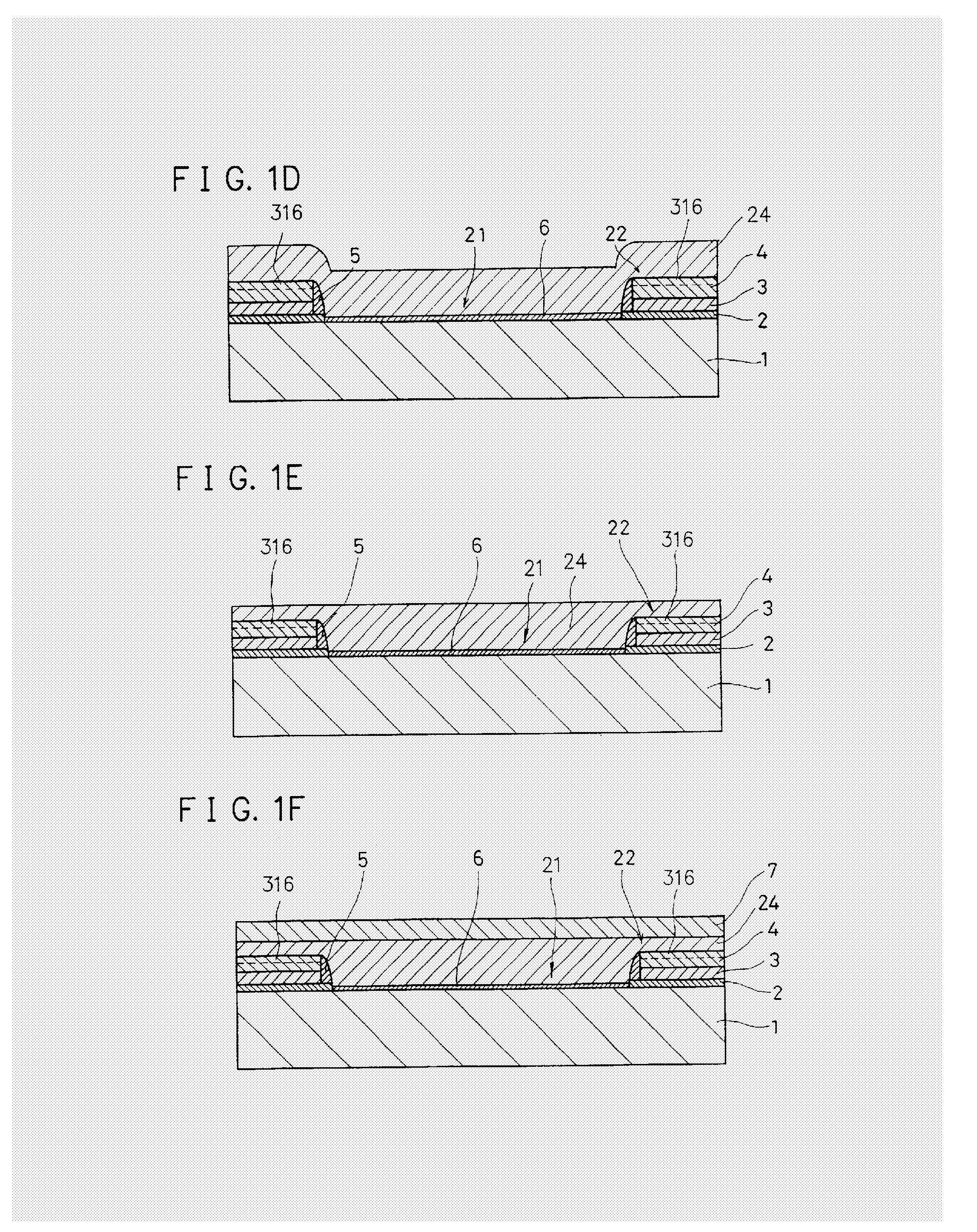

[0128] The second embodiment will be described next. As in the first embodiment, the structure of a MOS transistor and a manufacturing method therefore will be described together. The second embodiment is slightly different in the surface polishing method. A detailed description of the same steps as in the first embodiment will be omitted. The same reference numerals as in the first embodiment denote the same constituent elements in the second embodiment, and a detailed description thereof will be omitted.

[0129] In the second embodiment, in steps shown in FIGS. 1E and 1F of the above-described first embodiment, to easily and properly control polishing of a polysilicon film 24, silicon oxide films 4 serving as cap insulating films of field shield element isolation structures 22 are used as stoppers. When the cap insulating film is formed as an multilayered insulating film consisting of the silicon oxide film 4 and a silicon nitride film 316, the silicon nitride film 316 is used as a...

third embodiment

[0141] The third embodiment of the present invention will be described below. In the third embodiment, an example in which a semiconductor device according to the present invention and a manufacturing method therefore are applied to a MOS transistor will be described, as in the first embodiment. In the third embodiment, the structure of the MOS transistor and steps in manufacturing the MOS transistor will be described together. FIGS. 4A to 4G are schematic sectional views showing steps in manufacturing the MOS transistor of the third embodiment.

[0142] First, p- and n-type wells are formed in the surface region of a p-type silicon semiconductor substrate.

[0143] More specifically, as shown in FIG. 4A, the entire surface of a p-type silicon semiconductor substrate 41 is subjected to thermal oxidation to form a silicon oxide film (so-called preoxide film) 42 having a thickness of about 1,000 to 5,000 Å. A resist 43 is applied to the surface of the silicon oxide film 42. The resist 43 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More