Patents

Literature

99results about "Detecting faulty hardware using neural networks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Deep belief network feature extraction-based analogue circuit fault diagnosis method

ActiveUS20190243735A1Improve feature extraction performanceImprove the extraction effectDetecting faulty hardware using neural networksAnalog circuit testingRestricted Boltzmann machineFeature extraction

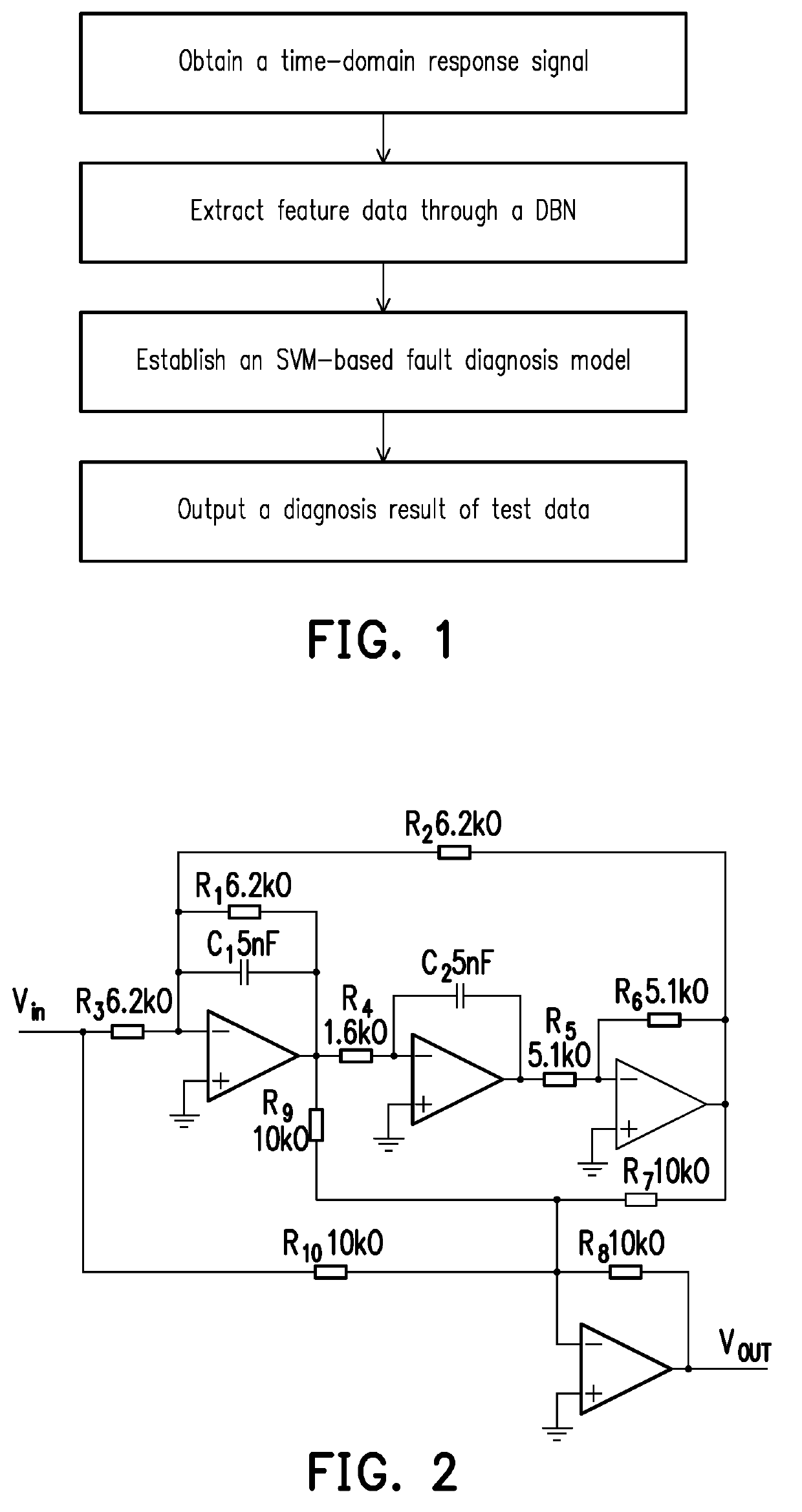

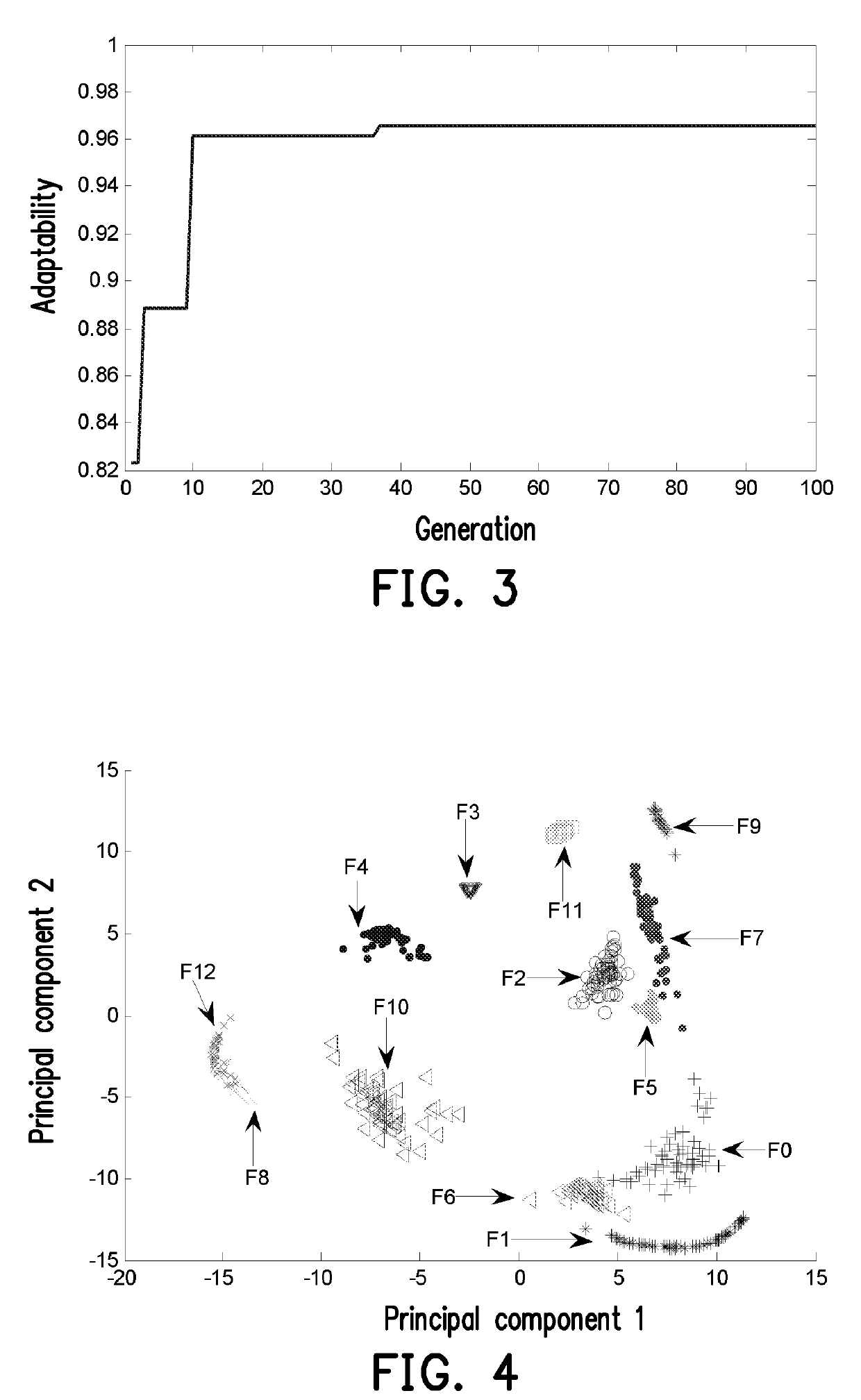

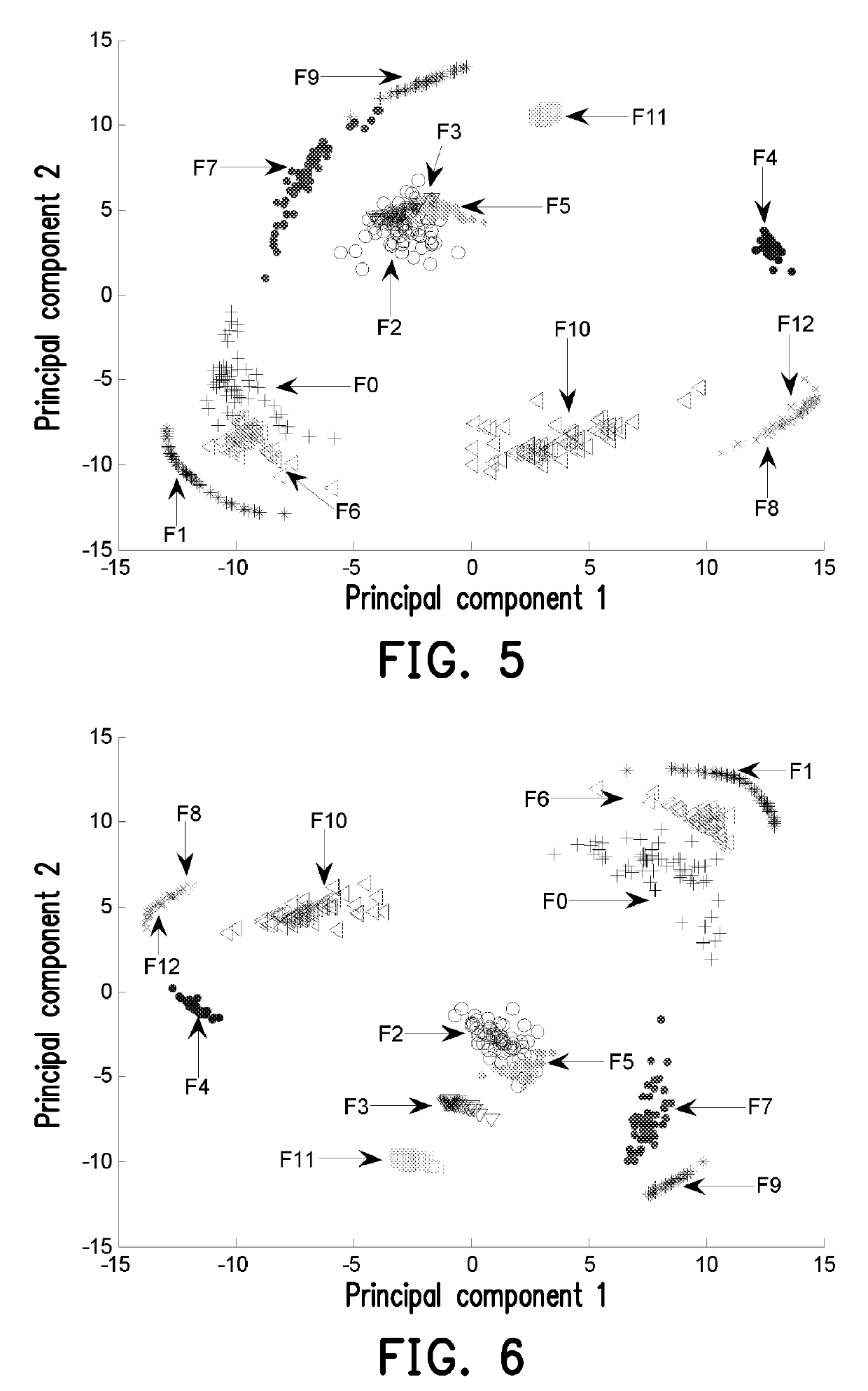

A Deep Belief Network (DBN) feature extraction-based analogue circuit fault diagnosis method comprises the following steps: a time-domain response signal of a tested analogue circuit is acquired, where the acquired time-domain response signal is an output voltage signal of the tested analogue circuit; DBN-based feature extraction is performed on the acquired voltage signal, wherein learning rates of restricted Boltzmann machines in a DBN are optimized and acquired by virtue of a quantum-behaved particle swarm optimization (QPSO); a support vector machine (SVM)-based fault diagnosis model is constructed, wherein a penalty factor and a width factor of an SVM are optimized and acquired by virtue of the QPSO; and feature data of test data are input into the SVM-based fault diagnosis model, and a fault diagnosis result is output, where the feature data of the test data is generated by performing the DBN-based feature extraction on the test data.

Owner:WUHAN UNIV

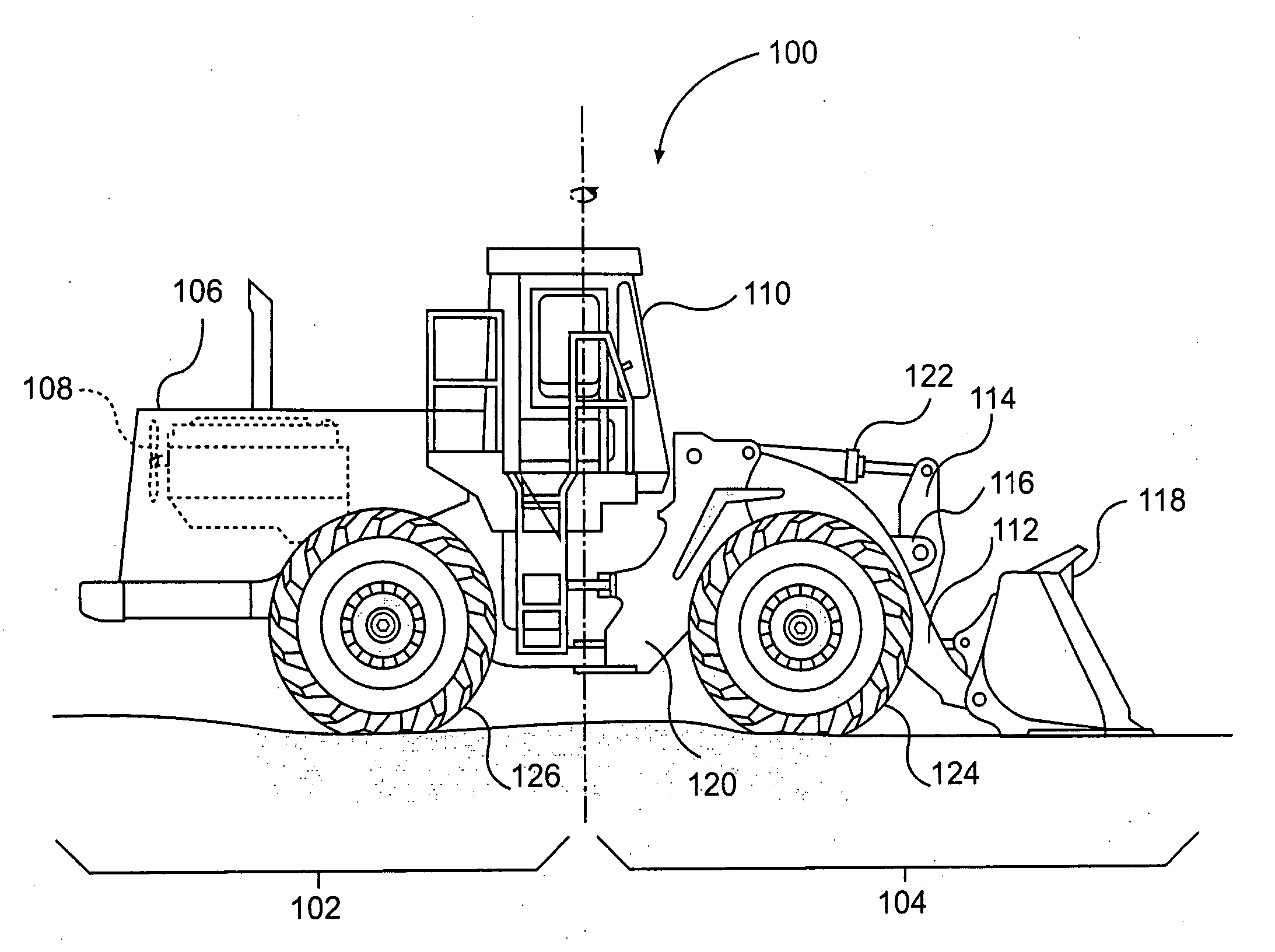

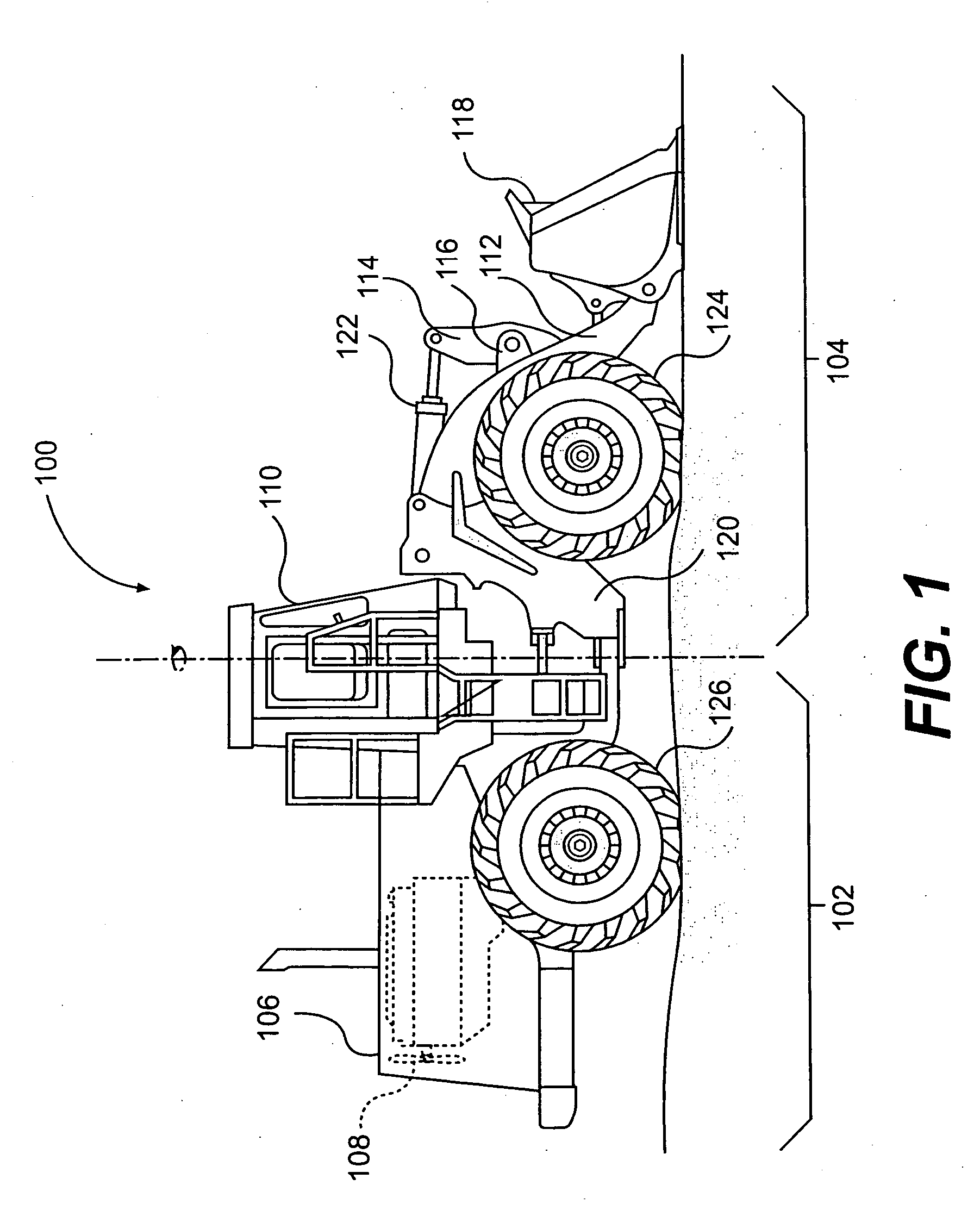

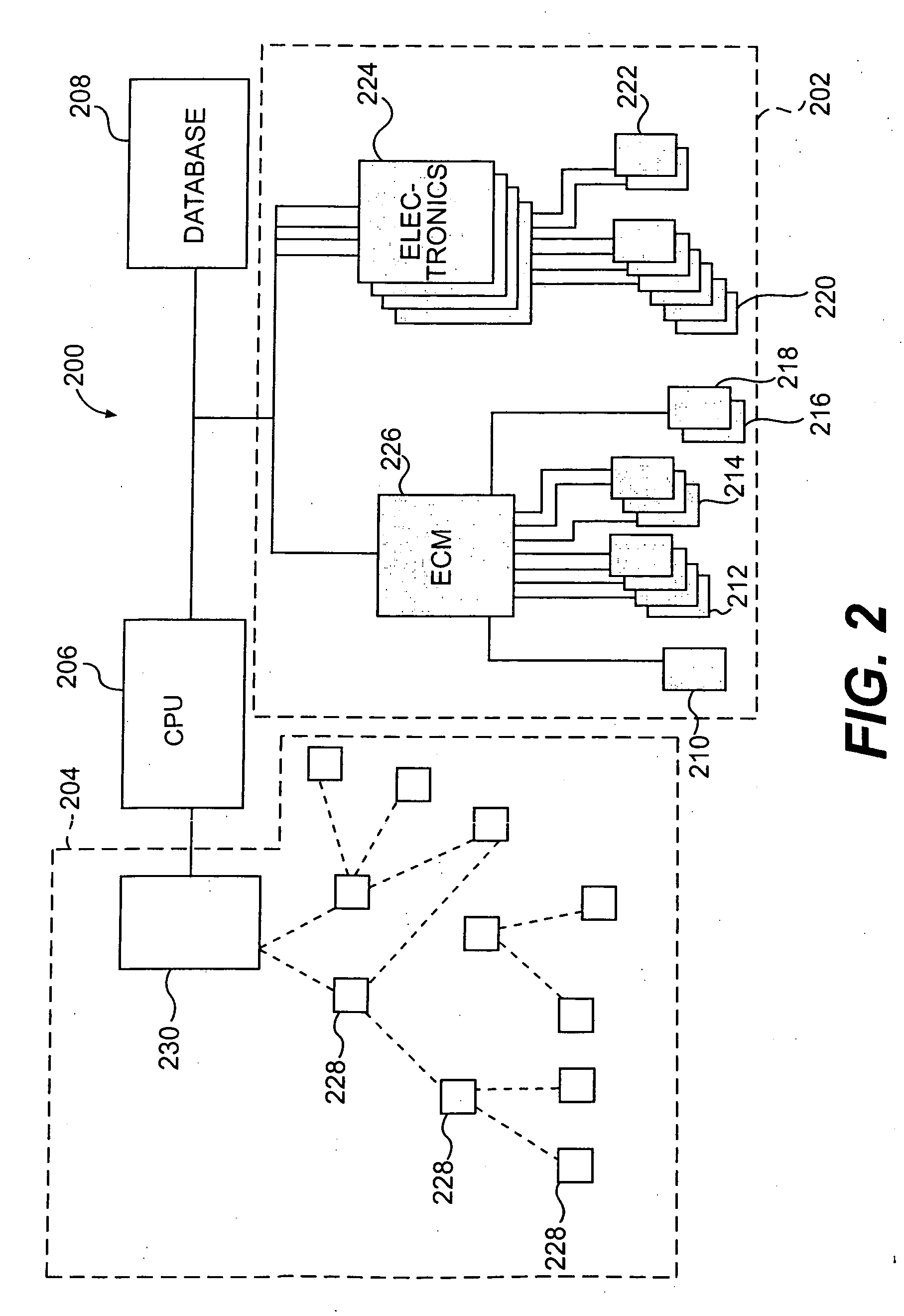

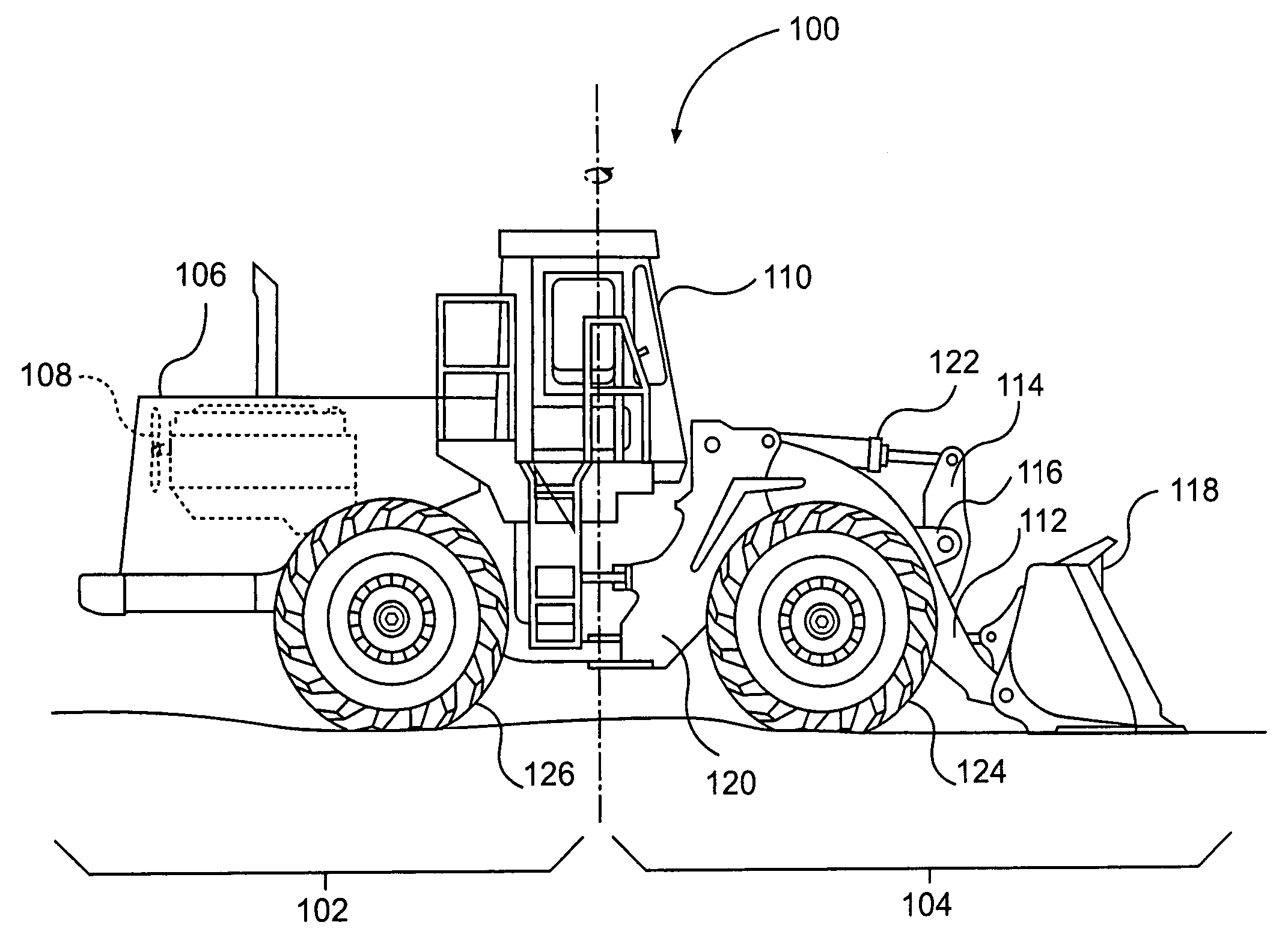

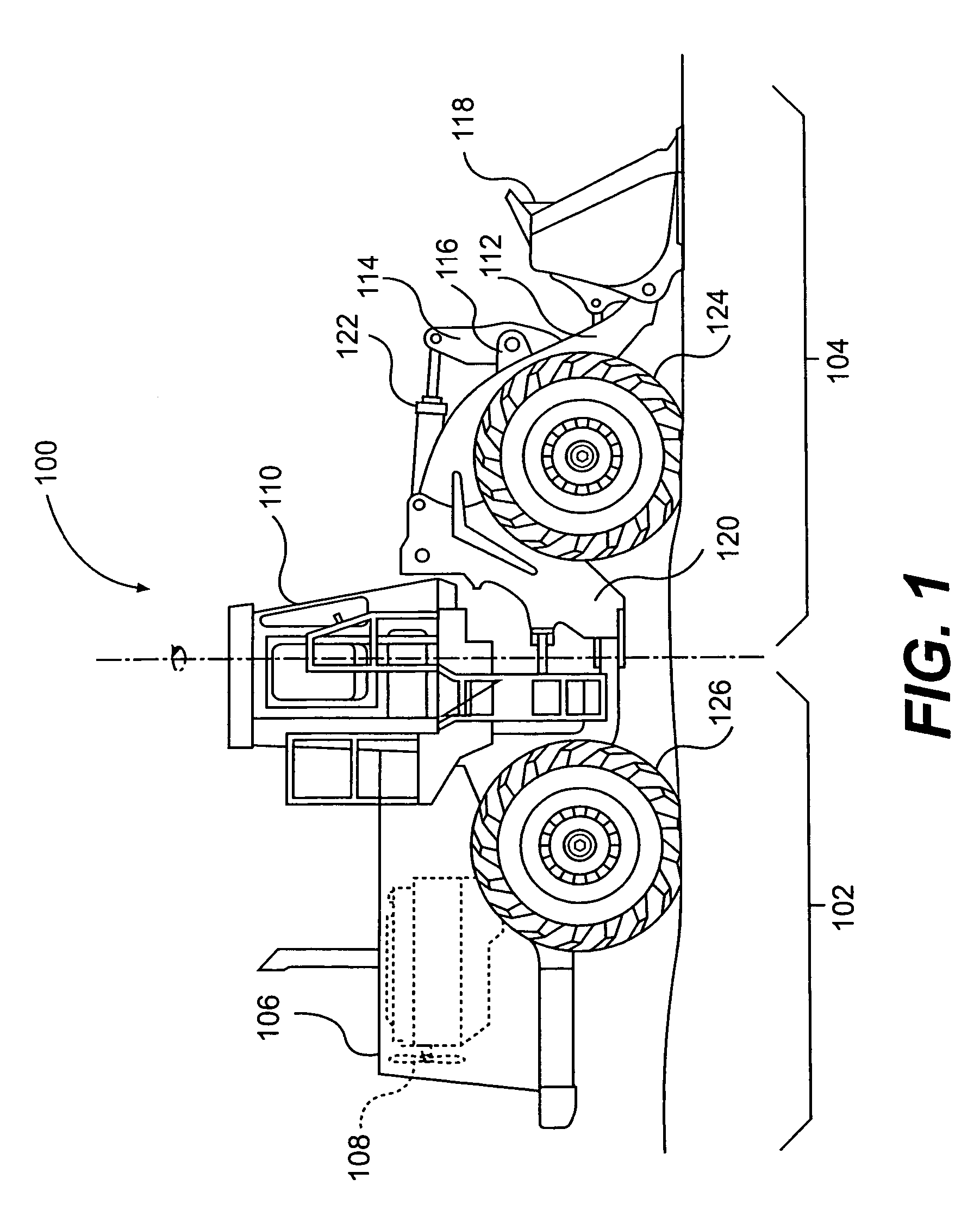

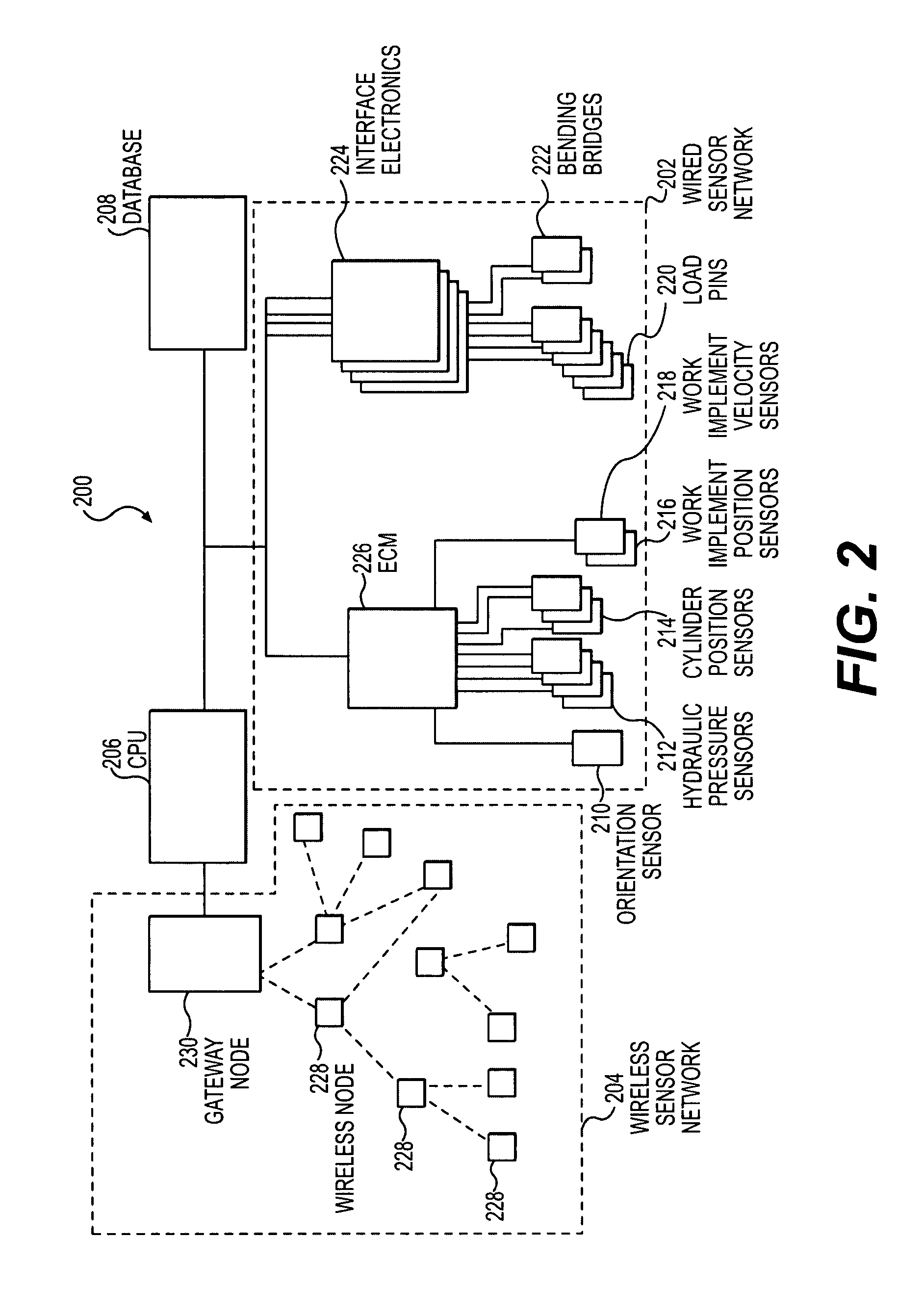

Classifying a work machine operation

ActiveUS20060243180A1Detecting faulty hardware using neural networksSewing apparatusNetwork onComputer science

A method for analyzing the use of a work machine is disclosed. In one embodiment, the method may include providing a computer with a neural network on the work machine. Further, the method may include inputting data to the computer, at least a portion of the data associated with a load experienced by one of the components of the work machine. The neural network, when executed by the computer may then classify a current operation of the work machine into one of a plurality of types of operations.

Owner:CATERPILLAR INC

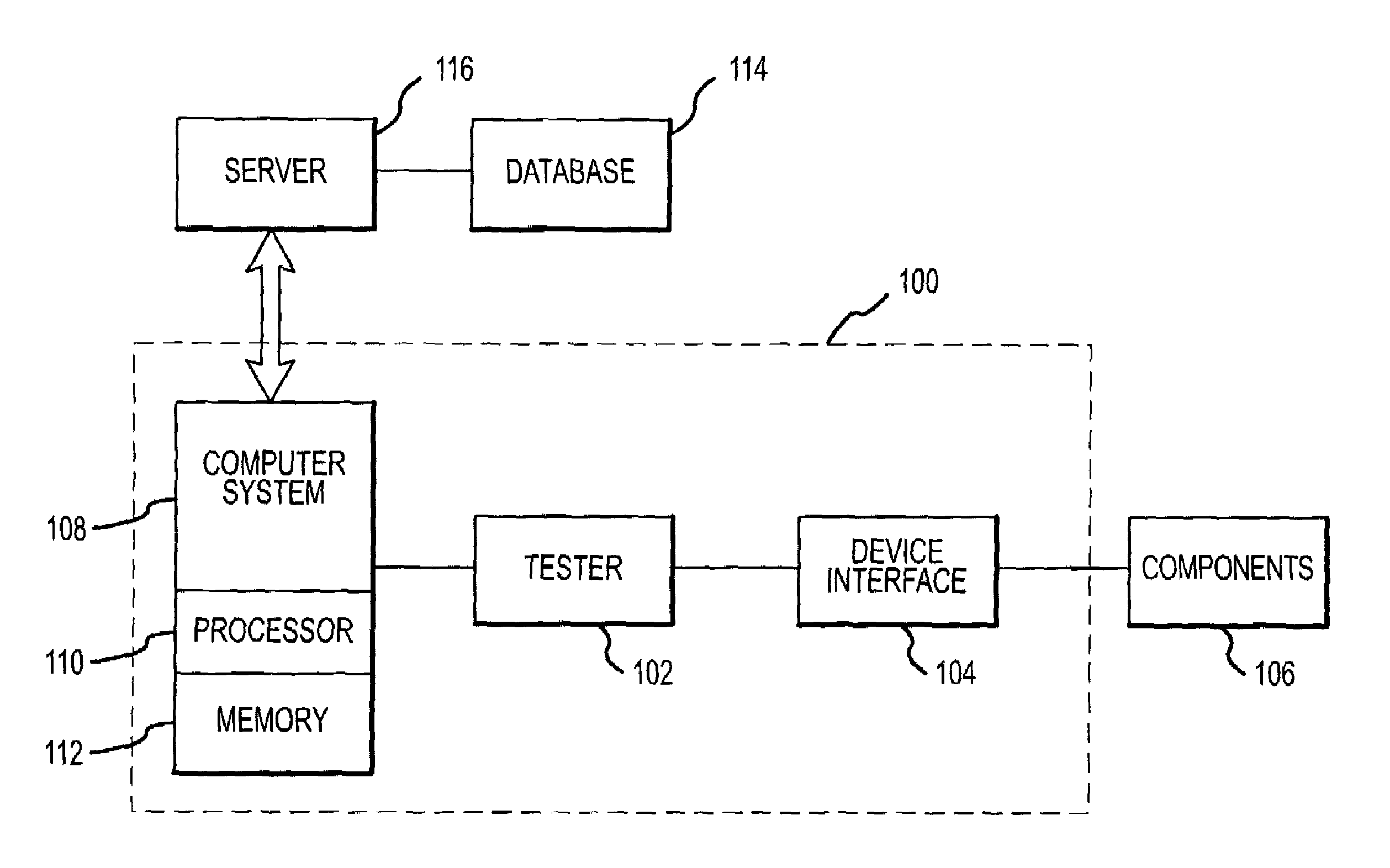

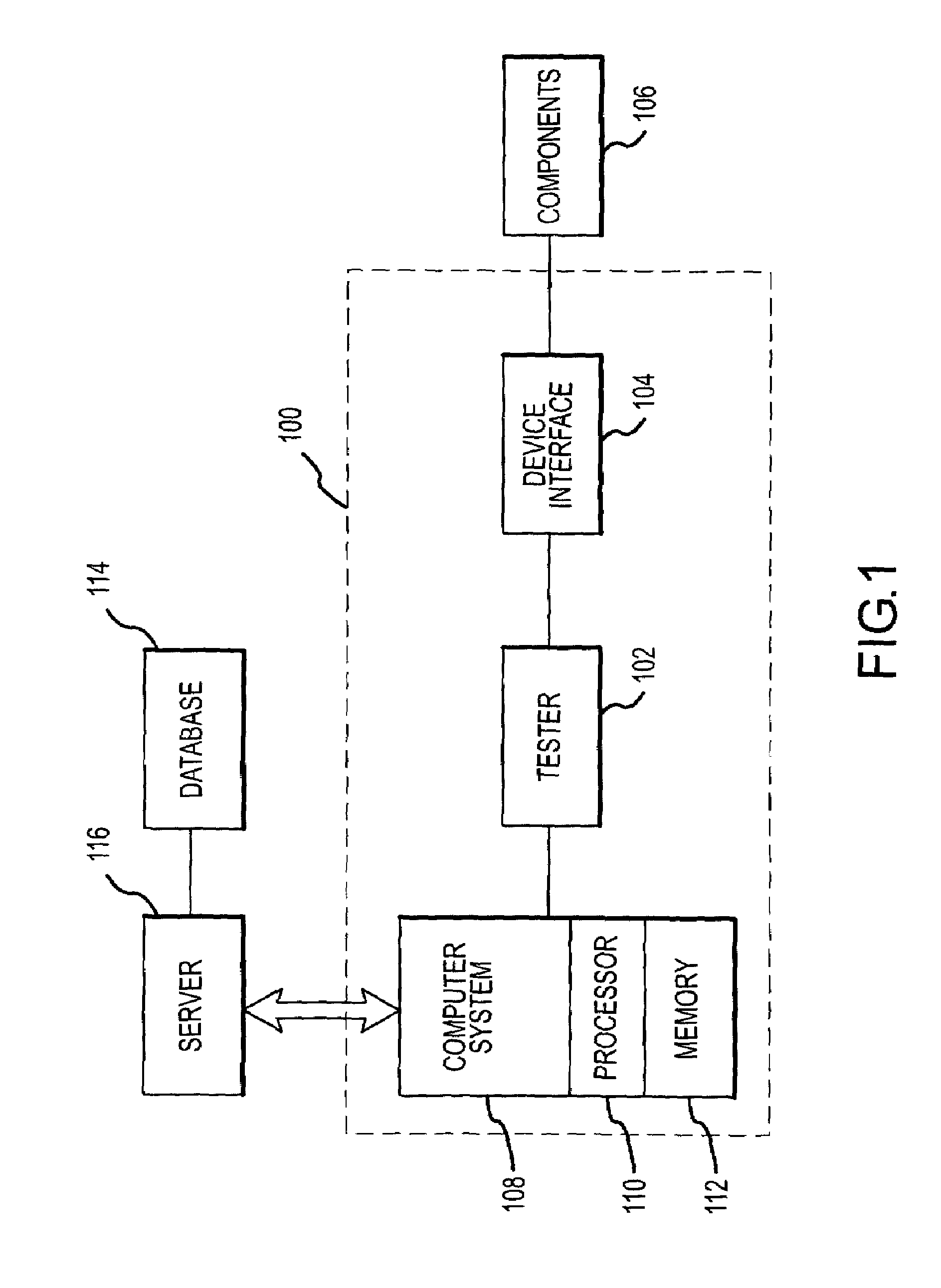

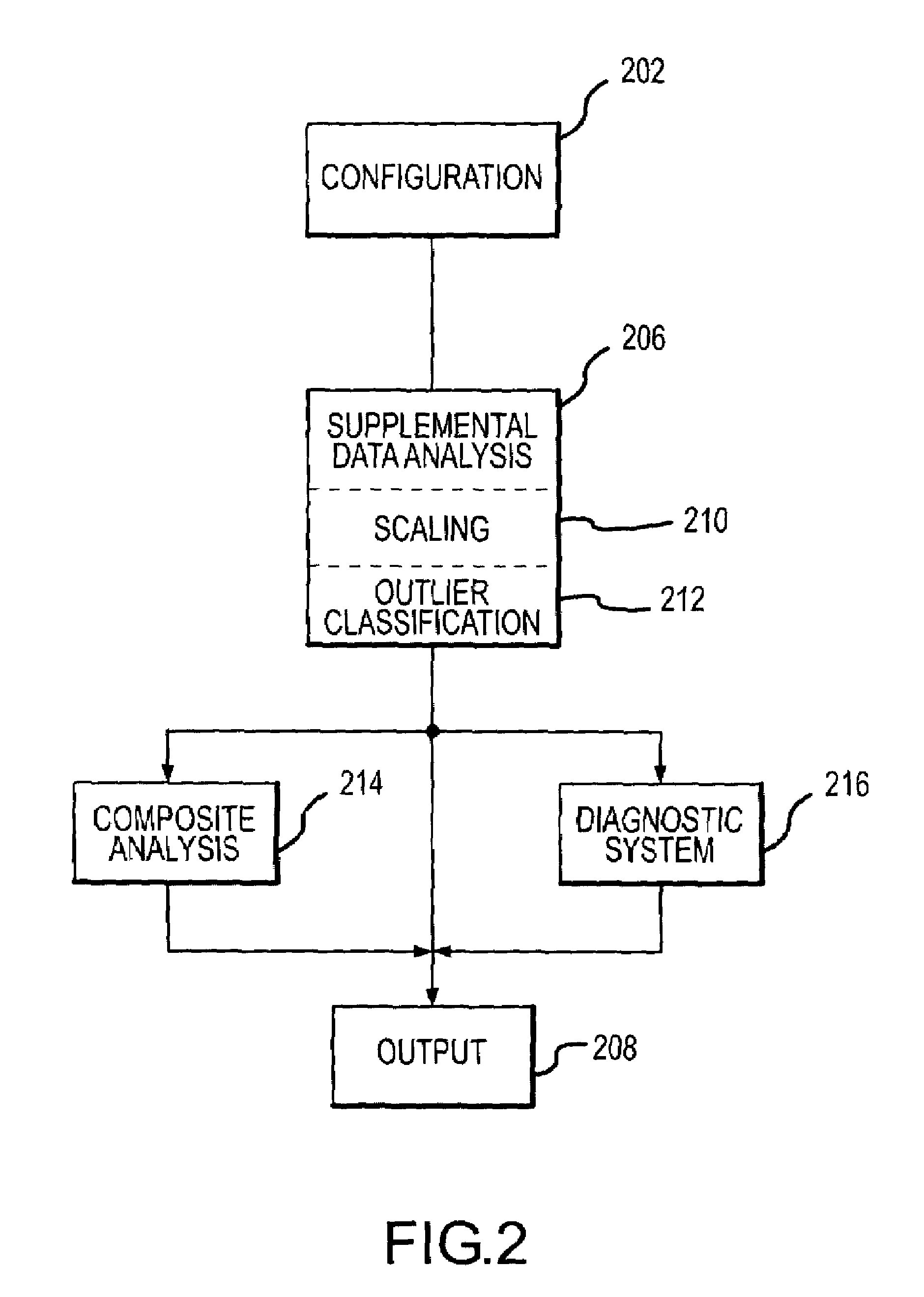

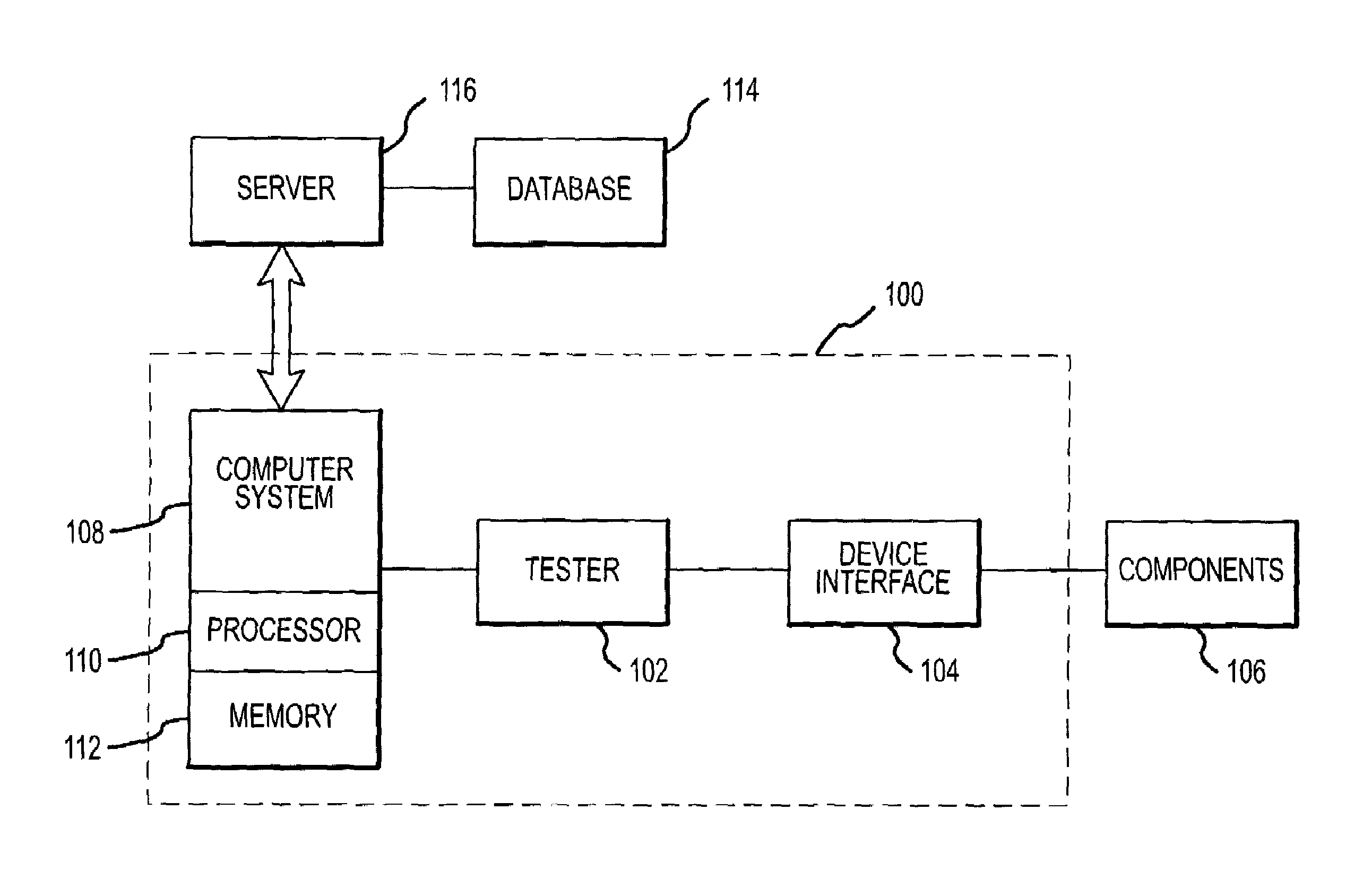

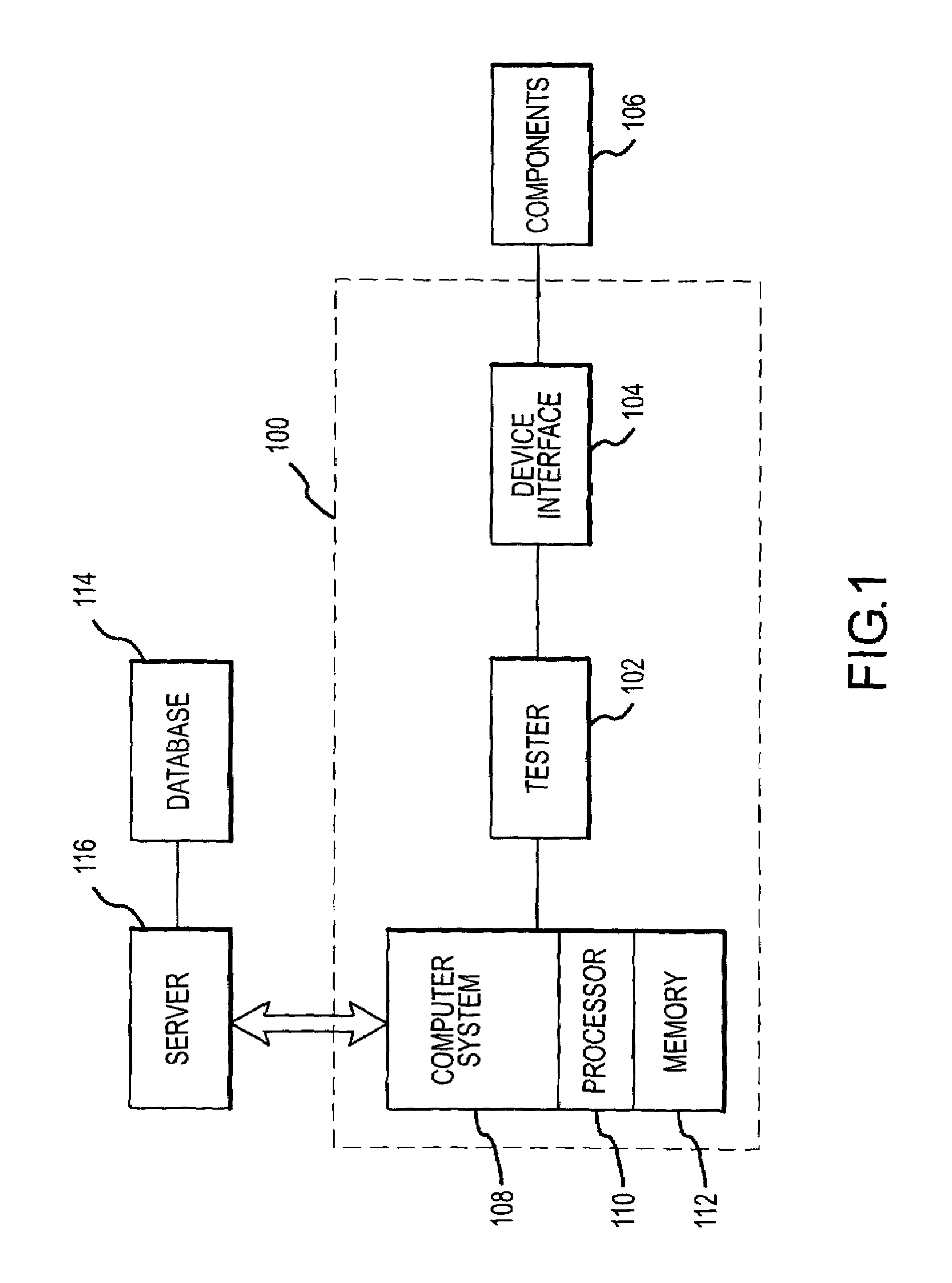

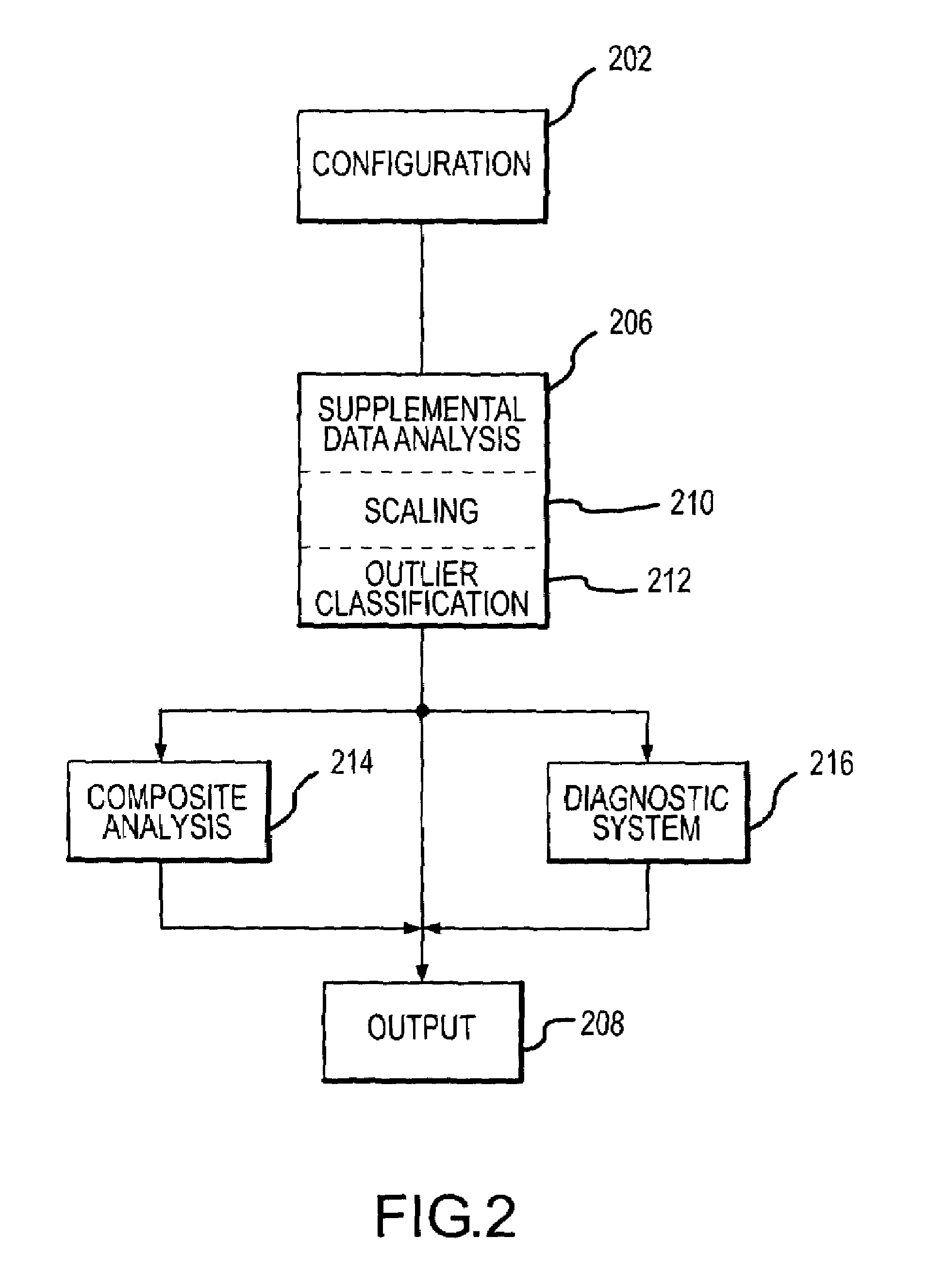

Methods and apparatus for data analysis

InactiveUS20110178967A1Detecting faulty hardware using neural networksSemiconductor/solid-state device testing/measurementMachine learningDiagnostic system

A method and apparatus for data analysis according to various aspects of the present invention is configured to test a set of components and generate test data for the components. A diagnostic system automatically analyzes the test data to identify a characteristic of a component fabrication process by recognizing a pattern in the test data and classifying the pattern using a neural network.

Owner:IN DEPTH TEST

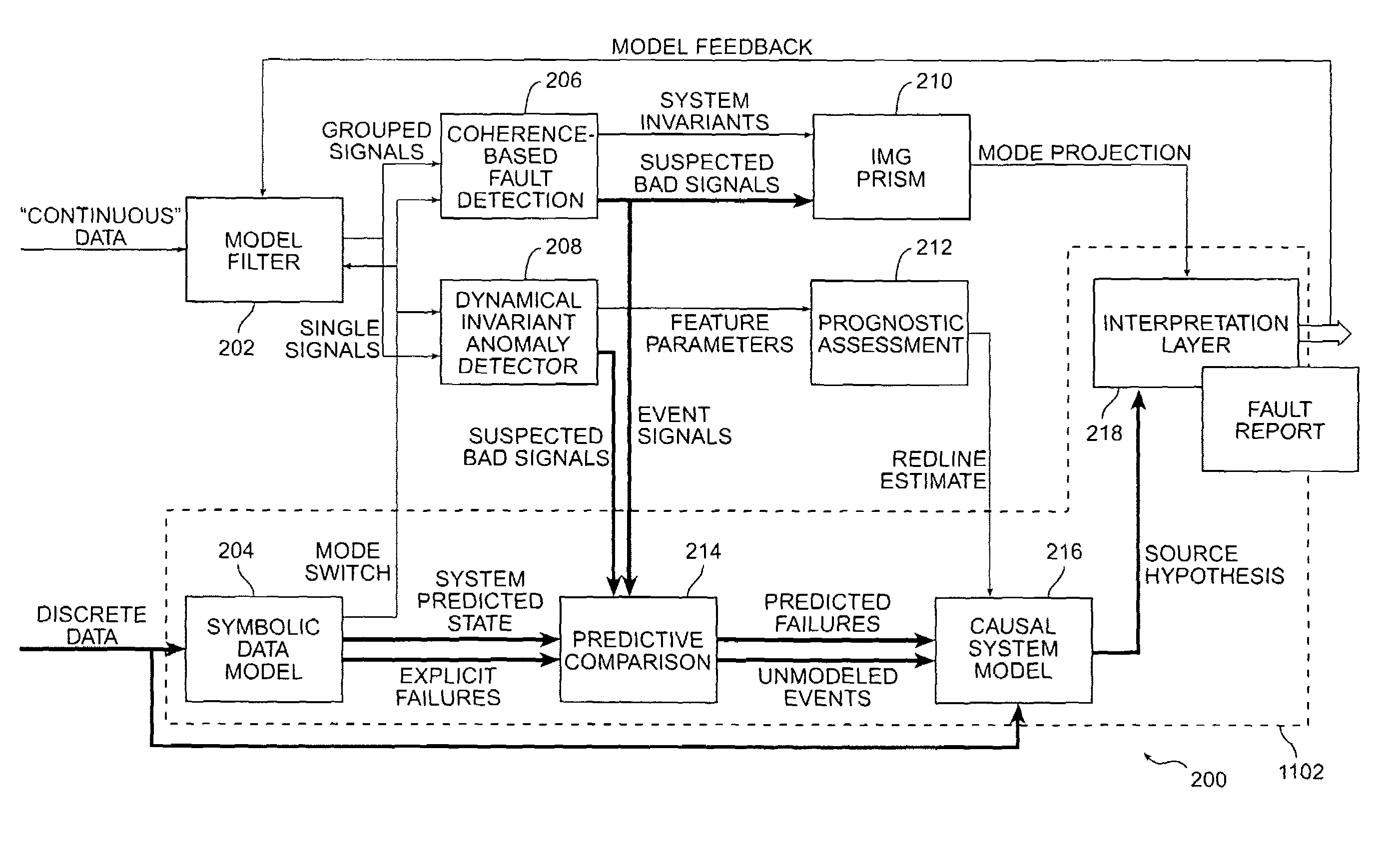

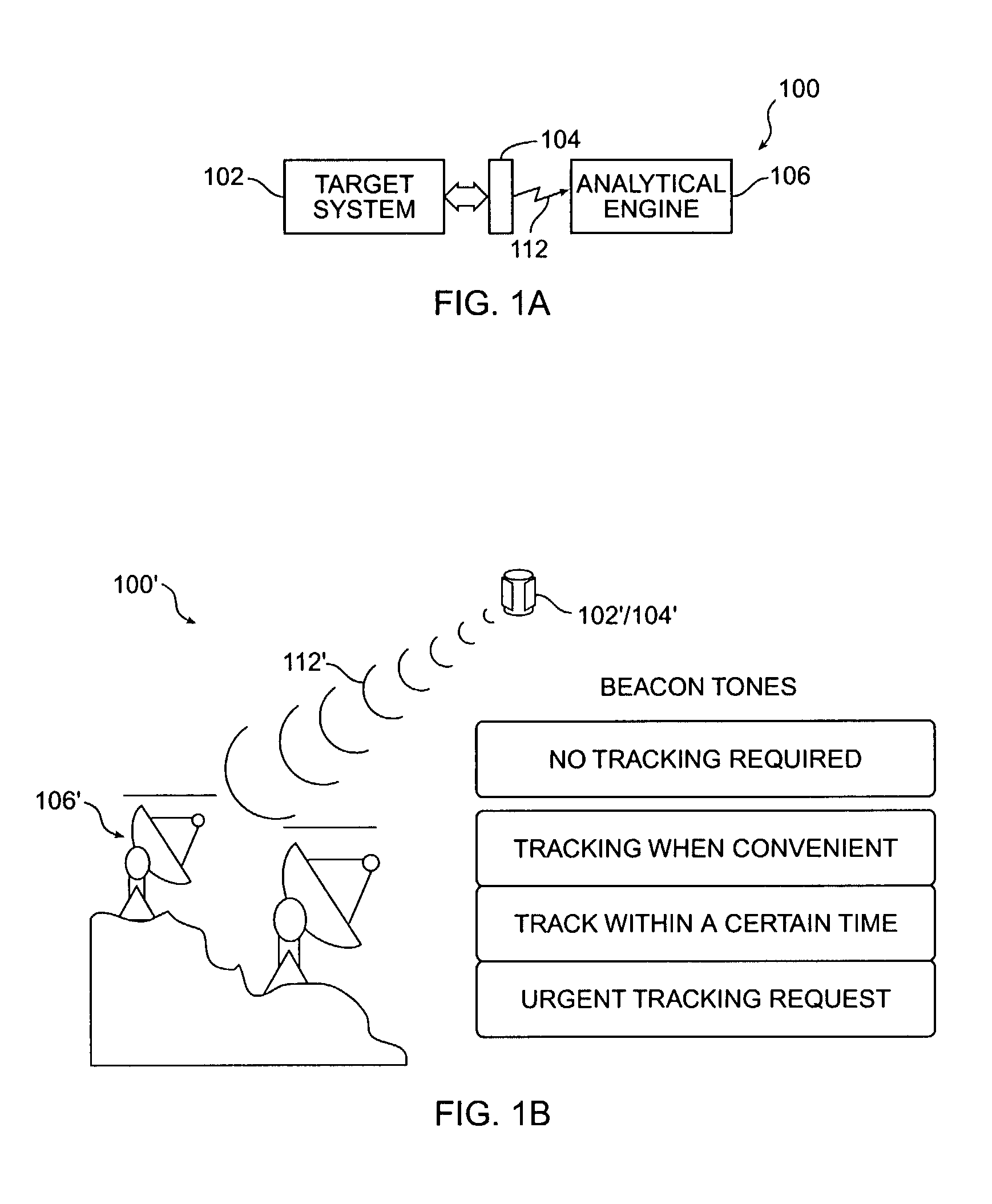

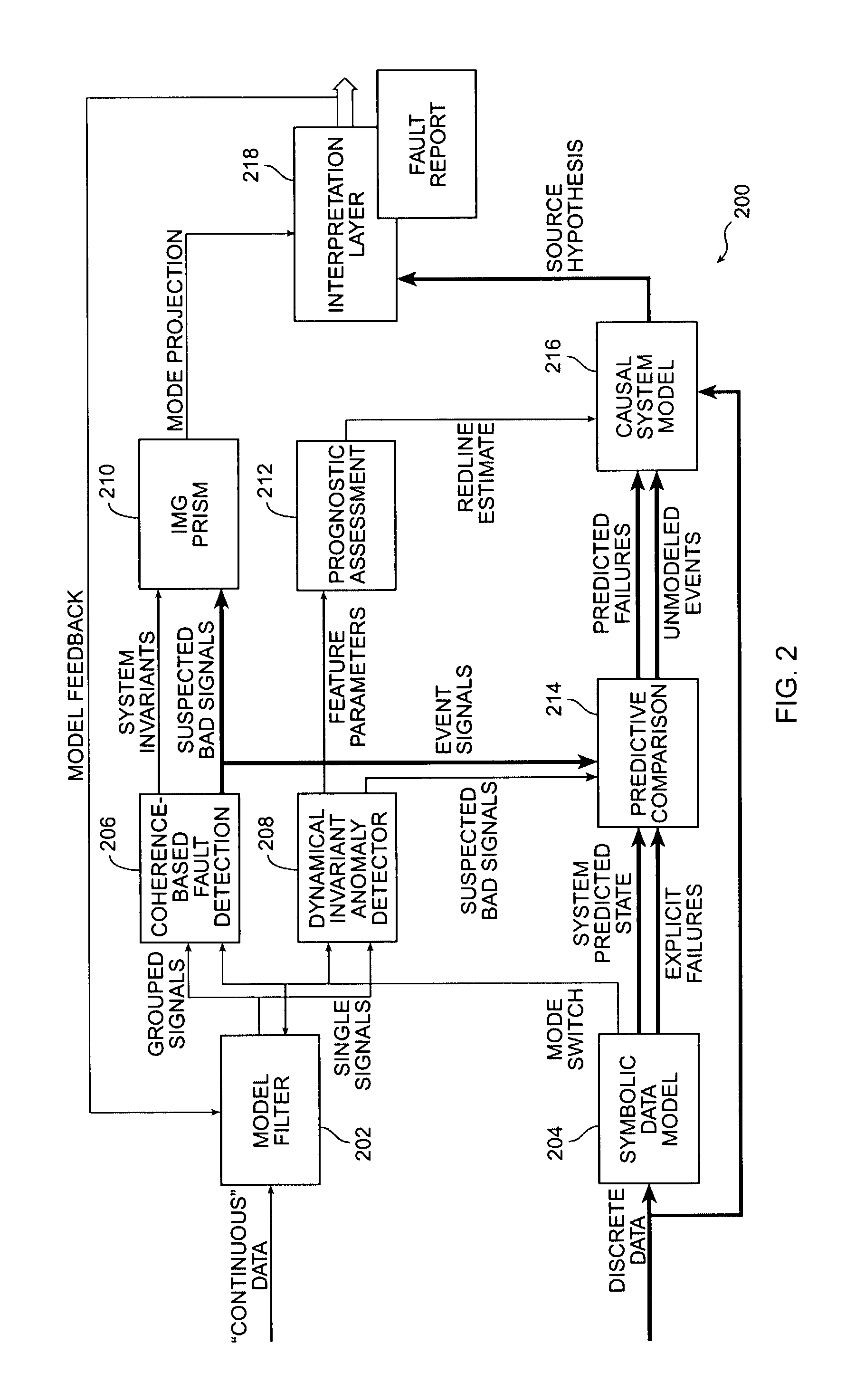

Exception analysis for multimissions

ActiveUS7080290B2Detecting faulty hardware using neural networksSimulator controlOn boardStandard form

A generalized formalism for diagnostics and prognostics in an instrumented system which can provide sensor data and discrete system variable takes into consideration all standard forms of data, both time-varying (sensor or extracted feature) quantities and discrete measurements, embedded physical and symbolic models, and communication with other autonomy-enabling components such as planners and schedulers. This approach can be adapted to on-board or off-board implementations with no change to the underlying principles.

Owner:CALIFORNIA INST OF TECH

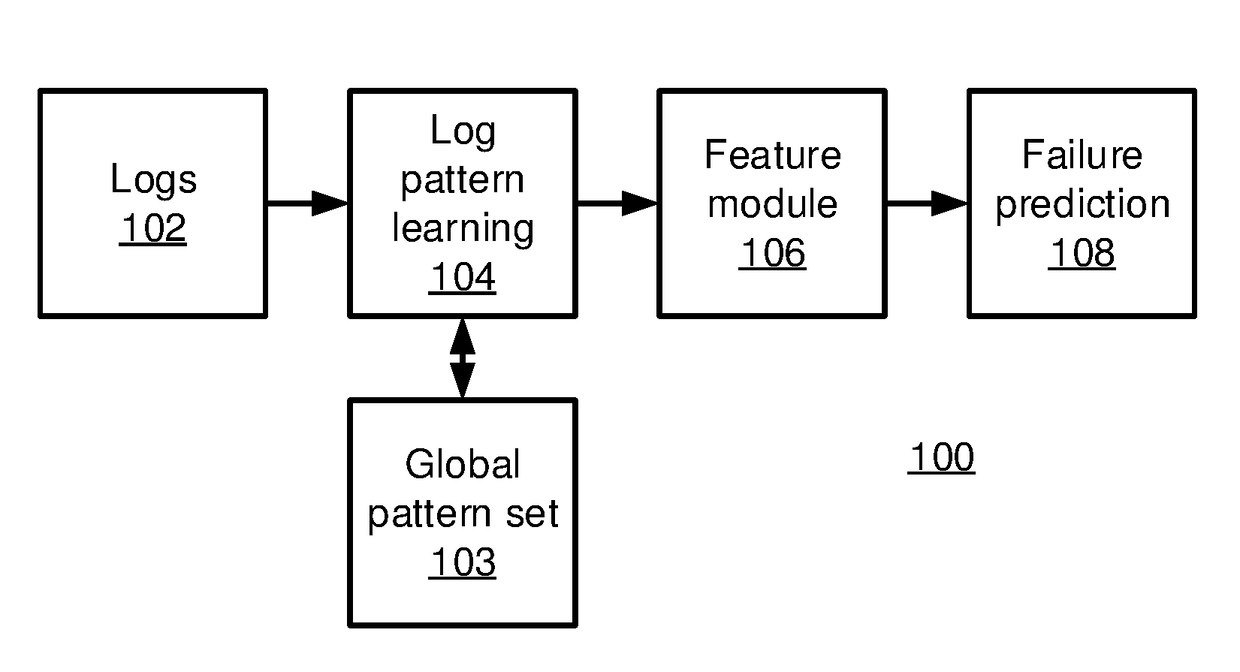

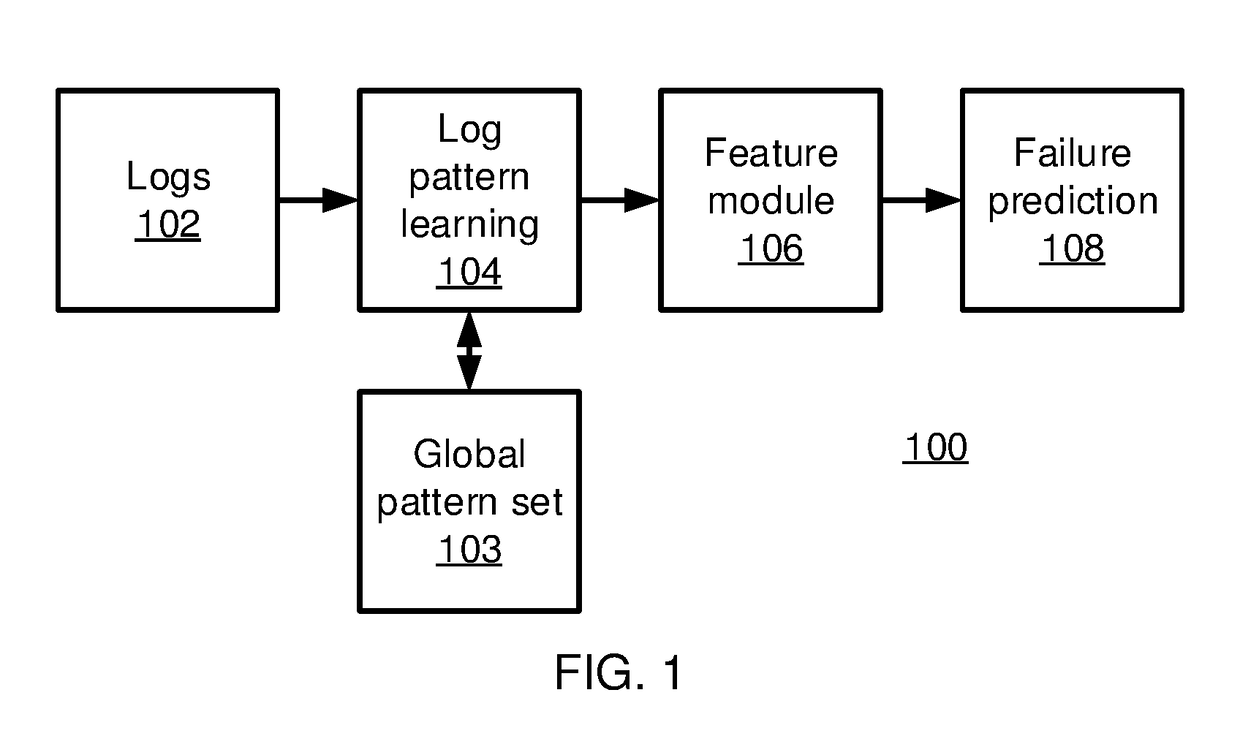

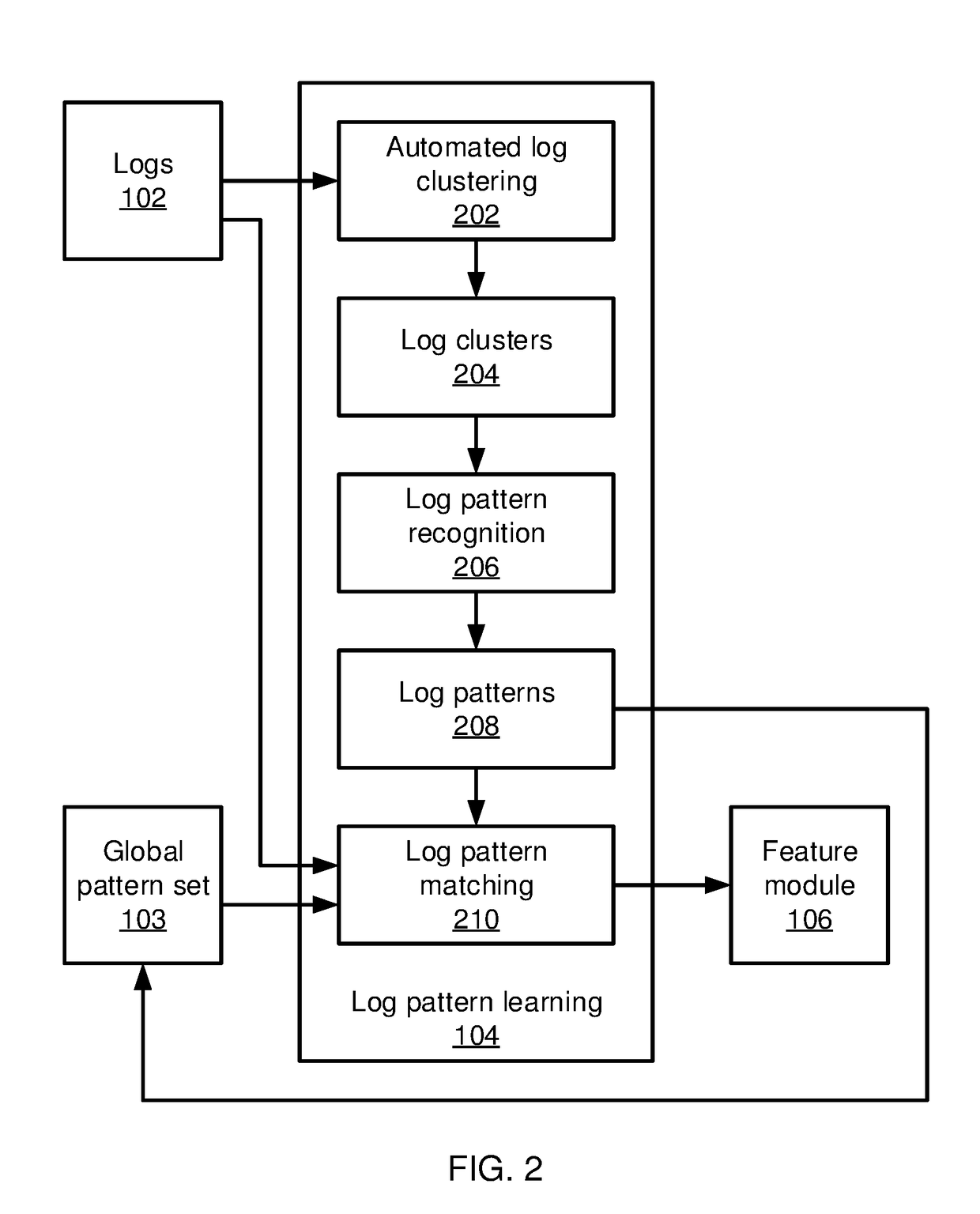

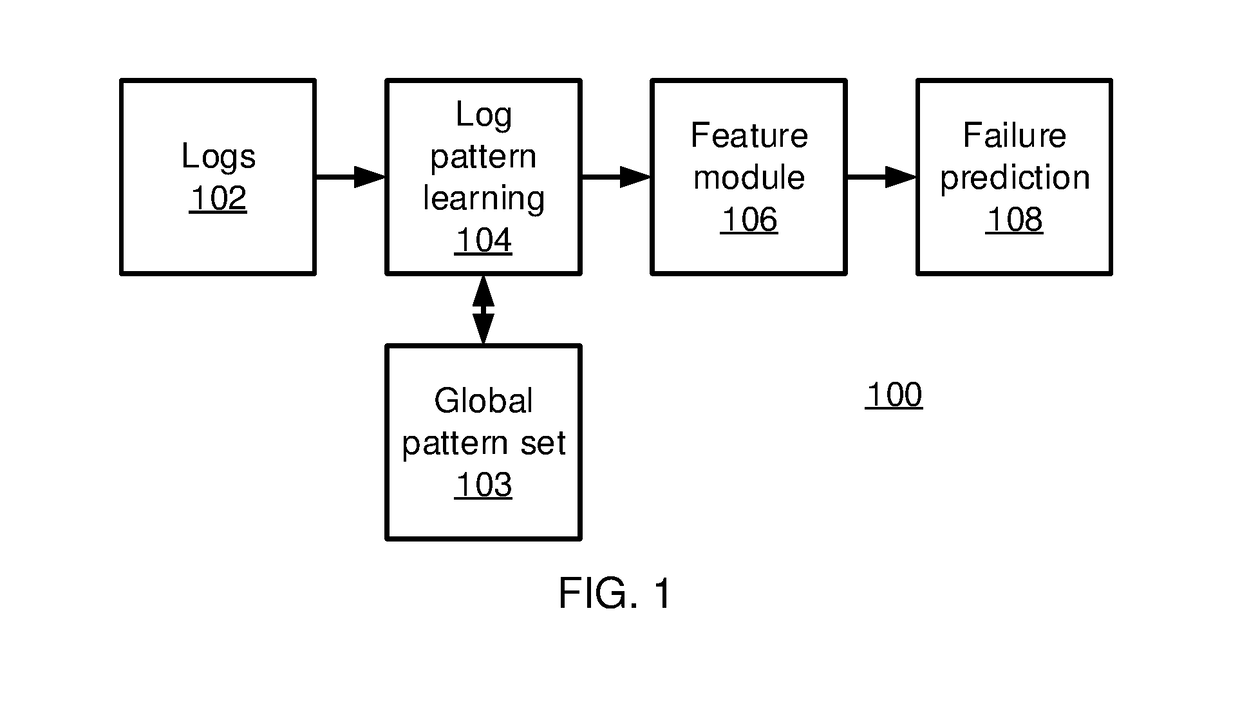

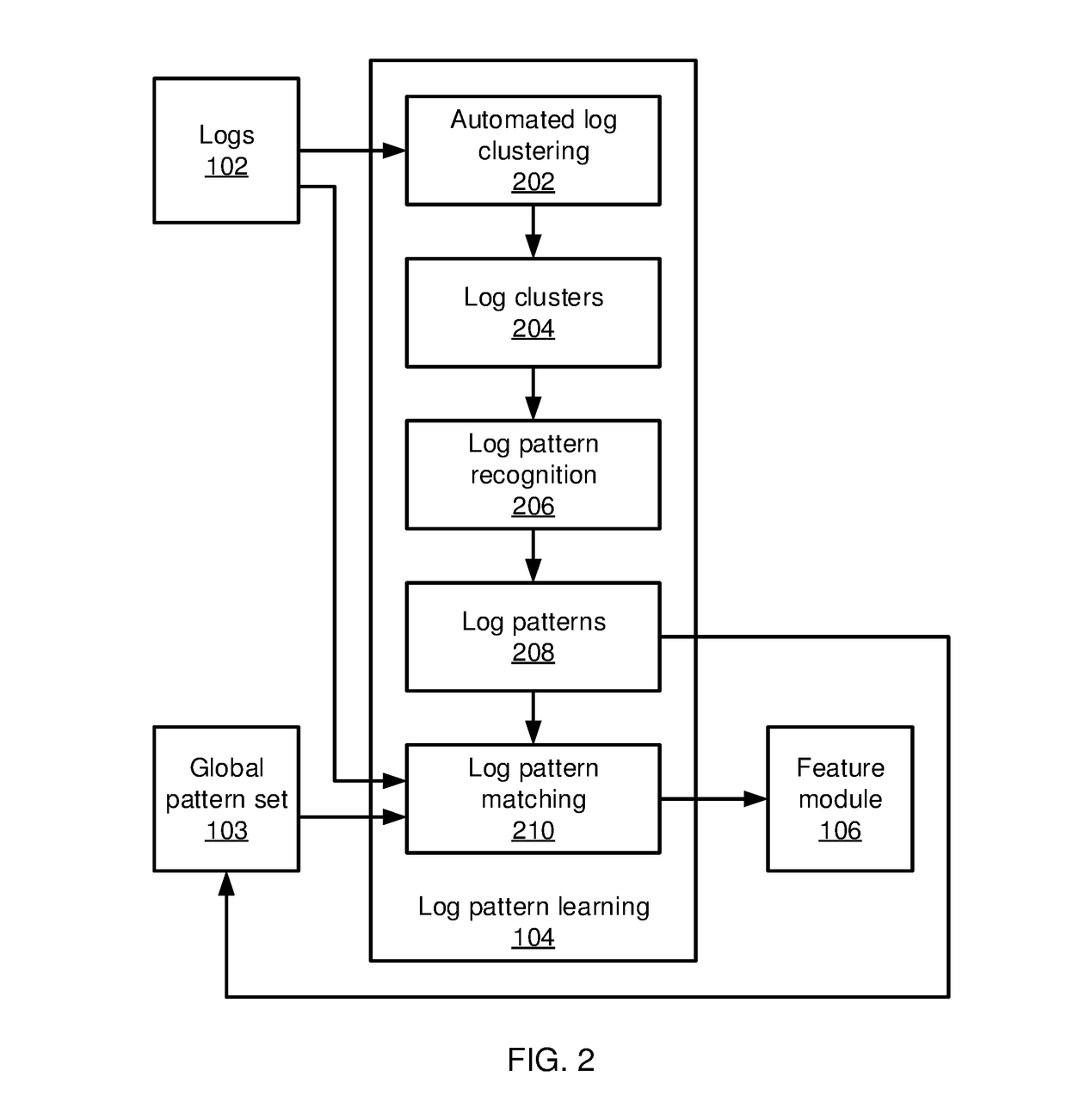

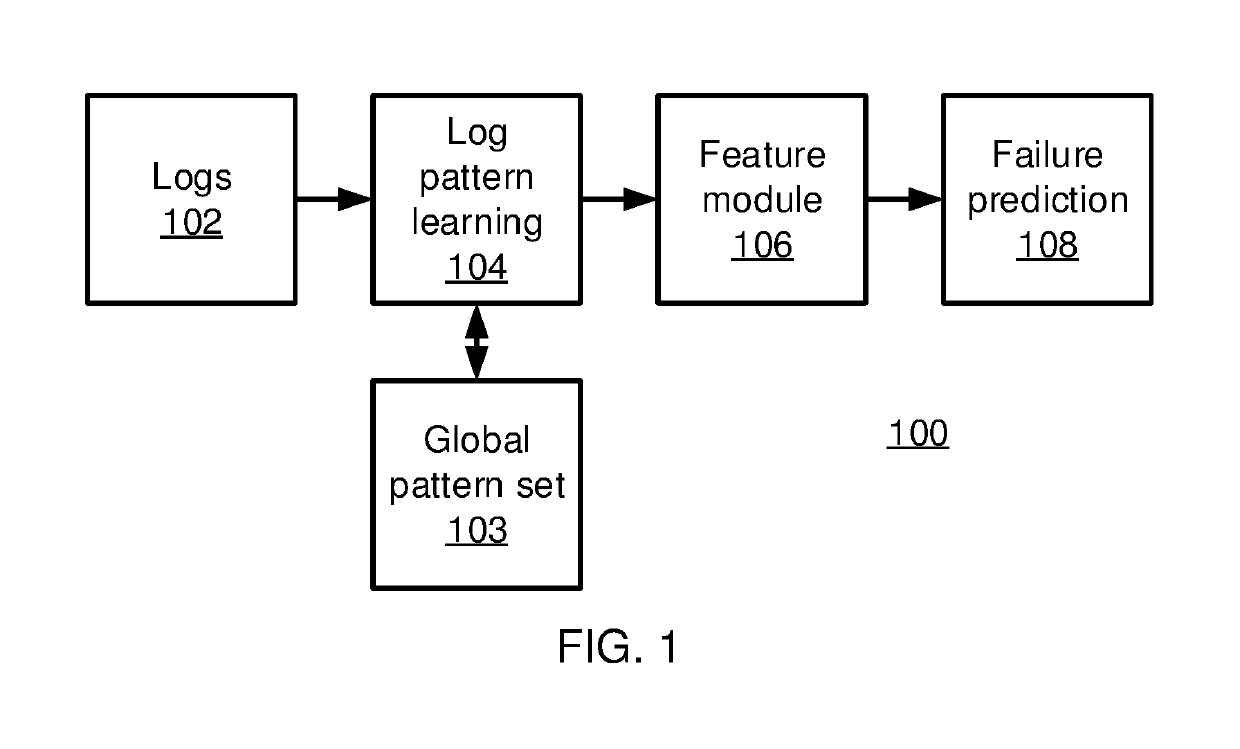

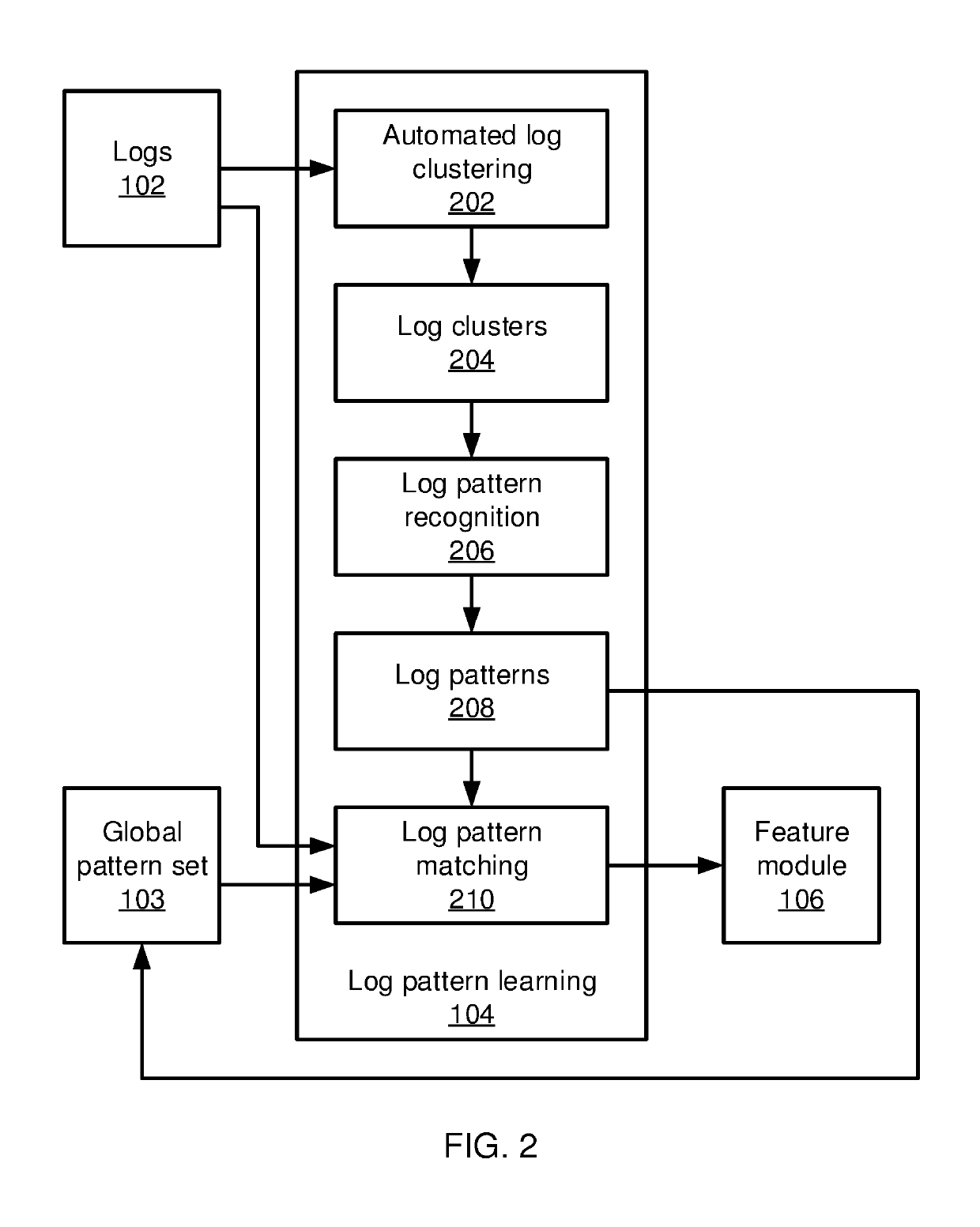

System failure prediction using long short-term memory neural networks

ActiveUS20170293542A1Detecting faulty hardware using neural networksReliability/availability analysisShort durationSystem failure

Methods for system failure prediction include clustering log files according to structural log patterns. Feature representations of the log files are determined based on the log clusters. A likelihood of a system failure is determined based on the feature representations using a neural network. An automatic system control action is performed if the likelihood of system failure exceeds a threshold.

Owner:NEC CORP

Mobile phone with system failure prediction using long short-term memory neural networks

ActiveUS20170293543A1Detecting faulty hardware using neural networksReliability/availability analysisSystem failureComputer science

Mobile phones and methods for mobile phone failure prediction include receiving respective log files from one or more mobile phone components, including at least one user application. The log files have heterogeneous formats. A likelihood of failure of one or more mobile phone components is determined based on the received log files by clustering the plurality of log files according to structural log patterns and determining feature representations of the log files based on the log clusters. A user is alerted to a potential failure if the likelihood of component failure exceeds a first threshold. An automatic system control action is performed if the likelihood of component failure exceeds a second threshold.

Owner:NEC CORP

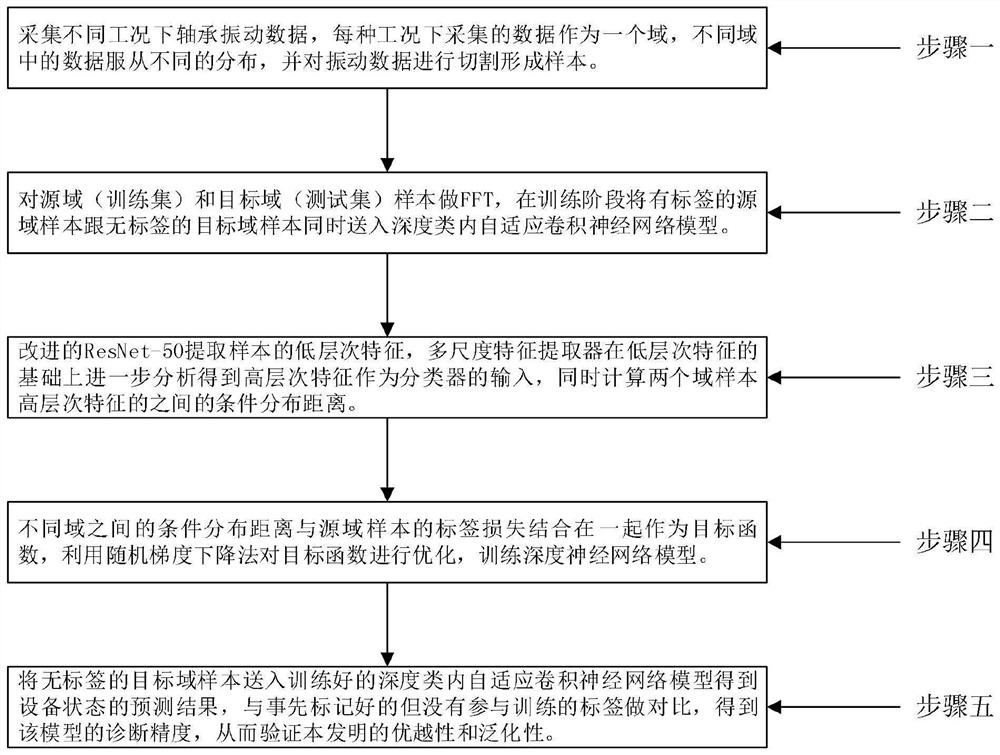

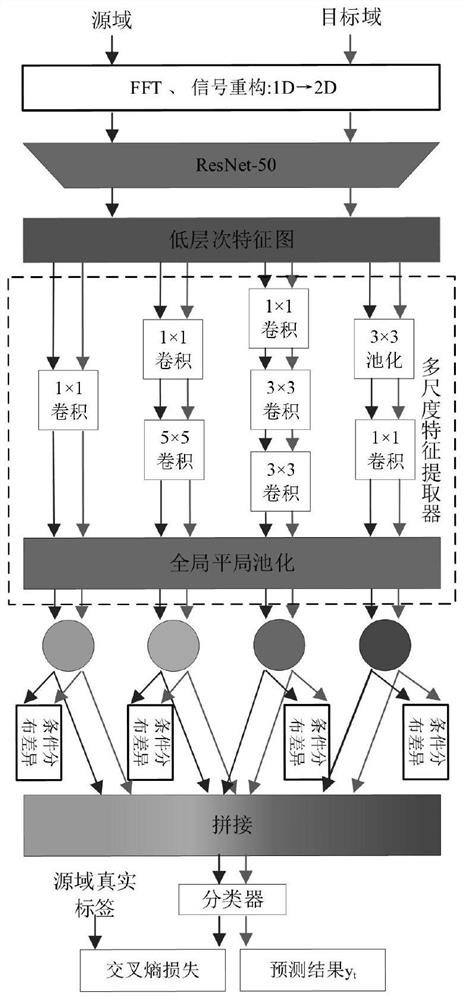

Fault diagnosis method for rolling bearing under variable working conditions

ActiveCN111651937AAchieve the effect of online diagnosisSave manpower and material resourcesDetecting faulty hardware using neural networksMachine part testingAlgorithmEngineering

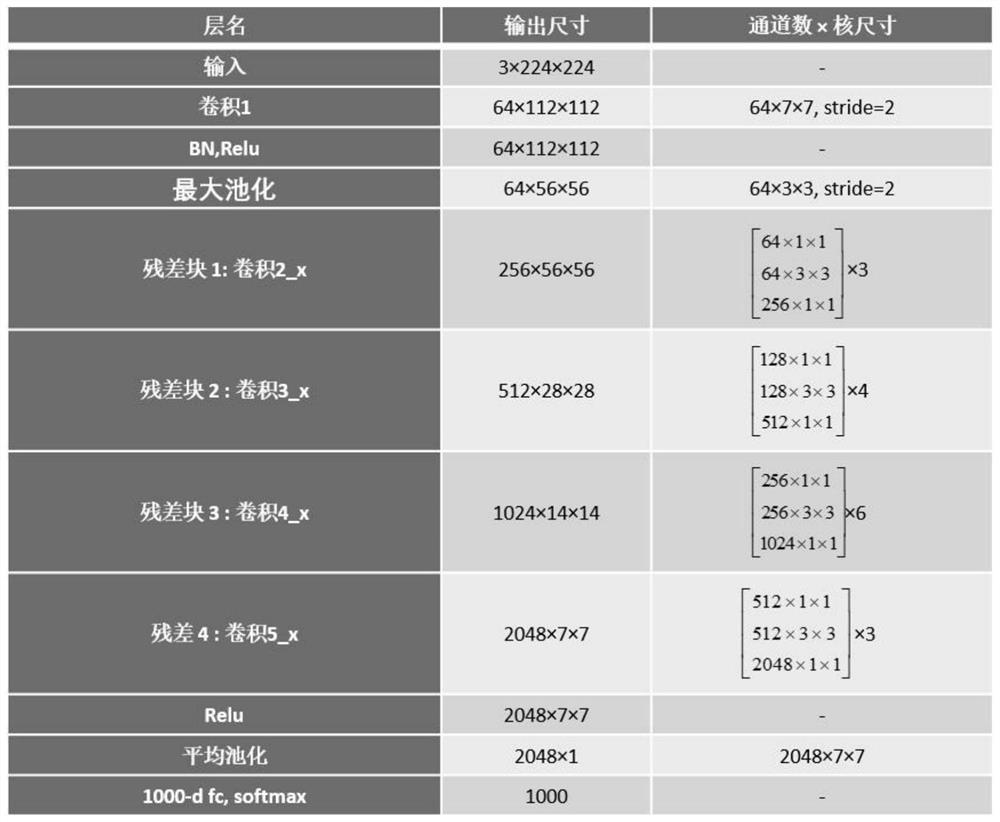

The invention relates to a fault diagnosis method for a rolling bearing under variable working conditions, and the method solves a problem that the universality of a deep learning model becomes poor because of the complex and variable working conditions of mechanical equipment through combining with a transfer learning algorithm on the basis of employing a convolutional neural network learning model. The method comprises the steps that firstly, data collected under different working conditions is cut to divide samples, the samples are preprocessed through FFT, then low-level features of the samples are extracted through improved ResNet-50, and then a multi-scale feature extractor analyzes the low-level features from different angles to obtain high-level features to serve as input of a classifier; in the training process, high-level features of a training sample and a test sample are extracted at the same time, the conditional distribution distance between the training sample and the test sample is calculated and serves as one part of back propagation of a target function to achieve intra-class self-adaption, the influence of domain drift is reduced, and a deep learning model can bebetter qualified for a fault diagnosis task under the variable working condition.

Owner:SUZHOU UNIV

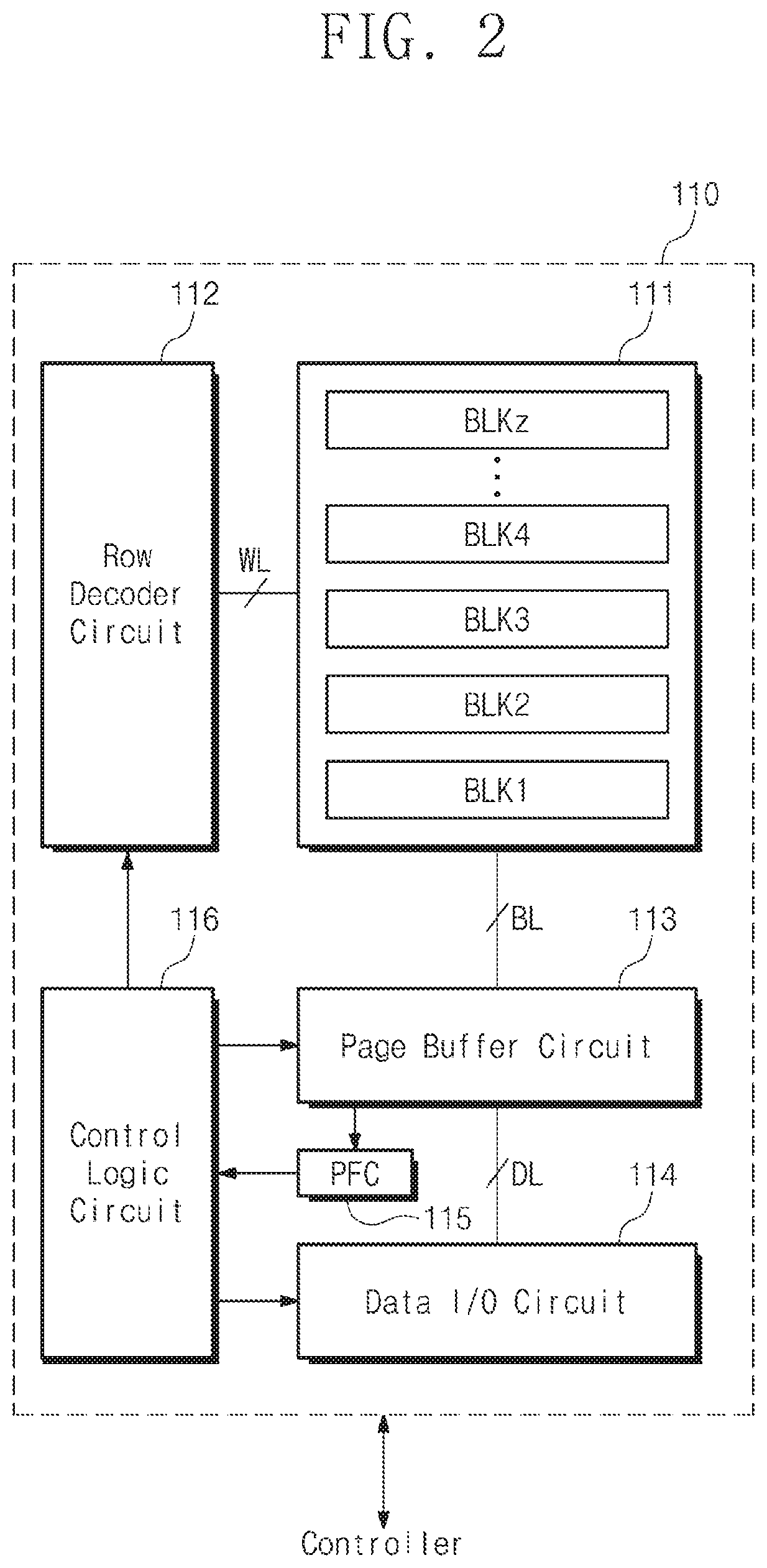

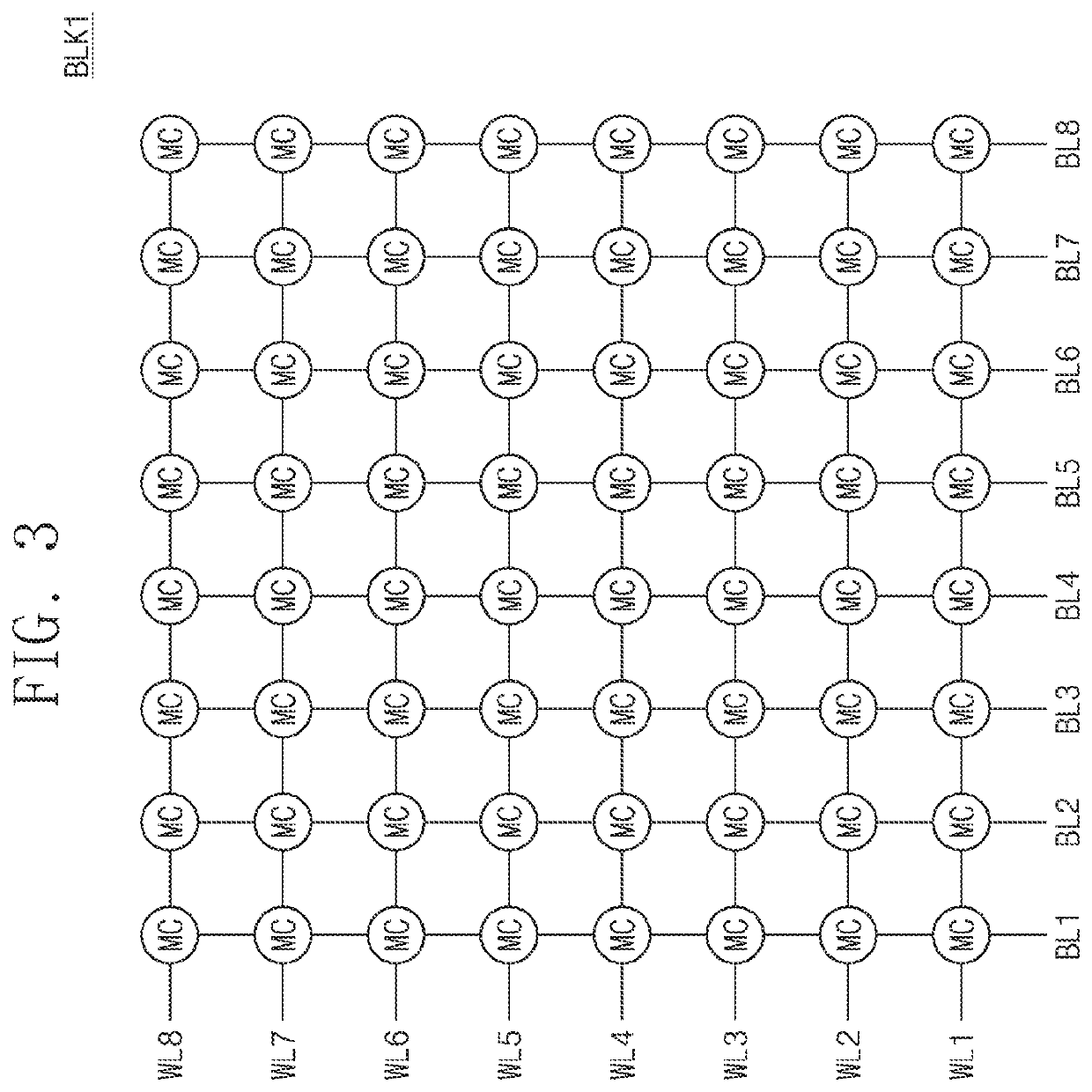

Storage device and operating method of storage device

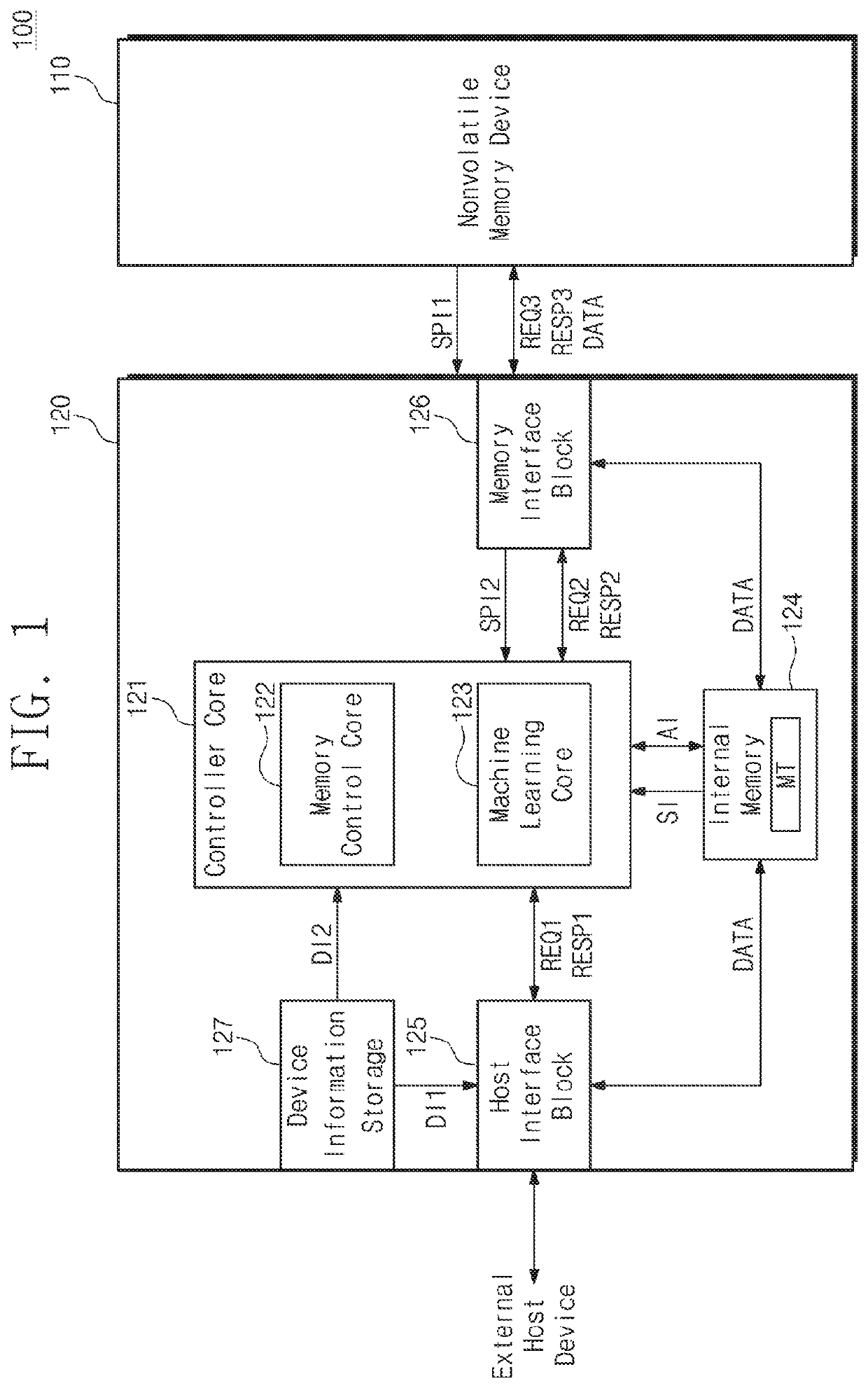

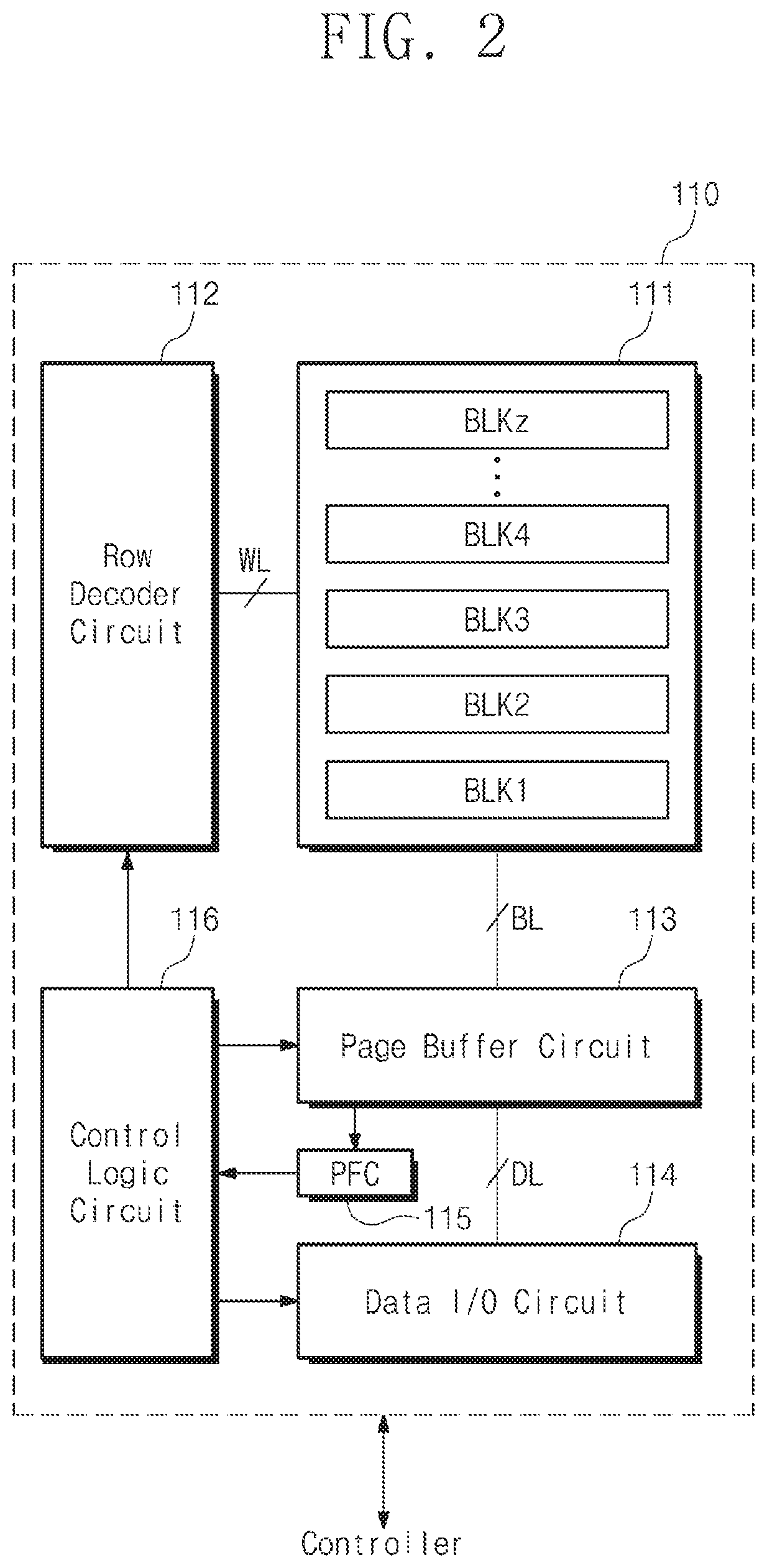

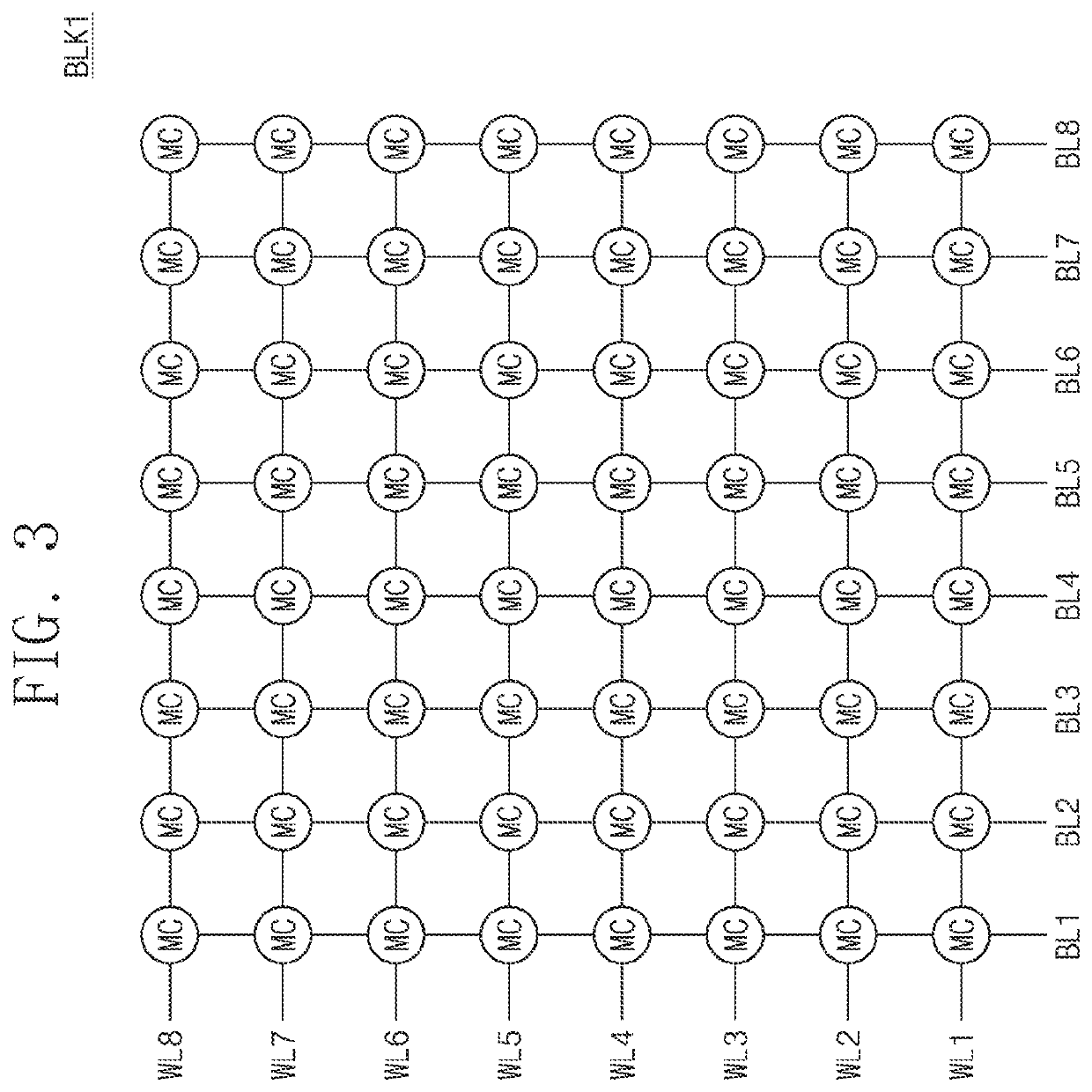

ActiveUS20200110547A1Reliable checkDetecting faulty hardware using neural networksInput/output to record carriersMemory cellEngineering

A storage device includes a nonvolatile memory device including a plurality of memory blocks, each including a plurality of memory cells connected to a plurality of word lines, and a controller configured to perform a first read operation on memory cells connected to a selected word line included in a selected memory block based on a request of an external host device. The controller is further configured to perform a check read operation that checks a reliability of the memory cells of the selected memory block after performing the first read operation. In the check read operation, the controller is further configured to select and perform one of an actual check and a machine learning-based check.

Owner:SAMSUNG ELECTRONICS CO LTD

Classifying a work machine operation

ActiveUS7487066B2Detecting faulty hardware using neural networksSewing apparatusNetwork onComputer science

A method for analyzing the use of a work machine is disclosed. In one embodiment, the method may include providing a computer with a neural network on the work machine. Further, the method may include inputting data to the computer, at least a portion of the data associated with a load experienced by one of the components of the work machine. The neural network, when executed by the computer may then classify a current operation of the work machine into one of a plurality of types of operations.

Owner:CATERPILLAR INC

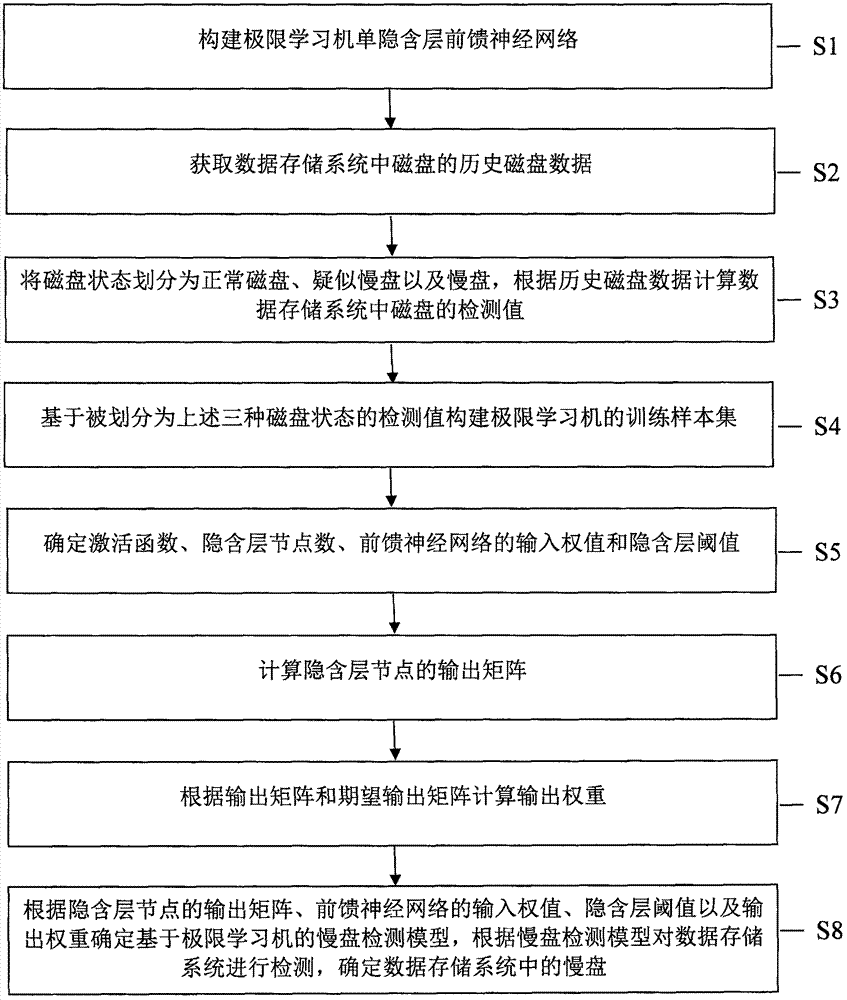

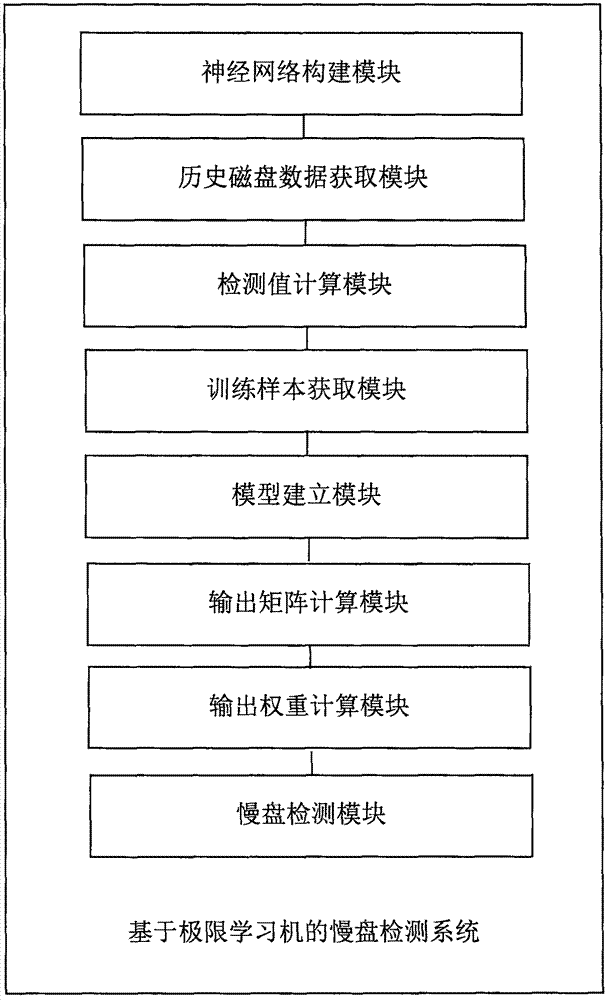

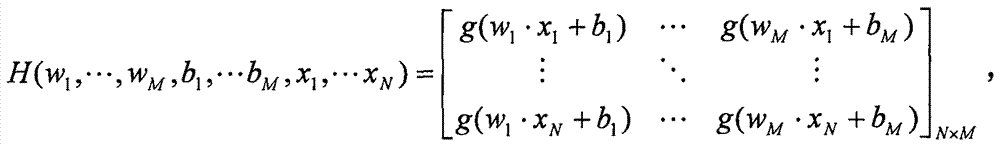

Extreme learning machine-based slow disk detection method and system

ActiveCN106897178AEasy to detectImprove detection accuracyDetecting faulty hardware using neural networksFaulty hardware testing methodsLearning machineComputation complexity

The invention provides an extreme learning machine-based slow disk detection method and system. By performing feature extraction on historical disk data, eigenvectors are selected from features to perform training, so that a scheme of detecting a slow disk based on a neural network is realized, a slow disk detection process is optimized, the accuracy of slow disk detection is improved, and the calculation complexity is lowered; and meanwhile, in an actual usage process, with increment of a historical disk data quantity, more and more samples are continuously trained, and model precision is higher and higher, so that the accuracy is further improved and a data storage system is ensured to be always in an optimal working state.

Owner:QUFU NORMAL UNIV

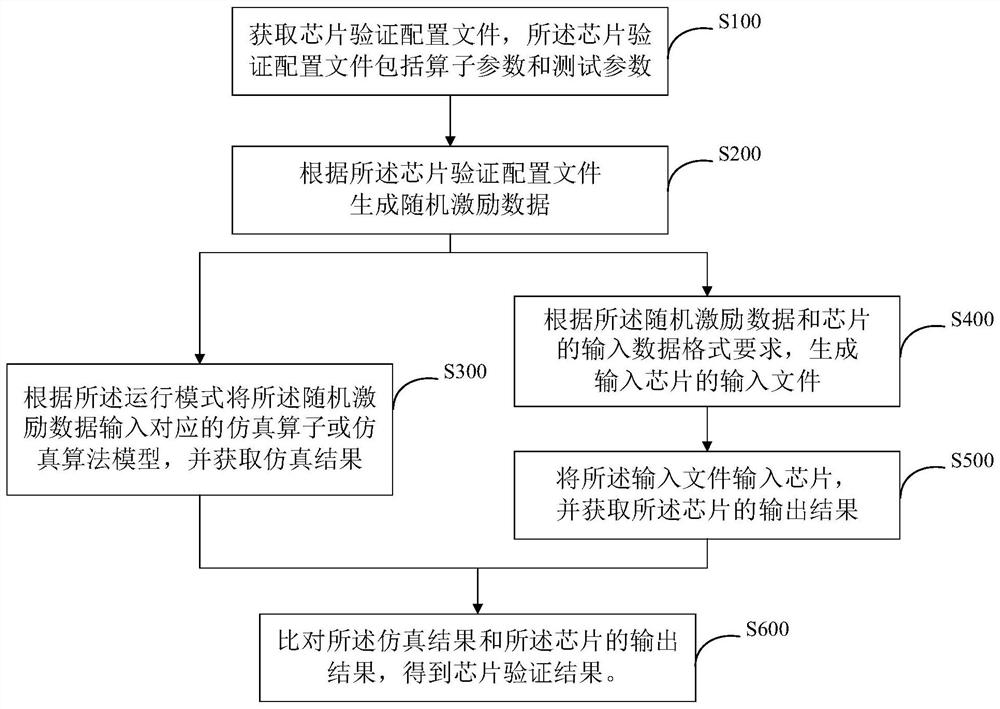

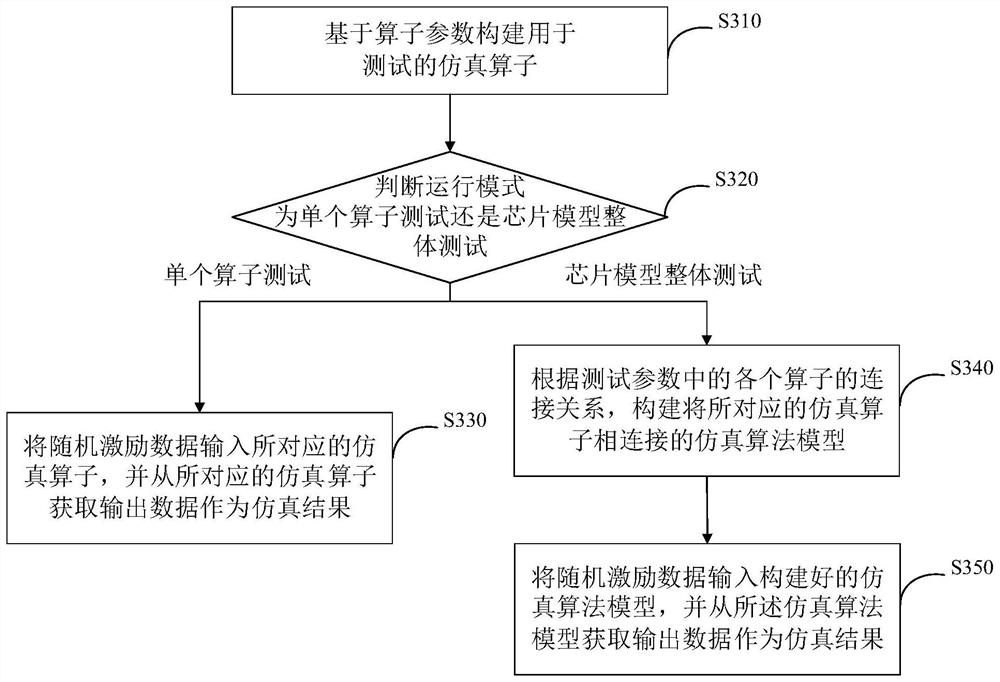

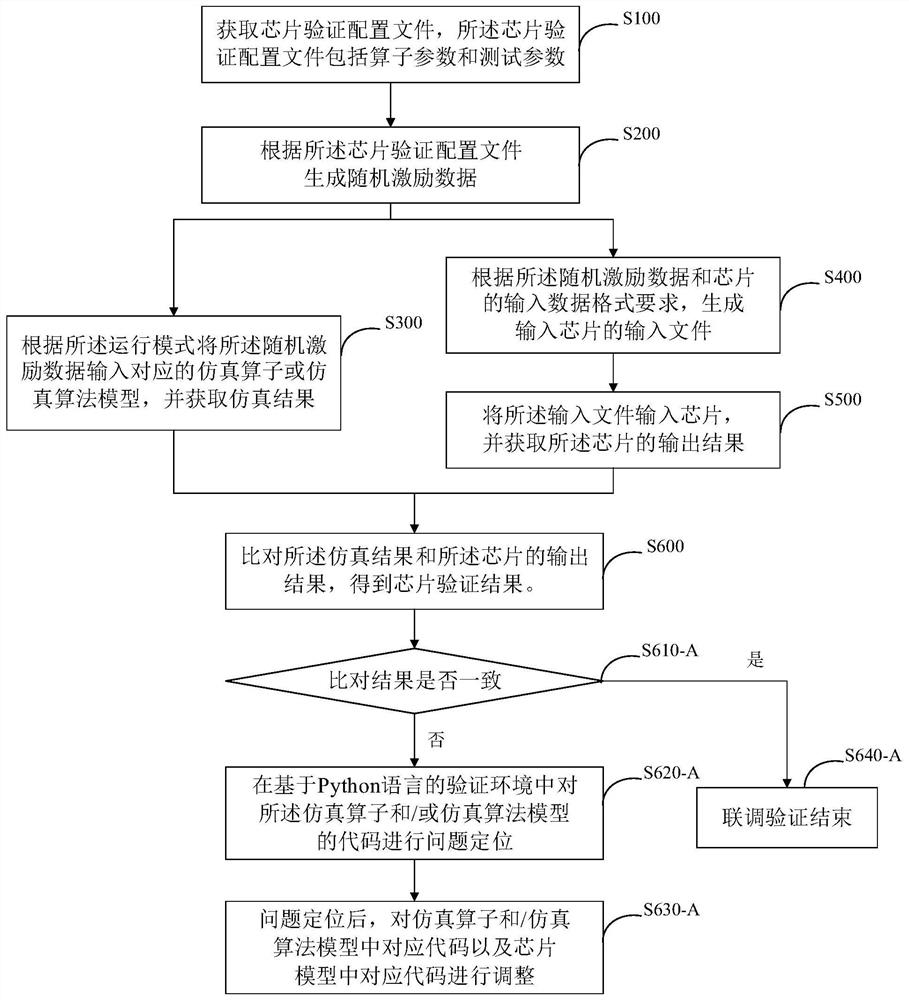

Chip simulation verification method, system and device and storage medium

ActiveCN113032195AAccelerate the speed of research and developmentImprove reuse rateDetecting faulty hardware using neural networksAlgorithmNetwork model

The invention provides a chip simulation verification method, system and device and a storage medium, and the method comprises the steps: obtaining a chip verification configuration file, wherein the chip verification configuration file comprises operator parameters and test parameters, the operator parameters comprise configuration parameters of each operator, and the test parameters comprise operation modes, the operation mode comprises a single operator test and / or a chip model overall test; generating random excitation data according to the chip verification configuration file; inputting the random excitation data into a corresponding simulation operator or simulation algorithm model, and obtaining a simulation result; generating an input file of the input chip according to the random excitation data and the input data format requirement of the chip; inputting the input file into the chip, and obtaining an output result of the chip; comparing the simulation result with an output result of the chip to obtain a chip verification result. The method is applied to simulation and verification of the neural network model reasoning chip, and rapid function verification of different neural network models and operators is achieved.

Owner:SHANGHAI WESTWELL INFORMATION & TECH CO LTD

Methods and Apparatus for Data Analysis

InactiveUS20160026915A1Detecting faulty hardware using neural networksSemiconductor/solid-state device testing/measurementData profilingMachine learning

A method and apparatus for data analysis according to various aspects of the present invention is configured to test a set of components and generate test data for the components. A diagnostic system automatically analyzes the test data to identify a characteristic of a component fabrication process by recognizing a pattern in the test data and classifying the pattern using a neural network.

Owner:IN DEPTH TEST

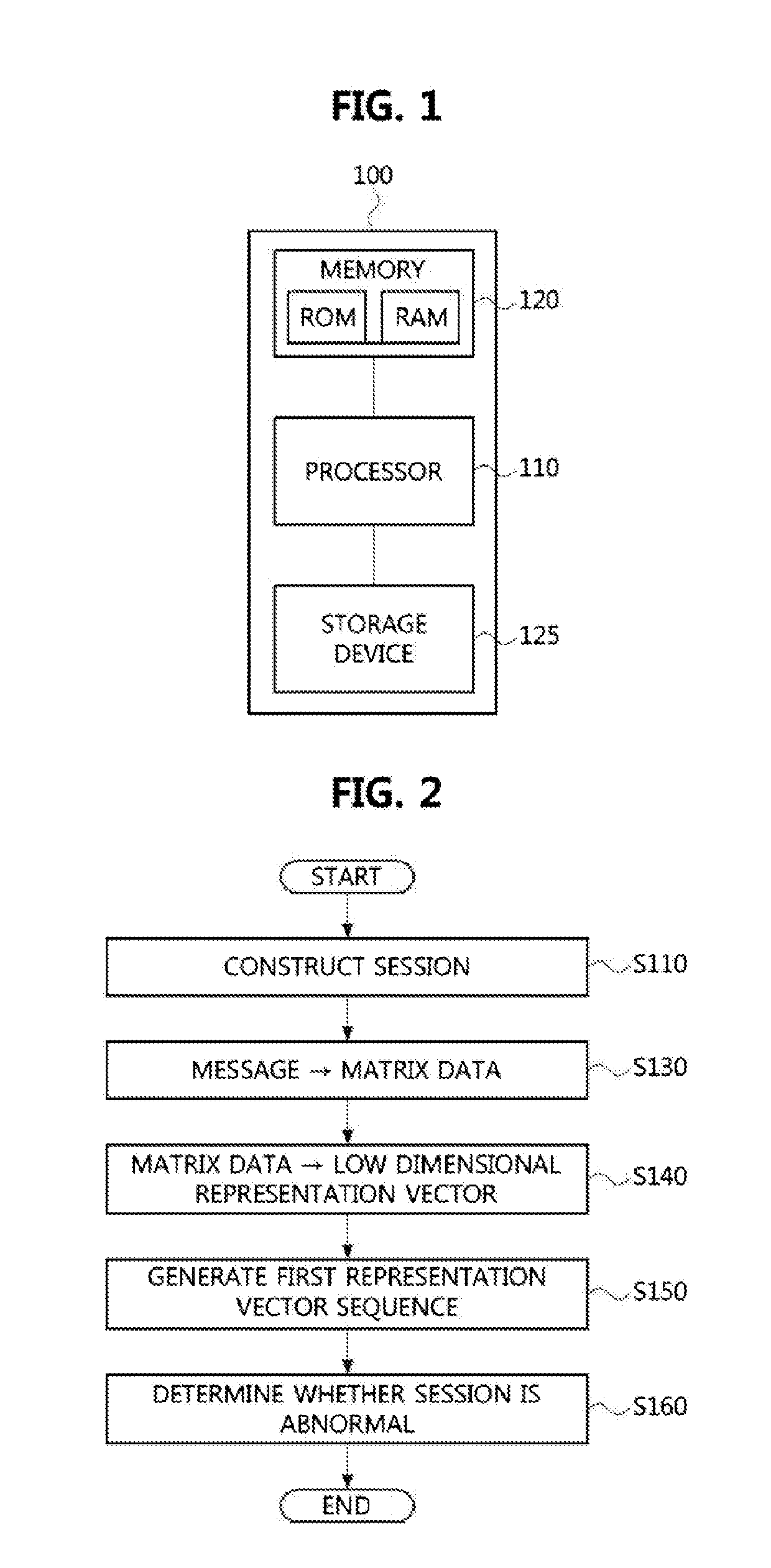

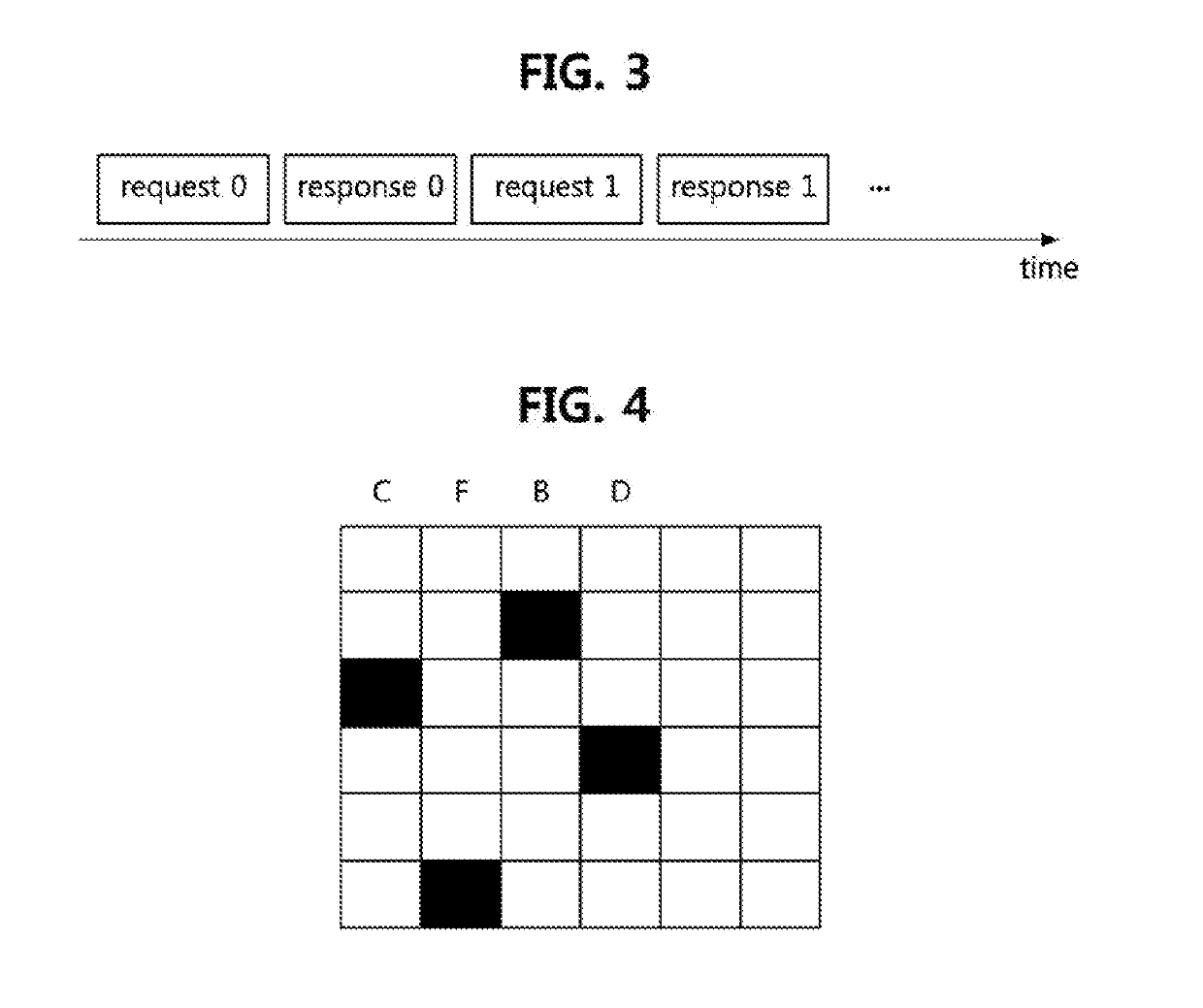

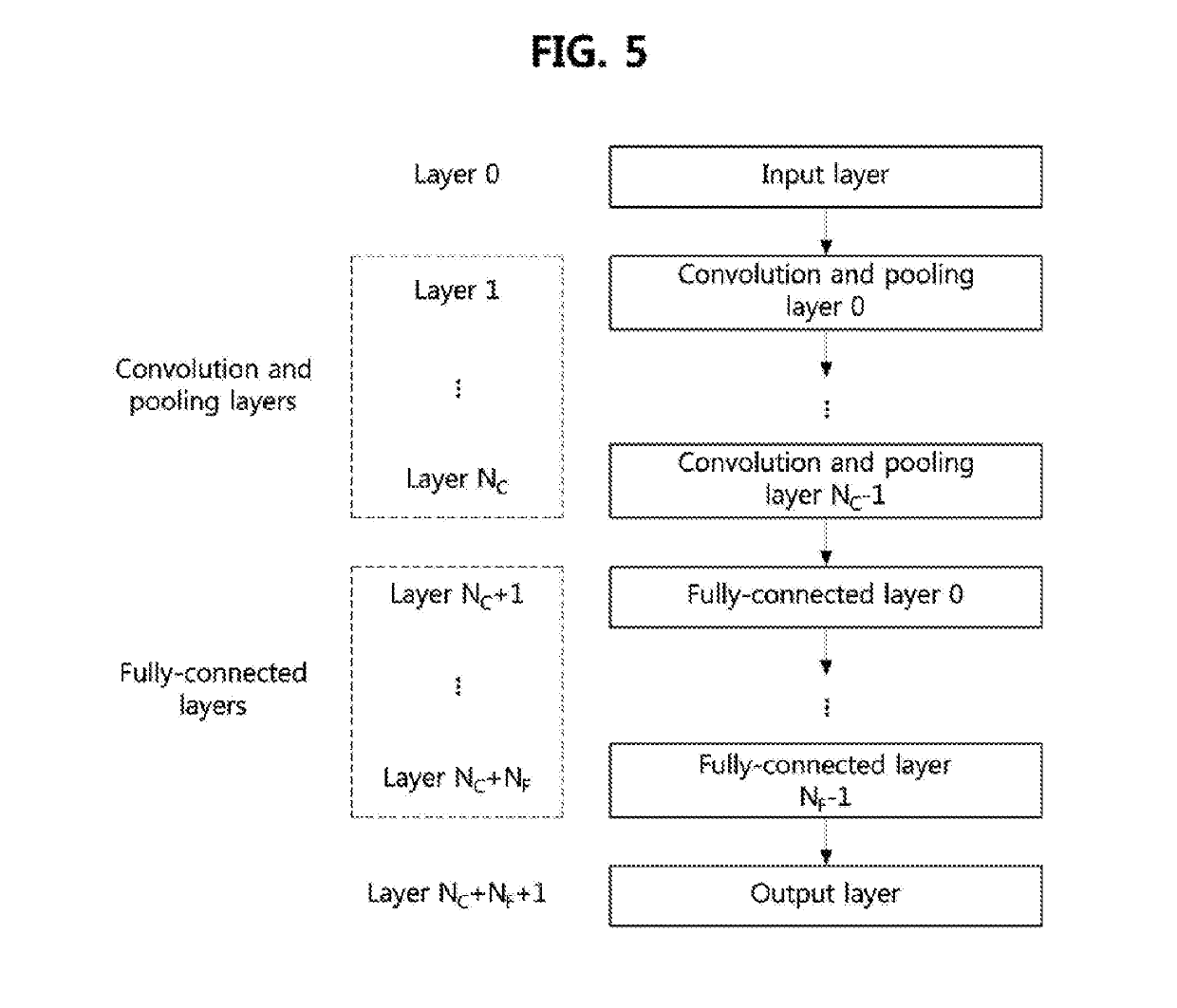

Method for detecting abnormal session

InactiveUS20190095301A1Detecting faulty hardware using neural networksNeural architecturesNeural network analysisComputer science

Provided is a method for detecting an abnormal session including a request message received by a server from a client and a response message generated by the server, the method including transforming at least a part of messages included in the session into data in the form of a matrix, transforming the data in the form of the matrix into a representation vector a dimension of which is lower than a dimension of the matrix of the data using a convolutional neural network, and determining whether the session is abnormal by arranging the representation vectors obtained from the messages in an order in which the messages are generated to compose a first representation vector sequence, and analyzing the first to representation vector sequence using an long short term memory (LSTM) neural network.

Owner:AUTOCRYPT CO LTD

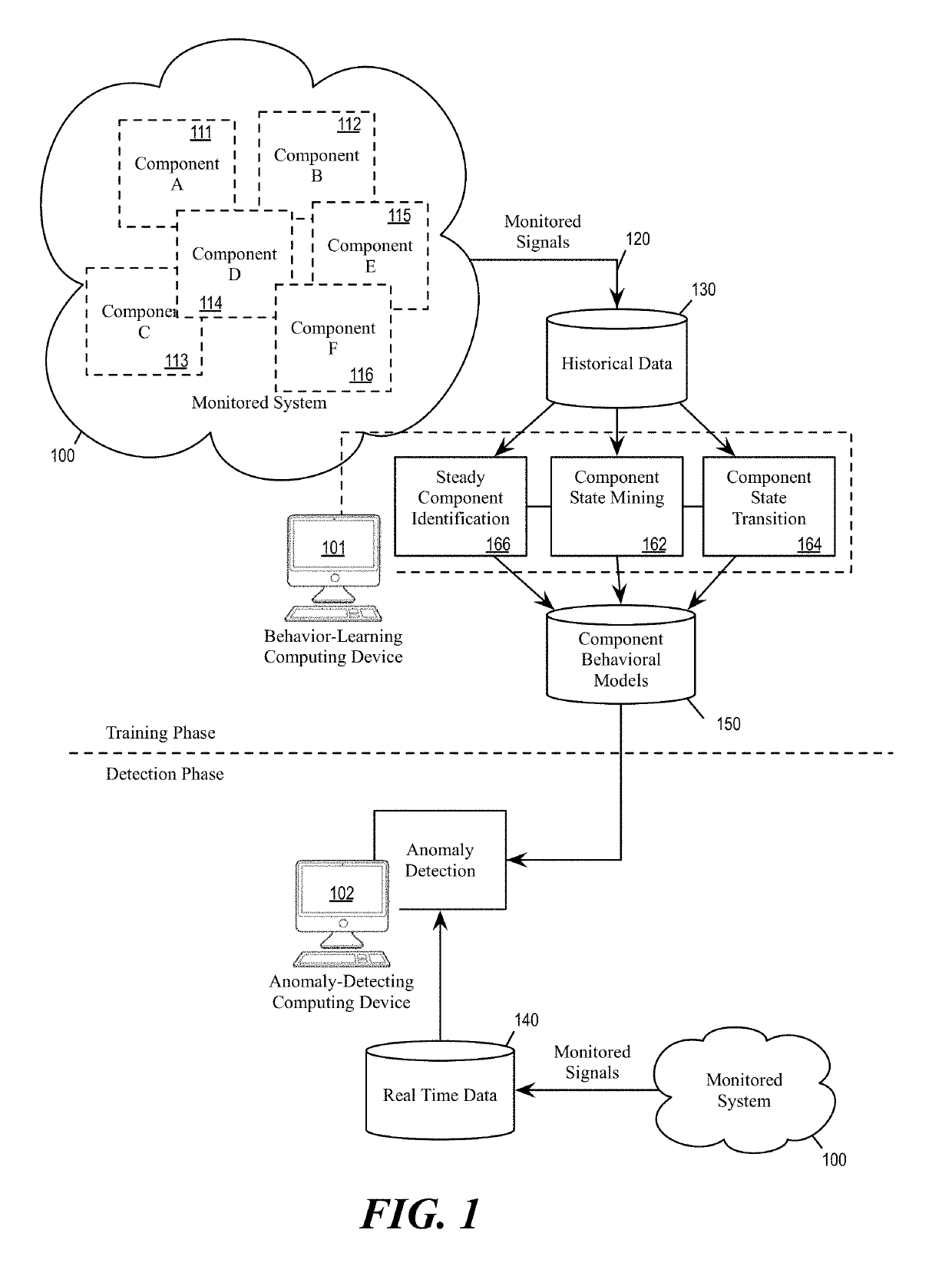

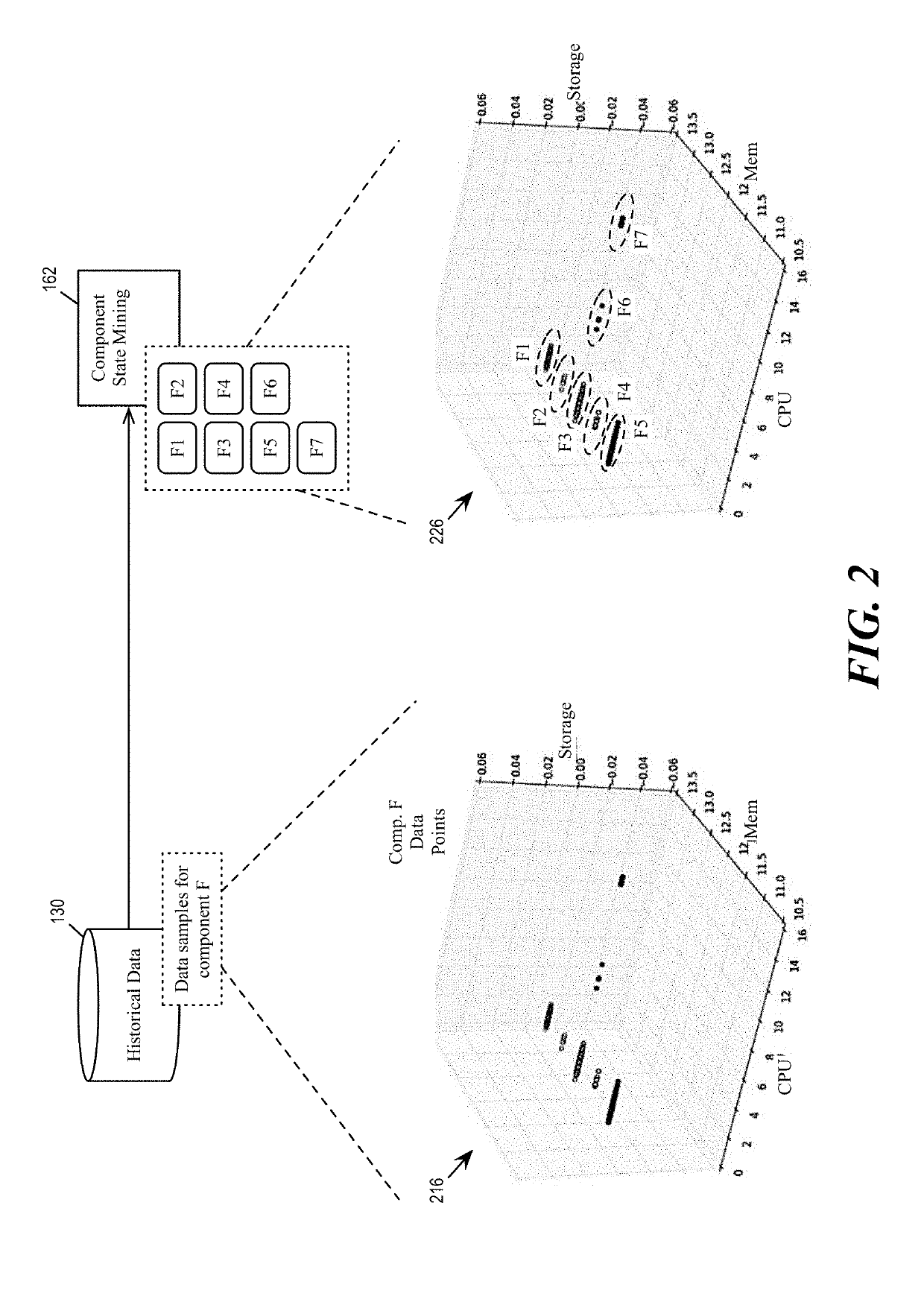

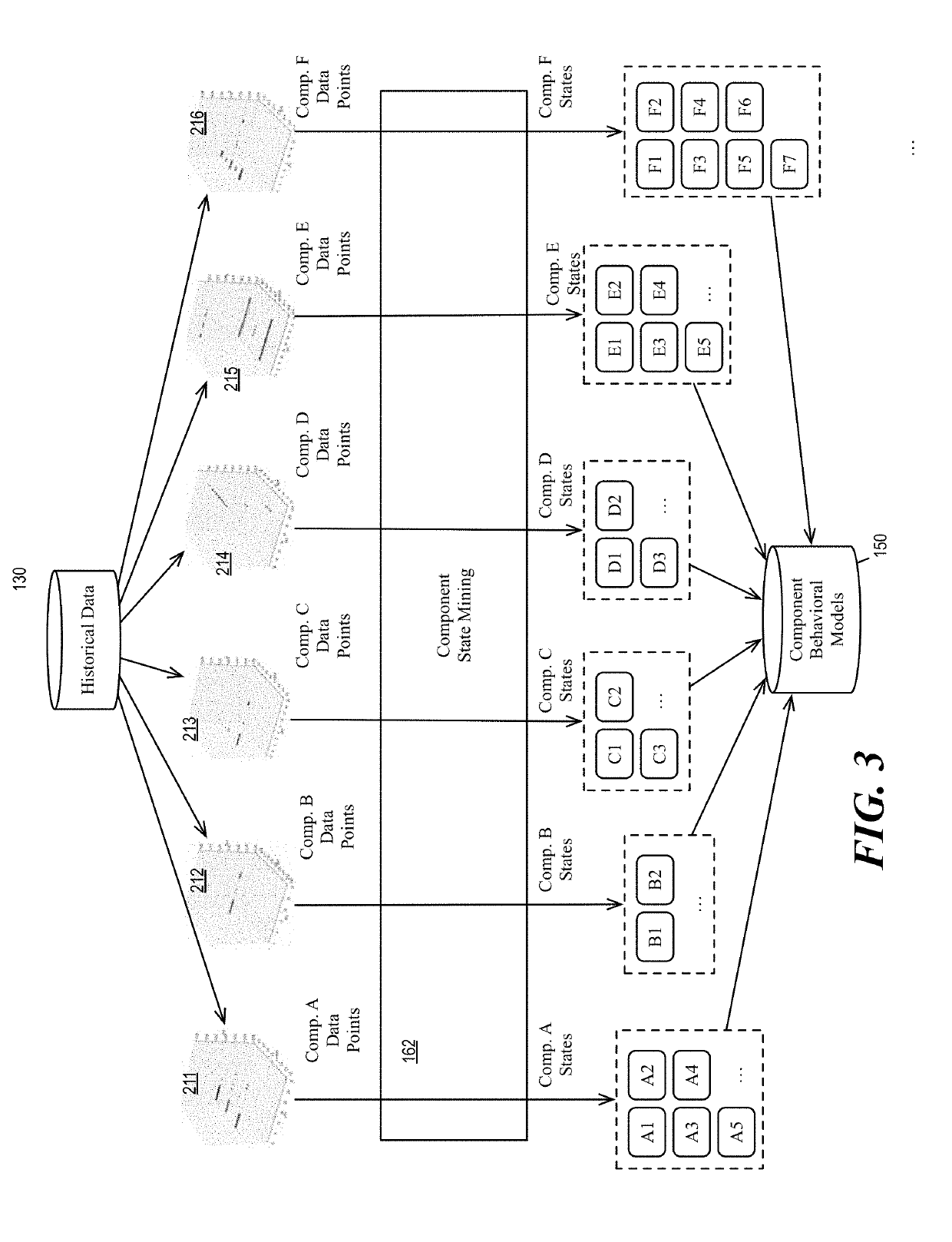

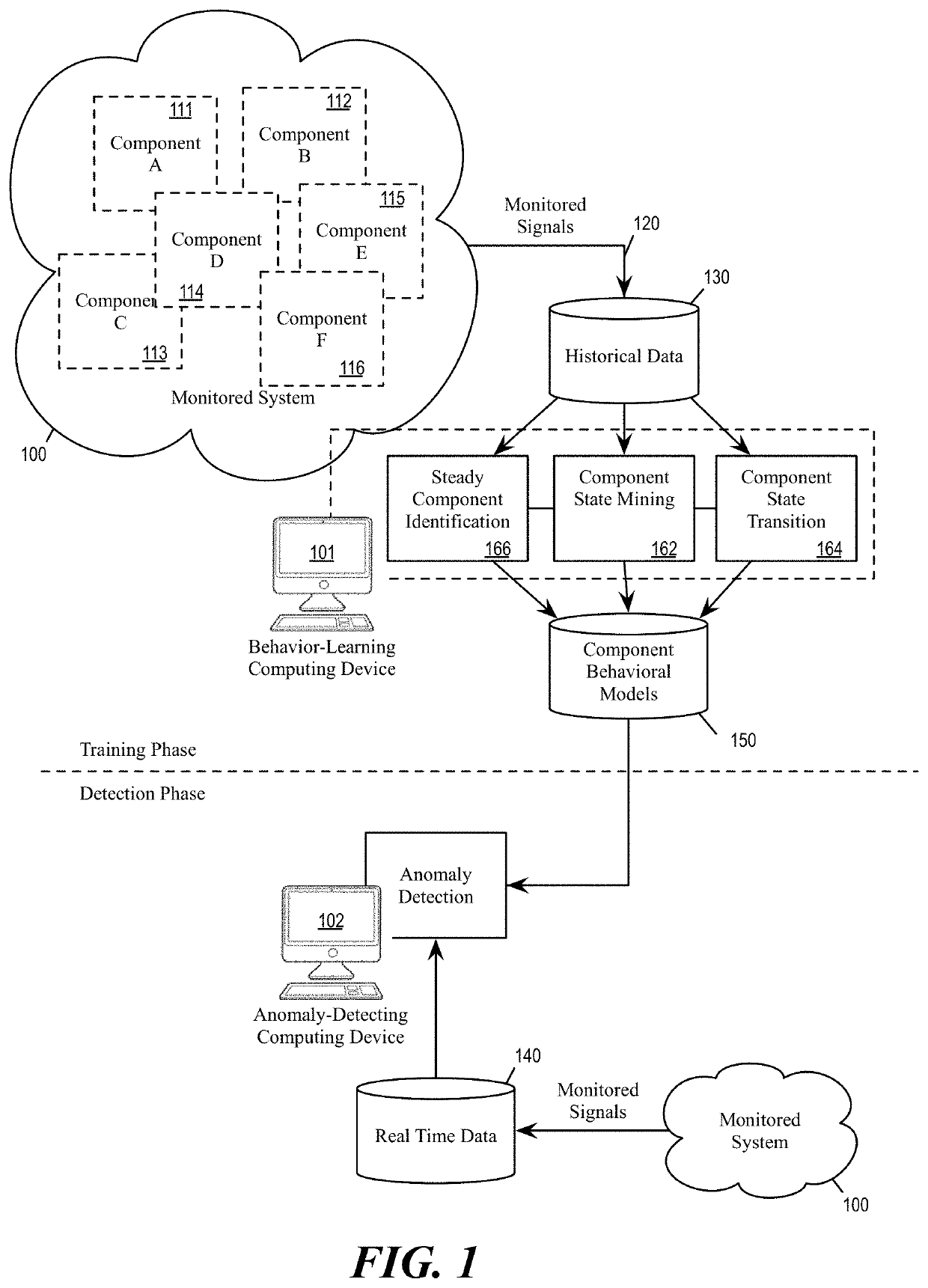

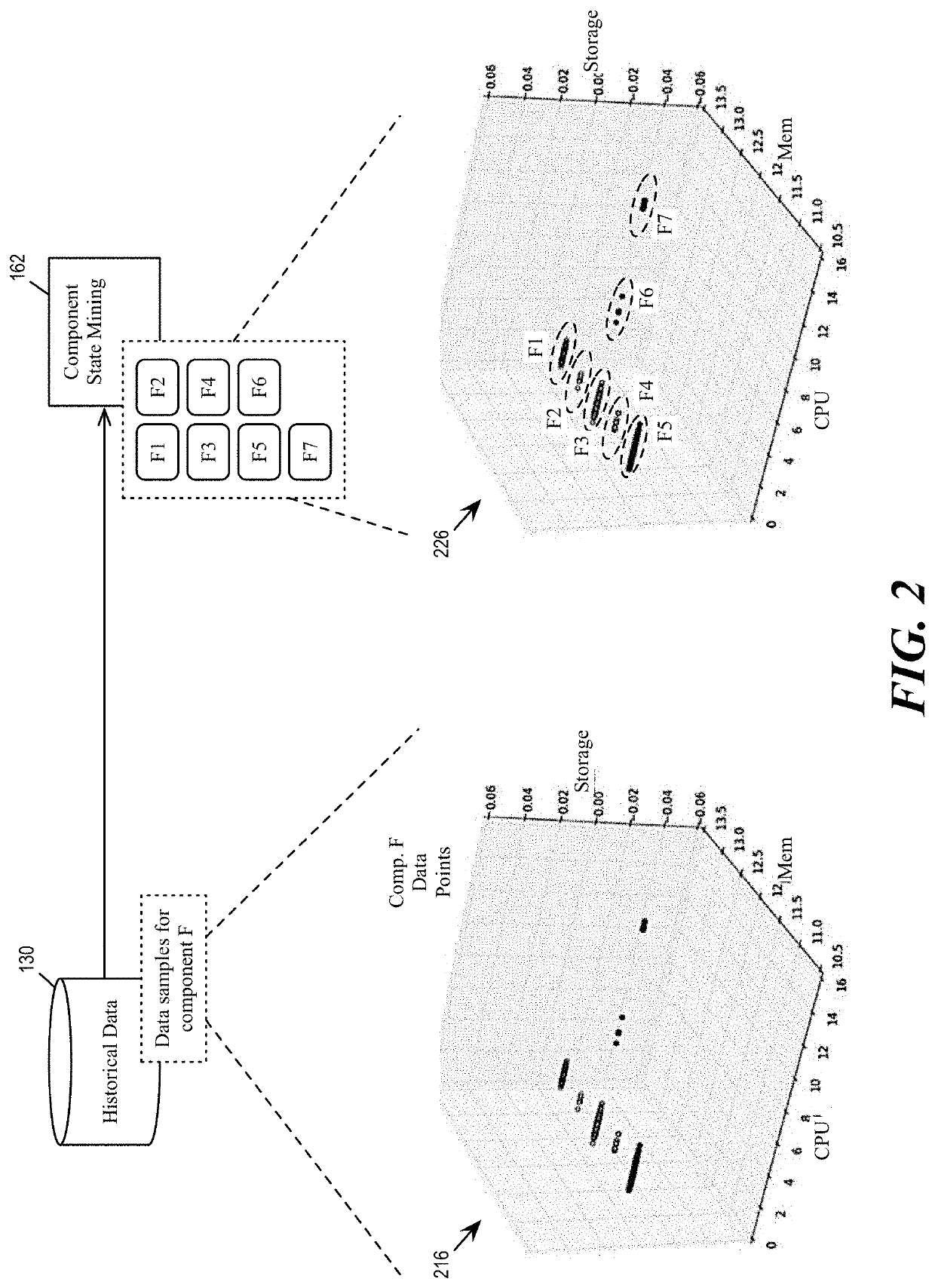

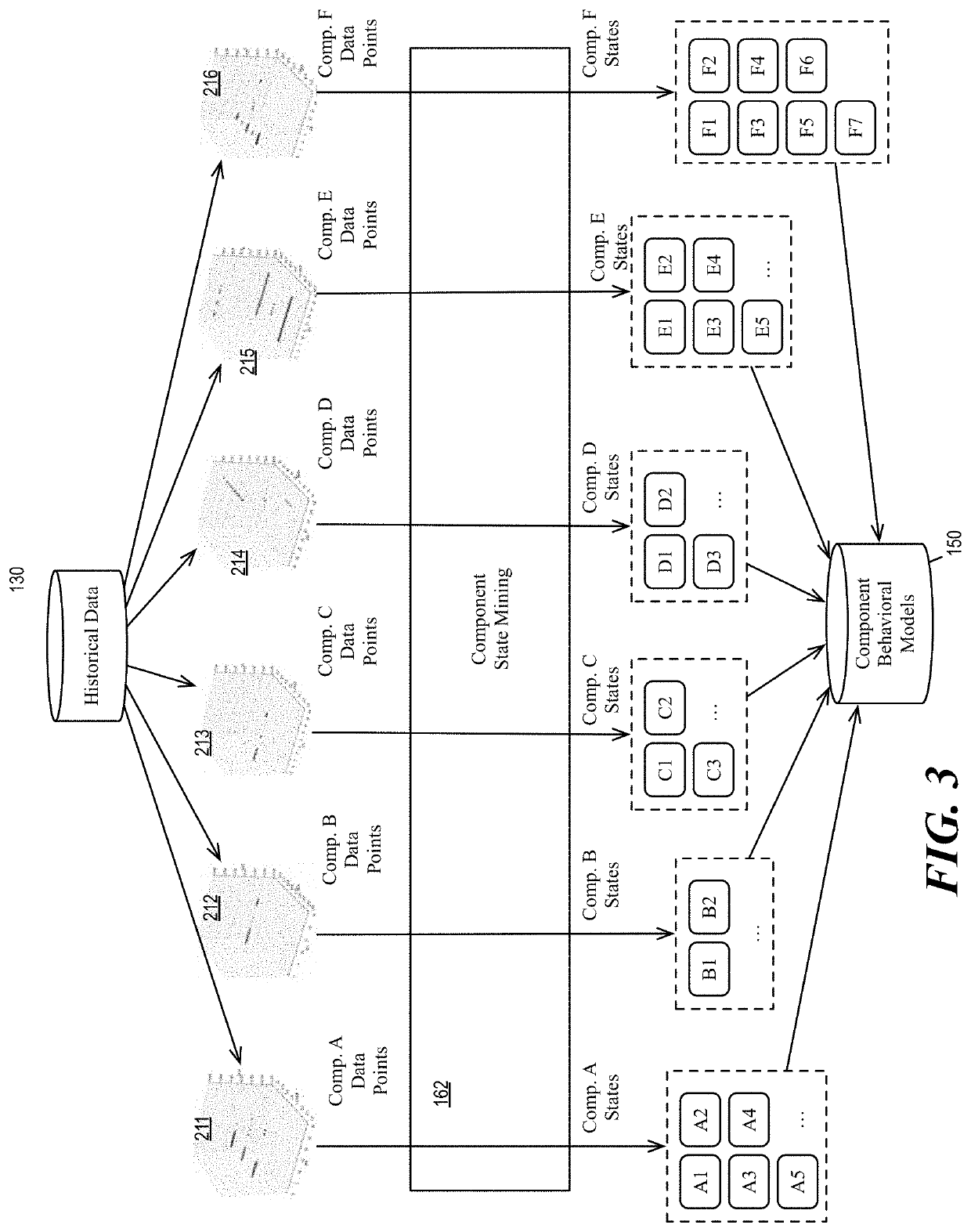

Detection of Misbehaving Components for Large Scale Distributed Systems

ActiveUS20190095266A1Detecting faulty hardware using neural networksHardware monitoringLearning basedReal-time data

A method or apparatus for monitoring a system by detecting misbehaving components in the system is presented. A computing device receives historical data points based on a set of monitored signals of a system. The system has components that are monitored through the set of monitored signals. For each monitored component, the computing device performs unsupervised machine learning based on the historical data points to identify expected states and state transitions for the component. The computing device identifies one or more steady components based on the identified states of the monitored components. The computing device also receives real-time data points based on monitoring the set of signals from the system. For each identified steady component, the computing device examines the received real-time data points for deviation from the expected state and state transitions of the steady component. The computing device reports anomaly in the system based on the detected deviations.

Owner:IBM CORP

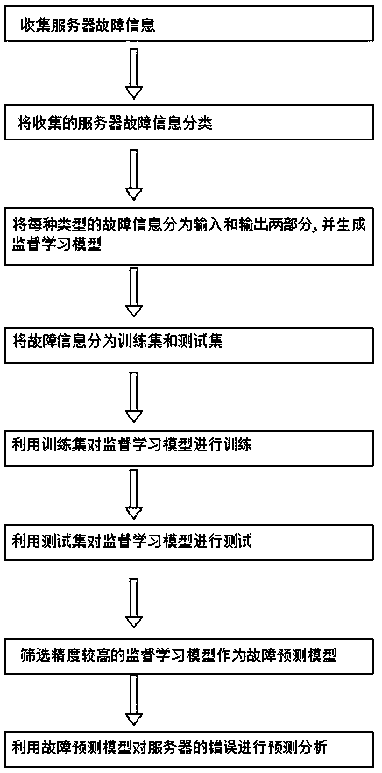

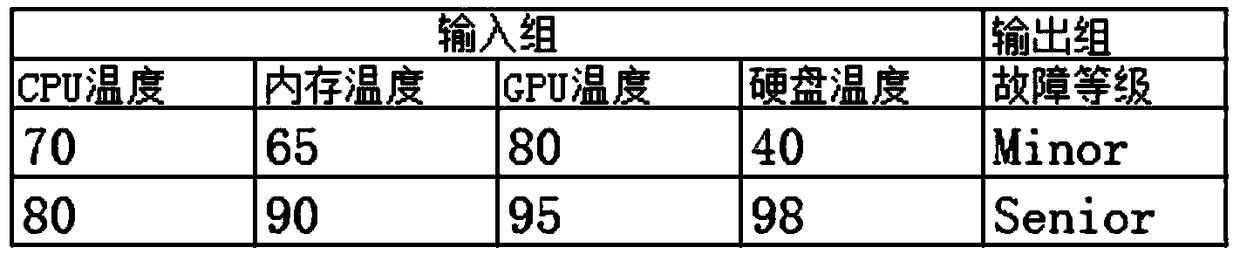

Server error diagnosis method based on supervised learning

InactiveCN108710555AReduce the risk of downtimeFlexible testing methodsDetecting faulty hardware using neural networksHardware monitoringDiagnosis methodsSupervised learning

The invention discloses a server error diagnosis method based on supervised learning. The method specifically includes: utilizing massive fault information to train a supervised-learning model to generate a fault prediction model, and utilizing a fault prediction model for prediction analysis on errors of a server. According to the server error diagnosis method based on supervised learning of theinvention, limitation of traditional methods of setting thresholds to detect faults is broken, a highly efficient algorithm is utilized to automatically analyze and predict log contents, time costs ofmanual server fault diagnosis are released, and fault levels are fully automatically analyzed and predicted.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

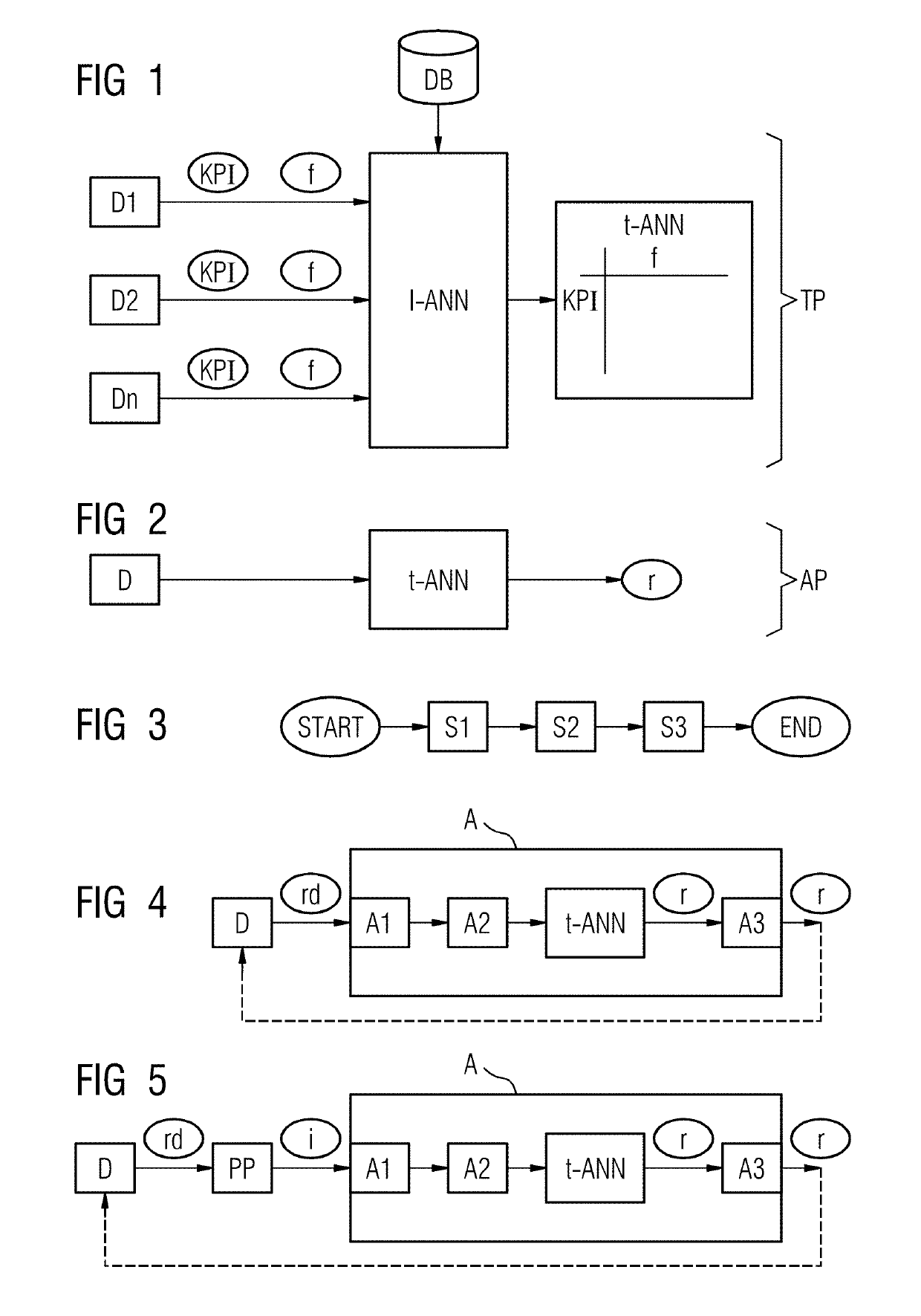

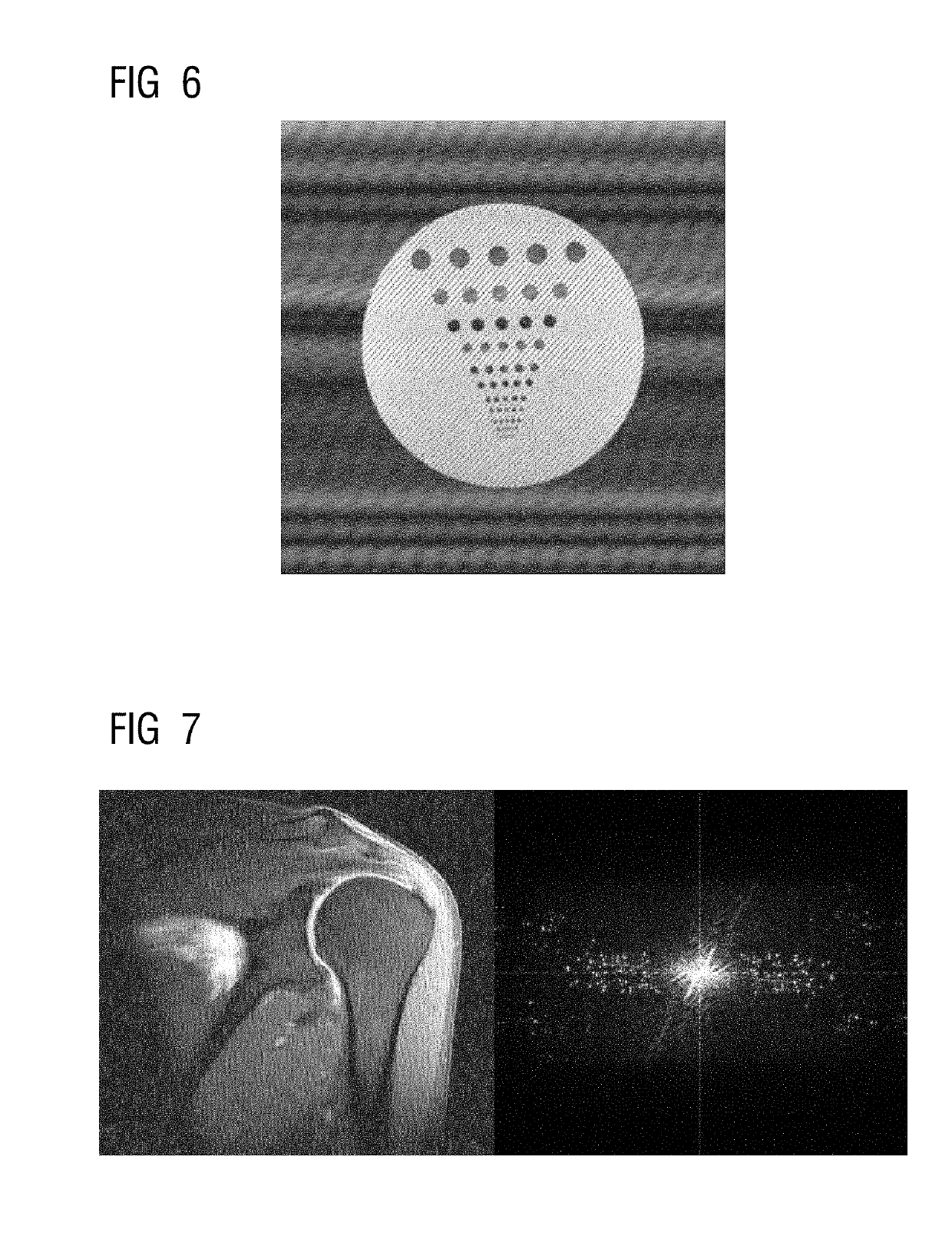

Automatic failure detection in magnetic resonance apparatuses

ActiveUS20190155709A1High sensitivityStrong specificityDetecting faulty hardware using neural networksMagnetic measurementsNeural network systemResonance

In a method, a computer and a medical computer for automatic failure analysis in order to provide a cause of failure of the medical imaging apparatus during operation, input data are read into the computer that include raw data or image data, acquired by the imaging apparatus. A set of performance indicators in the input data is calculated by the computer. A trained neural network system is accessed with the calculated performance indicators, in order to provide result data that, in the case of a failure, identify a failure source.

Owner:SIEMENS HEALTHCARE GMBH

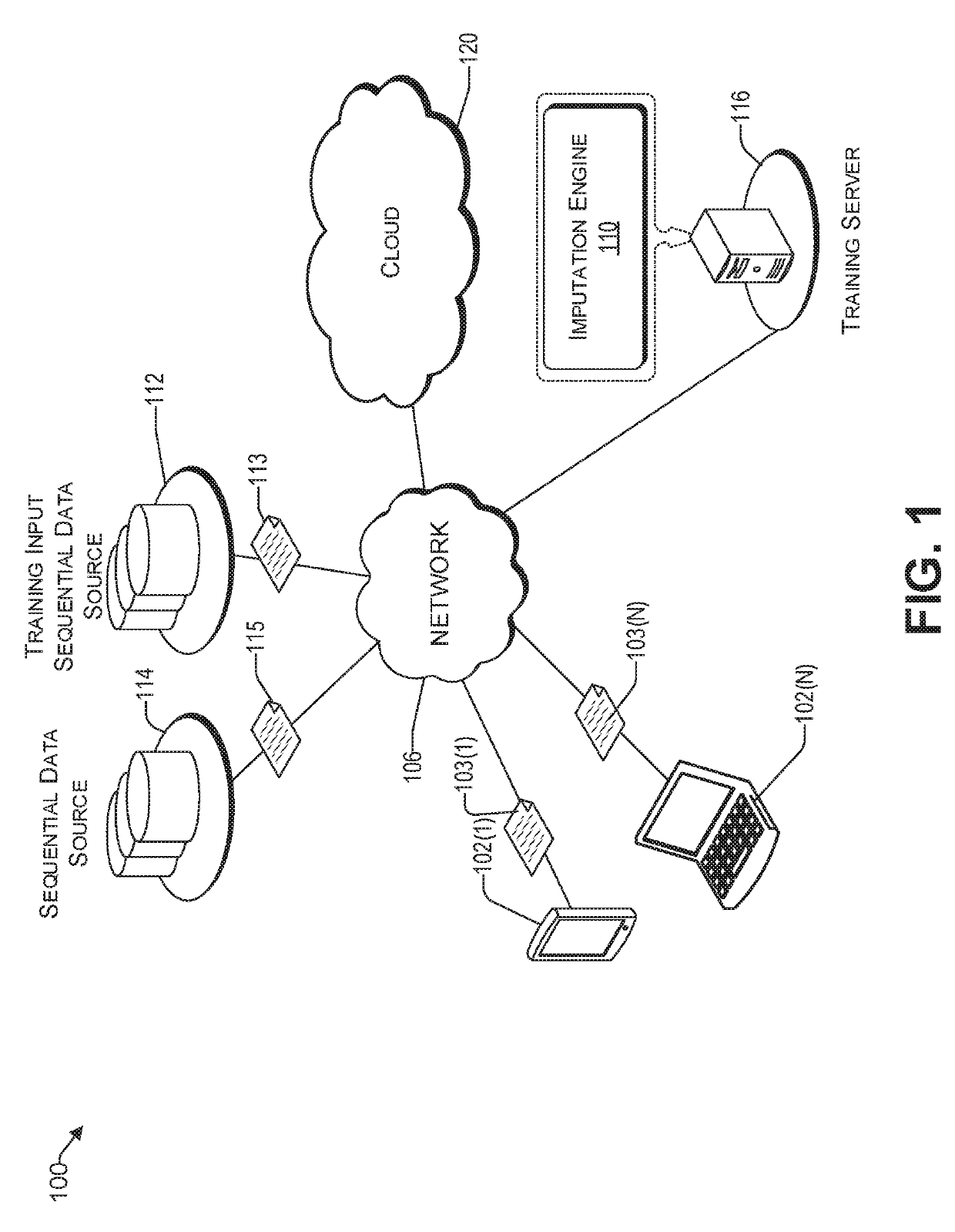

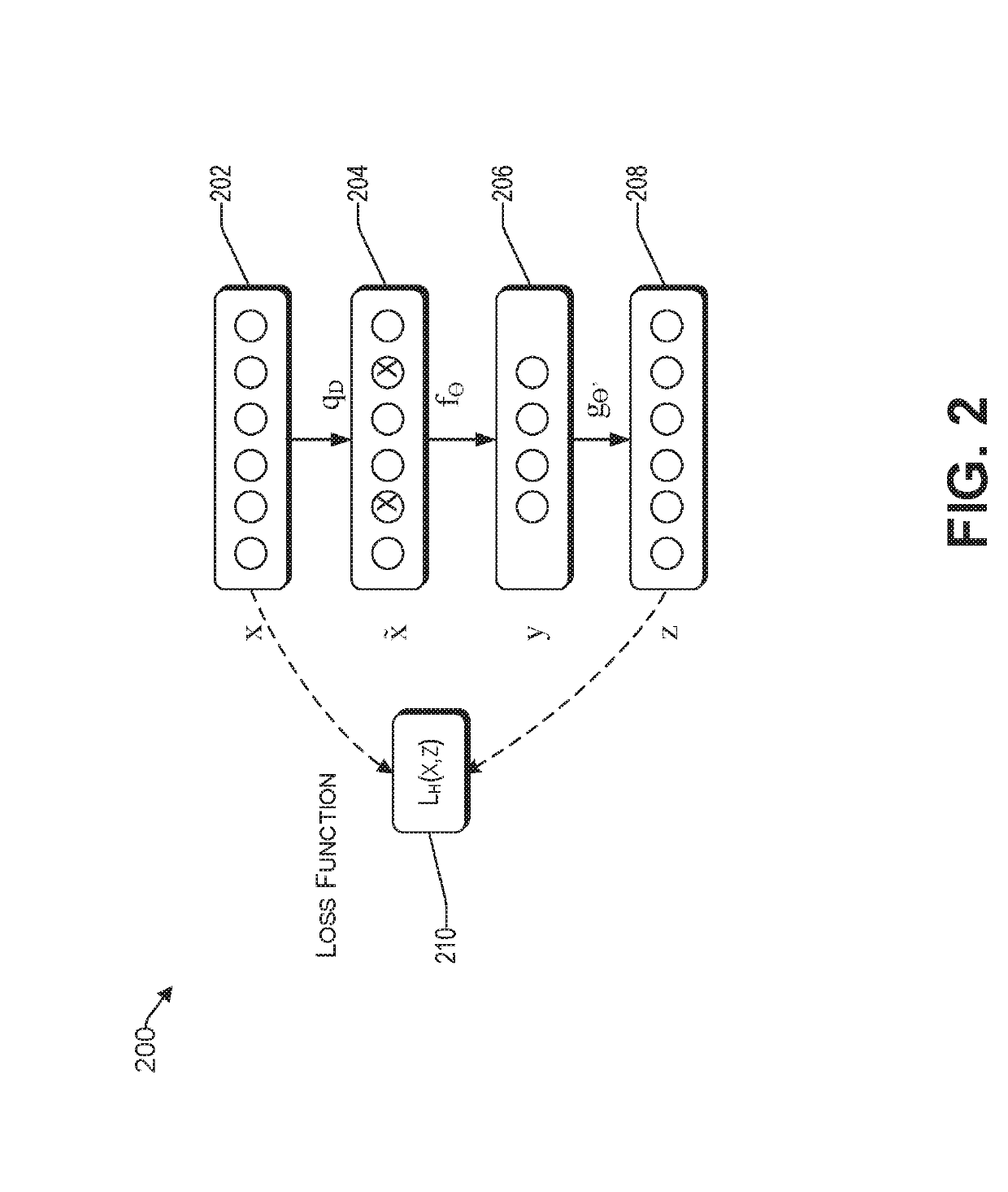

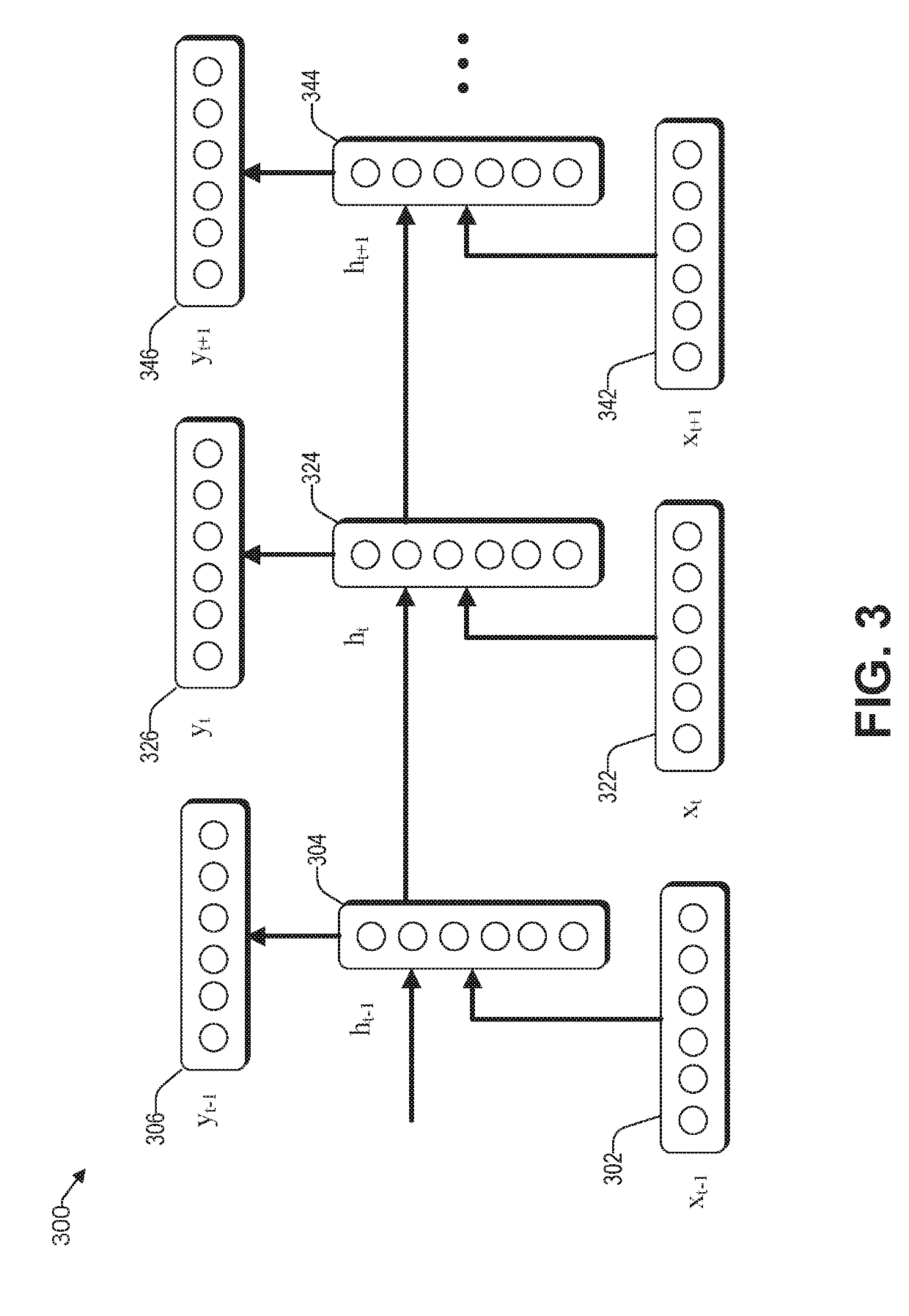

Missing Values Imputation of Sequential Data

ActiveUS20190129819A1Detecting faulty hardware using neural networksNeural architecturesHidden layerEngineering

A method and system of imputing corrupted sequential data is provided. A plurality of input data vectors of a sequential data is received. For each input data vector of the sequential data, the input data vector is corrupted. The corrupted input data vector is mapped to a staging hidden layer to create a staging vector. The input data vector is reconstructed based on the staging vector, to provide an output data vector. adjusted parameter of the staging hidden layer is iteratively trained until it is within a predetermined tolerance of a loss function. A next input data vector of the sequential data is predicted based on the staging vector. The predicted next input data vector is stored.

Owner:IBM CORP

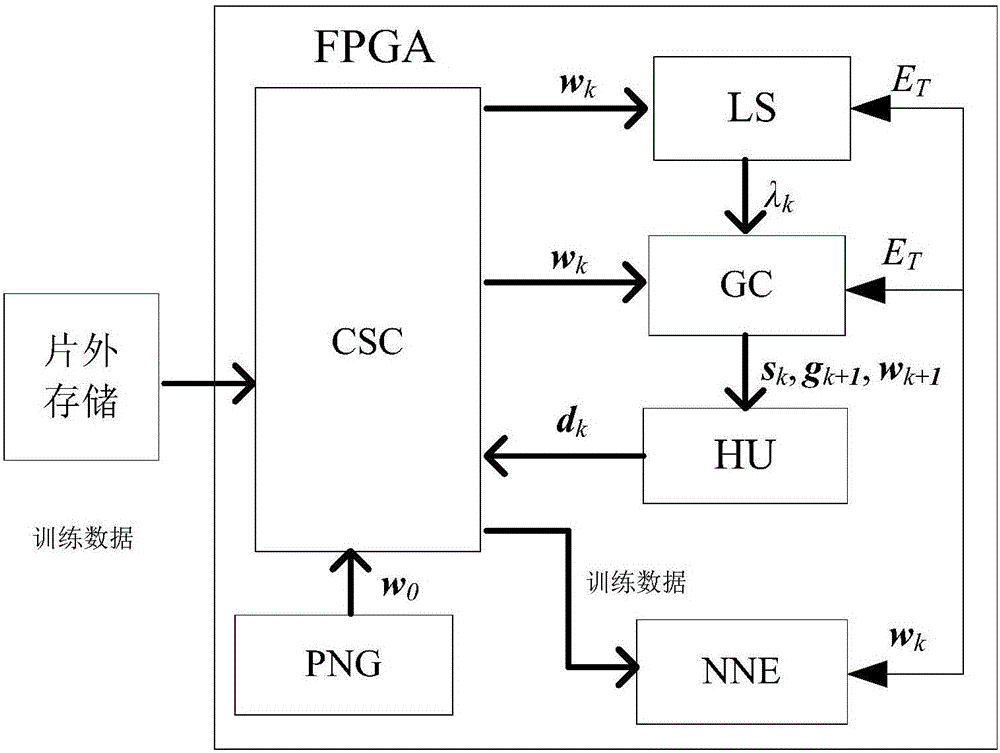

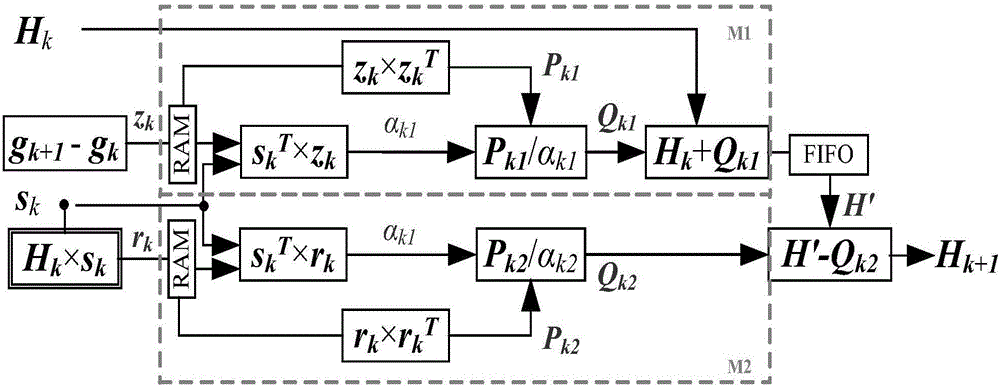

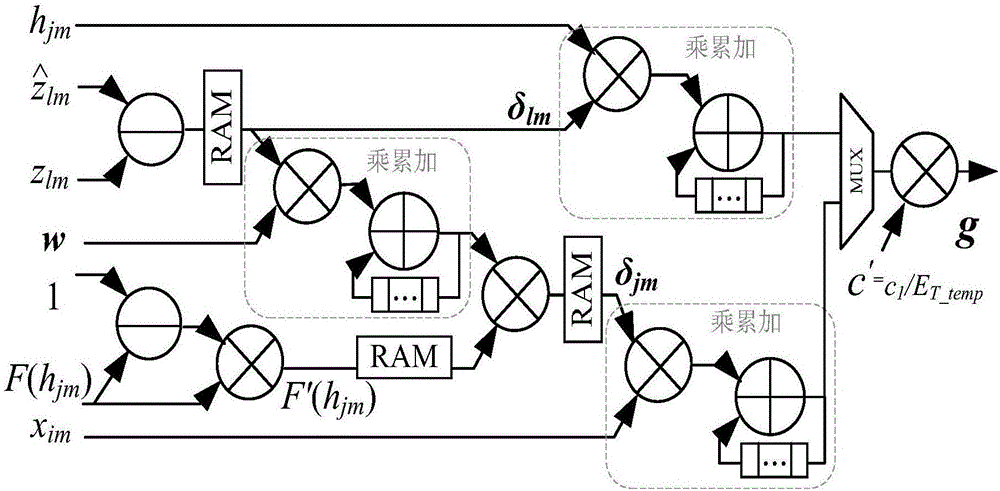

FPGA system and implementation method based on on-line training neural network of quasi-newton method

InactiveCN106528357AMeet the real-time needs of online trainingScalableDetecting faulty hardware using neural networksShift registerHardware structure

The invention discloses a FPGA system and implementation method based on an on-line training neural network of the quasi-newton method. The FPGA system comprises modules of LS, GC, HU, NNE, CSC and PNG. The implementation method includes 1 analyzing c++ codes of the quasi-newton method, dividing the algorithm into three calculation modules, and converting each calculation module into a hardware block by editing Verilog; 2 determining the hardware structure of a neural network evaluation module NNE by editing Verilog according to the topological structure, training method and excitation function of the neural network; 3 generating a module PNG by realizing the random number on the basis of a 32-bit linear shift register; 4 adopting a FPGA on-chip memory as a buffer to link the five hardware modules, storing the middle calculation results, and determining the operation order of the five modules and implementing data delivery between memory and corresponded modules in a manner of a finite state machine; 5 carrying out performance test through hardware design. The speed of neural network training can be increased through the FPGA, and the real-time capability requirements of neural network on-line training can be met.

Owner:TIANJIN UNIV

System failure prediction using long short-term memory neural networks

ActiveUS10289509B2Detecting faulty hardware using neural networksReliability/availability analysisNerve networkSystem failure

Methods for system failure prediction include clustering log files according to structural log patterns. Feature representations of the log files are determined based on the log clusters. A likelihood of a system failure is determined based on the feature representations using a neural network. An automatic system control action is performed if the likelihood of system failure exceeds a threshold.

Owner:NEC CORP

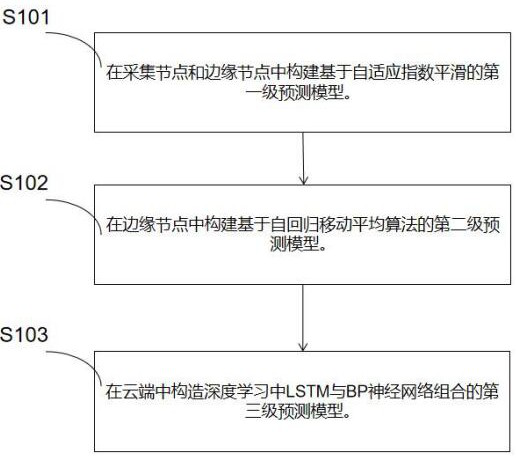

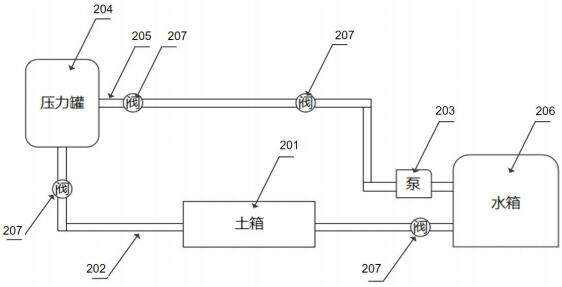

Equipment fault three-level bidirectional early warning method and system based on edge computing

ActiveCN111651312AReduce communication costsReduce false alarm rateDetecting faulty hardware using neural networksHardware monitoringMoving averageAlgorithm

The invention provides an equipment fault three-level bidirectional early warning method and system based on edge computing, and the method comprises the steps: building a first-level bidirectional data sensing prediction model based on an adaptive exponential smoothing algorithm, predicting the data of a collection node, carrying out preliminary screening of a fault signal, uploading the fault signal, and reducing the cost of normal signal transmission; a second-stage bidirectional data perception prediction model of an autoregressive moving average algorithm based on extended Kalman filtering is constructed, and is used for further confirming the accuracy of a fault signal, reducing the false alarm rate and reducing the communication cost between a side end and a cloud end; creating a third-stage bidirectional data perception prediction model based on LSTM and BP neural network combination so that strong computing power is achieved based on edge equipment, he accuracy of data is enhanced, underlying requirements are timely responded, thus reducing time delay of cloud layer transmission. According to the invention, bandwidth and time delay consumed in a data acoustic wave communication transmission process are greatly reduced, and early warning is effectively carried out on a fault signal.

Owner:杭州雪沉科技信息有限公司

Data stream fault detection mechanism in an artificial neural network processor

ActiveUS11221929B1Reduce riskMore efficientDetecting faulty hardware using neural networksNeural architecturesData streamSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

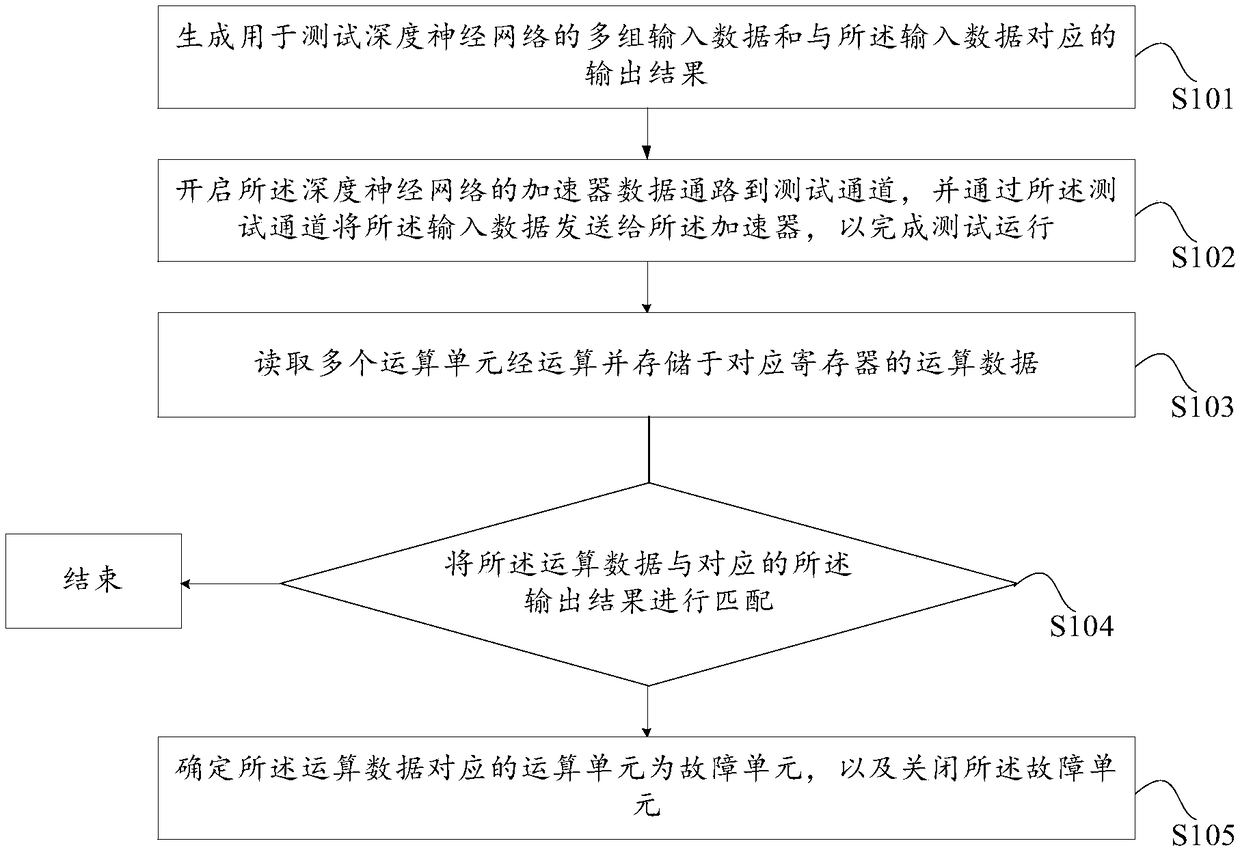

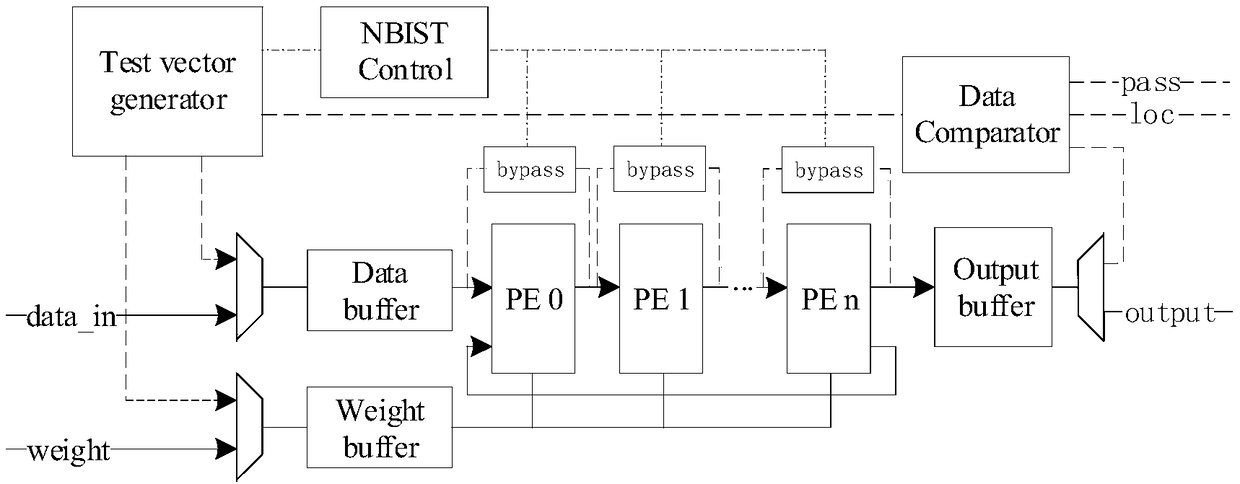

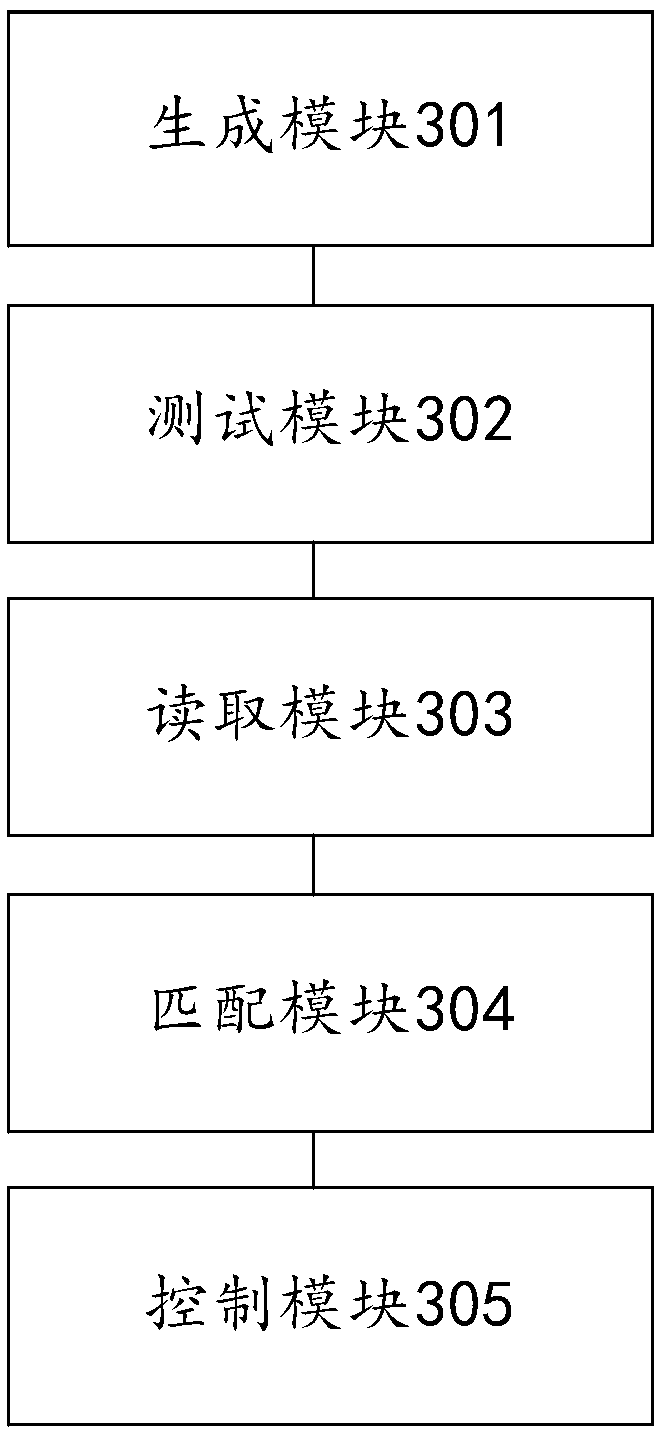

Deep neural network accelerator fault handling method and device

InactiveCN109358993AWith self-test capabilityReduce overheadDetecting faulty hardware using neural networksFaulty hardware testing methodsTest channelFault handling

The embodiment of the invention relates to a deep neural network accelerator fault handling method and device. The method comprises the following steps: generating a plurality of groups of input datafor testing the deep neural network and an output result corresponding to the input data; opening an accelerator data path of the depth neural network to a test channel, and sending the input data tothe accelerator through the test channel to complete the test operation; reading operation data of a plurality of operation units which are operated and stored in corresponding registers; matching theoperation data with a corresponding output result; If there is no match, the operation unit corresponding to the operation data is determined as a fault unit, and the fault unit is turned off, so that the DNN accelerator has the self-test ability, and the manufacturing fault is quickly tested and eliminated in the production stage, the test cost is reduced, and the available chip output is improved.

Owner:中科物栖(北京)科技有限责任公司

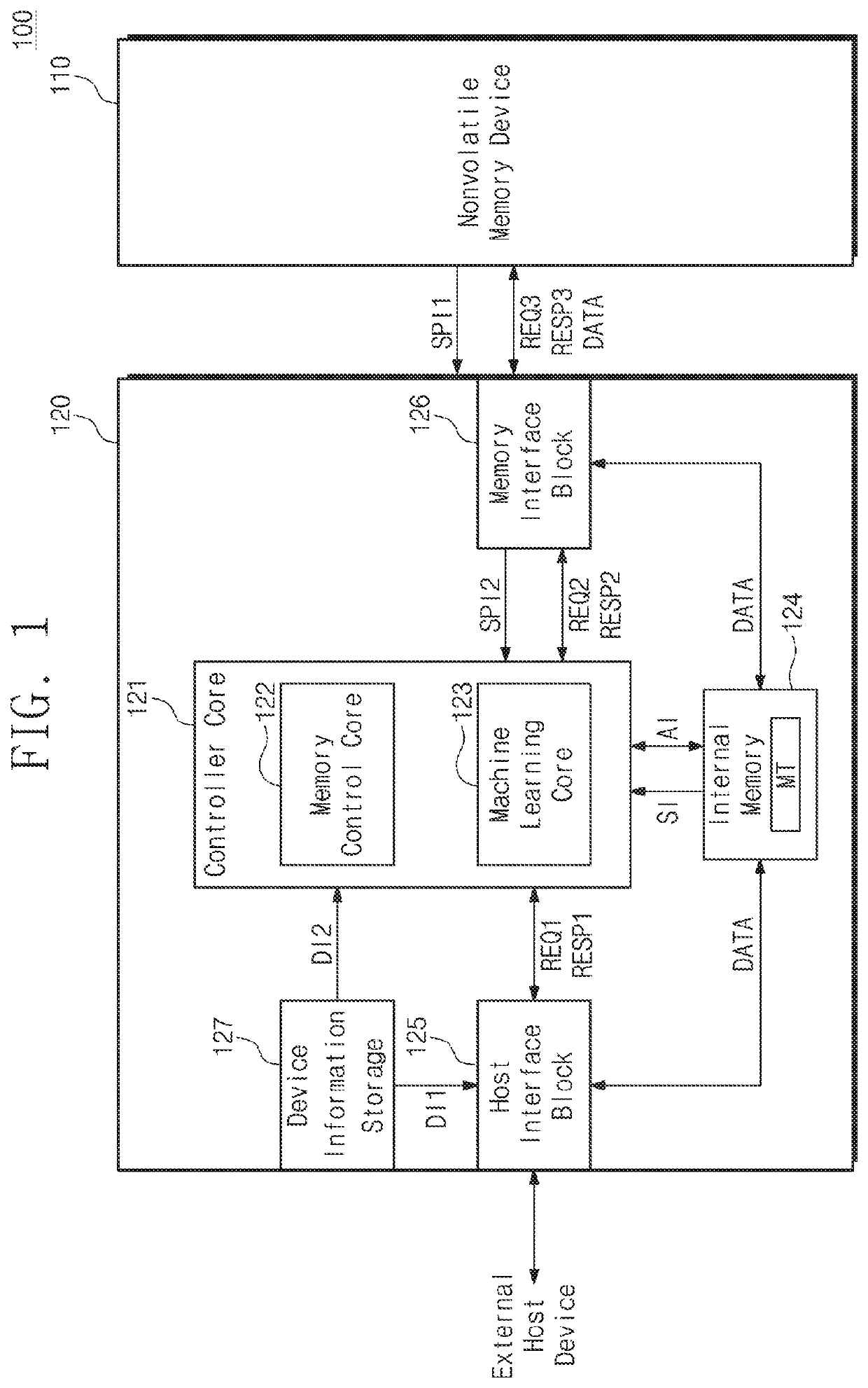

Storage device and operating method of storage device

ActiveUS10802728B2Reliable checkDetecting faulty hardware using neural networksInput/output to record carriersMemory cellEngineering

A storage device includes a nonvolatile memory device including a plurality of memory blocks, each including a plurality of memory cells connected to a plurality of word lines, and a controller configured to perform a first read operation on memory cells connected to a selected word line included in a selected memory block based on a request of an external host device. The controller is further configured to perform a check read operation that checks a reliability of the memory cells of the selected memory block after performing the first read operation. In the check read operation, the controller is further configured to select and perform one of an actual check and a machine learning-based check.

Owner:SAMSUNG ELECTRONICS CO LTD

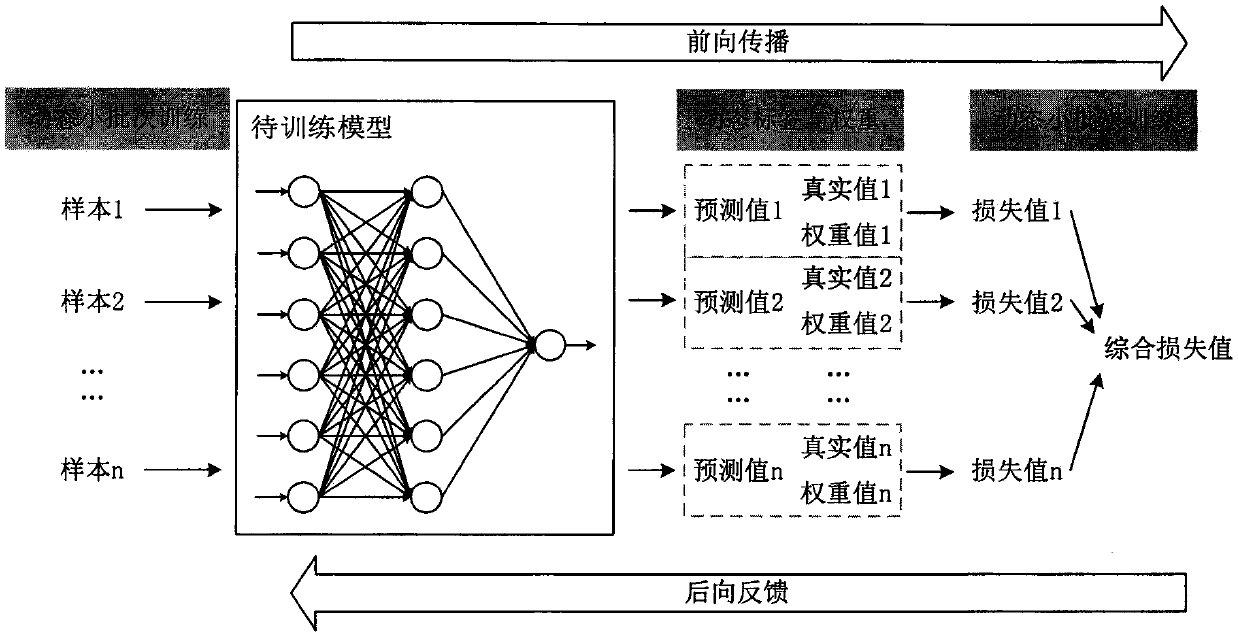

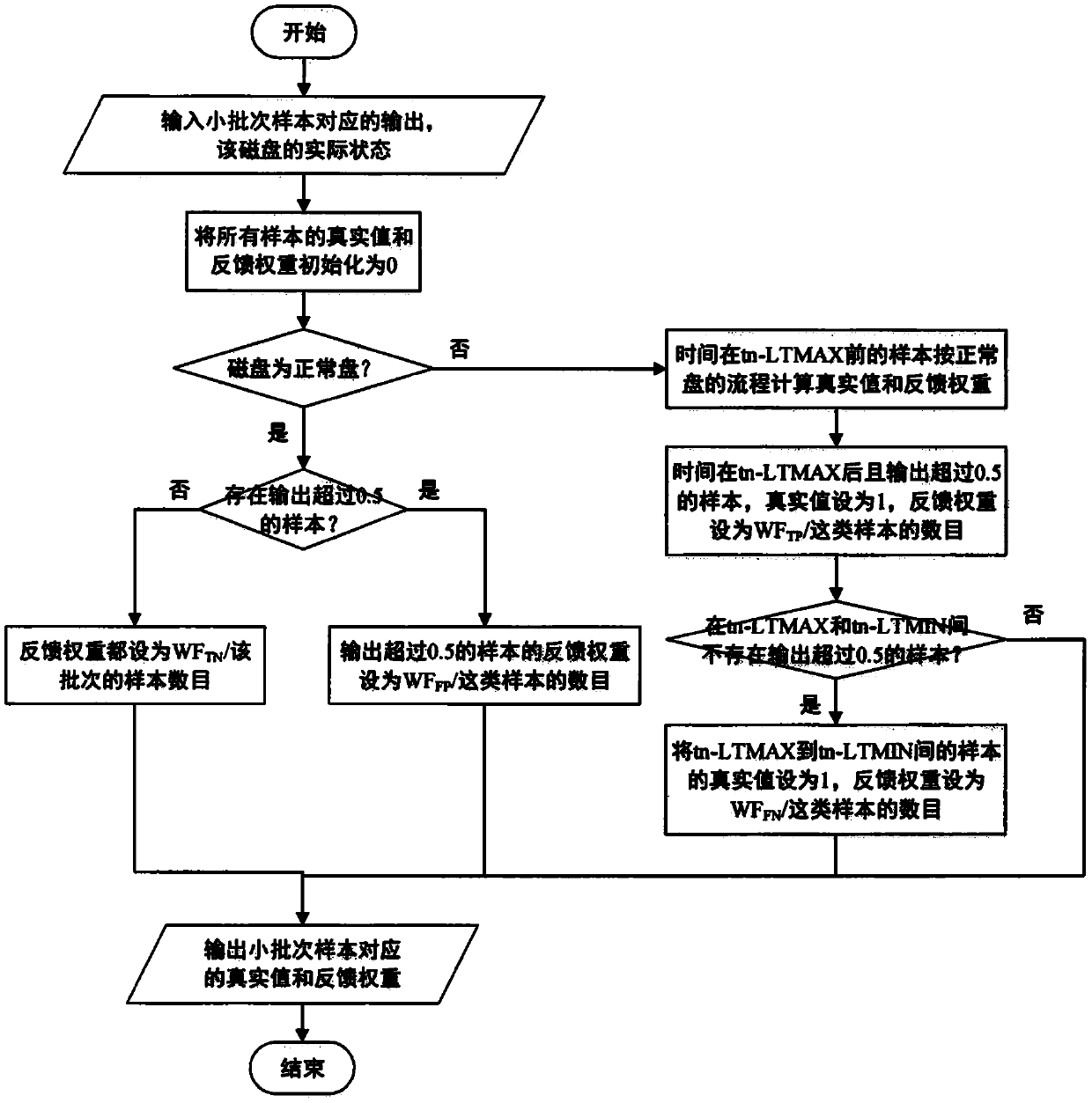

Storage device fault prediction method and system

ActiveCN110347538AStable trainingImprove accuracyDetecting faulty hardware using neural networksNeural architecturesPrediction methodsDevice failure

The invention discloses a storage device fault prediction method and system, and belongs to the technical field of computer storage. The method comprises the following steps: S1, acquiring SMART attribute data of N storage devices at different time points; S2, disordering the sequence of all the storage devices and selecting the j = 1 storage device; S3, using the SMART attribute data of the storage device at each time point as small-batch samples and input into a fault prediction model for training, and an output result is obtained; S4, dynamically adjusting the label and feedback weight of each sample according to the state of the time point tn of the storage device, the output result, the LTMIN and the LTMAX; s5, calculating the comprehensive loss Lossj of the batch; S6, selecting a next storage device, and repeating the steps S3 to S6; S5, calculating the total loss Lossfinal of all the storage devices in the period until all the storage devices are taken out; S7, judging whether Lossfinal is converged or not, if yes, obtaining a trained prediction model, entering the step S8, and otherwise, entering the step S2; and S8, inputting the current SMART attribute data of the to-be-predicted storage device into the trained prediction model to obtain a prediction result.

Owner:HUAZHONG UNIV OF SCI & TECH

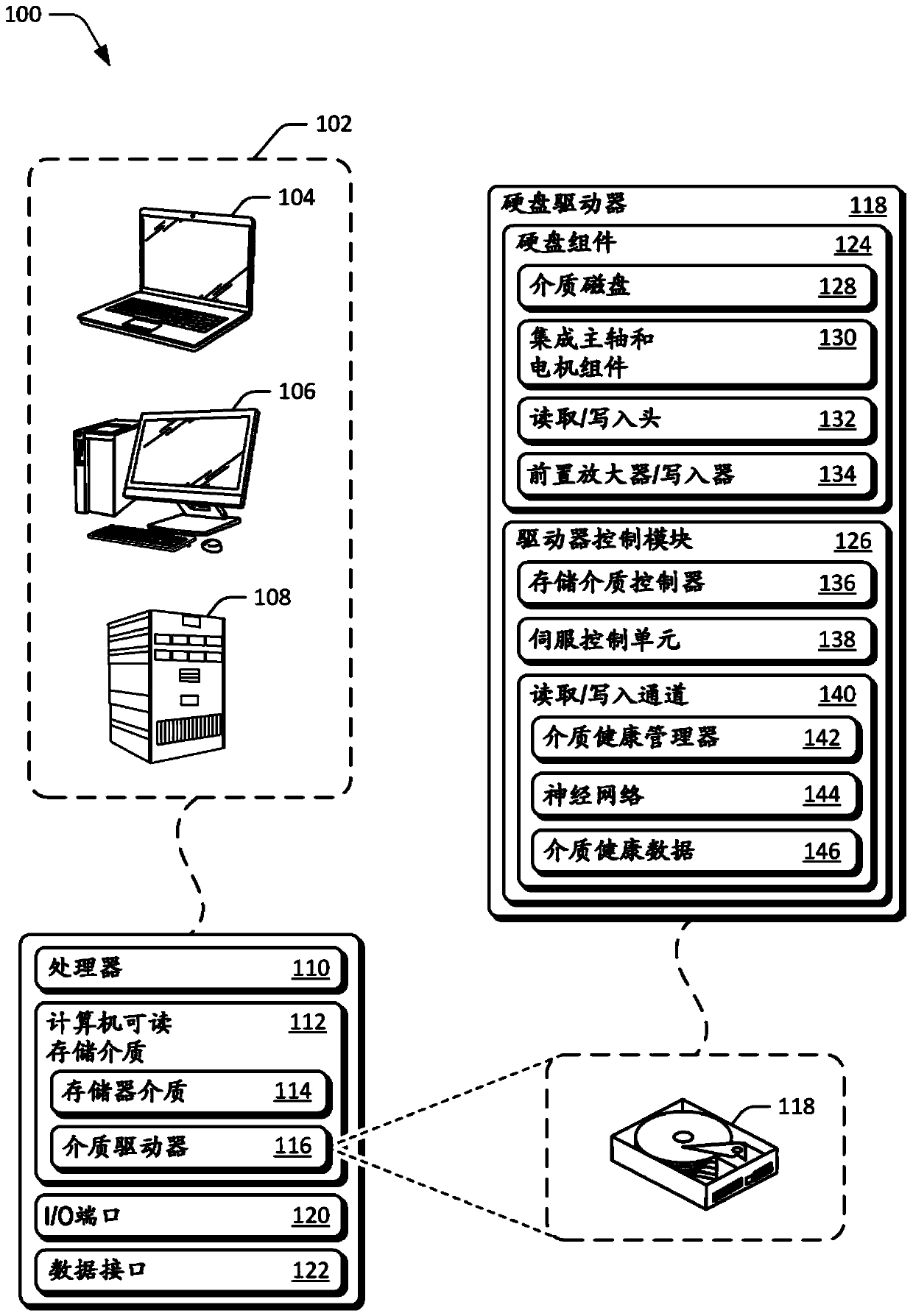

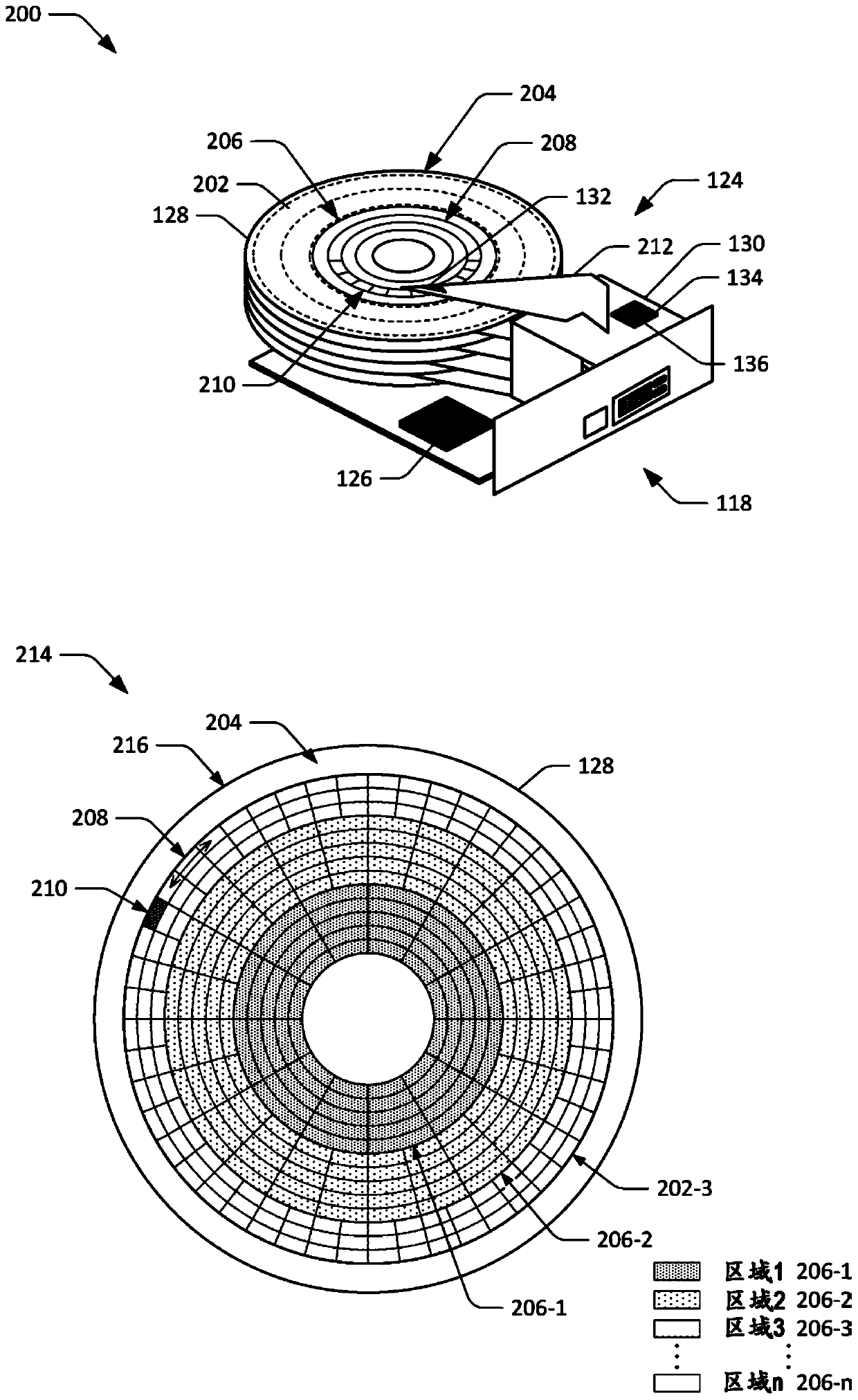

Health management for magnetic storage media

PendingCN111508532ADetecting faulty hardware using neural networksModification of read/write signalsNerve networkMagnetic storage

The present disclosure describes aspects of health management for magnetic storage media. In some aspects, a media health manager determines, with a read channel, read metrics for a sector of magneticstorage media that resides in a zone of magnetic storage media. The media health manager accesses read metrics of the zone and updates the read metrics of the zone based on the read metrics determined for the sector to provide updated read metrics for the zone of magnetic storage media. A health score for the zone of magnetic storage media is then determined with a neural network based on the updated read metrics of the zone of magnetic storage media. By so doing, gradual wear of the magnetic storage media may be predicted using the health score, enabling replacement of a magnetic storage media device before failure to improve reliability or availability of data stored to the device.

Owner:MARVELL ASIA PTE LTD

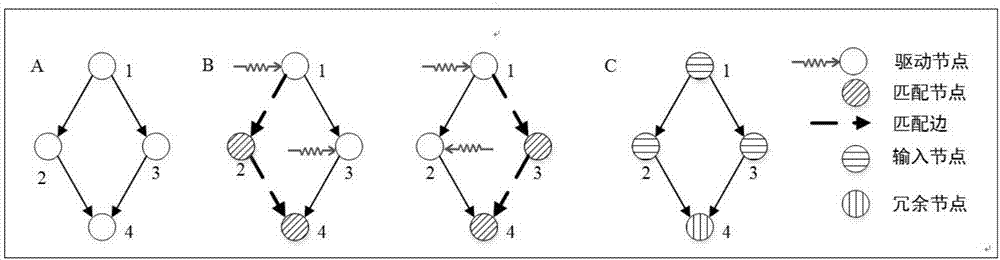

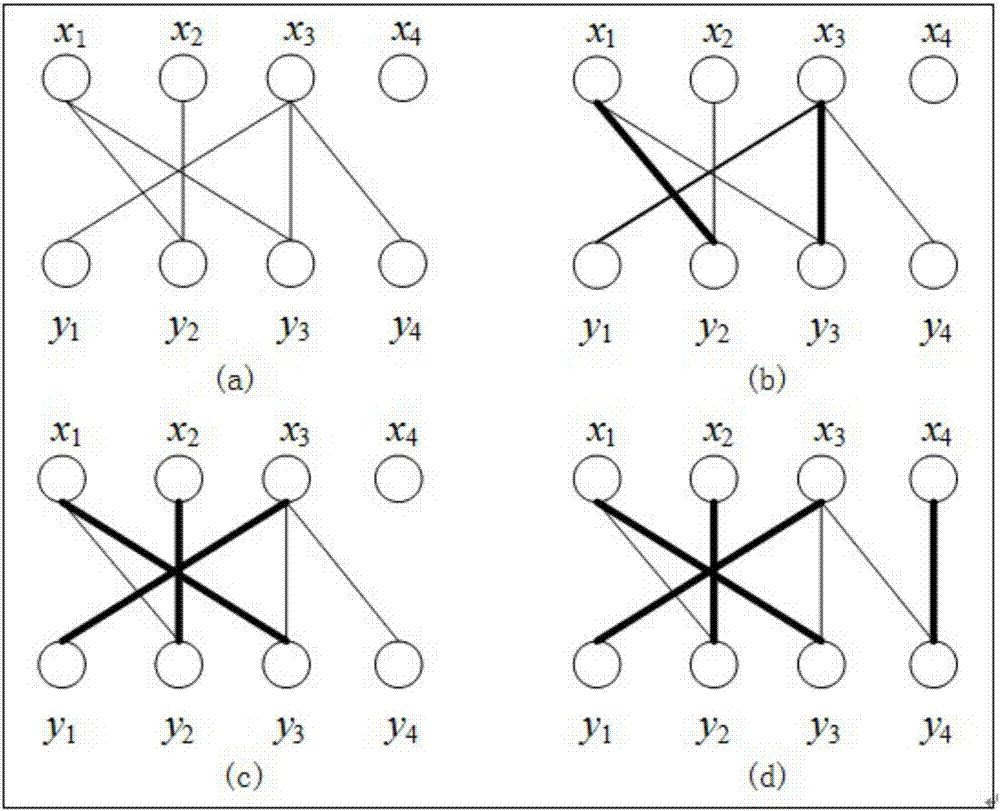

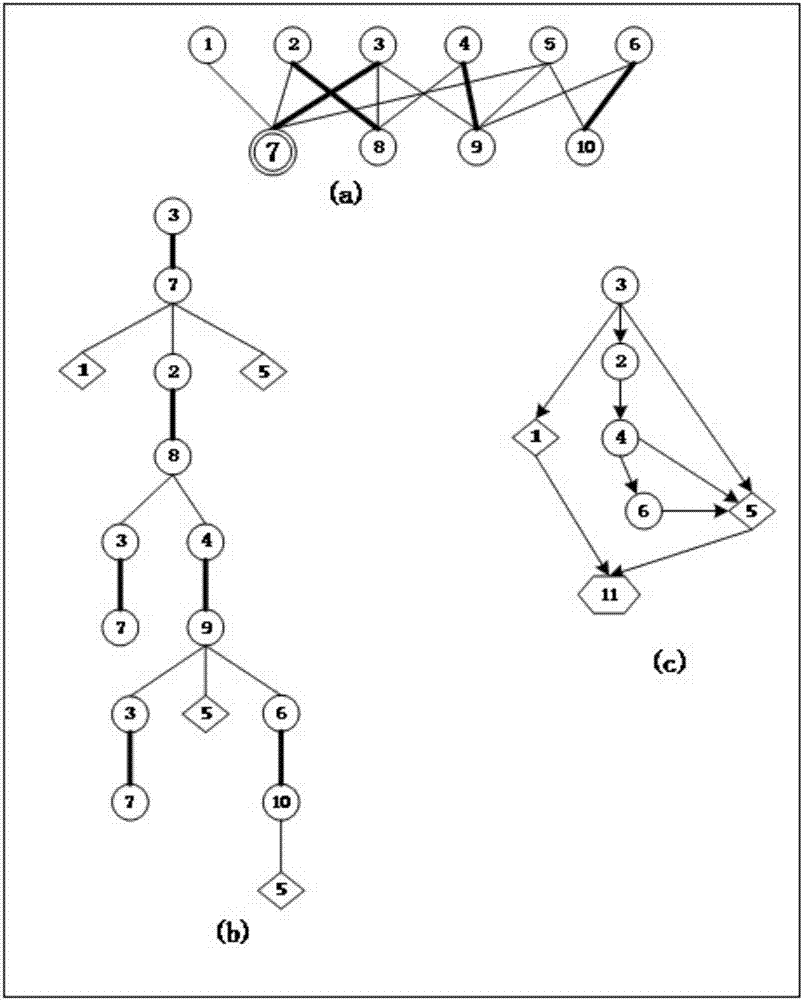

Method for changing node control category in complex network

ActiveCN108009061AImprove controllabilityLower conversion costDetecting faulty hardware using neural networksPhysical realisationNODALMinimum cut

The present invention provides a method for changing a node control category in a complex network. The method comprises: for a to-be-processed redundant node n, acquiring all unsaturated nodes in thenetwork that can arrive at the redundant node n through a staggered path; constructing a staggered network by taking the redundant node n as the starting point; using the minimum cut algorithm to process the staggered network to obtain a set of minimum edges that requires to be deleted when the redundant node n is disconnected from all the unsaturated nodes on the staggered path; identifying the alternative ring including the redundant node n in the network, and based on the identified alternative ring, determining contiguous edges that are required to destroy the alternative ring; deleting all the contiguous edges in the set of the minimum edges, and deleting the determined contiguous edges that require to be deleted in order to destroy the alternative ring; and selecting one staggered path from the redundant node n, and deleting a matched edge in the selected staggered path, so that the redundant node n is converted into an input node. The method provided by the present invention greatly reduces the conversion cost and has higher efficiency.

Owner:NORTHEASTERN UNIV

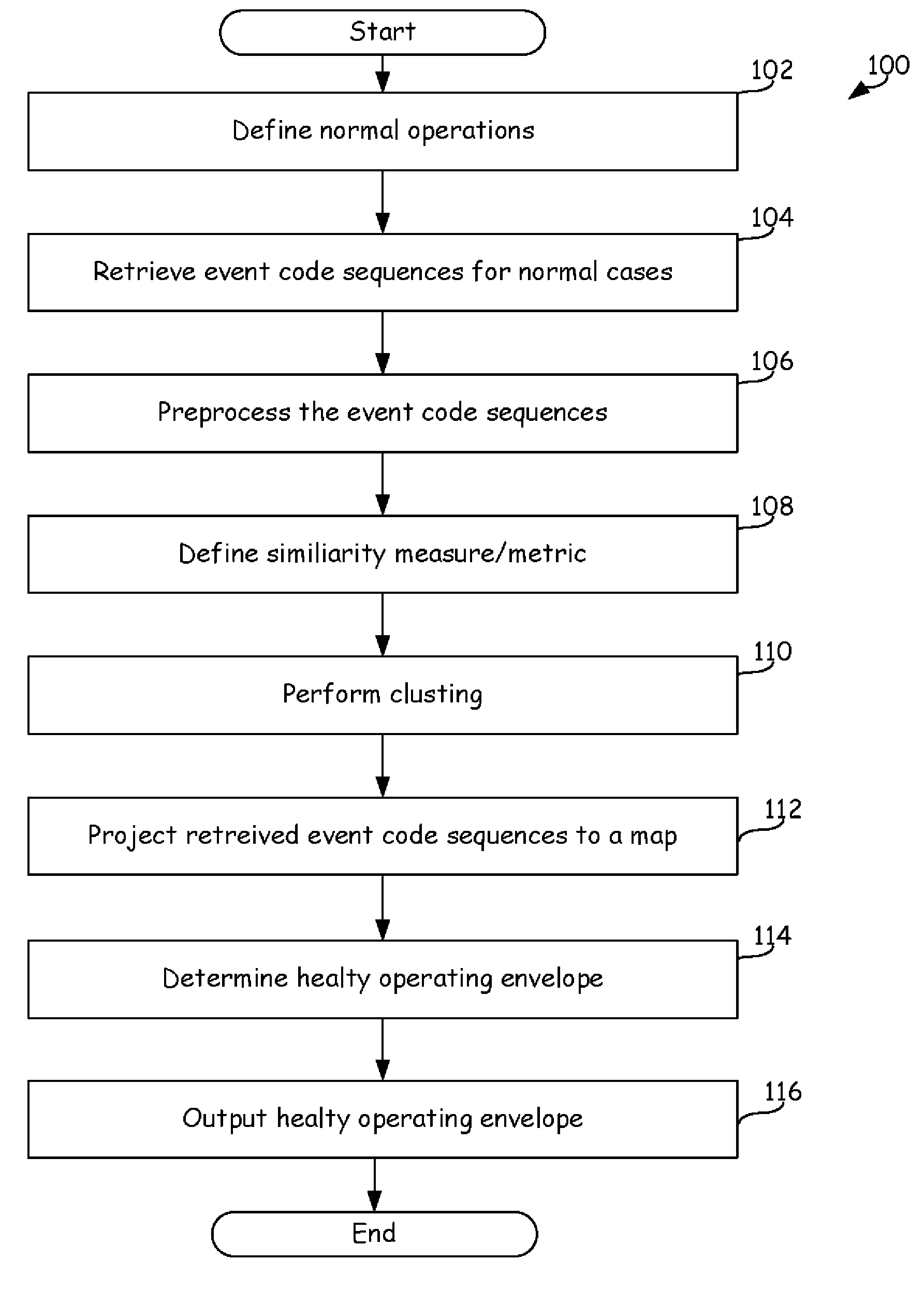

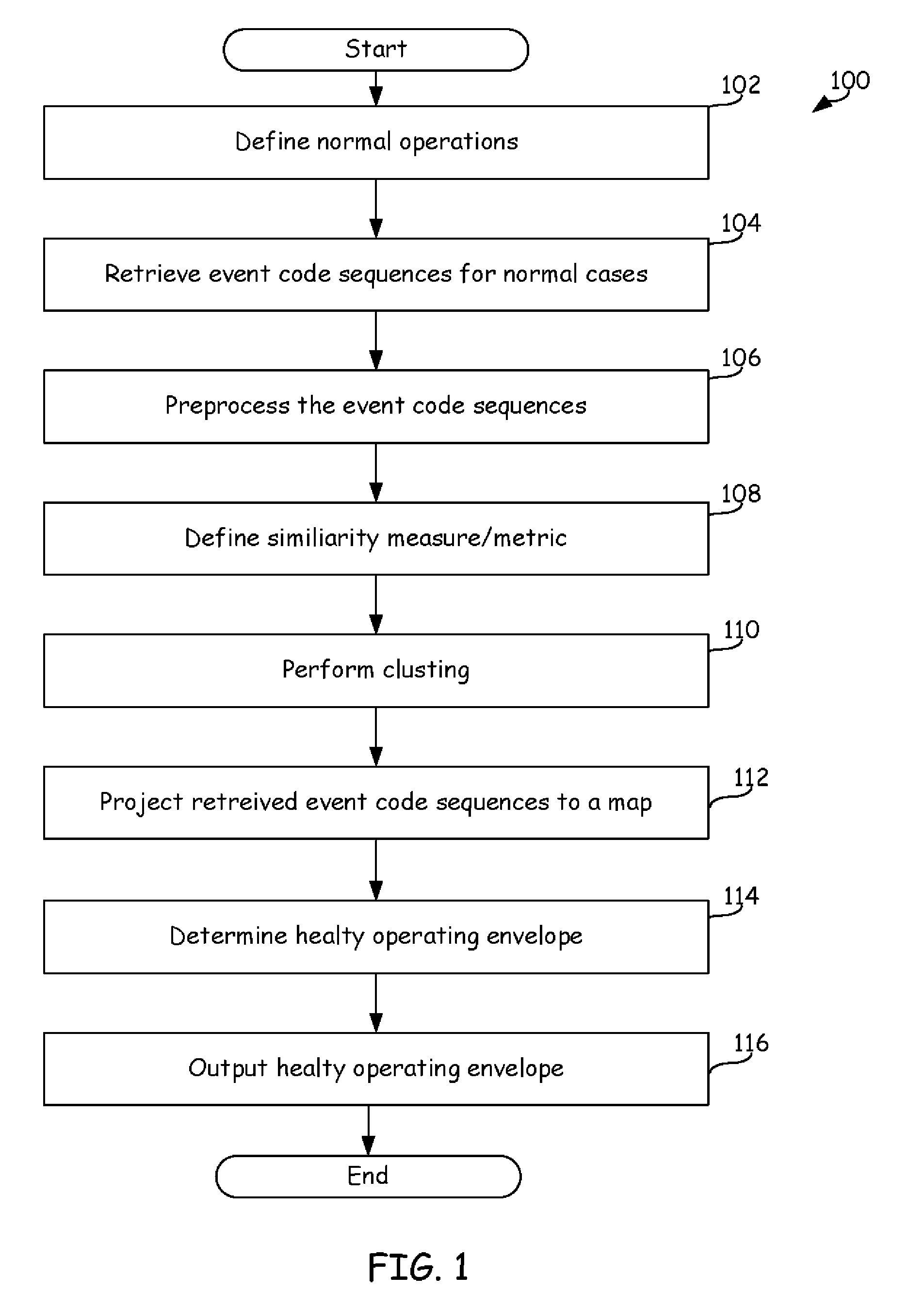

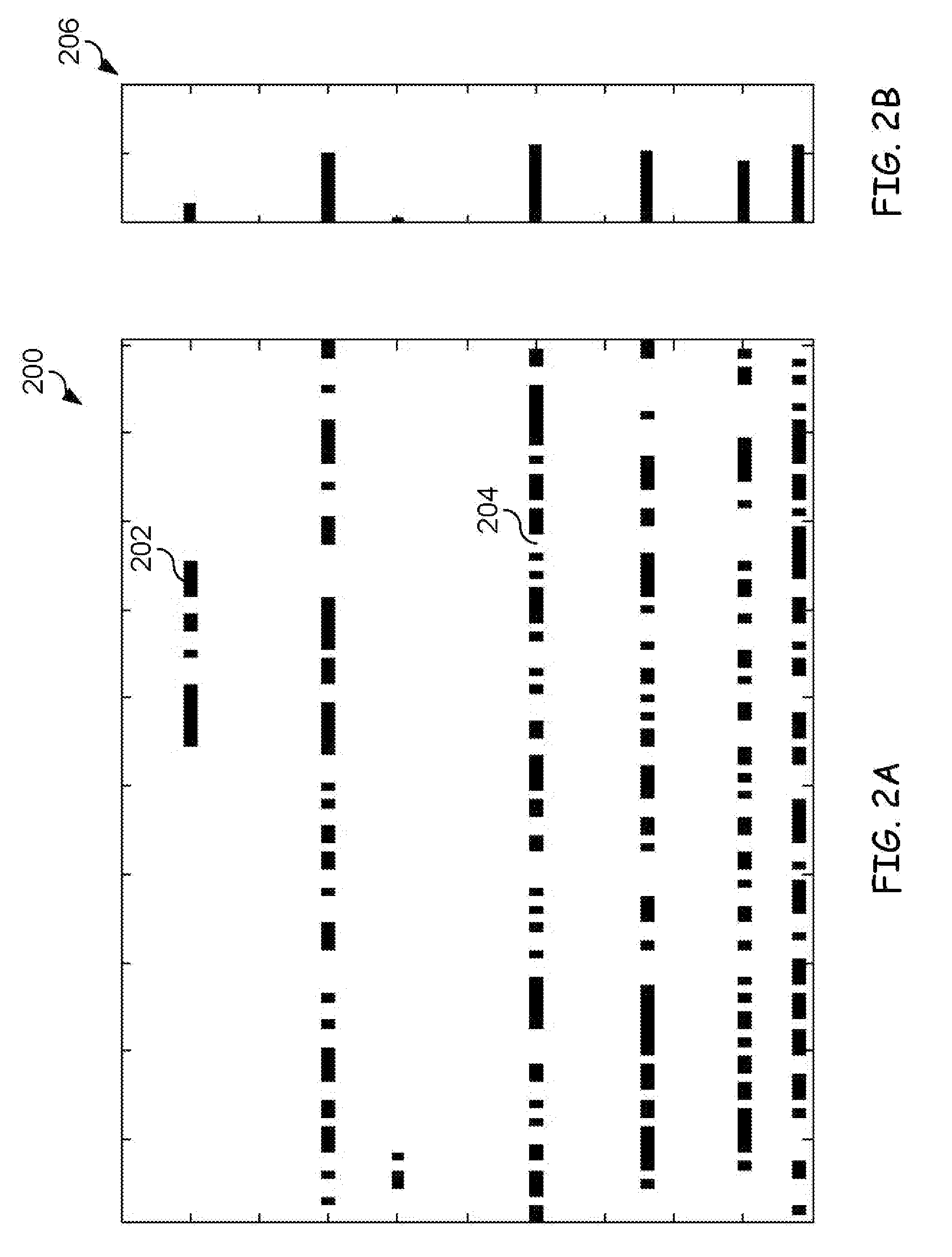

Method and system of creating health operating envelope for dynamic systems by unsupervised learning of a sequence of discrete event codes

InactiveUS20080091715A1Detecting faulty hardware using neural networksDigital computer detailsUnsupervised learningComputer science

A method and system for creating healthy operating envelope from only data samples obtained during normal operation / behavior of dynamic systems is provided. This method determines healthy operating envelope by clustering a stream of discrete event code sequences from the underlying system under normal operation condition only. The method is unsupervised, that is, requiring no prior knowledge of event code patterns corresponding to different operation conditions. Such created envelope can be used for fault detection and health monitoring of dynamic systems.

Owner:LOCKHEED MARTIN CORP

Detection of misbehaving components for large scale distributed systems

ActiveUS10585774B2Detecting faulty hardware using neural networksHardware monitoringReal-time dataEngineering

Owner:INT BUSINESS MASCH CORP

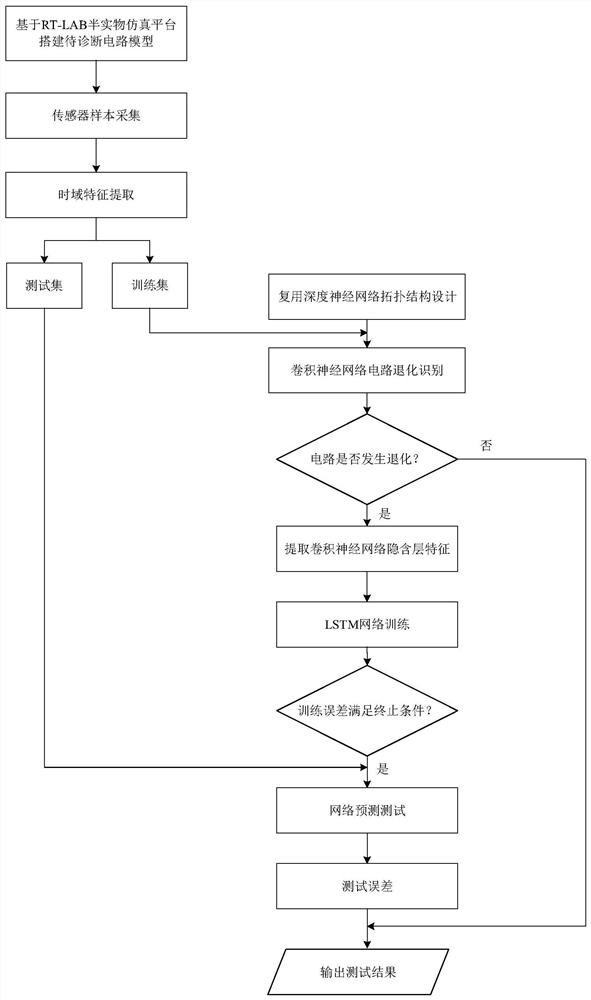

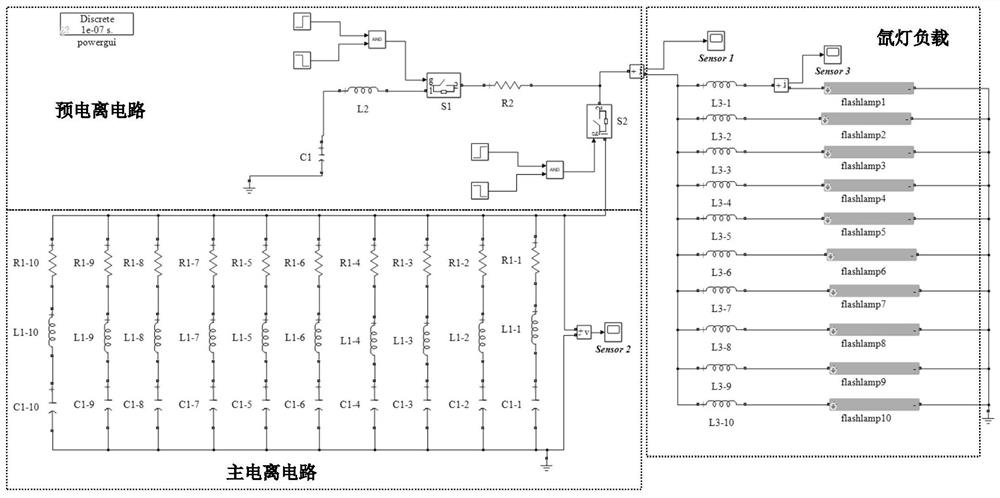

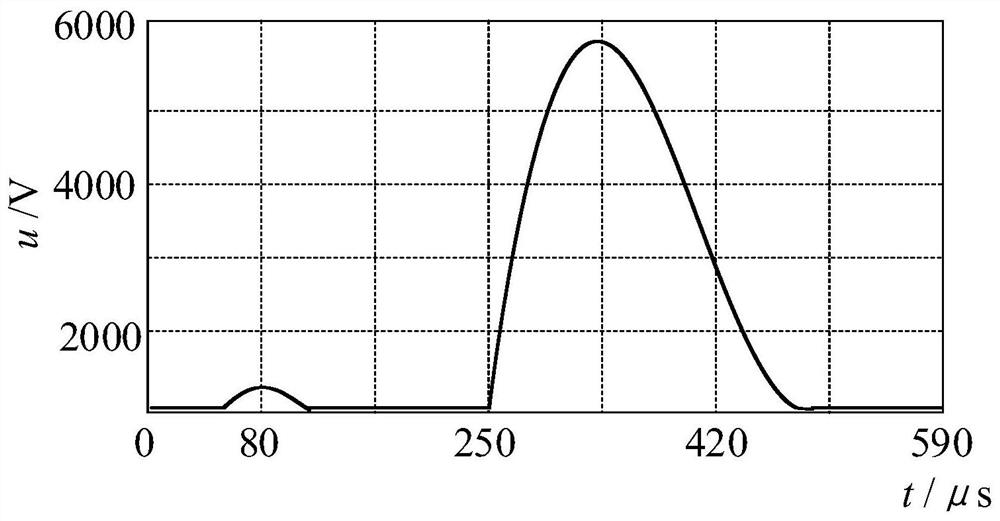

Complex analog circuit fault identification and estimation method and system

ActiveCN112149373AEfficient estimation of health statusAccurate identificationDetecting faulty hardware using neural networksKernel methodsHealth indexHemt circuits

The invention discloses a complex analog circuit fault identification and estimation method and system, and belongs to the field of power electronic circuit fault prediction, and the method comprisesthe steps: building a degradation simulation model of a to-be-diagnosed analog circuit, and carrying out parameter aging simulation experiment of different devices; extracting a series of time domainfeatures of the output signal by using a time sequence transformation method, and establishing health indices of the devices based on the angular similarity; whether the circuit is degraded and a degradation starting point are identified in combination with a time sliding window and a convolutional neural network; reusing a part of hidden layers in the previous identification network and the long-short-term memory cycle network to perform health state estimation on an analog circuit in degradation; and evaluating prediction accuracy. The health state of the analog circuit can be effectively estimated while the fault state starting point of the analog circuit is accurately recognized, and the invention has the advantages of being high in operation efficiency and accurate in recognition.

Owner:WUHAN UNIV

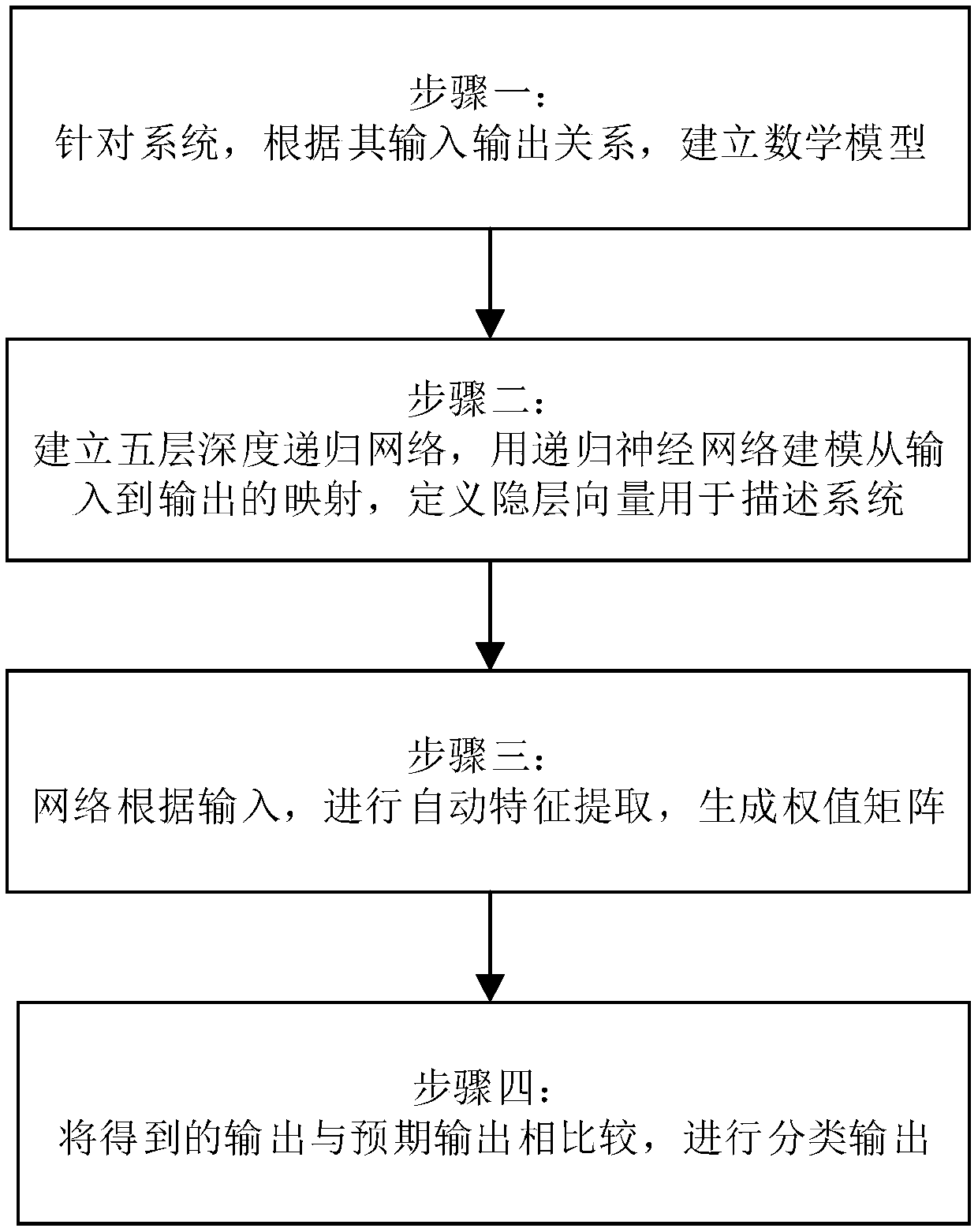

Big-data computer system fault detection method based on deep recursion network

ActiveCN108459933AFind the fault signatureQuick discoveryDetecting faulty hardware using neural networksNeural architecturesFeature extractionReal-time data

The invention relates to a computer system fault detection method, in particular to a big-data computer system fault detection method based on a deep recursion network. The big-data computer system fault detection method has the advantages that the deep recursion network is introduced to a fault detection step, training and learning are conducted according to historical data, and manual feature extraction is replaced; fault features are extracted automatically via the network, weights can be updated in real time, and the difficulty in manual section of the fault features is eliminated; throughreal-time data learning and feature extraction, faults are discovered quickly and accurately, the types of the faults are predicated, and system performance is improved.

Owner:哈尔滨工创智能科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com