Analog circuit fault diagnosis method based on Bayes-KFCM (Kernelized Fuzzy C-Means) algorithm

A technology for simulating circuit faults and diagnostic methods, which is applied in the direction of analog circuit testing, electronic circuit testing, etc., and can solve problems such as inability to diagnose new faults effectively and low diagnostic efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

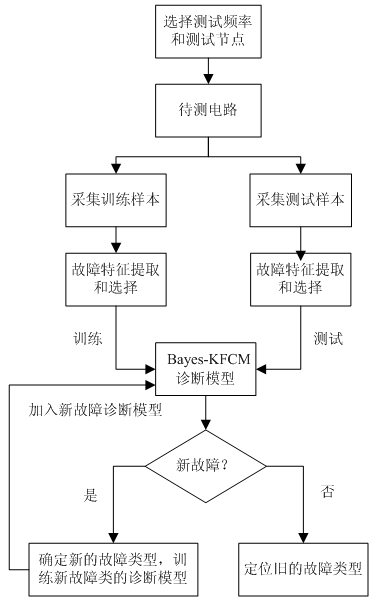

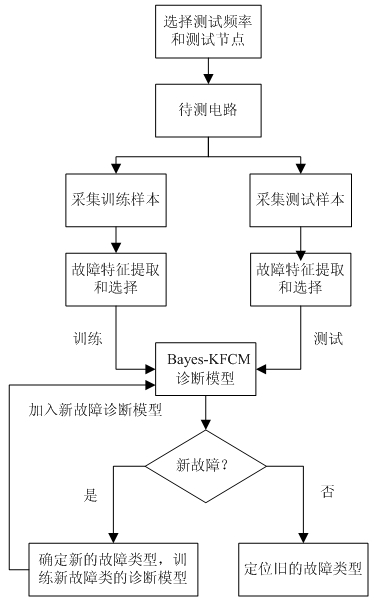

[0050] The technical scheme of the present invention is described in detail below in conjunction with accompanying drawing:

[0051] Analog circuit fault diagnosis method of the present invention, such as figure 1 shown, including the following steps:

[0052] Step A. Select the optimal measurable node and test signal frequency of the circuit to be tested.

[0053] In order to make the selection of the optimal measurable node and / or test signal frequency more representative, thereby improving the fault diagnosability, the present invention uses the maximum intra-class distance as the selection basis, and the optimal measurable node and / or test signal frequency Select the signal frequency. Specifically, step A specifically includes:

[0054] Step A1, obtaining the amplitude-frequency response curve of the circuit to be tested;

[0055] Step A2, select the inflection point on the amplitude-frequency response curve and the frequencies near it as the frequency set to be select...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More