Patents

Literature

133 results about "Logic error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer programming, a logic error is a bug in a program that causes it to operate incorrectly, but not to terminate abnormally (or crash). A logic error produces unintended or undesired output or other behaviour, although it may not immediately be recognized as such.

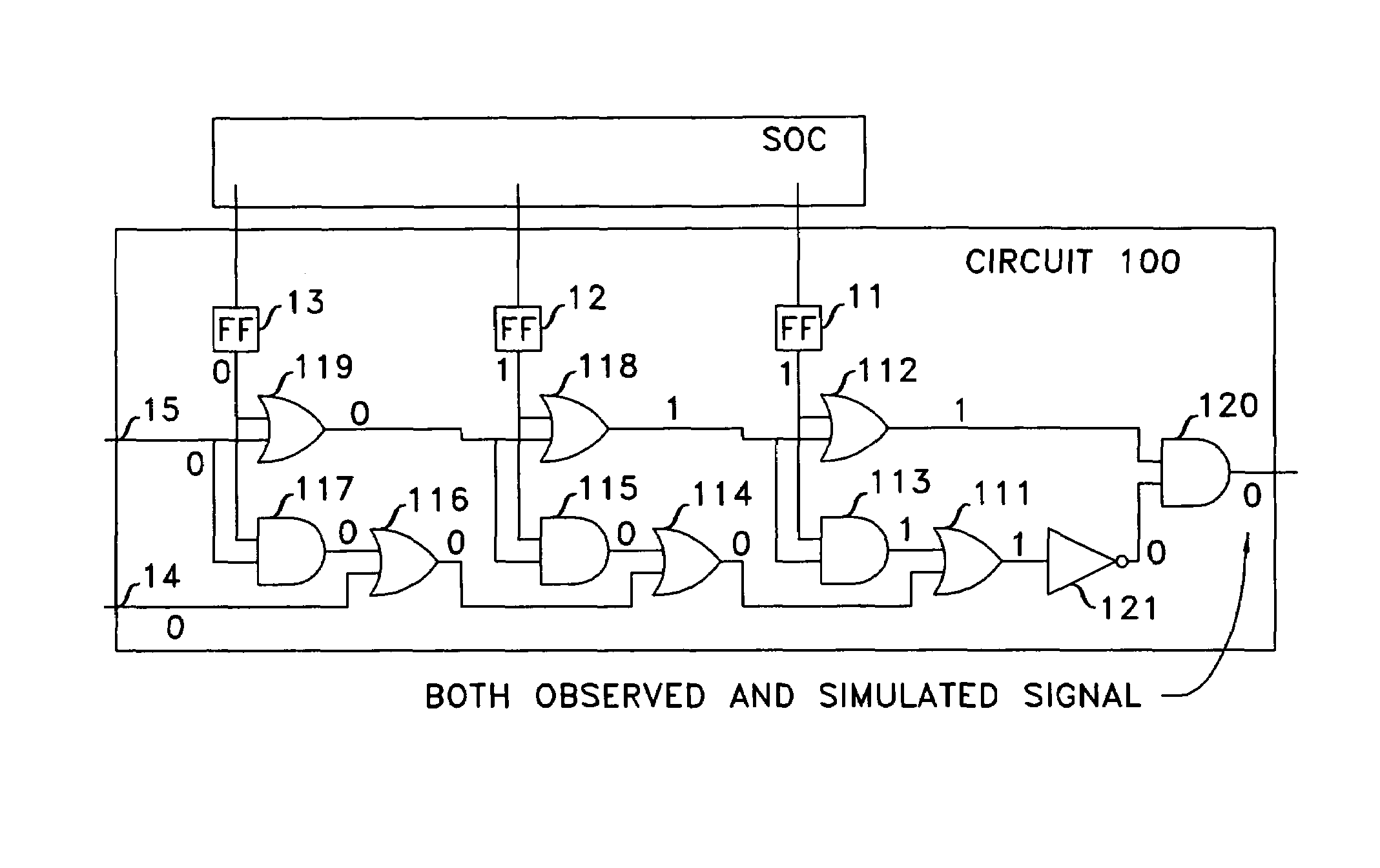

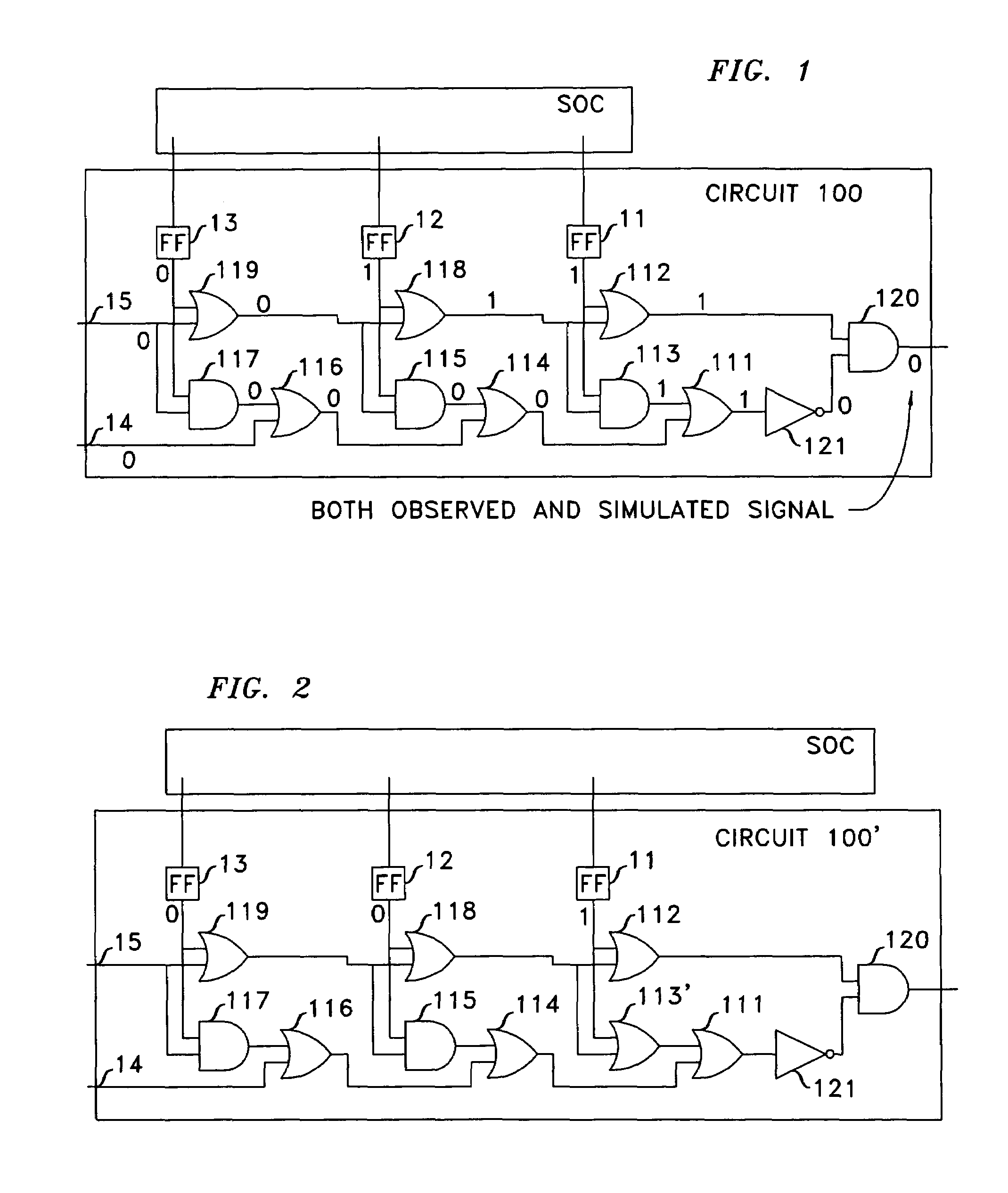

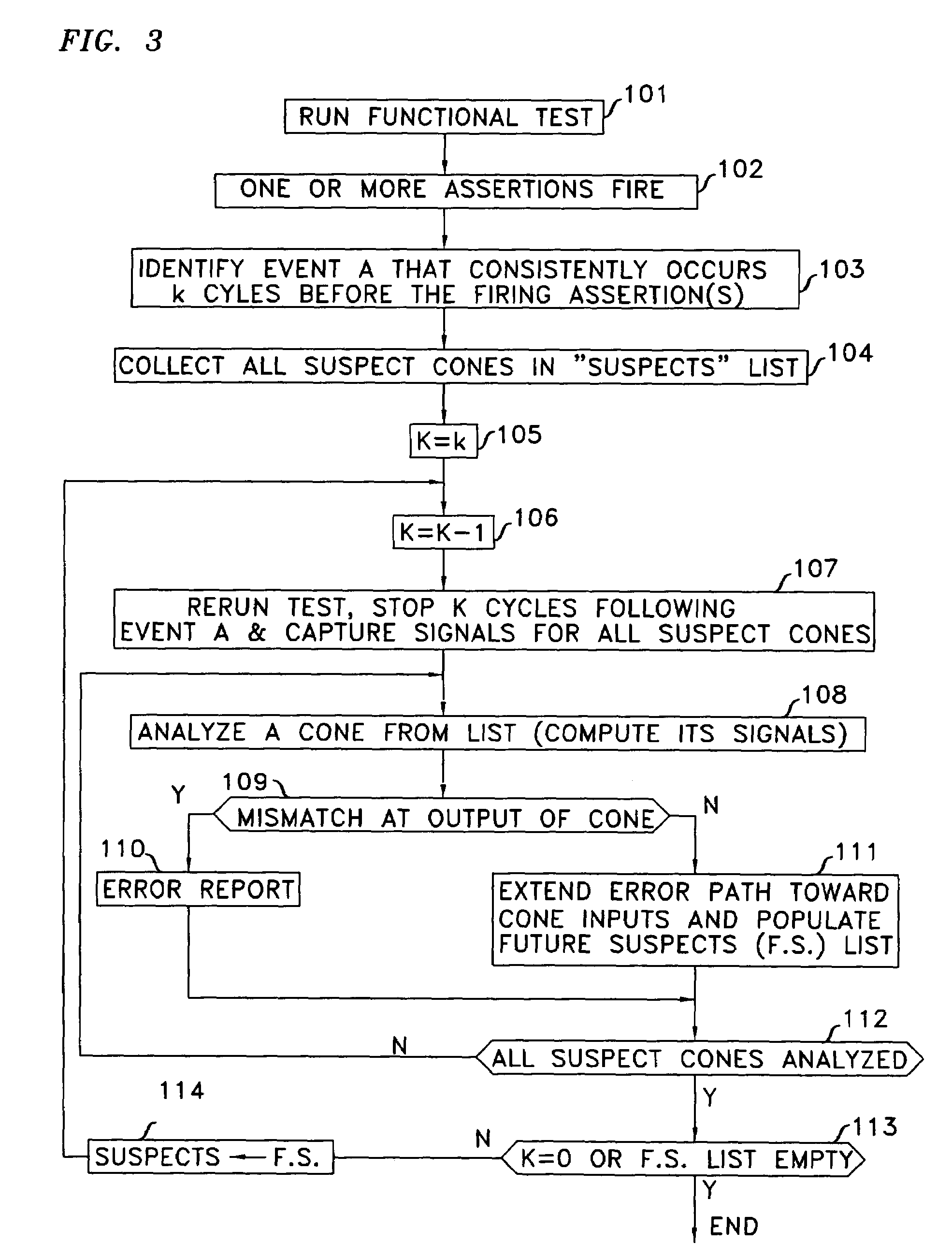

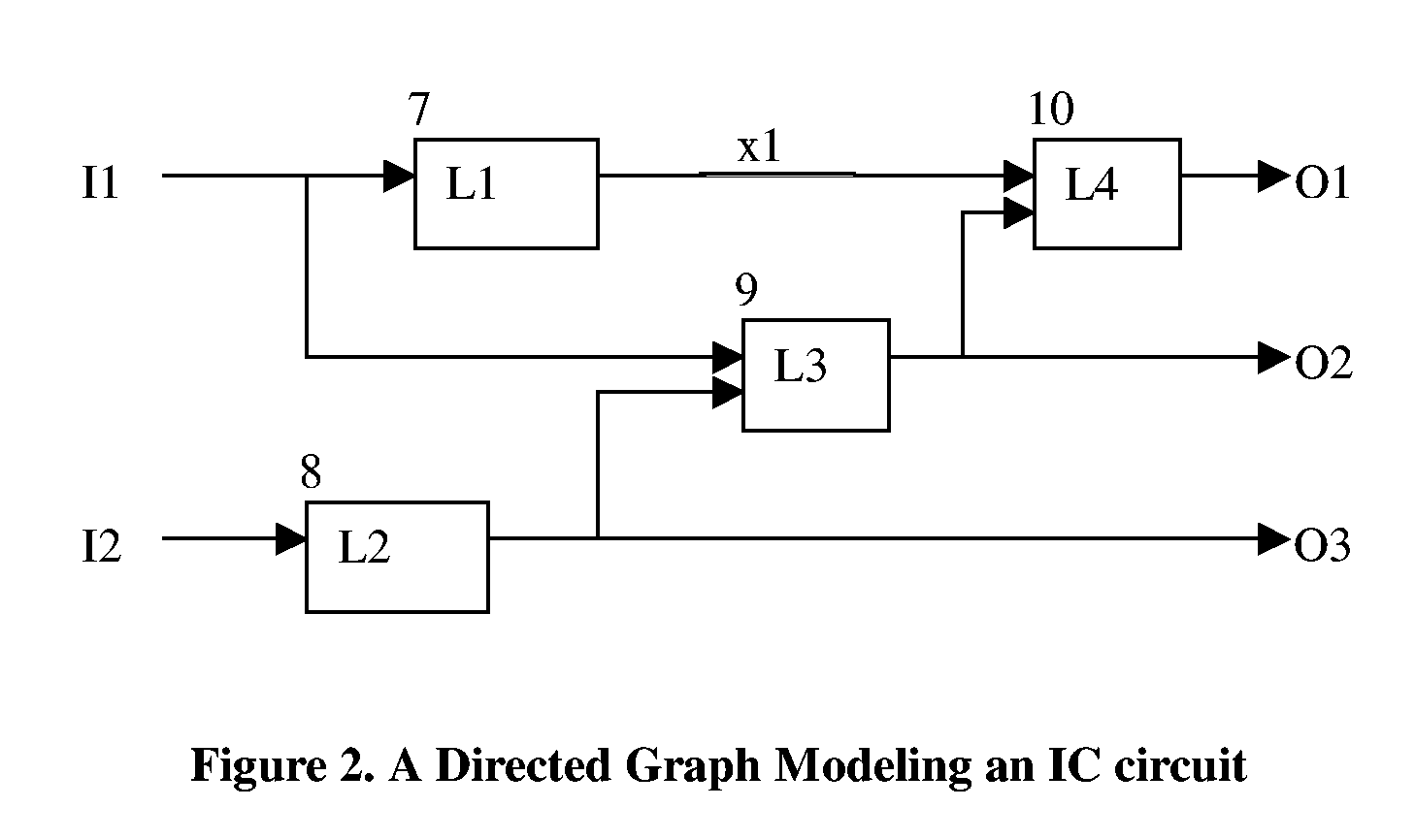

Method to locate logic errors and defects in digital circuits

When, in the course of an integrated circuit's functional test an assertion fires at clock k, the operational clock is stopped, the sequence is reapplied to capture inputs to the assertion circuit that fired, signals within the assertion circuit are computed, and the error is backtraced. Once one or more inputs of the assertion circuit are identified as potentially the source of the error, the process of backtracing is performed for each such input. When the input that is potentially the source of the error emanates from a memory circuit, the fanin cone of the memory circuit is identified and the process of backtracing through the last-identified fanin cone is undertaken for clock k−1. This is repeated iteratively until either a module of the integrated circuit is found to be the source of the error, or the error is extended to inputs of the SoC.

Owner:DAFCA

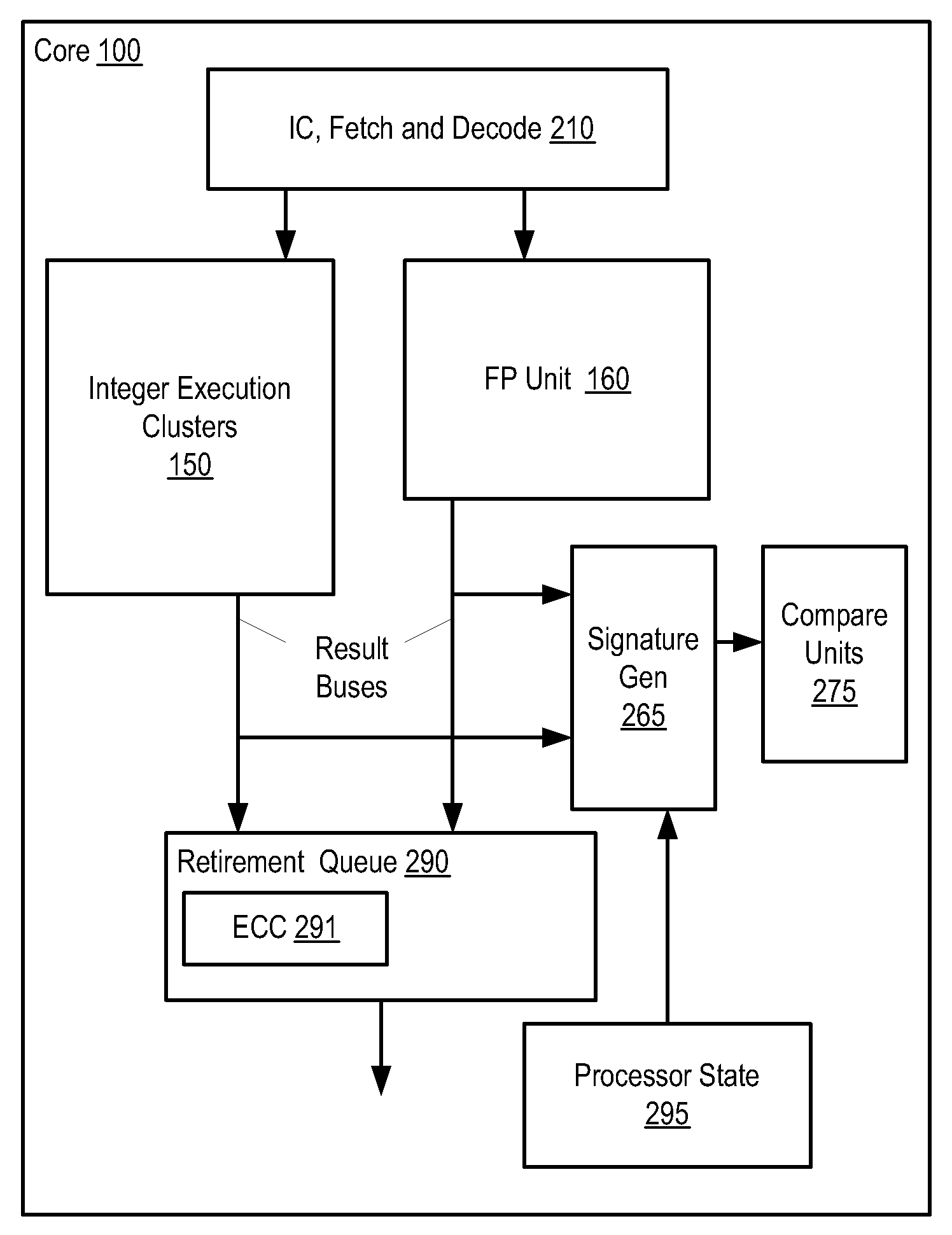

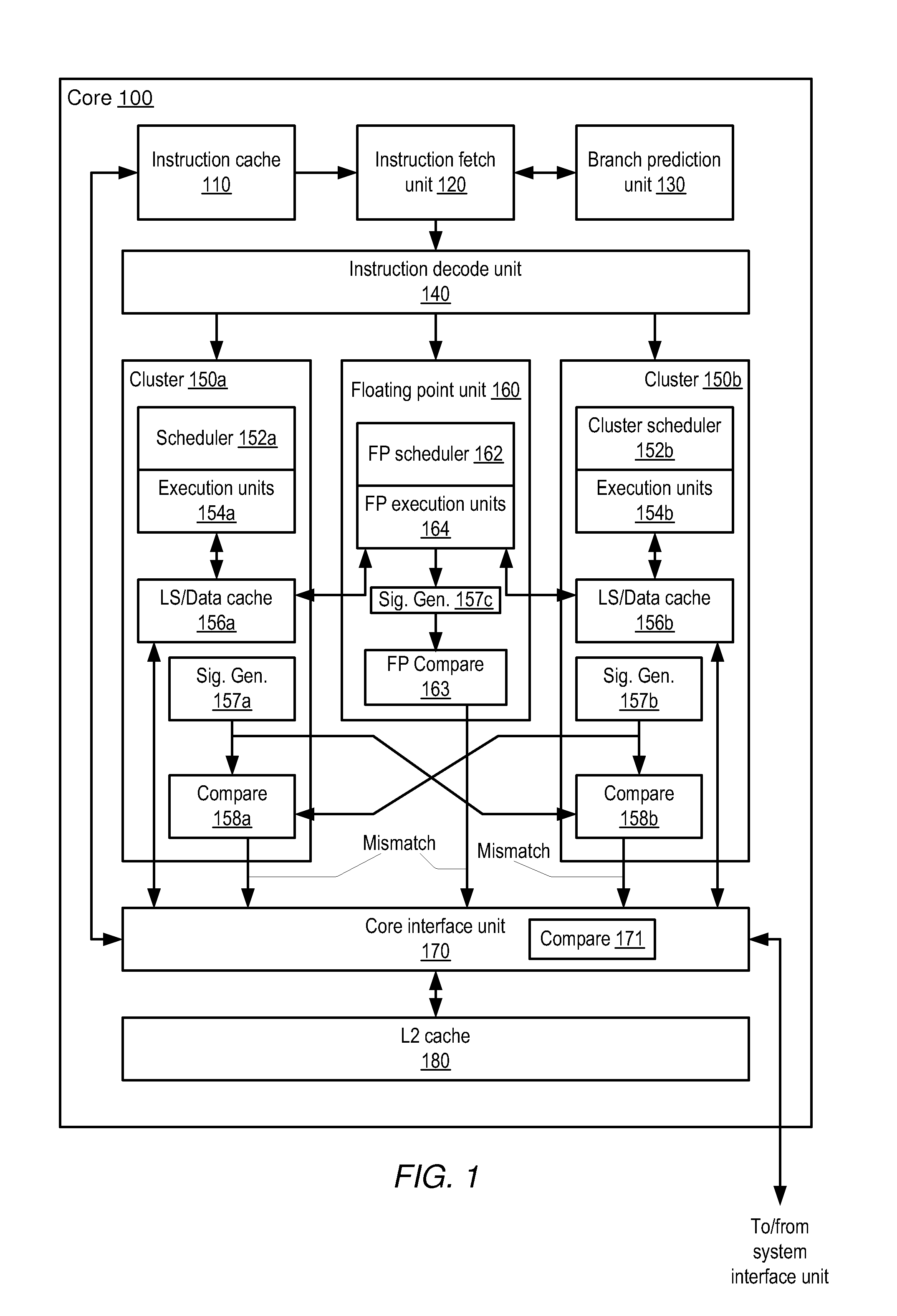

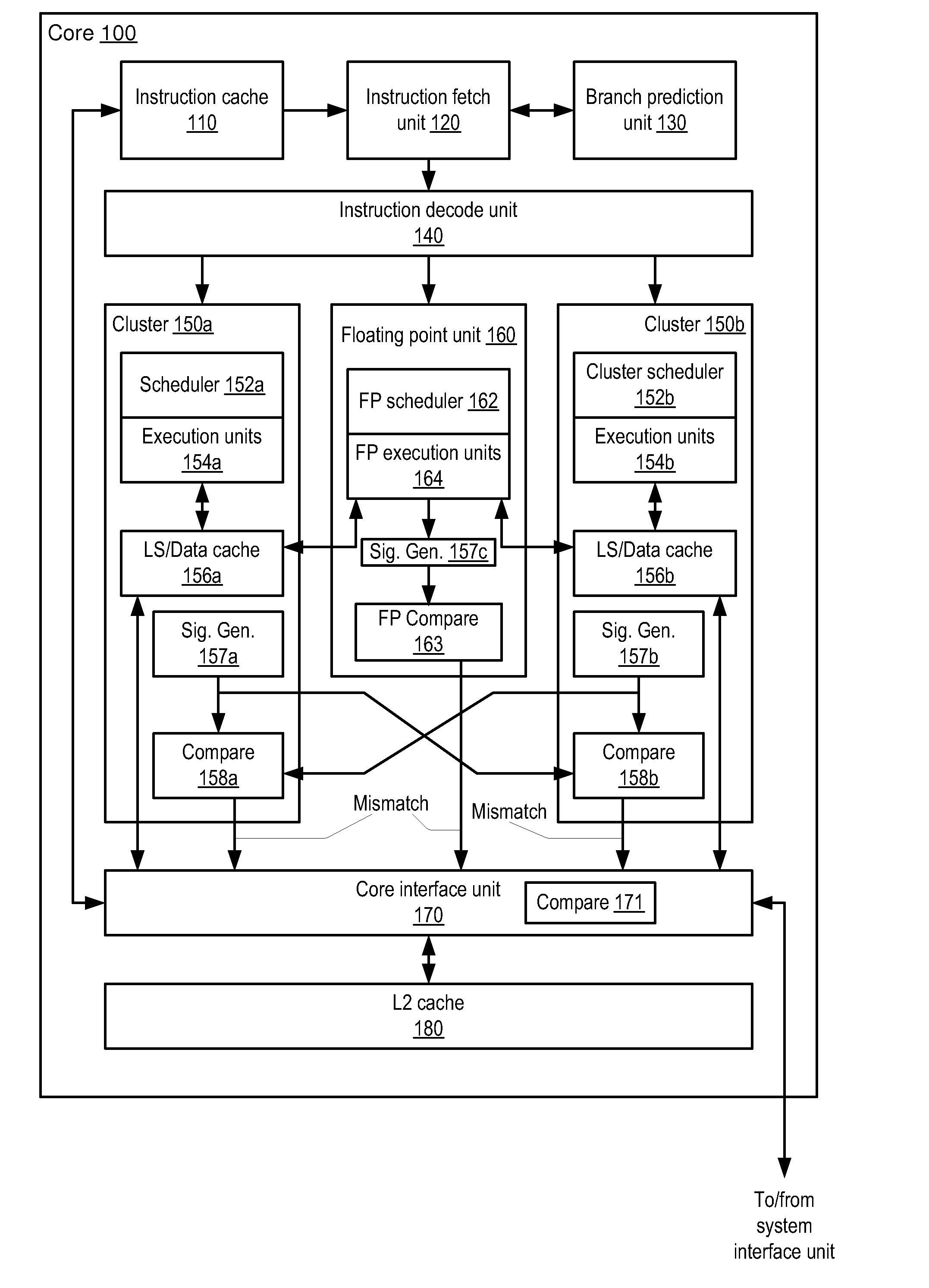

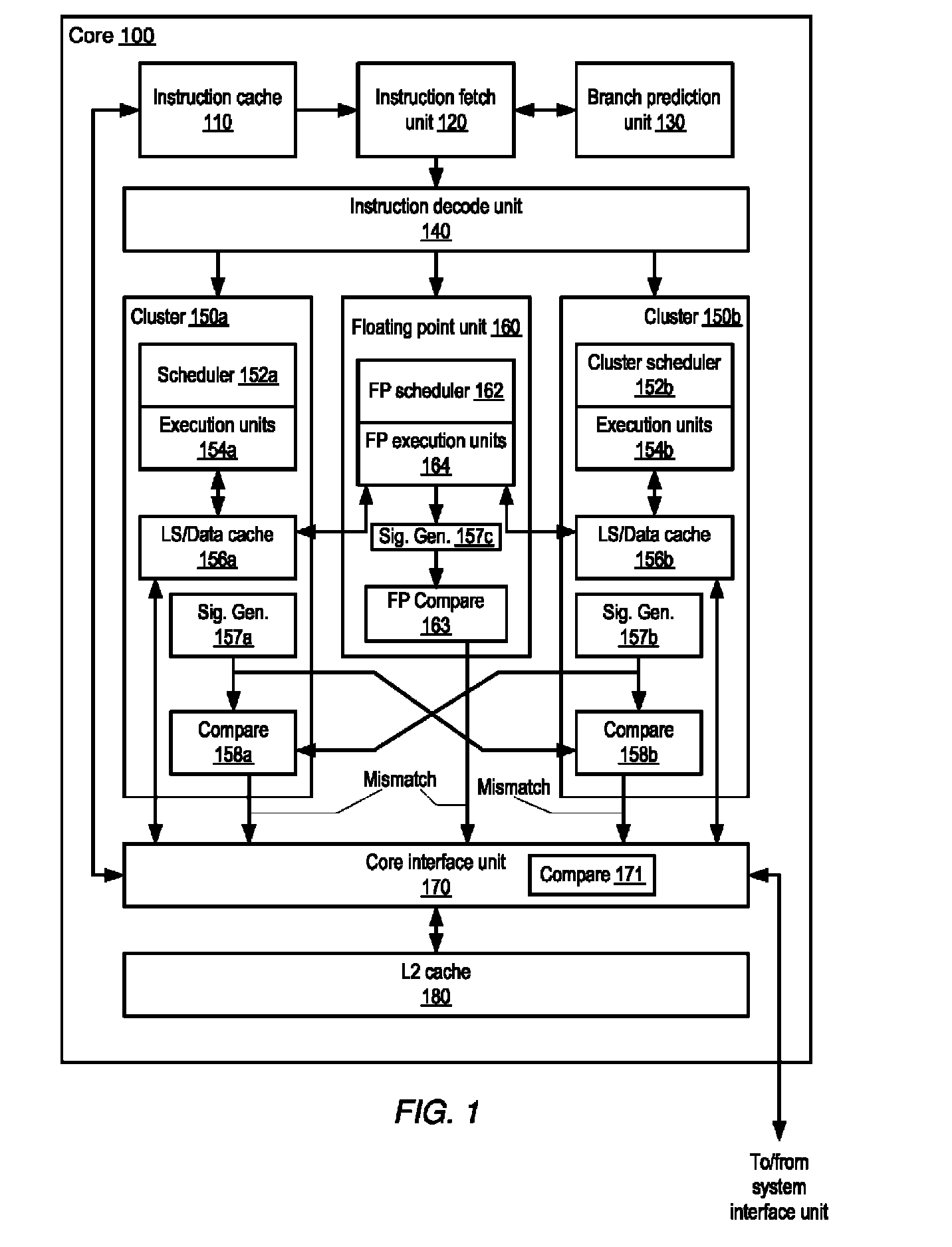

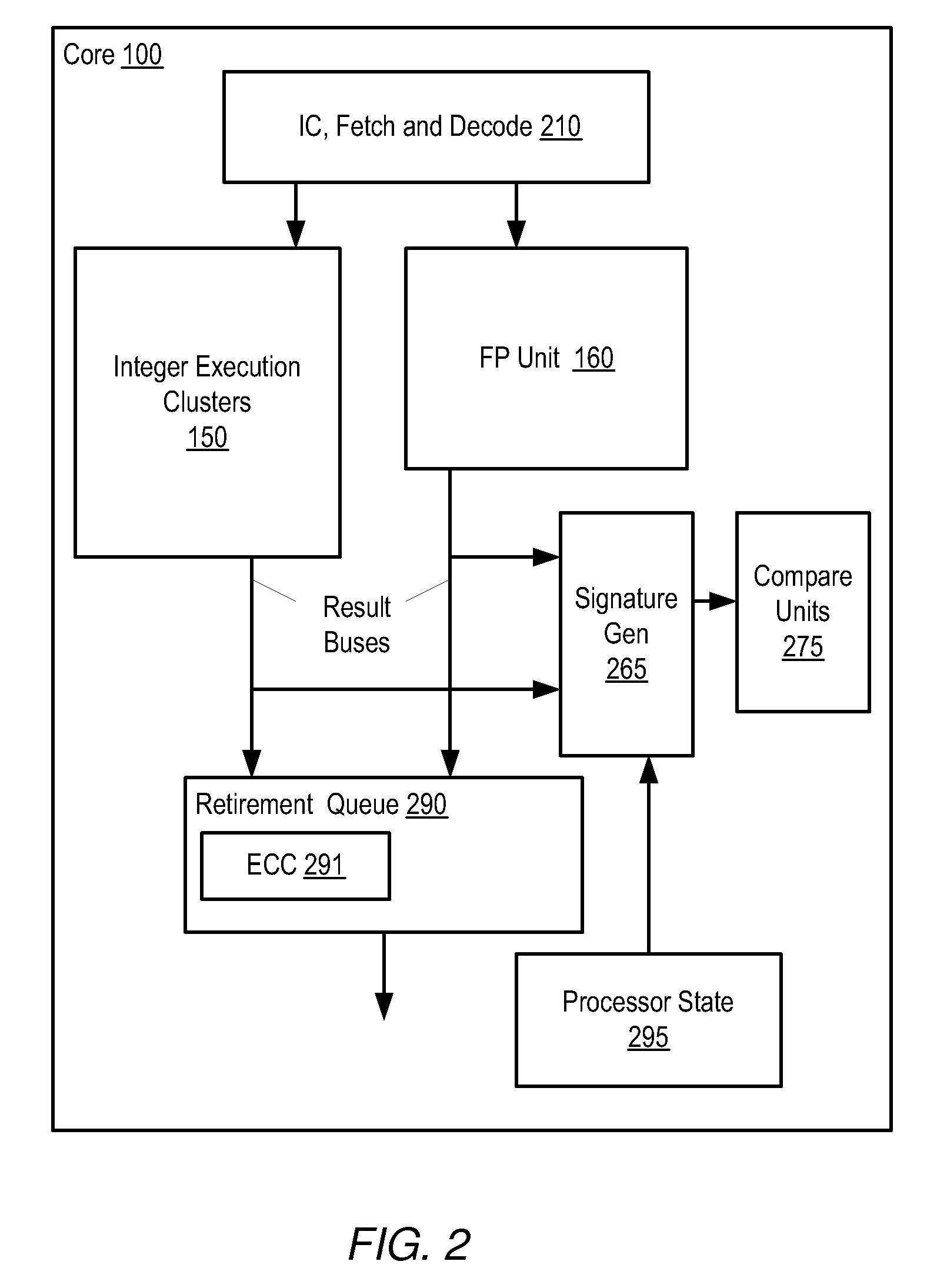

Processor including hybrid redundancy for logic error protection

InactiveUS20090183035A1Digital computer detailsRedundant operation error correctionFloating-point unitExecution unit

A processor core includes an instruction decode unit that may dispatch a same integer instruction stream to a plurality of integer execution units and may consecutively dispatch a same floating-point instruction stream to a floating-point unit. The integer execution units may operate in lock-step such that during each clock cycle, each respective integer execution unit executes the same integer instruction. The floating-point unit may execute the same floating-point instruction stream twice. Prior to the integer instructions retiring, compare logic may detect a mismatch between execution results from each of the integer execution units. In addition, prior to the results of the floating-point instruction stream transferring out of the floating-point unit, the compare logic may also detect a mismatch between results of execution of each consecutive floating-point instruction stream. Further, in response to detecting any mismatch, the compare logic may cause instructions causing the mismatch to be re-executed.

Owner:GLOBALFOUNDRIES INC

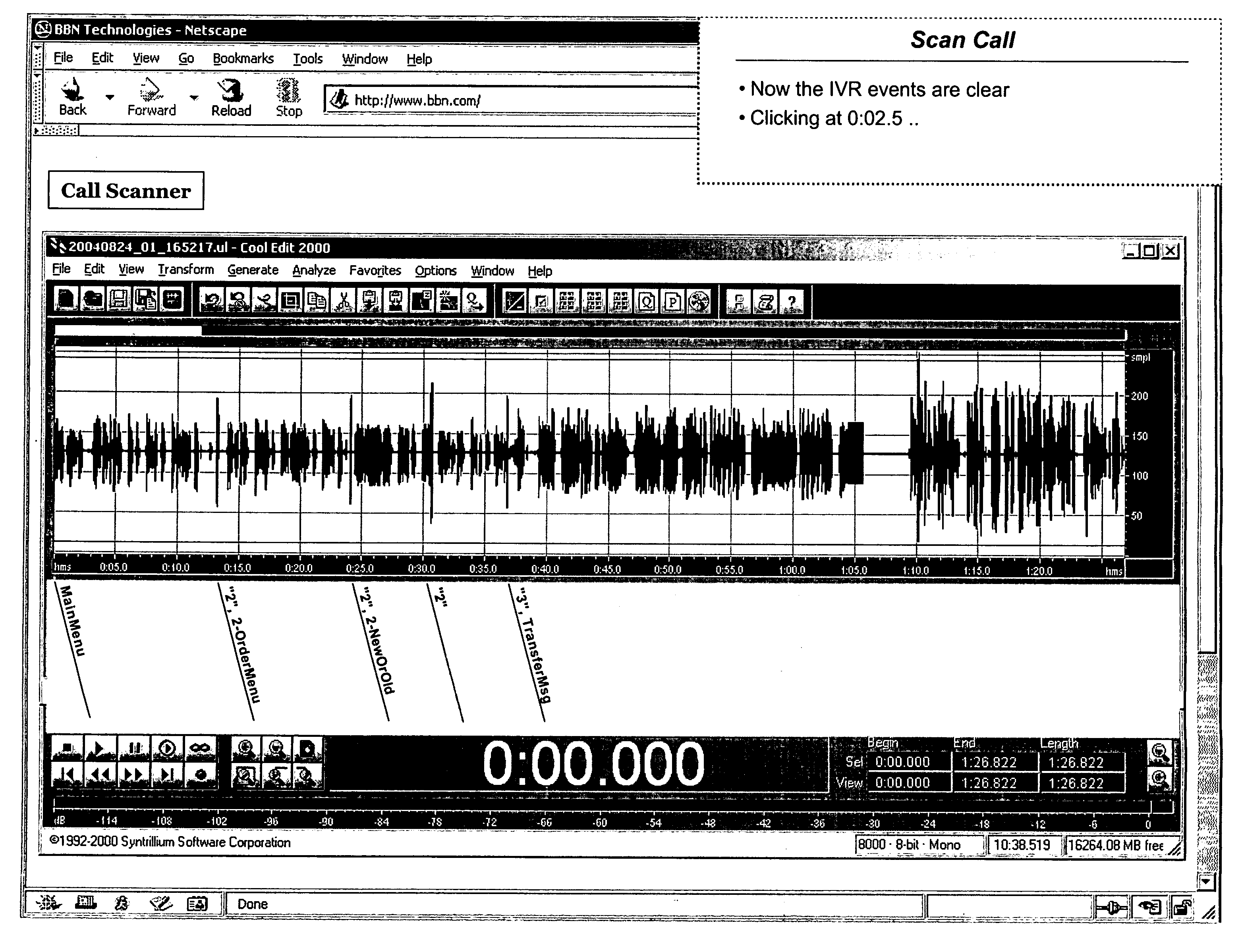

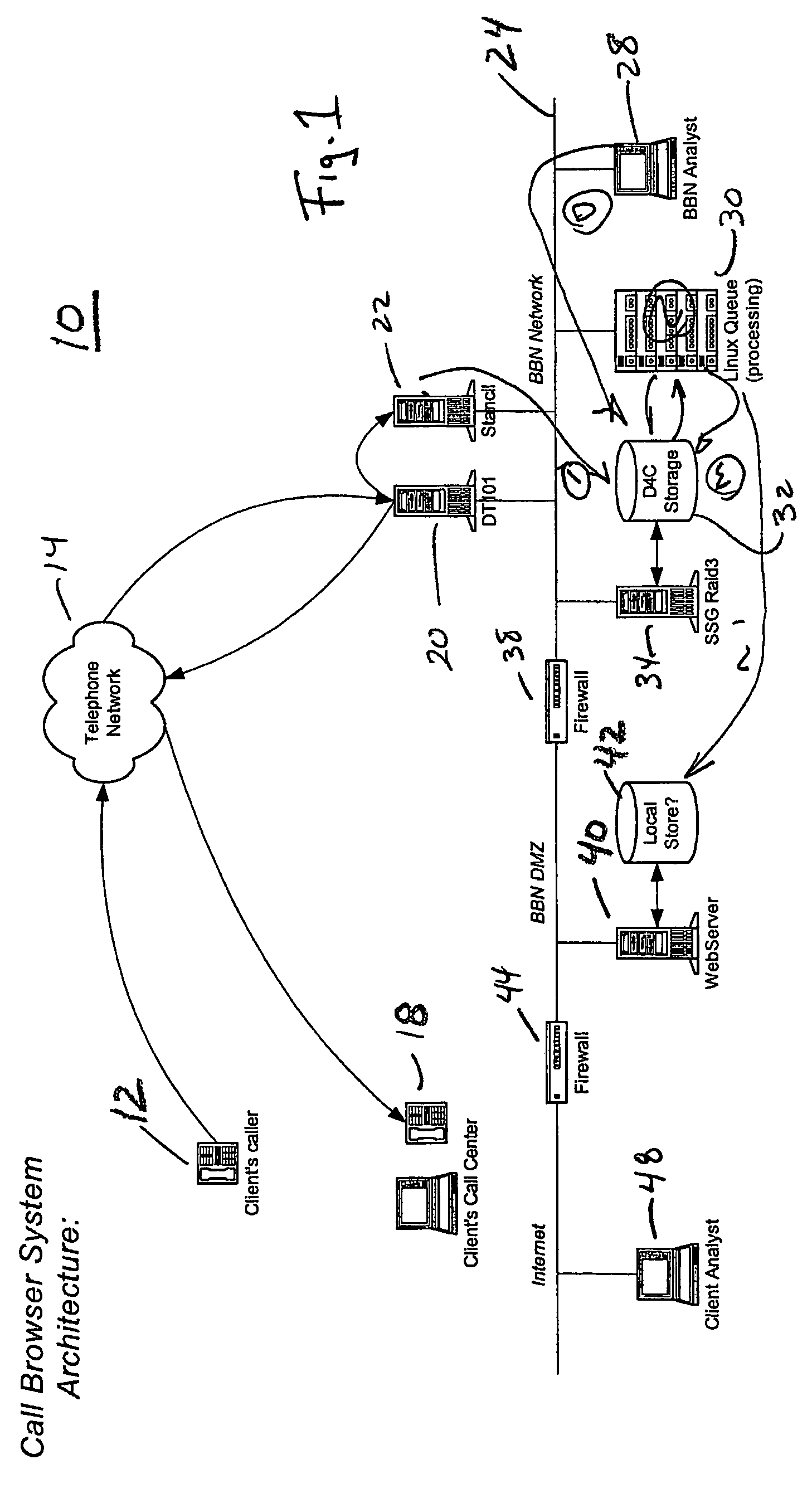

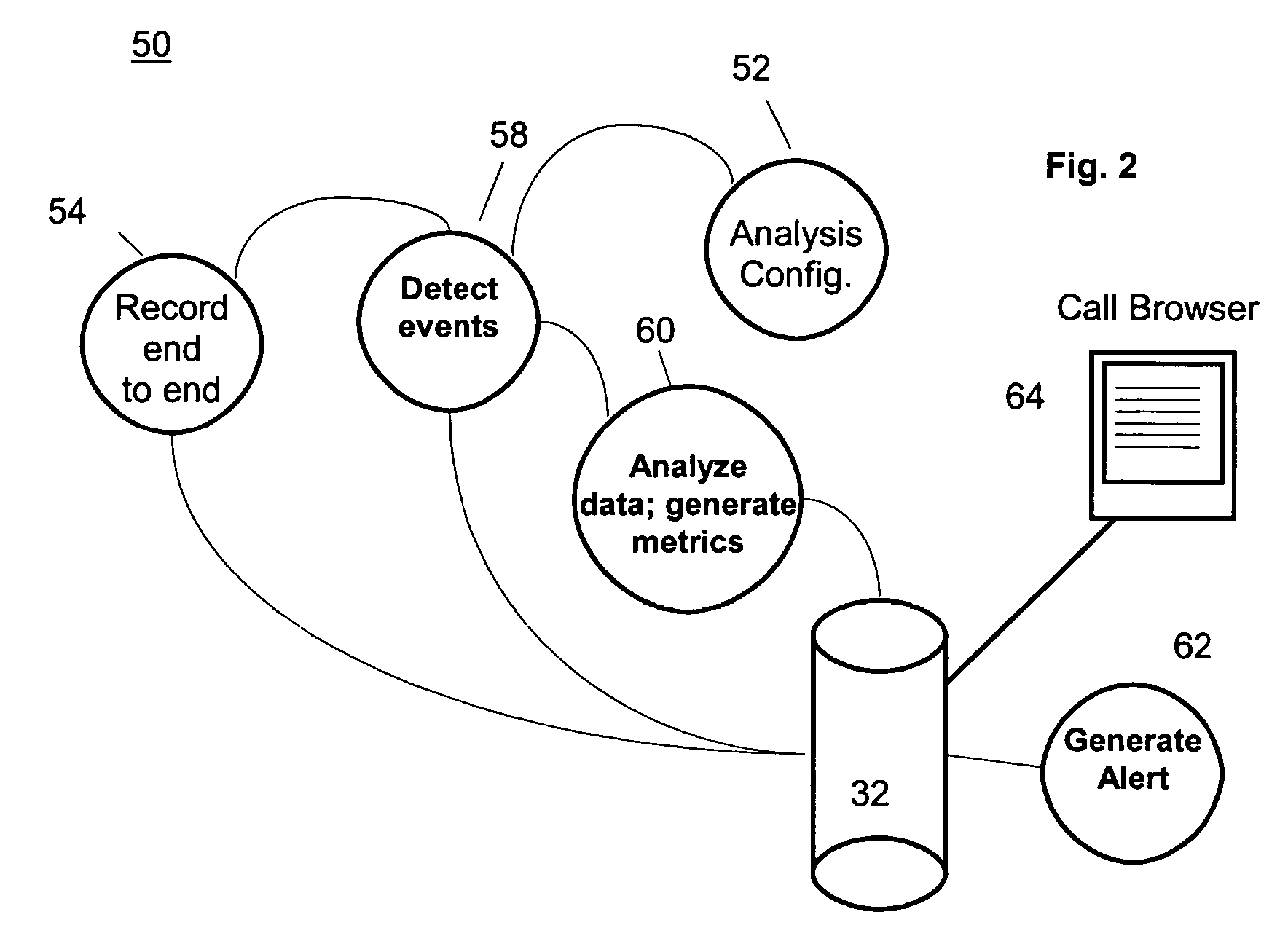

Systems and methods for presenting end to end calls and associated information

ActiveUS8102973B2Automatic call-answering/message-recording/conversation-recordingSupervisory/monitoring/testing arrangementsRelevant informationClient-side

Systems and methods that, among other things, analyze and monitor the performance of a call center including performance of the interactive voice response (IVR) systems, call center agents, and other components of the call center. The systems and methods record characteristics of the call such as the audio data, and analyze that record to identify the events and the actions that take place during the call. These events and actions may be defined as complex customer / call center interactions, such as dropped calls, logic errors or other event. A call center administrator may also identify a set of metrics, such as the number of dropped calls that occur during a day or for each agent, the number of times a client was left on hold for more than two minutes, or other such metrics that may be monitored by the systems described herein. The data collected about these events and the resulting metrics may be stored in a database and provided to a call center administrator through a user interface that allows the administrator to browse through the collected metric and recorded call data and directly review relevant portions of a call that are of interest to the administrator.

Owner:CX360 INC

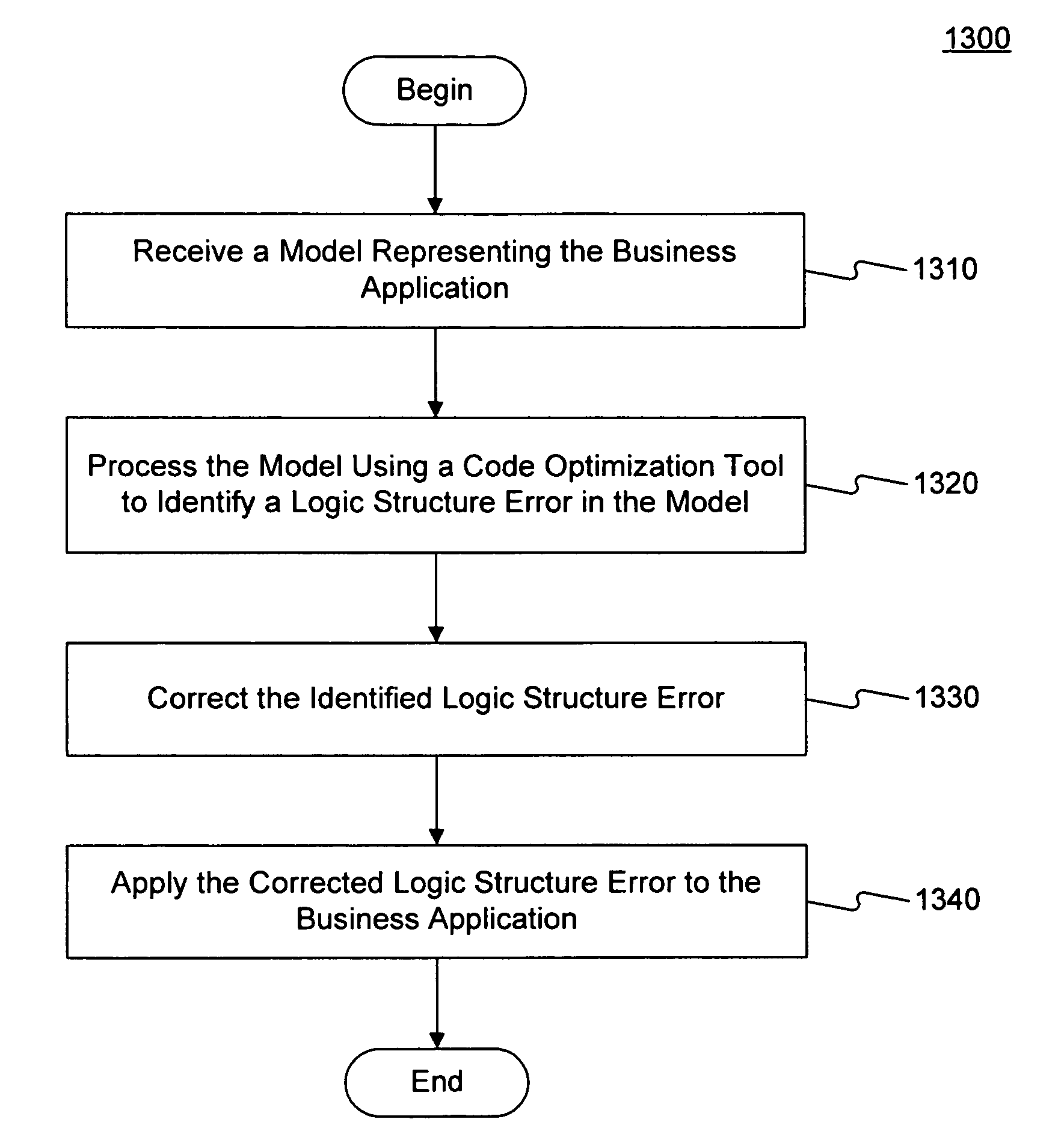

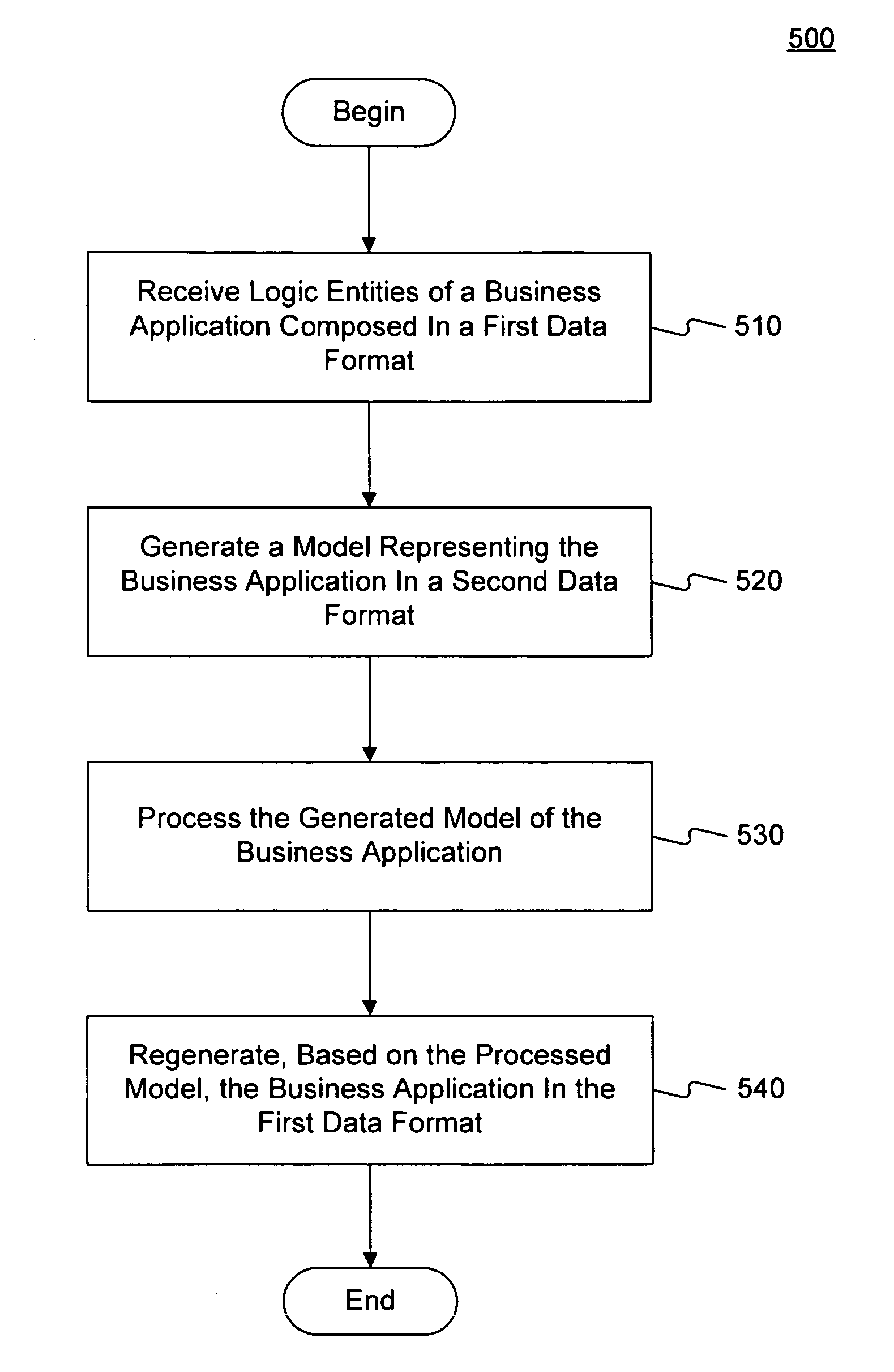

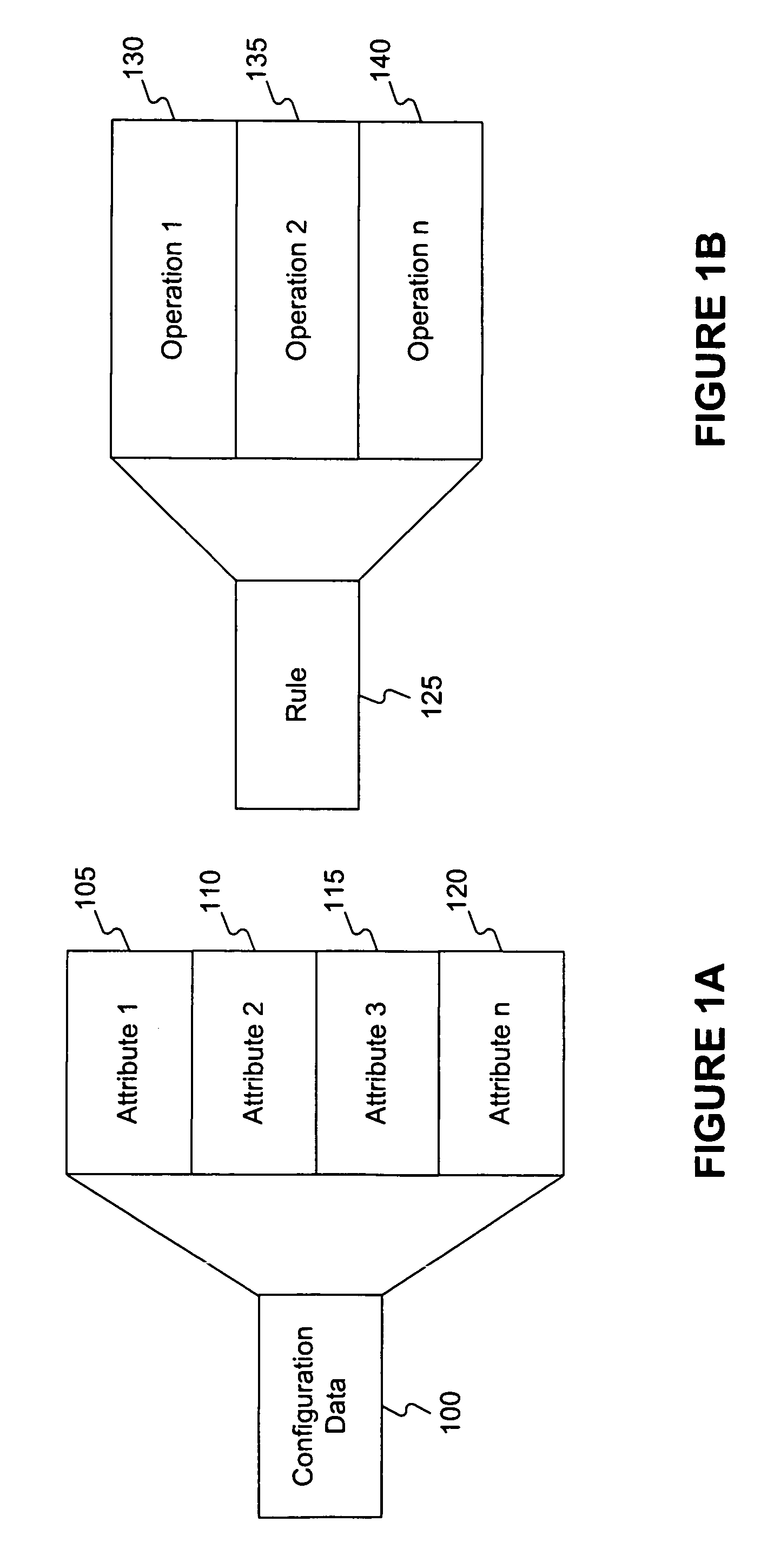

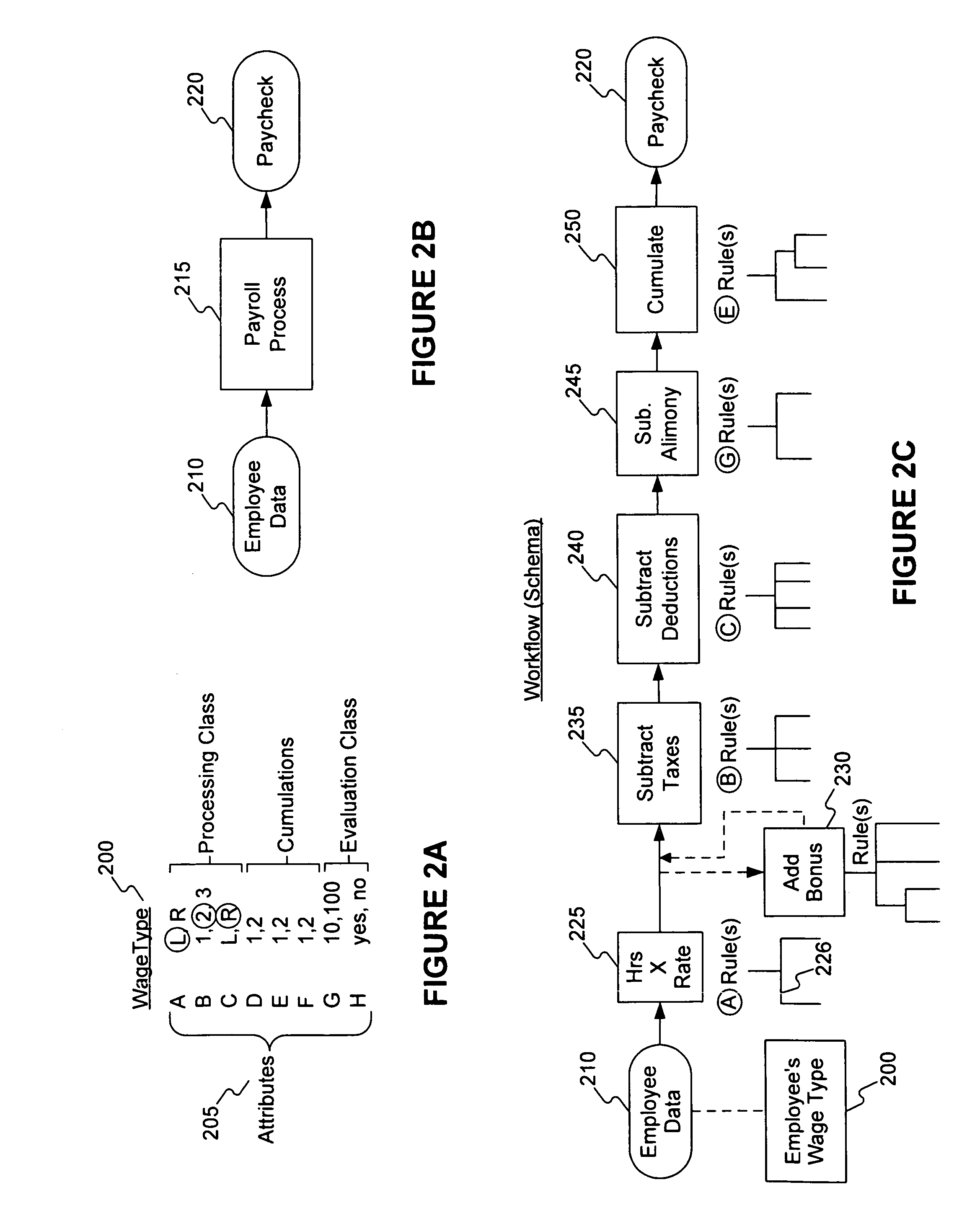

Systems and methods for using object-oriented tools to debug business applications

InactiveUS20060242174A1Digital data processing detailsCode refactoringTheoretical computer scienceLogic error

In accordance with embodiments of the present invention, methods and systems analyze potential logic errors or problems of a business application by receiving a model representing the business application and processing the model using an object-oriented tool. The errors or problems may be corrected in the model and the correction applied to the business application. In one exemplary embodiment, the logic errors or problems may be marked in the model for identification to a user.

Owner:SAP AG

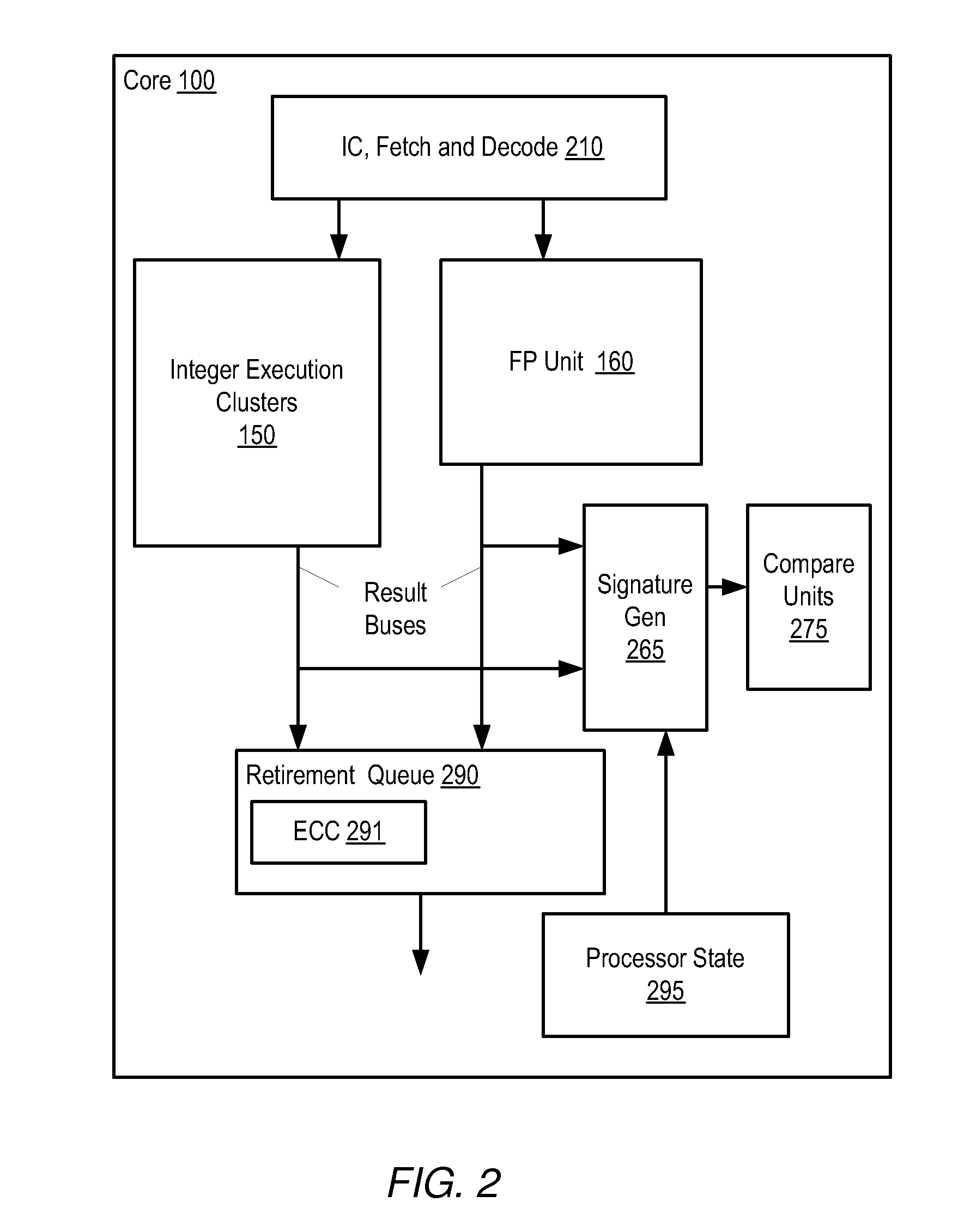

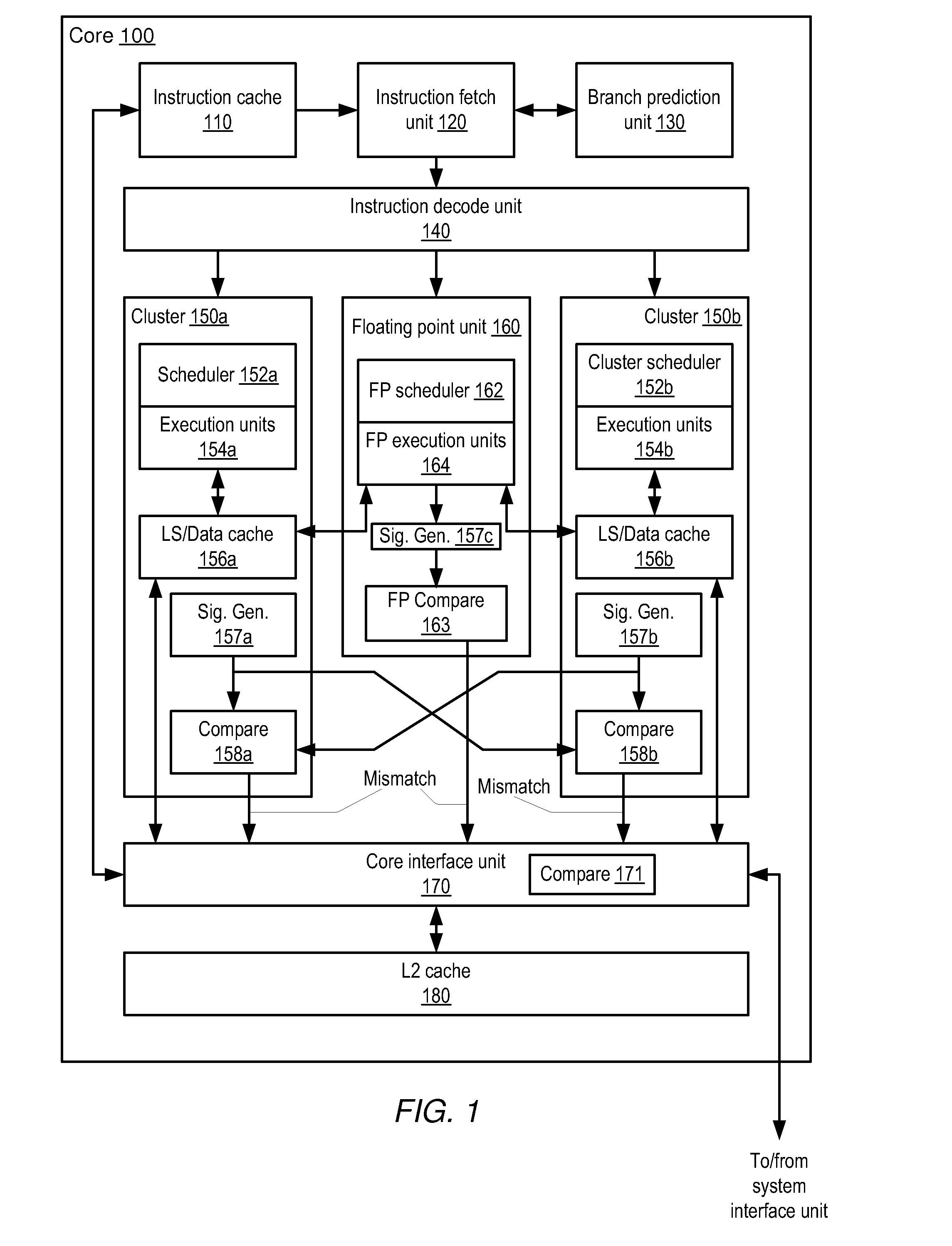

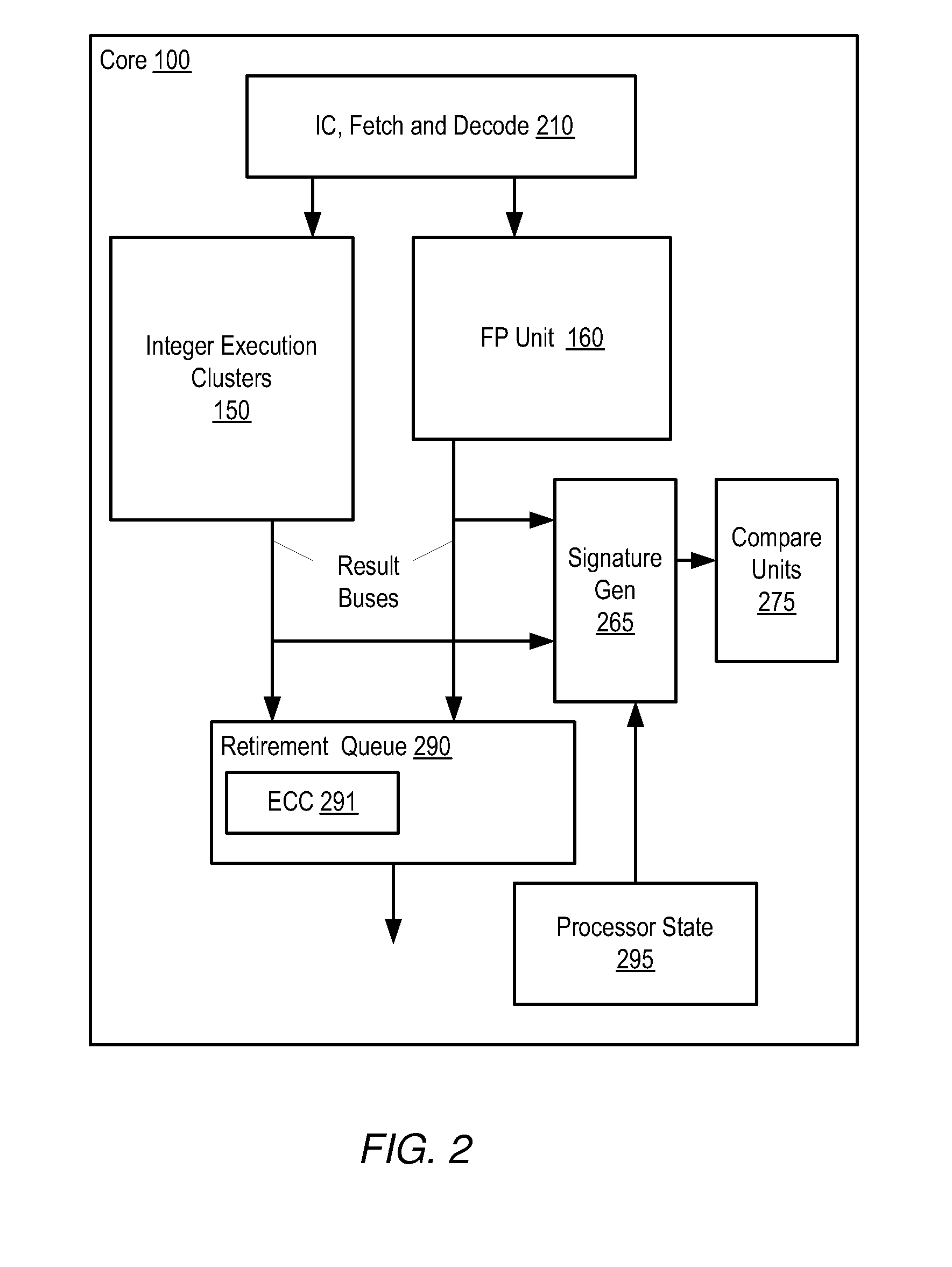

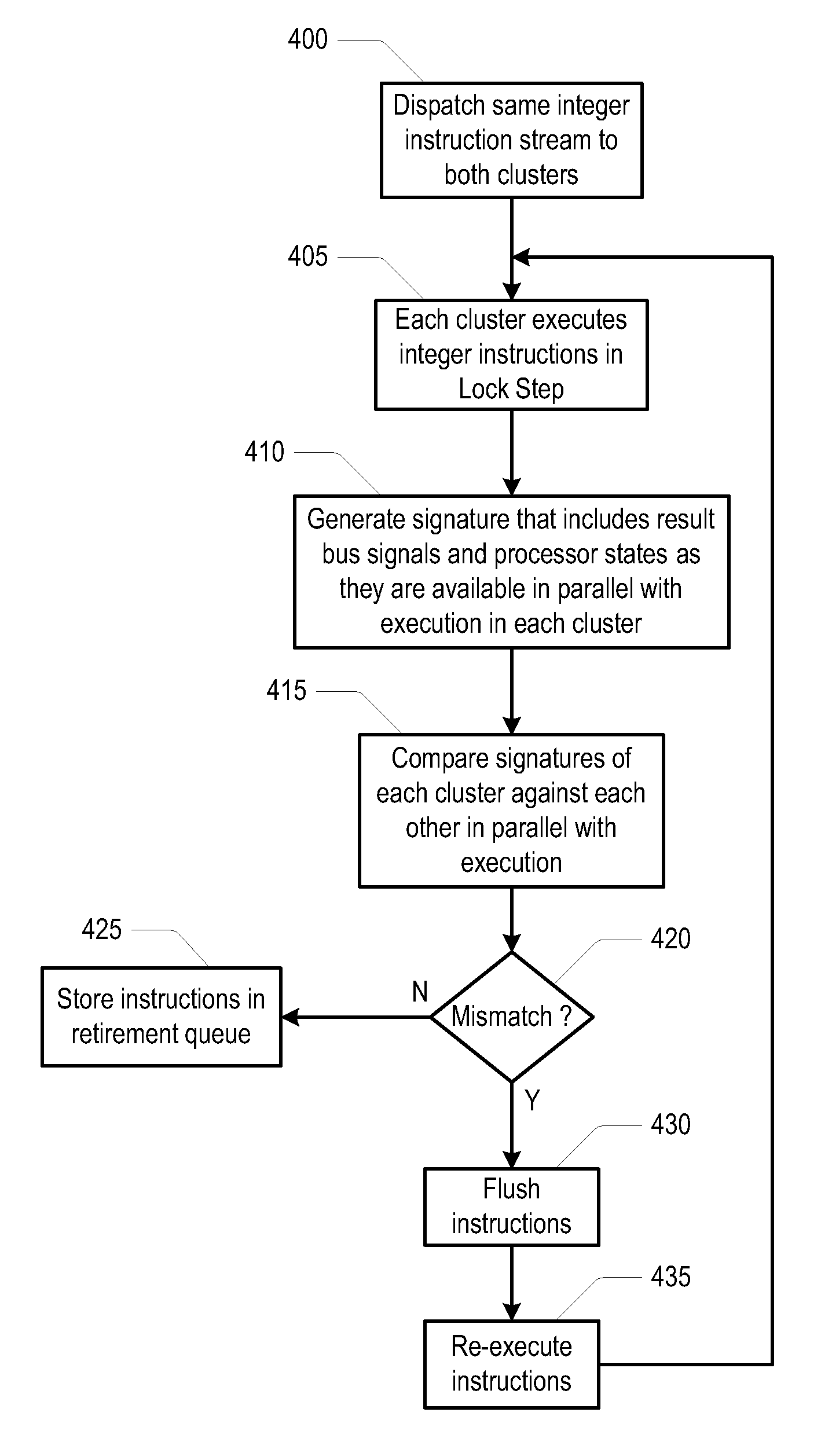

Processor including efficient signature generation for logic error protection

ActiveUS20090182991A1Generate efficientlyDigital computer detailsSpecific program execution arrangementsExecution unitLogic error

A processor core includes an instruction decode unit that may dispatch a same integer instruction stream to a plurality of integer execution units operating in lock-step. The processor core also includes signature generation logic that may generate, concurrently with execution of the integer instructions, a respective signature from result signals conveyed on respective result buses in one or more pipeline stages within each of the integer execution units in response to the result signals becoming available. The processor core also includes compare logic that may detect a mismatch between signatures from each of the integer execution units. Further, in response to the compare logic detecting any mismatch, the compare logic may cause instructions causing the mismatch to be re-executed.

Owner:ADVANCED MICRO DEVICES INC

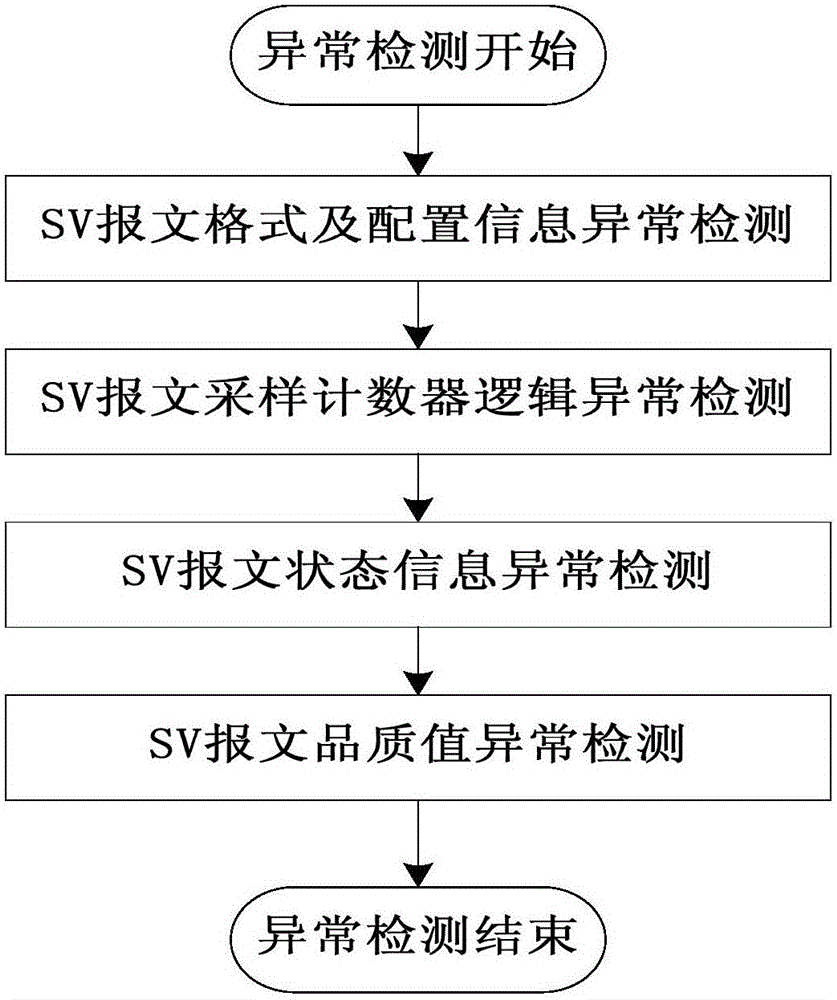

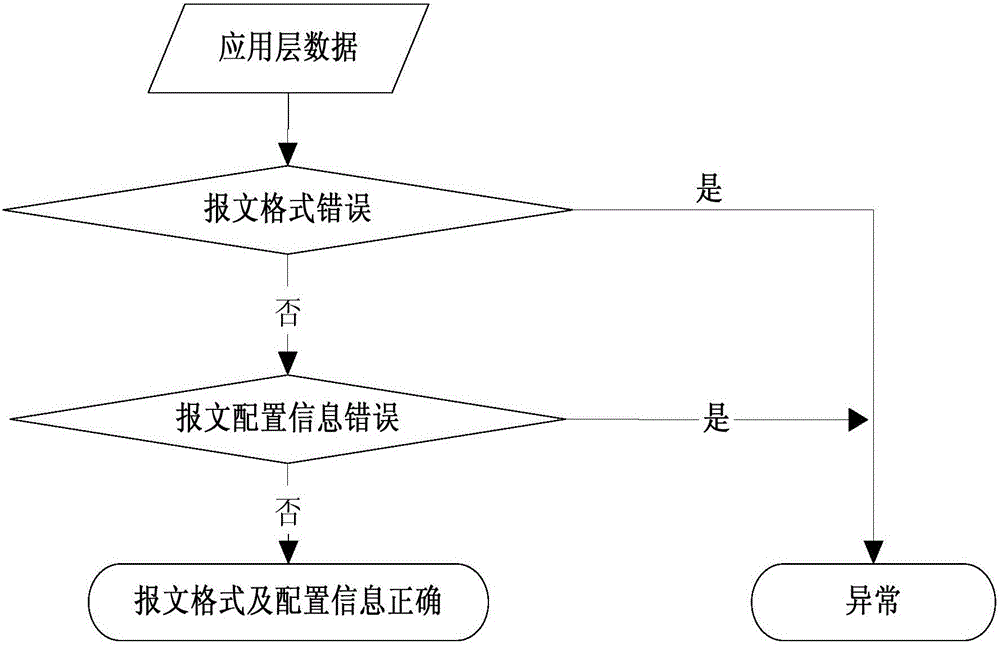

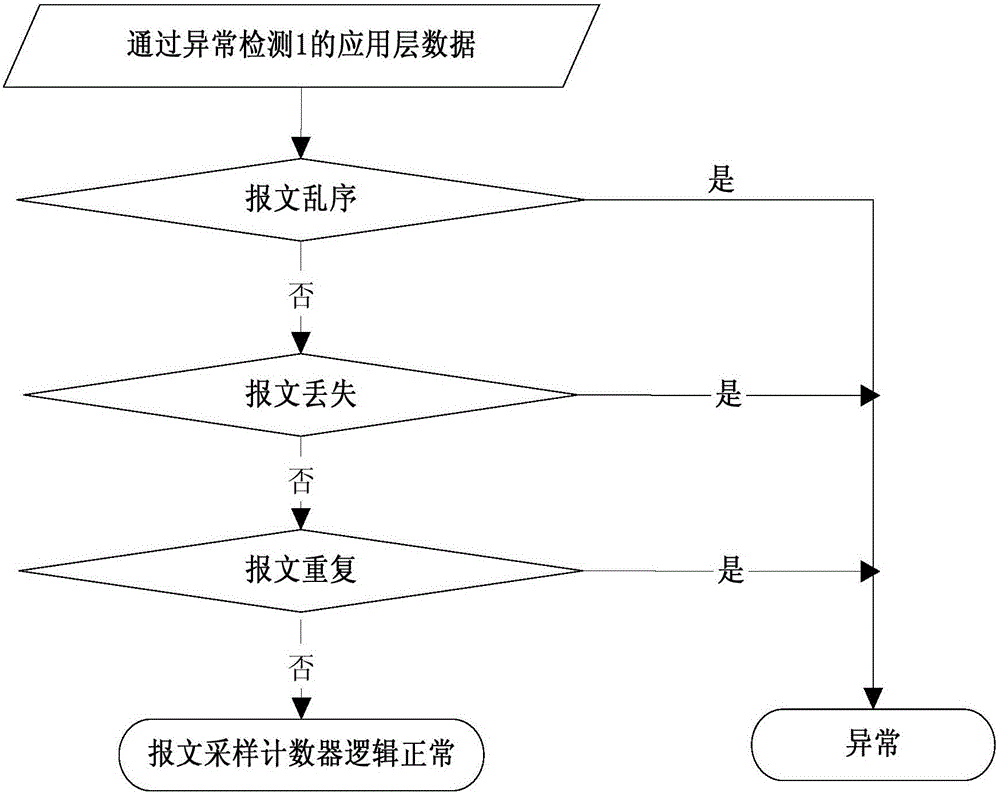

Anomaly detection method specific to IEC61850 protocol SV (Sample Value) message

InactiveCN106130950AConcise and comprehensive analysis and judgmentImprove debugging efficiencyTransmissionComputer hardwareAnomaly detection

The invention discloses an anomaly detection method specific to an IEC61850 protocol SV (Sample Value) message. The method comprises the following steps: firstly, detecting a format and configuration information of a frame of SV message, and ending subsequent detection if any of the format and the configuration information is wrong; if the format and the configuration information of the SV message are correct, continuing to perform logic analysis on an smpCnt value to judge whether abnormal phenomena such as disorder, loss and repetition of the message occur or not; if the smpCnt value is free from a logic error, continuing to detect state information of the SV message in order to detect whether the SV message is in an interrupt state or a synchronous state; and finally, if the message is not in an abnormal state, continuing to detect quality values (test and validity) of the message, and judging whether a quality factor of the message is abnormal or not. The method has the advantages of comprehensive analysis and clear logic, is simple, clear and efficient, and can be applied to online data analysis and anomaly detection of transformer substations.

Owner:NANJING UNIV OF SCI & TECH

Processor including efficient signature generation for logic error protection

A processor core includes an instruction decode unit that may dispatch a same integer instruction stream to a plurality of integer execution units operating in lock-step. The processor core also includes signature generation logic that may generate, concurrently with execution of the integer instructions, a respective signature from result signals conveyed on respective result buses in one or more pipeline stages within each of the integer execution units in response to the result signals becoming available. The processor core also includes compare logic that may detect a mismatch between signatures from each of the integer execution units. Further, in response to the compare logic detecting any mismatch, the compare logic may cause instructions causing the mismatch to be re-executed.

Owner:ADVANCED MICRO DEVICES INC

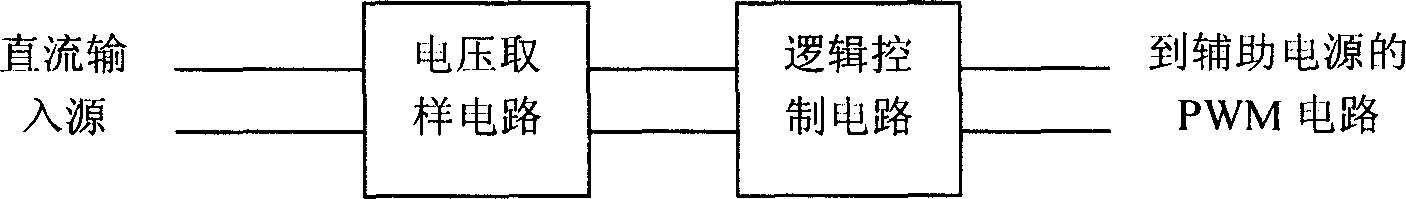

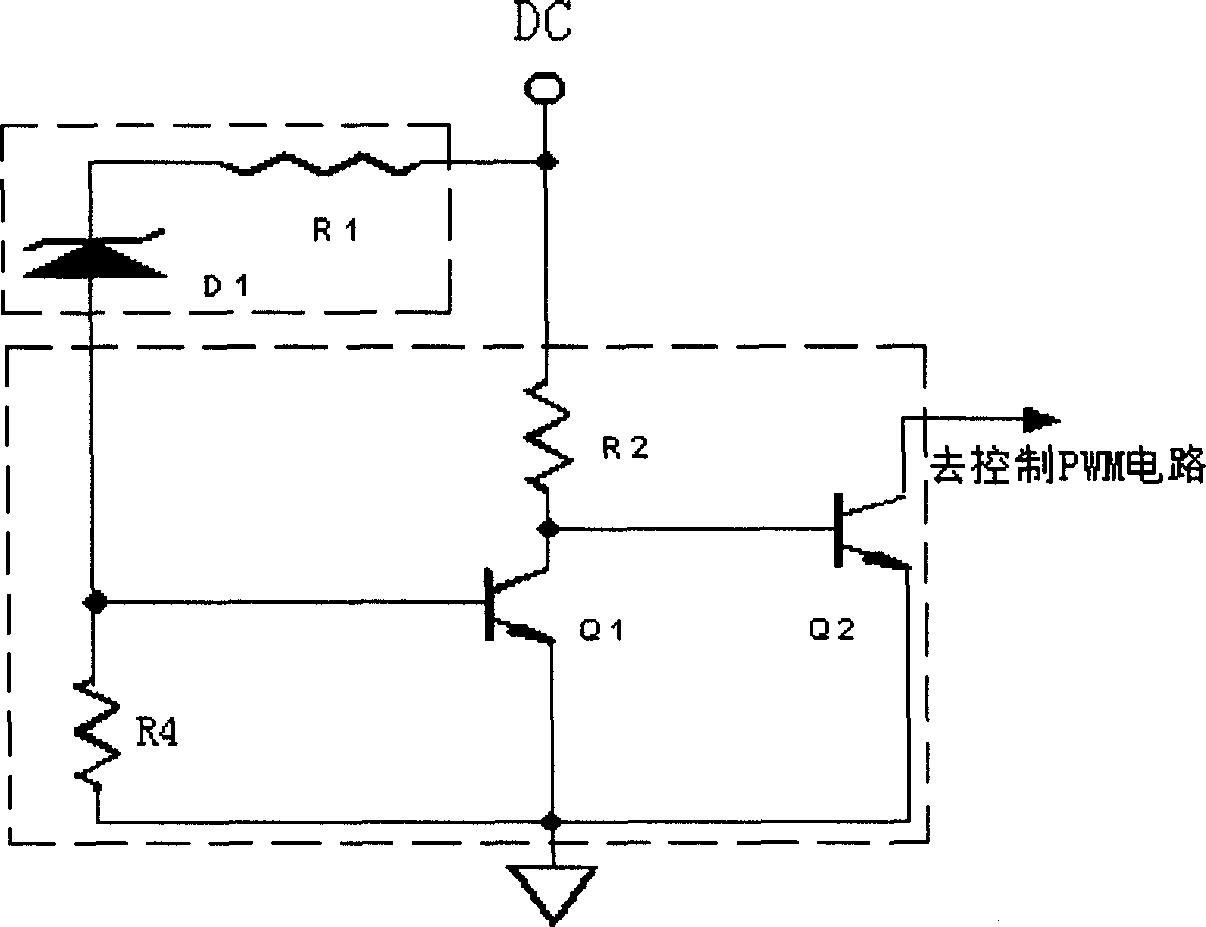

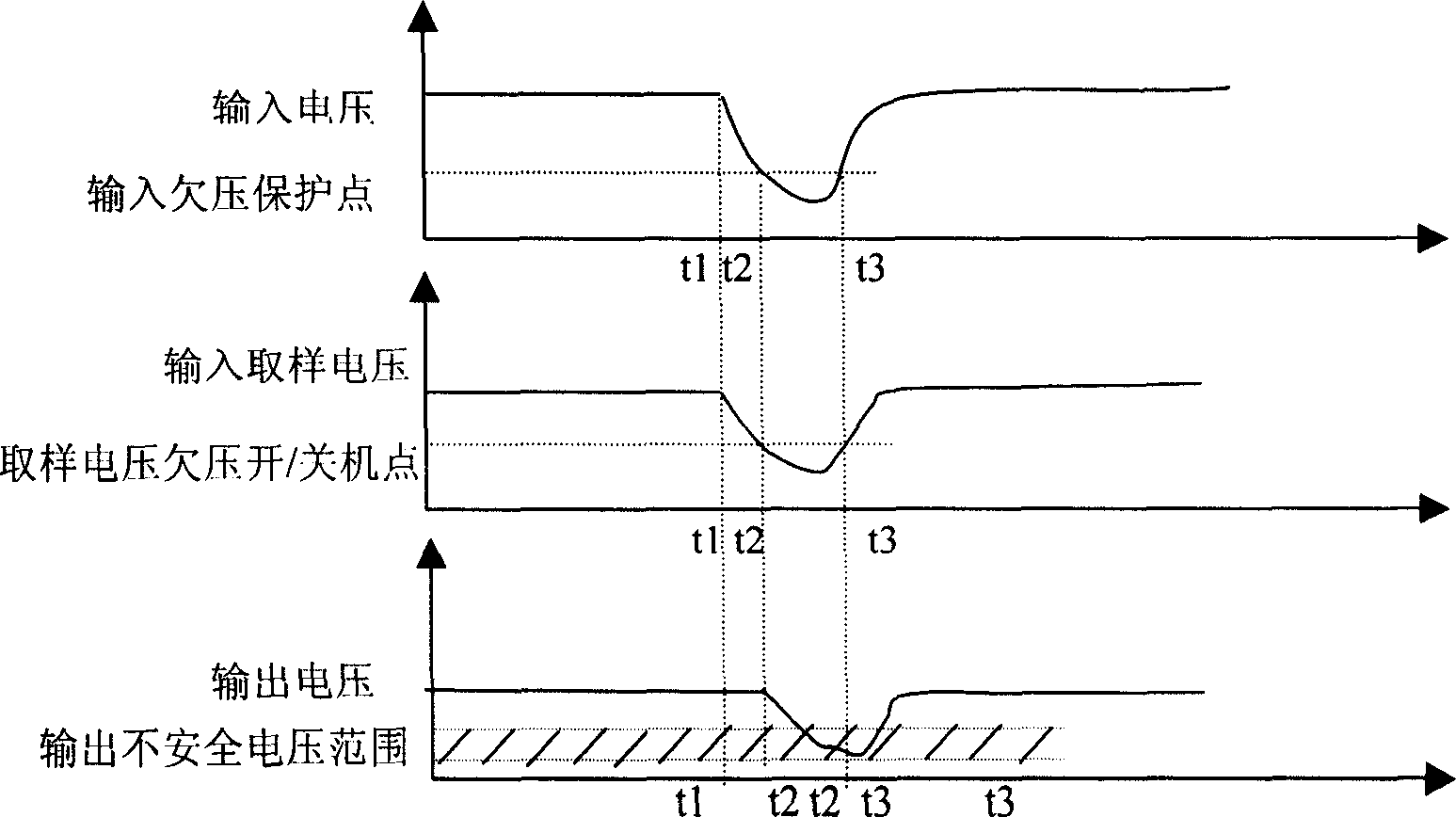

Input under-voltage/over-voltage protection circuit

ActiveCN1913272APrevent damage, etc.Prevent repeated switching on and offArrangements responsive to excess voltageArrangements responsive to undervoltageLow voltageEngineering

This invention relates to a new type of input low voltage / over voltage protection circuit used in assistant supply including a voltage sample circuit, a logic control circuit, a back lash control circuit used in low voltage back lash processing said sample output to be output to said logic control circuit, which ensures outputs of the assistant supply can fall to the safety low voltage and then starts up when the input meets with quick falling, transient, glittering or low frequency interference to avoid logic errors.

Owner:VERTIV CORP

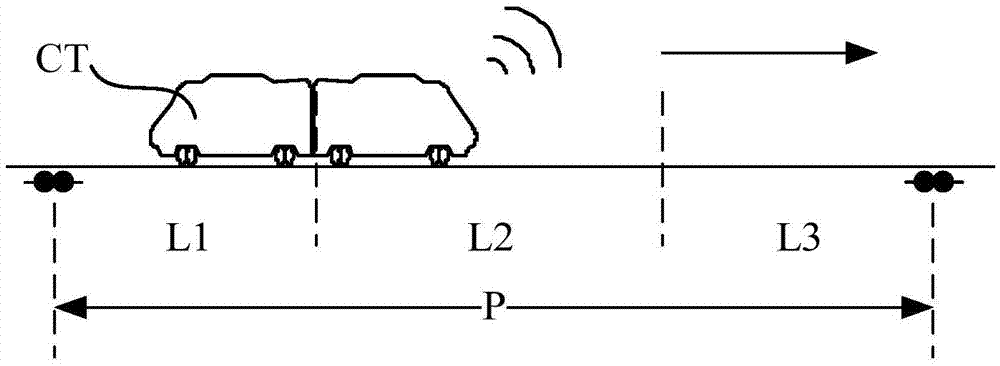

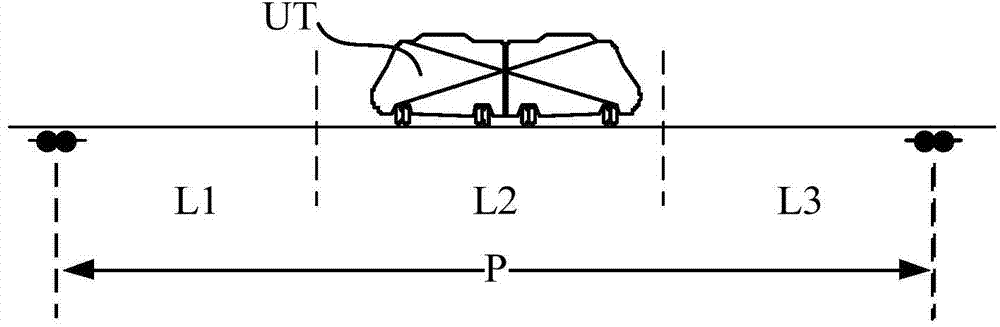

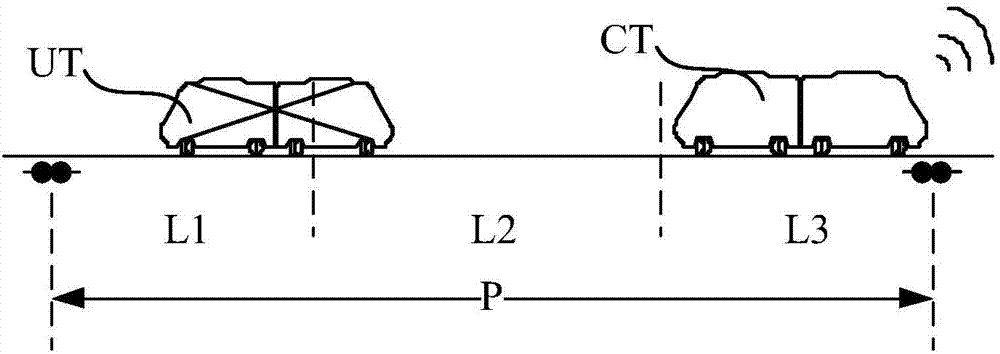

An orbital tracking method

ActiveCN104260761AAvoid situations that affect operational safetyAvoid exportingRailway signalling and safetyDowntimeEngineering

The invention discloses an orbital tracking method. The method comprises: searching, in an electronic map, a position of a physical section to be checked in an orbit line and the physical section round the physical section to be checked; determining whether the physical section to be checked and the physical section around the physical section to be checked are in an occupancy state or an idle state; if the sections are in the idle state, directly sending the state of the physical section to be checked to interlocking equipment; if the sections are in the occupancy state, further determining whether a logic section within the physical section to be checked and a logic section within the physical section around the physical section to be checked are in the occupancy state or the idle state; if the sections are in the idle state, directly guiding an automatic protecting system ATP of a ground train to a safe side, and warning in a downtime way that a logic error exists. The method avoids that the ground ATP system directly is directly guided to the safe side due to the logic error, and avoids a situation that affects the operation safety of the system like losing the car in a complex circumstance.

Owner:TRAFFIC CONTROL TECH CO LTD

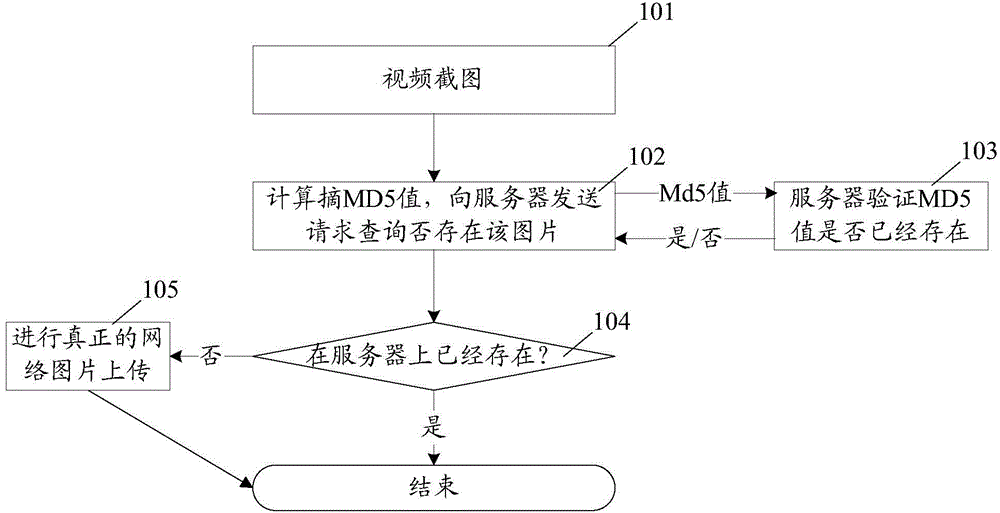

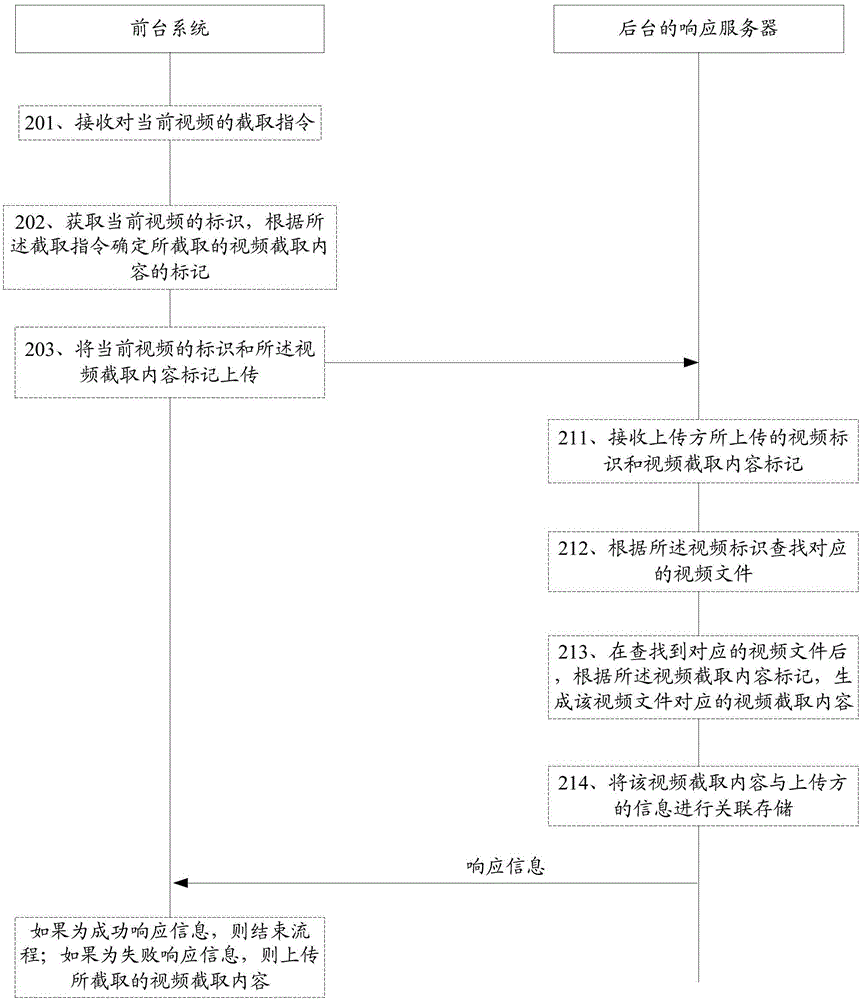

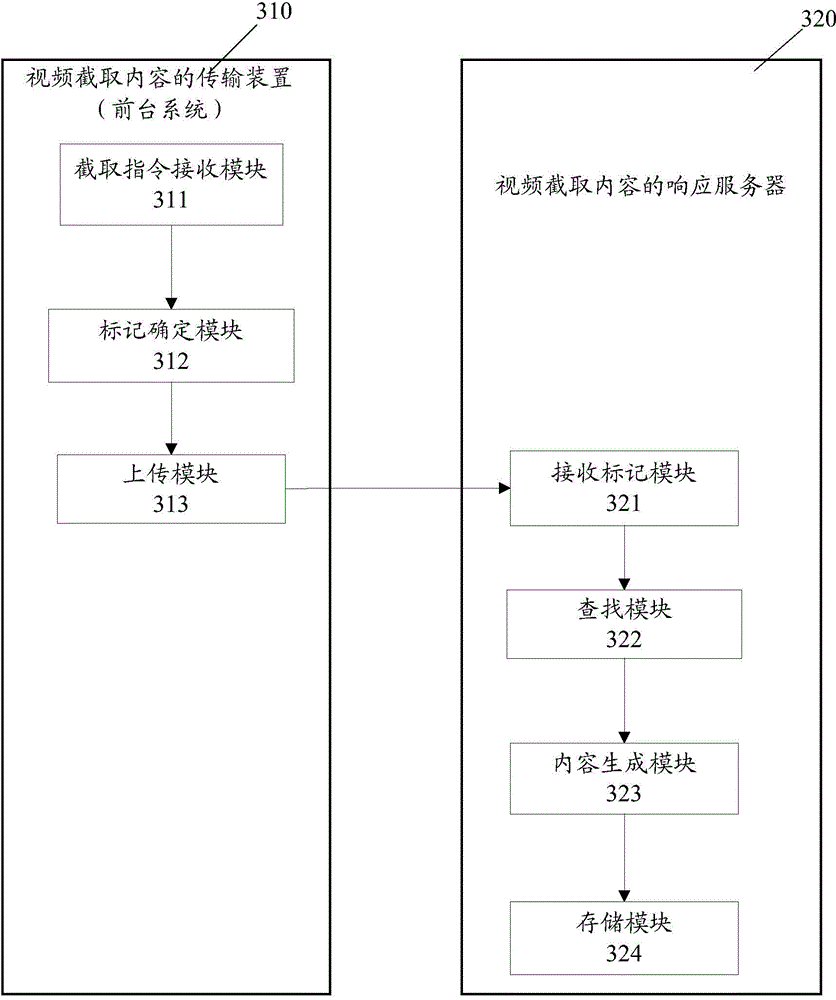

Transmission response method, device, server and system of video intercepted content

ActiveCN104602102AIncreased chance of screenshots being uploaded in secondsSave bandwidthSelective content distributionContent IdentifierComputer network

The invention discloses a transmission response method, device, server and system of a video intercepted content. The transmission response method comprises the following steps: receiving an interception instruction of current video by a foreground, acquiring an identifier of the current video, and determining an identifier of the video intercepted content according to the interception instruction; uploading the identifier of the current video and the video intercepted content identifier. The response server receives the video identifier and the video intercepted content identifier uploaded by an uploading party, searches a corresponding video file according to the video identifier, generates the video intercepted content corresponding to the video file according to the video intercepted content identifier after the corresponding video file is searched and performing associative storage on the video intercepted content and the information of the uploading party. A quick transmission function can be realized, the network bandwidth is saved, the transmission success rate is improved and the logic error rate is reduced.

Owner:TENCENT TECH (BEIJING) CO LTD

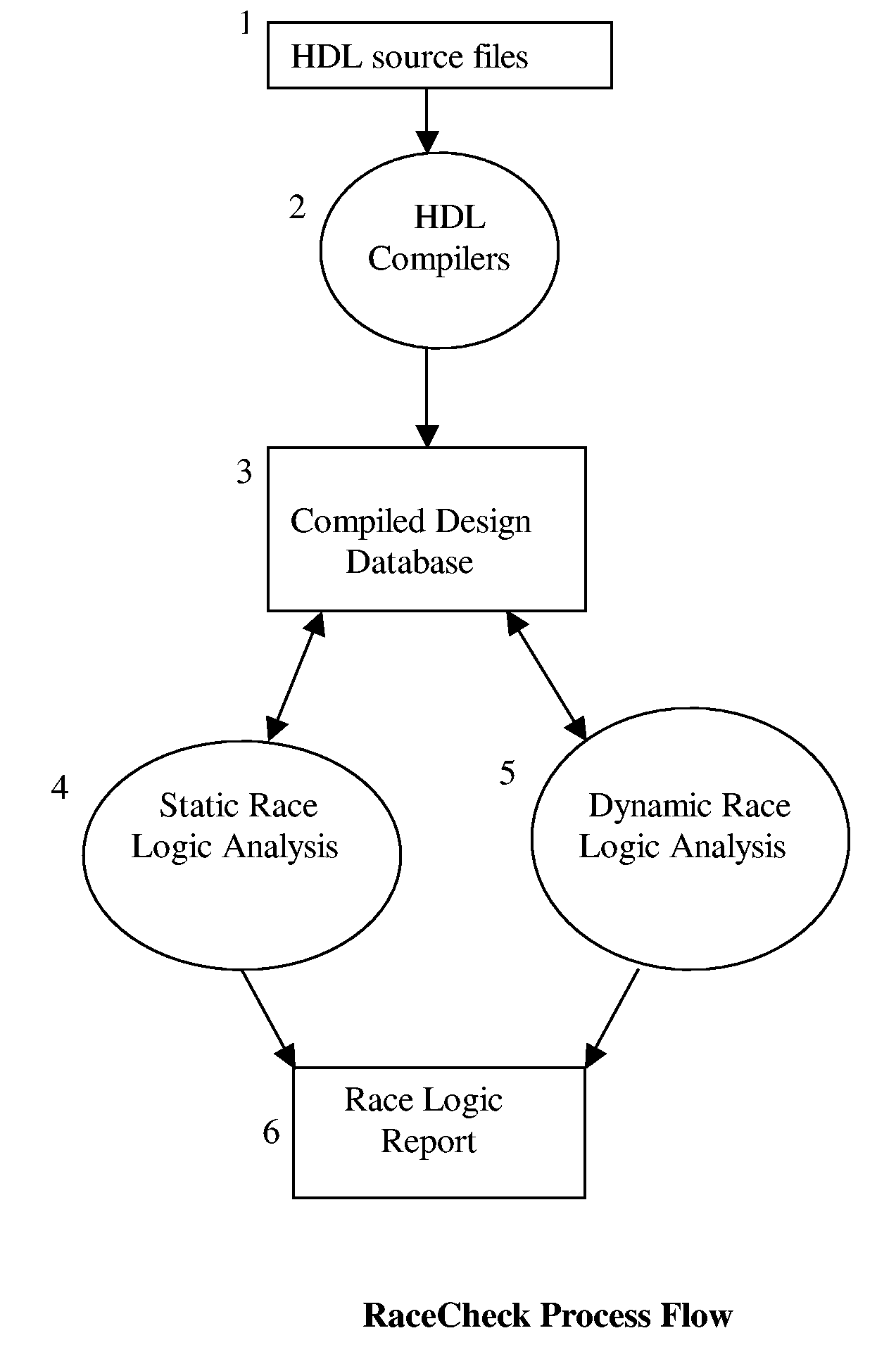

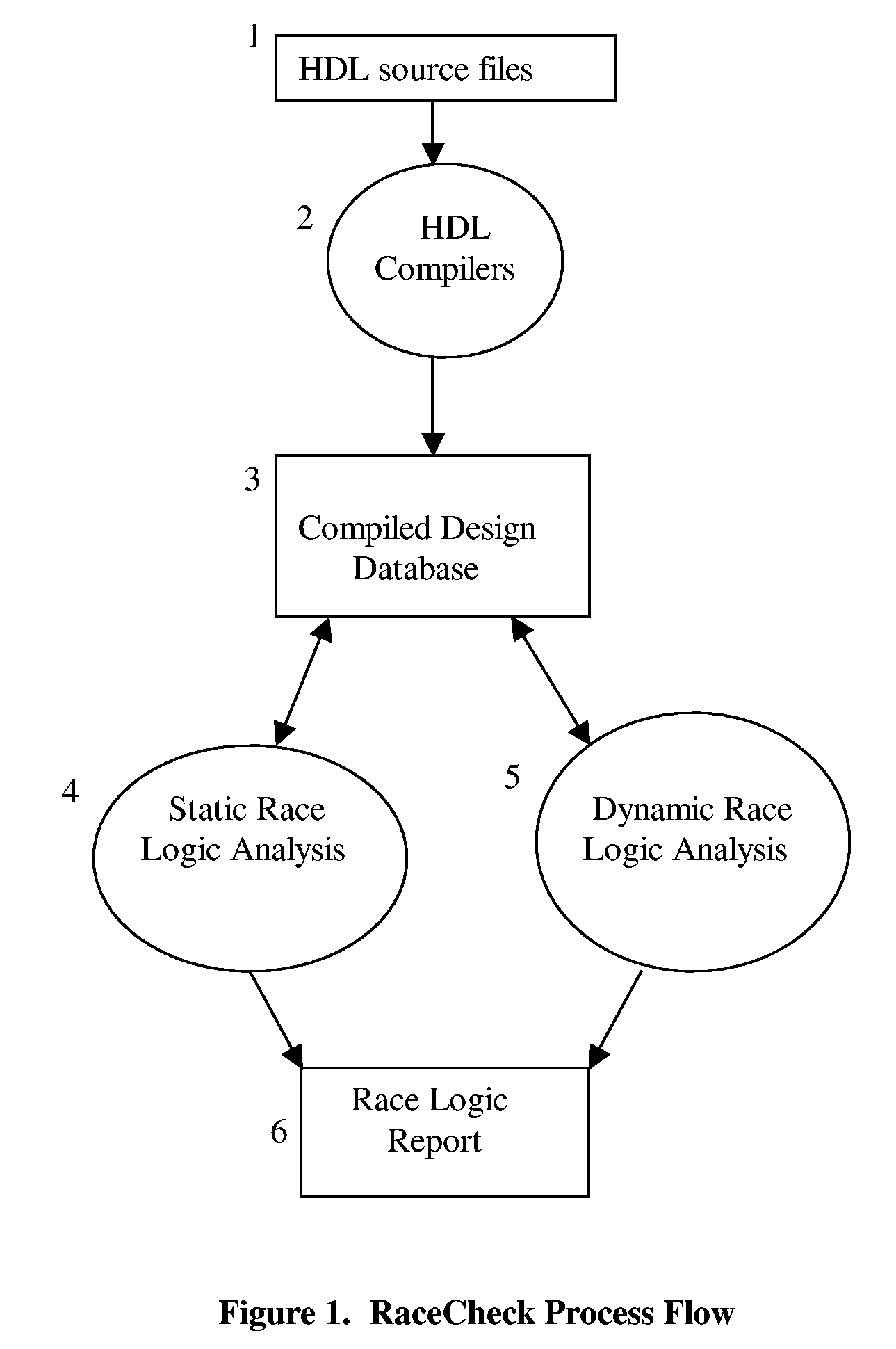

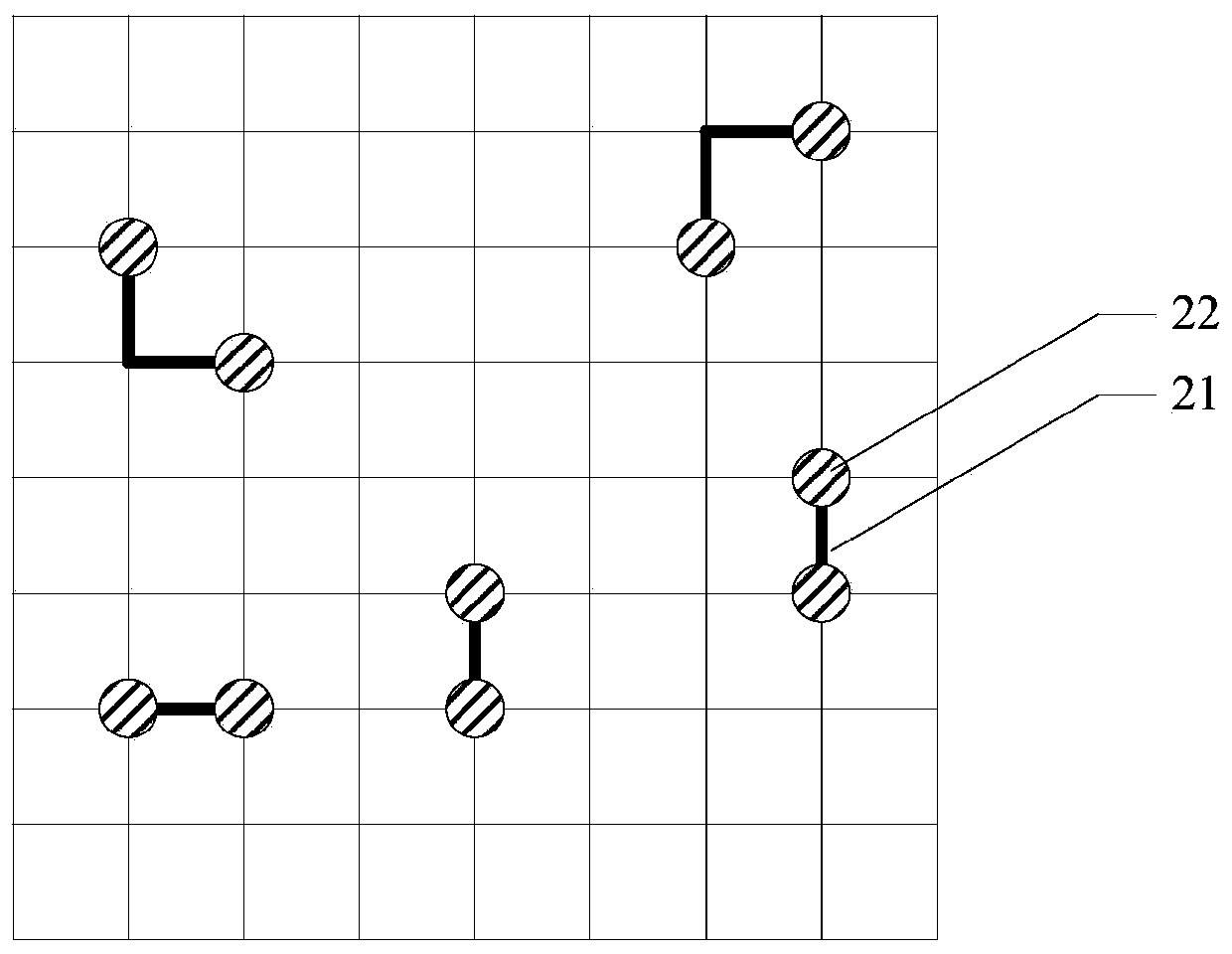

RaceCheck: a race logic analyzer program for digital integrated circuits

ActiveUS7334203B2Reduce effortShorten the timeElectrical testingDesign optimisation/simulationTheoretical computer scienceLogic error

Techniques for performing static and dynamic race logic analysis on an integrated circuit (IC) are described herein. According to one aspect of the invention, HDL (hardware description language) design source files of an IC design are compiled into a common design database, including recording full timing information of the IC design. A static race logic analysis is performed on the common design database to reveal all possible race logic in the IC design. A dynamic race logic analysis could also be performed on the common design database to reveal times and circuit locations where the race logic would occur when a physical IC chip for the IC design is implemented. A race logic analysis report is generated for the static and / or dynamic race logic analysis, where the race logic analysis report is used to eliminate race logic errors in IC designs, so as to render highest quality IC products that will not exhibit intermittent random failures in field operations.

Owner:DYNETIX DESIGN SOLUTIONS

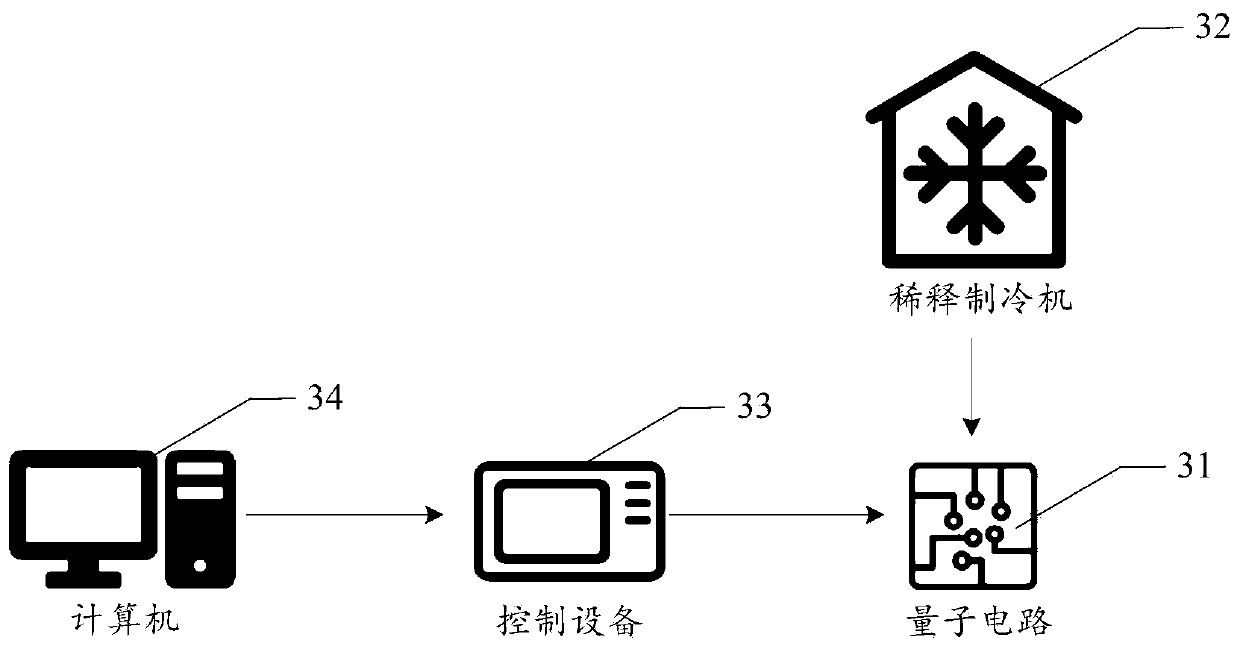

Fault-tolerant error correction decoding method and device of quantum circuit, and chip

ActiveCN111510158AImplement error-tolerant and error-correcting decodingError Tolerance Error Correction Decoding Real TimeQuantum computersNanoinformaticsDecoding methodsQuantum technology

The invention discloses a fault-tolerant error correction decoding method and a fault-tolerant error correction decoding device of a quantum circuit, and a chip, which relate to the technical field ofartificial intelligence and quanta. The fault-tolerant error correction decoding method comprises the following steps of: acquiring real error symptom information of a quantum circuit, wherein the real error symptom information is obtained by performing noisy error symptom measurement on the quantum circuit by adopting a quantum error correction code; decoding the real error symptom information to obtain a logic error class and perfect error symptom information corresponding to the real error symptom information; and determining error result information of the quantum circuit according to thelogic error class and the perfect error symptom information, wherein the error result information is used for indicating data quantum bits with errors in the quantum circuit and corresponding error types. According to the fault-tolerant error correction decoding method and the fault-tolerant error correction decoding device, fault-tolerant error correction decoding is equivalent to a classification problem, so that an efficient neural network classifier is suitable to be adopted for performing fault-tolerant error correction decoding on the error symptom information, the fault-tolerant errorcorrection decoding speed is increased, and real-time fault-tolerant error correction decoding can be realized.

Owner:TENCENT TECH (SHENZHEN) CO LTD

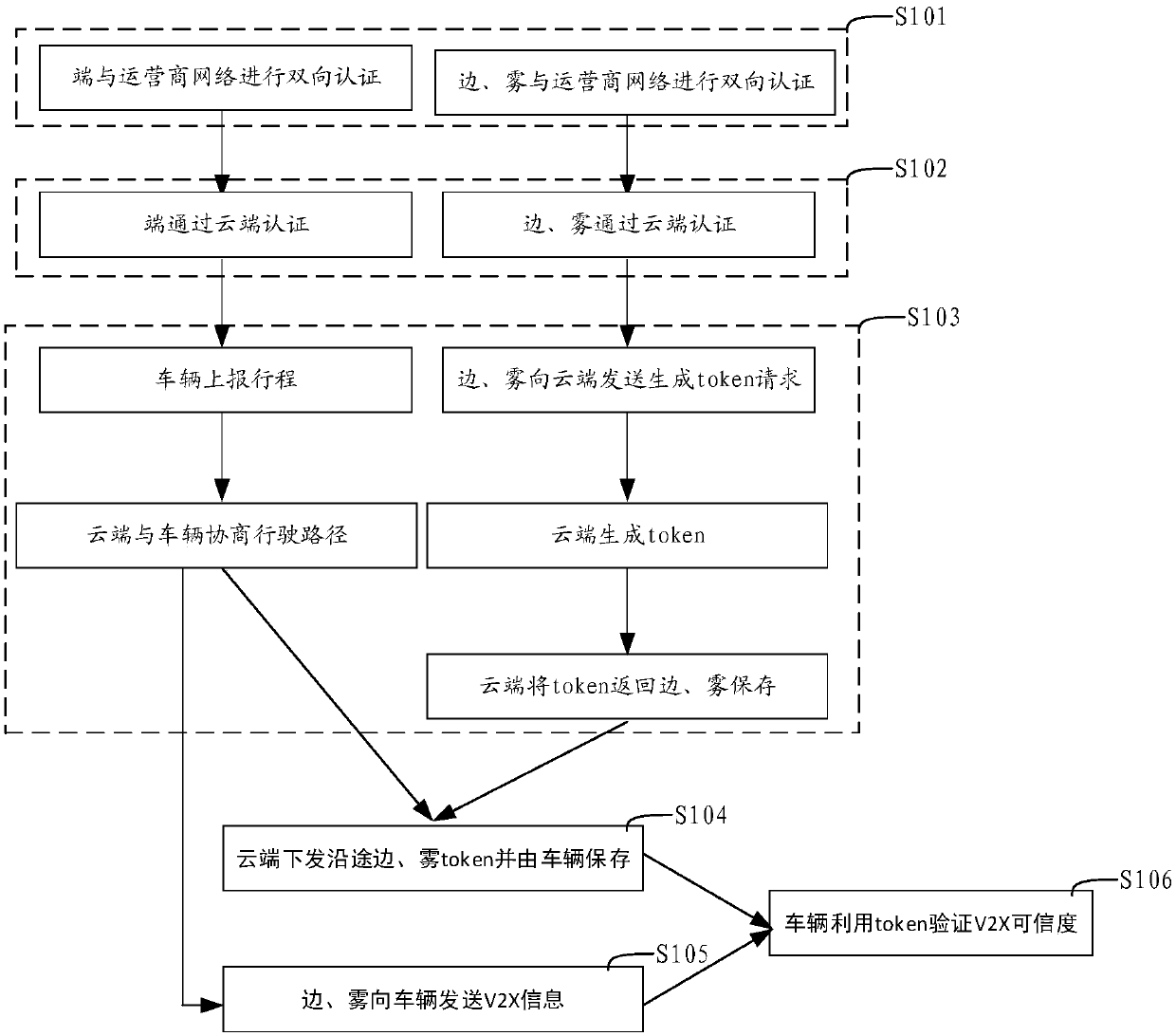

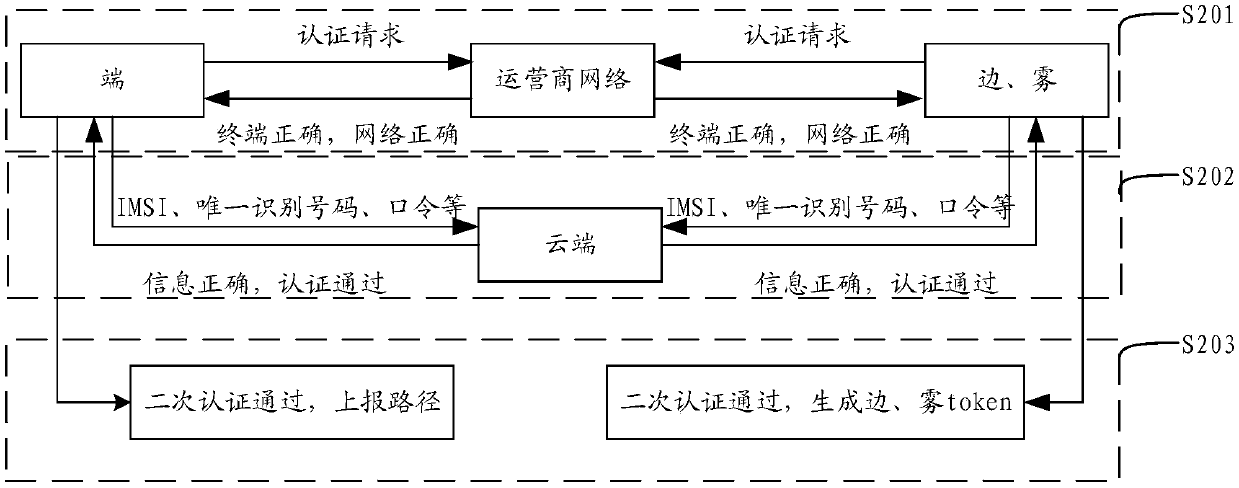

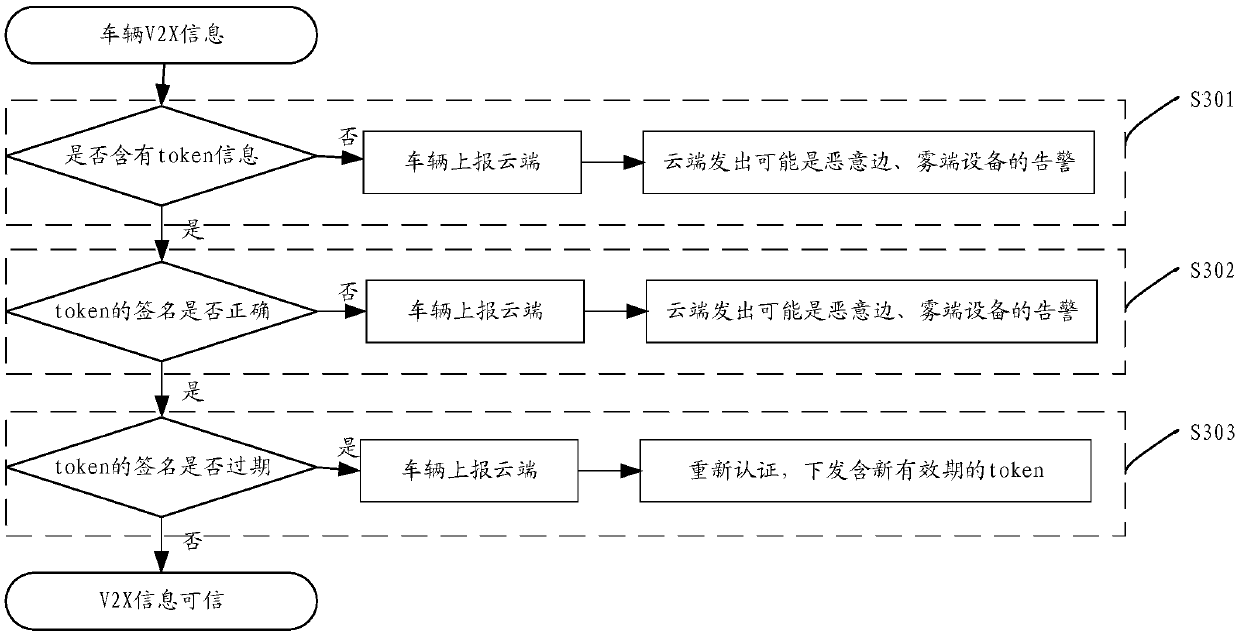

authentication and authorization mechanism and system for the Internet of Vehicles

ActiveCN109756897AParticular environment based servicesVehicle-to-vehicle communicationThe InternetLogic error

The invention provides an authentication and authorization mechanism and system for the Internet of Vehicles, and belongs to the field of information security. Through secondary authentication and token-based identity authentication, the credible problem of V2X information exchange is solved. Wherein the authentication and authorization mechanism comprises the steps that after secondary authentication of a terminal, an edge and fog passes through an operator network and a cloud end, the cloud end is the edge, and a token is generated by the fog; After the cloud end obtains the vehicle path information, side and fog token information is sent to the vehicle; and the vehicle receives the V2X information sent by the side and fog, and authenticates the credibility of the V2X information throughthe stored token. The invention also discloses an authentication and authorization system. The system comprises an operator authentication system, a cloud authentication system, a token system and aV2X system. The authentication and authorization mechanism and system provided by the invention are helpful for the cloud to discover malicious edge and fog equipment, or edge and fog equipment with own defects or logic errors.

Owner:云控智行科技有限公司

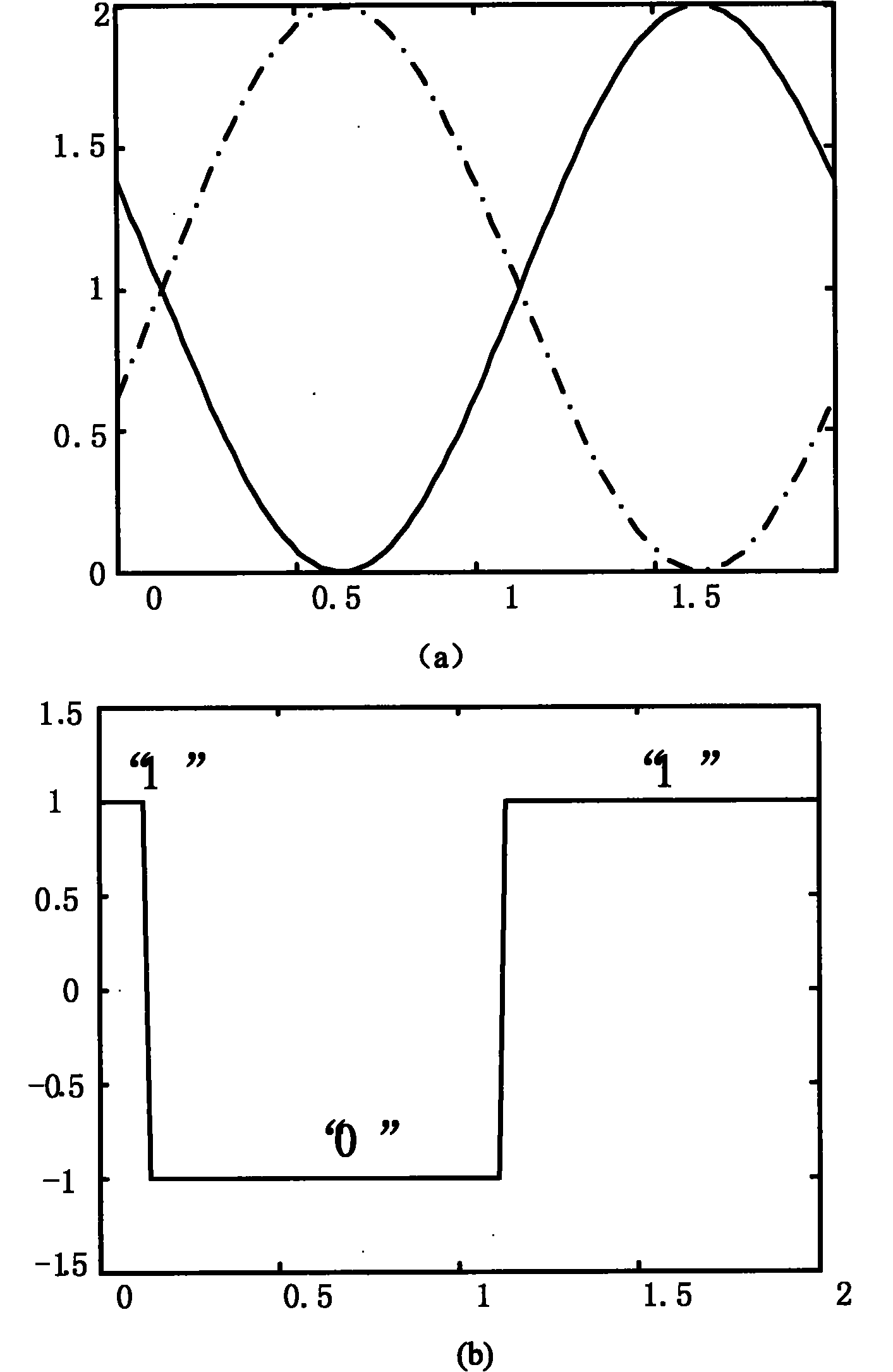

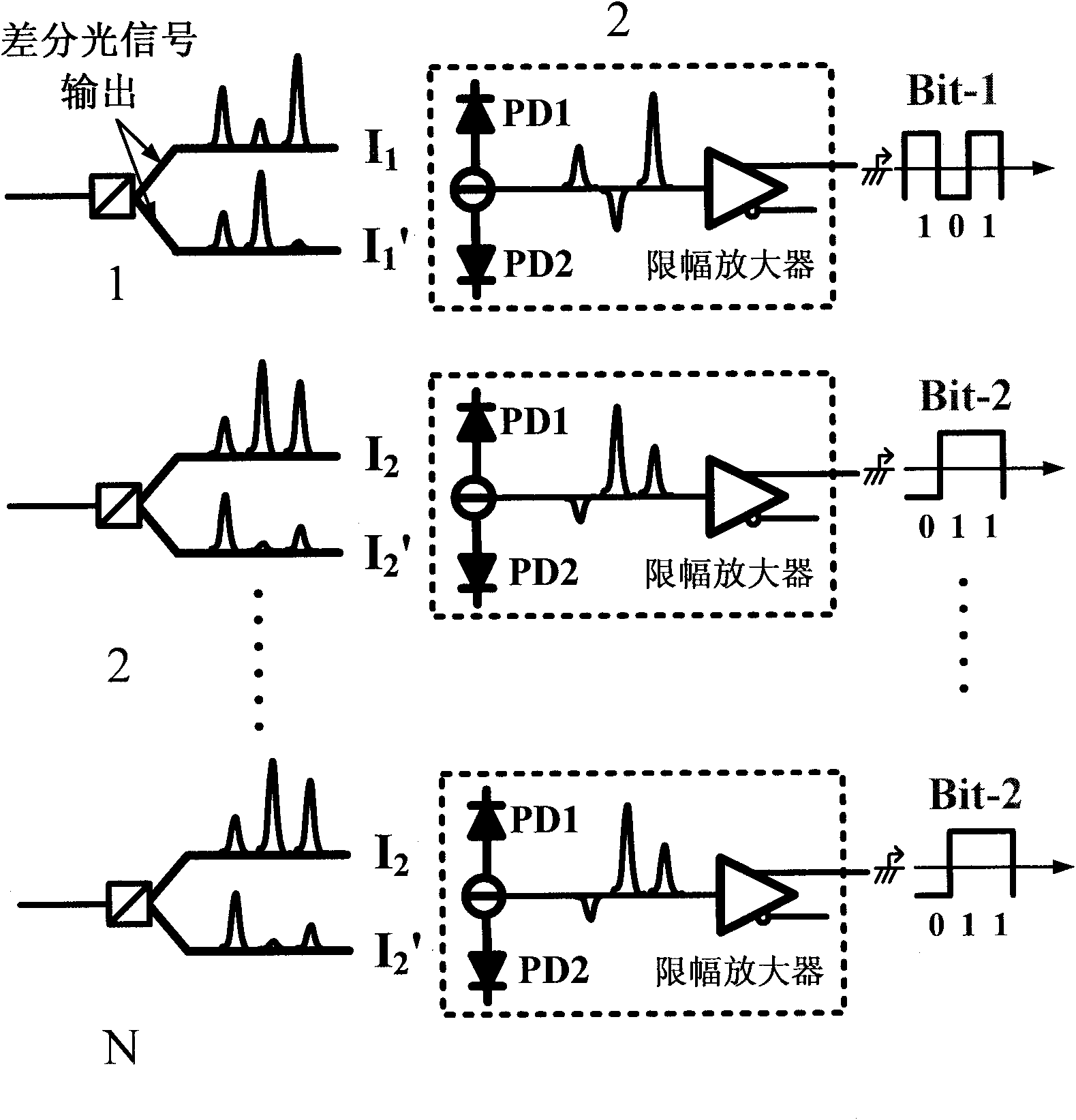

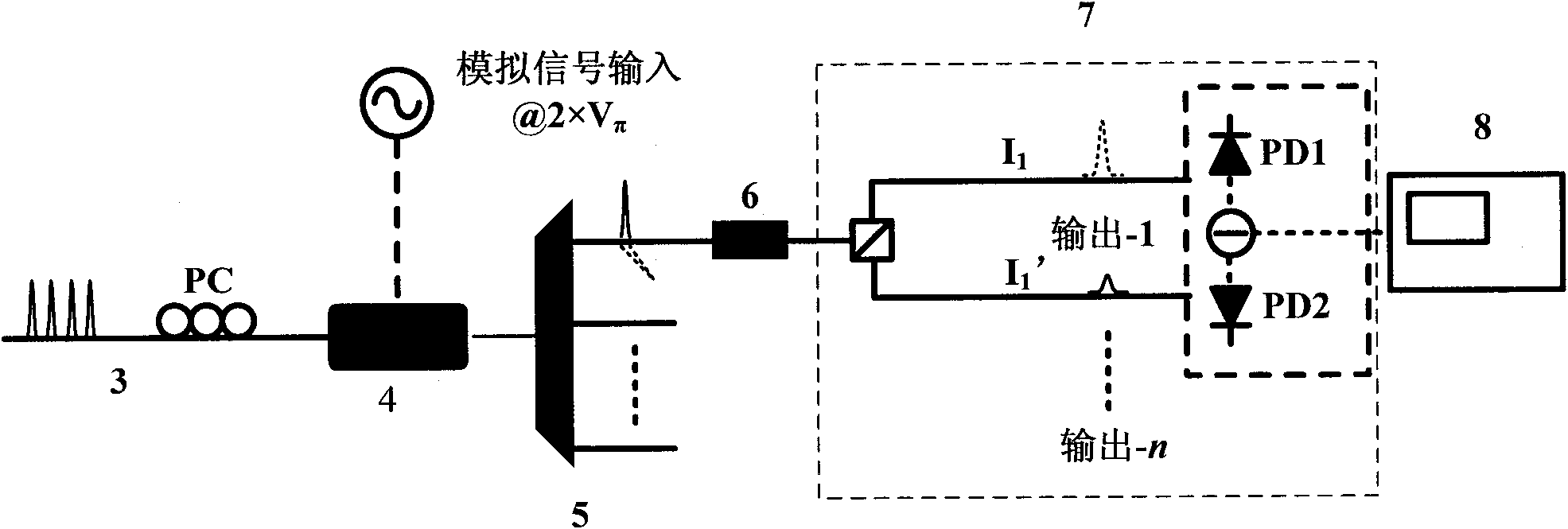

Phase-shift optical quantization receiver based on balance detection

InactiveCN101852968AAvoid the impact of judgmentImprove decision accuracyOptical analogue/digital convertersLogic circuits using opto-electronic devicesPhase shiftedTransimpedance amplifier

The invention discloses a phase-shift optical quantization receiver based on balance detection, belonging to the technical field of optical analog-digital converters. In the balance detection, signals to be judged and output by every quantization channel of a full optical quantizer are a group of difference optical signals of which the amplitudes are complementary; and after the balance receiver is used for receiving the difference optical signals, the difference signals are amplified into a digital signal level by the amplitude limiting of a transimpedance amplifier. The invention can eliminate influence of common-mode noise in a system and effectively reduce judgment logic errors caused by luminous power fluctuation without setting a judgment threshold, thereby eliminating the influenceof the threshold judgment errors, increasing the sensitivity and the tolerance to noise of the receiver, and realizing higher threshold judgment accuracy.

Owner:TSINGHUA UNIV

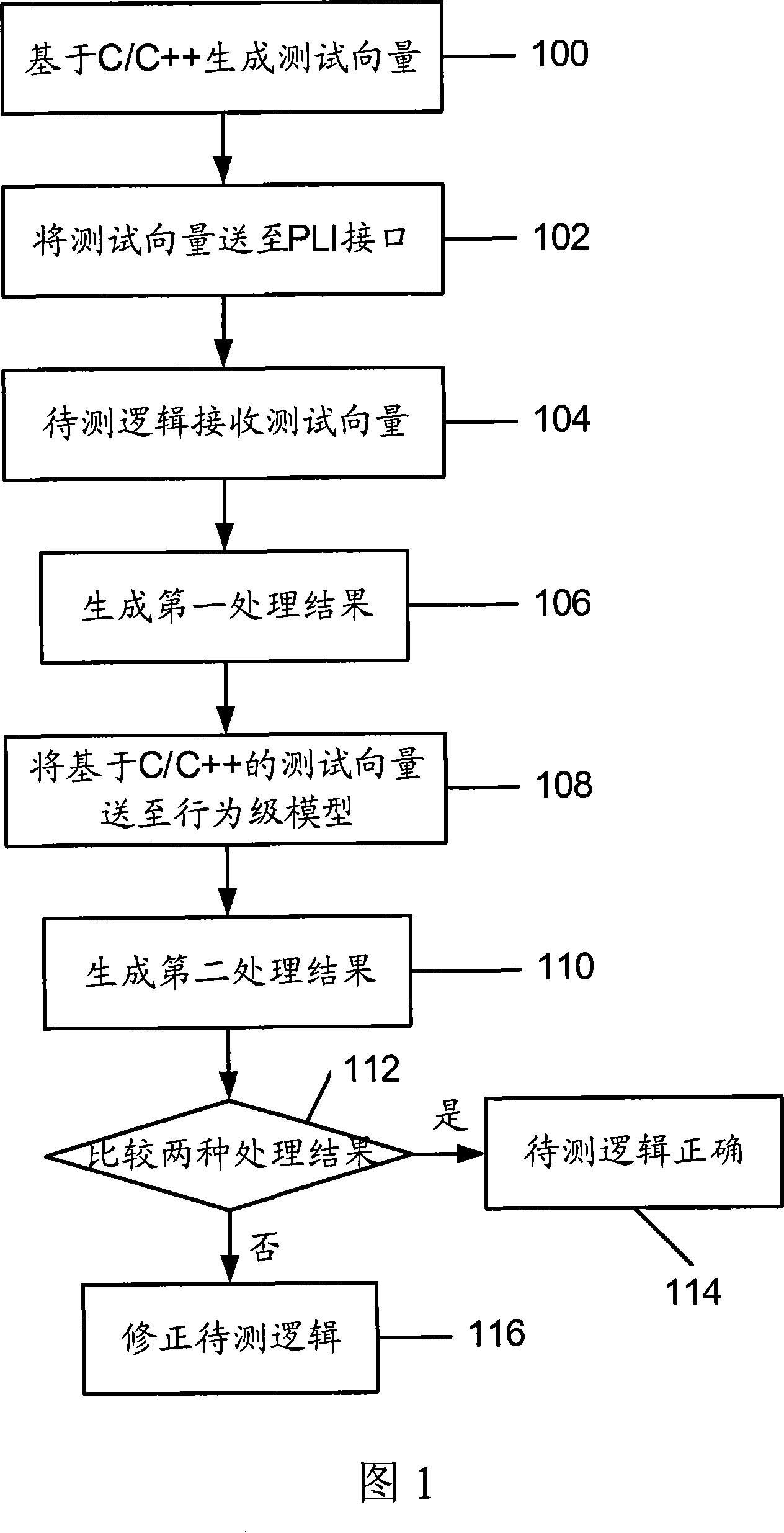

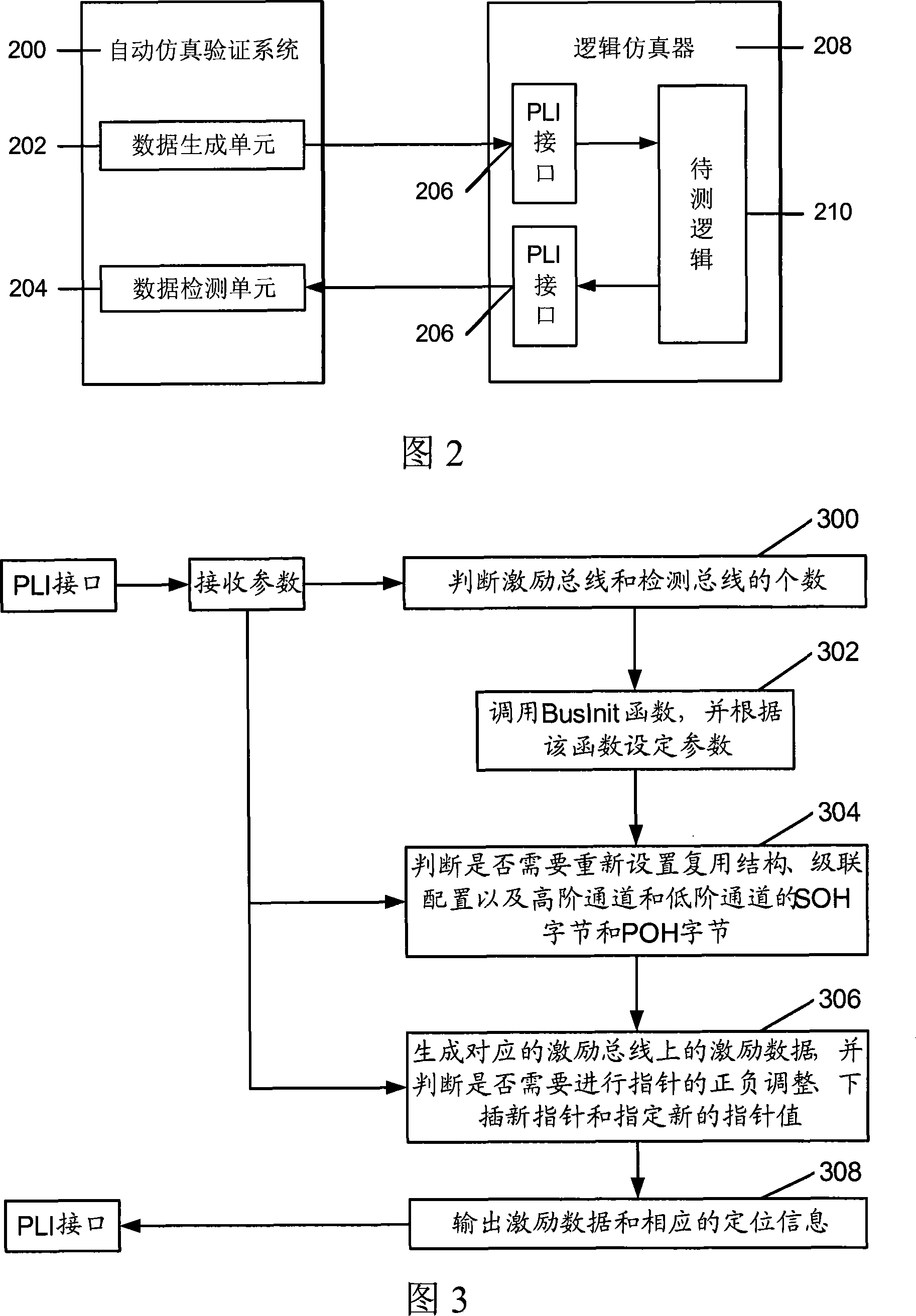

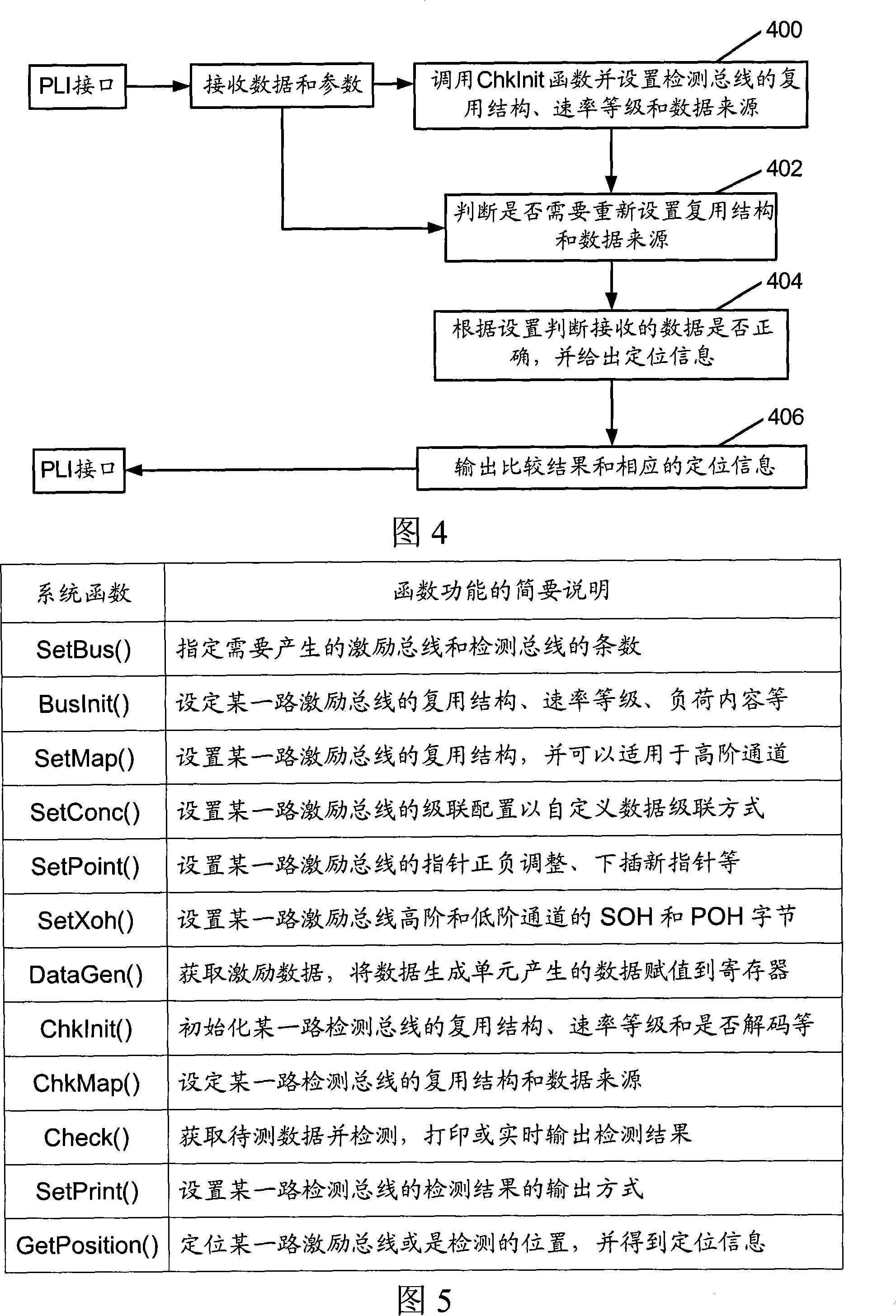

Simulation checking system and its method for SDH logical design

InactiveCN101159492AReduce workloadPrecise positioningTime-division multiplexTransmission monitoring/testing/fault-measurement systemsLogic errorVerification system

The invention discloses an automatic simulated verification system used for SDH / SONET logical design, which comprises a data generation unit for generating excitation data and positioning information, and a data detection unit for receiving the processed data of the logic to be test. The invention also discloses an automatic simulated verification method. The method comprises: determining the excitation bus and detection bus in the system, setting the corresponding configuration of the excitation bus, generating the excitation data and judging whether to adjust and process the pointer; outputting the excitation data and the corresponding positioning information; setting the corresponding configuration of the detection bus; and judging whether the data received by the detection bus is correct. The inventive system and method can rapidly, simply and efficiently provide a stimulating effect, realize the real-time detection of processed data of the logic to be test, and give an alarm when detecting logic error, thereby facilitating a user to position and modulate the logic error.

Owner:UTSTARCOM TELECOM CO LTD

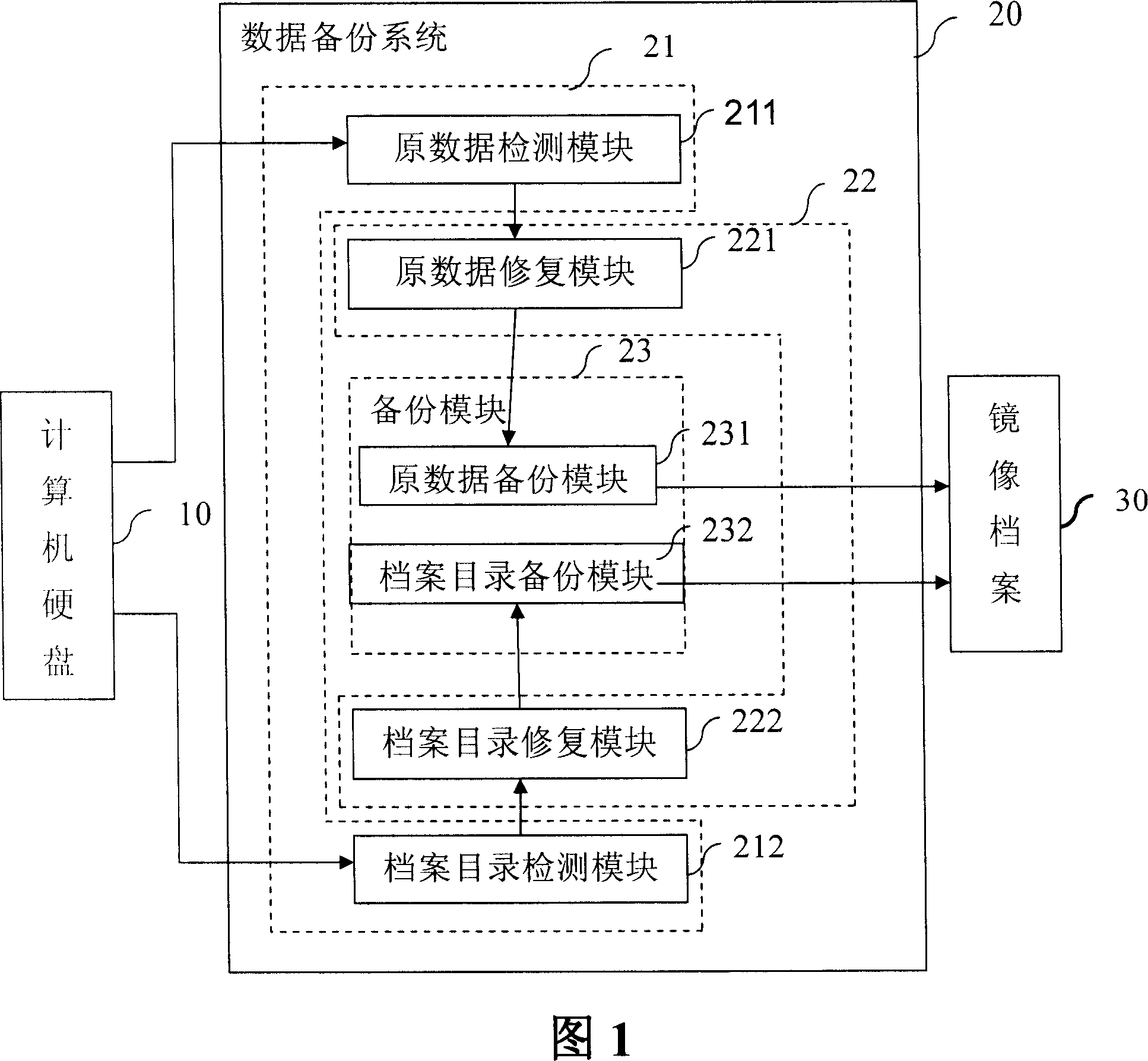

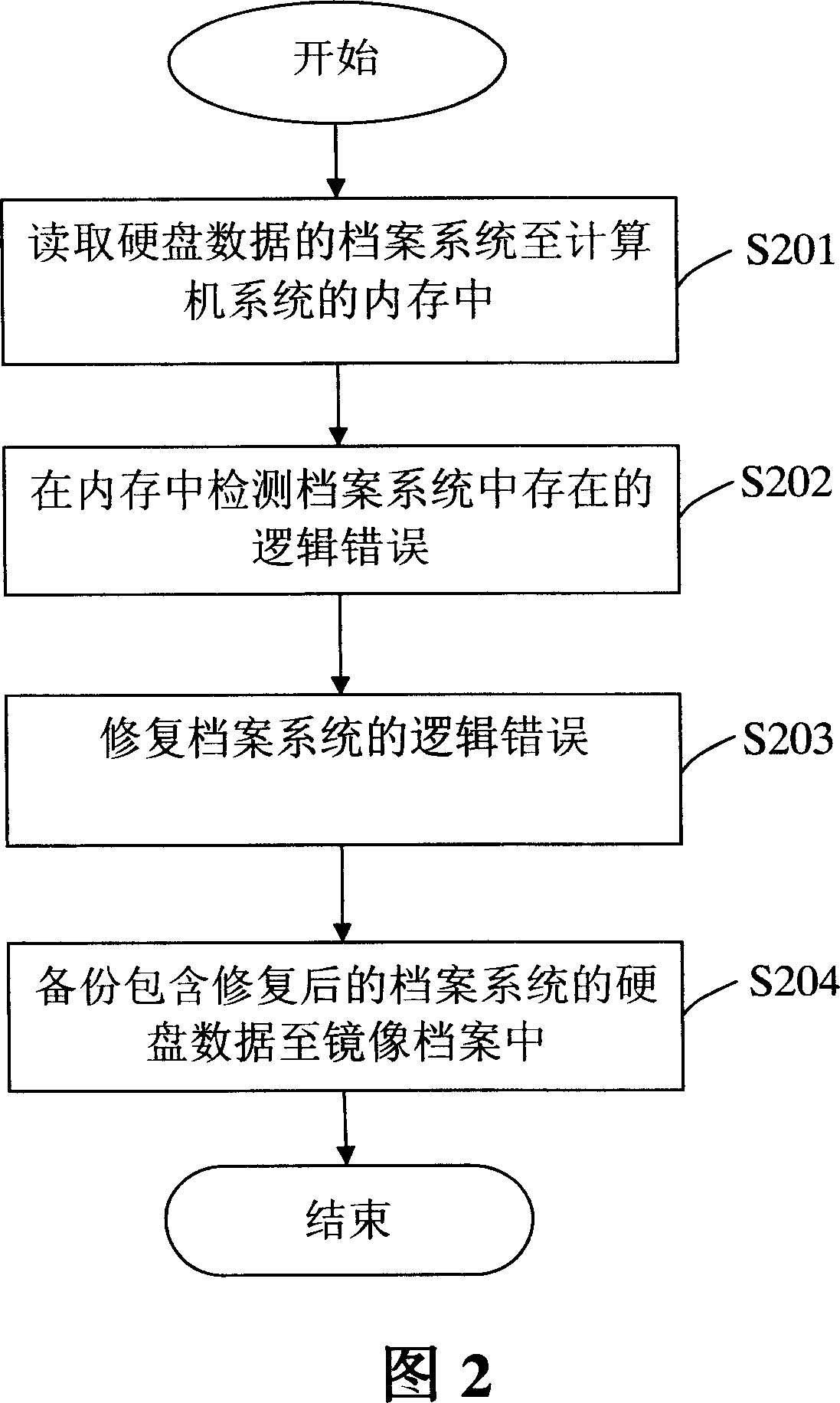

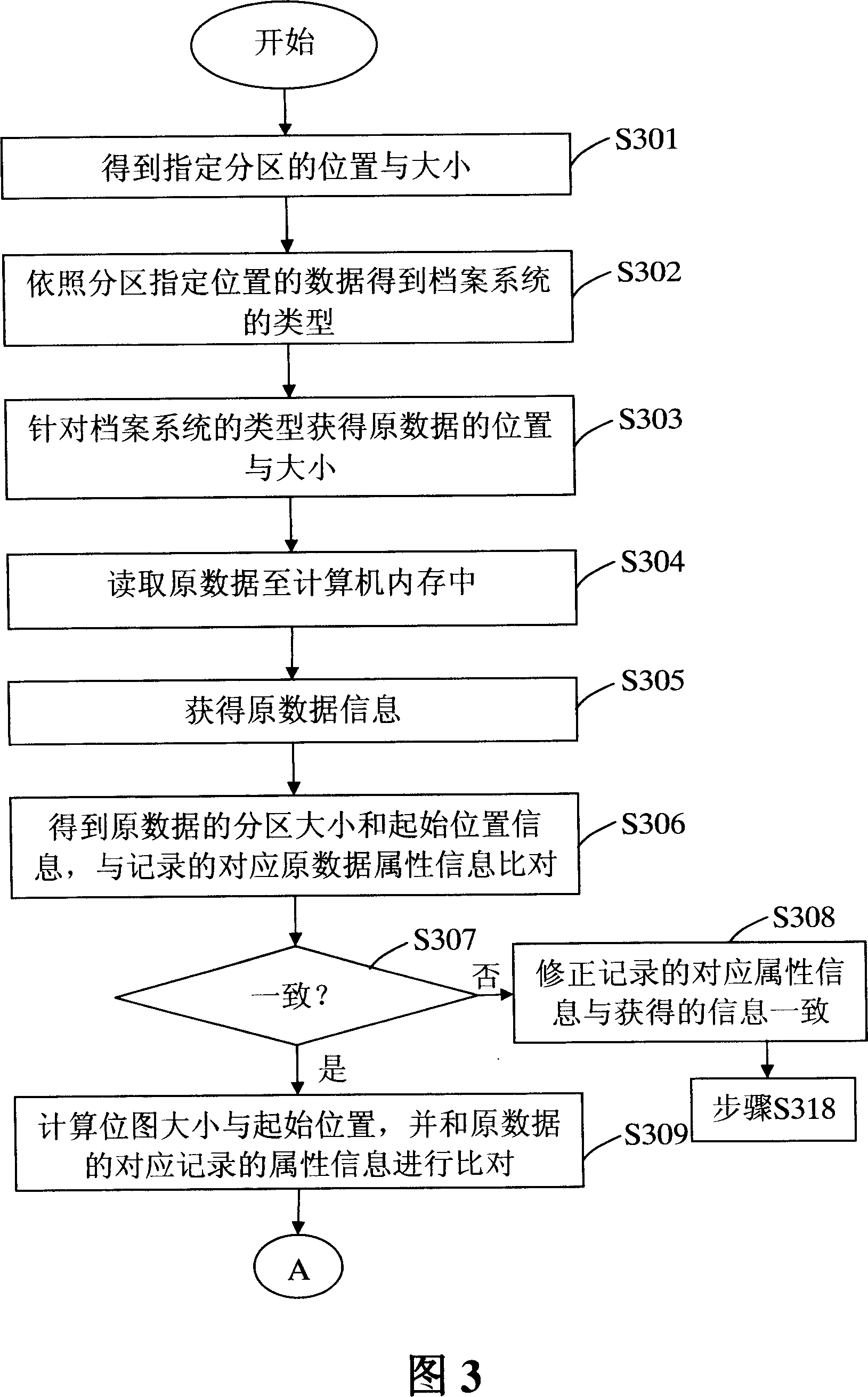

Hard disc data backup system and method

ActiveCN101051283AAvoid accidental damageRedundant operation error correctionInternal memoryFile system

A method for backing up data of hard disc includes fetching file system of hard disc data into internal memory of computer system before back-up, automatically detecting logic error existed in file system of hard disc data, repairing detected out logic error of file system according in internal memory and backing up hard disc data with correct file system to mirror image file.

Owner:ZHIGU HLDG

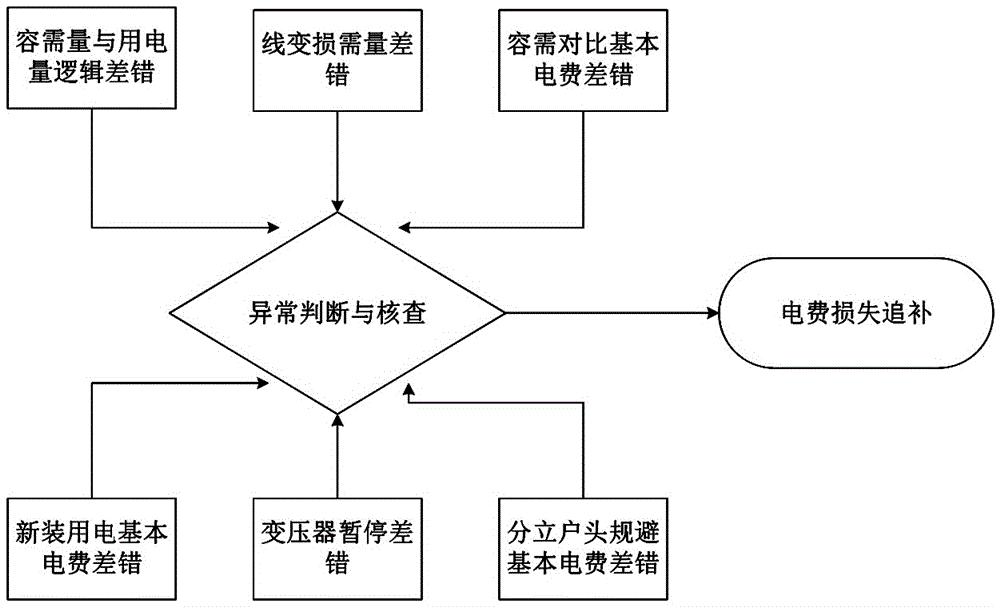

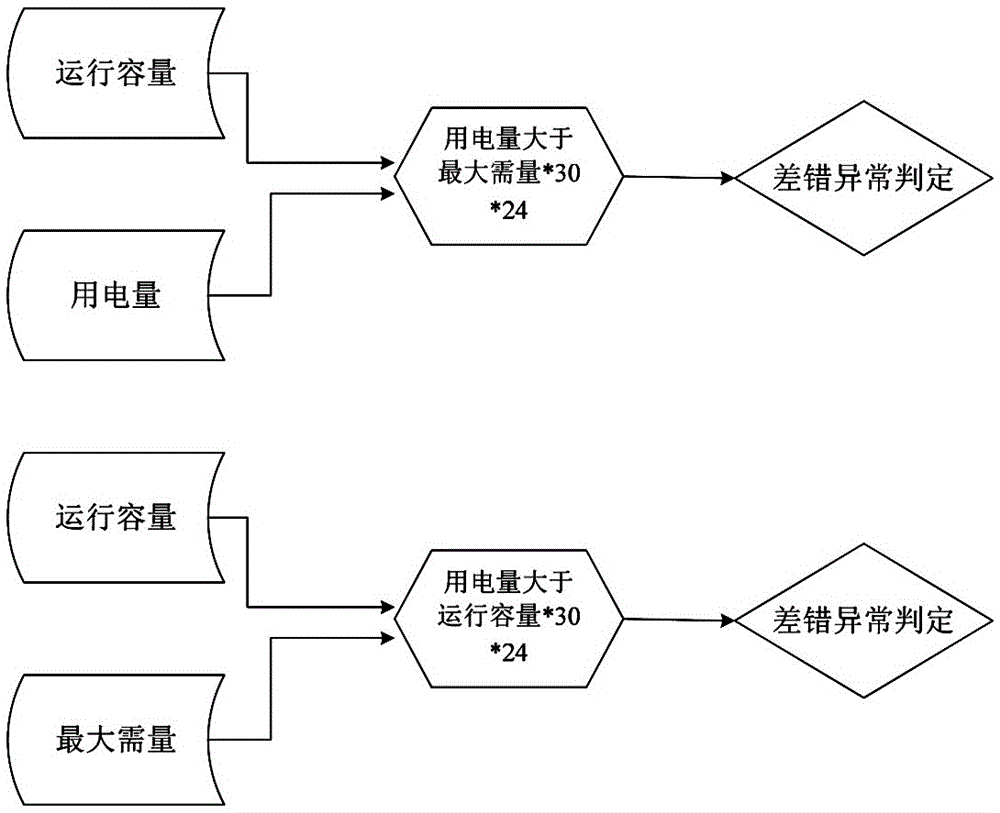

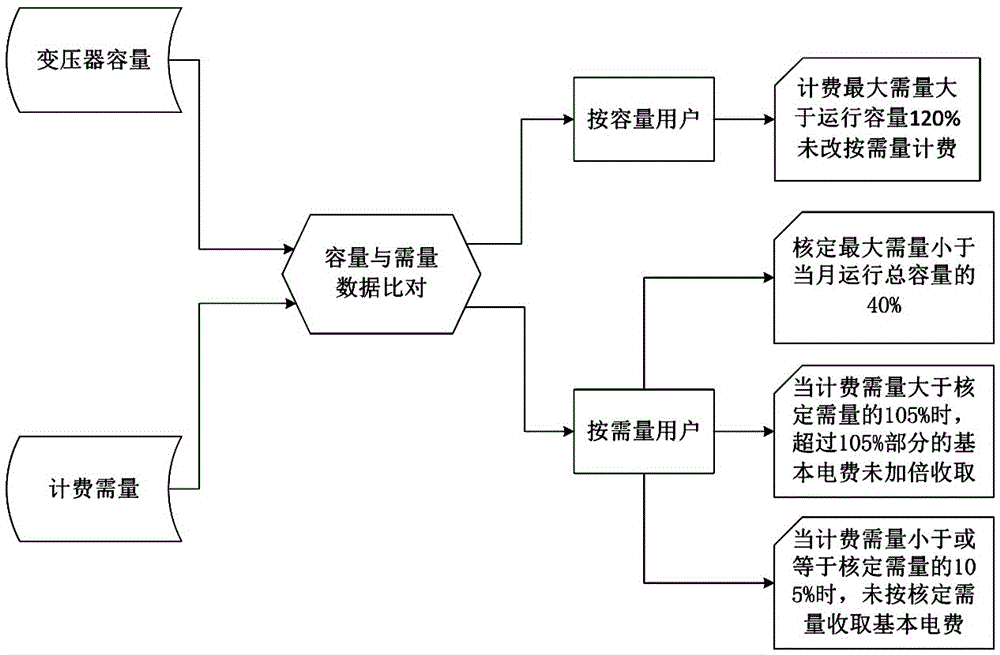

Basic electricity fee error detection method and system based on power grid charging system

Owner:STATE GRID HUNAN ELECTRIC POWER +2

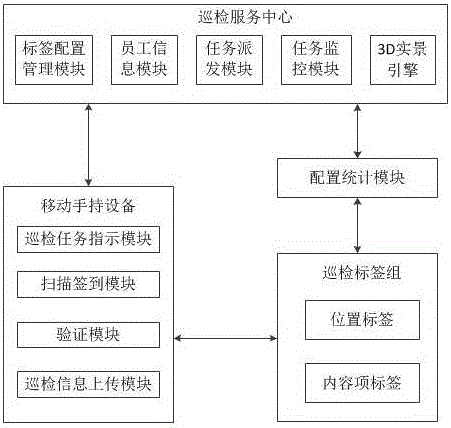

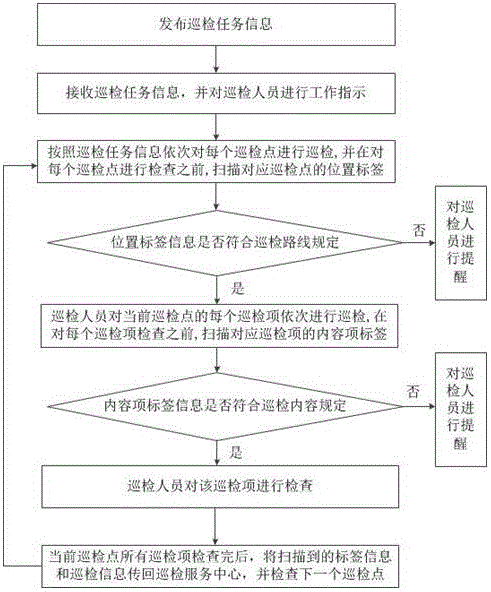

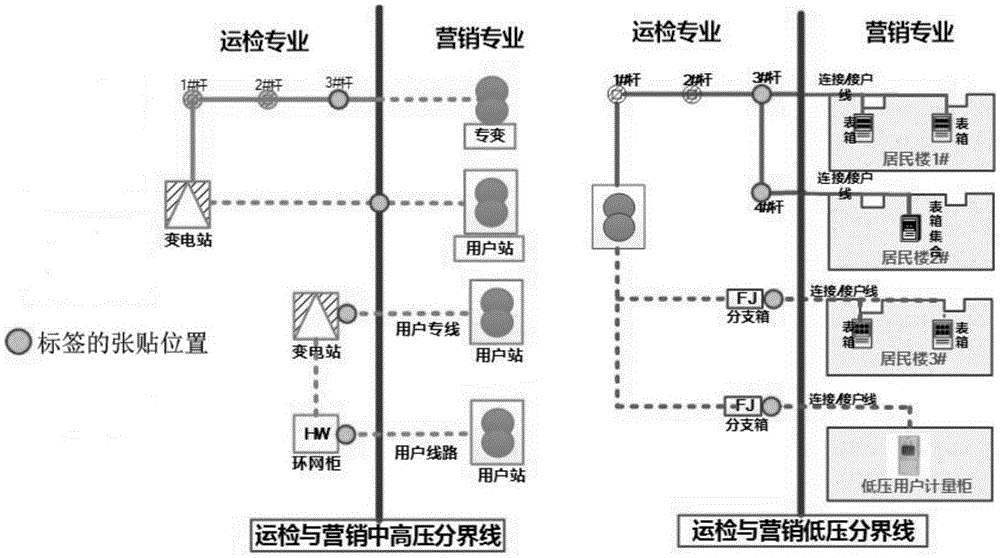

Logic error proofing leakproof inspection system and method based on mobile hand-held equipment and label scanning

InactiveCN106570541AGuarantee normal progressEasy to manageChecking time patrolsCo-operative working arrangementsHand heldHand held devices

The invention discloses a logic error proofing leakproof inspection system and method based on mobile hand-held equipment and label scanning; the system comprises an inspection service center, the mobile hand-held equipment and inspection label groups distributed on each inspection point; the inspection service center is used for issuing inspection task information and monitoring the inspection task; the mobile hand-held equipment is used for scanning the inspection label group and verifying the labels when inspection people execute the inspection task, and sending scanned label information and inspection information back to the inspection service center; the inspection label group comprises a position label and a content item label, wherein the position label is used for recording the inspection point position information, and the content item label is used for recording various inspection item information of the inspection point. The inspection people execute the inspection task, scan the inspection label group according to the inspection task information and verify the labels, thus ensuring normal operation of the inspection work, and preventing error detection and detection leakage conditions.

Owner:成都科曦科技有限公司

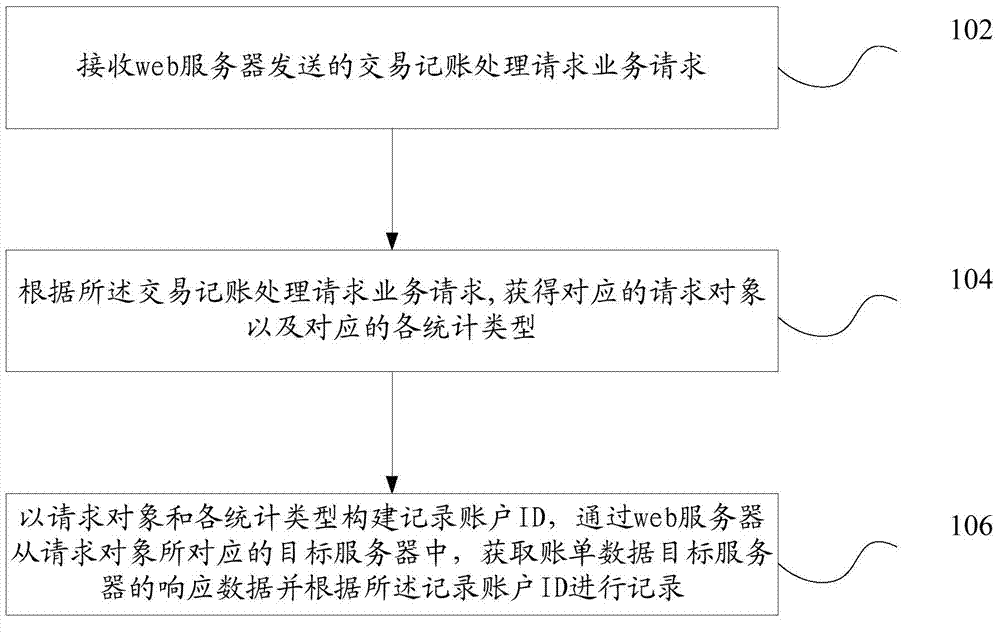

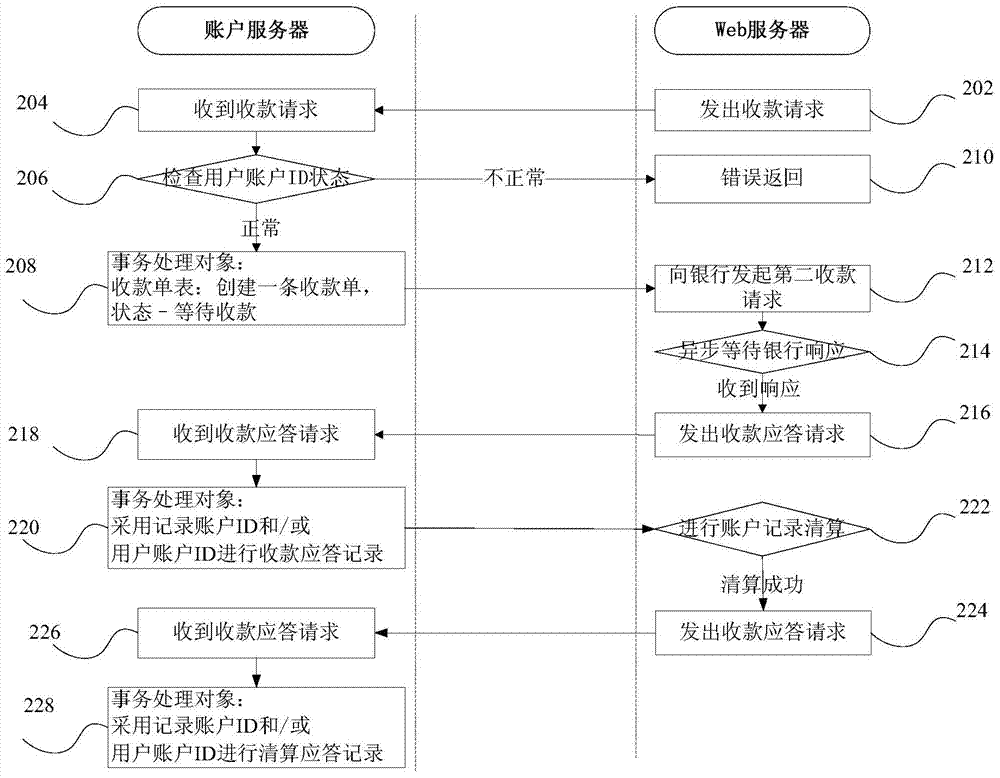

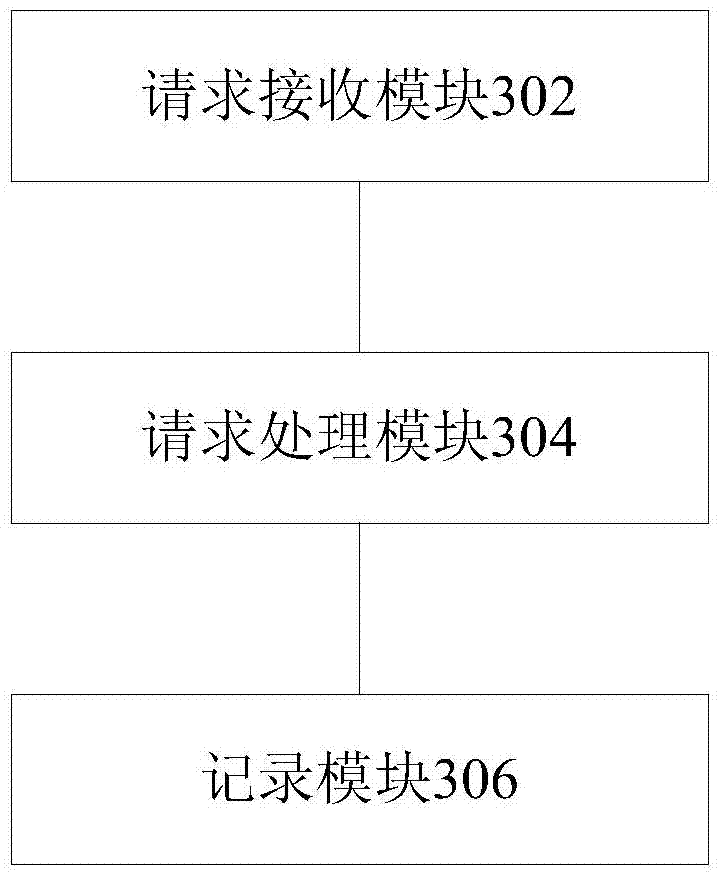

Data processing method and device

ActiveCN103578030AReduce data volumeImprove processing efficiencyFinanceTransmissionWeb serviceLogic error

The invention discloses a data processing method and device, and relates to the technical field of computers. The method comprises the steps that a service request sent by a web server is received; a corresponding request object and various corresponding statistics types are obtained according to the service request; a recording account ID is established by the request object and the various statistics types, responding data of a target server are obtained from the corresponding server of the request object through the web server, and recording is conducted according to the recording account ID. Accordingly, the data processing method and device solves the problems that the data size of analysis processing is large, the efficiency is low, the transaction process can not be recorded clearly, and logic errors can occur easily when late statistics is conducted. The advantages that the data size of analysis processing can be lowered, the processing efficiency is improved, interaction process data are recorded clearly, the service logic in the late statistics can be simple, and the statistics accuracy can be improved are achieved.

Owner:BEIJING QIHOO TECH CO LTD

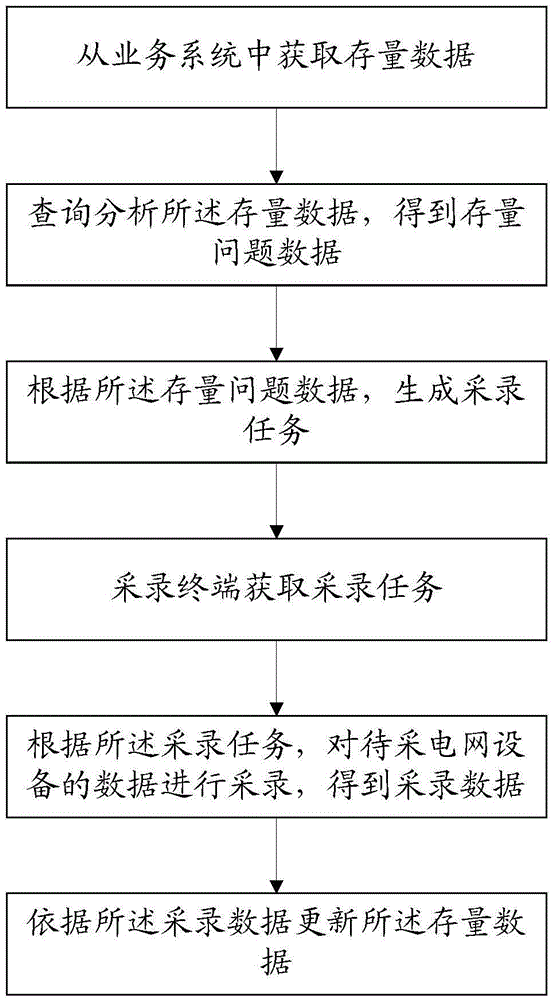

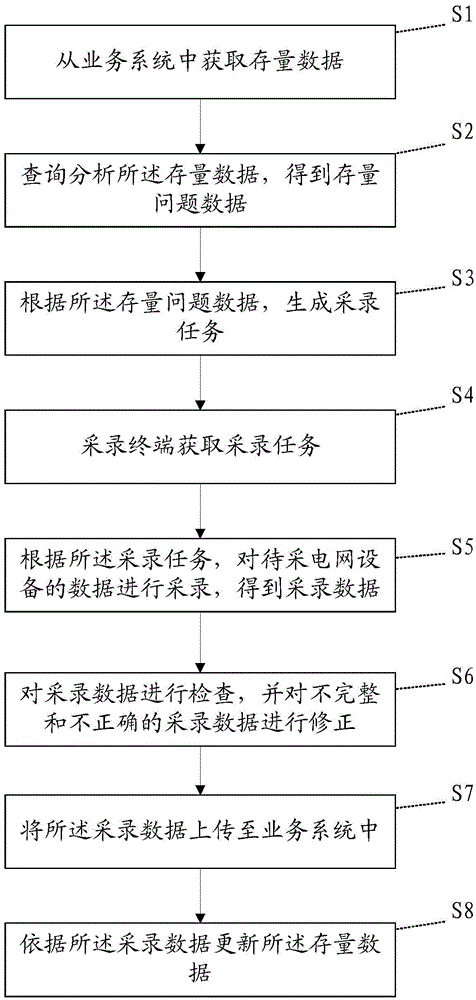

Power grid equipment data acquisition method and system

InactiveCN105608640AAccurate reacquisitionImprove collection efficiencyData processing applicationsPower gridData acquisition

The invention discloses a power grid equipment data acquisition method and system. The method comprises the following steps: obtaining storage data from a service system, querying and analyzing the storage data to obtain storage problem data; according to the storage problem data, generating an acquiring and recording task; an acquiring and recording terminal obtaining the acquiring and recording task; according to the acquiring and recording task, acquiring and recording data of power grid equipment to be acquired to obtain acquiring and recording data; and according to the acquiring and recording, updating the storage data. According to the invention, the storage problem data is obtained by analyzing the storage data and is taken as a basis for acquiring and recording, such that the acquiring and recording data amount can be greatly reduced, data with information errors or logic errors can be accurately re-acquired, and the data acquisition efficiency is improved; and the acquiring and recording data is uploaded to the service system such that the acquiring and recording data can be conveniently managed.

Owner:XIAMEN GREAT POWER GEO INFORMATION TECH +1

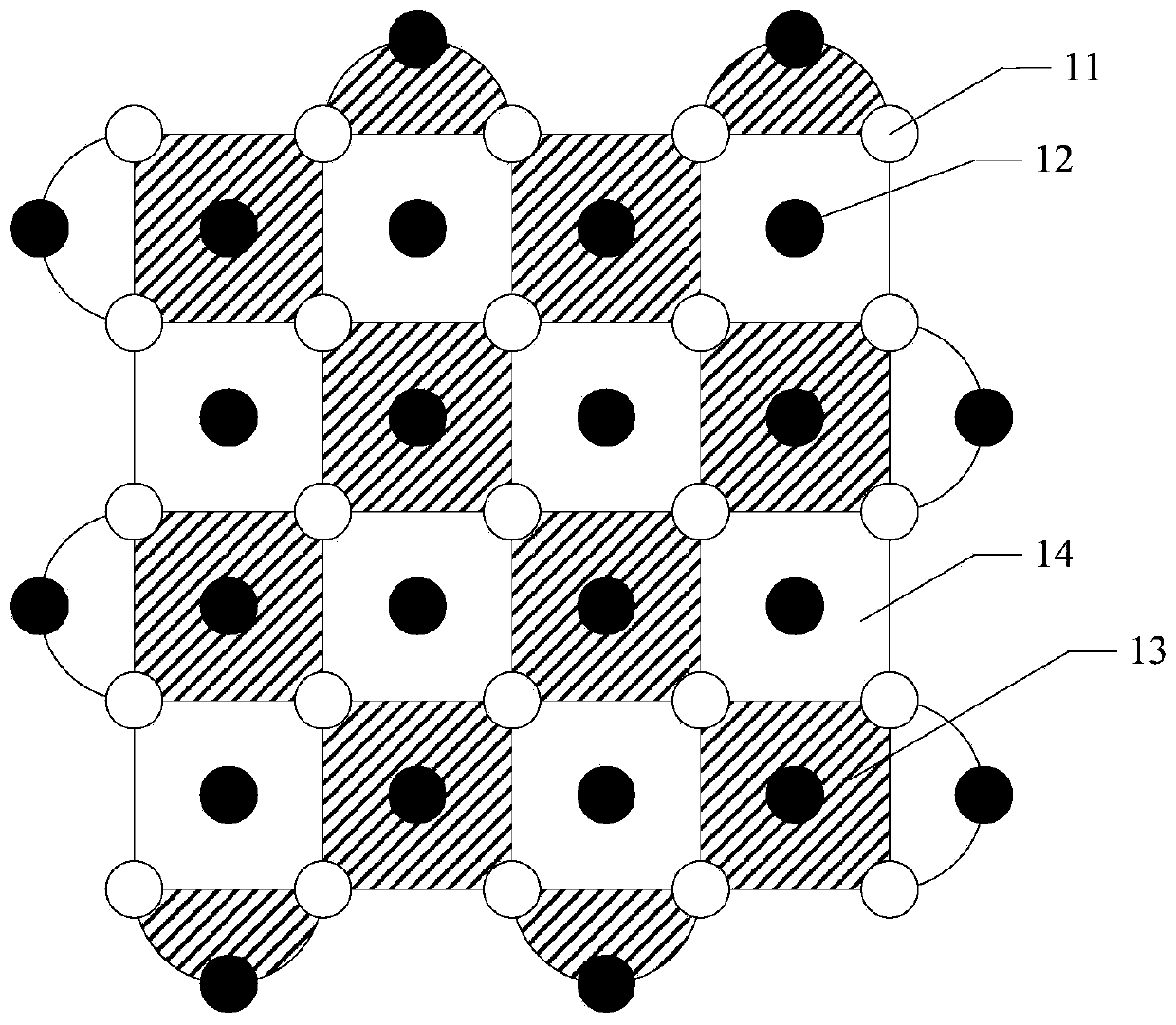

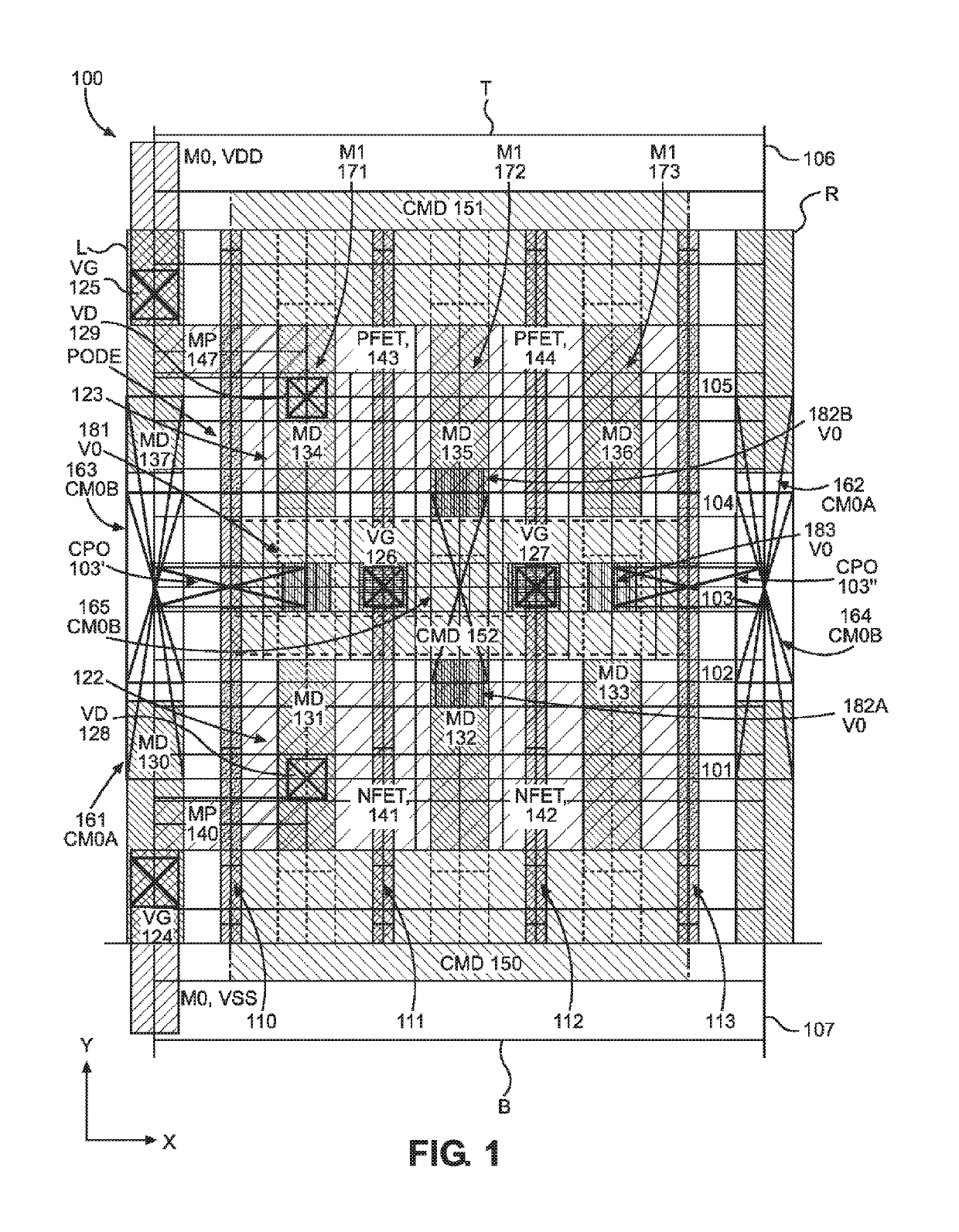

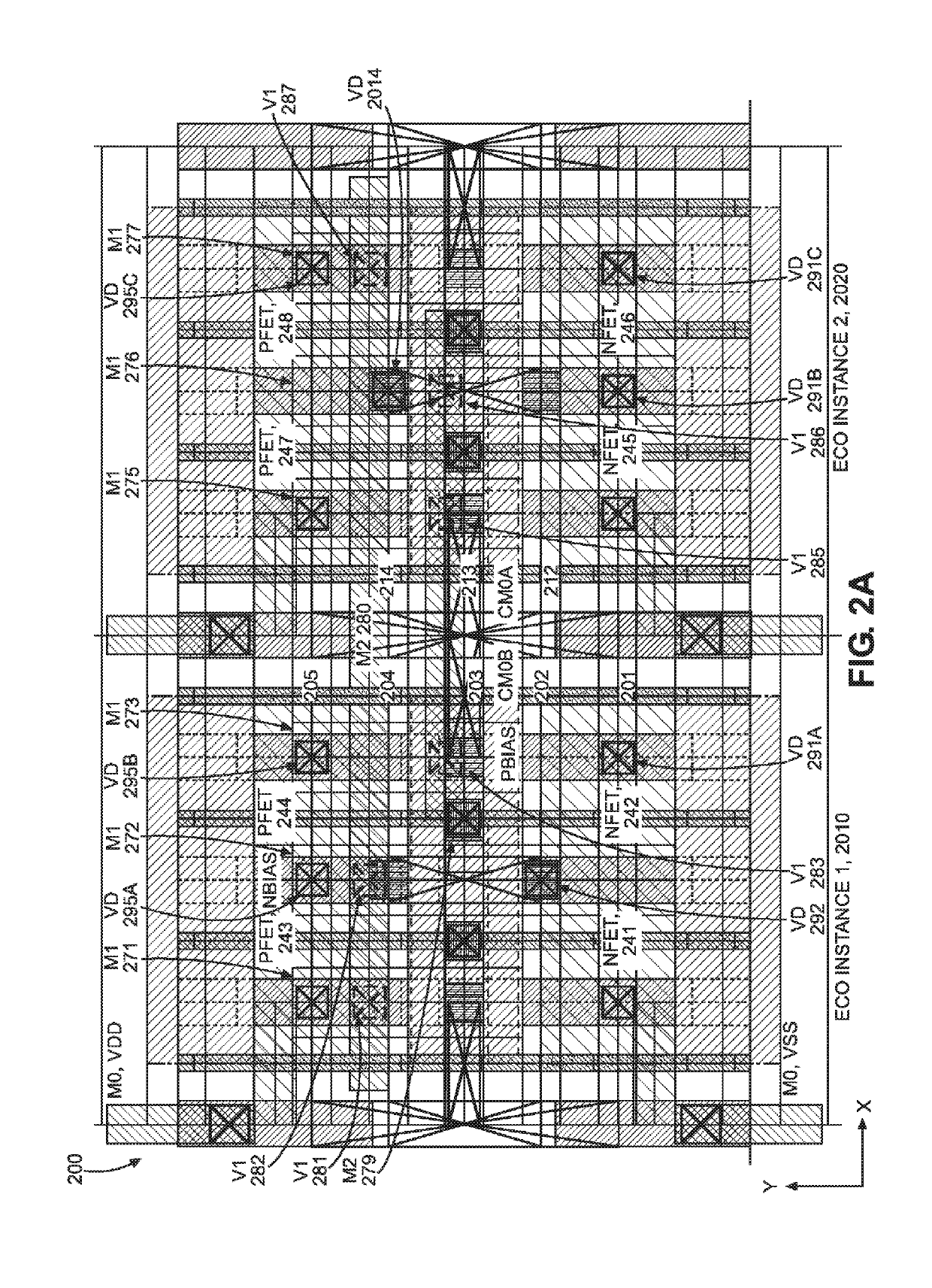

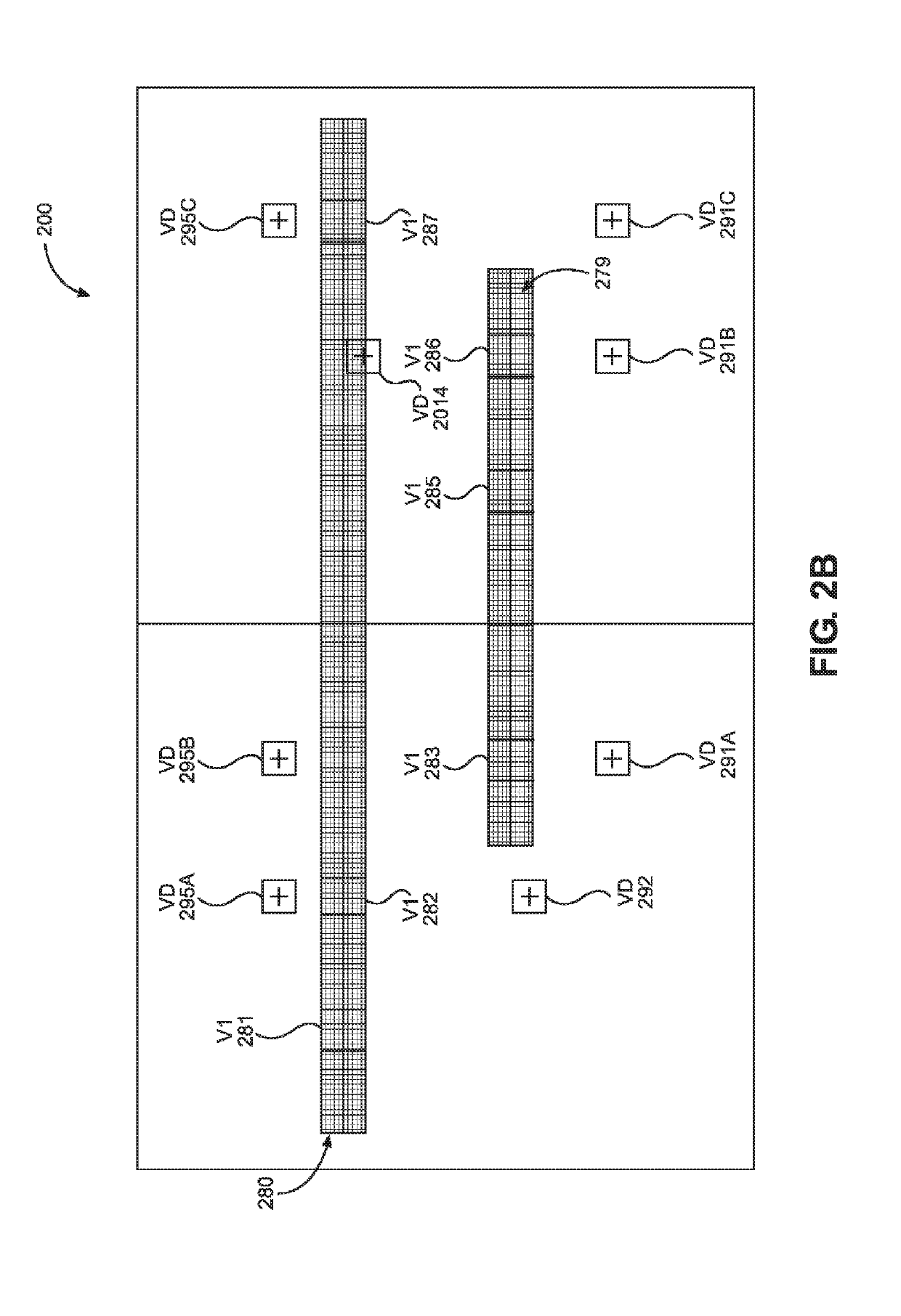

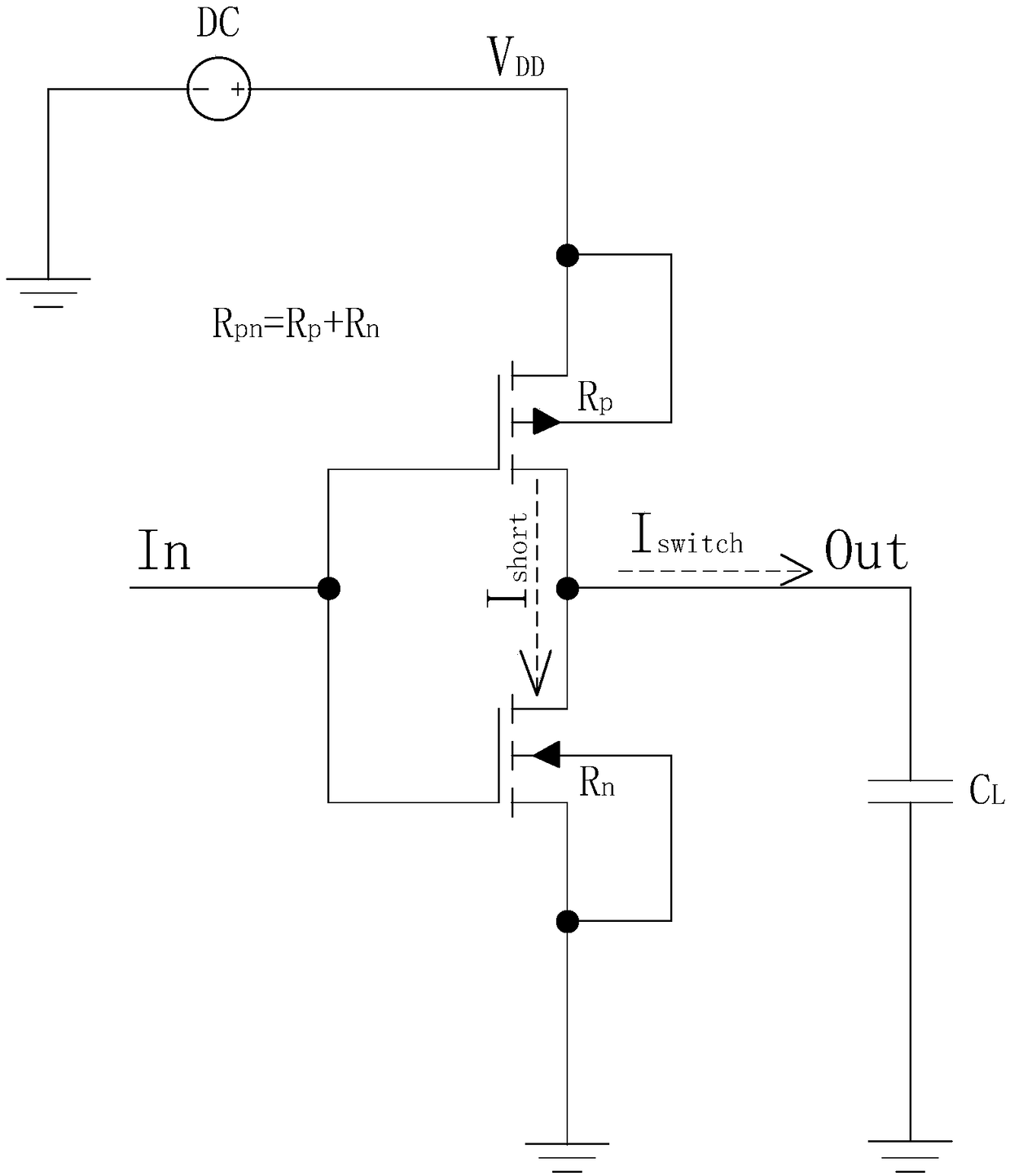

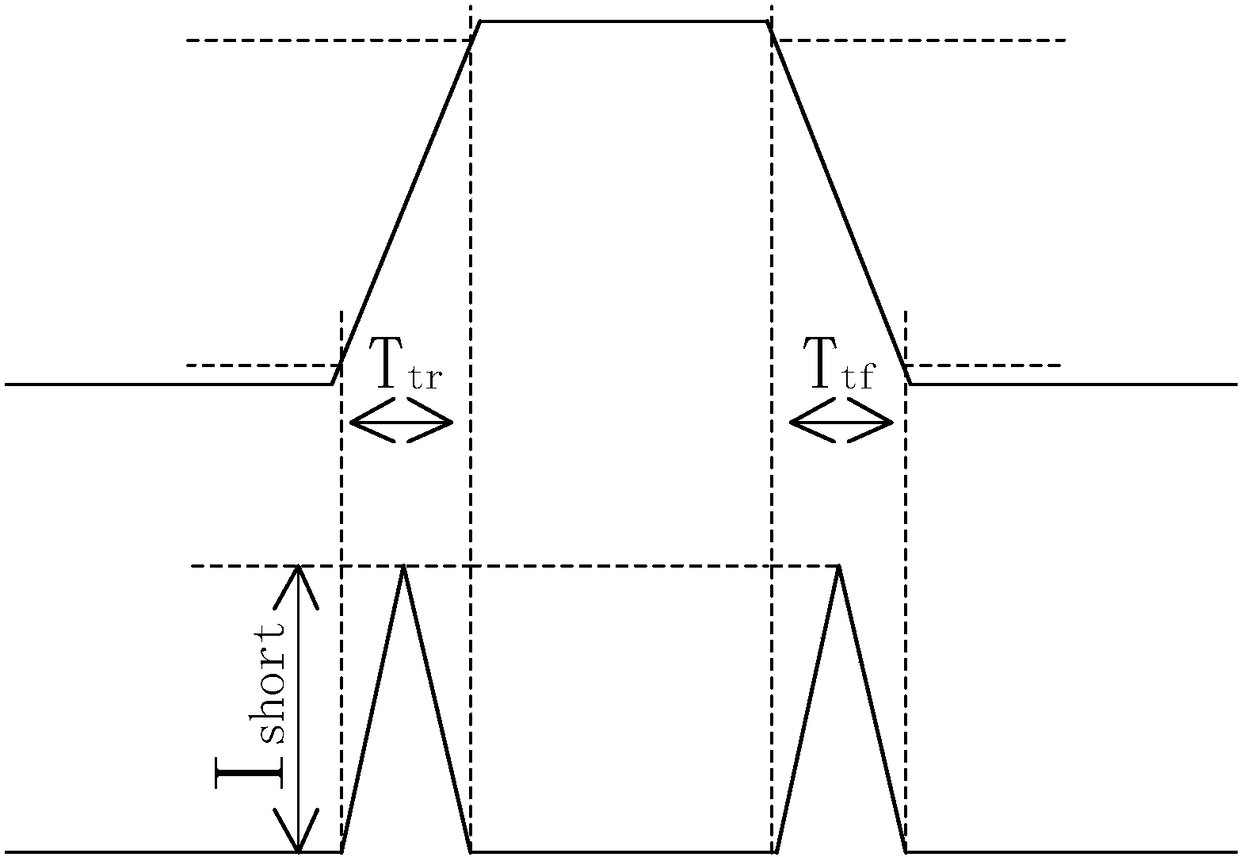

Integrated circuit (IC) design methods using engineering change order (ECO) cell architectures

ActiveUS20190188353A1Good flexibilityMinimal disruptionCAD circuit designSpecial data processing applicationsTime criticalEngineering

Aspects disclosed in the detailed description include integrated circuit (IC) design methods using engineering change order (ECO) cell architectures. In particular, exemplary aspects provide a fill algorithm that is both single- and multi-row aware, considers a poly-pitch count, and utilizes metallization of the “empty space” relative to a suite of available fill cells. The algorithm is also aware of timing critical logic elements and may place ECO fill cells in near proximity to such timing sensitive circuits or other margin critical circuits to allow for decoupling or, if there is a logic error, an ECO cell is placed such that the ECO cell is well positioned to be repurposed as a delay circuit or other function to aid in margin control. For maximum flexibility, the algorithm may also address both pre- and post-route applications.

Owner:QUALCOMM INC

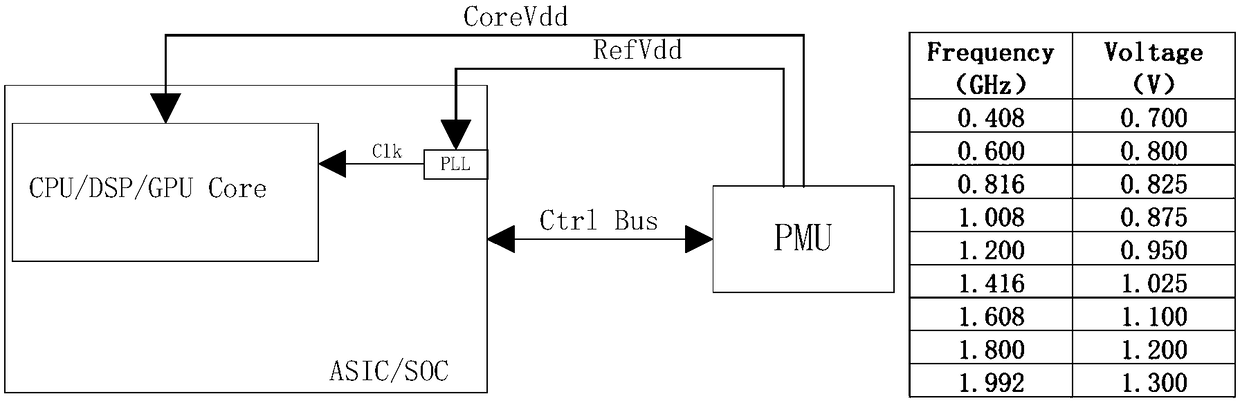

Method and device for adaptively adjusting voltage and frequency

ActiveCN109510621AImprove consistencyImprove stabilityPulse automatic controlControl signalEngineering

The invention provides a method and a device for adaptively adjusting a voltage and a frequency. In practical application, a system software only needs to set a target frequency of an ASIC / SOC chip according to a performance demand; when the supply voltage of the chip fails to meet the demand of the target frequency, the scheme can automatically adjust a working frequency to a frequency adapted toa current chip process, a power supply voltage and a temperature, and send a corresponding control signal to adjust a output voltage of a power supply module until the power supply voltage is matchedto the target frequency. The scheme does not cause digital logic errors by the insufficient power supply voltage, and can also automatically adjust the PLL output frequency and the power supply voltage according to differences of the chip process, the voltage, and the temperature, thereby improving the consistency and the stability of the chip, and omitting the waiting time for adjusting the power supply voltage, so that the frequency of the chip is adjusted more rapidly, and the purposes of rapidly changing the frequency and the voltage and saving the power consumption are achieved.

Owner:FUZHOU ROCKCHIP SEMICON

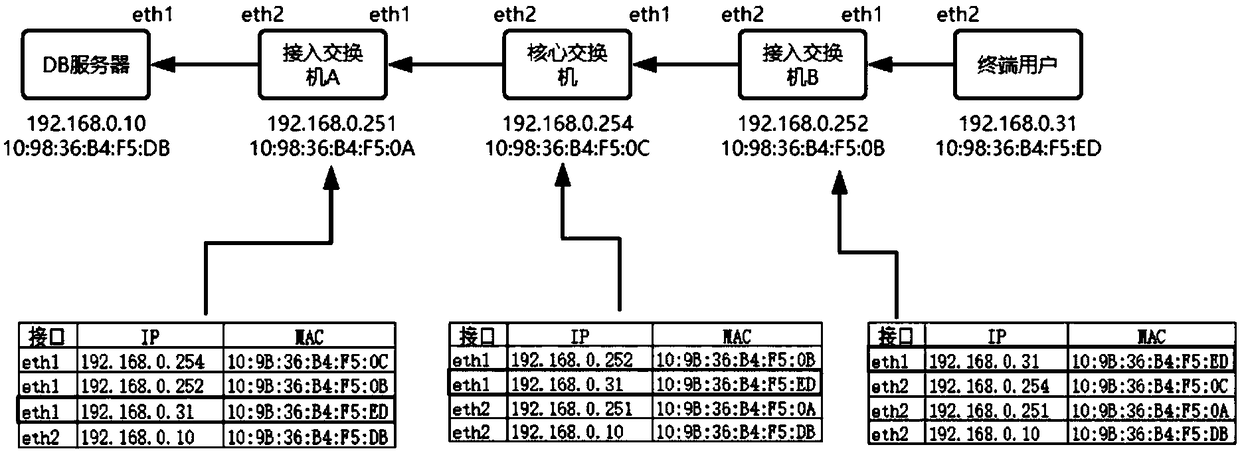

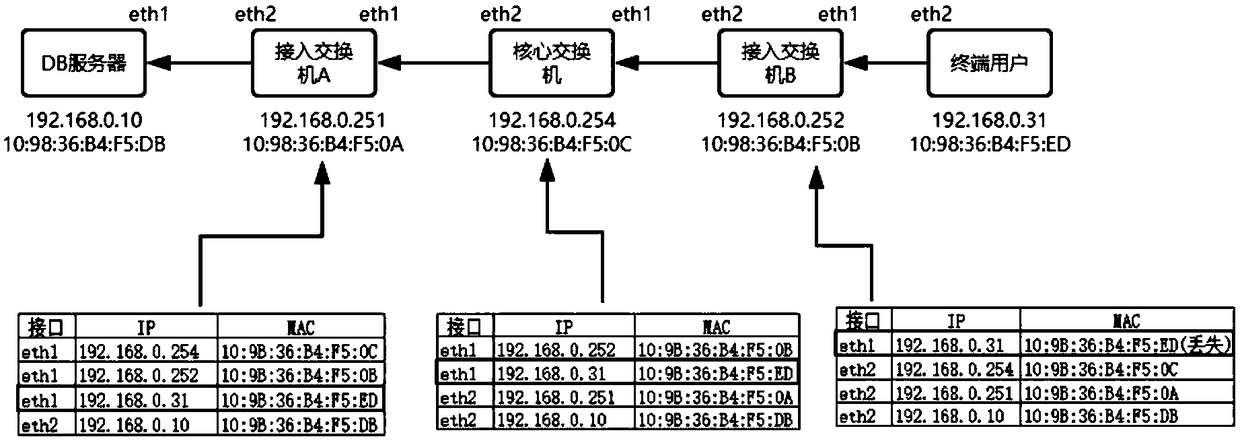

A visualization method of industrial control network topology structure

ActiveCN109067569AAvoid logic errorsData switching networksStructure of Management InformationNetwork structure

The invention relates to an industrial control system, aiming at providing a visualization method of industrial control network topology structure. The visualization method comprises the steps of: deploying a platform into the industrial control network which needs topology to ensure that the equipment in the industrial control network can reach; according to the position of the platform in the industrial control network, scanning the equipment in the industrial control network by the timing task, and saving the node information in the database, using the integrated node information to obtainthe topological line;according to the obtained topological line, returning the port connection information of each equipment, drawing the connection relationship between each equipment node, and finally obtaining the topological network diagram of the industrial control network. The invention adopts a very simple way, that is, the network structure requiring topology is obtained through the most basic ARP protocol and the SNMP protocol, and the structure is displayed on the visual interface, thereby avoiding the logic error that may occur in the complex algorithm.

Owner:HANGZHOU ANHENG INFORMATION TECH CO LTD

GOOSE message anomaly online detection method

InactiveCN103684903AImprove maintenance efficiencyReduce complexityCircuit arrangementsData switching networksCommunications systemAnomaly detection

A GOOSE message anomaly online detection method belongs to the field of electric power communication system. Format and configuration information judgment is firstly carried out on a frame message. If any one of the two items is erroneous, follow-up analysis of the frame message is terminated. Secondly, sqNum and stNum logic analysis is proceeding if there are no errors in both the format and the configuration information. Thirdly, no matter there are logic errors in sqNum and stNum, GOOSE message interrupt and delay judgments are both required. Finally, no matter there is delay, whether the message is in the test mode needs to be judged. Thus, concise and comprehensive analytical judgment of the frame message is realized, and various anomalies of the GOOSE message are positioned accurately based on the judgment results. The method provided by the invention has advantages of concise logic and comprehensive analysis. In addition, by the scheme, debugging efficiency of a substation can be raised effectively, and anomaly detection with meticulous logic can be realized.

Owner:SHANDONG UNIV

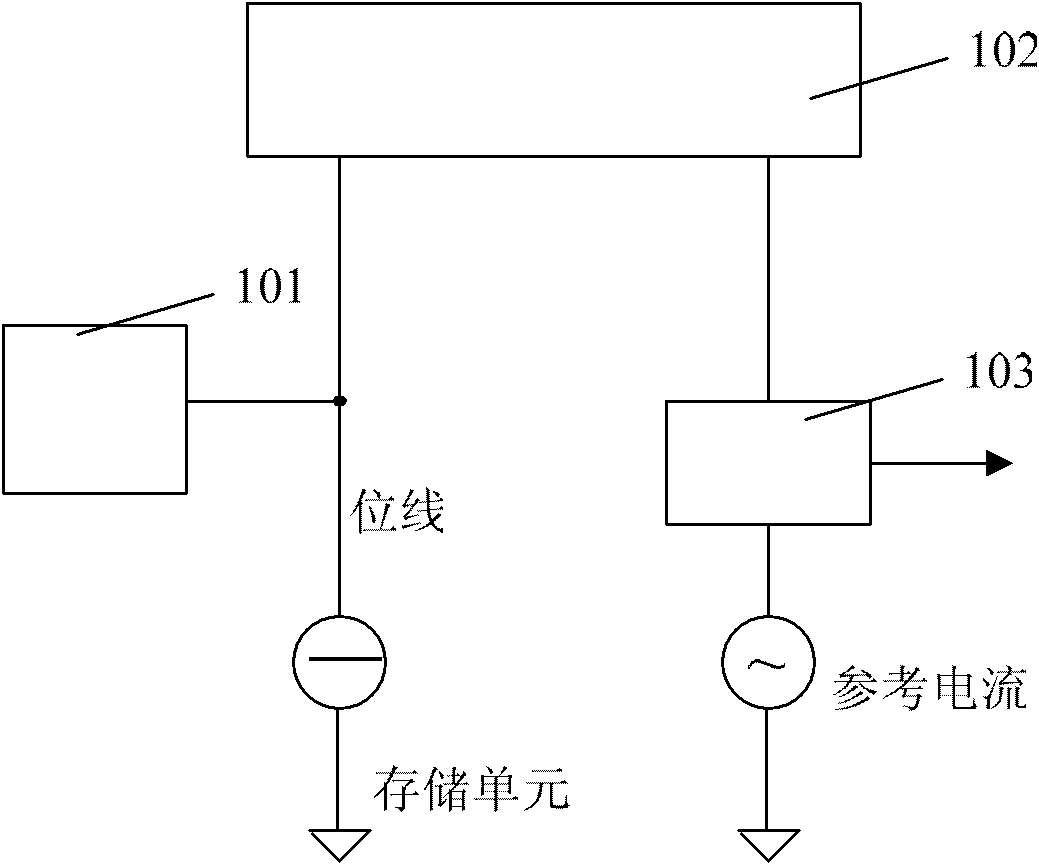

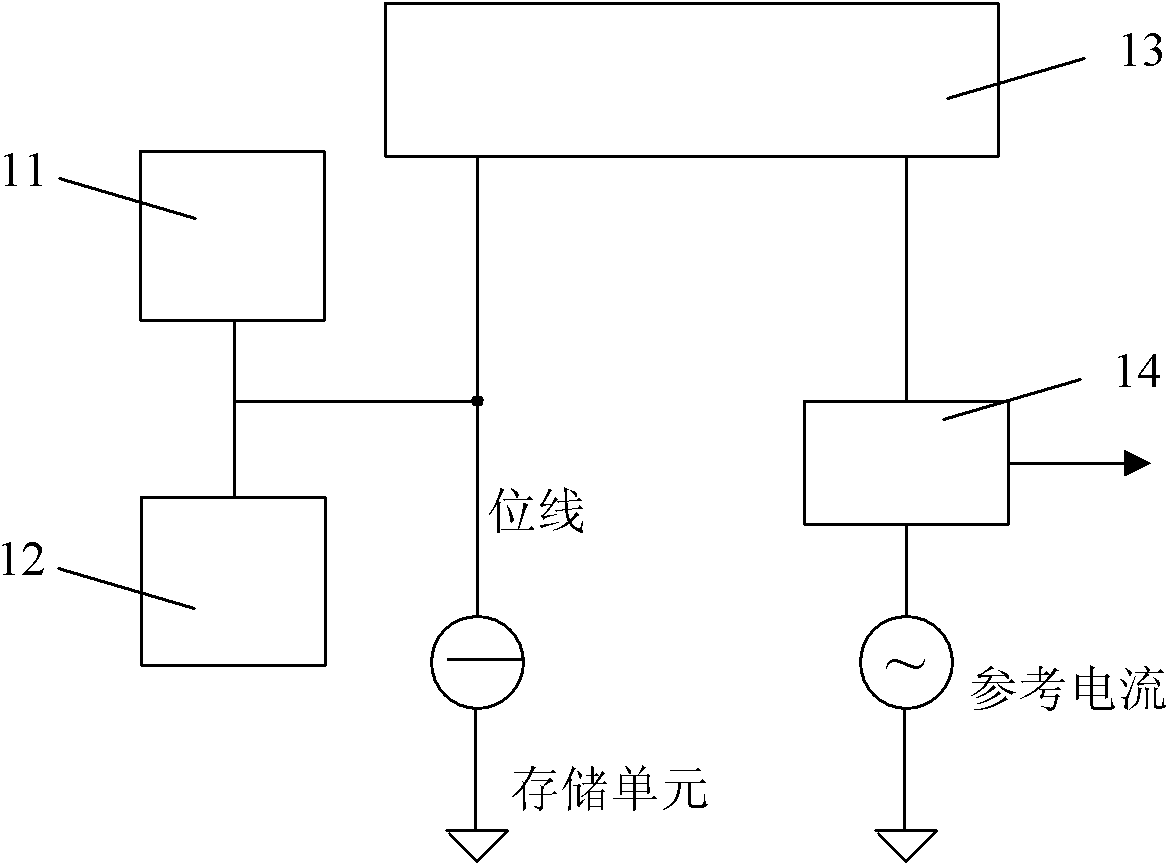

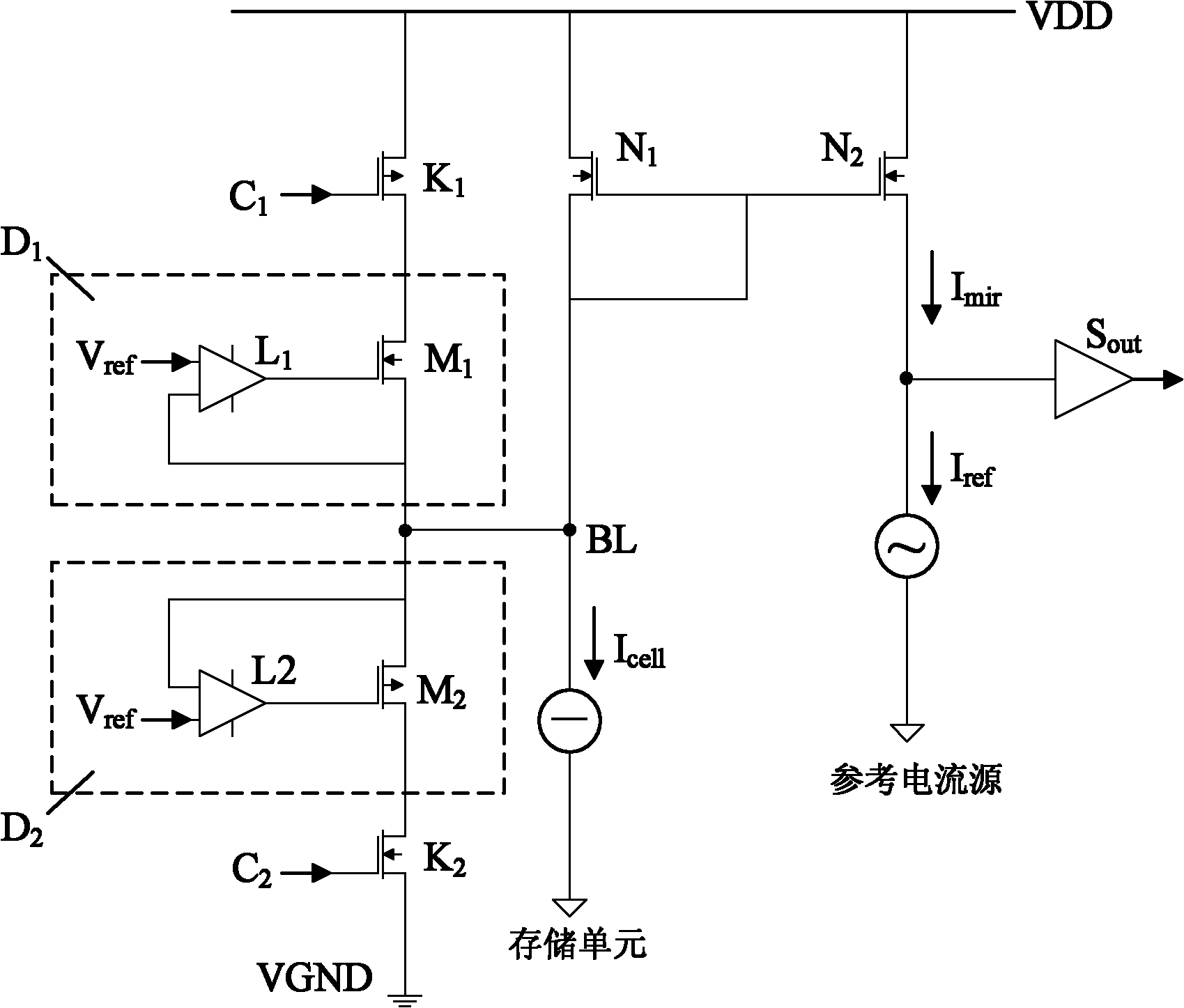

Non-volatile memory and read circuit thereof

The invention provides a non-volatile memory and a read circuit thereof. The read circuit comprises a mirror image unit, a data read unit, a pre-charging unit and a pre-discharging unit, wherein the mirror image unit is used for generating mirror image current which is the same as bit line current; the data read unit reads data of a memory unit according to the mirror image current; the pre-charging unit and the pre-discharging unit are connected with a bit line; the initial potential of the bit line is compared with a target potential by the pre-charging unit and the pre-discharging unit; and the bit line is charged or discharged to clamp the potential of the bit line to the target potential. By connecting the pre-charging unit and the pre-discharging unit with the bit line, the potential of the suspending bit line can be quickly ascended or descended to the target potential, so logic error is avoided, and data read speed is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

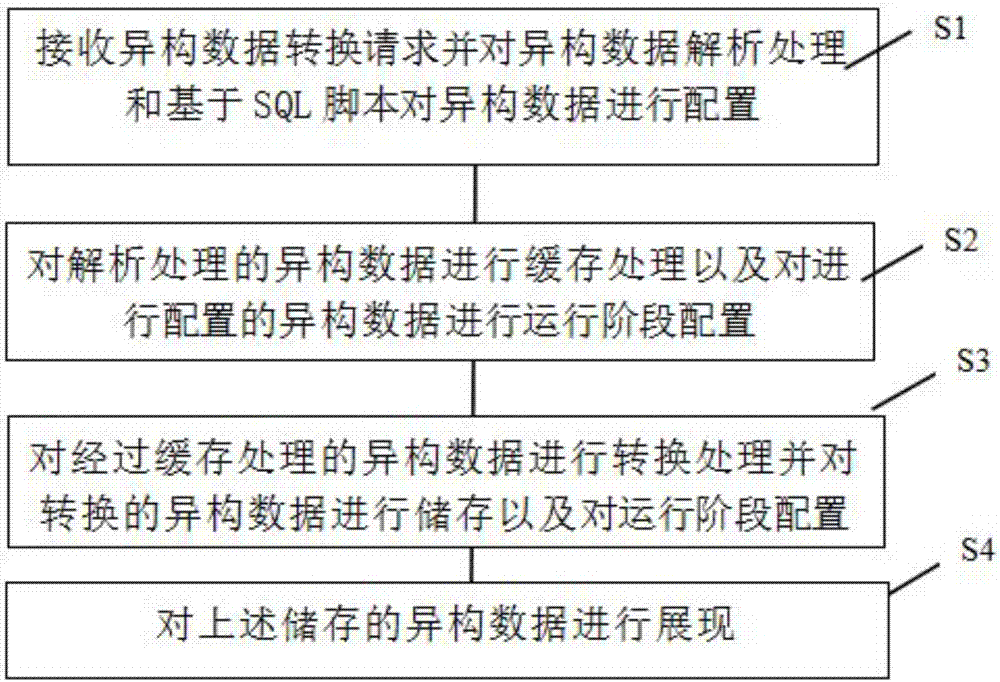

Big data conversion method and system based on adapter

InactiveCN107315743AReduce logic errorsImprove exchange efficiencyOther databases browsing/visualisationSpecial data processing applicationsData acquisitionStaging operation

The invention relates to a big data conversion method and system based on an adapter. The big data conversion method based on the adapter comprises the following steps that: receiving a heterogeneous data conversion request, carrying out analysis processing on the heterogeneous data, and configuring the heterogeneous data on the basis of an SQL (Structured Query Language) script; carrying out cache processing on the heterogeneous data subjected to the cache processing, and carrying out operation stage configuration on the configured heterogeneous data; carrying out conversion processing on the heterogeneous data subjected to the cache processing, storing the converted heterogeneous data, and carrying out operation stage operation on the heterogeneous data subjected to the operation stage configuration; and displaying the stored heterogeneous data. By use of the method, a batch data conversion script set is automatically executed, conversion script execution result information is stored, and then, an application analysis report is generated. When the method is adopted, logic errors generated when the heterogeneous data is converted can be reduced, conversion efficiency among the heterogeneous data is improved, and data collection and analysis cost of the heterogeneous data can be lowered.

Owner:上海赢华软件科技有限公司

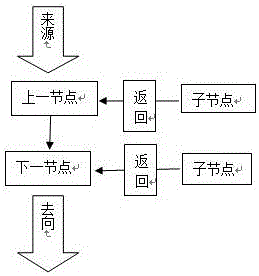

Logic node tree-shaped visual game editing engine

PendingCN105808260AImprove organizationEasy to readVisual/graphical programmingSpecific program execution arrangementsType errorLogic error

The invention relates to a logic node tree-shaped visual game editing engine. Different name lists are constructed by adopting tree-shaped programming, wherein the name lists of a logic set are arranged at the left side of a visual programming interface; the name lists correspond to the function lists in programming languages; a tree-shaped logic list is arranged at the right side of the visual programming interface; in a programming process, execution of the whole programming logic is started from a first line; the nodes are equipped with different icons for distinguishing different logic properties of the nodes; the part at the most right side of the visual programming interface is the attribute setting part of a single node; dynamical adjustment can be carried out according to the currently selected nodes; and the most lower part of the visual programming interface is equipped with a debugging operation interface. According to the method provided by the invention, logic errors resulting from typing errors can be reduced; the tree-shaped structure is clear in logic and is convenient for organizing and reading the logic; and the speed and efficiency of debugging the logic can be greatly improved.

Owner:成都神秘方块科技有限公司

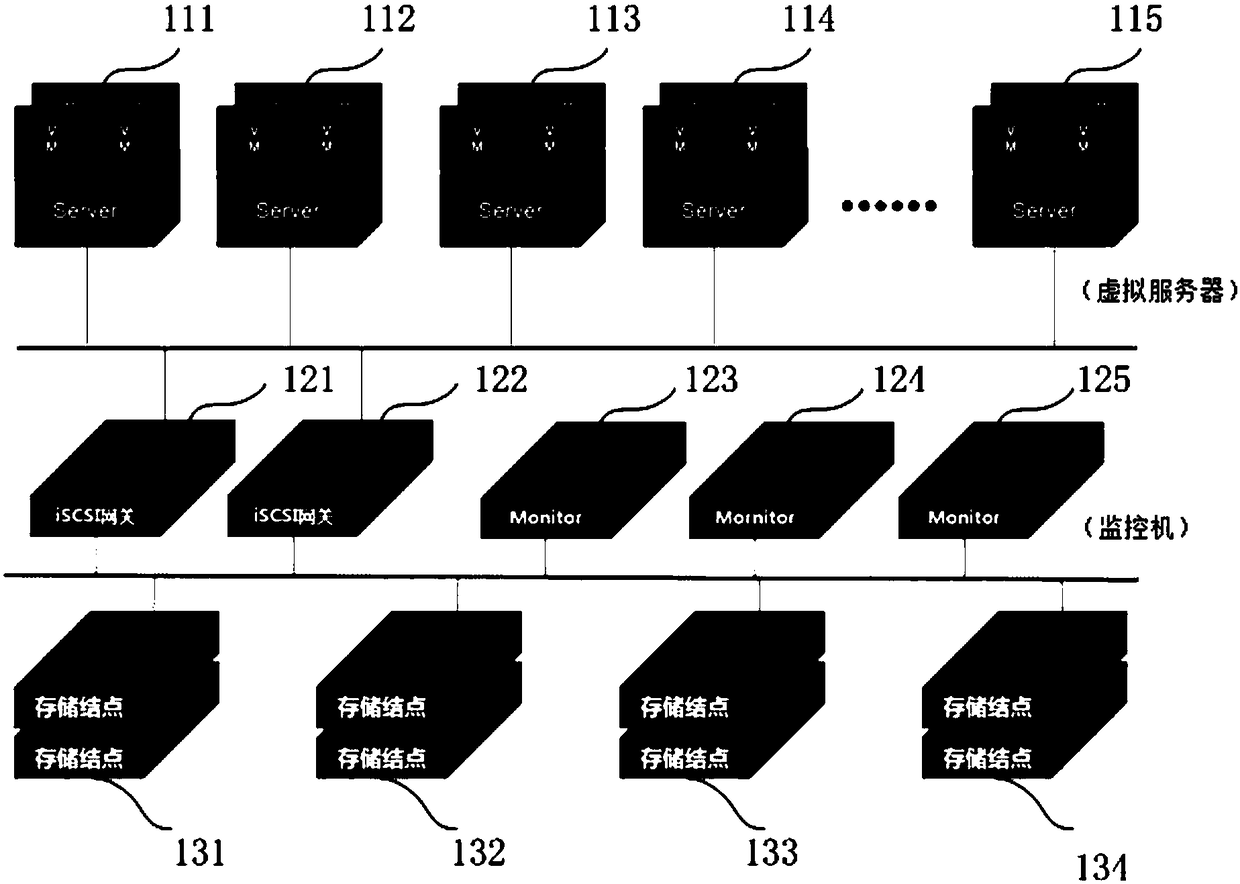

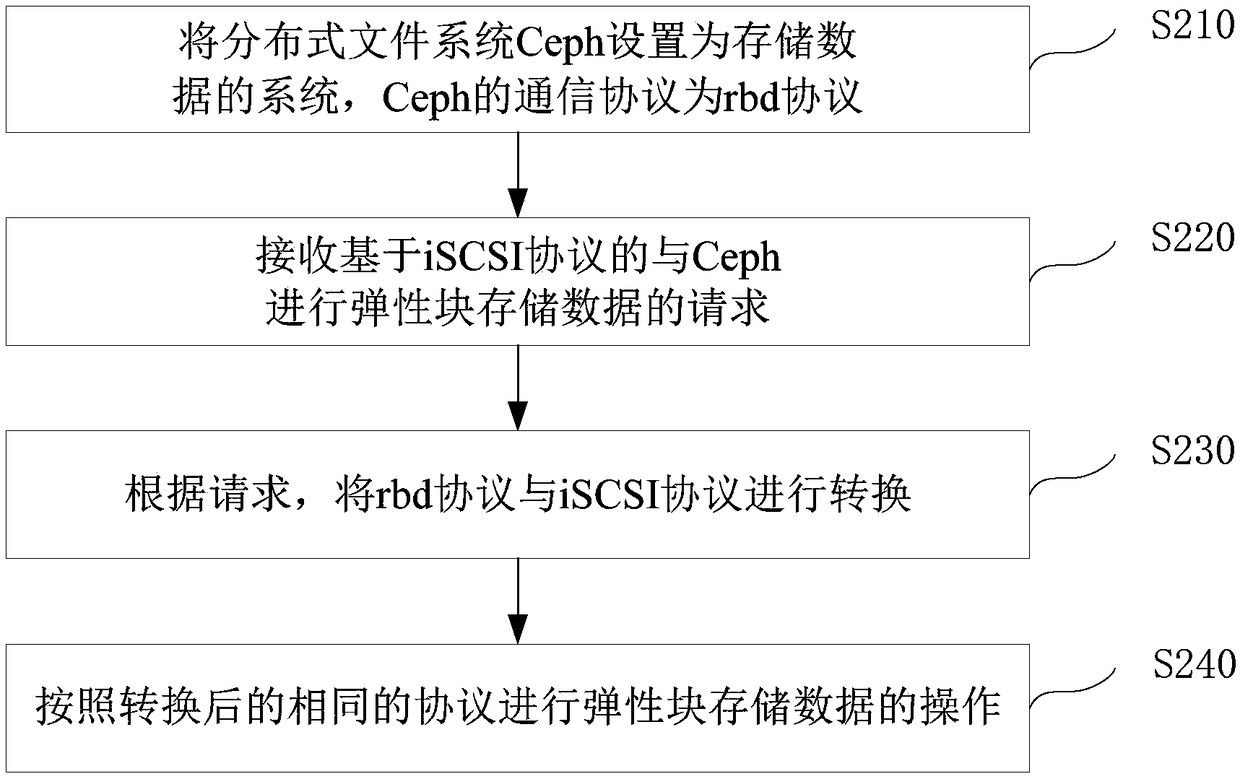

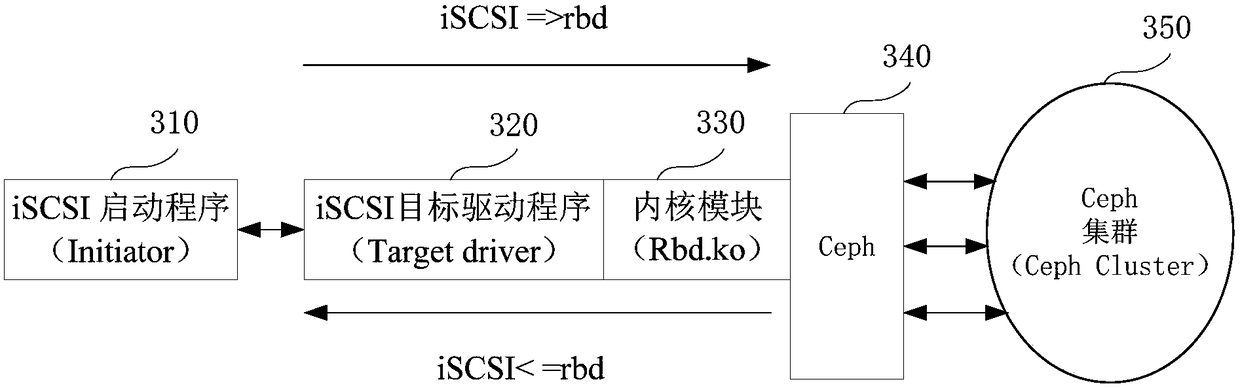

Method, apparatus, system and storage medium for elastic block to store data

InactiveCN109085996AAvoid the Risk of Logical ErrorsImprove storage efficiencyInput/output to record carriersTransmissionFailure rateDistributed File System

The invention discloses a method, a device, a system and a storage medium for storing data by an elastic block. The method comprises the following steps: a distributed file system Ceph is set as a system for storing data, and the communication protocol of the Ceph is an rbd protocol; a request for elastic block storage data with Ceph based on iSCSI protocol is received; upon request, the rbd protocol and the iSCSI protocol are converted; the elastic block stores data according to the converted same protocol. On the one hand, the embodiment of the invention can avoid the risk of logic error dueto the local hard disk mapped by ceph, effectively reduce the failure rate and improve the stability of the system; on the other hand, the embodiment of the invention can reduce the system performance consumption and the service response time delay by reducing one mapping.

Owner:中国移动通信集团重庆有限公司 +1

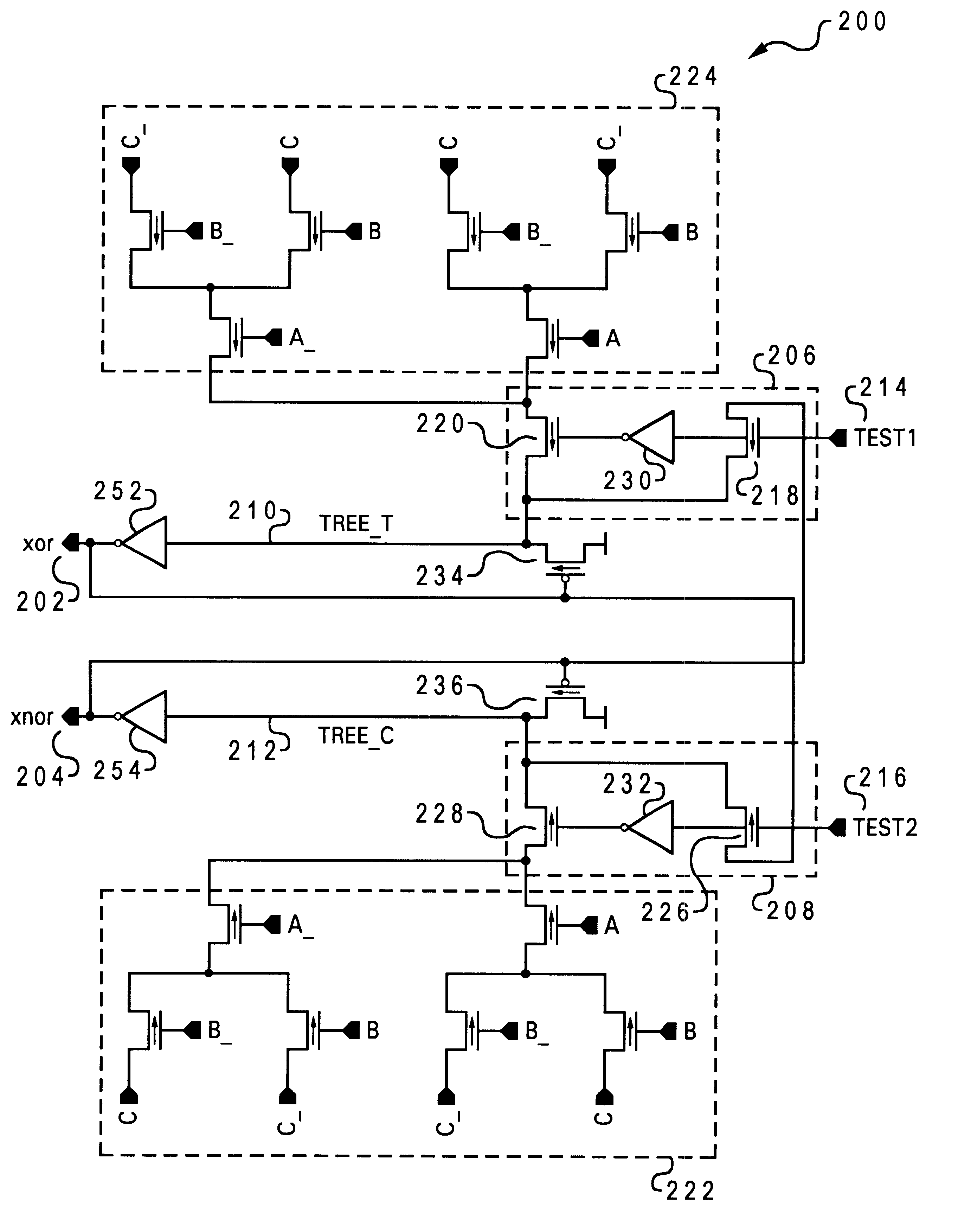

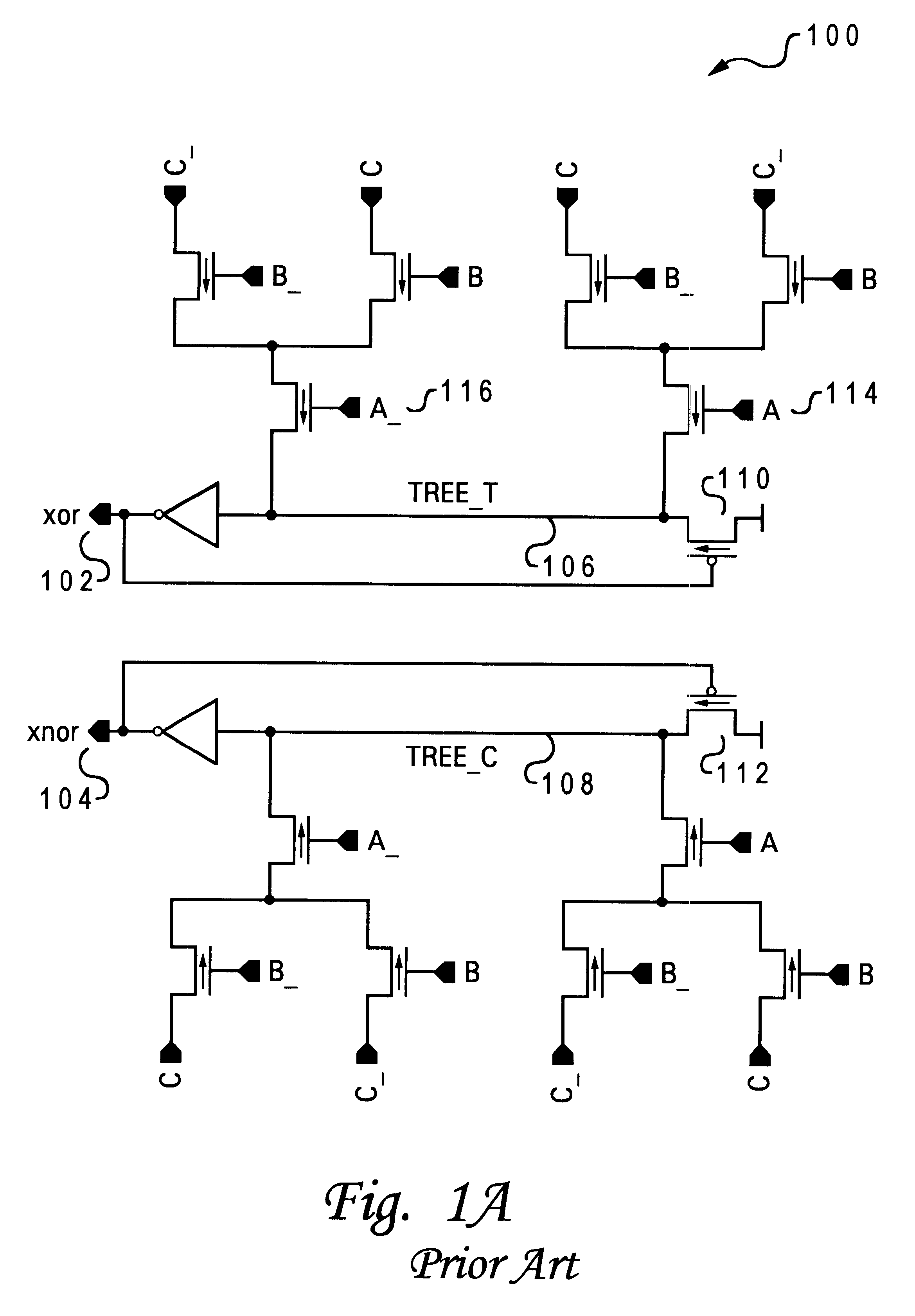

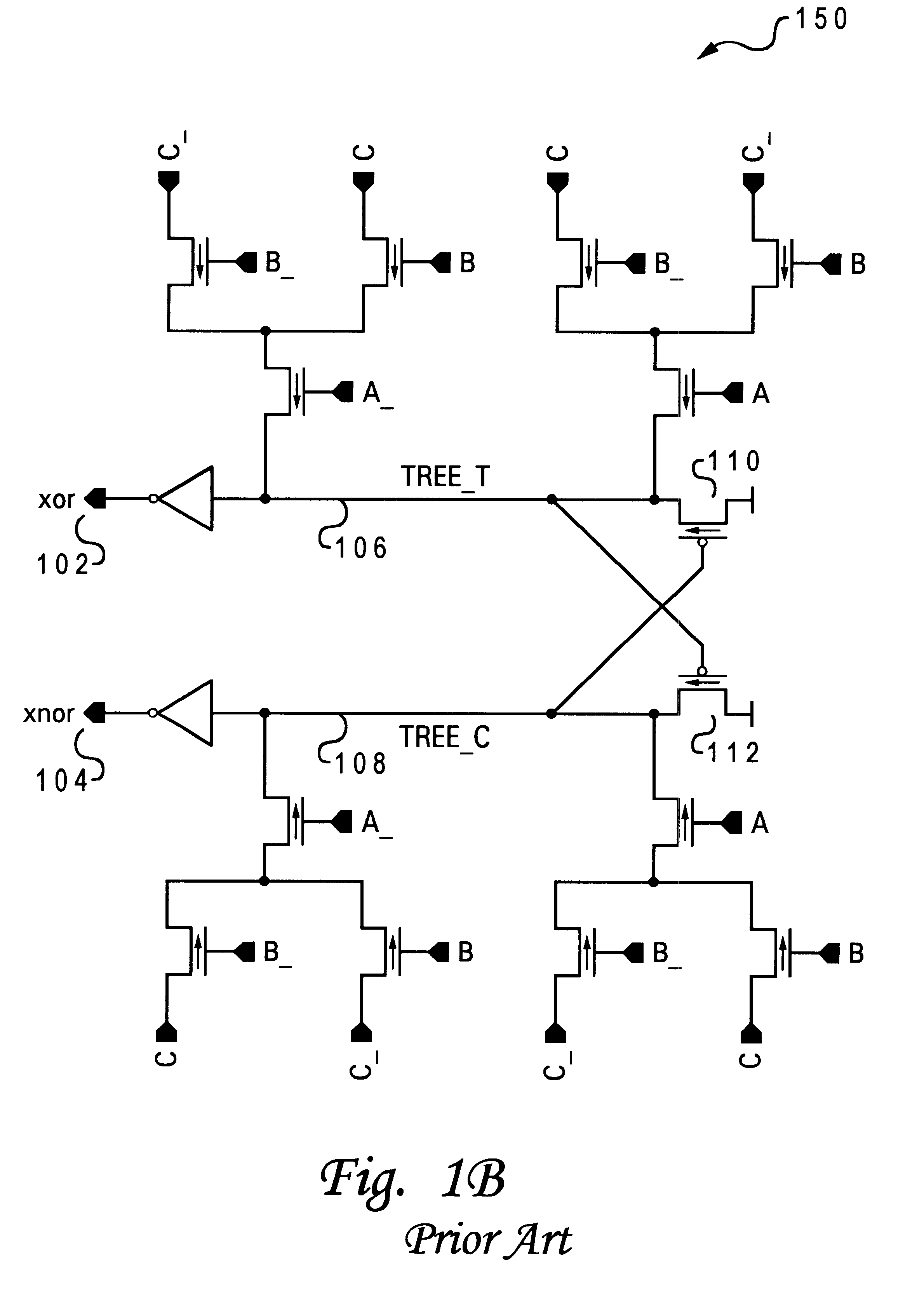

Complementary logic error detection and correction

InactiveUS6502220B1Logic circuits characterised by logic functionError prevention/detection by transmission repeatMultiplexingTheoretical computer science

A system and method for detecting and rectifying a proscribed non-complementary output from a complementary logic circuit. A complementary logic circuit having a true tree and a complement tree is provided. The true tree produces a true signal utilized to generate a true output signal from the complementary logic circuit. The complement tree produces a complement signal utilized to generate a complement output signal from the complementary logic circuit. Logic means coupled to the output of the complementary logic circuit detect an occurrence of a non-complementary output from the complementary logic circuit. Multiplexing means within the true tree is utilized to selectively replace the true signal with the complement signal within the true tree in response to detection by the logic means of a non-complementary output, such that a non-complementary output is seamlessly detected and rectified.

Owner:IBM CORP

Systems and methods for identifying problems of a business application in a customer support system

ActiveUS8539003B2Digital data processing detailsCode refactoringIdentifying problemsTheoretical computer science

In accordance with embodiments of the present invention, methods and systems analyze potential logic errors or problems of a business application by receiving a model representing the business application and processing the model using an object-oriented tool. The errors or problems may be corrected in the model and the correction applied to the business application. In one exemplary embodiment, the logic errors or problems may be marked in the model for identification to a user.

Owner:SAP AG