Method and device for adaptively adjusting voltage and frequency

A technology of self-adaptive voltage and frequency adjustment, applied in the direction of electrical components, automatic power control, etc., can solve the problems of complex calibration, slow control speed, high power consumption, etc., to improve consistency, rapid frequency adjustment, and stability. omitted effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

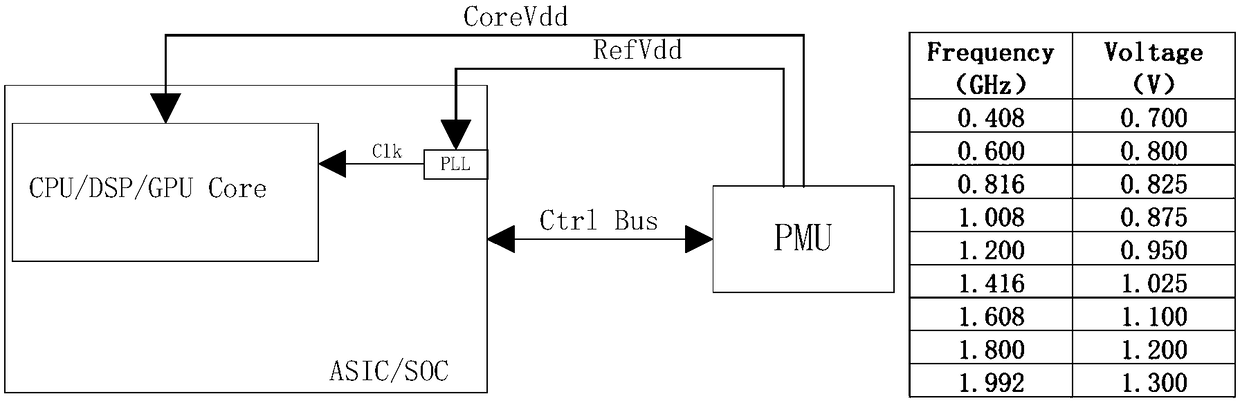

Embodiment 1

[0101] Embodiment one: when (F r -F n ) / F c ≥2 N-1When , an AC signal is generated, indicating that the actual output frequency of the ring oscillator is lower than the design expectation, and it also indicates that the actual performance of the chip is lower than the design expectation. The AC signal acts as a FastDown signal to quickly reduce the output frequency of the PLL, making F Clkout clkin , that is, let the PLL output frequency drop rapidly, and make F Clkout It is equal to the frequency of the ring oscillator; AC is also used as a power supply voltage up-regulation signal, and CoreVdd is increased accordingly until the voltage reaches enough to make the counter no longer generate AC signals.

Embodiment 2

[0102] Embodiment two: when (F n -F r ) / F c ≥2 N-1 When the BS signal is generated, it means that the actual output frequency of the ring oscillator is higher than the expected frequency, and the actual performance of the chip is higher than expected. The BS signal is used as a down-regulation signal of CoreVdd until the counter no longer generates the BS signal.

Embodiment 3

[0103] Embodiment three: when |F r -F n | / F c N-1 When , no BS or AC signal is generated, indicating that the actual performance of the chip meets the design expectations, and there is no need to adjust the frequency and voltage.

[0104] In summary, when debugging the chip, you only need to set an expected frequency that needs to be achieved, and set Clkin (the frequency received by the PLL clock circuit) to the required frequency. When the process, power supply or temperature cause the ring oscillator to When there is a deviation between the oscillation frequency and the design expectation, the device can adaptively adjust the voltage frequency to meet the performance requirements of the processor.

[0105] Such as Figure 8 As shown in FIG. 1 , it is a flow chart of an adaptive voltage-frequency adjustment method related to an embodiment of the present invention. The method is applied to an adaptive voltage frequency adjustment device, and the device includes a processo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More