Simulation checking system and its method for SDH logical design

A technology of simulation verification and logic design, applied in the field of simulation verification, can solve the problems of difficulty in ensuring the accuracy and reliability of analysis results, cumbersome, difficult modular programming, etc., to achieve rigorous and reliable simulation verification results, convenient positioning and debugging, and improve Effects of Simulation Efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Hereinafter, specific embodiments of the present invention will be described in detail with reference to the drawings.

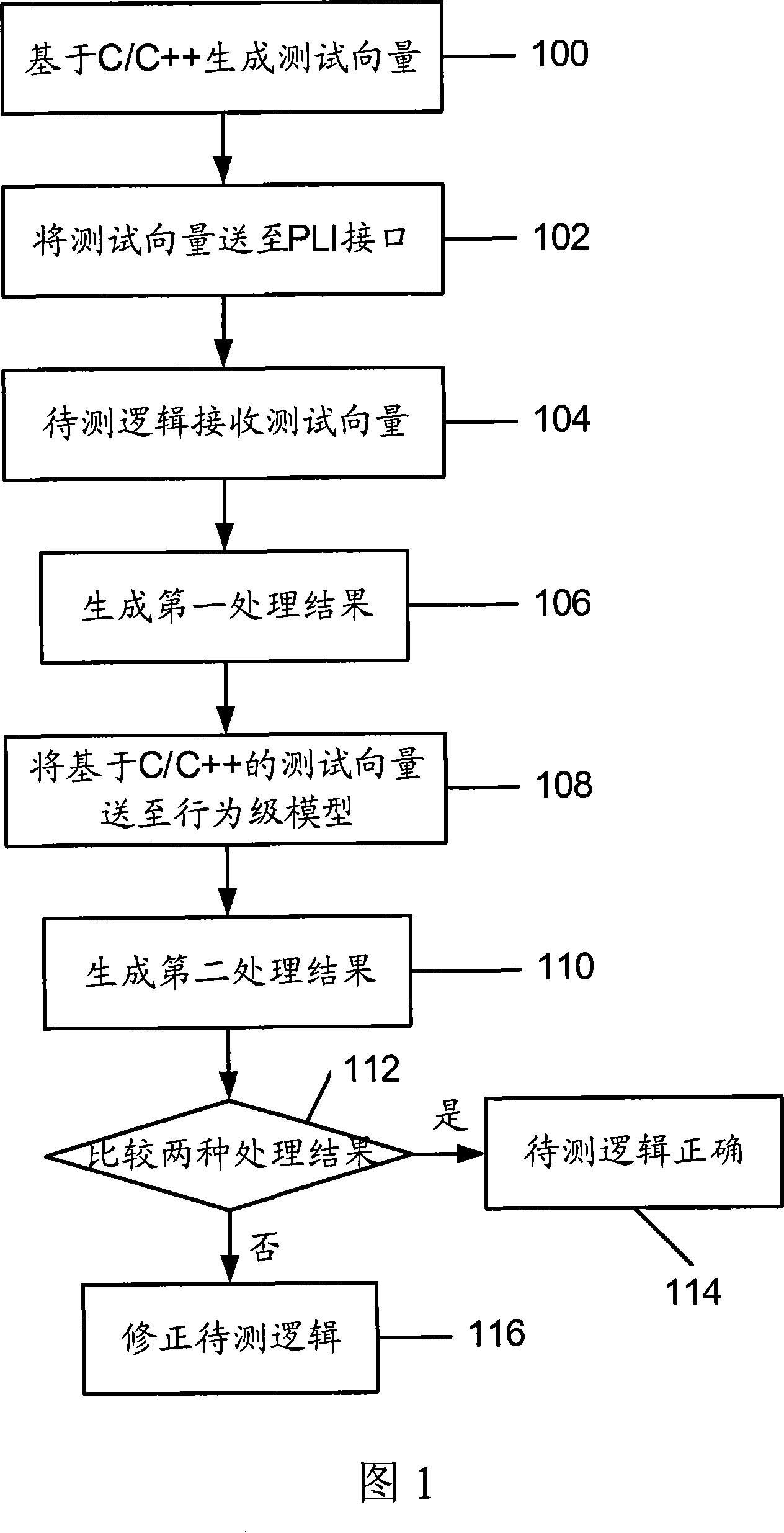

[0024] Fig. 1 shows a schematic structural diagram of a behavior-level model written in C / C++ in the prior art to imitate the logical behavior to be tested. Referring to Figure 1, the implementation principle of the test method is mainly that the test engineer uses the C / C++ high-level programming language to write a behavior-level model to imitate the logic to be tested, and send the same stimulus data used for the test to the logic and behavior to be tested. Level model, compare the results of the two processing. If the processing results are the same, it is determined that the function of the logic behavior to be tested is implemented correctly; if the processing results are inconsistent, the logic to be tested needs to be debugged and corrected. Specifically, it can be explained through the following steps:

[0025] Step 100: Generate a test vector ba...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More