Patents

Literature

43 results about "Real error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

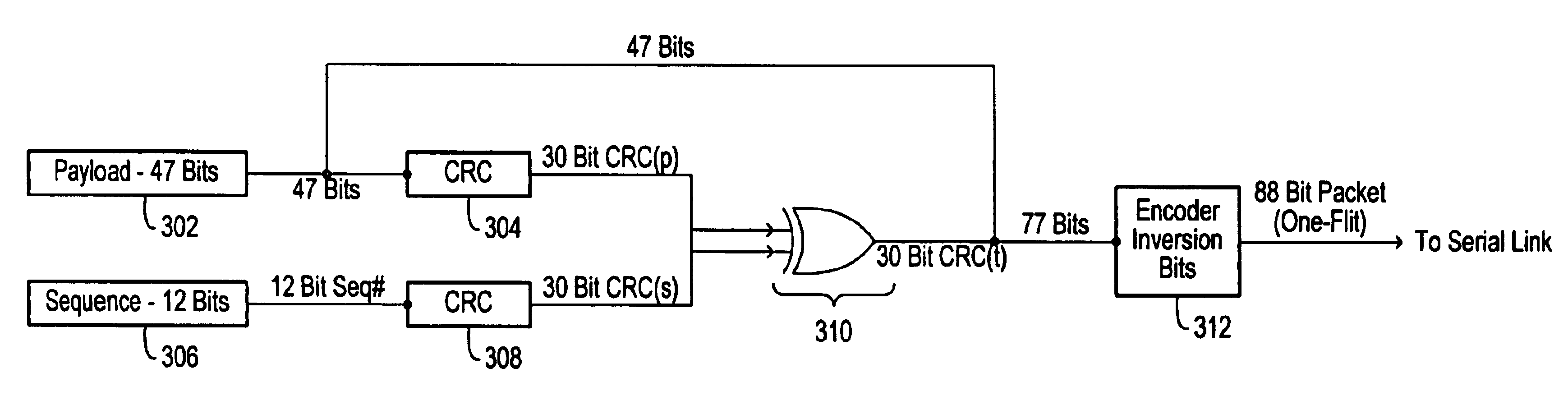

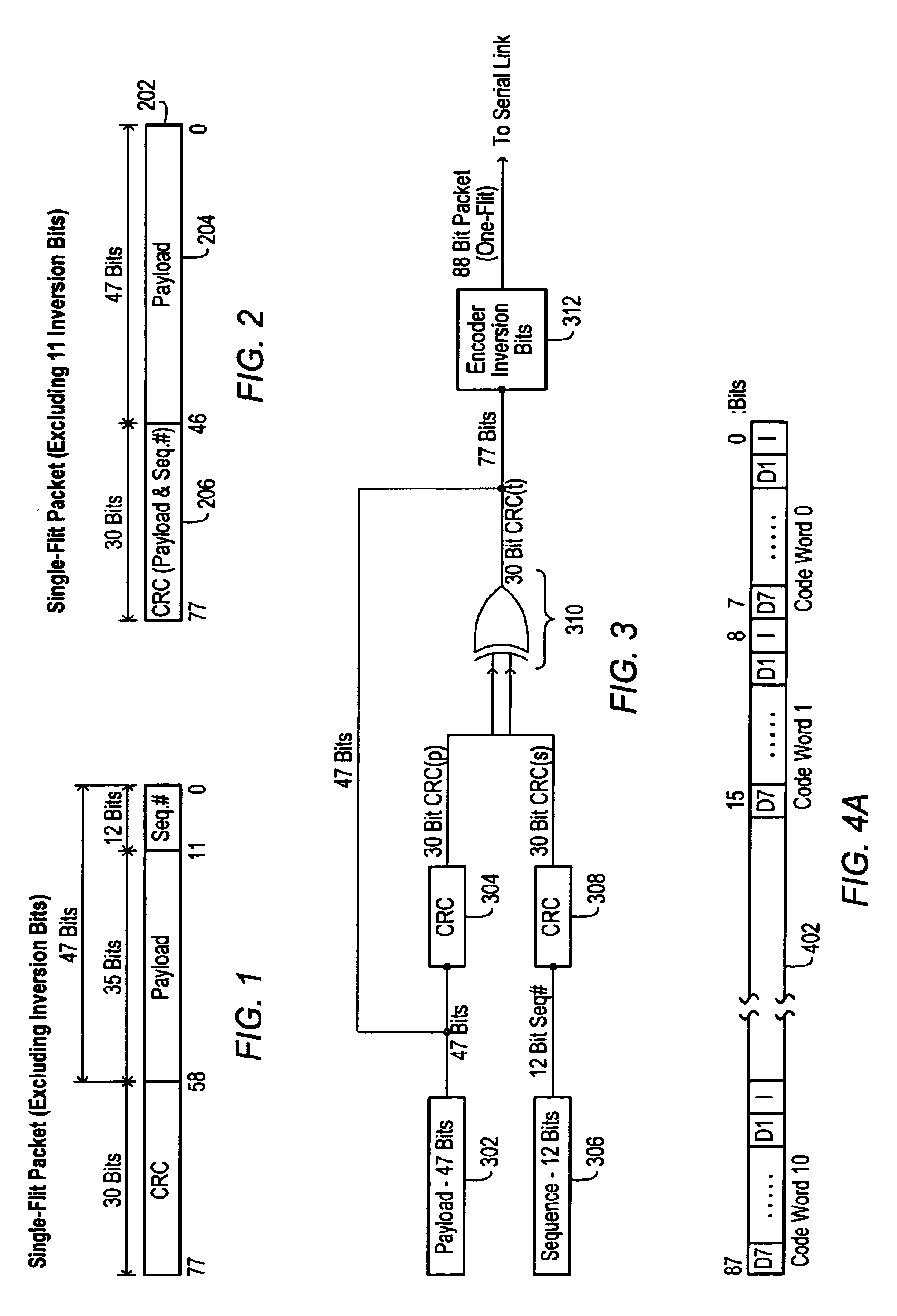

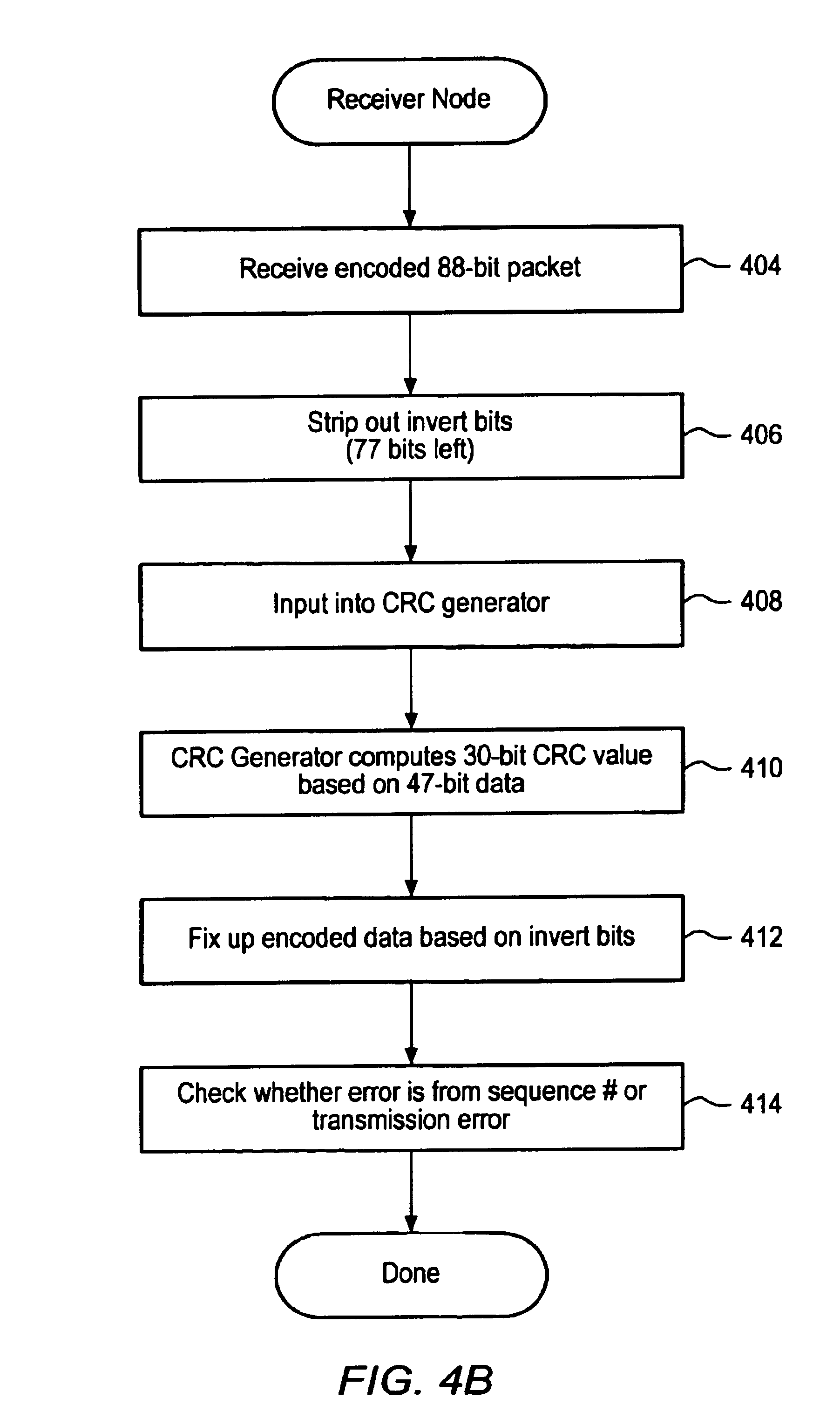

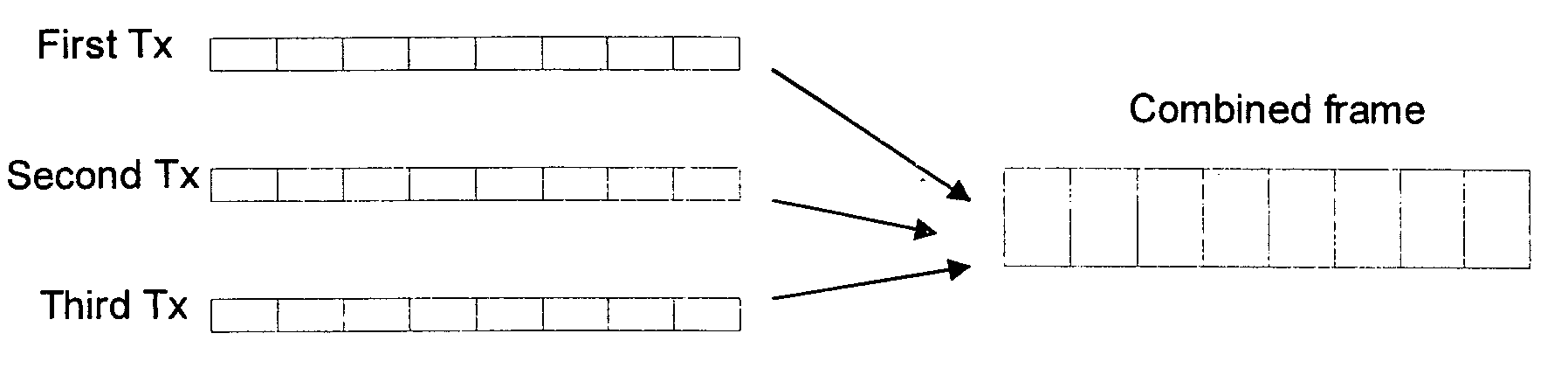

Method for superimposing a sequence number in an error detection code in a data network

A system and method for superimposing a sequence number of a packet into the CRC segment of the packet thereby allowing more bandwidth in the payload portion of the packet for carrying data is described. Also described is a method of acquiring additional information on the type of error in a packet, e.g., data transmission errors or sequence errors, from analyzing a CRC error. For example, a reported CRC error can be the result of the receipt of a packet with a sequence number the receiver is not expecting (which is a normal occurrence on transmission links due to transmitters resending packets that a receiver has already accepted) or can result from a real error in the transmission of a packet. A first error code check (CRC) value is calculated for the payload segment of a data packet. A second CRC value is calculated for the sequence number of the data packet. The first CRC value and the second CRC value are combined thereby creating a third CRC value. The third CRC value is then combined with the payload segment of the data packet thereby creating a data packet that can be transmitted across the link.

Owner:ORACLE INT CORP

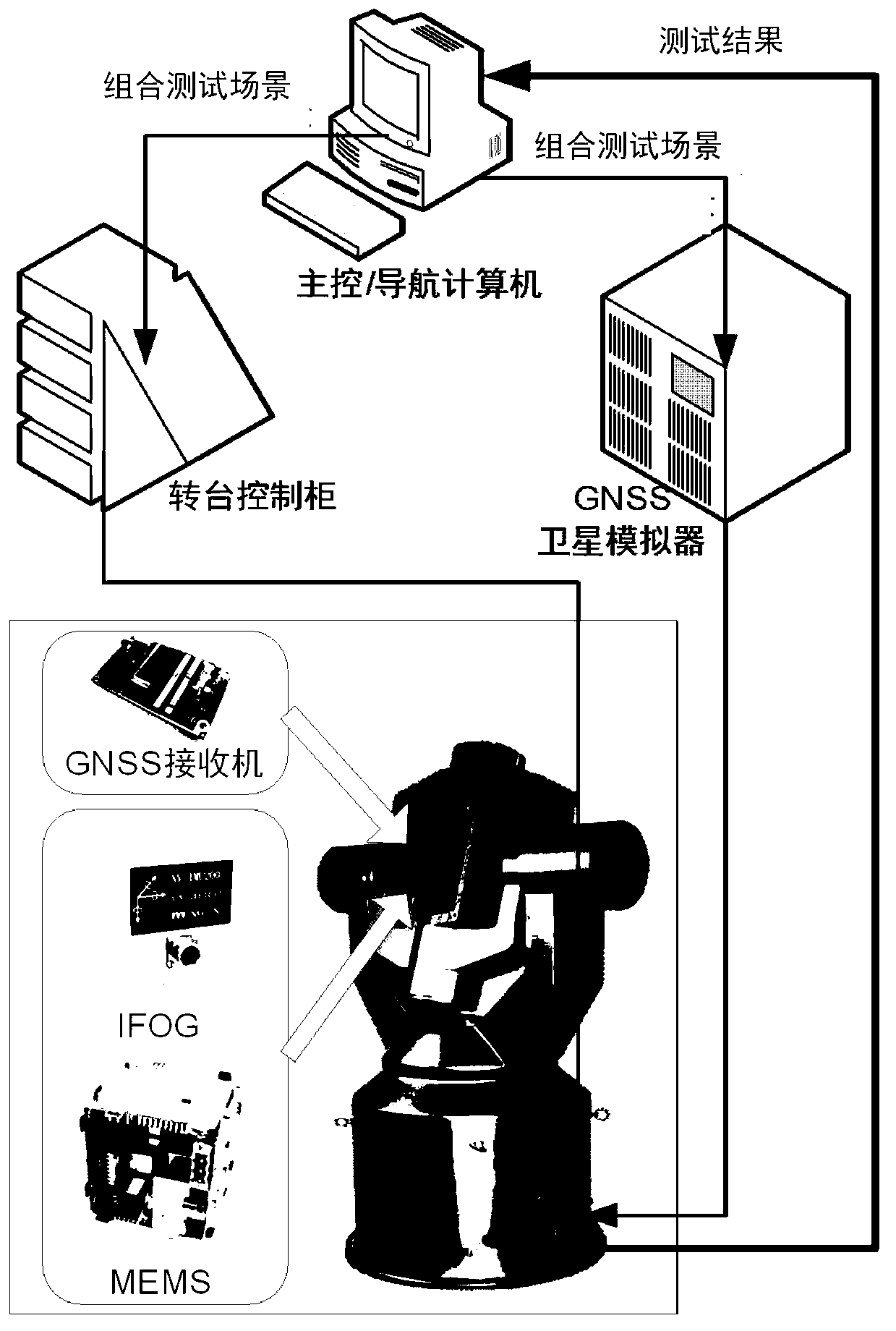

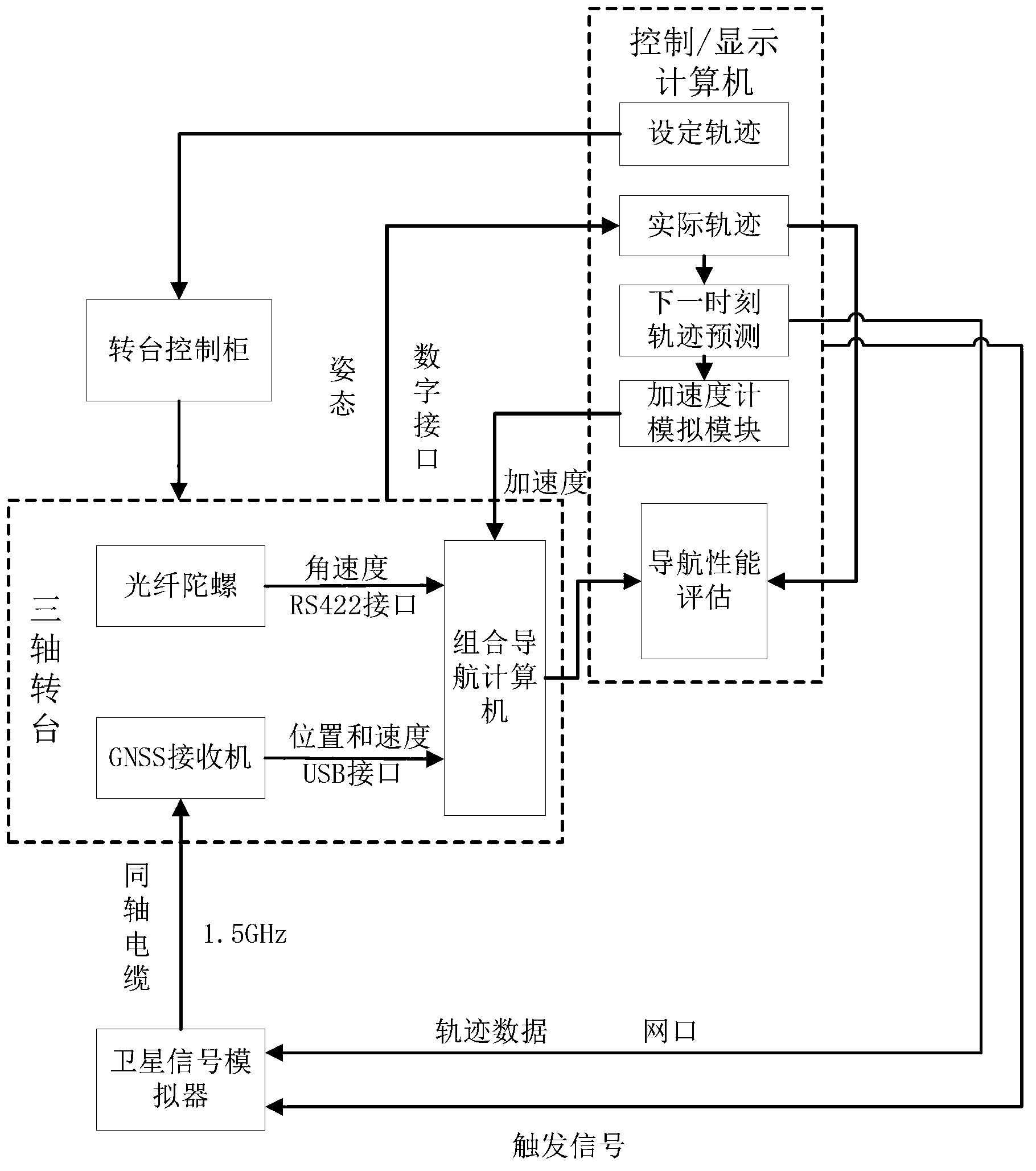

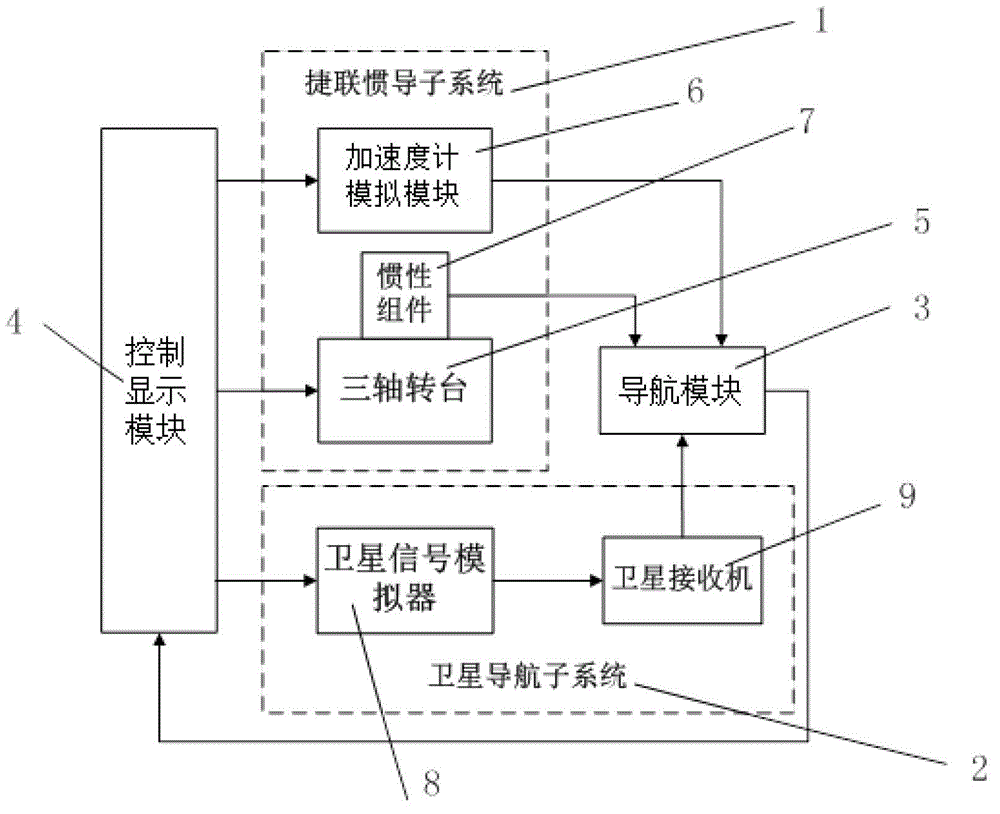

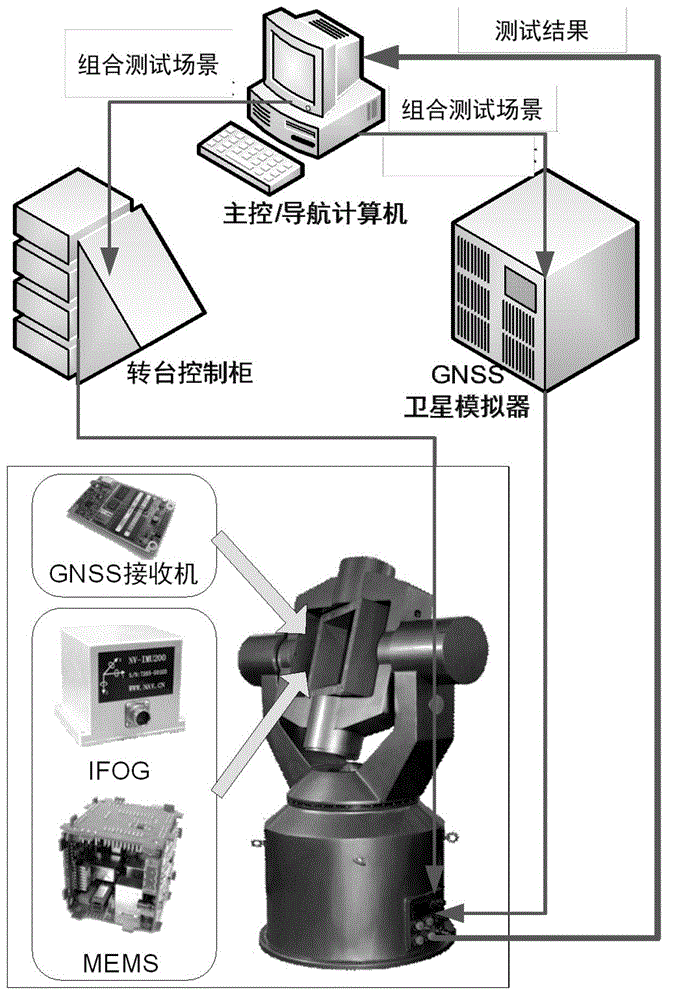

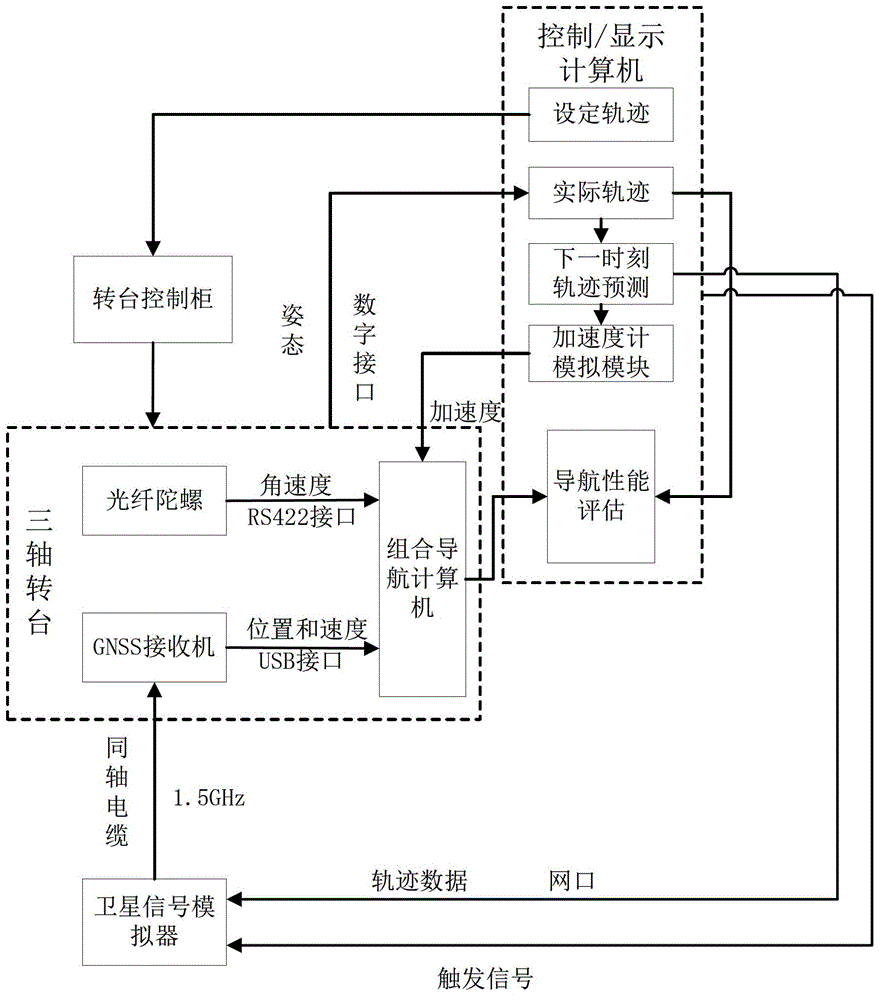

Strapdown inertial/satellite integrated navigation detecting system and simulation testing method thereof

ActiveCN103308073ARealize demonstration verificationRealize evaluationSatellite radio beaconingClosed loopComputer module

The invention relates to a strapdown inertial / satellite integrated navigation detecting system and a simulation testing method thereof. The system comprises a strapdown inertial subsystem, a satellite navigation subsystem, a navigation module and a control and display module, wherein the control and display module is connected with the strapdown inertial subsystem and the satellite navigation subsystem respectively to transmit track information; the strapdown inertial subsystem and the satellite navigation subsystem are respectively connected with the navigation module to transmit angular speed, accelerated speed and satellite signals; the output end of the navigation module is connected with the control and display module to feed an integrated navigation result back to the control and display module to form a closed-loop system. The system has real error characteristics. According to the system, optional tracks can be generated and do not need to be carried by actual carriers, so that the research and development cycle of an integrated navigation system is shortened, and the research and development cost is reduced; the real-time dynamic simulation on carrier movement according to a preset track can be realized and finished, and the universality is very strong.

Owner:SHANGHAI JIAO TONG UNIV

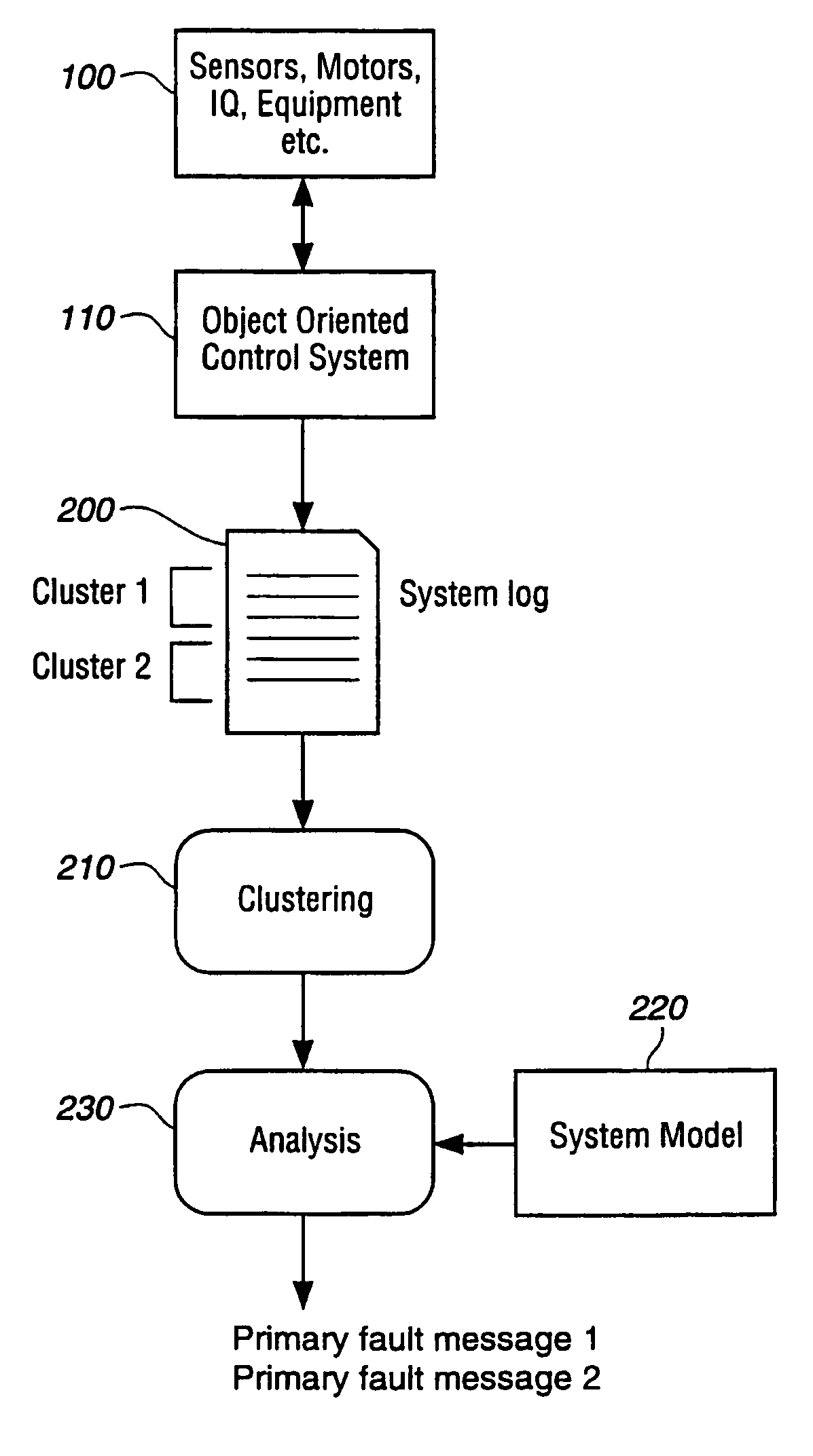

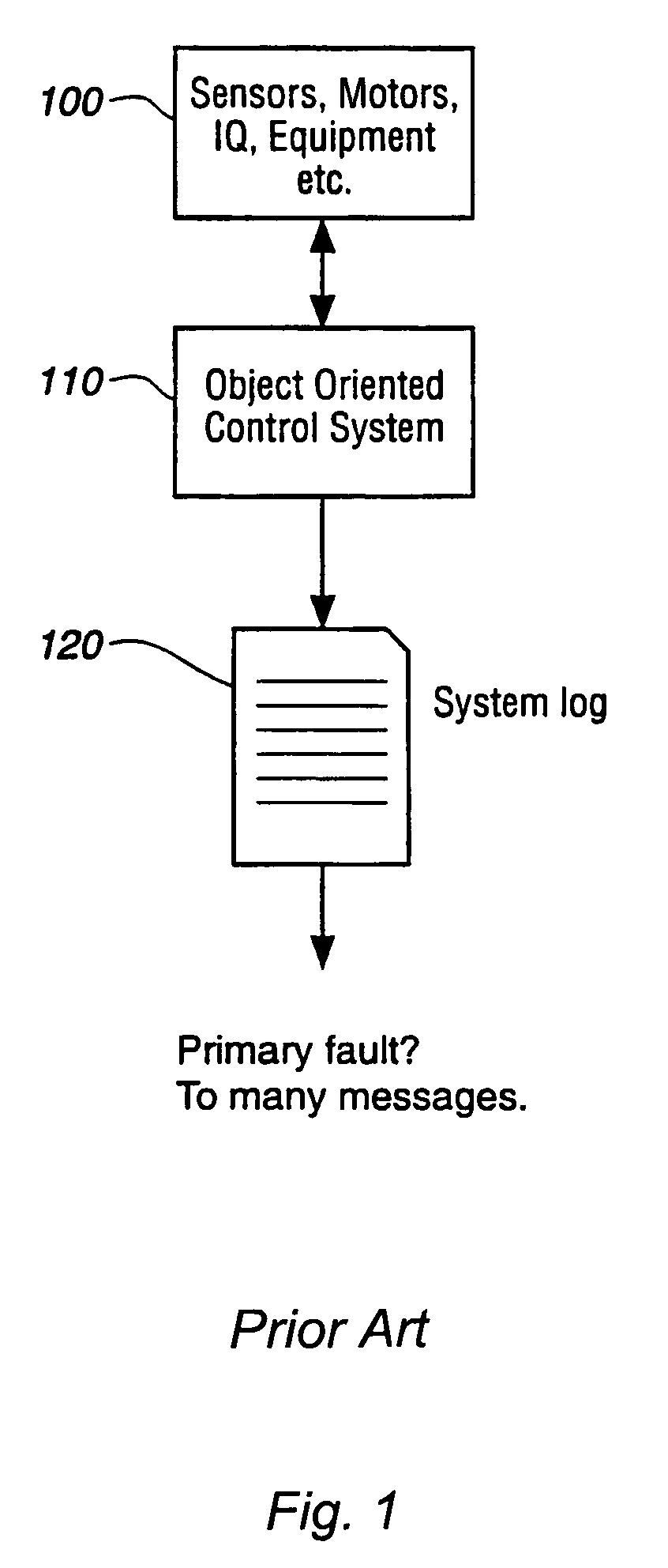

Method for isolating a fault from error messages

InactiveUS7124060B1Easy to deal withFault responseDetecting faulty computer hardwareCoded elementReal error

A method, a use of the method, a system, a use of the system, a computer program code element, and a computer readable medium for automatically isolating primary faults out from a system log including actual error messages in a system controlled by an object oriented program. Messages are isolated through clustering.

Owner:ABB (SCHWEIZ) AG

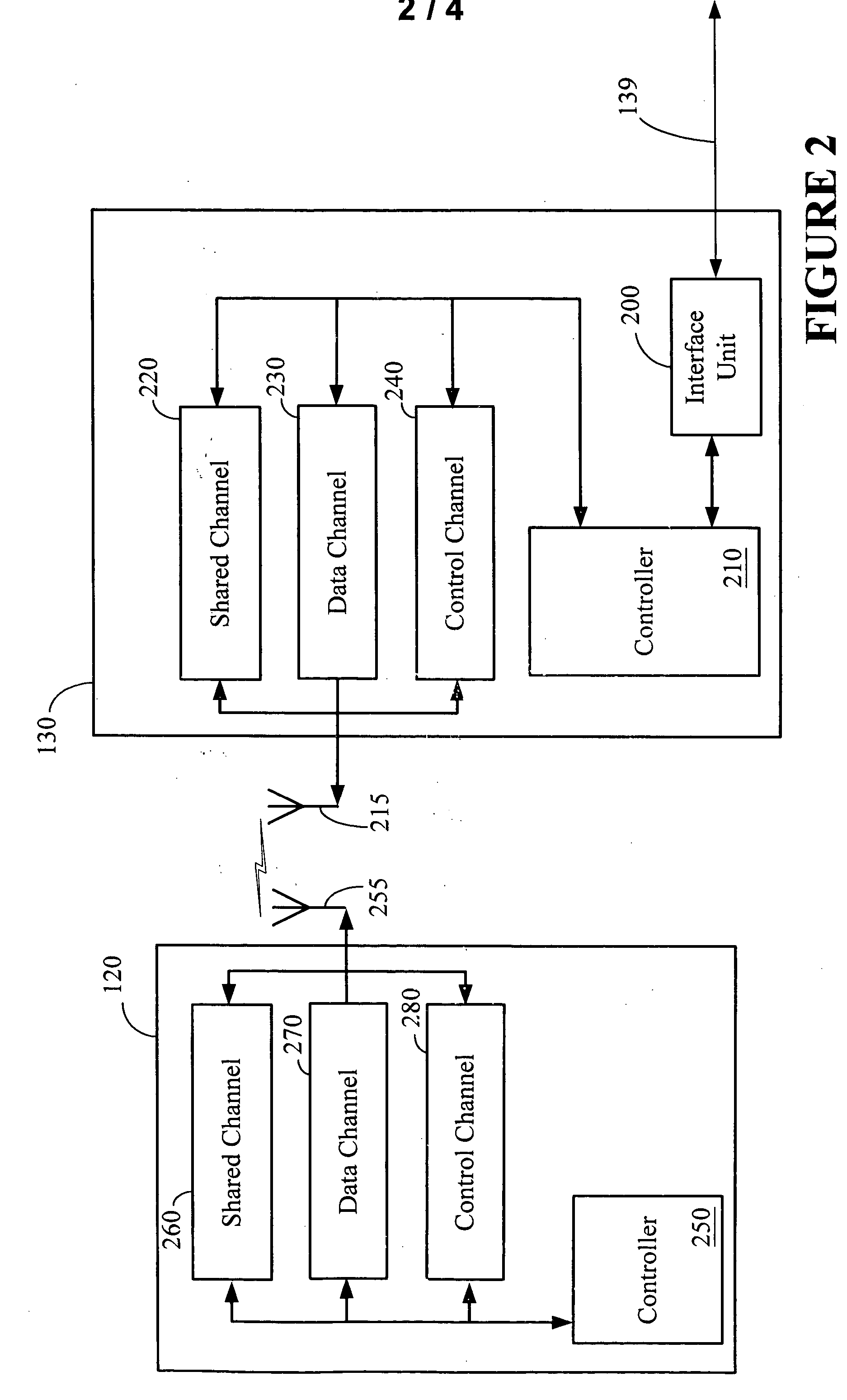

Method and apparatus for link error prediction in a communication system

InactiveUS20050182994A1Error prevention/detection by using return channelError detection/prevention using signal quality detectorCommunications systemSignal-to-noise ratio (imaging)

A method is provided to accurately predict the probability of successfully recovering frames of (coded) information received over a wireless link, without having to decode the frame. This method, which consists of three steps, requires only limited information about the received signals and the forward error correction code and retransmission scheme being used. First, the signal to noise ratio (SNR) of each of the received signals is measured, where the average SNR is determined for multiple segments that together constitute the frame. Next, an algorithm is employed that takes these SNR values as inputs and determines the so-called effective SNR. The algorithm translates the measured SNR values using an appropriate convex metric, and subsequently combines the resulting values, thereby factoring in the effects of fading, multi-path, and other signal degradations. In the third stage, the effective SNR is used to determine the frame error rate by using a look-up table of a single reference curve that specifies the frame error rate of the actual error control code over an additive white Gaussian noise channel. This suffices to accurately predict the performance of a wide range of mobile communication channels. This method can be applied to a variety of retransmission strategies, including hybrid automatic-repeat request (ARQ) and incremental redundancy (IR) and combinations of these two strategies.

Owner:LUCENT TECH INC

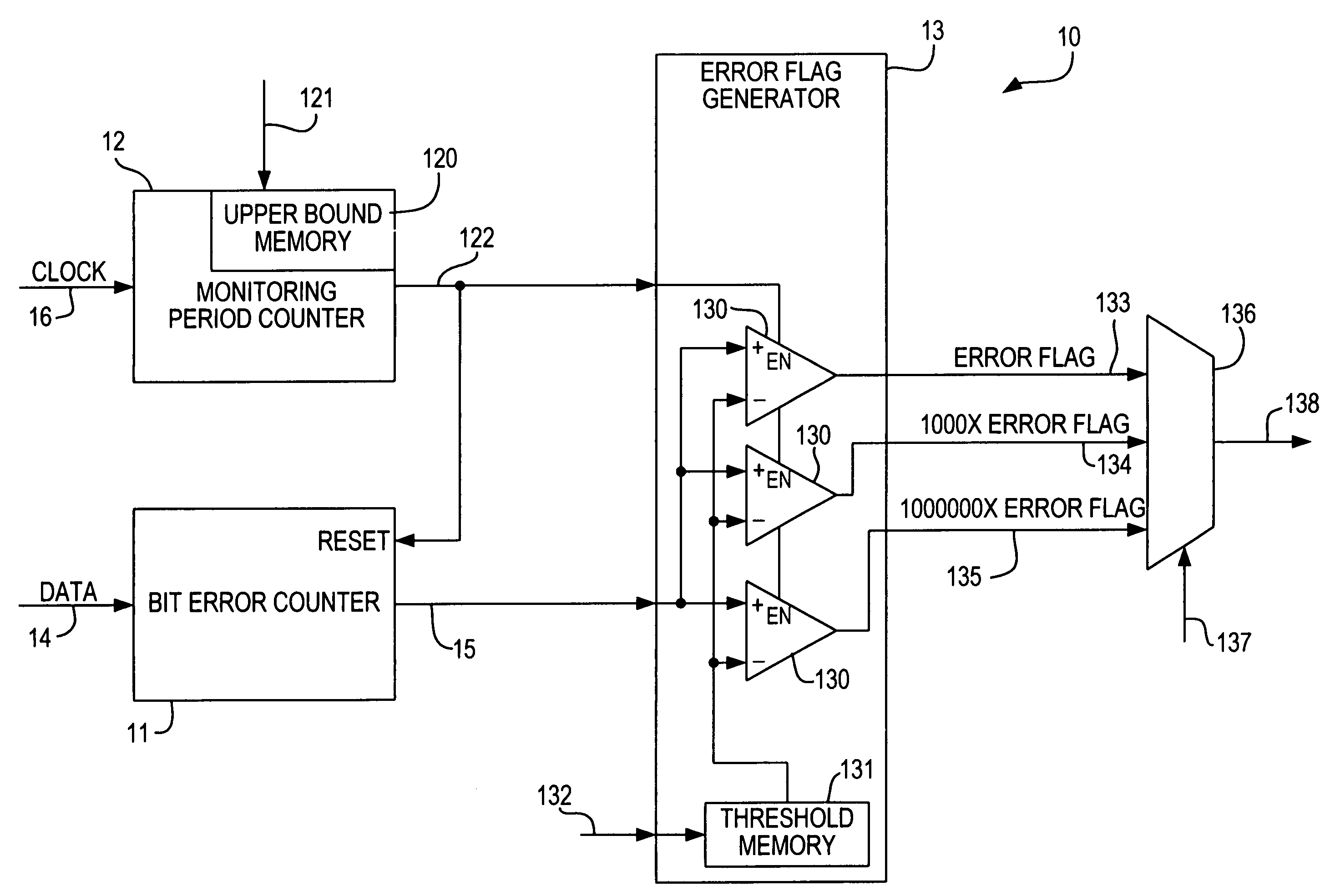

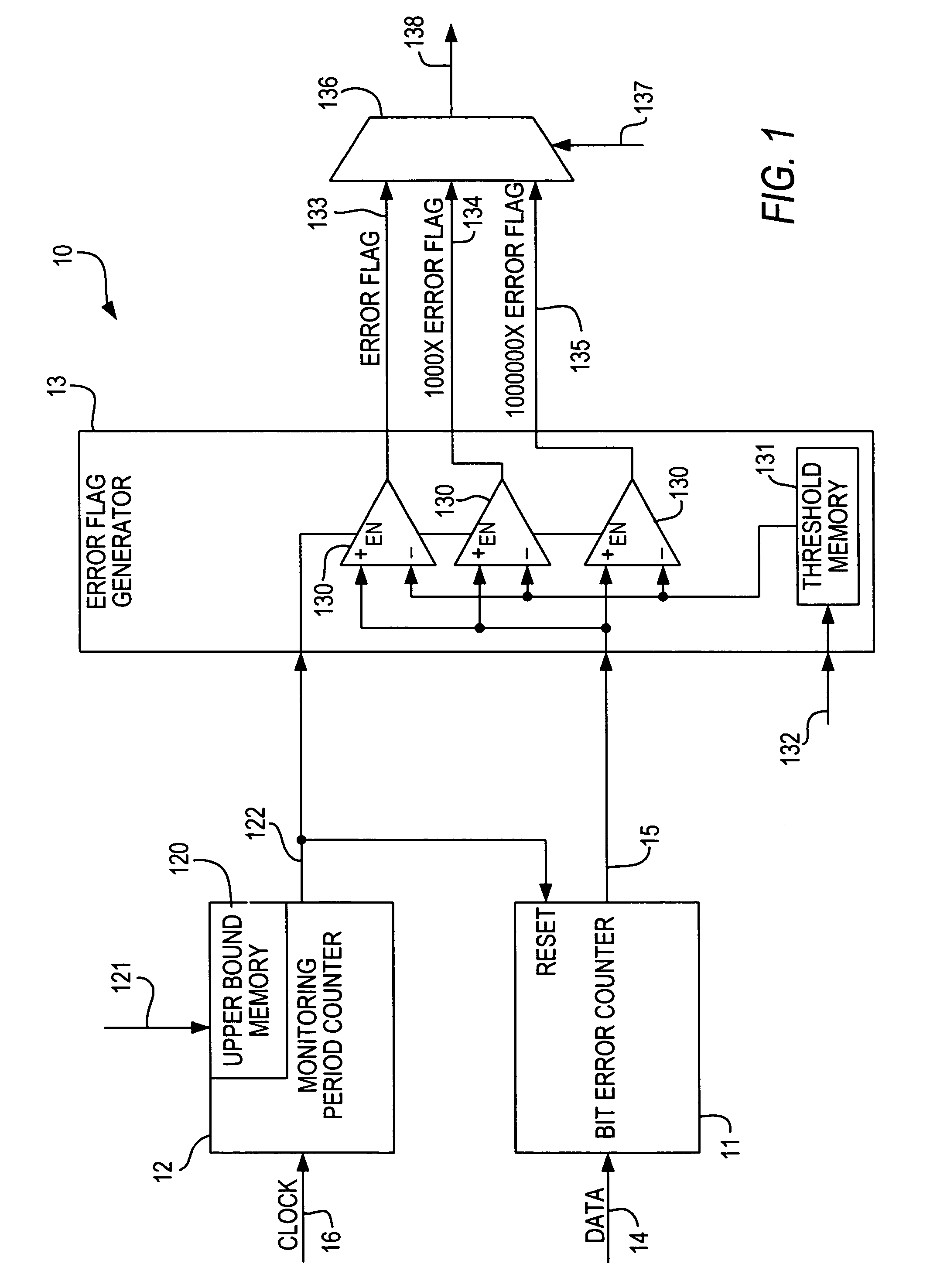

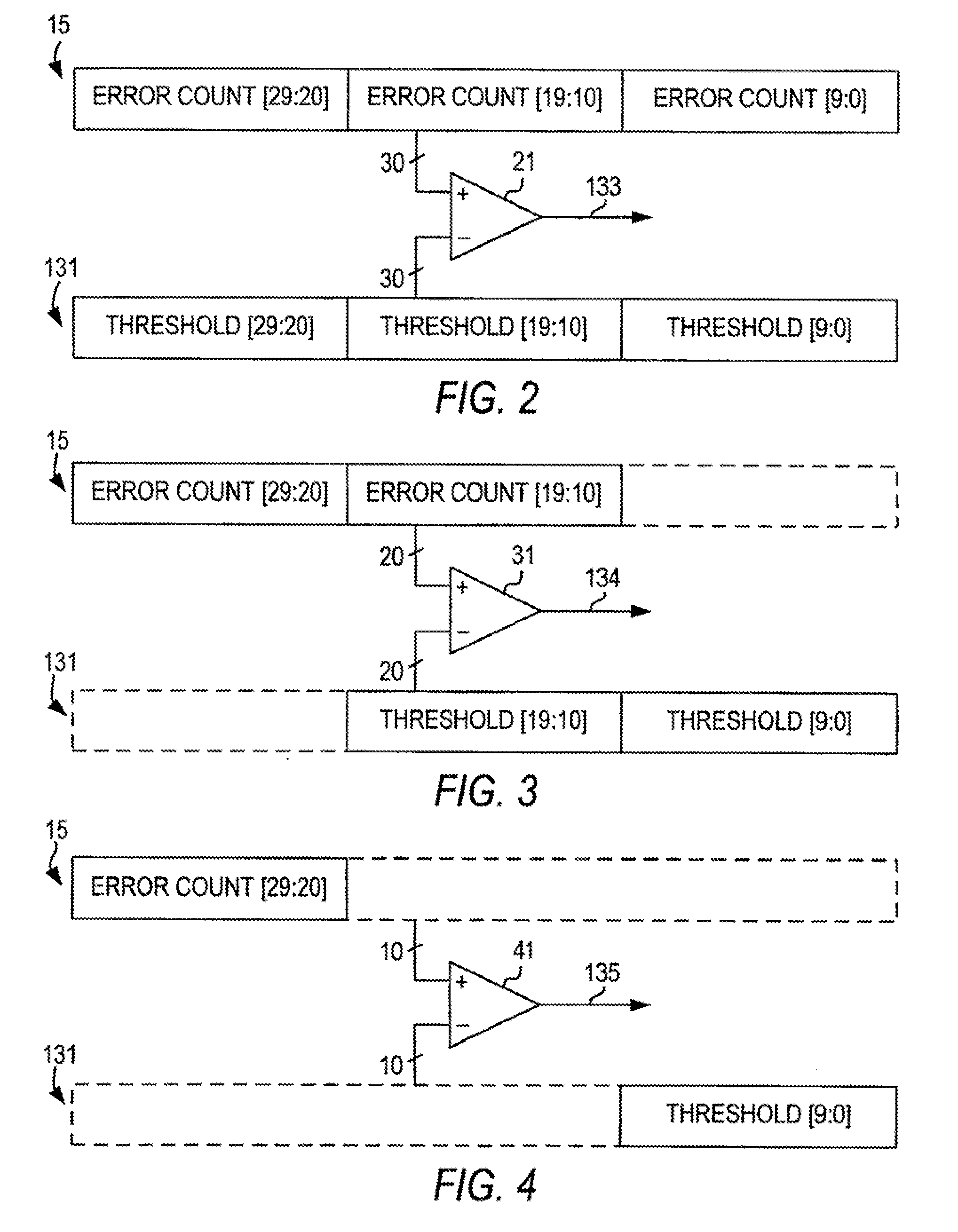

Programmable bit error rate monitor for serial interface

A programmable bit error rate monitor includes an error counter, a monitoring period counter with a programmable upper bound to set the monitoring period, and an error flag generator that compares the actual error count to a programmable threshold. The error flag generator may generate flags at different sensitivity levels, and the user may programmably select one of those flags. The three flags can be generated by independent comparators, or they can be extrapolated from the base error flag—e.g., by comparing only certain bits of the error count to corresponding bits of the threshold.

Owner:ALTERA CORP

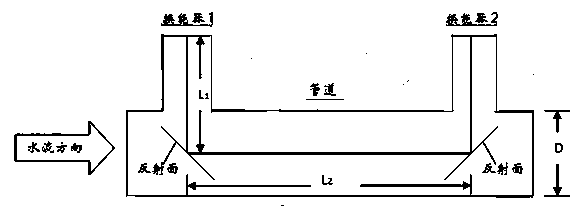

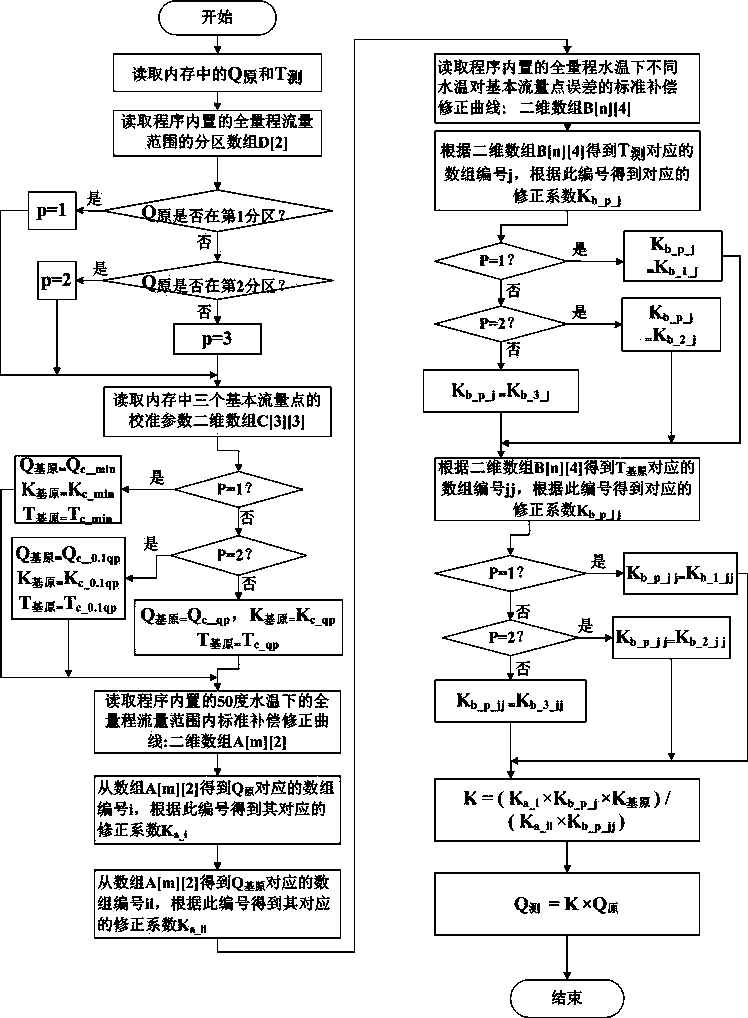

Flow error correction method for time difference type ultrasonic heat meter

ActiveCN104390680AGuaranteed accuracyIncrease productivityTesting/calibration apparatusTraffic volumeReal error

The invention discloses a flow error correction method for a time difference type ultrasonic heat meter. The flow error correction method comprises the steps of selecting three basic flow points which are respectively distributed in three regions within a full-measuring-range flow range, and setting a standard compensation correction curve within the full-measuring-range flow range under the water temperature being M DEG C and a standard compensation correction curve of different water temperatures under the full-measuring-range water temperature on the errors of the basic flow points; performing calibration correction on the flow points under the water temperature being M DEG C, and saving a non-corrected flow value, an error correction compensation coefficient and the water temperature during calibration; correcting the compensation coefficient and the water temperature according to the errors of the basic flow points during calibration, and upwards or downwards moving the two standard compensation correction curves in a subsection manner according to the region to obtain real compensation correction curves of the ultrasonic heat meter; obtaining a real error correction compensation coefficient according to the two real compensation correction curves. According to the flow error correction method, the accuracy of the full-measuring-range water temperature and the flow error within the full-measuring-range flow range can be guaranteed, and the production efficiency is improved.

Owner:HUNAN WEIMING ENERGY TECH CO LTD

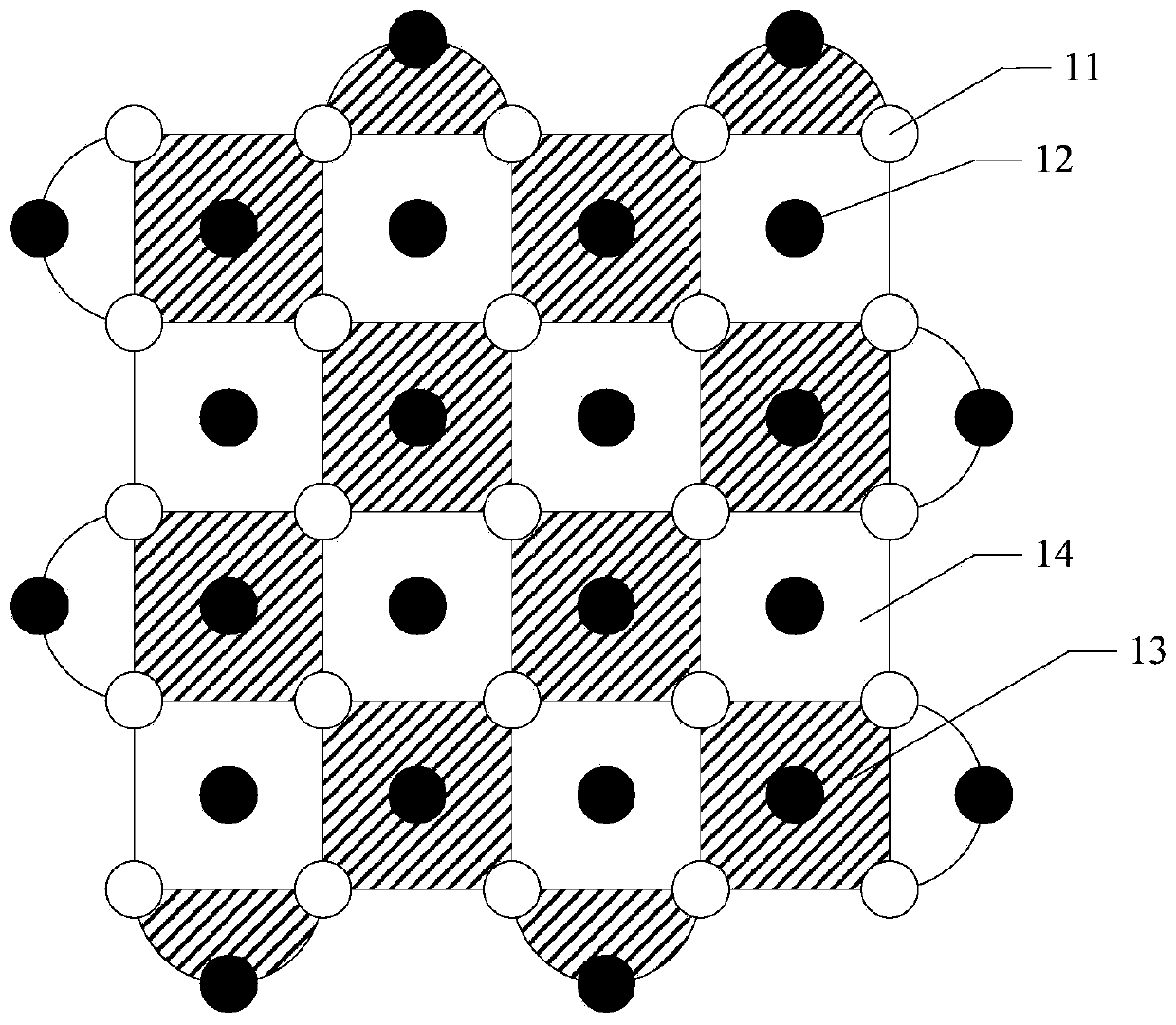

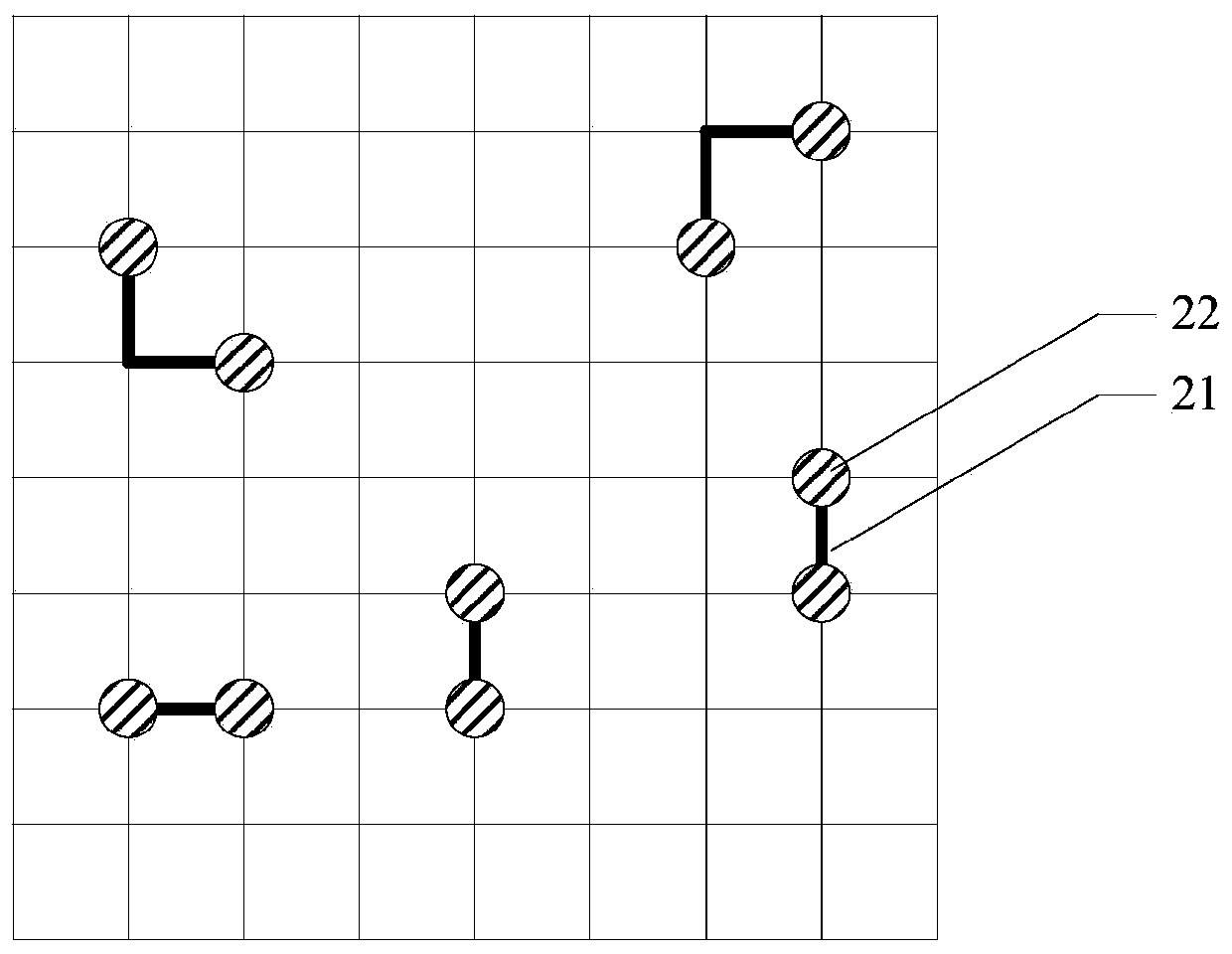

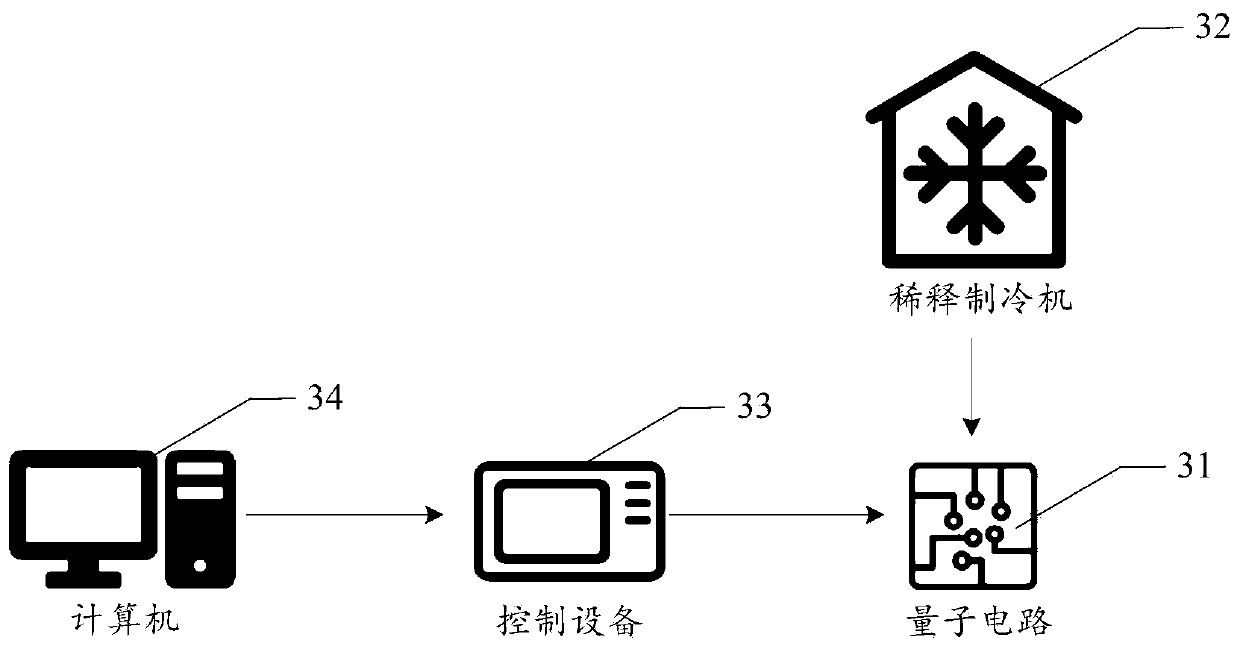

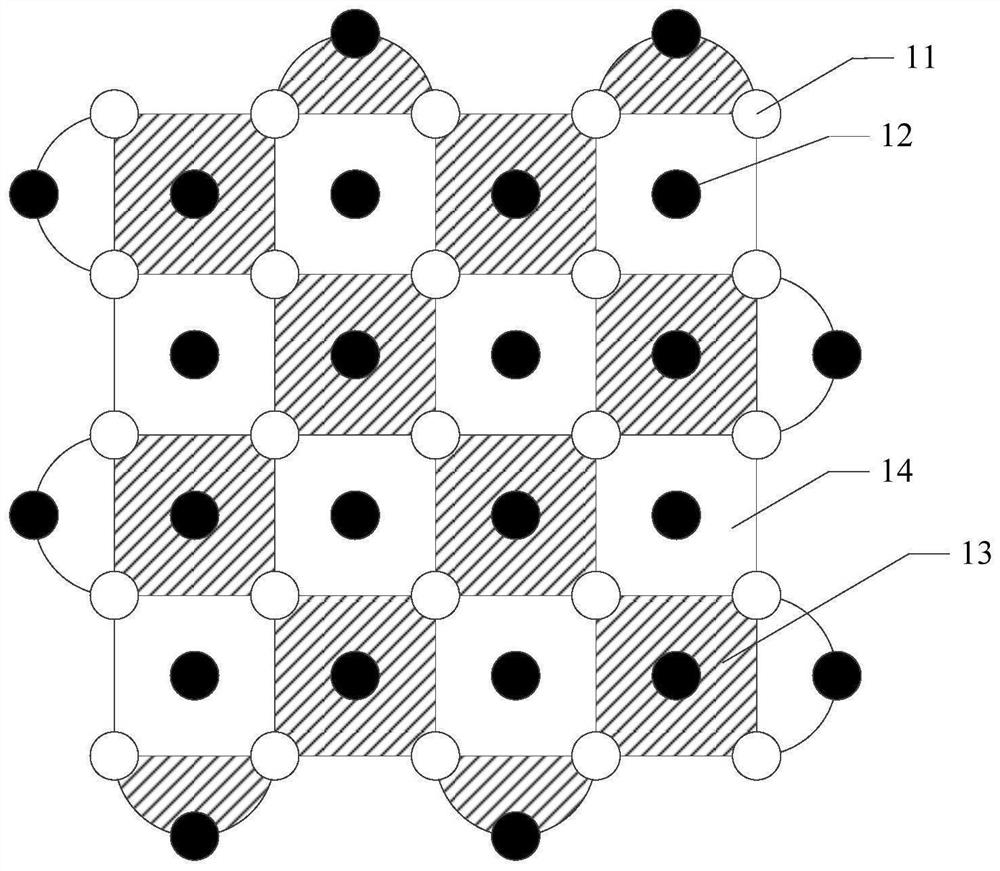

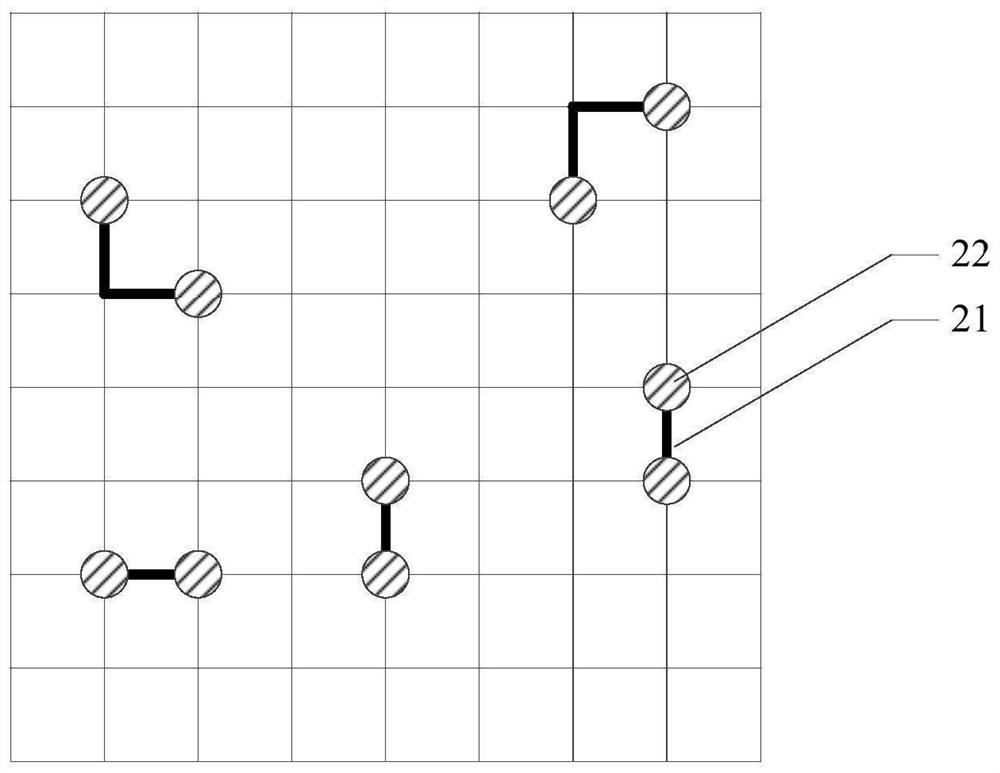

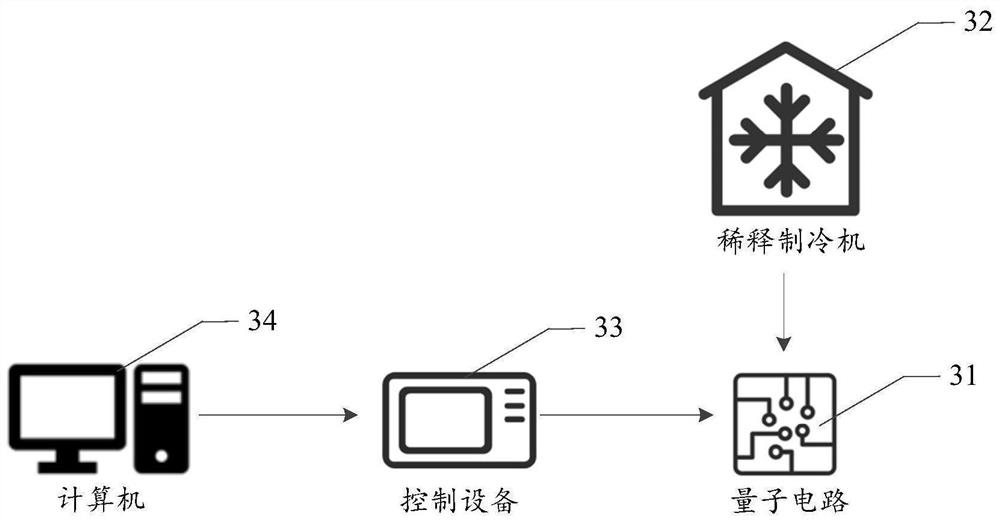

Fault-tolerant error correction decoding method and device of quantum circuit, and chip

ActiveCN111510158AImplement error-tolerant and error-correcting decodingError Tolerance Error Correction Decoding Real TimeQuantum computersNanoinformaticsDecoding methodsQuantum technology

The invention discloses a fault-tolerant error correction decoding method and a fault-tolerant error correction decoding device of a quantum circuit, and a chip, which relate to the technical field ofartificial intelligence and quanta. The fault-tolerant error correction decoding method comprises the following steps of: acquiring real error symptom information of a quantum circuit, wherein the real error symptom information is obtained by performing noisy error symptom measurement on the quantum circuit by adopting a quantum error correction code; decoding the real error symptom information to obtain a logic error class and perfect error symptom information corresponding to the real error symptom information; and determining error result information of the quantum circuit according to thelogic error class and the perfect error symptom information, wherein the error result information is used for indicating data quantum bits with errors in the quantum circuit and corresponding error types. According to the fault-tolerant error correction decoding method and the fault-tolerant error correction decoding device, fault-tolerant error correction decoding is equivalent to a classification problem, so that an efficient neural network classifier is suitable to be adopted for performing fault-tolerant error correction decoding on the error symptom information, the fault-tolerant errorcorrection decoding speed is increased, and real-time fault-tolerant error correction decoding can be realized.

Owner:TENCENT TECH (SHENZHEN) CO LTD

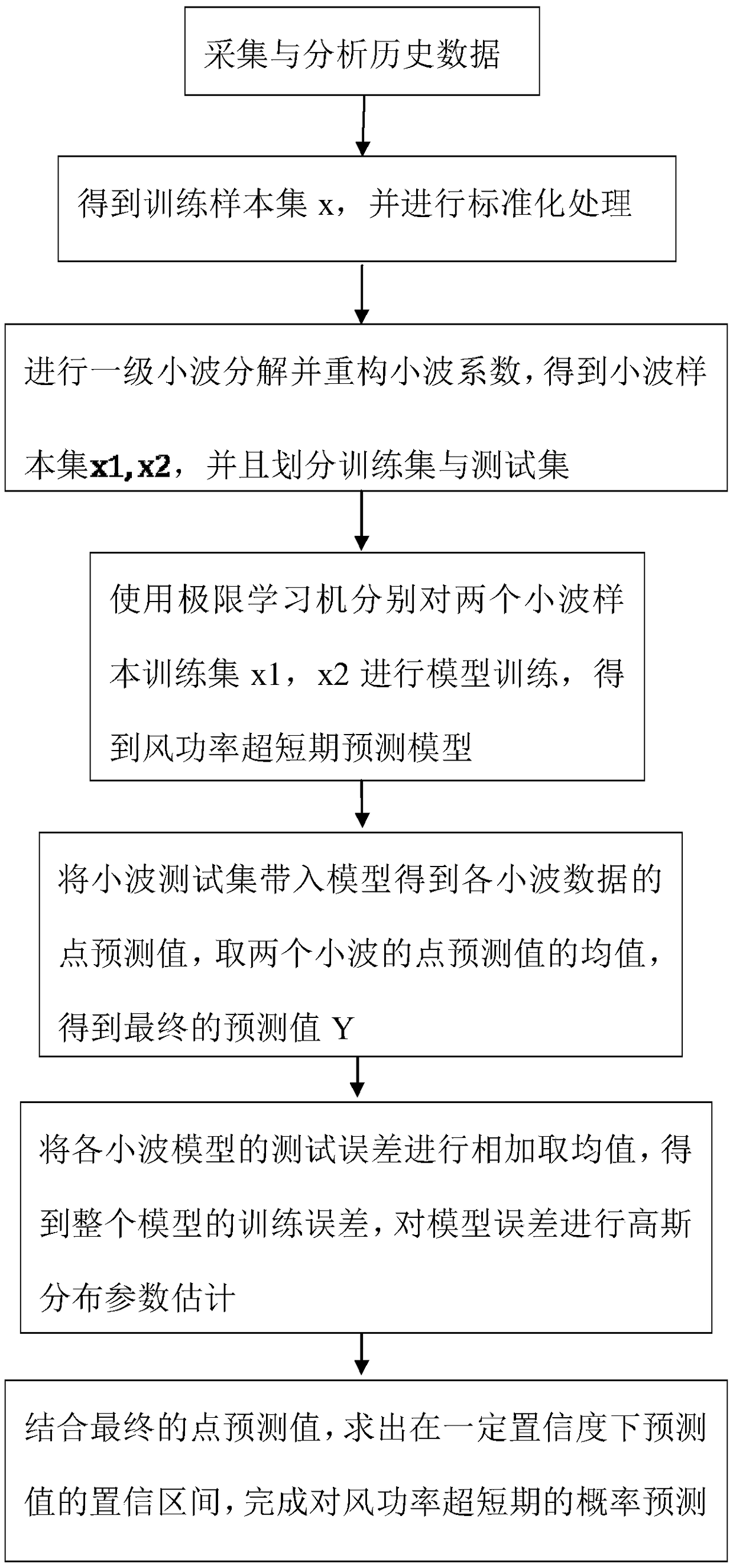

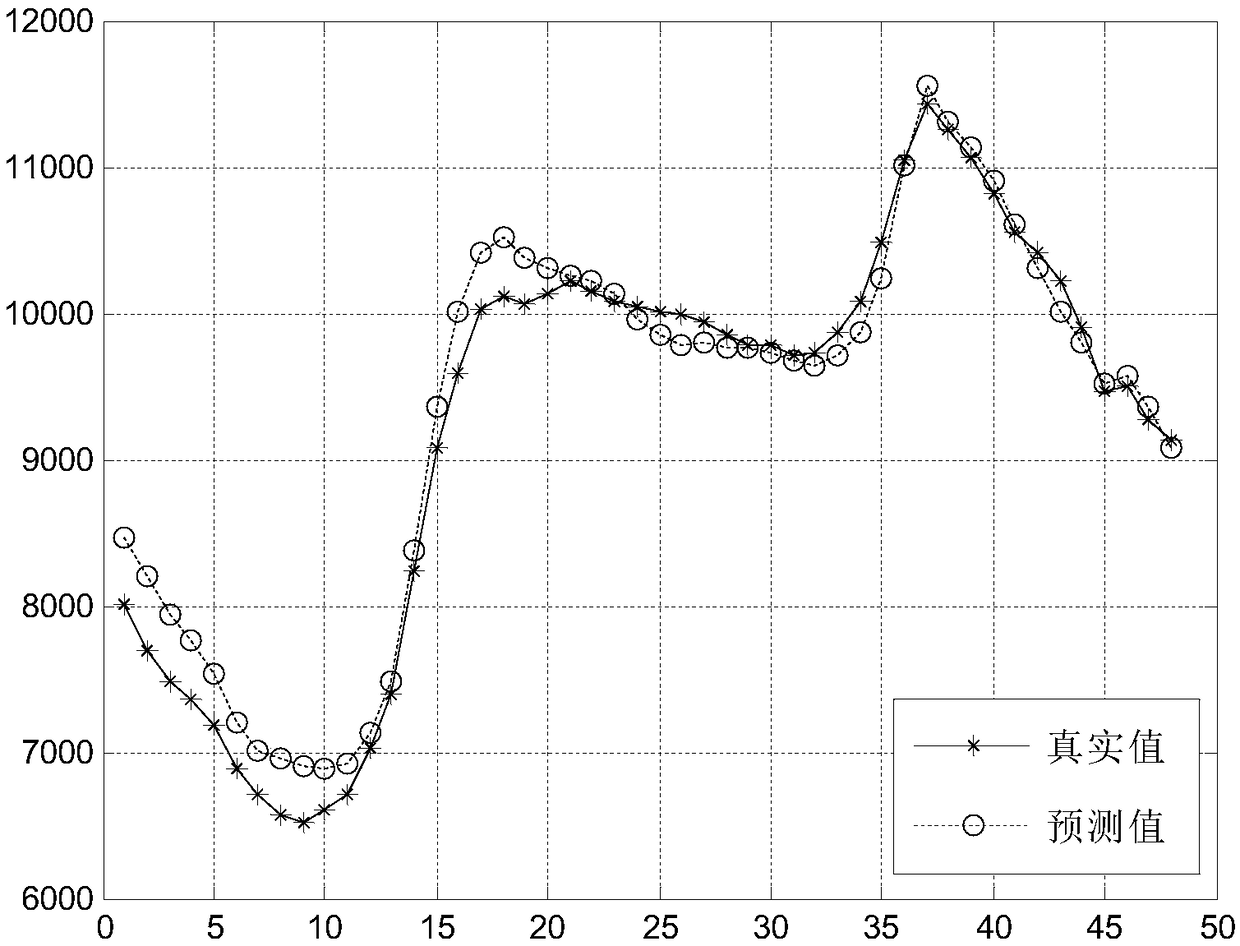

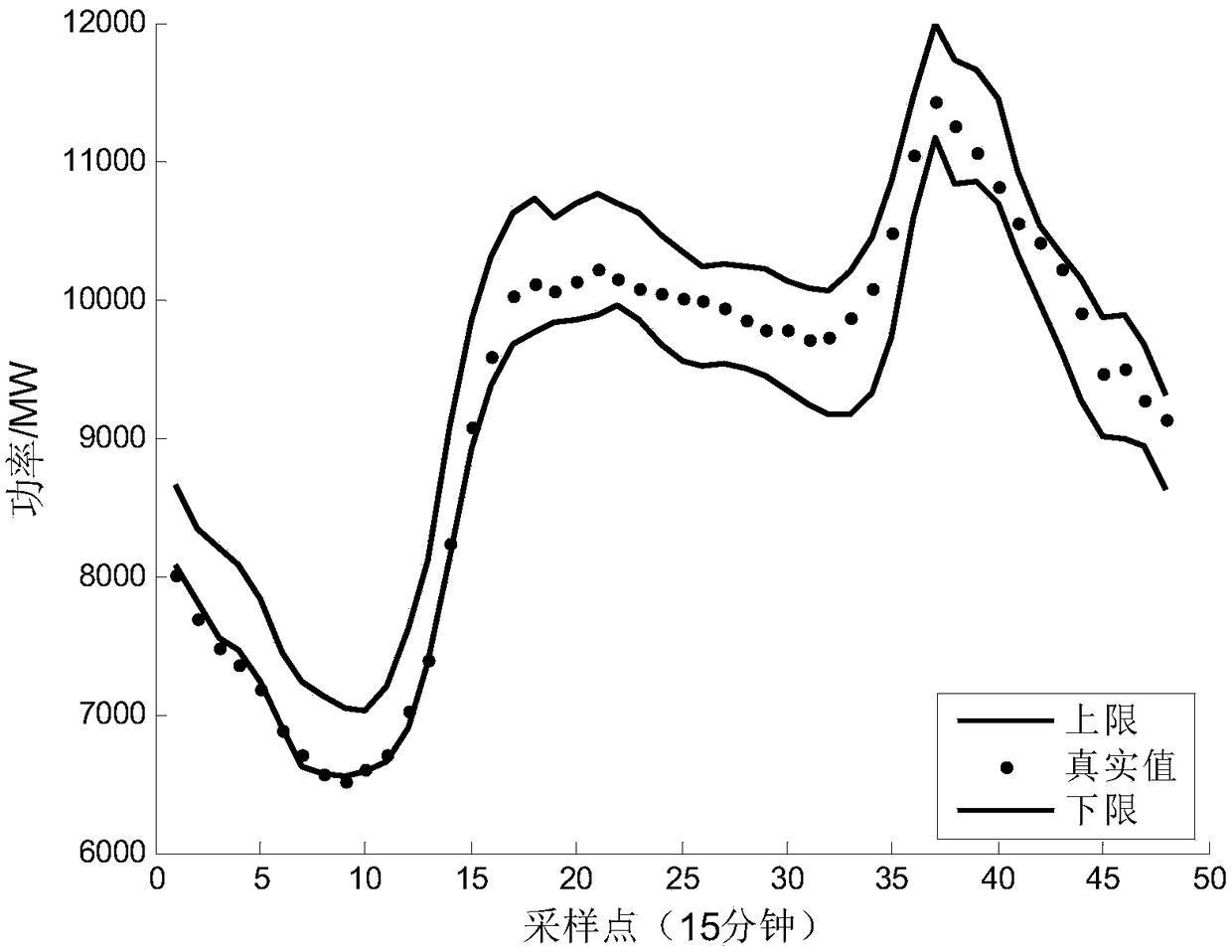

A ultra-short-term wind power probability prediction method

ActiveCN109272156ADelicate handlingHigh precisionForecastingMachine learningLearning machineModel parameters

The invention discloses an ultra-short-term wind power probability prediction method, which collects historical data of a wind farm and obtains a training sample set. According to the historical dataof the influencing factors, the input variables are generated and the sample set is obtained. Wavelet decomposition and wavelet coefficient reconstruction are used to get wavelet sample set. The parameters of each wavelet sample set are trained by the limit learning machine, the prediction model of wavelet limit learning machine is obtained, a test set is brought into the network to obtain a wavelet ultra-short-term point prediction value, the training error of each wavelet limit learning machine model and the point prediction value are stored and added and averaged, Gaussian distribution function of wavelet model training error is obtained by estimating the Gaussian distribution parameter of the real error of the model. The ultra-short-term probability prediction interval of wavelet can be obtained by the prediction value of the joint point according to the confidence requirement.

Owner:HOHAI UNIV

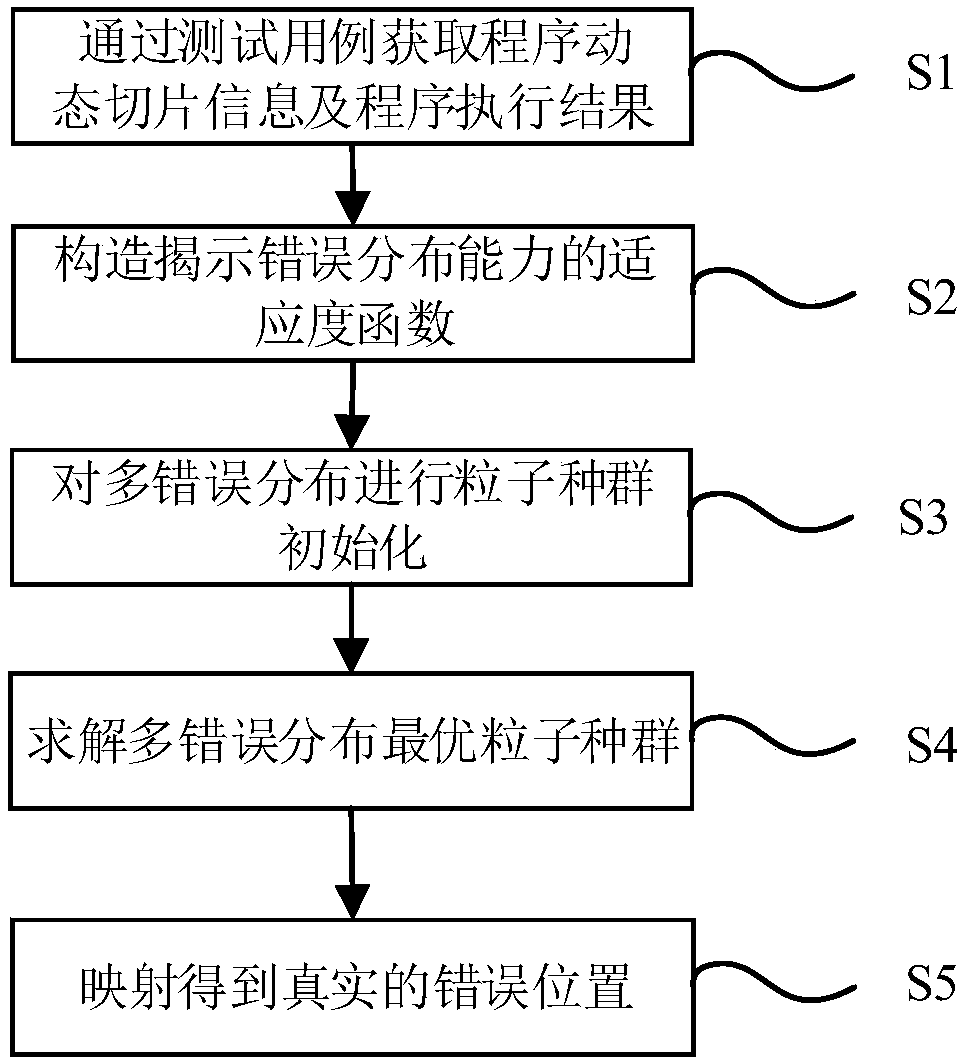

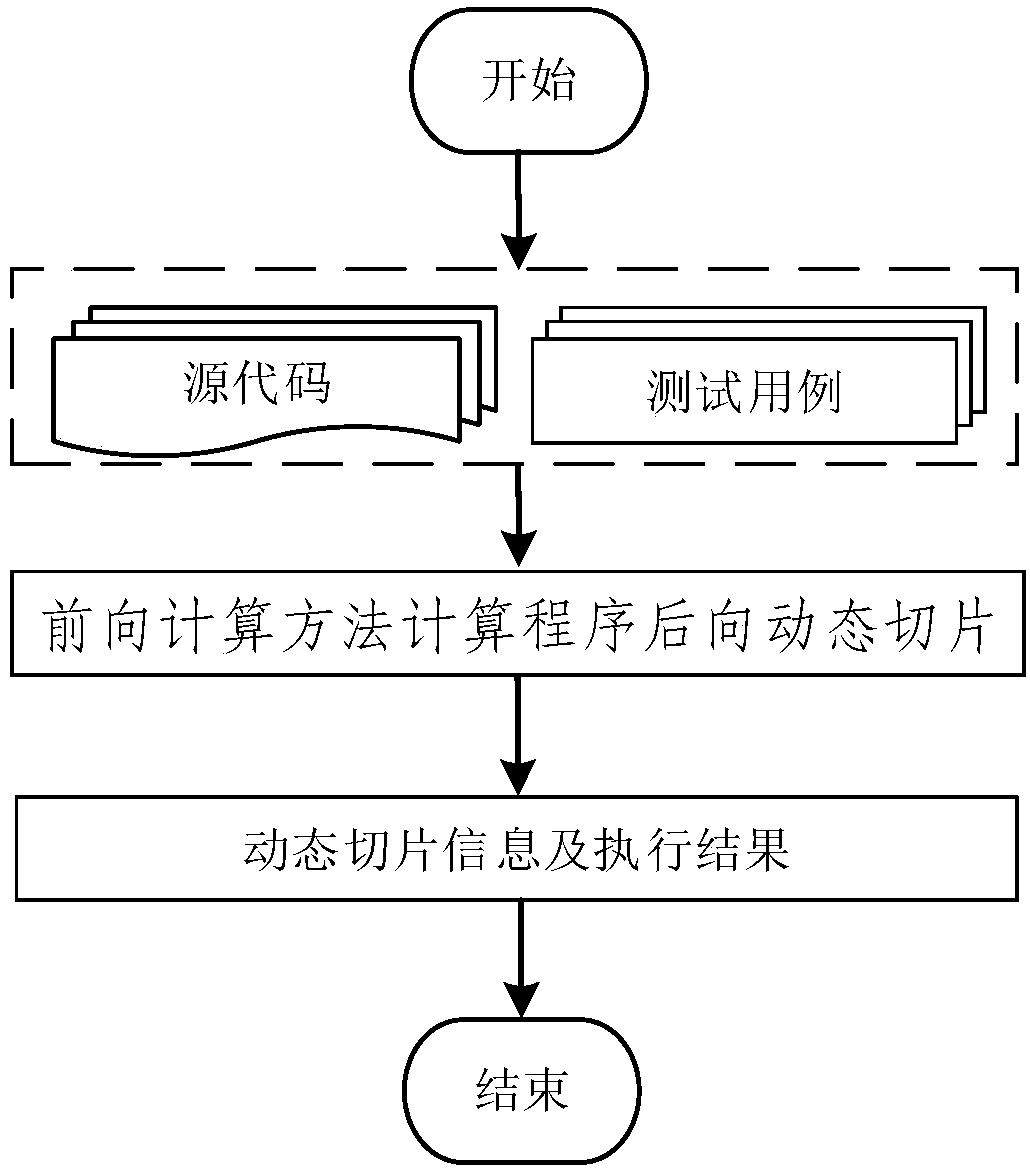

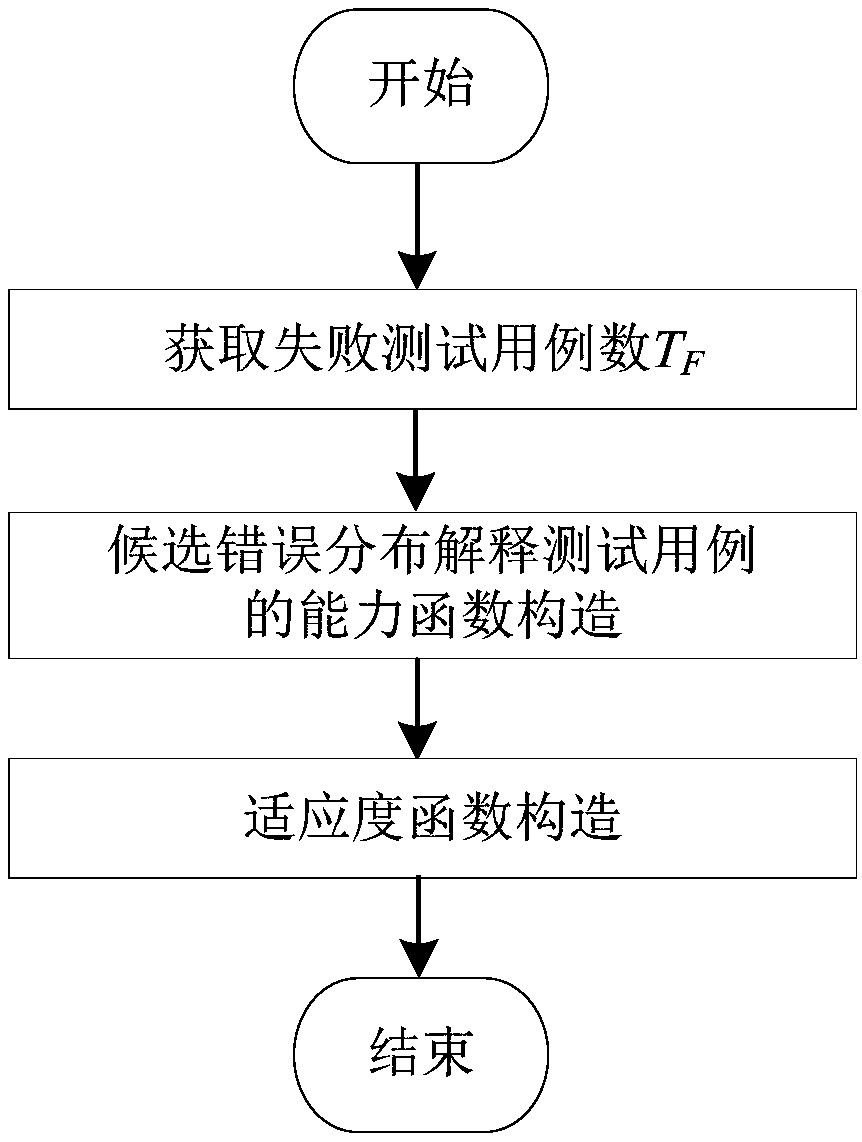

A software multi-error positioning method based on particle swarm optimization and a processing device

ActiveCN109885471AImprove the efficiency of error locationEfficient identificationSoftware testing/debuggingFrequency spectrumSoftware error

The invention relates to the technical field of software testing, in particular to a software multi-error positioning method and processing device based on particle swarm optimization. The error positioning range is reduced according to the dynamic slice; a theory and a method of a particle swarm optimization algorithm are combined; a fitness function constructed by a doubtful degree calculation formula is expanded based on the program frequency spectrum information and a program execution result, so that the optimal solution is obtained and mapped to the real error position, multiple errors in the software can be effectively recognized, the software error positioning efficiency can be remarkably improved, and therefore the problems that the current multi-error positioning effect is poor,and the efficiency is low, are solved.

Owner:HENAN UNIVERSITY OF TECHNOLOGY

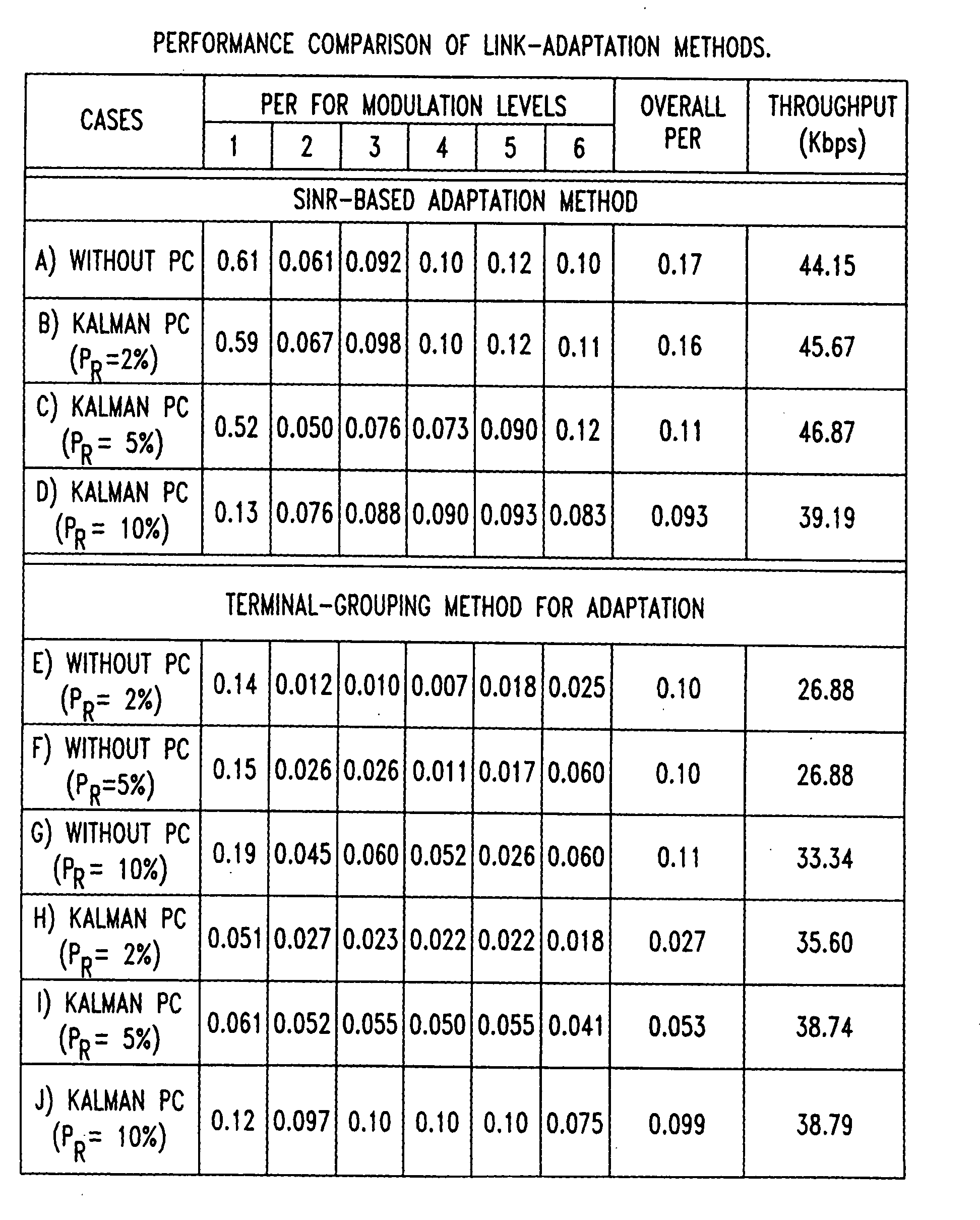

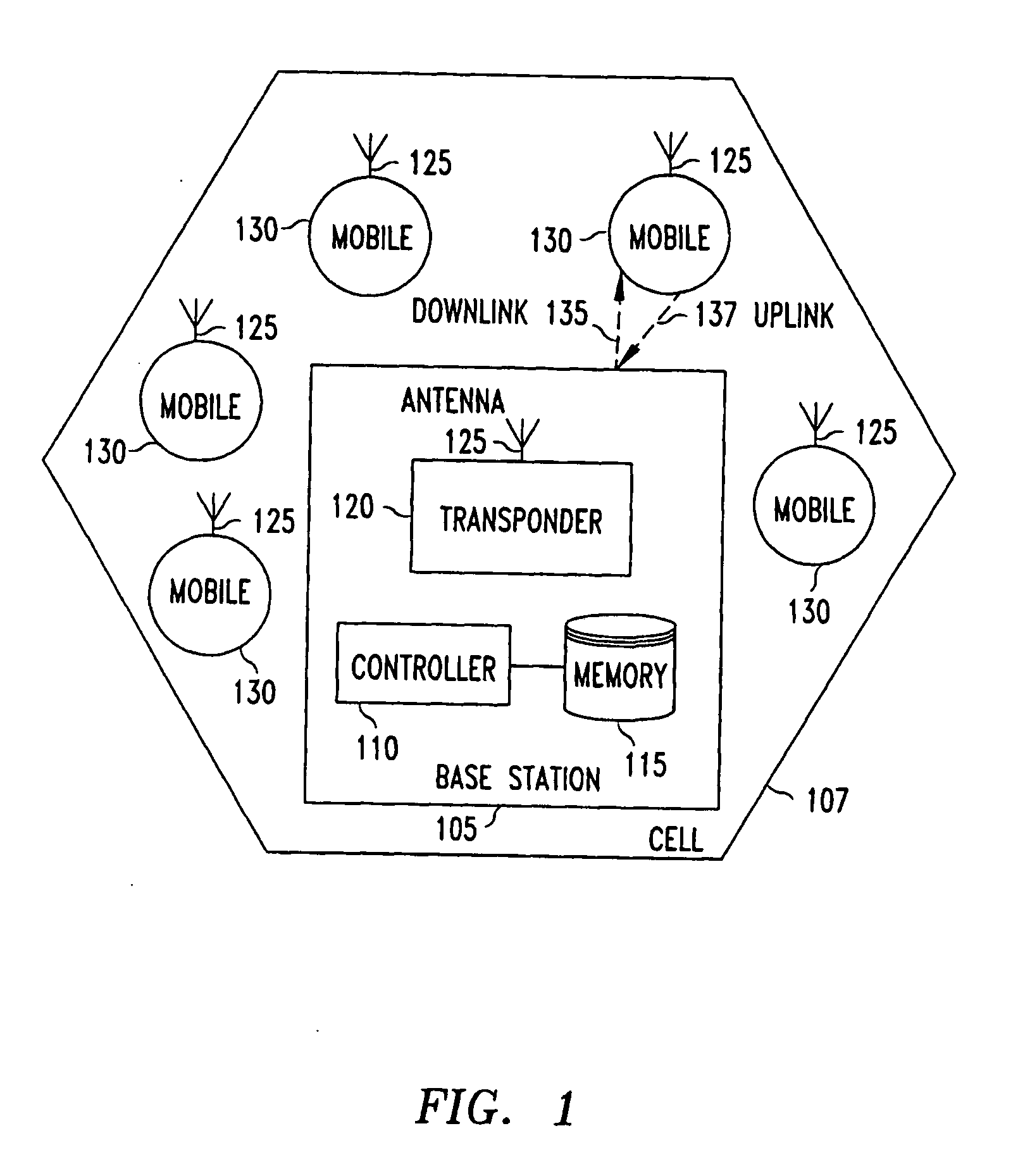

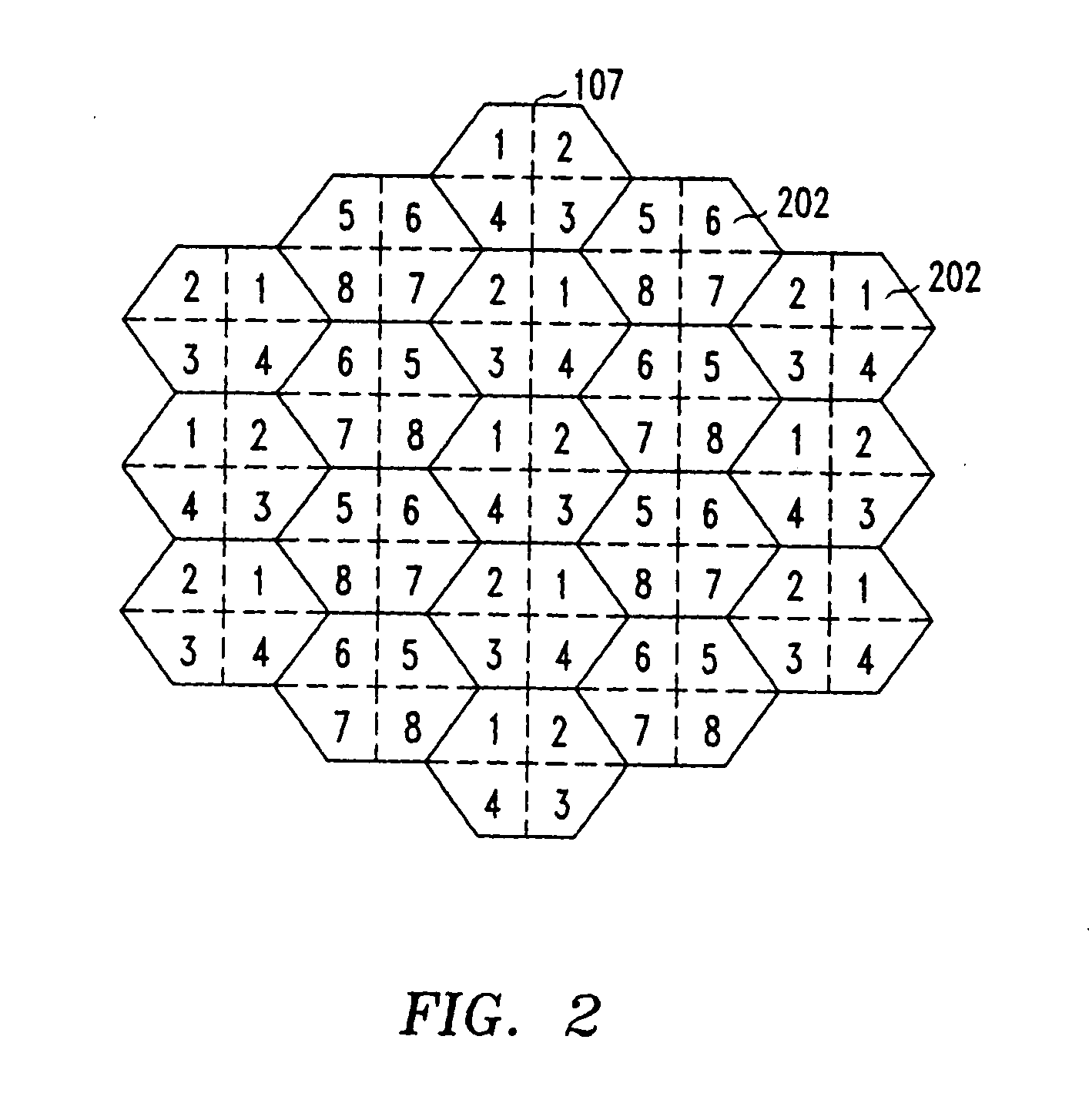

Method and system for integrated link adaptation and power control to improve error and throughput performance in wireless packet networks

InactiveUS20090175192A1Frequency-division multiplex detailsWireless commuication servicesKaiman filterLink adaptation

The invention provides a system that implements an algorithm for integrated link adaptation and power control to achieve specified error rates and to improve an overall throughput for real-time applications in wireless packet networks. The system initially divides wireless terminals into groups according to their signal path gains. Afterwards, the system can periodically adapt transmissions (i.e., link adaptations) based on the required error rates, actual error statistics and average transmission power for each wireless terminal group. Furthermore, transmission power can be adjusted by an enhanced Kalman-filter method to ensure successful reception.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

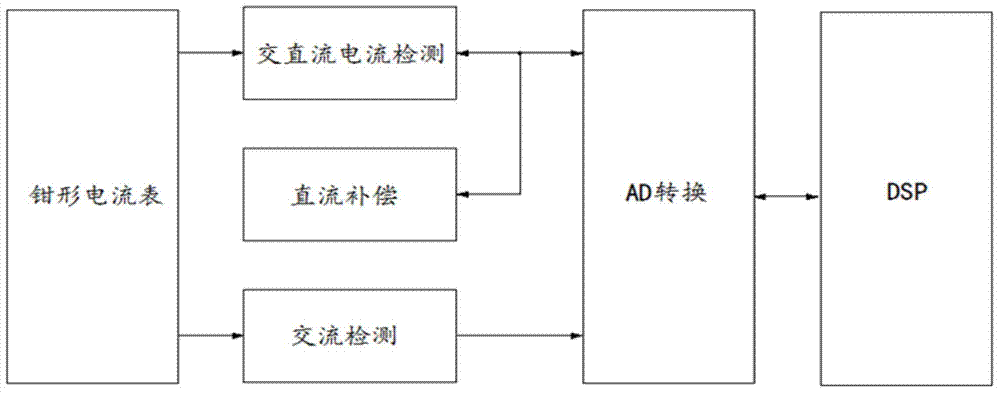

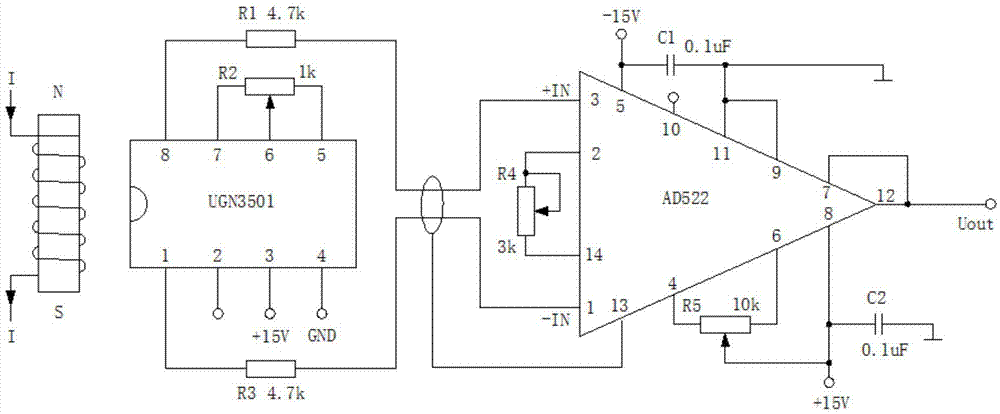

Novel on-site power meter calibration instrument

InactiveCN104749547AHigh measurement accuracySolve practical problems such as measurement differencesElectrical measurementsReal errorMagnetic core

The invention discloses a novel on-site power meter calibration instrument. The novel on-site power meter calibration instrument comprises a tong-type ammeter and a direct-current compensation circuit, wherein an alternating-current / direct-current detection circuit is arranged in the tong-type ammeter and used for detecting alternating current and direct current of the ammeter; the direct-current compensation circuit is used for neutralizing magnetic fluxes generated by direct-current components of the tong-type ammeter. In the calibration instrument, alternating current and direct current passing through the tong-type ammeter are detected by the alternating-current / direct-current detection circuit composed of hall elements; the calibration instrument is driven by the direct-current compensation circuit, and a reverse magnetic flux is injected into the iron core of the tong-type ammeter through compensation coils, so that the magnetic core in the tong-type ammeter cannot be saturated, real errors of a power meter can be accurately measured when the direct-current components are included in loads, the measurement accuracy of the tong-type ammeter is improved, and the actual problem of the measurement difference between an on-site customer power meter and a total measuring meter is solved.

Owner:STATE GRID CORP OF CHINA +1

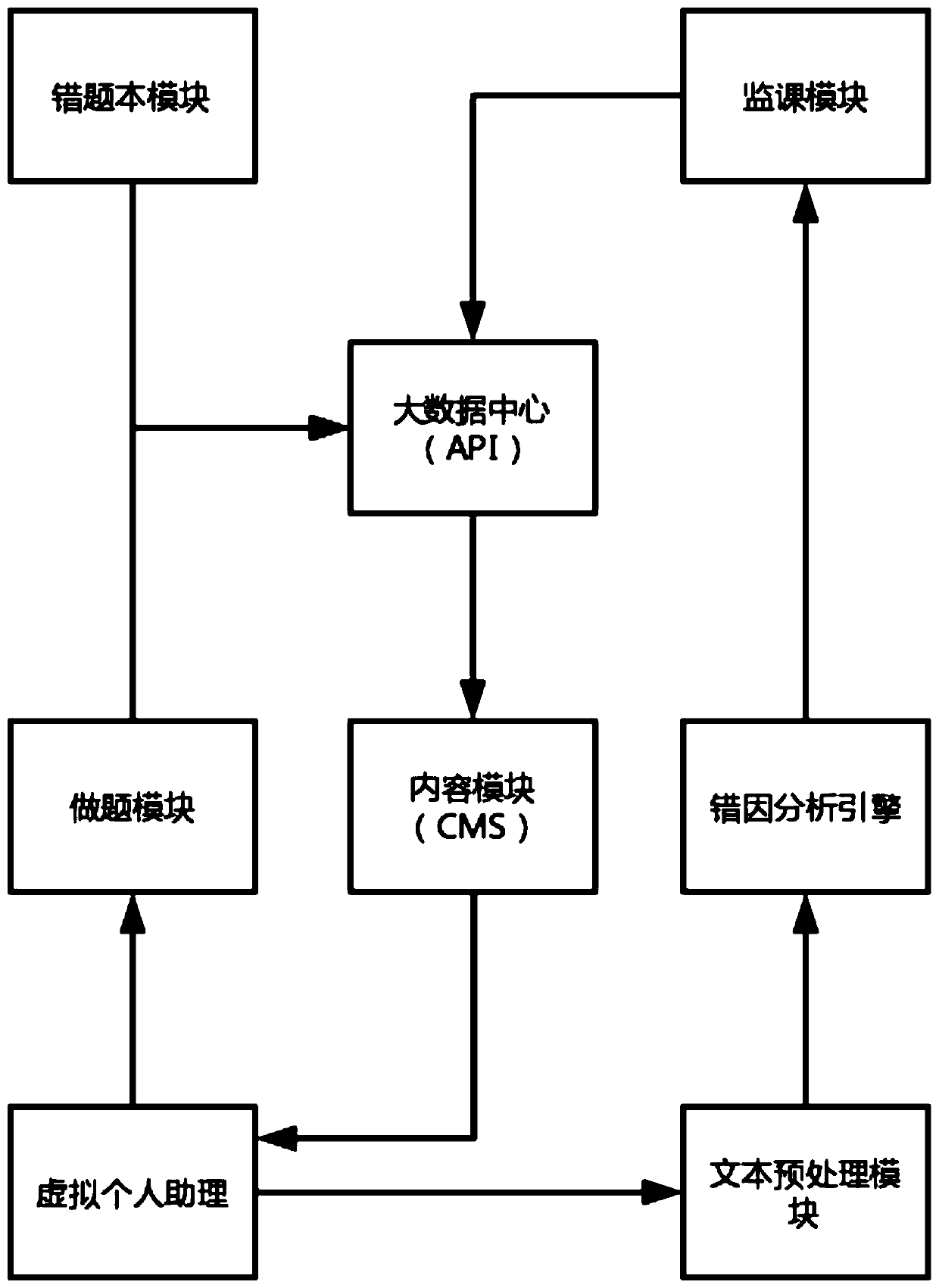

Human-computer interaction system based on error cause analysis

The invention discloses a human-computer interaction system based on error cause analysis. The system comprises an exercise module, an error book module, a class monitoring module, a big data center and an error cause analysis engine. The exercise module is used for collecting first-level error cause data of students for wrong questions and storing the collected first-level error cause data to thebig data center; the error book module is used for collecting secondary error cause data of the students for the errors and storing the collected secondary error cause data to the big data center; the error cause analysis engine is used for generating predicted error cause data of the error problem according to the first-level error cause data and the second-level error cause data of the error; and the course monitoring module is used for calling the predicted error cause data of the error questions under the knowledge points and generating third-level error cause data of the error questionsunder the knowledge points. According to the invention, in the learning process of students, the real error causes of the students can be collected.

Owner:SHANGHAI SQUIRREL CLASSROOM ARTIFICIAL INTELLIGENCE TECH CO LTD

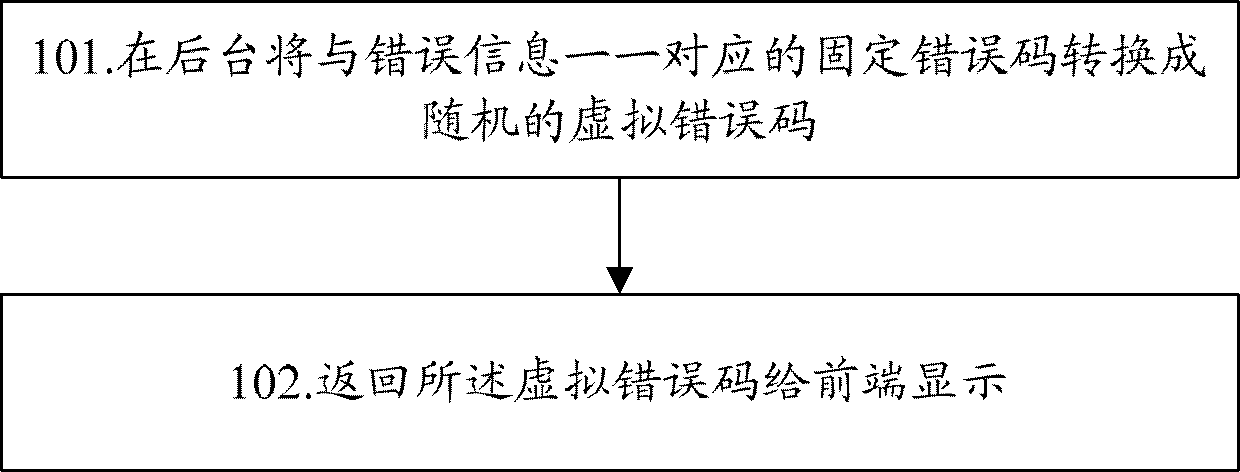

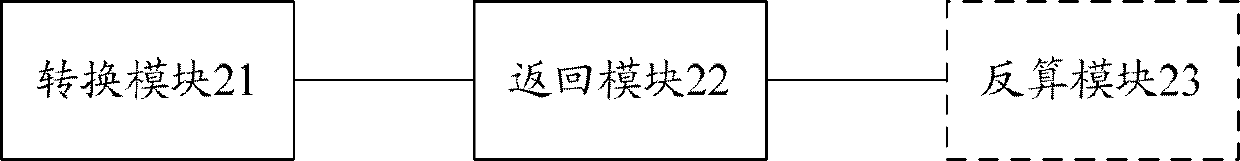

Error code returning method and device

The invention discloses an error code returning method. Fixed error codes which correspond to error information in a one-to-one mode are converted into random virtual error codes at a back-end, and the virtual error codes are returned to be displayed at a front-end. The invention further discloses an error code returning device. By means of the error code returning method and device, the virtual error codes returned for the same error are not necessarily the same, a malicious user is prevented from speculating real error information through multiple times of analyses and speculation on the error codes, and safety performance of operating systems or websites is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

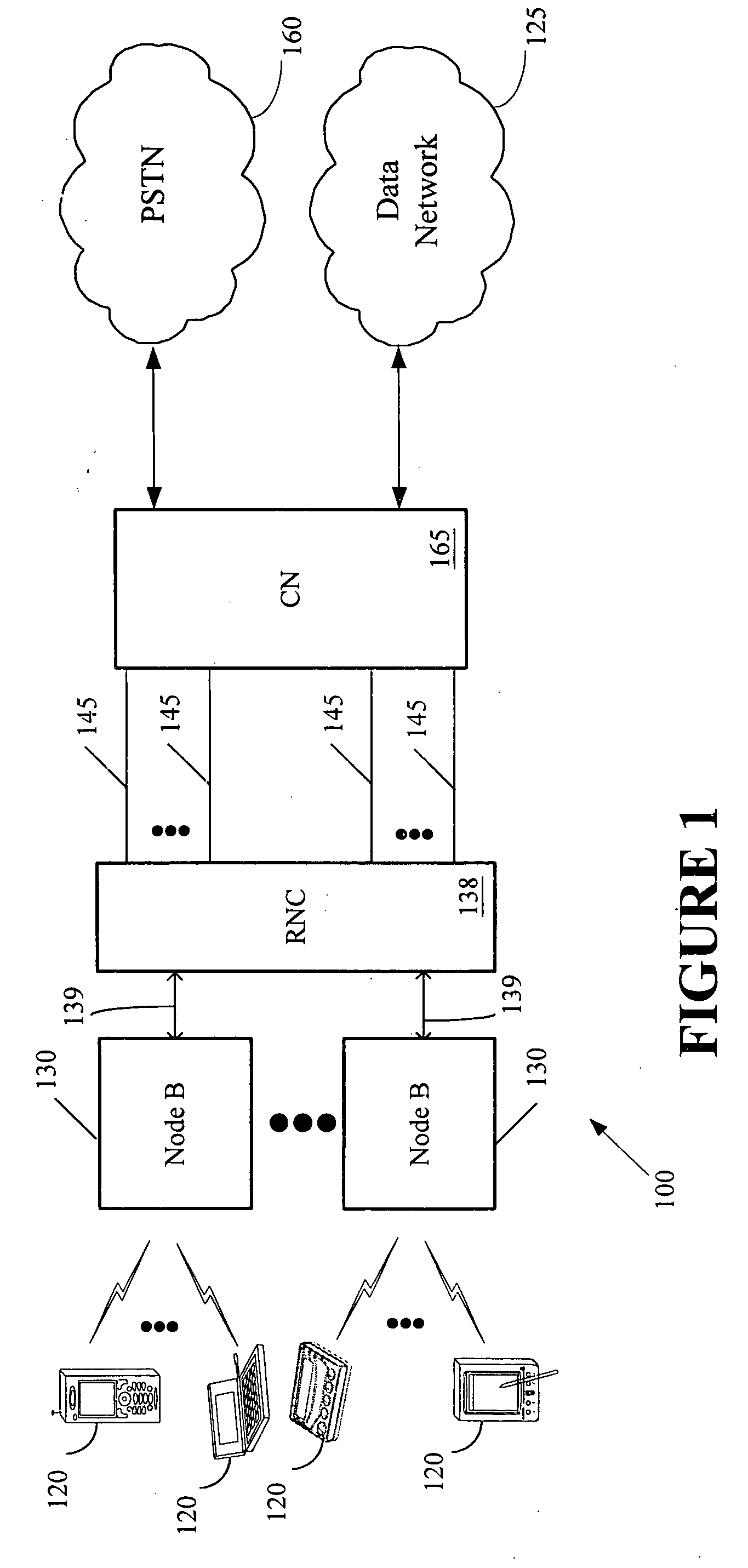

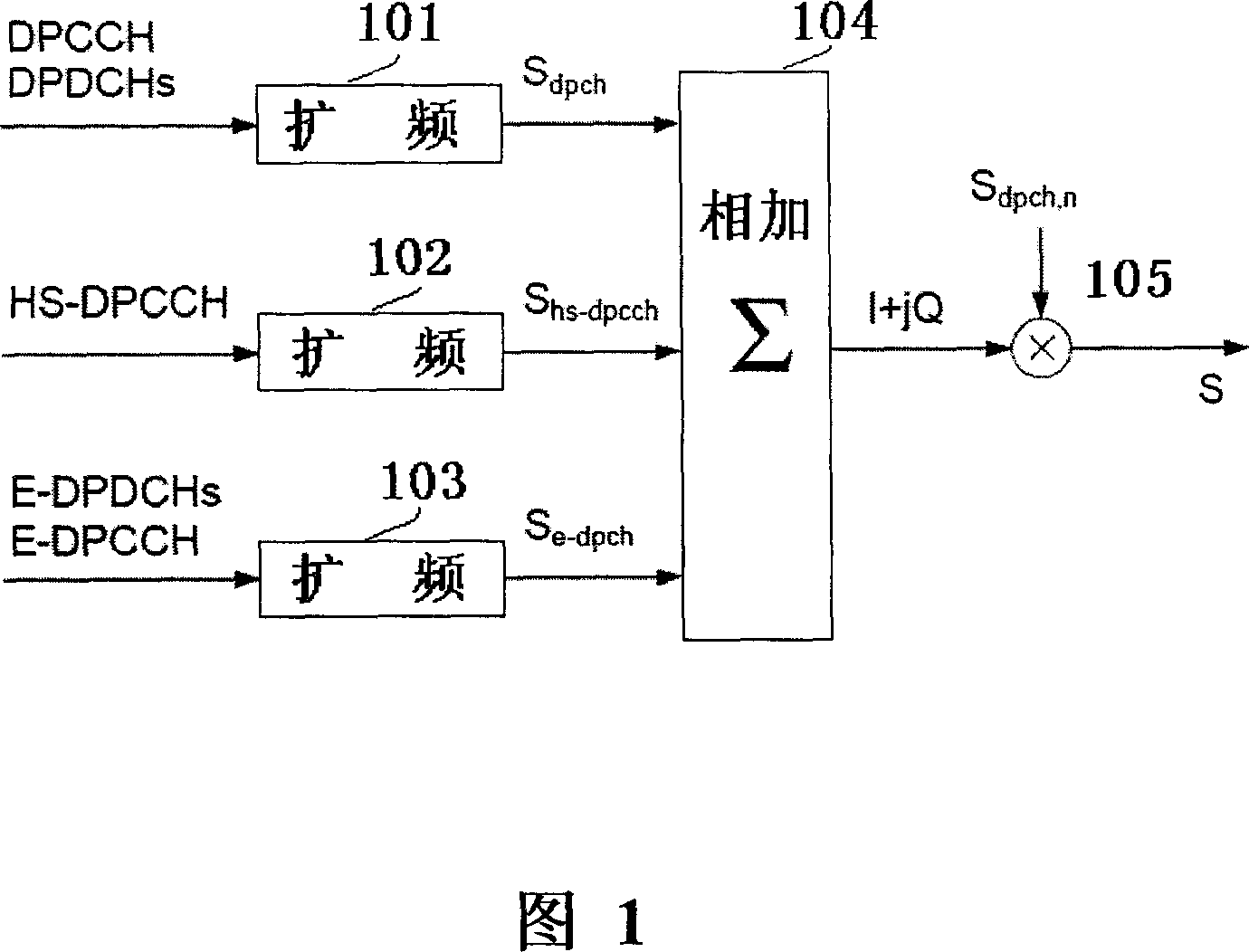

Power control method

ActiveCN1937441AReasonable power controlMeet different preferencesPower managementTransmission control/equalisingComputer scienceService quality

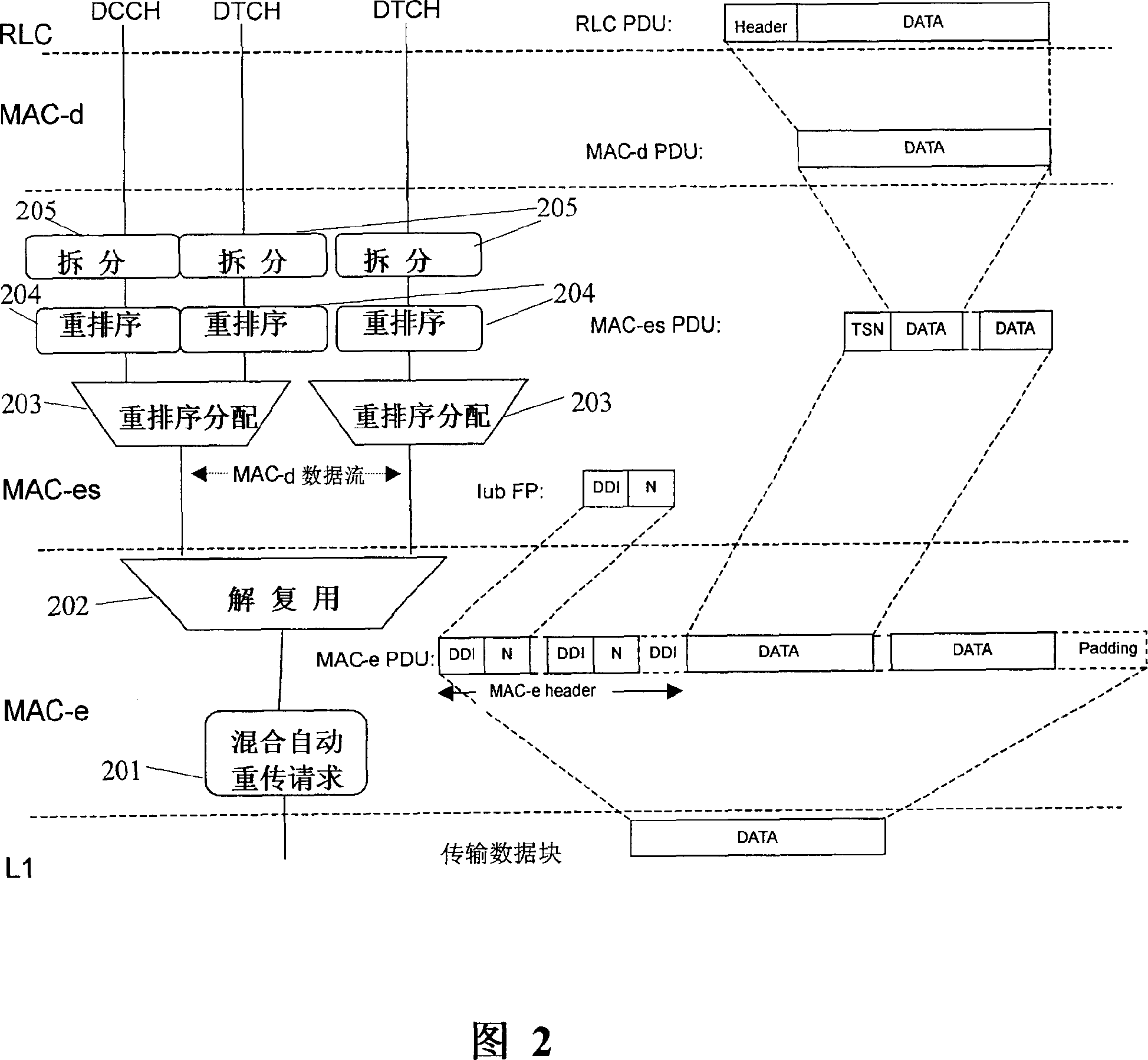

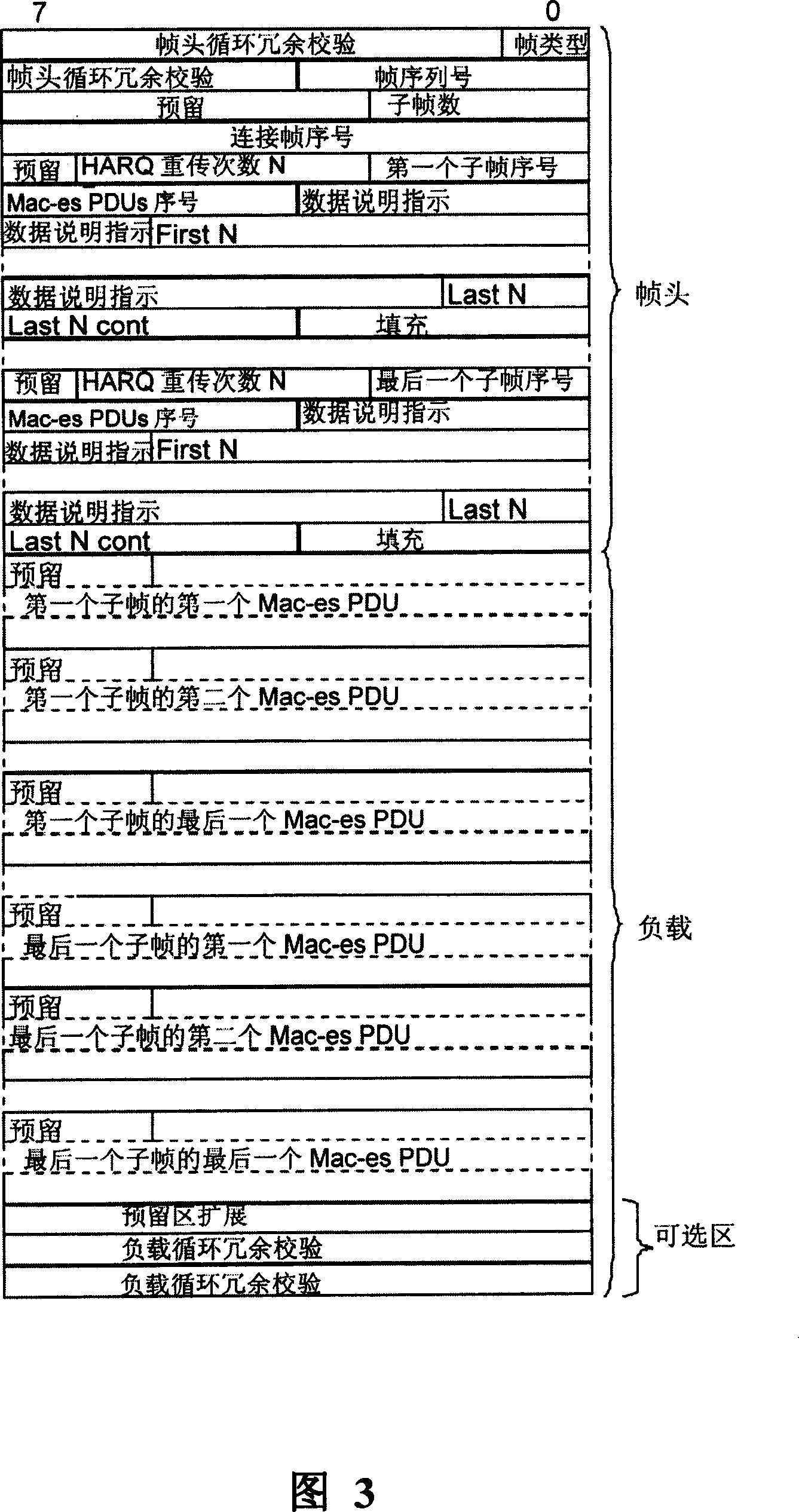

This method realizes power control on the up-going link of WCDMA system of using up-going boosting technique. It collects statistic of the error block ratio (EBT) on DPDCH. According to the aim value of EBT preset by the system, it calculates the signal interference ratio of renewed DPCCH, then according to the calculation result, regulates and controls the emitting power on DPCCH. The method collects statistic of real error block ratio and the number of re-transfer of MAC-d flow on E-DPDCH, calculates the power shift parameter of each MAC-d flow, then according to the calculation result, regulates the emitting power on each MAC-d flow. This power control method is applied on up-going link of WCDMA system of using up-going boosting technique. The invention regulates the emitting power of DPDCH and E-DPDCH periodically to ensure service quality and reduces interference inside the system.

Owner:HUAWEI TECH CO LTD

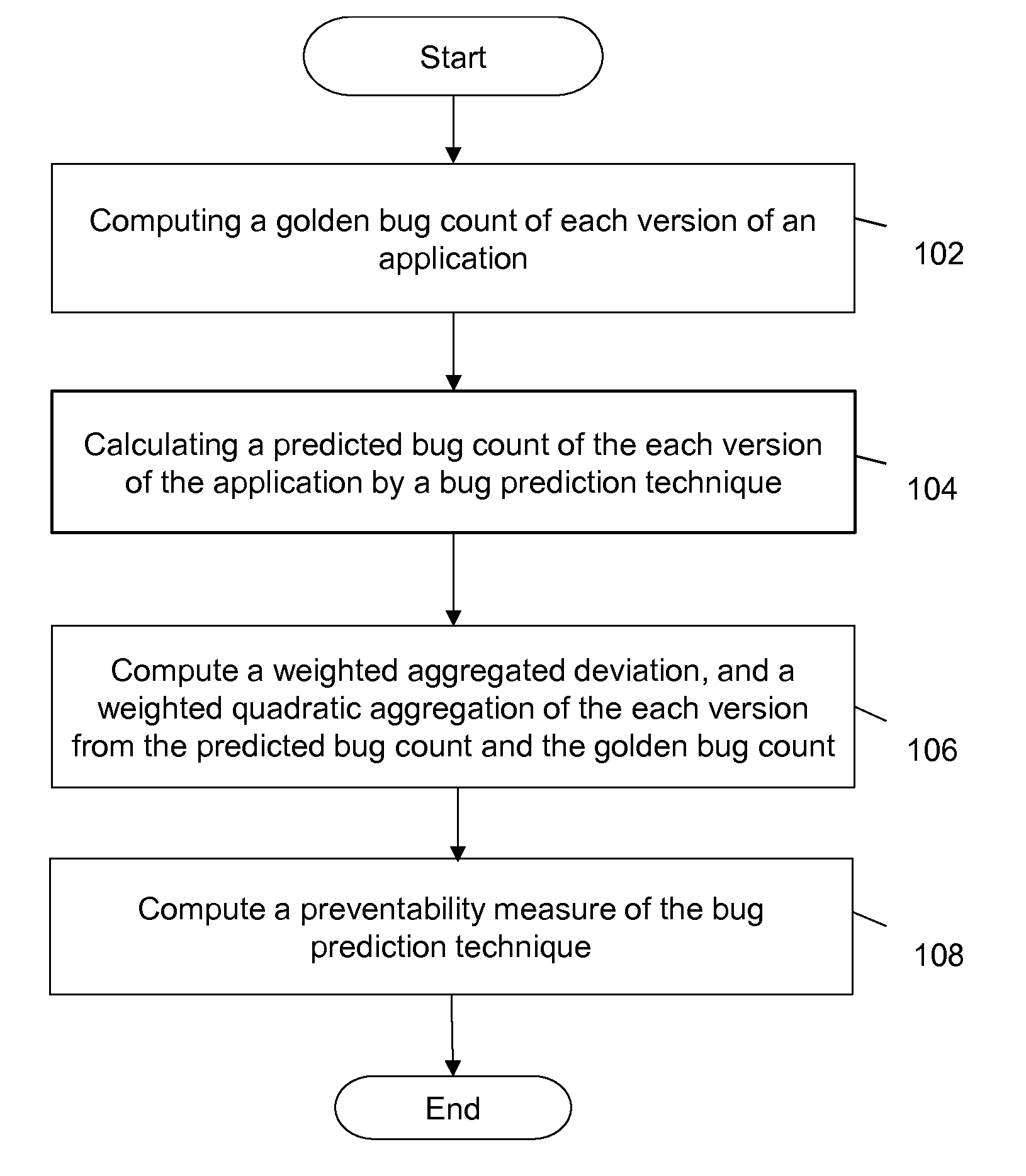

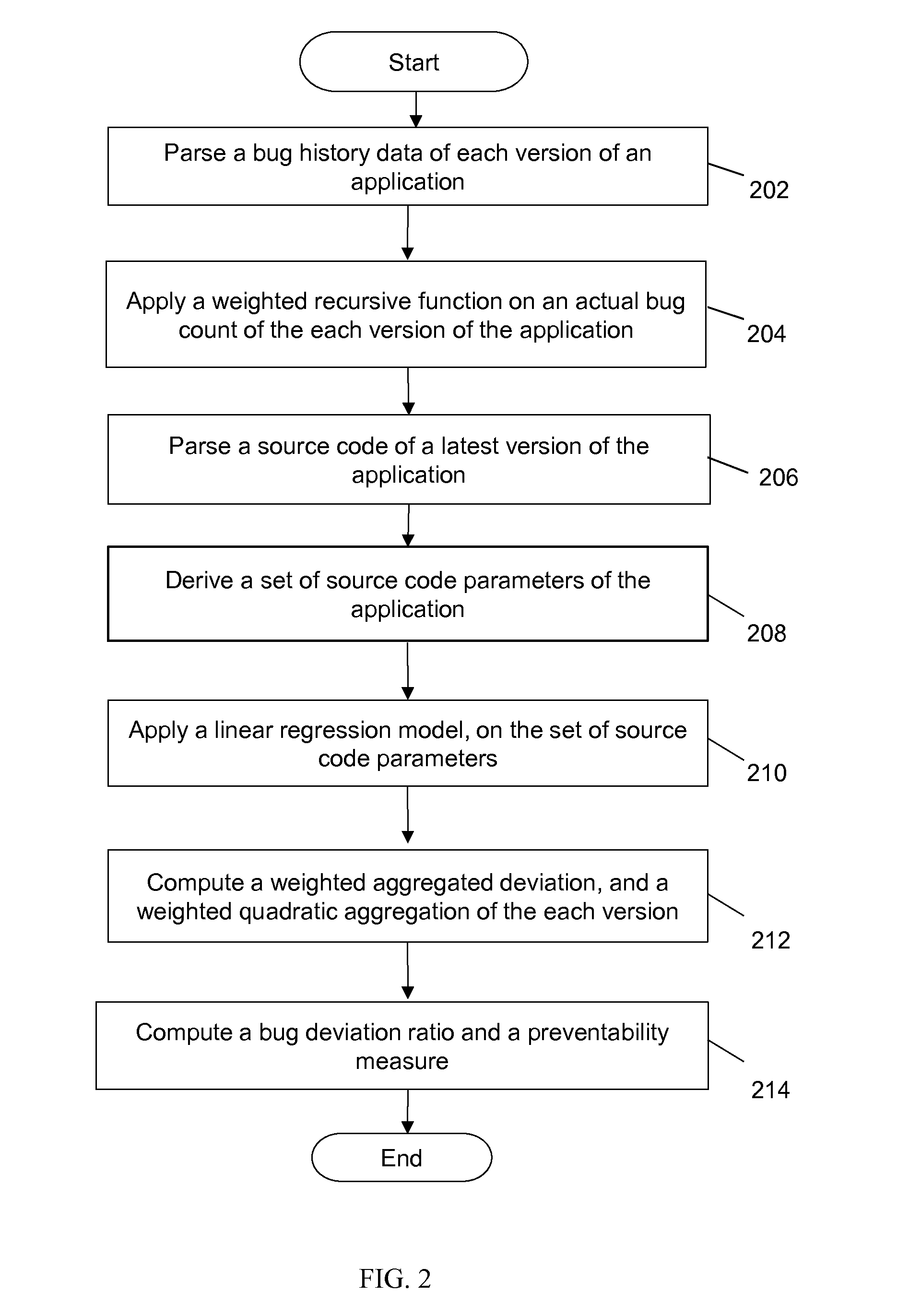

Methods, systems and computer-readable media for quantifying a bug detection efficiency of a bug prediction technique

InactiveUS20150089481A1Version controlSoftware testing/debuggingRecursive functionsLinear regression

The present invention provides a method and system for quantifying a bug preventability measure of a bug prediction technique. In accordance with a disclosed embodiment, the method may include applying a weighted recursive function, on an actual bug count of each version of an application, for computing a golden bug count of the each version. Further, the method shall include deriving a set of source code parameters of the application and applying a linear regression model, on the set of source code parameters of the each version of the application in order to calculate a predicted bug count for the each version. A bug deviation ratio, which shall be indicative the bug preventability measure, can be defined as a ratio of the weighted aggregated deviation and the weighted quadratic aggregation.

Owner:INFOSYS LTD

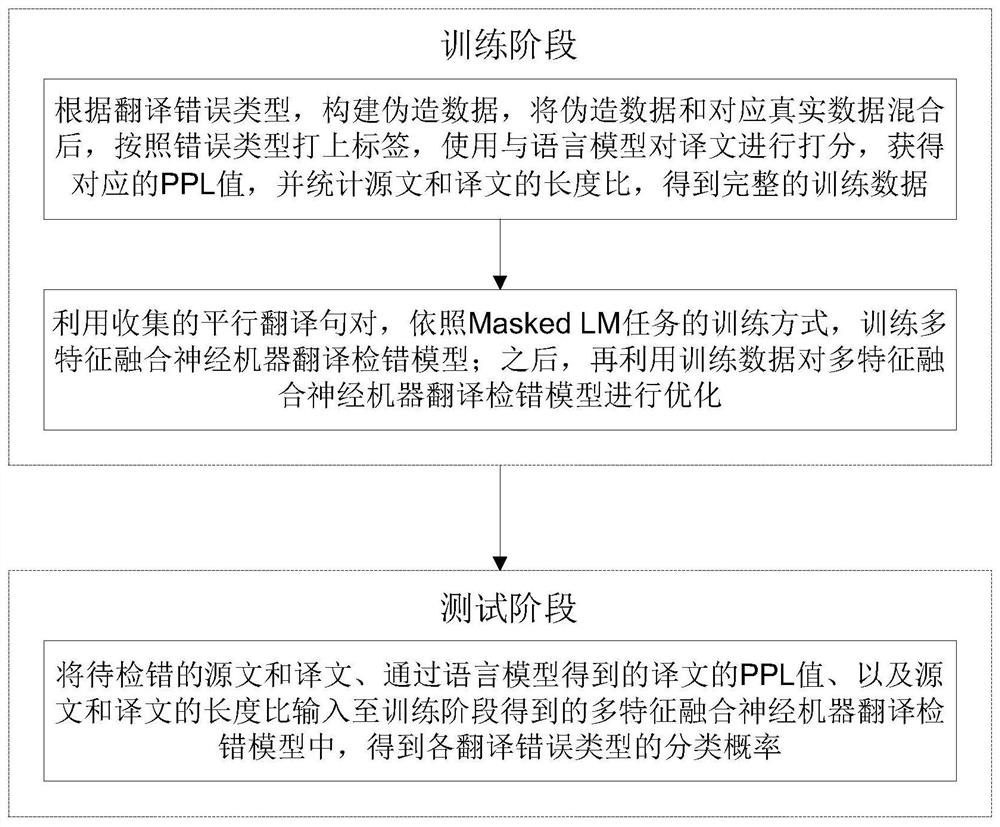

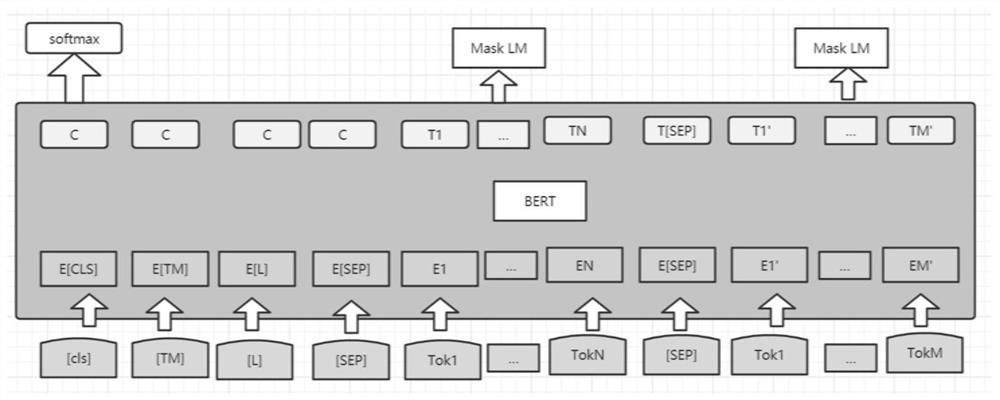

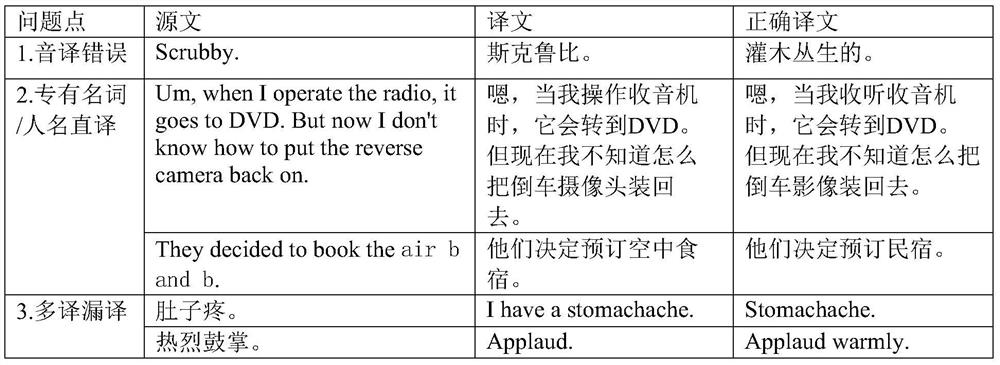

Multi-feature fusion neural machine translation error detection method based on data enhancement training

PendingCN112926345AGood effectImprove robustnessNatural language translationCharacter and pattern recognitionPattern recognitionTranslation language

The invention discloses a multi-feature fusion neural machine translation error detection method based on data enhancement training, which is used for artificially classifying and concluding real error sentences, counterfeiting a large amount of data through a data enhancement method, and enhancing the effect and robustness of a machine translation error detection model. In addition, source text and translation length ratio information and translation language model PPL score feature information are added into model input, so that the classification accuracy of the error detection model is further improved, and based on the error detection scheme, the detection result can be used for subsequent error correction and can also be used for error prompt, and translation user experience is provided; the invention can also be used for evaluation indexes of machine translation effects.

Owner:UNIV OF SCI & TECH OF CHINA

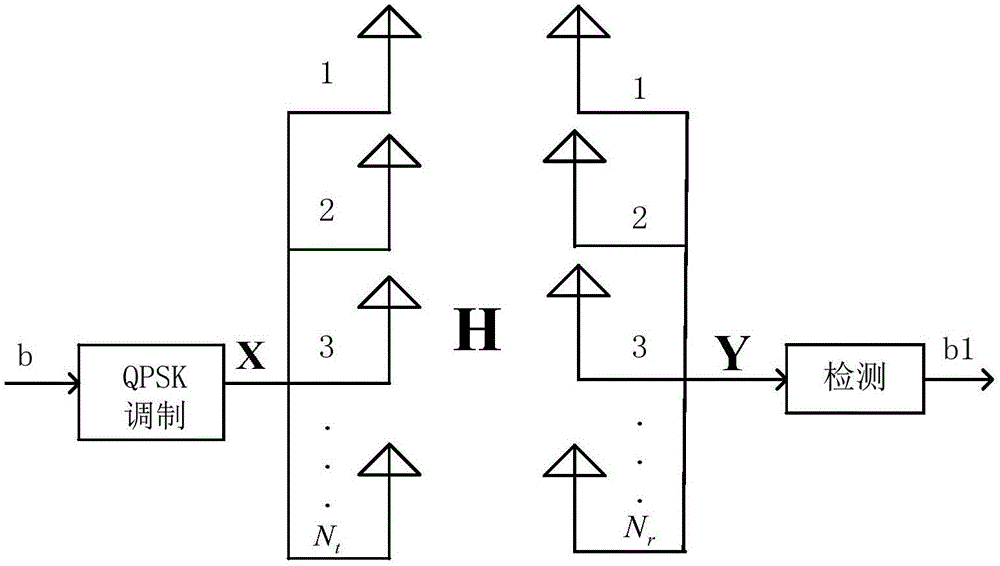

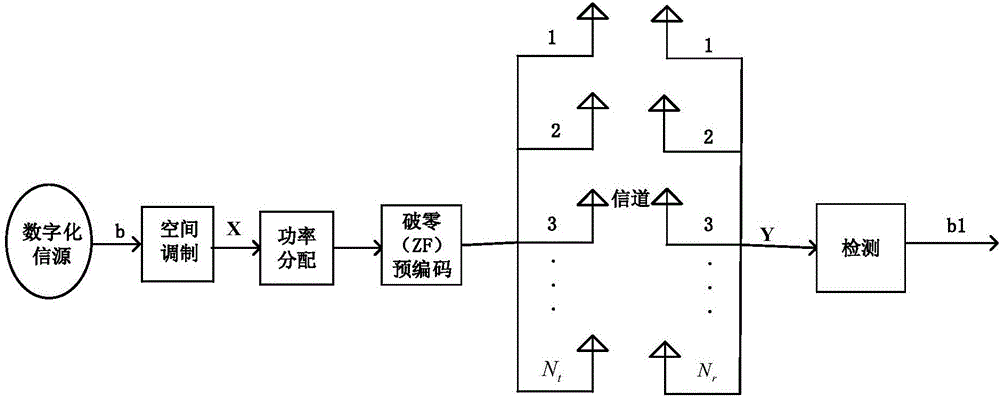

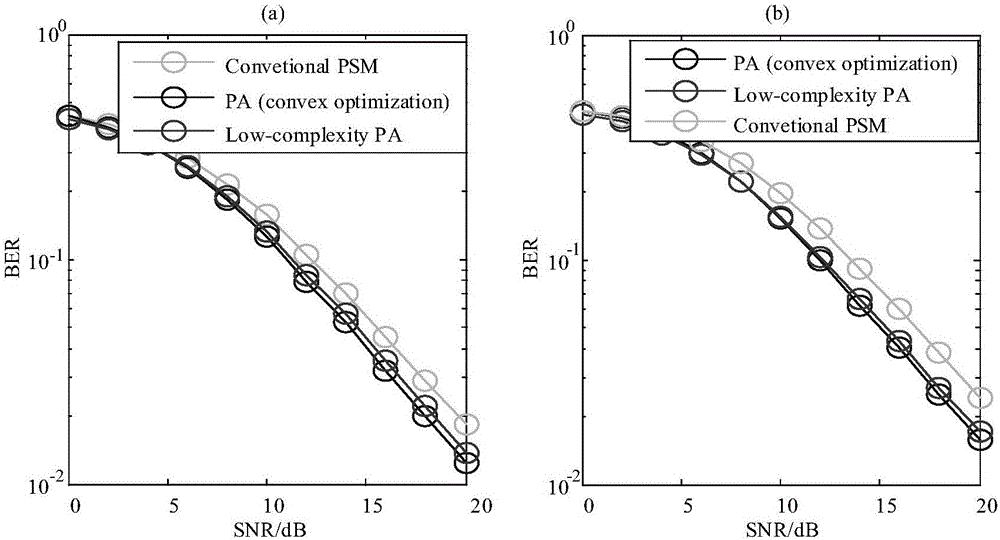

Power allocation method based on reducing upper bound of real error bit probability

ActiveCN106788630AAchieving high BER performance requirementsIncreased complexityRadio transmissionHigh level techniquesPrecodingAnti jamming

The invention belongs to the technical field of communication anti-jamming, and especially relates to an MIMO (Multiple Input Multiple Output) technology, a PSM (Precoding Aided Spatial Modulation) technology and a power allocation technology. The invention provides a power allocation method based on reducing an upper bound of the real error bit probability. The invention proposes an optimal adaptive power allocation algorithm based on convex optimization in view of the relatively poor bit error rate performance of a PSM-MIMO system when the channel condition is bad; and proposes a power allocation algorithm with low complexity and approaching the bit error rate performance of the optimal power allocation algorithm aiming at the problem that the first power allocation algorithm based on the convex optimization is higher in computational complexity.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

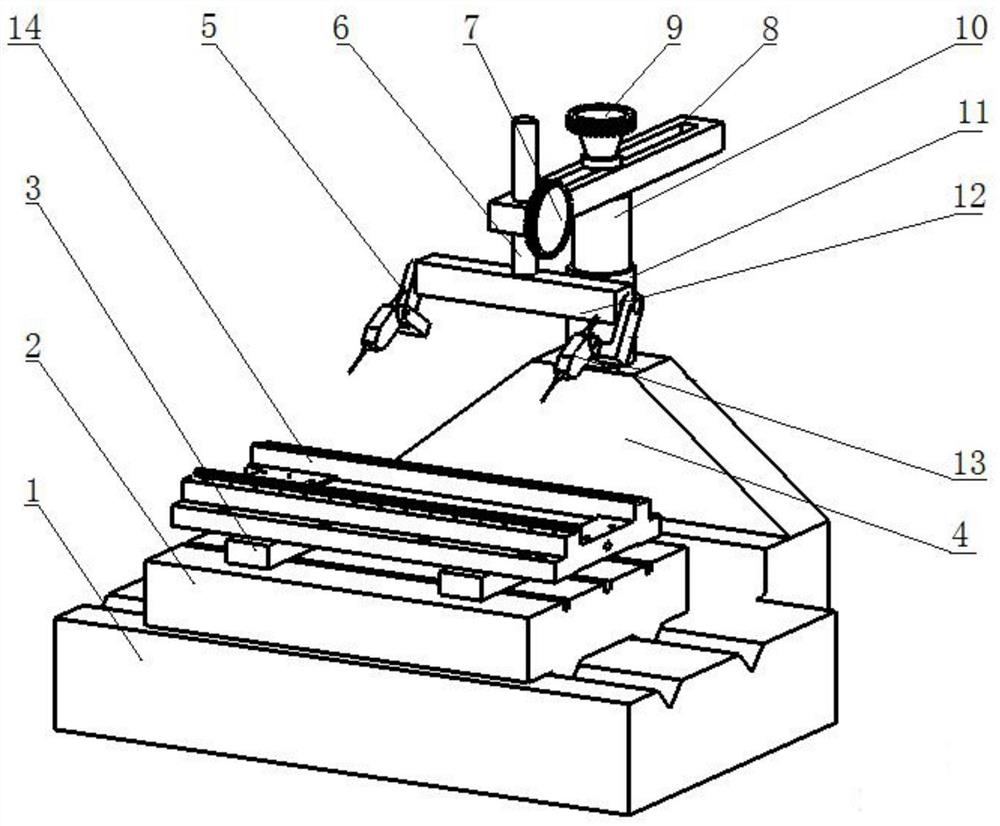

Device and method for geometric accuracy measurement and error compensation of dicing saw

ActiveCN112325816AMeet cutting needsClarify the error situationMeasurement devicesMicrometerControl engineering

The invention relates to a grinding wheel dicing saw, and particularly provides a device and a method for geometric accuracy measurement and error compensation of a dicing saw. The device comprises agrinding base, a moving platform, a cushion block, a supporting frame, a connecting arm, a lifting rod, a lifting fixed wheel, a front cantilever, a rear cantilever, a cantilever pressing wheel, a lifting guide column, a fixed guide sleeve, a horizontal connecting arm and an electronic micrometer. The precision of the base can be measured and verified, a clearer and more real error condition is displayed according to a measurement result, and local tiny errors are eliminated through manual grinding operation. And finally, a minimum error range is reached, and an error measurement structure isrecorded and ordered, and an actual error condition is simulated by using a nurbs curve principle, and the actual error condition is compensated by using software. Therefore, the highest reference precision is achieved, and the cutting requirement of the high-precision industry is met.

Owner:沈阳和研科技股份有限公司

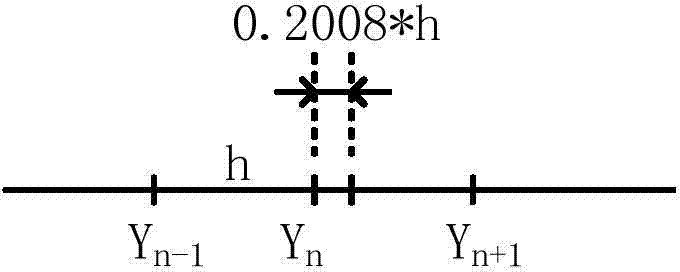

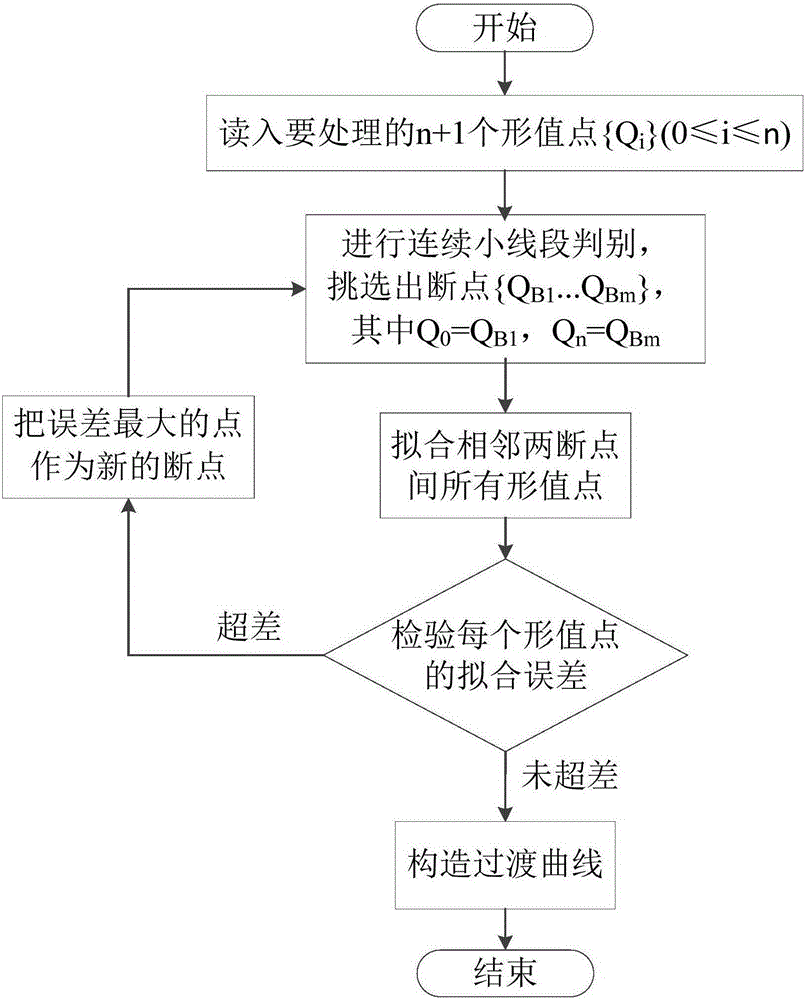

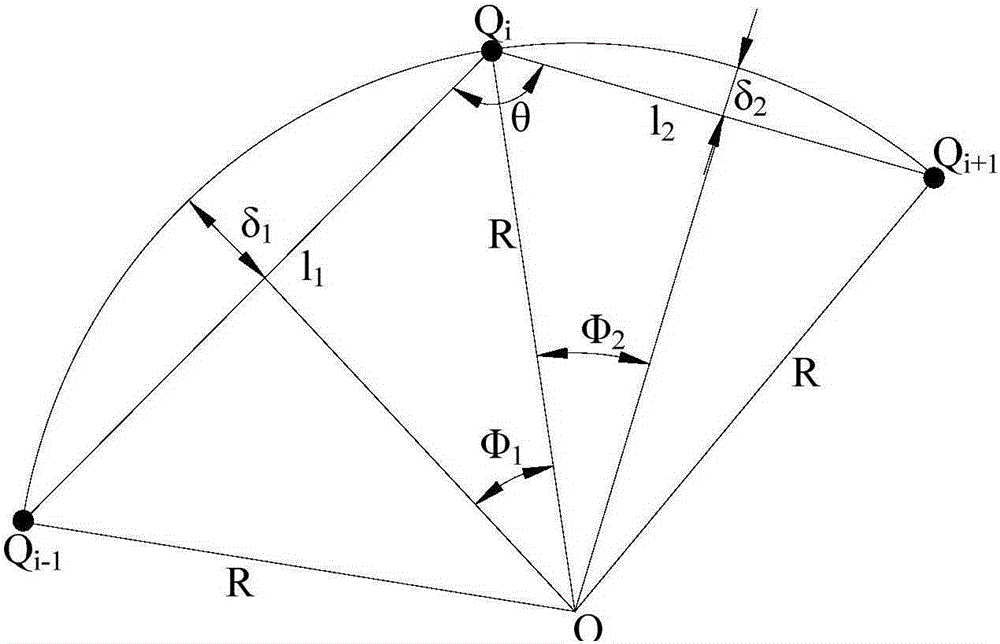

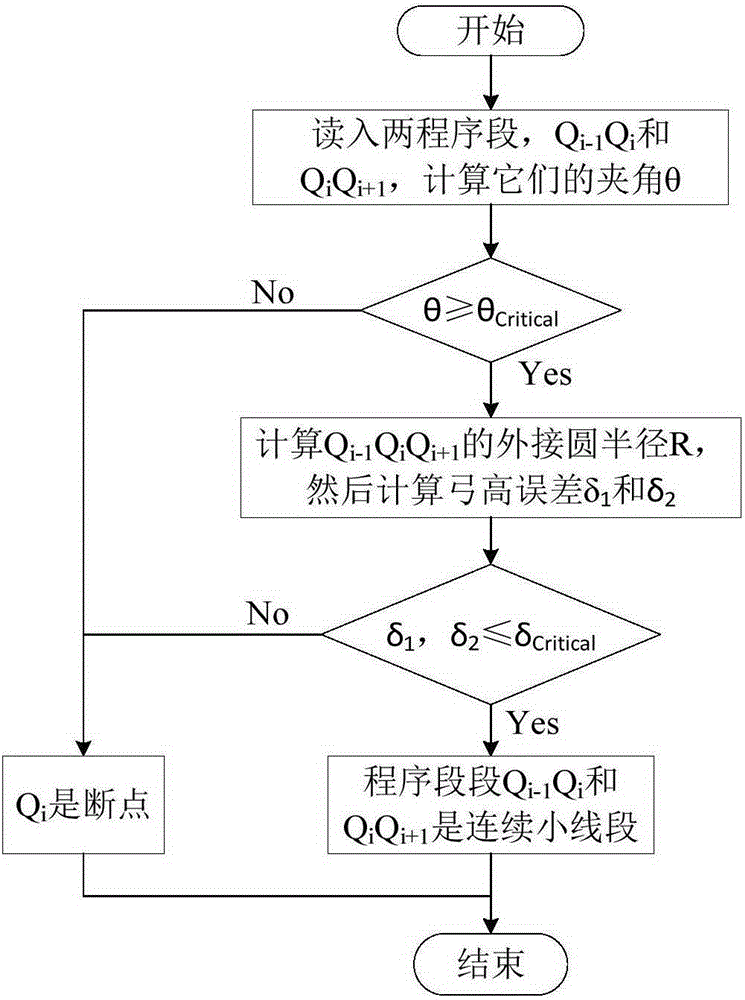

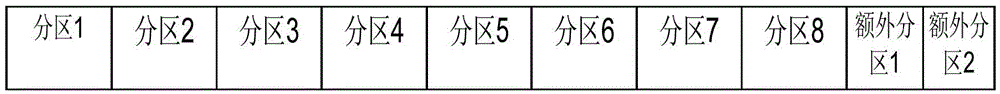

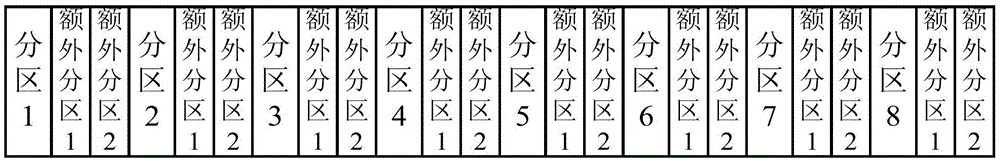

Tool path compression method based on g2 continuous bézier curve

ActiveCN103631198BImprove data compression ratioAlgorithm iterationNumerical controlNumerical controlData compression

The invention provides a gutter track compression method based on a G2 continuous Bezier curve. The method comprises the following steps of a continuous small-line-segment screening step: regions to be compressed are determined through the continuous small-line-segment screening step; a fitting step: shape value points in each region are fit into a three-order Bezier curve through the fitting step; an error estimation step: the error estimation step is adopted for controlling the precision during the fitting step execution; a transition fairing step: a G2 continuous firing processing path is generated through the transition fairing step. The gutter track compression method has the advantages that the linear cutter path in the numerical control processing code can be compressed into the G2 continuous Bezier curve, each section of Bezier curve only comprises one curvature extreme value point, the data compression rate is high, the whole algorithm does not have the iteration, the real-time performance is good, the estimated error is very similar to the real error, the fitting precision can be effectively controlled, and the method can be applied to the high-speed and high-precision numerical control processing.

Owner:SHANGHAI JIAO TONG UNIV

Method for scanning error bits

ActiveCN105607961AAverage number of error bitsOptimize write performanceRedundant data error correctionReal errorStorage cell

The invention discloses a method for scanning error bits. The method comprises the following steps: S1, averagely dividing a first data partition of a storage unit into N equal second data partitions; S2, forming a third data partition by using the second data partitions, scanning the third data partition and setting the permissible number of the error bits; S3, comparing the actual number of the error bits of the third data partition with the permissible number of the error bits, if the actual number of the error bits is greater than the permissible number of the error bits, executing step 4, if not, executing step 5; S4, carrying out one-time programming operation on the storage unit and returning to carry out the step S3; and S5, recording the current actual number of the error bits of the third data partition. According to the method, the qualification rate of storage chips can be adjusted through modifying the setting conditions; the corresponding data region and the error correcting capability of the own ECC (Error Correction Code) of a controller can be adjusted on the basis of final statistical results; and therefore, a better write performance is obtained.

Owner:GIGADEVICE SEMICON (BEIJING) INC

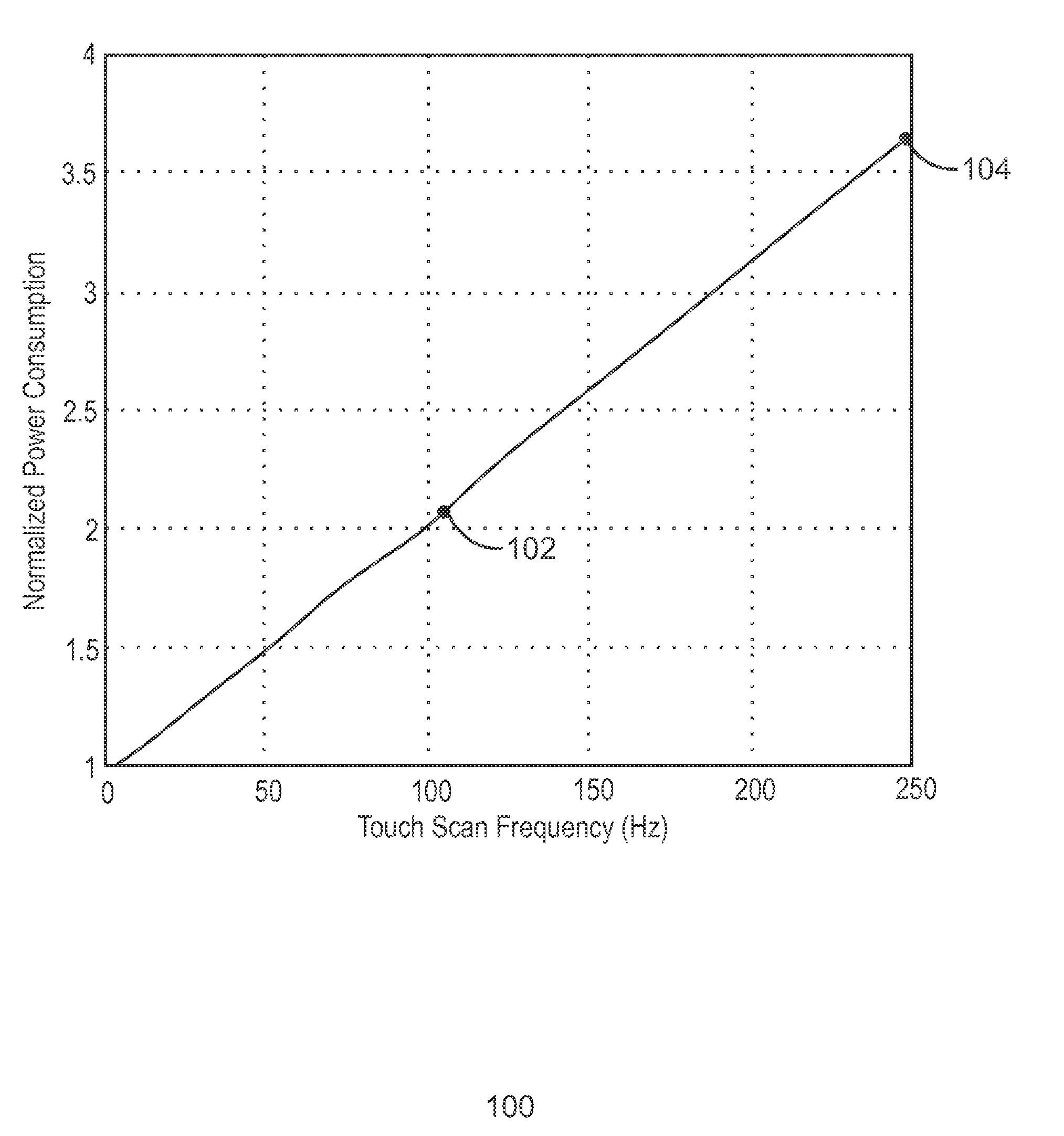

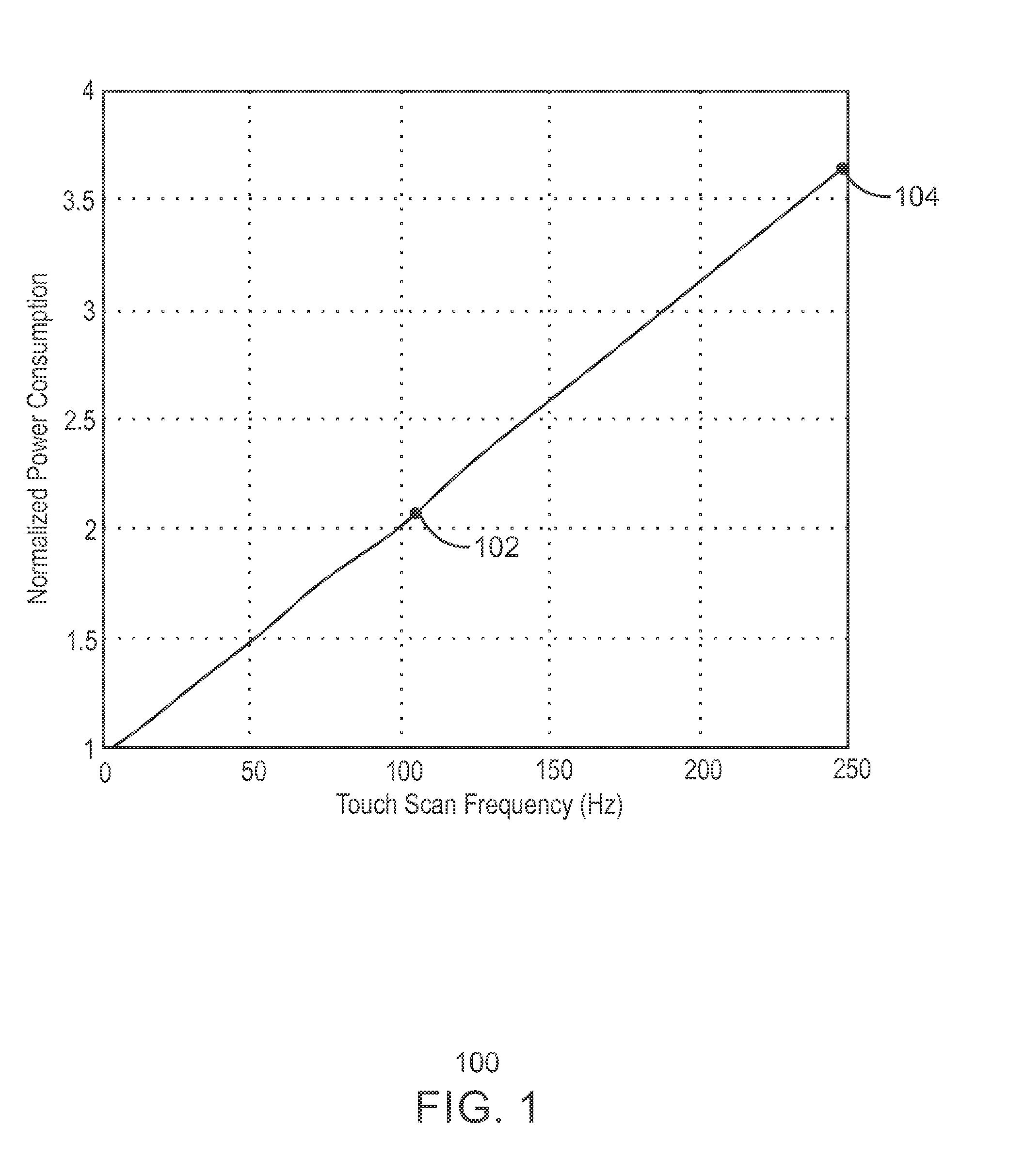

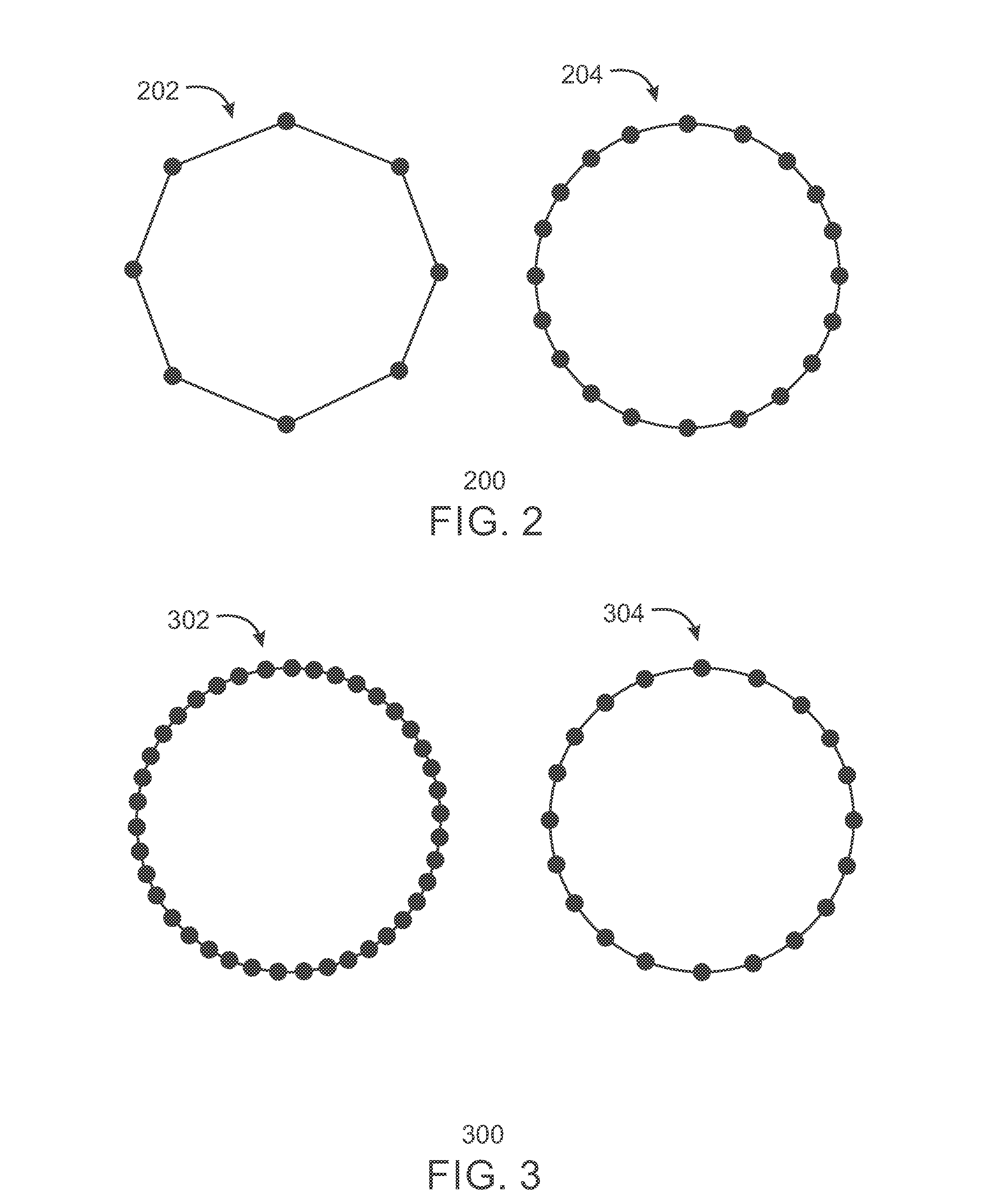

Adaptive touch scanning

ActiveUS20150084872A1Digital data processing detailsInput/output processes for data processingSimulationErrors and residuals

An apparatus, touch controller, and system for adaptive touch scanning is described herein. The apparatus includes logic to calculate a distance traveled between two consecutive touch samples, and logic to compare the distance traveled with a target distance to find an actual error. The apparatus also includes logic to update the scan rate based on the actual error.

Owner:INTEL CORP

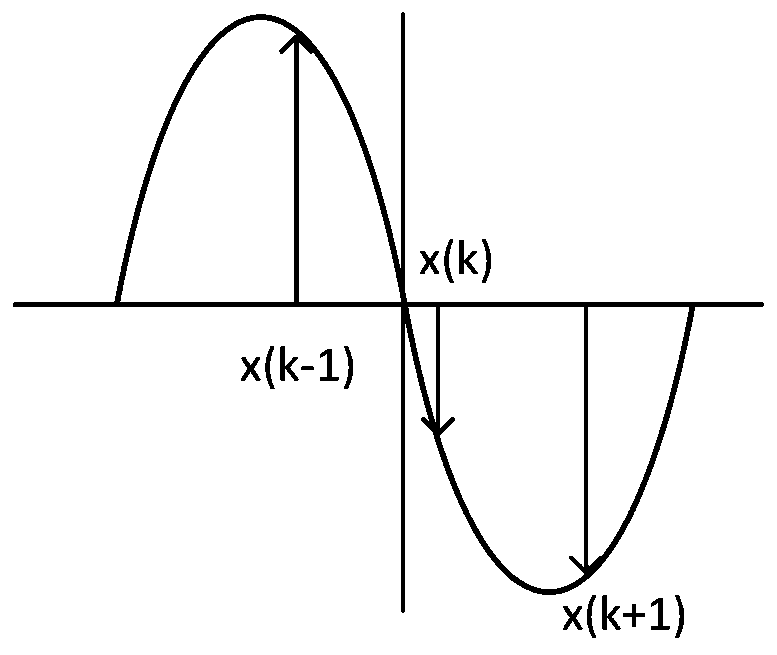

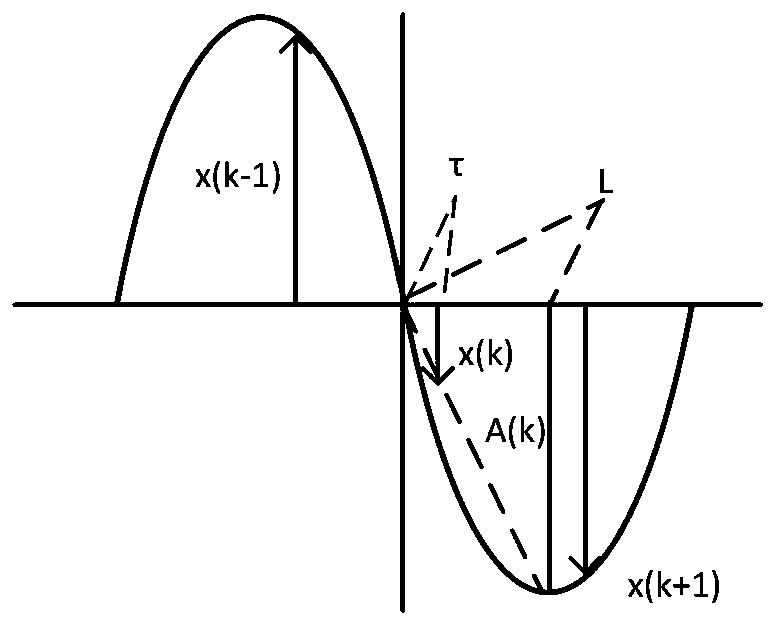

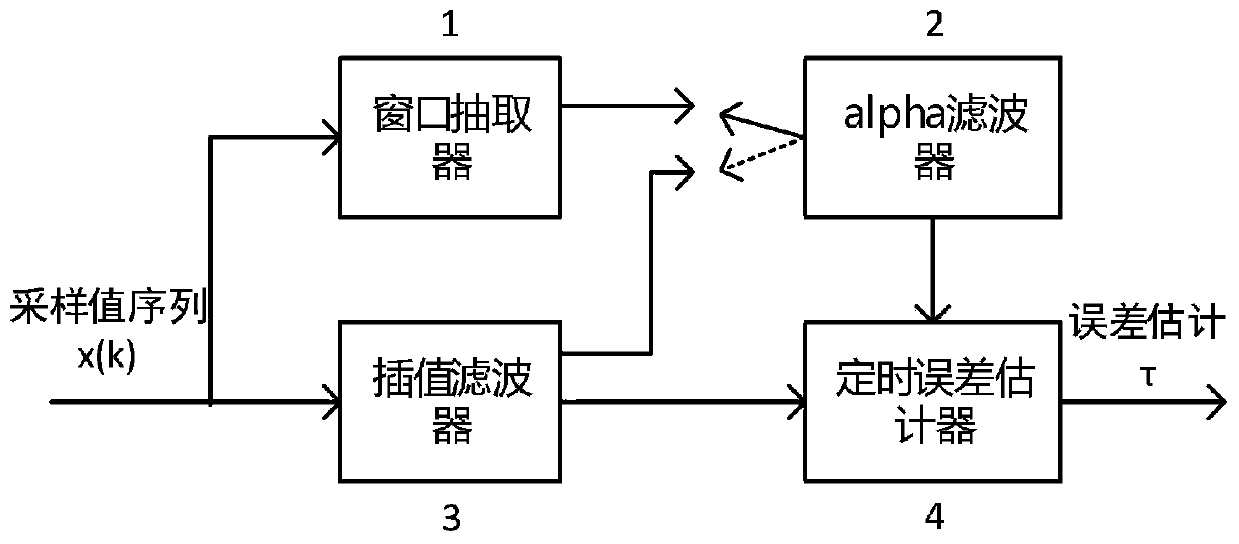

A simple self-adaptive improvement method of a timing error discriminator

ActiveCN109787653AImprove robustnessHigh feasibilityTransmissionDiscriminatorUltimate tensile strength

The invention provides a simple self-adaptive improvement method of a timing error discriminator, which is characterized by comprising the following steps of: (1) a loop convergence stage; Step (2), aloop stable tracking stage: the robustness of the loop to the signal intensity change is enhanced by utilizing simple normalization processing, and meanwhile, the direct estimation of a real error isalso obtained; And the treatment is simple, so that the method has very high feasibility in engineering practice.

Owner:SHANGHAI HUACE NAVIGATION TECH

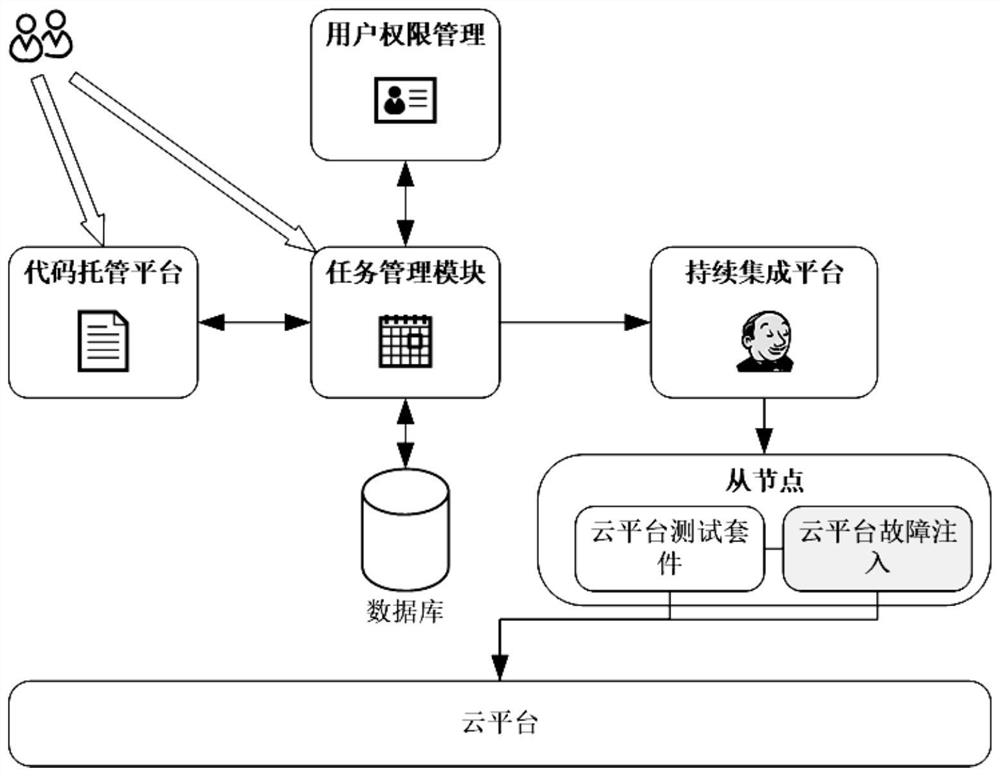

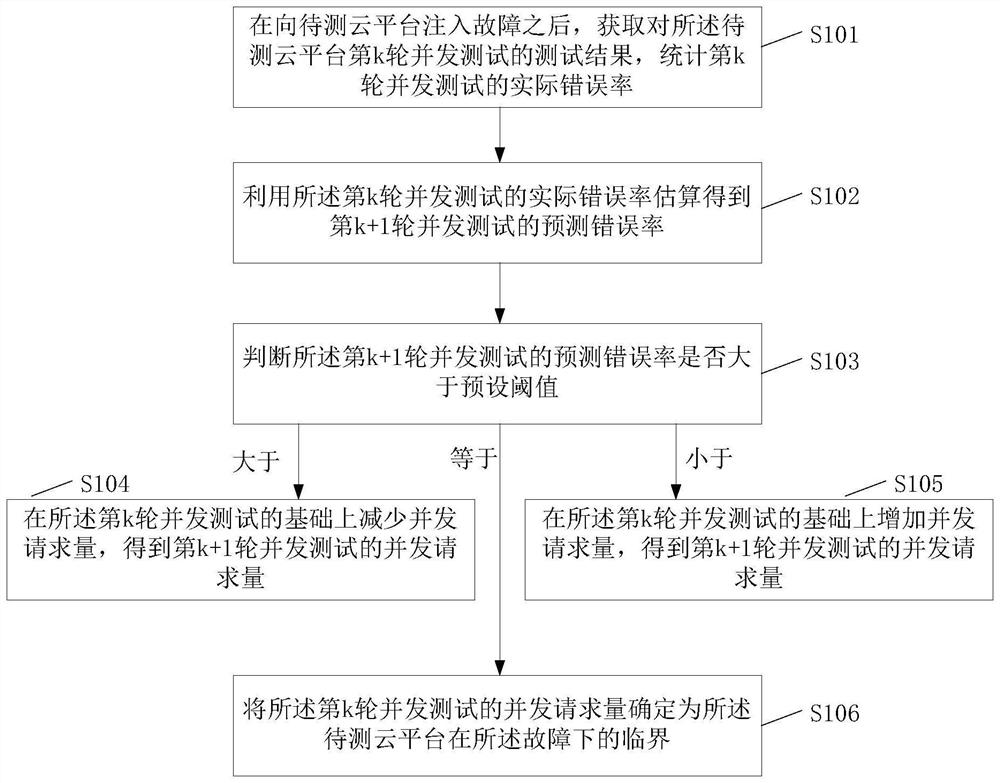

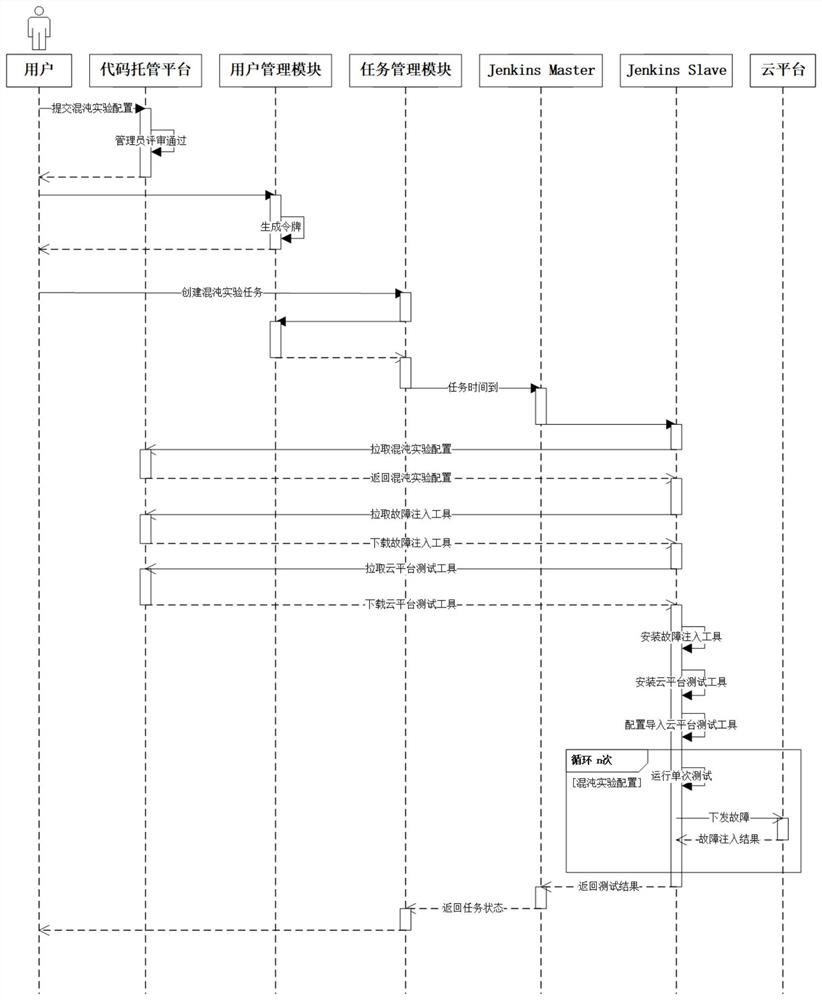

Cloud platform chaos test method and device

PendingCN114500349AIdentify performance degradationImprove assessment accuracyTransmissionEnergy efficient computingReal errorSelf adaptive

Owner:CHINA TELECOM CLOUD TECH CO LTD

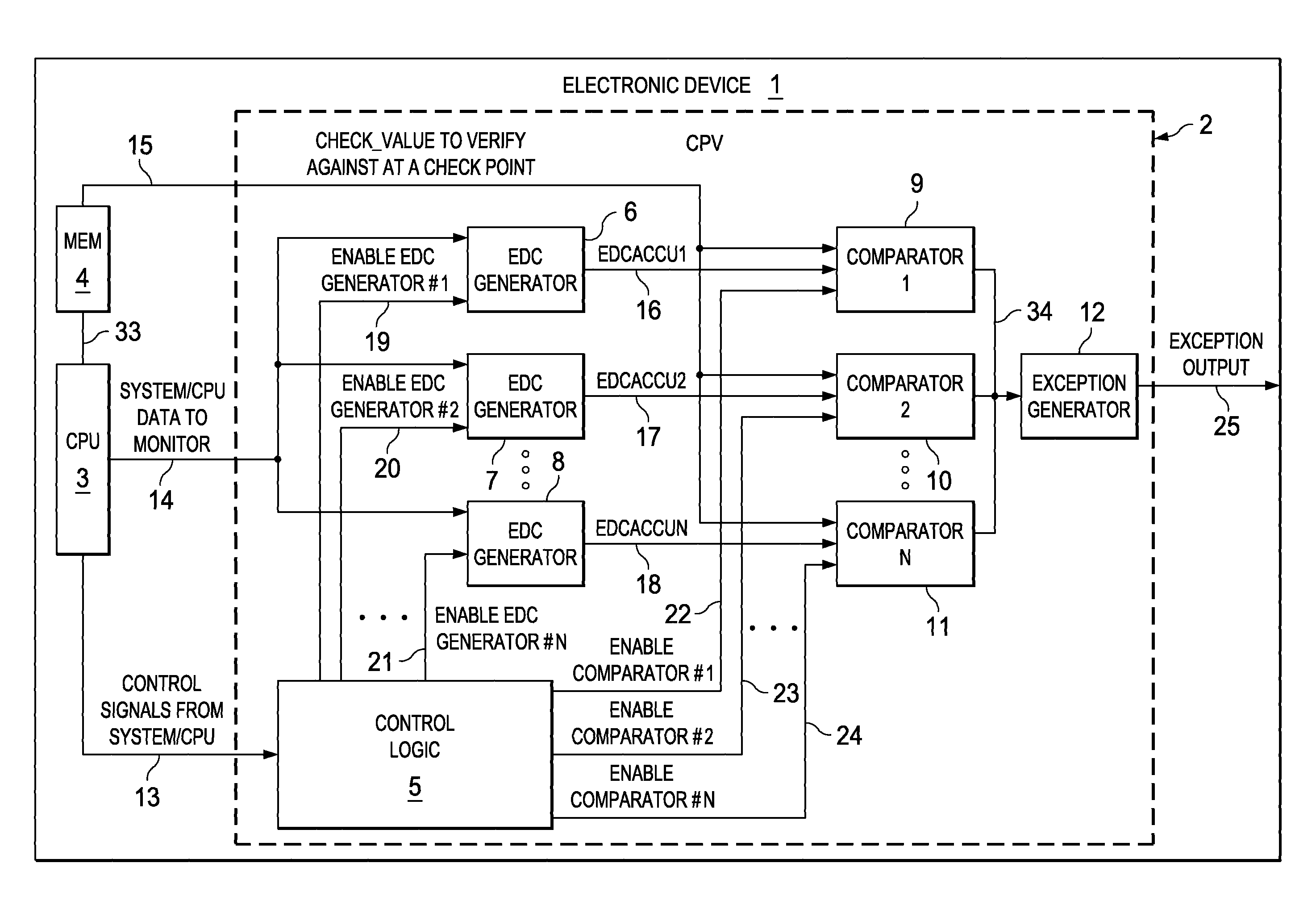

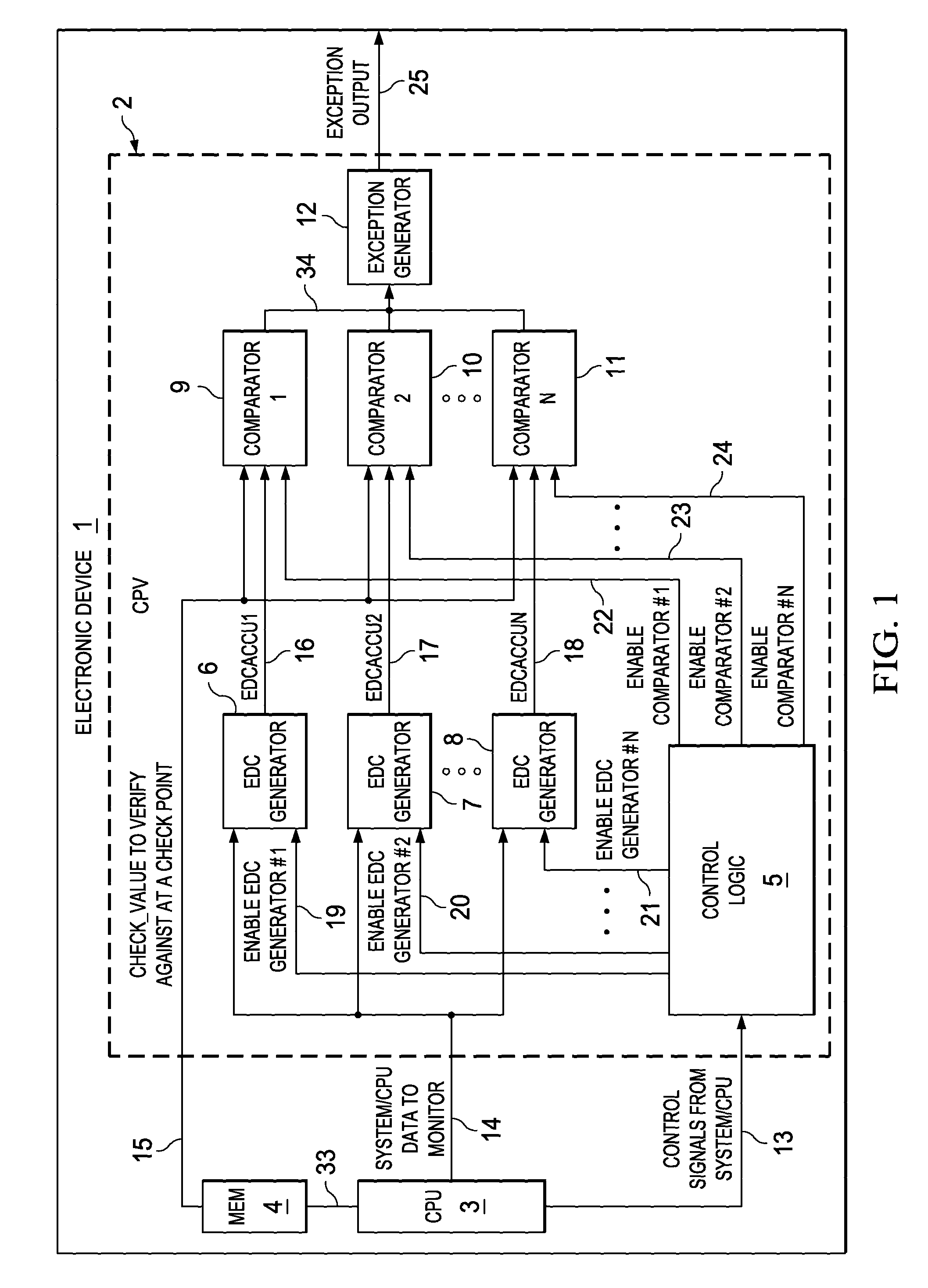

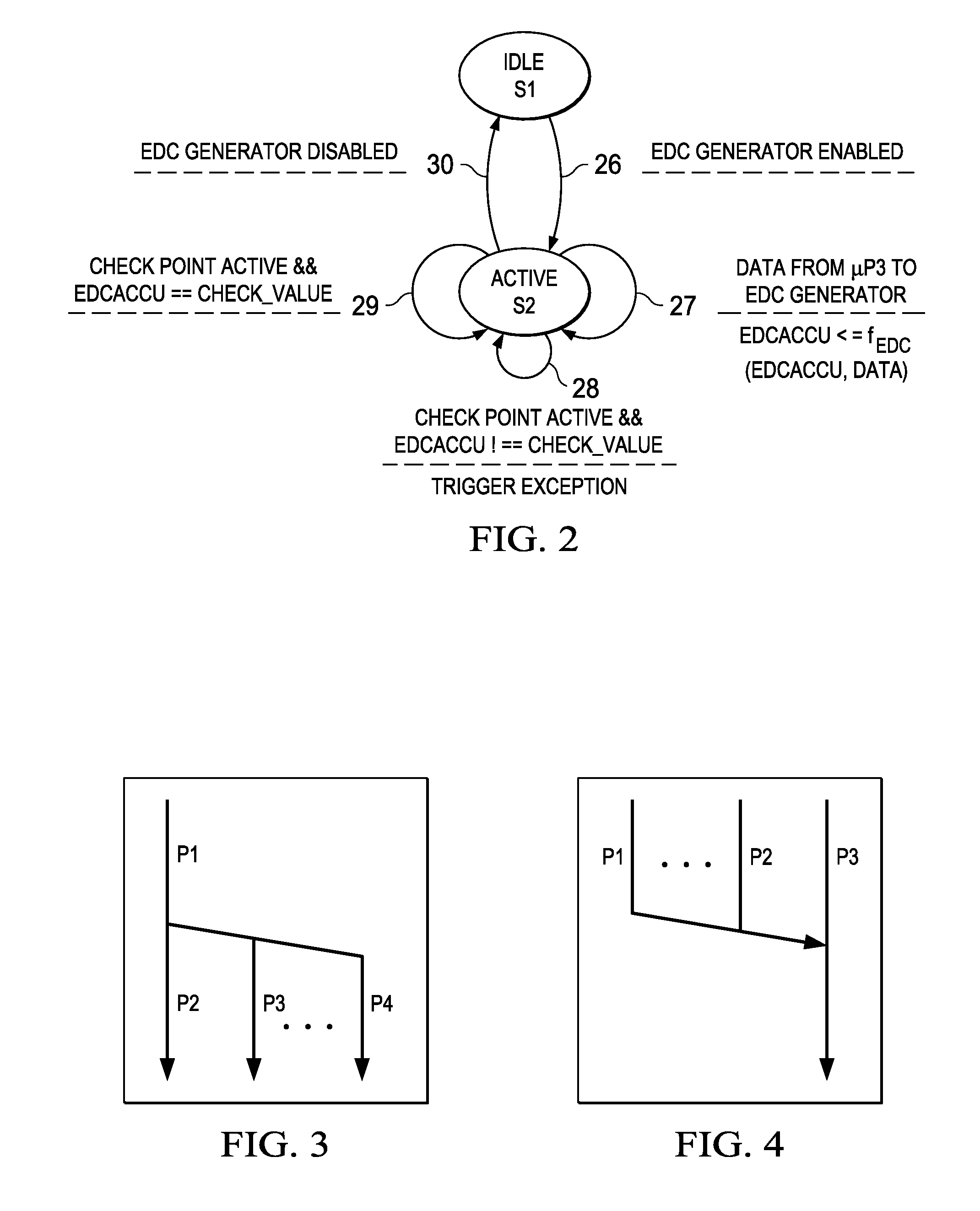

Electronic device and method for verifying correct program execution

ActiveUS8892943B2Fine granularityConsume additional data processing timeRedundant data error correctionError detection codeProgram code

An electronic device is provided which comprises a microprocessor for executing a program code and a first hardware code path verifying (CPV) stage coupled to the microprocessor. The hardware CPV stage comprises a first error detection code (EDC) generator configured to continuously determine an error detection code on a continuous sequence of code relating to an actually executed portion of the program code and to compare the actual error detection code with a predetermined error code so as to verify correct execution of the program code and to indicate an error.

Owner:TEXAS INSTR INC

Strapdown inertial/satellite integrated navigation detection system and its simulation test method

ActiveCN103308073BWith true error propertiesImplement hardware-in-the-loop testingSatellite radio beaconingClosed loopNavigation system

The invention relates to a strapdown inertial / satellite integrated navigation detecting system and a simulation testing method thereof. The system comprises a strapdown inertial subsystem, a satellite navigation subsystem, a navigation module and a control and display module, wherein the control and display module is connected with the strapdown inertial subsystem and the satellite navigation subsystem respectively to transmit track information; the strapdown inertial subsystem and the satellite navigation subsystem are respectively connected with the navigation module to transmit angular speed, accelerated speed and satellite signals; the output end of the navigation module is connected with the control and display module to feed an integrated navigation result back to the control and display module to form a closed-loop system. The system has real error characteristics. According to the system, optional tracks can be generated and do not need to be carried by actual carriers, so that the research and development cycle of an integrated navigation system is shortened, and the research and development cost is reduced; the real-time dynamic simulation on carrier movement according to a preset track can be realized and finished, and the universality is very strong.

Owner:SHANGHAI JIAO TONG UNIV

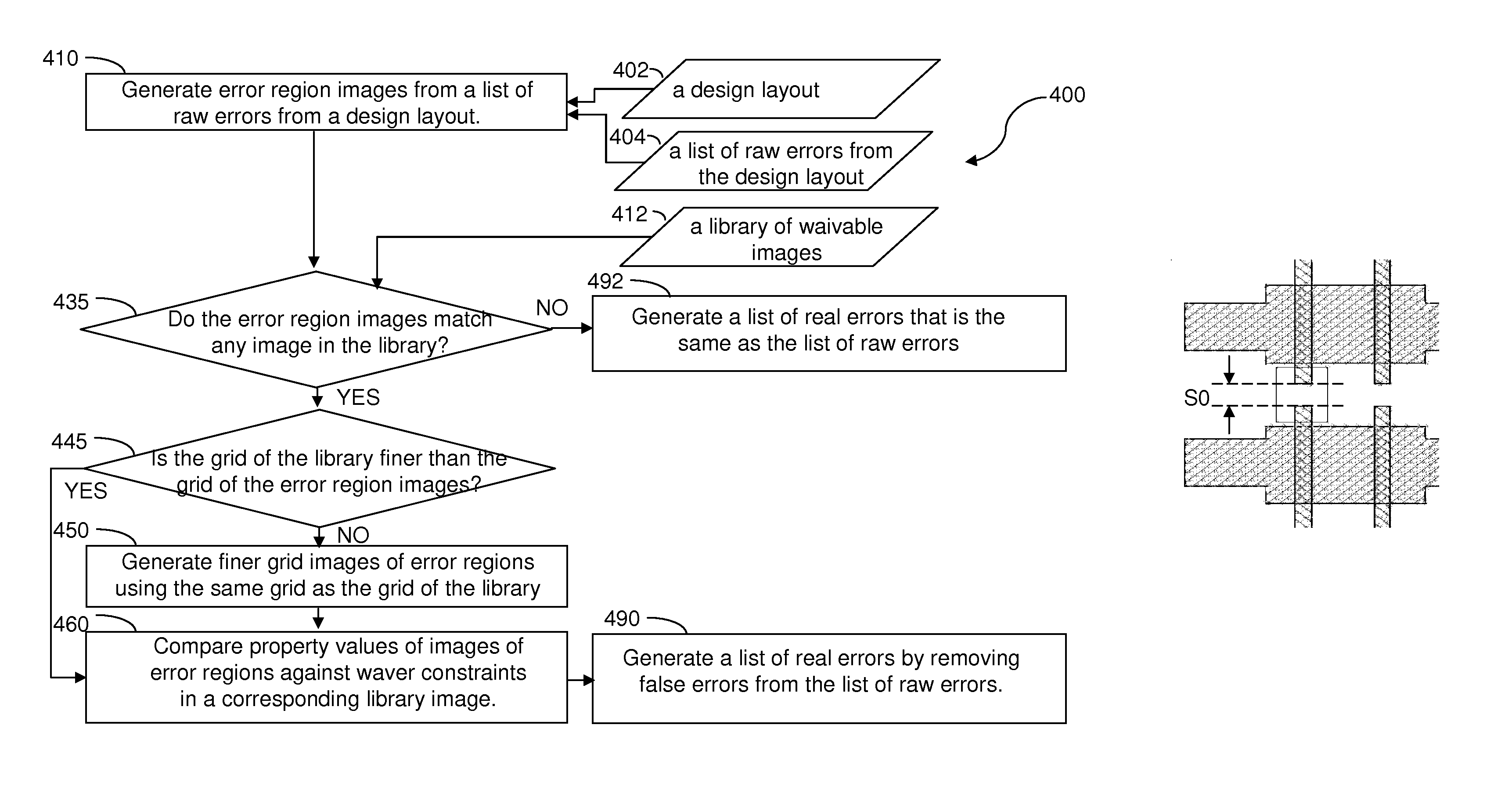

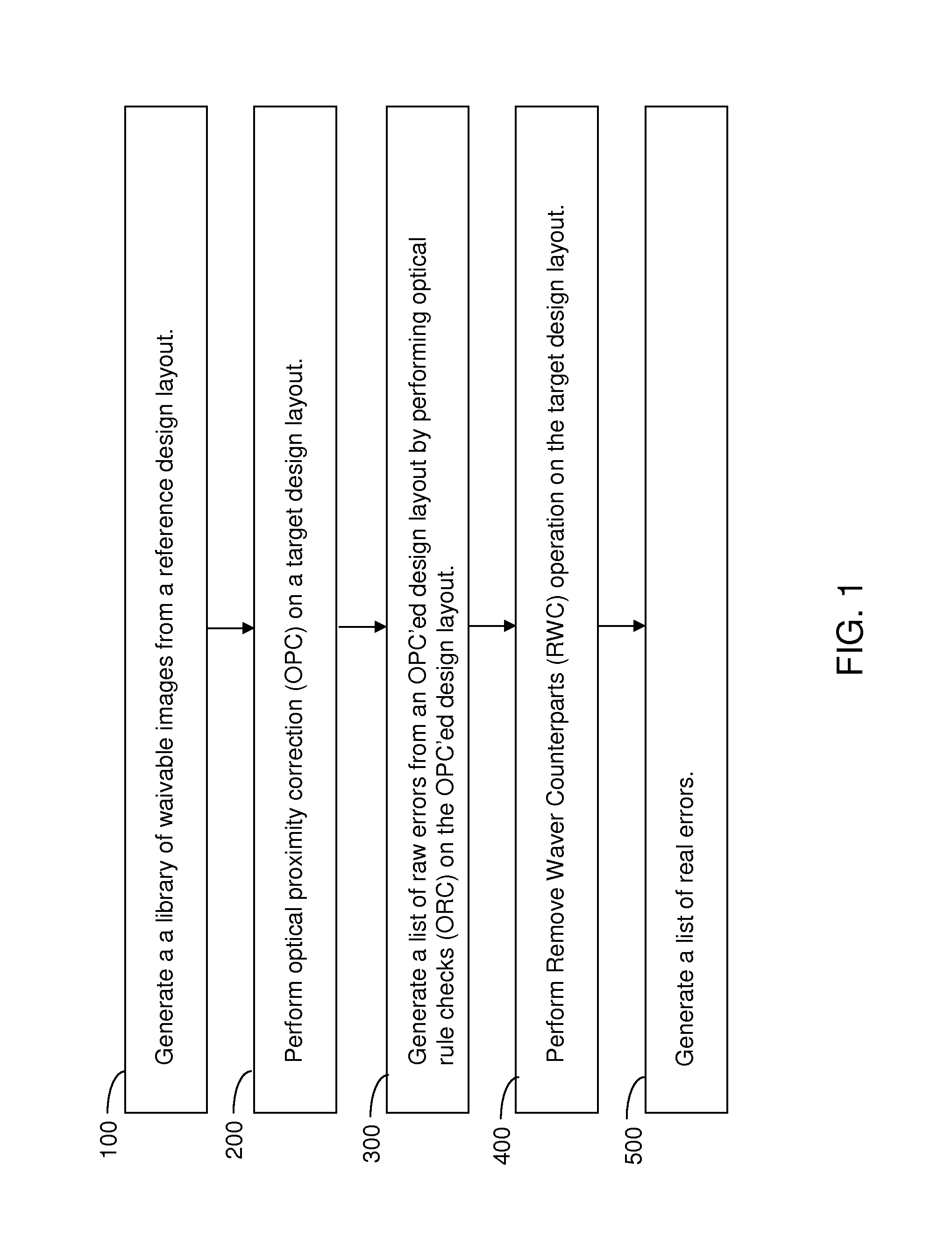

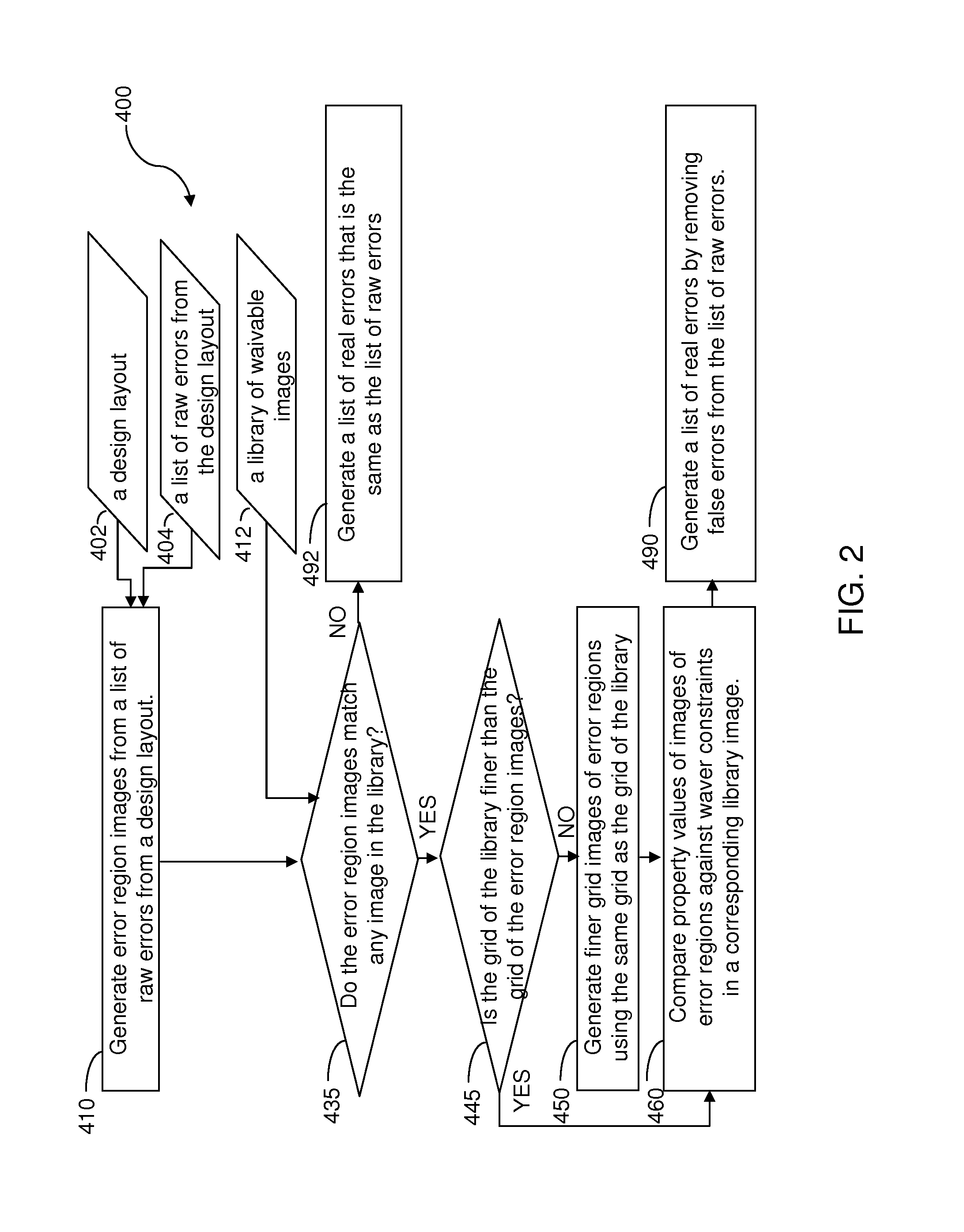

Lithographic error reduction by pattern matching

InactiveUS8495525B1Originals for photomechanical treatmentSoftware simulation/interpretation/emulationError reductionPattern matching

A library of waivable images with corresponding waiver constraints is generated. Each of the waivable images is an image of a region of a reference design layout including a raw error as determined by an optical rule checks (ORC) program and does not require a correction for printability on a photoresist layer. A list of raw errors is generated by running the ORC program on a target design layout. Error region images corresponding to the list of raw errors are generated by selecting a region of the target design layout around points corresponding to the raw errors. A list of matches between the library of waivable images and the error region images is generated. By removing a subset of raw errors that correspond to a subset of the list of matches from the list of raw errors, a list of real errors is generated.

Owner:GLOBALFOUNDRIES INC

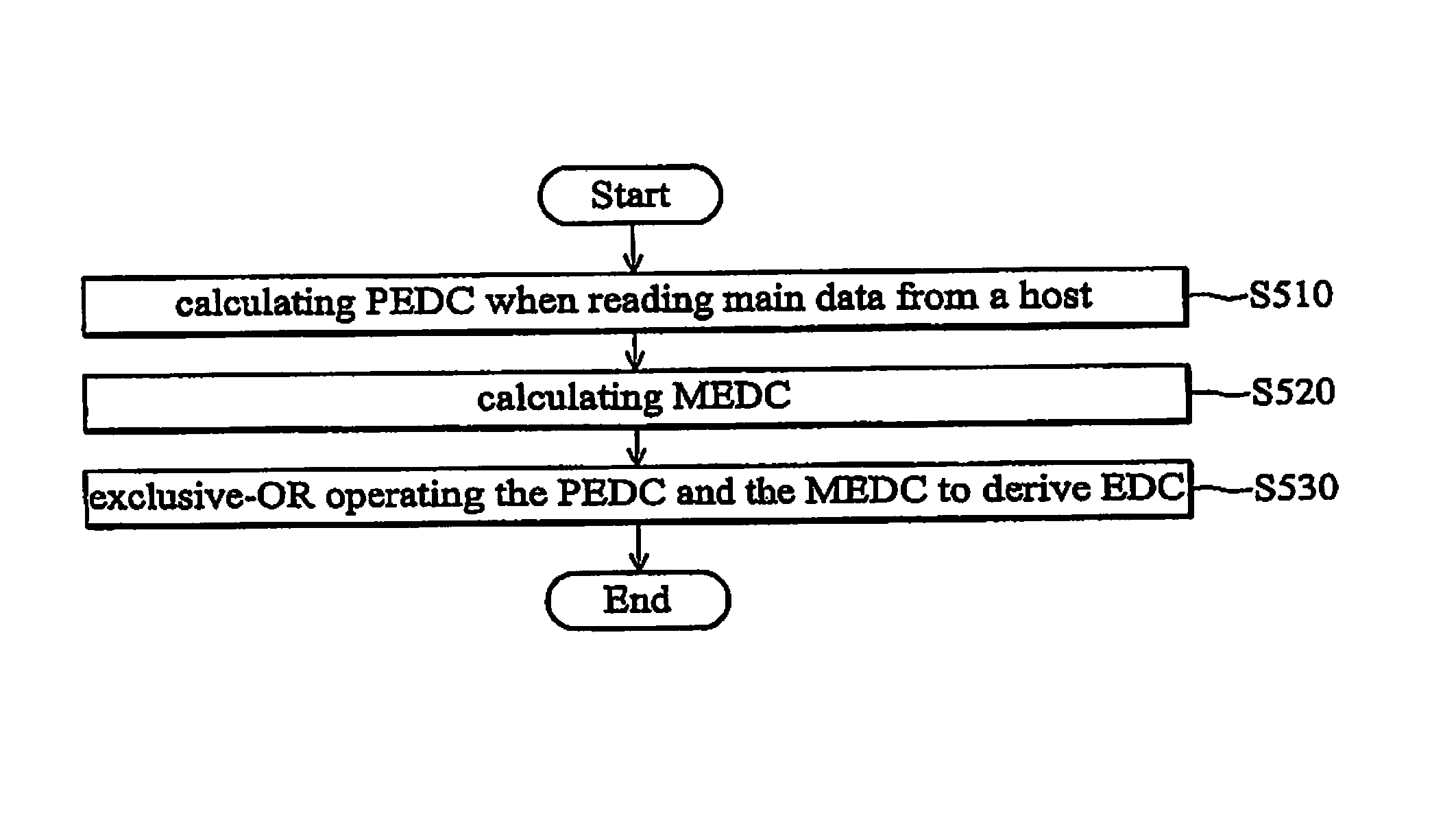

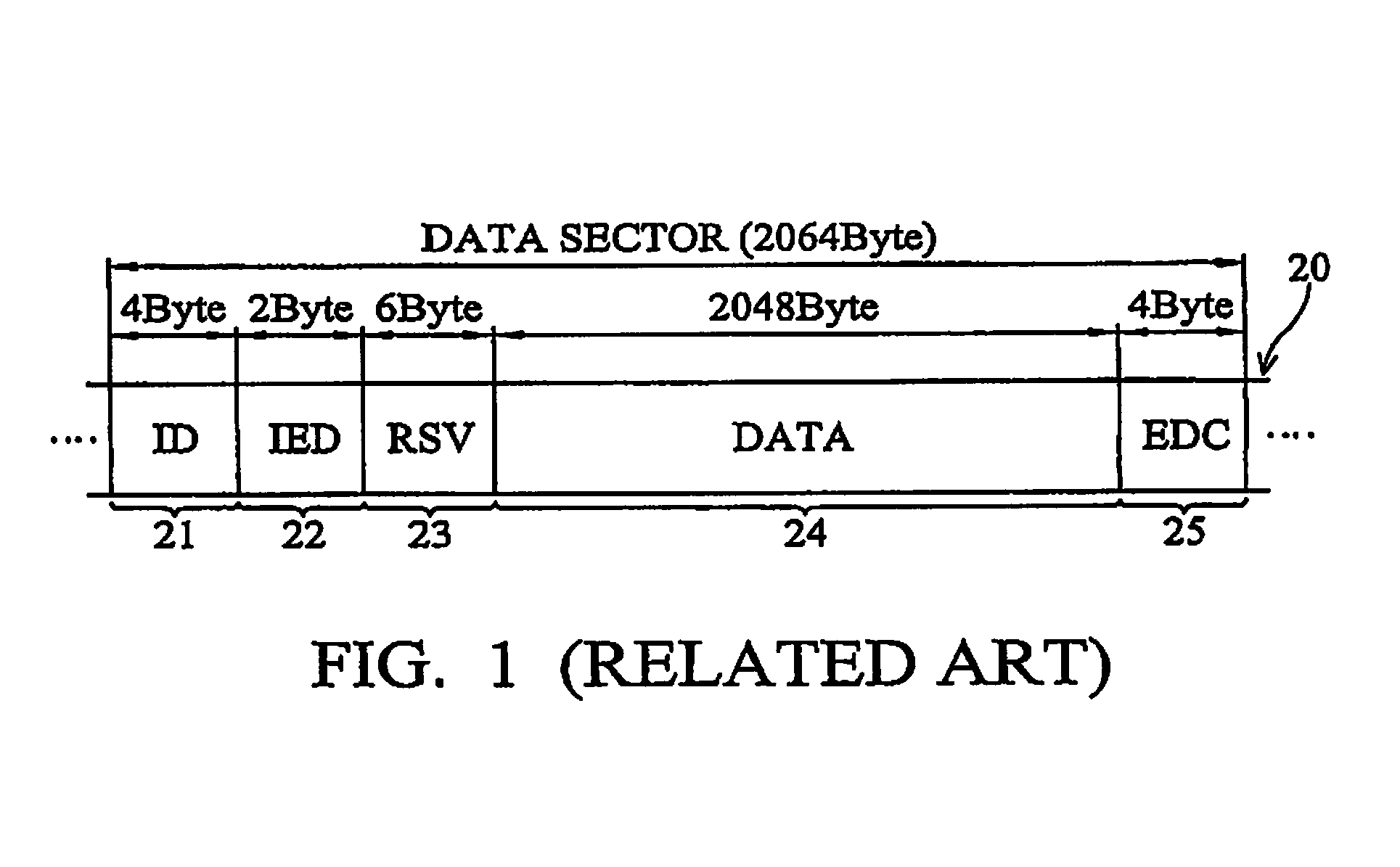

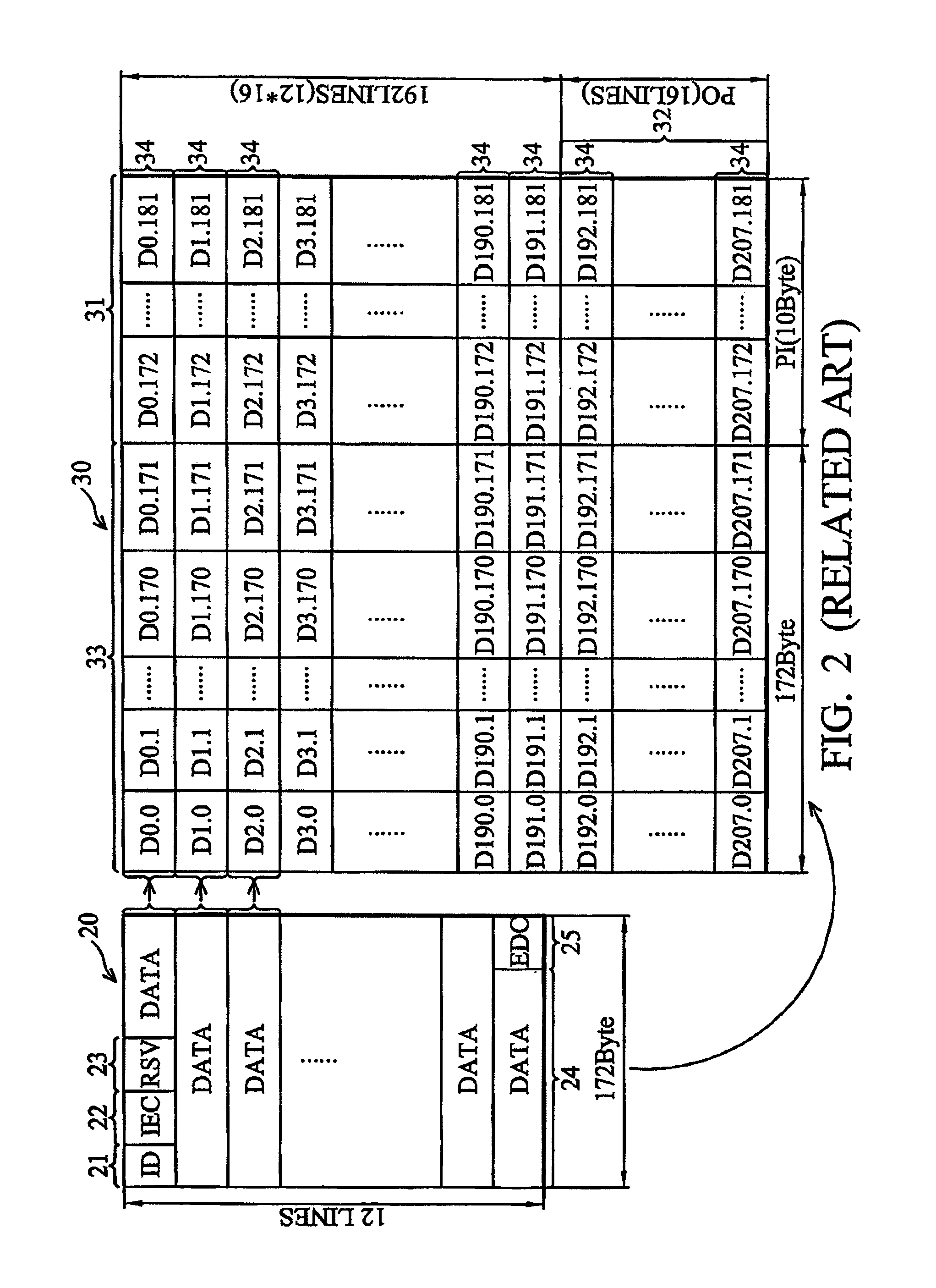

Method of generating error detection codes

ActiveUS8225179B2Reduce data transferError preventionTransmission systemsData informationExclusive or

A method for generating error detection code is disclosed. Firstly, a first error detection code PEDC is derived by using 12-byte unknown sector data information including ID, IED, RSV and the 2048-byte main data while the main data is delivered from a host. Secondly, a second error detection code MEDC is obtained by using known 12-byte sector data information including ID, IED, RSV and the 2048-byte main data. Thereafter, the real error detection code EDC is obtained by applying an exclusive-OR operation to both the PEDC and MEDC.

Owner:TIAN HLDG LLC

Error-tolerant and error-correcting decoding method, device and chip for quantum circuits

ActiveCN111510158BImplement error-tolerant and error-correcting decodingError Tolerance Error Correction Decoding Real TimeQuantum computersNanoinformaticsFault toleranceDecoding methods

The application discloses an error-tolerant and error-correcting decoding method, device and chip for a quantum circuit, and relates to the fields of artificial intelligence and quantum technology. The method includes: obtaining real error symptom information of the quantum circuit, the real error symptom information is information obtained by measuring the noisy error symptom of the quantum circuit by using a quantum error correction code; decoding the real error symptom information to obtain the real error symptom information The logical error class and perfect error symptom information corresponding to the symptom information; according to the logical error class and perfect error symptom information, the error result information of the quantum circuit is determined, and the error result information is used to indicate the wrong data qubit in the quantum circuit and the corresponding error type. This application realizes that error-tolerant and error-correcting decoding is equivalent to a classification problem, so that it is suitable to use an efficient neural network classifier to perform error-tolerant and error-correcting decoding on error symptom information, thereby improving the speed of error-tolerant and error-correcting decoding, and realizing real-time Error-tolerant and error-correcting decoding.

Owner:TENCENT TECH (SHENZHEN) CO LTD

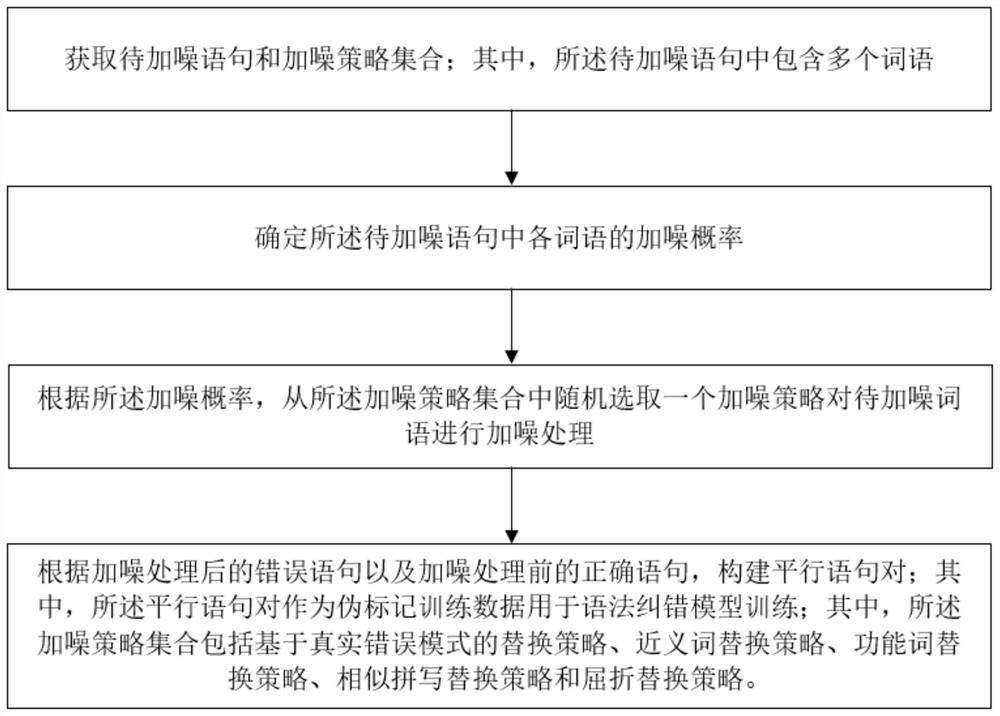

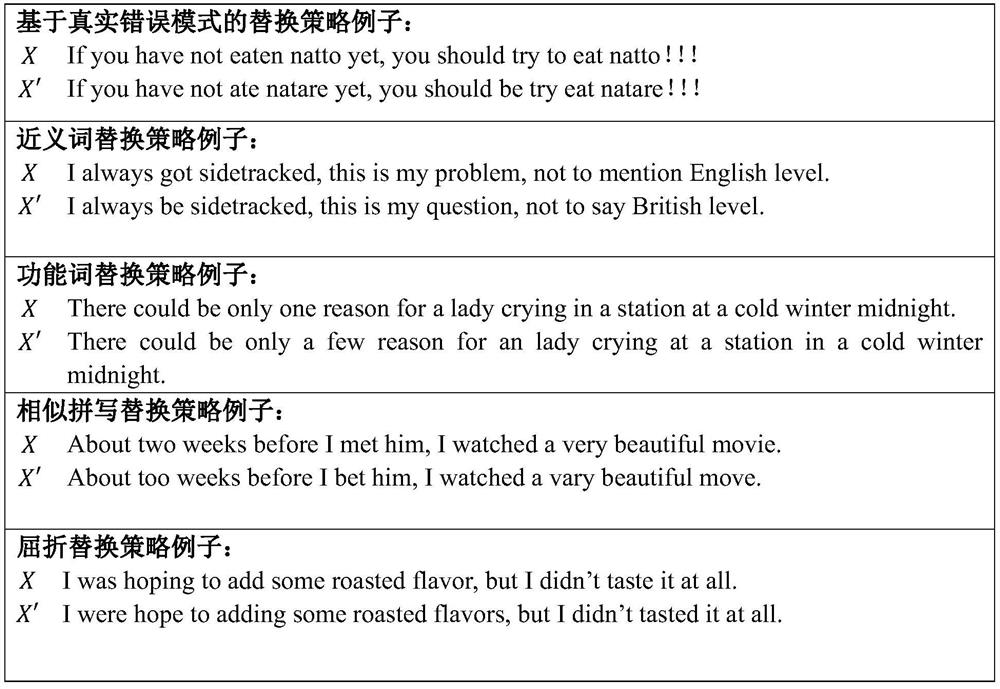

Method and device for enhancing grammar error correction data based on real error mode

The invention discloses a method and a device for enhancing grammar error correction data based on a real error pattern. The method comprises the following steps: acquiring a to-be-noise-added statement and a noise adding strategy set; determining the noise adding probability of each word in the statement to be subjected to noise adding; randomly selecting a noise adding strategy from a noise adding strategy set according to the noise adding probability to carry out noise adding processing on the to-be-noise-added word; and constructing parallel statement pairs according to the error statements subjected to noise addition processing and the correct statements before noise addition processing. The noise adding strategy set comprises a real error pattern-based replacement strategy, a synonym replacement strategy, a function word replacement strategy, a similar spelling replacement strategy and a flexion replacement strategy. According to the embodiment of the invention, through introduction of real errors and simulation of various real errors, high-quality artificial error enhancement data which is more real and closer to real errors of learners can be generated; and various grammar errors can be manufactured through various types of noise schemes, and the method and the device can be widely applied to the technical field of data processing.

Owner:GUANGDONG UNIVERSITY OF FOREIGN STUDIES

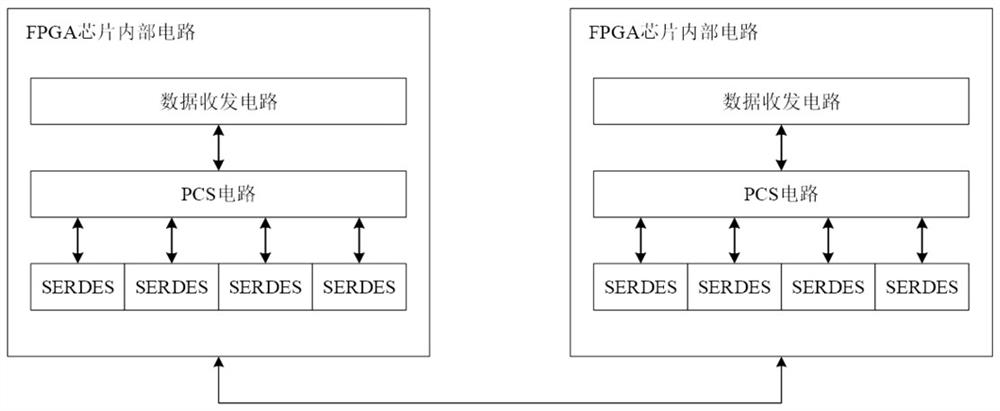

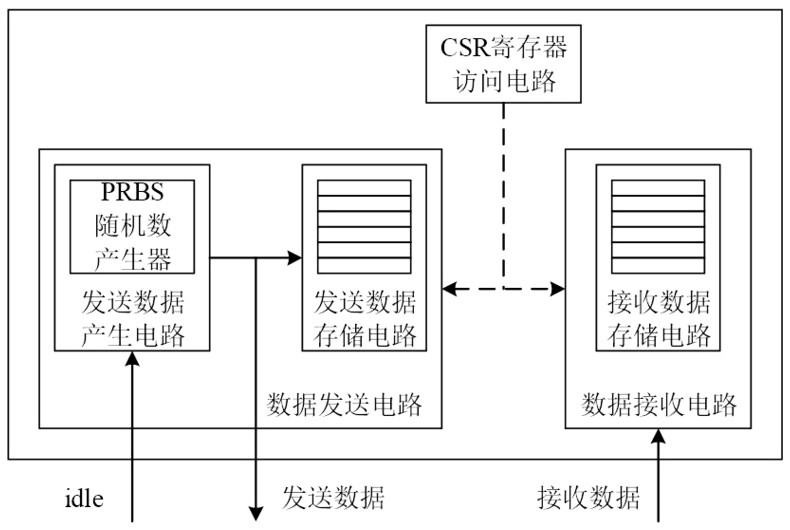

Physical layer transmission real error code acquisition device and equipment

ActiveCN111654358AReal-timeRealize analysisError detection/prevention using signal quality detectorData switching networksComputer hardwareReliable transmission

The invention discloses a physical layer transmission real error code collection device and equipment, and the device comprises an error code rate detection circuit and a data receiving and transmitting circuit connected with a physical coding sub-layer circuit PCS, and the data receiving and transmitting circuit comprises a CSR register access circuit, a data transmitting circuit, and a data receiving circuit. The CSR register access circuit is respectively connected with the data sending circuit and the data receiving circuit, the CSR register access circuit is further connected with an out-of-band access interface, and the data receiving circuit is provided with an output interface used for outputting stored data so as to detect the bit error rate of the data. According to the invention, a physical layer transmission error code can be collected and analyzed in real time when data is transmitted on a high-speed serial link; therefore, the data sent by the sender and the data receivedby the receiver can be analyzed to detect the bit error rate passing through the physical link, and the obtained distribution characteristics and rules of the bit error rate can lay a foundation forthe design of a link fault-tolerant function when the physical link cannot ensure reliable transmission.

Owner:NAT UNIV OF DEFENSE TECH