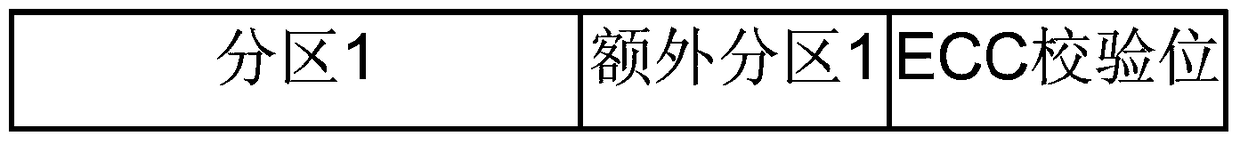

Patents

Literature

32results about How to "Optimize write performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

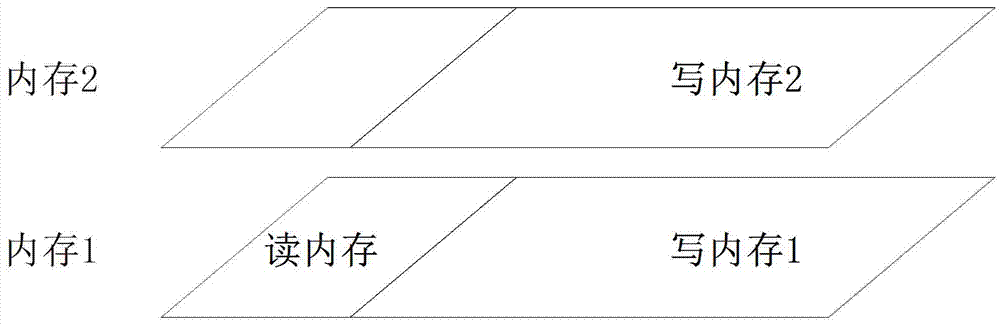

Read-write method and system for database

InactiveCN102999519AFast read and writeWrite quicklySpecial data processing applicationsData segmentDatabase

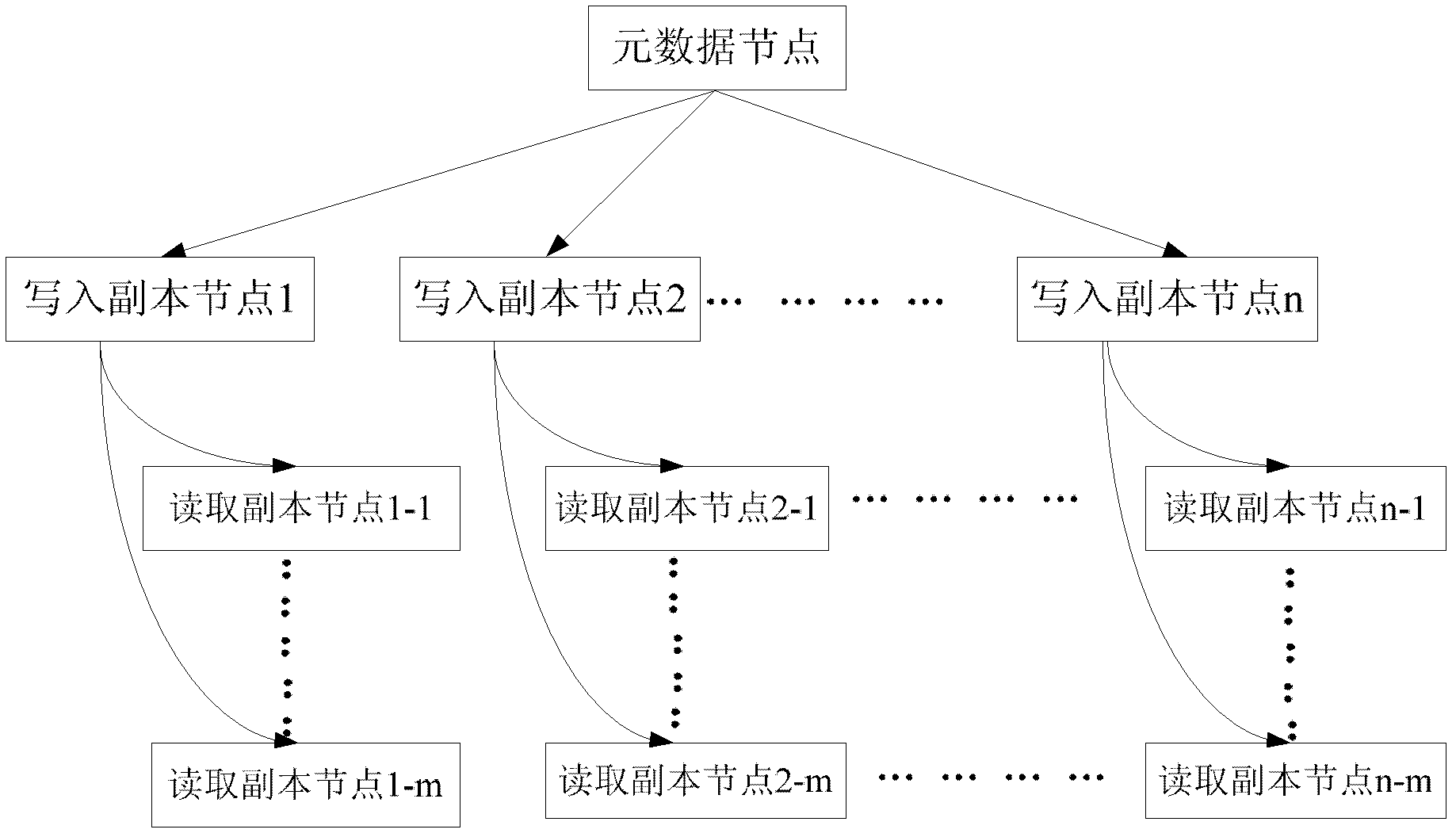

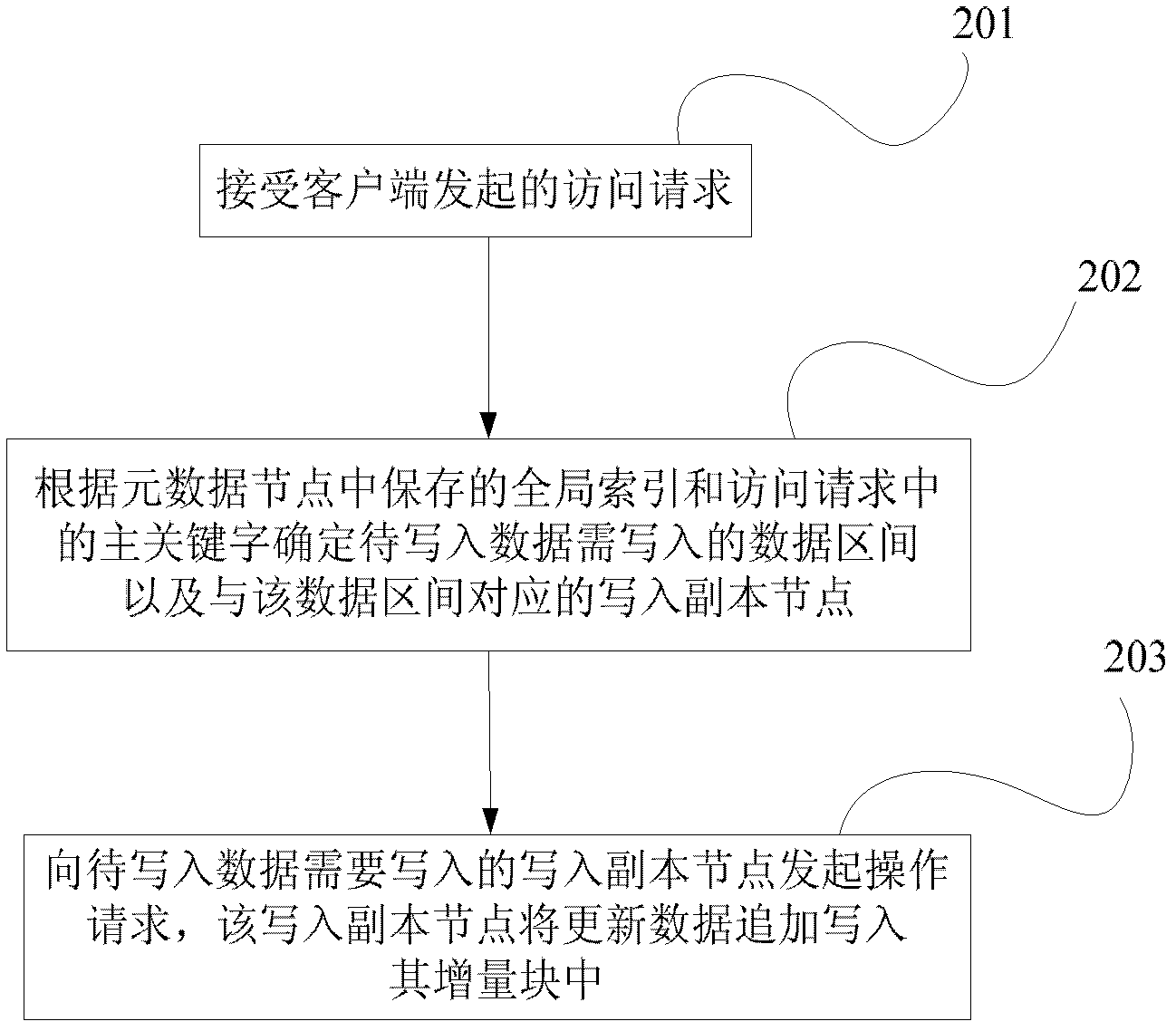

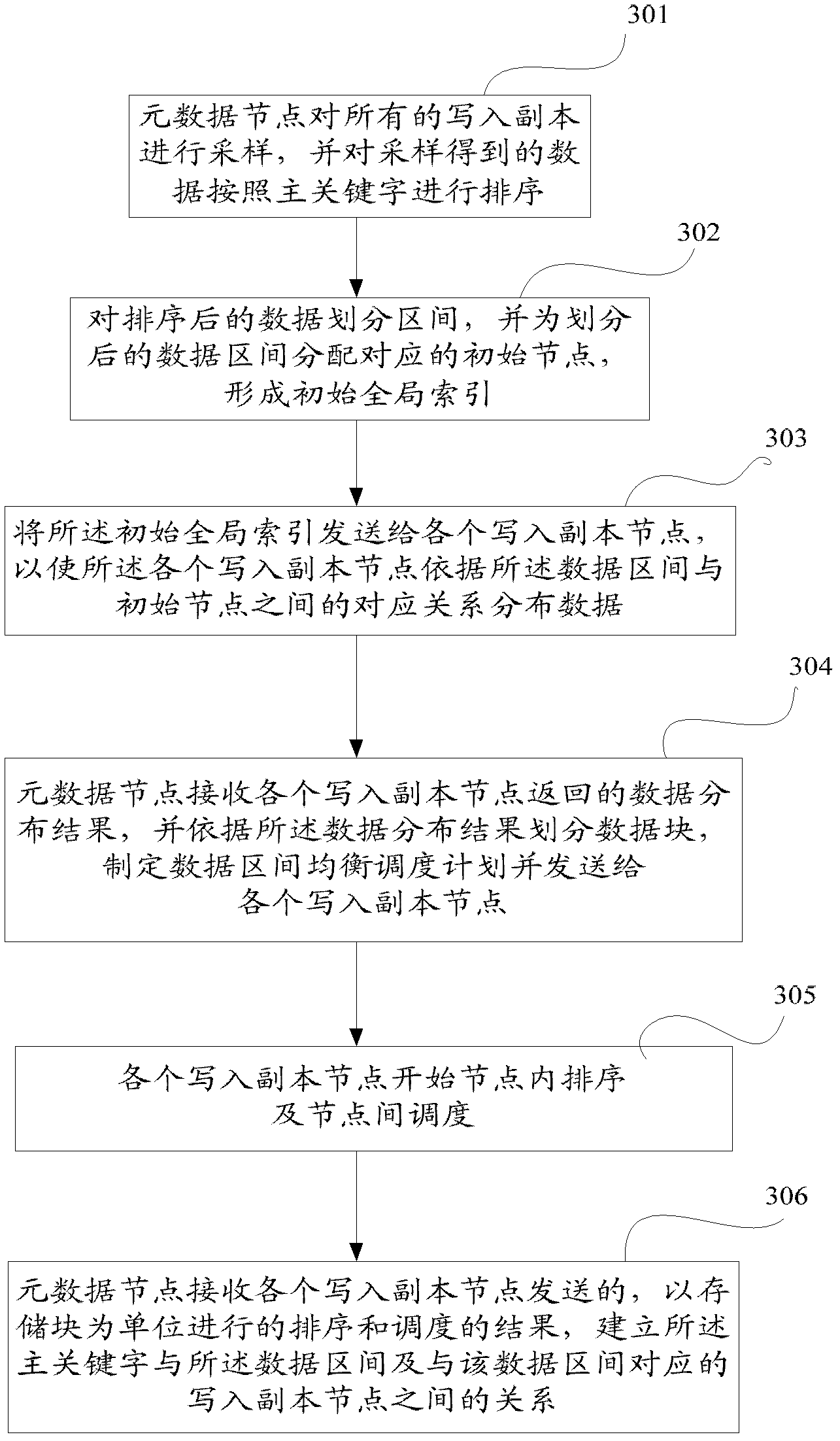

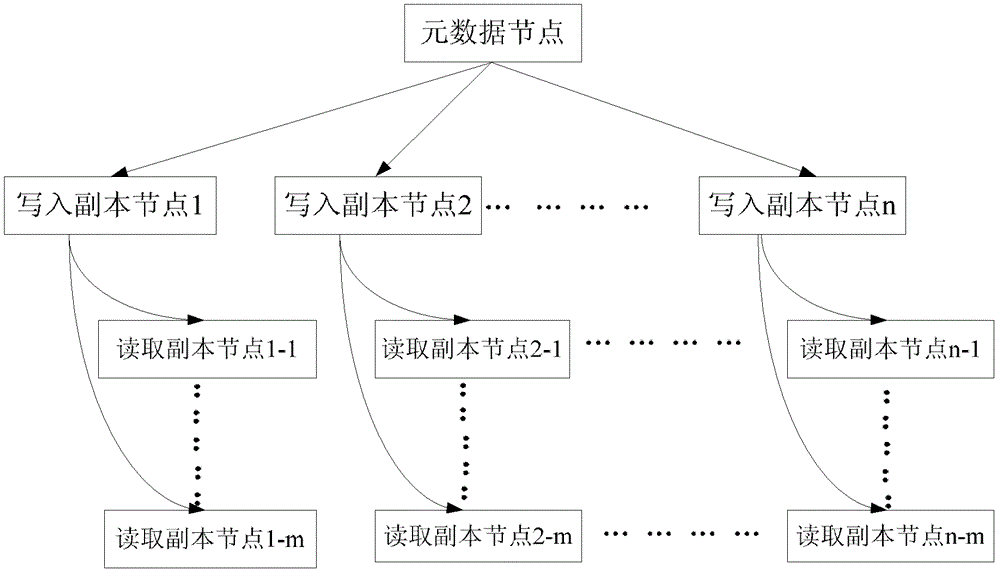

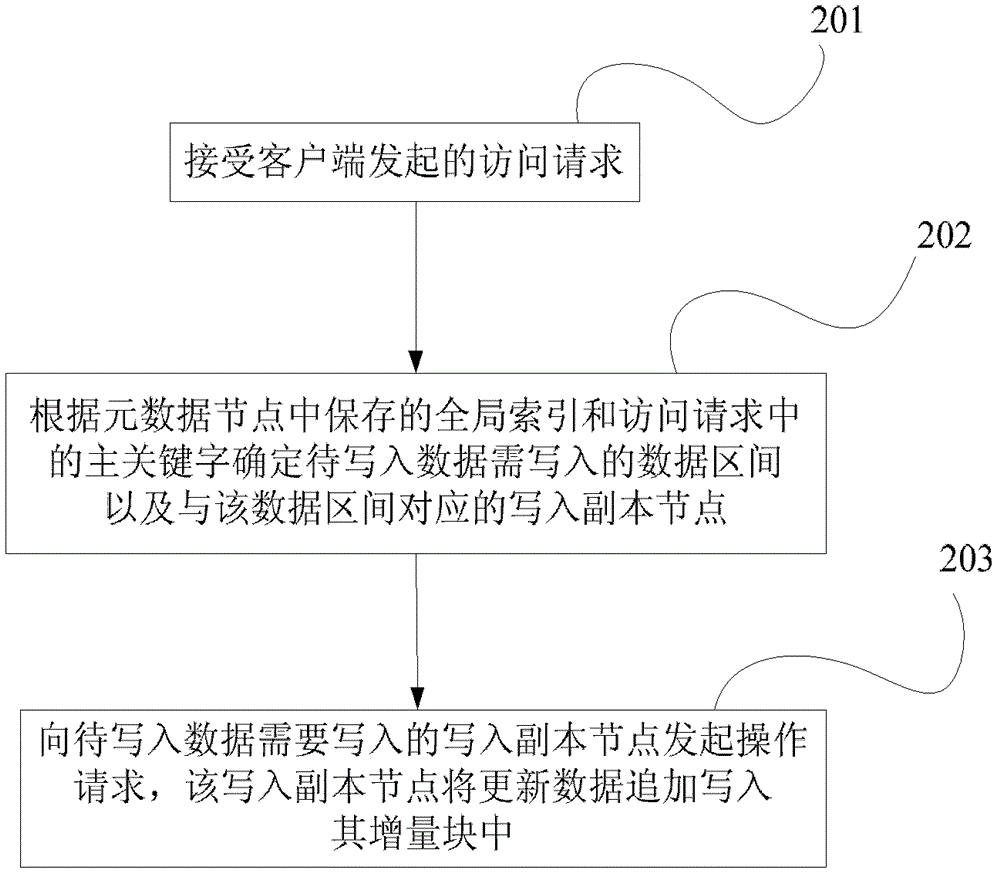

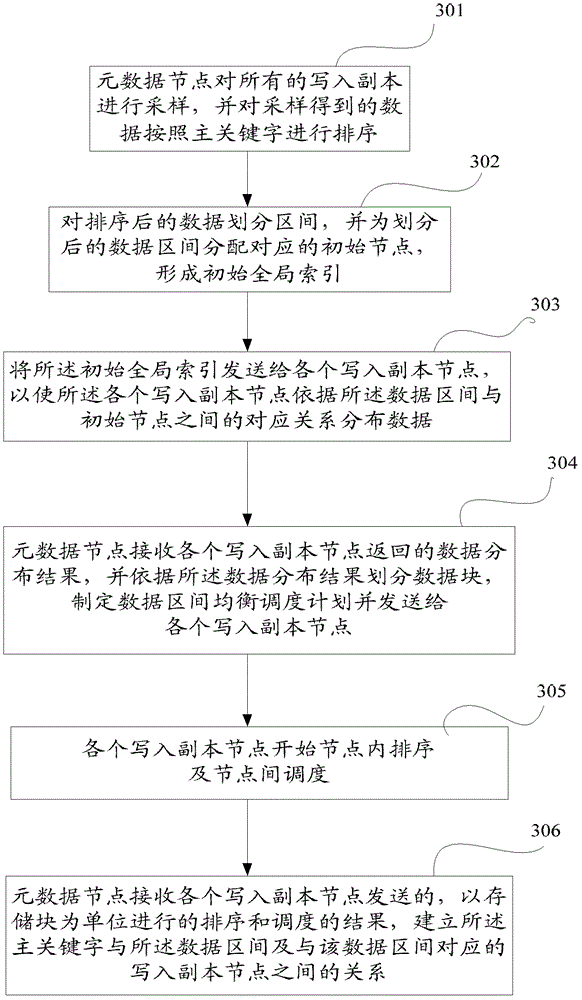

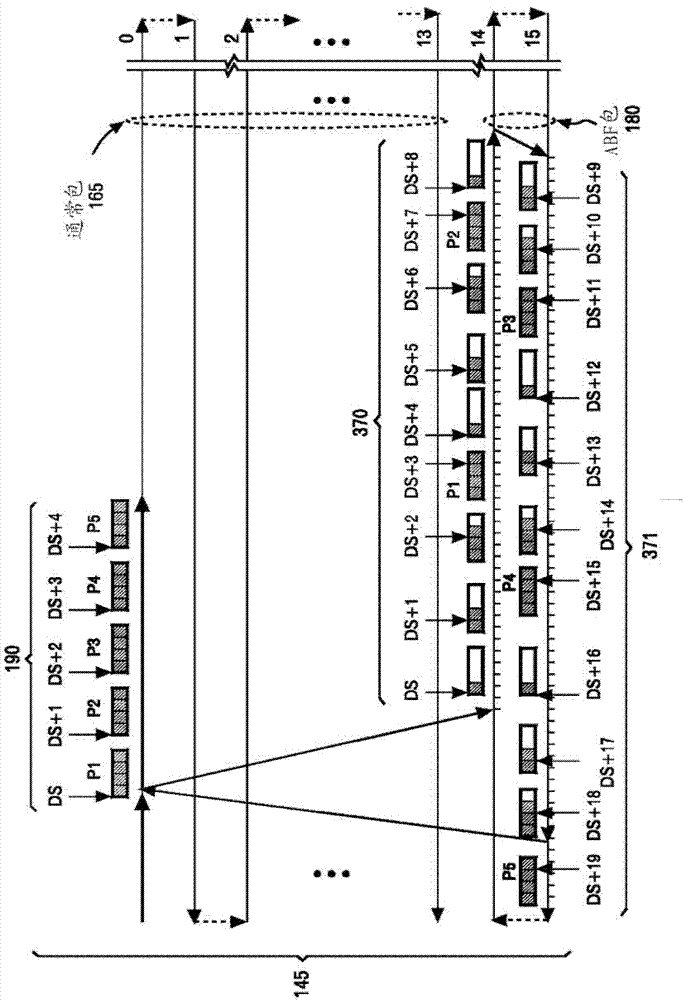

The embodiment of the invention discloses a read-write method and system for a database. The method comprises the steps of: transversely cutting record data according to a main keyword into a plurality of data segments, wherein each data segment is stored as a write copy and corresponding read copies, and the write copy is stored in form of line storage, so that the write performance of the database is optimized; the read copies are stored in form of column storage, and data in each read copy is organized in different manners, so that the read performance of the database is optimized. According to the method, an overall index and a local index are further established, so that the operating position of data to be written or to be read can be quickly positioned when data is written or read. According to the embodiment of the method or system, not only is data quickly written, but also data can be quickly read.

Owner:SHANGHAI SHENGPAY E PAYMENT SERVICE CO LTD

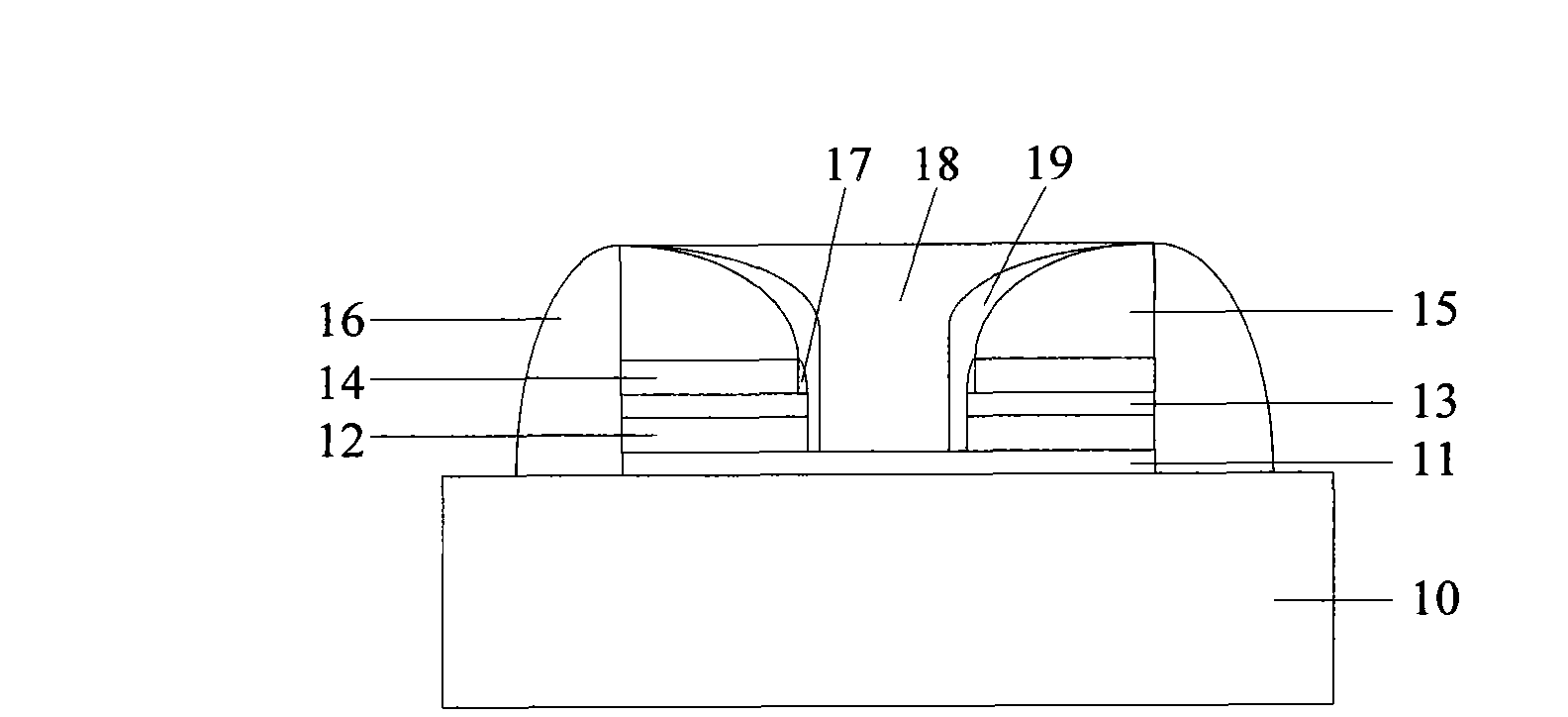

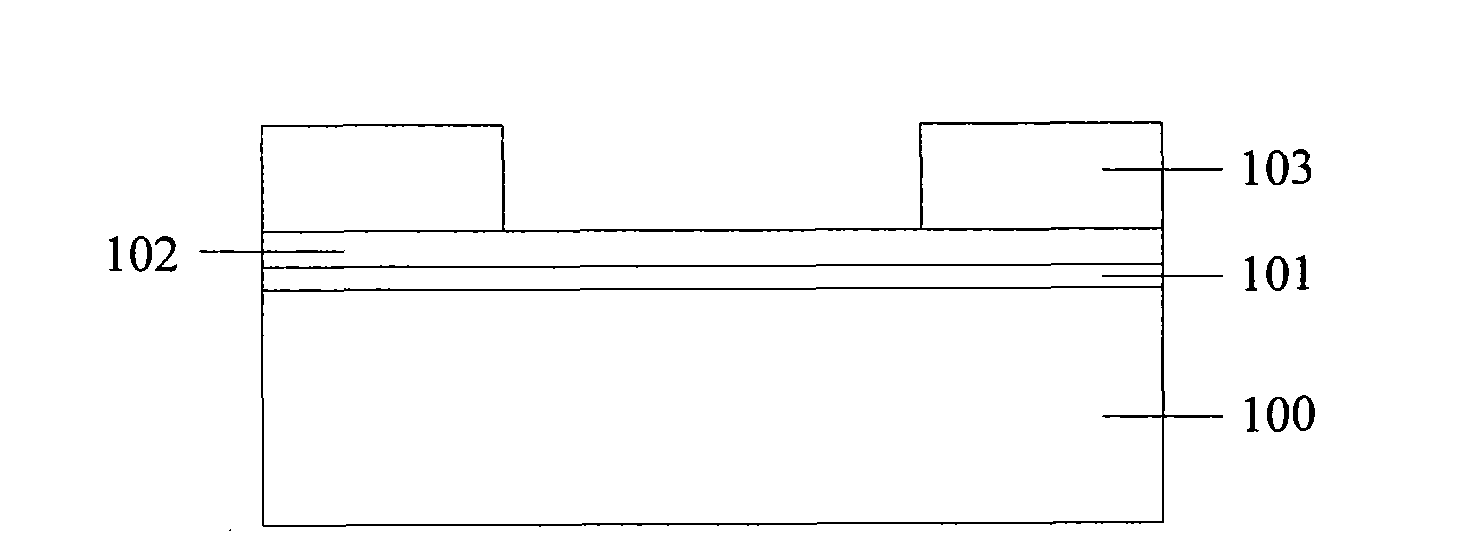

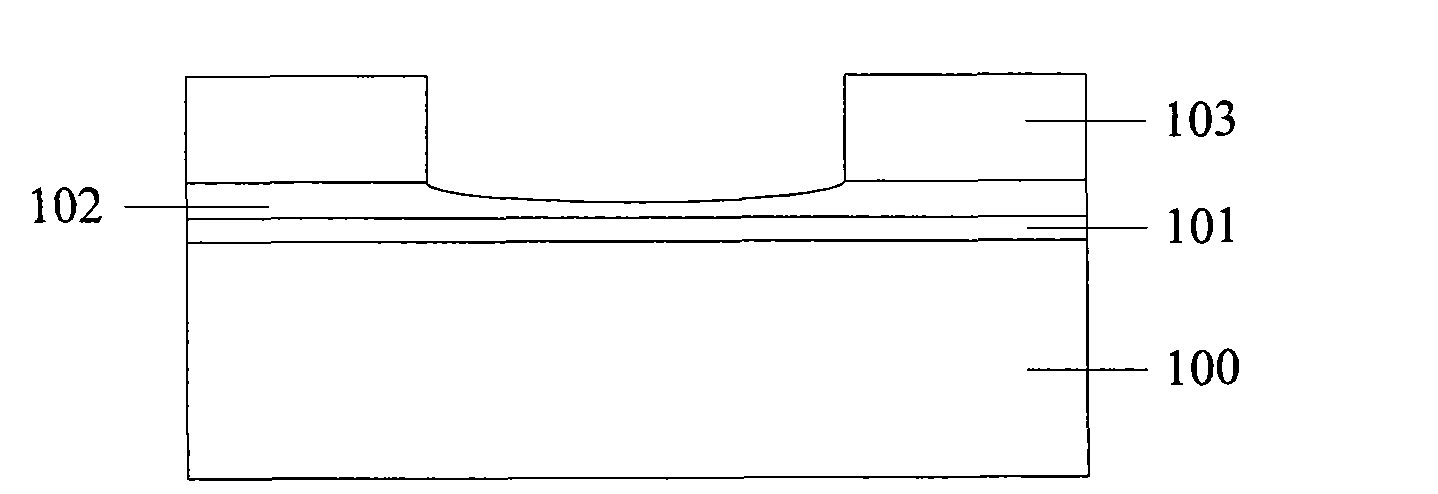

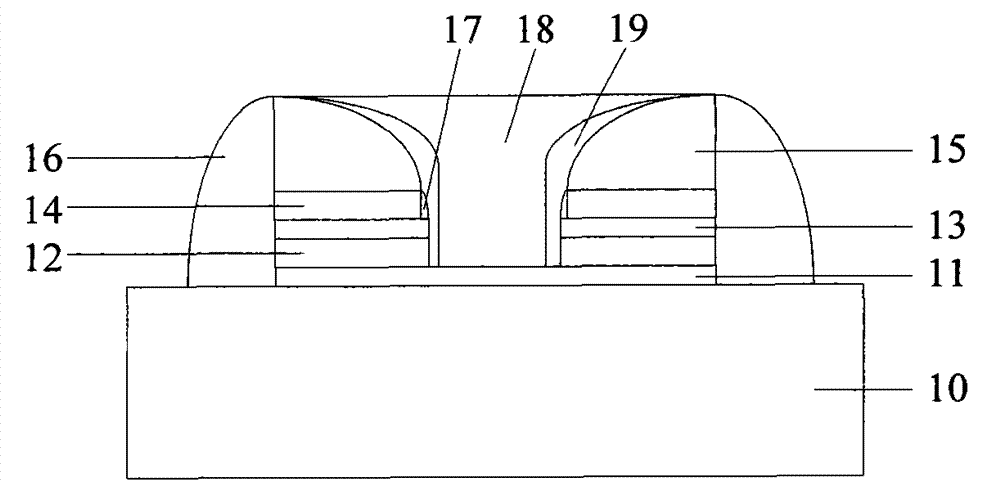

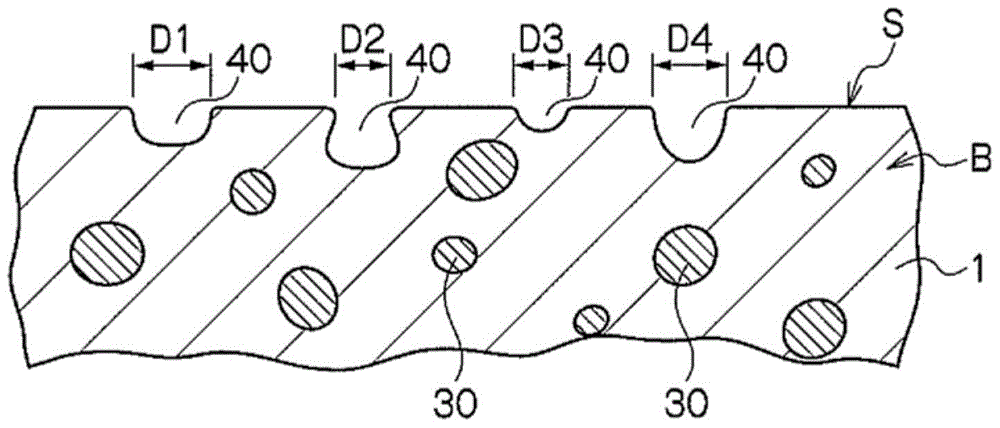

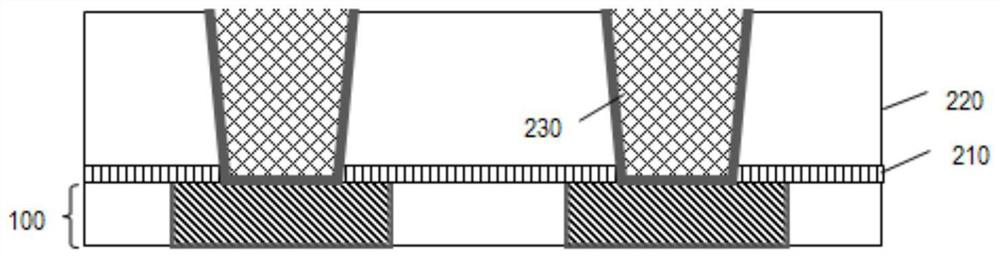

Split gate flash memory and manufacture method thereof

ActiveCN101807577AIncrease surface areaIncrease contact areaSolid-state devicesSemiconductor/solid-state device manufacturingGratingGate oxide

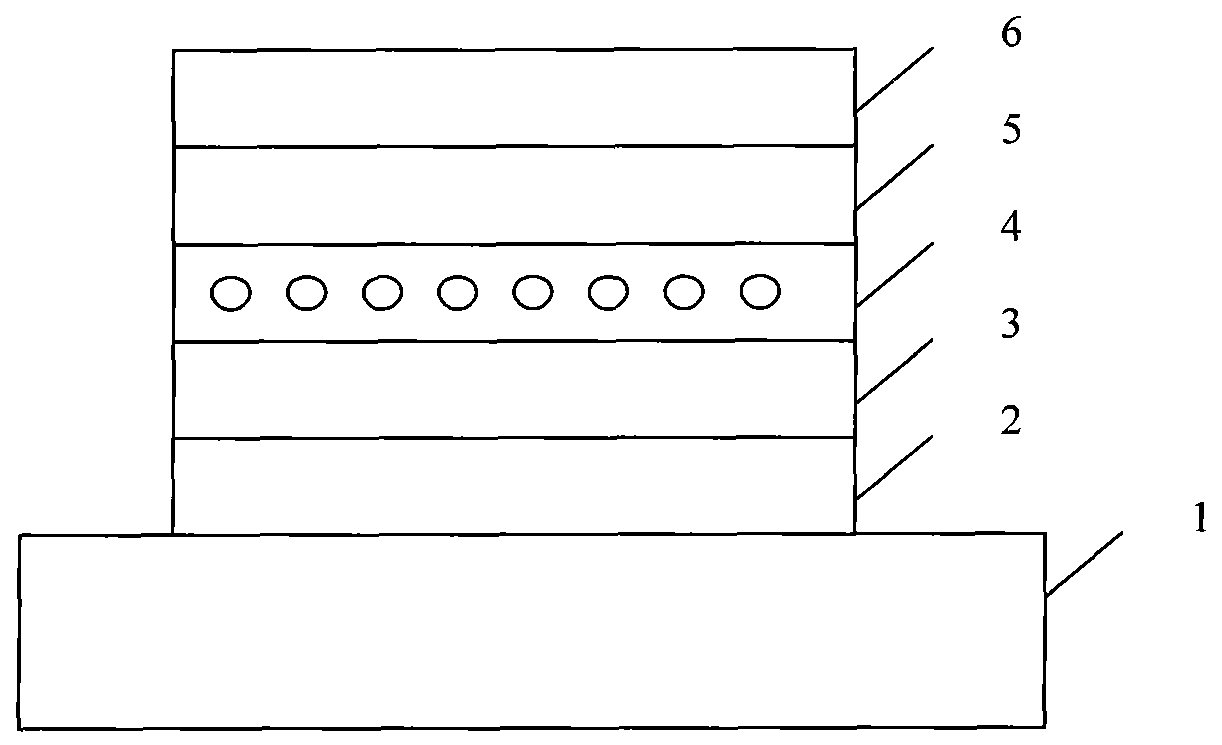

The invention provides a split grating flash memory and a manufacture method thereof. The split gate flash memory comprises a semiconductor substrate, a gate oxide and split structure units, wherein the gate oxide is positioned on the surface of the semiconductor substrate; and the split structure units are positioned on the gate oxide. Each split structure unit is provided with a floating gate, a gate medium layer, a control gate, a first side wall layer, a second side wall layer, a third side wall layer, a word line and side walls, wherein the floating gate is positioned on the gate oxide, and the surface of the floating gate is in a cambered shape with an inclined angle; the gate medium layer is positioned on the surface of the floating gate; the control gate is positioned on the gate medium layer; the first side wall layer is positioned on the control gate; the second side wall layer is positioned on the inner side wall of the control gate; the third side wall layer is positioned in the first side wall, the second side wall layer, the gate medium layer and the inner side wall of the floating gate; the word line is positioned between two split structure units and fills a gap; and the side walls are positioned at the outside walls of the split structure units. The invention improves the performance of flash memory erasure or writing and the electric performance of the flash memory.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

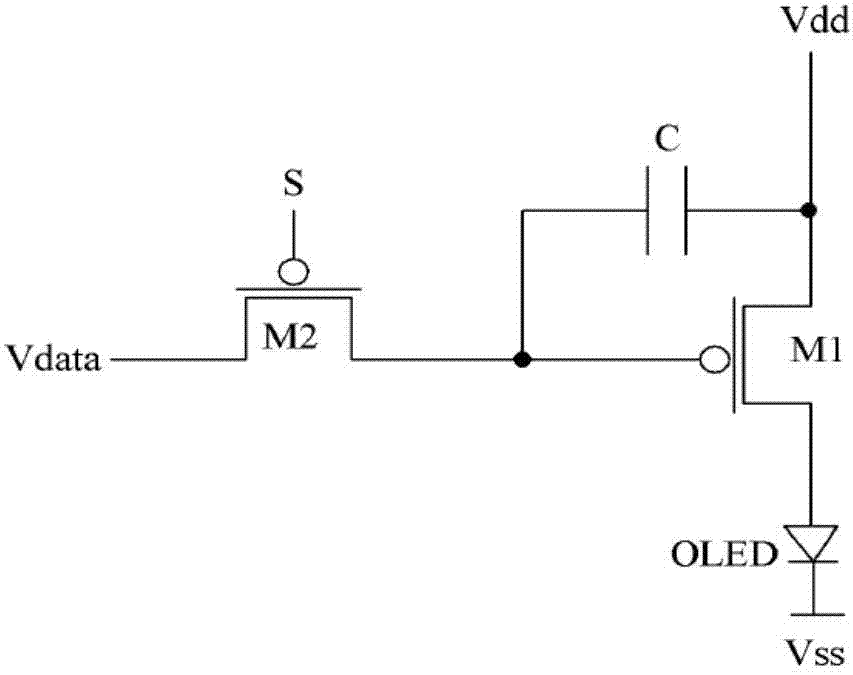

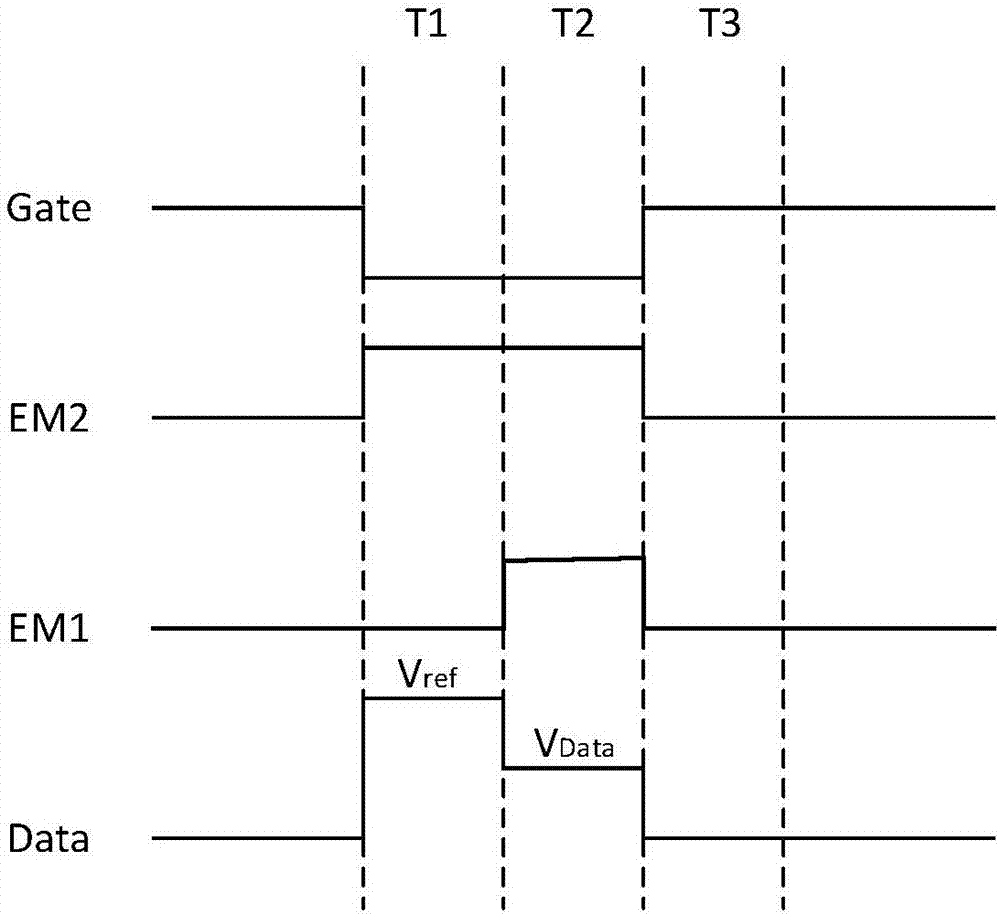

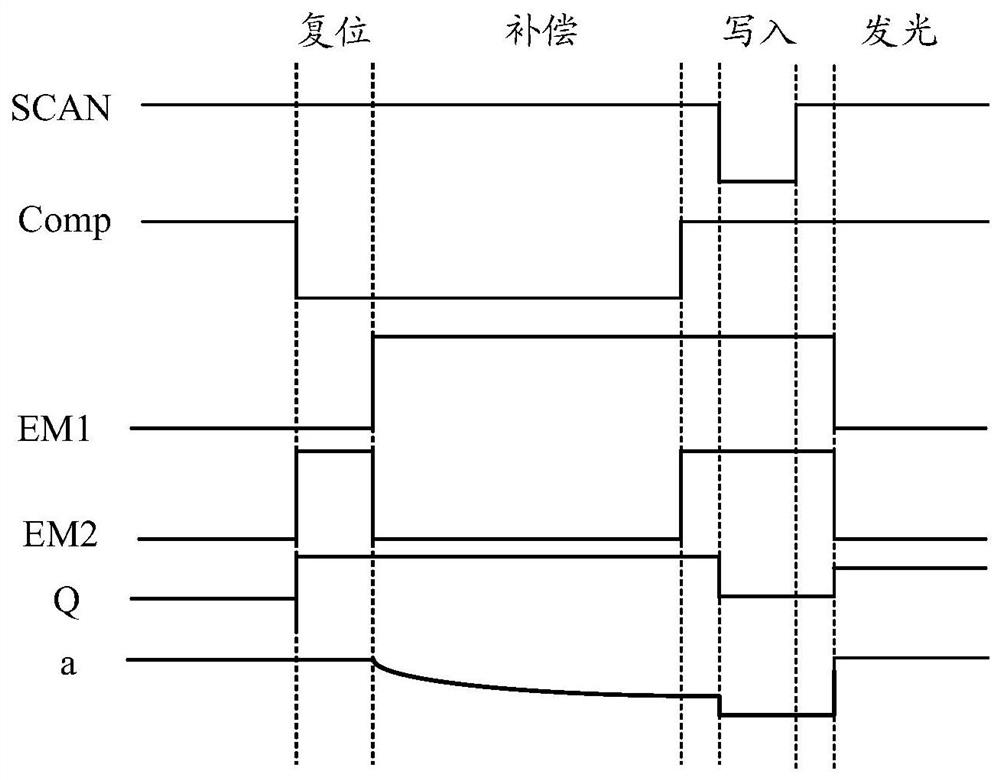

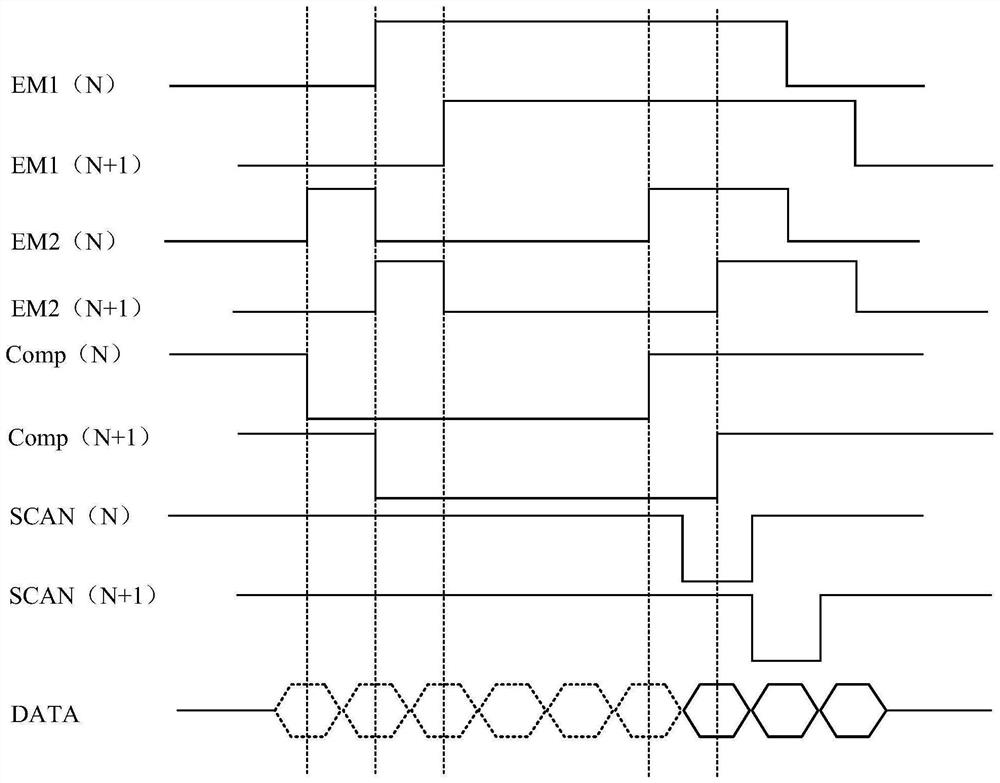

Pixel driving circuit, driving method thereof, array substrate and display device

PendingCN107481675ASolve the problem of uneven brightnessReduce the numberStatic indicating devicesBackplanePower flow

The invention discloses a pixel driving circuit. The pixel driving circuit comprises a driving transistor, a first switching element, a second switching element, a third switching element, a fourth switching element and a storage capacitor. Different control signals control the on-off states of the switching elements so as to achieve the compensation function of the pixel driving circuit, and the light emitting current of an OLED is only related to a threshold voltage and data signals of the OLED and is irrelevant to a threshold voltage of the driving transistor and the voltage drop of a back plate power supply, so that the problem that the light emitting brightness is uneven due to the deviation of the threshold voltage of the driving transistor and the voltage drop of the back plate power supply is solved. The invention further discloses a driving method, an array substrate and a display device.

Owner:BOE TECH GRP CO LTD

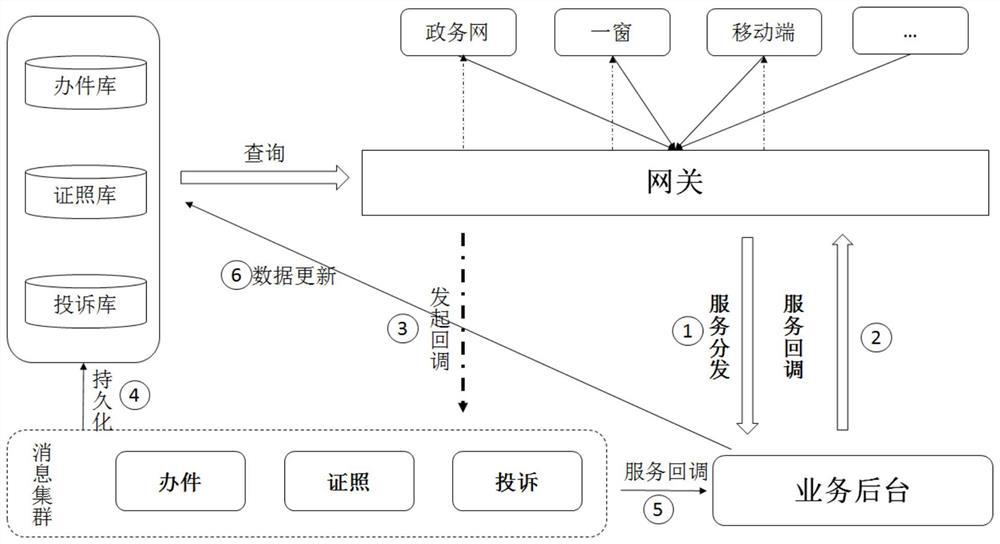

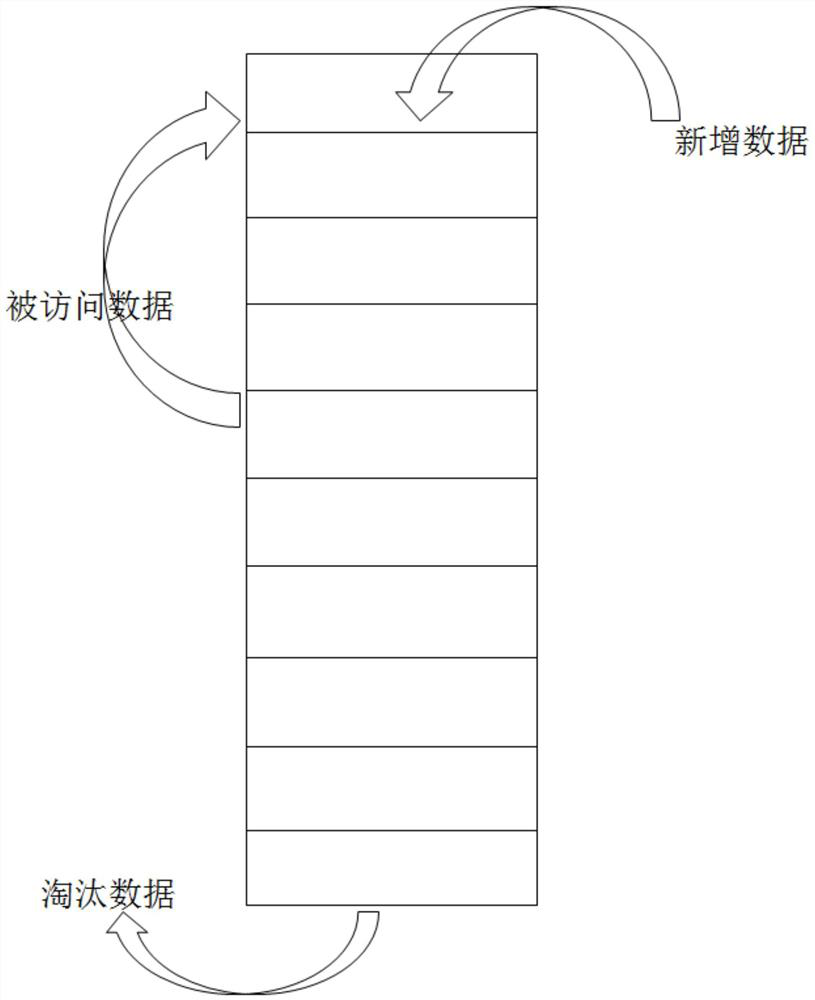

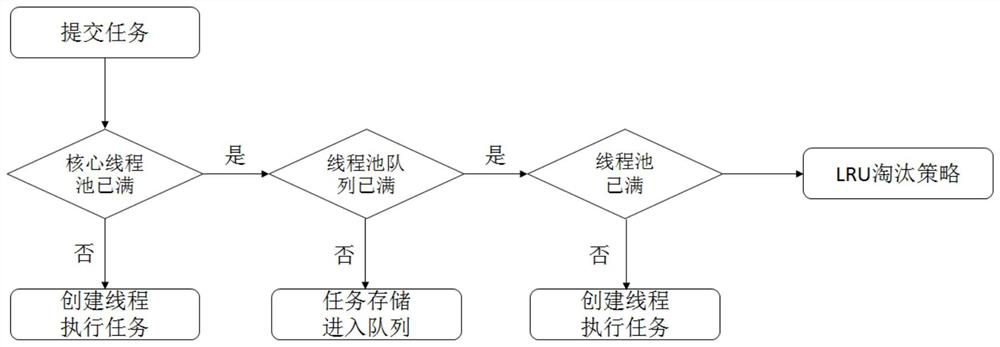

Method for realizing service callback based on message queue and search engine

ActiveCN112799860AImprove scalabilityOptimize write performanceInterprogram communicationOther databases indexingMessage queueEngineering

The invention discloses a method for realizing service callback based on a message queue and a search engine, belongs to the field of information technology service, and aims to solve the technical problem of how to ensure high performance of callback service realization and meet actual use of business requirements. According to the technical scheme, the method specifically comprises the following steps: a client initiates a service function request; the business background decides to request the server to initiate a callback service according to the business function request; the server initiates a callback service request, and request information enters a RabbitMq message queue; the request information is subjected to persistence and enters an Elasticsearch search engine; the Consumer executes a callback service according to the callback rule; and the server updates the data record according to the execution result of the callback service.

Owner:SHANDONG LANGCHAO YUNTOU INFORMATION TECH CO LTD

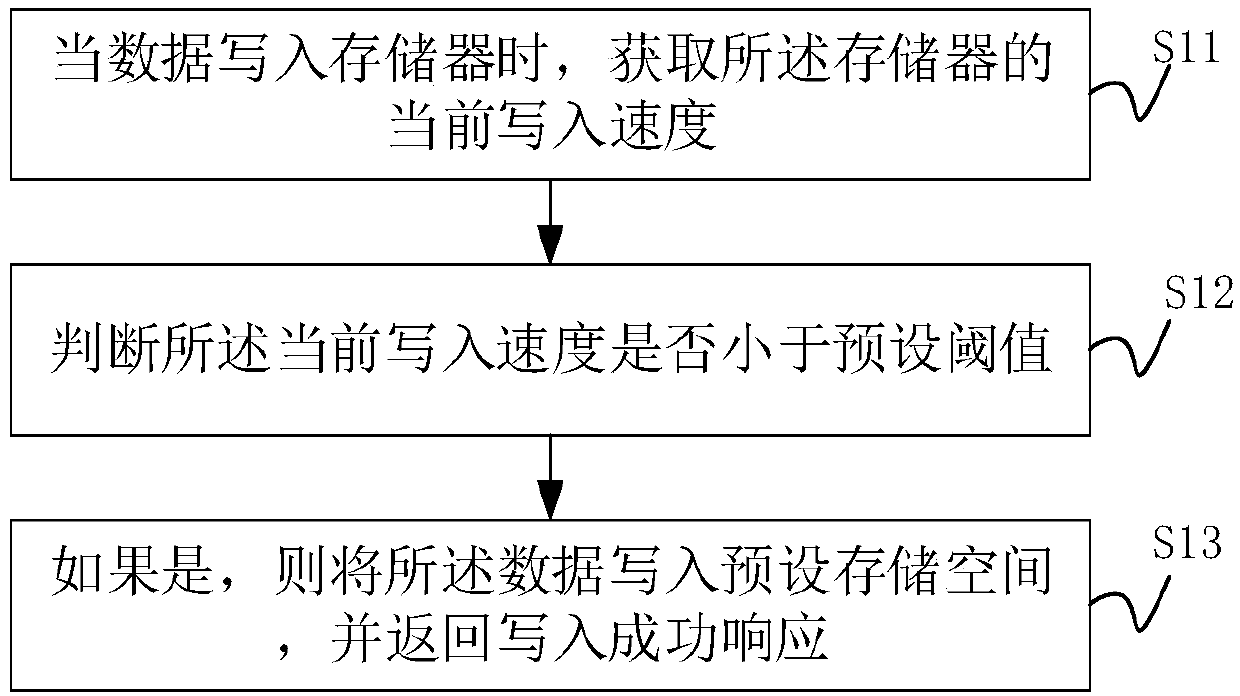

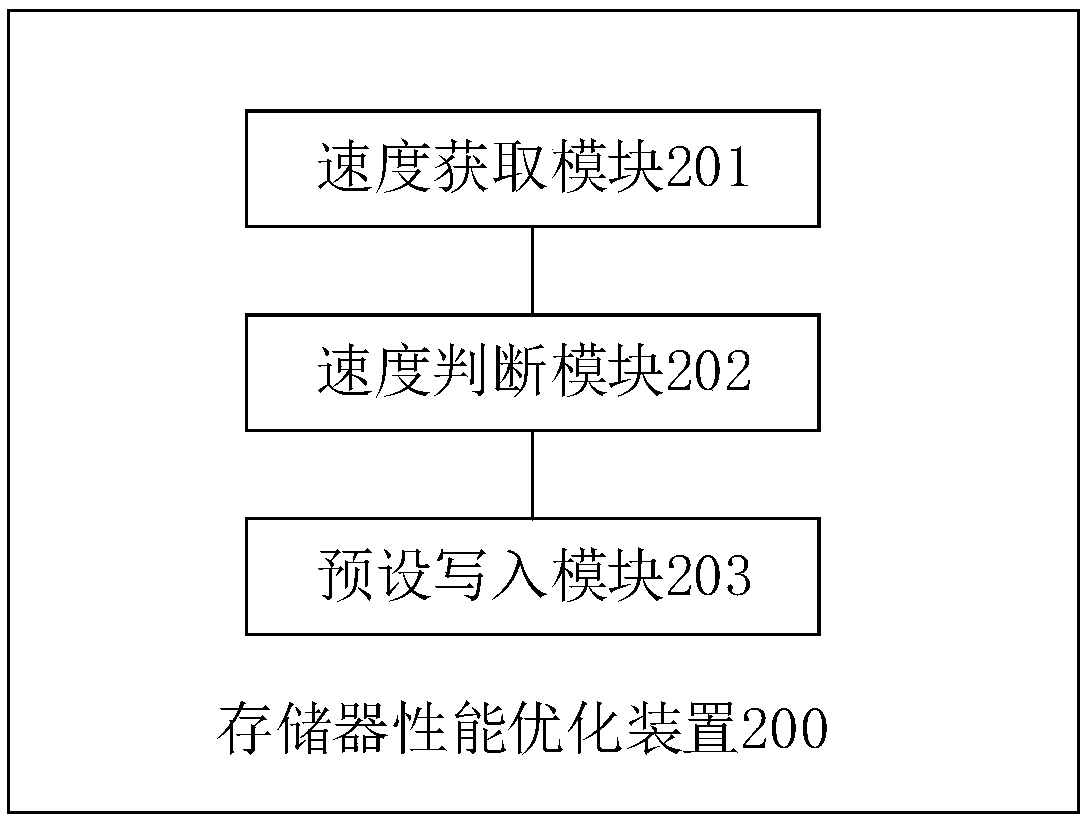

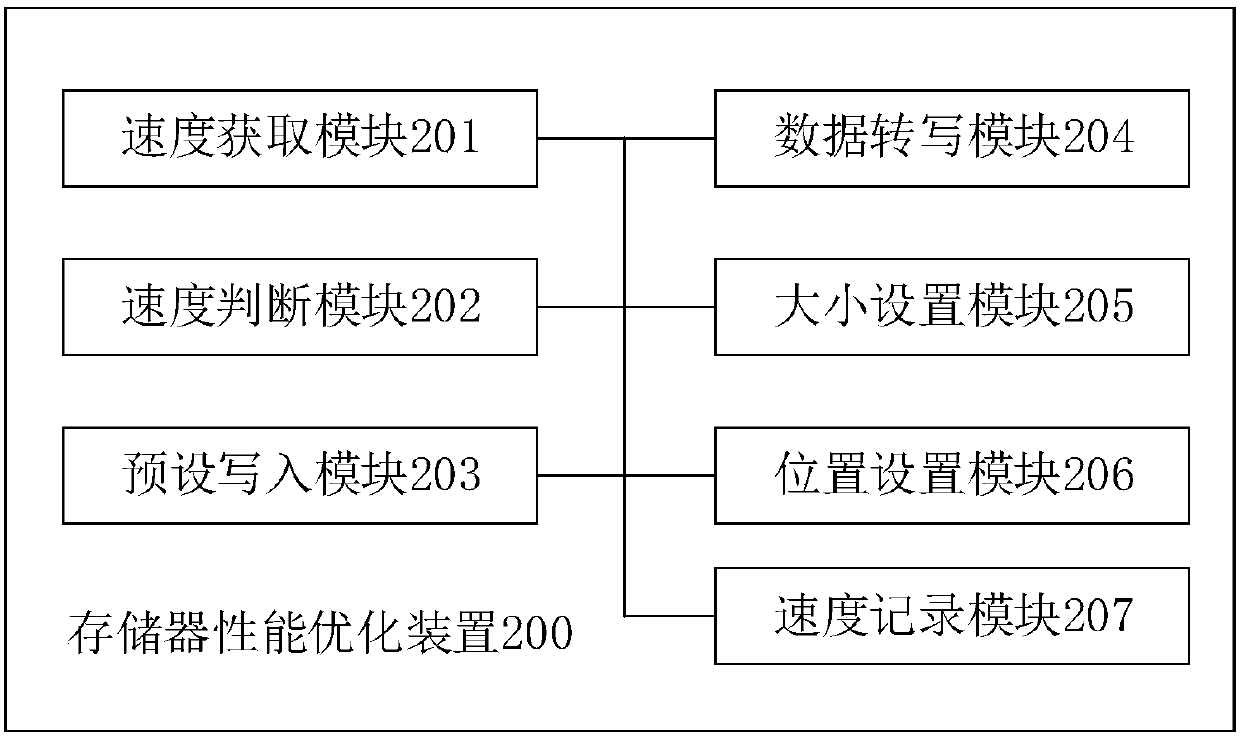

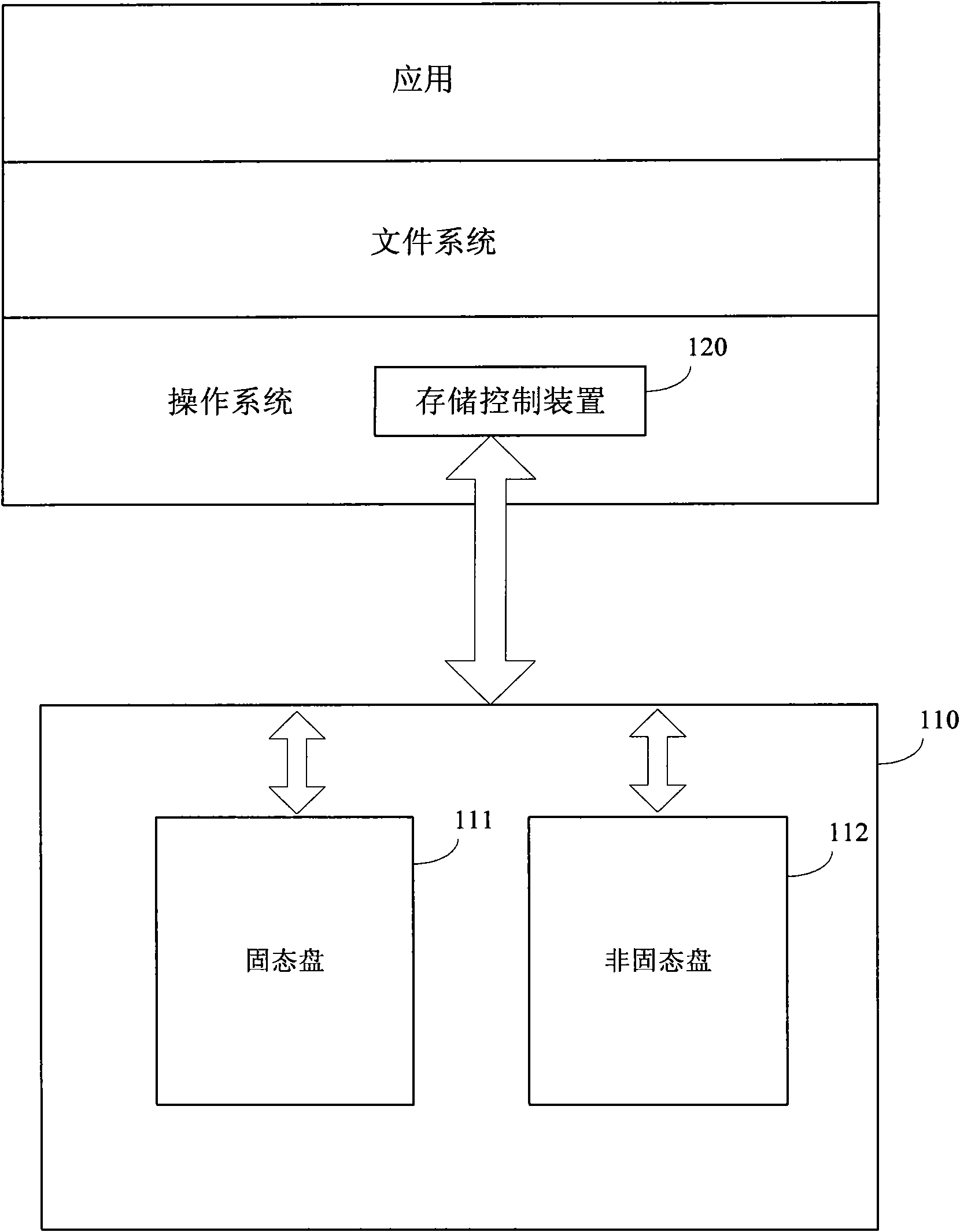

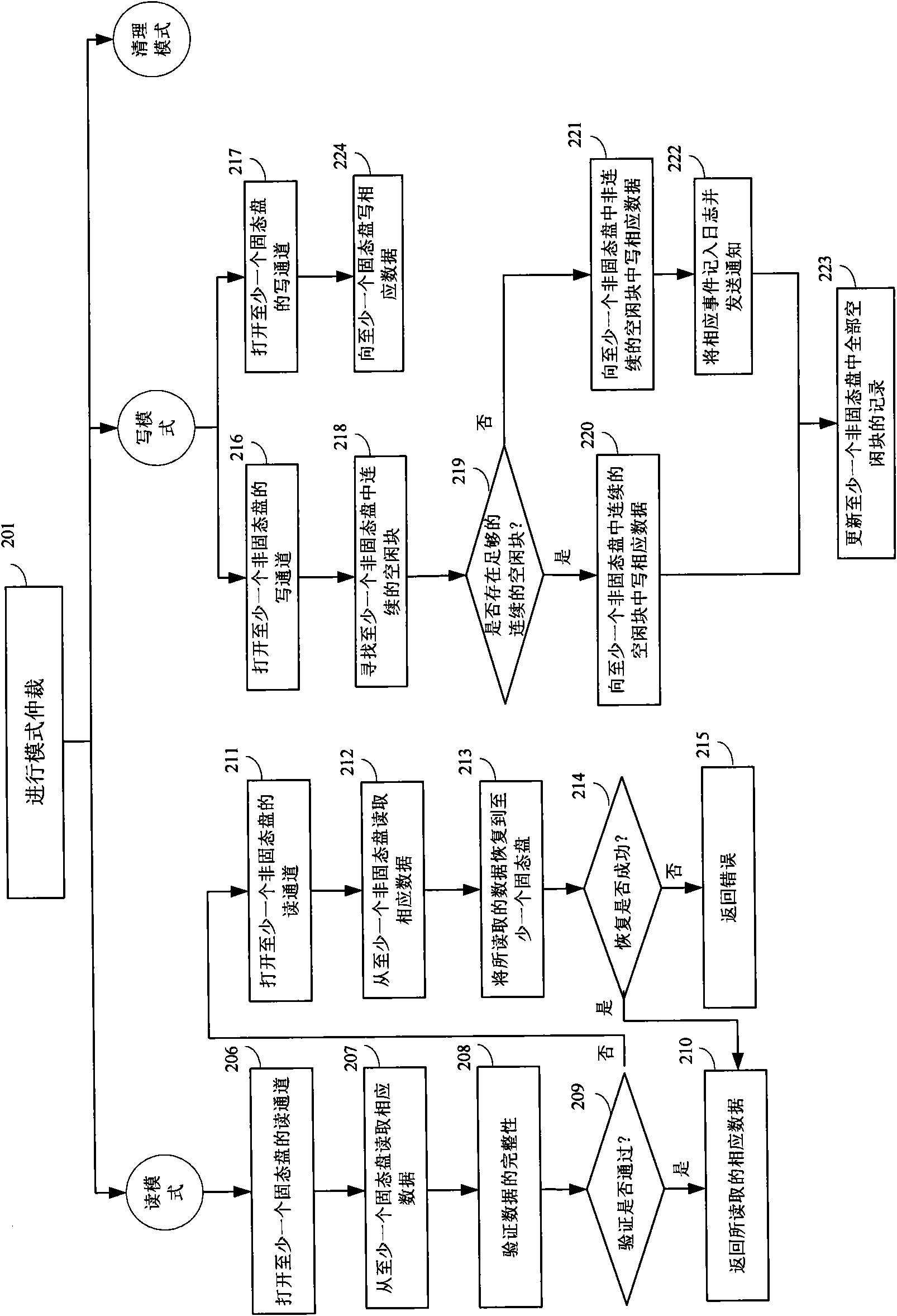

Memorizer performance optimizing method and device and computer equipment

InactiveCN107728948AOptimize write performanceImprove work efficiencyInput/output to record carriersData informationComputer engineering

The invention provides a memorizer performance optimizing method and device and computer equipment. The method includes the steps that when data is written into a memorizer, the current writing speedof the memorizer is obtained; whether the current writing speed is smaller than a preset threshold value or not is judged; if yes, the data is written into preset storage space, and write success response is returned. Whether writing of the memorizer is slow is judged by adopting the mode of obtaining and comparing memorizer writing data information, so that the data is written into the preset storage space, and the write success response is returned. The problem of hard disk falling speed problem in the hard disk writing process is found, the hard disk writing performance is optimized, and the working efficiency is improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

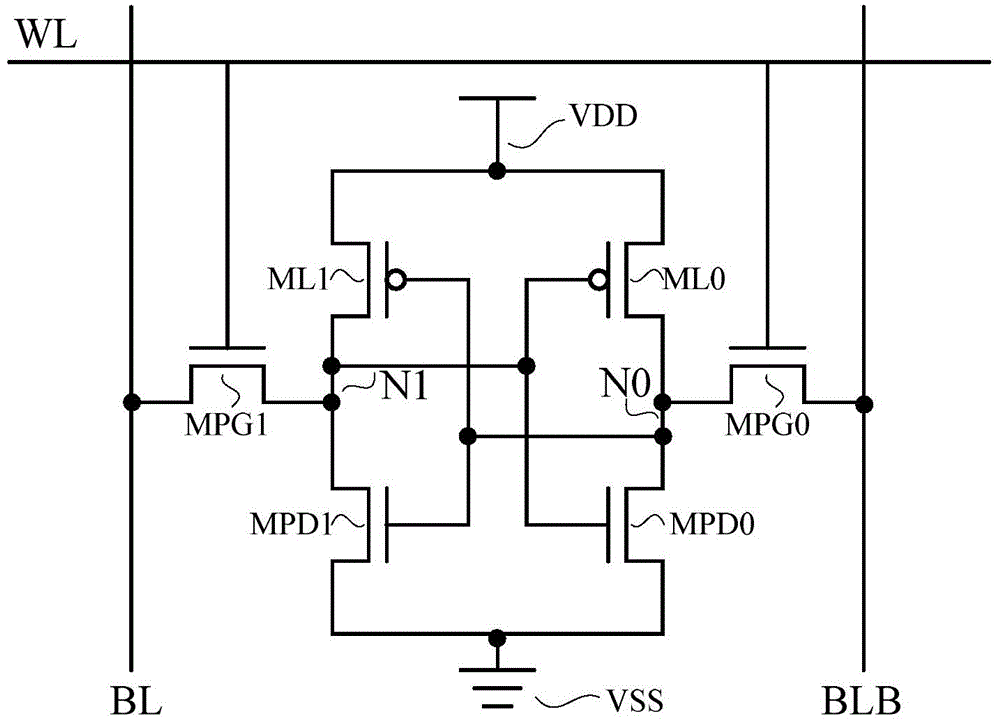

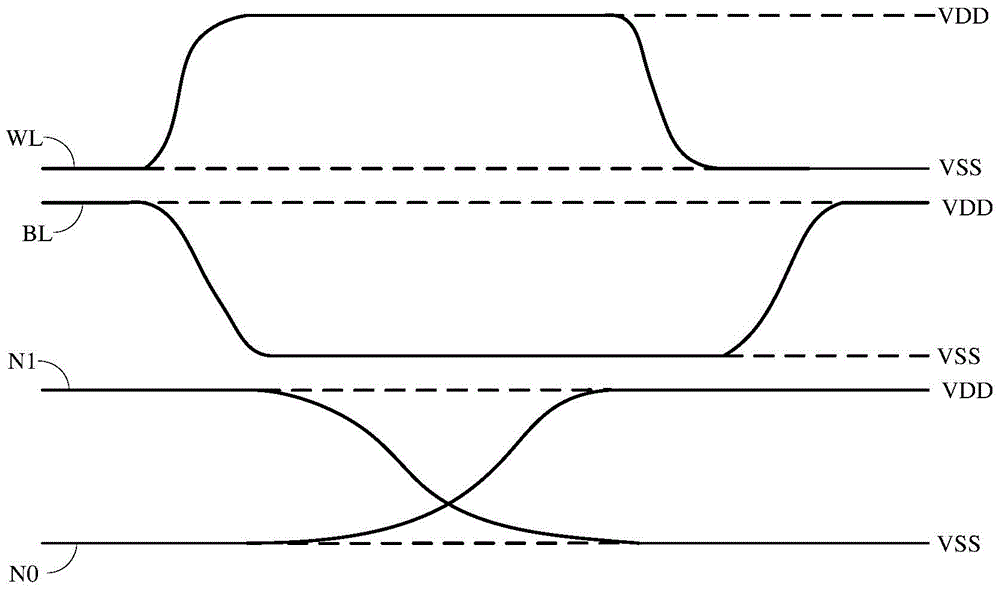

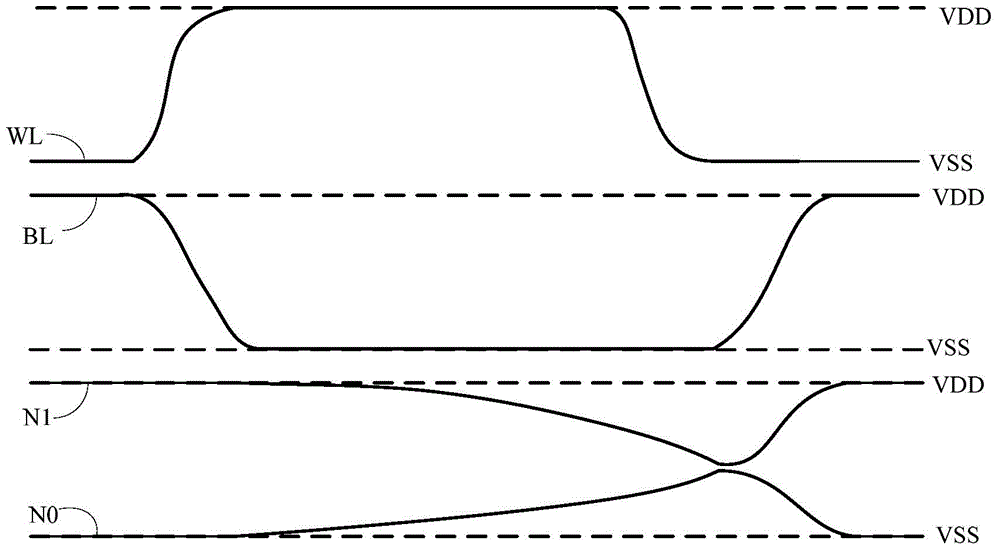

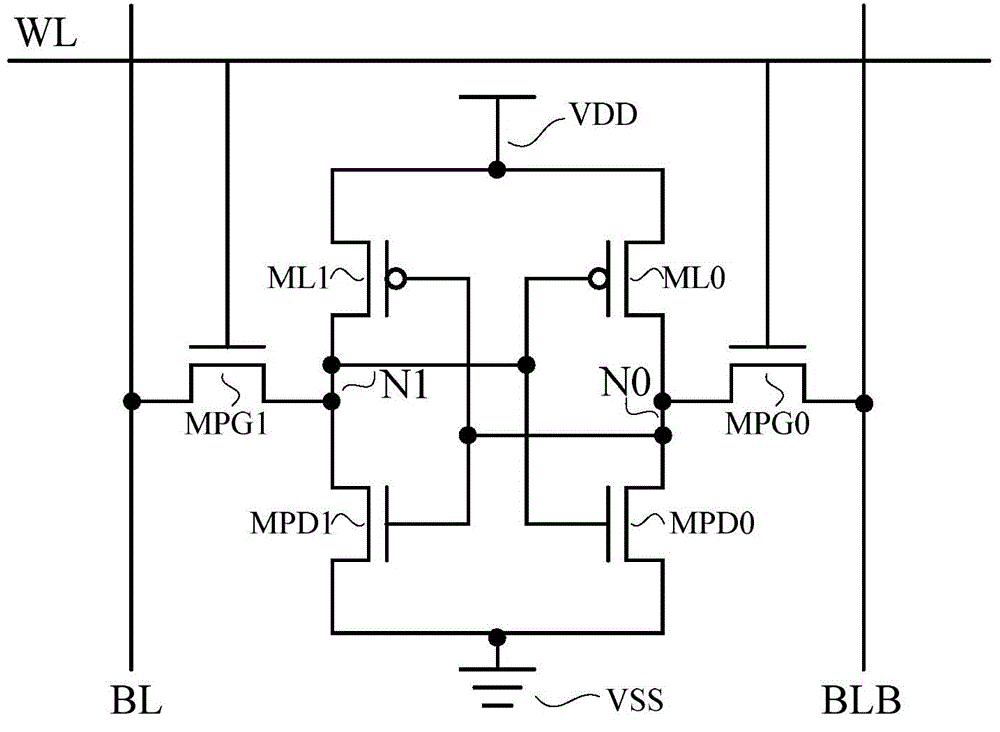

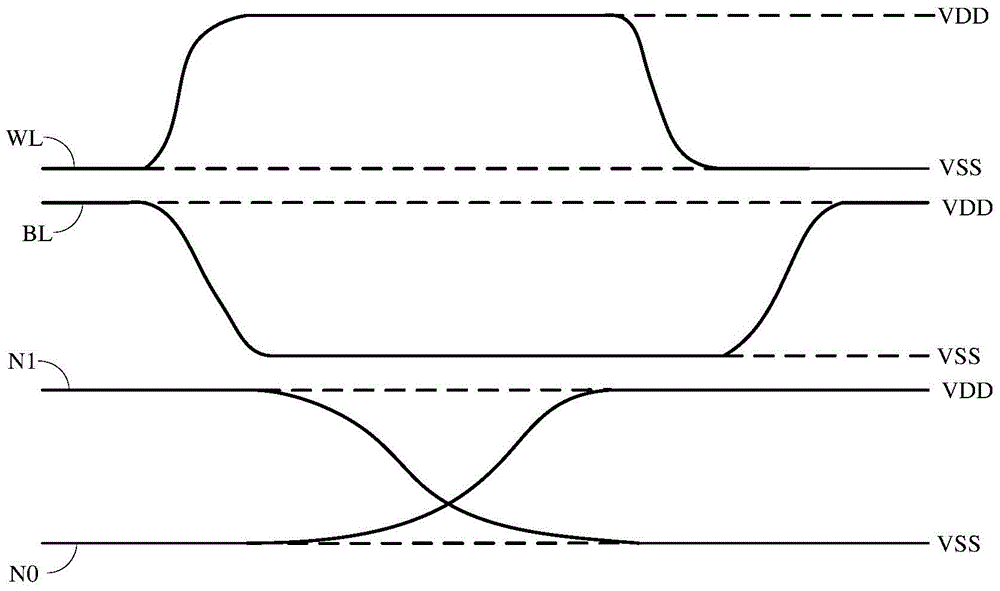

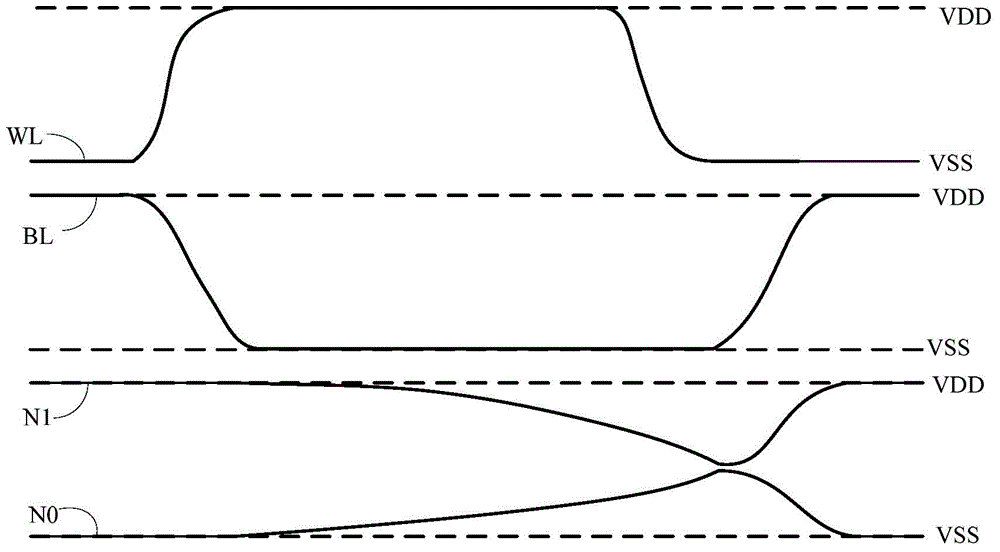

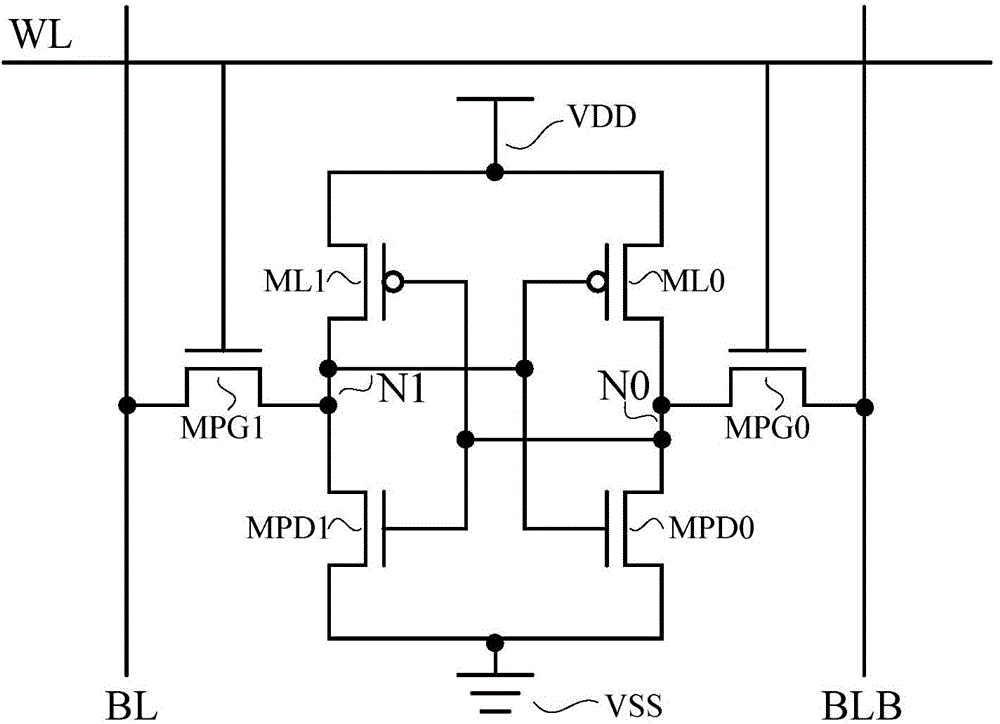

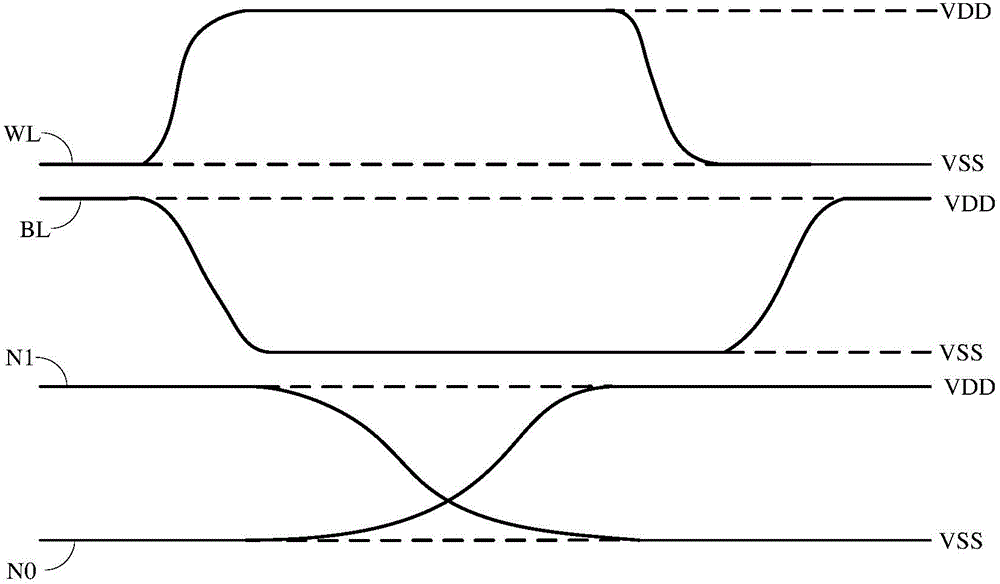

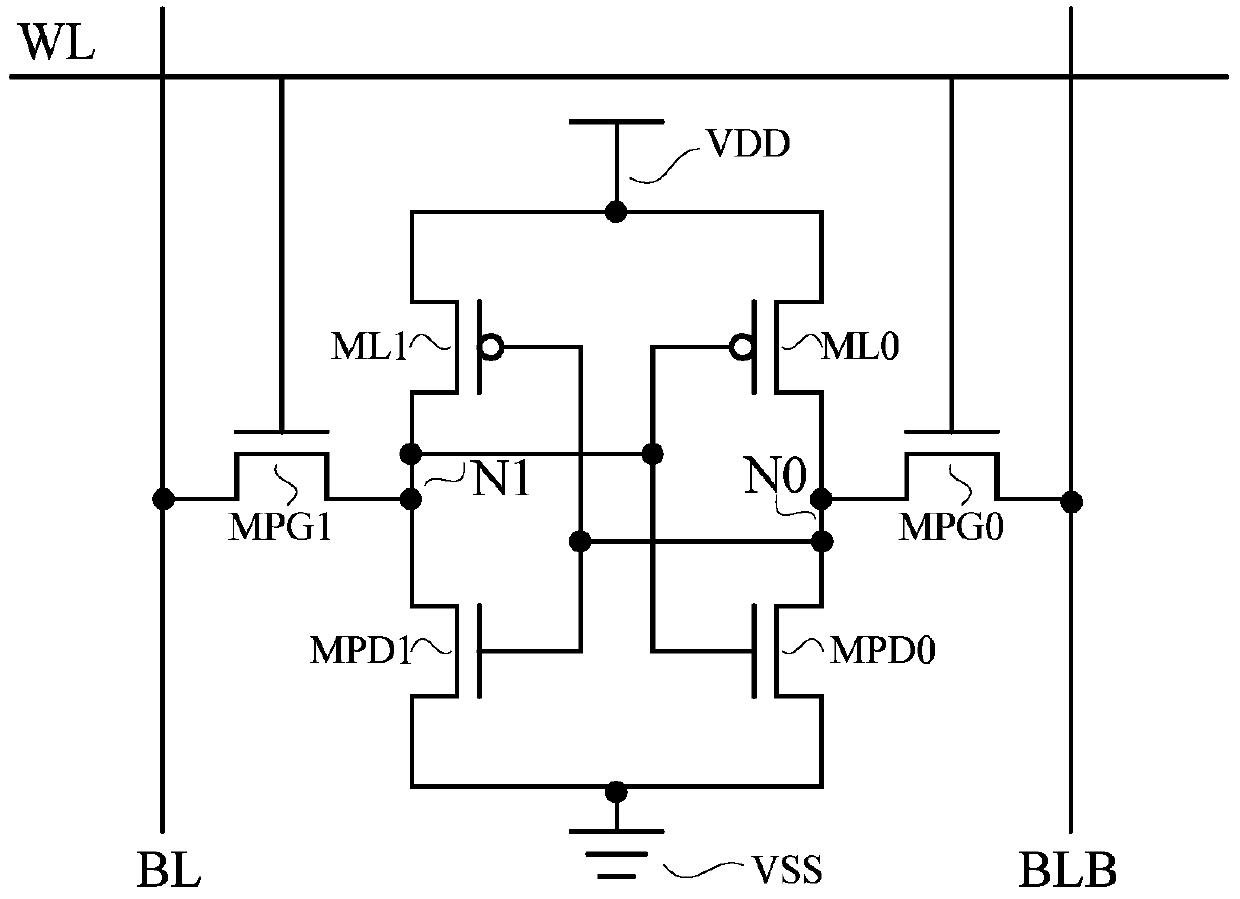

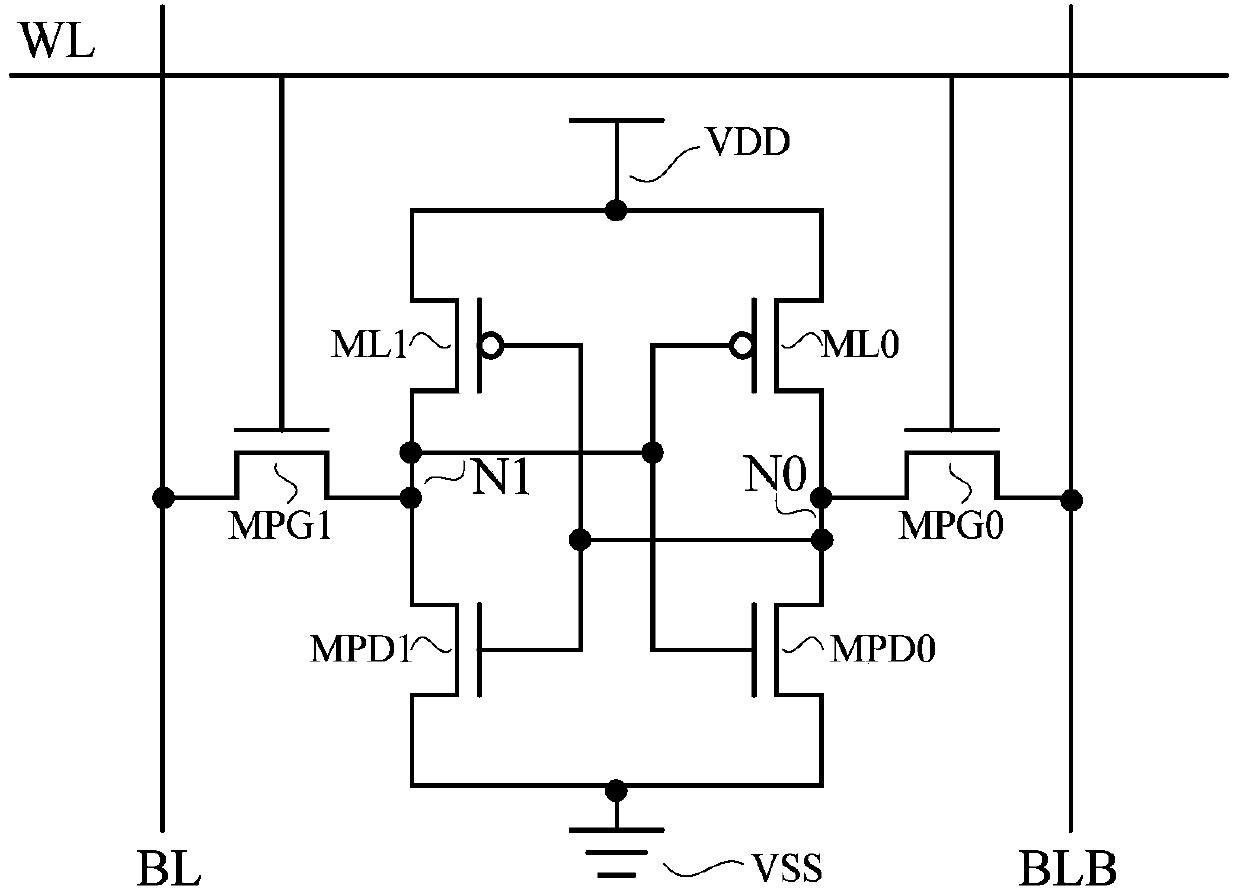

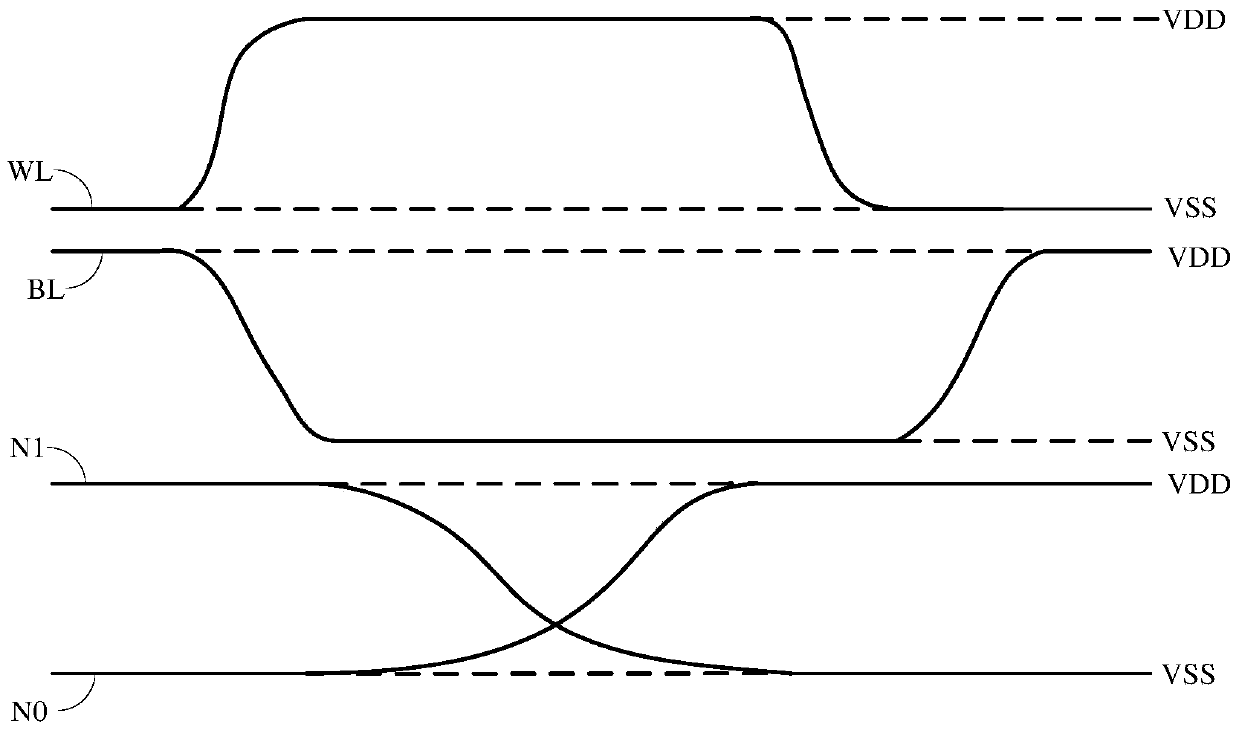

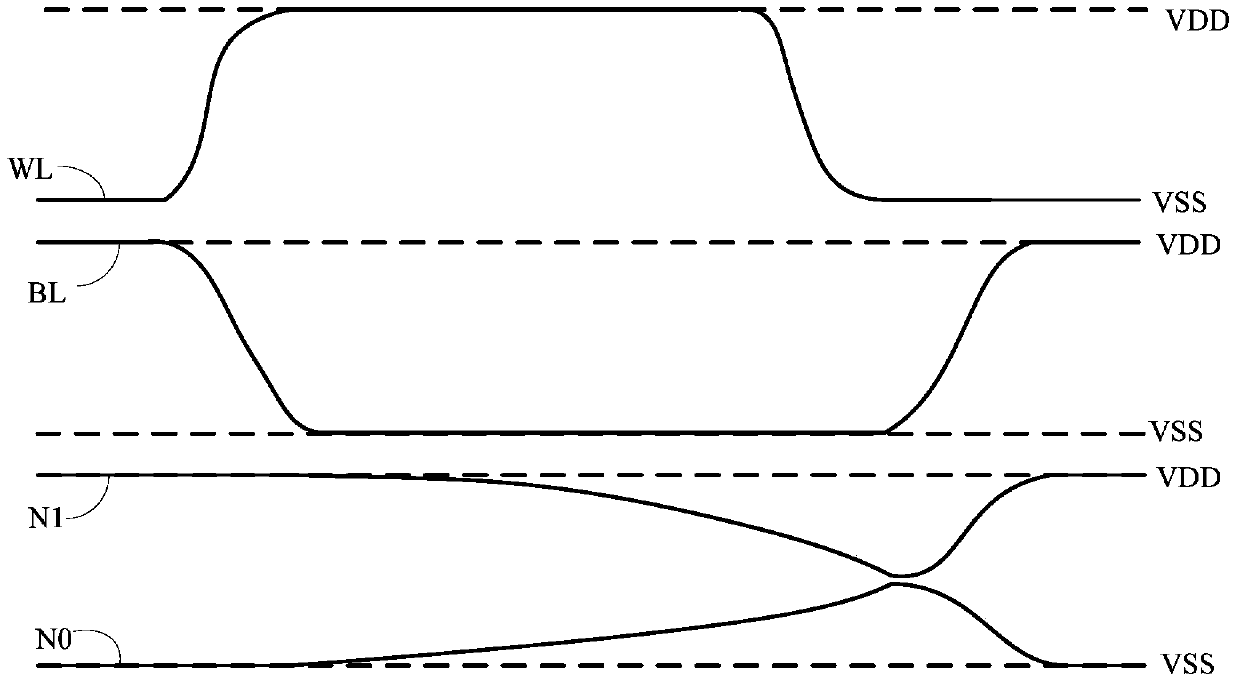

SRAM memory cell, storage array and memory

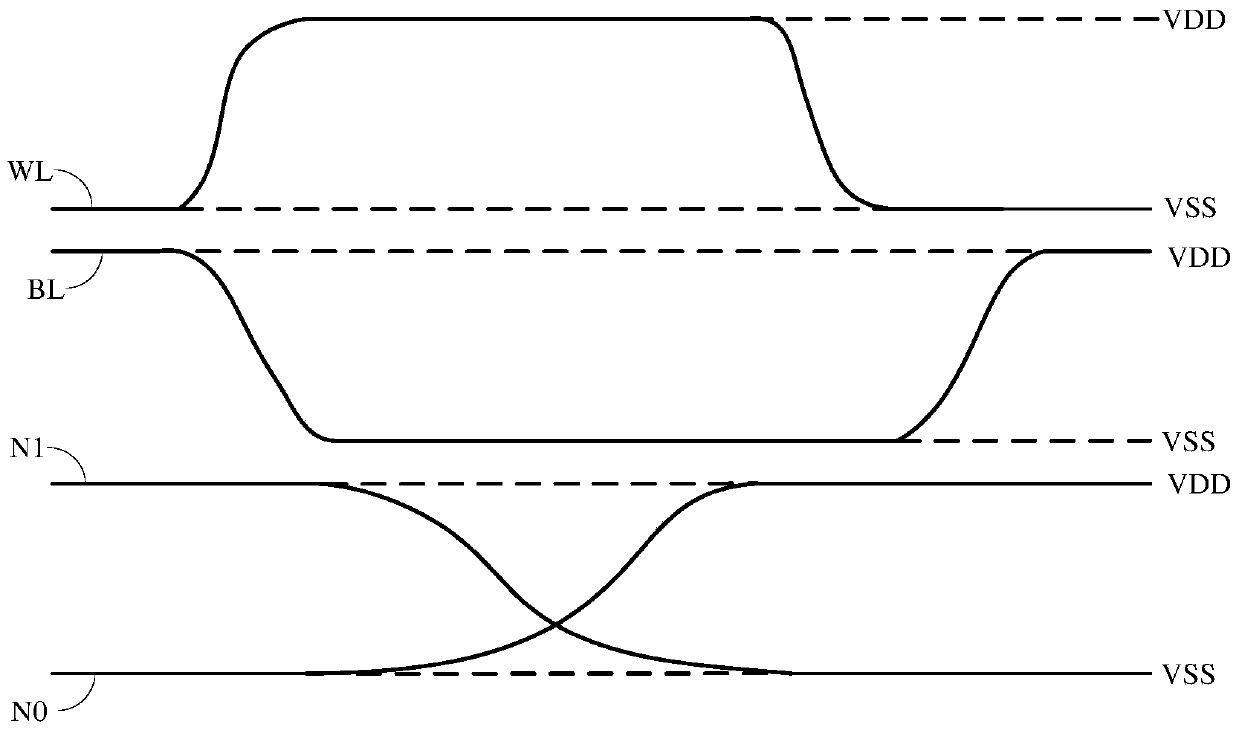

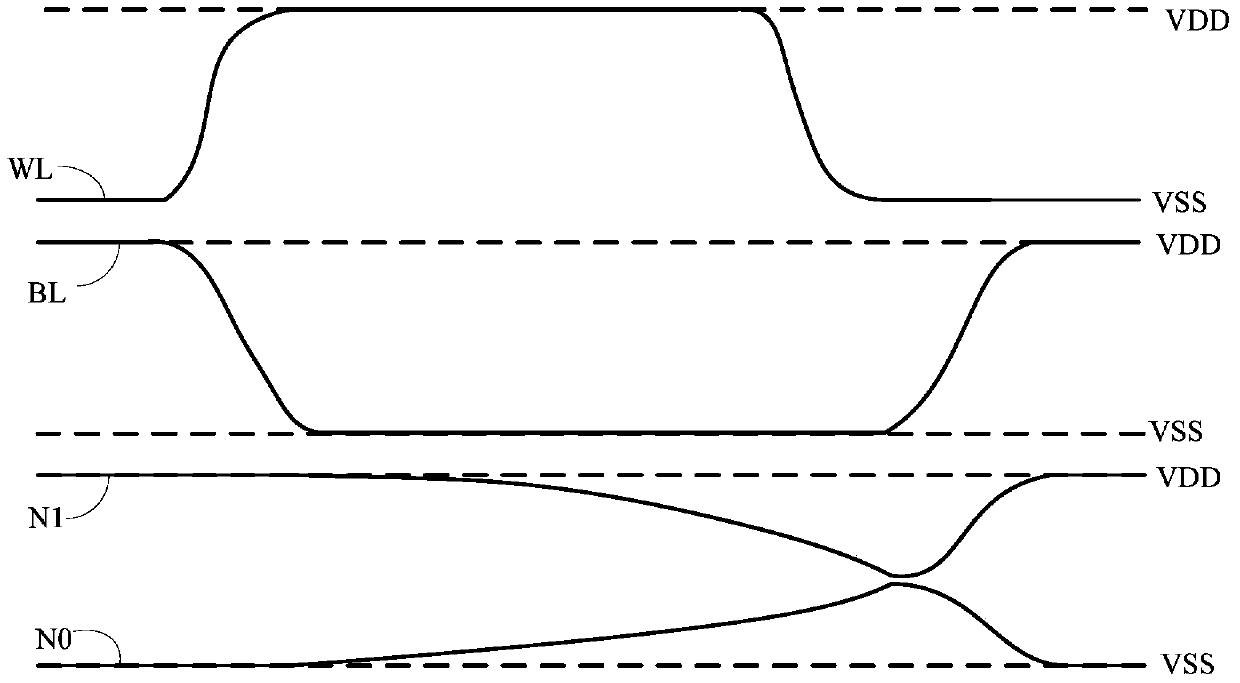

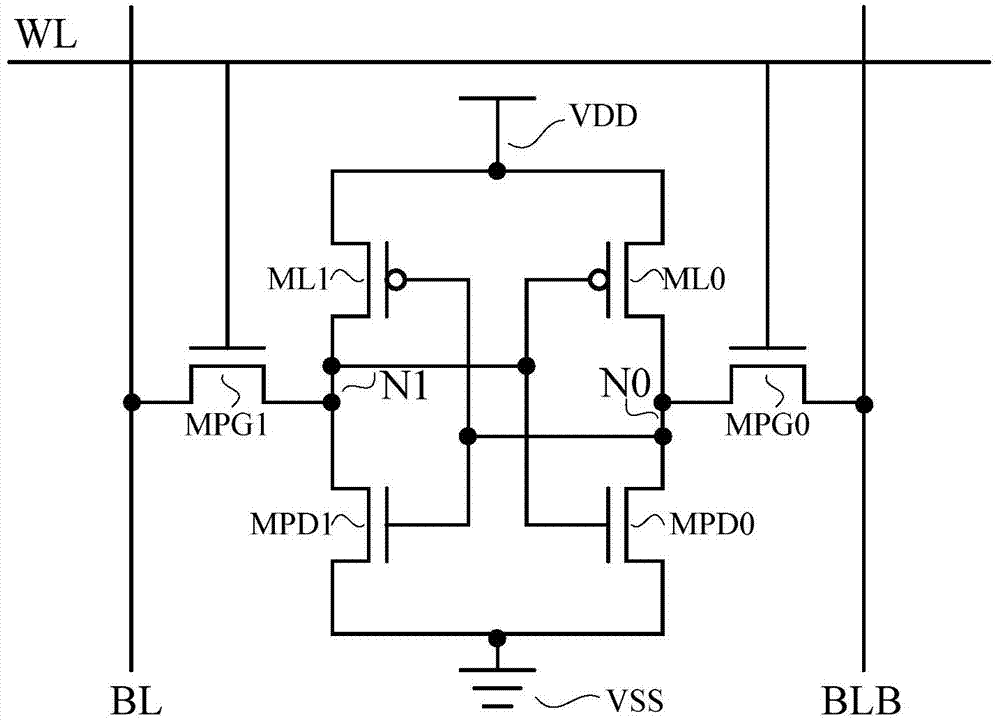

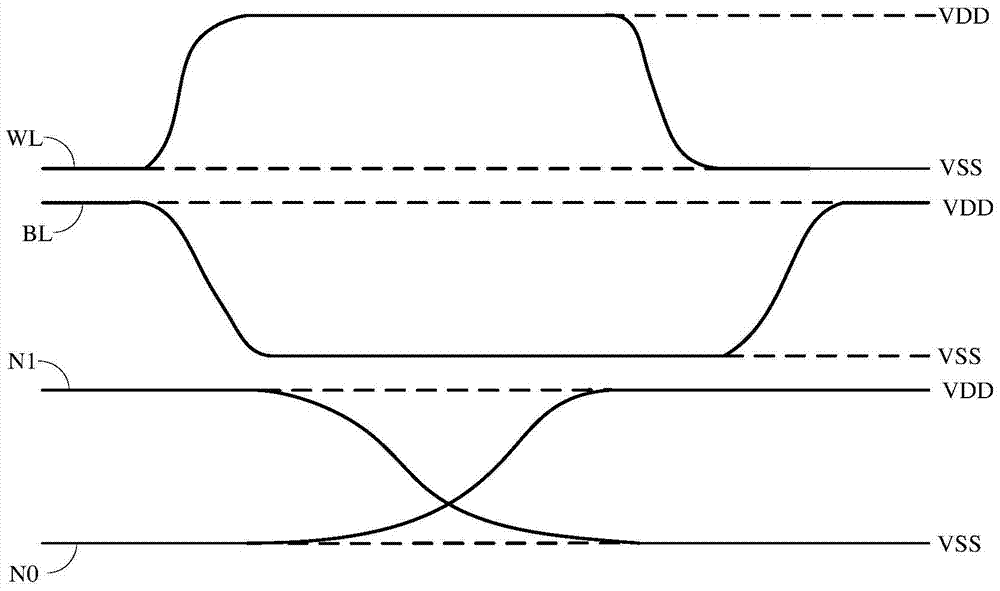

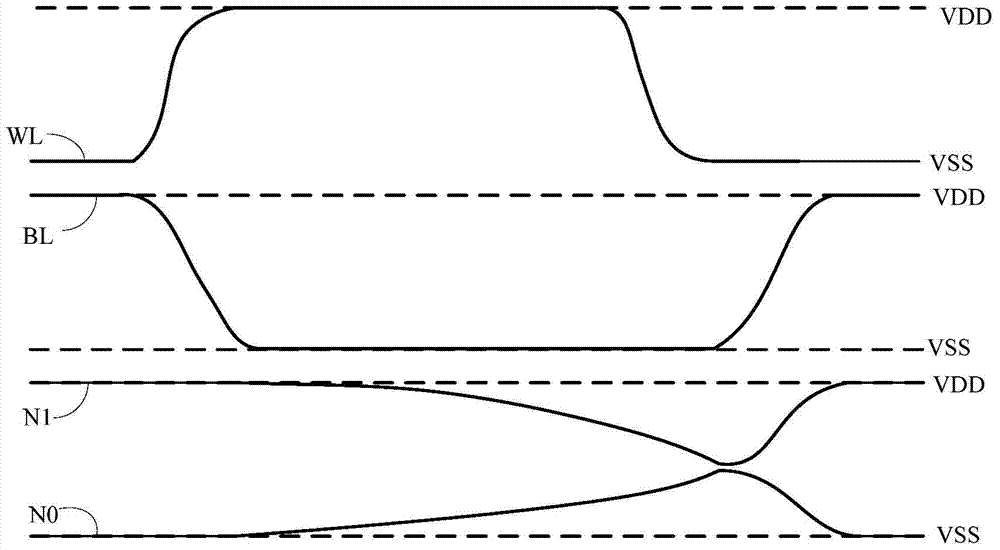

ActiveCN105336364ATroubleshoot write operation failuresBoost reverse voltageDigital storageTransistorElectrical and Electronics engineering

The invention relates to a SRAM memory cell, a storage array and a memory. The SRAM memory cell comprises a first PMOS transistor, a second PMOS transistor, a first NMOS transistor, a second NMOS transistor, a first transmission transistor, a second transmission transistor, a first double-grid NMOS transistor, and a second double-grid NMOS transistor. According to the invention, the possible failure problem of write-in operation of the SRAM memory cell can be solved.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

Pixel circuit and display panel

ActiveCN112071259AImprove writing effectExtended voltage rangeStatic indicating devicesVoltage rangeCapacitance

The invention discloses a pixel circuit and a display panel. The pixel circuit comprises a driving transistor, a writing transistor, a first capacitor and a second capacitor, wherein the ratio of thecapacitance value of the second capacitor to the capacitance value of the first capacitor is not less than 50% and not more than 150%; by configuring the proportional relation between the capacitancevalue of the second capacitor and the capacitance value of the first capacitor, the write-in effect of data signals can be improved; moreover, the voltage range of the data signal is increased, and the gray-scale precision can be improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

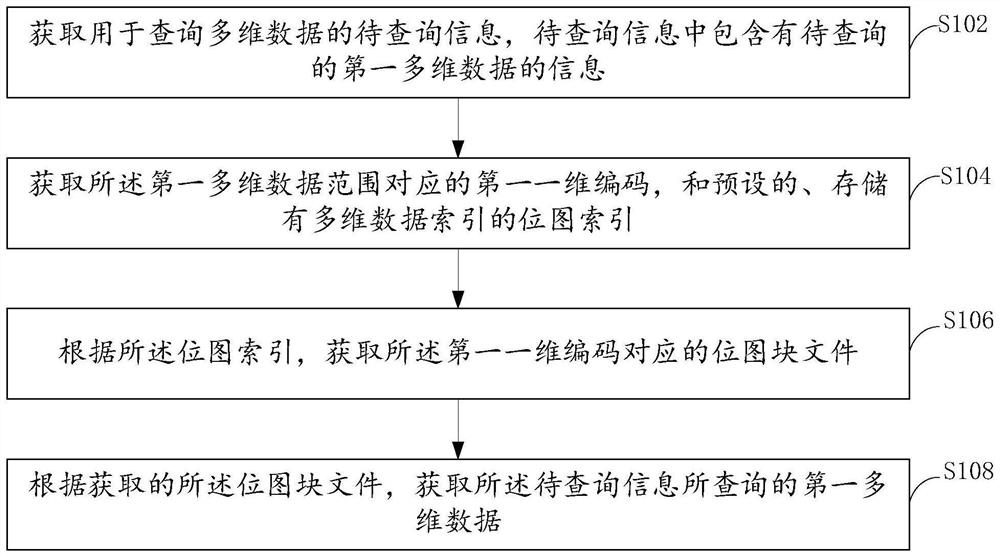

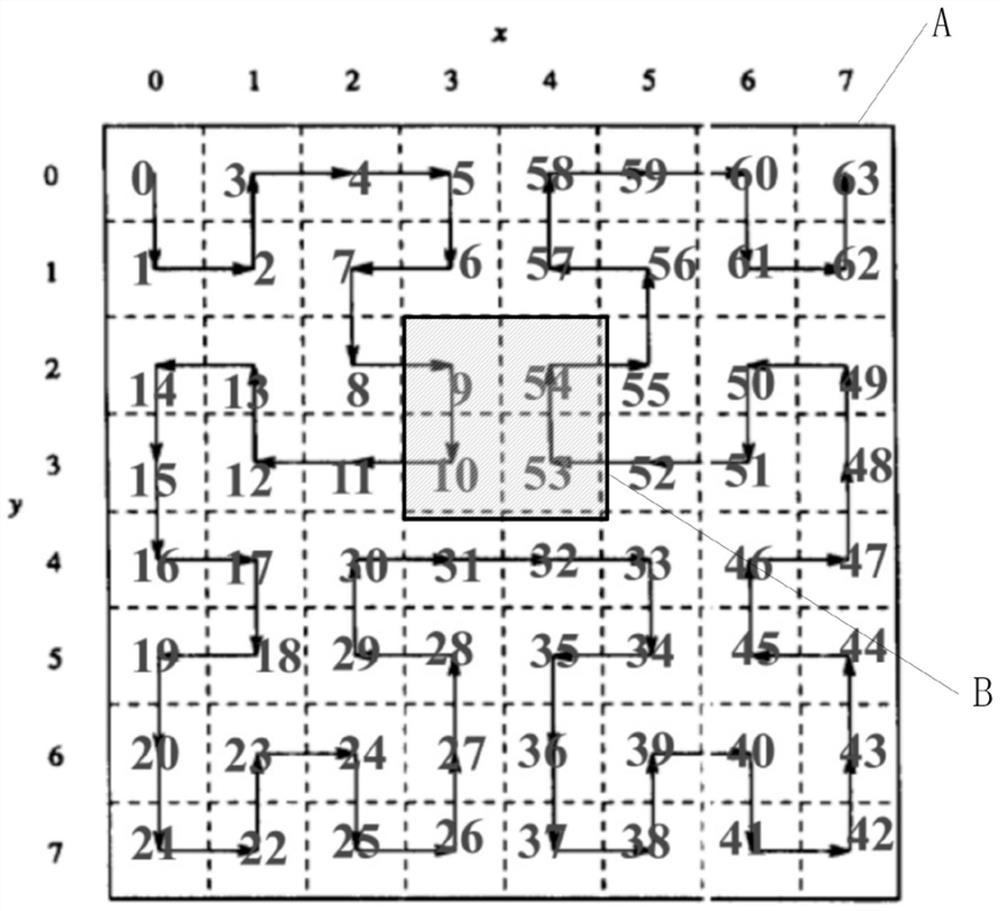

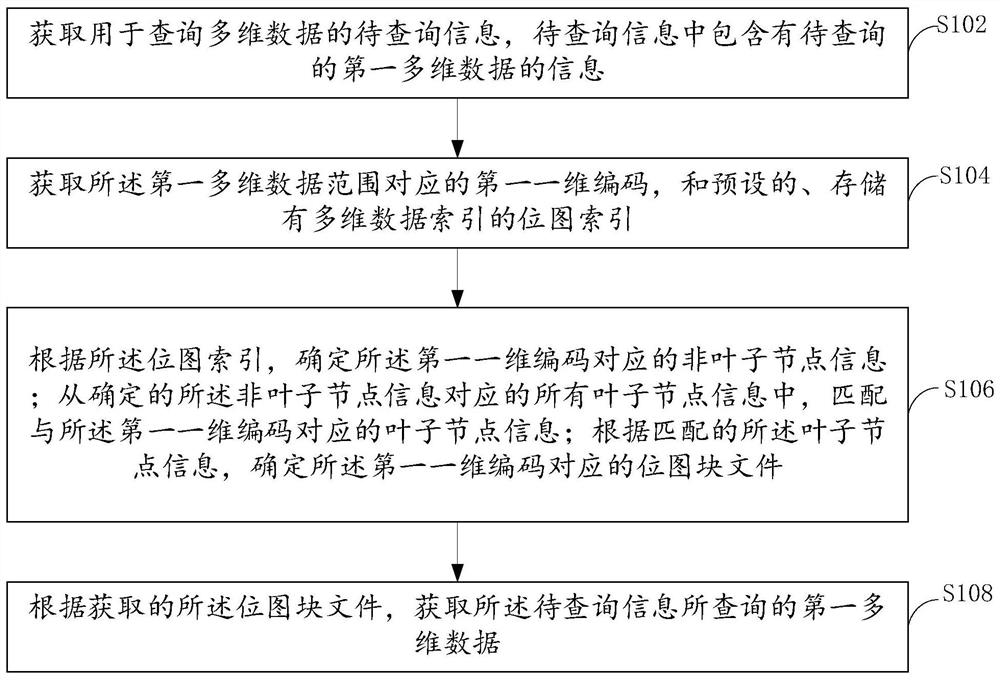

Data query method and device, index generation method and device and electronic equipment

PendingCN113076334AReduce storage space usageAvoid high storage costsMulti-dimensional databasesSpecial data processing applicationsEngineeringMulti dimensional data

The embodiment of the invention provides a data query method and device, an index generation method and device and electronic equipment. The data query method comprises the steps that to-be-queried information used for querying multi-dimensional data is obtained, and the to-be-queried information comprises information of first multi-dimensional data to be queried; a first one-dimensional code corresponding to the first multi-dimensional data and a preset bitmap index storing a multi-dimensional data index are obtained, and the multi-dimensional data index is generated according to a second one-dimensional code corresponding to second multi-dimensional data; collecting a bitmap block file corresponding to the first one-dimensional code according to the bitmap index; According to the obtained bitmap block file, obtaining first multi-dimensional data queried by the to-be-queried information. Through the embodiment of the invention, the retrieval efficiency is higher.

Owner:ALIBABA GRP HLDG LTD

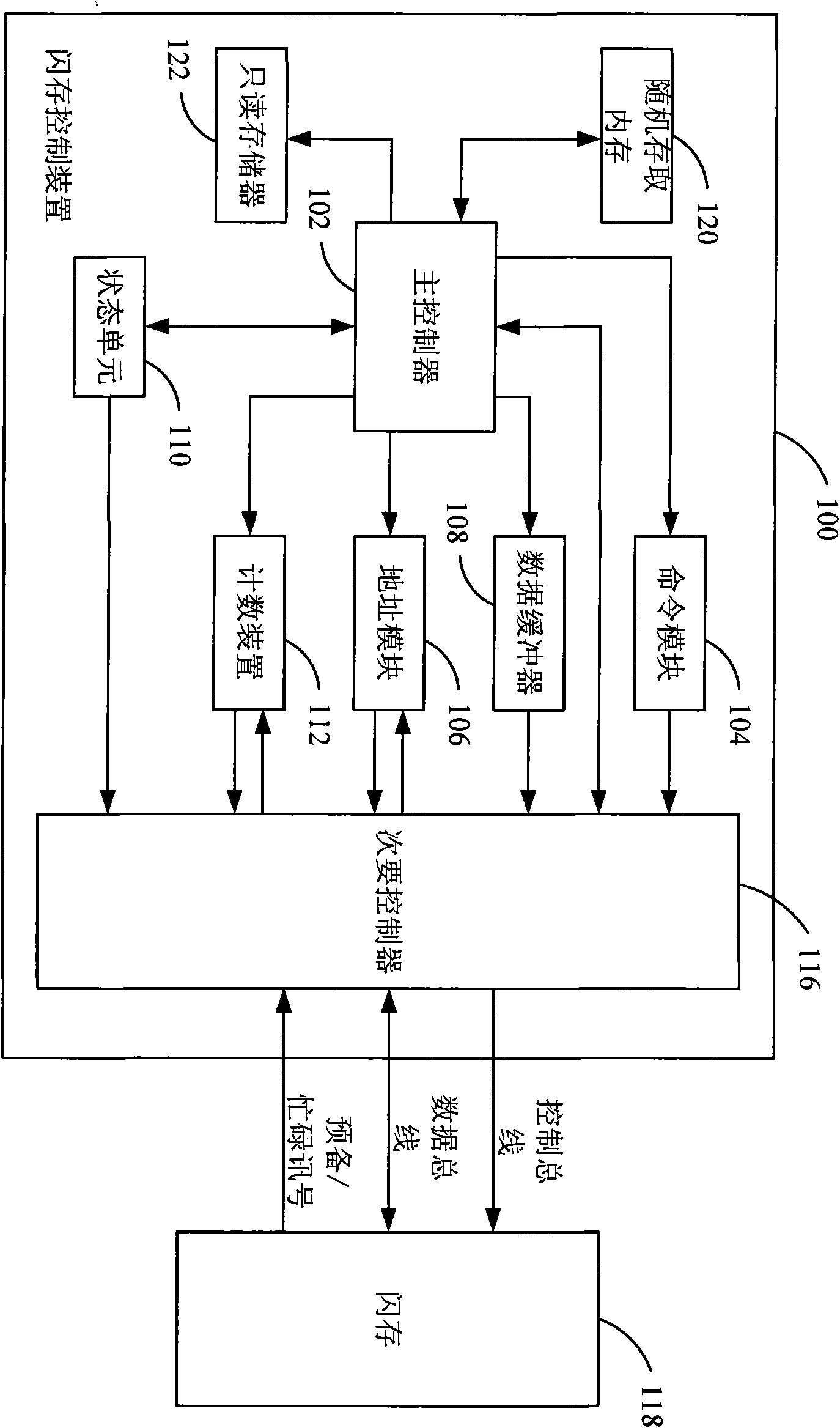

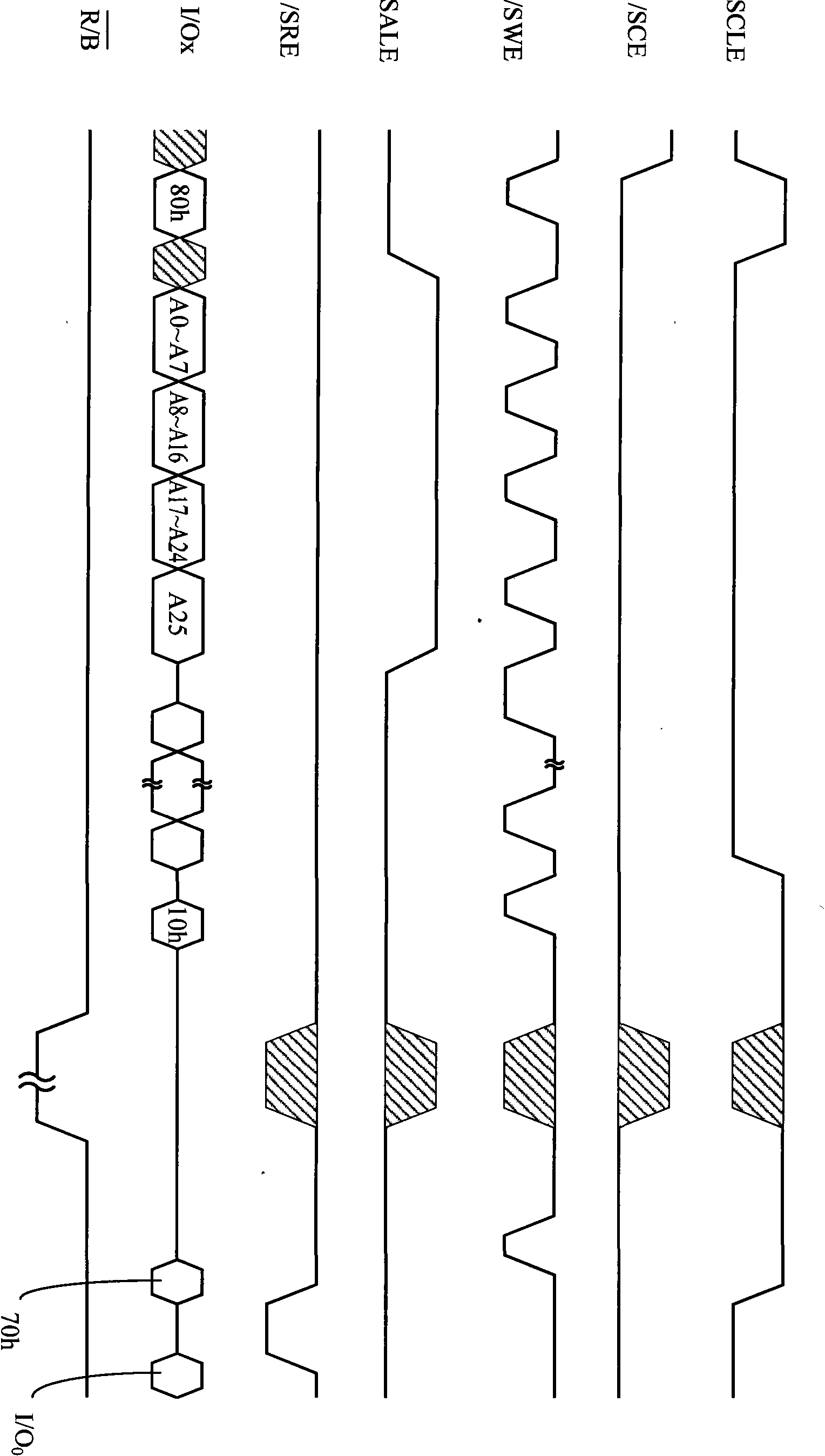

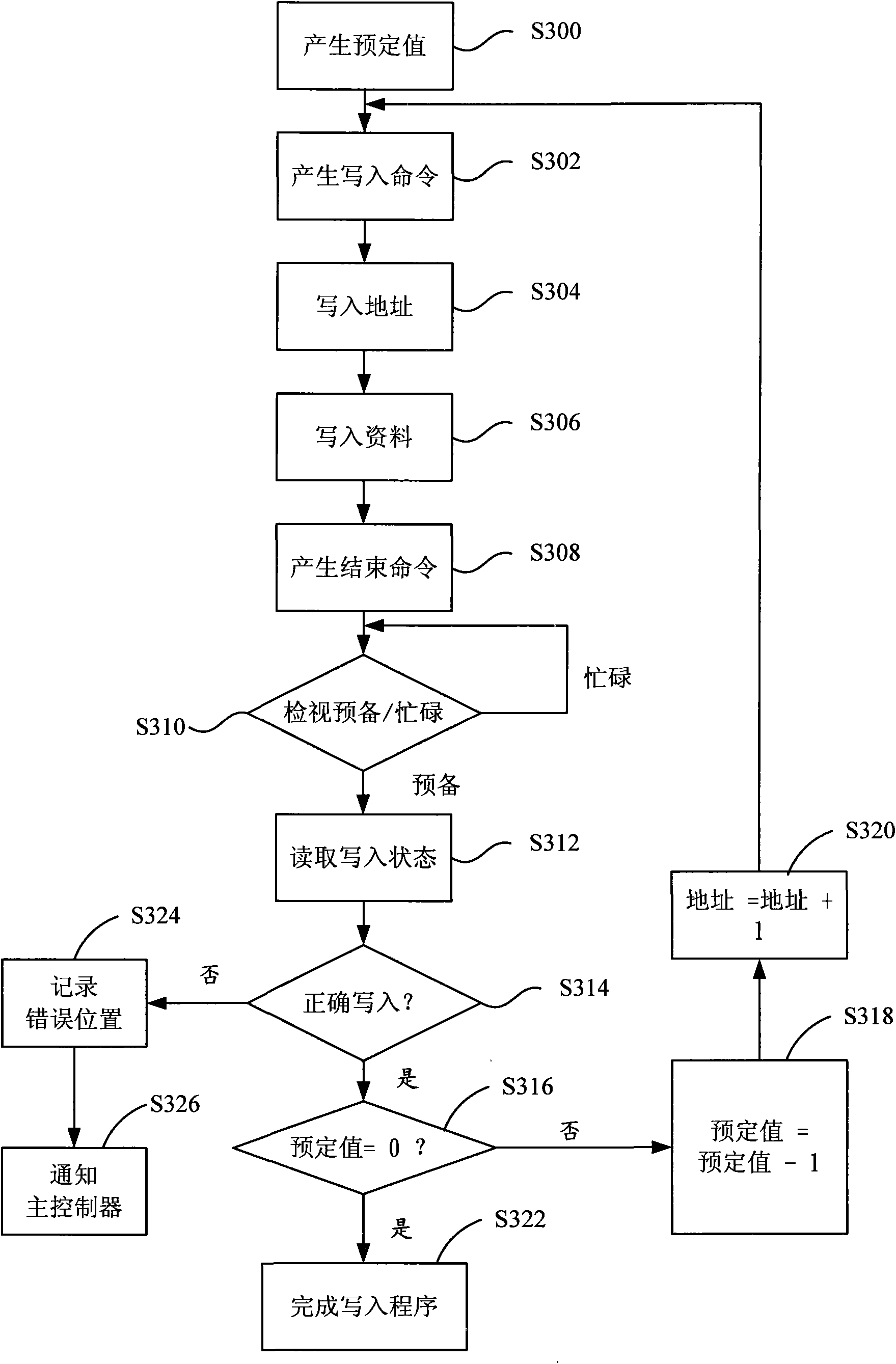

Flash memory control device with sequential write and control method

InactiveCN101673241AOptimize write performanceMemory adressing/allocation/relocationMaster controllerData buffer

The invention discloses a flash memory control device with sequential write and a control method thereof. The flash memory control device comprises a main controller, a command module, an address module, a data buffer, a state unit and a counting device, wherein the main controller generates a preset value; the command module stores a write command in a period of executing a write procedure; the address module stores a current address and carries out addressing of a current page; the data buffer stores data; the state unit decides that a flash memory is in a standby mode or a busy mode; and when the command module correctly writes the data to the current page, the address module generates at least one downstream adjacent address, and the command module orderly and continuously write the data to at least one downstream adjacent page so as to completely and continuously write the data to all the pages in the period of executing the write procedure.

Owner:GENESYS LOGIC INC

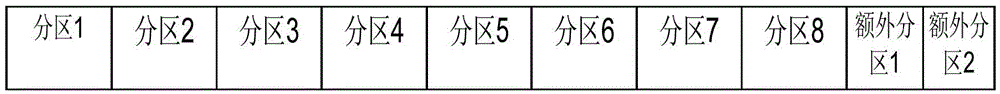

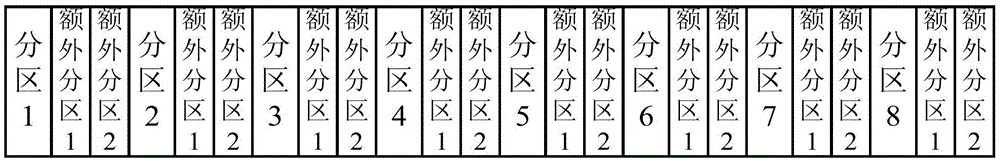

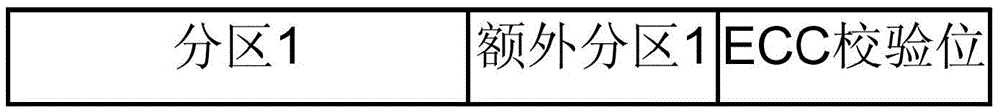

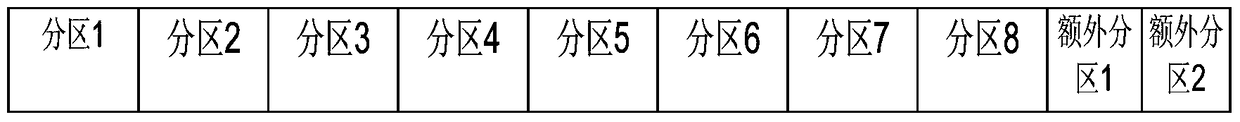

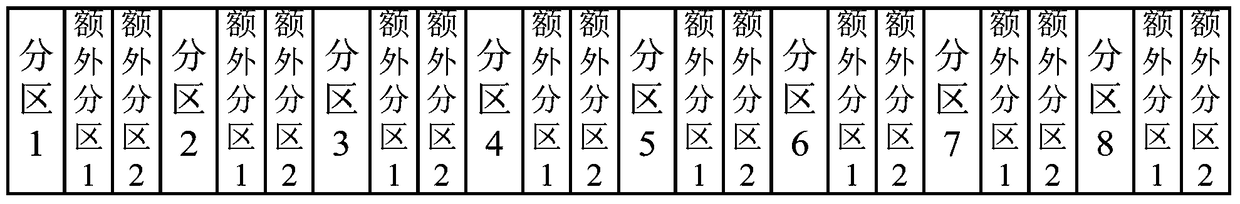

Method for scanning error bits

ActiveCN105607961AAverage number of error bitsOptimize write performanceRedundant data error correctionReal errorStorage cell

The invention discloses a method for scanning error bits. The method comprises the following steps: S1, averagely dividing a first data partition of a storage unit into N equal second data partitions; S2, forming a third data partition by using the second data partitions, scanning the third data partition and setting the permissible number of the error bits; S3, comparing the actual number of the error bits of the third data partition with the permissible number of the error bits, if the actual number of the error bits is greater than the permissible number of the error bits, executing step 4, if not, executing step 5; S4, carrying out one-time programming operation on the storage unit and returning to carry out the step S3; and S5, recording the current actual number of the error bits of the third data partition. According to the method, the qualification rate of storage chips can be adjusted through modifying the setting conditions; the corresponding data region and the error correcting capability of the own ECC (Error Correction Code) of a controller can be adjusted on the basis of final statistical results; and therefore, a better write performance is obtained.

Owner:GIGADEVICE SEMICON (BEIJING) INC

SRAM memory cell, memory array and memory

ActiveCN105206298ATroubleshoot write operation failuresBoost reverse voltageDigital storageEngineeringMemory array

The invention relates to a SRAM memory cell, a memory array and a memory. The SRAM memory cell comprises a first PMOS transistor, a second PMOS transistor, a first NMOS transistor, a second NMOS transistor, a first transmission transistor, a second transmission transistor, a first dual-gate PMOS transistor, a second dual-gate PMOS transistor, a first dual-gate NMOS transistor and a second dual-gate NMOS transistor. The SRAM memory cell solves the problem that the existing SRAM memory cell has write operation failure possibility.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

SRAM memory cell, storage array and memory

ActiveCN105336363ATroubleshoot write operation failuresBoost reverse voltageDigital storageTransistorElectrical and Electronics engineering

The invention relates to a SRAM memory cell, a storage array and a memory. The SRAM memory cell comprises a first PMOS transistor, a second PMOS transistor, a first NMOS transistor, a second NMOS transistor, a first transmission transistor, a second transmission transistor, a first double-grid PMOS transistor and a second double-grid PMOS transistor. The possible failure problem of write-in operation of the SRAM memory cell can be solved.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

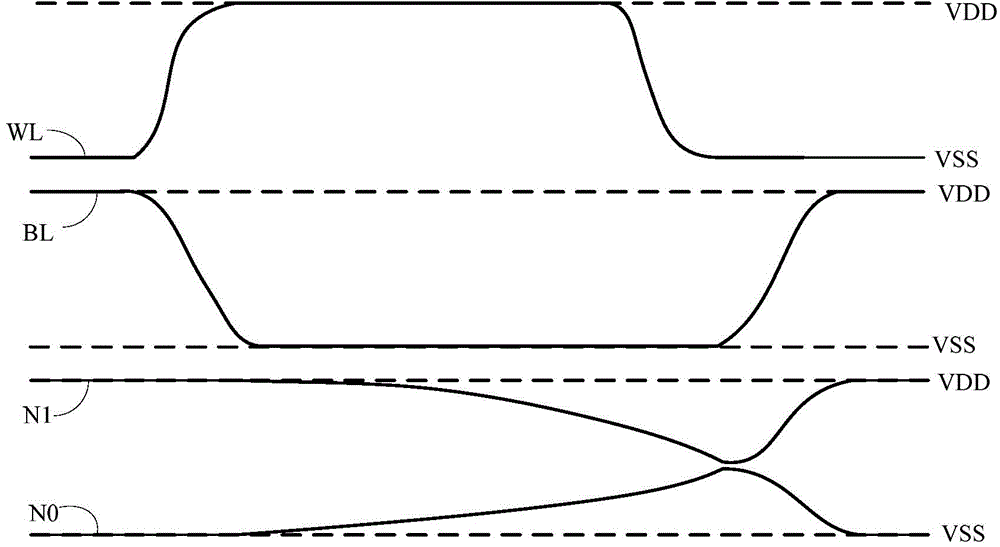

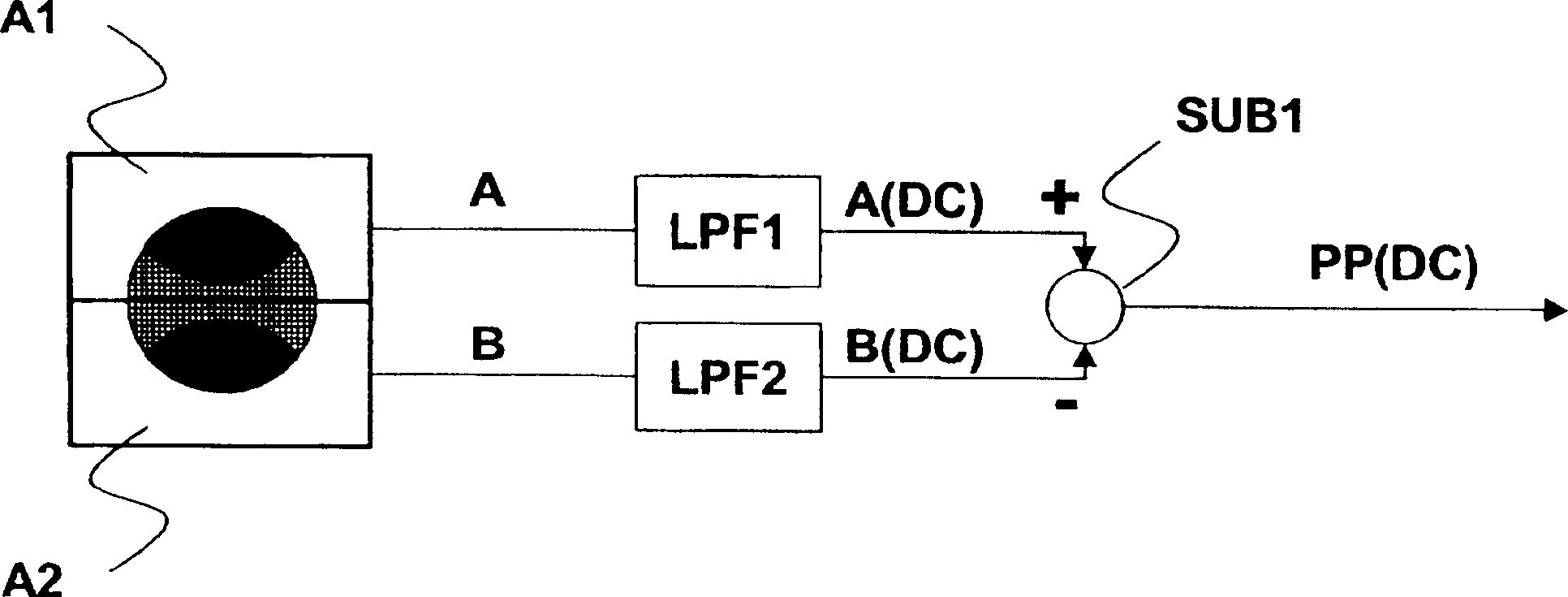

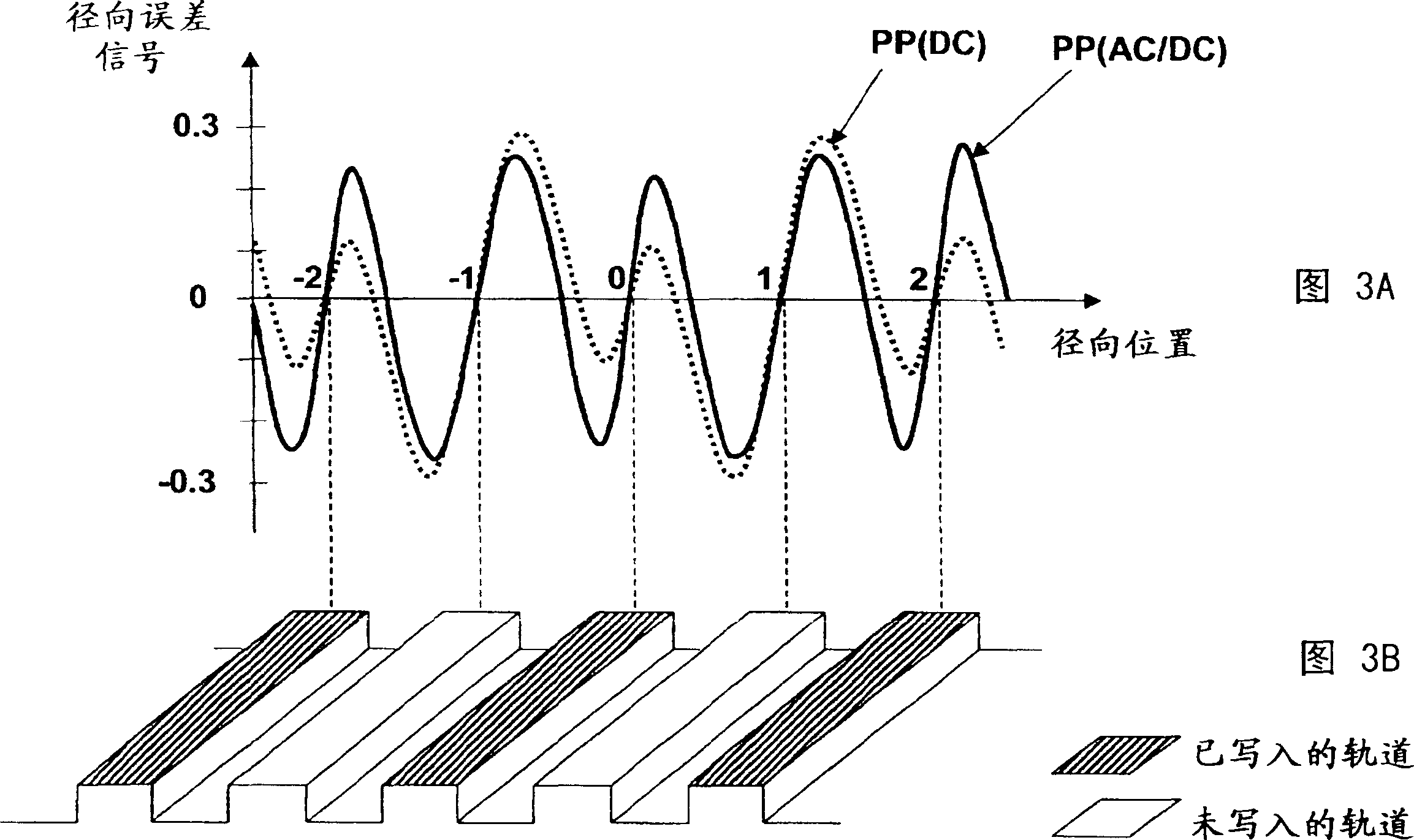

Tracking system and method

InactiveCN1675695AOptimize write performanceReduce the number of lost tracksRecord information storageDisposition/mounting of headsPhotodetectorDifferential signaling

Tracking system for guiding an optical beam on tracks on an optical disc, said tracking system comprising a photodetector (A1, A2) for detecting optical beams derived from said optical beam, said photodetector generating a first output signal (A) and a second output signal (B), said tracking system comprising first processing means for generating a first differential signal (PP(DC)) corresponding to the low-frequency part of a difference between said first and second output signals. The tracking system comprises second processing means for generating a tracking error signal (PP(AC / DC)) defined by the addition of said first differential signal (PP(DC)) to a second differential signal (PP'(AC)), said second differential signal corresponding to a fraction of the difference in amplitude of the high-frequency components of said first and second output signals. Use: Optical disc player / writer.

Owner:KONINKLIJKE PHILIPS NV

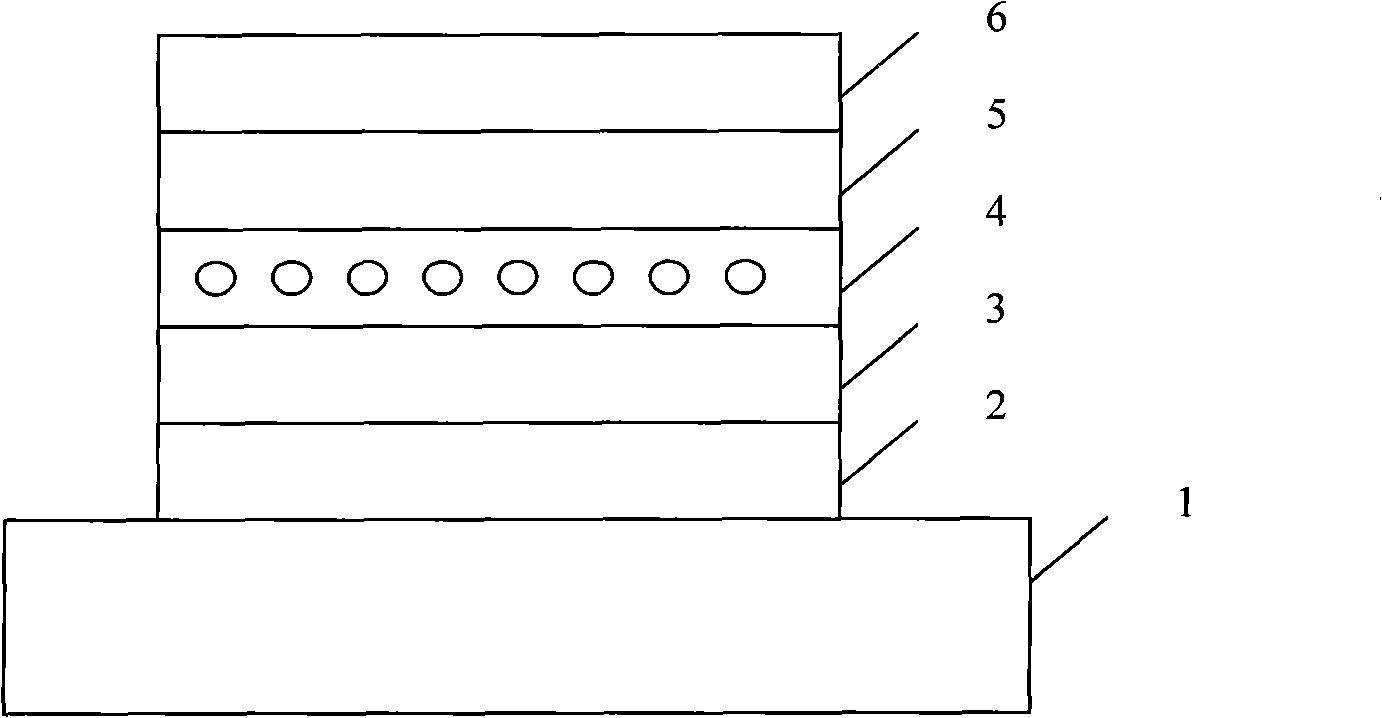

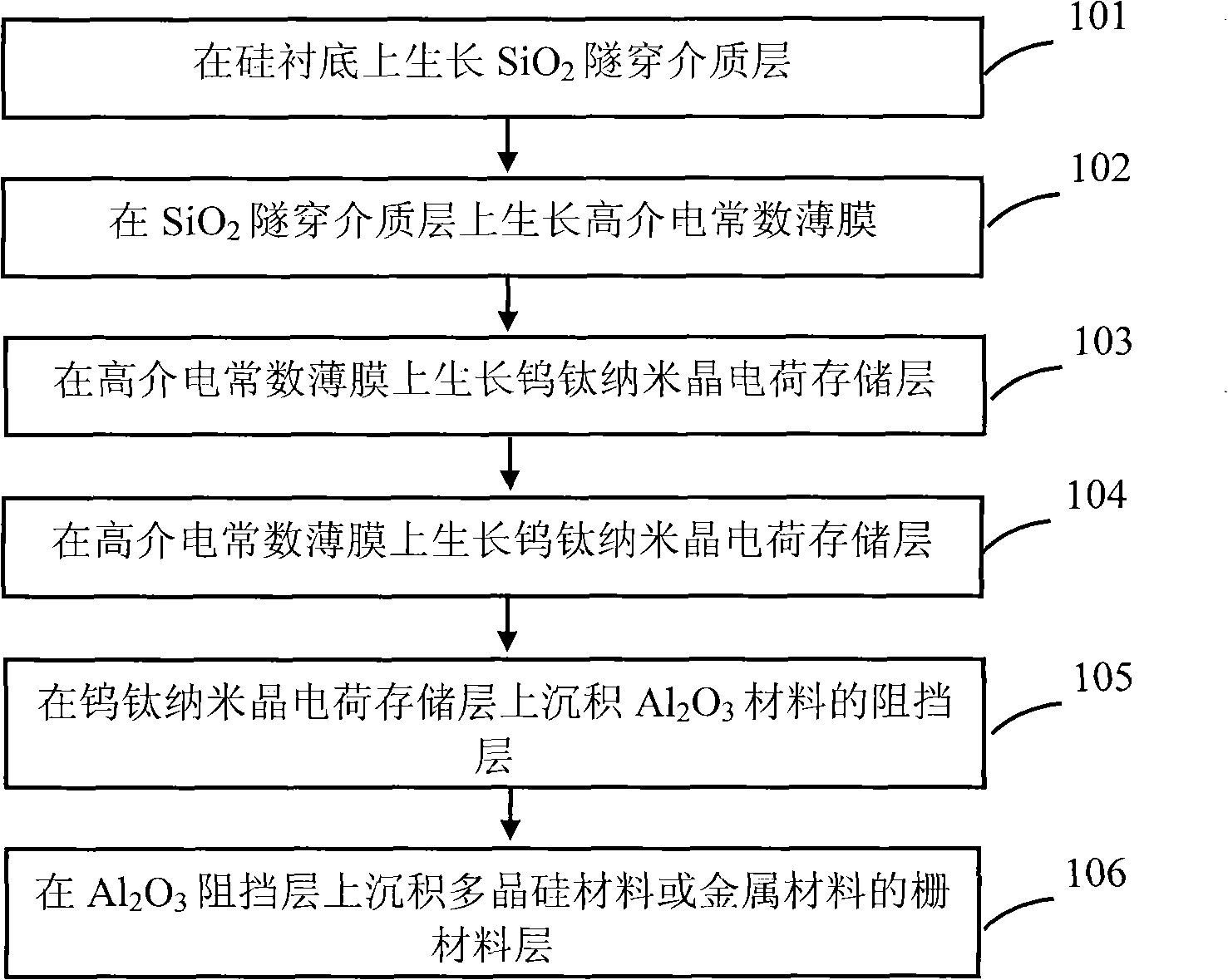

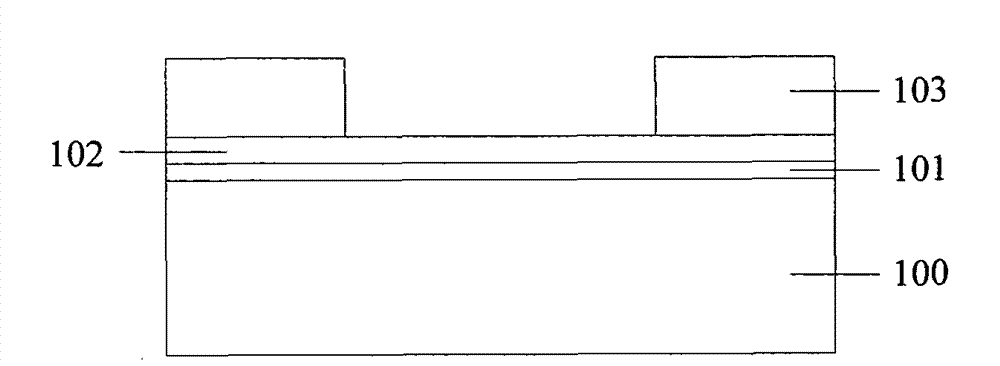

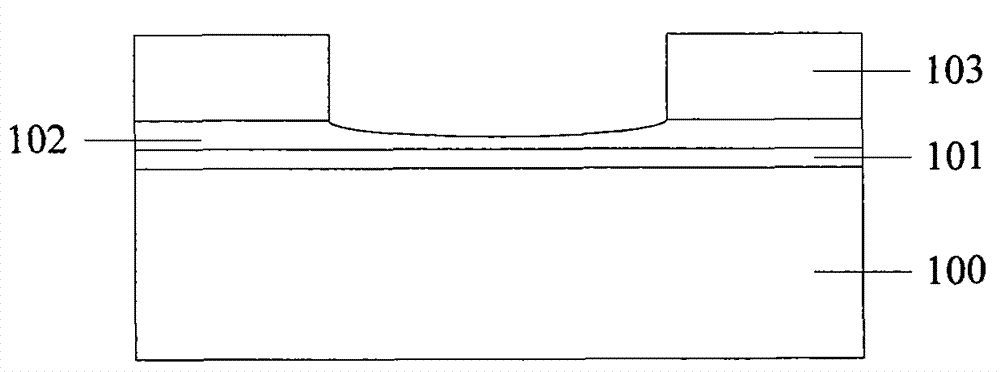

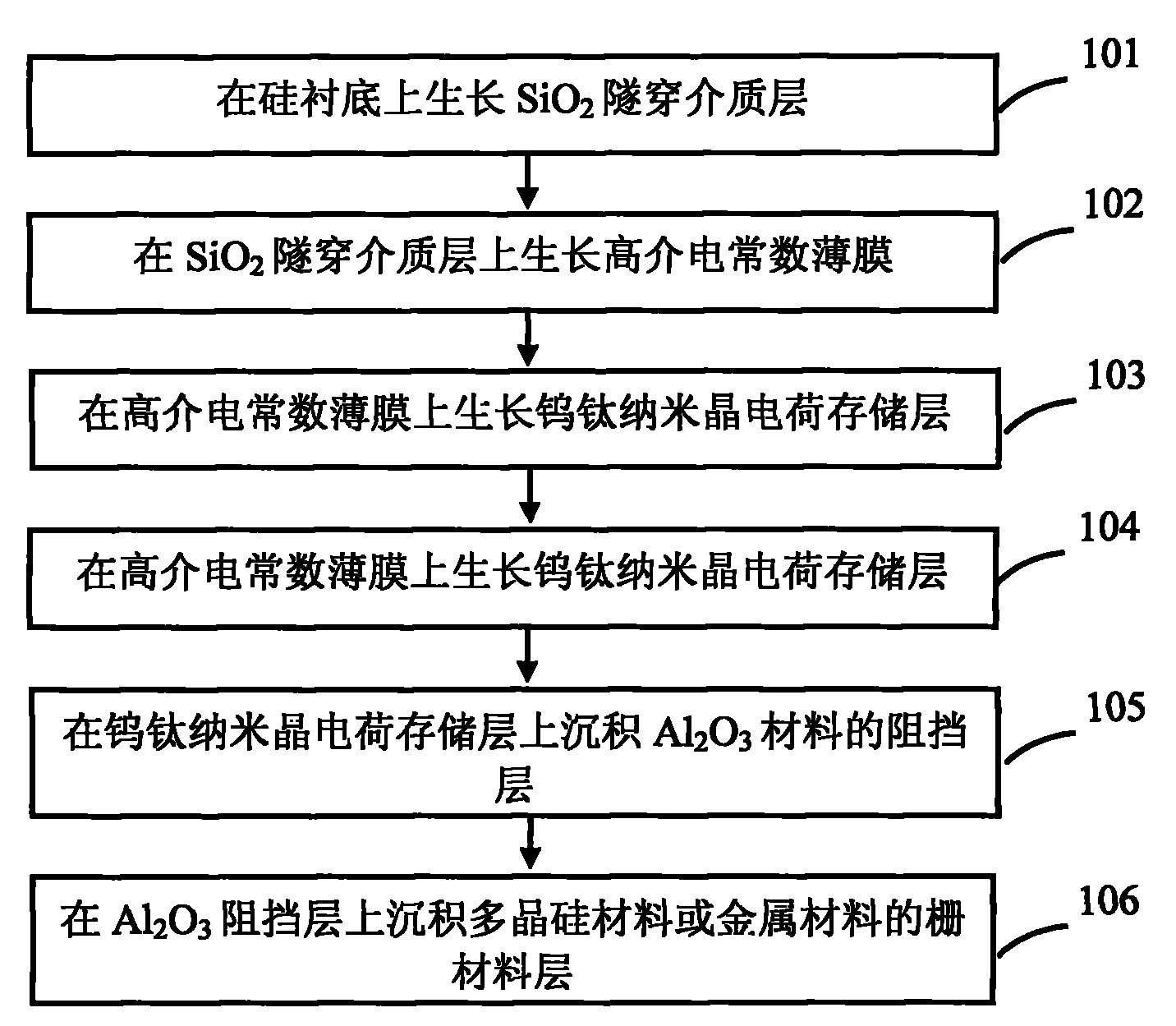

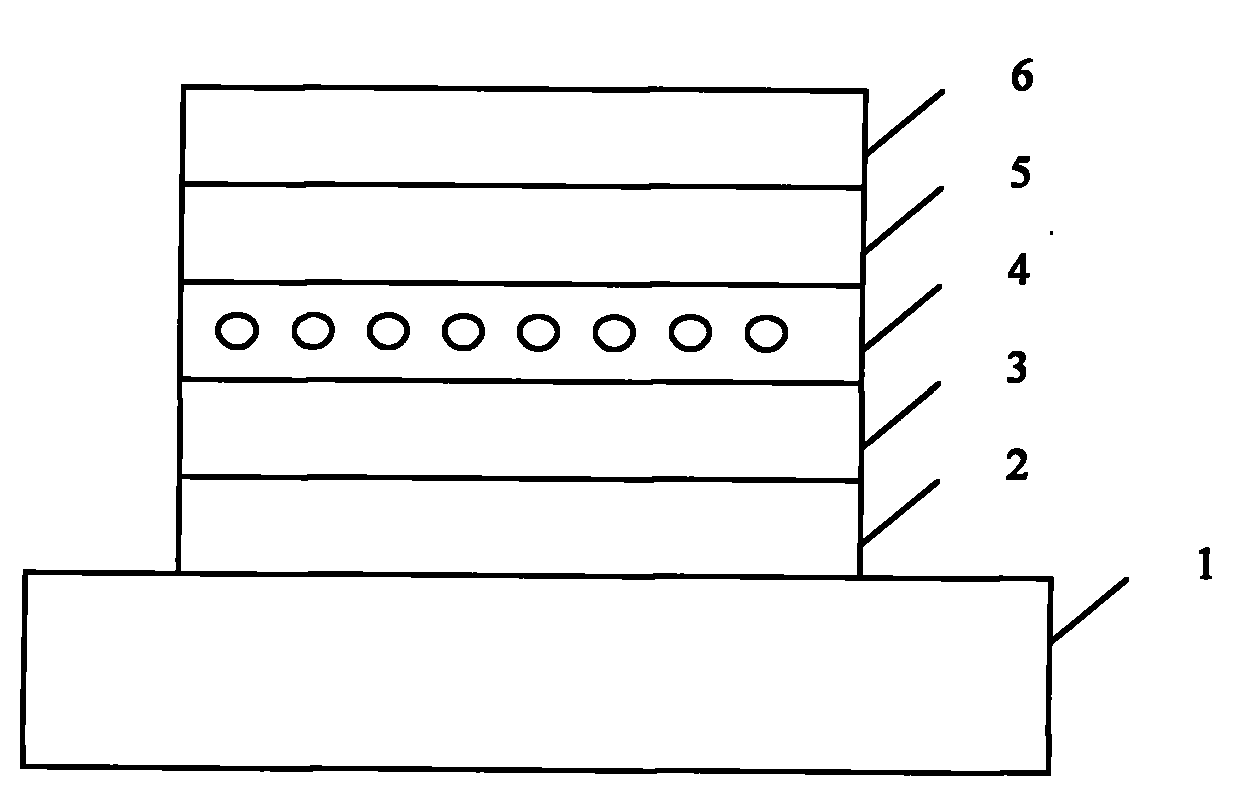

Tungsten titanium alloy nanocrystalline gate-floating structure and preparation method thereof

InactiveCN101494237APrevent leakageImproved data retention featuresSemiconductor devicesCMOSDielectric

The invention discloses a tungsten-titanium alloy nanocrystalline floating grid structure used for a flash memory, pertaining to the technical field of micro-electronics. The structure comprises a silicon substrate as well as a silicon oxide layer, a high k (dielectric constant) thin film, a tungsten-titanium alloy nanocrystalline charge storage layer, a barrier layer and a grid material layer which are covered on the silicon oxide layer successively. The structure improves memory properties of a non-volatile memory unit of the floating grid structure, such as programming / erasing efficiency, programming / erasing (P / E) speed, effective charge memory power, data maintenance property and programming / erasing tolerance. The invention also discloses a method for manufacturing the tungsten-titanium alloy nanocrystalline floating grid structure. The method is simple and convenient and is compatible with the traditional CMOS silicon planar technology.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

sram storage unit, storage array and memory

ActiveCN105336363BOptimize write performanceTroubleshoot write operation failuresDigital storageEngineeringComputer science

The invention relates to an SRAM memory unit, a memory array and a memory. The SRAM storage unit includes: a first PMOS transistor, a second PMOS transistor, a first NMOS transistor, a second NMOS transistor, a first pass transistor, a second pass transistor, a first double-gate PMOS transistor, and a second double-gate PMOS transistor . The invention can solve the problem that the writing operation failure of the SRAM storage unit may exist.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

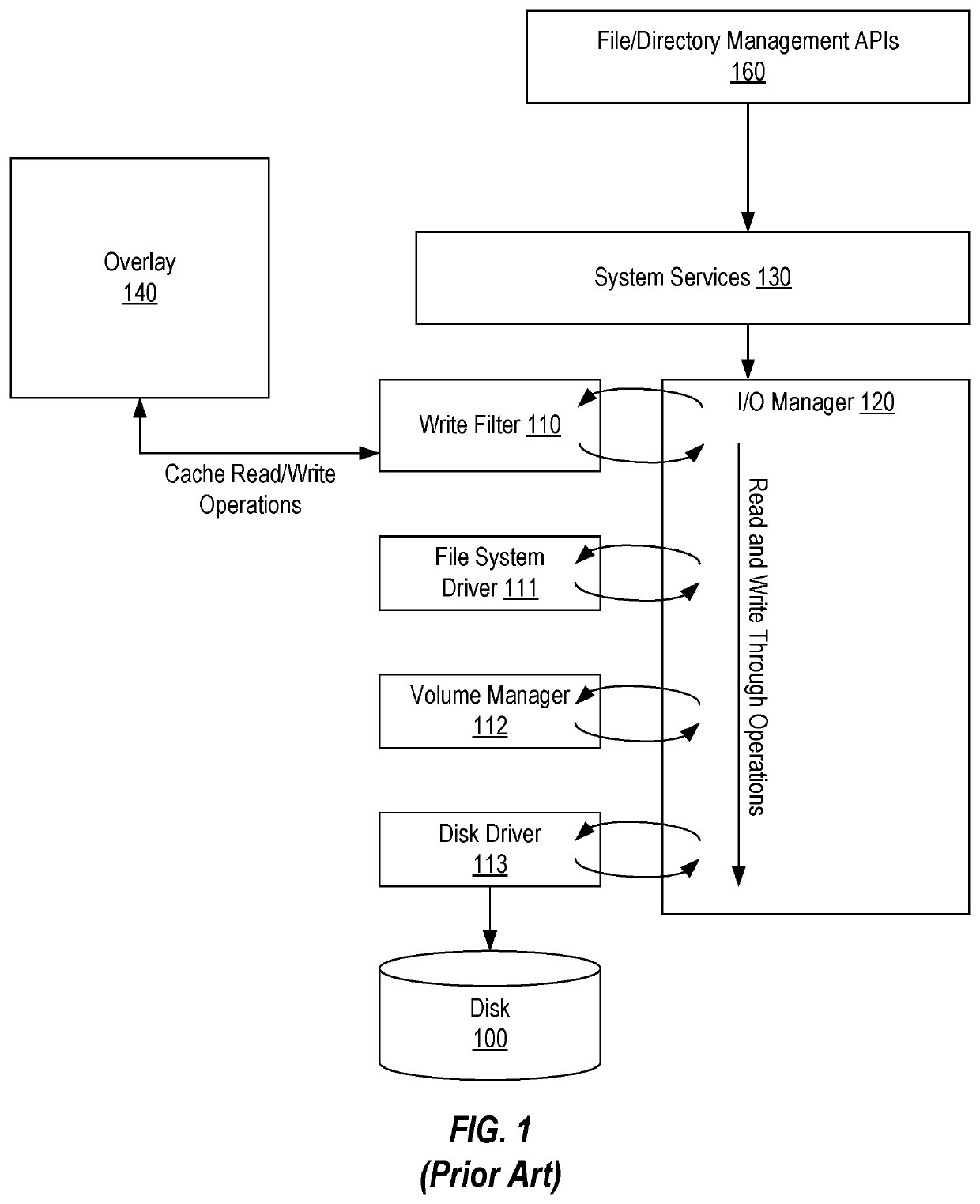

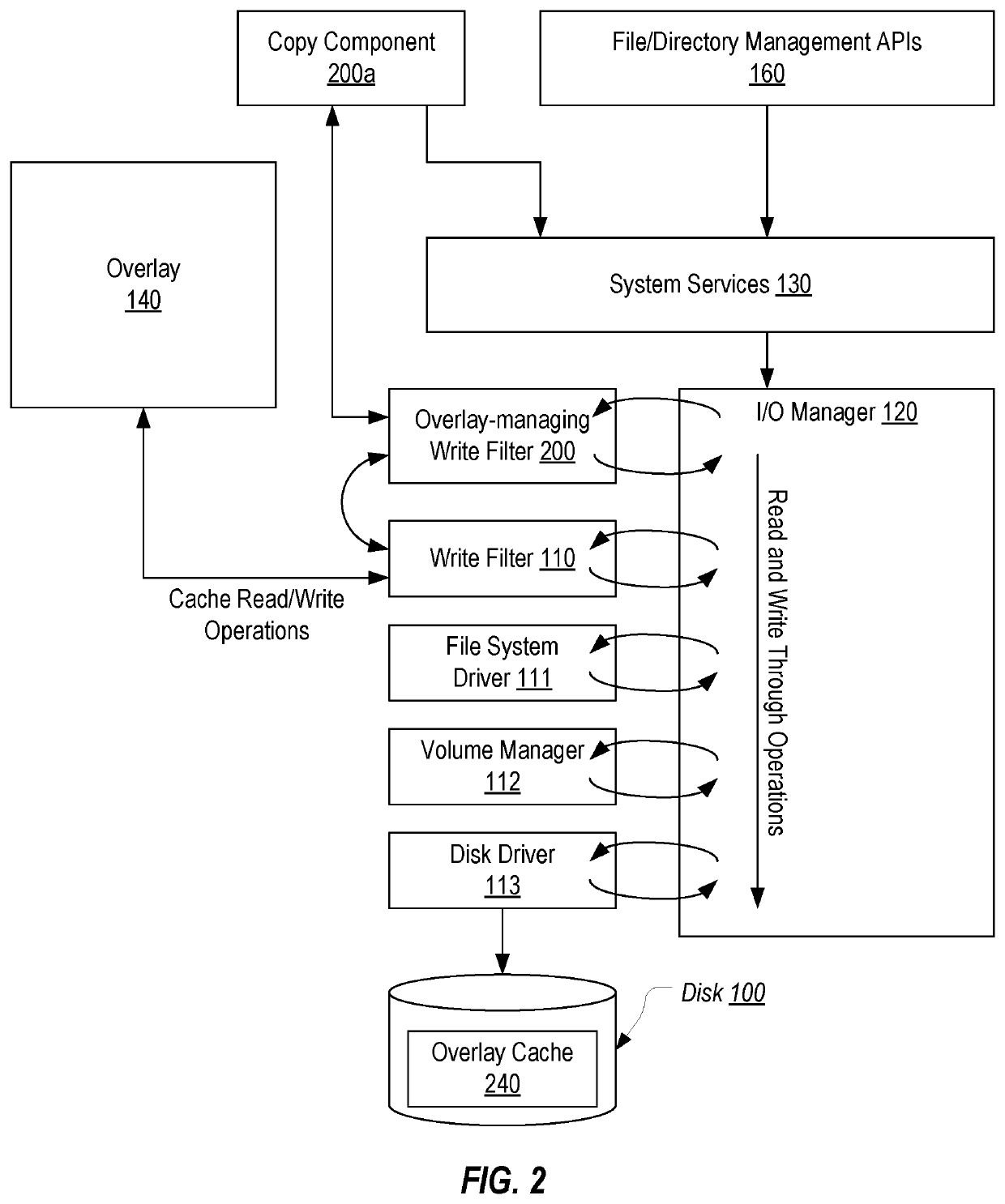

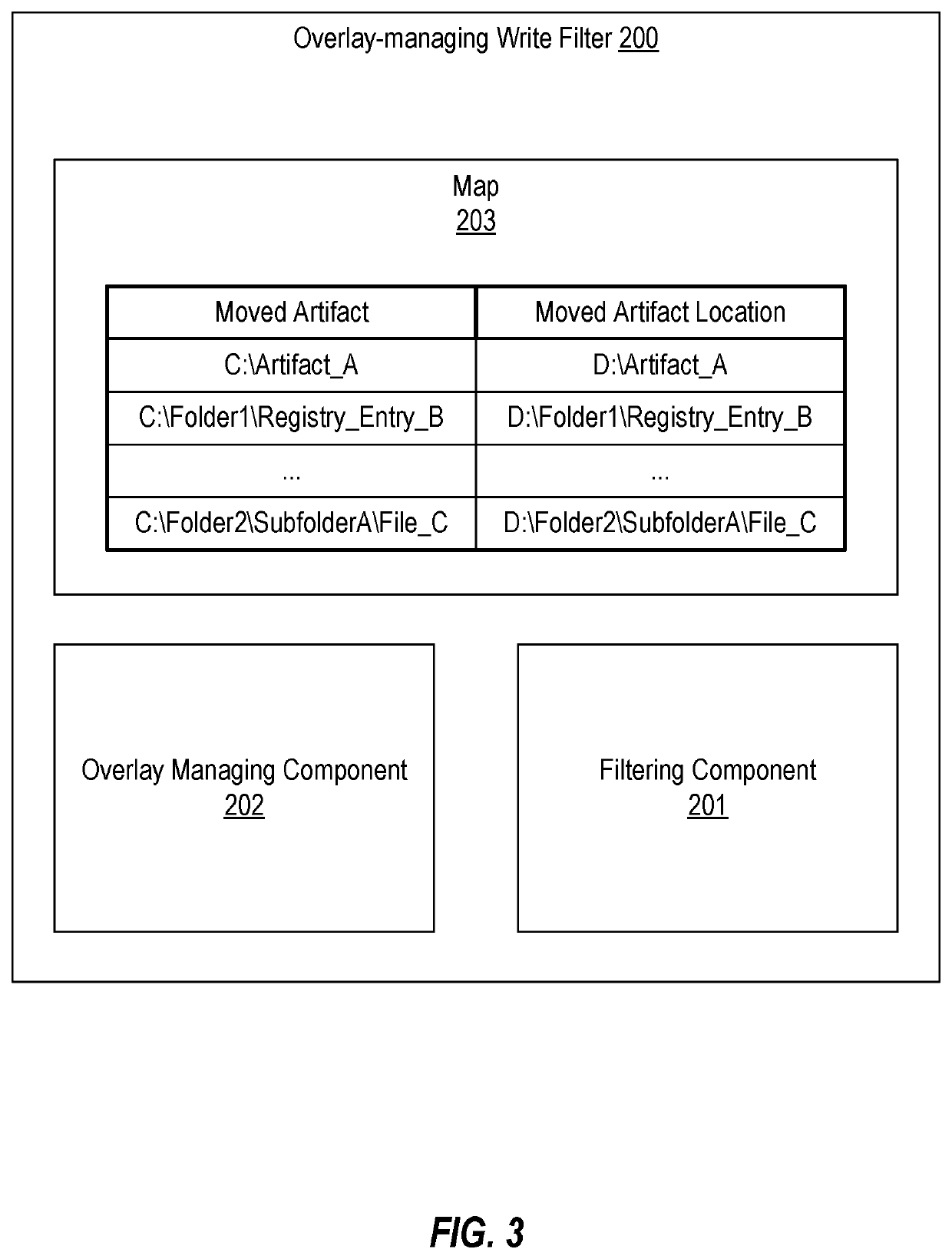

Preventing cross-volume file moves in an overlay optimizer

ActiveUS10789014B2Preventing cross-volume movesOptimize write performanceDatabase updatingInput/output to record carriersParallel computingDirectory

An overlay optimizer can prevent cross-volume moves to optimize the performance of a write filter. The overlay optimizer can be configured to detect when a file move is being attempted and can modify the handling of the file move so that a cross-volume move is not performed. In the case where the file move would result in a file being moved from the volume where the overlay cache is implemented, the overlay optimizer can create a copy of the target directory tree in the overlay cache and redirect the move to the newly created directory. In the case where the file move would result in a file being moved to the volume where the overlay cache is implemented, the overlay optimizer can forgo redirection so that the file will be moved within the same volume.

Owner:DELL PROD LP

A way to scan for error bits

ActiveCN105607961BAverage number of error bitsOptimize write performanceRedundant data error correctionError correctingStorage cell

The invention discloses a method for scanning error bits. The method comprises the following steps: S1, averagely dividing a first data partition of a storage unit into N equal second data partitions; S2, forming a third data partition by using the second data partitions, scanning the third data partition and setting the permissible number of the error bits; S3, comparing the actual number of the error bits of the third data partition with the permissible number of the error bits, if the actual number of the error bits is greater than the permissible number of the error bits, executing step 4, if not, executing step 5; S4, carrying out one-time programming operation on the storage unit and returning to carry out the step S3; and S5, recording the current actual number of the error bits of the third data partition. According to the method, the qualification rate of storage chips can be adjusted through modifying the setting conditions; the corresponding data region and the error correcting capability of the own ECC (Error Correction Code) of a controller can be adjusted on the basis of final statistical results; and therefore, a better write performance is obtained.

Owner:GIGADEVICE SEMICON (BEIJING) INC

Split gate flash memory and manufacture method thereof

ActiveCN101807577BIncrease surface areaIncrease contact areaSolid-state devicesSemiconductor/solid-state device manufacturingGratingGate oxide

The invention provides a split grating flash memory and a manufacture method thereof. The split gate flash memory comprises a semiconductor substrate, a gate oxide and split structure units, wherein the gate oxide is positioned on the surface of the semiconductor substrate; and the split structure units are positioned on the gate oxide. Each split structure unit is provided with a floating gate, a gate medium layer, a control gate, a first side wall layer, a second side wall layer, a third side wall layer, a word line and side walls, wherein the floating gate is positioned on the gate oxide, and the surface of the floating gate is in a cambered shape with an inclined angle; the gate medium layer is positioned on the surface of the floating gate; the control gate is positioned on the gate medium layer; the first side wall layer is positioned on the control gate; the second side wall layer is positioned on the inner side wall of the control gate; the third side wall layer is positioned in the first side wall, the second side wall layer, the gate medium layer and the inner side wall of the floating gate; the word line is positioned between two split structure units and fills a gap; and the side walls are positioned at the outside walls of the split structure units. The invention improves the performance of flash memory erasure or writing and the electric performance of the flash memory.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

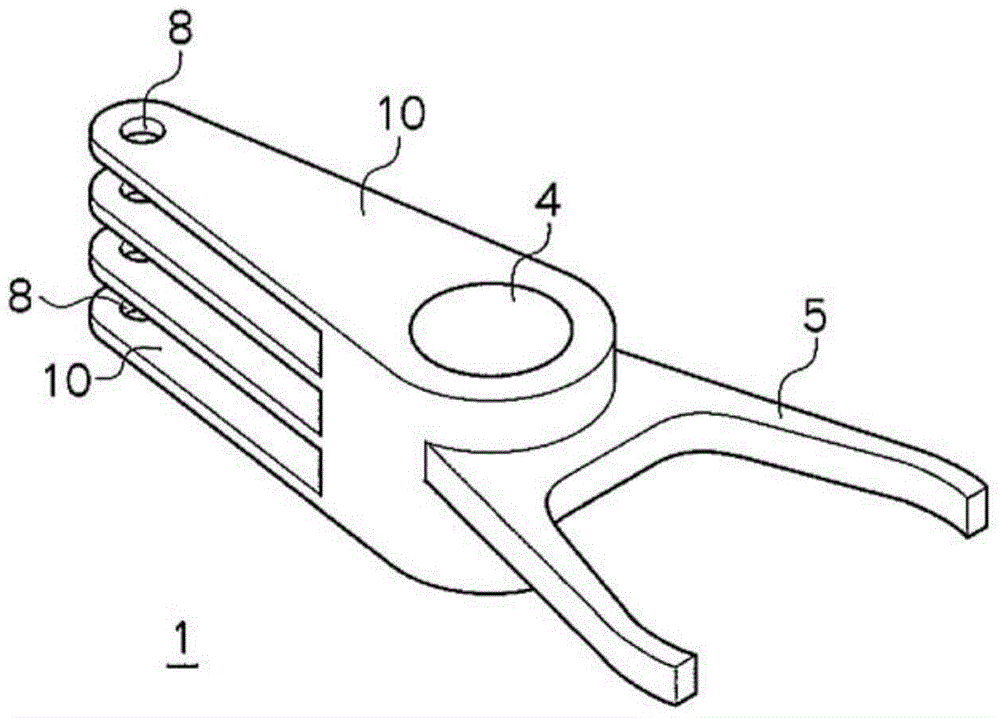

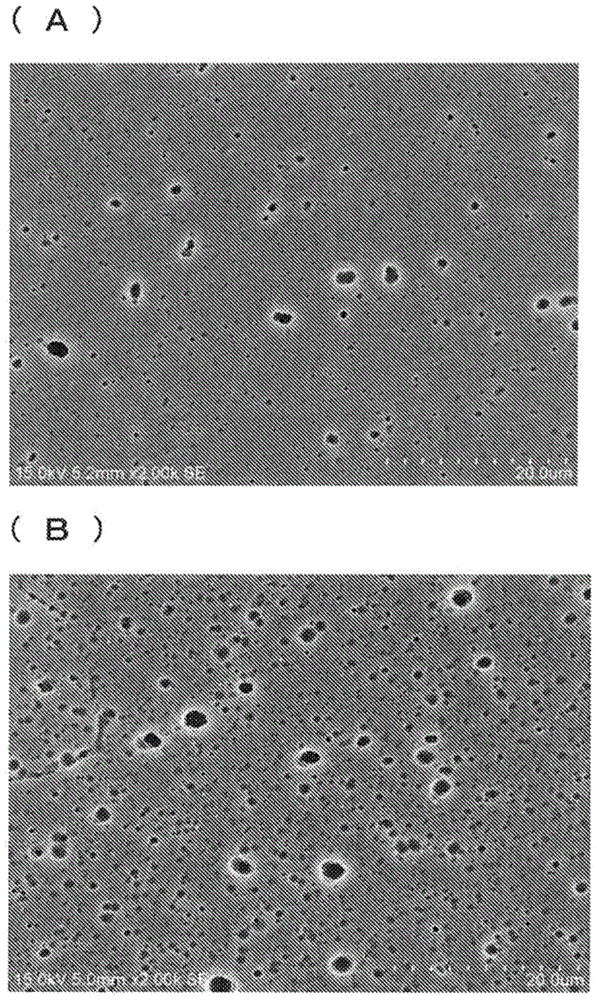

Magnetic head driving arm, its manufacturing method and surface treatment method

ActiveCN104271806BInhibit sheddingEasy to readDriving/moving recording headsStructure of arm assemblyAlloyFluoride

The present invention provides a magnetic head actuating arm in which very few oxide particles fall off from the surface of an aluminum alloy magnetic head actuating arm and a manufacturing method thereof. There are no protrusions formed by the oxide particles 30 on the surface S of the aluminum alloy magnetic head drive arm 1, and the average diameter D of the pits 40 formed by the traces after the oxide particles 30 are removed is 1 μm or more and 5 μm or less. The head drive arm solves the above problems. At this time, it is preferable that pits 40 that are 1 / 2 to 2 times the average diameter of the pits 40 exist in a range of 10 to 100 in a measurement area of 20 μm in length and width, and the reflectivity of the surface S of the head drive arm 1 In the wavelength range of 500 nm to 600 nm, it is 10% or more and 40% or less. This magnetic head drive arm 1 can be manufactured by contacting a solution containing fluoride ions after chemical polishing.

Owner:TOTOKU ELECTRIC CO LTD

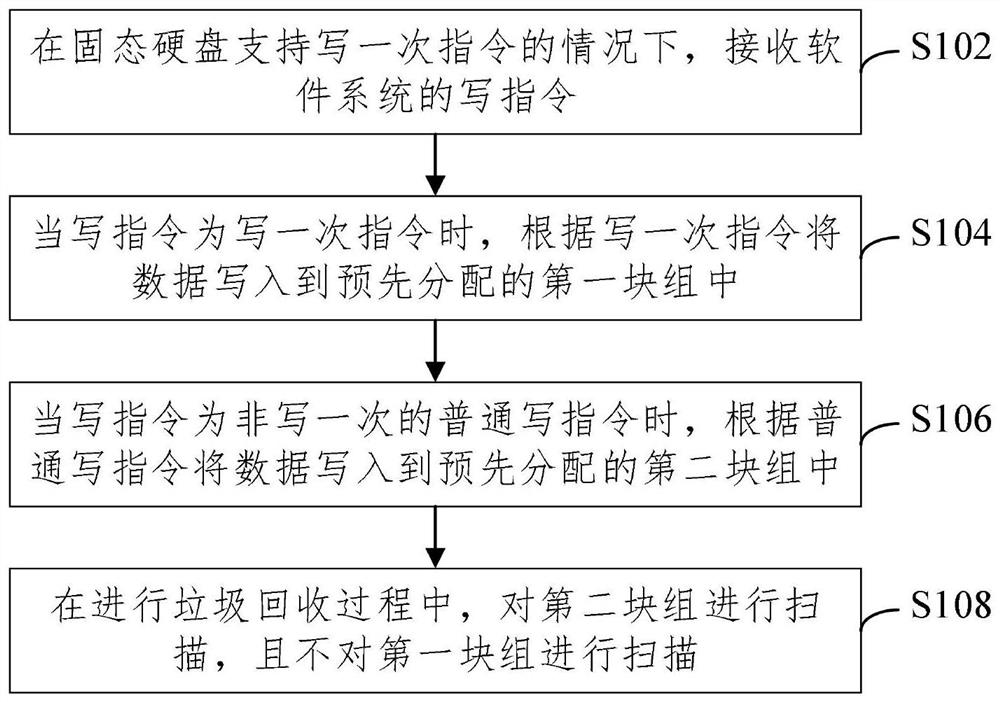

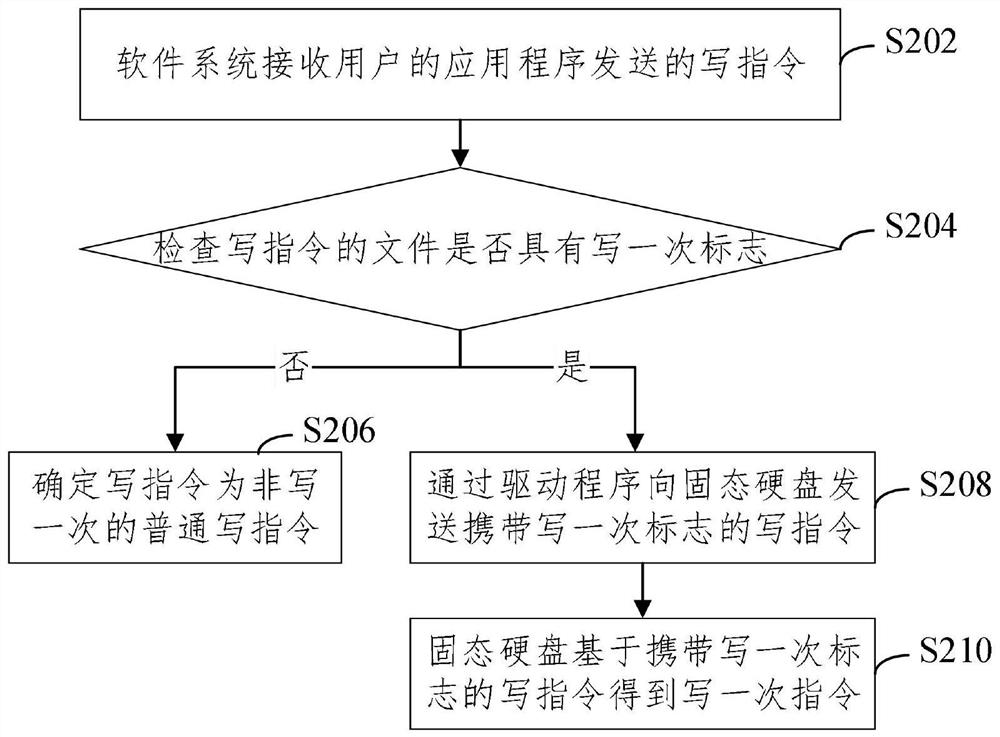

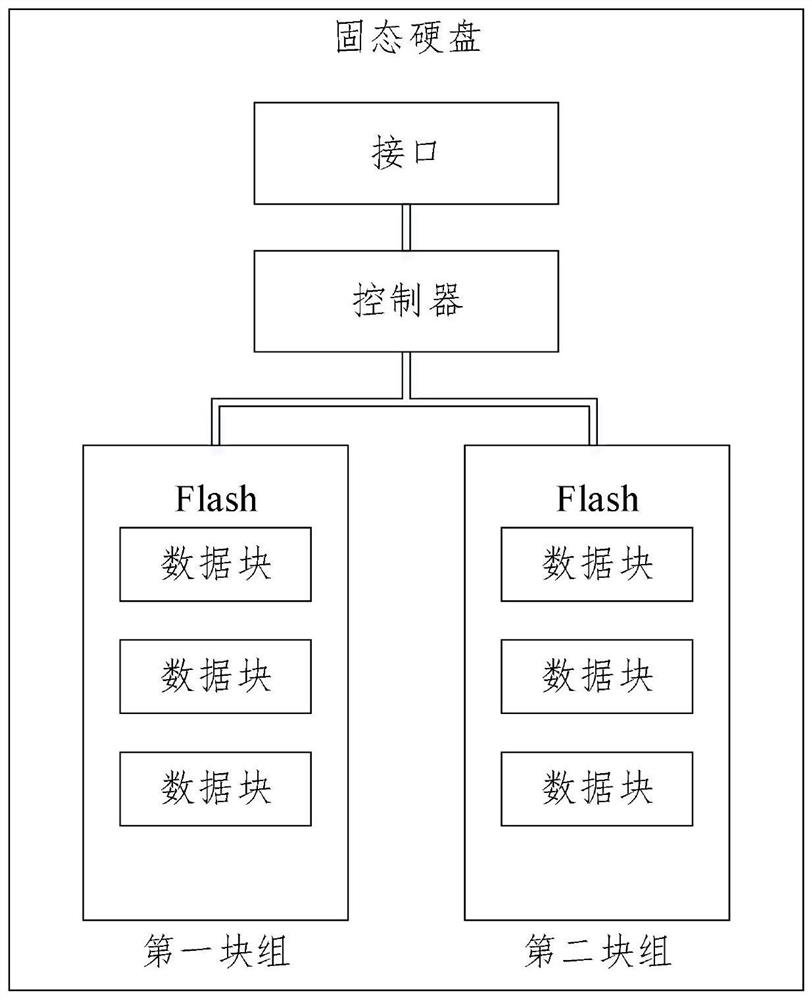

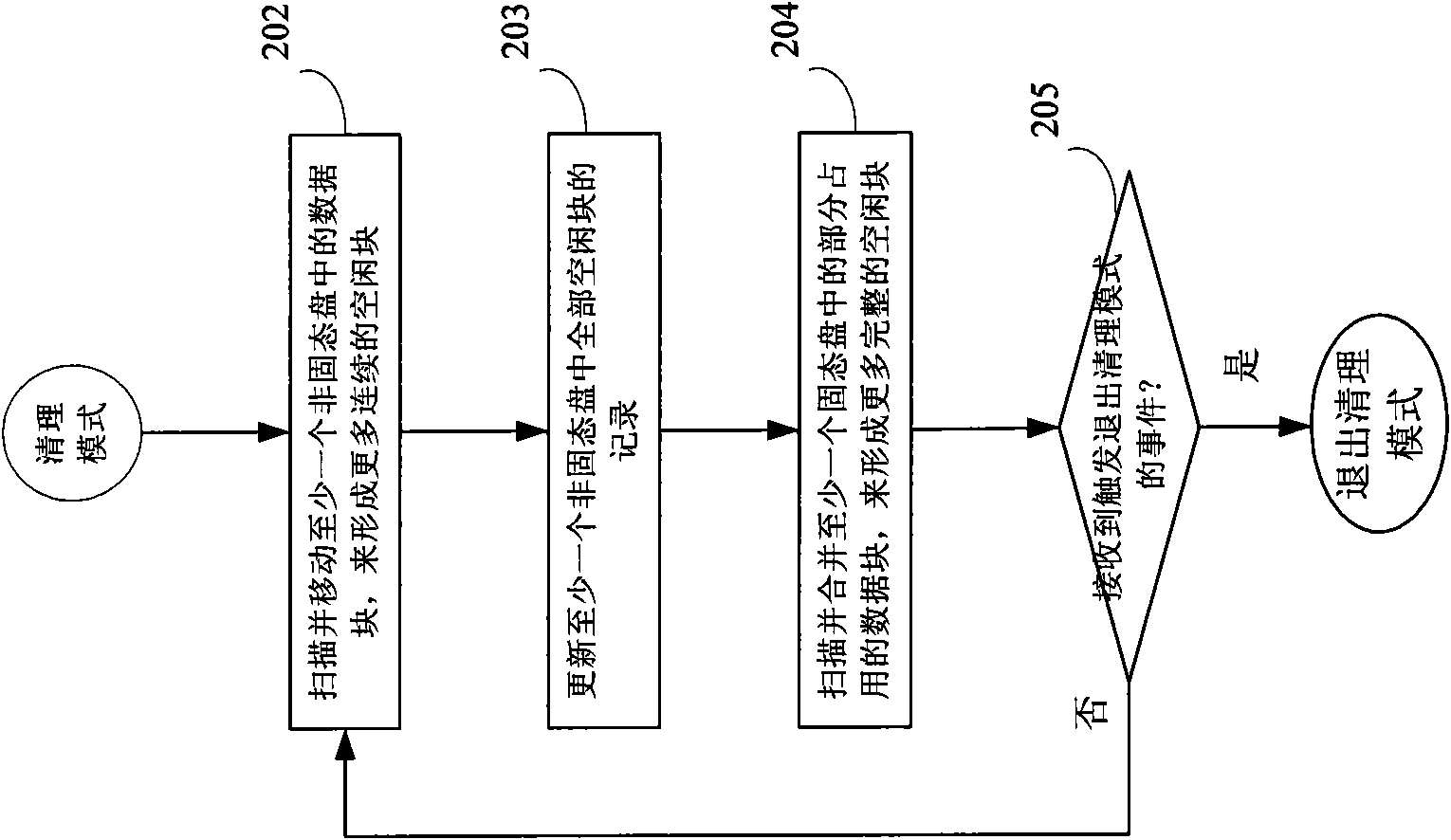

Garbage recycling method and device

PendingCN114741327AImprove recycling efficiencyOptimize write performanceMemory adressing/allocation/relocationSoftware systemSoftware engineering

The embodiment of the invention relates to a garbage collection method and device, and the method comprises the steps: receiving a writing instruction of a software system under the condition that a solid state disk supports a writing instruction for one time; when the write instruction is a write-once instruction, writing the data into a pre-allocated first block group according to the write-once instruction; when the write instruction is a common write instruction which is not written once, writing the data into a pre-allocated second block group according to the common write instruction; and in the garbage collection process, the second block group is scanned, and the first block group is not scanned. The garbage collection efficiency can be improved, and then the write-in performance of the solid state disk is optimized.

Owner:YUSUR TECH CO LTD

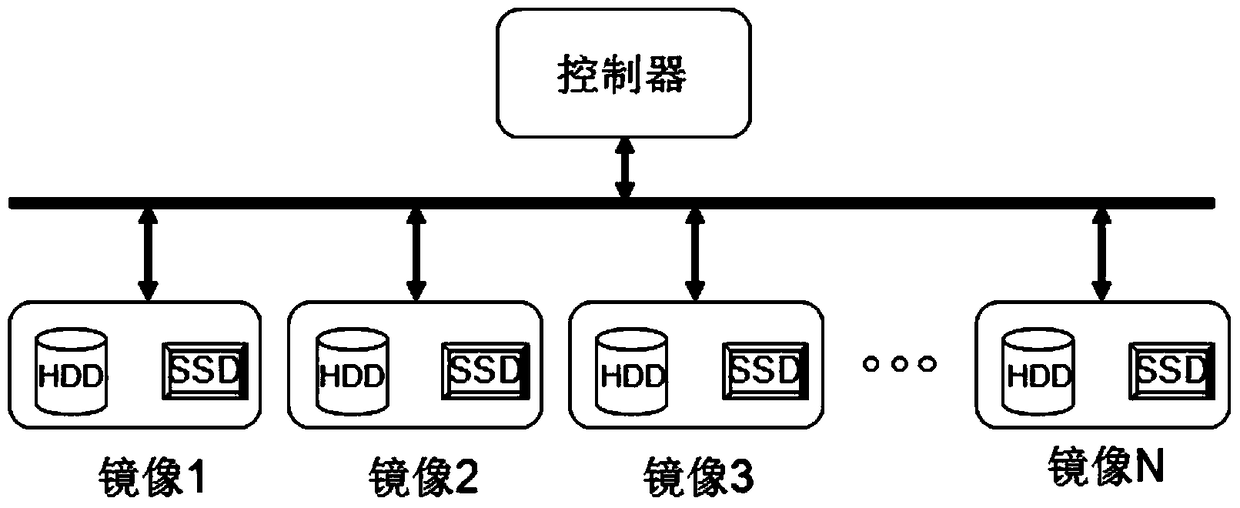

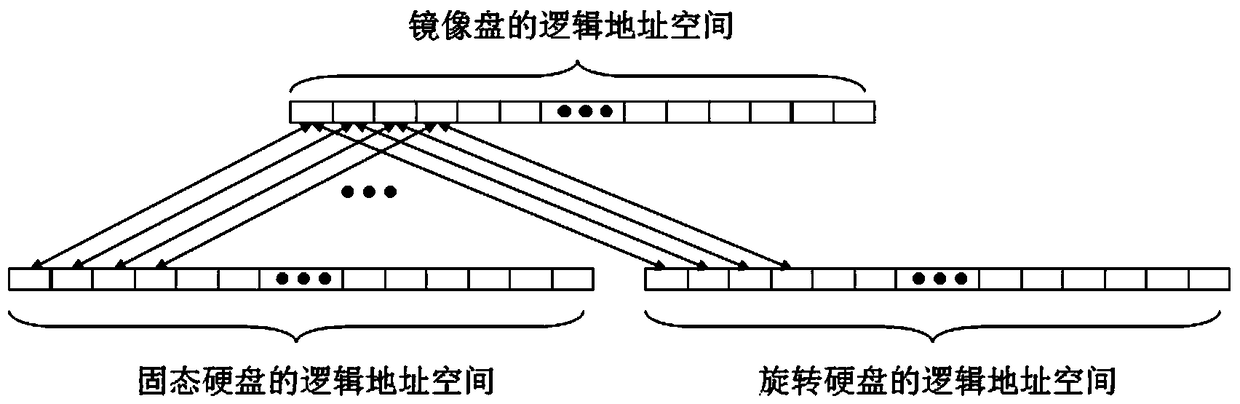

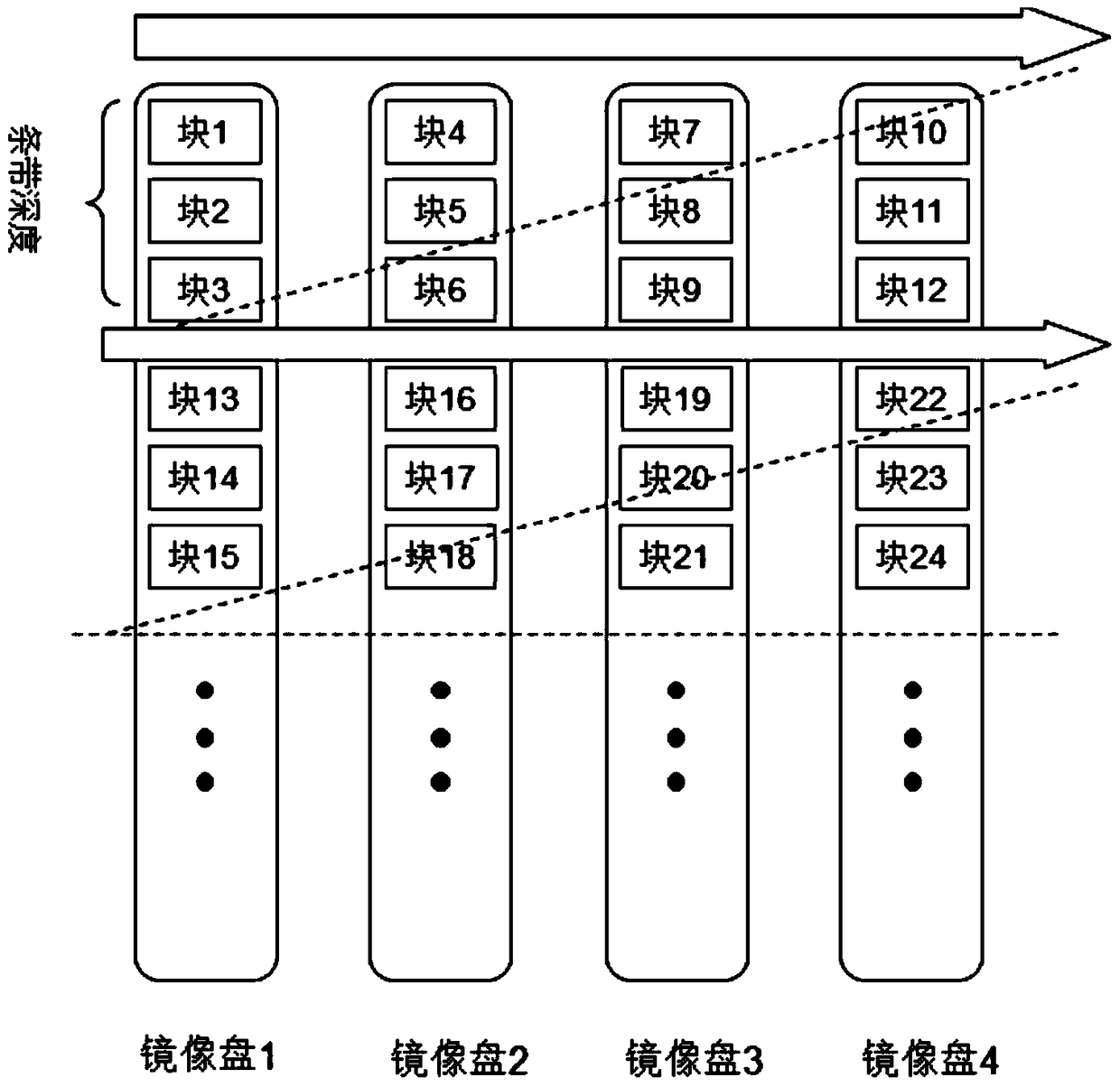

Wide-stripe disk array and storage method based on asymmetric hybrid disk mirroring

ActiveCN104778018BImprove read and write performanceImprove reliabilityInput/output to record carriersRedundant operation error correctionHybrid typeData connection

Owner:南京道熵信息技术有限公司

A database reading and writing method and system

InactiveCN102999519BFast read and writeWrite quicklySpecial data processing applicationsData segmentDatabase

The embodiment of the invention discloses a read-write method and system for a database. The method comprises the steps of: transversely cutting record data according to a main keyword into a plurality of data segments, wherein each data segment is stored as a write copy and corresponding read copies, and the write copy is stored in form of line storage, so that the write performance of the database is optimized; the read copies are stored in form of column storage, and data in each read copy is organized in different manners, so that the read performance of the database is optimized. According to the method, an overall index and a local index are further established, so that the operating position of data to be written or to be read can be quickly positioned when data is written or read. According to the embodiment of the method or system, not only is data quickly written, but also data can be quickly read.

Owner:SHANGHAI SHENGPAY E PAYMENT SERVICE CO LTD

Tungsten titanium alloy nanocrystalline gate-floating structure and preparation method thereof

InactiveCN101494237BPrevent leakageImproved data retention featuresSemiconductor devicesCMOSDielectric

The invention discloses a tungsten-titanium alloy nanocrystalline floating grid structure used for a flash memory, pertaining to the technical field of micro-electronics. The structure comprises a silicon substrate as well as a silicon oxide layer, a high k (dielectric constant) thin film, a tungsten-titanium alloy nanocrystalline charge storage layer, a barrier layer and a grid material layer which are covered on the silicon oxide layer successively. The structure improves memory properties of a non-volatile memory unit of the floating grid structure, such as programming / erasing efficiency, programming / erasing (P / E) speed, effective charge memory power, data maintenance property and programming / erasing tolerance. The invention also discloses a method for manufacturing the tungsten-titanium alloy nanocrystalline floating grid structure. The method is simple and convenient and is compatible with the traditional CMOS silicon planar technology.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

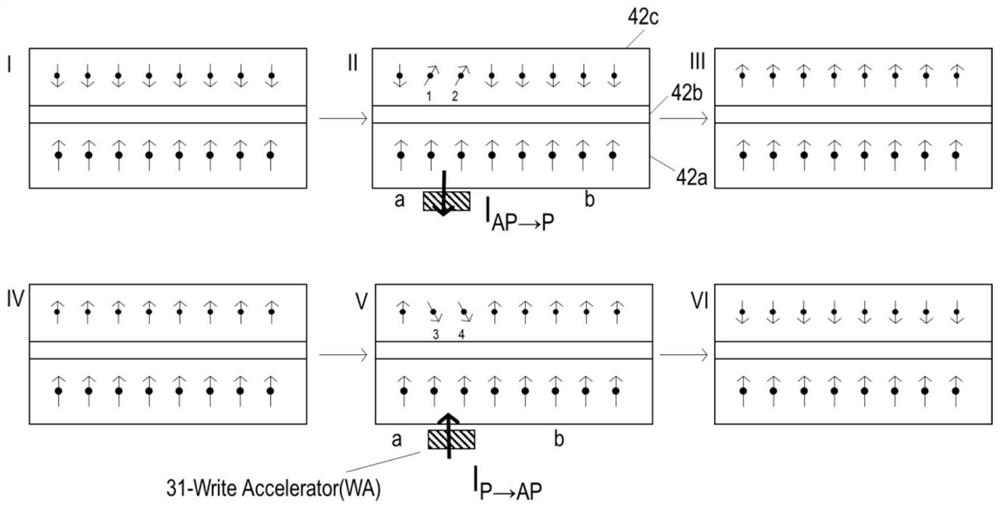

Structure for optimizing writing performance of magnetic random access memory and preparation method thereof

PendingCN112186097AOptimize write performanceReduce power consumptionMagnetic-field-controlled resistorsGalvano-magnetic device detailsCMOSChemical-mechanical planarization

The invention discloses a structure for optimizing the writing performance of a magnetic random access memory. The structure comprises a writing accelerator, the writing accelerator is positioned on the lower side of a bottom electrode of the magnetic random access memory and the upper side of a bottom electrode through hole, and the writing accelerator is directly connected with the bottom electrode and the bottom electrode through hole. The invention further discloses a preparation method of the structure for optimizing the writing performance of the magnetic random access memory. The preparation method comprises the following steps: 1, providing a CMOS substrate with a polished surface and a metal connecting line Mx; 2, manufacturing a bottom electrode through hole in the flattened CMOSsubstrate, and grinding the bottom electrode through hole; 3, on the bottom electrode through hole, performing graphical definition and etching to manufacture writing accelerator metal, filling a writing accelerator dielectric medium, and grinding the writing accelerator dielectric medium by adopting chemical mechanical planarization; and 4, sequentially depositing a bottom electrode, a magnetictunnel junction multilayer film and a top electrode on the writing accelerator, manufacturing a magnetic tunnel junction storage unit, and finally manufacturing bit line connection on the top electrode.

Owner:SHANGHAI CIYU INFORMATION TECH

A method of data writing based on memory replacement

ActiveCN103744626BKeep intactNot easy to loseInput/output to record carriersComputer architectureAlternative methods

The present invention provides a method for writing data based on memory replacement, the realization process of which is as follows: setting up the memory structure, independently designing the part used for data reading and writing in the memory, and integrating two integrated circuits with exactly the same capacity ; Perform memory switching, the system starts in general mode when it is just started, and after running for a period of time, the system-related applications are completely loaded, and the memory management unit detects the capacity used by the stack according to the switching mode set by the system, and then according to The actual capacity plus a certain amount of redundancy sets the stack area, then detects the memory used for reading, and adds a certain amount of redundancy to set the read memory, and the remaining memory is completely mapped to the write memory to complete the memory switching process . Compared with the prior art, the method for writing data based on memory replacement can smooth the entire writing process by replacing the memory when writing files, improve the writing performance, have strong practicability, and be easy to popularize.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

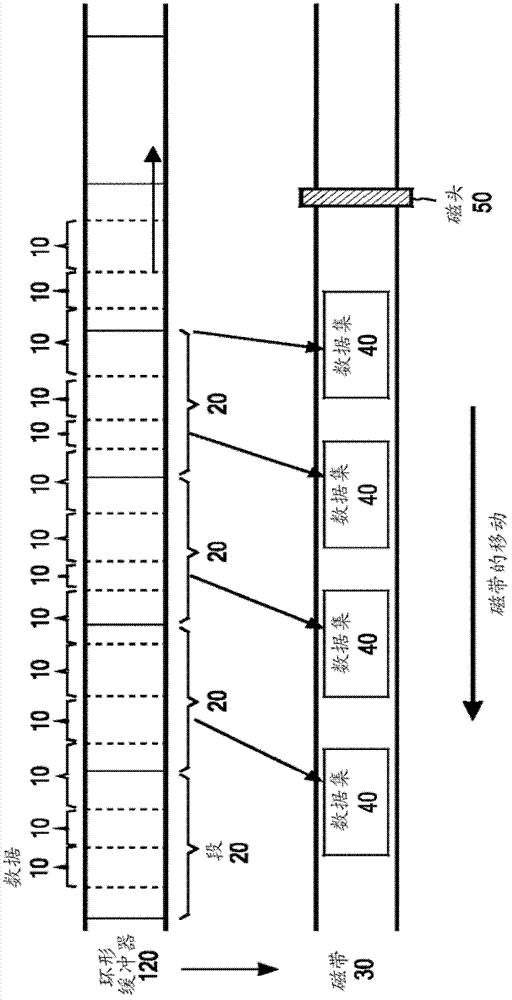

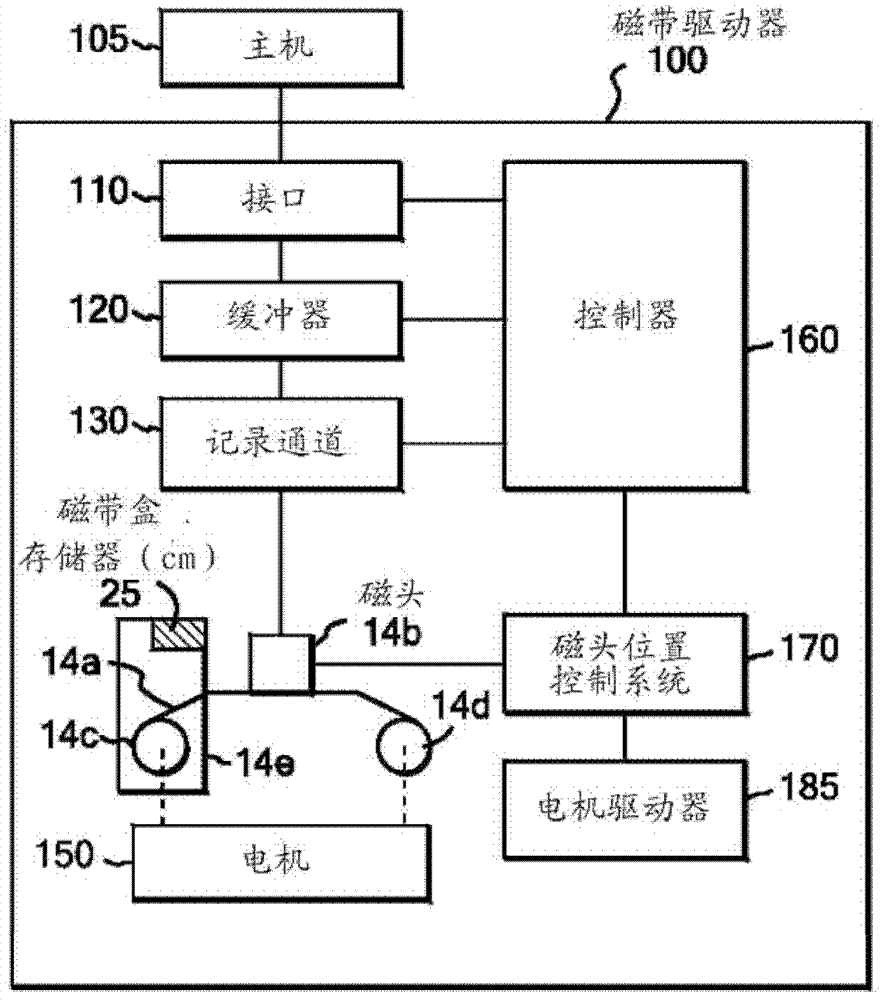

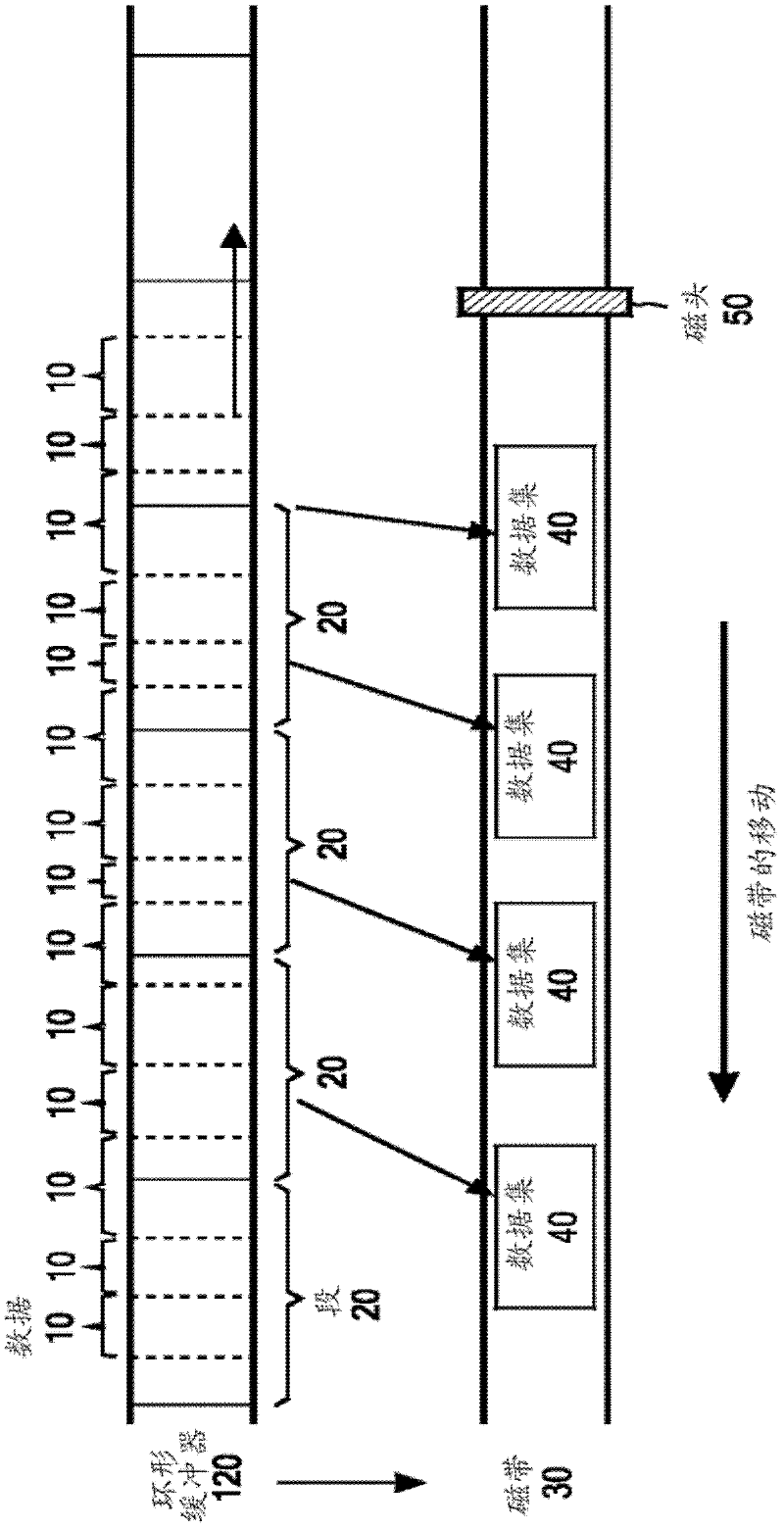

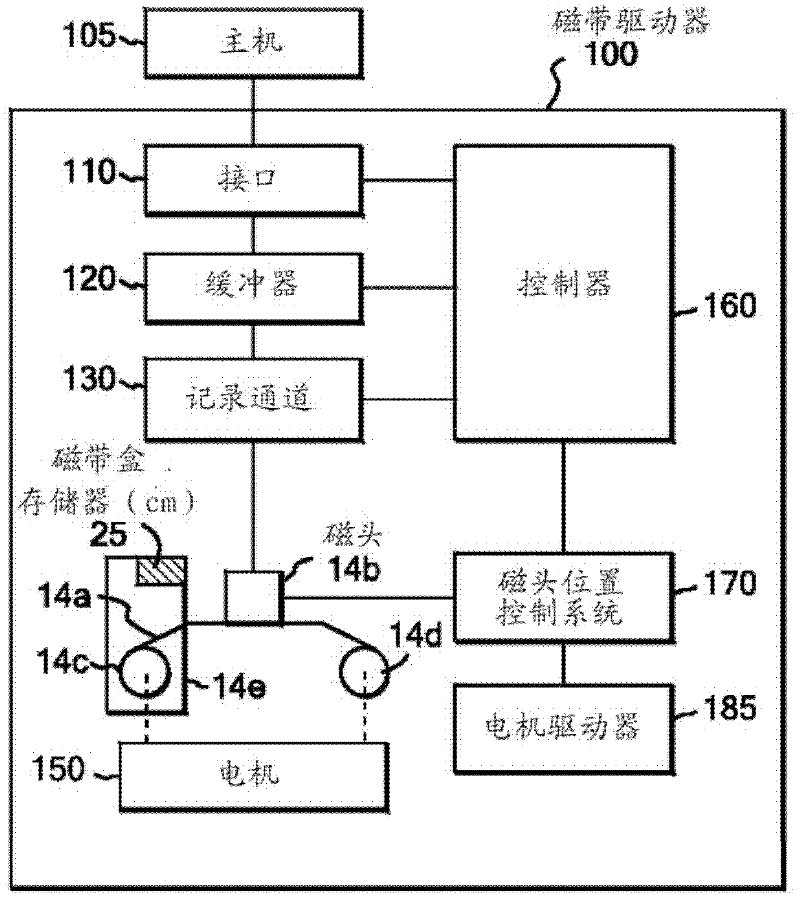

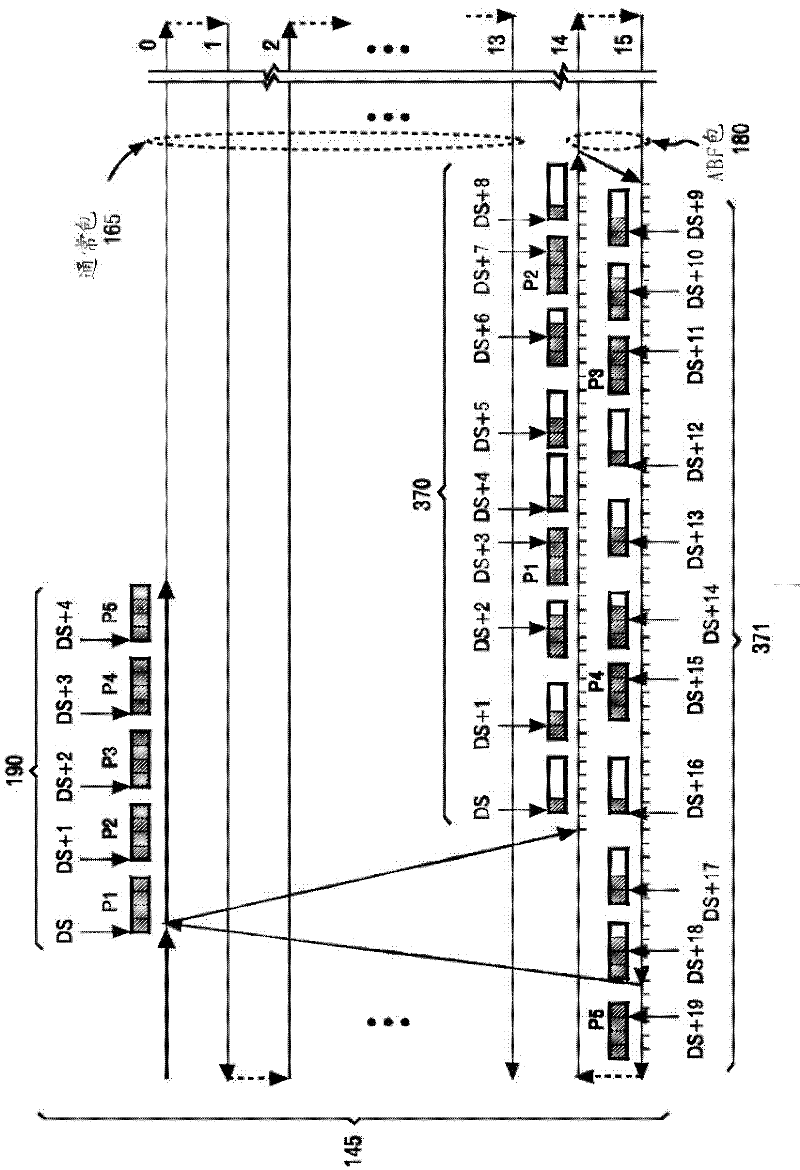

Tape storage system including a plurality of tape recording devices

ActiveCN102414753BMaintain storage densityOptimize write performanceRecording carrier detailsInput/output to record carriersMagnetic tapeRecording density

Owner:INT BUSINESS MASCH CORP

sram storage unit, storage array and memory

ActiveCN105336364BOptimize write performanceBoost reverse voltageDigital storageComputer scienceStorage cell

The invention relates to an SRAM memory unit, a memory array and a memory. The SRAM storage unit includes: a first PMOS transistor, a second PMOS transistor, a first NMOS transistor, a second NMOS transistor, a first pass transistor, a second pass transistor, a first double-gate NMOS transistor, and a second double-gate NMOS transistor . The invention can solve the problem that the writing operation failure of the SRAM storage unit may exist.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

sram storage unit, storage array and memory

ActiveCN105206298BOptimize write performanceTroubleshoot write operation failuresDigital storageEngineeringMemory array

The invention relates to a SRAM memory cell, a memory array and a memory. The SRAM memory cell comprises a first PMOS transistor, a second PMOS transistor, a first NMOS transistor, a second NMOS transistor, a first transmission transistor, a second transmission transistor, a first dual-gate PMOS transistor, a second dual-gate PMOS transistor, a first dual-gate NMOS transistor and a second dual-gate NMOS transistor. The SRAM memory cell solves the problem that the existing SRAM memory cell has write operation failure possibility.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

Tape storage system including a plurality of tape recording devices

ActiveCN102414753AMaintain storage densityOptimize write performanceRecording carrier detailsInput/output to record carriersMagnetic tapeRecording density

Disclosed is a tape recording device system wherein tape recording density can be maintained and writing performance can be improved in respect of write requests for a plurality of data items accompanying a large number of synchronisation requests from a host. This system is a tape storage system including two or more tape drives in which respective tapes are mounted and having buffers divided into segments of fixed length; the tape storage system is connected with a host that sends synchronisation requests at a prescribed timing and a plurality of data items to these tape drives. This tape recording system is provided with: a tape drive that receives a plurality of data items delivered from the host to which it is connected and that, when a buffer segment is filled with accumulated data, writes this accumulated data onto a tape; and another tape drive which is connected with the first-mentioned tape drive and receives a plurality of data items delivered from the host through this first-mentioned tape drive, and exports to a tape a prescribed number of data items accumulated in a segment at the timing with which a synchronisation request is received.

Owner:IBM CORP

Storage system and method for implementing the same

ActiveCN102298506BIncrease write speedExtended service lifeInput/output to record carriersComputer hardwareUsability

Owner:INT BUSINESS MASCH CORP