Patents

Literature

60 results about "Reference design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reference design refers to a technical blueprint of a system that is intended for others to copy. It contains the essential elements of the system; however, third parties may enhance or modify the design as required. When discussing computer designs, the concept is generally known as a reference platform.

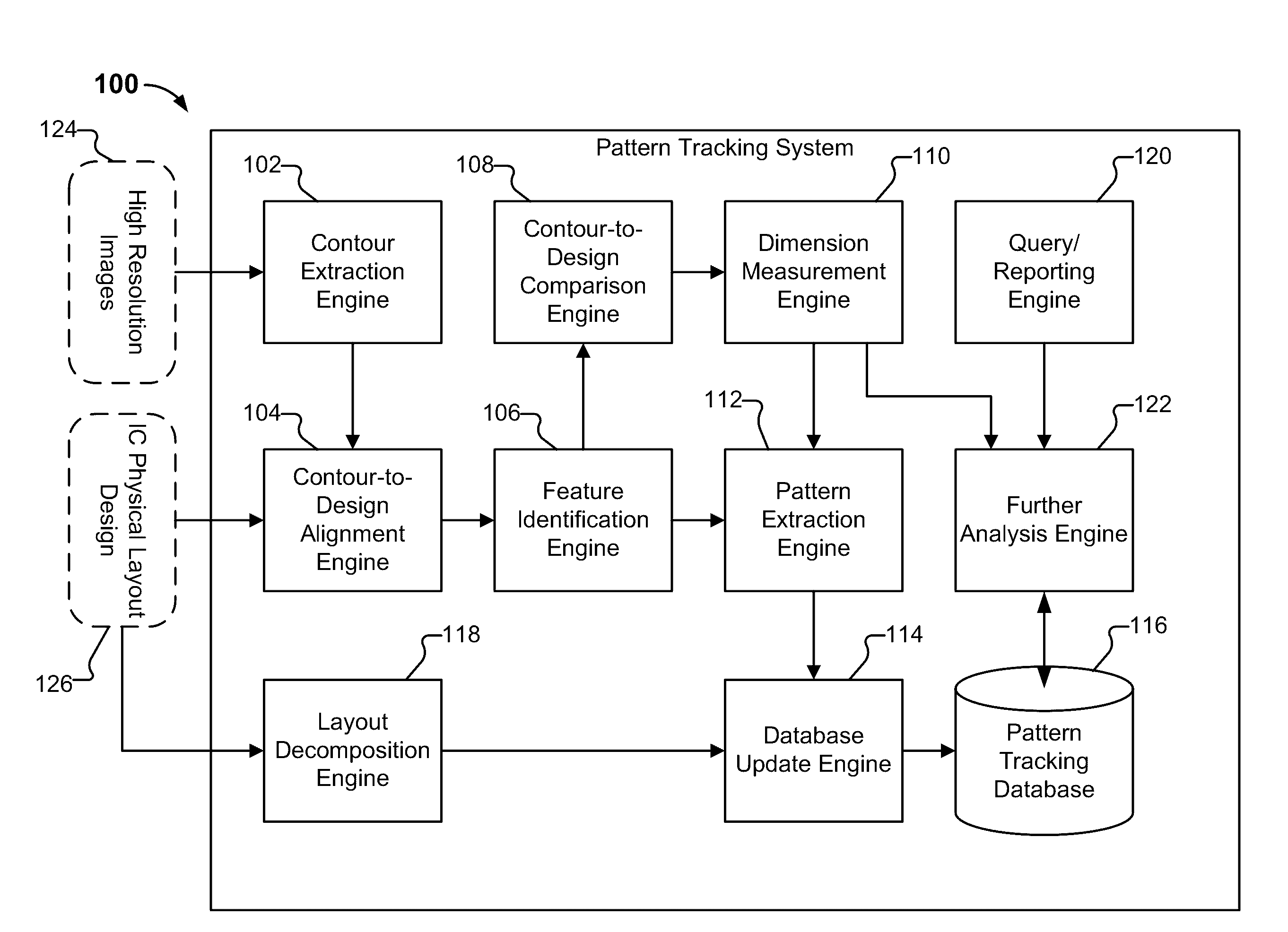

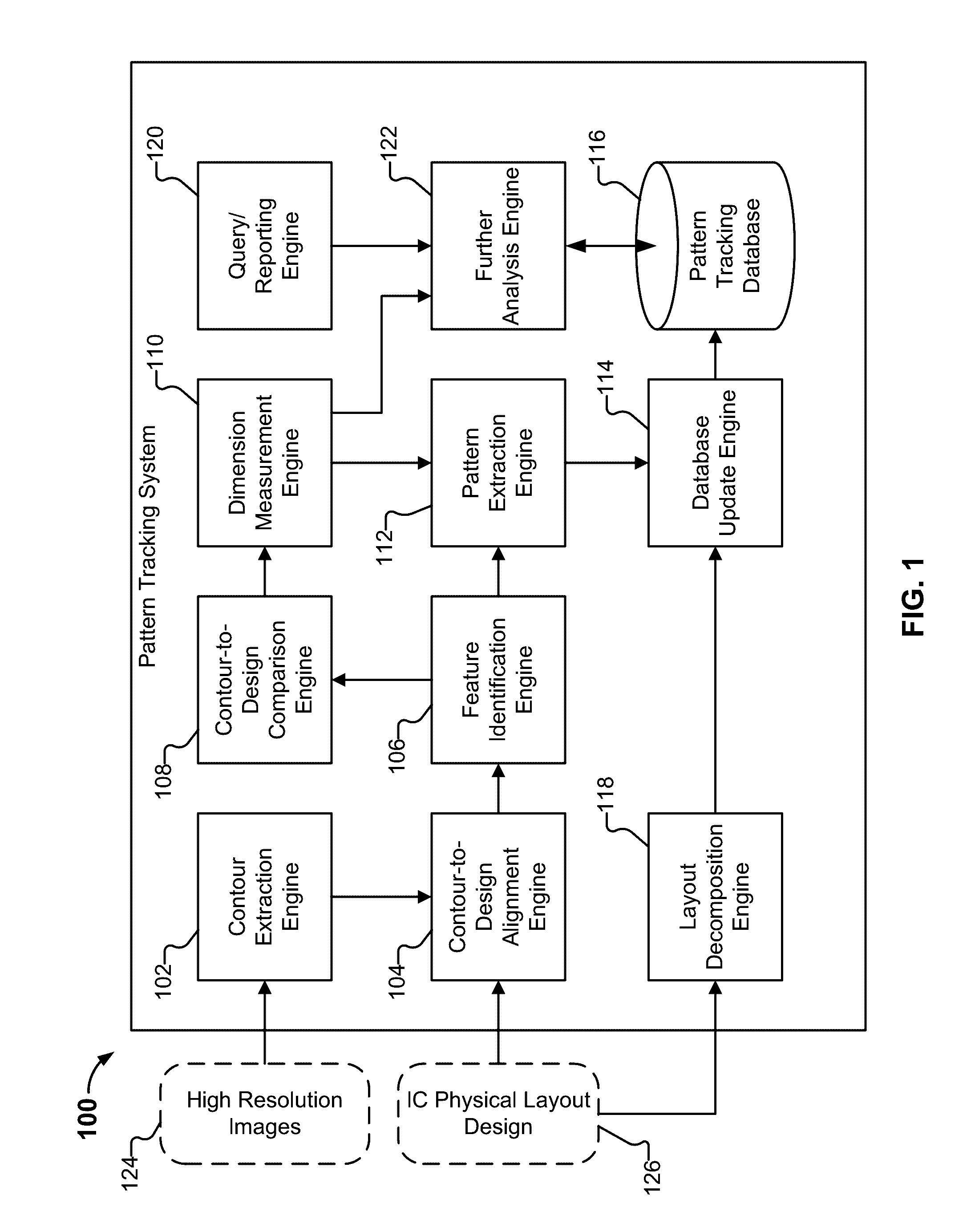

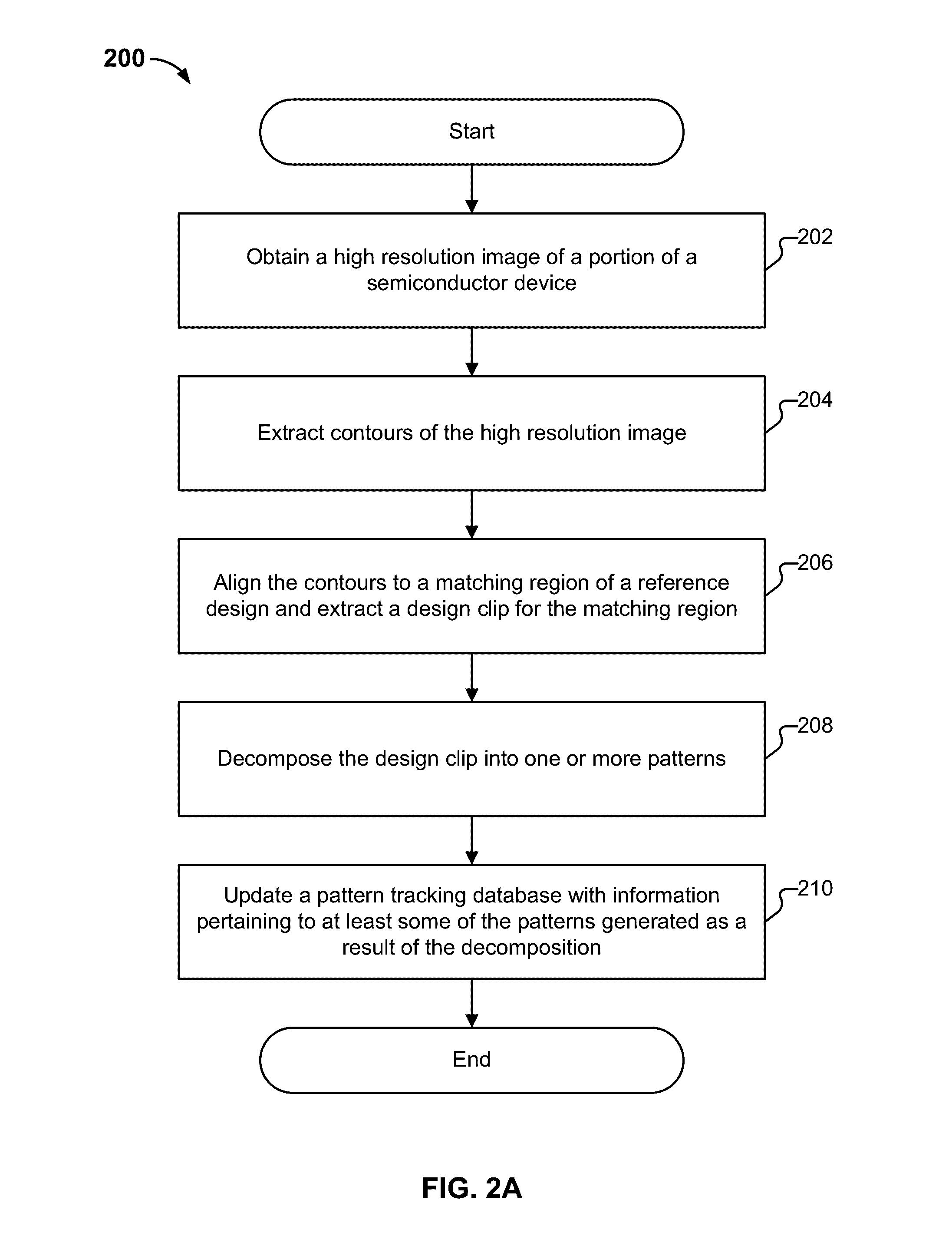

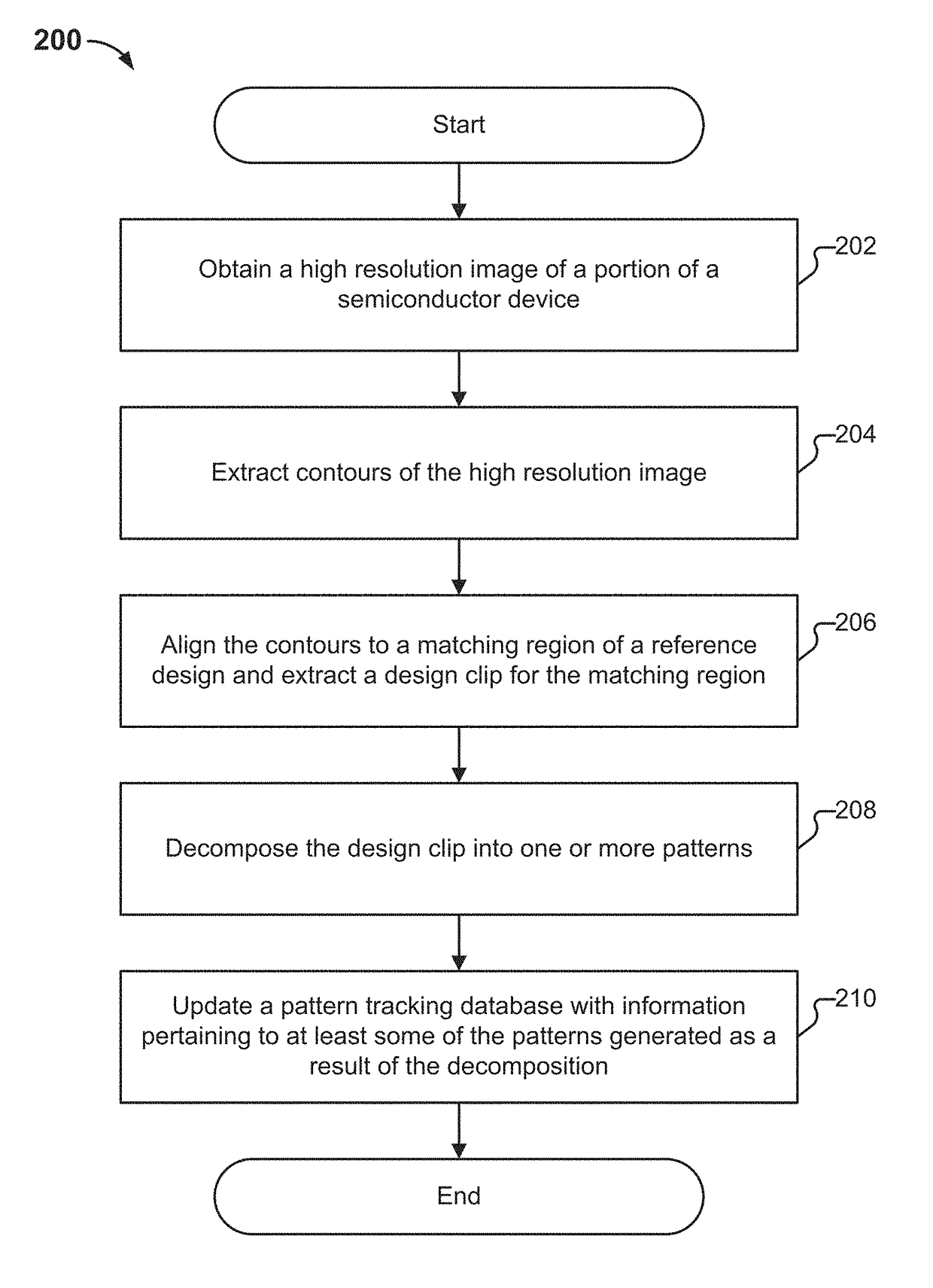

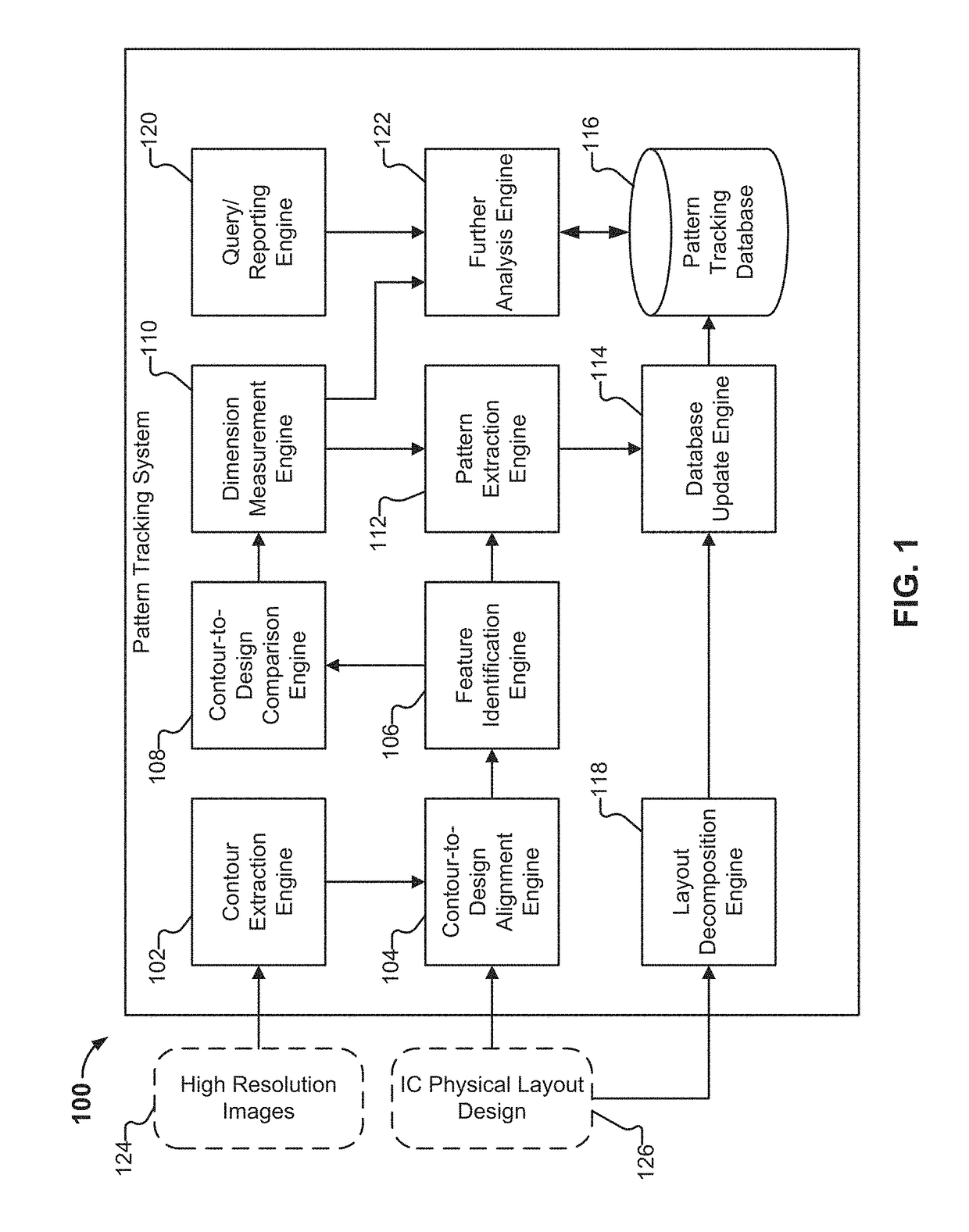

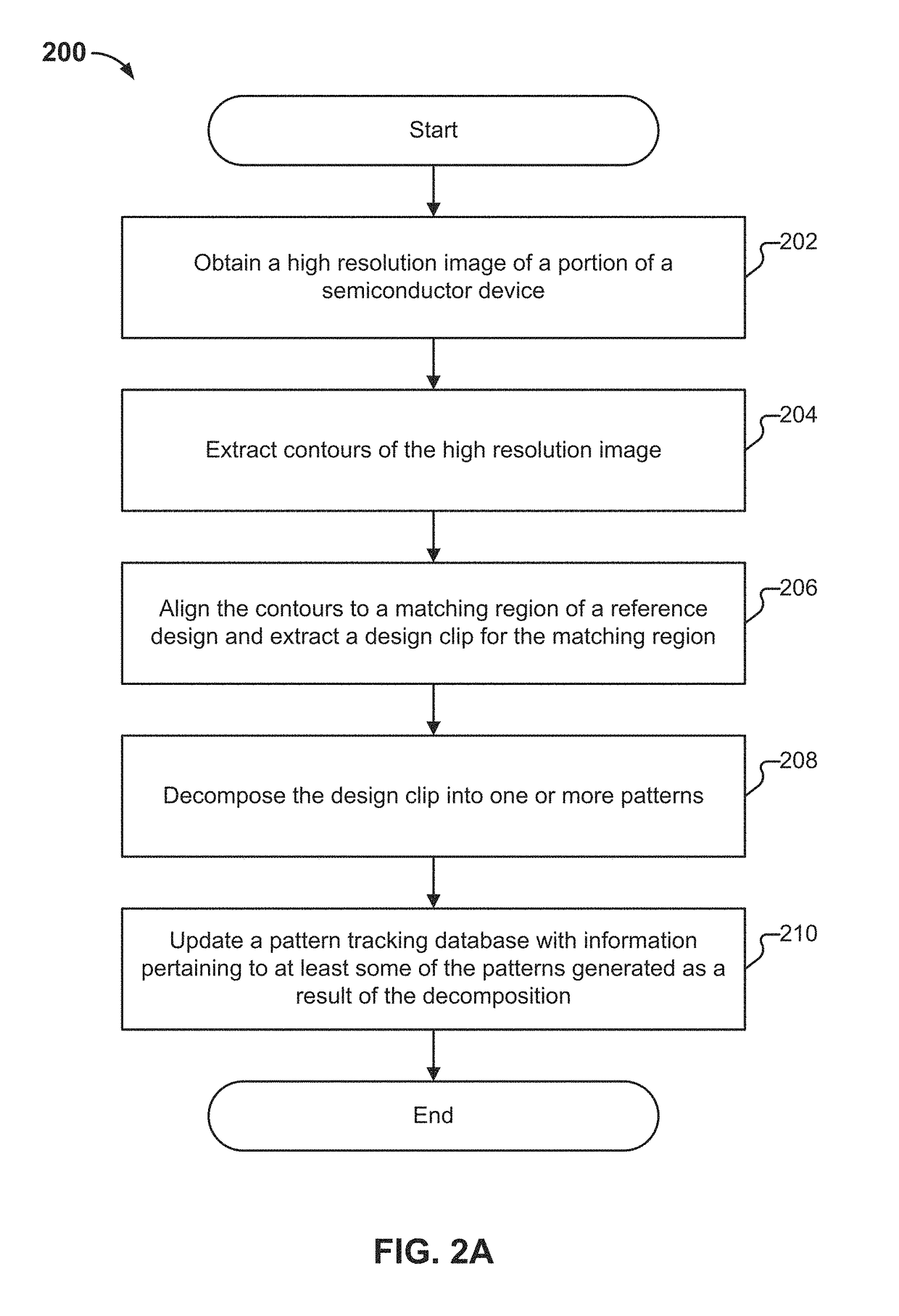

Pattern weakness and strength detection and tracking during a semiconductor device fabrication process

ActiveUS20160300338A1Image enhancementMaterial analysis using wave/particle radiationDecompositionReference design

Tracking patterns during a semiconductor fabrication process includes: obtaining an image of a portion of a fabricated device; extracting contours of the portion of the fabricated device from the obtained image; aligning the extracted contour to a matching section of a reference design; decomposing the matching section of the reference design into one or more patterns; and updating a pattern tracking database with information pertaining to at least one pattern in the one or more patterns generated as a result of the decomposition.

Owner:ANCHOR SEMICON

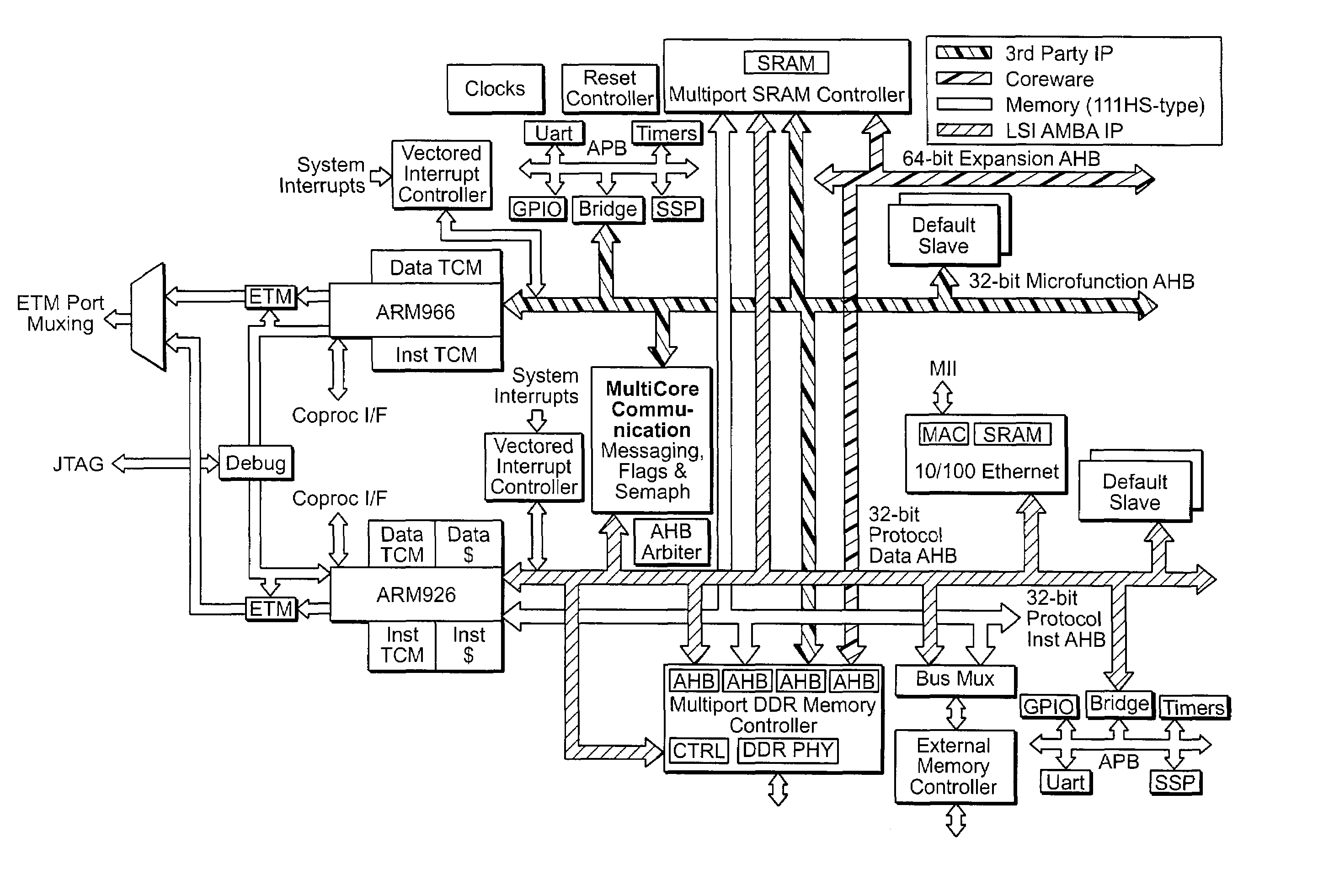

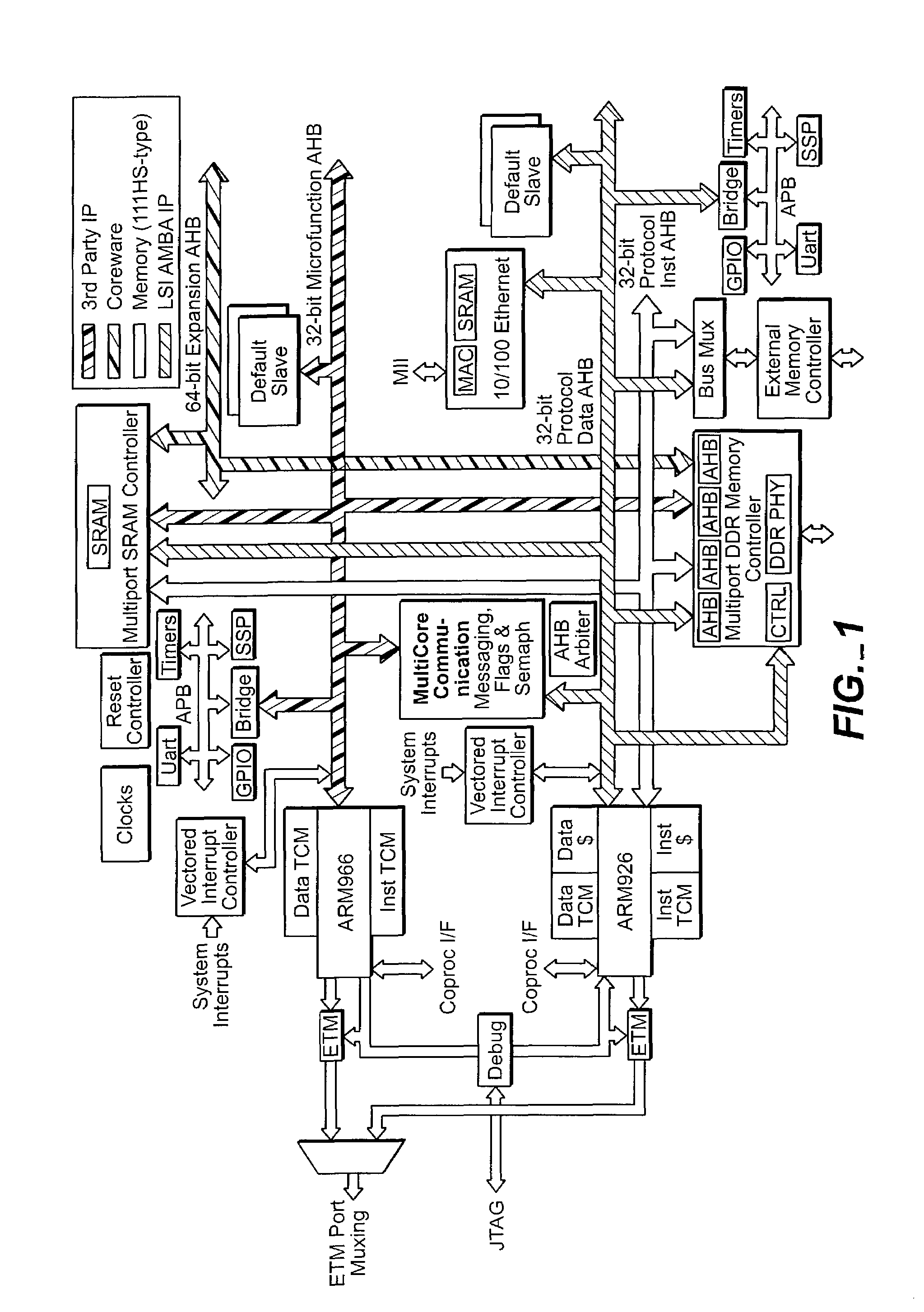

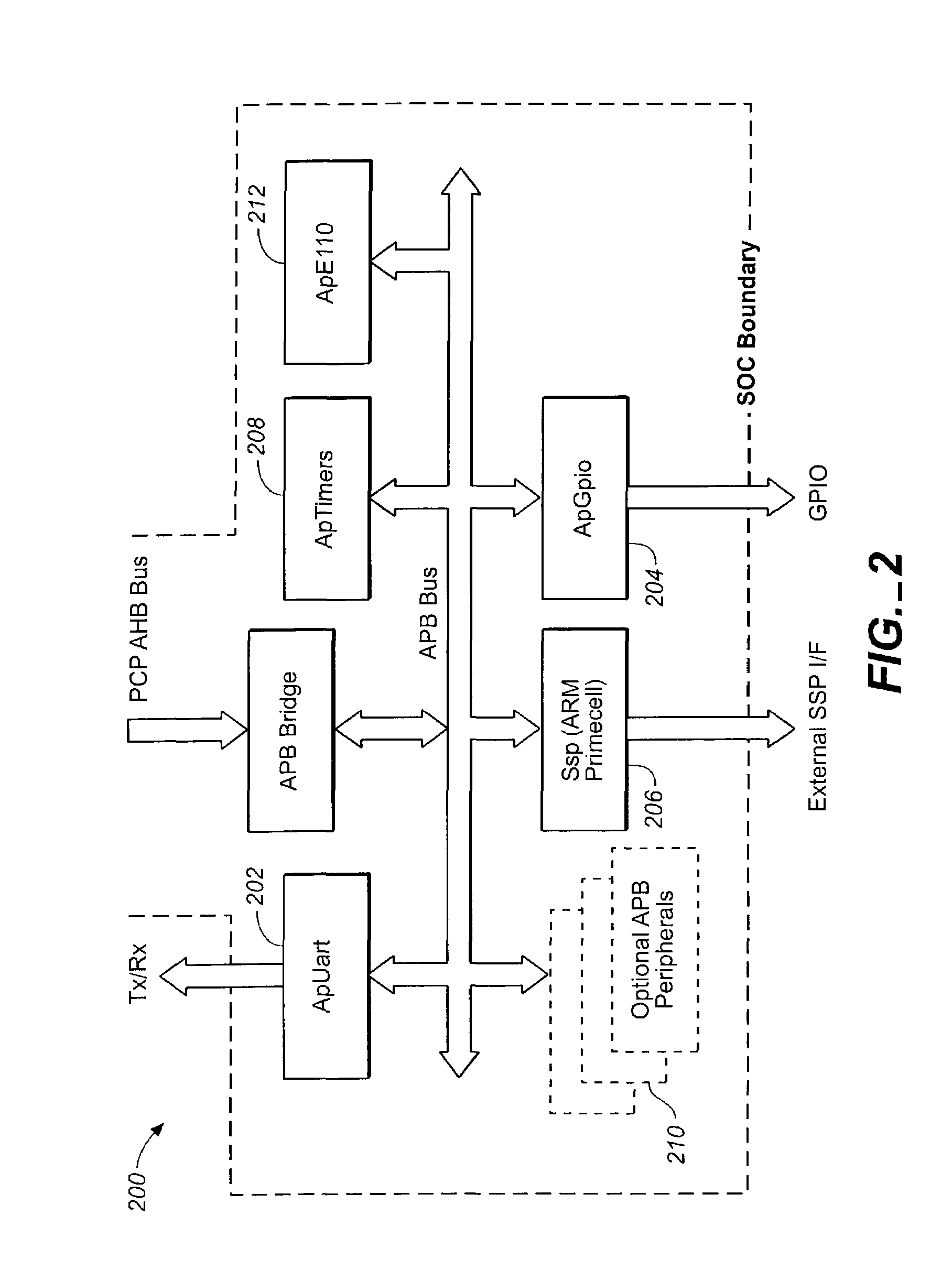

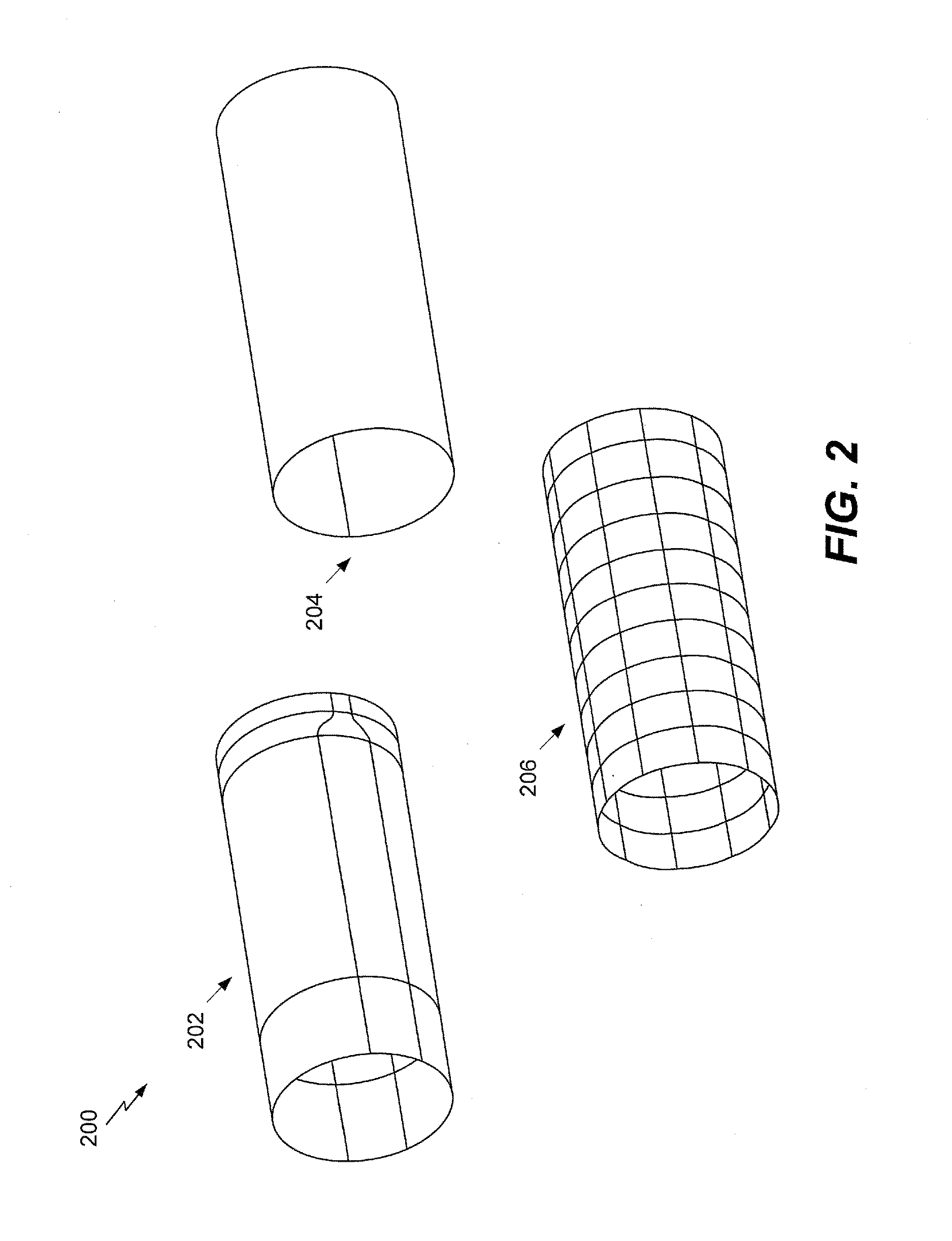

Heterogeneous multi-processor reference design

InactiveUS7000092B2General purpose stored program computerMultiple digital computer combinationsComputer architectureMulti processor

The present invention is directed to a system and method for heterogeneous multiprocessor reference design. In an aspect of the present invention, a method of designing a multiprocessor integrated circuit may include receiving a specification for an integrated circuit having multiprocessors, the specification having a desired functionality. Functional components are chosen which provide the desired functionality of the received specification. The functional components are implemented in a modular multiprocessor reference design as an example system for the multiprocessor integrated circuit. The implemented functional components of the modular multiprocessor reference design may be suitable for testing software for operation by the multiprocessor integrated circuit. Moreover, the modular multiprocessor reference design enables testing of interaction of functional components for providing the desired functionality of the received specification.

Owner:AVAGO TECH INT SALES PTE LTD

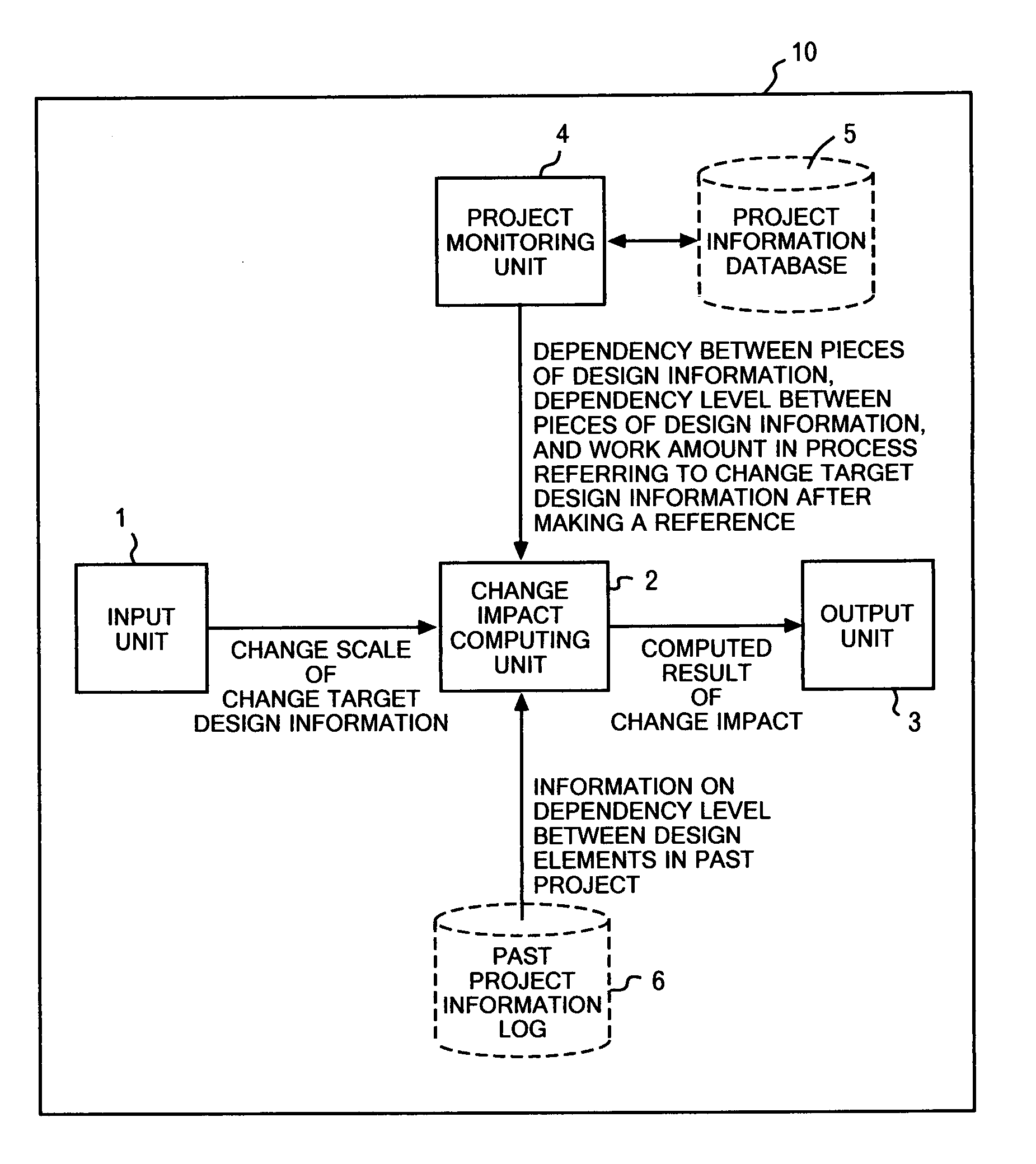

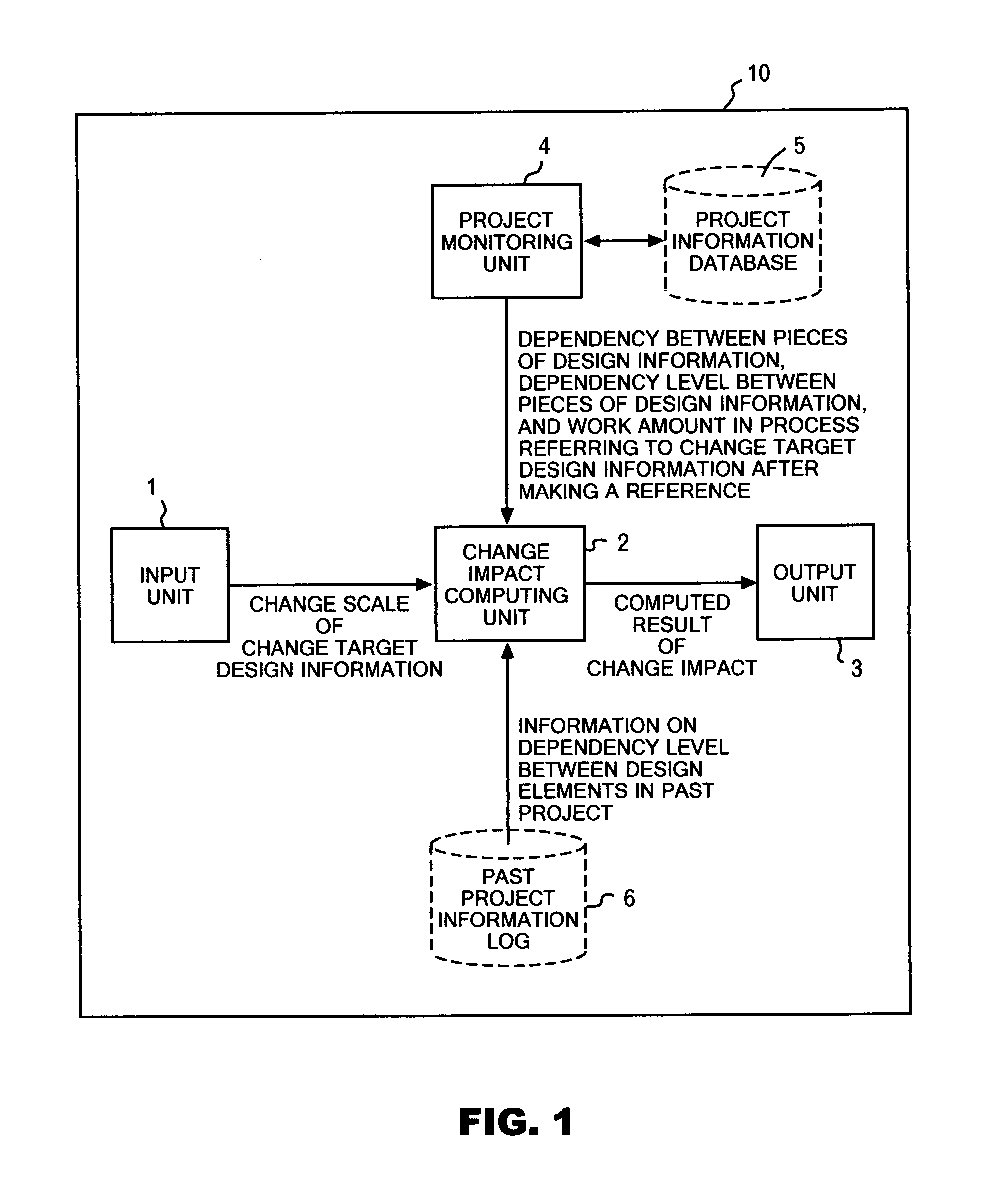

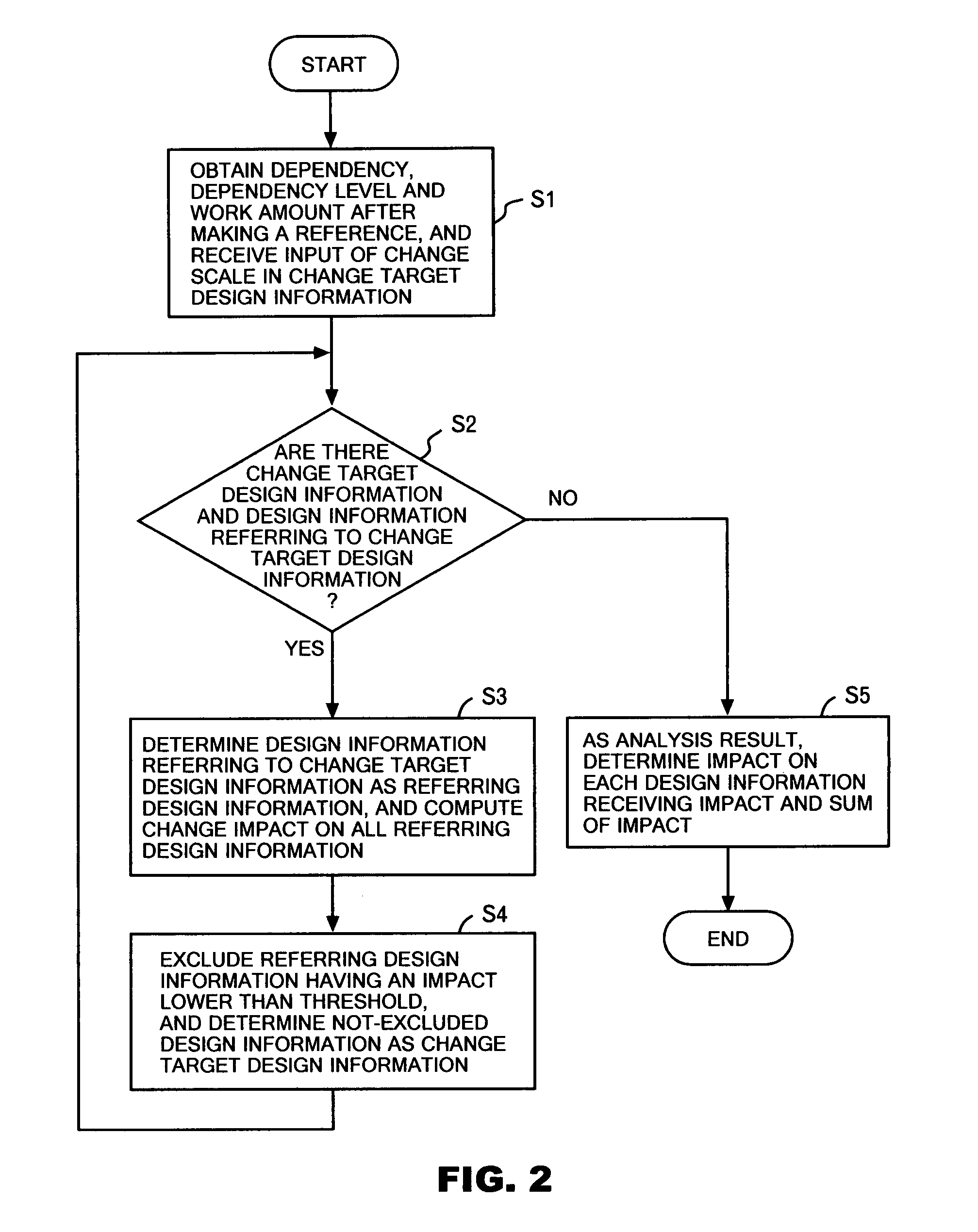

Apparatus and method for analyzing design change impact on product development process

An impact of a change in design information is defined as a sum of an additional work amount that must be reworked in each design process referring to the design information. At a time of requesting an impact analysis of a design change, all processes referring to certain design information to be changed are extracted from a project monitoring unit. An impact of the change in the referred design information on each extracted process is calculated. With respect to design information created on the basis of the referred design information in each extracted process, the maturity levels at a time when the process makes a reference and at a time when the reference design information is changed are obtained. Then, the difference therebetween is determined as the work amount that may possibly become useless.

Owner:IBM CORP

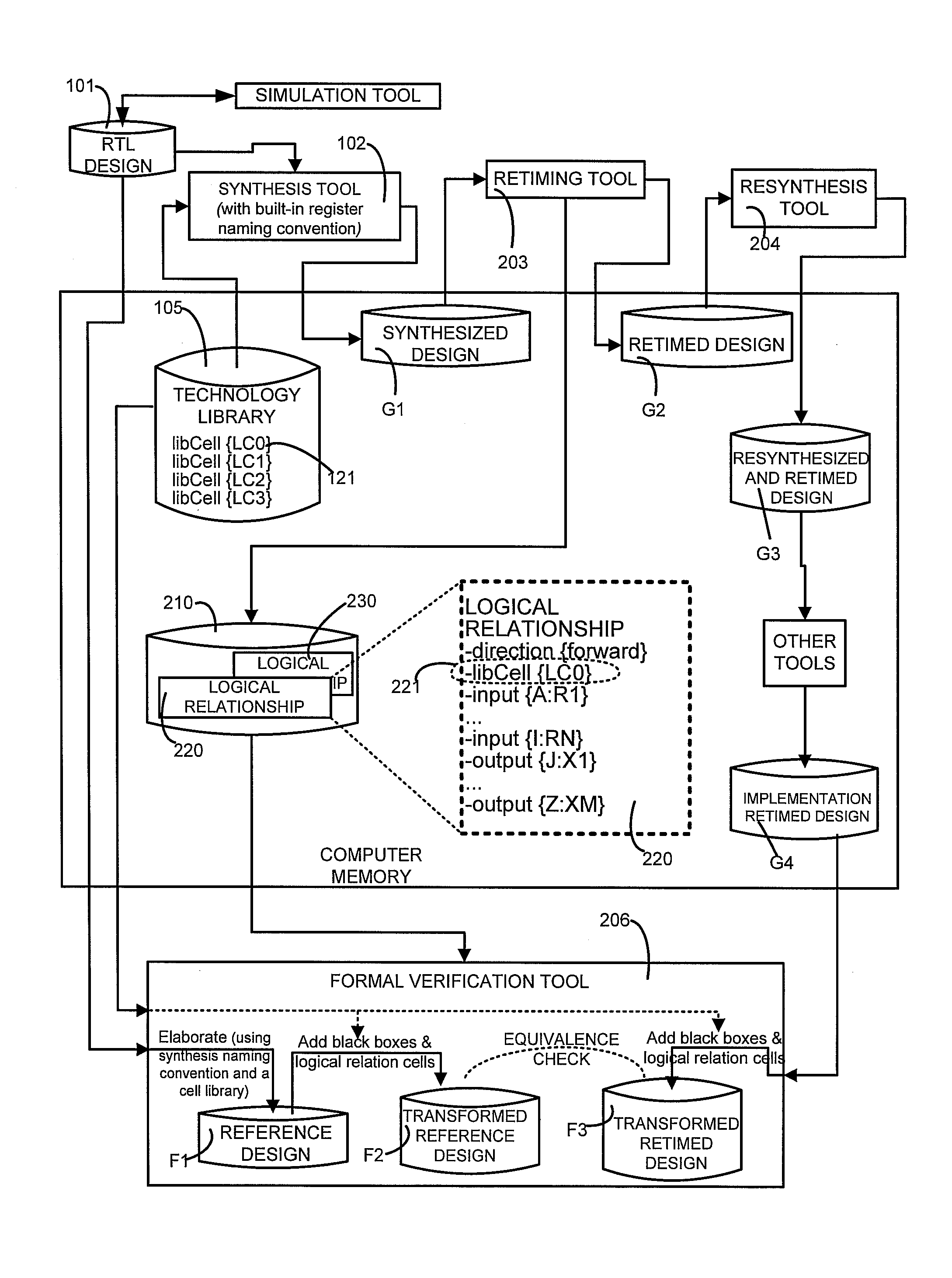

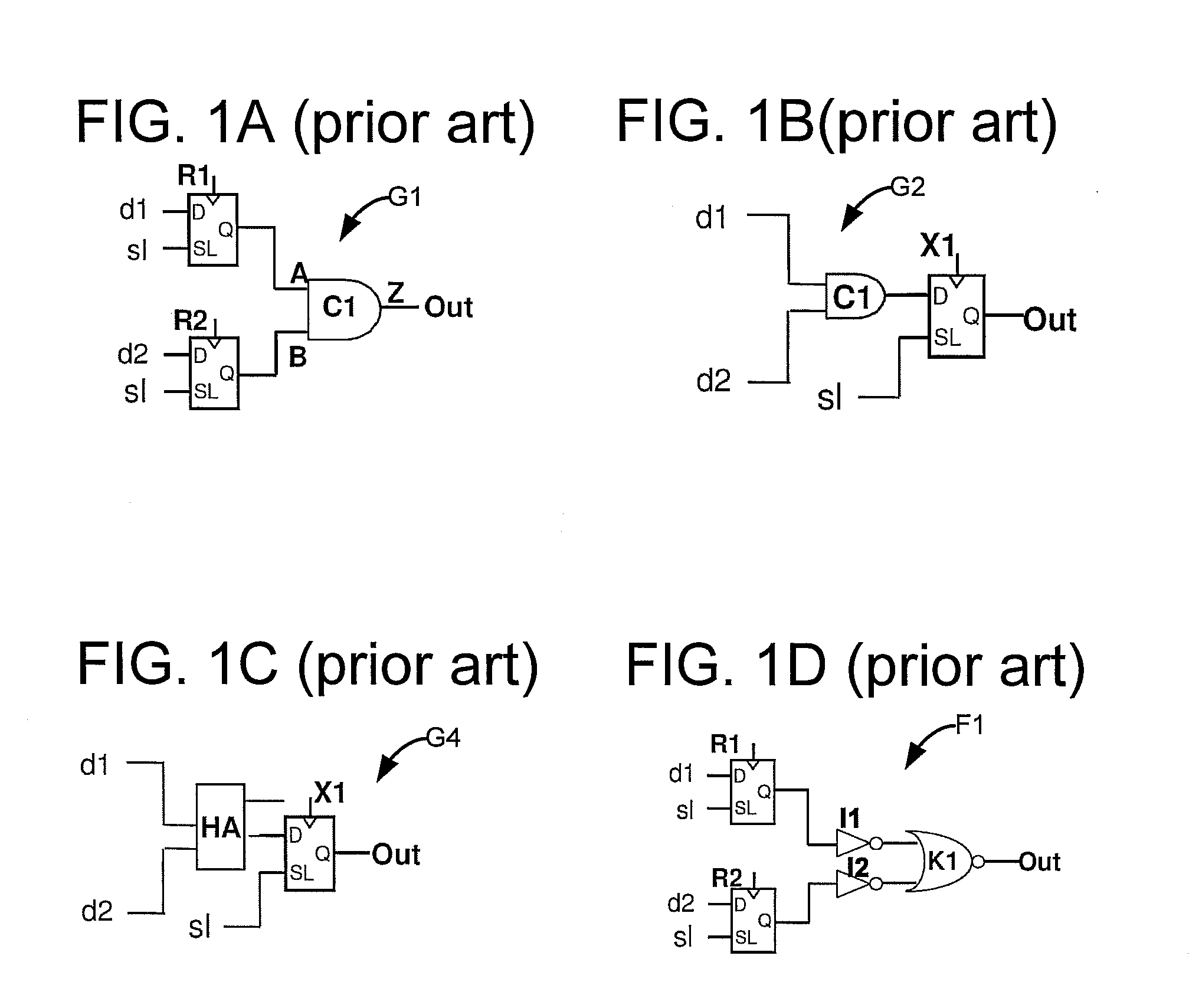

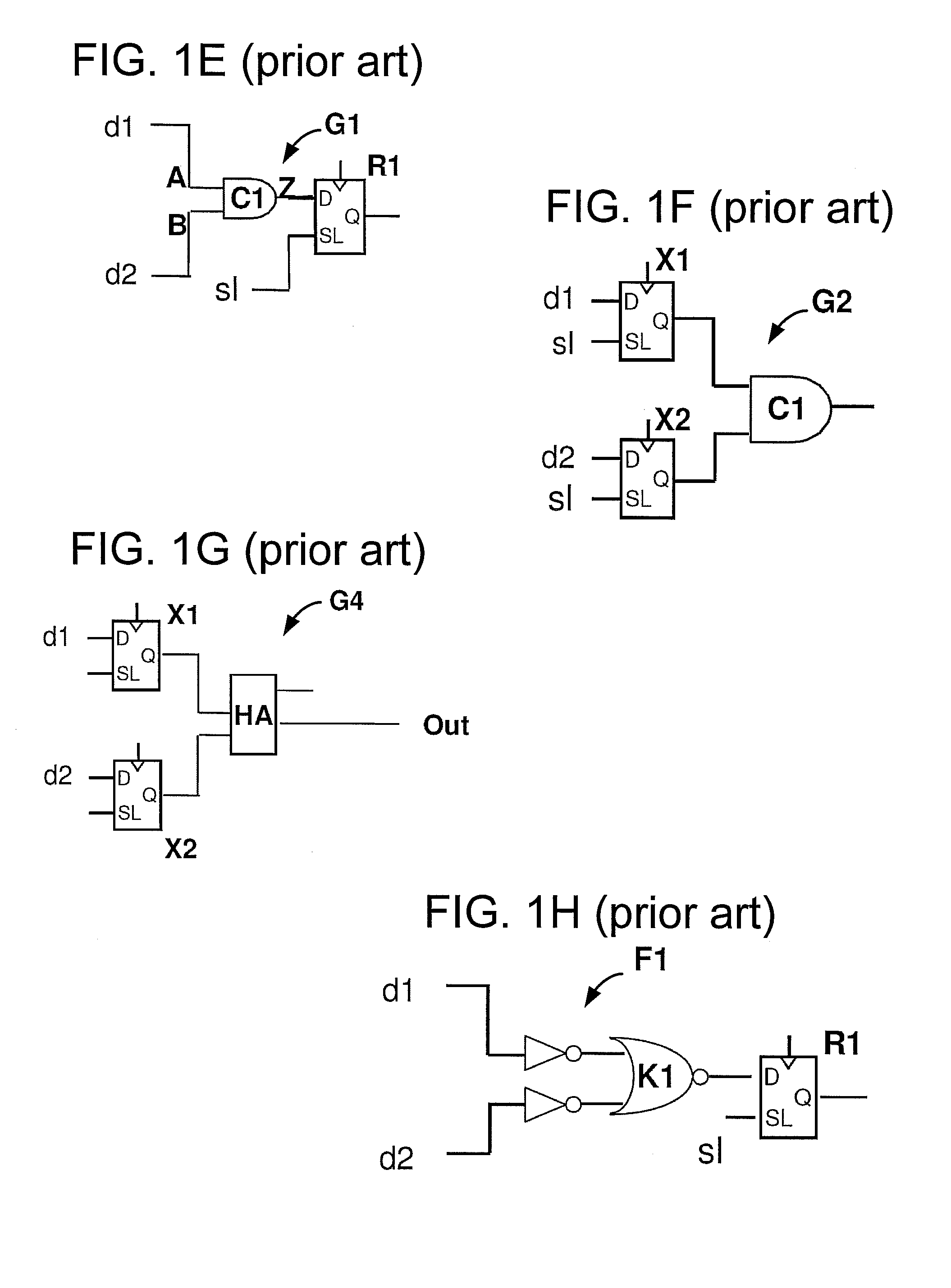

Transformation of IC designs for formal verification

ActiveUS20090293028A1Computer aided designSoftware simulation/interpretation/emulationBlack boxCombinational logic

A memory is encoded with data that represents a reference IC design, a retimed IC design, and logical relationships, wherein at least one logical relationship describes combinational logic without reference to structural information, such as actual cells that have been instantiated in the IC designs. The logical relationships are used to instantiate logic described therein, and to define one or more black boxes as being functionally inverse of the logic. Each instantiated logic and its functionally inverse black box are thereafter added to the reference IC design to obtain a transformed reference IC design. A transformed retimed IC design is also obtained by addition of the instantiated logic(s) and functionally inverse black box(es) to the retimed IC design. These two transformed IC designs are then supplied to an equivalence checker, for formal verification.

Owner:SYNOPSYS INC

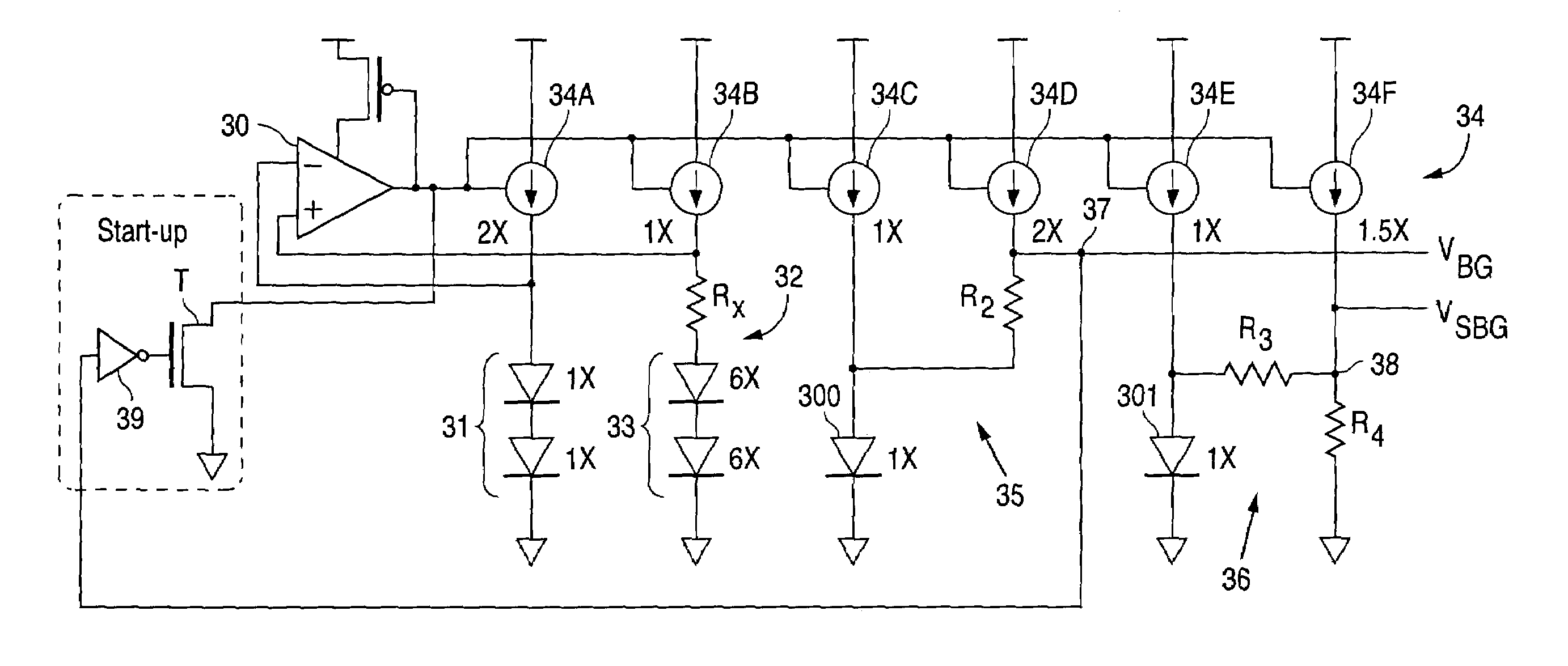

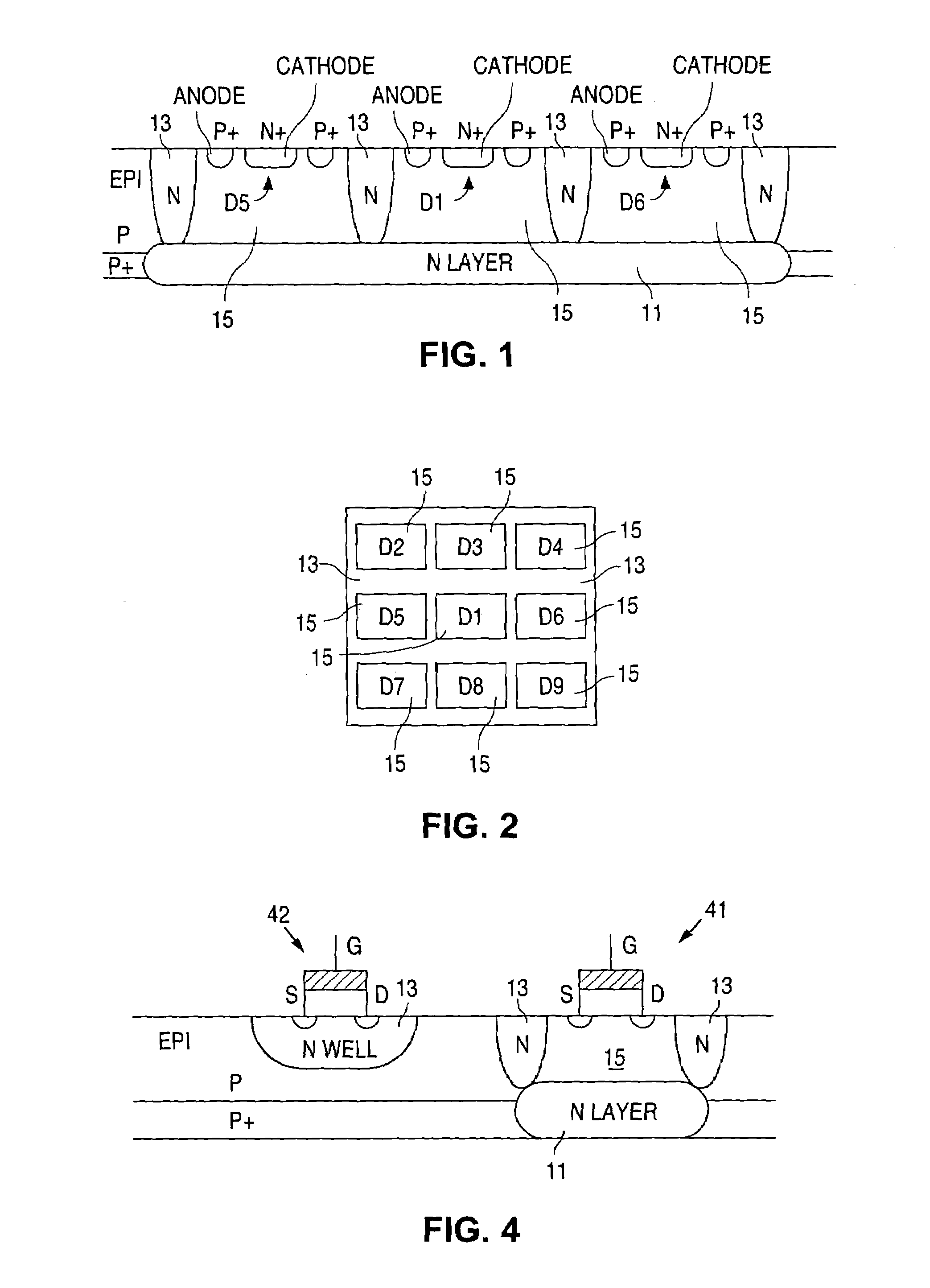

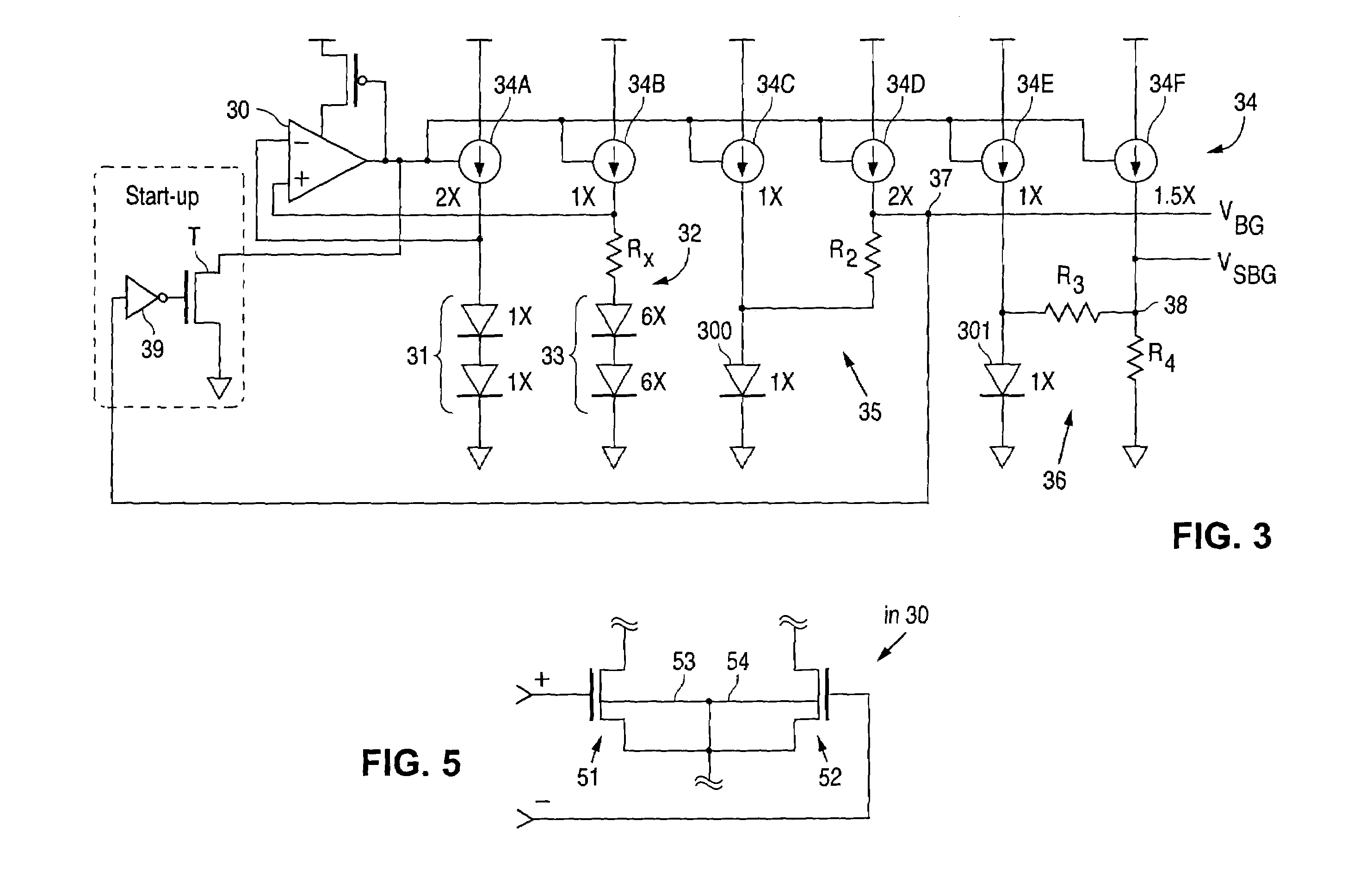

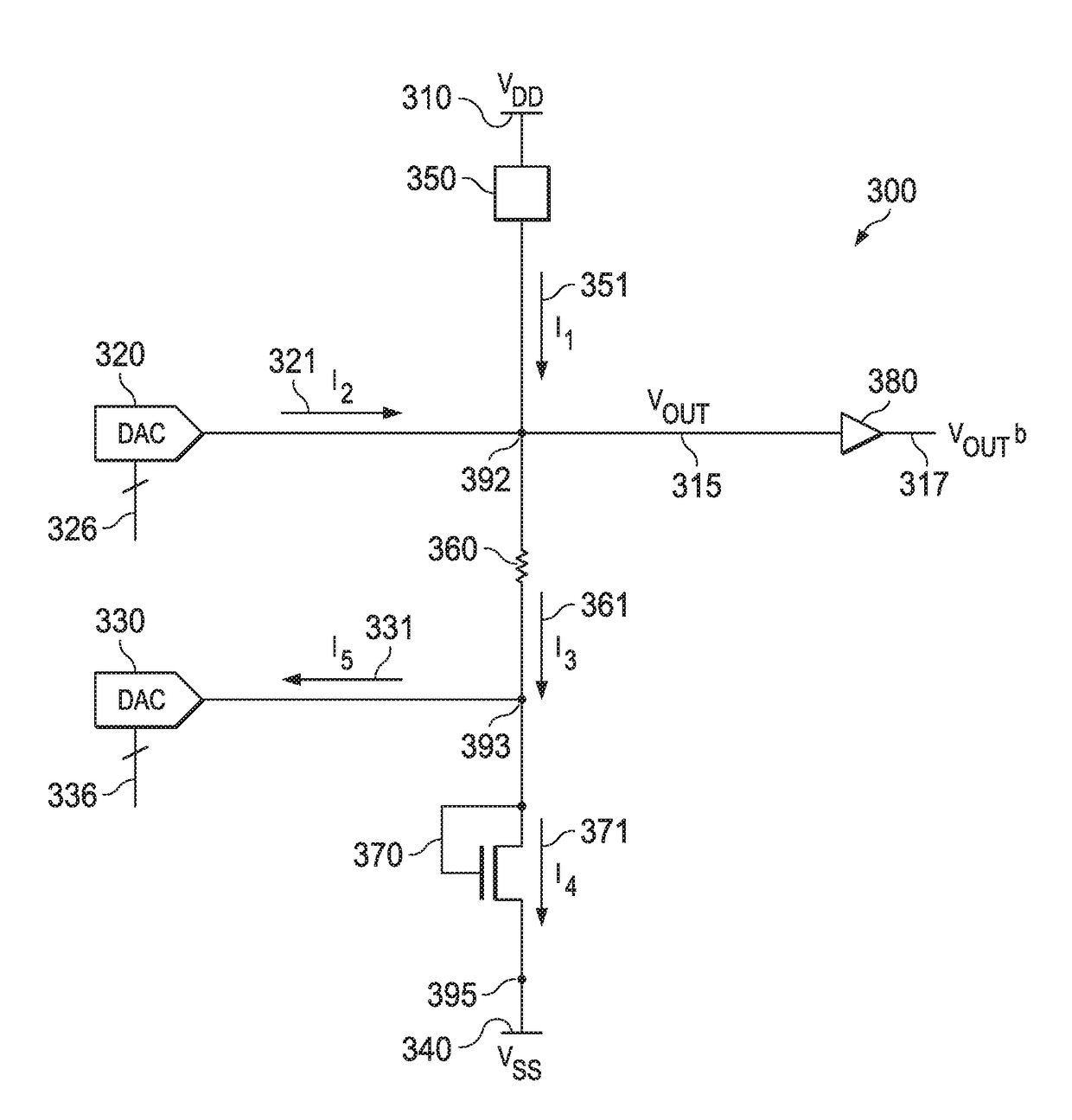

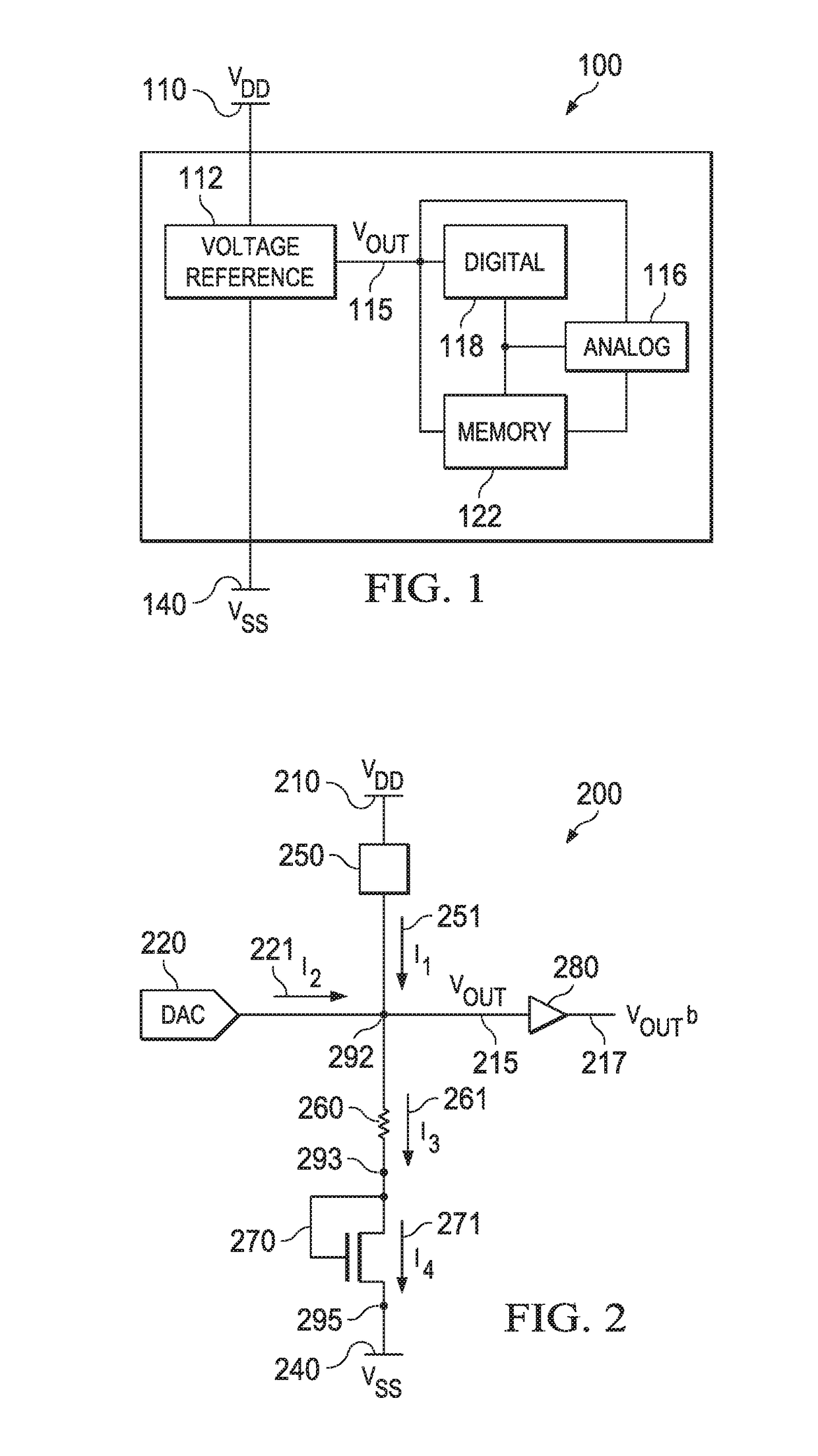

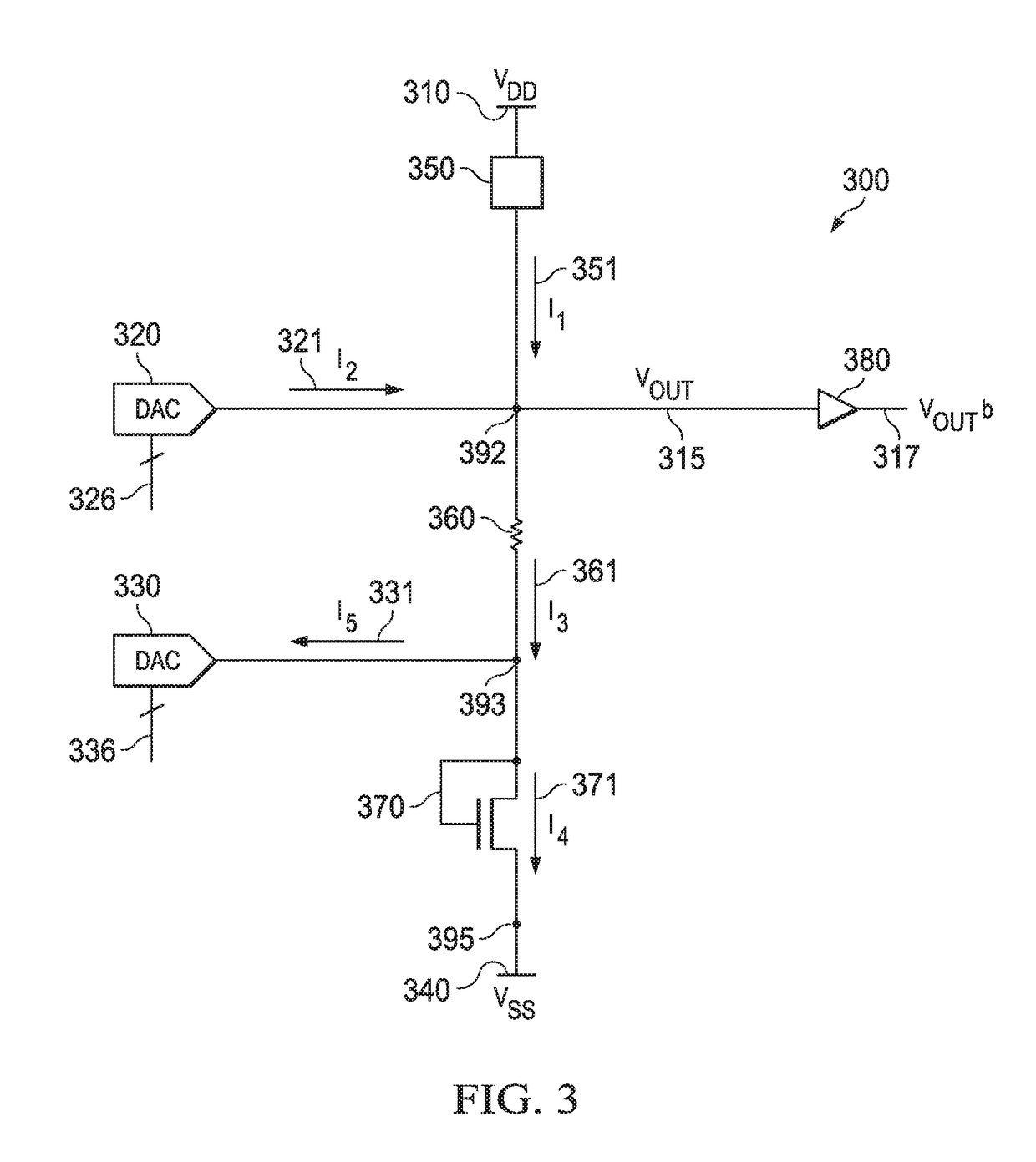

Bandgap reference designs with stacked diodes, integrated current source and integrated sub-bandgap reference

ActiveUS7253598B1Improve bandgap reference circuit performanceLower input sensitivityElectric variable regulationAudio power amplifierReference design

The performance of a bandgap reference circuit is improved by increasing the ΔVBE, and thereby correspondingly decreasing the input sensitivity of the error amplifier in the control loop. The ΔVBE can be increased by presenting stacked diode configurations at the amplifier inputs, by increasing the diode ratio presented at the amplifier inputs, and by providing a higher current in the CTAT leg than in the PTAT leg. The stacked diode configuration is achieved by producing isolated diodes with a triple well CMOS process. The stacked diode configuration and the triple well CMOS process also permit the input stage of the amplifier to use N-channel transistors operating in the threshold region.

Owner:NAT SEMICON CORP

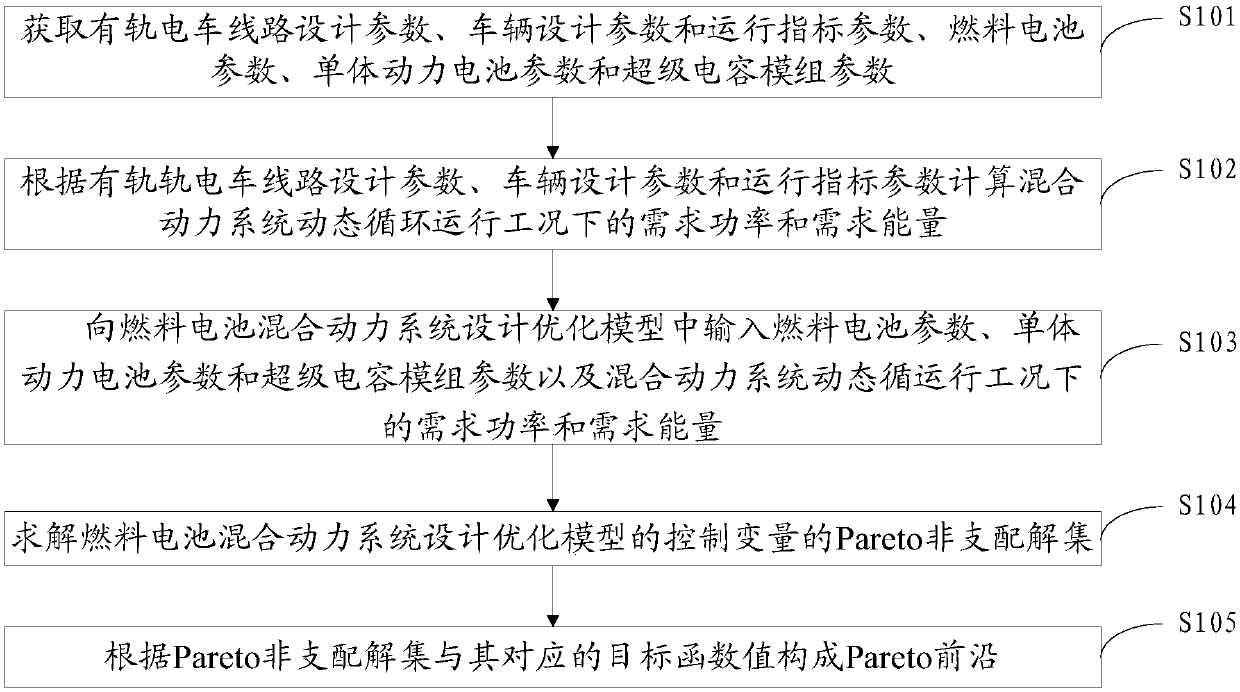

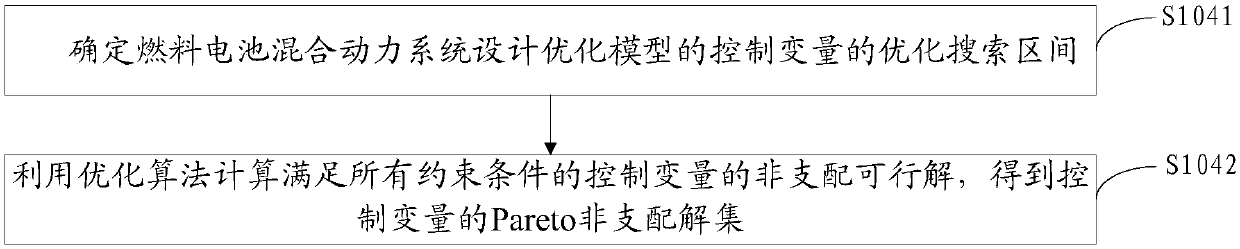

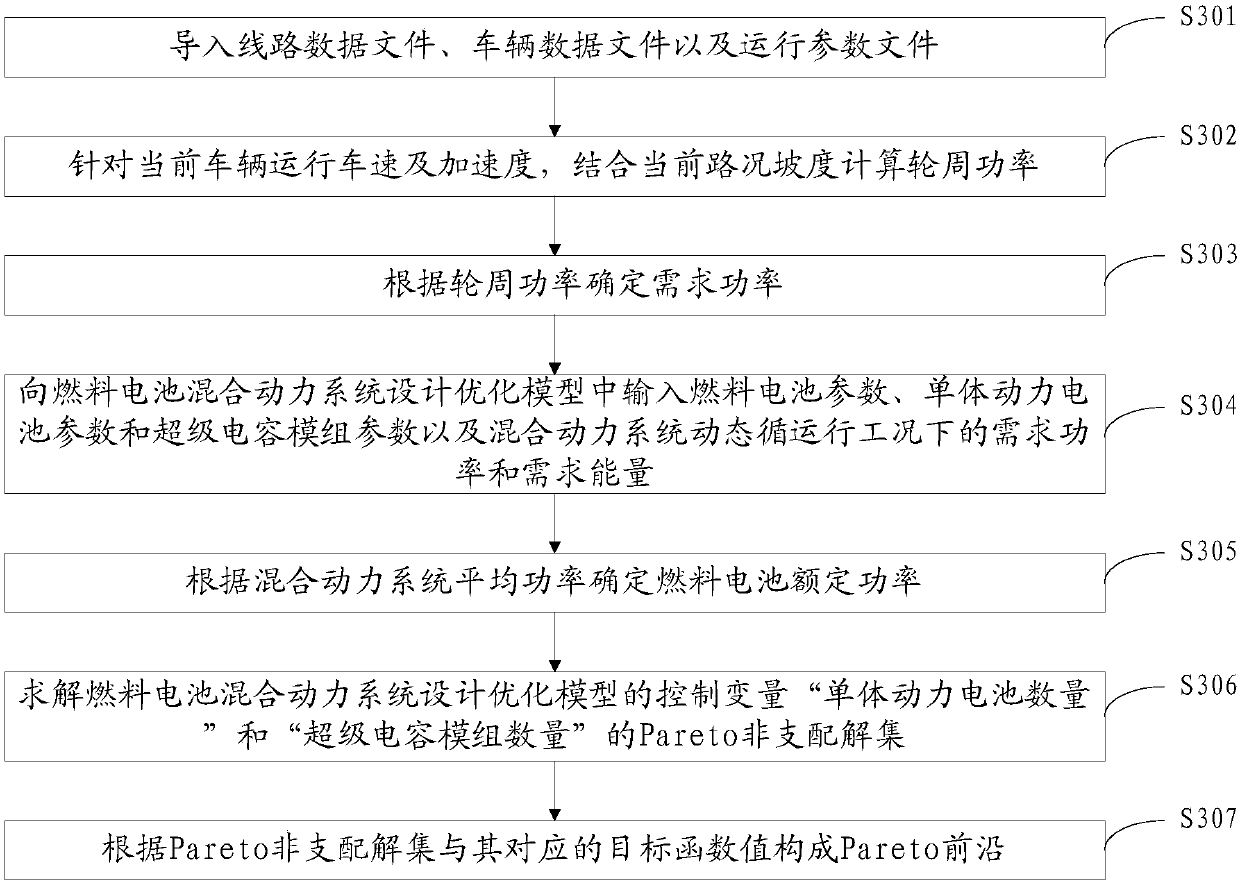

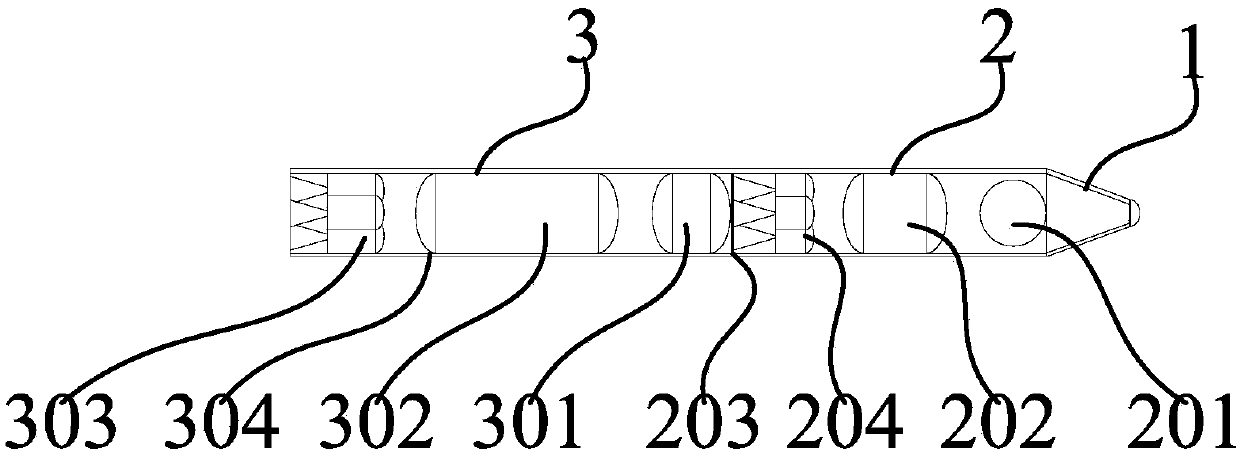

Vehicle-mounted fuel cell hybrid power system designing method and device

InactiveCN107813718AEconomy prioritySize priorityGeometric CADInternal combustion piston enginesCapacitanceLeading edge

The embodiment of the invention discloses a vehicle-mounted fuel cell hybrid power system designing method. The method comprises the steps of obtaining tramcar line designing parameters, vehicle design parameters, running index parameters, fuel cell parameters, monomer power battery parameters and super capacitor module parameters; calculating needed power and needed energy of a hybrid power system under a dynamic cycle running condition according to the parameters; inputting the parameters, the needed power and the needed energy into a fuel cell hybrid power system design optimization model;solving a Pareto non-dominated solution set of control variables of the fuel cell hybrid power system design optimization model; constituting a Pareto leading edge according to the Pareto non-dominated solution set and target function values corresponding to the Pareto non-dominated solution set. In this way, a reference design scheme for designing the fuel cell hybrid power system which meets user requirements is provided for design personnel. The embodiment of the invention further discloses a vehicle-mounted fuel cell hybrid power system designing device.

Owner:CRRC QINGDAO SIFANG CO LTD

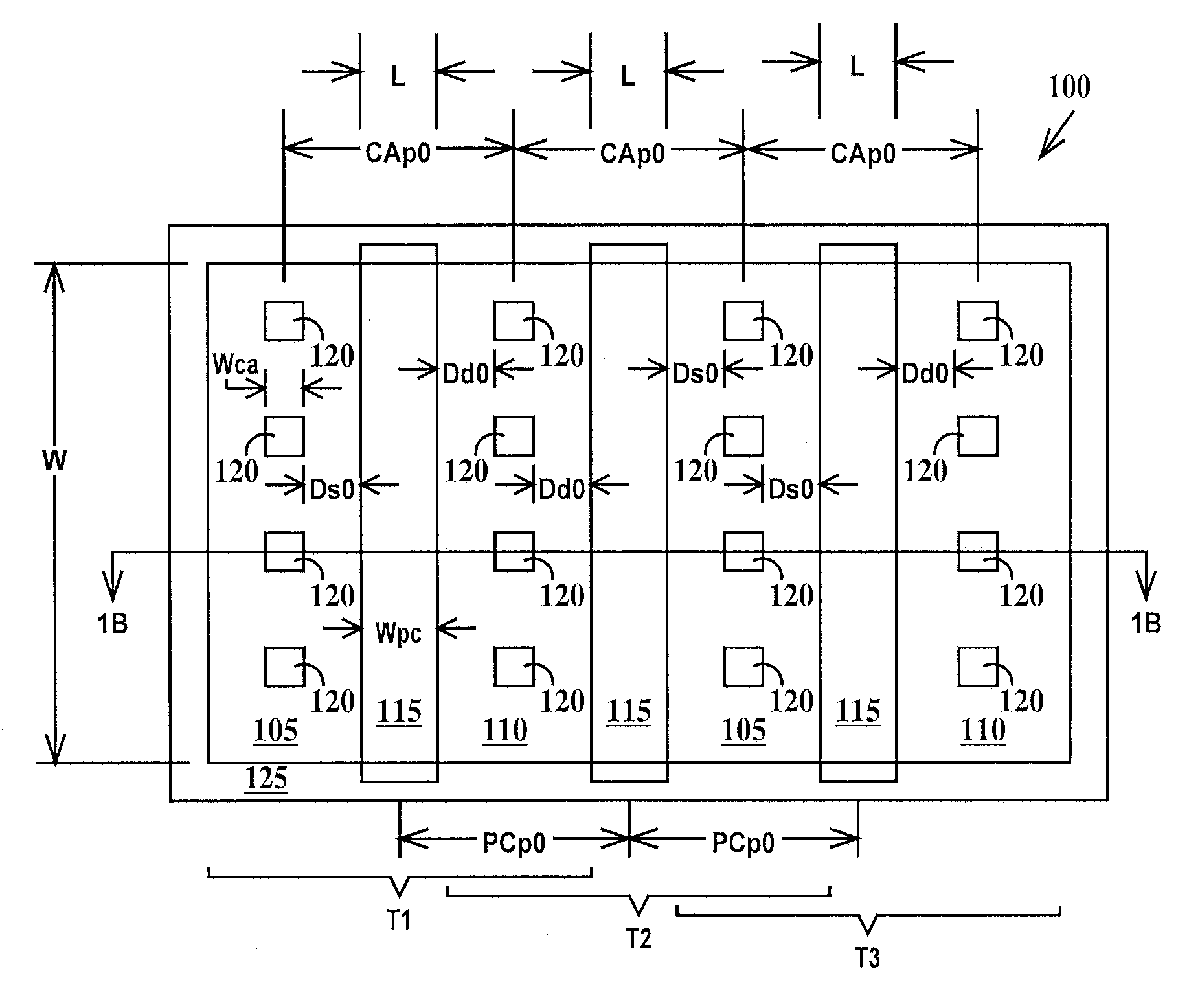

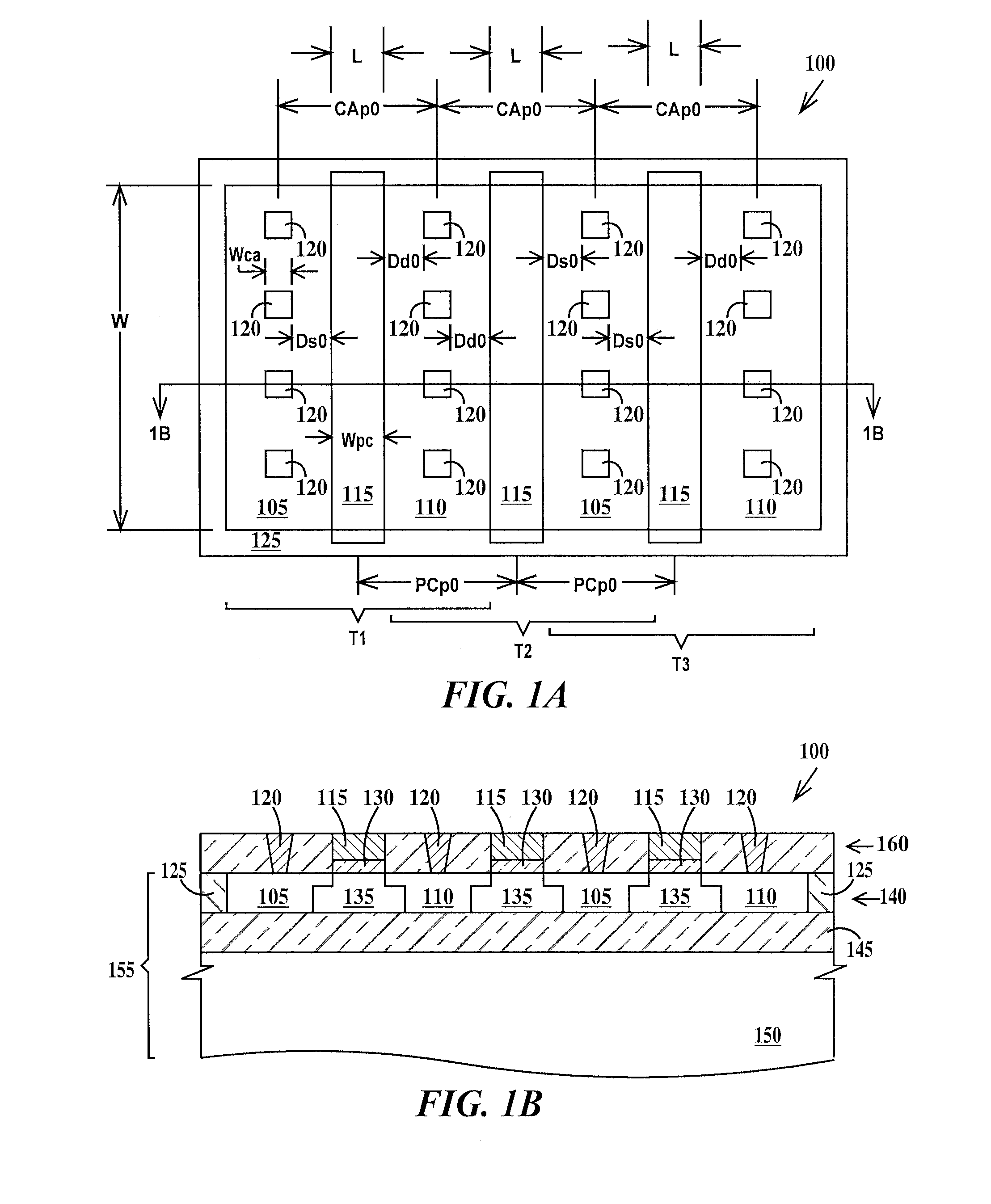

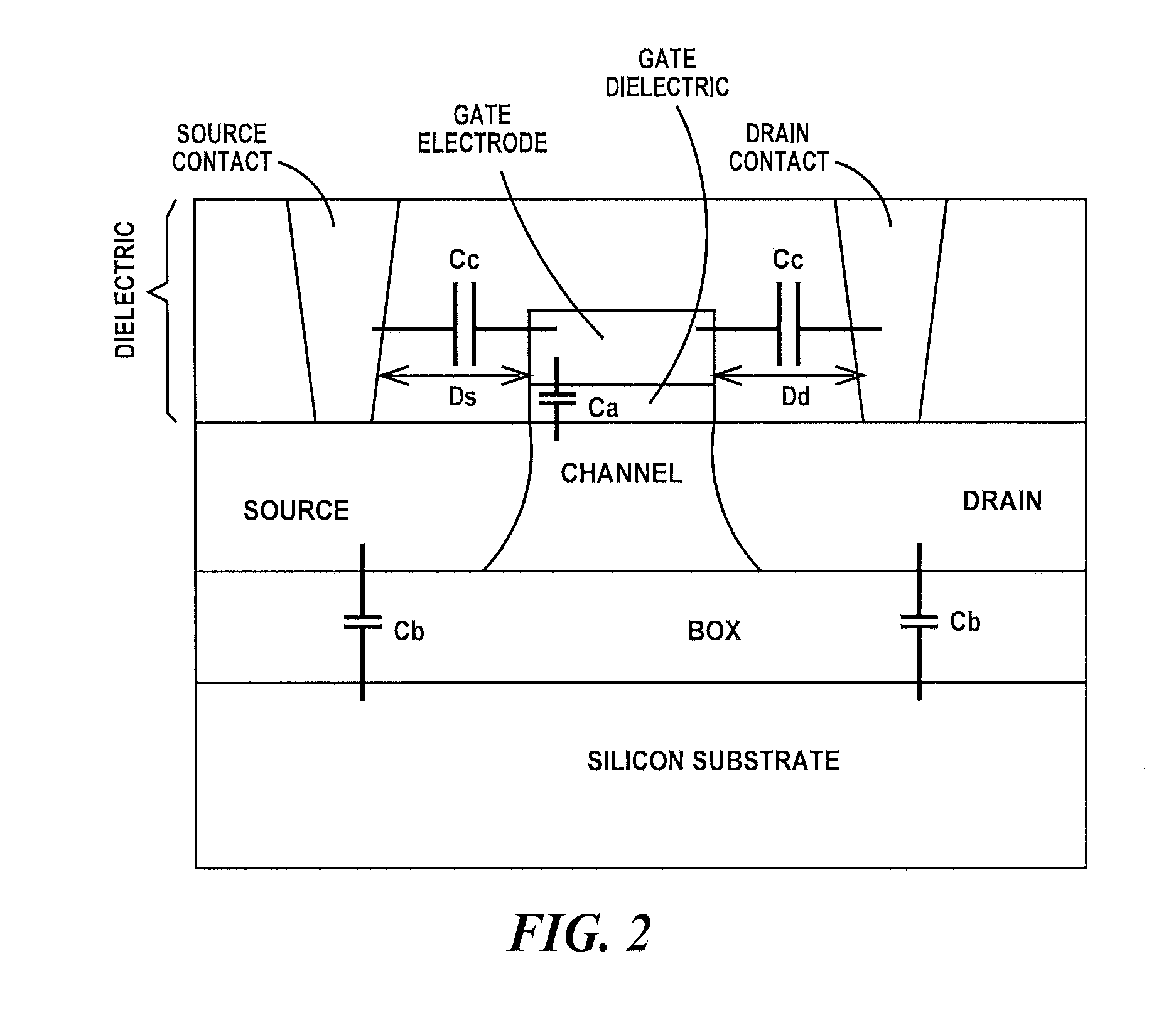

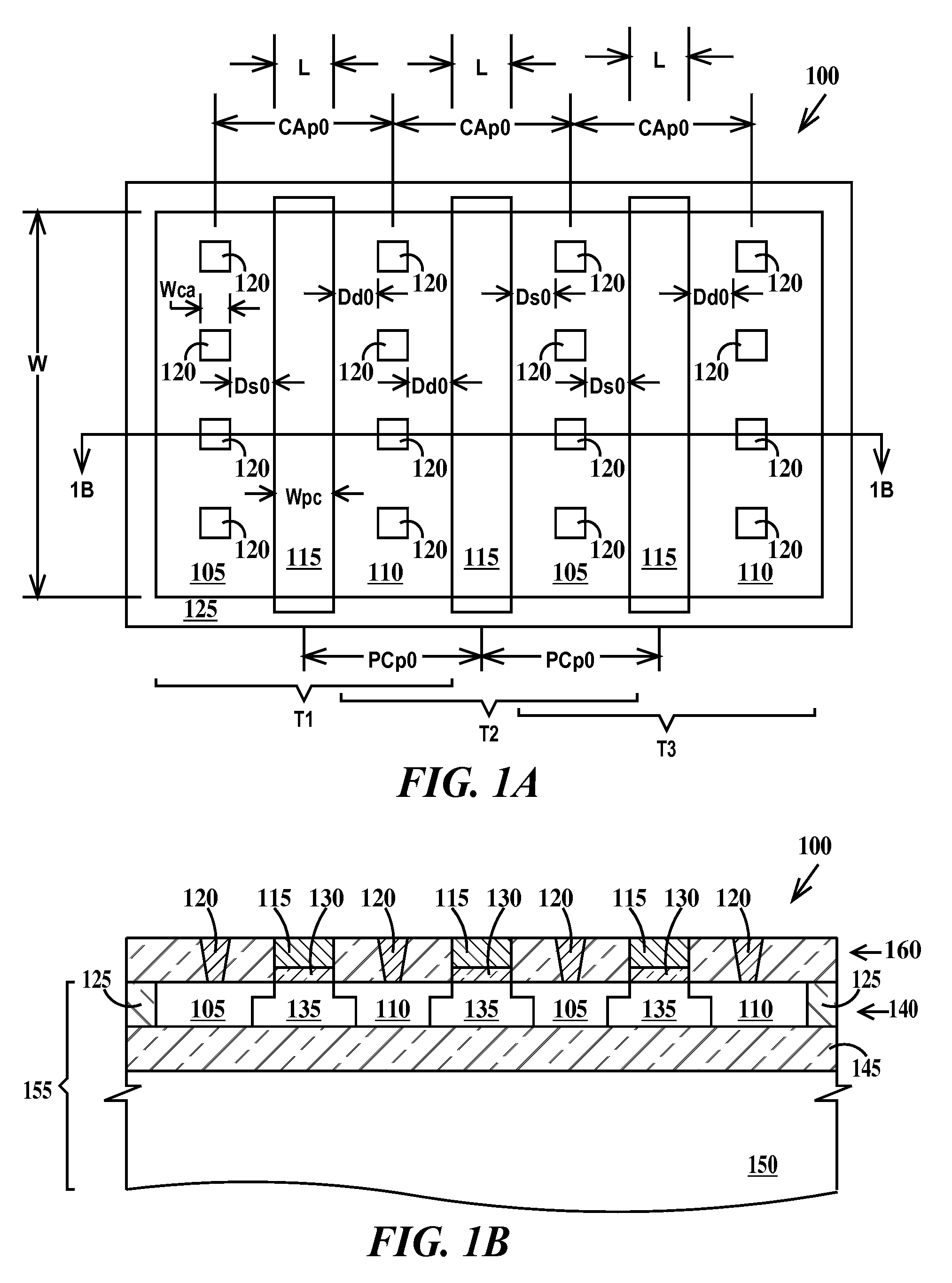

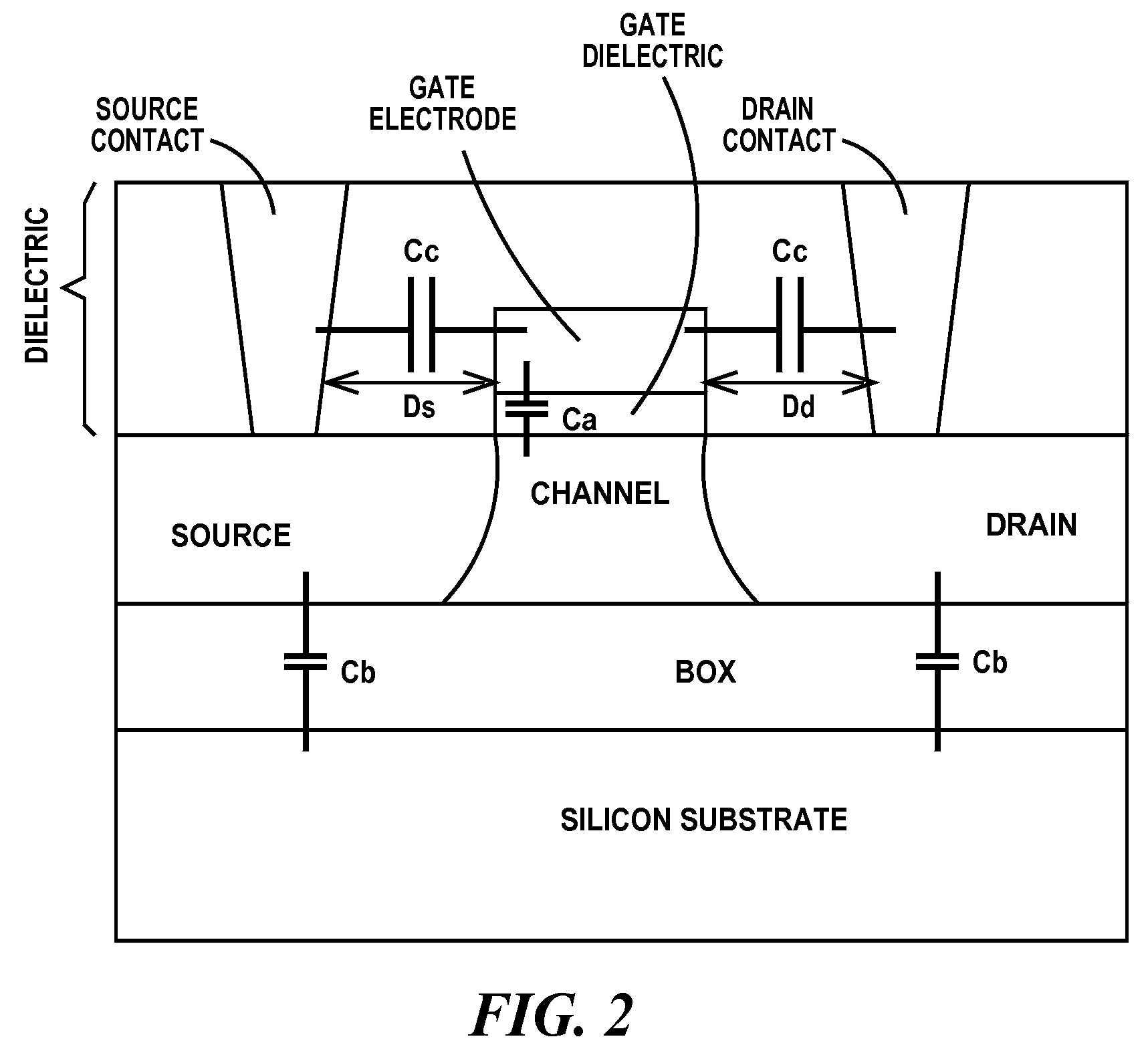

High-performance fet device layout

InactiveUS20080109770A1Performance maximizationRapid designDetecting faulty computer hardwareCAD circuit designEngineeringReference design

A fast FET and a method and system for designing the fast FET. The method includes: selecting a reference design for a field effect transistor, the field effect transistor including a source, a drain, a channel between the source and drain, a gate electrode over the channel, at least one source contact to the source and at least one contact to the drain, the at least one source contact spaced a first distance from the gate electrode and the at least one drain contact spaced a second distance from the gate electrode; and adjusting the first distance and the second distance to maximize a performance parameter of the field effect transistor to create a fast design for the field effect transistor.

Owner:GLOBALFOUNDRIES INC

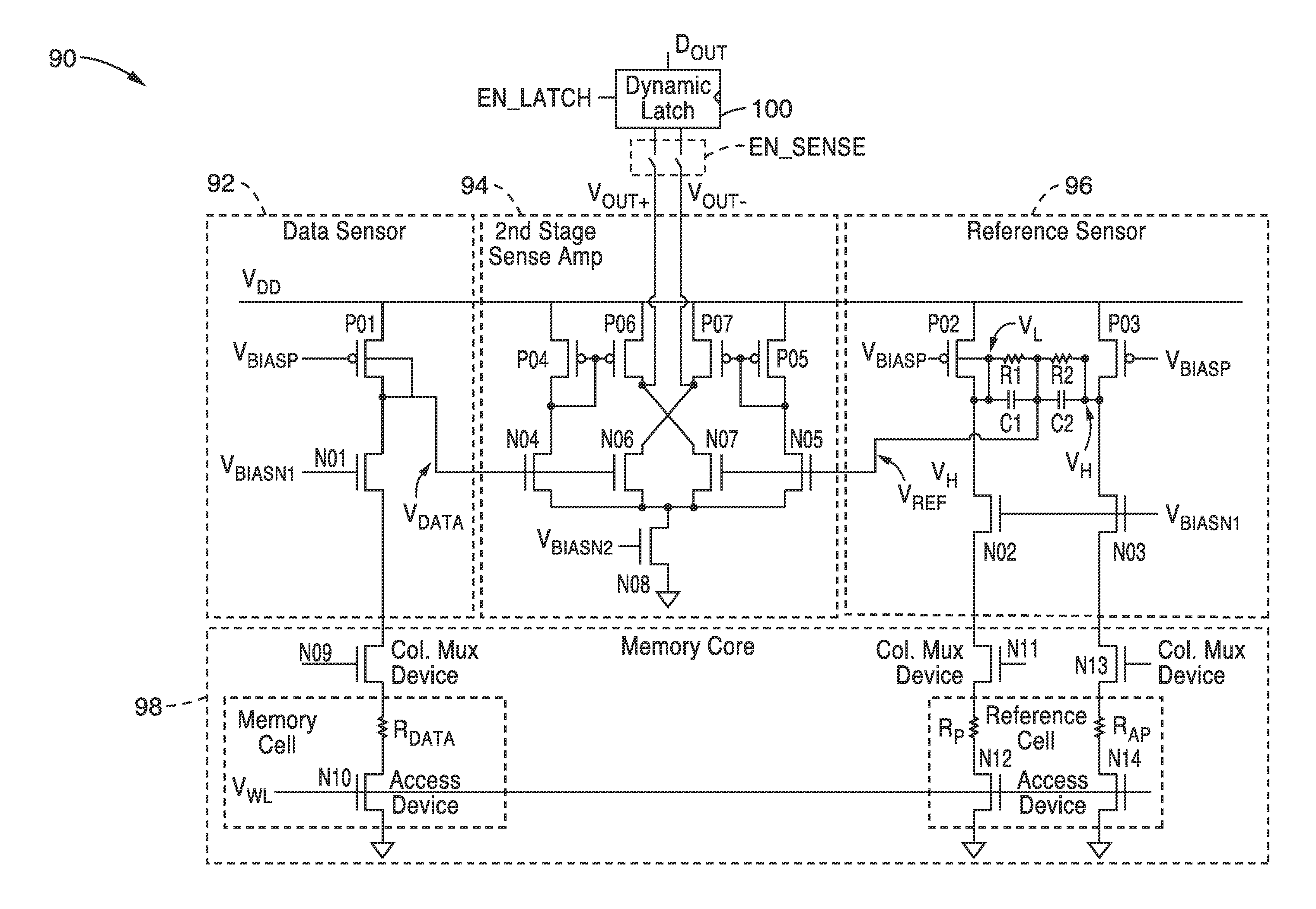

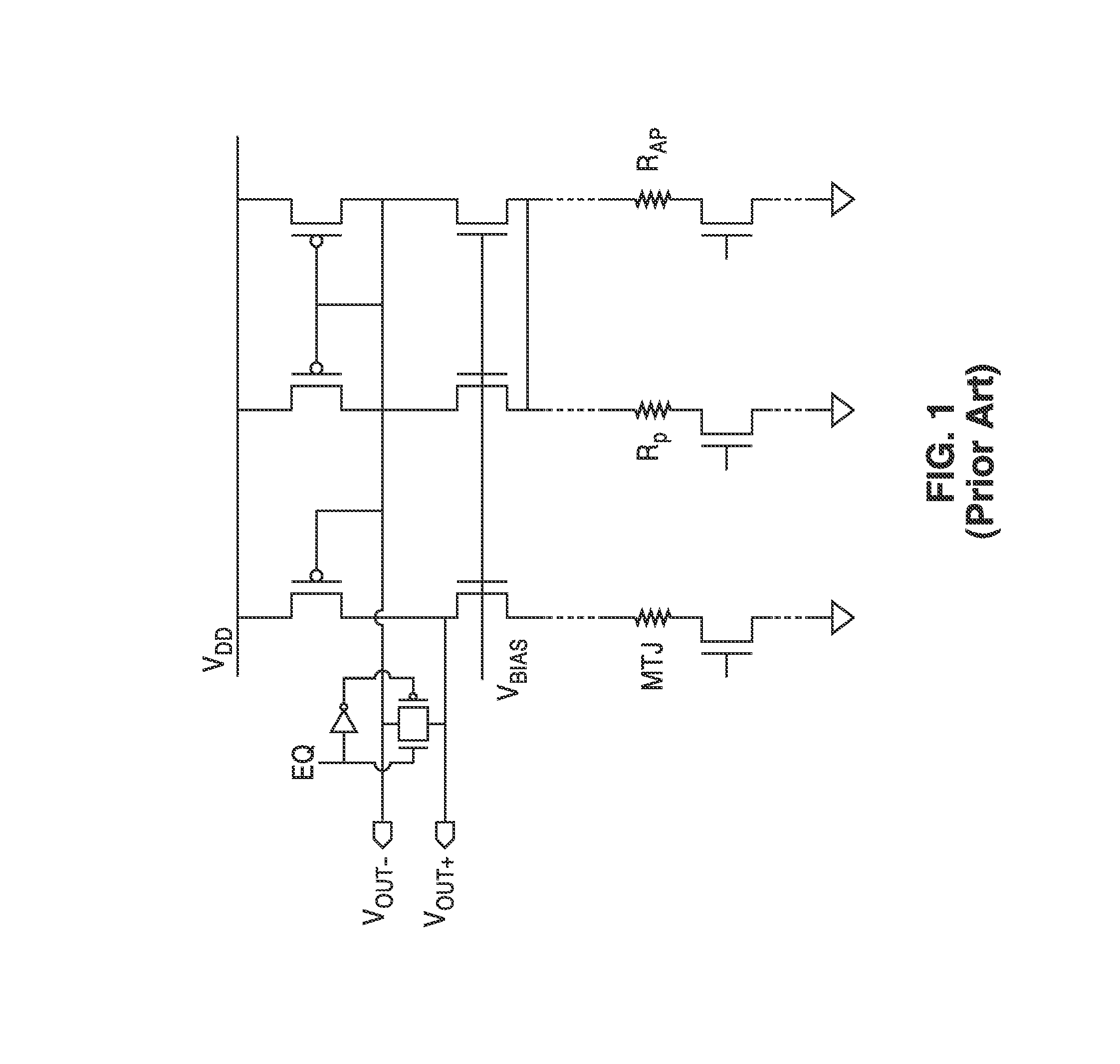

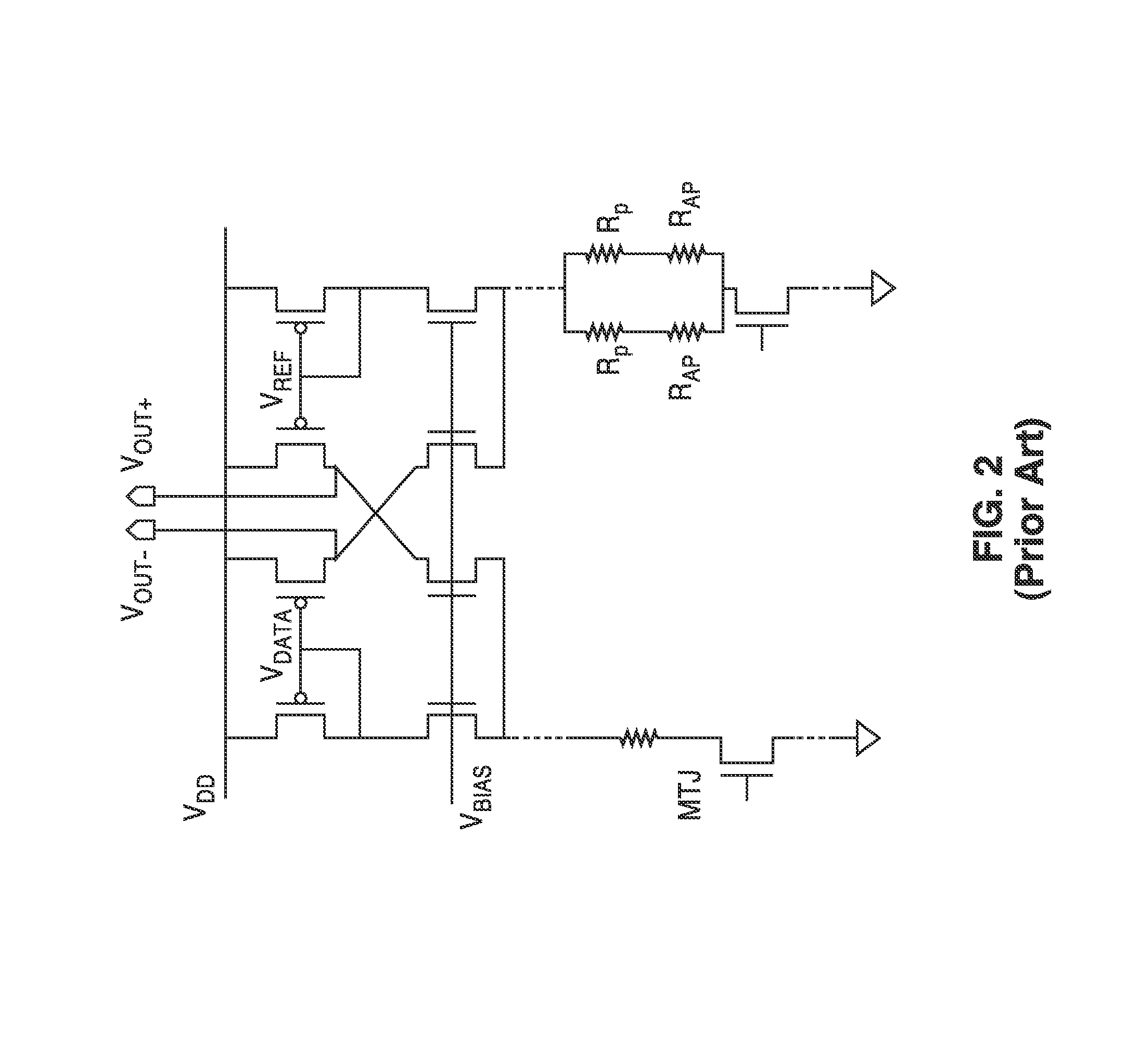

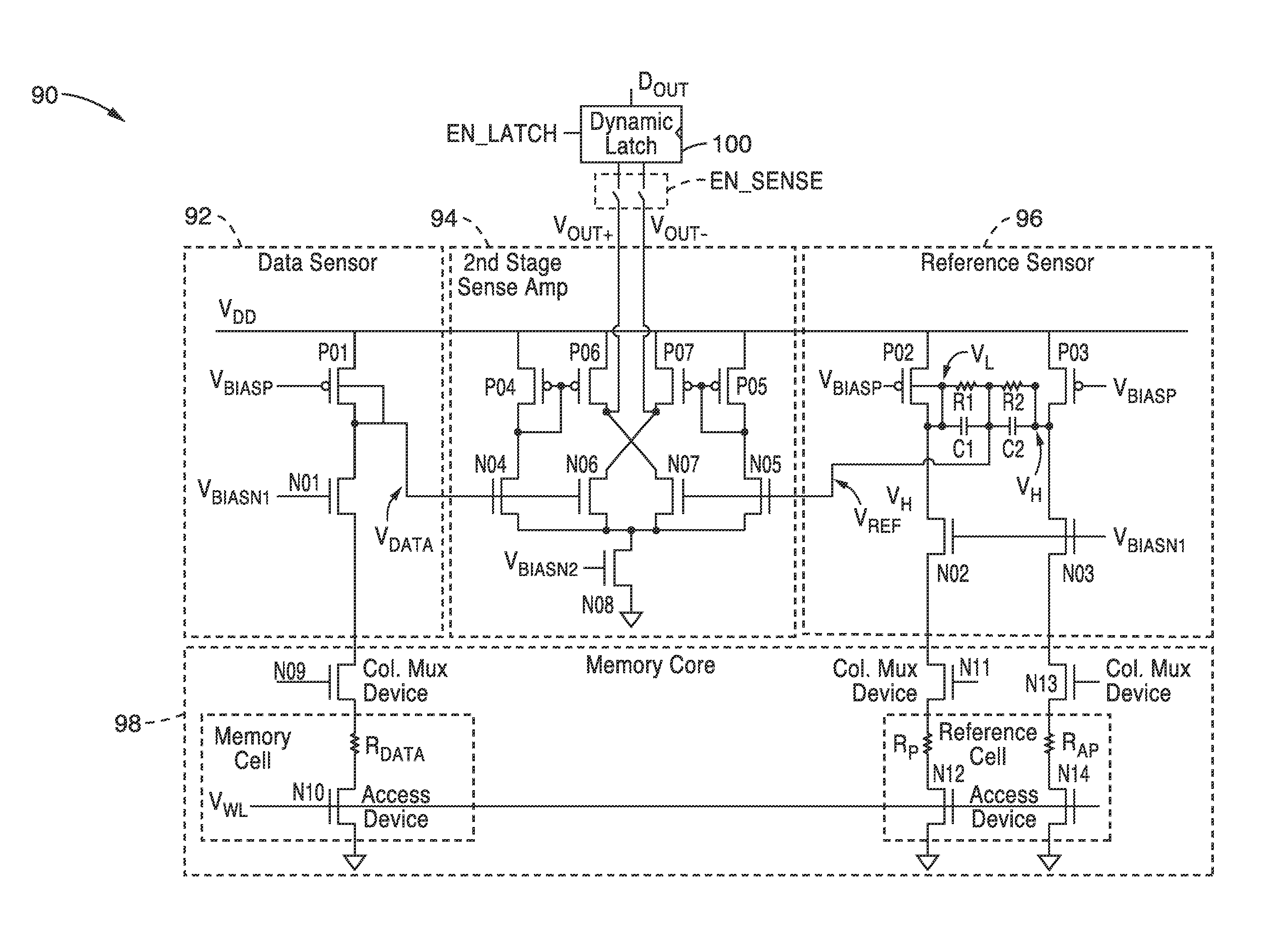

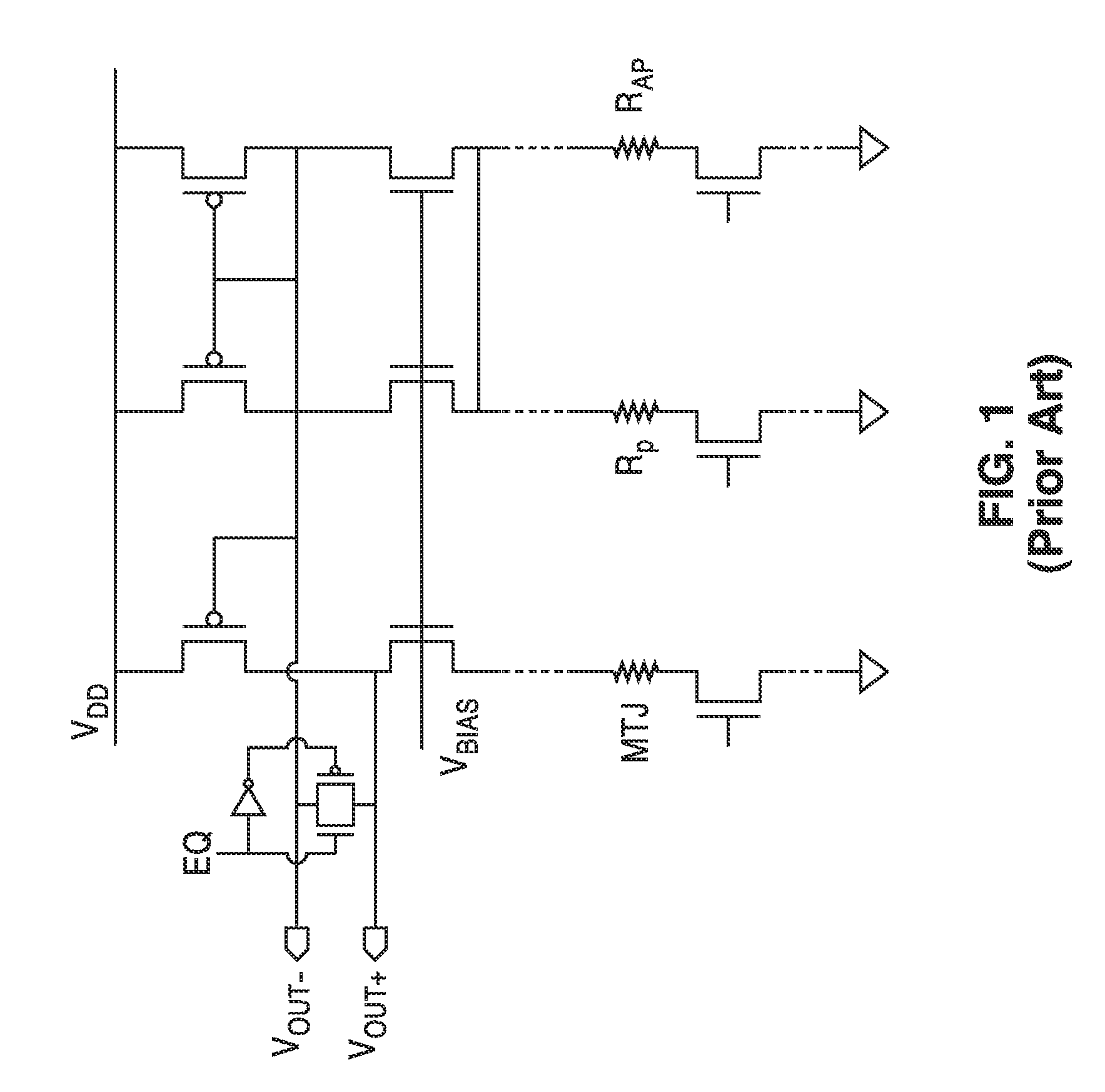

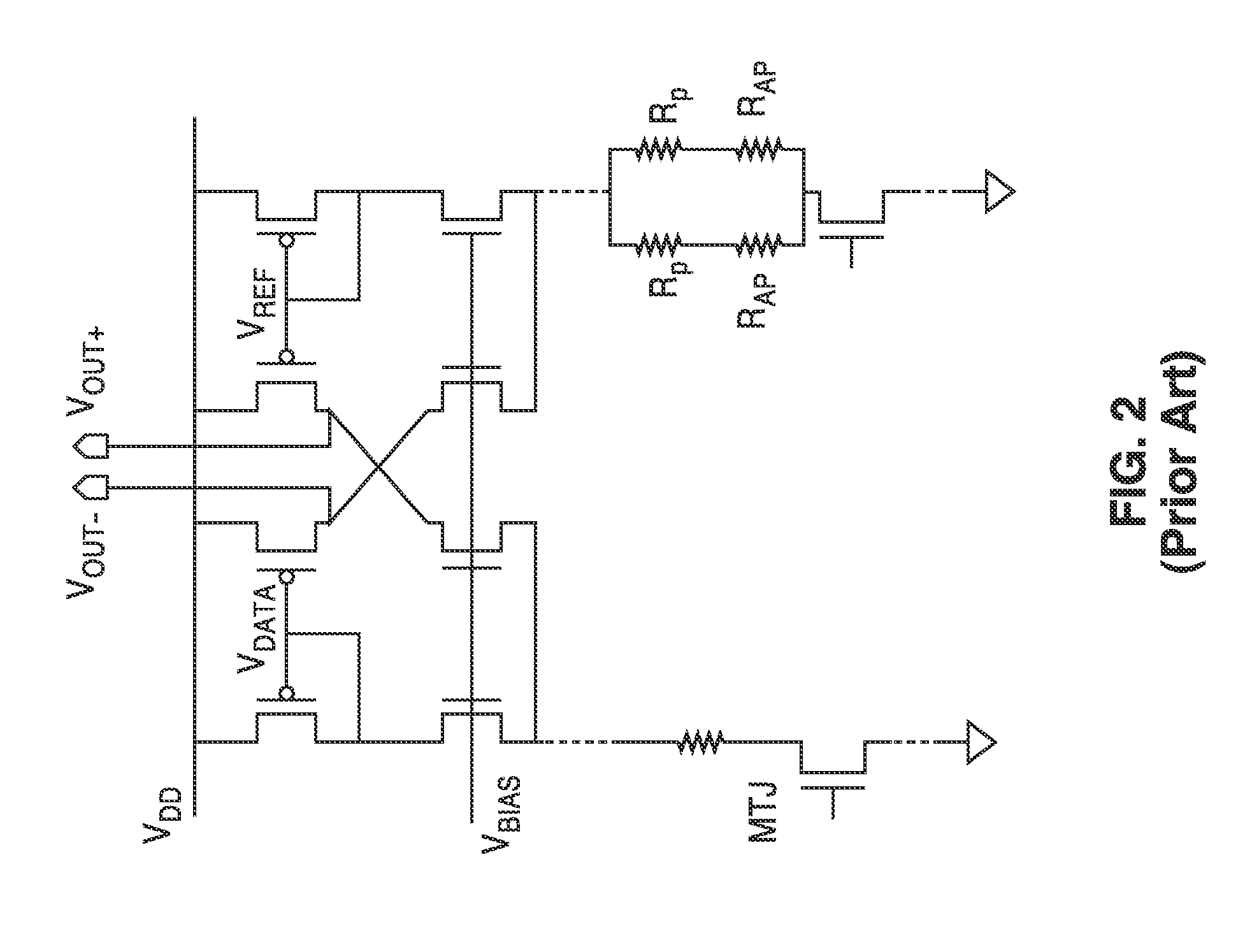

Body voltage sensing based short pulse reading circuit

InactiveUS20140153325A1Decrease read disturbance probabilityImprove read reliabilityDigital storageEngineeringShort read

As memory geometries continue to scale down, current density of magnetic tunnel junctions (MTJs) make conventional low current reading scheme problematic with regard to performance and reliability. A body-voltage sense circuit (BVSC) short pulse reading (SPR) circuit is described using body connected load transistors and a novel sensing circuit with second stage amplifier which allows for very short read pulses providing much higher read margins, less sensing time, and shorter sensing current pulses. Simulation results (using 65-nm CMOS model SPICE simulations) show that our technique can achieve 550 mV of read margin at 1 ns performance under a 1V supply voltage, which is greater than reference designs achieve at 5 ns performance.

Owner:RGT UNIV OF CALIFORNIA

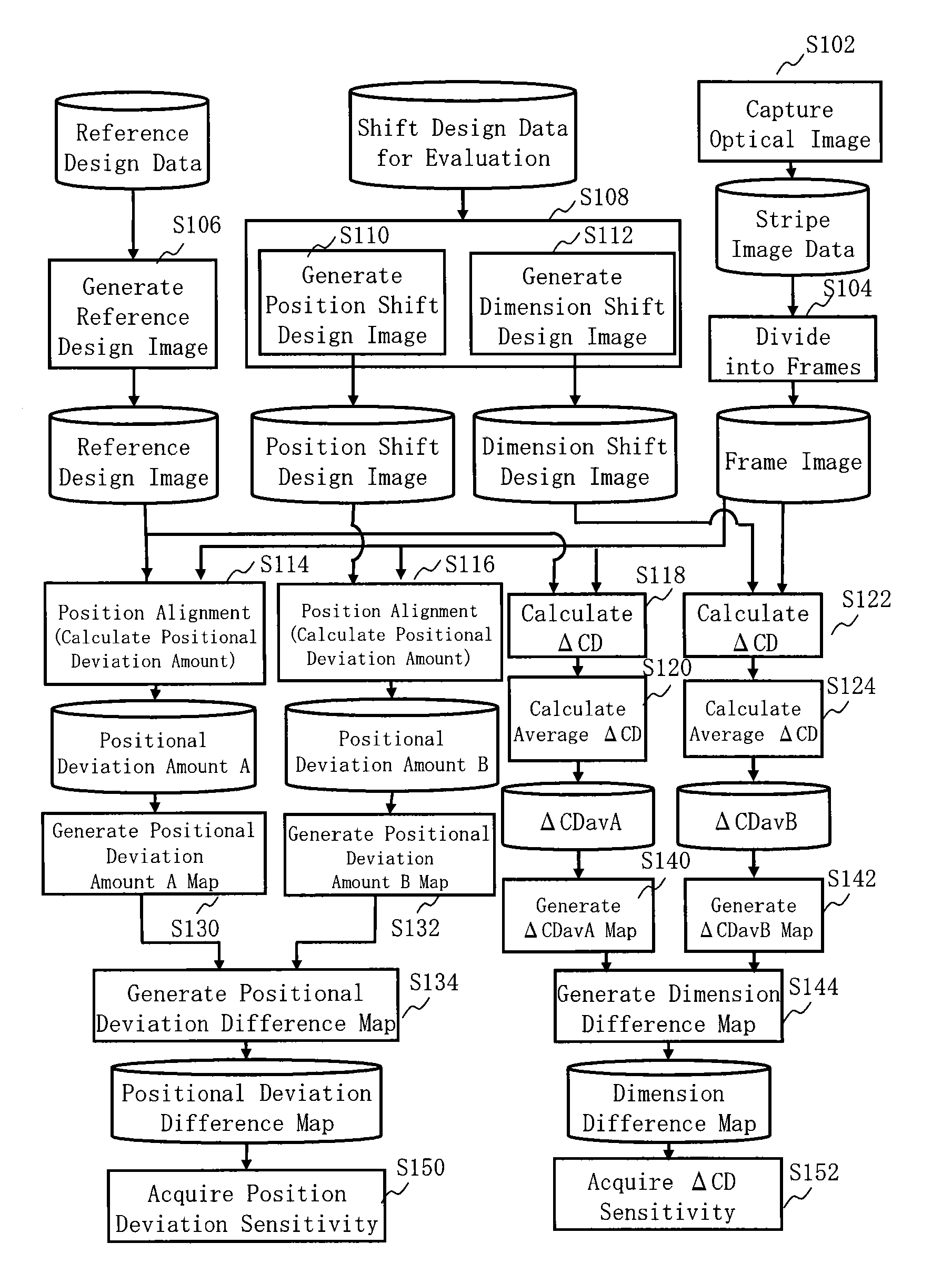

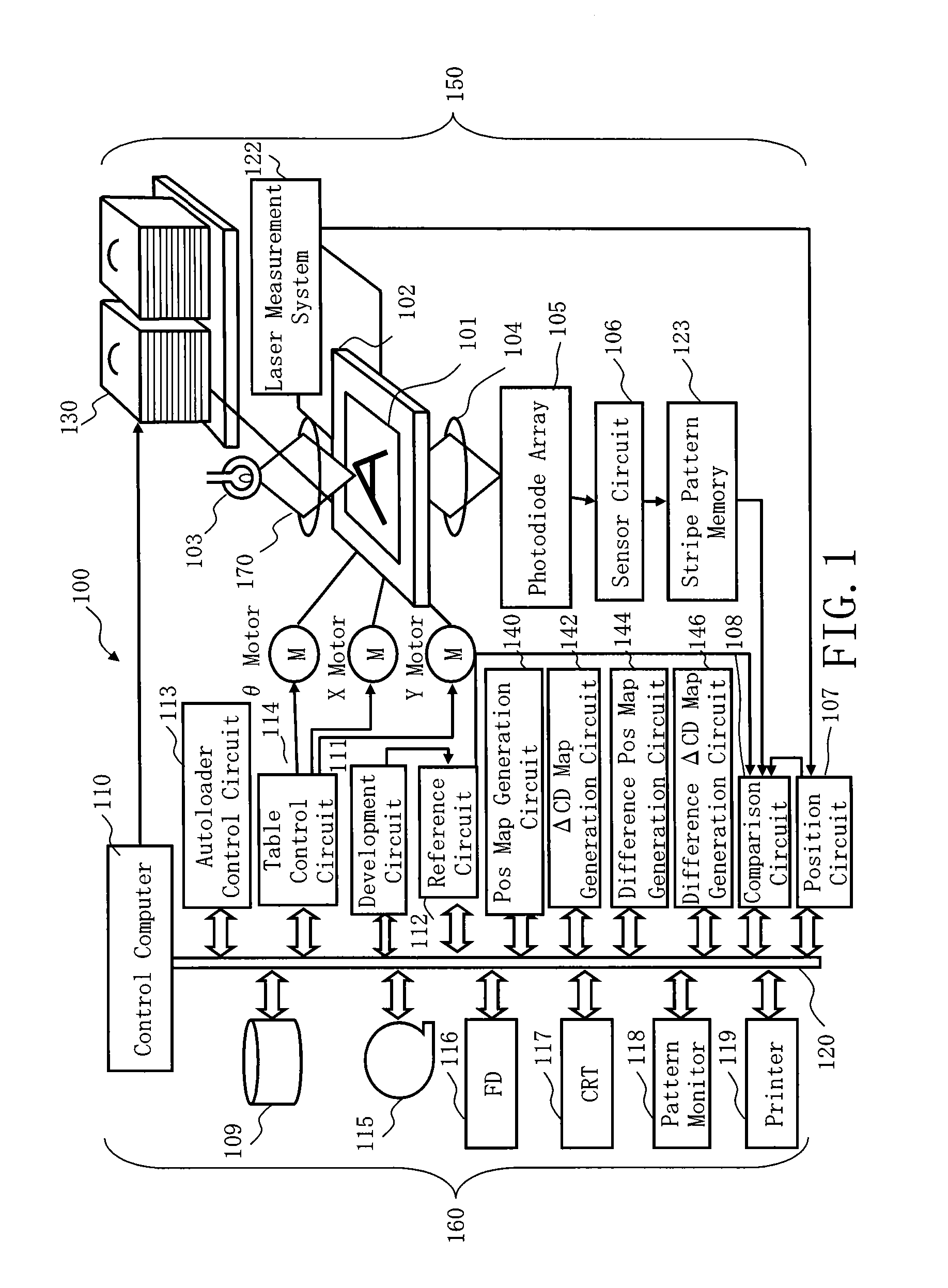

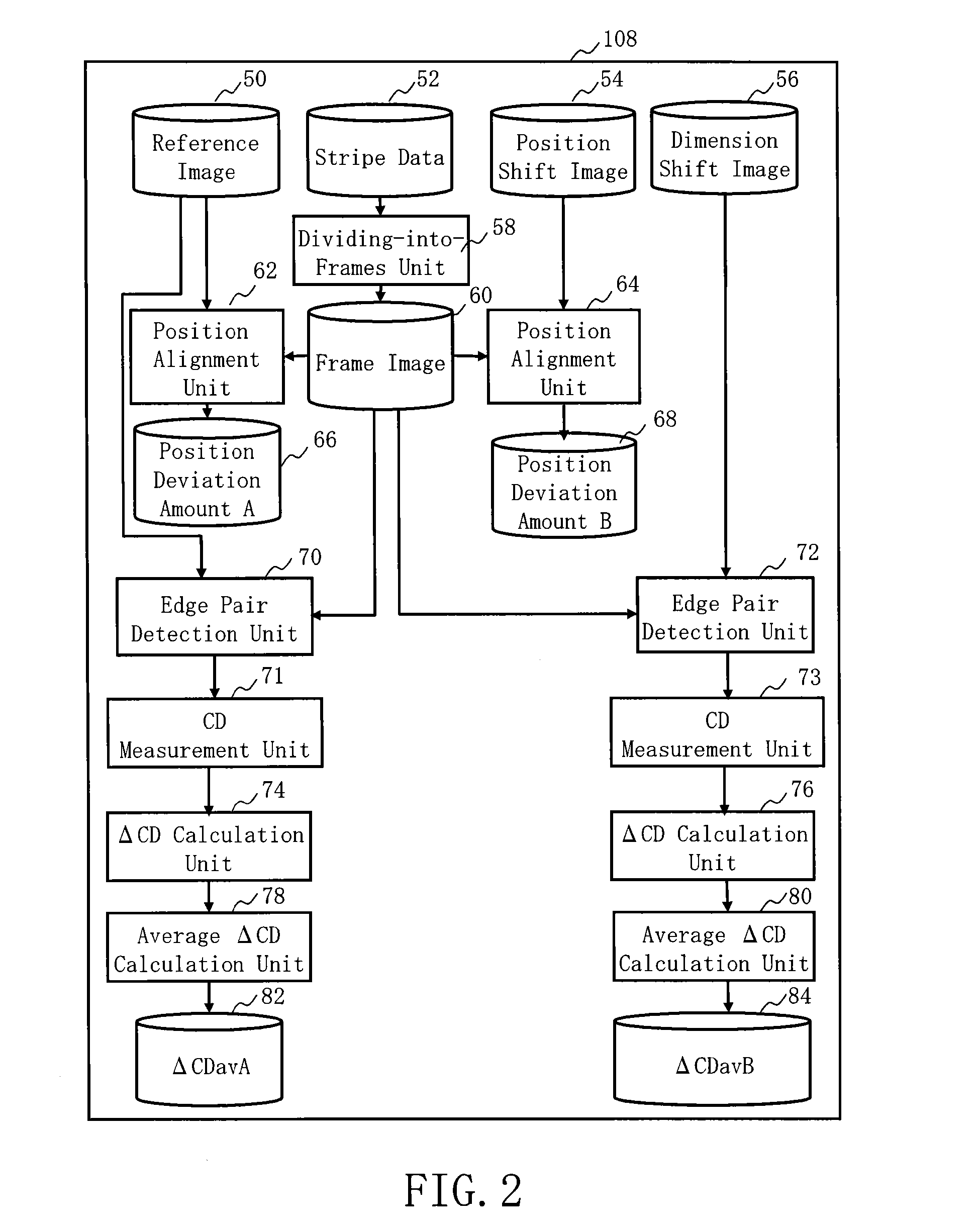

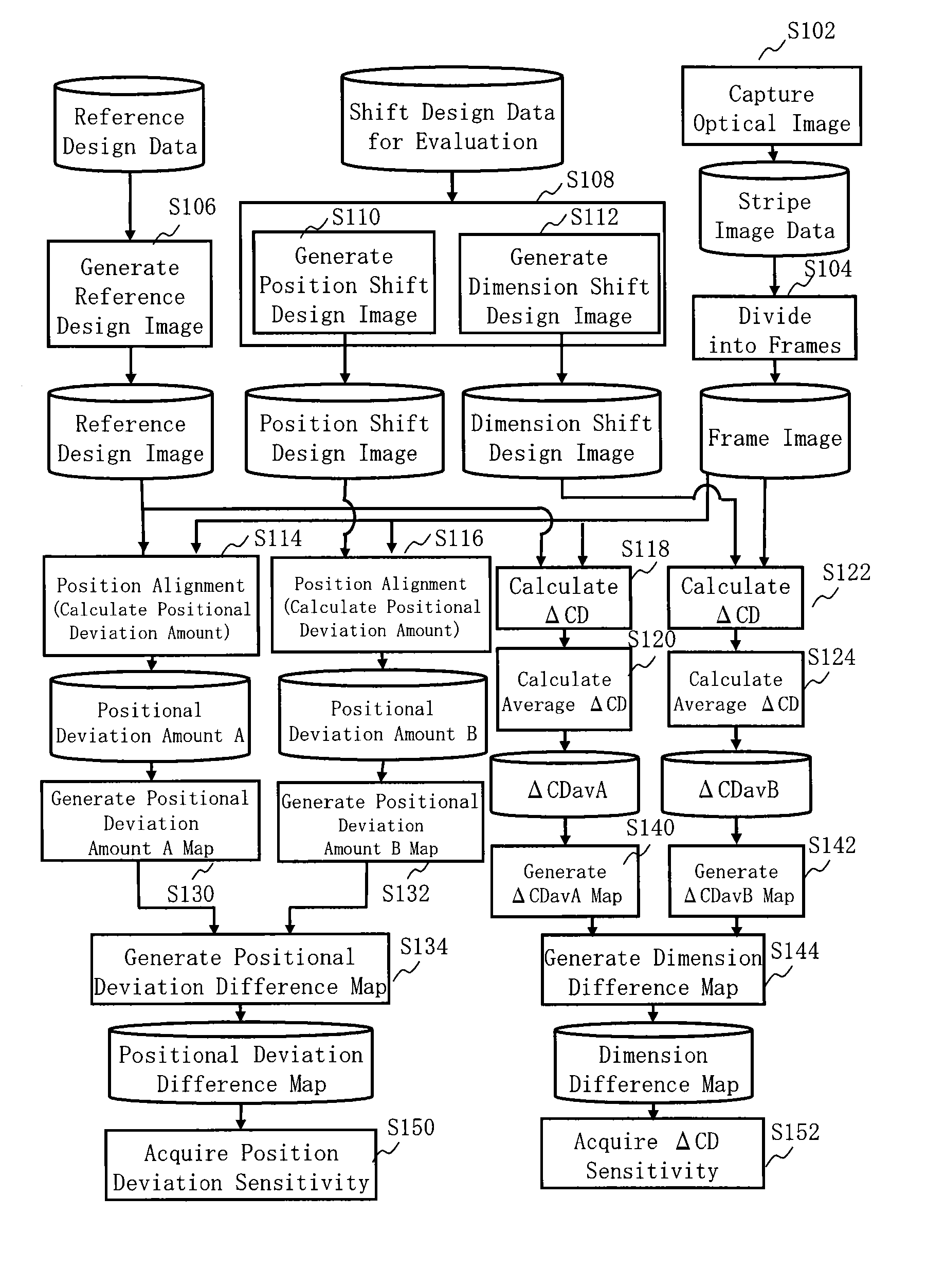

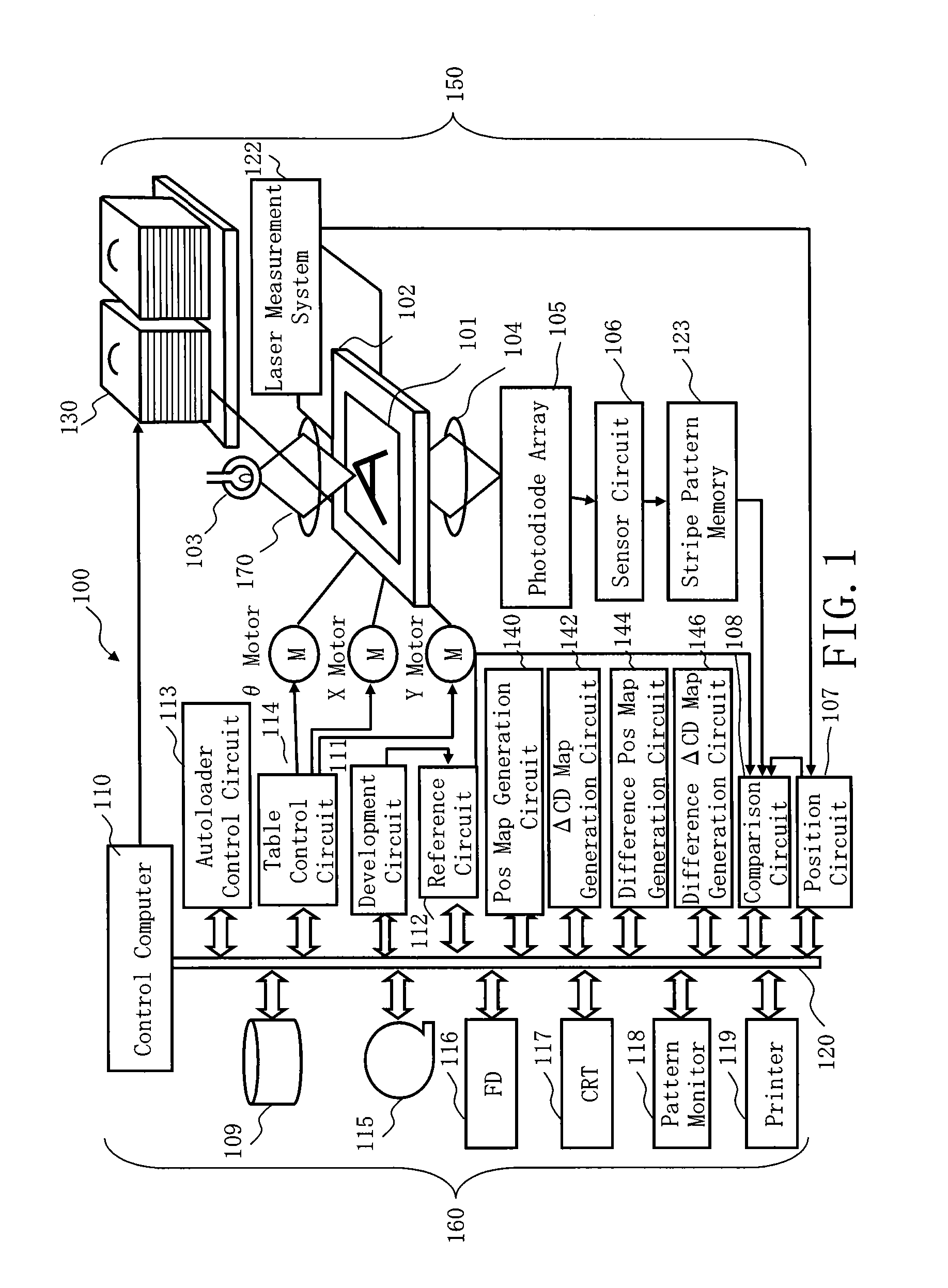

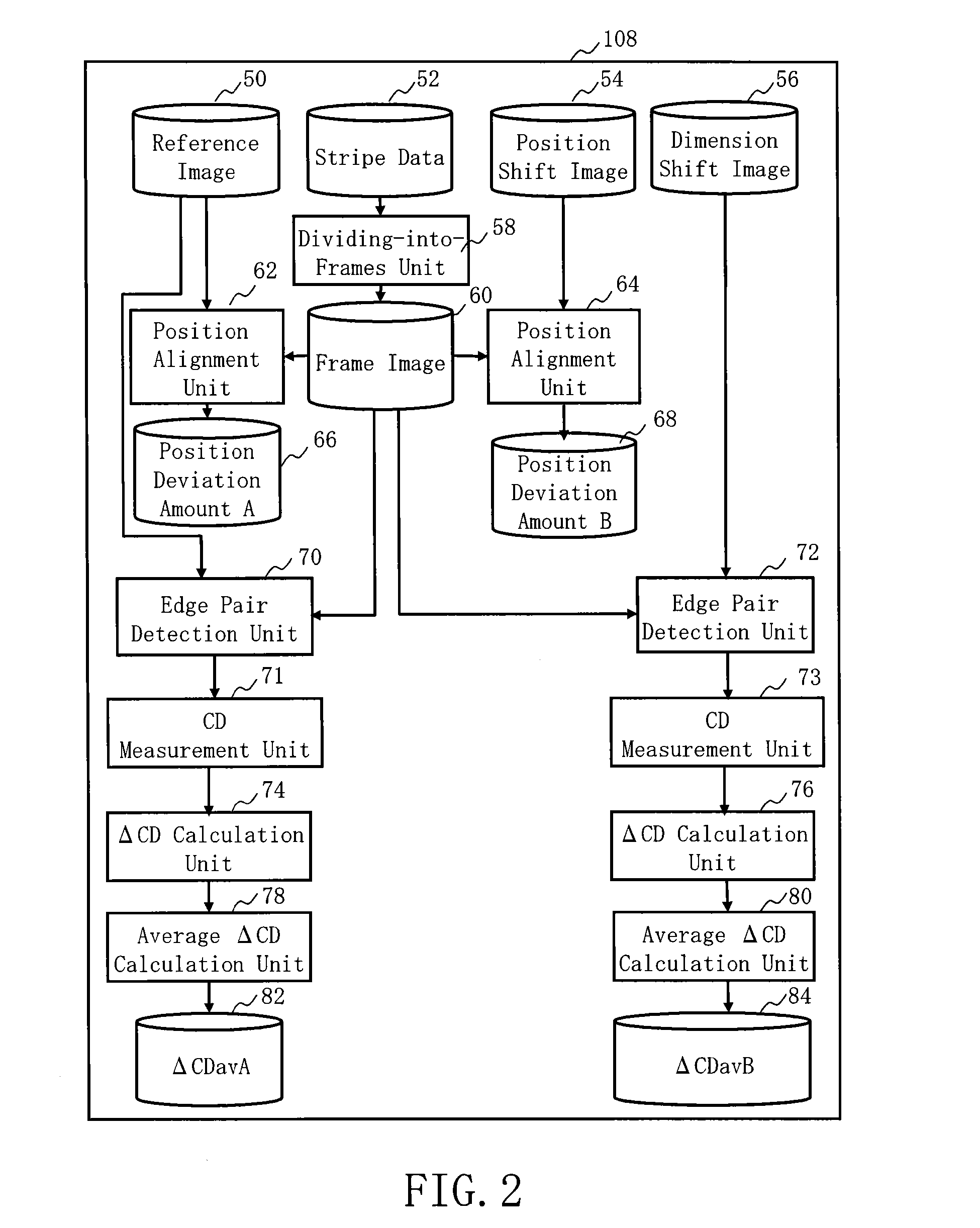

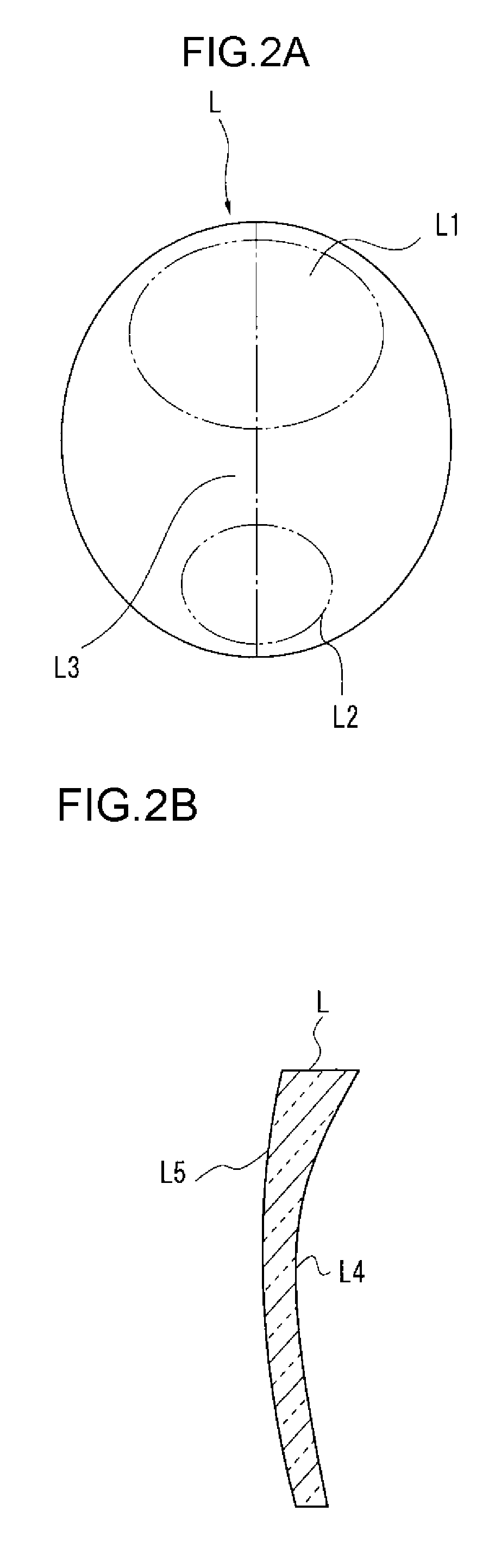

Inspection sensitivity evaluation method

An inspection sensitivity evaluation method includes generating a reference design image where plural figure patterns are arranged, based on reference design data, generating plural position shift design images whose positional deviation amounts are mutually different such that positions of the plural figure patterns in the reference design image are uniformly shifted, acquiring an optical image of a photo mask fabricated based on the reference design data where there is no positional deviation from the plural figure patterns, calculating a first positional deviation amount between the reference design image and the optical image, calculating plural second positional deviation amounts each of which is a respective positional deviation amount between a corresponding position shift design image of the plural position shift design images and the optical image, and acquiring a detectable positional deviation amount by using the first and the plural second positional deviation amounts.

Owner:NUFLARE TECH INC

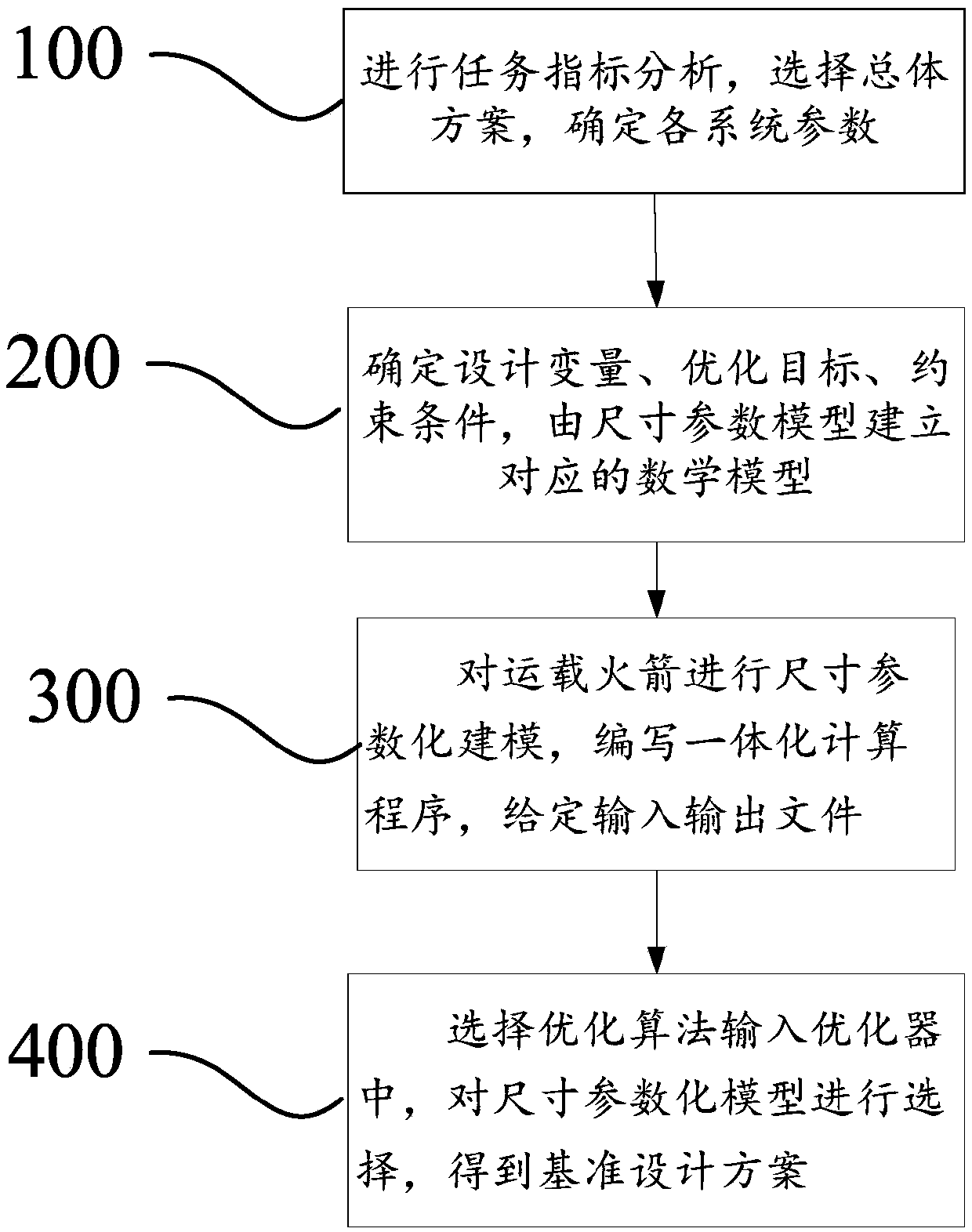

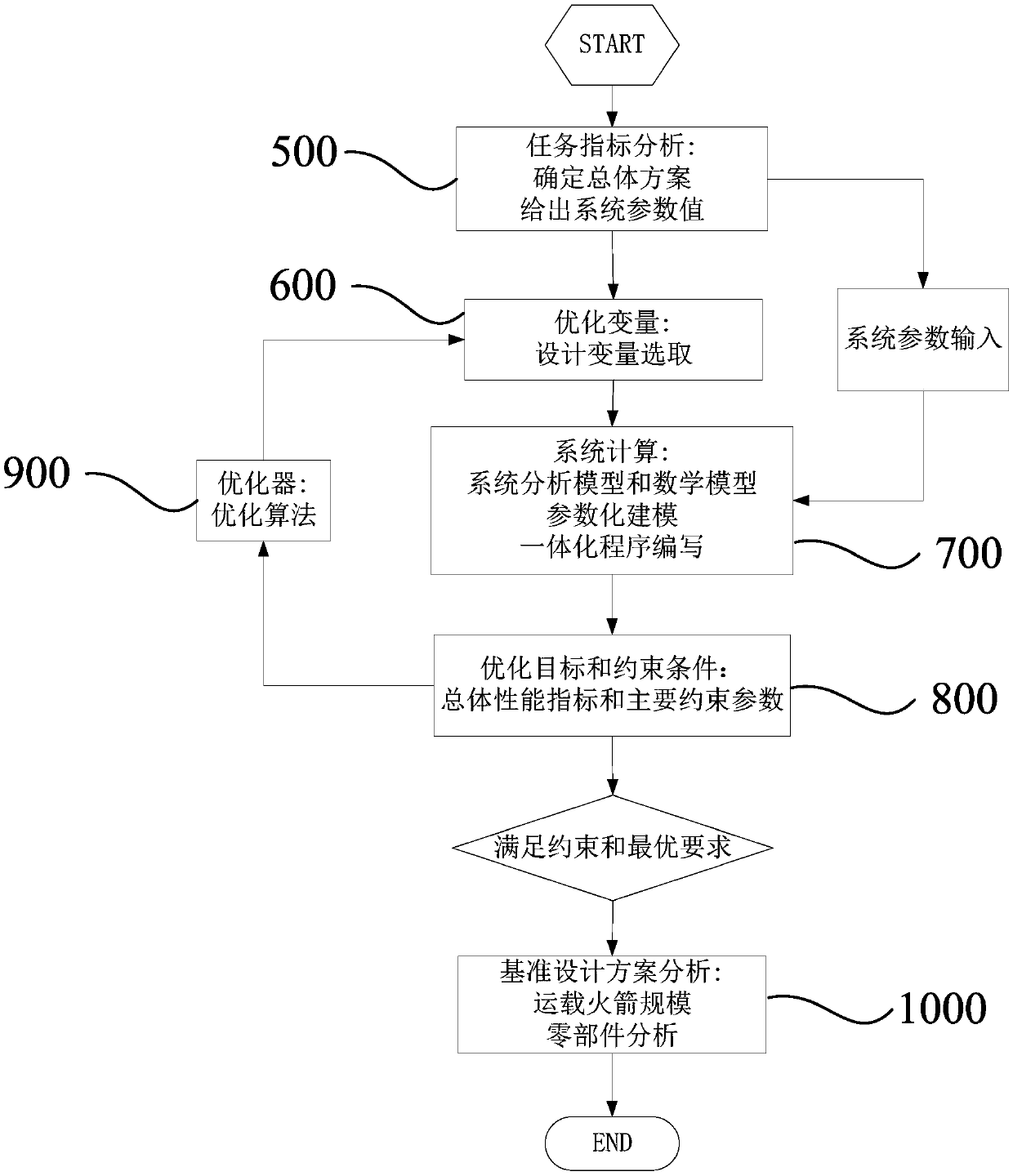

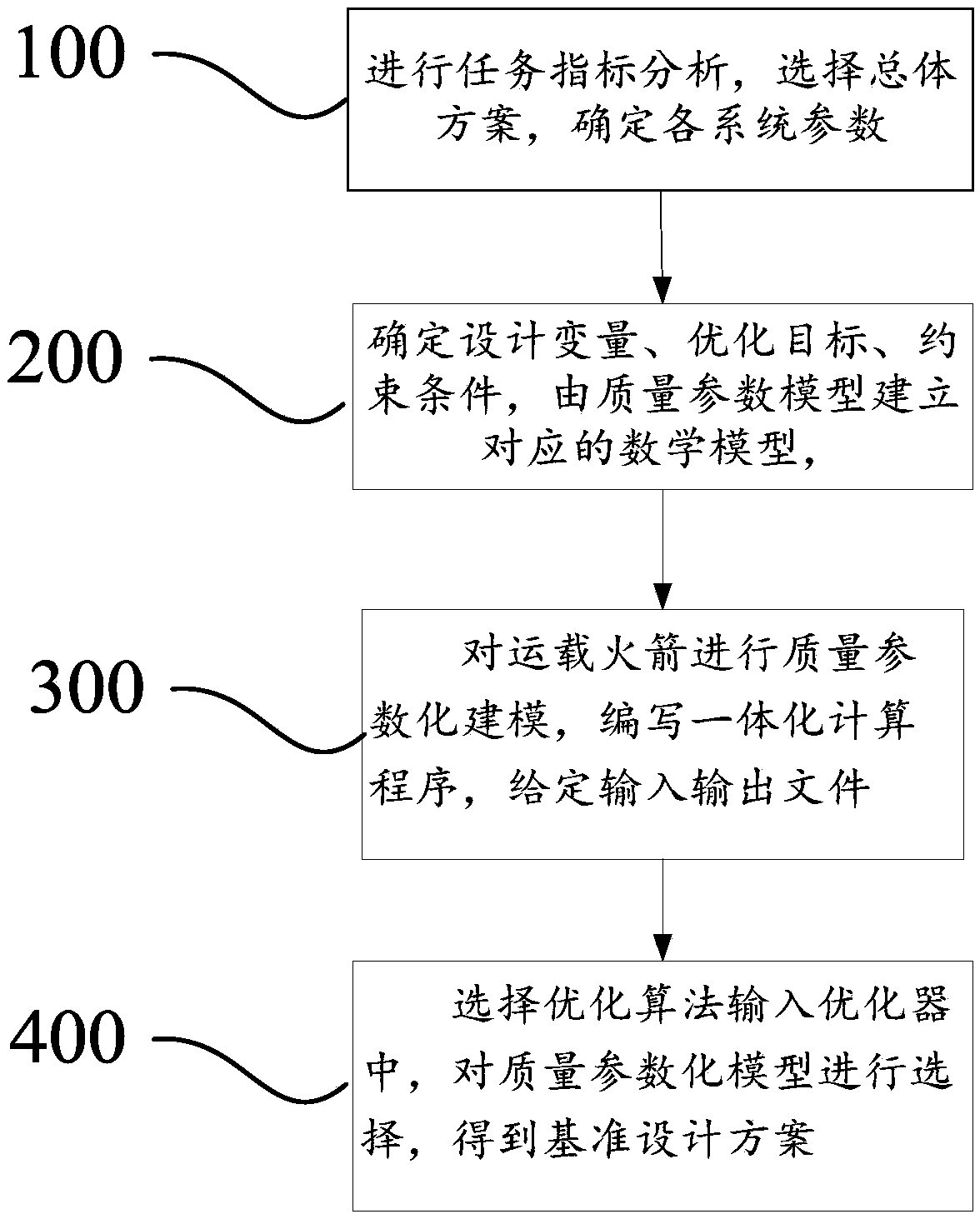

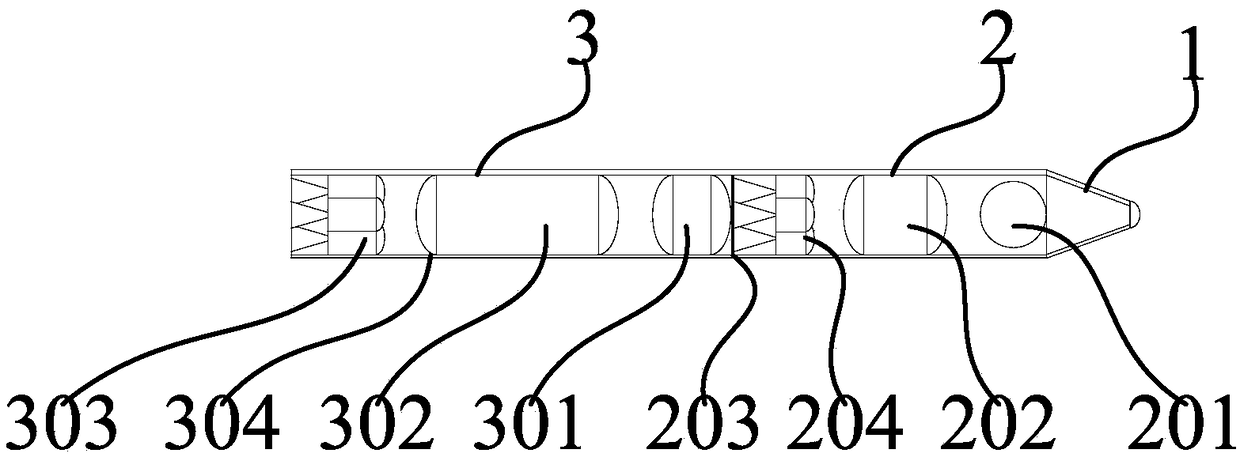

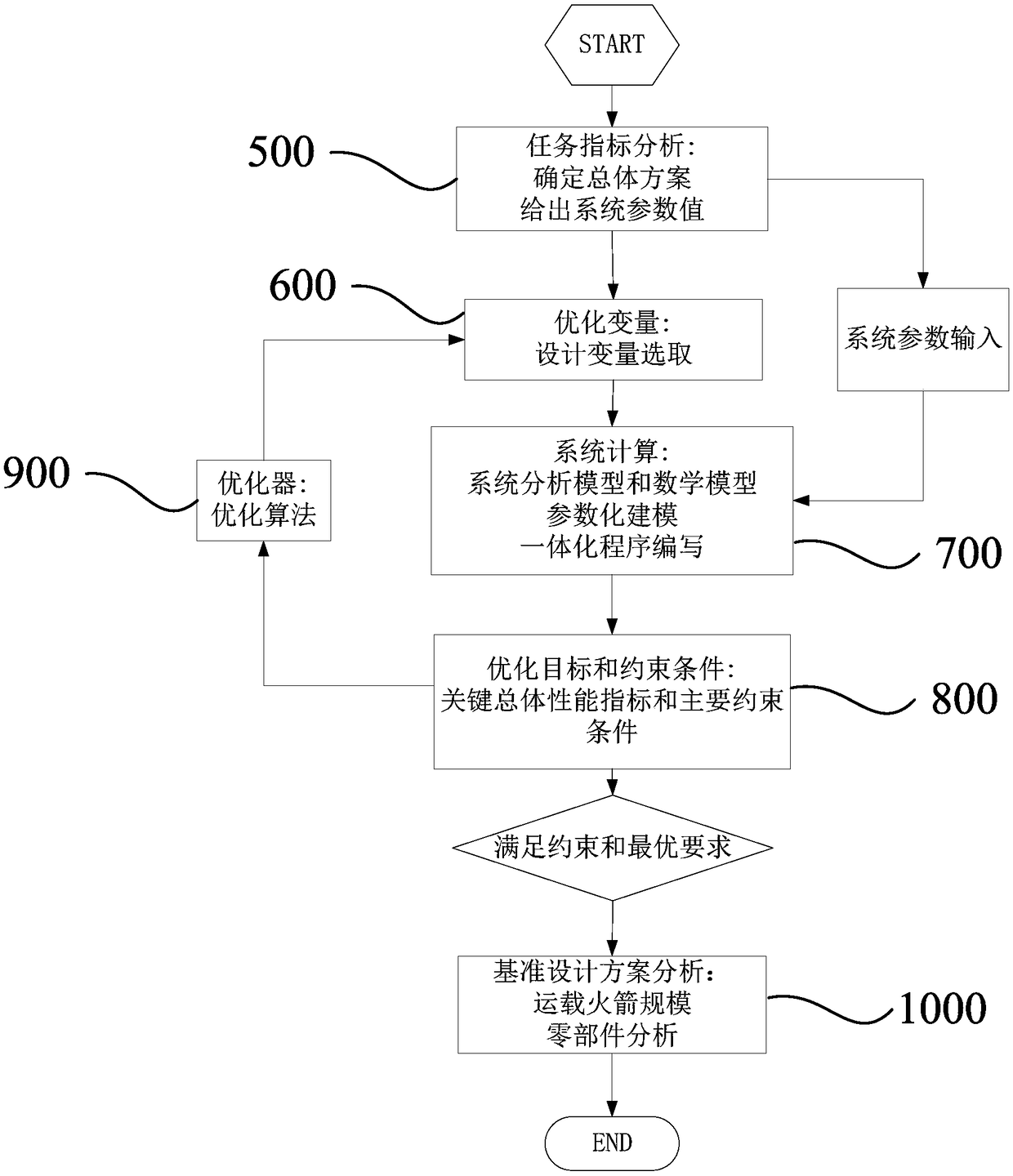

Method for estimating size parameter of carrier rocket

ActiveCN108763747ASmall amount of calculationReduce design iterationsGeometric CADInternal combustion piston enginesAviationMathematical model

The invention discloses a method for estimating the size parameter of a carrier rocket, belongs to the technical field of aerospace and aims to solve the technical problem of large calculation amountand inaccuracy during conventional size parameter selection. The method for estimating the size parameter comprises the following steps of: carrying out task index analysis, selecting an overall scheme and determining each system parameter; determining design variables, an optimization target and constraint conditions and building a corresponding mathematical model on the basis of a size parametermodel, wherein the size model comprises a part size calculating module, an engine size calculating module and an overall size calculating module for sequential calculation; carrying out size parametric modeling on the carrier rocket, writing an integrated calculation program and giving input and output files; selecting an optimization algorithm, inputting to an optimizer and selecting a size parametric model to obtain a reference design scheme. The method disclosed by the invention has the advantages that the iterative design times of the carrier rocket in the overall scheme stage is reduced;and the method is simple in process, small in calculation amount and high in efficiency.

Owner:BEIHANG UNIV

High-performance FET device layout

InactiveUS7791160B2Performance maximizationRapid designTransistorSolid-state devicesEngineeringReference design

A fast FET, a method and system for designing the fast FET and a design structure of the fast FET. The method includes: selecting a reference design for a field effect transistor, the field effect transistor including a source, a drain, a channel between the source and drain, a gate electrode over the channel, at least one source contact to the source and at least one contact to the drain, the at least one source contact spaced a first distance from the gate electrode and the at least one drain contact spaced a second distance from the gate electrode; and adjusting the first distance and the second distance to maximize a performance parameter of the field effect transistor to create a fast design for the field effect transistor.

Owner:GLOBALFOUNDRIES INC

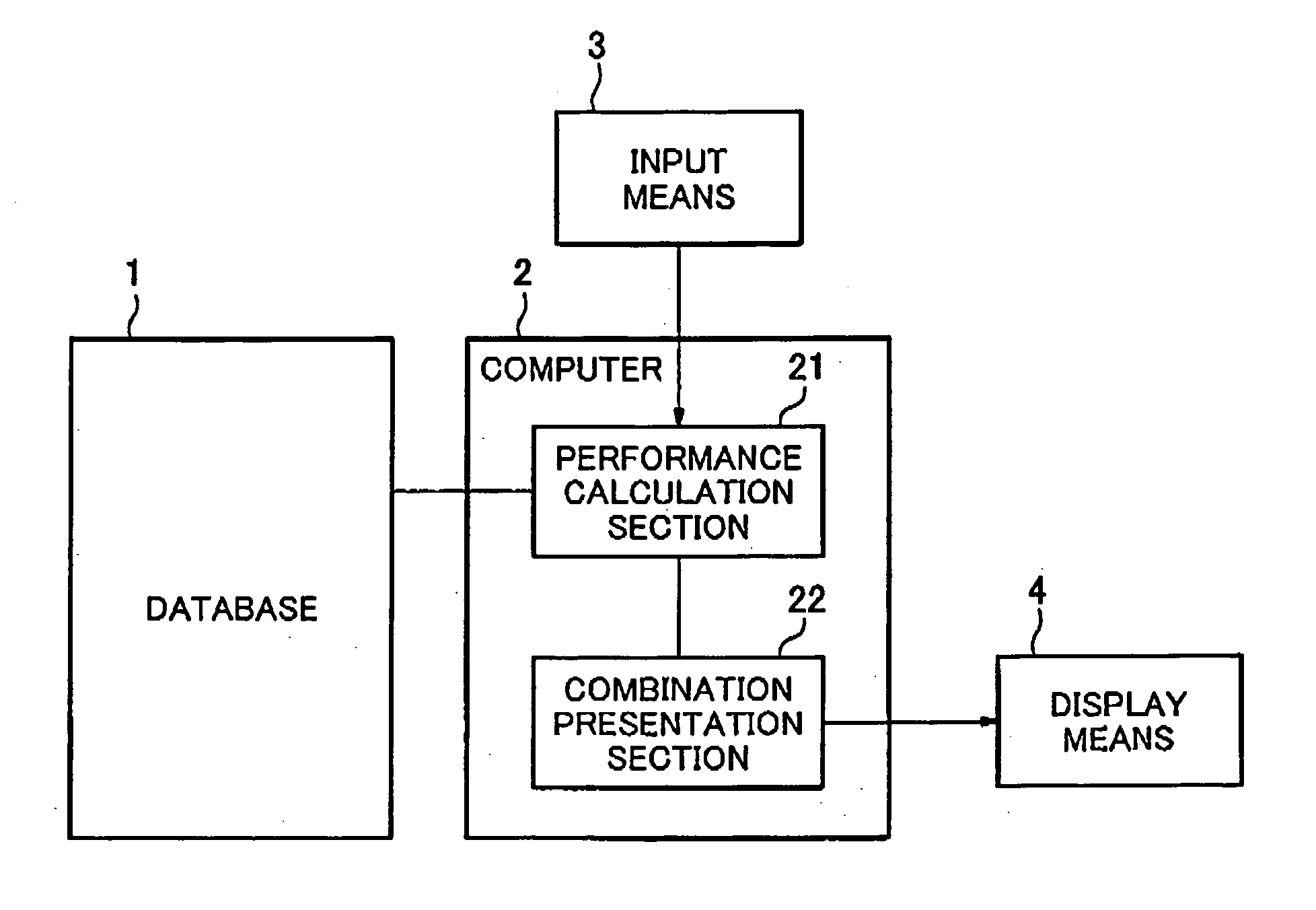

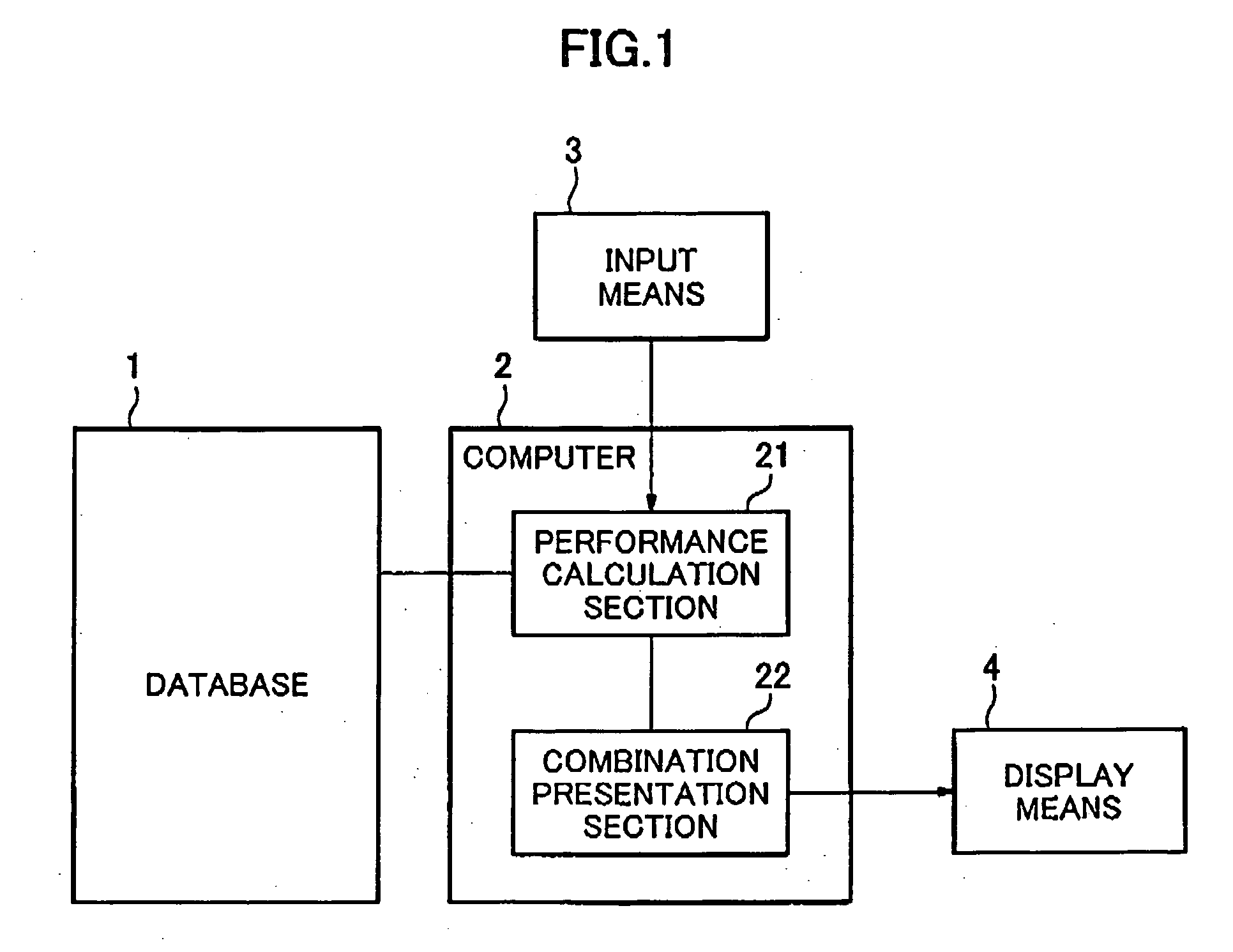

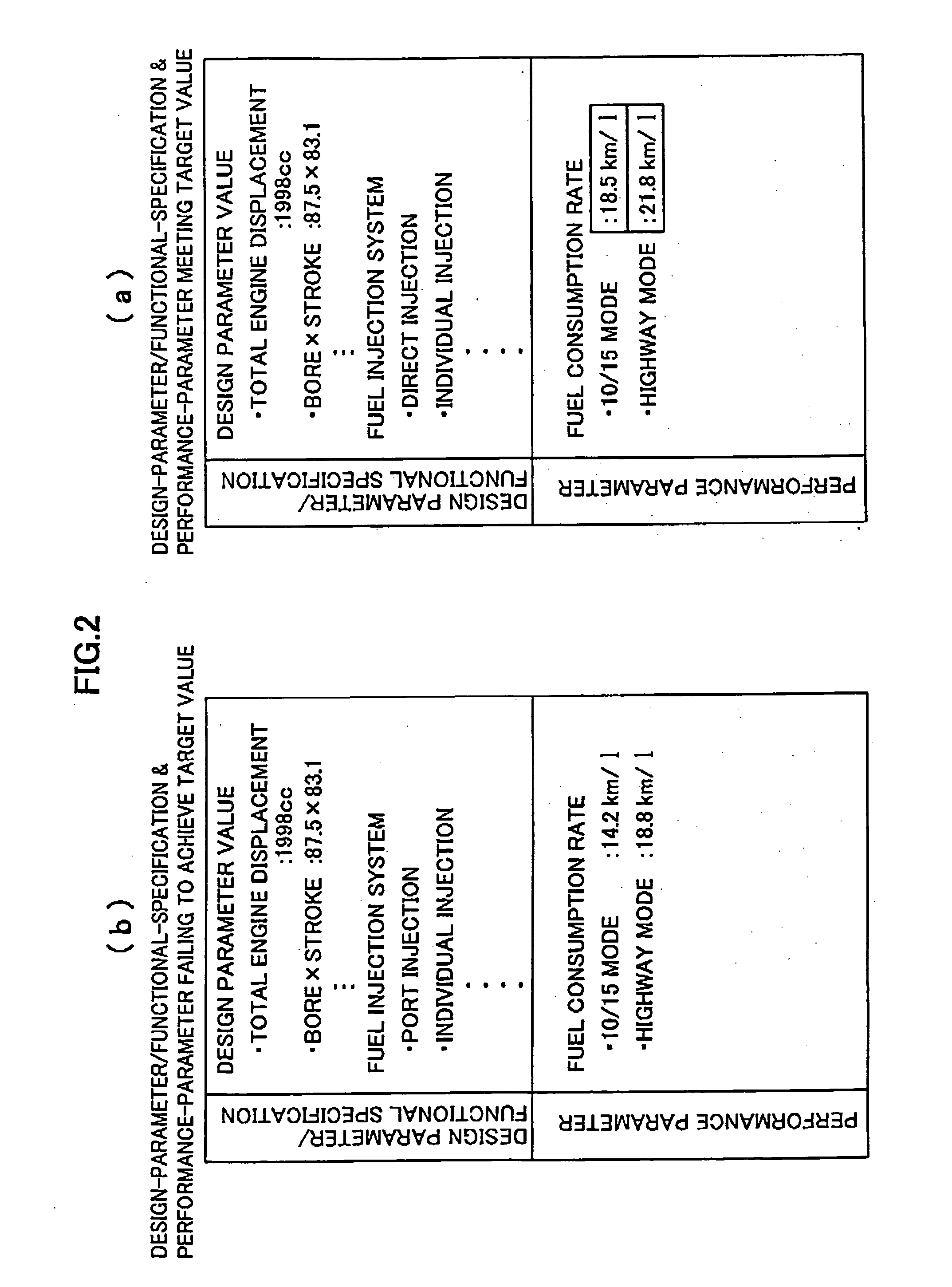

Internal-combustion engine design support system

InactiveUS20070106453A1Improve efficiencyGeometric CADAnalogue computers for vehiclesCombustionValue set

Disclosed is an internal-combustion engine design support system for presenting a combination of functional specification types or the like of a design-target engine in connection with a target performance parameter value set out in a new vehicle. The system comprises a database (1) storing data about a design parameter value of a given design parameter, a functional specification type of a given functional specification and a performance parameter value of a given performance parameter, which are associated with each of a plurality of existing internal-combustion engines, a performance calculation section (21) for calculating a performance parameter value of the given performance parameter of at least one of an internal-combustion engine model set by changing a combination of a reference design parameter value and / or a reference functional specification type of a base internal-combustion engine selected from the existing internal-combustion engines, and a combination presentation section (22) for outputting at least one combination of a design parameter value and a functional specification type of the internal-combustion engine model having the performance parameter value calculated by the performance calculation section (21), according to a given presentation condition.

Owner:MAZDA MOTOR CORP

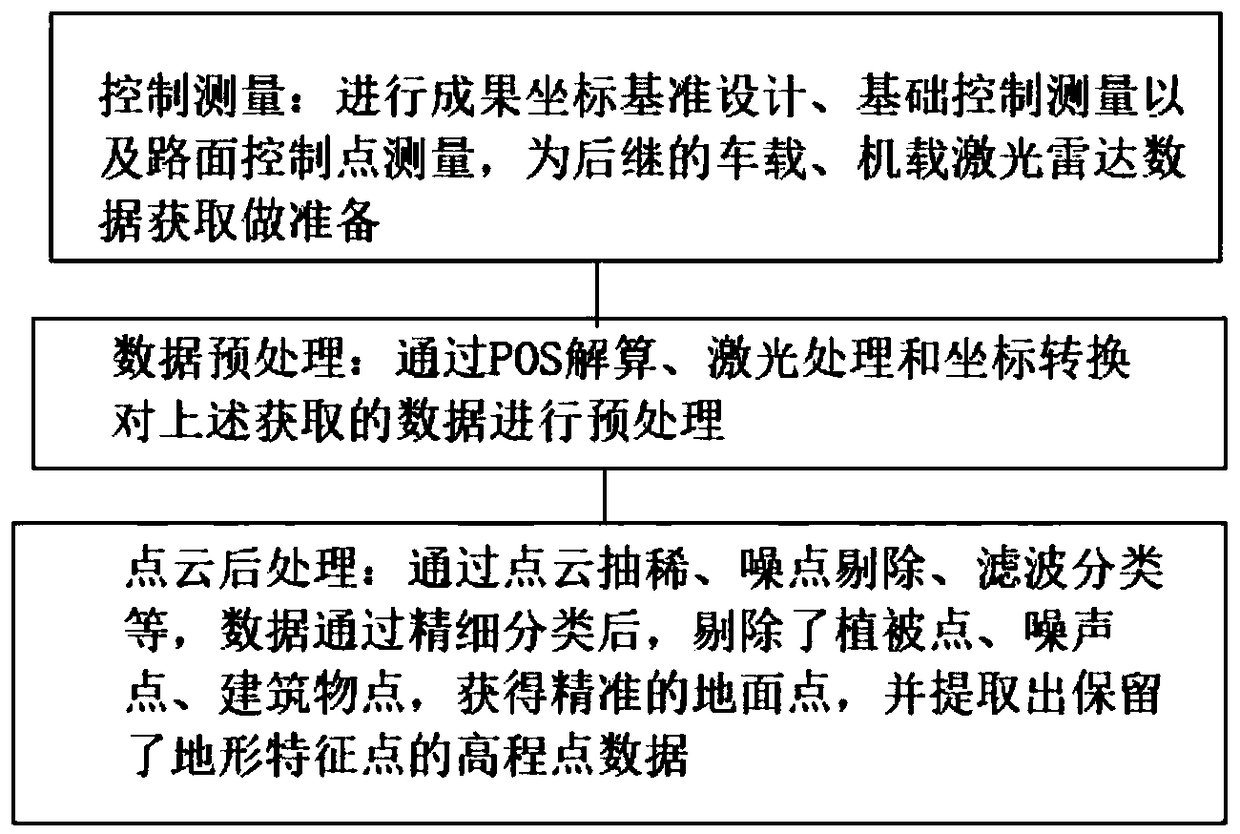

The application of vehicle-mounted lidar system in highway reconstruction and expansion survey

InactiveCN109024199AHigh degree of automationImprove work efficiencyRoads maintainenceRadar systemsData acquisition

The invention provides the application of the vehicle-mounted laser radar system in the highway reconstruction and expansion survey, comprising the following steps: control survey: carrying out the result coordinate reference design, the foundation control survey and the pavement control point measurement to prepare for the subsequent vehicle-mounted and airborne laser radar data acquisition; andthe vehicle-mounted laser radar system is used for the road reconstruction and expansion survey. Data pre-processing: POS solution, laser processing and coordinate conversion are used to pre-process the obtained data. Point cloud post-processing: through point cloud thinning, noise elimination, filtering classification and the like, after data is classified, vegetation points, noise points and building points are eliminated to obtain accurate ground points, and elevation point data retaining topographic characteristic points are extracted. Compared with the traditional method, the invention collects 100 kilometers of road data every day, and improves the operation efficiency by 5-7 times. The automation degree of indoor software is as high as 80 percent. Due to the improvement of operationefficiency and the decrease of manpower input, the comprehensive cost of indoor software is reduced by 4-5 times.

Owner:SHANGHAI HUACE NAVIGATION TECH

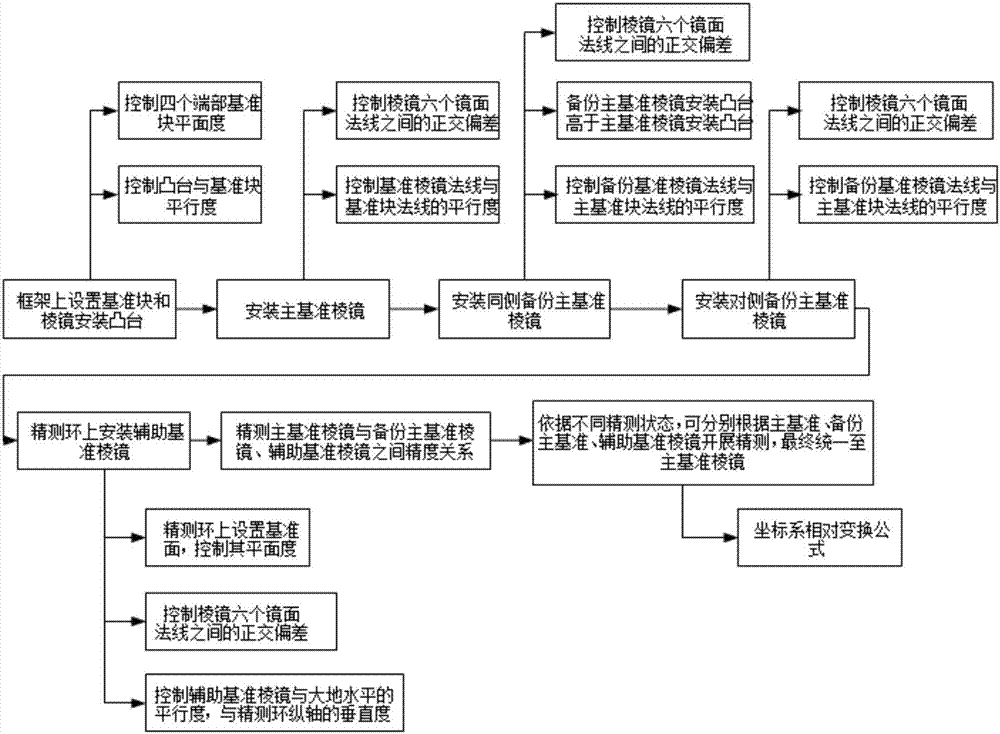

Precise measurement reference design method for SAR satellite

ActiveCN107300701AEliminate installation deviationImprove the efficiency of precision measurement workRadio wave reradiation/reflectionRadarSynthetic aperture radar

The invention provides a precise measurement reference design method for an SAR satellite, and the method comprises the following steps: 1, respectively setting reference blocks in regions of the external surfaces of four end parts of an antenna frame, setting a prism installation boss on the frame, controlling the levelness of the reference blocks and the levelness of the boss and the reference blocks in a mode of combined machining; 2, leveling the antenna frame, enabling a main reference prism of the satellite to be installed on the boss of the antenna frame through the reference blocks at four end parts of the antenna frame and the tool conversion, and controlling the levelness of the main reference prism and the reference blocks. The method can achieve the high consistency of the coordinate system of the main reference prism with the coordinate system of a load antenna, directly eliminates the installation deviation between the main reference prism and the load antenna. A single-chip computer with other precision on the satellite and the precision of the load antenna, relative to the on-orbit to-be-reached target precision of the whole satellite, achieve the unification, thereby reducing the transmission links of precision errors, and improving the precision measurement efficiency of the whole satellite.

Owner:SHANGHAI SATELLITE ENG INST

Pattern weakness and strength detection and tracking during a semiconductor device fabrication process

ActiveUS9846934B2Image enhancementMaterial analysis using wave/particle radiationDecompositionReference design

Tracking patterns during a semiconductor fabrication process includes: obtaining an image of a portion of a fabricated device; extracting contours of the portion of the fabricated device from the obtained image; aligning the extracted contour to a matching section of a reference design; decomposing the matching section of the reference design into one or more patterns; and updating a pattern tracking database with information pertaining to at least one pattern in the one or more patterns generated as a result of the decomposition.

Owner:ANCHOR SEMICON

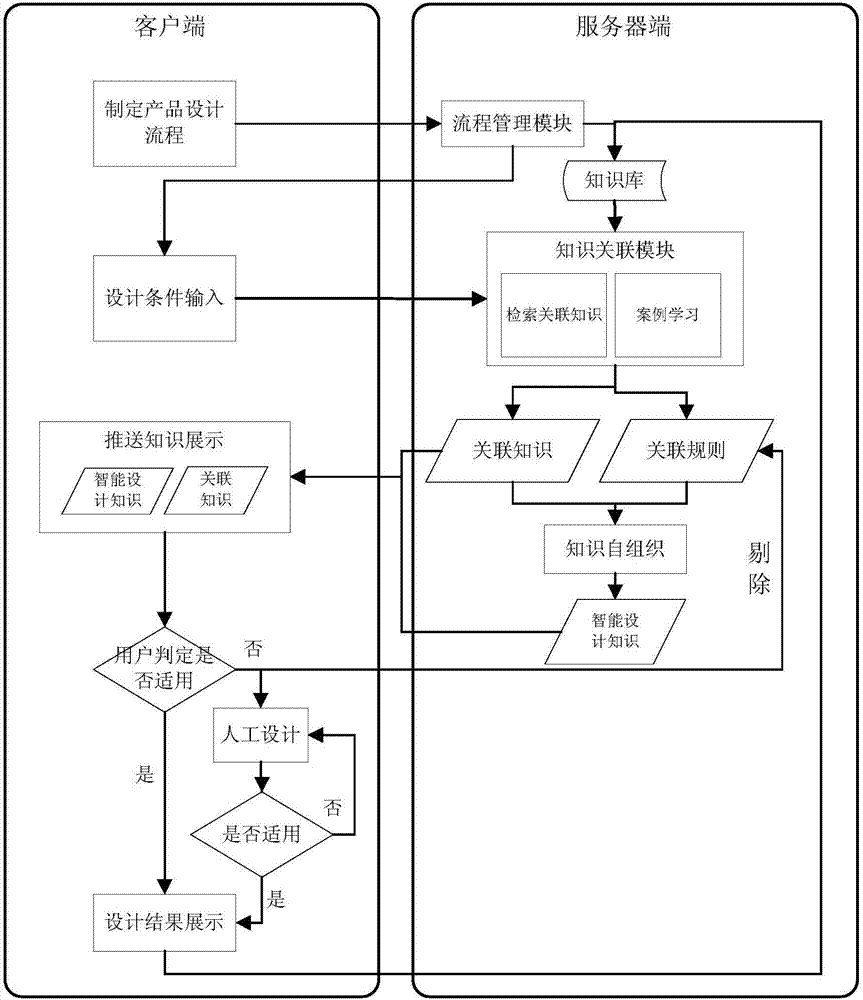

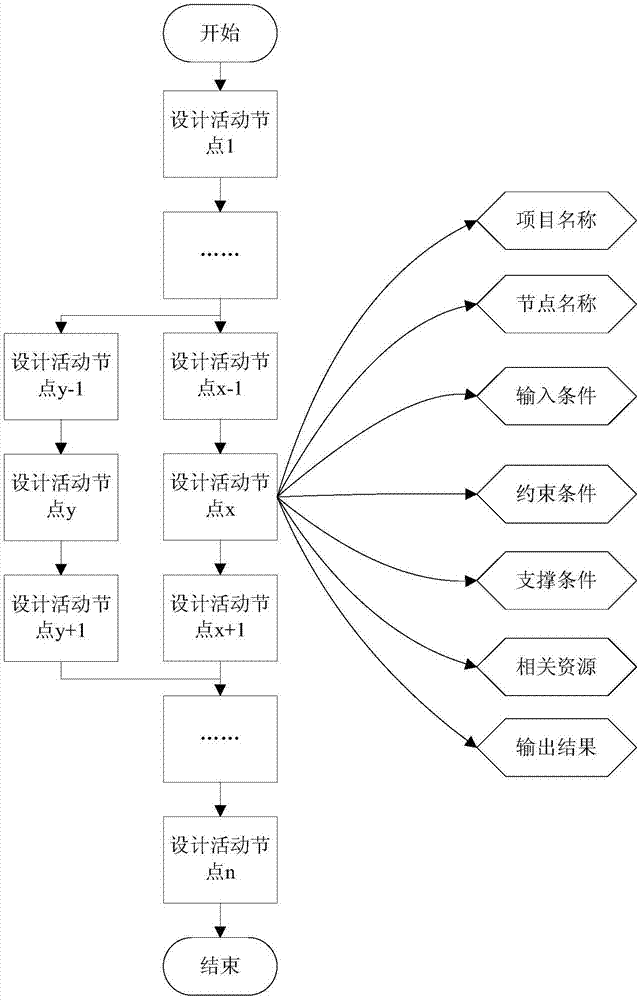

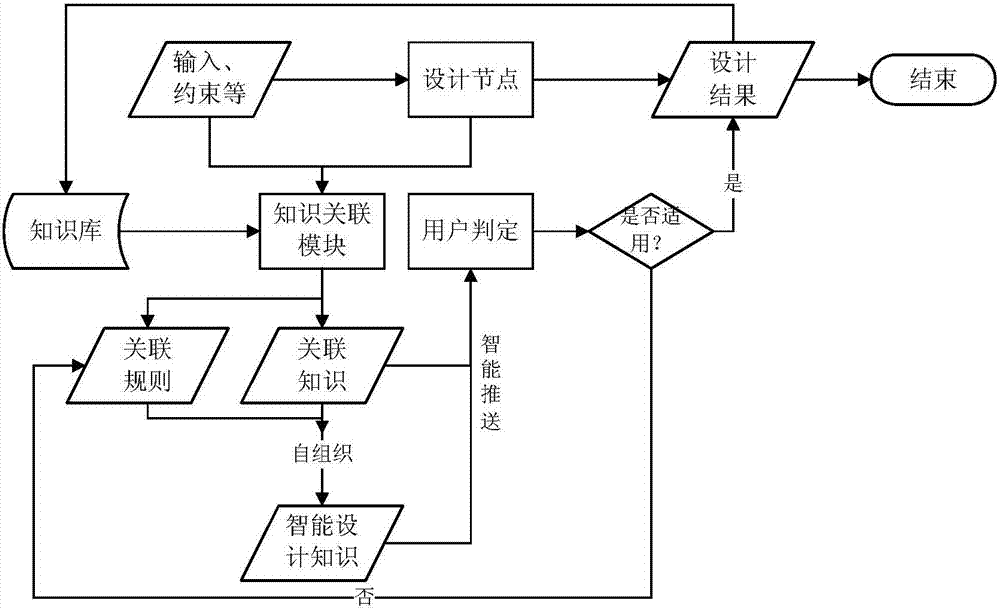

Automatic knowledge association system and method based on product design

ActiveCN107967518ARealize automatic creationEasy to reuseOffice automationKnowledge representationIntelligent designReference design

The invention relates to an automatic knowledge association system and method based on product design. The ontology technology, a machine learning algorithm and a solr index are utilized to realize fast retrieval and association of the design knowledge based on complex product design nodes, in the process of complex product design, the associated knowledge is self-organized through association rules based on case learning in the Bayesian networks, a user is provided with a reference design solution scheme, the design demand index situation is satisfied by the user according to the intelligentdesign knowledge pushed by a system, and applicability of the intelligent design knowledge is determined; if the intelligent design knowledge is adopted, the intelligent design knowledge is displayedas the design result at a client and is stored in a knowledge database; if the intelligent design knowledge is not adopted, the associated knowledge is referred by the client for manual design till the design result satisfies the design demand index, and the design result is uploaded to the knowledge database and stored as a product design case. The system is advantaged in that effective design knowledge reuse is realized, design efficiency is improved, the product design period is shortened, and manpower cost is reduced.

Owner:CHINA ACAD OF LAUNCH VEHICLE TECH

Body voltage sensing based short pulse reading circuit

InactiveUS8917562B2Large sensing marginImprove the sense of speedDigital storageEngineeringShort read

Owner:RGT UNIV OF CALIFORNIA

Mass parameter estimation method of carrier rocket

ActiveCN108763746ASimple processReduce design iterationsGeometric CADDesign optimisation/simulationAviationMass ratio

The invention discloses a mass parameter estimation method of a carrier rocket, and belongs to the field of aerospace technology. The technical problems of large calculated amount and inaccuracy in the existing mass parameter selection are solved. The mass parameter estimation method comprises the following steps: performing task index analysis, selecting an overall scheme, and determining systemparameters; determining design variables, optimization objectives and constraint conditions, and establishing a corresponding mathematical model via a mass parameter model, wherein the mass parametermodel comprises a sequential calculation propellant mass fraction calculation module, a coefficient Ki calculation module, an inter-stage mass ratio calculation module and an overall mass calculationmodule; performing mass parameter modeling on the carrier rocket, compiling an integrated calculation program, and giving an input and output file; selecting and inputting an optimization algorithm inan optimizer, and selecting the mass parameter model to obtain a reference design scheme. By adoption of the carrier rocket mass parameter estimation method disclosed by the invention, the iterativedesign times of the carrier rocket are reduced, and the method is simple in process, small in calculated amount and high in efficiency.

Owner:BEIHANG UNIV

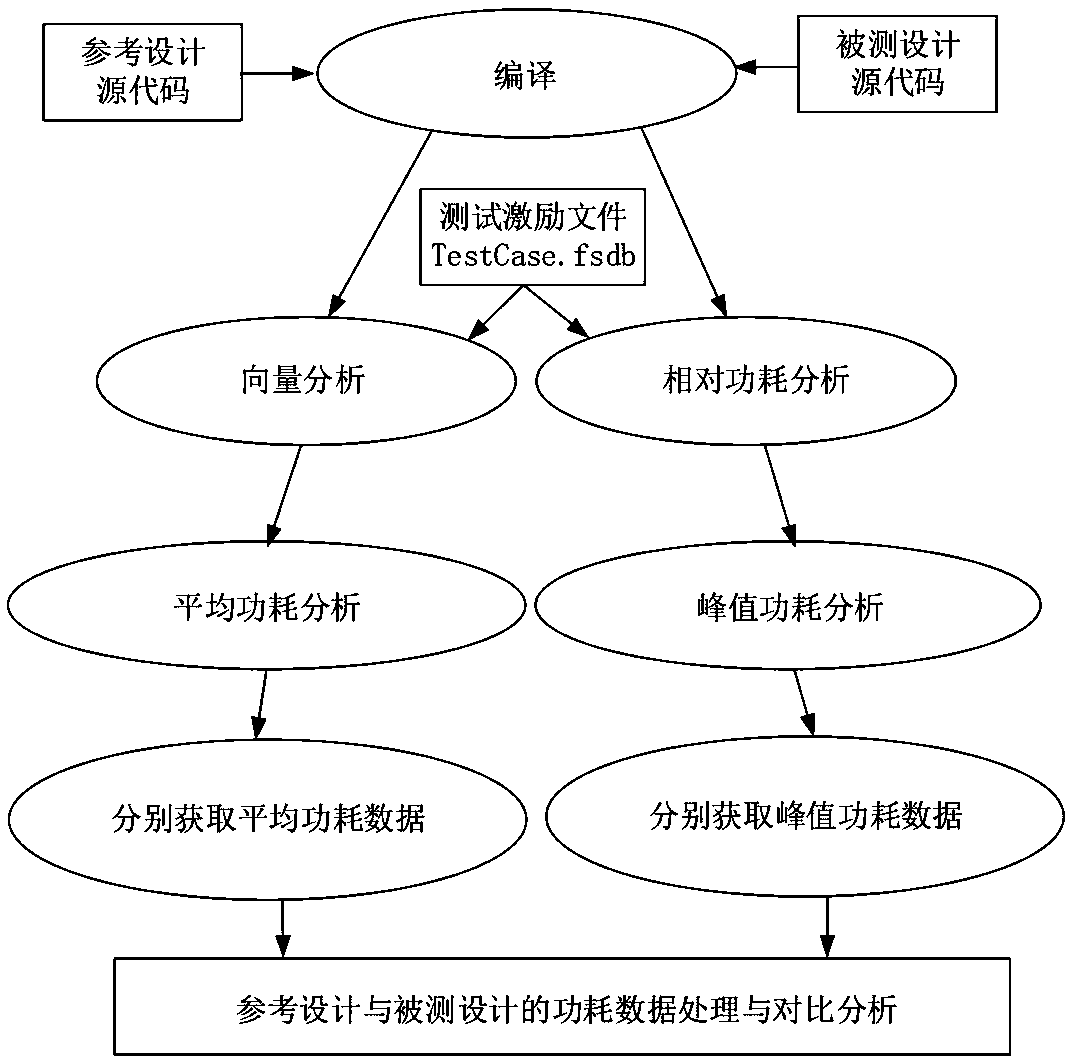

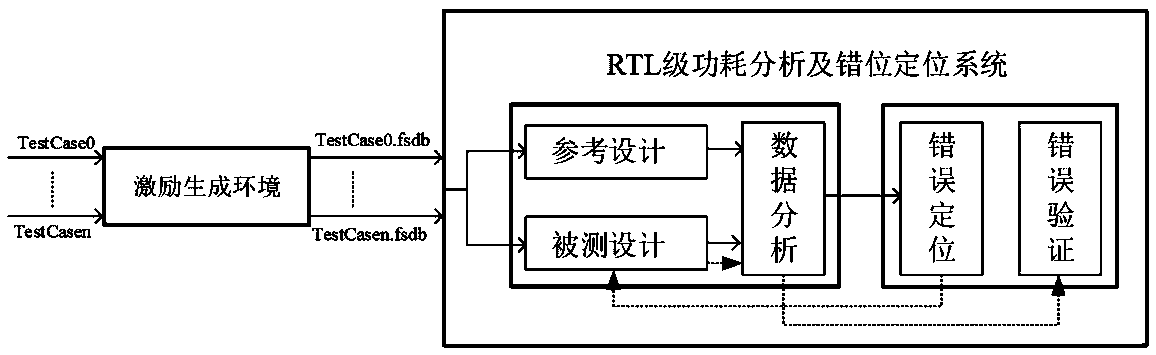

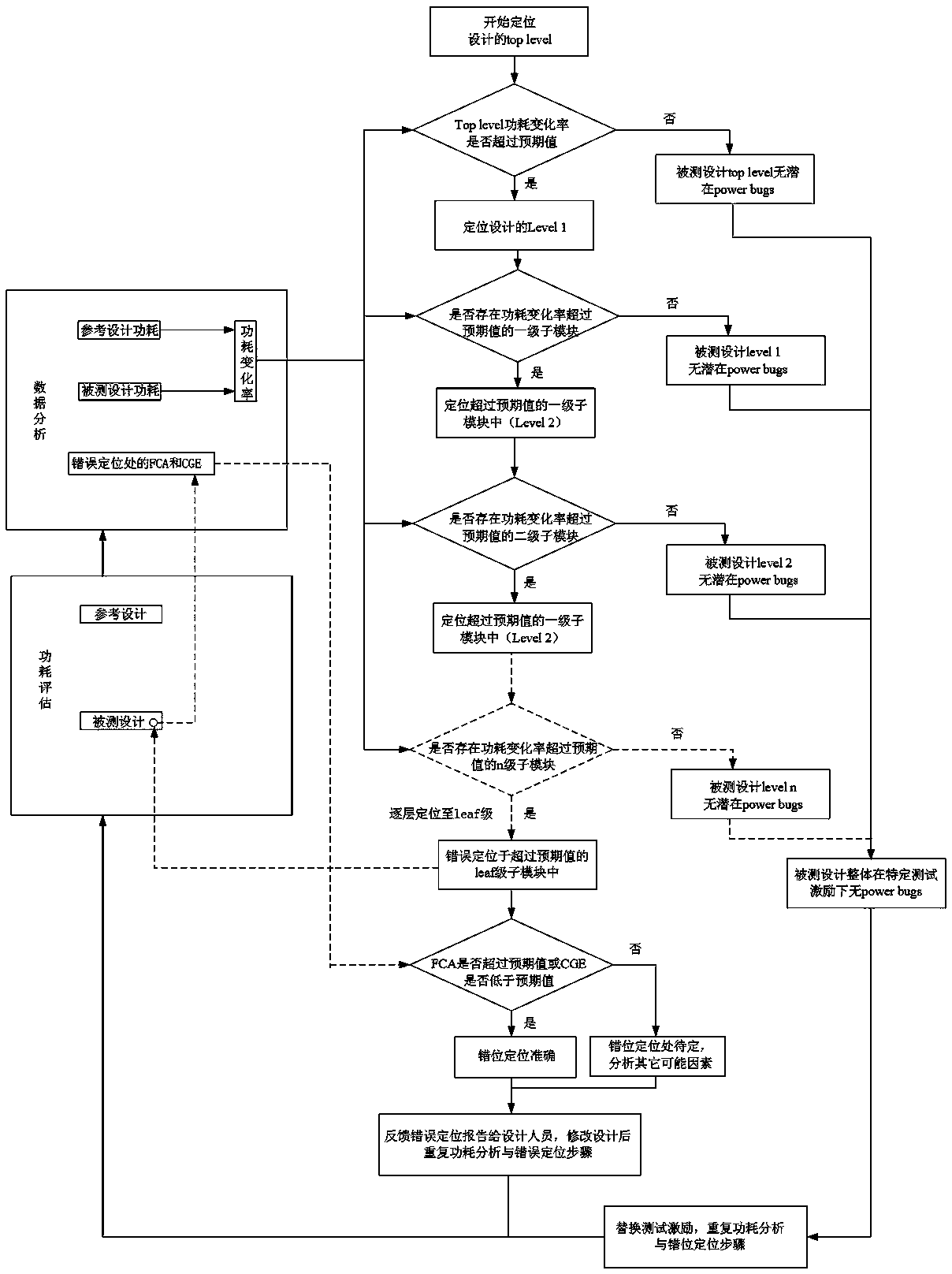

Error positioning method and system based on RTL-level power consumption analysis

ActiveCN108897652AAccelerate error locationGuaranteed accuracyFaulty hardware testing methodsSpecific testTest design

The invention discloses an error positioning method and system based on RTL-level power consumption analysis. The error positioning method includes the steps that an executable tested design DUT, a reference design REF and a test case set are obtained; test cases sequentially run, and the tested design DUT and the reference design REF are subjected to power consumption evaluation respectively; power consumption of the tested design DUT and power consumption of the reference design REF under specific test excitation are obtained respectively, and power consumption results are compared and analyzed; according to the power-consumption comparison results, the designs are subjected to error positioning analysis of power consumption defects layer by layer from top to bottom; the accuracy of thepower consumption defects positioned in the tested design DUT is verified; a dislocation positioning report of the power consumption defects is fed back to designers. According to the error positioning method and system based on RTL-level power consumption analysis, limitation that functional errors in designs can be only positioned with the main verification technology can be overcome, the defects that in the physical design stage, power-consumption optimizing space is low, and the design iteration cycle is long can also be overcome, and the function that the power consumption defects are early positioned can be achieved in the logical design stage of a microprocessor.

Owner:NAT UNIV OF DEFENSE TECH

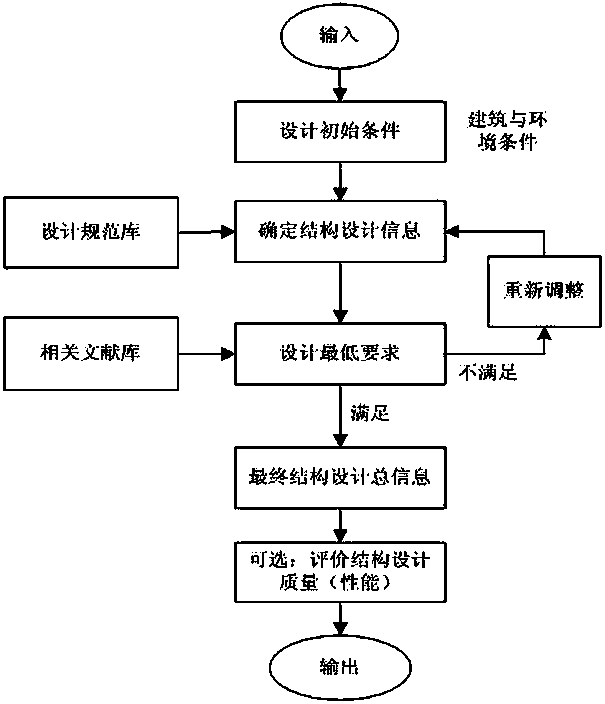

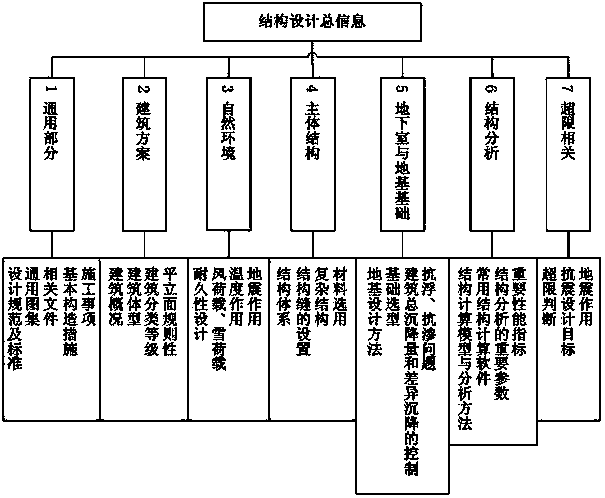

Aided design method of building structure

InactiveCN104318029AFully determinedDetermine scienceSpecial data processing applicationsDesign standardReference design

The invention relates to an aided design method of a building structure. The aided design method includes the steps of 1, inputting design initial conditions including building and environment conditions; 2, determining structure design information according to the design initial conditions and reference design standards of a design standard base; 3, based on a relevant constraint conditions, judging whether or not the structure design information and calculated amount acquired from the structure design information meet the minimum design requirement, and if so, enters the step 4; if not, back to the step 2 to re-adjust the structure design information; 4, outputting the structure design information to acquire the final total structure design information. By the use of the aided design method, structure design is more accurate and integral, and design efficiency is increased.

Owner:STATE GRID CORP OF CHINA +2

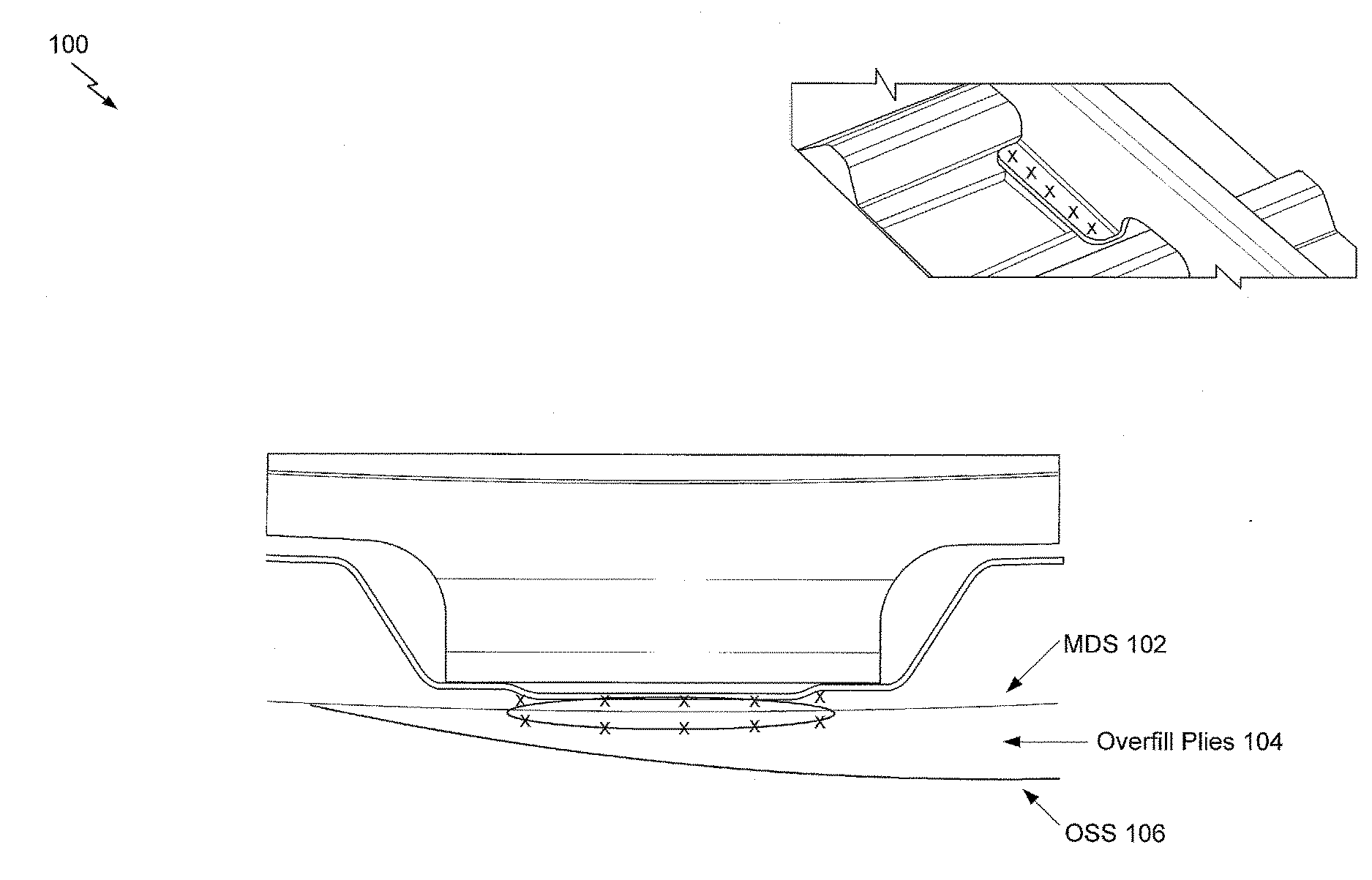

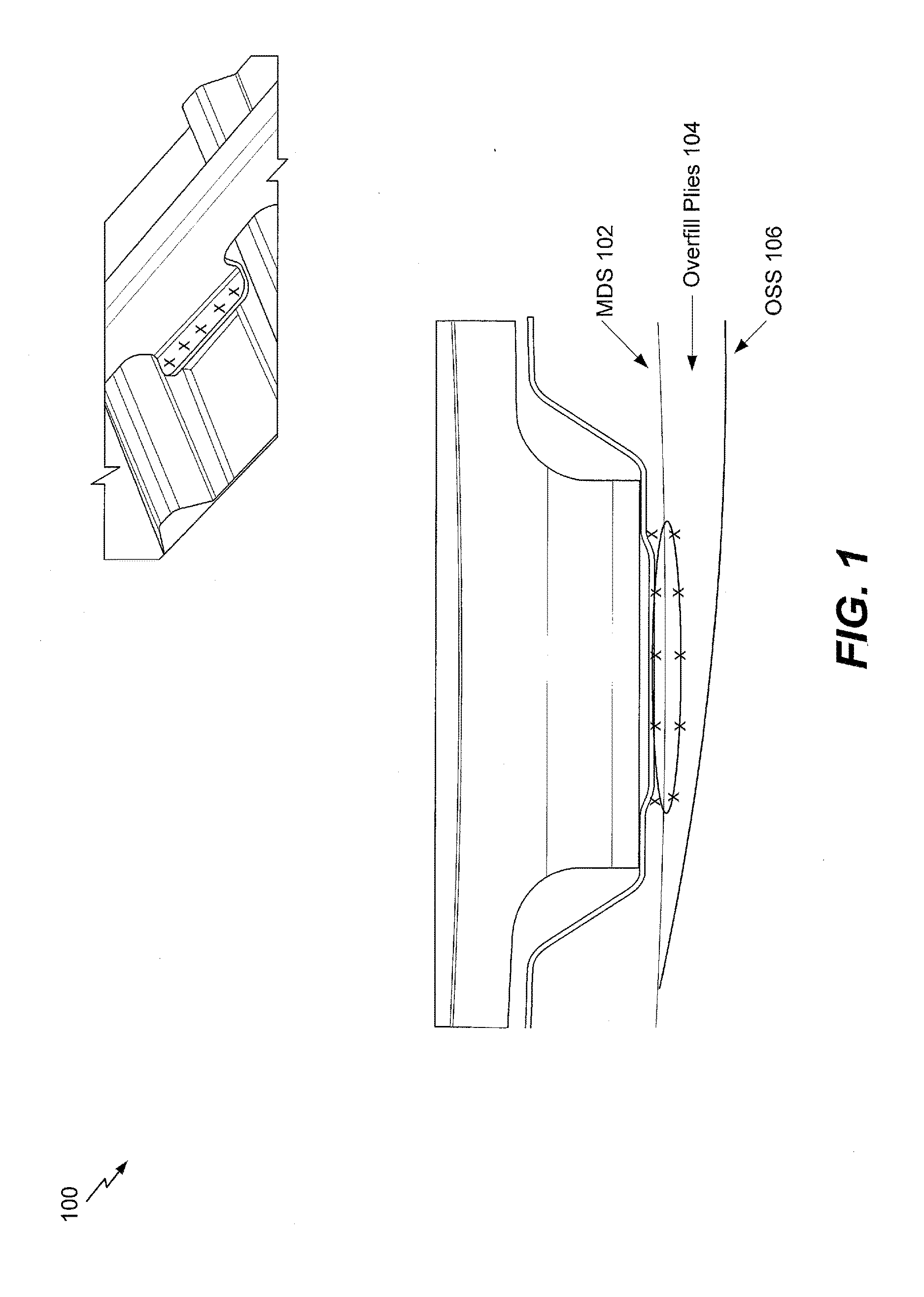

Surface modeling

A method includes receiving a reference design at a computing device. The reference design includes first geometrical information associated with a first set of composite materials to form a reference surface. The method includes receiving second geometrical information at the computing device. The second geometrical information is associated with a second set of composite materials associated with a second design. The method includes determining, based on a comparison of the first geometrical information and the second geometrical information, an offset surface relative to the reference surface. The method further includes generating a model of a surface of the second design based on the reference surface and the offset surface.

Owner:THE BOEING CO

Inspection sensitivity evaluation method

An inspection sensitivity evaluation method includes generating a reference design image where plural figure patterns are arranged, based on reference design data, generating plural position shift design images whose positional deviation amounts are mutually different such that positions of the plural figure patterns in the reference design image are uniformly shifted, acquiring an optical image of a photo mask fabricated based on the reference design data where there is no positional deviation from the plural figure patterns, calculating a first positional deviation amount between the reference design image and the optical image, calculating plural second positional deviation amounts each of which is a respective positional deviation amount between a corresponding position shift design image of the plural position shift design images and the optical image, and acquiring a detectable positional deviation amount by using the first and the plural second positional deviation amounts.

Owner:NUFLARE TECH INC

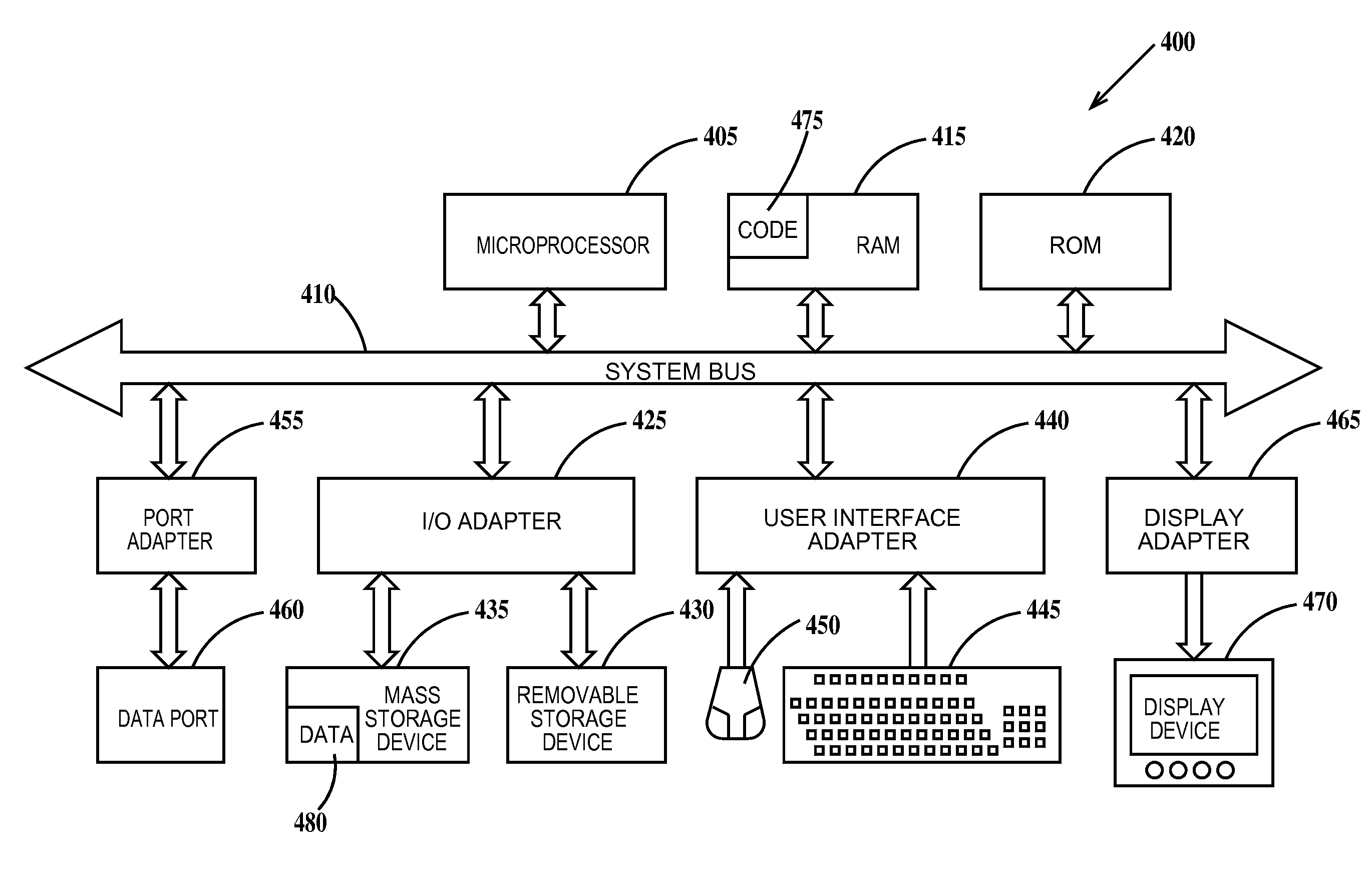

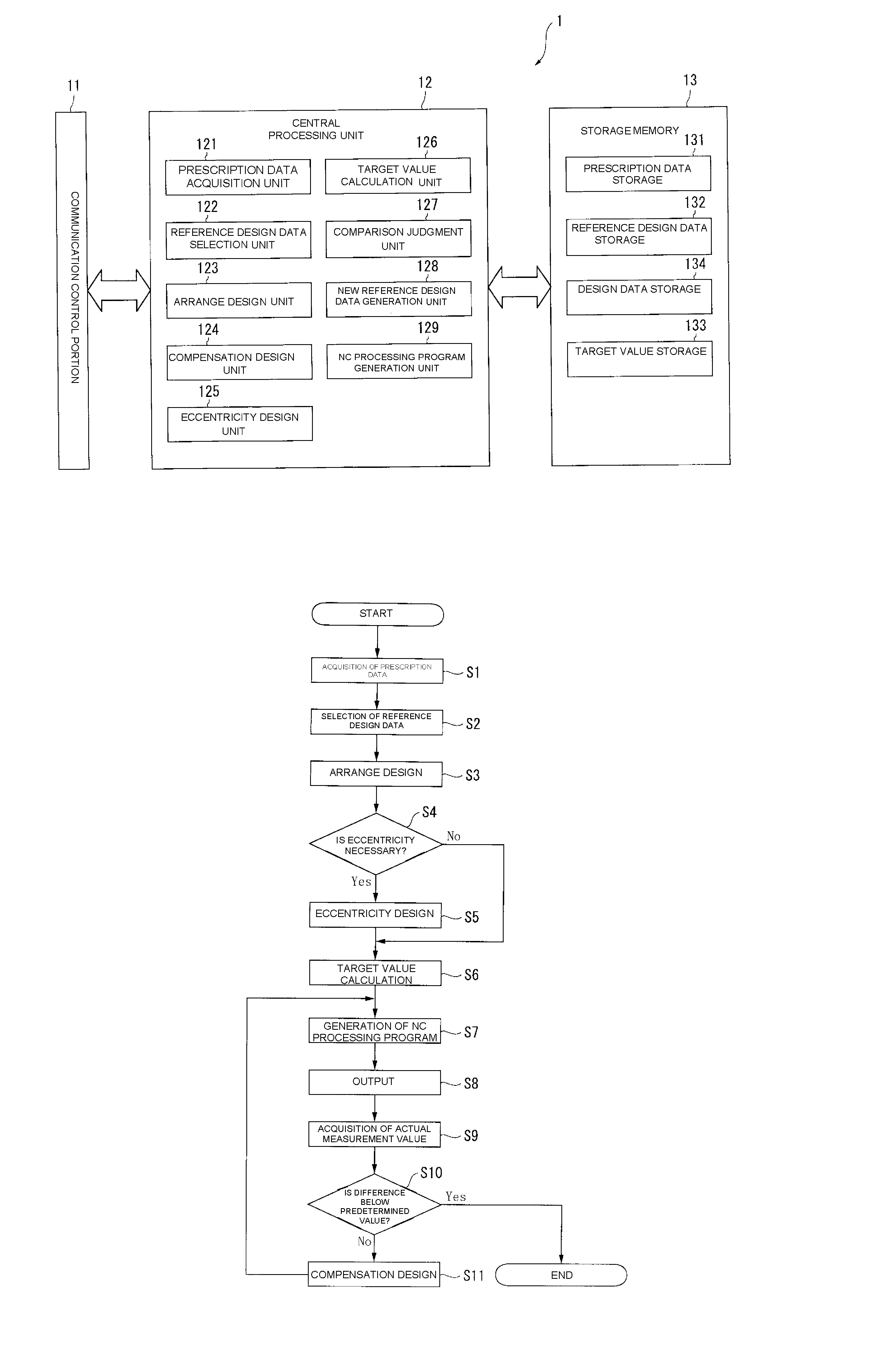

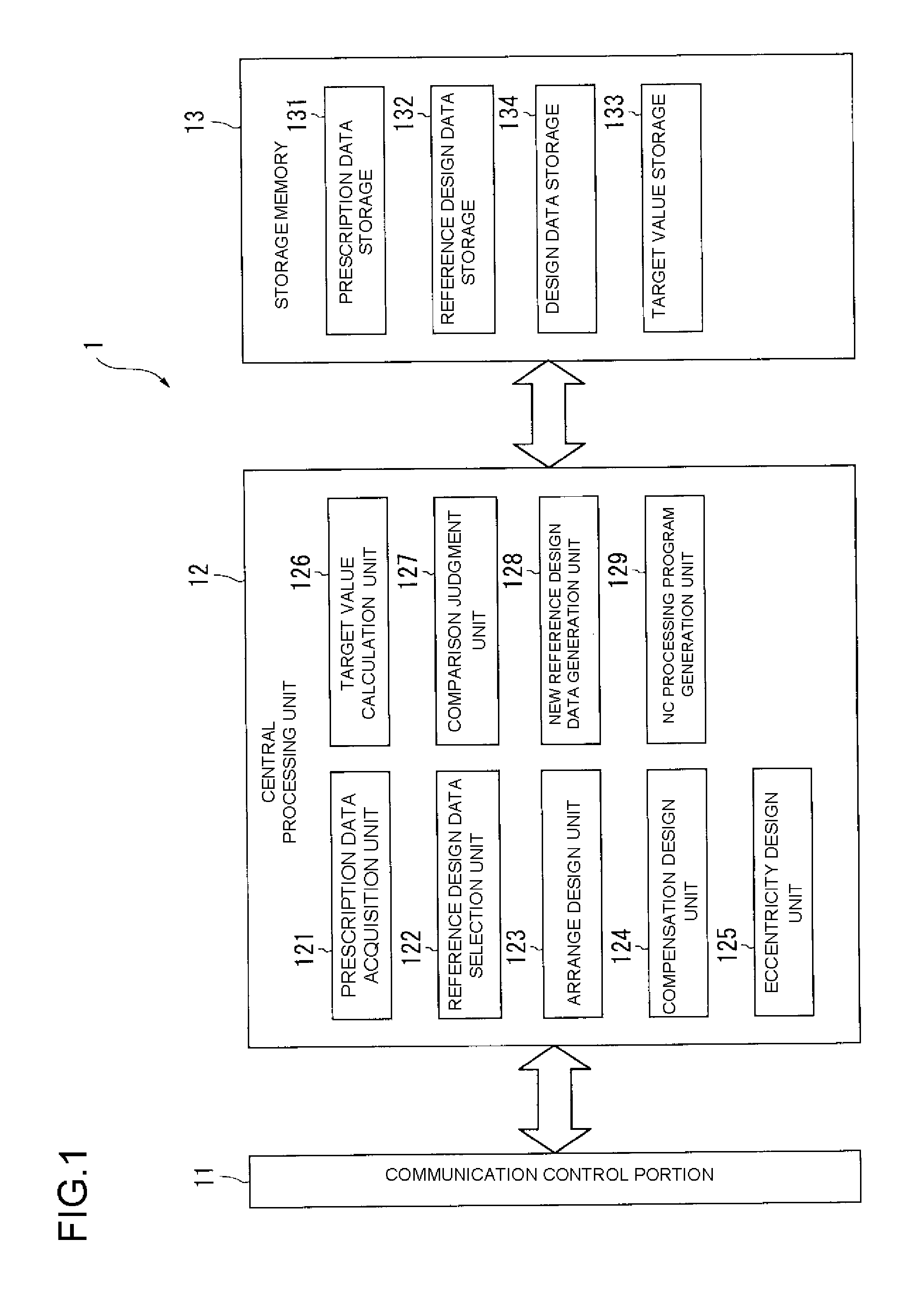

Generation system of design data, generation method of design data, recording medium and program

ActiveUS7175277B2Quickly generating design dataTime necessary for generating the design data can be reducedProgramme controlComputer controlComputer architectureData selection

A central processing unit of a calculation server apparatus includes a reference design data selection unit for selecting reference design data from a plurality of reference design data stored in reference design data storage of storage memory, and an arrange design unit 123 for processing the reference design data so acquired on the basis of prescription data. The reference design data has point groups having coordinates of points and obtained by dividing a progressive surface as a reference into a lattice form.

Owner:EHS LENS PHILIPPINES

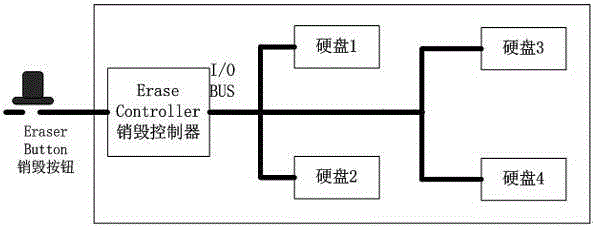

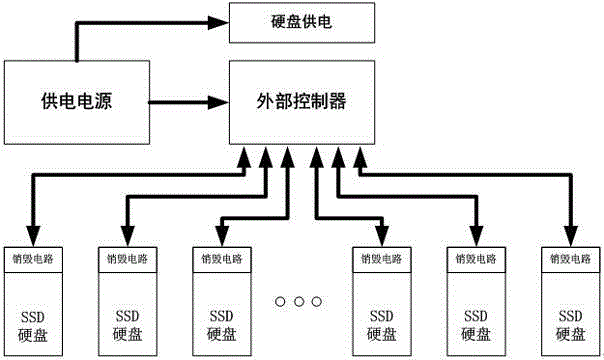

Design method of multi-hard disc sub-time destroying

InactiveCN105184195ARealize low-power physical destructionContinuous safe and reliable power supplyInternal/peripheral component protectionMass storageReference design

The invention particularly relates to a design method of multi-hard disc sub-time destroying. According to the design method of multi-hard disc sub-time destroying, destroyable hard discs, a destroying circuit, an external controller and a power supply are arranged, wherein the power supply is used for supplying power for the hard disc and the external controller at the same time; the external controller is connected with the destroyable hard discs through the destroying circuit; and through the external controller, hard disc destroying signals are output at different times, so that the sub-time physical destroying of the hard discs is realized. According to the design method of multi-hard disc sub-time destroying,, the safe privacy of stored data and the power consumption problem of the physical destroying of stored mediums are comprehensively considered, so that the condition that destroying is carried out twice at the same time is avoided, continuous, safe and reliable power supply can be ensured in the hard disc destroying process, the low-power consumption physical destroying of multi-hard disc storage equipment is realized, and a feasible conference design is provided for the physical destroying of the large-capacity storage equipment.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

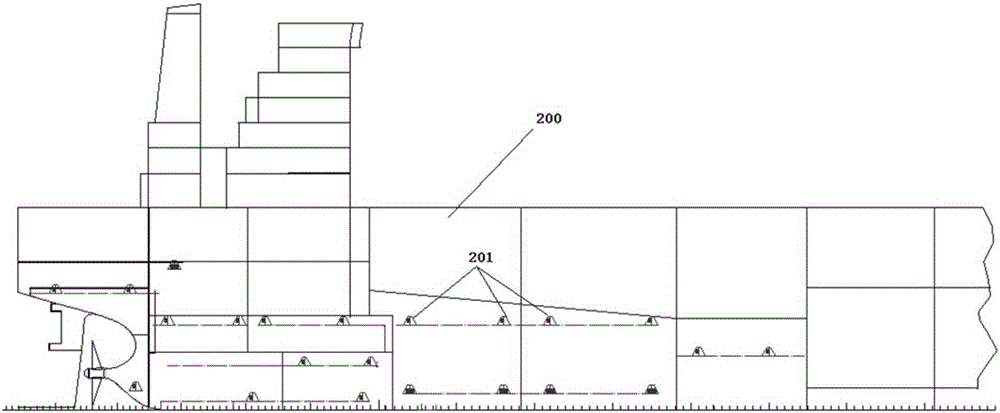

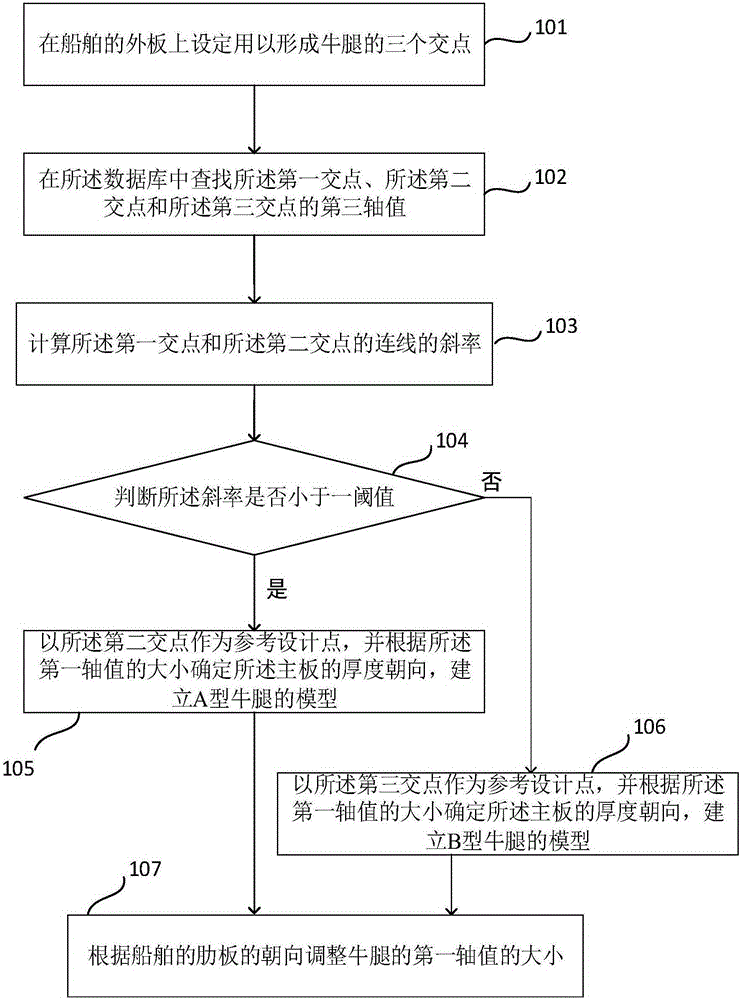

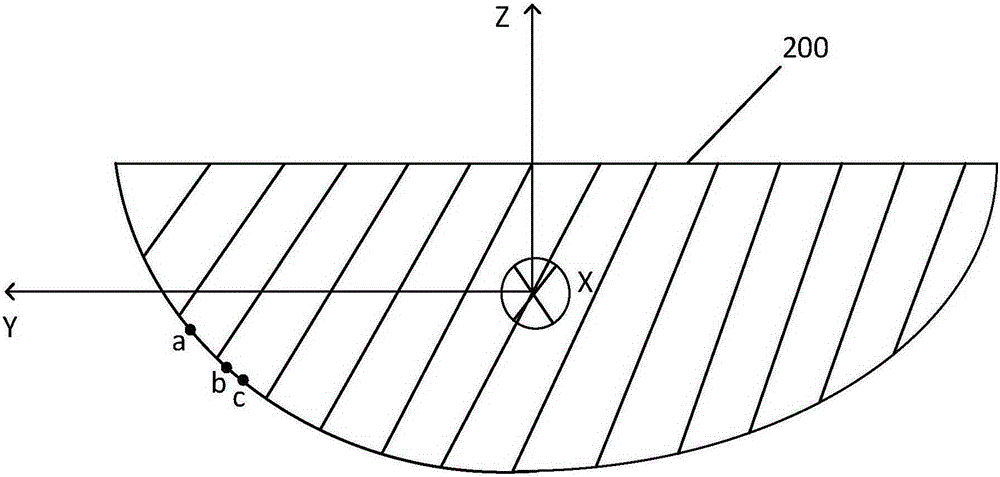

Modeling method and modeling apparatus for bracket of ship and bracket

ActiveCN105260535ANot easy to make mistakesEnsure consistencySpecial data processing applicationsModel methodIntersection of a polyhedron with a line

Owner:SHANGHAI WAIGAOQIAO SHIP BUILDING CO LTD

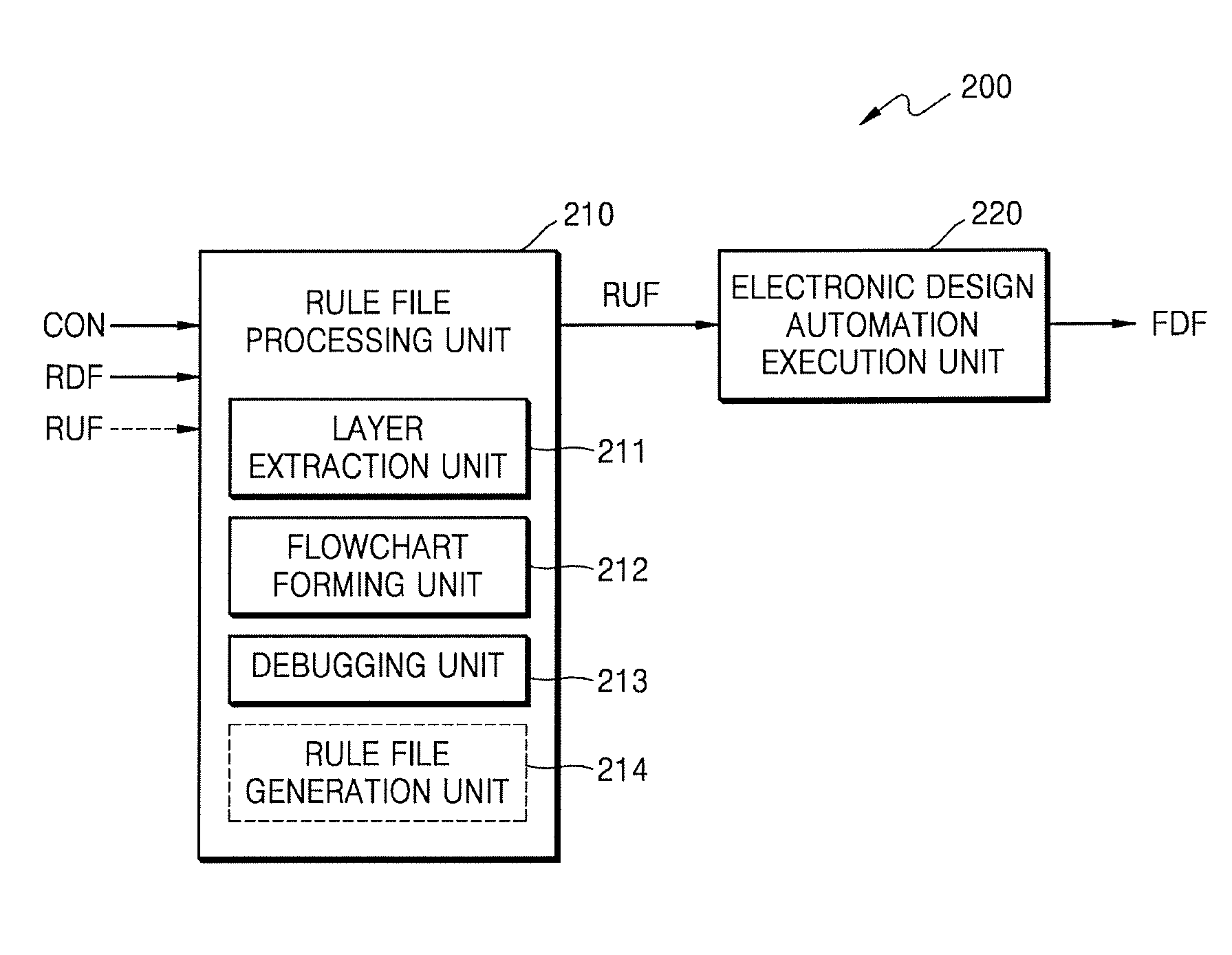

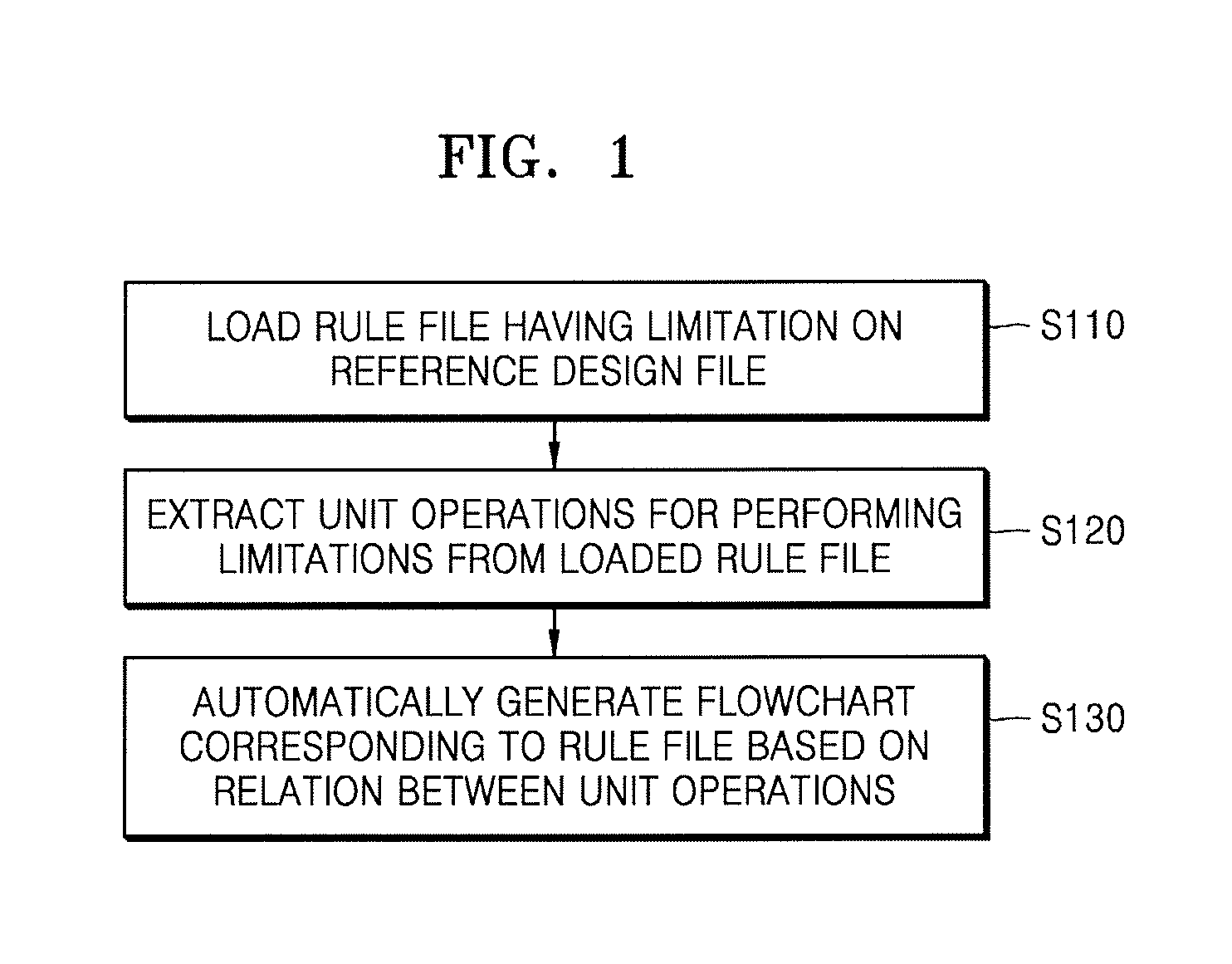

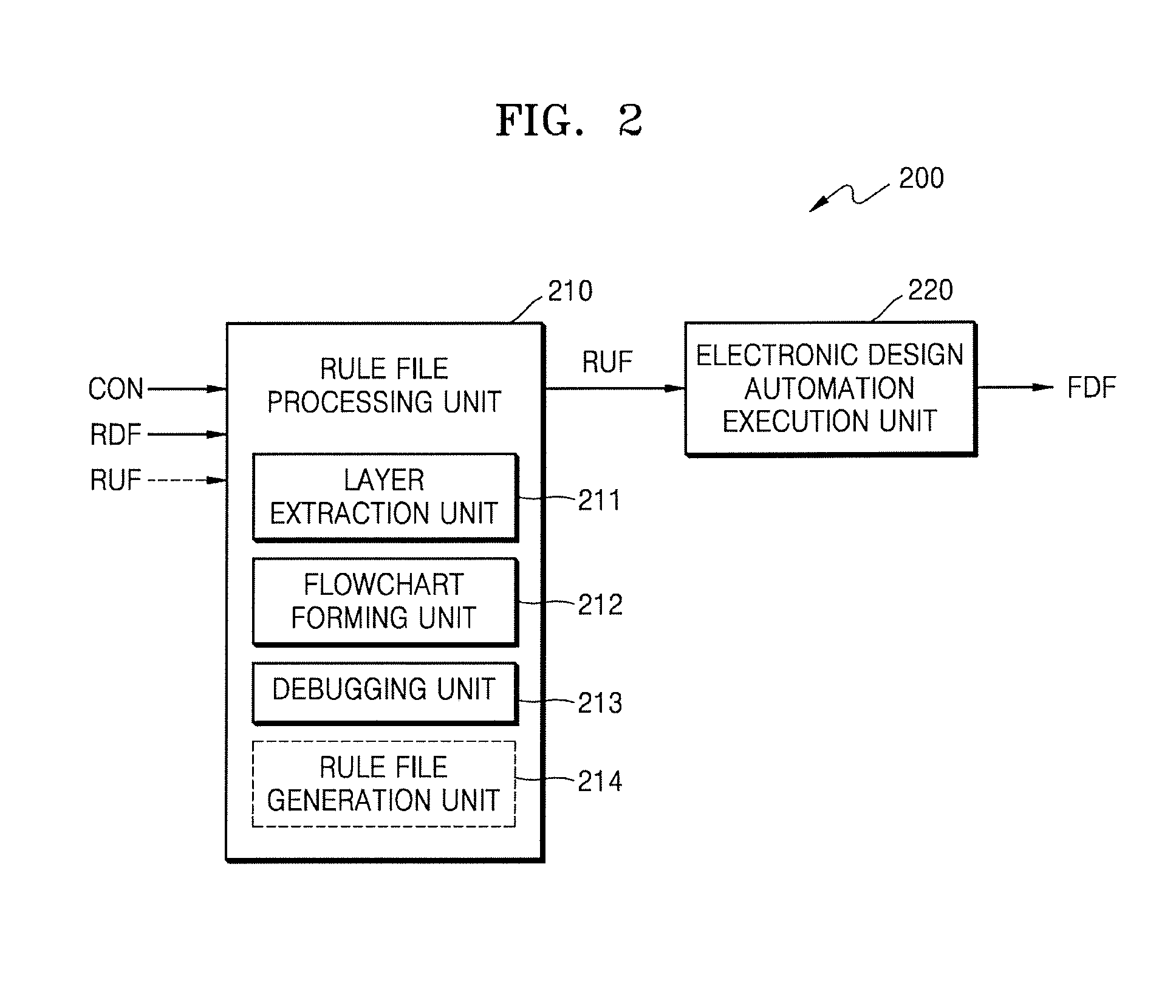

Electronic design automation method and apparatus thereof

InactiveUS20160188773A1Easy to usePrecise designGeometric CADDesign optimisation/simulationComputer architectureUnit operation

Provided are an electronic design automation apparatus and method. The electronic design automation method includes: loading, by a processor, a rule file having limitations on a reference design file; extracting, by the processor, a plurality of unit operations for respectively performing the limitations from the loaded file; and automatically forming, by the processor, a flowchart corresponding to the rule file based on relations between the plurality of unit operations.

Owner:SAMSUNG ELECTRONICS CO LTD

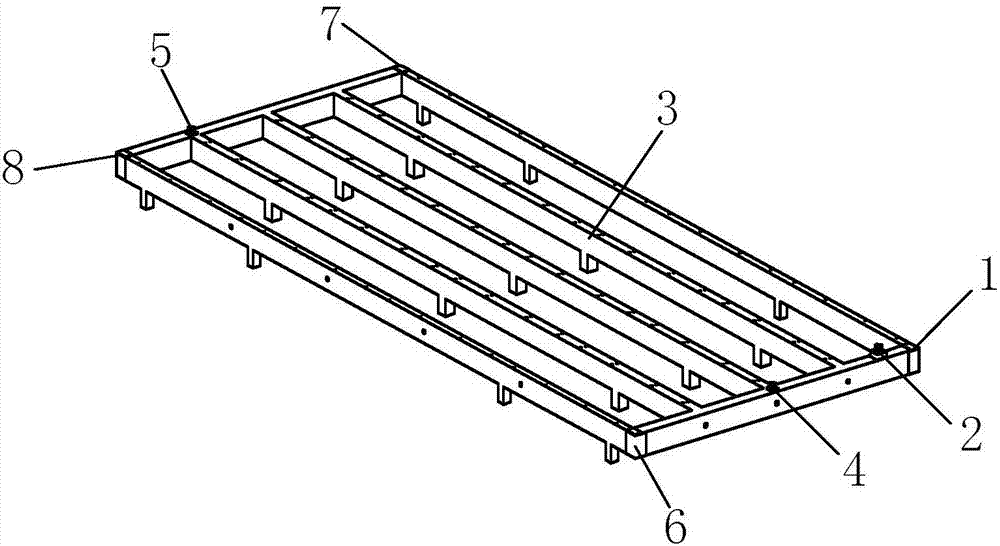

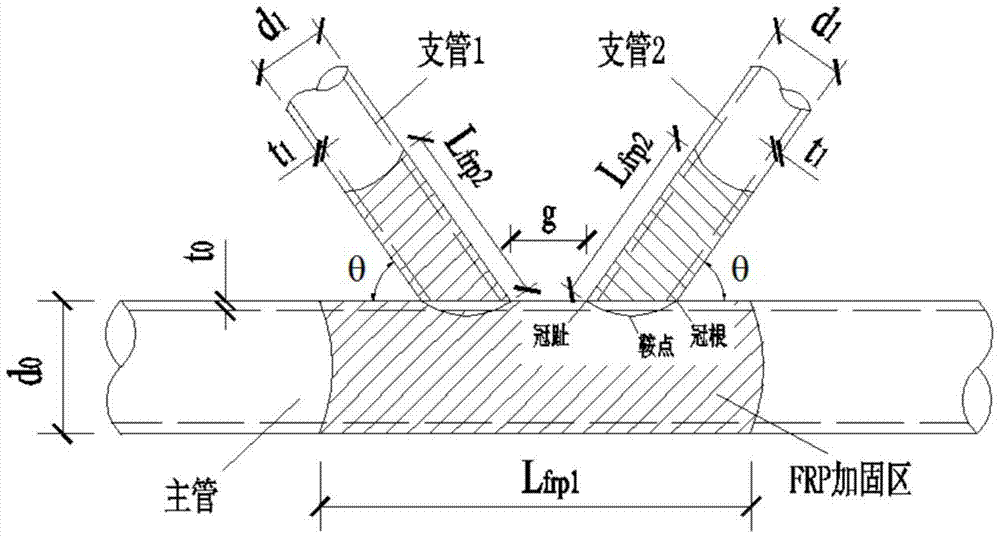

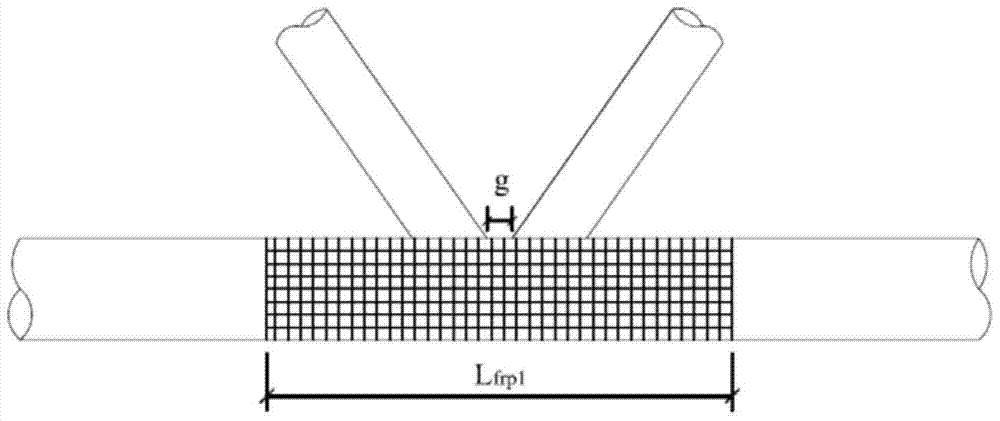

A Method for Strengthening Metal Pipe Joints Using Fiber Reinforced Composite Materials

ActiveCN104790683BImprove static performanceImprove fatigue lifeBuilding repairsAdhesiveReference design

The invention discloses a method for reinforcing metal pipe joints with fiber-reinforced composite materials. There are three steps of reinforced composite material cloth reinforcement and end anchorage, and finally curing. The method of the invention is simple and convenient in construction, does not need complex equipment, and is suitable for complex geometric shapes of pipe joints. At the same time, the pasted FRP material is light and high-strength, without additional node load. After the reinforcement is completed, the node has a beautiful appearance and good durability. The method of the present invention aims at common metal pipe nodes, by making the FRP material and the metal pipe nodes work together and suppressing the deformation of the nodes, to improve the static performance and fatigue performance of the nodes such as stiffness, ductility, bearing capacity; the method can also be Other types of pipe nodes provide reference for design ideas.

Owner:TONGJI UNIV +1

CMOS low voltage bandgap reference design with orthogonal output voltage trimming

Bandgap Voltage Reference circuits configured to produce reference voltages with both voltage offset and a voltage temperature slope are disclosed. By generating the voltage offset from a temperature-independent current, the voltage offset of the reference voltage may be temperature-independent, while generating the voltage temperature slope from a temperature-dependent current allows the voltage temperature slope to vary with temperature. To ensure that the voltage offset remains independent from the voltage temperature slope, an apparatus is disclosed for orthogonal trimming of voltage offset and voltage temperature slope.

Owner:SYNOPSYS INC

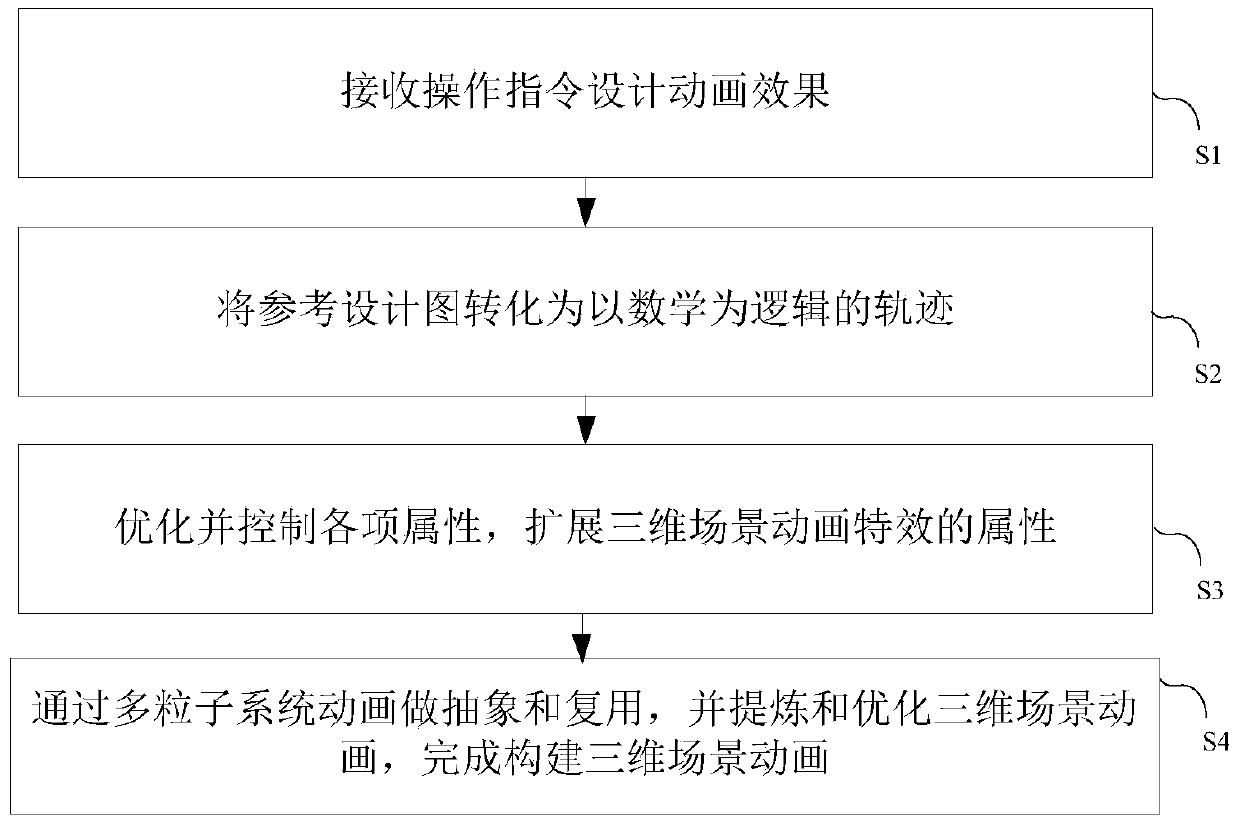

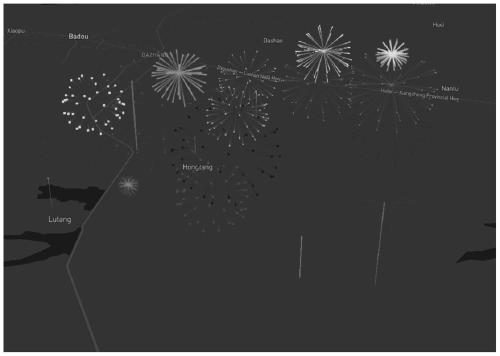

Method and device for constructing three-dimensional scene animation in GIS system based on particle system

ActiveCN111292399AImprove attributesImprove implementation efficiencyAnimationInternal combustion piston enginesComputational scienceAnimation

The invention relates to a method and device for constructing a three-dimensional scene animation based on a particle system in a GIS system. The method comprises the steps that an operation instruction is received to design an animation effect; converting the reference design animation into a track taking mathematics as logic; optimizing and controlling each attribute, and expanding the attributeof the animation special effect of the three-dimensional scene; abstraction and reuse are carried out through multi-particle system animation, three-dimensional scene animation is extracted and optimized, and construction of the three-dimensional scene animation is completed. The three-dimensional animation effect with high efficiency and vivid effect is realized at the WebGis front end, and themethod is low in cost, high in efficiency and high in universality.

Owner:GENEW TECH

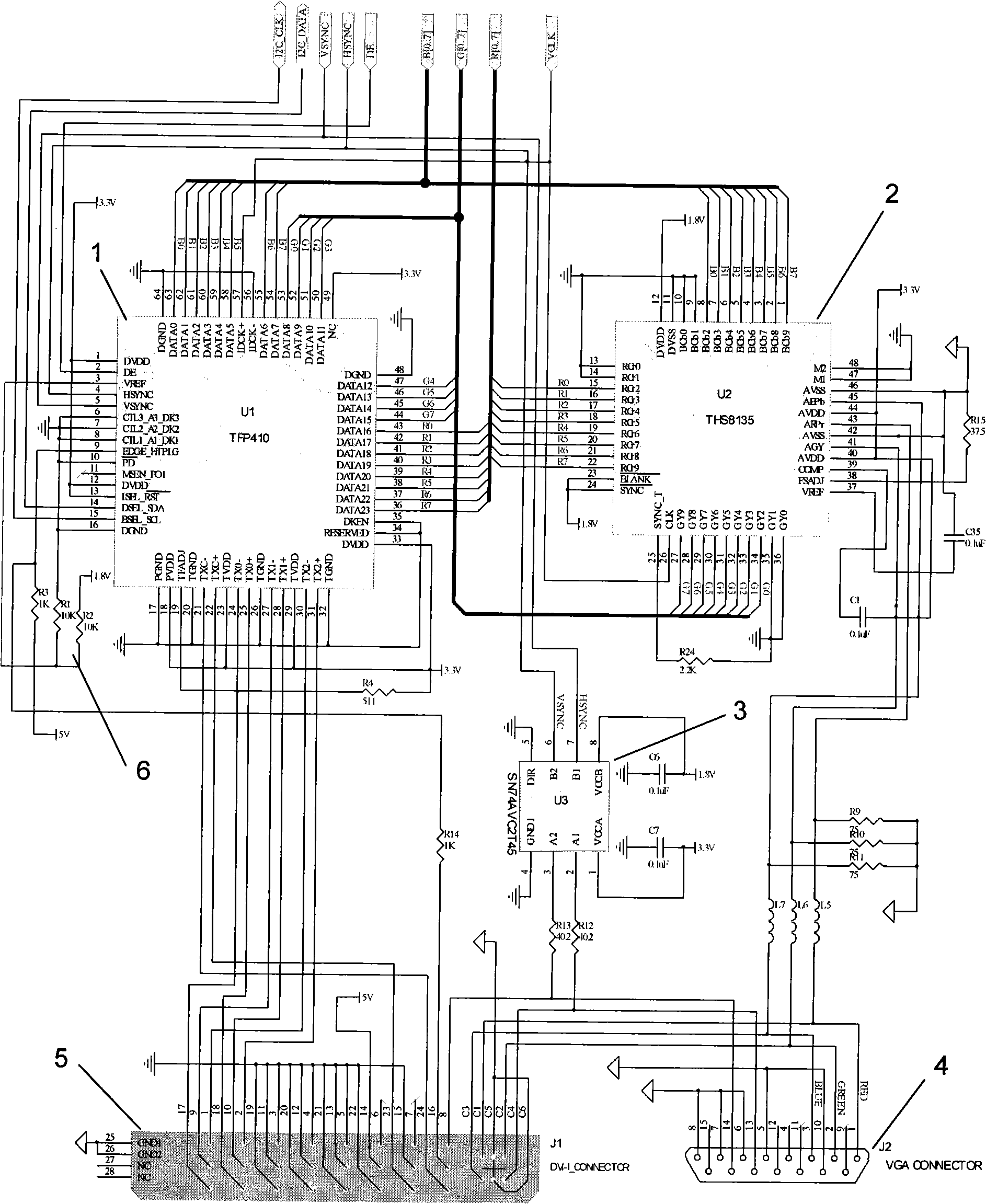

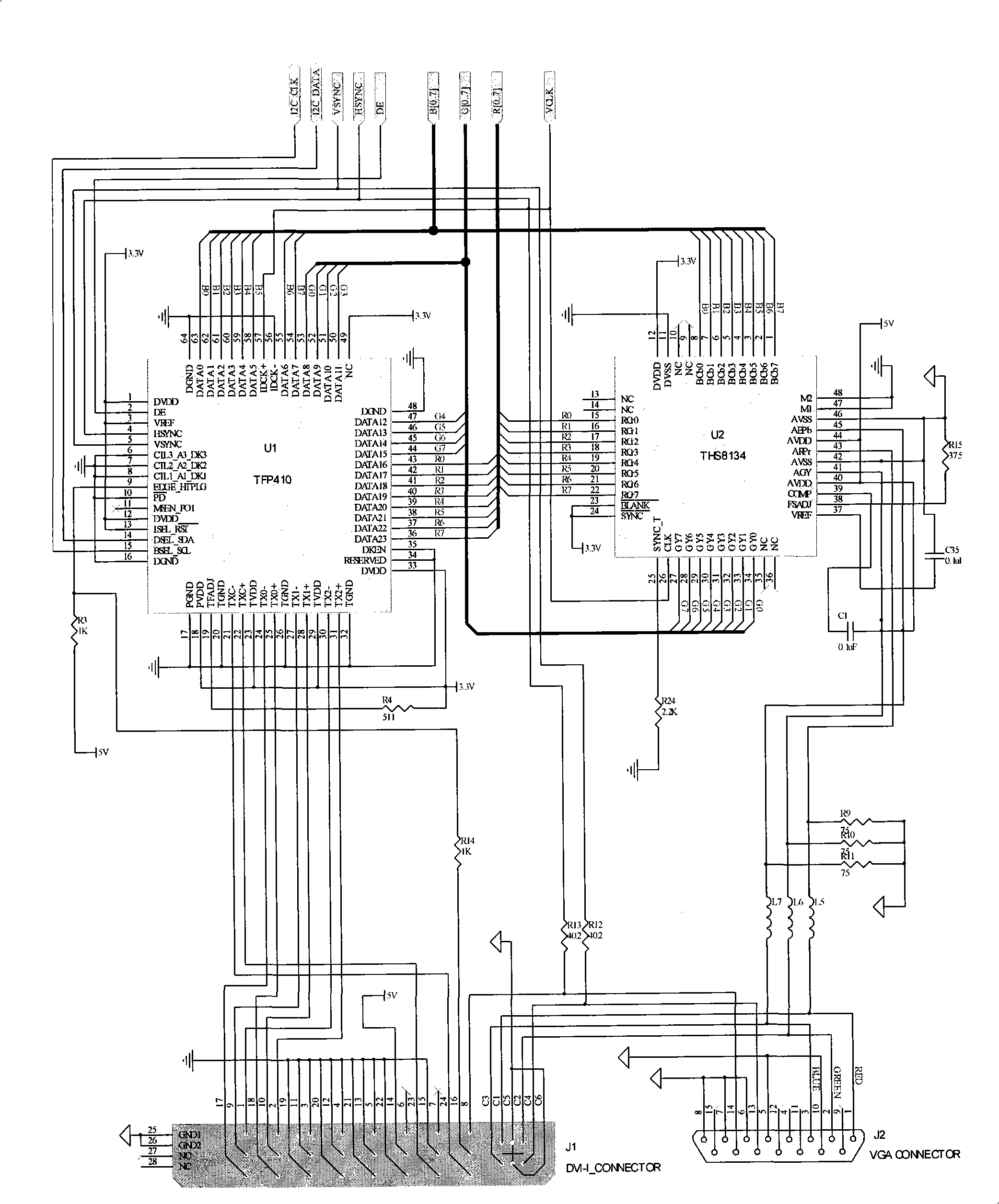

DVI-I and VGA interface circuit

InactiveCN101404149ASimple structureCathode-ray tube indicatorsElectrical resistance and conductanceMonitoring system

The present invention relates to a DVI-I and VGA interface circuit, in particular to the design of a DVI and VGA output circuit for an embedded system, which belongs to the technical field of high vision display. The DVI-I and VGA interface circuit is a processing circuit which can be applied to an embedded system, can be based on a digital medium processor and can output DVI and VGA at the same time. The interface circuit of the invention comprises a DVI transmitter chip (1), a three-channel video DAC conversion chip (2), a 1.8V to 3.3V of level conversion chip (3), a VGA output socket (4), a DVI-I output socket (5) and a reference voltage division resistor (6). The interface circuit has simple structure, practicability and high efficiency, stability and reliability. Being used as the reference design of the DVI and VGA output circuit in an embedded video decoding playing device, the interface circuit can be widely applied to the embedded fields of digital monitoring systems, IP machine top boxes, KTV machine top boxes and multimedia information issuing systems.

Owner:YUNNAN UNIV