Error positioning method and system based on RTL-level power consumption analysis

A technology for power analysis and error localization, applied in error detection/correction, faulty hardware testing methods, detection of faulty computer hardware, etc. It solves problems such as long generation iteration time, and achieves the effect of mining power consumption optimization space, low power consumption design goals, and reducing design iteration time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

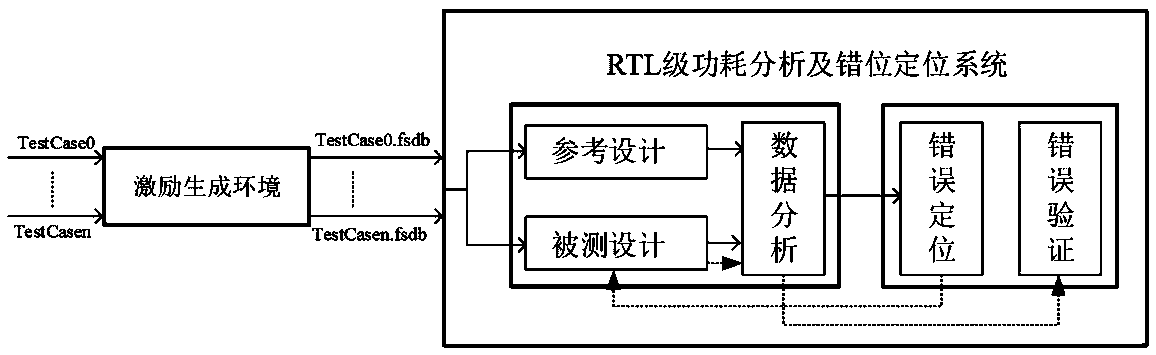

[0036] The following will be a test case set containing two test cases {TestCase i} as an example, the error location method and system based on RTL-level power consumption analysis of the present invention are further described in detail, wherein the test case set {TestCase i} The two test cases included are TestCase0 for testing integer programs and TestCase1 for testing vector floating-point programs.

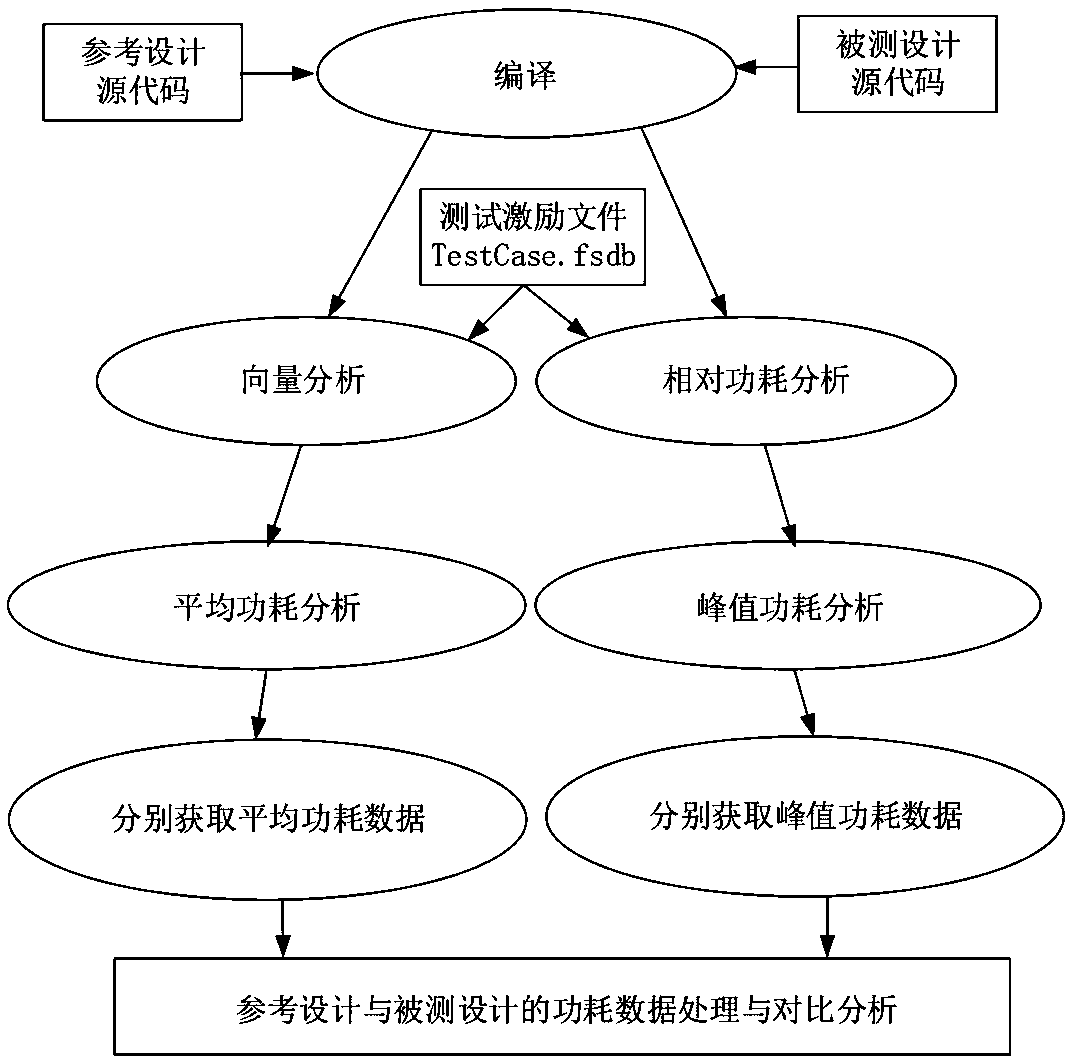

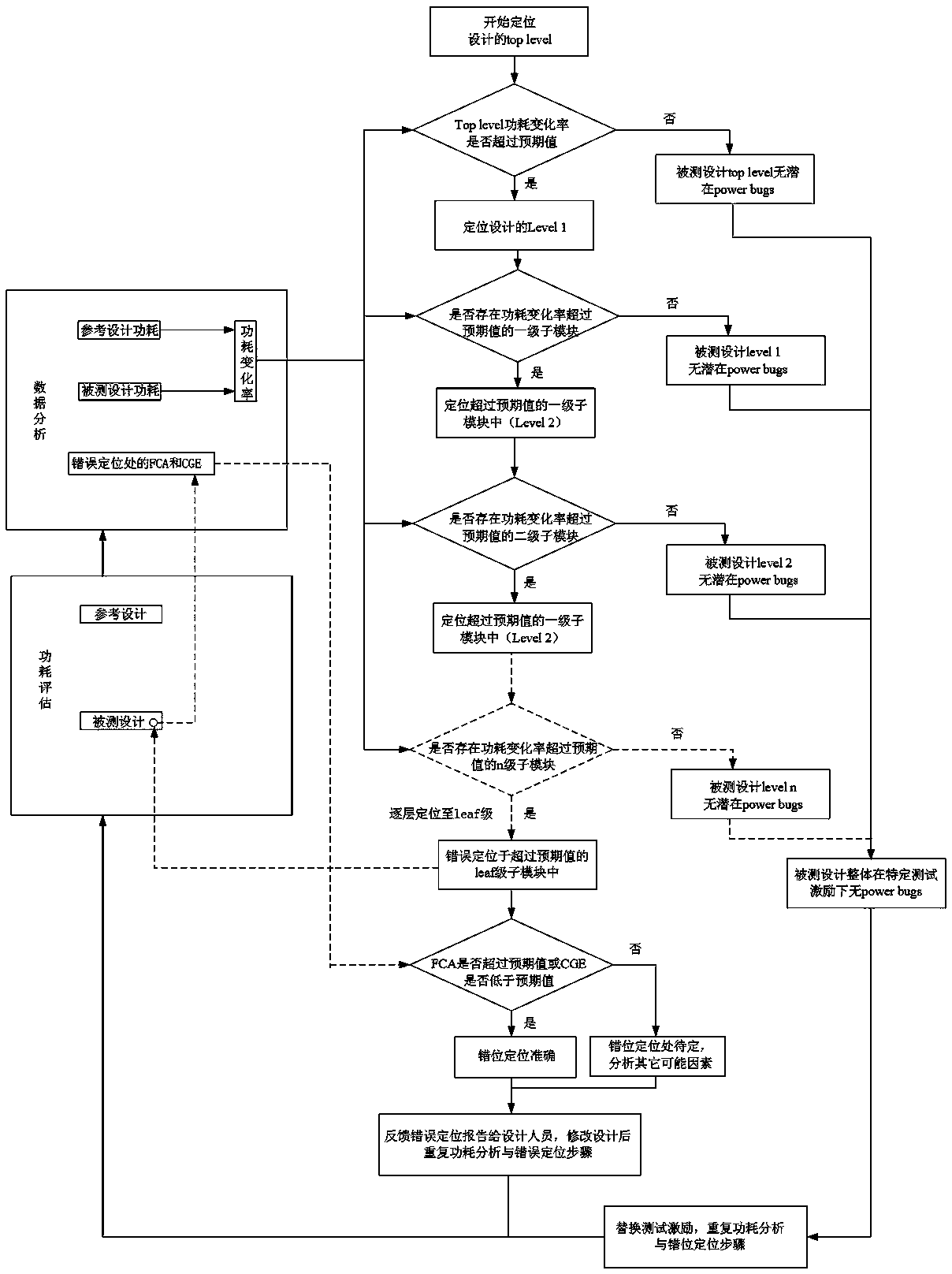

[0037] Such as figure 2 and image 3 As shown, the implementation steps of the error location method based on RTL-level power consumption analysis in this embodiment include:

[0038] 1) Obtain executable DUT under test, reference design REF, and test case set {TestCase i};

[0039]2) from TestCaseSet {TestCase i} traverse to select a current test case TestCase i , to run the current test case TestCase i , with the help of EDA power consumption analysis tool to evaluate the power consumption of the DUT under test and the reference design REF respectively;

[0040] 3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More