Physical layer transmission real error code acquisition device and equipment

A technology of acquisition device and physical layer, which is applied in the field of real error code acquisition device and equipment for transmission of physical layer, and can solve problems such as inability to guarantee reliable transmission.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

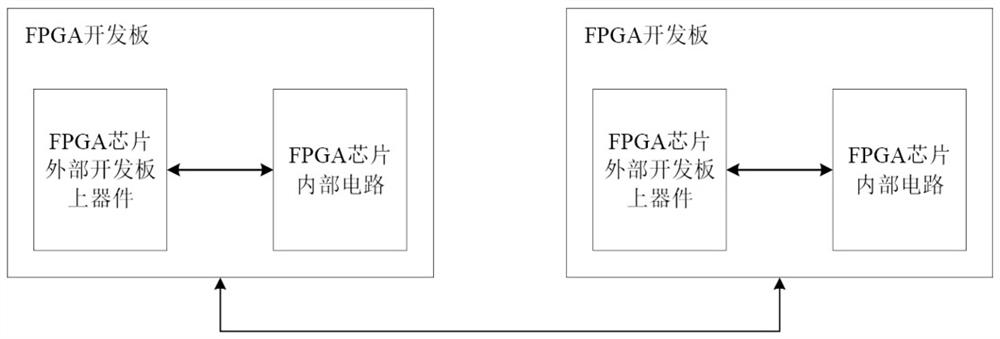

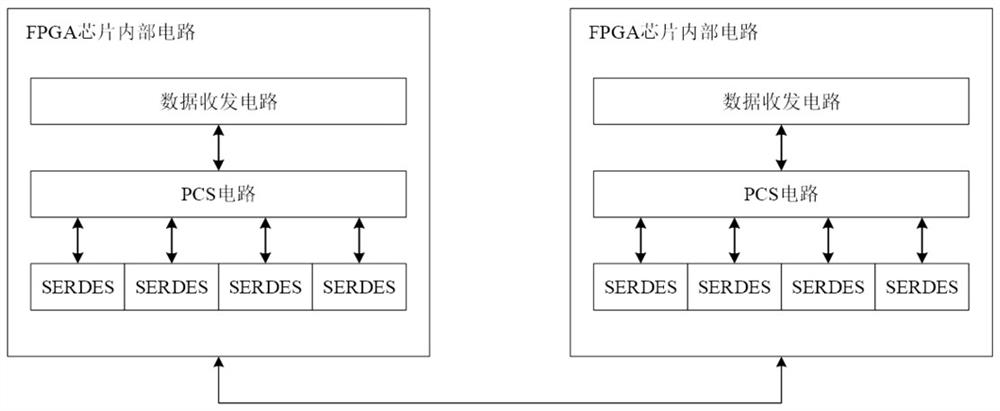

[0032] The real bit error acquisition device for physical layer transmission of the present invention will be further described in detail below by taking the real bit error acquisition device for physical layer transmission implemented in the FPGA development version as a specific example. It should be noted that the carrier of the physical layer transmission real bit error acquisition device of the present invention is not limited to the FPGA chip, and can also be used in other types of processing chips. like figure 1 As shown, the physical layer transmission real error bit acquisition device in this embodiment uses two FPGA development boards with high-speed serial communication interfaces as carriers, and the bottom layer uses optical fibers to connect them, and data is transmitted between the two FPGA development boards. To transmit and collect its error code, each FPGA development board contains the internal circuits of the FPGA chip and the devices on the external develo...

Embodiment 2

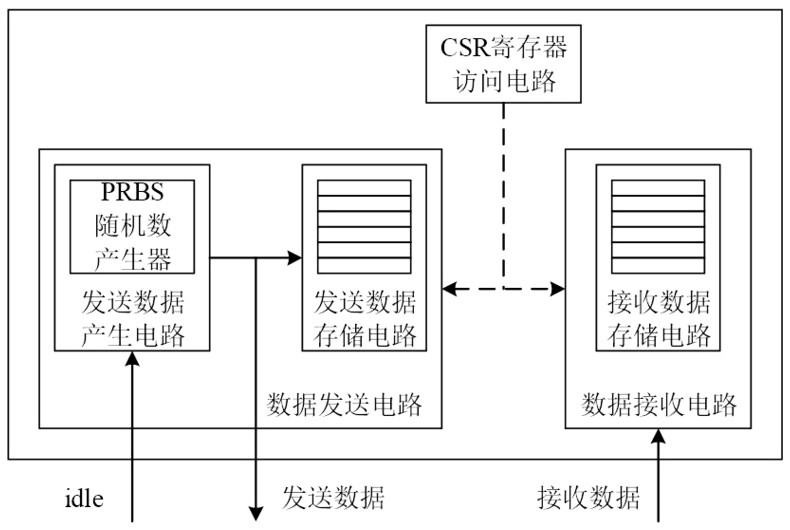

[0050] In the aforementioned first embodiment, the transmission data generation circuit generates pseudo-random data through a PRBS random number generator. However, considering that in some test scenarios it is necessary to test the bit error rate of specific data passing through the physical link, a function of testing specific data is added on the basis of Embodiment 1.

[0051] like Figure 4As shown, the data transmission circuit includes a transmission data generation circuit and a transmission data storage circuit, and the transmission data generation circuit includes a random number generator, a mode configurable data generator and an output selector, a random number generator, a mode configurable data generator They are respectively connected to the input end of the output selector, and the output end of the output selector is connected to the physical coding sublayer circuit PCS. The mode configurable data generator is used to generate specified mode data according t...

Embodiment 3

[0056] In the first and second embodiments above, the physical layer transmission real bit error collection device at the sending end and the physical layer transmission real bit error collection device at the receiving end respectively use their own storage circuits to store the sent data and the received data. However, inside the FPGA chip, the resources of the Block RAM are limited. When the link rate is relatively high, the storage resources of the Block RAM in the FPGA chip will be consumed quickly, resulting in short test time and low test data. Not much. For example, the FPGA chip we usually use has an internal Block RAM with a capacity of about 1000*32Kb, that is, it can store about 120*1024 pieces of 256b data. Under the bandwidth of 4 lanes*2.5Gbps, only about 122880 pieces of 256 data can be sent, and the duration is 3ms. If the consumption of the memory can be reduced, a larger amount of data can be sent and the test time can be increased. Therefore, in order to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More