Clock recovery device and method

A clock recovery and digital clock technology, which is applied in the direction of synchronization devices, electromagnetic wave transmission systems, digital transmission systems, etc., can solve the problem that digital clock recovery circuits cannot provide synchronous clocks, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

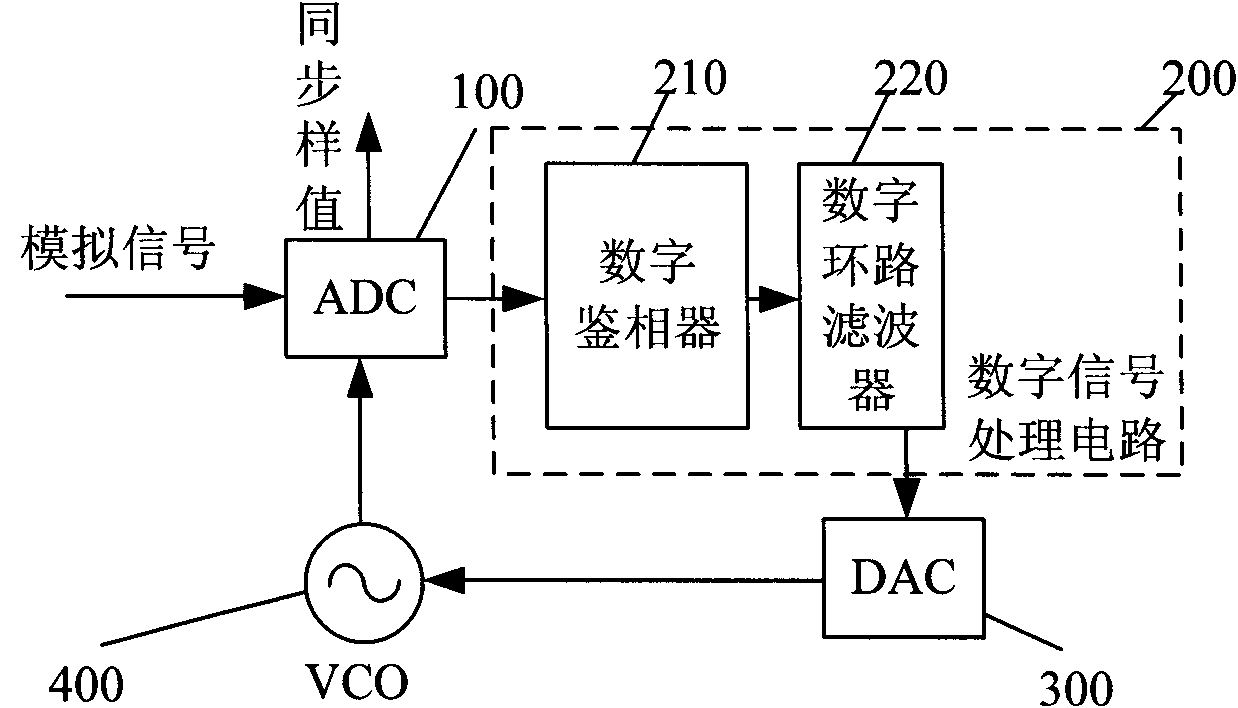

[0045] figure 2 Shown is the clock recovery device of this embodiment, including: analog-to-digital converter (ADC) 100, digital signal processing circuit 200, digital-to-analog converter (DAC) 300 and VCO400, wherein, ADC100, digital signal processing circuit 200, DAC300 It is connected with VCO400 in turn, and VCO400 is also connected with ADC100 to provide reference clock to ADC100;

[0046] The ADC100 converts the received analog signal to be processed into a digital signal, and sends the digital signal to the digital signal processing circuit 200; after synchronization is established, the ADC100 outputs a synchronous sampling value;

[0047] The digital signal processing part 200 includes: a digital phase detector 210 and a digital loop filter 220. The digital phase detector 210 receives the digital signal sent by the ADC100, performs phase detection processing on the digital signal, obtains a phase error signal, and converts the phase error signal Send to the loop filt...

Embodiment 2

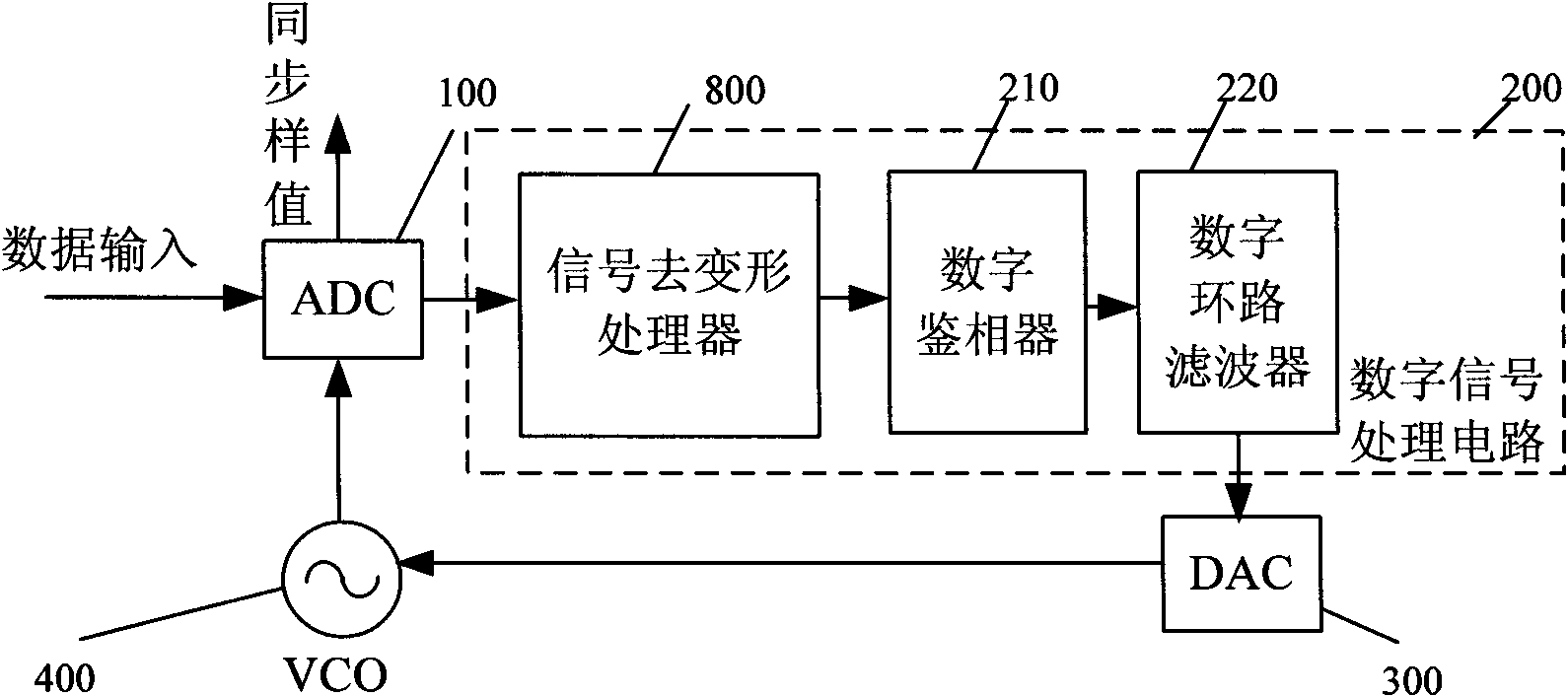

[0051] For a signal with serious distortion, a processing circuit can be added in the digital signal processing circuit 200 to weaken the distortion of the signal, and then perform clock recovery, such as image 3As shown, a signal de-distortion processor 800 is also connected between the ADC100 and the digital phase detector 210. After the digital signal converted by the ADC100 is processed by the signal de-distortion processor 800, a recoverable clock signal is obtained, and then the clock is processed. recover. The signal dewarping processor 800 may be an FIR filter for equalization.

Embodiment 3

[0053] For the case where the sampling rate of the ADC100 is different from the required sampling rate of the digital phase detector 210, such as Figure 4 As shown, a resampling circuit 900 can be added between the ADC100 and the digital phase detector 210, and the resampling circuit 900 resamples the digital signal converted by the ADC100 to obtain a digital signal with a sampling rate required by the digital phase detector 210, and then Then perform clock recovery.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More