Patents

Literature

320results about How to "Data transfer speed is fast" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electronic device and coordination device and method for implementing coordinated transmission between the same

ActiveUS20150189042A1Data transfer speed is fastConnection managementMultiple digital computer combinationsTelecommunications linkCommunication link

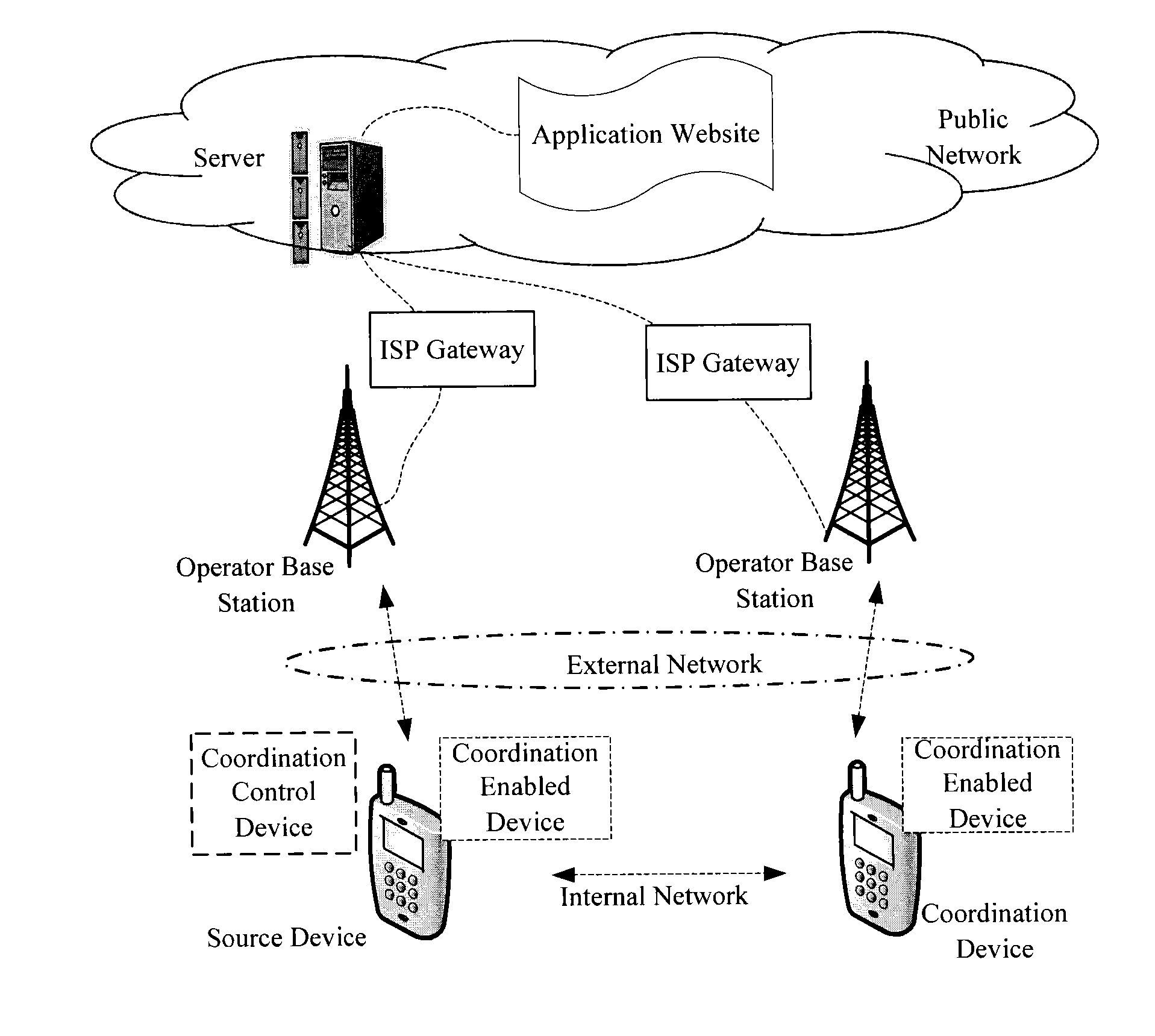

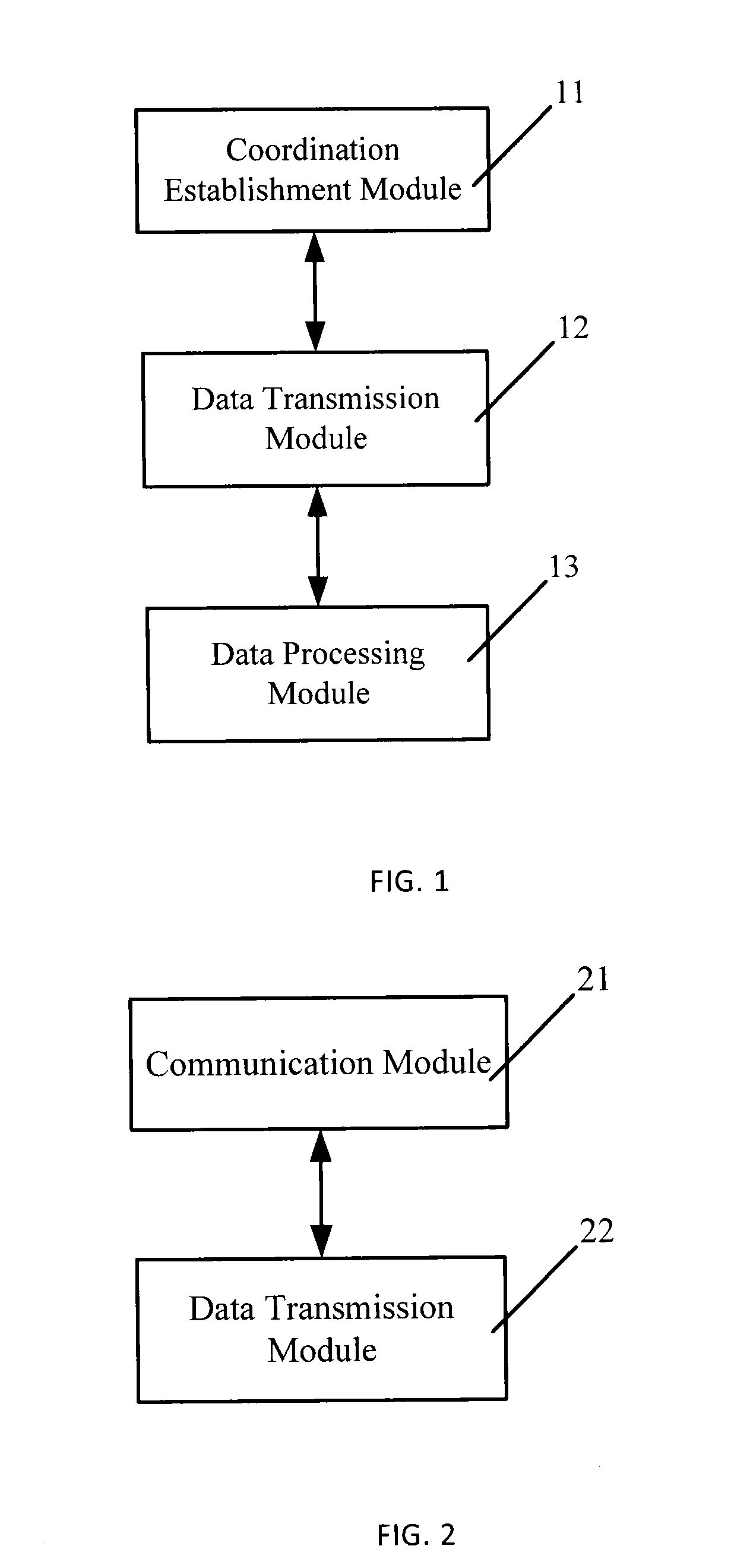

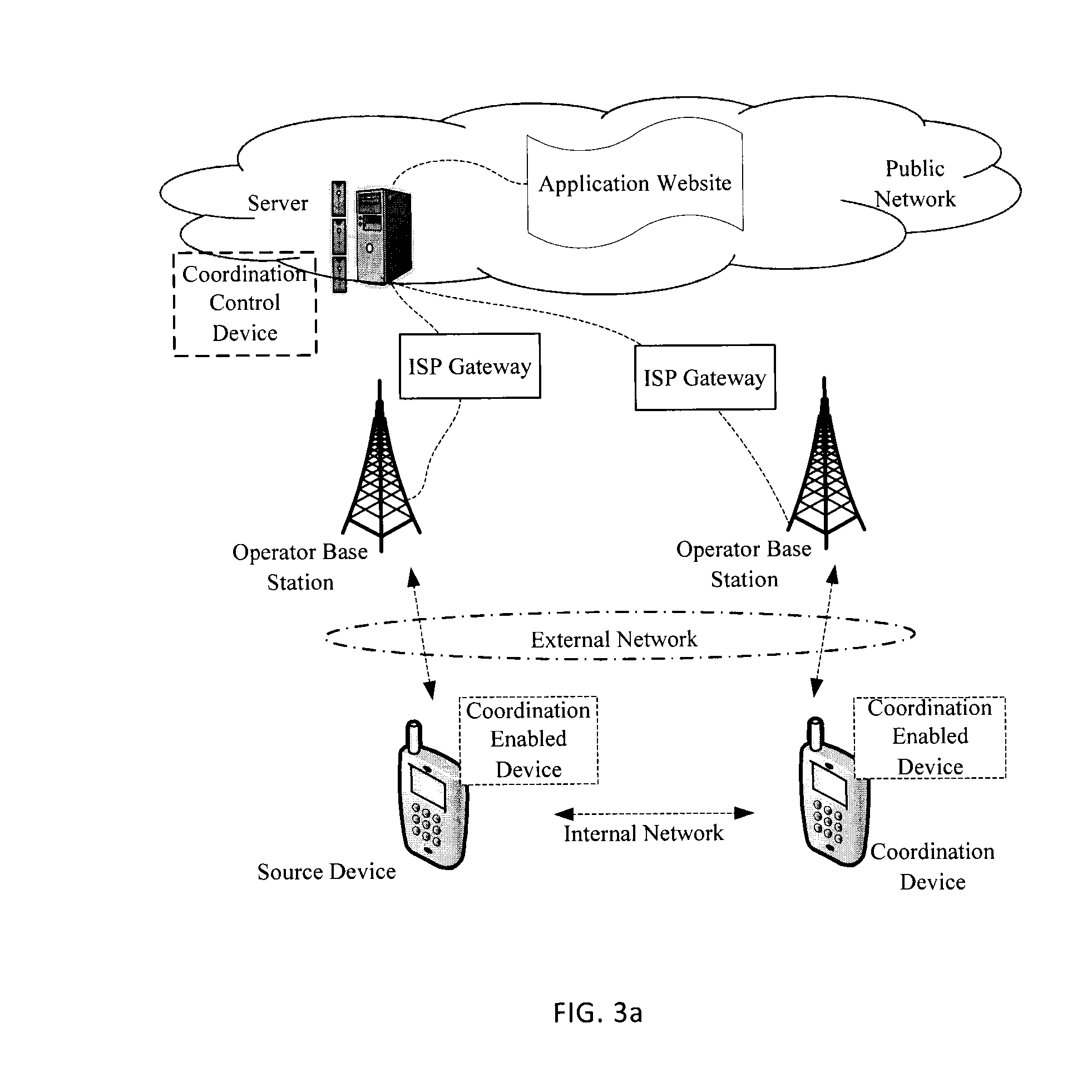

The invention discloses an electronic device and a method and device for implementing coordinated transmission between electronic devices. The electronic device comprises a coordination establishment module configured to send a coordination request signal to candidate coordination devices as well as determine coordination devices in accordance with a response of the candidate coordination device and establish coordination connection with the determined coordination device, and a data transmission module configured to transmit target data by a plurality of communication links, the plurality of communication links comprising communication links between the electronic device and the coordination device. The present invention can establish the coordination connection reasonably by initiating the coordination through the request and transmitting the data through the plurality of communication links by the coordination device, thereby effectively improving the data transmission speed through the plurality of the communication links.

Owner:SONY CORP

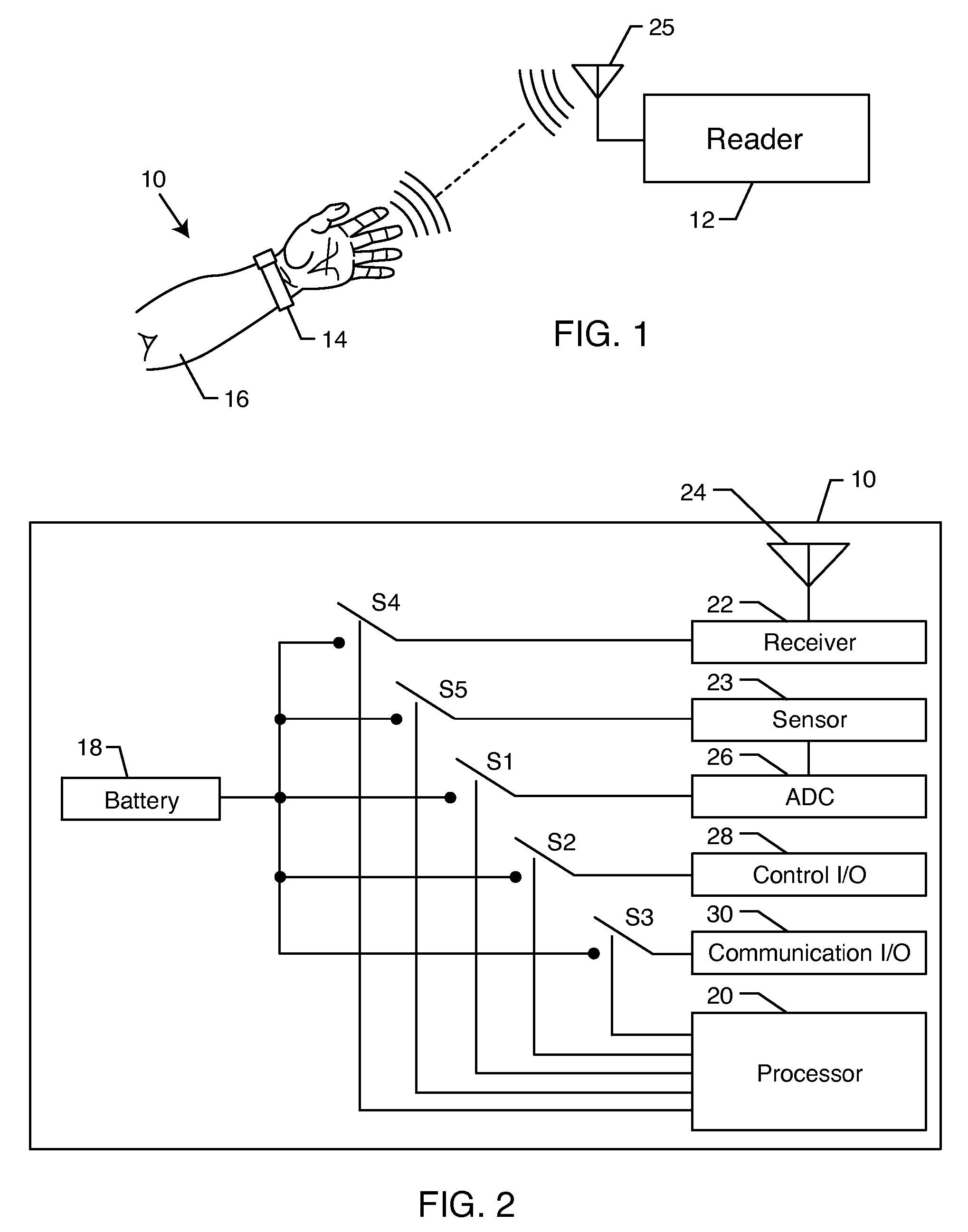

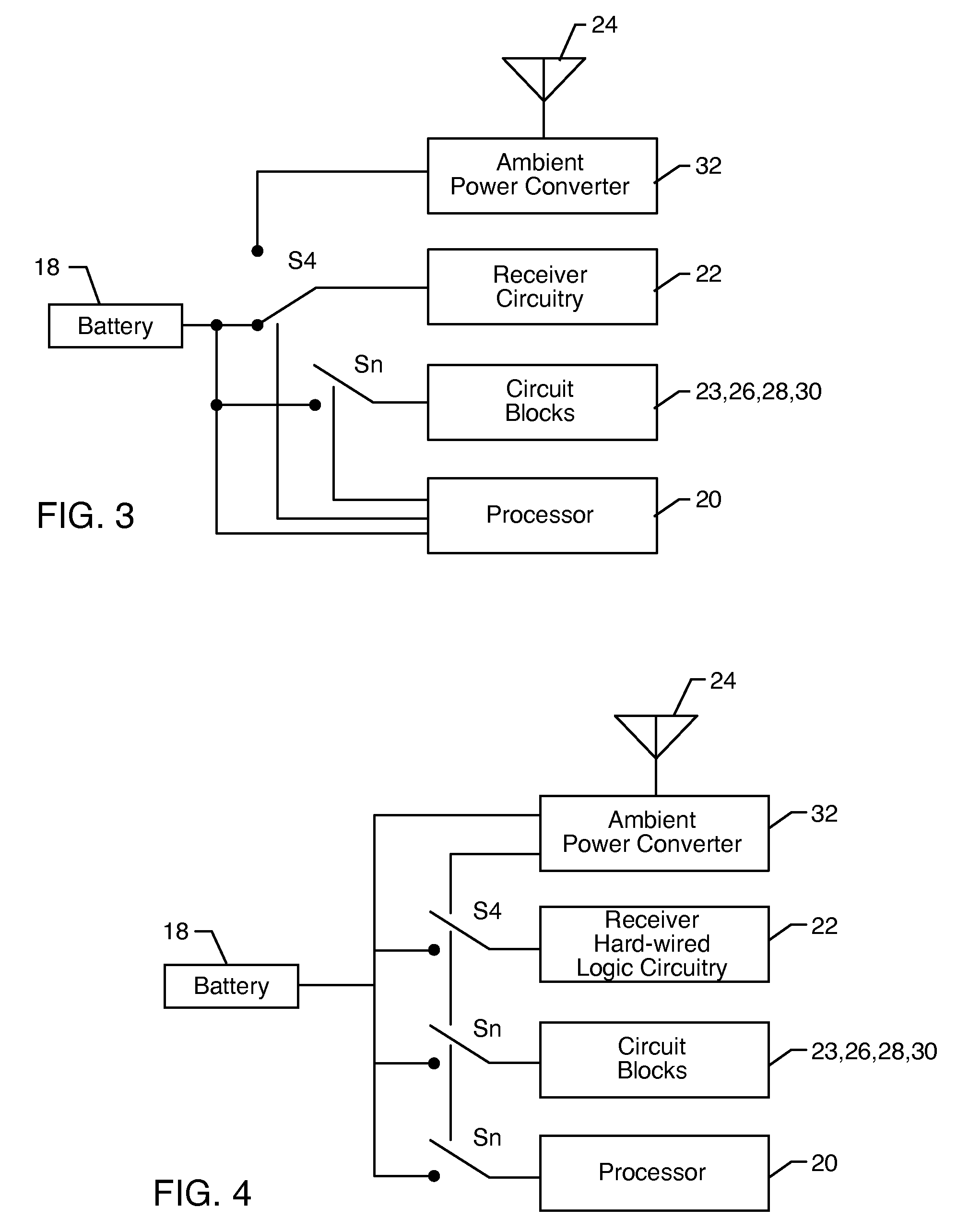

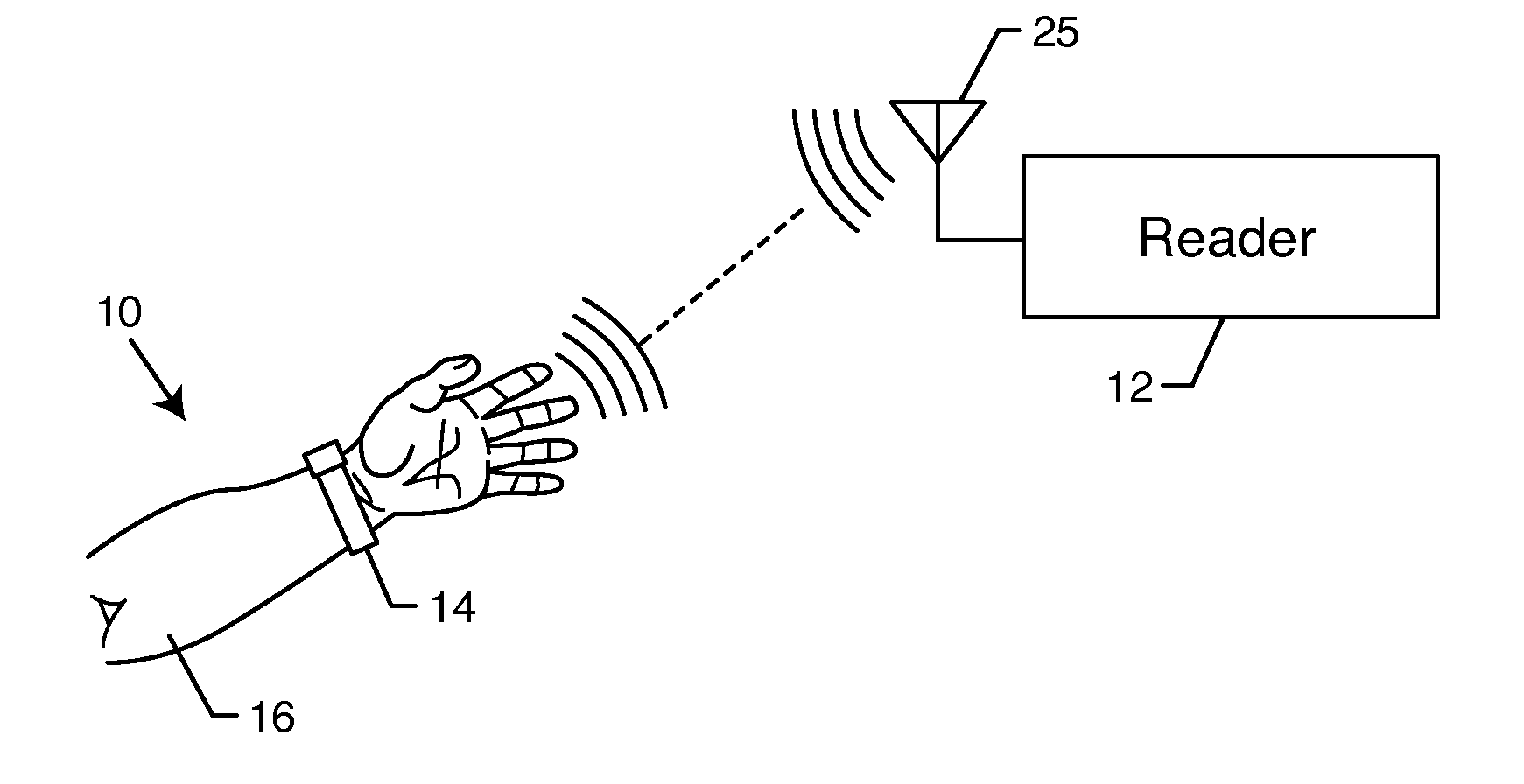

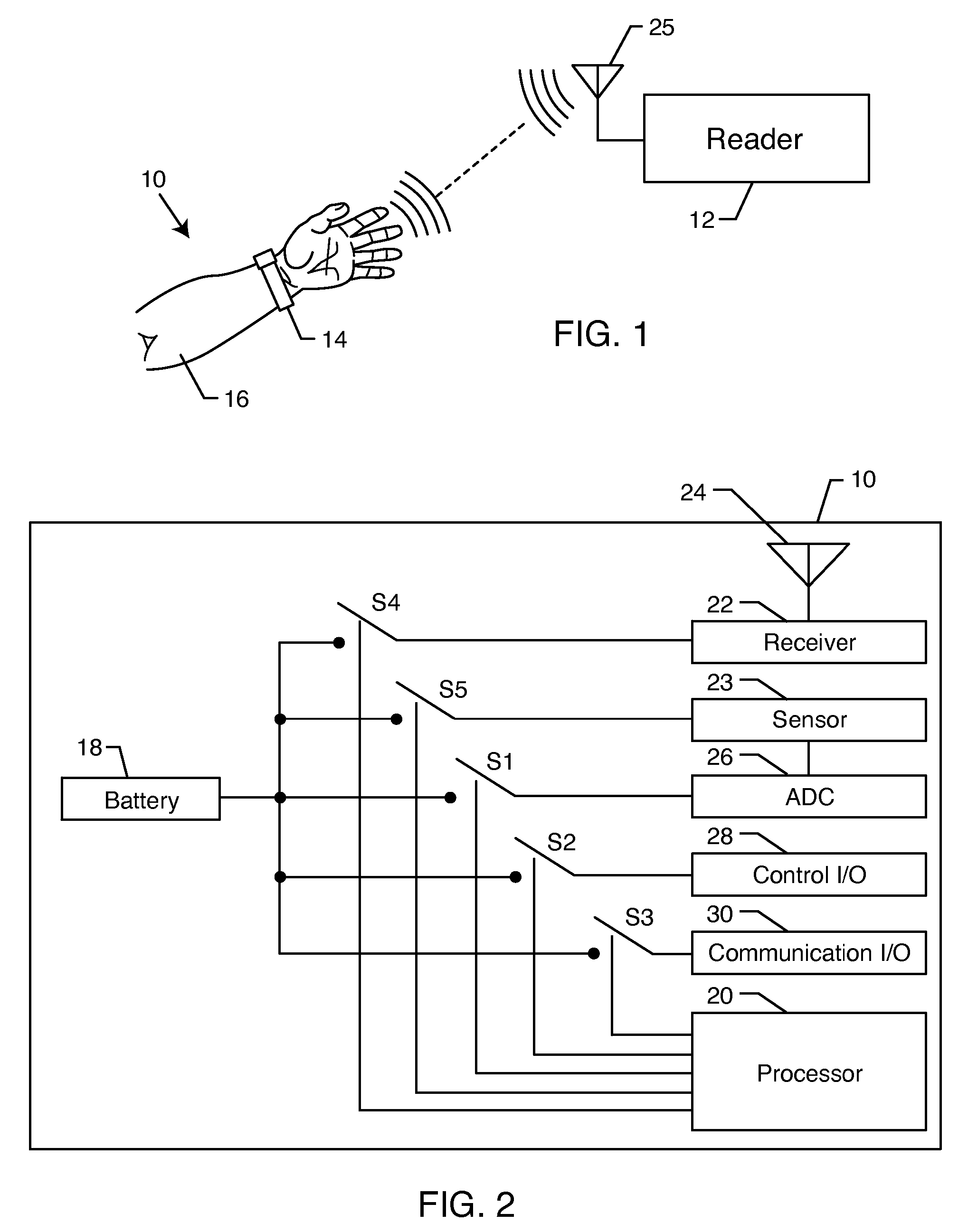

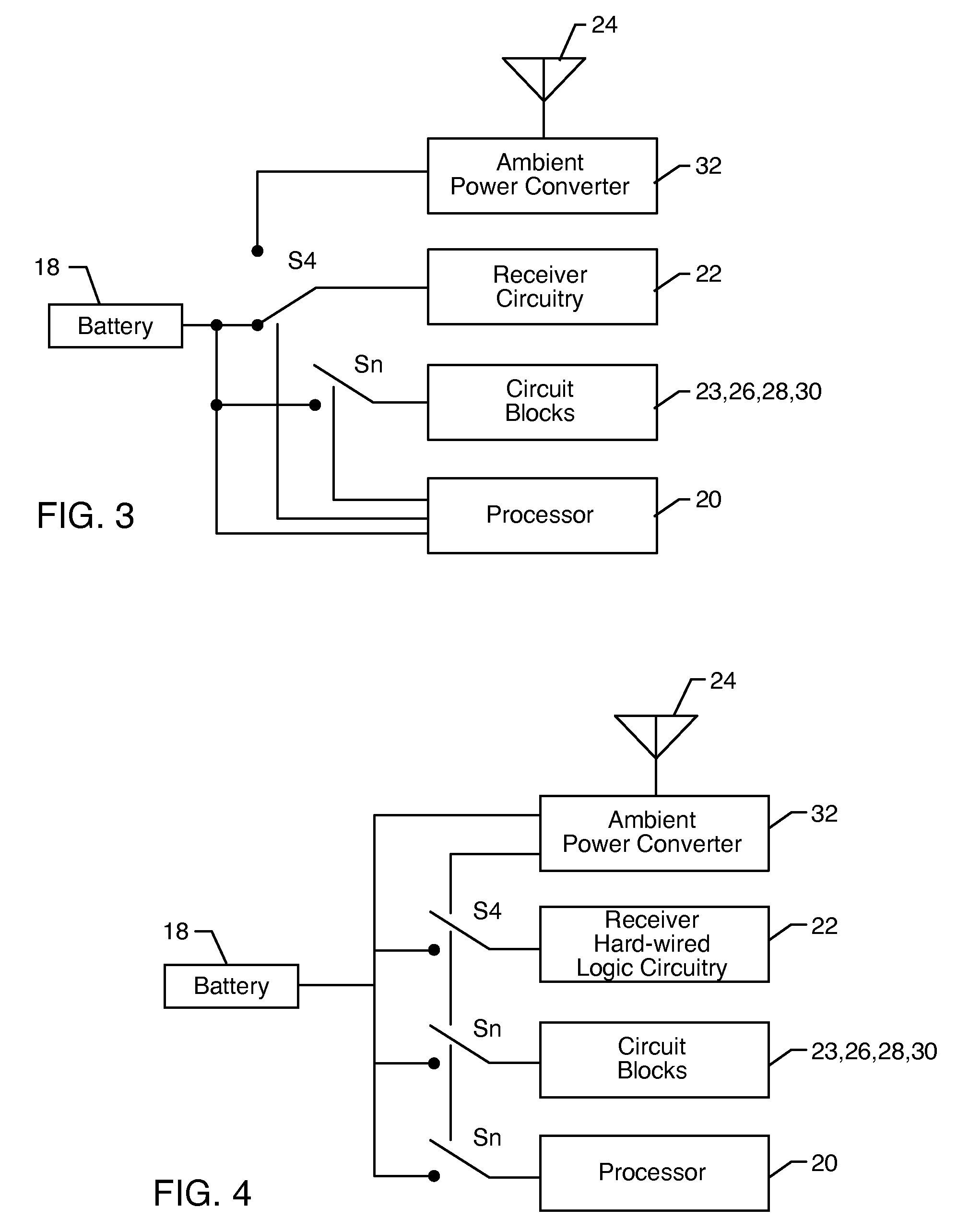

Semi-active RFID tag and related processes

ActiveUS20070018832A1Probability of successfulSuccessful transactionAntenna equipments with additional functionsSubscribers indirect connectionSemi activeDual mode

An improved radio frequency identification (RFID) tag and related reader system and process are provided, wherein the RFID tag includes an on-board battery for enhanced signal transmission range, relatively rapid signal transmission speed, and optimized completion of a data transaction between the tag and a reader. The RFID tag further includes a power management system for activating the tag battery on an as-needed basis, and for thereupon enabling limited portions of the tag circuitry as required for a specific communication protocol, thereby conserving battery power and prolonging battery service life. In one preferred form, the battery is integrated with an antenna structure of single or dual mode with respect to frequency or type. This combination battery-antenna may be designed for recharging from a source of ambient energy.

Owner:PRECISION DYNAMICS CORPORATION

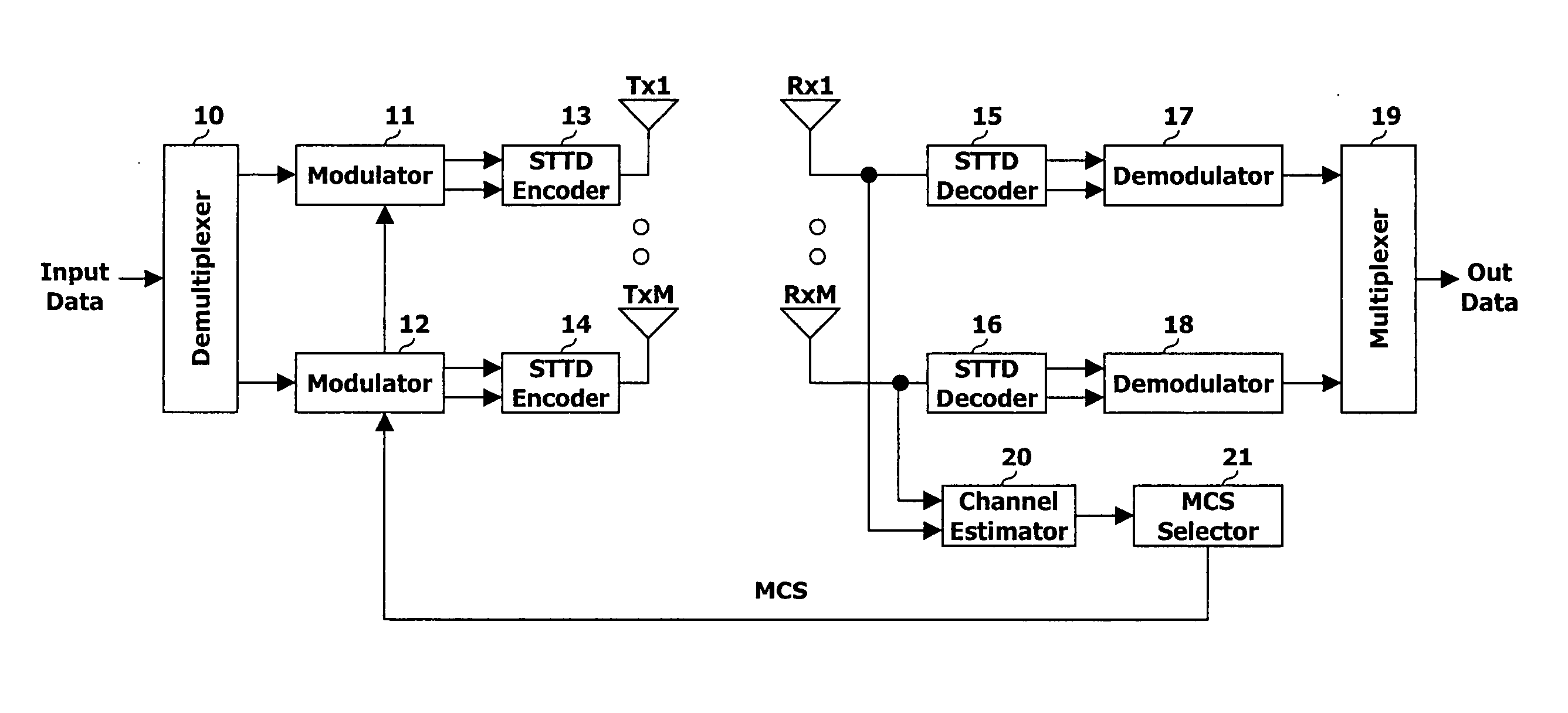

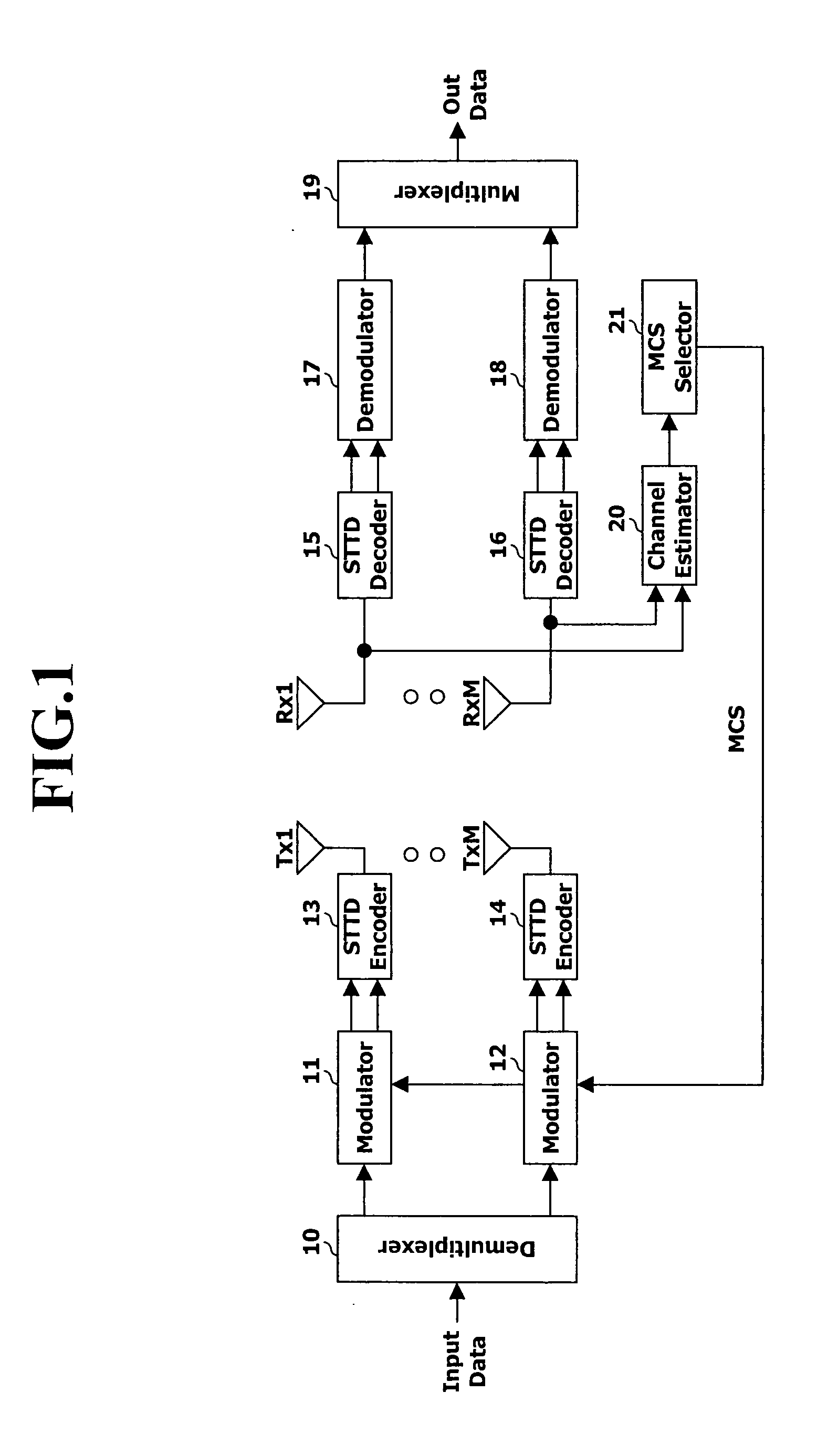

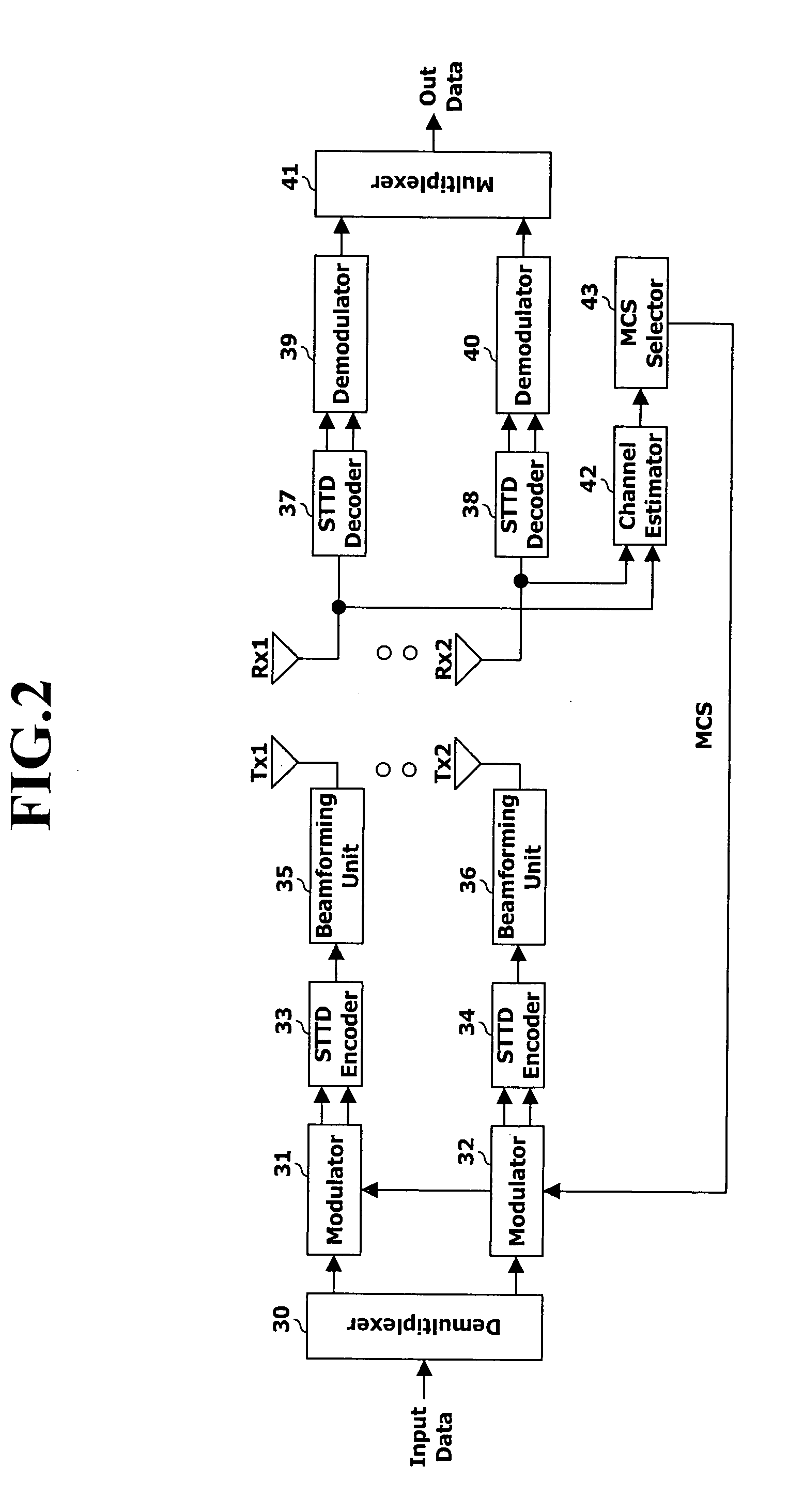

Method for transmitting/receiving signal in MIMO system

InactiveUS20050157807A1Solve the slow data transmission speedIncrease ratingsSpatial transmit diversityMultiplex communicationMultiplexingFeature vector

Disclosed is a method for transmitting a signal in a mobile communications system using a plurality of transmit / receive antennas. A method for transmitting a signal in accordance with an embodiment of the present invention comprises the steps of: a receiving end's calculating a signal to interference noise ratio (SINR) with respect to every antenna pairs configuring STTD pairs to be transmittable from a transmitting end; feedbacking information indicating an antenna pair having the greatest SINR to the transmitting end; and the transmitting end's performing a D-STTD transmission through the antenna pair determined by the feedbacked information. A method for transmitting a signal in accordance with another embodiment of the present invention comprises the steps of: a receiving end's feedbacking information of an antenna pair and / or an eigenvector (weight vector) of a channel matrix with respect to transmit antennas included in the space-time multiplexing (STTD) pair to a transmitting end; and the transmitting end's forming beam by multiplying a symbol with respect to each STTD pair by the eigenvector, and thereafter transmitting the beam through each transmit antenna (in case of using two antennas) or a transmit antenna pair (in case of using more than four antennas) determined by the information of the antenna pair.

Owner:LG ELECTRONICS INC

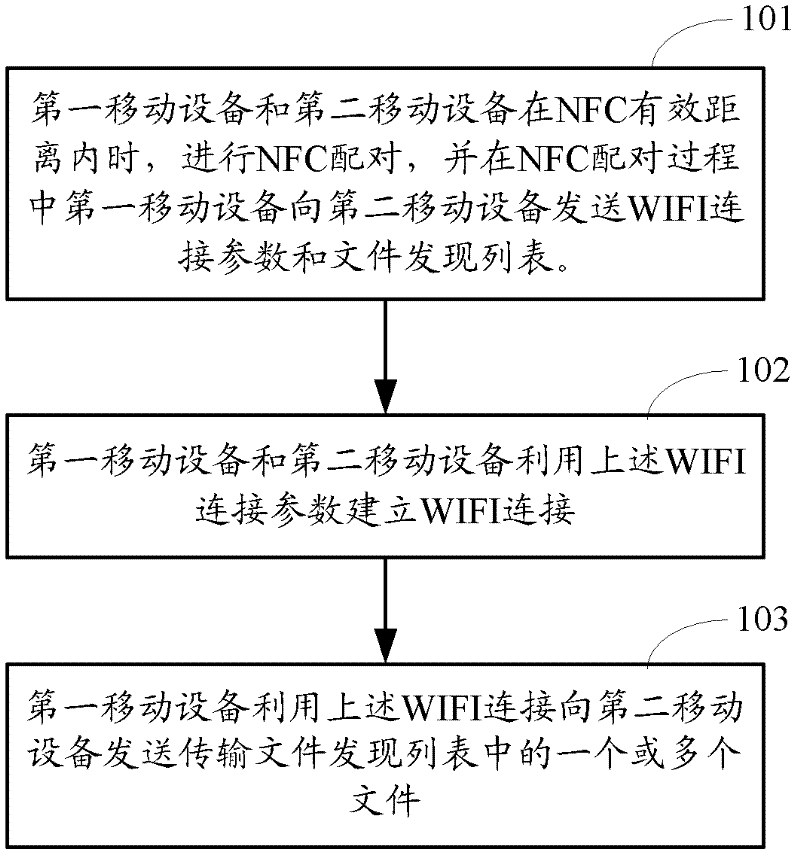

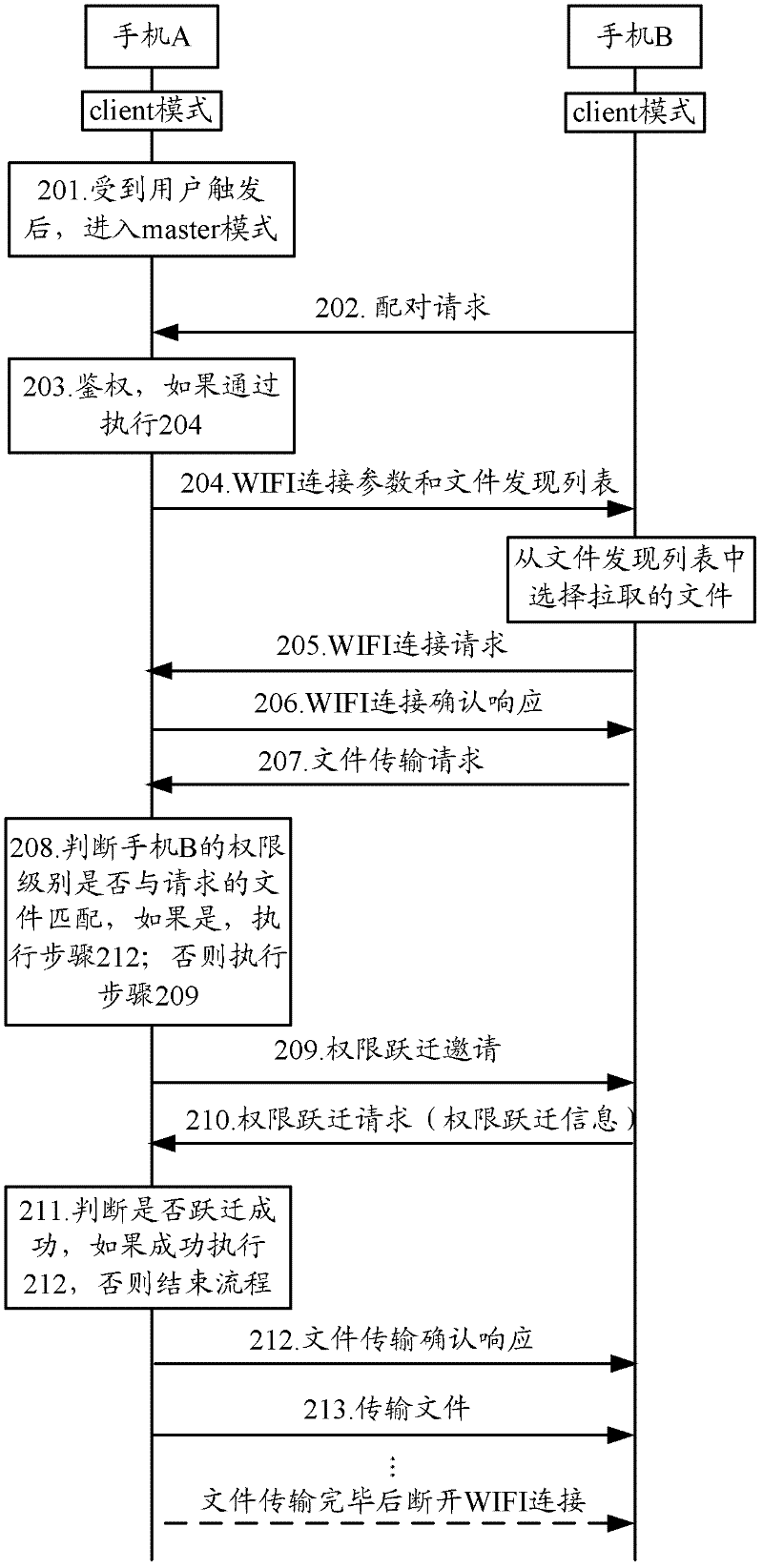

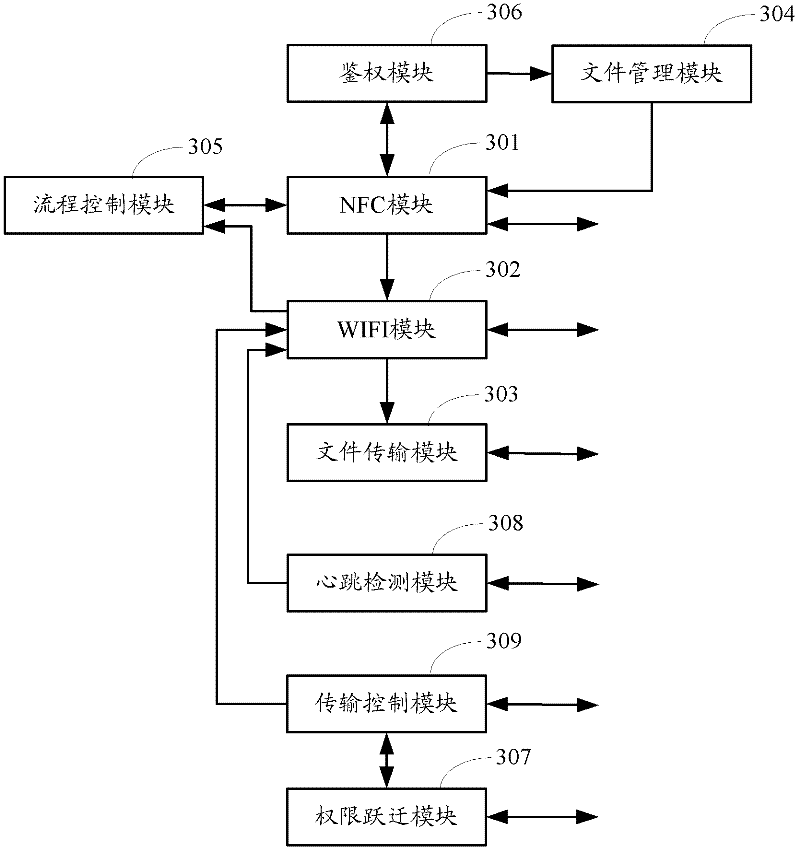

Method of point-to-point data transmission for mobile device and device

ActiveCN102315864AEasy pairingFirmly connectedNear-field transmissionNetwork topologiesBroadbandWireless broadband

The invention provides a method of point-to-point data transmission for a mobile device and a device. The method comprises the following steps that: a first mobile device and a second mobile device performs NFC pairing within the effective distance of NFC (Near-Field Communication), and the first mobile device sends wireless broadband (Wireless Fidelity(WIFI)) connection parameters and a file finding list to the second mobile device in the process of NFC pairing; and the first mobile device and the second mobile device utilize the WIFI connection parameters to build WIFI connection; and the first mobile device utilizes the WIFI connection to send one or more files in the file finding list to the second mobile device. The point-to-point data transmission for the mobile devices provided by the invention can achieve the objects of simple operation, increased effective distance, improved stability of connection and improved data transmission speed.

Owner:BAIDU ONLINE NETWORK TECH (BEIJIBG) CO LTD

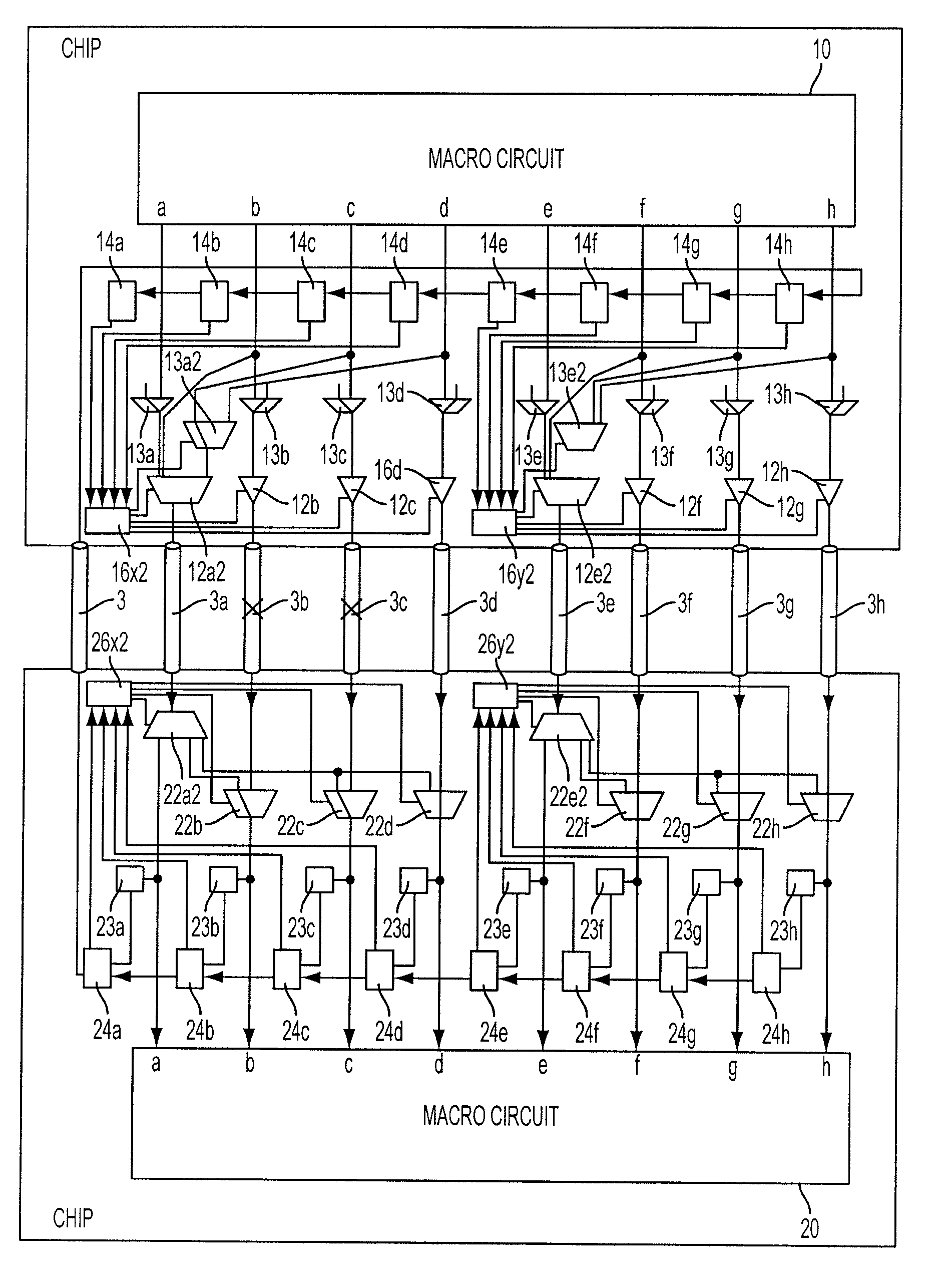

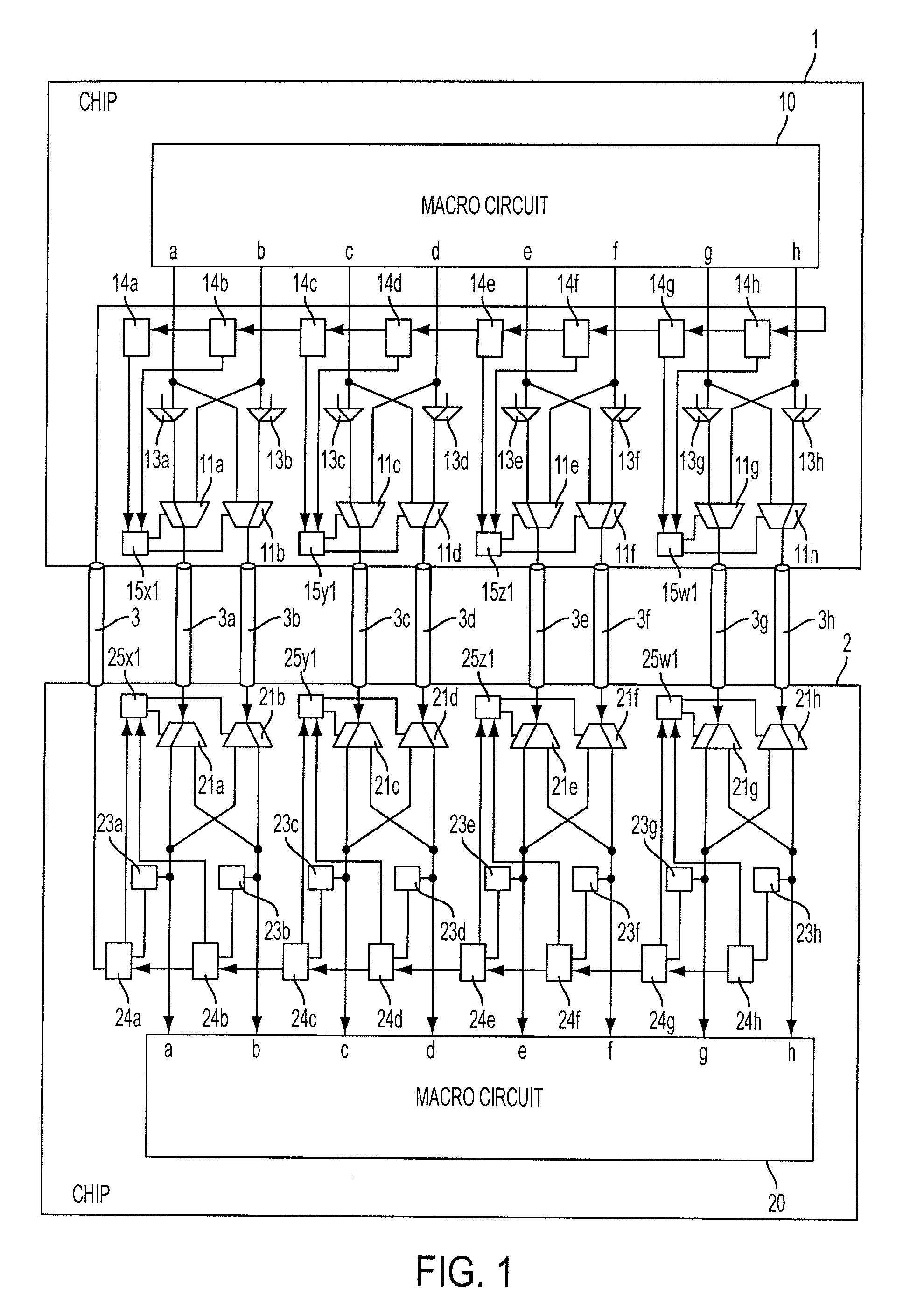

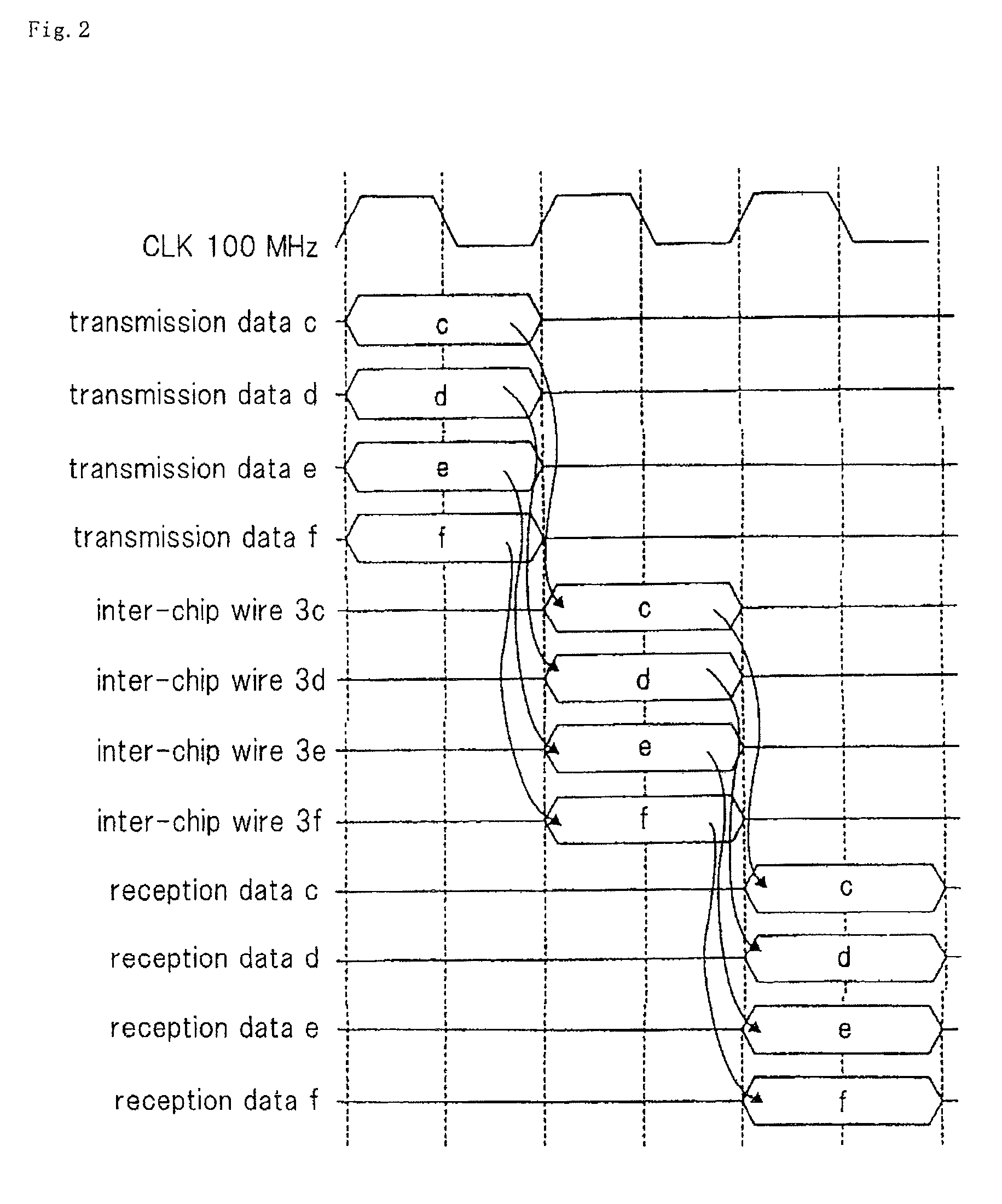

Data transfer between chips in a multi-chip semiconductor device with an increased data transfer speed

ActiveUS8149906B2Reduce the amount requiredIncrease the number ofModulated-carrier systemsSolid-state devicesData transmissionSemiconductor

A data transfer method is disclosed in a multi-chip semiconductor device which comprises a plurality of inter-chip wires. First, a test is conducted to determine whether or not each inter-chip wire is capable of normally transferring data, on circuits arranged on chips between which the inter-chip wire is connected. When an inter-chip wire incapable of normally transferring data exists, the data transfer speed of the buffer circuit that is on the chip on the transmission and that is connected to an inter-chip wire capable of normally transferring data is increased. The buffer circuit, whose data transfer speed has been increased, transfers data which would otherwise be transferred through the inter-chip wire incapable of normally transferring data, together with the data which should be transferred thereby, to the chip on the reception side chip through an inter-chip wire connected to the buffer circuit at the data transfer speed.

Owner:NEC CORP +1

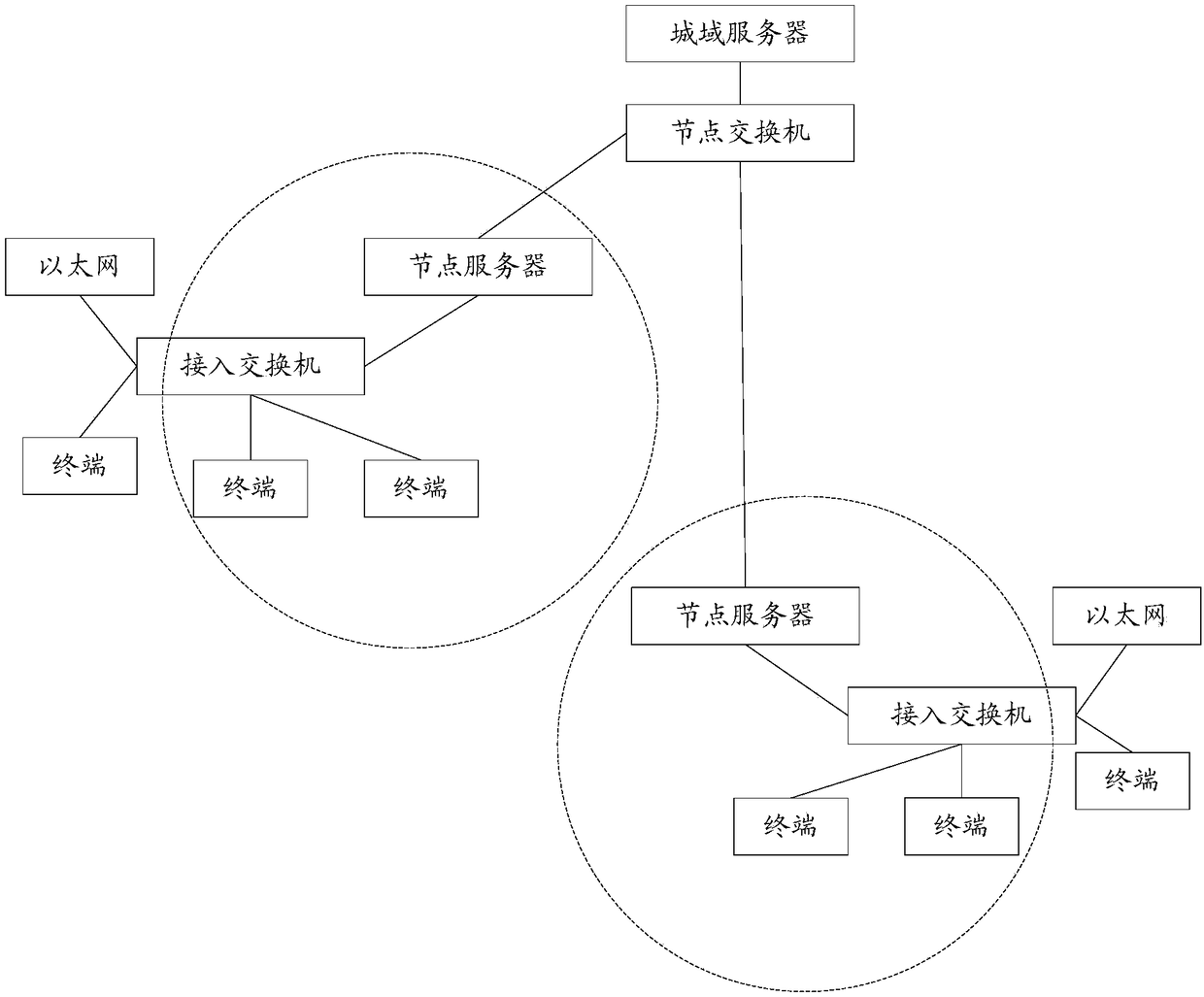

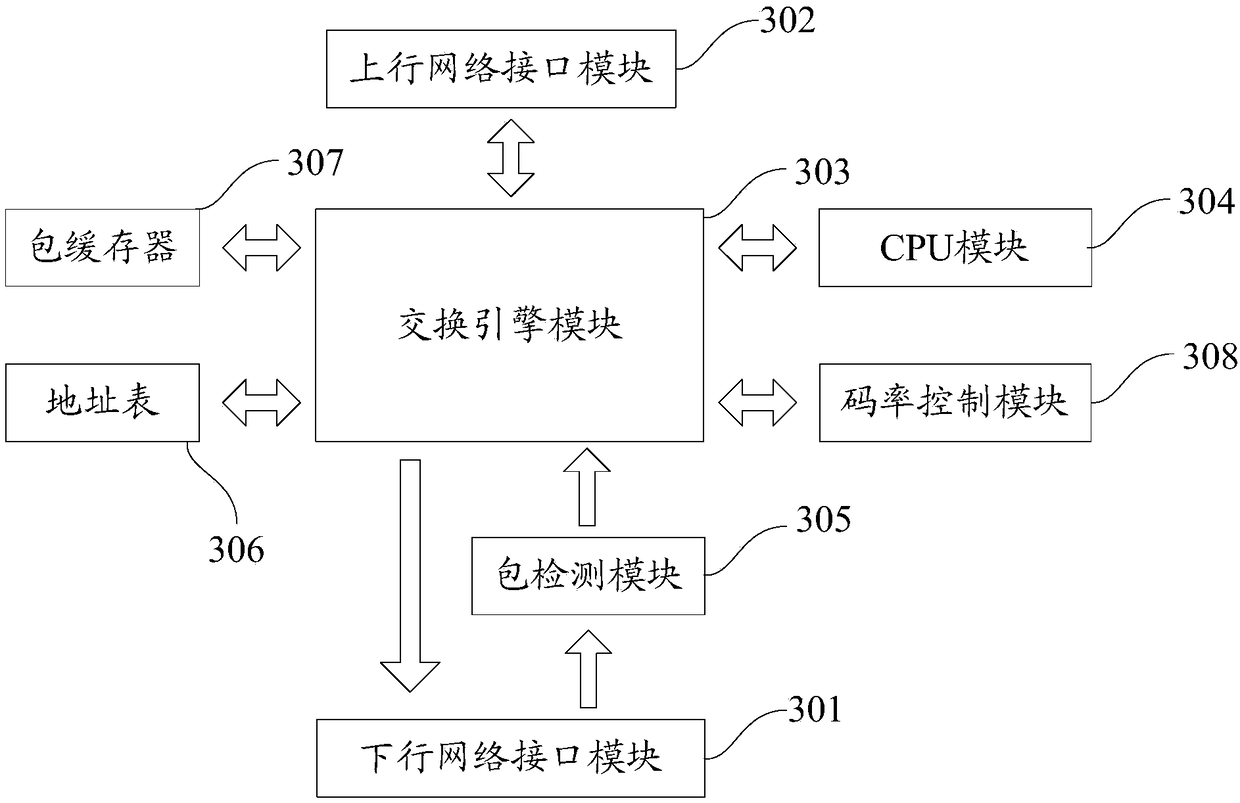

Communication method and device of internet and internet of scenes, and interaction system

InactiveCN108418778AImprove convenienceAccelerateTransmissionSelective content distributionProtocol for Carrying Authentication for Network AccessApplication software

The embodiment of the invention provides an interaction system applied to an internet of scenes. The system comprises first terminal equipment, a streaming media server, an internet of scenes server and second terminal equipment; the second terminal equipment comprises an internet of scenes terminal, the first terminal equipment is an internet terminal, a specified application is installed in thefirst terminal equipment, and the specified application program provides an input interface for user information input; the first terminal equipment communicates with the streaming media server through an internet protocol; the streaming media server is used for converting the internet protocol into the internet of scenes protocol and communicating with the internet of scenes server through the internet of scenes protocol; the internet of scenes server is communicated with the second terminal equipment through the internet of scenes protocol. Through the interaction system provided by the embodiment of the invention, the convenience of communicating the internet and the internet of scenes can be improved, and the transmission speed of the video and other multimedia data is accelerated.

Owner:VISIONVERA INFORMATION TECH CO LTD

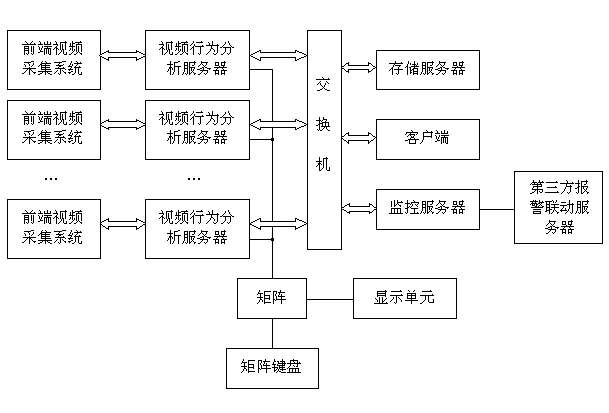

Wisdom skynet video behavior analyzing system

InactiveCN103297751AEffective trackingSave burdenClosed circuit television systemsBurglar alarmVisual technologyDistributed structure

The invention discloses a wisdom skynet video behavior analyzing system which comprises a plurality of front end video collecting systems and a central monitoring system. The central monitoring system comprises a plurality of video behavior analyzing servers, a storage server, a monitoring server and a client side, wherein each video behavior analyzing server receives video information of one front end video collecting system respectively, automatically analyzes all kinds of exception behaviors by the adoption of an advanced image analyzing processing technology, a computer vision technology, a computer network technology and an artificial intelligent technology and generates alarming signals, the video behavior analyzing servers are respectively connected with the storage server, the monitoring sever and the client end through an interchanger, and the monitoring server is further connected with a third party alarm linkage server. The wisdom skynet video behavior analyzing system is provided with multiple detection modules, users can selectively install certain modules according to actual needs, installation is convenient, the operation is simple, and video behavior analysis can be carried out automatically. A distribution type structure is adopted by the wisdom skynet video behavior analyzing system, and data transmitting and processing speed can be improved.

Owner:四川天翼网络股份有限公司

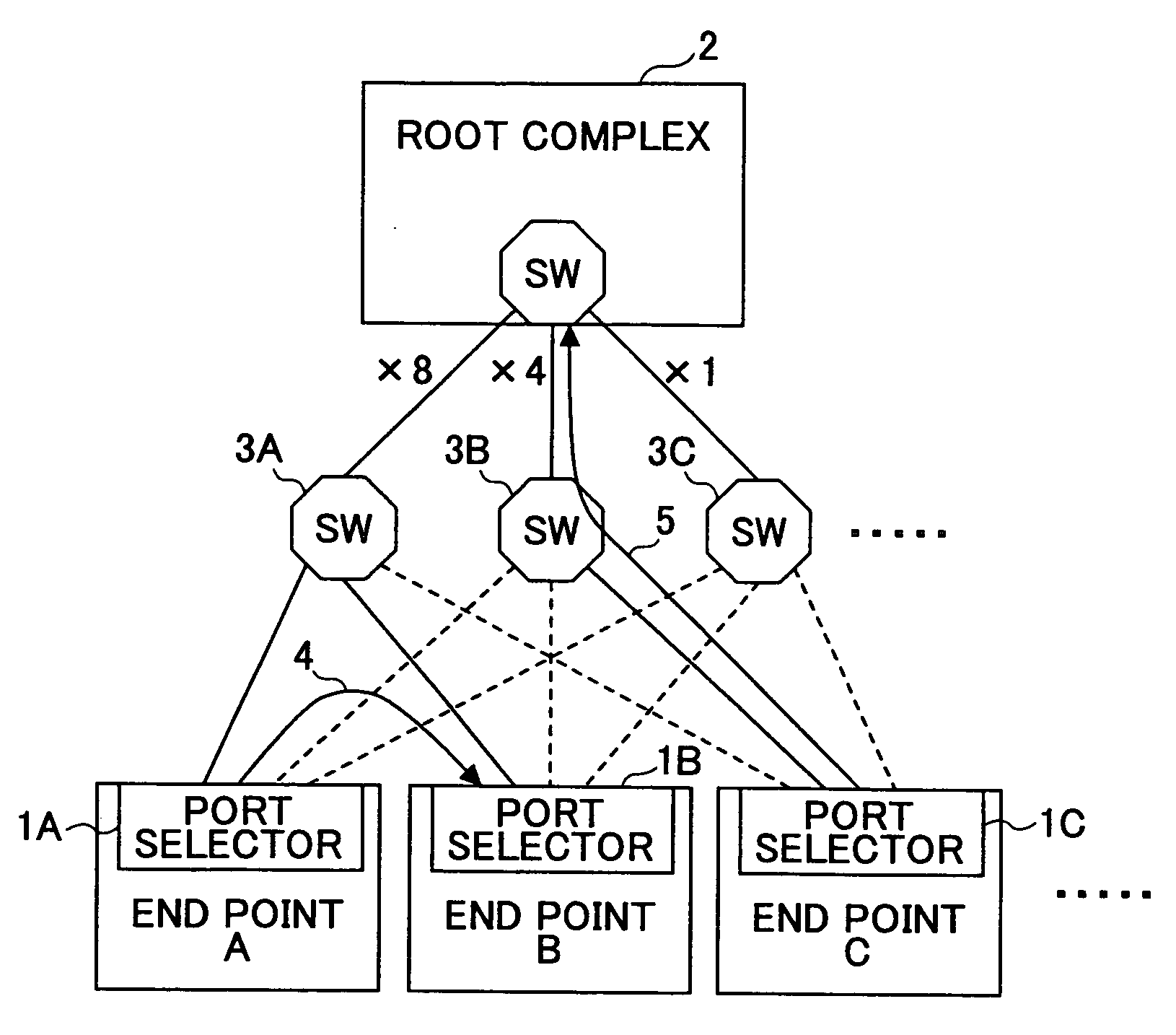

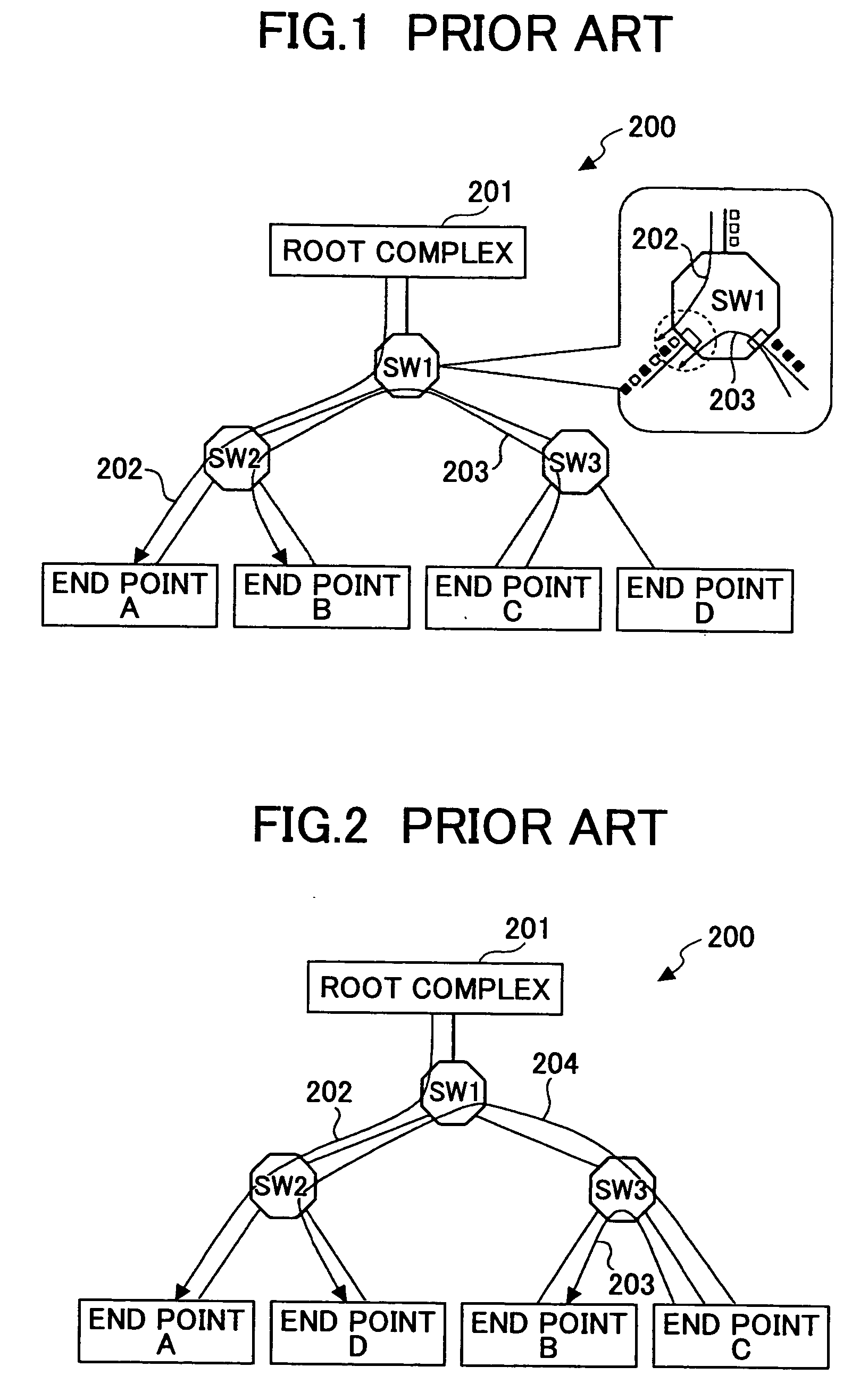

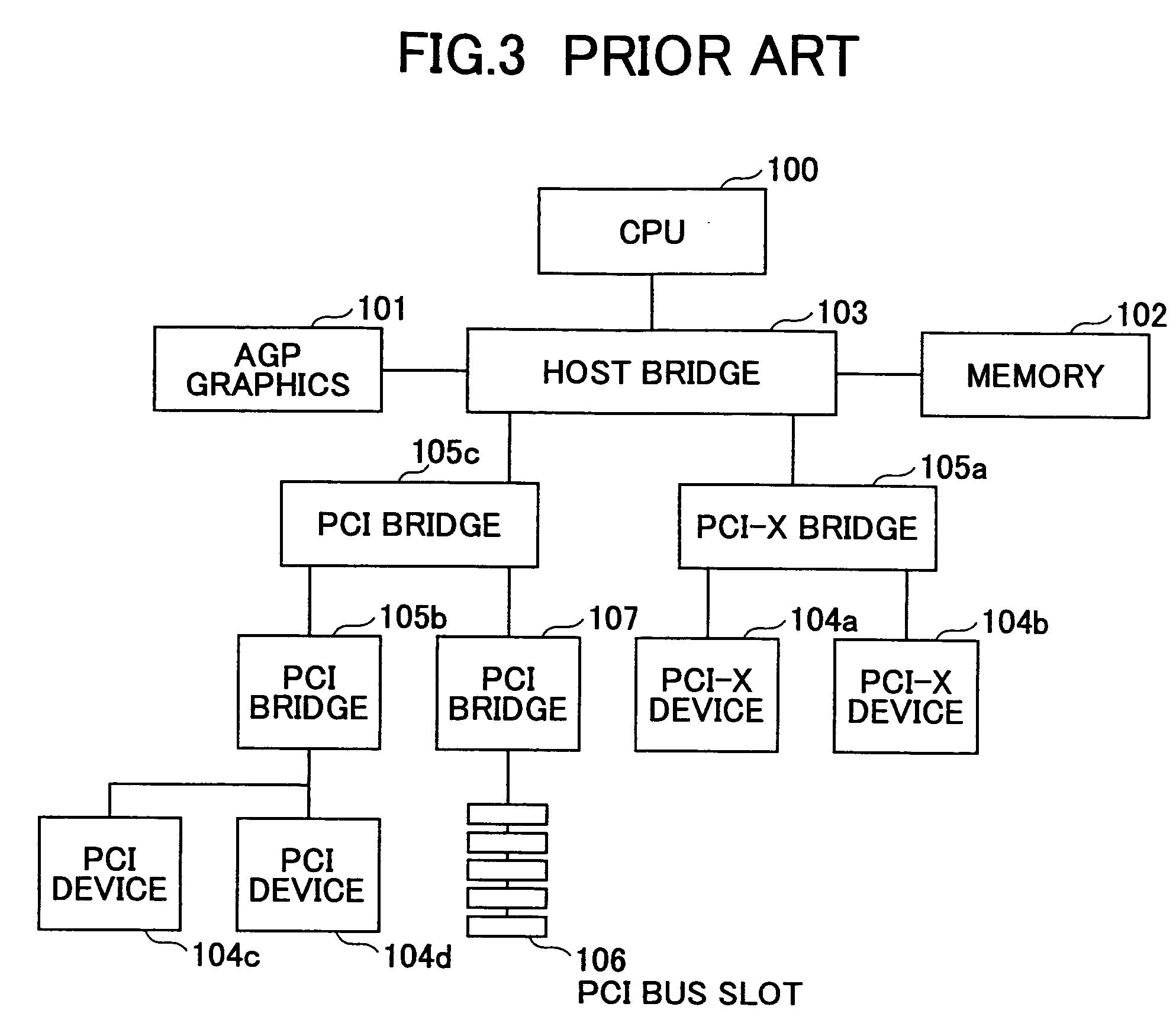

Data transfer system, data transfer method, and image apparatus system

InactiveUS20060114918A1Improve data transfer efficiencyAvoid contentionData switching by path configurationTransfer systemOperation mode

A data transfer system using a high-speed serial interface system that forms a tree structure in which point-to-point communication channels are established for data sending and data receiving independently is provided. The data transfer system includes plural end points each having plural upper ports each of which is connected to a switch of an upper side, wherein each end point includes a port selecting part for selecting a port to be used according to an operation mode of the data transfer system so as to dynamically change the tree structure.

Owner:RICOH KK

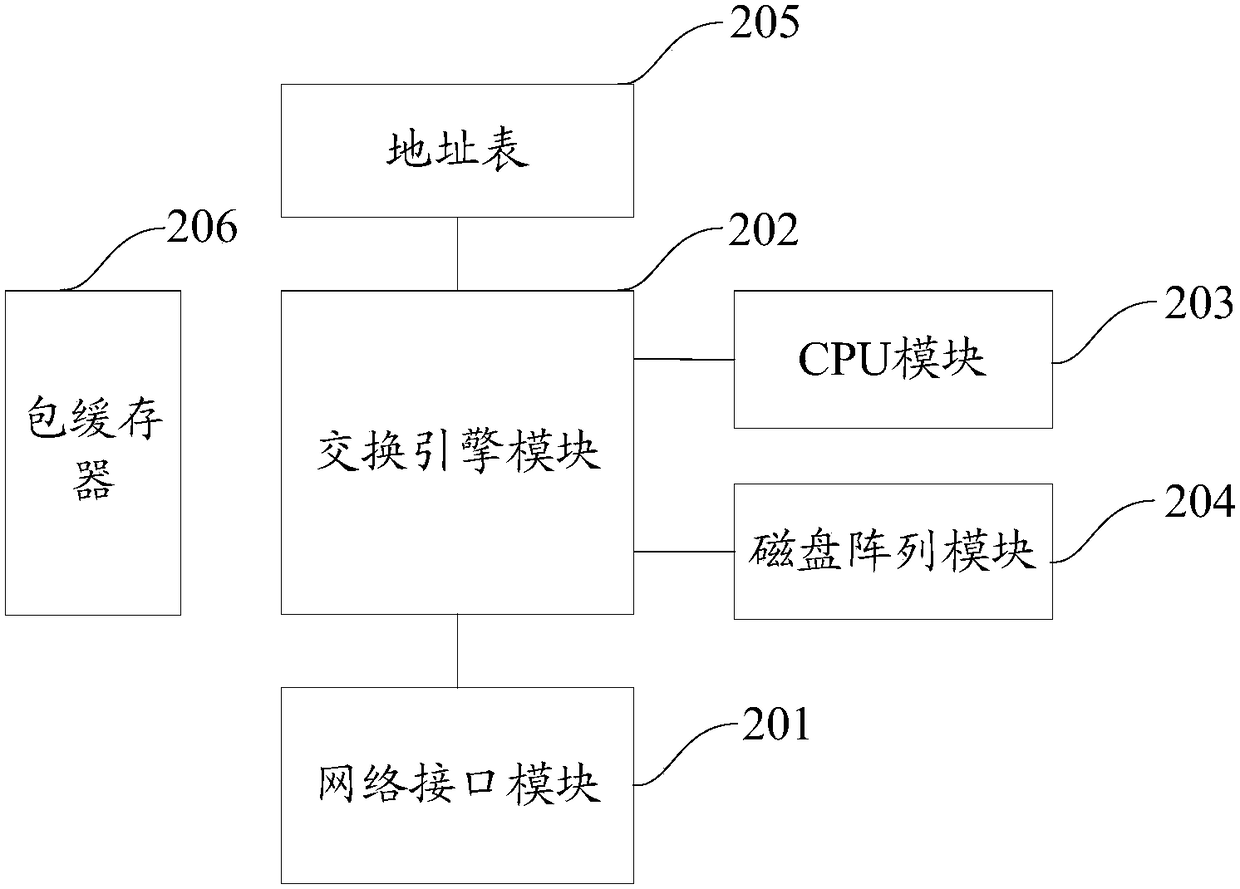

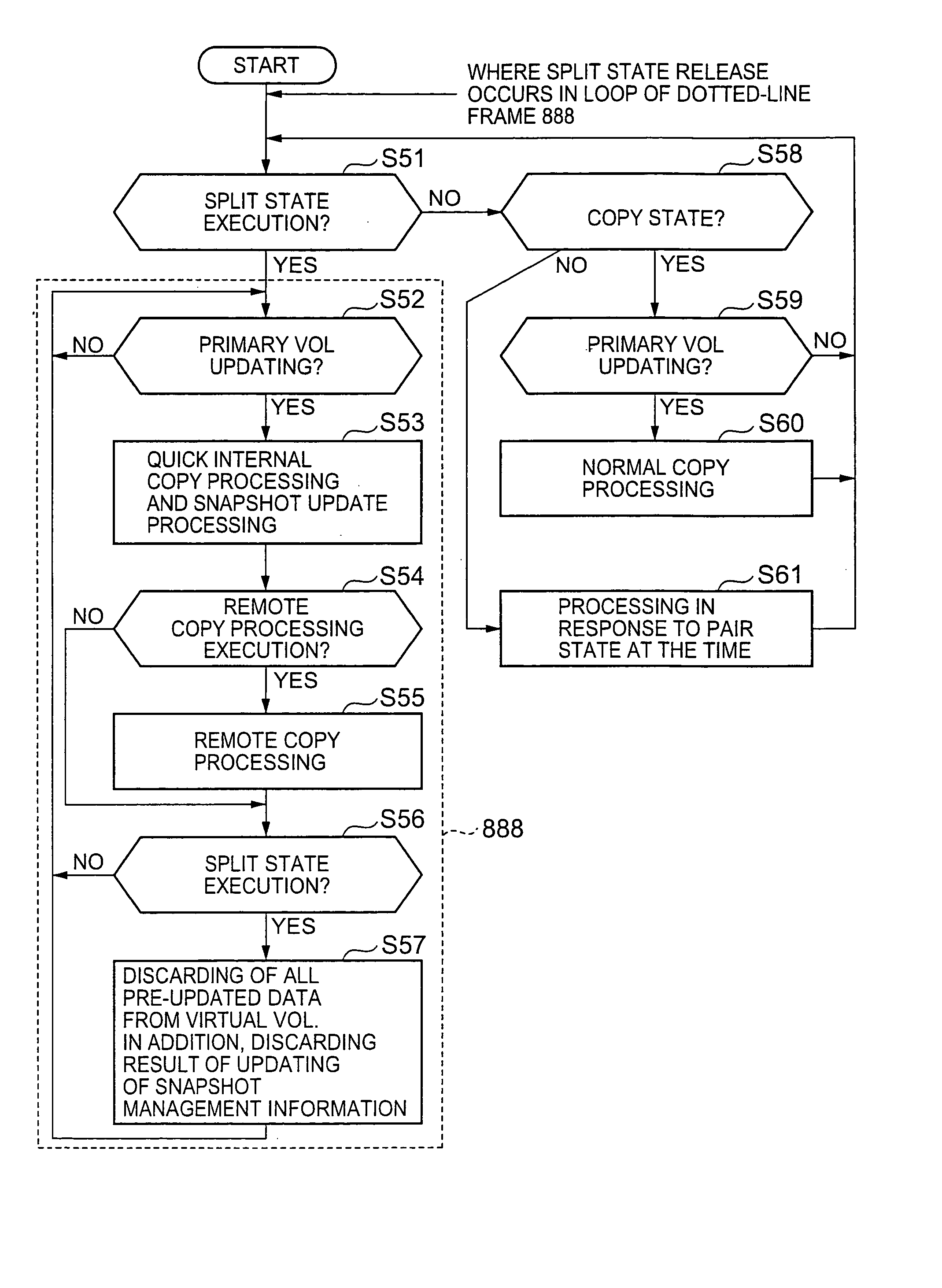

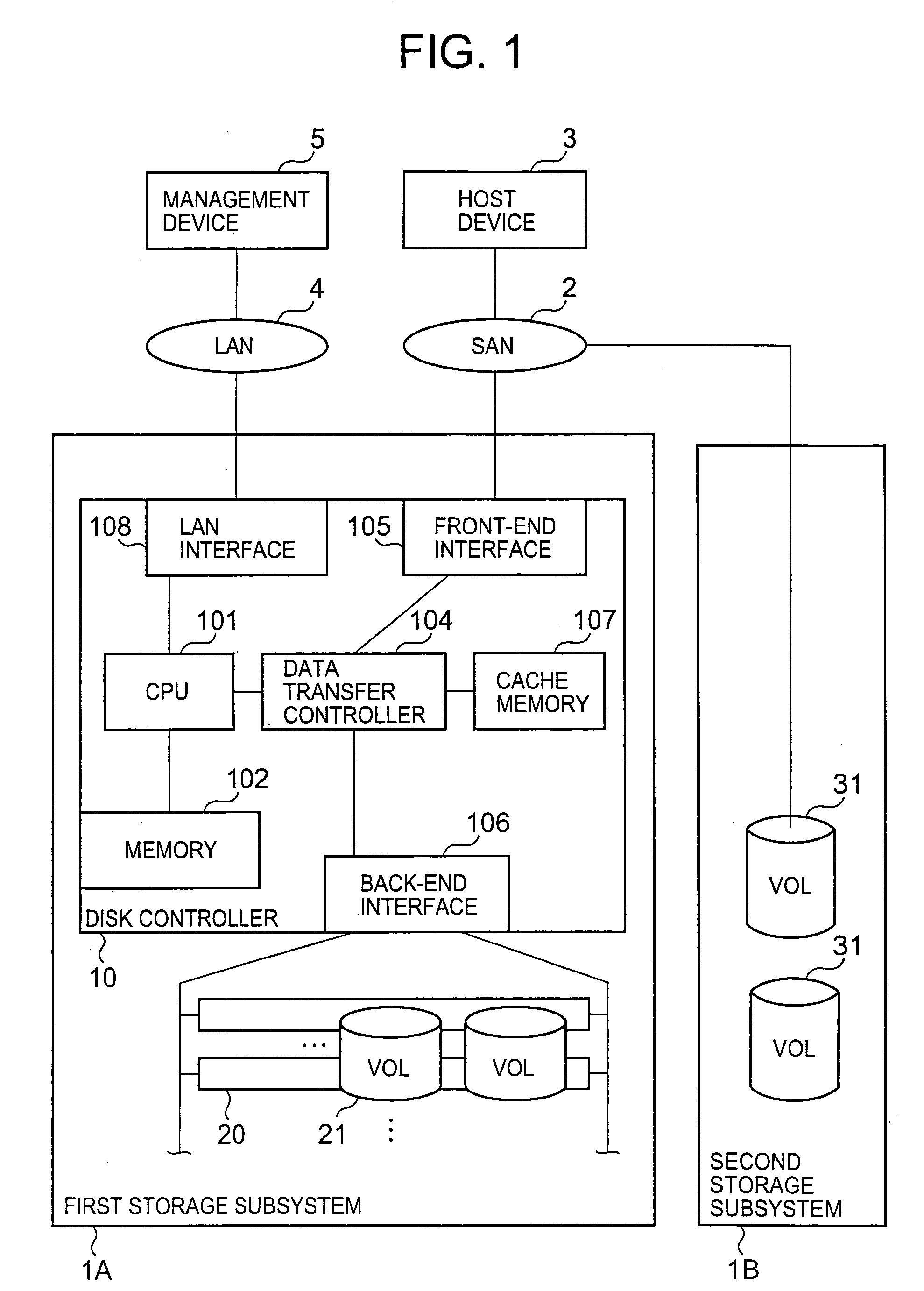

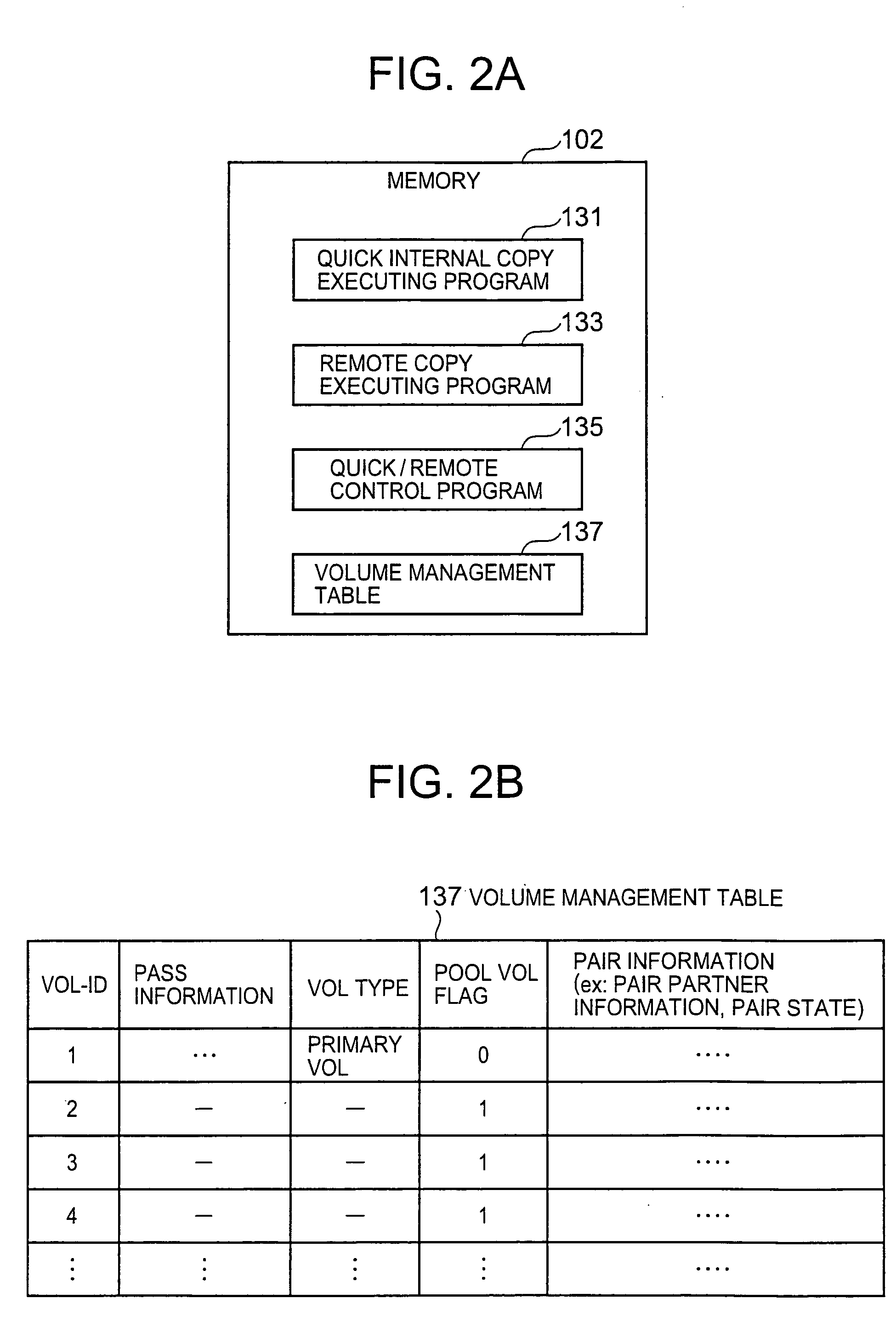

Storage subsystem and storage system

InactiveUS20050210210A1Promote disseminationShorten the timeMemory loss protectionError detection/correctionData memoryData store

The first storage subsystem, when new data is written in a first memory device beyond a certain timing, writes pre-updated data prior to update by said new data into a pre-updated data memory region and, in addition, updates snapshot management information that expresses a snapshot of a data group within the first memory device to information that expresses the snapshot at the certain timing and, at a later timing than the certain timing, judges, on the basis of the snapshot management information, in which of either the pre-updated data memory region or the first memory device the data constituting the data group at a certain timing exists, acquires data from the one in which the data exists and writes it into the second memory device of the second storage subsystem, and generates the certain timing repeatedly.

Owner:HITACHI LTD

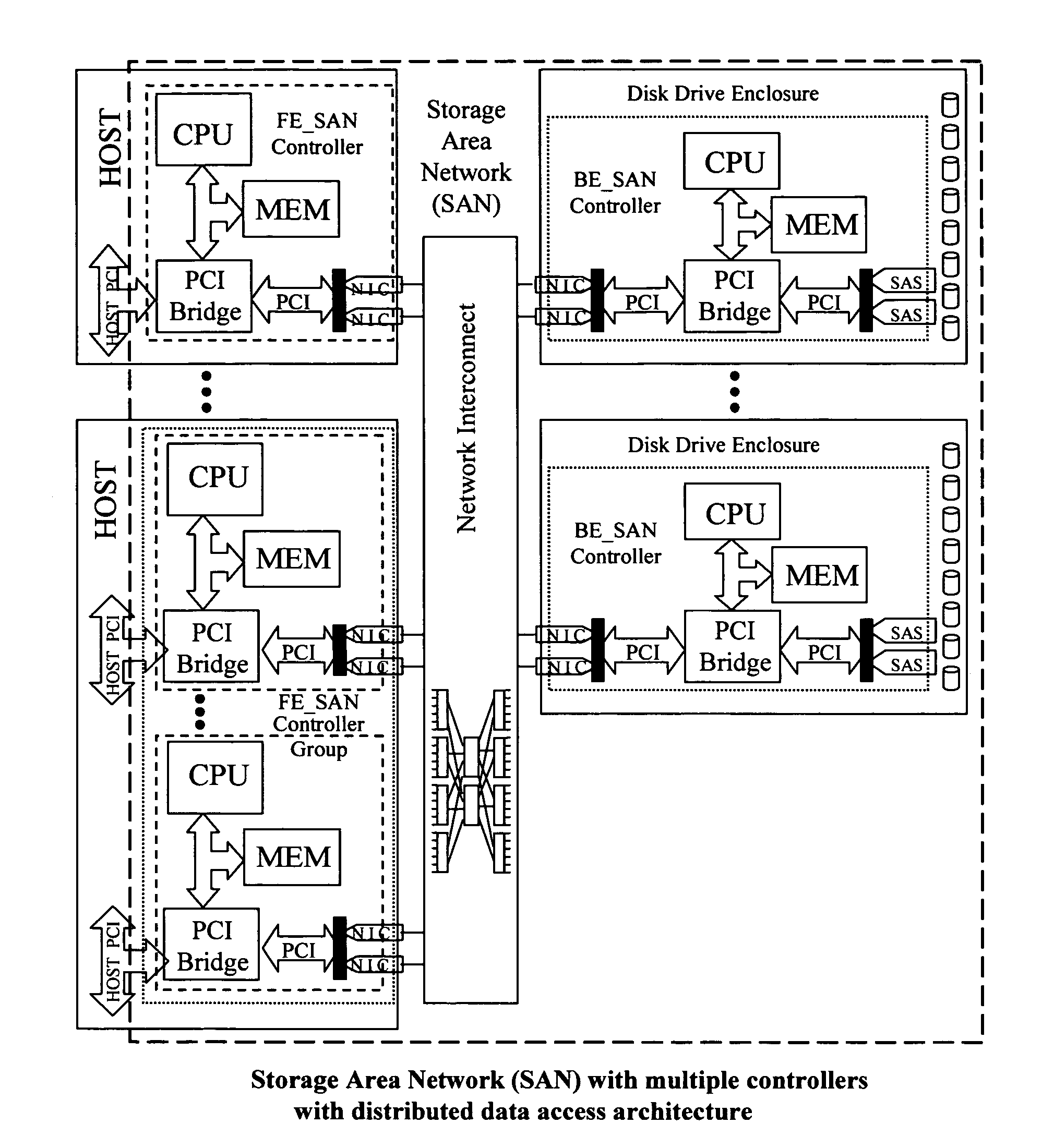

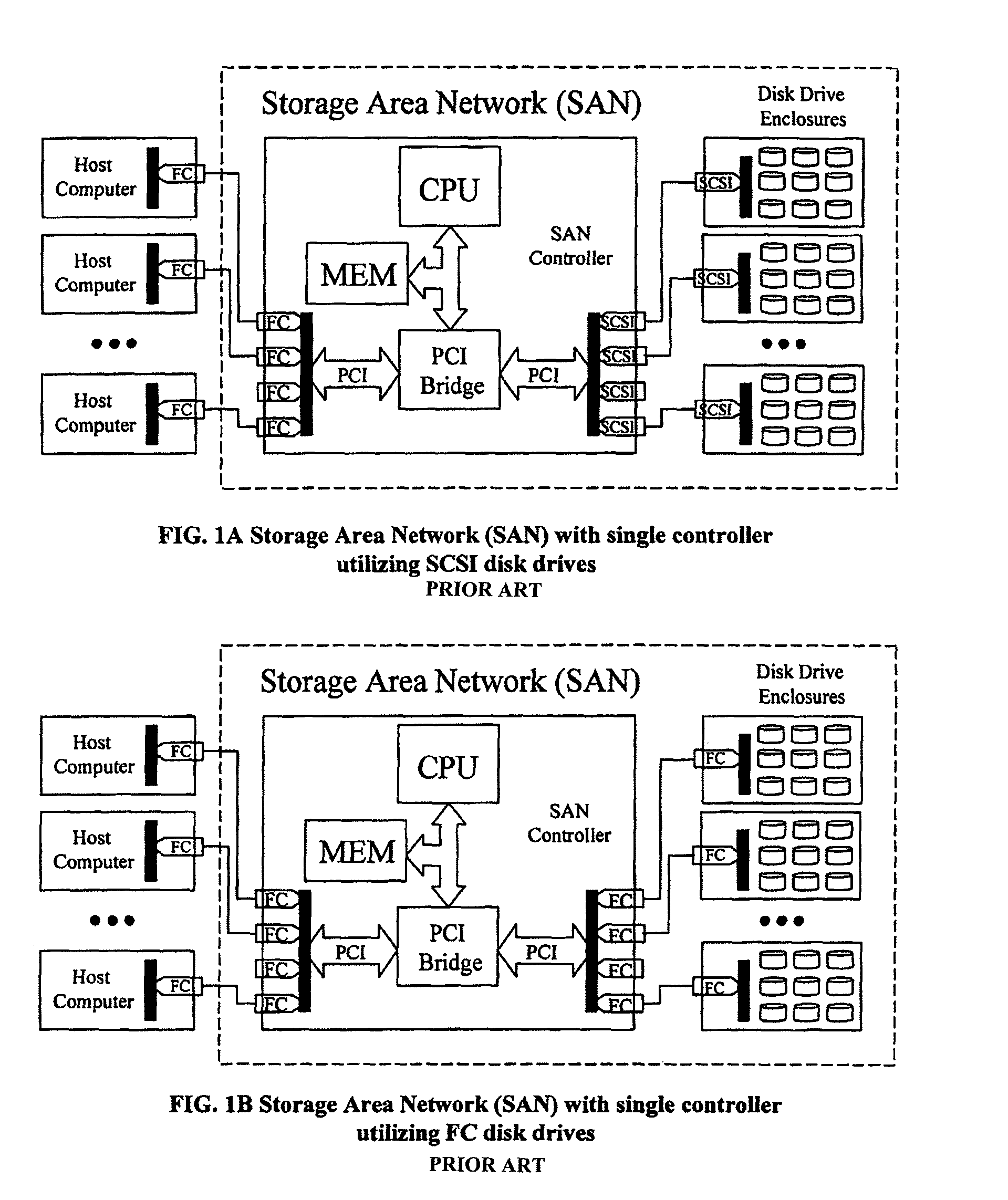

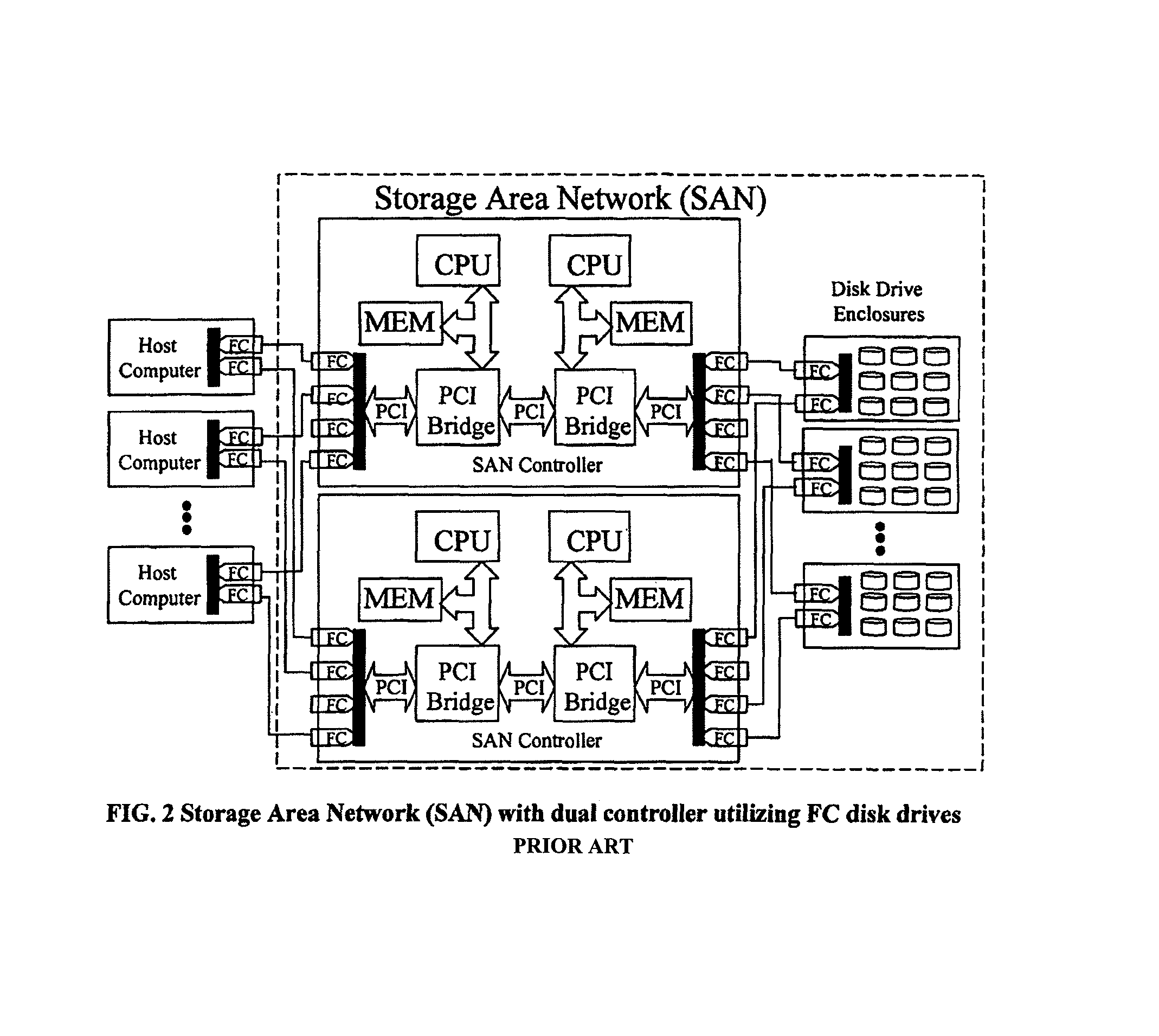

Scalable data storage architecture and methods of eliminating I/O traffic bottlenecks

ActiveUS8347010B1Increase storage capacityImprove system performanceMemory systemsInput/output processes for data processingExtensibilityFiber

An apparatus and method implemented in hardware and embedded software that improves performance, scalability, reliability, and affordability of Storage Area Network (SAN) systems or subsystems. The apparatus contains host computers (application servers, file servers, computer cluster systems, or desktop workstations), SAN controllers connected via a bus or network interconnect, disk drive enclosures with controllers connected via network interconnect, and physical drive pool or cluster of other data storage devices that share I / O traffic, providing distributed high performance centrally managed storage solution. This approach eliminates I / O bottlenecks and improves scalability and performance over the existing SAN architectures. Although this architecture is network interconnect (transport) neutral, additional improvements and cost savings could be made by utilizing existing, of the shelf, low latency and high speed hardware such as Advanced Switching (AS) or Myrinet networks as a transport for data, Small Computer System Interface (SCSI) and other commands and messages. Using AS or Myrinet network as a replacement for Fiber Channel (FC) would significantly reduce the cost of such SAN systems and at the same time boost performance (higher data transfer rates and lower latencies). This invention is about defining hardware and software architectural solution that is specifically designed to eliminate I / O traffic bottlenecks, improve scalability, and reduce the overall cost of today's SAN systems or subsystems. This innovative solution, in addition to it's performance superiority compared to the existing solutions, should also provide 100% compatibility with the all existing Operating Systems (OS), File Systems (FS), and existing applications.

Owner:RADOVANOVIC BRANISLAV

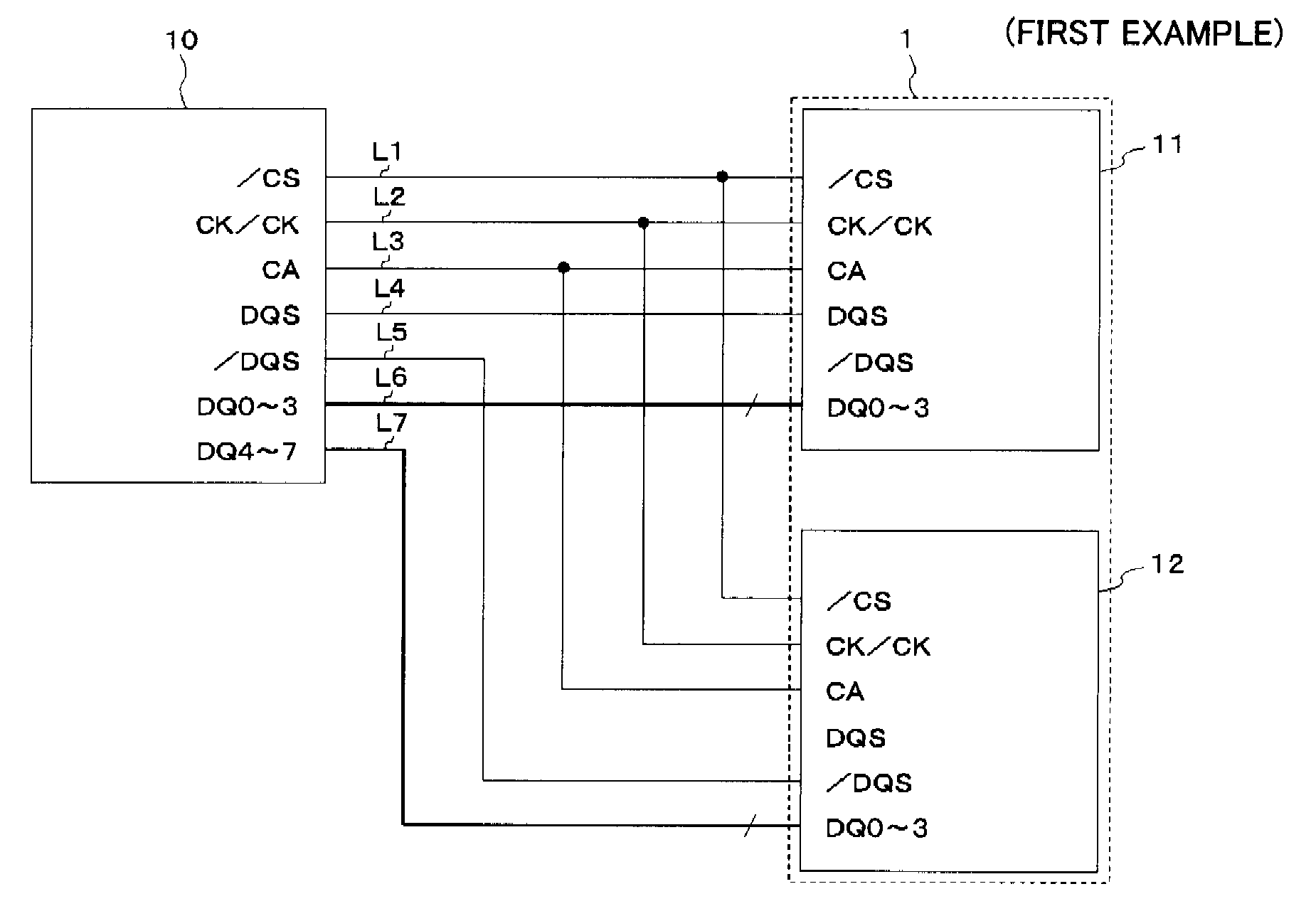

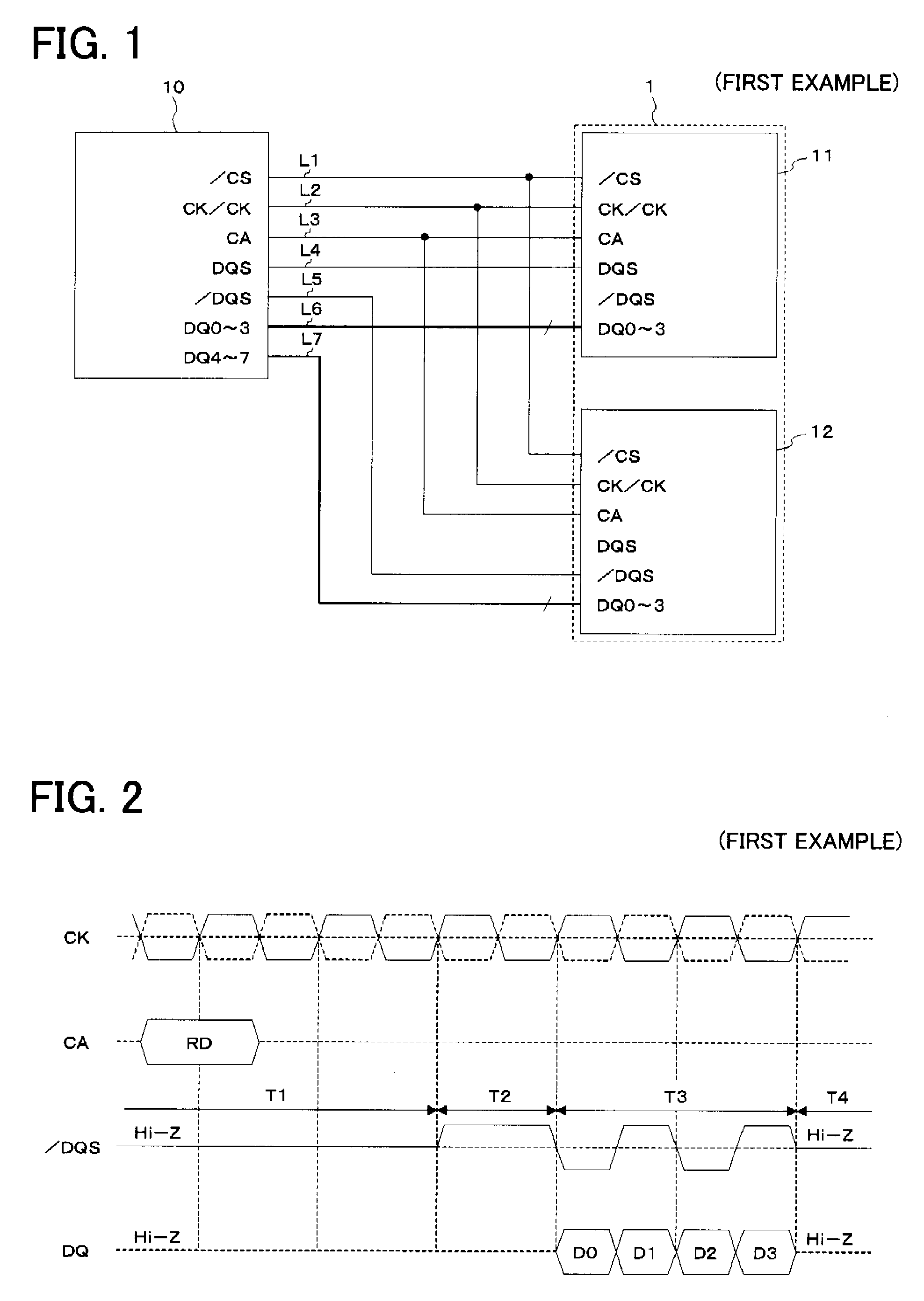

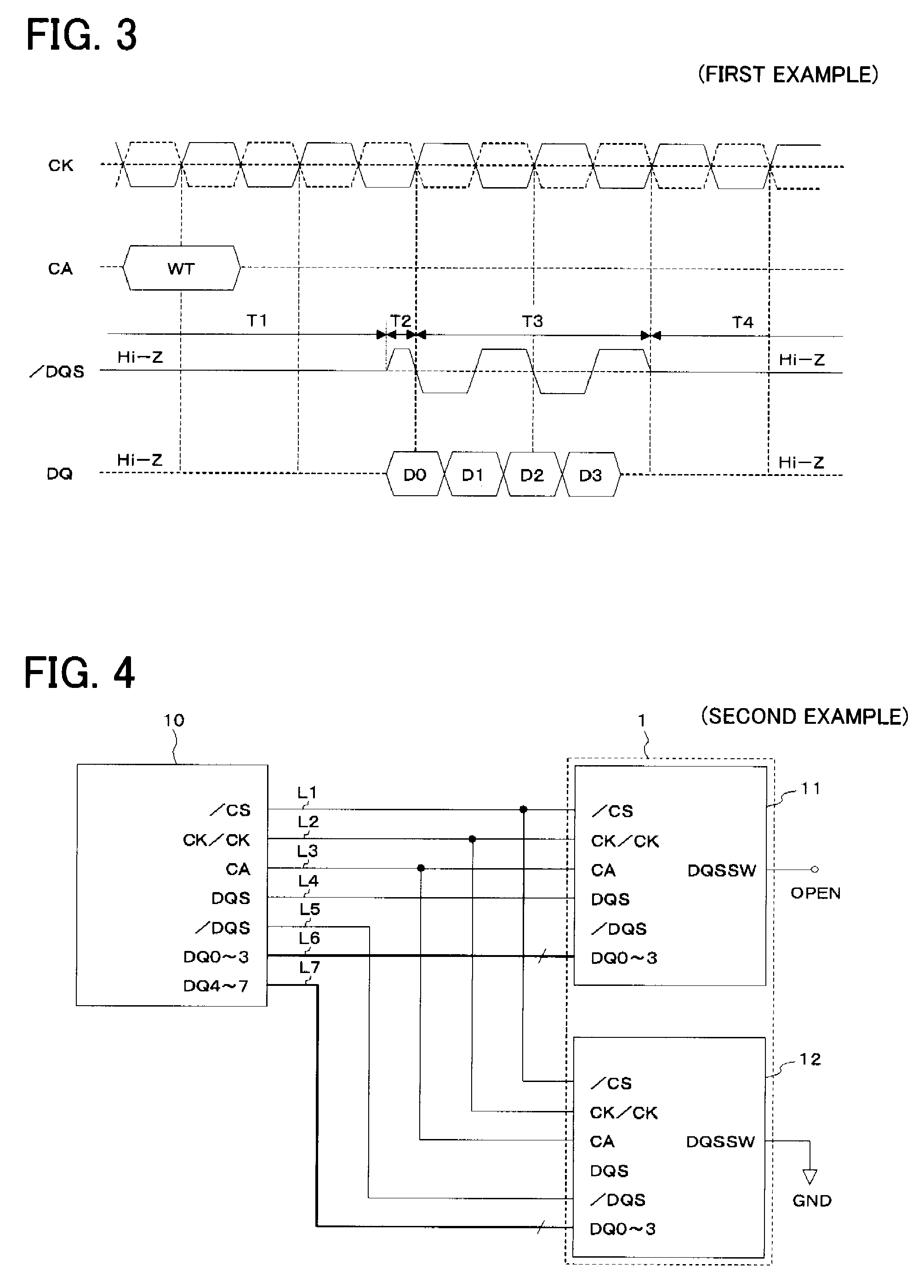

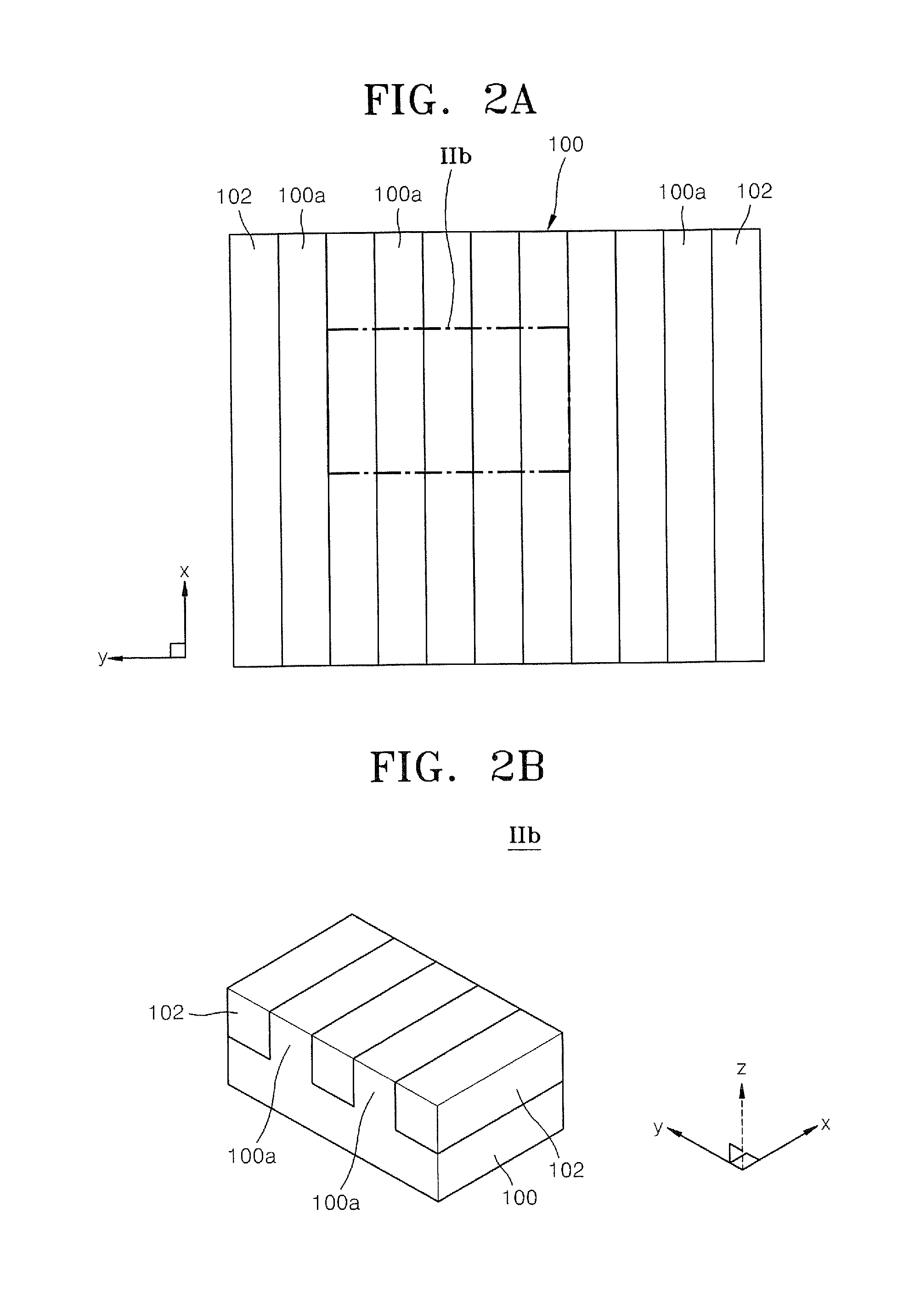

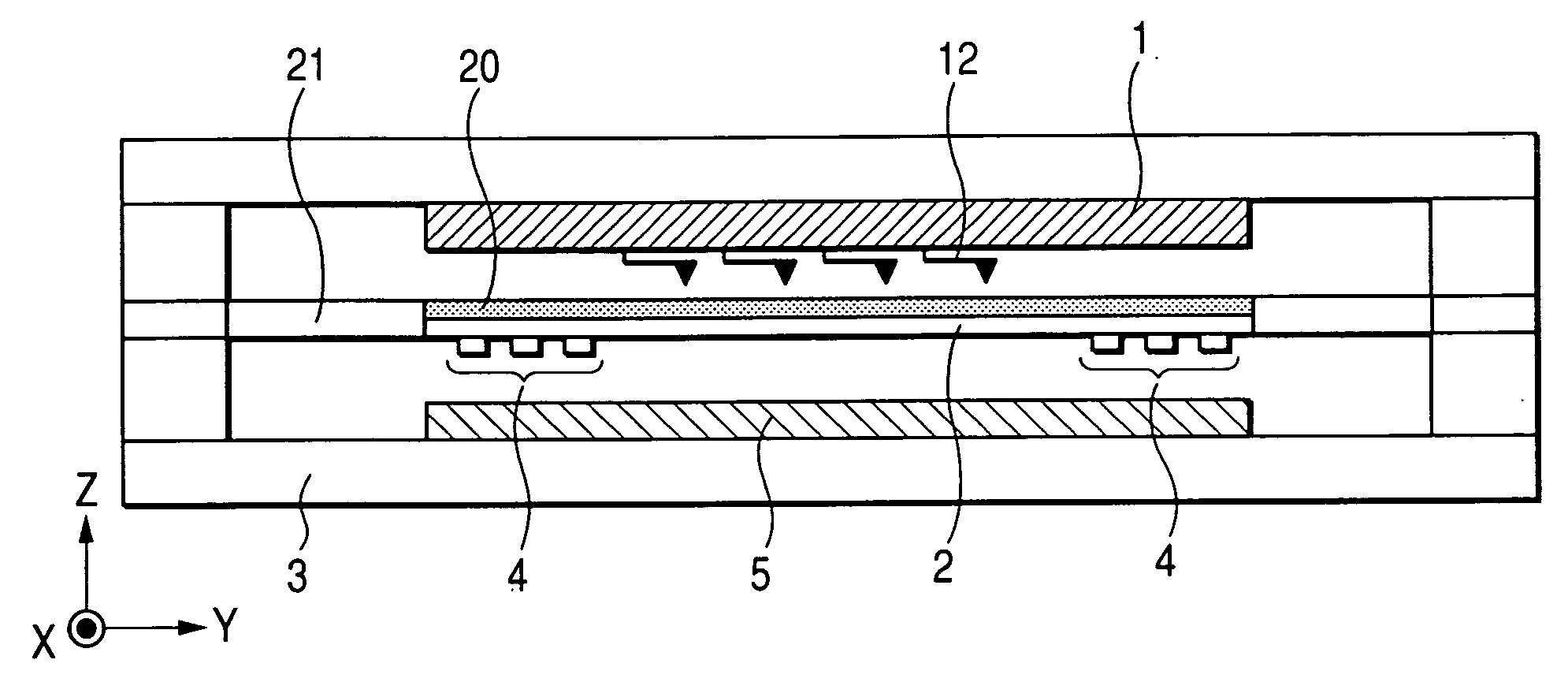

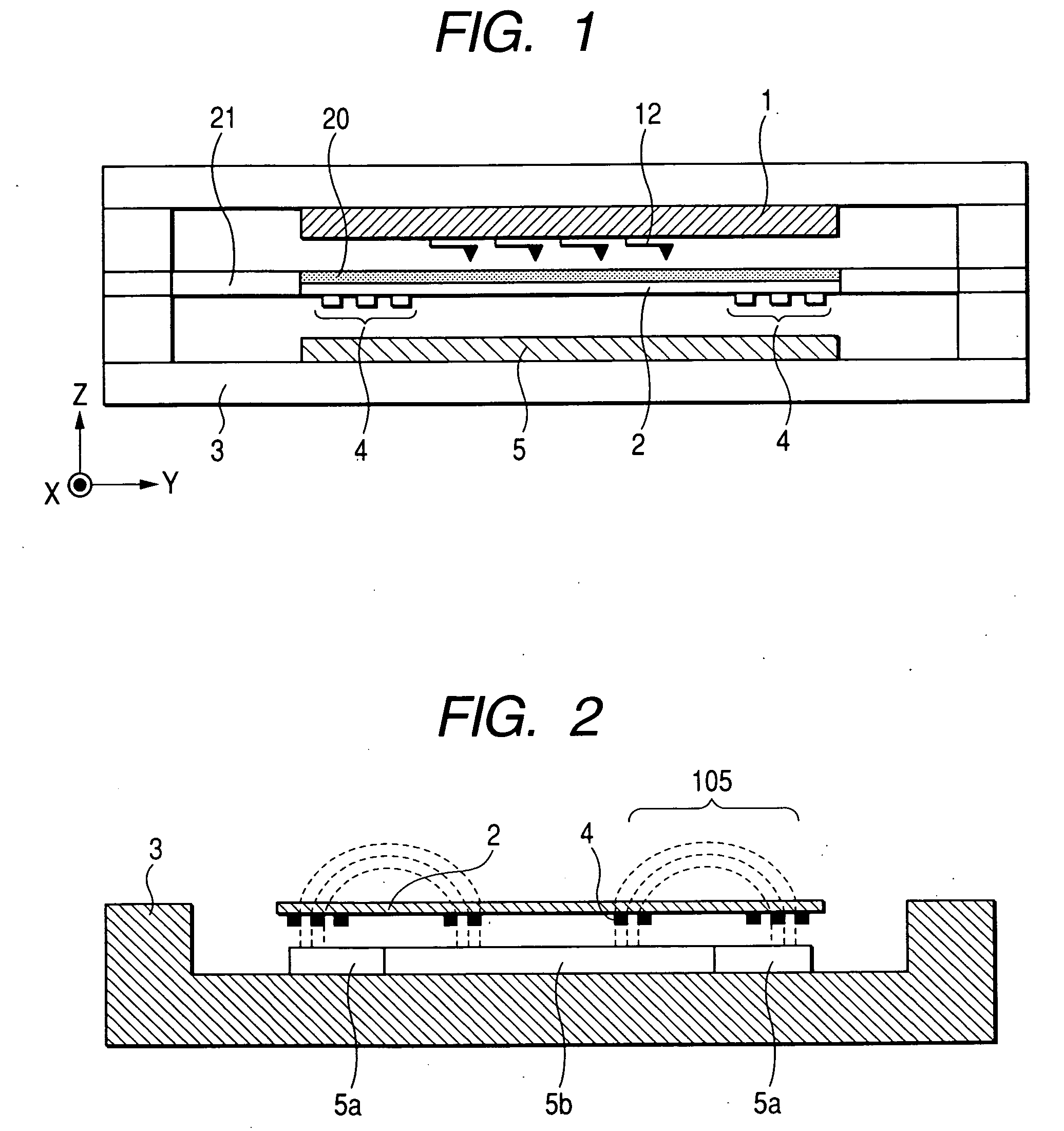

Stacked semiconductor device

InactiveUS20070291557A1Remove distortionIncrease speedSolid-state devicesDigital storageMemory chipControl signal

Stacked semiconductor device includes plural memory chips, stacked together, in which waveform distortion at high speed transmission is removed. Stacked semiconductor device 1 includes plural memory chips 11, 12 stacked together. Data strobe signal (DQS) and inverted data strobe signal ( / DQS), as control signals for inputting / outputting data twice per cycle, are used as two single-ended data strobe signals. Data strobe signal and inverted data strobe signal mate with each other. Data strobe signal line for the data strobe signal L4 is connected to data strobe signal (DQS) pad of first memory chip 11. Inverted data strobe signal line for / DQS signal L5 is connected to inverted data strobe signal ( / DQS) pad of second memory chip 12.

Owner:LONGITUDE SEMICON S A R L

Semi-active RFID tag and related processes

ActiveUS8237561B2Probability of successfulSuccessful transactionAntenna equipments with additional functionsSubscribers indirect connectionSemi activeDual mode

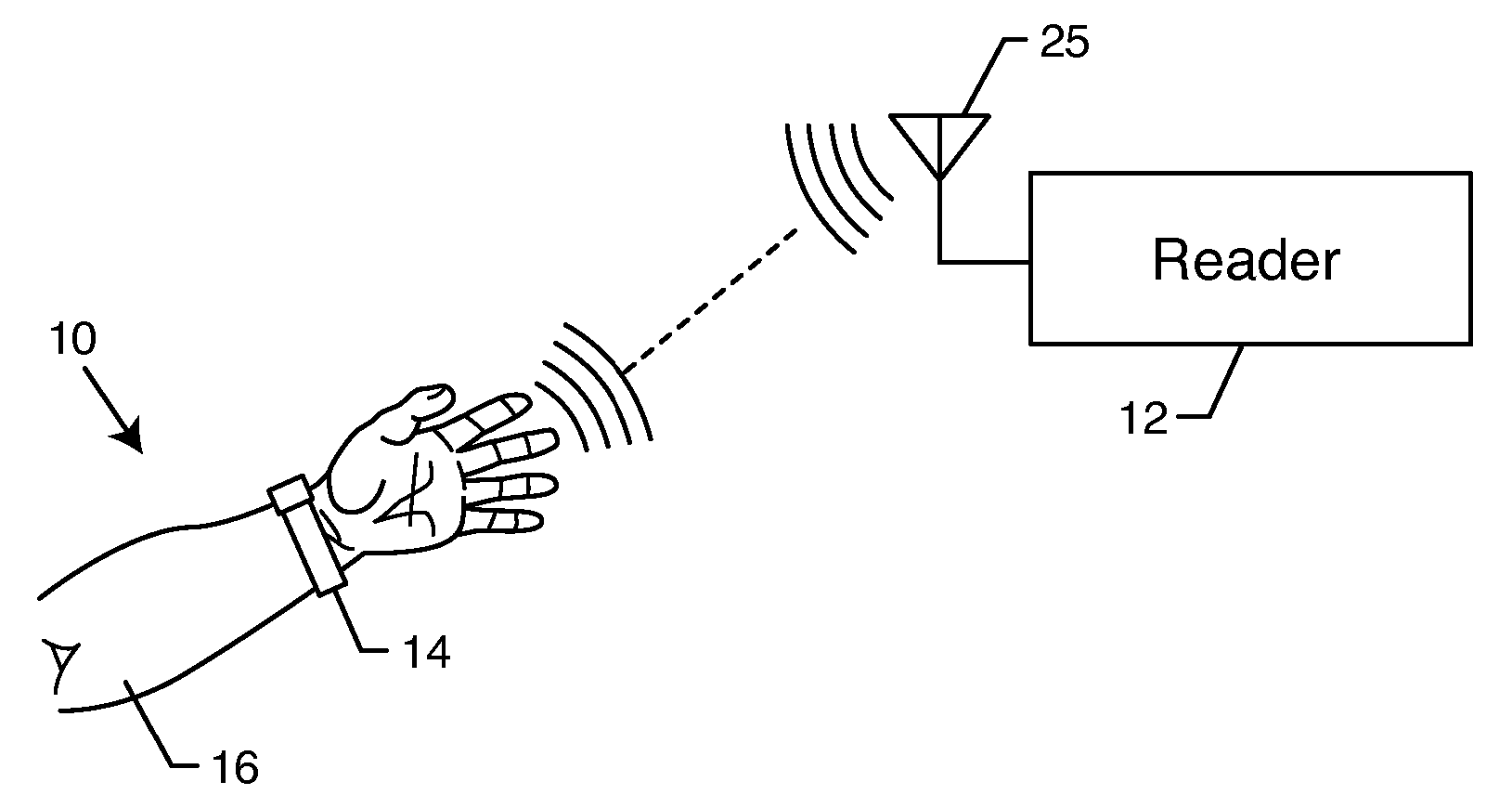

An improved radio frequency identification (RFID) tag and related reader system and process are provided, wherein the RFID tag includes an on-board battery for enhanced signal transmission range, relatively rapid signal transmission speed, and optimized completion of a data transaction between the tag and a reader. The RFID tag further includes a power management system for activating the tag battery on an as-needed basis, and for thereupon enabling limited portions of the tag circuitry as required for a specific communication protocol, thereby conserving battery power and prolonging battery service life. In one preferred form, the battery is integrated with an antenna structure of single or dual mode with respect to frequency or type. This combination battery-antenna may be designed for recharging from a source of ambient energy.

Owner:PRECISION DYNAMICS CORPORATION

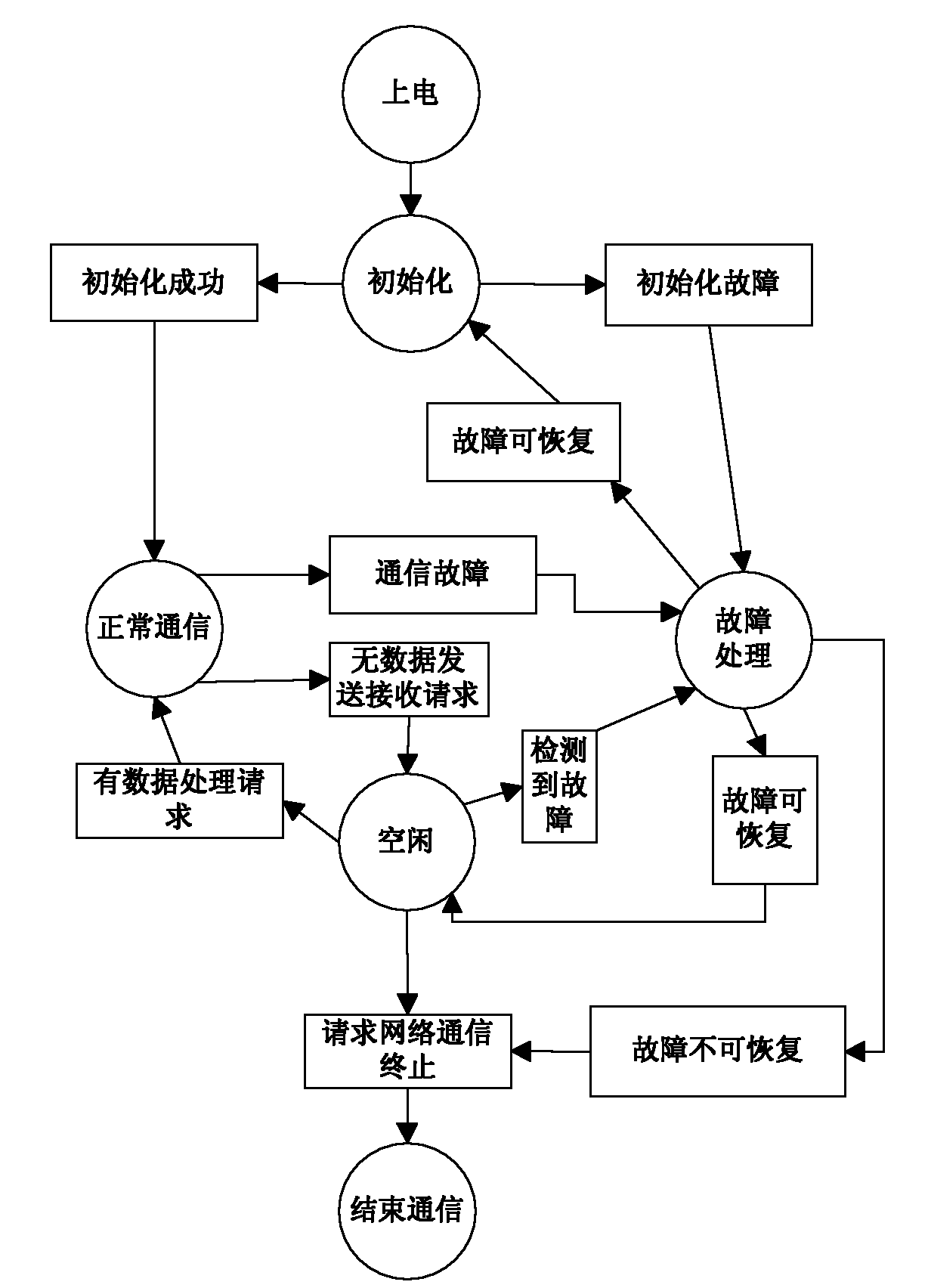

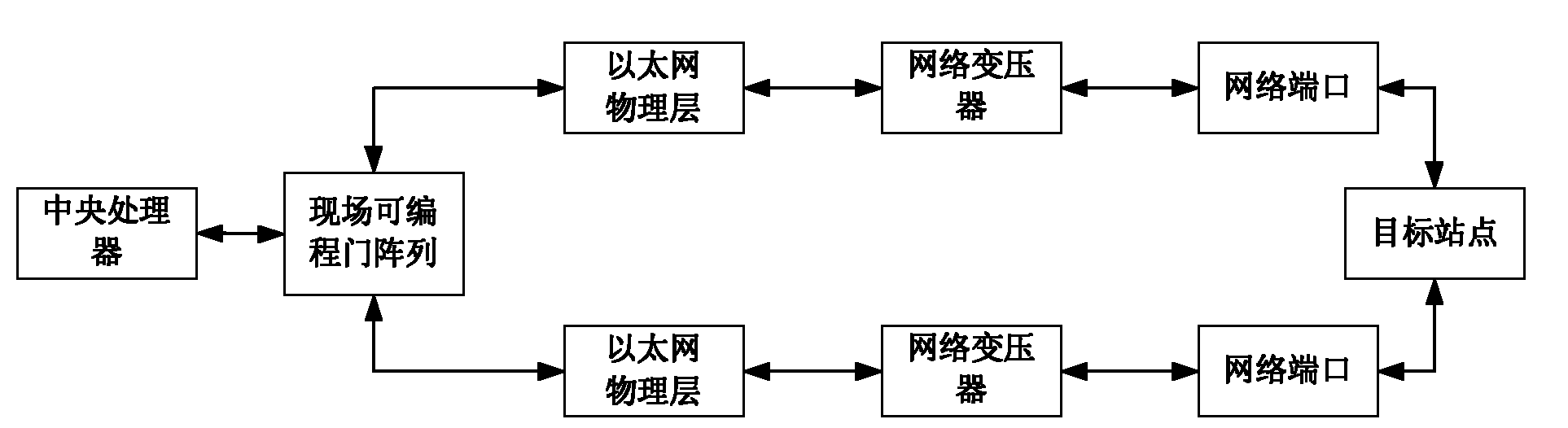

Implementation method of high-speed fieldbus based on industrial Ethernet

ActiveCN101950175AData transfer speed is fastImprove data transfer efficiencyTotal factory controlProgramme total factory controlComplete dataElectricity

The invention provides an implementation method of a high-speed fieldbus based on industrial Ethernet, which comprises the following steps: (1) electrifying a fieldbus system, and carrying out initialization setting; carrying out the step (3) if the initialization setting is successful, otherwise, carrying out fault treatment of the step (2); (2) carrying out the fault treatment; (3) carrying out data communication, and returning to the step (2) for carrying out the fault treatment if a fault emerges; entering into the idle state if the cycle further has remaining time after completing data transmission of all station points, waiting for the next data sending or receiving request, returning to the step (2) for carrying out the fault treatment if the fault emerges during the waiting process, otherwise, carrying out the step (4); and (4) finishing the communication. The invention further provides the high-speed fieldbus system based on the industrial Ethernet for implementing the method, that is a GSK-Link high-speed fieldbus system. Slave stations can mutually carry out the data communication, thereby greatly improving the data transmission speed and the efficiency.

Owner:GSK CNC EQUIP

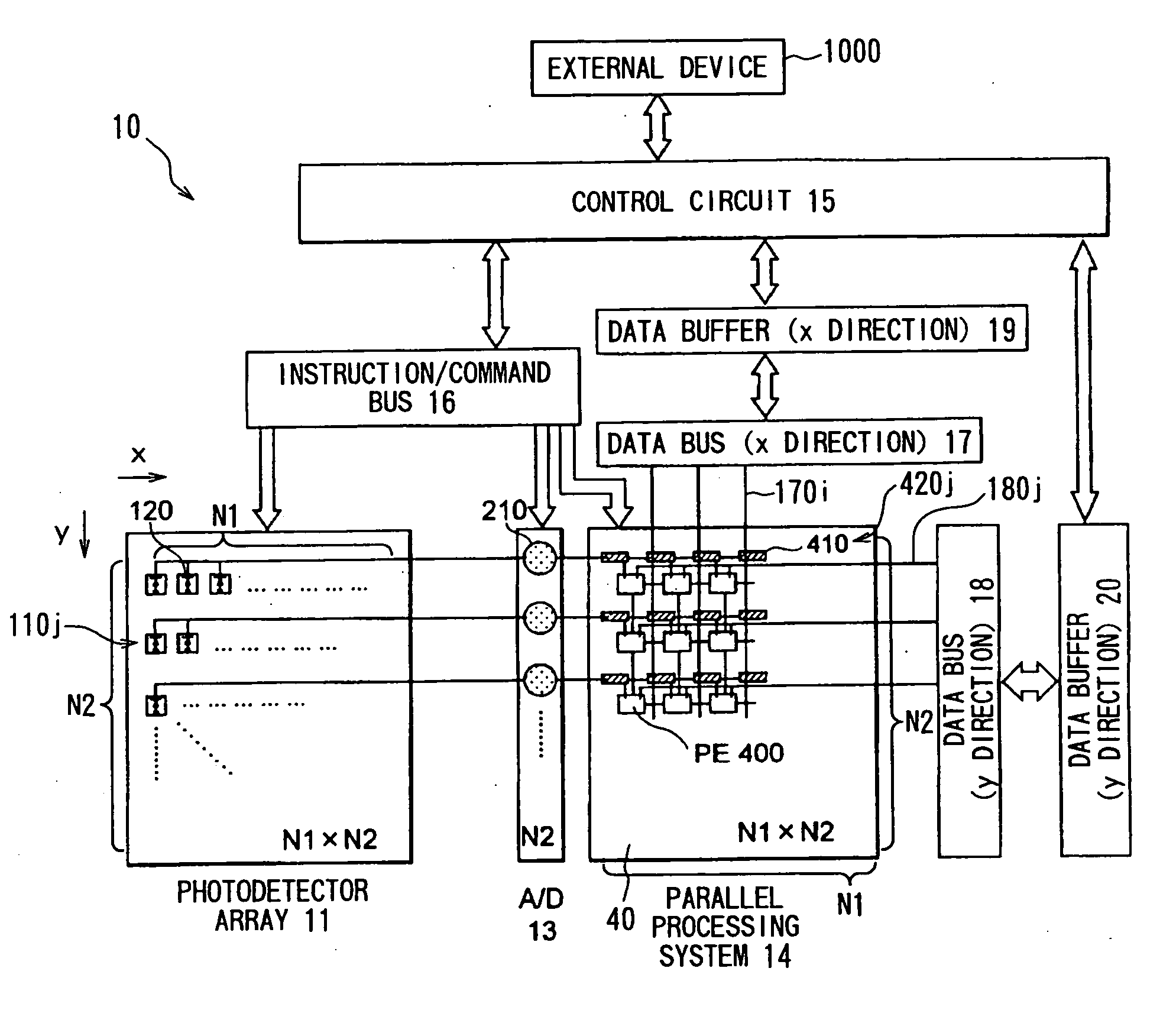

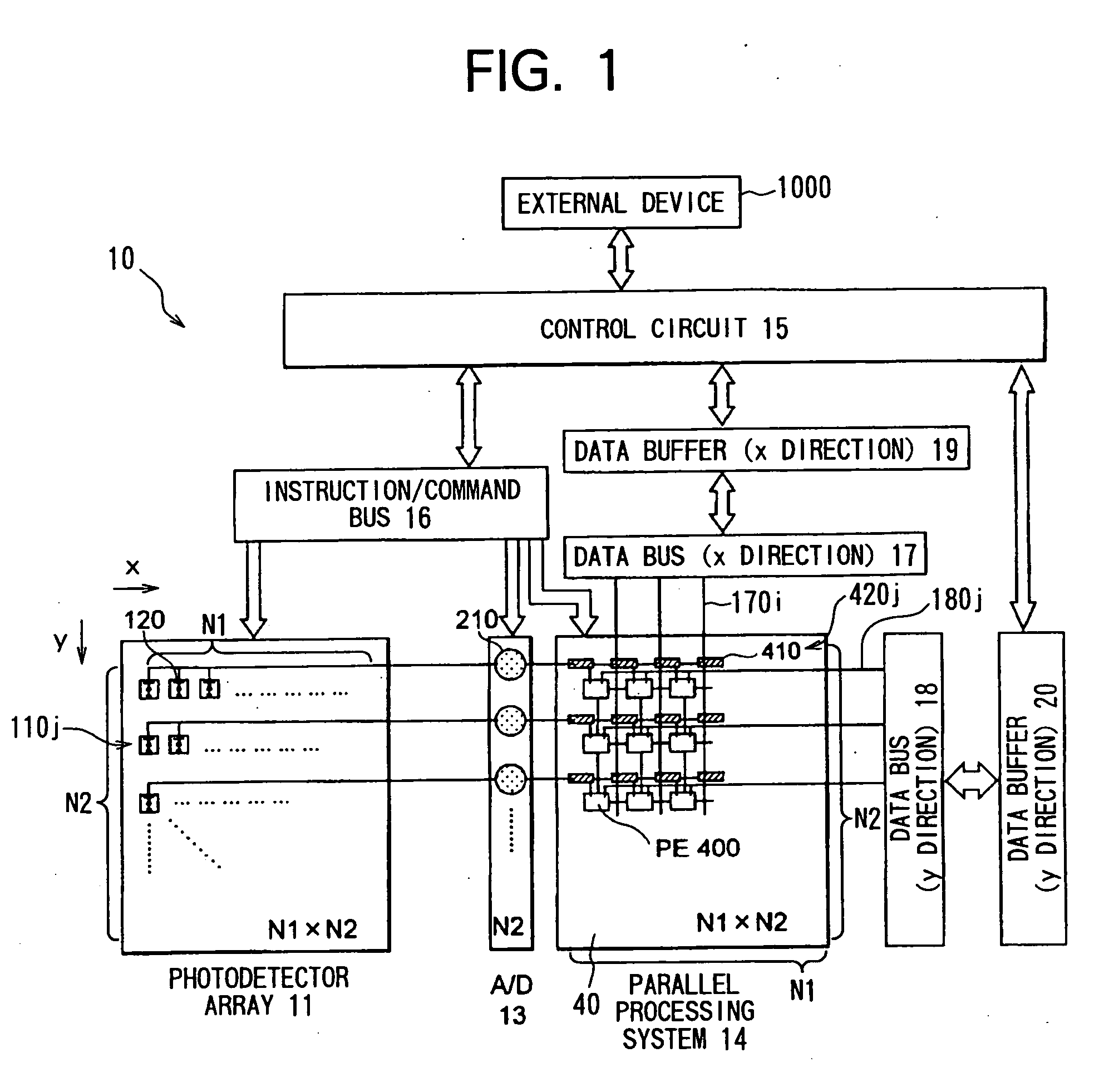

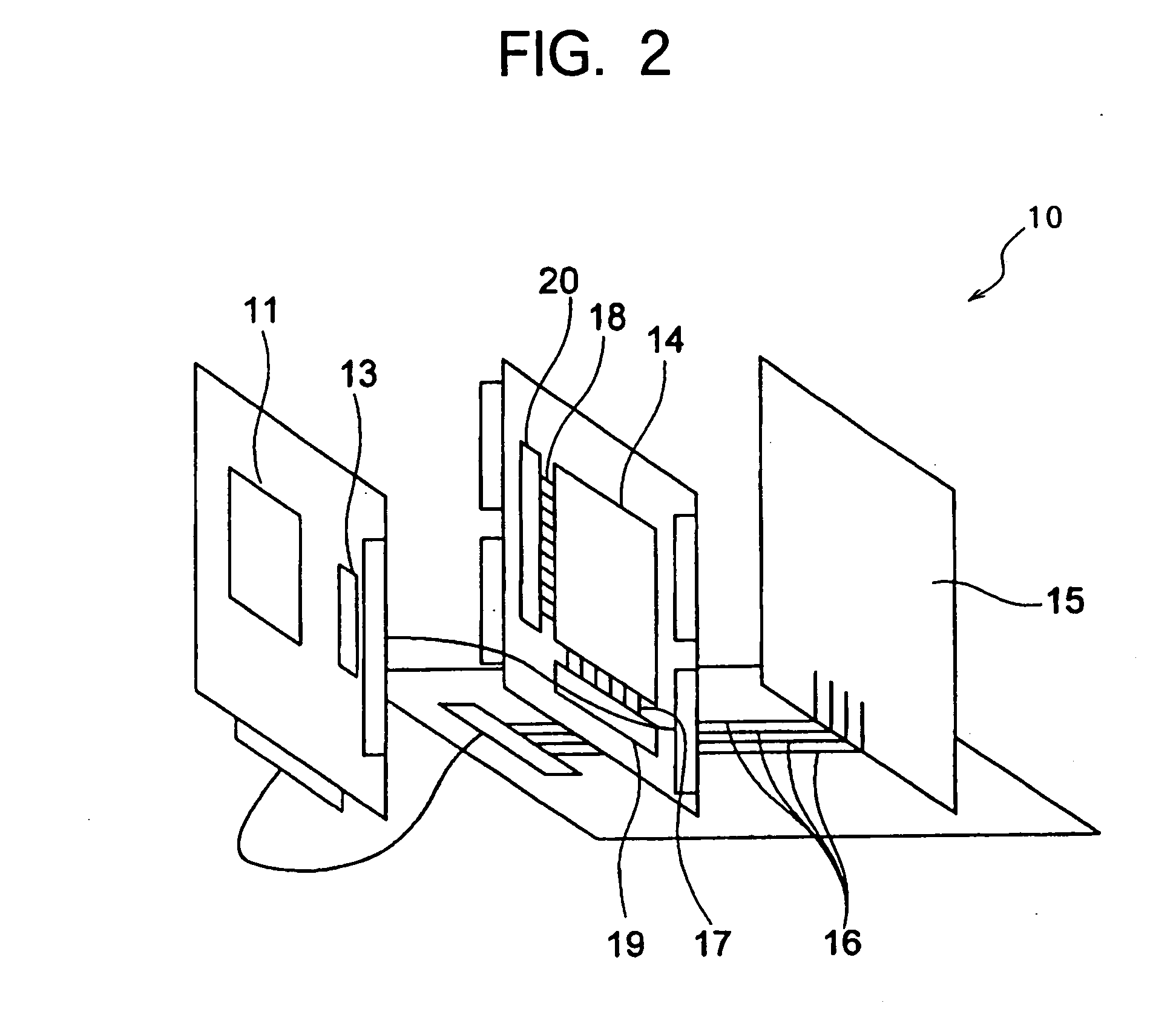

High-speed vision sensor

InactiveUS20050280728A1Simple circuit structureIncrease speedProgramme controlTelevision system detailsShift registerHigh rate

A high-speed vision sensor includes: an analog-to-digital converter array 13, in which one analog-to-digital converter 210 is provided in correspondence with all the photodetector elements 120 that are located on each row in a photodetector array 11; a parallel processing system 14 that includes processor elements 400 and shift registers 410, both of which form a one-to-one correspondence with the photodetector elements 120; and data buses 17, 18 and data buffers 19 and 20 for data transfer to processing elements 400. The processing elements 400 perform high-speed image processing between adjacent pixels by parallel processings. By using the data buses 17, 18, it is possible to attain, at a high rate of speed, such calculation processing that requires data supplied from outside.

Owner:HAMAMATSU PHOTONICS KK

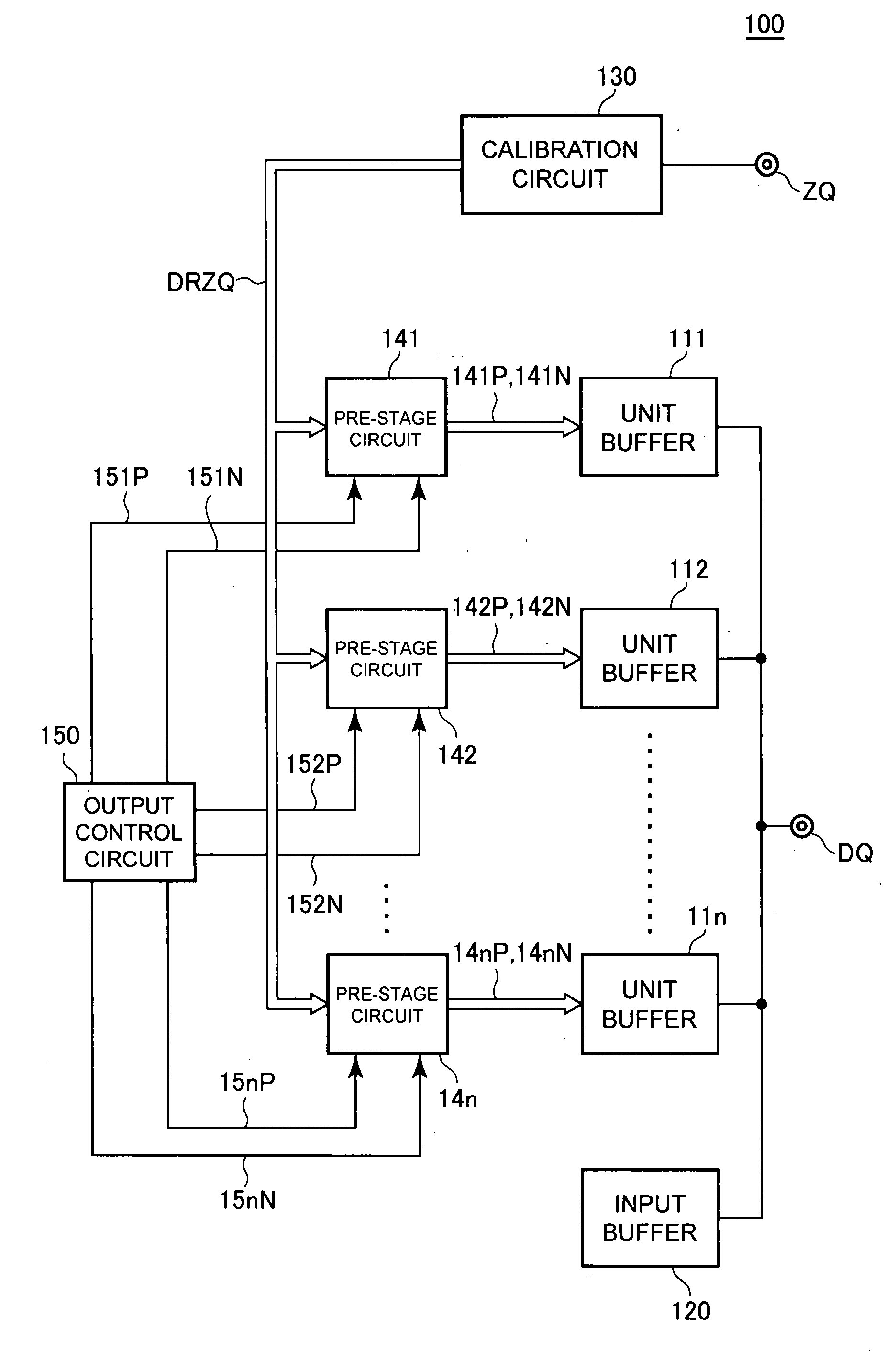

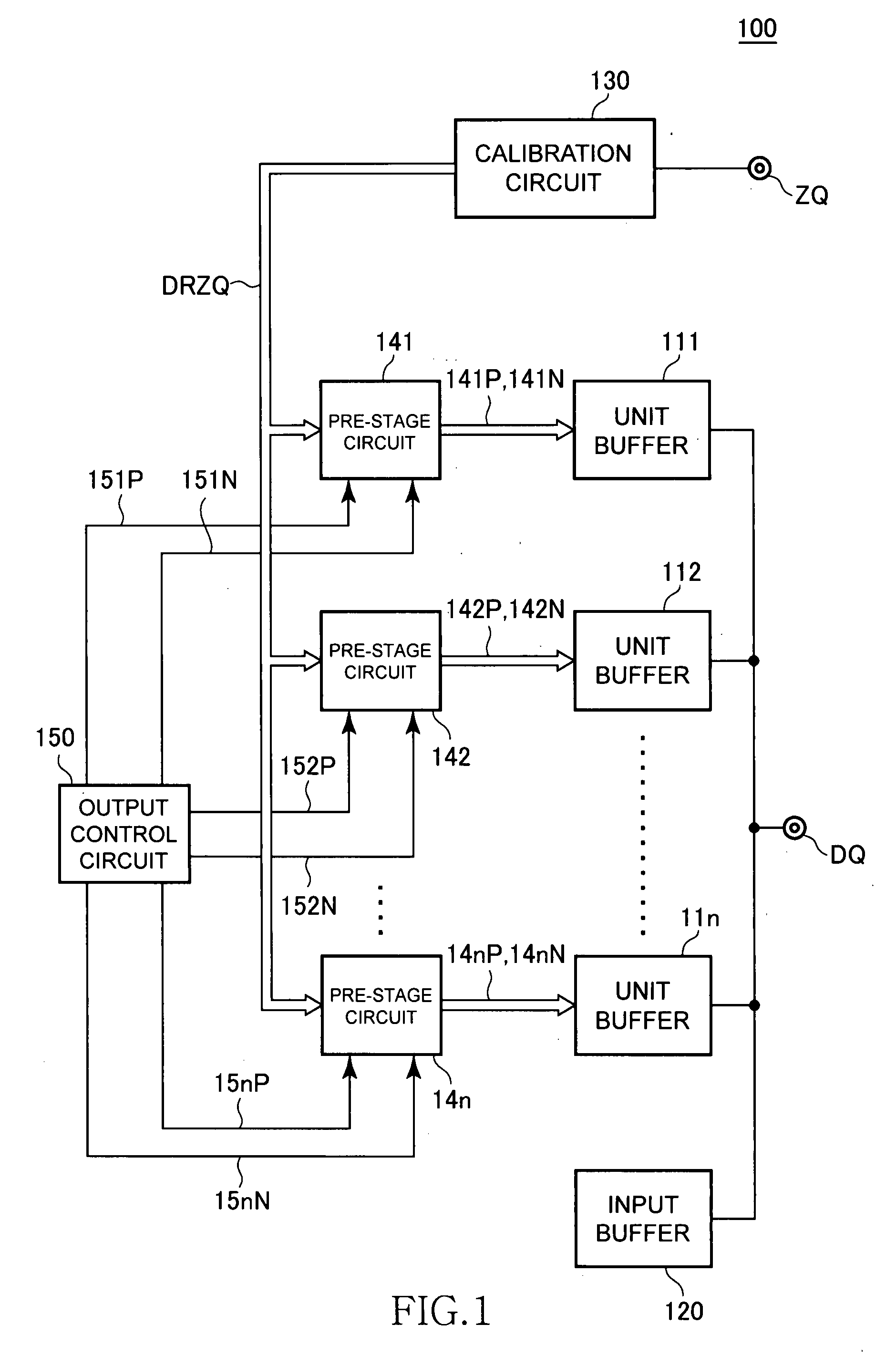

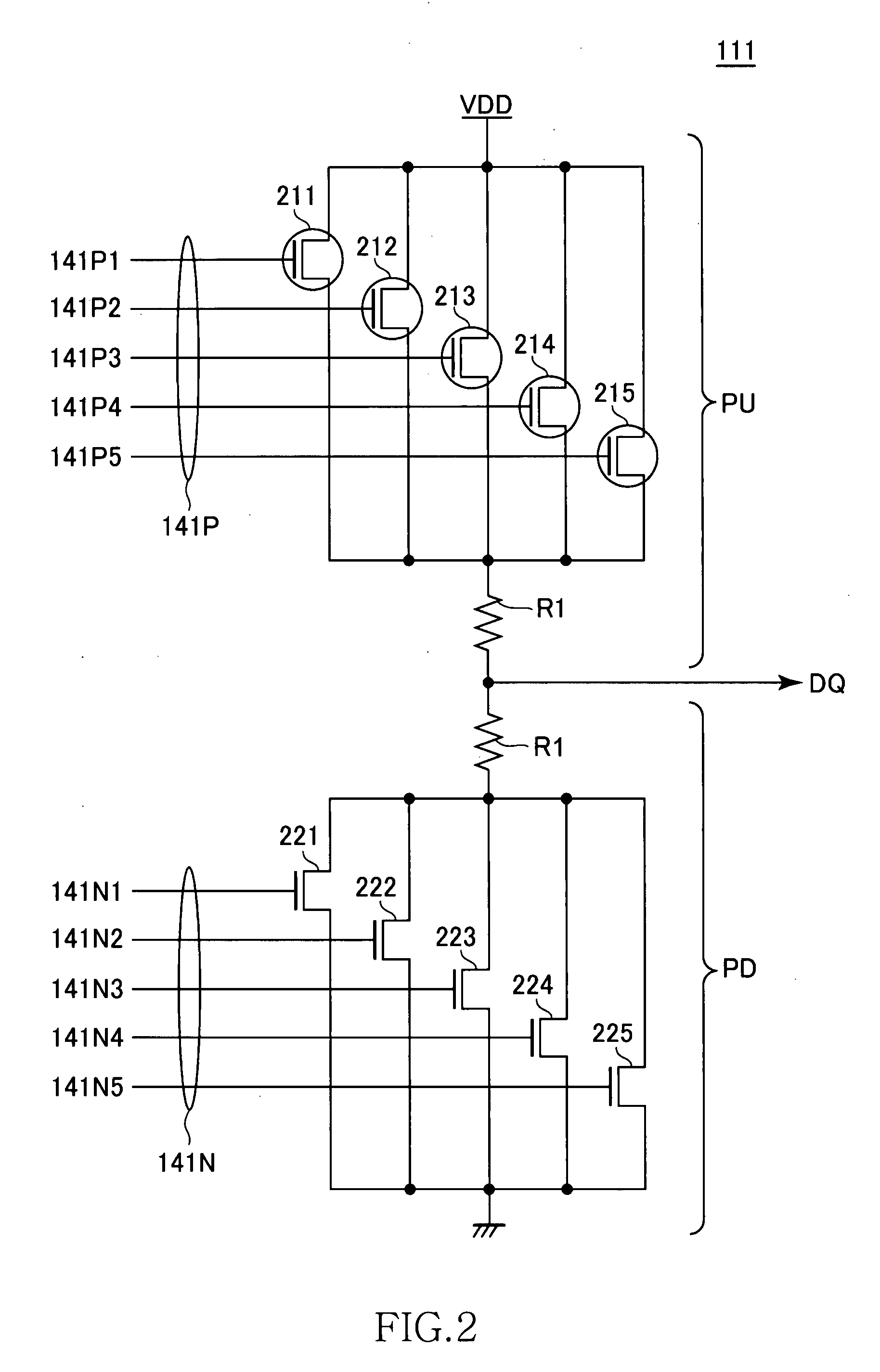

Output circuit of semiconductor device

ActiveUS20080054937A1Deviation and offsetIncrease speedInput/output impedence modificationReliability increasing modificationsElectrical resistance and conductancePower semiconductor device

An output circuit of a semiconductor includes unit buffers, each unit buffer having transistors and resistors connected between a power source terminal VDDQ and an output terminal DQ, and transistors and resistors connected between a power source terminal VSSQ and an output terminal DQ. On-resistance values of transistors included in the unit buffers are mutually substantially the same, and resistance values of resistors included in the unit buffers are mutually different. A deviation of impedances attributable to a power source resistance can be offset based on a difference between resistance values of the resistors.

Owner:LONGITUDE LICENSING LTD

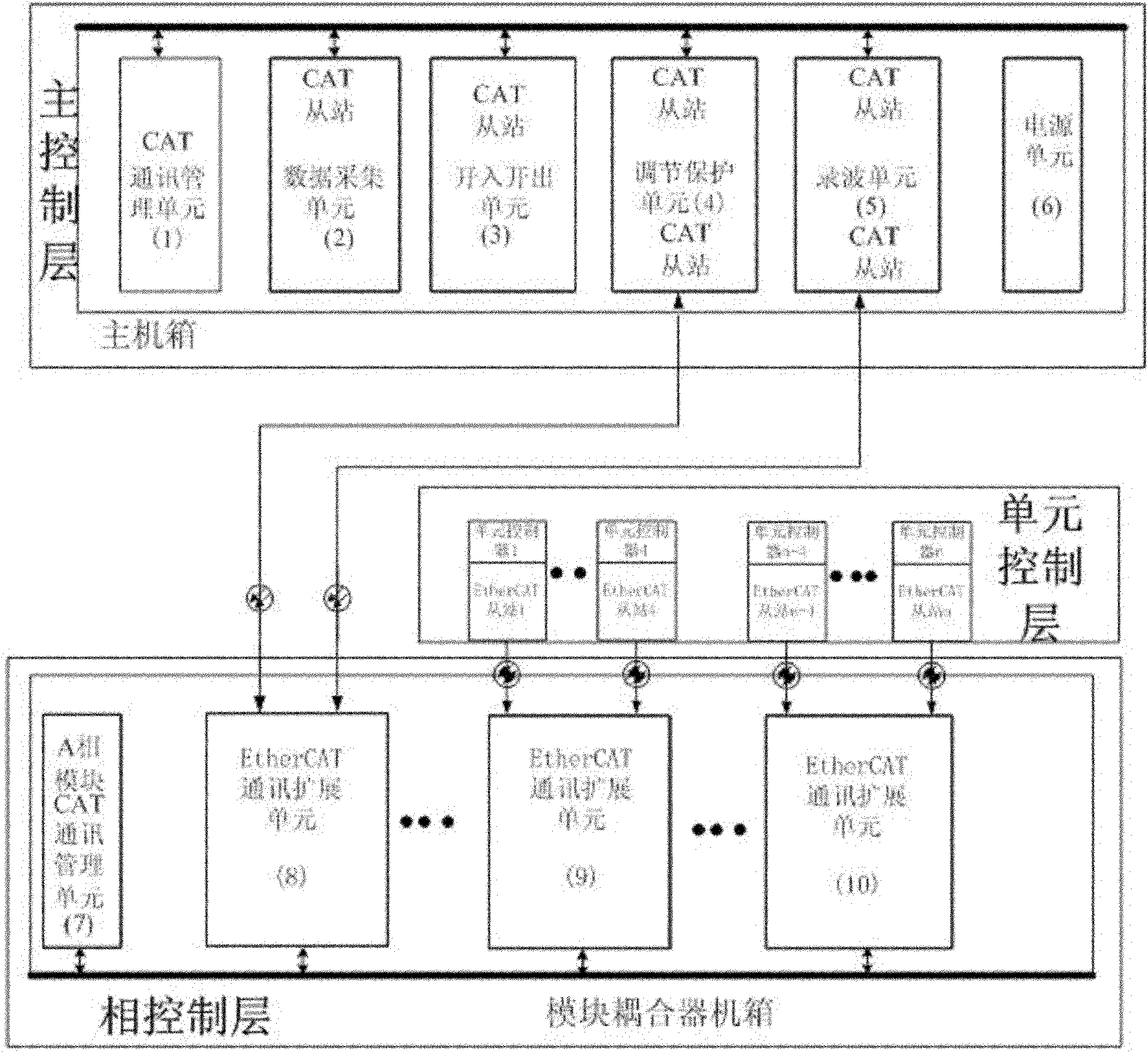

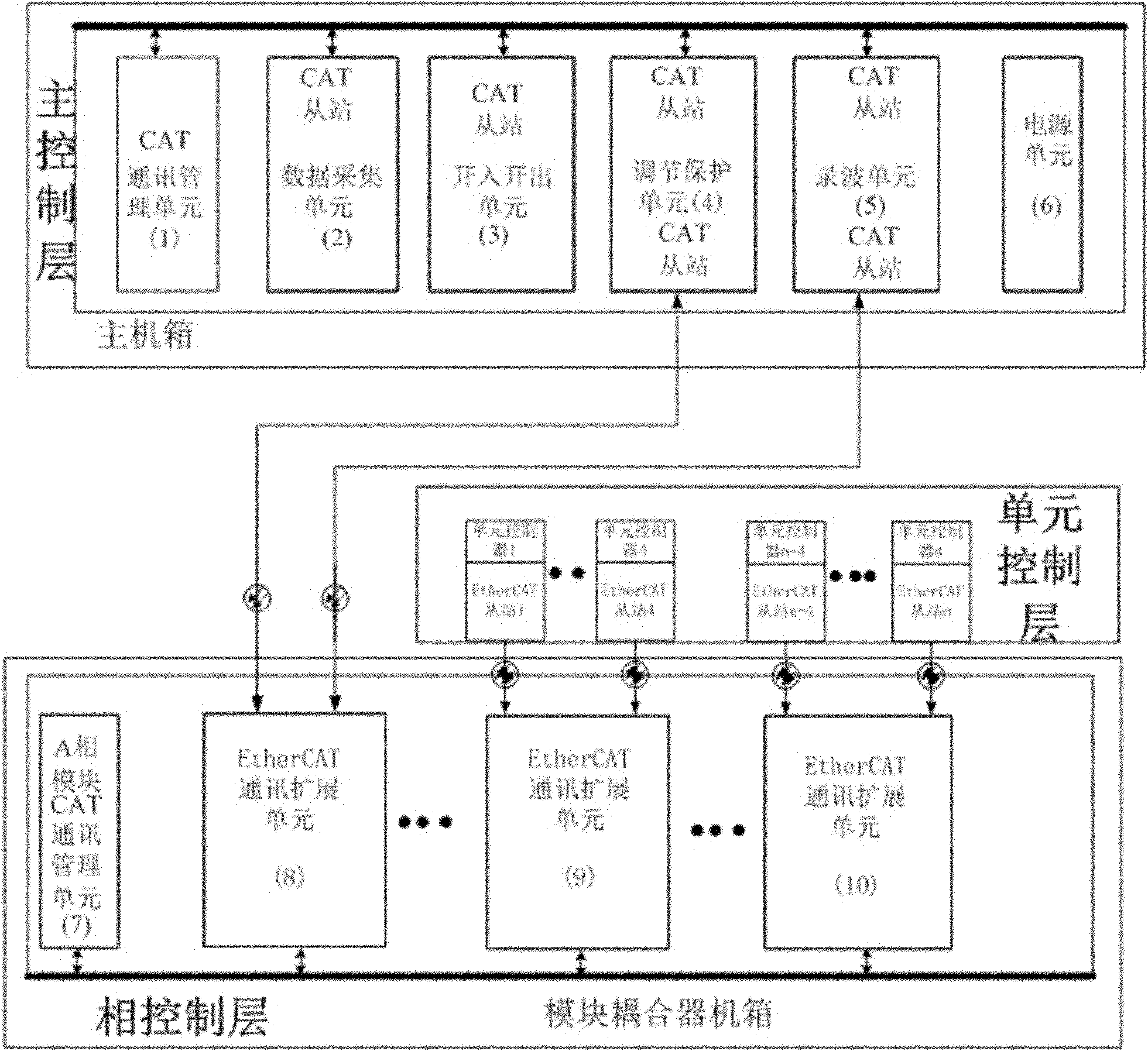

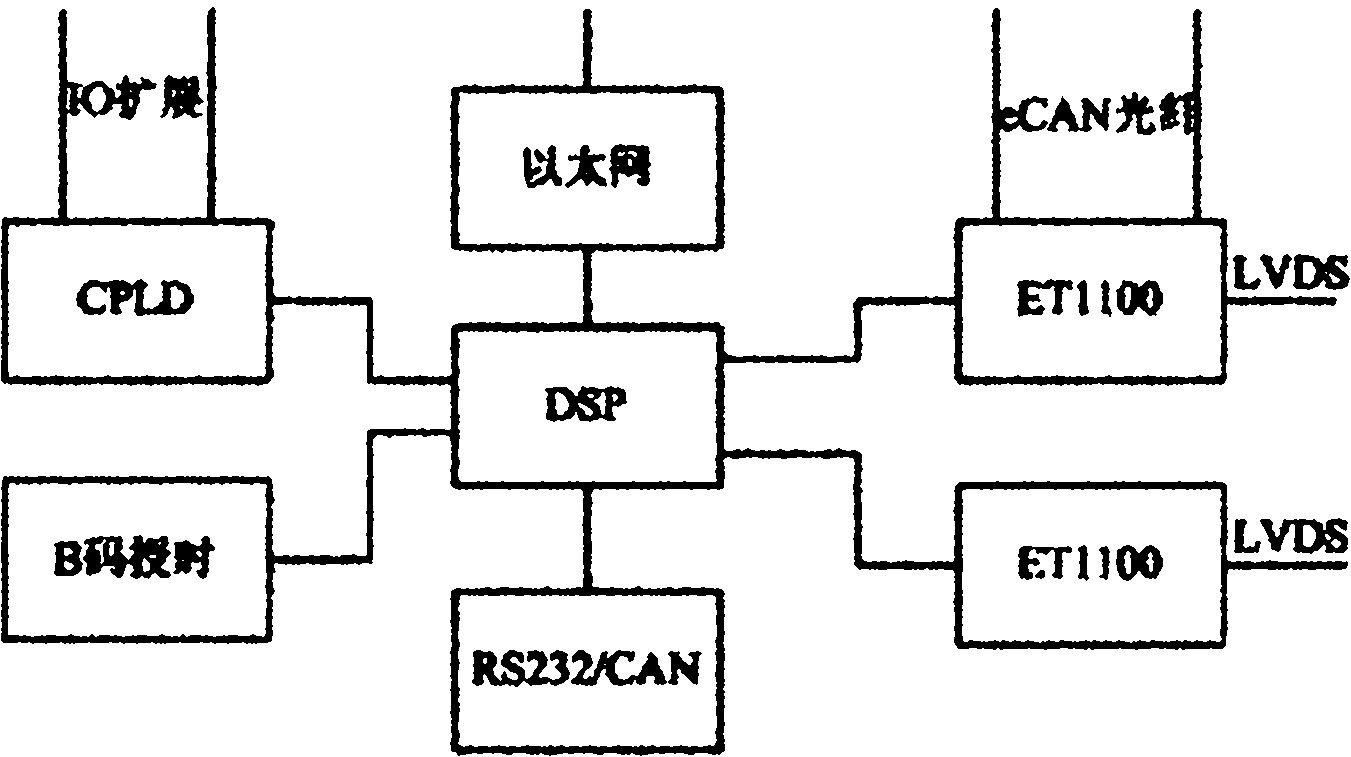

Chain type STATCOM control system based on EtherCA technology

ActiveCN102096407AData transfer speed is fastGuaranteed reliabilityFlexible AC transmissionReactive power adjustment/elimination/compensationIndustrial EthernetControl layer

The invention provides a chain type STATCOM (Static Synchronous Compensator) control system based on EtherCA technology, wherein the chain type STATCOM control system uses real-time industrial Ethernet EtherCA as a channel of data transferring, and the control system uses a layered distribution topology structure. The layered distribution topology structure of the STATCOM control system comprises a main control layer, a phase control layer and a unit control layer. The main control layer comprises a main control case and the like functional cases, the phase control layer is composed of a phase coupler case, and the unit control unit is composed of a unit controller. The communication between the main case and the phase coupler case is carried out by means of firewire connected EtherCA. The chain type STATCOM control system based on EtherCA technology provided by the invention has the advantages that the data transferring speed is high, the number of the cable is less, the exchange speed is fast, the expansion is convenient, the accurate synchronism and the diagnosis ability are strong and the configuration is flexible.

Owner:CHINA EPRI SCIENCE & TECHNOLOGY CO LTD +2

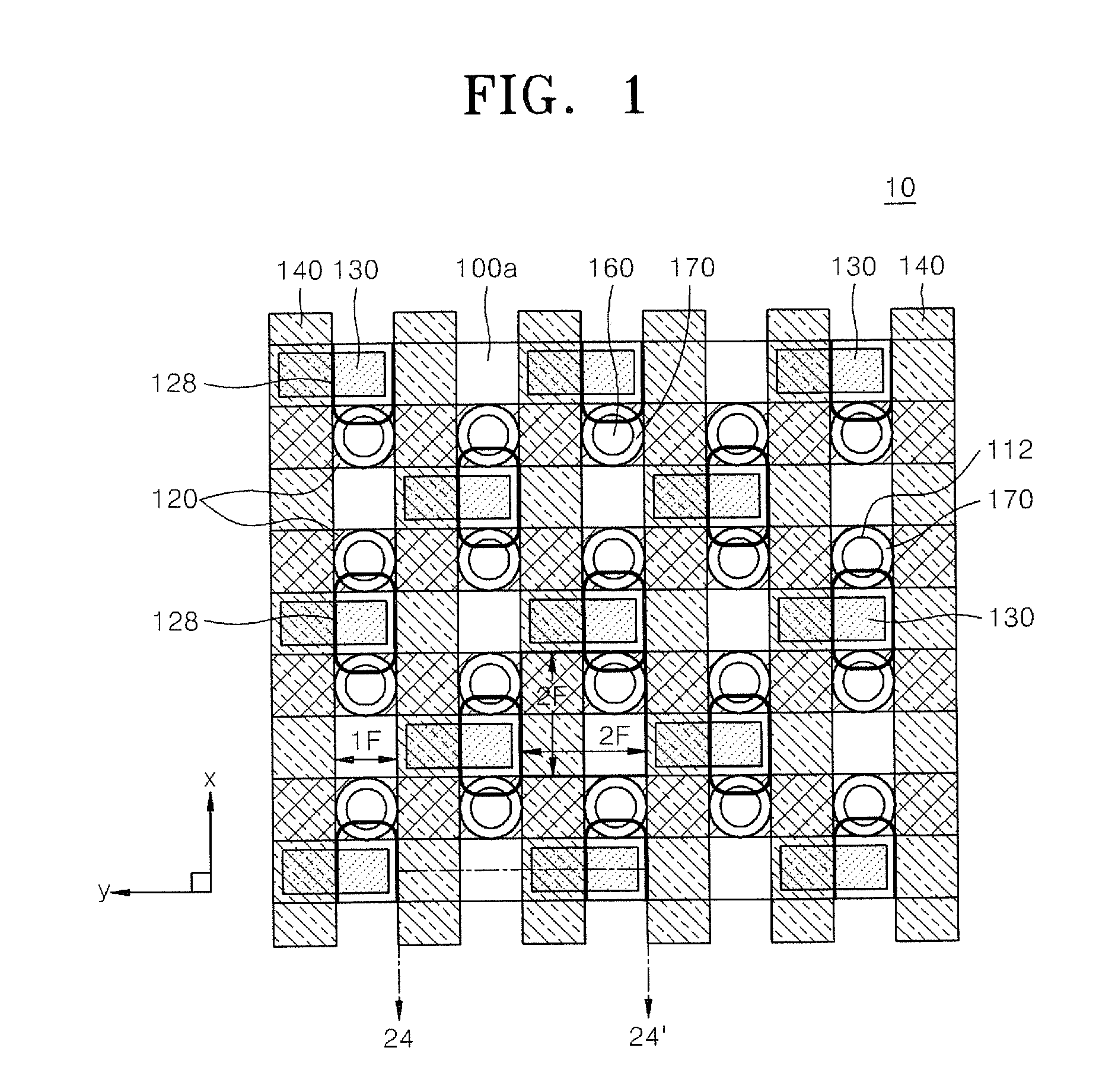

Semiconductor Memory Devices Having Vertical Channel Transistors and Related Methods

ActiveUS20090121268A1Data transfer speed is fastShorten access timeTransistorSolid-state devicesVertical channelSemiconductor memory

A semiconductor memory device may include a semiconductor substrate with an active region extending in a first direction parallel with respect to a surface of the semiconductor substrate. A pillar may extend from the active region in a direction perpendicular with respect to the surface of the semiconductor substrate with the pillar including a channel region on a sidewall thereof. A gate insulating layer may surround a sidewall of the pillar, and a word line may extend in a second direction parallel with respect to the surface of the semiconductor substrate. Moreover, the first and second directions may be different, and the word line may surround the sidewall of the pillar so that the gate insulating layer is between the word line and the pillar. A contact plug may be electrically connected to the active region and spaced apart from the word line, and a bit line may be electrically connected to the active region through the contact plug with the plurality of bit lines extending in the first direction. Related methods are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

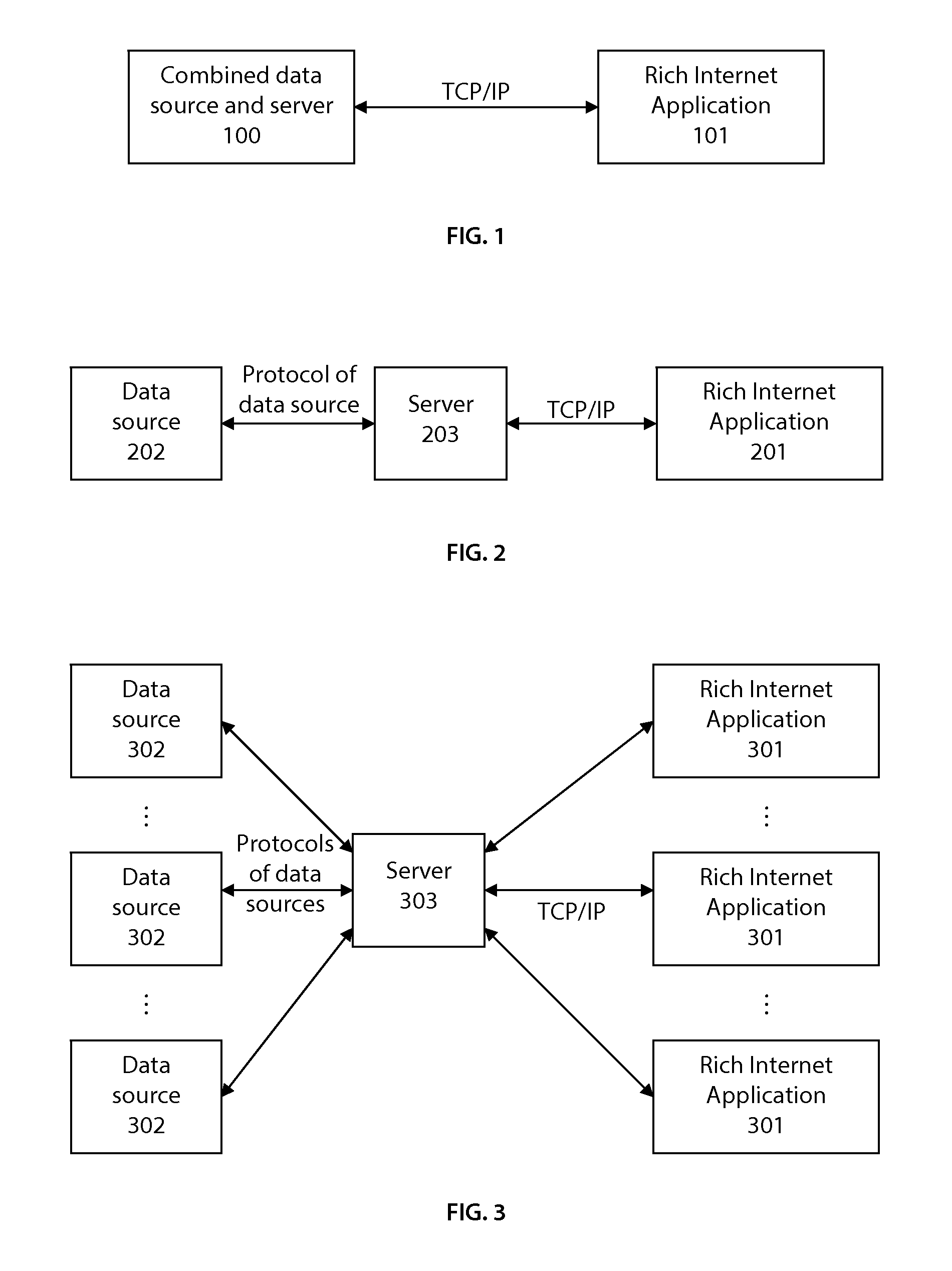

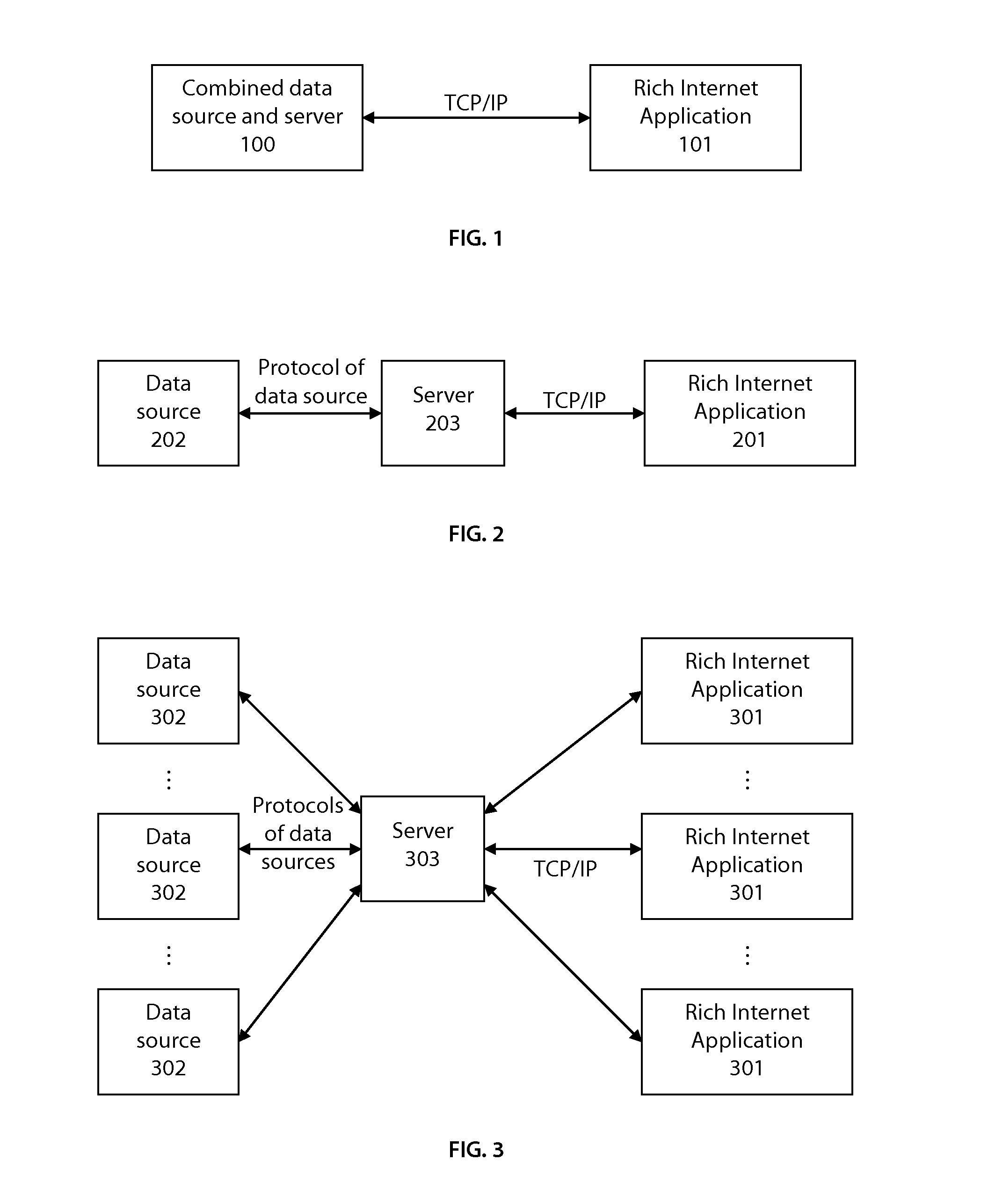

System and method for streaming data via HTTP

InactiveUS20130212227A1Data efficientEfficiently madeMultiple digital computer combinationsTransmissionProtocol for Carrying Authentication for Network AccessClient-side

A system and method for providing bi-directional streaming communication over the HTTP or HTTPS protocol between a client and a server is disclosed. The method provides a long-lived, bi-directional communication mechanism from a web client that is performed entirely over HTTP or HTTPS, using existing HTTP verbs such as GET and POST, and is operable with existing browser and RIA technology. The graphical and networking features of RIA frameworks in conjunction with the disclosed method provide low-latency, real-time data applications in a web browser.

Owner:COGENT REAL TIME SYST

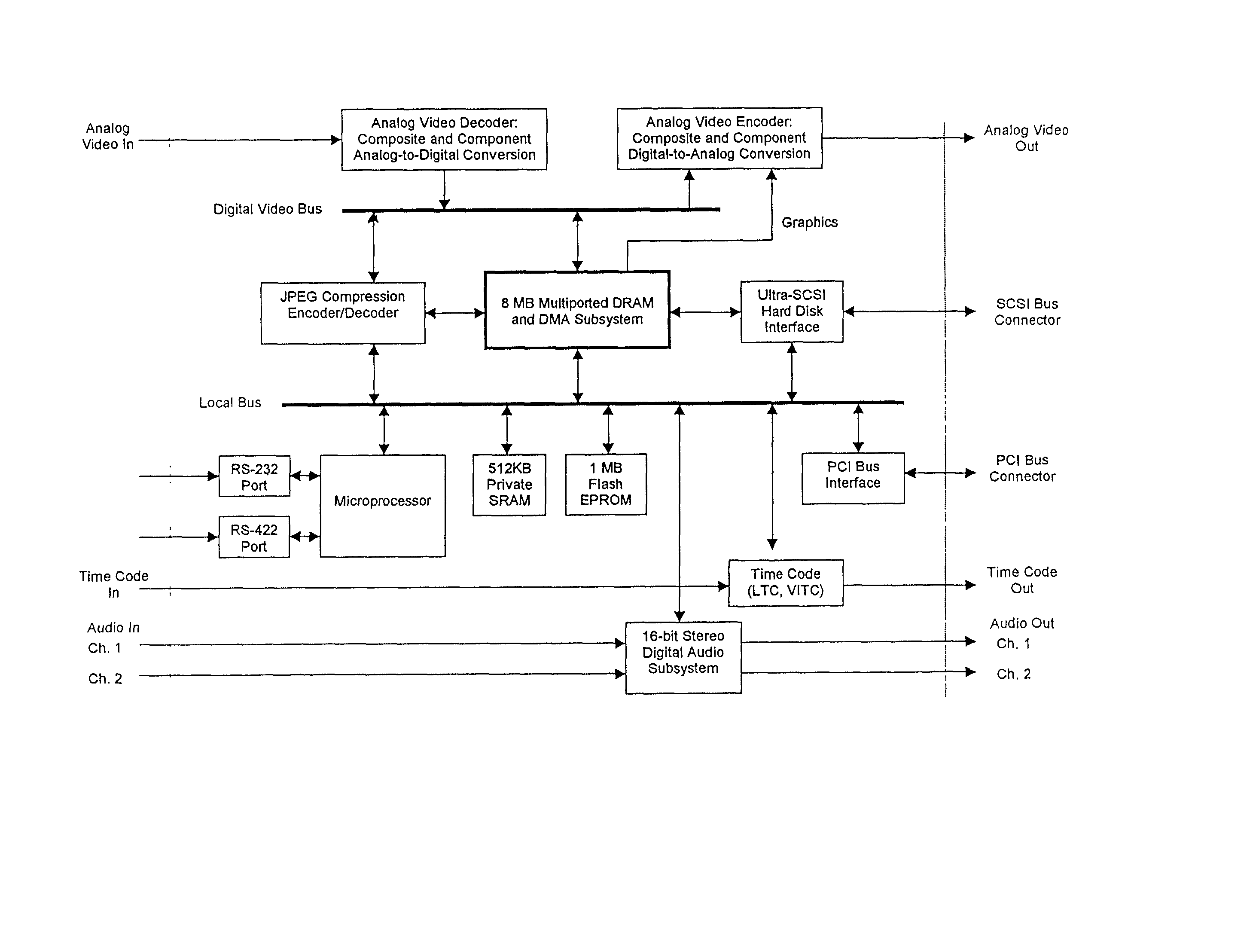

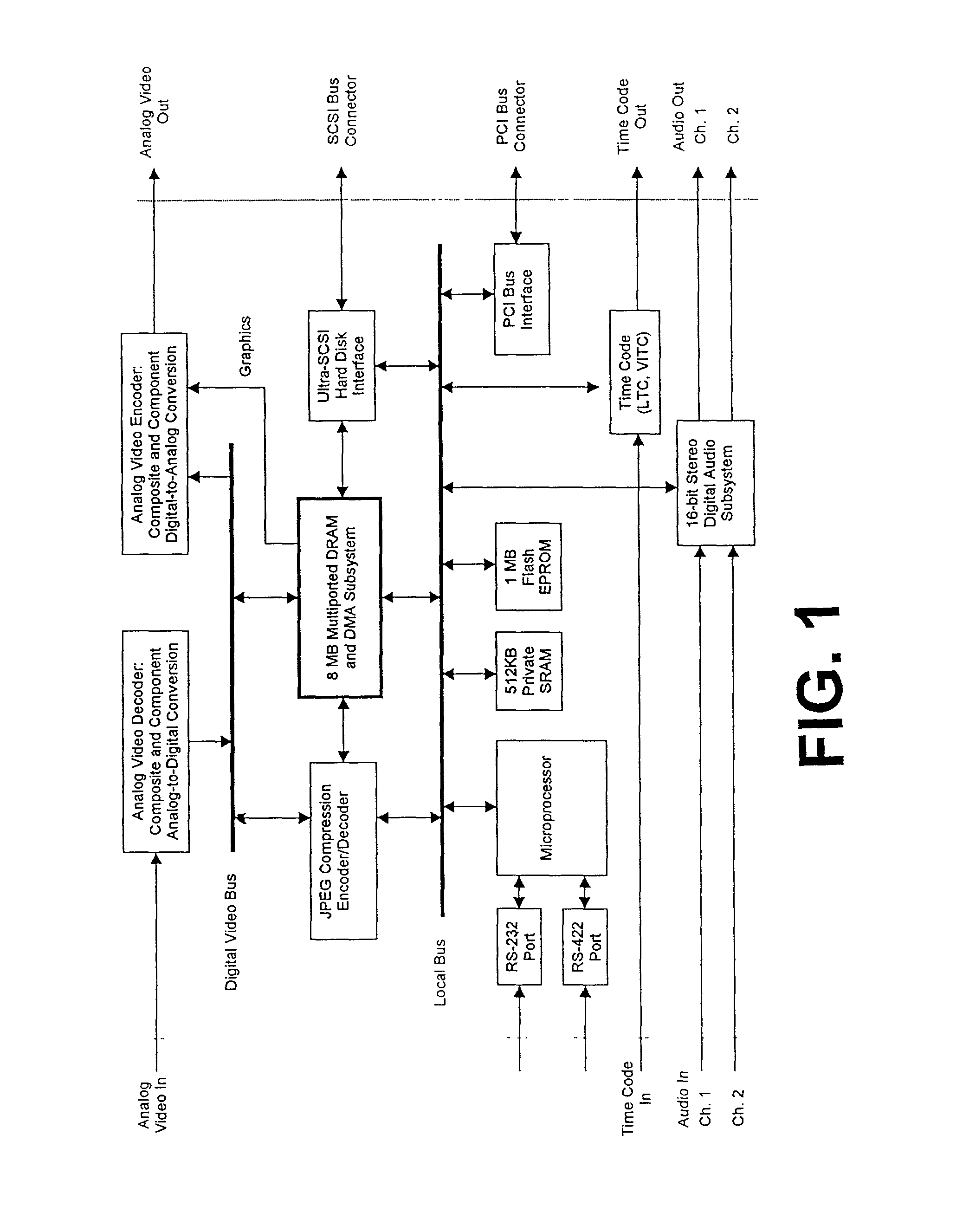

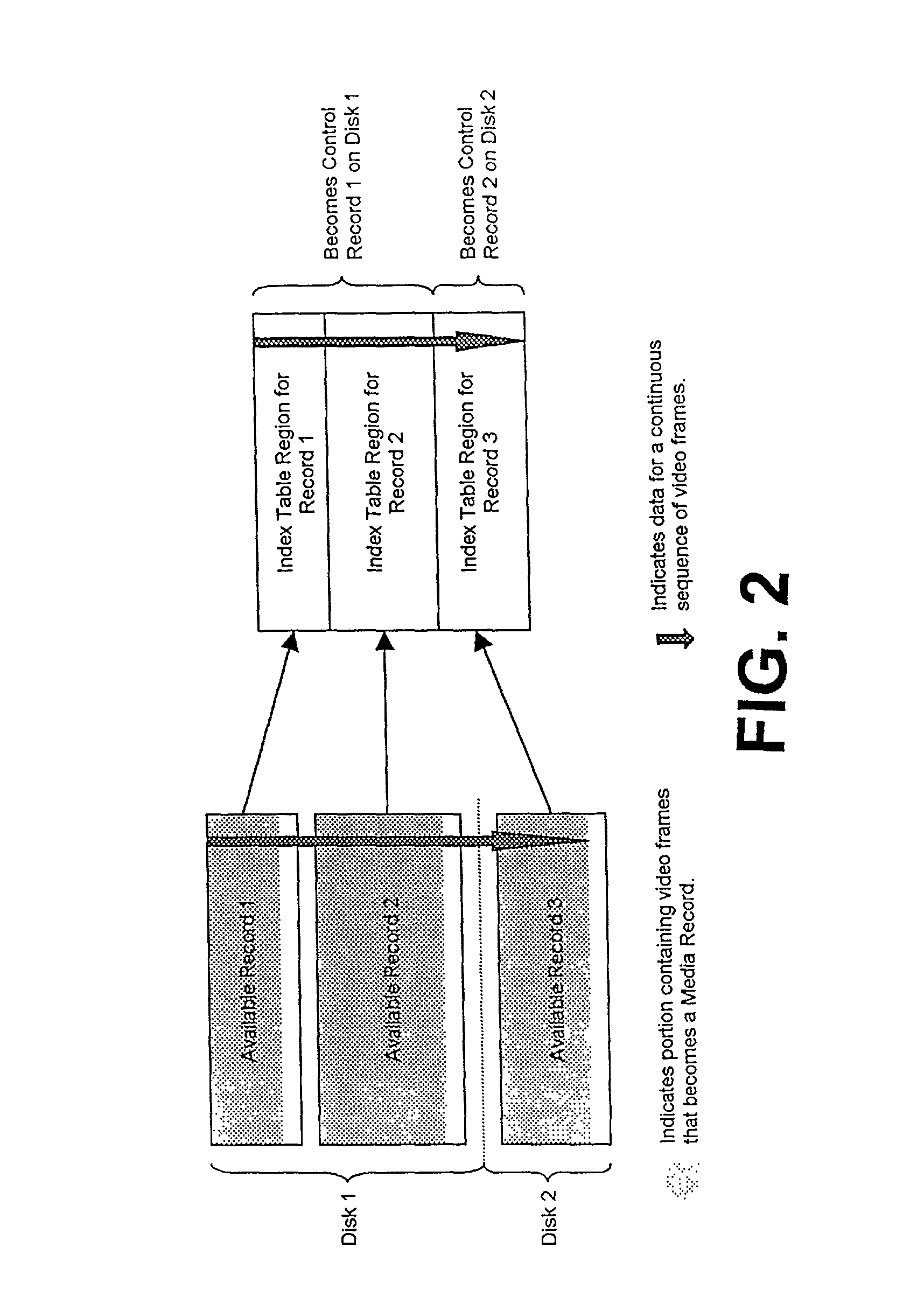

Digital video recorder

InactiveUS20020131765A1Data transfer speed is fastTelevision system detailsColor television detailsHard disc driveBus interface

A unique high performance digital video recorder having a number of novel features. The recorder's electronics are all on a unitary printed circuit board. The recorder also requires at least one hard disk drive and audio and video input analog signals (from a source such as video camera or broadcast media) as well as a suitable monitor for receiving output audio and video analog signals. A external time code generator (i.e., VITC digital clock) is also required for synchronization. Also required are various manual control devices (i.e., panel controls) for mode selection. The electronics of the preferred embodiment comprise A-to-D and D-to-A converters, a hard disk interface, a JPEG compression encoder / decoder, a multi-port DRAM and DMA subsystem, a microprocessor with RS-232 and RS-422 access ports, various working memory devices and bus interfaces and a 16-bit stereo digital audio subsystem. Novel features of the preferred embodiment include use of an index table for disk addresses of recorded frames, a multi-port memory controller in the form of a field programmable gate array (FPGA), loop recording using dual channels, and dynamic JPEG compression compensation.

Owner:FFV SYST

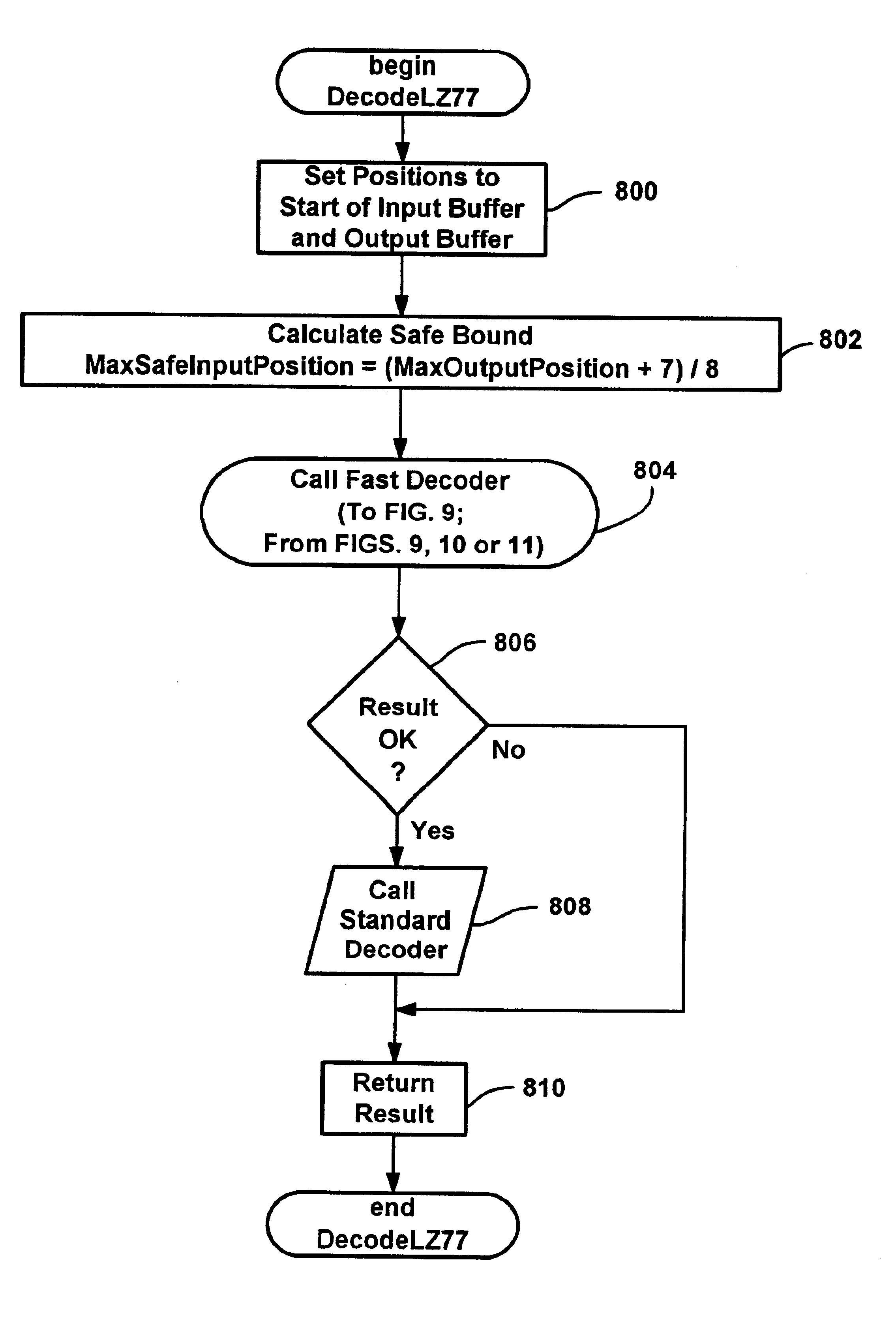

Fast data decoder that operates with reduced output buffer bounds checking

InactiveUS6883037B2Increase speed of data transferReduce in sizeInput/output to record carriersDigital computer detailsSubstringComputer science

Described is an improved decoder that reduces the number of bounds checks needed for typical compressed data by first guaranteeing that there is sufficient room to decode small symbol substrings and literal symbols, whereby bounds checking need not be performed on each symbol. Because literal symbols and small substrings of symbols form the majority of compressed data, the reduced checking significantly speeds up decoding on average. In one implementation, a fast LZ77 decoder that operates without bounds checking is used in a first phase until the end of the output buffer is neared at which time a second phase standard decoder, which performs bounds checks on each to ensure that the buffer does not overflow, is used. Normally the standard decoder decompresses only a small amount of data relative to the amount of data decompressed with the fast decoder, greatly improving decompression speed while not compromising safety.

Owner:MICROSOFT TECH LICENSING LLC

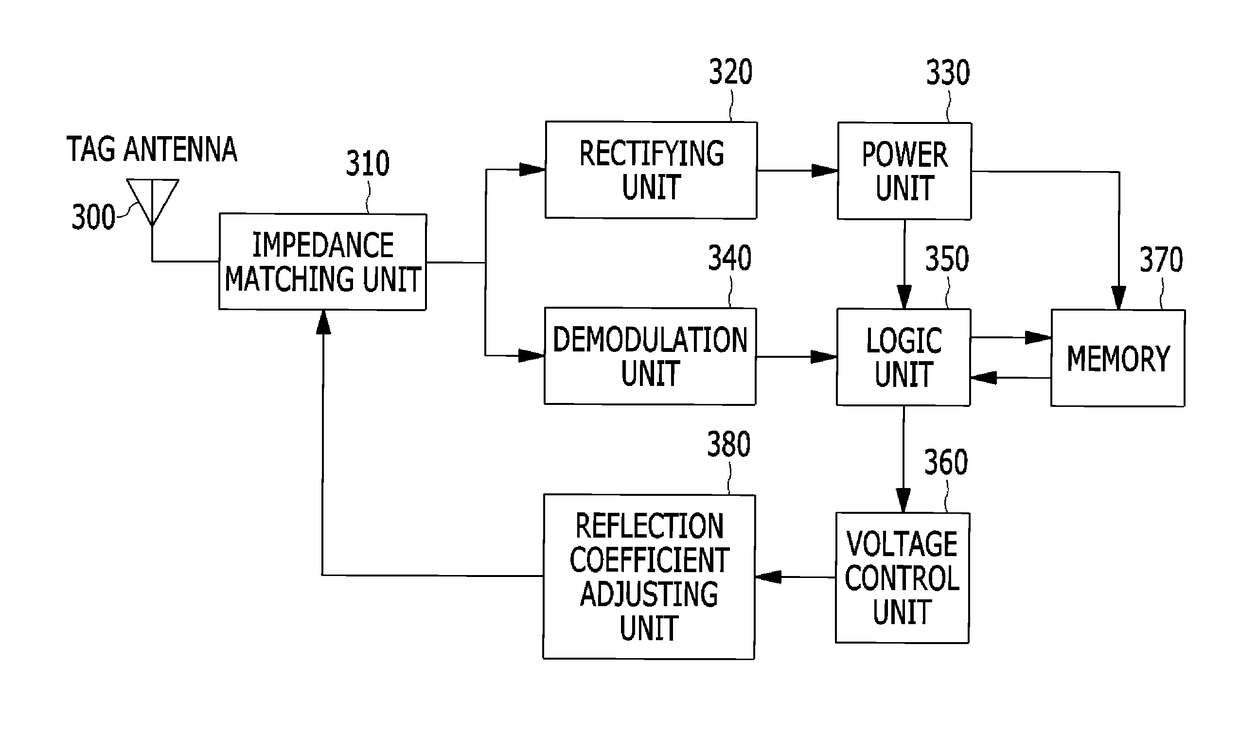

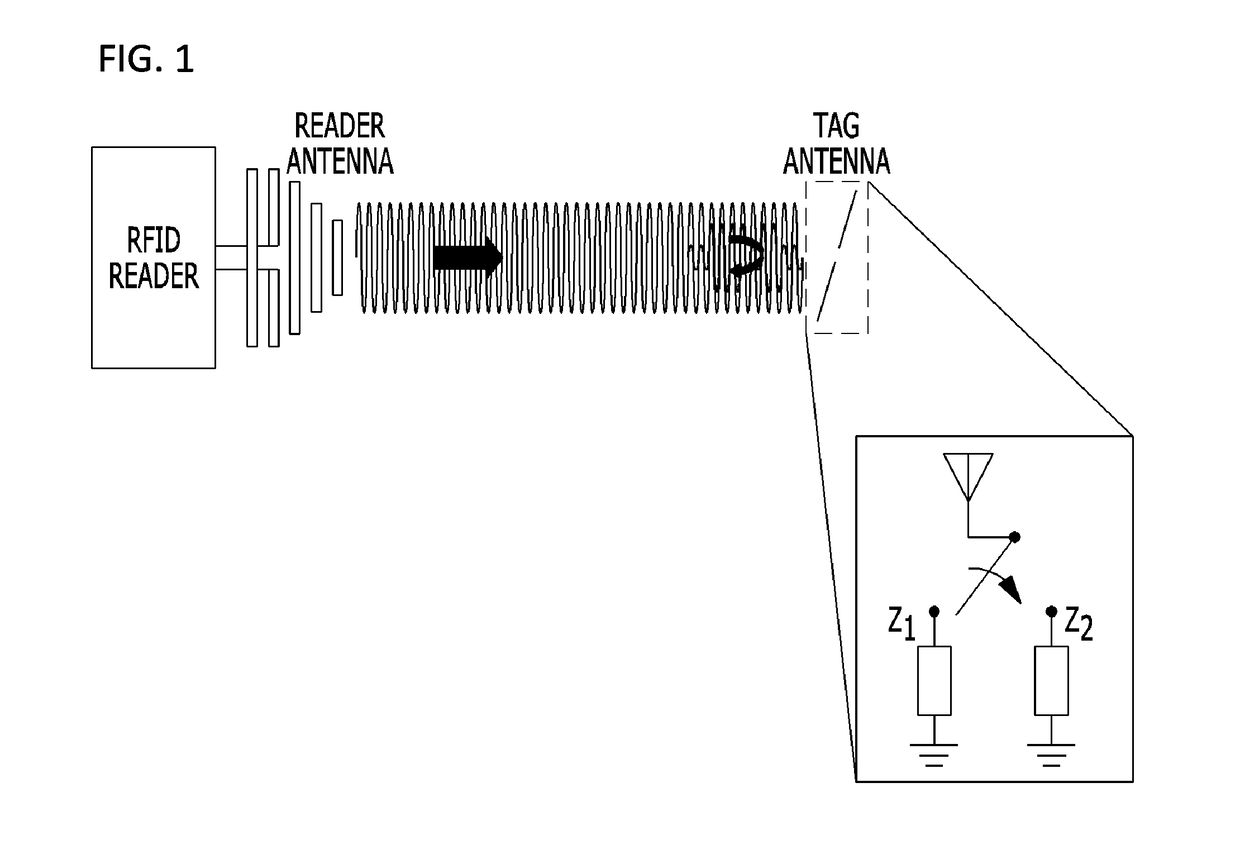

RFID tag and method of controlling the same

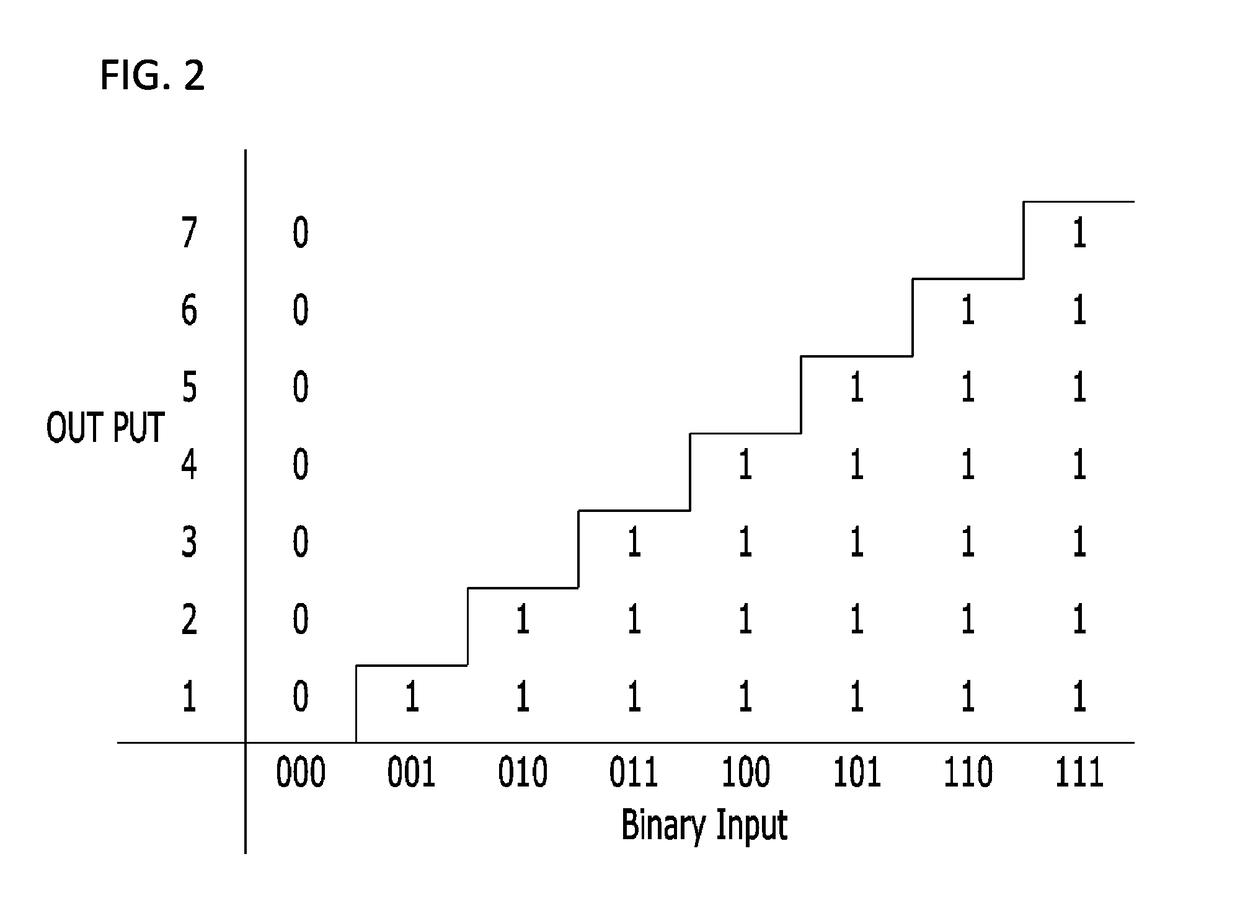

InactiveUS20170193256A1Solve the slow data transmission speedIncrease rangeRecord carriers used with machinesSensing by electromagnetic radiationData transmissionEmbedded system

Disclosed are a high speed wide range RFID tag capable of improving a data transmission speed and a recognition distance between an RFID tag and an RFID reader by controlling a reflected power as multi levels through adjustment of a reflection coefficient in the RFID tag, and a method of controlling the same. The RFID tag includes a data converting unit configured to convert stored RFID serial tag data into a number of multi-level parallel data according to a request of an RFID reader, a reflection coefficient adjusting unit configured to generate a plurality of reflection coefficients corresponding to a number of the converted parallel data, and a transmitting unit configured to transmit a number of the multi-level parallel data according to the generated plurality of tag reflection coefficients through an antenna to the RFID reader.

Owner:ELECTRONICS & TELECOMM RES INST

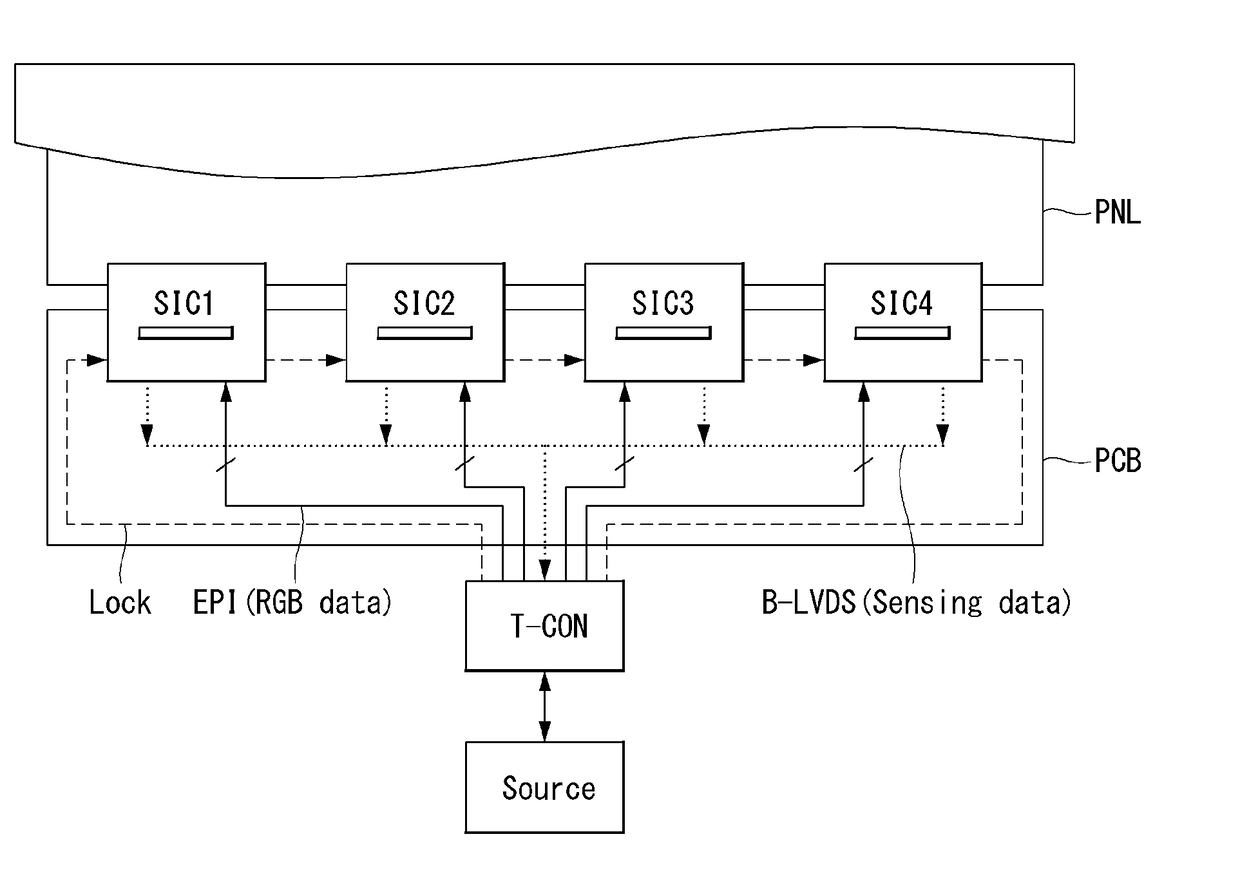

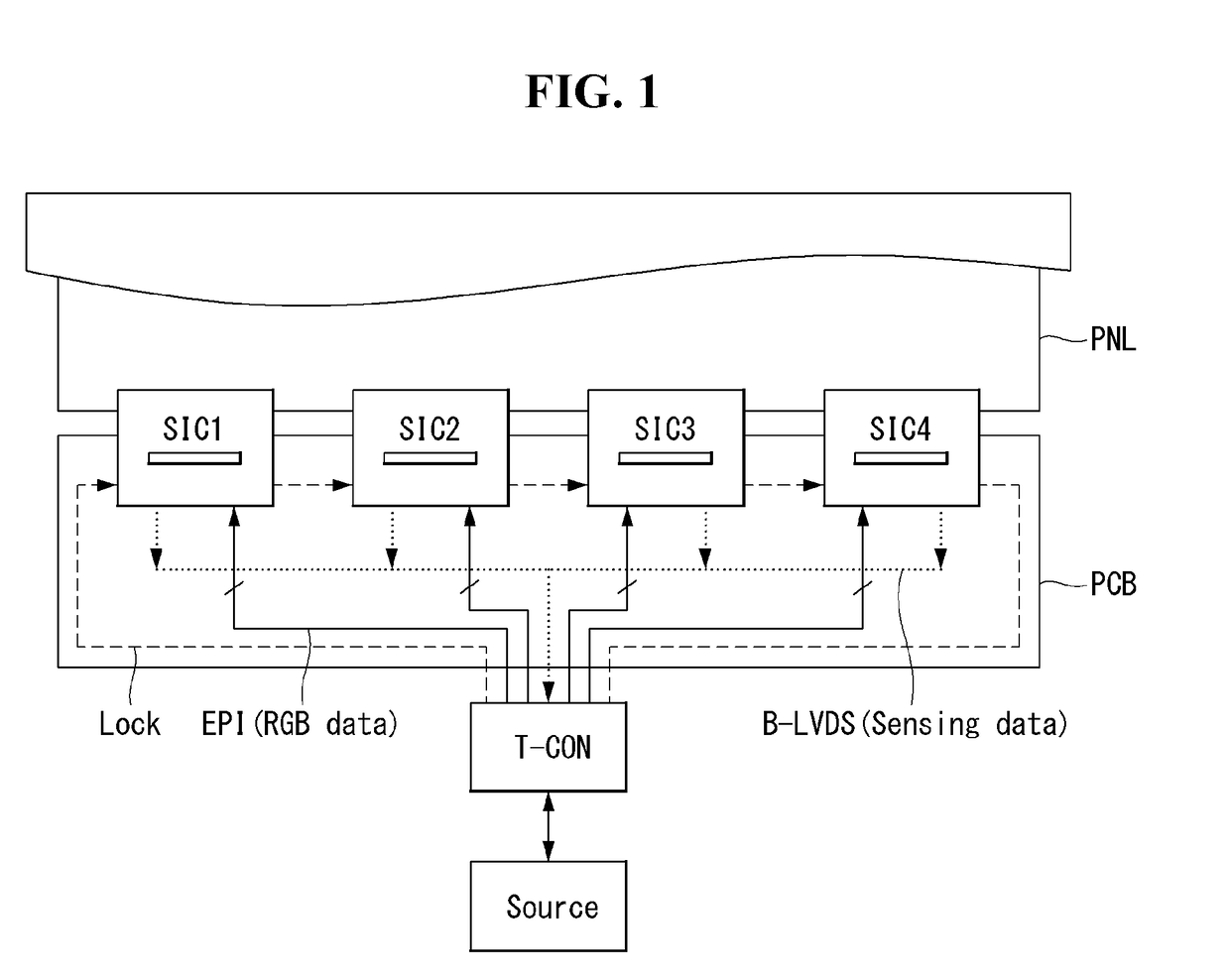

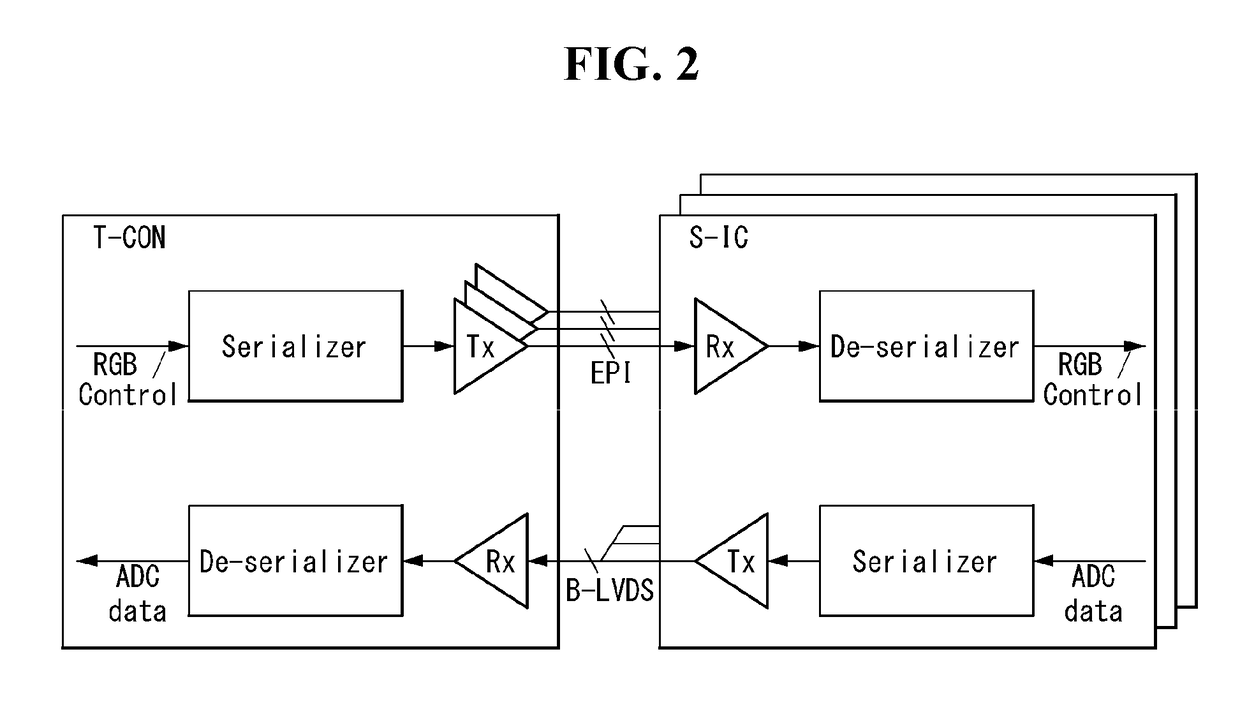

Display Device

ActiveUS20180122294A1Reduce in quantityConnection structureCathode-ray tube indicatorsSensing dataNetwork packet

The display device according to an embodiment of the present disclosure comprises a display panel; a source drive IC configured to provide data voltages to the pixels, convert signals indicating driving characteristics of the pixels into sensing data and output the sensing data; and a timing controller configured to transmit a control data packet and a video data packet to the source drive IC through first and second wire pairs and receive the sensing data from the source drive IC through the second wire pair, wherein the timing controller is configured to load lock information indicating whether a clock extracted from a signal provided from the source drive IC through the second wire pair is locked or not into the control data packet and provide the control data packet to the source drive IC through the first wire pair, when receiving data from the source drive IC.

Owner:LG DISPLAY CO LTD

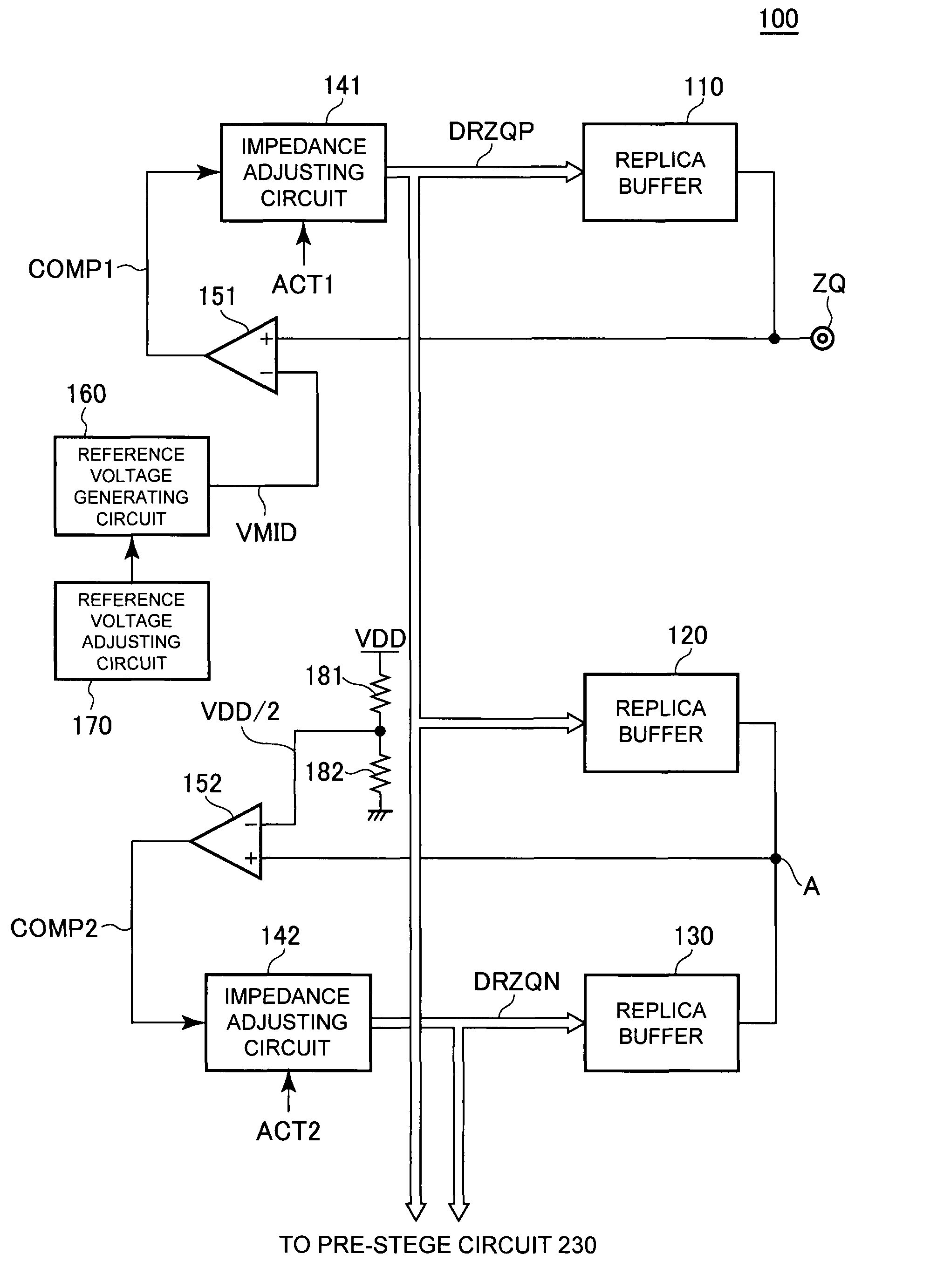

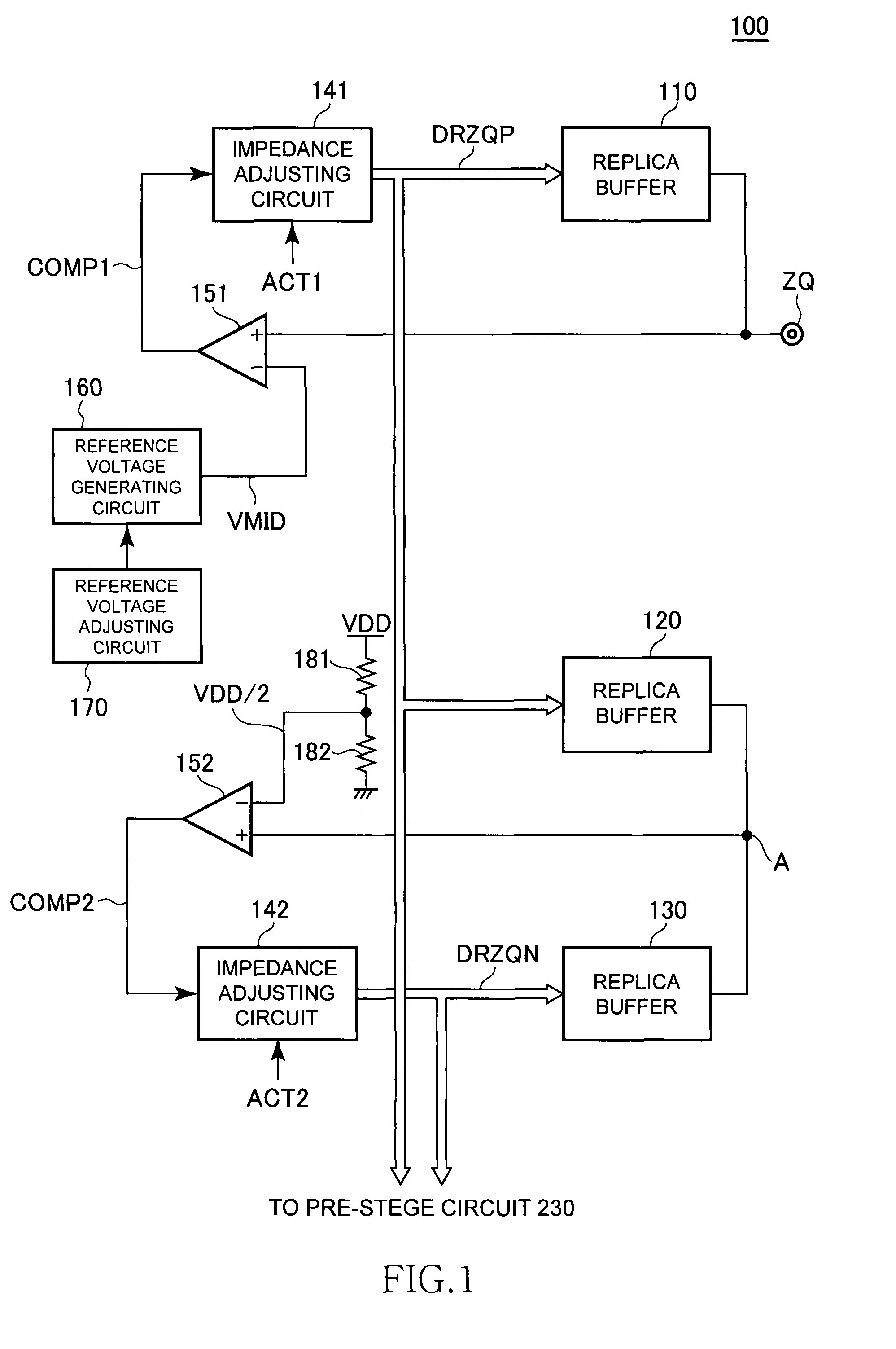

Calibration circuit, semiconductor device including the same, and method of adjusting output characteristics of semiconductor device

InactiveUS7755366B2Exact impedanceAccurate operationPulse automatic controlElectrical measurementsVoltage referenceOutput impedance

A calibration circuit includes: a replica buffer that drives a calibration terminal ZQ; a reference voltage generating circuit that generates a reference voltage VMID; a comparing circuit that compares a voltage appearing in the calibration terminal ZQ with the reference voltage VMID; an impedance adjusting circuit that changes an output impedance of the replica buffer based on a result of comparison carried out by the comparing circuit; and a reference voltage adjusting circuit that adjusts the reference voltage VMID. With this arrangement, the reference voltage VMID can be offset by taking into account a resistance component present between the calibration terminal ZQ and the external terminal, and therefore, a more accurate calibration operation can be carried out.

Owner:LONGITUDE LICENSING LTD

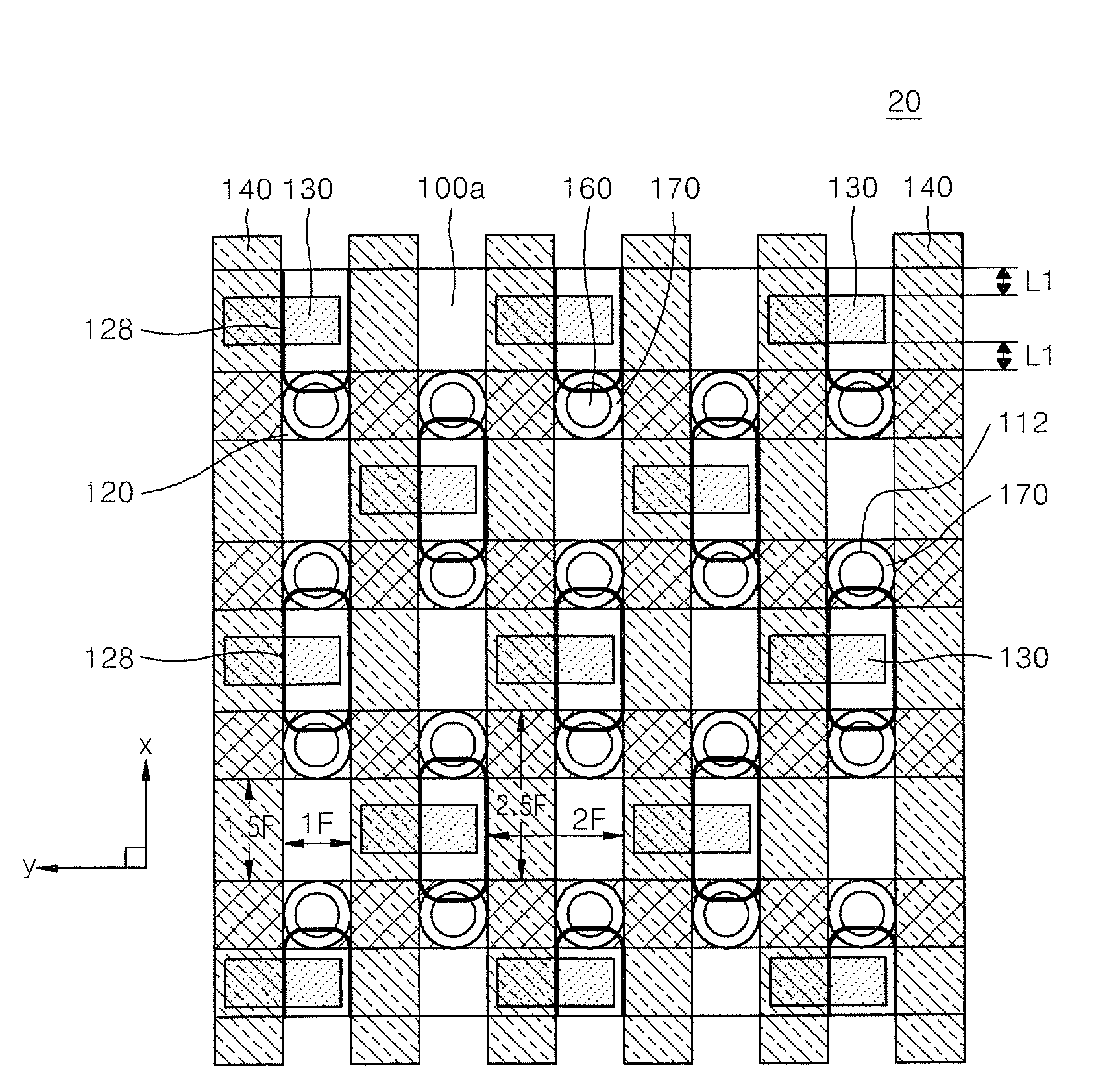

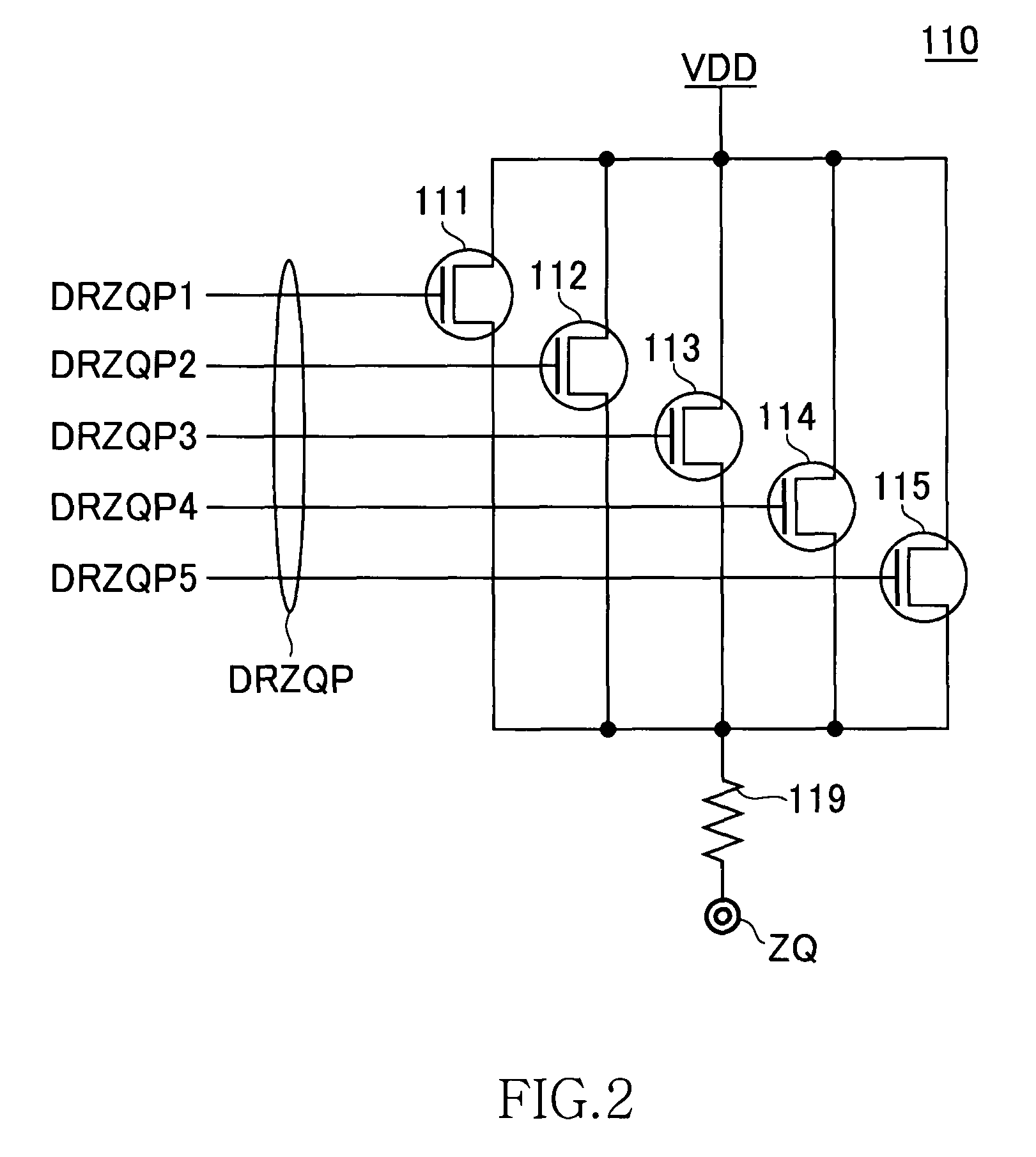

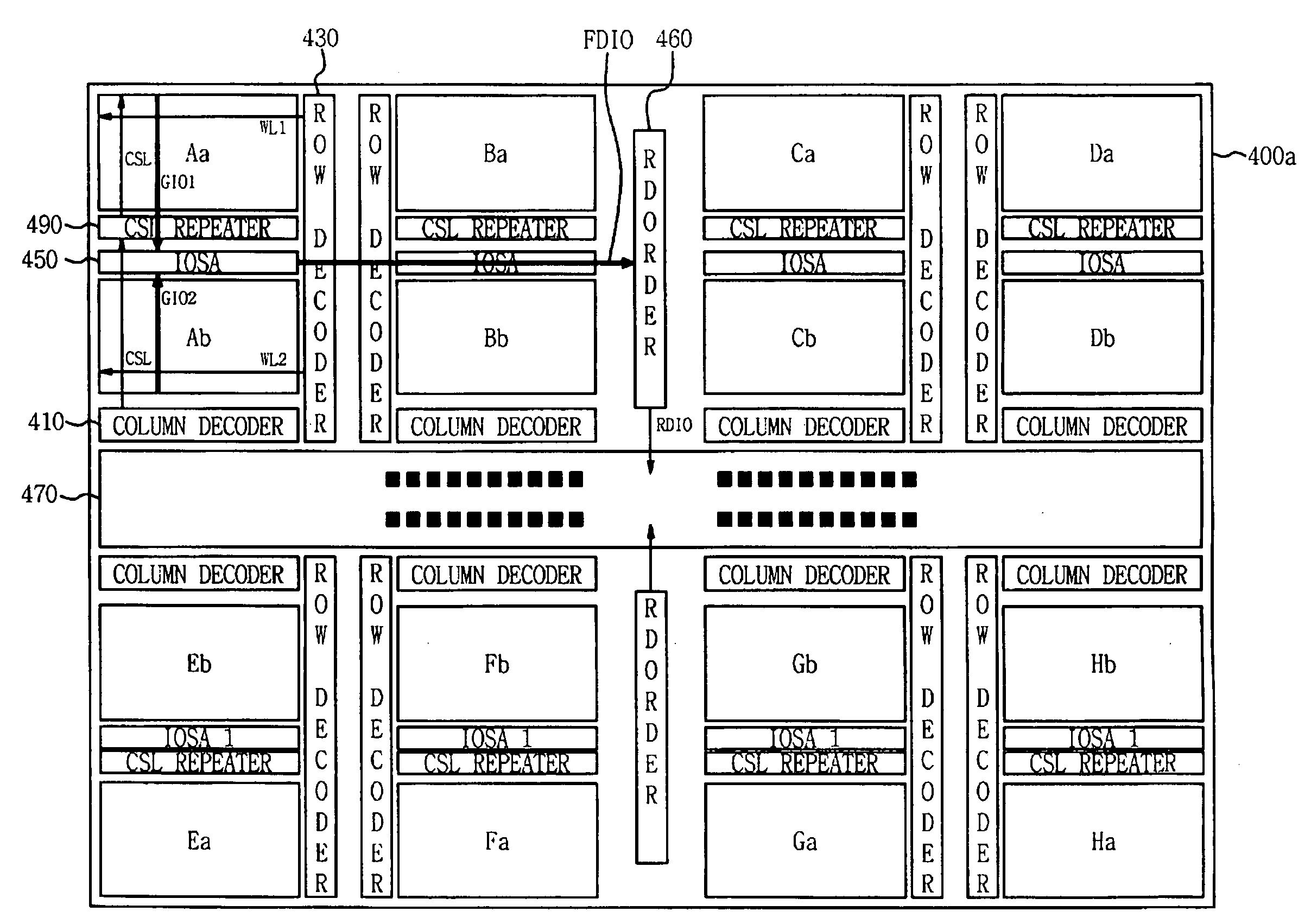

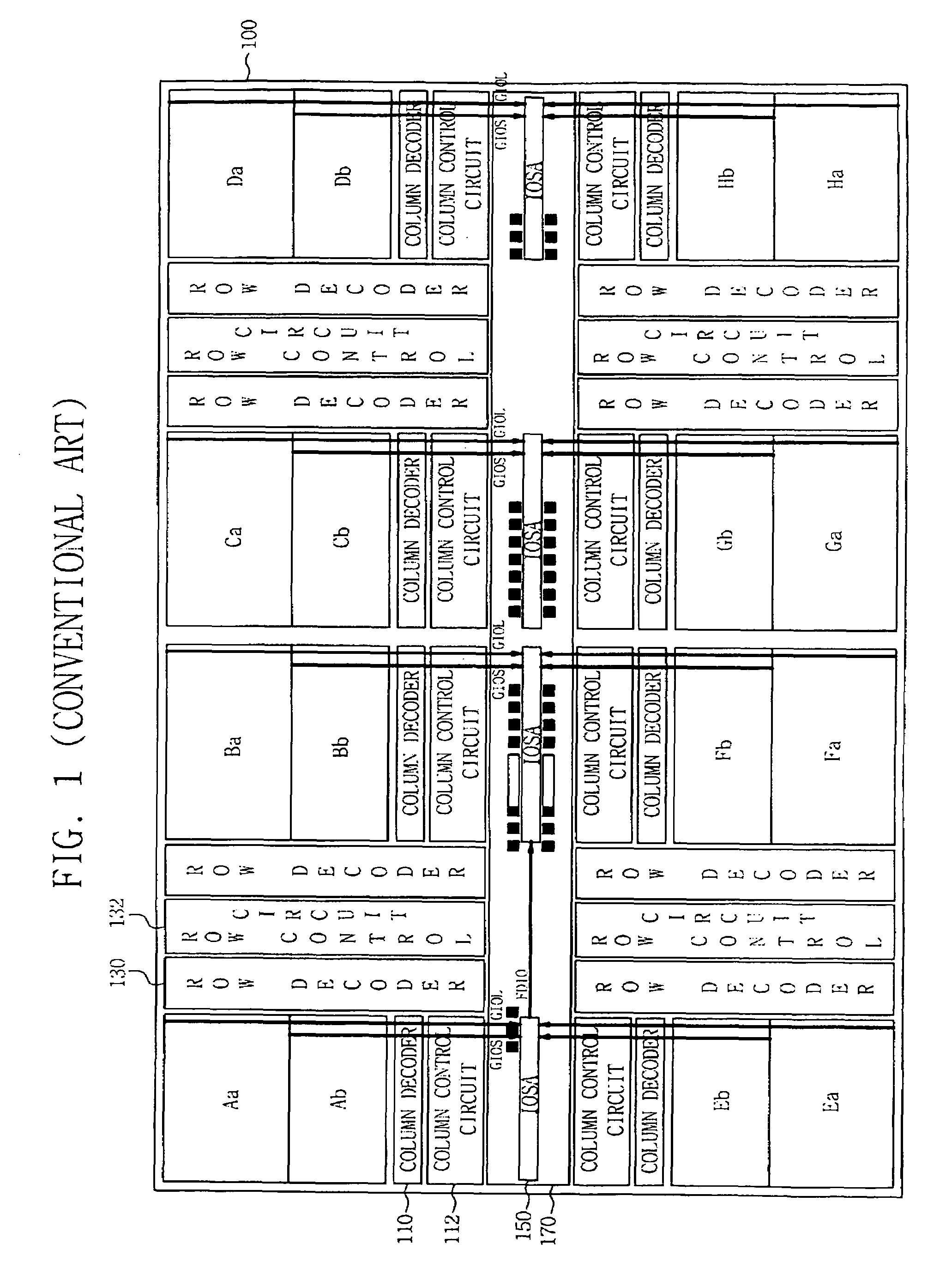

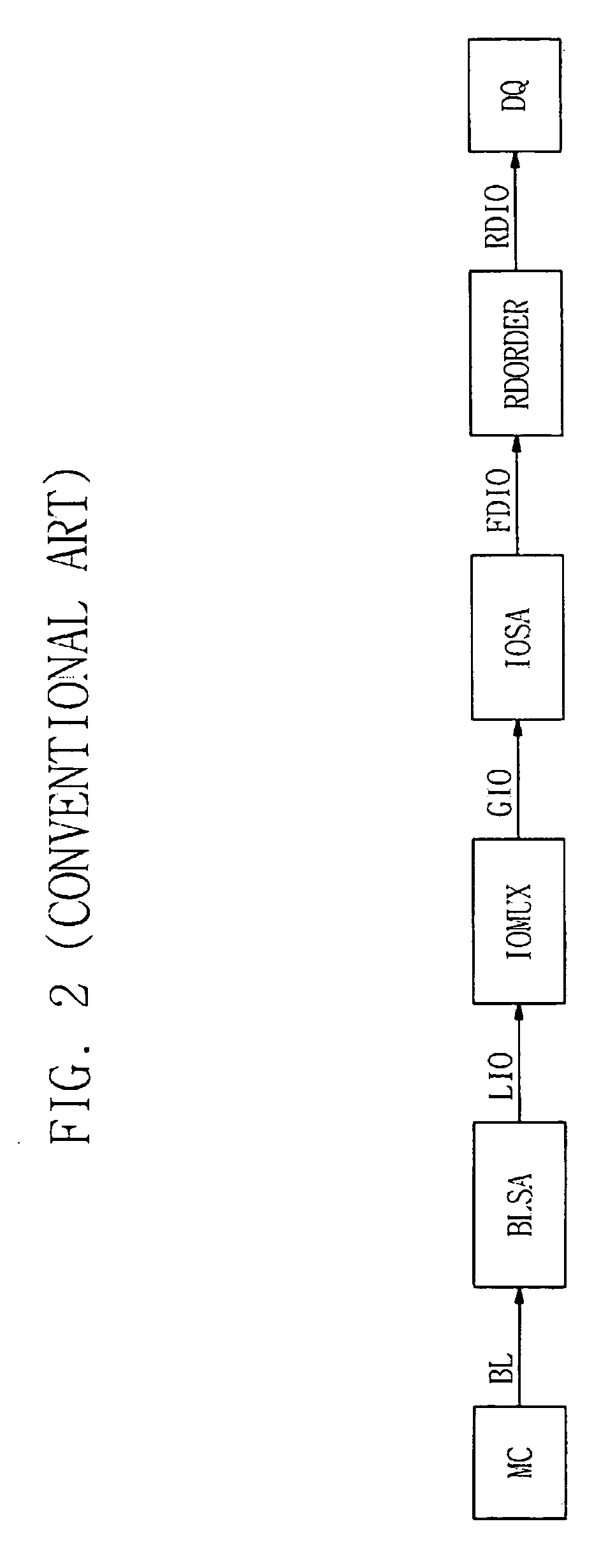

Layout structure of semiconductor memory device having iosa

ActiveUS20080205177A1Improve densityImprove the layout densityDigital storageData transmissionSense amplifier

Embodiments of the invention provide a layout for a semiconductor memory device that splits each memory bank into two blocks. Embodiments of the invention dispose input / output sense amplifiers between the two memory blocks to achieve relatively short global input / output lines to all areas of the memory bank. Shorter global input / output lines have less loading and therefore enable higher-speed data transfer rates. Some embodiments of the invention include column selection line repeaters between the two memory blocks. The column selection line repeaters reduce loading in the column selection lines, and increase column selection speed. Embodiments of the invention include both input / output sense amplifiers and column selection line repeaters disposed between the two memory blocks to increase data transfer rates on the global input / output lines and also increase column selection speed.

Owner:SAMSUNG ELECTRONICS CO LTD

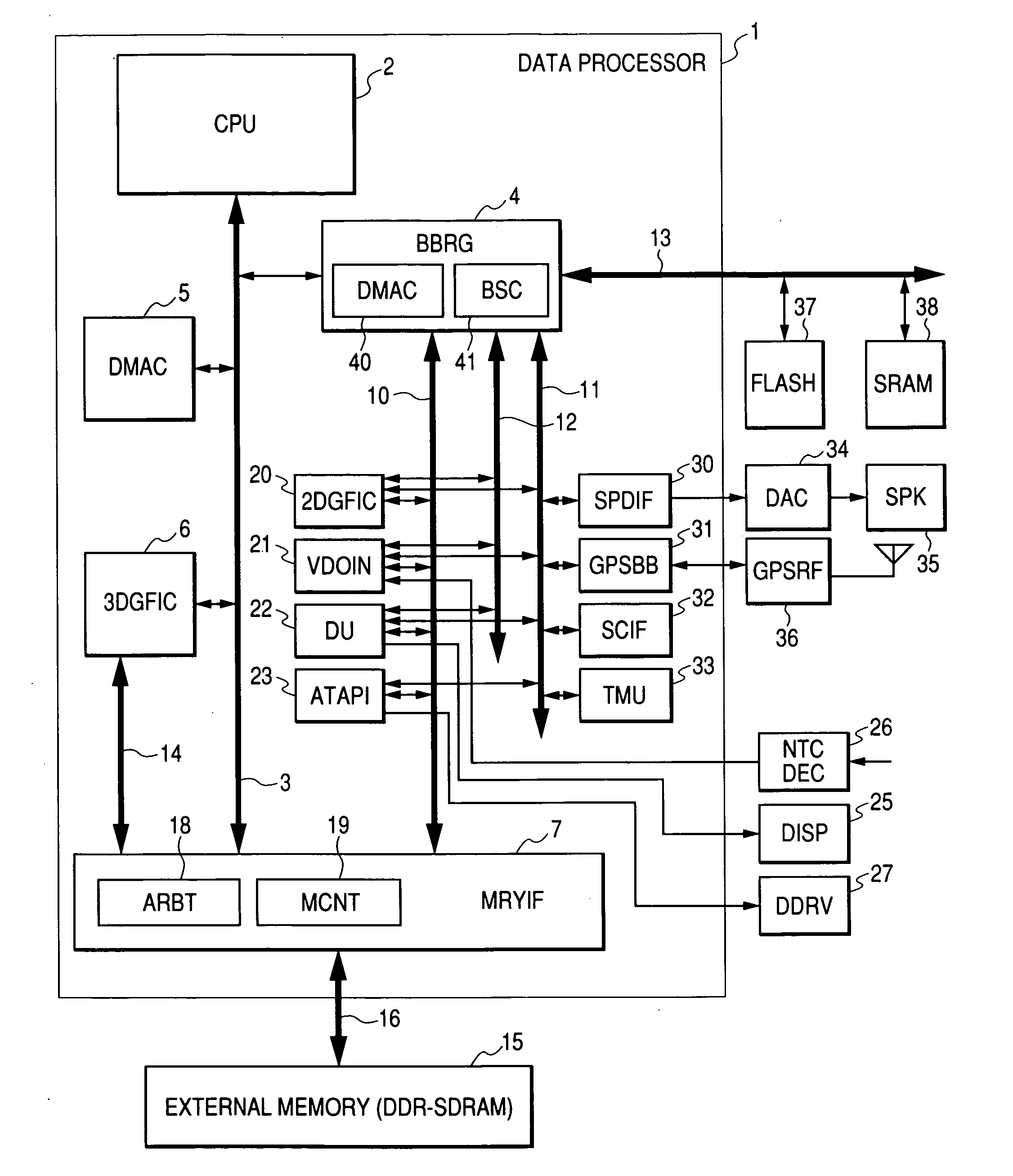

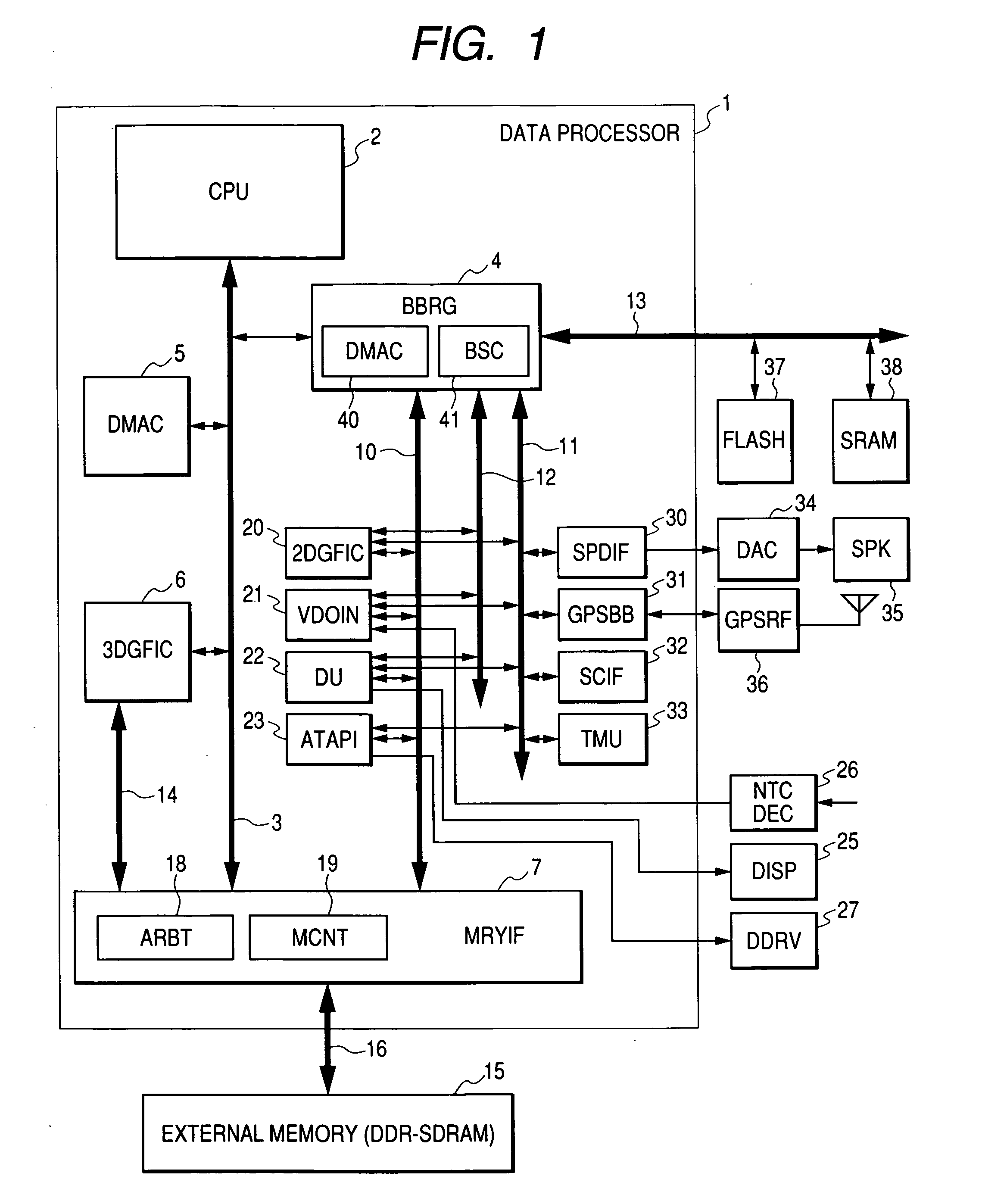

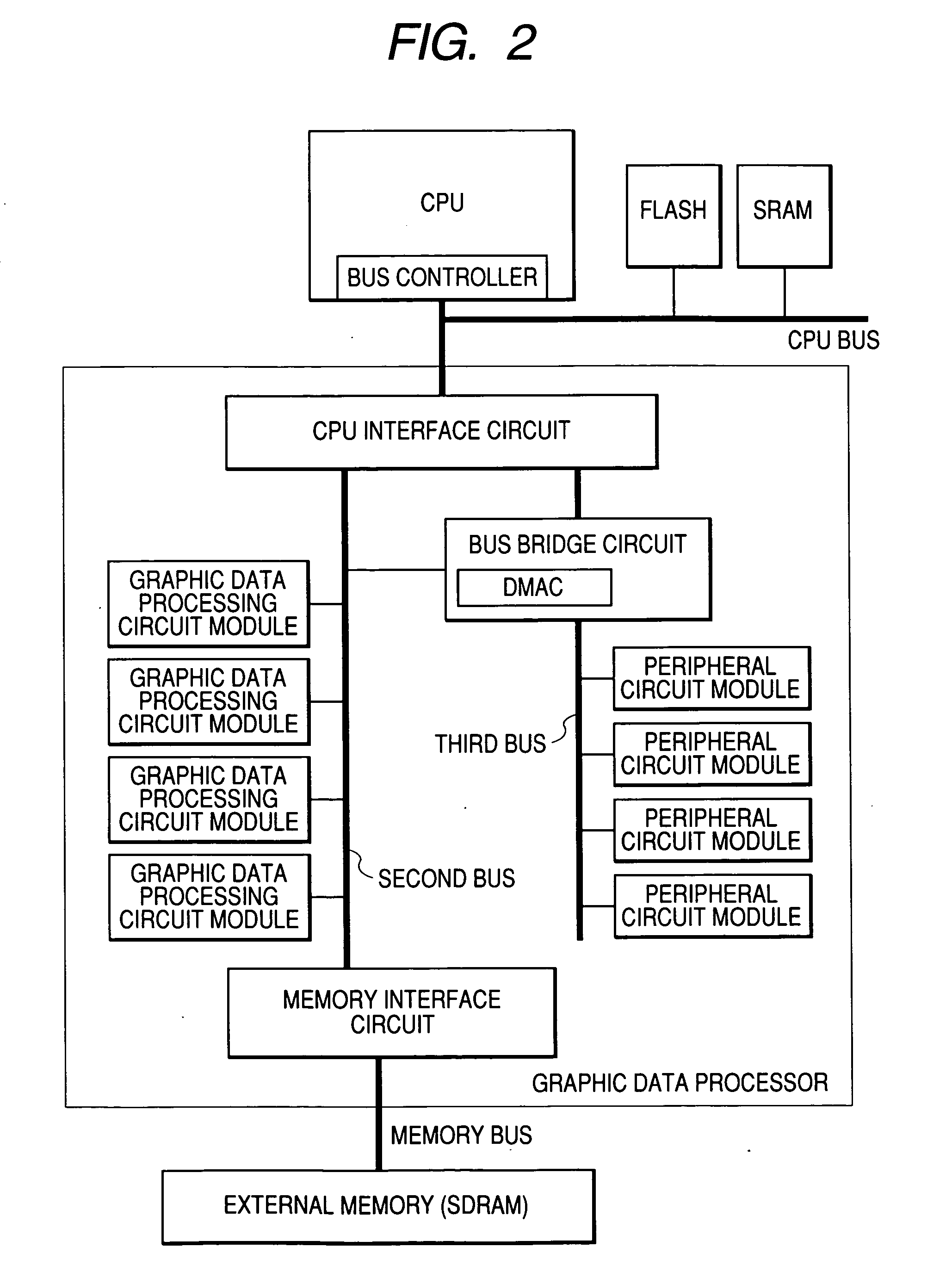

Data processor and graphic data processing device

ActiveUS20050030311A1Improve data processing speedData transfer speed is fastDrawing from basic elementsProcessor architectures/configurationDirect memory accessExternal storage

An object of the present invention is to improve efficiency of transfer of control information, graphic data, and the like for drawing and display control in a graphic data processor. A graphic data processor includes: a CPU; a first bus coupled to the CPU; a DMAC for controlling a data transfer using the first bus; a bus bridge circuit for transmitting / receiving data to / from the first bus; a three-dimensional graphics module for receiving a command from the CPU via the first bus and performing a three-dimensional graphic process; a second bus coupled to the bus bridge circuit and a plurality of first circuit modules; a third bus coupled to the bus bridge circuit and second circuit modules; and a memory interface circuit coupled to the first and second buses and the three-dimensional graphic module and connectable to an external memory, wherein the bus bridge circuit can control a direct memory access transfer between an external circuit and the second bus.

Owner:RENESAS ELECTRONICS CORP

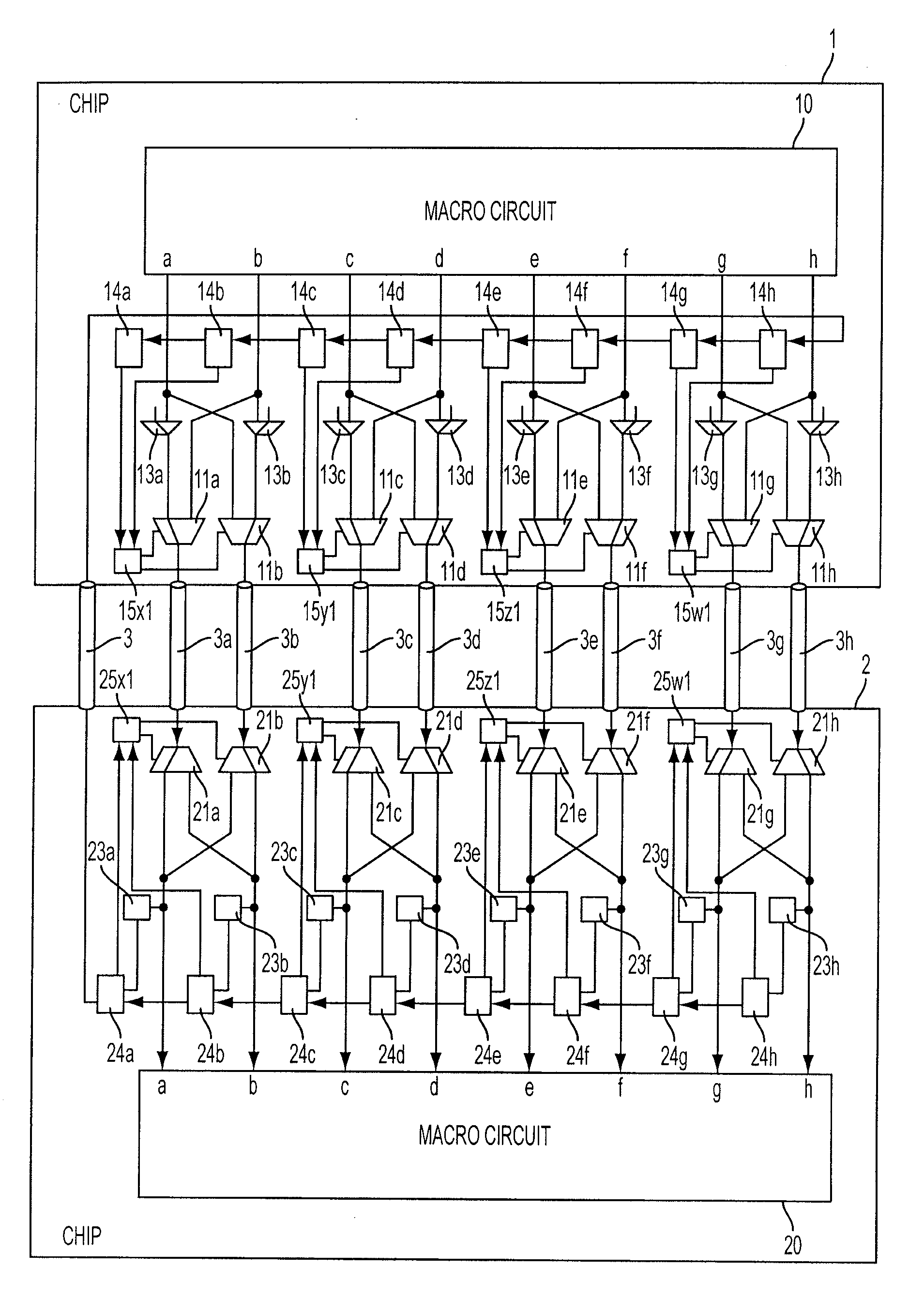

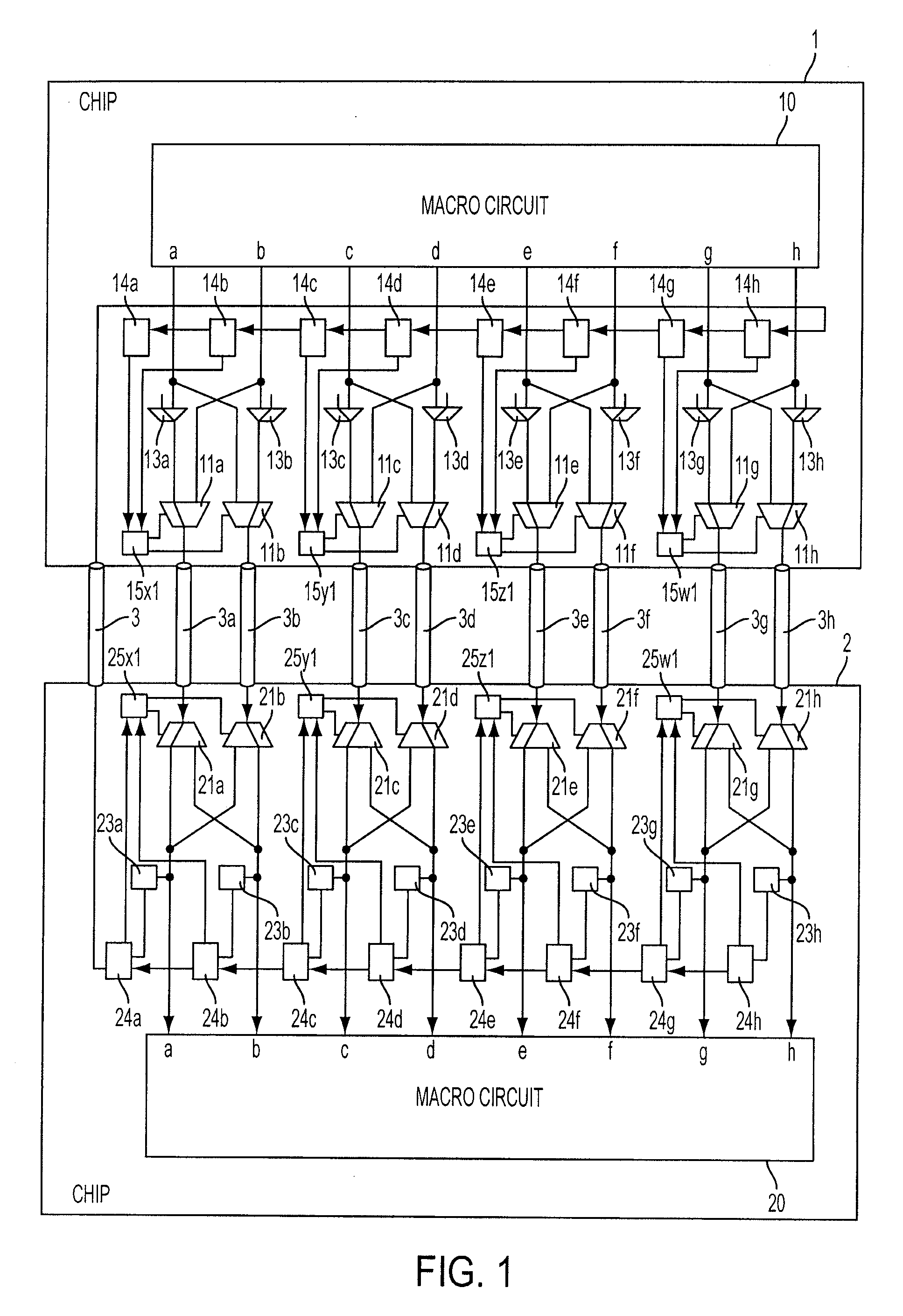

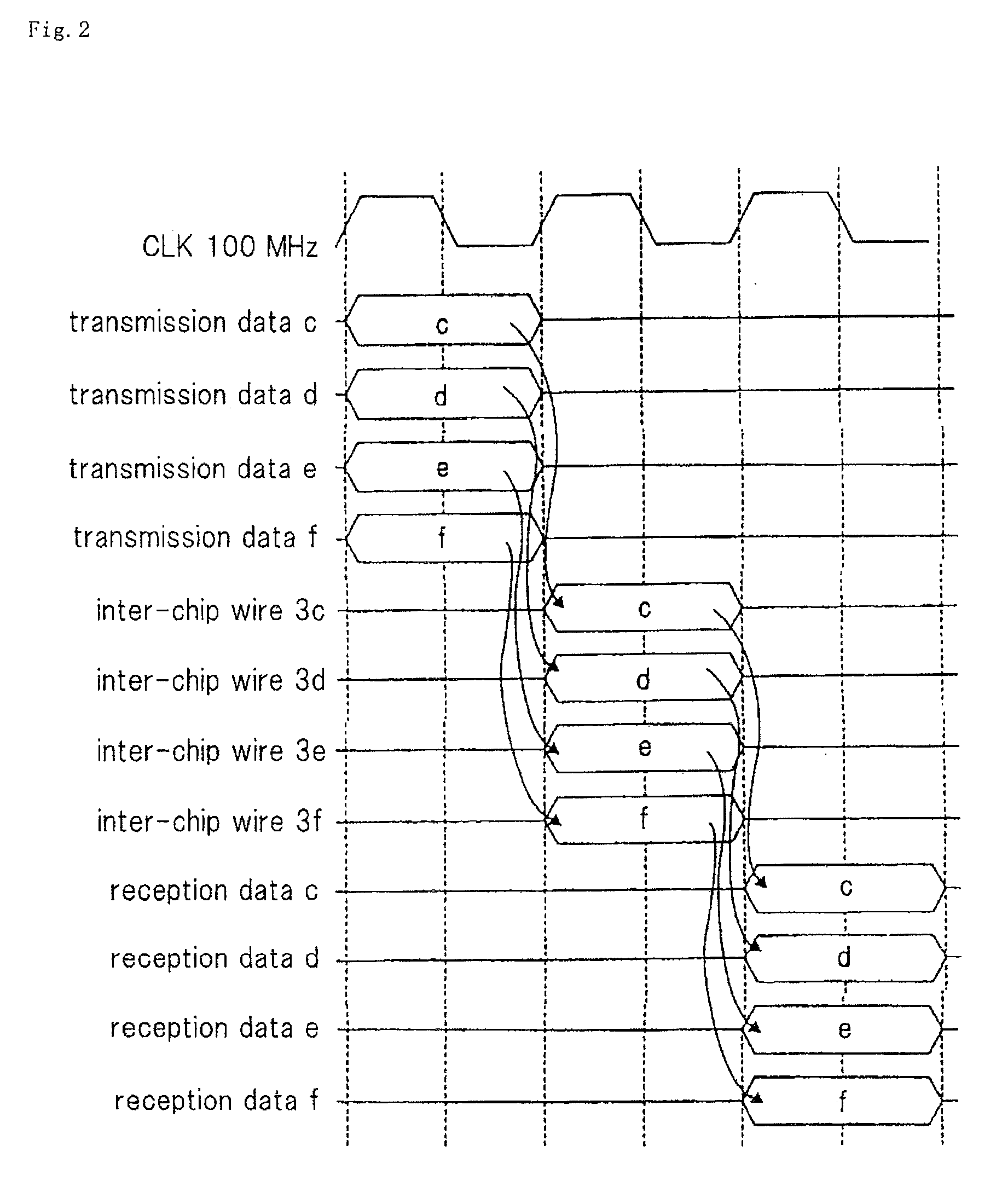

Data transfer between chips in a multi-chip semiconductor device with an increased data transfer speed

ActiveUS20090141827A1Reduce the amount of dataReduce the amount requiredModulated-carrier systemsSolid-state devicesData transmissionSemiconductor

A data transfer method is disclosed in a multi-chip semiconductor device which comprises a plurality of inter-chip wires. First, a test is conducted to determine whether or not each inter-chip wire is capable of normally transferring data, on circuits arranged on chips between which the inter-chip wire is connected. When an inter-chip wire incapable of normally transferring data exists, the data transfer speed of the buffer circuit that is on the chip on the transmission and that is connected to an inter-chip wire capable of normally transferring data is increased. The buffer circuit, whose data transfer speed has been increased, transfers data which would otherwise be transferred through the inter-chip wire incapable of normally transferring data, together with the data which should be transferred thereby, to the chip on the reception side chip through an inter-chip wire connected to the buffer circuit at the data transfer speed.

Owner:NEC CORP +1

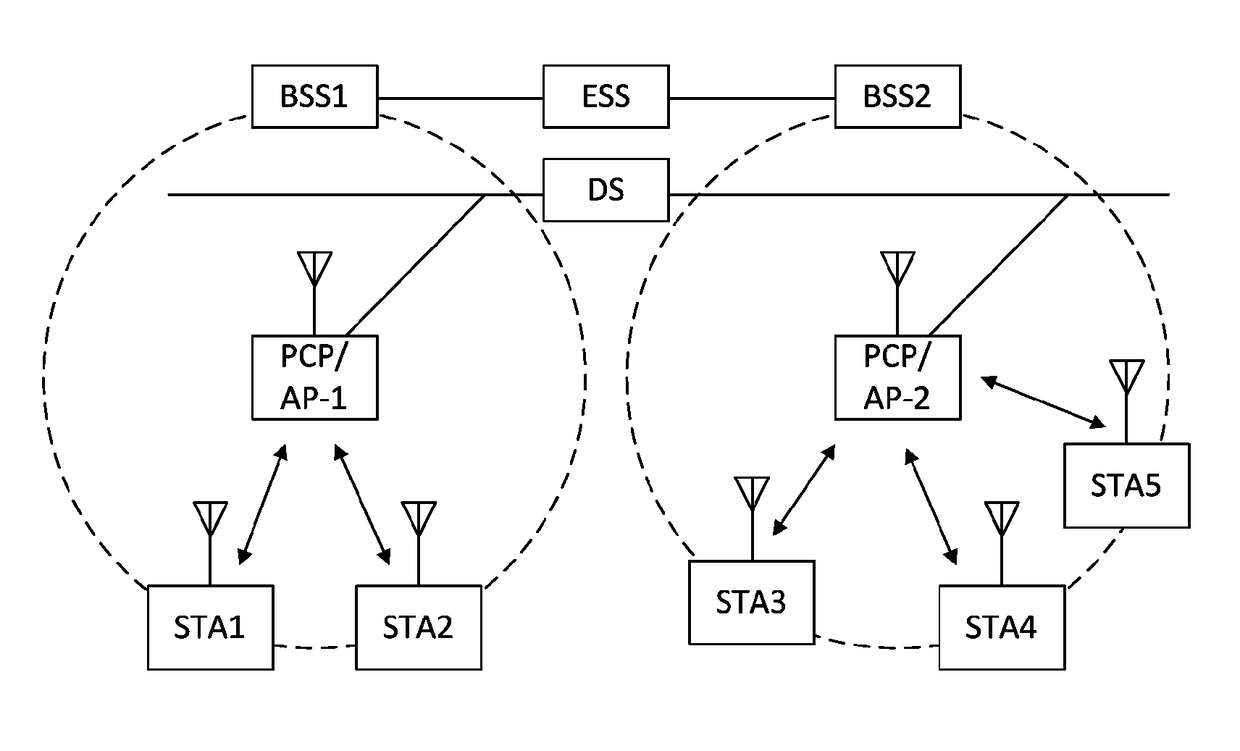

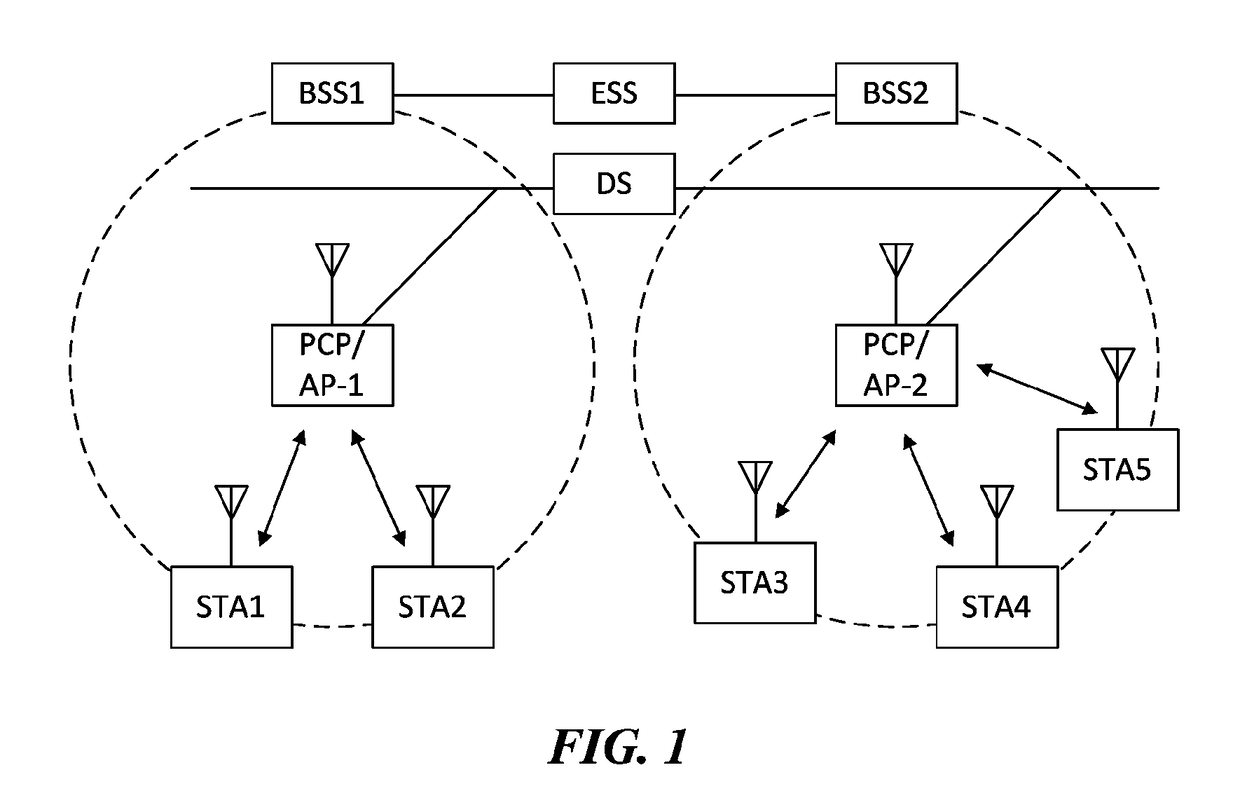

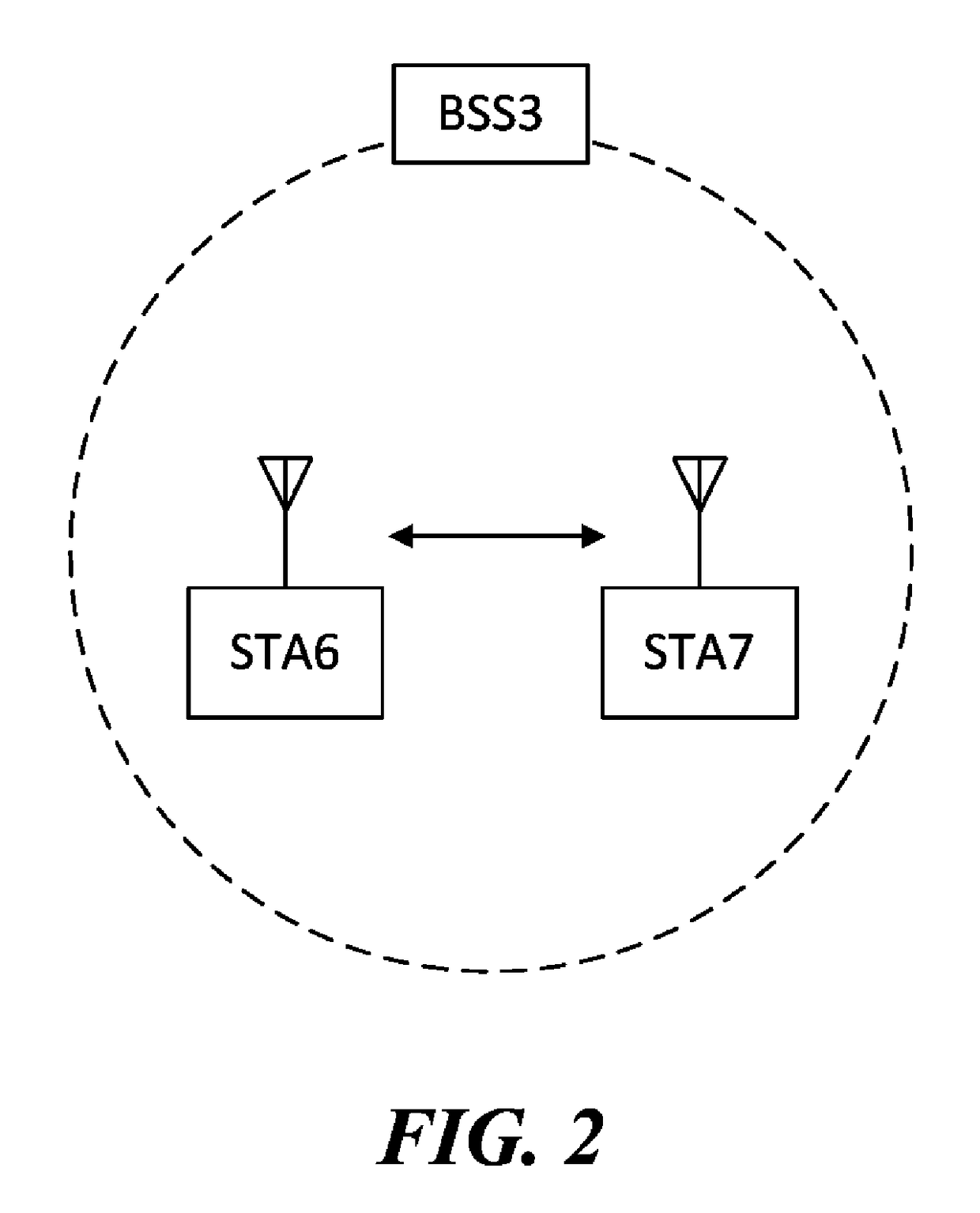

Wireless communication method and wireless communication device for broadband link configuration

ActiveUS20170188336A1Data transfer speed is fastIncrease overall channel use rateNetwork topologiesTransmission path multiple useData transmissionPrimary channel

The present invention relates to a wireless communication method and a wireless communication terminal for wideband link setup, and more particularly, a wireless communication method and a wireless communication terminal for increasing data communication efficiency by extending a data transmission bandwidth of a terminal.To this end, provided are a wireless communication method of a terminal, including: obtaining first primary channel information of a basic service set (BSS) with which the terminal is associated; performing clear channel assessment (CCA) for one or more secondary channels of the BSS; and setting a second primary channel among one or more secondary channels determined to be idle based on a result of the CCA, and a wireless communication terminal using the same.

Owner:WILUS INST OF STANDARDS & TECH +1

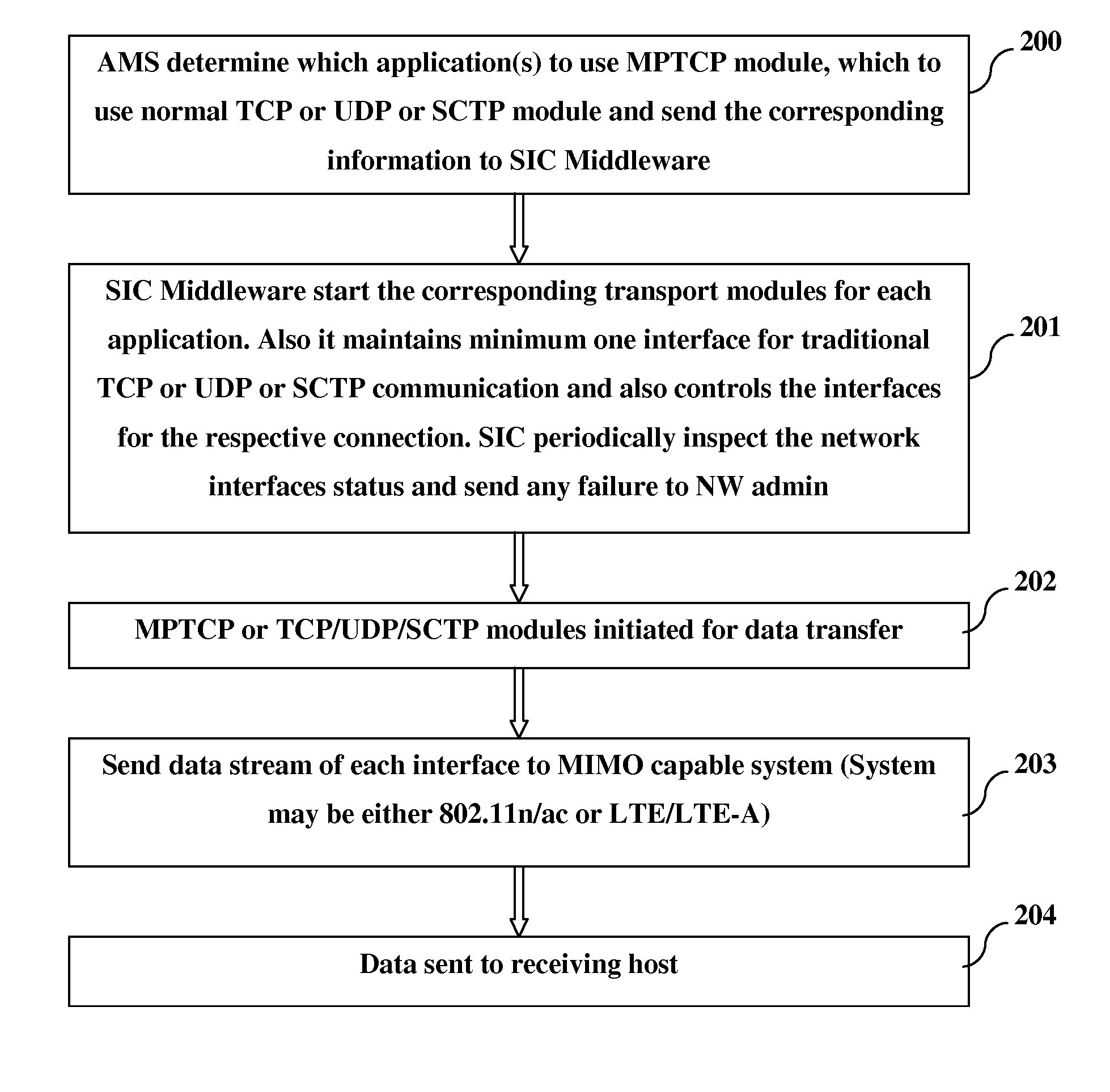

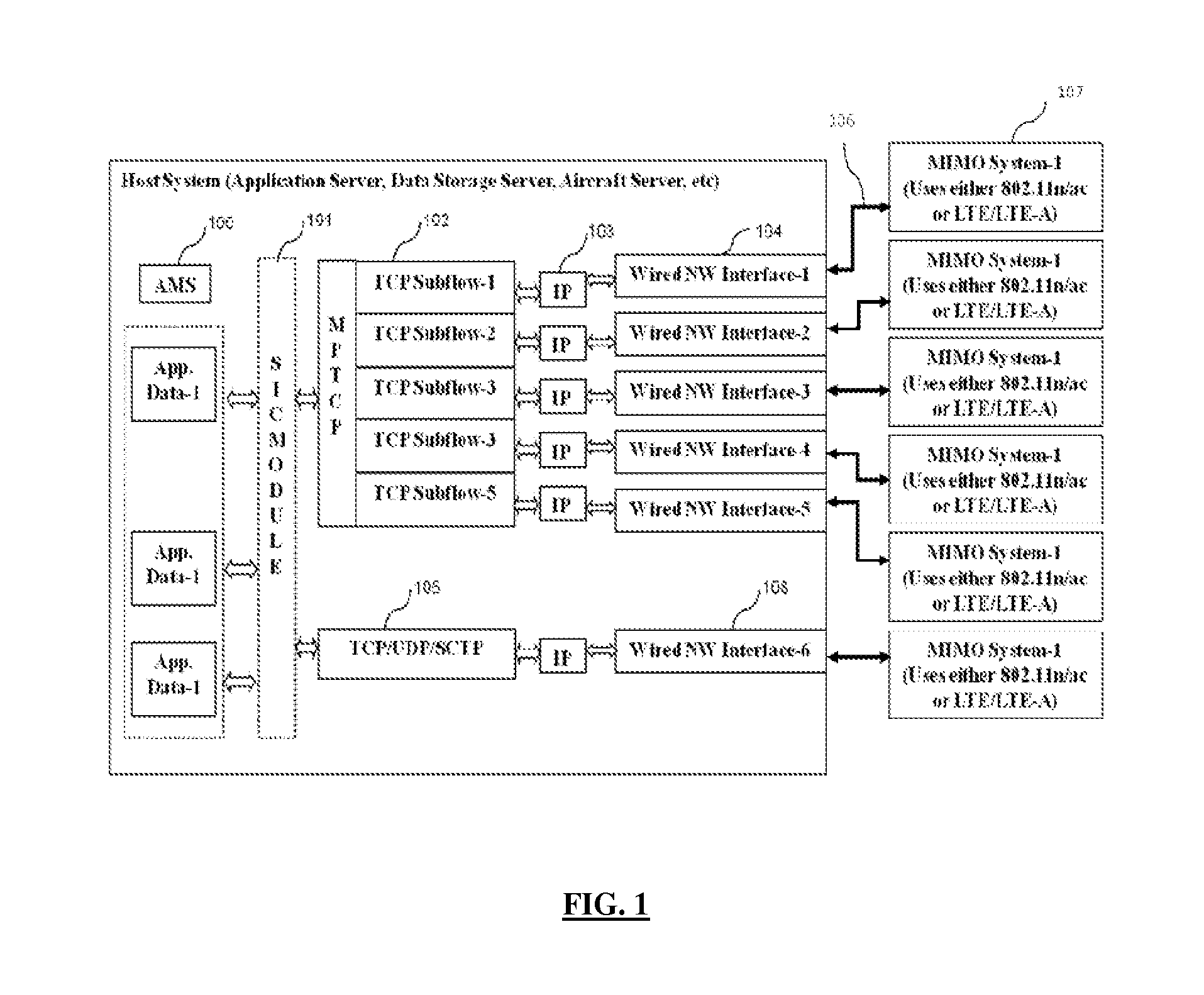

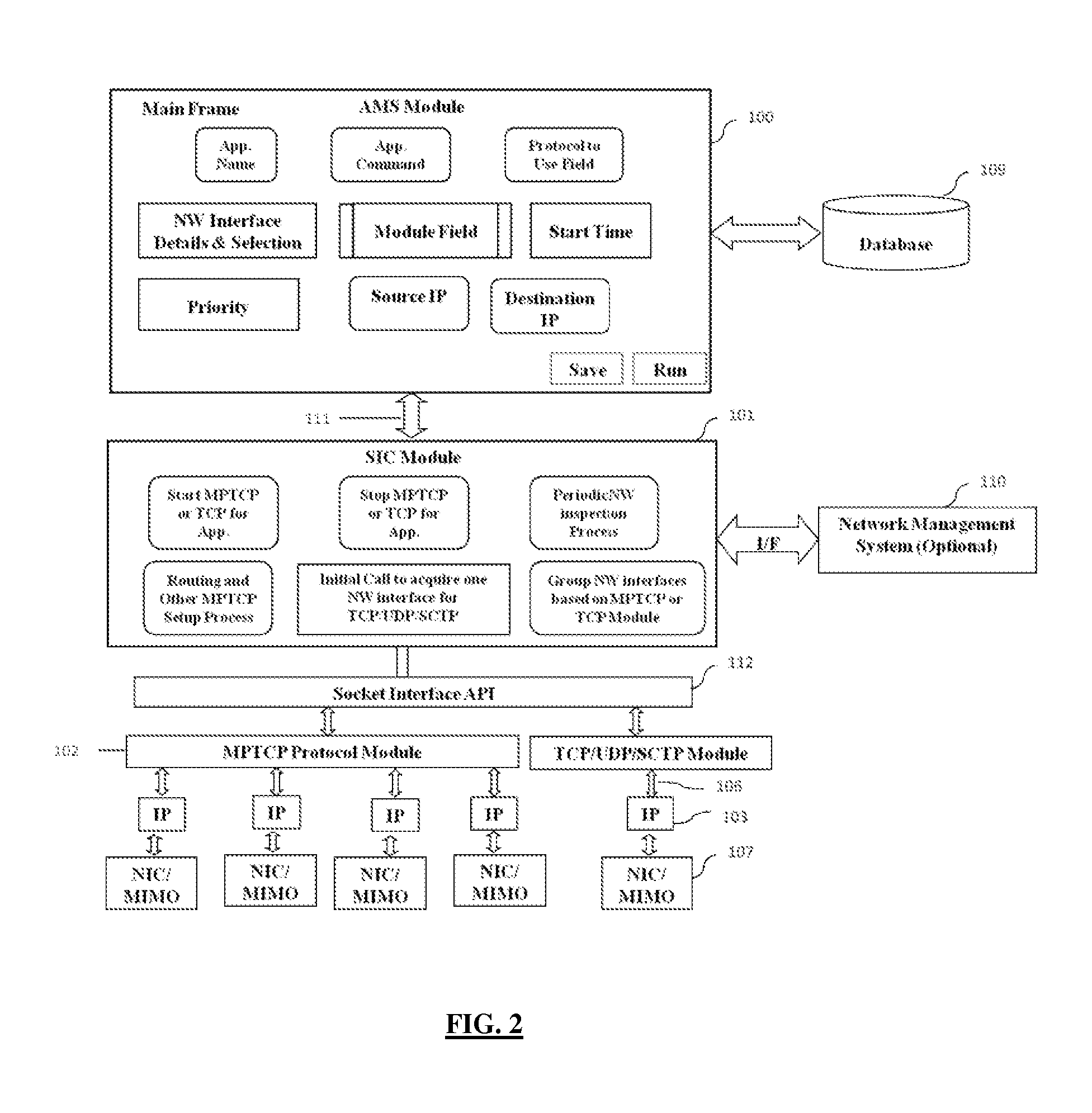

efficient mechanism to improve data speed between systems by MPTCP and MIMO combination

ActiveUS20150295782A1Improve speedData transfer speed is fastDigital computer detailsRadio transmissionData transmissionApplication management system

An apparatus for improving data transfer speed by using Multipath Transport Control Protocol (MPTCP) and Multiple-Input Multiple-Output (MIMO) combination, wherein the apparatus comprises a user interface module called Application Management System (AMS) module (100) to receive user inputs for managing transport protocol (MPTCP or conventional TCP / UDP / SCTP) usage selection. The apparatus also includes a Selection, Inspection Control (SIC) middleware module (101) which STARTs and STOPs the corresponding MPTCP module or conventional TCP / UDP / SCTP module based on the user inputs received from AMS. The MPTCP module splits the data traffic into multiple TCP subflows and sends the subflows via wired network interface (104), wherein each network interface is connected to one MIMO systems (107) for achieving efficient data transfer.

Owner:HCL TECH LTD

Probe memory device and positioning method therefor

InactiveUS20070030791A1Small dimensionImprove accuracyNanoinformaticsRecord information storageHigh densityHigh stiffness

In a probe memory device, a technique of realizing consistency of high-density recording and high-speed reading / writing is provided. A recording medium is placed to a probe array chip on which a plurality of probes are arranged in such a way as to maintain a constant spacing thereto by adopting a high-stiffness elastic support structure. The recording medium is equipped with a stage scanner that is driven continuously while drawing a constant trajectory on an X-Y plane almost in parallel to a probe array chip plane. The probes are equipped with respective actuators each being driven in a Z direction almost perpendicular to the X-Y plane. Each of the probes is made to write or read by altering a distance between the probe and the recording medium in parallel processing. The X-Y actuator is controlled so that the probe may continue a predetermined cyclic movement. Moreover, a tracking area is provided in a portion of the recording medium, and a trajectory of the probe by actuation is controlled so as to have a fixed geometry.

Owner:HITACHI LTD

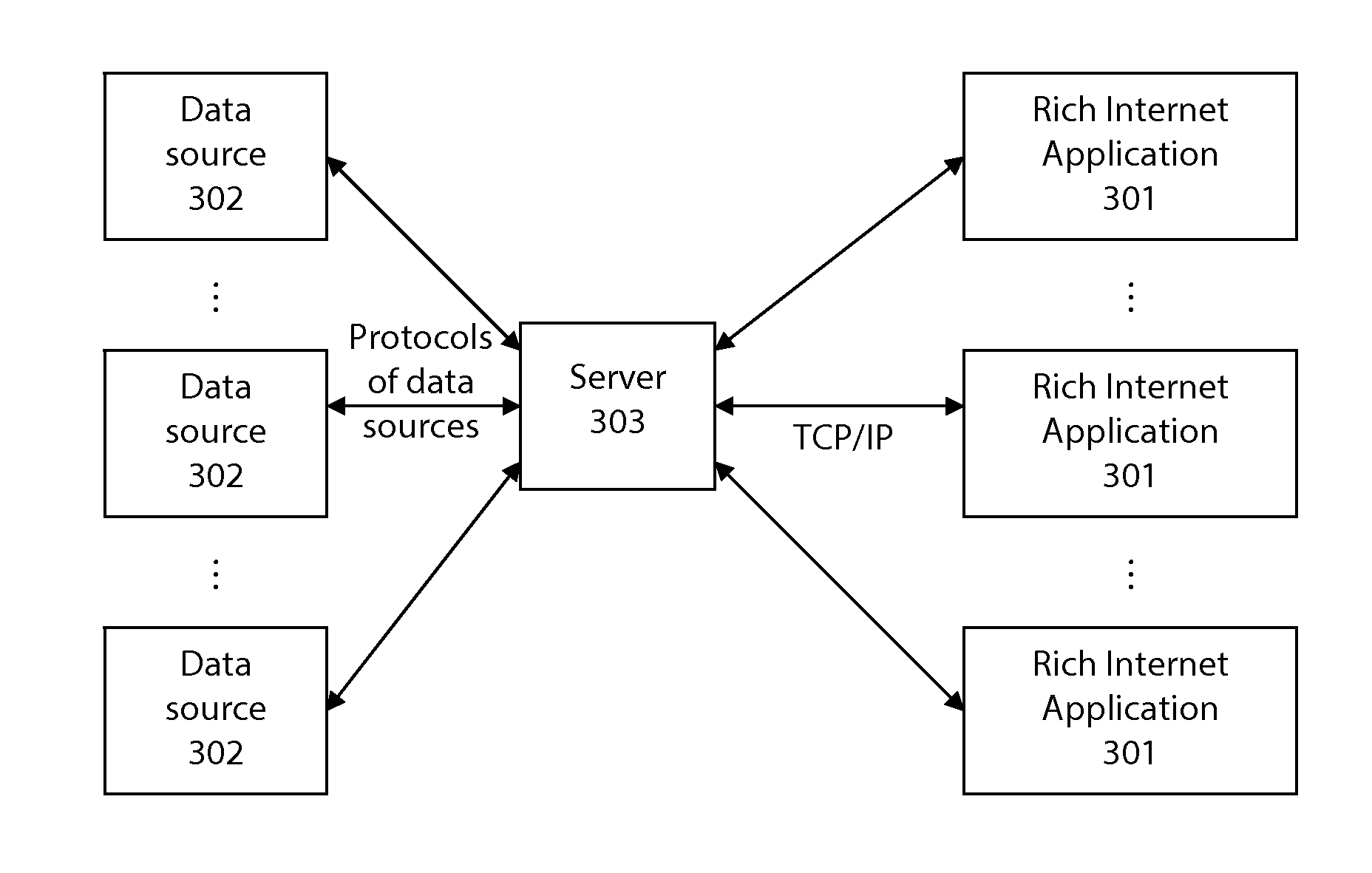

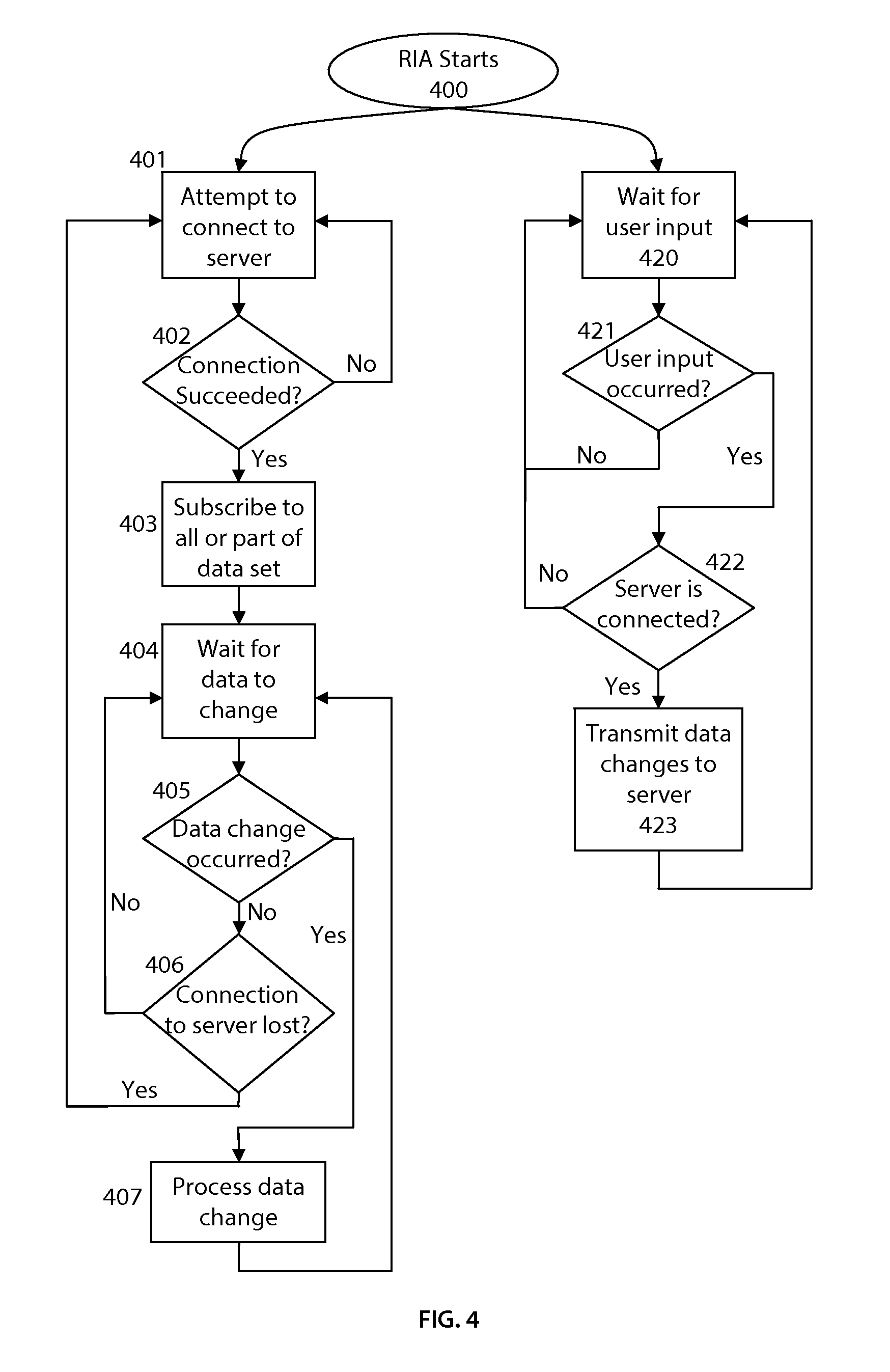

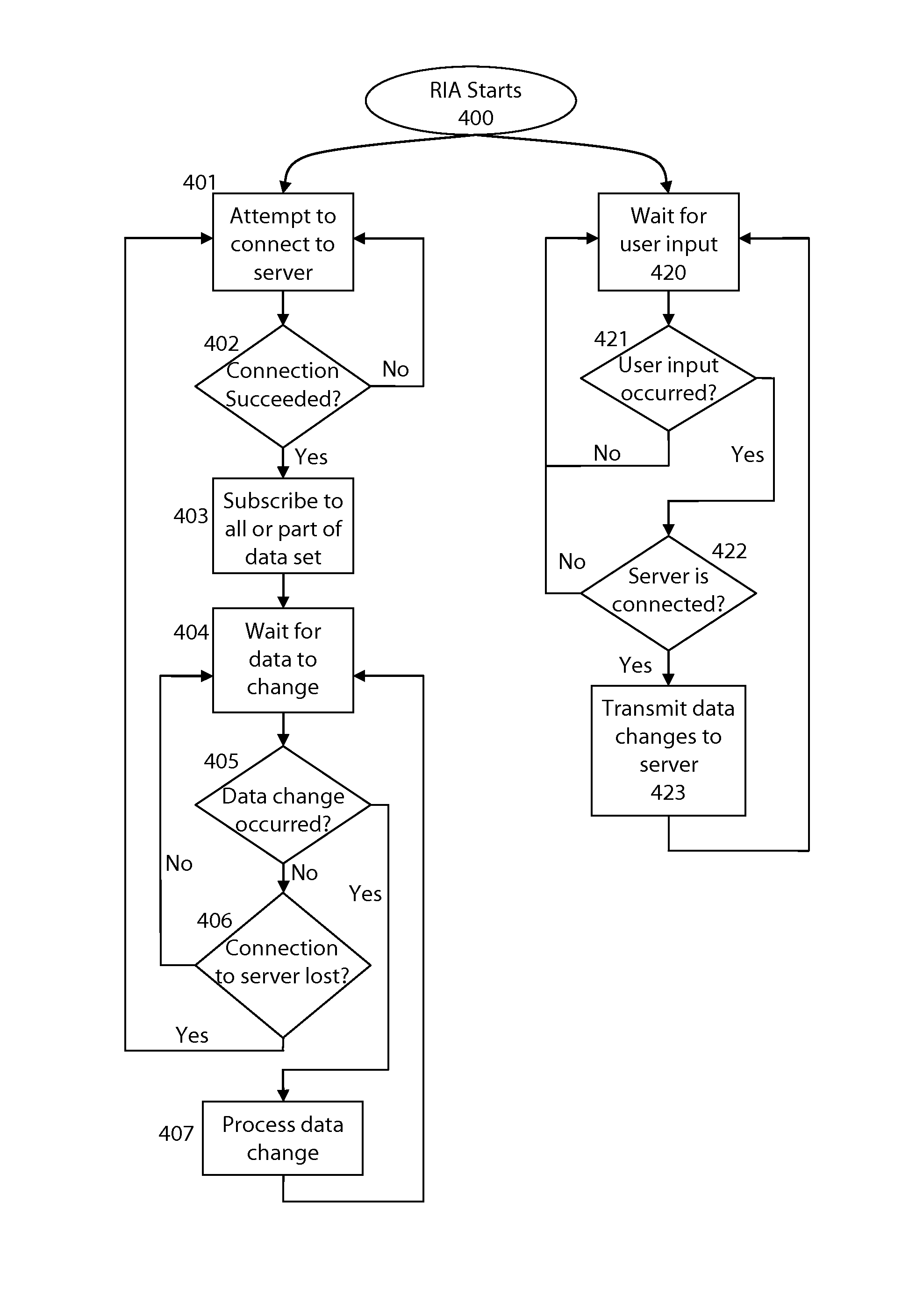

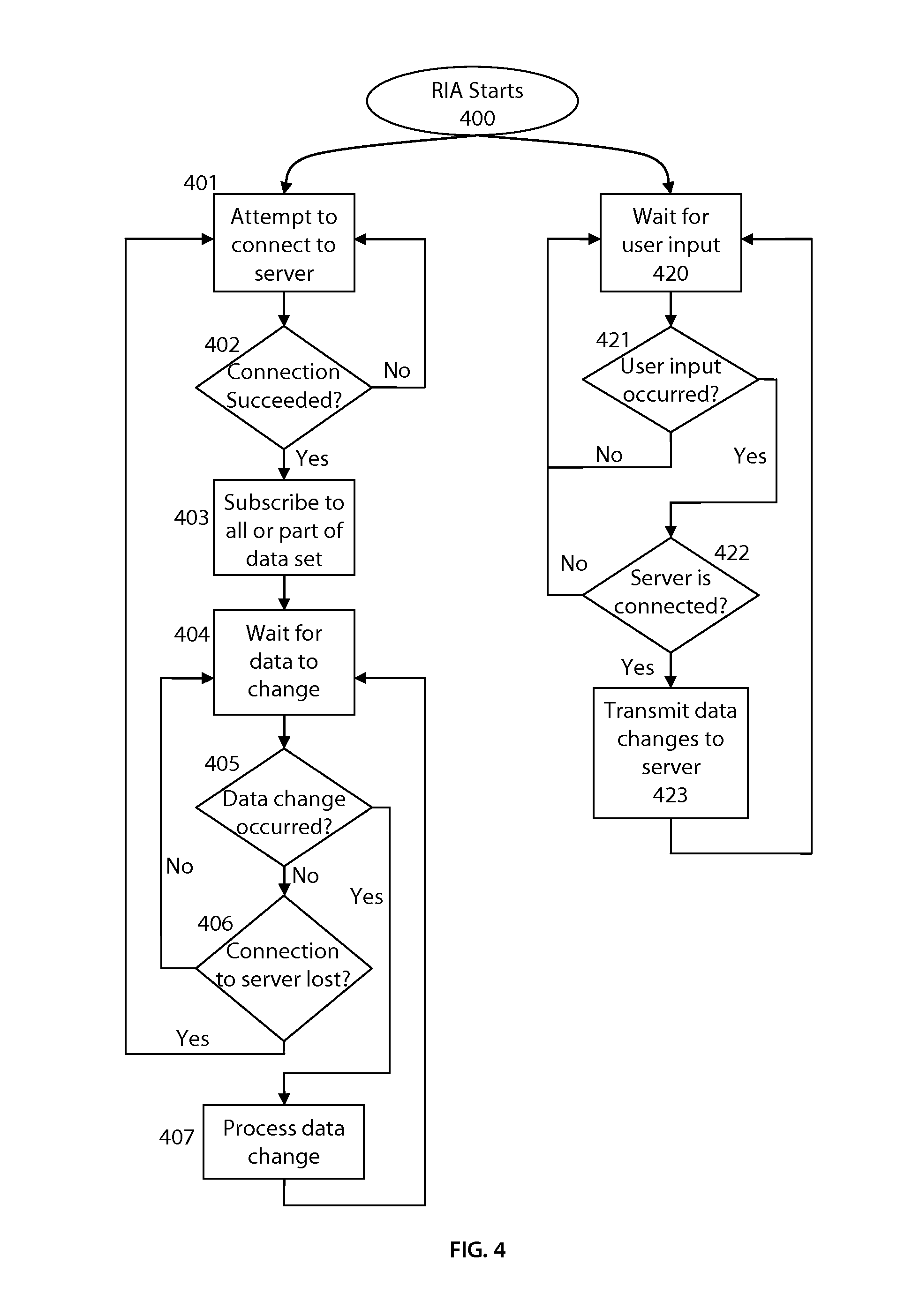

System and method for providing real-time data

ActiveUS20110093568A1Efficiently modifyOvercome limitationsMultiple digital computer combinationsTransmissionApplication softwareGraphics

A system and method for providing real-time data to a Rich Internet Application is disclosed. The graphical and networking features of RIA frameworks in conjunction with at least one real-time data server provides low-latency, real-time data applications in a web browser. In one embodiment, data is produced at a data source, propagated to a server, and collected at the server. A persistent connection is created from a RIA to the server, and the RIA is subscribed to the data, wherein the subscribed data comprises at least some of the data collected at the server, and wherein the server propagates the subscribed data to the RIA through the persistent connection as the data is collected at the server.

Owner:REAL INNOVATIONS INT