Digital clock duty ratio calibrating circuit

A technology for calibrating circuits and digital clocks, which is applied in the direction of transforming a continuous pulse train into a pulse train device with a required mode, which can solve the problems of system stability design difficulties, small edge jitter, and long settling time, and achieve no accumulation. effect, resistance to PVT deviation, good effect of PVT deviation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

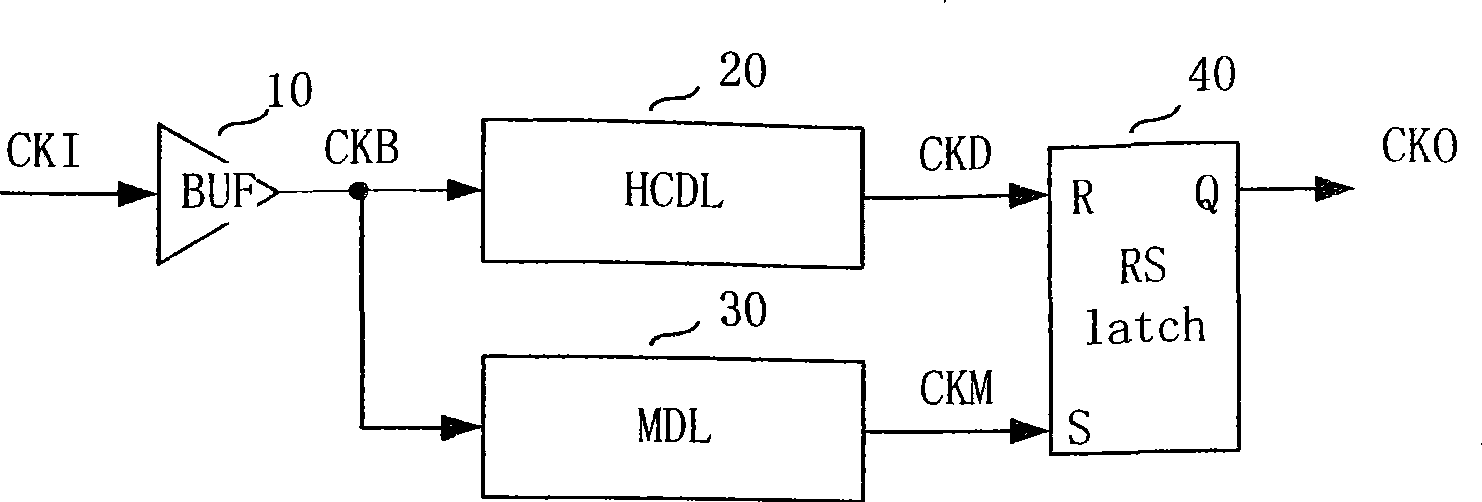

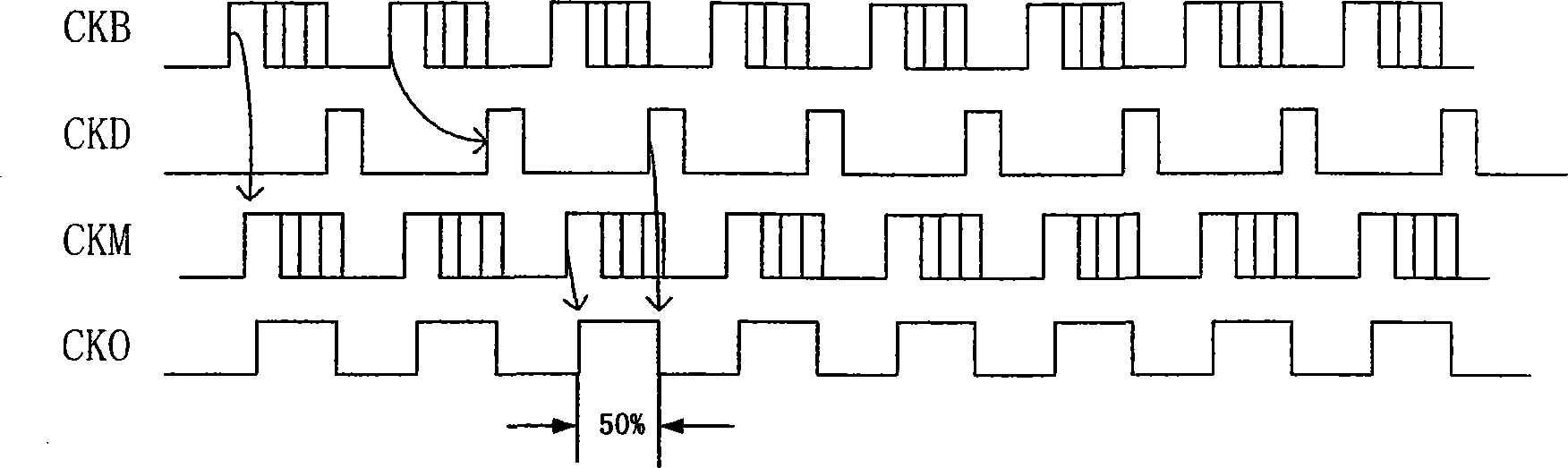

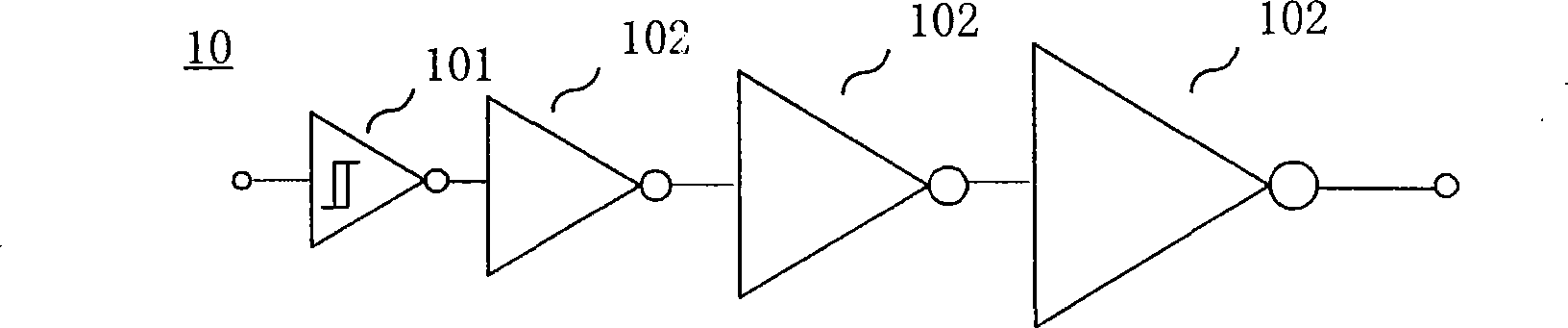

[0035]The input terminal of the input buffer stage 10 in this circuit receives the calibrated original input clock signal CKI; the output signal of the input buffer stage 10 is the buffered input clock signal CKB, which is simultaneously connected to the clock input of the half-period delay line HCDL20 end and the clock input end of the matching delay line 30; the output signal of the half-cycle delay line HCDL 20 is the half-cycle delay clock signal CKD, and the output signal of the matching delay line 30 is the matching delay clock signal CKM respectively connected to the RS flip-flop The reset input terminal R of 40 and the set input terminal S; the signal at the output terminal Q of the RS flip-flop 40 is the calibrated clock signal CKO with a 50% duty cycle after calibration; the function of the input buffer stage 10 is to ensure that the cl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More