Gating clock for on-site programmable gate array and implementing method thereof

A gated clock and gate array technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of large occupied area, inability to accurately estimate power consumption, etc., and achieve the effect of reducing area consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, specific embodiments will be described in detail below with reference to the accompanying drawings.

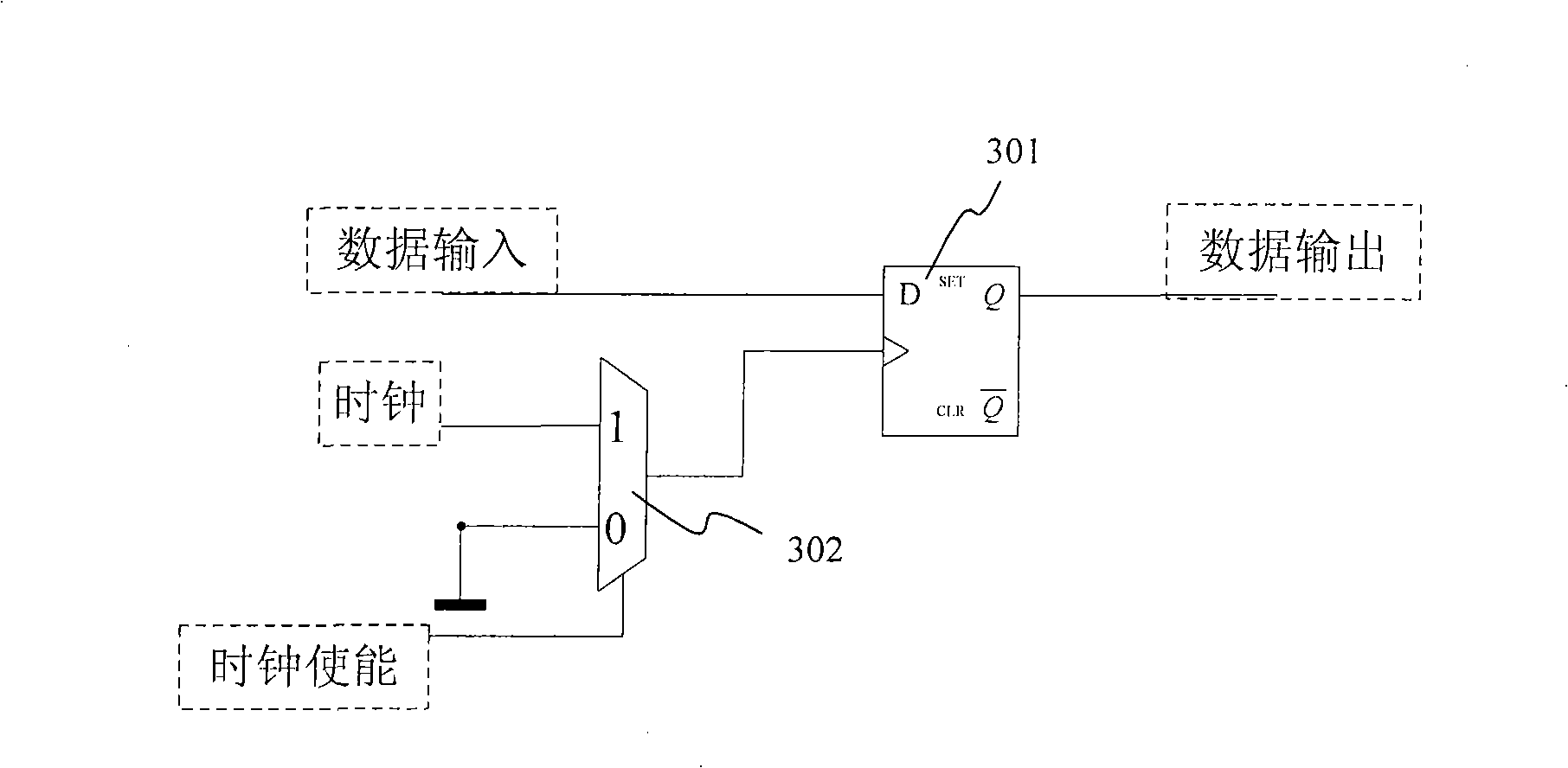

[0043] There is a resource in the FPGA called BUFGMUX (global clock buffer multiplexer). BUFGMUX is not a simple clock buffer. It is a multiplexer with low clock skew, high drive capability and a selector. The BUFGMUX is instantiated using different primitives, and the BUFGMUX can constitute a clock selector, a clock gate, or a simple clock buffer.

[0044] Considering that the FPGA has its own unique clock resources, the embodiments of the present invention will use these resources flexibly and correctly, so as to not only meet the clock tree requirements inside the FPGA, but also satisfy the design verification requirements to the greatest extent.

[0045] image 3The circuit structure diagram of using BUFGMUX to realize the gating clock of FPGA pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More