FPGA (field programmable gate array) removable high-speed operation verification development board

A development board, high-speed technology, applied in the field of verification development board, can solve problems such as expensive, FPGA chip damage, speed can not meet the demand, etc., to achieve the effect of easy disassembly and assembly, and meet the needs of design verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The present invention will be further described and defined below in conjunction with the accompanying drawings and specific embodiments.

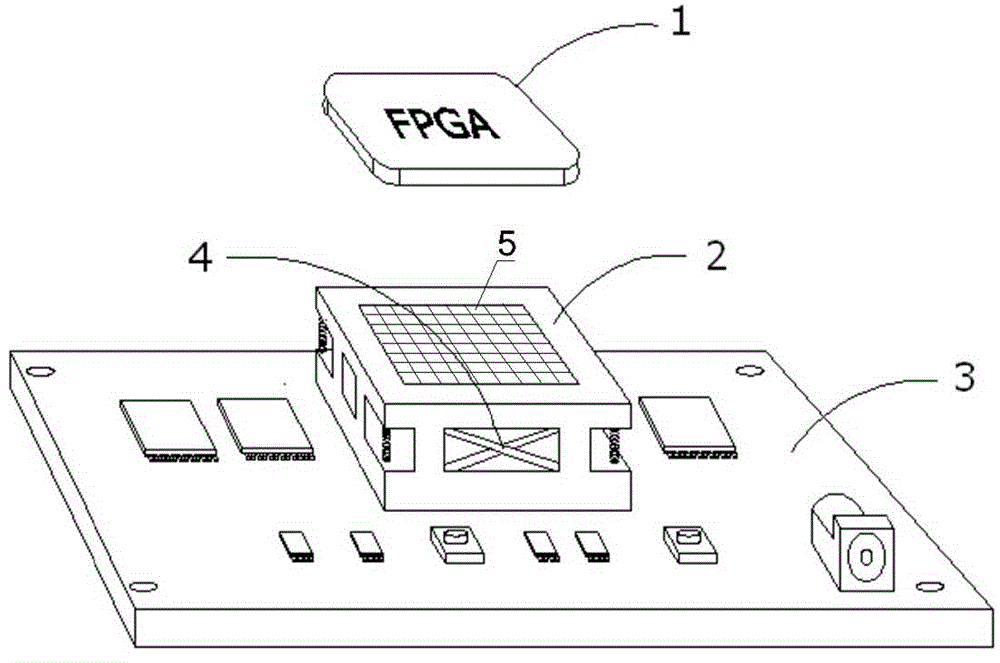

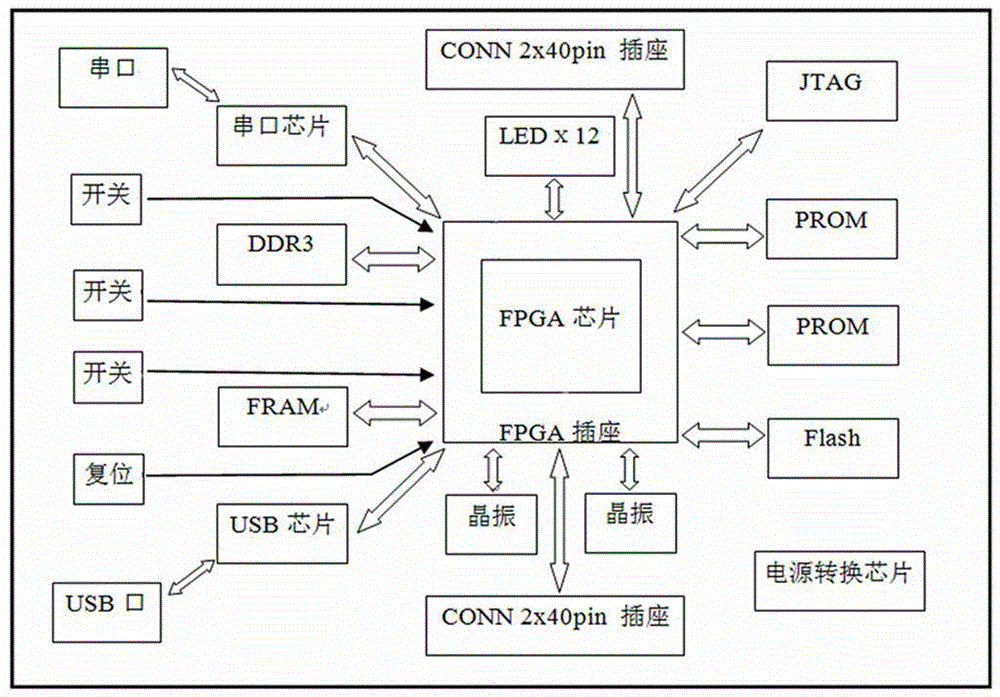

[0015] Such as figure 1 Shown, a kind of FPGA detachable and the verification development board of high-speed operation, comprise development board 3, be positioned at the socket 2 on the development board 3 and detachably be connected on the FPGA chip 1 on the socket 2, development board 3 is provided with and The pad corresponding to the packaging form of the socket 2, the socket 2 is soldered on the pad; the socket 2 is provided with a pin 5 corresponding to the solder ball of the FPGA chip 1, and the upper end of the pin 5 is connected to the solder ball of the FPGA chip 1 The lower end is connected to the wiring on the development board 3, and the FPGA chip 1 is electrically connected to each component on the development board 3 through the pin 5 of the socket 2.

[0016] In this embodiment, the FPGA chip 1 is detachably conne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More