SoC verification platform with high efficiency and high coverage rate for virtual clock synchronization

A verification platform and virtual clock technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as different control logic, complicated synchronization, redesign, etc., achieve good versatility, reduce work difficulty, and solve problems The effect of clocks being difficult to synchronize

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

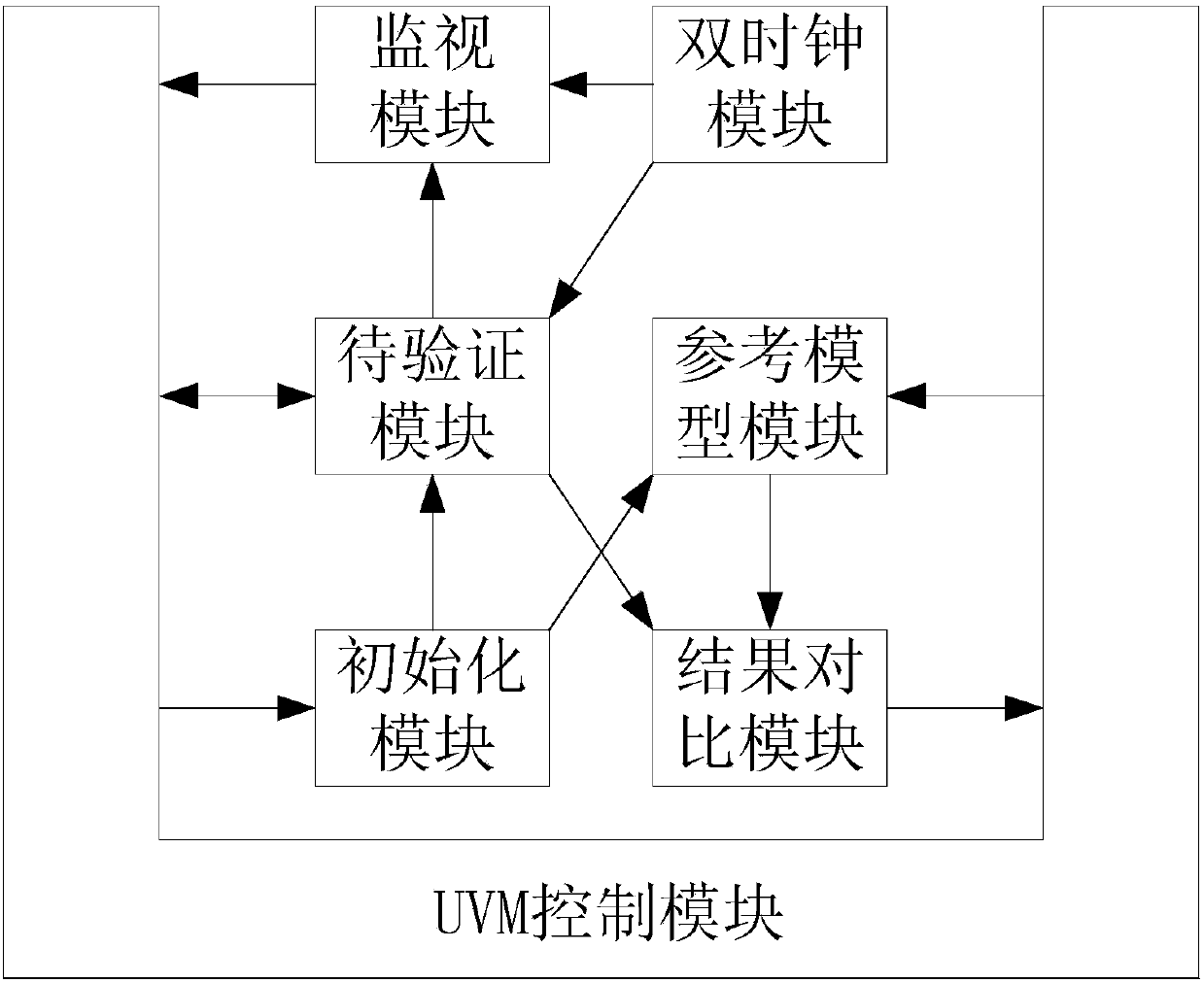

[0038] Such as figure 1 Shown is a schematic diagram of the composition of the SoC verification platform with virtual clock synchronization. It can be seen from the figure that the platform includes a dual clock module, a module to be verified, a reference model module, a monitoring module, an initialization module, a result comparison module, and a UVM control module.

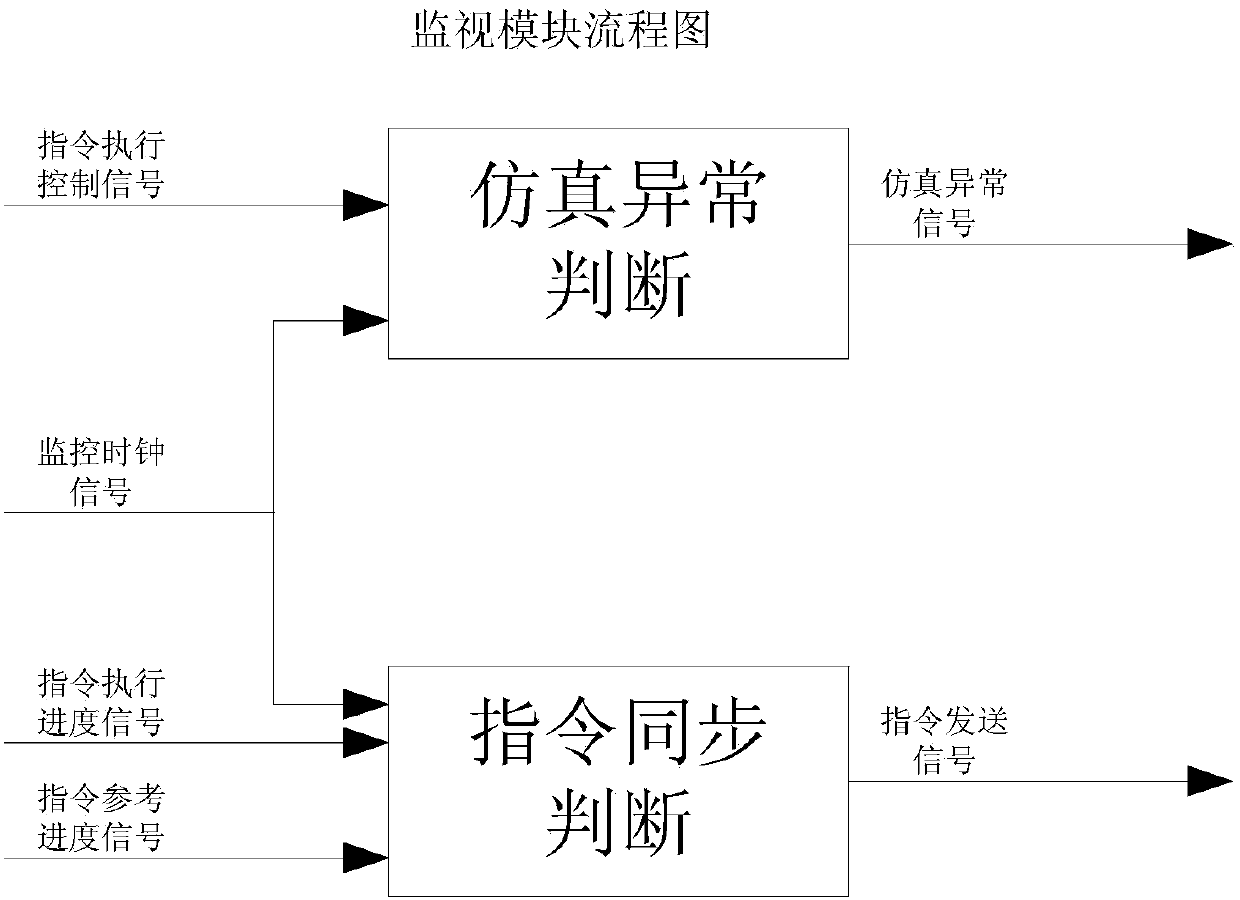

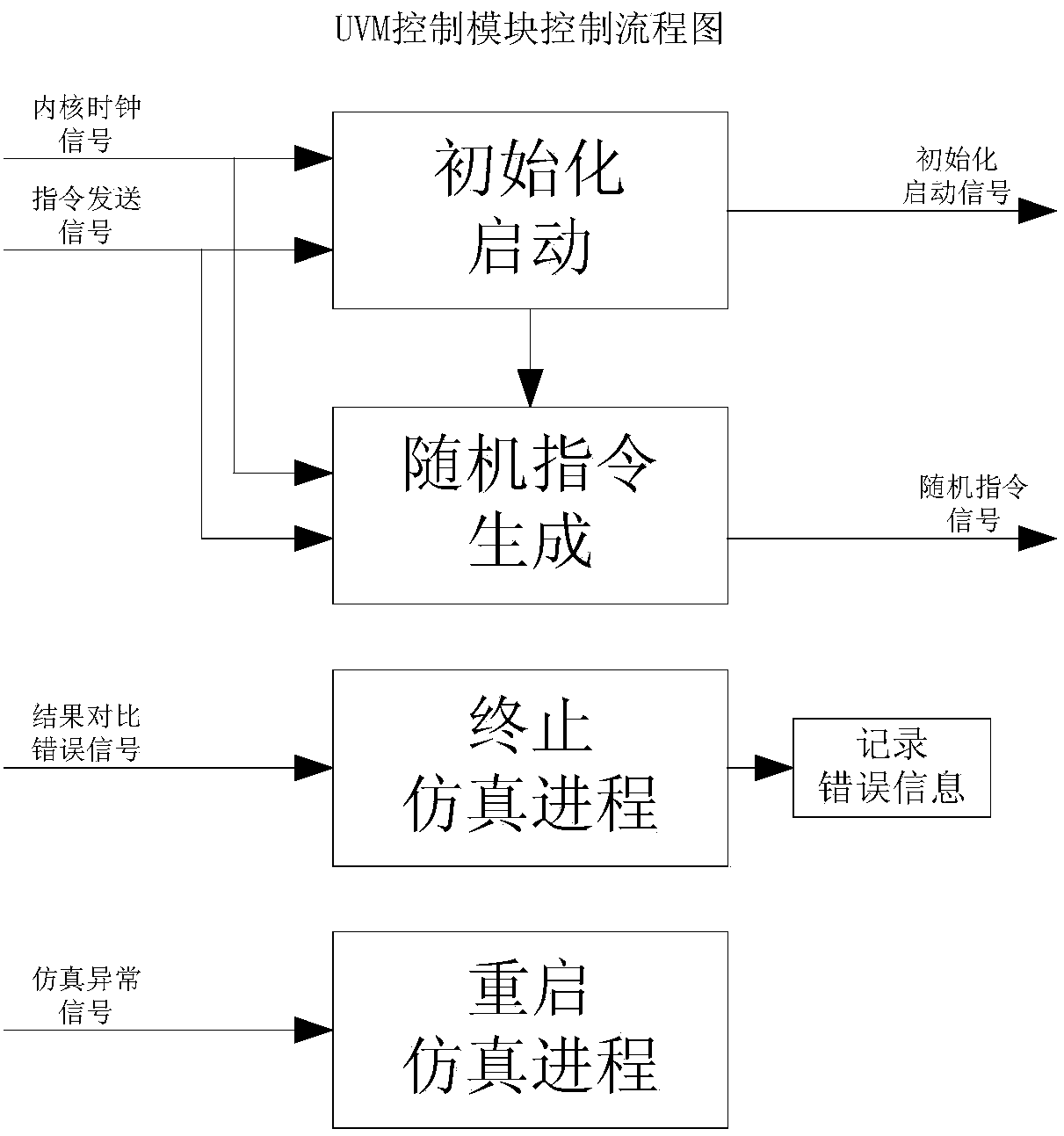

[0039] The monitoring clock cycle configuration parameters and the system clock cycle configuration parameters are entered in the dual clock module, and the monitoring clock and the system clock are generated according to the monitoring clock cycle configuration parameters and the system clock cycle configuration parameters; and the monitoring clock is transmitted to the monitoring module, and the system clock is transmitted to the The module to be verified; the setting of the m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More