Patents

Literature

33 results about "Polyphase decomposition" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

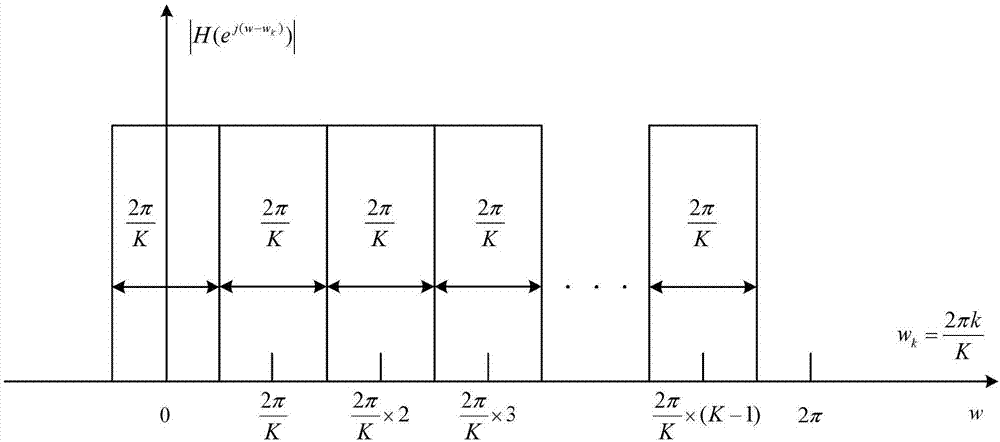

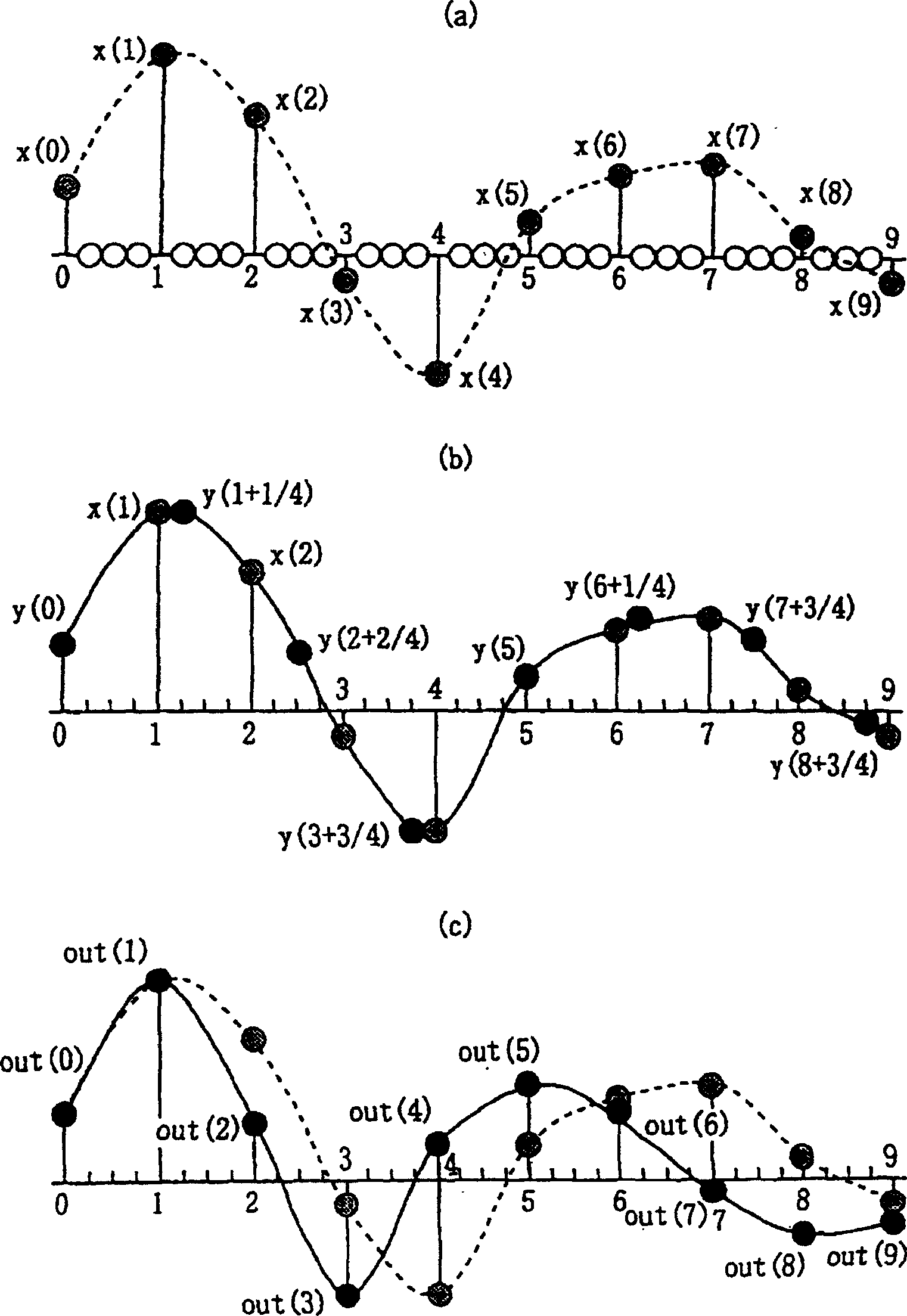

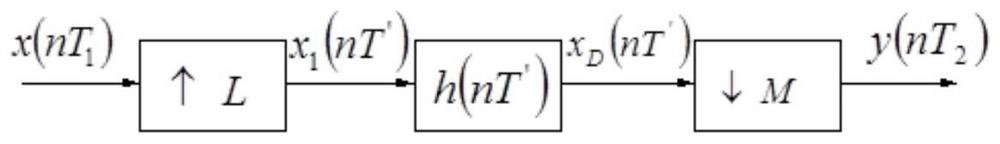

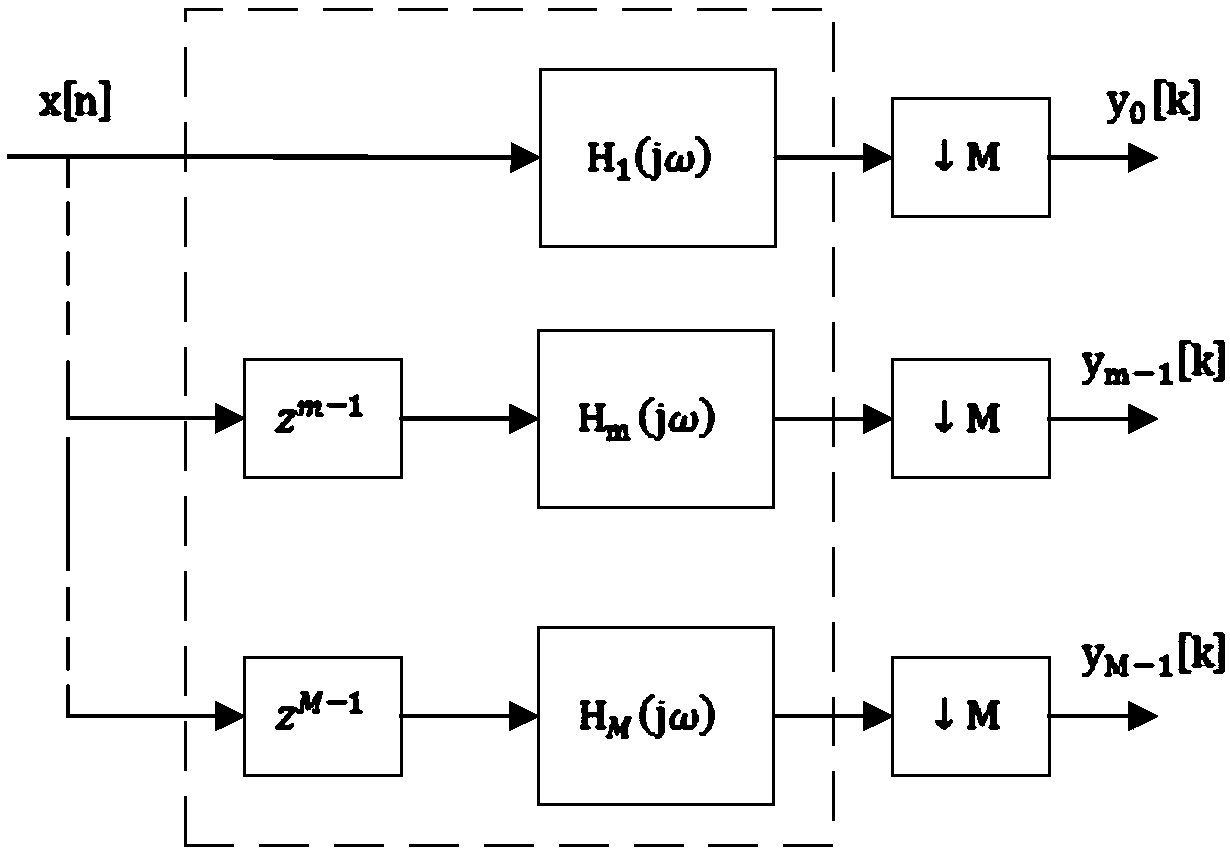

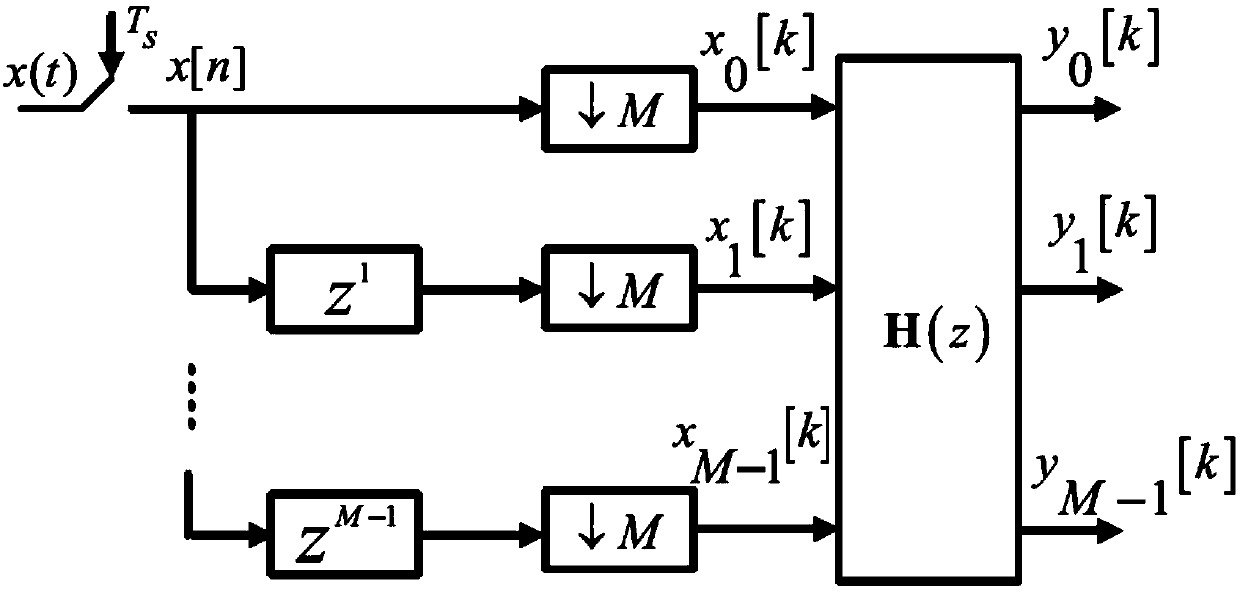

Polyphase Decomposition. The multirate operations of decimation and interpolation that were introduced in the previous section will now be used to decompose any system function. H(z) into its polyphase representation.

Sample rate converter

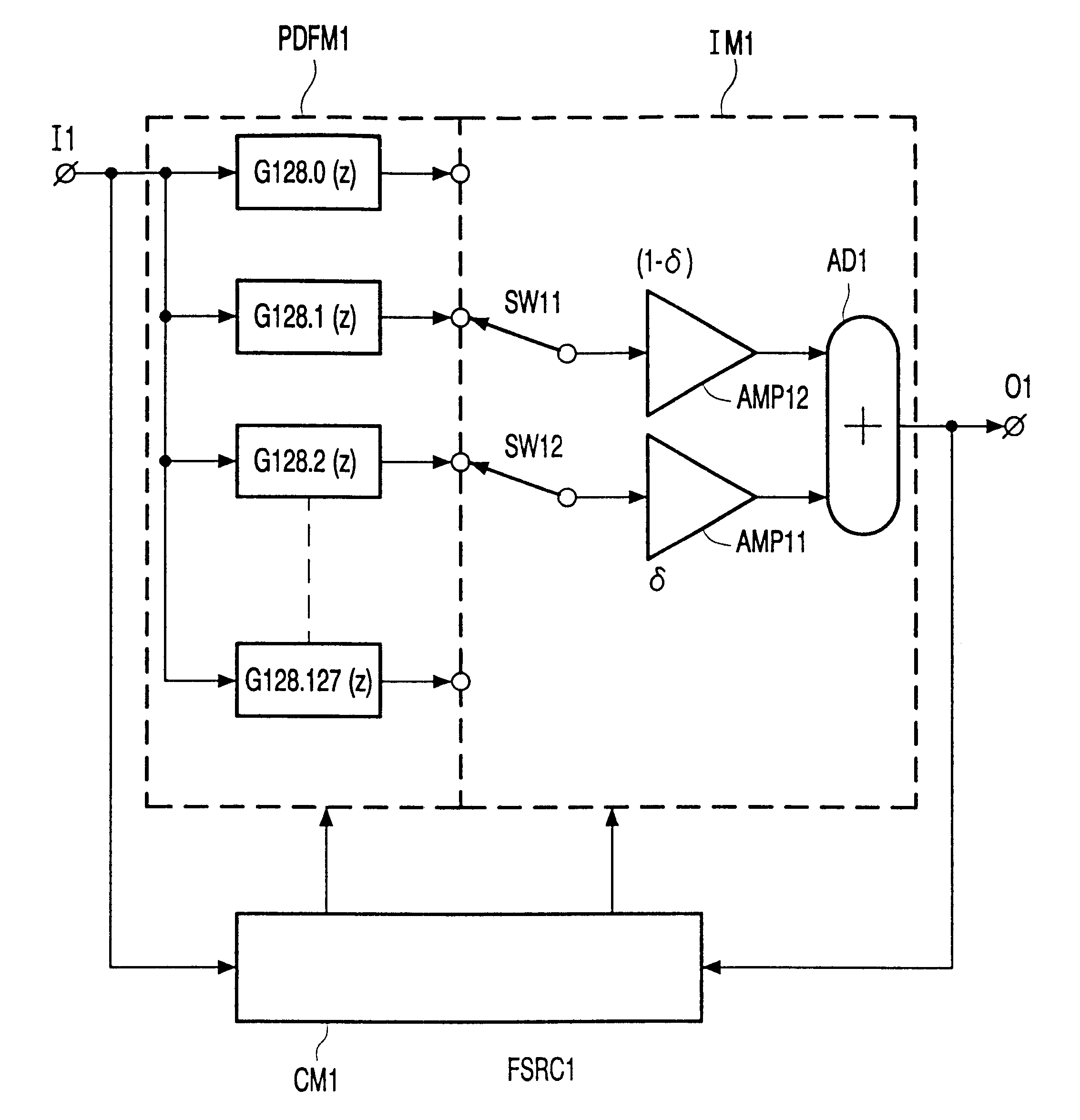

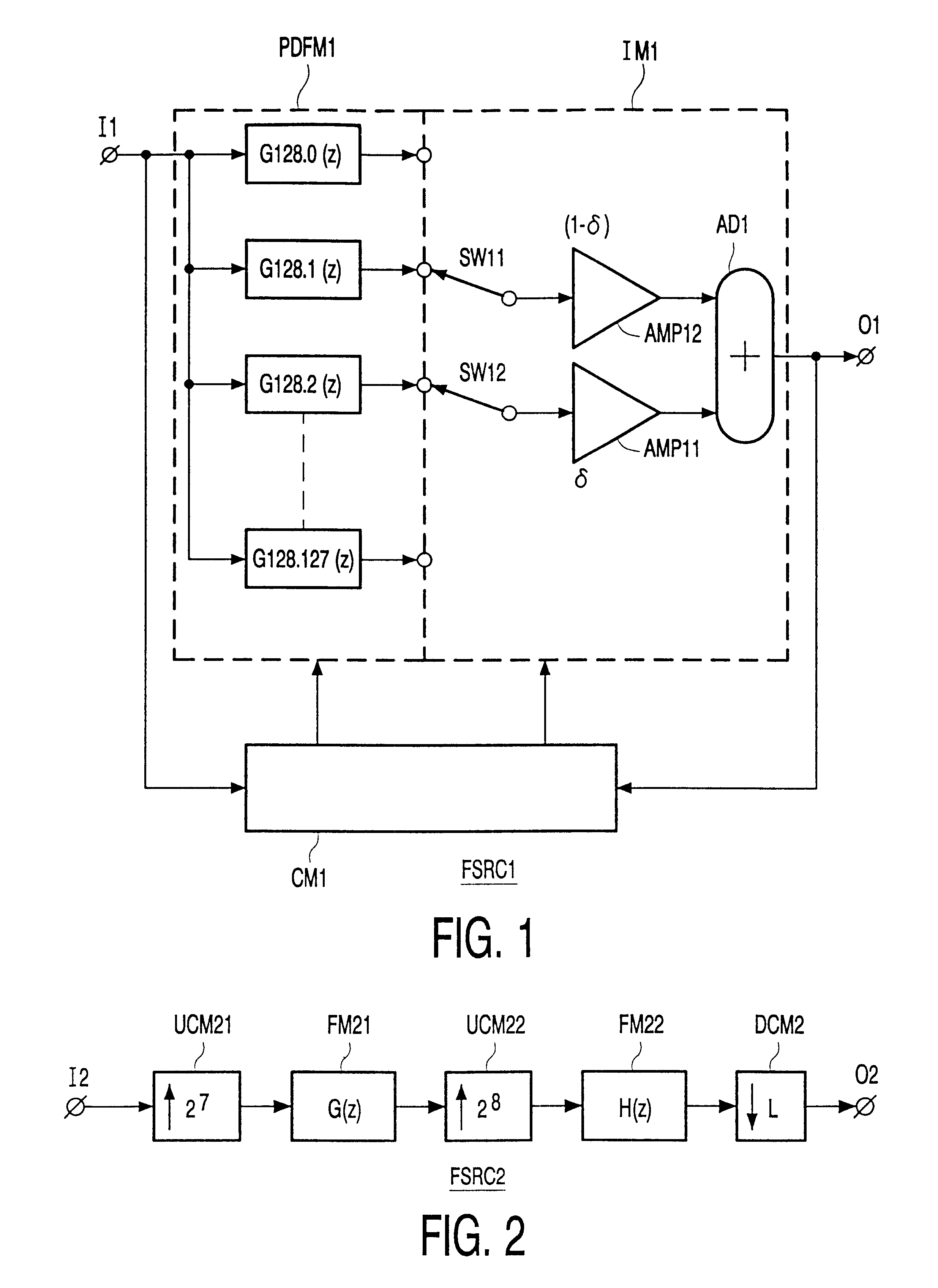

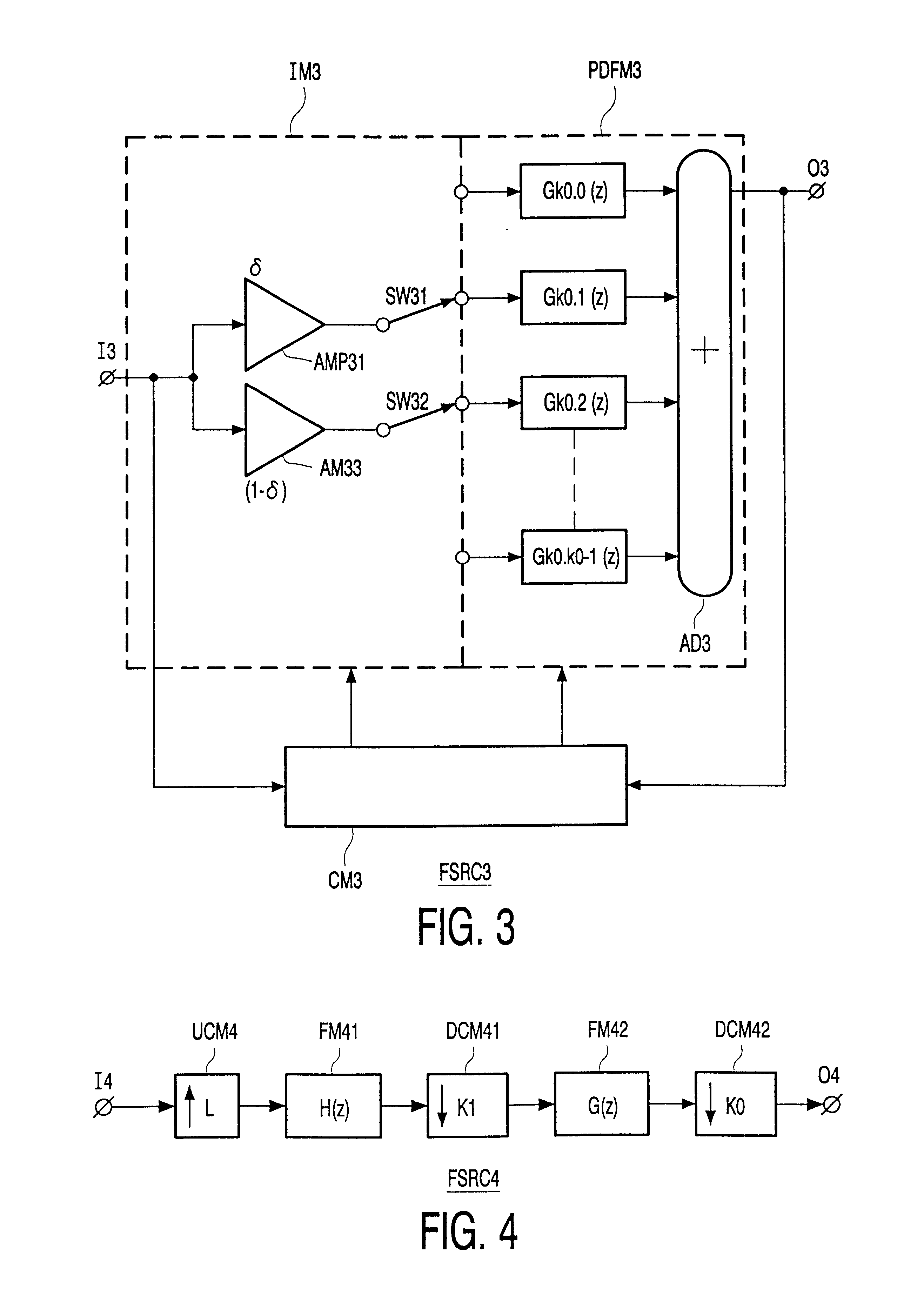

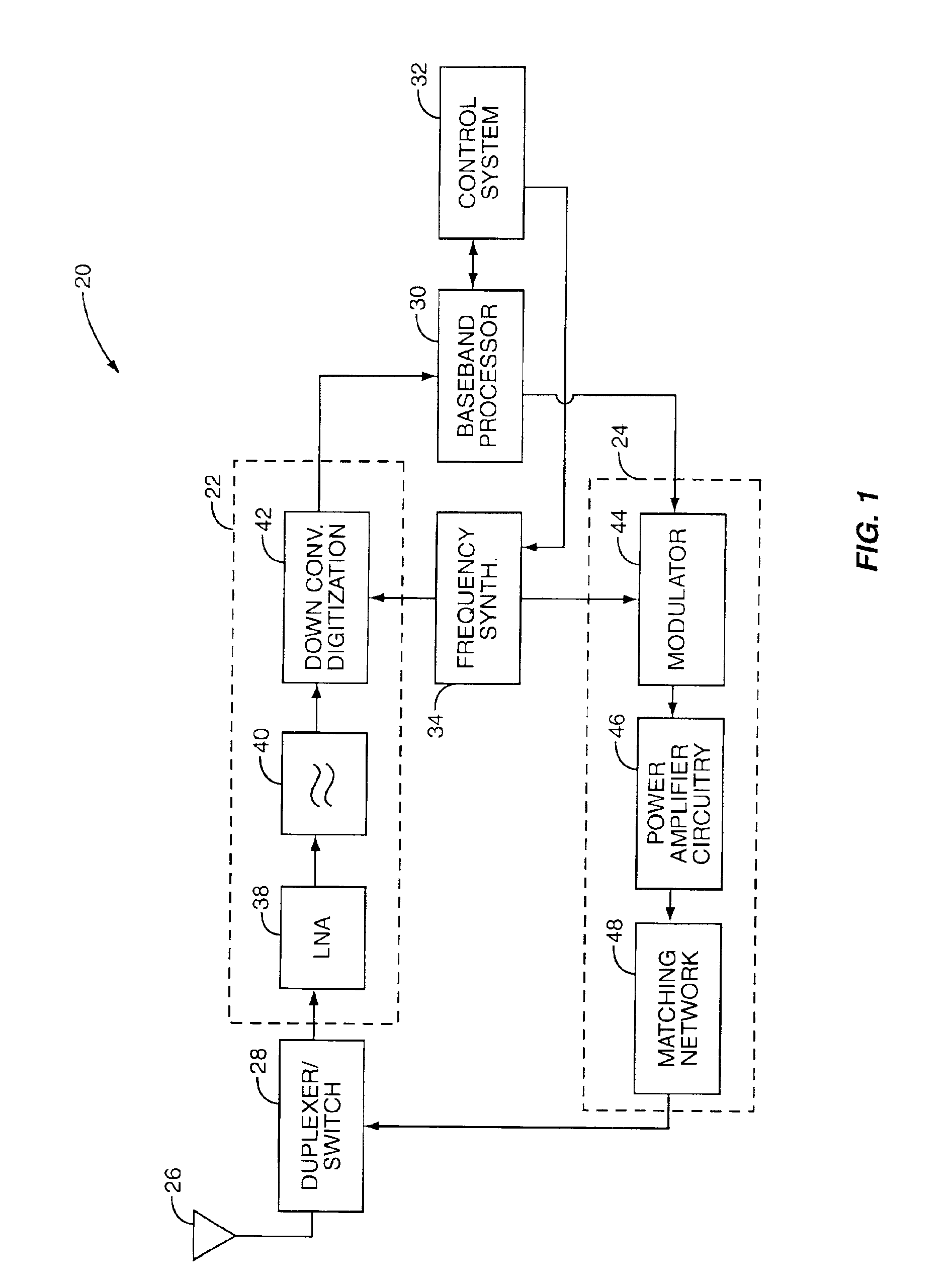

InactiveUS6411225B1Efficient flexible sample rate converterEasy to operateDigital technique networkDelta modulationSignal transitionPhysics

Sample rate converters are known, and are used to convert a signal with a first sample rate (sampling frequency) into a signal with a second sample rate (sampling frequency). To obtain a flexible sample rate converter with sampling frequencies that are not known beforehand, until now only sample rate converters with very high intermediate sampling frequencies are known. The invention provides a flexible sample rate converter, which is able to handle unknown input and output sampling frequencies. This is achieved by using polyphase decomposition filter means in combination with interpolation means.

Owner:NXP BV

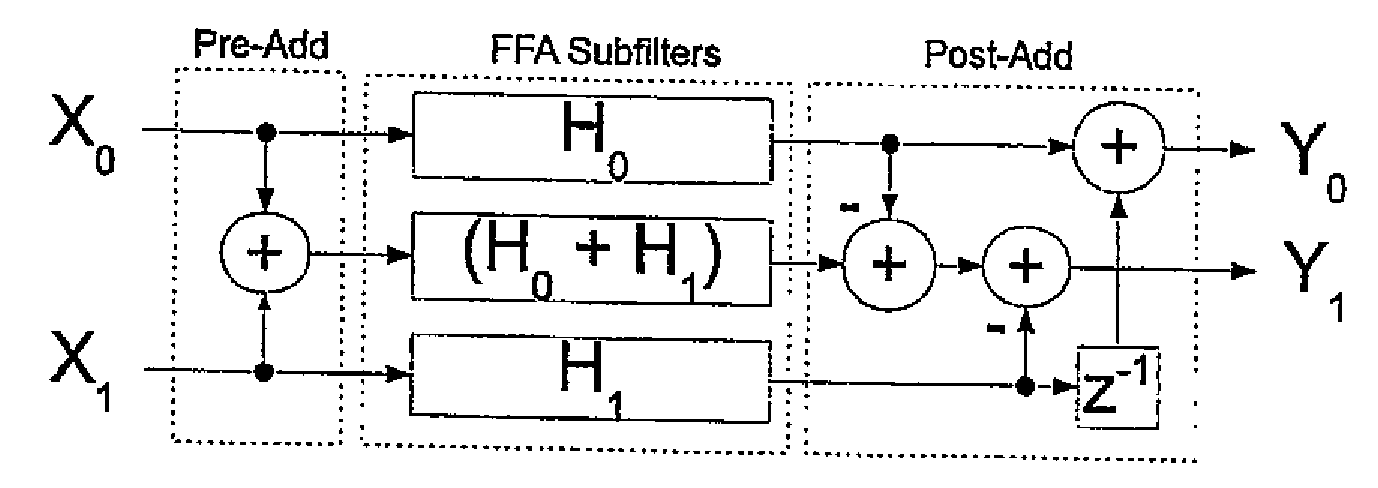

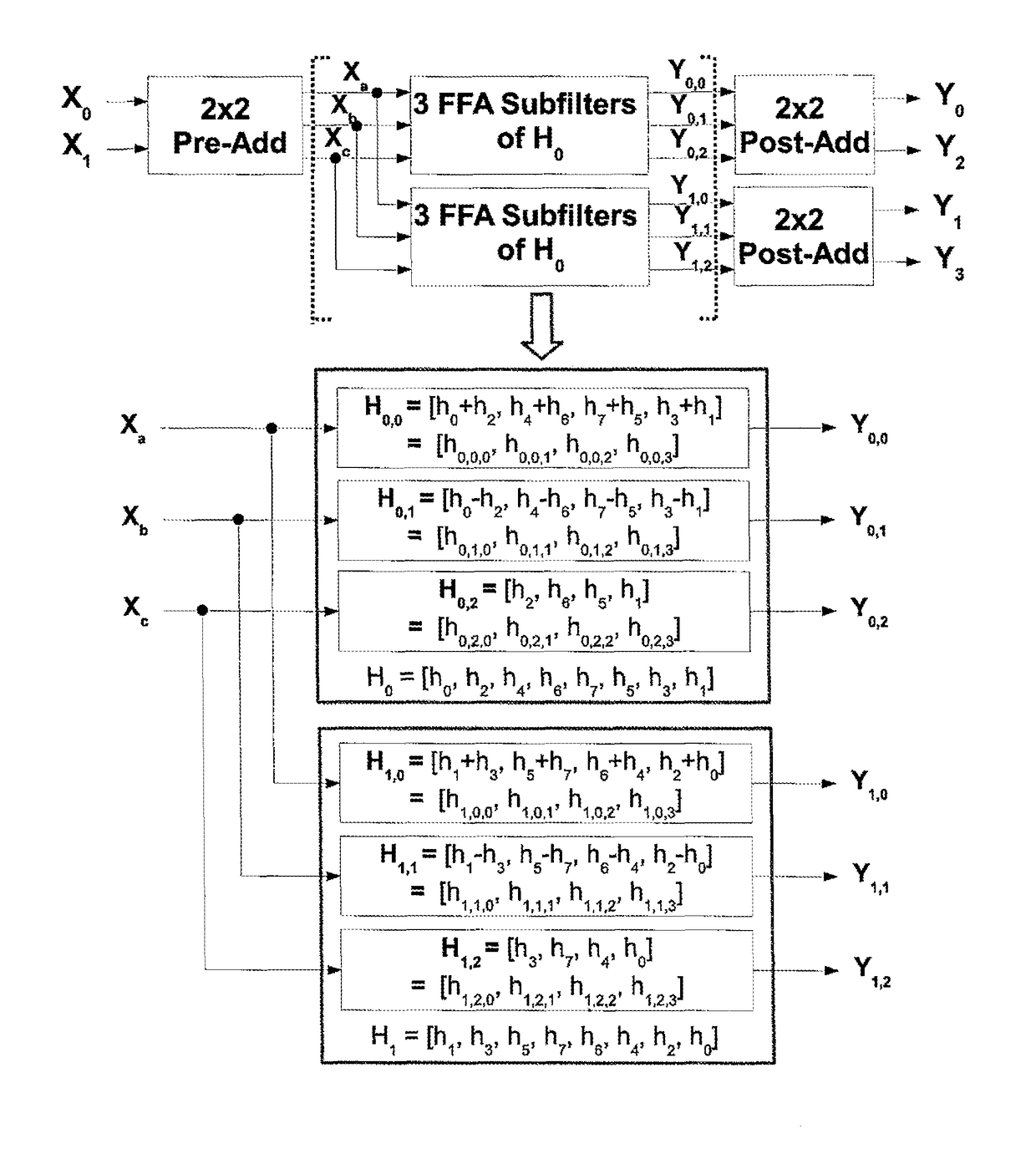

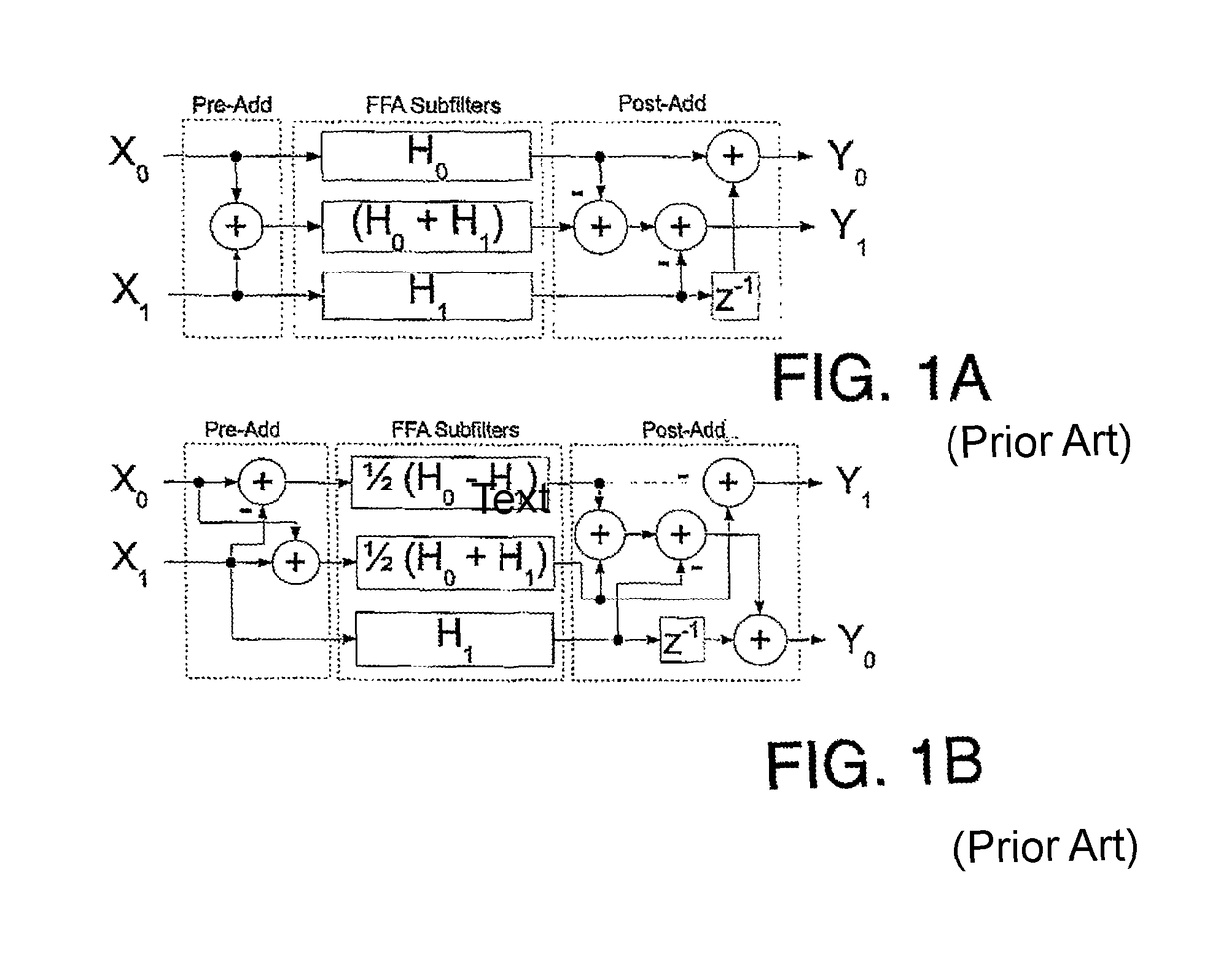

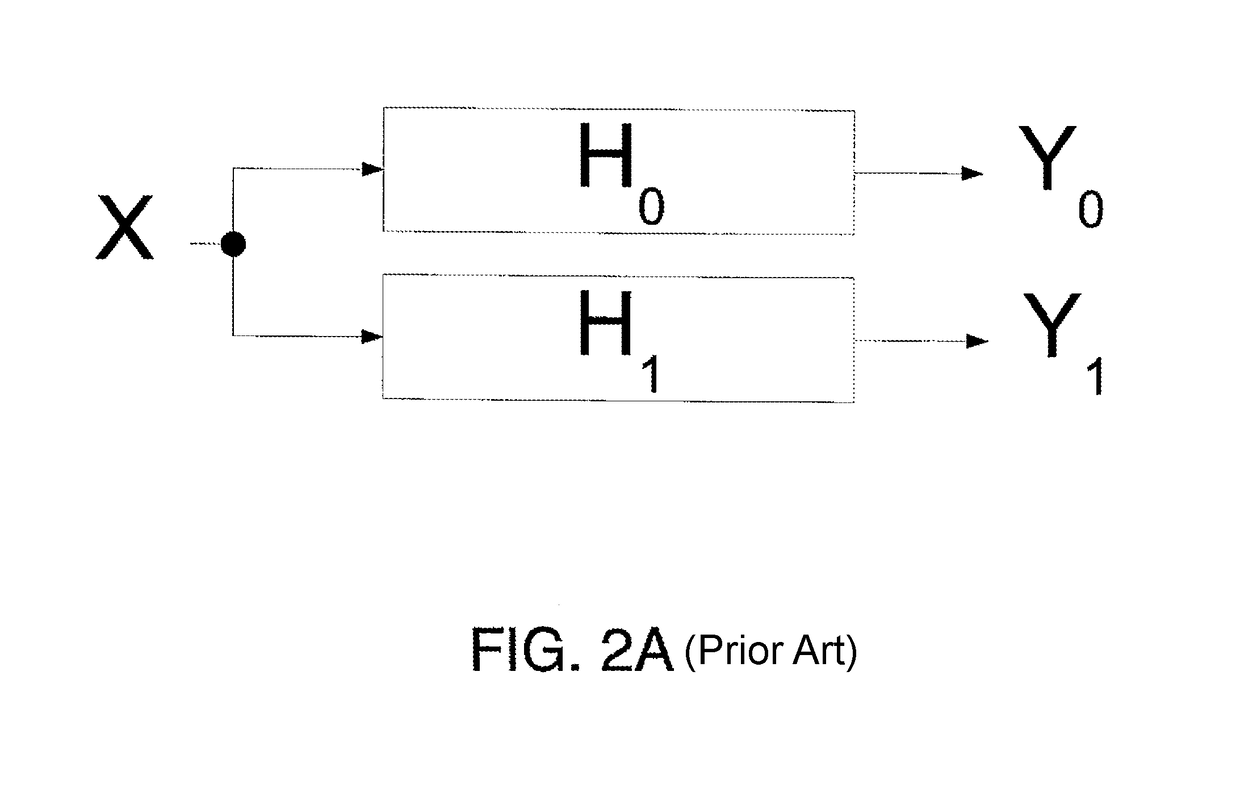

Fast FIR Filtering Technique for Multirate Filters

ActiveUS20160079960A1Digital technique networkComplex mathematical operationsPattern recognitionData stream

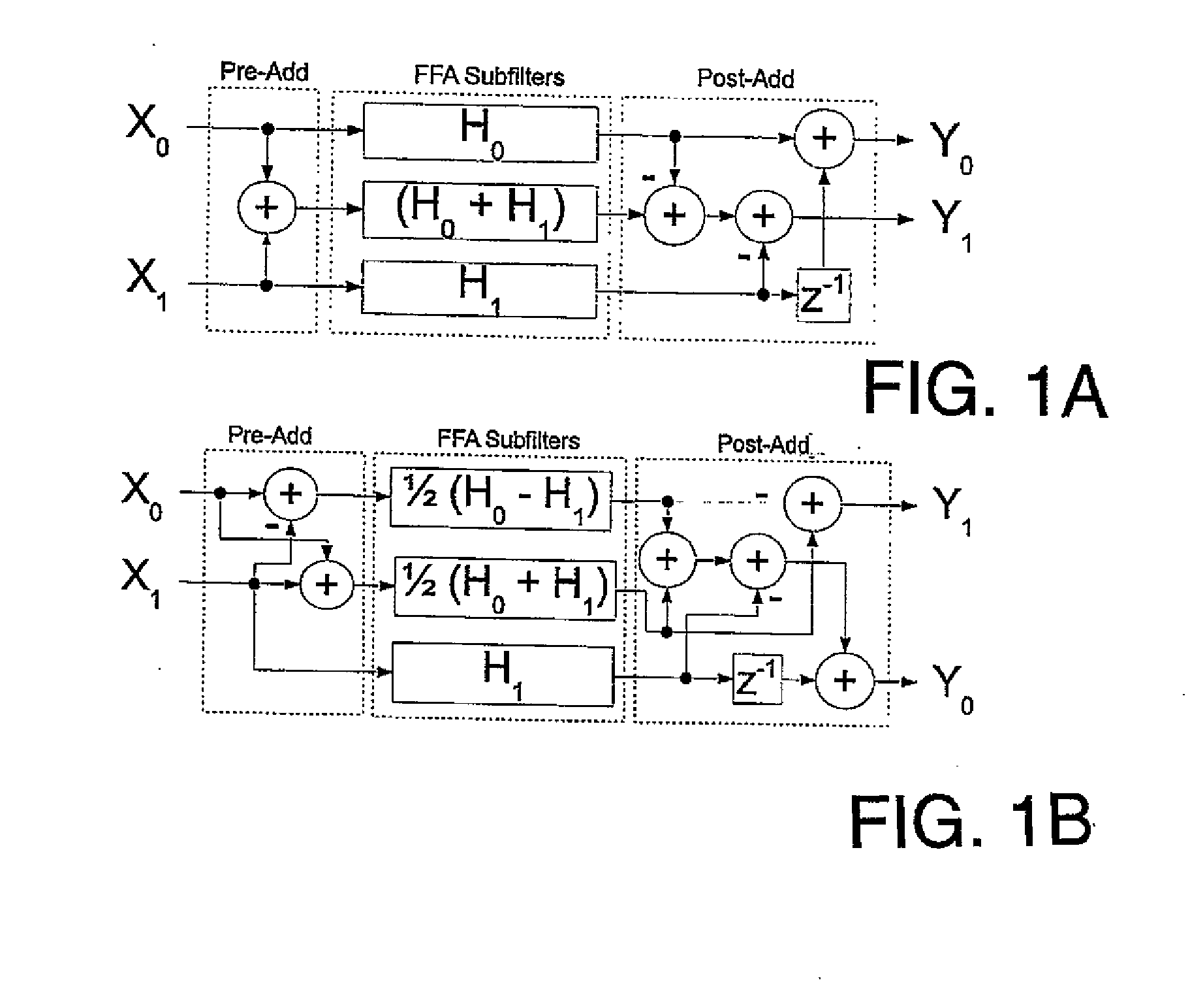

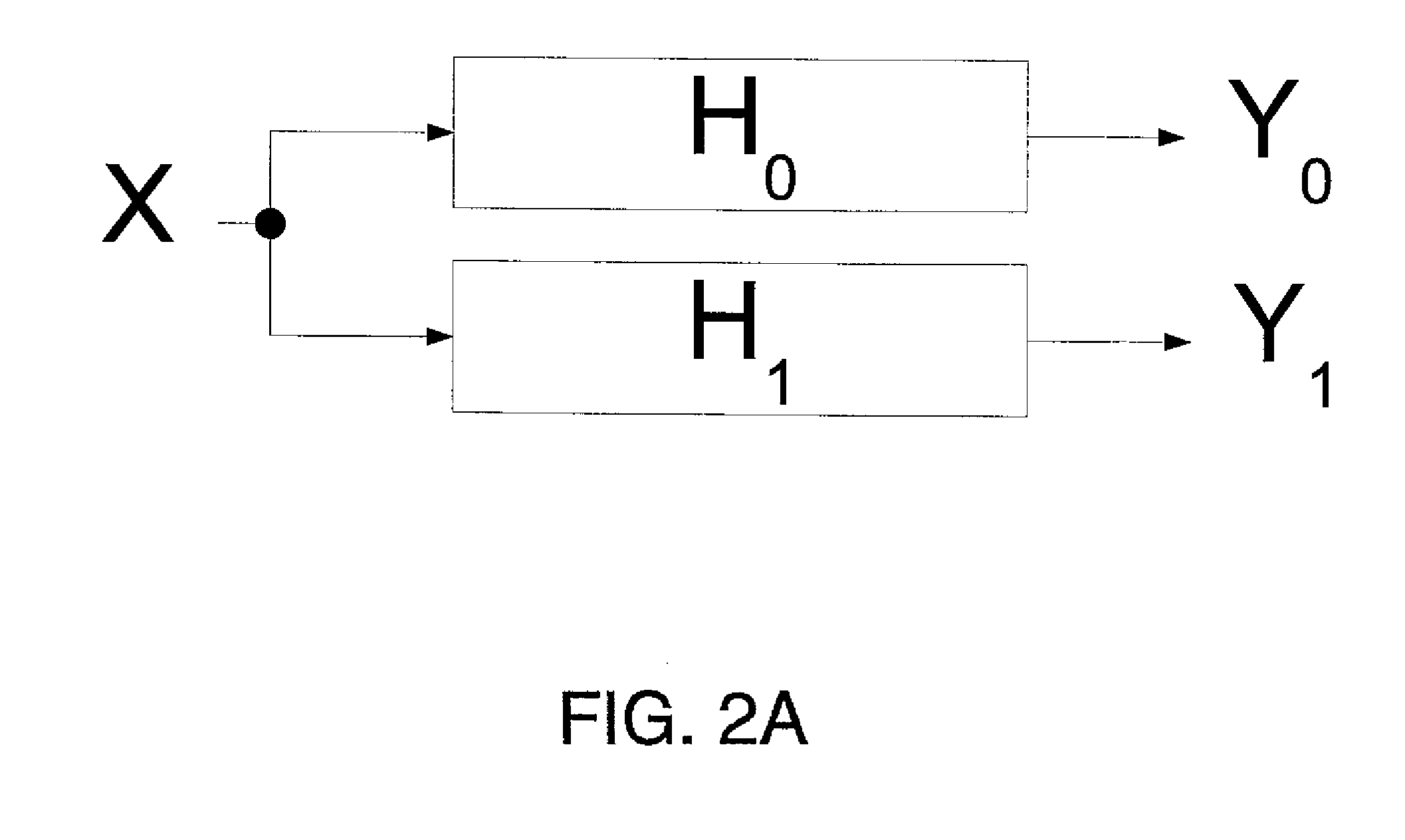

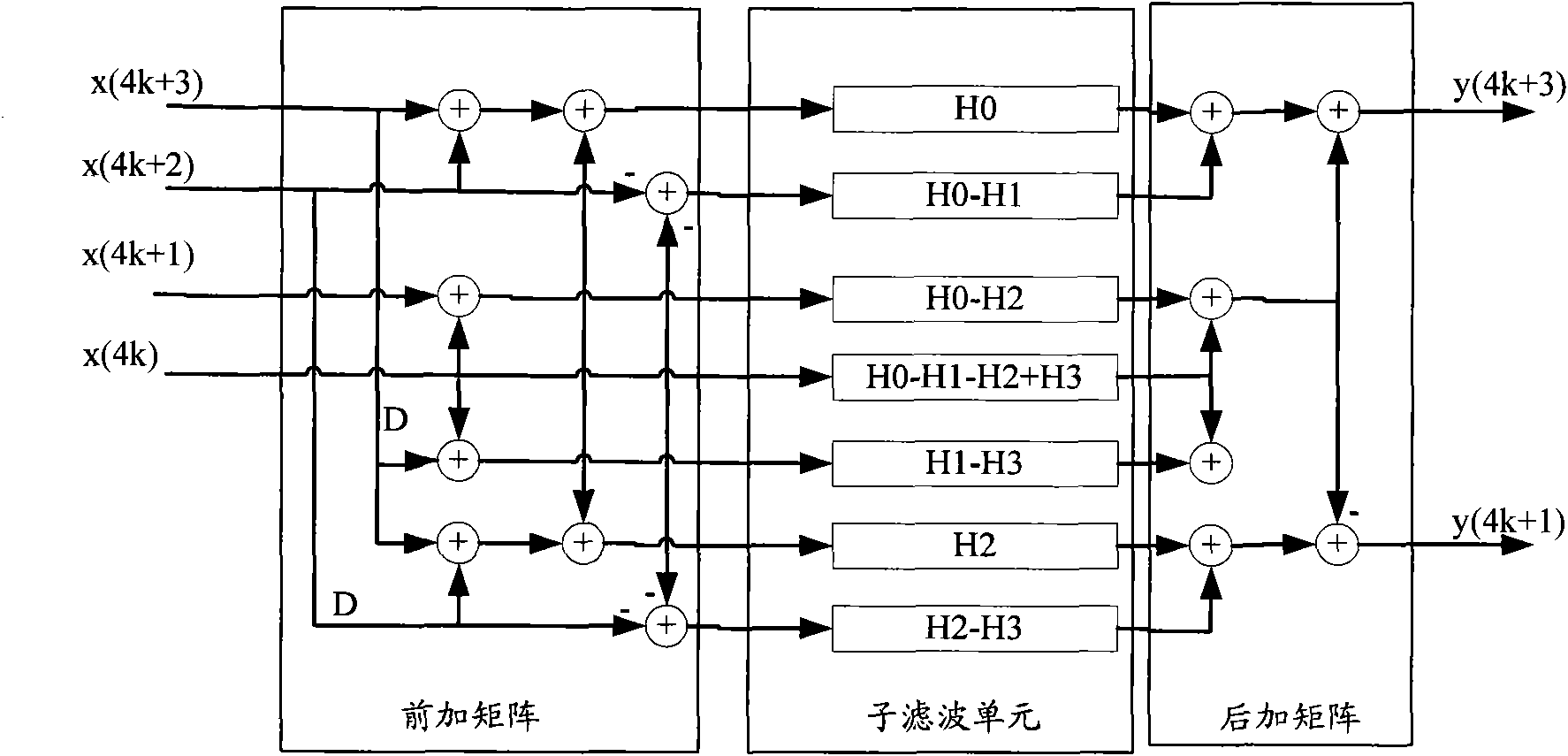

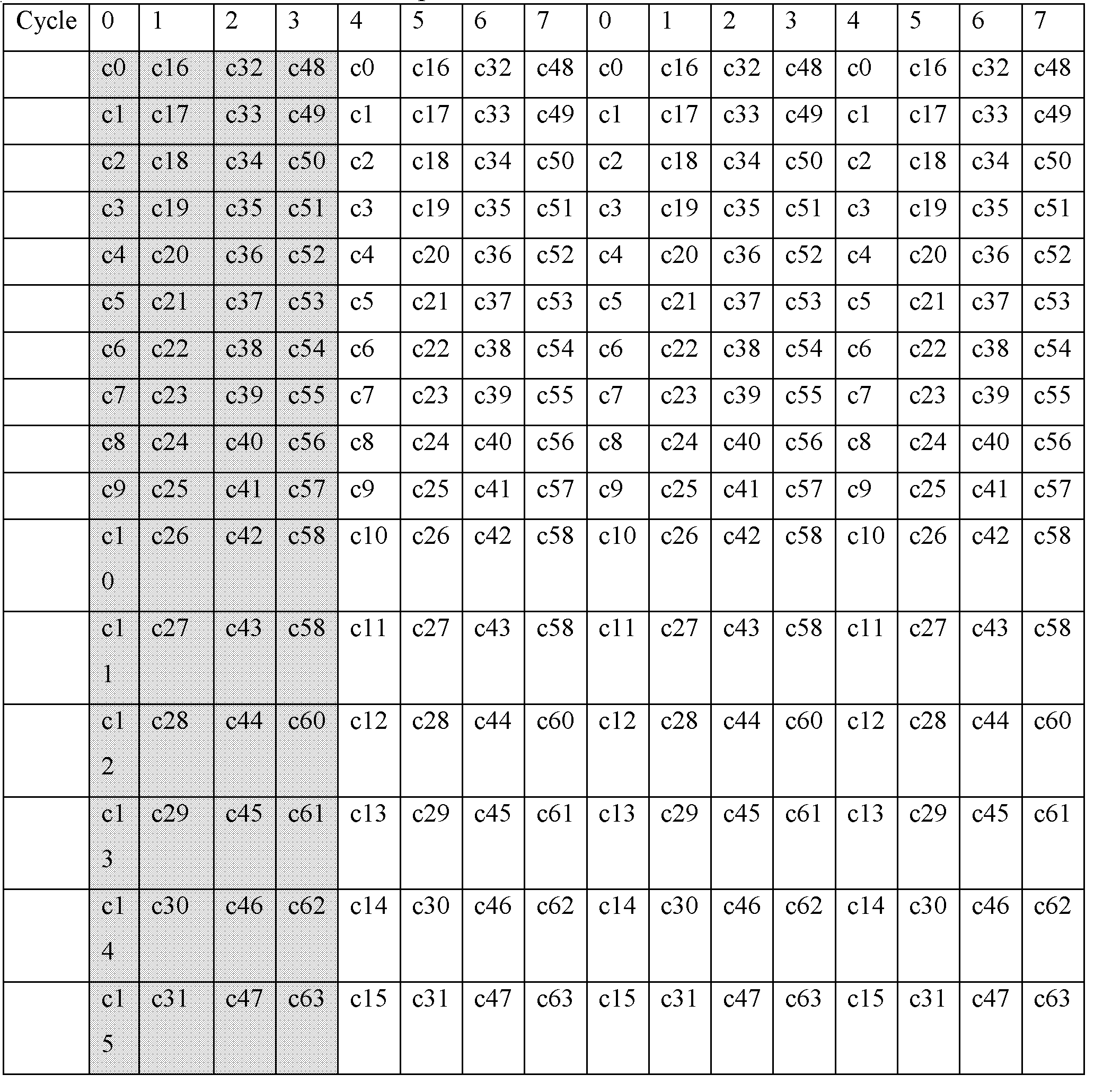

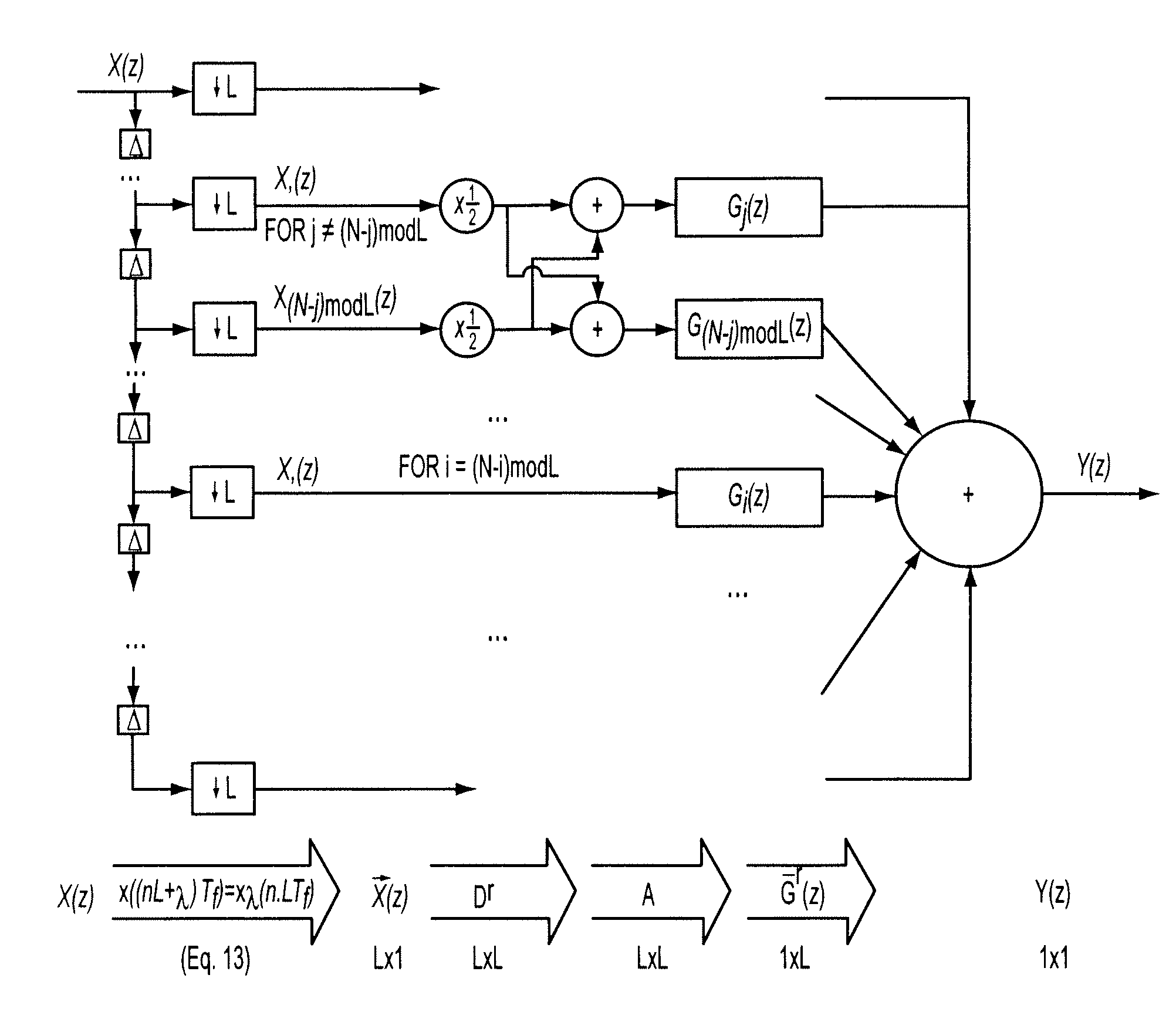

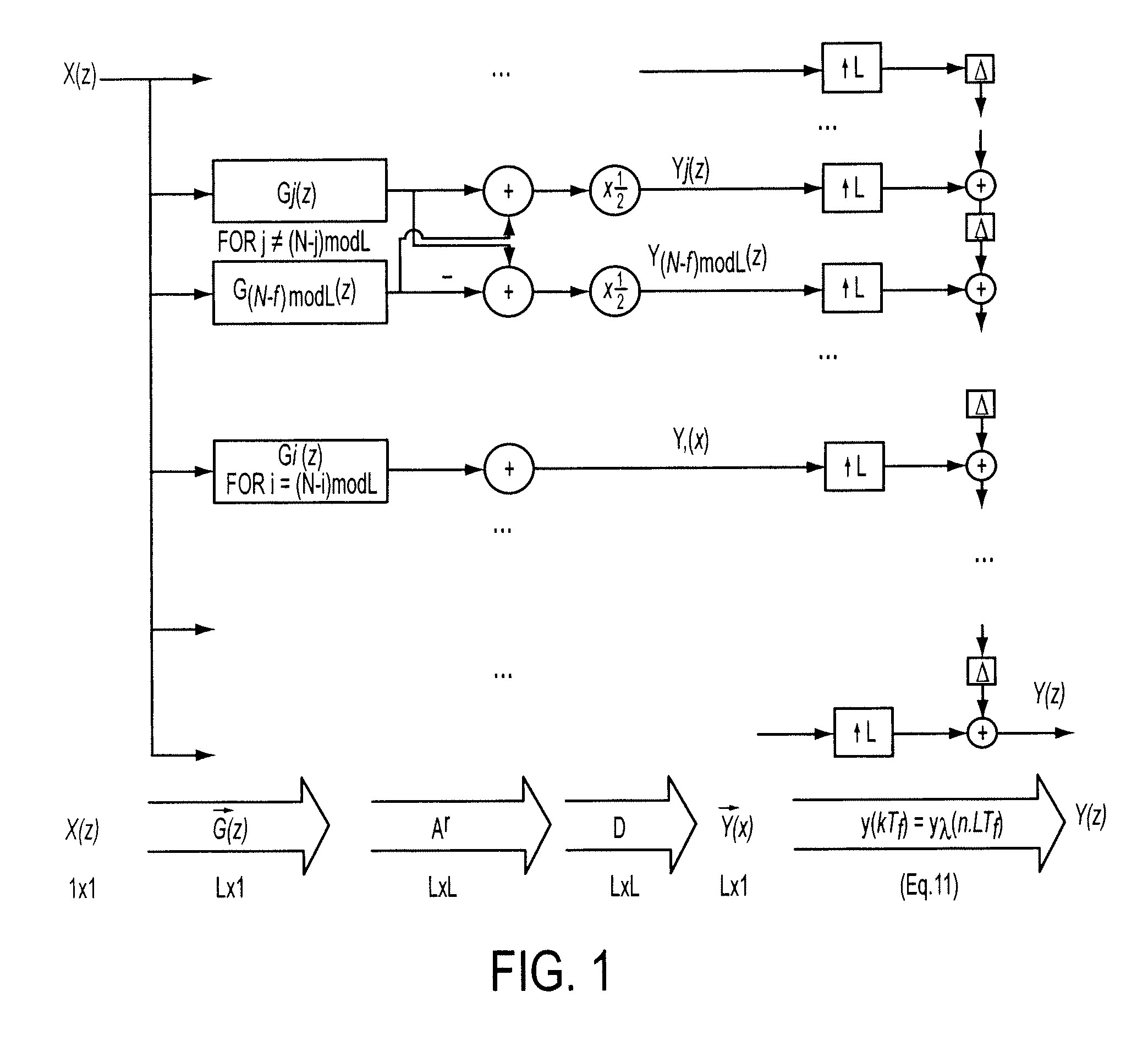

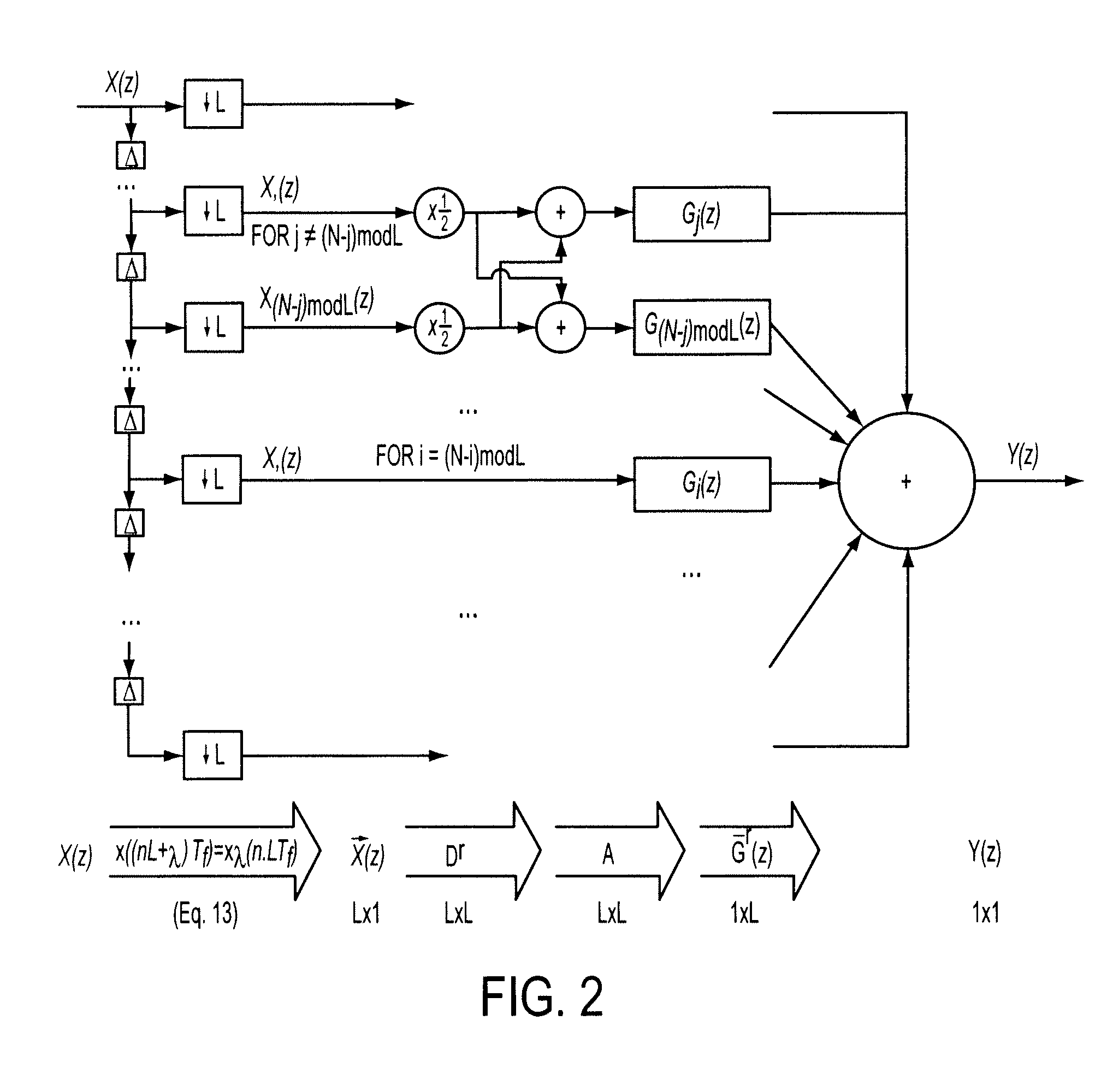

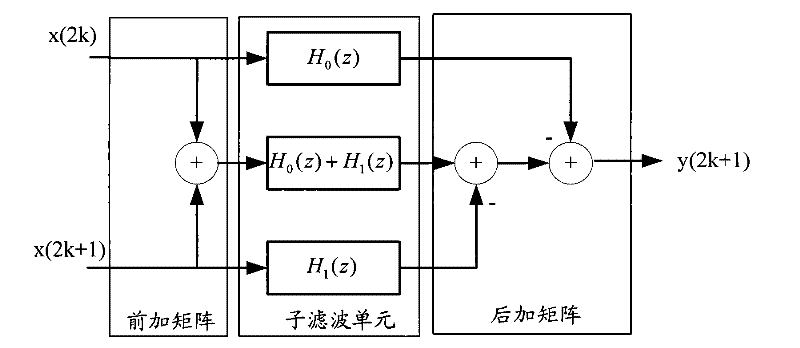

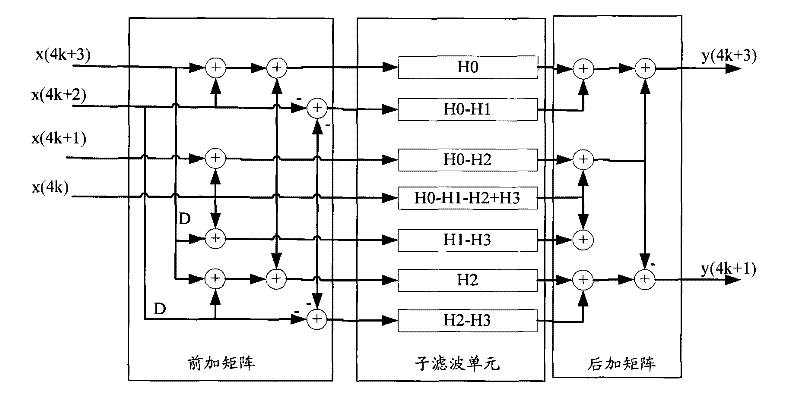

Data samples are filtered by using a digital filter where the length of an impulse response of the digital filter is finite, an impulse response of the digital filter is symmetric and the operation of the digital filter is multi-rate. The method uses a polyphase decomposition to break down the input data stream into N parallel substreams and the multi-rate digital filter is separated by a polyphase decomposition into multiple lower-rate sub-filters where each of the sub-filters is separated into a set of simpler sub-sub-filters which operate upon the same set of input samples and which have impulse responses which are jointly centro-symmetric, a set of pre-filtering arithmetic structures, and a set of post-filtering arithmetic structures and performing each such pair of sub-sub-filtering operations using a single shared filter structure, a set of pre-filtering combining adders, and a set of post-filtering separating adders.

Owner:VECIMA NETWORKS

Antenna arraying full-spectrum correlated combining system based on broadband signal frequency domain

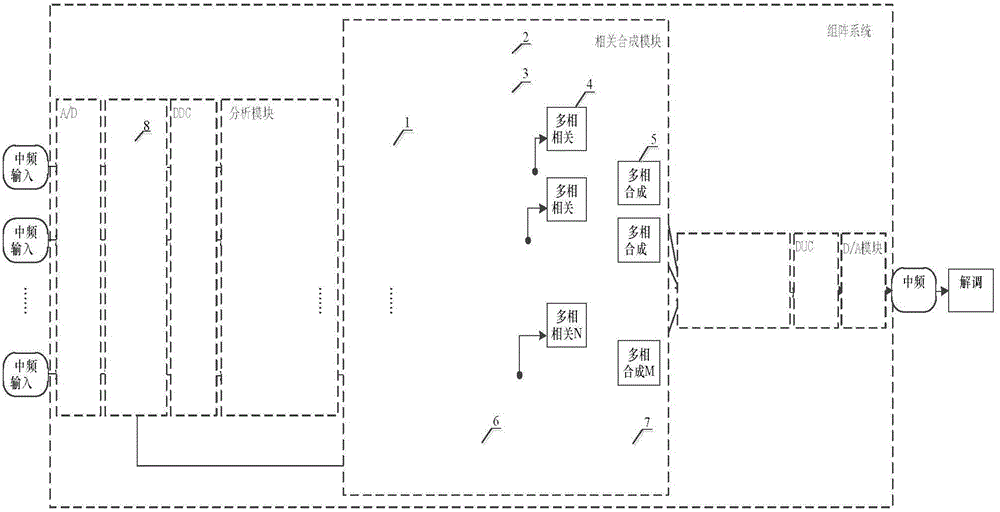

The invention provides an antenna arraying full-spectrum correlated combining system based on a broadband signal frequency domain and aims to provide a frequency domain based arraying system capable of saving hardware computing resources and overcoming phase ambiguity. The technical scheme includes that the antenna arraying full-spectrum correlated combining system is implemented according to that an A / D (analog / digital) module is used for sampling inputted broadband medium-frequency analog signals; obtained digital medium-frequency signals are subjected to sampling clock full-period delay by a delay module according to N antenna signal time delay estimation values fed back by a correlated combining module, then subjected to frequency conversion by a DDC (digital down converter ) module, polyphase decomposition by an analysis module to obtain M falling-rate narrow-band branches with uniform frequency domain ranges, polyphase correlation, time delay estimation and feedback, fractional time delay correction and polyphase combining by a correlated combining module, polyphase synthesis by a synthesis module, and finally are outputted to a demodulation receiver through a DUC (digital up converter) module and a D / A (digital / analog) module. The antenna arraying full-spectrum correlated combining system based on the broadband signal frequency domain solves the problem of phase ambiguity through integer multiples of sampling clock delay and fractional delay compensation.

Owner:10TH RES INST OF CETC

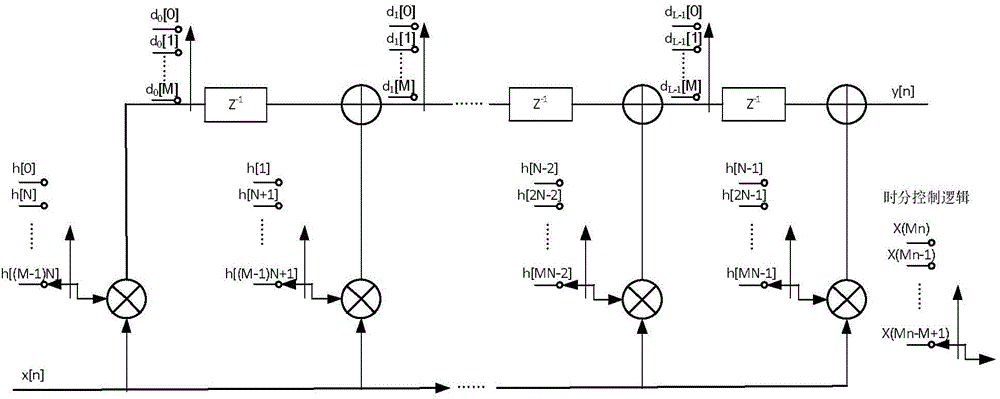

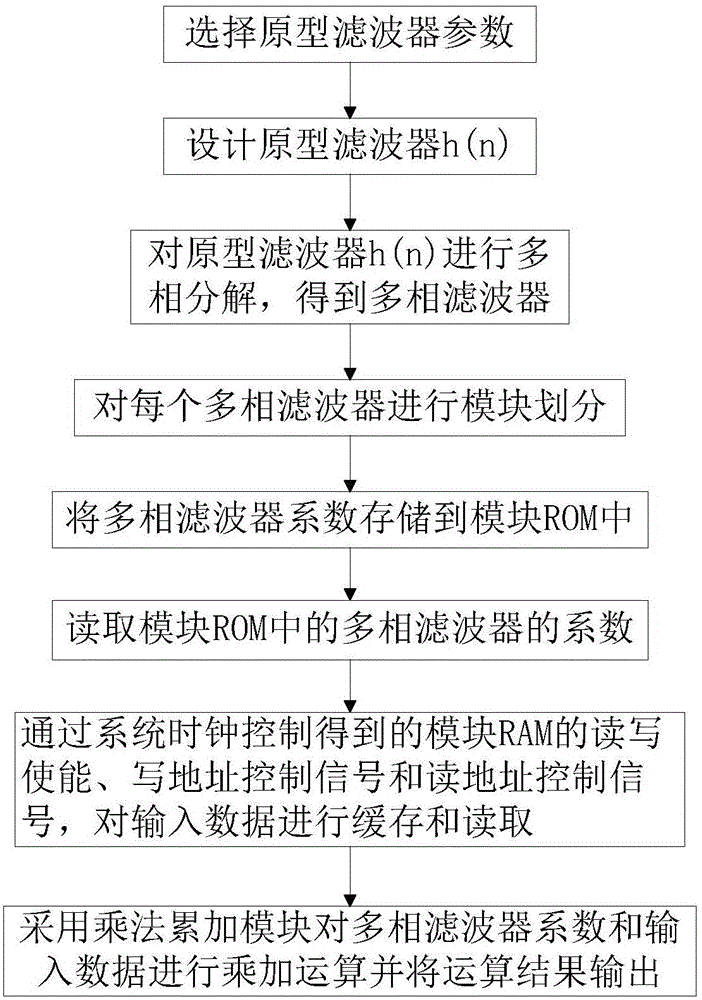

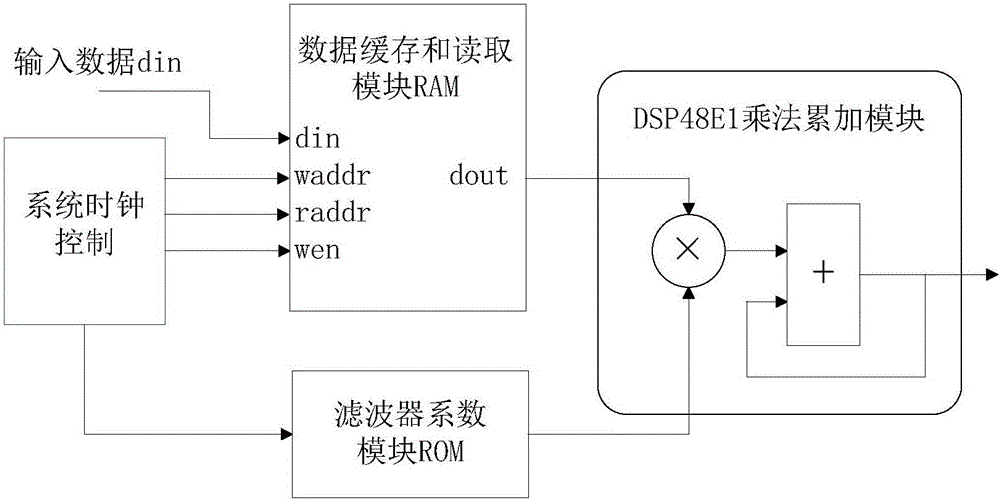

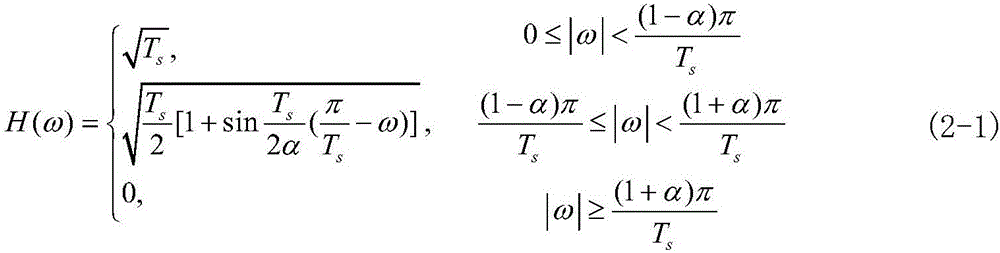

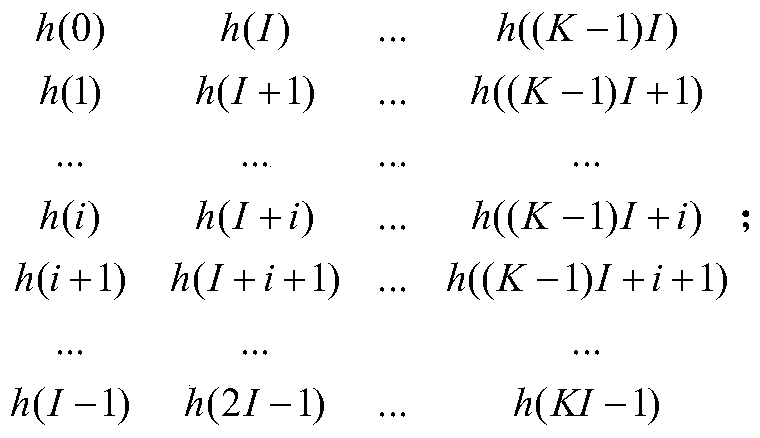

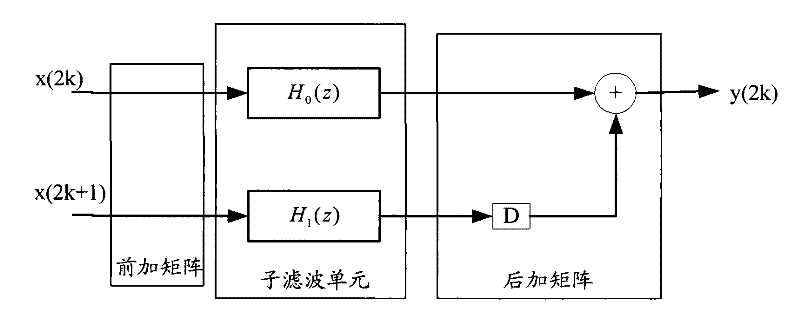

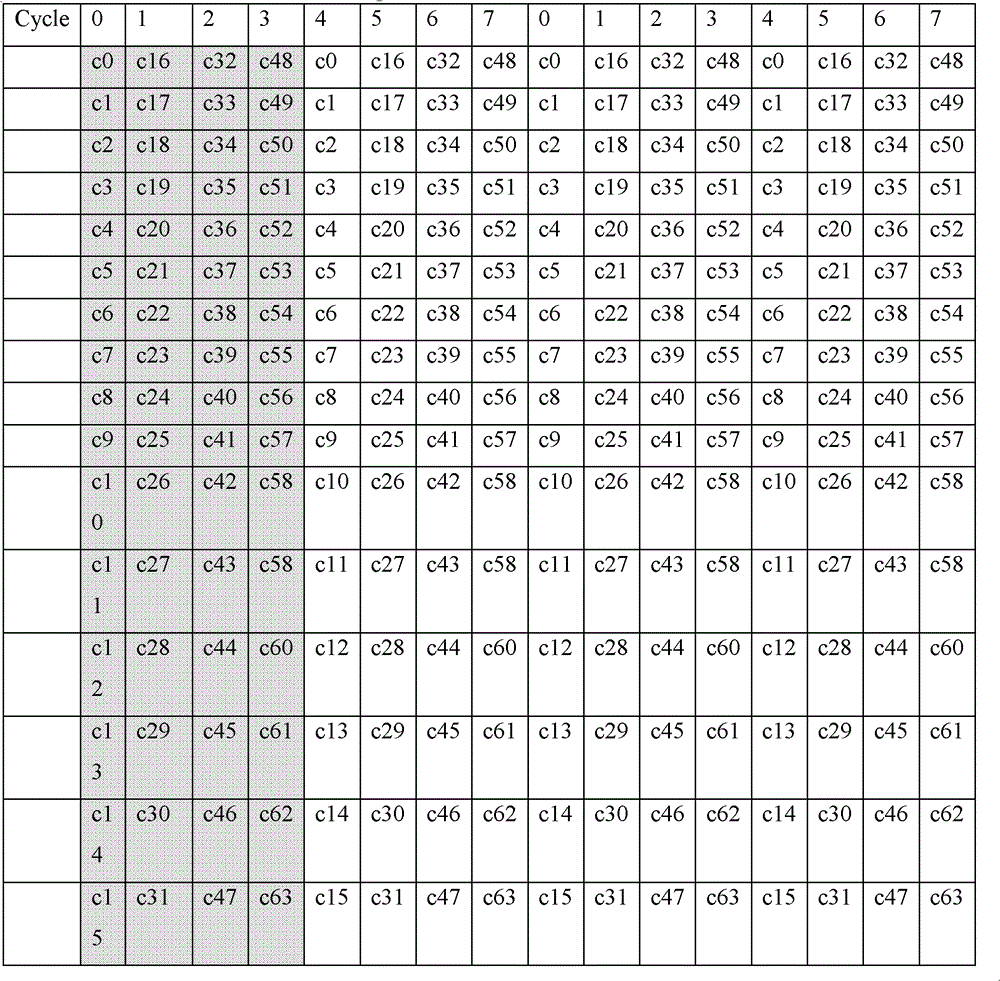

Method for realizing high-order FIR filter based on FPGA

ActiveCN106549650AReduce occupancyGuaranteed real-time processingDigital technique networkComputer architectureDecomposition

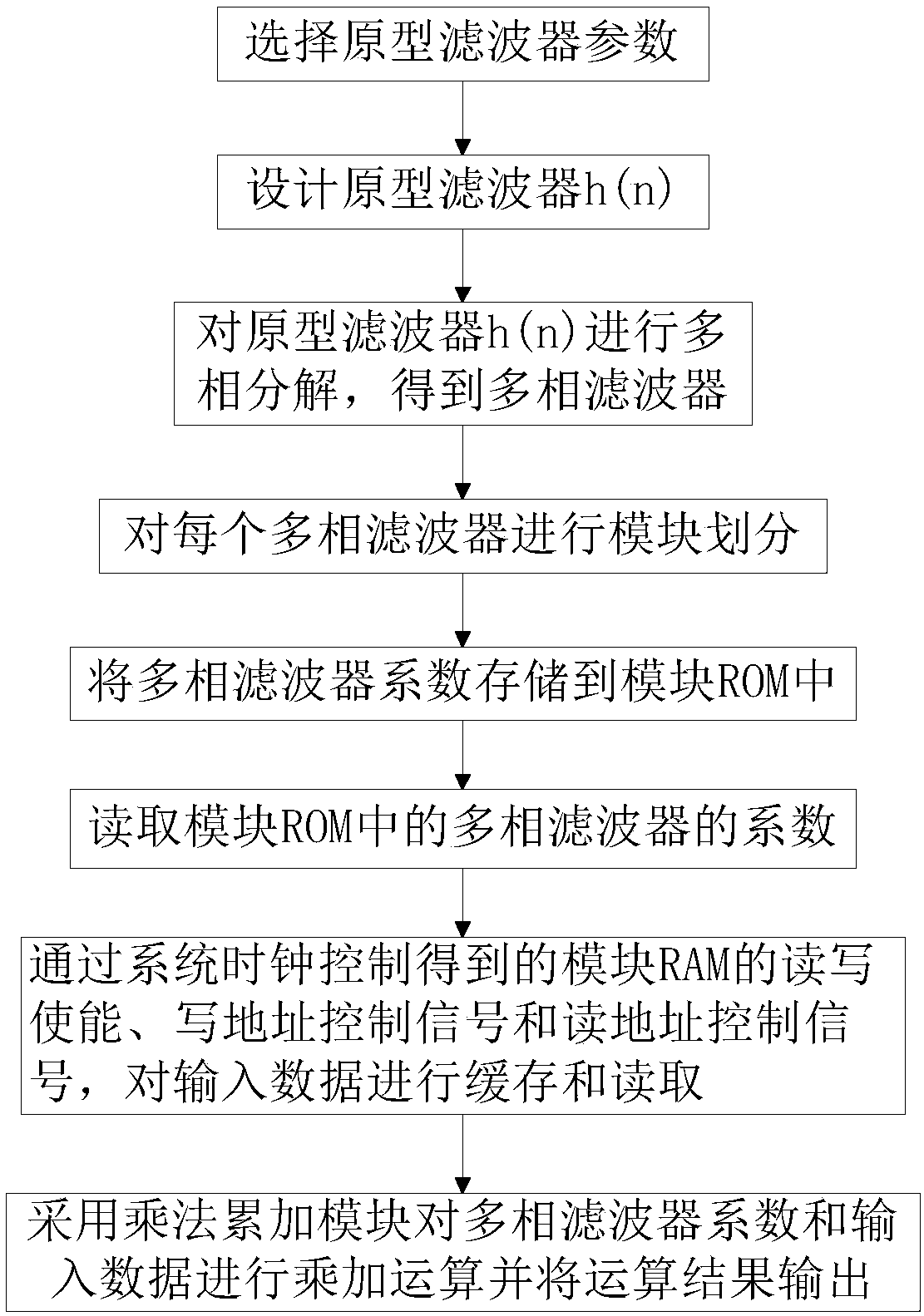

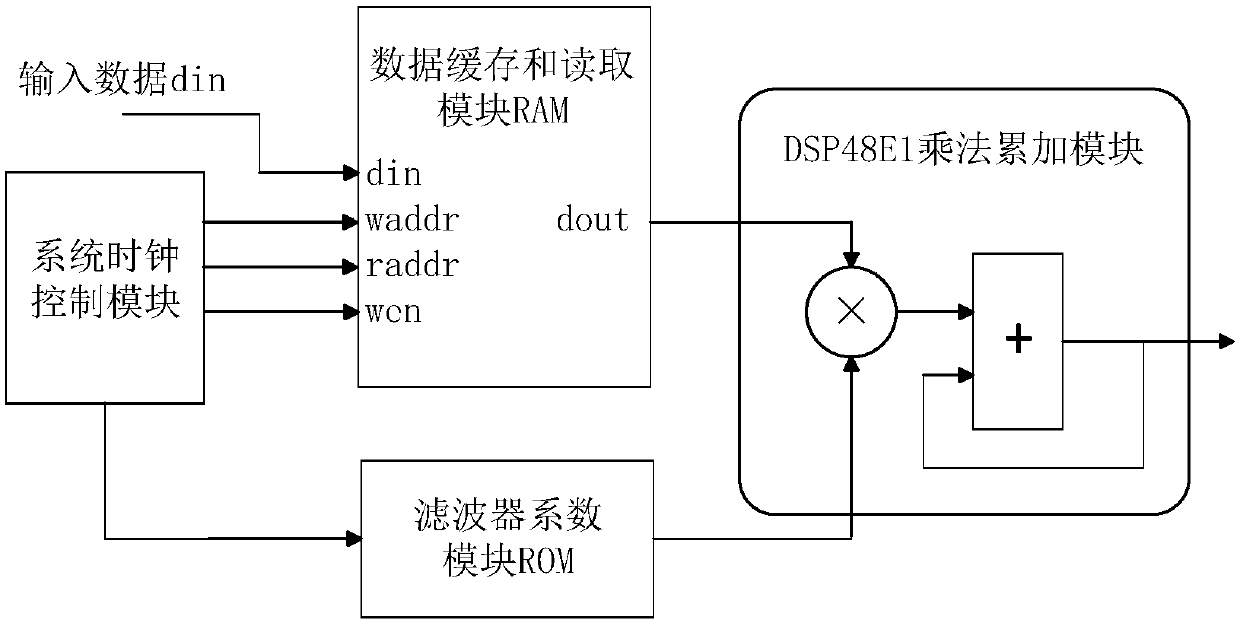

The invention provides a method for realizing a high-order FIR filter based on an FPGA, used for solving the technical problem of excessive occupation of the high-order FIR filter to logic units in the FPGA in the existing method for realizing high-order FIR multiphase filtering. The method comprises the following steps: selecting parameters of a prototype filter; designing the prototype filter h (n); performing multiphase decomposition on the prototype filter h (n) to obtain multiphase filters; performing module division on each multiphase filter; storing coefficients of the multiphase filters in a module ROM; reading the coefficients of the multiphase filters in the module ROM; caching and reading input data by read-write enable, a write address control signal and a read address control signal of a module RAM obtained by system clock control; and performing multiplication and addition operations on the coefficients of the multiphase filters and the input data by using a multiplication accumulation module, and outputting an operation result. The method provided by the invention is little in occupation of the logic units in the FPGA, simple, efficient and is easy to realize.

Owner:XIDIAN UNIV

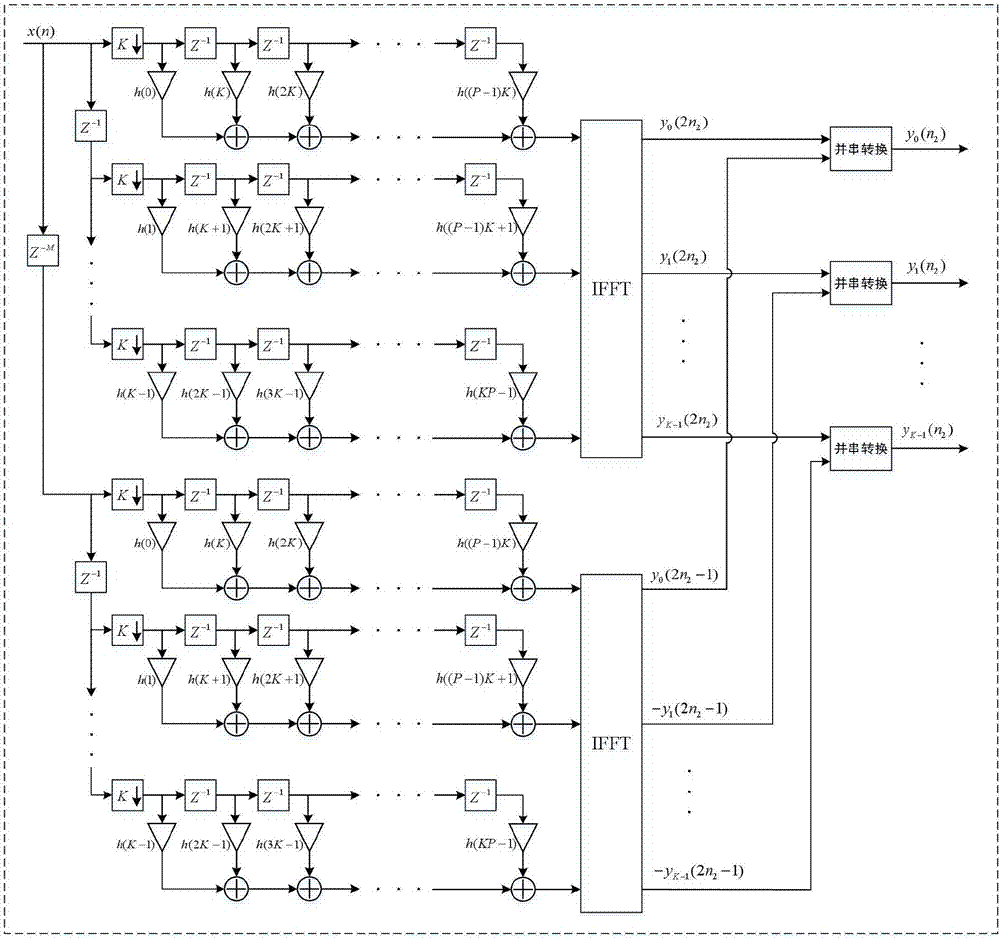

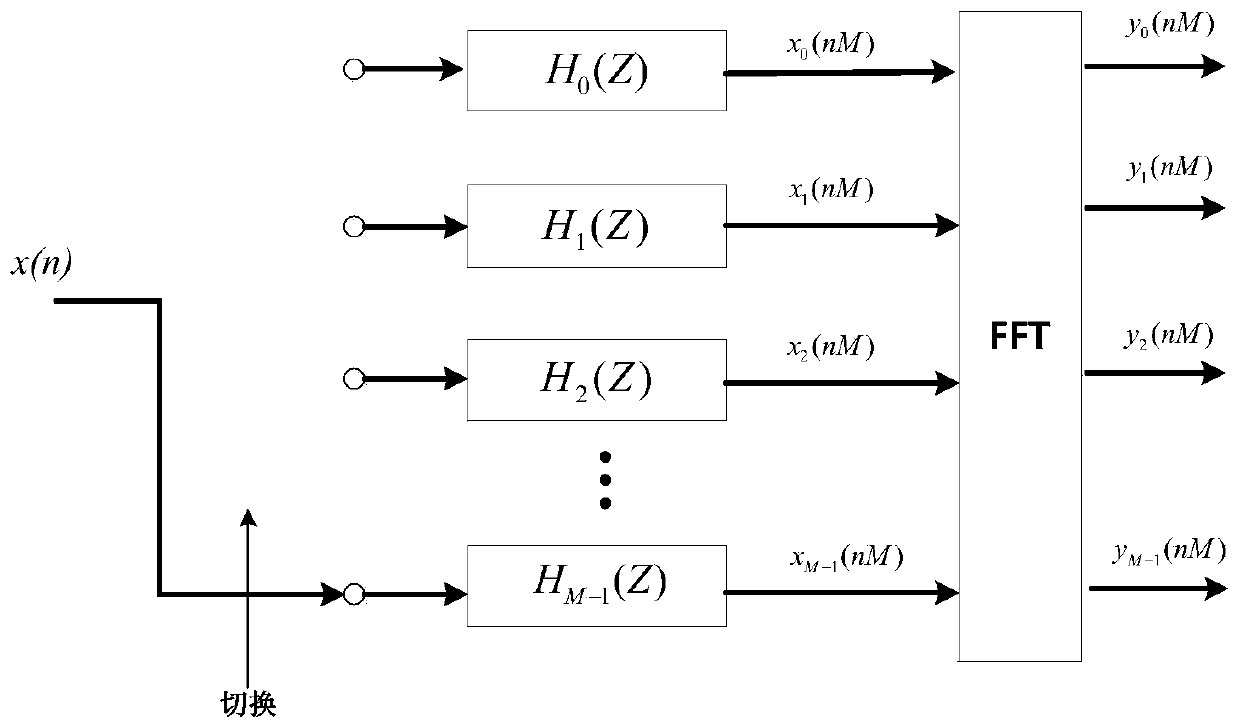

Implementation method for digital channelized filter bank

ActiveCN107241107AReduce computationReduce resource consumptionDigital technique networkTransmissionComputer architectureFiltering theory

The invention belongs to the technical field of communication, relates to an implementation method for a digital channelized filter bank and provides a digital channelized filter bank implementation technology based on low computation burden, low resource consumption and high adaptability of a multi-channel filter and application thereof in implementation of digital channelization. When the required frequency resolution is changed, only coefficient of a lowpass prototype filter needs to be calculated again, and a new filter coefficient is reallocated into a multi-channel filter bank of the original structure according to multi-phase decomposition and multichannel filter theories, and an expression and an implementation structure do not need to be deduced again, so that the implementation method provided by the invention is applicable to platforms such as FPGA and DSP, and digital channelization processing is realized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Time variant filter implementation

ActiveUS6961395B2Effectively implement spreadingEffectively scramblingError preventionLine-faulsts/interference reductionComputation complexityComputer science

The present invention relates to the efficient realization of a time variant multi-rate FIR filter cascaded with a time invariant FIR filter. Preferably, the time invariant FIR filter response provides filtering based on channel estimates and the time variant FIR filter provides filtering to effectively implement spreading and scrambling with appropriate coding. The realization of the combined filters is accomplished by transforming the pair of filters into a single “combined” polyphase filter with coefficients that are time variant in a specific manner. The invention provides for pre-calculating the coefficients of the combined filter; a memory storage and addressing scheme for the resulting coefficients that ensures that the combined filter behaves like the original pair of filters; and overall polyphase decomposition of the resulting filter to significantly reduce the computational complexity as compared to the requirements of the original pair of filters.

Owner:RPX CORP

Method and device for digital down converter and filtering extraction

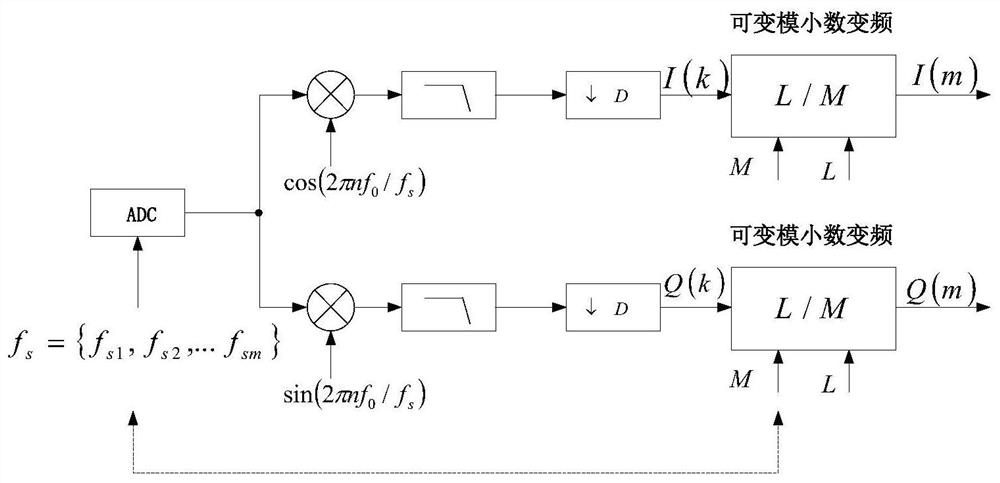

ActiveCN101621279ALower requirementReduce power consumptionDigital technique networkMulti-frequency-changing modulation transferenceInformation processingDigital down converter

The invention provides a method and a device for digital down converter and filtering extraction, belonging to the field of signal and information processing. The method comprises the following steps: receiving a middle frequency digital signal, and carrying out polyphase decomposition processing with a polyphase decomposition factor of n on the middle frequency digital signal to obtain n paths of signals subjected to the polyphase decomposition processing and output the signals; receiving n paths of signals subjected to the polyphase decomposition processing, carrying out mixed frequency processing on each path of signal subjected to the polyphase decomposition processing to obtain n paths of signals subjected to the mixed frequency processing and output the signals; and receiving n paths of signals subjected to the mixed frequency processing and carrying out filtering extraction processing on the n paths of signals subjected to the mixed frequency processing according to an extraction factor m to obtain n / m paths of digital down converter signals, wherein m, n and n / m are natural numbers which are not equal to zero, and m is more than or equal to n. The device comprises a polyphase decomposition circuit, a mixed frequency circuit and a filtering extraction circuit. The scheme reduces the operation complexity, improves the stability of the processor, and effectively improves the precision and real-time property of the operation at the same time.

Owner:成都市天珑科技有限公司 +1

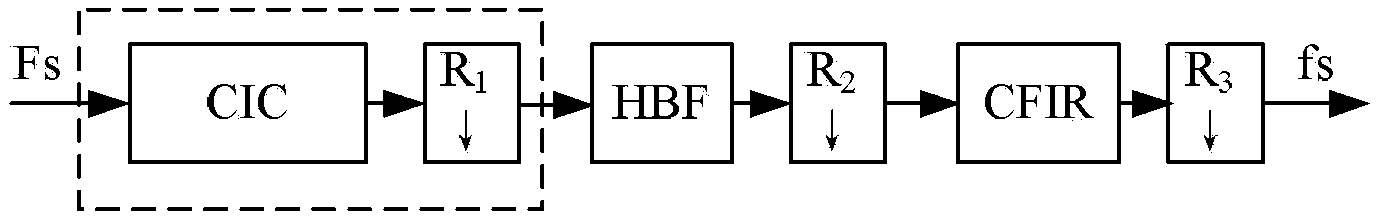

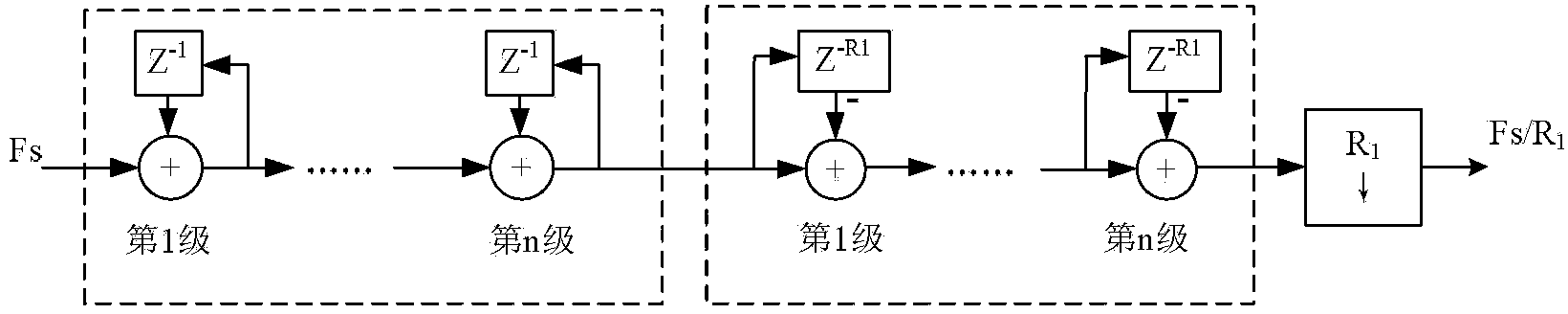

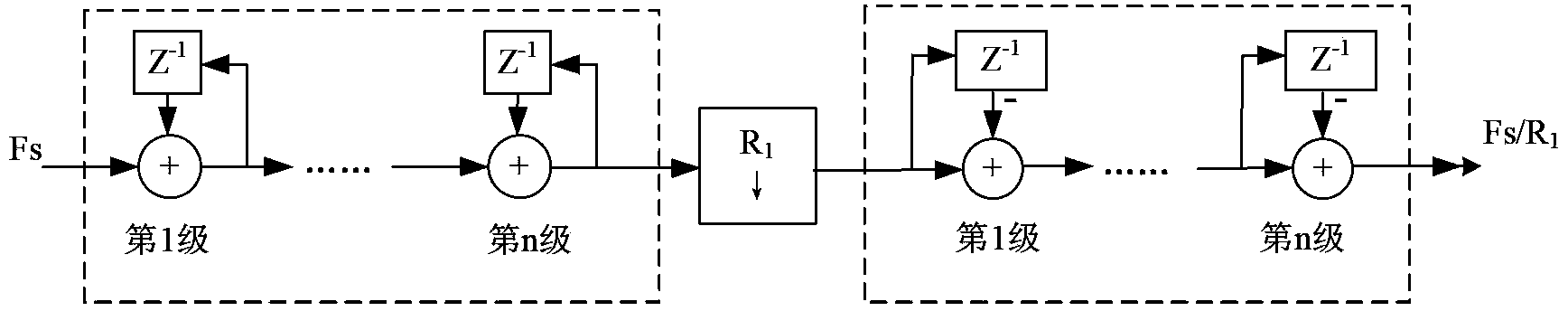

Low-consumption digital decimation filter bank with variable decimation multiples and digital decimation and filtering method

InactiveCN103457574AReduce the numberReduce consumptionDigital technique networkDecompositionEngineering

The invention discloses a low-consumption digital decimation filter bank with variable decimation multiples and a digital decimation and filtering method. The low-consumption digital decimation filter bank and the digital decimation and filtering method are used for the filtering and the decimation of data. The filter bank comprises a first stage, a second stage and a third stage, wherein the first stage is a cascading comb-shaped integrating filter which is used for achieving the decimation movement with large multiples, the second stage is a half-band filter of at least one stage which is used for achieving the decimation movement of the second stage, the third stage is a compensating filter which is used for compensating pass band damping and carrying out filtering decimation movement, and the first stage is the cascading comb-shaped integrating filter with variable decimation multiples in a non-recursion mode. The method comprises the steps of determining decimation ratios and the system structure of the decimation filter bank, decomposing the transfer function of the cascading comb-shaped integrating filter, selecting the decimation ratios meeting requirements to for combination and carrying out multi-phase decomposition on the cascading comb-shaped integrating filter, the half-band filter and the compensating filter. The low-consumption digital decimation filter bank with the variable decimation multiples and the digital decimation and filtering method have the advantages that the number of registers working close to high frequency can be reduced, resource consumption is reduced, and power dissipation is reduced.

Owner:湘潭芯力特电子科技有限公司

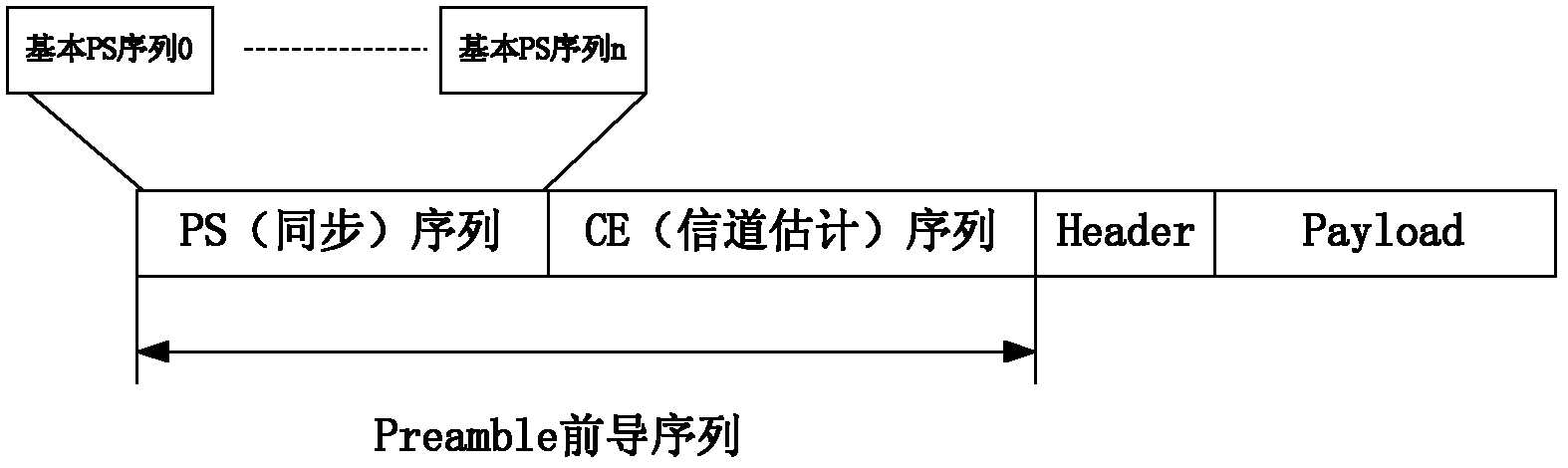

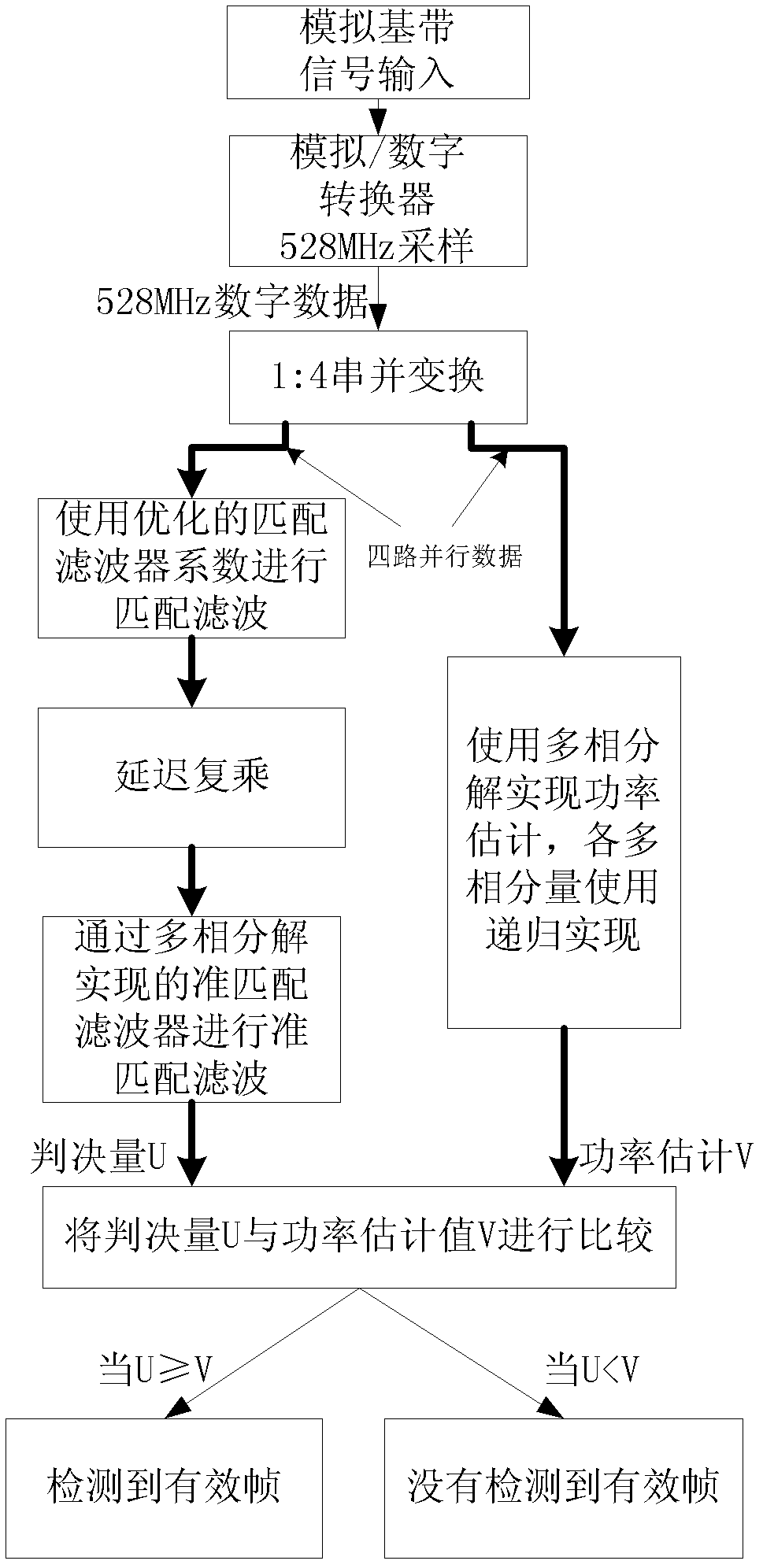

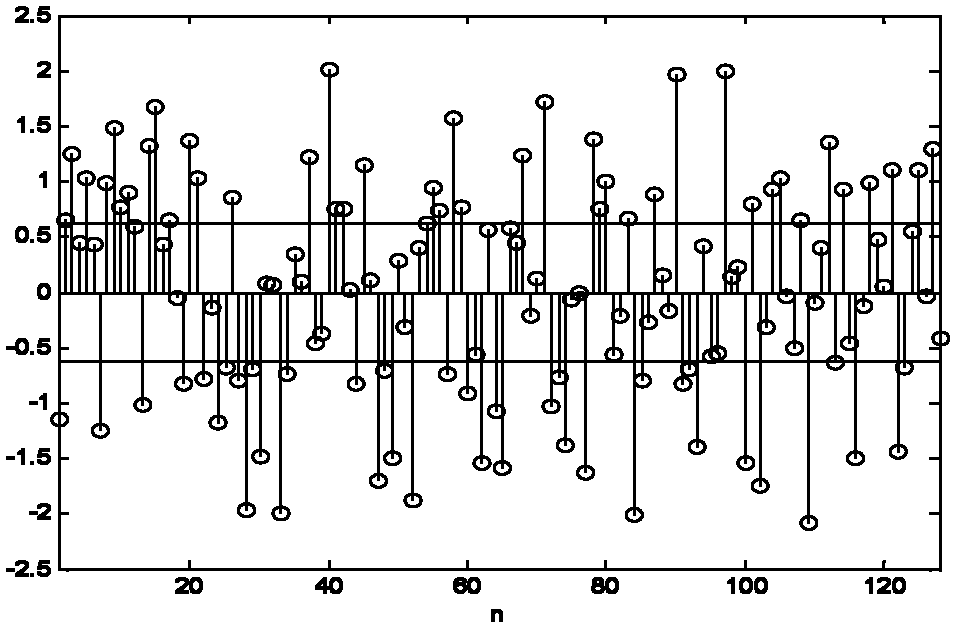

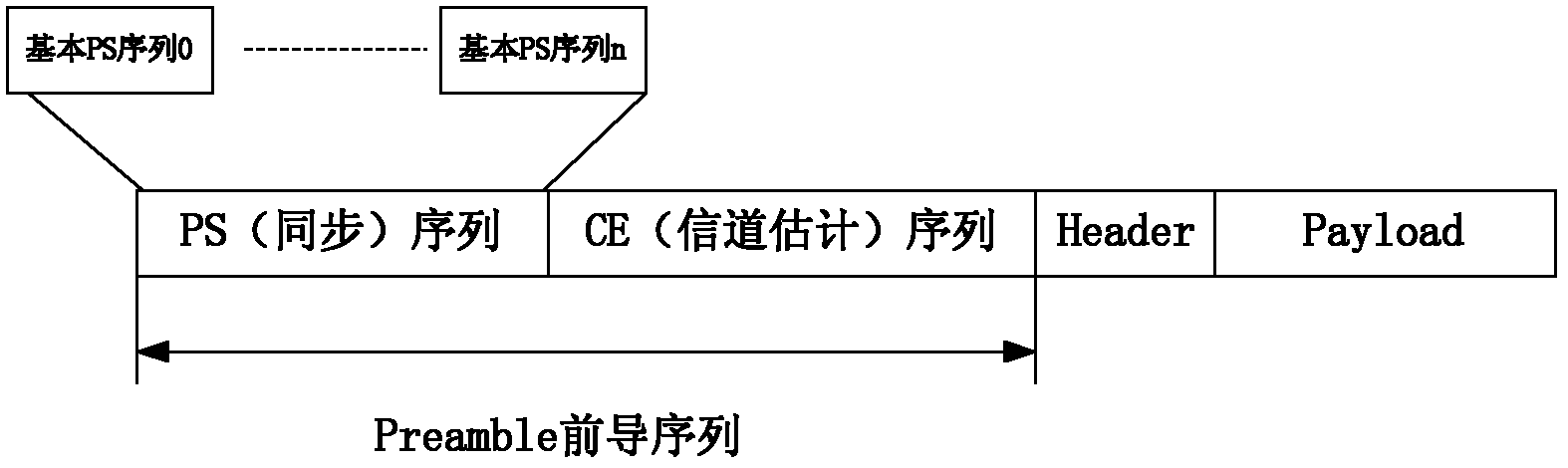

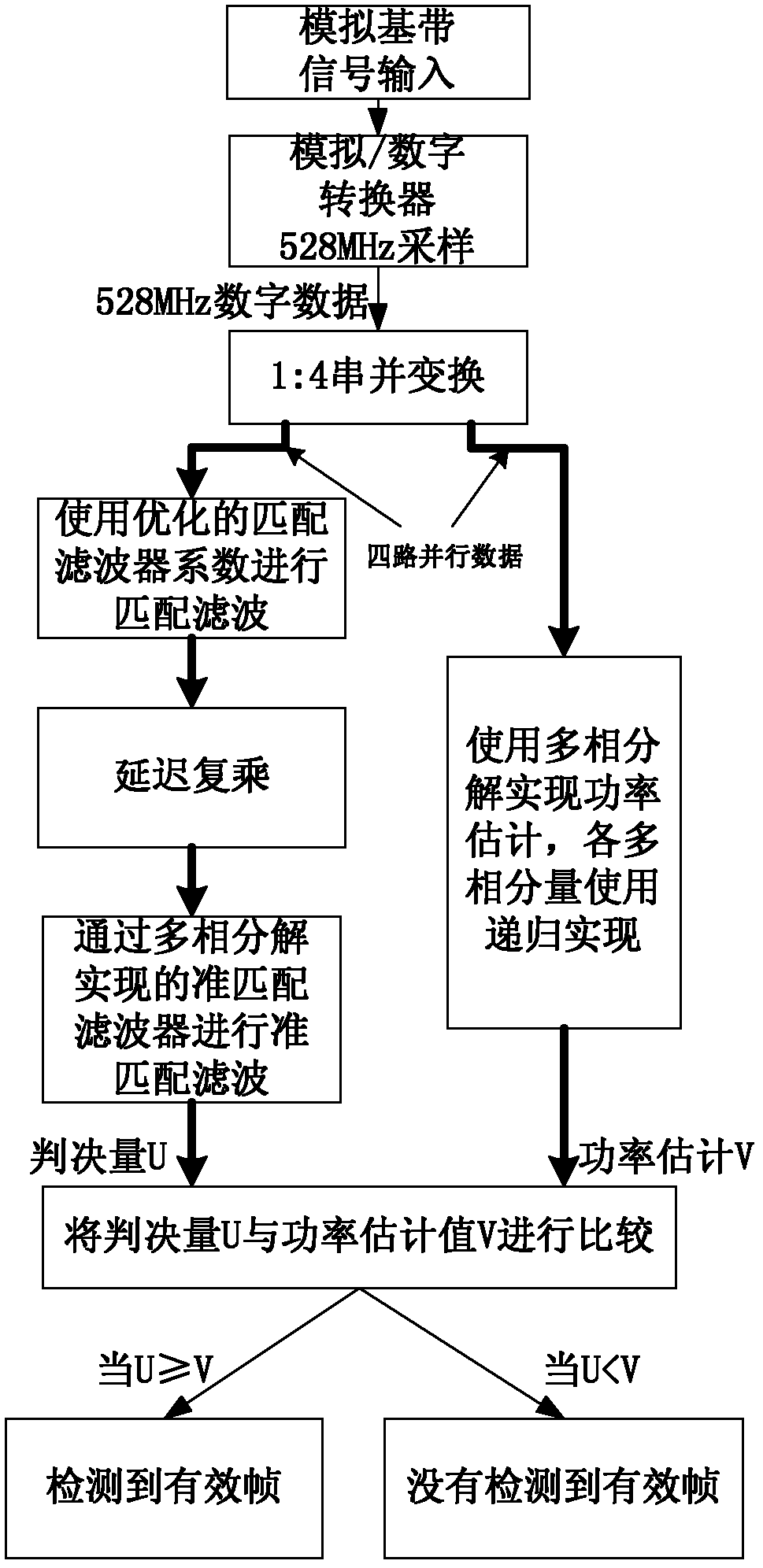

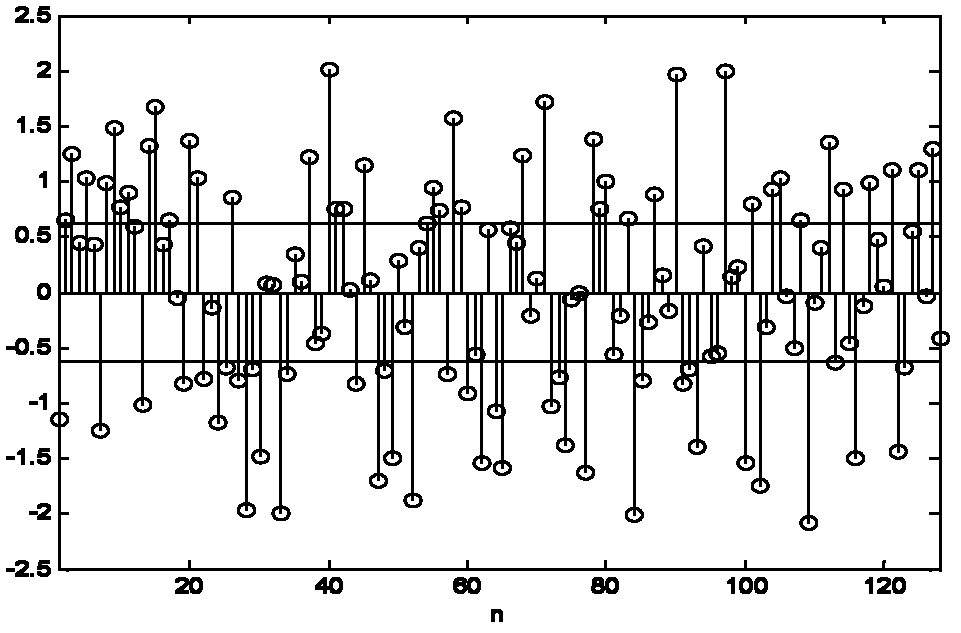

Frame detection method for orthogonal frequency division multiplexing ultra-wideband system

InactiveCN102255832AFacilitate hardware logic verificationReduce implementation complexityMulti-frequency code systemsTransmitter/receiver shaping networksUltra-widebandA d converter

The invention provides a frame detection method for an orthogonal frequency division multiplexing ultra-wideband system. The method comprises the following steps: performing 1:4 serial-parallel conversion on a received sampling data of an analog-to-digital converter; dividing the data subject to the serial-parallel conversion into two paths; utilizing an optimized matching filter coefficient to perform matching filtering on one path of the data, performing a delaying multiplying operation on a matching filtering result, and then utilizing a weighting coefficient in an exponential form to perform accurate matching filtering on a delaying multiplying result so as to acquire a decision, and finally performing quadruple downsampling treatment on the decision, wherein multiphase decomposition is used for reducing the calculation quantity of weighting accumulation; and estimating the power of the other path of the data to acquire an estimated power value and then performing the quadruple downsampling treatment on the estimated power value, wherein the calculating quantity is reduced since the multiphase decomposition is used for realizing the power estimation and the quadruple downsampling treatment, and a recursive algorithm is used for realizing each multiphase component; and finally, inputting calculated results of the two paths of the data into a comparator, and judging whether a frame exists.

Owner:SOUTHEAST UNIV +1

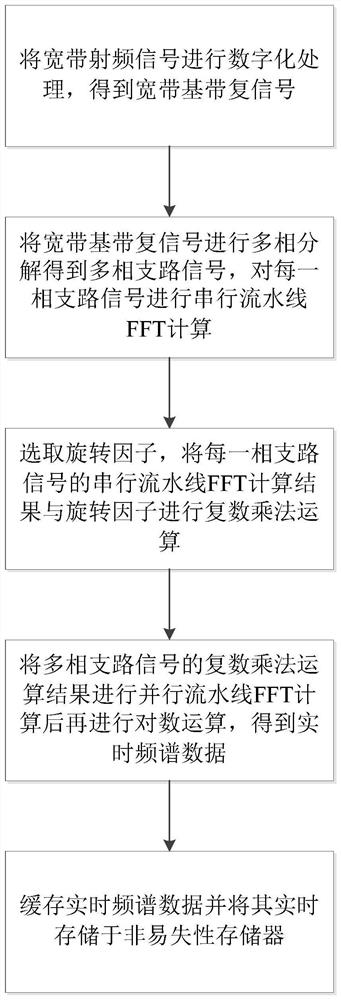

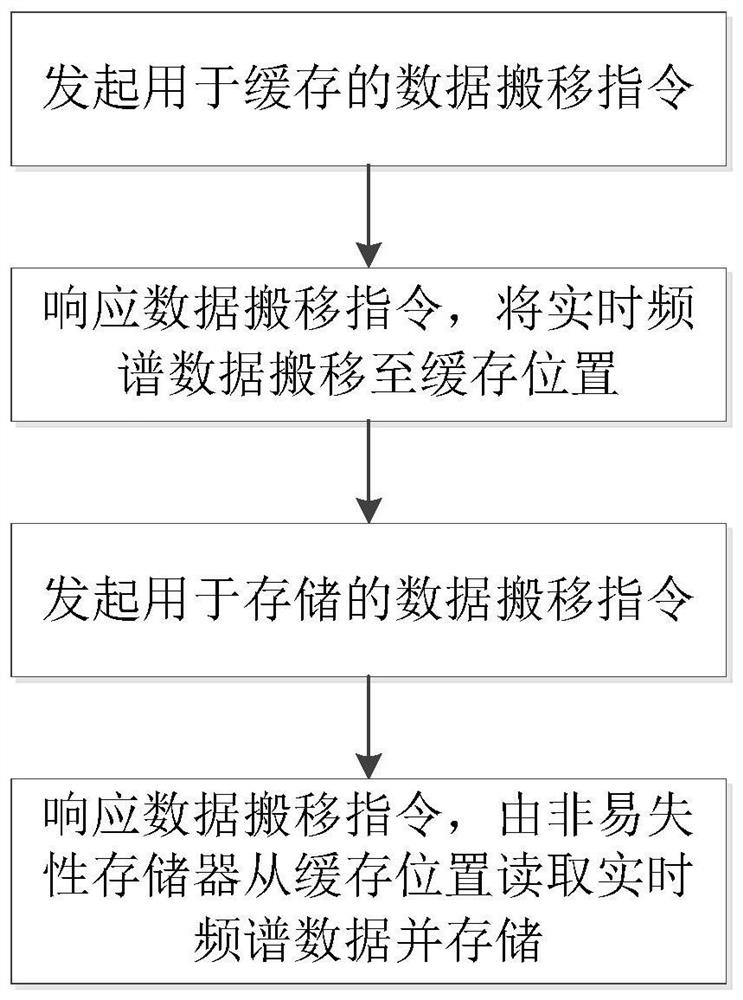

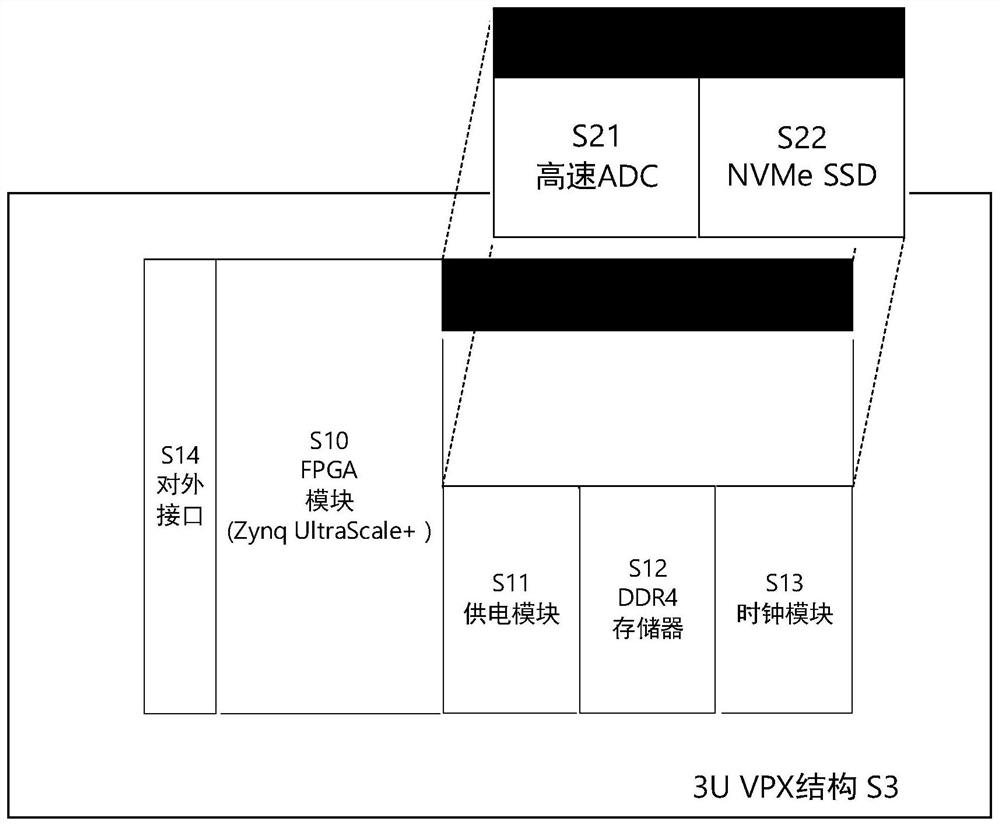

Real-time broadband spectrum analysis and storage method and device

PendingCN113267677AReduce volumeReduce complexitySpectral/fourier analysisFrequency spectrumTime spectrum

The invention provides a real-time broadband spectrum analysis and storage method and device. The invention relates to a real-time broadband spectrum analysis and storage method, which comprises the following steps of: carrying out digital processing on a broadband radio frequency signal to obtain a broadband baseband complex signal; carrying out multiphase decomposition on the broadband baseband complex signal to obtain multiphase branch signals, and carrying out serial pipeline FFT calculation on each phase branch signal; selecting a twiddle factor, and performing complex multiplication on the serial pipeline FFT calculation result of each phase of branch signal and the twiddle factor; performing parallel pipeline FFT calculation on a complex multiplication result of the multi-phase branch signal, and then performing logarithmic operation to obtain real-time spectrum data; caching and storing real-time spectrum data in a non-volatile memory in real time. According to the invention, full-parallel FFT calculation is directly carried out on the broadband signal acquired by the high-speed ADC, the frequency spectrum of the GHz-level broadband signal can be calculated in real time, and real-time frequency spectrum data can be recorded in a gapless and lossless manner.

Owner:嘉兴军创电子科技有限公司

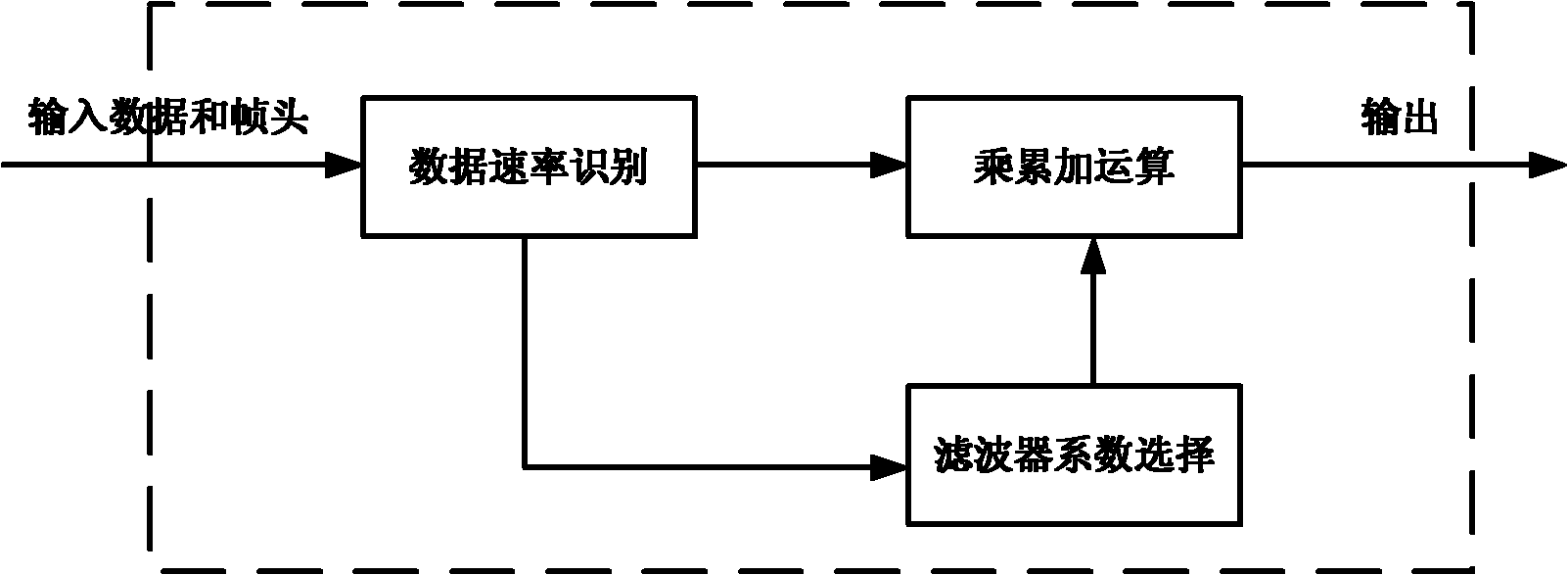

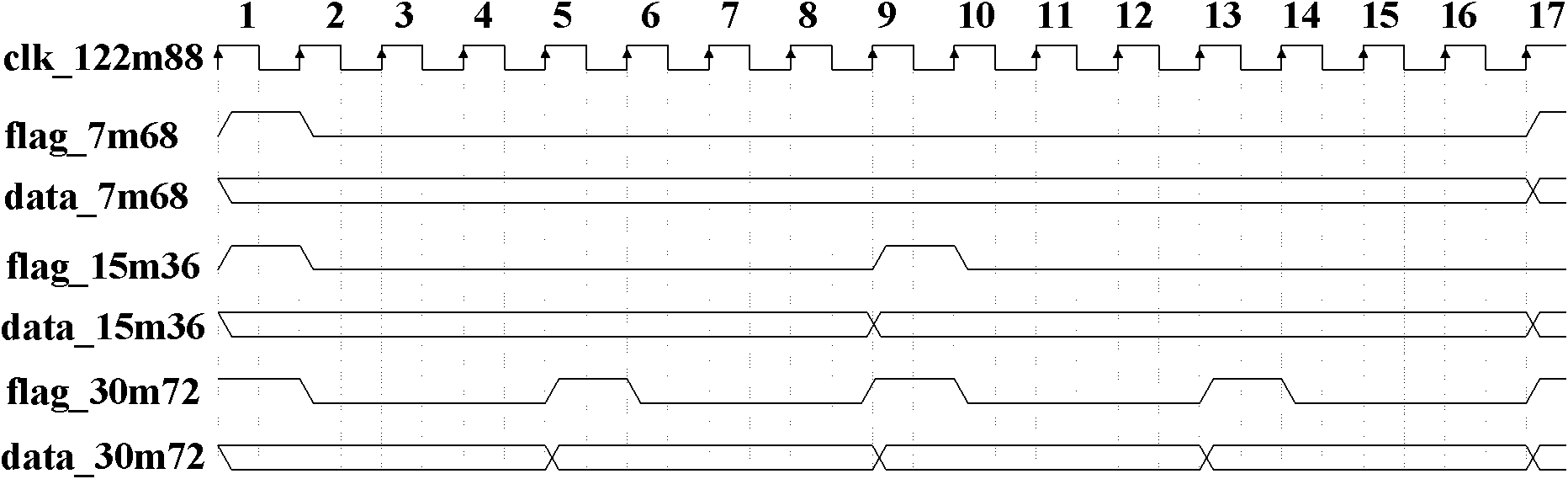

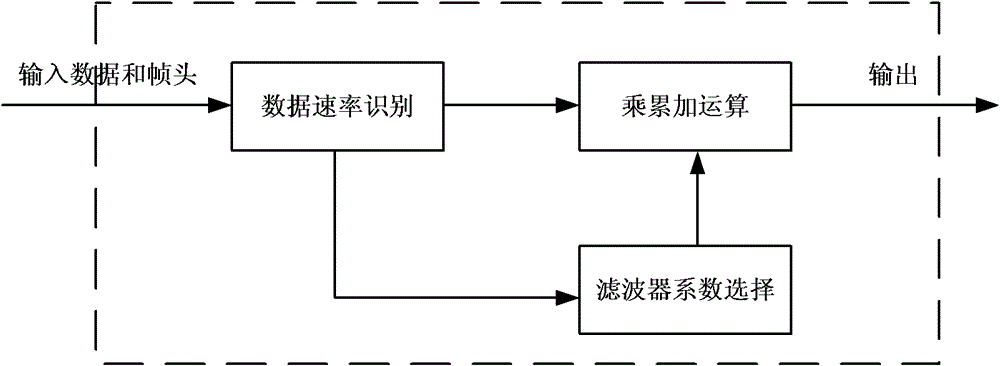

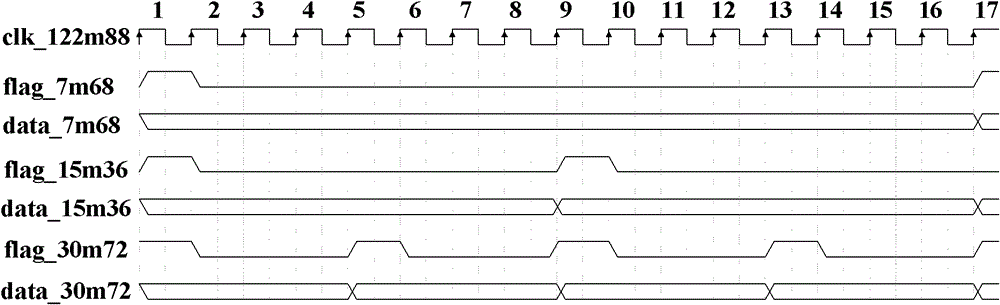

Multi-standard digital filtering implementation method and system

The invention relates to a multi-standard digital filtering implementation method and system, wherein the method comprises the following steps of: identifying data speed according to data frame head; respectively calculating sample point periods of the identified signals with different data speeds, and determining a minimum common sample point period number of each signal; performing multi-phase decomposition on a filter, and completing multiplication-accumulation operation of each phase in clock periods of the minimum common sample point period number. The invention automatically determines the sampling rate by judging the data frame head, without the selection of switch, and reduces the consumption of the clock domain by the using of the same operating clock; furthermore, the data with different bandwidth shares the multiplication-accumulation operation so that the resource consumption is greatly reduced.

Owner:ZTE CORP

Circuit for sample rate conversion

ActiveUS20090058692A1Digital technique networkAnalogue conversionSample rate conversionImpulse response

The present invention is related to a circuit for converting the sample rate of a digital signal, comprisingan input for applying the digital signal,a conversion filter having either a symmetrical or anti-symmetrical impulse response and implemented as a plurality of subfilters in parallel, each subfilter having a symmetrical or anti-symmetrical response derived from components of a polyphase decomposition of said impulse response,combining means for deriving from said applied digital signal input signals of said plurality of subfilters or for combining output signals of said plurality of subfilters into a digital signal with converted sample rate,an output for outputting said digital signal with converted sample rate.

Owner:KEYSIGHT TECH

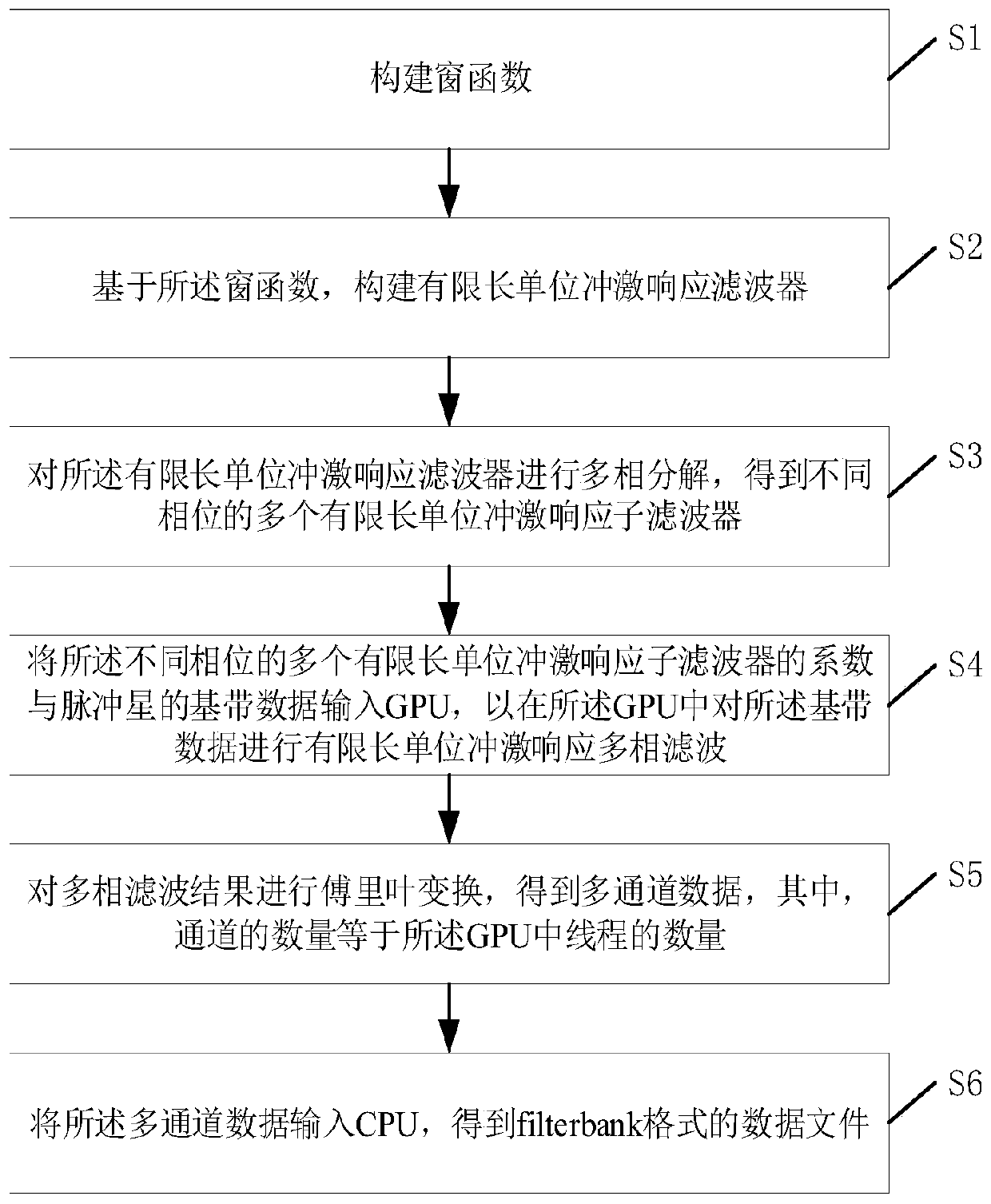

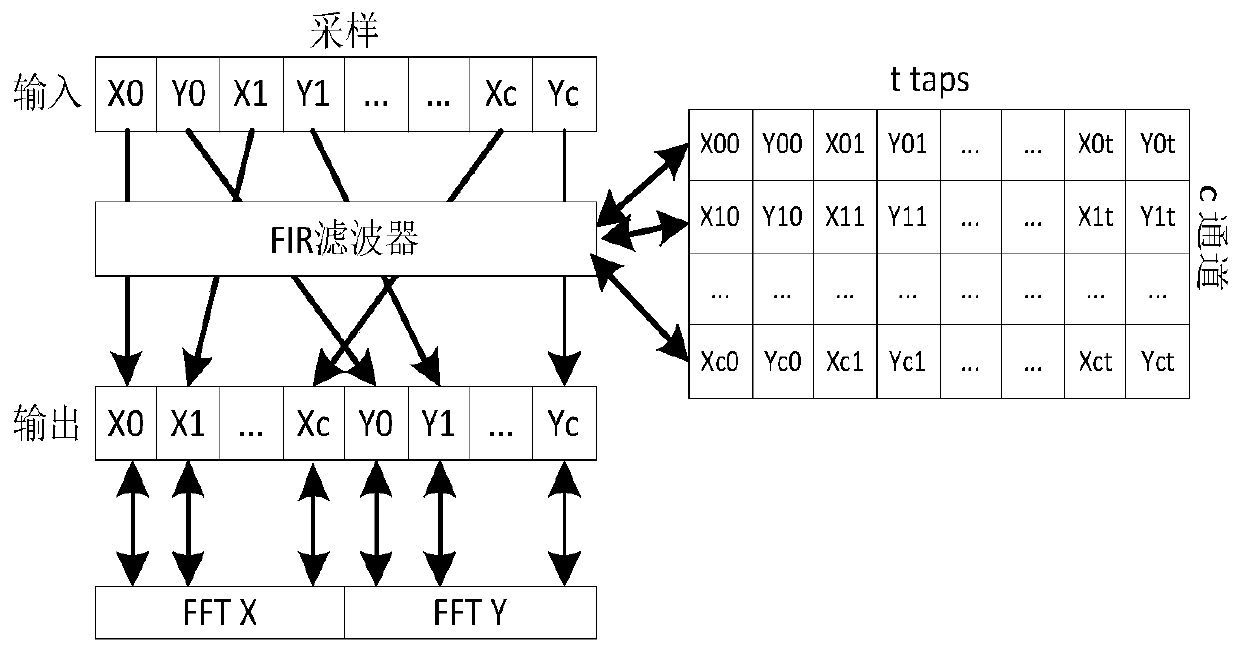

Pulsar signal multichannel filtering method and device and storage medium

PendingCN111414257AImprove observation resolutionIncrease the number of frequency channelsResource allocationComplex mathematical operationsFrequency spectrumData file

The invention provides a pulsar signal multichannel filtering method and device and a storage medium. The method comprises: constructing a window function; constructing a finite length unit impulse response filter based on the window function; carrying out multiphase decomposition on the finite-length unit impulse response filter to obtain a plurality of finite-length unit impulse response sub-filters with different phases; inputting the coefficients of the plurality of finite-length unit impulse response sub-filters with different phases and the baseband data of the pulsar into a GPU so as tocarry out finite-length unit impulse response multiphase filtering on the baseband data in the GPU; performing fourier transform on the multiphase filtering result to obtain multichannel data, wherein the number of channels is equal to the number of threads in the GPU; and inputting the multichannel data into the CPU to obtain a data file in a filterbank format. According to the method provided by the invention, spectrum leakage can be avoided, and the real-time high-speed channel division requirement of radio signals can be met.

Owner:XINJIANG ASTRONOMICAL OBSERVATORY CHINESE ACADEMY OF SCI

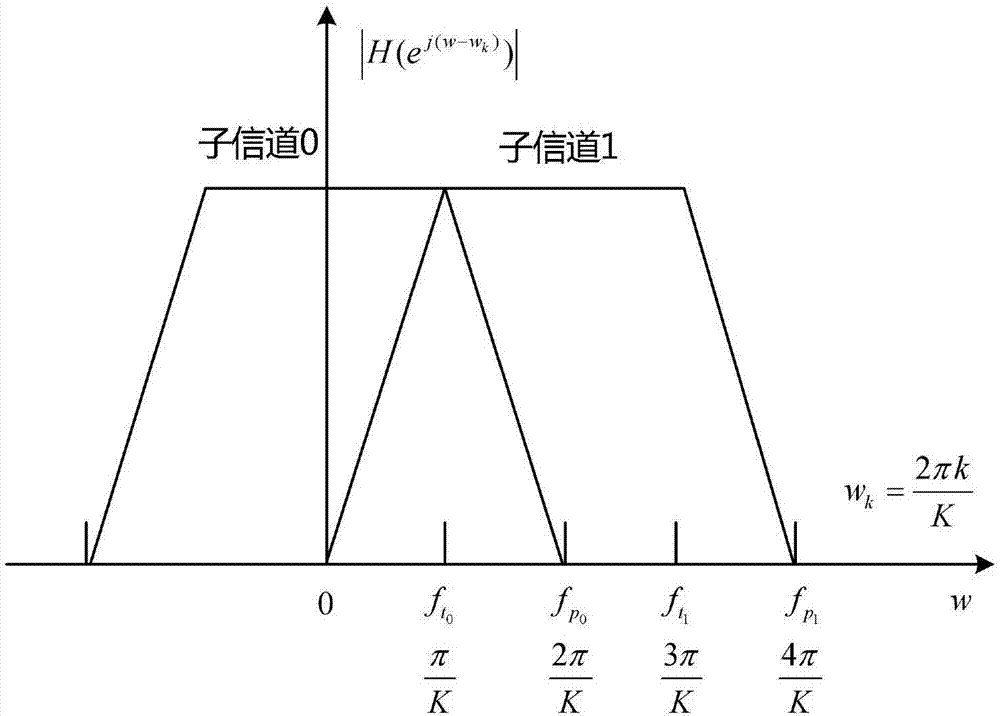

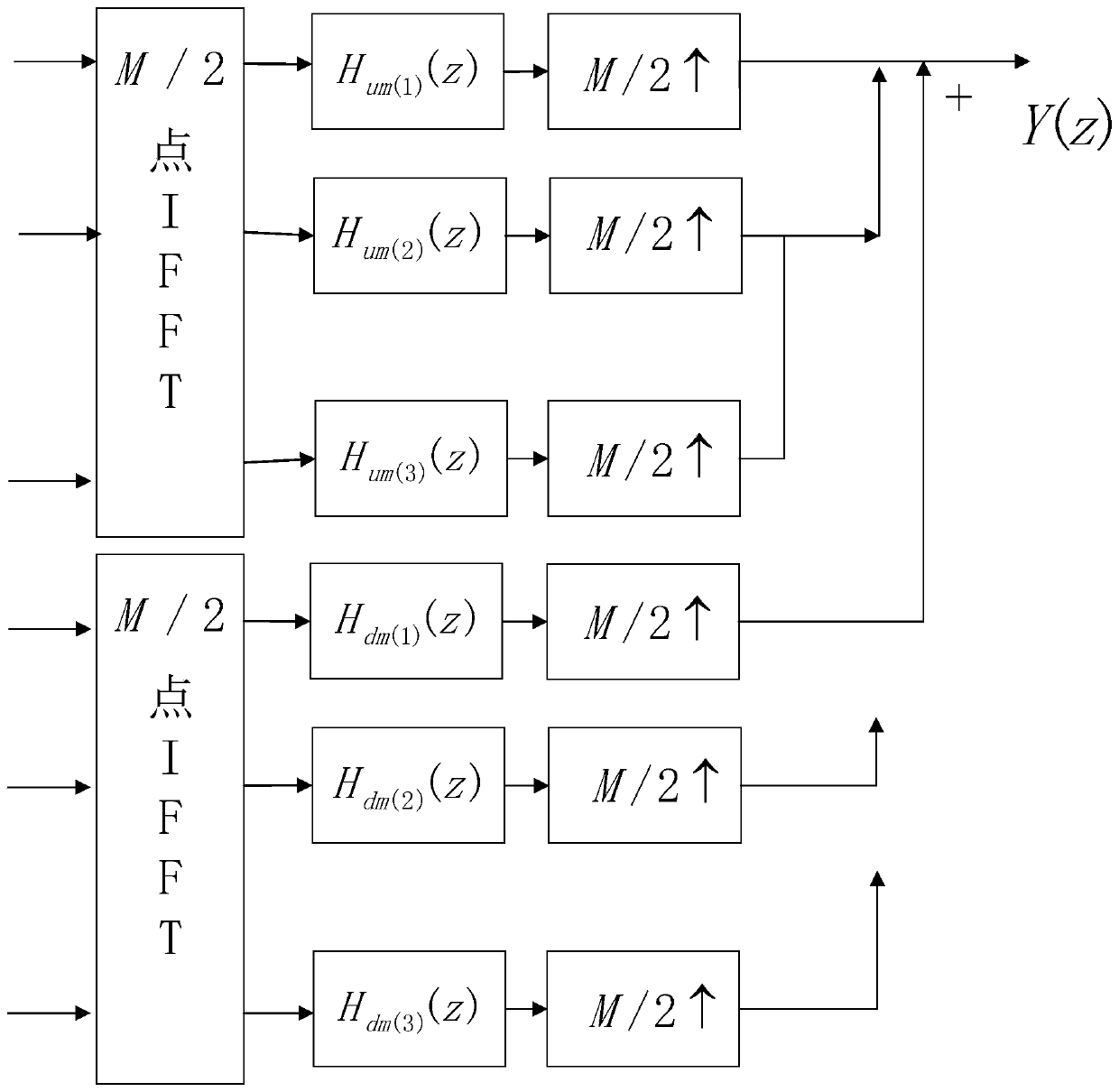

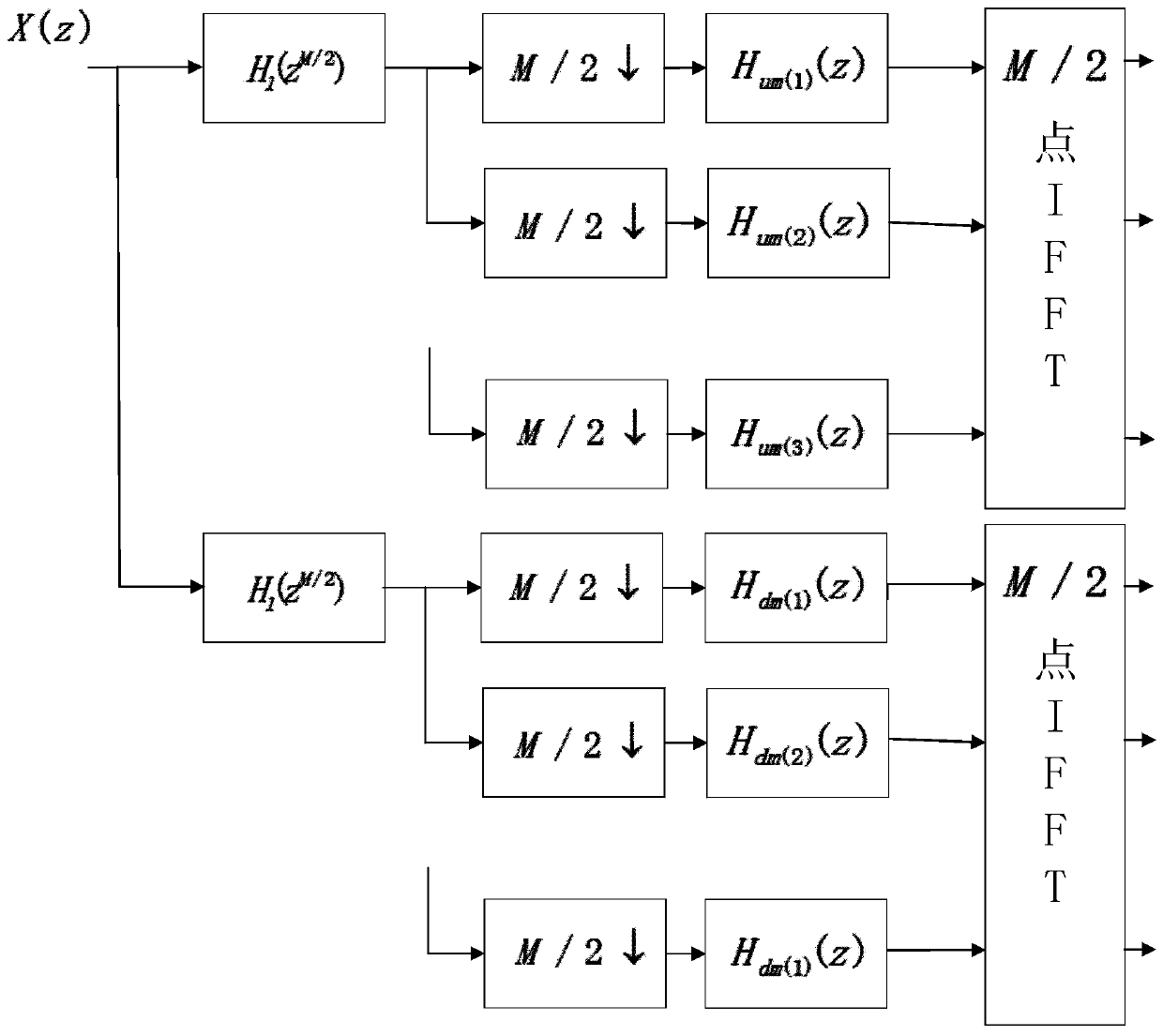

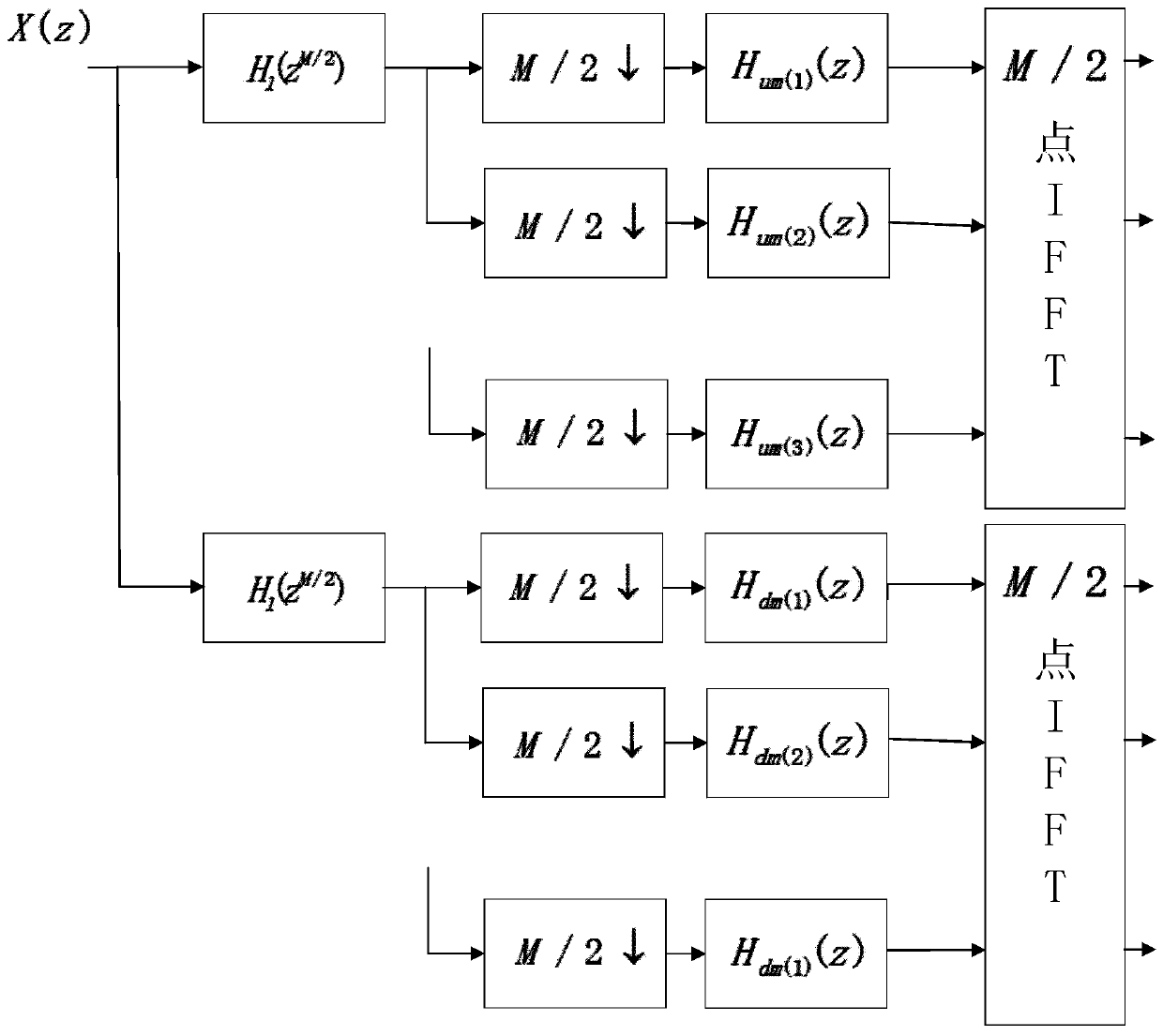

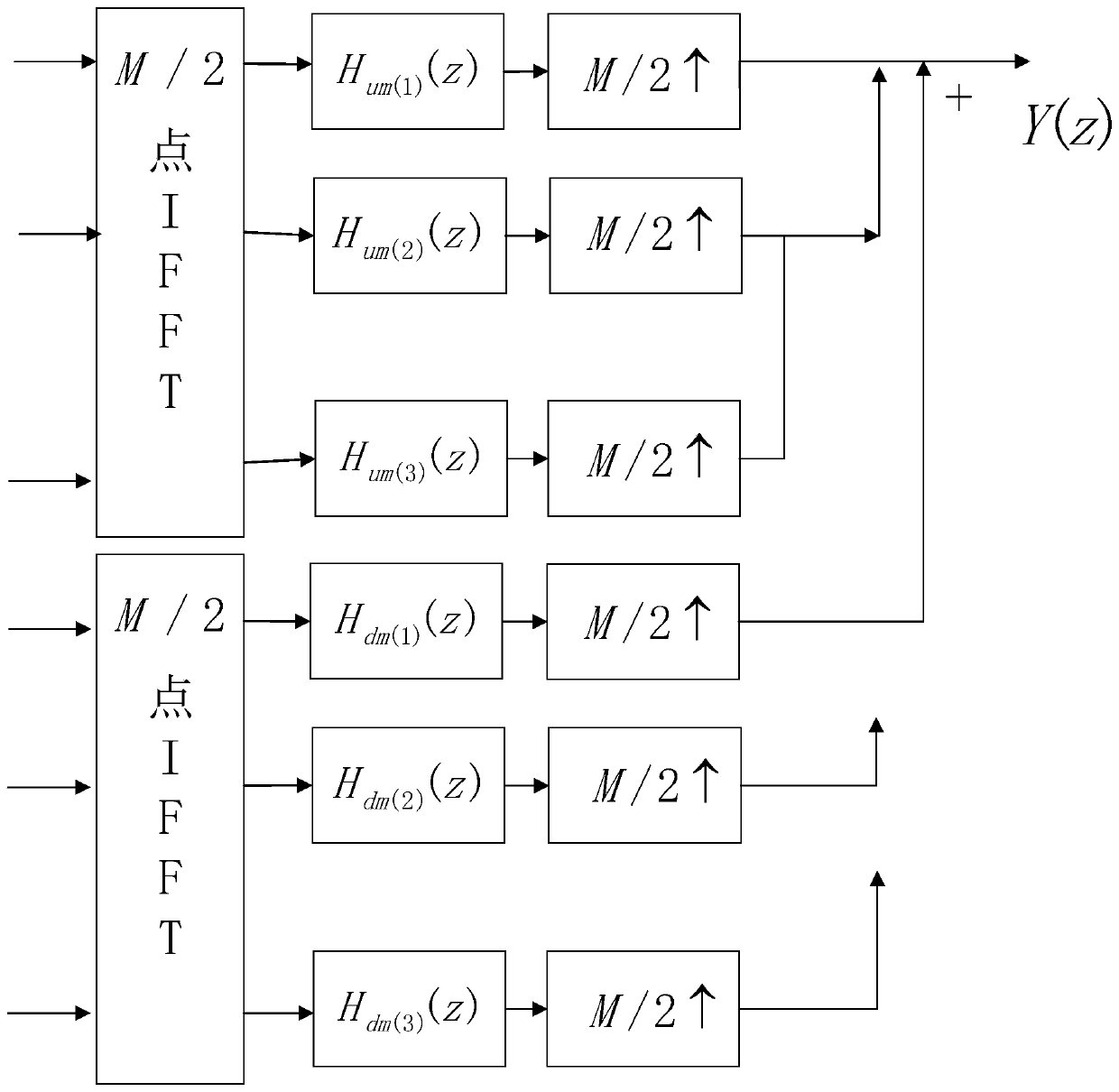

Approximately completely reconstructed satellite-borne low-complexity non-uniform bandwidth digital channelizer

ActiveCN109962731AReduce reconstruction errorNarrow reconstruction errorRadio transmissionComputation complexityRound complexity

The invention provides an approximately completely reconstructed satellite-borne low-complexity non-uniform bandwidth digital channelization device, which is used for solving the technical problems ofhigh reconstruction error, wide protection interval and high calculation complexity of the existing satellite-borne digital channelization device. The implementation method comprises the following steps: designing a prototype low-pass half-band filter; designing a corresponding complementary high-pass half-band filter according to the prototype low-pass half-band filter; taking the prototype low-pass half-band filter up-sampling as an upper branch primary filter, and taking the prototype complementary high-pass half-band filter up-sampling as a lower branch primary filter; designing an upperbranch secondary filter and a lower branch secondary filter and performing multiphase decomposition; signal reconstruction is completed through transposition of multiphase decomposition of upper and lower branch secondary filters. According to the method, the reconstruction error of the original spaceborne digital channelizer is reduced, the guard interval width is reduced, the calculation complexity is reduced, and the method is simple, efficient and easy to implement.

Owner:XIDIAN UNIV

Coefficient fitting method of FARROW filter

ActiveCN110708039ADigital technique networkHarmonic reduction arrangementLow-pass filterPhase filter

The invention discloses a coefficient fitting method of a FARROW filter based on wavelet function fitting. According to the method, the method comprises the following steps: firstly carrying out the multi-phase decomposition of a low-pass filter, and obtaining a multi-phase filter coefficient matrix; secondly, conducting wavelet fitting on each column of coefficients of the coefficient matrix, andobtaining wavelet fitting coefficients through calculation by means of a least square method; and finally, loading a coefficient obtained by fitting into a FARROW filter structure, and outputting a resampling output value at an expected position by an input signal through the structure. According to the method, the oscillation phenomenon occurring during filter coefficient fitting can be reduced,and compared with traditional polynomial fitting, under the condition of the same fitting order, the fitting precision can be effectively improved by changing the scale factor, and the calculation efficiency of the general demodulator is improved.

Owner:GUANGXI NORMAL UNIV

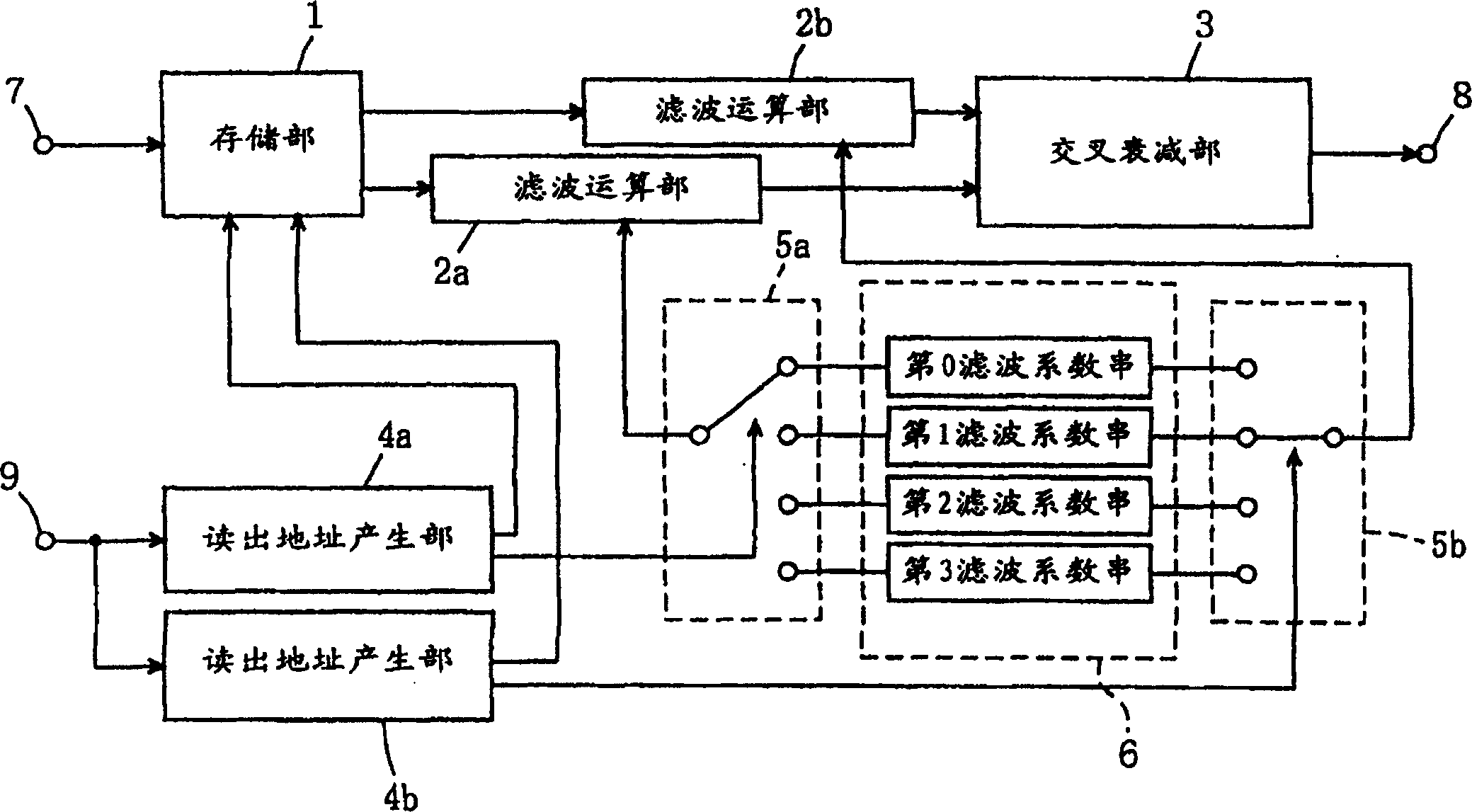

Musical interval changing device

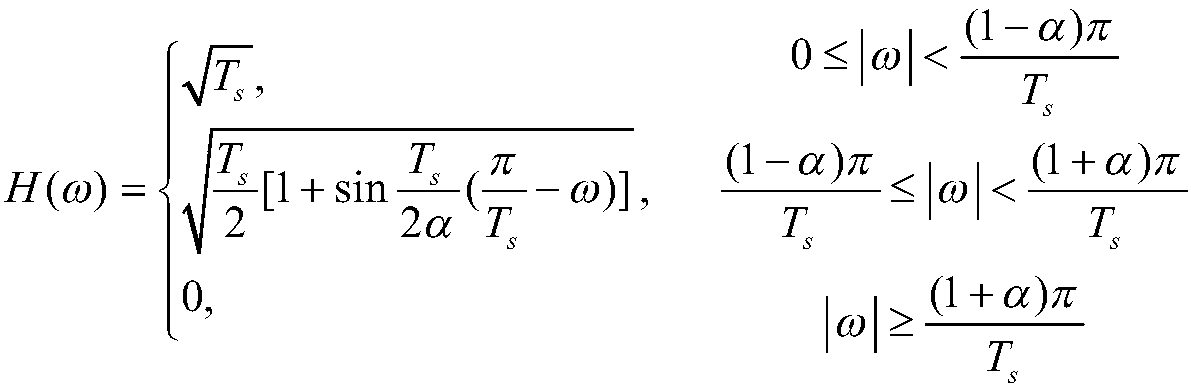

InactiveCN1160704CHigh-precision interval transformationElectrophonic musical instrumentsAnalogue recording/reproducingLow-pass filterAddress generator

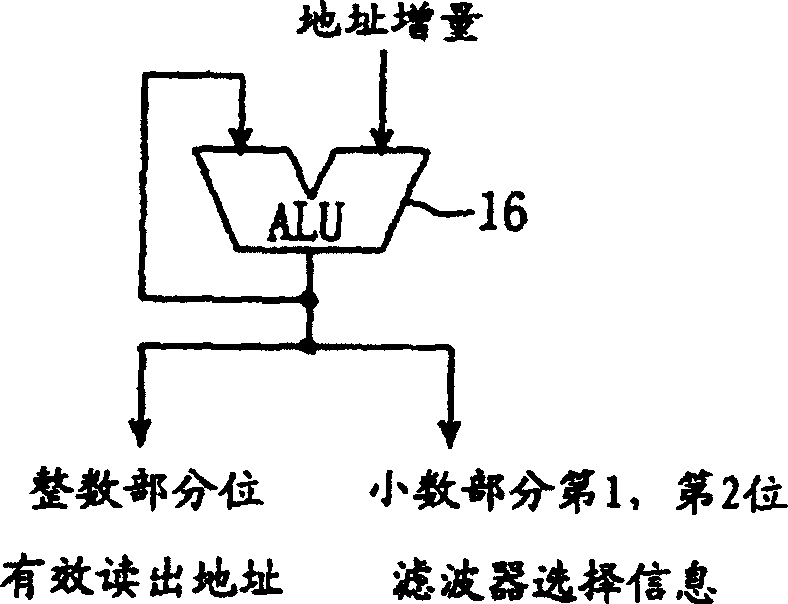

A pitch shifter capable of shifting an acoustic signal in pitch to an arbitrary level with a high degree of accuracy without any change in reproduction time, and also sufficiently reducing high-frequency distortion without being increased in size or speeded-up is provided. Stored in a filter coefficient string storage 6, four filter coefficient strings corresponding to four sub-filters produced through polyphase decomposition of a low-pass filter for 4-fold oversampling. Filter coefficient string selectors 5a and 5b select, based on the first and second bits of the decimal part of each of read addresses generated by the read address generators 4a and 4b, respectively, any one of the four filter coefficient strings stored in the filter coefficient string storage 6. Filter operation units 2a and 2b receive paired sound data strings, and carry out a filter operation by using the filter coefficient strings selected by the filter coefficient string selector 5a and 5b, respectively.

Owner:PANASONIC CORP

Variable-modulus fractional frequency conversion serial signal processing method and device

PendingCN111884655ASave processing resourcesHigh precisionAnalogue-digital convertersEnergy efficient computingComputer hardwareBinary multiplier

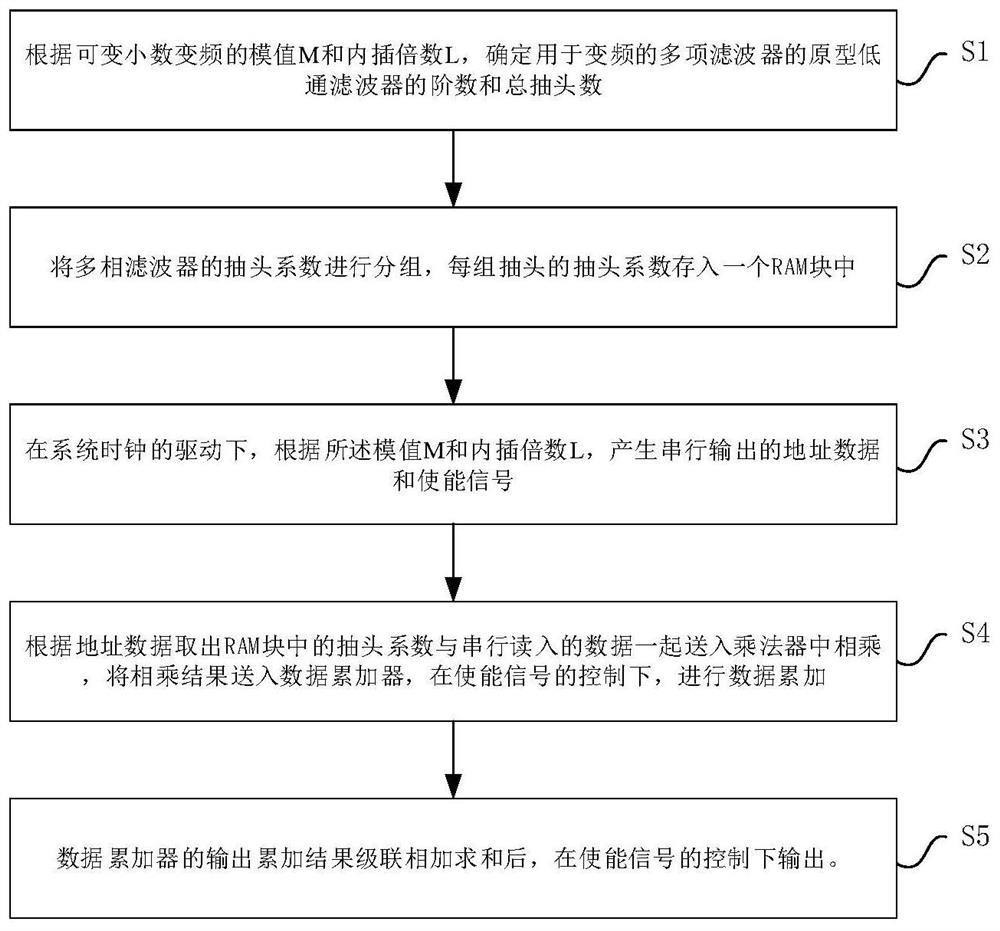

The invention relates to a variable-modulus fractional frequency conversion serial signal processing method and device, and the method comprises the steps: determining the order and total tap number of a prototype low-pass filter of a multi-phase filter according to the modulus M and interpolation multiple L of variable-modulus fractional frequency conversion; carrying out multiphase decompositionon the prototype low-pass filter, and grouping and storing tap coefficients into corresponding RAM blocks; generating address data and an enable signal which are output in series under the driving ofa system clock; transmitting address data to an RAM block to take out a tap coefficient, sending the tap coefficient and read-in data to a multiplier for multiplication, sending a multiplication result to a data accumulator corresponding to the RAM block, and under the control of an enable signal, carrying out data accumulation to output an accumulation result; performing cascade addition summation on the output accumulation result, and outputting the result under the control of an enable signal to serve as a final result after frequency conversion. Under the condition of variable-rate blindarea sampling, fixed digital intermediate frequency is obtained through efficient frequency conversion, the structure is simple, processing resources are small, and precision is high.

Owner:36TH RES INST OF CETC

A realization method of high order fir filter based on fpga

ActiveCN106549650BReduce occupancyGuaranteed real-time processingDigital technique networkComputer architectureDecomposition

The invention provides a method for realizing a high-order FIR filter based on an FPGA, used for solving the technical problem of excessive occupation of the high-order FIR filter to logic units in the FPGA in the existing method for realizing high-order FIR multiphase filtering. The method comprises the following steps: selecting parameters of a prototype filter; designing the prototype filter h (n); performing multiphase decomposition on the prototype filter h (n) to obtain multiphase filters; performing module division on each multiphase filter; storing coefficients of the multiphase filters in a module ROM; reading the coefficients of the multiphase filters in the module ROM; caching and reading input data by read-write enable, a write address control signal and a read address control signal of a module RAM obtained by system clock control; and performing multiplication and addition operations on the coefficients of the multiphase filters and the input data by using a multiplication accumulation module, and outputting an operation result. The method provided by the invention is little in occupation of the logic units in the FPGA, simple, efficient and is easy to realize.

Owner:XIDIAN UNIV

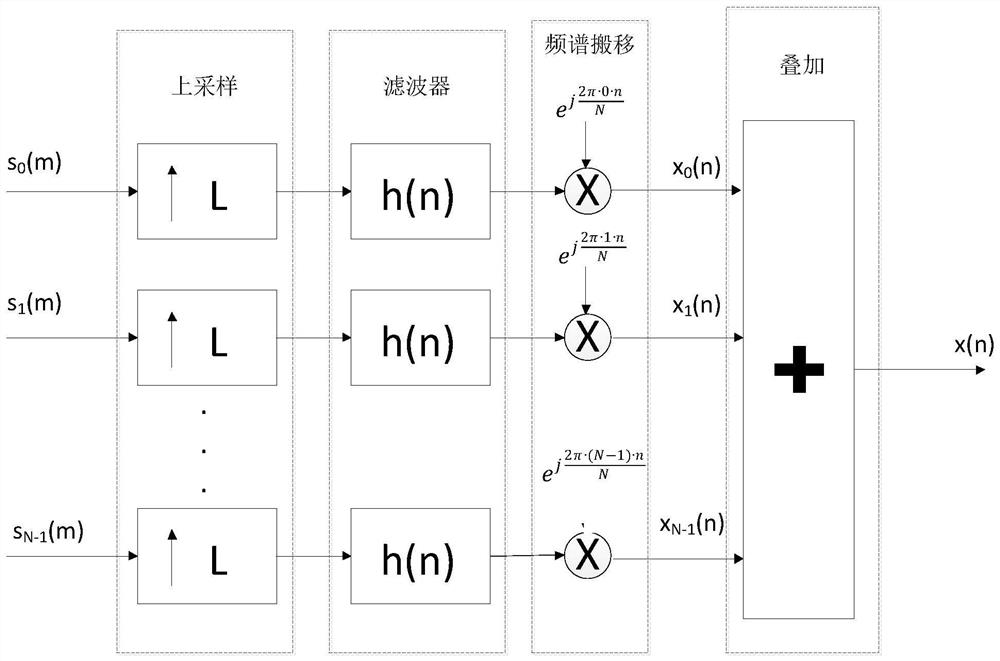

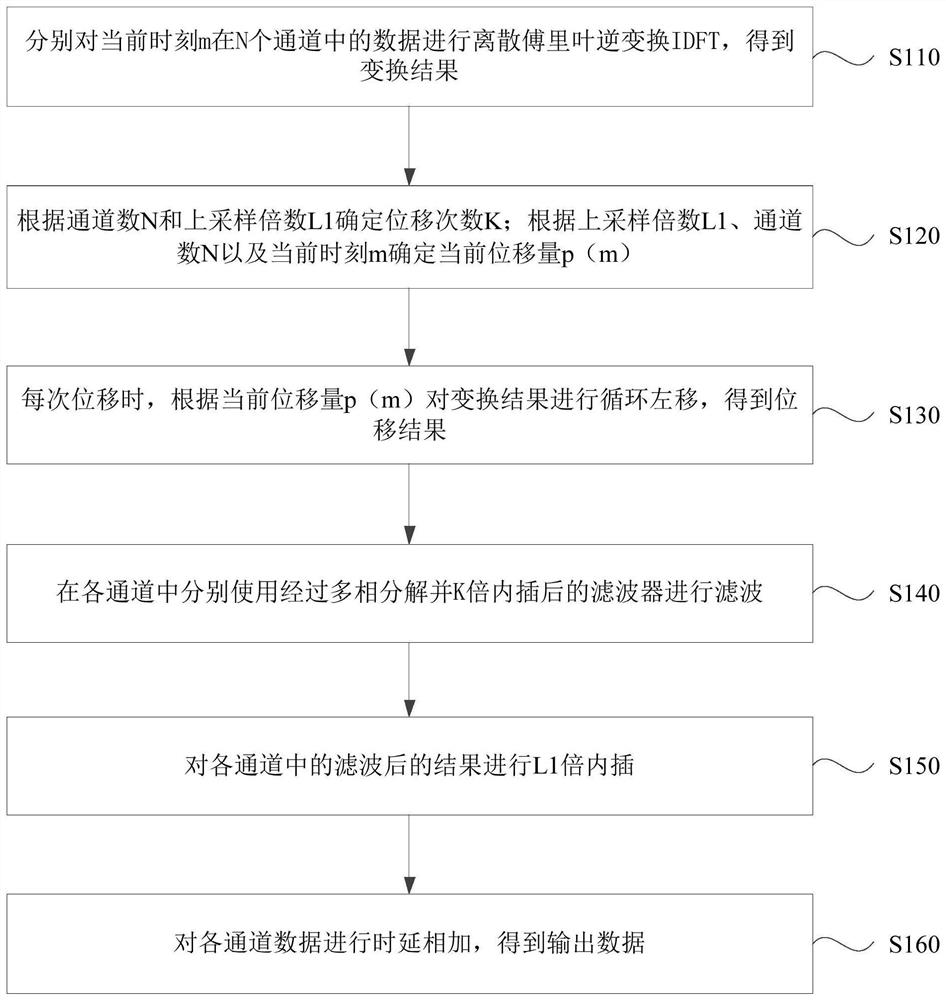

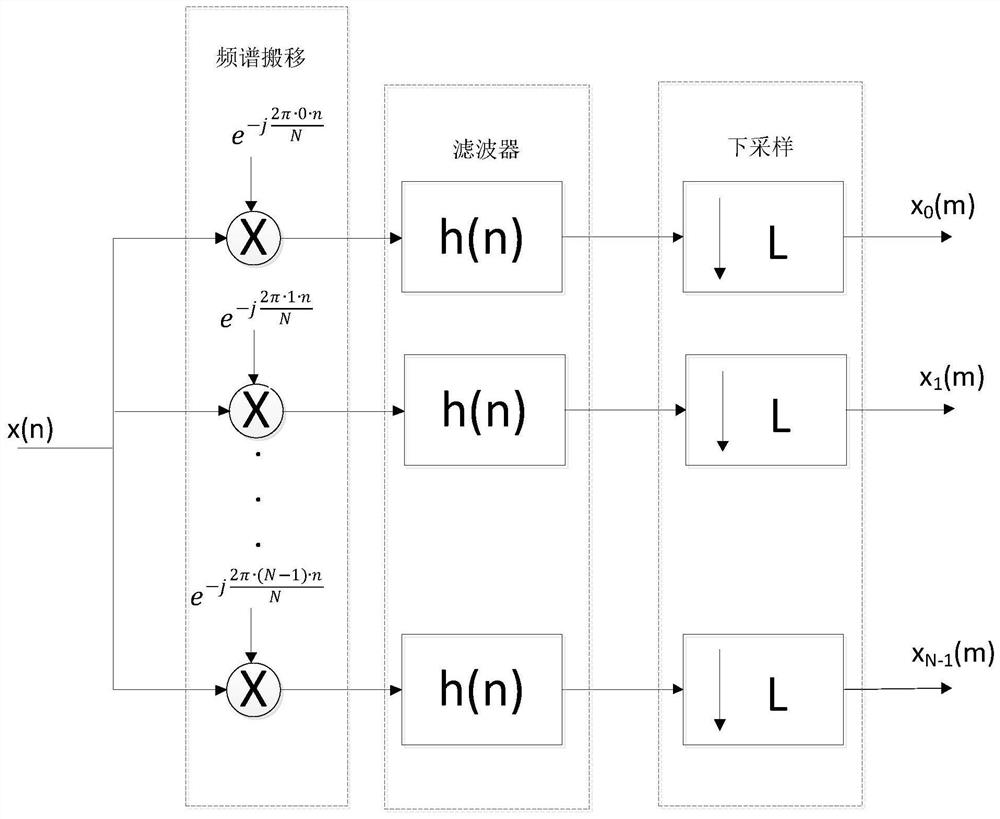

Signal processing method and device, equipment and storage medium

PendingCN111651716AImprove signal processing efficiencyImprove processing efficiencyTransmissionComplex mathematical operationsInverse discrete fourier transformFilter (signal processing)

The invention discloses a signal processing method and device, equipment and a storage medium, and the method comprises the steps out of performing the inverse discrete Fourier transform (IDFT) of data in N channels at a current moment m by a transmitting terminal, and obtaining a transformation result; determining a displacement frequency K according to the channel number N and the up-sampling multiple L1; determining the current displacement according to the up-sampling multiple L1, the channel number N and the current moment m; during each displacement, performing cyclic left shift on the transformation result according to the current displacement to obtain a displacement result; using a filter subjected to multiphase decomposition and K-time interpolation for filtering in each channel;performing L1-time interpolation on the filtered result in each channel, and performing time delay addition on the data of each channel to obtain output data. Through multiple times of displacement,signal processing with a small sampling multiplying power L matched with a high channel number N is achieved, and the signal processing efficiency is improved.

Owner:北京东土军悦科技有限公司 +1

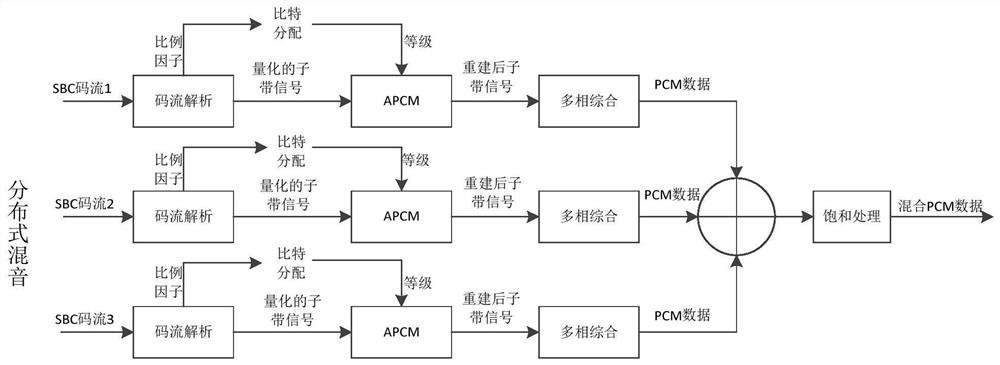

Sound mixing method and device of SBC code stream, medium and equipment

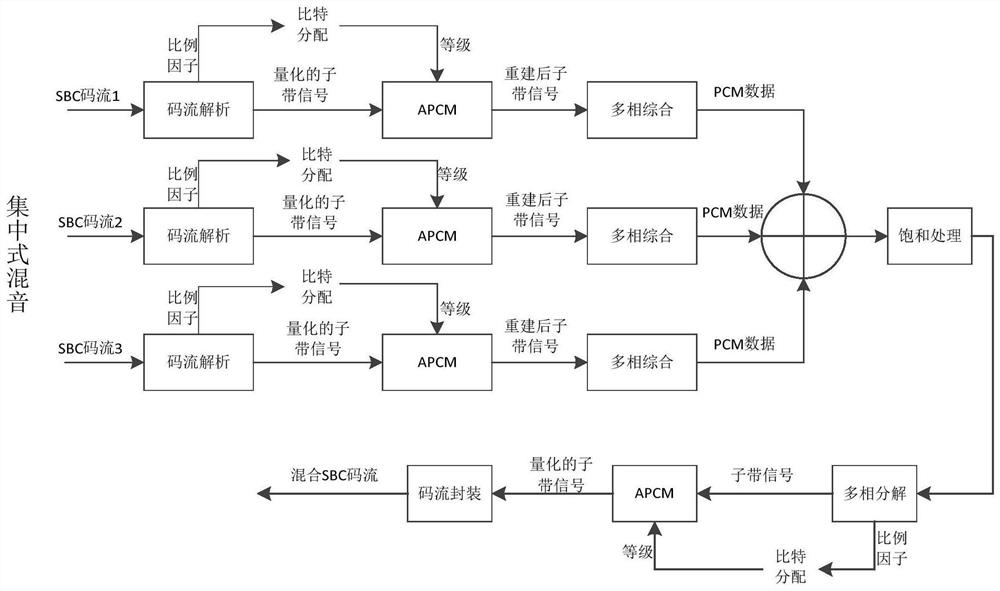

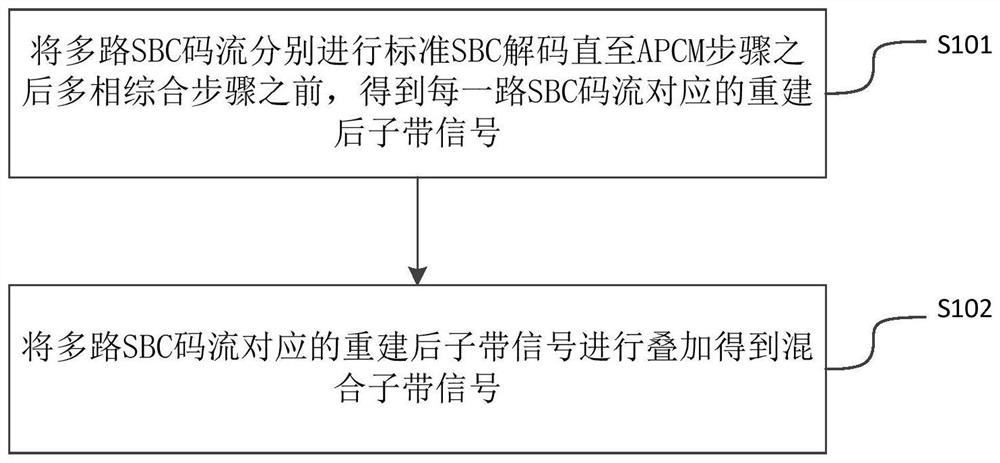

ActiveCN113160837AReduce total computing power requirementsReduce the number of calculationsSpeech analysisEngineeringSound quality

The invention discloses a sound mixing method for SBC code streams, which comprises the following steps of respectively carrying out standard SBC decoding on multiple paths of SBC code streams until the standard SBC decoding is carried out after an APCM step and before a multi-phase synthesis step, and obtaining a reconstructed sub-band signal corresponding to each path of SBC code stream; and superposing the reconstructed sub-band signals corresponding to the multiple paths of SBC code streams to obtain a mixed sub-band signal. The application of the invention reduces the calculation times of the multiphase synthesis step in the audio mixing process, omits the operation of the multiphase decomposition step, effectively reduces the total computing power demand in the audio mixing server, reduces the operand in the audio mixing process, saves the power consumption, reduces the cost, and ensures that the voice quality is not reduced.

Owner:BEIJING BAIRUI INTERNET TECH CO LTD

Moiré Elimination Method of Screen Capture Image Based on Multi-channel Decomposition

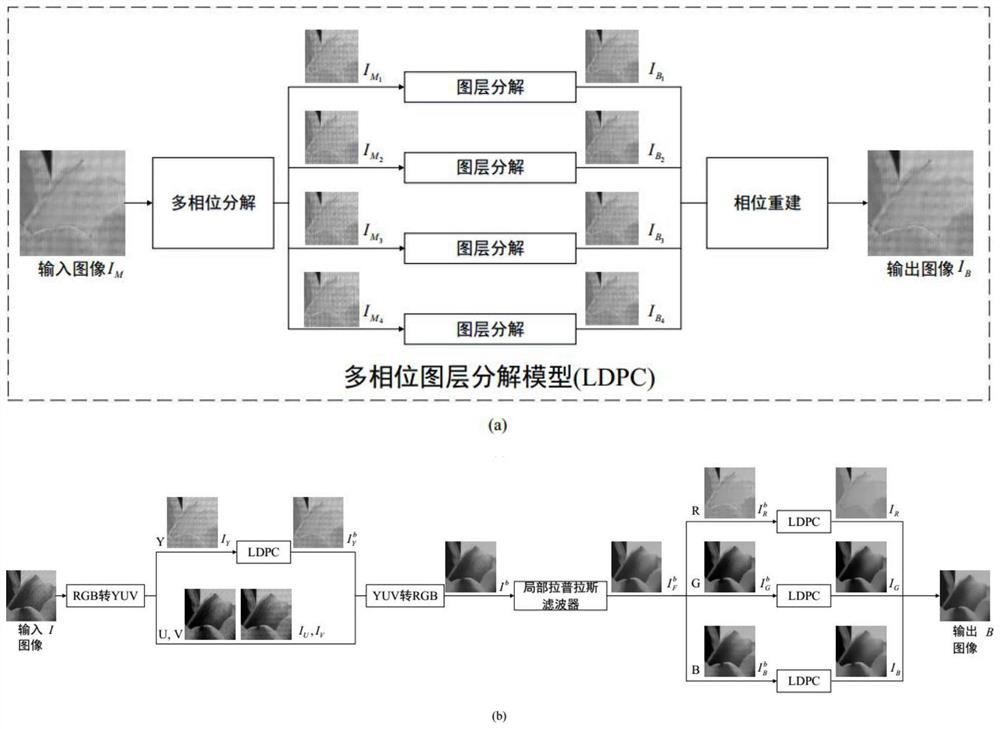

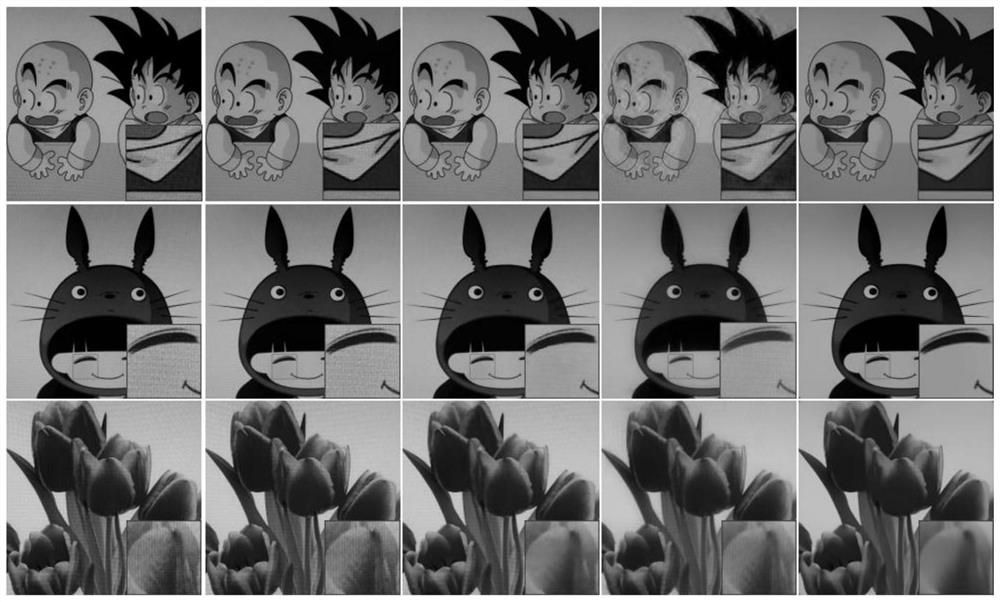

ActiveCN108154487BAvoid remodelingEliminate moiréImage enhancementImage analysisPattern recognitionComputer graphics (images)

The invention belongs to the field of digital image processing, and aims to provide a method for eliminating moiré patterns in screen shots that do not exist in the prior art, so as to realize the elimination of moiré patterns in screen shot images. The technical solution adopted by the present invention is to provide a multi-phase layer decomposition model based on the multi-channel decomposition method for eliminating moiré in screen-shot images, and use the model in the Y channel to realize the desalination of moiré color stripes and high-frequency parts ; Input the obtained results into an improved Laplacian filter to further eliminate the color fringes; finally, apply the multi-phase decomposition layer model to the RGB channels of the results obtained in the previous step to obtain the final result. The invention is mainly applied to digital image processing occasions.

Owner:TIANJIN UNIV

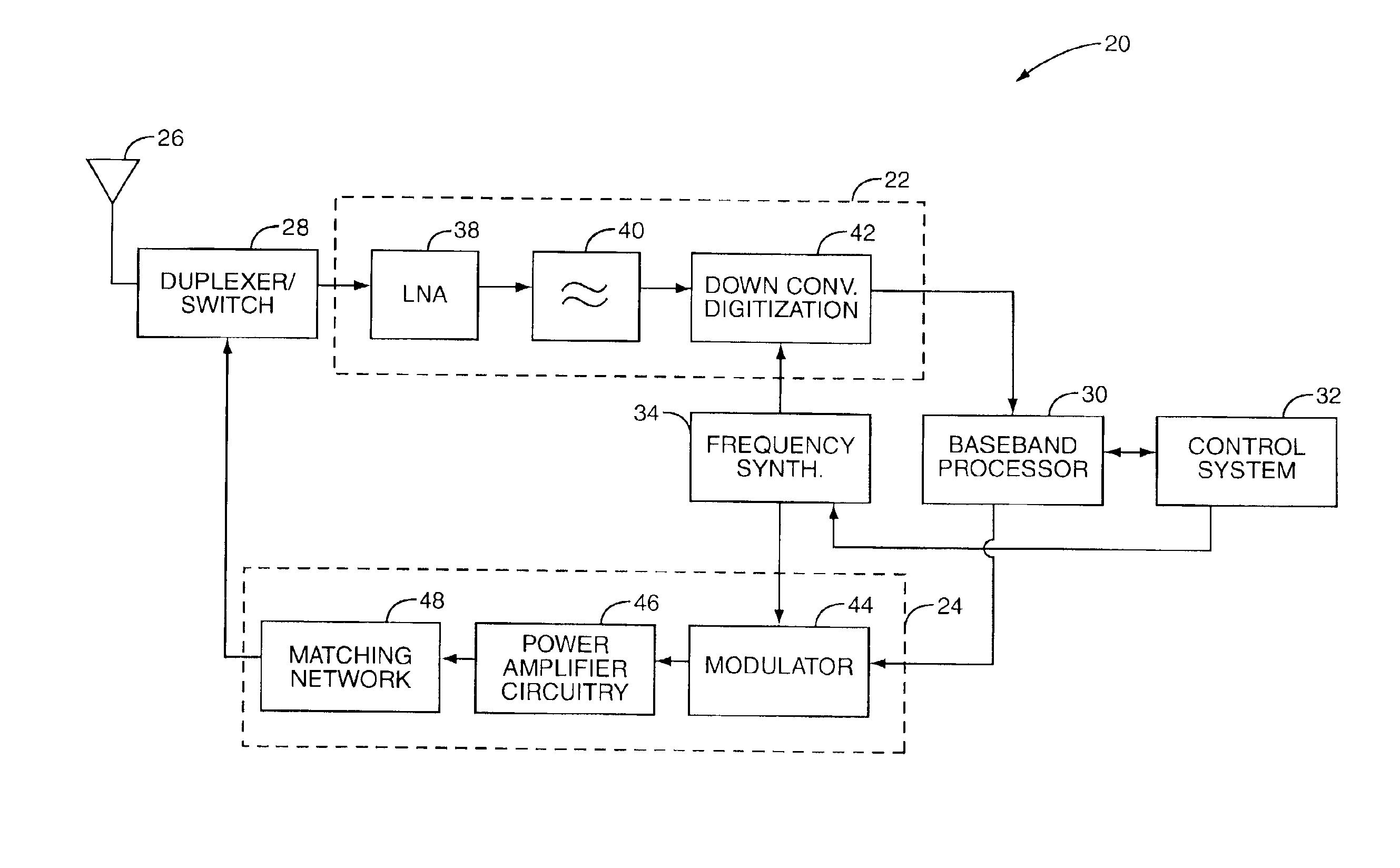

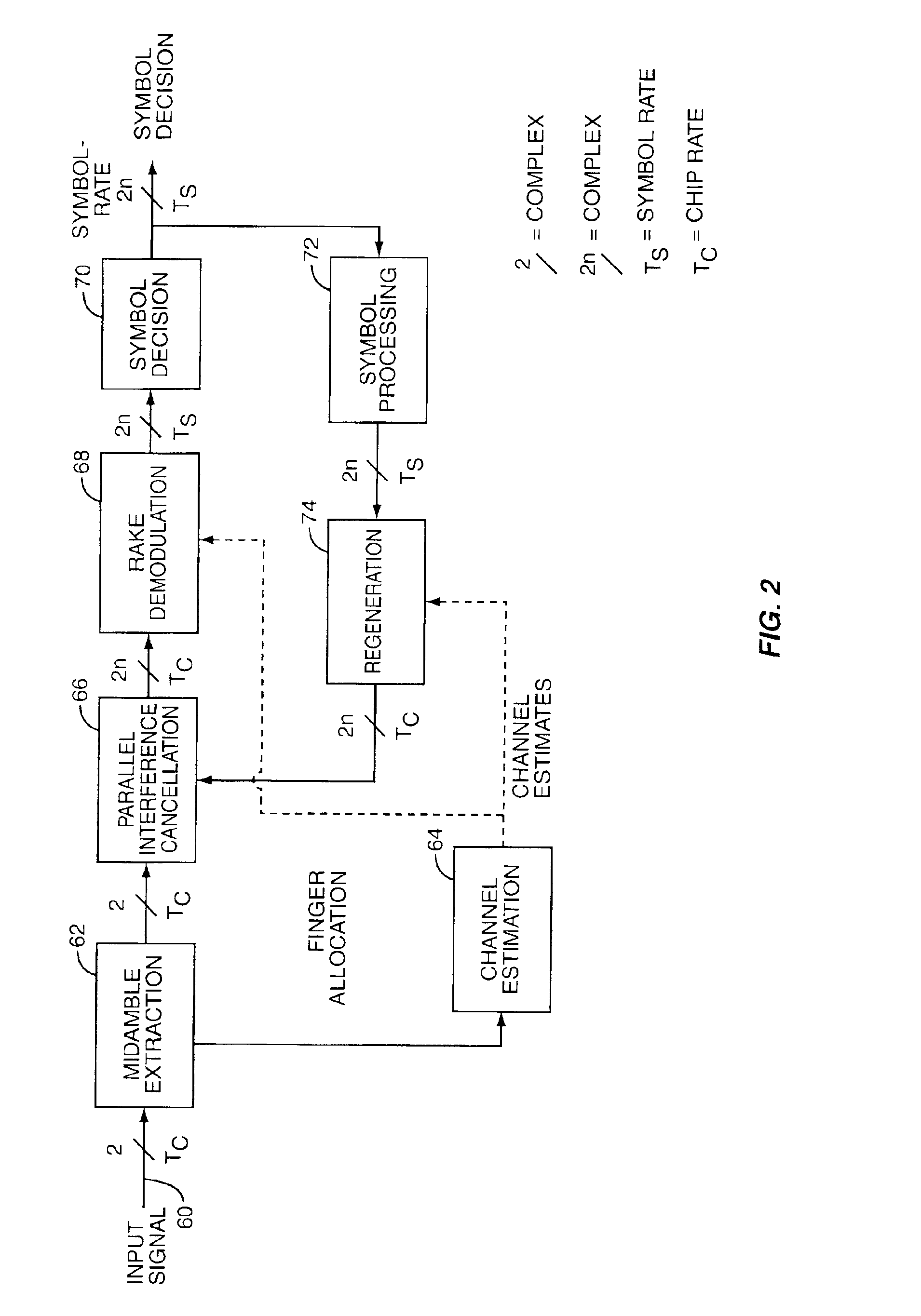

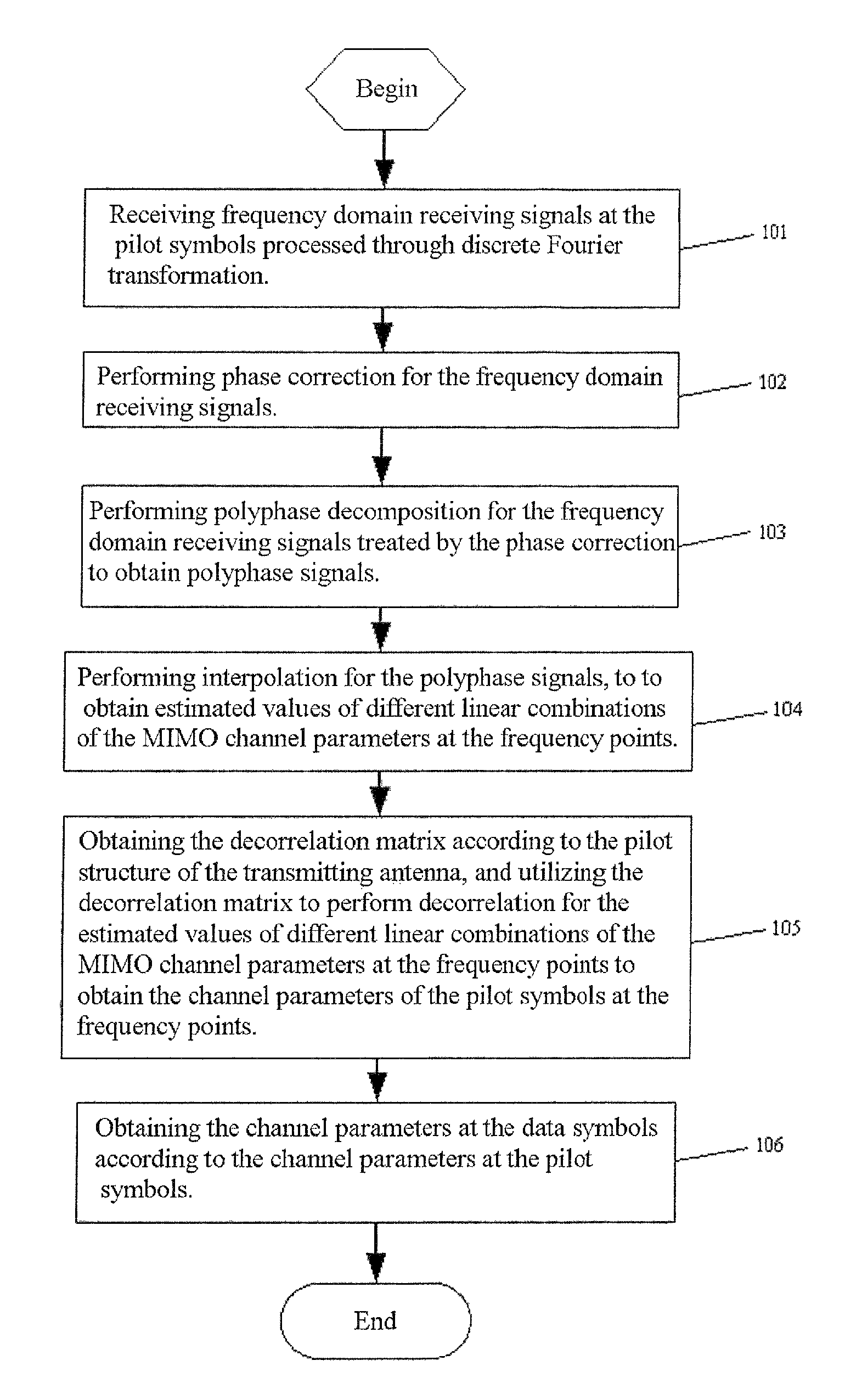

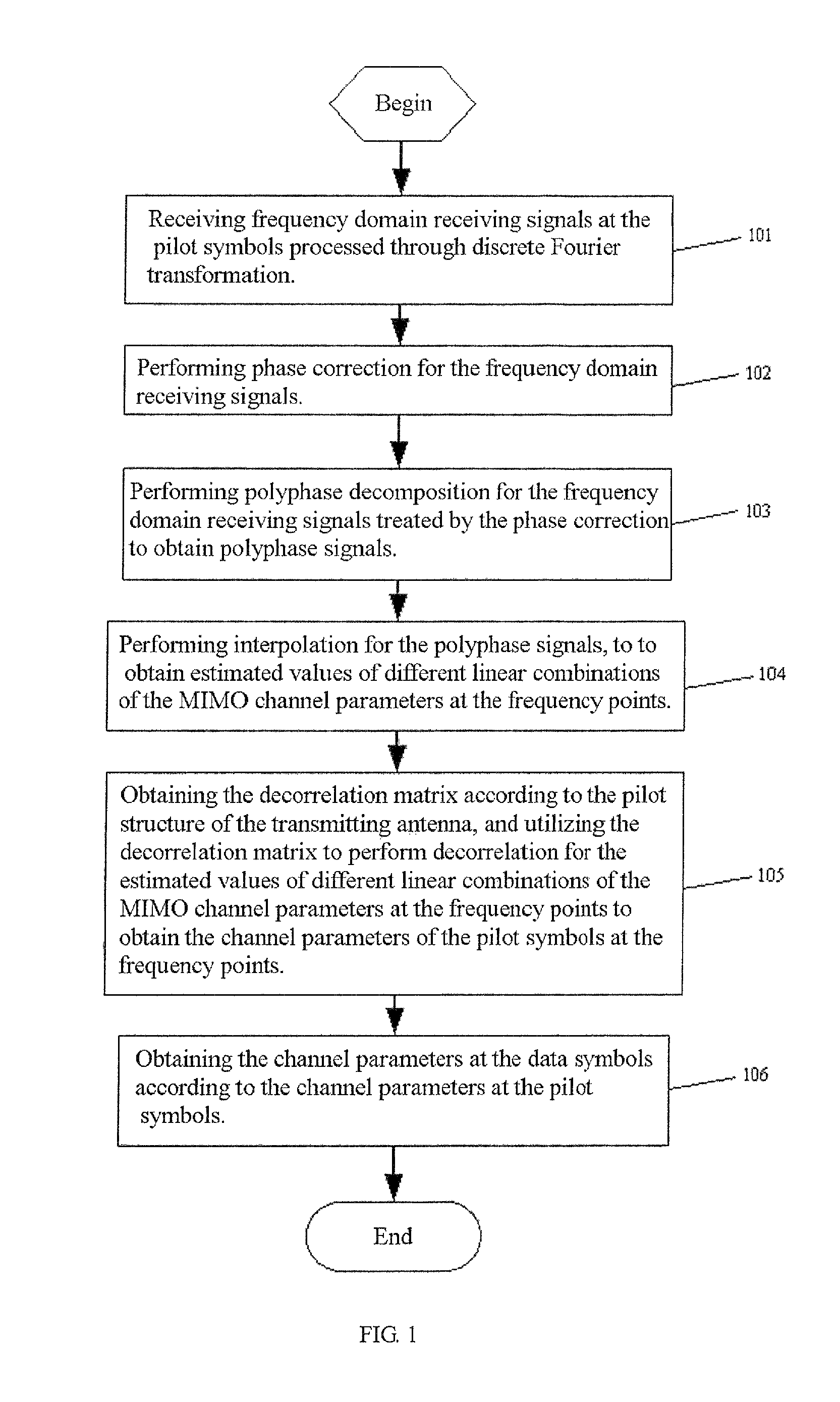

Multi-antenna channel estimation method based on polyphase decomposition

ActiveUS8654879B2Reduce complexityAmplitude-modulated carrier systemsDiversity/multi-antenna systemsChannel parameterTransmitter antenna

A multi-antenna channel estimation method based on polyphase decomposition includes: receiving frequency domain received signals transformed using discrete fourier transformation (DFT) in pilot symbols; performing phase correction on the frequency domain received signals; performing polyphase decomposition on the frequency domain received signals which are corrected using phase correction and acquiring polyphase signals; performing interpolation on the polyphase signals and acquiring the estimation values of the multi-antenna channel parameters with various linear combinations on each frequency; acquiring decorrelation array based on the pilot structure of the transmission antenna and decorrelating the estimation values of the multi-antenna channel parameters with various linear combination on each frequency using the decorrelation array and acquiring channel parameters of the pilot symbols on each frequency; acquiring channel parameters of data symbols based on the channel parameters of the pilot symbols. With the present invention, the inversion problem in multi-antenna channel estimation is avoided with lower complexity, and results of the multi-antenna channel estimation method become more accurate since the DFT and filtering are performed in the interpolation after polyphase decomposition.

Owner:HUAWEI TECH CO LTD

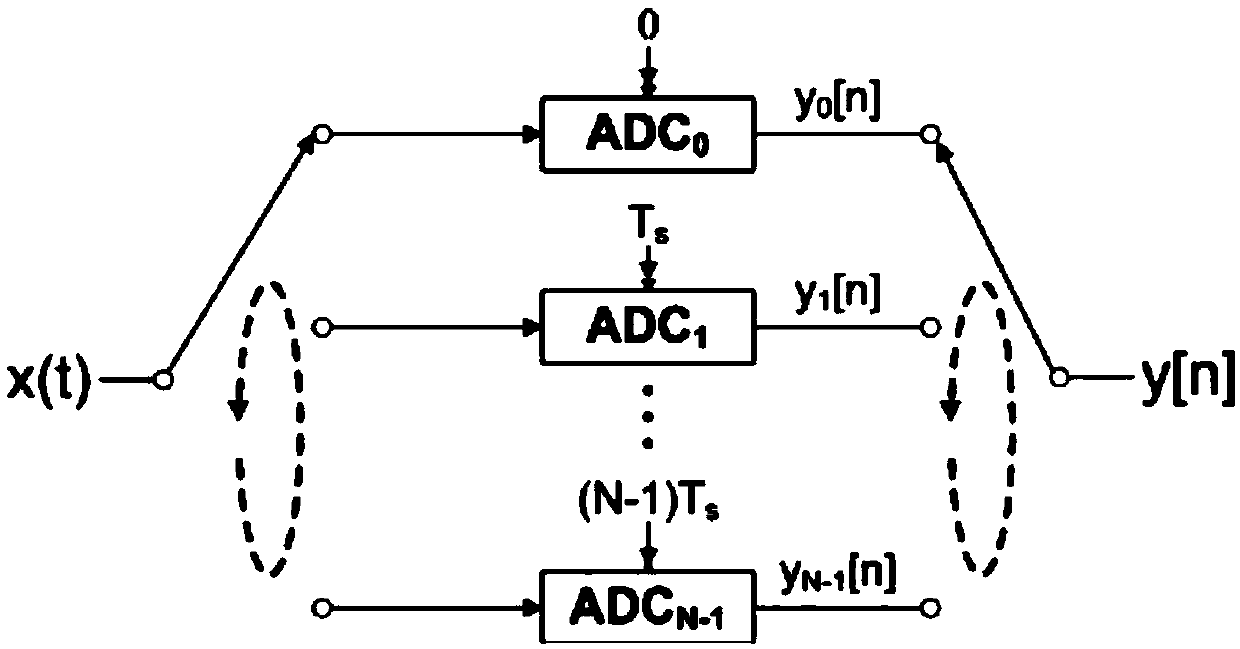

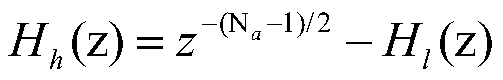

Linear Distortion Correction Method for Time-Interleaved Analog-to-Digital Converter Based on Polyphase Decomposition

ActiveCN106374921BLow working speed requirementsGood compensationPhysical parameters compensation/preventionAnalogue/digital conversion calibration/testingDifferentiatorComputation complexity

The invention provides a linear distortion correction method of a time interleaved analog-digital converter based on multiphase decomposition having low computational complexity. The method comprises the following steps: expressing spectral characteristics of a channel by a transfer function, then mapping the spectral characteristics into frequency response of a high order differentiator, carrying out multiphase decomposition processing on the constructed differentiators separately, providing an equivalent TIADC analysis module based on a multiphase structure, and extracting crosstalk and errors from an out[ut signal according to the model to complete multichannel correction. Experiments prove that the method has low requirements on the working speed of a correction filter, is simple and feasible, good in compensation effect and has universality to the correction of general frequency distortion errors.

Owner:SYSU CMU SHUNDE INT JOINT RES INST +1

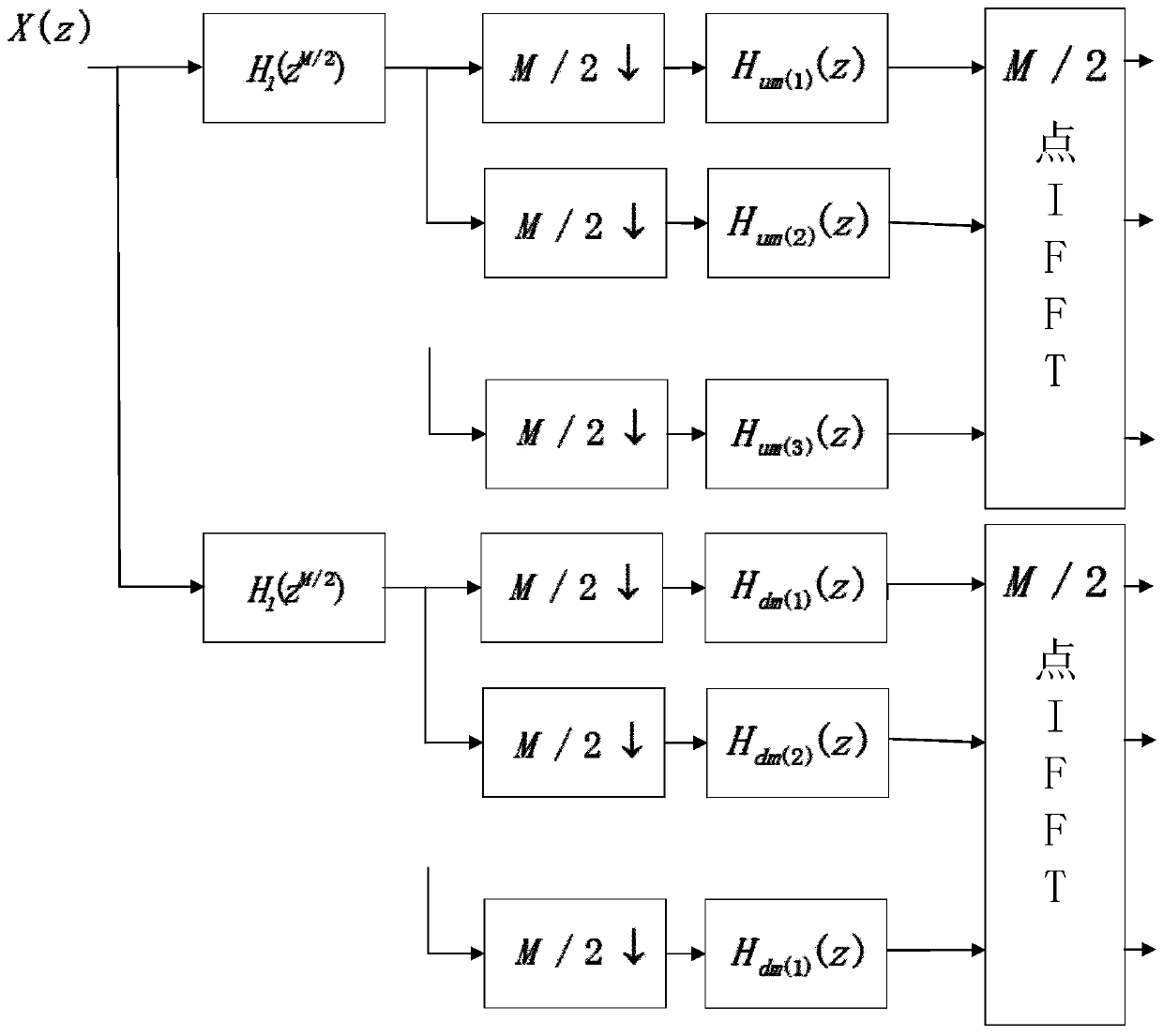

Approximate complete reconstruction of space-borne low-complexity non-uniform bandwidth digital channelization method

ActiveCN109962731BReduce reconstruction errorNarrow reconstruction errorRadio transmissionComputation complexityTelecommunications

The invention provides an approximately completely reconstructed satellite-borne low-complexity non-uniform bandwidth digital channelization device, which is used for solving the technical problems ofhigh reconstruction error, wide protection interval and high calculation complexity of the existing satellite-borne digital channelization device. The implementation method comprises the following steps: designing a prototype low-pass half-band filter; designing a corresponding complementary high-pass half-band filter according to the prototype low-pass half-band filter; taking the prototype low-pass half-band filter up-sampling as an upper branch primary filter, and taking the prototype complementary high-pass half-band filter up-sampling as a lower branch primary filter; designing an upperbranch secondary filter and a lower branch secondary filter and performing multiphase decomposition; signal reconstruction is completed through transposition of multiphase decomposition of upper and lower branch secondary filters. According to the method, the reconstruction error of the original spaceborne digital channelizer is reduced, the guard interval width is reduced, the calculation complexity is reduced, and the method is simple, efficient and easy to implement.

Owner:XIDIAN UNIV

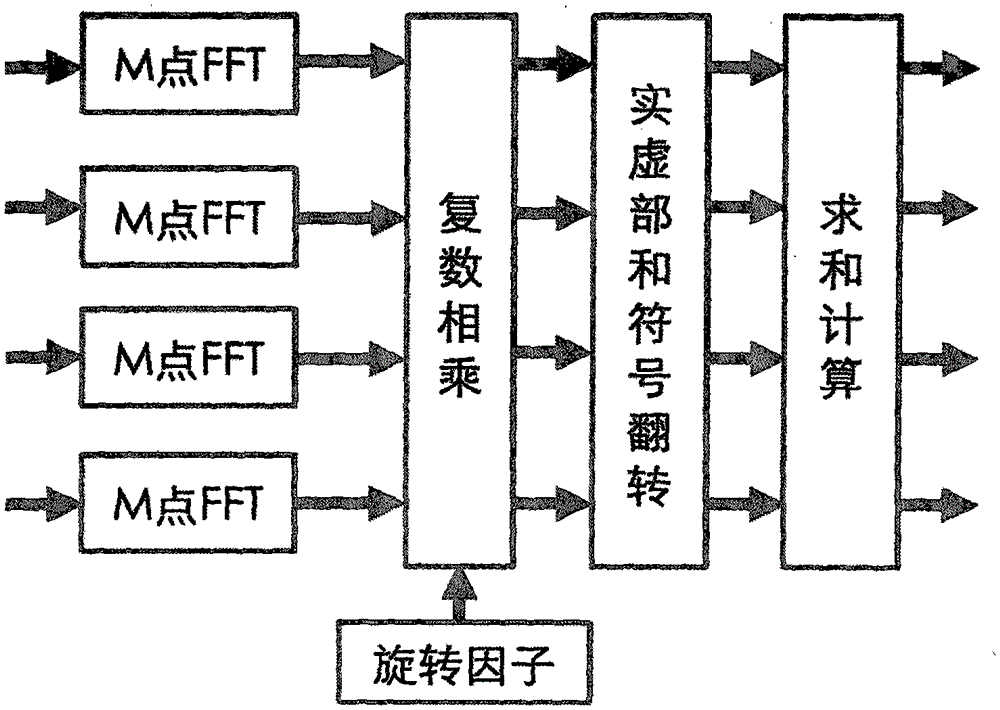

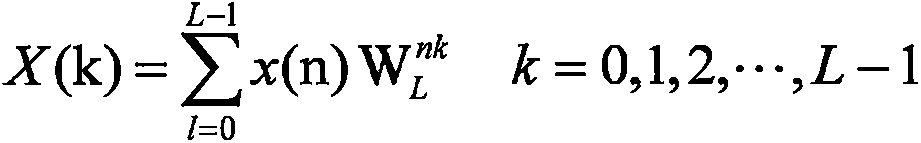

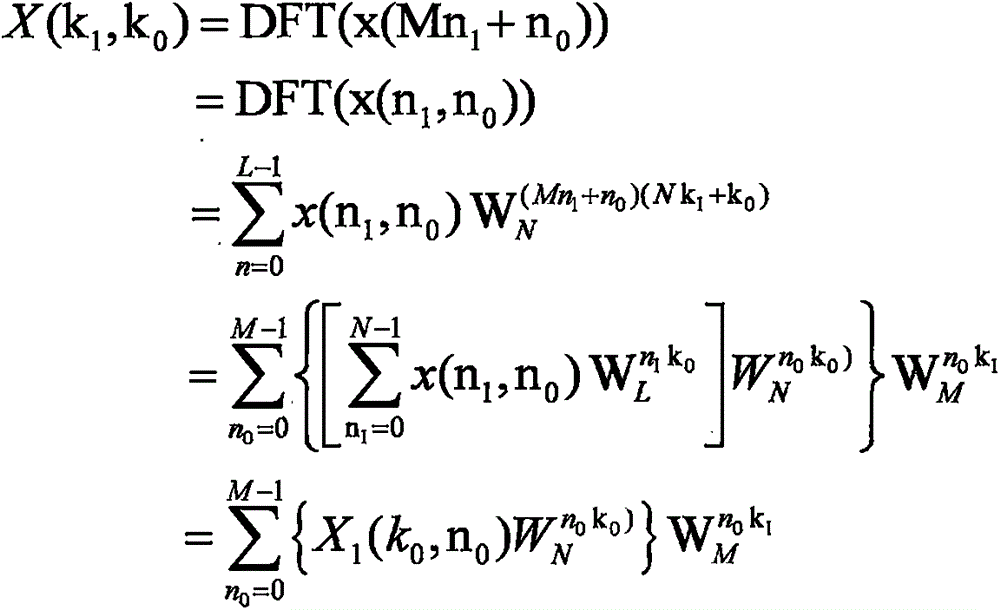

Polyphase decomposition based variable point number fast Fourier transform method for GHz high-speed sampling signal

InactiveCN105608052AReduce resource usageIncrease flexibilityComplex mathematical operationsTime domainFast Fourier transform

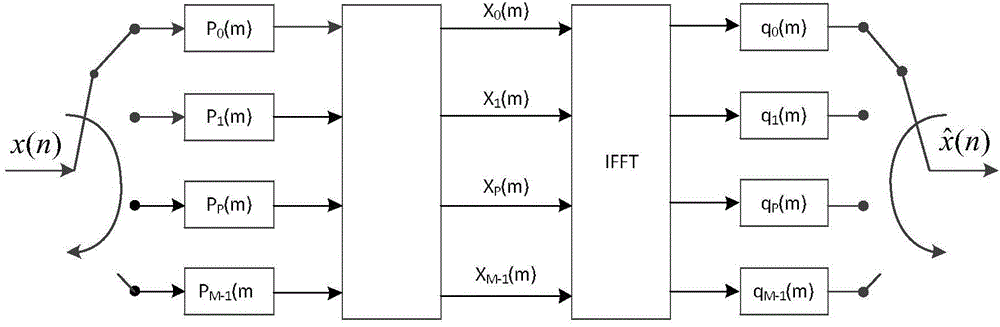

The invention proposes a polyphase decomposition based variable point number fast Fourier transform (FFT) method for a GHz high-speed sampling signal. A conventional FFT processing method is decomposed and the FFT processing of the high-speed sampling signal is decomposed into the processing of a plurality of low-speed signals through a time domain polyphase decomposition technology, so that a possibility is provided for the FFT processing of the high-speed sampling signal; and after the conventional FFT processing method is decomposed into the processing of the low-speed signals in the polyphase manner, low-speed processing results are subjected to weighted synthesis to obtain a final high-speed sampling signal FFT processing result. According to the method, a new polyphase twiddle factor is established, so that the final FFT result is obtained through simple pipelining multiplication and summation operations.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

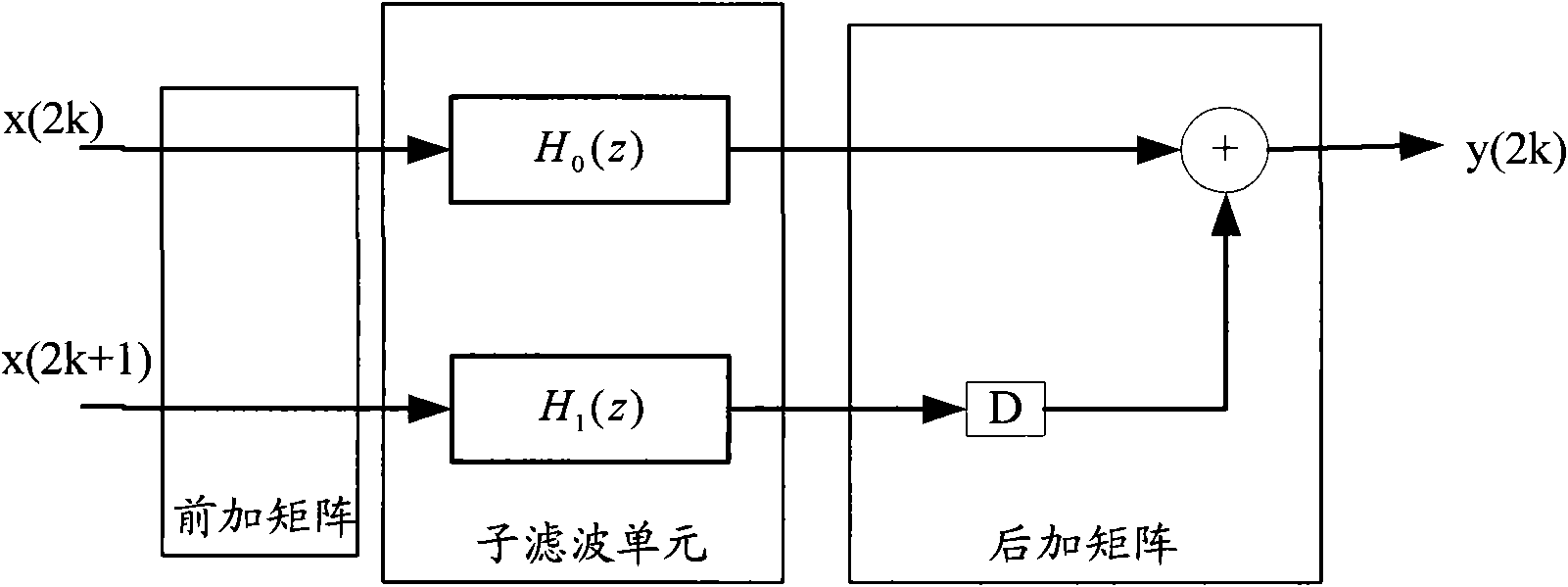

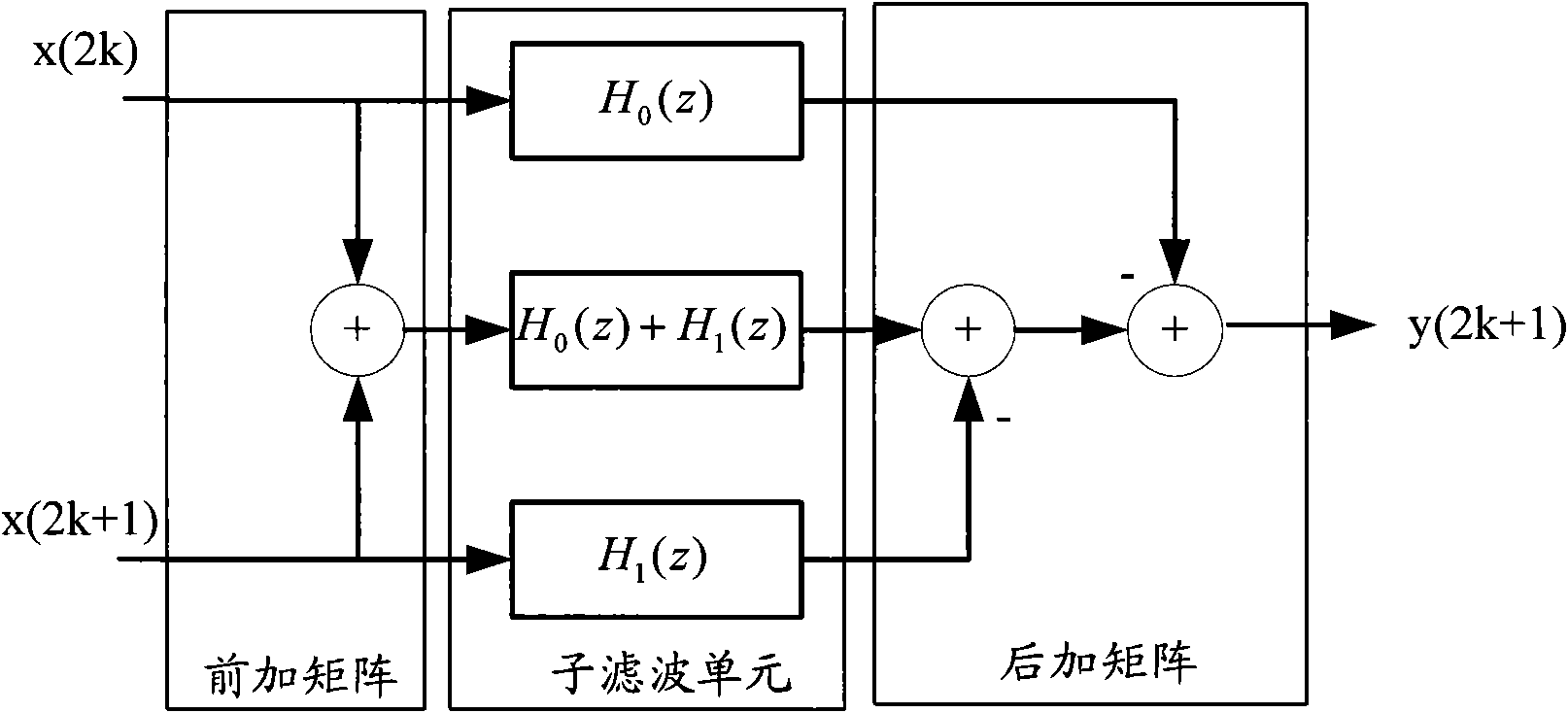

Fast FIR filtering technique for multirate filters

Data samples are filtered by using a digital filter where the length of an impulse response of the digital filter is finite, an impulse response of the digital filter is symmetric and the operation of the digital filter is multi-rate. The method uses a polyphase decomposition to break down the input data stream into N parallel substreams and the multi-rate digital filter is separated by a polyphase decomposition into multiple lower-rate sub-filters where each of the sub-filters is separated into a set of simpler sub-sub-filters which operate upon the same set of input samples and which have impulse responses which are jointly centro-symmetric, a set of pre-filtering arithmetic structures, and a set of post-filtering arithmetic structures and performing each such pair of sub-sub-filtering operations using a single shared filter structure, a set of pre-filtering combining adders, and a set of post-filtering separating adders.

Owner:VECIMA NETWORKS

Frame detection method for orthogonal frequency division multiplexing ultra-wideband system

InactiveCN102255832BFacilitate hardware logic verificationReduce implementation complexityMulti-frequency code systemsTransmitter/receiver shaping networksUltra-widebandA d converter

Owner:SOUTHEAST UNIV +1

Method and device for digital down converter and filtering extraction

ActiveCN101621279BLower requirementReduce power consumptionDigital technique networkMulti-frequency-changing modulation transferenceInformation processingDigital down conversion

The invention provides a method and a device for digital down converter and filtering extraction, belonging to the field of signal and information processing. The method comprises the following steps: receiving a middle frequency digital signal, and carrying out polyphase decomposition processing with a polyphase decomposition factor of n on the middle frequency digital signal to obtain n paths of signals subjected to the polyphase decomposition processing and output the signals; receiving n paths of signals subjected to the polyphase decomposition processing, carrying out mixed frequency processing on each path of signal subjected to the polyphase decomposition processing to obtain n paths of signals subjected to the mixed frequency processing and output the signals; and receiving n paths of signals subjected to the mixed frequency processing and carrying out filtering extraction processing on the n paths of signals subjected to the mixed frequency processing according to an extraction factor m to obtain n / m paths of digital down converter signals, wherein m, n and n / m are natural numbers which are not equal to zero, and m is more than or equal to n. The device comprises a polyphase decomposition circuit, a mixed frequency circuit and a filtering extraction circuit. The scheme reduces the operation complexity, improves the stability of the processor, and effectively improves the precision and real-time property of the operation at the same time.

Owner:成都市天珑科技有限公司 +1

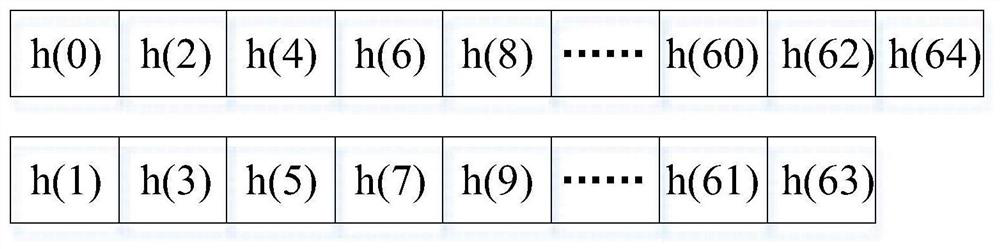

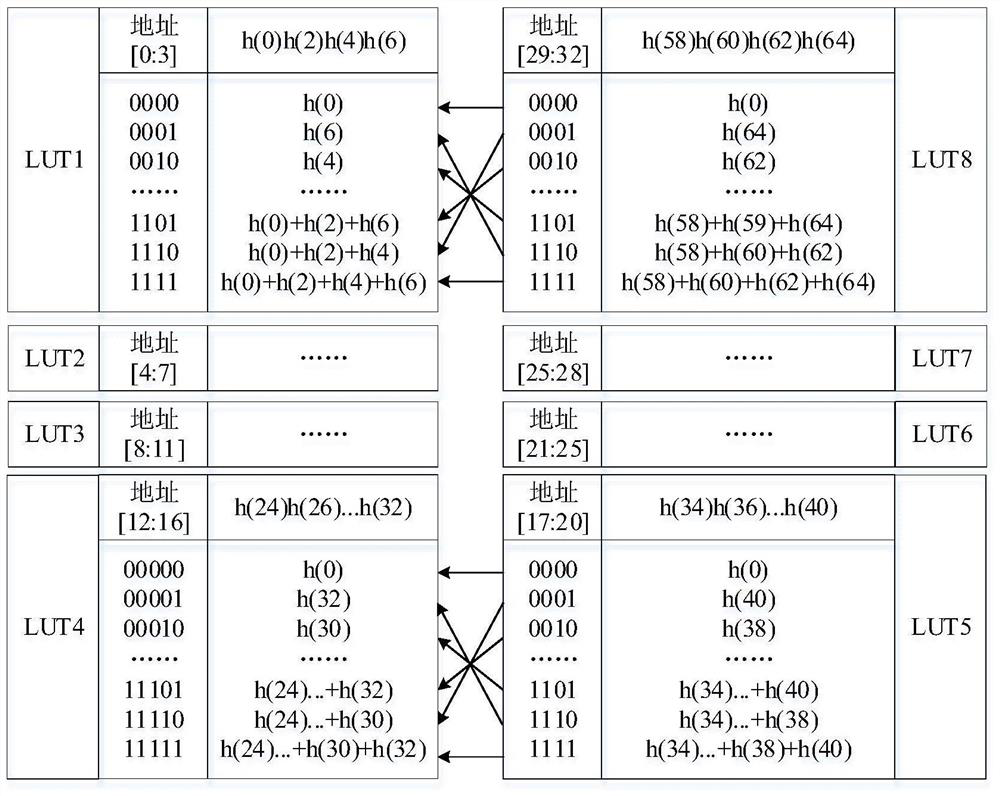

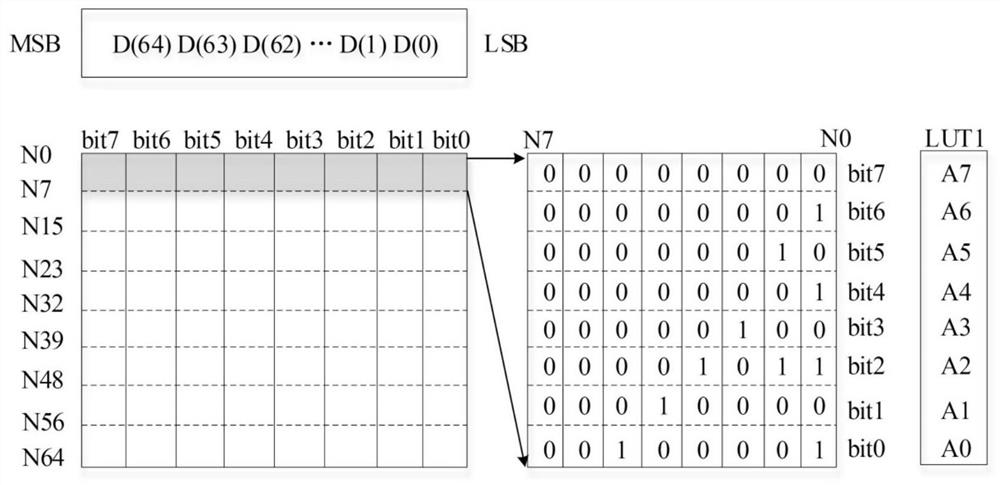

High-order multiphase digital filtering sampling method and system

PendingCN114614795AIncrease working frequencyReduce storage sizeDigital technique networkSoftware engineeringDigital filter

The invention provides a high-order multi-phase digital filtering sampling method and system aiming at the problem that hardware cannot be realized due to the fact that the filtering rate of a broadband communication system is too high and the order of a filter is too high. The method comprises the following steps: firstly, carrying out interpolation operation on a digital signal, then carrying out multiphase decomposition on a coefficient of a filter by utilizing symmetry of the filter, then designing a split lookup table by adopting a parallel distribution algorithm, and finally, optimizing the number of stored lookup tables by utilizing symmetry of content of the lookup table. According to the implementation scheme, the storage scale of the lookup table is greatly reduced, resource consumption is reduced, the operation rate and the operation amount are effectively reduced, the working frequency of the filter is greatly improved, and the method is suitable for engineering implementation.

Owner:中科南京移动通信与计算创新研究院

A method and system for realizing multi-standard digital filtering

The invention relates to a multi-standard digital filtering implementation method and system, wherein the method comprises the following steps of: identifying data speed according to data frame head; respectively calculating sample point periods of the identified signals with different data speeds, and determining a minimum common sample point period number of each signal; performing multi-phase decomposition on a filter, and completing multiplication-accumulation operation of each phase in clock periods of the minimum common sample point period number. The invention automatically determines the sampling rate by judging the data frame head, without the selection of switch, and reduces the consumption of the clock domain by the using of the same operating clock; furthermore, the data with different bandwidth shares the multiplication-accumulation operation so that the resource consumption is greatly reduced.

Owner:ZTE CORP