Variable-modulus fractional frequency conversion serial signal processing method and device

A processing method and serial signal technology, applied in the information field, can solve problems such as inability to adapt to frequency conversion requirements, and achieve the effects of simple structure, small processing resources, and high precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

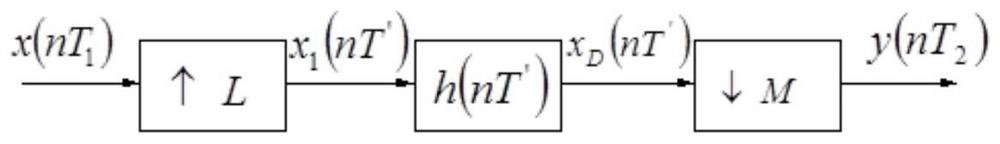

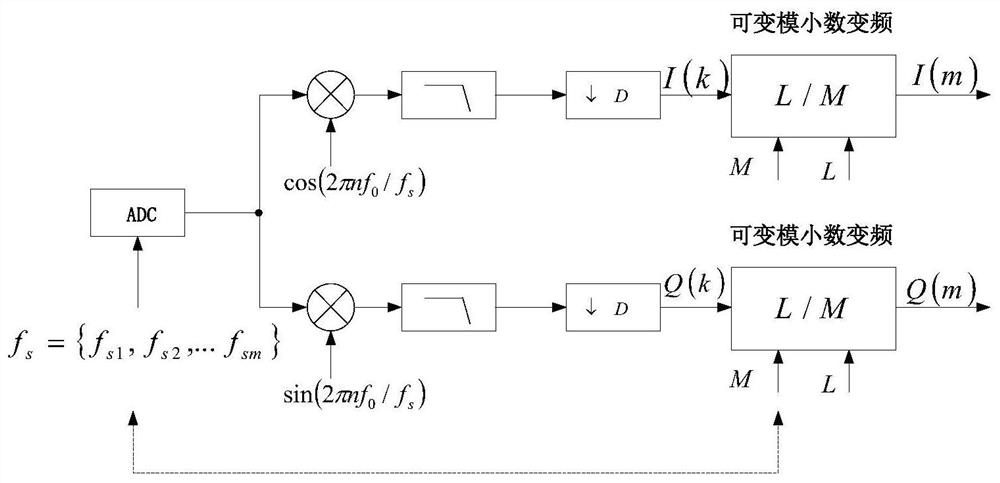

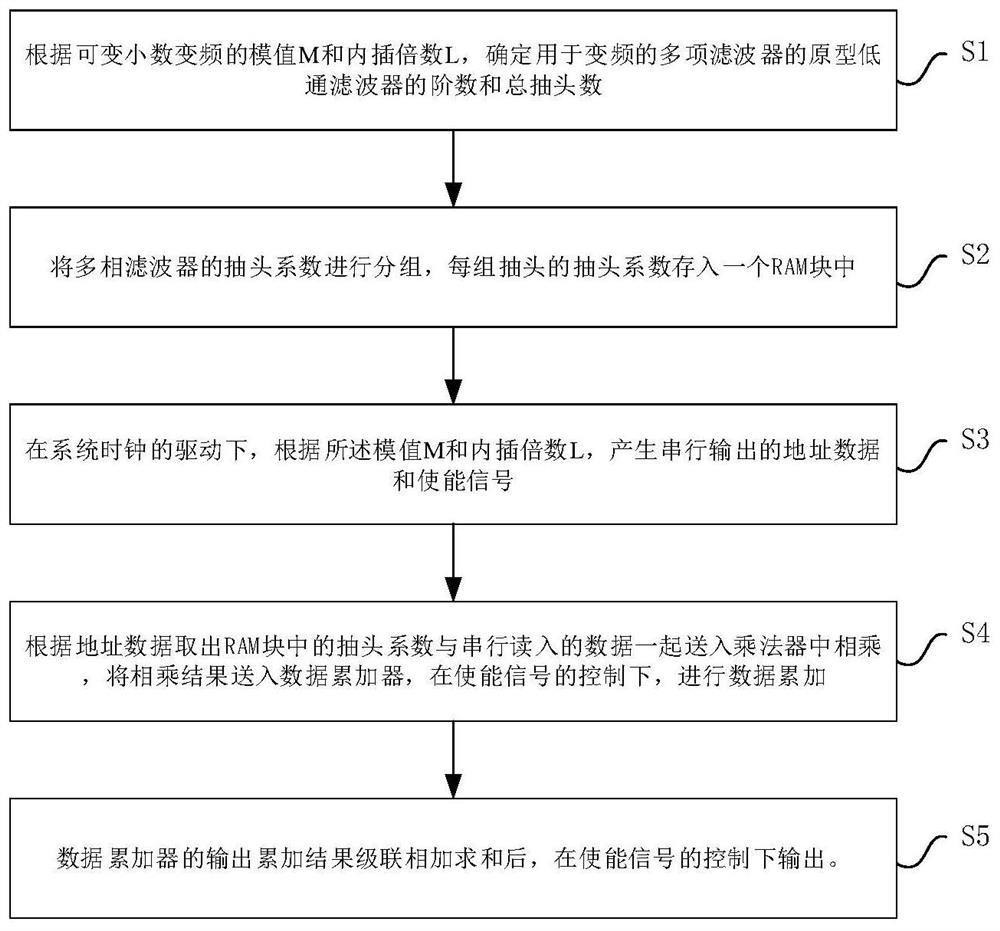

[0049] This embodiment discloses a serial signal processing method with variable modulus and decimal frequency conversion. In the input and output relationship of the rational number decimal frequency conversion, the rational number multiplication decimal conversion process of the interpolation multiple L and the decimation multiple M, where L and M are integers, and the rational number decimation rate is

[0050]

[0051] T 2 Is the output data clock cycle, T 1 Is the input data clock period. In theory, there is a low-pass filter after internal decimation and before decimation. The interpolated filter is used to filter out image spurious, and the pre-decimation filter is used for anti-aliasing. When two filters are cascaded, the frequency response of the equivalent filter h(nT') is equal to the convolution of the two low-pass filters, so it can be represented by one filter. Among them, the frequency response of h(nT’) satisfies

[0052]

[0053] Note that ω above is the normaliz...

Embodiment 2

[0093] This embodiment discloses a serial signal processing device with variable modulus and decimal frequency conversion, such as Image 6 As shown, it includes P one-to-one corresponding RAM blocks, multipliers and data accumulators, and P-1 adders and address generators;

[0094] The P RAM blocks are used to store the filter tap coefficients after polyphase decomposition of the prototype low-pass filter; one RAM block is a memory bank to store M tap coefficients, and the total number of P RAM blocks is N=M ×P tap coefficient of the filter.

[0095] The address generator is used to generate serial output address data and enable signals according to the modulus value M and the interpolation multiple L.

[0096] One multiplier of each multiplier is the data read in serially, and the other multiplier is the tap coefficient extracted from the address data output by the address generator in the corresponding RAM block, and the output terminal of the multiplier is connected to the corres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More