Intra-frame sub-block predictor circuit for video encoder and method for implementing same

A technology of video encoder and prediction circuit, which is applied in digital video signal modification, television, electrical components, etc., can solve the problems of reducing time and space costs, reducing encoding quality, etc., to improve efficiency, realize hardware area and circuit design the effect of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention will be described in further detail below with reference to the accompanying drawings and in combination with specific embodiments.

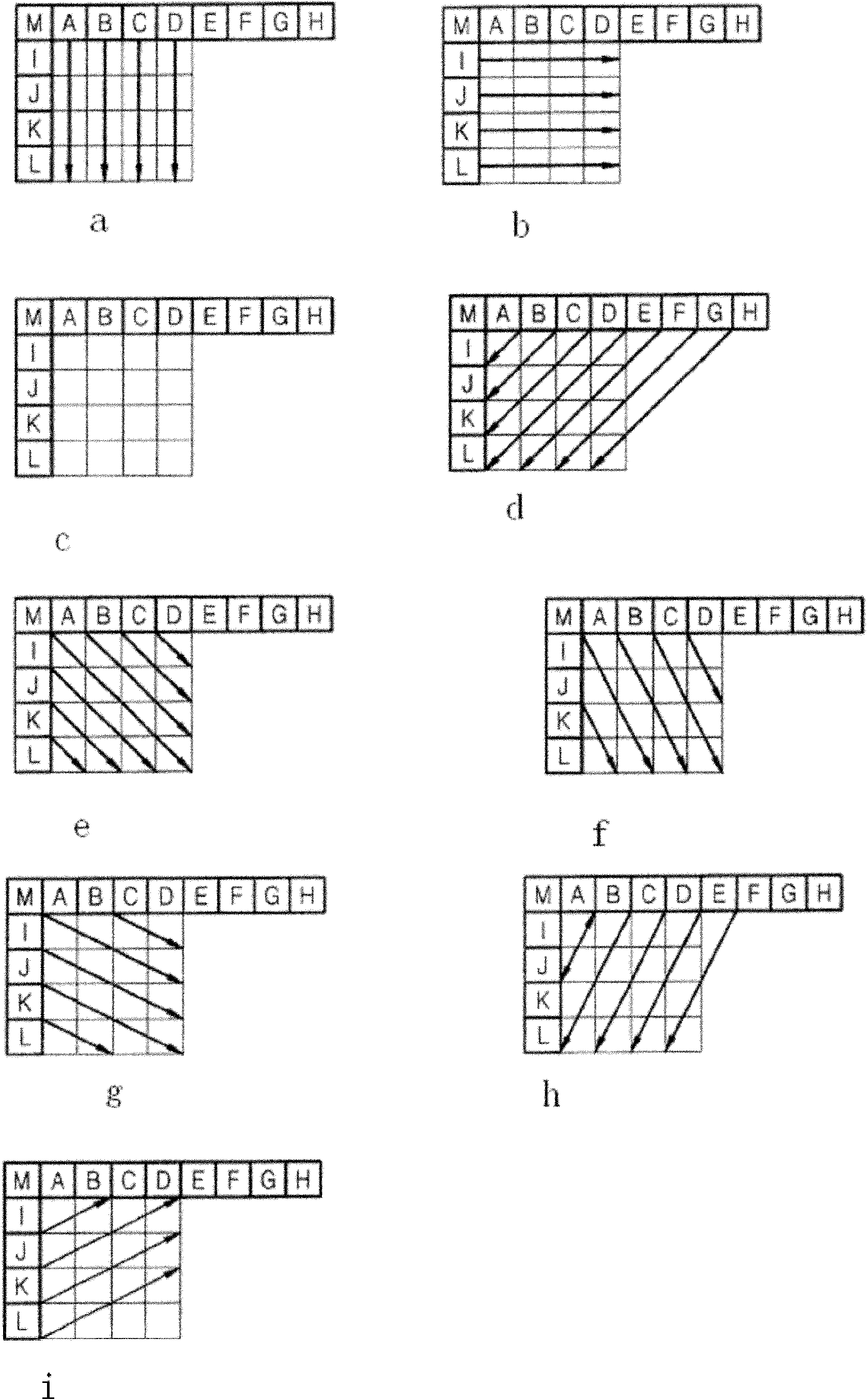

[0051] The invention discloses a method for realizing an intra-frame sub-block prediction circuit of a video encoder, which includes: mapping each functional block of the intra-frame sub-block prediction circuit of a video encoder described by a computer program language algorithm to be composed of an operator unit The hardware logic description; the hardware logic description composed of the operator unit generates the hardware integrated circuit of the intra-frame sub-block prediction circuit.

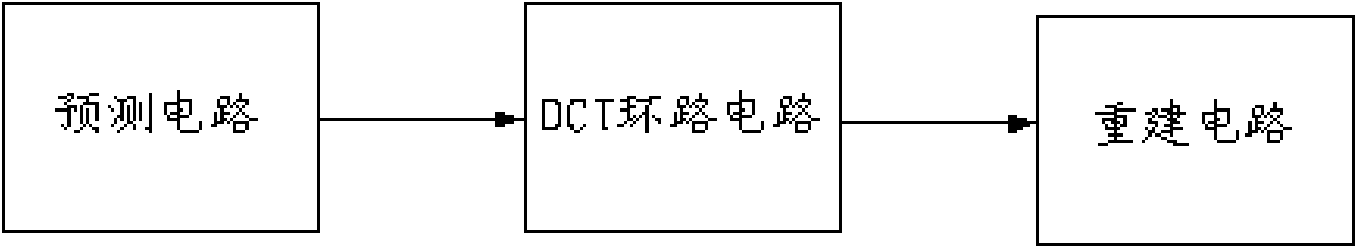

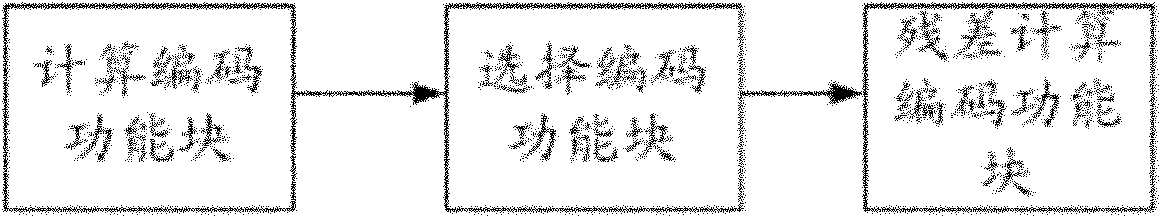

[0052] The intra-frame sub-block prediction circuit of the video encoder implemented by the above method includes a calculation function block for calculating the prediction value, a selection function block for selecting the optimal prediction value from the prediction values, and a function block for selecting the optimal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More