Method for dividing cycle task by means of software and hardware and device thereof

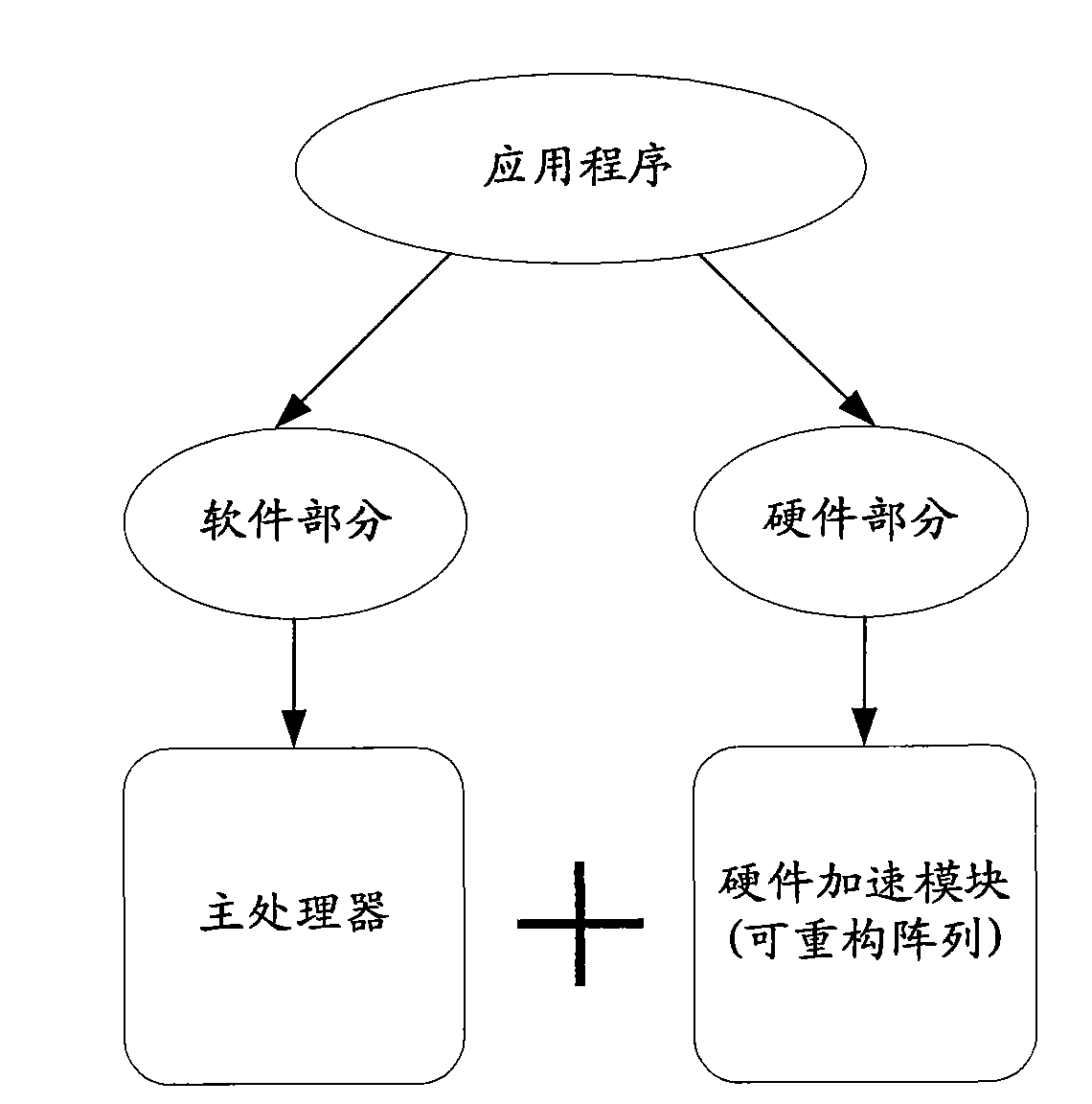

A technology of hardware and software division and task, applied in the direction of multi-programming device, resource allocation, etc., can solve the problems of increasing the execution time of the application program, limiting the size of the loop body, and the loop body cannot map all the reconfigurable arrays at one time. Reduced execution time and increased scale

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

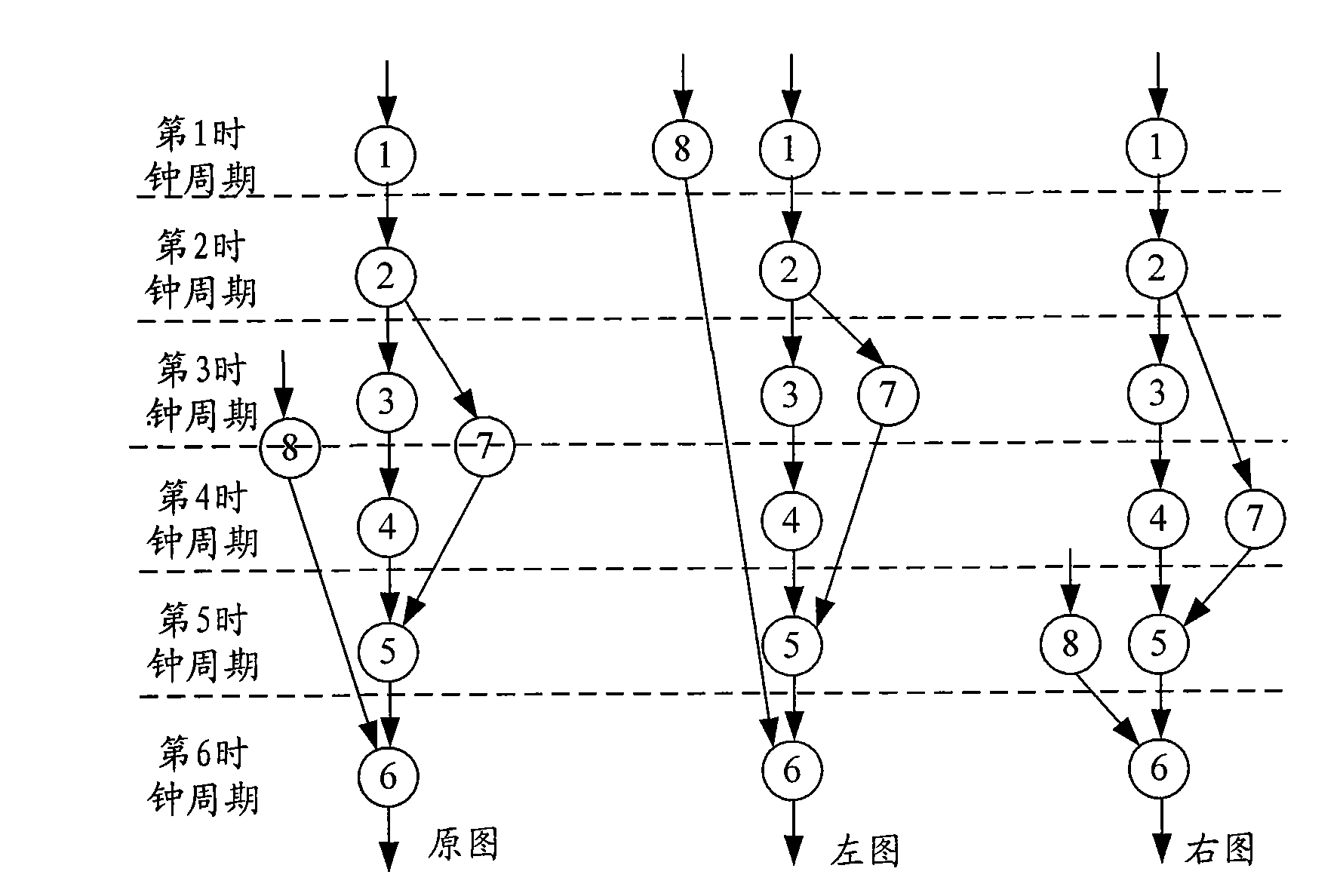

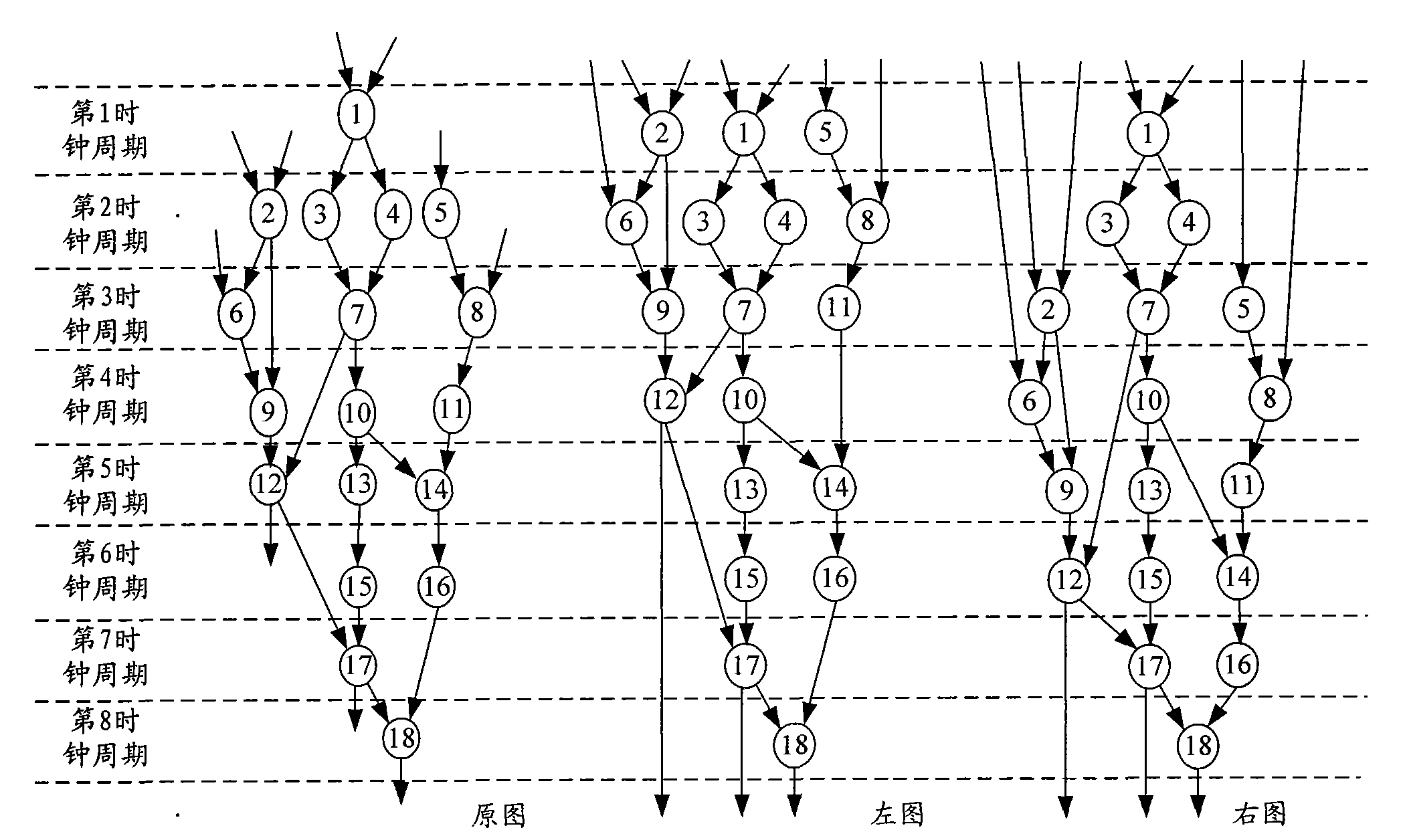

[0088] The execution process of the division algorithm is described below with a specific embodiment, and the specific execution process is as follows:

[0089] Taking the scale of the reconfigurable array as 4×4 as an example, that is, it can support the mapping of a maximum of 16 nodes. Among them, G1 represents a reconfigurable array, and G2 represents a main processor.

[0090] see image 3 The original graph in is the data flow graph of the loop body to be divided, and there are 18 nodes in the graph.

[0091] Figure 8 For the flow chart of the method for dividing the software and hardware of the cyclic task provided by the embodiment of the present invention, see Figure 8 .

[0092] Step S1: First, all nodes are executed on G1 by default.

[0093] That is, G1=18, G2=0.

[0094] Step S2: Determine whether the number of nodes on G1 is greater than the maximum number of nodes that G1 can support, if the number of nodes on G1 is greater than the maximum number of nodes...

Embodiment 2

[0134] see Figure 9 , which is a schematic diagram of an apparatus for implementing software and hardware division of cyclic tasks provided by an embodiment of the present invention, Figure 10 It is a specific schematic diagram of a device for realizing software and hardware division of cyclic tasks provided by the embodiment of the present invention, which is used to perform software and hardware division of large-scale cyclic bodies, including:

[0135] The scheduling module 101 is configured to perform operator scheduling on nodes currently executing data streams of the reconfigurable array.

[0136] Among them, specifically include:

[0137] The first scheduling unit 101A is configured to perform first operator scheduling on nodes currently executing data flows;

[0138] The second scheduling unit 101B is configured to perform second operator scheduling on the node currently executing the data flow;

[0139] Correspondingly, the scheduling module specifically includes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More