Dynamic reconfigurable processor

A processor and dynamic technology, applied to the architecture with a single central processing unit, general-purpose stored-program computer, etc., can solve problems such as short delay of calculation path, low efficiency of array usage, inconsistent delay of calculation path, etc., to reduce calculation efficiency effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the above objects, features and advantages of the present application more obvious and comprehensible, the present application will be further described in detail below in conjunction with the accompanying drawings and specific implementation methods.

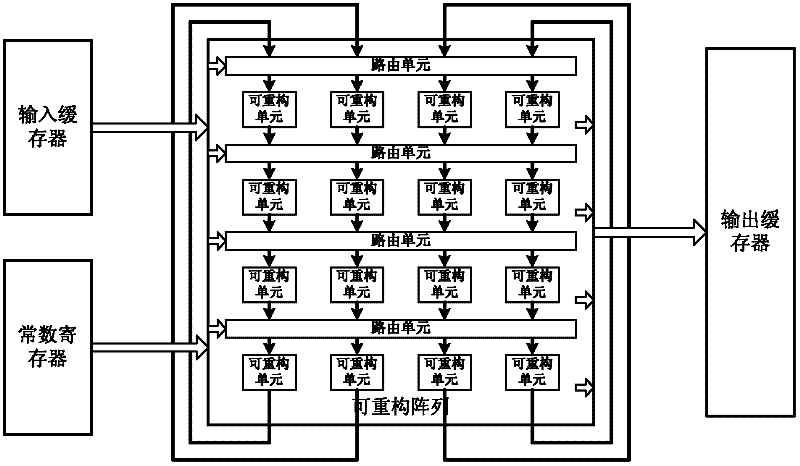

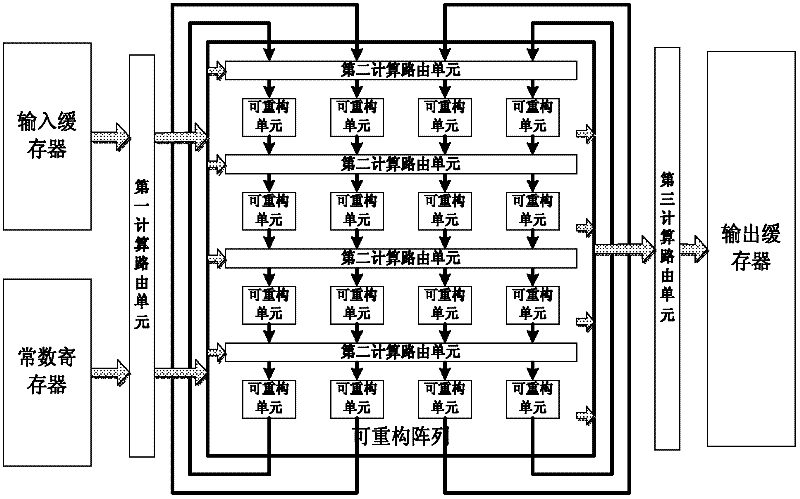

[0037] refer to figure 2 , which shows a schematic structural diagram of a dynamically reconfigurable processor of the present application, including:

[0038] The input buffer is used for buffering external data and outputting the data to the first computing routing unit;

[0039] The constant register is used to store the constants required by the reconfigurable array for operation, and output the constants to the first calculation routing unit;

[0040] The first calculation routing unit is used to receive the data input into the buffer, perform calculation processing on the data, and output the calculation result data to the reconfigurable array;

[0041] For some data processing operations such a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More