Patents

Literature

54results about How to "Reduce junction depth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

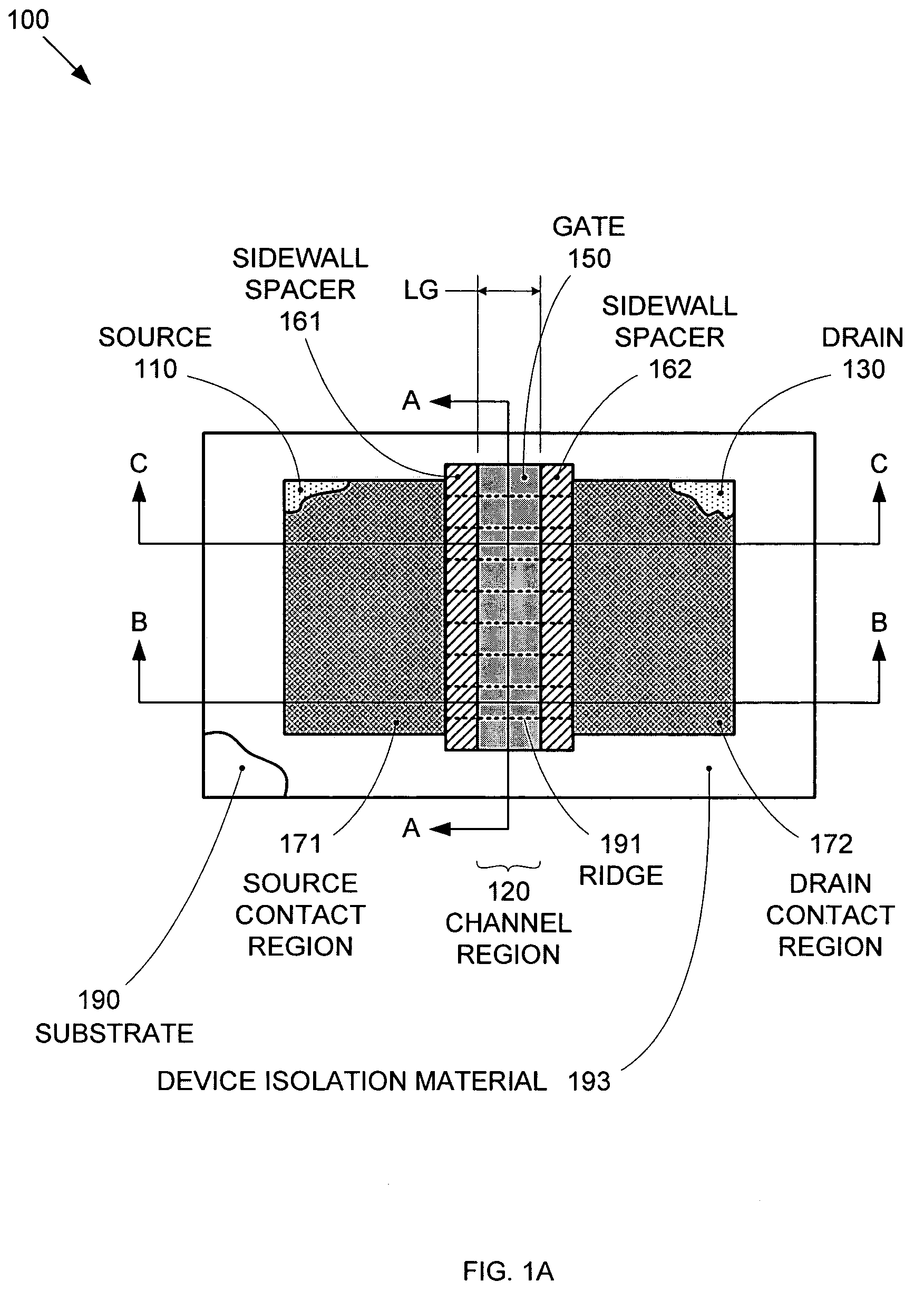

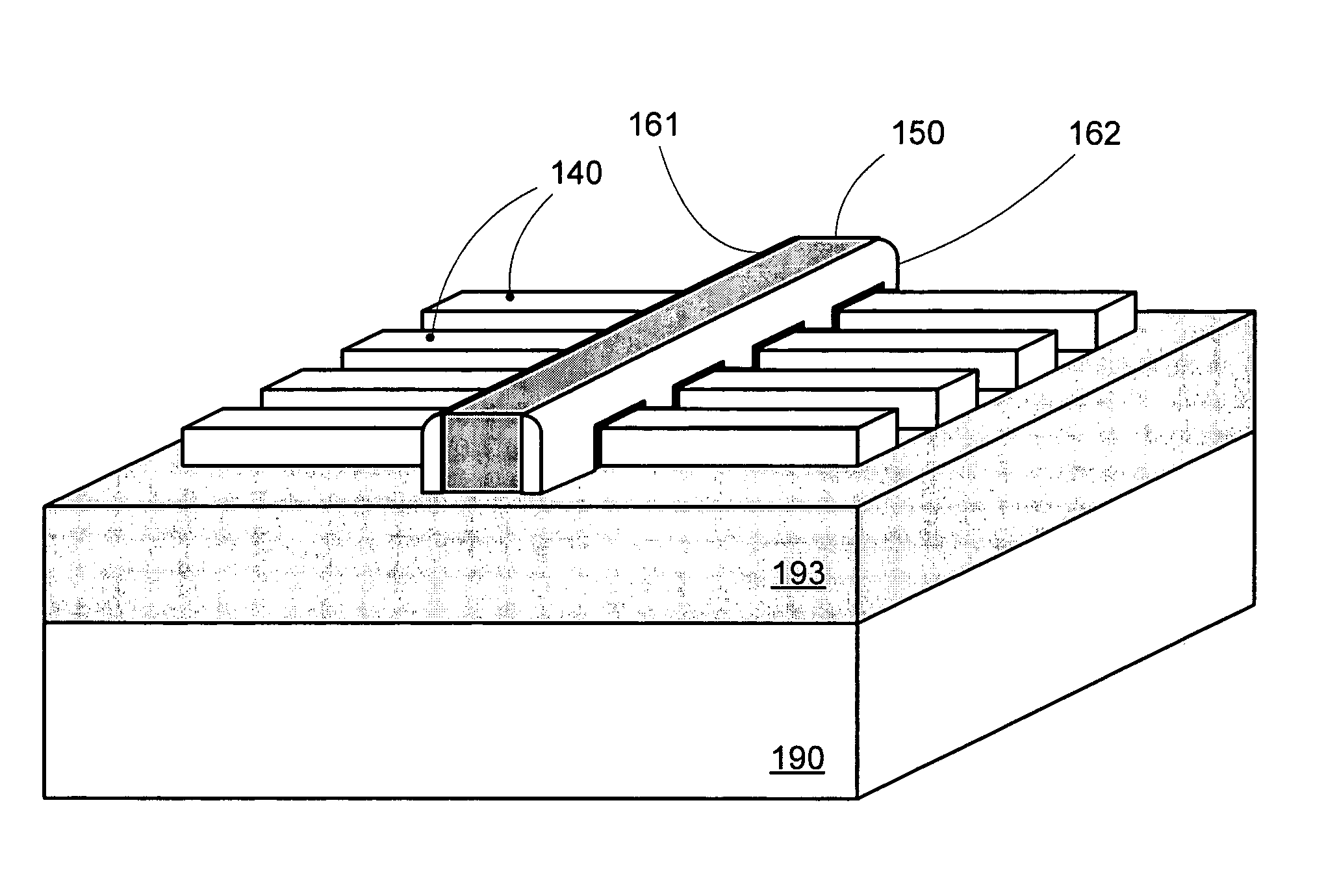

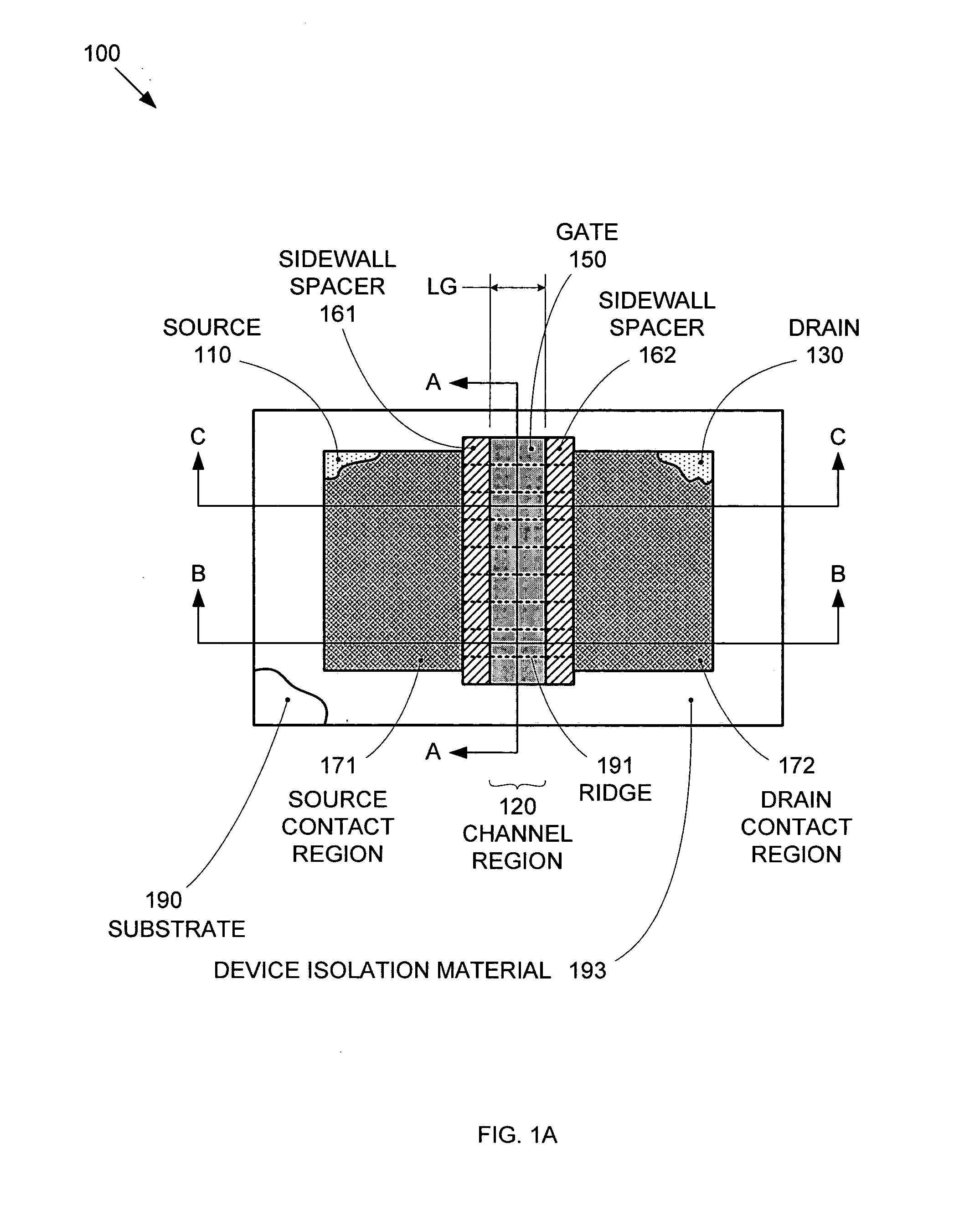

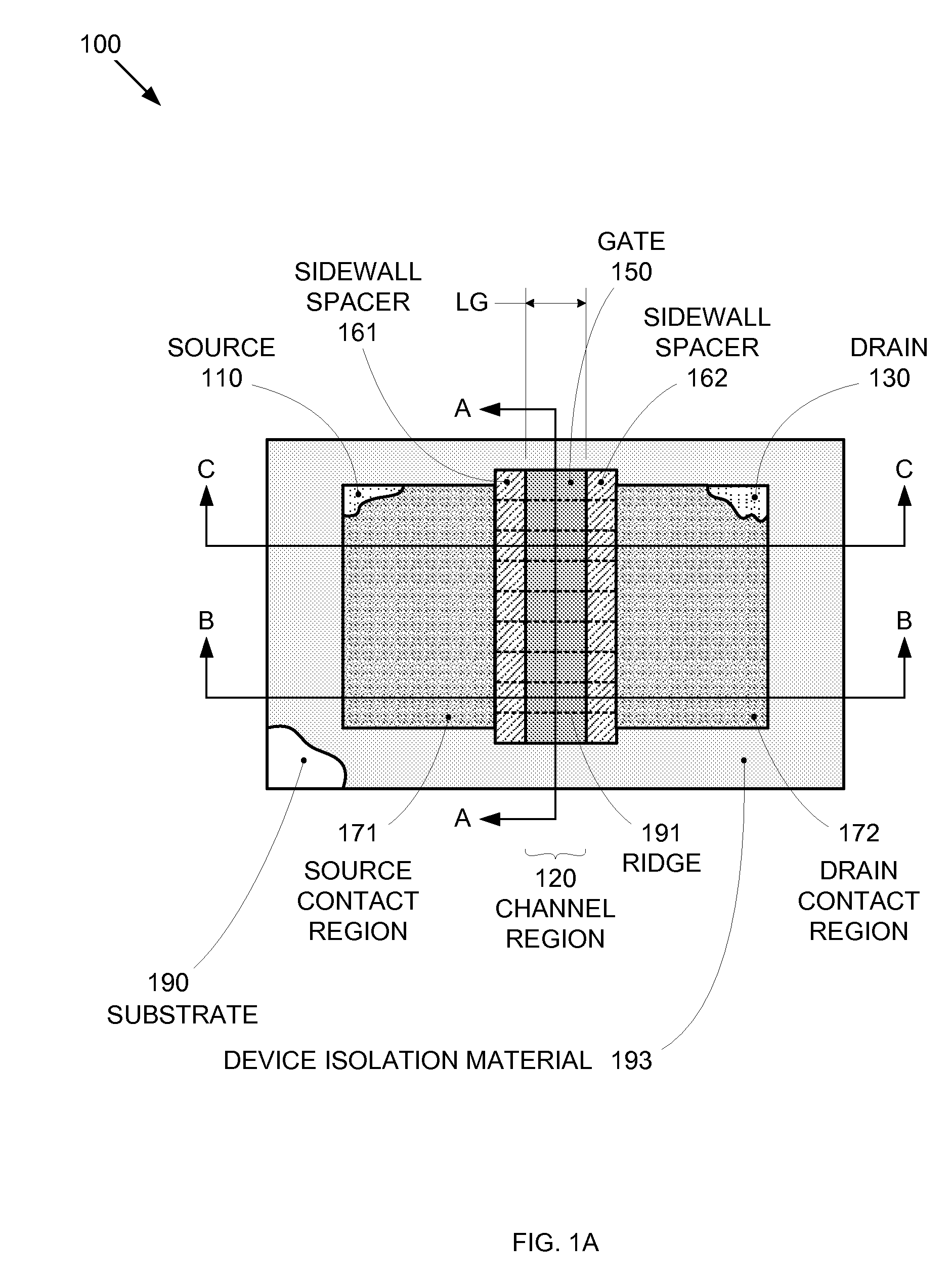

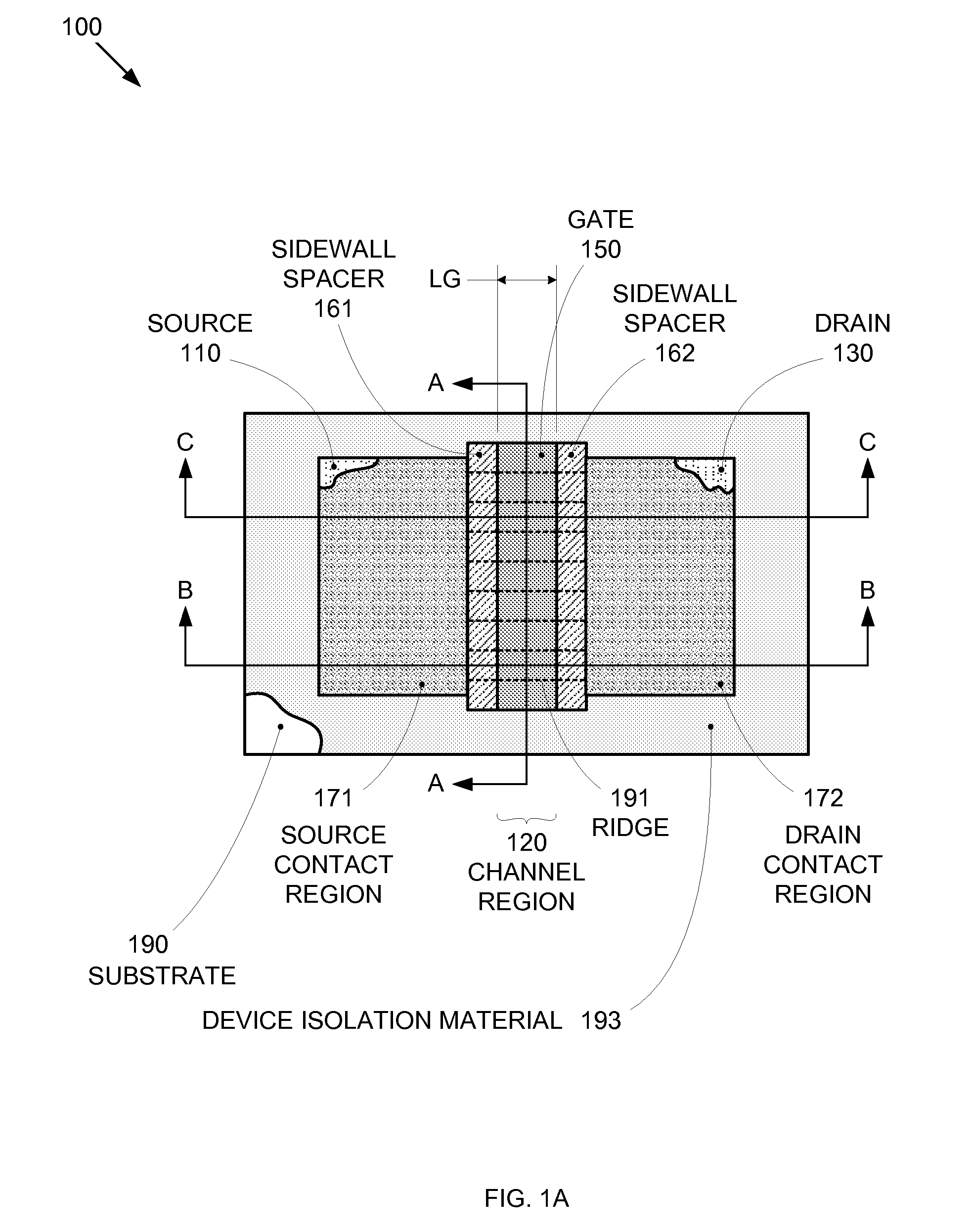

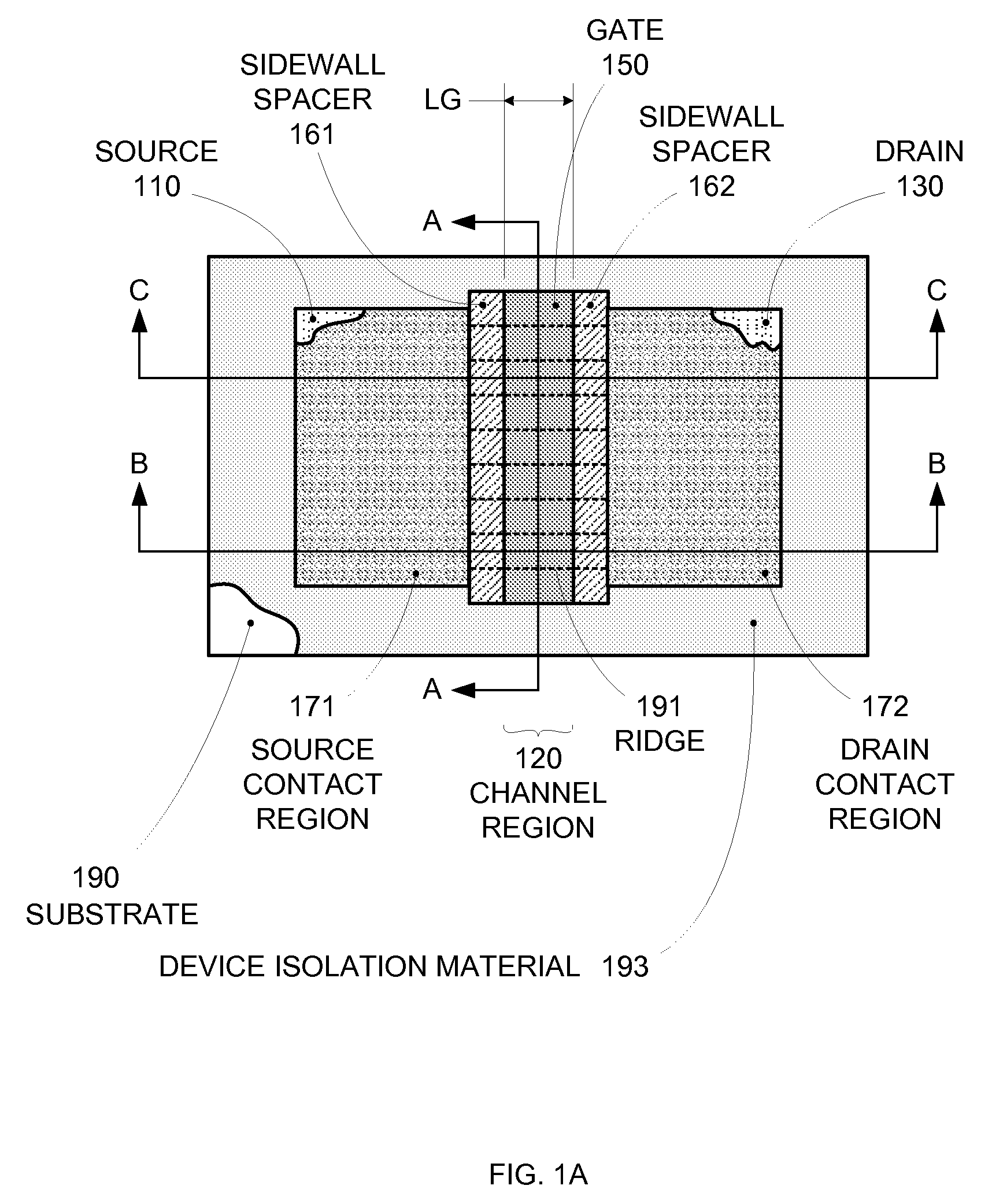

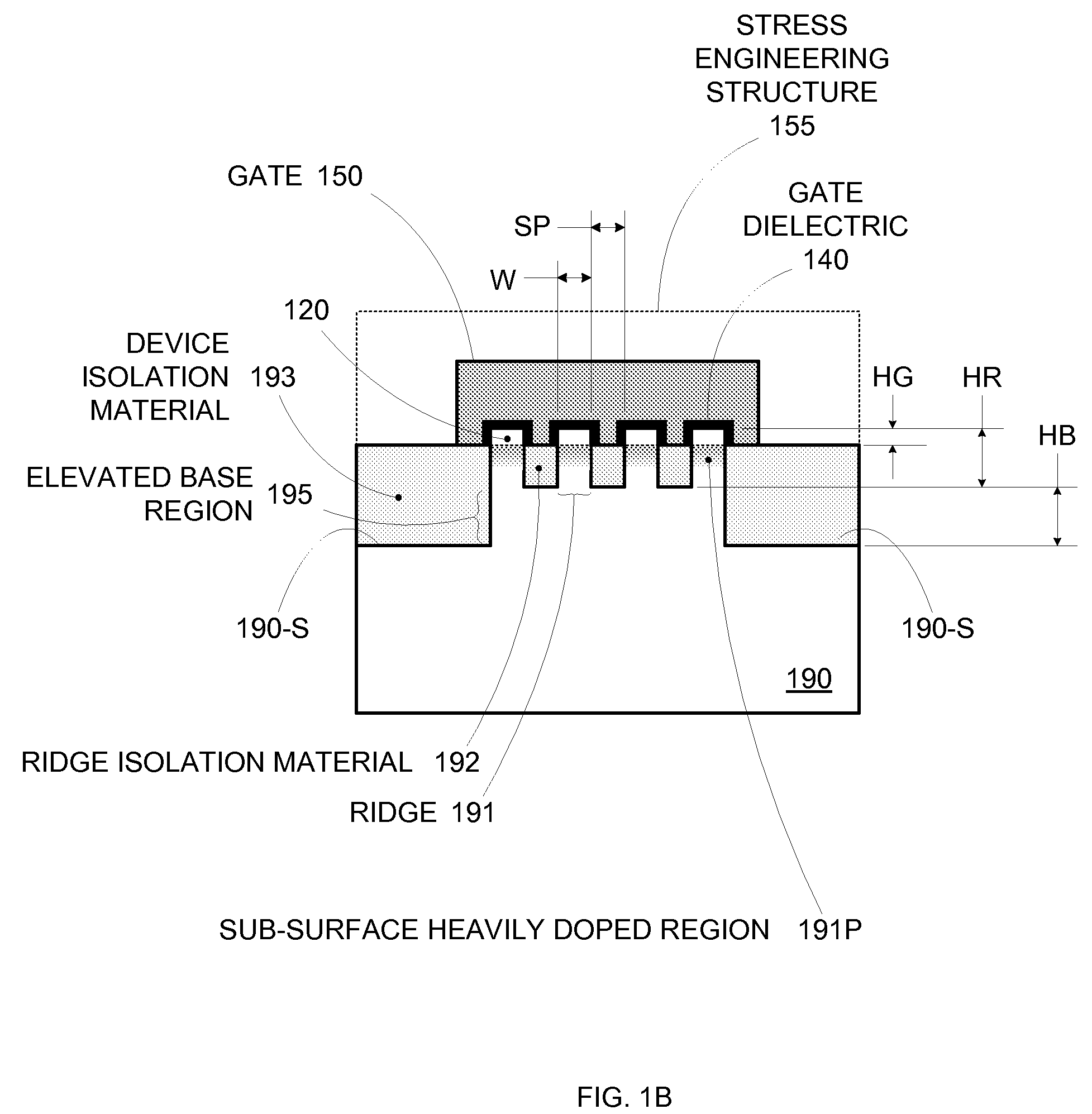

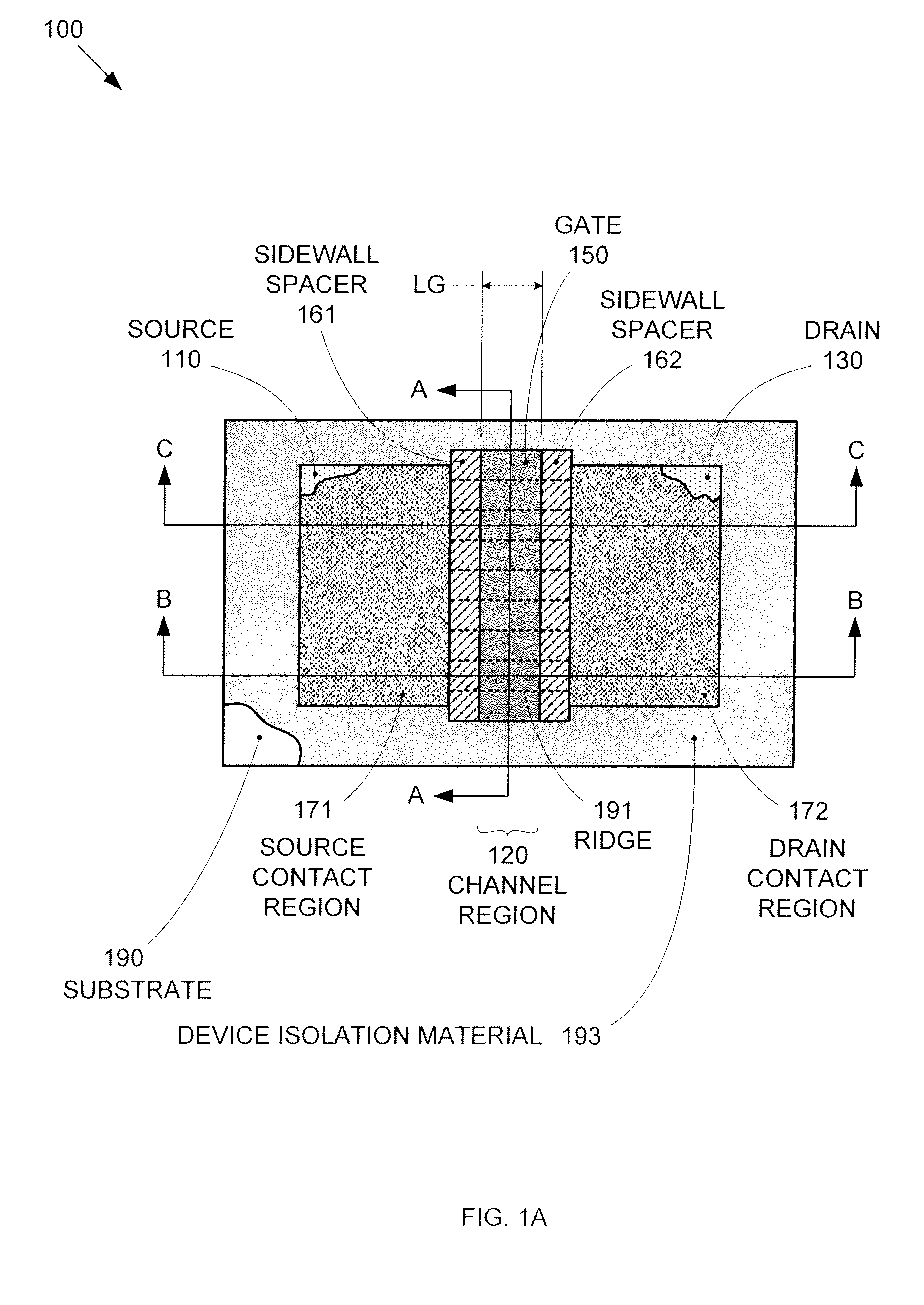

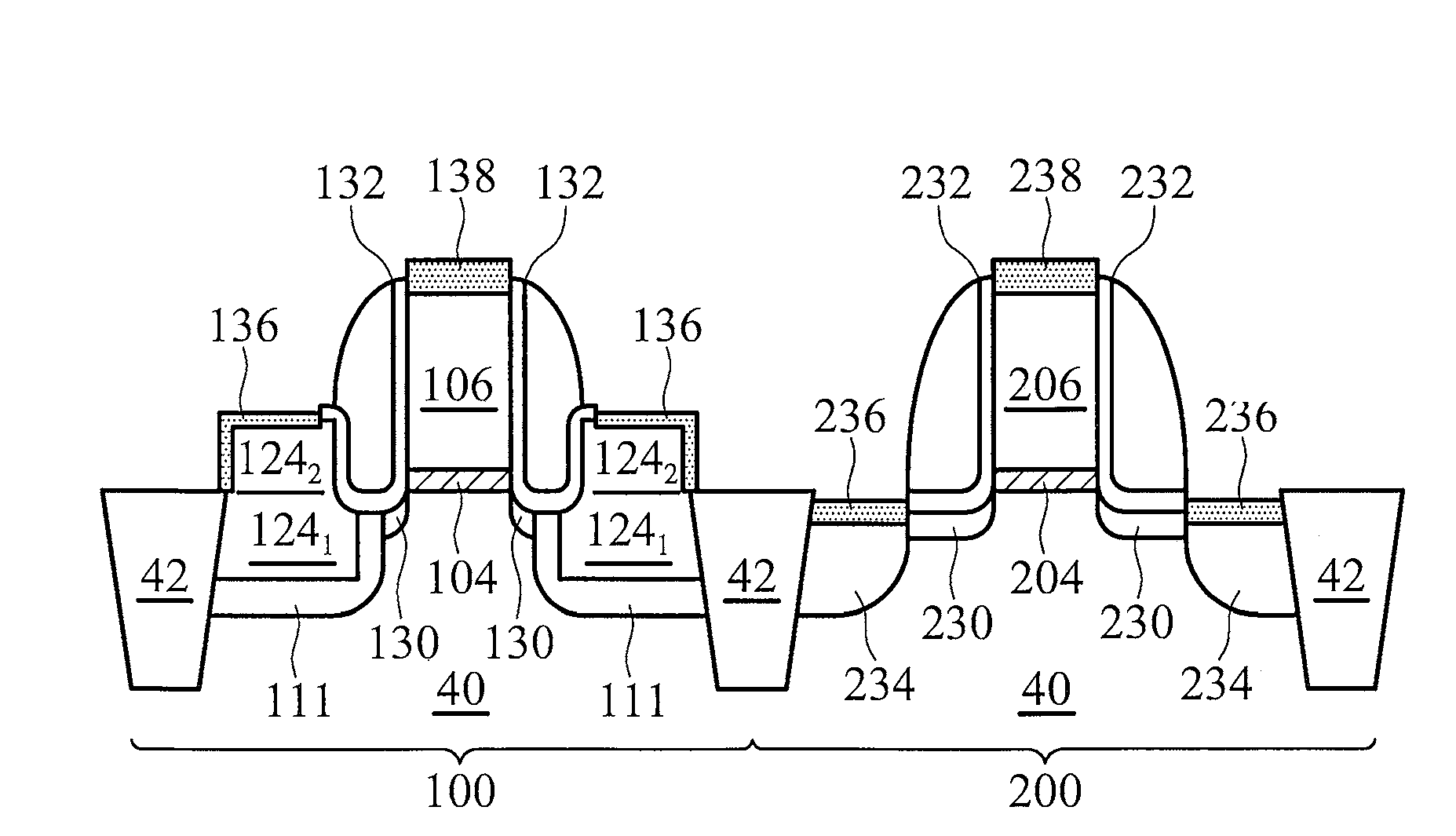

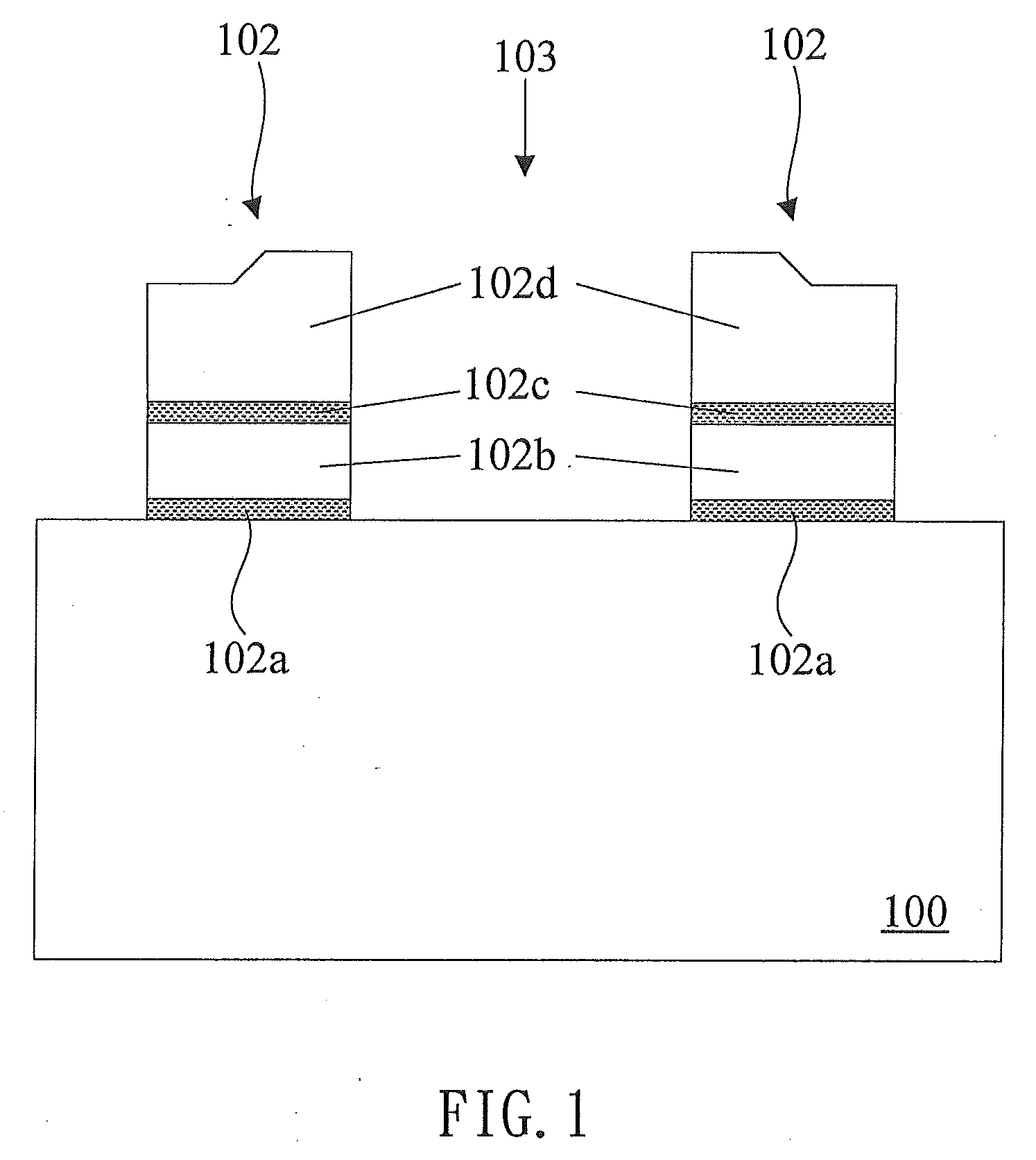

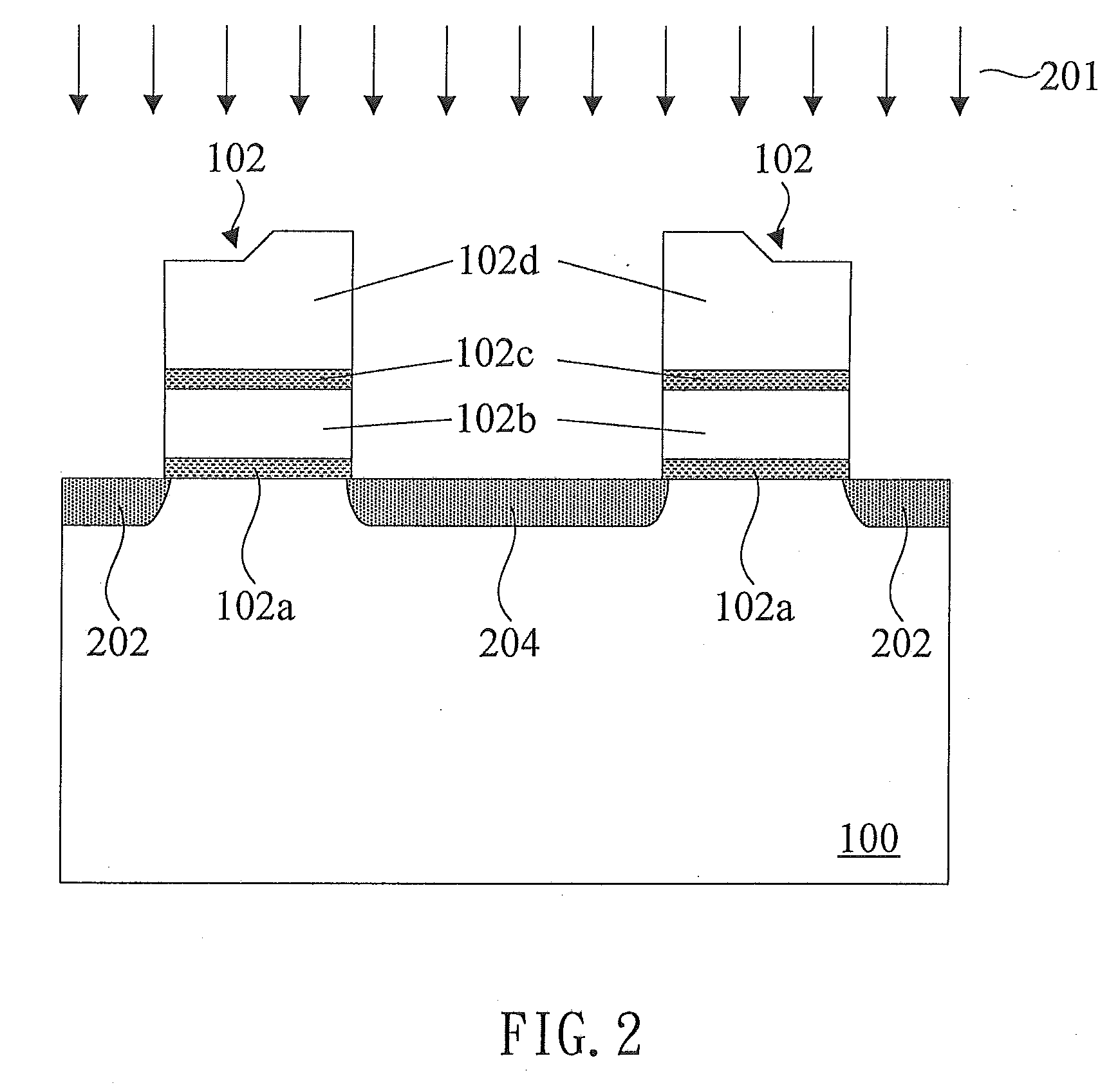

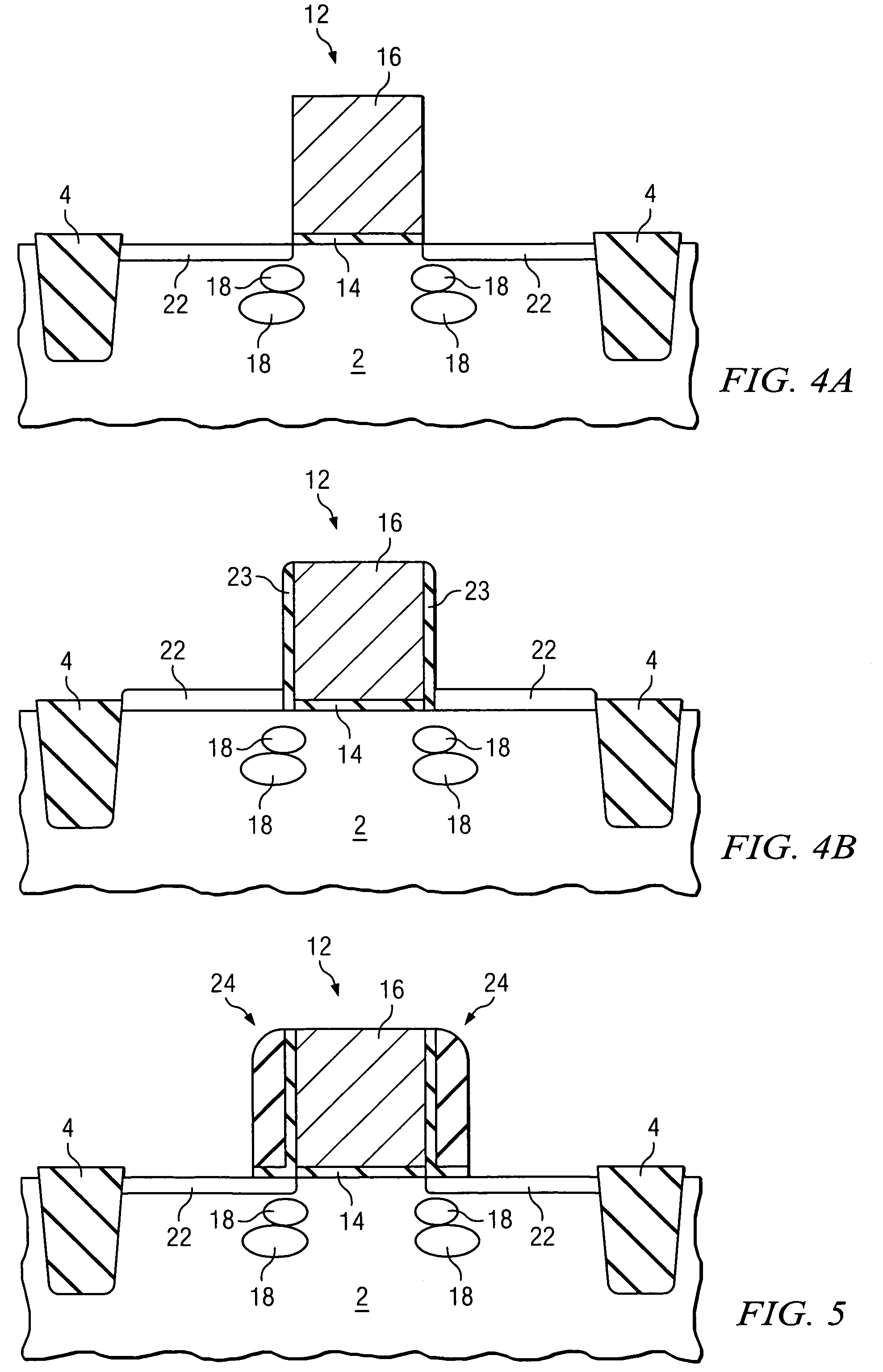

Segmented channel MOS transistor

ActiveUS7247887B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETLithographic artist

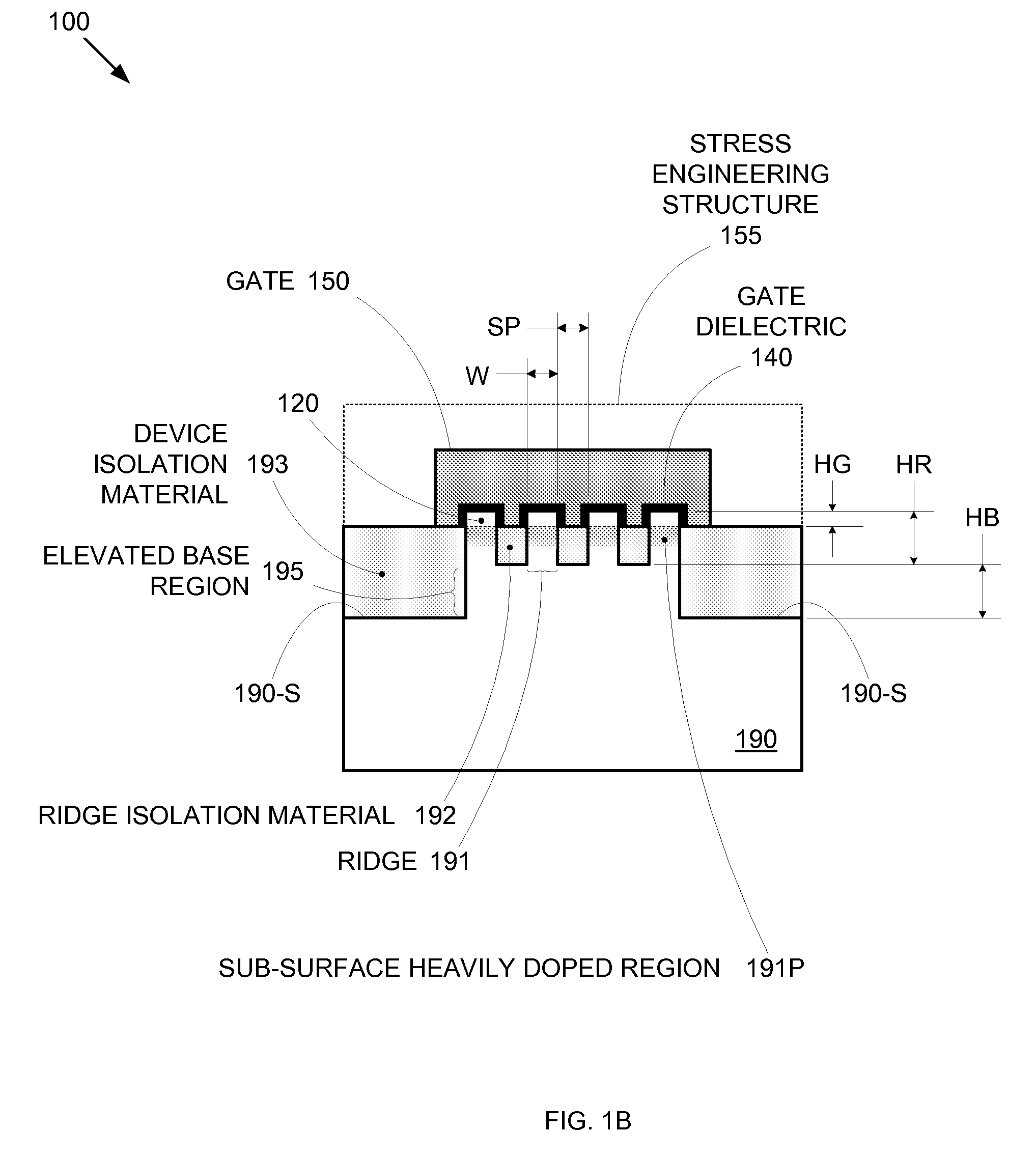

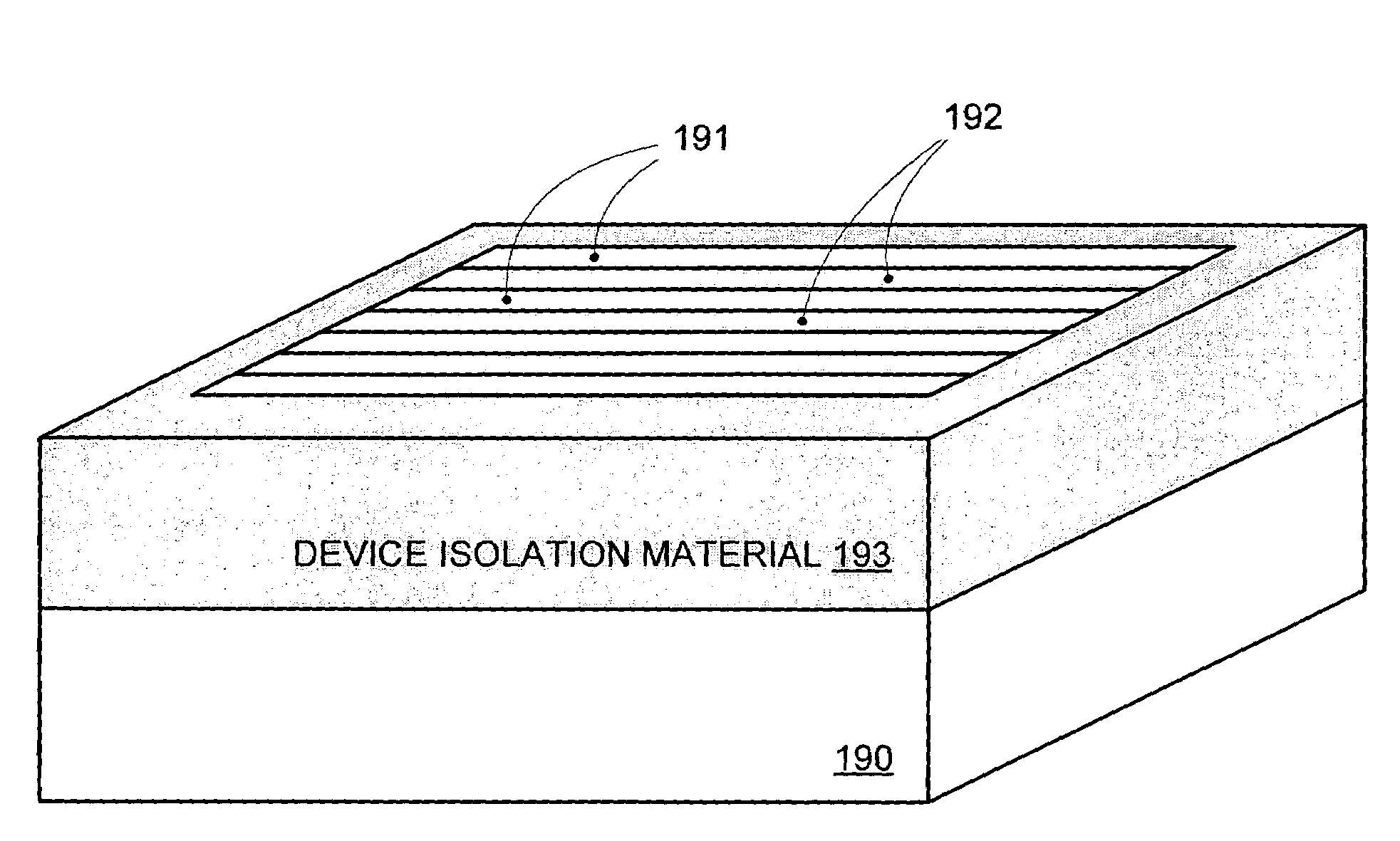

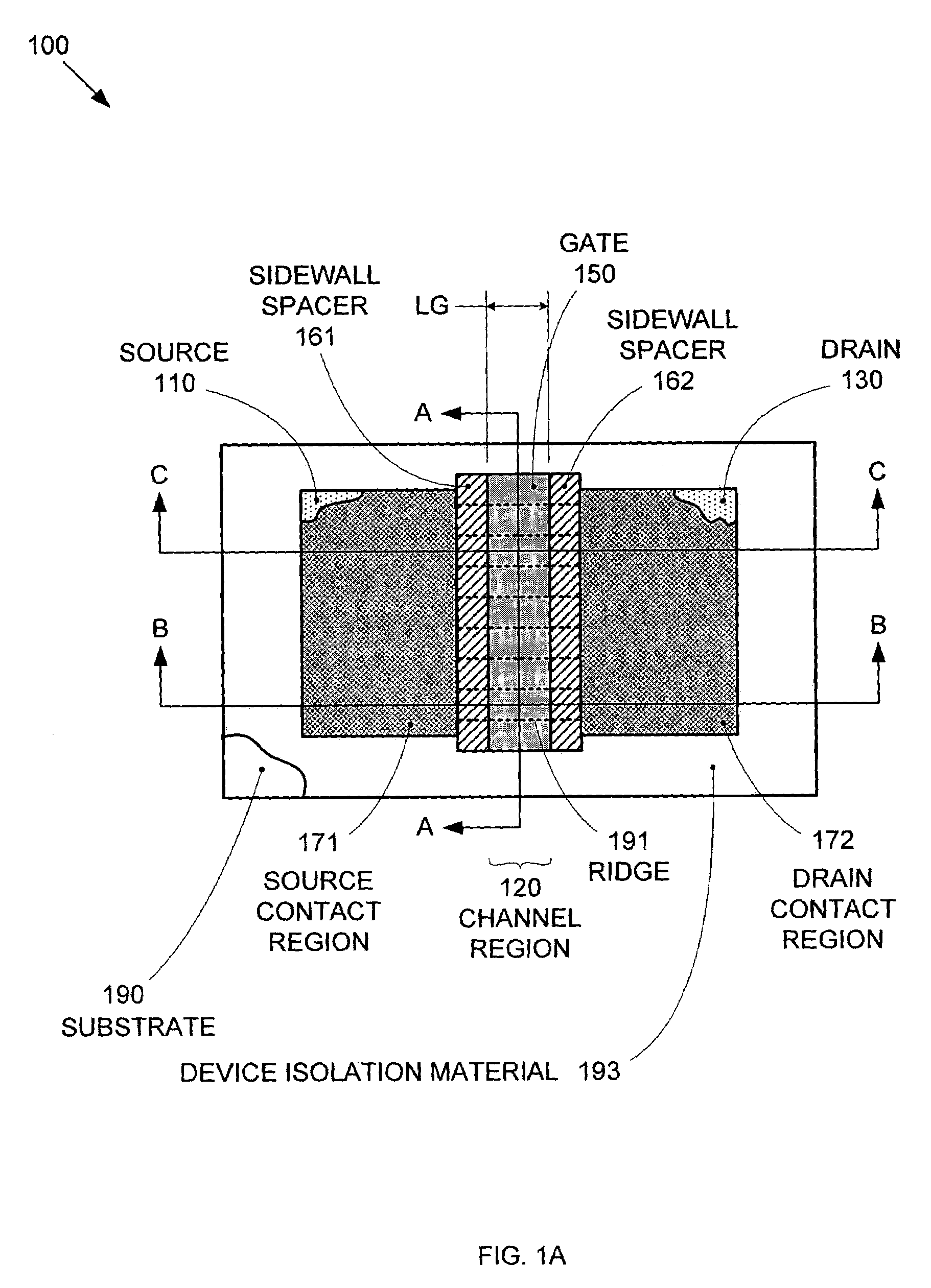

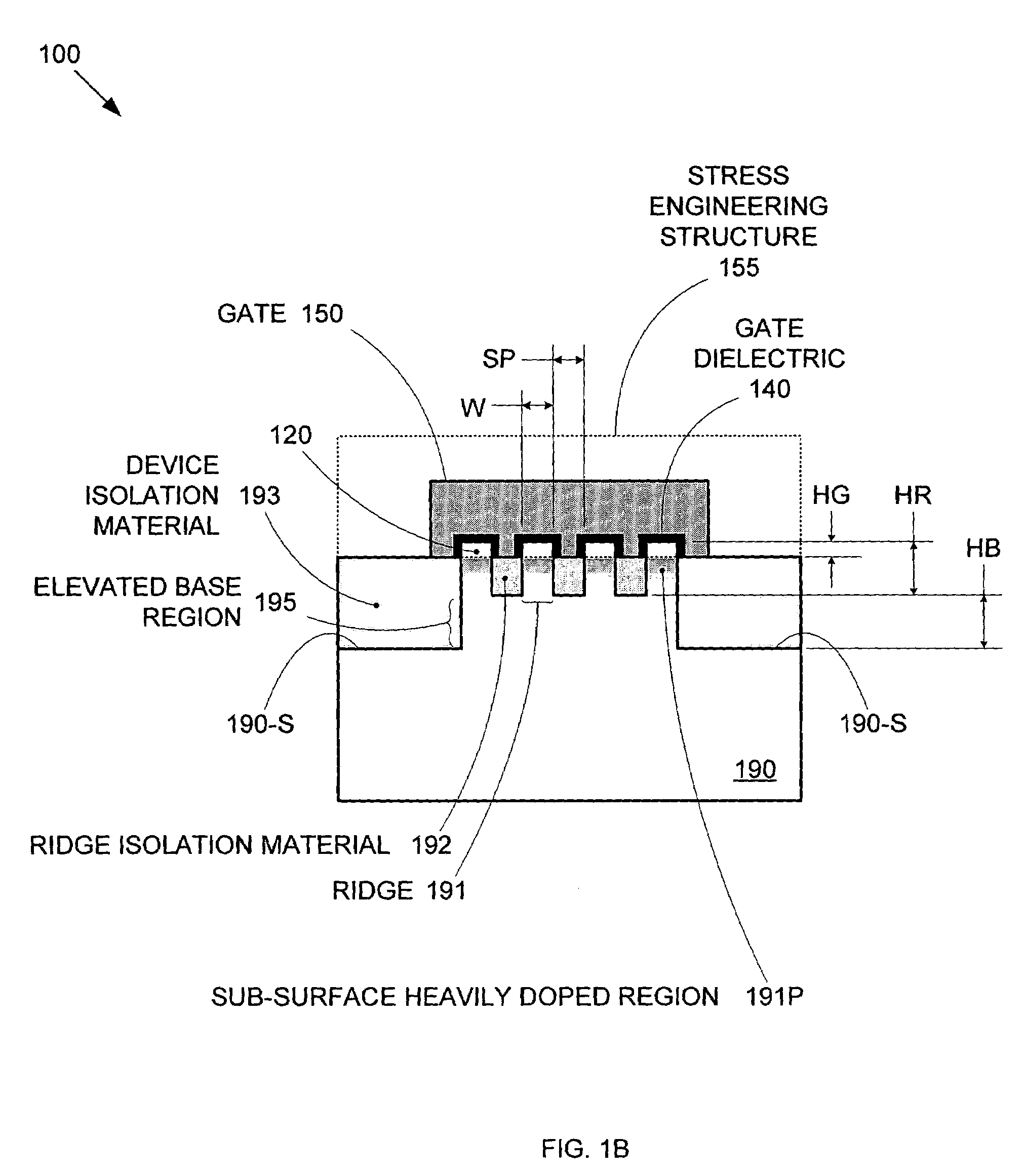

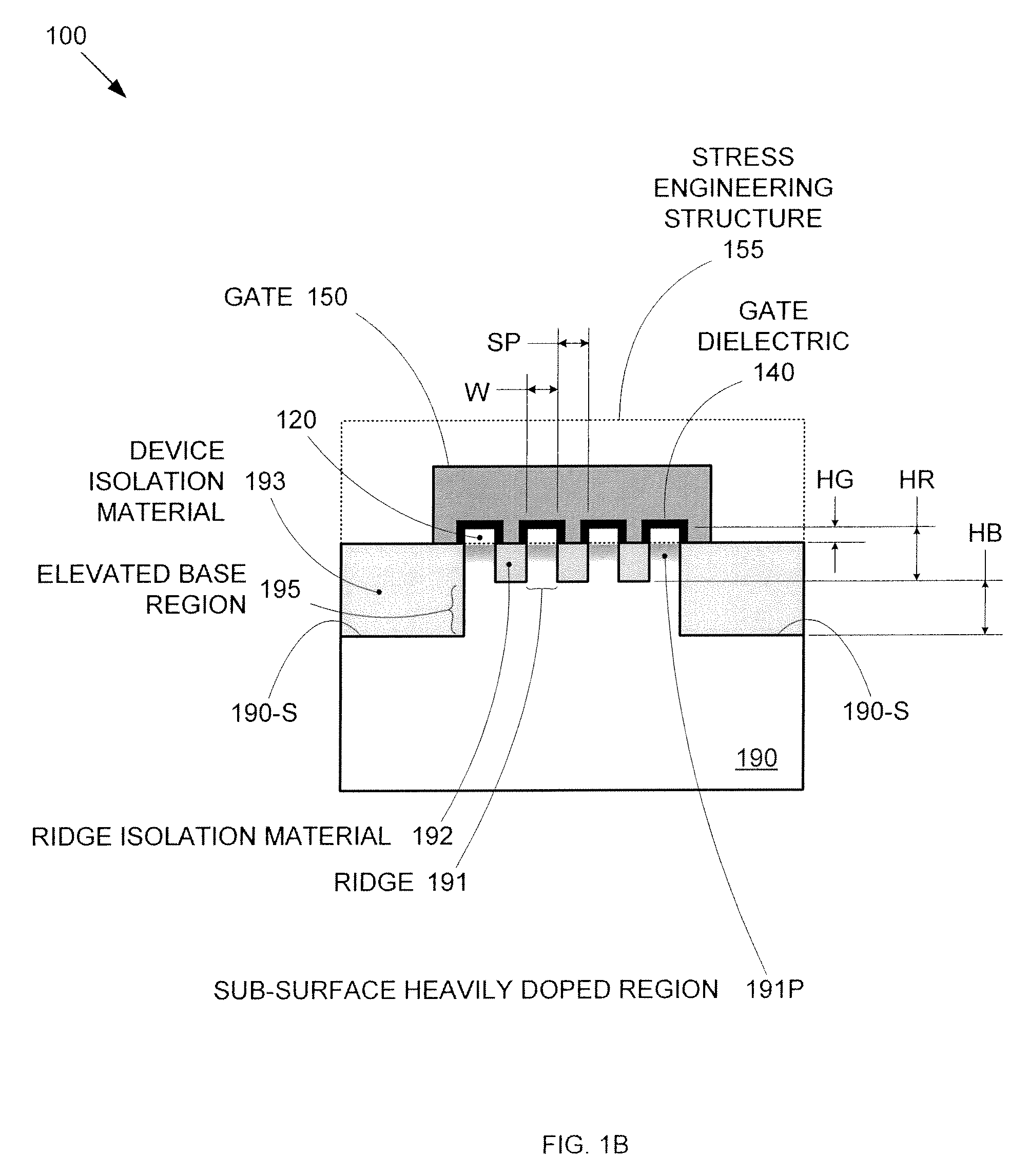

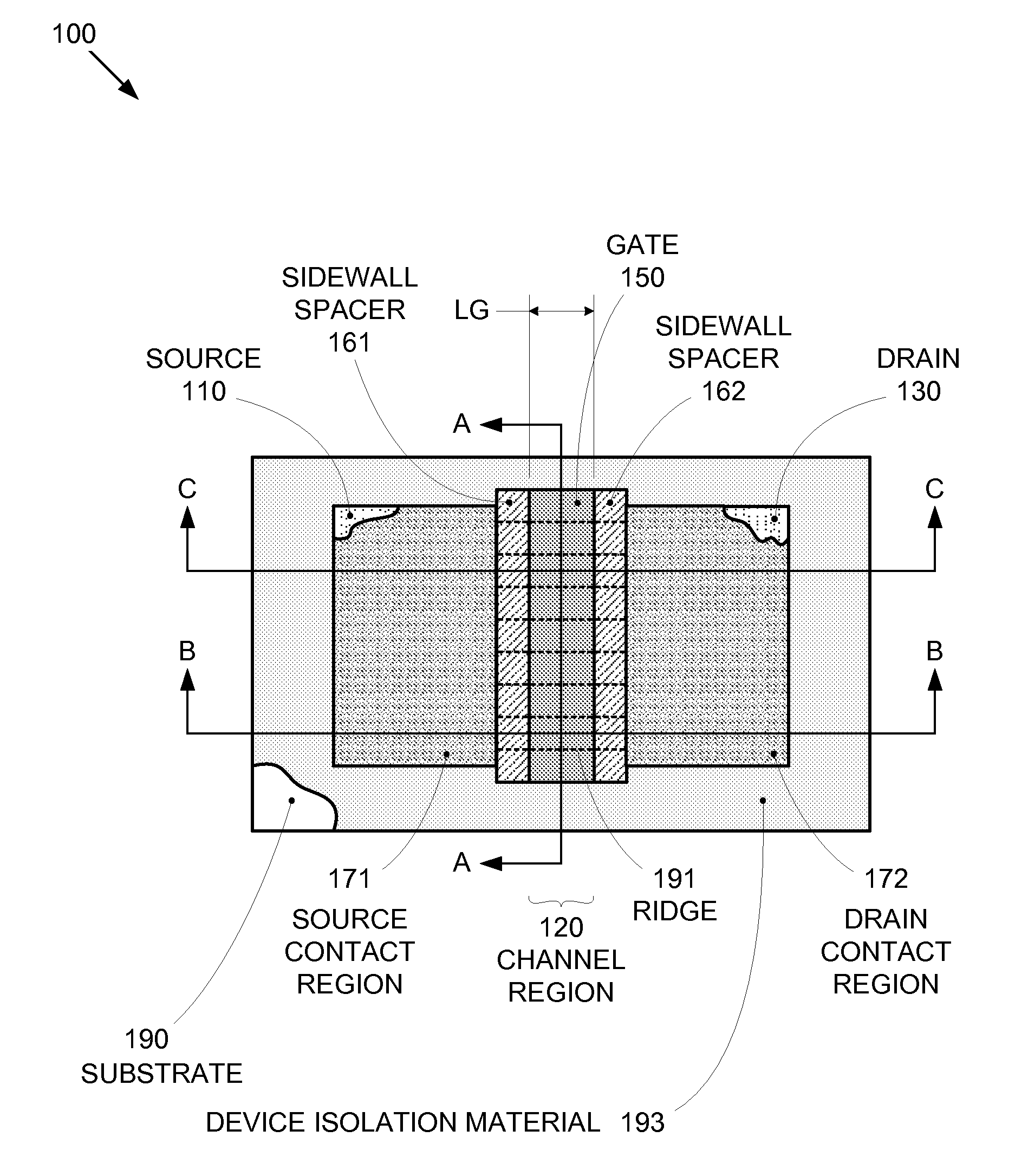

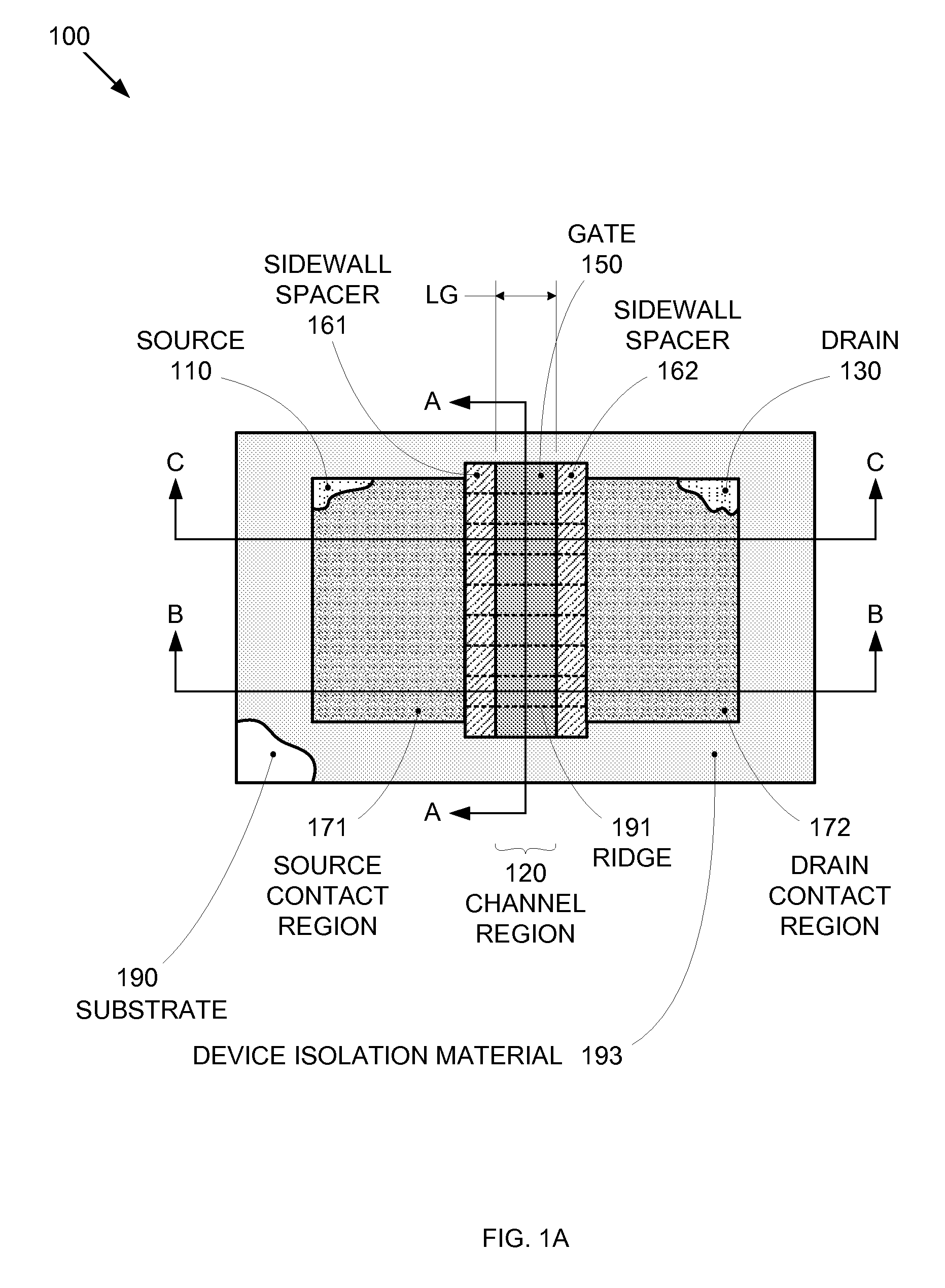

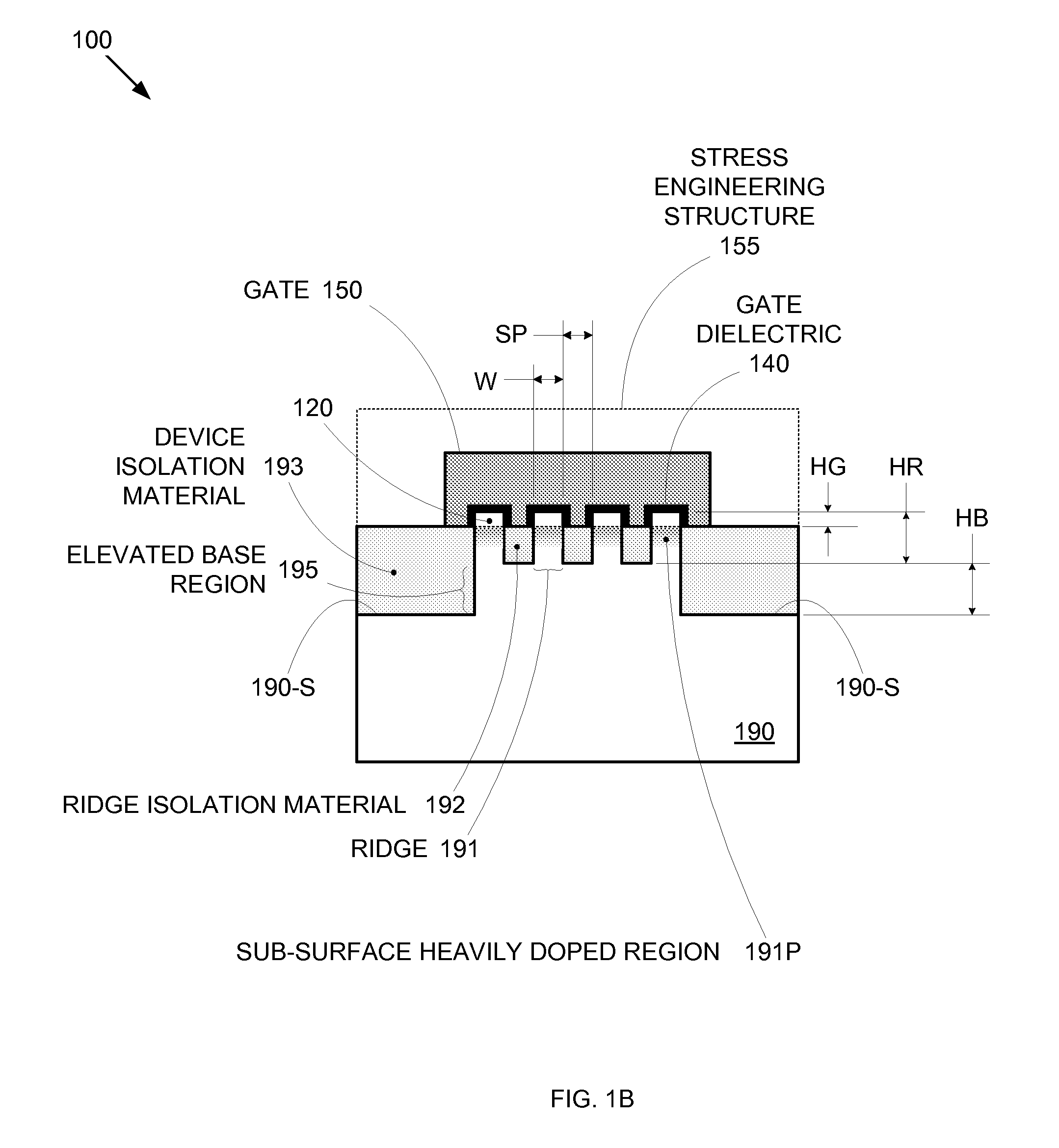

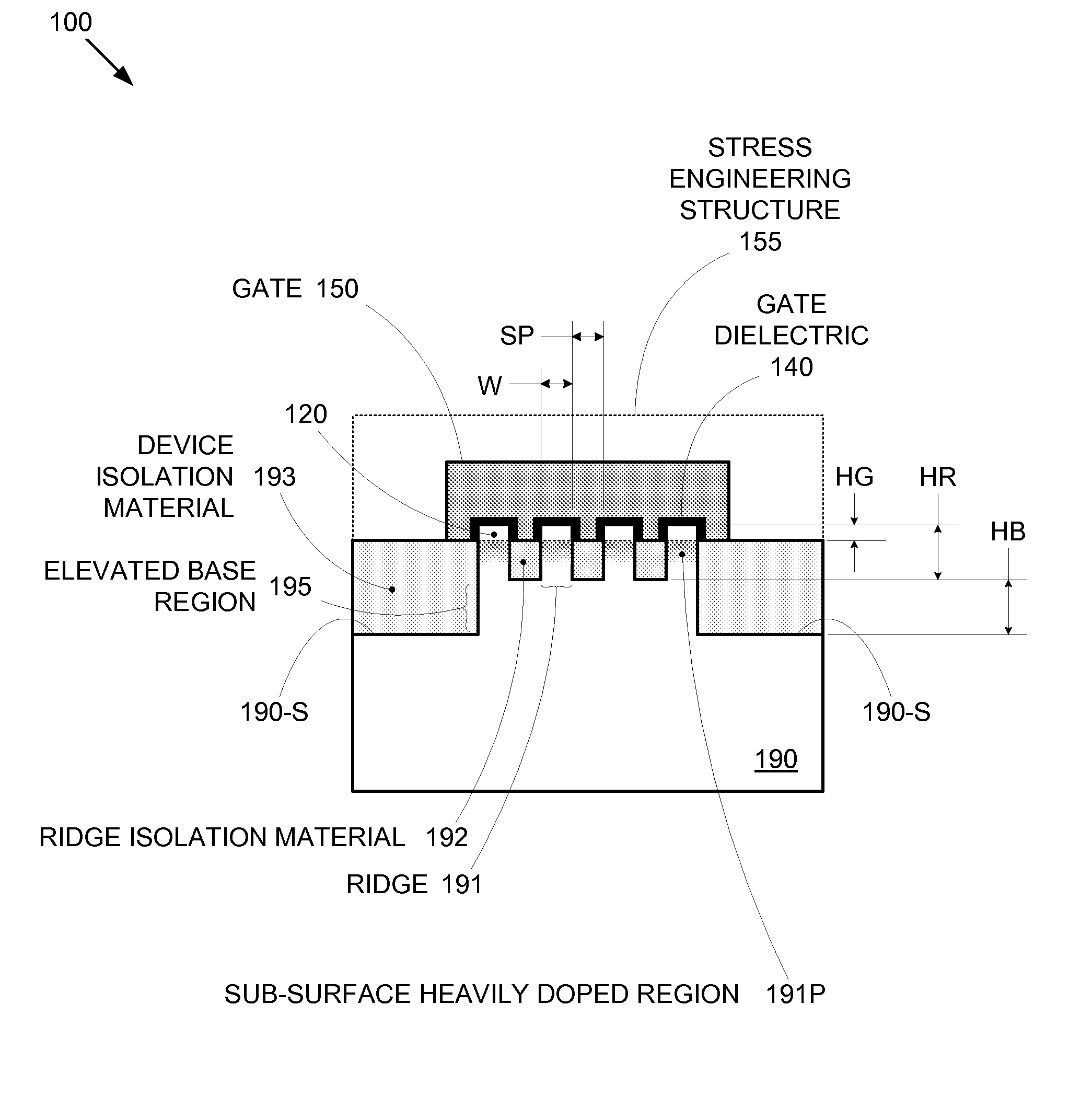

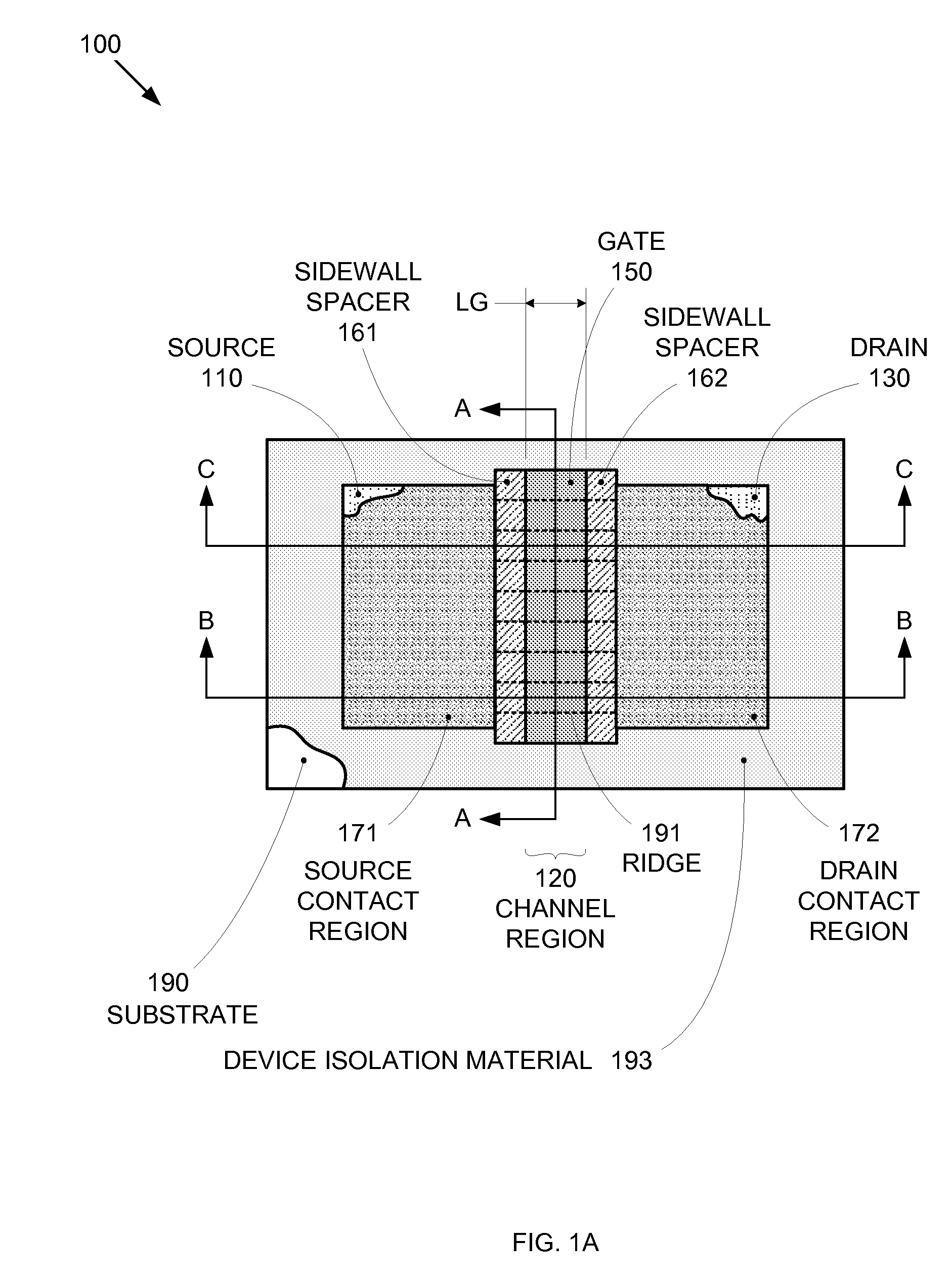

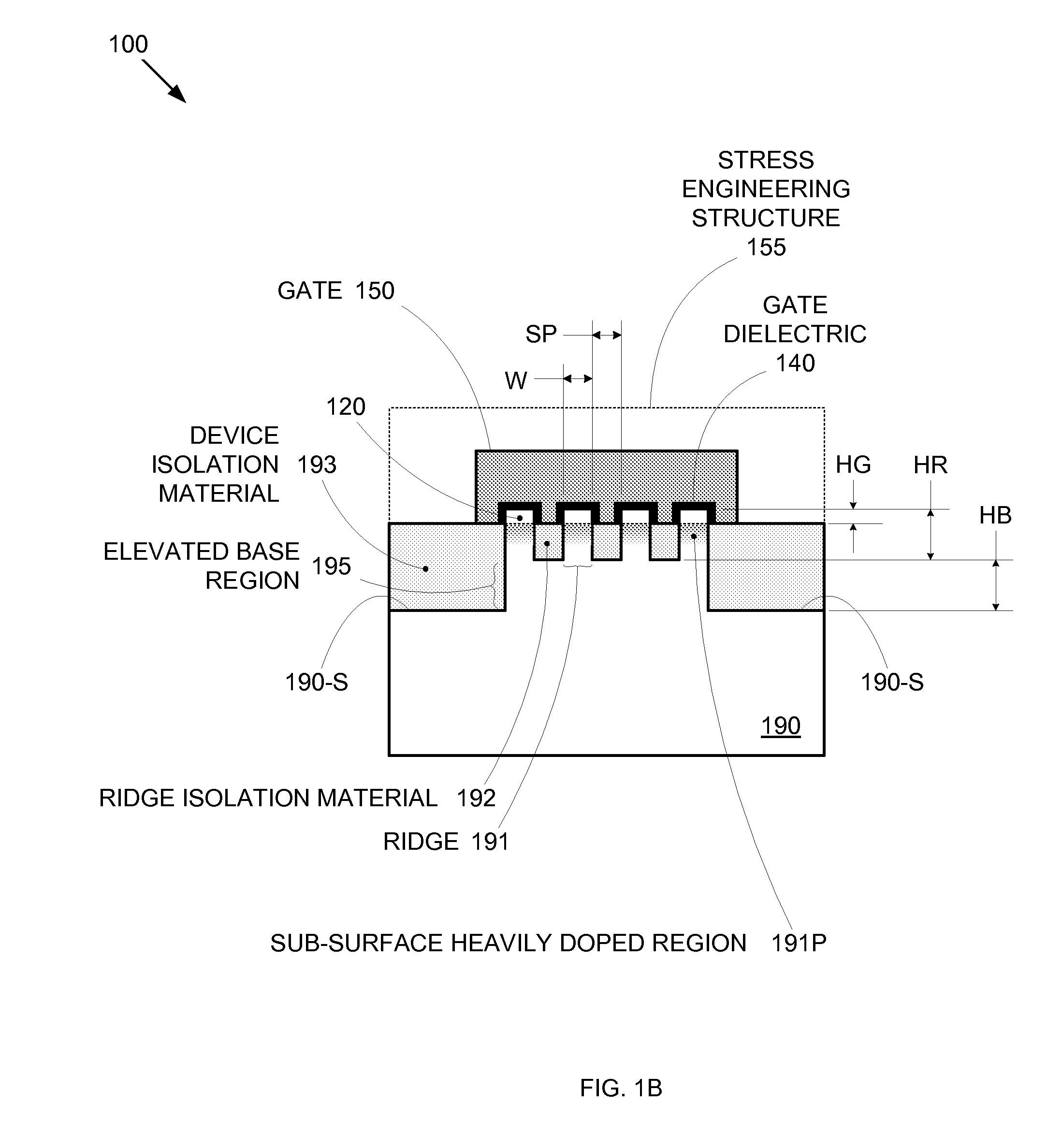

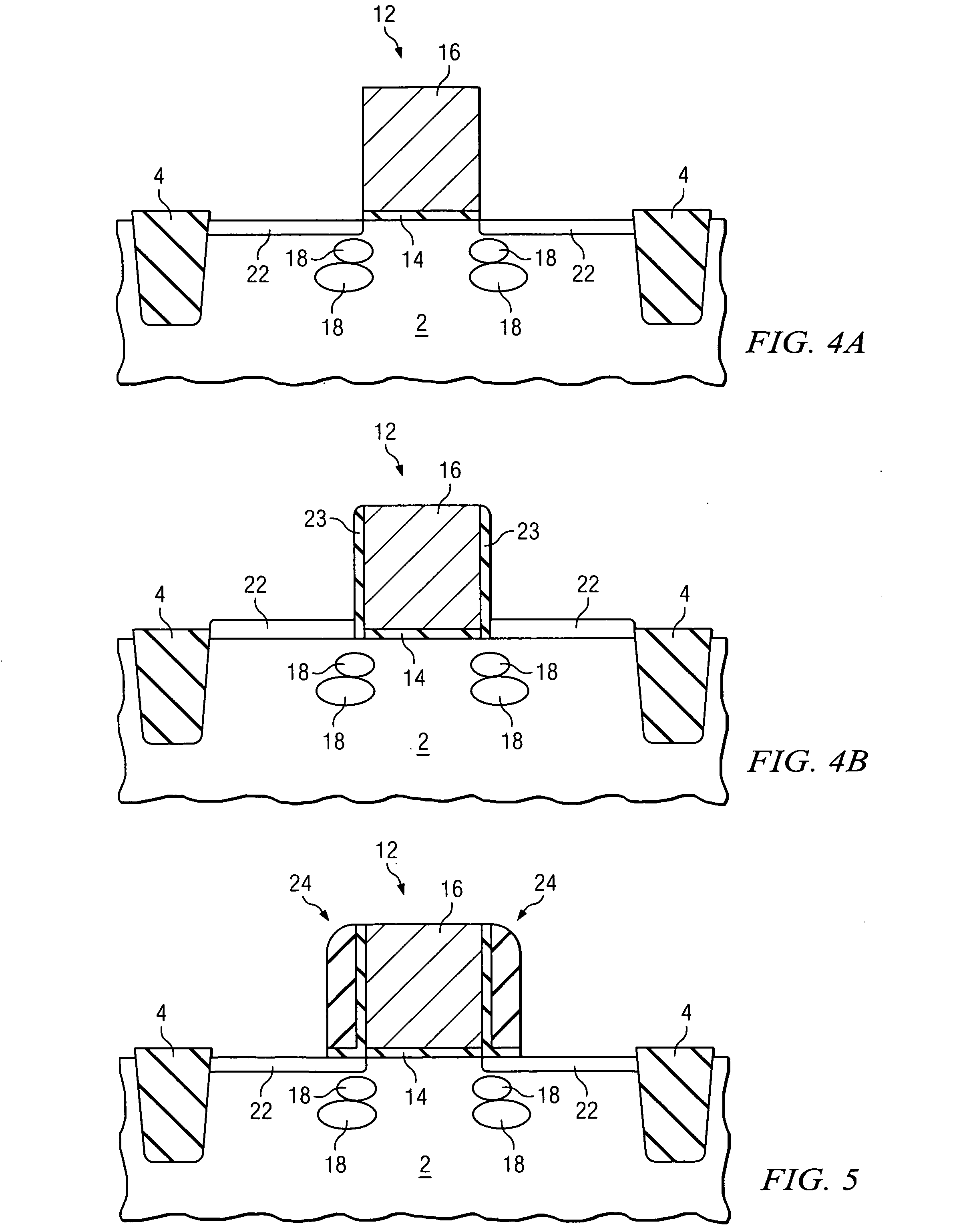

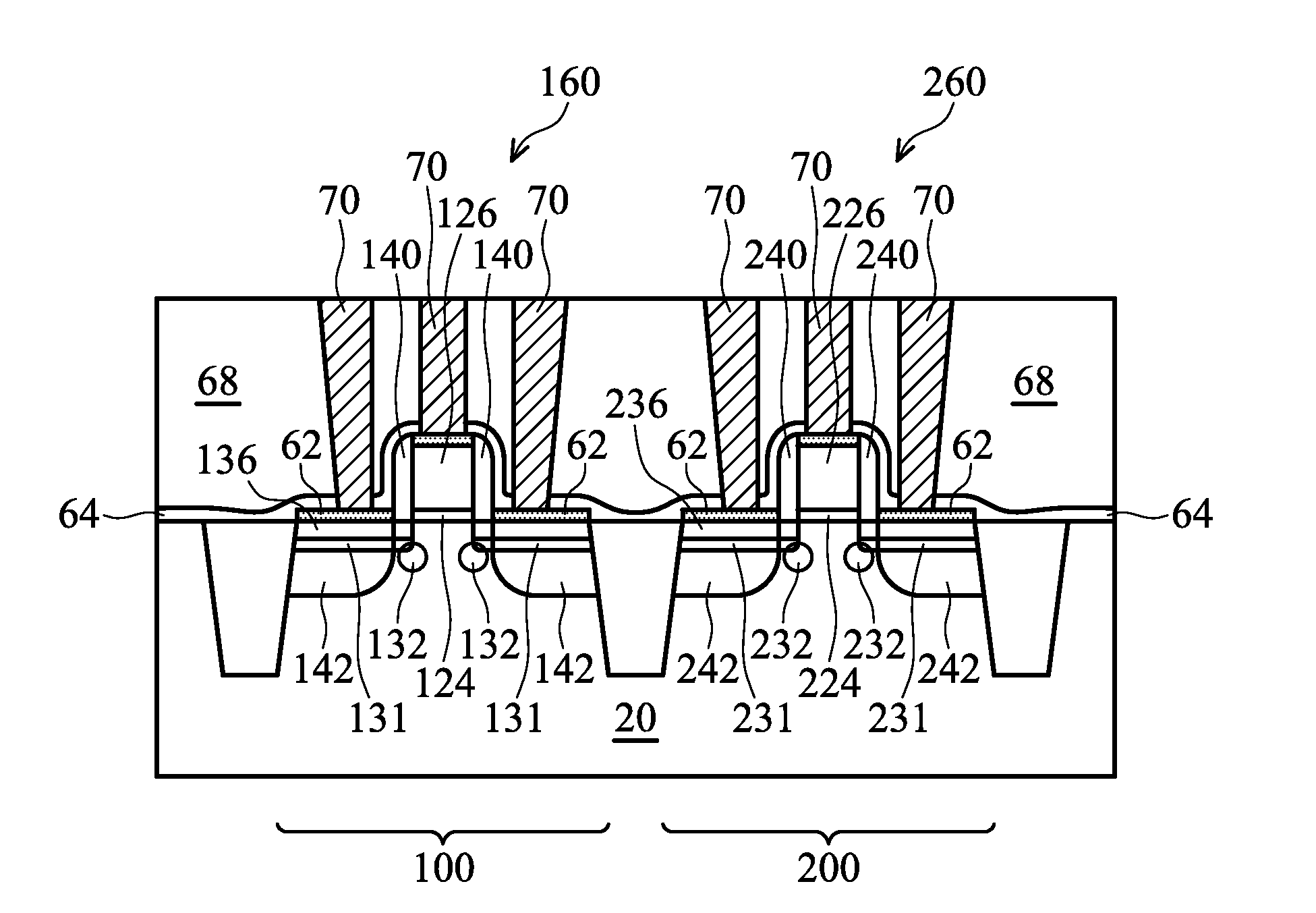

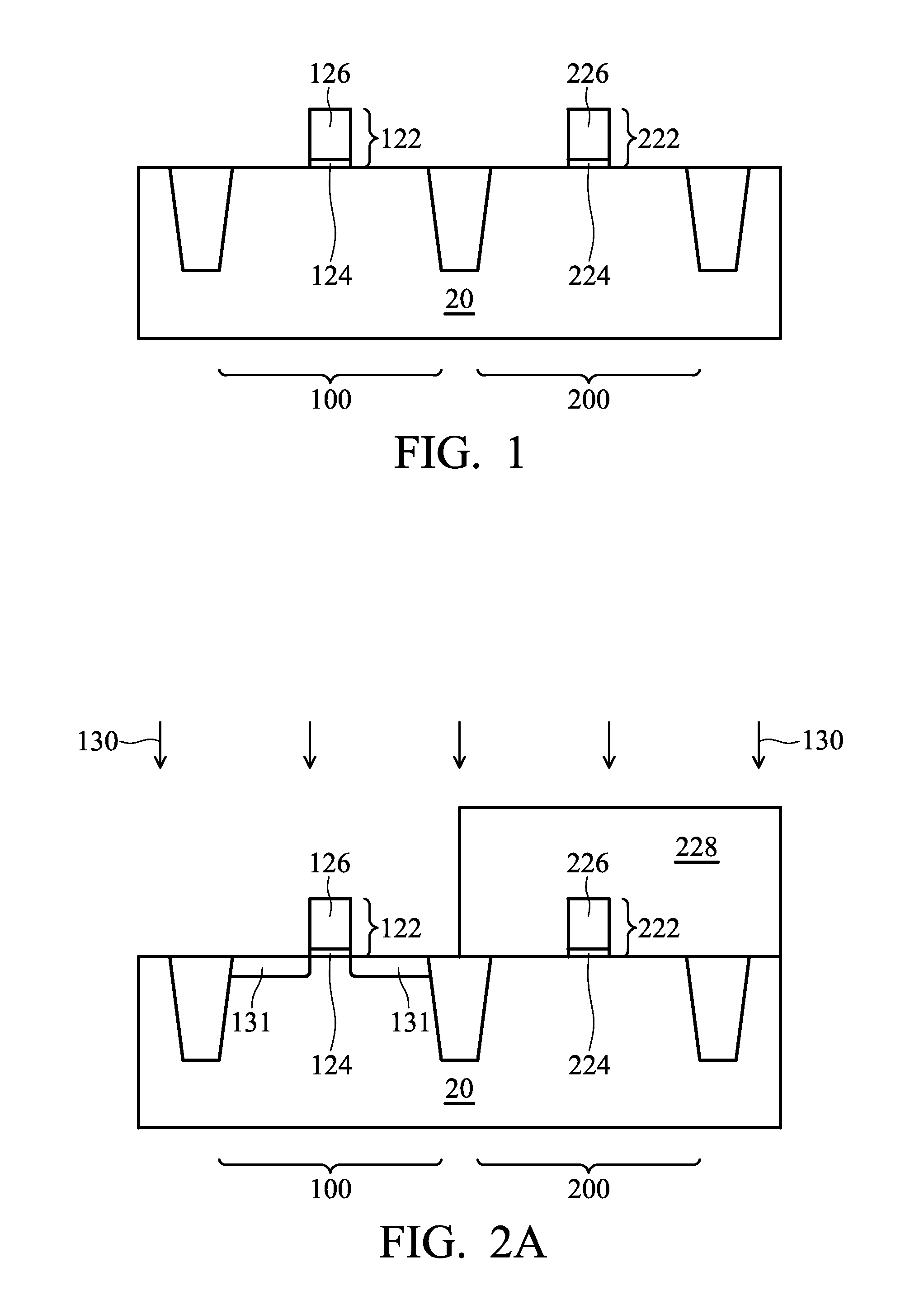

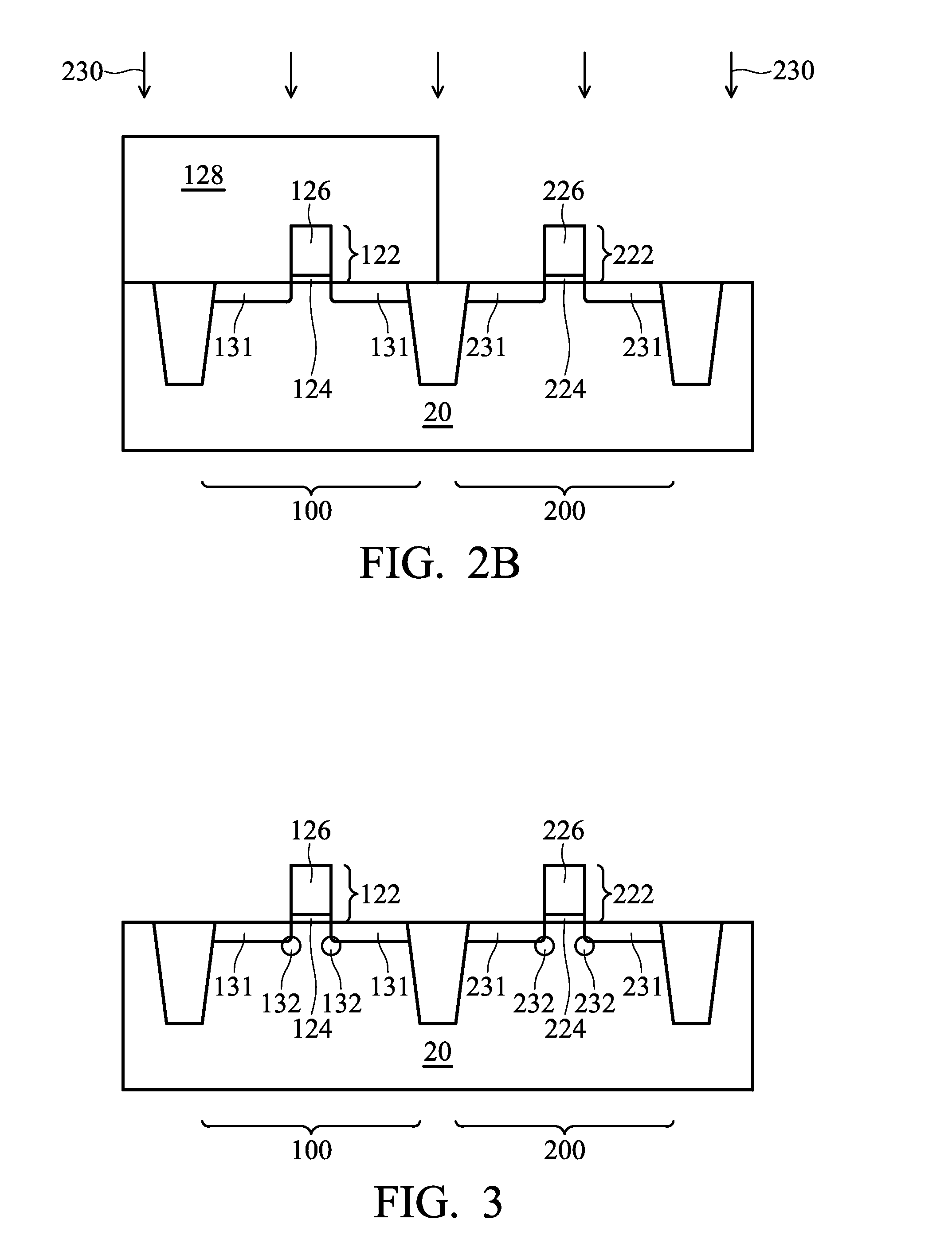

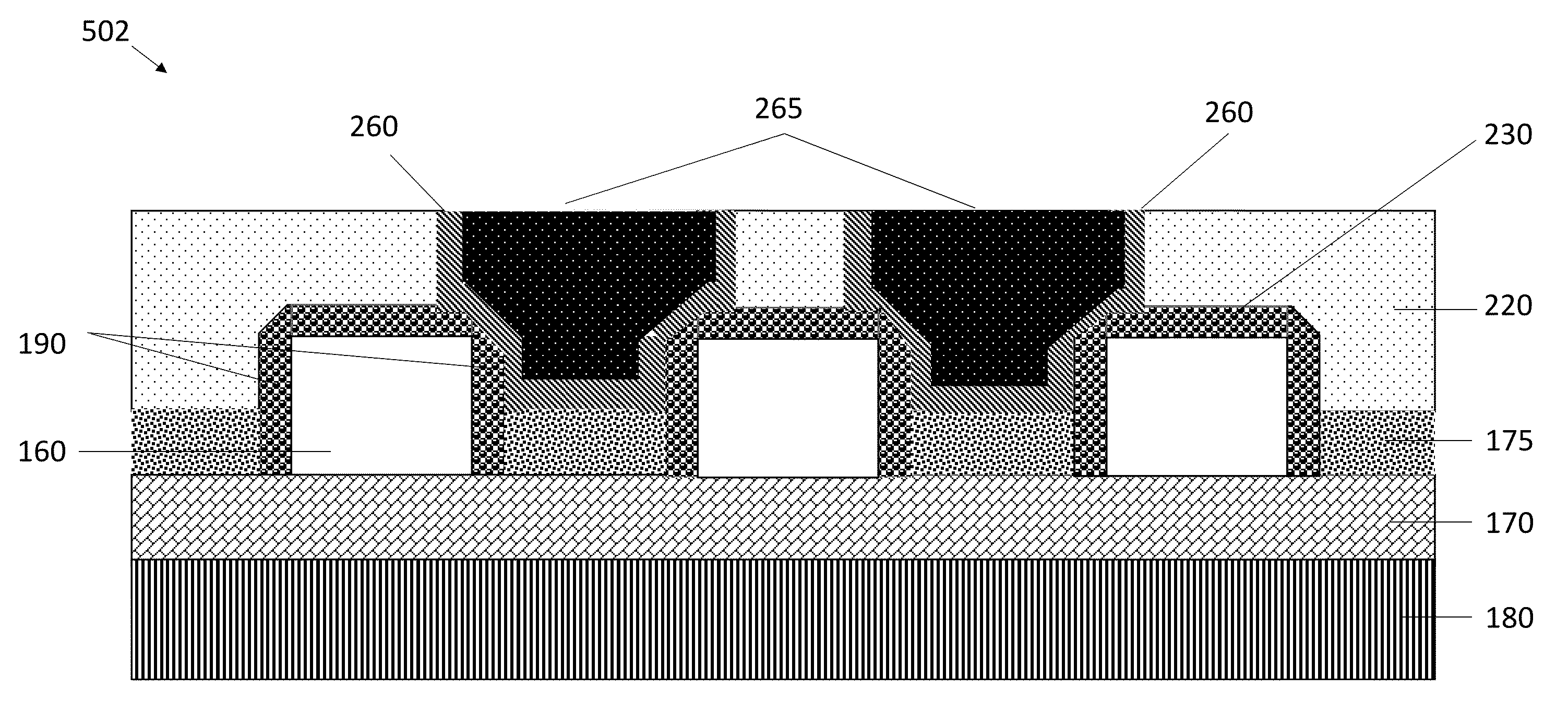

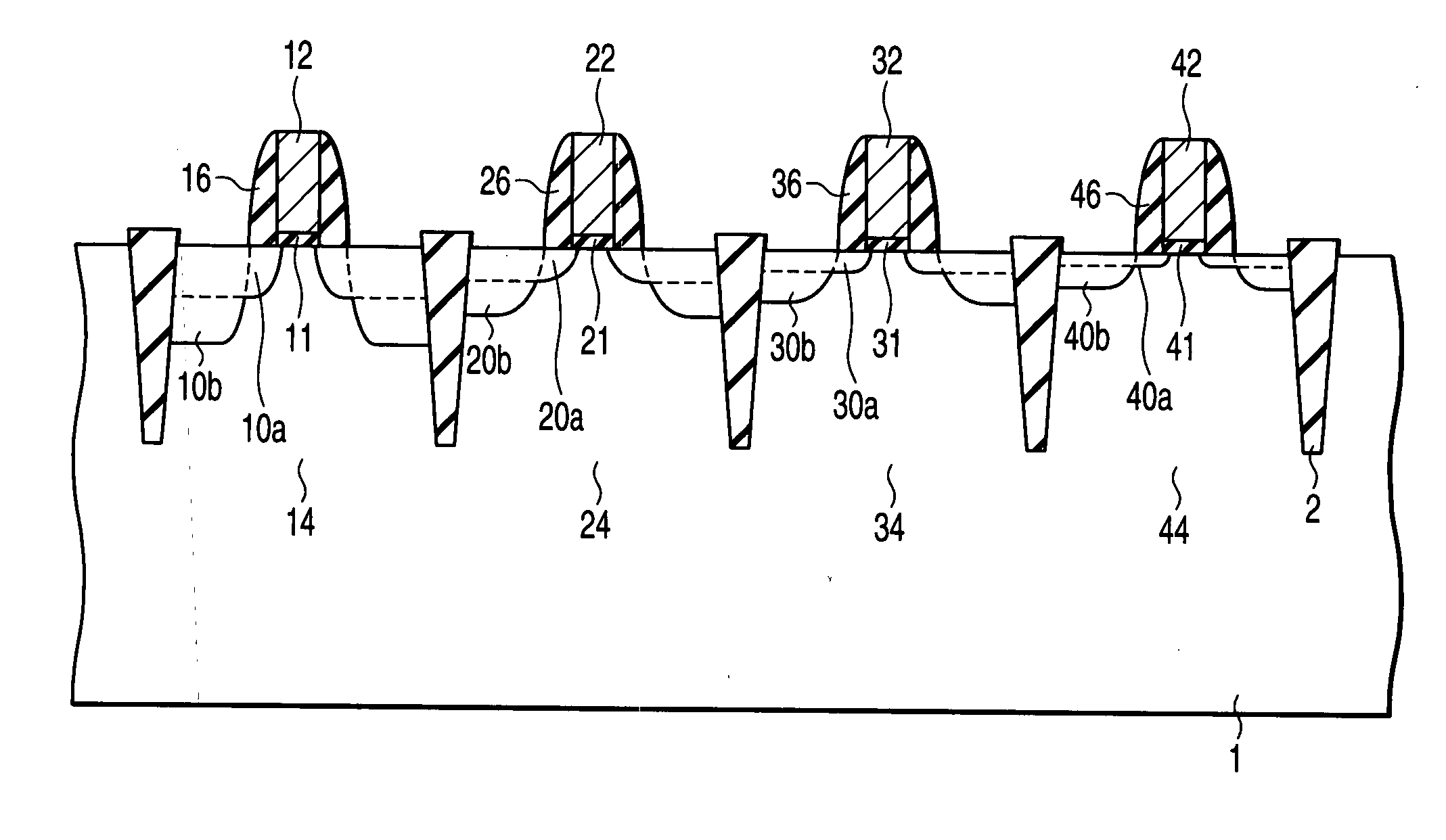

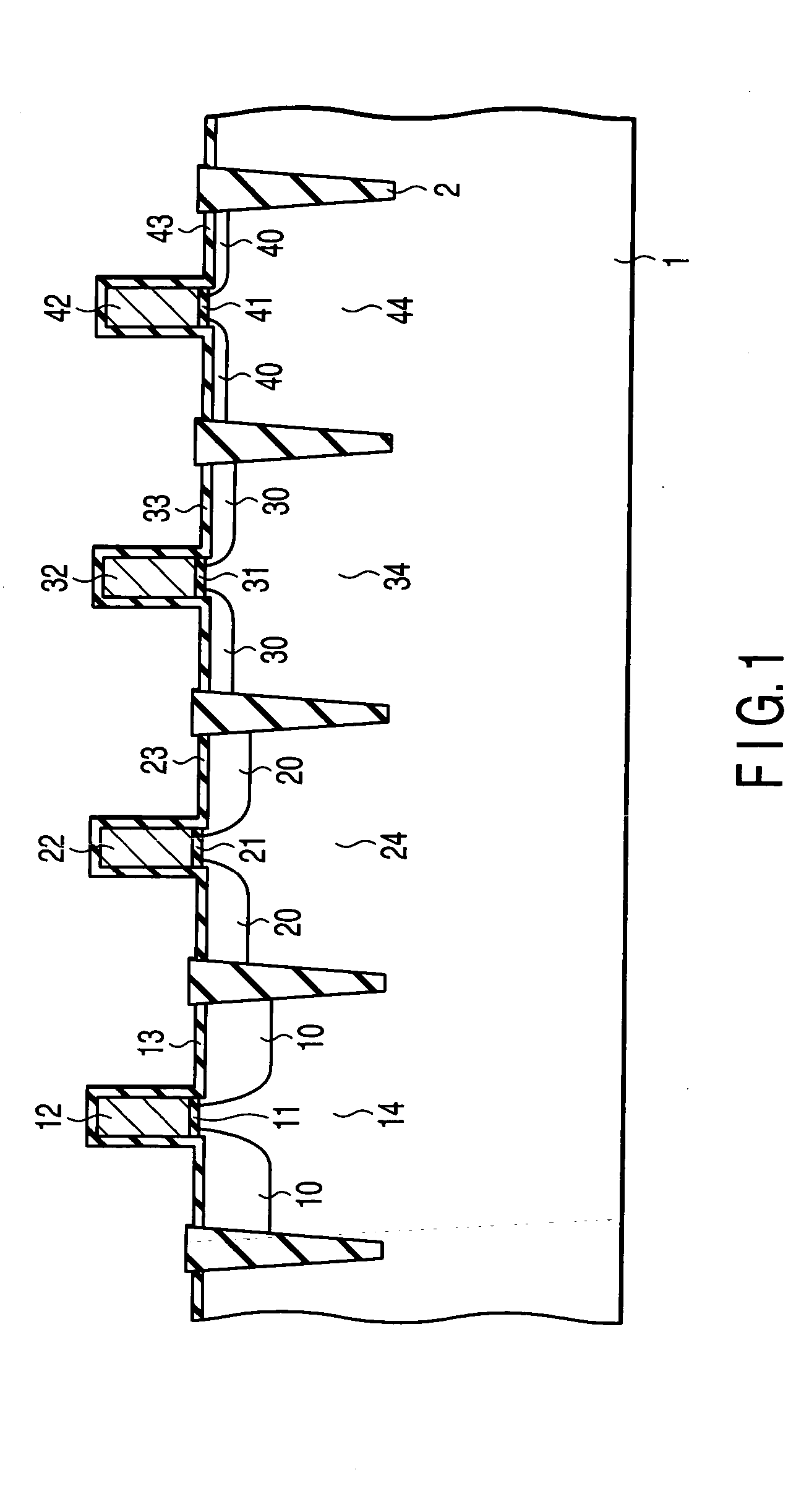

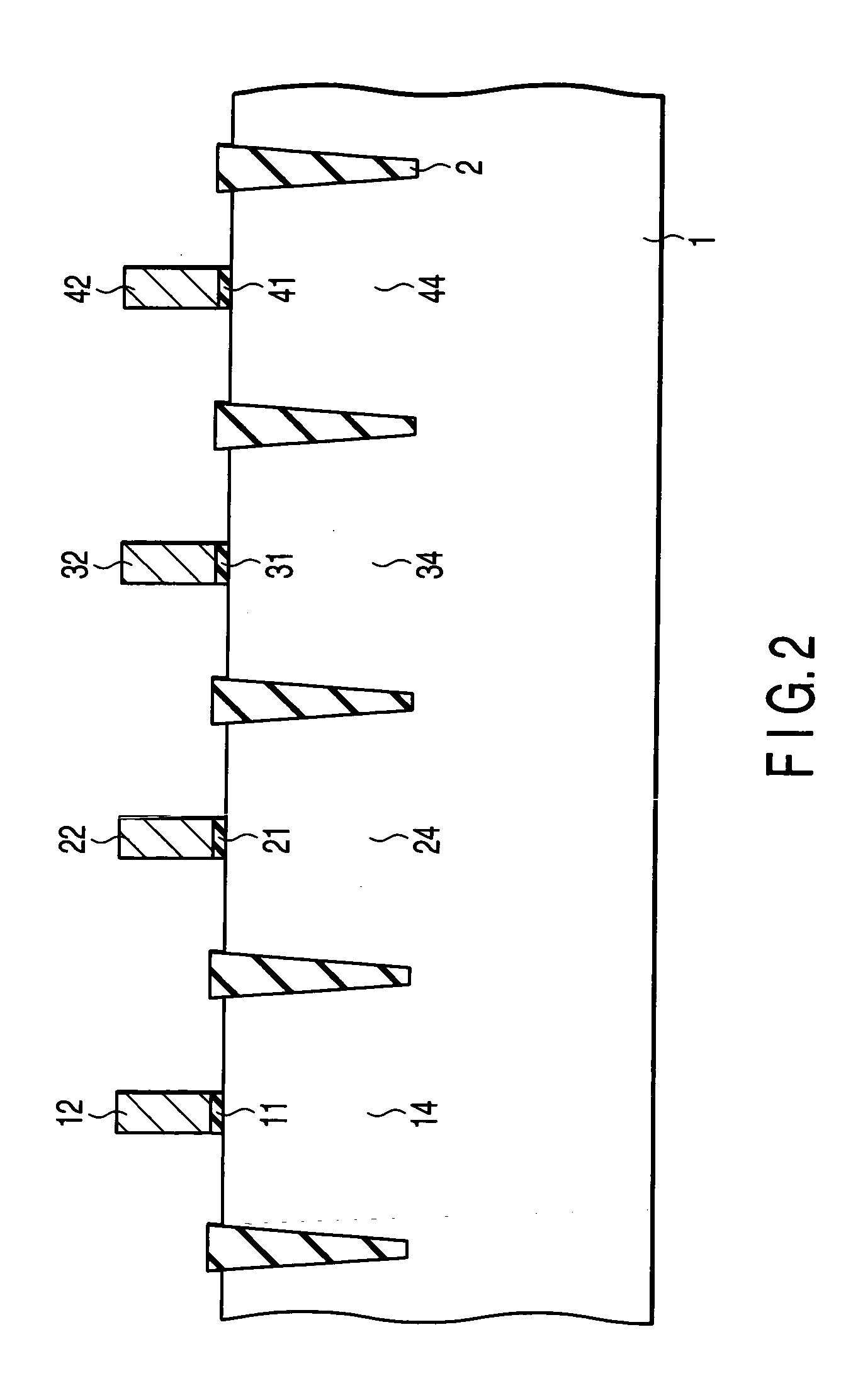

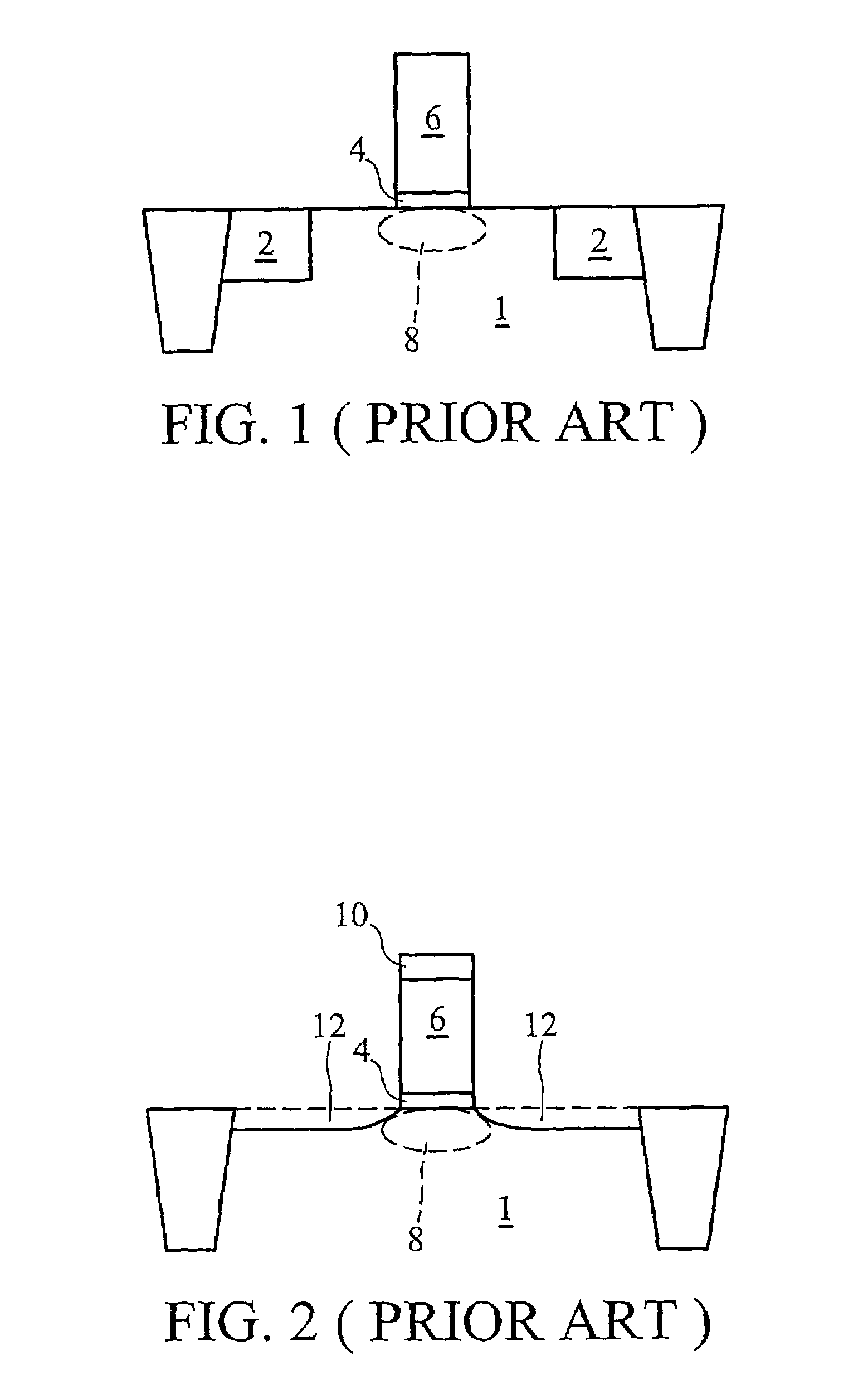

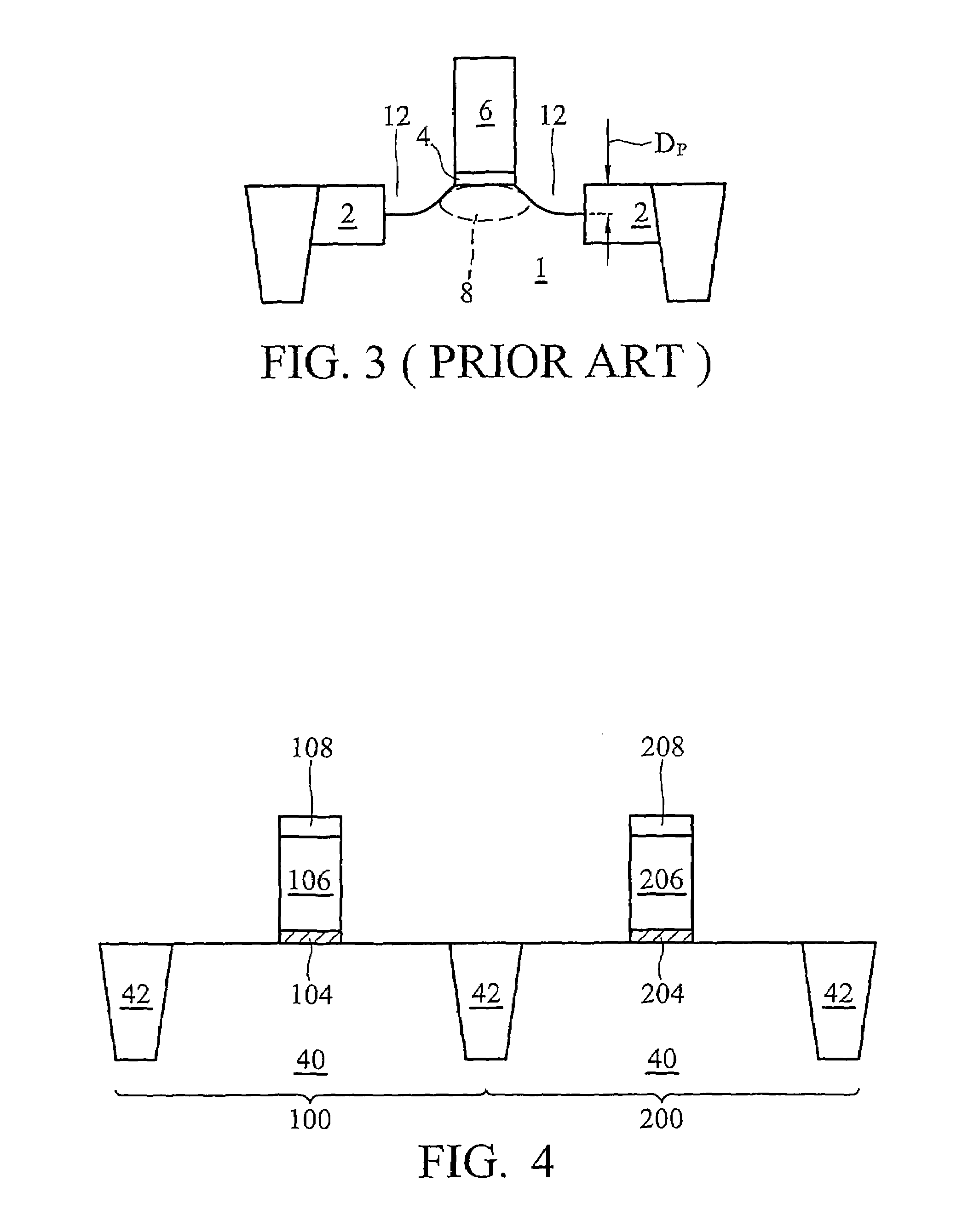

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

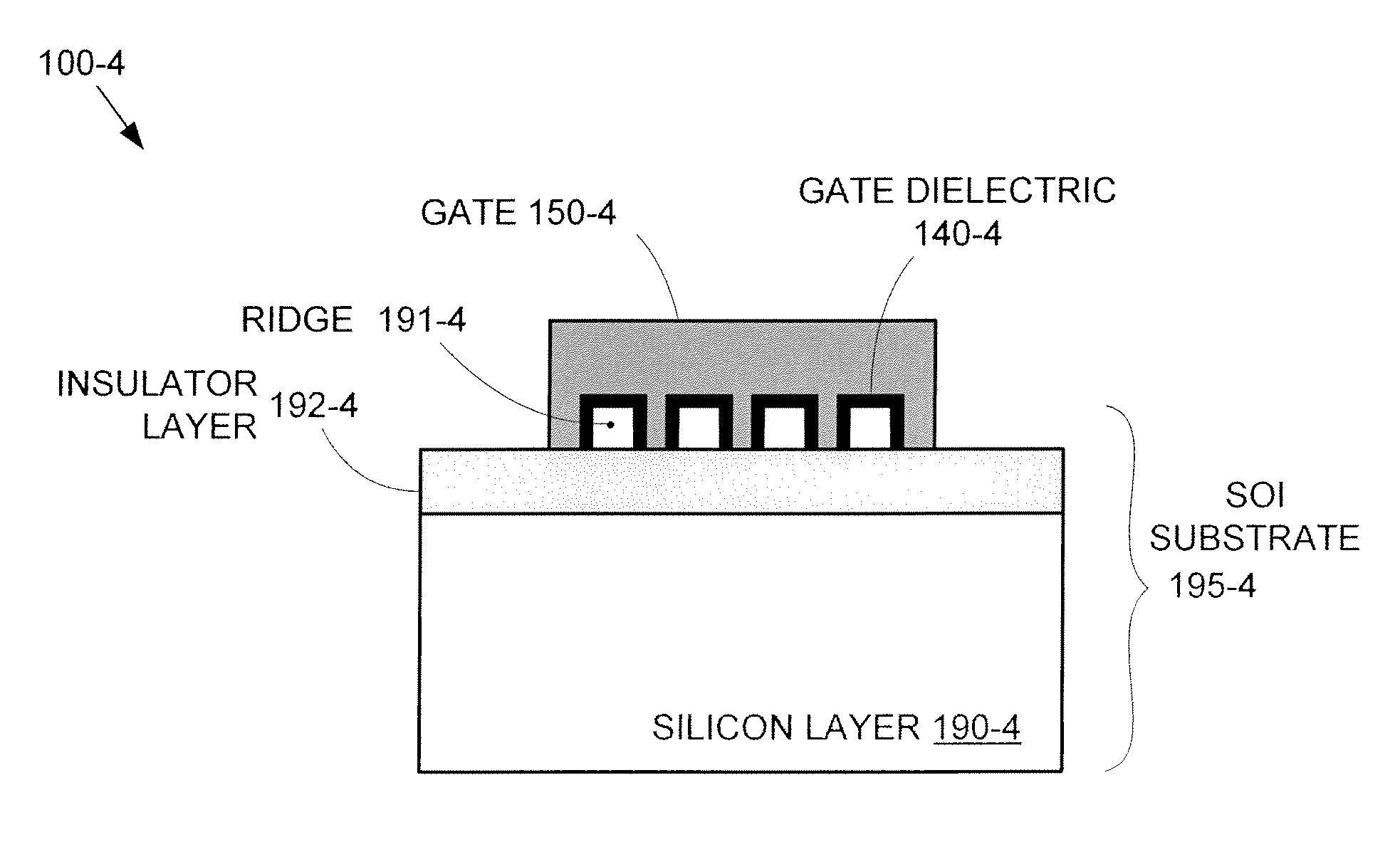

Integrated circuit on corrugated substrate

ActiveUS7190050B2Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

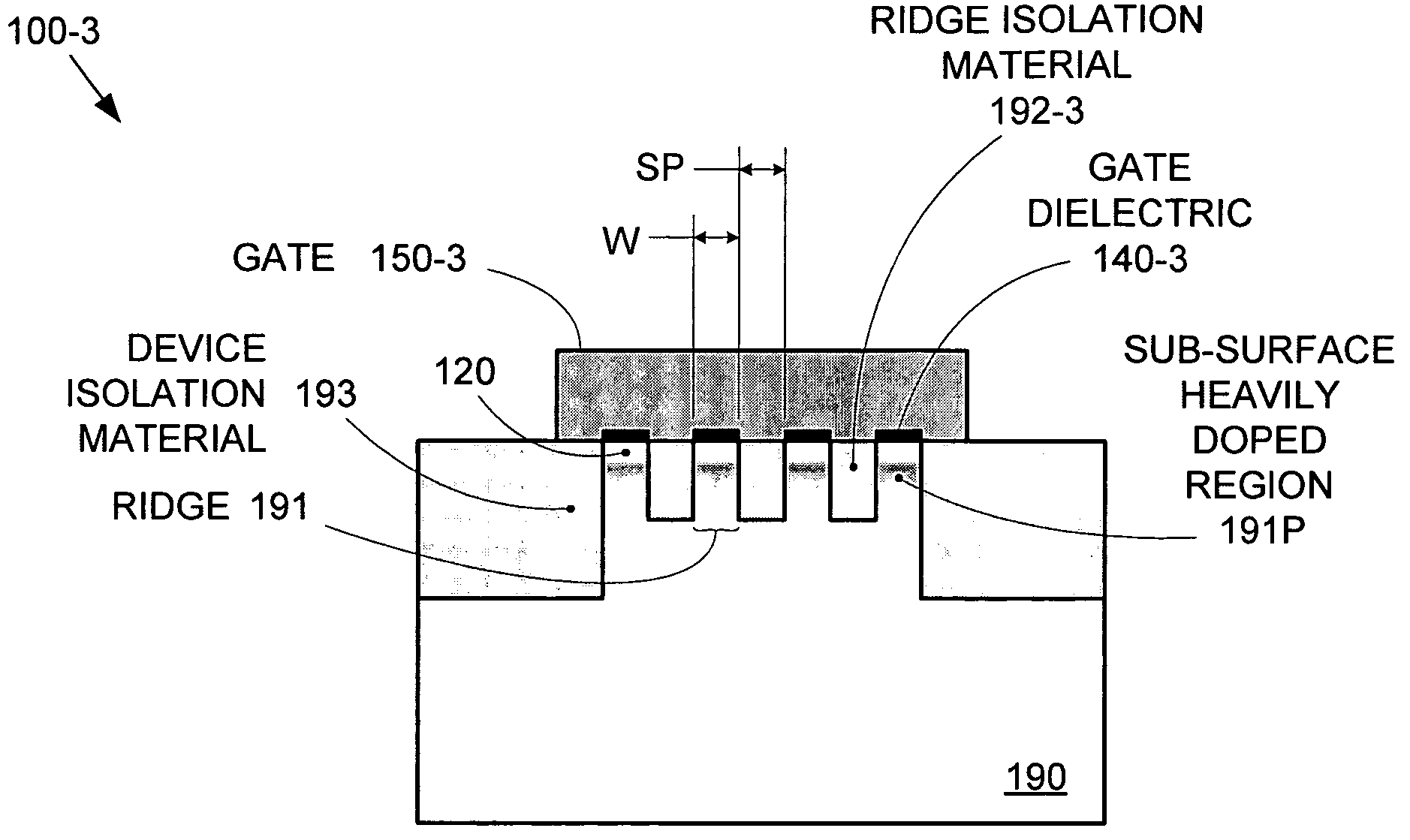

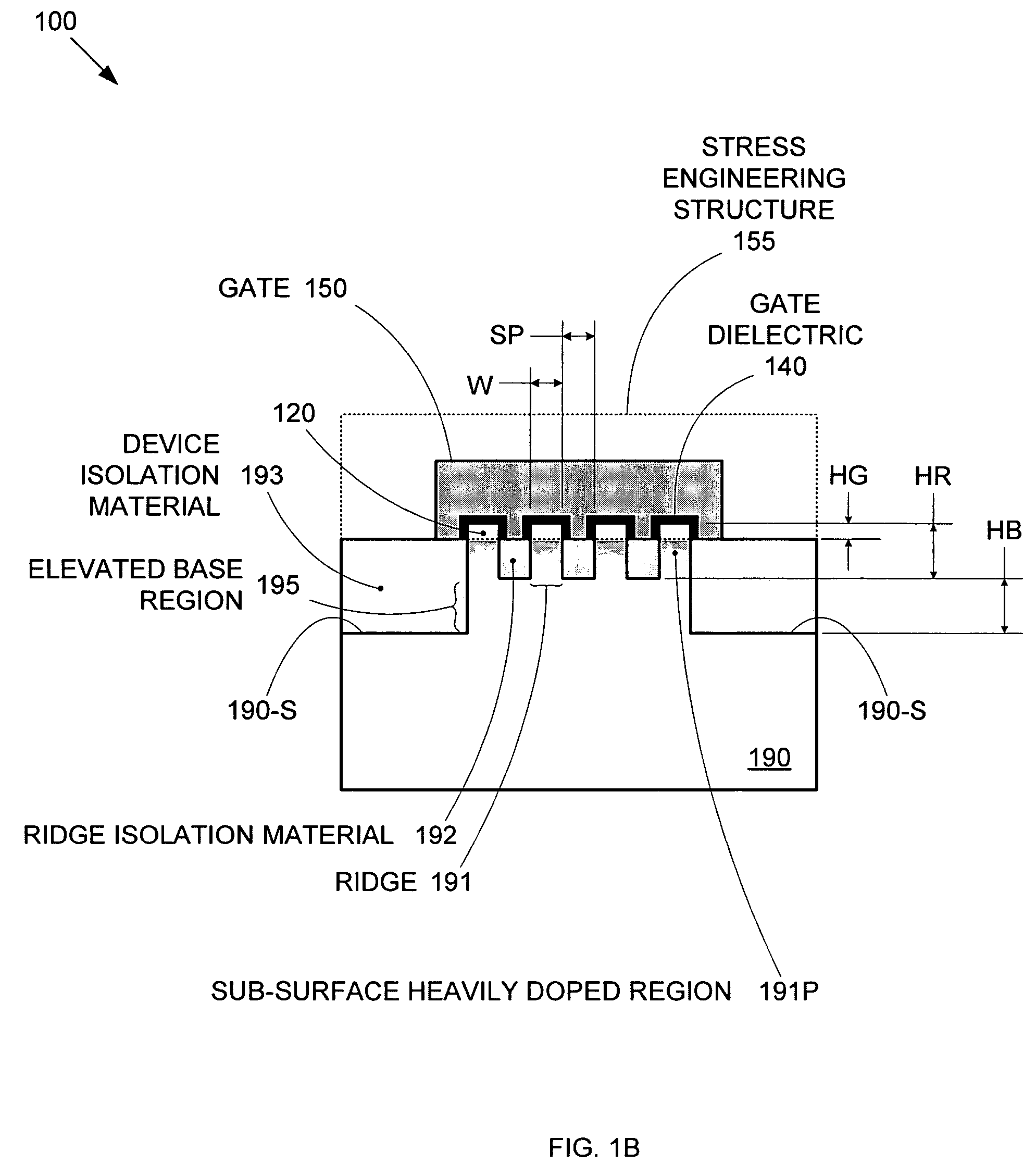

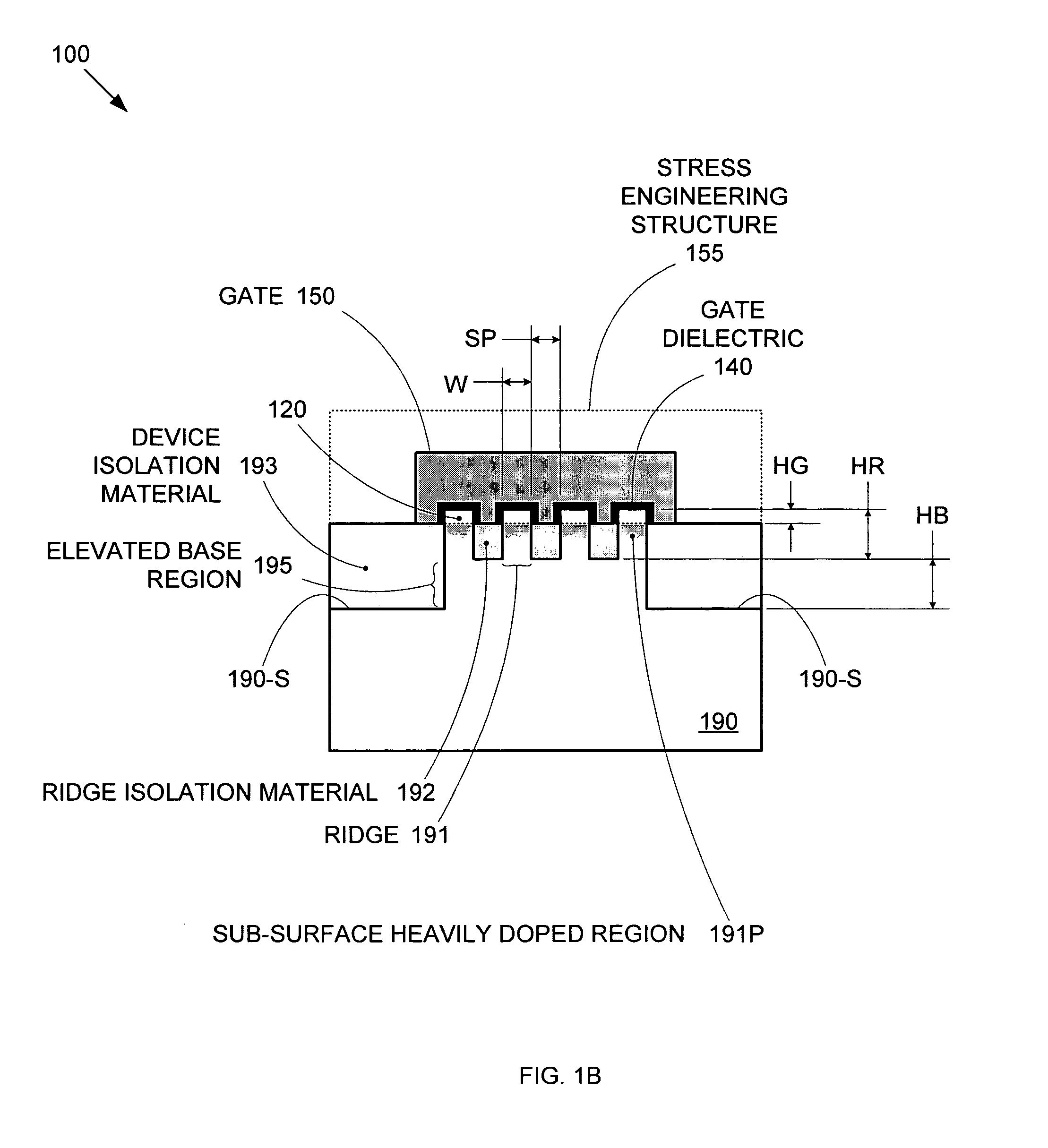

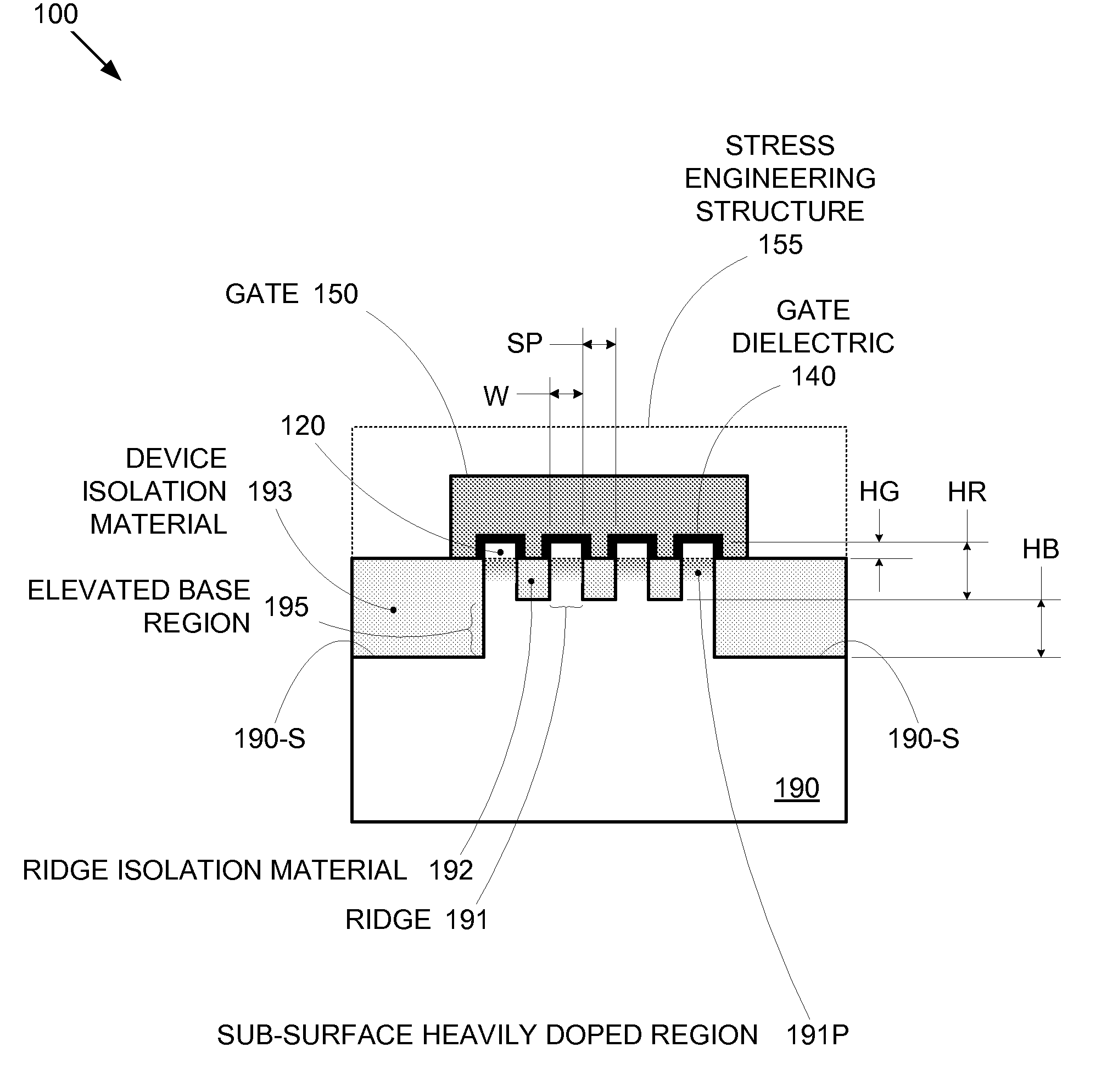

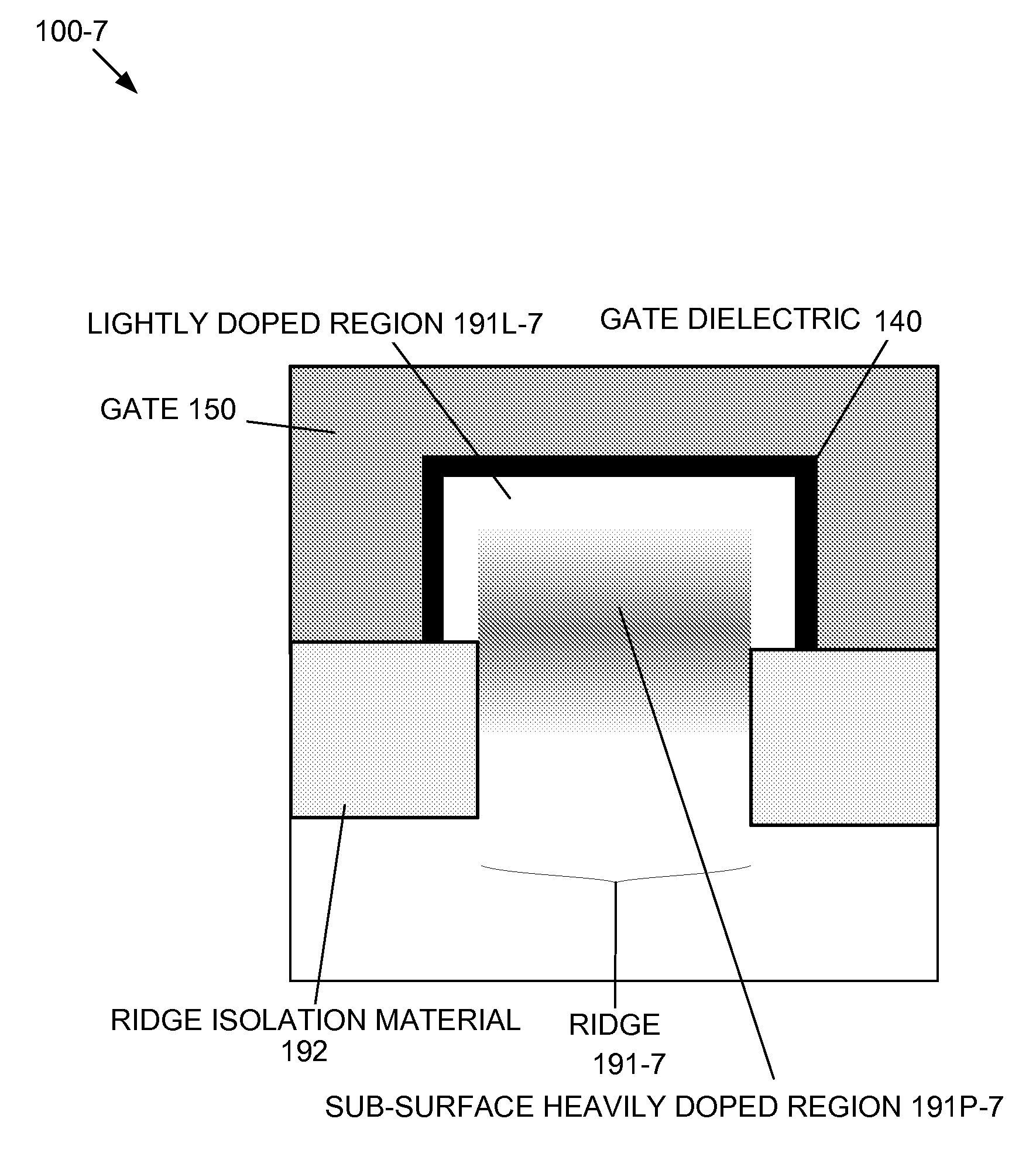

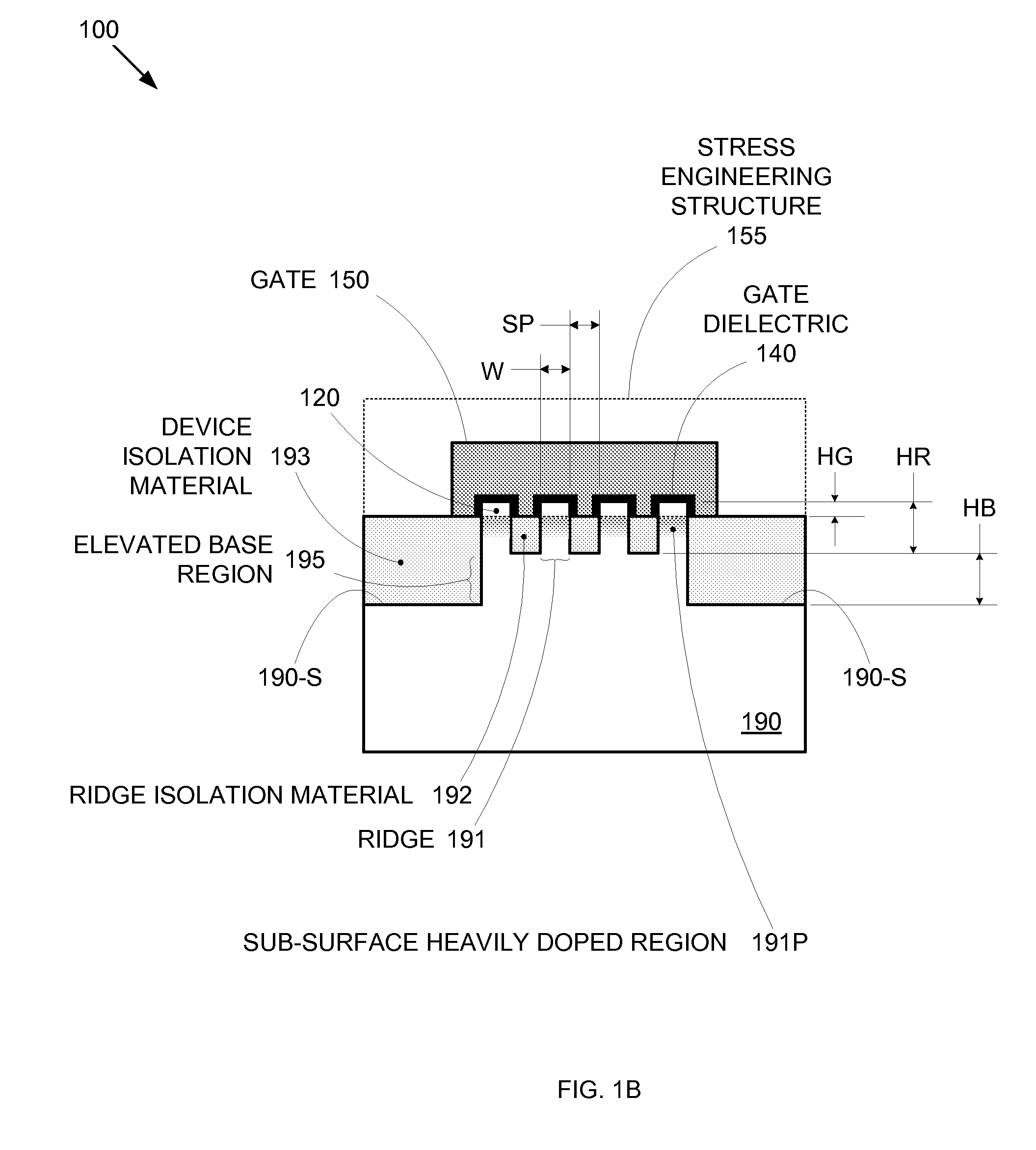

Enhanced Segmented Channel MOS Transistor with Multi Layer Regions

ActiveUS20070120156A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Method of IC production using corrugated substrate

ActiveUS7265008B2Improve performance consistencyImprove performanceLaser detailsSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with narrowed base regions

ActiveUS7508031B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably produced. Ridges on the corrugated substrate can be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials, high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

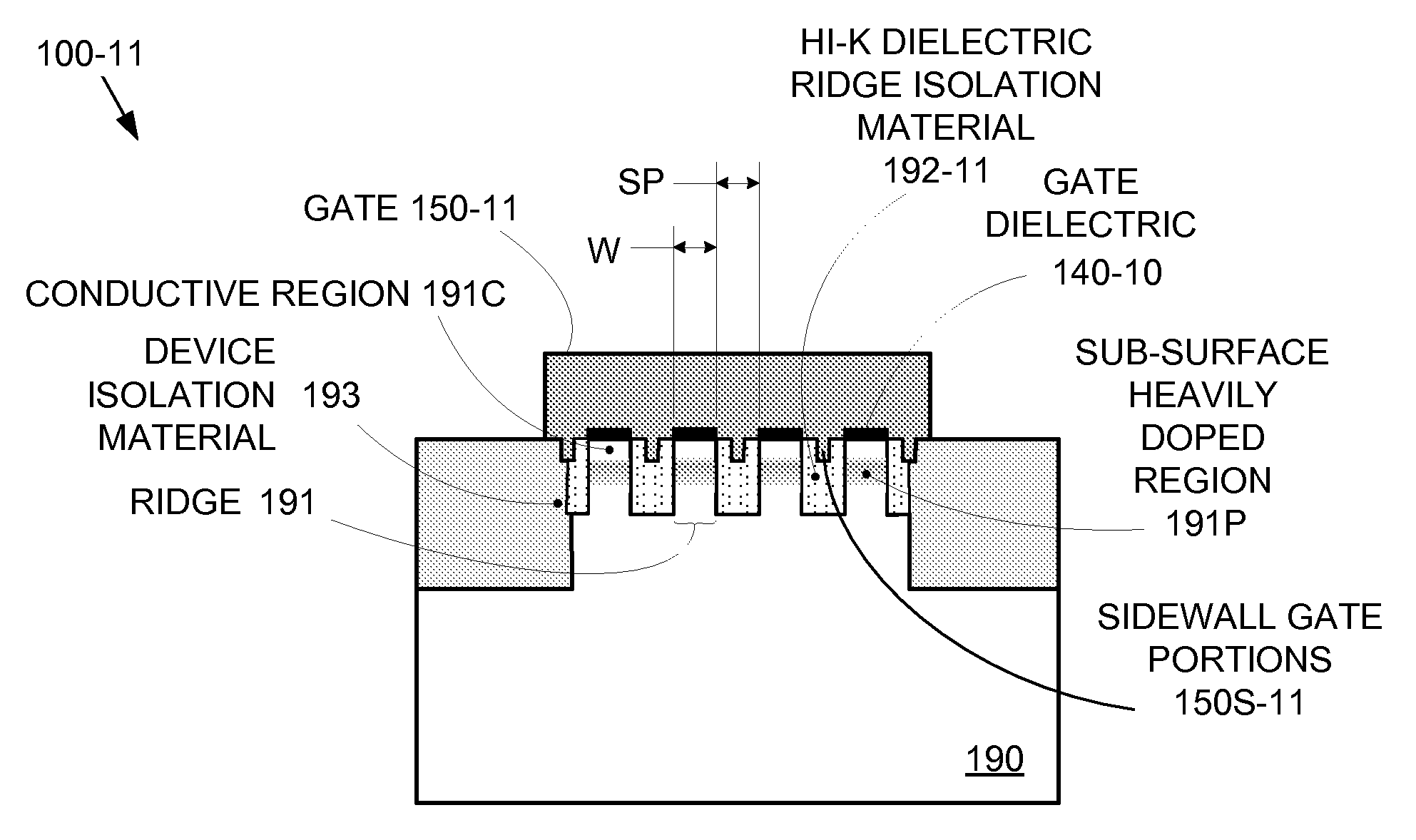

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Integrated Circuit On Corrugated Substrate

ActiveUS20070132053A1Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETSemiconductor materials

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Sequential selective epitaxial growth

ActiveUS7807523B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCMOS

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. A multi step epitaxial process can be used to extend the ridges with different dopant types, high mobility semiconductor, and or advanced multi-layer strutures. For CMOS integrated circuits a capping layer is formed over the a first region. Epitaxial layers are formed in a second region. Then the capping layer is removed from the first region and a capping layer is formed over the second region. Epitaxial layers can than be formed in the first region.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with multi layer regions

ActiveUS8466490B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETSemiconductor materials

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably produced. Ridges on the corrugated substrate can be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials, high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

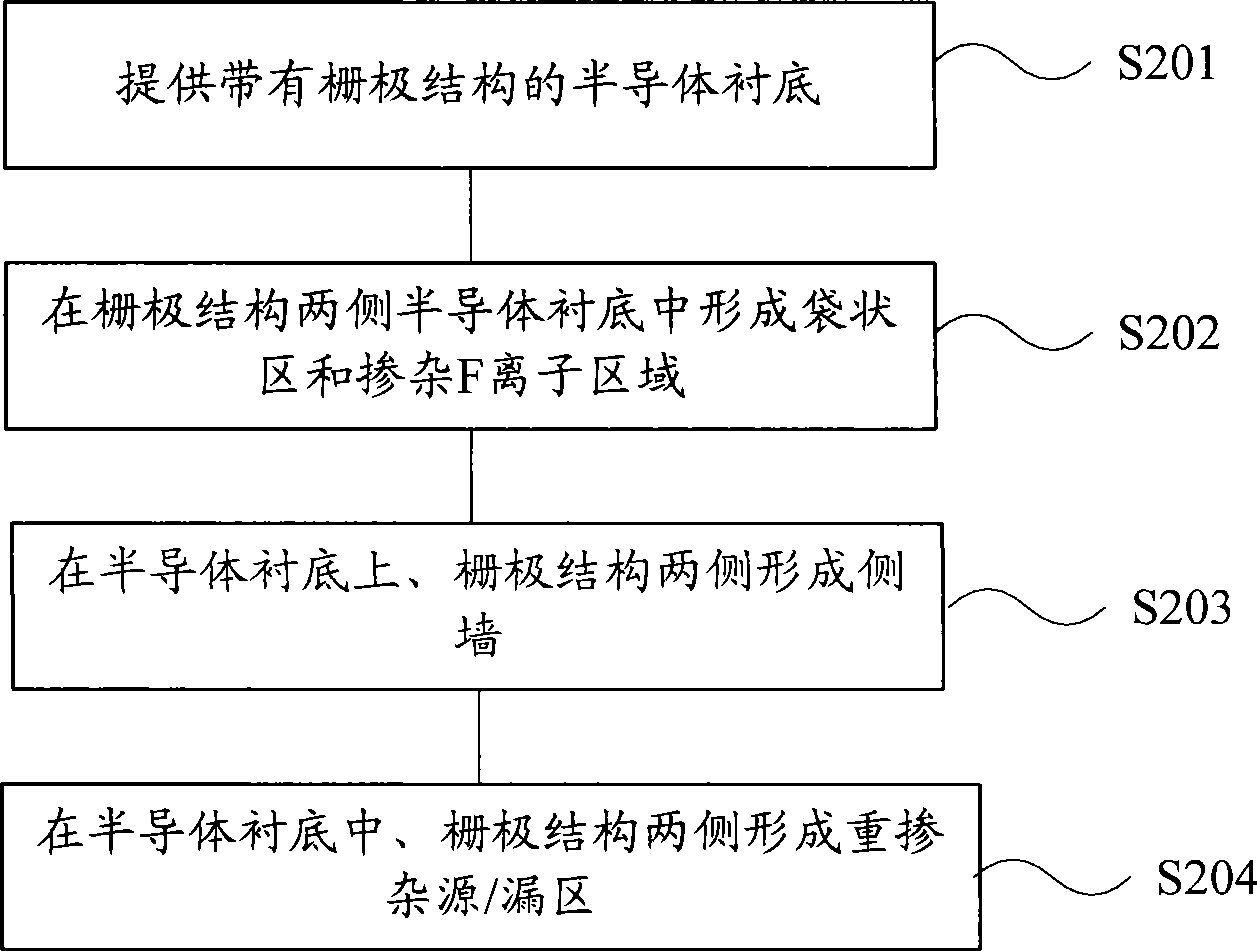

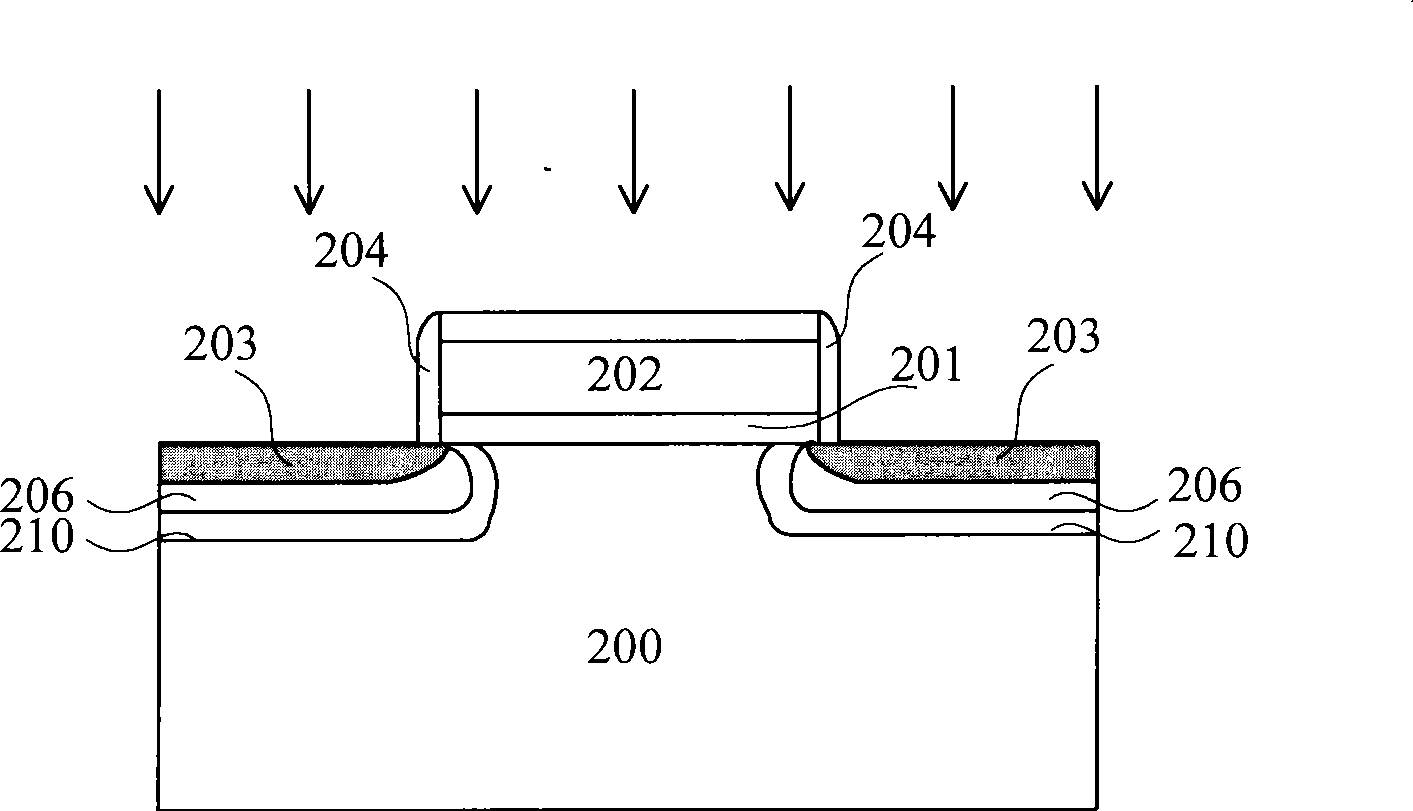

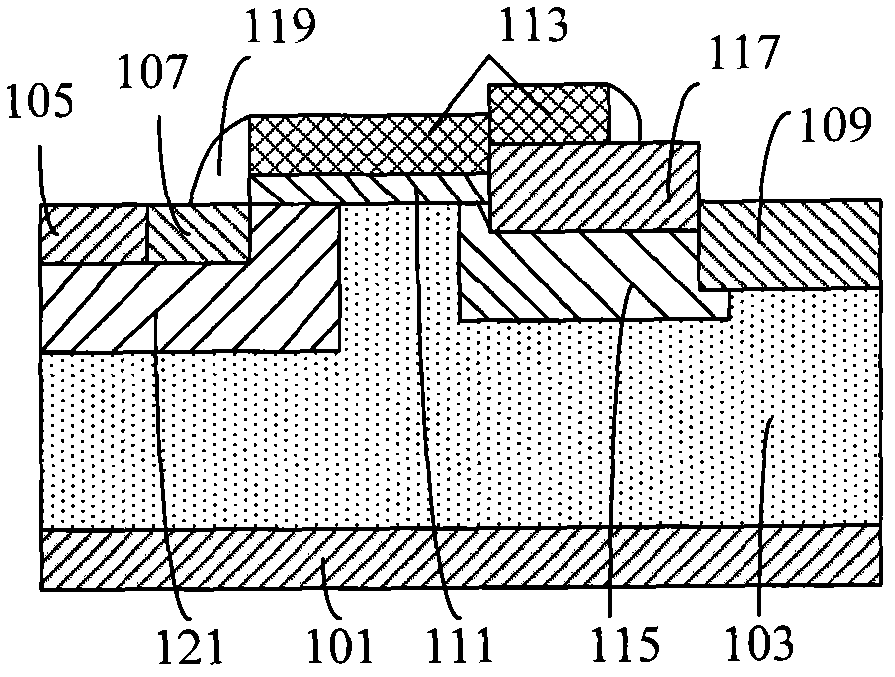

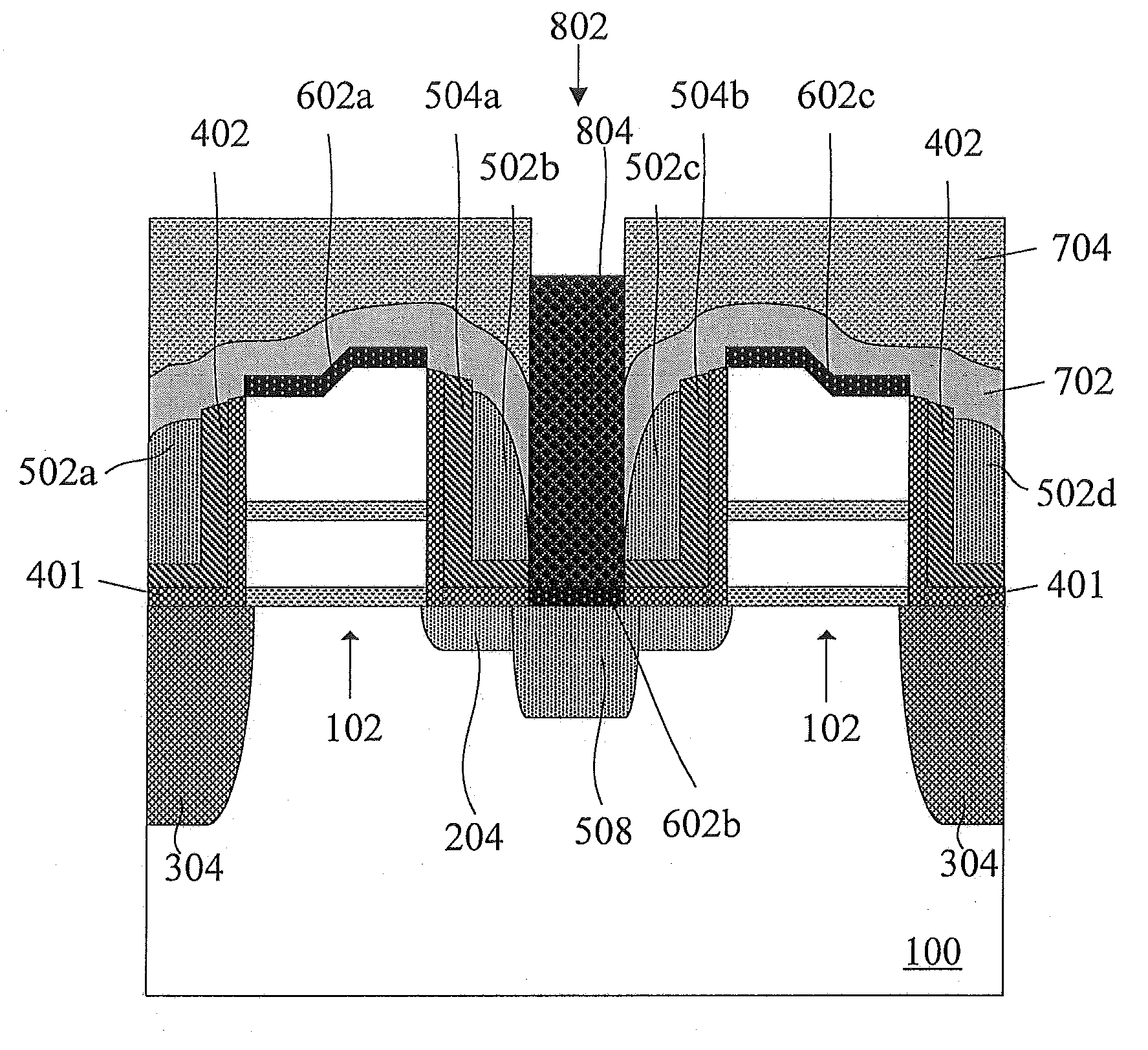

MOS transistor and forming method thereof

ActiveCN101459082AImprove performanceReduce junction depthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorJunction depth

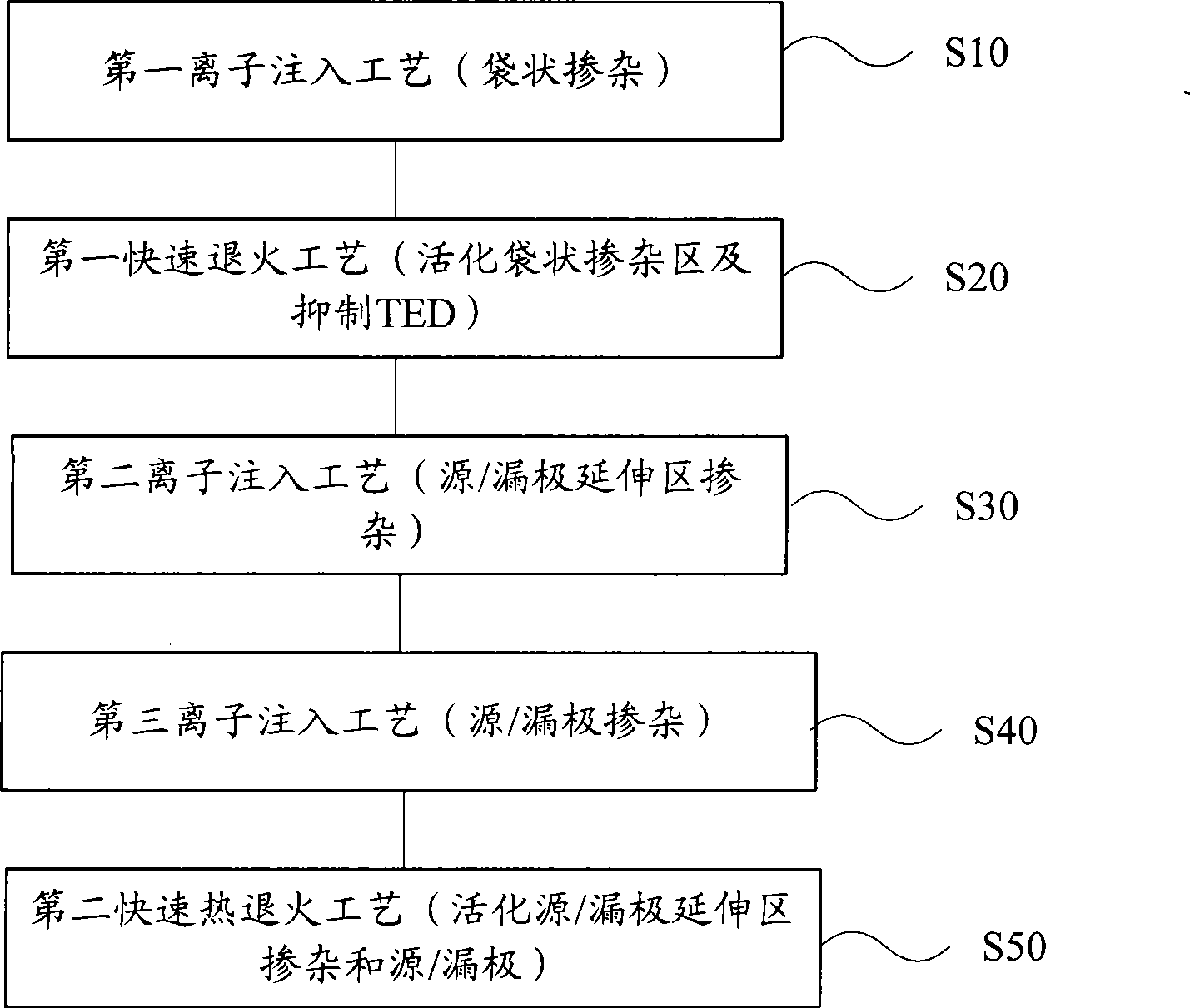

An MOS transistor comprises low doped source / drain extended regions in a semiconductor substrate and on two sides of a grid structure, sidewalls located on the semiconductor substrate on two sides of the grid structure, heavily doped source / drain regions located in the semiconductor and on two sides of the grid structure, and pocket regions and F-ion doped regions respectively located in the semiconductor substrate and on two sides of the grid structure, wherein the F-ion doped regions are located around the pocket regions. The invention further provides a method of forming the MOS transistors. By forming the F-ion doped regions around the pocket regions of the MOS transistor, transient enhanced diffusion effect of ions from the pocket regions into the semiconductor substrate can be prevented, thereby reducing junction depth, decreasing junction current leakage, and improving the performance of the MOS transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

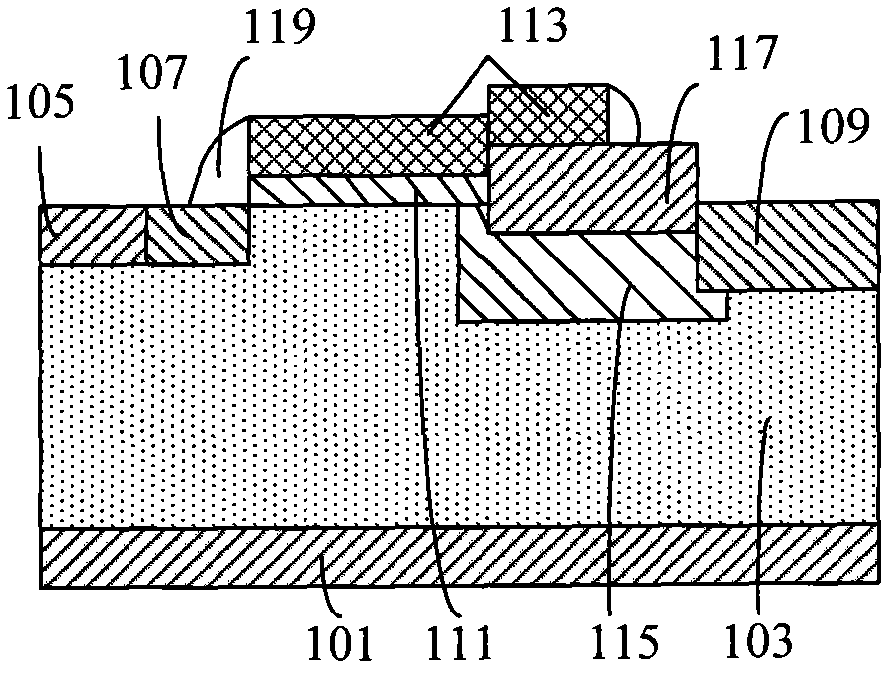

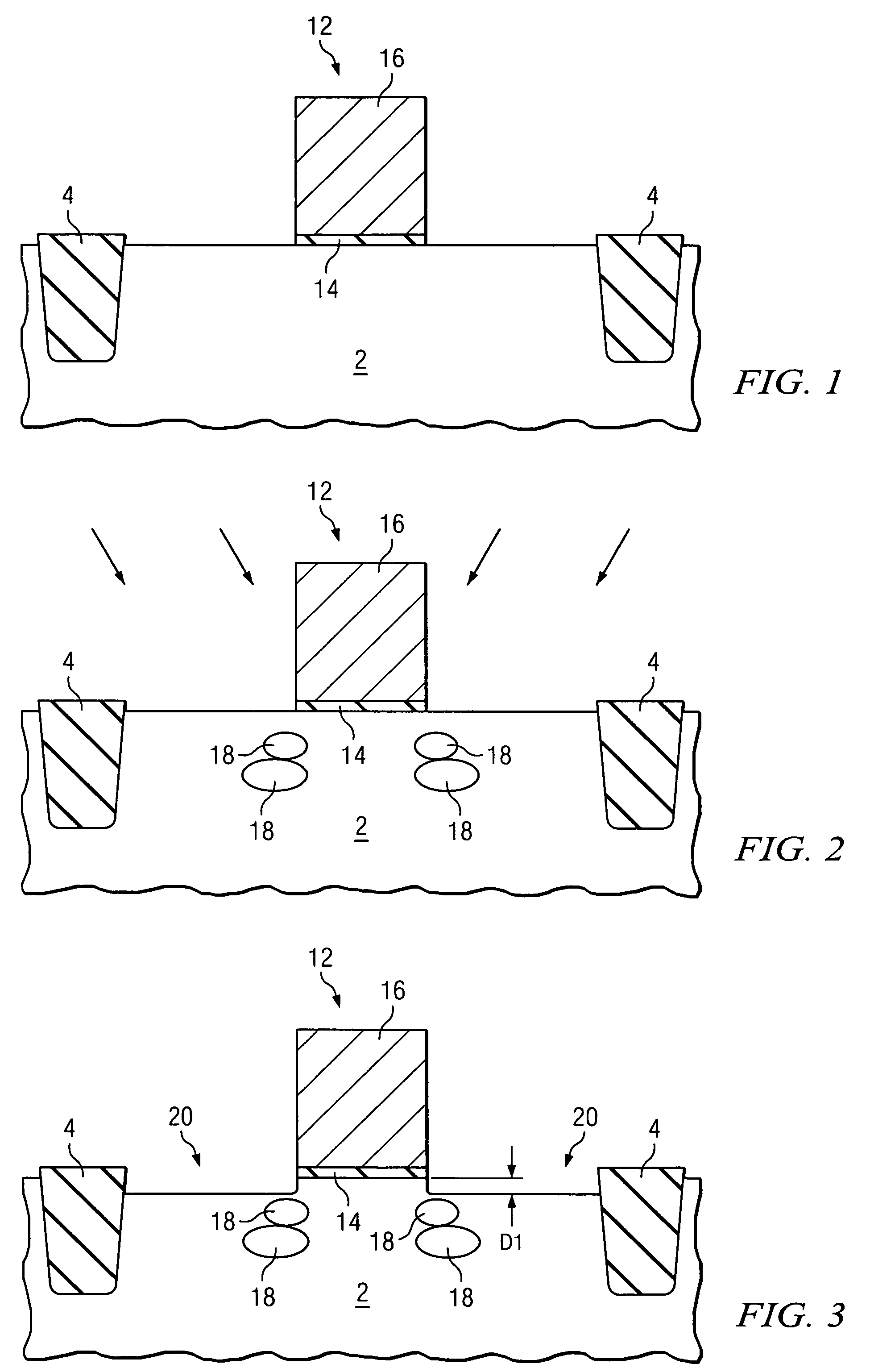

Short channel effect engineering in MOS device using epitaxially carbon-doped silicon

InactiveUS20080132019A1Reduce impurity diffusionReduce junction depthSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon dopedShort-channel effect

A method for forming a semiconductor structure includes providing a semiconductor substrate, forming a gate stack on the semiconductor substrate, and epitaxially growing a lightly-doped source / drain (LDD) region adjacent the gate stack, wherein carbon is simultaneously doped into the LDD region.

Owner:TAIWAN SEMICON MFG CO LTD

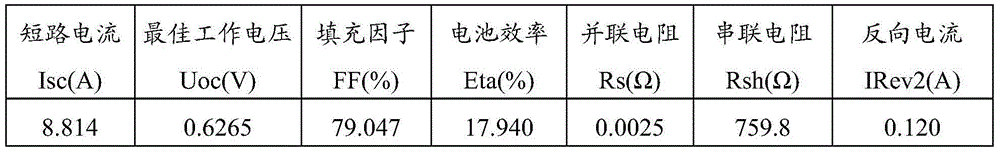

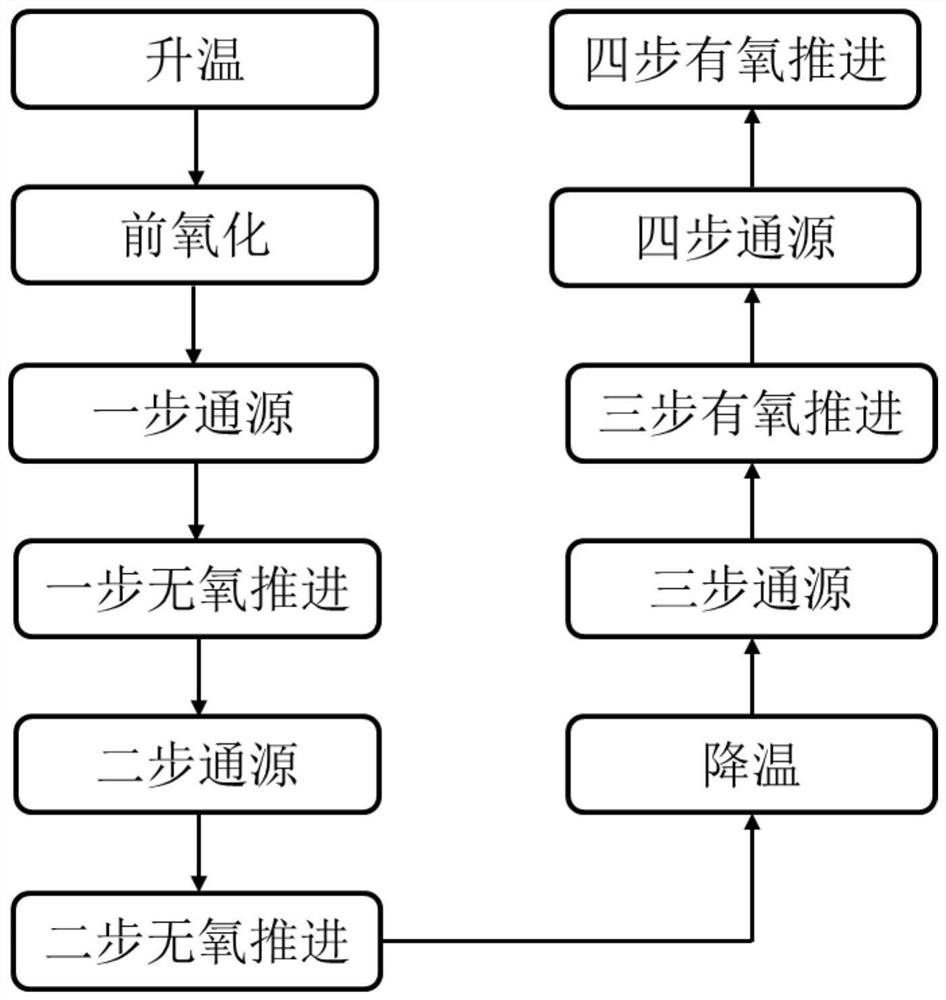

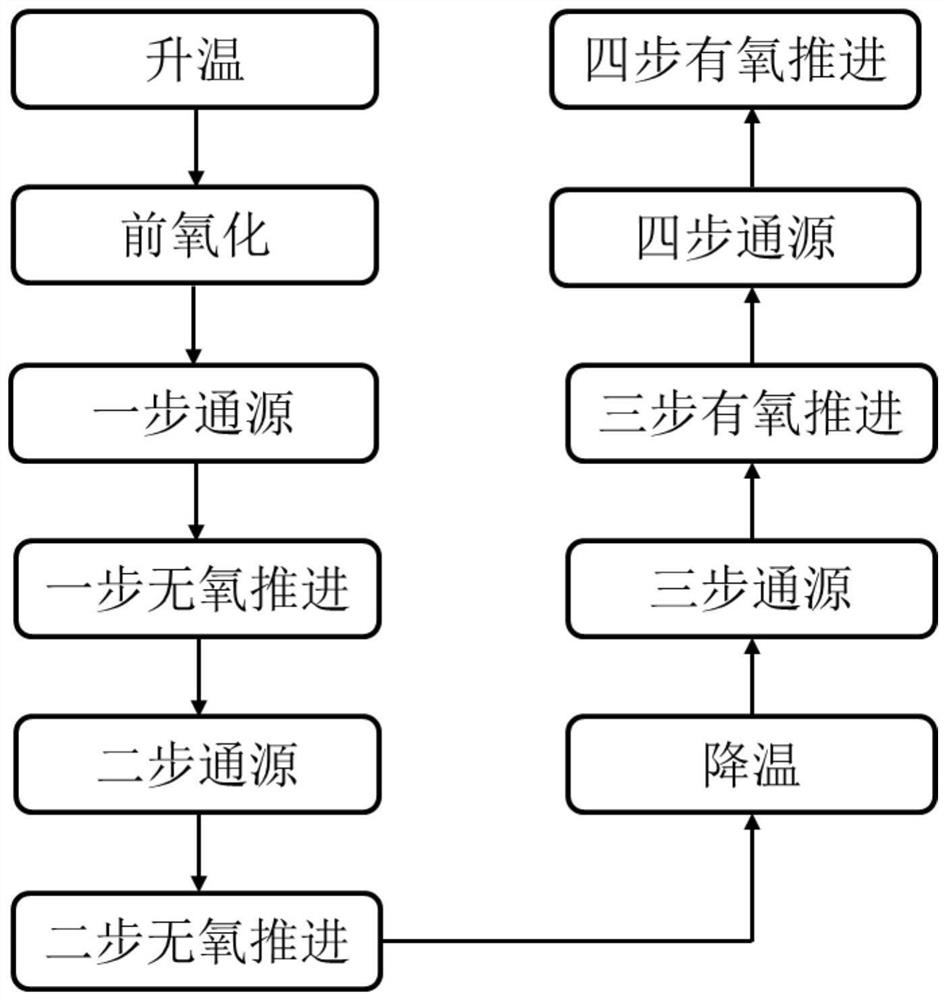

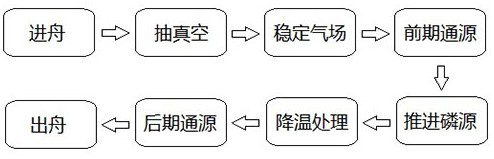

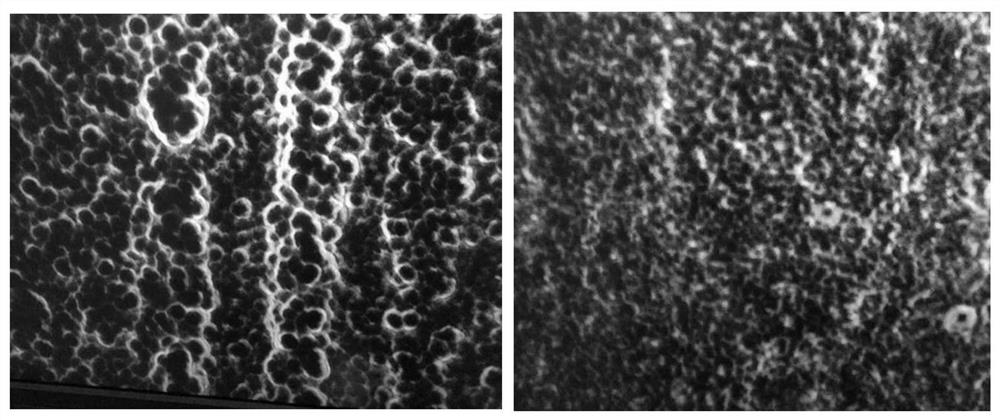

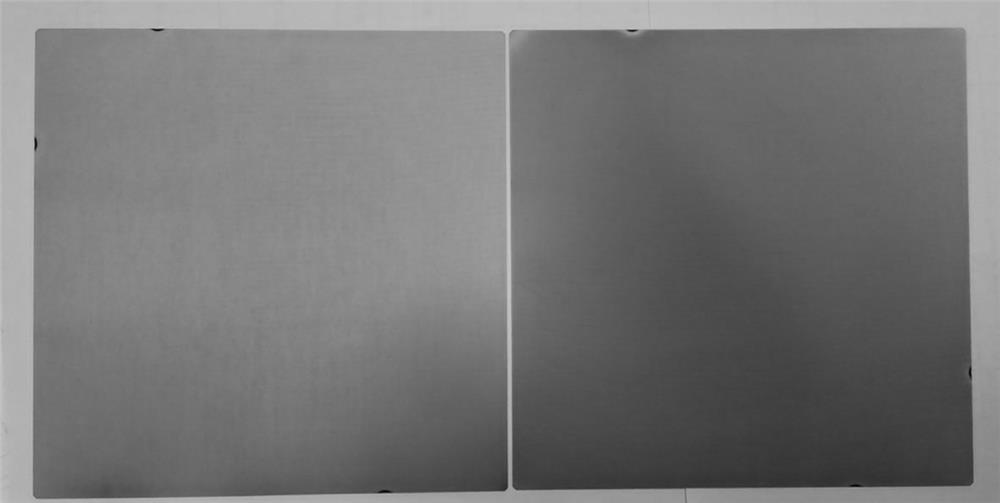

P diffusion method of silicon wafer and preparation method of solar cell

ActiveCN104409339AImprove square resistance uniformityImprove conversion efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingSurface concentrationDiffusion methods

The invention provides a P diffusion method of a silicon wafer; a textured silicon wafer is subjected to P diffusion; in the P diffusion process, the steps of increasing the temperature for the first time, depositing for the first time, propelling for the first time, increasing the temperature for the second time, depositing for the second time, propelling for the second time, increasing the temperature for the third time, depositing for the third time, propelling for the third time, decreasing the temperature and absorbing impurities are carried out in sequence; by means of the depositing processes, the propelling processes and the impurity-absorbing processes step by step, the sheet resistance uniformity of the silicon wafer containing a PN junction is increased; the surface concentration and the junction depth are reduced; therefore, the conversion efficiency of the solar cell is effectively increased; furthermore, the method provided by the method is incapable of increasing existing production of production lines, and has better economic benefits.

Owner:ZHEJIANG JINKO SOLAR CO LTD +1

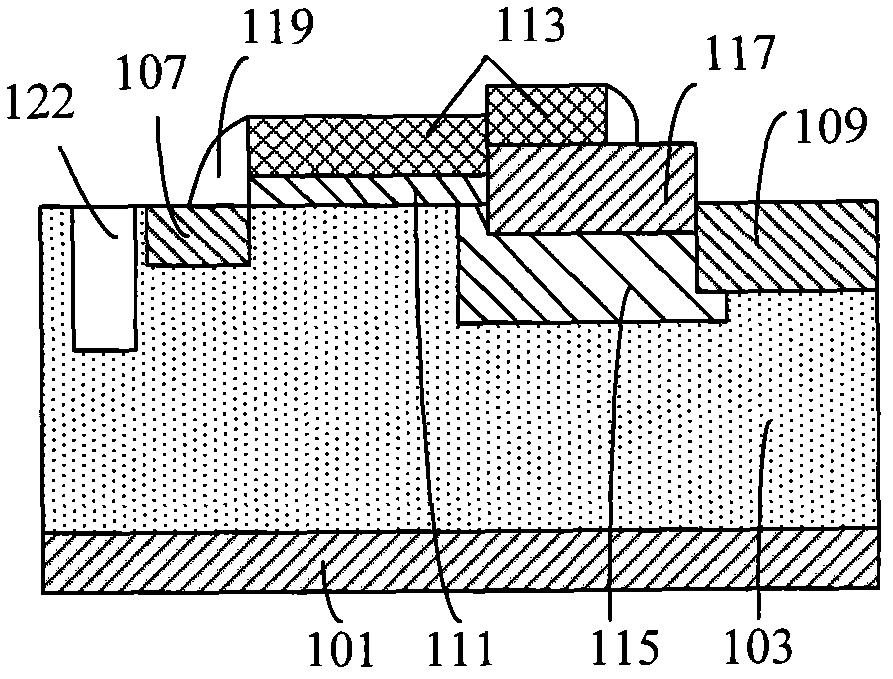

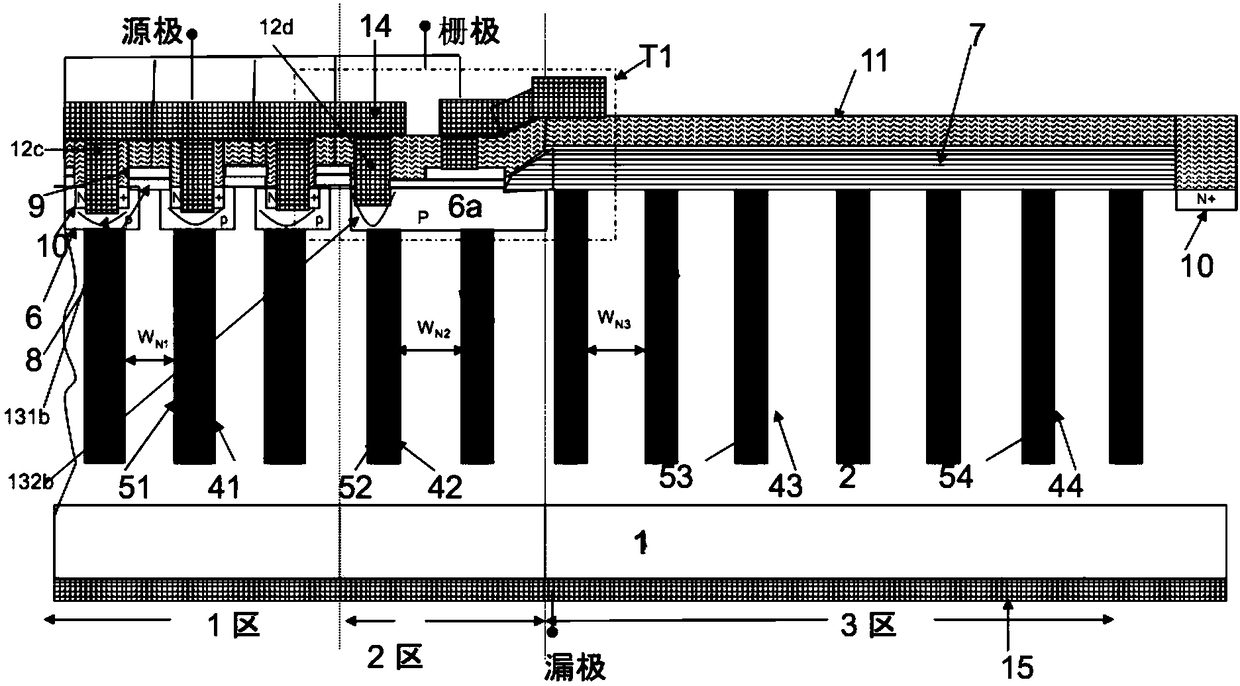

LDMOS device and fabrication method thereof

ActiveCN102386211AIncreasing the thicknessReduce junction depthSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSBody region

The invention discloses a laterally diffused metal oxide semiconductor (LDMOS) device; the LDMOS device comprises a source region, a gate region, a drain region, a body region, and a drifting region with doped type opposite to the body region; the body region is arranged on a substrate region, and the drifting region is arranged between the drain region and the body region. The LDMOS device also comprises an insulated dielectric layer, and the insulated dielectric layer is positioned on the drifting region and below the gate region. By using the structure of the LDMOS device provided by the invention, the puncture voltage of the device can be enhanced, so that the on-resistance is lowered and the power consumption of the device is reduced; and in the adjusting and fabricating process, junction depth for adjusting the insulated dielectric layer and the drifting region has smaller effect on the other devices.

Owner:CSMC TECH FAB2 CO LTD

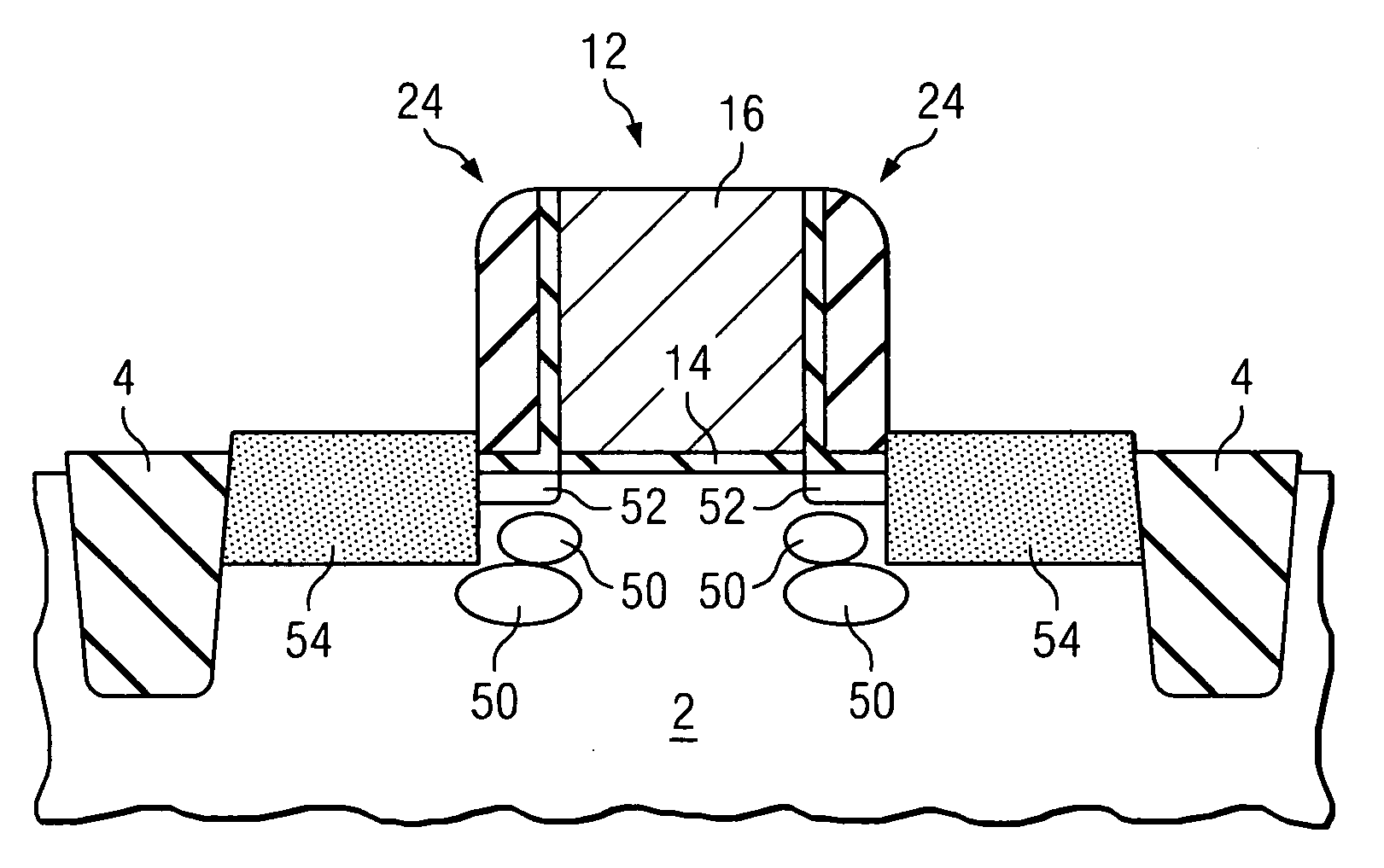

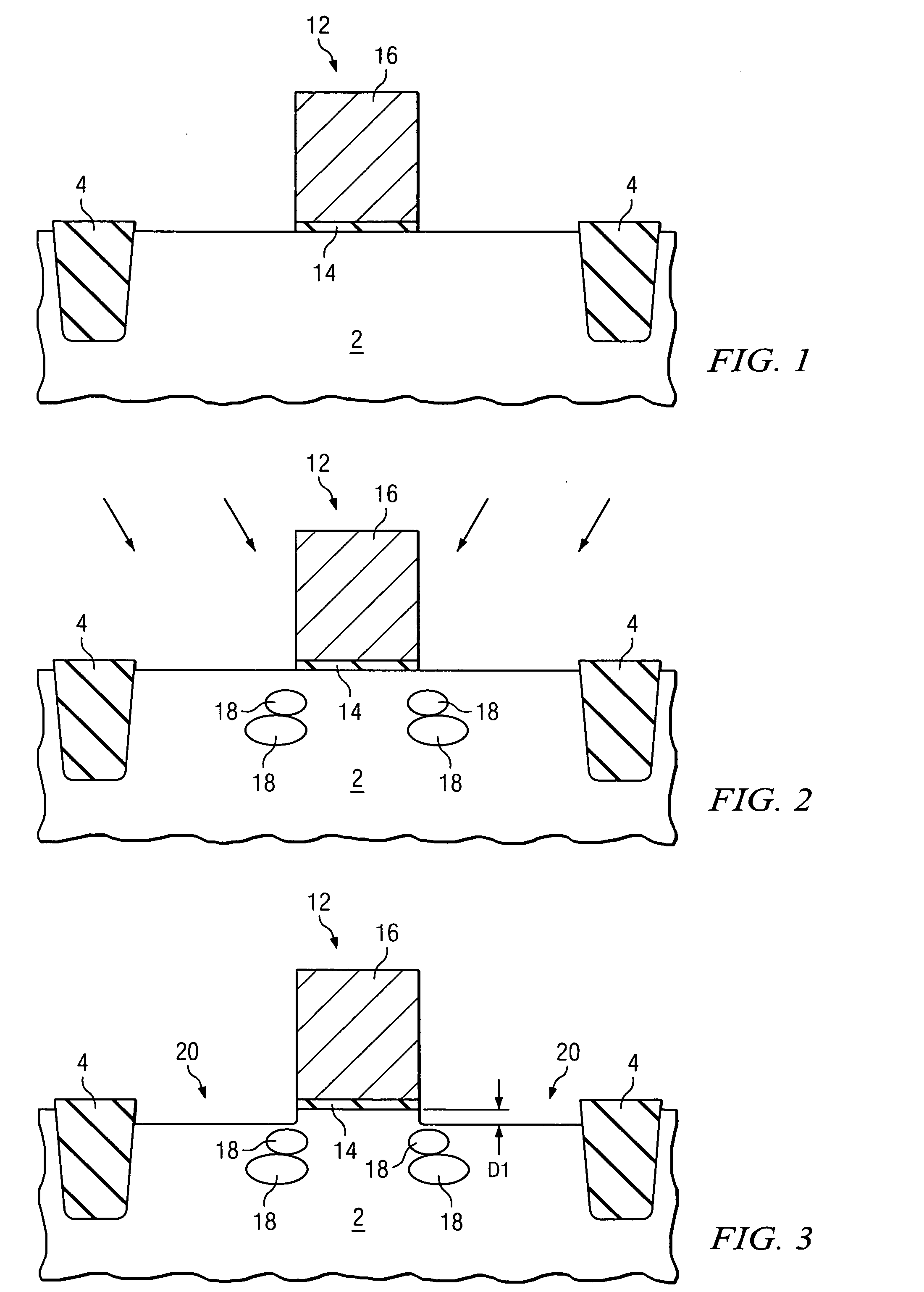

Fabrication of Source/Drain Extensions with Ultra-Shallow Junctions

ActiveUS20100216288A1Reduce sheet resistanceReduce junction depthSemiconductor/solid-state device manufacturingIndiumEngineering

A method of forming an integrated circuit device includes providing a semiconductor substrate; forming a gate structure on the semiconductor substrate; and performing a pre-amorphized implantation (PAI) by implanting a first element selected from a group consisting essentially of indium and antimony to a top portion of the semiconductor substrate adjacent to the gate structure. The method further includes, after the step of performing the PAI, implanting a second element different from the first element into the top portion of the semiconductor substrate. The second element includes a p-type element when the first element includes indium, and includes an n-type element when the first element includes antimony.

Owner:TAIWAN SEMICON MFG CO LTD

Method for Forming an Electrical Contact

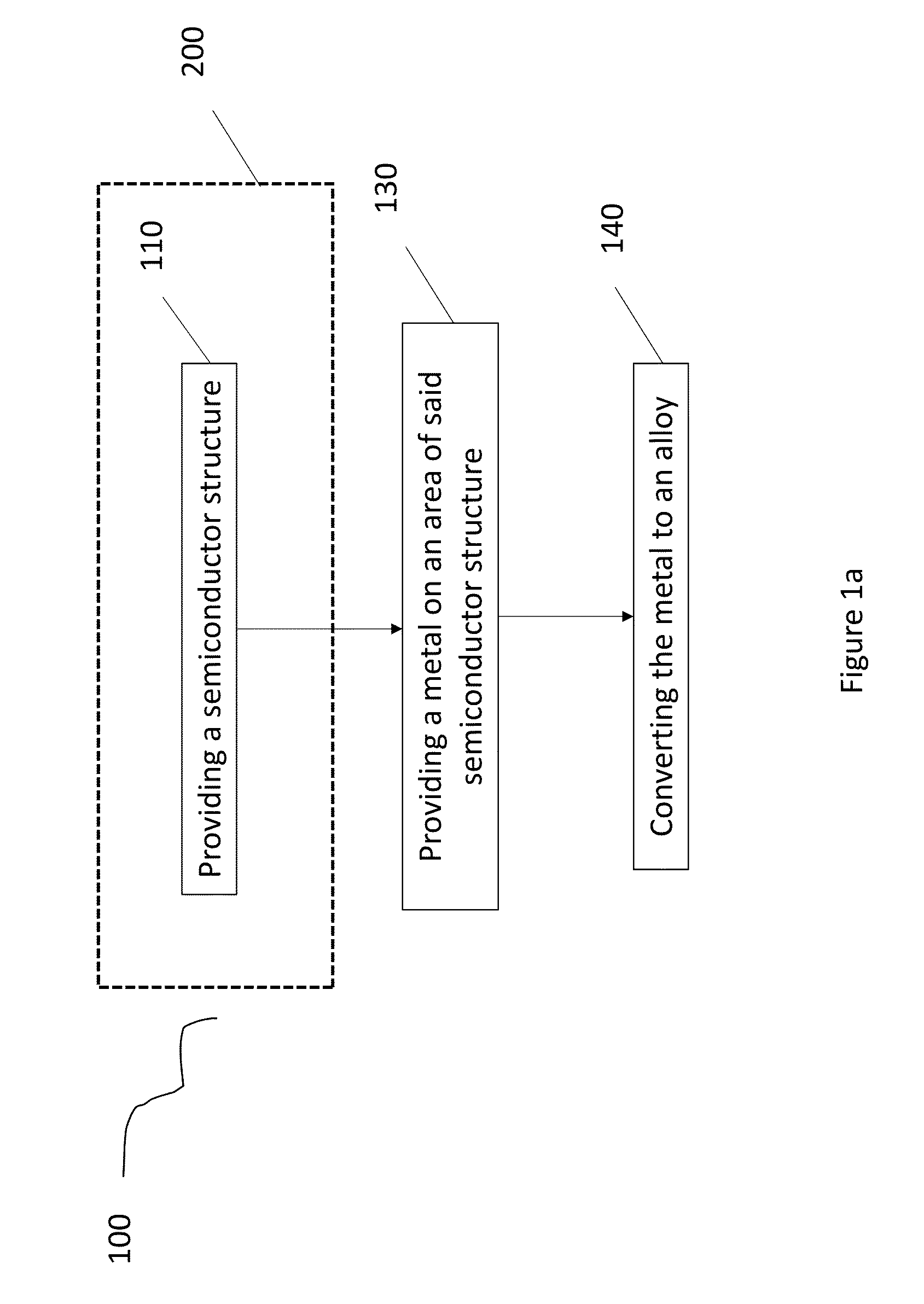

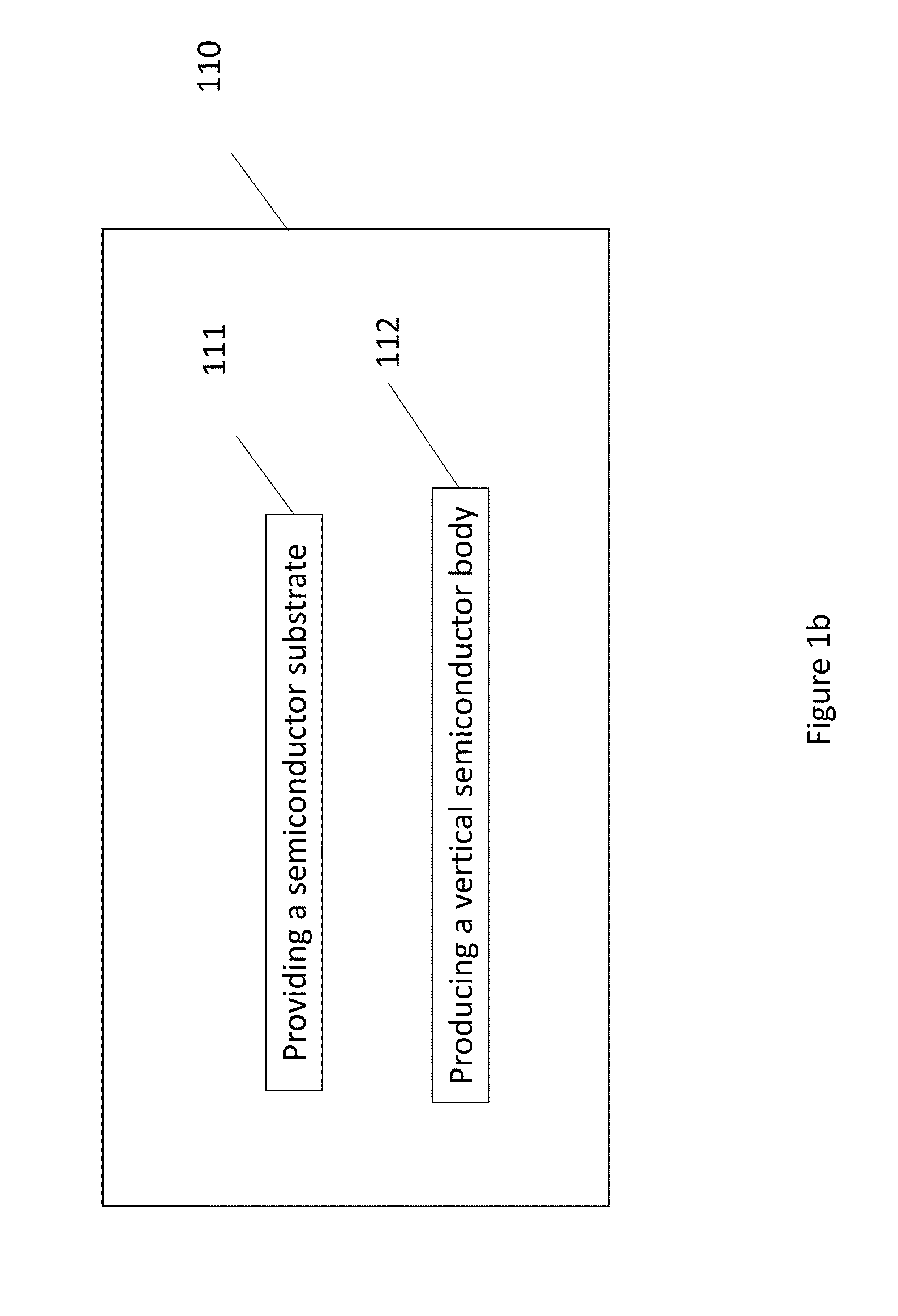

ActiveUS20160163648A1Simplifies electrical contact formationLower performance requirementsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsSemiconductor structure

A method for forming an electrical contact to a semiconductor structure is provided. The method includes providing a semiconductor structure, providing a metal on an area of said semiconductor structure, wherein said area exposes a semiconductor material and is at least a part of a contact region, converting said metal to a Si-comprising or a Ge-comprising alloy, thereby forming said electrical contact on said area, wherein said converting is done by performing a vapor-solid reaction, whereby said semiconductor structure including said metal is subjected to a silicon-comprising precursor gas or a germanium-comprising precursor gas.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

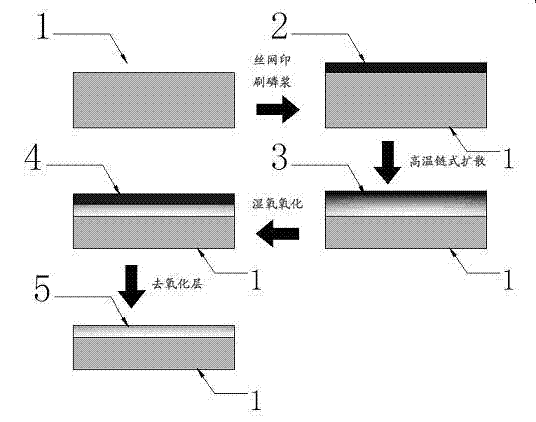

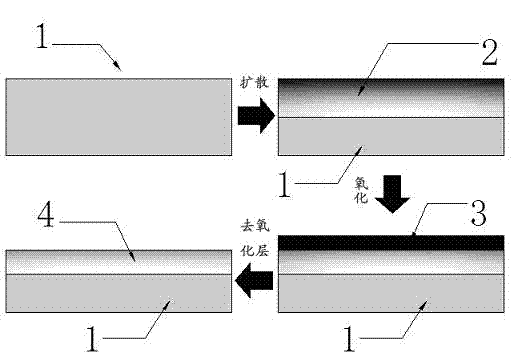

Chained diffusion process for solar cell

InactiveCN102881767AExtend your lifeImprove conversion efficiencyFinal product manufactureDiffusion/dopingSurface concentrationWater vapor

The invention discloses a chained diffusion process for a solar cell. The chained diffusion process is to remove a highly-doped area on a diffused surface and improve the minority carrier lifetime of a diffused silicon wafer by growing a thick oxidation layer on the surface of a silicon wafer subjected to chained diffusion and washing off the oxidation layer, and comprises the following steps: making a reaction between steam and the diffused surface of the silicon wafer at a high temperature to quickly grow the thick oxidation layer in a short time; and finally, removing the oxidation layer. The chained diffusion process avoids the phenomenon that the ordinary diffusion process cannot avoid generating a 'dead layer', further reduces the surface concentration, improves the minority carrier lifetime and the conversion efficiency of the cell, and reduces the production cost of the solar cell.

Owner:TIANWEI NEW ENERGY HLDG

Method of manufacturing semiconductor device

InactiveUS20050186748A1Reduce junction depthTransistorSemiconductor/solid-state device manufacturingLithographic artistImpurity diffusion

A method of manufacturing a semiconductor device including a plurality of MIS transistors formed on a semiconductor substrate, includes forming a plurality of gate electrodes associated with the MIS transistors on the semiconductor substrate, with a plurality of gate insulating films interposed between the gate electrodes and the semiconductor substrate, respectively, and successively forming a plurality of impurity diffusion regions for LDD regions in the semiconductor substrate, at decreasing junction depths, respectively, by using lithography and ion implantation, such that each of the impurity diffusion regions being provided on both sides of a respective one of the gate electrodes.

Owner:KK TOSHIBA

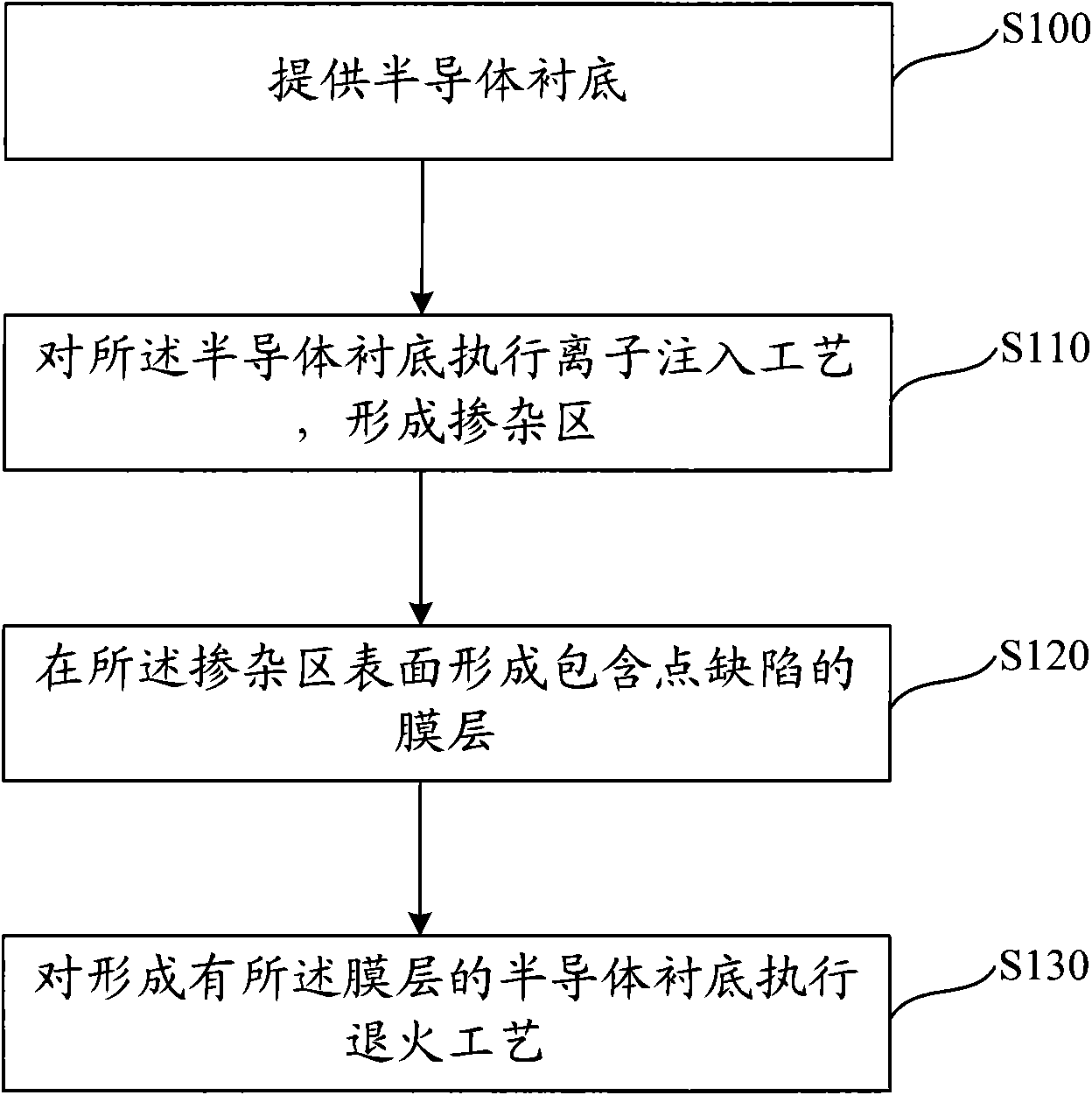

Doping method and method for forming LDD doped area

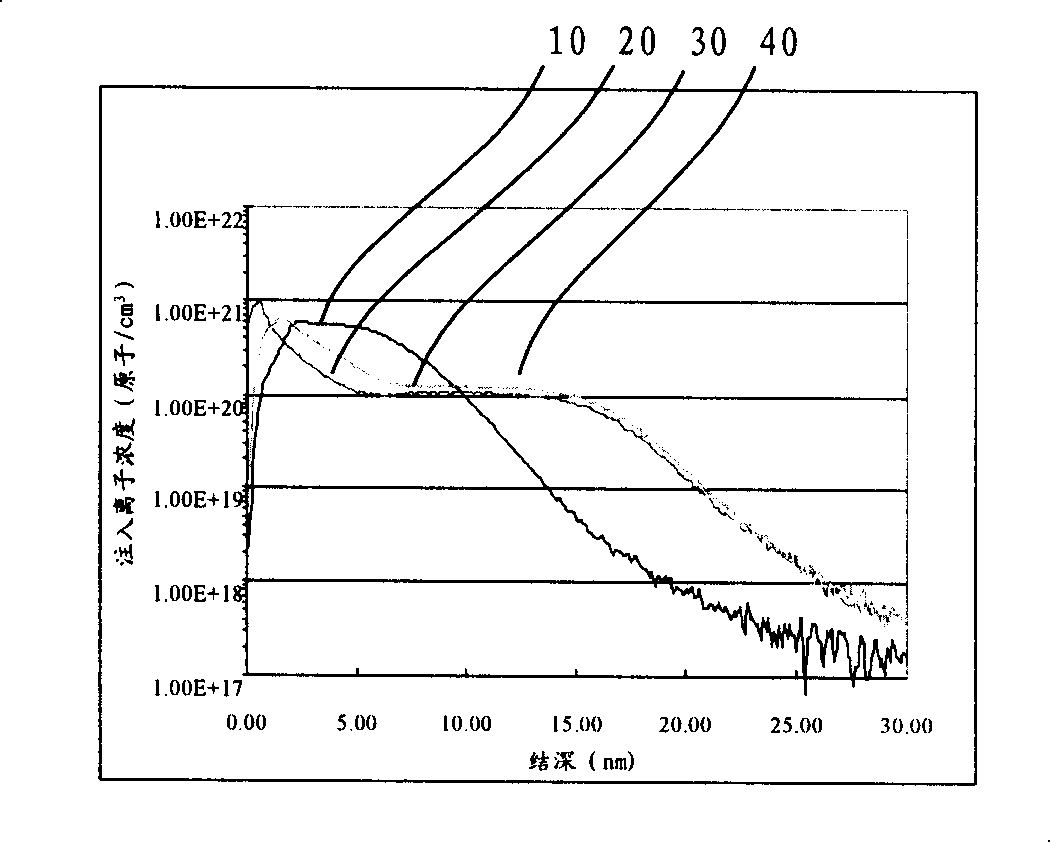

InactiveCN101577222AReduce junction depthDiffusion inhibition or reductionSemiconductor/solid-state device manufacturingSemiconductorIon implantation

The invention relates to a doping method comprising the following steps: providing a semiconductor substrate; processing the semiconductor substrate with an ion injection process to form a doped area; forming a film containing point defect on the surface of the doped area; and processing the semiconductor substrate with the film formed thereon with an anneal process. The invention also provides a method for forming an LDD doped area. The junction depth of the doped area formed in the invention is shallower.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Process for manufacturing emitter of solar cell

InactiveCN102881766AExtend your lifeImprove conversion efficiencyFinal product manufactureSemiconductor devicesSurface concentrationP–n junction

The invention discloses a process for manufacturing an emitter of a solar cell, which comprises the following steps: step A, manufacturing a PN junction on the surface of a matrix silicon wafer (1) by a diffusion process to form a surface impurity distribution layer (2); step B, oxidizing the surface impurity distribution layer (2) obtained in step A to quickly grow an oxidation layer (3) distributed uniformly on the surface of the surface impurity distribution layer (2); and step C, removing the oxidation layer (3) in step B. The process avoids the phenomenon that the ordinary diffusion process cannot avoid generating a 'dead layer', further reduces the surface concentration, improves the minority carrier lifetime and the conversion efficiency of the cell, and reduces the production cost of the solar cell.

Owner:TIANWEI NEW ENERGY HLDG

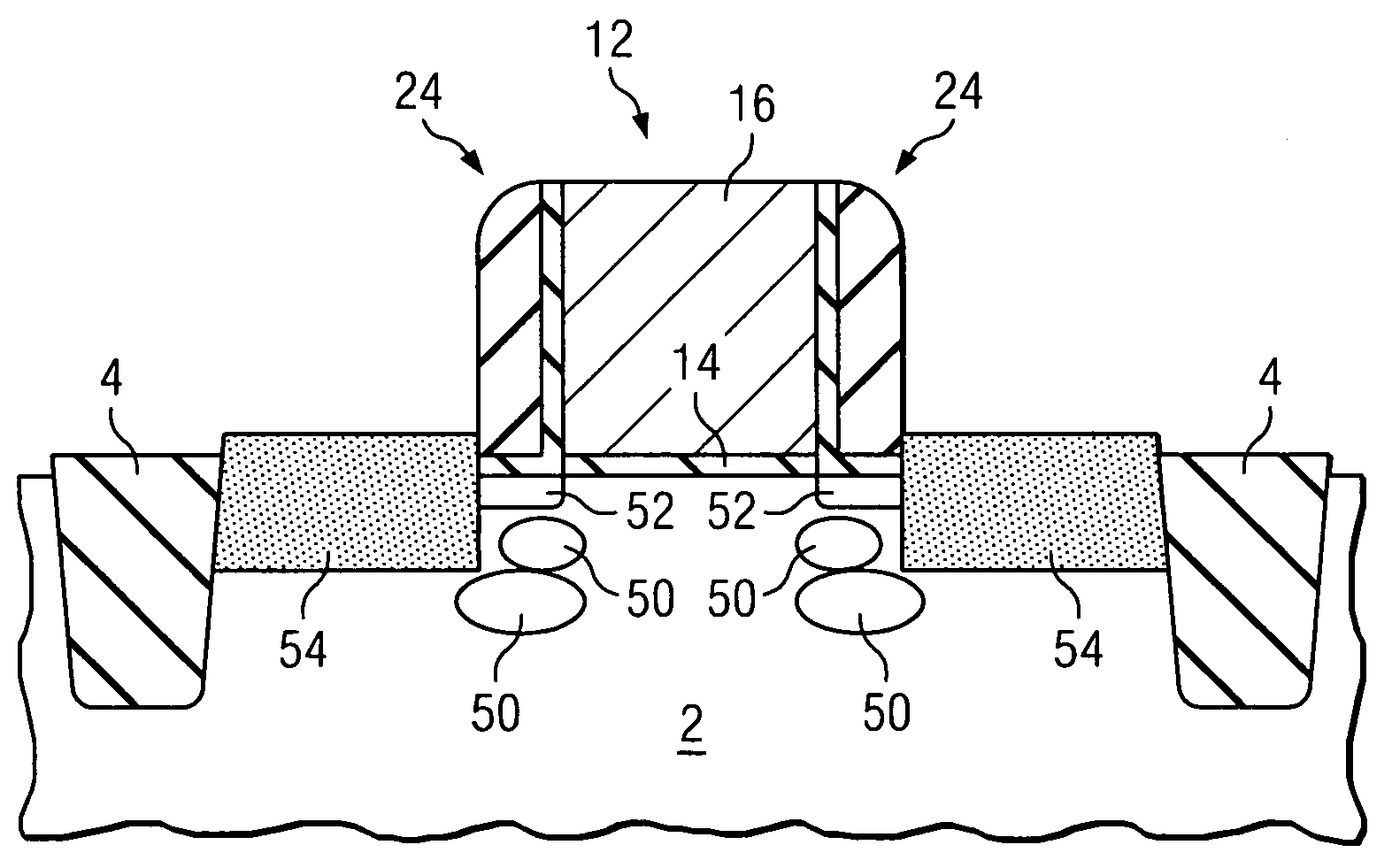

MOS devices with reduced recess on substrate surface

ActiveUS7642607B2Reduce depthImprove short channel effectTransistorSemiconductor/solid-state device manufacturingSilicon alloySubstrate surface

A MOS device having reduced recesses under a gate spacer and a method for forming the same are provided. The MOS device includes a gate structure overlying the substrate, a sidewall spacer on a sidewall of the gate structure, a recessed region having a recess depth of substantially less than about 30 Å underlying the sidewall spacer, and a silicon alloy region having at least a portion in the substrate and adjacent the recessed region. The silicon alloy region has a thickness of substantially greater than about 30 nm. A shallow recess region is achieved by protecting the substrate when a hard mask on the gate structure is removed. The MOS device is preferably a pMOS device.

Owner:TAIWAN SEMICON MFG CO LTD

Method for forming ultra-shallow junction

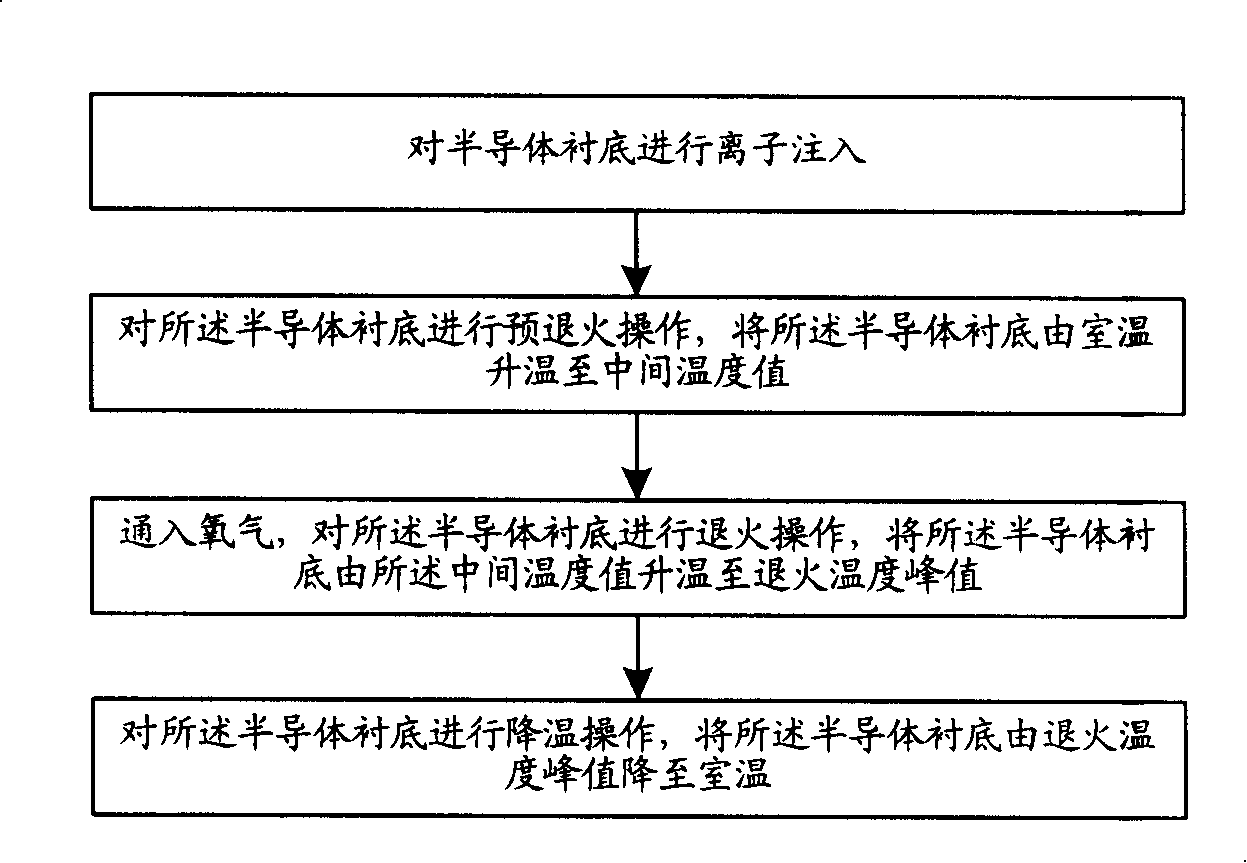

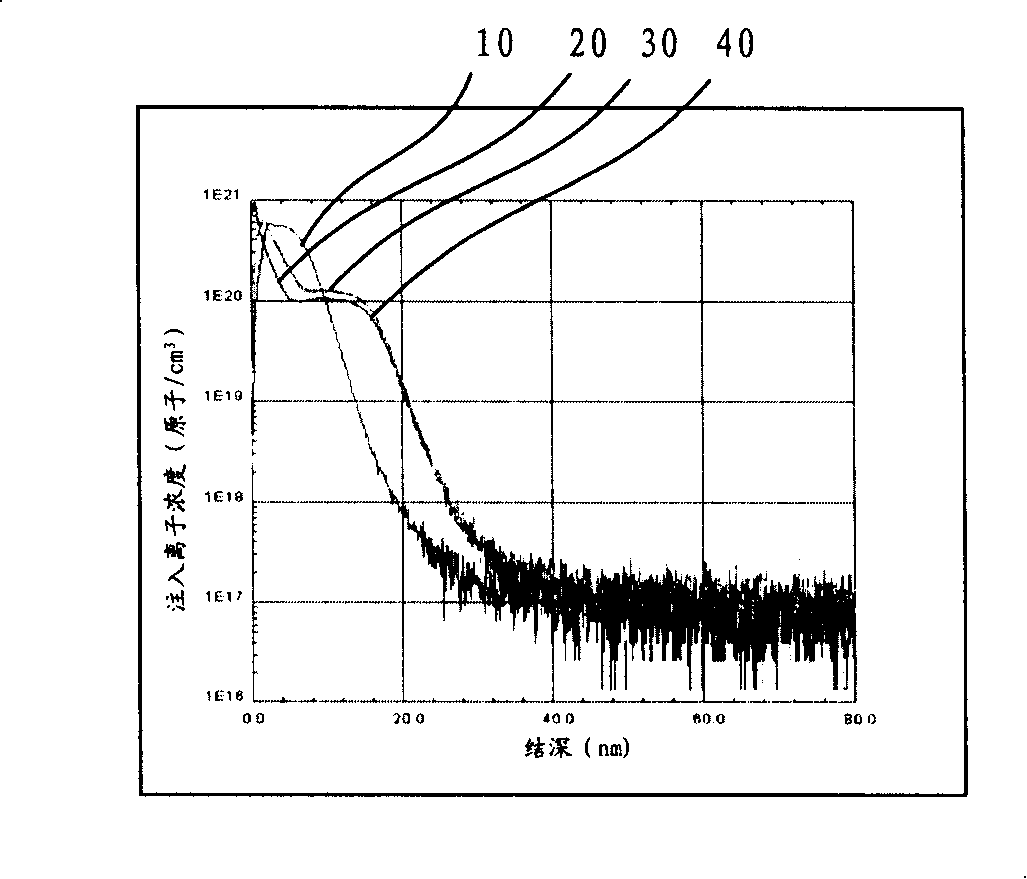

InactiveCN101207020AReduce spreadReduce junction depthSemiconductor/solid-state device manufacturingIonic diffusionRoom temperature

The invention relates to a method of forming an ultra-shallow junction. The invention comprises the following steps: ions are infused into a semiconductor substrate; the pre-annealing operation is carried on to the semiconductor substrate, to heat up the semiconductor substrate from the room temperature to the intermediate temperature value; oxygen is filled, the annealing operation is carried on to the semiconductor substrate, to heat up the semiconductor substrate from the intermediate temperature value to the annealing temperature peak value; the cooling operation is carried on to the semiconductor substrate, to cool the semiconductor substrate from the annealing temperature peak value to the room temperature. A peak value annealing method is adopted in the forming process of the ultra-shallow junction, doping material activation and crystal lattice damage reconstruction can be completed simultaneously in one thermal treatment process; the oxygen is filled in the peak value annealing process, and the doping ionic diffusion is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Nor flash memory structure with highly-doped drain region and method of manufacturing the same

InactiveUS20100230738A1Reduce junction depthIncrease in SCETransistorSolid-state devicesEngineeringIon implantation

In a method of manufacturing a NOR flash memory structure, a highly-doped ion implantation process is performed to form a highly-doped drain region to overlap with a lightly-doped drain region. Therefore, the flash memory structure can have a reduced drain junction depth to improve the short channel effect while protecting the lightly-doped drain region from being punched through during an etching process for forming a contact hole.

Owner:EON SILICON SOLUTION

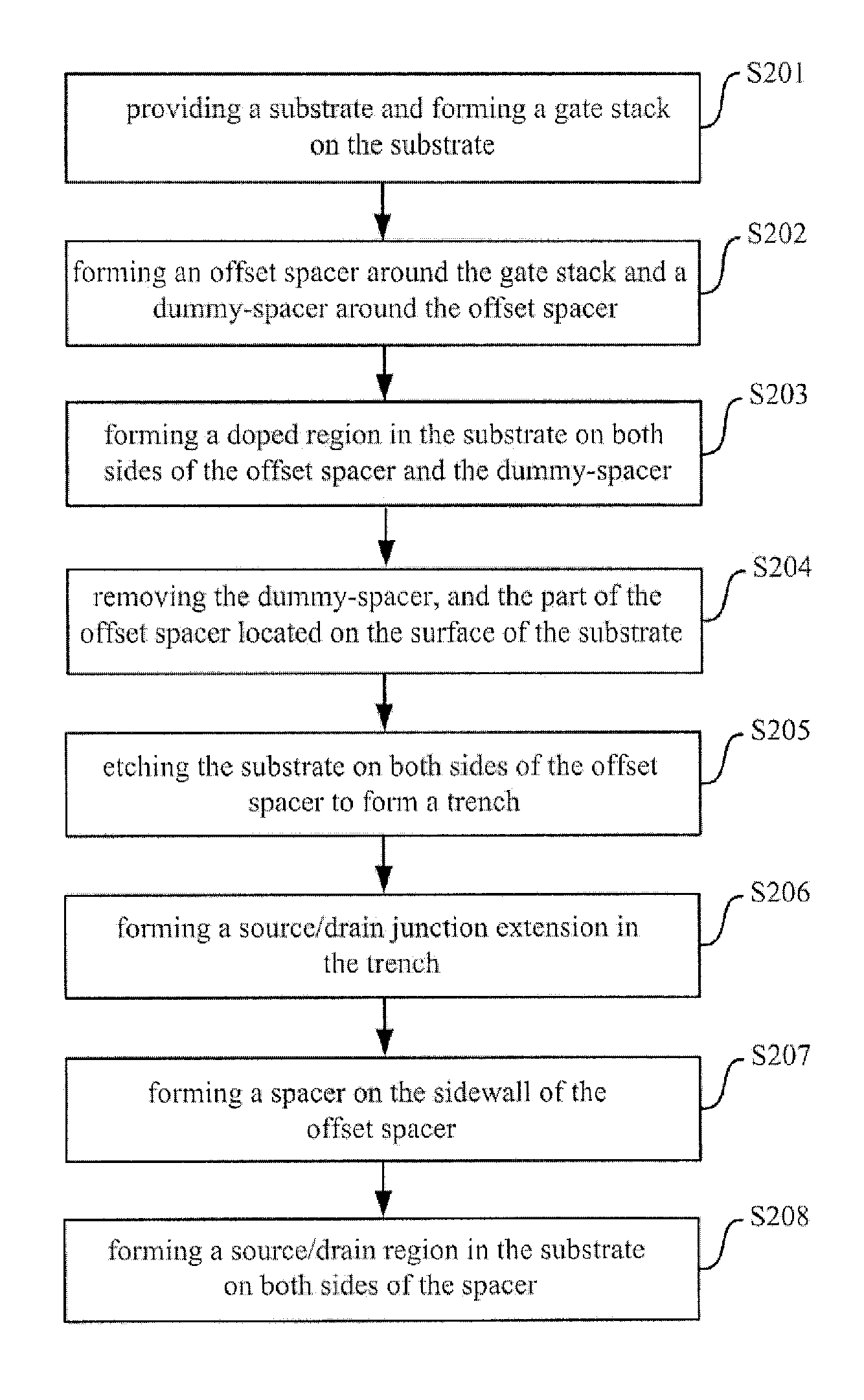

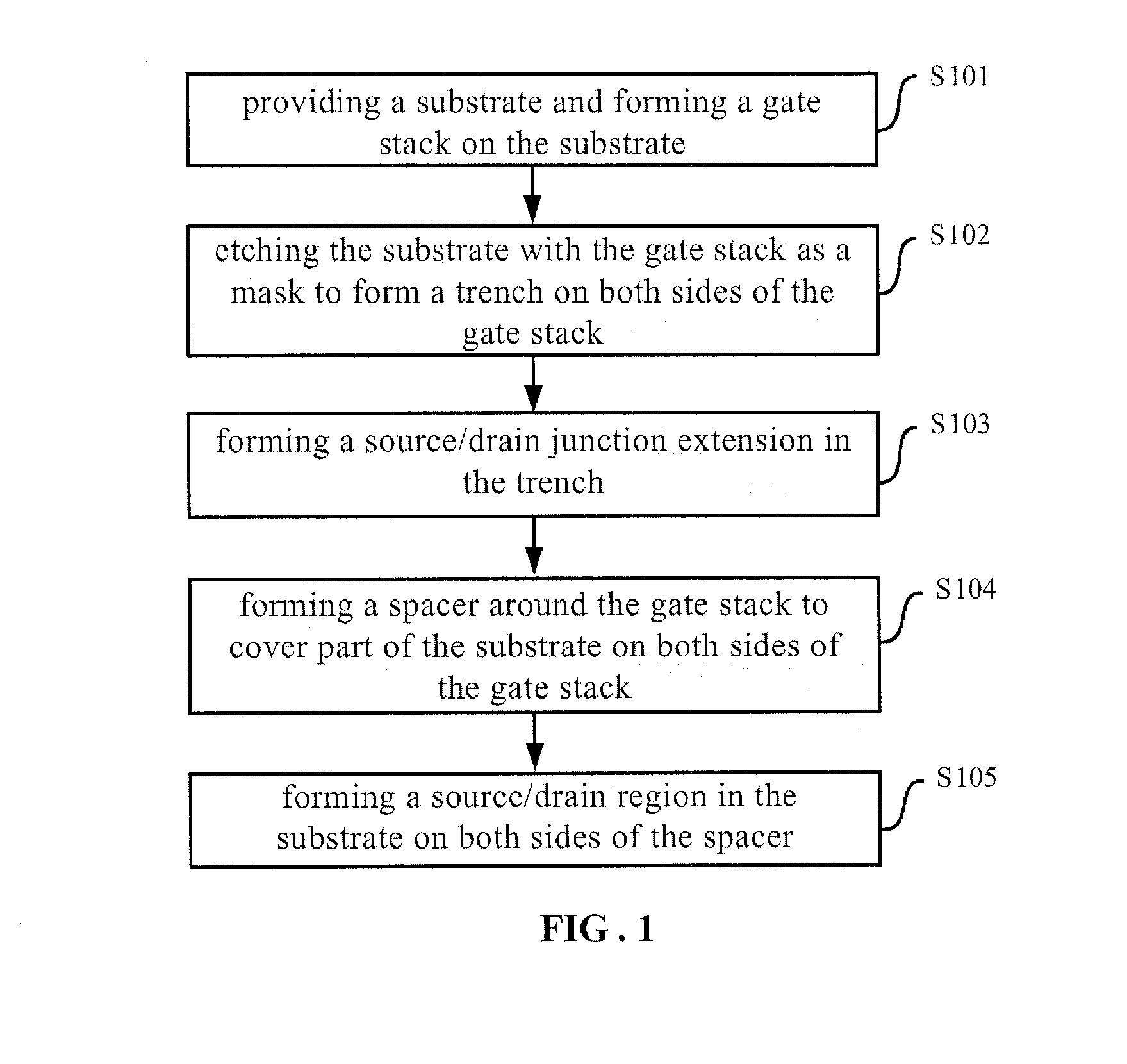

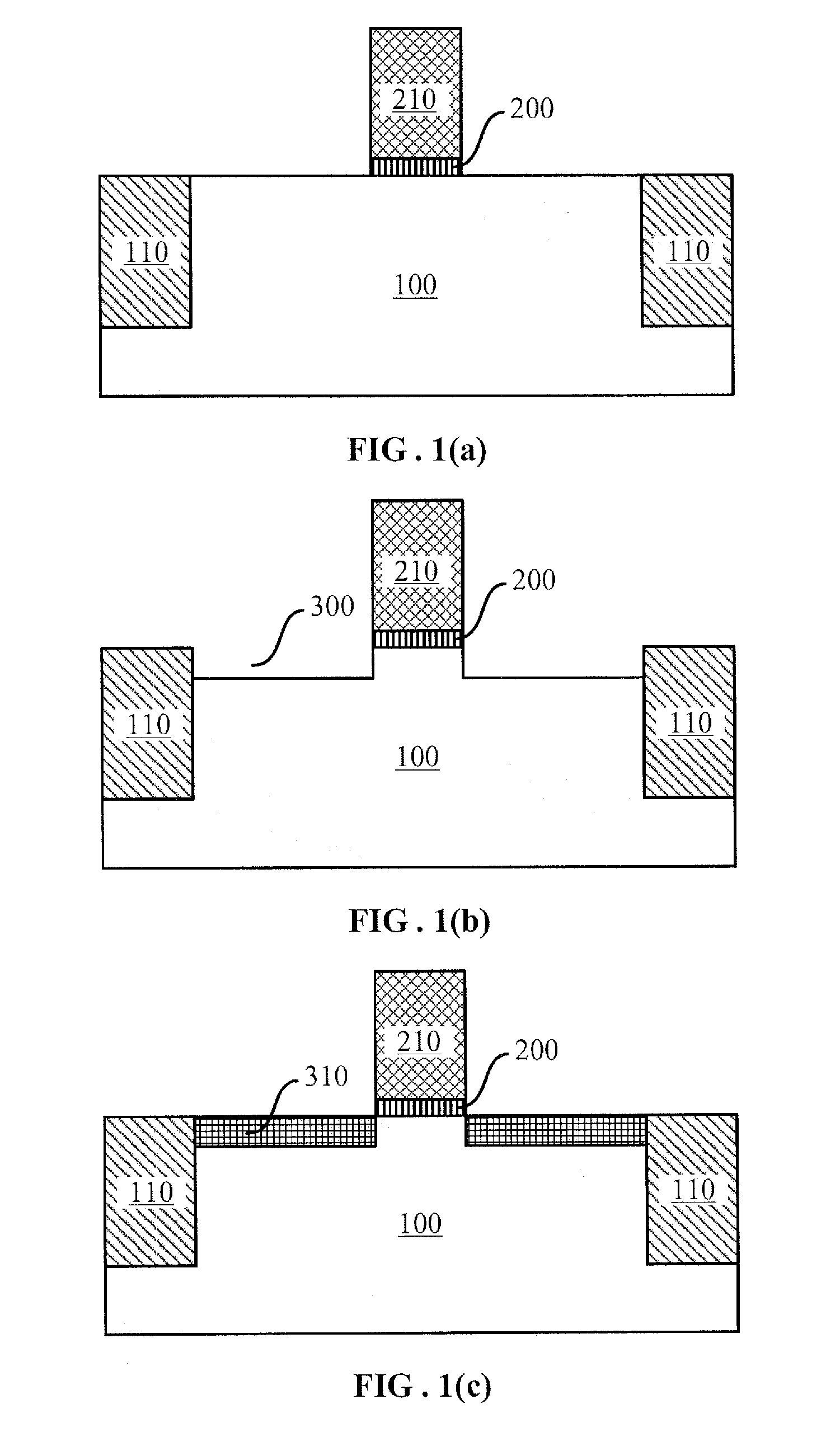

Semiconductor structure and method for manufacturing the same

ActiveUS9276085B2Easy to controlIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureGate stack

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

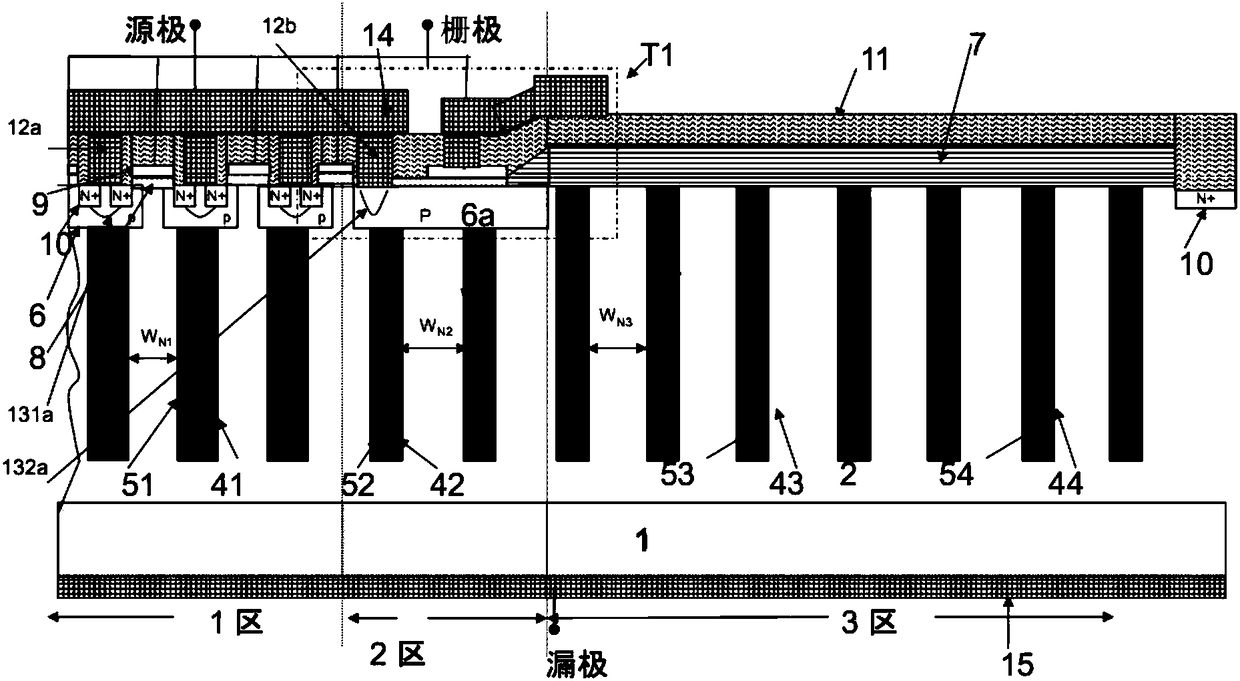

Super-junction device and manufacturing method thereof

ActiveCN108428732AImprove softness factorImprove reverse recovery characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryEngineering

The invention discloses a super-junction device, which is characterized in that a protective epoxy film exposes a charge flow region, completely covers a transition region and completely or mostly covers a terminal region, a second contact hole at the top of a P-type ring of the transition region is enabled to penetrate deeper than a first contact hole at the top of a P-type well of the charge flow region by the thickness of one protective epoxy film, and thus the junction depth of a second P+ contact region at the bottom of the second contact hole is enabled to be less than the junction depthof a first P+ contact region at the bottom of the first contact hole, so that the distance between a hole collected by the P-type ring to the second P+ contact region, and a softness factor of reverse recovery of a body diode of the device is increased. The invention further discloses a manufacturing method of the super-junction device. According to the invention, the reverse recovery characteristics of device can be improved, and the avalanche tolerance of the device is enhanced at the same time.

Owner:SHENZHEN SANRISE TECH CO LTD

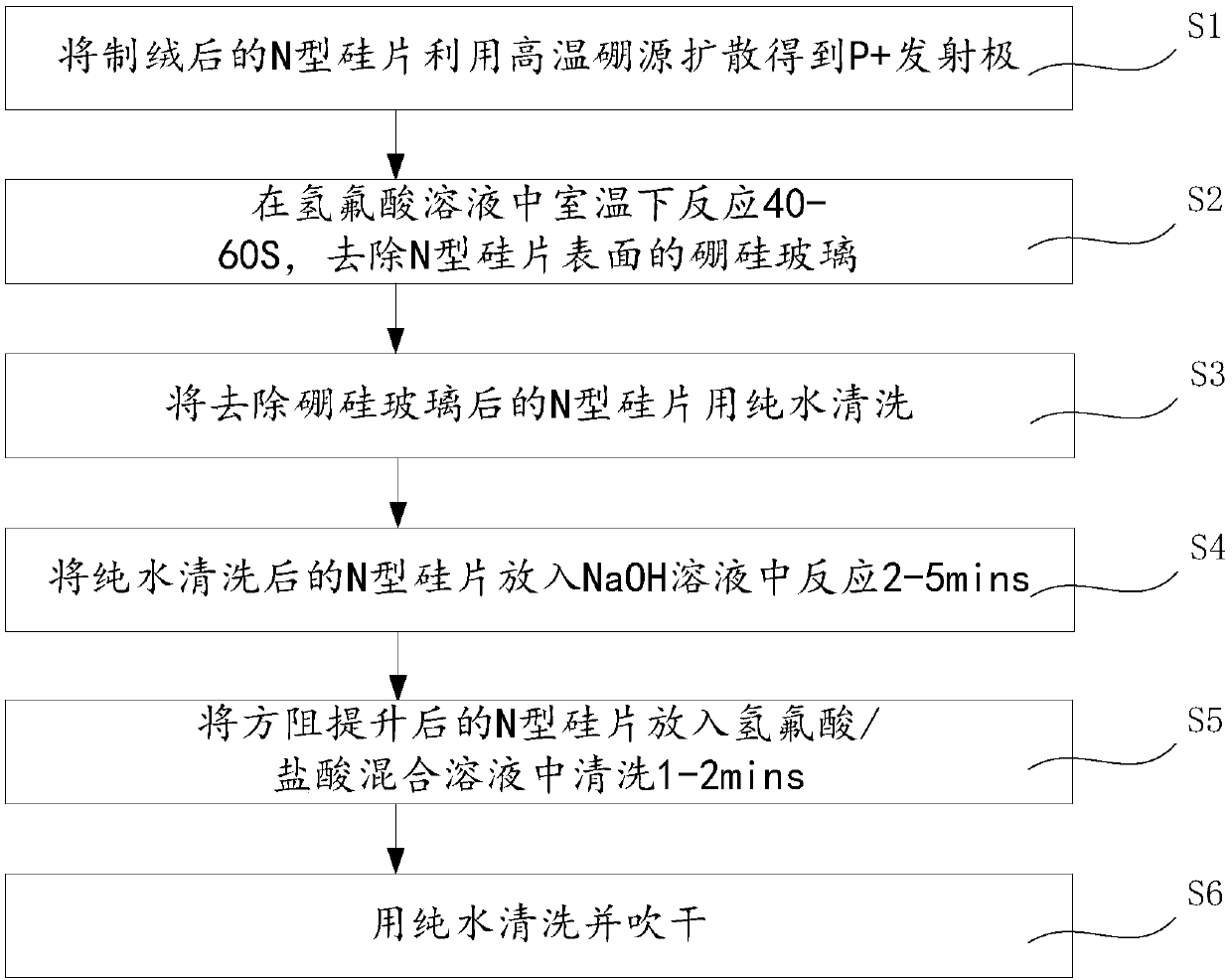

Boron diffusion method for N-type solar cell

InactiveCN107863418AIncrease contactReduce junction depthFinal product manufactureSemiconductor/solid-state device manufacturingSolar cellBorosilicate glass

The invention discloses a boron diffusion method for an N-type solar cell. The boron diffusion method comprises the following steps: (1) carrying out high-temperature boron source diffusion on an N-type silicon wafer after texturing so as to obtain a P+ emitting electrode; (2) carrying out a reaction for 40 to 60 s at room temperature in a hydrofluoric acid solution to remove borosilicate glass onthe surface of the N-type silicon wafer; (3) washing the N-type silicon wafer with pure water after the borosilicate glass is removed to remove the hydrofluoric acid solution remaining on the surface; (4) putting the N-type silicon wafer after being cleaned with pure water into an NaOH solution for carrying out a reaction for 2 to 5 min so that the square resistance of the N-type silicon wafer isimproved by 8 to 20 ohm / sq; (5) putting the N-type silicon wafer after the square resistance is improved into a hydrofluoric acid and hydrochloric acid mixed solution for washing for 1 to 2 min to remove metal ions and a back oxidation layer; and (6) washing with pure water and drying. According to the method, the square resistance on the surface of the silicon wafer after boron expansion can beuniformly improved, the condition that the concentration of the surface after the boron diffusion of the N-type cell is effectively solved, and the junction depth is improved.

Owner:SPIC XIAN SOLAR POWER CO LTD

Short channel effect engineering in MOS device using epitaxially carbon-doped silicon

InactiveUS7504292B2Reduce impurity diffusionReduce junction depthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureGate stack

A method for forming a semiconductor structure includes providing a semiconductor substrate, forming a gate stack on the semiconductor substrate, and epitaxially growing a lightly-doped source / drain (LDD) region adjacent the gate stack, wherein carbon is simultaneously doped into the LDD region.

Owner:TAIWAN SEMICON MFG CO LTD

Low-pressure diffusion process of solar single crystal PERC

ActiveCN113964239AReduce surface concentrationIncrease the diffusion lengthFinal product manufactureSemiconductor/solid-state device manufacturingSingle crystalSolar cell

The invention provides a low-pressure diffusion process of solar single crystal PERC. The low-pressure diffusion process comprises one-step source introduction, one-step oxygen-free propulsion, two-step source introduction, two-step oxygen-free propulsion, three-step source introduction, three-step aerobic propulsion, four-step source introduction and four-step aerobic propulsion which are carried out in sequence. According to the method, four-step source introduction, two-step anaerobic propulsion and two-step aerobic propulsion are combined, the two-step anaerobic propulsion is firstly carried out after early-stage source introduction so that the surface concentration can be reduced, and the two-step aerobic propulsion is carried out after later-stage source introduction so that the diffusion length can be increased, and then the sheet resistance uniformity is improved; according to the low-voltage diffusion technology, the solar cell piece which is low in surface concentration, small in junction depth and high in uniformity can be manufactured, high open-circuit voltage and short-circuit current are achieved, and the conversion efficiency is high.

Owner:HENGDIAN GRP DMEGC MAGNETICS CO LTD

A kind of p-diffusion method of silicon chip and preparation method of solar cell

ActiveCN104409339BImprove square resistance uniformityImprove conversion efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingDiffusion methodsProduction line

The invention provides a P diffusion method of a silicon wafer; a textured silicon wafer is subjected to P diffusion; in the P diffusion process, the steps of increasing the temperature for the first time, depositing for the first time, propelling for the first time, increasing the temperature for the second time, depositing for the second time, propelling for the second time, increasing the temperature for the third time, depositing for the third time, propelling for the third time, decreasing the temperature and absorbing impurities are carried out in sequence; by means of the depositing processes, the propelling processes and the impurity-absorbing processes step by step, the sheet resistance uniformity of the silicon wafer containing a PN junction is increased; the surface concentration and the junction depth are reduced; therefore, the conversion efficiency of the solar cell is effectively increased; furthermore, the method provided by the method is incapable of increasing existing production of production lines, and has better economic benefits.

Owner:ZHEJIANG JINKO SOLAR CO LTD +1

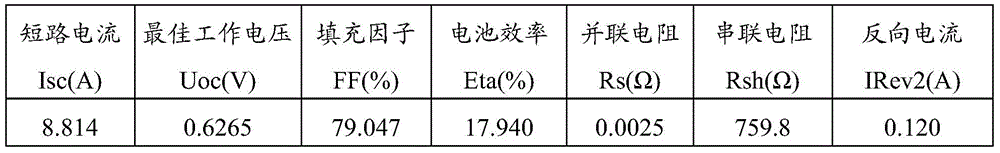

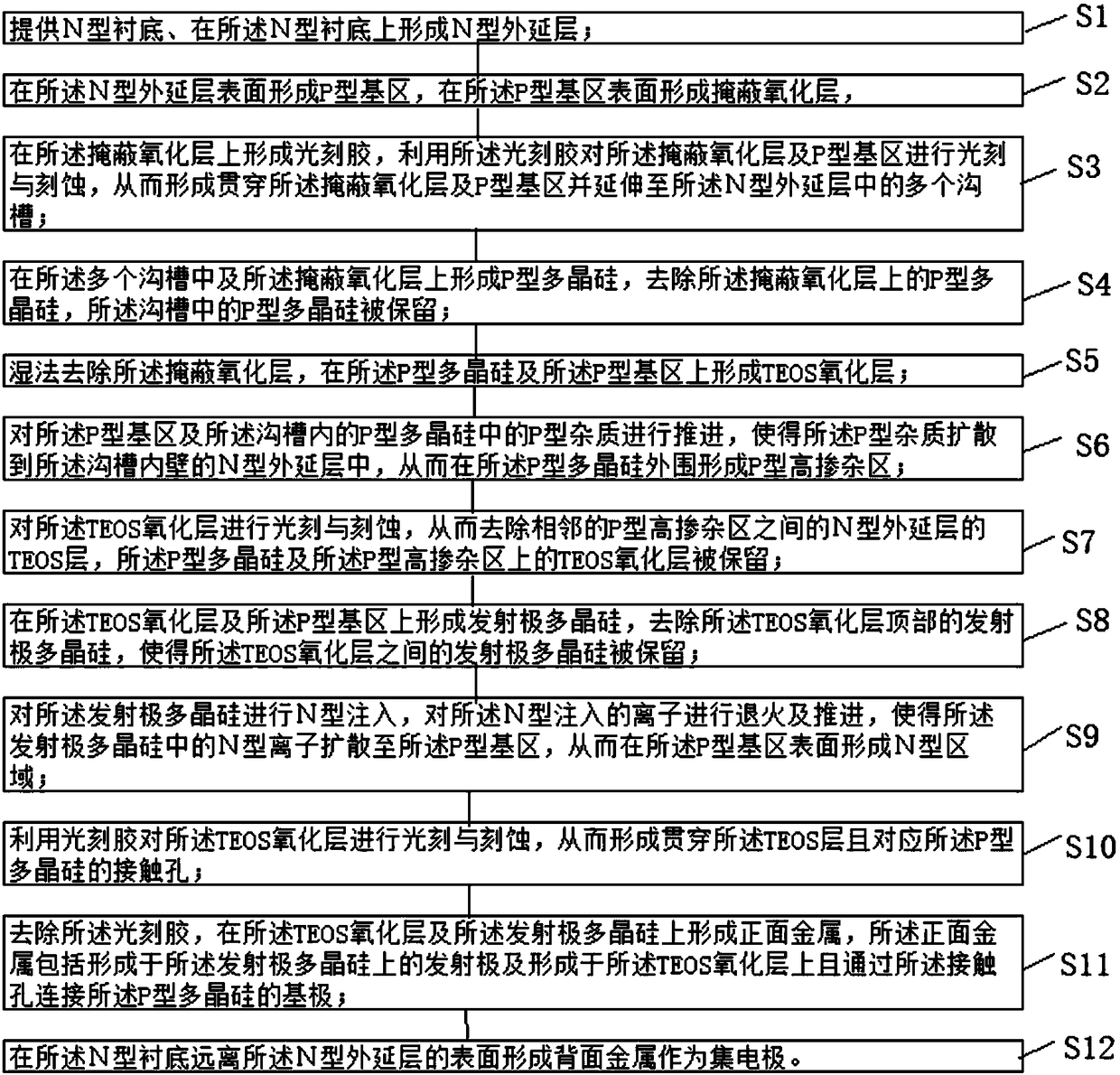

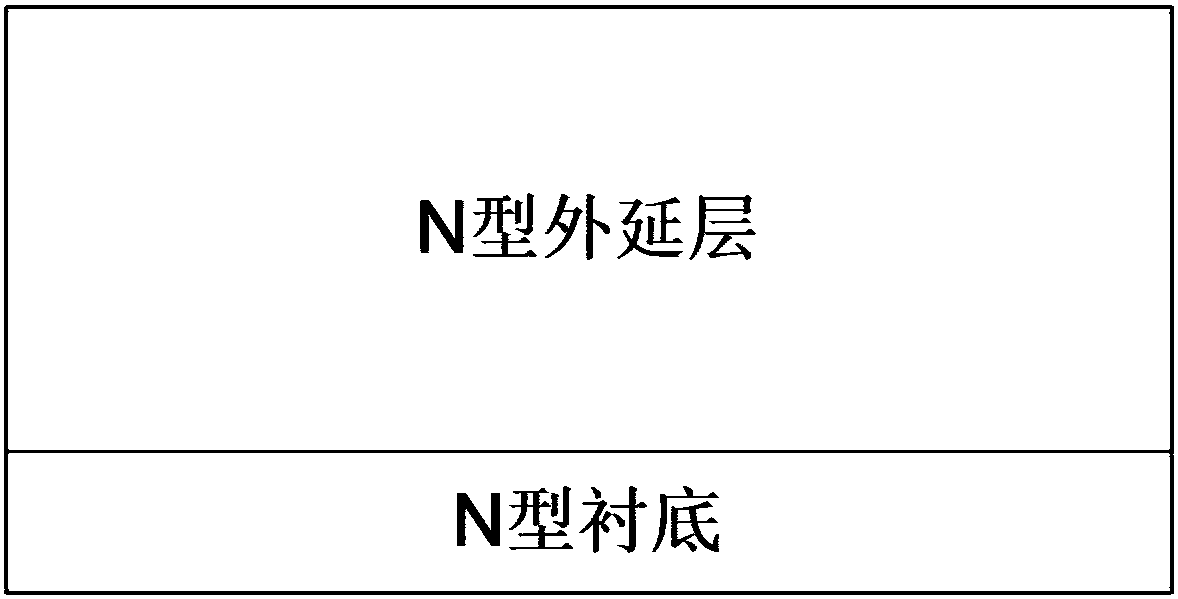

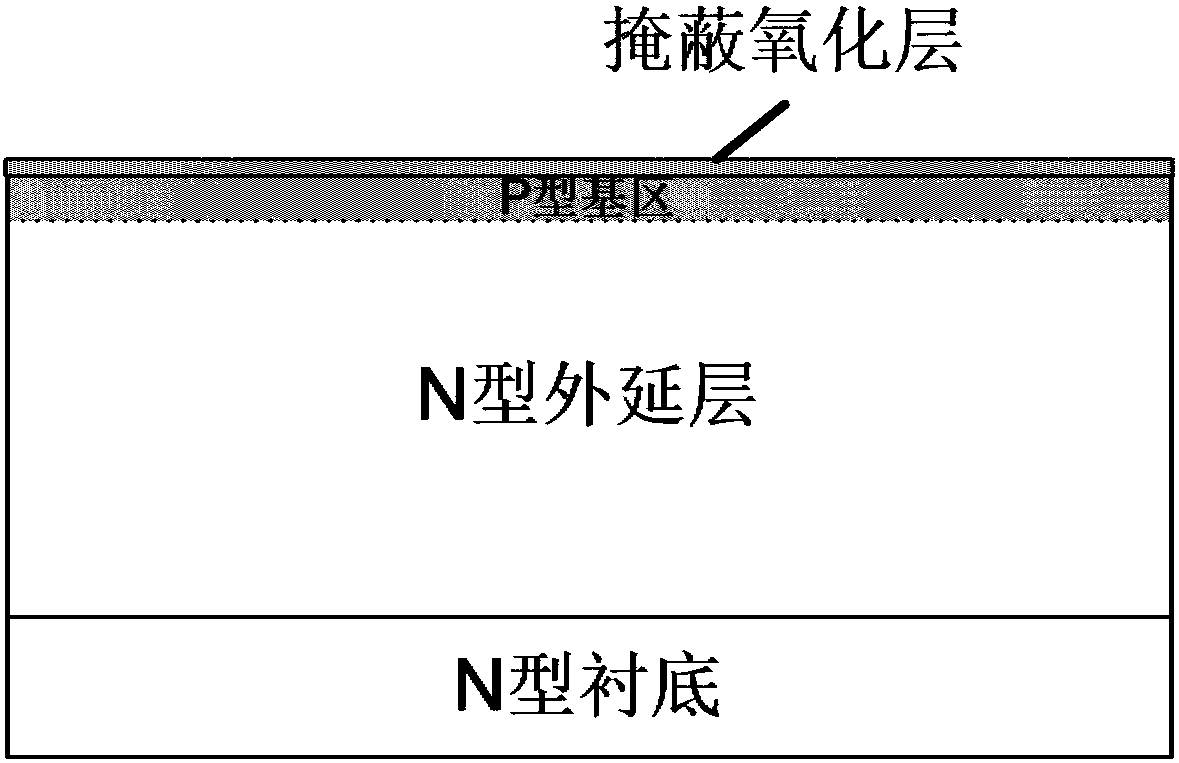

Trench triode and manufacturing method thereof

ActiveCN108133959AReduce partial pressureLower resistanceTransistorSemiconductor/solid-state device manufacturingEngineeringPolycrystalline silicon

The invention relates to a trench triode and a manufacturing method thereof. The trench triode comprises an N-type substrate, an N-type epitaxial layer which is formed on the N-type substrate, a P-type base region which is formed on the surface of the N-type epitaxial layer, multiple trenches which penetrate through the P-type base region and extend to the N-type epitaxial layer, a P-type high doped region which is formed on the side wall of multiple trenches, P-type polycrystalline silicon which is arranged in multiple trenches, an N-type region which is formed on the surface of the P-type base region, a TEOS oxide layer which is formed on the P-type polycrystalline silicon and the -type high doped region, emitter polysilicon which is formed on the N-type region, a contact hole which penetrates through the TEOS oxide layer and is corresponding to the P-type polycrystalline silicon, front metal and back metal. The front metal comprises an emitter which is formed on the emitter polysilicon and a base electrode which is formed on the TEOS oxide layer and connected with the P-type polycrystalline silicon through the contact hole. The back metal is formed on the surface, which is awayfrom the N-type epitaxial layer, of the N-type substrate to act as the collecting electrode.

Owner:浙江昌新生物纤维股份有限公司

Preparation method of PERC battery

PendingCN112635617AReduce tensionIncrease profitFinal product manufactureChemical vapor deposition coatingRefractive indexPhysical chemistry

The invention belongs to the technical field of photovoltaics, and particularly relates to a preparation method of a PERC battery. The method is mainly used for improving the efficiency of the PERC battery. The method comprises a diffusion step, an etching step and a back film step which are carried out in sequence, an etching solution is adopted in the etching step, and chemical components of the etching solution comprise HNO3, HF, H2SO4 and H2O; and in the back film step, SiH4 and NH3 are adopted to carry out film coating deposition on the back surface of the silicon wafer, and the film coating deposition times is twice. Compared with the prior art, the method increases the refractive index of the silicon wafer substrate, increases the light absorption rate of the PERC cell, and increases the efficiency of the PERC cell.

Owner:ZHEJIANG BEYONDSUN PV