P-type FET and manufacturing method thereof

A manufacturing method, N-type technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of inability to further reduce device leakage and increase junction leakage current, and achieve the goal of eliminating subthreshold leakage current and junction leakage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

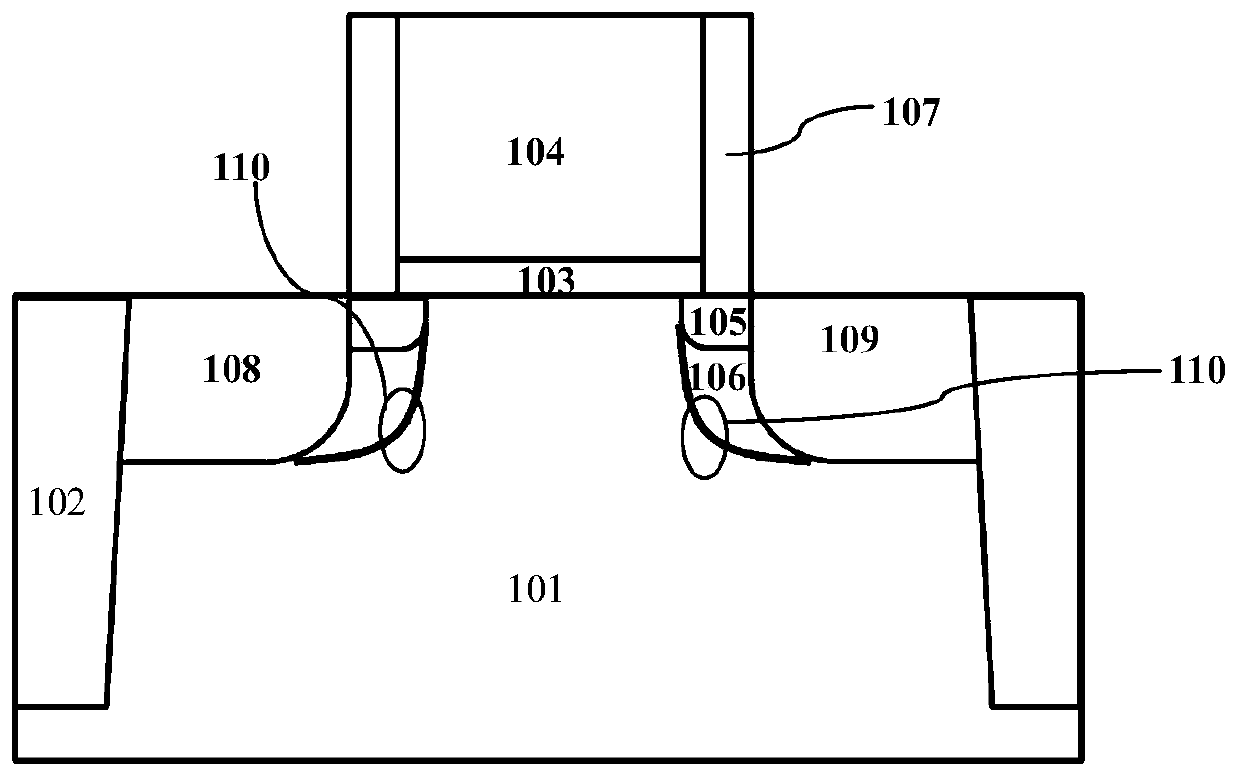

[0070] Such as Figure 4 Shown is a schematic diagram of the structure of the P-type FET of the embodiment of the present invention; the P-type FET of the embodiment of the present invention includes a gate structure, a side wall 7, a channel region, a P-type lightly doped drain region 5, a source region 8, and a drain region. region 9 and halo implant region 6.

[0071] The gate structure is formed on the surface of the semiconductor substrate 1 . Field oxygen 2 is also formed on the semiconductor substrate 1, and the field oxygen 2 isolates an active region.

[0072] An N-type well is formed on the semiconductor substrate 1, the formation region of the P-type FET is located in the formation region of the N-type well, and the gate structure is formed on the surface of the N-type well; N The channel region doped with the N type is composed of the N-type well located between the lightly doped drain regions 5 and between the source region 8 and the drain region 9 and covered b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More