Transistor and manufacturing method for same

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of obvious short-channel effect of transistors and unsatisfactory device performance, etc., to improve short-channel effect and improve performance , The effect of reducing the junction leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The short channel effect of the transistor manufactured by the existing method is obvious, and the performance of the device is not ideal. With the development of semiconductor technology, ultra-shallow junction technology is applied to make the source region and the drain region, and the ion lateral diffusion between the source region and the drain region is more serious, which makes the short channel effect more obvious, and the source region and the drain region There is a large junction capacitance and junction leakage current between the drain region and the semiconductor substrate, which reduces the response speed of the device and affects the performance of the device.

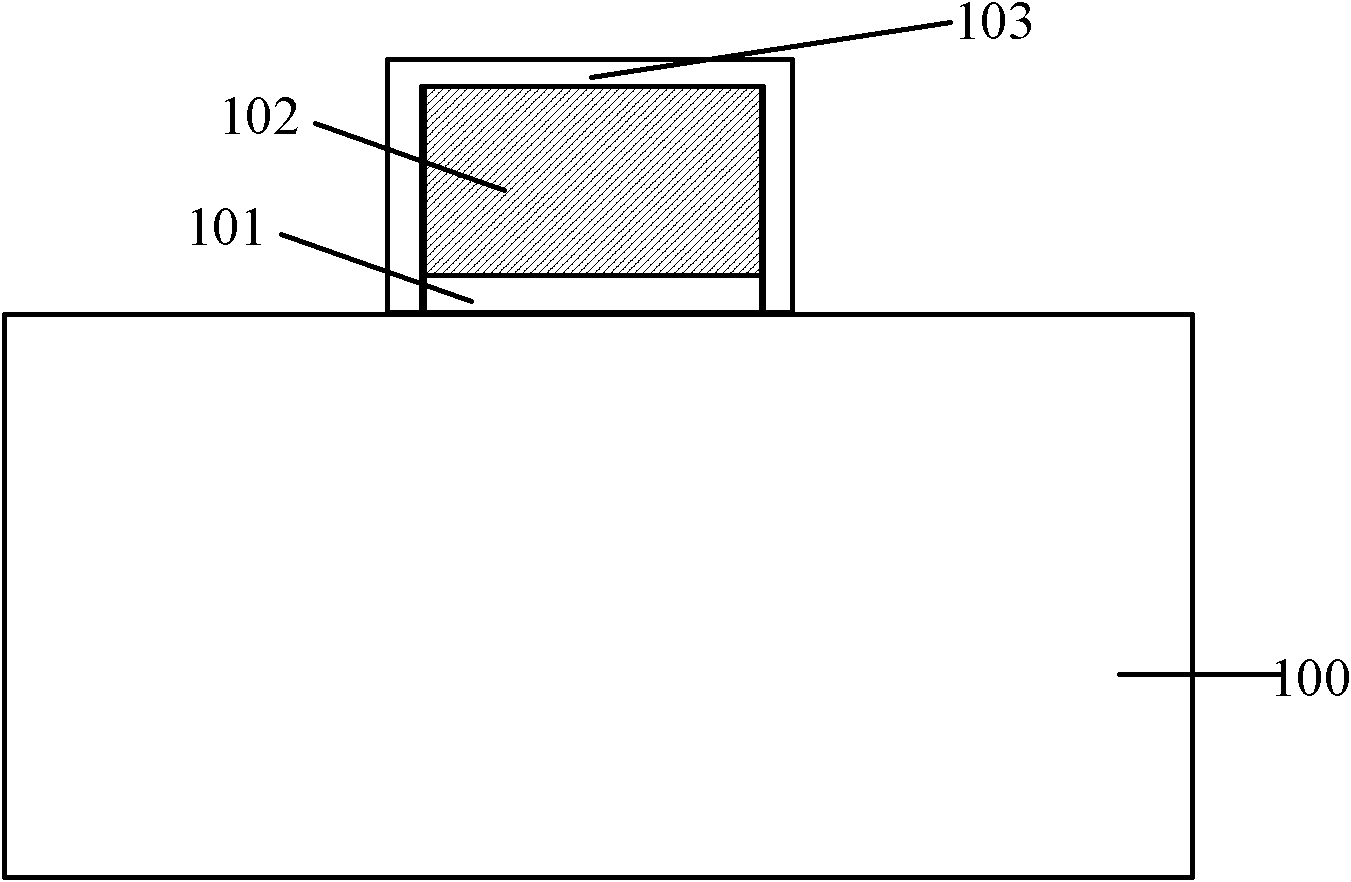

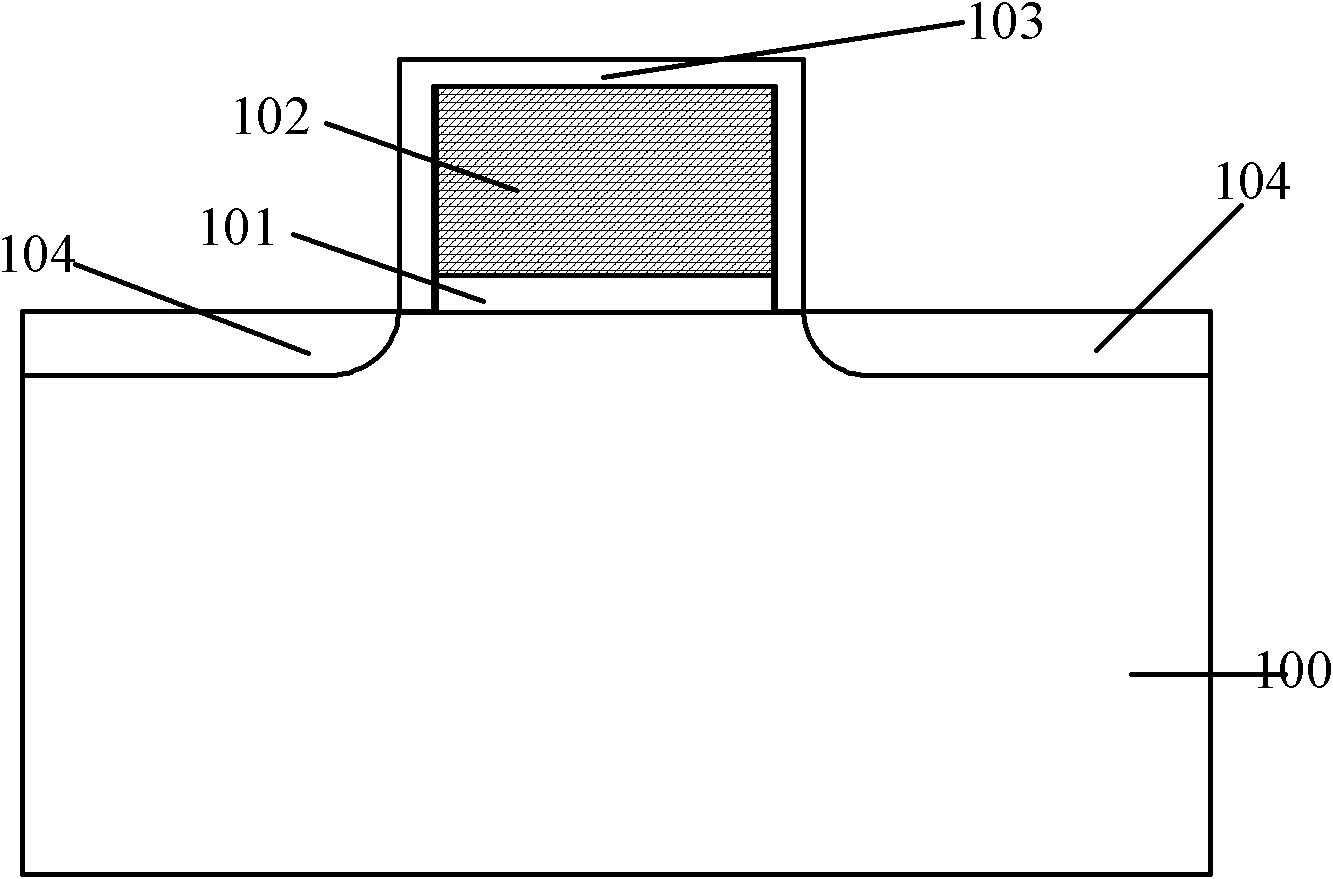

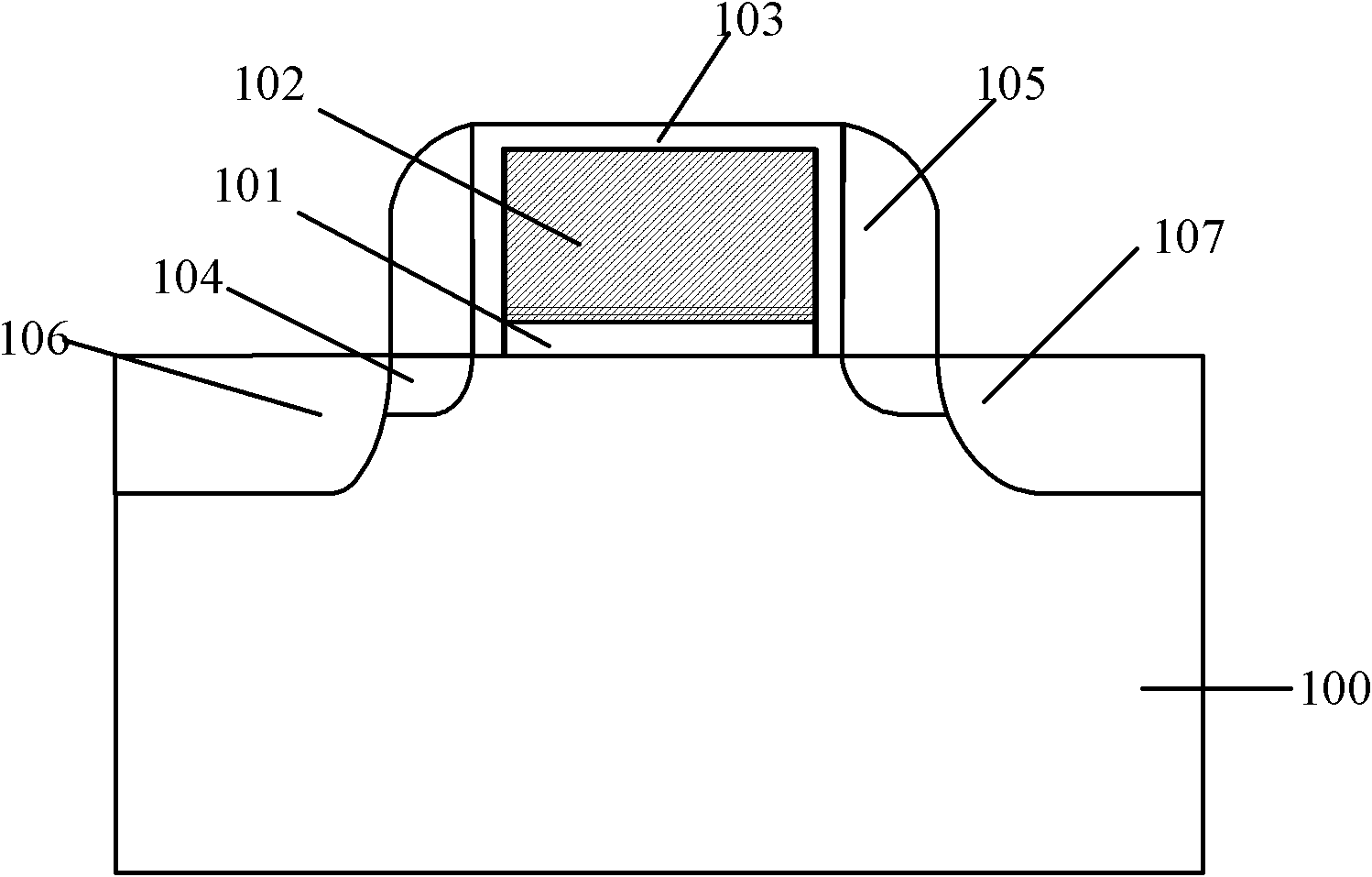

[0054] In order to solve the above problems, the inventor proposes a method for making a transistor, please refer to Figure 4 The schematic flow chart of the transistor manufacturing method of the present invention shown, the method includes:

[0055] Step S1, providing a semiconductor substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More