Patents

Literature

31results about How to "Improve data retention characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

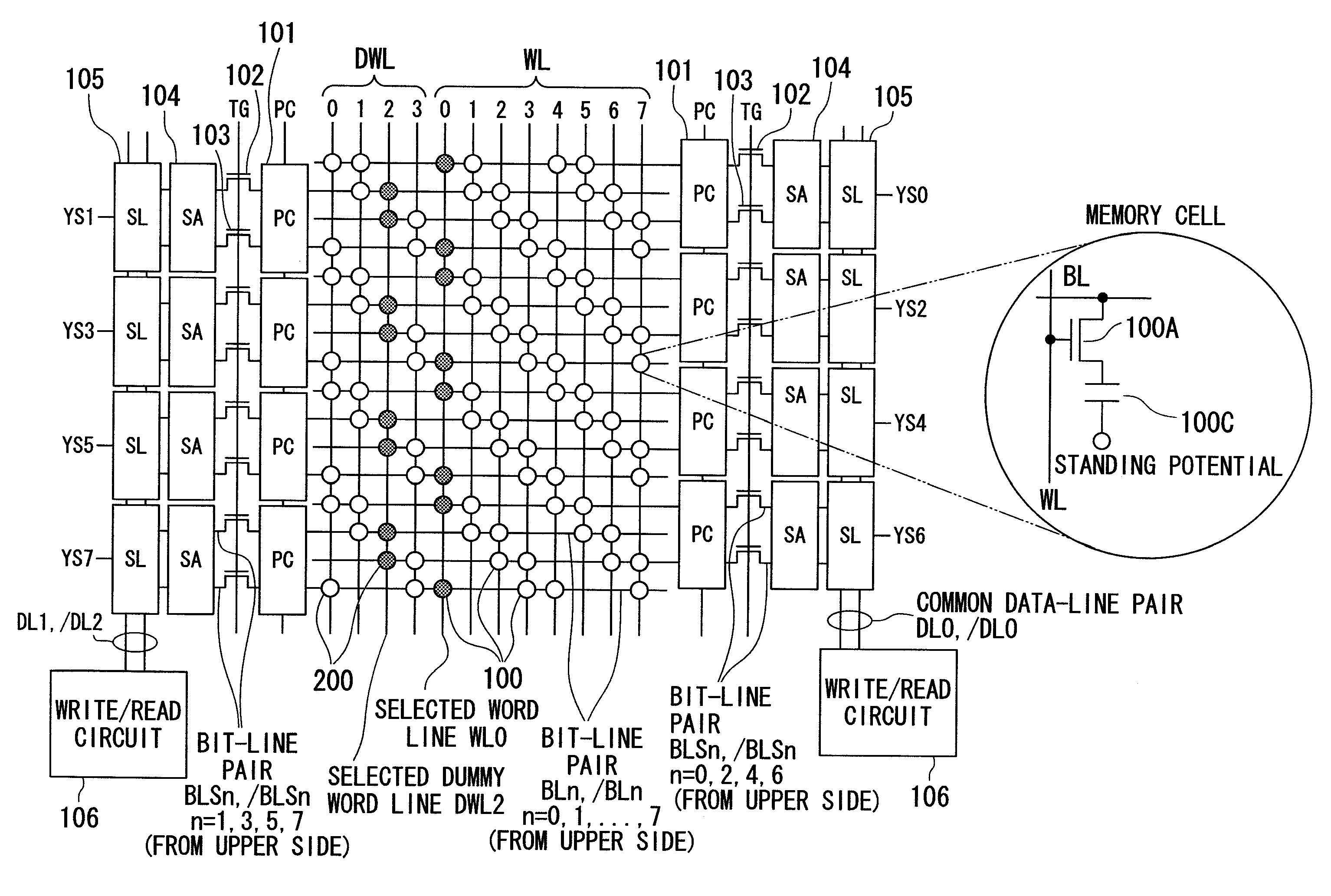

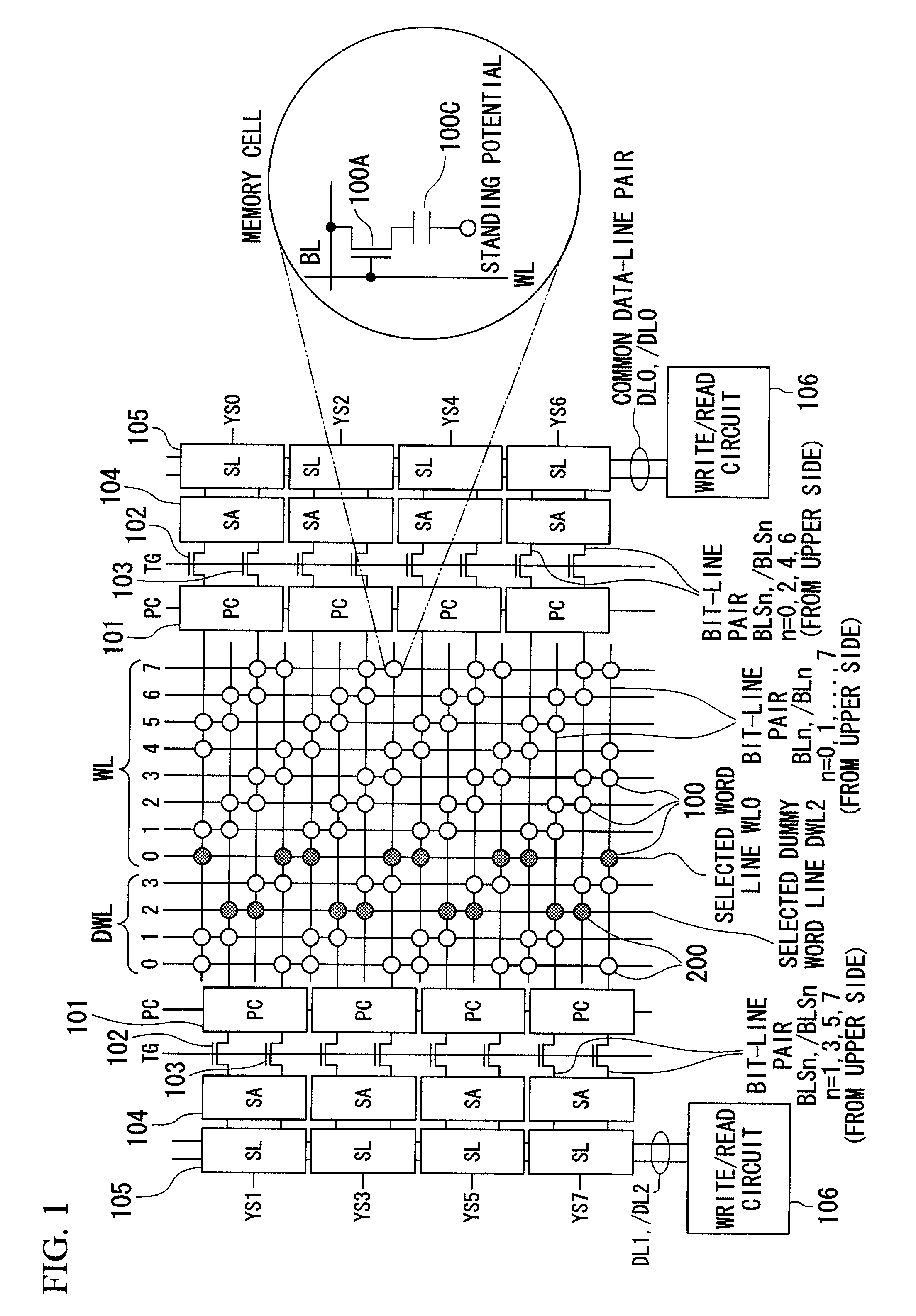

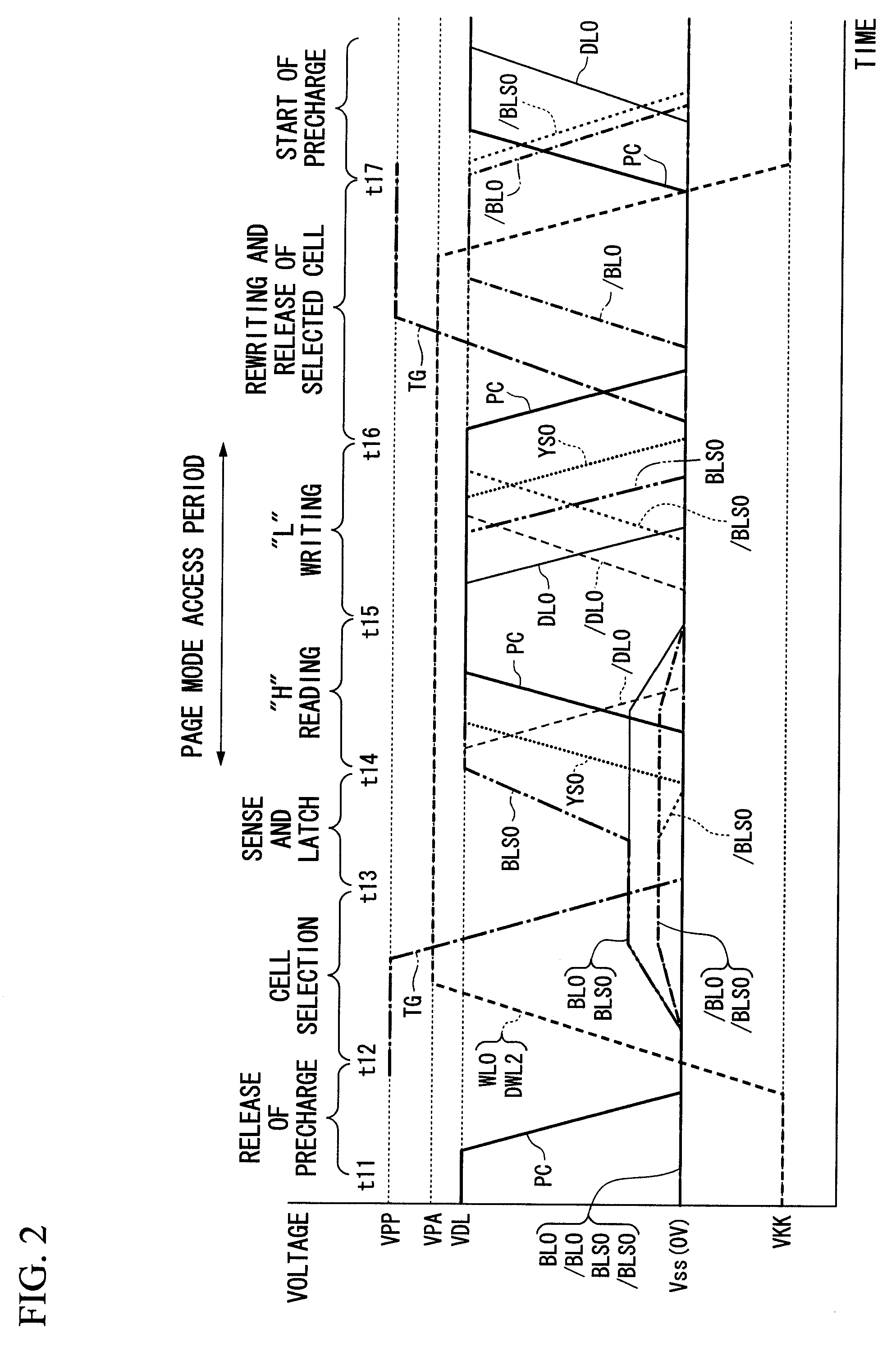

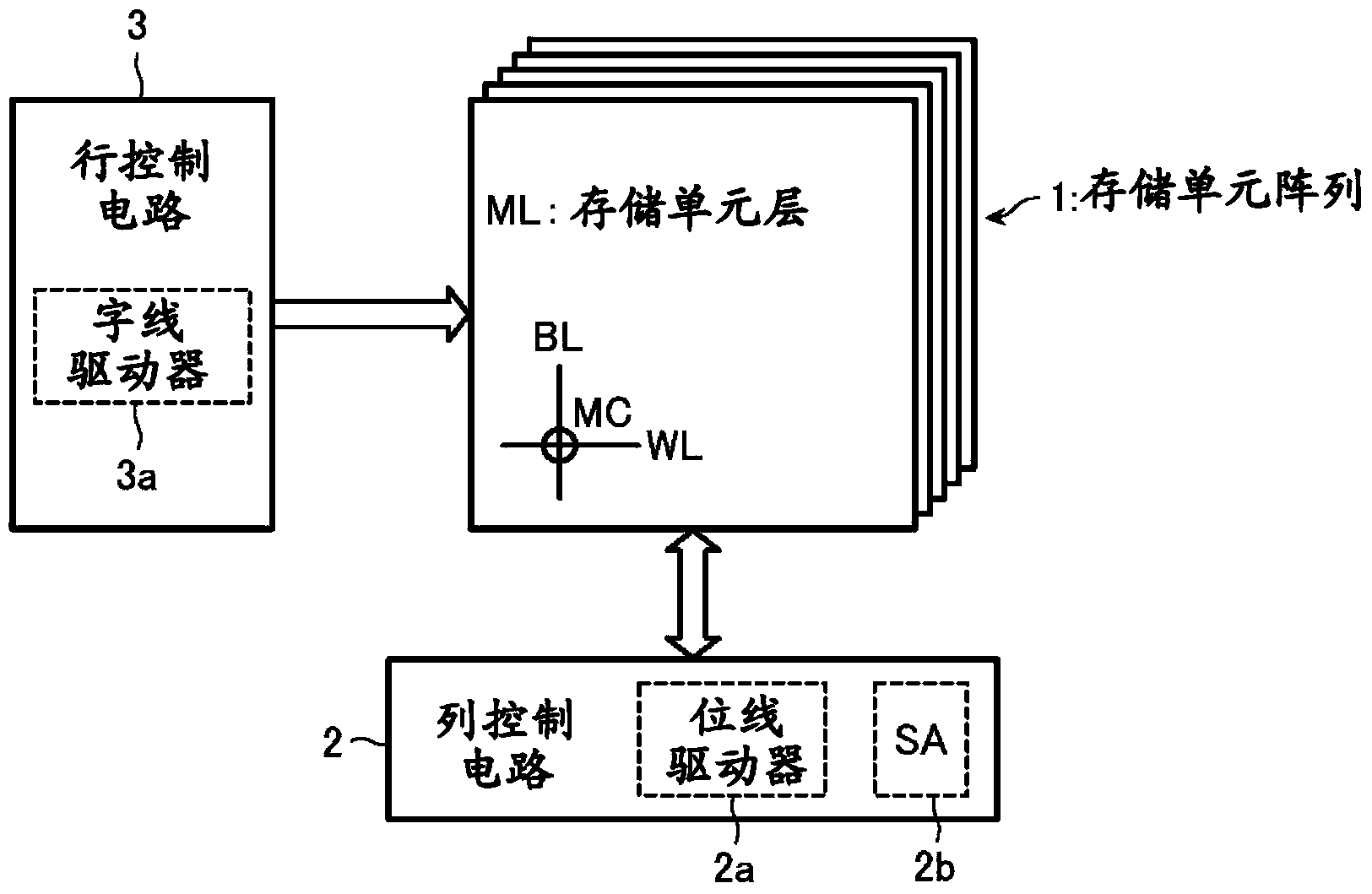

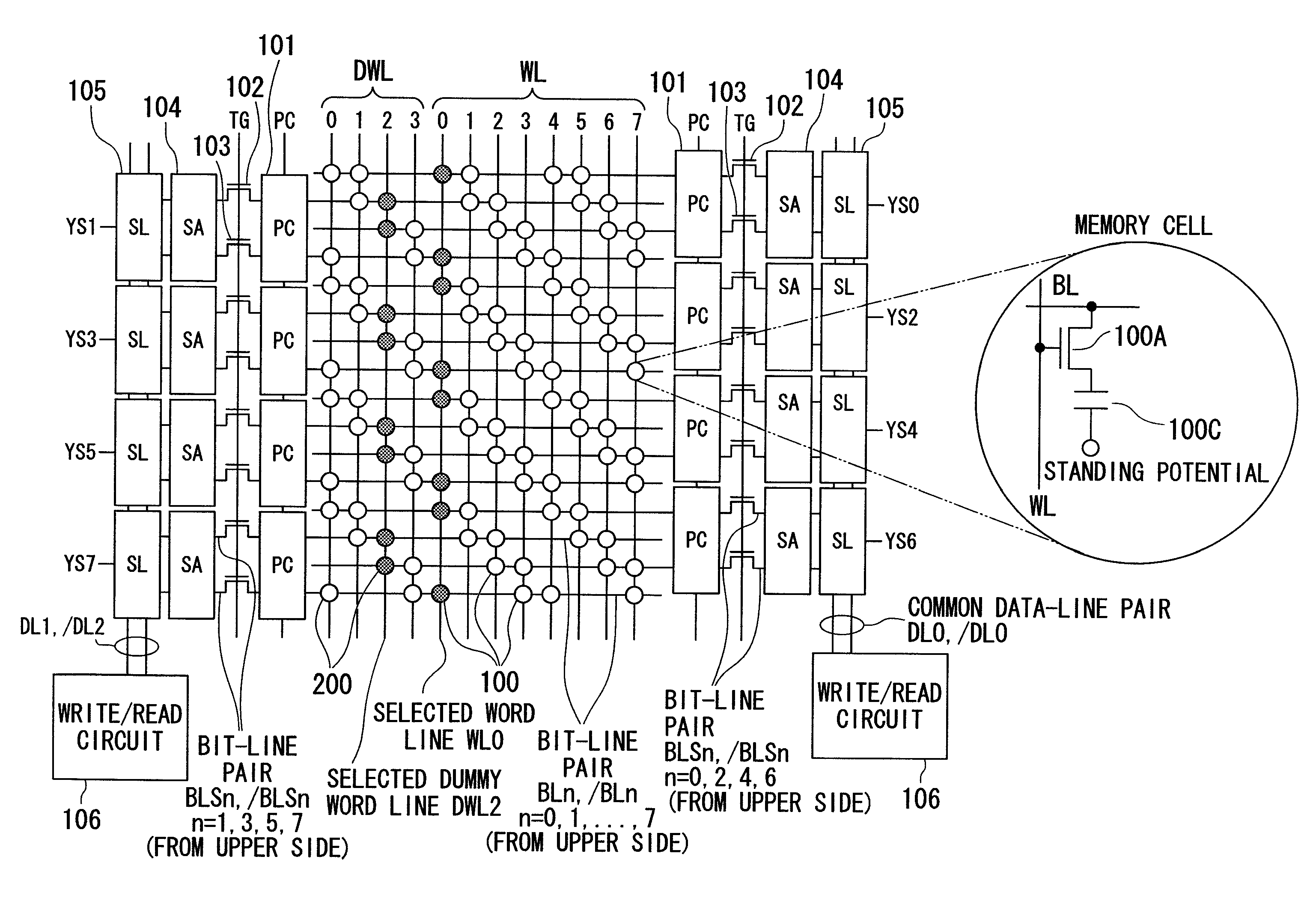

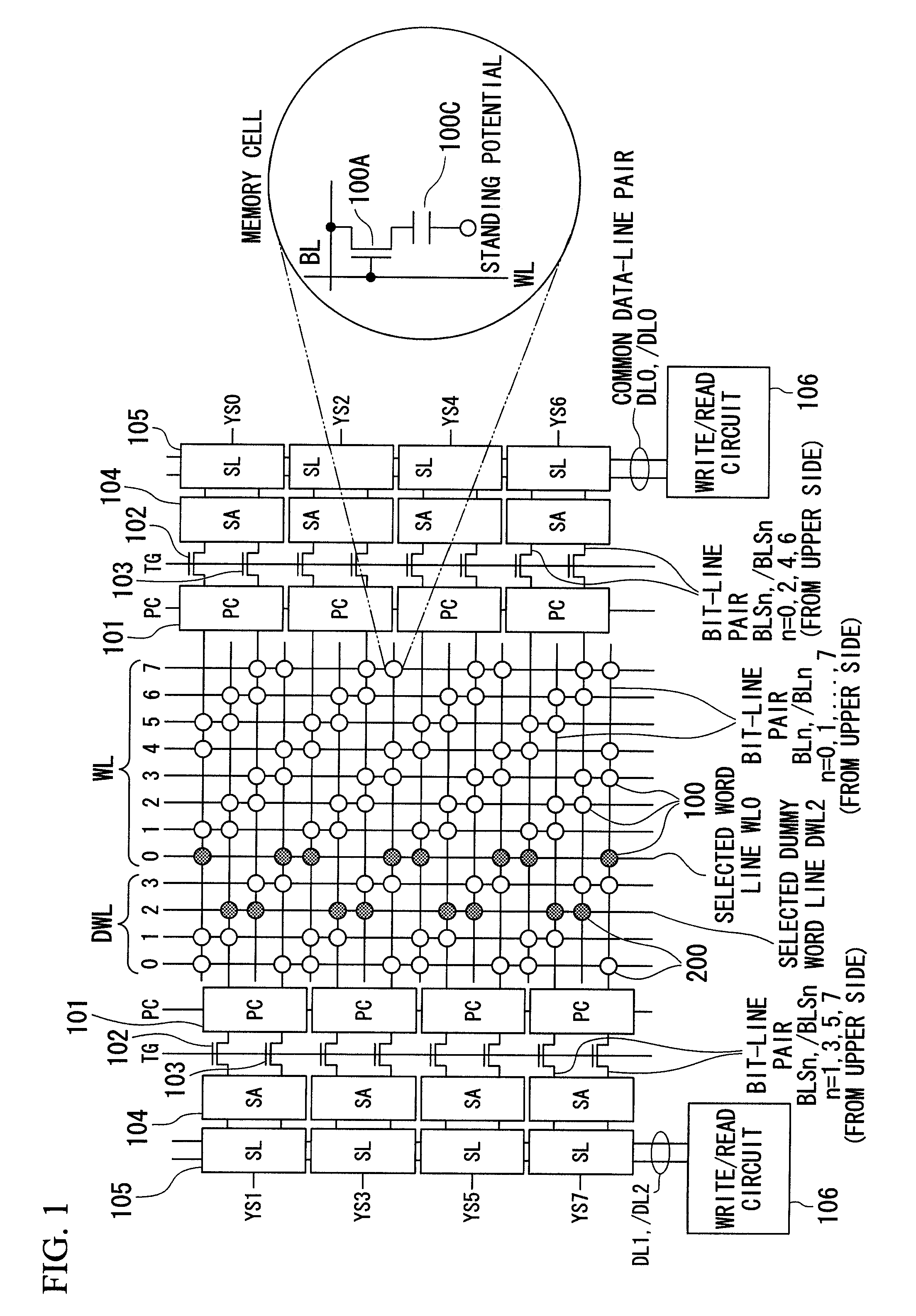

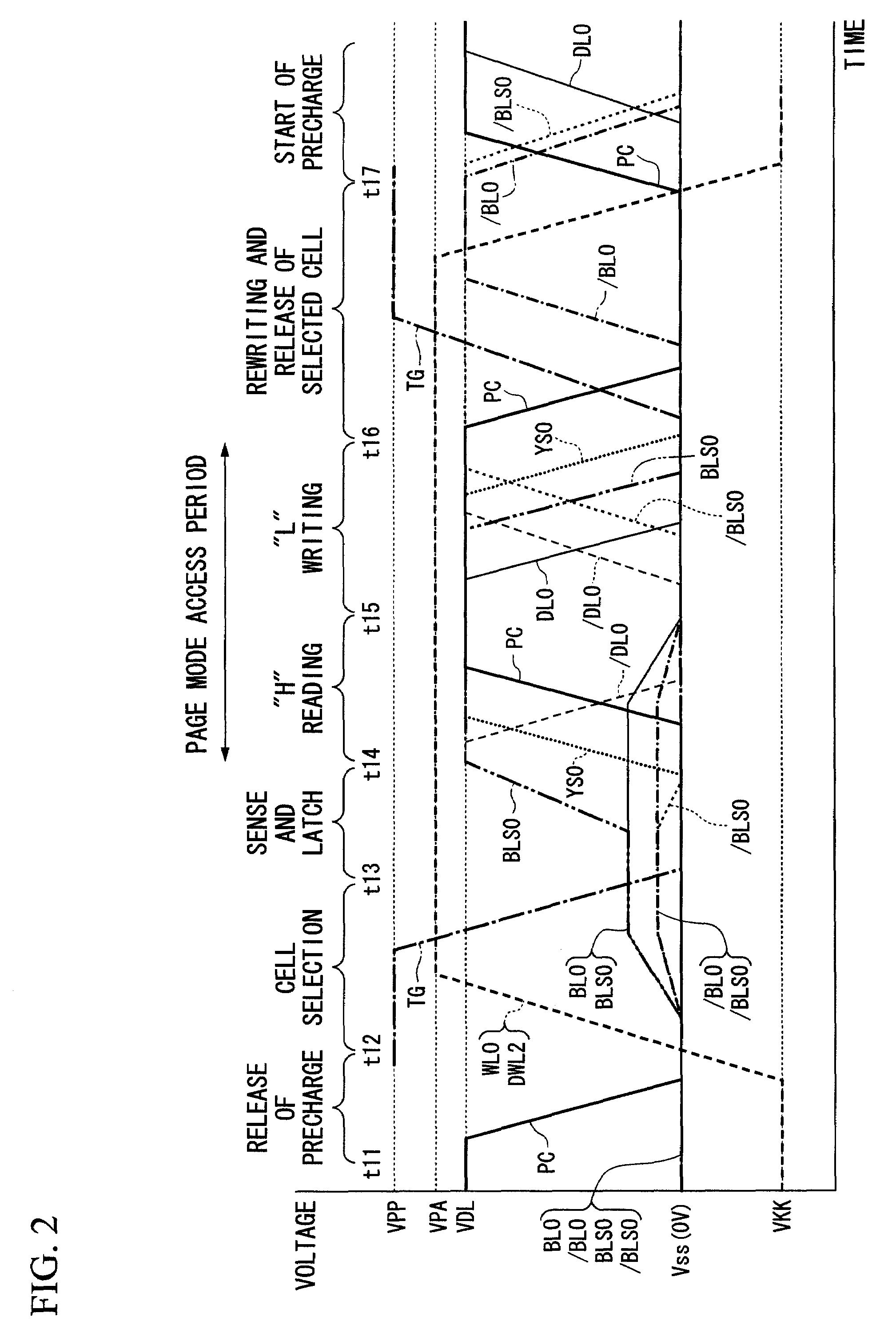

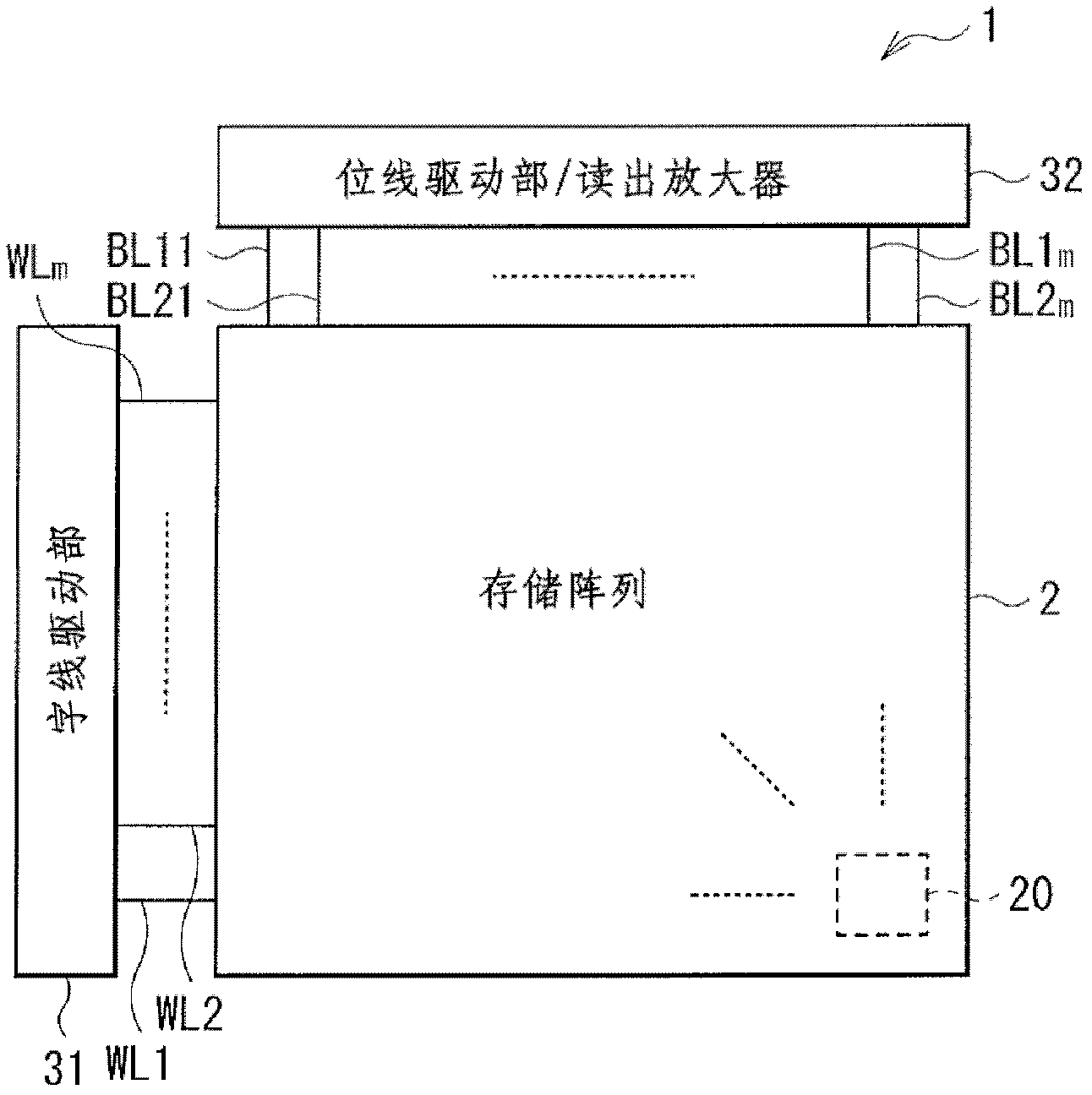

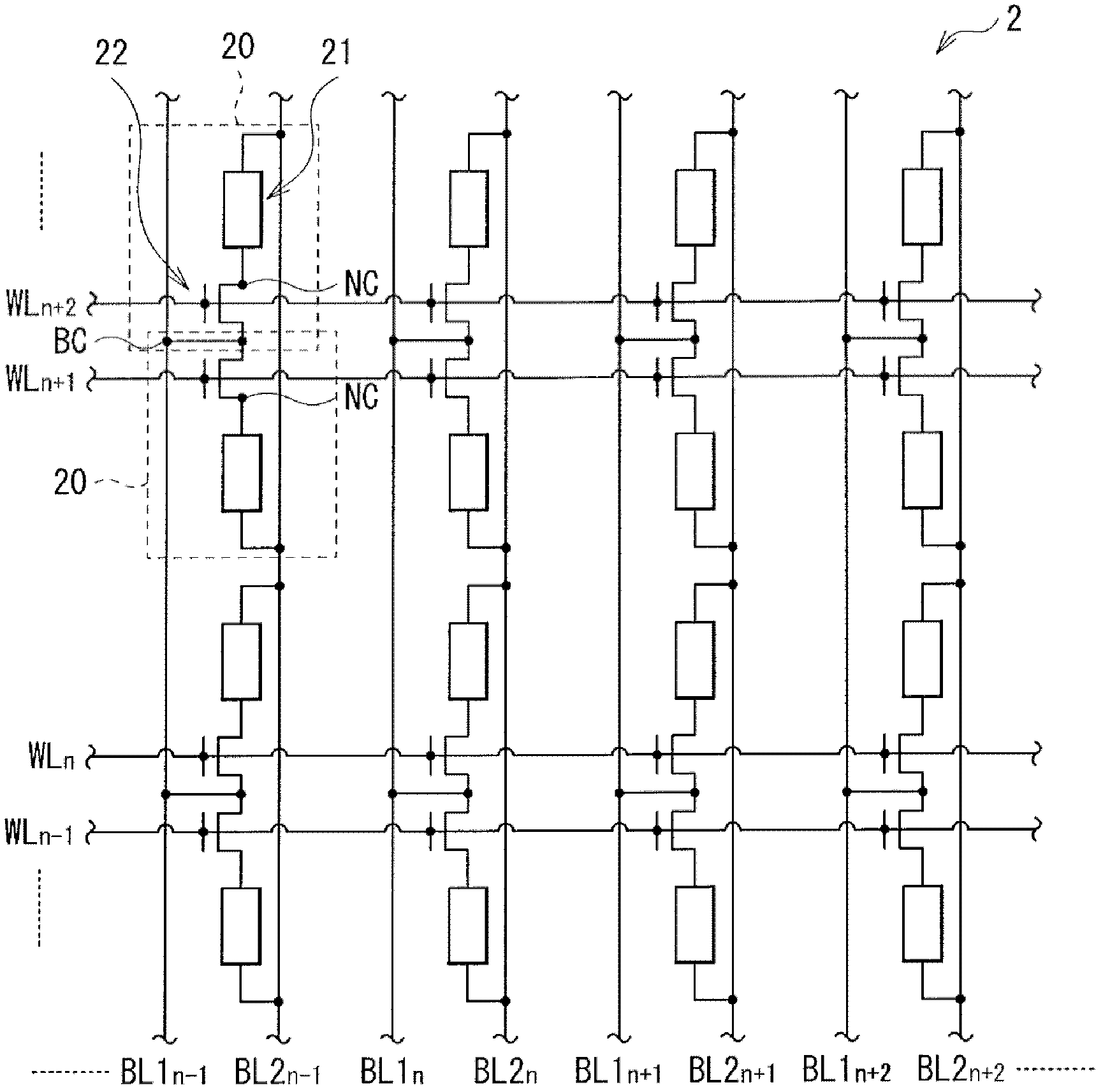

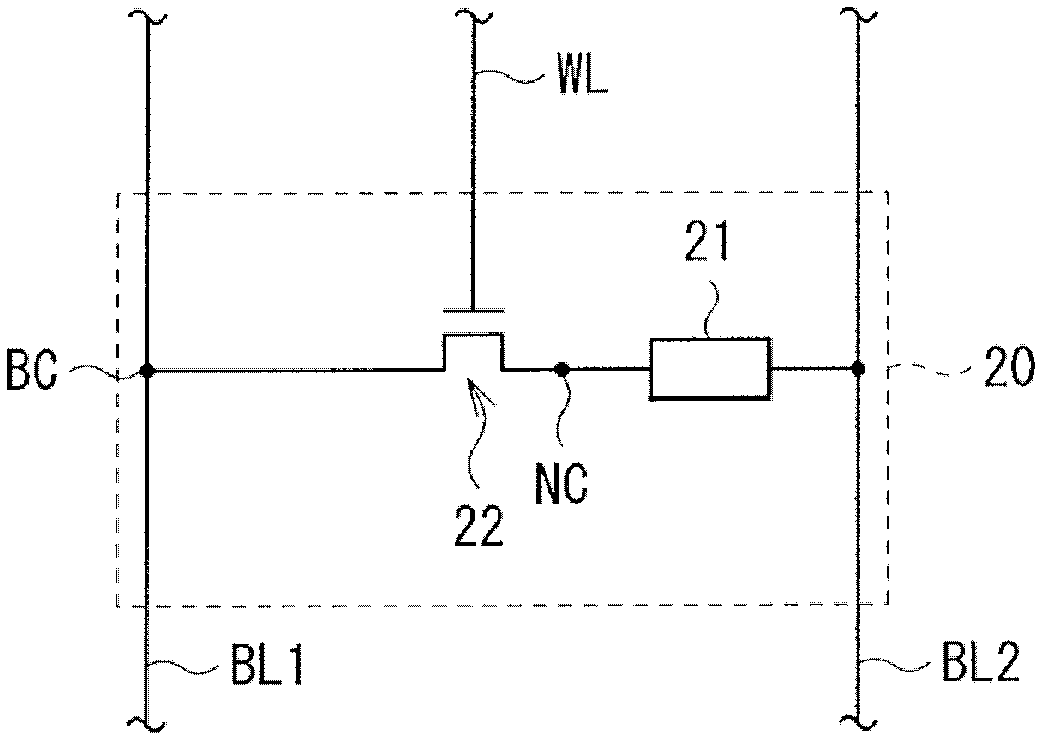

Semiconductor memory device for precharging bit lines except for specific reading and writing periods

InactiveUS20080291762A1Improve characteristicPrevent data-charge lossDigital storageSense amplifierBit plane

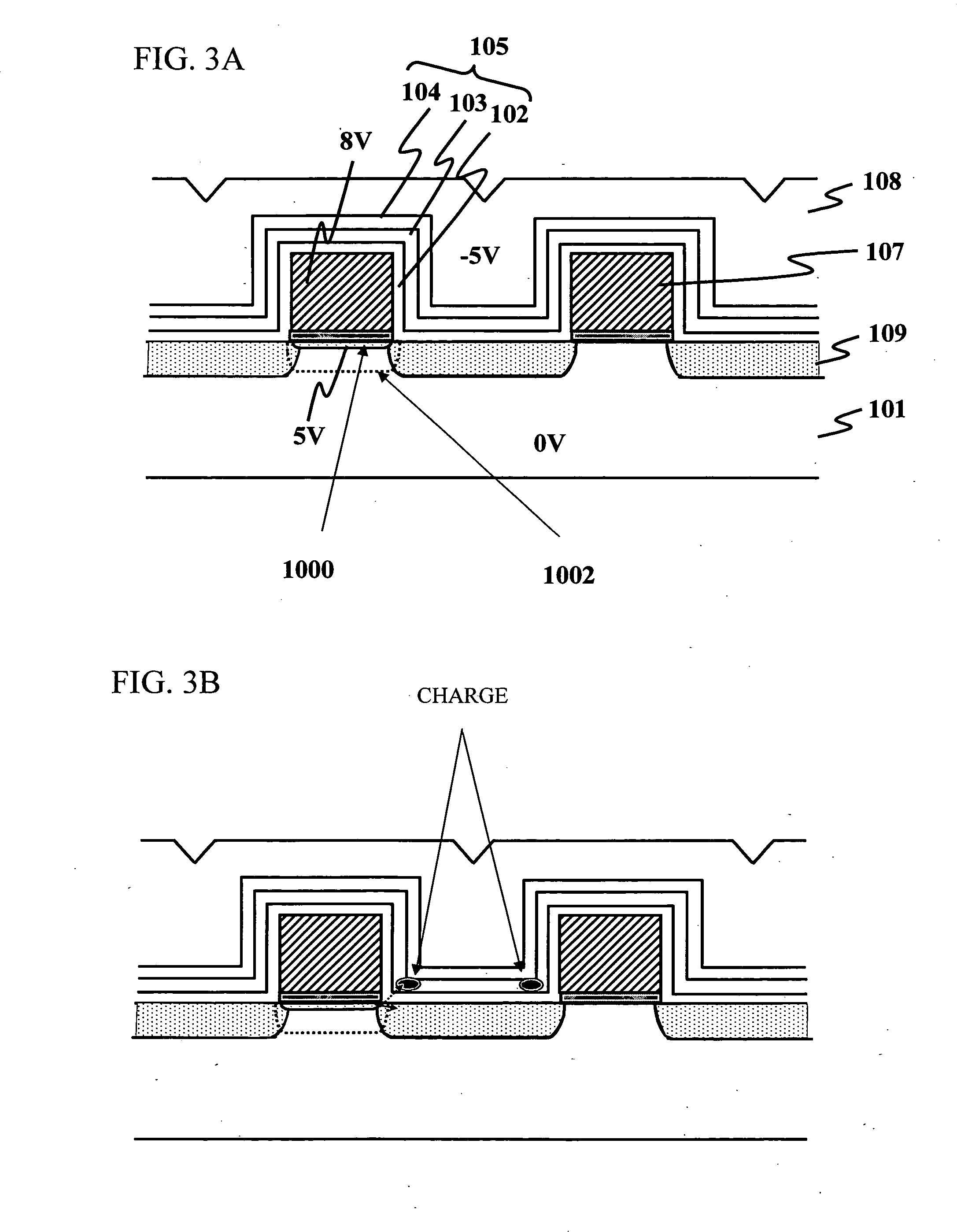

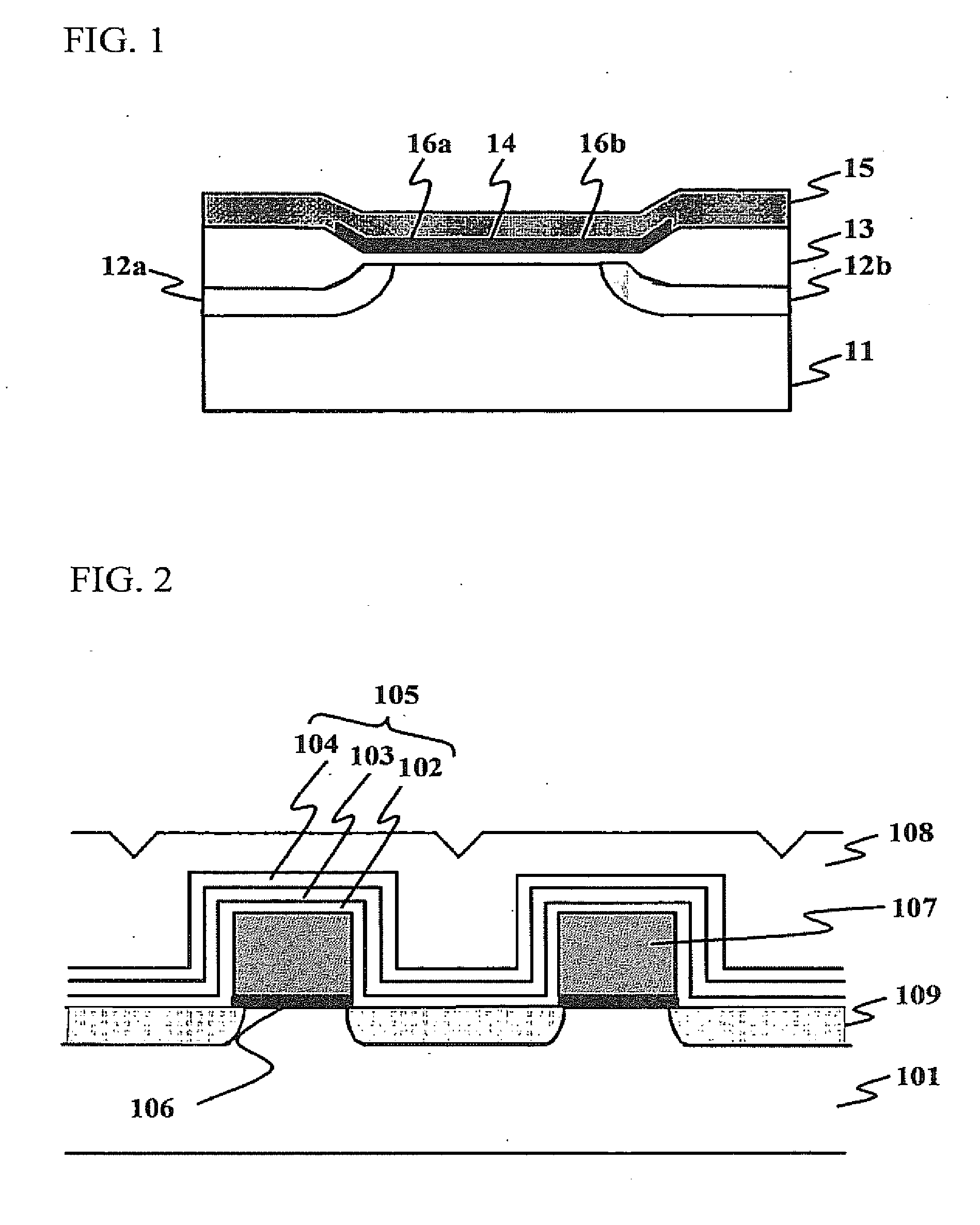

A semiconductor memory device includes a memory cell having an FET of a floating body type, and a capacitor for storing a data charge; a bit line to which the source or the drain of the FET is connected; a precharging device for performing precharge control so that the bit line has a predetermined precharge voltage; a sense amplifier for amplifying and storing the potential of the bit line, which is set in accordance with the data charge read from the memory cell; a switching device, provided between the bit line and the sense amplifier, for performing selective connection therebetween; and a control part for controlling the precharging device, the sense amplifier, and the switching device. Except for each period for performing data reading or writing, the control part makes the precharging device perform the precharge control and makes the switching device disconnect the bit line from the sense amplifier.

Owner:LONGITUDE SEMICON S A R L

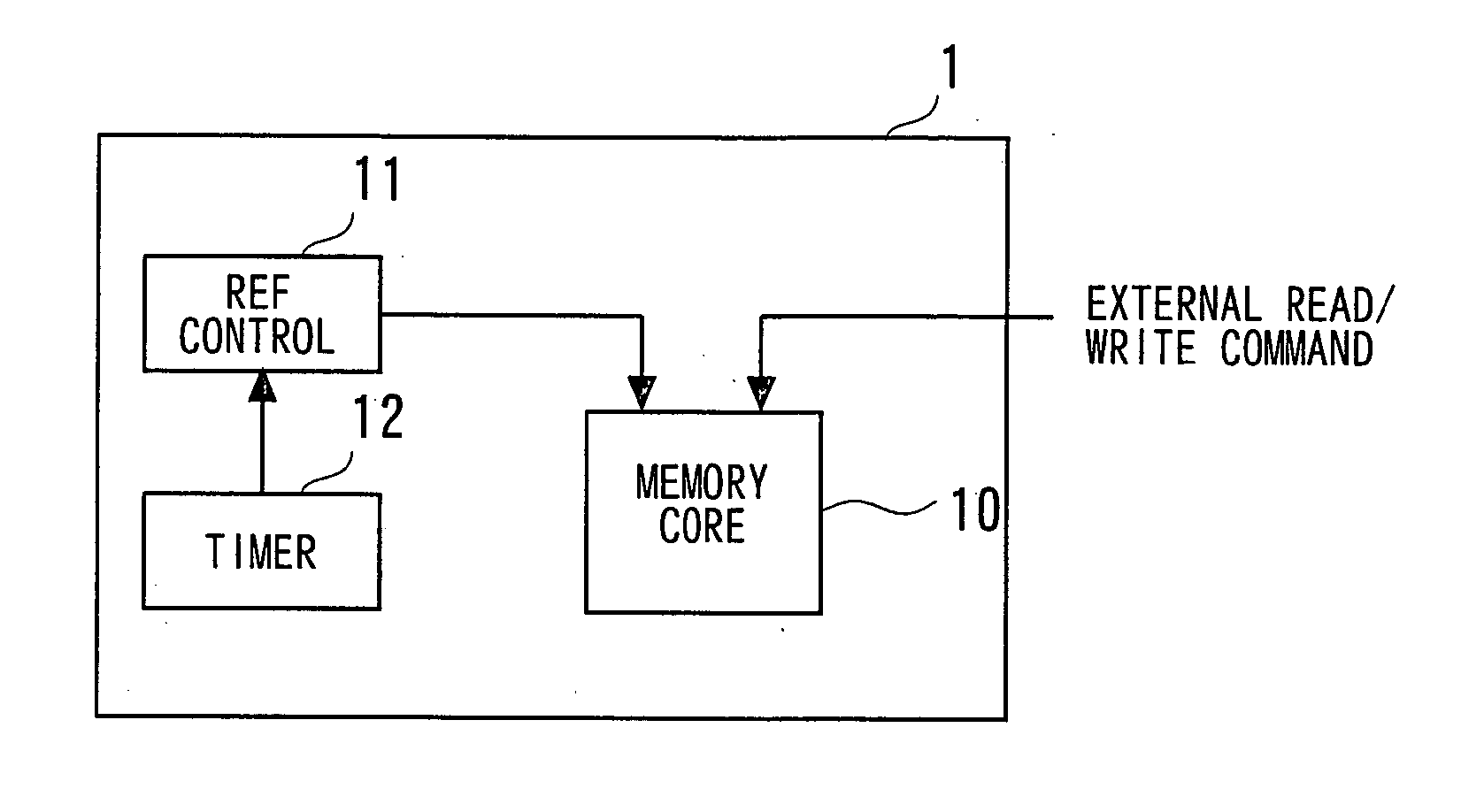

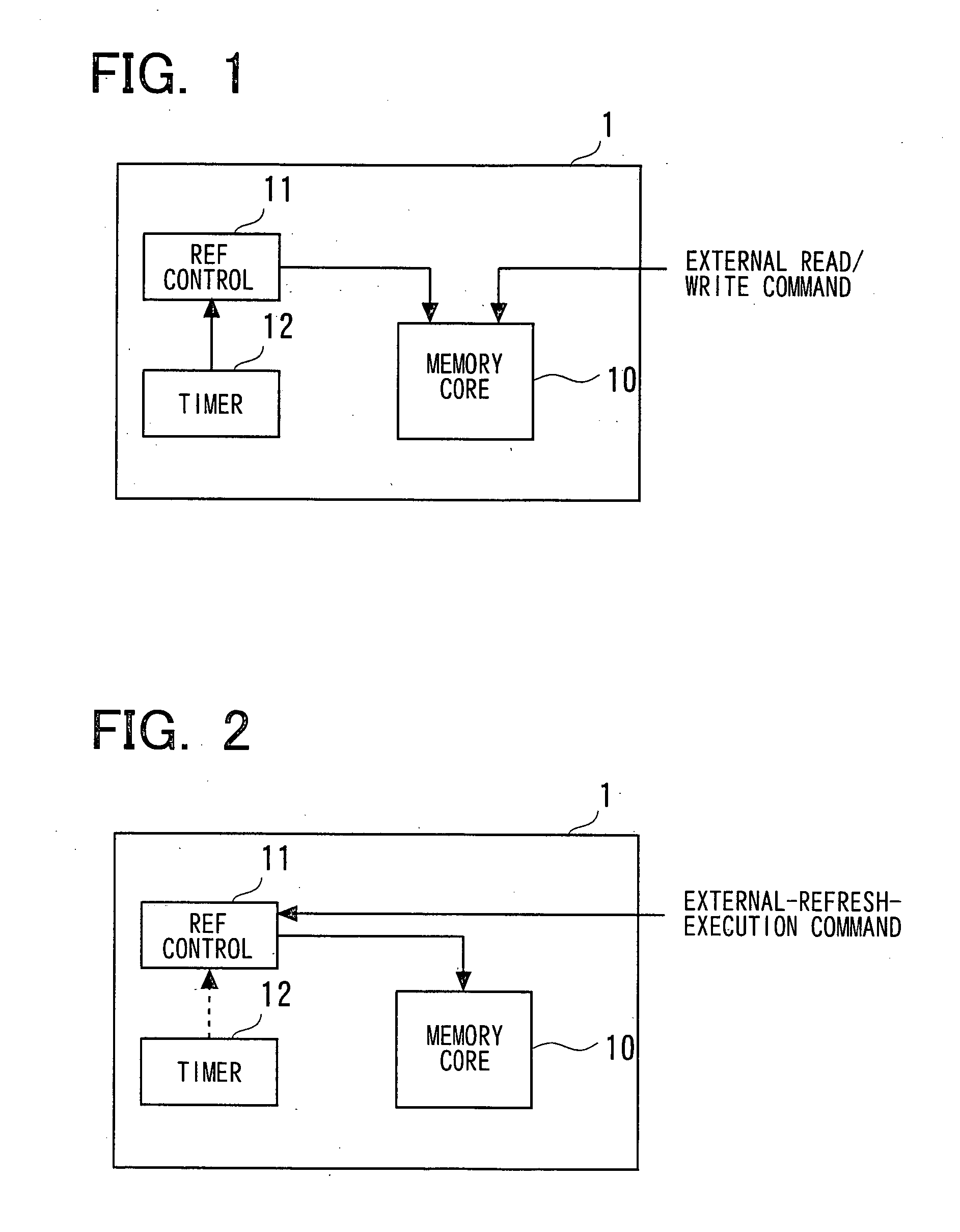

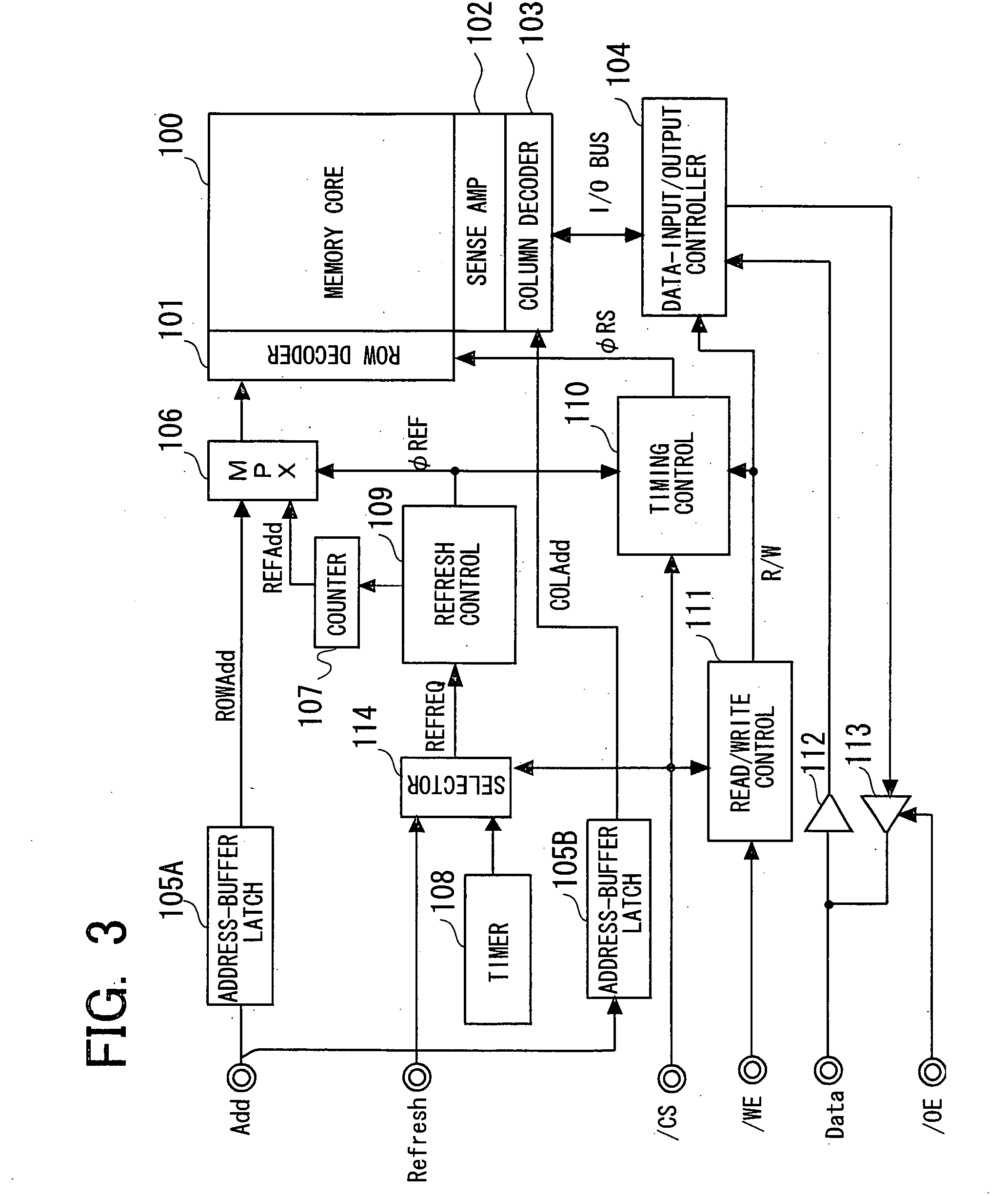

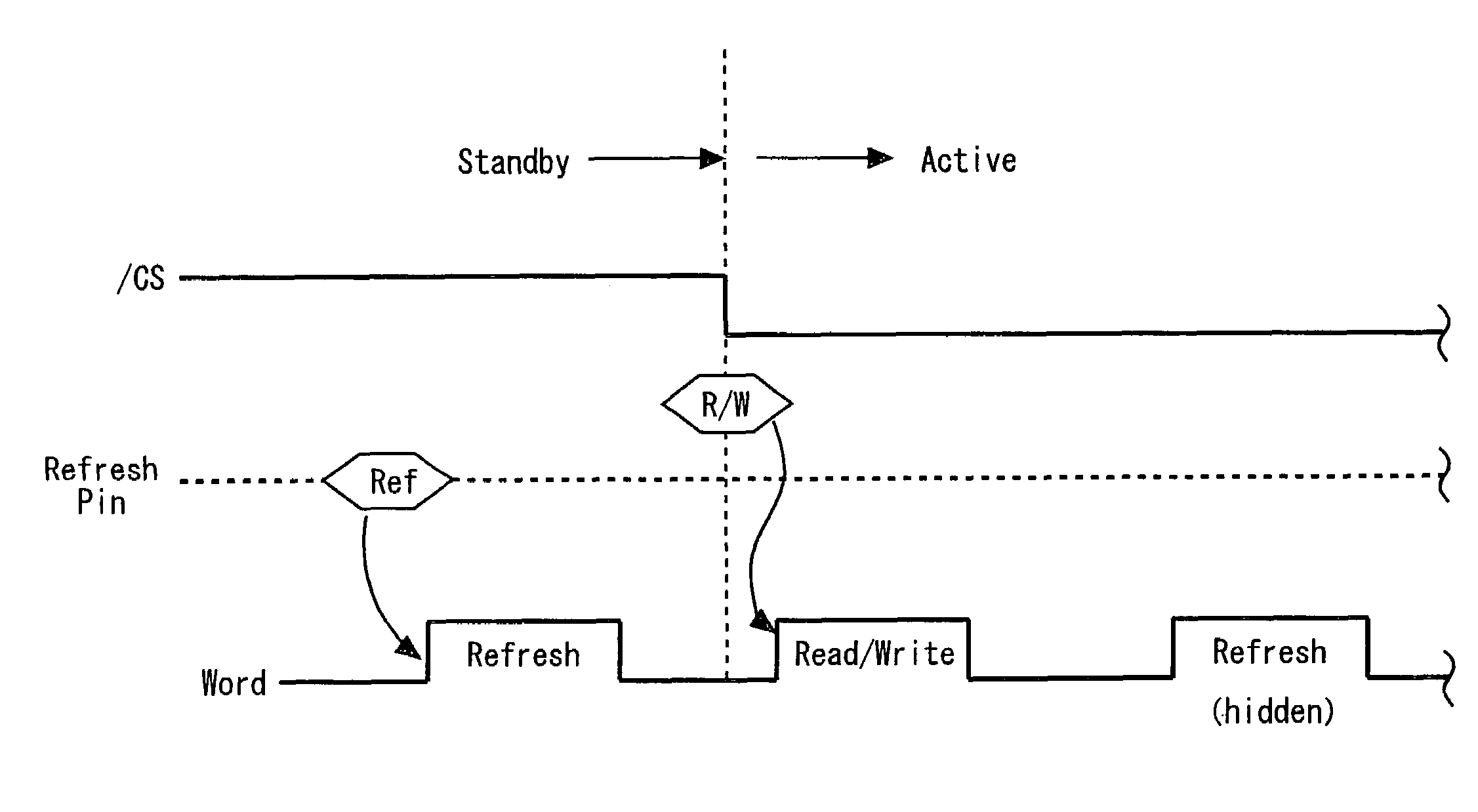

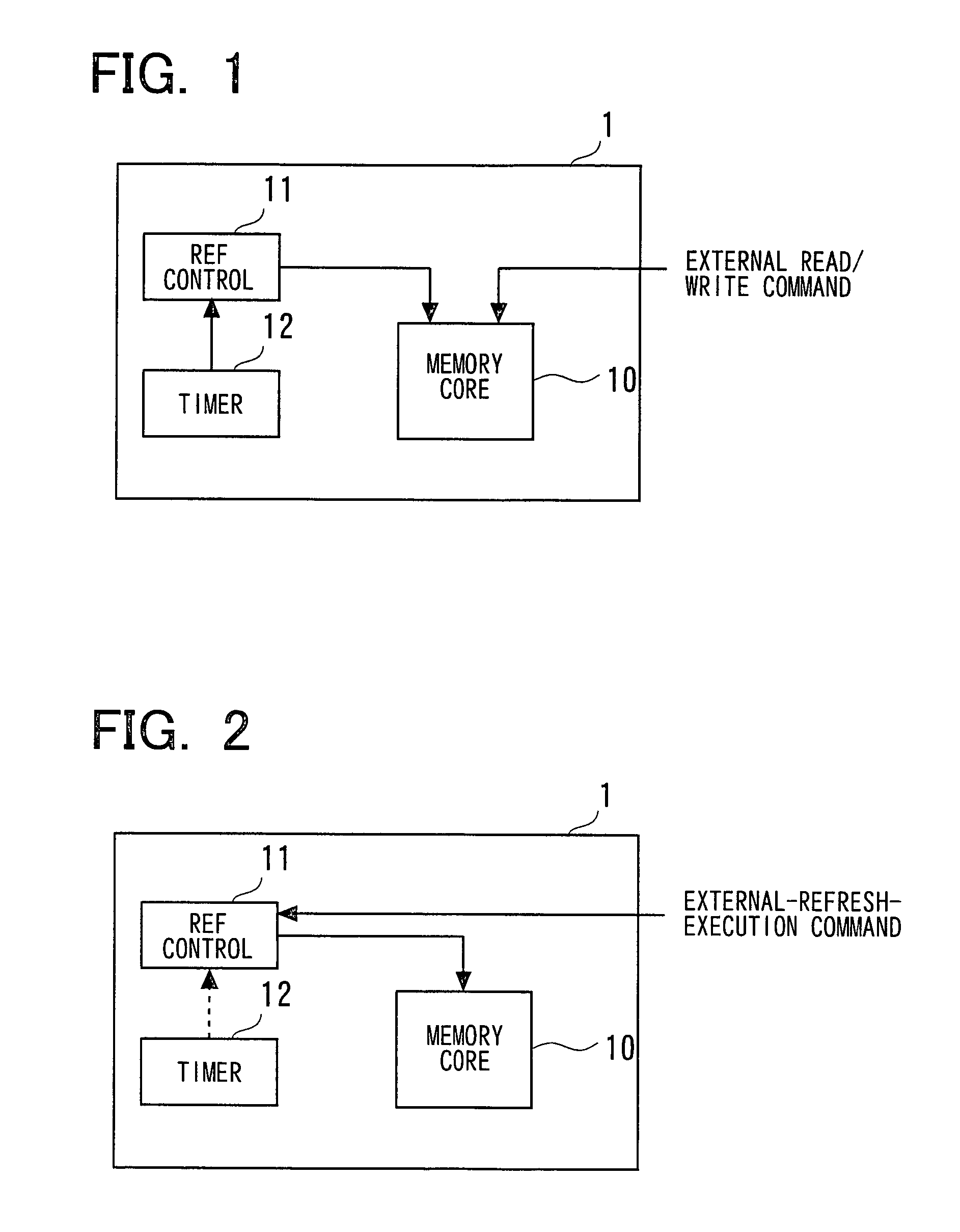

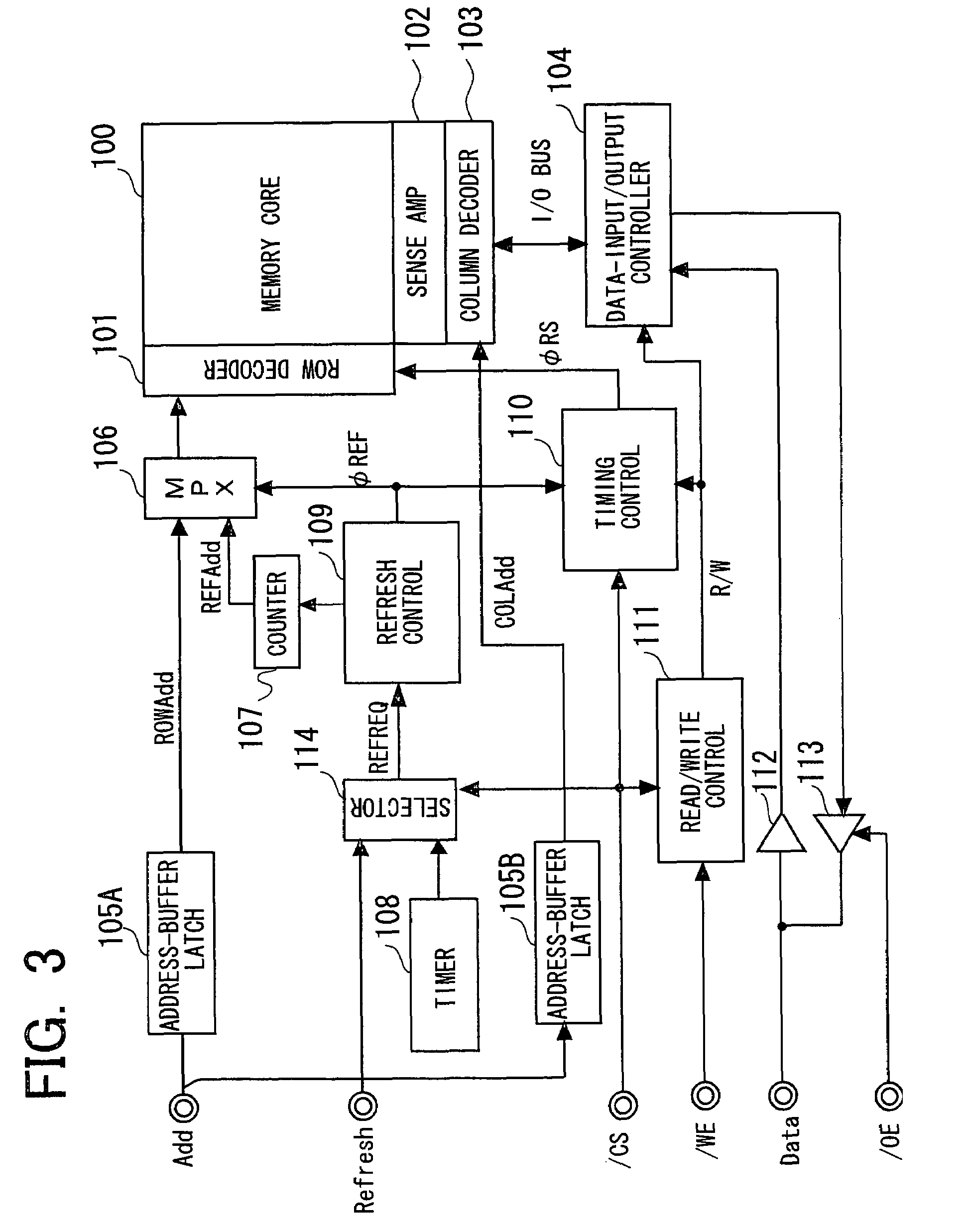

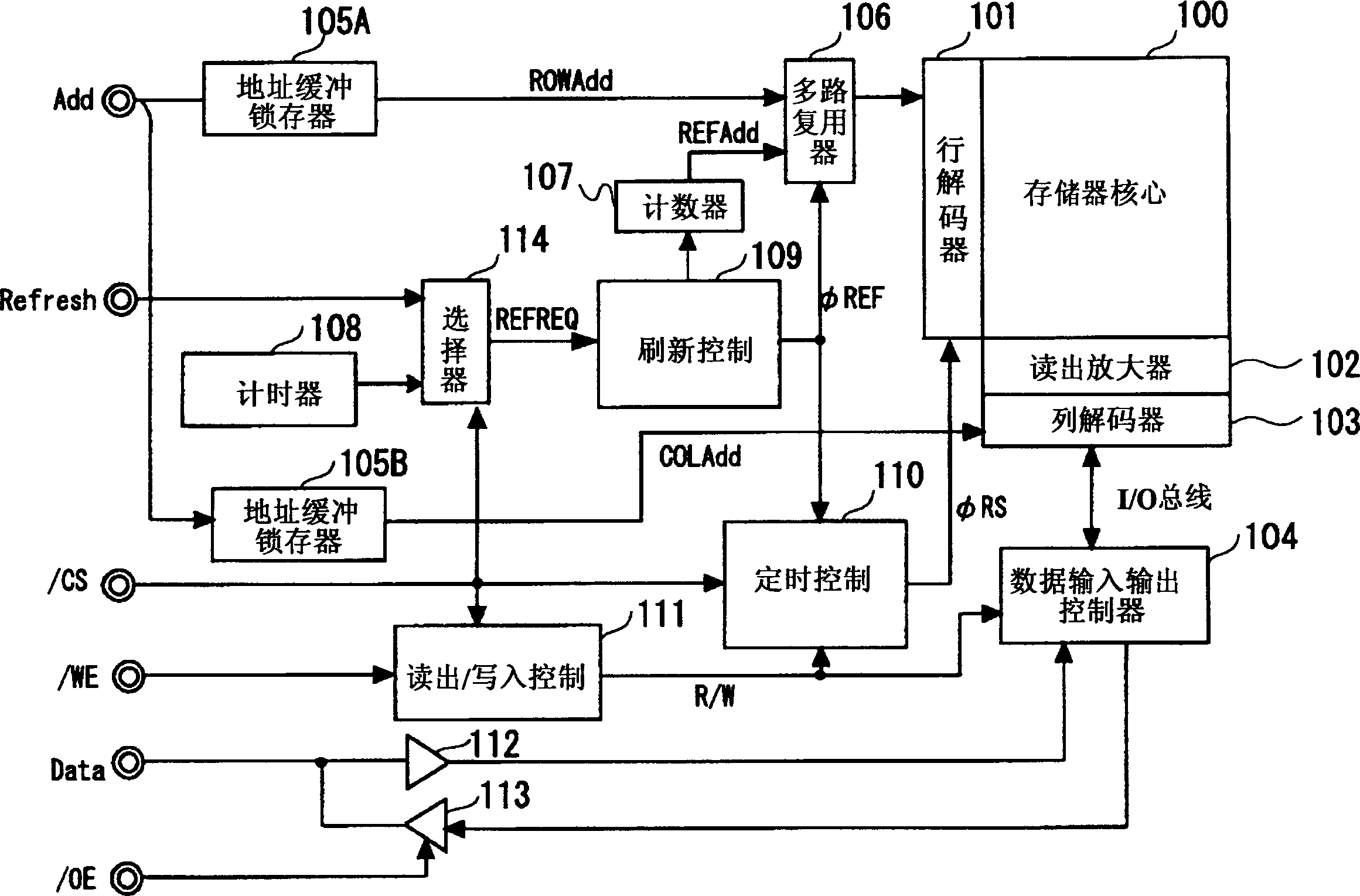

Semiconductor memory device and refresh control method

InactiveUS20060114735A1Shorten test timeImprove data retention characteristicsDigital storageEmbedded systemSemiconductor memory

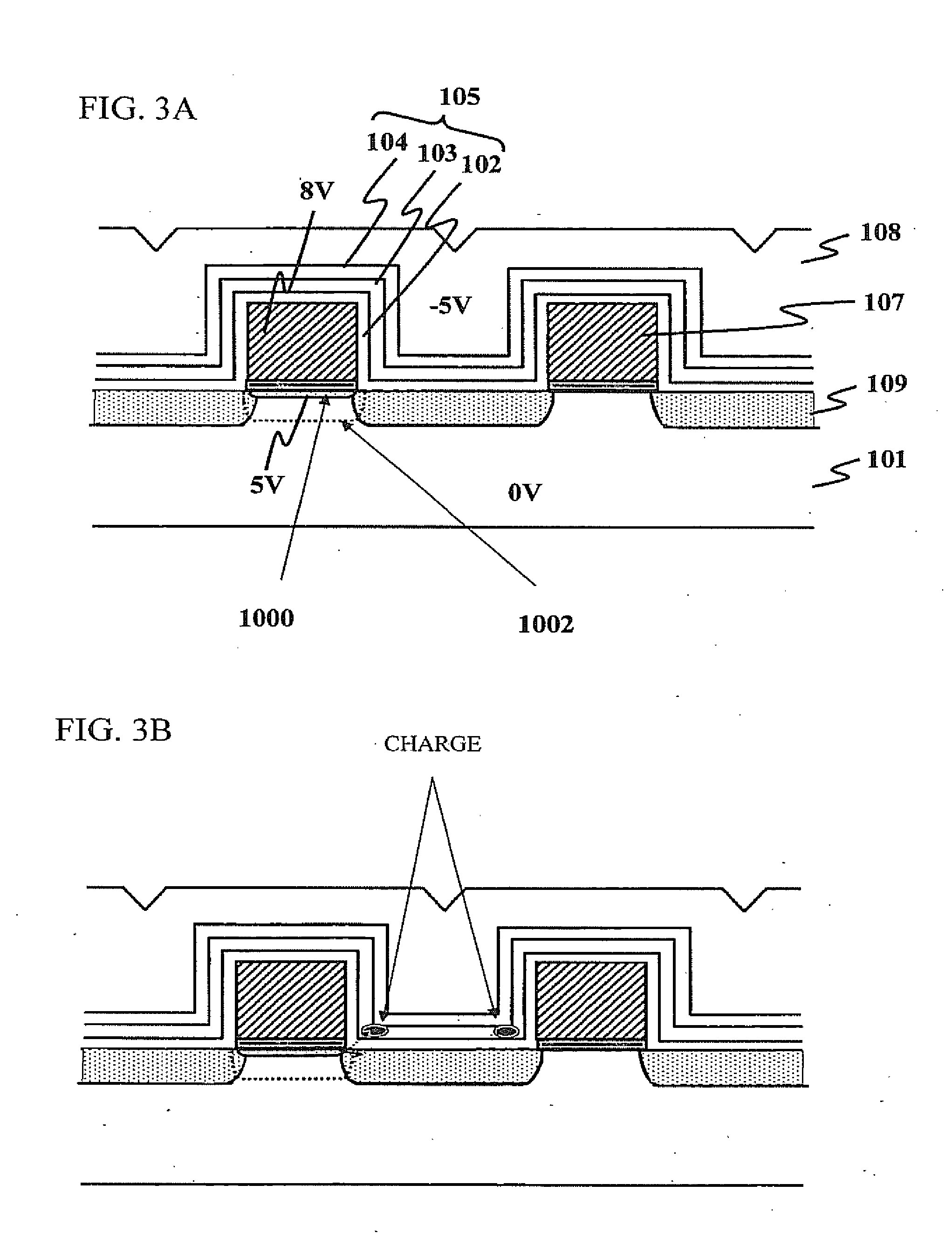

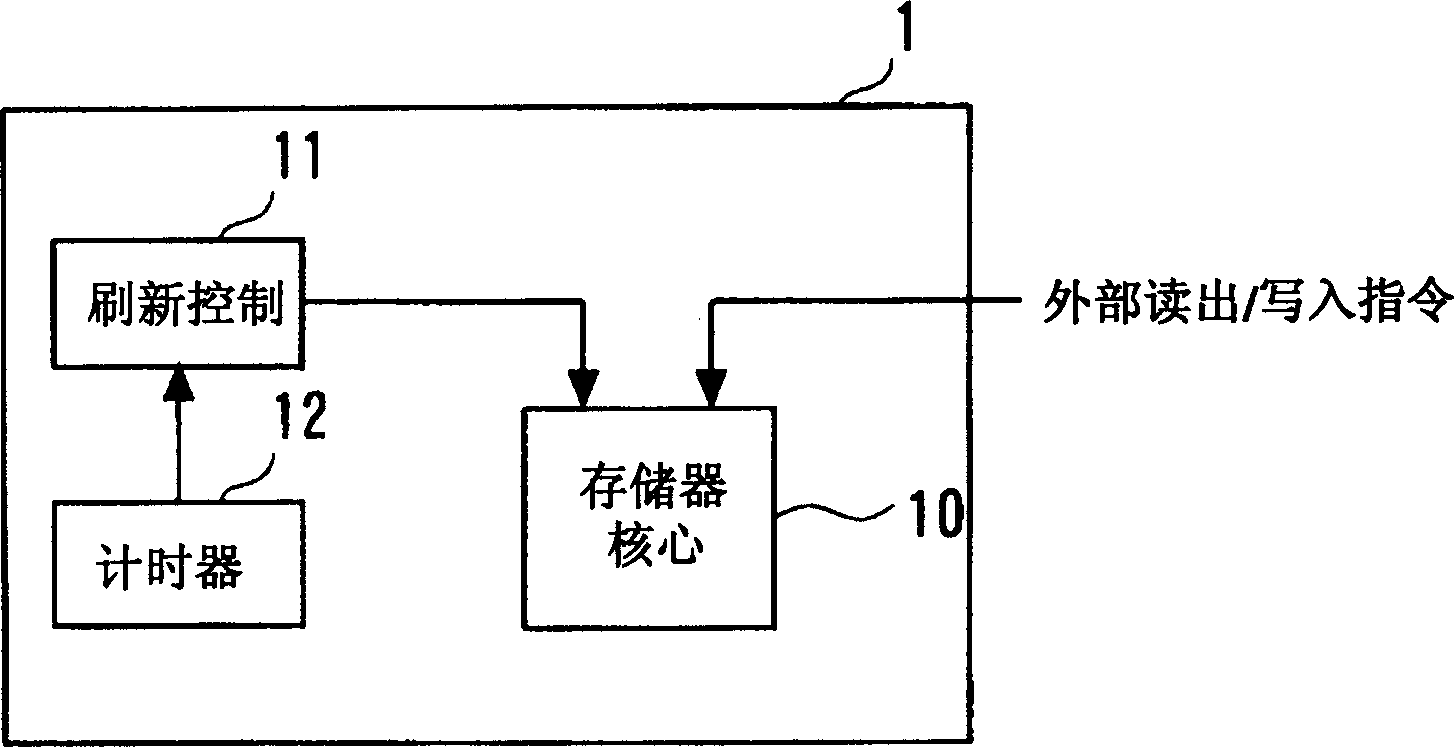

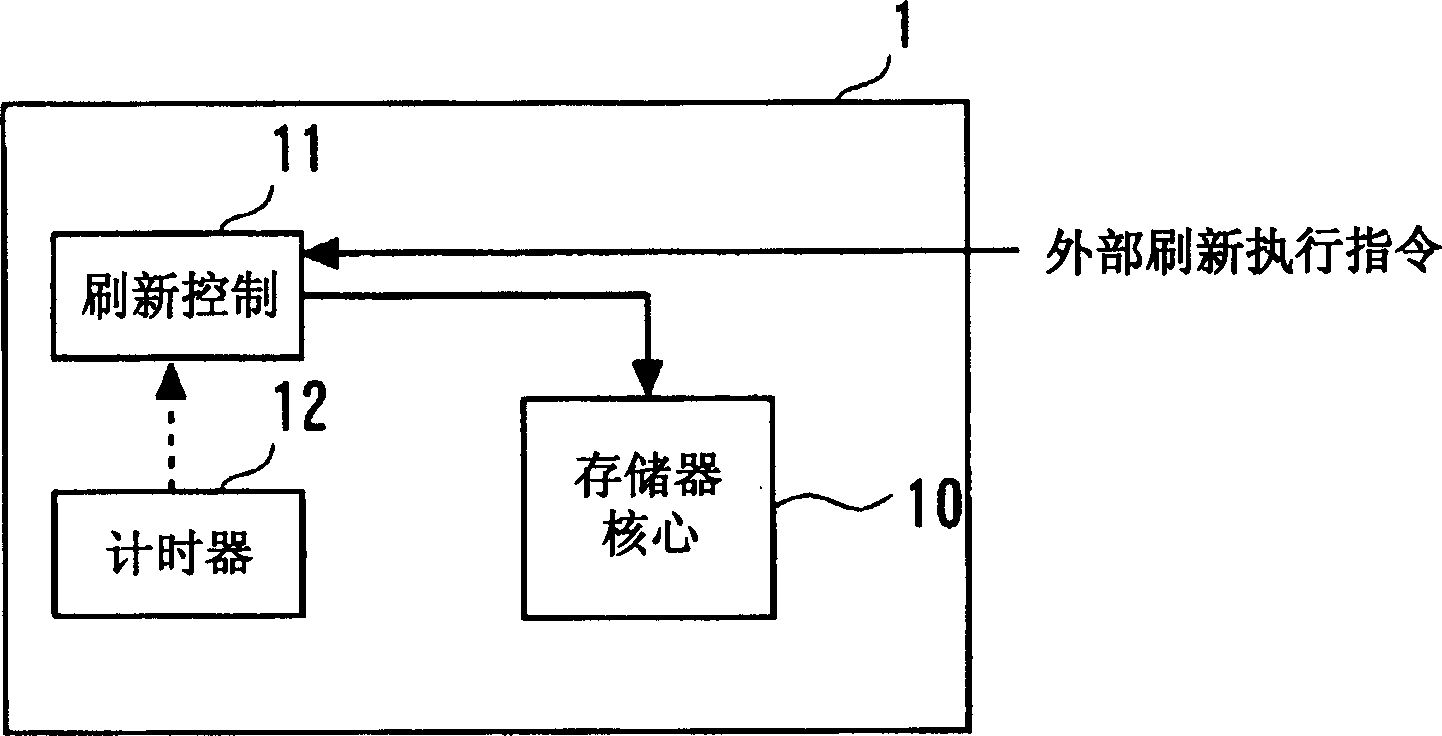

Disclosed is a semiconductor-memory device comprising a selector for performing switching control such that in the standby state the refresh operation is performed responsive to an external-refresh-execution command supplied from outside the semiconductor-memory device, while in the active state, the refresh operation is performed, not under the control from outside the semiconductor-memory device, but under the control from a built-in timer.

Owner:RENESAS ELECTRONICS CORP

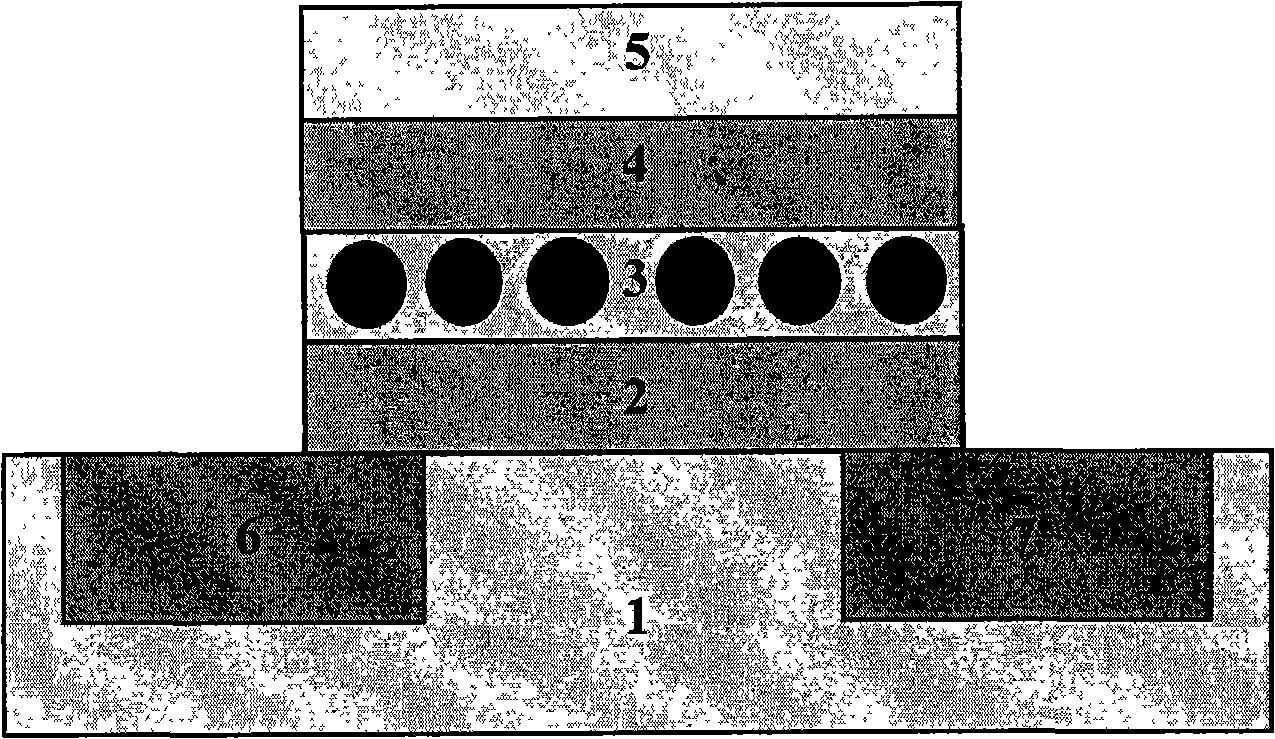

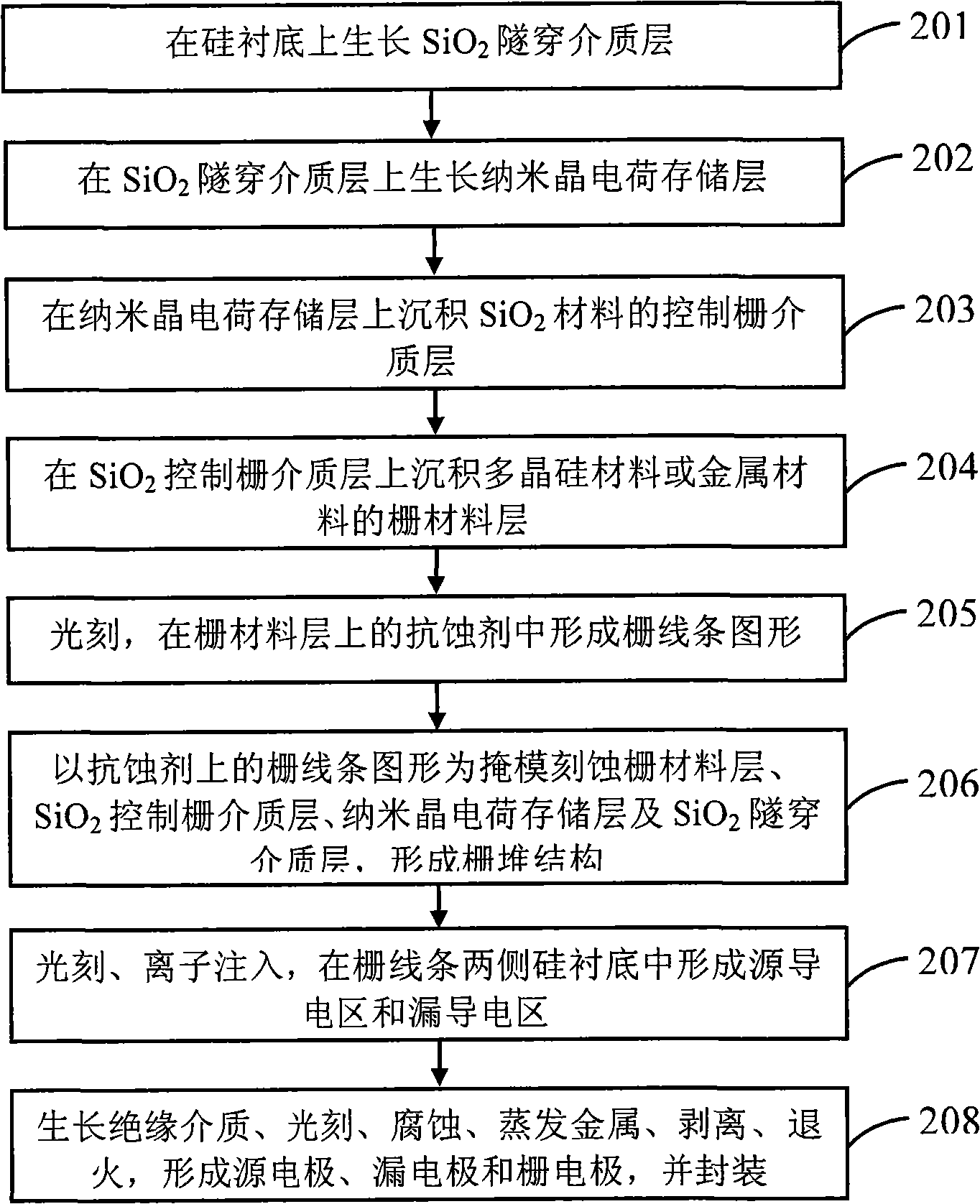

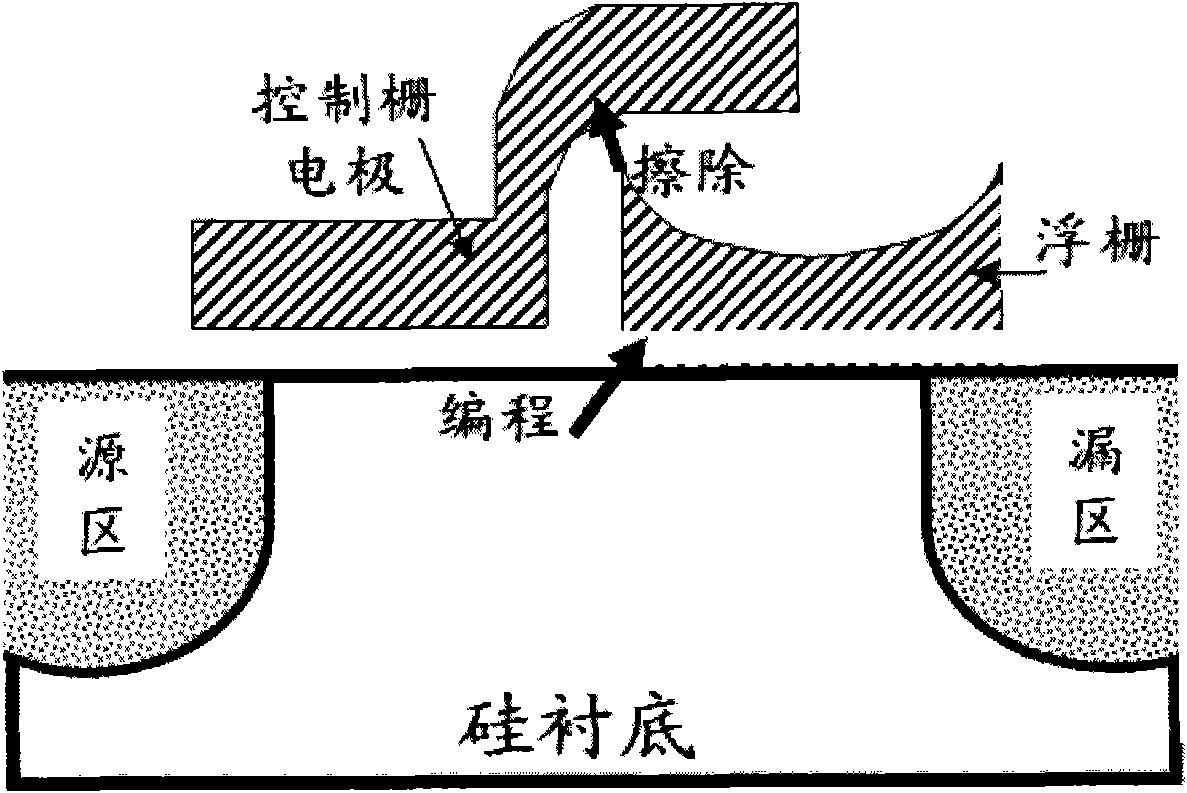

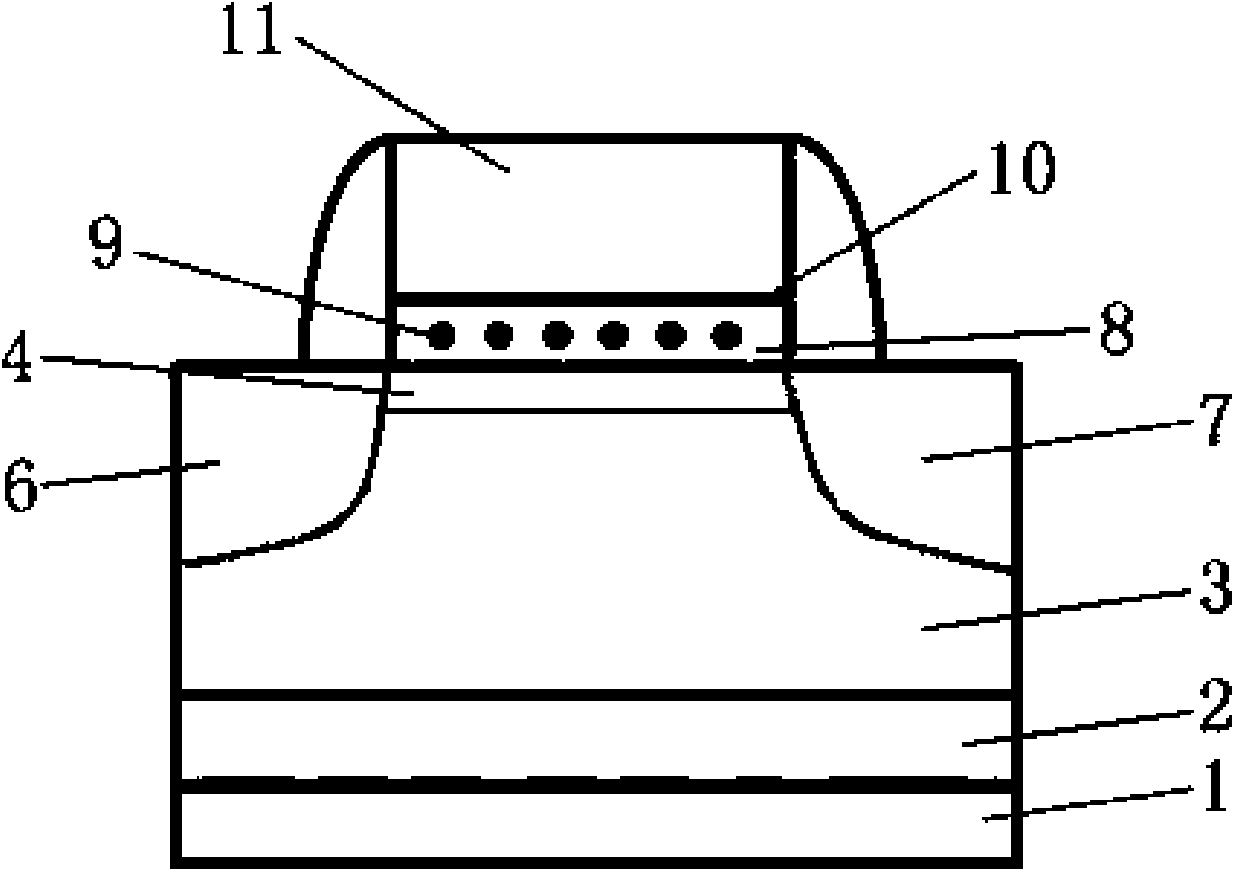

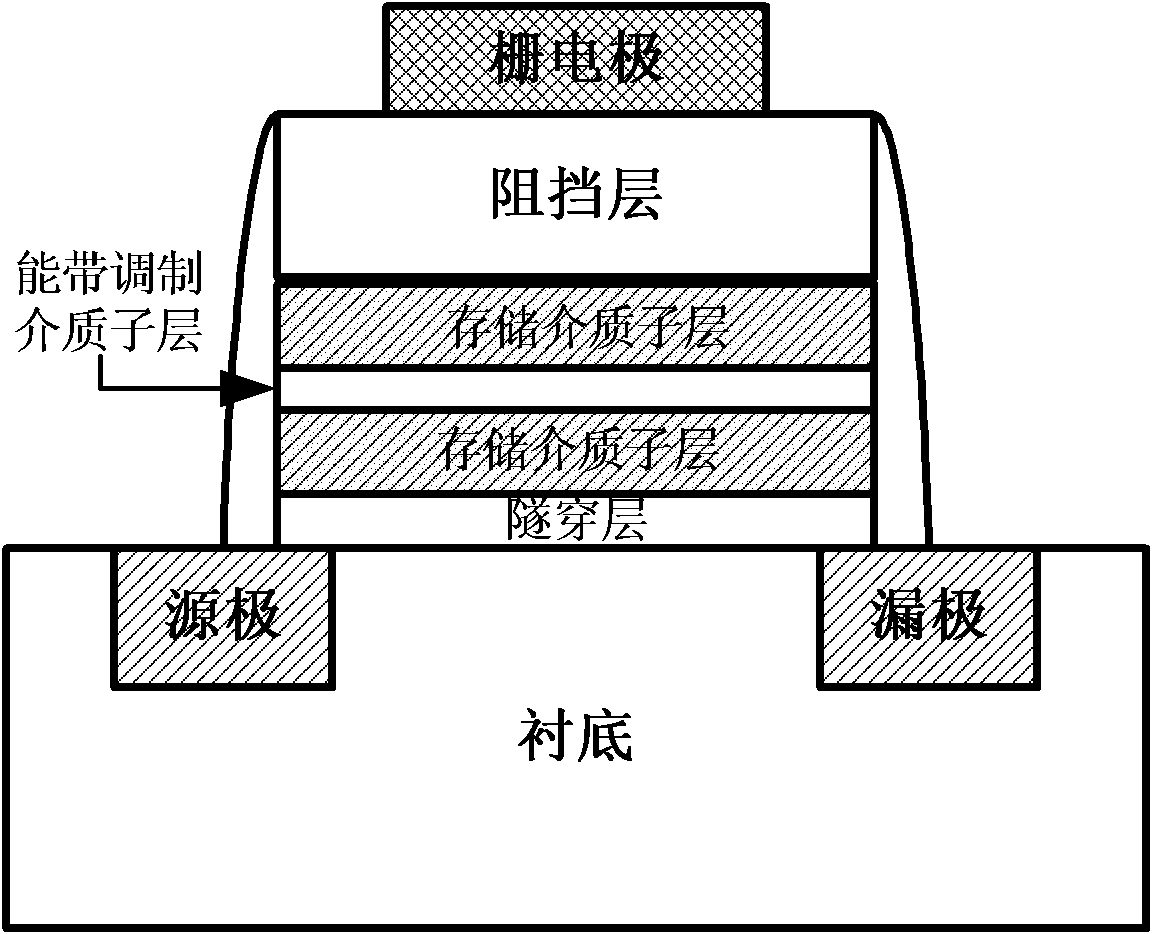

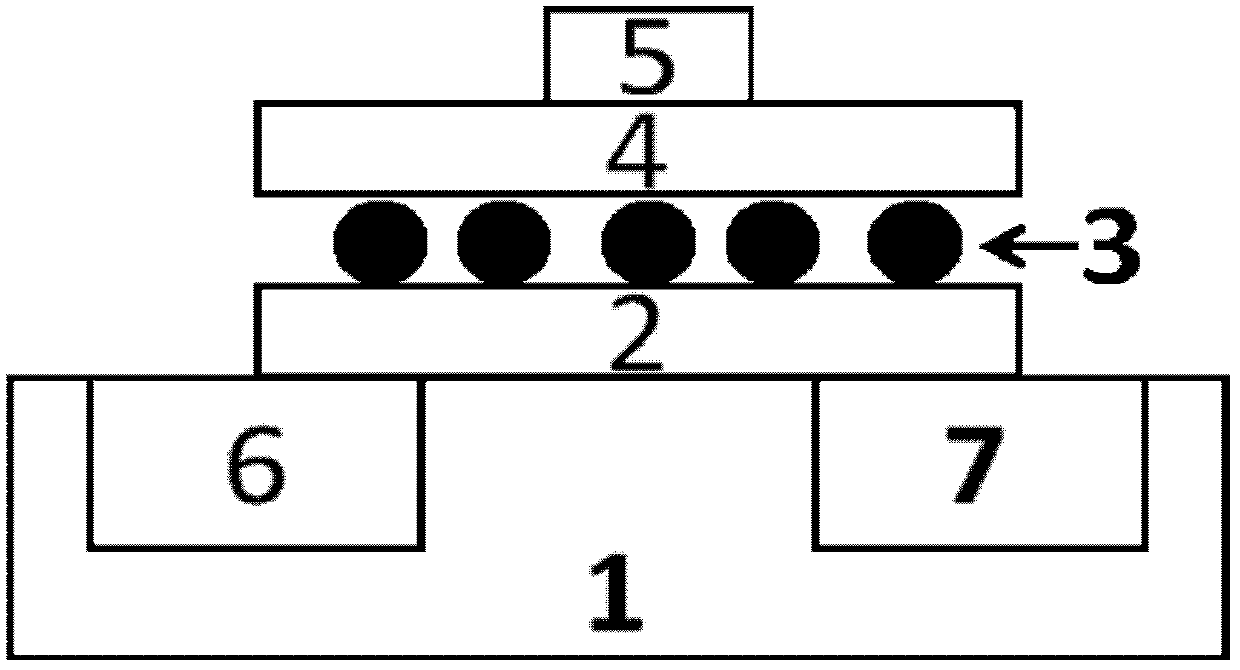

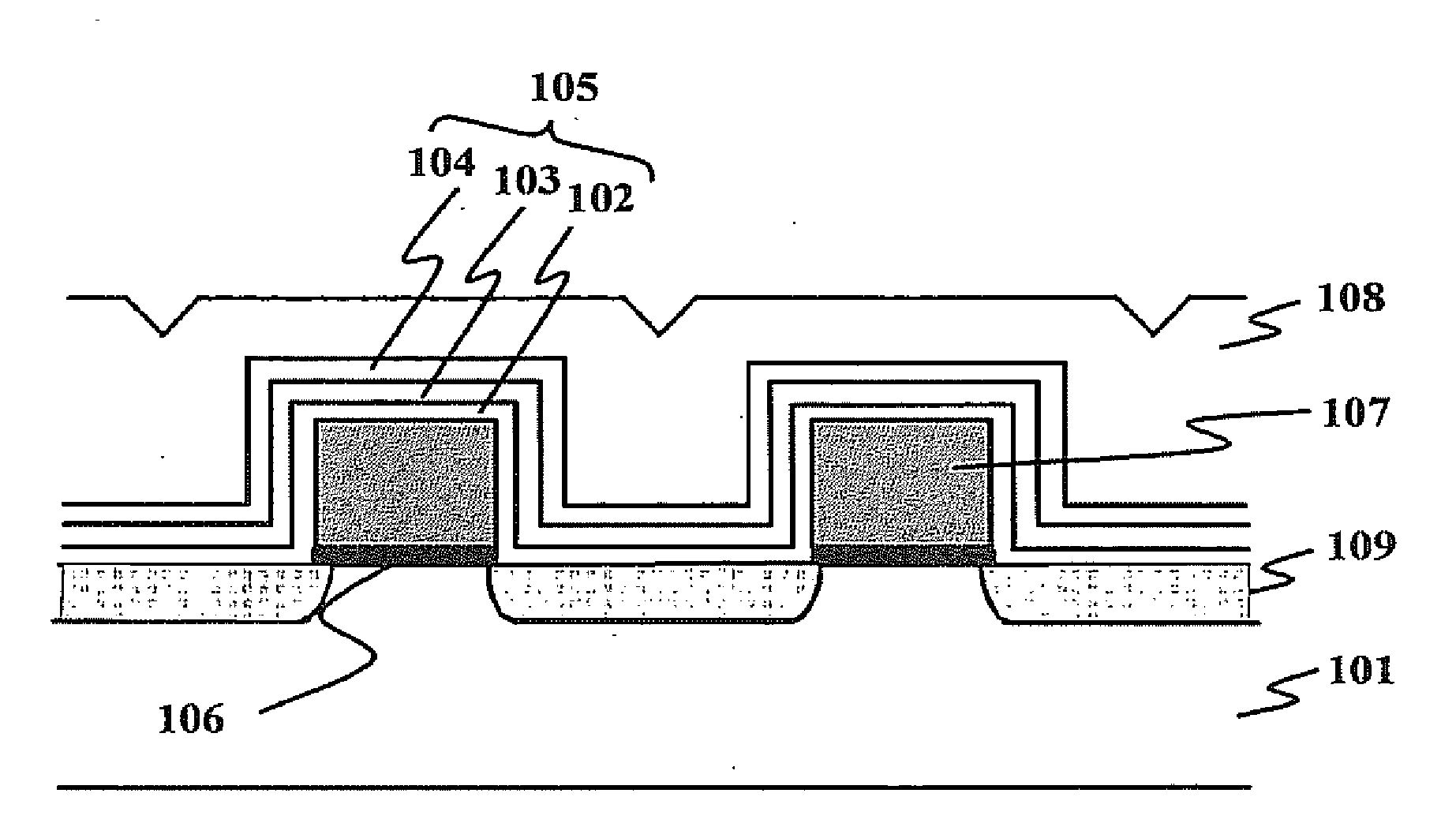

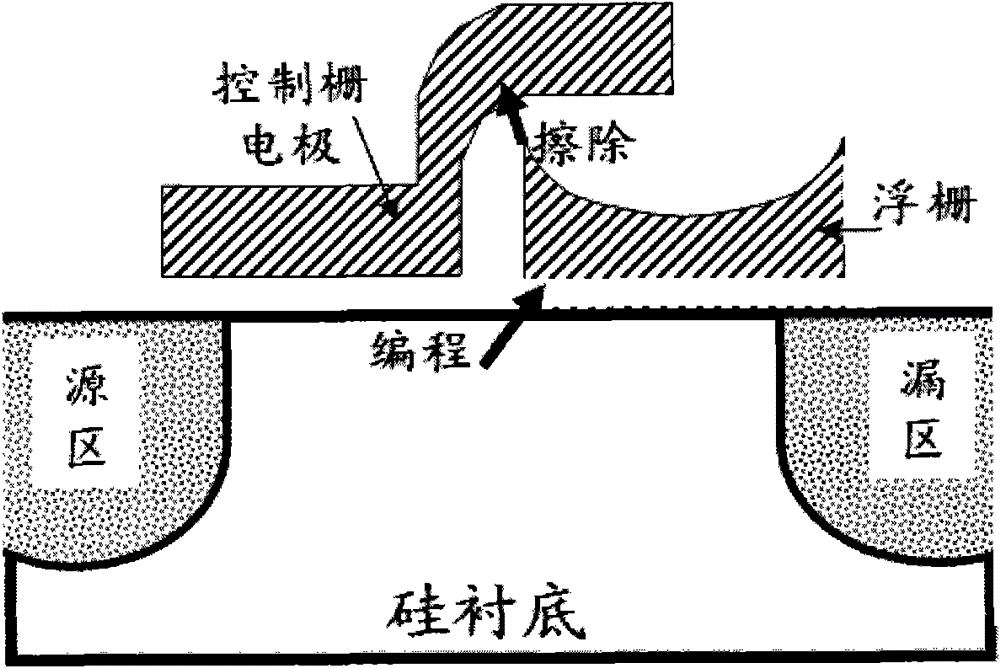

Nanocrystalline floating gate structure non-volatility memory cell and its manufacture method

InactiveCN101312213AImprove cooling effectExtended service lifeTransistorSolid-state devicesCMOSGate dielectric

The invention relates to the micro-electronics technical field, and discloses a non-volatile storage unit of a nanocrystal floating gate structure, which comprises a silicon substrate, a source conduction region 6, a drain conduction region 7, a tunneling dielectric layer 2, a nanocrystal charge storage layer 3, a control gate dielectric layer 4 and a gate material layer 5, wherein the source conduction region 6 and the drain conduction region 7 which are heavily doped are arranged on two ends of the silicon substrate 1, the tunneling dielectric layer 2 is covered on a current carrier channel between the source conduction region 6 and the drain conduction region 7, the nanocrystal charge storage layer is covered on the tunneling dielectric layer, the control gate dielectric layer 4 is covered on the nanocrystal charge storage layer, and the gate material layer 5 is covered on the control gate dielectric layer. The invention simultaneously discloses a process for preparing the non-volatile storage unit of a nanocrystal floating gate structure. The non-volatile storage unit of a nanocrystal floating gate structure increases programming / erasing speed of the non-volatile storage unit of a floating gate structure, effective storage capacity, data retention, programming / erasing durability and the like, and the process for preparing the non-volatile storage unit of a nanocrystal floating gate structure simplifies manufacturing technique, increases manufacturing efficiency and reduces manufacturing cost based on the conventional CMOS technique.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

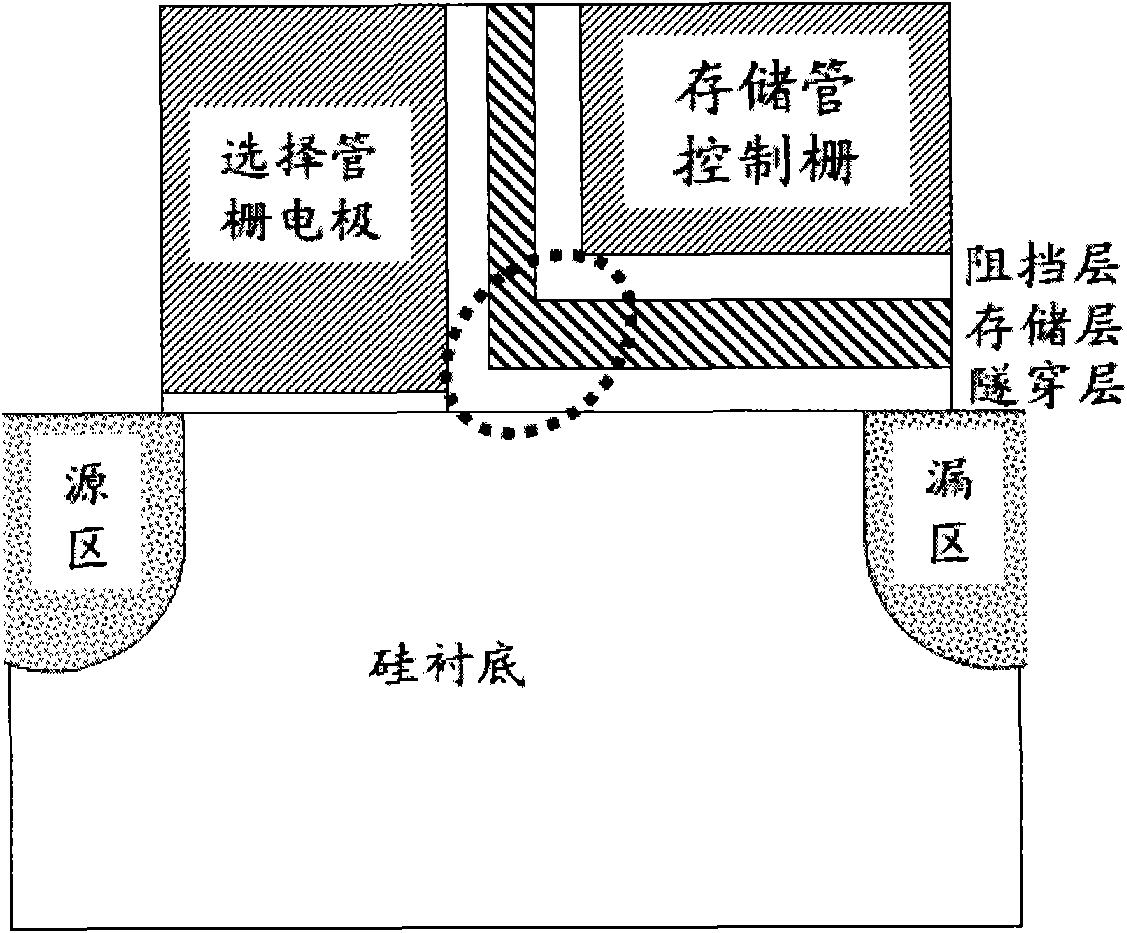

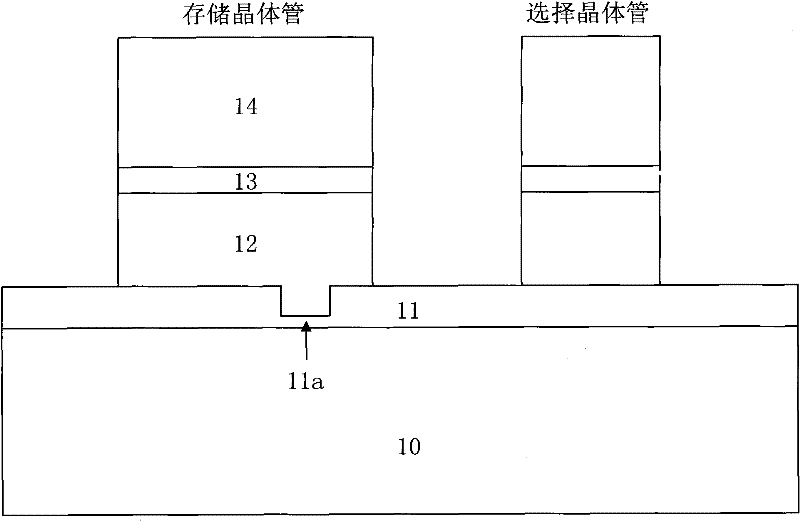

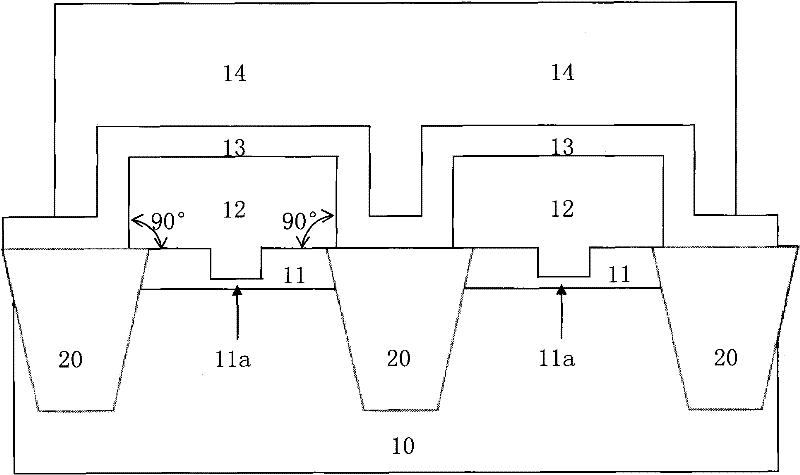

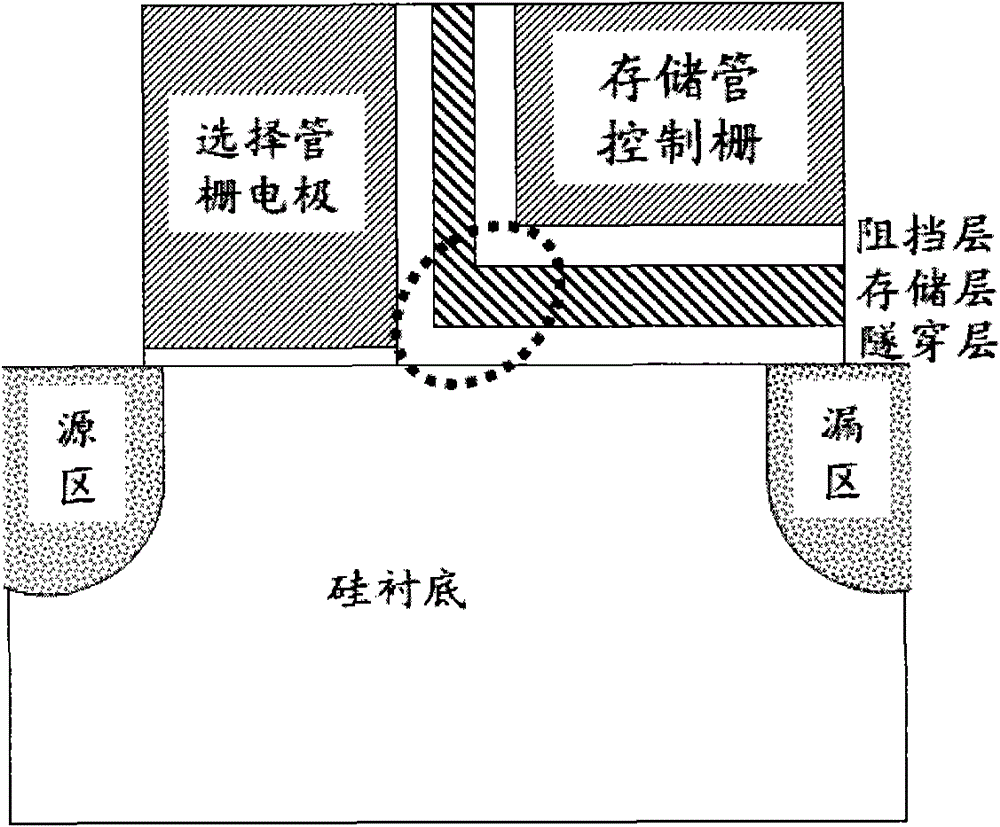

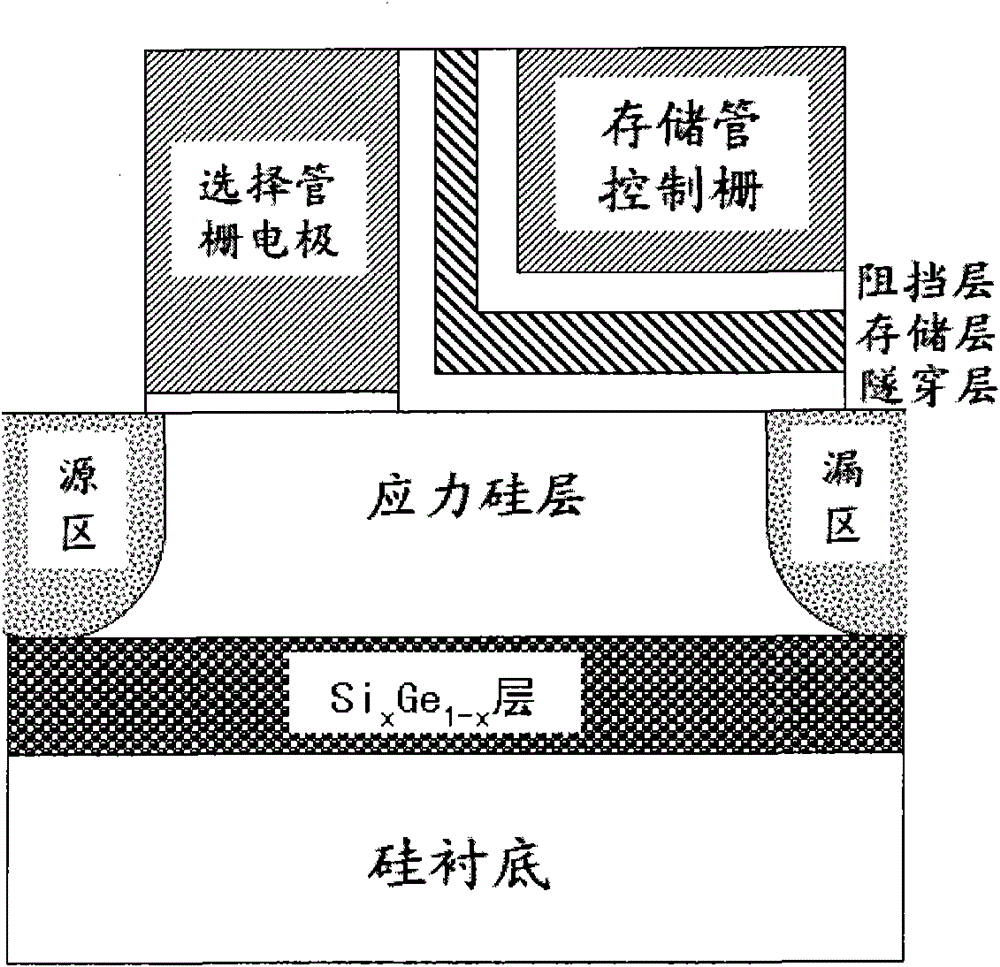

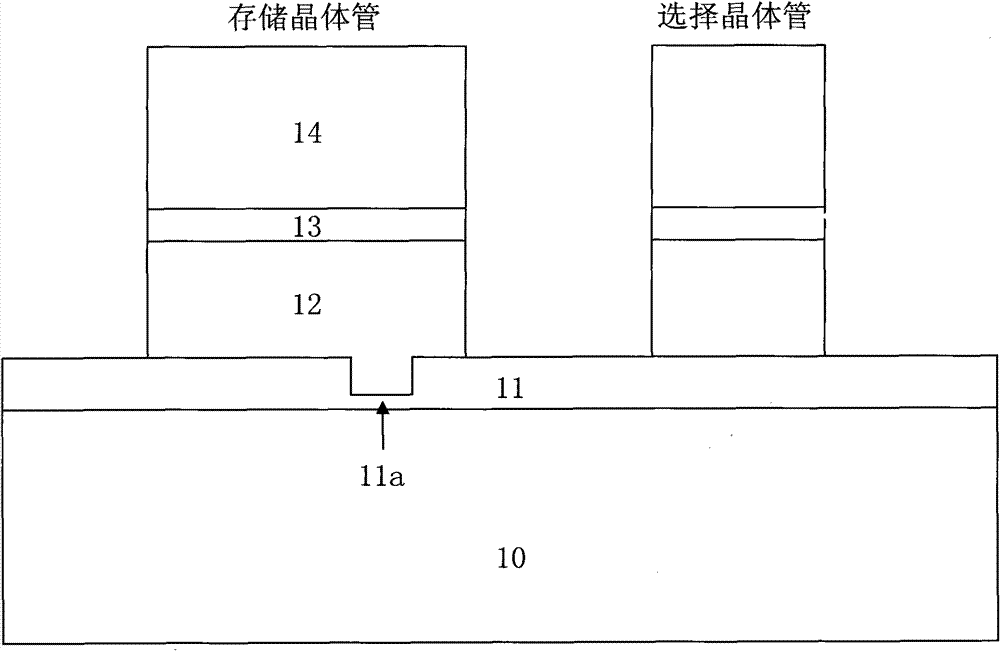

High-reliability split-gate nonvolatile memory structure with high-speed low-voltage operation function

ActiveCN102339833AImprove programming efficiencyEvenly distributedSolid-state devicesSemiconductor devicesCMOSLow voltage

The invention discloses a high-reliability split-gate nonvolatile memory structure with a high-speed low-voltage operation function, which is characterized in that the structure comprises a selection transistor and a memory transistor, the selection transistor and the memory transistor share a substrate region and a source / drain doped region, the memory transistor is provided with a stack structure and information is stored in a charge storage layer below a grid region. By adopting a dual-layer or multilayer substrate made of stress silicon / germanium-silicon and by comprehensively utilizing high collision ionization rate brought by primary collision ionization of the channels of the stress silicon, high collision ionization rate brought by the introduction of a SixGel-x layer and wider transverse electron distribution produced resultantly, the programming efficiency of a split-gate structure can be greatly improved, the programming voltage is reduced, the data hold characteristic of adevice is improved and the high-reliability operation of the device is facilitated. Since the charge-trap-type split-gate memory preparation process disclosed by the invention is compatible with the traditional silicon planar complementary metal oxide semiconductor (CMOS) process, the wide application is facilitated.

Owner:宁夏储芯科技有限公司

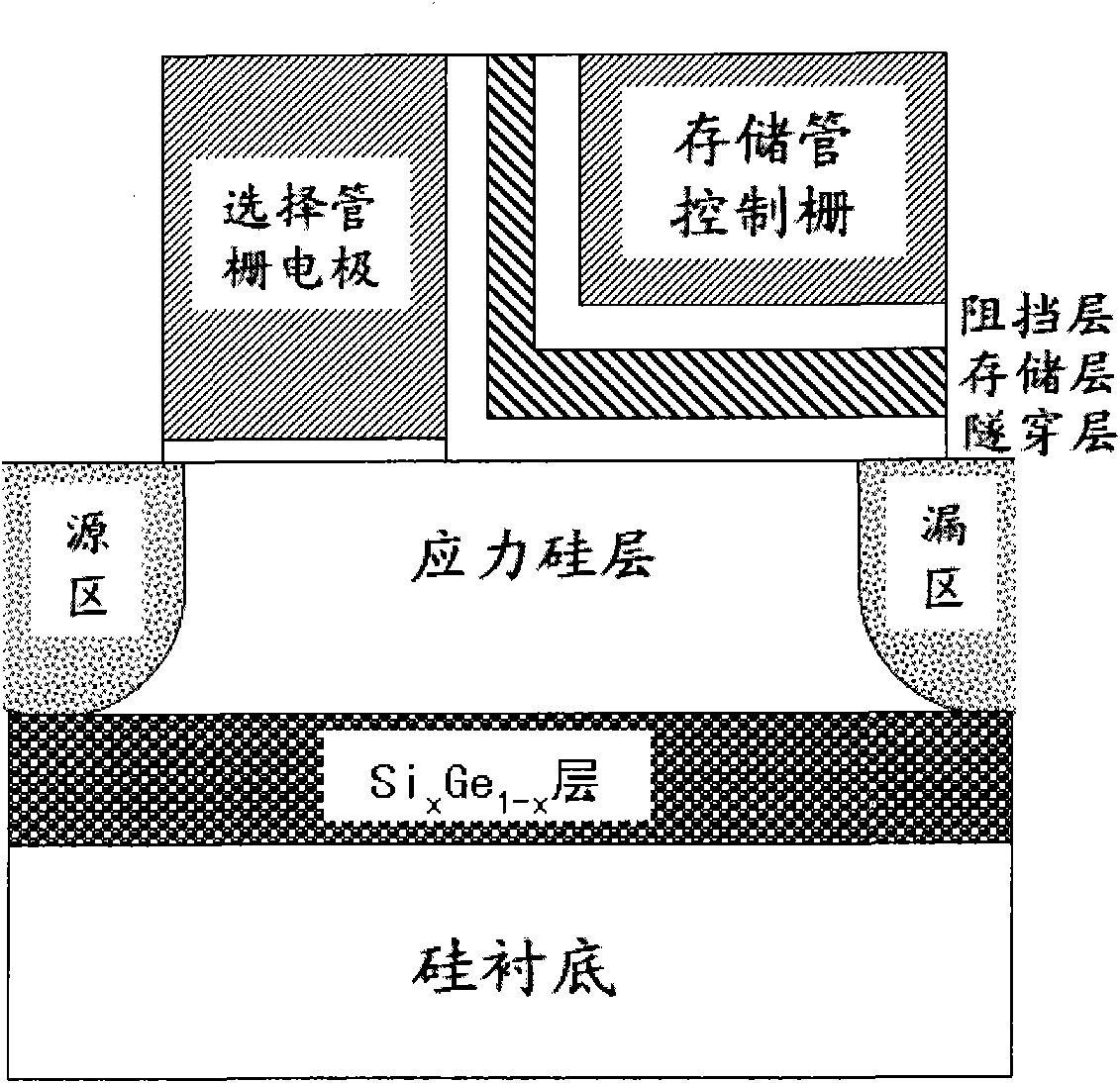

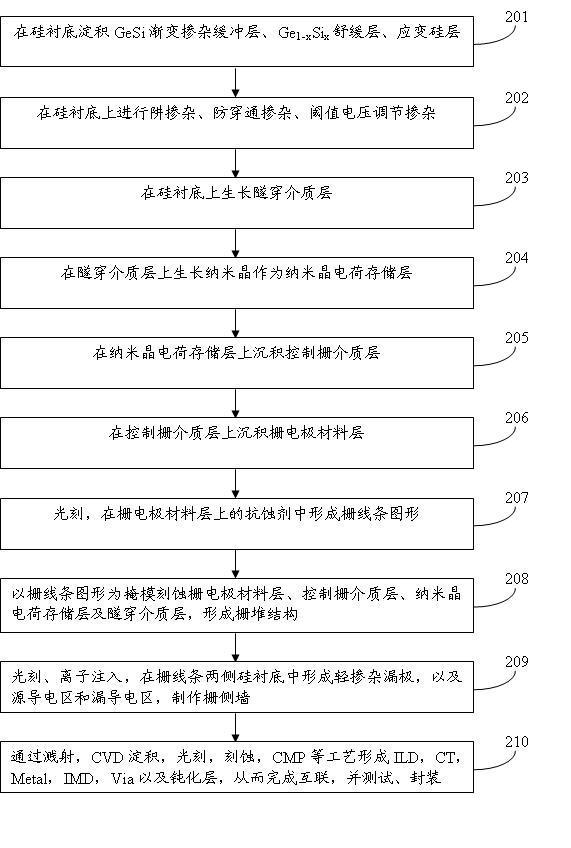

Nanocrystal nonvolatile memory based on strained silicon and manufacturing method of memory

InactiveCN102117812AImprove mobilityIncrease read currentSolid-state devicesSemiconductor/solid-state device manufacturingNanometreStrained silicon

The invention relates to a nanocrystal nonvolatile memory based on strained silicon in the technical fields of nano electronic components and nano processing. The nanocrystal nonvolatile memory based on strained silicon comprises a silicon substrate, a GeSi gradually-doped buffer layer, a Gel-xSix relieving layer, a strained silicon layer, lightly-doped drain electrodes, a source conduction region, a drain conduction region, a tunneling dielectric layer, a nanocrystal charge storage layer, a control grid dielectric layer and a grid electrode material layer, wherein the GeSi gradually-doped buffer layer, the Gel-xSix relieving layer and the strained silicon layer are deposited on the silicon substrate; the lightly-doped drain electrodes, the source conduction region and the drain conduction region are arranged at two sides in the silicon substrate; the tunneling dielectric layer covers a current carrier channel arranged between the source conduction region and the drain conduction region; the nanocrystal charge storage layer covers the tunneling dielectric layer; the control grid dielectric layer covers the tunneling dielectric layer; and the grid electrode material layer covers the control grid dielectric layer. According to the invention, the mobility is increased by utilizing the strained silicon, thereby increasing the reading current, and simplifying a peripheral circuit; the nanocrystal nonvolatile memory based on strained silicon adopts the nanocrystal as a floating grid material, so that the performance of a storage device is improved, and particularly, the storage performance, such as storage windows, programming / erasing speed, data retention characteristic and the like, is improved comprehensively.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

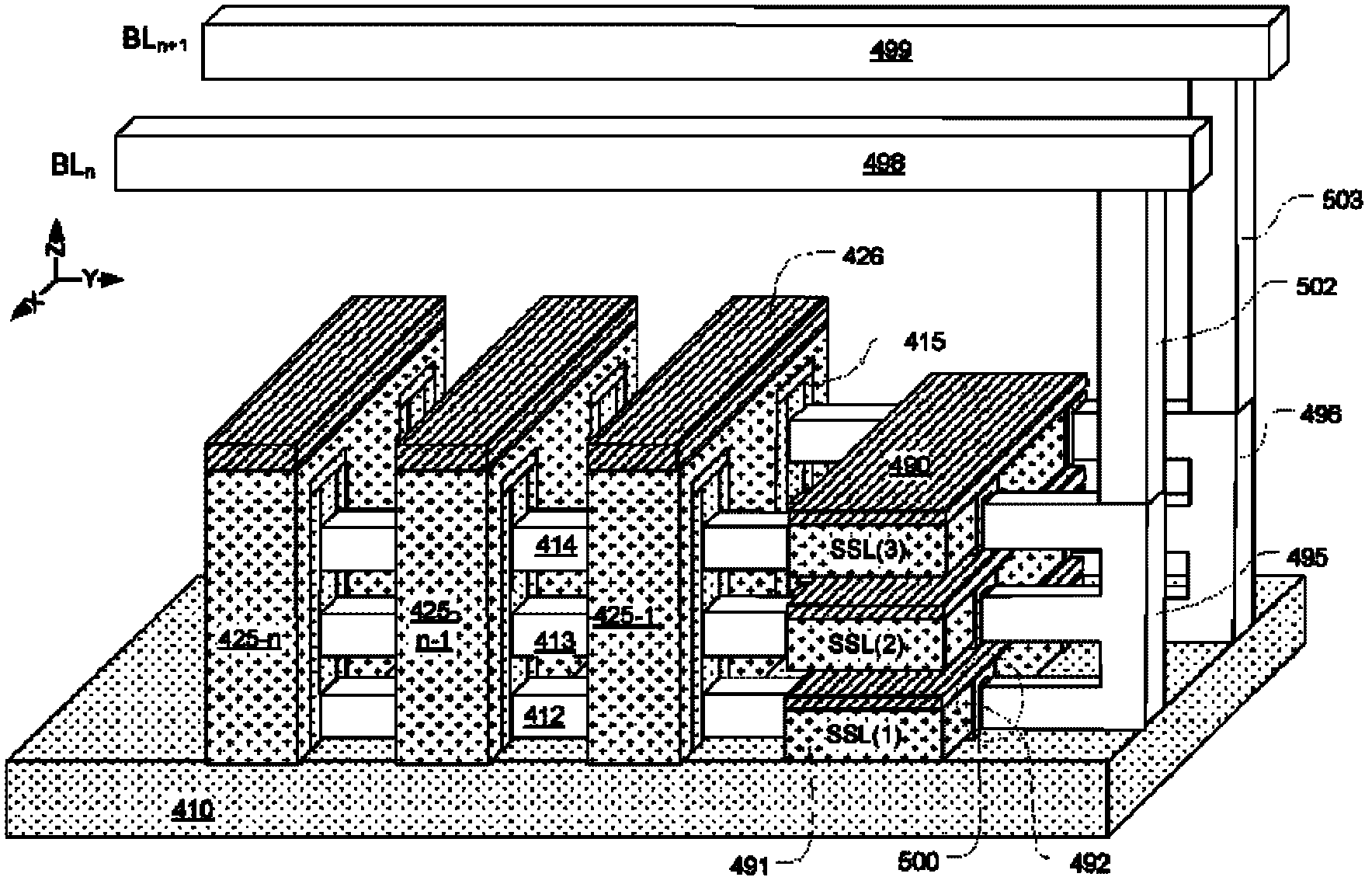

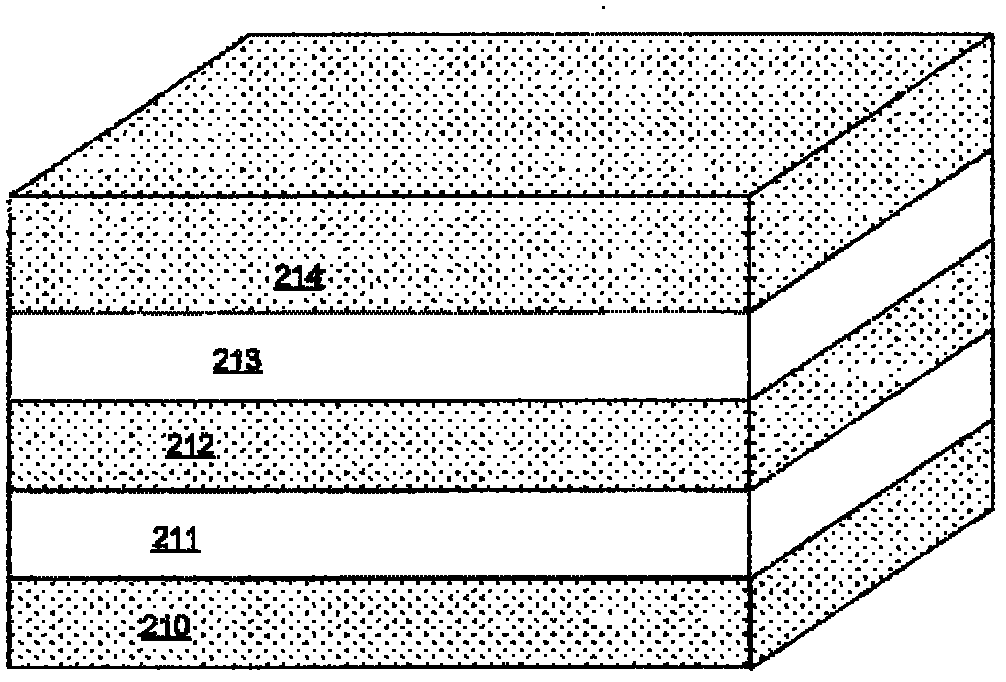

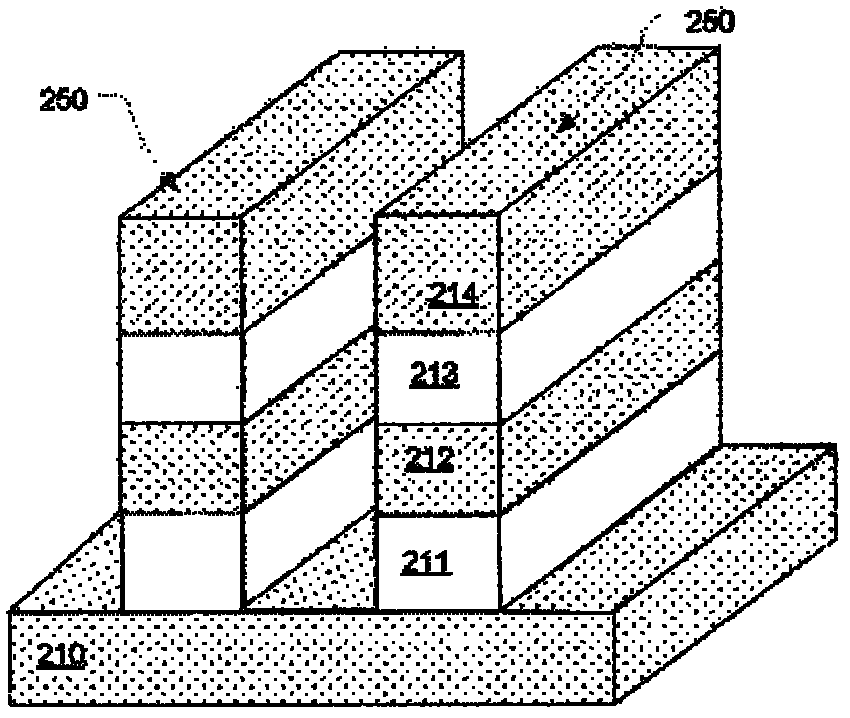

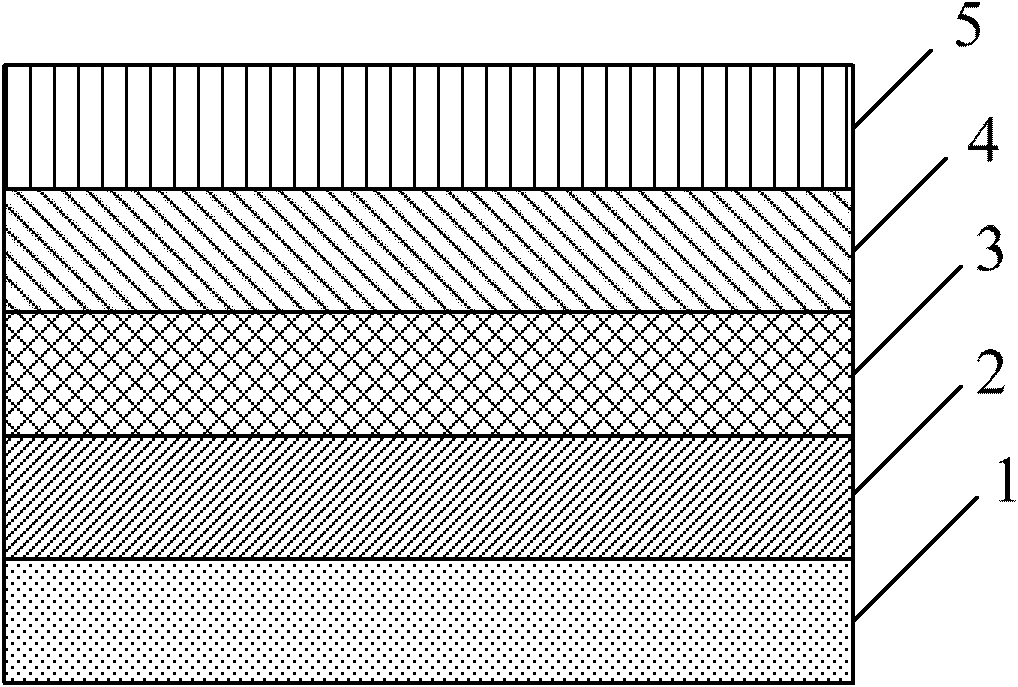

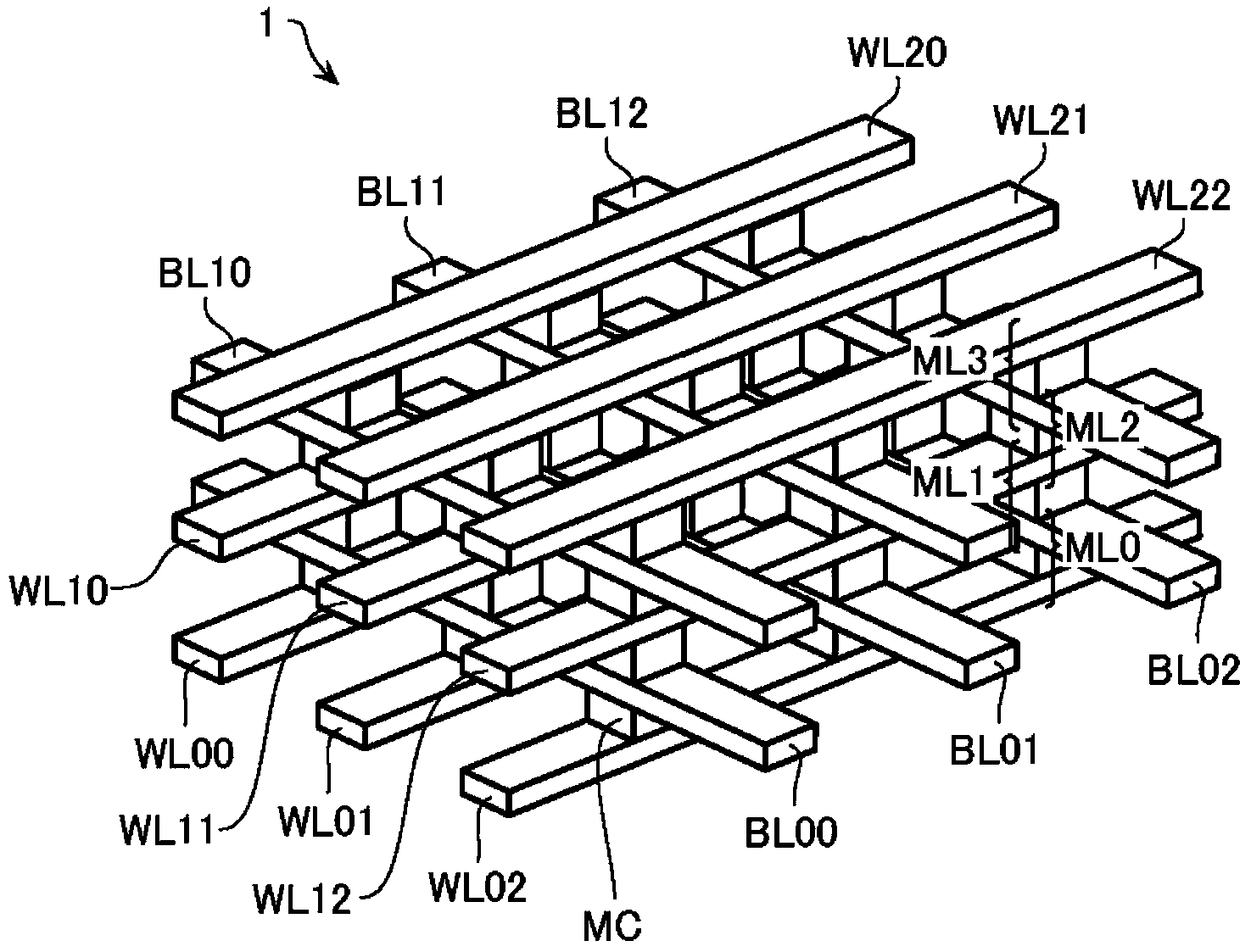

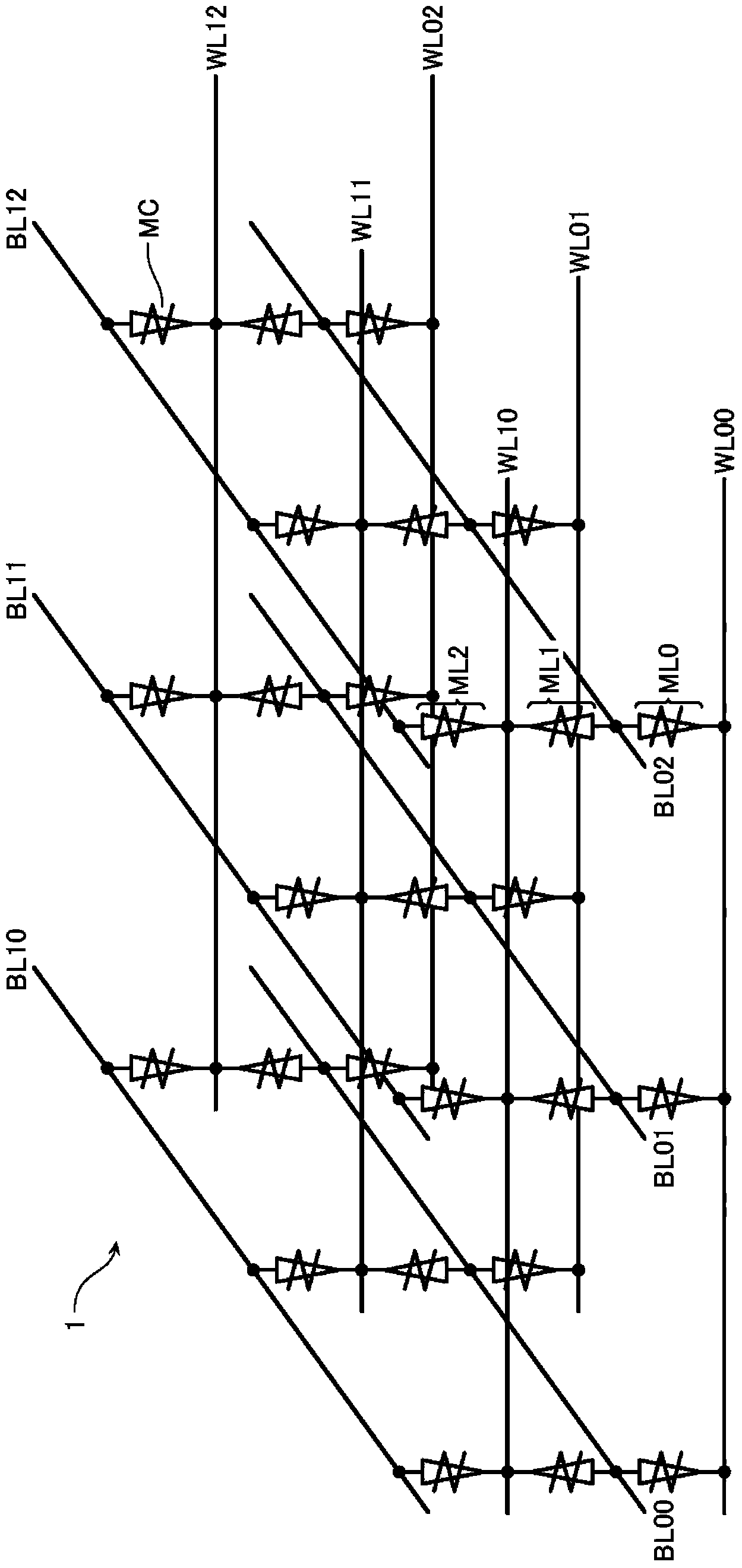

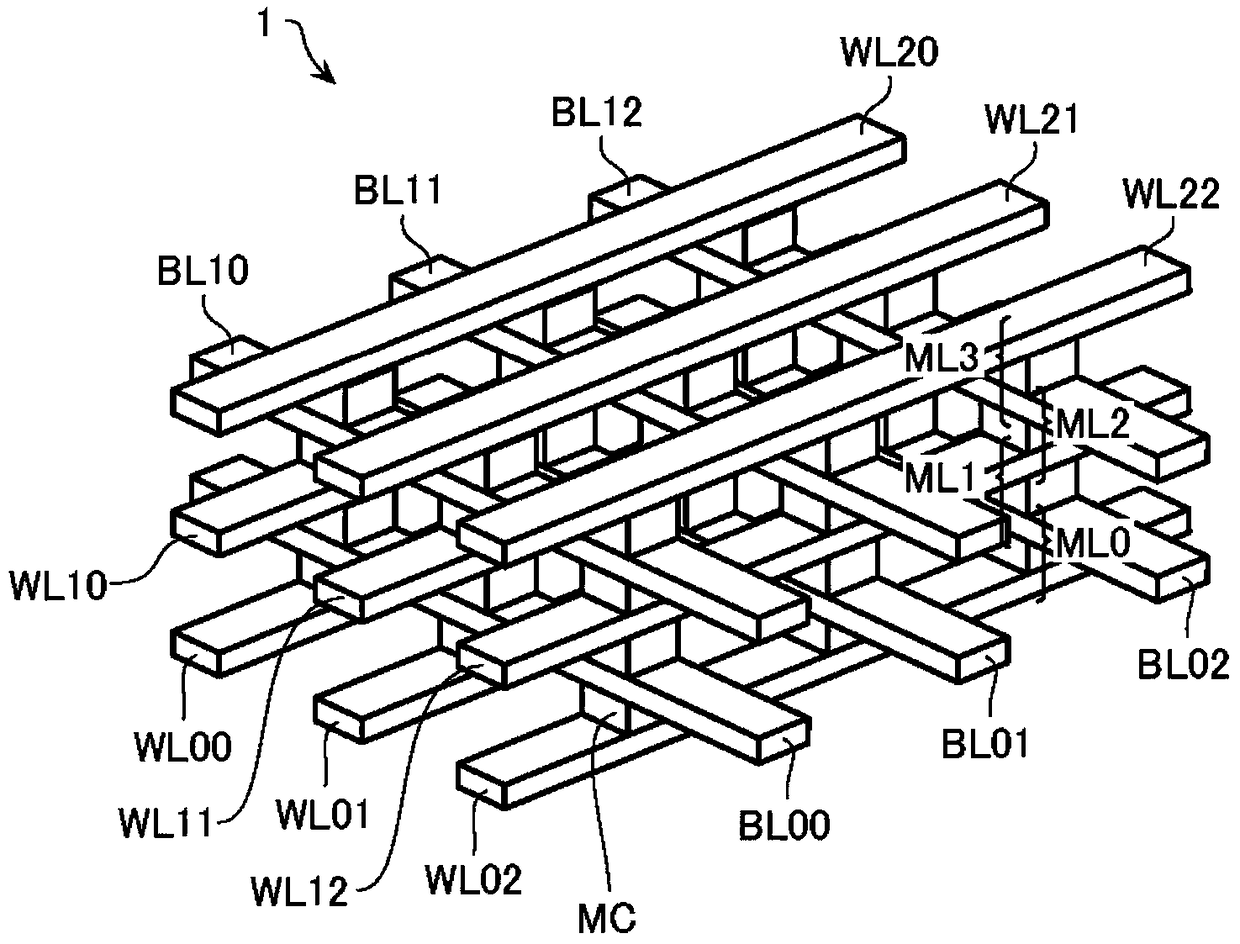

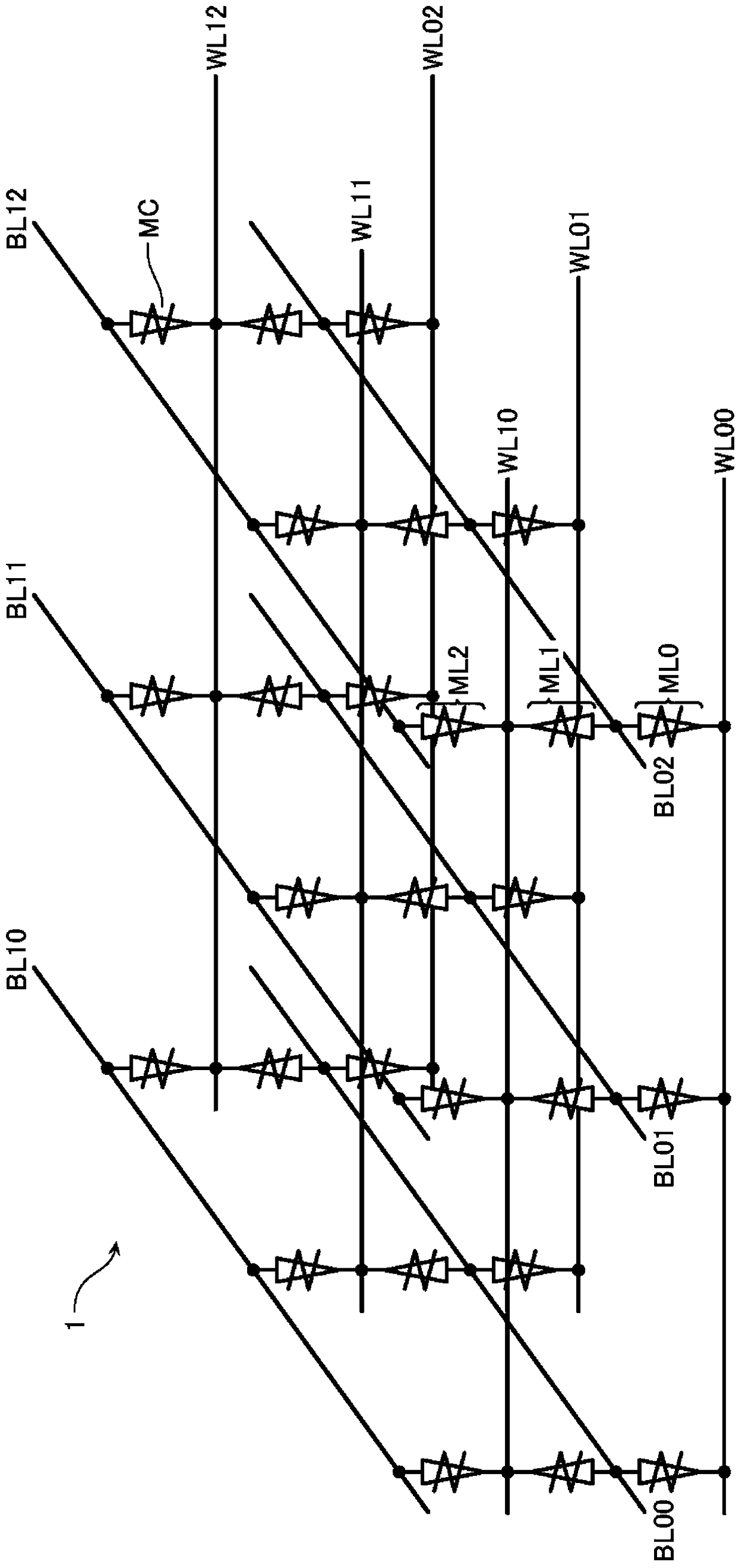

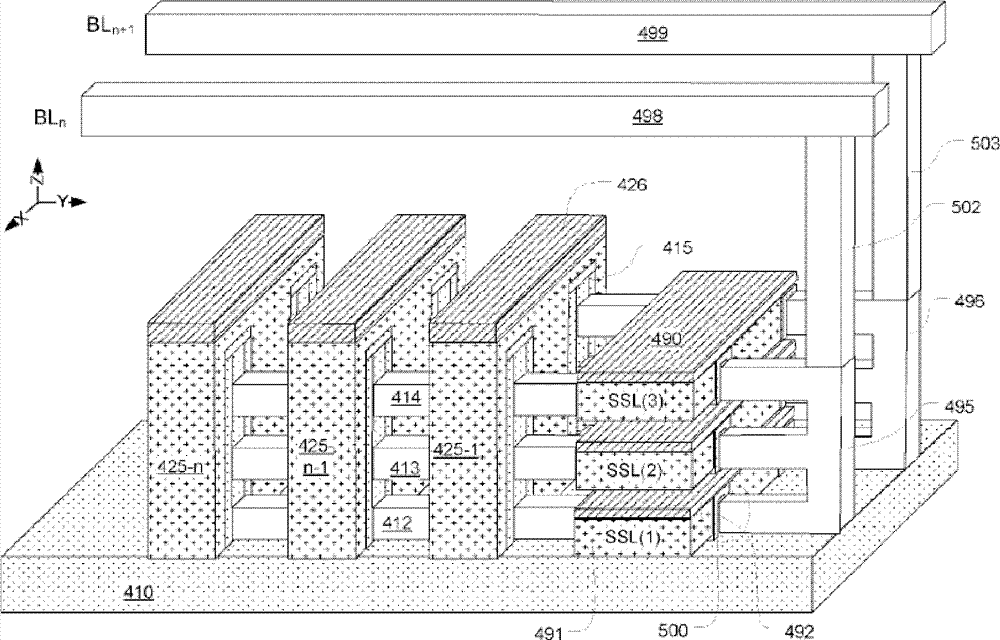

Nonvolatile three-dimensional semiconductor memory device and preparing method

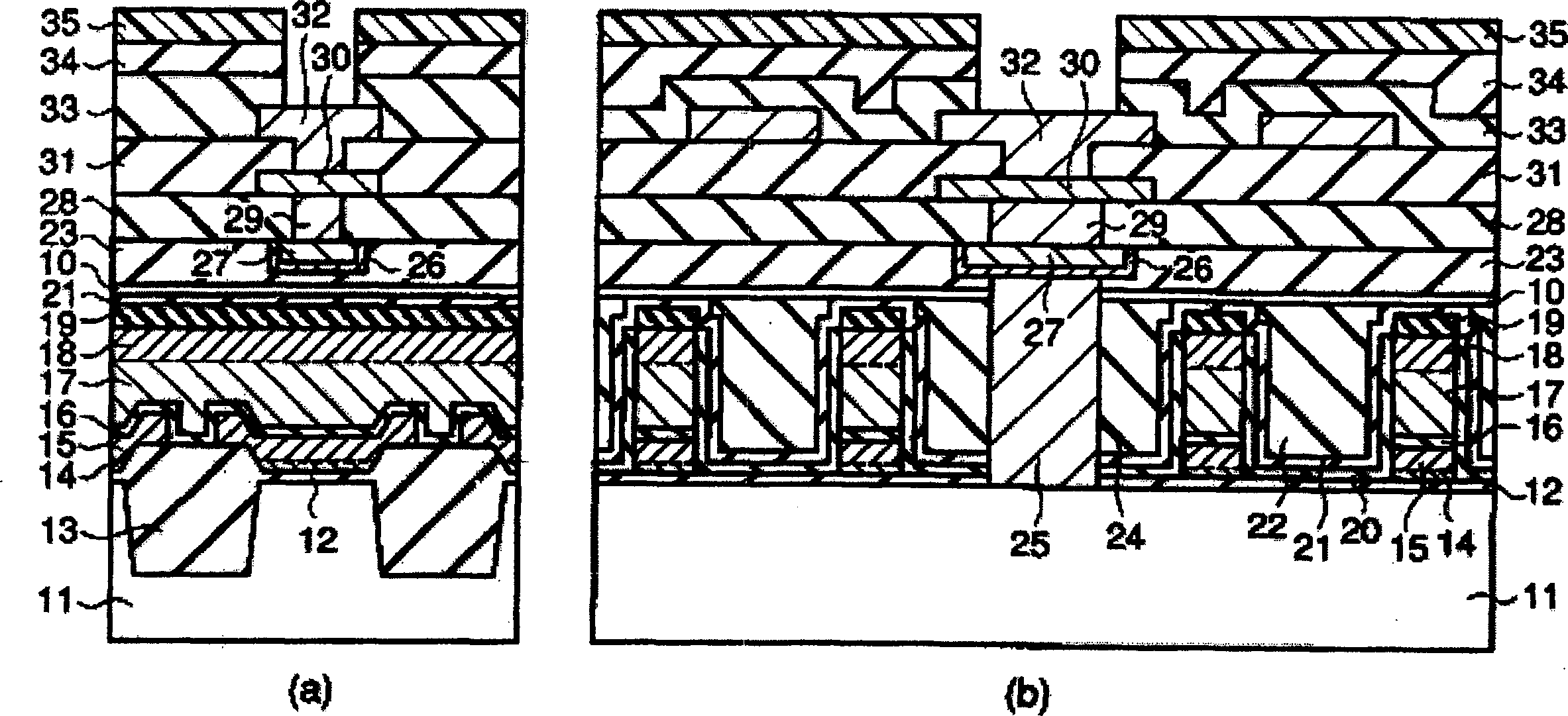

ActiveCN103137860AImprove integration densitySimple processElectrical apparatusDigital storageStorage materialAND gate

The invention relates to the technical field of microelectronics, and discloses a nonvolatile three-dimensional semiconductor memory device and a preparing method. The three-dimensional semiconductor memory device comprises bit lines made of strip-shaped connecting materials which are isolated by a plurality of insulating layers; each strip-shaped connecting bit line is provided with two surface zones along the side direction; word lines made of connecting materials are arranged in the direction orthogonal with the connecting bit lines; and storage materials are placed in the middle of a cross-shaped overlapping zone which is then used as an electric charge capturing stack zone or a resistance changing function zone. High-dielectric-constant materials can be used in a function zone of the three-dimensional semiconductor memory device, and high-work function materials such as metal nitride are used in a gate electrode. Therefore, according to the preparing method of the three-dimensional semiconductor memory device, partitioning zones arranged between the word lines are introduced first, then storage function layer materials and gate materials are deposited in a back-gate technology, a technology is simplified, material pollution is avoided, and meanwhile performance of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor memory device and refresh control method

Disclosed is a semiconductor-memory device comprising a selector for performing switching control such that in the standby state the refresh operation is performed responsive to an external-refresh-execution command supplied from outside the semiconductor-memory device, while in the active state, the refresh operation is performed, not under the control from outside the semiconductor-memory device, but under the control from a built-in timer.

Owner:RENESAS ELECTRONICS CORP

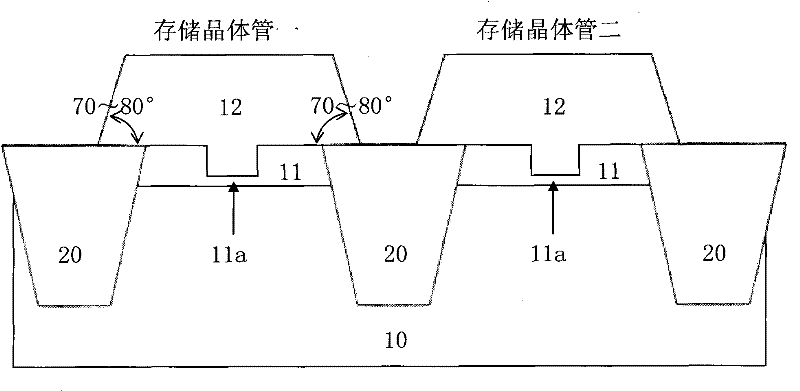

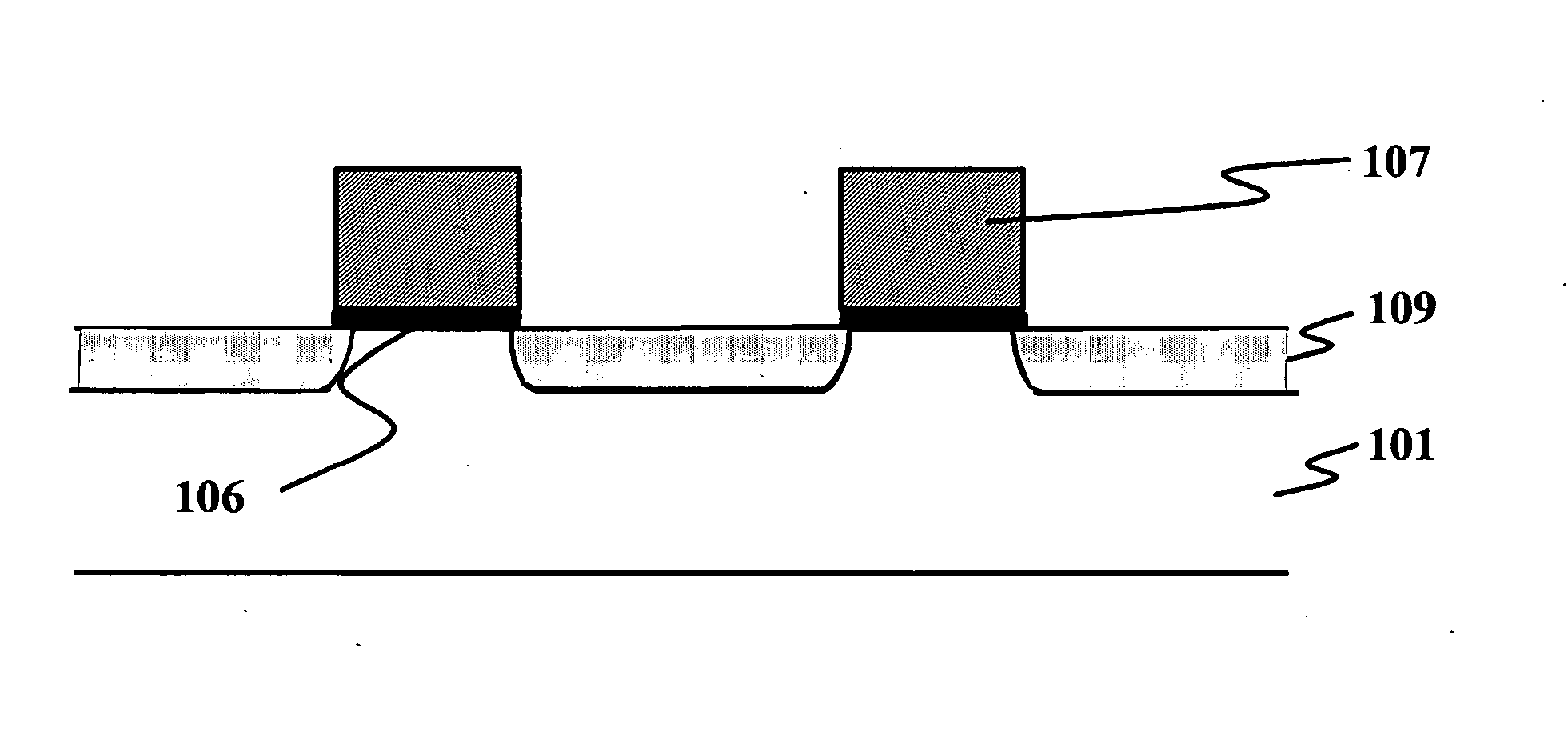

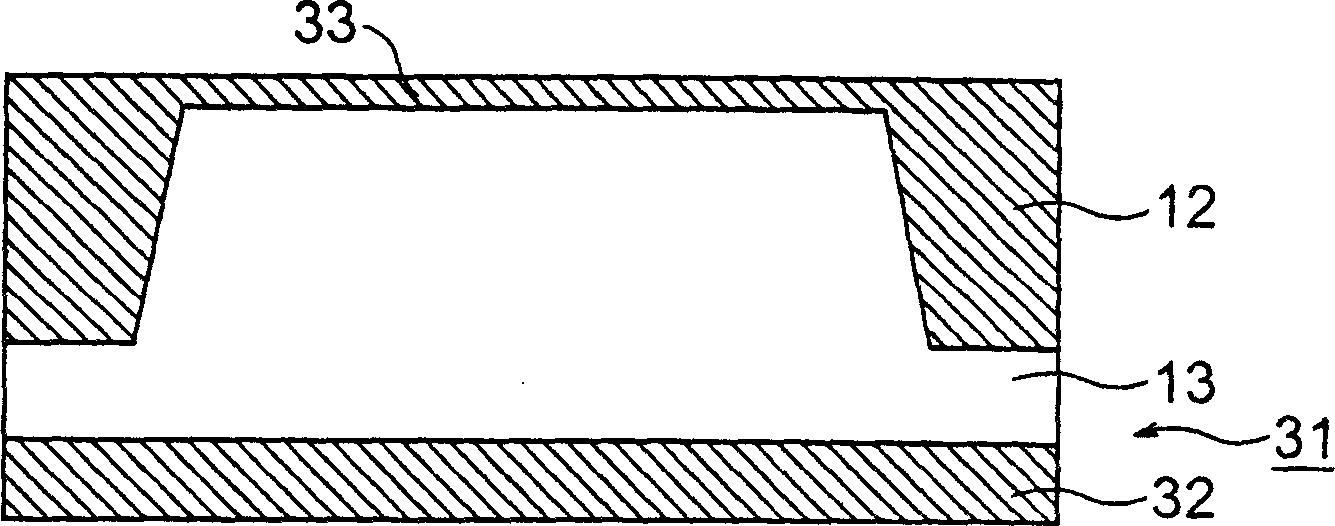

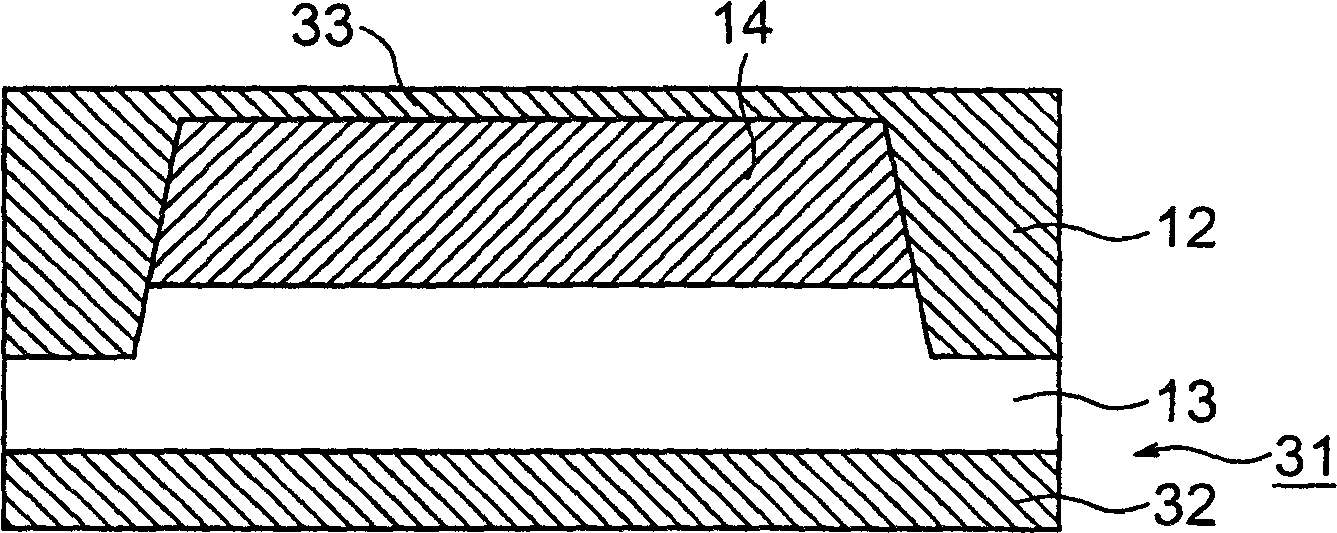

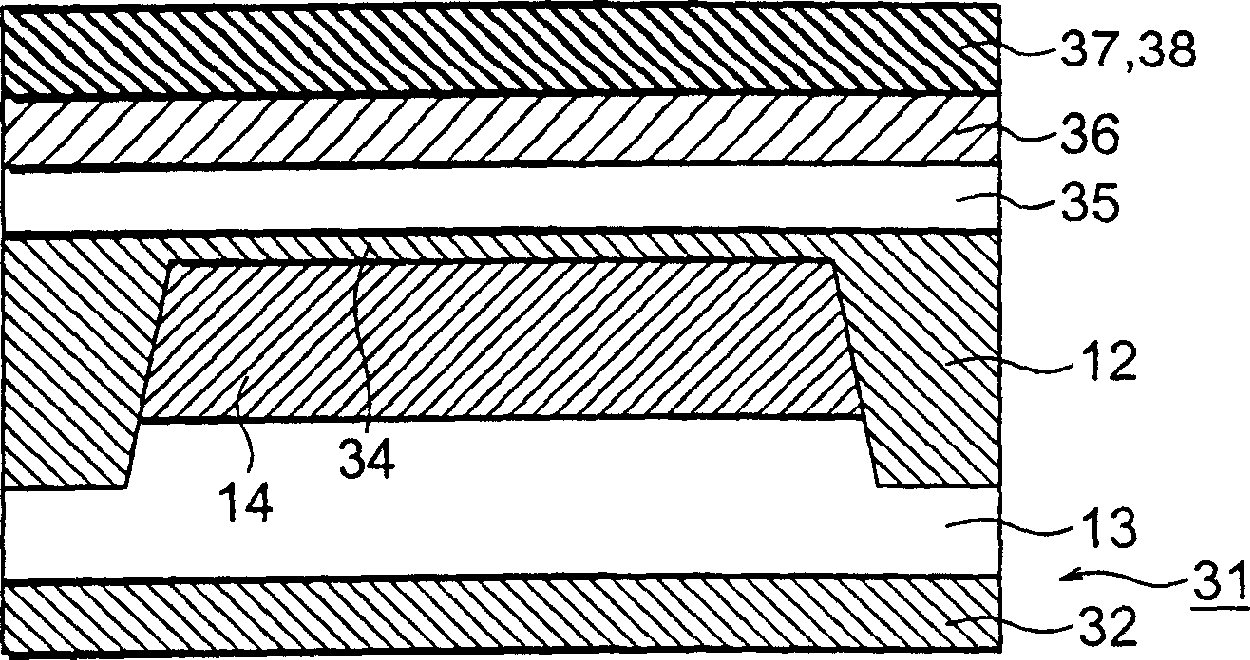

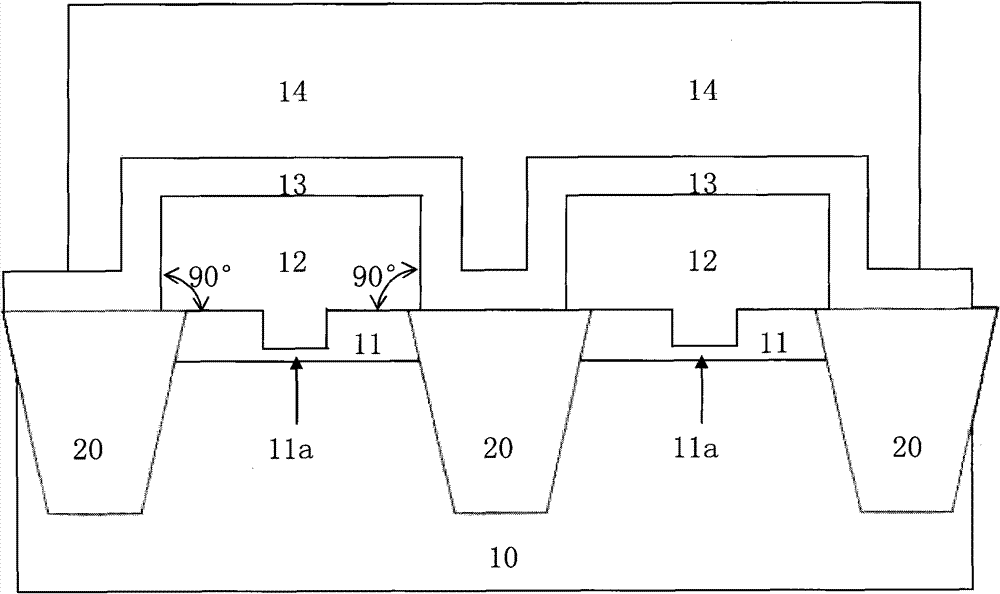

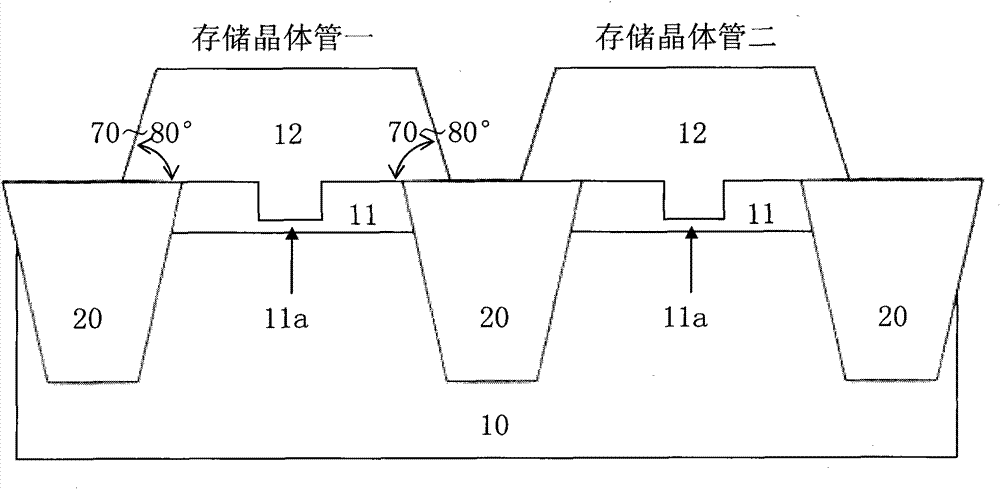

Floating gates of EEPROM (electrically erasable programmable read-only memory) and manufacturing method thereof

ActiveCN102129976AImprove data retention characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesProgrammable read-only memorySilicon oxide

The invention discloses a manufacturing method of floating gates of an EEPROM (electrically erasable programmable read-only memory). The method comprises the following steps: 1. etching a polysilicon layer on the surface of a silicon wafer to form floating gates, wherein the side walls of the floating gates have angle of inclination being 70-80 degrees; and the silicon wafer is characterized in that gate oxide layers and tunnelling oxide layers have been formed on the silicon substrate; isolation structures have existed in the silicon substrate; and the polysilicon layer has been deposited onthe surface of the silicon substrate; 2. growing silicon oxide layers on the surfaces of the floating gates by adopting the thermal oxide growth process; and 3. depositing a silicon nitride layer anda silicon oxide layer on the surface of the silicon wafer in sequence, wherein the silicon oxide layers, the silicon nitride layers and the silicon oxide layers on the floating gates form ONO (oxide-nitride-oxide) layers. The topography of the floating gates after etching becomes oblique through improvement and the upper angles of the floating gates are chamfered through the thermal oxide growth process, thus improving the data retention of the EEPROM.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

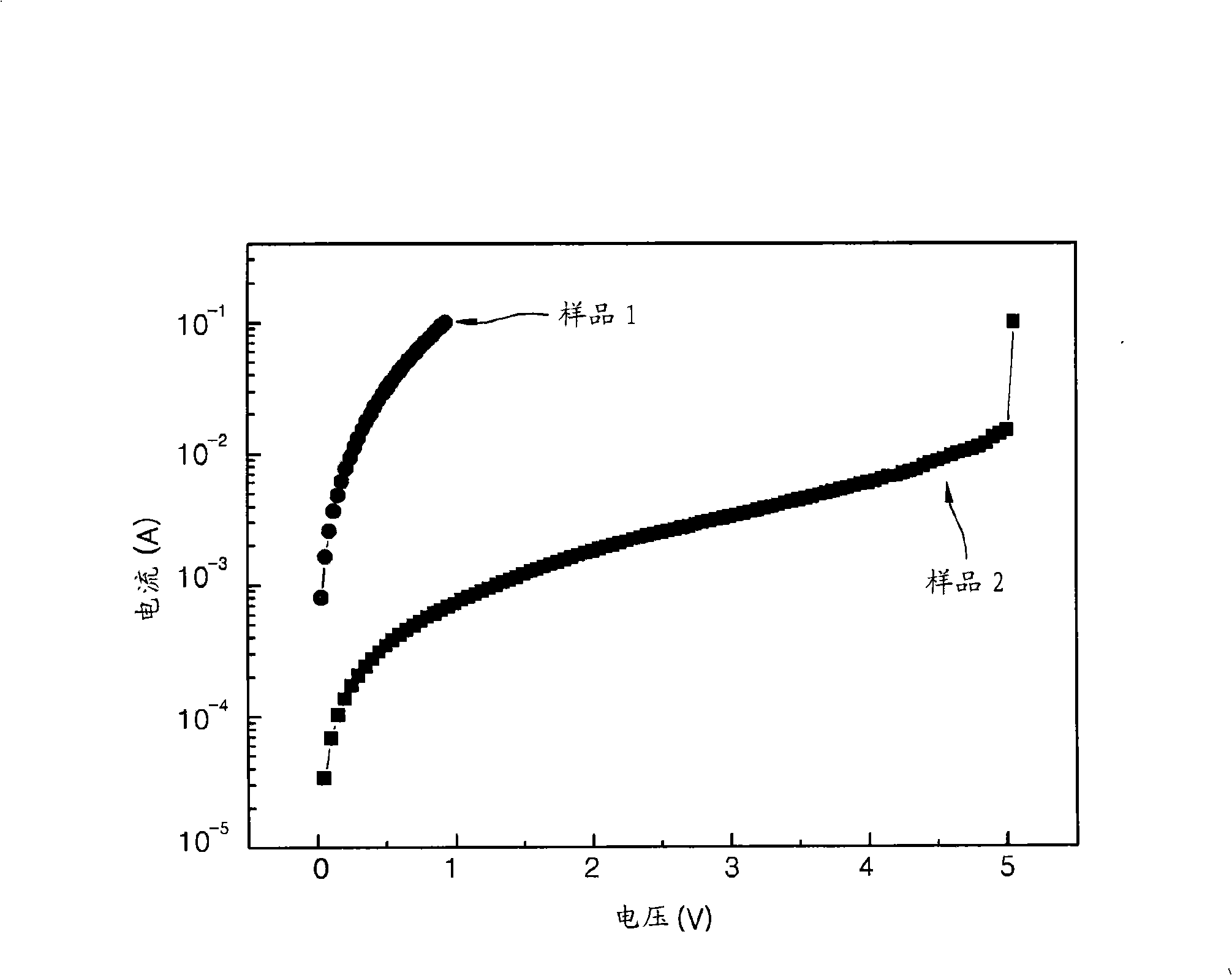

Oxide resistor storage device and preparation method thereof

ActiveCN102148328AGood reliabilitySimple preparation processElectrical apparatusControl layerData retention

The invention discloses an oxide resistor storage device, which comprises a substrate, a bottom electrode positioned on the substrate, an oxide control layer positioned on the bottom electrode, an oxide resistance change layer positioned on the oxide control layer, and a top electrode positioned on the oxide resistance change layer. The device is simple in preparation process and reliable in performance, the circulating durability of the resistance change of an oxide resistance change storage is improved and the data retention performance is improved.

Owner:PEKING UNIV

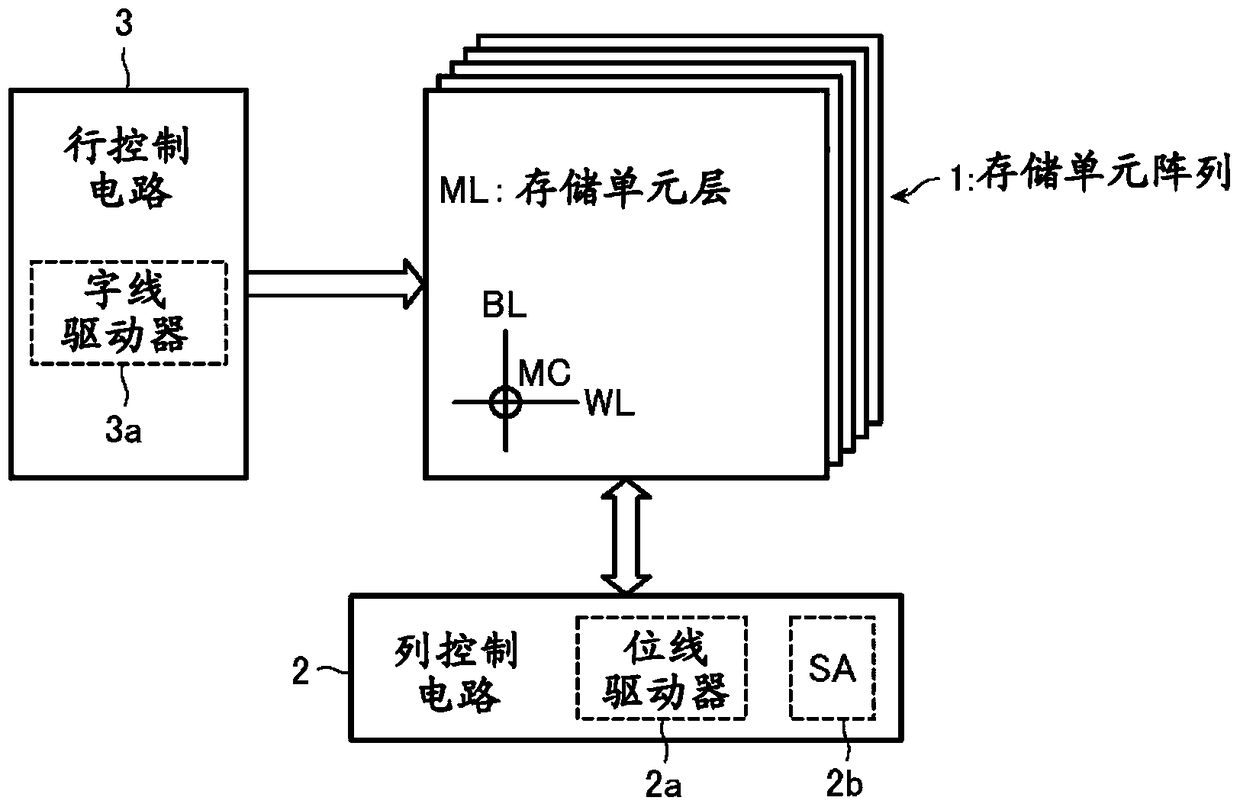

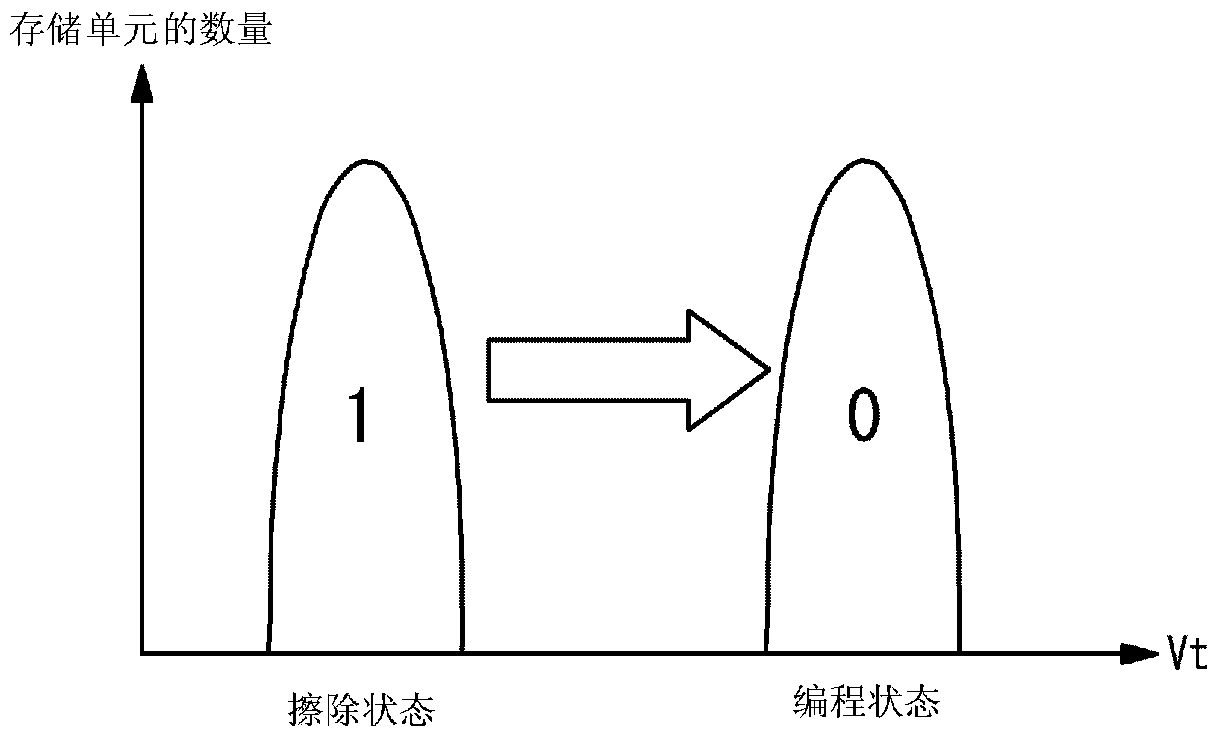

Nonvolatile semiconductor memory device

ActiveCN104282335AImprove data retention characteristicsRead-only memoriesDigital storageElectrical polarityControl circuit

A nonvolatile semiconductor memory device according to an embodiment comprises: a memory cell array including a plurality of memory cells provided one at each of intersections of a plurality of first lines and a plurality of second lines and each storing data by a data storing state of a filament; and a control circuit configured to execute a write sequence that writes data to the memory cell, the write sequence including: a setting operation that applies a setting pulse having a first polarity to the memory cell; and a removing operation that applies a removing pulse having a second polarity opposite to the first polarity to the memory cell; and the control circuit, during execution of the write sequence, is configured to repeatedly execute the setting operation until the memory cell attains a desired data storing state, and then to execute the removing operation.

Owner:KIOXIA CORP +1

Resistive random access memory and manufacturing method for the same

InactiveCN101257089AHighly integratedImprove data retention characteristicsSolid-state devicesRead-only memoriesDopantStatic random-access memory

Provided are a resistance random access memory including a resistance layer having a metal oxide and / or a metal ion dopant, which may be deposited at room temperature and which may have variable resistance characteristics, and a method of manufacturing the same.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device for precharging bit lines except for specific reading and writing periods

InactiveUS7692986B2Prevent data-charge lossData augmentationDigital storageBit lineAudio power amplifier

Owner:LONGITUDE SEMICON S A R L

Method of manufacturing flash memory

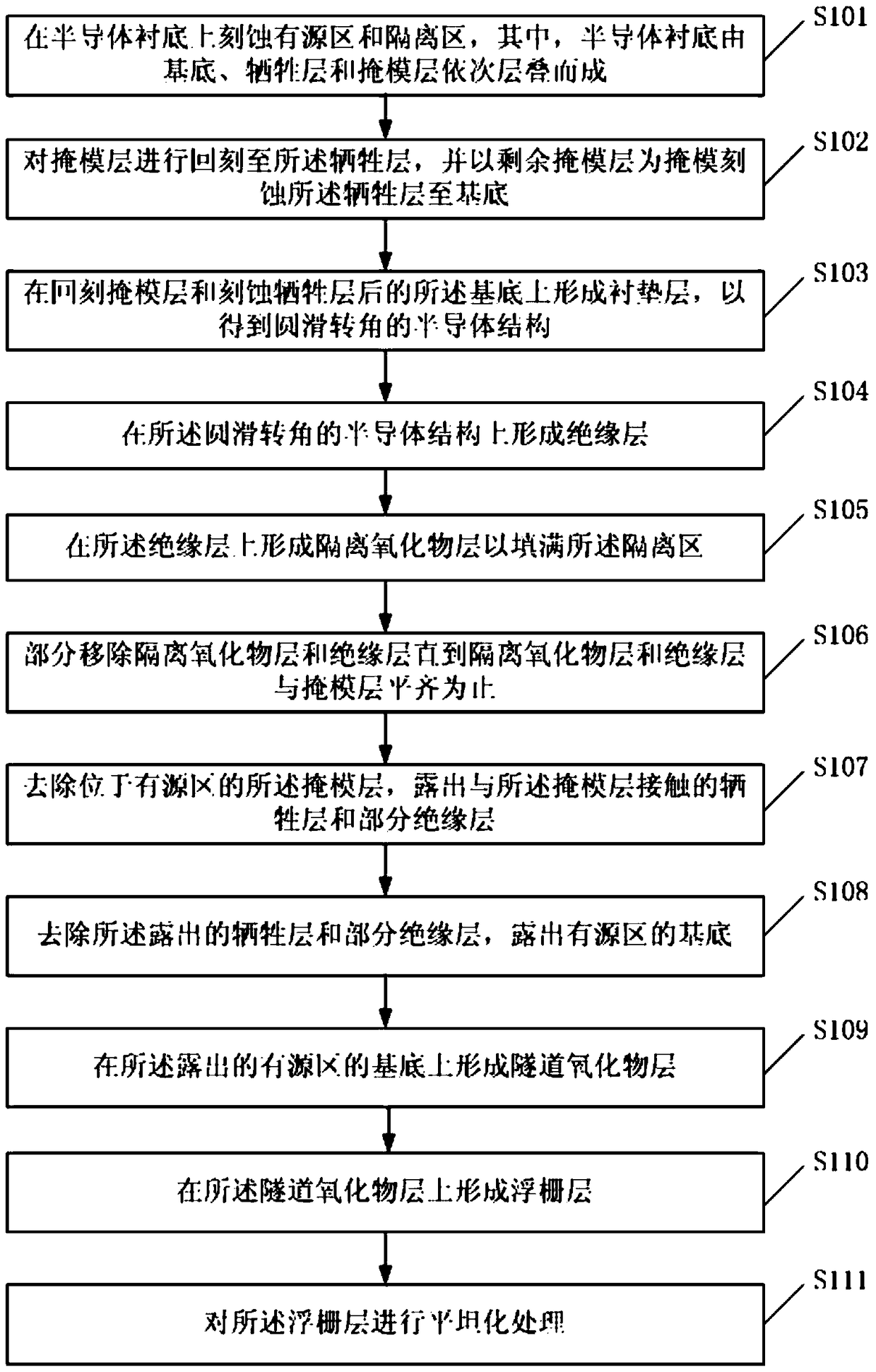

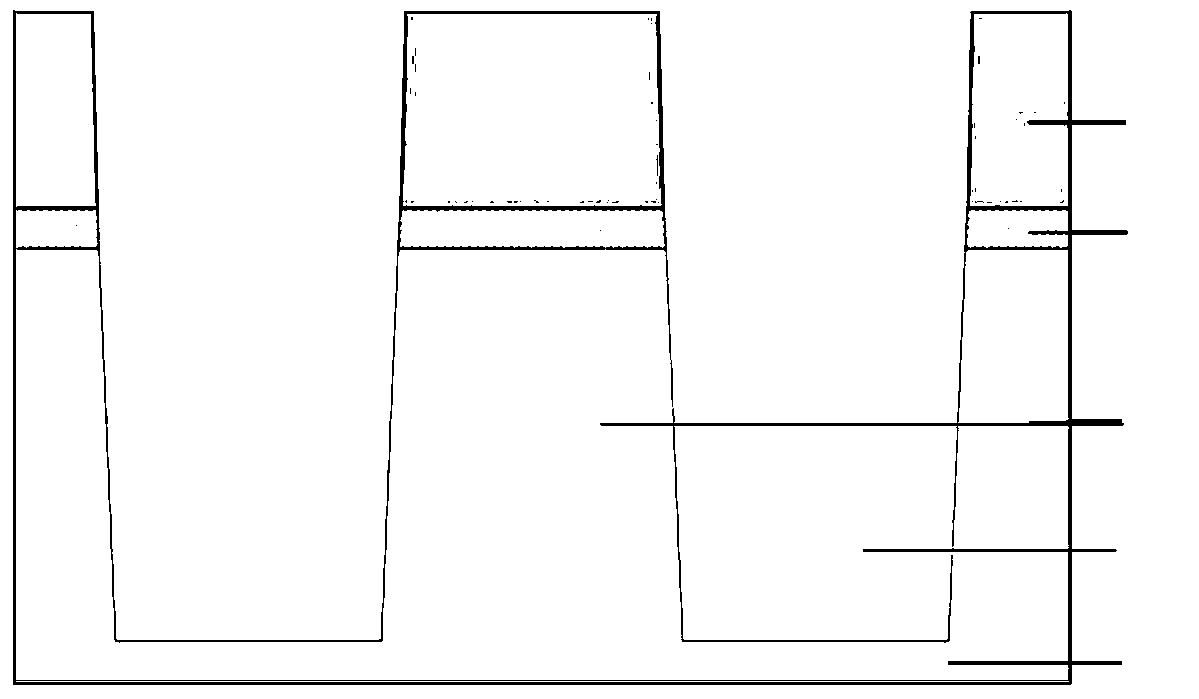

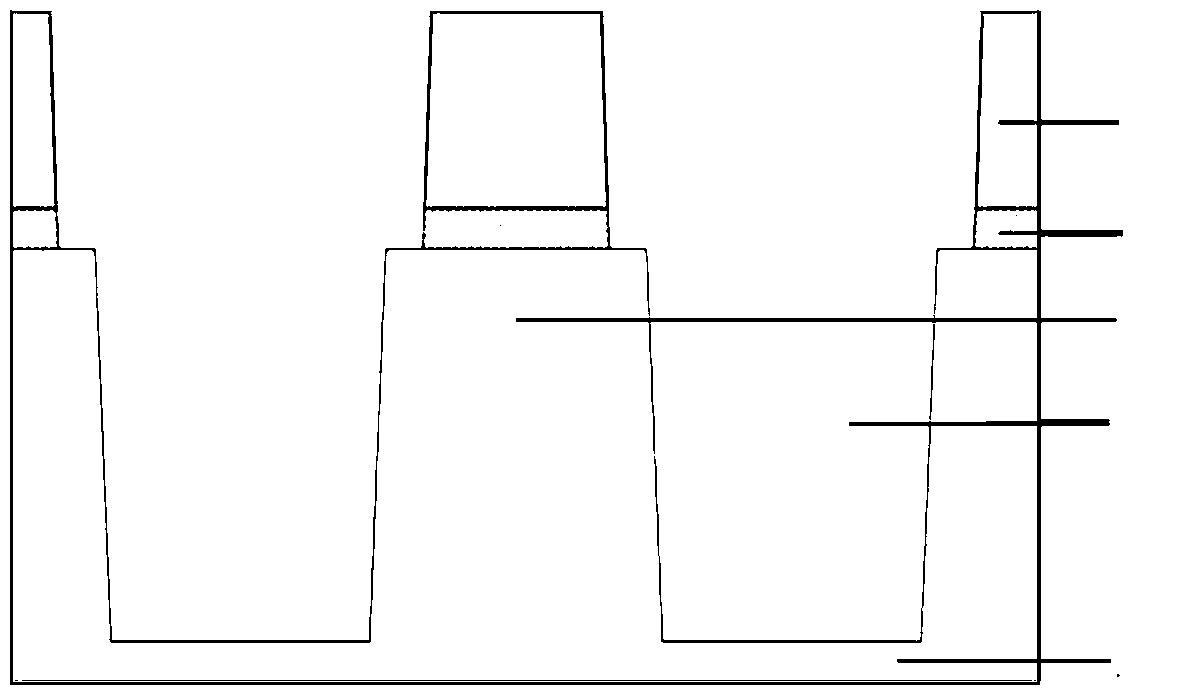

ActiveCN105405809AImprove data retention characteristicsAvoid influenceSemiconductor/solid-state device manufacturingInsulation layerEtching

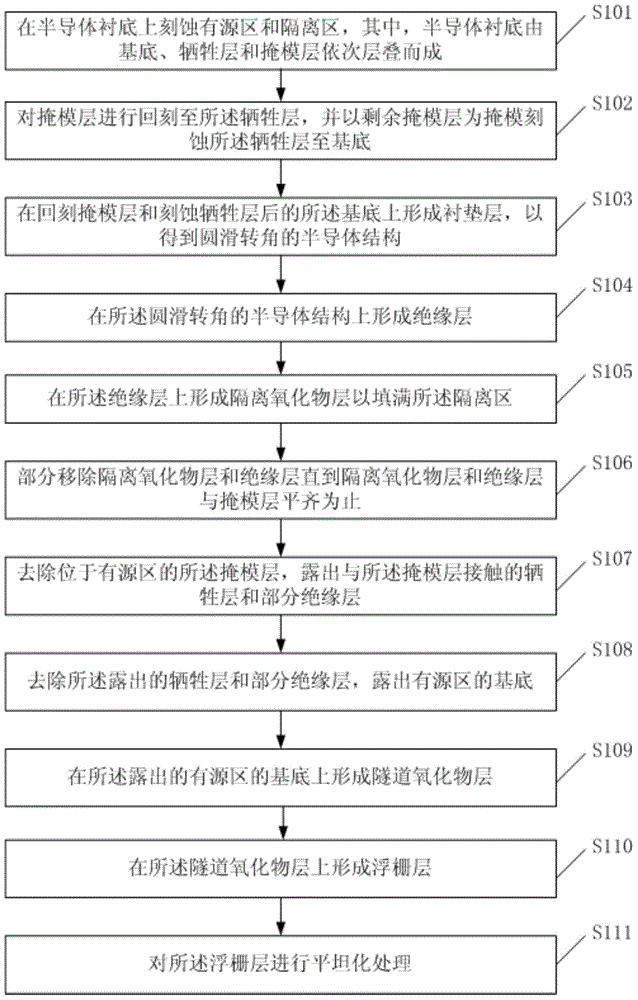

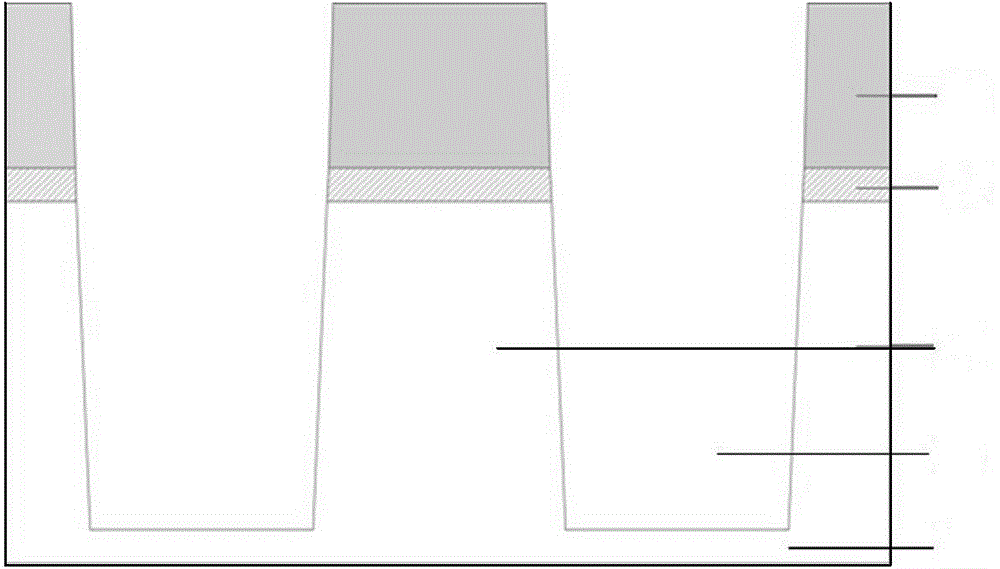

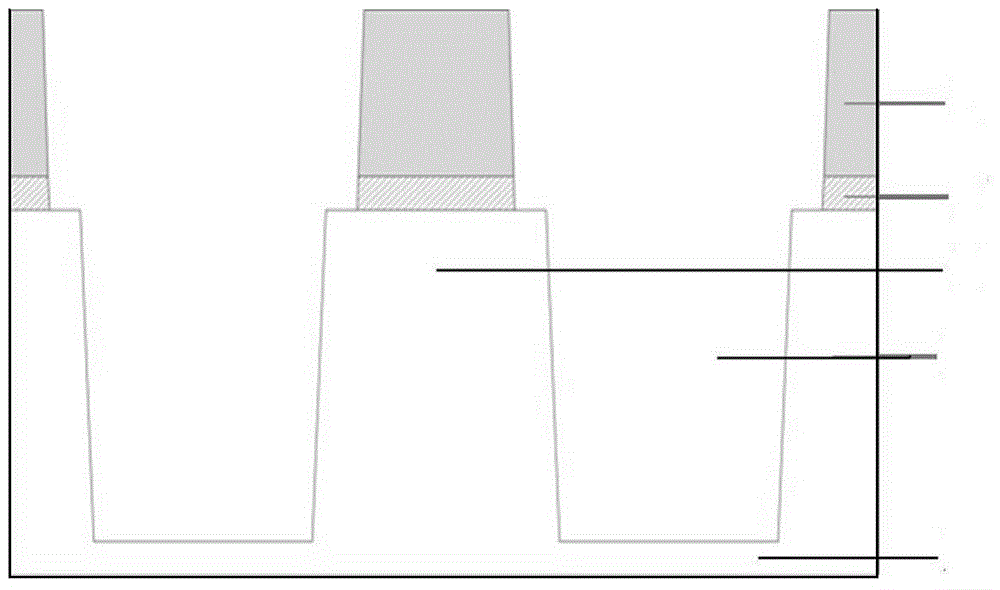

The invention discloses a method of manufacturing a flash memory. The method comprises the steps of etching an active region and an isolation region on a semiconductor substrate which is stacked by a substrate, a sacrificial layer and a mask layer in sequence, forming a lining layer on the substrate after the etching of the mask layer and the sacrificial layer to obtain a semiconductor structure of a smooth corner; forming an insulation layer on the semiconductor structure of the smooth corner; forming an isolation oxide layer on the insulation layer to fill the isolation region; removing the isolation oxide layer and the insulation layer partially until the isolation oxide layer levels with the insulation layer and the mask layer; removing the mask layer located on the active region to expose the sacrificial layer and the partial insulation layer which are in contact with the mask layer; removing the exposed sacrificial layer and the partial insulation layer to expose the substrate of the active region; and forming a tunnel oxide layer and a floating gate layer on the exposed substrate of the active region. The invention can prevent the tunnel oxide layer and the floating gate layer from being influenced by the isolation oxide of the isolation region, thereby improving the data holding characteristics of the flash memory.

Owner:GIGADEVICE SEMICON SHANGHAI INC +1

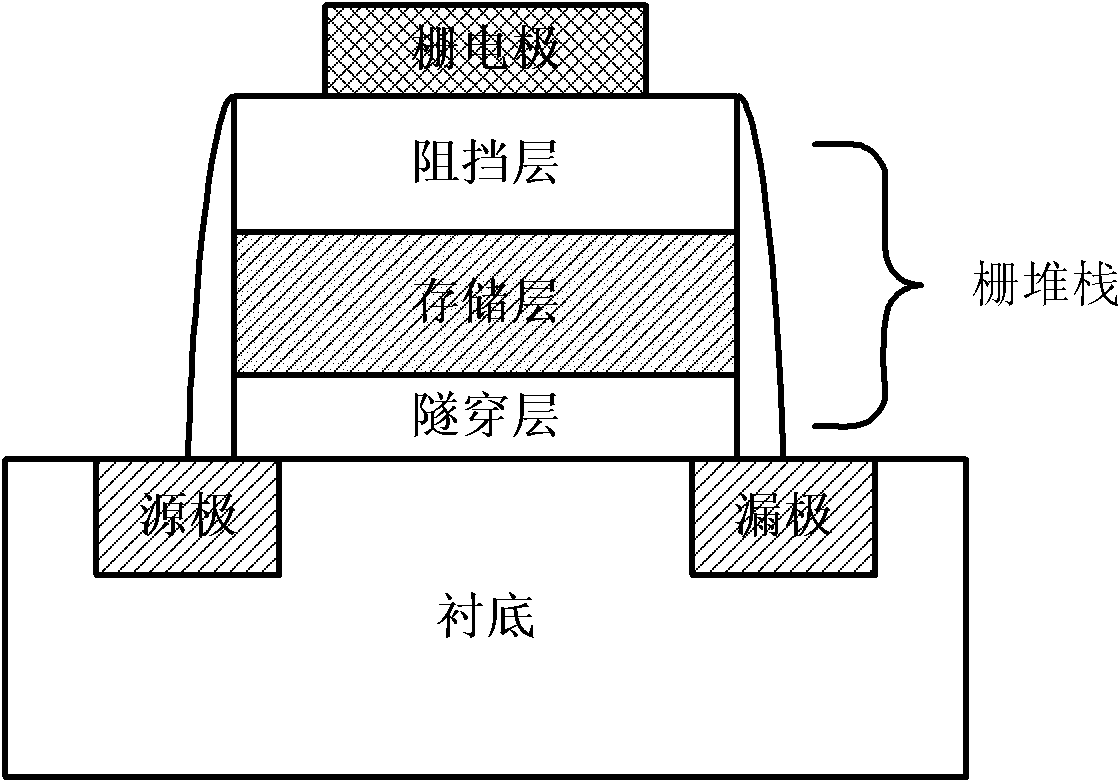

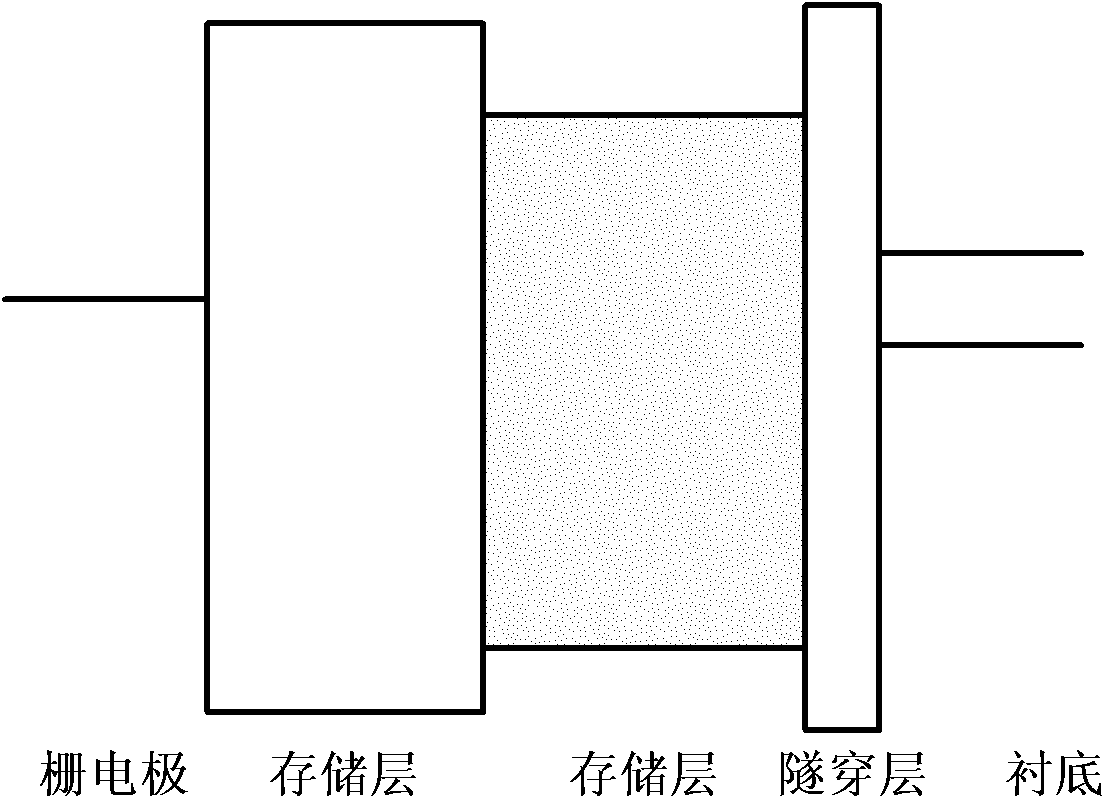

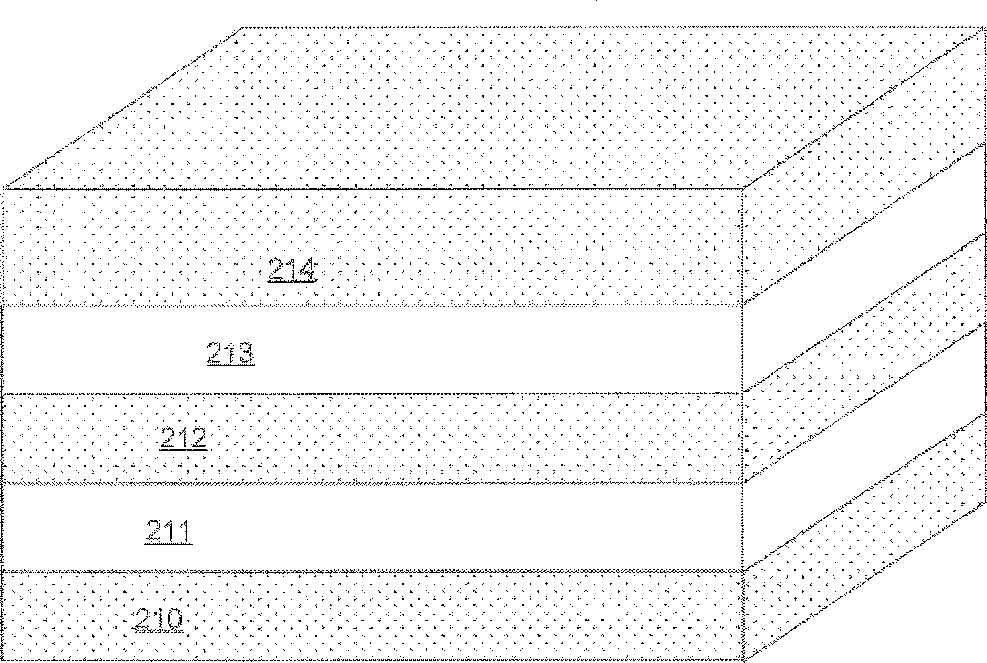

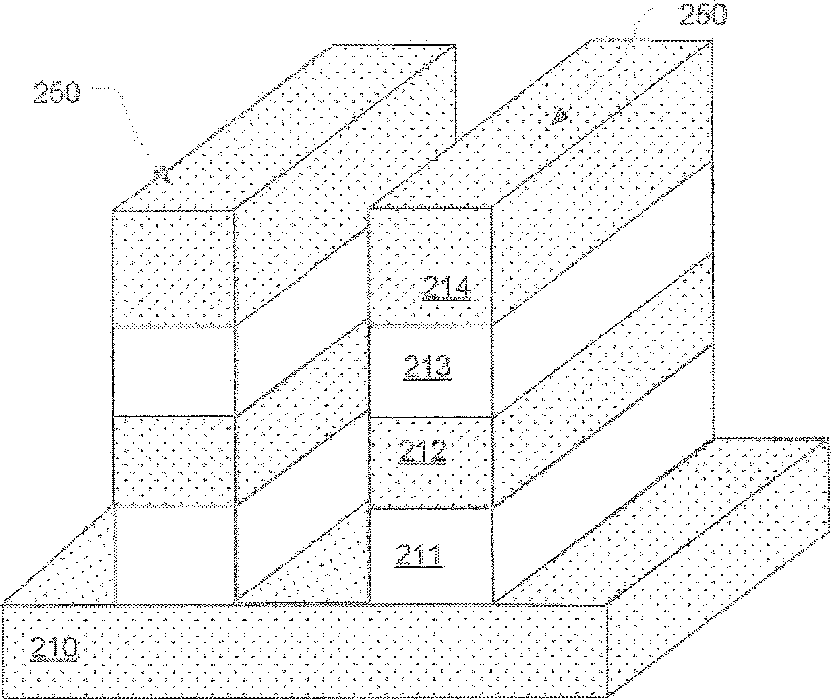

Charge-trapping type gate stack and storage unit

InactiveCN102655167AImprove data retention characteristicsHigh reliability operationSemiconductor devicesTrappingGate stack

The invention discloses a charge-trapping type gate stack and a storage unit. The gate stack is formed by stacking a tunneling layer, a storage layer and a blocking layer from bottom to top, wherein the storage layer is formed by stacking at least three medium sub-layers including at least two storage medium sub-layers and at least one modulation medium sub-layer sandwiched between the storage medium sub-layers, and the modulation medium sub-layer is used for changing the charge distribution in the storage layer so as to reduce charges close to the blocking layer and gather the charges in the storage layer. According to the invention, through effectively controlling the charge distribution in the storage layer, the data retention property of the storage layer of the gate stack for the charge constraint capacity can be improved, and high-reliability operation for a device can be realized. In addition, through introducing a modulation structure of the storage layer, device performances such as the programming efficiency, the operation voltage of a charge-trapping type nonvolatile memory device are optimized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

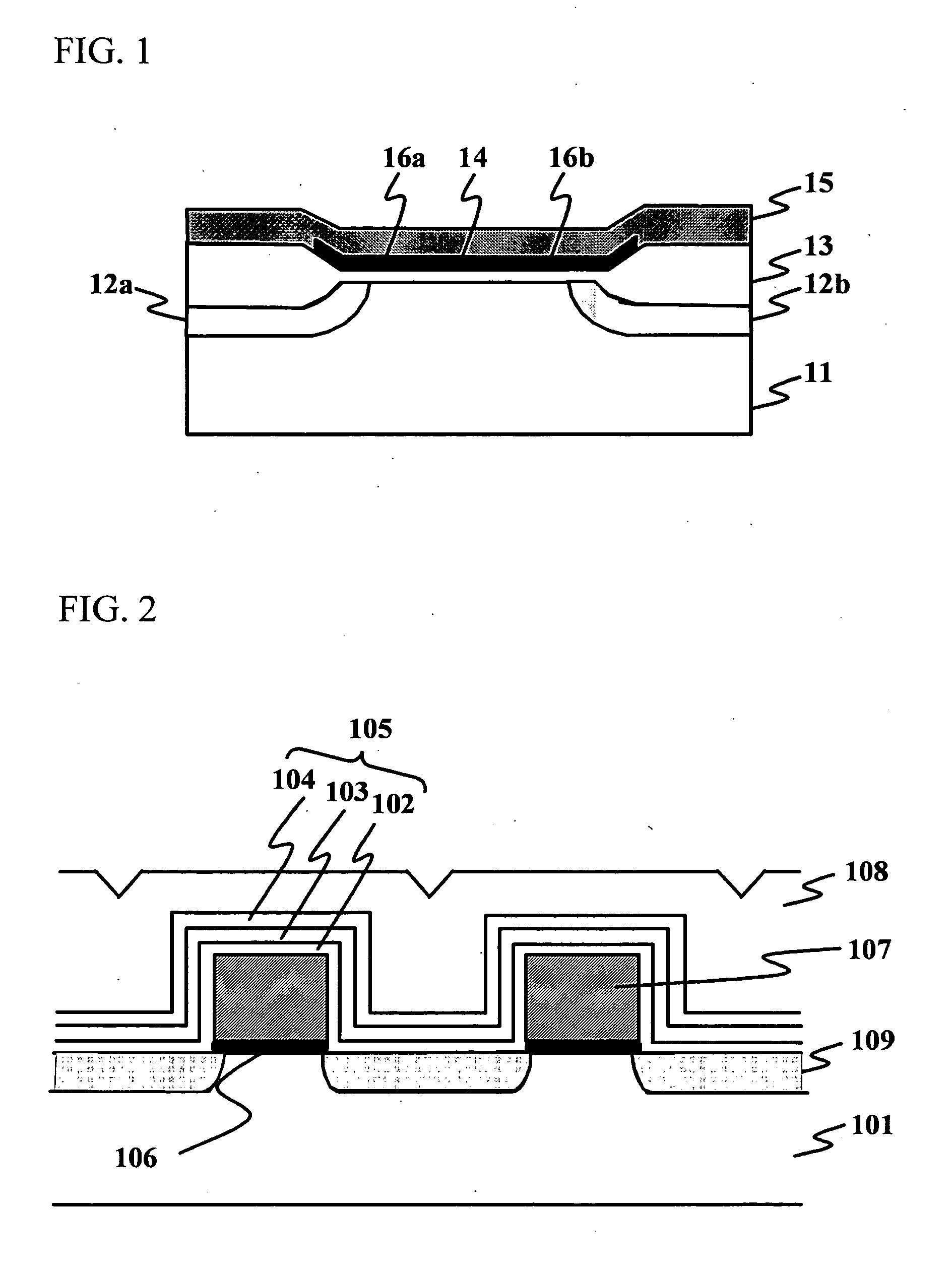

Semiconductor device

ActiveUS20060231883A1Improve data retention characteristicsEasy to eraseSolid-state devicesRead-only memoriesHigh concentrationSemiconductor memory

A semiconductor memory device, firstly, has both the thickness of a tunnel film and that of a top film provided thereon and configured to be in the FN tunneling region (4 nm or more). The data retention characteristics can be improved by configuring both the thickness of a tunnel film and that of a top film to have a thickness of in the FN tunneling region. Secondly, a high-concentration impurity region of a conductivity type the same as that of the substrate is provided in a substrate region arranged between assist gates provided adjacently to each other. The aforementioned high-concentration impurity region makes a depletion layer extremely thin when bias is applied to the assist gates. Hot holes generated between bands in the depletion region are injected into a charge storage region and the holes and electrons make pairs and disappear, enabling easy data erasing.

Owner:MONTEREY RES LLC

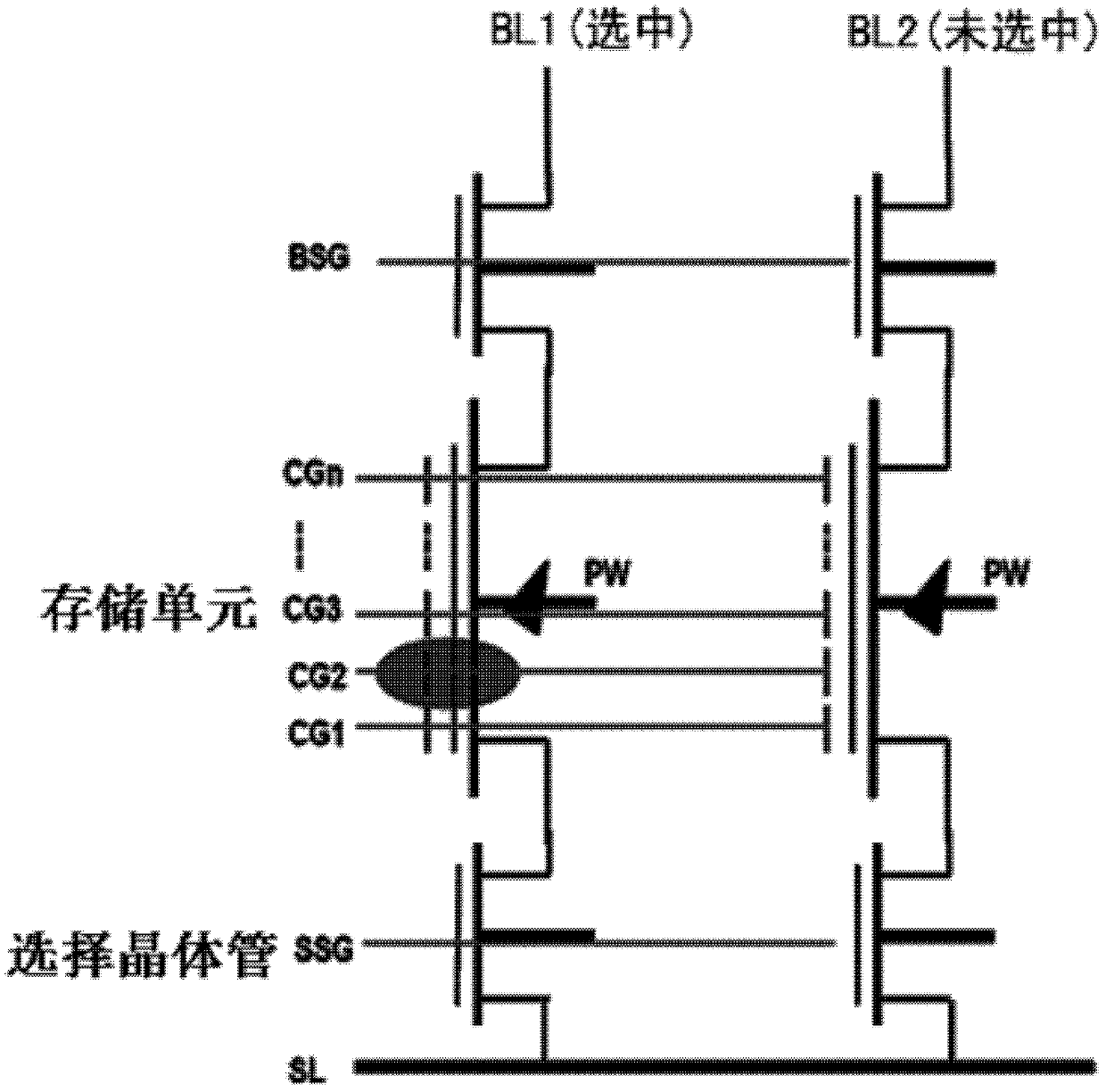

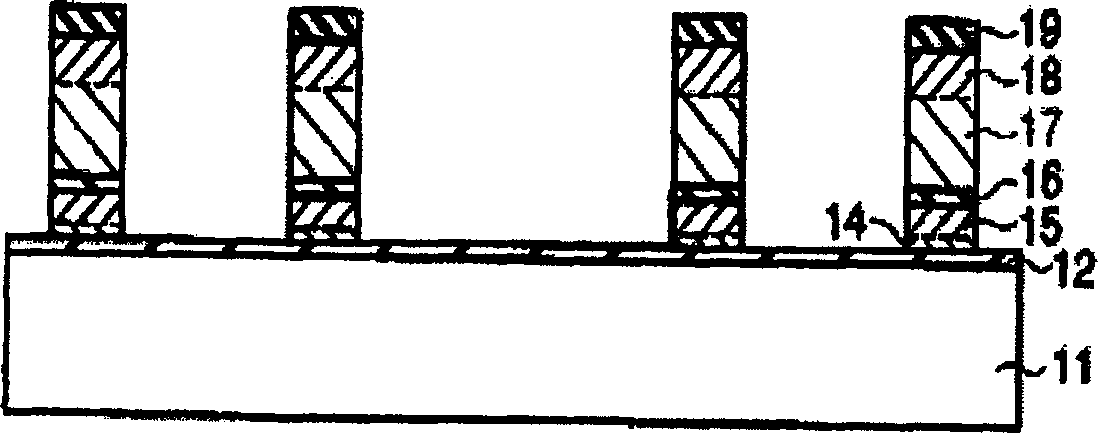

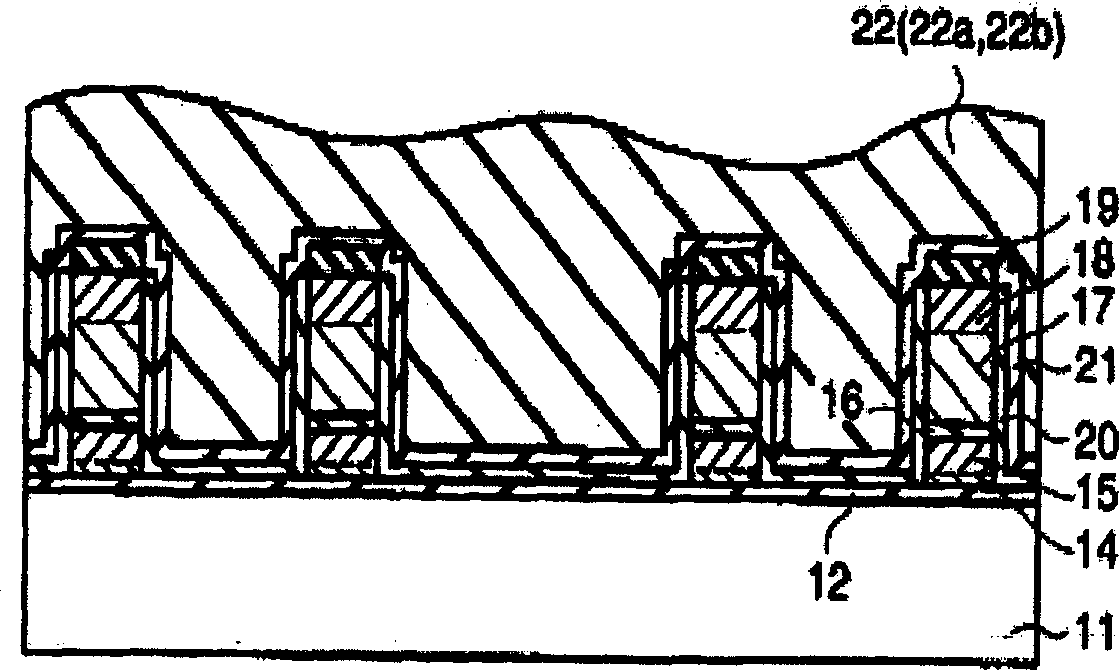

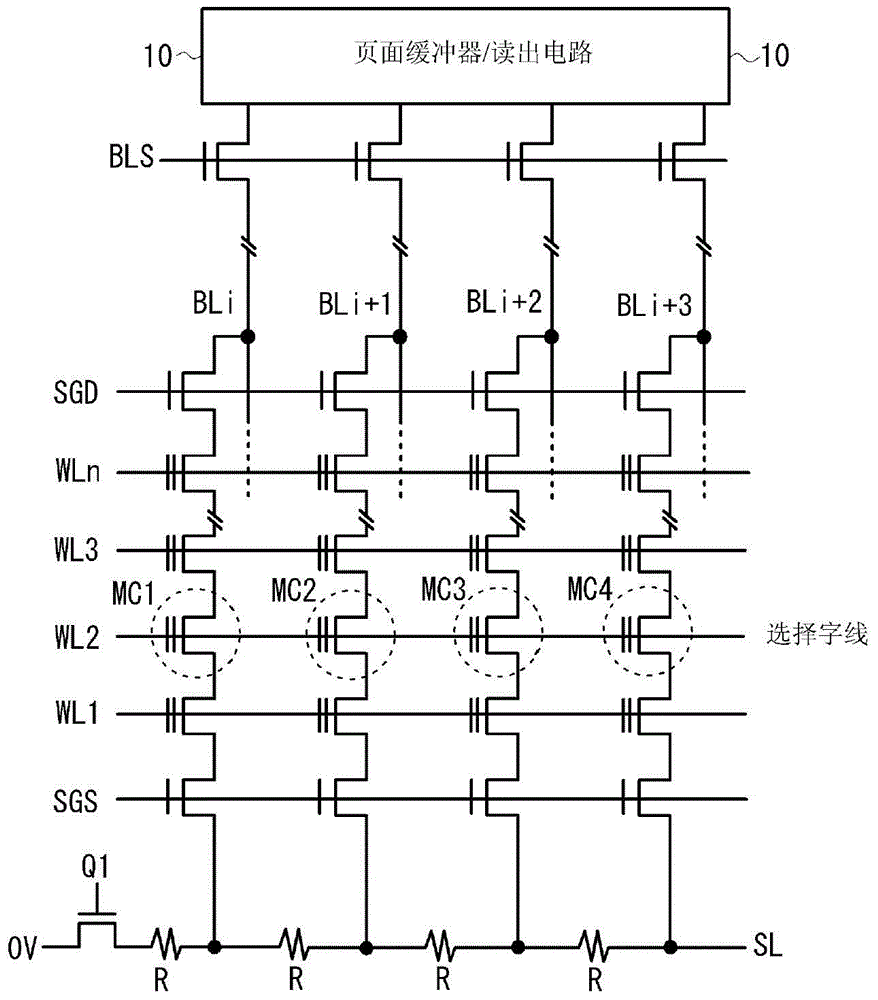

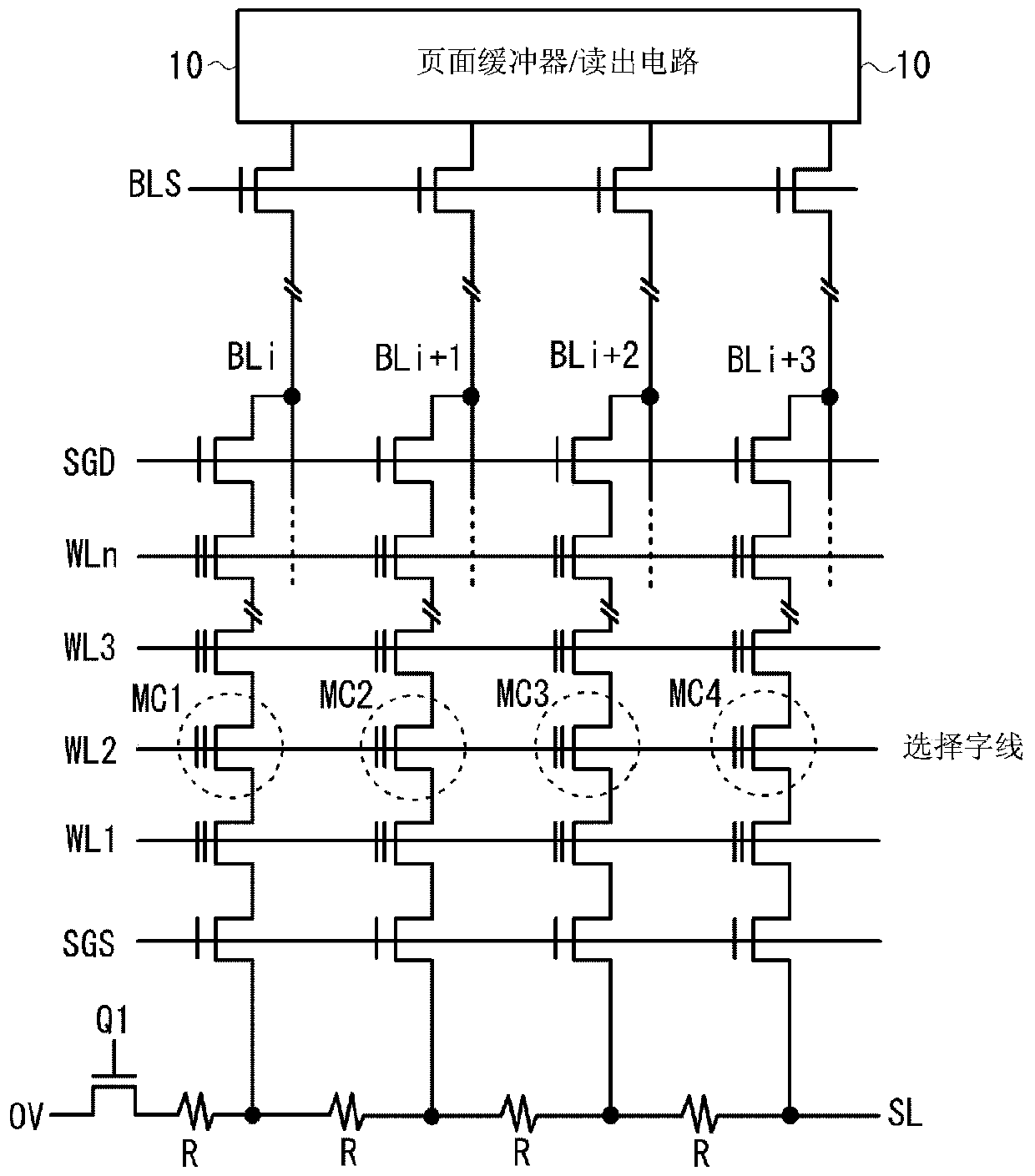

NAND memory based on nanocrystalline and manufacturing method thereof

InactiveCN103296070AReduce areaImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingCharge carrierMaterials science

The invention relates to an NAND memory based on nanocrystalline and a manufacturing method of the NAND memory based on the nanocrystalline. The NAND memory comprises a nanocrystalline storage unit and a selective transistor. The nanocrystalline storage unit comprises a silicon base, a conduction source region and a conductive leakage area which are arranged at two sides of the silicon base, a tunneling medium layer covering on the charge carrier channel between the source conductive region and the conductive leakage area, a nanocrystalline charge storage layer covering on the tunneling medium layer, a control grid medium layer covering on the nanocrystalline charge storage layer, and a grid electrode material layer covering on the control grid medium layer. The transistor comprises a silicone base, a conductive source region and a conductive leakage region which are arranged at two sides of the silicone base, a medium layer covering on the charge carrier channel between the conductive source region and the conductive leakage region, and a grid electrode material layer covering on the medium layer. The NAND memory based on the nanocrystalline and the manufacturing method of the NAND memory based on the nanocrystalline can reduce the area of a chip in a large-scale mode, meanwhile can save one to two lines of photomask due to the fact that the source-drain junction in the middle part of a storage unit is removed, and preparation is made for the memory of next generation.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

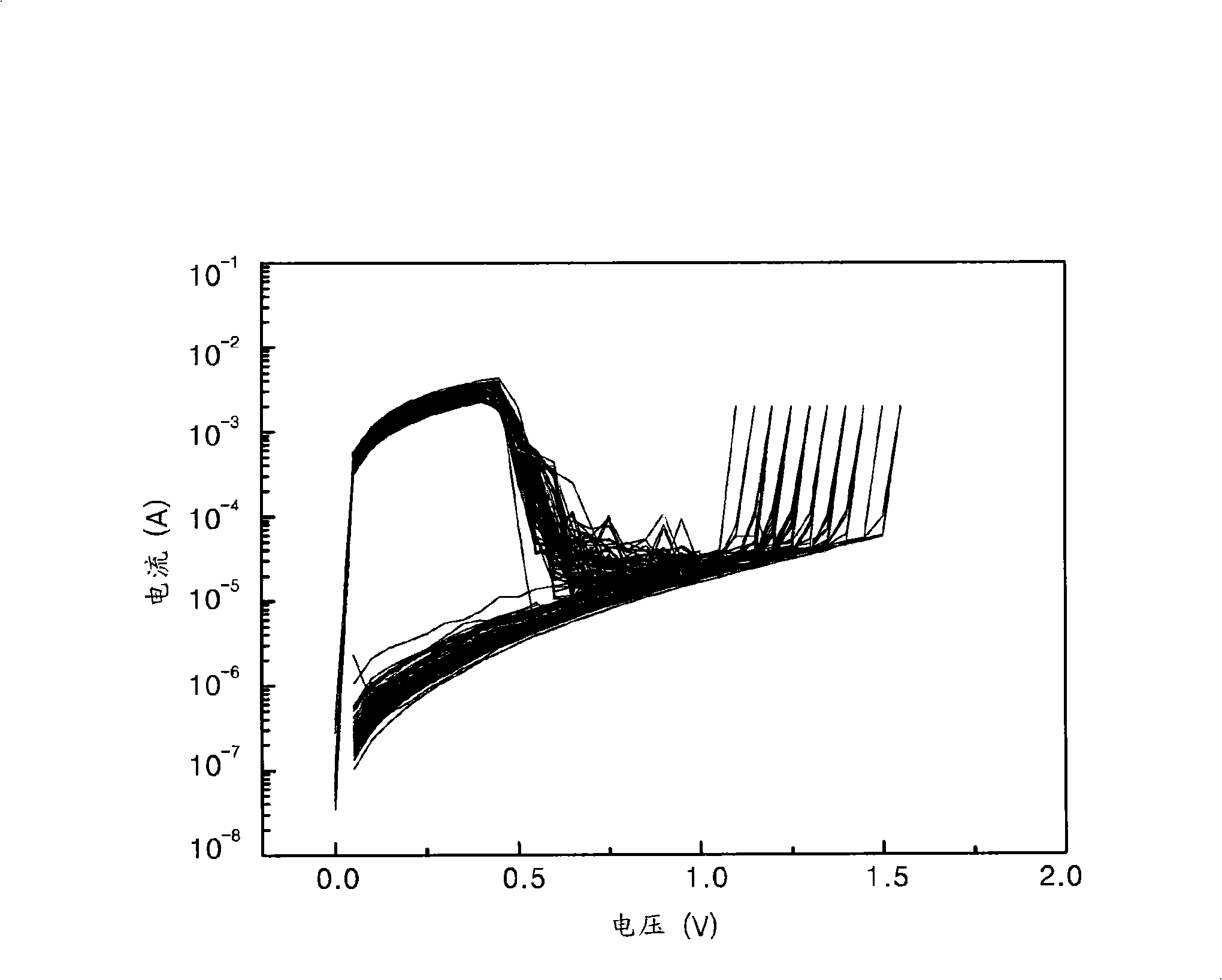

Memory unit and method of operating the same

InactiveCN102629486AImprove data retention characteristicsImprove long-term reliabilityDigital storageEngineeringHigh resistance

A memory unit includes memory elements and a drive section. In executing a first operation out of the first operation for changing resistance state of the memory element from one resistance state out of low resistance state and high resistance state to the other resistance state and a second operation for changing the resistance state of the memory element from the other resistance state to the one resistance state, the drive section performs stepwise operation, in which the drive section repeatedly performs, at least one time, a step in which strong stress application step for applying a stress for performing the first operation to the memory element as the drive target relatively strongly is performed and subsequently weak stress application step for applying a stress for performing the second operation to the memory element as the drive target relatively weakly is performed, and subsequently performs the strong stress application step.

Owner:SONY CORP

Non-volatile sonos-type memory device

ActiveUS20100022081A1Improve data retentionSimple dataSolid-state devicesRead-only memoriesHigh concentrationElectron

A semiconductor memory device with the thickness of both a tunnel film and a top film provided thereon configured to be in the FN tunneling region (4 nm or more). Data retention characteristics can be improved by configuring both a tunnel film and a top film to have a thickness in the FN tunneling region. Secondly, a high-concentration impurity region of a conductivity type the same as that of the substrate is provided in a substrate region arranged between assist gates provided adjacently to each other. The aforementioned high-concentration impurity region makes a depletion layer extremely thin when bias is applied to the assist gates. Hot holes generated between bands in the depletion region are injected into a charge storage region and the holes and electrons make pairs and disappear, enabling easy data erasing.

Owner:MONTEREY RES LLC

Semiconductor memory device and refresh control method

InactiveCN1805048AImprove data retention characteristicsShorten test timeDigital storageControl signalTimer

Disclosed is a semiconductor-memory device comprising a selector for performing switching control such that in the standby state the refresh operation is performed responsive to an external-refresh-execution command supplied from outside the semiconductor-memory device, while in the active state, the refresh operation is performed, not under the control from outside the semiconductor-memory device, but under the control from a built-in timer.

Owner:NEC ELECTRONICS CORP

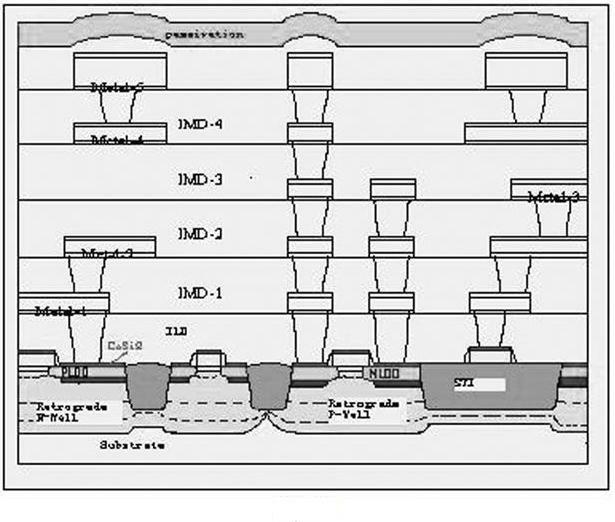

Method for manufacturing a semiconductor device

InactiveCN1649113AReduce standby currentImprove data retention characteristicsTransistorSolid-state devicesDopantBiomedical engineering

A method for manufacturing a MOS transistors in a semiconductor device includes the step of implanting a dopant in a channel layer or source / drain regions by using a multi-step implantation and an associated multi-step heat treatment, wherein the multi-step implantation includes a number of steps of implantation each for implanting the dopant at a dosage lower than 1x1013 / cm2. The total dosage of the multi-step implantation ranges between 1x1013 / cm2 and 3x1013 / cm2.

Owner:ELPIDA MEMORY INC

Semiconductor storage device and its making method

InactiveCN1449044AImprove data retention characteristicsTransistorSolid-state devicesSemiconductor storage devicesSilicon oxide

Provided are a nonvolatile semiconductor memory device capable of improving data retention characteristics and a method of manufacturing the same. On the upper layer of the memory element, there is at least one layer including at least one of the following groups: a silicon oxide film doped with nitrogen; a silicon oxide film doped with Al; an oxide of Al; a silicon oxide film doped with Ti; Nitrogen and two of the three kinds of Al and Ti silicon oxide film; silicon oxide film with nitrogen and three kinds of Al and Ti added; Ti oxide; Ti and Al oxide; made of Ti, Ni, Co , Zr, Cu, Pt, V, Mg, U, Nd, La, Sc metal group consisting of a single metal layer; metals containing two or more of these metal groups account for at least 50% of the whole A layer composed of a binary or higher alloy; a layer composed of a nitride of the alloy; or a layer composed of a hydride of the alloy (such as the Al2O3 film 10).

Owner:KK TOSHIBA

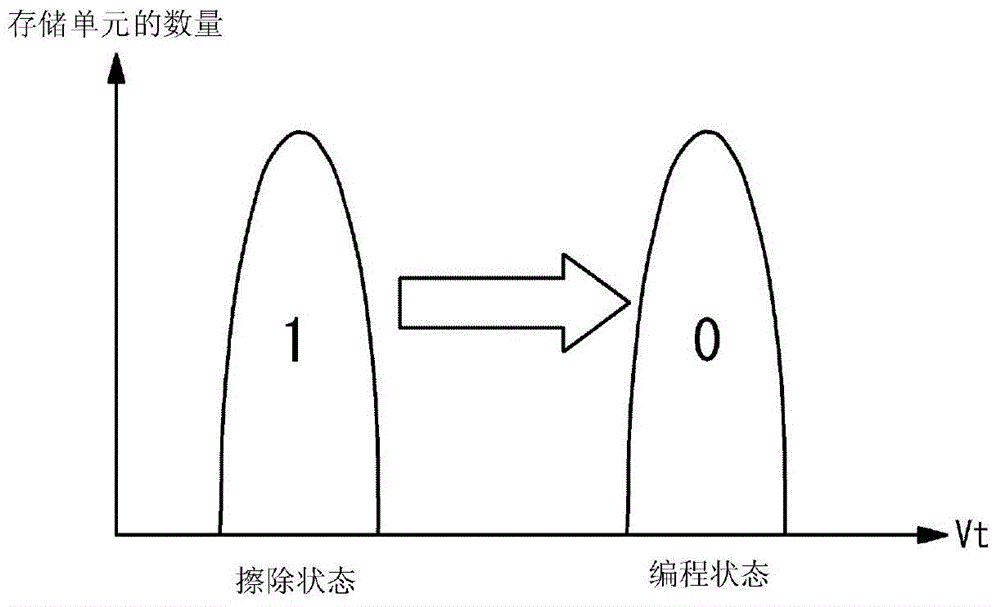

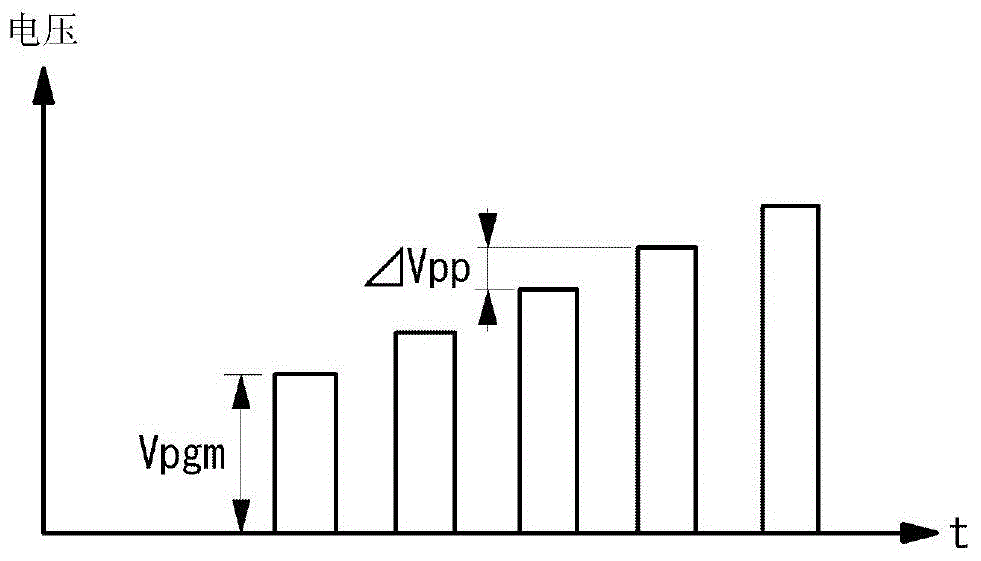

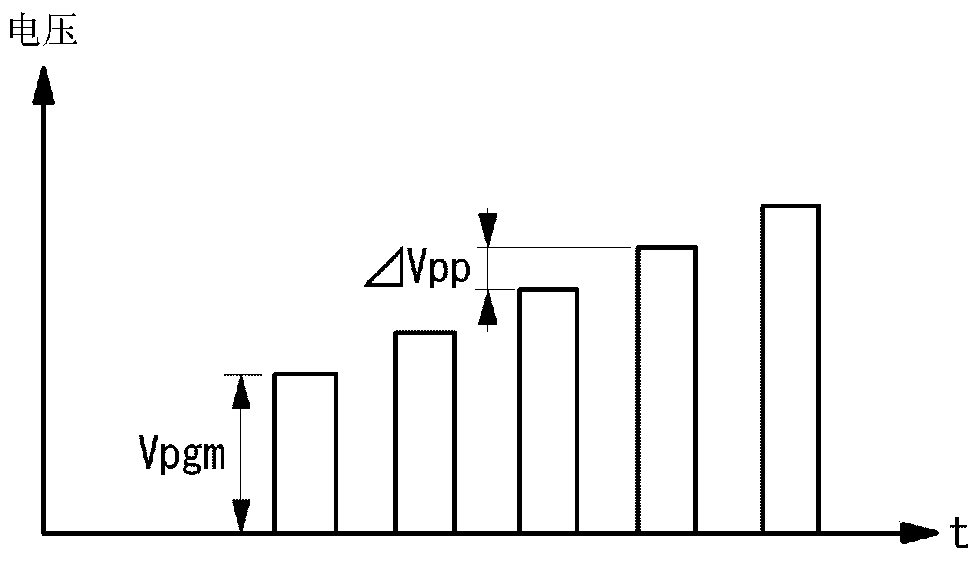

Flash memory and programming method thereof

ActiveCN106158028AImprove data retention characteristicsAccurate verificationRead-only memoriesDigital storageBit linePre-charge

A programming method of an NAND flash memory is provided, for narrowing a distribution width of a threshold voltage. The method includes a step of verification reading for verifying a threshold voltage of a selected memory cell after a programming voltage is applied to a selected word line. The verification reading further includes a step of pre-charging a voltage to a bit line, a step of discharging the pre-charged bit line to a source line, and a step of reading the voltage of the bit line after the discharging step. Regarding the discharge period from starting the discharging of the bit line to starting the read out, the discharge period of the verification reading after the initial programming voltage is applied is set longer than the discharge period of the verification reading after the subsequent programming voltage is applied.

Owner:WINBOND ELECTRONICS CORP

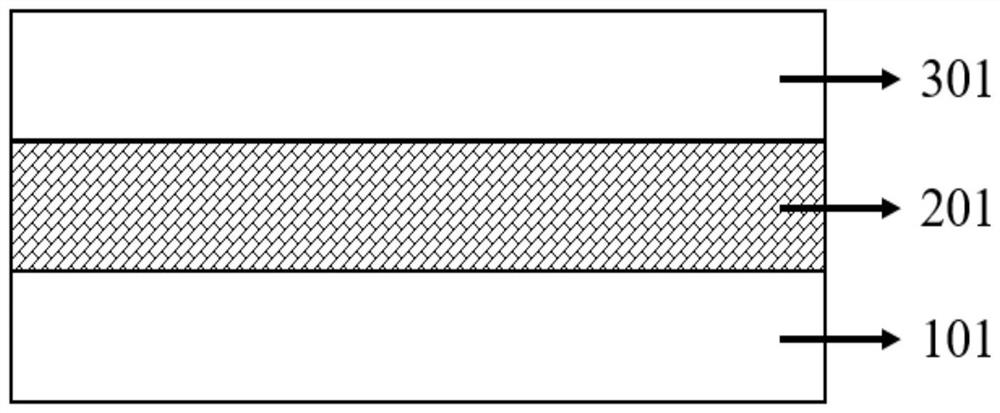

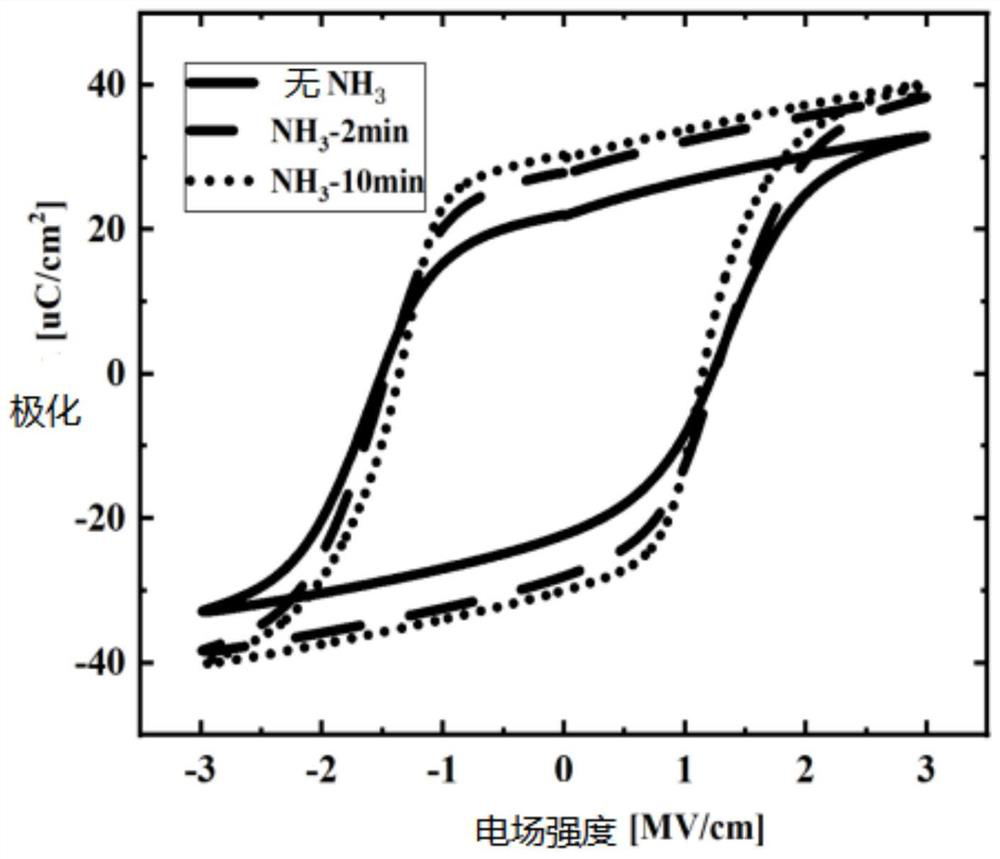

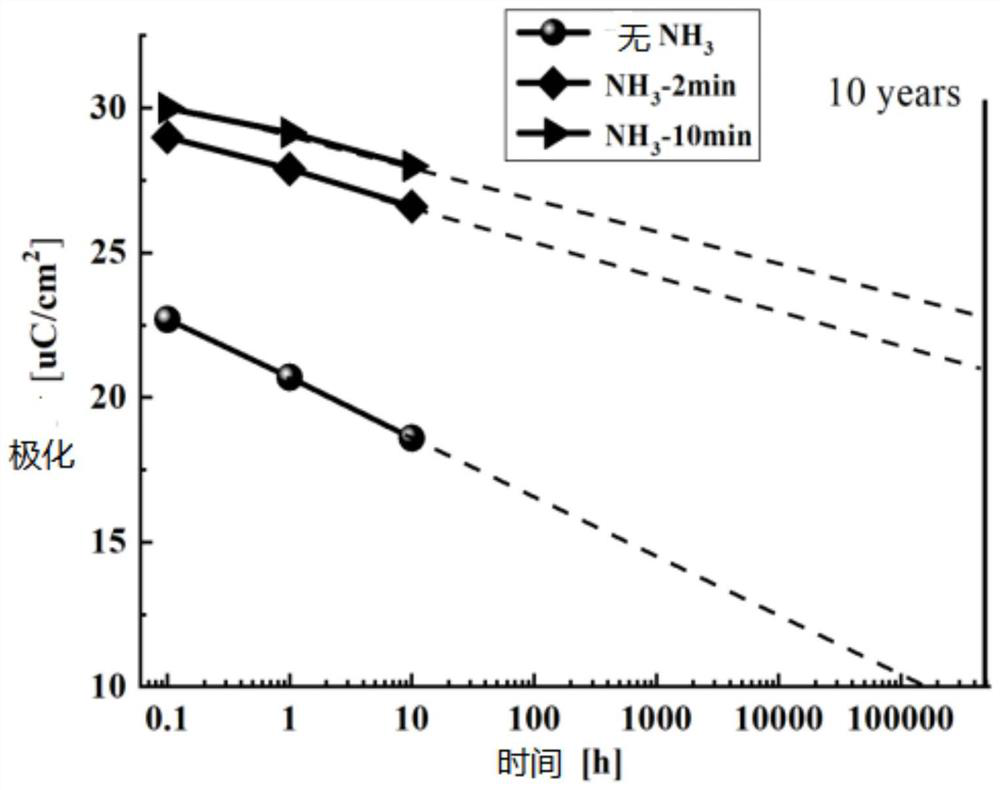

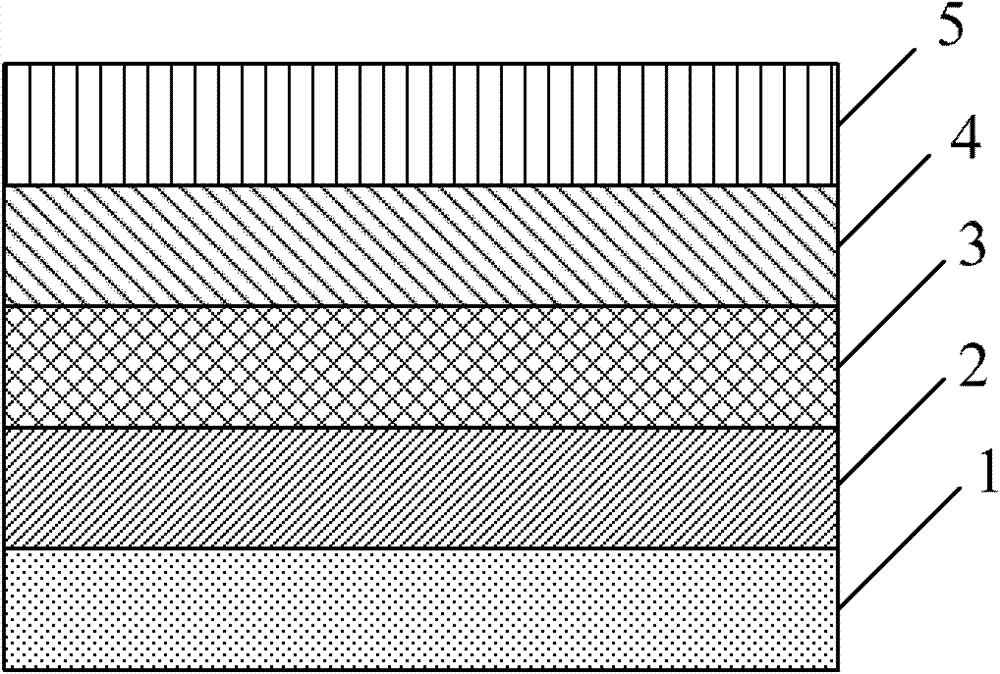

Ferroelectric memory and preparation method thereof

PendingCN114709214AHigh remnant polarizationImprove data retention characteristicsSolid-state devicesDigital storageEngineeringEngineering physics

The invention discloses a ferroelectric memory and a preparation method thereof, relates to the technical field of microelectronic manufacturing and memories, and aims to provide a ferroelectric memory which is relatively high in polarization intensity and has data retention time capable of meeting the retention period requirement proposed by the industry. The ferroelectric memory includes: a lower electrode; the ferroelectric material layer is formed on the lower electrode, and the interface of the lower electrode and the ferroelectric material layer is processed by NH3; and the upper electrode is formed on the ferroelectric material layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Oxide resistor storage device and preparation method thereof

ActiveCN102148328BGood reliabilitySimple preparation processElectrical apparatusControl layerData retention

The invention discloses an oxide resistor storage device, which comprises a substrate, a bottom electrode positioned on the substrate, an oxide control layer positioned on the bottom electrode, an oxide resistance change layer positioned on the oxide control layer, and a top electrode positioned on the oxide resistance change layer. The device is simple in preparation process and reliable in performance, the circulating durability of the resistance change of an oxide resistance change storage is improved and the data retention performance is improved.

Owner:PEKING UNIV

non-volatile semiconductor storage device

ActiveCN104282335BImprove data retention characteristicsRead-only memoriesDigital storageComputer architectureElectrical polarity

The present invention relates to a nonvolatile semiconductor memory device. A nonvolatile semiconductor memory device according to an embodiment includes: a memory cell array including a plurality of memory cells, wherein one memory cell is provided at each intersection of a plurality of first lines and a plurality of second lines, each storing a cell stores data according to the state of the filament; and a control circuit that executes a write sequence for writing data into the memory cell, the write sequence including a set step applying a set pulse to the memory cell , the set pulse has a first polarity; and a removal step of applying a removal pulse to the memory cell, the removal pulse having a second polarity different from the first polarity; and the controlling The circuitry repeatedly performs the setting step during the write sequence until the memory cell reaches a desired state, and then performs the removing step.

Owner:KIOXIA CORP +1

Flash memory and its programming method

ActiveCN106158028BImprove data retention characteristicsAccurate verificationRead-only memoriesDigital storagePre-chargeBit plane

Owner:WINBOND ELECTRONICS CORP

High-reliability split-gate nonvolatile memory structure with high-speed low-voltage operation function

ActiveCN102339833BImprove programming efficiencyEvenly distributedSolid-state devicesSemiconductor devicesCMOSLow voltage

The invention discloses a high-reliability split-gate nonvolatile memory structure with a high-speed low-voltage operation function, which is characterized in that the structure comprises a selection transistor and a memory transistor, the selection transistor and the memory transistor share a substrate region and a source / drain doped region, the memory transistor is provided with a stack structure and information is stored in a charge storage layer below a grid region. By adopting a dual-layer or multilayer substrate made of stress silicon / germanium-silicon and by comprehensively utilizing high collision ionization rate brought by primary collision ionization of the channels of the stress silicon, high collision ionization rate brought by the introduction of a SixGel-x layer and wider transverse electron distribution produced resultantly, the programming efficiency of a split-gate structure can be greatly improved, the programming voltage is reduced, the data hold characteristic of adevice is improved and the high-reliability operation of the device is facilitated. Since the charge-trap-type split-gate memory preparation process disclosed by the invention is compatible with the traditional silicon planar complementary metal oxide semiconductor (CMOS) process, the wide application is facilitated.

Owner:宁夏储芯科技有限公司

Nonvolatile three-dimensional semiconductor memory device and preparing method

ActiveCN103137860BImprove integration densitySimple processElectrical apparatusDigital storageStorage materialAND gate

The invention relates to the technical field of microelectronics, and discloses a nonvolatile three-dimensional semiconductor memory device and a preparing method. The three-dimensional semiconductor memory device comprises bit lines made of strip-shaped connecting materials which are isolated by a plurality of insulating layers; each strip-shaped connecting bit line is provided with two surface zones along the side direction; word lines made of connecting materials are arranged in the direction orthogonal with the connecting bit lines; and storage materials are placed in the middle of a cross-shaped overlapping zone which is then used as an electric charge capturing stack zone or a resistance changing function zone. High-dielectric-constant materials can be used in a function zone of the three-dimensional semiconductor memory device, and high-work function materials such as metal nitride are used in a gate electrode. Therefore, according to the preparing method of the three-dimensional semiconductor memory device, partitioning zones arranged between the word lines are introduced first, then storage function layer materials and gate materials are deposited in a back-gate technology, a technology is simplified, material pollution is avoided, and meanwhile performance of the device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

A kind of manufacturing method of flash memory

ActiveCN105405809BImprove data retention characteristicsSolid-state devicesSemiconductor devicesSemiconductor structureEngineering

The invention discloses a method for manufacturing a flash memory, which comprises etching an active region and an isolation region on a semiconductor substrate, wherein the semiconductor substrate is formed by stacking a substrate, a sacrificial layer and a mask layer in sequence, and the mask is etched back after the semiconductor substrate is sequentially stacked. A liner layer is formed on the substrate after the sacrificial layer is etched to obtain a semiconductor structure with rounded corners, an insulating layer is formed on the semiconductor structure with rounded corners, an isolation oxide layer is formed on the insulating layer to fill the isolation region, and part of Remove the isolation oxide layer and insulating layer until the isolation oxide layer and the insulating layer are flush with the mask layer, remove the mask layer located in the active area, expose the sacrificial layer and part of the insulating layer in contact with the mask layer, remove The exposed sacrificial layer and part of the insulating layer expose the substrate of the active region, and a tunnel oxide layer and a floating gate layer are sequentially formed on the exposed substrate of the active region. The present invention can prevent the isolation oxide of the isolation region from affecting the tunnel oxide and the pad layer, thereby improving the data retention characteristics of the flash memory.

Owner:GIGADEVICE SEMICON SHANGHAI INC +1

Floating gates of EEPROM (electrically erasable programmable read-only memory) and manufacturing method thereof

ActiveCN102129976BImprove data retention characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSilicon oxide

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP