Flash memory and programming method thereof

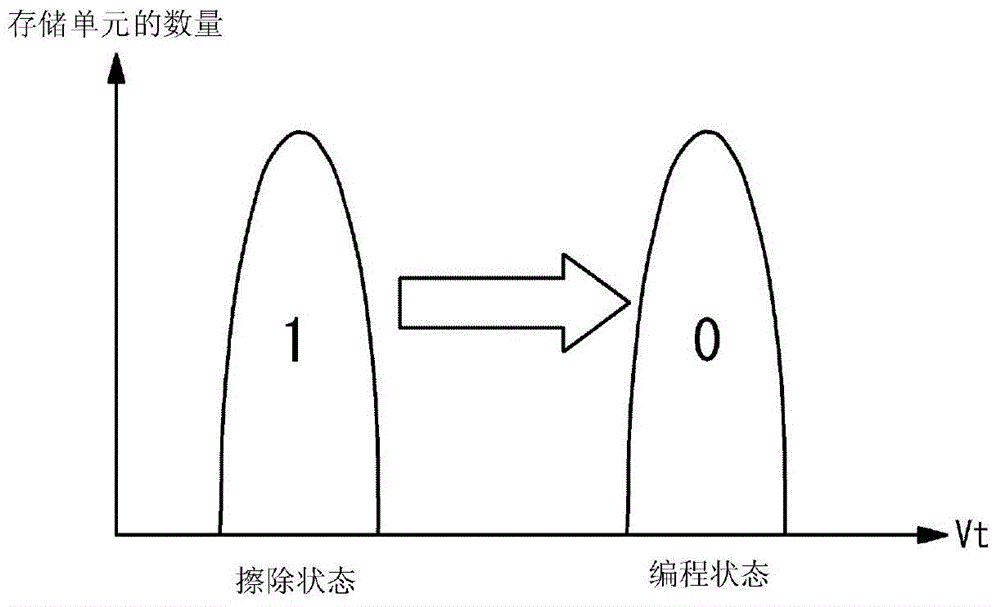

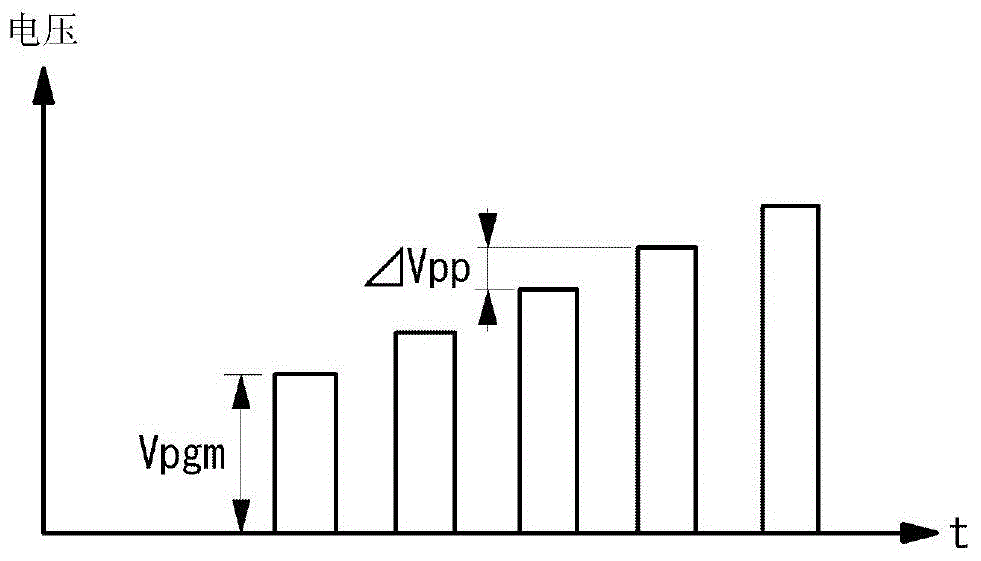

A programming method and memory technology, applied in static memory, read-only memory, digital memory information, etc., can solve the problem that the memory cells are not uniform, and achieve the effect of realizing the threshold distribution range and improving the data retention characteristics.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

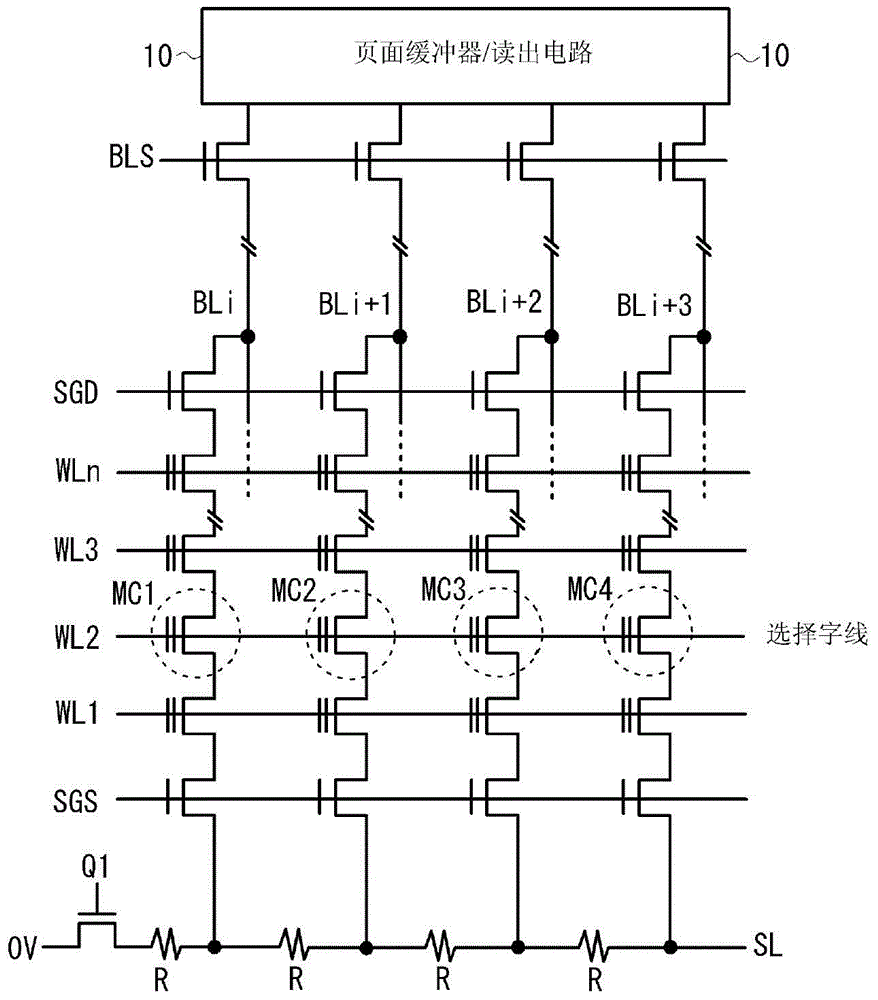

[0107] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. In addition, it should be noted that in the drawings, each part is emphasized for easy understanding, and the scale of the actual device (device) is not the same.

[0108] Figure 6 It is a block diagram of the overall structure of the NAND flash memory according to an embodiment of the present invention. Such as Figure 6As shown, the flash memory 100 includes: a memory array 110, formed with a plurality of memory cells arranged in rows and columns; an input / output buffer (buffer) 120, connected to an external input / output terminal I / O; an address register 130, Receive address data from the input / output buffer 120; cache memory (cache memory) 140 keeps the input / output data; controller 150 generates control signals C1, C2, C3, etc., the control signals C1, C2, C3 etc. are based on the command data (command data) from the input / output buffer 120 and external ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More