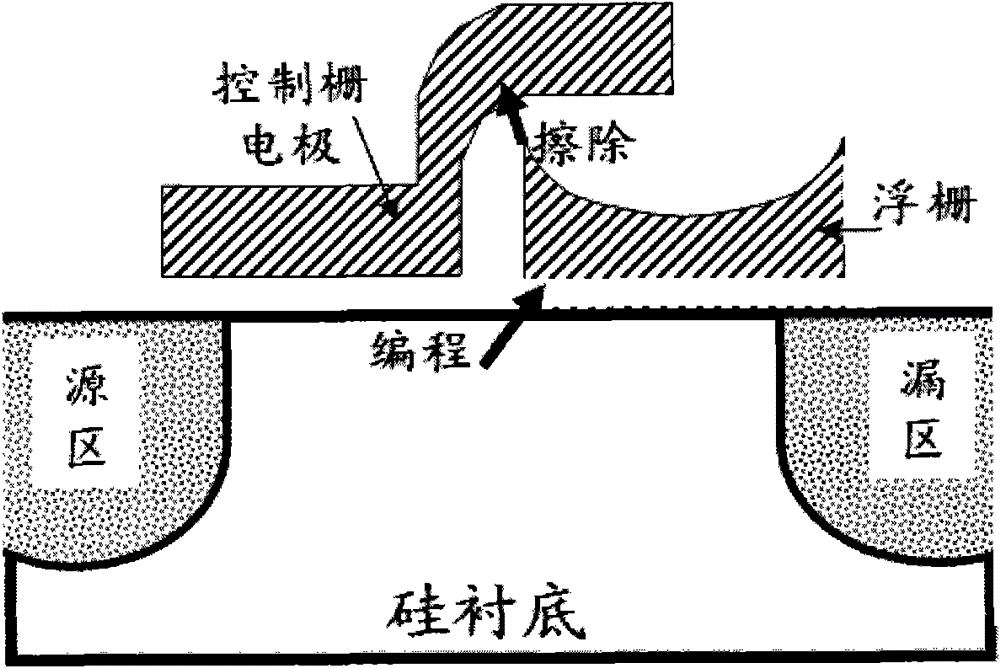

High-reliability split-gate nonvolatile memory structure with high-speed low-voltage operation function

A non-volatile, high-speed and low-voltage technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of degraded data retention time, increased mismatch, mismatch of electron and hole injection positions, etc., to achieve improved collision ionization rate, achieve uniform distribution, and reduce the effect of programming voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

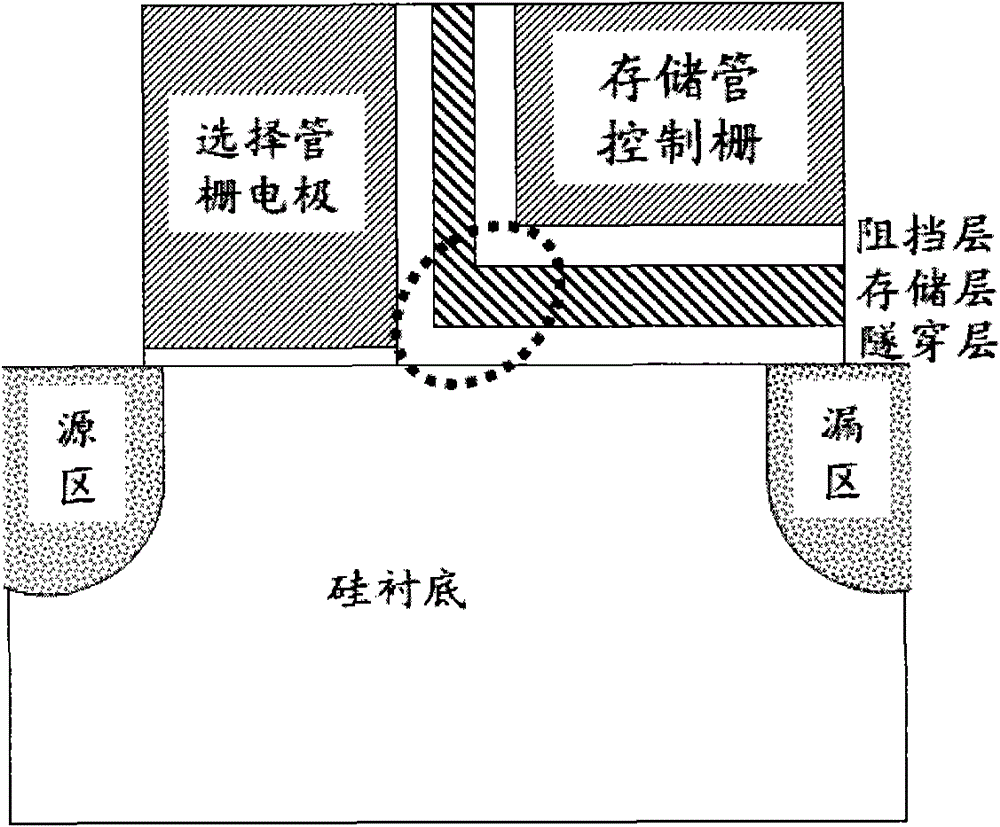

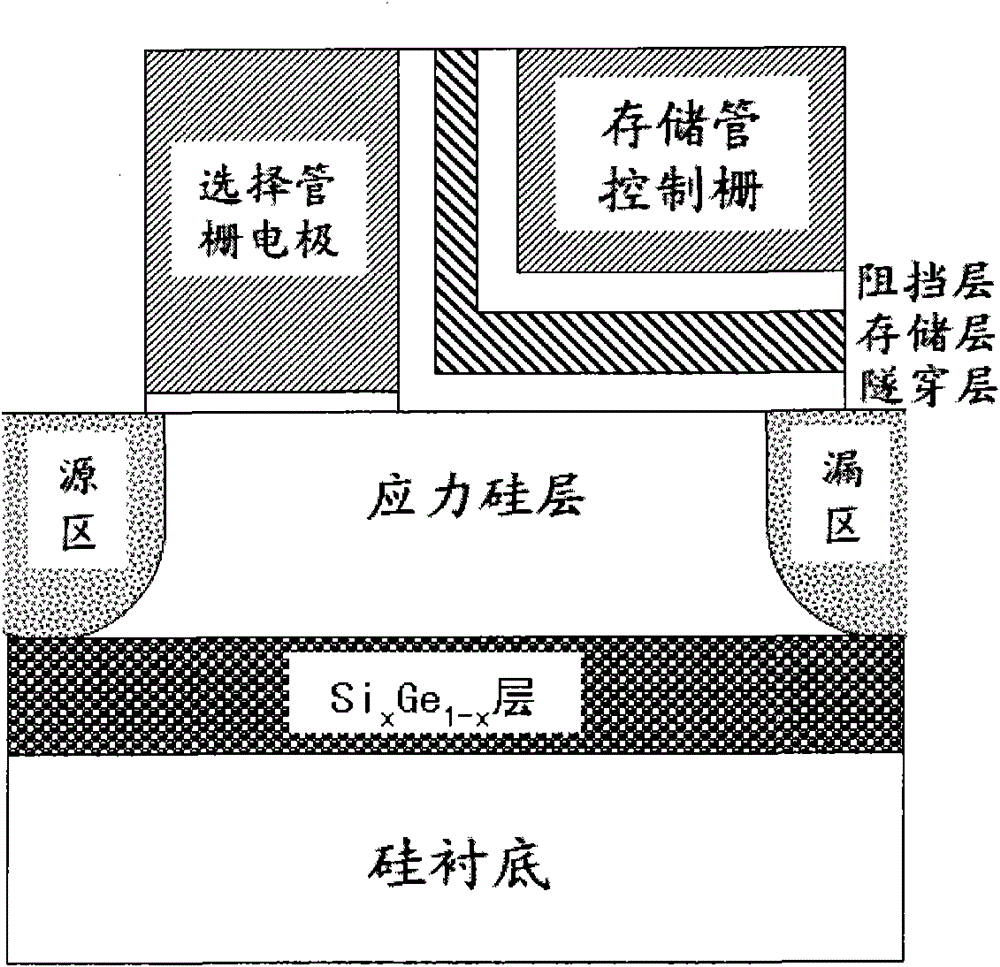

[0031] like image 3 , 4 As shown in and 5, the high-reliability split-gate non-volatile memory structure with high-speed and low-voltage operation provided by the present invention includes a selection transistor and a memory transistor, and the selection transistor and the memory transistor share the substrate region and source-drain doping area, while memory transistors have a stack structure, and information is stored in the charge storage layer below the gate area. Its preparation method and required technology are compatible with traditional technology.

[0032] Wherein, the substrate region shared by the selection transistor and the memory transistor is a double-layer structure or a multi-layer structure composed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More