Floating gates of EEPROM (electrically erasable programmable read-only memory) and manufacturing method thereof

A manufacturing method and floating gate technology, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problems of affecting the effect of blocking electrons, uneven film thickness, etc., and achieve the effect of improving data retention characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

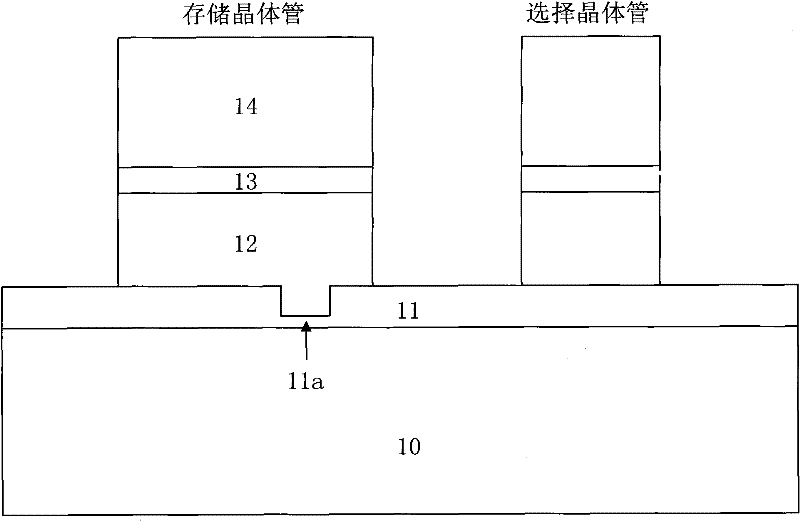

[0018] The floating gate manufacturing method of EEPROM of the present invention comprises the steps:

[0019] Step 1, see Figure 3a , which is a schematic cross-sectional view of the EEPROM memory array in the direction of the bit line. Before this step, a gate oxide layer 11 and a tunnel oxide layer 11a have been formed on the silicon substrate 10, an isolation structure 20 has existed in the silicon substrate 10 to isolate each storage transistor, and a silicon substrate 10 has been deposited on the surface. Layer 1500~ thick polysilicon as the floating gate material. The isolation structure 20 is a field oxygen isolation (LOCOS) structure or a shallow trench isolation (STI) structure.

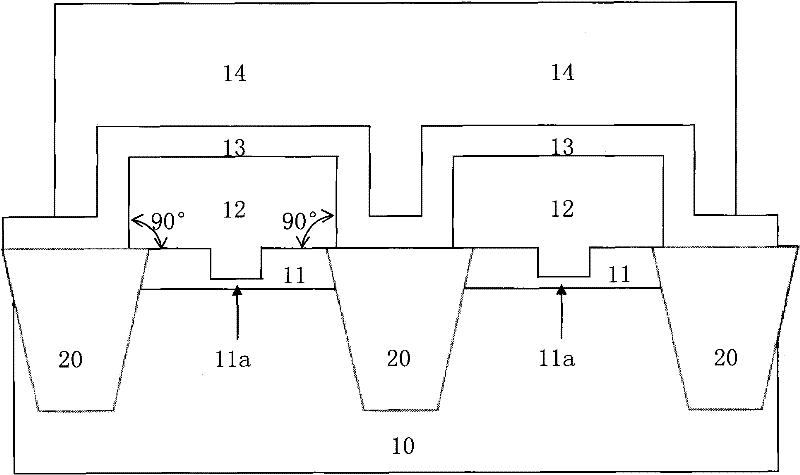

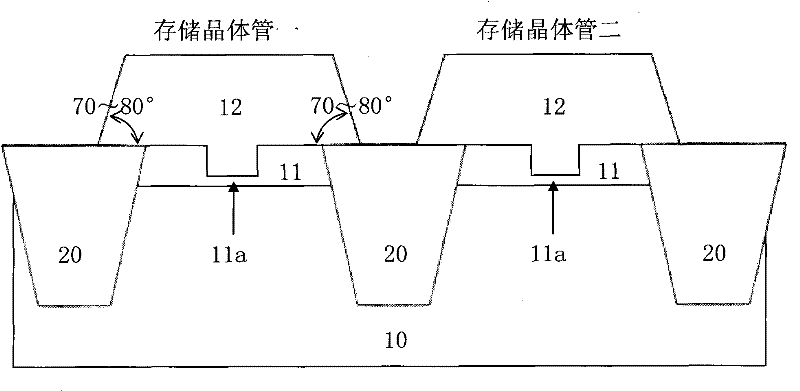

[0020] The operation in this step is to etch the polysilicon layer to form the floating gate 12, the sidewall of the floating gate 12 has an inclination angle of 70-80 degrees. From another perspective, for the trench between the two floating gates 12, it has a tapered etching profile...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com