Patents

Literature

32results about How to "Increase drive strength" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

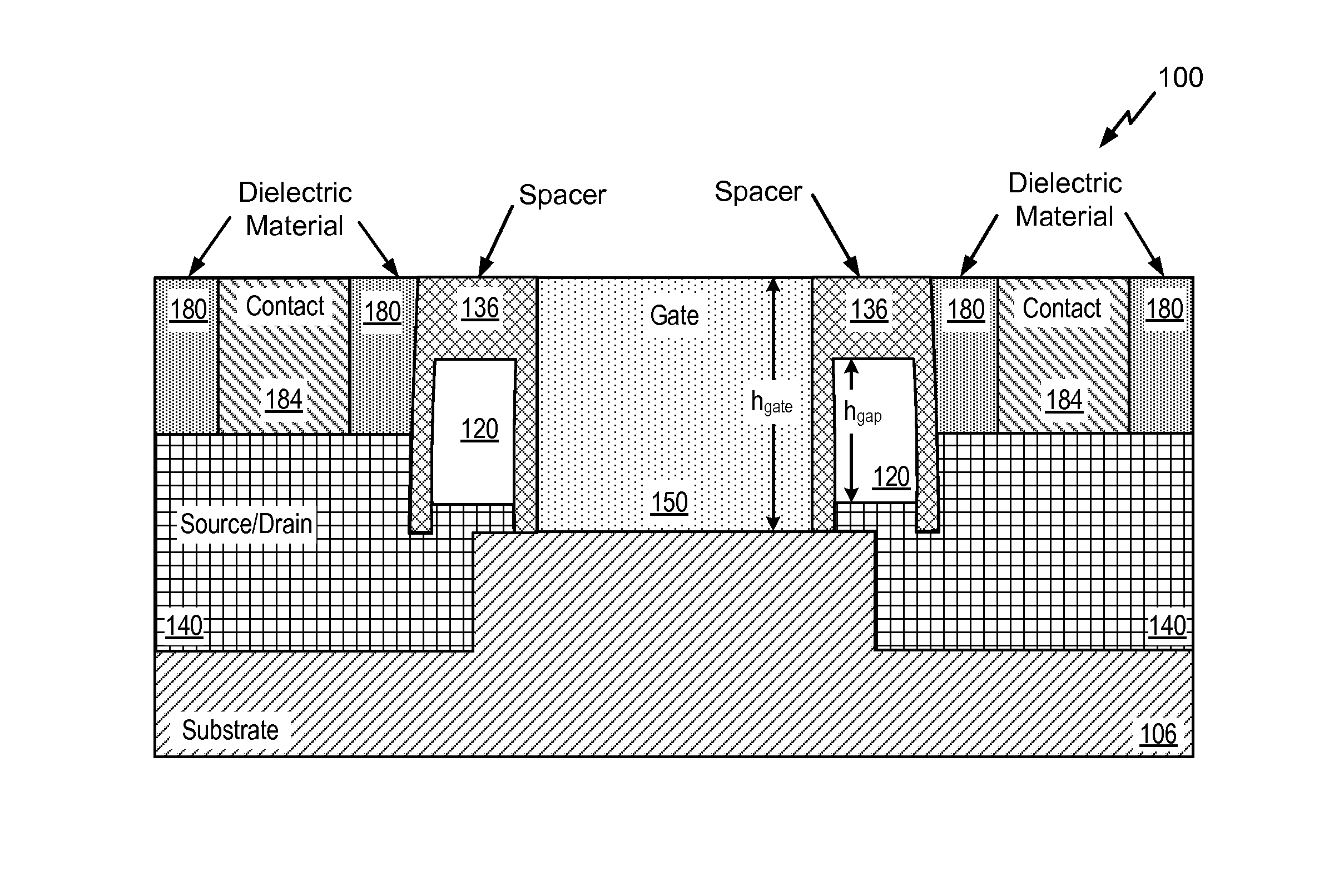

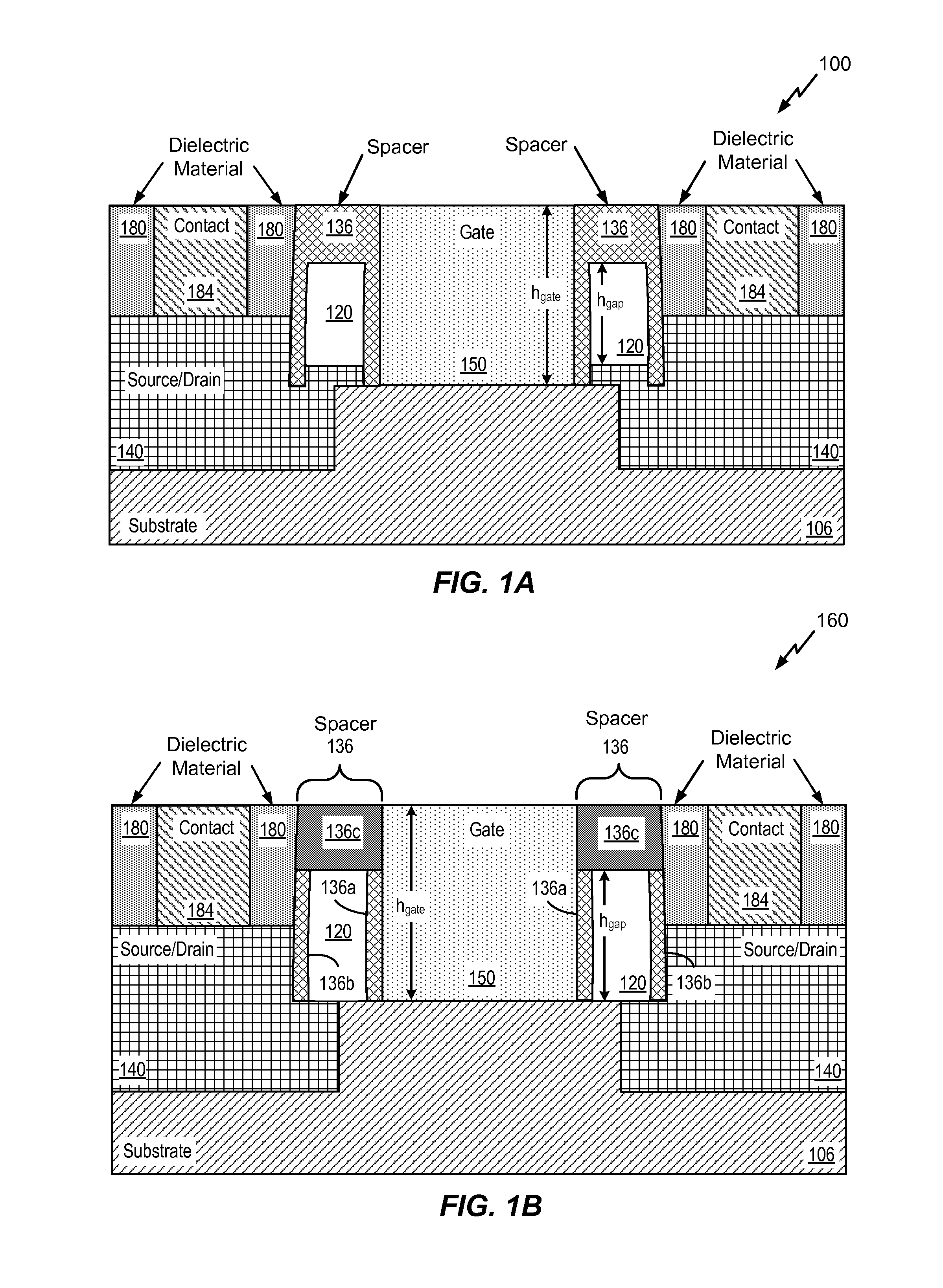

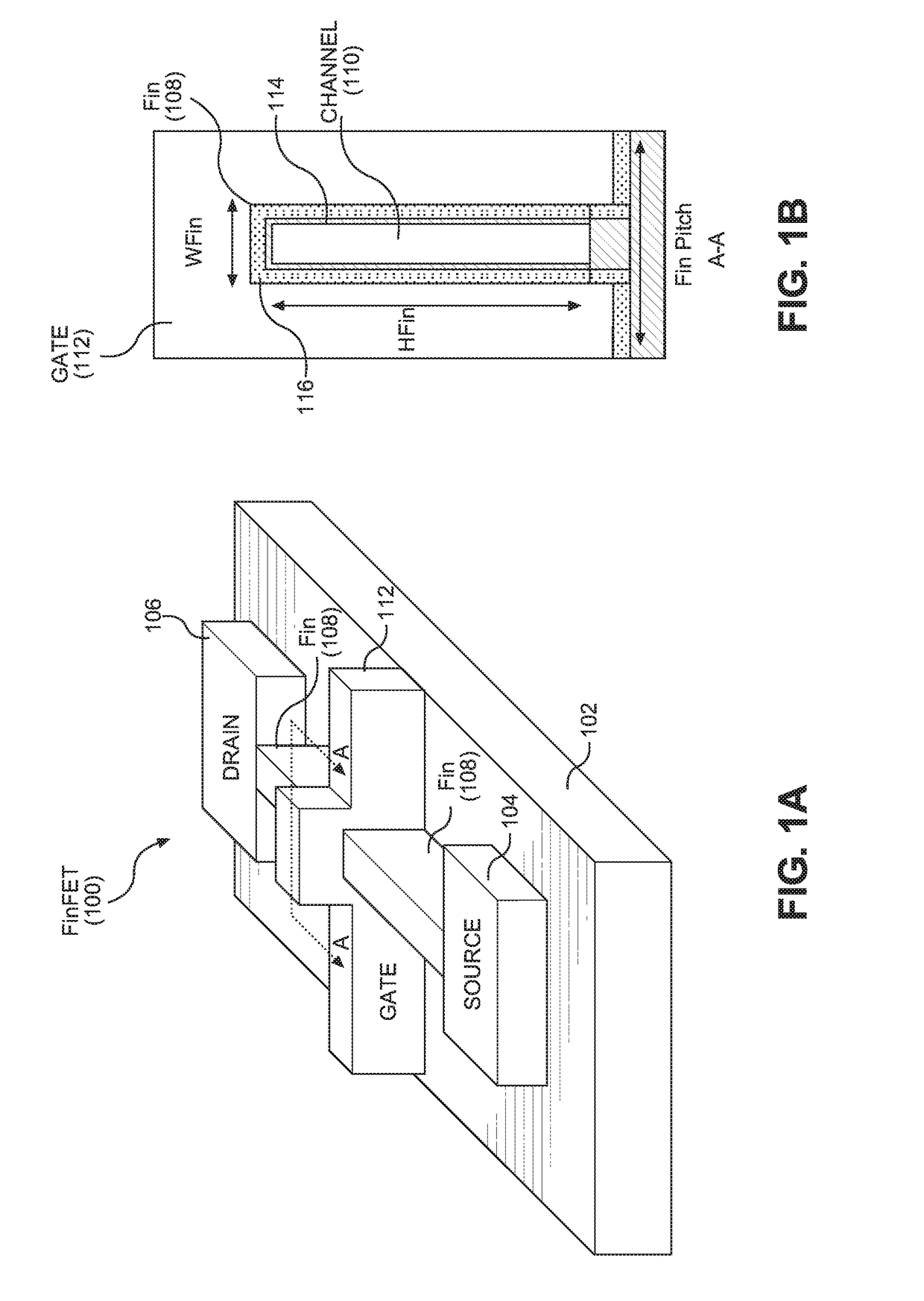

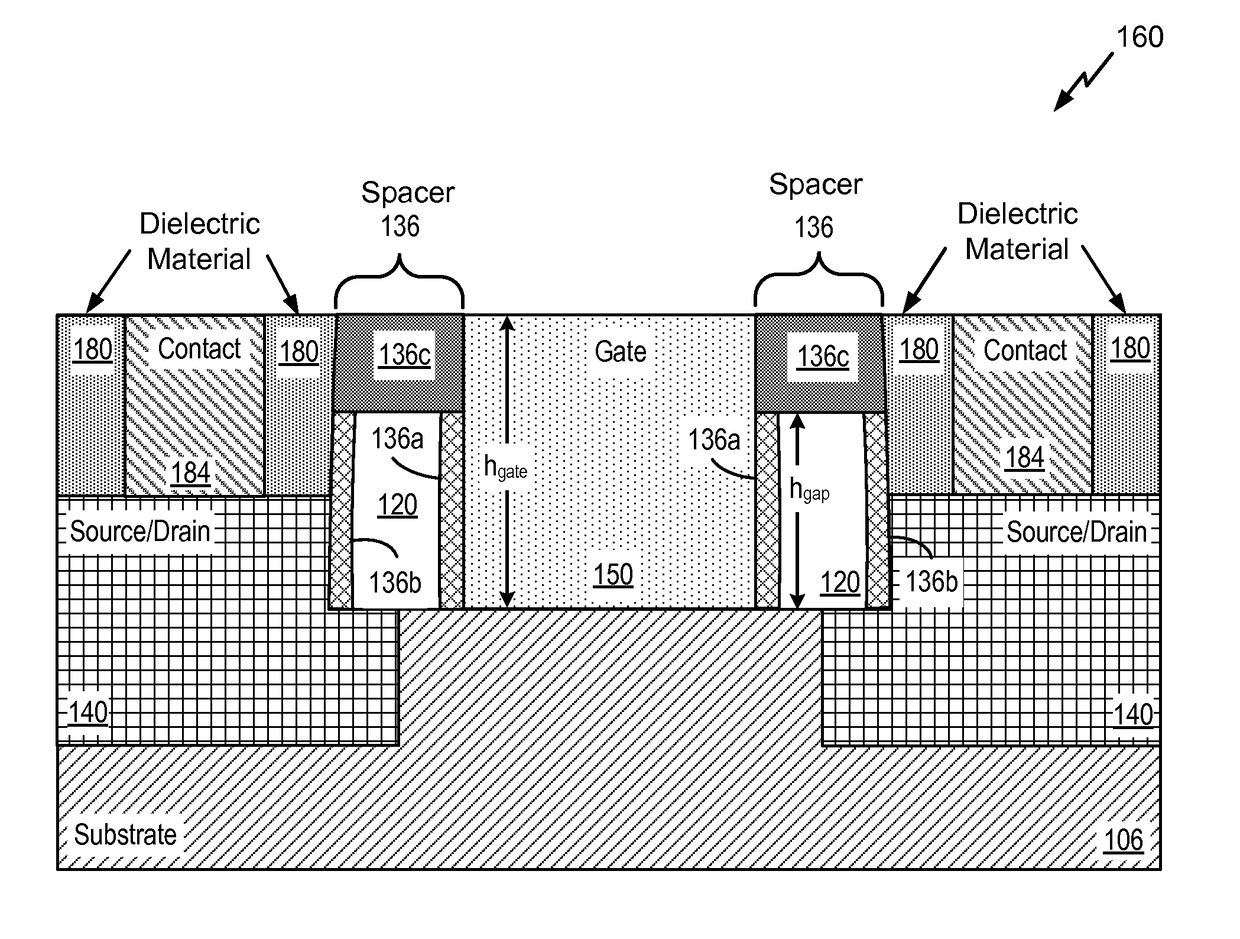

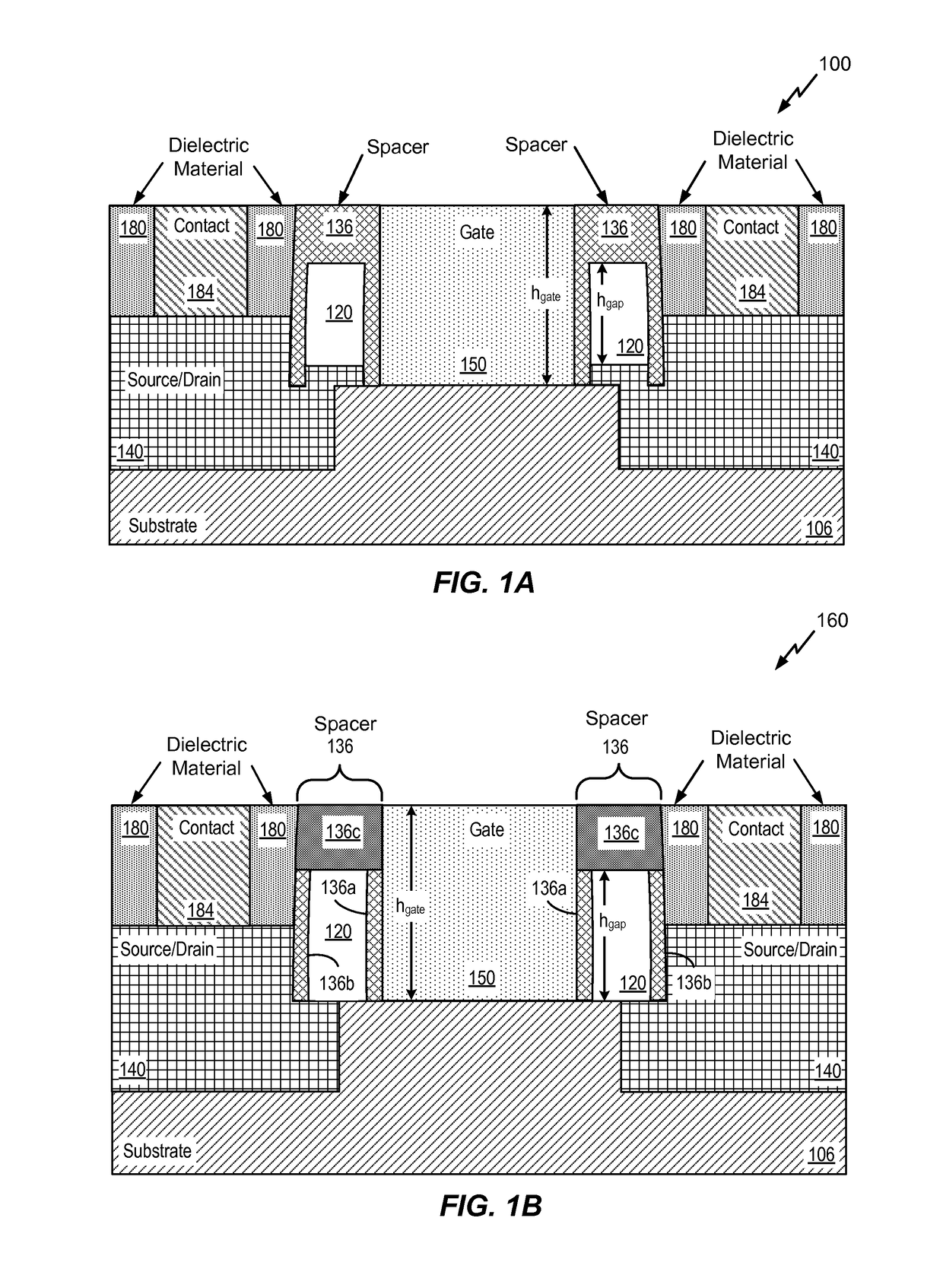

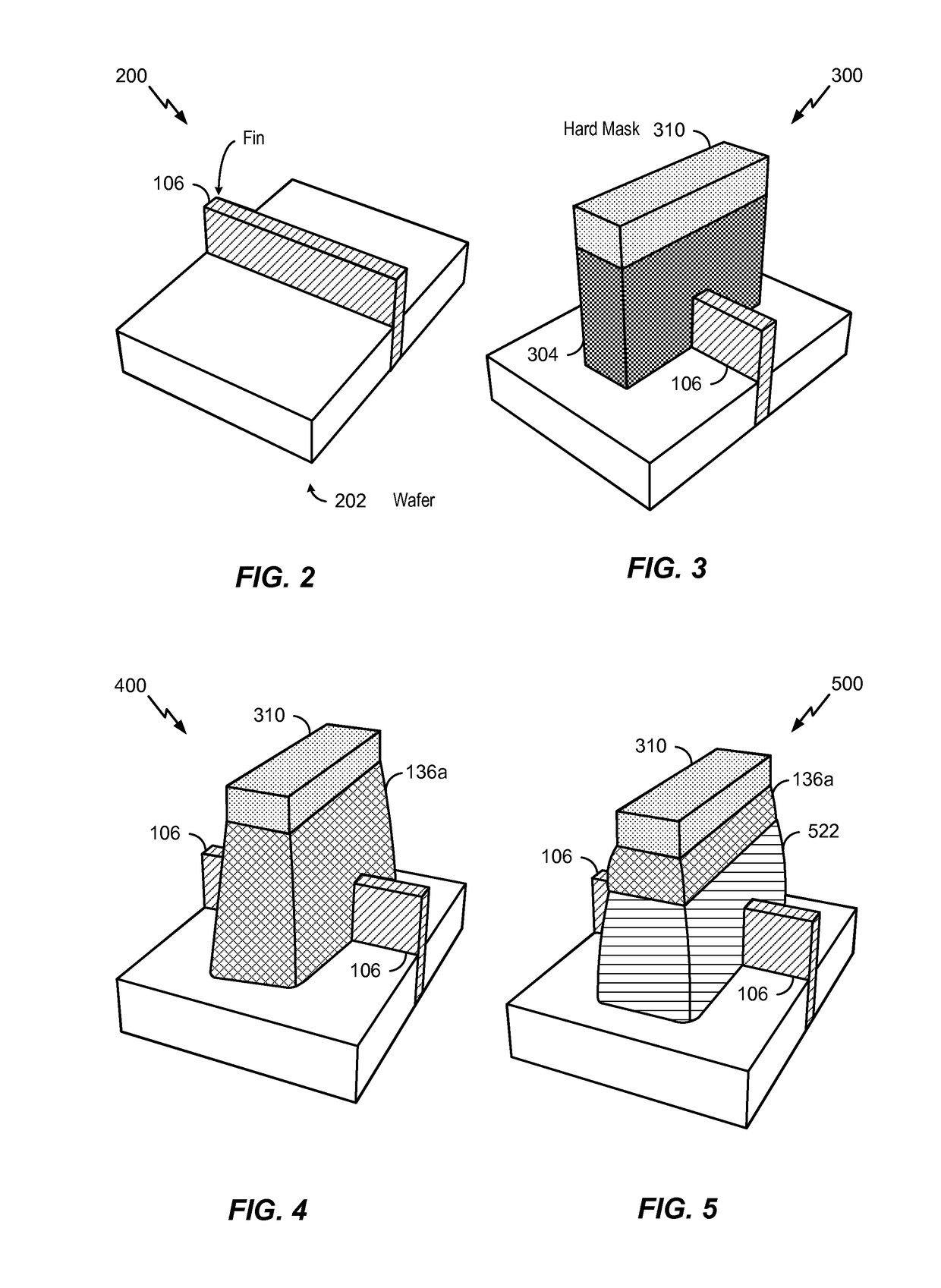

Semiconductor device having a gap defined therein

ActiveUS20150255571A1Increase drive strengthReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

In a particular embodiment, a method includes forming a first spacer structure on a dummy gate of a semiconductor device and forming a sacrificial spacer on the first spacer structure. The method also includes etching a structure of the semiconductor device to create an opening, removing the sacrificial spacer via the opening, and depositing a material to close to define a gap.

Owner:QUALCOMM INC

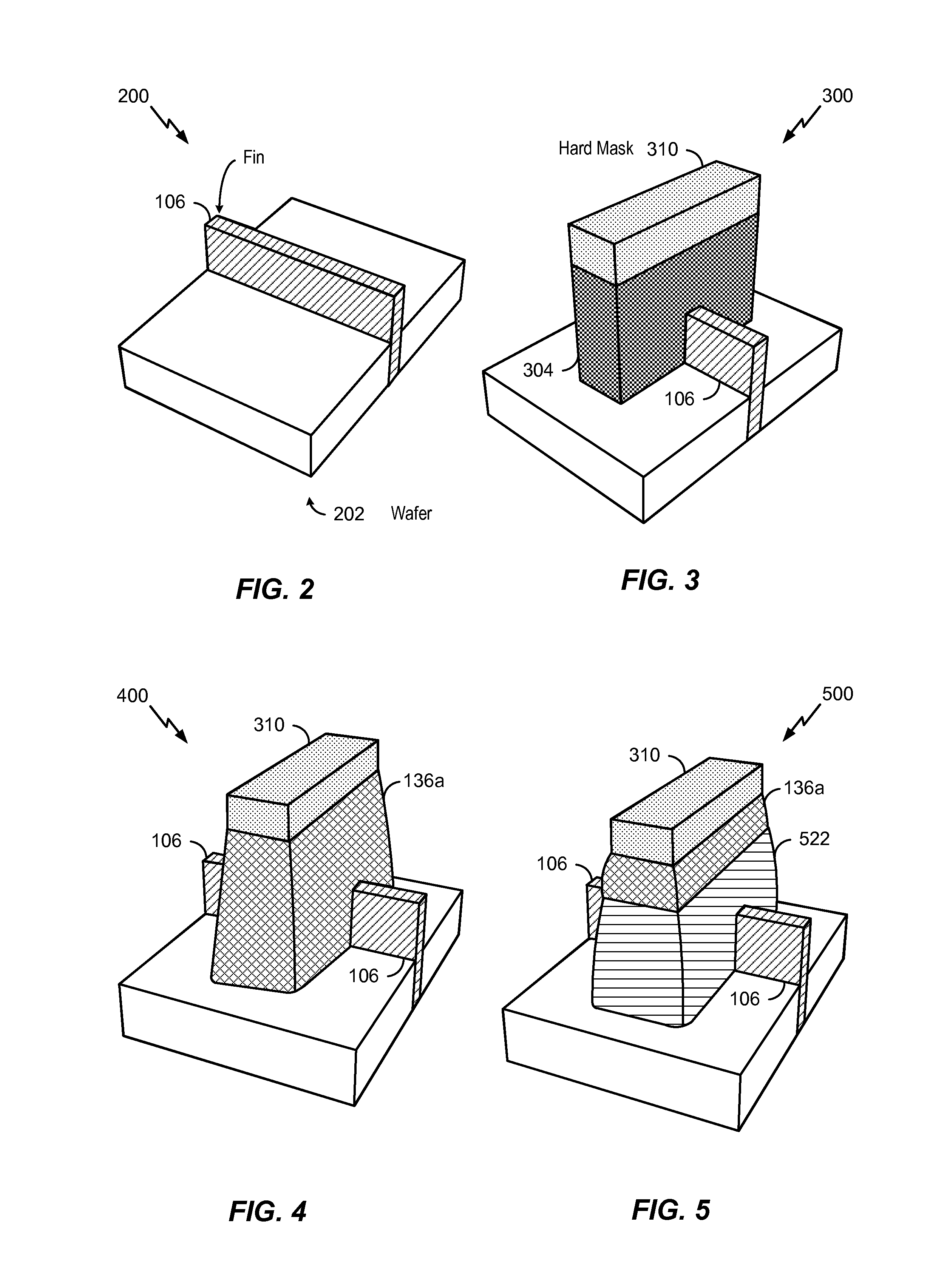

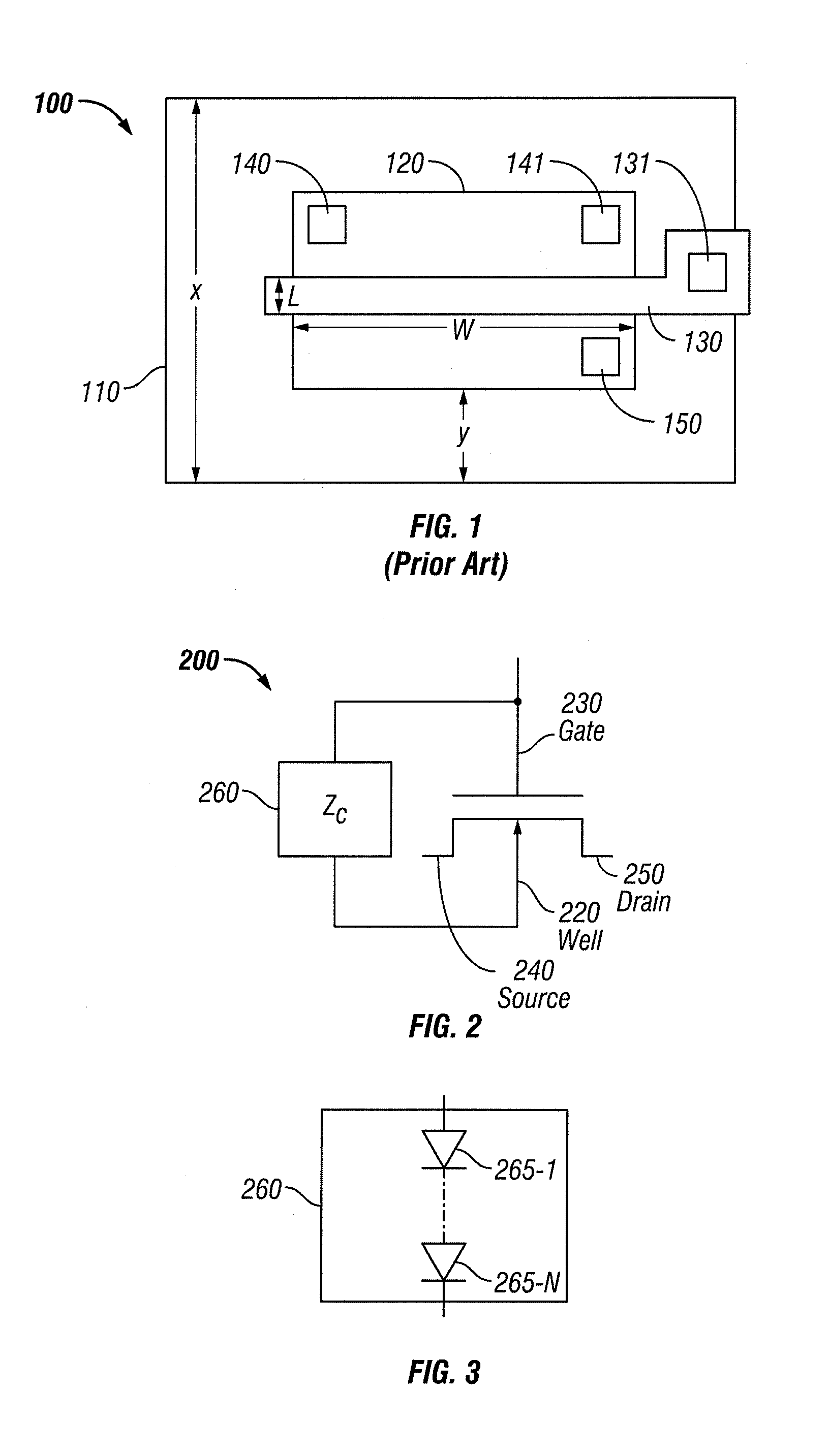

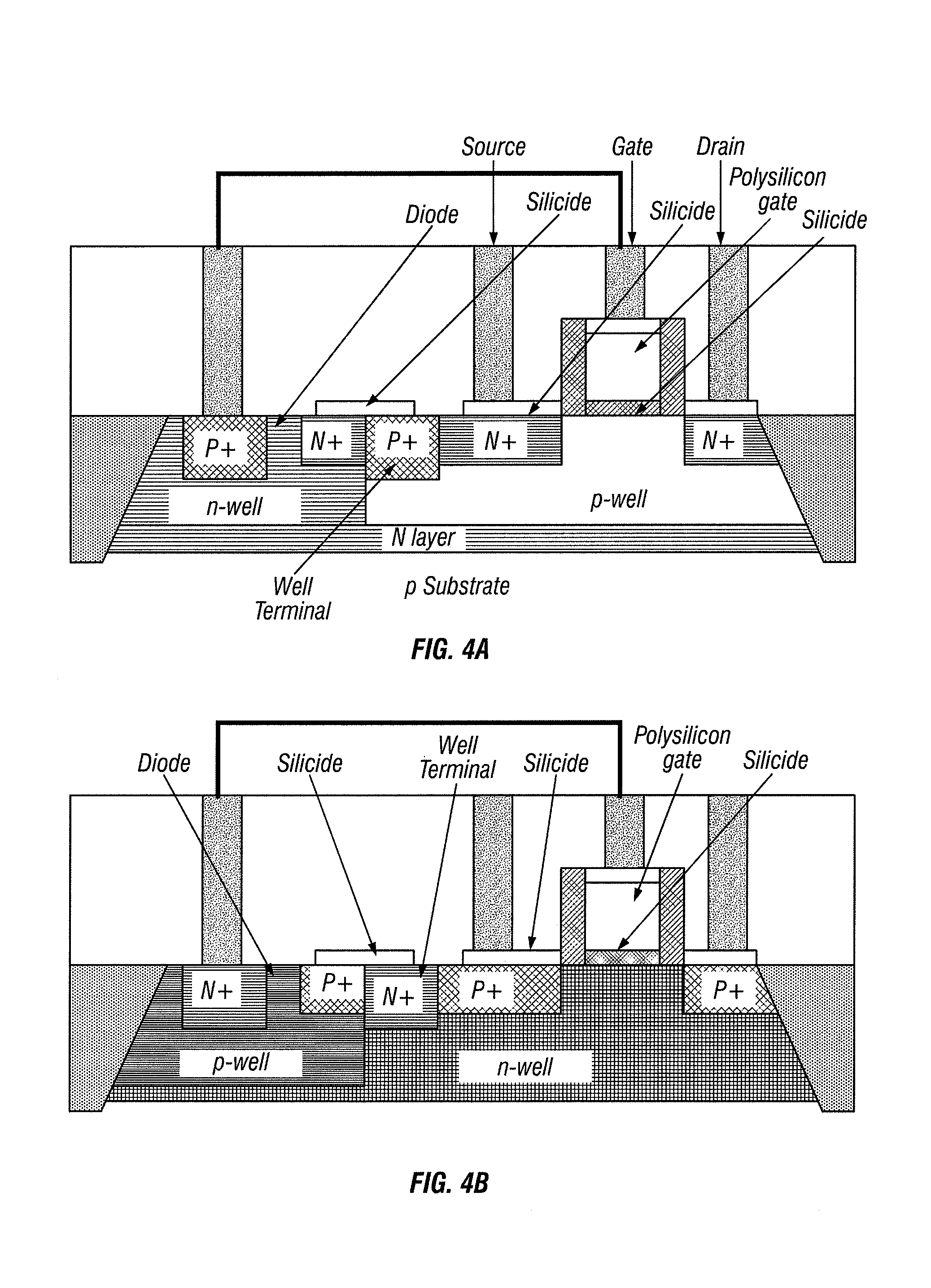

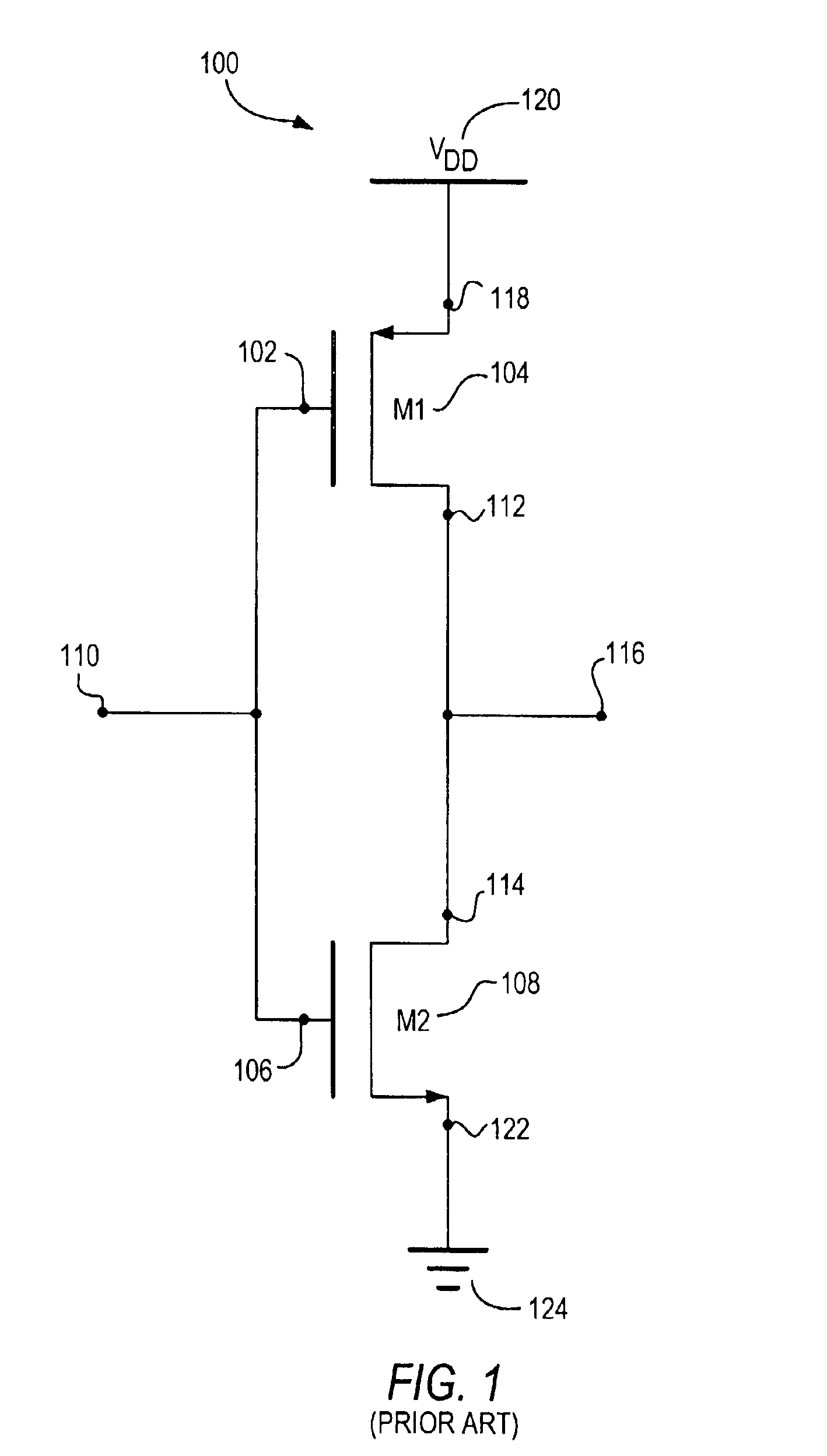

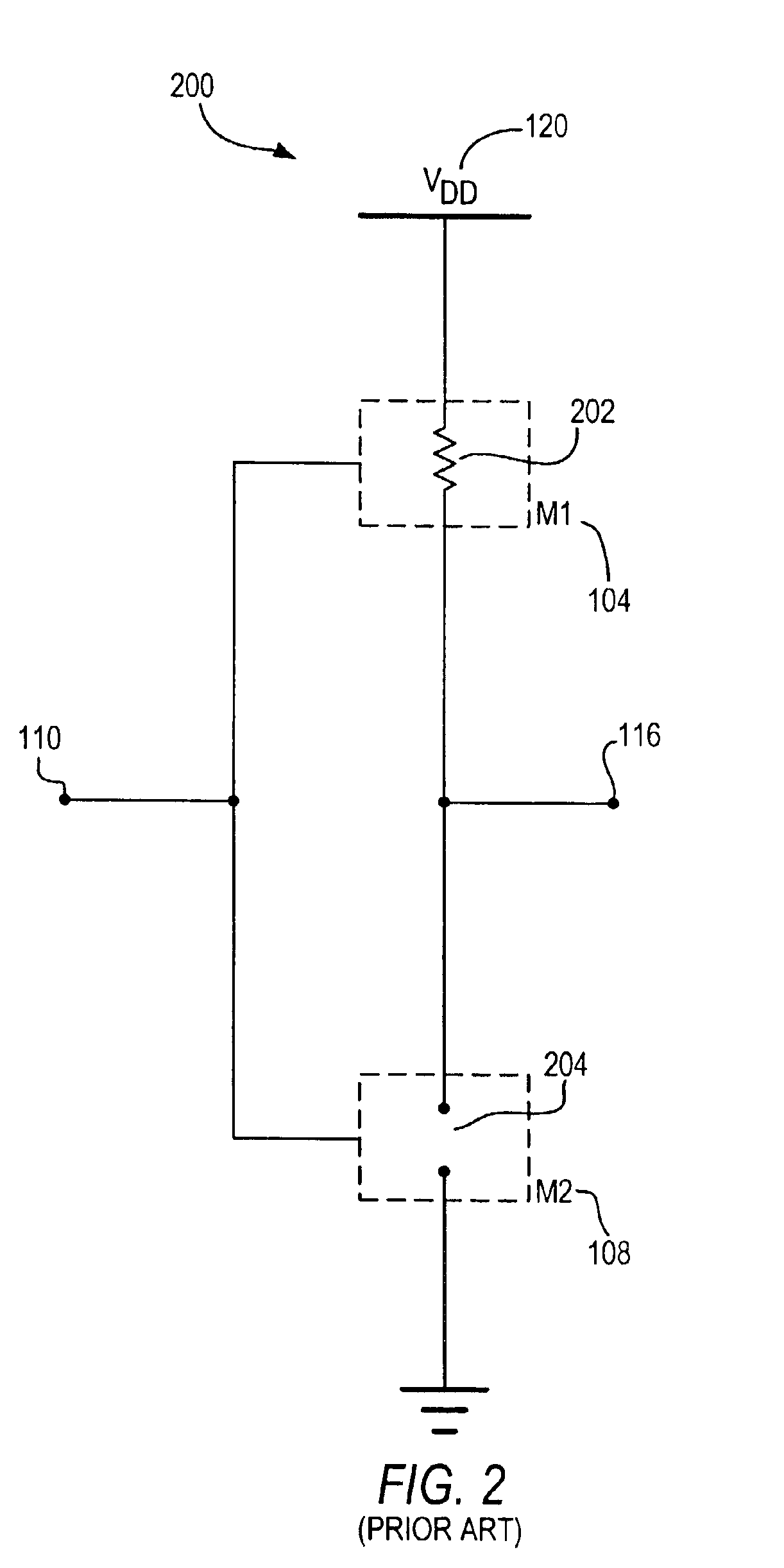

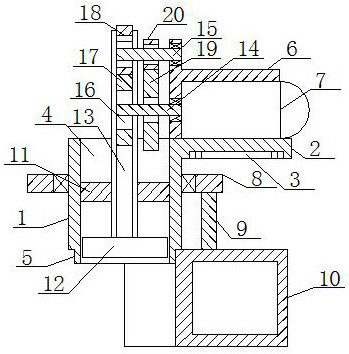

Apparatus and method for improving drive-strength and leakage of deep submicron MOS transistors

InactiveUS7683433B2Increase drive strengthReduce leakage currentTransistorInput/output impedence modificationCMOSEngineering

An apparatus and method of manufacture for metal-oxide semiconductor (MOS) transistors is disclosed. Devices in accordance with the invention are operable at voltages below 2V. The devices are area efficient, have improved drive strength, and have reduced leakage current. A dynamic threshold voltage control scheme comprised of a forward biased diode in parallel with a capacitor is used, implemented without changing the existing MOS technology process. This scheme controls the threshold voltage of each transistor. In the OFF state, the magnitude of the threshold voltage of the transistor increases, keeping the transistor leakage to a minimum. In the ON state, the magnitude of the threshold voltage decreases, resulting in increased drive strength. The invention is particularly useful in MOS technology for both bulk and silicon on insulator (SOI) CMOS. The use of reverse biasing of the well, in conjunction with the above construct to further decrease leakage in a MOS transistor, is also shown.

Owner:SEMI SOLUTIONS LLC

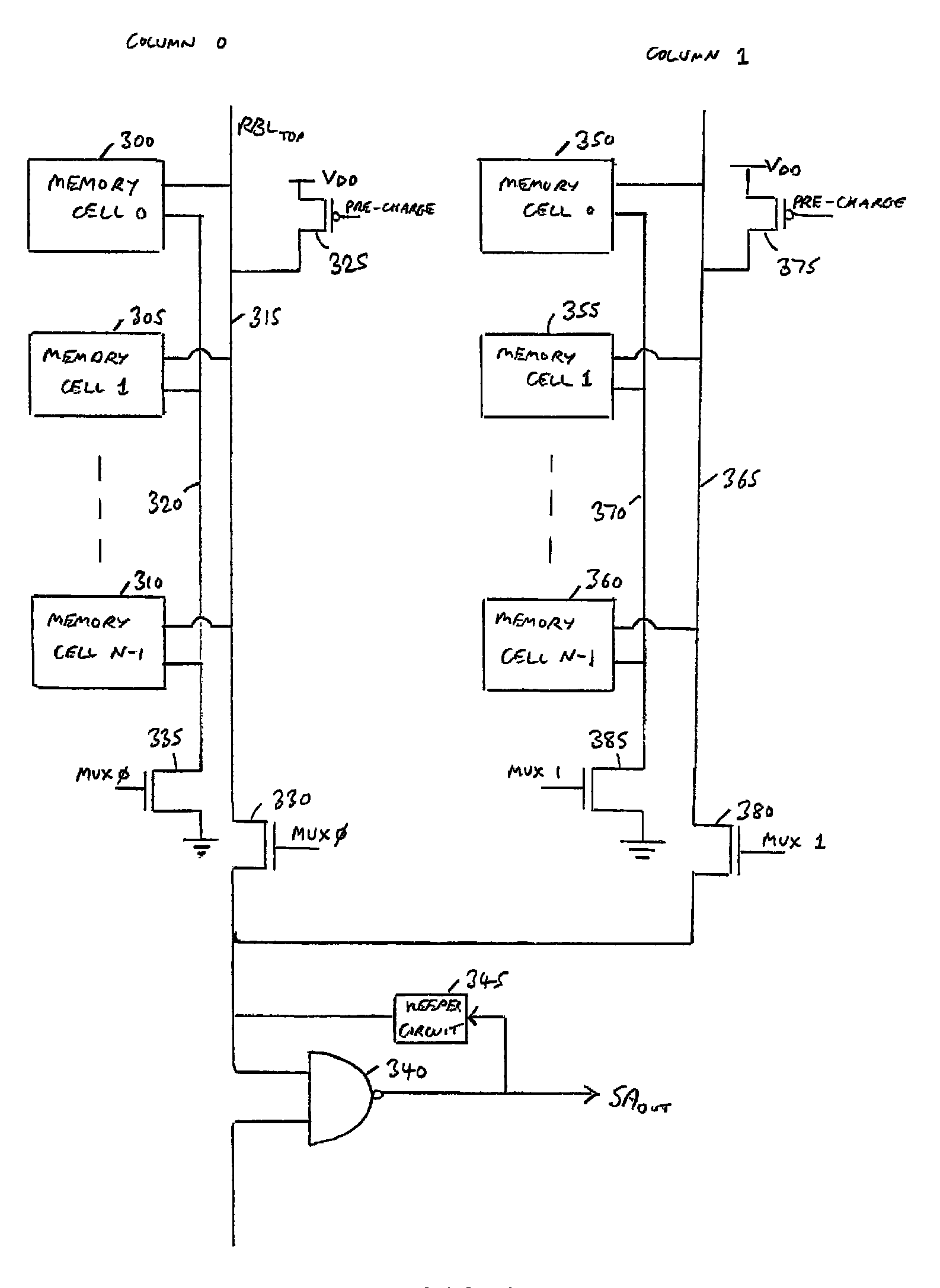

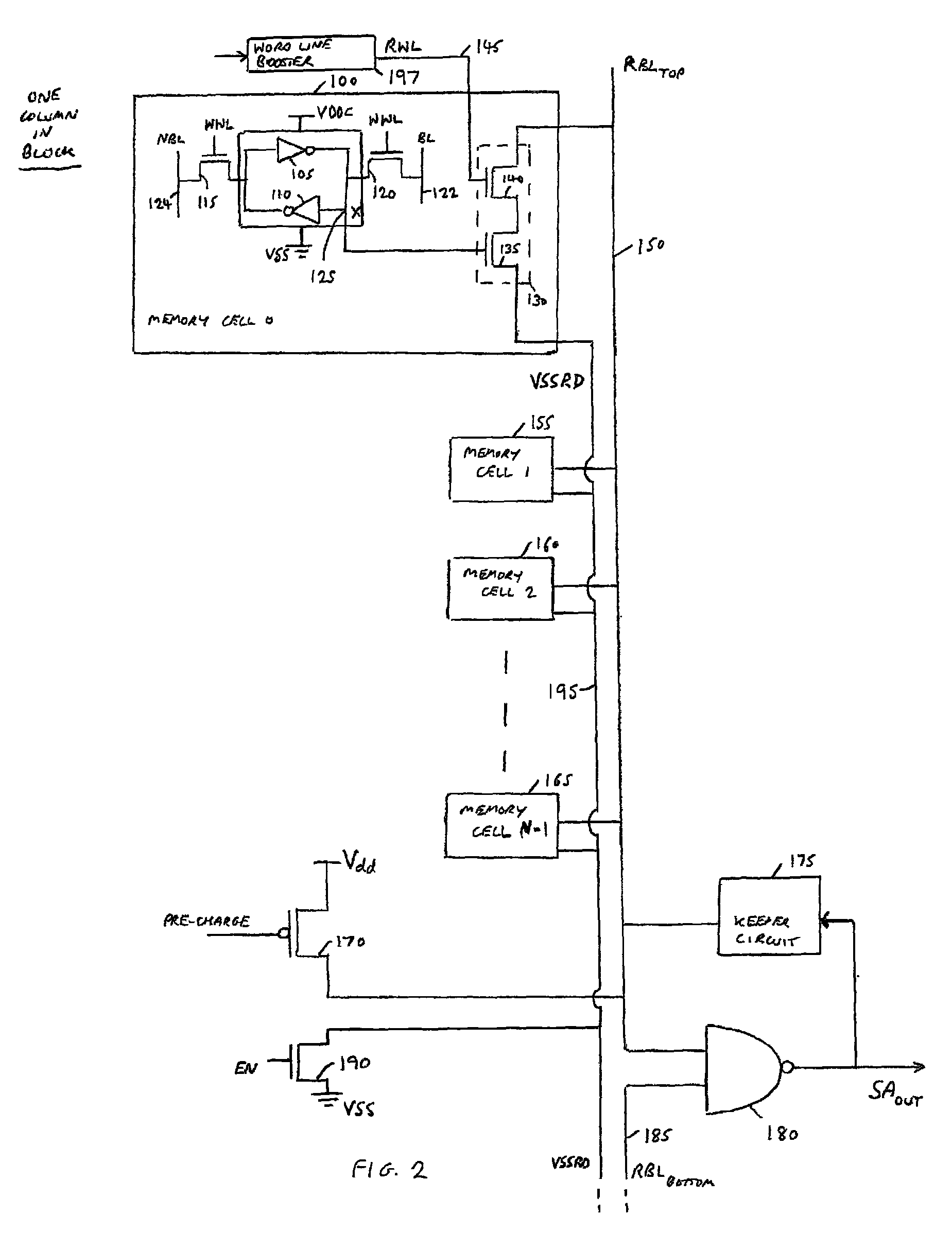

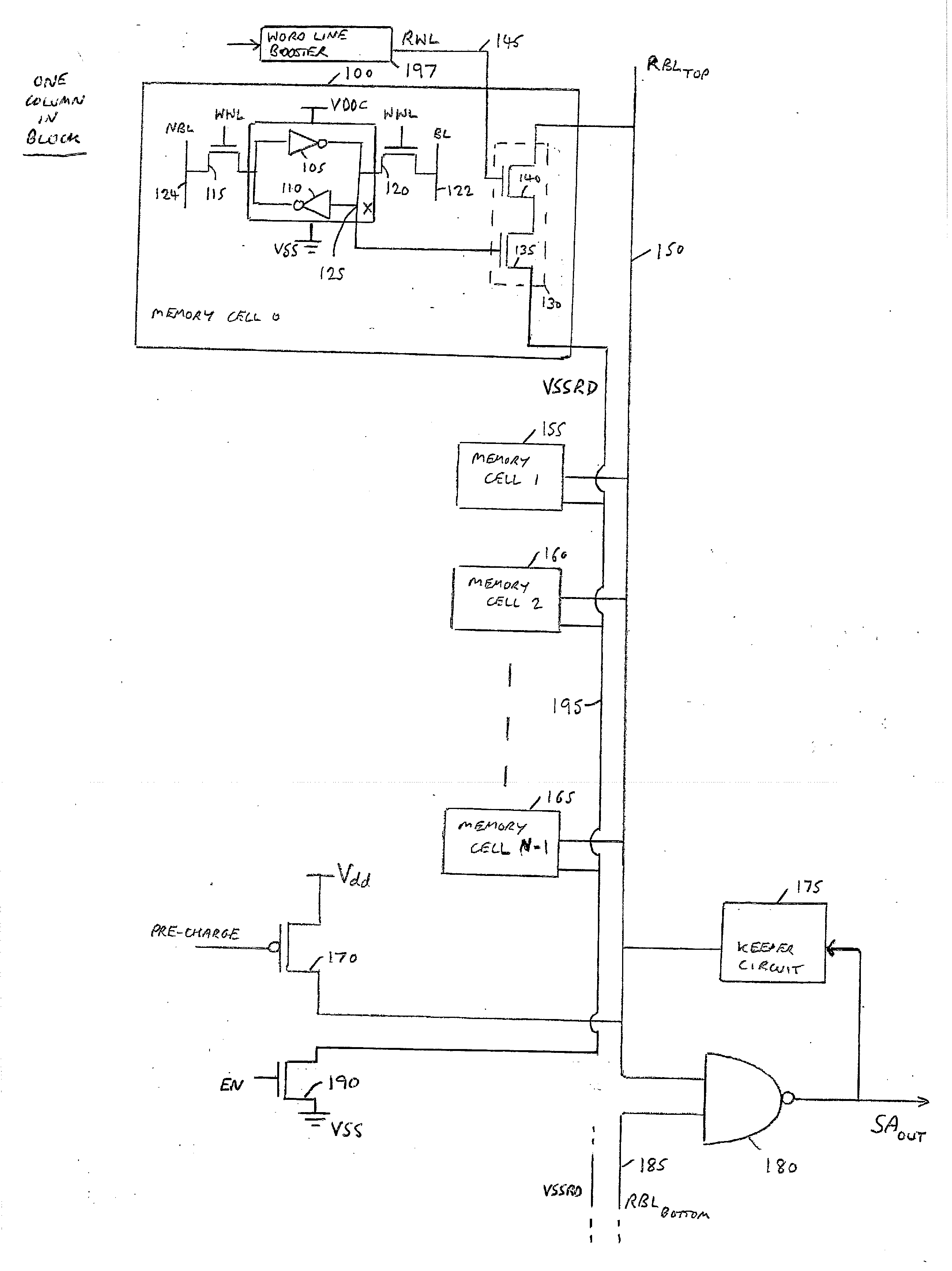

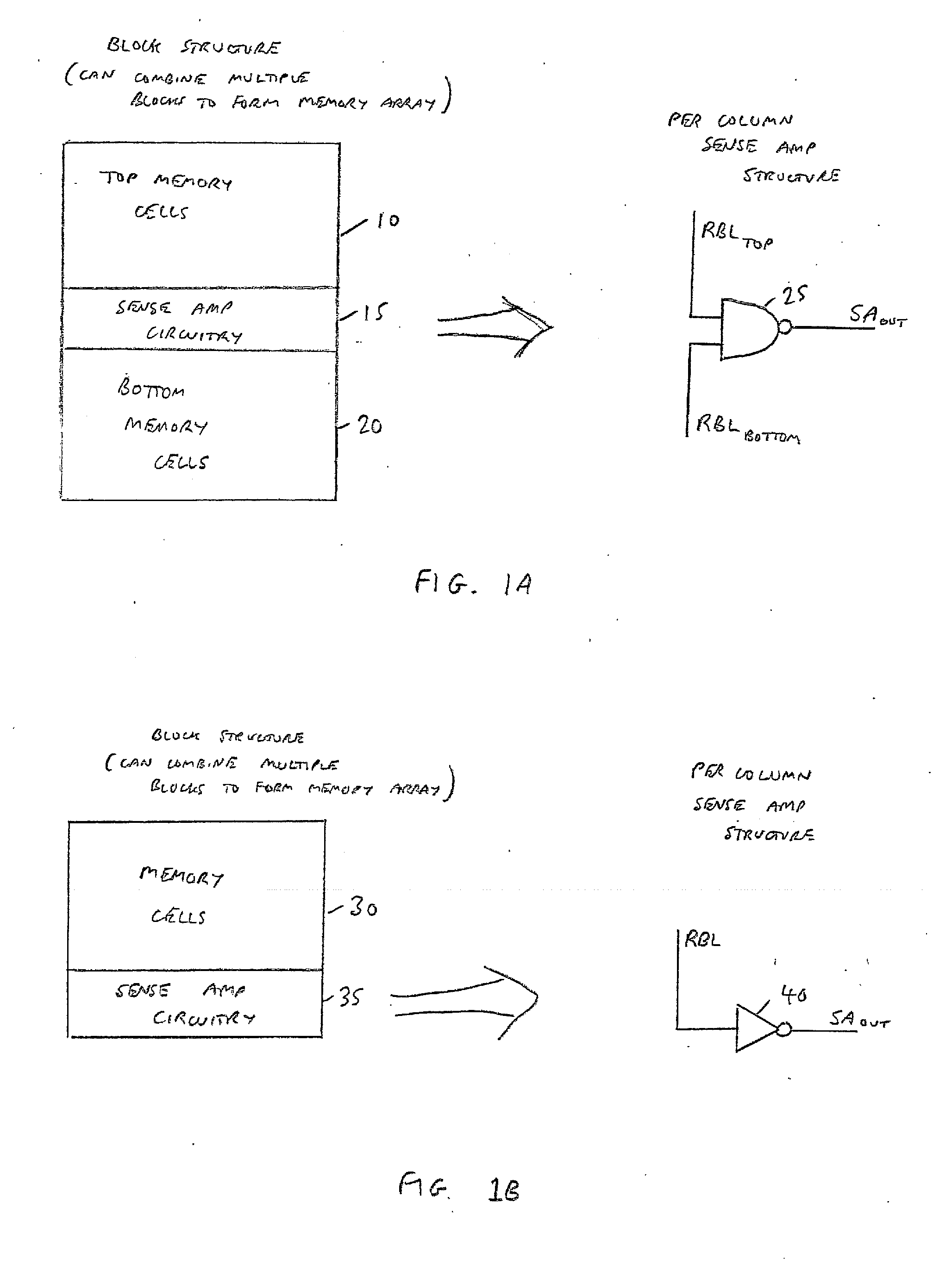

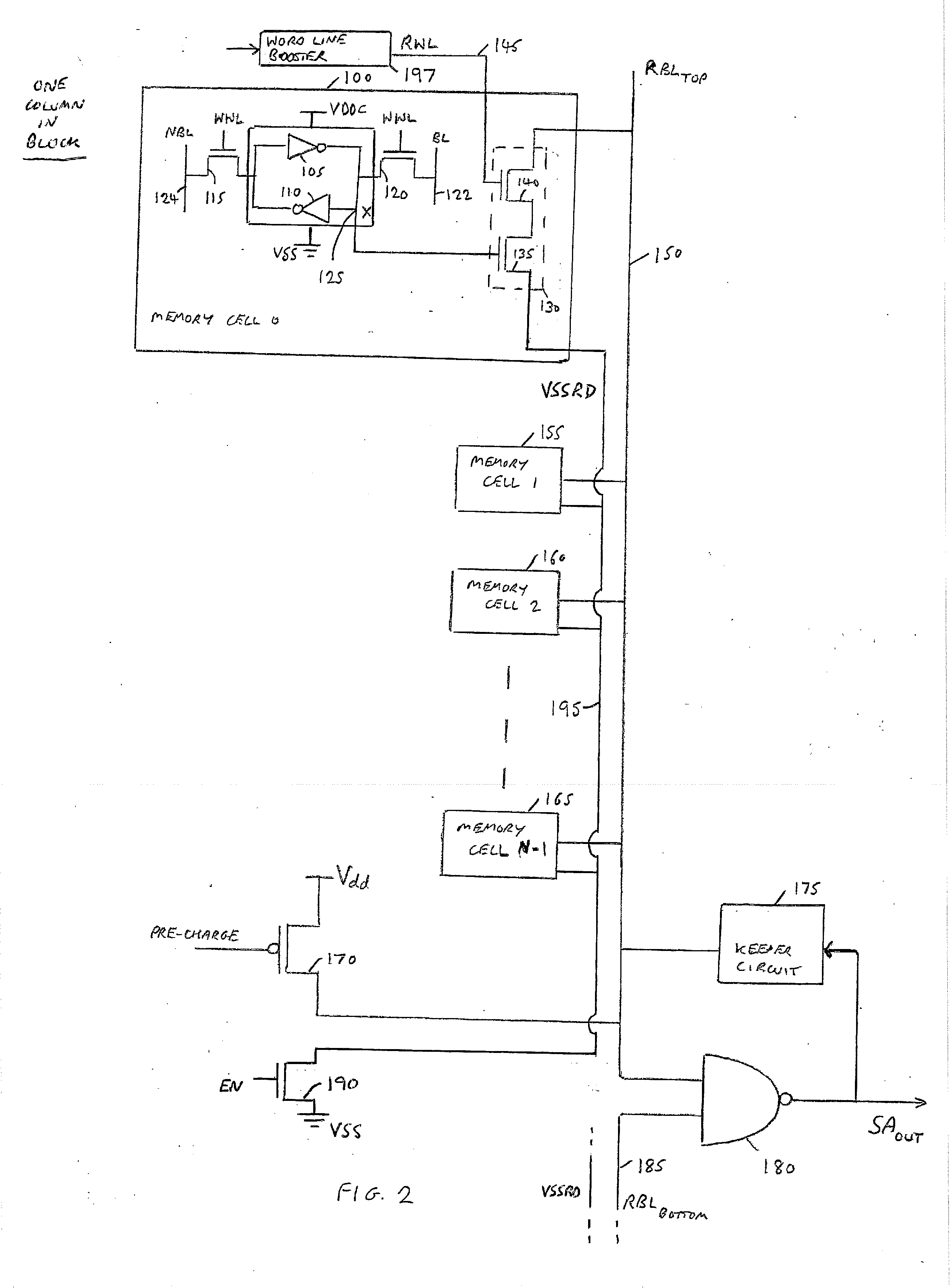

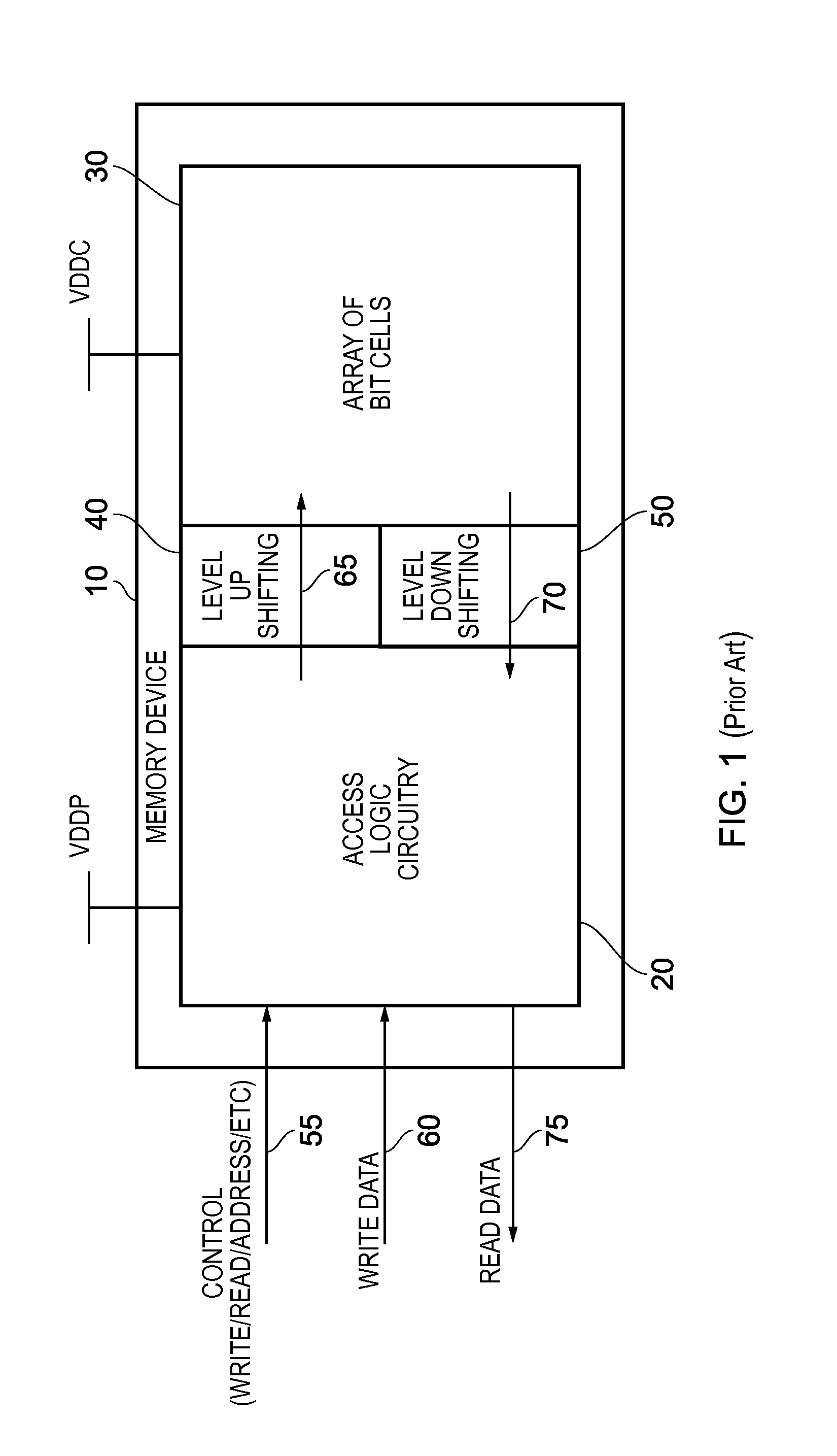

Memory device and method of controlling leakage current within such a memory device

ActiveUS9171634B2Reduce leakage currentImprove performanceRead-only memoriesDigital storageComputer architectureDrain current

A memory device includes an array of memory cells arranged as a plurality of rows and columns, each row being coupled to an associated read word line, and each column forming at least one column group, where the memory cells of each column group are coupled to an associated read bit line. Each column has an active mode of operation where a read operation may be performed on an activated memory cell within that column group, and a non-active mode of operation where the read operation is not performable. Precharge circuitry is used, for each column group, to precharge the associated read bit line to a first voltage level prior to the read operation. Each memory cell includes coupling circuitry connected between the associated read bit line and a reference line associated with the column group containing that memory cell.

Owner:ARM LTD

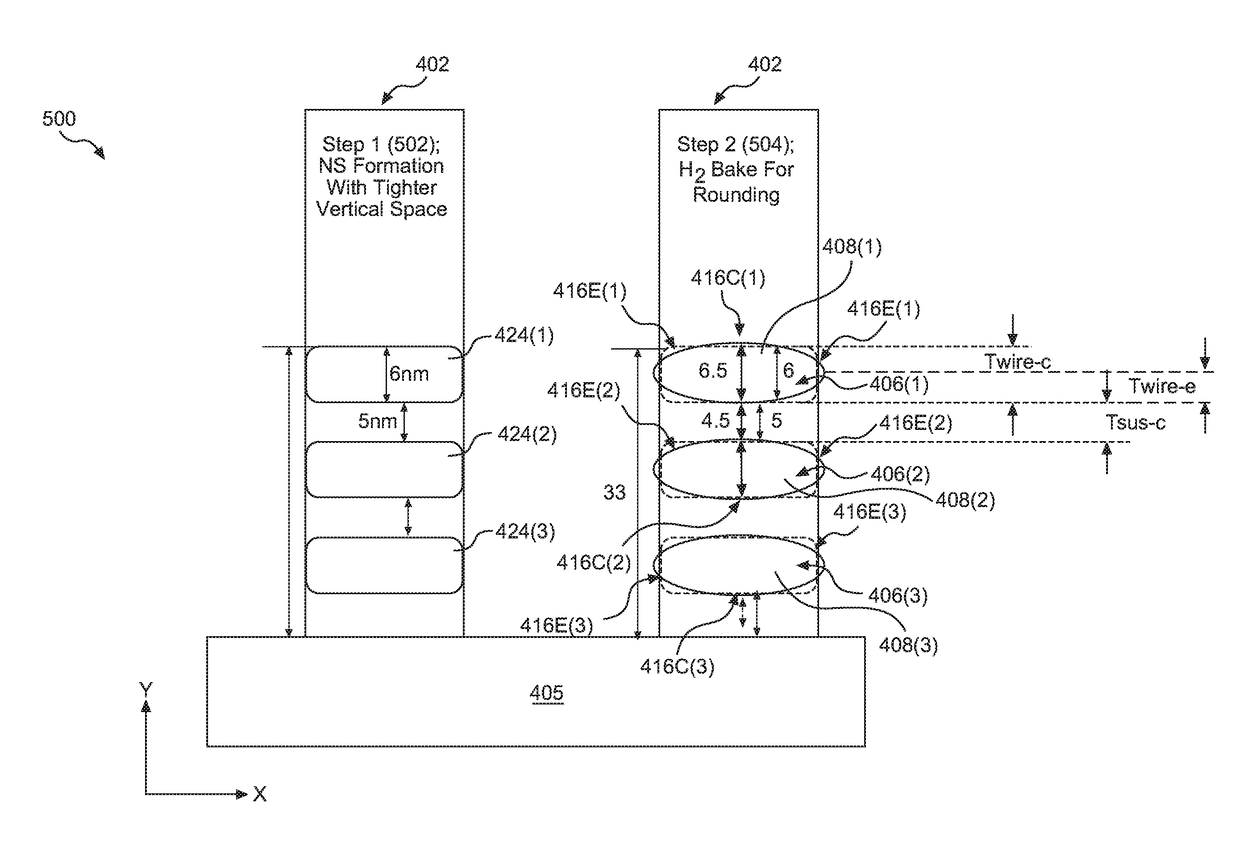

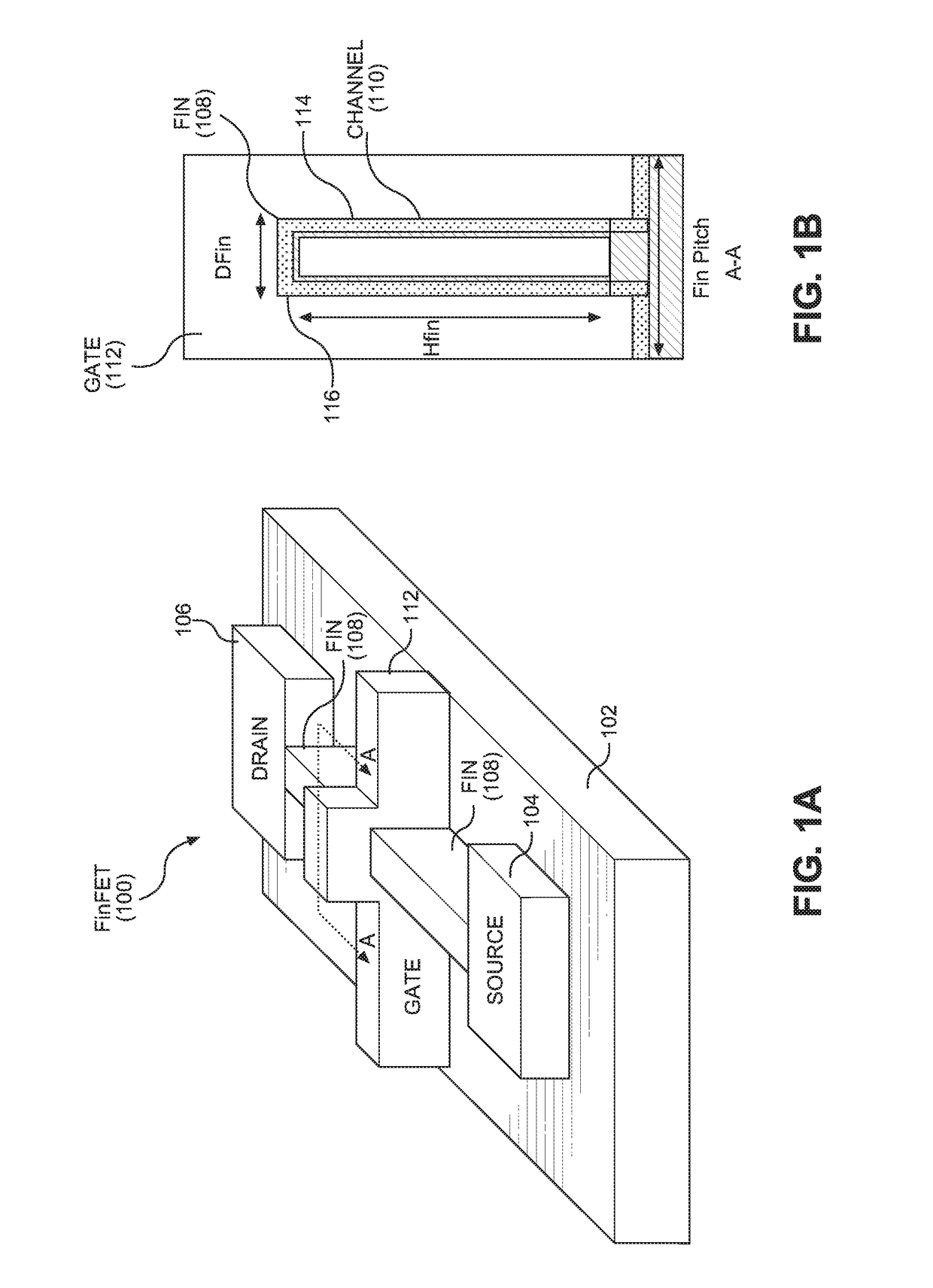

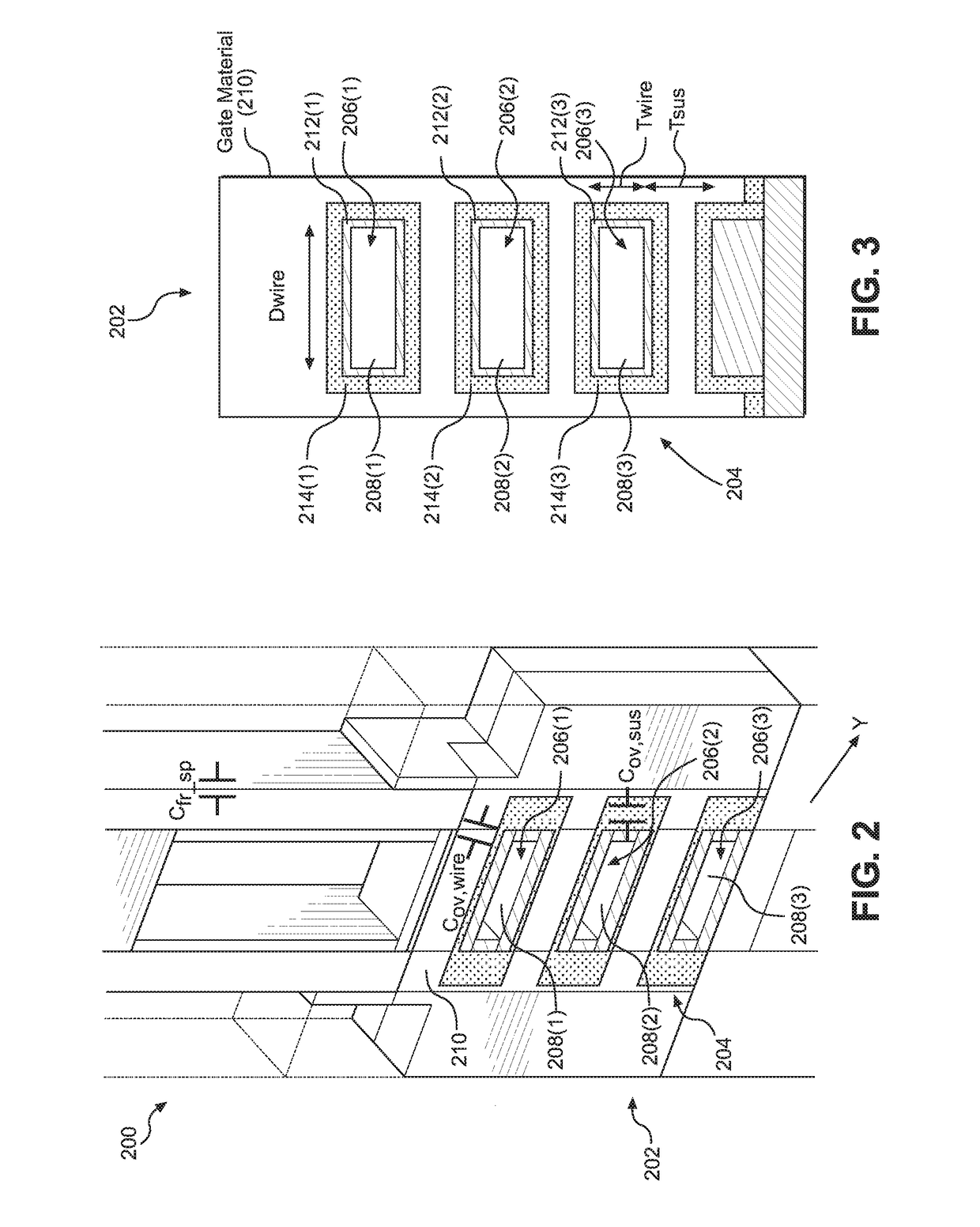

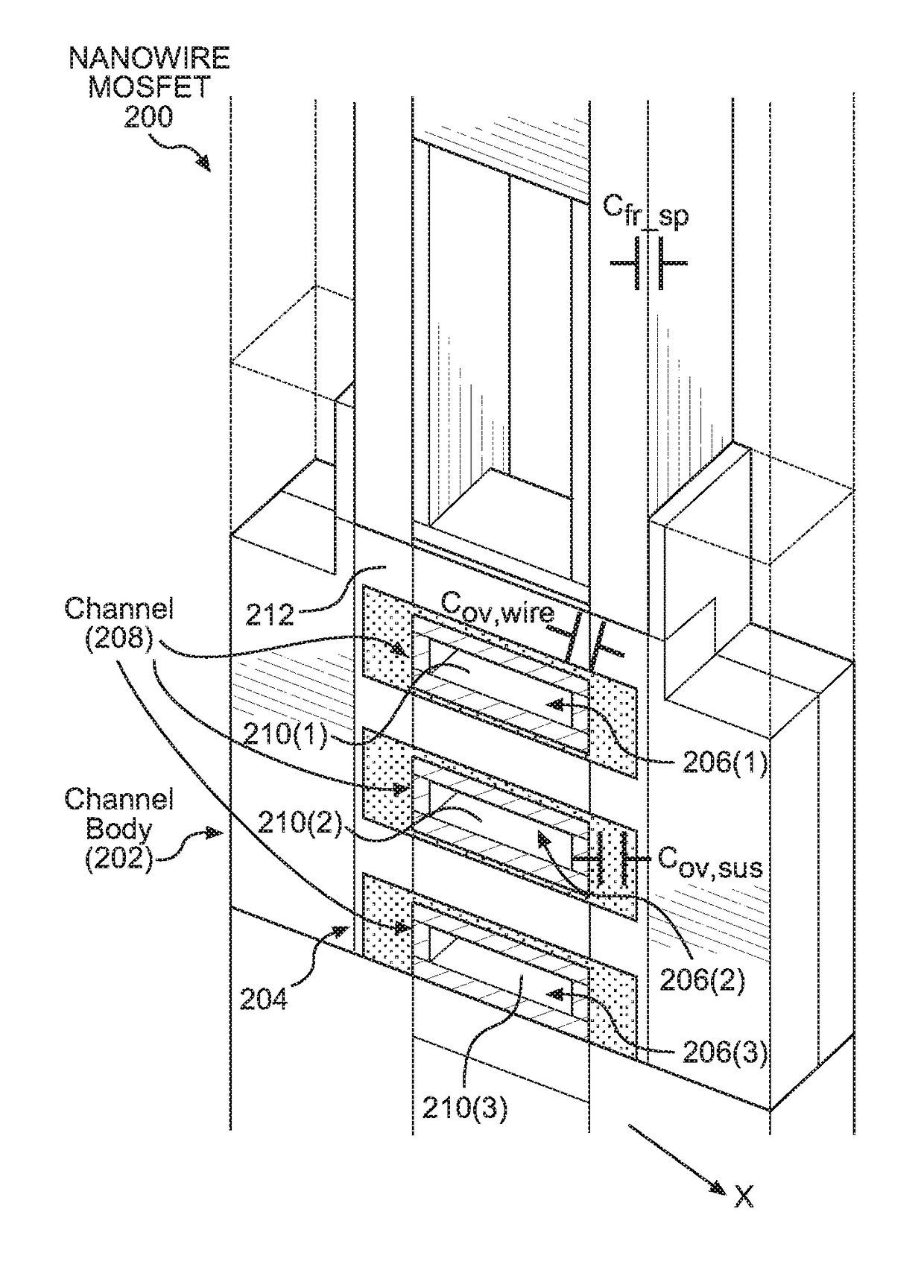

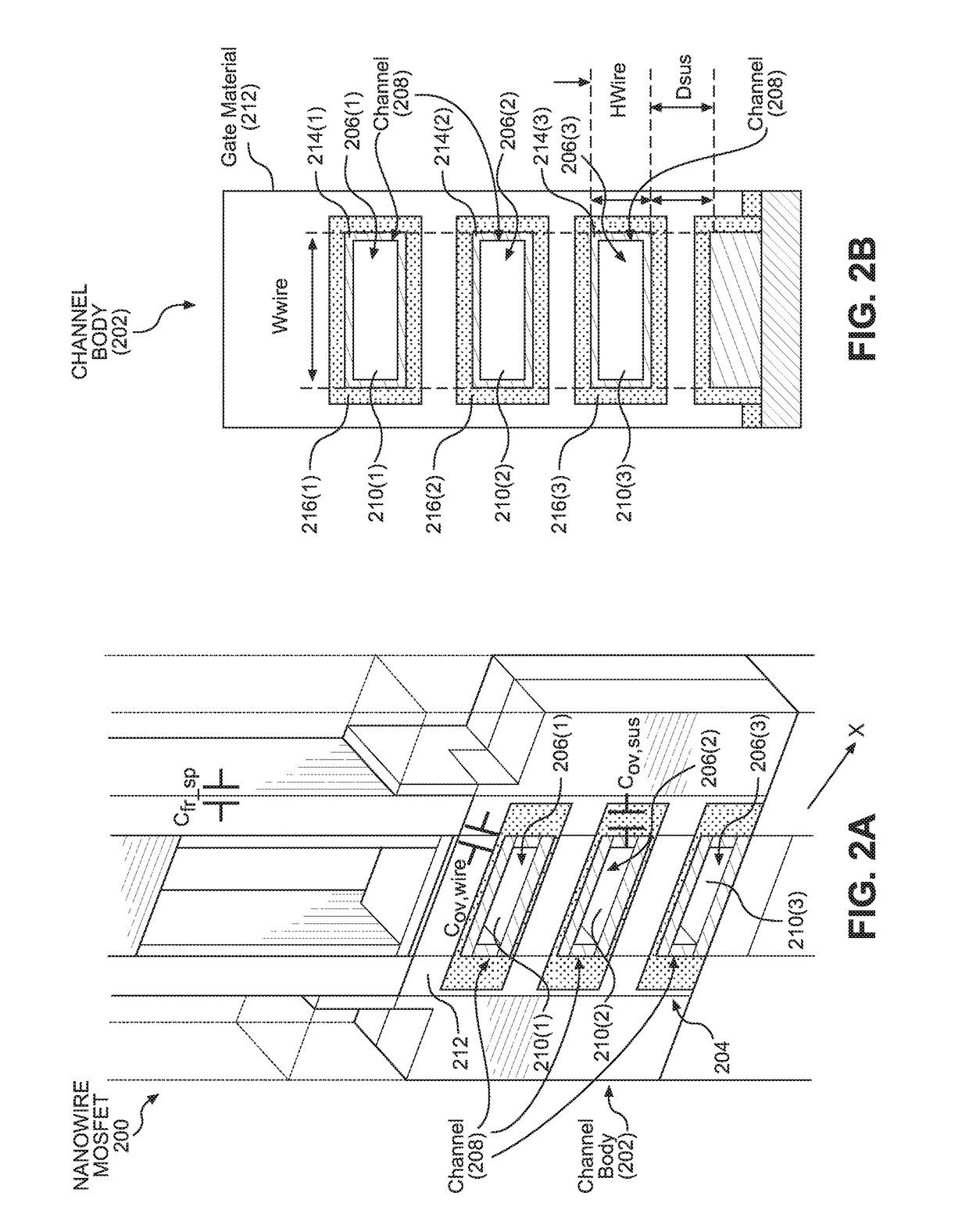

NANOWIRE METAL-OXIDE SEMICONDUCTOR (MOS) FIELD-EFFECT TRANSISTORS (FETs) (MOSFETs) EMPLOYING A NANOWIRE CHANNEL STRUCTURE HAVING ROUNDED NANOWIRE STRUCTURES

InactiveUS20170170268A1Reduce distanceSmall channel lengthTransistorSolid-state devicesMOSFETNanowire

Nanowire metal-oxide semiconductor (MOS) Field-Effect Transistors (FETs) (MOSFETs) employing a nanowire channel structure having rounded nanowire structures is disclosed. To reduce the distance between adjacent nanowire structures to reduce parasitic capacitance while providing sufficient gate control of the channel, the nanowire channel structure employs rounded nanowire structures. For example, the rounded nanowire structures provide for a decreased height from a center area of the rounded nanowire structures to end areas of the rounded nanowire structures. Gate material is disposed around rounded ends of the rounded nanowire structures to extend into a portion of separation areas between adjacent nanowire structures. The gate material extends in the separation areas between adjacent nanowire structures sufficient to create a fringing field to the channel where gate material is not adjacently disposed, to provide strong gate control of the channel even though gate material does not completely surround the rounded nanowire structures.

Owner:QUALCOMM INC

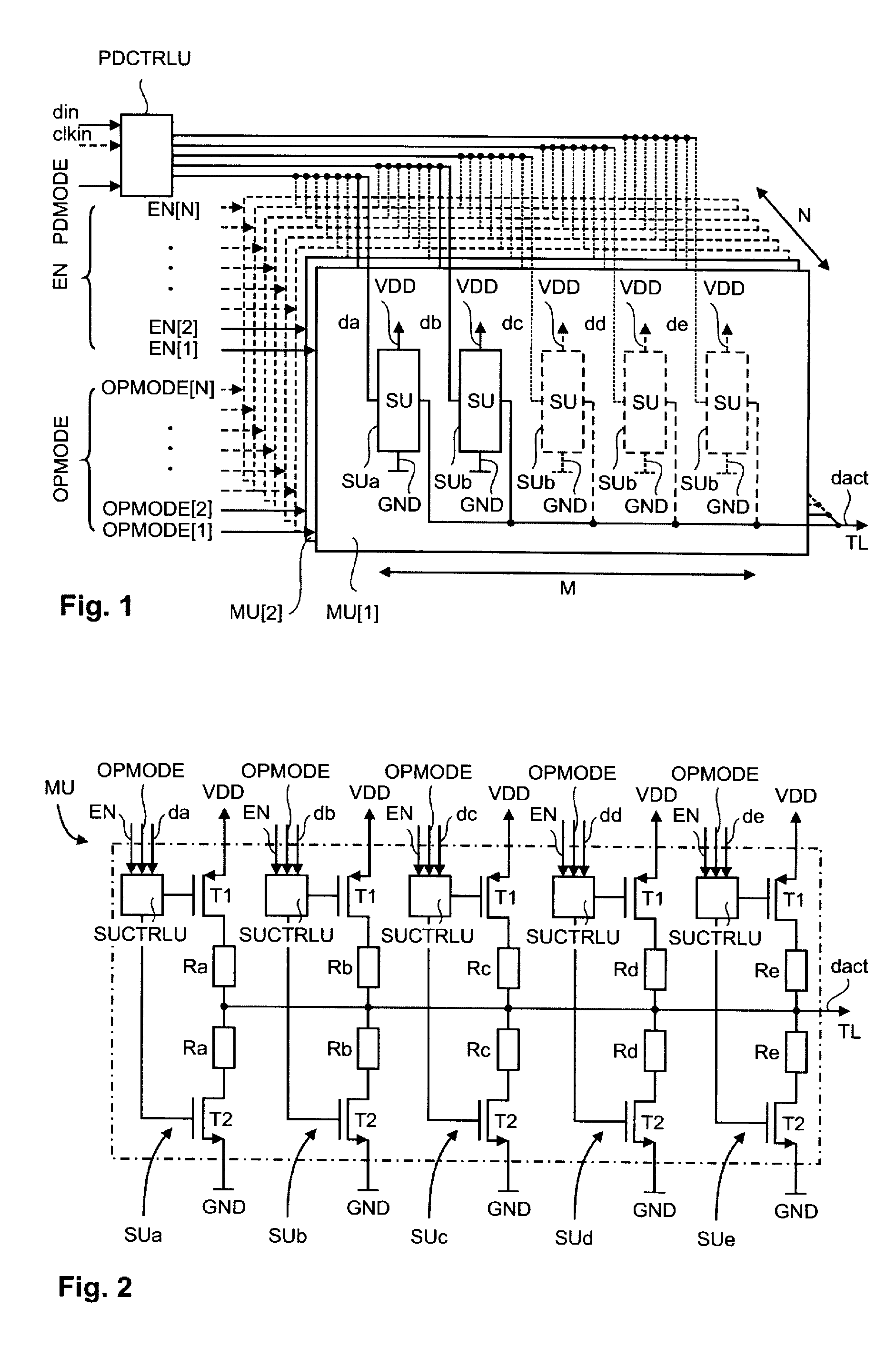

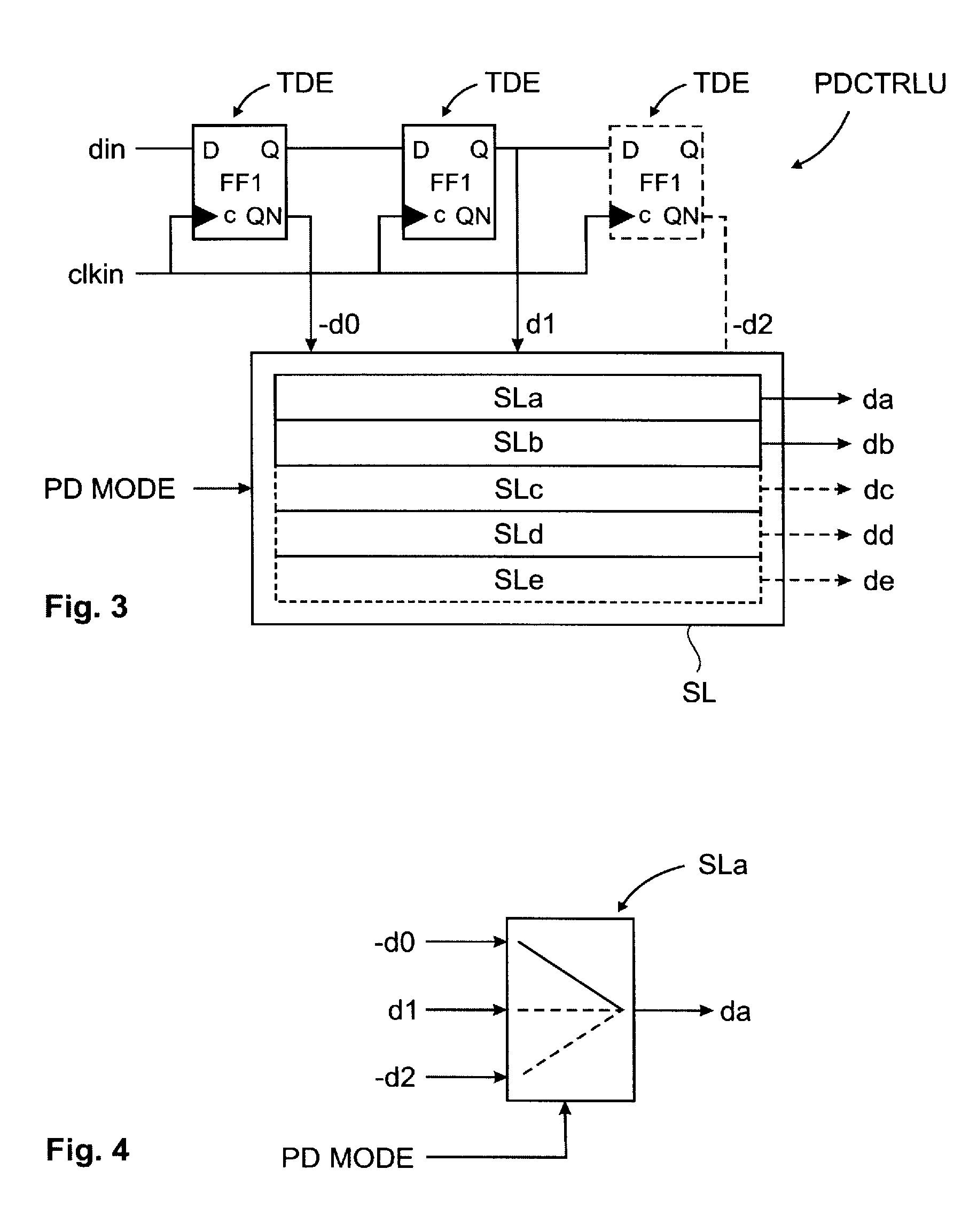

Driver circuit

InactiveUS7692447B2Increase drive strengthReduced strengthInput/output impedence modificationReliability increasing modificationsDriver circuitData signal

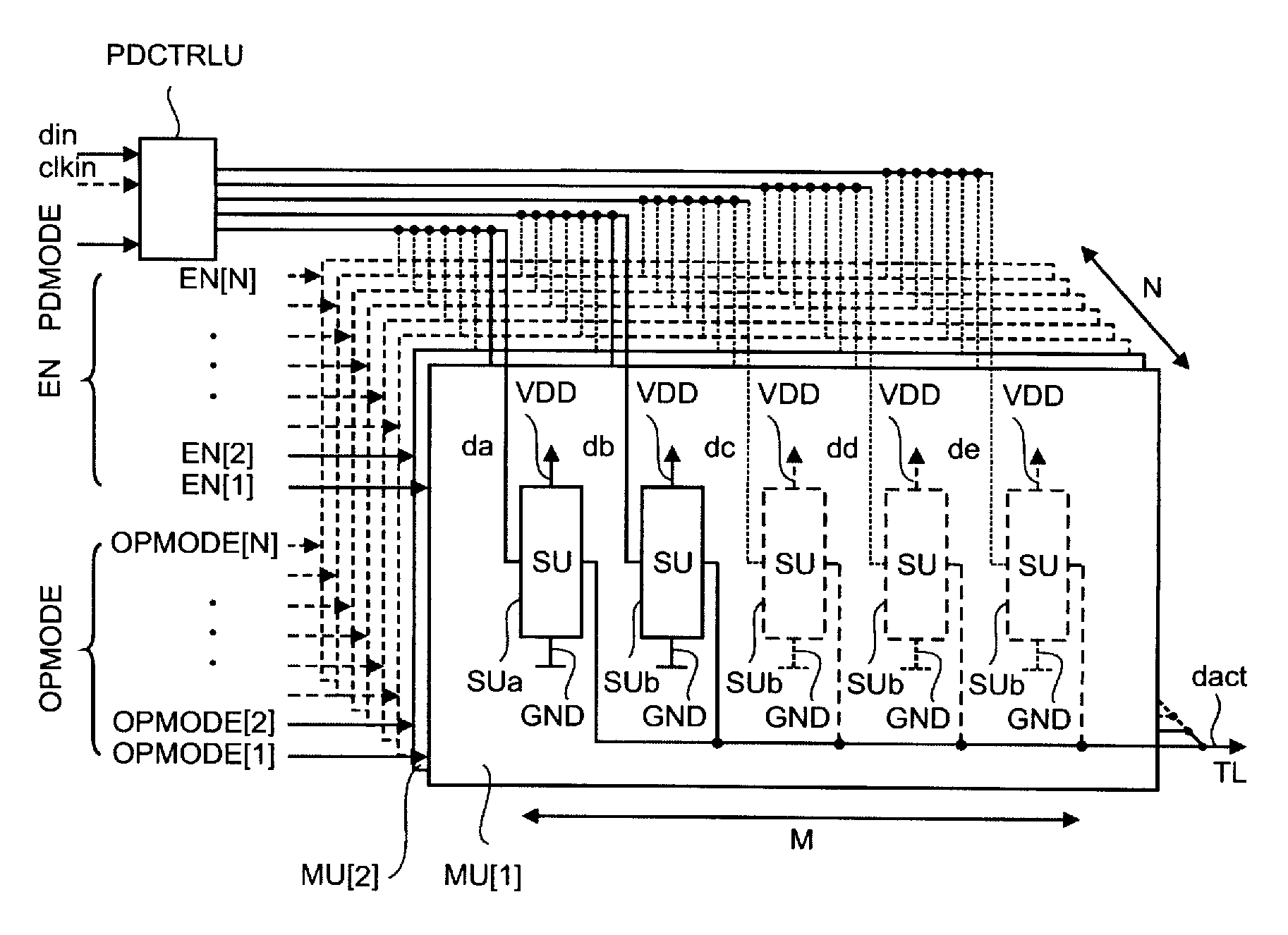

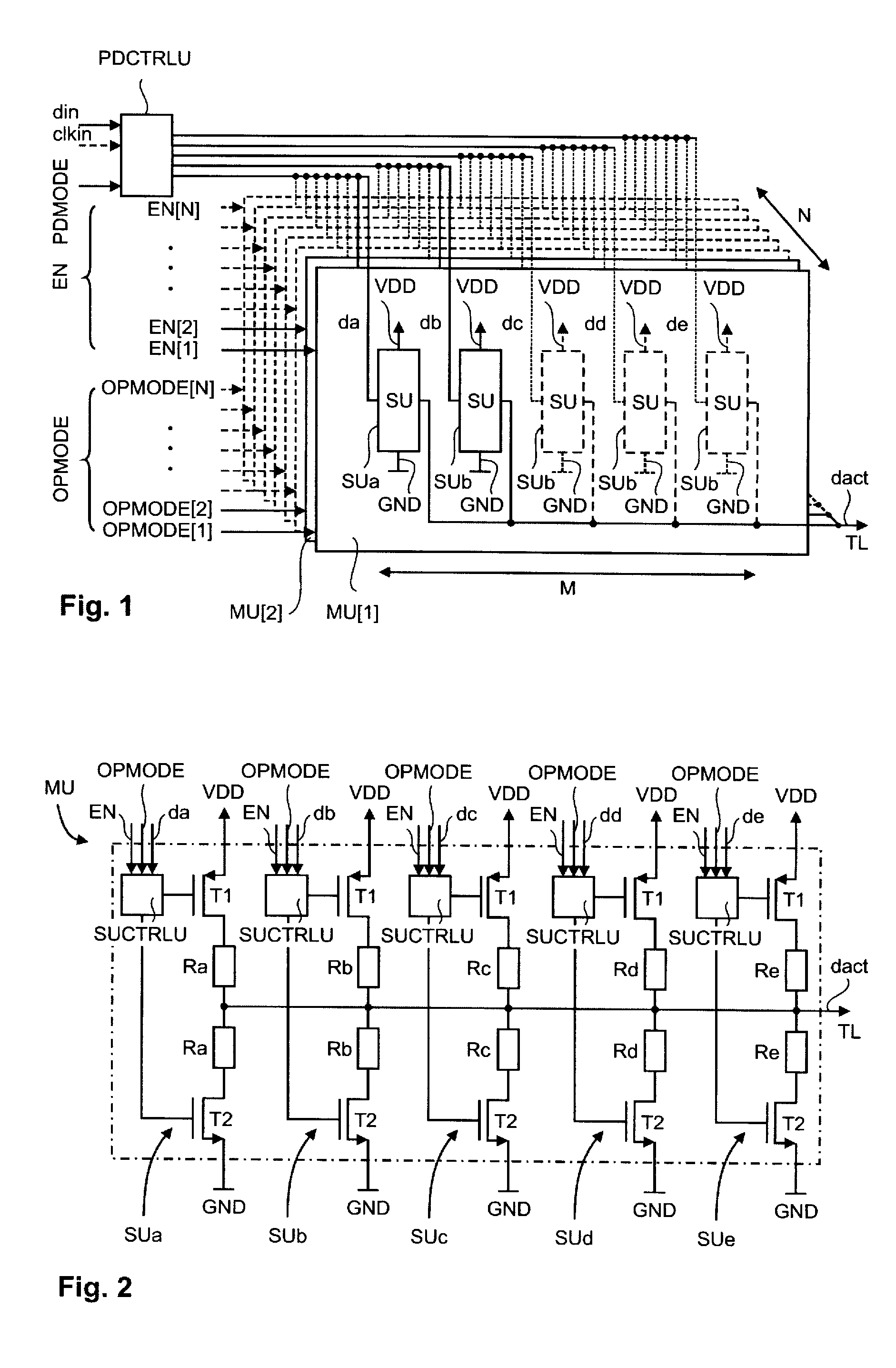

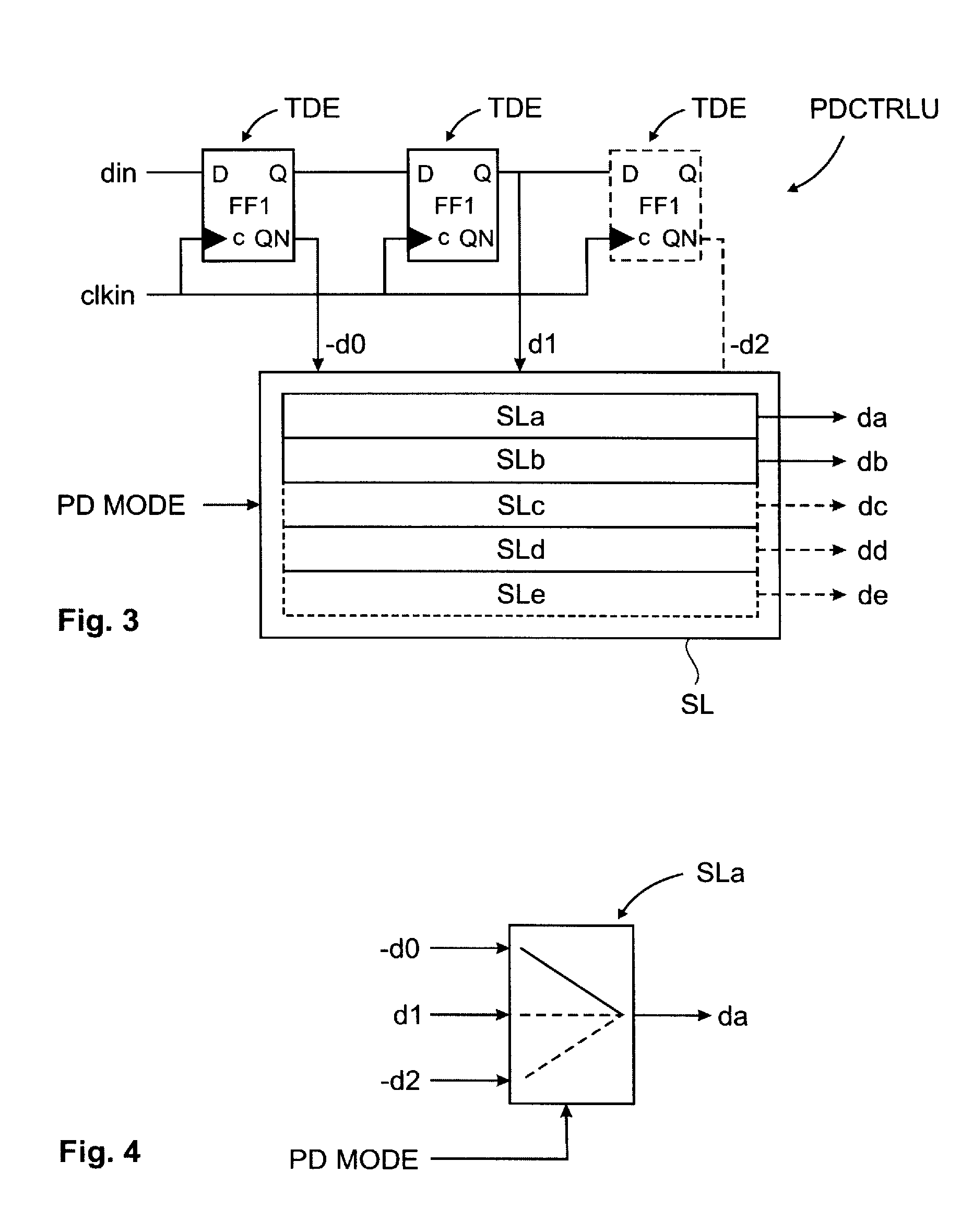

A driver circuit is provided comprising at least two equal main units (MU) each comprising at least two sub units (SU) coupled to a data output (dout). Each sub unit (SU) is adapted to represent a respective predetermined impedance. Each main unit (MU) is adapted to that, when in a data mode, each sub unit (SU) of the respective main unit (MU) is switchable to either a first or second reference potential depending on a data signal to transmit. Each main unit (MU) is further adapted to that, when in a termination mode, the sub units (SU) of the respective main unit (MU) are switched to either the first or second reference potential such that an output of the respective main unit (MU) is neutral with respect to the driving of the data output (dout) to the first or second reference potential.

Owner:GLOBALFOUNDRIES INC

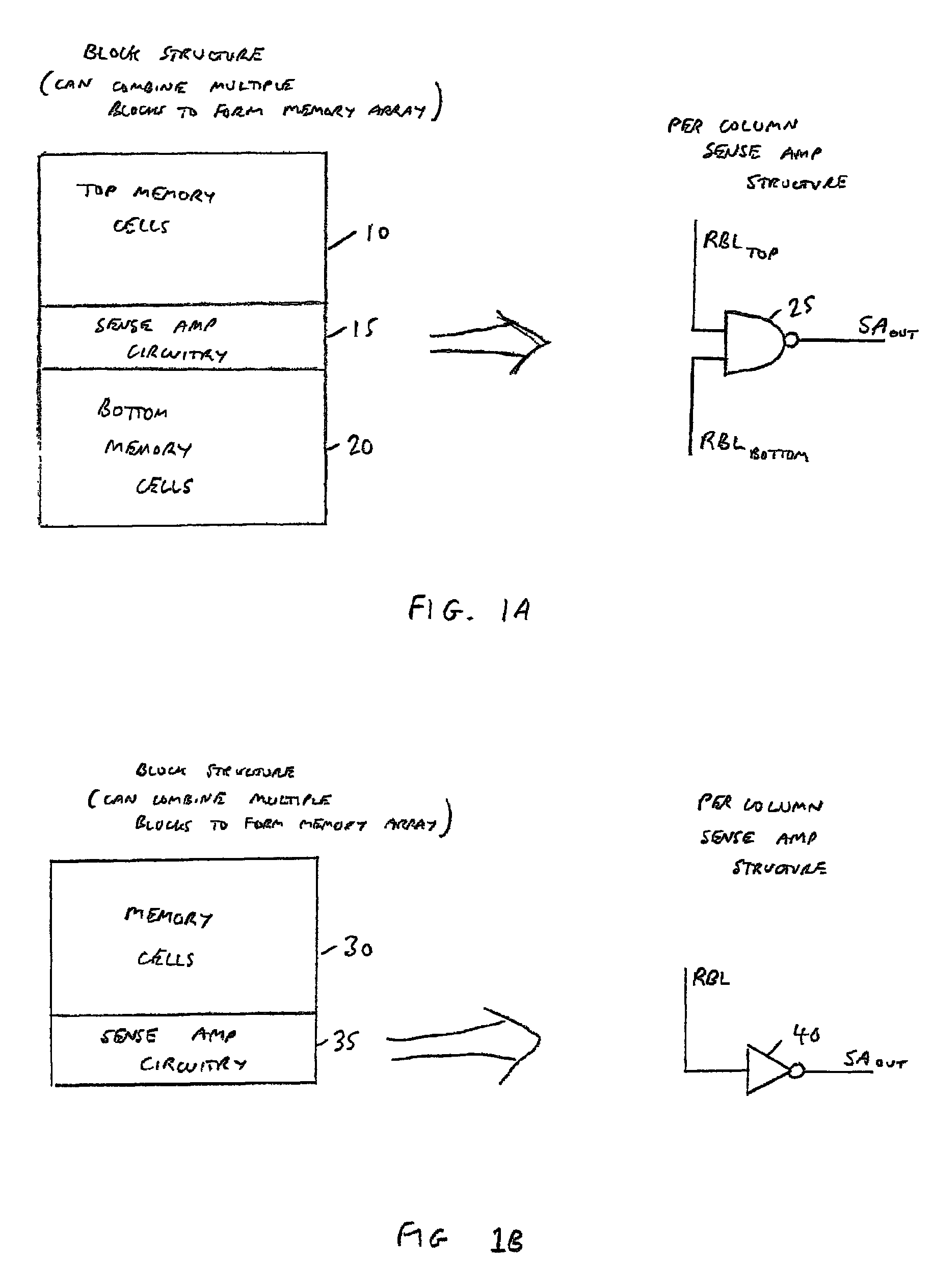

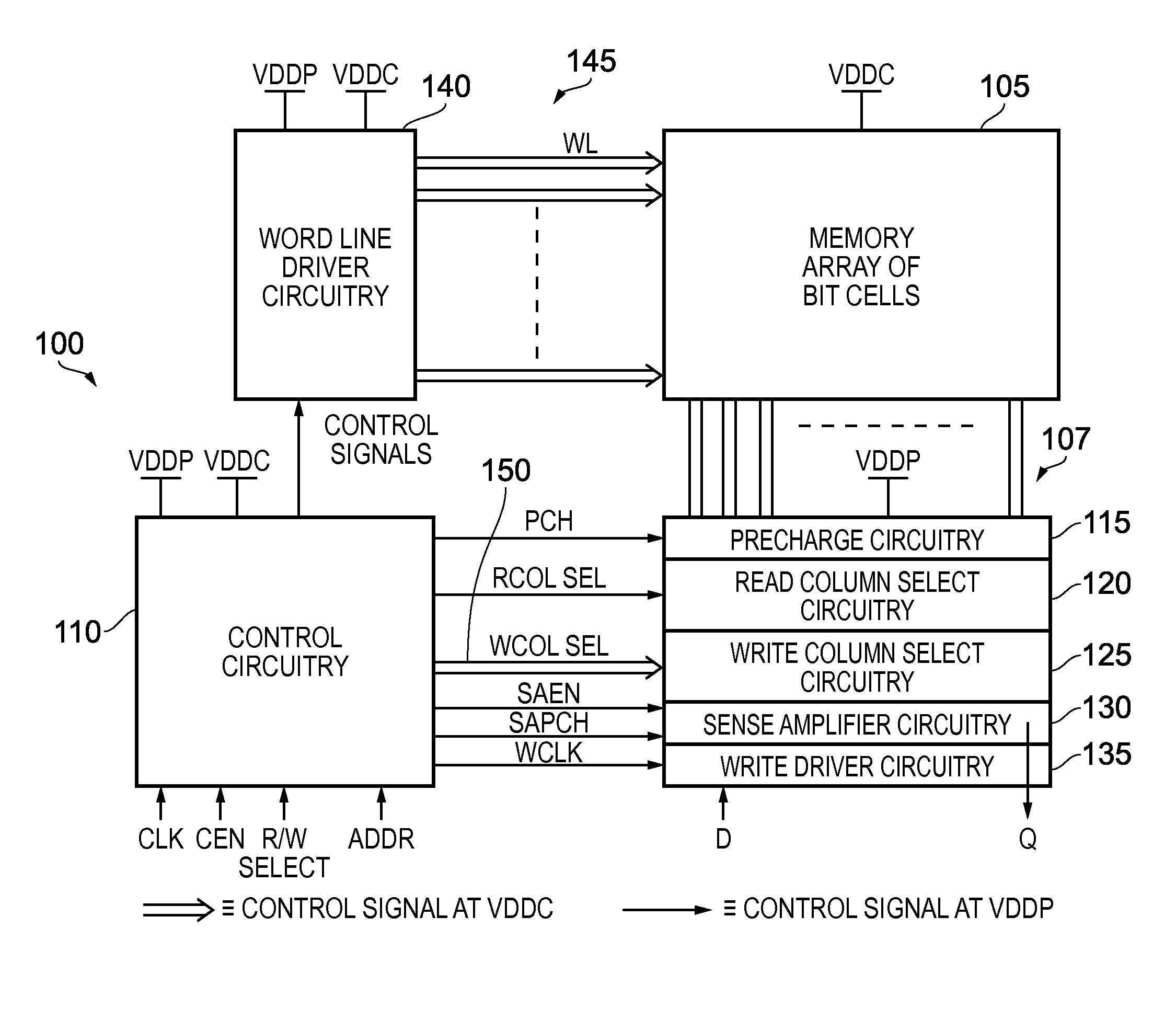

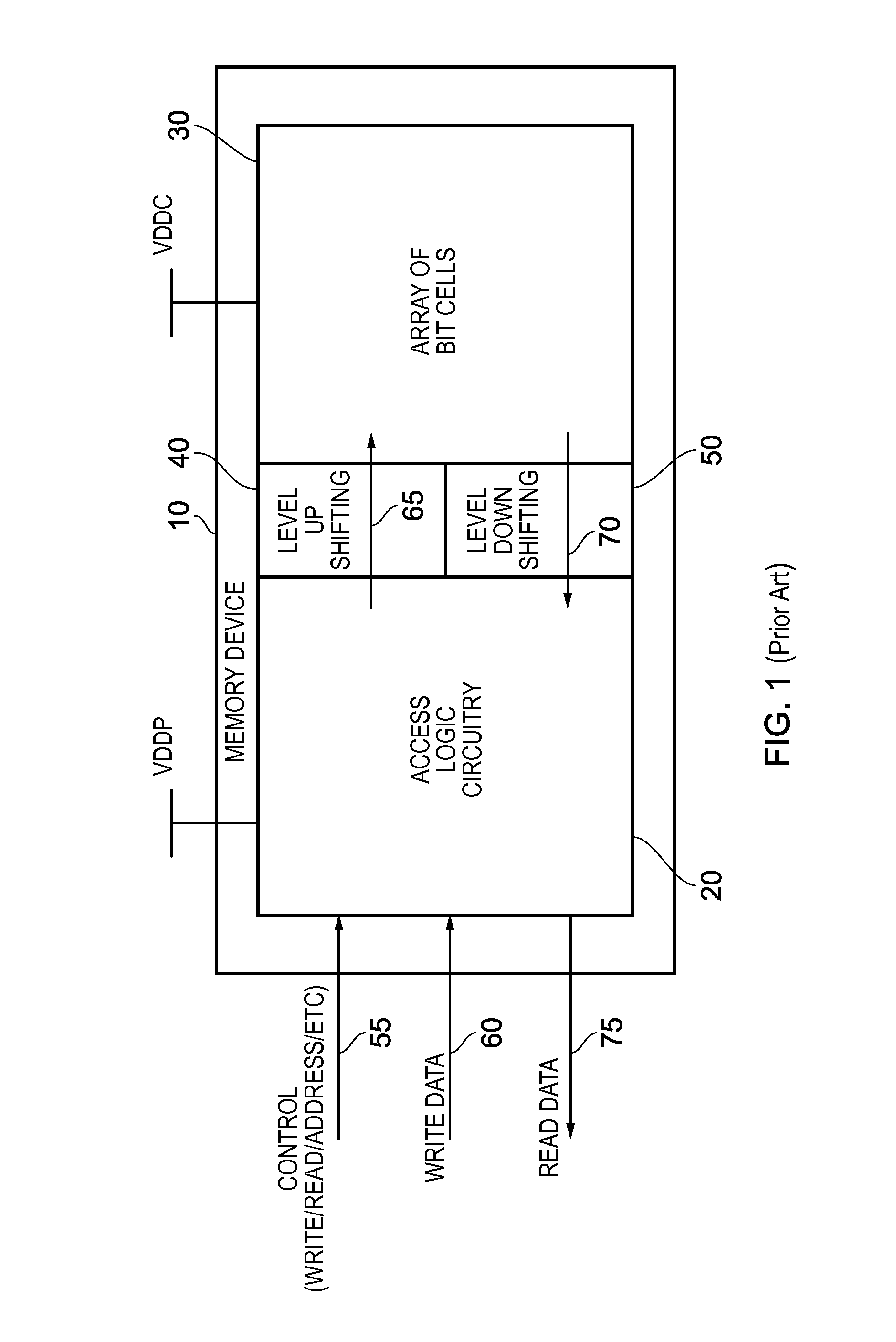

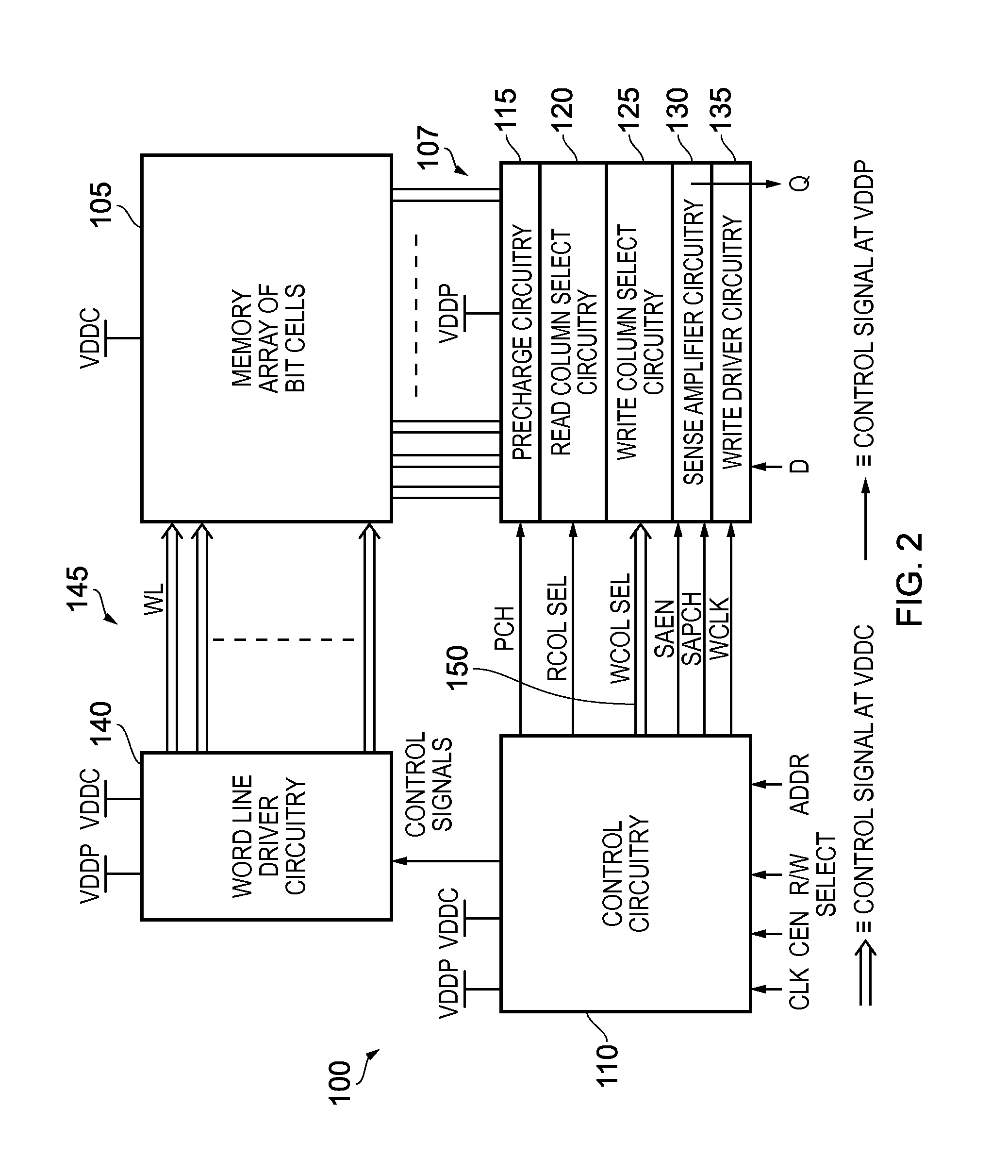

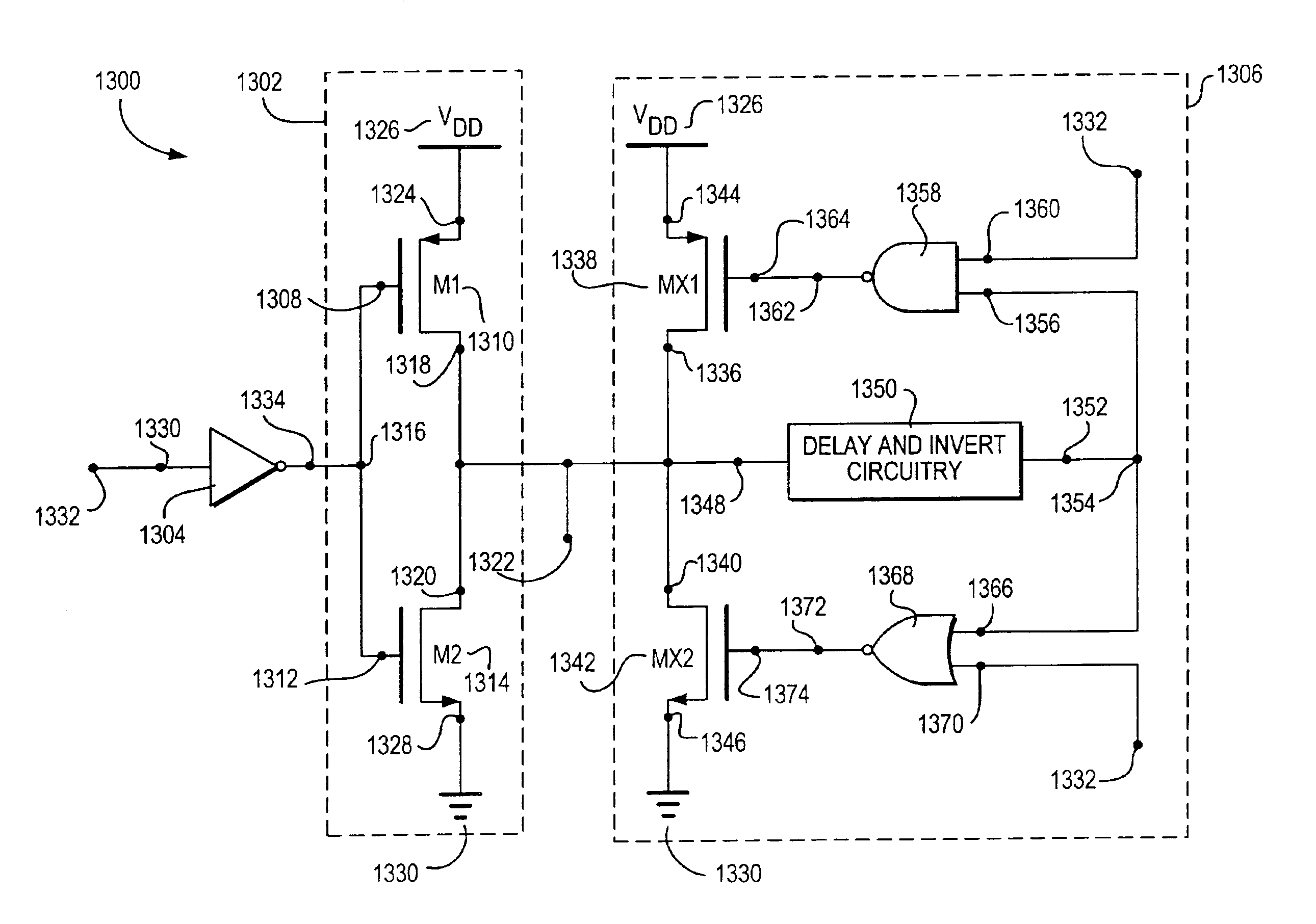

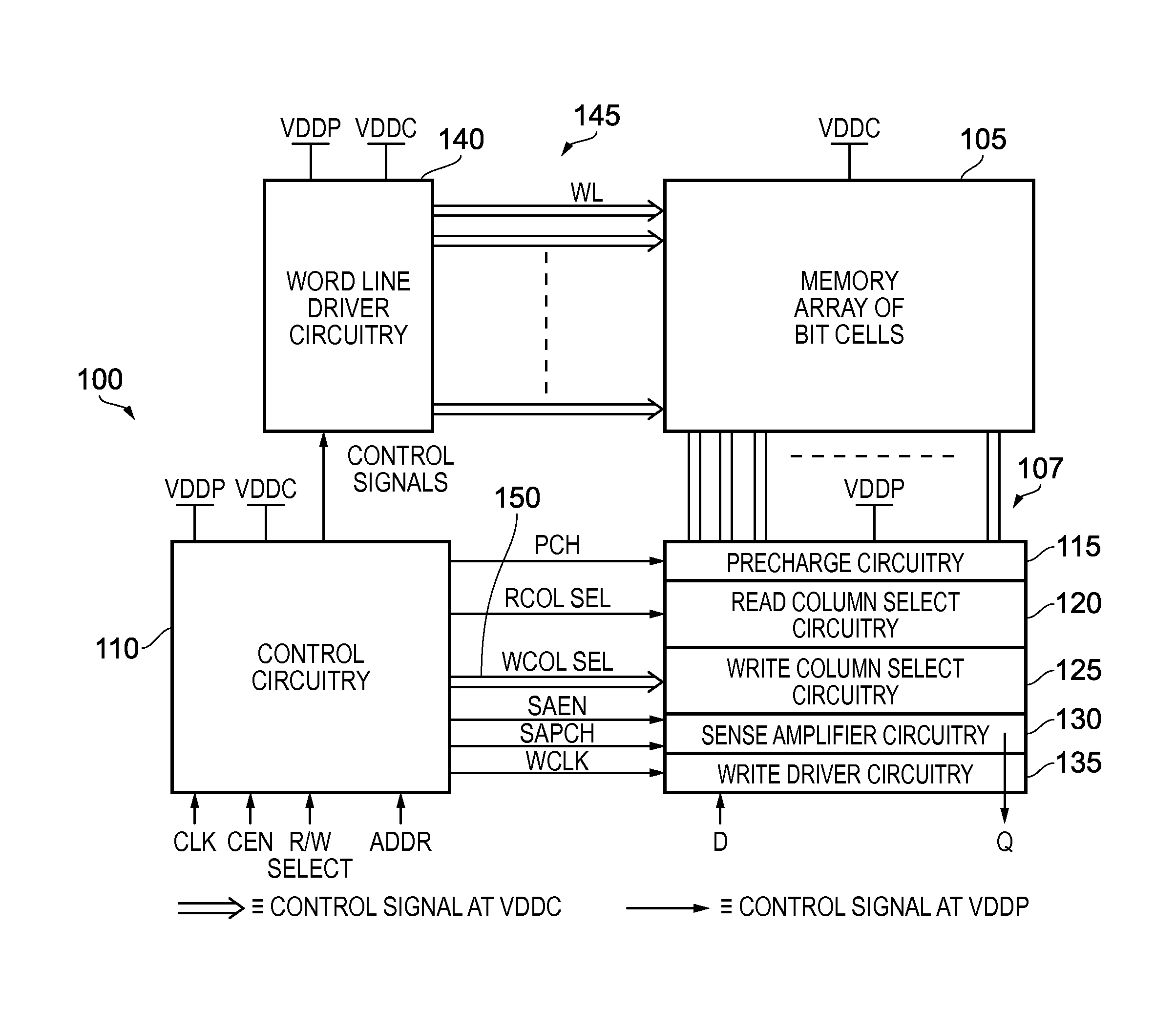

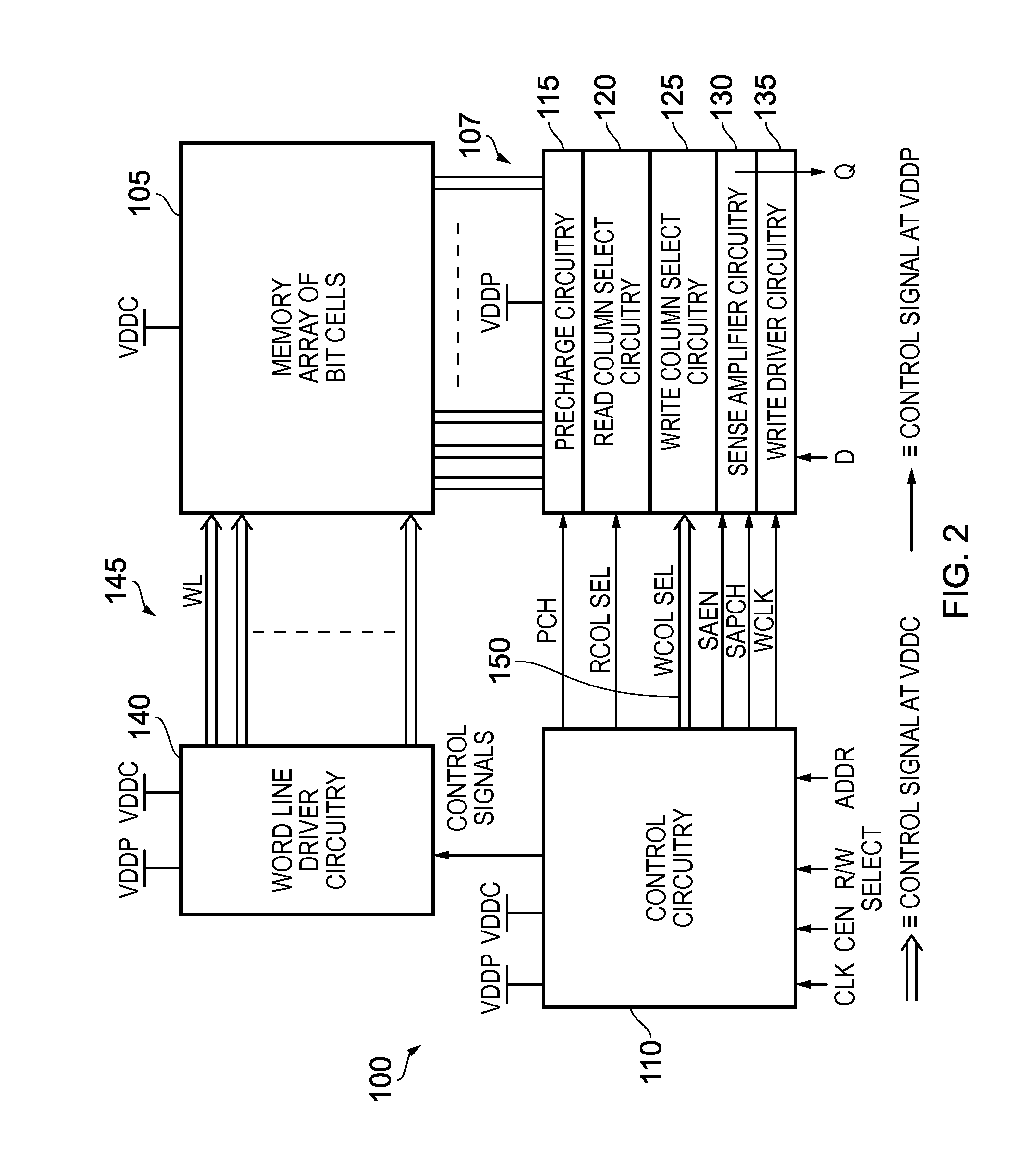

Memory device and method of operation of such a memory device

ActiveUS8971133B1Sufficient write marginReduce power consumptionRead-only memoriesElectronic switchingMuxponderLine driver

A memory device having an array of memory cells connected to a core voltage level, and access circuitry used to perform a write operation in order to write data into a plurality of addressed memory cells. At least one bit line associated with at least each column in the array containing an addressed memory cell is precharged to the peripheral voltage level prior to the write operation being performed. Word line driver circuitry is then configured to assert a word line signal at the core voltage level on the word line associated with the row of the array containing the addressed memory cells. Write multiplexing driver circuitry asserts a mux control signal to write multiplexing circuitry which then couples the bit line of each addressed memory cell to the write driver circuitry in dependence on the mux control signal identifying which column contains the addressed memory cells.

Owner:ARM LTD

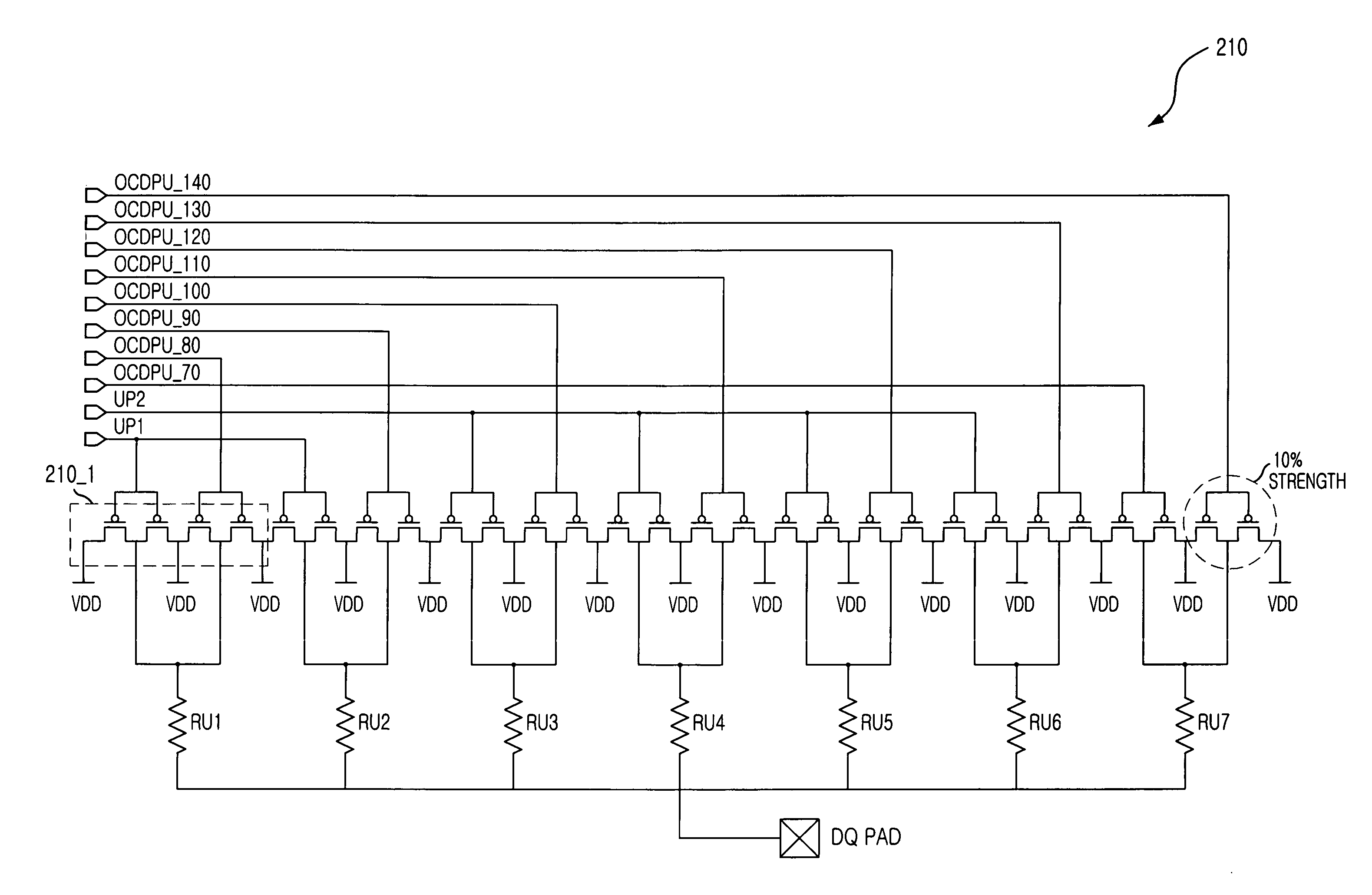

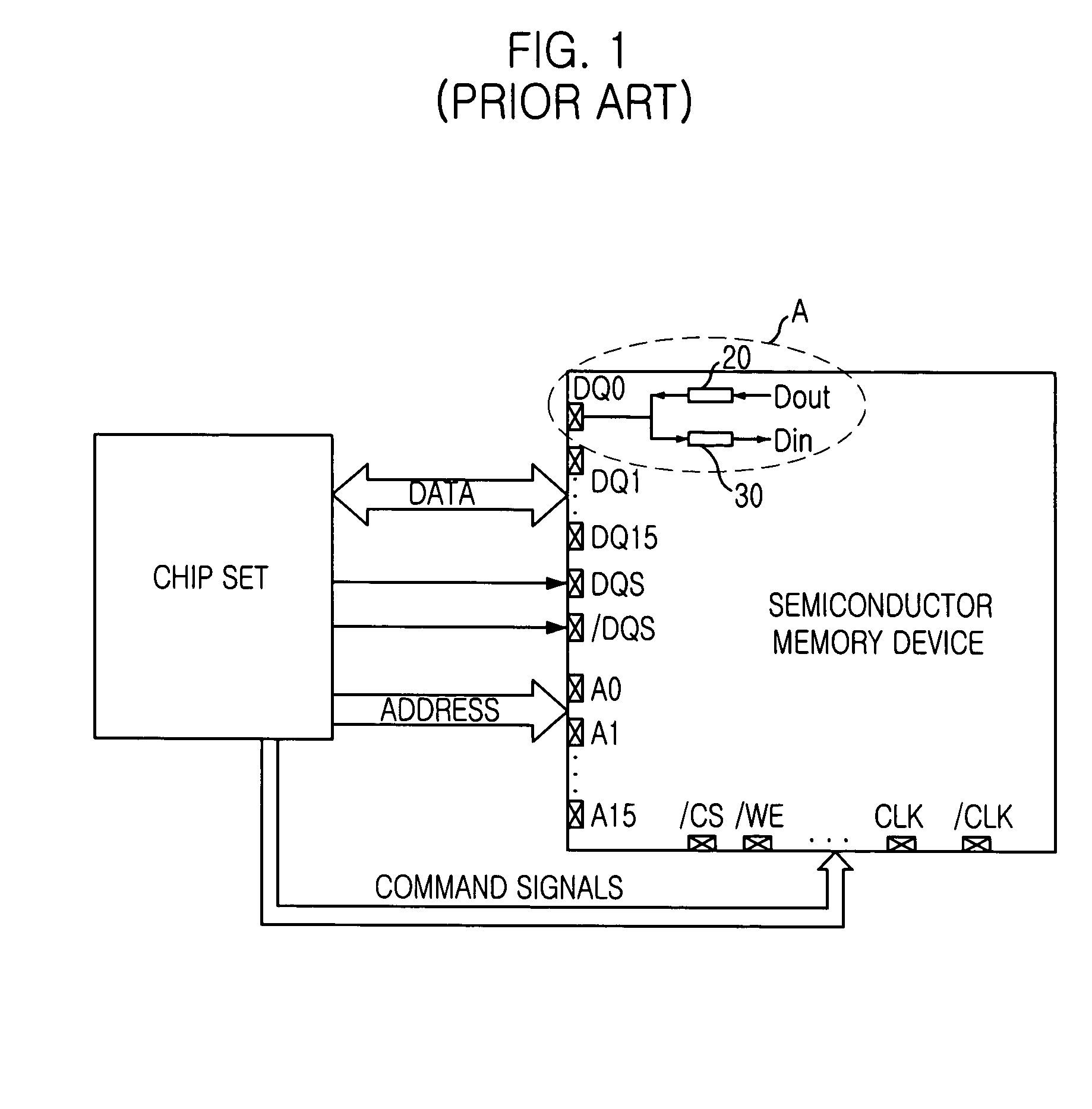

Data output driver

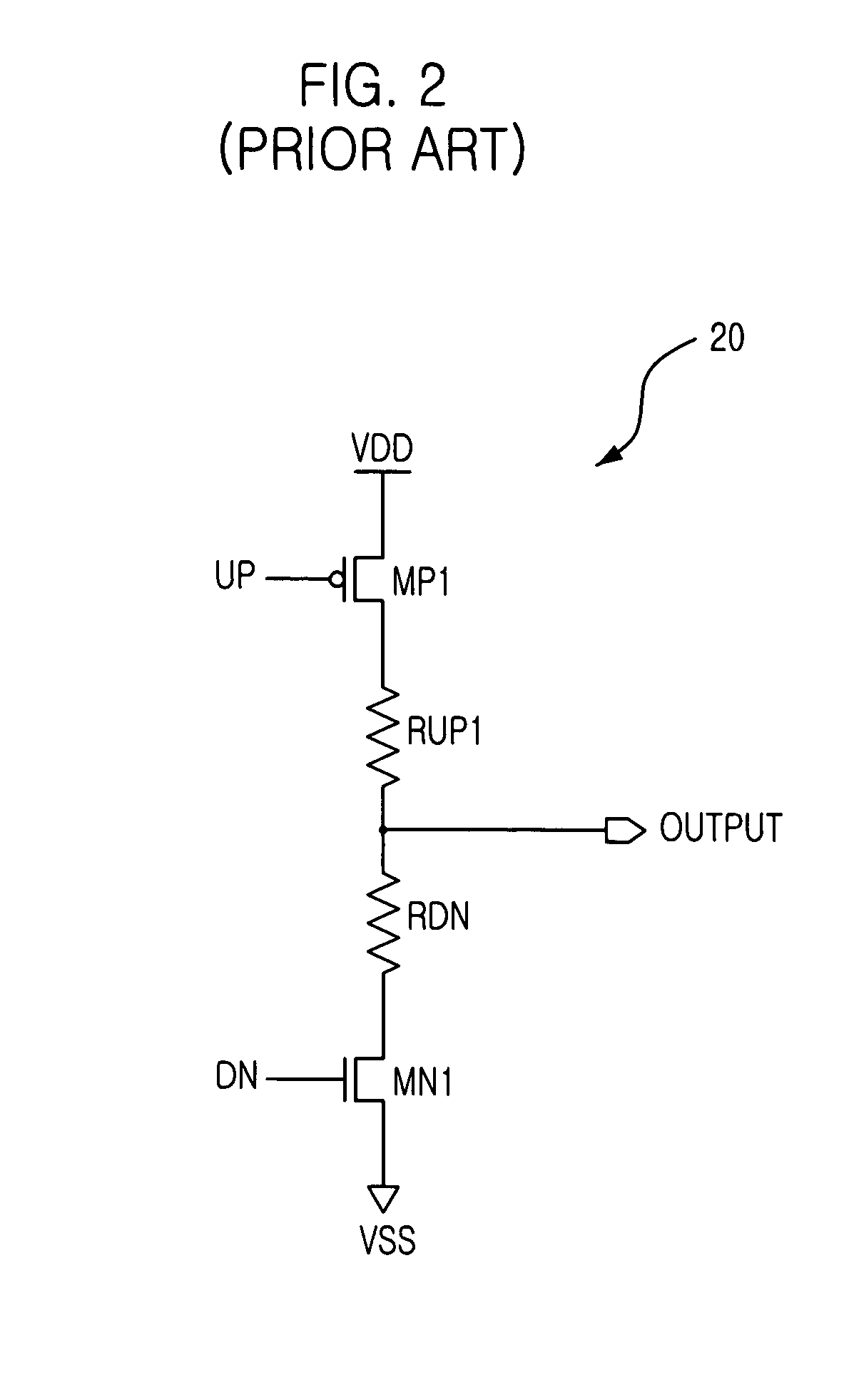

InactiveUS7068078B2Increase drive strengthReliability increasing modificationsElectronic switchingControl signalData signal

A data output driver, for use in a semiconductor memory device, includes a pull-up driving unit, having N numbers of unit pull-up drivers and N numbers of pull-up resistors, turned on by selected pull-up control signals for pull-up driving the output terminal in response to a pull-up data signal; and a pull-down driving unit, having N numbers of unit pull-down drivers and N numbers of pull-down resistors, turned on by selected pull-down control signals for pull-down driving the output terminal in response to a pull-down data signal, wherein each of the N numbers of unit pull-up drivers has the same driving strength, and the N numbers of pull-up resistors are connected between the output terminal and the N numbers of unit pull-up drivers; and each of the N numbers of unit pull-down drivers has the same driving strength, and the N numbers of pull-down resistors are connected between the output terminal and the N numbers of unit pull-down drivers.

Owner:SK HYNIX INC

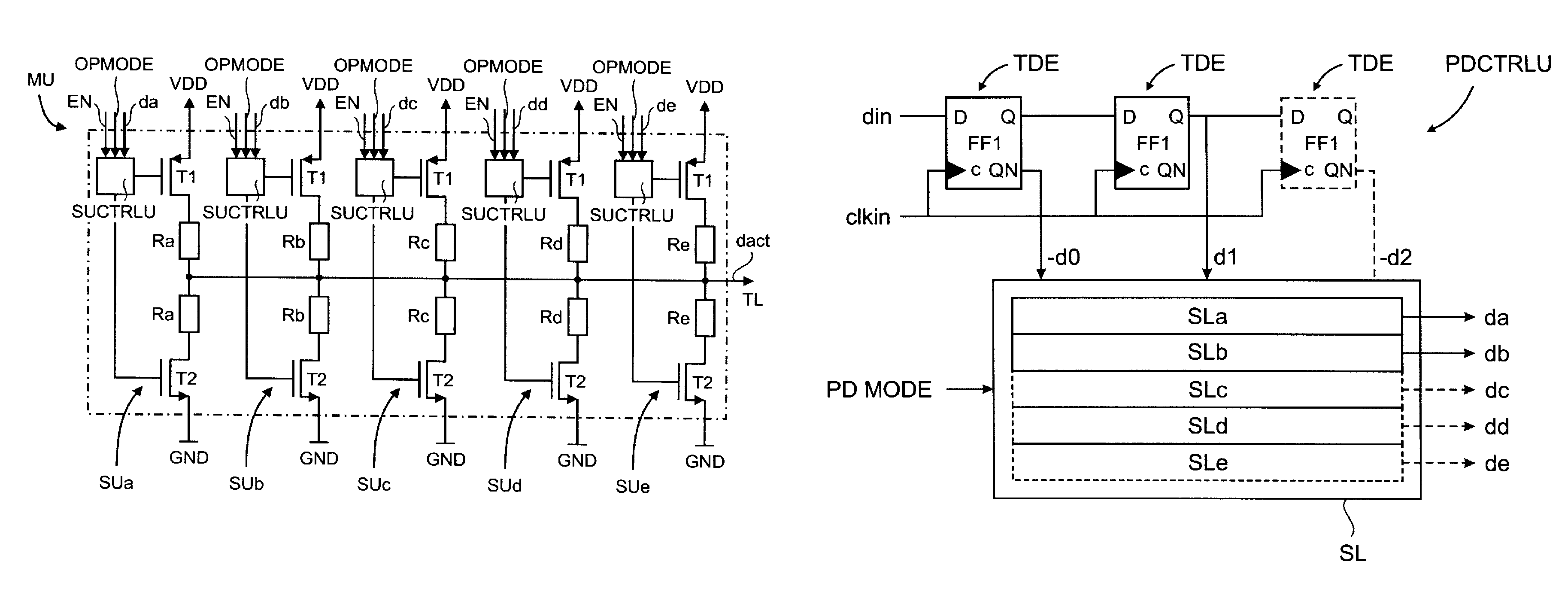

Driver Circuit

InactiveUS20080284466A1Easy to implementEasy to provideInput/output impedence modificationReliability increasing modificationsDriver circuitData signal

A driver circuit is provided comprising at least two equal main units (MU) each comprising at least two sub units (SU) coupled to a data output (dout). Each sub unit (SU) is adapted to represent a respective predetermined impedance. Each main unit (MU) is adapted to that, when in a data mode, each sub unit (SU) of the respective main unit (MU) is switchable to either a first or second reference potential depending on a data signal to transmit. Each main unit (MU) is further adapted to that, when in a termination mode, the sub units (SU) of the respective main unit (MU) are switched to either the first or second reference potential such that an output of the respective main unit (MU) is neutral with respect to the driving of the data output (dout) to the first or second reference potential.

Owner:GLOBALFOUNDRIES INC

NANOWIRE METAL-OXIDE SEMICONDUCTOR (MOS) FIELD-EFFECT TRANSISTORS (FETs) (MOSFETs) EMPLOYING A NANOWIRE CHANNEL STRUCTURE EMPLOYING RECESSED CONDUCTIVE STRUCTURES FOR CONDUCTIVELY COUPLING NANOWIRE STRUCTURES

InactiveUS20170207313A1Increase widthIncrease channel current densitySemiconductor devicesMOSFETNanowire

Nanowire metal-oxide semiconductor (MOS) Field-Effect Transistors (FETs) (MOSFETs) employing a nanowire channel structure employing recessed conductive structures for conductively coupling nanowire structures are disclosed. Conductive structures are disposed between adjacent nanowire structures to conductively couple nanowire structures. Providing conductive structures in the nanowire channel structure increases the average cross-sectional area of nanowire structures, as compared to a similar nanowire channel structure not employing conductive structures, thus increasing effective channel width and drive strength for a given channel structure height. The precision of a gate material filling process is also eased, because gate material does not have to be disposed in areas between adjacent nanowire structures occupied by conductive structures. The conductive structure width can also be recessed with regard to width of nanowire structures in the nanowire channel structure to allow for a thicker metal gate to lower the gate resistance, while providing excellent electrostatic gate control of the channel.

Owner:QUALCOMM INC

Semiconductor device having a gap defined therein

ActiveUS9871121B2Increase drive strengthReduce parasitic capacitanceSemiconductor devicesPower semiconductor deviceEngineering

In a particular embodiment, a method includes forming a first spacer structure on a dummy gate of a semiconductor device and forming a sacrificial spacer on the first spacer structure. The method also includes etching a structure of the semiconductor device to create an opening, removing the sacrificial spacer via the opening, and depositing a material to close to define a gap.

Owner:QUALCOMM INC

Memory device and method of controlling leakage current within such a memory device

ActiveUS20140269091A1Reduce leakage currentImprove performanceRead-only memoriesDigital storageComputer architectureDrain current

A memory device includes an array of memory cells arranged as a plurality of rows and columns, each row being coupled to an associated read word line, and each column forming at least one column group, where the memory cells of each column group are coupled to an associated read bit line. Each column has an active mode of operation where a read operation may be performed on an activated memory cell within that column group, and a non-active mode of operation where the read operation is not performable. Precharge circuitry is used, for each column group, to precharge the associated read bit line to a first voltage level prior to the read operation. Each memory cell includes coupling circuitry connected between the associated read bit line and a reference line associated with the column group containing that memory cell.

Owner:ARM LTD

Increasing drive strength and reducing propagation delays through the use of feedback

InactiveUS6909308B2Reduce degradationIncrease drive strengthReliability increasing modificationsElectronic switchingDriving currentPropagation delay

Techniques of increasing drive strength and reducing propagation delays of a digital logic circuit through the use of feedback are presented. Logic circuitry operative to receive an input signal of the digital logic circuit and a delayed version of an output signal of the digital logic circuit turns “ON” a supplemental drive transistor for a digital state transition of the output signal. The supplemental drive transistor provides supplemental drive current to the digital logic circuit during the output signal digital state transition, thus advantageously reducing propagation delay and increasing fan-out capability. The logic circuitry turns “OFF” the drive transistor once the output signal digital state transition is complete.

Owner:ROUND ROCK RES LLC

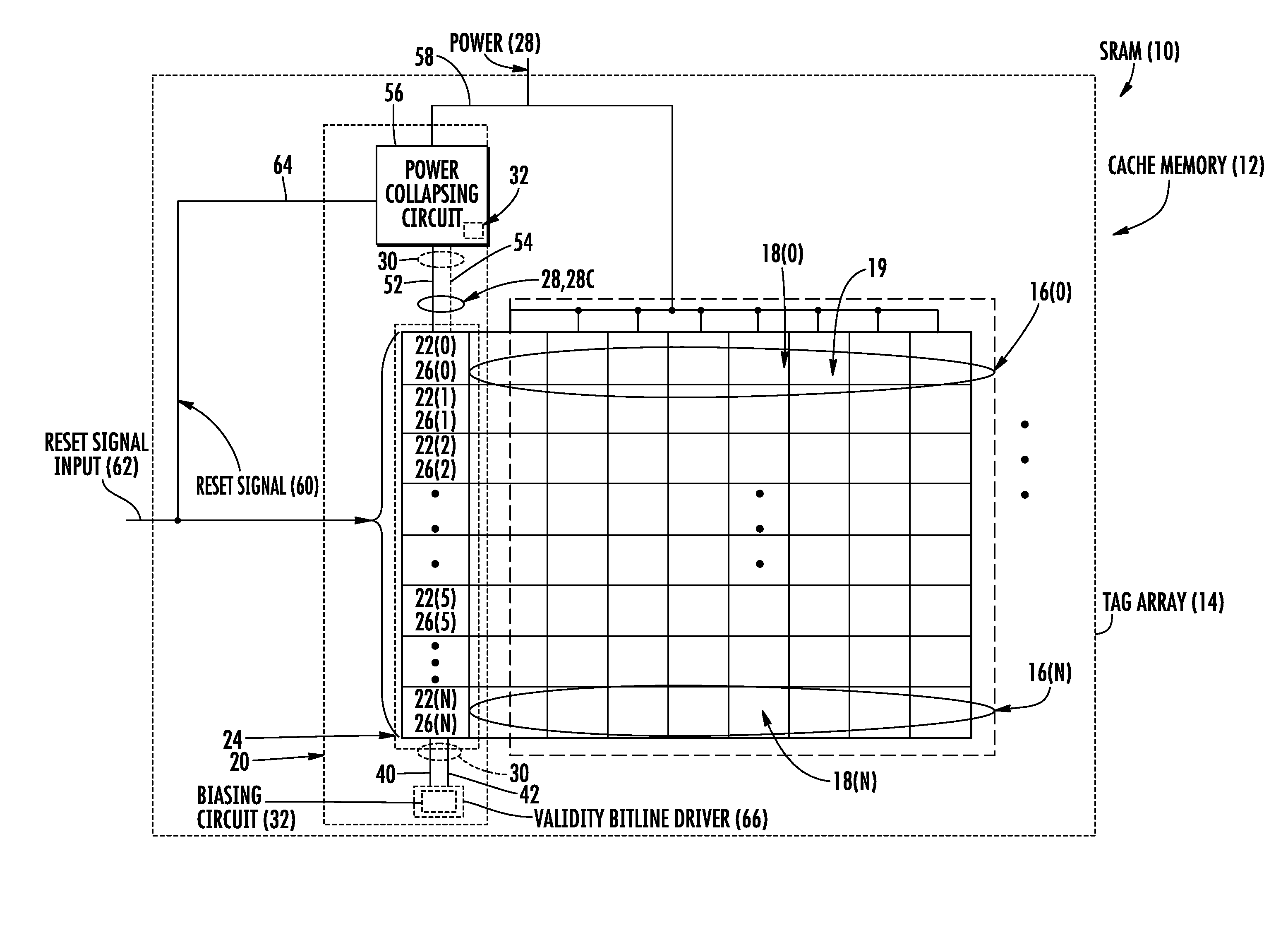

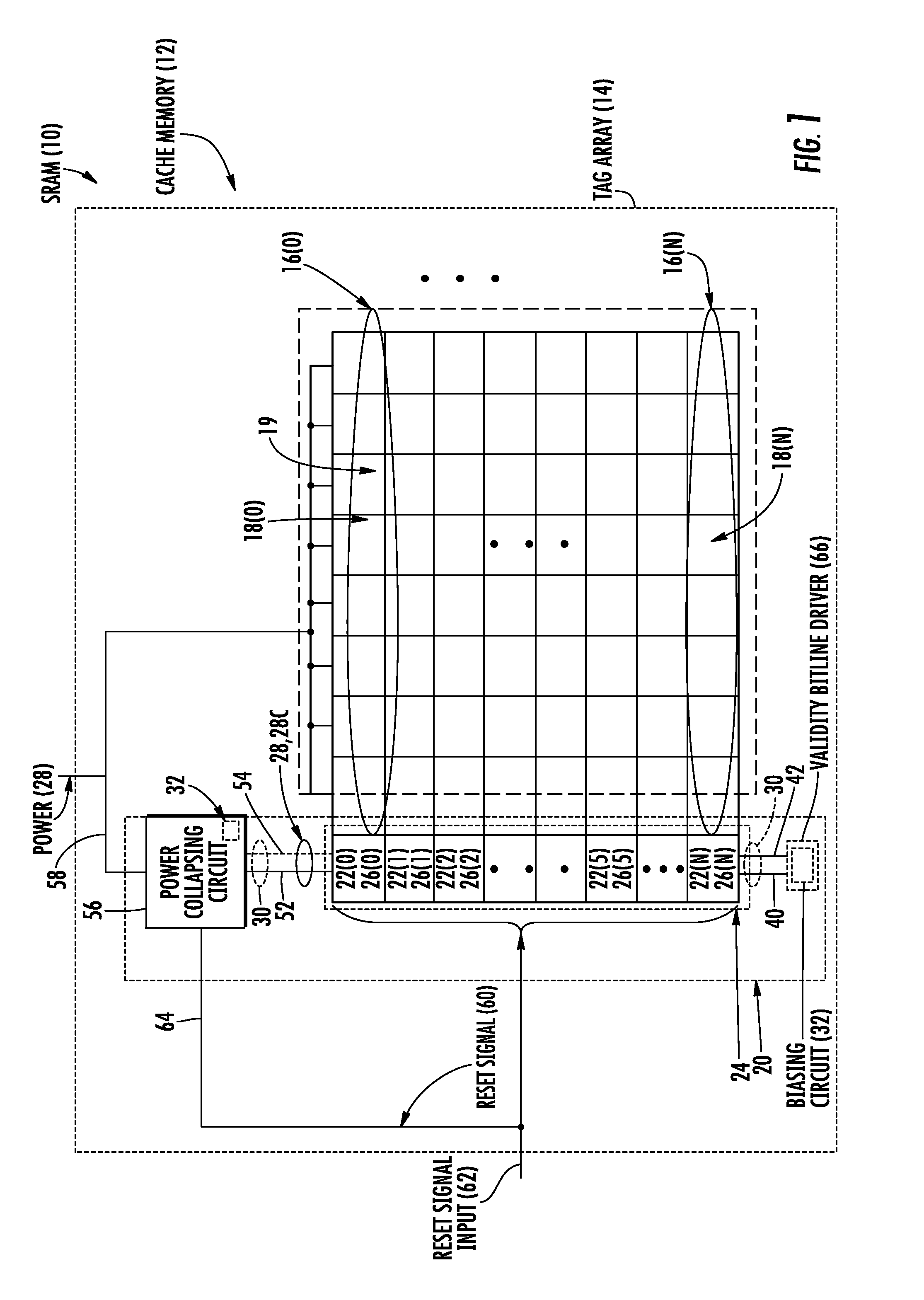

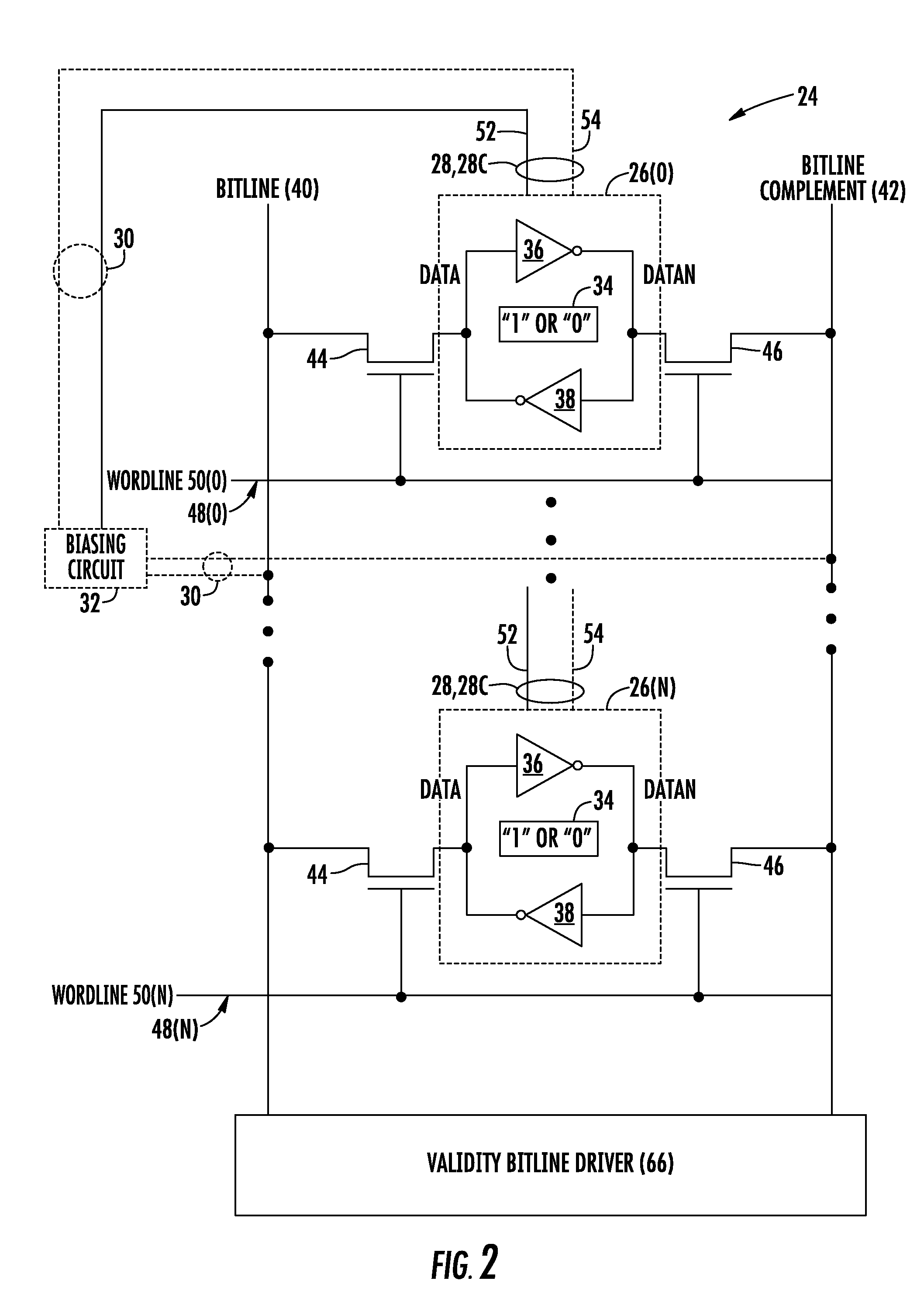

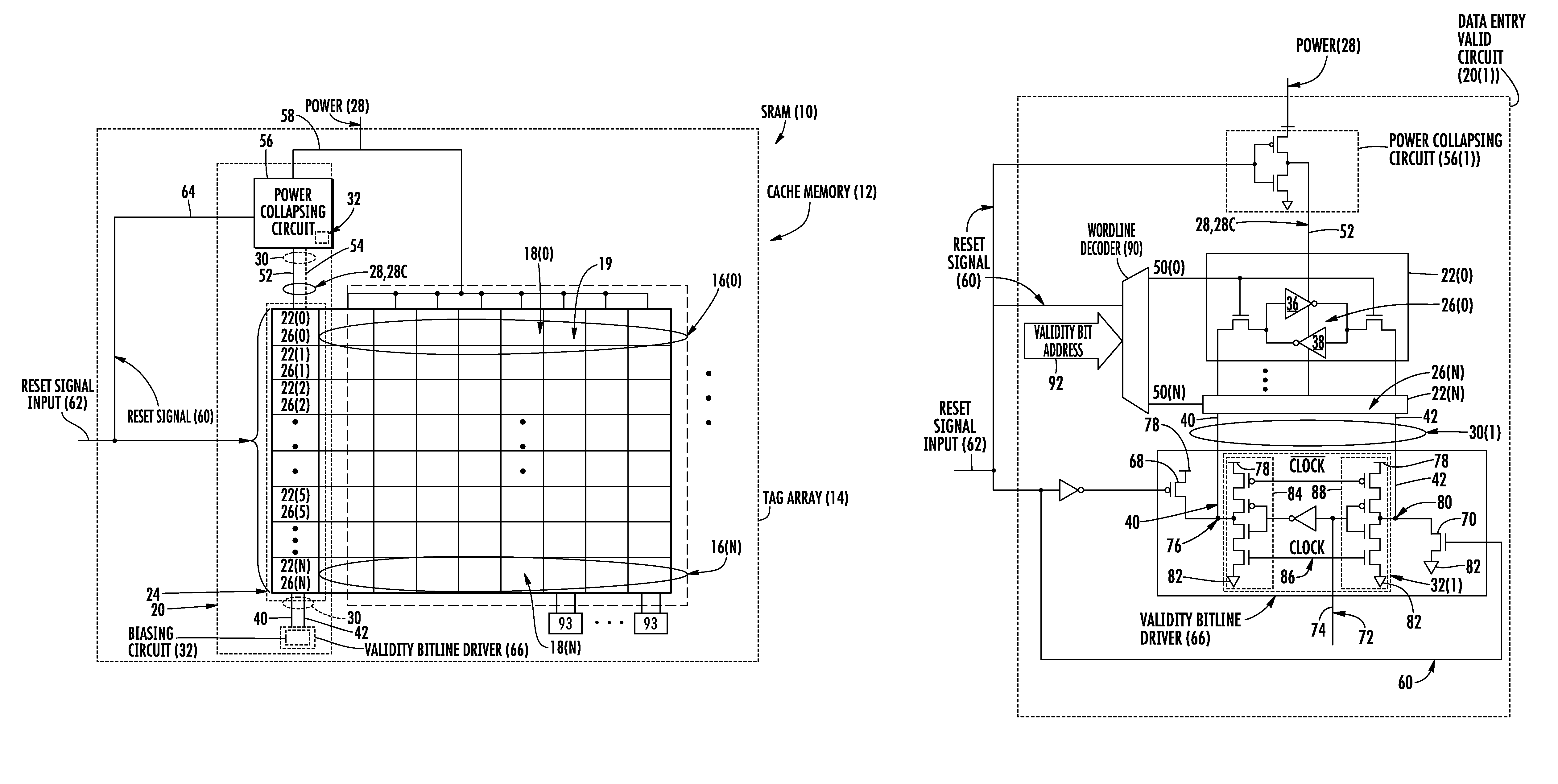

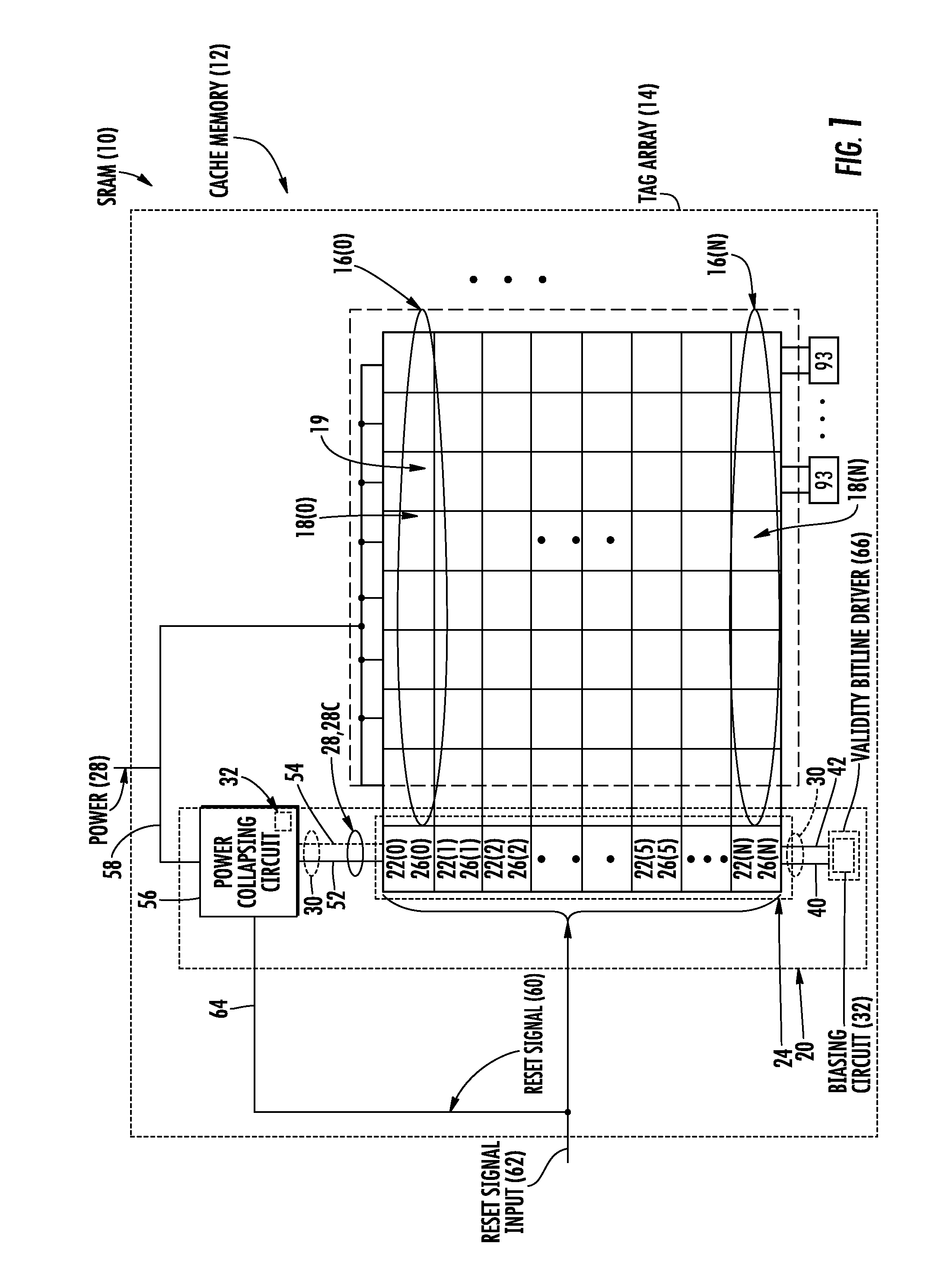

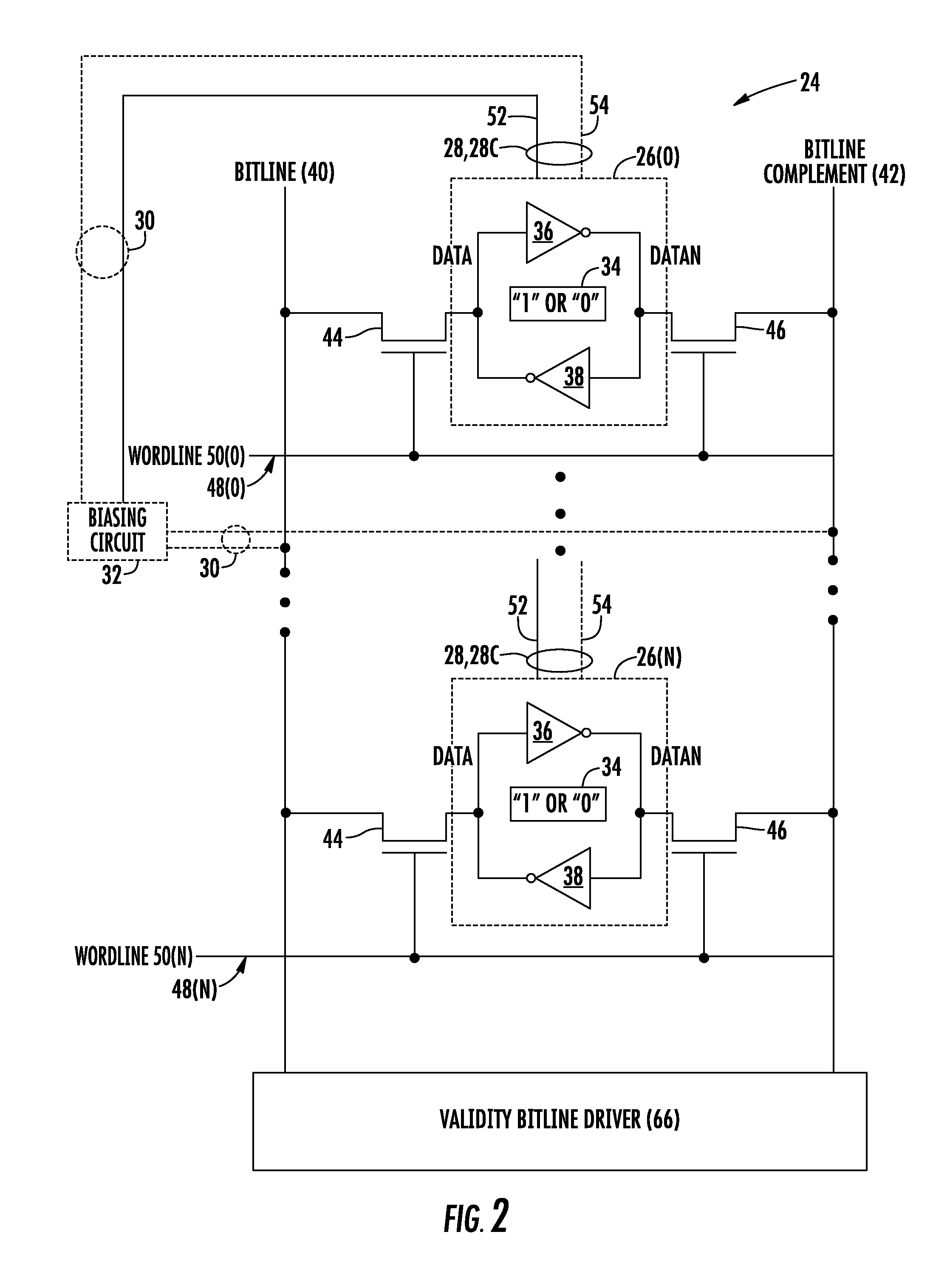

Circuits for voltage or current biasing static random access memory (SRAM) bitcells during SRAM reset operations, and related systems and methods

Circuits for voltage or current biasing static random access memory (SRAM) bitcells during SRAM reset operations are disclosed. Related systems and methods are also disclosed. To reset a plurality of SRAM bitcells in a single reset operation, a biasing circuit is provided and coupled to the plurality of SRAM bitcells. The biasing circuit is configured to apply a voltage or current bias to the SRAM bitcells during a reset operation after power provided to the SRAM bitcells is collapsed to a collapsed power level below an operational power level. The bias is applied as the power to the SRAM bitcells is restored to an operational power level, thus forcing the SRAM bitcells into a desired state. In this manner, the SRAM bitcells can be reset in a single reset operation without need for an increased drive strength from a reset circuit and without need to provide specialized SRAM bitcells.

Owner:QUALCOMM INC

Memory device and method of operation of such a memory device

ActiveUS20150085586A1Sufficient write marginReduce power consumptionRead-only memoriesElectronic switchingMultiplexingControl signal

A memory device having an array of memory cells connected to a core voltage level, and access circuitry used to perform a write operation in order to write data into a plurality of addressed memory cells. At least one bit line associated with at least each column in the array containing an addressed memory cell is precharged to the peripheral voltage level prior to the write operation being performed. Word line driver circuitry is then configured to assert a word line signal at the core voltage level on the word line associated with the row of the array containing the addressed memory cells. Write multiplexing driver circuitry asserts a mux control signal to write multiplexing circuitry which then couples the bit line of each addressed memory cell to the write driver circuitry in dependence on the mux control signal identifying which column contains the addressed memory cells.

Owner:ARM LTD

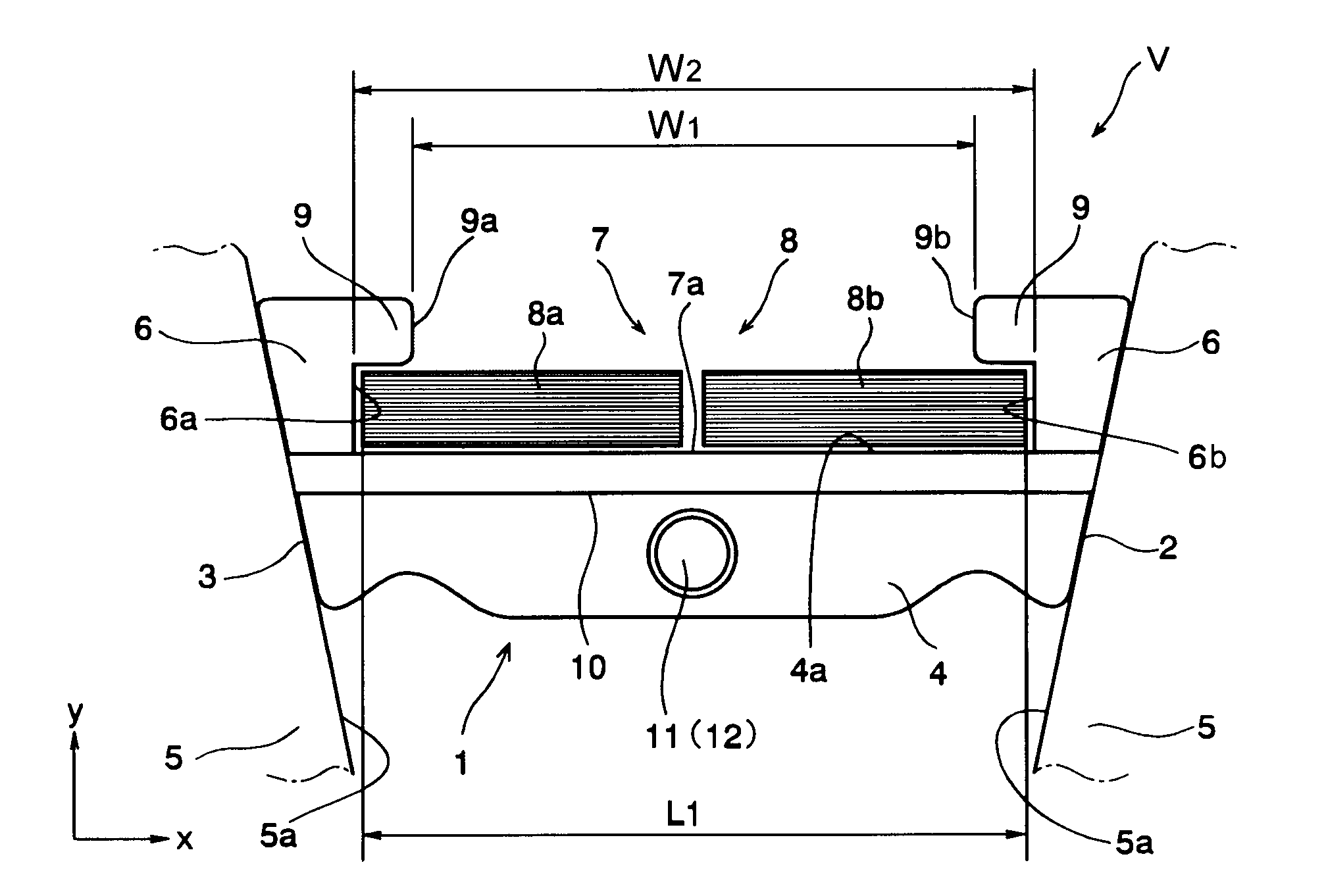

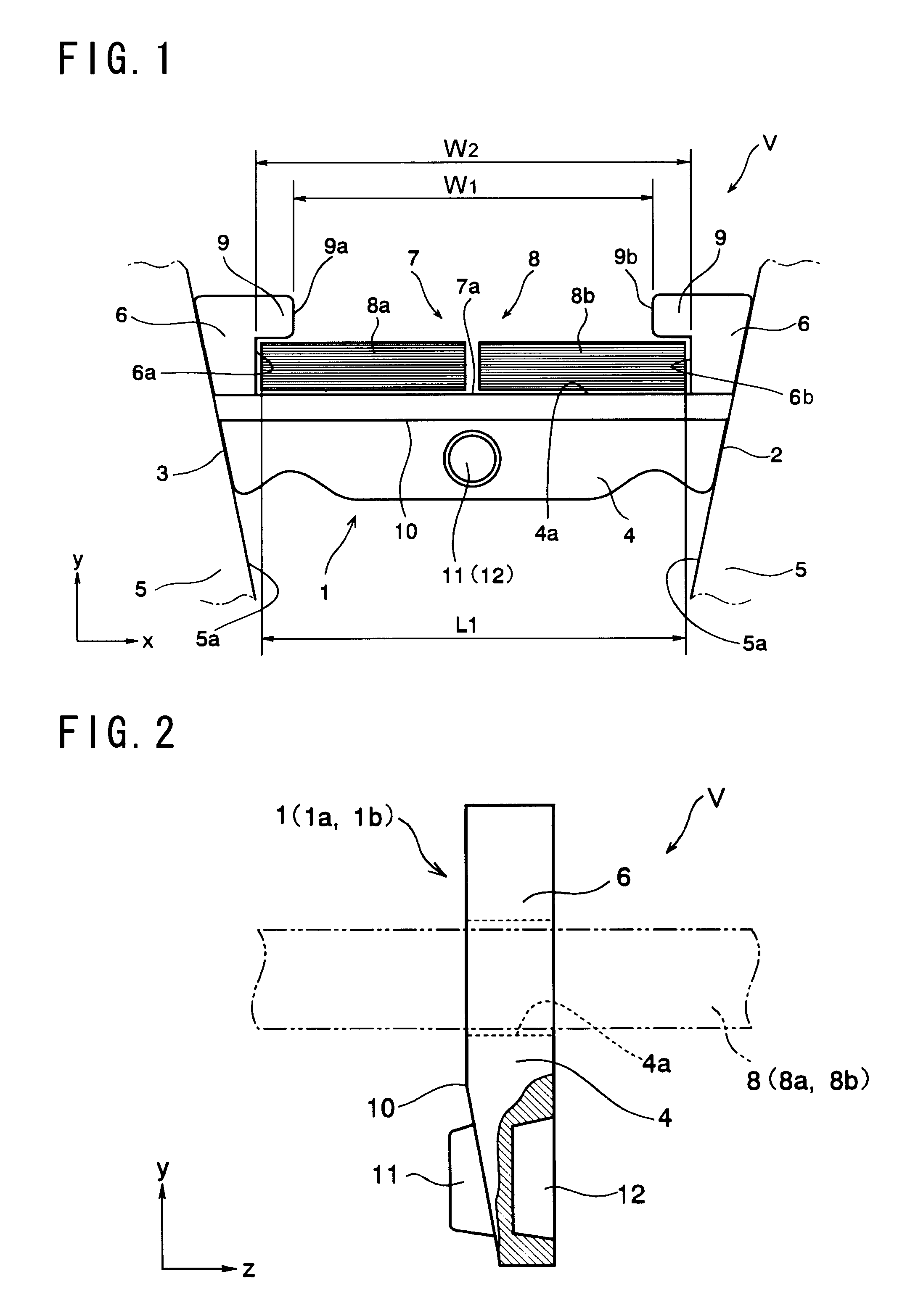

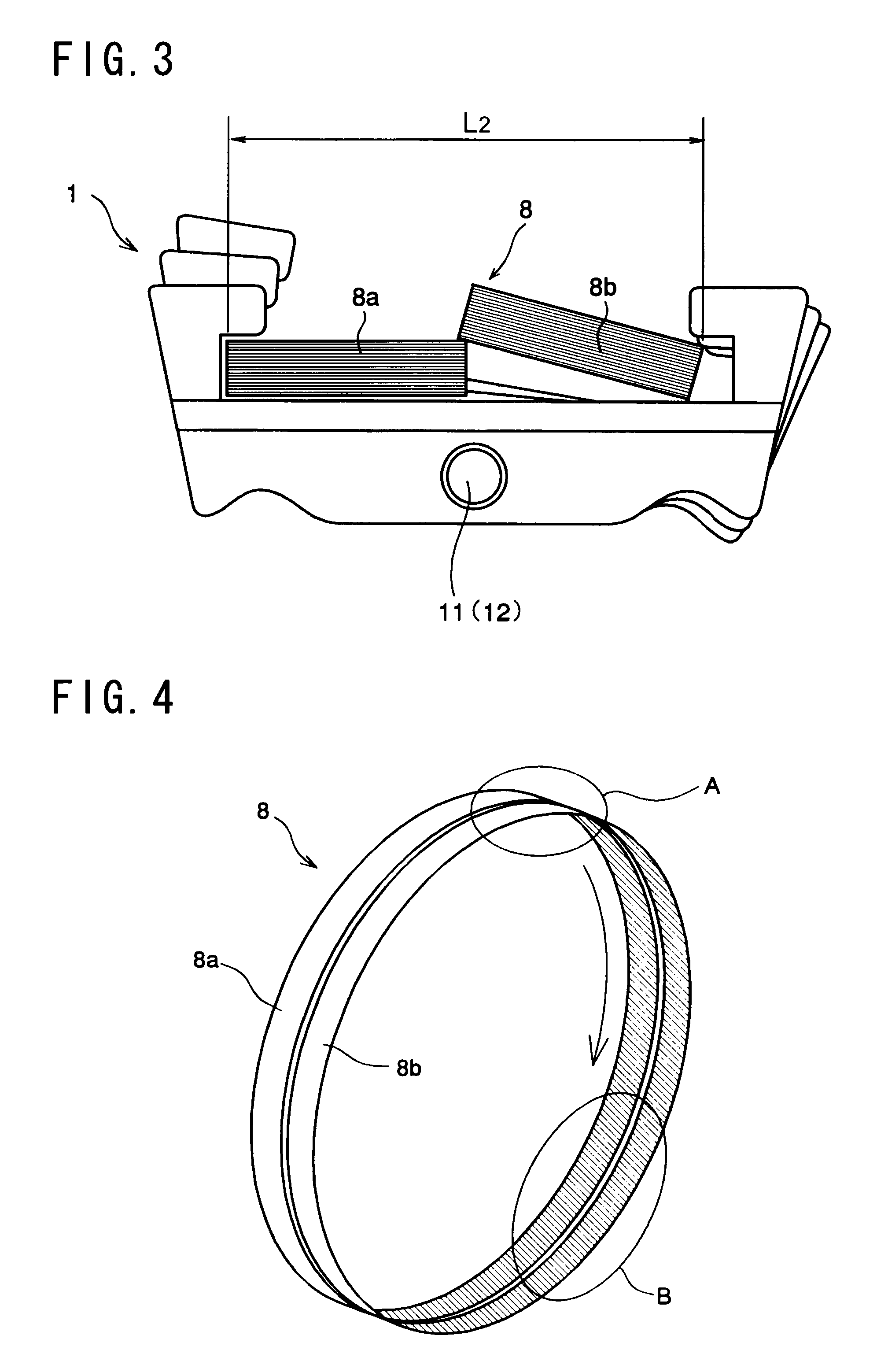

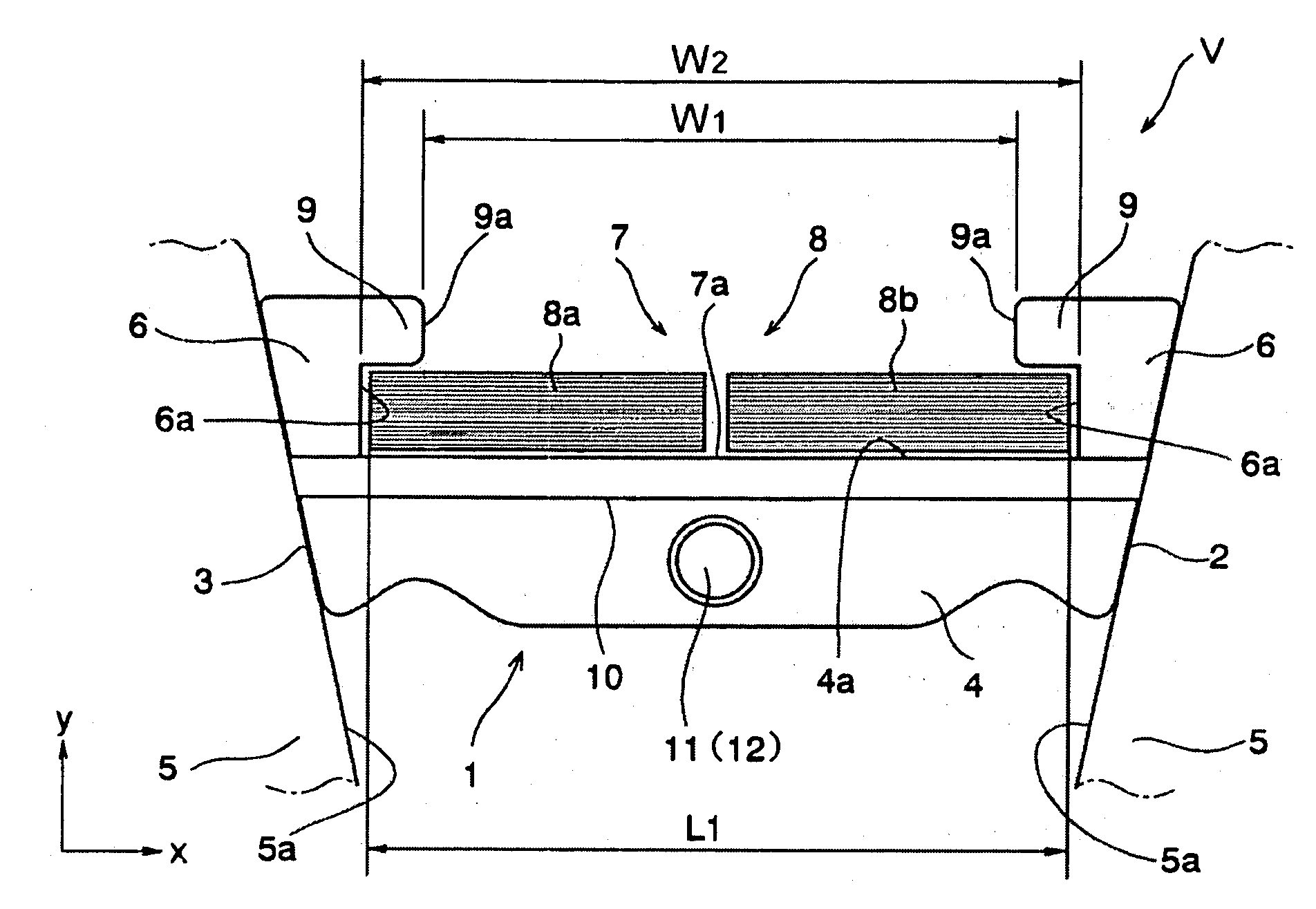

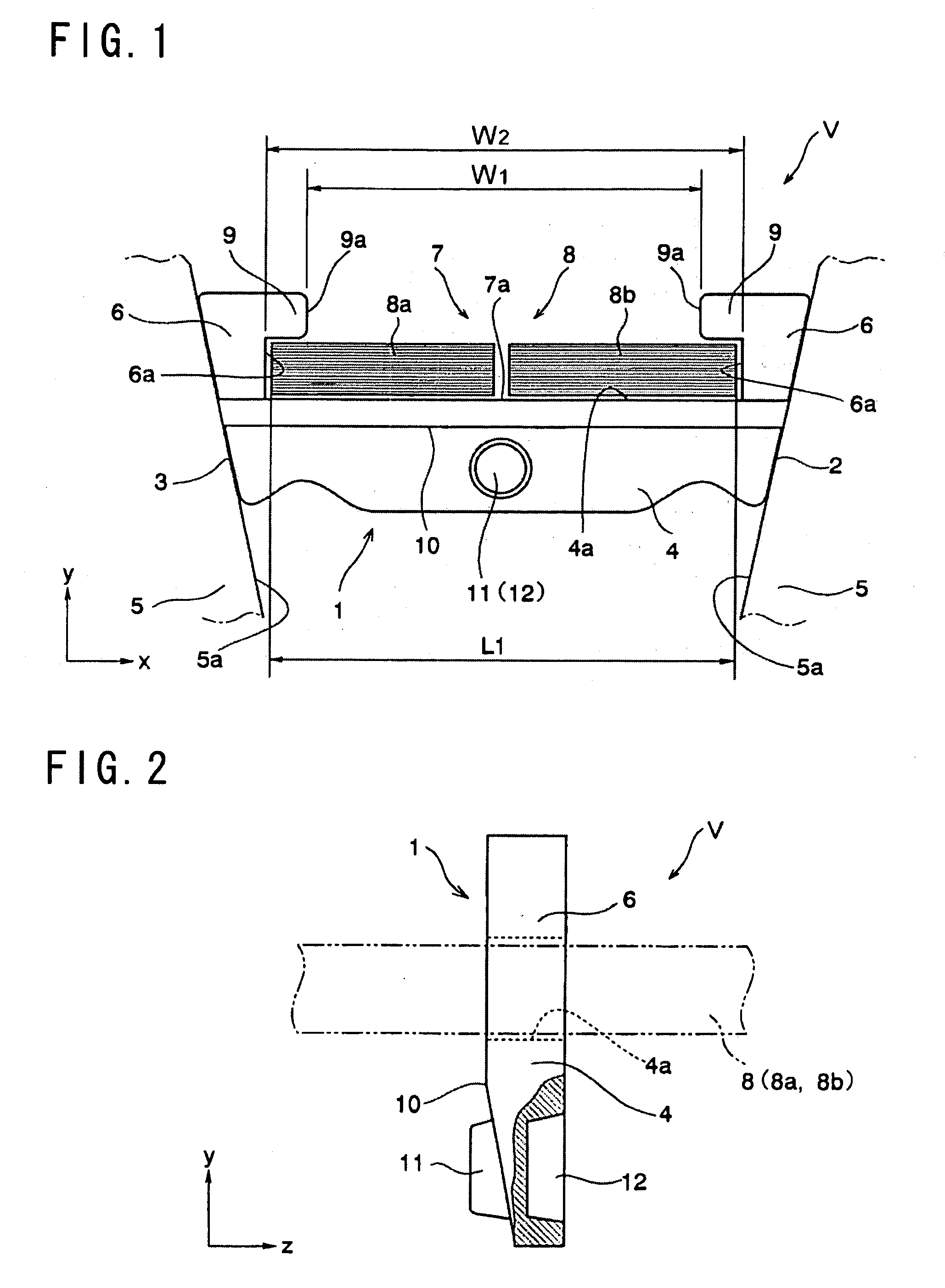

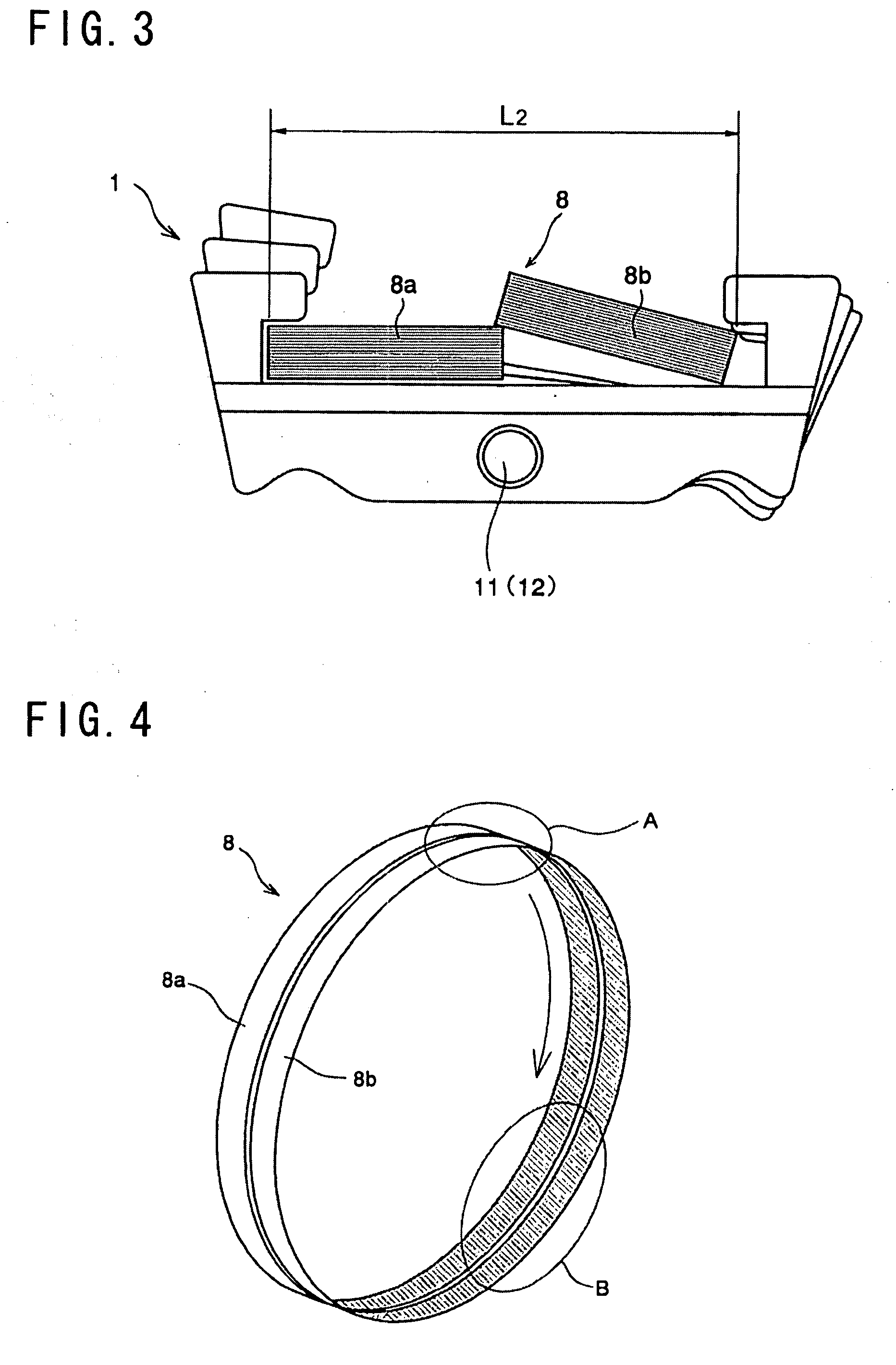

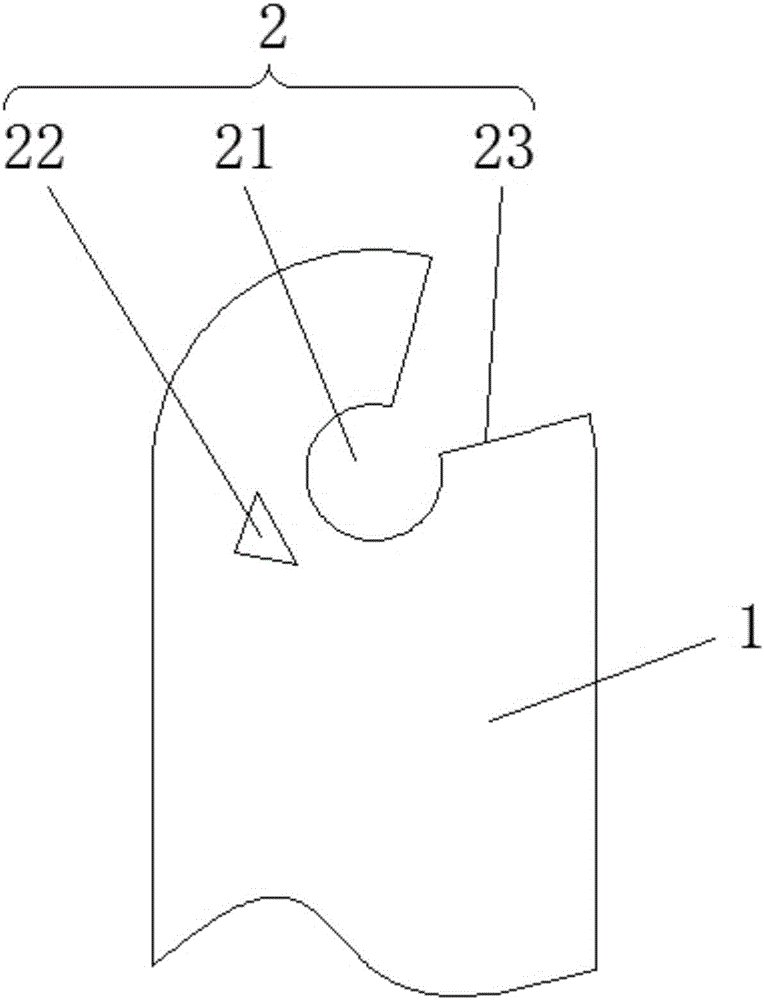

Driving belt and method for assembling same

InactiveUS20100016112A1Increasing the thicknessIncrease drive strengthV-belt fasteningsV-beltsMechanical engineering

Owner:TOYOTA JIDOSHA KK

Driving belt and method for assembling same

InactiveUS20090258743A1Prevent disengagementIncreasing the thicknessV-beltsDriving beltsEngineeringMechanical engineering

Owner:TOYOTA JIDOSHA KK

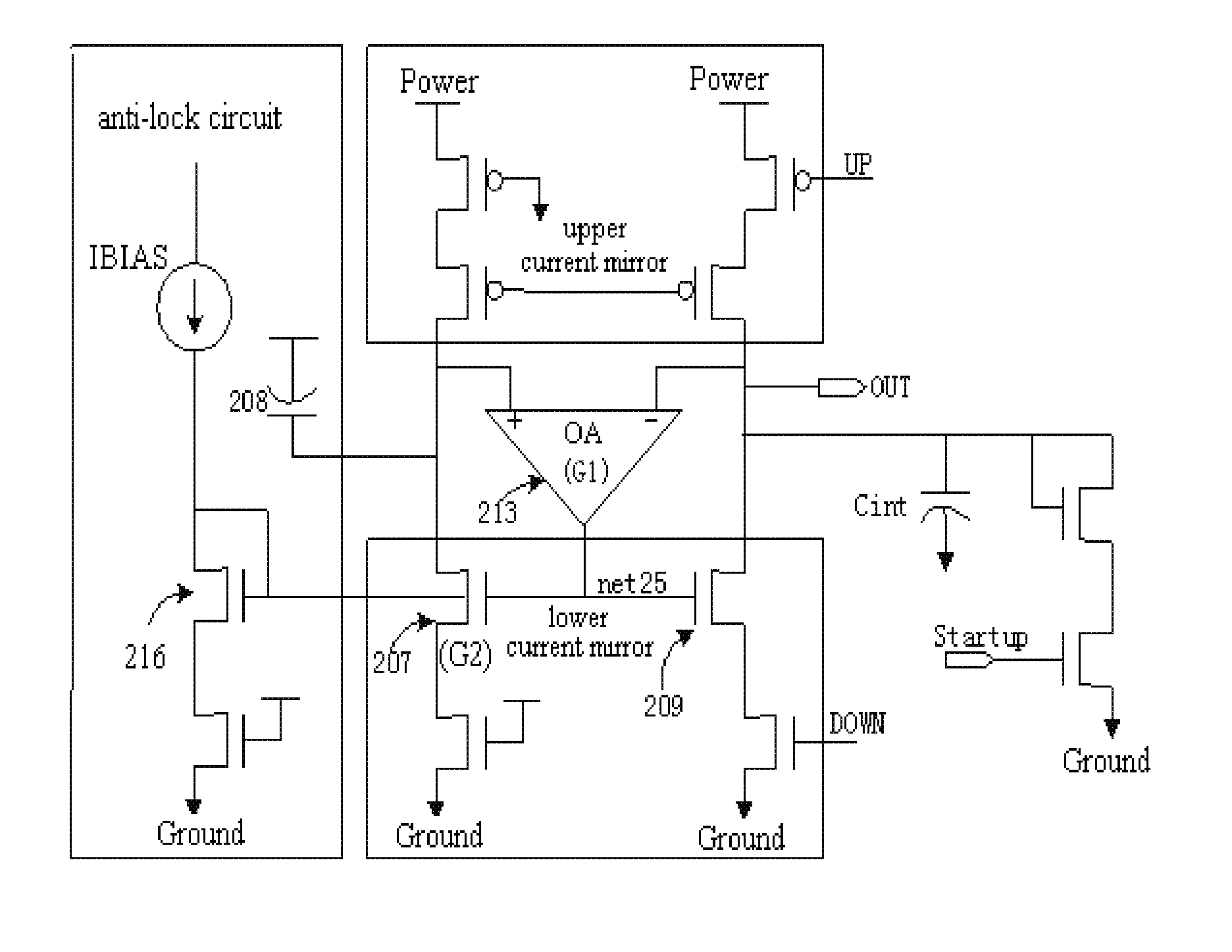

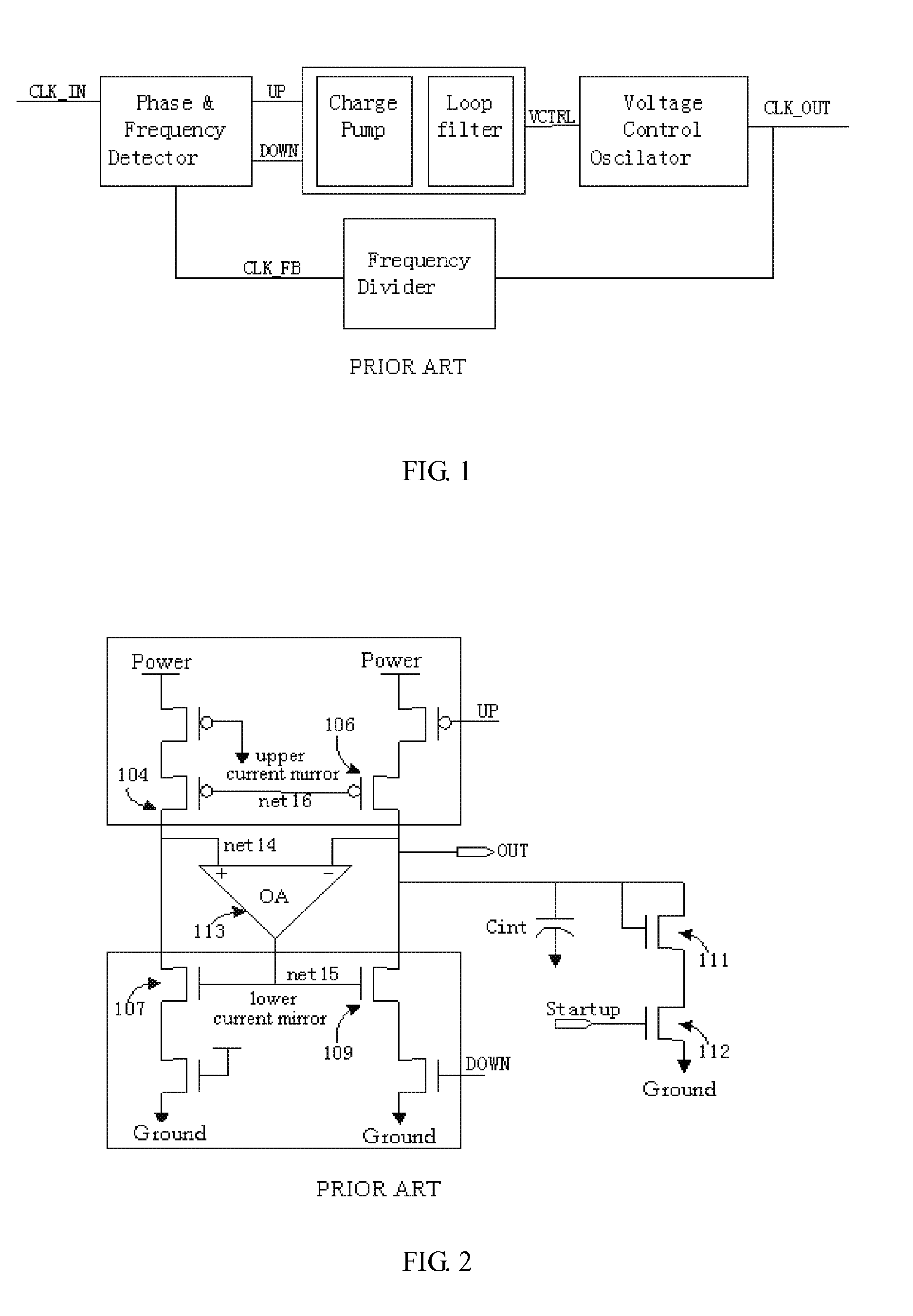

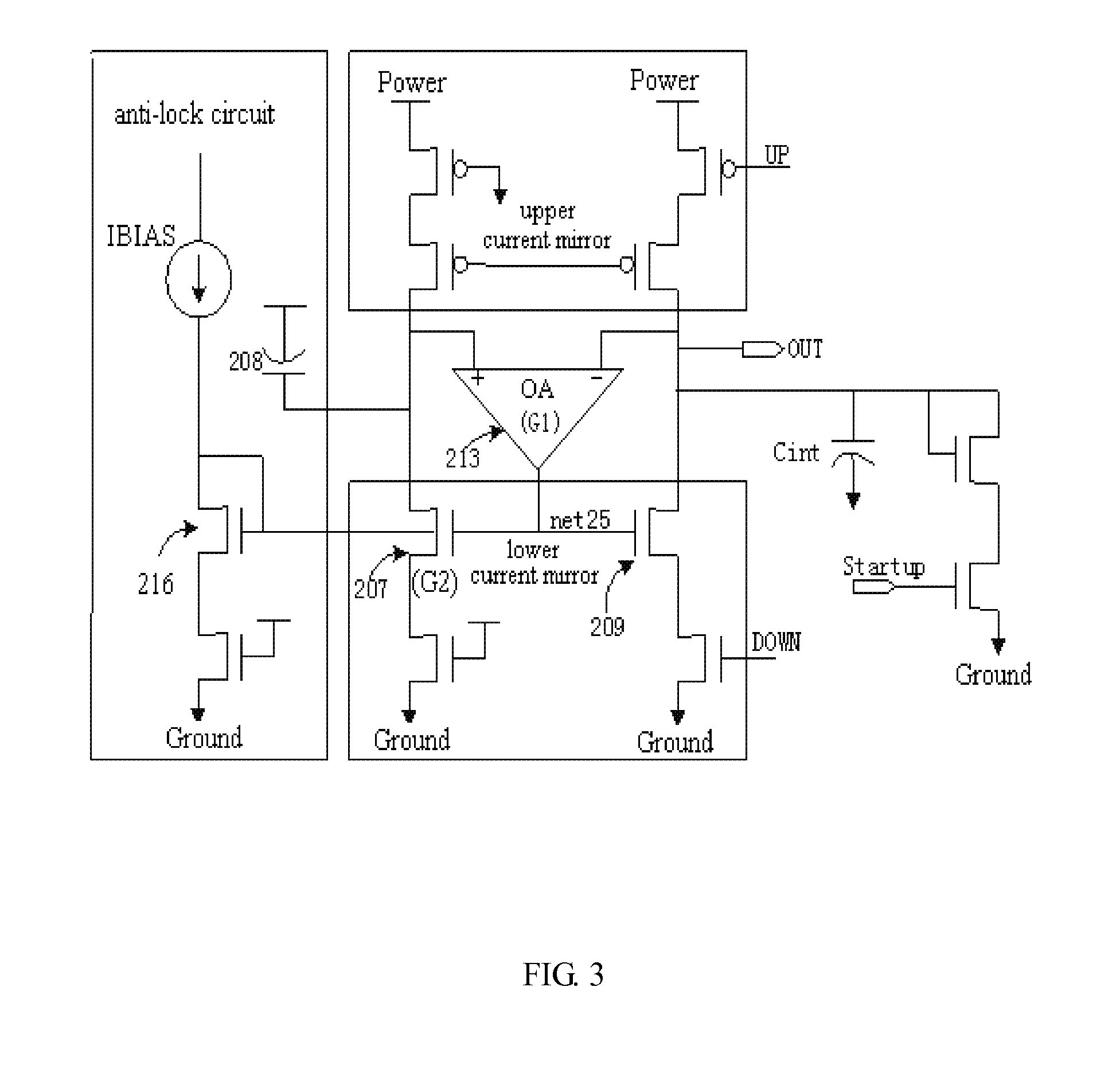

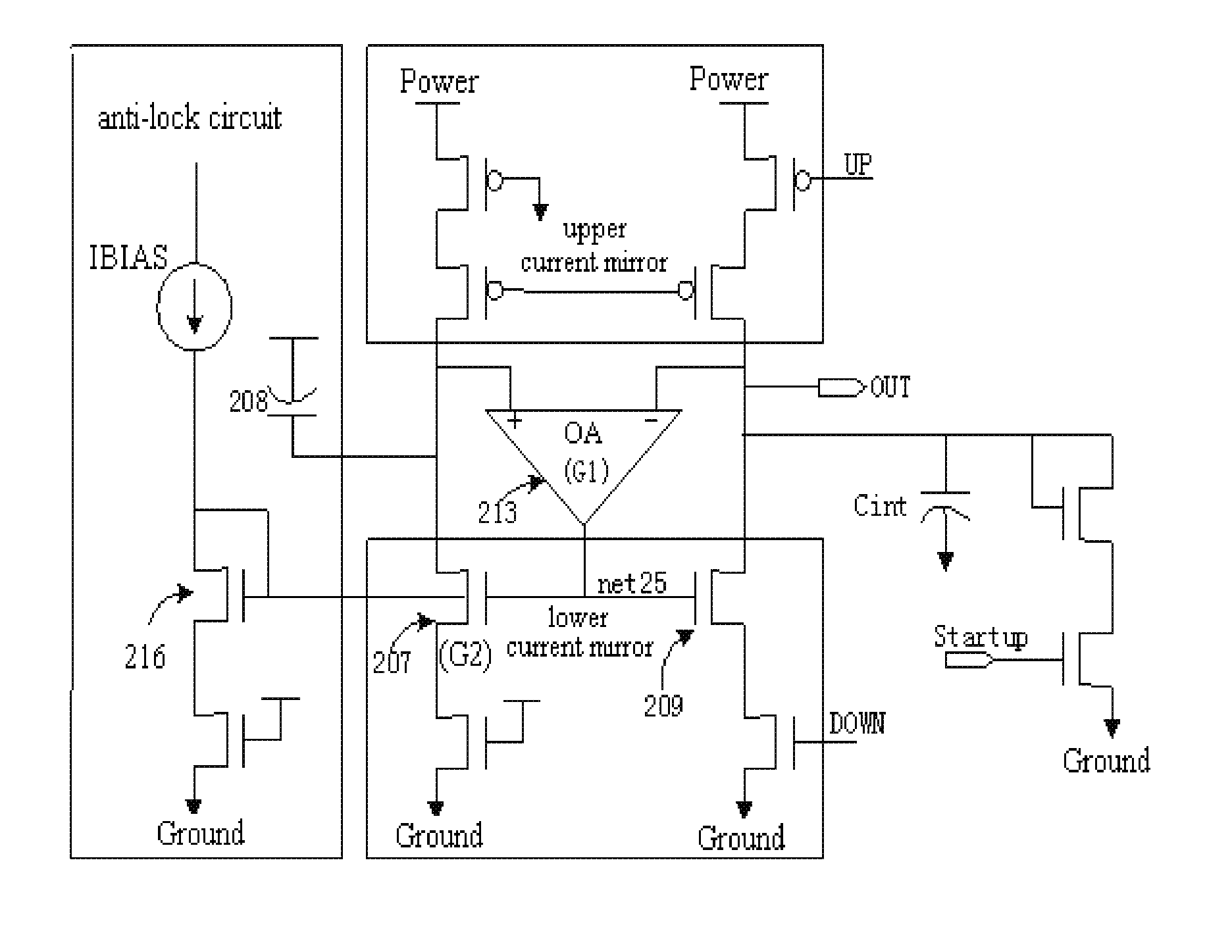

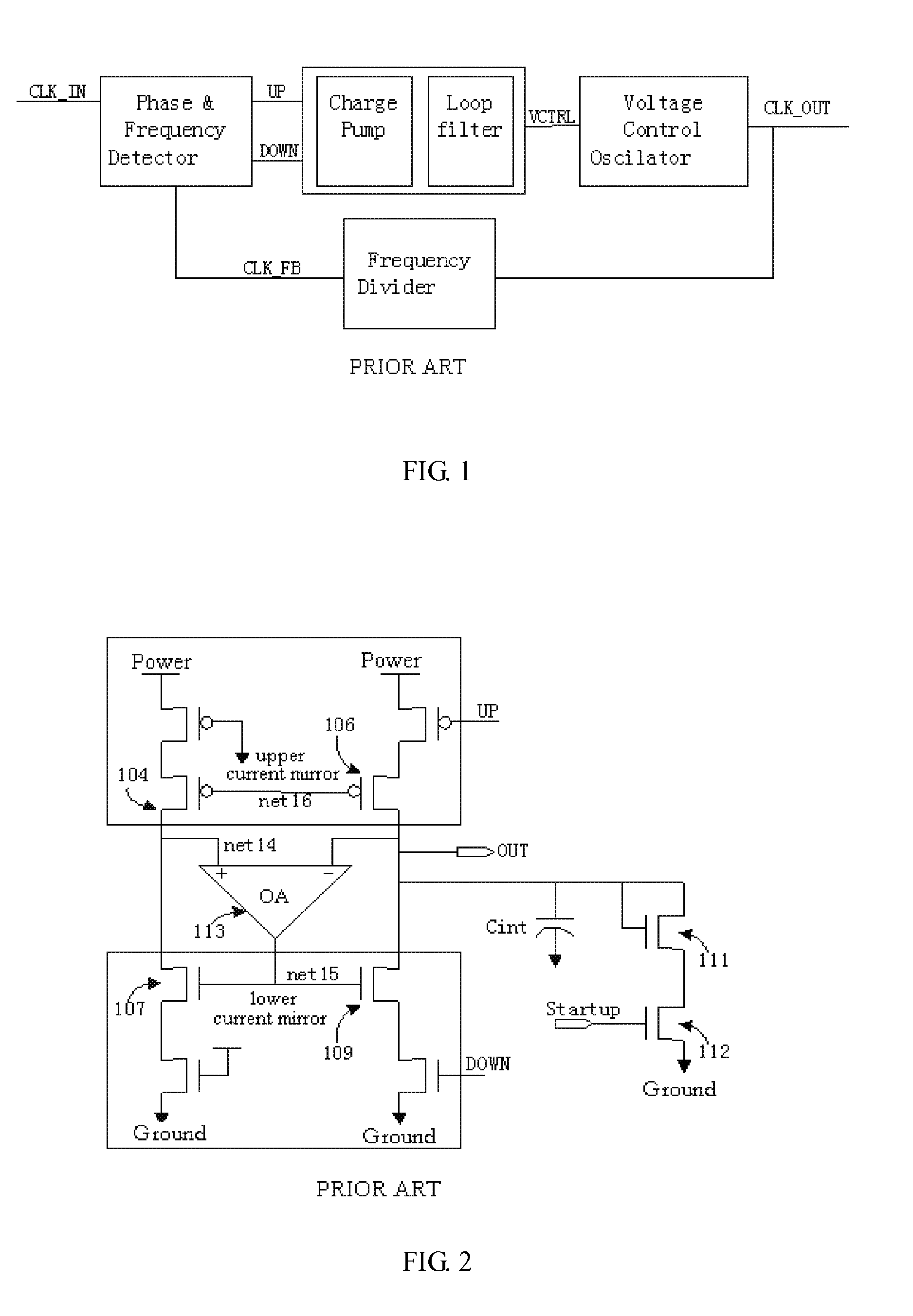

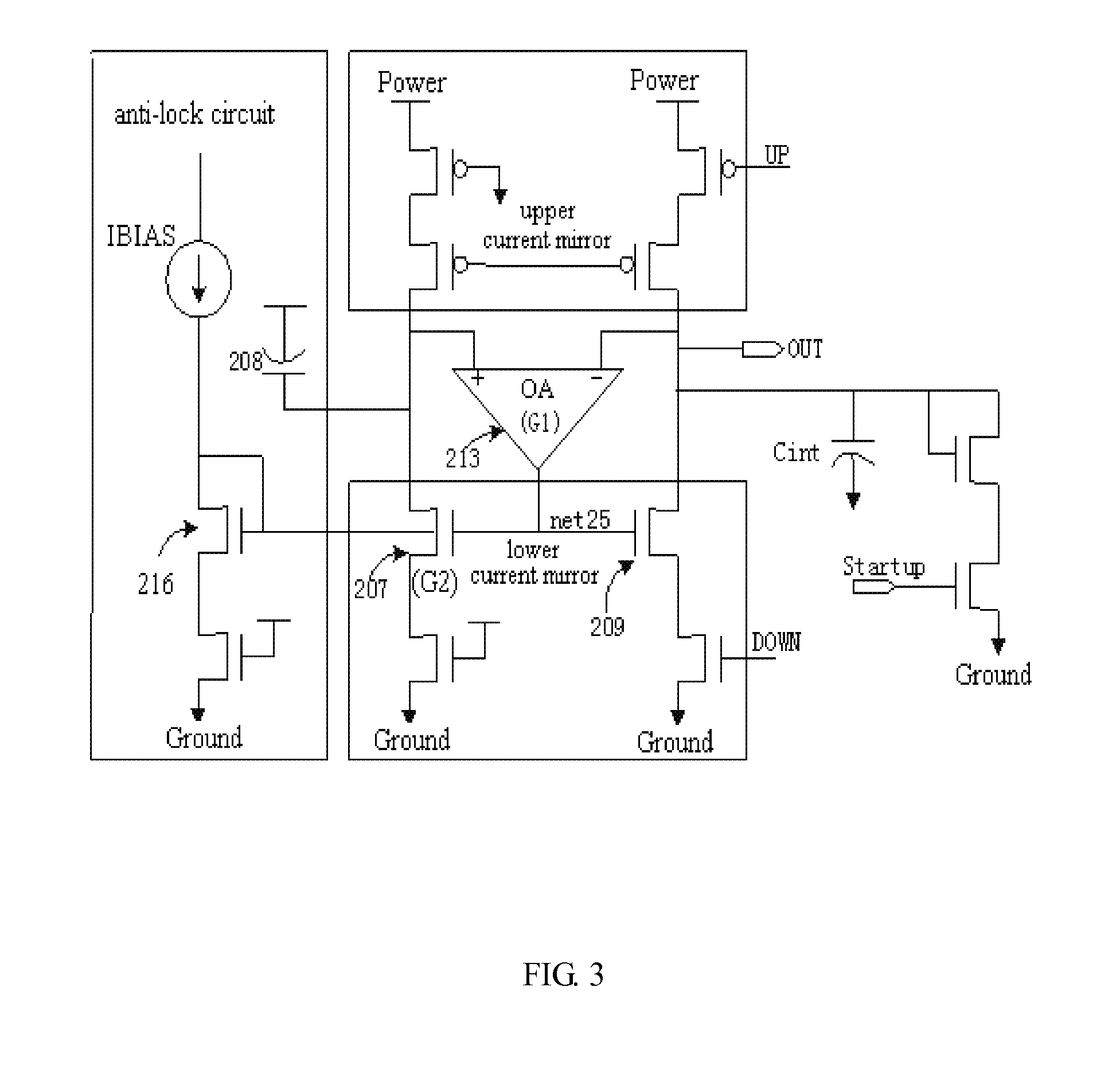

Reliable Charge Pump Circuit

InactiveUS20100315154A1Avoid deadlockAvoid oscillationPulse automatic controlElectric variable regulationAudio power amplifierStable status

A reliable charge pump circuit includes an operational amplifier; an upper current mirror; a lower current mirror; a startup circuit; and an anti-lock circuit, wherein the anti-lock circuit includes a current source and a diode-connected NMOS transistor, which increases the driving strength of the operational amplifier to two NMOS transistors connected to an output node of the operational amplifier, so as to prevent deadlock caused by multiple stable status and improve production yield.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

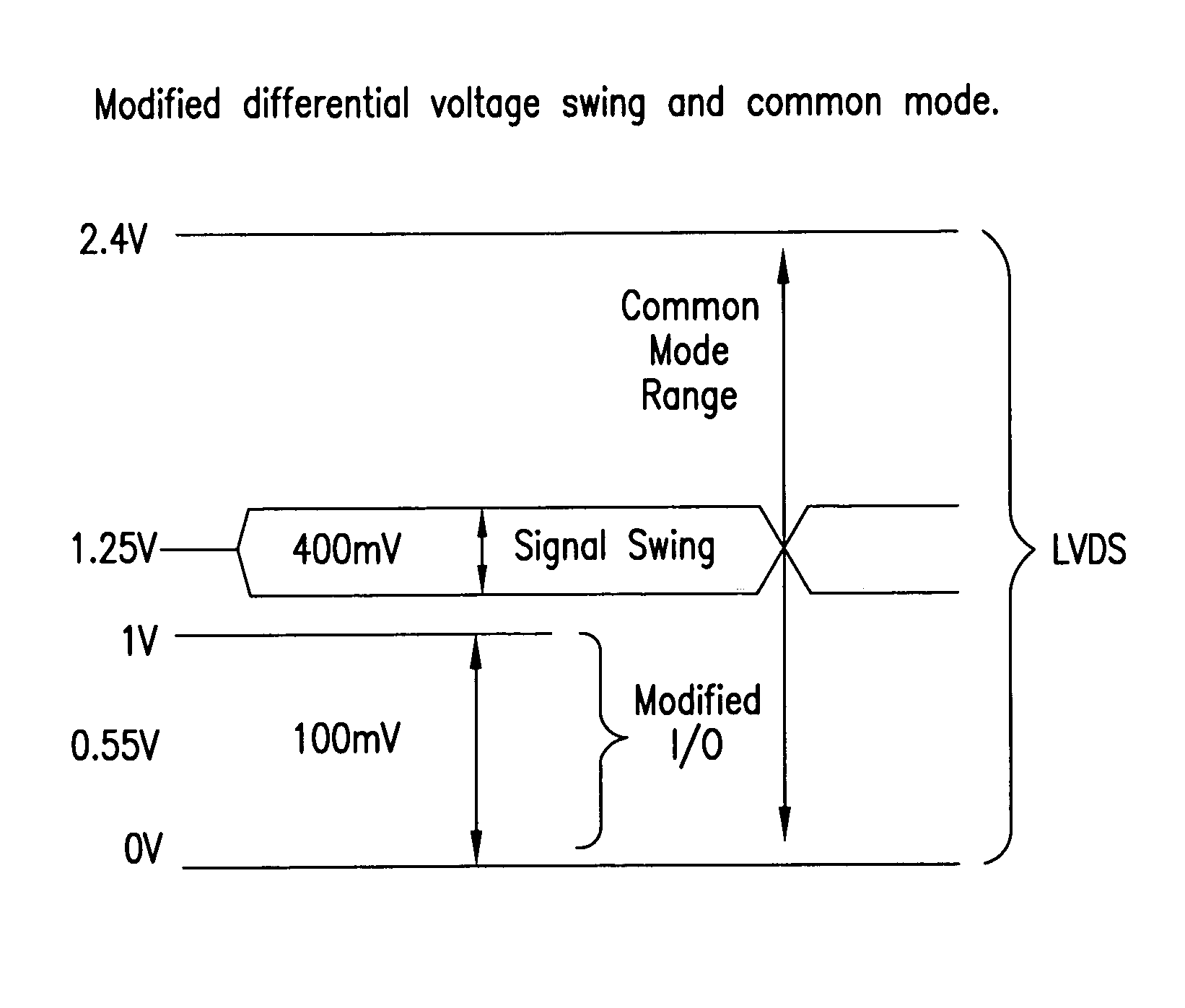

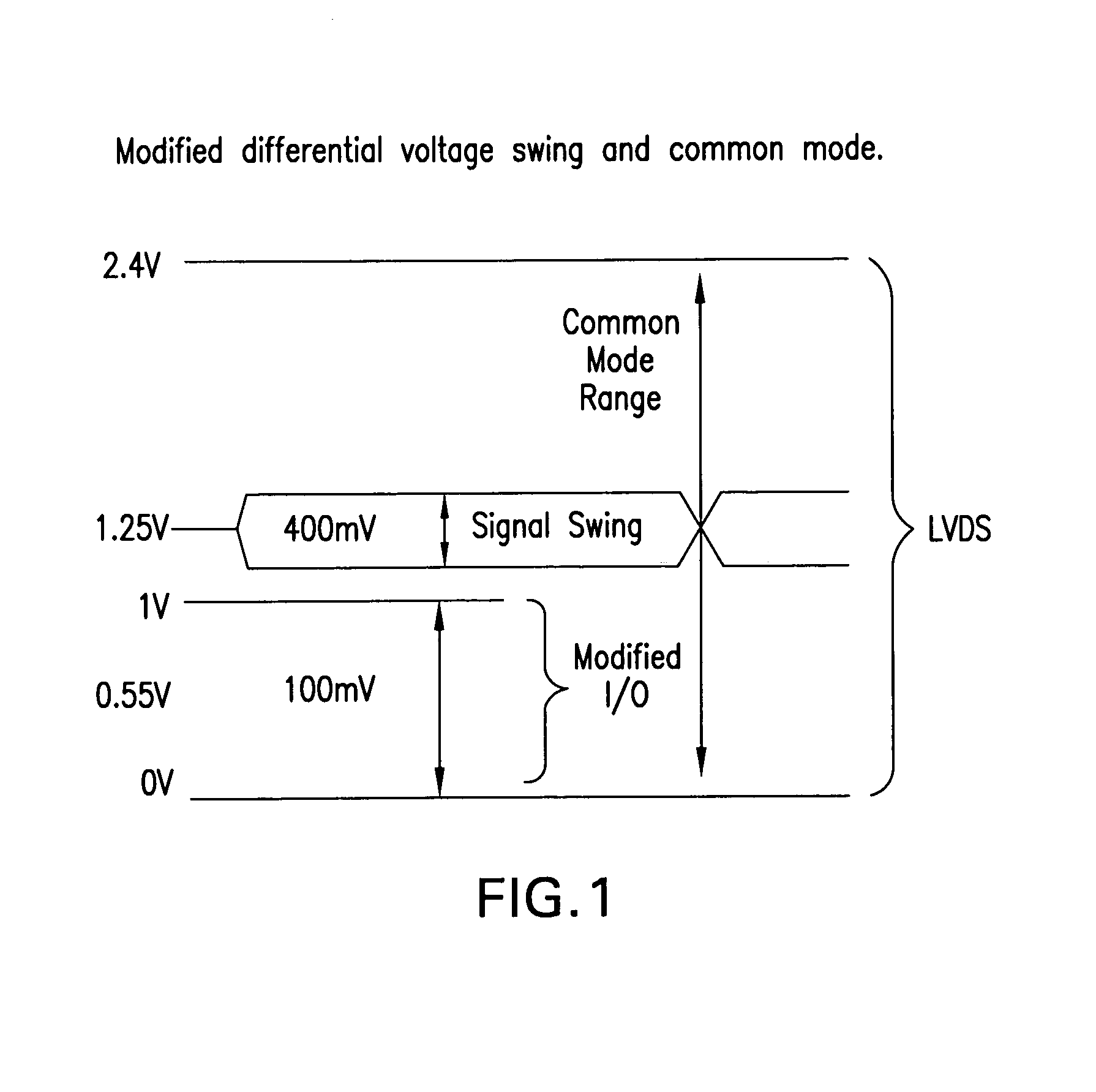

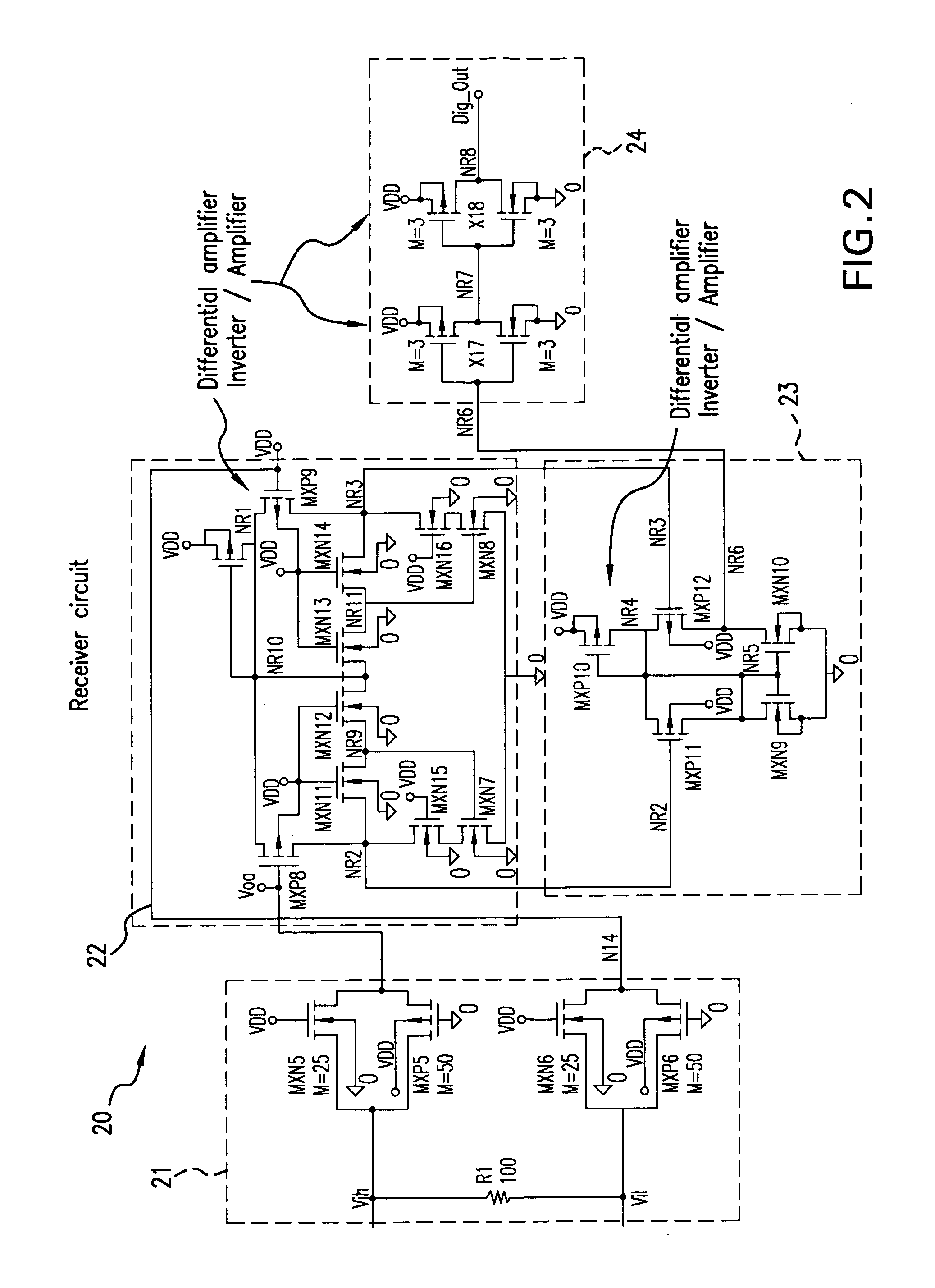

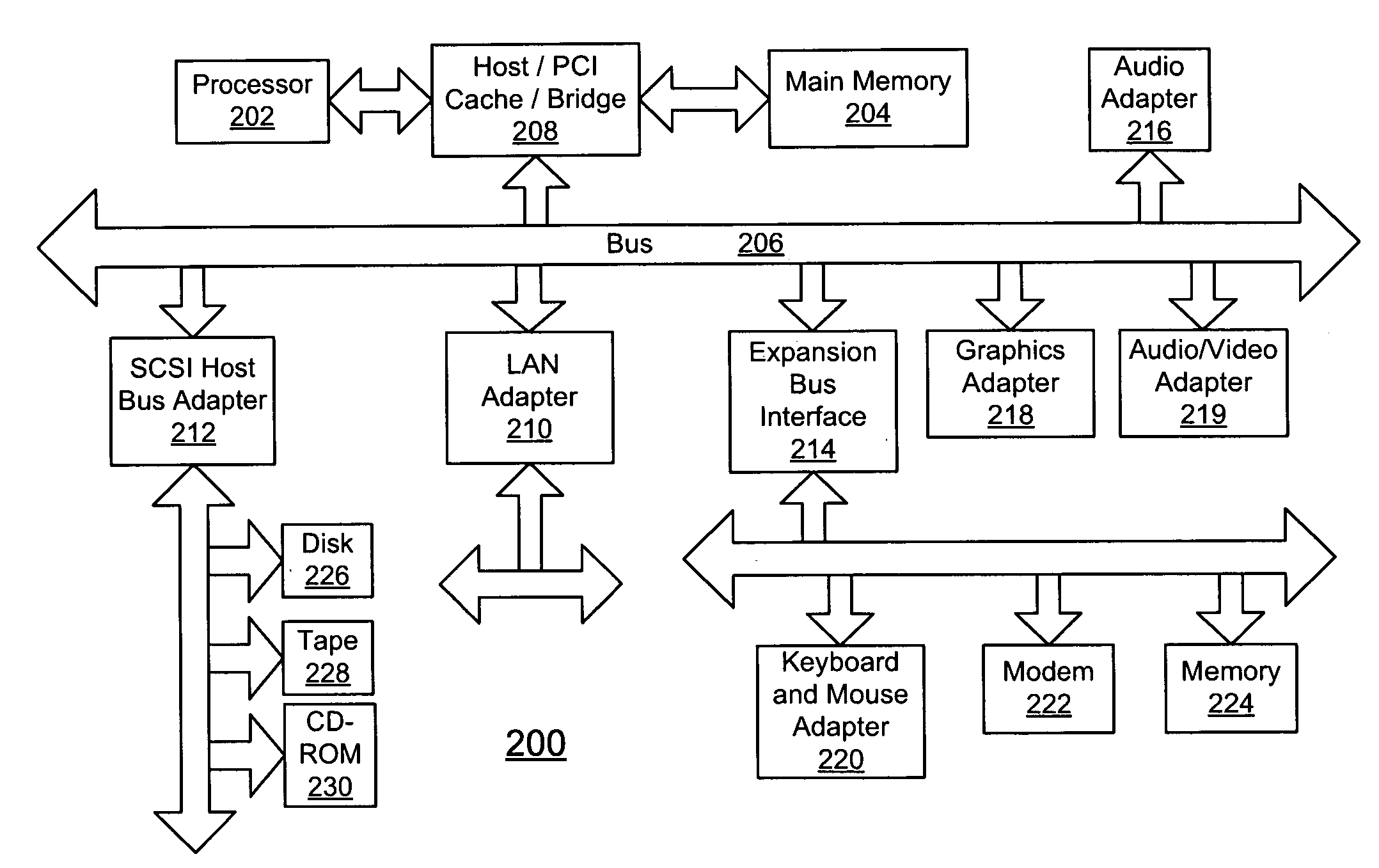

High speed chip-to-chip communication links

ActiveUS7176724B1Increase data rateReduce power consumptionReliability increasing modificationsElectronic switchingDouble data rateDifferential signaling

A very low voltage swing is used to achieve very high data rates (up to 4 Gbps double data rate) at very low power consumption. A differential signaling approach is used for noise rejection, and a constant current approach also is used to minimize switching noise.

Owner:NORTHROP GRUMMAN SYST CORP

Reliable charge pump circuit

InactiveUS8179175B2Avoid oscillationIncrease drive strengthPulse automatic controlElectric variable regulationAudio power amplifierStable status

A reliable charge pump circuit includes an operational amplifier; an upper current mirror; a lower current mirror; a startup circuit; and an anti-lock circuit, wherein the anti-lock circuit includes a current source and a diode-connected NMOS transistor, which increases the driving strength of the operational amplifier to two NMOS transistors connected to an output node of the operational amplifier, so as to prevent deadlock caused by multiple stable status and improve production yield.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

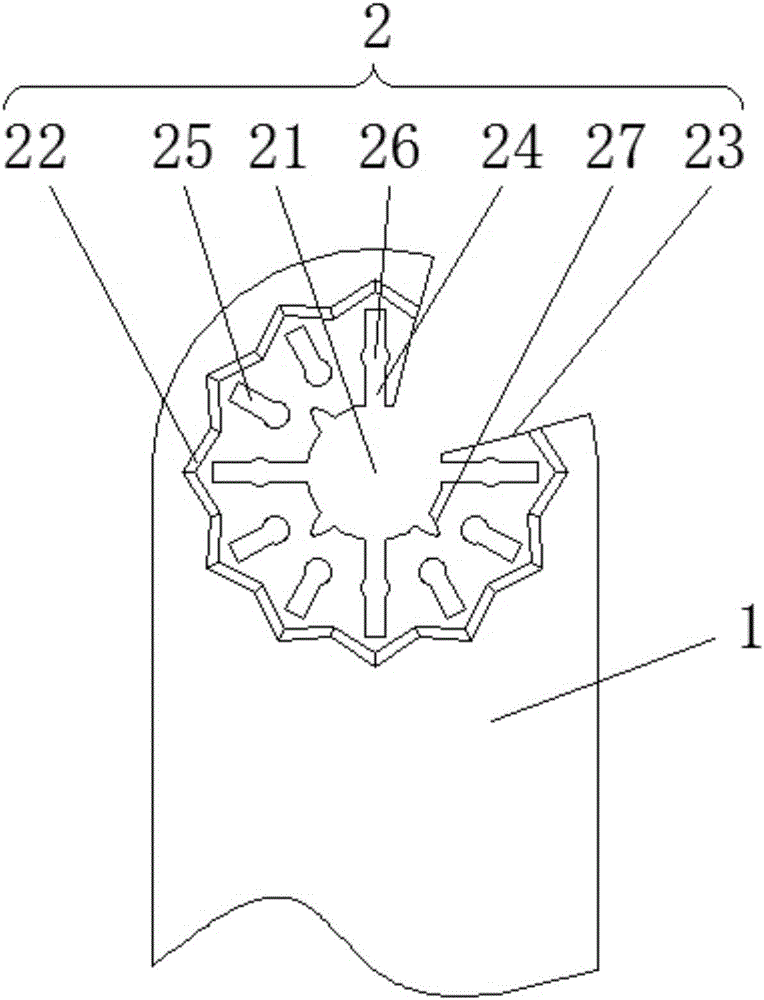

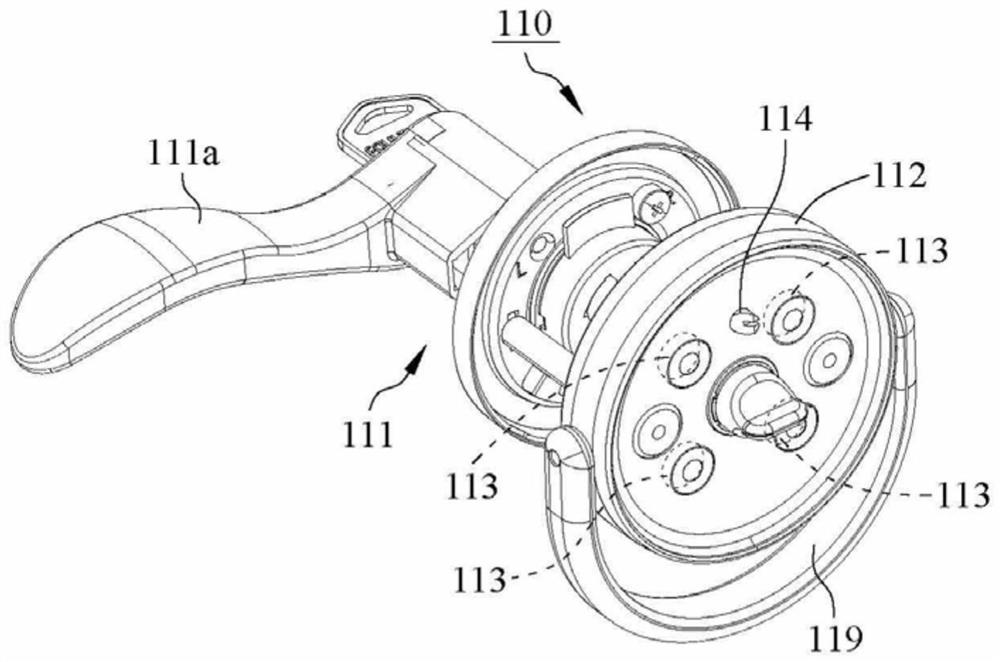

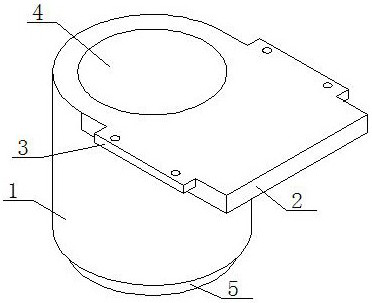

Quick connection function head for electric tool

InactiveCN106272268AQuick installationAvoid displacementPortable power-driven toolsExterior spacePower tool

The invention relates to a quick connection function head for an electric tool. The function head is provided with a body, a connecting portion connected with the electric tool is arranged on the body and comprises an inserting hole and at least one drive convex block, an opening communicated with the exterior space is formed in the edge of one side of the inserting hole, and the inserting hole is in matched connection with an output shaft of the electric tool. The drive convex block is matched with a drive mounting groove in the output shaft of the electric tool. The quick connection function head is ingenious in structural design, rapid mounting of the function head can be achieved, the drive effect of the connecting portion is good, generality is high, and the displacement problem of the function head can be effectively solved.

Owner:江苏美之轮工具有限公司

System and method for amplitude optimization in high-speed serial transmissions

InactiveUS20070121496A1Increase drive strengthPower managementError preventionData signalComputer science

A method, system, and computer usable program code for increasing drive strength using various steps. First, a data signal is received at a receiving device. The receiving device determines whether the data is successfully received once the data signal is received at the receiving device. If the receiving device determines that the data signal is unsuccessfully received, the receiving device requests an increase in a signal amplitude of the data signal transmitted by a transmitting device that sent the data signal for increasing the drive strength.

Owner:LSI CORPORATION

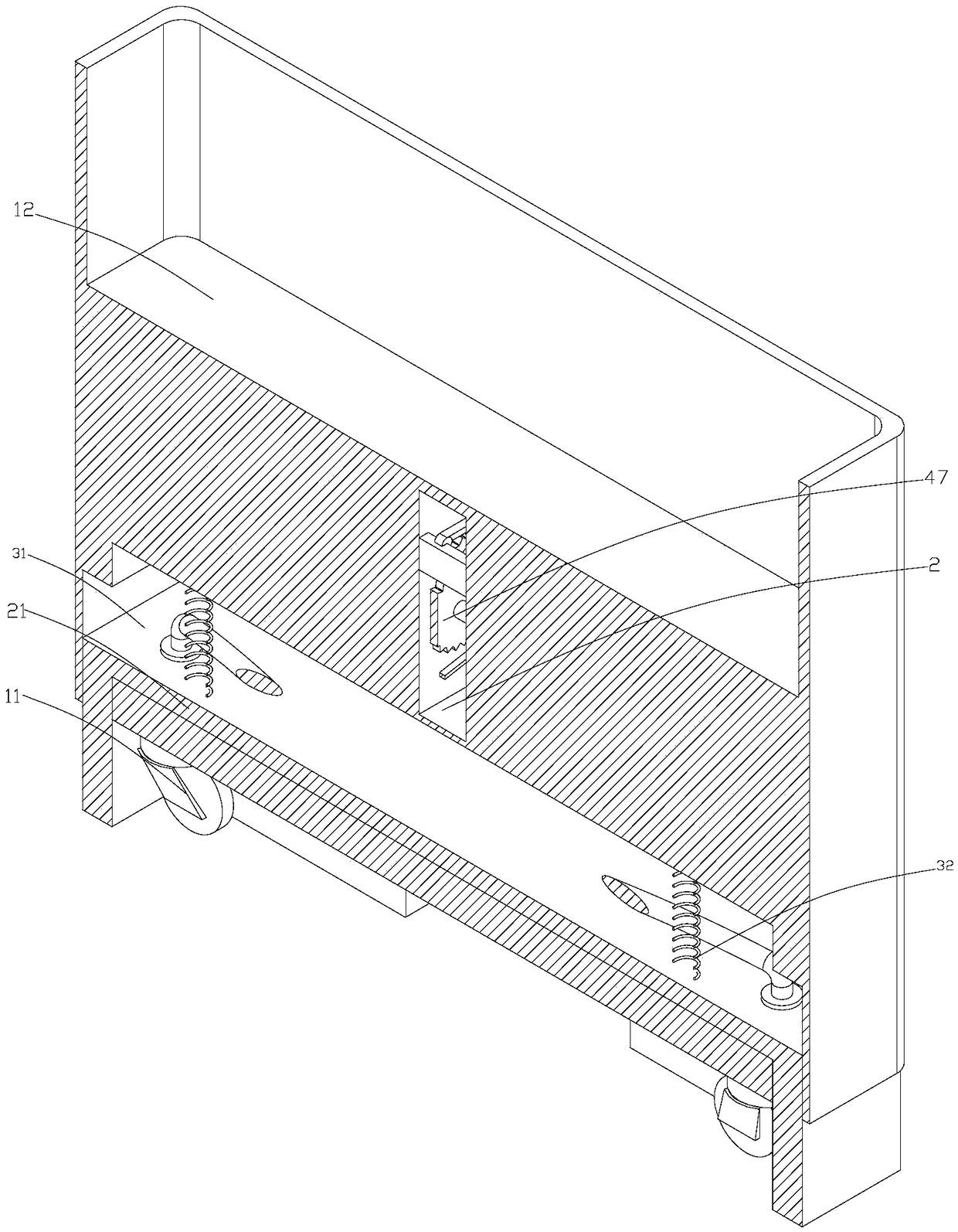

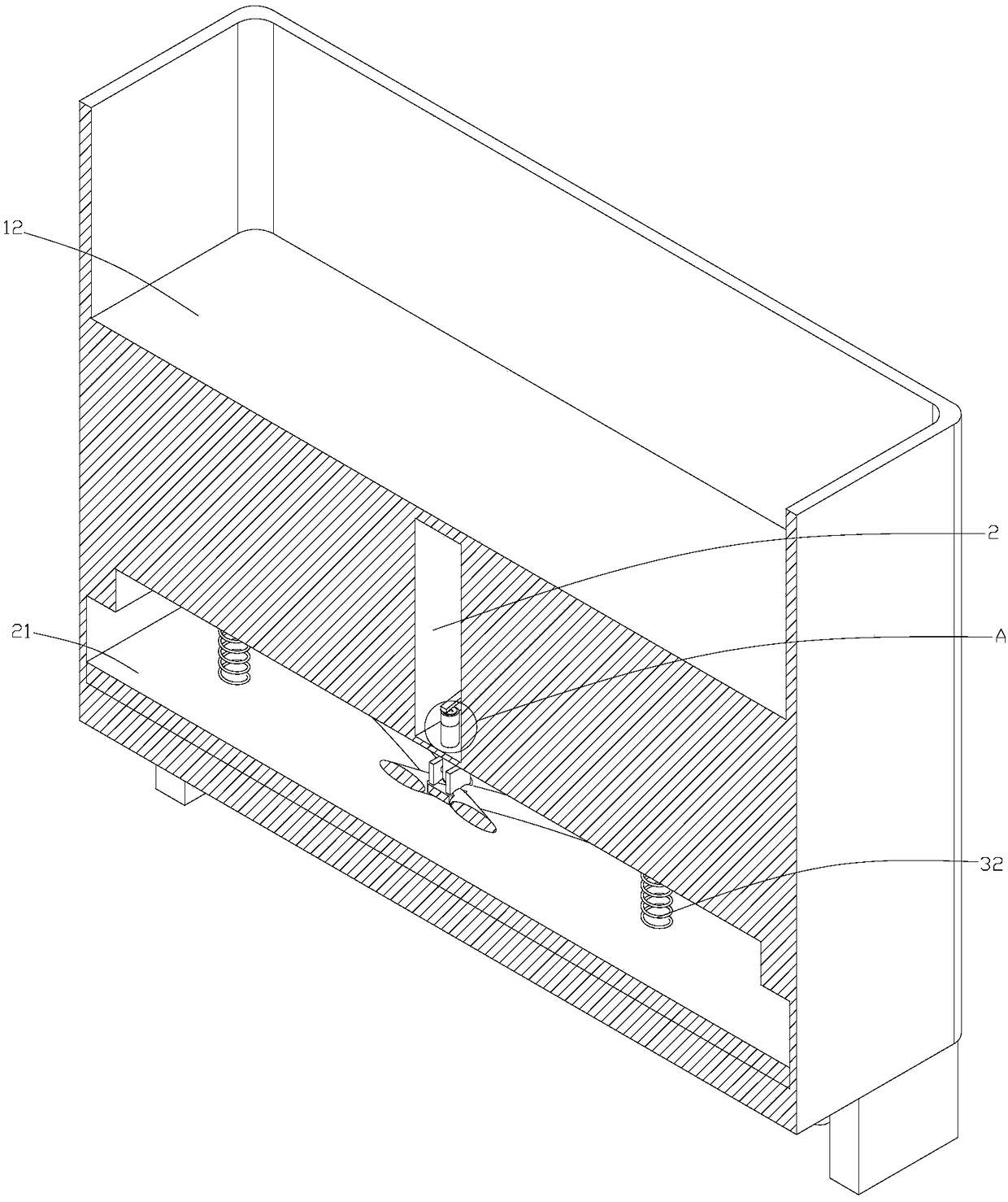

Movable planting box for garden engineering

The invention discloses a movable planting box for garden engineering, comprising a planting box body for planting plants, wherein the bottom of the planting box body is provided with a plurality of universal wheel sets for assisting movement of the planting box body, a planting chamber for planting plants is arranged in the planting box body, and the planting box body is provided with a braking mechanism for fixing the planting box body on designated ground and a braking chamber for accommodating working of the braking mechanism. Through arrangement of the above structure, carrying and fixingof the planting box can be effectively realized, carrying movement of the planting box is more easy and labor-saving, and the carrying efficiency of the planting box is improved. And the planting boxcan be reliably braked and fixed after carried, so that the planting box can be stably placed on the designated ground, deviation of the planting box when placed is avoided, and the stability of theplanting box is strengthened.

Owner:南京幸庄科技创新产业园管理有限公司

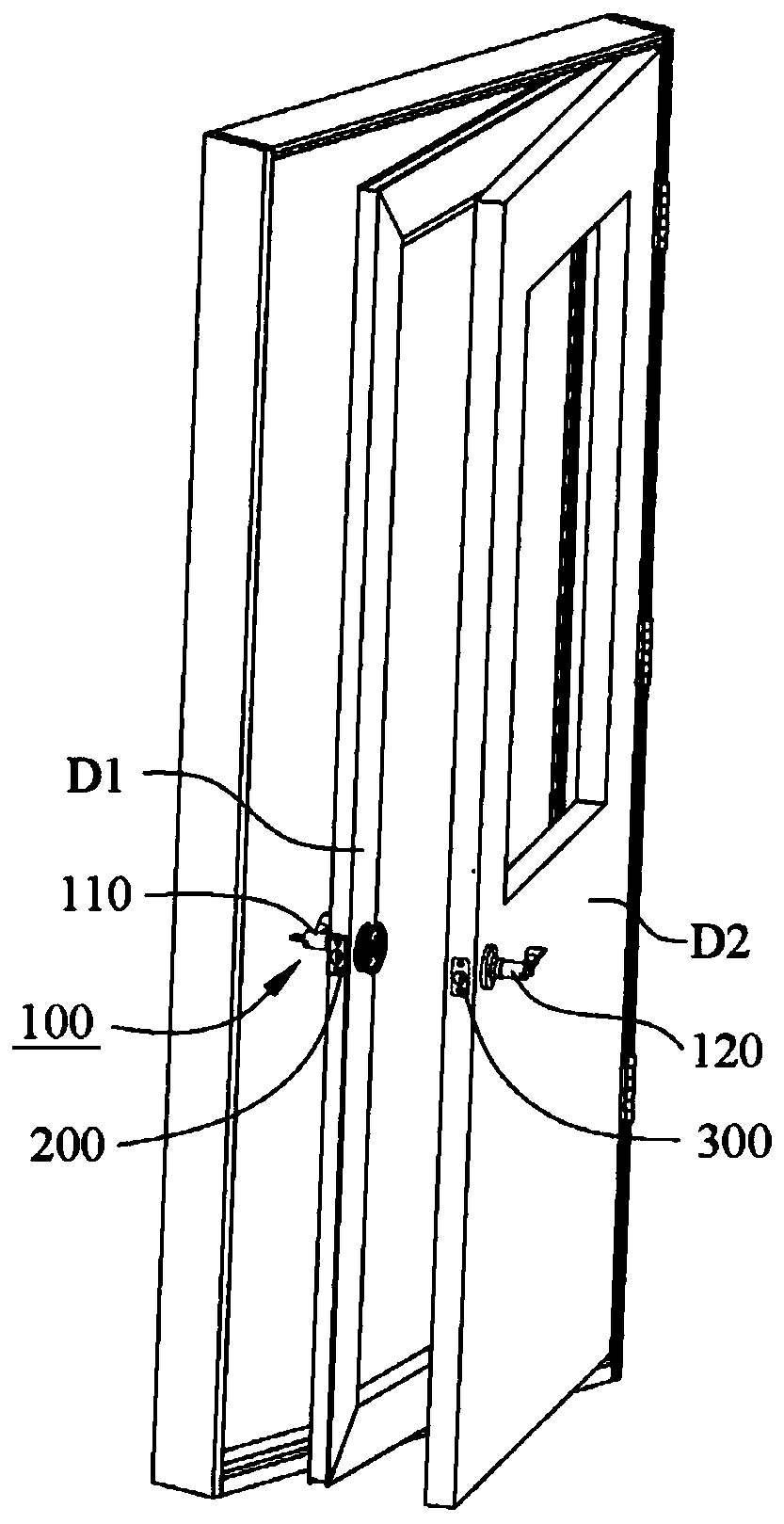

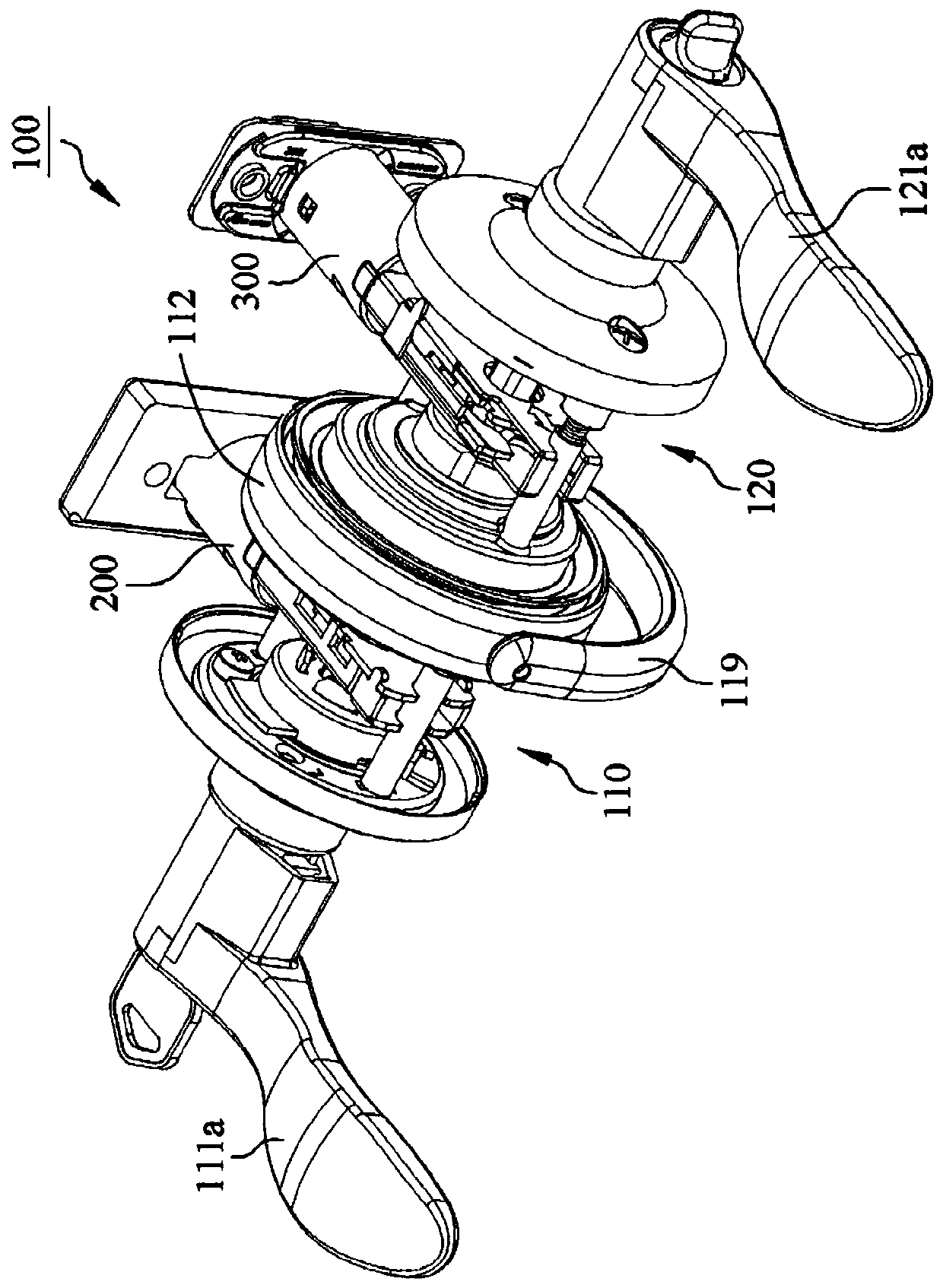

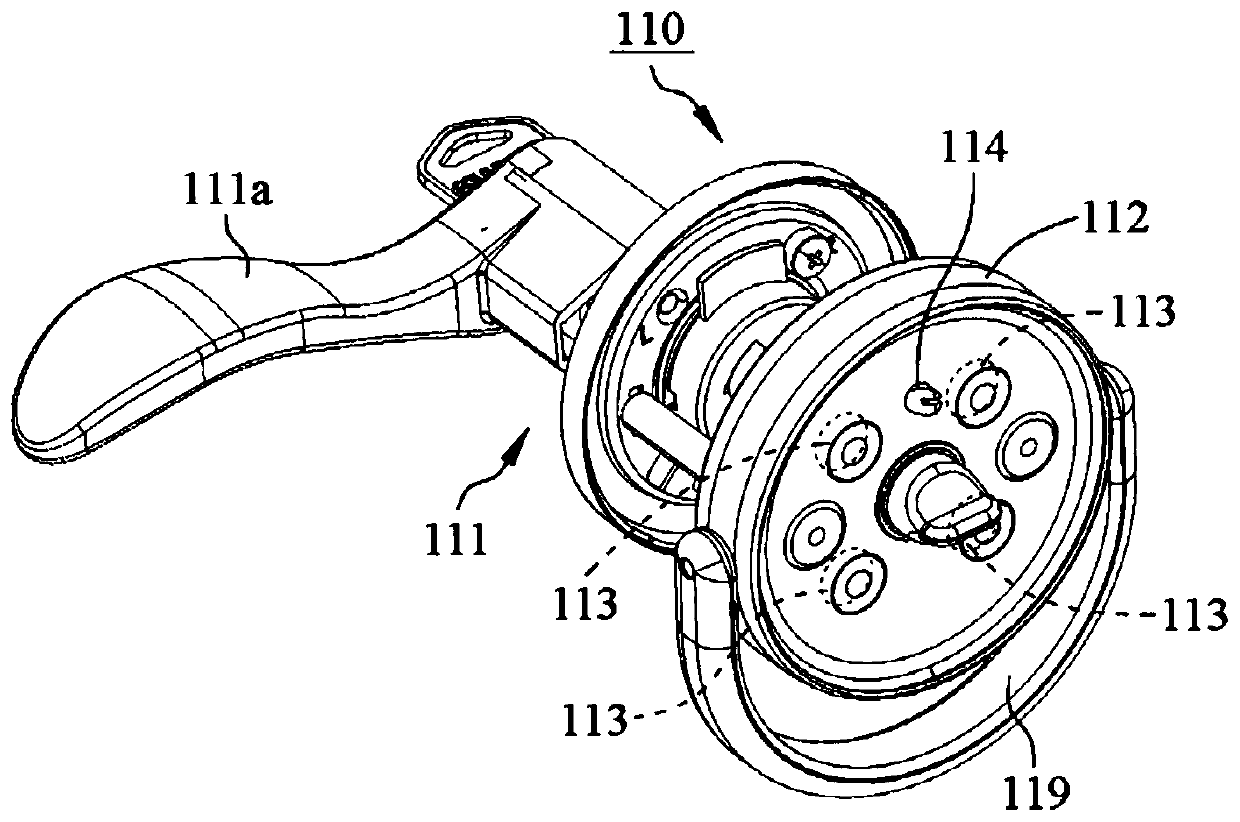

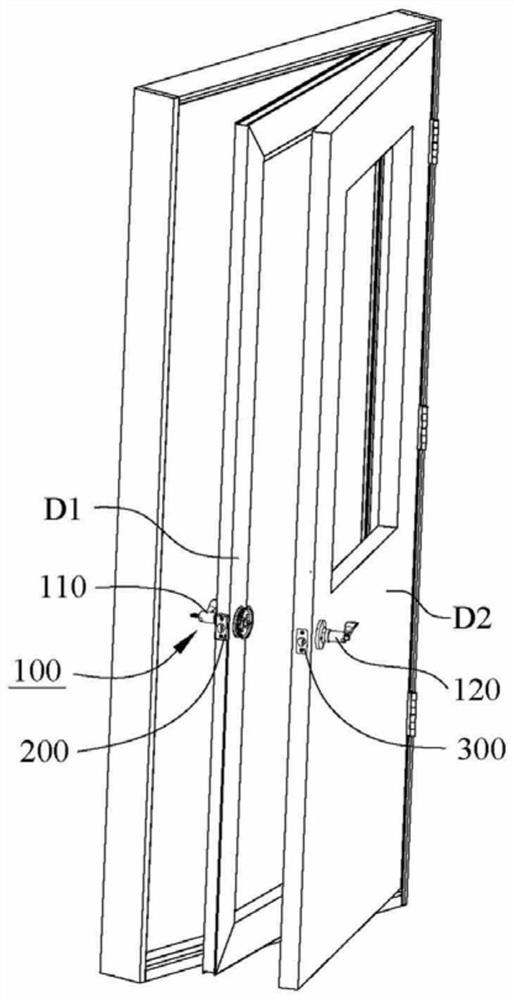

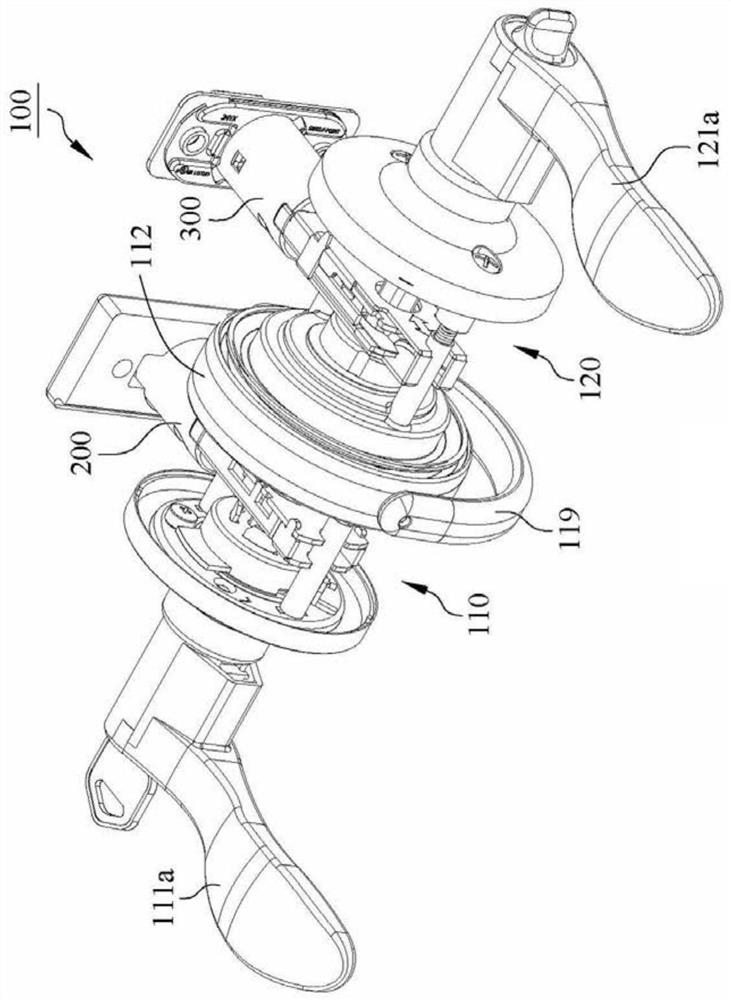

Double-door lock assembly

A double-door lock assembly includes a first lock and a second lock which are respectively mounted on a first door and a second door. The first lock includes a first rotating member, a first magneticmember and a linkage member. The second lock includes a second rotating member with a driving portion and a second magnetic member. According to the lock assembly the first magnetic member and the second magnetic member are magnetically attracted to each other, and the driving portion provided on the second rotating member abuts against the linkage member provided on the first rotating member, sothat the second rotating member and the first rotating member rotate synchronously to open / close the first door and the second door synchronously.

Owner:TAIWAN FU HSING INDAL

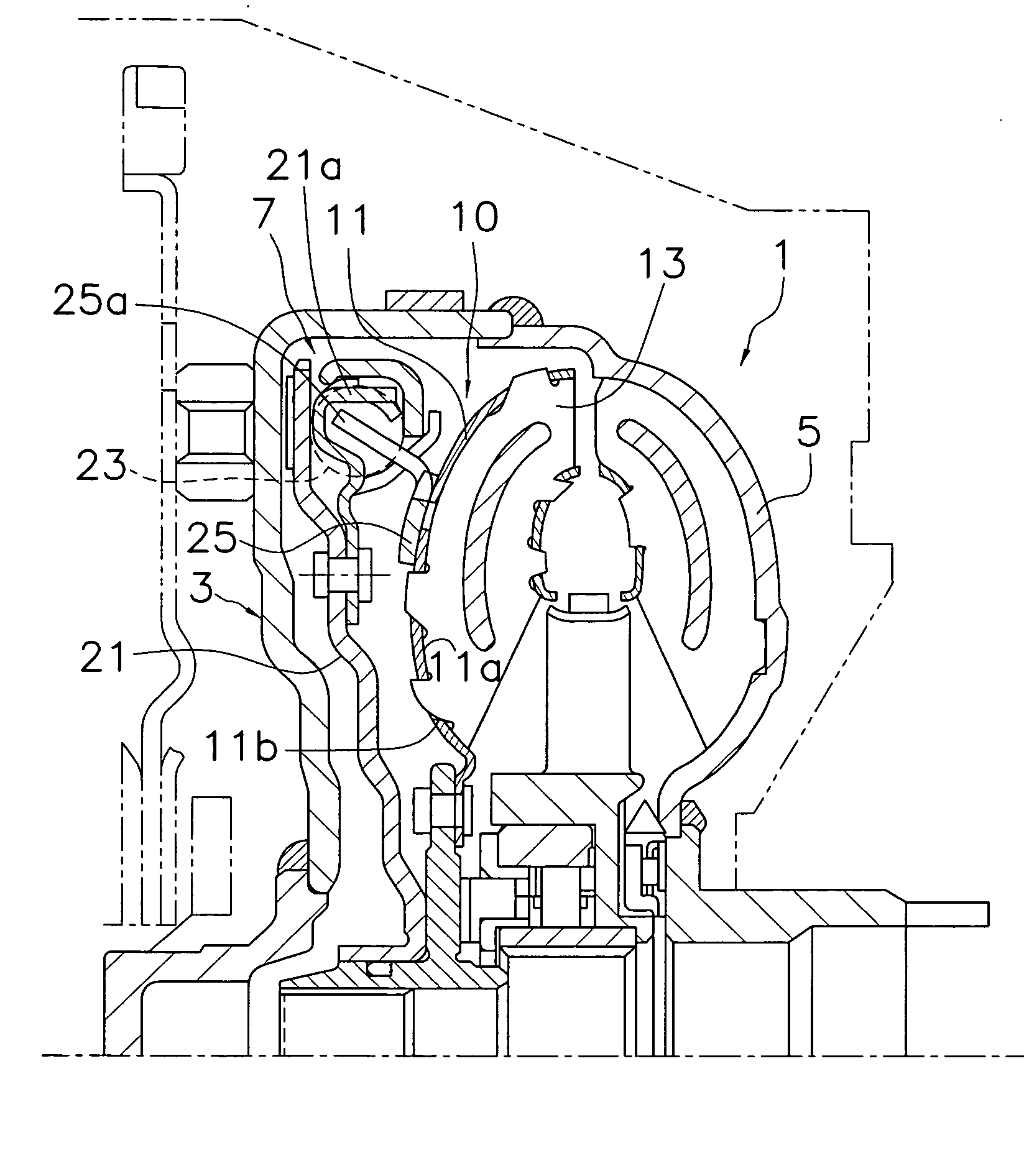

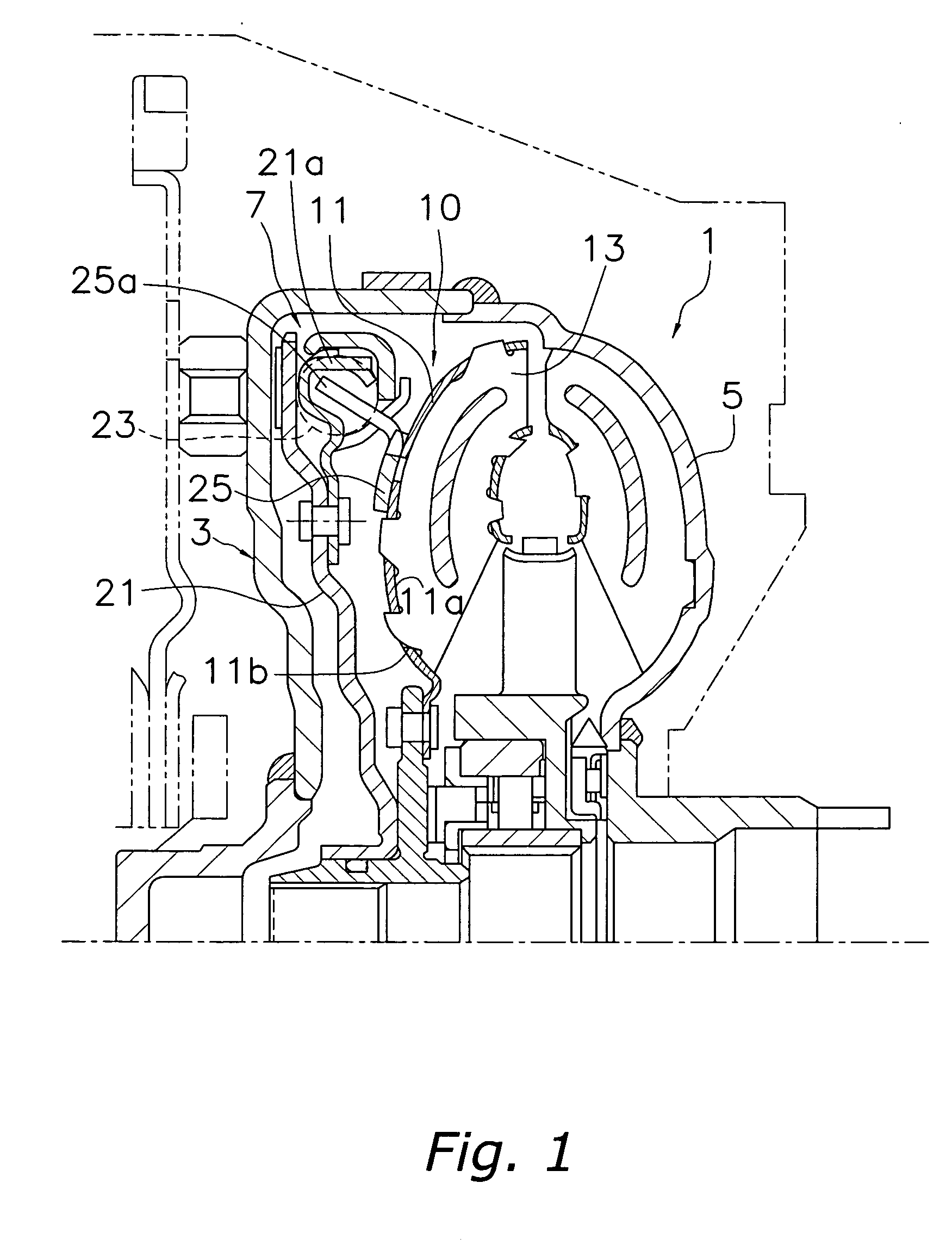

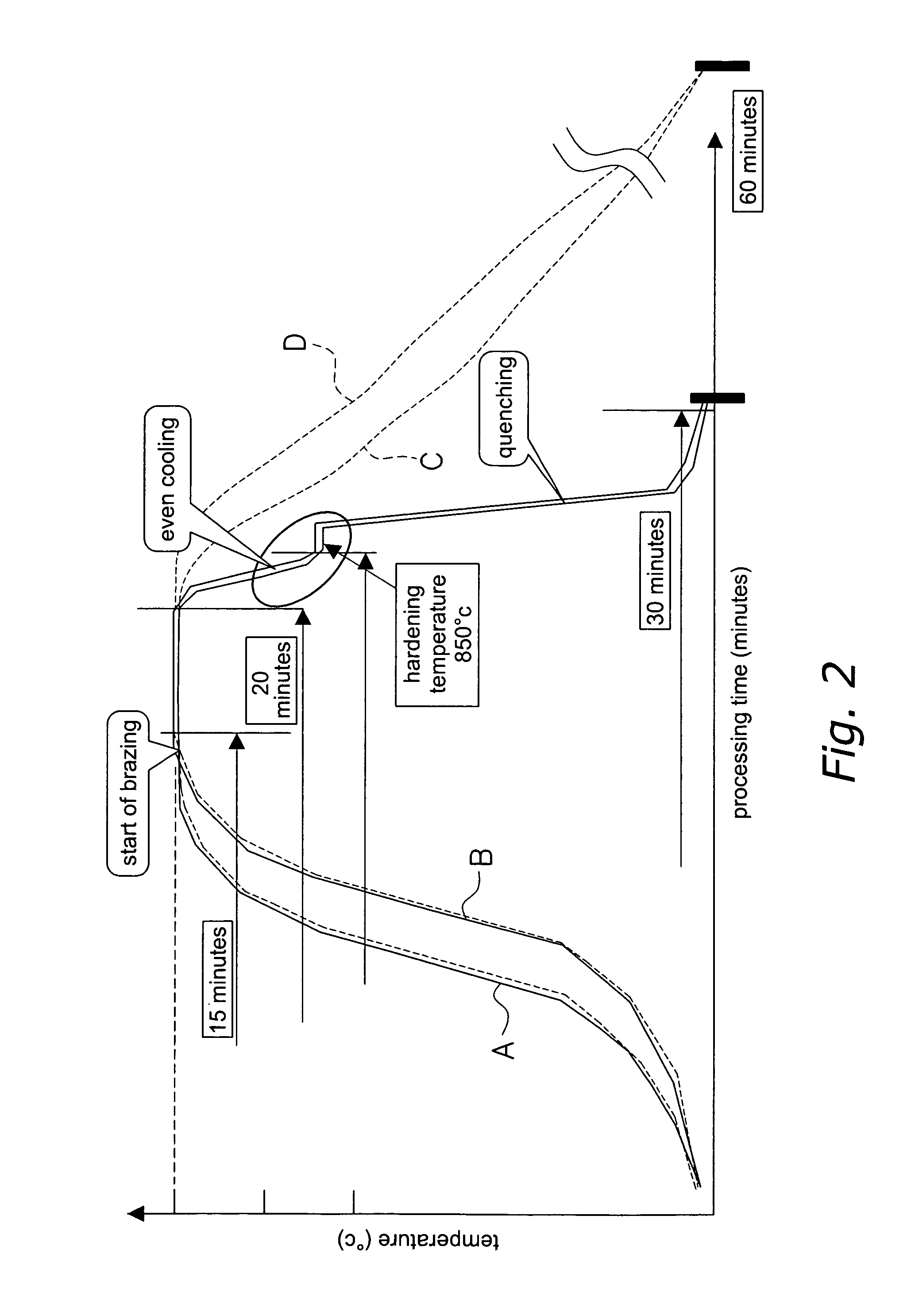

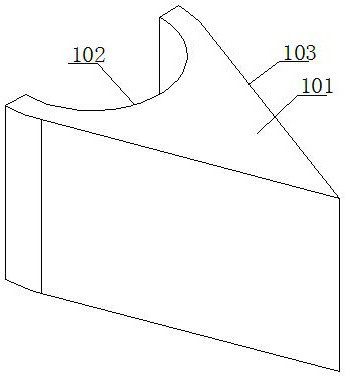

Method for manufacturing a rotary member of a torque converter and a rotary member of a torque converter manufactured by the method

InactiveUS20070137033A1Increase the number ofConsumed energy is largeGearing controlFluid gearingsTurbine bladeHeat treated

It is an object of the present invention to cut costs in manufacturing a rotary member of a torque converter. A method for manufacturing a rotary member of a torque converter 1 is a method for includes manufacturing a rotary member 10 constituted by a turbine shell 11 of the torque converter 1, a plurality of turbine blades 13 fixed to an inner face 11a of the turbine shell 11, and a driven plate 25 of a lock-up device 7 fixed to an outer face 11b of the turbine shell 11. The method includes a first step, a second step, and a third step. In the first step, the driven plate 25 is fixed to the turbine shell 11. In the second step, the turbine blades 13 are brazed to the turbine shell 13 by heating the turbine shell 11 and the turbine blades 13. In the third step, the rotary member 10 is quenched after the heat treatment in the second step.

Owner:EXEDY CORP

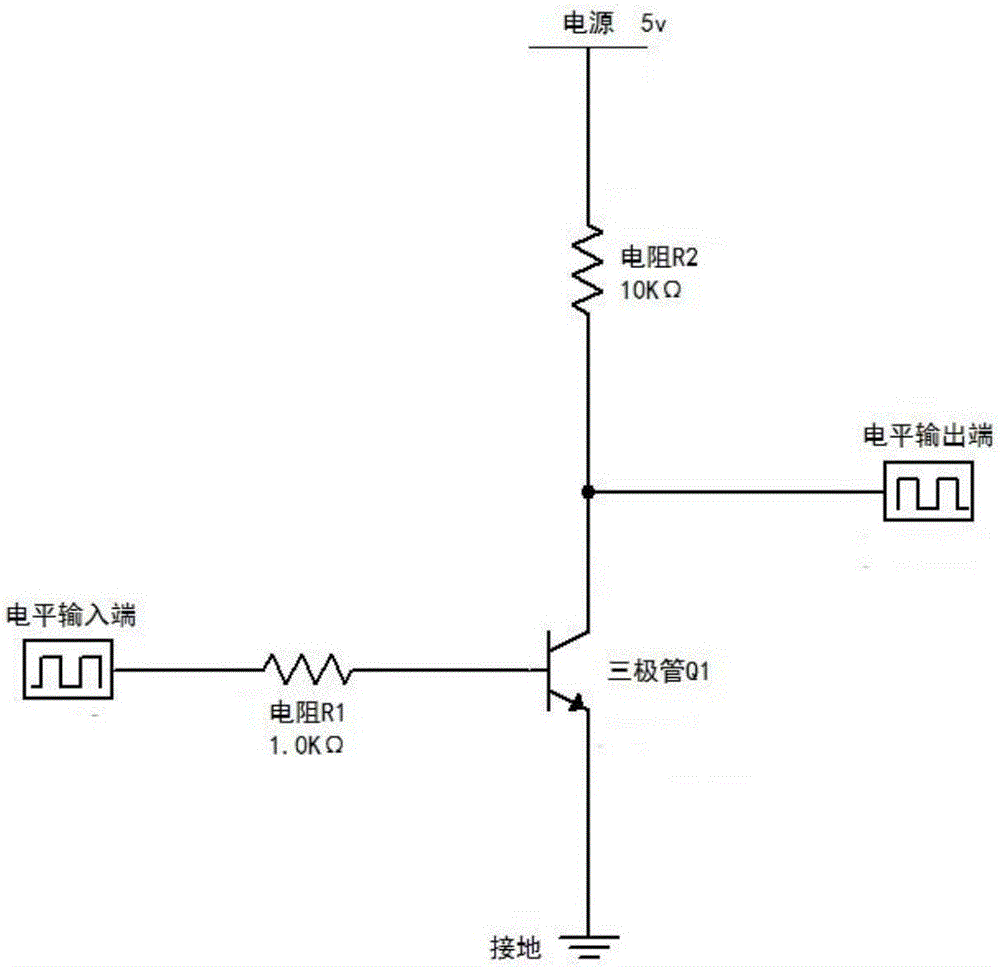

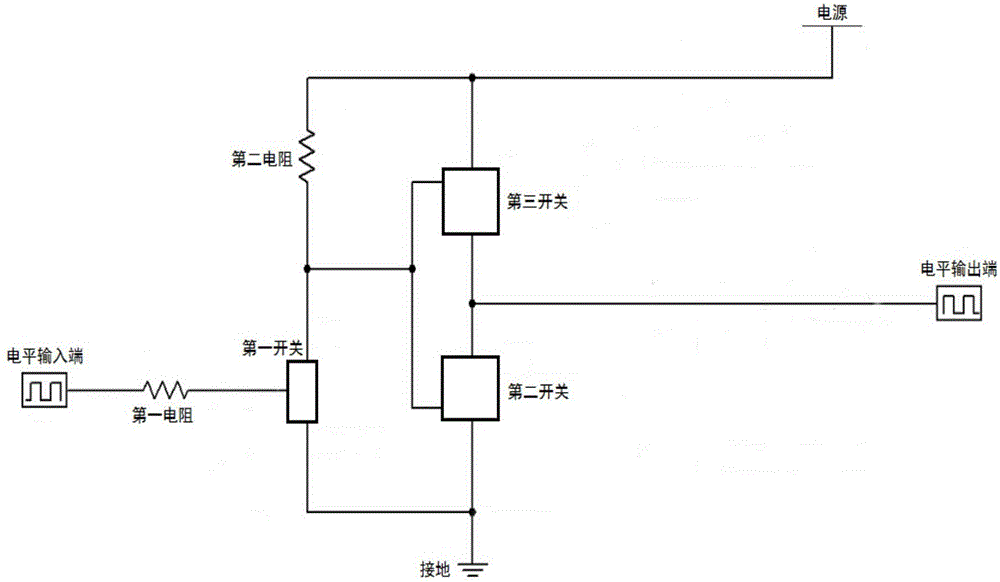

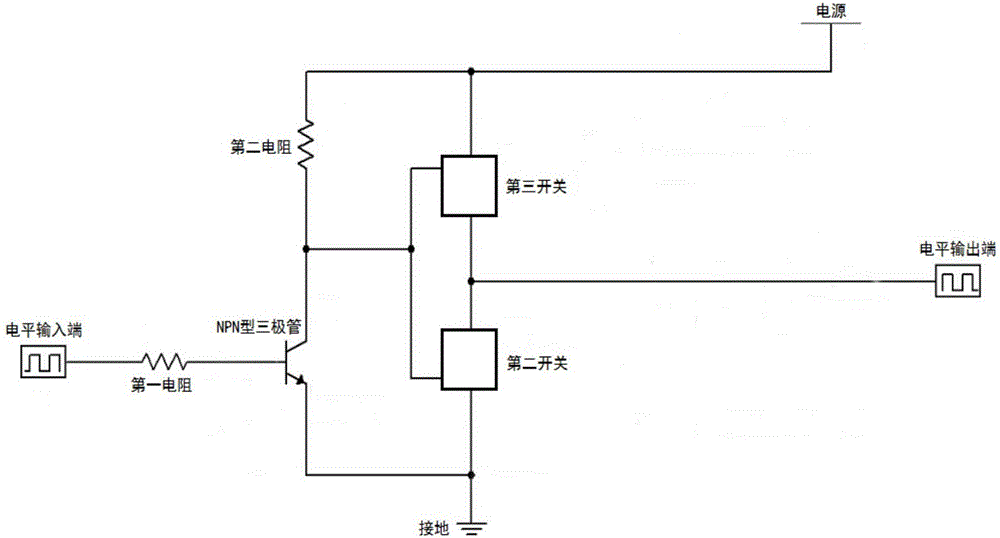

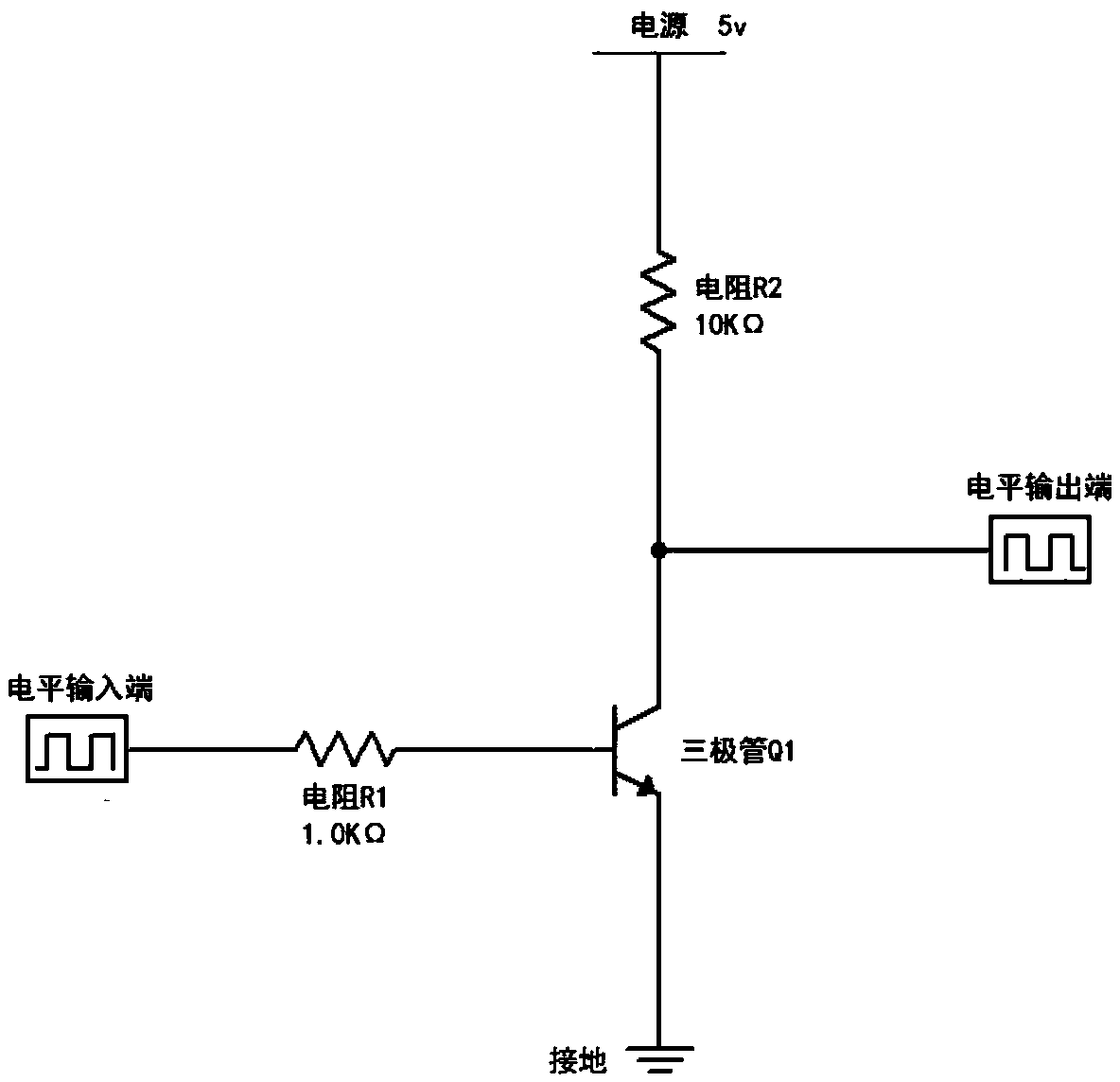

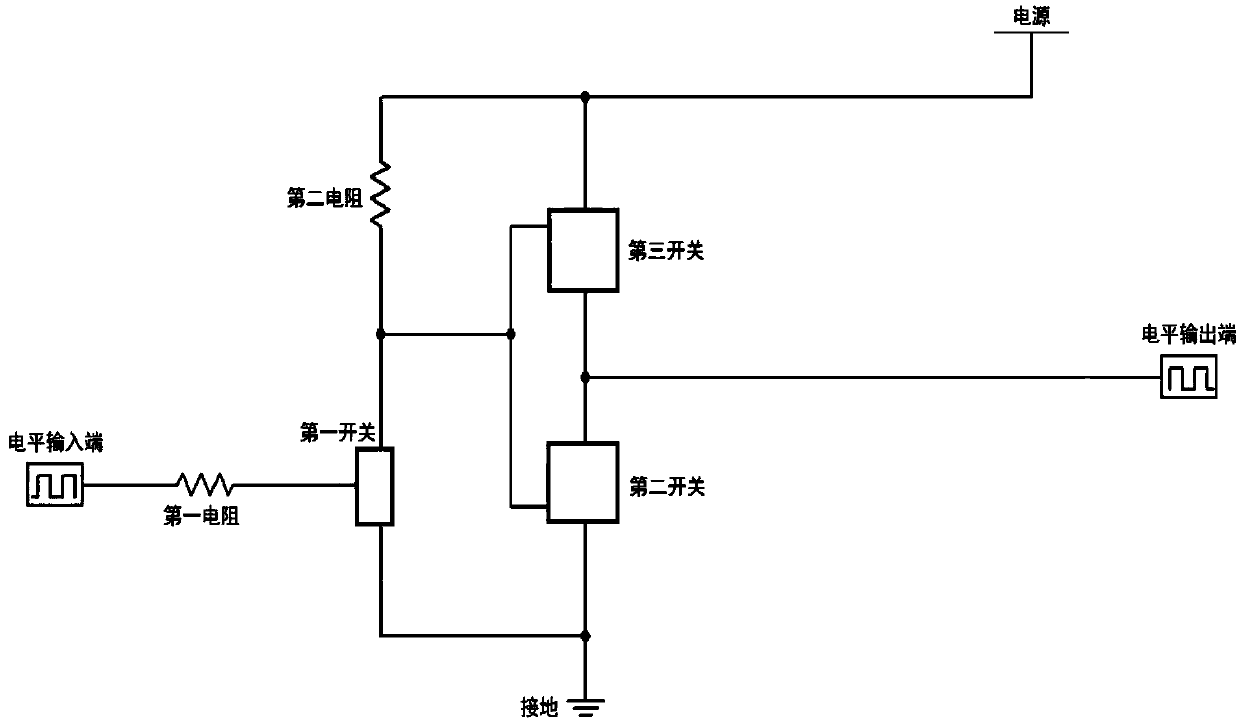

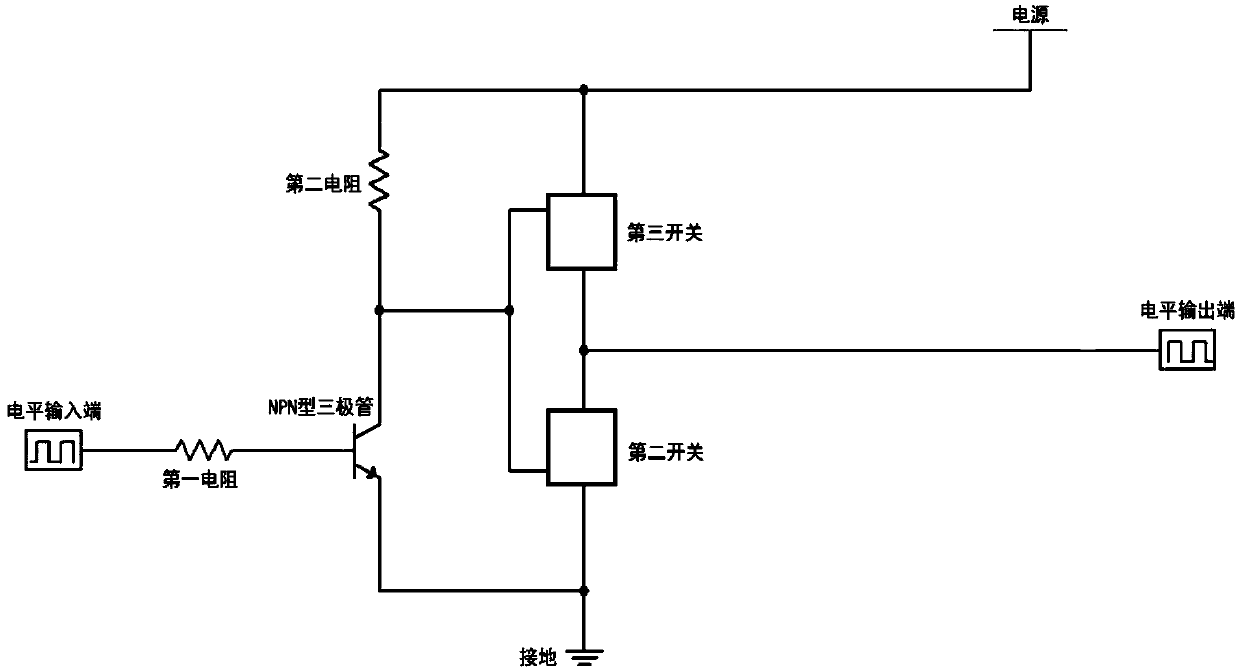

Circuit for remote transmission and biological recognition device and access control system

ActiveCN105809792ASimple structureEnhanced drive strengthIndividual entry/exit registersVIT signalsMedia access control

The invention discloses a circuit for remote transmission and a biological recognition device and access control system.The circuit comprises the electric level input end, a first resistor, a second resistor, a first switch, a second switch, a third switch and the electric level output end; the electric level input end is connected with the control end of the first switch through the first resistor, the first end of the first switch is connected with a power supply through the second resistor, the second end of the first switch is grounded, the first end of the first switch is connected with the control end of the second switch and the control end of the third switch, the first end of the second switch is connected with the first end of the third switch, the first end of the second switch is connected with the electric level output end, the second end of the second switch is grounded, and the second end of the third switch is connected with the power supply.In this way, the problem that transmitted signals generate quality deformation due to the fact that the signal driving capacity of the remote transmission circuit is poor and other problems are solved.

Owner:BEIJING EYECOOL TECH CO LTD +1

Lock structure installed on double doors

ActiveCN111219105BIncrease drive strengthNon-mechanical controlsStructural engineeringMechanical engineering

Owner:TAIWAN FU HSING INDAL

Circuits for voltage or current biasing static random access memory (SRAM) bitcells during SRAM reset operations, and related systems and methods

Circuits for voltage or current biasing static random access memory (SRAM) bitcells during SRAM reset operations are disclosed. Related systems and methods are also disclosed. To reset a plurality of SRAM bitcells in a single reset operation, a biasing circuit is provided and coupled to the plurality of SRAM bitcells. The biasing circuit is configured to apply a voltage or current bias to the SRAM bitcells during a reset operation after power provided to the SRAM bitcells is collapsed to a collapsed power level below an operational power level. The bias is applied as the power to the SRAM bitcells is restored to an operational power level, thus forcing the SRAM bitcells into a desired state. In this manner, the SRAM bitcells can be reset in a single reset operation without need for an increased drive strength from a reset circuit and without need to provide specialized SRAM bitcells.

Owner:QUALCOMM INC

Tidal power generator for new energy

InactiveCN114876714AImprove conversion rateIncrease drive strengthMachines/enginesEngine componentsSea wavesNew energy

The invention relates to the technical field of new energy, and discloses a tidal power generator for new energy. According to the tidal power generator for the new energy, longitudinal displacement can be converted into rotating motion through the gears and the one-way mechanism, the power is directly generated from liquid level contact, therefore, the liquid level difference formed by tides and sea waves can be effectively converted into kinetic energy, then the kinetic energy is converted into electric energy, the effective conversion rate is high, and the power generation efficiency is improved through size limitation among the four gears. The phenomenon that resetting cannot be achieved or resetting is not timely due to insufficient gravity is prevented, a power source formed by tides can act on the generator to the maximum extent through control of the four one-way bearings, potential energy of the entering tides can be utilized to the maximum extent through the guide mechanism, energy conversion is improved, and then the power generation efficiency is improved. Electric energy can be generated when the buoyancy valve moves upwards and can also be generated when the buoyancy valve moves downwards, so that the electric energy is continuously generated, and the electric energy conversion rate is increased.

Owner:刘梦梅

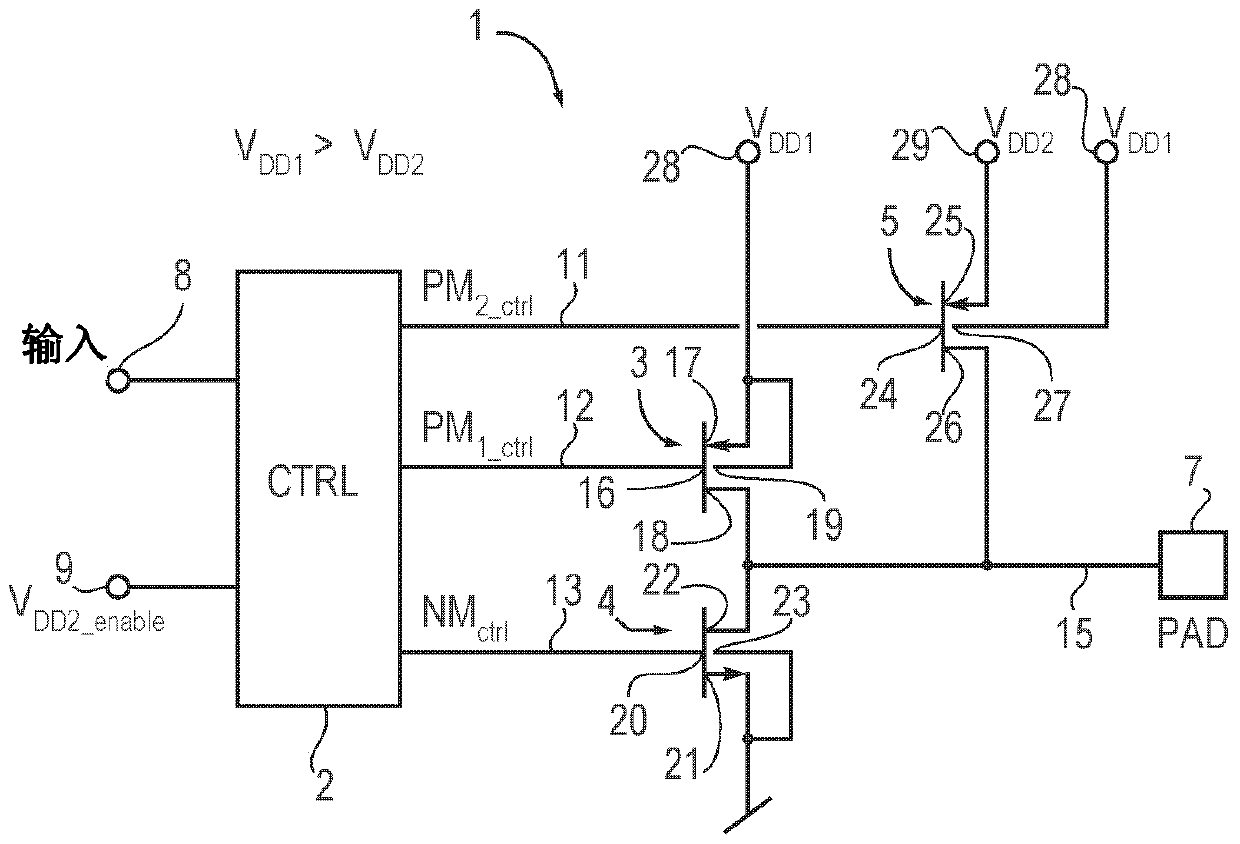

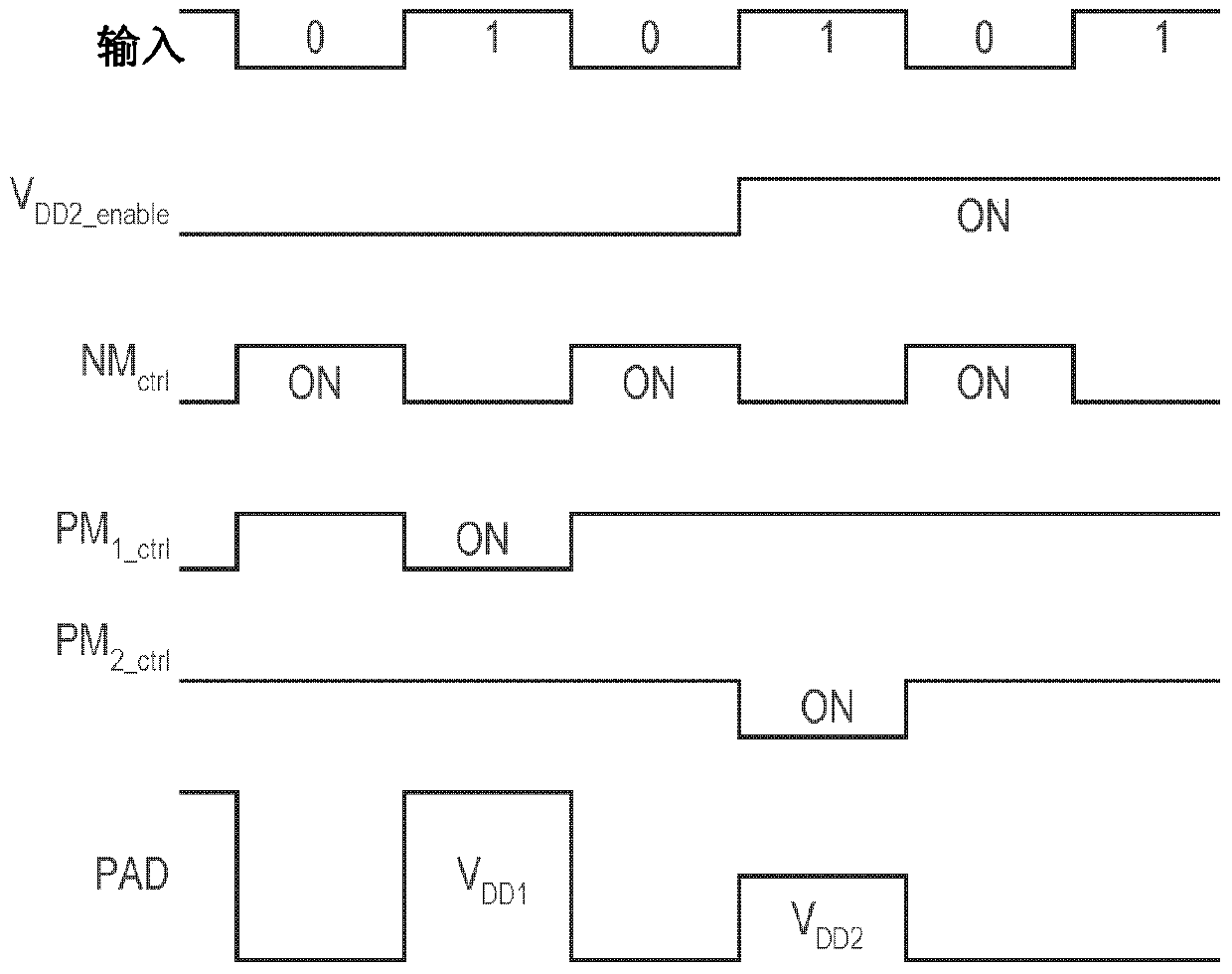

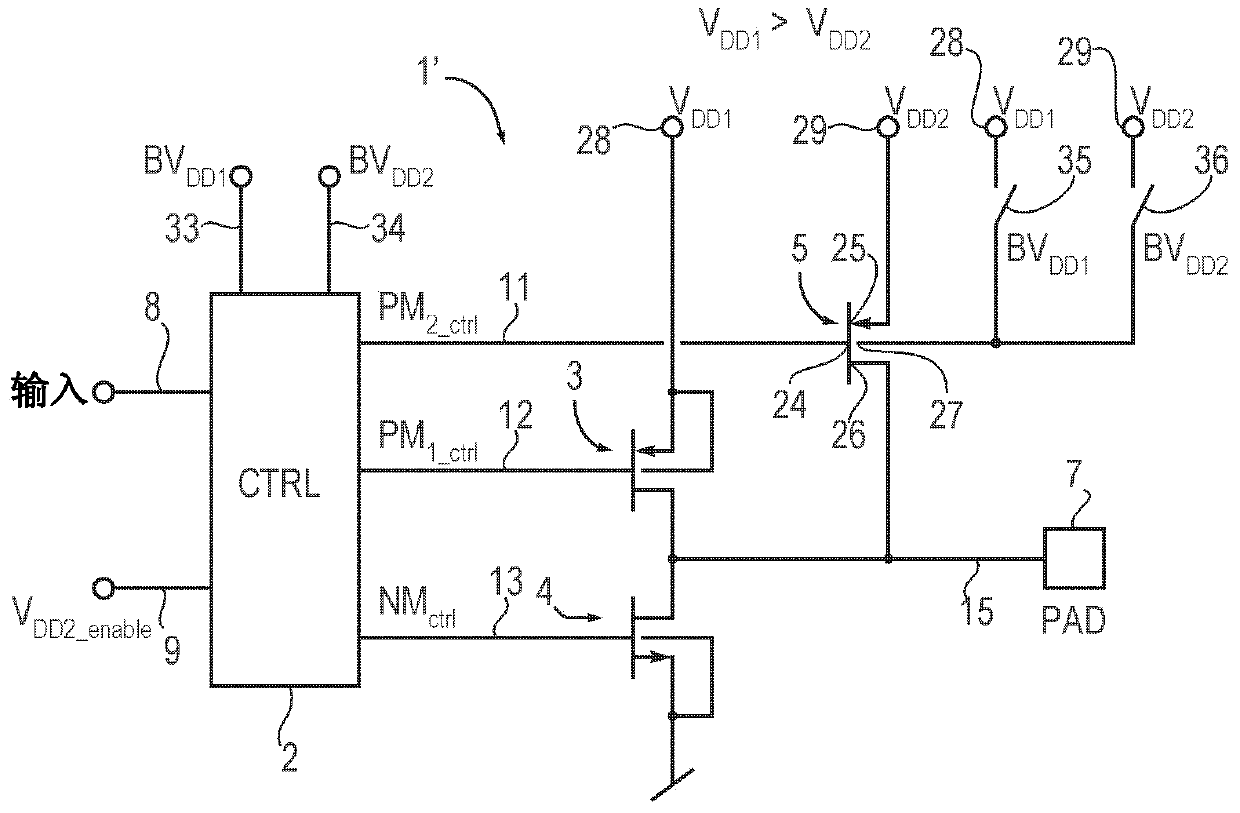

Hearing aid interface circuit and method

ActiveCN105282673BIncrease drive strengthLow Dynamic Power ConsumptionHearing device energy consumption reductionDeaf-aid setsSemiconductor chipHemt circuits

An interface pad circuit configured for conveying an electrical signal from a semiconductor chip component to a component external to the semiconductor chip component, the interface pad circuit includes: a control circuit; a plurality of semiconductor elements, the semiconductor elements having respective bulk terminals and being controlled by the control circuit; and a connection pad; wherein at least two of the semiconductor elements are configured for providing a plurality of non-zero logic voltage levels to the connection pad; and wherein the control circuit is configured to apply a voltage level to the bulk terminals of the at least two of the semiconductor elements providing the non-zero logic voltage levels, the voltage level applied by the control circuit corresponding to the highest voltage level of the plurality of non-zero logic voltage levels.

Owner:GN HEARING AS

Circuits for long-distance transmission and biometric devices, access control systems

ActiveCN105809792BSimple structureImprove stabilityIndividual entry/exit registersElectrical resistance and conductanceEngineering

The invention discloses a circuit for remote transmission and a biological recognition device and access control system.The circuit comprises the electric level input end, a first resistor, a second resistor, a first switch, a second switch, a third switch and the electric level output end; the electric level input end is connected with the control end of the first switch through the first resistor, the first end of the first switch is connected with a power supply through the second resistor, the second end of the first switch is grounded, the first end of the first switch is connected with the control end of the second switch and the control end of the third switch, the first end of the second switch is connected with the first end of the third switch, the first end of the second switch is connected with the electric level output end, the second end of the second switch is grounded, and the second end of the third switch is connected with the power supply.In this way, the problem that transmitted signals generate quality deformation due to the fact that the signal driving capacity of the remote transmission circuit is poor and other problems are solved.

Owner:BEIJING EYECOOL TECH CO LTD +1