Layout method of SiC JBS device

A layout method and device technology, which are applied in the manufacture of electrical solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problem of affecting the pinch-off ability of Schottky junctions, the strip structure is difficult to achieve uniformity, and it cannot effectively reduce the size of the To solve the problems such as the electric field on the surface of the Teky, to increase the contact area of the Schottky, increase the area of the Schottky barrier area, and ensure the reverse breakdown characteristics.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0056] The purpose of the present invention is to provide a SiC JBS device, which mainly lies in the arrangement of the P-type region in the active region. Compared with the traditional layout method, while ensuring the reverse blocking voltage of the device, it increases the Schottke as much as possible. The area of the base contact area is small, and the process is easy to realize, achieving a reasonable compromise between breakdown voltage, on-resistance characteristics and process difficulty.

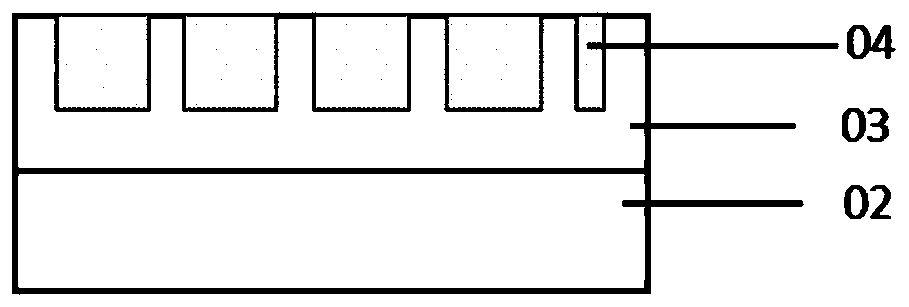

[0057] an active area and a terminal protection area, the terminal protection area is arranged around the active area, and the active area includes a plurality of P-type areas and Schottky contact areas; the active area is a rectangular structure;

[0058] The multiple P-type regions are arranged alternately in multiple rows and columns, and the Schottky contact regions are filled between the P-type regions.

[0059] The P-type region includes a complete P-type region and a half-P...

Embodiment 2

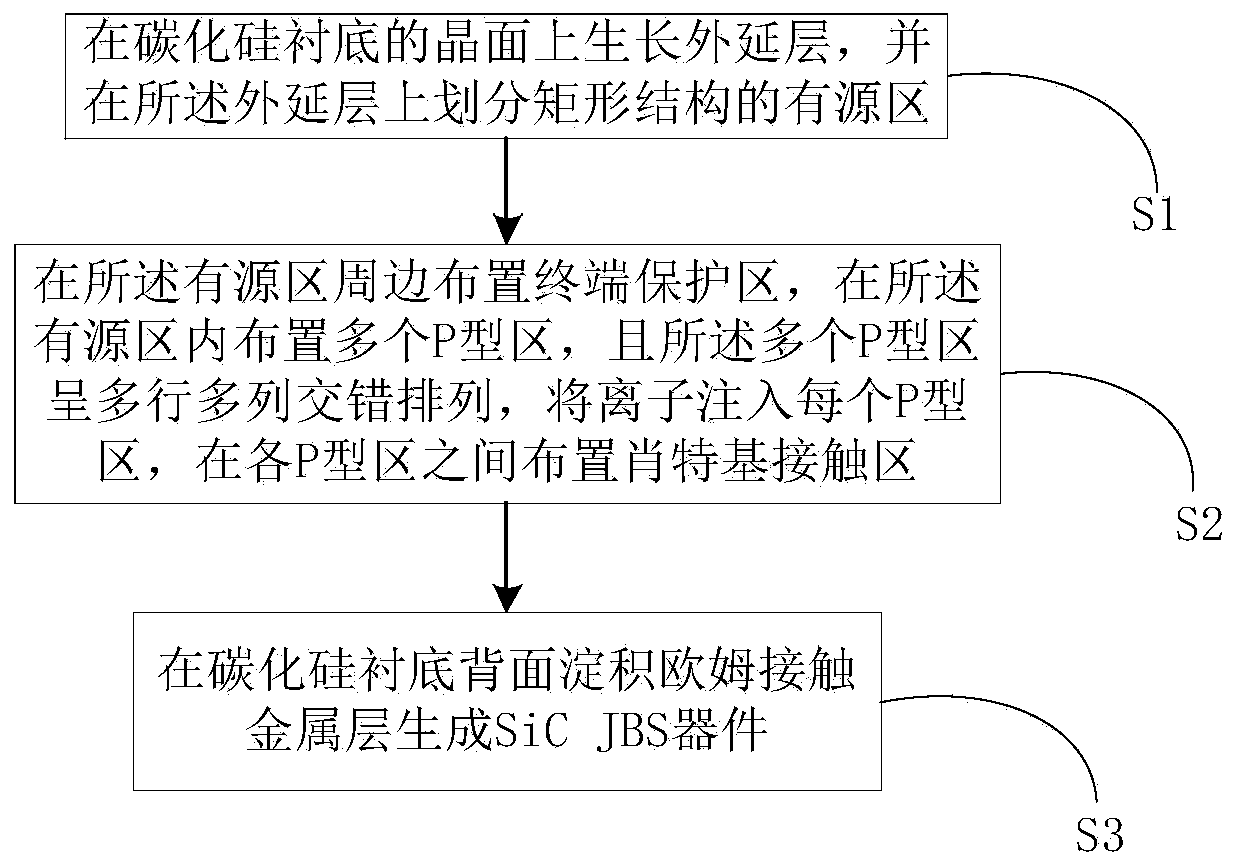

[0070] Based on the same inventive concept, this embodiment also provides a layout method for SiC JBS devices, which is suitable for manufacturing processes, such as figure 1 shown, including:

[0071] Step S1, growing an epitaxial layer on the crystal plane of the silicon carbide substrate, and dividing an active region of a rectangular structure on the epitaxial layer;

[0072] Step S2, arranging a plurality of P-type regions in the active region, and the plurality of P-type regions are arranged alternately in multiple rows and columns, implanting ions into each P-type region, and arranging between the P-type regions Schottky contact area;

[0073] Step S3, depositing an ohmic contact metal layer on the back surface of the silicon carbide substrate to form a SiC JBS device.

[0074] The specific layout methods of SiC JBS devices include:

[0075] Step S1, growing an epitaxial layer on the crystal plane of the silicon carbide substrate, and dividing an active region of a r...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More